## (19) 대한민국특허청(KR)

## (12) 공개특허공보(A)

(51) Int. Cl.<sup>7</sup>

G09G 3/36

(11) 공개번호 특2001-0007288

(43) 공개일자 2001년01월26일

(21) 출원번호 10-2000-0031263

(22) 출원일자 2000년06월08일

(30) 우선권주장 1999-162268 1999년06월09일 일본(JP)

(71) 출원인 가부시키가이샤 히타치세이사쿠쇼 가나이 쓰토무

일본 도쿄토 치요다쿠 간다스루가다이 4쪽메 6반치

(72) 발명자 미야자와도시오

일본지바겐지바시미도리꾸시이나사끼즈931

사또우도모히고

일본지바겐지바시미도리꾸아스미가오까2쪽메20-11

(74) 대리인 장수길, 구영창

**심사청구 : 없음****(54) 액정 표시 장치****요약**

액정 표시 소자의 표시 화면의 표시 품질을 향상시킨 액정 표시 장치를 제공한다.

각 영상 신호선에 화소 구동 전압을 공급하는 복수의 영상 신호 수신 수단을 구비하고, 각 영상 신호 수신 수단은 전계 효과형 트랜지스터와, 전계 효과형 트랜지스터의 제어 전극의 전압치를 공통 화소 구동 전압에 대하여 전계 효과형 트랜지스터의 임계지 전압분만큼 보정한 전압치로 설정하는 제1 수단과, 전계 효과형 트랜지스터의 제어 전극의 전압치를 제1 수단에서 보정된 전압치에 영상 신호 전압이 중첩된 전압으로 하는 제2 수단과, 제2 수단에서 제어 전극의 전압치가 제1 수단에서 보정된 전압치에 영상 신호 전압이 중첩된 전압이 된 전계 효과형 트랜지스터와 함께, 공통 화소 구동 전압에 영상 신호 전압이 중첩된 전압을 형상 신호선에 공급하는 제3 수단을 구비한다.

**대표도****도3****색인어**

영상 신호 수단, 제어 전극, 전계 효과형 트랜지스터, 화소 구동 전압, 비디오 신호 수신 회로

**명세서****도면의 간단한 설명**

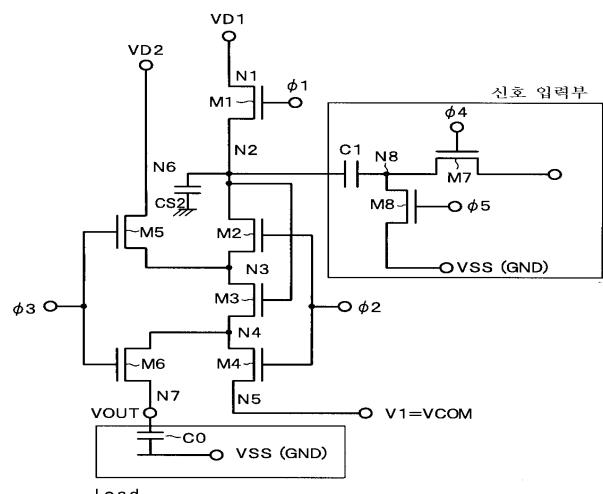

도 1은 본 발명의 Poly-SiTr-TFT 액정 표시 모듈에 적용되는 전압 재생 회로의 일례의 회로 구성을 나타내는 회로도이다.

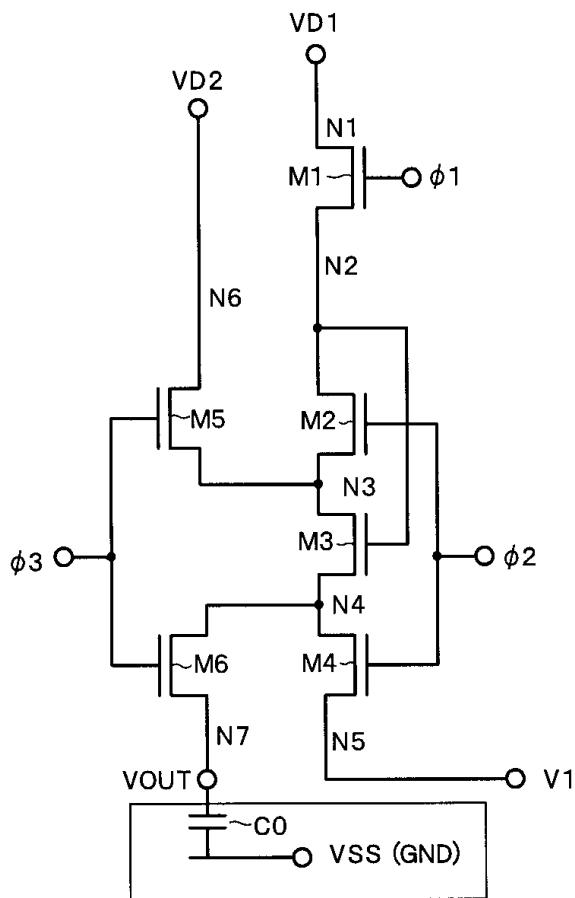

도 2는 도 1에 도시하는 전압 재생 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 3$ )의 일례와, 각 외부 펄스 파형( $\phi 1 \sim \phi 3$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면.

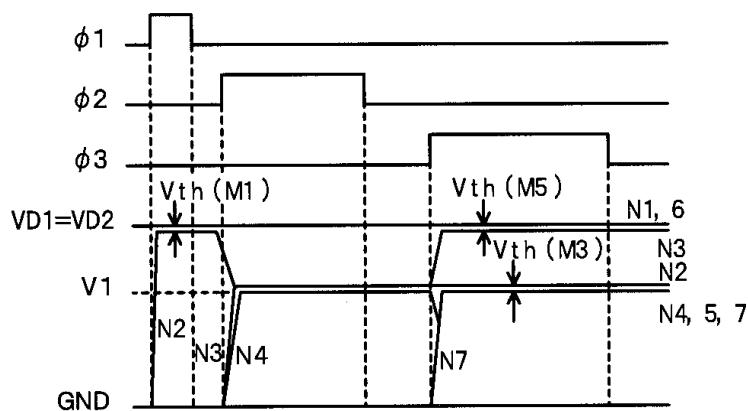

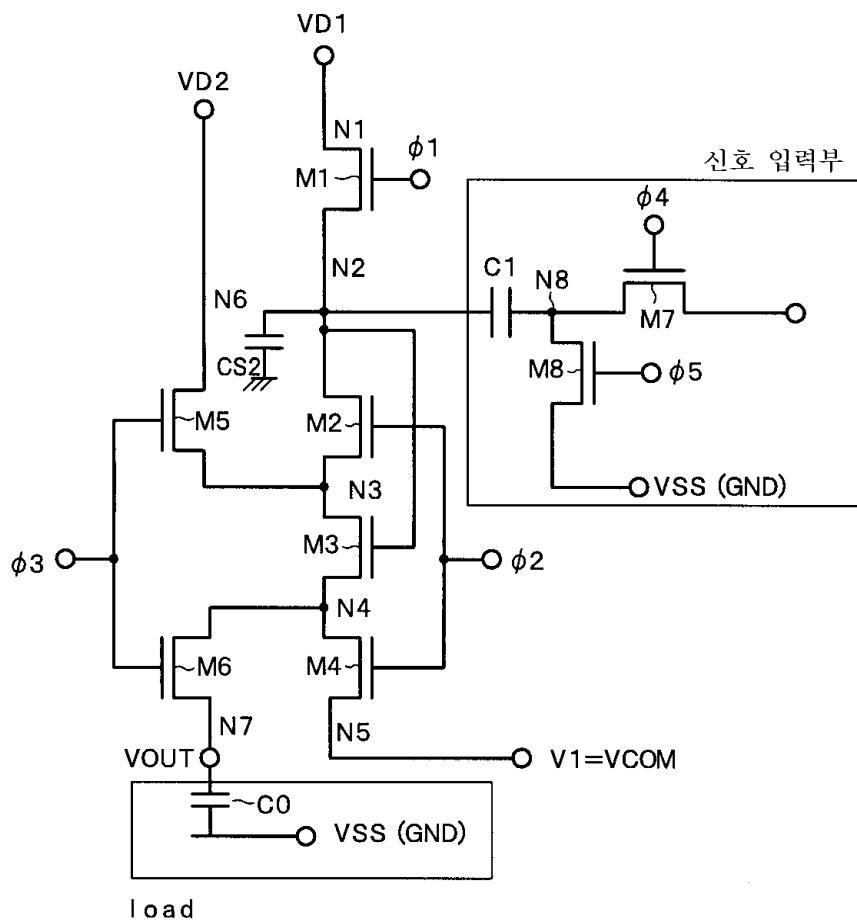

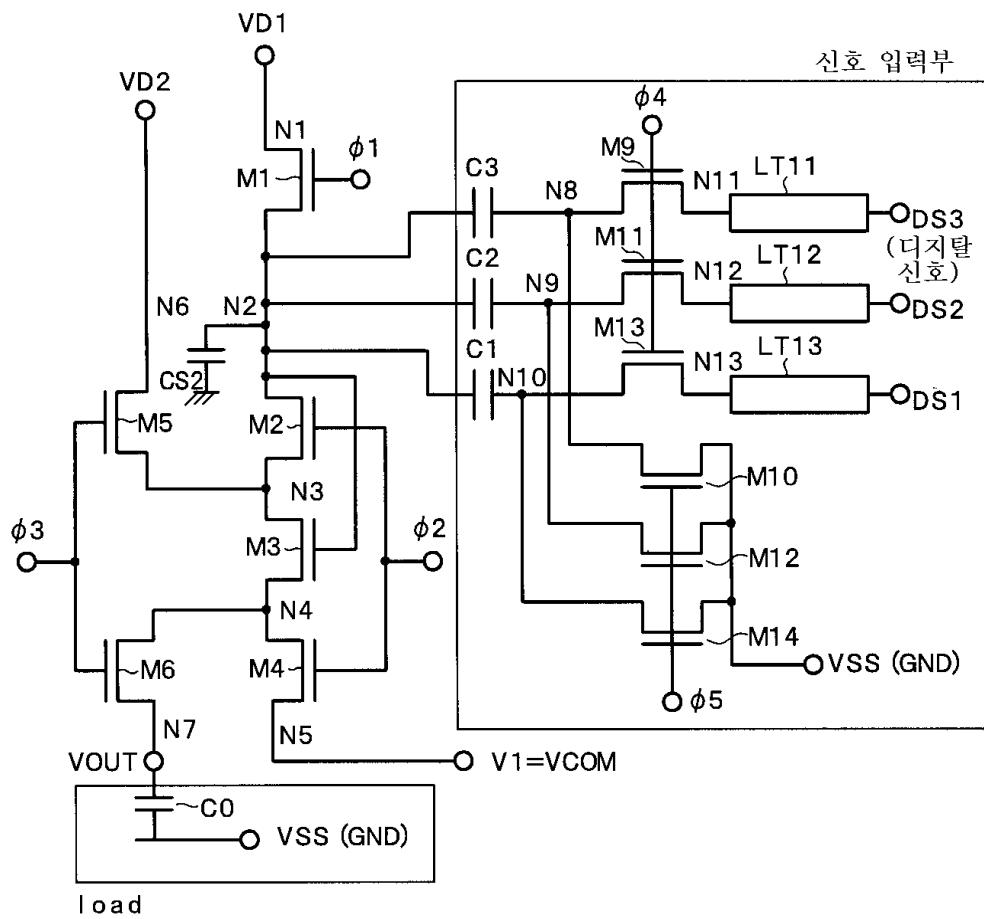

도 3은 도 1에 도시하는 전압 재생 회로를 응용한 응용 회로의 일례의 회로 구성을 나타내는 회로도.

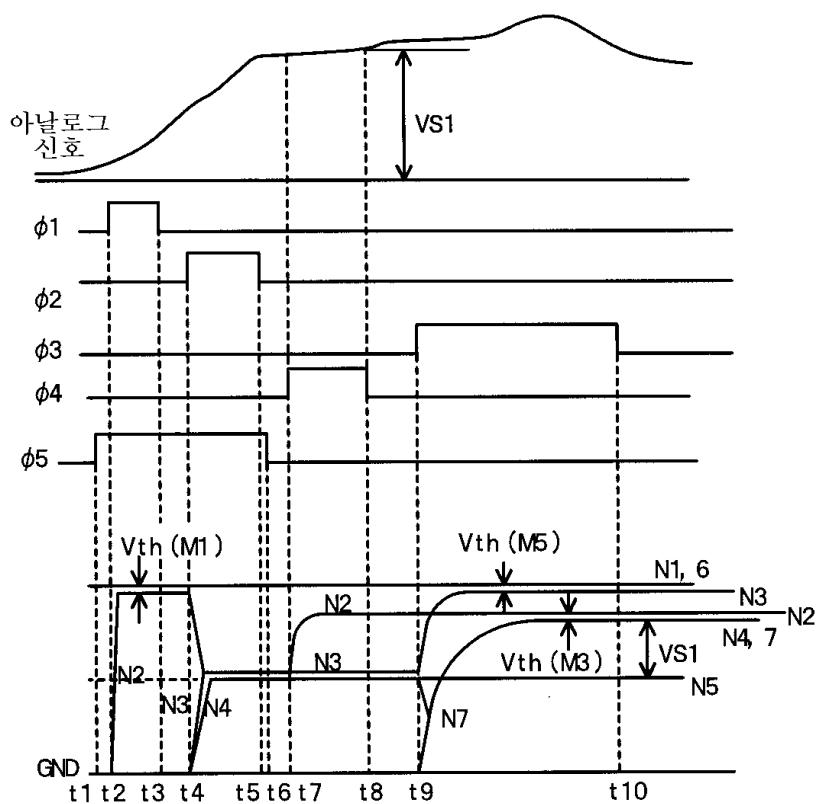

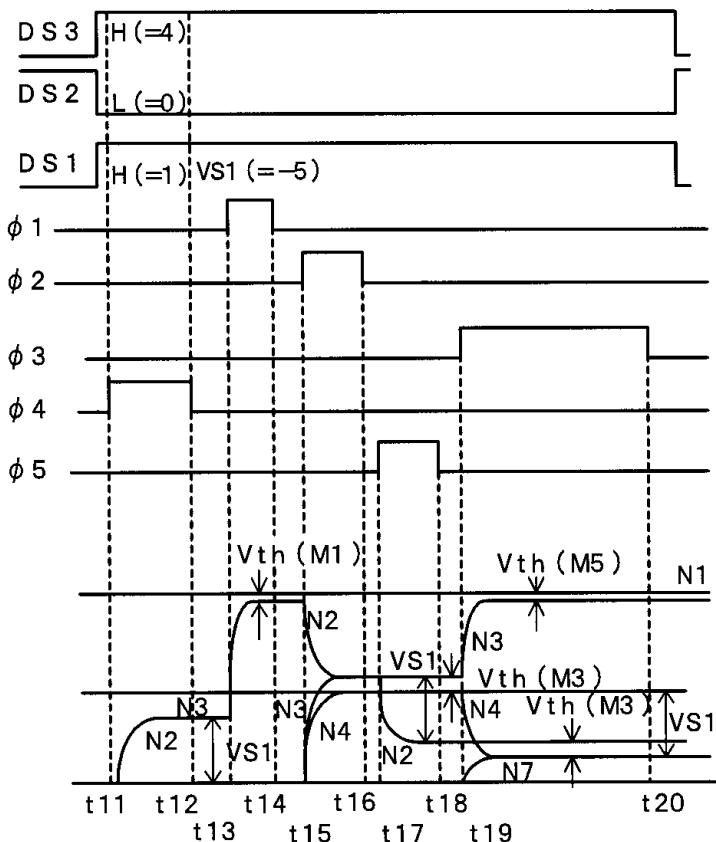

도 4는 도 3에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 일례와, 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면.

도 5는 도 3에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 다른 예와, 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면.

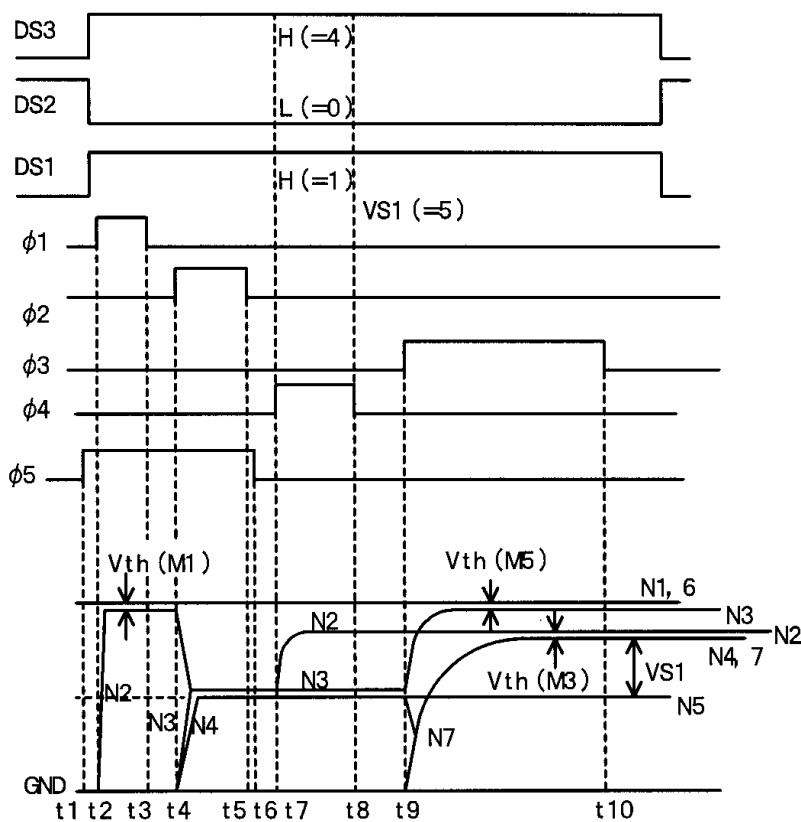

도 6은 도 1에 도시하는 전압 재생 회로를 응용한 응용 회로의 다른 예의 회로 구성을 나타내는 회로도.

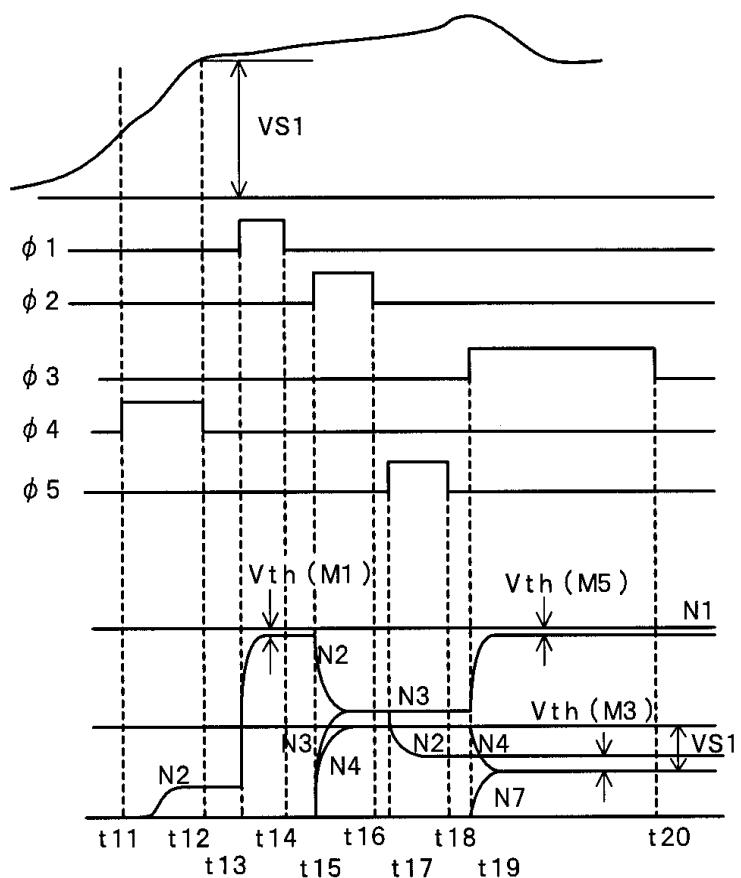

도 7은 도 6에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 일례와, 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면.

도 8은 도 6에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 다른 예와, 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면.

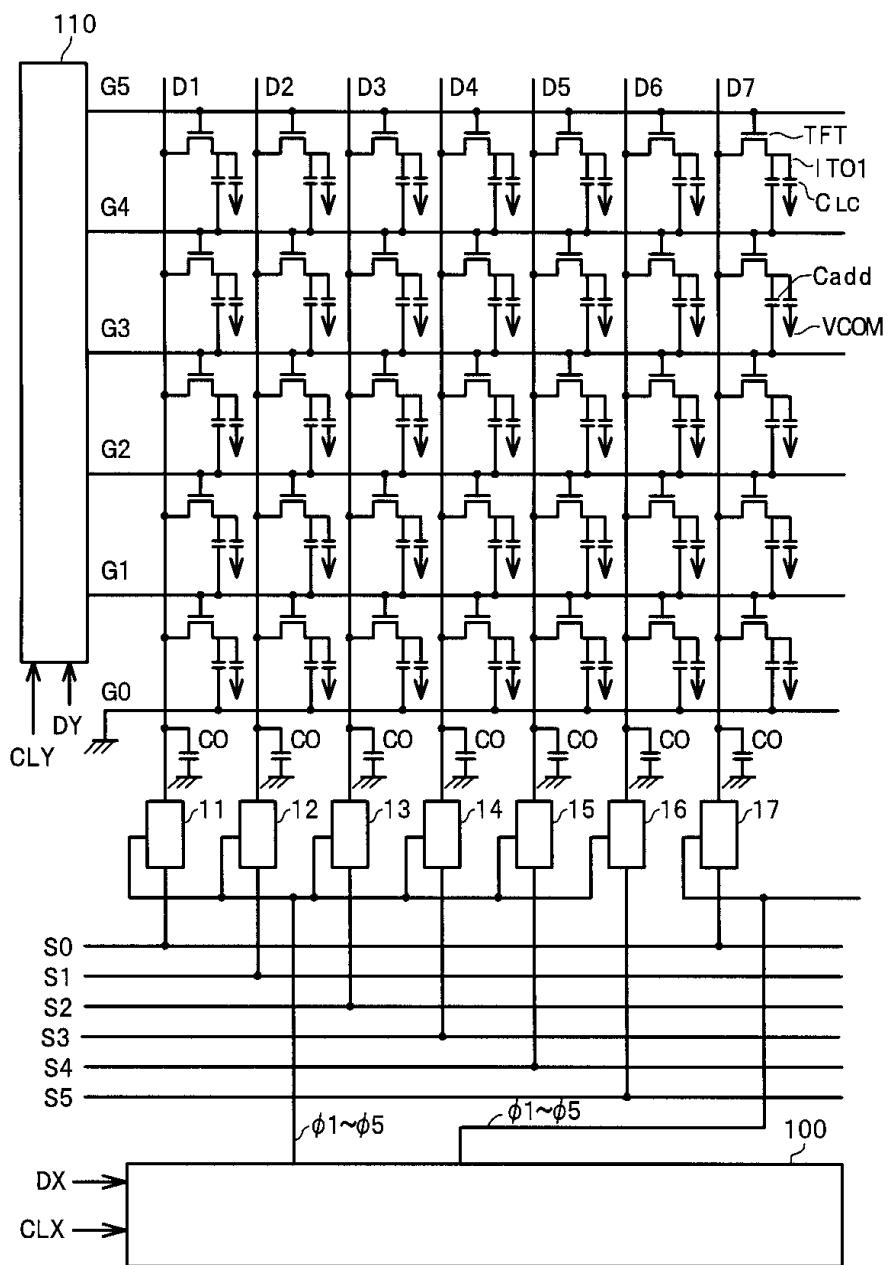

도 9는 본 발명의 실시예 1의 Poly-SiTr-TFT 액정 표시 모듈의 액정 표시 패널의 등화 회로를 나타낸 도면.

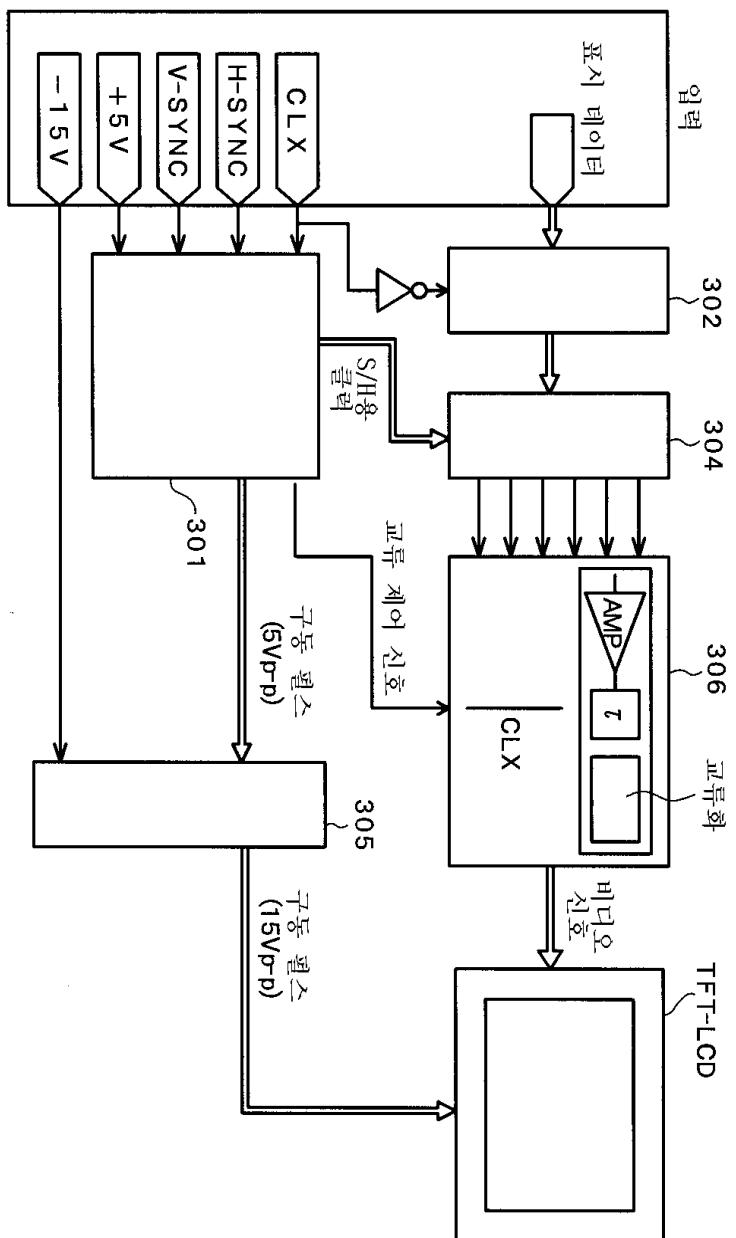

도 10은 본 발명의 실시예 1의 Poly-SiTr-TFT 액정 표시 모듈의 주변 회로의 개략 회로 구성을 나타내는 블

록도.

도 11은 본 발명의 실시예 1의 Poly-SiTr-TFT 액정 표시 모듈을 도트 반전법으로 구동하는 경우의 일 구성 예를 나타내는 주요부 구성도.

도 12는 본 발명의 실시예 1의 Poly-SiTr-TFT 액정 표시 모듈을 도트 반전법으로 구동하는 경우의 다른 구성 예를 나타내는 주요부 구성도.

도 13은 본 발명의 실시예 2의 TFT 방식의 액정 표시 모듈의 전체의 개략 구성을 나타내는 블록도.

도 14는 각 MOS 트랜지스터의 임계치 전압( $V_{th}$ )의 전압 레벨의 변동을 회피하기 위한 일회로 구성을 나타내는 회로도.

<도면의 주요 부분에 대한 부호의 설명>

11~17, 21, 22, 31a, 31b, 32a, 32b, 411~41n : 비디오 신호 수신 회로

100, 202 : 제어 회로부

110, 230 : 수직 주사 회로

200, TFT-LCD : 액정 표시 패널

201 : 표시 제어 장치

210 : 표시부

220 : 수평 주사 회로

221 : 메모리 어드레스 선택 회로(수평 레지스터)

222 : 래치 회로부

301 : 컨트롤 IC 회로

302 : 디지털/아날로그(D/A) 변환기

304 : 샘플 훌드 회로

305 : 드라이버 IC 회로

306 : 신호 처리 회로

Cadd : 유지 용량

CLC : 액정 용량

C0 : 부하 용량

C1~C3 : 결합 용량

CS2 : 기생 용량

D : 영상 신호선(드레인 신호선 또는 수직 신호선)

FFT : 박막 트랜지스터

G : 주사 신호선(게이트 신호선 또는 수평 신호선)

IT01 : 화소 전극

LT : 데이터 래치부

M, TR : 전계 효과형 트랜지스터(MOS 트랜지스터)

N : 노드

S : 비디오 신호선

TG : 트랜스퍼 게이트 회로

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시 장치에 관하여 특히 폴리 · 실리콘 · 트랜지스터로 구성되는 TFT(Thin Film Transistor) 방식의 액정 표시 장치에 적용하여 유익한 기술에 관한 것이다.

종래 액정 표시 장치의 하나로서 화소마다 능동 소자를 구비하고, 이 능동 소자를 스위칭 동작시키는 액티브 매트릭스형 액정 표시 장치가 알려지고 있다.

이 액티브 매트릭스형 액정 표시 장치의 하나로, 능동 소자로서 비정질 · 실리콘 · MOS 트랜지스터 혹은 폴리 · 실리콘 · MOS 트랜지스터로 구성되는 박막 트랜지스터를 사용하는 TFT 방식의 액티브 매트릭스형 액정 표시 모

들이 알려지고 있다.

또 이 이후, 본 명세서 중에서는 비정질 · 실리콘 · MOS 트랜지스터를 비정질-SiTr, 폴리 · 실리콘 · MOS 트랜지스터를 Poly-SiTr, 비정질 · 실리콘 · MOS 트랜지스터를 사용한 TFT 방식의 액정 표시 모듈을 비정질-SiTr-TFT 액정 표시 모듈, 폴리 · 실리콘 · MOS 트랜지스터를 사용한 TFT 방식의 액정 표시 모듈 Poly-SiTr-TFT 액정 표시 모듈이라고 칭한다.

비정질-SiTr-TFT 액정 표시 모듈은 패스널 컴퓨터 혹은 텔레비전의 표시 장치로서 널리 사용되고 있다.

그러나, 비정질-SiTr-TFT 액정 표시 모듈에서는 액정을 구동하기 위한 구동 회로를 액정 표시 패널의 주변에 설치할 필요가 있었다.

이에 대하여, 최근, Poly-SiTr 소자를 사용한 TFT 방식의 모듈이 개발되며, 예를 들면 액정 프로젝터 혹은 헤드 마운트(안경형) 디스플레이 등에 사용되고 있다.

이 Poly-SiTr-TFT 액정 표시 모듈의 액정 표시 패널에서는 비정질-SiTr-TFT 액정 표시 모듈의 액정 표시 패널과 마찬가지로, 석영 혹은 유리 기판 상에 Poly-SiTr을 매트릭스형으로 배치 · 형성한다.

또한, Poly-SiTr의 동작 속도가 비정질-SiTr보다도 고속이기 때문에 Poly-SiTr-TFT 액정 표시 모듈의 액정 패널에서는 그 주변 회로도 동일 기판 상에 제조한 것이 가능하다.

또, 이러한 기술에 대해서는 예를 들면 「일경 일렉트로닉스」, 일경 마그로힐사, 1994년 2월 28일, pp103~pp109에 기재되고 있다.

### 발명이 이루고자 하는 기술적 과제

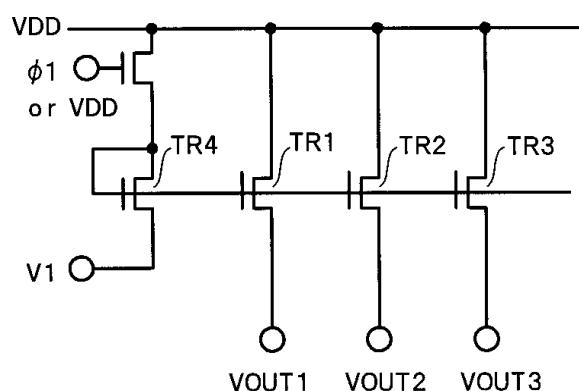

현상의 단결정 Si 반도체 MOS 트랜지스터에서는 예를 들면 도 14에 도시한 바와 같은 비교적 간단한 회로 구성으로, 실용 레벨로 각 MOS 트랜지스터(TR1~TR3)의 임계치 전압(Vth)의 전압 레벨의 변동을 회피할 수 있다.

그러나, 채널 형성 영역이 다결정 실리콘으로 이루어지는 Poly-SiTr에서 현상에서는 게이트 하에서도 다수의 결정 입계가 존재하는 것이 일반적이며 따라서 동일 기판의 근방에 동일 치수의 트랜지스터를 배치하여도 임계치 전압(Vth)은 실용적으로 근사 가능할수록 일치하지 않는 것이 일반적이다.

그 때문에, Poly-SiTr을 사용하고 도 14에 도시한 바와 같은 회로 구성으로 한 경우에, 각 MOS 트랜지스터(TR1~TR3)의 출력 전압(VOUT1~VOUT3)이 실용 상 허용할 수 없을 정도로 변동되는 것이 일반적이다.

그리고, Poly-SiTr-TFT 액정 표시 모듈의 액정 표시 패널의 각 화소에 화소 구동 전압(또는 계조 전압)을 공급하는 목적을 위하여, 예를 들면, Poly-SiTr을 사용하여 상기 도 14에 도시한 바와 같은 회로 구성을 채용한 경우에 각 Poly-SiTr의 임계치 전압(Vth)의 변동에 의해 생기는 출력 전압(VOUT1~VOUT3)의 변동에 의해 액정 표시 패널의 표시 화면에 선형의 모양이 생기고, 액정 표시 패널의 표시 화면의 표시 품질이 현저하게 손상된다는 문제점이 있었다.

본 발명은 상기 종래 기술의 문제점을 해결하기 위하여 이루어진 것으로, 본 발명의 목적은 액정 표시 장치에서 액정 표시 소자의 표시 화면의 표시 품질을 향상시키는 것이 가능해지는 기술을 제공하는데 있다.

본 발명의 상기 및 그 외의 목적과 신규인 특징은 본 명세서의 기술 및 첨부 도면에 의해서 명확해진다.

본원에 있어서 개시되는 발명 중 대표적이지만 개요를 간단하게 설명하면 하기 그대로이다.

즉, 본 발명은 매트릭스형으로 설치되는 복수의 화소와, 상기 복수의 화소의 열(또는 행) 방향의 화소에 화소 구동 전압을 인가하는 복수의 영상 신호선과, 상기 복수의 영상 신호선에 화소 구동 전압을 공급하는 구동 수단을 구비하는 액정 표시 장치에 있어서, 상기 구동 수단은 상기 각 영상 신호선에 화소 구동 전압을 공급하는 복수의 영상 신호 수신 수단을 가지며, 상기 각 영상 신호 수신 수단은 제1 전계 효과형 트랜지스터와, 상기 제1 전계 효과형 트랜지스터의 제어 전극의 전압차를 공통 화소 구동 전압에 대하여, 상기 제1 전계 효과형 트랜지스터의 임계치 전압분만큼 보정한 전압차로 설정하는 제1 수단과, 상기 제1 전계 효과형 트랜지스터의 제어 전극의 전압치를, 상기 제1 수단에서 보정된 전압치에 영상 신호 전압이 중첩된 전압으로 하는 제2 수단과,

상기 제2 수단에서 제어 전극의 전압치가 상기 제1 수단에서 보정된 전압치에 영상 신호 전압이 중첩된 전압이 된 제1 전계 효과형 트랜지스터와 함께, 상기 공통 화소 구동 전압에 영상 신호 전압이 중첩된 전압을 화소 구동 전압으로서 상기 영상 신호선에 공급하는 제3 수단을 갖는 것을 특징으로 한다.

또한, 본 발명은 상기 구동 수단이 상기 각 영상 신호 수신 수단을 제어하는 제어 수단에 있어서, 상기 각 영상 신호 수신 수단에 대하여 제1 모드의 제어 신호를 송출하고, 상기 각 영상 신호 수신 수단으로부터 상기 영상 신호선에 상기 공통 화소 구동 전압에 영상 신호 전압이 가산된 전압을 화소 구동 전압으로서 공급시키고 또한 상기 각 영상 신호 수신 수단에 대하여 제2 모드의 제어 신호를 송출하여 상기 각 영상 신호 수신 수단으로부터 상기 영상 신호선에 상기 공통 화소 구동 전압으로부터 영상 신호 전압이 감산된 전압을 화소 구동 전압으로서 공급시키는 제어 수단을 갖는 것을 특징으로 한다.

또한, 본 발명은 상기 제어 수단으로부터 송출되는 제1 모드의 제어 신호가 제1 내지 제5 제어 신호를 가지며, 상기 제1 내지 제5 제어 신호는 상기 제5 제어 신호, 상기 제4 제어 신호 및 상기 제3 제어 신호의 순서로 또한 상기 제5 제어 신호가 송출되고 있는 동안에 상기 제1 제어 신호 및 상기 제2 제어 신호의 순서로, 각 영상 신호 수신 수단에 대하여 송출되는 것을 특징으로 한다.

또한, 본 발명은 상기 제어 수단으로부터 송출되는 제2 모드의 제어 신호가 제1 내지 제5 제어 신호를 가지고, 상기 제1 내지 제5 제어 신호는 상기 제4 제어 신호, 상기 제1 제어 신호, 상기 제2 제어 신호, 상기 제5 제어 신호 및 상기 제3 제어 신호의 순서로 각 영상 신호 수신 수단에 대하여 송출되는 것을 특징으로 한다.

또한, 본 발명은 상기 제1 수단이 제2 전극에 제1 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제어 전극에 접속되는 제2 전계 효과형 트랜지스터와, 제2 전극이 상기 제2 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제3 전계 효과형 트랜지스터와, 제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되는 전계 효과형 트랜지스터로, 제1 전극에 상기 공통 화소 구동 전압이 인가되는 제4 전계 효과형 트랜지스터로 구성되며, 상기 제3 수단이 제2 전극이 제2 기준 전압에 접속되는 전계 효과형 트랜지스터로, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제5 전계 효과형 트랜지스터와, 제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 영상 신호선에 접속되는 제6 전계 효과형 트랜지스터로 구성되며, 상기 제2 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제1 제어 신호가 제어 전극에 인가되었을 때 온이 되며, 상기 제3 및 제4 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제2 제어 신호가 제어 전극에 인가되었을 때 온이 되며 상기 제5 및 제6 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제3 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 한다.

또한, 본 발명은 상기 제2 수단이 제2 전극에 영상 신호 전압이 인가되는 제7 전계 효과형 트랜지스터와, 제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형 트랜지스터와, 상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되고, 상기 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며, 상기 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 한다.

또한, 본 발명은 상기 제2 수단이 표시 데이터의 비트수만큼 설치되는 복수의 데이터 입력 수단을 가지며, 각 데이터 입력 수단은 표시 데이터의 각 비트치를 저장하는 래치부와, 제2 전극이 상기 래치부에 접속되는 제7 전계 효과형 트랜지스터와, 제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형 트랜지스터와, 상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되며, 상기 각 데이터 입력 수단의 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며 상기 각 데이터 입력 수단의 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 한다.

또한, 본 발명은 상기 구동 수단이 상기 영상 신호 수신 수단을 2계통 가지며 또한 상기 2계통 영상 신호 수신 수단으로부터 각 영상 신호선에 대하여, 교대로 화소 구동 전압을 공급하는 복수의 선택 수단을 갖는 것을 특징으로 한다.

또한, 본 발명은 상기 각 전계 효과형 트랜지스터가 제어 전극 하의 채널 형성 영역이 다결정 실리콘인 것을 특징으로 한다.

또한, 본 발명은 상기 매트릭스형으로 설치되는 복수의 화소, 상기 복수의 영상 신호선 및 상기 구동 수단이 액정 표시 소자 내에 삽입되고 있는 것을 특징으로 한다.

### 발명의 구성 및 작용

이하, 도면을 참조하여 본 발명의 실시예를 상세하게 설명한다.

또, 실시예를 설명하기 위한 전 도면에 있어서, 동일 기능을 갖는 것은 동일 부호를 붙여서 그 반복된 설명은 생략한다.

#### [실시예 1]

도 1은 본 발명의 Poly-SiTr-TFT 액정 표시 모듈에 적용되는 전압 재생 회로의 일례의 회로 구성을 나타내는 회로도이다.

도 2는 도 1에 도시하는 전압 재생 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 3$ )의 일례와, 각 외부 펄스 파형( $\phi 1 \sim \phi 3$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면이다.

이 도 1에 도시하는 전압 재생 회로는 NMOS 트랜지스터만으로 구성한 것이며 도 1에서 M1~M6은 MOS 트랜지스터, C0는 부하 용량이다.

또한, N1~N7은 도 1에 도시하는 전압 재생 회로의 각 노드를 나타내고 노드(N7)는 도 1에 도시하는 전압 재생 회로의 출력단(VOUT)이다.

또한, 바이어스 전압(VD1, VD2, V1)이 접속되고 있는 노드(N1, N5, N6) 이외의 노드는 간단하게 하기 위하여 초기 상태(GND)에 있다고 한다.

또한, VD1, VD2는 고전압으로 여기서는 간단하게 하기 위하여 VD1=VD2로 한다.

또한, V1은 출력하고자 하는 전압으로, 이 경우 하기 수학식 1의 조건을 만족하는 것으로 한다.

$$V1 < VD1 - Vth(M3) - Vth(M2 \text{ 또는 } M5)$$

여기서,  $Vth(Mn)$ 는 MOS 트랜지스터( $Mn$ )의 임계 전압이다.

이하에, 상기 조건 하에서 도 1에 도시하는 전압 재생 회로의 동작을 설명한다.

(1) 외부 펄스( $\phi 1$ )가 Low 레벨(GND ; 이하, 단순하게 L 레벨이라고 칭한다.)로부터 High 레벨(PVH1 ; 이

하, 단순하게 H 레벨이라고 칭한다.)로 변하면 MOS 트랜지스터(M1)가 ON 상태가 된다.

또, H 레벨(PVH1)은 하기 수학식 2를 만족할 필요가 있다.

$PVH1 > V1 + Vthh$  (M4 또는 M6)

$$+ Vthh (M3) + Vthh (M2 또는 M5)$$

여기서는 간단하게 하기 위해서,  $PVH1=VD1$ 로 하면, MOS 트랜지스터(M1)가 ON 상태가 되면 노드(N2)의 전압은 GND로부터 ( $VD1-Vth(M1)$ )가 된다.

여기서, 외부 펄스( $\phi 1$ )가 다시 L 레벨이 되며 MOS 트랜지스터(M1)가 OFF 상태가 된다.

또, 엄밀하게는 이 때 MOS 트랜지스터(M1)의 게이트와 노드(N2)와의 결합 용량( $C12$ )에 의해  $\Delta V$  정도의 전압 변동이 있지만, 용량( $C2$ )을 십분 크게 함으로서 실용 상 무시할 수 있는 값으로 할 수 있기 때문에 이후의 논의에서는 언급하지 않는다.

$$\Delta V \asymp C12 \times (VD1 - Vthh (M1)) / C2$$

여기서,  $C2$ 는 노드(N2)의 전체 용량이다.

(2) 외부 펄스( $\phi 2$ )가 L 레벨(GND)로부터 H 레벨(PVH2)로 변하면 MOS 트랜지스터(M2)와 MOS 트랜지스터(M4)가 ON 상태가 된다.

또, H 레벨(PVH2)은 하기 수학식 4를 만족할 필요가 있다.

$PVH2 > V1 + Vthh (M4 또는 M6)$

$$+ Vthh (M3) + Vthh (M2 또는 M5)$$

이 때, MOS 트랜지스터(M3)는 노드(N2)의 전압을 게이트 전압으로 하는 다이오드 접속으로 되어 있으므로, 노드(N2)의 전압이 ( $V1+Vth(M3)$ )가 된 것으로 MOS 트랜지스터(M3)는 펀치 오프하여 전류는 멈춘다.

여기서, 외부 펄스( $\phi 2$ )가 다시 L 레벨이 되며 MOS 트랜지스터(M2) 및 MOS 트랜지스터(M4)는 OFF 상태가 된다.

따라서, MOS 트랜지스터(M3)의 게이트 전압인 노드(N2)는  $V1-Vth(M3)$ 으로 유지된다.

(3) 외부 펄스( $\phi 3$ )가 L 레벨(GND)로부터 H 레벨(PVH3)로 변하면 MOS 트랜지스터(M5)와 MOS 트랜지스터(M6)가 ON 상태가 된다.

또, H 레벨(PVH3)은 하기 수학식 5를 만족할 필요가 있다.

$PVH3 > V1 + Vthh (M4 또는 M6)$

$$+ Vthh (M3) + Vthh (M2 또는 M5)$$

이에 따라, 노드(N6)  $\rightarrow$  MOS 트랜지스터(M5)  $\rightarrow$  노드(N3)  $\rightarrow$  MOS 트랜지스터(M3)  $\rightarrow$  노드(N4)  $\rightarrow$  MOS 트랜지스터(M6)  $\rightarrow$  출력단(VOUT)과 연결되는 전압(전류) 출력 회로로 계통이 ON 상태가 되며 노드(N6)로부터 출력단(VOUT)에 전류가 공급된다.

이 때, 출력단(VOUT)의 먼저 전압( $V0$ ;  $V0 < V1$ )의 부하 용량( $C0$ )이 접속되고 있으면, 부하 용량( $C0$ )의 전압이  $V1$ 이 된 것으로 MOS 트랜지스터(M3)가 다시 펀치 오프하여 전류 공급이 멈춘다.

즉, 부하 용량( $C0$ )의 값 및 MOS 트랜지스터(M3)의 임계치 전압( $Vth(M3)$ )에 상관없이 부하 용량( $C0$ )의 전압을  $V1$ 로 할 수 있다.

또, 도 1에서는 NMOS 트랜지스터만을 사용하는 전압 재생 회로에 대하여 설명하였지만, 도 1에 도시하는 전압 재생 회로는 PMOS 트랜지스터만을 사용하는 회로 구성으로 하는 것도 가능하며 또한 CMOS 구성으로 하는 것도 가능하다.

예를 들면, MOS 트랜지스터(M2, M5)를 PMOS 트랜지스터, MOS 트랜지스터(M4, M6)를 NMOS 트랜지스터로 하는 CMOS 구성으로 해도 좋다.

도 3은 도 1에 도시하는 전압 재생 회로를 응용한 응용 회로의 일례의 회로 구성은 나타내는 회로도이다.

도 4는 도 3에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 일례와, 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면이다.

도 3에 도시하는 회로는 도 1에 도시하는 전압 재생 회로에 노드(N2)에 용량 접속하기 위한 용량( $C1$ )과, 외부 펄스( $\phi 4$ ,  $\phi 5$ )에 의해 제어되는 2개의 MOS 아날로그 스위치 트랜지스터(M7, M8)로 이루어지는 신호 입력부를 부가한 것이다.

MOS 아날로그 스위치 트랜지스터(M7)의 드레인에는 외부에서 공급되는 아날로그 신호 전압이 입력되며 MOS 아날로그 스위치 트랜지스터(M8)의 소스에는 기준 바이어스 전압(여기서는  $VSS=GND$ )이 인가된다.

또한, V1=VCOM으로 한다.

이하, 도 4를 이용하여, 도 3에 도시하는 응용 회로의 동작을 설명한다.

(1) 도 4의 시각(t7)까지는 도 1에 도시하는 전압 재생 회로의 동작과 동일하므로, 시각(t7)까지의 동작으로 노드(N2)는 VCOM+Vth(M3)의 전압이 된다.

이 시각(t7)까지 동안에 외부 펄스( $\phi$ 5)를 H 레벨로 하는 것은 외부 펄스( $\phi$ 1,  $\phi$ 2)의 펄스 동작과는 상관없이 노드(N8)를 VSS(=GND)로 하기 때문이다.

(2) 시각(t7) 내지 시각(t8)의 기간, 외부 펄스( $\phi$ 4)가 H 레벨이 되면, 이 기간의 아날로그 신호 전압이 노드(N8)에 판독되며 용량(C1, CS2)과 MOS 트랜지스터(M7)의 ON 저항으로 결정되는 시상수로 노드(N2)가 아날로그 신호 전압으로 향하여 변화한다.

이 시각(t8)까지 받아들인 전압으로 시각(t8) 이후의 노드(N2)의 전압 레벨이 결정된다.

또, 용량(CS2)은 노드(N2)의 기생 용량으로 용량(C1) 이외의 용량이다.

시각(t7) 내지 시각(t8)까지의 노드(N2)의 전압 변동을 VS1로 하면 시각(t8) 이후의 노드(N2)의 전압은 VCOM+Vth(M3)+VS1이 된다.

(3) 시각(t9)으로 외부 펄스( $\phi$ 3)가 H 레벨이 되면, MOS 트랜지스터(M5, M6)가 ON 상태가 되며, 전압(전류) 출력 회로 계통이 ON 상태가 되면, 노드(N6)로부터 출력단(VOUT)에 전류가 공급되며, MOS 트랜지스터(M3)가 펀치 오프하는 (VCOM+VS1)의 전압까지 부하 용량(C0)을 충전한다.

즉, MOS 트랜지스터(M7)로 판독한 아날로그 신호 전압(VS1)을 전압 변동없이 더 MOS 트랜지스터(M3)의 임계 전압(Vth(M3))의 영향없이, 어느 기준 전압(VCOM)에 가산할 수 있다.

도 3에 도시하는 응용 회로에서, 외부 펄스의 입력 타이밍을 바꿈으로서, 어느 기준 전압(VCOM)으로부터 아날로그 신호 전압(VS1)을 빼는 것도 용이하다.

이하, 도 5를 이용하여, 도 3에 도시하는 응용 회로에서 어떤 기준 전압(VCOM)으로부터 아날로그 신호 전압(VS1)을 빼는 경우의 동작을 설명한다.

또, 도 5는 도 3에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi$ 1~ $\phi$ 5)의 다른 예와, 각 외부 펄스 파형( $\phi$ 1~ $\phi$ 5) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면이다.

(1) 우선, 시각(t11) 내지 시각(t12)의 기간에 외부 펄스( $\phi$ 4)를 H 레벨로 한다.

이 때, 도 4의 경우와 마찬가지로 노드(N8)는 아날로그 신호 전압(VS1')이 된다.

여기서, VS1'는 하기 수학식 6을 만족하는 전압이다.

$$VS1' = (VS1 \times C1) / (C1 + CS2)$$

(2) 이 후, 시각(t12)으로부터 시각(t16)까지의 동안, 외부 펄스( $\phi$ 1)를 H 레벨로 하고, 다음에 외부 펄스( $\phi$ 2)를 H 레벨로 하는 일련의 동작을 행한다.

이에 따라, 시각(t16) 직후의 노드(N2)의 전압은 노드(N8)가 (VS1')라는 조건 하에서 VCOM+Vth(M3)가 된다.

(3) 시각(t17)에서 외부 펄스( $\phi$ 5)를 H 레벨로 하면, 노드(N8)는 VSS(=GND) 레벨로 변화하고, 이 결과 노드(N2)의 전압은 VCOM+Vth(M3)-VS1이 된다.

(4) 시각(t19)에서 외부 펄스( $\phi$ 3)가 H 레벨로 하면, MOS 트랜지스터(M5, M7)가 ON 상태가 되며, 전압(전류) 출력 회로 계통이 ON 상태가 되면, 노드(N6)로부터 출력단(VOUT)에 전류가 공급되며, MOS 트랜지스터(M3)가 펀치 오프하는 (VCOM-VS1)의 전압까지 부하 용량(C0)을 충전한다.

즉, MOS 트랜지스터(M7)로 판독된 아날로그 신호 전압(VS1)을 전압 변동없이 더 MOS 트랜지스터(M3)의 임계 전압(Vth(M3))의 영향없이, 어느 기준 전압(VCOM)으로부터 뺄 수 있다.

도 3에 도시하는 응용 회로는 특히 공통 전극에 인가되는 공통 전압(본 발명의 공통 화소 구동 전압)에 대하여, 정극성 혹은 부극성의 화소 구동 전압을 필요로 하는 액정 표시 모듈의 표시 패널의 내장 구동 회로로서 유용하다.

예를 들면, 어느 기준 전압(VCOM)을 공통 전극에 인가되는 공통 전압이라고 하면, 도 3에 도시하는 응용 회로에서, 도 4, 도 5에 도시한 바와 같은 펄스 구동을 행함으로써 각 화소 전극에 정극성 혹은 부극성을 간단하게 공급할 수 있다.

도 6은 도 1에 도시하는 전압 재생 회로를 응용한 응용 회로의 다른 예의 회로 구성을 나타내는 회로도이다.

도 7은 도 6에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi$ 1~ $\phi$ 5)의 일례와, 각 외부 펄스 파형( $\phi$ 1~ $\phi$ 5) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면이다.

도 6에 도시하는 회로는 도 3에 도시하는 회로에서 입력 신호를 3비트의 디지털 신호로 한 것이다.

도 6에 도시하는 회로에서는 비트수(도 6에서는 3비트)에 따른 수만큼의 결합 용량(C1~C3)을 노드(N2)에 접속한다.

각 결합 용량(C3)을 통하여 노드(N2)에 접속되는 노드(N8)에는 MOS 아날로그 스위치 트랜지스터(M9)와 MOS 아날로그 스위치 트랜지스터(M10)가 접속된다.

여기서, MOS 아날로그 스위치 트랜지스터(M9)의 드레인에는 데이터 래치부(LT1)로부터 공급되는 입력 디지털 신호(DS3)의 신호 전압이 입력되며, MOS 스위치 트랜지스터(M10)의 소스에는 기준 바이어스 전압(VSS=GND)이 인가된다.

마찬가지로, 결합 용량(C2)을 통하여 노드(N2)에 접속되는 노드(N9)에는 MOS 아날로그 스위치 트랜지스터(M11)와 MOS 아날로그 스위치 트랜지스터(M12)가 접속되며, MOS 아날로그 스위치 트랜지스터(M11)의 드레인에는 데이터 래치부(LT2)로부터 공급되는 입력 디지털 신호(DS2)의 신호 전압이 입력되며, MOS 스위치 트랜지스터(M12)의 소스에는 기준 바이어스 전압(VSS=GND)이 인가된다.

마찬가지로, 결합 용량(C1)을 통하여 노드(N2)에 접속되는 노드(N10)에는 MOS 아날로그 스위치 트랜지스터(M13)와 MOS 아날로그 스위치 트랜지스터(M14)가 접속되며, MOS 아날로그 스위치 트랜지스터(M13)의 드레인에는 데이터 래치부(LT3)로부터 공급되는 입력 디지털 신호(DS1)의 신호 전압이 입력되며, MOS 스위치 트랜지스터(M14)의 소스에는 기준 바이어스 전압(VSS=GND)이 인가된다.

입력 디지털 신호(DS1~DS3)는 각각의 데이터 래치부(LT1~LT3)로 래치되며 원하는 타이밍으로 각 노드(N11~N13)에 출력된다.

이 각 노드(N11~N13)에 출력되는 디지털 신호 전압은 아날로그 신호 전압으로 변환하며, 노드(N2)에 출력하고 상기 도 4와 마찬가지로 동작시킴으로써 데이터 래치부(LT1~LT3)로부터 출력되는 3 비트의 디지털 신호 전압에 대응하는 아날로그 신호 전압(VS1)을 전압 변동없이 더 MOS 트랜지스터(M3)의 임계치 전압(Vth(M3))의 영향없이 어느 기준 전압(VCOM)에 중첩할 수 있다.

이 경우의 동작은 상기 도 4를 이용하여 설명한 경우와 동일하므로 그 상세한 설명은 생략한다.

디지털 · 아날로그 변환은 출력 노드(N11~N13)에 신호 전압을 출력할 때(예를 들면, 3 비트의 경우) 그 전압을 VA, 2VA, 4VA가 되는 것과 같은 구성으로 하고, 결합 용량(C1~C3)을 동일 용량의 값으로 해도 좋으며 혹은 출력 노드(N11~N13)의 신호 전압은 일정치로 하고 결합 용량(C1~C3)의 값을 각각 CA, 2CA, 4CA로 해도 좋다.

이 때, 용량(CS2)에 의한 전압 효과가 실용 상 문제가 되지 않는 레벨로 결합 용량(C1~C3)을 설정하면 된다.

도 8은 도 6에 도시하는 응용 회로에 입력되는 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 다른 예와 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ ) 입력 시의 각 노드의 전압 파형을 모식적으로 나타낸 도면이다.

도 8은 도 6에 도시하는 회로에서 어느 기준 전압(VCOM)으로부터 아날로그 신호 전압(VS1)을 빼는 경우의 각 외부 펄스 파형( $\phi 1 \sim \phi 5$ )의 입력 타이밍을 나타낸 도면이다.

도 6에 도시하는 회로에서 상기 도 5에 도시하는 타이밍으로 동작시킴으로써, 데이터 래치부(LT1~LT3)로부터 출력되는 3 비트의 디지털 신호에 대응하는 아날로그 신호 전압(VS1)을 전압 변동없이 또한 MOS 트랜지스터(M3)의 임계치 전압(Vth(M3))의 영향없이 어느 기준 전압(VCOM)으로부터 뺄 수 있다.

이 경우의 동작은 상기 도 5를 이용하여 설명한 경우와 동일하므로 그 상세한 설명은 생략한다.

또, 상기 설명에서는 간단하게 하기 위해서 MOS 트랜지스터의 게이트의 ON/OFF에 의한 부유 노드의 변동을 무시하여 기재하였지만 현실의 적용 시에는 이것을 고려해야 할 것은 물론이다.

또한, 통상의 반도체와 같은 깊은 WELL 또는 SUB 구조를 갖는 디바이스에서는 소스 변동에 의한 기판 효과 상수가 크며, 상기 응용 회로와 같은 임계치 전압(Vth) 설정 후에 게이트 전압을 변동시키는 사용법은 기판 효과에 의한 임계치 전압(Vth) 시프트량이 지나치게 크며, 본 발명의 목적인 임계치 전압(Vth)의 상쇄가 불충분할 가능성이 있지만, Poly-SiTr 소자의 TFT 또는 SOI와 같은 박막 트랜지스터로서는 기판 효과가 작기 때문에 실용 가능하다.

도 9는 본 발명의 실시예 1의 Poly-SiTr-TFT 액정 표시 모듈의 표시 패널의 등화 회로를 나타낸 도면이다.

또, 도 9는 회로도이지만 실제의 기하학적 배치에 대응하여 나타내고 있으며 또한 본 실시예의 액정 표시 패널(본 발명의 액정 표시 소자)에서는 주사 신호선(G)이 (m)개로 구성되며, 영상 신호선(D)이 (n)개로 구성되고 있지만, 도 9에서는 주사 신호선(G)은 6개, 영상 신호선(D)은 7개밖에 도시하지 않는다.

본 실시예의 액정 표시 패널은 매트릭스형으로 배치되는 화소를 가지며, 각 화소는 인접하는 2개의 주사 신호선(게이트 신호선 또는 수평 신호선 ; G)과, 인접하는 2개의 영상 신호선(드레인 신호선 또는 수직 신호선 ; D)과의 교차 영역(4개의 신호선에서 둘러싸인 영역) 내에 배치된다.

각 화소는 예를 들면, Poly-SiTr로 이루어지는 박막 트랜지스터(TFT)를 가지며, 매트릭스형으로 배치된 각 화소의 각 열마다의 각 박막 트랜지스터(TFT)의 드레인은 각각 영상 신호선(D)에 접속되며 또한 매트릭스형으로 배치된 각 화소의 각 박막 트랜지스터(TFT)의 소스는 화소 전극(IT01)에 접속된다.

또, 드레인 및 소스는 본래 그 사이의 바이어스 극성에 의해서 결정됨으로서, 본 실시예의 모듈에서는 그 극성은 동작 중 반전하므로, 드레인, 소스는 동작 중 교체하는 것이지만, 본 명세서에서는 편의상 한쪽을 드레인, 다른쪽을 소스와 고정하여 설명한다.

영상 신호선(D)은 비디오 신호 수신 회로(11~17)를 통하여 대응하는 비디오 신호선(S0~S5)에 접속된다.

여기서, 각 비디오 신호 수신 회로(11~17)는 상기 도 4에 도시하는 응용 회로로 구성되며 또한 각 비디오 신호 수신 회로(11~17)는 6개씩 그룹화되며, 각 그룹마다 비디오 신호 수신 회로(11~16)에는 동일 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 제어 회로부(100)로부터 입력된다.

또한, 매트릭스형으로 배치된 각 화소의 각 행마다의 각 박막 트랜지스터(TFT)의 게이트는 각각 주사 신호선(G)에 접속되며 이 주사 신호선(G)은 수직 주사 회로(110)에 접속된다.

각 박막 트랜지스터(TFT)는 게이트에 플러스의 바이어스 전압을 인가하면 도통하고, 게이트에 마이너스의 바이어스 전압을 인가하면 비도통이 된다.

또한, 화소 전극(IT01)과 공통 전극 간에 액정층이 설치되므로, 각 화소 전극(IT01)에는 액정 용량( $C_{LC}$ )이 등화적으로 접속되며 또한 전단의 주사 신호선(G)과 화소 전극(IT01) 간에는 유지 용량( $C_{add}$ )이 접속된다.

또, 비디오 신호 수신 회로(11~17), 제어 회로부(100), 수직 주사 시프트 레지스터(VSR) 및 수직 주사 회로(110)는 액정 표시 패널에 삽입되고 있으며, 박막 트랜지스터(TFT)와 동일하게 Poly-SiTr로 구성되고 동일한 기판 상에 형성된다.

이하, 본 실시예의 액정 표시 패널의 동작에 대하여 간단하게 설명한다.

도 9에 도시하는 수직 주사 회로(110)는 스타트 펄스(DY) 및 수직 구동용 클럭 신호(CLY)에 의해 주사 신호선(G)을 순차 선택하여 선택한 주사 신호선(G)에 플러스의 바이어스 전압을 출력한다.

이에 따라, 선택된 주사 신호선(G)을 게이트로 하는 박막 트랜지스터(TFT)가 온이 된다.

또한, 제어 회로부(100)는 스타트 펄스(DX) 및 수평 구동용 클럭 신호(CLX)에 의해 각 그룹마다의 비디오 신호 수신 회로(11~16)에 외부 펄스( $\phi 1 \sim \phi 5$ )를 출력하여, 이에 따라, 각 그룹을 구성하는 각 비디오 신호 수신 회로(11~16)에 의해 비디오 신호선(S0~S5)으로부터 6분할된 비디오 신호가 대응하는 6개의 영상 신호선(D)에 출력된다.

따라서, 선택된 주사 신호선(G)을 게이트로 하는 박막 트랜지스터(TFT)에 대응하는 화소에, 수신된 비디오 신호(비디오 신호의 전압)가 기입되며 액정 표시 패널에 표시된다.

도 10은 본 실시예의 Poly-SiTr-TFT 액정 표시 모듈의 주변 회로의 개략 회로 구성을 나타내는 블록도이다.

도 10에서 TFT-LCD는 액정 표시 패널, 참조 번호 301은 컨트롤 IC 회로, 참조 번호 302는 디지털/아날로그(D/A) 변환기, 참조 번호 304는 샘플 훌드 회로, 참조 번호 305는 드라이버 IC 회로, 참조 번호 306은 신호 처리 회로이다.

본체측에서부터 송신되는 표시 데이터[R(적) · G(녹) · B(청) 중 1개]는 D/A 변환기(302)로 아날로그의 비디오 신호가 된다.

또, 본체측에서부터 비디오 신호가 공급되는 경우에는 상기 D/A 변환기(302)는 필요없다.

도 9에 도시하는 액정 표시 패널에서는 영상 신호선(D)을 6상으로 나누어서 구동(주사)하기 때문에, 비디오 신호도 그에 더불어 6상으로 분할할 필요가 있다.

그 때문에, D/A 변환기(302)로부터의 비디오 신호는 수평 구동용 클럭 신호(CLX)와 동기한 샘플 훌드(S/H)용 클럭에 기초하여, 샘플 훌드 회로(304)에서 6상으로 분할된다.

또한, 이 6상으로 분할된 비디오 신호는 타이밍이 조정되어 동일한 위상이 되며 샘플 훌드 회로(304)로부터 출력된다.

또한, 6상으로 분할된 비디오 신호는 신호 처리 회로(306)에서, 증폭 처리 ·  $\gamma$  처리 · 교류화 처리가 실시되며 액정 표시 패널(TFT-LCD)의 비디오 신호선(S1~S6)에 공급된다.

여기서,  $\gamma$  처리는 액정층의 감마 특성을 보정하기 위한 신호 처리이며 교류화 처리는 액정층에 직류 전압이 인가되는 것을 방지하기 위한 신호 처리이다.

또, 샘플 훌드 회로(304)와 신호 처리 회로(306)의 순서를 교체한 회로 구성으로 하는 것도 가능하다.

또한, 상기 도 9에 도시하는 액정 표시 패널은 다색 표시 가능한 컬러 액정 표시 패널이어도 좋으며, 그 경우에는 R · G · B의 각 표시 데이터를 각각 D/A 변환기(302)에서 비디오 신호로 변환하고, 해당 각 비디오 신호를 각각 샘플 훌드 회로(304)로 6상으로 분할하고 액정 표시 패널의 비디오 신호선(S1~S6)에 공급하도록 하면 된다.

단지, 다색 표시 가능한 컬러 액정 표시 패널에서는 상기 도 9에 도시하는 액정 표시 패널에 R · G · B용 박막 트랜지스터(TFT), R · G · B용 영상 신호선(D) 및 컬러 필터를 설치하고, R · G · B의 비디오 신호를 각각의 영상 신호선(D)에 공급할 필요가 있다.

또한, 1개의 반도체 집적 회로(LSI)로 구성되는 컨트롤 IC 회로(301)는 본체측에서부터의 수평 동기 신호(H-SYNC), 수직 동기 신호(V-SYNC), 클럭 펄스(CLK)에 기초하여 수평 구동용 클럭 신호(CLX), 수직 구동용 클럭 신호(CLY) 등을 생성한다.

또한, 드라이버 IC 회로(305)는 수평 구동용 클럭 신호(CLX), 수직 구동용 클럭 신호(CLY) 등을 액정 표시 패널(TFT-LCD)을 동작시키기 위해서 필요한 전압까지 증폭한다.

일반적으로, 액정층은 장시간 동일 전압(직류 전압)이 인가되고 있으면, 액정층의 기울기가 고정화되며, 결과로서 잔상 현상을 야기하고 액정층의 수명을 단축하게 된다.

이것을 방지하기 위해서, 액정 표시 장치에서는 공통 전극에 인가하는 전압을 기준으로 하여, 화소 전극(IT01)에 인가하는 구동 전압을 일정 시간마다 플러스 전압측/マイ너ス 전압측으로 변화(일반적으로, 이것을 교류화라고 부르고 있다.)시키도록 하고 있다.

이하, 본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에서의 교류화 구동 방법에 대하여 설명한다.

액정층에 교류 전압을 인가하는 구동 방법으로서 공통 대칭법과 공통 반전법의 2가지 방법이 알려지고 있다.

본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에서는 제어 회로부(100)로부터 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 도 4에 도시하는 타이밍의 제1 모드의 펄스 신호 혹은 도 5에 도시하는 타이밍의 제2 모드의 펄스

신호로 변화시킴으로써 어느 방식에도 대응 가능하다.

예를 들면, 훌수 프레임의 훌수 라인에 정극성의 비디오 신호를 훌수 프레임의 짹수 라인에 부극성의 비디오 신호를 인가하고 또한 짹수 프레임의 훌수 라인에 부극성의 비디오 신호를 또한 짹수 프레임의 짹수 라인에 정극성의 비디오 신호를 인가하는 교류화 구동 방법을 채용하는 경우라도 일주사 라인마다 제어 회로부(100)로부터 도 4에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ ) 혹은 도 5에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )를 각 비디오 신호 수신 회로(11~17)에 공급함으로써 용이하게 대응 가능하다.

또한, 상기 공통 대칭법의 하나로 도트 반전법이 알려져 있다.

이 도트 반전법에서는 예를 들면 훌수 프레임의 훌수 라인에서는 훌수번째의 영상 신호선(D)에 부극성의 계조 전압이 또한 짹수번째의 영상 신호선(D)에 정극성의 계조 전압이 인가된다.

또한, 훌수 프레임의 짹수 라인에서는 훌수번째의 영상 신호선(D)에 정극성의 계조 전압이 또한 짹수번째의 영상 신호선(D)에 부극성의 계조 전압이 인가된다.

또한, 각 라인마다의 극성은 프레임마다 반전되며 짹수 프레임의 훌수 라인에서는 훌수번째의 영상 신호선(D)에 정극성의 계조 전압이 또한 짹수번째의 영상 신호선(D)에 부극성의 계조 전압이 인가된다.

또한, 짹수 프레임의 짹수 라인에서는 훌수번째의 영상 신호선(D)에 부극성의 계조 전압이 또한 짹수번째의 영상 신호선(D)에 정극성의 계조 전압이 인가된다.

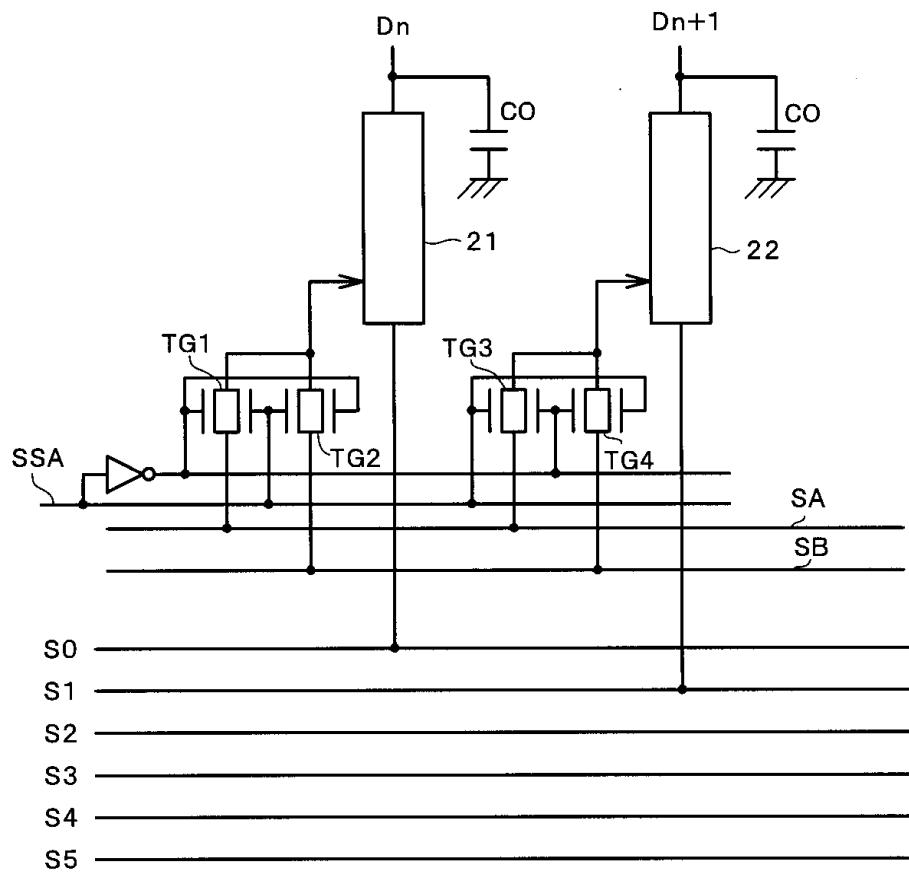

본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에 있어서, 상기 도트 반전법을 채용하는 경우에는 예를 들면 도 11에 도시한 바와 같이, 영상 신호선(Dn)에 설치되는 비디오 신호 수신 회로(21)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 4에 도시하는 타이밍으로 하고, 영상 신호선(Dn)에 인접하는 영상 신호선(Dn+1)에 설치되는 비디오 신호 수신 회로(22)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면, 도 5에 도시하는 타이밍으로 하고, 1라인마다 또한 1 프레임마다 전환하도록 하면 된다.

또, 도 11에서 TG1~TG4는 트랜스퍼 게이트 회로, SA는 도 4에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 공급되는 신호선, SB는 도 5에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 공급되는 신호선이다.

또한, SSA는 게이트 전환 신호가 공급되는 신호선이며 이 게이트 전환 신호(SSA)를 1 라인마다 또한 1 프레임마다 H 레벨 혹은 L 레벨로 전환함으로써, 인접하는 영상 신호선(Dn, Dn+1)마다 설치되는 비디오 신호 수신 회로(21, 22)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을, 1라인마다 또한 1 프레임마다 전환한다.

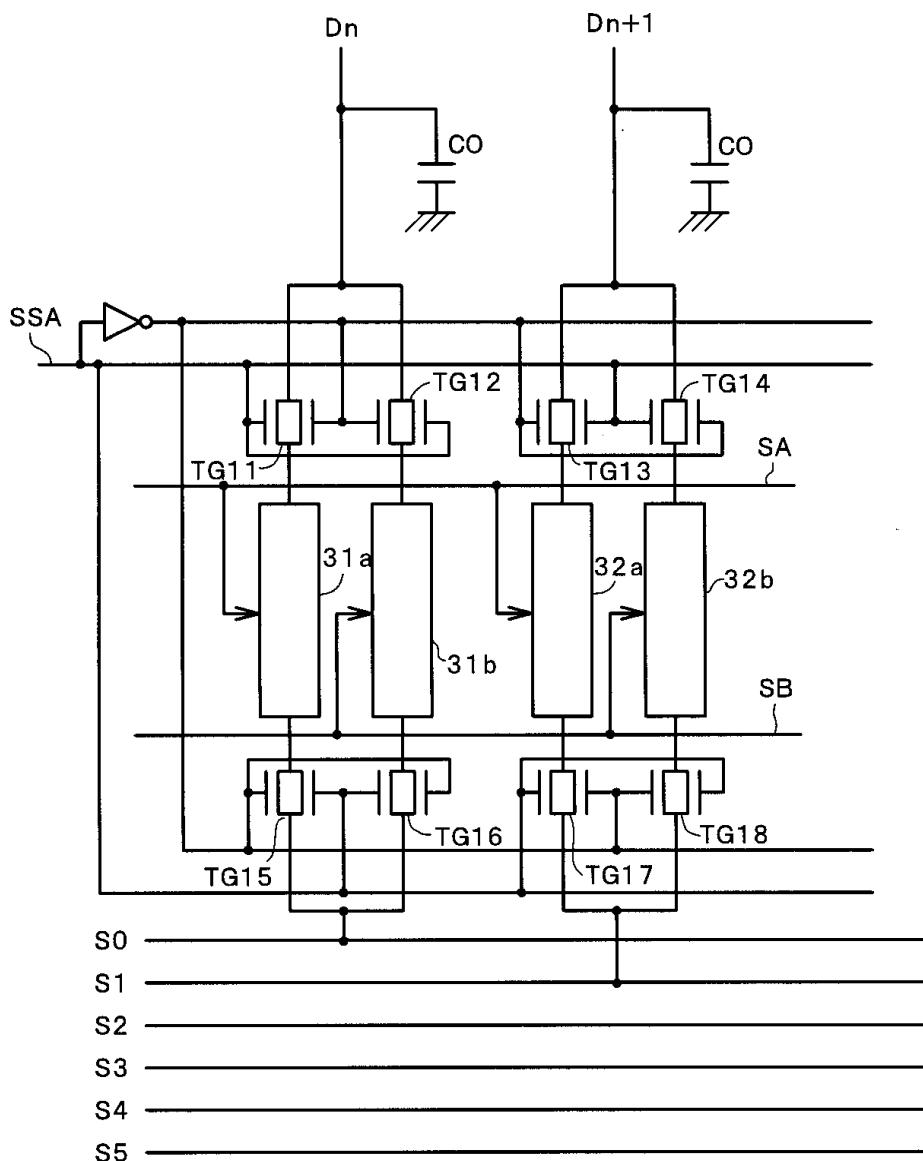

또한 본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에 있어서, 상기 도트 반전법을 채용하는 경우에도 도 12에 도시한 바와 같은 구성을 채용해도 된다.

도 12에 도시하는 구성으로는 각 영상 신호마다 2계통의 비디오 신호 수신 회로(31a, 31b, 32a, 32b)를 설치하고, 이 2계통의 비디오 신호 수신 회로의 한쪽에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍과, 다른쪽에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 다르게 하다.

즉, 비디오 신호 수신 회로(31a, 32a)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 4에 도시하는 타이밍으로 하고 또한 비디오 신호 수신 회로(31b, 32b)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 5에 도시하는 타이밍으로 한다.

또, 도 12에서 TG11~TG18은 트랜스퍼 게이트 회로, SA는 도 4에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 공급되는 신호선, SB는 도 5에 도시하는 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 공급되는 신호선이다.

또한, SSA는 게이트 전환 신호가 공급되는 신호선이며 이 게이트 전환 신호(SSA)에 의해 트랜스퍼 게이트 회로(TG11~TG14)를 교대로 온으로 함으로써, 1 라인마다 2계통의 비디오 신호 수신 회로를 교대로 전환하여 영상 신호선과 접속하고 또한 1 프레임마다 영상 신호선에 접속하는 2계통의 비디오 신호 수신 회로의 접속순을 교환한다.

즉, 훌수 프레임의 훌수번째의 라인에서 예를 들면 비디오 신호 수신 회로(31a)를 영상 신호선(Dn)에 접속하고 또한 짹수 라인에서 비디오 신호 수신 회로(31b)를 영상 신호선(Dn)에 접속하고 또한 짹수 프레임의 훌수번째의 라인에서 비디오 신호 수신 회로(31b)를 영상 신호선(Dn)에 접속하고 또한 짹수 라인에서 비디오 신호 수신 회로(31a)를 영상 신호선(Dn)에 접속한다.

또, 도 12에 도시하는 구성에서는 트랜스퍼 게이트 회로(TG15~TG18)에 의해, 비디오 신호가 1라인마다 교대로 비디오 신호 수신 회로(31a) 혹은 비디오 신호 수신 회로(31b)로 수신된다.

즉, 비디오 신호 수신 회로(31a)가 영상 신호선(Dn)에 접속되어 있는 경우에 비디오 신호 수신 회로(31b)에는 비디오 신호선(S0)으로부터 비디오 신호가 입력된다.

이에 따라, 회로 구성은 복잡해지지만, 비디오 신호 수신과 비디오 신호의 화소 기입이 분리되므로 타이밍 조정 등의 점에서 유리해진다.

또, 상기 본 실시예에서는 제어 회로부(100) 및 수직 주사 회로(110)를 액정 표시 패널 내에 삽입된 실시예에 대하여 설명하였지만, 본 발명은 이에 한정되지는 않고 제어 회로부(100) 및 수직 주사 회로(110)는 액정 표시 패널의 외부에 설치하도록 해도 좋다.

## [실시예 2]

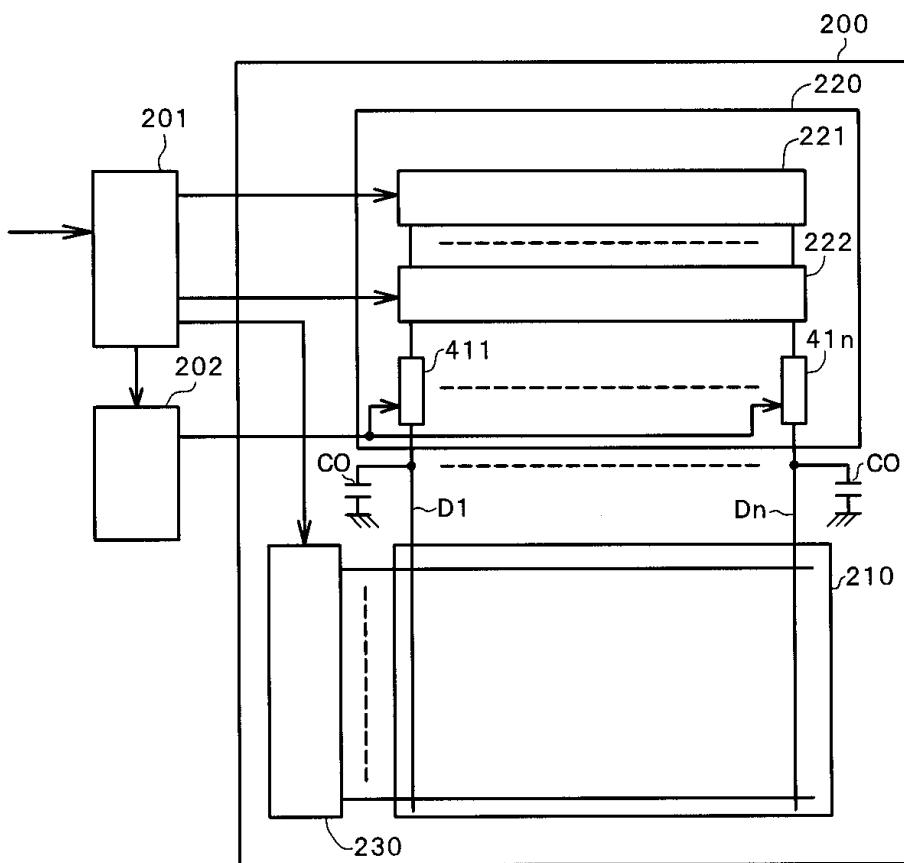

도 13은 본 발명의 실시예 2의 TFT 방식의 액정 표시 모듈의 전체의 개략 구성을 나타내는 블록도이다.

본 실시예의 액정 표시 모듈은 비디오 신호가 디지털 신호로 입력되는 액정 표시 모듈이며, 본 실시예의 액정 표시 모듈은 액정 표시 패널(200)과, 표시 제어 장치(201)와, 제어 회로부(202)로 구성된다.

액정 표시 패널(200)은 표시부(210)와, 수평 주사 회로(220)와, 수직 주사 회로(230)로 구성된다.

여기서, 수평 주사 회로(220)는 메모리 어드레스 선택 회로(이하, 수평 시프트 레지스터 회로라고 칭한다. ; 221)와, 래치 회로부(222)와, 비디오 신호 수신 회로(411~41n)로 구성된다.

각 비디오 신호 수신 회로(411~41n)는 상기 도 7에 도시하는 응용 회로에서 구성되며 또한 각 비디오 신호 수신 회로(411~41n)에는 동일 타이밍의 외부 펄스( $\phi 1 \sim \phi 5$ )가 제어 회로부(202)로부터 입력된다.

또한, 액정 표시 패널(200)의 표시부(210)는 상기 도 9에 도시하는 것과 동일하다.

표시 제어 장치(201)는 1개의 반도체 집적 회로(LSI)로 구성되며, 표시 제어 장치(201)에는 클럭 신호, 디스플레이 타이밍 신호, 수평 동기 신호, 수직 동기 신호의 각 표시 제어 신호 및 표시용 데이터(R·G·B)가 컴퓨터 본체측에서부터 송신된다.

다음에, 표시 데이터가 3비트인 경우에서의 본 실시예의 액정 표시 모듈의 동작의 개략을 설명한다.

표시 제어 장치(201)는 수직 동기 신호 입력 후에 제1번째의 디스플레이 타이밍 신호가 입력되면, 이것을 제1 번째의 표시 라인이라고 판단하여 수직 주사 회로(230)에 스타트 펄스(SY)를 출력한다.

또한, 표시 제어 장치(201)는 수평 동기 신호에 기초하여 1수평 주사 시간마다 표시부(210)의 각 주사 신호선(G)에 순차 플러스의 바이어스 전압을 인가하도록, 수직 주사 회로(230)에 1수평 주사 시간 주기의 시프트 클럭인 수직 구동용 클럭 신호(CLY)를 출력한다.

이에 따라, 수직 주사 회로(230)는 주사 신호선(G)을 순차 선택하여 선택한 주사 신호선(G)에 플러스의 바이어스 전압을 출력하고, 선택된 주사 신호선(G)에 게이트가 접속되는 박막 트랜지스터(TFT)를 1 주사 기간 온으로 한다.

표시 제어 장치(201)는 디스플레이 타이밍 신호가 입력되면 이것을 표시 개시 위치라고 판단하고, 수취한 단순 1열의 3 비트의 표시 데이터를 수평 주사 회로(220)의 래치 회로부(222)에 출력한다.

동시에 표시 제어 장치(201)는 수평 시프트 레지스터 회로(221)에 스타트 펄스(DX)와, 표시 데이터 래치용 클럭을 출력한다.

이에 따라, 수평 시프트 레지스터 회로(221)는 래치 회로부(222)에 표시 데이터 취득용 시프트 펄스를 순차 출력한다.

래치 회로부(222)는 이 표시 데이터 취득용 시프트 펄스에 의해, 표시 데이터를 순차 저장하고, 비디오 신호 수신 회로(411~41n)의 각 데이터 래치부(도 6에 도시하는 LT1~LT3)에 입력한다.

각 데이터 래치부(LT1~LT3)는 외부 펄스( $\phi 1 \sim \phi 5$ )의 입력 전에 래치 회로부(222)로부터의 데이터를 래치하고, 상기 도 7, 도 8을 이용하여 설명한 순서로 각 영상 신호선(D1~Dn)에 비디오 신호를 공급한다.

이에 따라, 선택된 주사 신호선(G)에 게이트가 접속되는 박막 트랜지스터(TFT)를 갖는 화소에 표시 데이터에 대응한 계조 전압이 기입되며 표시부(210)에 화상이 표시된다.

본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에서도 제어 회로부(202)로부터 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 도 7 혹은 도 8에 도시하는 타이밍으로 변화시킴으로써, 상기한 공통 대칭법 혹은 공통 반전법 중 어느쪽의 교류화 구동에도 대응 가능하다.

또한, 본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에 있어서 상기 도트 반전법을 채용하는 경우라도 예를 들면 상기 도 11에 도시한 바와 같은 방법에 의해 용이하게 대응 가능하다.

즉, 영상 신호선(Dn)에 설치되는 비디오 신호 수신 회로(21)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 7에 도시하는 타이밍으로 하고, 영상 신호선(Dn)에 인접하는 영상 신호선(Dn+1)에 설치되는 비디오 신호 수신 회로(22)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 8에 도시하는 타이밍으로 하고, 1 라인마다 또한 1 프레임마다 전환하도록 하면 된다.

또한, 본 실시예의 Poly-SiTr-TFT 액정 표시 모듈에서도 상기 도트 반전법을 채용하는 경우에 상기 도 12에 도시한 바와 같은 구성을 채용하여도 된다.

즉, 각 영상 신호마다 2계통의 비디오 신호 수신 회로(31a, 31b, 32a, 32b)를 설치하고, 비디오 신호 수신 회로(31a, 32a)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 7에 도시하는 타이밍으로 하고 또한 비디오 신호 수신 회로(31b, 32b)에 공급하는 외부 펄스( $\phi 1 \sim \phi 5$ )의 타이밍을 예를 들면 도 8에 도시하는 타이밍으로 하고, 1 라인마다 2계통의 비디오 신호 수신 회로를 교대로 전환하여 영상 신호선과 접속하고 또한 1 프레임마다 영상 신호선에 접속하는 2계통의 비디오 신호 수신 회로의 접속순을 교환하면 된다.

또, 도 13에 도시하는 수평 주사 회로(220) 및 수직 주사 회로(230)는 액정 표시 패널에 삽입되고 있고, 박막 트랜지스터(TFT)와 동일하게 Poly-SiTr에서 구성되며 동일한 기판 상에 형성된다.

또, 상기 각 실시예에서는 본 발명을 폴리·실리콘·트랜지스터를 사용한 TFT 방식의 모듈에 적용한 실시예에 대하여 설명하였지만, 본 발명은 이에 한정되지는 않고, 본 발명은 비정질·실리콘·트랜지스터를 사용한 TFT 방식의 모듈에 적용 가능하다.

이상, 본 발명자에 의해서 이루어진 발명을 상기 실시예에 기초하여 구체적으로 설명하였지만, 본 발명은 상기 실시예에 한정되지는 않고 그 요지를 일탈하지 않은 범위에서 여러가지 변경 가능한 것은 물론이다.

### 발명의 효과

본원에서 개시되는 발명 중 대표적인 것에 의해서 얻어지는 효과를 간단하게 설명하면 하기 그대로이다.

본 발명에 따르면, 각 화소에 구동 전압을 공급하는 전계 효과형 트랜지스터의 임계치 전압의 변동에 의해, 액정 표시 소자의 표시 화면에 생기는 선형의 모양을 방지하여 액정 표시 소자의 표시 화면의 표시 품질을 향상

시키는 것이 가능해진다.

### (57) 청구의 범위

#### 청구항 1

매트릭스형으로 설치되는 복수의 화소와,

상기 복수의 화소의 열(또는 행) 방향의 화소에 화소 구동 전압을 인가하는 복수의 영상 신호선과,

상기 복수의 영상 신호선에 화소 구동 전압을 공급하는 구동 수단을 구비하는 액정 표시 장치에 있어서,

상기 구동 수단은 상기 각 영상 신호선에 화소 구동 전압을 공급하는 복수의 영상 신호 수신 수단을 구비하고,

상기 각 영상 신호 수신 수단은 제1 전계 효과형 트랜지스터와,

상기 제1 전계 효과형 트랜지스터의 제어 전극의 전압치를, 공통 화소 구동 전압에 대하여, 상기 제1 전계 효과형 트랜지스터의 임계지 전압분만큼 보정한 전압치로 설정하는 제1 수단과,

상기 제1 전계 효과형 트랜지스터의 제어 전극의 전압치를, 상기 제1 수단으로 보정된 전압치에 영상 신호 전압이 중첩된 전압으로 하는 제2 수단과,

상기 제2 수단에서, 제어 전극의 전압치가 상기 제1 수단으로 보정된 전압치에 영상 신호 전압이 중첩된 전압이 된 제1 전계 효과형 트랜지스터와 함께, 상기 공통 화소 구동 전압에 영상 신호 전압이 중첩된 전압을 화소 구동 전압으로서, 상기 영상 신호선에 공급하는 제3 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 2

제1항에 있어서, 상기 구동 수단은 상기 각 영상 신호 수신 수단을 제어하는 제어 수단에 있어서, 상기 각 영상 신호 수신 수단에 대하여 제1 모드의 제어 신호를 송출하고, 상기 각 영상 신호 수신 수단으로부터 상기 영상 신호선에 상기 공통 화소 구동 전압에 영상 신호 전압이 가산된 전압을 화소 구동 전압으로서 공급시키고 또한 상기 각 영상 신호 수신 수단에 대하여 제2 모드의 제어 신호를 송출하여 상기 각 영상 신호 수신 수단으로부터 상기 영상 신호선에, 상기 공통 화소 구동 전압으로부터 영상 신호 전압이 감산된 전압을 화소 구동 전압으로서 공급시키는 제어 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 3

제2항에 있어서, 상기 제어 수단으로부터 송출되는 제1 모드의 제어 신호는 제1 내지 제5 제어 신호를 구비하고,

상기 제1 내지 제5 제어 신호는 상기 제5 제어 신호, 상기 제4 제어 신호, 및 상기 제3 제어 신호의 순서로 또한 상기 제5 제어 신호가 송출되고 있는 동안에 상기 제1 제어 신호 및 상기 제2 제어 신호의 순서로, 각 영상 신호 수신 수단에 대하여 송출되는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 4

제2항에 있어서, 상기 제어 수단으로부터 송출되는 제2 모드의 제어 신호는 제1 내지 제5 제어 신호를 구비하고,

상기 제1 내지 제5 제어 신호는 상기 제4 제어 신호, 상기 제1 제어 신호, 상기 제2 제어 신호, 상기 제5 제어 신호 및 상기 제3 제어 신호의 순서로 각 영상 신호 수신 수단에 대하여 송출되는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 5

제3항에 있어서, 상기 제1 수단은 제2 전극에 제1 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제어 전극에 접속되는 제2 전계 효과형 트랜지스터와,

제2 전극이 상기 제2 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제3 전계 효과형 트랜지스터와,

제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되는 전계 효과형 트랜지스터로, 제1 전극에 상기 공통 화소 구동 전압이 인가되는 제4 전계 효과형 트랜지스터로 구성되며,

상기 제3 수단은 제2 전극이 제2 기준 전압에 접속되는 전계 효과형 트랜지스터로, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제5 전계 효과형 트랜지스터와,

제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 영상 신호선에 접속되는 제6 전계 효과형 트랜지스터로 구성되며,

상기 제2 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제1 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제3 및 제4 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제2 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제5 및 제6 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제3 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 6

제5항에 있어서, 상기 제2 수단은 제2 전극에 영상 신호 전압이 인가되는 제7 전계 효과형 트랜지스터와, 제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형 트랜지스터와,

상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되며,

상기 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 7

제5항에 있어서, 상기 제2 수단은 표시 데이터의 비트수만큼 설치되는 복수의 데이터 입력 수단을 구비하고, 각 데이터 입력 수단은 표시 데이터의 각 비트치를 저장하는 래치부와,

제2 전극이 상기 래치부에 접속되는 제7 전계 효과형 트랜지스터와, 제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트랜지스터로, 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형 트랜지스터와,

상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되며,

상기 각 데이터 입력 수단의 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 각 데이터 입력 수단의 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 8

제4항에 있어서, 상기 제1 수단은 제2 전극에 제1 기준 전압이 인가되는 전계 효과형 트랜지스터로 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제어 전극에 접속되는 제2 전계 효과형 트랜지스터와,

제2 전극이 상기 제2 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제3 전계 효과형 트랜지스터와,

제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되는 전계 효과형 트랜지스터로 제1 전계에 상기 공통 화소 구동 전압이 인가되는 제4 전계 효과형 트랜지스터로 구성되며,

상기 제3 수단은 제2 전극이 제2 기준 전압에 접속되는 전계 효과형 트랜지스터로 제1 전극이 상기 제1 전계 효과형 트랜지스터의 제2 전극에 접속되는 제5 전계 효과형 트랜지스터와,

제2 전극이 상기 제1 전계 효과형 트랜지스터의 제1 전극에 접속되며, 제1 전극이 상기 영상 신호선에 접속되는 제6 전계 효과형 트랜지스터로 구성되며,

상기 제2 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제1 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제3 및 제4 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제2 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제5 및 제6 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제3 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 9

제8항에 있어서, 상기 제2 수단은 제2 전극에 영상 신호 전압이 인가되는 제7 전계 효과형 트랜지스터와,

제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트래진스터로 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형 트랜지스터와,

상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되며,

상기 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

### 청구항 10

제8항에 있어서, 상기 제2 수단은 표시 데이터의 비트수만큼 설치되는 복수의 데이터 입력 수단을 구비하고, 각 데이터 입력 수단은 표시 데이터의 각 비트치를 저장하는 래치부와,

제2 전극이 상기 래치부에 접속되는 제7 전계 효과형 트랜지스터와, 제1 전극에 제3 기준 전압이 인가되는 전계 효과형 트랜지스터로 제2 전극이 상기 제7 전계 효과형 트랜지스터의 제1 전극에 접속되는 제8 전계 효과형

트랜지스터와,

상기 제7 전계 효과형 트랜지스터의 제1 전극과, 상기 제2 전계 효과형 트랜지스터의 제1 전극 간에 접속되는 결합 용량으로 구성되며,

상기 각 데이터 입력 수단인 제7 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제4 제어 신호가 제어 전극에 인가되었을 때 온이 되며,

상기 각 데이터 입력 수단의 제8 전계 효과형 트랜지스터는 상기 제어 수단으로부터 출력되는 제5 제어 신호가 제어 전극에 인가되었을 때 온이 되는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 11

제2항에 있어서, 상기 제어 수단은 각 영상 신호 수신 수단에 대하여, 각 프레임으로  $n(n \geq 1)$  라인마다 또한 1 프레임마다 송출되는 제어 신호의 모드가 다르도록, 상기 제1 모드의 제어 신호 혹은 상기 제2 모드의 제어 신호를 교대에 송출하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 12

제2항에 있어서, 상기 제어 수단은 홀수번째의 영상 신호선에 화소 구동 전압을 공급하는 각 영상 신호 수신 수단에 대하여, 각 프레임으로  $n(n \geq 1)$  라인마다 또한 1 프레임마다 송출되는 제어 신호의 모드가 다르도록 상기 제1 모드의 제어 신호 혹은 상기 제2 모드의 제어 신호를 교대로 송출하고,

또한, 짹수번째의 영상 신호선에 화소 구동 전압을 공급하는 각 영상 신호 수신 수단에 대하여, 각 프레임으로  $n(n \geq 1)$  라인마다 또한 1 프레임마다 송출되는 제어 신호의 모드가 다르도록 상기 제2 모드의 제어 신호 혹은 상기 제1 모드의 제어 신호를 교대에 송출하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 13

제1항에 있어서, 상기 구동 수단은 상기 영상 신호 수신 수단을 2계통 구비하고,

또한, 상기 2계통 영상 신호 수신 수단으로부터 각 영상 신호선에 대하여, 교대로 화소 구동 전압을 공급하는 복수의 선택 수단을 포함하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 14

제13항에 있어서, 상기 제어부는 상기 2계통의 한쪽 계통의 각 영상 신호 수신 수단에 대하여 상기 제1 모드의 제어 신호를 또한 상기 2계통의 다른쪽의 계통의 각 영상 신호 수신 수단에 대하여 상기 제2 모드의 제어 신호를 송출함과 함께, 상기 각 선택 수단에 대하여 전환 제어 신호를 송출하고,

홀수번째의 영상 신호선에 화소 구동 전압을 공급하는 선택 수단은 각 프레임으로 1 라인마다 또한 1 프레임마다 화소 구동 전압을 공급하는 계통이 다르도록, 상기 2계통의 한쪽 계통의 영상 신호 수신 수단 혹은 상기 2계통의 다른쪽의 계통의 영상 신호 수신 수단으로부터의 화소 구동 전압을 각 영상 신호선에 교대로 공급하고, 짹수번째의 영상 신호선에 화소 구동 전압을 공급하는 선택 수단은 각 프레임으로 1 라인마다 또한 1 프레임마다 화소 구동 전압을 공급하는 계통이 다르도록, 상기 2계통의 다른쪽 계통의 영상 신호 수신 수단, 혹은 상기 2계통의 한쪽 계통의 영상 신호 수신 수단으로부터의 화소 구동 전압을 각 영상 신호선에 교대로 공급하는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 15

제1항에 있어서, 상기 각 전계 효과형 트랜지스터는 제어 전극 하의 채널 형성 영역이 다결정 실리콘인 것을 특징으로 하는 액정 표시 장치.

#### 청구항 16

제1항에 있어서, 상기 매트릭스형으로 설치되는 복수의 화소, 상기 복수의 영상 신호선 및 상기 구동 수단은 액정 표시 소자 내에 삽입되고 있는 것을 특징으로 하는 액정 표시 장치.

## 도면

도면1

도면2

도면3

도면4

도면5

## 도면6

## 도면7

## 도면8

## 도면9

도면10

도면11

도면12

도면13

도면14

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR1020010007288A</a>                                                                               | 公开(公告)日 | 2001-01-26 |

| 申请号            | KR1020000031263                                                                                                | 申请日     | 2000-06-08 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA                                                                                        |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                                      |         |            |

| [标]发明人         | MIYAZAWA TOSHIO<br>미야자와 도시오<br>SATOU TOMOHIKO<br>사토우 도모히코                                                      |         |            |

| 发明人            | 미야자와 도시오<br>사토우 도모히코                                                                                           |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                    |         |            |

| CPC分类号         | G09G2300/0408 G09G2310/027 G09G3/3659 G09G3/3614 G09G2310/0297 G09G3/3688 G09G2352/00 G09G2320/0276 G09G3/3648 |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                                 |         |            |

| 优先权            | 1999162268 1999-06-09 JP                                                                                       |         |            |

| 其他公开文献         | KR100787698B1                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                      |         |            |

## 摘要(译)

一种液晶显示装置，具有改善的液晶显示元件的显示屏的显示质量。多个视频信号接收的装置，用于提供像素驱动电压施加到每个视频信号线的，接收装置的每个视频信号是一个场效应晶体管，并且对所述控制电极的电压值的场效应型场效应到晶体管的共用像素驱动电压第一种用于将场效应晶体管的控制电极的电压值设置为其中视频信号电压叠加在由第一装置校正的电压值上的电压的装置，在与视频信号电压的电压的电压值的控制电压值的第二装置在所述电极的所述第一装置被叠加的电场效应晶体管校正，图像信号电压的形状叠加电压施加到共用像素驱动电压信号线第三种方法是提供第三种方法。3指数方面视频信号装置，控制电极，场效应晶体管，像素驱动电压，视频信号接收电路