(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0054300

(43) 공개일자 2009년05월29일

(51) Int. Cl.

G02F 1/133 (2006.01) G02F 1/1343 (2006.01)

(21) 출원번호 10-2007-0121092

(22) 출원일자 2007년11월26일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 벌명자

양영철

경기 성남시 분당구 정자동 한솔마을주공6단지아파트 610동1104호

투지안강

경기 수원시 영통구 영통동 벽적골8단지아파트 833-404

이승훈

경기 용인시 기흥구 공세동 청구아파트 102동 1104호

(74) 대리인

특허법인가산

전체 청구항 수 : 총 9 항

## (54) 액정 표시 장치

## (57) 요 약

측면 시인성을 높이면서 휙도 감소를 방지할 수 있는 액정 표시 장치가 제공된다. 액정 표시 장치는, 나란히 배열되고 순차적으로 게이트 전압을 전달하는 제1 및 제2 게이트선과, 제1 및 제2 게이트선과 교차하고 데이터 전압을 전달하는 데이터선과, 하나의 화소 내에 위치하여 서로 전기적으로 분리된 제1 및 제2 부화소 전극으로 이루어진 화소 전극과, 제1 게이트선, 데이터선, 및 제1 부화소 전극에 접속하는 제1 스위칭 소자와, 제1 게이트선, 데이터선, 및 제2 부화소 전극에 접속하는 제2 스위칭 소자와, 전하 분배 커패시터를 사이에 두고 제1 부화소 전극과 접속하는 제3 스위칭 소자와, 제2 게이트선 및 제2 부화소 전극에 접속하고, 전하 분배 커패시터를 사이에 두고 제1 부화소 전극에 접속하는 제4 스위칭 소자를 포함한다.

## 대 표 도 - 도2

## 특허청구의 범위

### 청구항 1

나란히 배열되고 순차적으로 게이트 전압을 전달하는 제1 및 제2 게이트선;

상기 제1 및 제2 게이트선과 교차하고 데이터 전압을 전달하는 데이터선;

하나의 화소 내에 위치하여 서로 전기적으로 분리된 제1 및 제2 부화소 전극으로 이루어진 화소 전극;

상기 제1 게이트선, 상기 데이터선, 및 상기 제1 부화소 전극에 접속하는 제1 스위칭 소자;

상기 제1 게이트선, 상기 데이터선, 및 상기 제2 부화소 전극에 접속하는 제2 스위칭 소자;

전하 분배 커패시터를 사이에 두고 상기 제1 부화소 전극과 접속하는 제3 스위칭 소자; 및

상기 제2 게이트선 및 상기 제2 부화소 전극에 접속하고, 상기 전하 분배 커패시터를 사이에 두고 상기 제1 부화소 전극에 접속하는 제4 스위칭 소자를 포함하는 액정 표시 장치.

### 청구항 2

제1 항에 있어서,

상기 게이트선과 평행하고 공통 전압을 전달하는 스토리지선을 더 포함하고,

상기 제3 스위칭 소자는, 상기 제1 게이트선에 접속하는 제어 단자와, 상기 전하 분배 커패시터에 접속하는 출력 단자와, 상기 스토리지선에 접속하는 입력 단자를 포함하는 액정 표시 장치.

### 청구항 3

제2 항에 있어서,

상기 제3 스위칭 소자의 입력 단자는 상기 스토리지선에 직접 접속하는 액정 표시 장치.

### 청구항 4

제3 항에 있어서,

상기 제1 게이트선에 게이트 온 전압이 인가되는 경우, 상기 전하 분배 커패시터에는 상기 데이터 전압과 상기 공통 전압의 차이에 해당하는 전압이 충전되는 액정 표시 장치.

### 청구항 5

제2 항에 있어서,

상기 제3 스위칭 소자의 입력 단자는 보조 커패시터를 사이에 두고 상기 스토리지선에 접속하는 액정 표시 장치.

### 청구항 6

제1 항에 있어서,

상기 데이터선과 평행하고 전하 분배용 전압을 전달하는 전하 분배용 배선을 더 포함하고,

상기 제3 스위칭 소자는, 상기 제1 게이트선에 접속하는 제어 단자와, 상기 전하 분배 커패시터에 접속하는 출력 단자와, 상기 전하 분배용 배선에 접속하는 입력 단자를 포함하는 액정 표시 장치.

### 청구항 7

제6 항에 있어서,

상기 전하 분배용 전압의 극성은 상기 데이터 전압의 극성과 반대인 액정 표시 장치.

### 청구항 8

제6 항에 있어서,

상기 제1 및 제2 부화소 전극의 화소 전압 사이에 전하 분배가 일어난 후, 상기 제1 부화소 전극의 화소 전압 및 상기 제2 부화소 전극의 화소 전압이 상기 데이터 전압보다 높은 액정 표시 장치.

### 청구항 9

제8 항에 있어서,

상기 제1 스위칭 소자에 병렬로 접속하는 제1 액정 캐퍼시터 및 제1 스토리지 커패시터와, 상기 제2 스위칭 소자에 병렬로 접속하는 제2 액정 커패시터 및 제2 스토리지 커패시터를 더 포함하고,

$$\frac{|Vm|}{|Vp|} \geq \frac{Ch}{2Cb + Ch}$$

상기 데이터 전압 및 상기 전하 분배용 전압은  $\frac{|Vm|}{|Vp|} \geq \frac{Ch}{2Cb + Ch}$  을 만족하는 액정 표시 장치.

(여기서, Vp는 데이터 전압이고, Vm은 전하 분배용 전압이고, Ch는 제1 액정 커패시터와 제1 스토리지 커패시터의 커패시턴스 합이고, Cb는 전하 분배 커패시터의 커패시턴스이다.)

## 명세서

### 발명의 상세한 설명

#### 기술 분야

<1> 본 발명은 디스플레이 장치 및 그 구동 방법에 관한 것으로서, 더욱 상세하게는 액정 표시 장치에 관한 것이다.

#### 배경 기술

<2> 액정 표시 장치는 현재 가장 널리 사용되고 있는 평판 표시 장치 중 하나로서, 화소 전극과 공통 전극 등 전계 생성 전극이 형성되어 있는 두 장의 표시판과 그 사이에 삽입되어 있는 액정층으로 이루어지며, 전계 생성 전극에 전압을 인가하여 액정층에 전계를 생성하고 이를 통하여 액정층의 액정 분자들의 배향을 결정하고 입사광의 편광을 제어함으로써 영상을 표시한다.

<3> 또한 전계가 인가되지 않은 상태에서 액정 분자의 장축을 상하 표시판에 대하여 수직을 이루도록 배열한 수직 배향 모드 액정 표시 장치는 대비비가 크고 넓은 기준 시야각 구현이 용이하여 각광받고 있다. 여기에서 기준 시야각이란 대비비가 1:10인 시야각 또는 계조간 희도 반전 한계 각도를 의미한다.

<4> 수직 배향 모드 액정 표시 장치에서 광시야각을 구현하기 위한 수단으로는 전계 생성 전극에 절개부를 형성하는 방법과 전계 생성 전극 위에 돌기를 형성하는 방법 등이 있다. 절개부와 돌기로 액정 분자가 기우는 방향을 결정할 수 있으므로, 이들을 사용하여 액정 분자의 경사 방향을 여러 방향으로 분산시킴으로써 기준 시야각을 넓힐 수 있다.

### 발명의 내용

#### 해결 하고자하는 과제

<5> 종래의 수직 배향 방식의 액정 표시 장치는 전면 시인성에 비하여 측면 시인성이 떨어지는 문제점이 있다. 예를 들어, 절개부가 구비된 PVA(patterned vertically aligned) 방식 액정 표시 장치의 경우에는 측면으로 갈수록 영상이 밝아져서, 심한 경우에는 높은 계조 사이의 희도 차이가 없어져 그림이 풍그려져 보이는 경우도 발생한다.

<6> 본 발명이 해결하고자 하는 과제는, 측면 시인성을 높이면서 희도 감소를 방지할 수 있는 액정 표시 장치를 제공하고자 하는 것이다.

<7> 본 발명이 해결하고자 하는 과제들은 이상에서 언급한 과제로 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 과제 해결수단

- <8> 상기 과제를 달성하기 위한 본 발명의 일 실시예에 따른 액정 표시 장치는, 나란히 배열되고 순차적으로 게이트 전압을 전달하는 제1 및 제2 게이트선과, 상기 제1 및 제2 게이트선과 교차하고 데이터 전압을 전달하는 데이터 선과, 하나의 화소 내에 위치하여 서로 전기적으로 분리된 제1 및 제2 부화소 전극으로 이루어진 화소 전극과, 상기 제1 게이트선, 상기 데이터선, 및 상기 제1 부화소 전극에 접속하는 제1 스위칭 소자와, 상기 제1 게이트선, 상기 데이터선, 및 상기 제2 부화소 전극에 접속하는 제2 스위칭 소자와, 전하 분배 커패시터를 사이에 두고 상기 제1 부화소 전극과 접속하는 제3 스위칭 소자와, 상기 제2 게이트선 및 상기 제2 부화소 전극에 접속하고, 상기 전하 분배 커패시터를 사이에 두고 상기 제1 부화소 전극에 접속하는 제4 스위칭 소자를 포함한다.

- <9> 기타 실시예들의 구체적인 사항들은 상세한 설명 및 도면들에 포함되어 있다.

### 효과

- <10> 상술한 바와 같이 본 발명에 따른 액정 표시 장치에 의하면, 하나의 화소 전극을 한 쌍의 부화소 전극으로 분할한 후 전하 분배(charge sharing)를 통하여 각 부화소 전극의 화소 전압에 차이를 발생시킴으로써 측면 시인성을 높일 수 있다. 또한 전하 분배를 일으키는 전하 분배 커패시터의 일단에 스위칭 소자를 연결함으로써 한 쌍의 부화소 전극의 화소 전압의 차이가 커져서 측면 시인성이 더욱 향상될 수 있다. 또한 상기 스위칭 소자는 데이터 전압보다 화소 전압이 지나치게 감소하는 것을 방지함으로써 전하 분배에 따른 휘도 감소를 억제할 수 있다.

### 발명의 실시를 위한 구체적인 내용

- <11> 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

- <12> 하나의 소자(elements)가 다른 소자와 "접속된(connected to)" 또는 "커플링된(coupled to)"이라고 지칭되는 것은, 다른 소자와 직접 연결 또는 커플링된 경우 또는 중간에 다른 소자를 개재한 경우를 모두 포함한다. 반면, 하나의 소자가 다른 소자와 "직접 접속된(directly connected to)" 또는 "직접 커플링된(directly coupled to)"으로 지칭되는 것은 중간에 다른 소자를 개재하지 않은 것을 나타낸다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. "및/또는"은 언급된 아이템들의 각각 및 하나 이상의 모든 조합을 포함한다.

- <13> 비록 제1, 제2 등이 다양한 소자, 구성요소 및/또는 섹션들을 서술하기 위해서 사용되나, 이들 소자, 구성요소 및/또는 섹션들은 이들 용어에 의해 제한되지 않음은 물론이다. 이들 용어들은 단지 하나의 소자, 구성요소 또는 섹션들을 다른 소자, 구성요소 또는 섹션들과 구별하기 위하여 사용하는 것이다. 따라서, 이하에서 언급되는 제1 소자, 제1 구성요소 또는 제1 섹션은 본 발명의 기술적 사상 내에서 제2 소자, 제2 구성요소 또는 제2 섹션일 수도 있음을 물론이다.

- <14> 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다(comprises)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

- <15> 다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않는 한 이상적으로 또는 과도하게 해석되지 않는다.

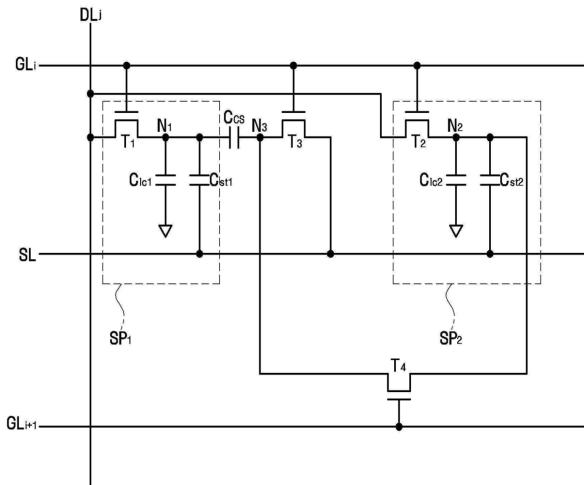

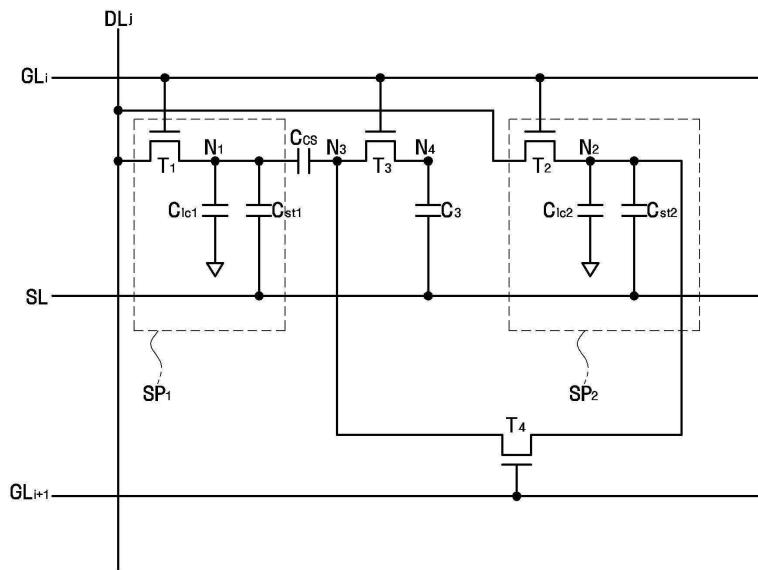

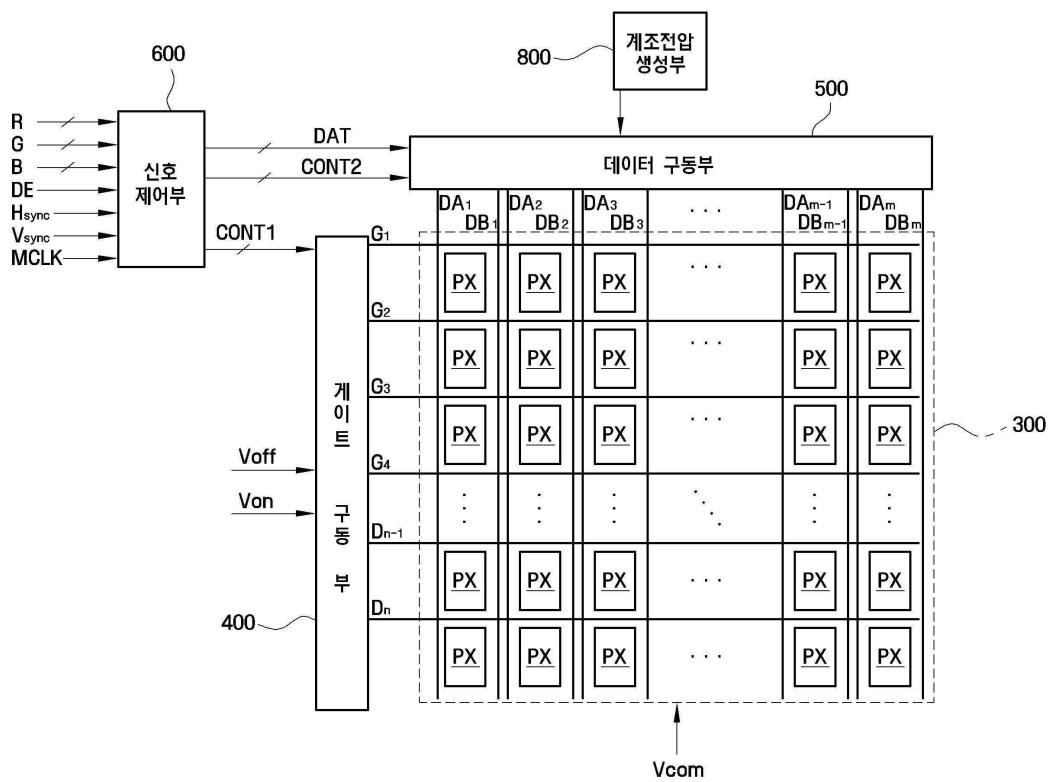

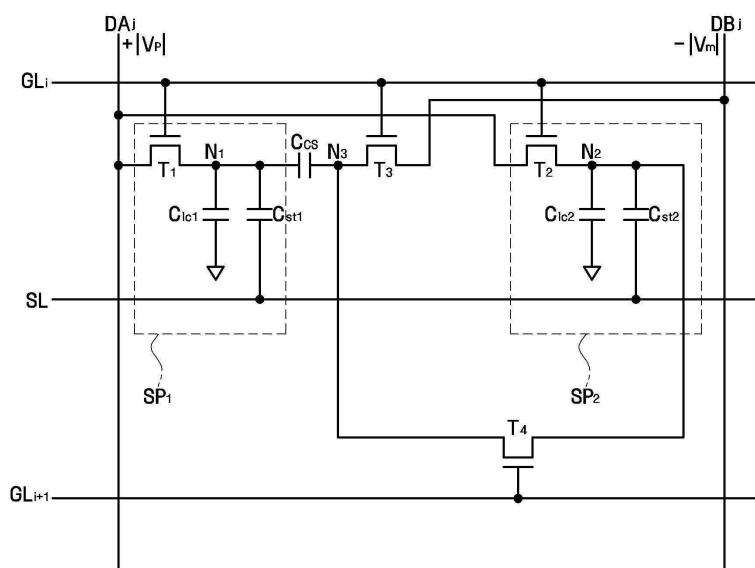

- <16> 이하 도 1 내지 도 3을 참조하며 본 발명의 제1 실시예에 따른 액정 표시 장치에 대하여 설명한다. 도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치의 블록도이다. 도 2는 본 발명의 제1 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다. 도 3은 본 발명의 제1 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그림이다.

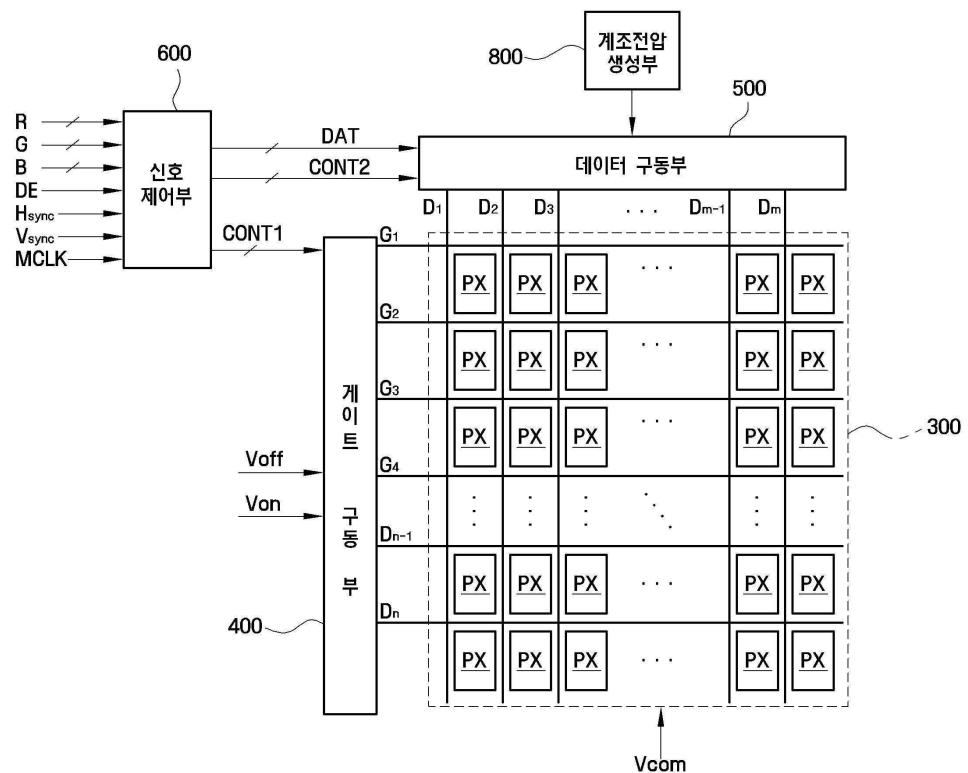

- <17> 도 1을 참조하면, 본 발명의 제1 실시예에 따른 액정 표시 장치는 액정 패널 어셈블리(liquid crystal panel

assembly)(300), 이에 연결된 게이트 구동부(400) 및 데이터 구동부(500), 데이터 구동부(500)에 연결된 계조 전압 생성부(800), 그리고 이들을 제어하는 신호 제어부(600)를 포함한다.

- <18> 액정 패널 어셈블리(300)는 등가 회로로 볼 때 다수의 표시 신호선과 이에 연결되어 있으며 대략 행렬의 형태로 배열된 다수의 화소(PX)를 포함한다. 여기서, 액정 패널 어셈블리(300)는 서로 마주 보는 하부 표시판, 상부 표시판 및 이들 사이에 개재된 액정층을 포함한다.

- <19> 표시 신호선은 하부 표시판에 구비되어 있으며, 게이트 신호를 전달하는 다수의 게이트선(G1-Gn)과 데이터 신호를 전달하는 데이터선(D1-Dm)을 포함한다. 게이트선(G1-Gn)은 대략 행 방향으로 뻗어 있으며 서로가 거의 평행하고 데이터선(D1-Dm)은 대략 열 방향으로 뻗어 있으며 서로가 거의 평행하다.

- <20> 각 화소(PX)는 해당 게이트선(G1-Gn) 및 데이터선(D1-Dm)에 연결되어 있는 스위칭 소자와, 이에 연결된 액정 커페시터(liquid crystal capacitor)를 포함한다. 여기서 필요에 따라 스위칭 소자에 스토리지 커페시터(storage capacitor)를 액정 커페시터와 병렬로 연결할 수 있다.

- <21> 여기서 각 화소(PX)의 스위칭 소자는 박막 트랜지스터 등으로 이루어지며, 각각 해당 게이트선(G1-Gn)에 연결되어 있는 제어 단자, 데이터선(D1-Dm)에 연결되어 있는 입력 단자, 그리고 액정 커페시터에 연결되어 있는 출력 단자를 가지는 삼단자 소자이다.

- <22> 게이트 구동부(400)는 게이트선(G1-Gn)에 연결되어 외부로부터 하이 레벨의 게이트 신호(이를 게이트 온 전압(Von)라 한다)와 로우 레벨의 게이트 신호(이를 게이트 오프 전압(Voff)라 한다)의 조합으로 이루어진 게이트 신호를 게이트선(G1-Gn)에 인가한다. 도 1에 도시된 게이트 구동부(400)는 액정 패널 어셈블리(300)의 한 쪽에 위치하며 모든 게이트선(G1-Gn)에 연결되어 있다. 다만 본 발명은 이에 한정되지 않으며 한 쌍의 게이트 구동부가 각각 액정 패널 어셈블리(300)의 좌우에 위치하여 각 게이트선(G1-Gn)에 동시에 연결될 수 있다. 예를 들어, 대형 액정 표시 장치의 경우 하나의 게이트 구동부만으로는 게이트선(G1-Gn)의 끝까지 게이트 온 전압(Von) 또는 게이트 오프 전압(Voff)을 충분히 전달하기 어렵기 때문에 이와 같이 한 쌍의 게이트 구동부를 각 게이트선(G1-Gn)의 양쪽에 연결할 수 있다. 또한 이러한 게이트 구동부(400)는 액정 패널 어셈블리(300)의 하부 표시판 상에 적어도 하나의 박막 트랜지스터로 이루어진 접적 회로 형태로 내장될 수 있다.

- <23> 계조 전압 생성부(gray voltage generator)(800)는 화소의 투과율과 관련된 계조 전압을 생성한다. 계조 전압은 각 화소에 제공되며, 공통 전압(Vcom)에 대하여 양의 값을 가지는 것과 음의 값을 가지는 것을 포함한다.

- <24> 데이터 구동부(500)는 액정 패널 어셈블리(300)의 데이터선(D1-Dm)에 연결되어 계조 전압 생성부(800)로부터의 계조 전압, 즉 데이터 전압을 화소에 인가한다. 여기서 계조 전압 생성부(800)가 모든 계조에 대한 전압을 모두 제공하는 것이 아니라 기본 계조 전압만을 제공하는 경우, 데이터 구동부(500)는 기본 계조 전압을 분압하여 전체 계조에 대한 계조 전압을 생성하고 이 중에서 데이터 전압을 선택할 수 있다.

- <25> 게이트 구동부(400) 또는 데이터 구동부(500)는 표시 신호선(G1-Gn, D1-Dm)과 박막 트랜지스터 등과 함께 액정 패널 어셈블리(300)에 접적될 수 있다. 이와는 달리 게이트 구동부(400) 또는 데이터 구동부(500)는 가요성 인쇄 회로막(flexible printed circuit film)(미도시) 위에 장착되어 테이프 캐리어 패키지(tape carrier package)의 형태로 액정 패널 어셈블리(300)에 부착될 수도 있다.

- <26> 신호 제어부(600)는 게이트 구동부(400) 및 데이터 구동부(500) 등의 동작을 제어한다.

- <27> 신호 제어부(600)는 외부의 그래픽 제어기(미도시)로부터 입력 영상 신호(R, G, B) 및 이의 표시를 제어하는 입력 제어 신호, 예를 들면 수직 동기 신호(Vsync)와 수평 동기 신호(Hsync), 메인 클록(MCLK), 데이터 인에이블 신호(DE) 등을 제공받는다. 신호 제어부(600)의 입력 영상 신호(R, G, B)와 입력 제어 신호를 기초로 영상 신호(R, G, B)를 액정 패널 어셈블리(300)의 동작 조건에 맞게 적절히 처리하고 게이트 제어 신호(CONT1) 및 데이터 제어 신호(CONT2) 등을 생성한 후, 게이트 제어 신호(CONT1)를 게이트 구동부(400)로 내보내고 데이터 제어 신호(CONT2)와 처리한 영상 신호(DAT)를 데이터 구동부(500)로 내보낸다.

- <28> 게이트 제어 신호(CONT1)는 게이트 구동부(400)의 동작의 시작, 즉 주사 시작을 지시하는 주사 시작 신호(STV)와 게이트 온 전압(Von)의 출력 시간을 제어하는 적어도 하나의 클록 신호를 포함한다. 게이트 제어 신호(CONT1)는 또한 게이트 온 전압(Von)의 지속 시간을 한정하는 출력 인에이블 신호(OE)를 포함할 수 있다. 여기에서 클록 신호는 선택 신호(SE)로 사용될 수 있다.

- <29> 데이터 제어 신호(CONT2)는 한 뷰어의 화소(PX)에 대한 데이터의 전송을 알리는 수평 동기 시작 신호(STH)와 데이터선(D1-Dm)에 해당 데이터 전압을 인가하라는 로드 신호(LOAD) 및 데이터 클록 신호(HCLK)를 포함한다. 또한

데이터 제어 신호(CONT2)는 공통 전압(Vcom)에 대한 데이터 전압의 극성(이하 "공통 전압에 대한 데이터 전압의 극성"을 줄여 "데이터 전압의 극성"이라 함)을 반전시키는 반전 신호(RVS)를 포함할 수 있다.

- <30> 신호 제어부(600)로부터의 데이터 제어 신호(CONT2)에 따라, 데이터 구동부(500)는 화소(PX)에 대한 영상 데이터(DAT)를 수신하고, 계조 전압 생성부(800)로부터의 영상 데이터(DAT)에 대응하는 계조 전압을 선택함으로써 영상 데이터(DAT)를 해당 데이터 전압으로 변환한 후, 이를 해당 데이터선(D1-Dm)에 인가한다.

- <31> 게이트 구동부(400)는 신호 제어부(600)로부터의 게이트 제어 신호(CONT1)에 따라 게이트 온 전압(Von)을 게이트선(G1-Gn)에 인가하여 이 게이트선(G1-Gn)에 연결된 스위칭 소자를 턴온시키며, 이에 따라 데이터선(D1-Dm)에 인가된 데이터 전압이 턴온된 스위칭 소자를 통하여 해당 화소(PX)에 인가된다.

- <32> 각 화소(PX)에 인가된 데이터 전압과 공통 전압(Vcom)의 차이는 액정 커패시터의 충전 전압, 즉 화소 전압으로서 나타난다. 액정 분자들은 화소 전압의 크기에 따라 그 배열을 달리하며 이에 따라 액정층을 통과하는 빛의 편광이 변화하고, 이는 빛의 투과율 변화로 나타난다.

- <33> 본 발명의 제1 실시예에 따른 액정 표시 장치는 화소(PX)를 이루는 한 쌍의 부화소에 동일한 데이터 전압을 제공한 후, 이웃하는 게이트선에 게이트 온 전압(Von)이 인가될 때 상기 한 쌍의 부화소 중 어느 한 부화소에 충전된 데이터 전압을 전하 분배(charge sharing) 방식에 의해 떨어뜨린다. 이와 같이 한 쌍의 부화소에 서로 다른 데이터 전압이 충전되므로, 한 화소(PX)의 감마 곡선은 한 쌍의 부화소의 감마 곡선을 합성한 것이 된다. 전하 분배에 의하여 각 부화소에 충전되는 데이터 전압을 결정할 때에는, 정면에서의 합성 감마 곡선이 정면에서의 기준 감마 곡선에 가깝게 되도록 하고 측면에서의 합성 감마 곡선이 정면에서의 기준 감마 곡선과 가장 가깝게 되도록 함으로써, 측면 시인성을 향상시킬 수 있다.

- <34> 도 2를 참조하면, 본 발명의 제1 실시예에 따른 액정 표시 장치는, 게이트 전압을 전달하는 다수의 게이트선(GLi, GLi+1)과, 게이트선(GLi, GLi+1)에 교차하여 형성되며 데이터 전압을 전달하는 다수의 데이터선(DLj)을 포함한다.

- <35> 각 화소는 제1 부화소(SP1)와 제2 부화소(SP2)로 이루어진다. 제1 부화소(SP1)는 제1 스위칭 소자(T1), 제1 액정 커패시터(Cl<sub>c</sub>1) 및 제1 스토리지 커패시터(Cst1)를 포함하고, 제2 부화소(SP2)는 제2 스위칭 소자(T2), 제2 액정 커패시터(Cl<sub>c</sub>2) 및 제2 스토리지 커패시터(Cst2)를 포함한다.

- <36> 제i 게이트선(GLi)과 제j 데이터선(DLj)이 교차하는 지점에 제1 스위칭 소자(T1) 및 제2 스위칭 소자(T2)가 형성되고, 제i 게이트선(GLi)에 연결된 제3 스위칭 소자(T3)가 형성되고, 제i+1 게이트선(GLi+1)에 연결된 제4 스위칭 소자(T4)가 형성된다. 여기서 제1 스위칭 소자(T1), 제2 스위칭 소자(T2), 제3 스위칭 소자(T3) 및 제4 스위칭 소자(T4)는 박막 트랜지스터로 이루어질 수 있다.

- <37> 제1 스위칭 소자(T1)는 제i 게이트선(GLi)에 접속된 제어 단자와, 제j 데이터선(DLj)에 접속된 입력 단자와, 제1 액정 커패시터(Cl<sub>c</sub>1) 및 제1 스토리지 커패시터(Cst1)에 접속된 출력 단자를 포함한다. 제2 스위칭 소자(T2)는 제i 게이트선(GLi)에 접속된 제어 단자와, 제j 데이터선(DLj)에 접속된 입력 단자와, 제2 액정 커패시터(Cl<sub>c</sub>2) 및 제2 스토리지 커패시터(Cst2)에 접속된 출력 단자를 포함한다. 제3 스위칭 소자(T3)는 제i 게이트선(GLi)에 접속된 제어 단자와, 전하 분배 커패시터(Ccs)를 사이에 두고 제1 스위칭 소자(T1)의 출력 단자와 접속된 출력 단자와, 스토리지선(SL)에 접속된 입력 단자를 포함한다. 더욱 구체적으로, 제3 스위칭 소자(T3)의 입력 단자는 스토리지선(SL)에 직접 접속되어 있다. 제4 스위칭 소자(T4)는 제i+1 게이트선(GLi+1)에 접속된 제어 단자와, 제2 스위칭 소자(T2)의 출력 단자에 접속된 입력 단자와, 제3 스위칭 소자(T3)의 출력 단자와 접속된 출력 단자를 포함한다. 따라서 제4 스위칭 소자(T4)의 출력 단자는 전하 분배 커패시터(Ccs)를 사이에 두고 제1 스위칭 소자(T1)의 출력 단자와 접속되어 있다.

- <38> 이러한 구조의 하부 표시판을 구성하는 각 화소마다, 제1 스위칭 소자(T1)의 출력 단자에 접속된 제1 부화소 전극, 및 제2 스위칭 소자(T2)의 출력 단자에 접속된 제2 부화소 전극으로 이루어진 화소 전극이 형성되어 있다. 그리고 하부 표시판에 대향하는 상부 표시판에는 공통 전극이 형성되어 있다.

- <39> 제1 액정 커패시터(Cl<sub>c</sub>1)는 제1 스위칭 소자(T1)에 접속된 제1 부화소 전극, 공통 전극 및 이들 사이에 개재된 액정 물질로 이루어진다. 제1 스토리지 커패시터(Cst1)는 제1 부화소 전극, 하부 표시판에 형성된 스토리지선(SL) 및 이들 사이에 개재된 유전 물질로 이루어진다.

- <40> 제2 액정 커패시터(Cl<sub>c</sub>2)는 제2 스위칭 소자(T2)에 접속된 제2 부화소 전극, 공통 전극 및 이들 사이에 개재된 액정 물질로 이루어진다. 제2 스토리지 커패시터(Cst2)는 제2 부화소 전극, 하부 표시판에 형성된 스토리지선

(SL) 및 이들 사이에 개재된 유전 물질로 이루어진다.

<41> 전하 분배 커패시터(Ccs)는 제1 스위칭 소자(T1)의 출력 단자, 제3 스위칭 소자의 출력 단자 및 이들 사이에 개재된 유전 물질로 이루어진다. 전하 분배 커패시터(Ccs) 및 제3 스위칭 소자(T3)는 제2 액정 커패시터(ClC2)에 충전된 화소 전압을 낮추고 제1 액정 커패시터(ClC1)에 충전된 화소 전압을 높이는 역할을 한다.

<42> 제1 스토리지 커패시터(Cst1) 및 제2 스토리지 커패시터(Cst2)는 각각 제1 액정 커패시터(ClC1) 및 제2 액정 커패시터(ClC2)에 충전된 화소 전압을 유지시키는 역할을 한다. 스토리지선(SL)에는 고정 전압, 예를 들어 공통 전압(Vcom)이 인가될 수 있다.

<43> 제i 게이트선(GLi)에 게이트 온 전압(Von)이 인가되면, 제1 스위칭 소자(T1) 및 제2 스위칭 소자(T2)를 통하여 제i 행(row)에 위치하는 제1 부화소 전극 및 제2 부화소 전극에 동일한 데이터 전압이 전달된다. 즉, 제i 게이트선(GLi)에 연결된 제1 액정 커패시터(ClC1) 및 제2 액정 커패시터(ClC2)에 동일한 데이터 전압이 충전된다. 이와 같이 제1 액정 커패시터(ClC1) 및 제2 액정 커패시터(ClC2)에 충전된 데이터 전압을 화소 전압이라고 한다.

<44> 또한 제i 게이트선(GLi)에 게이트 온 전압(Von)이 인가되면, 제3 스위칭 소자(T3)가 턴온되고 제3 스위칭 소자(T3)의 출력 단자에 공통 전압(Vcom)이 전달된다. 따라서 전하 분배 커패시터(Ccs)에는 데이터 전압과 공통 전압(Vcom)의 차이에 해당하는 전압이 충전된다.

<45> 이어서 제i 게이트선(GLi)에 게이트 오프 전압(OFF)이 인가되면, 제1 부화소(SP1)와 제2 부화소(SP2)는 서로 전기적으로 분리된다. 즉, 제1 부화소 전극과 제2 부화소 전극에 각각 동일한 데이터 전압이 인가된 후 제1 부화소 전극과 제2 부화소 전극은 플로팅(floating) 상태를 유지한다.

<46> 제i+1 게이트선(GLi+1)에 게이트 온 전압(Von)이 인가되면, 제i+1 게이트선(GLi+1)에 연결된 한 쌍의 제1 스위칭 소자(미도시) 및 제2 스위칭 소자(미도시)를 통하여 제i+1 행에 위치한 한 쌍의 부화소 전극에 각각 동일한 데이터 전압이 전달된다.

<47> 또한 제i+1 게이트선(GLi+1)에 게이트 온 전압(Von)이 인가되면, 제4 스위칭 소자(T4)가 턴온된다. 따라서 제2 스위칭 소자(T2)에 연결된 제2 부화소 전극에 저장된 데이터 전압이 제4 스위칭 소자(T4)를 통하여 전하 분배 커패시터(Ccs)에 분배된다. 이는 제4 스위칭 소자(T4)의 입력 단자는 제2 스위칭 소자(T2)의 출력 단자에 접속되어 있고, 제4 스위칭 소자(T4)의 출력 단자는 전하 분배 커패시터(Ccs)에 접속되어 있기 때문이다. 따라서 제i 행에 위치하며 제1 스위칭 소자(T1) 및 제2 스위칭 소자(T2)에 각각 연결된 제1 부화소 전극 및 제2 부화소 전극에 저장된 데이터 전압이 서로 다른 값을 가지게 된다.

<48> 이하 전하량 보존 법칙을 이용하여 제1 부화소 전극과 제2 부화소 전극의 화소 전압을 구체적으로 살펴본다. 여기서 제1 노드(N1)는 제1 스위칭 소자(T1)의 출력 단자와 전하 분배 커패시터(Ccs) 사이의 노드를 말하고, 제2 노드(N2)는 제2 스위칭 소자(T2)의 출력 단자와 제4 스위칭 소자(T4)의 입력 단자 사이의 노드를 말하고, 제3 노드(N3)는 전하 분배 커패시터(Ccs)와 제3 스위칭 소자(T3)의 출력 단자 사이의 노드를 말한다. 또한 제3 노드(N3)는 전하 분배 커패시터(Ccs)와 제4 스위칭 소자(T4)의 출력 단자 사이의 노드를 말할 수도 있다.

<49> 제i 게이트선(GLi)에 게이트 온 전압(Von)이 인가되면, 제1 스위칭 소자(T1) 및 제2 스위칭 소자(T2)가 턴온되면서 제1 노드(N1) 및 제2 노드(N2)에 데이터 전압(Vd)이 인가된다. 또한 제3 스위칭 소자(T3)가 턴온되면서 제3 노드(N3)에 공통 전압(Vcom)이 인가된다. 이하 설명의 편의를 위하여 공통 전압(Vcom)을 0 V로 가정하고, 데이터 전압(Vd)을 공통 전압(Vcom)에 대한 상대적인 전압이라고 한다. 따라서 제1 노드(N1), 제2 노드(N2) 및 제3 노드(N3)에서의 각 전압은 Vd, Vd, 0이 된다. 또한 제1 액정 커패시터(ClC1)와 제1 스토리지 커패시터(Cst1)의 커패시턴스 합을 Ch이라 하고, 제2 액정 커패시터(ClC2)와 제2 스토리지 커패시터(Cst2)의 커패시턴스 합을 C1이라 하고, 전하 분배 커패시터(Ccs)의 커패시턴스를 Cb이라 한다.

<50> 이 때 제1 액정 커패시터(ClC1)와 제1 스토리지 커패시터(Cst1)의 전하량 Qh와, 제2 액정 커패시터(ClC2)와 제2 스토리지 커패시터(Cst2)의 전하량 Ql과, 전하 분배 커패시터(Ccs)의 전하량 Qb는 다음과 같다.

## 수학식 1

$$Qh = Ch \times Vd$$

$$Ql = C1 \times Vd$$

<53>  $Q_b = C_b \times V_d$

<54> 이어서 제*i* 게이트선(GL*i*)에 게이트 오프 전압(V<sub>off</sub>)이 인가되고 제*i*+1 게이트선(GL*i*+1)에 게이트 온 전압(V<sub>on</sub>)이 인가되면, 제1 스위칭 소자(T1), 제2 스위칭 소자(T2) 및 제3 스위칭 소자(T3)는 턴오프되고 제4 스위칭 소자(T4)가 턴온된다.

<55> 이 때 제1 노드(N1), 제2 노드(N2) 및 제3 노드(N3)에서의 각 전압을 V1, V2 및 V3(=V2)라 할 때, 제1 액정 커페시터(C1c1)와 제1 스토리지 커페시터(Cst1)의 전하량 Q<sub>h'</sub>와, 제2 액정 커페시터(C1c2)와 제2 스토리지 커페시터(Cst2)의 전하량 Q<sub>l'</sub>과, 전하 분배 커페시터(Ccs)의 전하량 Q<sub>b'</sub>는 다음과 같다.

## 수학식 2

<56>  $Q_h' = C_h \times V_1$

<57>  $Q_l' = C_l \times V_2$

<58>  $Q_b' = C_b \times (V_1 - V_2)$

<59> 제1 노드(N1)에 연결된 커페시터들의 총 전하량은 보존되므로 다음의 관계식이 성립한다.

## 수학식 3

<60>  $Q_h + Q_b = Q_h' + Q_b'$

<61> 제3 노드(N3)에 연결된 커페시터들의 총 전하량은 보존되므로 다음의 관계식이 성립한다.

## 수학식 4

<62>  $Q_l - Q_b = Q_l' - Q_b'$

<63> 수학식 1 내지 수학식 4의 관계를 정리하면 다음과 같이 제1 노드(N1) 및 제2 노드(N2)에서의 전압 V1 및 V2를 얻을 수 있다.

## 수학식 5

$$V_1 = V_d \left( 1 + \frac{C_l \cdot C_b}{C_l \cdot C_h + C_h \cdot C_b + C_b \cdot C_l} \right)$$

$$V_2 = V_d \left( 1 - \frac{C_h \cdot C_b}{C_l \cdot C_h + C_h \cdot C_b + C_b \cdot C_l} \right)$$

<64>

<65> 데이터 전압(V<sub>d</sub>)이 공통 전압(V<sub>com</sub>)보다 큰 양극성 전압인 경우, 제1 부화소(SP1)의 화소 전압(V1)은 데이터 전압(V<sub>d</sub>)보다 상승하고, 제2 부화소(SP2)의 화소 전압(V2)은 데이터 전압(V<sub>d</sub>)보다 하강한다. 데이터 전압(V<sub>d</sub>)이 공통 전압(V<sub>com</sub>)보다 작은 음극성 전압인 경우는 이와 반대가 된다. 따라서 제1 부화소(SP1)의 화소 전압(V1)의 절대값이 제2 부화소(SP2)의 화소 전압(V2)의 절대값보다 항상 크게 된다.

<66>

이와 같이 하나의 화소 내에 위치하는 제1 부화소(SP1) 및 제2 부화소(SP2)의 화소 전압(V1, V2)이 서로 다른 값을 가지게 되는 경우 측면 시인성을 향상시킬 수 있다. 즉 제1 부화소(SP1) 및 제2 부화소(SP2)에 하나의 영상 정보로부터 얻어진 서로 다른 감마 곡선을 가지는 한 쌍의 계조 전압 집합이 저장되고, 제1 부화소(SP1) 및 제2 부화소(SP2)로 이루어진 하나의 화소의 감마 곡선은 이들을 합성한 감마 곡선이 된다. 한 쌍의 계조 전압 집합을 결정할 때에는 정면에서의 합성 감마 곡선이 정면에서의 기준 감마 곡선에 가깝게 되도록 하고, 측면에서의 합성 감마 곡선이 정면에서의 기준 감마 곡선과 가장 가깝게 되도록 함으로써, 측면 시인성을 향상시킬 수 있다.

<67>

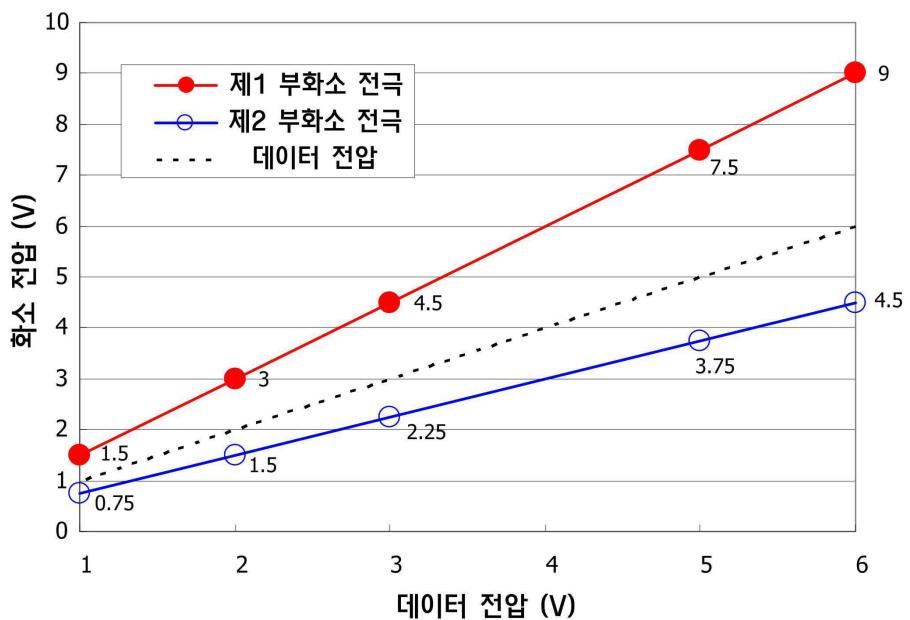

도 3은 데이터선을 통하여 인가되는 데이터 전압에 대하여 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압의 변화를 나타낸 그래프이다. 본 그래프는 C<sub>l</sub> : C<sub>h</sub> : C<sub>b</sub> = 2 : 1 : 2인 경우를 예로 들어 화소 전압을 계산한 그래프이다.

<68>

도 3에 도시된 바와 같이, 6 V의 데이터 전압을 인가하는 경우 제1 부화소 전극의 화소 전압은 9V가 되어 3V 상

승하고, 제2 부화소 전극의 화소 전압은 4.5V가 되어 1.5V 하강하는 것을 알 수 있다. 따라서 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압 사이의 충분한 전압 차이를 확보할 수 있다. 또한 제2 부화소 전극의 화소 전압의 경우 데이터 전압에 비하여 지나치게 감소되는지 않으므로 휘도 감소를 억제할 수 있다.

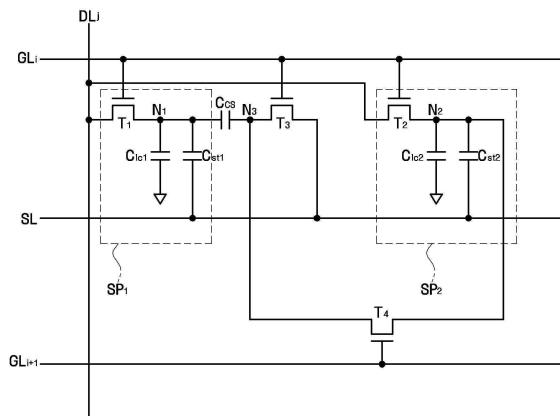

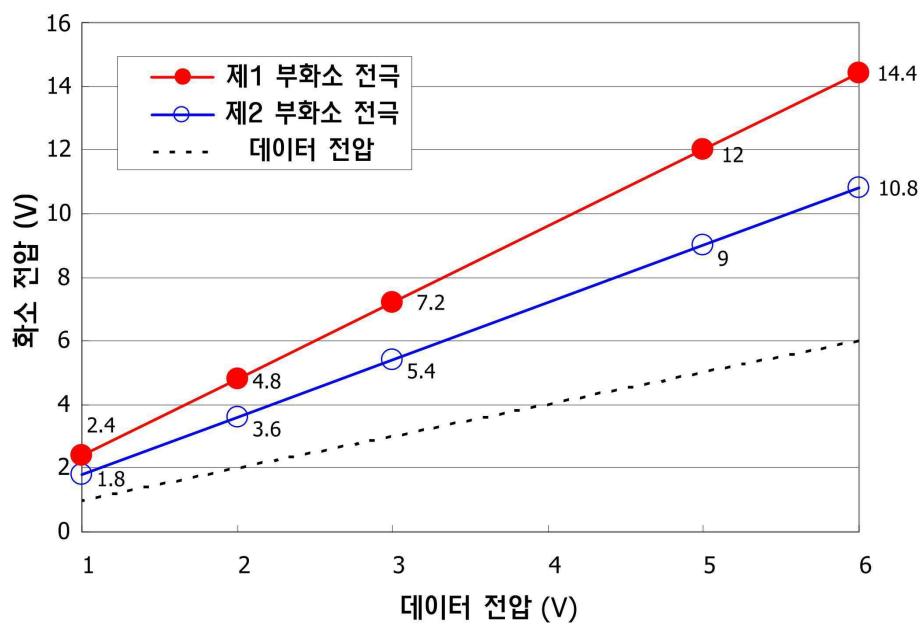

<69> 이하 도 4 및 도 5를 참조하여 본 발명의 제2 실시예에 따른 액정 표시 장치를 설명한다. 여기서 도 4는 본 발명의 제2 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다. 도 5는 본 발명의 제2 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그래프이다. 설명의 편의상, 제1 실시예의 도면(도 1 내지 도 3)에 나타낸 각 부재와 동일 기능을 갖는 부재는 동일 부호로 나타내고, 따라서 그 설명은 생략하며, 이하 차이점을 위주로 설명한다.

<70> 도 4를 참조하면, 제3 스위칭 소자(T3)는 제i 게이트선(GLi)에 접속된 제어 단자와, 전하 분배 커패시터(Ccs)를 사이에 두고 제1 스위칭 소자(T1)의 출력 단자와 접속된 출력 단자와, 스토리지선(SL)에 접속된 입력 단자를 포함한다. 더욱 구체적으로, 제3 스위칭 소자(T3)의 입력 단자는 보조 커패시터(C3)를 사이에 두고 스토리지선(SL)과 접속되어 있다. 액정 표시 장치의 제조 공정에 있어서 제3 스위칭 소자(T3)의 입력 단자와 스토리지선(SL)가 서로 다른 층에 형성되어서 이들이 직접 접속하기 어려울 때 상기 보조 커패시터(C3)를 이용하여 서로 커플링 될 수 있다.

<71> 이하 전하량 보전 법칙을 이용하여 제1 부화소 전극과 제2 부화소 전극의 화소 전압을 구체적으로 살펴본다. 여기서 제4 노드(N4)는 제3 스위칭 소자(T3)의 입력 단자와 보조 커패시터(C3) 사이의 노드를 말한다. 또한 설명의 편의를 위하여 공통 전압(Vcom)을 0 V로 정의하고, 데이터 전압(Vd)을 공통 전압(Vcom)에 대한 상대적인 전압이라고 한다. 또한 보조 커패시터(C3)의 커패시턴스를 Cc이라 한다.

<72> (n-1)번째 프레임에서 제1 노드(N1), 제2 노드(N2), 제3 노드(N3) 및 제4 노드(N4)에서의 전압을 V1, V2, V3 및 V4라고 할 때,  $V_2 = V_3$ 이다. 제1 액정 커패시터(C1c1)와 제1 스토리지 커패시터(Cst1)의 전하량 Qh와, 제2 액정 커패시터(C1c2)와 제2 스토리지 커패시터(Cst2)의 전하량 Ql과, 전하 분배 커패시터(Ccs)의 전하량 Qb과, 보조 커패시터(C3)의 전하량 Qc는 다음과 같다.

## 수학식 6

$$<73> Q_h = C_h \times V_1$$

$$<74> Q_l = C_l \times V_2$$

$$<75> Q_b = C_b \times (V_1 - V_3) = C_b \times (V_1 - V_2)$$

$$<76> Q_c = C_c \times V_4$$

<77> n번째 프레임에서 제i 게이트선(GLi)에 게이트 온 전압(Von)이 인가되면, 제1 스위칭 소자(T1) 및 제2 스위칭 소자(T2)가 터온되면서 제1 노드(N1) 및 제2 노드(N2)에 데이터 전압(Vd)이 인가된다. 또한 제3 스위칭 소자(T3)가 터온되면서 제3 노드(N3)와 제4 노드(N4)가 연결된다. 이 때 제1 노드(N1), 제2 노드(N2), 제3 노드(N3) 및 제4 노드(N4)에서의 각 전압을 V1', V2', V3', V4'이라 할 때,  $V_1' = V_2' = V_d$ 이고  $V_3' = V_4'$ 이다.

<78> 이 때 제1 액정 커패시터(C1c1)와 제1 스토리지 커패시터(Cst1)의 전하량 Qh'과, 제2 액정 커패시터(C1c2)와 제2 스토리지 커패시터(Cst2)의 전하량 Ql'과, 전하 분배 커패시터(Ccs)의 전하량 Qb'과, 보조 커패시터(C3)의 전하량 Qc'는 다음과 같다.

## 수학식 7

$$<79> Q_h' = C_h \times V_1' = C_h \times V_d$$

$$<80> Q_l' = C_l \times V_2' = C_l \times V_d$$

$$<81> Q_b' = C_b \times (V_1' - V_3') = C_b \times (V_d - V_3')$$

$$<82> Q_c' = C_c \times V_4' = C_c \times V_3'$$

<83> 제3 노드(N3) 및 제4 노드(N4)에 연결된 커패시터들의 총 전하량은 보존되므로 다음의 관계식이 성립한다.

## 수학식 8

<84>  $Qc - Qb = Qc' - Qb'$

<85> 이어서 제*i* 게이트선(GL*i*)에 게이트 오프 전압(V<sub>off</sub>)이 인가되고 제*i*+1 게이트선(GL*i*+1)에 게이트 온 전압(V<sub>on</sub>)이 인가되면, 제1 스위칭 소자(T1), 제2 스위칭 소자(T2) 및 제3 스위칭 소자(T3)는 턴오프되고 제4 스위칭 소자(T4)가 턴온된다.

<86> 이 때 제1 노드(N1), 제2 노드(N2), 제3 노드(N3) 및 제4 노드(N4)에서의 각 전압을 V1", V2", V3" 및 V4"이라 할 때, V2"=V3"이다. 제1 액정 커패시터(Cl<sub>c1</sub>)와 제1 스토리지 커패시터(Cst<sub>1</sub>)의 전하량 Qh"와, 제2 액정 커패시터(Cl<sub>c2</sub>)와 제2 스토리지 커패시터(Cst<sub>2</sub>)의 전하량 Q1"과, 전하 분배 커패시터(Ccs)의 전하량 Qb"과, 보조 커패시터(C3)의 전하량 Qc"는 다음과 같다.

### 수학식 9

<87>  $Qh'' = Ch \times V1''$

<88>  $Q1'' = Cl \times V2''$

<89>  $Qb'' = Cb \times (V1'' - V3'') = Cb \times (V1'' - V2'')$

<90>  $Qc'' = Cc \times V4''$

<91> 제1 노드(N1)에 연결된 커패시터들의 총 전하량은 보존되므로 다음의 관계식이 성립한다.

### 수학식 10

<92>  $Qh' + Qb' = Qh'' + Qb''$

<93> 제3 노드(N3)에 연결된 커패시터들의 총 전하량은 보존되므로 다음의 관계식이 성립한다.

### 수학식 11

<94>  $Q1' + Qc' - Qb' = Q1'' + Qc'' - Qb''$

<95> 수학식 11 내지 수학식 25의 관계를 정리하면 다음과 같이 제1 노드(N1) 및 제2 노드(N2)에서의 전압 V1" 및 V2"을 얻을 수 있다.

### 수학식 12

$$V1'' = Vd + (Vd - V0) \frac{Cl \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl}$$

$$V2'' = Vd - (Vd - V0) \frac{Ch \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl}$$

<96>

<97> 여기서,

$$V0 = \frac{(Cb \cdot Vd + Cc \cdot V4) - Cb(V1 - V2)}{Cb + Cc}$$

<98> 이다.

<99> 따라서 데이터 전압(Vd)이 공통 전압(V<sub>com</sub>)보다 큰 양극성 전압인 경우, 제1 부화소(SP1)의 화소 전압(V1")은 데이터 전압(Vd)보다 상승하고 제2 부화소(SP2)의 화소 전압(V2")은 데이터 전압(Vd)보다 하강한다. 데이터 전압(Vd)이 공통 전압(V<sub>com</sub>)보다 작은 음극성 전압인 경우는 이와 반대가 된다. 따라서 제1 부화소(SP1)의 화소 전압(V1")의 절대값이 제2 부화소(SP2)의 화소 전압(V2")의 절대값보다 항상 크게 된다.

<100> 이와 같이 하나의 화소 내에 위치하는 제1 부화소(SP1) 및 제2 부화소(SP2)의 화소 전압(V1", V2")이 서로 다른 값을 가지게 되는 경우 측면 시인성을 향상시킬 수 있다.

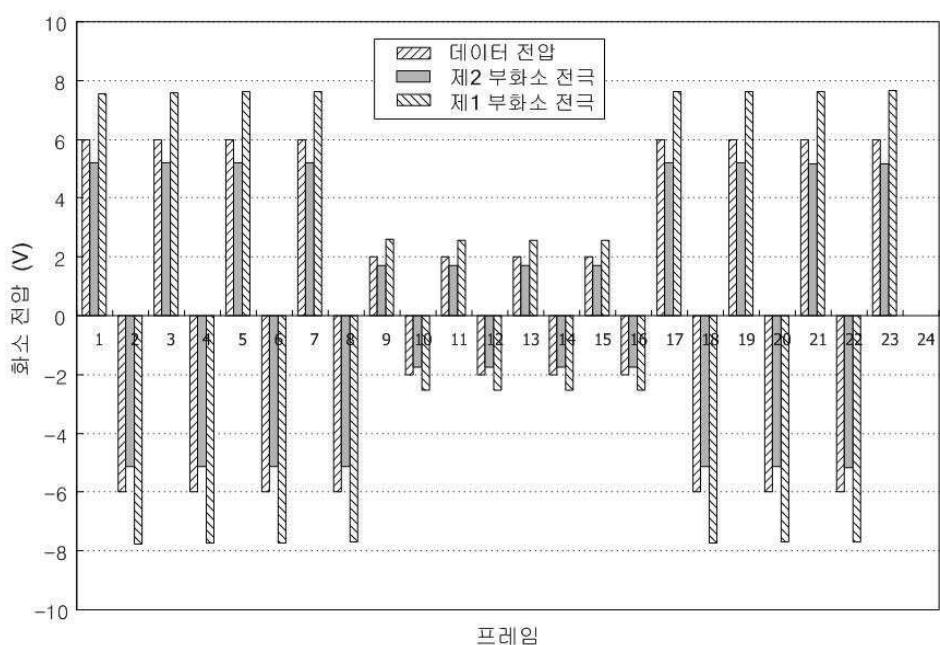

- <101> 도 5은 프레임마다 데이터 전압에 대하여 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압의 변화를 나타낸 그래프이다. 본 그래프는 Cl : Ch : Cb : Cc = 2 : 1 : 0.8 : 2이고 데이터 전압이 6V에서 2V로, 다시 6V로 변하는 경우를 예로 들어 화소 전압을 계산한 그래프이다.

- <102> 도 5에 도시된 바와 같이, 제1 부화소 전극의 화소 전압은 데이터 전압보다 상승하고, 제2 부화소 전극의 화소 전압은 데이터 전압보다 하강하며, 따라서 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압 사이의 충분한 전압 차이를 확보할 수 있다. 또한 제2 부화소 전극의 화소 전압의 경우 데이터 전압에 비하여 지나치게 감소되는지 않으므로 휘도 감소를 억제할 수 있다.

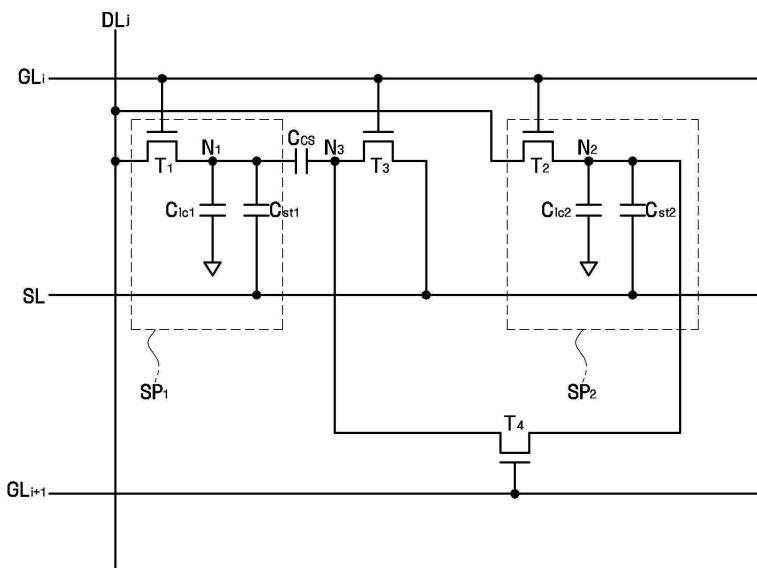

- <103> 이하 도 6 내지 도 8을 참조하여 본 발명의 제3 실시예에 따른 액정 표시 장치를 설명한다. 여기서 도 6은 본 발명의 제3 실시예에 따른 액정 표시 장치의 블록도이다. 도 7은 본 발명의 제3 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다. 도 8은 본 발명의 제3 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그래프이다. 설명의 편의상, 제1 실시예의 도면(도 1 내지 도 3)에 나타낸 각 부재와 동일 기능을 갖는 부재는 동일 부호로 나타내고, 따라서 그 설명은 생략하며, 이하 차이점을 위주로 설명한다.

- <104> 도 6을 참조하면, 액정 패널 어셈블리(300)는 등가 회로로 볼 때 다수의 표시 신호선과 이에 연결되어 있으며 대략 행렬의 형태로 배열된 다수의 화소(PX)를 포함한다. 여기서, 액정 패널 어셈블리(300)는 서로 마주 보는 하부 표시판, 상부 표시판 및 이들 사이에 개재된 액정층을 포함한다.

- <105> 표시 신호선은 하부 표시판에 구비되어 있으며, 게이트 신호를 전달하는 다수의 게이트선(G1-Gn)과, 데이터 신호를 전달하는 데이터선(DA1-DAm)과, 전하 분배 신호를 전달하는 전하 분배용 배선(DB1-DBm)을 포함한다. 게이트선(G1-Gn)은 대략 행 방향으로 뻗어 있으며 서로가 거의 평행하고, 데이터선(DA1-DAm)은 대략 열 방향으로 뻗어 있으며 서로가 거의 평행하고, 전하 분배용 배선(DB1-DBm)은 데이터선(DB1-DBm)과 실질적으로 평행하게 뻗어 있다. 게이트선(G1-Gn)은 게이트 전압을 전달하고, 데이터선(DA1-DAm)은 데이터 전압을 전달하고, 전하 분배용 배선(DB1-DBm)은 전하 분배를 위한 스위칭 소자에 전하 분배용 전압을 전달한다.

- <106> 도 7을 참조하면, 본 발명의 제3 실시예에 따른 액정 표시 장치의 경우 제1 실시예와 비교하여 각 화소마다 데이터선(DAj)과 실질적으로 평행하게 전하 분배용 배선(DBj)이 형성되어 있다. 또한 제3 스위칭 소자(T3)는 제i 게이트선(GLi)에 접속된 제어 단자와, 전하 분배 커패시터(Ccs)를 사이에 두고 제1 스위칭 소자(T1)의 출력 단자와 접속된 출력 단자와, 전하 분배용 배선(DBj)에 접속된 입력 단자를 포함한다.

- <107> 데이터선(DAj)에 공통 전압(Vcom)보다 큰 양극성 전압을 가지는 데이터 전압, 예를 들어  $+|Vp|$ 이 인가되고 전하 분배용 배선(DBj)에 공통 전압(Vcom)보다 작은 음극성 전압을 가지는 전하 분배용 전압, 예를 들어  $-|Vm|$ 이 인가되는 경우를 생각해 보자. 여기서 양극성 전압은 공통 전압(Vcom)보다 높은 전압을 말하고, 음극성 전압은 공통 전압(Vcom)보다 낮은 전압을 말한다.

- <108> 제1 실시예의 경우 제3 스위칭 소자(T3)의 입력 단자에 공통 전압(Vcom)이 인가되지만(이하 공통 전압(Vcom)을 0V라 가정한다), 본 실시예의 경우 제3 스위칭 소자(T3)의 입력 단자에는 공통 전압(Vcom)보다 낮은 전하 분배용 전압, 즉  $-|Vm|$ 이 인가된다. 따라서 제i 게이트선(GLi)에 게이트 온 전압(Von)이 인가되고 제3 스위칭 소자(T3)가 터온되면, 전하 분배 커패시터(Ccs)에는  $|Vp| + |Vm|$ 의 전압이 충전된다. 따라서 제1 부화소(SP1)와 제2 부화소(SP2)에 대하여 전하 분배가 더 효과적으로 일어난다. 제1 실시예에서 언급한 계산과정을 거치면, 결과적으로 제1 부화소 전극 및 제2 부화소 전극에 충전된 화소 전압, 즉 제1 노드(N1)의 전압 V1과 제2 노드(N2)의 전압 V2는 다음과 같은 수식을 만족한다.

### 수학식 13

$$V1 = |Vp| + (|Vp| + |Vm|) \frac{Cl \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl} + 2|Vm| \frac{Cb \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl}$$

$$V2 = |Vp| - (|Vp| - |Vm|) \frac{Ch \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl} + 2|Vm| \frac{Cb \cdot Cb}{Cl \cdot Ch + Ch \cdot Cb + Cb \cdot Cl}$$

- <109> 수학식 13으로부터 제1 부화소(SP1)의 화소 전압(V1)은 데이터 전압,  $|Vp|$ 보다 높아진다. 제2 부화소(SP2)의 화소 전압(V2)은 화소 전압(V1)보다 낮아진다.

<111> 나아가 다음의 수식을 만족하는 경우 제1 부화소(SP1)의 화소 전압(V1)뿐만 아니라 제2 부화소(SP2)의 화소 전압(V2)도 데이터 전압  $|V_p|$ 보다 높아질 수도 있다.

### 수학식 14

$$\frac{|V_m|}{|V_p|} \geq \frac{Ch}{2Cb + Ch}$$

<112>

<113> 수학식 14에 나타난 바와 같이,  $|V_m|$ 이  $|V_p|$ 보다 매우 작지 않는 한, 거의 대부분의 경우에 화소 전압(V1) 및 화소 전압(V2)이 모두 승압되는 효과가 있다. 이러한 경우 데이터 구동부로부터 낮은 데이터 전압이 출력되더라도 제1 부화소(SP1) 및 제2 부화소(SP2)에 서로 다른 2개의 높은 화소 전압을 발생시킬 수 있다. 일반적으로 수직전계를 이용한 VA(vertical alignment) 모드의 액정 표시 장치에서는 높은 데이터 전압을 필요로 하는데, 본 실시예에서와 같이 전하 분배용 배선(DBj)을 통하여 적절한 전하 분배용 전압을 제3 스위칭 소자(T3)에 인가하는 경우 낮은 데이터 전압으로도 높은 화소 전압을 얻을 수 있다. 여기서 전하 분배용 전압의 극성은 데이터 전압의 극성과 반대인 것이 바람직하다. 예를 들어 데이터 전압이 양극성 전압인 경우 전하 분배용 전압은 음극성 전압이고, 데이터 전압이 음극성인 경우 전하 분배용 전압은 양극성인 것이 바람직하다.

<114> 이상에서 설명한 동작은 데이터 전압이 공통 전압(Vcom)보다 작은 음극성 전압인 경우도 동일하게 적용될 수 있다.

<115> 도 8은 데이터선을 통하여 인가되는 데이터 전압에 대하여 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압의 변화를 나타낸 그래프이다. 본 그래프는  $Cl : Ch : Cb = 2 : 1 : 2$ 인 경우를 예로 들어 화소 전압을 계산한 그래프이다.

<116> 도 8에 도시된 바와 같이, 6 V의 데이터 전압을 인가하는 경우 제1 부화소 전극의 화소 전압은 14.4V로 상승하고, 제2 부화소 전극의 화소 전압은 10.8V로 상승하는 것을 알 수 있다. 따라서 제1 부화소 전극의 화소 전압과 제2 부화소 전극의 화소 전압 사이의 충분한 전압 차이를 확보하면서, 동시에 제1 부화소 전극의 화소 전압 및 제2 부화소 전극의 화소 전압을 승압시킬 수 있다. 따라서 휘도 감소를 방지할 수 있다.

<117> 이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

### 도면의 간단한 설명

<118> 도 1은 본 발명의 제1 실시예에 따른 액정 표시 장치의 블록도이다.

<119> 도 2는 본 발명의 제1 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다.

<120> 도 3은 본 발명의 제1 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그래프이다.

<121> 도 4는 본 발명의 제2 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다.

<122> 도 5는 본 발명의 제2 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그래프이다.

<123> 도 6은 본 발명의 제3 실시예에 따른 액정 표시 장치의 블록도이다.

<124> 도 7은 본 발명의 제3 실시예에 따른 액정 표시 장치의 한 화소를 나타내는 회로도이다.

<125> 도 8은 본 발명의 제3 실시예에 따른 액정 표시 장치에 있어서 데이터 전압에 따른 화소 전압을 나타낸 그래프이다.

<126> (도면의 주요부분에 대한 부호의 설명)

<127> 300: 액정 패널 어셈블리

400: 게이트 구동부

|       |                  |               |

|-------|------------------|---------------|

| <128> | 500: 데이터 구동부     | 600: 신호 제어부   |

| <129> | 800: 계조 전압 생성부   | DLj: 데이터선     |

| <130> | GLi, GLi+1: 케이트선 | SLi: 스토리지선    |

| <131> | SP1: 제1 부화소      | SP2: 제2 부화소   |

| <132> | T1: 제1 스위칭 소자    | T2: 제2 스위칭 소자 |

| <133> | T3: 제3 스위칭 소자    | T4: 제4 스위칭 소자 |

## 도면

도면1

## 도면2

## 도면3

## 도면4

## 도면5

도면6

도면7

도면8

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">KR1020090054300A</a>                                                                                          | 公开(公告)日 | 2009-05-29 |

| 申请号            | KR1020070121092                                                                                                           | 申请日     | 2007-11-26 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                                                                                 |         |            |

| [标]发明人         | YANG YOUNG CHOL<br>양영철<br>LU JIANGANG<br>루지안강<br>LEE SEUNG HOON<br>이승훈                                                    |         |            |

| 发明人            | 양영철<br>루지안강<br>이승훈                                                                                                        |         |            |

| IPC分类号         | G02F1/133 G02F1/1343                                                                                                      |         |            |

| CPC分类号         | G02F2001/134345 G09G2300/0443 G09G2300/0842 G09G2300/0814 G09G2320/068 G09G3/3659<br>G02F1/1393 G02F1/13624 G09G2300/0447 |         |            |

| 其他公开文献         | KR101371604B1                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                 |         |            |

**摘要(译)**

提供一种能够在提高横向可视性的同时防止亮度降低的液晶显示装置。液晶显示装置包括并布置的第一和第二栅极线，依次传输栅极电压，与第一和第二栅极线交叉的数据线以及传输数据电压，第一开关元件连接到第一栅极线，数据线和第一子像素电极，第二开关元件连接到第一栅极线，数据线和第二子电路连接到像素电极的第二开关元件，经由电荷共享电容器连接到第一子像素电极的第三开关元件，以及连接到第二栅极线和第二子像素电极的第三开关元件，第四开关元件连接在第一子像素电极和第一子像素电极之间。