(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년12월29일

(11) 등록번호 10-0934524

(24) 등록일자 2009년12월21일

(51) Int. Cl.

*G02F 1/1343* (2006.01)

(21) 출원번호 10-2007-0080458

(22) 출원일자 2007년08월10일

심사청구일자 2007년08월10일

(65) 공개번호 10-2008-0014679

(43) 공개일자 2008년02월14일

(30) 우선권주장

JP-P-2006-00219322 2006년08월11일 일본(JP)

JP-P-2007-00065078 2007년03월09일 일본(JP)

(56) 선행기술조사문헌

KR1020020007483 A\*

KR1020030061352 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

엔이씨 엘씨디 테크놀로지스, 엘티디.

일본 가나가와쿄 가와사끼시 나카하라구 시모누마 베 1753

(72) 발명자

콘노 타카유키

일본국 가나가와쿄 가와사끼시 나카하라구 시모누마베 1753엔이씨 엘씨디 테크놀로지스. 엘티디. 내

니시다 신이치

일본국 가나가와쿄 가와사끼시 나카하라구 시모누마베 1753엔이씨 엘씨디 테크놀로지스. 엘티디. 내

(뒷면에 계속)

(74) 대리인

최달용

전체 청구항 수 : 총 6 항

심사관 : 윤성주

(54) 액티브 매트릭스 액정 디스플레이 장치

**(57) 요약**

기판 및 액정층을 포함하는 액티브 매트릭스 액정 디스플레이 장치에 대해 설명한다. 상기 기판은: 주사 신호 배선; 공통 신호 배선; 상기 배선들과 교차하는 비디오 신호 배선; 및 상기 주사 신호 배선 및 상기 비디오 신호 배선으로 둘러싸인 픽셀을 포함한다. 각 픽셀은: 박막 트랜지스터; 상기 비디오 신호 배선을 구비한 층의 소스 전극; 상기 소스 전극과 접속된 픽셀 전극; 및 상기 공통 신호 배선과 접속된 공통 전극을 포함한다. 상기 소스 전극은 상기 주사 신호 배선과 중첩하는 제1의 부분과 상기 비디오 신호 배선 사이의 중앙부 부근에 위치한 픽셀 전극과 접속하는 제2의 부분을 포함한다. 상기 액정층의 분자축은 상기 픽셀 전극과 상기 공통 전극 사이에 인가된 전계하에서 회전한다.

**대 표 도** - 도1a

(72) 발명자

스즈키 테루아키

일본국 가나가와깨 가와사끼시 나카하라구 시모누

마베 1753엔이씨 엘씨디 테크놀로지스. 엘티디. 내

---

노가미 유스케

일본국 가나가와깨 가와사끼시 나카하라구 시모누

마베 1753엔이씨 엘씨디 테크놀로지스. 엘티디. 내

**특허청구의 범위**

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

액티브 매트릭스 액정 디스플레이 장치에 있어서,

주사 신호 배선과,

상기 주사 신호 배선에 평행한 공통 신호 배선과,

상기 주사 신호 배선 및 상기 공통 신호 배선과 교차하는 영상 신호 배선과,

상기 주사 신호 배선 및 상기 영상 신호 배선에 의해 둘러싸인 제 1의 영역에 마련되고, 박막 트랜지스터와, 상기 영상 신호 배선과 같은 층에 형성되는 상기 박막 트랜지스터의 소스 전극과, 상기 소스 전극에 접속되는 픽셀 전극과, 상기 공통 신호 배선에 접속되는 공통 전극을 갖는 픽셀을 포함하는 제 1의 기판;

상기 제 1의 기판에 대향하는 제 2의 기판; 및

상기 제 1의 기판과 상기 제 2의 기판에 끼워 지지되는 액정층을 포함하고,

상기 픽셀 전극과 상기 공통 전극 사이에 인가되고, 상기 제 1의 기판의 표면에 평행한 전계에 의해, 상기 액정 층의 분자축이 상기 제 1의 기판에 평행한 면 내에서 회전함에 의해 표시가 행해지고,

상기 주사 신호 배선과 상기 공통 신호 배선은 같은 층에 형성되고, 제 1의 절연막을 통하여 상기 영상 신호 배선보다 하층에 형성되고,

상기 픽셀 전극과 상기 공통 전극은 같은 층에 형성되고, 제 2의 절연막을 통하여 상기 영상 신호 배선보다 상층에 형성되고,

상기 픽셀 전극은, 전극의 단부에서 공통 신호 배선과 오버랩하고,

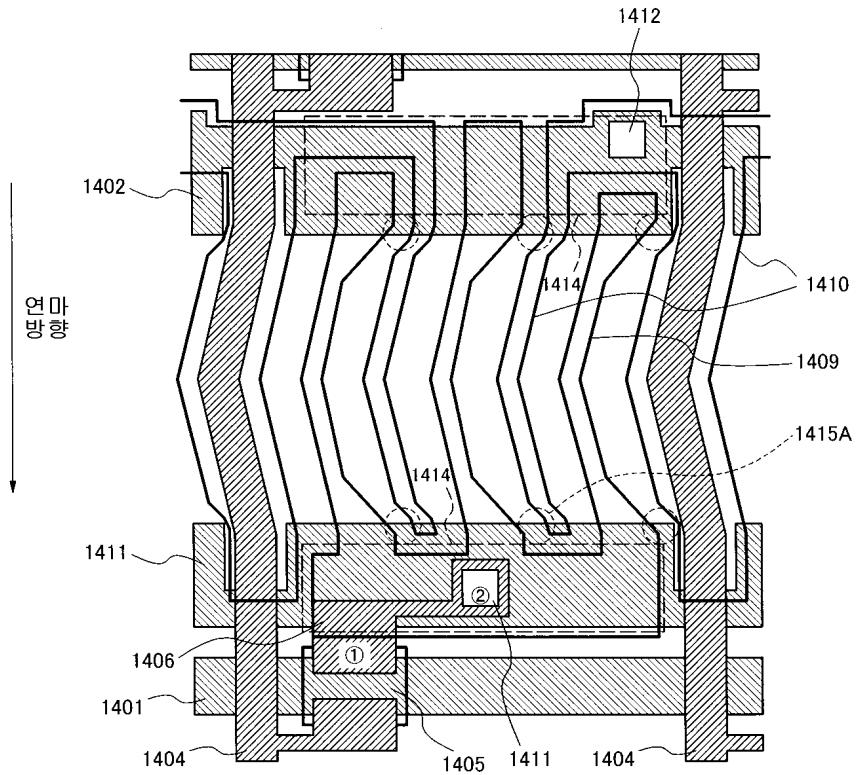

상기 픽셀 전극이 상기 공통 신호 배선과 오버랩하는 개소에서,

상기 개소에 인접하는 표시 영역에서, 상기 픽셀 전극과 이에 대향하는 공통 전극 사이의 전계에 의해 액정 분자가 회전하는 방향을 제 1의 회전 방향으로 할 때,

상기 픽셀 전극의 에지 중, 공통 신호 배선의 표시부측의 에지와의 사이에 형성되는 전계에 의해, 상기 액정 분자가 상기 제 1의 회전 방향과 다른 회전 방향으로 회전하는 층에서, 상기 공통 전극에 의해 끼여진 전극 간격으로 대향하도록 픽셀 전극의 폭이 벌어져 있고,

상기 픽셀 전극의 전극 폭이 벌어진 부분의 표시 영역측의 에지는, 상기 공통 신호 배선의 표시 영역측의 에지와 평행하게 형성된 것을 특징으로 하는 액티브 매트릭스 액정 디스플레이 장치.

청구항 22

제 21항에 있어서,

상기 픽셀 전극의 전극 폭이 벌어진 부분의 픽셀 전극의 에지는 대향하는 공통 전극의 에지와 평행한 것을 특징

으로 하는 액티브 매트릭스 액정 디스플레이 장치.

### 청구항 23

제 21항에 있어서,

상기 픽셀 전극의 단의 폭이 큰 영역의 상기 표시 영역측의 에지는, 한 쌍의 상기 공통 신호 배선의 상기 표시 영역측에 대해, 상기 한 쌍의 공통 신호 배선의  $1\mu m$  내측부터  $4\mu m$  외측까지의 어느 하나의 위치에 있는 것을 특징으로 하는 액티브 매트릭스 액정 디스플레이 장치.

### 청구항 24

제 21항에 있어서,

상기 픽셀 전극의 단의 폭이 크게 되는 측에 인접하는 상기 공통 전극의 에지는, 상기 픽셀 전극의 형상에 맞추어서 굴곡하는 것을 특징으로 하는 액티브 매트릭스 액정 디스플레이 장치.

### 청구항 25

제 24항에 있어서,

상기 픽셀 전극의 단에서, 상기 픽셀 전극의 에지에 맞추어서 에지를 굴곡한 상기 공통 전극이 크랭크의 형상으로 굴곡하는 것을 특징으로 하는 액티브 매트릭스 액정 디스플레이 장치.

### 청구항 26

제 21항에 있어서,

한 쌍의 상기 공통 신호 배선의 상기 표시 영역측의 에지에서, 상기 픽셀의 상기 표시 영역의 경계를 정의하는 부위는 직선 형상을 포함하는 것을 특징으로 하는 액티브 매트릭스 액정 디스플레이 장치.

### 청구항 27

삭제

## 명세서

### 발명의 상세한 설명

#### 기술 분야

<1> 본 발명은 일본 출원 제2006-219322호(2006.08.11) 및 일본 출원 제2007-060758호(2007.03.09)의 우선권 주장을 특허출원이다.

<2> 본 발명은 액정 디스플레이 장치(LCD), 특히, 높은 개구율 및 높은 콘트라스트의 IPS(In-Plane Switching) 모드에서의 액티브 매트릭스 LCD 장치에 관한 것이다.

#### 배경 기술

<3> 높은 콘트라스트의 TN(Twisted Nematic) 시스템의 디스플레이가 널리 사용되고 있다. 그러나, 액정(LC) 분자의 분자축이 수직 전계에 의해 상승되므로, TN 시스템의 디스플레이 장치는 시야각 의존도가 매우 높다. 최근, 대형 모니터 TV에 대한 요구가 높아지면서, IPS 모드가 보급되고 있다. IPS 모드의 디스플레이 장치에서, LC 분자의 분자축은 기판에 평행인 면에서 수평 전계에 의해 회전하여 디스플레이를 수행한다. IPS 모드가 분자축의 상승각 이상의 시야각 의존도를 포함하지 않으므로, 그 시야각 특성은 TN 시스템에서보다 더 양호하다.

<4> IPS 모드의 디스플레이 장치에서, 픽셀 전극 및 공통 전극은 빗살 형상으로 배열되고, 수평 전계가 픽셀 전극과 공통 전극 사이에 인가된다. 상기와 같은 이유로, 디스플레이 영역에 대한 전극 영역의 비율이 크다. 즉, IPS 모드의 디스플레이 장치는 낮은 개구율을 갖는다. IPS 모드의 디스플레이 장치가 수평 전계에 의해 구동되므로, 디스플레이 영역에서 LC 분자는 비디오 신호 배선으로부터 누출된 전계에 의해 영향을 받기 쉽고, 수직 크로스 토크(vertical cross talk)가 쉽게 발생한다.

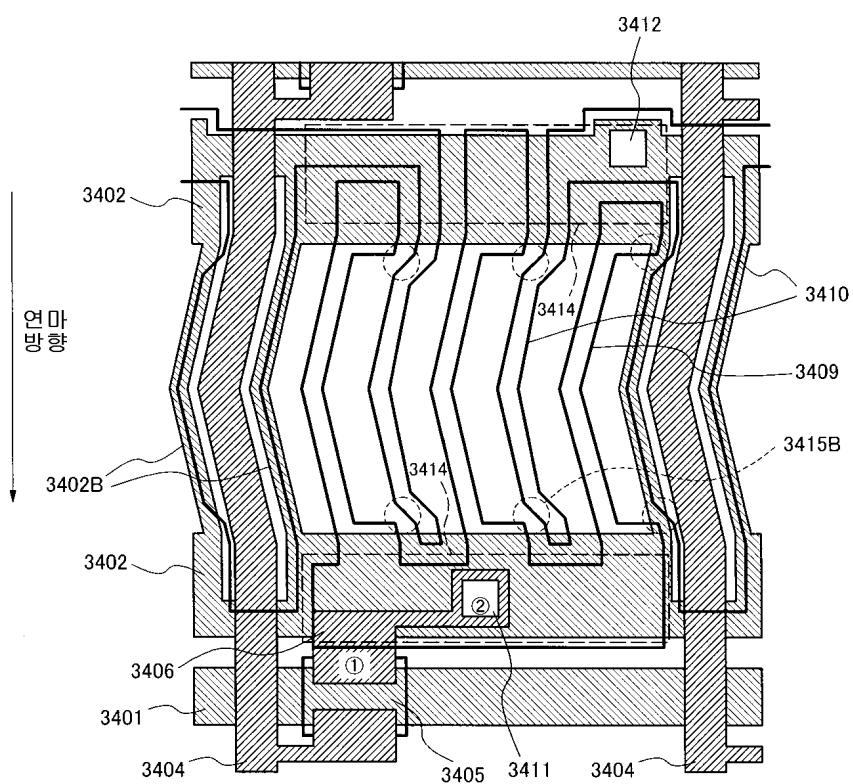

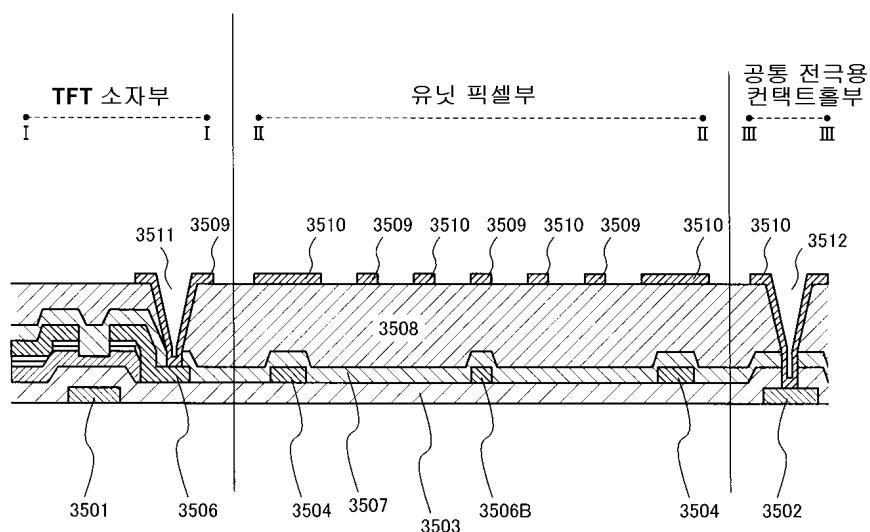

- <5> 예를 들어, 이러한 문제에 대한 해결책이 일본 공개 특허 출원 제2002-323706호(특허문헌1)에 기재되어 있다. 도 35a는 하나의 픽셀 평면도를 도시하고, 도 35b는 I-I, II-II, III-III를 따라 취해지는 단면도를 도시한다. 제1의 금속층인 복수의 주사 신호 배선(3501) 및 이와 평행한 두개의 공통 신호 배선(3502)이 기판 상에 형성된다. 제2의 금속층인 복수의 비디오 신호 배선(3504), 박막 트랜지스터(TFT)(3505) 및 소스 전극(3506)이 제1의 절연막상에 형성된다. 소스 전극(3506)은 복수의 픽셀의 양 측에 배치되고, 소스 전극과 같은 층에 배치된 픽셀 보조 배선(3506B)에 접속된다. 각 소스 전극(3506)은 복수의 공통 신호 배선(3502)이 중첩된 영역에서 기억 용량(storage capacitance)을 형성한다. 소스 전극(3506) 및 복수의 공통 신호 배선(3502)이 톱니 형상으로 패턴된다.

- <6> 디스플레이 영역의 에지에서, 톱니형 패턴부는 LC 분자의 역회전을 야기하는 전계를 억제한다. 제2의 절연막(3507)은 복수의 비디오 신호 배선(3504), TFT(3505) 및 소스 전극(3506)상에 형성된다. 투명 절연막인 제3의 절연막(3508)은 제2의 절연막(3507) 상에 형성된다. 투명 전극인 공통 전극(3510) 및 픽셀 전극(3509)이 제3의 절연막(3508) 상에 형성된다. 복수의 비디오 신호 배선(3504)은 제2의 절연막(3507)과 제3의 절연막(3508)을 통해 배선 폭 방향에서 공통 전극(3510)에 의해 완전히 피복된다. 픽셀 전극(3509) 및 공통 전극(3510)은 컨택트홀(3511 및 3512)을 통해 각각 소스 전극(3506) 및 복수의 공통 신호 배선(3502)에 전기적으로 접속된다.

- <7> 빗살형으로 배열된 공통 전극(3510) 및 픽셀 전극(3509)은 투명 전극이다. 따라서, 전극상의 영역은 투과율에 기여한다. 시뮬레이션에 따라, 투명 전극의 투과율에 대한 기여는 유효 개구율을 약 8%증가시킨다. 복수의 비디오 신호 배선 상의 영역이 배선 폭 방향에서 공통 전극에 의해 완전히 피복되므로, 복수의 비디오 신호 배선 부근 영역에 개구를 연장하는 것이 가능하다. 따라서, 디스플레이 영역의 에지에서 액정 분자의 역회전이 방지되고, 광활용에 대한 효율이 최대로 높아진다.

- <8> 복수의 비디오 신호 배선으로부터 누설된 전계가 공통 전극에 의해 차폐된다. 따라서, 수직 크로스 토크이 감소된다. 또한, 복수의 비디오 신호 배선 및 공통 전극 사이에서 부하 용량이 발생하더라도, 부하 용량은 절연막이 낮은 유전율을 갖기 때문에 디스플레이 장치의 구동에 영향을 미치지 않는다.

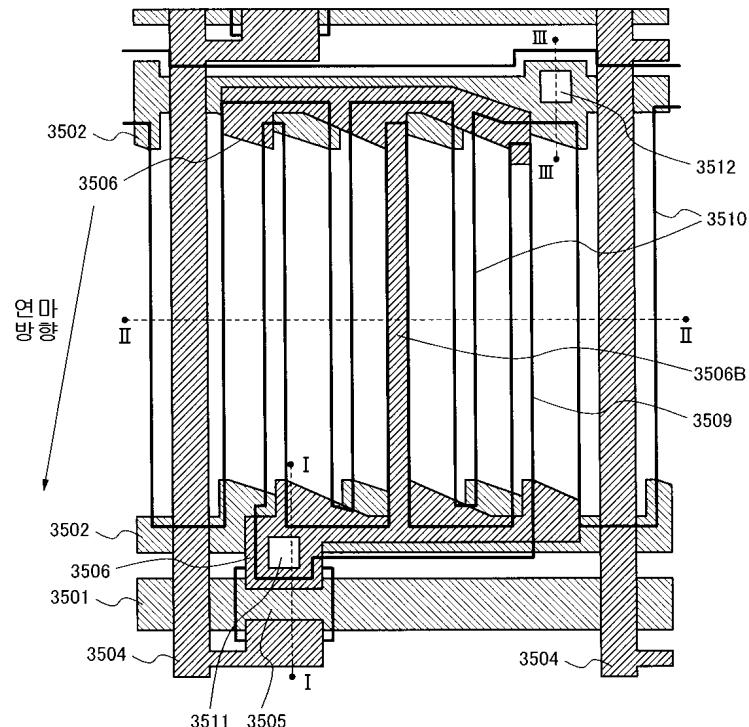

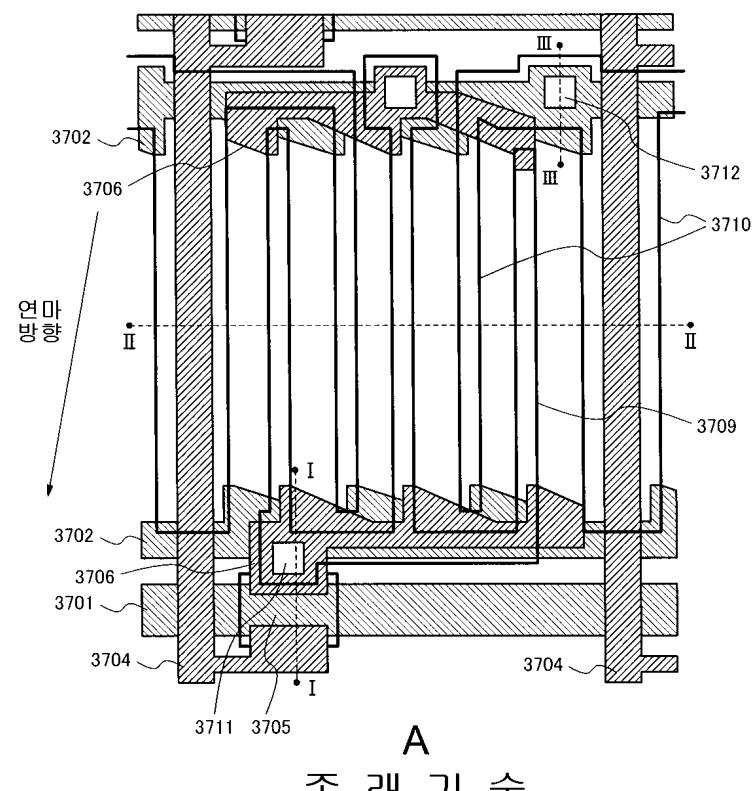

- <9> 상기 문제에 대한 해결책이 일본 공개 특허 출원 2003-207803(특허문헌2)에 기재되어 있다. 도 37a는 하나의 픽셀의 평면도를 도시하고, 도 37b는 I-I, II-II, III-III선을 따라 취해지는 단면도를 도시한다. 제1의 금속층인 복수의 주사 신호 배선(3701) 및 이와 평행한 두개의 공통 신호 배선(3702)이 형성된다. 제1의 절연막(3703)이 복수의 주사 신호 배선(3701) 및 복수의 공통 신호 배선(3702) 상에 형성된다. 제2의 금속층인 복수의 비디오 신호 배선(3704), TFT(3705), 소스 전극(3706)이 제1의 절연막 상에 형성된다. 도 37a에서 소스 전극(3706)이 복수의 픽셀의 양측에 마련되지만, 소스 전극은 같은 층에서 서로 접속되지 않는다. 각 소스 전극(3706)은 컨택트홀(3711, 3713) 및 픽셀 전극(3709)을 통해 전기적으로 접속된다. 각 소스 전극(3706)은 복수의 공통 신호 배선(3702)이 중첩된 영역에서 기억용량을 형성한다.

- <10> 소스 전극(3706) 및 복수의 공통 신호 배선(3702)은 톱니형으로 패턴된다. 디스플레이 영역의 에지에서, 톱니형 패턴은 LC 분자의 역회전을 야기하는 전계를 억제한다. 제2의 절연막(3707)이 복수의 비디오 신호 배선(3704), TFT(3705), 소스전극(3706) 상에 형성된다. 제3의 절연막(3708)은 제2의 절연막(3707)상에 형성된다. 투명 전극인 공통 전극(3710) 및 픽셀 전극(3709)은 제3의 절연막(3708) 상에 형성된다. 복수의 비디오 신호 배선(3704)은 제2의 절연막(3707) 및 제3의 절연막(3708)을 통해 배선 폭 방향에서 공통 전극(3710)에 의해 완전히 피복된다. 픽셀 전극(3709) 및 공통 전극(3710)은 컨택트홀(3711, 3712, 3713)을 통해 각각 복수의 공통 신호 배선(3702) 및 소스 전극(3706)에 전기적으로 접속된다.

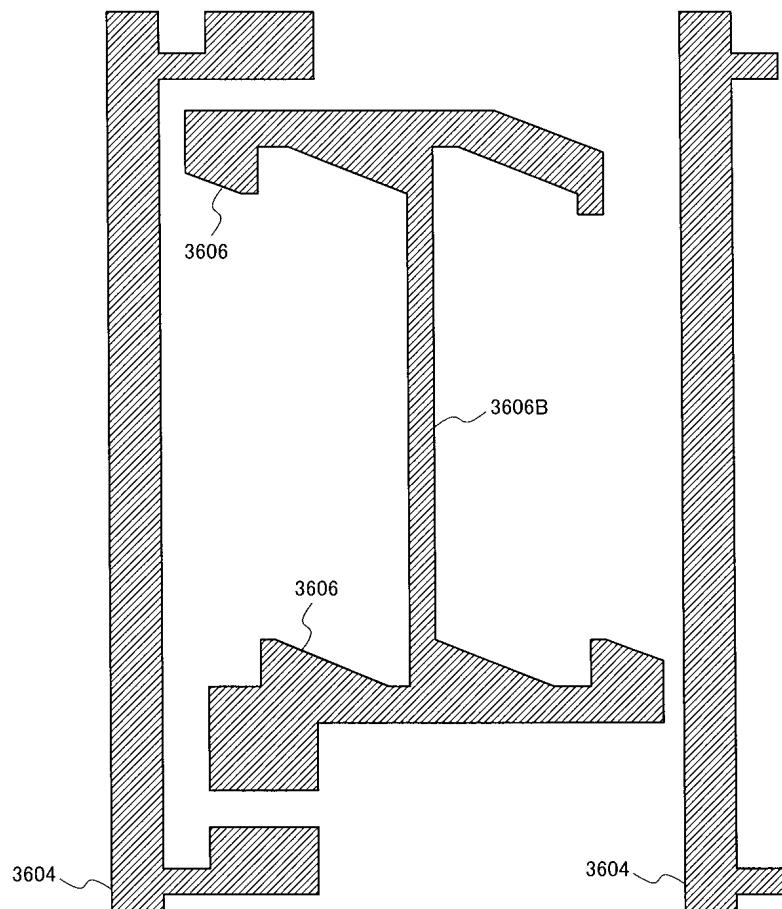

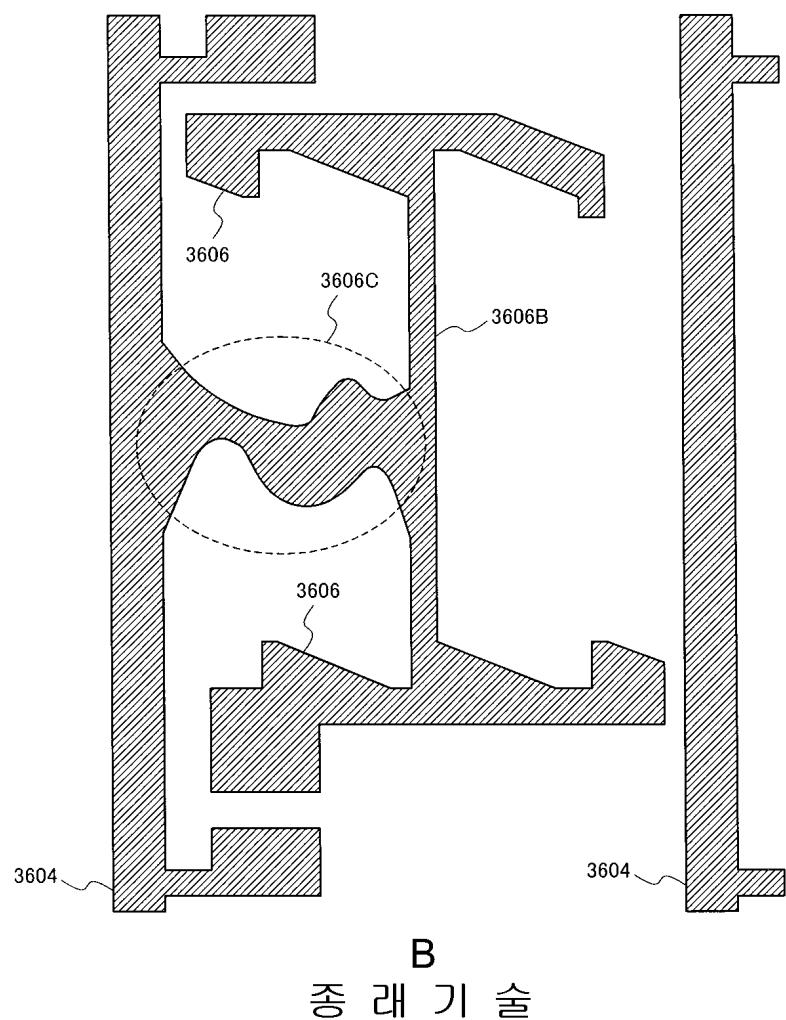

- <11> 최근, 고해상도의 액정 디스플레이 장치(LCD)가 요구된다. 특허문헌1에서는, 고해상도 LCD가 구현되지 않는다. 제2의 금속층이 도36A에 도시되어 있다. 복수의 비디오 신호 배선(3604) 및 픽셀 보조 배선(3606B)이 같은 층에서 가깝게(close) 되면, 외부 입자 등이 그 사이에서 단락을 일으킬 수 있다. 도 36b는 두 배선 이 단락된 예를 나타낸다. 복수의 비디오 신호 배선(3604) 및 픽셀 보조 배선(3606B)이 누설 패스(3606C)를 통해 접속된다. 이 상태에서 비디오 신호 배선(3604)의 전위 변화에 의해 픽셀 전극의 전위가 영향을 받는다. 누설 패스는 어두운 화면에서 밝은 점과 같이 보이고, 밝은 화면에서는 어두운 점과 같이 보인다. 이하, 상기와 같은 점 결함을 '누설 명점(leak bright point)'라고 부른다. 화질에 대한 요구가 최근 증가하고 있고, 특히, 누설 명점이 없는 디스플레이 장치가 강하게 요구되고 있다.

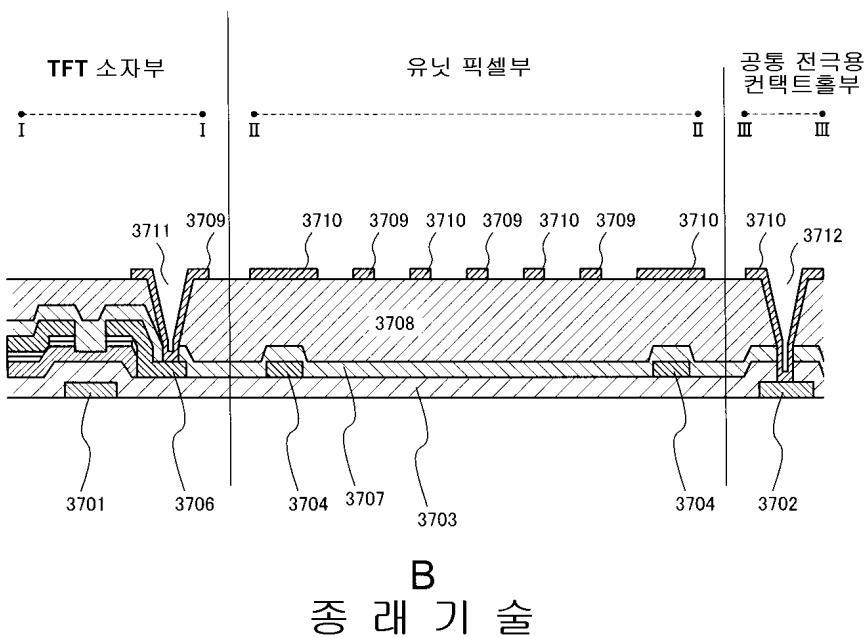

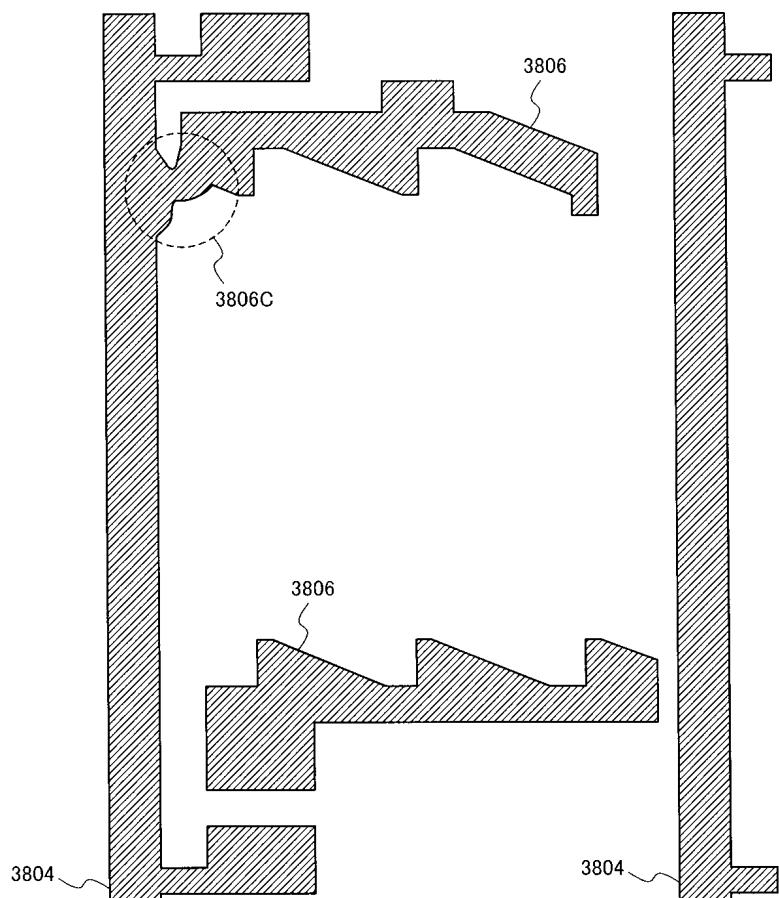

- <12> 특허문헌2에서, 컨택트홀(3713)이 배치되고, 두개의 소스 전극(3706)이 투명 픽셀 전극(3709)을 통해 접속된다. 같은 층에서 픽셀 보조 배선을 제거함으로써, 같은 층에서 복수의 비디오 신호 배선에 대한 단락이 감소된다. 그러나, 이러한 구성에도 불구하고, 소스 전극 및 복수의 비디오 신호 배선은 매우 단락되기 쉽다. 도 38a는 제

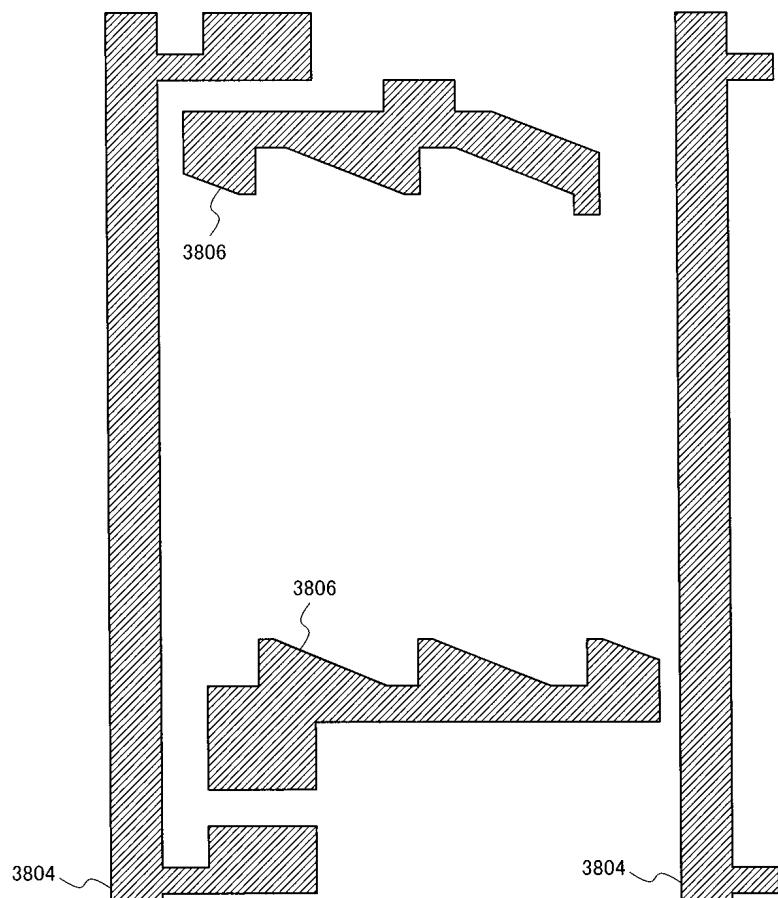

2의 금속층만을 도시한다. 기억 용량이 소스 전극(3806)과 복수의 공통 신호 배선(3802) 사이에 형성되므로, 소스 전극(3806)은 픽셀 보조 배선보다 복수의 비디오 신호 배선(3804)에 더 가깝게 되도록 배치되어야 한다. 도 38b는 같은 층에 형성된 복수의 비디오 신호 배선(3804) 및 소스 전극(3806)이 누설 패스(3806C)를 통해 단락되는 것을 도시한다. 이러한 구성에서, 픽셀 전극의 전위는 복수의 비디오 신호 배선(3804)의 전위 변화에 의해 영향을 받으며, 특허문헌1에서 언급된 누설 명점이 발생한다. 픽셀 보조 배선을 제거함으로써, 특허문헌1에 비해 동일층에서의 단락이 어느 정도 감소된다. 그러나, 실질적인 감소는 이루어지지 않는다.

<13> 종래 기술에서의 디스플레이 장치는 복수의 공통 신호 배선 및 소스 전극 사이의 오버래핑에 의해 기억 용량을 형성한다. 디스플레이 장치에서, 복수의 비디오 신호 배선 및 소스 전극 사이의 단락은 여전히 가능하다. 따라서, 종래 기술에서 실제 수율을 향상시키는 것은 어렵다.

### 발명의 내용

#### 해결 하고자하는 과제

<14> 본 발명의 목적은 복수의 비디오 배선과 소스 전극 사이의 단락을 억제하여 높은 수율을 이룰 수 있는 측면 전계형 액티브 매트릭스 LCD 장치를 제공하는 것이다.

#### 과제 해결手段

<15> 본 발명의 양상에 따르면, 액티브 매트릭스 액정 디스플레이 장치는: 제1의 기판, 제1의 기판과 대면하는 제2의 기판, 및 제1의 기판과 제2의 기판 사이에 삽입된 액정층을 포함한다. 제1의 기판은: 복수의 주사 신호 배선; 복수의 주사 신호 배선을 따라 배치된 복수의 공통 신호 배선; 복수의 주사 신호 배선 및 복수의 공통 신호 배선을 교차하는 복수의 비디오 신호 배선; 및 복수의 픽셀을 포함한다. 복수의 픽셀은 복수의 주사 신호 배선 및 복수의 비디오 신호 배선으로 둘러싸인 제1의 영역에 배치된다. 픽셀은: 박막 트랜지스터; 복수의 비디오 신호 배선이 배치된 층에 형성된 박막 트랜지스터의 소스 전극; 소스 전극에 접속된 픽셀 전극; 및 복수의 공통 신호 배선에 접속된 공통 전극을 포함한다. 소스 전극은 복수의 주사 신호 배선으로 중첩된 제1의 부분 및 픽셀 전극과 접속하는 제2의 부분을 포함한다. 제2의 부분은 복수의 픽셀의 측면에서 비디오 신호 배선 사이의 중앙부 주위에 위치한다. 액정층에서 액정 분자의 분자축은 제1의 기판에 거의 평행하고 픽셀 전극 및 공통 전극 사이에 인가된 전계하에서 제1의 기판에 거의 평행한 면에서 제1의 방향으로 회전한다.

#### 효과

<16> 본 발명의 측면 전계의 액티브 매트릭스 LCD 장치에 따르면, 다음과 같은 효과를 얻을 수 있다.

<17> 첫째로, 소스 전극과 복수의 비디오 신호 배선 사이의 단락이 크게 감소되므로, 고해상도 제품에서 높은 수율을 얻는 것이 가능해진다. 상기 이유는 다음과 같다. 복수의 픽셀의 측면에 배치된 소스 전극 및 픽셀 보조 배선은 복수의 비디오 신호 배선이 배치된 층과 상이한 층에 형성된다. 복수의 비디오 신호 배선과 같은 층 및 픽셀의 다른 층에 배치된 소스 전극의 면적이 감소된다. 동일층에서 패턴의 에지 사이의 거리(패턴의 대면측의 간격)가 커진다.

<18> 두 번째로, 상기 구조에서 LC 분자의 역회전도 방지된다. LC층에서 프린지 전계에 의거한 분자축 회전 방향 및 거기에서 분자축 회전의 소망의 방향은 상층에서 픽셀 전극과 하부층에서 복수의 공통 신호 배선이 교차하는 영역에서 동일하다. 정회전 방향으로 분자축을 회전하는 강력한 전계가 이 영역에서 발생한다. 따라서, 소스 전극이 제거되더라도, 새로운 역회전 방지 구조에 의해 LC 분자의 역회전이 방지된다.

<19> 본 발명의 다른 특징 및 장점은 첨부된 도면을 참조하여 이하의 설명으로부터 더욱 명확해 질 것이다.

#### 발명의 실시를 위한 구체적인 내용

<20> 본 발명의 예시적인 실시예가 첨부된 도면을 참조하여 설명될 것이다.

<21> 실시예에 있어서, IPS 모드의 액티브 매트릭스 액정 디스플레이 장치는 TFT의 소스 전극을 포함한다. TFT의 소스 전극은 TFT와 연결되는 제1의 부분과, 픽셀 전극과 연결되는 제2의 부분 및 상기 제1 및 제2의 부분과 연결되는 제3의 부분에 형성된다. 제2의 부분은 비디오 신호 배선 라인 사이의 거의 중앙 부분에 배치된다. 소스 전극과 비디오 신호 배선 라인 사이의 위치 관계는, 다수의 비디오 신호 배선 라인의 적어도 일부와 마주보는 소스 전극의 각 영역의 폭이 다수의 비디오 신호 배선 라인과 상기 영역 사이의 거리에 의해 분할될 때 얻어지는

전체 값에 의해 규정된다. 전체 값을 제어하는 것에 의해, 다수의 비디오 신호 배선 라인과 소스 전극의 단락은 억제된다. 따라서, 높은 수율의 고선명 디스플레이 장치가 생산될 수 있다. 픽셀 전극이 다수의 공통 신호 배선 라인과 기판의 수직 방향으로 중첩하는 부분에서 기억 용량이 형성된다. 픽셀 전극 바로 아래의 제2의 절연막의 적어도 일부가 제거되어 오목부를 형성하면, 기억 용량이 형성된다. 최상층 픽셀 전극이 바닥층 공통 신호 배선 라인과 교차하는 영역에서, LC층의 LC 분자의 분자축은 프린지 전계(fringe electric field)에 의해 소정의 회전 방향으로 회전한다. 이 영역에서, 순방향 회전을 위한 강한 전계가 발생한다. 이러한 구성에서 소스 전극이 감소되더라도, LC 분자의 역회전은 방지된다. 이하, 도면을 참조하여 예시적인 실시예를 설명한다.

## &lt;22&gt; [제 1의 실시예]

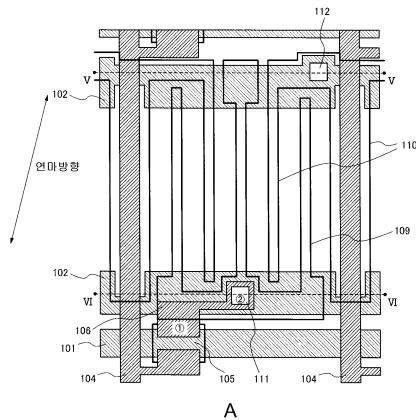

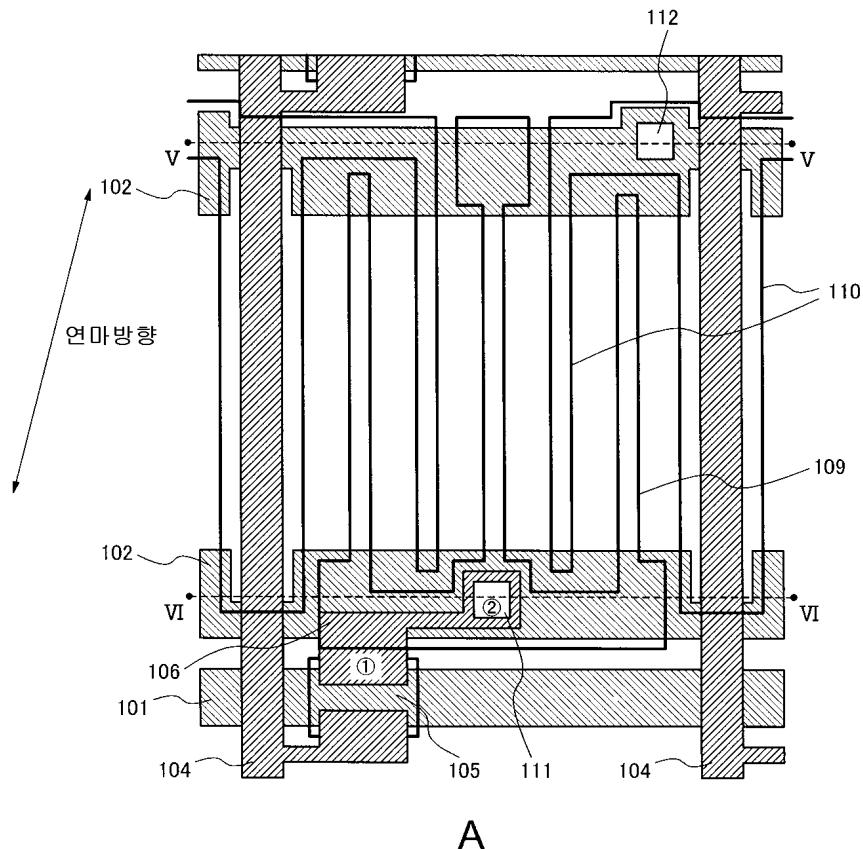

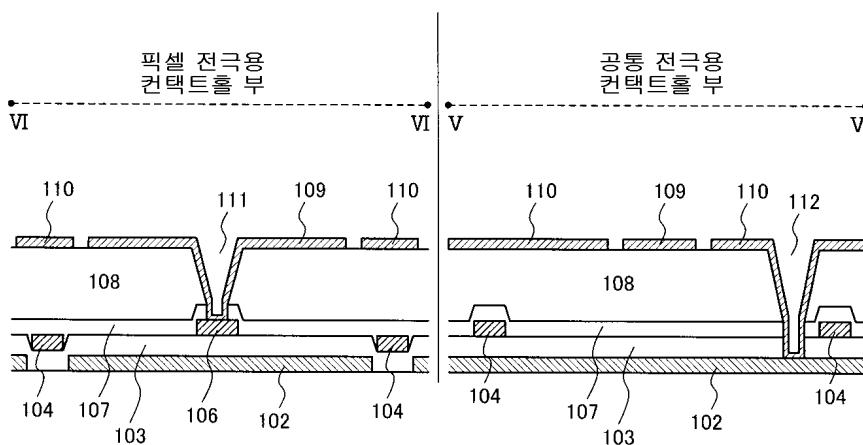

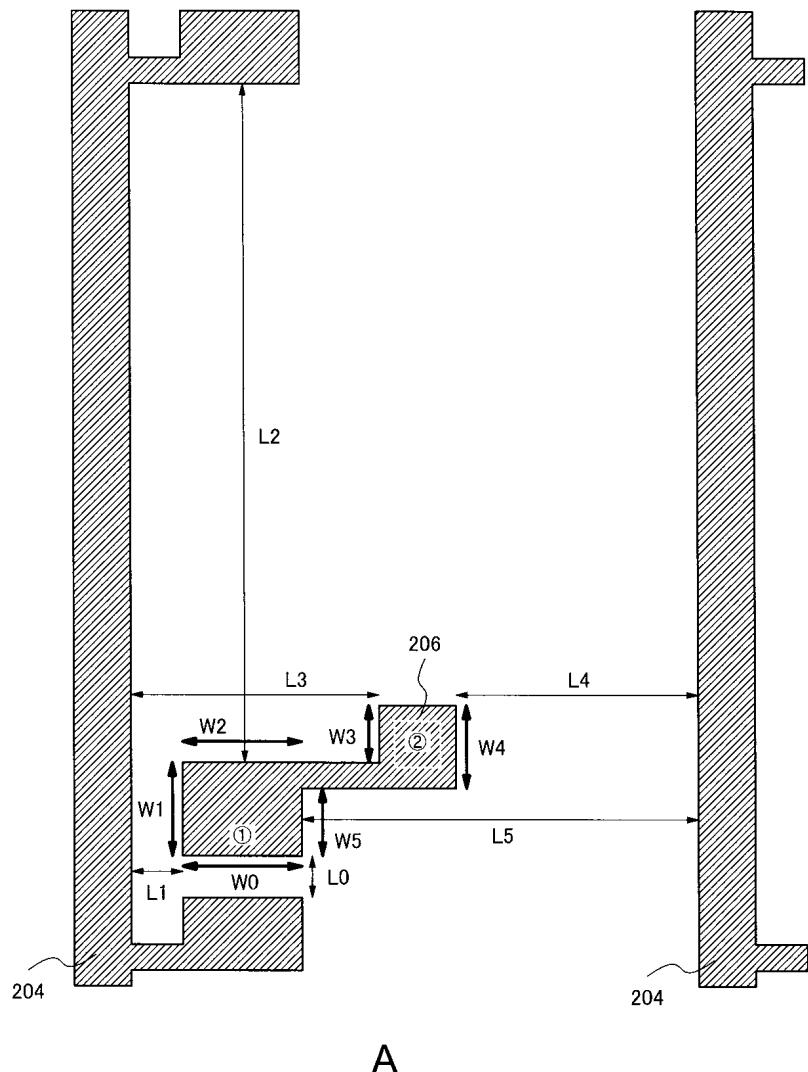

<23> 도 1a 및 b를 참조하여 제1의 실시예를 설명한다. 도 1a는 LCD 장치의 픽셀 구성을 도시하는 평면도이다. 도 1b는 도 1a의 IV-IV라인과 V-V 라인을 따른 단면도이다.

<24> 도 1a 및 b에 도시된 바와 같이, LCD 장치의 TFT 기판은 제1의 금속층인 다수의 주사 신호 배선 라인(101)과 이 주사 신호 배선 라인을 따르는 두 개의 공통 신호 배선 라인(102)을 포함한다. 다수의 주사 신호 배선 라인(101)과 공통 신호 배선(102) 상에는 제1의 절연막(103)이 형성된다. 제1의 절연막(103) 상에는 제2의 금속층인 다수의 비디오 신호 배선 라인(104)과, TFT(105) 및 소스 전극(106)이 형성된다. 여기서, 소스 전극(106)은 TFT(105)와 연결된 제1의 부분(1)과 픽셀 전극(109)과 연결된 제2의 부분(2)을 포함한다. 제2의 부분(2)은 다수의 픽셀의 양측의 비디오 신호 배선 라인(104)의 거의 중앙에 배치된다. 소스 전극(106)은 제1 및 제2의 부분을 포함하지만, 그 형상은 도면에 도시된 구성으로 제한되는 것은 아니다.

<25> 다수의 비디오 신호 배선 라인(104), TFT(105) 및 소스 전극(106) 상에는 제2의 절연막(107)이 형성된다. 제2의 절연막(107) 상에는 제3의 투명 절연막(108)이 형성된다. 제3의 절연막(108) 상에는 투명 전극인 공통 전극(110)과 픽셀 전극(109)이 형성된다. 다수의 비디오 신호 배선 라인(104)은 제2의 절연막(107)과 제3의 절연막(108)을 통해 배선 라인의 방향에서 공통 전극(110)에 의해 완전히 피복된다. 다수의 비디오 신호 배선 라인(104)이 배치되는 충에 위치된 소스 전극(106)은 도 1a에 도시된 바와 같이 픽셀 아래에만 형성된다. 픽셀의 위쪽에 있어서, 최상층에서의 픽셀 전극(109)의 폭은 증가한다. 다수의 공통 신호 배선 라인(102)이 픽셀 전극(109)과 중첩하는 영역에, 기억 용량이 형성된다.

<26> 픽셀 전극(109)과 공통 전극(110)은, 콘택트홀(111 및 112)을 통해 소스 전극(106)의 제2의 부분(2)과 다수의 공통 신호 배선 라인(102)에 각각 전기적으로 연결된다.

<27> 종래기술과 비교하여, 제1의 실시예에서는 픽셀의 위쪽에 형성되며 다수의 비디오 신호 배선 라인이 배치되는 충에 형성되는 소스 전극이 제거된다. 따라서, 다수의 픽셀의 하부충에 형성되는 소스 전극과 픽셀 전극을 전기적으로 연결하기 위한 콘택트홀이 불필요하게 된다. 따라서, 단락이 크게 감소하게 된다.

<28> 소스 전극의 제2의 부분과 다수의 비디오 신호 배선 라인은 동일충에 존재한다. 소스 전극의 제2의 부분이, 픽셀의 양측에 위치된 비디오 신호 배선 라인 사이의 거의 중앙에 배치되면, 신호 배선과 제2의 부분 사이의 단락은 최소로 감소될 수 있다. 결과적으로, 높은 수율의 LCD 장치가 실현될 수 있다.

<29> 픽셀 전극이 다수의 공통 신호 배선 라인과 중첩하는 부분에 기억 용량의 절반 이상이 형성된다. 그 결과, 소스 전극의 영역이 감소되는 경우에도 충분한 기억 용량이 형성된다. 따라서 우수한 이미지 품질이 얻어진다.

## &lt;30&gt; [제 2의 실시예]

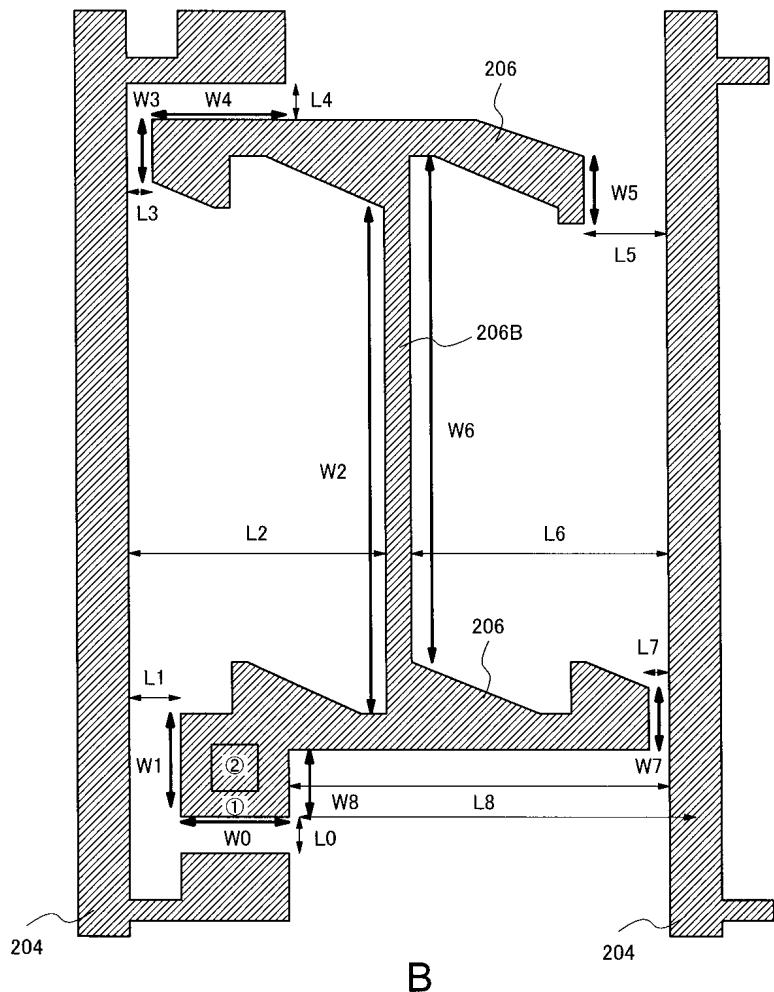

<31> 다음으로, 도 2a 및 b를 참조하여 제2의 실시예를 설명한다. 도 2a는 LCD 장치의 제2의 금속층의 구조를 도시하는 평면도이다. 도 2b는 종래기술에 따른 LCD 장치의 제2의 금속층의 구조를 도시하는 평면도이다.

<32> 제 2의 실시예는 소스 전극의 영역과, 소스 전극의 영역의 각 폭, 및 상기 영역과 대향 비디오 신호 배선 라인 사이의 거리를 규정한다.

<33> 도 2a에 도시된 바와 같이, 예지가 다수의 비디오 신호 배선 라인(204)의 적어도 일부와 마주보는 소스 전극(206)의 영역 각각에 있어서,  $W_i$ 는 영역의 폭을 나타내고  $L_i$ 는 영역과 다수의 비디오 신호 배선 라인(204)의 거리를 나타낸다. 픽셀에서  $\sum W_i / L_i$ 의 합( $\Sigma W_i / L_i$ )은 동일충에서의 단락의 주파수를 나타내는 양호한 파라미터로서 기능한다. 작은 값의  $\Sigma W_i / L_i$ 는 바람직한 상태를 의미한다.  $\Sigma W_i / L_i$ 의 값이, TFT의 채널폭( $W_0$ )을 채널 간격( $L_0$ )으로 나누어서 얻어지는 값( $W_0 / L_0$ )의 두 배 이내이면, 소스 전극과 다수의 비디오 신호 배선 라인 사이의 단락의 주파수는 아주 작게 된다. 이러한 상태하에서, 높은 수율이 얻어진다.

- <34> 종래기술의 디스플레이 장치에 있어서, 패널 내에서 세 개 또는 네 개의 누설 명점(leak bright point)이 검출된다. 본 실시예에 있어서는, 누설 명점이 검출되지 않는다.

- <35> 다른 관점에서, 소스 전극(206)의 면적이 작은 것이 바람직하다. 소스 전극의 전체 면적이 소스 전극의 제1의 부분과 제2의 부분의 두 면적의 합의 네 배 또는 그 이하이면, 소스 전극과 다수의 비디오 신호 배선 라인 사이의 단락의 주파수는 충분히 작게 된다. 따라서, 높은 수율이 디스플레이 장치가 얻어진다. 소스 전극의 전체 면적이 제1의 부분과 제2의 부분의 두 면적의 합의 네 배 이하이면, 누설 명점은 0개 또는 1개가 나타난다. 소스 전극의 전체 면적이 제1의 부분과 제2의 부분의 두 면적의 합의 세 배 이하이면, 누설 명점은 나타나지 않는다.

- <36> 다음에, 제2의 실시예를 상세히 설명한다. 도 2a에 도시된 실시예의 구성에 있어서, 소스 전극(206)의 영역이 작기 때문에, 파라미터  $\Sigma W_i/L_i$ , 즉,  $(W_1/L_1 + \dots + W_5/L_5)$ 의 값도 작다. 소스 전극의 전체 면적은 제1의 부분과 제2의 부분의 두 면적의 합의 약 2.5배이다. 파라미터  $\Sigma W_i/L_i$ 의 값은 약 2.5이고  $W_0/L_0$ 의 값과 거의 동일하다. 이 상태에서, 누설 명점은 나타나지 않는다.

- <37> 한편, 도 2b에 도시된 종래기술의 구성에 있어서, 소스 전극(206)의 면적은 크다.  $W_i$ 가 크고  $L_i$ 가 작은 영역이 다수 존재한다. 파라미터  $\Sigma W_i/L_i$ , 즉,  $(W_1/L_1 + \dots + W_5/L_5)$ 의 값은 크다. 소스 전극의 전체 면적은 제1의 부분과 제2의 부분의 두 면적의 합의 약 9배이다. 파라미터  $\Sigma W_i/L_i$ 는 약 20이며  $W_0/L_0$ 의 값의 약 8배이다. 이 상태에서, 누설 명점은 4개 또는 3개 나타난다.

- <38> 따라서, 제2의 실시예에 따르면, 단락을 크게 감소시키는 픽셀 구조가 제공된다.

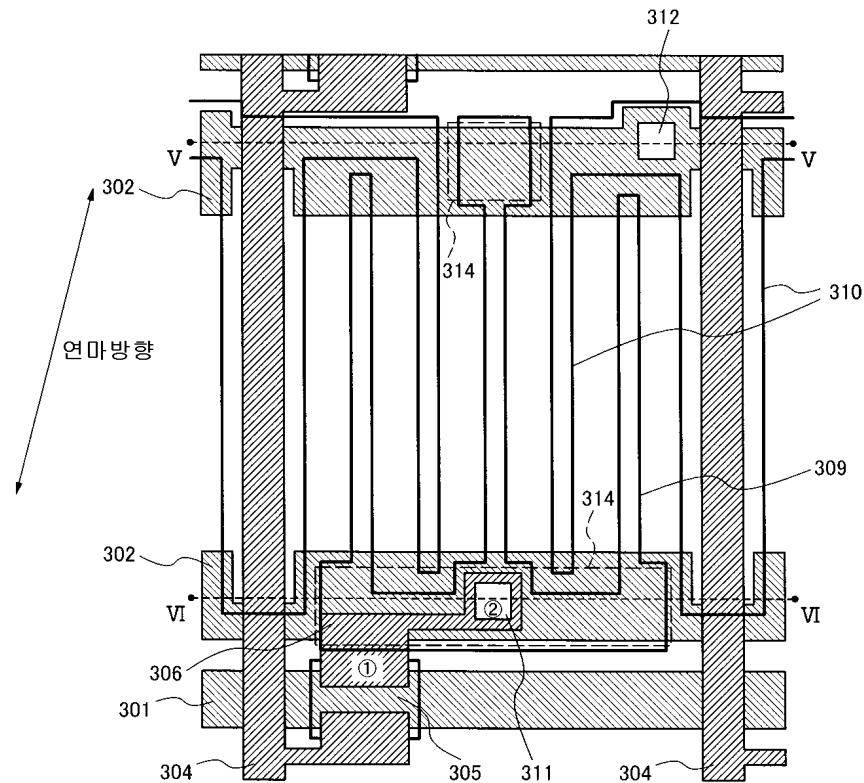

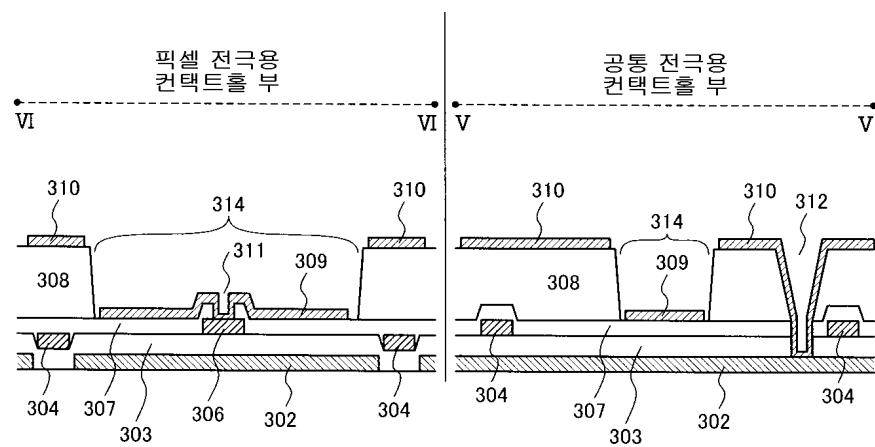

- <39> [제 3의 실시예]

- <40> 다음에, 도 3a 및 b를 참조하여 제3의 실시예를 설명한다. 도 3a는 LCD 장치의 하나의 픽셀 구성을 도시하는 평면도이고, 도 3b는 도 3a의  $\Sigma - \Sigma$  라인과  $\Sigma - \Sigma$ 을 따라 취해진 단면도이다. 제1의 실시예와는 달리, 기억 용량이 형성되는 영역에서, 픽셀 전극 바로 아래에 위치된 제3의 절연층의 일부가 소정의 두께만큼 제거된다.

- <41> 제 3의 실시예를 상세히 설명한다. 제1의 실시예에서 최상층의 픽셀 전극과 바닥층의 다수의 공통 신호 배선 라인 사이에 기억 용량이 형성된다. 그러나, 제1의 실시예에서 다수의 공통 신호 배선 라인과 픽셀 전극 사이에 세 개의 절연층이 배치되기 때문에, 기억 용량을 위한 절연층의 두께는 두껍다. 따라서, 기억 용량의 용량이 작다. 본 실시예에 따르면, 기억 용량이 형성되는 영역에서, 픽셀 전극(309) 바로 아래에 위치된 제3의 절연층(308)이 제거되어 오목부(314)를 형성하게 된다. 용량 형성 영역의 절연층의 두께가 얇기 때문에, 더 큰 용량의 기억 용량이 형성된다.

- <42> 또한, 예를 들면, 제1의 절연막(303)과 제2의 절연막(307)으로서 실리콘 질화막이 CVD(Chemical Vapor Deposition)법에 의해 형성된다. 그 후, 아크릴 수지로 이루어진 감광성 유기막이 제3의 절연막으로서 도포된다. 다음에, 노광 및 현상에 의해 제3의 절연층(308)을 선택적으로 제거하는 것에 의해 오목부(314)가 형성된다. 아크릴 수지는 낮은 유전상수를 갖는다. 절연층을 통해 다수의 비디오 신호 배선 라인(304) 상에 공통 전극이 형성되더라도, 다수의 비디오 신호 배선 라인과 공통 전극 사이의 기억 용량의 용량값은 작다. 기억 용량은 다수의 픽셀의 구동에 영향을 끼치지 않는다.

- <43> 제 3의 절연막(308)은 CVD법에 의해 형성되고, 오목부(314)는 예칭에 의해 형성될 것이다. 픽셀 전극(309) 바로 아래에 위치된 제3의 절연막(308)은 완전히 제거될 것이다. 제3의 절연막(308)은 얇게 남을 수도 있다.

- <44> 다수의 비디오 신호 배선 라인(304) 상에 배치된 절연막은 하나의 층으로 형성된 제2의 절연막(307)만을 포함할 수도 있고, 기억 용량 형성 영역에서, 제2의 절연막의 일부는 제거될 것이다.

- <45> 다수의 비디오 신호 배선 라인(304) 상에 배치된 절연층이 3층 이상의 층을 포함하는 경우, 하나 이상의 층의 적층 절연층은 기억 용량 형성 영역에서 제거될 수 있다.

- <46> 따라서, 제3의 실시예에 따르면, 단락의 주파수는 기억 용량을 형성하는 동안 크게 감소될 수 있다.

- <47> [제 4의 실시예]

- <48> 다음에, 도 3a 및 b를 참조하여 제4의 실시예를 설명한다. 본 실시예에서는, 오목부의 에지에서 디스플레이 영역까지의 간격이 규정된다. 오목부는 픽셀 전극 바로 아래에 위치된 제3의 절연층을 제거하는 것에 의해 형성된다. 디스플레이 영역은 한 쌍의 공통 신호 배선 라인(302) 사이의 영역이다.

- <49> 제 4의 실시예를 상세히 설명한다. 제3의 절연막(308)을 제거하는 것에 의해 형성되는 오목부(314)의 에지가 디

스플레이 영역에 가까우면, 단차에 의한 광누설이 발생한다. 이러한 광누설은 블랙 레벨 휘도를 증가시킨다. 본 실시예에서는, 제3의 절연막(308)을 제거하는 것에 의해 형성되는 오목부(314)의 에지에서 디스플레이 영역까지의 간격이 규정된다. 이 간격이 커지면, 광누설은 잘 억제될 수 있을 것이다. 이 간격이  $2\mu m$  이상이면, 단차로 인한 광누설은 공통 신호 배선 라인(302)에 의해 차단되고, 블랙 레벨 휘도는 증가하지 않는다.

<50> 따라서, 제4의 실시예에 따르면, 단락의 주파수가 크게 감소되고, 종래기술의 기억 용량과 등가의 기억 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 디스플레이 스크린의 콘트라스트는 향상된다.

<51> [제 5의 실시예]

<52> 다음에, 도 4를 참조하여 제5의 실시예를 설명한다. 제1의 기억 용량 형성부와 제2의 기억 용량 형성부에 각각 대응하는 픽셀의 상부 및 하부에 배치된 두 개의 공통 신호 배선 라인은 다수의 비디오 신호 배선 라인을 따라 배치된 접속부에 의해 전기적으로 연결된다.

<53> 픽셀의 상부와 하부의 두개의 공통 신호 배선 라인(402)이 접속부(402B)에 의해 전기적으로 연결되기 때문에, 공통 신호의 지연은 감소되고 플리커 레벨(flicker level) 또는 휘도의 면내 분포는 균일하게 된다. 이 구성은 고선명 디스플레이에 기여하게 된다. 따라서, 장치가 크고 고선명이 크게 요구되면, 이와 같은 구성이 유효하게 된다. 본 실시예에 있어서, 접속부(402B)는 다수의 비디오 신호 배선 라인의 측면을 따라 배치되고, 다수의 비디오 신호 배선 라인으로부터 디스플레이 영역으로의 누설 전계는 강하게 억제되어, 수직 크로스 토크가 억제된다.

<54> 따라서, 제5의 실시예에 따르면, 단락의 주파수가 크게 감소되고 공통 신호의 지연이 감소되기 때문에, 이미지 품질이 향상되고 수율이 더 높아진다.

<55> [제 6의 실시예]

<56> 다음에, 도 5를 참조하여 제6의 실시예를 설명한다. 제2의 기억 용량 형성부에 있는 상부 공통 신호 배선 라인은, 다수의 비디오 신호 배선 라인이 교차하는 영역에서, 횡방향으로, 다른 라인 또는 다른 전극에 연결되지 않는다.

<57> 상부 공통 신호 배선 라인은 접속부(502B)를 통해 하부 공통 신호 배선 라인과 전기적으로 연결된다. 다수의 비디오 신호 배선 라인과 다수의 공통 신호 배선 라인 사이의 교차 용량(crossing capacity)은 거의 절반으로 된다.

<58> [제 7의 실시예]

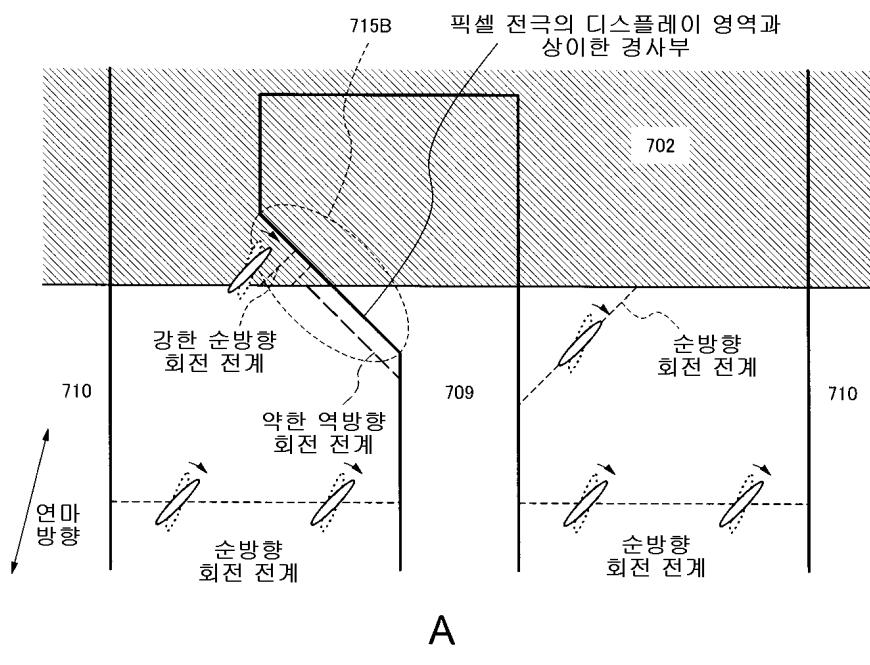

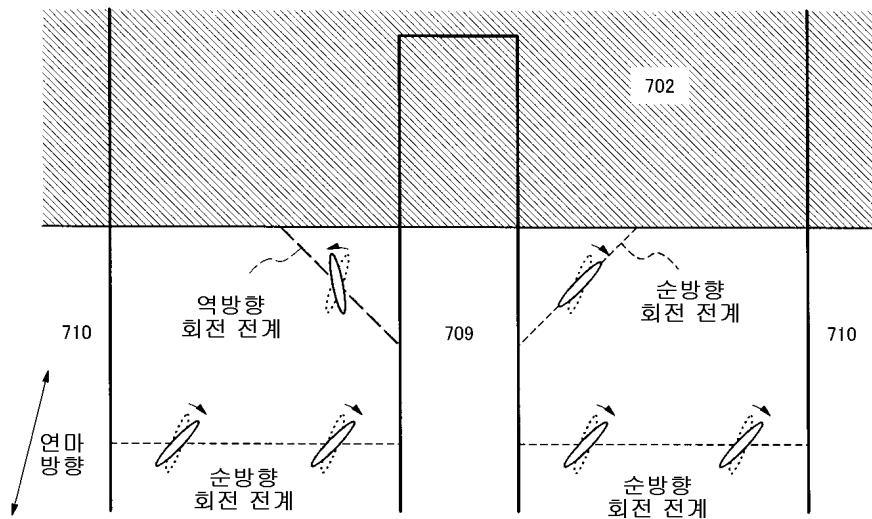

<59> 다음에, 도 6a 및 도 7b를 참조하여 제7의 실시예를 설명한다. 도 6a는 본 실시예에 따른 LCD 장치의 한 픽셀의 구성을 도시하는 평면도이다. 도 6b는 역회전 방지 구조를 구비하지 않은 한 픽셀 구성을 도시하는 평면도이다. 도 7a는 본 실시예의 역회전 방지 구조를 구비하는 구성에서의 LC 문자의 동작을 도시한다. 도 7b는 역회전 방지 구조를 구비하지 않은 구성에서의 LC 문자의 동작을 도시한다.

<60> 도 35a 및 도 37a에 도시된 종래기술의 디스플레이 장치에 있어서, 다수의 공통 신호 배선 라인과 소스 전극 둘다는 톱니 형상으로 패턴화되고 적층된다. 이러한 구성은 LC 문자의 역회전을 야기하는 전계를 억제시킨다. 역회전은 하기에 간략히 설명된다. LC 문자에 전계가 인가되지 않으면, LC 문자는 도면에 도시된 바와 같이 러빙 방향으로 균질하게(homogeneously) 배향된다. 픽셀 전극과 공통 전극 사이에 전위차가 주어지면, 도 35a의 횡방향으로 전계가 인가된다. 이러한 상황에서, 전계와 LC 문자의 초기 배향 방향 사이의 관계에 기초하여, LC 문자는 변형되어 전계의 방향에 대응하게 된다. 도면에 도시된 예에 있어서, 이러한 움직임은 시계방향 회전이다. 이 회전 방향은 순방향으로 정의된다. 순방향 회전과 반대의 회전 방향에서의 LC 문자의 회전은 역회전으로 정의된다. 도 35a에 있어서, 공통 전극과 픽셀 전극의 에지는 톱니 형상으로 형성된다. 그 결과, 전극 에지부에 있어서, LC 문자의 초기 배향 상태에서 LC 문자가 순방향 회전을 수행하는 방향으로 전계가 형성된다. 따라서, LC 문자의 잘 배향된 상태가 전극 에지부에서 유지된다. 한편, 도 1a에 있어서, 소스 전극의 영역이 작기 때문에, 도 35a와 동일한 구조는 형성되지 않는다. 예를 들면, 도 1a에서, 픽셀 전극의 좌상측에서 오른쪽 대각선 방향으로 전계가 형성된다. LC 문자는 이 영역에서 반시계 방향으로 회전한다. LC 문자가 역회전하는 영역이 이 영역 내에 형성되고, 회위(回位; disclination)가 발생한다. 회위는 콘트라스트와 백색 휘도를 감소시킨다. 따라서, 역회전을 야기하는 전계가 발생하는 영역은 LC층의 LC 문자축의 소망하는 회전 방향에 따르지 않는 부분으로서 정의된다. 한편, 도 1a에 있어서, 전계의 방향은 픽셀 전극의 우상측에서 대각선 방향이다. 이 부분에서의 LC 문자는 시계 방향으로 회전된다. 이 부분은 액정층의 LC 문자축의 소망의 회전 방향에 일치하는 부분으로

정의된다. 본 실시예에 있어서, 소스 전극의 영역을 줄이는 제1의 실시예의 구성과 마찬가지로 역회전을 방지하는 대책이 취해진다.

<61> 도 6a에 구체적으로 도시된 바와 같이, 바닥층의 다수의 공통 신호 배선 라인(602)이 최상층의 픽셀 전극(609)과 교차하는 부분(즉, 도면에서 점선으로 둘러싸인 부분)에서, 픽셀 전극(609)은, 한 쌍의 공통 신호 배선 라인(602) 사이의 영역인 디스플레이 영역에서의 방향과는 다른 방향으로 기울어진다. 다수의 공통 신호 배선 라인(602)의 영역에서, 픽셀 전극(609)의 에지 근처에서 생성된 프린지 전계에 따른 LC층의 LC 분자축의 회전이 순방향이 되도록 역회전 방지 구조(615A)가 형성된다. 러빙 방향에 따르면, 역회전 방지 구조(615A)의 경사 방향은 도 6a의 다수의 픽셀의 양측(즉, 도 6a의 좌우측)에서 서로 반대가 된다.

<62> 도 7a 및 b를 참조하여 이러한 역회전 방지 구조를 설명한다. 도 7b에서, LC 분자의 역회전을 만드는 전계가 발생하는 영역은 디스플레이 영역의 에지에 위치된다. 한편, 도 7a에서, 역회전 방지 구조(715B)는 LC 분자의 역회전을 위한 전계가 발생하는 영역에 배치된다. 역회전 방지 구조(715B)는, 다수의 공통 신호 배선 라인의 에지가, 디스플레이 영역에서의 방향과는 다른 방향으로 기울어진 픽셀 전극의 부분과 교차하는 구성을 포함한다. 다수의 공통 신호 배선 라인(702)의 영역에서, 순방향 회전을 위한 프린지 전계가 발생한다. 또한, 역회전 전계의 영향은 차단된다. 그 결과, 전체 디스플레이 영역에서, LC 분자는 순방향으로 회전한다. 이하, 도 7a에 도시된 역회전 방지 구조를 제1의 역회전 방지 구조라고 칭한다.

<63> 따라서, 제7의 실시예에 따르면, 단락의 주파수가 크게 감소하고, 디스플레이 영역 전체에서 LC 분자의 역회전이 방지되어, 광 활용 효율이 증가한다.

<64> [제 8의 실시예]

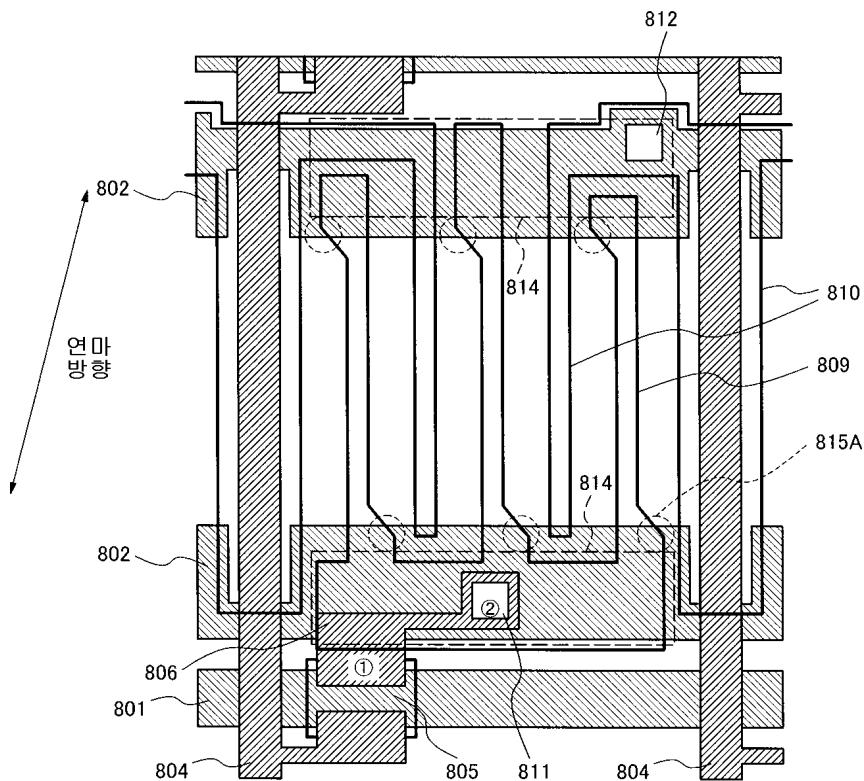

<65> 다음으로, 도 8을 참조하여 제8의 실시예를 설명한다. 도 8은 LCD 장치의 다수의 픽셀의 구성을 도시하는 평면도이다. 본 실시예에 있어서, 픽셀 전극 바로 아래의 제3의 절연막은 기억 용량이 형성되는 영역에서 제거된다.

<66> 구체적으로는, 기억 용량은 바닥층의 다수의 공통 신호 배선 라인과 최상층의 픽셀 전극 사이에 형성된다. 이러한 구성에서, 다수의 공통 신호 배선 라인과 픽셀 전극 사이에 세 개의 절연막이 배치되기 때문에, 막두께는 두껍고, 기억 용량은 작다. 본 실시예에서, 기억 용량이 형성되는 영역의 픽셀 전극(809) 바로 아래의 제3의 절연막을 제거하는 것에 의해 오목부(814)가 형성된다. 결과적으로, 기억 용량 형성 영역에 두 개의 절연층이 배치된다. 따라서, 큰 용량의 기억 용량이 이 영역에서 형성된다.

<67> 제 1 및 제2의 절연막으로서, 예를 들면, CVD법에 의해 실리콘 질화막이 형성된다. 아크릴 수지의 감광성 유기막이 제3의 절연막으로서 도포된다. 그리고, 노광 및 현상에 의해 제3의 절연층을 선택적으로 제거하는 것에 의해 오목부(814)가 형성된다. 제3의 절연막은 CVD법에 의해 형성될 수 있고, 오목부(314)는 애칭에 의해 형성될 수 있다. 픽셀 전극(809) 바로 아래의 제3의 절연막은 완전히 제거될 수도 있고 또는 얇게 남겨질 수도 있다.

<68> 제 8의 실시예에 따르면, 단락의 주파수가 크게 감소하고 LC 분자의 역회전이 전체 디스플레이 영역에서 방지되며 더 큰 기억 용량이 형성될 수 있다.

<69> [제 9의 실시예]

<70> 다음으로, 도 8을 참조하여 제9의 실시예를 설명한다. 또한, 제8의 실시예의 장치와 동일한 구성이지만, 픽셀 전극 바로 아래의 제3의 절연막을 제거하는 것에 의해 형성된 오목부의 에지에서 디스플레이 영역까지의 간격이 본 실시예에서 규정된다.

<71> 제 3의 절연막을 제거함으로써 형성되는 오목부(814)의 에지가 디스플레이 영역에 가까우면, 단차로 인한 광누설이 발생한다. 광누설은 블랙 레벨 휘도를 증가시킨다. 본 실시예에 있어서, 제3의 절연막을 제거함으로써 형성되는 오목부(814)의 에지에서 디스플레이 영역까지의 간격이 규정된다. 상기 간격이 클 때, 광누설은 효과적으로 억제된다. 이 간격이  $2\mu\text{m}$  이상으로 유지되면, 단차로 인한 광누설은 공통 신호 배선 라인(802)에 의해 차단된다. 그에 따라, 블랙 레벨 휘도가 증가하지 않는다.

<72> 본 실시예에 따르면, 단락 회로의 주파수가 크게 감소하고, LC 분자의 역회전이 전체 디스플레이 영역에서 방지된다. 충분한 기억 용량이 형성되고 블랙 레벨 휘도가 증가하지 않기 때문에, 디스플레이 장치의 스크린의 콘트라스트가 향상된다.

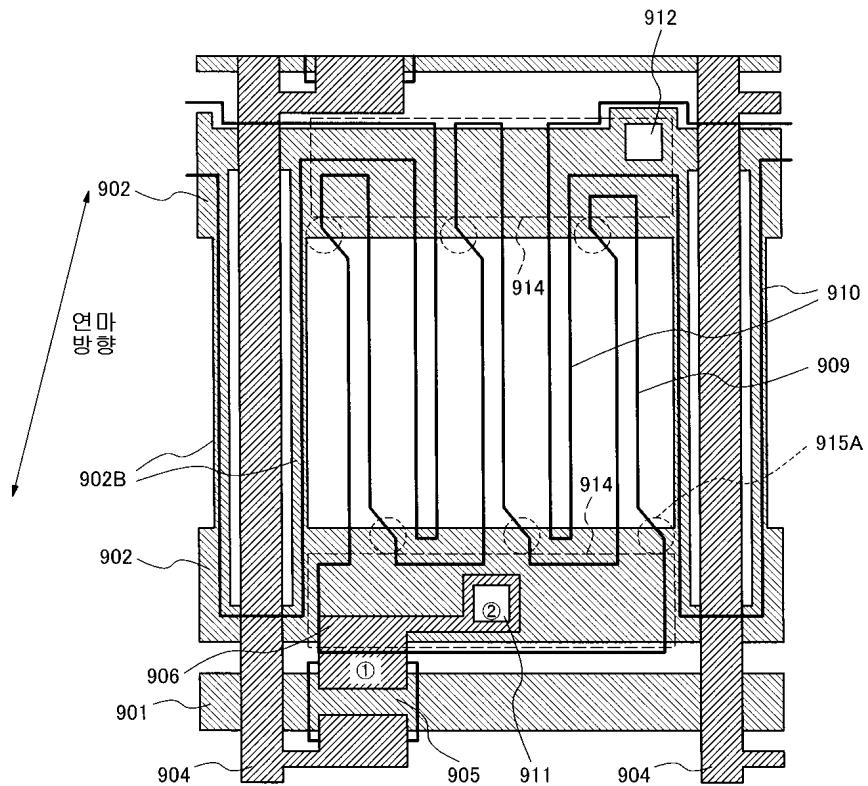

<73> [제 10의 실시예]

<74> 다음에, 도 9를 참조하여 제10의 실시예를 설명한다. 제1의 기억 용량 형성부와 제2의 기억 용량 형성부에 있는

픽셀의 상부 및 하부에 배치된 두 개의 공통 신호 배선은 다수의 비디오 신호 배선 라인을 따라 배치된 접속부를 통해 서로 전기적으로 연결된다.

<75> 픽셀의 상측과 하측의 두 개의 공통 신호 배선 라인(902)이 접속부(902B)를 통해 연결되면, 공통 신호의 지연이 감소되고 플리커 레벨 또는 휘도의 면내 분포(in-plane distribution)는 일정하게 된다. 이 구성은 디스플레이의 고선명에 기여하게 된다. 이 구성은 장치가 크고 고선명이 요구될 때, 디스플레이의 고선명화에 아주 효과적이다. 본 실시예에 있어서, 접속부(902B)가 다수의 비디오 신호 배선 라인을 따라 배치되면, 다수의 비디오 신호 배선 라인에서 디스플레이 영역으로의 누설 전계는 강하게 억제되고, 수직 크로스 토크가 억제된다.

<76> 제 10의 실시예에 따르면, 단락의 주파수가 크게 감소하고, 공통 신호의 지연이 감소되며, 이미지 품질 및 수율 향상이 도모된다.

<77> [제 11의 실시예]

<78> 다음에, 도 10을 참조하여 제11의 실시예를 설명한다. 도 10은 LCD 장치의 다수의 픽셀의 구성을 도시하는 평면도이다.

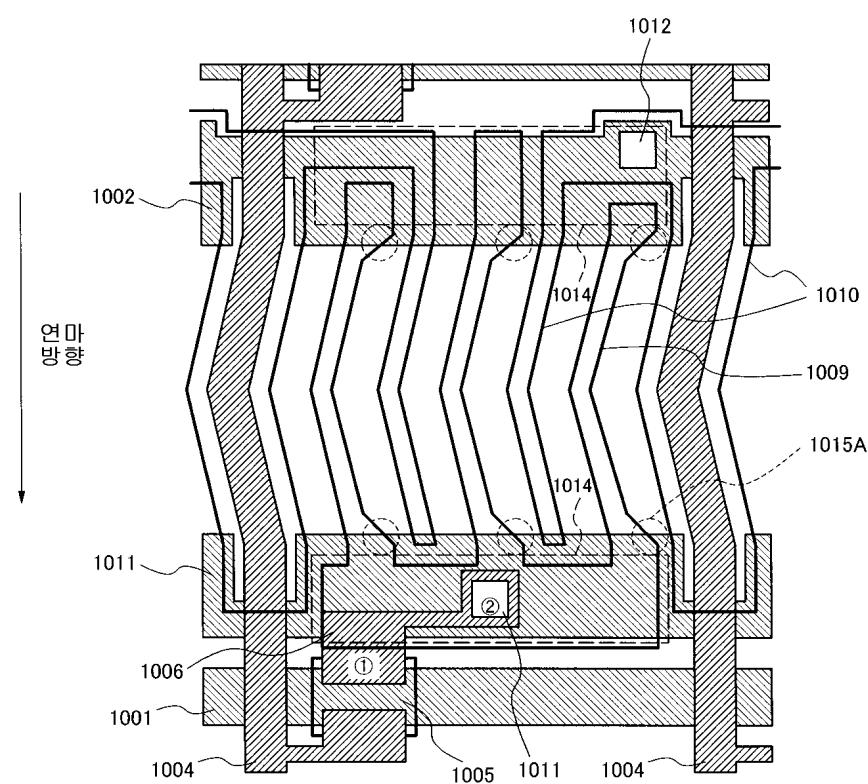

<79> 본 실시예에 있어서, 공통 전극(1010), 픽셀 전극(1009) 및 다수의 비디오 신호 배선 라인(1004)은 굴곡되어 멀티-도메인 구조(multi-domain structure)를 형성한다. 이 구조에 따르면, 제1의 역회전 방지 구조(1015A)의 방향은 싱글 도메인의 방향으로부터 변경된다.

<80> 제 11의 실시예에 따르면, 단락 회로의 주파수는 크게 감소하고 디스플레이 영역 전체에서 LC 문자의 역회전이 방지된다. 또한, 충분한 기억 용량이 형성된다. 본 실시예의 디스플레이 장치에서, 블랙 레벨 휘도가 증가하지 않기 때문에, 높은 콘트라스트가 얻어진다. 본 실시예의 디스플레이 장치에서는, 스크린을 비스듬한 방향에서 보는 경우에도, 멀티-도메인 구조에 의해 색상 전이(color shift)가 억제된다.

<81> [제 12의 실시예]

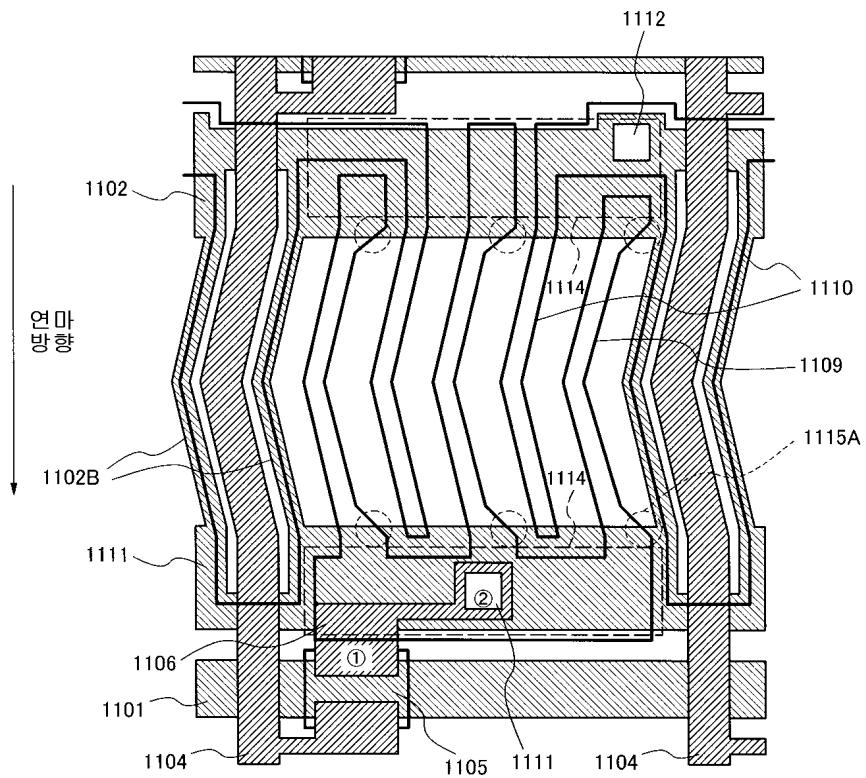

<82> 도 11을 참조하여 제12의 실시예를 설명한다. 제1의 기억 용량 형성부와 제2의 기억 용량 형성부에 있는 픽셀의 상부와 하부에 배치된 두 개의 공통 신호 배선 라인은 다수의 비디오 신호 배선 라인을 따라 배치된 접속부에 의해 전기적으로 연결된다.

<83> 픽셀의 상측 및 하측의 두 개의 공통 신호 배선 라인(1102)이 접속부(1102B)를 통해 서로 전기적으로 연결되면, 공통 신호의 지연은 감소되고 플리커 레벨 또는 휘도의 면내 분포는 균일하게 된다. 이 구성은 디스플레이의 고선명에 기여하게 된다. 이 구성은 장치가 크고 고선명이 요구될 때, 디스플레이의 고선명화에 아주 효과적이다. 본 실시예에 있어서, 접속부(1102B)가 다수의 비디오 신호 배선 라인을 따라 배치되면, 다수의 비디오 신호 배선 라인에서 디스플레이 영역으로의 누설 전계는 강하게 억제되고, 수직 크로스 토크가 억제된다.

<84> 제 12의 실시예에 따르면, 단락 회로의 주파수는 크게 감소하고 전체 디스플레이 영역에서 역회전이 방지된다. 본 실시예에 있어서, 충분한 기억 용량이 형성된다. 본 실시예의 디스플레이 장치에서, 블랙 레벨 휘도가 증가하지 않기 때문에, 높은 콘트라스트가 얻어진다. 스크린을 비스듬한 방향에서 보는 경우에도, 멀티-도메인 구조에 의해 색상 전이가 억제된다. 단락이 크게 감소하고 공통 신호의 지연이 감소하기 때문에, 본 실시예의 디스플레이에서는 이미지 품질과 수율이 향상된다.

<85> [제 13의 실시예]

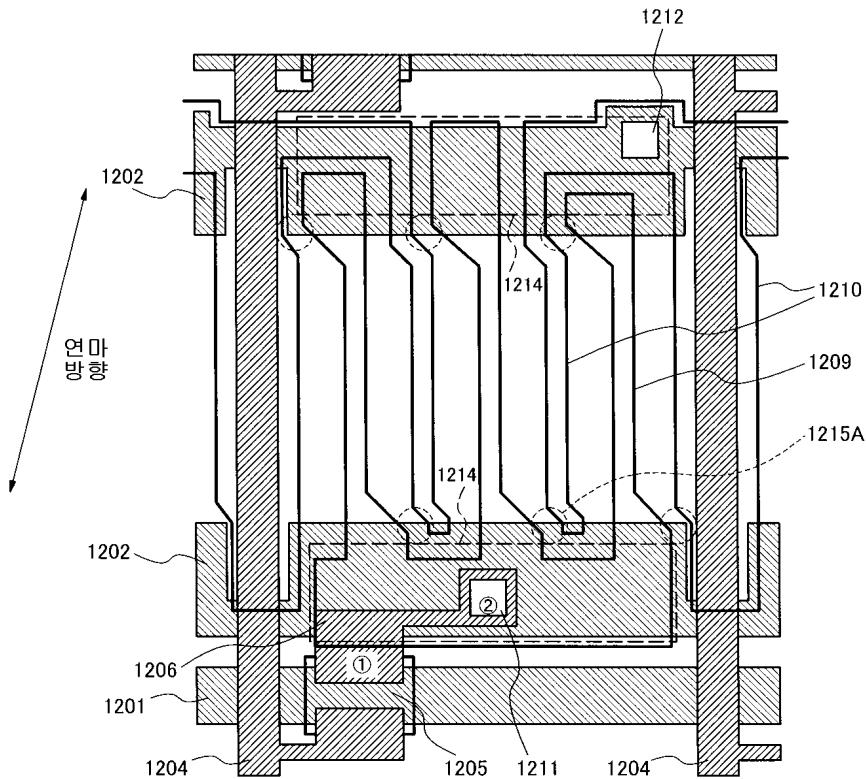

<86> 다음에, 도 12를 참조하여 제13의 실시예를 설명한다. 제1의 역회전 방지 구조(1215A)에서 프린지 전계를 생성하는 측의 픽셀 전극(1209)에 인접한 공통 전극(1210)은 픽셀 전극(109)의 형상에 따른 거의 크랭크 형상을 포함한다. 공통 전극에 기초한 인클로저 효과(enclosure)가 프린지 전계의 효과에 더해져서, 강한 역회전 방지 효과가 얻어진다.

<87> 따라서, 제13의 실시예에 따르면, 단락의 주파수가 크게 감소하고 LC 문자의 역회전이 디스플레이 영역 전체에서 방지되며, 광 활용 효율이 향상된다.

<88> [제 14의 실시예]

<89> 도 12를 참조하여 제14의 실시예를 설명한다. 픽셀 전극 바로 아래의 제3의 절연막을 제거하는 것에 의해 형성된 오목부(1214)의 에지에서 디스플레이 영역까지의 간격이 규정된다.

<90> 픽셀 전극 바로 아래의 제3의 절연막을 제거하는 것에 의해 형성된 오목부(1214)의 에지가 디스플레이 영역에

가까우면, 단차로 인한 광누설이 발생하여 블랙 레벨 휘도의 증가를 야기시킨다. 본 실시예에 있어서, 제3의 절연막을 제거하는 것에 의해 형성된 오목부(1214)의 에지에서 디스플레이 영역까지의 간격이 규정된다. 이 간격이 크면, 광누설은 효율적으로 억제된다. 이 간격이  $2\mu m$  이상으로 유지되면, 단차로 인한 광누설은 공통 신호 배선 라인(1202)에 의해 차단되고, 블랙 레벨 휘도가 증가하지 않는다.

<91> 제 14의 실시예에 따르면, 단락의 주파수는 크게 감소하고 디스플레이 영역 전체에서 LC 분자의 역회전이 방지되며 충분한 기억 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 스크린의 콘트라스트가 향상한다.

<92> [제 15의 실시예]

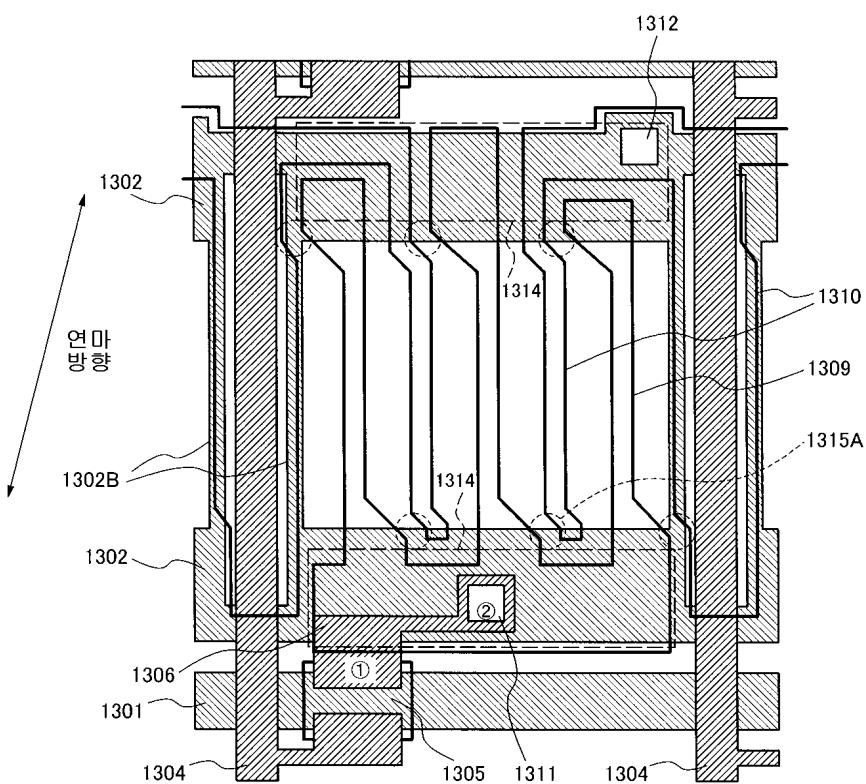

<93> 다음에, 도 13을 참조하여 제15의 실시예를 설명한다. 제1의 기억 용량 형성부와 제2의 기억 용량 형성부에 있는 픽셀의 상부와 하부에 배치된 두 개의 공통 신호 배선 라인은 다수의 비디오 신호 배선 라인을 따라 배치된 접속부(1302B)에 의해 전기적으로 연결된다.

<94> 픽셀의 상측 및 하측의 두 개의 공통 신호 배선 라인(1302)이 접속부(1302B)를 통해 전기적으로 연결되면, 공통 신호의 지연이 감소되고 플리커 레벨 또는 휘도의 면내 분포는 균일하게 된다. 이 구성은 디스플레이의 고선명에 기여하게 된다. 이 구성은 장치가 크고 고선명이 요구될 때, 디스플레이의 고선명화에 아주 효과적이다. 본 실시예에 있어서, 접속부(1302B)가 다수의 비디오 신호 배선 라인을 따라 배치되면, 다수의 비디오 신호 배선 라인에서 디스플레이 영역으로의 누설 전계는 강하게 억제되고, 수직 크로스 토크가 억제된다.

<95> 제 15의 실시예에 따르면, 단락의 주파수가 크게 감소하고, 디스플레이 영역 전체에서 LC 분자의 역회전이 방지되며, 광 활용 효율이 증가한다. 플리커 레벨 또는 휘도의 면내 분포는 균일하게 되고, 수직 크로스 토크가 억제되며, 디스플레이 품질이 향상한다.

<96> [제 16의 실시예]

<97> 다음에, 도 14를 참조하여 제16의 실시예를 설명한다. 본 실시예에 있어서, 공통 전극(1410), 픽셀 전극(1409) 및 다수의 비디오 신호 배선 라인(1404)은 굴곡되어 디스플레이 영역의 중앙에 멀티-도메인 구조(multi-domain structure)를 형성한다. 이 구조에 따르면, 제1의 역회전 방지 구조(1015A)의 방향은 상기 제13 및 제14의 실시예에서 언급된 성글 도메인의 방향과 상이하다.

<98> 제 16의 실시예에 따르면, 단락 회로의 주파수는 크게 감소하고 디스플레이 영역 전체에서 LC 분자의 역회전이 방지되고 광 활용 효율이 증가한다. 본 실시예의 디스플레이 장치에 있어서, 멀티-도메인 구조에 의해, 스크린을 비스듬히 볼 때에도, 색상 전이가 억제된다.

<99> [제 17의 실시예]

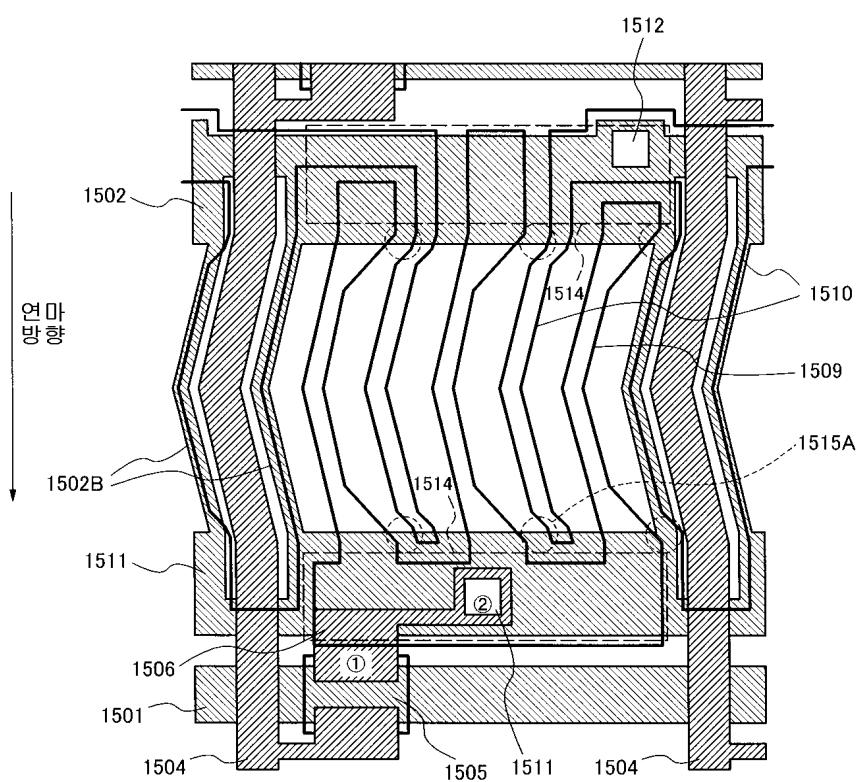

<100> 도 15를 참조하여 제17의 실시예를 설명한다. 제1의 기억 용량 형성부와 제2의 기억 용량 형성부에 있는 픽셀의 상부와 하부에 배치된 두 개의 공통 신호 배선 라인은 다수의 비디오 신호 배선 라인을 따라 배치된 접속부에 의해 전기적으로 연결된다.

<101> 픽셀의 상측 및 하측의 두 개의 공통 신호 배선 라인(1502)이 접속부(1502B)를 통해 서로 전기적으로 연결되면, 공통 신호의 지연은 감소되고 플리커 레벨 또는 휘도의 면내 분포는 균일하게 된다. 이 구성은 디스플레이의 고선명에 기여하게 된다. 이 구성은 장치가 크고 고선명이 요구될 때, 디스플레이의 고선명화에 아주 효과적이다. 본 실시예에 있어서, 접속부(1502B)가 다수의 비디오 신호 배선 라인을 따라 배치되면, 다수의 비디오 신호 배선 라인에서 디스플레이 영역으로의 누설 전계는 강하게 억제되고, 수직 크로스 토크가 억제된다.

<102> 제 17의 실시예에 따르면, 단락 회로의 주파수는 크게 감소하고 전체 디스플레이 영역에서 역회전이 방지되며, 광 활용 효율이 증가한다. 스크린을 비스듬히 볼 때에도, 멀티-도메인 구조에 의해 색상 전이가 억제된다. 플리커 레벨 또는 휘도의 면내 분포가 균일하게 되고, 수직 크로스 토크가 억제되고, 이미지 품질이 향상된다.

<103> [제 18의 실시예]

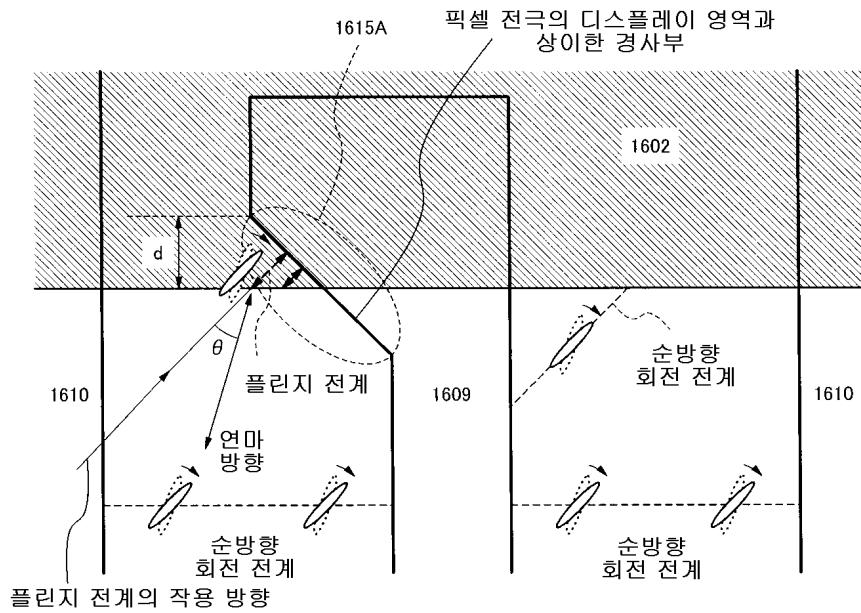

<104> 다음에, 도 16을 참조하여 제18의 실시예를 설명한다. 본 실시예에 있어서는, 제1의 역회전 방지 구조(1615A)의 근처에서 발생하는 프린지 전계가 작용하는 방향과 LC층에서의 LC 분자의 초기 배향 방향의 각(angle)이 규정된다.

<105> 도 16에 있어서, 프린지 전계가 작용하는 방향과 액정층의 초기 배향 방향, 즉 러빙 방향 사이의 작은  $\theta$ 로 조정된다. 이 각( $\theta$ )이 45도이면, 제1의 역회전 방지 구조(1615A) 근처의 LC층에서의 LC 분자에 제일 강한 기동

토오크(running torque)가 인가되고 역회전 방지 효과가 커진다. 따라서, 상기 각  $\theta$ 는 45도인 것이 바람직하다. 그러나, 다수 픽셀의 피치와 레이아웃으로 인해, 이 각도  $\theta$ 가 45도로 설정될 수 없으면,  $\theta$ 의 값에 마진이 주어질 수도 있다. 이 각도  $\theta$ 가 45도를 중심으로 하여 소정의 범위 내에 설정되면, 충분한 역회전 방지 효과가 실질적으로 얻어진다. 구체적으로, 이 각도가 30도에서 60도이면, 충분한 역회전 방지 효과가 얻어진다. 이 각도  $\theta$ 가 50도에서 40도로 조정되면, 손가락 누름과 같은 교란이 발생하더라도, 안정한 배향이 유지될 수 있다. 이 각도  $\theta$ 는 다수의 공통 신호 배선 라인(1602)의 예지와 디스플레이 영역에서의 방향과 상이한 방향으로 기울어진 픽셀 전극(1609)의 일부의 예지 사이의 각도에 거의 일치한다.

<106> 제 18의 실시예에 따르면, 프린지 전계가 작용하는 방향과 LC층에서의 LC 분자의 초기 배향 방향에 의해 형성되는 각도( $\theta$ )를 규정함으로써, 강한 역회전 방지 효과가 얻어진다.

<107> [제19의 실시예]

<108> 다음에, 제19의 실시예가 도 16을 참조하여 설명된다. 프린지 전계(fringe electric field)에 기인한 액정층의 액정 분자의 분자 축의 회전 방향 및 LC 분자의 분자 축의 소요의 회전 방향이 동일한 영역의 길이는 예시로서 정의된다.

<109> 상기 정의된 길이는 이하에서 설명된다. 공통 신호 배선의 예지로부터의 길이(d)가 LC층의 두께보다 더 길게 조절되는 경우에, 강한 역회전 방지 효과가 얻어진다.

<110> 따라서, 제19의 실시예에 따르면, 전술한 각( $\theta$ ) 및 길이(d)가 정의되고, 강한 역회전 방지 효과가 얻어진다.

<111> [제20의 실시예]

<112> 다음에, 제20의 실시예가 도 16을 참조하여 설명된다. 복수의 공통 신호 배선의 형상은 본 실시예에서 정의된다.

<113> 표시 영역과 대면하고 픽셀의 표시 영역의 경계를 결정하는 복수의 공통 신호 배선의 예지는 직선으로 형성된다. 종래 기술에서, 공통 신호 배선의 예지는 톱니(saw)형상을 포함하는데, 그 이유는 역회전 방지 구조가 그 상부에 형성되기 때문이다.

<114> 따라서, 투과광은 배선 예지에서 산란된다.

<115> 제20의 실시예에 따르면, 픽셀의 표시 영역의 경계를 결정하는 복수의 공통 신호 배선의 예지가 단순한 선형 형상이 되도록 형성되는 경우에, 배선 예지에서의 투과광의 산란이 억제된다. 본 실시예의 복수의 공통 신호 배선은 톱니 형상을 포함하지 않기 때문에, 투과광의 산란이 억제되고 특히 블랙 표시시의 선형 편광(linearly polarized light) 상태가 나빠지지 않는다. 블랙 레벨 휘도가 증가하지 않기 때문에, 높은 콘트라스트가 얻어진다.

<116> [제21의 실시예]

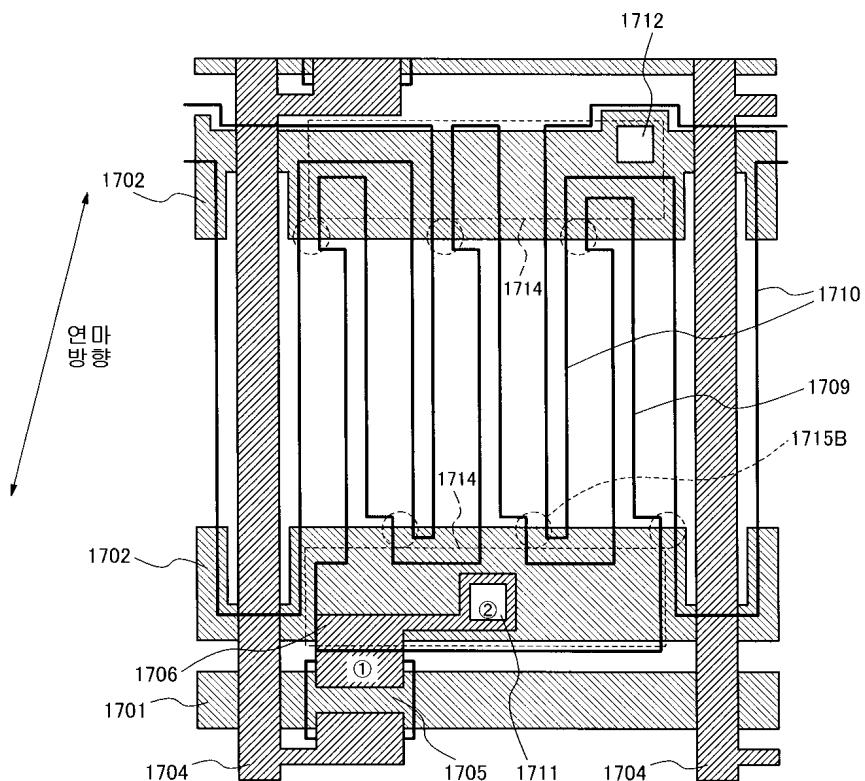

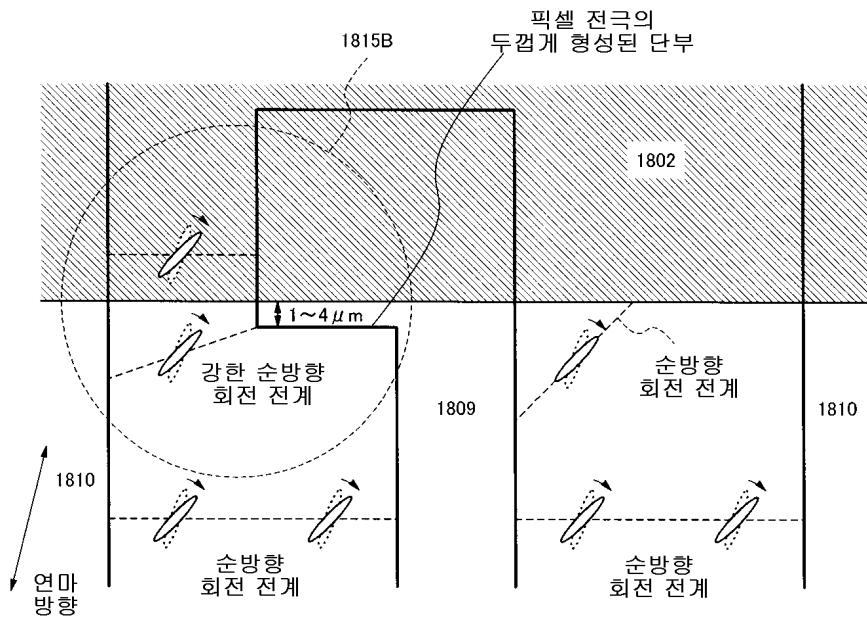

<117> 다음에, 제21의 실시예가 도 17 및 도 18을 참조하여 설명된다. 본 실시예의 표시 장치에는 상기 언급한 제1의 역회전 방지 구조와는 다른 역회전 방지 구조가 마련된다. 도 17은 본 실시예의 LCD 장치의 픽셀 구성을 도시하는 평면도이고, 도 18은 본 실시예의 역회전 방지 구조에서 LC 분자의 동작을 도시하는 도면이다.

<118> 특히, 픽셀 전극(1709)의 양쪽 단의 전극 폭은 역회전 전계가 생성되는 측부를 향해 두꺼워지도록 제조된다. 픽셀 전극(1709)의 단부에서의 전극 폭이 두껍게 제조되는 영역의 대부분은 바닥층의 복수의 공통 신호 배선(1702)과 중첩된다.

<119> 도 18은 상기 구조에 의해 역회전이 방지되는 이유와 제1의 역회전 방지 구조와의 상이점을 도시한다. 도 18에 있어서, 역회전 전계가 생성되는 영역 부근에서, 픽셀 전극(1809)의 폭은 두껍고, 픽셀 전극(1809)과 공통 전극(1810) 사이의 간격은 협소하다. 상기 구조에 기인하여, 강한 순방향 회전 전계가 발생하고 역회전 전계의 동작이 억제된다. 도 7a에서 도시된 제1의 역회전 방지 구조에 있어서, 복수의 공통 신호 배선(702)의 예지는 표시 영역에서의 그 방향과는 상이한 방향으로 경사지는 픽셀 전극의 일부와 교차한다. LC 분자의 순방향에 대한 프린지 전계는 복수의 공통 신호 배선(702)과 픽셀 전극(709)의 예지 사이에서 발생한다. 따라서, 역회전 전계의 영향이 억제된다. 도 18에 도시된 역회전 방지 구조에 있어서, 강한 순방향 회전 전계가 픽셀 전극(1809)과 공통 전극(1810) 사이에서 발생한다. 이하, 도 18에 도시된 역회전 방지 구조는 제2의 역회전 방지 구조라고 한다.

- <120> 본 제21의 실시예에 따르면, 단락 주파수(frequency of a short circuit)가 실질적으로 감소하고, 전체 표시 영역에서 LC 분자의 역회전을 방지하는 효과가 증가하고, 광 이용 효율이 증가한다. 손가락의 놀린 자국이 LC 패널의 스크린상에 남지 않는다.

- <121> [제22의 실시예]

- <122> 다음에, 제22의 실시예가 도 17을 참조하여 설명될 것이다. 픽셀 전극 직하의 제3의 절연층을 제거함에 의해 형성된 오목부의 에지로부터 표시 영역까지의 거리가 정의된다.

- <123> 제3의 절연막을 제거함에 의해 형성된 오목부(1714)의 에지가 표시 영역에 대해 근접한 경우에, 단차에 기인한 광 누설이 발생하여 블랙 레벨 휘도를 증가시킨다. 따라서, 본 실시예에 있어서, 제3의 절연막을 제거함에 의해 형성된 오목부(1714)의 에지로부터 표시 영역까지의 거리가 정의된다. 상기 거리가 큰 경우에 광 누설이 양호하게 억제된다. 적어도  $2\mu\text{m}$ 의 거리가 유지되면, 단차에 기인한 광 누설이 공통 신호 배선(1702)에 의해 저지되고, 블랙 레벨 휘도는 증가하지 않는다.

- <124> 제22의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고 LC 분자의 역회전이 전체 표시 영역에서 방지되고 충분한 축적 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 콘트라스트가 개선된다.

- <125> [제23의 실시예]

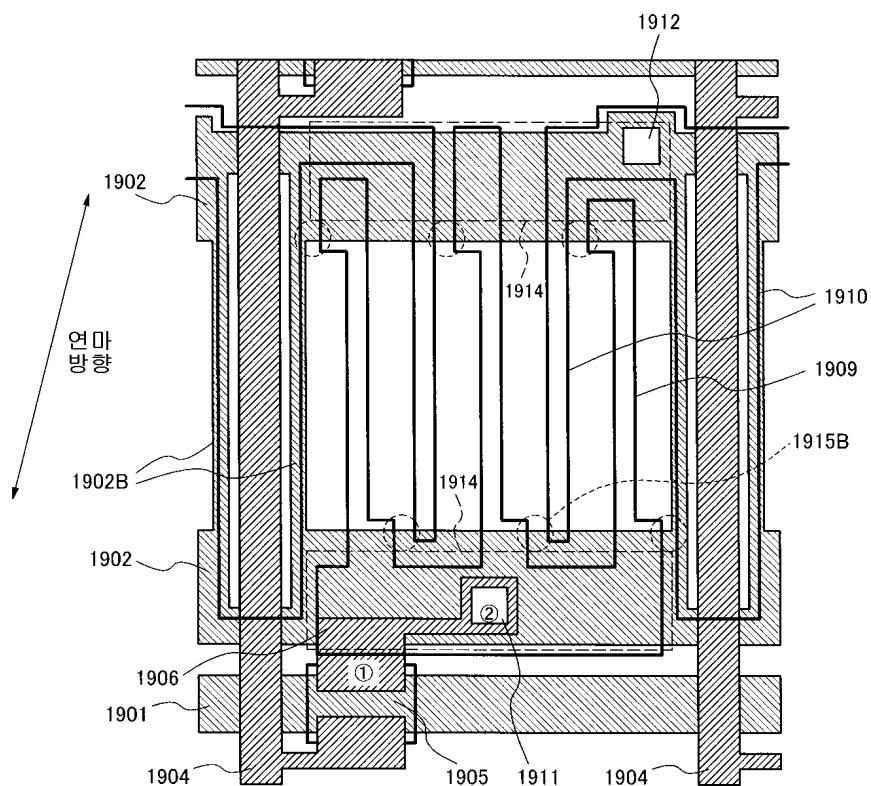

- <126> 다음에 제23의 실시예가 도 19를 참조하여 설명될 것이다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 픽셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부(1902B)에 의해 전기적으로 접속된다.

- <127> 픽셀의 상부측과 하부측의 2개의 공통 신호 배선(1902)을 접속부(1902B)와 접속함에 의해, 공통 신호의 지연이 감소하고 휘도의 평면내 분포(in-plane distribution) 또는 플리커(flicker) 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여한다. 상기 구성은 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(1902B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

- <128> 제23의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 분자의 역회전을 방지하는 효과가 증가하고, 광 이용 효율이 증가한다. 손가락 놀림 자국은 LC 패널의 스크린상에서 남지 않는다. 휘도의 평면내 분포 또는 플리커 레벨이 균일해지고, 수직 크로스 토크가 억제되고 화질이 개선된다.

- <129> [제24의 실시예]

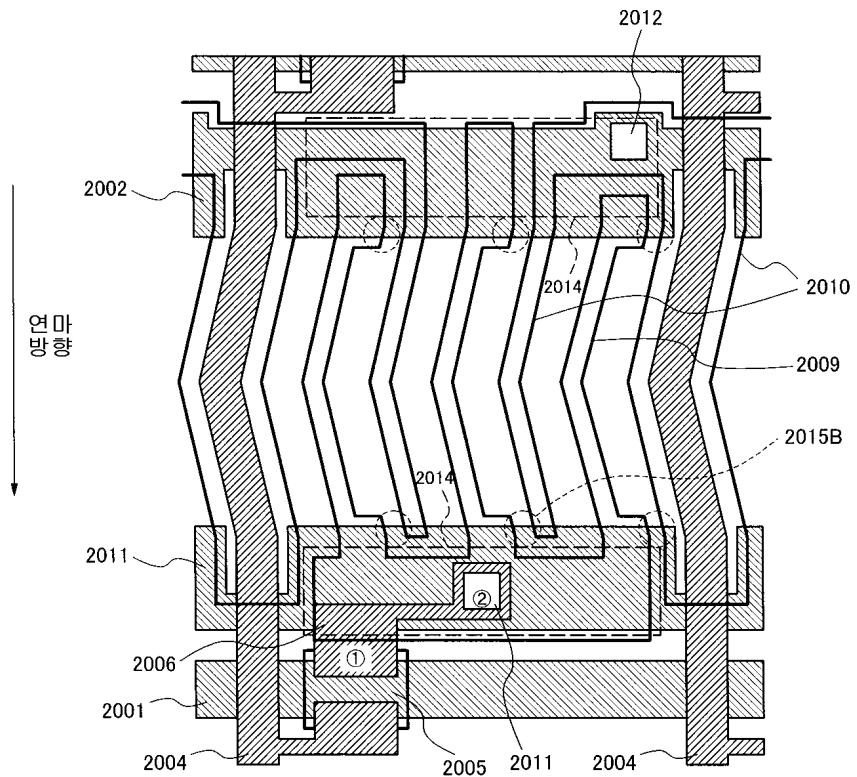

- <130> 다음에 제24의 실시예가 도 20을 참조하여 설명된다. 공통 전극(2010), 픽셀 전극(2009), 및 복수의 영상 신호 배선(2004)은 굽어져 표시 영역의 중심에서 멀티 도메인 구조를 형성한다.

- <131> 본 구조에 따르면, 제2의 역회전 방지 구조(2015B)의 방향이 제21 및 제22의 실시예에서 설명된 싱글 도메인의 방향으로부터 변한다.

- <132> 제24의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, LC 분자의 역회전 방지 효과가 전체 표시 영역에서 증가하고, 광 이용 효율이 증가한다. 손가락의 놀린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 색상 전이(color shift)가 멀티 도메인 구조에 의해 억제된다.

- <133> [제25의 실시예]

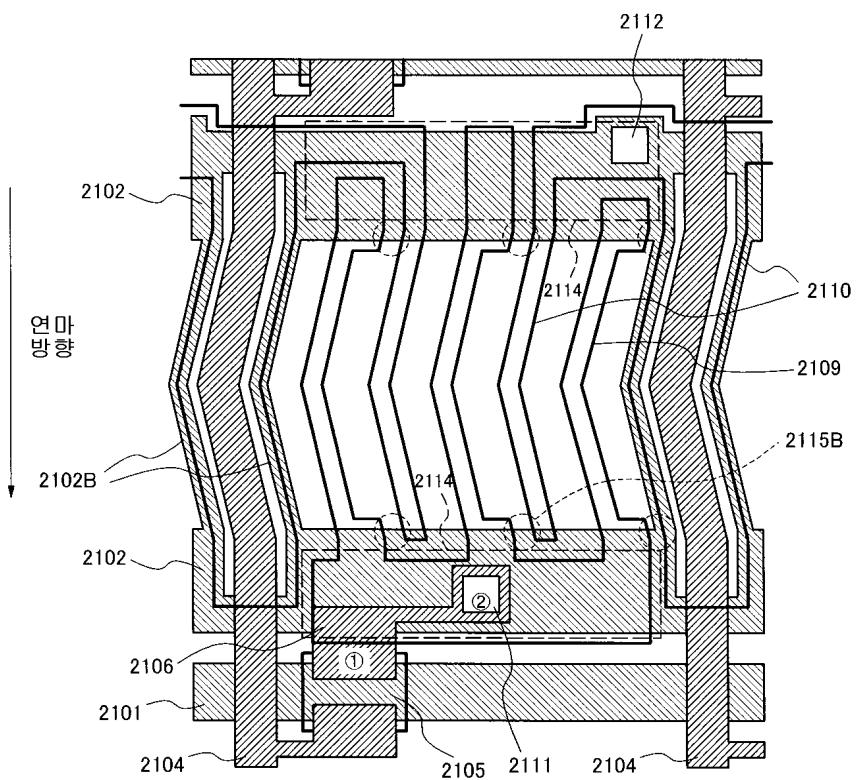

- <134> 다음에, 제25의 실시예가 도 21을 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 픽셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부에 의해 전기적으로 접속된다.

- <135> 픽셀의 상부측과 하부측의 2개의 공통 신호 배선(2102)을 접속부(2102B)에 접속함에 의해 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(2102B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

- <136> 제25의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 분자의 역회전을 방지하는 효과가 증가하고, 광 이용 효율이 증가한다. 손가락의 놀린 자국이 LC 패널의 스크린상에 남지 않는다. 스크

린을 경사방향으로 보더라도, 색상 전이가 멀티 도메인 구조에 의해 억제된다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

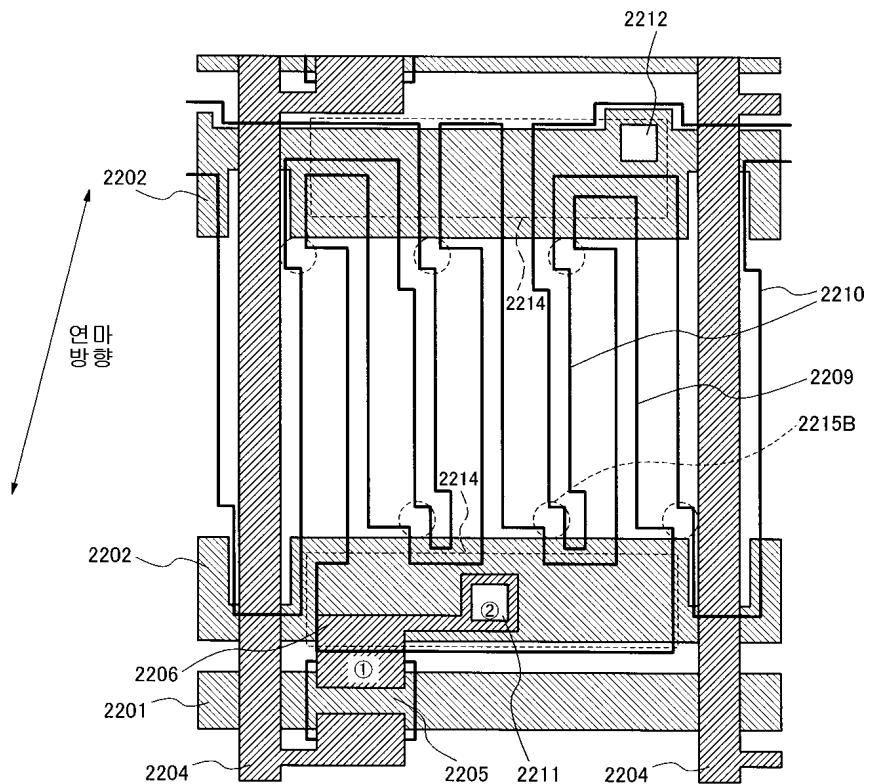

<137> [제26의 실시예]

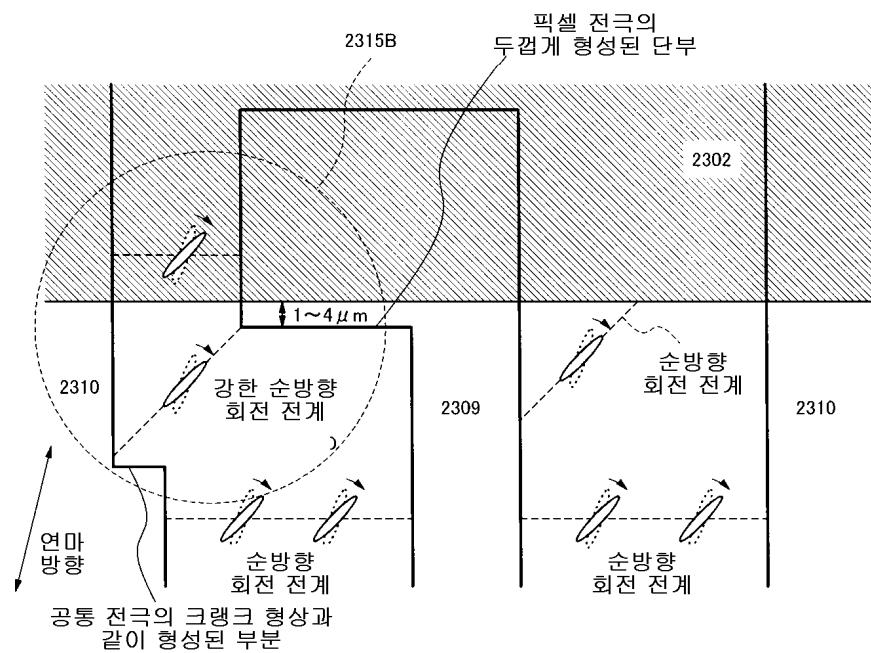

다음에, 제26의 실시예가 도 22 및 도 23을 참조하여 설명된다. 제2의 역회전 방지 구조(2215B)에 있어서, 넓은 에지를 갖는 핵셀 전극(2209)에 인접한 공통 전극(2210)은 핵셀 전극(2209)의 형상에 따른 개략 크랭크(crank) 형상이다. 역회전 전계를 억제하는 효과는 본 실시예에서 한층 더 높게 될 것이다.

<139> 상기 효과에 대한 이유는 도 23을 참조하여 설명된다. 전극 에지의 코너부가 서로 근접한 영역에서, 강한 순방향 회전 전계가 발생한다. 상기 전계는 LC 분자의 초기 배향 방향으로 강한 회전 토크를 가한다. 특히, LC 분자의 초기 배향 방향 및 순방향 회전 전계가 작용하는 방향은 약 45도를 이룬다. 역회전 전계를 억제하는 효과는 본 실시예에서 한층 더 높게 된다.

<140> 제26의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, 전체 표시 영역에서 LC 분자의 역회전을 방지하는 효과가 증가되고, 광 이용 효율은 증가한다. 손가락의 누름 자국이 LC 패널의 스크린상에 남지 않는다.

<141> [제27의 실시예]

<142> 다음에, 제27의 실시예가 도 22를 참조하여 설명될 것이다. 핵셀 전극 직하의 제3의 절연층을 제거함에 의해 형성된 오목부의 에지로부터 표시 영역까지의 거리가 본 실시예에서 정의된다.

<143> 본 실시예가 상세히 설명된다. 제3의 절연막을 제거함에 의해 형성된 오목부(2214)의 에지가 표시 영역에 근접한 경우에, 단차에 의해 발생한 광 누설이 일어나 블랙 레벨 휘도의 증가를 초래한다. 따라서, 본 실시예에 있어서, 제3의 절연막을 제거함에 의해 형성된 오목부(2214)의 에지로부터 표시 영역까지의 거리가 정의된다. 상기 거리가 큰 경우에 광 누설이 양호하게 억제된다. 적어도 2mm의 거리가 유지되면, 단차에 기인한 광 누설은 복수의 공통 신호 배선(1702)에 의해 저지되고, 블랙 레벨 휘도는 증가하지 않는다.

<144> 따라서, 제27의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고 LC 분자의 역회전이 전체 표시 영역에서 방지되고 충분한 축적 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 콘트라스트가 개선된다.

<145> [제28의 실시예]

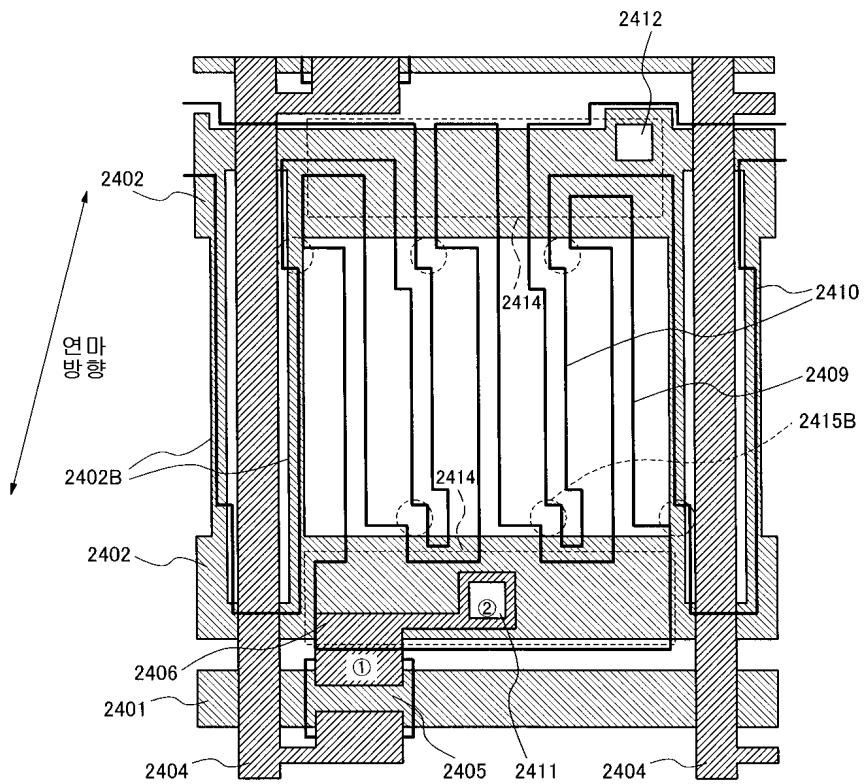

<146> 다음에, 제28의 실시예가 도 24를 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 핵셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부를 경유하여 전기적으로 접속된다.

<147> 핵셀의 상부측과 하부측의 2개의 공통 신호 배선(2402)과, 접속부(2402B)가를 접속됨에 의해, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여한다. 상기 구성은 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(2402B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

<148> 제28의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 분자의 역회전이 방지되고, 광 이용 효율이 증가한다. 손가락의 놀린 자국이 LC 패널의 스크린상에 남지 않는다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

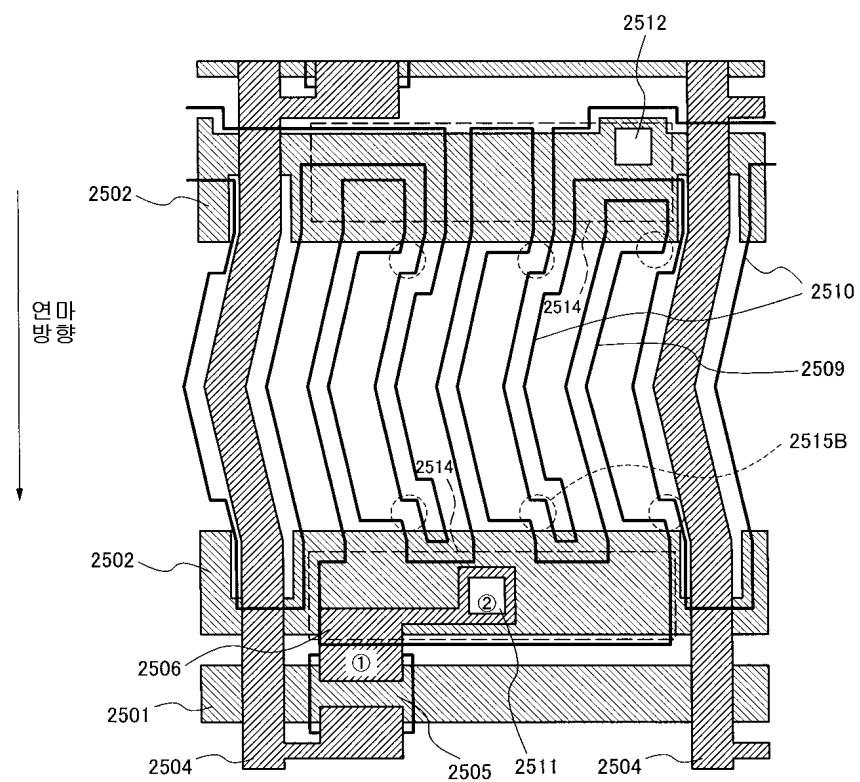

<149> [제29의 실시예]

<150> 다음에, 제29의 실시예가 도 25를 참조하여 설명된다. 공통 전극(2510), 핵셀 전극(2509) 및 복수의 영상 신호 배선(2504)은 굽어져 표시 영역의 중심에서 멀티 도메인 구조를 형성한다. 본 구조에 따르면, 제2의 역회전 방지 구조(2515B)는 제26 및 제27의 실시예에서 설명된 싱글 도메인의 방향으로부터 변한다.

<151> 제29의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, LC 분자의 역회전 방지 효과가 전체 표시 영역에서 증가하고, 광 이용 효율이 증가한다. 손가락의 놀린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 색상 전이가 멀티 도메인 구조에 의해 억제된다.

<152> [제30의 실시예]

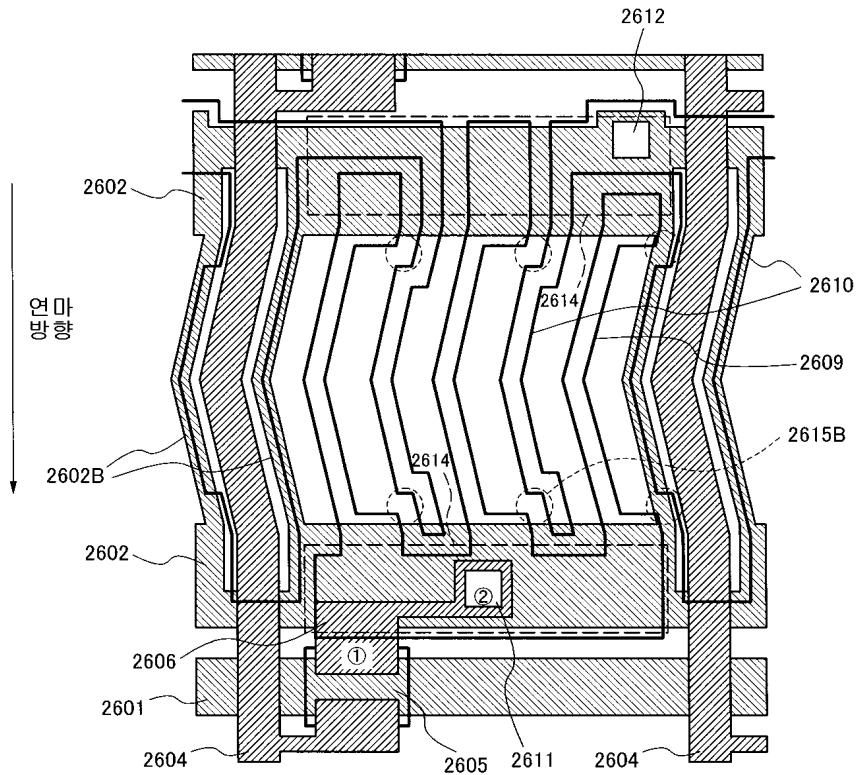

<153> 다음에, 제30의 실시예가 도 26을 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 핵셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부를 경

유하여 의해 전기적으로 접속된다.

<154> 핵셀의 상부측과 하부측의 2개의 공통 신호 배선(2602)과 접속부(2602B)가 접속되는 경우에, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(2602B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

<155> 제30의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 문자의 역회전이 방지되고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 색상 전이가 멀티 도메인 구조에 의해 억제된다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

<156> [제31의 실시예]

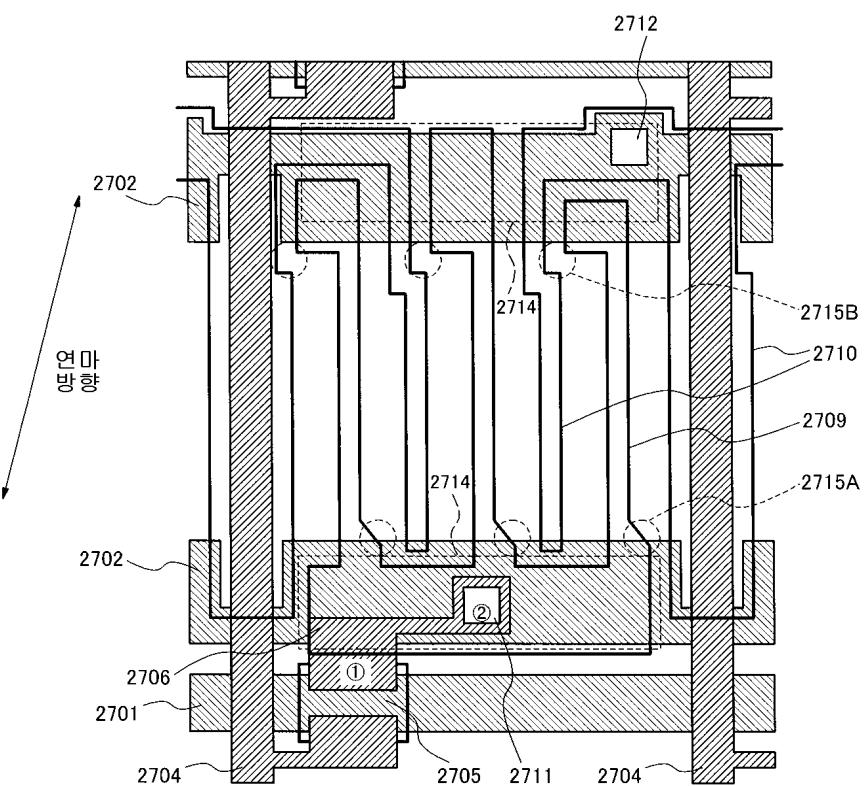

<157> 다음에, 제31의 실시예가 도 27을 참조하여 설명된다. 제1의 역회전 방지 구조(2715A)는 핵셀의 한쪽 측(예를 들면, 하부측)에서 사용되고, 제2의 역회전 방지 구조(2715B)는 핵셀의 다른 쪽 측(예를 들면, 상부측)에서 사용된다. 상기와 같은 역회전 방지 구조의 조합은 뒤집을 수도 있고, 설계 조건에 따라 자유롭게 설정할 수 있다.

<158> 본 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, 전체 표시 영역에서 LC 문자의 역회전을 방지하는 효과가 증대되고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다.

<159> [제32의 실시예]

<160> 다음에, 제32의 실시예가 도 27을 참조하여 설명될 것이다. 핵셀 전극 직하의 제3의 절연층을 제거함에 의해 형성된 오목부의 에지로부터 표시 영역까지의 거리가 정의된다.

<161> 제3의 절연막을 제거함에 의해 형성된 오목부(2714)의 에지가 표시 영역에 대해 근접한 경우에, 단차에 기인한 광 누설이 발생하여 블랙 레벨 휘도를 증가시킨다. 따라서, 본 실시예에 있어서, 제3의 절연막을 제거함에 의해 형성된 오목부(2714)의 에지로부터 표시 영역까지의 거리가 정의된다. 상기 거리가 큰 경우에 광 누설이 양호하게 억제된다. 적어도  $2\mu m$ 의 거리가 유지되면, 단차에 기인한 광 누설이 공통 신호 배선(1702)에 의해 저지되고, 블랙 레벨 휘도는 증가하지 않는다.

<162> 제32의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고 LC 문자의 역회전이 전체 표시 영역에서 방지되고 충분한 축적 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 콘트라스트가 개선된다.

<163> [제33의 실시예]

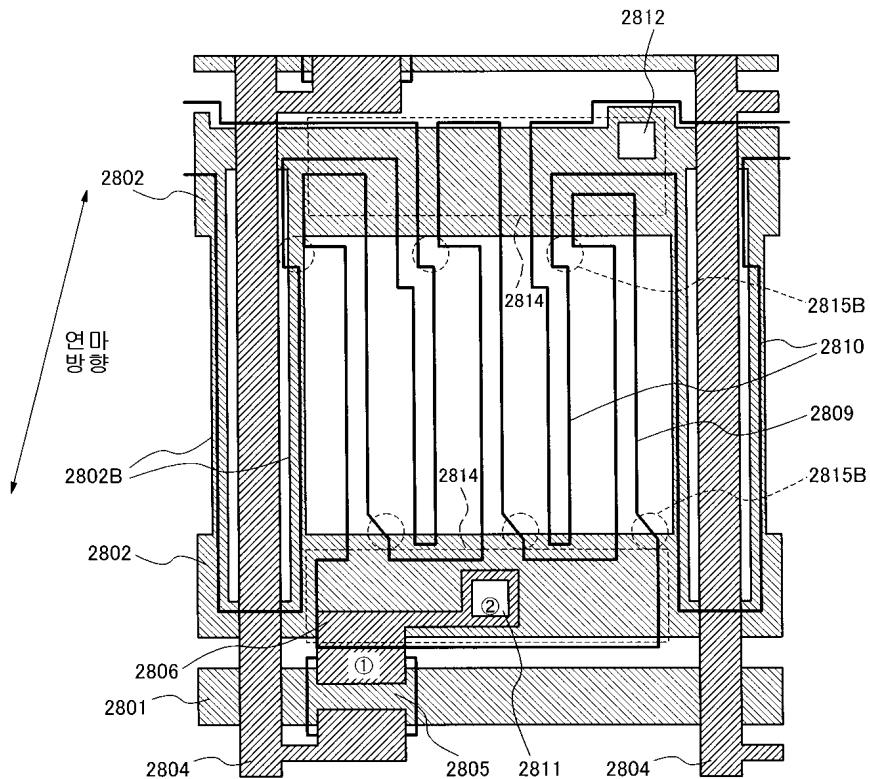

<164> 다음에, 제33의 실시예가 도 28을 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 핵셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부를 경유하여 전기적으로 접속된다.

<165> 핵셀의 상부측과 하부측의 2개의 공통 신호 배선(2802)이 접속부(2802B)에 의해 접속되는 경우에, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(2802B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

<166> 제33의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 문자의 역회전이 방지되고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

<167> [제34의 실시예]

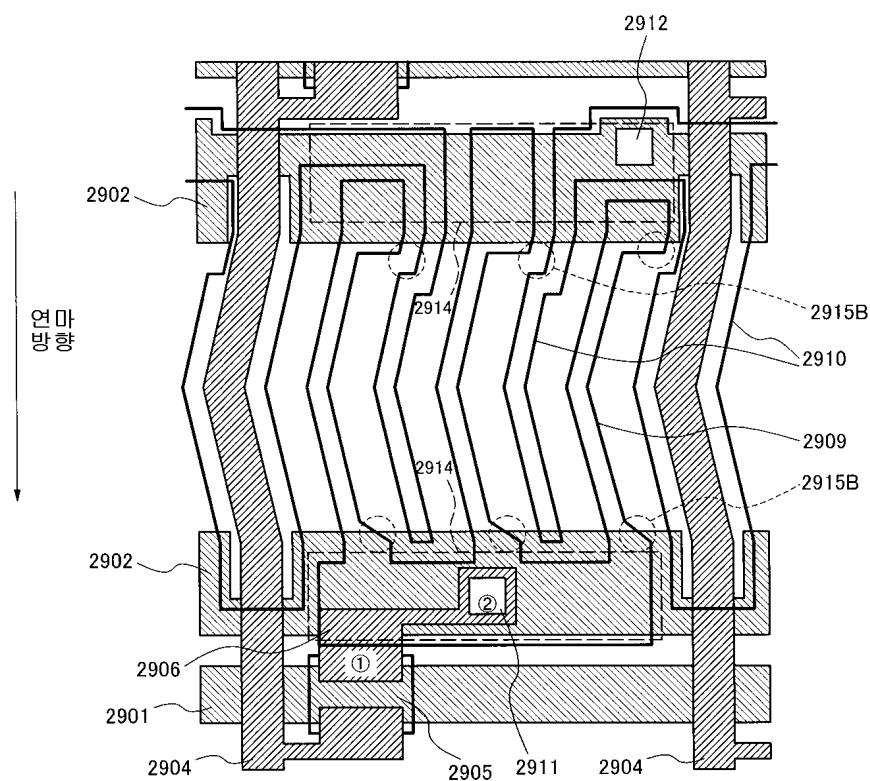

<168> 다음에, 제34의 실시예가 도 29를 참조하여 설명된다. 공통 전극(2910), 핵셀 전극(2909) 및 복수의 영상 신호 배선(2904)은 굽어져 표시 영역의 중심에서 멀티 도메인 구조를 형성한다. 본 구조에 따르면, 제2의 역회전 방지 구조(2915B)의 방향은 제23의 실시예에서 설명된 싱글 도메인의 방향으로부터 변한다.

<169> 제34의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, LC 문자의 역회전 방지 효과가 전체 표시 영역에

서 증가하고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 색상 전이가 멀티 도메인 구조에 의해 억제된다.

<170> [제35의 실시예]

다음에, 제35의 실시예가 도 30을 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 픽셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부(1902B)에 의해 전기적으로 접속된다.

픽셀의 상부측과 하부측의 2개의 공통 신호 배선(2102)이 접속부(3002B)에 의해 접속되는 경우에, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 폴리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(3002B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

제35의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 문자의 역회전을 방지하는 효과가 증가하고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 본 실시예의 표시 장치에 있어서, 멀티 도메인 구조에 기인하여, 스크린을 경사방향으로 보더라도, 색상 전이가 억제된다. 휘도의 평면내 분포 또는 폴리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

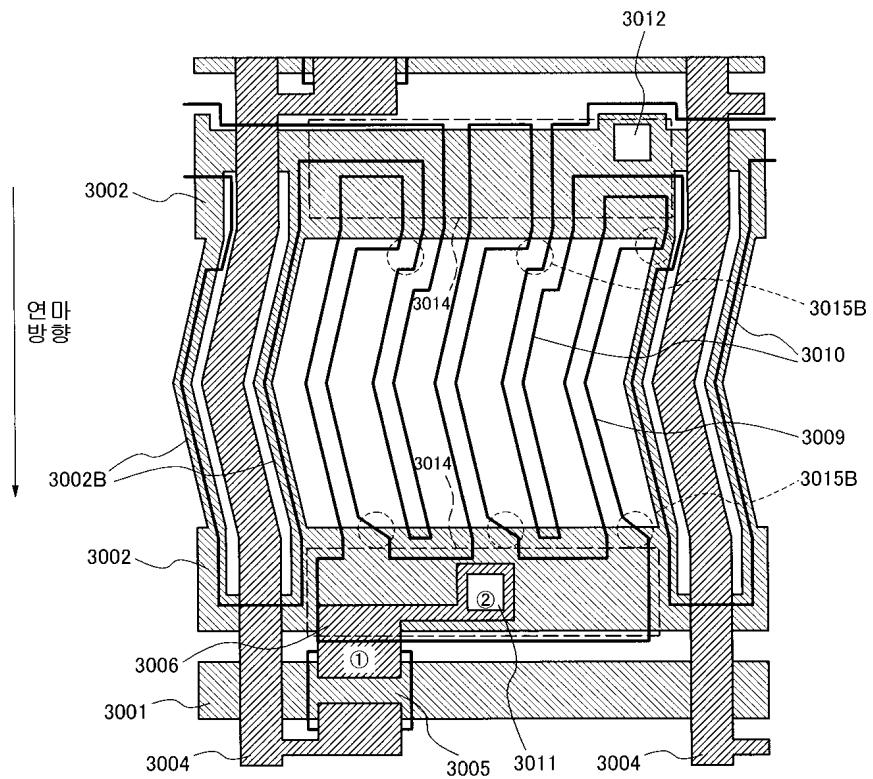

<174> [제36의 실시예]

다음에, 제36의 실시예가 도 31을 참조하여 설명된다. 제2의 역회전 방지 구조(3115B)에 있어서, 픽셀 전극(3109)과 인접한 공통 전극(3110)은 픽셀 전극(3109)의 형상에 완전히 따른 형상을 포함하지 않지만, 그 첨단(tip) 부근에서 경사진 형상을 포함한다. 형상을 변경하는 경우에도, 역회전 전계를 방지하는 효과는 그대로 변하지 않고, 공통 전극(3110)의 형상은 설계 조건에 따라 자유롭게 형성될 수 있다. 본 실시예에 따른 공통 전극(3110)의 형상은 열(column) 폭이 협소하고 직각 크랭크 형상이 용이하게 제조되지 못하는 경우에 유효하다.

제36의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, LC 문자의 역회전 방지 효과가 전체 표시 영역에서 증가하고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다.

<177> [제37의 실시예]

다음에, 제37의 실시예가 도 31을 참조하여 설명될 것이다. 픽셀 전극 직하의 제3의 절연층을 제거함에 의해 형성된 오목부의 에지로부터 표시 영역까지의 거리가 정의된다.

제3의 절연막을 제거함에 의해 형성된 오목부(3114)의 에지가 표시 영역에 근접한 경우에, 단차에 의해 발생한 광 누설이 일어나 블랙 레벨 휘도의 증가를 초래한다. 따라서, 본 실시예에 있어서, 제3의 절연막을 제거함에 의해 형성된 오목부(3114)의 에지로부터 표시 영역까지의 거리가 정의된다. 상기 거리가 큰 경우에 광 누설이 양호하게 억제된다. 적어도  $2\mu\text{m}$ 의 거리가 유지되면, 단차에 기인한 광 누설은 복수의 공통 신호 배선(1702)에 의해 저지되고, 블랙 레벨 휘도는 증가하지 않는다.

제37의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고 LC 문자의 역회전이 전체 표시 영역에서 방지되고 충분한 축적 용량이 형성된다. 블랙 레벨 휘도가 증가하지 않기 때문에, 콘트라스트가 개선된다.

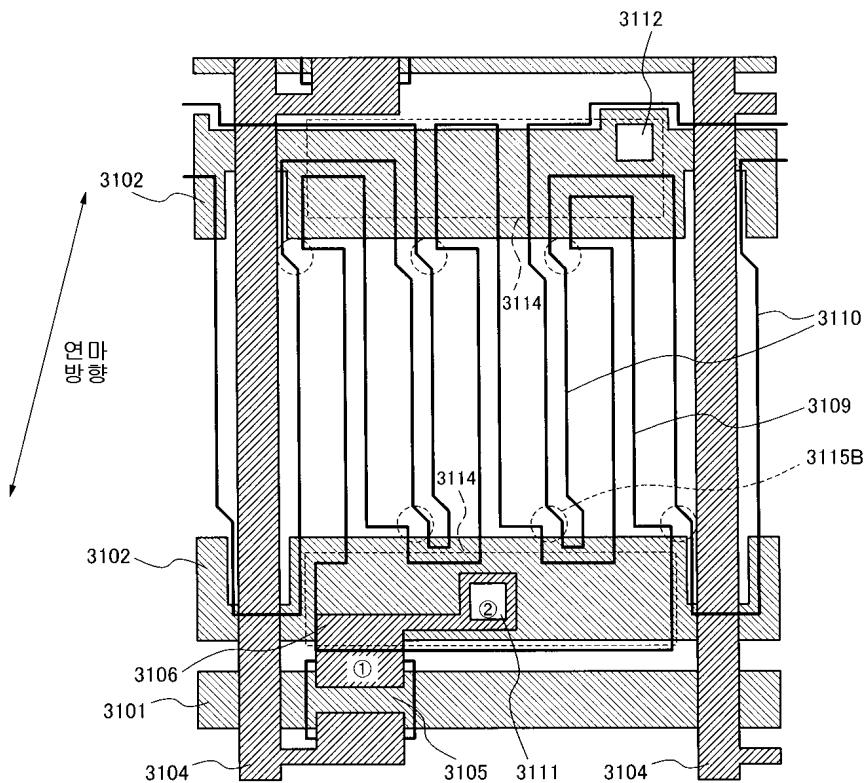

<181> [제38의 실시예]

다음에, 제38의 실시예가 도 32를 참조하여 설명된다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 픽셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부(1902B)에 의해 전기적으로 접속된다.

픽셀의 상부측과 하부측의 2개의 공통 신호 배선(3202)이 접속부(3202B)에 의해 접속되는 경우에, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 폴리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(3202B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

제38의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 문자의 역회전이 방지되

고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

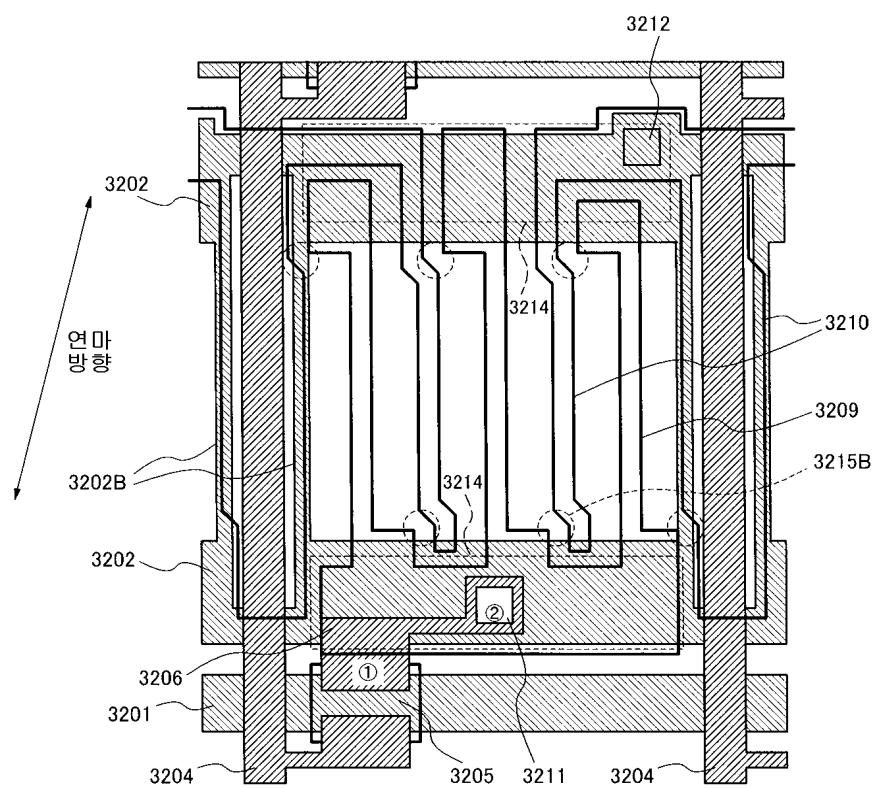

<185> [제39의 실시예]

다음에, 제39의 실시예가 도 33을 참조하여 설명된다. 공통 전극(3310), 픽셀 전극(3309) 및 복수의 영상 신호 배선(3304)은 굽어져 표시 영역의 중심에서 멀티 도메인 구조를 형성한다. 본 구조에 따르면, 제2의 역회전 방지 구조(3315B)의 방향은 제36의 실시예 및 제37의 실시예에서 설명된 싱글 도메인의 방향으로부터 변한다.

<187> 제39의 실시예에 따르면, 단락 주파수가 실질적으로 감소하고, LC 분자의 역회전 방지 효과가 전체 표시 영역에서 증가하고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 색상 전이가 멀티 도메인 구조에 의해 억제된다.

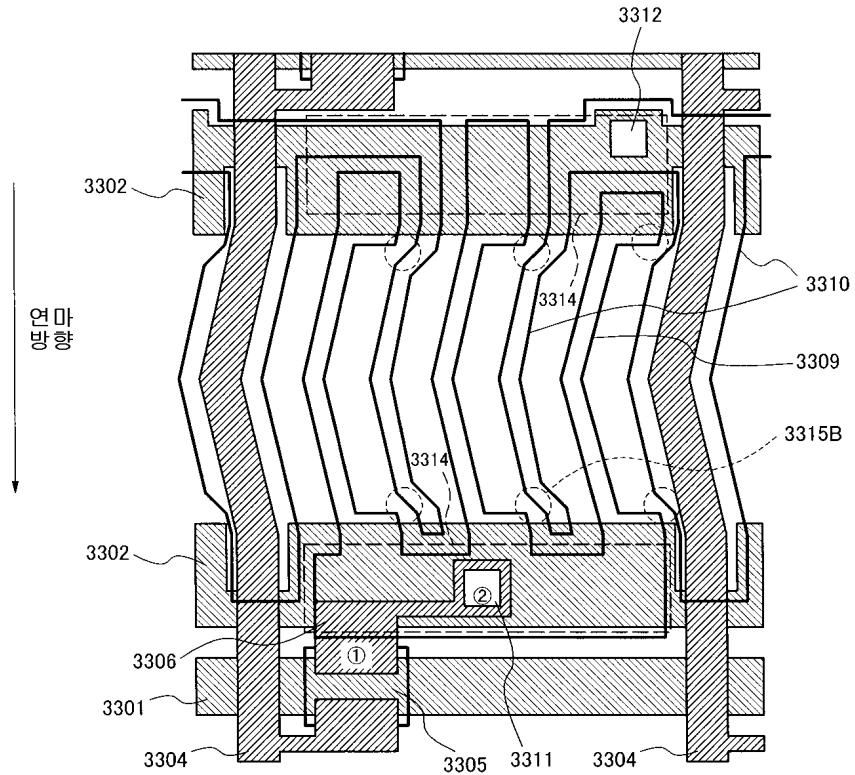

<188> [제40의 실시예]

다음에, 제40의 실시예가 도 34를 참조하여 설명될 것이다. 제1의 축적 용량 형성부와 제2의 축적 용량 형성부 내에 있는 픽셀의 상부 및 하부에 배치된 2개의 공통 신호 배선은 복수의 영상 신호 배선을 따라 배치된 접속부(1902B)에 의해 전기적으로 접속된다.

<190> 픽셀의 상부측과 하부측의 2개의 공통 신호 배선(3402)이 접속부(3402B)에 의해 접속되는 경우에, 공통 신호의 지연이 감소하고 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 된다. 상기 구성은 표시의 고화질에 기여하고, 장치가 대형이고 고화질이 요구되는 경우에 고화질 표시에 효과적이다. 실시예에 있어서, 접속부(3402B)가 복수의 영상 신호 배선의 측면을 따라 배치되는 경우에, 복수의 영상 신호 배선으로부터 표시 영역까지의 누설 전계가 강하게 억제되고 수직 크로스 토크가 억제된다.

<191> 제40의 실시예에 따르면, 단락 주파수가 실질적으로 감소되고, 전체 표시 영역에서 LC 분자의 역회전이 방지되고, 광 이용 효율이 증가한다. 손가락의 눌린 자국이 LC 패널의 스크린상에 남지 않는다. 스크린을 경사방향으로 보더라도, 멀티 도메인 구조에 의해 색상 전이가 억제된다. 휘도의 평면내 분포 또는 플리커 레벨이 균일하게 되고, 수직 크로스 토크가 억제되고 화질이 개선된다.

<192> [제41의 실시예]

다음에, 제41의 실시예가 도 18 및 도 23을 참조하여 설명된다. 픽셀 전극의 양단에서 넓은 폭을 갖는 영역의 에지와 복수의 공통 신호 배선의 에지 사이의 위치 관계가 정의된다.

<194> 도 18 및 도 23에 따르면, 역회전 전계를 억제하기 위해, 픽셀 전극의 단부의 넓은 폭 영역의 에지가 복수의 공통 신호 배선의 에지로부터  $1\mu m$  내지  $4\mu m$  정도 돌출하는 것이 바람직하다. 그러나, 픽셀 전극의 단부의 넓은 폭 영역의 에지가 복수의 공통 신호 배선의 에지로부터 약  $1\mu m$  정도 물러나더라도 LC 분자의 역회전이 방지된다. 따라서, 픽셀 전극의 단부의 넓은 폭 영역의 에지는 복수의 공통 신호 배선의 에지에 대해 안쪽으로  $1\mu m$  내지 바깥쪽으로  $4\mu m$ 의 범위내에서 형성될 수 있다.

<195> 제41의 실시예에 따르면, 전체 표시 영역에서의 LC 분자에 대한 역회전 방지 구조는 마스크 등을 용이하게 정렬하는 큰 제조 마진을 포함한다.

<196> [제42의 실시예]

다음에, 제42의 실시예가 도 18 및 도 23을 참조하여 설명된다. 복수의 공통 신호 배선의 형상이 본 실시예에서 정의된다.

<198> 표시 영역을 대면하고 픽셀의 표시 영역의 경계를 정의하는 복수의 공통 신호 배선의 에지는 직선 형상을 포함한다. 종래 기술에서, 공통 신호 배선의 에지는, 역회전 방지 구조가 그곳에 형성되기 때문에, 톱니 형상을 포함한다. 따라서, 투과광은 배선의 에지에서 산란된다.

<199> 제42의 실시예에 따르면, 픽셀의 표시 영역의 경계를 정의하는 복수의 공통 신호 배선의 에지가 단순한 선형 형상이 되도록 형성되기 때문에, 배선 에지에서의 투과광의 산란이 억제된다. 투과광의 산란이 억제되기 때문에, 블랙 표시에서의 선형 편광 상태가 나빠지지 않는다. 또한 블랙 레벨 휘도가 증가하기 않기 때문에, 높은 콘트라스트가 얻어진다.

<200> 상기 실시예에 있어서, TFT가 스위칭 소자로서 설명되었다. 그러나, 본 발명에 있어서, 박막 다이오드(TFD) 등의 다른 소자가 스위칭 소자로서 사용될 수 있다. TFT 기판에 대향하는 기판의 구성, TFT 기판, 대향 기판, 및

LC층을 포함하는 액정 패널의 외측상에 배치된 광학 부재의 구성, 및 LC 패널을 조명하는 백라이트의 구성 등은 상기 실시예에 한정되지 않고 다른 이용 가능한 기술을 채택할 수 있다.

<201> 제1 및 제2의 역회전 방지 구조 및 소스 전극이 줄어드는 구조가 상기 언급한 실시예에서 조합될 수 있다. 그러나, 상기의 역회전 방지 구조는 소스 전극이 줄어드는 구조에만 반드시 적용되는 것이 아니다. 상기와 같은 역회전 방지 구조는 복수의 공통 신호 배선 및 그 상부의 공통 전극과 픽셀 전극을 포함하는 장치에 적용될 수 있고, 복수의 픽셀의 단부의 어긋남을 방지하여 높은 콘트라스트를 실현할 수 있다.

<202> 상기 실시예는 2개의 절연층이 복수의 영상 신호 배선상에 배치되고 그 상부에 픽셀 전극과 공통 전극이 배치되는 실시예를 설명한다. 그러나, 상기 구조에서, 하나의 절연층 또는 그 이상의 절연층이 이용 가능하다.

<203> [산업상 이용 가능성]

<204> 본 발명은 횡전계 타입의 액티브 매트릭스형 LCD 장치 및 표시 장치로서 상기 LCD 장치를 이용하는 임의의 기구 (instrument)에 이용 가능하다.

<205> 본 발명은 예시적인 실시예를 참조하여 특별히 설명 및 도시되었지만, 본 발명은 상기 실시예에 한정되지 않는다. 본 분야의 당업자는 청구범위에 의해 정의된 바와 같은 본 발명의 본질 및 범위를 벗어남이 없이 형태 및 상세의 변경이 이루어질 수 있다는 것은 자명하다.

<206> 또한, 본 발명자는 청구범위가 보정되어도 본 발명의 등가적인 기술적 사상을 유지하고자 한다.

### 도면의 간단한 설명

<207> 도 1a는 제1의 실시예에 따른 LCD 장치의 하나의 픽셀의 구조를 도시하는 평면도.

<208> 도 1b는 제1의 실시예에 따른 LCD 장치의 도 1a의 특정 부분의 구조를 도시하는 단면도.

<209> 도 2a는 제2의 실시예에 따른 LCD 장치의 제2의 금속층의 구성을 도시하는 평면도.

<210> 도 3a는 제3 및 제4의 실시예에 따른 LCD 장치의 하나의 픽셀의 구성을 도시하는 평면도.

<211> 도 3b는 제3 및 제4의 실시예에 따른 LCD 장치의 도 3a에서의 특정 부분 구성을 도시하는 단면도.

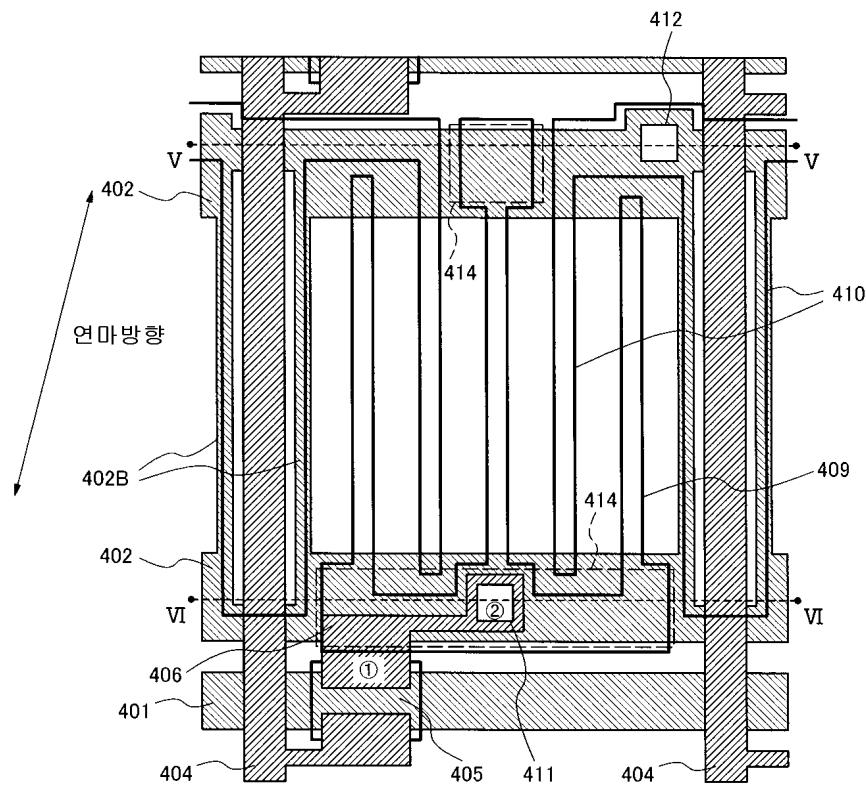

<212> 도 4는 제5의 실시예에 따른 LCD 장치의 하나의 픽셀의 구성을 도시하는 평면도.

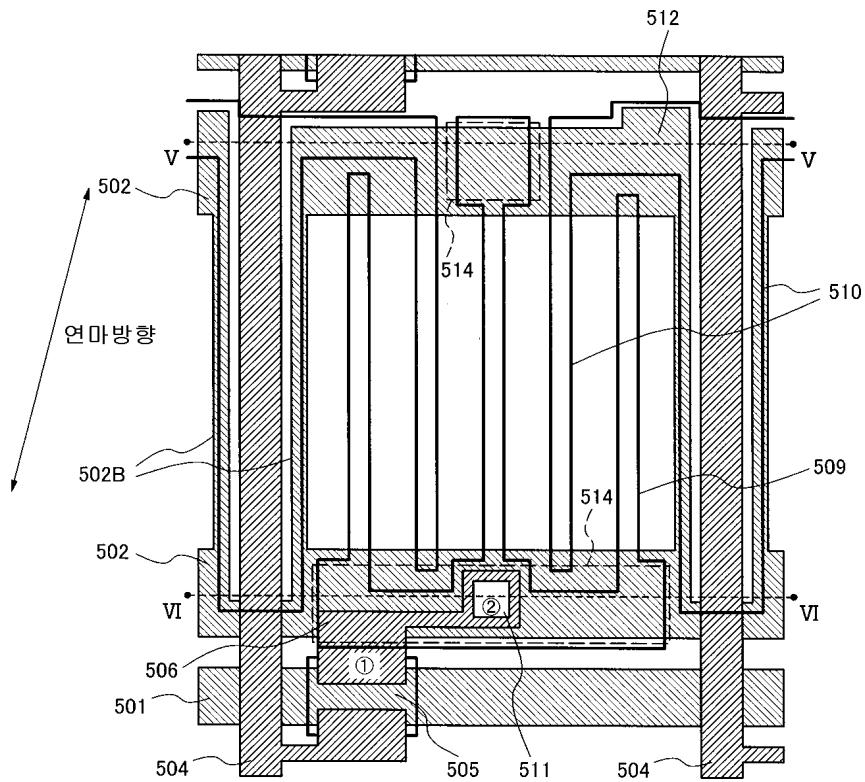

<213> 도 5는 제6의 실시예에 따른 LCD 장치의 픽셀의 구성의 도시하는 평면도.

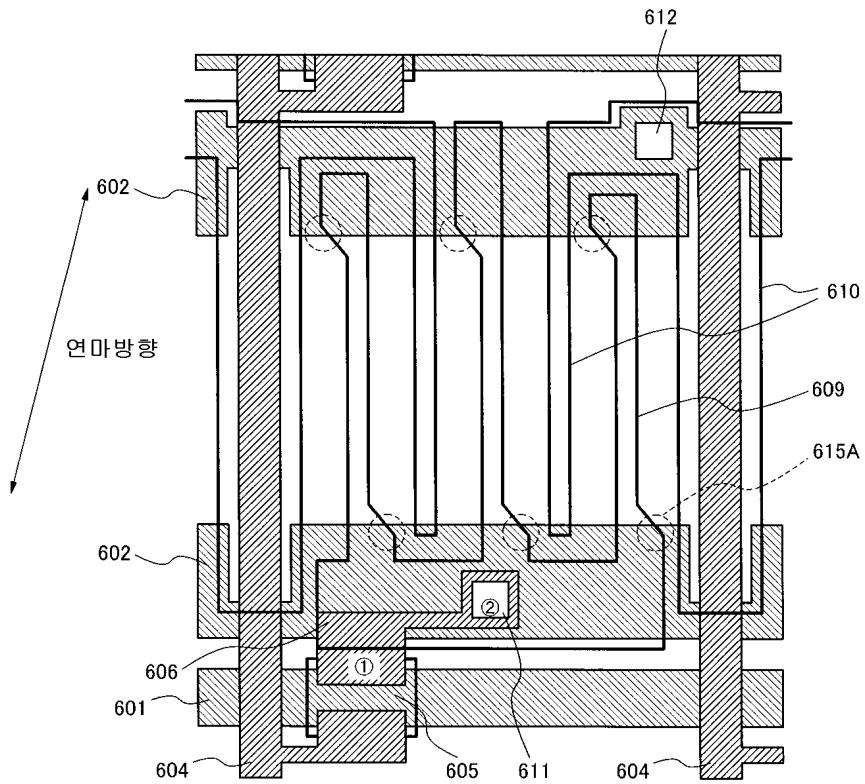

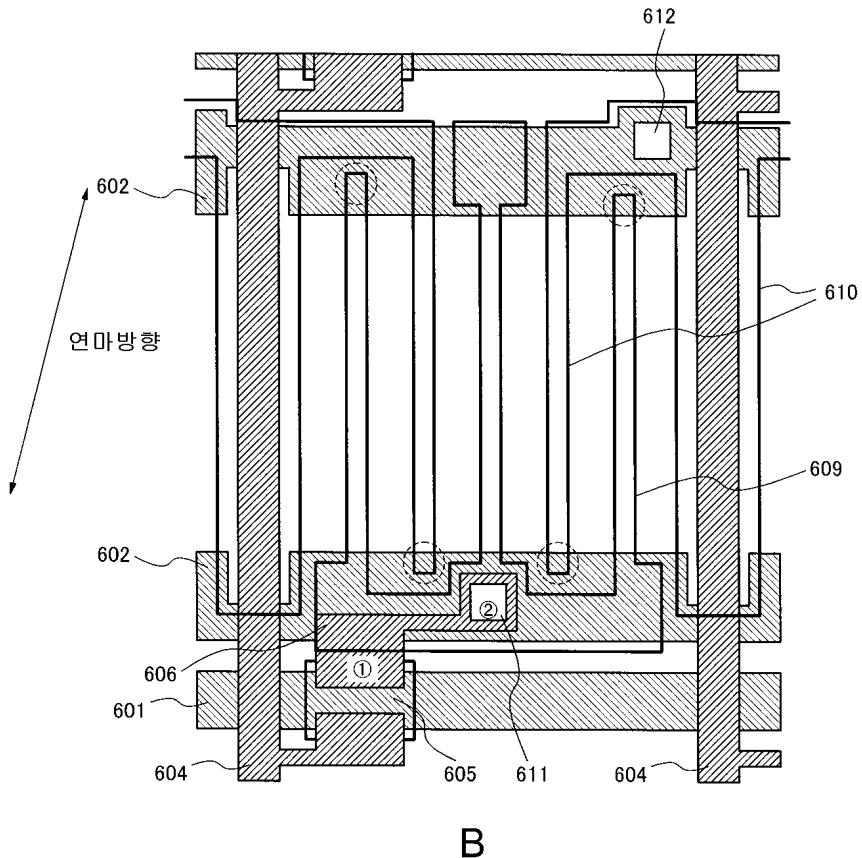

<214> 도 6a 및 도 6b는 제7의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<215> 도 7a 및 도 7b는 제7의 실시예에 따른 LCD 장치에서 제1의 역회전 방지 구조를 방지하는 구조를 도시하는 도면.

<216> 도 8은 제8 및 제9의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<217> 도 9는 제10의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<218> 도 10은 제11의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<219> 도 11은 제12의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<220> 도 12는 제13 및 14의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<221> 도 13은 제15의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<222> 도 14는 제16의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<223> 도 15는 제17의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<224> 도 16은 제18 내지 20의 실시예에 따른 LCD 장치의 제1의 역회전 방지 구조를 도시하는 도면.

<225> 도 17은 제21 내지 22의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

<226> 도 18은 제21의 실시예에 따른 LCD 장치의 제2의 역회전 방지 구조를 도시하는 도면.

<227> 도 19는 제23의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <228> 도 20은 제24의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <229> 도 21은 제25의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <230> 도 22는 제26 및 27의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <231> 도 23은 제26의 실시예에 따른 LCD 장치의 제2의 역회전 방지 구조를 도시하는 도면.

- <232> 도 24는 제28의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <233> 도 25는 제29의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <234> 도 26은 제30의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <235> 도 27은 제31 및 32의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <236> 도 28은 제33의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <237> 도 29는 제34의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <238> 도 30은 제35의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <239> 도 31은 제36 및 37의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <240> 도 32는 제38의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <241> 도 33은 제39의 실시예에 따른 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <242> 도 34는 제40의 실시예에 따른 LCD 장치의 제2의 역회전 방지 구조를 도시하는 도면.

- <243> 도 35a는 종래 기술의 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <244> 도 35b는 종래 기술에서 LCD 장치의 도 35a에서 특정 부분 구성을 도시하는 단면도.

- <245> 도 36a는 종래 기술에서 LCD 장치의 제2의 금속층의 구성을 도시하는 평면도.

- <246> 도 36b는 종래 기술의 LCD 장치의 제2의 금속층에서, 동일층에서 발생하는 복수의 비디오 신호 배선과 소스 전극 사이의 단락의 예를 도시하는 도면.

- <247> 도 37a는 다른 종래 기술에서 LCD 장치의 픽셀의 구성을 도시하는 평면도.

- <248> 도 37b는 종래 기술에서 LCD 장치의 도 37a에 도시된 특정 부분 구성을 도시하는 단면도.

- <249> 도 38a는 종래 기술에서 LCD 장치의 제2의 금속층의 구성을 도시하는 평면도.

- <250> 도 38b는 종래 기술의 LCD 장치의 제2의 금속층에서, 동일층에서 발생하는 복수의 비디오 신호 배선과 소스 전극 사이의 단락의 예를 도시하는 도면.

## 도면

도면1a

A

도면1b

B

도면2a

A

도면2b

도면3a

A

도면3b

B

## 도면4

## 도면5

도면6a

A

### 도면6b

### 도면7a

도면7b

B

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

도면28

도면29

도면30

도면31

도면32

도면33

도면34

도면35a

A

종 래 기 술

도면35b

B

종 래 기 술

도면36a

A

종 래 기 술

도면36b

도면37a

도면37b

도면38a

A

종 래 기 술

도면38b

B

종 래 기 술

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵液晶显示装置                                                                                                     |         |            |

| 公开(公告)号        | KR100934524B1                                                                                                  | 公开(公告)日 | 2009-12-29 |

| 申请号            | KR1020070080458                                                                                                | 申请日     | 2007-08-10 |

| [标]申请(专利权)人(译) | NEC液晶技术株式会社                                                                                                    |         |            |

| 申请(专利权)人(译)    | 日元号技术可否让这个夏                                                                                                    |         |            |

| 当前申请(专利权)人(译)  | 日元号技术可否让这个夏                                                                                                    |         |            |

| [标]发明人         | KONNO TAKAYUKI<br>콘노타카유키<br>NISHIDA SHINICHI<br>니시다신이치<br>SUZUKI TERUAKI<br>스즈키테루아키<br>NOGAMI YUSUKE<br>노가미유스케 |         |            |

| 发明人            | 콘노타카유키<br>니시다신이치<br>스즈키테루아키<br>노가미유스케                                                                          |         |            |

| IPC分类号         | G02F1/1343                                                                                                     |         |            |

| CPC分类号         | G02F1/134363 G02F1/136227 G02F1/136213                                                                         |         |            |

| 优先权            | 2007065078 2007-03-09 JP<br>2006219322 2006-08-11 JP                                                           |         |            |

| 其他公开文献         | KR1020080014679A                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                      |         |            |

### 摘要(译)

公开了一种包括基板和液晶层的有源矩阵液晶显示装置。基板包括：扫描信号布线；公共信号线；视频信号布线与这些布线相交；用扫描信号布线和视频信号布线包围的像素。每个像素包括：薄膜晶体管；具有视频信号布线的层中的源电极；像素电极连接到源电极；和公共电极连接到公共信号布线。源电极包括与扫描信号布线重叠的第一部分和与像素电极连接的第二部分，第二部分位于视频信号布线之间的中心部分周围。液晶层中的分子轴在施加在像素电极和公共电极之间的电场下旋转。