(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

G02F 1/133 (2006.01)

(45) 공고일자

2007년04월23일

(11) 등록번호

10-0710120

(24) 등록일자

2007년04월16일

(21) 출원번호 10-2000-0058462

(22) 출원일자 2000년10월05일

심사청구일자 2005년08월05일

(65) 공개번호 10-2001-0040002

(43) 공개일자 2001년05월15일

(30) 우선권주장 1999-283830 1999년10월05일 일본(JP)

(73) 특허권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

(72) 발명자 안도마사히코

일본이바라끼肯히타치나까시니시오시마3조메14-4

와까기마사또시

일본이바라끼肯히타치시모리야마조3조메17-1-501

(74) 대리인 장수길

구영창

(56) 선행기술조사문현

KR1019980010547 A

\* 심사관에 의하여 인용된 문현

심사관 : 이동윤

전체 청구항 수 : 총 3 항

(54) 액티브 매트릭스형 액정 표시 장치

(57) 요약

전력 소비가 적은 개선된 액정 표시 장치가 개시되어 있다. 액정 표시 장치는 스위칭 소자로서 박막 트랜지스터를 갖는다. 박막 트랜지스터는 게이트 전극상에 순차 적층된 게이트 절연층, 반도체층, 드레인 전극 및 소스 전극, 보호성 절연층을 구비한다. 박막 트랜지스터는 게이트 절연층과 반도체층 사이 및 보호성 절연층과 반도체층 사이에 산화실리콘을 더 구비한다.

대표도

도 1

특허청구의 범위

## 청구항 1.

적어도 한쪽이 투명한 한 쌍의 기판과, 상기 한 쌍의 기판에 협지된 액정층을 가지고, 상기 한 쌍의 기판 중 한쪽에는, 복수의 주사 배선(게이트 전극)과, 상기 복수의 주사 배선과 매트릭스 형태로 형성된 복수의 신호 배선(드레인 전극)과, 상기 복수의 신호 배선과 상기 복수의 주사 배선과의 각각의 교점에 대응하여 형성된 복수의 스위칭 소자와, 상기 스위칭 소자에 접속된 복수의 화소 전극(소스 전극)과, 상기 복수의 주사 배선에 접속되고 상기 복수의 화소 전극과의 사이에, 상기 한 쌍의 기판의 한쪽에 대하여 지배적으로 평행한 전계가 발생하도록 형성된 복수의 공통 전극을 가지는 액티브 매트릭스형 액정 표시 장치로서,

상기 스위칭 소자는, 게이트 전극상에 순차적으로 적층된, 게이트 절연층, 반도체층, 드레인 전극 및 소스 전극, 및 보호성 절연층을 가지고, 상기 게이트 절연층 및 상기 보호성 절연층의 반도체와의 인접 부분에 산화실리콘(SiO<sub>x</sub>)을 갖는 박막 트랜지스터를 가지고, 상기 산화실리콘(SiO<sub>x</sub>)의 조성비(x)가 1.7 이상이고 2 이하인 것을 특징으로 하는 액티브 매트릭스형 액정 표시 장치.

## 청구항 2.

제1항에 있어서,

상기 박막 트랜지스터의 상기 게이트 절연층은 산화실리콘 단층막 또는 질화실리콘과 산화실리콘의 적층막으로 구성되며, 상기 박막 트랜지스터의 상기 보호성 절연층은 산화실리콘으로 구성되는 것을 특징으로 하는 액티브 매트릭스형 액정 표시 장치.

## 청구항 3.

제1항에 있어서,

상기 박막 트랜지스터의 상기 게이트 절연층은 산화실리콘 단층막 또는 질화실리콘과 산화실리콘의 적층막으로 구성되며, 상기 박막 트랜지스터의 상기 보호성 절연층은 상기 반도체층 표면을 산화함으로써 형성된 산화실리콘층으로 구성되는 것을 특징으로 하는 액티브 매트릭스형 액정 표시 장치.

## 청구항 4.

삭제

## 청구항 5.

삭제

## 청구항 6.

삭제

명세서

### 발명의 상세한 설명

#### 발명의 목적

발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액티브 매트릭스형 액정 표시 장치에 관한 것으로, 특히 시야각이 넓고 전력 소비가 적은 평면 스위칭(In-Plane Switching:IPS) 방식에 적합한 액티브 매트릭스형 액정 표시 장치에 관한 것이다.

최근, 박막 트랜지스터로 대표되는 스위칭 소자를 이용한 액티브 매트릭스형 액정 표시 장치는 그 화질이 CRT와 동등하면서도 전력 소비가 적고 사이즈가 작으므로, 퍼스널 컴퓨터, 워크 스테이션 등의 모니터로 사용되고 있다. 이러한 액티브 매트릭스형 액정 표시 장치에서는, 주사 배선, 신호 배선, 공통 배선이 동일 기판상에 배치되고, 화소 전극과 공통 전극 등 2개의 전극이 빗살 형태로 형성된다. 그러므로, 액정에 인가되는 전계의 방향은 기판의 표면에 거의 평행하다. IPS 방식의 액정 표시 장치는 종래의 액정 표시 장치와 비교하여 시야각이 넓으므로, 직시형 모니터용으로는 최적이다.

IPS 방식이 상술한 특징을 갖지만, 광이 투과될 수 있는 개구 면적이 좁고, 따라서 표시 스크린이 비교적 어두우므로, IPS 형 액정 표시 장치에서는 밝은 백라이트를 사용할 필요가 있다. 말하자면, IPS 방식의 액정 표시 장치에서는 전력 소비가 매우 크다.

IPS 방식의 액정 표시 장치의 개구 면적을 확대하기 위해, 일본 특개평 8-62578호는, 공통 전극에 외부로부터 전압을 공급하는 공통 배선의 역할을 주사 배선이 맡도록 하여 공통 배선을 생략한 개선된 표시 장치를 개시하고 있다. 이러한 IPS 방식을 공통 배선 생략(common-wiring-less) IPS 방식이라 호칭한다.

일반적인 액티브 매트릭스형 액정 표시 장치용 스위칭 소자로 사용되는 박막 트랜지스터에서는, 트랜지스터의 드레인과 소스간에 전류가 흐르기 시작하여 트랜지스터가 "온(ON)" 상태로 시프트되는 게이트 전압인 임계 전압  $V_{th}$ 이 1 볼트이다. 이에 비해, 일본 특개평 8-62578에 기재된 이유에 의하면, 액정을 광학적으로 변조하는데 필요한 최대 구동 전압 이상의  $V_{th}$ , 바람직하게는 10볼트 이상의  $V_{th}$ 를 갖는 박막 트랜지스터가 공통 배선 생략 IPS 방식에 사용된다. 그러므로, 인핸스먼트형 스위칭 특성을 보이는 박막 트랜지스터에 균일한 특성을 제공하고, 저가의 표시 장치를 제공하는 것이 바람직하다.

### 발명이 이루고자 하는 기술적 과제

본 발명은 저가의 공통 배선 생략 IPS 방식에 적합한 개선된 액티브 매트릭스형 액정 표시 장치를 제공하려는 것이다. 또한 본 발명은 균일한 인핸스먼트형 스위칭 특성을 보이는 개선된 박막 트랜지스터를 제공하려는 것이다.

### 발명의 구성

본 발명의 액티브 매트릭스형 액정 표시 장치는 스위칭 소자로서 박막 트랜지스터를 갖는다. 박막 트랜지스터는 게이트 전극상에 순차 적층된 게이트 절연층, 반도체층, 드레인 전극 및 소스 전극, 보호성 절연층을 구비한다. 박막 트랜지스터는 게이트 절연층과 반도체층 사이 및 보호성 절연층과 반도체층 사이에 산화실리콘을 더 구비한다. 그러므로, 본 발명에서는 단층의 산화실리콘층 또는 질화실리콘과 산화실리콘의 적층막으로 이루어진 게이트 절연층과, 산화실리콘으로 이루어진 보호성 절연층이 사용된다. 산화실리콘으로 이루어진 보호성 절연층 대신에, 반도체의 표면을 산화하여 보호성 절연층을 형성할 수도 있다. 게이트 절연층과 반도체층 사이 및 보호성 절연층과 반도체층 사이에 사용되는 산화실리콘(SiO<sub>x</sub>)의 조성비(x)는 1.7 이상으로 선택되는 것이 바람직하다. 상기와 같이 제조하면, 임계 전압이 10볼트 이상인 인핸스먼트형 TFT 특성을 보이는 박막 트랜지스터를 얻는 것이 가능하다.

본 발명의 목적, 특성 및 장점은 첨부 도면을 참조하여 후술하는 상세한 설명을 보면 더욱 명확해질 것이다.

### <실시예 1>

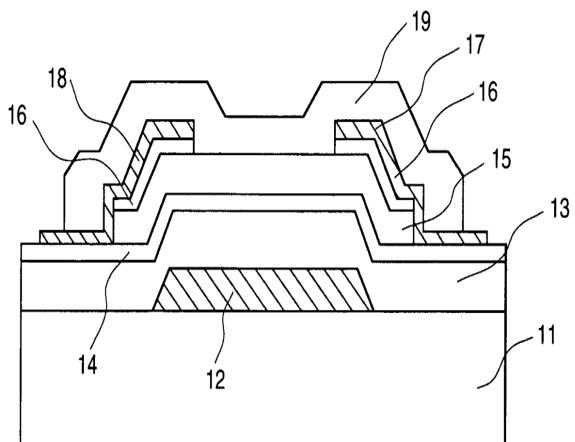

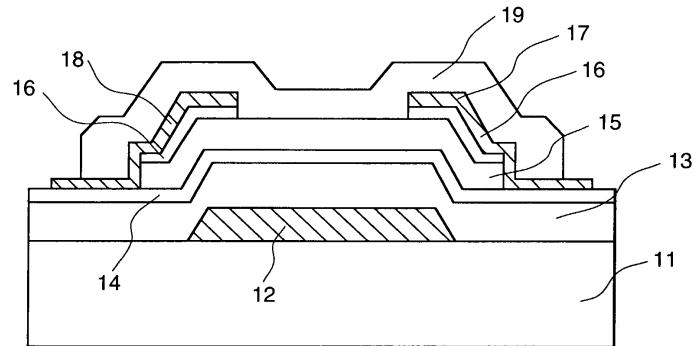

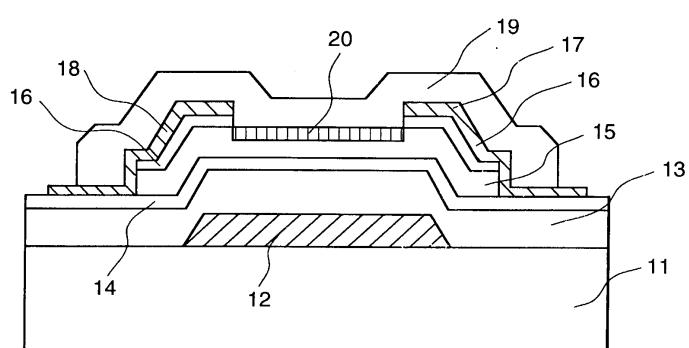

도 1은 본 발명의 액정 표시 장치의 한 실시예에서 사용된 박막 트랜지스터의 단면 구조를 도시한 것이다.

이 구조는 소스/드레인 전극이 게이트 전극에 대해 상방에 배치된 소위 역스태거(inverse stagger) 구조를 갖는다. 도 1에서, 참조 번호 11은 유리 기판을 가리키고, 12는 Cr로 이루어진 게이트 전극, 13은 질화실리콘으로 이루어진 제1 게이트 절연층, 14는 산화실리콘으로 이루어진 제2 게이트 절연층, 15는 아몰퍼스 실리콘으로 이루어진 반도체층, 16은 인이 도프된 n+ 아몰퍼스 실리콘으로 이루어진 콘택층, 17 및 18은 Cr로 이루어진 소스 및 드레인 전극, 19는 산화실리콘으로 이루어진 보호성 절연층을 가리킨다. 이러한 박막 트랜지스터는 다음과 같이 제조된다. 먼저, 코팅 1737 유리 기판(11)상에 120 nm 두께의 Cr막이 스퍼터링 방법을 사용하여 형성된다. 다음, 포토 에칭법을 사용하여 Cr을 패터닝함으로써 게이트 전극(12)이 형성된다. 플라즈마 화학 기상 성장(CVD) 법을 사용하여, 다음과 같은 순서로 박막이 형성된다. 먼저, 질화실

리콘막으로 이루어진 250 nm 두께의 제1 게이트 절연층(13)이 SiH<sub>4</sub>, NH<sub>3</sub>, N<sub>2</sub>, 등등의 혼합 가스를 사용하여 형성된다. 다음으로, 제1 절연층상에 SiH<sub>4</sub> 와 N<sub>2</sub>O 의 혼합 가스를 사용하여 산화실리콘으로 이루어진 제2 게이트 절연층을 10 nm 두께로 형성한다. 제2 절연층에는, SiH<sub>4</sub> 와 H<sub>2</sub> 의 혼합 가스를 사용하여 150 nm 의 아몰퍼스 실리콘막을 형성한 다음, SiH<sub>4</sub> 와 PH<sub>3</sub> 를 사용하여 30 nm 두께의 n+ 아몰퍼스 실리콘막을 형성한다. 상술한 박막의 형성에 있어서, 진공을 유지한 채로 연속적으로 공정으로 행하는 것이 바람직하다. 포토 에칭에 의해, n+ 아몰퍼스 실리콘막 및 아몰퍼스 실리콘막을 동시에 아일랜드 형상으로 가공하여 반도체층을 형성한다. 반도체층(15)상에는, 스팍터링 방법으로 형성된 120 nm 두께의 Cr 막을 포토 에칭 및 패터닝하여 소스 전극(17) 및 드레인 전극(18)이 형성된다. 또한, 소스 및 드레인 전극 사이의 n+ 아몰퍼스 실리콘막을 에칭 제거함으로써, 소스 전극(17)과 반도체층(15) 사이 및 드레인 전극(18)과 반도체층(15) 사이에 콘택트(16)이 형성된다. 마지막으로, 예컨대 SiH<sub>4</sub> 와 N<sub>2</sub>O 의 혼합 가스를 사용하여 플라즈마 CVD 법으로 퇴적된 대략 300 nm 두께의 산화실리콘막을 포토 에칭 및 패턴 가공하여 보호성 절연층(19)을 형성한다.

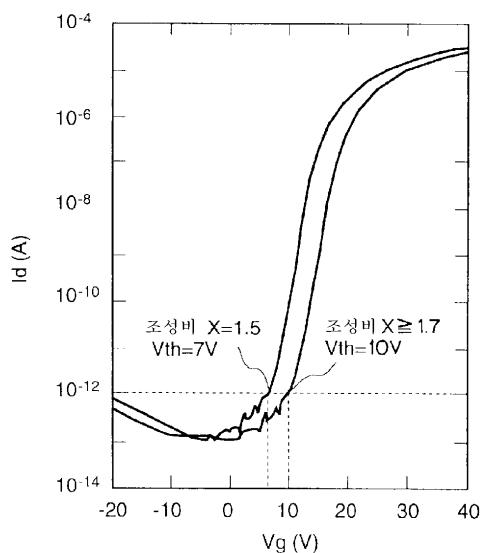

도 2는 상술한 본 발명의 실시예에 따른 박막 트랜지스터의 게이트 전압(Vg)에 대한 드레인 전류(Id)의 의존성(Id-Vg 특성)을 보여준다. 상기 박막 트랜지스터에서, 임계 전압은 드레인 전류가  $1 \times 10^{-12}$  암페어가 되는 게이트 전압으로 정의되는 10 볼트이다. 말하자면, 목적하는 인핸스먼트형 TFT 특성이 얻어지므로, 박막 트랜지스터의 완성후 임계 전압을 제어할 필요가 없다.

본 실시예에 따른 박막 트랜지스터에서 10 볼트 이상의 Vth를 얻기 위해서는, 게이트 절연층(14) 및 보호성 절연층(19)에 사용된 산화실리콘(SiOx)의 조성비(x)를 1.7 이상의 값으로 설정하는 것이 바람직하다. 예를 들어, x = 1.5인 산화실리콘이 보호성 절연층으로 사용되면, 도 2에 도시된 것처럼 Vth는 7 볼트이다.

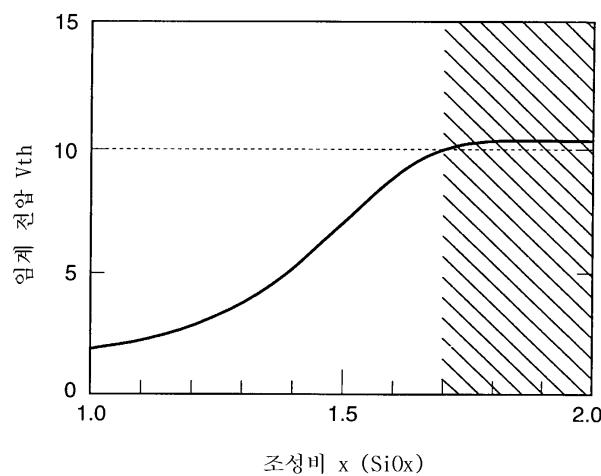

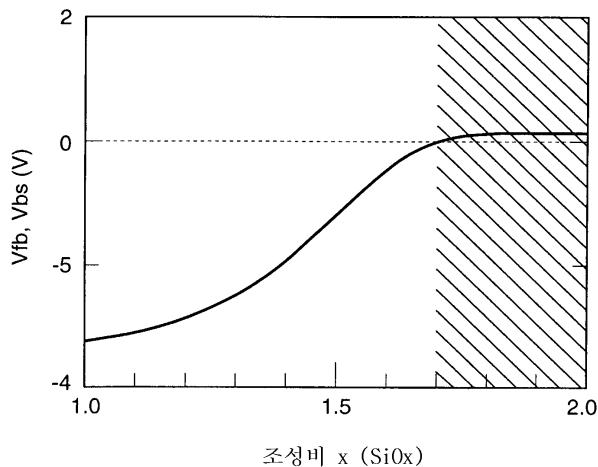

도 3은 게이트 절연층 및 보호성 절연층에 사용된 산화실리콘 SiOx의 조성비(x)에 대한 박막 트랜지스터의 임계 전압 Vth의 존성을 도시한다. 도 3에 도시된 바와 같이, Vth는 조성비(x) 증가에 따라 단조 증가한다. x < 1.7 이면 Vth < 10 V이고, x ≥ 1.7 이면 Vth ≥ 10 V이며 점점 포화된다. 산화실리콘 SiOx의 조성비는 SiOx막이 형성될 때의 SiH<sub>4</sub> 가스에 대한 N<sub>2</sub>O 가스의 유량비(flow rate)에 의존한다. 유량비가 100 이상의 값으로 되면 x가 1.7 이상인 산화실리콘 SiOx이 얻어진다.

이상과 같이, 반도체층(15)에 인접한 게이트 절연층(14) 및 보호성 절연층은 모두 산화실리콘 SiOx으로 구성하고, 이들 산화실리콘의 조성비를 1.7 이상으로 설정하는 것이 바람직하다. 적어도 하나의 산화실리콘의 조성비가 1.7 이하로 설정되거나 적어도 하나의 층이 예컨대 질화실리콘(산화실리콘이 아님)으로 구성되면, Vth는 10 볼트 미만으로 된다.

이하에서는 Vth가 10 볼트 미만으로 되는 이유를 설명하겠다. 예를 들어, 문헌 "반도체 디바이스의 기초"(마사쓰요 기시노(Masatuyo Kishino)저, 옴 출판사, 1985) p167에 기재된 바와 같이, 박막 트랜지스터의 임계 전압 Vth은, 일반적으로 플랫 밴드 전압 Vfb과, 드레인 전류가 흐르기 시작하도록 반도체층(15)에 공급되는 최소 전압 ψf과, 반도체층(15)과 보호성 절연층(19) 사이의 인접 표면에서의 표면 전압 Vbs과의 합으로 결정된다. 즉,

$$Vth = Vfb + \psi_f + Vbs$$

Vfb, ψf, Vbs의 값은 게이트 절연층(14), 반도체층(15), 보호성 절연층(19)의 재질에 의해 각각 결정된다. 아몰퍼스 실리콘으로 이루어진 반도체층(15)의 최소 전압은 대략 15 볼트이고, 질화실리콘이 사용되면, Vfb = Vbs = -4.5 볼트이다.

플라즈마 CVD법으로 형성된 산화실리콘막 SiOx에서, 일반적으로 조성비(x)는 화학양론적 조성에 있어 2 이하의 값을 보인다. 도 4에 도시된 바와 같이, Vfb 및 Vbs는 조성비(x)가 증가함에 따라 단조 증가하며, x = 1.7 이면 Vfb (= Vbs) = 0에서 포화한다.

따라서, 게이트 절연층(14) 및 보호성 절연층(19)에 질화실리콘이 사용되는 종래의 박막 트랜지스터에서는, Vth = -4.5 + 10 - 4.5 = 1 볼트이고, 임계 전압은 10 볼트 이하이다. 한편, 반도체층에 인접한 보호성 절연층의 일부에서 산화실리콘 SiOx의 조성비(x)가 1.7 이상인 본 발명의 박막 트랜지스터에서는, 임계 전압 Vth = 0 + 10 + 0 = 10 볼트이므로 원하는 인핸스먼트형 TFT 특성이 얻어질 수 있다. 그러나, 게이트 절연층 및 보호성 절연층중 어느 하나에 조성비(x) < 1.7인 산화실리콘이 사용되면, Vth < 10 볼트이므로 원하는 인핸스먼트형 TFT 특성을 얻을 수 없다. 또한, 게이트 절연층과 보호성 절연층중 하나에 질화실리콘이 사용되면, 다른 산화실리콘의 조성비가 1.7 이상이더라도 Vth = 0 + 10 - 4.5V = 5.5V 이므로, 소정의 인핸스먼트형 TFT 특성을 얻을 수 없다.

본 실시예에서 박막 구조로서 역스태거 구조가 채택되었지만, 게이트 절연막 및 보호성 절연막이 산화실리콘으로 구성된다면 스태거 구조(stagger structure)나 코플래너 구조(co-planner structure)도 채택될 수 있다. 또한, 본 실시예에서 반도체층이 아몰퍼스 실리콘으로 구성되었지만, 미결정 실리콘, 다결정 실리콘 또는 단결정 실리콘도 사용될 수 있다.

### <실시예 2>

도 5는 본 발명의 액정 표시 장치의 제2 실시예에 사용된 박막 트랜지스터의 단면 구조의 도면이다. 상기 구조 및 본 실시예의 제조 방법은, 산화실리콘층(20)으로 구성된 보호성 절연층이 반도체층(15)의 표면을 산화시킴으로써 형성된다는 것을 제외하고는, 도 1에서의 것과 같다. 산화실리콘층(20)은 다음과 같이 형성된다. 먼저, 콘택층(16)이 소스와 드레인 전극 사이의 n+ 아몰퍼스 실리콘 막을 에칭 제거하는 단계에 의해 형성된다. 다음으로, 반도체층(15)의 표면은 산소(02)에 5분간 노출된다. 반도체층(15)의 표면을 산화시킴으로써 20nm 두께의 산화실리콘층(20)이 형성된다. 이러한 산화 프로세스는 n+ 아몰퍼스 실리콘막에 대한 에칭 디바이스 내에서, 가능하면 진공이 유지된 상태에서 실행되는 것이 바람직하다. 그 결과, 도 2에 도시된 V<sub>th</sub>가 10V인 인핸스먼트형 TFT 특성이 상기 박막 트랜지스터에서도 얻어진다. 박막 트랜지스터의 완성 후에도 임계치를 제어할 필요가 없다. 제1 실시예와 동일한 이유로 V<sub>th</sub>가 10V 이상인 인핸스먼트형 TFT 특성을 얻기 위해서는 산화실리콘층(20)의 조성비(x)를 1.7 이상의 값으로 설정하는 것이 바람직하다는 것이 드러났다. 이러한 목적으로, 산소 플라즈마의 고주파 전력이 500W 이상의 값으로 설정되었다.

임계 전압 V<sub>th</sub>가 본 실시예에서 산화실리콘층(20)에 의해 10 볼트 이상의 값으로 고정되었기 때문에, 보호성 절연층(19)으로서 조성비(x)가 1.7 이상인 산화실리콘을 사용하는 것이 요구되지 않는다. 플라즈마 CVD 방법에 의해 형성된 500nm 두께의 질화실리콘이 사용될 수도 있다. 또한, 진공 설비가 요구되는 플라즈마 CVD 방법 대신에, 스핀 코팅 방법 같은 보다 간단하고 저렴한 코팅 방법에 의해 형성될 수 있는 절연층(예, 1μm 두께의 폴리이미드로 구성된 유기 절연층)이 채택될 수 있으며, 폴리 디 실라잔(poli-di-silazane)을 200°C에서 열처리함으로써 얻어지는 코팅형 산화실리콘막이 채택될 수도 있다. 종래 기술에서는, 이러한 코팅형 절연층이 반도체층(15) 상에 직접 형성될 경우 전기적 불안정성으로 인해 임계 전압(V<sub>th</sub>)이 저하되고 변동한다. 그러나, 본 실시예에서는, 산화실리콘층(20)이 코팅형 절연층의 영향을 차단하기 때문에 안정적이고, 일정한 임계 전압 V<sub>th</sub>가 얻어질 수 있다.

또한, 제1 실시예 및 제2 실시예에 기술된 박막 트랜지스터에 대한 게이트 절연층(13), 반도체층(15), 보호성 절연층(19), 및 산화실리콘층(20) 각각의 두께에 대한 임계 전압 V<sub>th</sub>의 의존성이 관찰되었다. 그 결과, 임계 전압 V<sub>th</sub>의 변동은 ± 1 볼트 이내이고, 따라서 일정한 V<sub>th</sub>가 얻어진다.

### <실시예 3>

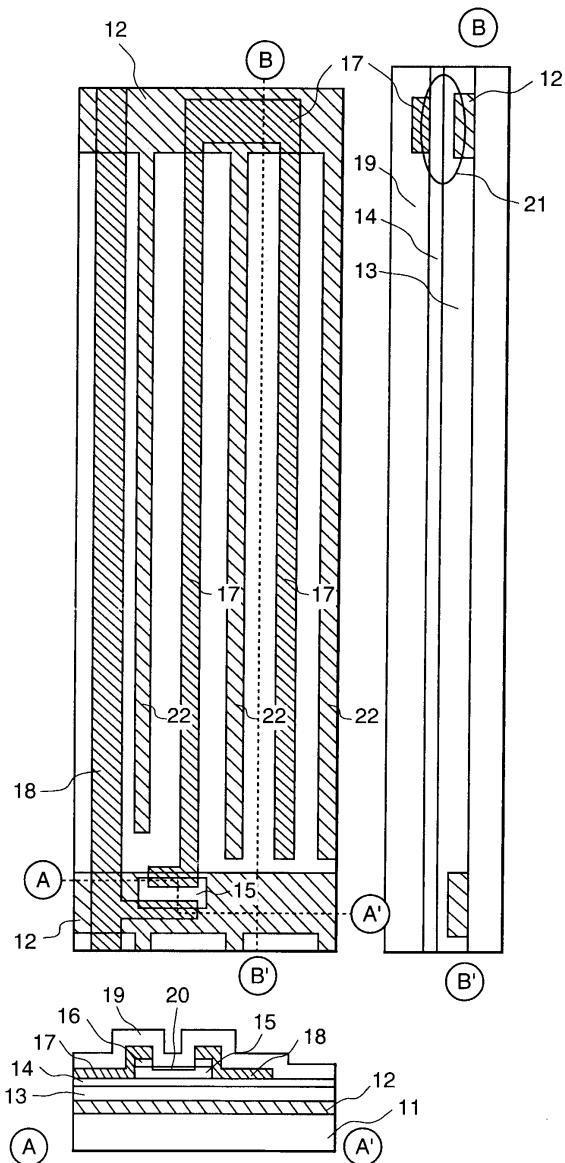

도 6은 본 발명의 한 실시예에 따른 공통 배선 생략 IPS 방식의 액티브 매트릭스형 액정 표시 장치 내의 화소 부분의 평면의 구조의 도면이다. 또한, 도 6은 점선 (A)-(A') 및 (B)-(B')을 따라 취해진 화소 부분의 단면의 구조도 도시하고 있다. 도 6에서 대향 기판은 도시가 생략되어 있다. 참조 번호 11은 유리 기판, 12는 Cr로 구성된 게이트 전극(주사 배선), 13은 질화실리콘으로 구성된 제1 게이트 절연층, 14는 산화실리콘으로 구성된 제2 게이트 절연층, 15는 아몰퍼스 실리콘으로 구성된 반도체층, 16은 인이 도프된 n+ 아몰퍼스 실리콘으로 구성된 콘택층, 17 및 18은 각각이 Cr로 구성된 소스 전극(화소 전극) 및 드레인 전극(신호 배선), 19는 산화실리콘으로 구성된 보호성 절연층을 표시한다. 단일 산화실리콘층이 질화실리콘 대신에 게이트 절연층으로서 사용될 수 있다. 산화실리콘층(20)이 반도체층(15)의 표면 상에 형성되는 경우, 산화실리콘이 아닌 재료들이 보호성 절연층(19)으로서 사용될 수 있다. 보유 용량(21)은 드레인 전극(18)과 게이트 전극(주사 배선)(12)의 교차 부분 사이에 삽입된 게이트 절연층(13, 14)에 의해 형성된다. 액정층의 배향 방향은 프론트 스테이지 게이트 전극(12)으로부터 연장된 공통 전극(22)과 공통 전극들 사이에 평행하게 연장된 드레인 전극(18) 사이에 인가된 전계에 의해 제어된다. 광은 공통 전극(22)과 드레인 전극(18) 사이를 통과한다. 다음으로, 광은 액정층 내로 입사되고 그 안에서 변조된다. 프론트 스테이지 게이트 전극(12)이 공통 배선 생략 IPS 방식에서 공통 배선의 역할을 맡고 있기 때문에, 공통 배선은 필요치 않다.

상술된 바와 같이, 제1 실시예 및 제2 실시예에 기술된 박막 트랜지스터를 사용함으로써 공통 배선 생략 IPS 방식의 액티브 매트릭스형 액정 표시 장치를 실현할 수 있다. 본 실시예에 따른 박막 트랜지스터에서, 특별한 임계 전압 제어 설비를 사용함으로써 임계 전압을 제어할 필요는 없다.

특히, 반도체(15)의 표면 상에 산화실리콘층을 형성하는 제2 실시예에 따른 박막 트랜지스터를 사용한 경우, 스핀 코팅 방법 같은 코팅 방법을 사용하여 형성할 수 있는 코팅형 산화실리콘 또는 폴리이미드로 구성된 유기 절연층이 보호성 절연층으로서 사용될지라도, 안정적이고 일정한 인핸스먼트형 TFT 특성(V<sub>th</sub> = 10 V)이 얻어진다.

## &lt;실시예 4&gt;

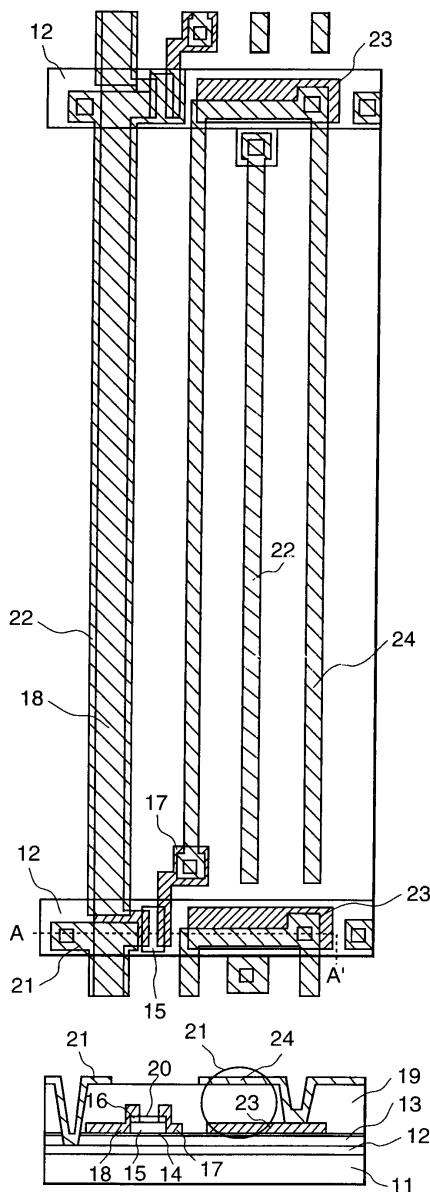

도 7은 본 발명의 또 다른 실시예에 따른 공통 배선 생략 IPS 방식의 액티브 매트릭스형 액정 표시 장치내 화소부의 평면 구조를 나타내고 있다. 더욱이, 도 7은 점선 (A)-(A')을 따라 취한 화소부의 부분적 구조를 나타내고 있다. 도 7에서 대향 기판은 도시되어 있지 않다. 참조부호 11은 유리 기판을 나타내고, 12는 질화실리콘으로 이루어지는 주사 배선(게이트 전극)을 나타내며, 14는 산화실리콘으로 이루어지는 제2 게이트 절연층을 나타내고, 15는 아몰퍼스 실리콘으로 이루어지는 반도체층을 나타내고, 16은 인이 도핑되는 n+ 아몰퍼스 실리콘으로 이루어지는 콘택트층을 나타내며, 17은 Cr로 이루어지는 소스 배선을 나타내고, 18은 Cr로 이루어지는 드레인 전극 신호 배선을 나타내고, 19는 유기막으로 이루어지는 보호성 절연층을 나타내고, 22와 22'는 공통 전극을 나타내고, 23은 Cr로 이루어지는 유지 용량 단자(holding capacitance terminal)를 나타내고, 24는 화소 전극을 나타낸다.

본 실시예에서는 산화실리콘막이 제공된다. 더욱이, 게이트 절연층(14)과 산화 실리콘층(20)을 형성하는 실리콘 산화막의 조성비는 1.7 이상이다.

예를 들어, TFT 기판은 다음과 같은 방식으로 제조된다. 먼저, 스퍼터링법을 이용하여 코닝 1737 유리 기판(11)상에 300nm 두께의 Cr막이 형성된다. 다음에 포토 에칭법에 의해 Cr을 패터닝함으로써 주사 배선이 되는 게이트 전극(12)을 형성한다. 플라즈마 화학 기상 성장(CVD)법을 이용하여, 250nm 두께의 질화실리콘층, 50nm 두께의 산화실리콘층, 200nm 두께의 아몰퍼스 실리콘층, 인이 도핑되는 n+ 아몰퍼스 실리콘층이 순서대로 형성된다. 각각의 층 형성을 위해 사용되는 소스 가스는 다음과 같다.  $\text{SiH}_4 + \text{NH}_3 + \text{N}_2$  (질화실리콘층);  $\text{SiH}_4 + \text{N}_2\text{O}$  (산화실리콘층);  $\text{SiH}_4 + \text{H}_2$  (아몰퍼스 실리콘층);  $\text{SiH}_4 + \text{H}_3 + \text{PH}_3$  (n+ 아몰퍼스 실리콘층). 다음에 포토 에칭에 의해 n+ 아몰퍼스 실리콘층, 아몰퍼스 실리콘층, 및 산화실리콘층을 동시에 아일랜드 형상으로 가공하여 반도체층(15)을 형성한다.

반도체막(15) 위에, 스퍼터링 법을 이용하여 형성한 300nm 두께의 Cr막을 포토 에칭에 의해 패터닝하여, 신호 배선(18), 소스 전극(17) 및 유지 용량 단자(23)를 형성한다. 그리고, 신호 배선(18)과 소스 전극(17)으로 덮여 있지 않은 n+ 아몰퍼스 실리콘층을 에칭하여, 소스 전극(17)과 반도체층(15) 사이에 그리고 신호 배선(18)과 반도체층(15) 사이에 콘택트층(16)을 형성한다. 더욱이, 스핀 코팅법에 의해 폴리이미드로 이루어지는 두께 1000nm의 보호막인 보호성 절연층(19)를 형성한다. 포토 에칭에 의해 보호성 절연층(19)과 제1 게이트 절연층(14)내에 콘택트 홀을 형성한 후에, 스퍼터링법을 이용하여 300nm 두께의 금속막을 형성한다. 그리고, 포토 에칭에 의해 금속막을 에칭하여 공통 전극(22, 22')을 형성한다.

이것에 의해, 화소 전극(24), 소스 전극(17) 그리고 유지 용량 단자(105)가 콘택트홀을 통해 접속되고, 공통 전극(22)과 게이트 전극(12)이 서로 접속된다.

제1 게이트 절연층(14)의 게이트 전극(12)과 용량 유지 단자(105) 사이에 협지된 부분이 유지 용량이 된다. 그 위에, 200nm 두께의 배향막이 스핀 코팅법을 이용하여 형성된다.

도 6 및 도 7에서, 도시 생략한 대향 기판은 다음과 같이 구성된다. 먼저, 500nm 두께의 컬러 필터는 스핀 코팅법에 의해 코닝 1737 유리 기판상에 형성된다. 다음에, 500nm 두께의 보호막과 200nm 두께의 배향막이 스핀 코팅법에 의해 형성된다.

TFT와 대향 기판 각각의 표면을 배향처리한 후에는, 산화실리콘으로 이루어지는 대략  $4\mu\text{m}$ 직경의 비드를 삽입하도록, 서로 대향시켜 형성한 셀 캡의 공간에 액정 조성 재료를 충전한다. 그 결과, 액정층이 형성된다. 최종적으로, TFT와 대향 기판 각각의 표면에 편광판을 부착하여 액정 패널을 완성한다.

산화 실리콘층(20)을 형성하는 방법은 실시예 2와 동일하다. 배선과 전극이 차지하는 화소부의 면적을 줄여 개구 면적을 증가시키기 위해, 공통 배선 생략 방식을 채택한다. 더욱이, 이러한 구조에서, 보호성 절연층(19)을 통해 신호 배선(18)과 공통 전극(22)이 중첩된다. 중첩부에 삽입되는 보호성 절연층(19)에 의해 접유되는 기생 용량을 감소시키기 위해서는, 보호성 절연층(19)은 저유전 재료, 구체적으로는 유전 상수가 3.5인 폴리이미드 등의 유기막으로 이루어져야 한다. 이 막의 두께는  $2\mu\text{m}$  이상이 바람직하다. 폴리이미드로 이루어지는 보호성 절연층(19)이 반도체층(15)과 바로 접촉하는 경우에는, 박막 트랜지스터는 전기적으로 불안정한 보호성 절연층(19)의 영향으로 인해, 그 임계 전압  $V_{th}$ 가  $\pm 2\text{ V}$  이상 변동될 가능성이 있다. 본 실시예에서, 반도체층(15)과 보호성 절연층(19) 사이에는 산화실리콘층(20)이 놓여지기 때문에, 보호성 절연층(19)의 영향없이 임계 전압  $V_{th}$ 의 안정성이 크게 향상된다. 본 실시예에서는 임계 전압을 제어하기 위한 추가 단계가 요구되지 않는다. 따라서, 공정을 단순화할 수 있고, 이에 따라 비용을 저감할 수 있다.

## 발명의 효과

본 발명에 의하면, 공통 배선 생략 IPS 방식에 필요한 균일하고 안정한 인핸스먼트형 스위칭 특성을 보이는 박막 트랜지스터를 제공할 수 있어서, 전력 소비가 적은 공통 배선 생략 IPS 방식 액티브 매트릭스형 액정 표시 장치를 제공하는 효과가 있다.

## 도면의 간단한 설명

도 1은 본 발명의 액정 표시 장치의 한 실시예에서 사용된 박막 트랜지스터의 단면 구조를 도시한 도면.

도 2는 박막 트랜지스터의  $Id-Vg$  특성을 도시한 도면.

도 3은 박막 트랜지스터의 임계 전압의 산화실리콘 조성비에 대한 의존성을 도시한 도면.

도 4는 박막 트랜지스터에 사용된 산화실리콘의 플랫 밴드 전압 및 표면 전위의 조성비에 대한 의존성을 도시한 도면.

도 5는 본 발명의 액정 표시 장치의 다른 실시예에서 사용된 박막 트랜지스터의 단면 구조를 도시한 도면.

도 6은 본 발명의 액정 표시 장치에서 화소부의 평면 및 단면 구조의 한 실시예를 도시한 도면.

도 7은 본 발명의 액정 표시 장치에서 화소부의 평면 및 단면 구조의 다른 실시예를 도시한 도면.

<도면의 주요부분에 대한 부호의 설명>

11 : 유리 기판

12 : 게이트 전극

13 : 제1 게이트 절연층

14 : 제2 게이트 절연층

15 : 반도체층

17 : 소스 전극

18 : 드레인 전극

22 : 공통 전극

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

## 도면7

|                |                                                                          |         |            |

|----------------|--------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵型液晶显示器                                                               |         |            |

| 公开(公告)号        | <a href="#">KR100710120B1</a>                                            | 公开(公告)日 | 2007-04-23 |

| 申请号            | KR1020000058462                                                          | 申请日     | 2000-10-05 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA                                                  |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                |         |            |

| [标]发明人         | ANDO MASAHIKO<br>안도마사히코<br>WAKAGI MASATOSHI<br>와까기마사도시                   |         |            |

| 发明人            | 안도마사히코<br>와까기마사도시                                                        |         |            |

| IPC分类号         | G02F1/133 G09F9/30 G02F1/1343 G02F1/136 G02F1/1362 G02F1/1368 H01L29/786 |         |            |

| CPC分类号         | G02F1/1362 G02F1/134363                                                  |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                           |         |            |

| 优先权            | 1999283830 1999-10-05 JP                                                 |         |            |

| 其他公开文献         | KR1020010040002A                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                |         |            |

#### 摘要(译)

目的：提供一种无需普通接线的IPS（面内切换）模式有源矩阵液晶显示器件，其特点是功耗低，不会增加工序。