**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl. (45) 공고일자 2006년03월15일

*G02F 1/133* (2006.01) (11) 등록번호 10-0561150

(24) 등록일자 2006년03월08일

|                           |                           |

|---------------------------|---------------------------|

| (21) 출원번호 10-2003-0075079 | (65) 공개번호 10-2004-0079820 |

| (22) 출원일자 2003년10월27일     | (43) 공개일자 2004년09월16일     |

(30) 우선권주장 JP-P-2003-00061778 2003년03월07일 일본(JP)

(73) 특허권자 미쓰비시덴키 가부시키가이샤

일본국 도쿄도 지요다구 마루노우치 2쵸메 7반 3고

(72) 발명자 노지리이사오

일본도쿄도지요다꾸마루노우찌2쵸메2-3미쓰비시덴키가부시키가이샤

내

무라이히로유끼

일본도쿄도지요다꾸마루노우찌2쵸메2-3미쓰비시덴키가부시키가이샤

내

(74) 대리인 장수길

구영창

**심사관 : 김정훈**

---

**(54) 검사 단자를 포함한 화상 표시 장치**

---

**요약**

본 발명의 LCD 모듈은, 검사 시에 각 제1 N형 TFT(26) 및 디멀티플렉서(20)를 통하여 각 홀수번의 조의 데이터선(6)에 홀수 데이터 신호(DO)를 제공하기 위한 홀수 데이터 단자(36)와, 검사 시에 각 제2 N형 TFT(27) 및 디멀티플렉서(20)를 통하여 각 짹수번의 조의 데이터선(6)에 짹수 데이터 신호(DE)를 제공하기 위한 짹수 데이터 단자(35)와, 검사 시에 제1, 제2 N형 TFT(26, 27)의 게이트에 제어 신호(ΦC)를 제공하기 위한 제어 단자(34)를 포함한다. 따라서, 검사 시에 사용하는 단자수가 적어져 검사 장비의 저비용화를 도모할 수 있다.

**대표도**

도 3

**색인어**

데이터선, 제어 신호, 제어 단자, 단자수, LCD 모듈, 디멀티플렉서

**명세서**

## 도면의 간단한 설명

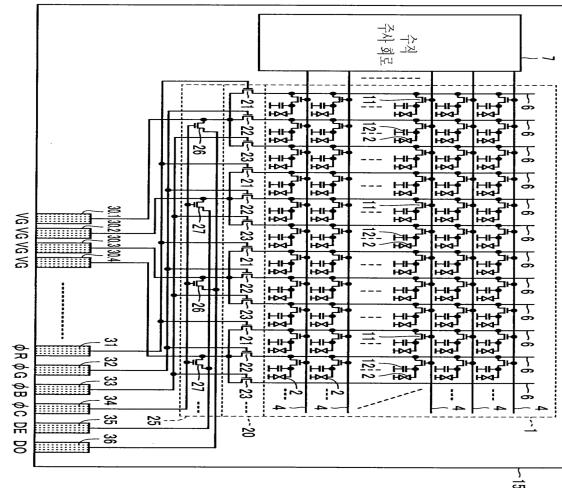

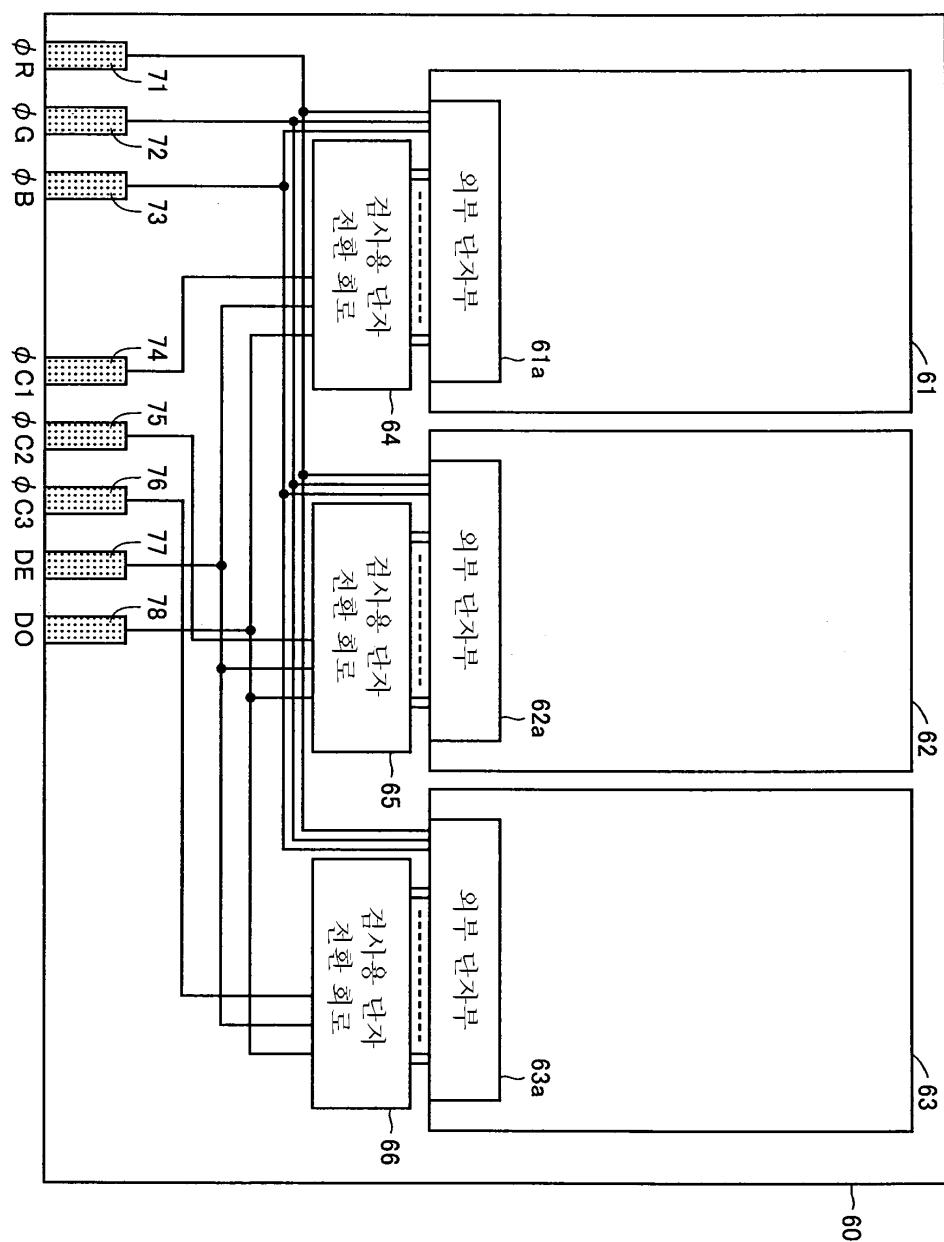

도 1은 본 발명의 실시예 1에 따른 컬러 액정 화상 장치의 구성을 도시하는 블록도.

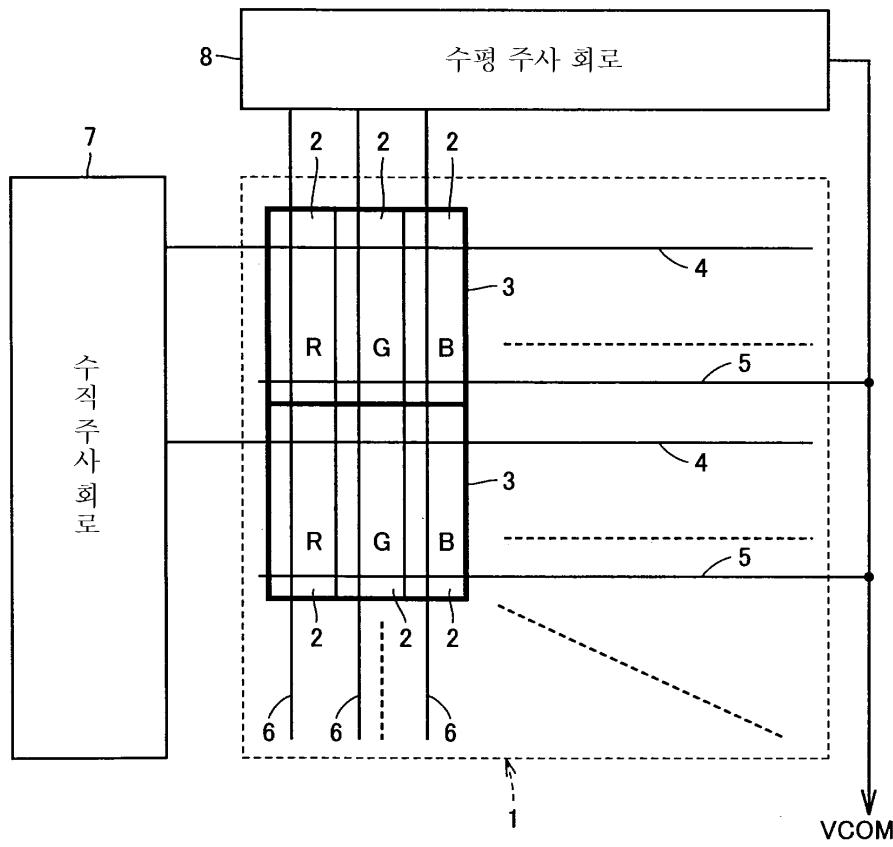

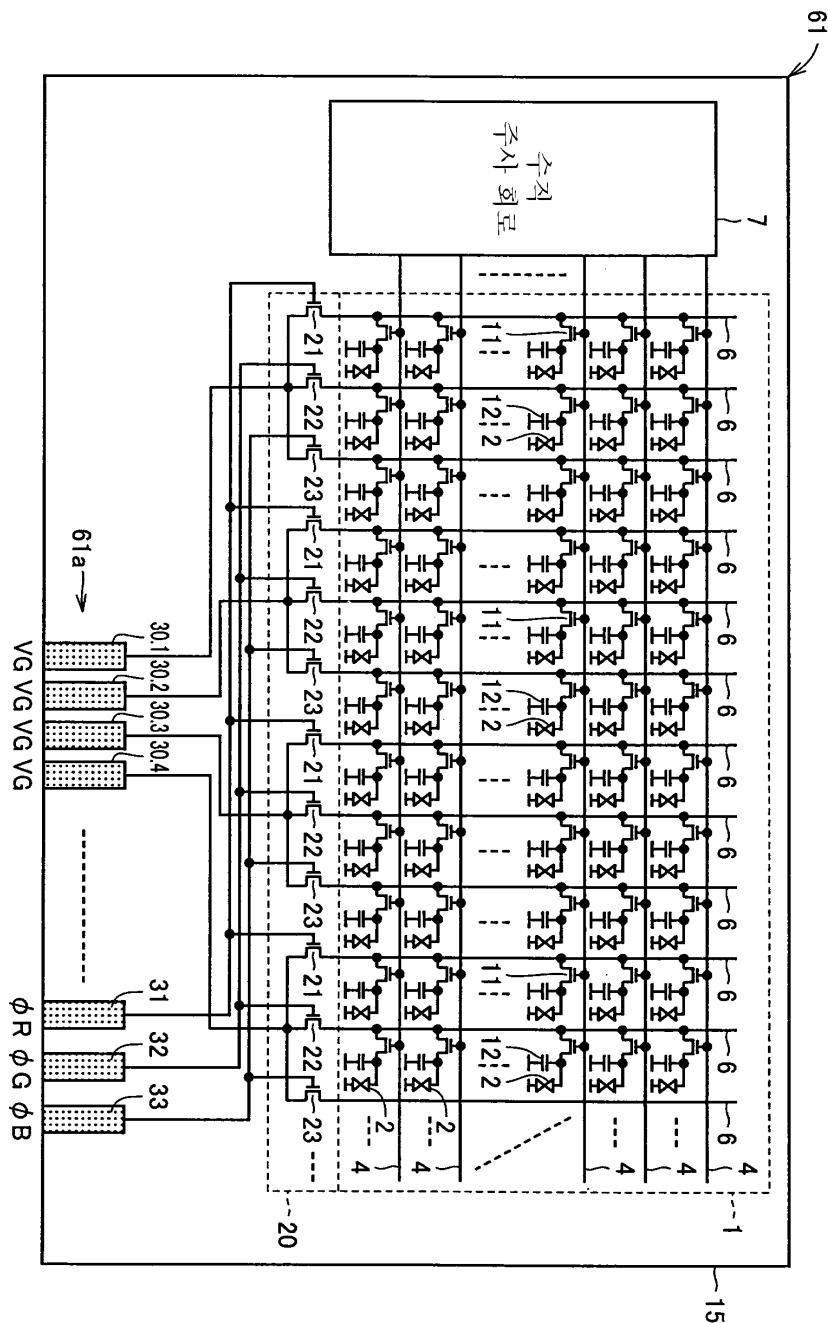

도 2는 도 1에 도시한 액정 셀에 대응하여 설치되는 액정 구동 회로의 구성을 도시하는 회로도.

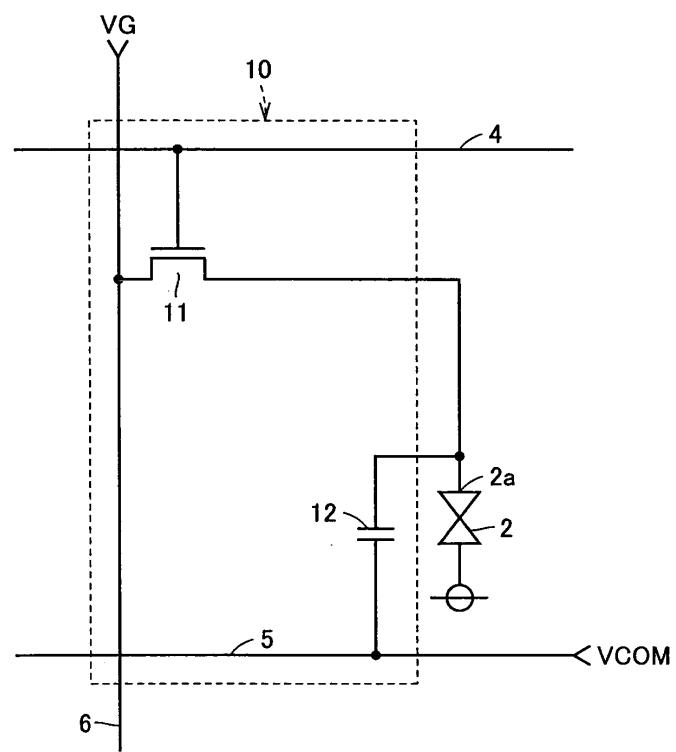

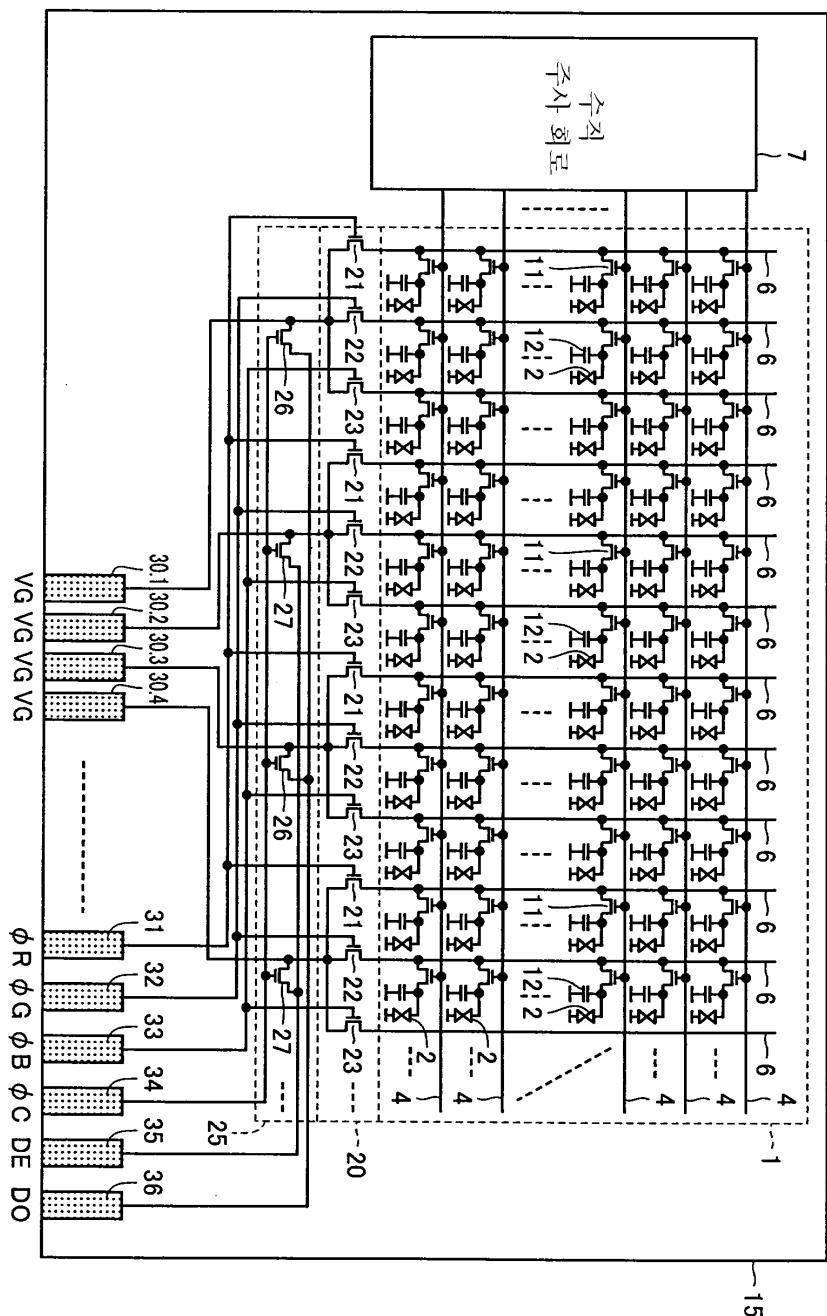

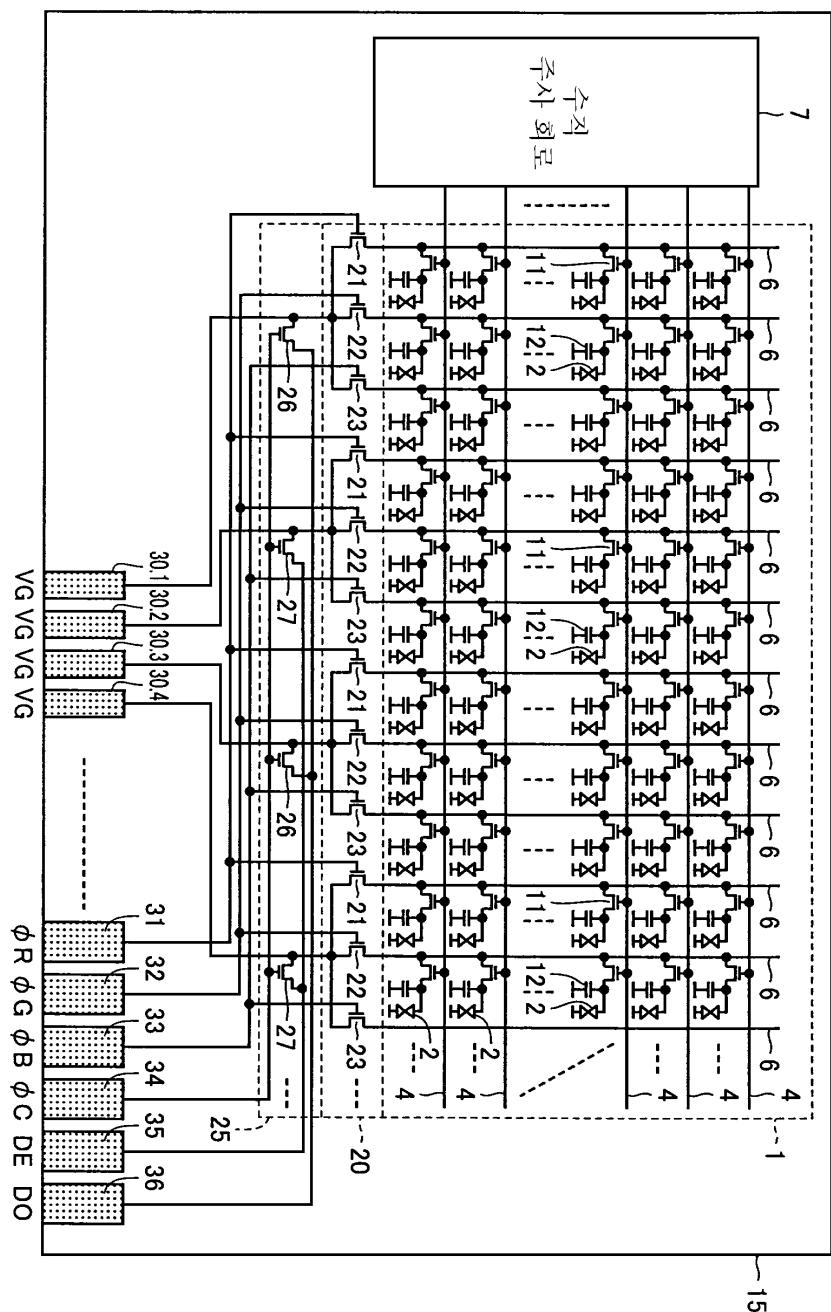

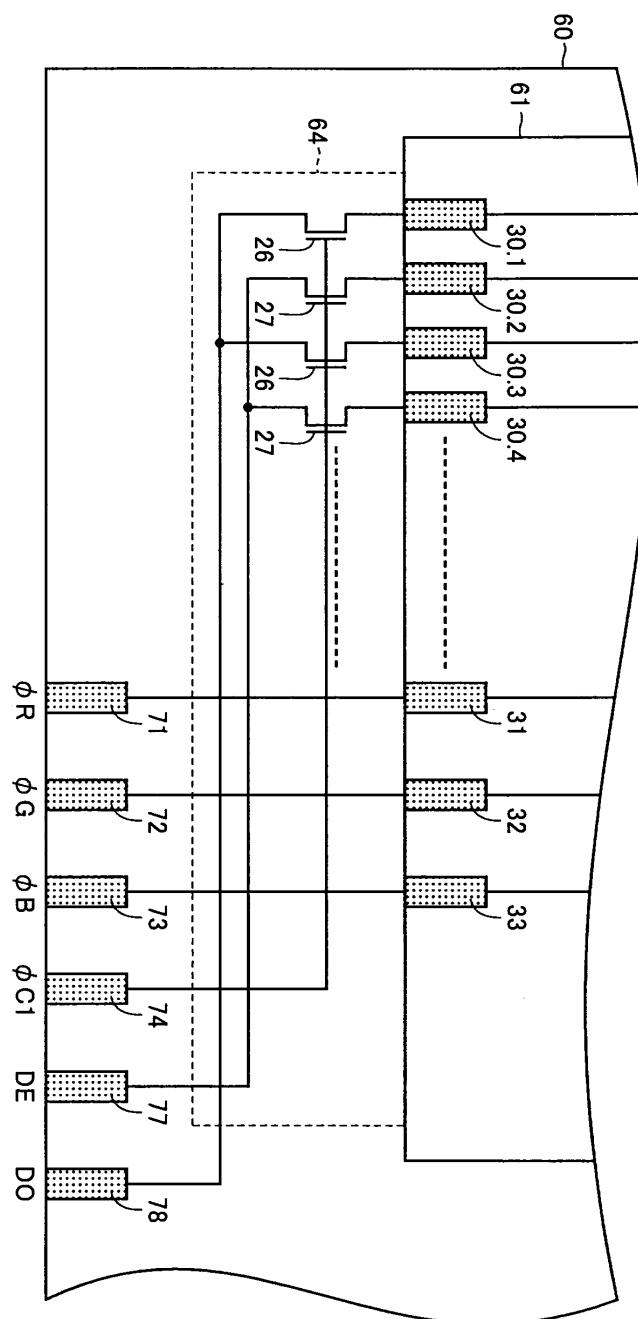

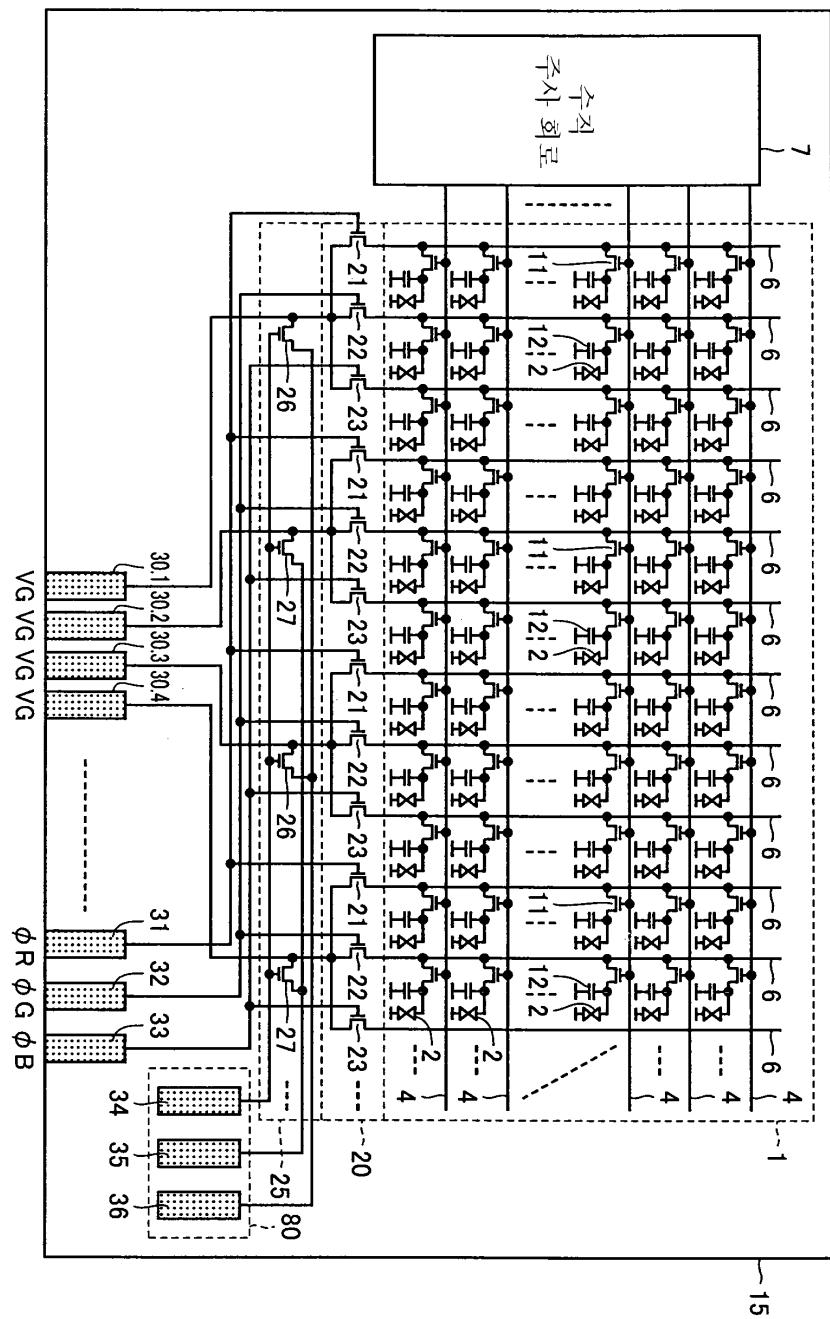

도 3은 도 1에 도시한 컬러 액정 표시 장치의 조립 부품인 LCD 모듈의 구성을 도시하는 회로 블록도.

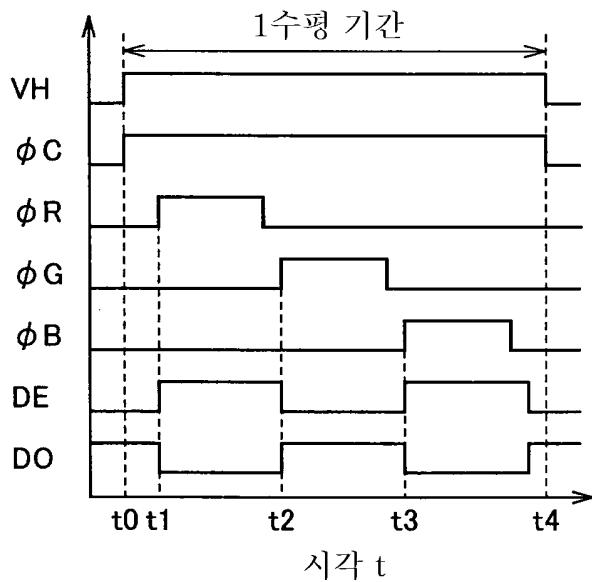

도 4는 도 3에 도시한 LCD 모듈의 검사 방법을 설명하기 위한 타임차트.

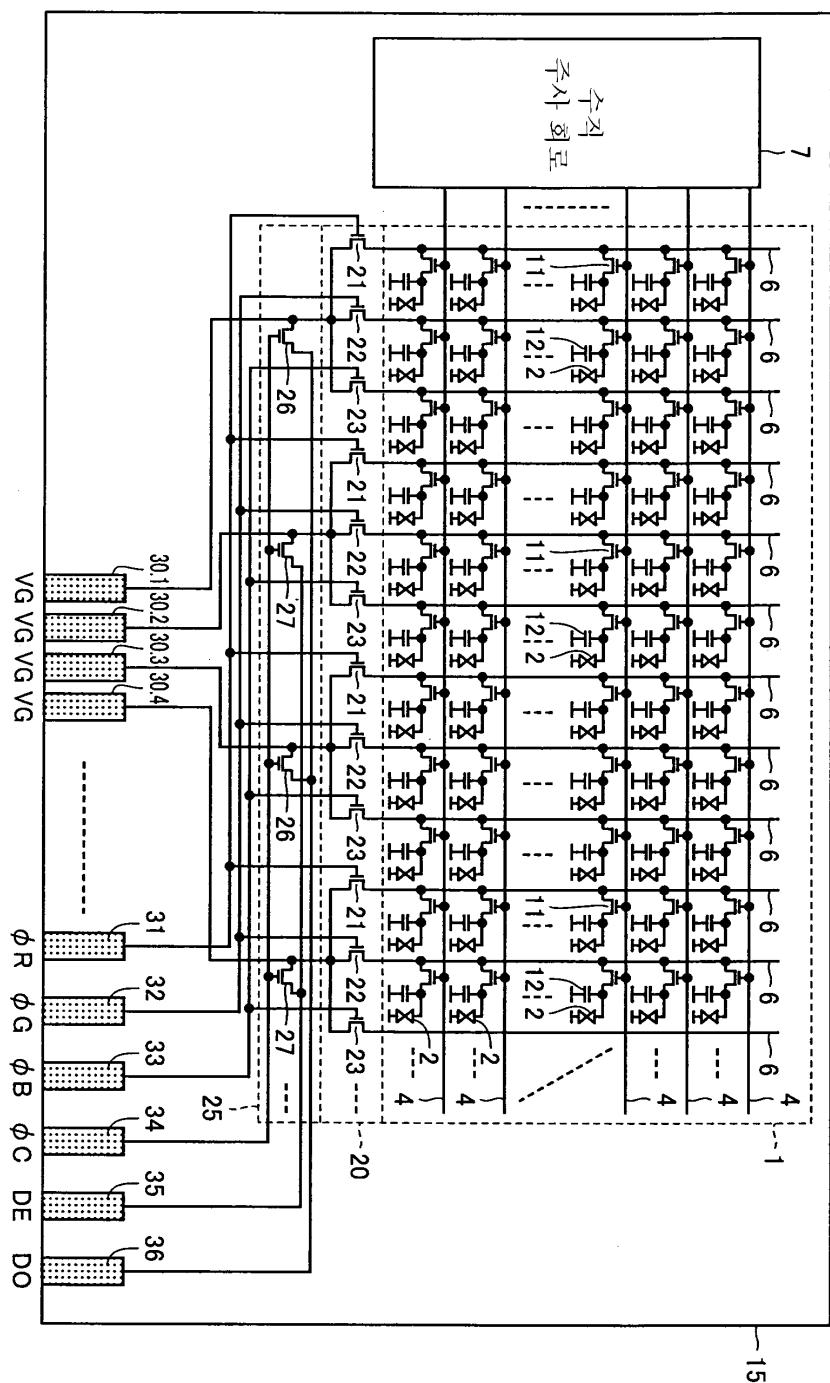

도 5는 실시예 1의 변경예를 도시하는 회로 블록도.

도 6은 실시예 1의 다른 변경예를 도시하는 회로 블록도.

도 7은 본 발명의 실시예 2에 따른 LCD 모듈의 검사 방법을 설명하기 위한 도면.

도 8은 본 발명의 실시예 3에 따른 LCD 모듈의 검사 방법을 설명하기 위한 도면.

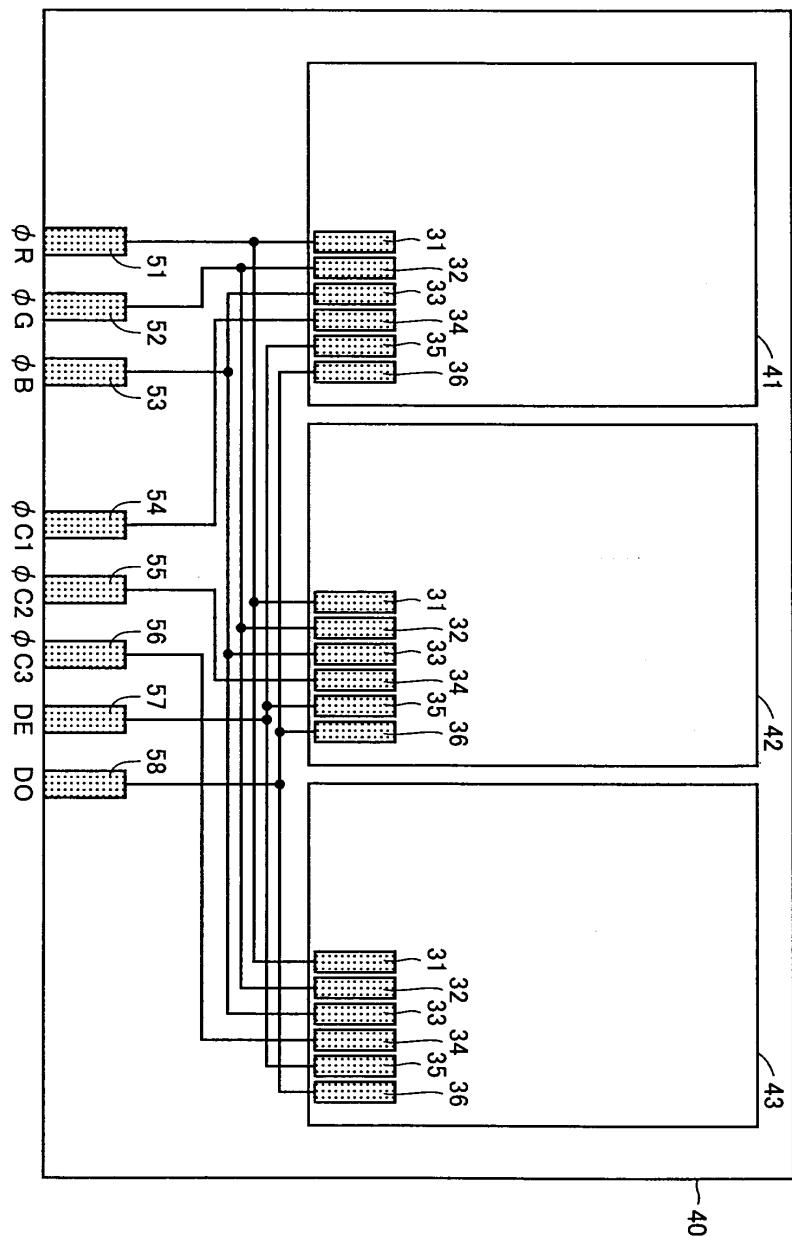

도 9는 도 8에 도시한 LCD 모듈의 구성을 도시하는 회로 블록도.

도 10은 도 8에 도시한 검사용 단자 전환 회로의 구성을 도시하는 회로 블록도.

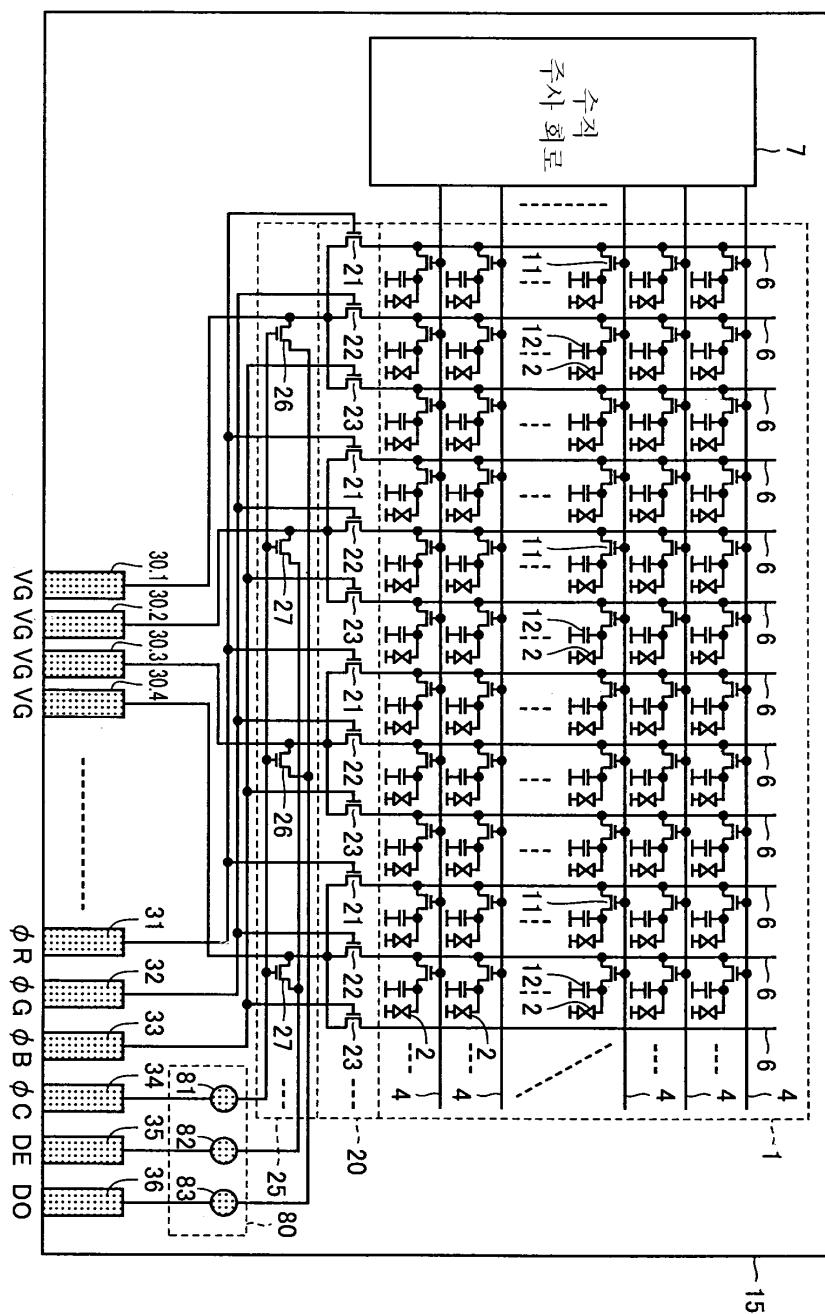

도 11은 본 발명의 실시예 4에 따른 LCD 모듈의 구성을 도시하는 회로 블록도.

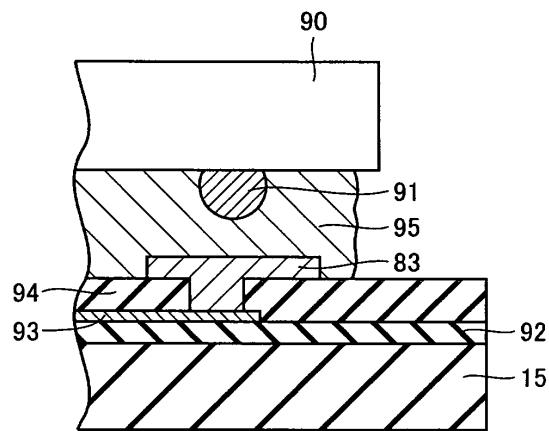

도 12는 도 11에 도시한 LCD 모듈에의 반도체 칩의 실장 방법을 설명하기 위한 단면도.

도 13은 실시예 4의 변경예를 도시하는 회로 블록도.

<도면의 주요 부분에 대한 부호의 설명>

1 : 액정 패널

2 : 액정 셀

3 : 화소

4 : 주사선

5 : 공통 전위선

6 : 데이터선

7 : 수직 주사 회로

8 : 수평 주사 회로

10 : 액정 구동 회로

11, 21~23, 26, 27 : N형 TFT

12 : 캐패시터

15, 40, 60 : 유리 기판

20 : 1:3 디멀티플렉서

25, 64~66 : 검사용 단자 전환 회로

30 : 데이터 단자

31, 51, 71 : R 단자

32, 52, 72 : G 단자

33, 53, 73 : B 단자

34, 54~56, 74~76 : 제어 단자

35, 57, 77 : 짹수 데이터 단자

36, 58, 78 : 홀수 데이터 단자

41~43, 61~63 : LCD 모듈

61a~63a : 외부 단자부

80 : COG 실장 영역

81~83 : 패드

90 : 반도체 칩

91 : 범프 전극

92, 94 : 절연막

93 : 금속 배선

95 : 이방성 도전 수지

**발명의 상세한 설명**

**발명의 목적**

**발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 화상 표시 장치에 관한 것으로, 특히, 절연 기판 상에 형성되어, 출하 전에 검사되는 화상 표시 장치에 관한 것이다.

최근, 액정 패널의 고해상도화가 진행되어, LCD(liquid crystal display) 모듈과 FPC(flexible printed circuit board)를 접속하기 위한 단자의 수가 증가하고 있다. 또, LCD 모듈의 소형화가 진행되어, 단자의 피치가 좁다. 액정 패널의 검사는 각 단자에 프로브를 적용하여 행하는데 단자 수의 증가 및 단자 피치의 협소화에 수반하여 검사 장치의 비용 상승이 발생하고 있다.

검사 장치의 비용 절감을 도모하는 방법으로서는 액정 패널의 홀수번의 데이터선을 1개의 검사 단자에 접속함과 함께, 짹수번의 데이터선을 또 다른 하나의 검사 단자에 접속하여, 2개의 검사 단자를 이용하여 검사한 후에 2개의 단자를 제거하는 방법이 있다(예, 일본 특개평5-5897호 공보).

## 발명이 이루고자 하는 기술적 과제

이러한 2개의 검사 단자를 복수의 액정 패널에 공통으로 설치하면, 검사 장치의 비용을 더욱 절감할 수 있을 것으로 생각된다. 그러나, 단순히 복수의 액정 패널의 홀수번의 데이터선을 1개의 검사 단자에 접속함과 함께 짝수번의 데이터선을 또 다른 1개의 검사 단자에 접속하는 것만으로는 각 액정 패널을 개별적으로 정확하게 검사할 수는 없다.

그 때문에, 본 발명의 주된 목적은, 검사를 저비용으로 정확하게 행하는 것이 가능한 화상 표시 장치를 제공하는 것이다.

## 발명의 구성 및 작용

본 발명에 따른 화상 표시 장치에서는, 복수 행 복수 열로 배치된 복수의 화소 표시 회로와, 각각 복수 행에 대응하여 설치된 복수의 주사선과, 각각 복수 열에 대응하여 설치된 복수의 데이터선을 포함하는 화상 표시 패널과, 이들의 제1 전극이 각각 복수의 데이터선에 접속되어, 화상 표시 패널의 통상 동작 시에 비도통이 되는 복수의 트랜지스터와, 복수의 트랜지스터 중의 각 홀수번의 트랜지스터의 제2 전극에 접속된 제1 검사 단자와, 복수의 트랜지스터 중의 각 짝수번의 트랜지스터의 제2 전극에 접속된 제2 검사 단자와, 복수의 트랜지스터의 게이트에 접속되어, 검사 시에 복수의 트랜지스터를 제어하기 위한 제어 신호를 받는 제1 제어 단자가 설치된다. 따라서, 제1 검사 단자, 제2 검사 단자 및 제1 제어 단자를 검사 장치에 접속하면 검사할 수 있기 때문에, 검사에 사용하는 단자의 수가 적어지게 되어, 검사 장치의 비용 절감을 도모할 수 있다. 또한, 복수의 화상 표시 장치의 복수의 제1 검사 단자를 상호 접속함과 함께 복수의 제2 검사 단자를 상호 접속한 경우라도, 화상 표시 장치를 1개씩 정확하게 검사할 수 있다.

<발명의 실시예>

### [실시예 1]

도 1은, 본 발명의 실시예 1에 따른 컬러 액정 표시 장치의 구성을 도시하는 블록도이다. 도 1에 있어서, 이 컬러 액정 표시 장치는 액정 패널(1), 수직 주사 회로(7) 및 수평 주사 회로(8)를 포함하고, 예를 들면 휴대 전화기에 설치된다.

액정 패널(1)은, 복수 행 복수 열로 배치된 복수의 액정 셀(2)과, 각각 복수 행에 대응하여 설치된 복수의 주사선(4)과, 각각 복수 행에 대응하여 설치된 복수의 공통 전위선(5)과, 각각 복수 열에 대응하여 설치된 복수의 데이터선(6)을 포함한다. 복수의 공통 전위선(5)은 상호 접속되어 있다.

액정 셀(2)은 각 행에서 3개씩 미리 그룹화되어 있다. 각 그룹의 3개의 액정 셀(2)에는 각각 R, G, B의 컬러 필터가 설치되어 있다. 각 그룹의 3개의 액정 셀(2)은 1개의 화소(3)를 구성하고 있다.

각 액정 셀(2)에는 도 2에 도시한 바와 같이, 액정 구동 회로(10)가 설치되어 있다. 액정 구동 회로(10)는 N형 TFT(박막 트랜지스터)(11) 및 캐패시터(12)를 포함한다. N형 TFT(11)은 데이터선(6)과 액정 셀(2)의 한쪽 전극(2a)의 사이에 접속되고, 그 게이트는 주사선(4)에 접속된다. 캐패시터(12)는 액정 셀(2)의 한쪽 전극(2a)과 공통 전위선(5)의 사이에 접속된다. 공통 전위선(5)에는 공통 전위 VCOM이 주어진다. 액정 셀(2)의 다른 쪽 전극은 대향 전극에 접속된다. 대향 전극에는 일반적으로는 공통 전위 VCOM과 동 전위가 주어진다.

도 1로 되돌아가, 수직 주사 회로(7)는, 화상 신호에 따라서, 복수의 주사선(4)을 소정 시간 씩 순차 선택하고, 선택한 주사선(4)을 선택 레벨의 「H」 레벨로 한다. 주사선(4)이 선택 레벨의 「H」 레벨이 되면, 도 2의 N형 TFT(11)가 도통하여, 그 주사선(4)에 대응하는 각 액정 셀(2)의 한쪽 전극(2a)과 그 액정 셀(2)에 대응하는 데이터선(6)이 결합된다.

수평 주사 회로(8)는, 화상 신호에 따라, 수직 주사 회로(7)에 의해서 1개의 주사선(4)이 선택되어 있는 사이에, 각 데이터선(6)에 계조 전위 VG를 제공하면서 공통 전위선(5)에 공통 전위 VCOM을 제공한다. 액정 셀(2)의 광투과율은 그 전극 간 전압에 따라 변화한다.

수직 주사 회로(7) 및 수평 주사 회로(8)에 의해서 액정 패널(1)의 전 액정 셀(2)이 주사되면, 액정 패널(1)에 1개의 컬러 화상이 표시된다.

도 3은, 도 1 및 도 2에 도시한 컬러 액정 표시 장치의 조립 부품인 LCD 모듈의 구성을 도시하는 회로 블록도이다. 도 3에 있어서, 이 LCD 모듈은 유리 기판(15)과, 그 표면에 형성된 액정 패널(1), 수직 주사 회로(7), 1:3 디멀티플렉서(20), 검사 용 단자 전환 회로(25), 복수(예를 들면 240)의 데이터 단자(30.1~30.4, …), R 단자(31), G 단자(32), B 단자(33), 제어 단자(34), 짹수 데이터 단자(35), 및 홀수 데이터 단자(36)를 포함한다.

단자(30.1~30.4, …, 31~36)는 유리 기판(15)의 1 번에 따라서 소정의 피치로 배치된다. 검사 시에는 단자(31~36) 각각이 프로브를 통하여 검사 장치에 접속된다. 검사 후에는 단자(30.1~30.4, …, 31~36)가 FPC에 접속된다. 데이터 단자(30.1~30.4, …) 각각에는 FPC로부터 계조 전위 VG가 주어진다. R 단자(31)에는 R용의 데이터선(6)을 선택하기 위한 신호  $\phi R$ 이 주어진다. G 단자(32)에는 G용의 데이터선(6)을 선택하기 위한 신호  $\phi G$ 가 주어진다. B 단자(33)에는 B용의 데이터선(6)을 선택하기 위한 신호  $\phi B$ 가 주어진다. 제어 단자(34)에는 제어 신호  $\phi C$ 가 주어진다. 짹수 데이터 단자(35)에는 짹수 데이터 신호 DE가 주어진다. 홀수 데이터 단자(36)에는 홀수 데이터 신호 DO가 주어진다.

1:3 디멀티플렉서(20)는 액정 패널(1)의 240조의 R용 데이터선(6), G용 데이터선(6) 및 B용 데이터선(6)에 대응하여 설치된 240조의 N형 TFT(21~23)을 포함한다. N형 TFT(21~23)은 각각 대응하는 조의 R용 데이터선(6), G용 데이터선(6) 및 B용 데이터선(6)의 한쪽 끝과 대응하는 데이터 단자(예를 들면 30.1)의 사이에 접속되고, 게이트는 각각 R 단자(31), G 단자(32) 및 B 단자(33)에 접속된다.

신호  $\phi R$ ,  $\phi G$ ,  $\phi B$  중의 신호  $\phi R$ 이 「H」 레벨이 되면, 각 N형 TFT(21)이 도통하여, 각 R용 데이터선(6)과 대응하는 데이터 단자가 결합된다. 신호  $\phi R$ ,  $\phi G$ ,  $\phi B$  중의 신호  $\phi G$ 가 「H」 레벨이 되면, 각 N형 TFT(22)이 도통하여, 각 G용 데이터선(6)과 대응하는 데이터 단자가 결합된다. 신호  $\phi R$ ,  $\phi G$ ,  $\phi B$  중의 신호  $\phi B$ 가 「H」 레벨이 되면, 각 N형 TFT(23)이 도통하여, 각 B용 데이터선(6)과 대응하는 데이터 단자가 결합된다.

검사용 단자 전환 회로(25)는 240조의 R용 데이터선(6), G용 데이터선(6) 및 B용 데이터선(6) 중의 각 홀수번의 조에 대응하여 설치된 N형 TFT(26)과, 각 짹수번의 조에 대응하여 설치된 N형 TFT(27)을 포함한다. 각 N형 TFT(26)은 대응하는 N형 TFT(21~23)의 드레인과 홀수 데이터선(36)의 사이에 접속되고, 그 게이트는 제어 단자(34)에 접속된다. 각 N형 TFT(27)은 대응하는 N형 TFT(21~23)의 드레인과 짹수 데이터 단자(35)의 사이에 접속되고, 그 게이트는 제어 단자(34)에 접속된다.

제어 신호  $\phi C$ 가 「H」 레벨이 되면, N형 TFT(26, 27)이 도통하여, 홀수번째의 조의 N형 TFT(21~23)의 드레인과 홀수 데이터 단자(36)가 접속됨과 함께, 짹수번째의 조의 N형 TFT(21~23)의 드레인과 짹수 데이터 단자(35)가 접속된다.

도 4는 도 3에 도시한 LCD 모듈의 검사 방법을 도시하는 타임차트이다. 검사 시에는 단자(31~36) 각각은 프로브를 통하여 검사 장치에 접속된다. 어떤 시각 t0에 있어서 복수의 주사선(4) 중의 어느 하나의 주사선(4)이 선택되고, 그 주사선(4)의 전위 VH가 「H」 레벨로 상승된다. 이에 따라, 그 주사선(4)에 대응하는 각 N형 TFT(11)이 도통하여, 각 데이터선(6)이 도통한 N형 TFT(11)을 통하여 액정 셀(2)에 접속된다. 또한 시각 t0에 있어서 제어 신호  $\phi C$ 가 「H」 레벨로 상승하여 N형 TFT(26, 27)이 도통하여, 홀수번의 조의 N형 TFT(21~23)의 드레인이 N형 TFT(26)을 통하여 홀수 데이터 단자(36)에 접속됨과 함께, 짹수번의 조의 N형 TFT(21~23)의 드레인이 N형 TFT(27)을 통하여 짹수 데이터 단자(35)에 접속된다.

계속해서 시각 t1에 있어서 신호  $\phi R$ 이 「H」 레벨로 상승하여 각 N형 TFT(21)이 도통하여, 각 홀수번의 R용 데이터선(6)이 N형 TFT(21, 26)을 통하여 홀수 데이터 단자(36)에 접속됨과 함께, 각 짹수번의 R용 데이터선(6)이 N형 TFT(21, 27)을 통하여 짹수 데이터 단자(35)에 접속된다. 또한 시각 t1에 있어서 홀수 데이터 신호 DO가 「L」 레벨로 하강됨과 함께 짹수 데이터 신호 DE가 「H」 레벨로 상승되고, 각 홀수번의 R용 데이터선(6)이 「L」 레벨이 됨과 함께 각 짹수번의 R용 데이터선(6)이 「H」 레벨이 된다. 시각 t1으로부터 소정 시간 경과 후에 신호  $\phi R$ 이 「L」 레벨로 하강되어 각 N형 TFT(21)이 비도통이 되어, 선택된 주사선(4)에 대응하는 각 R용 액정 셀(2)에의 데이터 신호의 기입이 종료한다.

다음에, 시각 t2에 있어서 신호  $\phi G$ 가 「H」 레벨로 상승되어 각 N형 TFT(22)이 도통하여, 각 홀수번의 G용 데이터선(6)이 N형 TFT(22, 26)을 통하여 홀수 데이터 단자(36)에 접속됨과 함께, 각 짹수번의 G용 데이터선(6)이 N형 TFT(22, 27)을 통하여 짹수 데이터 단자(35)에 접속된다. 또한 시각 t2에 있어서 홀수 데이터 신호 DO가 「H」 레벨로 상승됨과 함께 짹수 데이터 신호 DE가 「L」 레벨로 하강되어, 각 홀수번의 G용 데이터선(6)이 「H」 레벨이 됨과 함께 각 짹수번의 G용 데이터선(6)이 「L」 레벨이 된다. 시각 t2으로부터 소정 시간 경과 후에 신호  $\phi G$ 가 「L」 레벨로 하강되어 각 N형 TFT(22)이 비도통이 되어, 선택된 주사선(4)에 대응하는 각 G용 액정 셀(2)에의 데이터 신호의 기입이 종료한다.

계속해서 시각 t3에 있어서 신호  $\phi B$ 가 「H」 레벨로 상승하여 각 N형 TFT(23)이 도통하여, 각 홀수번의 B용 데이터선(6)이 N형 TFT(23, 26)을 통하여 홀수 데이터 단자(36)에 접속됨과 함께, 각 짝수번의 B용 데이터선(6)이 N형 TFT(23, 27)을 통하여 짝수 데이터 단자(35)에 접속된다. 또한 시각 t3에 있어서 홀수 데이터 신호 DO가 「L」 레벨로 하강됨과 함께 짝수 데이터 신호 DE가 「H」 레벨로 상승되고, 각 홀수번의 B용 데이터선(6)이 「L」 레벨이 됨과 함께 각 짝수번의 B용 데이터선(6)이 「H」 레벨이 된다. 시각 t3으로부터 소정 시간 경과 후에 신호  $\phi B$ 가 「L」 레벨로 하강되어 각 N형 TFT(23)이 비도통이 되어, 선택된 주사선(4)에 대응하는 각 B용 액정 셀(2)에의 데이터 신호의 기입이 종료한다. 다음에, 시각 t4에 있어서 주사선(4)의 전위 VH가 「L」 레벨로 하강되어, 1개의 주사선(4)에 대응하는 각 액정 셀(2)에의 데이터 신호의 기입이 종료한다.

이상의 동작을 각 주사선(4)마다 행함으로써, 액정 패널(1)의 전 액정 셀(2)에 「H」 레벨 또는 「L」 레벨의 데이터 신호를 기입할 수 있다. 액정 패널(1)이 정상인가 아닌가는 예를 들면 각 액정 셀(2)의 광투과율을 검출함으로써 판정된다. 예를 들면 인접하는 2개의 데이터선(6)이 단락되어 있는 경우에는, 이들의 데이터선(6)에 대응하는 각 액정 셀(2)에는, 「H」 레벨과 「L」 레벨의 사이의 중간 레벨의 전위가 기입되어, 그 액정 셀(2)은 정상적인 데이터선(6)에 대응하는 액정 셀(2)과 상이한 광투과율을 나타낸다. 따라서, 액정 패널(1)이 정상이 아니라는 것을 용이하게 판정할 수 있다.

검사에 있어서 정상이라고 판정된 LCD 모듈의 단자(30.1~30.4, … 31~36)는 FPC에 접속된다. 단자(34~36) 각각은 FPC에 의해, N형 TFT(26, 27)을 비도통으로 하는 전위(예를 들면 접지 전위 GND)로 고정된다. 계조 전위 VG의 기입은 도 4에서 도시한 데이터 신호 DE, DO의 기입과 마찬가지로 행해진다. 즉, 도 4의 시각 t1~t2의 사이는 데이터 단자(30.1~30.4, …) 각각에 R용 계조 전위 VG가 주어지고, R용 액정 셀(2) 각각에 R용 계조 전위 VG가 기입된다. 시각 t2~t3의 사이는 데이터 단자(30.1~30.4, …) 각각에 G용 계조 전위 VG가 주어지고, G용 액정 셀(2) 각각에 G용 계조 전위 VG가 기입된다. 시각 t3~t4의 사이는, 데이터 단자(30.1~31.4, …) 각각에 B용 계조 전위 VG가 주어지고, B용 액정 셀(2) 각각에 B용 계조 전위 VG가 기입된다. 이와 같이 하여, 액정 패널(1)의 각 액정 셀(2)에 계조 전위 VG가 기입되어, 액정 패널(1)의 하나의 컬러 화상이 표시된다.

이 실시예 1에서는, 각 홀수번의 조의 N형 TFT(21~23)의 드레인과 홀수 데이터 단자(36)의 사이에 N형 TFT(26)을 접속하고, 각 짝수번의 조의 N형 TFT(21~23)의 드레인과 짝수 데이터 단자(35)의 사이에 N형 TFT(27)을 접속하고, N형 TFT(26, 27)의 게이트를 제어 단자(34)에 접속한다. 검사 시에는 N형 TFT(26, 27)을 도통시켜 단자(35, 36)에 검사용의 데이터 신호 DE, DO를 제공하고, 통상 동작 시에는 N형 TFT(26, 27)을 비도통 상태로 고정한다. 따라서, 검사 시에 필요한 단자의 수가 적게 되어, 검사 장치의 저비용화를 도모할 수 있다. 또한, 복수의 LCD 모듈의 복수의 홀수 데이터 단자(36)를 상호 접속함과 함께 복수의 짝수 데이터 단자(35)를 상호 접속한 경우라도, 각 LCD 모듈용의 제어 신호  $\phi C$ 의 레벨을 제어하는 것에 의해, 각 LCD 모듈을 개별적으로 정확하게 검사할 수 있다.

또, 액정 패널(1)은 유리 기판(15) 표면의 소정 영역에 주사선(4), 데이터선(6), N형 TFT(11) 및 캐패시터(12)를 포함하는 어레이 기판을 형성한 후에, 그 어레이 기판의 표면에 액정을 개재하여 대향 기판을 배치함으로써 형성된다. 실시예 1에서는, 액정 패널(1)의 조립 후에 액정 셀(2)의 광투과율을 검사하도록 하였지만, 액정 패널(1)의 조립 전 즉 대향 기판을 배치하기 전의 상태에서, 캐패시터(12)의 전하량을 모니터링 함으로써 어레이 기판을 검사해도 된다.

또한, 이 실시예 1에서는, 검사용 단자 전환 회로(25)를 N형 TFT으로 구성하였지만, P형 TFT으로 구성해도 되고, N형 TFT 및 P형 TFT의 병렬 접속체 즉 트랜스퍼 게이트로 접속해도 된다.

또한, 도 5에 도시한 바와 같이, 검사 시에 사용하는 단자(31~36) 각각의 사이즈를 데이터 단자(30.1~30.4, …) 각각의 사이즈보다 크게 해도 된다. 이에 따라, 프로브의 위치 정밀도를 저하시킬 수 있고, 검사 장치의 비용 절감을 도모할 수 있다.

또한, 도 6에 도시한 바와 같이, 검사 시에 사용하는 단자(31~36)의 피치를 데이터 단자(30.1~30.4, …)의 피치보다 크게 해도 된다. 이 경우에도, 프로브의 위치 정밀도를 저하시킬 수 있어, 검사 장치의 비용 절감을 도모할 수 있다. 또한, 도 5의 변경 예와 도 6의 변경 예를 조합하여, 검사 시에 사용하는 단자(31~36)의 크기 및 피치를 데이터 단자(30.1~30.4, …)의 크기 및 피치보다도 크게 하면, 검사 장치의 한 층의 비용 절감을 도모할 수 있다.

## [실시예 2]

도 7은 본 발명의 실시예 2에 의해 LCD 모듈의 검사 방법을 설명하기 위한 도면이다. 도 7에 있어서, 이 검사 방법에서는 유리 기판(40)의 표면에 복수(도 7에서는 3개)의 LCD 모듈(41~43)이 형성된다. LCD 모듈(41~43) 각각은 도 3에 도시

한 것과 동일하다. LCD 모듈(41~43) 각각의 검사 시에 사용되는 단자(31~36)는 유리 기판(40)의 1변에 대향하여 배치된다. 또한, 유리 기판(40)의 1변을 따라서, R 단자(51), G 단자(52), B 단자(53), 제어 단자(54~56), 짹수 데이터 단자(57), 및 훌수 데이터 단자(58)가 배치된다.

LCD 모듈(41~43)의 R 단자(31)는 모두 R 단자(51)에 접속된다. LCD 모듈(41~43)의 G 단자(32)는 모두 G 단자(52)에 접속된다. LCD 모듈(41~43)의 B 단자(33)는 모두 B 단자(53)에 접속된다. LCD 모듈(41~43)의 제어 단자(34)는 모두 제어 단자(54~56)에 접속된다. LCD 모듈(41~43)의 짹수 데이터 단자(35)는 모두 짹수 데이터 단자(57)에 접속된다. LCD 모듈(41~43)의 훌수 데이터 단자(36)는 모두 훌수 데이터 단자(58)에 접속된다.

검사 시에는 단자(51~58) 각각이 프로브를 통하여 검사 장치에 접속된다. 단자(51~58)에는 각각 신호  $\phi R$ ,  $\phi G$ ,  $\phi B$ ,  $\phi C1$ ,  $\phi C2$ ,  $\phi C3$ , DE, DO가 주어진다. LCD 모듈(41~43)을 검사하는 경우에는 각각 제어 신호  $\phi C1 \sim \phi C3$ 이 「H」 레벨이 된다. LCD 모듈(41~43) 각각은 실시 예 1과 동일한 방법으로 검사된다. 검사의 종료 후에는 LCD 모듈(41~43) 각각은 유리 기판(40)으로부터 추출된다. 이 때, LCD 모듈(41~43) 각각은 불필요해진 단자(51~58) 및 배선으로부터 분리된다.

이 실시 예 2에서는 1회의 프로빙으로 복수의 LCD 모듈(41~43)을 검사할 수 있기 때문에, 분단된 LCD 모듈을 1개씩 검사하는 경우에 비교하여, 프로빙의 횟수가 적어지게 되어, 프로빙의 전환에 필요한 시간이 짧아지게 된다. 또한, 프로빙의 횟수가 적어지게 되기 때문에, 프로브의 마모나 절곡을 경감할 수가 있어, 프로브의 수명을 연장시킬 수 있다. 따라서, 테스트 비용의 대폭적인 저감화를 도모할 수 있다.

또, 이 실시 예 2에서도, 액정 패널(1)을 조립하기 전의 상태에서, 캐패시터(12)의 전하량을 모니터링함으로써 각 어레이 기판을 검사해도 된다.

### [실시 예 3]

도 8은 본 발명의 실시 예 3에 따른 LCD 모듈의 검사 방법을 설명하기 위한 도면이다. 도 8에 있어서, 이 검사 방법에서는, 유리 기판(60)의 표면에 복수(도 8에서는 3개)의 LCD 모듈(61~63)이 형성된다. LCD 모듈(61~63)의 외부 단자부(61a~61c)는 유리 기판(60)의 1변에 대향하여 배치된다. LCD 모듈(61~63)의 외부 단자부(61a~61c)에 따라서, 각각 검사용 단자 전환 회로(64~66)가 설치된다. 또한, 유리 기판(60)의 1변을 따라서, R 단자(71), G 단자(72), B 단자(73), 제어 단자(74~76), 짹수 데이터 단자(77), 및 훌수 데이터 단자(78)가 설치된다.

도 9는 LCD 모듈(61)의 구성을 도시하는 회로 블록도로서, 도 3과 대비되는 도면이다. 도 9를 참조하면, LCD 모듈(61)이 도 3의 LCD 모듈과 다른 점은 검사용 단자 전환 회로(25), 제어 단자(34), 짹수 데이터 단자(35) 및 훌수 데이터 단자(36)가 제거되어 있는 점이다. 외부 단자부(61a)는 데이터 단자(30.1~30.4, …), R 단자(31), G 단자(32), 및 B 단자(33)를 포함한다. 유리 기판(15)은 유리 기판(60)의 일부를 구성하고 있다. LCD 모듈(62, 63)도 LCD 모듈(61)과 동일한 구성을이다.

검사용 단자 전환 회로(64)는 도 10에 도시한 바와 같이, 훌수번의 데이터 단자(30.1, 30.3, …) 각각에 대응하여 설치된 N형 TFT(26)과, 짹수번의 데이터 단자(30.2, 30.4, …) 각각에 대응하여 설치된 N형 TFT(27)을 포함한다. 각 N형 TFT(26)은 대응하는 훌수번의 데이터 단자와 훌수 데이터 단자(78)의 사이에 접속되고, 그 게이트는 제어 단자(74)에 접속된다. 각 N형 TFT(27)은 대응하는 짹수번의 데이터 단자와 짹수 데이터 단자(77)의 사이에 접속되고, 그 게이트는 제어 단자(74)에 접속된다. 또, 도 10에서 제어 단자(75, 76)는 도시가 생략되어 있다. 검사용 단자 전환 회로(65, 66)도 검사용 단자 전환 회로(64)와 동일한 구성을이다. 단, 검사용 단자 전환 회로(65)의 N형 TFT(26, 27)의 게이트는 제어 단자(75)에 접속되고, 검사용 단자 전환 회로(66)의 N형 TFT(26, 27)의 게이트는 제어 단자(76)에 접속된다.

검사 시에는 단자(71~78) 각각이 프로브를 통하여 검사 장치에 접속된다. 단자(71~78)에는 각각 신호  $\phi R$ ,  $\phi G$ ,  $\phi B$ ,  $\phi C1$ ,  $\phi C2$ ,  $\phi C3$ , DE, DO가 주어진다. LCD 모듈(61~63)을 검사하는 경우에는 각각 제어 신호  $\phi C1 \sim \phi C3$ 이 「H」 레벨이 된다. LCD 모듈(61~63) 각각은 실시 예 1과 같이 검사된다. 검사의 종료 후에는 LCD 모듈(61~63) 각각은 유리 기판(60)으로부터 추출된다. 이 때, LCD 모듈(61~63) 각각은 불필요해진 검사용 단자 전환 회로(64~66), 단자(71~78) 및 배선으로부터 분리된다.

이 실시 예 3에서는, 실시 예 2와 동일한 효과가 얻어지는 외에, 불필요해진 N형 TFT(26, 27)을 비도통 상태로 고정하는 쳐리(N형 TFT(26, 27)의 게이트 및 드레인에 접지 전위 GND를 인가하는 것)가 불필요해진다. 또한, LCD 모듈의 구성이 간단해진다.

또, 이 실시예 3에서는, 유리 기판(60) 상에 복수의 LCD 모듈(61~63)을 설치한 경우에 대해 설명하였지만, 도 10으로부터 알 수 있는 바와 같이, 이 검사 방법은 유리 기판(60) 상에 1개의 LCD 모듈(61)을 설치한 경우라도 유효하다.

#### [실시예 4]

도 11은 본 발명의 실시예 4에 따른 LCD 모듈의 구성을 도시하는 회로 블록도로서, 도 3과 대비되는 도면이다. 도 11을 참조하면, 이 LCD 모듈이 도 3의 LCD 모듈과 다른 점은, 단자(34~36)와 검사용 단자 전환 회로(25)의 사이의 3개의 배선이 COG(chip on glass) 실장 영역(80)을 통과하여, 3개의 배선의 COG 실장 영역(80) 내의 소정의 위치에 패드(81~83)가 각각 설치되어 있는 점이다. 검사의 종료 후에는 COG 실장 영역(80)을 덮도록 반도체 칩이 실장된다. 이 때, 반도체 칩의 접지 전위 GND의 전극이 3개의 패드(81~83)와 도통 상태에 되어, 패드(81~83)는 접지 전위 GND로 고정된다. 반도체 칩에는, 도시가 생략된 전원 단자 및 접지 단자로부터, 전원 전위 VDD 및 접지 전위 GND가 주어진다. 반도체 칩은 DC-DC 컨버터 등을 포함하고 있다.

도 12는 COG 실장 영역(80)에 실장된 반도체 칩(90)의 일부를 도시하는 단면도이다. 도 12에 있어서, 유리 기판(15)의 표면에 절연막(92)이 형성되고, 절연막(92)의 표면에 금속 배선(93)이 형성된다. 이 금속 배선(93)은 홀수 데이터 단자(36) 및 각 N형 TFT(26)의 드레인에 접속된다.

금속 배선(93)을 덮도록 하여 절연막(94)이 형성되고, 절연막(94)의 소정 영역에 개구부가 형성되어, 금속 배선(93)의 소정 부분이 노출된다. 절연막(94)의 개구부를 덮도록 하여 금속 단자인 패드(83)가 형성된다. 패드(83)의 표면에 이방성 도전 수지(95)가 도포되고, 반도체 칩(90)의 접지 단자인 범프 전극(91)이 패드(83) 상에 위치하도록 반도체 칩(90)이 탑재된다. 이에 따라, 범프 전극(91)과 패드(83)는 전기적으로 접속된다.

이 실시예 4에서는, 검사 후에 반도체 칩(90)을 실장함으로써, 검사용 단자 전환 회로(25)의 N형 TFT(26, 27)을 비도통 상태로 고정한다. 따라서, LCD 모듈의 외부로부터 단자(34~36)에 접지 전위 GND를 제공할 필요가 없게 되기 때문에, FPC의 단자 수를 적게 할 수 있어, FPC의 폭을 좁게 할 수 있다.

또, 도 13에 도시한 바와 같이, 단자(34~36)를 COG 실장 영역(80) 내에 설치하여도 된다. 단자(34~36)는 반도체 칩(90)의 실장에 의해, 접지 전위 GND로 고정된다. 이 변경예에서는 실시예 4와 동일한 효과가 얻어지는 외에, 패드(81~83)를 별도 설치할 필요가 없다.

본 명세서에 개시된 실시예는 모든 점에서 예시이고 제한적인 것이 아니라고 생각돼야 된다. 본 발명의 범위는 상기한 설명이 아니라 특허 청구의 범위에 의해서 기술되고, 특히 청구의 범위와 균등의 의미 및 범위 내에서의 모든 변경이 포함되는 것으로 의도된다.

#### 발명의 효과

이상과 같이, 본 발명에 따르면, 제1 검사 단자, 제2 검사 단자 및 제1 제어 단자를 검사 장치에 접속하면 검사할 수 있기 때문에, 검사에 사용하는 단자의 수가 적어지게 되어, 검사 장치의 비용 절감을 도모할 수 있다. 또한, 복수의 화상 표시 장치의 복수의 제1 검사 단자를 상호 접속함과 함께 복수의 제2 검사 단자를 상호 접속한 경우라도 화상 표시 장치를 1개씩 정확하게 검사할 수 있다.

#### (57) 청구의 범위

##### 청구항 1.

절연 기판 상에 형성된 화상 표시 장치로서,

복수 행 복수 열로 배치된 복수의 화소 표시 회로와, 각각 상기 복수 행에 대응하여 설치된 복수의 주사선과, 각각 상기 복수 열에 대응하여 설치된 복수의 데이터선을 포함하는 화상 표시 패널,

이들의 제1 전극이 각각 상기 복수의 데이터선에 접속되어, 상기 화상 표시 패널의 통상 동작 시에 비도통이 되는 복수의 트랜지스터,

상기 복수의 트랜지스터 중의 각 홀수번의 트랜지스터의 제2 전극에 접속된 제1 검사 단자,

상기 복수의 트랜지스터 중의 각 짝수번의 트랜지스터의 제2 전극에 접속된 제2 검사 단자, 및

상기 복수의 트랜지스터의 게이트에 접속되어, 상기 화상 표시 패널의 검사 시에 상기 복수의 트랜지스터를 제어하기 위한 제어 신호를 받는 제1 제어 단자

를 포함하는 화상 표시 장치.

## 청구항 2.

제1항에 있어서,

각각 상기 복수의 데이터선에 대응하여 설치되고, 각각이 상기 통상 동작 시에 상기 화소 표시 회로에 화소를 표시시키기 위한 화소 전위를 받는 복수의 데이터 단자를 더 포함하고,

상기 제1 검사 단자, 상기 제2 검사 단자 및 상기 제1 제어 단자 각각의 사이즈는 상기 데이터 단자의 사이즈보다 큰 화상 표시 장치.

## 청구항 3.

제1항에 있어서,

각각 상기 복수의 데이터선에 대응하여 설치되고, 각각이 상기 통상 동작 시에 상기 화소 표시 회로에 화소를 표시시키기 위한 화소 전위를 받는 복수의 데이터 단자를 더 포함하고,

상기 복수의 데이터 단자는 소정의 피치로 배열되고,

상기 제1 검사 단자, 상기 제2 검사 단자 및 상기 제1 제어 단자는 상기 복수의 데이터 단자의 피치보다도 큰 피치로 배열되어 있는 화상 표시 장치.

도면

도면1

도면2

### 도면3

도면4

도면5

## 도면6

도면7

도면8

## 도면9

도면10

## 도면11

도면12

### 도면13

|                |                                                                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种包括检查终端的图像显示装置                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">KR100561150B1</a>                                                                                                                 | 公开(公告)日 | 2006-03-15 |

| 申请号            | KR1020030075079                                                                                                                               | 申请日     | 2003-10-27 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三菱电机有限公司                                                                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 三菱电机有限公司                                                                                                                                      |         |            |

| [标]发明人         | NOJIRI ISAO<br>노지리이사오<br>MURAI HIROYUKI<br>무라이히로유끼                                                                                            |         |            |

| 发明人            | 노지리이사오<br>무라이히로유끼                                                                                                                             |         |            |

| IPC分类号         | G02F1/133 G02F1/1345 G01R31/00 G02F1/13 G02F1/1343 G02F1/136 G02F1/1362 G02F1/1368<br>G09F9/00 G09F9/30 G09G3/00 G09G3/20 G09G3/36 H01L21/336 |         |            |

| CPC分类号         | G09G3/006 G09G3/3688 G02F1/1345 G09G2310/0297 G02F1/1309 G02F2001/136254 G09G3/3648<br>G09G2330/12 G02F2203/69                                |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                                                                |         |            |

| 优先权            | 2003061778 2003-03-07 JP                                                                                                                      |         |            |

| 其他公开文献         | KR1020040079820A                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                     |         |            |

## 摘要(译)

在测试过程中对于每个奇一对数据线(6)本发明的液晶显示模块提供所述奇数数据信号(DO),通过各1N型TFT(26)和多路分解器(20)的奇数据终端(36),并且在每个在检查由每个2N型TFT(27)的时候甚至一对数据线(6)的偶数编号的数据信号(DE))和多路分解器(20)并且控制端子34用于在检查时向第一和第二N型TFT26和27的栅极提供控制信号 $\varphi C$ 。因此,减少了检查时使用的端子的数量,并且可以降低检查设备的成本。3指数方面数据线,控制信号,控制端子,端子数量,LCD模块,解复用器