(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

G02F 1/136 (2006.01)

(45) 공고일자

2007년03월09일

(11) 등록번호

10-0692434

(24) 등록일자

2007년03월02일

(21) 출원번호 10-2000-0024573

(22) 출원일자 2000년05월09일

심사청구일자 2005년05월03일

(65) 공개번호 10-2001-0020822

(43) 공개일자 2001년03월15일

(30) 우선권주장 99-244468 1999년08월31일 일본(JP)

(73) 특허권자 샤프 가부시키가이샤

일본 오사카후 오사카시 아베노구 나가이께조 22방 22고

(72) 발명자 나가세요지

일본국가나가와켄가와사키시나가하라구가미고다나카4-1-1후지쓰가부

시끼가이샤내

다나까요시노리

일본국가나가와켄가와사키시나가하라구가미고다나카4-1-1후지쓰가부

시끼가이샤내

후지까와태쓰야

일본국가나가와켄가와사키시나가하라구가미고다나카4-1-1후지쓰가부

시끼가이샤내

나수야수히로

일본국가나가와켄가와사키시나가하라구가미고다나카4-1-1후지쓰가부

시끼가이샤내

(74) 대리인

문두현

문기상

(56) 선행기술조사문헌

JP05198806 A \*

KR1019980080705 A \*

\* 심사관에 의하여 인용된 문헌

심사관 : 임동재

전체 청구항 수 : 총 10 항

(54) 액정 표시 장치

(57) 요약

본 발명은 정전기 보호 소자를 갖춘 액정 표시 장치에 관한 것이며, 용장성(冗長性)이 우수하고, 비교적 낮은 전압이 장시간 발생되는 정전기에 대해서도 충분한 보호 기능을 갖춘 액정 표시 장치를 제공하는 것을 목적으로 한다.

정전기 보호 소자부(28, 30)는 외부 인출 전극(16, 18)에 접속되는 소스 전극(S)과 공통선(22, 24)에 접속되는 드레인 전극(D)을 갖는 제 1 TFT(32)와 제 1 TFT(32) 게이트 전극(G)에 접속된 도전체(42)와, 외부 인출 전극(16, 18)에 접속된 소스 전극(S)과 도전체(42)에 접속된 드레인 전극(D)과 전기적으로 고립되어 있는 게이트 전극(G)을 갖는 제 2 TFT(38)와, 공통선(22, 24)에 접속된 소스 전극(S)과 도전체(42)에 접속된 드레인 전극(D)과 전기적으로 고립되어 있는 게이트 전극(G)을 갖는 제 3 TFT(40)를 구비하고 있다.

## 대표도

도 3

### 특허청구의 범위

#### 청구항 1.

복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

상기 버스라인에 접속되는 소스/드레인 전극과, 상기 쇼트 링에 접속되는 드레인/소스 전극을 갖는 박막 트랜지스터와,

상기 박막 트랜지스터의 게이트 전극을 상기 버스라인에 접속하는 제 1 저항체와,

상기 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 제 2 저항체

를 구비하고 있는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 2.

제 1 항에 있어서,

상기 제 2 저항체는 복수의 상기 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 공용 저항체인 것을 특징으로 하는 액정 표시 장치.

#### 청구항 3.

복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

인접하는 상기 버스라인의 한쪽에 접속되는 소스/드레인 전극과, 상기 버스라인의 다른 쪽에 접속되는 드레인/소스 전극을 갖는 박막 트랜지스터와,

상기 박막 트랜지스터의 게이트 전극을 상기 버스라인의 한쪽에 접속하는 제 1 저항체와,

상기 박막 트랜지스터의 상기 게이트 전극을 상기 버스라인의 다른 쪽에 접속하는 제 2 저항체를 구비하고 있는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 4.

복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

상기 버스라인에 접속되는 소스/드레인 전극과, 상기 쇼트 링에 접속되는 드레인/소스 전극을 갖는 제 1 박막 트랜지스터와,

상기 제 1 박막 트랜지스터의 게이트 전극에 접속된 도전체와,

상기 버스라인에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 2 박막 트랜지스터와,

상기 쇼트 링에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 3 박막 트랜지스터

를 구비하고 있는 것을 특징으로 하는 액정 표시 장치.

#### 청구항 5.

제 4 항에 있어서,

상기 제 3 박막 트랜지스터는 복수의 상기 제 1 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 공용 트랜지스터인 것을 특징으로 하는 액정 표시 장치.

#### 청구항 6.

복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

인접하는 상기 버스라인의 한쪽에 접속되는 소스/드레인 전극과, 상기 버스라인의 다른 쪽에 접속되는 드레인/소스 전극을 갖는 제 1 박막 트랜지스터와,

상기 제 1 박막 트랜지스터의 게이트 전극에 접속된 도전체와,

상기 버스라인의 한쪽에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 2 박막 트랜지스터와,

상기 버스라인의 다른 쪽에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 3 박막 트랜지스터

를 구비하고 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 7.

제 4 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 제 1 박막 트랜지스터의 게이트 전극은 상기 도전체와 용량을 통해서 접속되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 8.

제 4 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 제 2 및 제 3 박막 트랜지스터 중 적어도 한쪽의 채널 길이는 상기 제 1 박막 트랜지스터의 채널 길이보다 짧은 것을 특징으로 하는 액정 표시 장치.

### 청구항 9.

복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

복수의 금속층과,

상기 복수의 금속층 상에 형성된 절연층과,

상기 복수의 금속층 상의 상기 절연층을 개구시켜 형성한 컨택트 홀과,

상기 컨택트 홀을 통하여 상기 금속층 사이를 전기적으로 접속하는 접속층

을 갖고 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 10.

복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서,

상기 정전기 보호 소자부는,

복수의 금속층과,

상기 복수의 금속층상에 형성된 절연층과,

상기 복수의 금속층상의 상기 절연층을 개구시켜 형성한 컨택트 홀과,

상기 컨택트 홀을 통하여 상기 금속층 사이를 전기적으로 접속하는 접속층

을 갖고 있는 것을 특징으로 하는 액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 박막 트랜지스터(Thin Film Transistor: 이하, TFT라 함)를 스위칭 소자로서 구비한 액티브 매트릭스형의 액정 표시 장치(Liquid Crystal Display)에 관한 것이며, 특히, 어레이측 기판상에 형성된 TFT나 버스라인 사이를 정전기에 의한 파괴나 단락으로부터 보호하는 정전기 보호 소자를 구비한 액정 표시 장치에 관한 것이다.

액티브 매트릭스형의 LCD는 우수한 화상 품질이 얻어지는 플랫 패널·디스플레이로서 컴퓨터나 OA 기기 등에 다용되고 있다. 이 액티브 매트릭스형의 LCD는 TFT 및 화소 전극이 형성된 어레이측 기판과 공통 전극이 형성된 대향 기판 사이에 밀봉된 액정층에 대해서 양 전극으로부터 전압을 인가하여 액정을 구동하도록 되어 있다.

어레이측 기판상에는, 구동하는 표시 화소를 선택하기 위한 주사 신호가 순차 입력되는 복수의 게이트 버스라인이 서로 평행하게 형성되어 있다. 또, 복수의 게이트 버스라인 상에는 절연막이 형성되고, 절연막 상에는 게이트 버스라인에 거의 직교하는 복수의 데이터 버스라인이 형성되어 있다. 서로 직교하는 복수의 게이트 버스라인과 데이터 버스라인에서 매트릭스 형상으로 확정되는 각 영역이 화소 영역으로 되고, 각 화소 영역 내에는 TFT와 표시 전극이 형성되어 있다. TFT의 게이트 전극은 소정의 게이트 버스라인에 접속되고, 드레인 전극은 소정의 데이터 버스라인에 접속되고, 소스 전극은 화소 영역내의 표시 전극에 접속되어 있다.

그런데, TFT-LCD의 액정 동작을 제어하는 TFT나 게이트 버스라인, 데이터 버스라인 등은 절연물인 유리 기판상에 형성되기 때문에 기본적으로 정전기에 약하다. 따라서, TFT를 만들어 넣는 어레이측 기판 공정으로부터 어레이측 기판과 대향 기판을 맞대어 액정을 밀봉하고 드라이버 IC 등을 탑재시키는 패널 공정까지의 사이에서 어레이측 기판상에 정전기가 발생되면, TFT가 파괴되거나 그 특성이 변동되어 버리거나, 또는 각 버스라인 사이가 단락되는 문제가 발생하여 패널의 제조 제품 비율이 현저하게 저하해 버린다. 이 때문에, 어레이측 기판상의 소자나 버스라인을 정전기로부터 보호하는 확실한 수단이 필요해진다.

어레이측 기판을 정전기로부터 보호하는 수단으로서, 예를 들면, 버스라인을 모두 공통 전극(쇼트 링)에 접속하여 동전위로 유지하는 방법이 알려져 있다. 쇼트 링은 데이터 버스라인 또는 게이트 버스라인의 형성시에 이들의 형성 재료로 형성된다. 이 때문에, 수 k $\Omega$ 이하의 저항값으로 각 버스라인이 전기적으로 접속된다. 따라서, 패널상의 특정 장소에 대전이 있어도 순간에 전하 분산이 발생하기 때문에, 표시부 내의 TFT의 소자 파괴 또는 특성 변화를 방지할 수 있다.

그러나, 이 방법에서는 각 버스라인끼리 단락되어 버리기 때문에 버스라인마다 독립의 신호를 인가할 수 없다. 이 때문에, 표시 패널의 화소 전극과 공통(common) 전극간에 전하를 유지시켜, 그 충전량을 검출하여 각 화소의 TFT의 특성 시험을 고정밀도로 행하는 어레이 검사(TFT 검사)를 할 수 없게 된다는 문제가 발생한다. 또, 쇼트 링은 인접하는 버스라인을 저저항으로 전기적으로 접속하기 위해 패널 공정 또는 패널 완성 이후의 유닛 조립 공정에 있어서 제거할 필요가 있고, 그 이후의 공정에서는 정전기 대책이 행해지지 않는다는 문제가 있다.

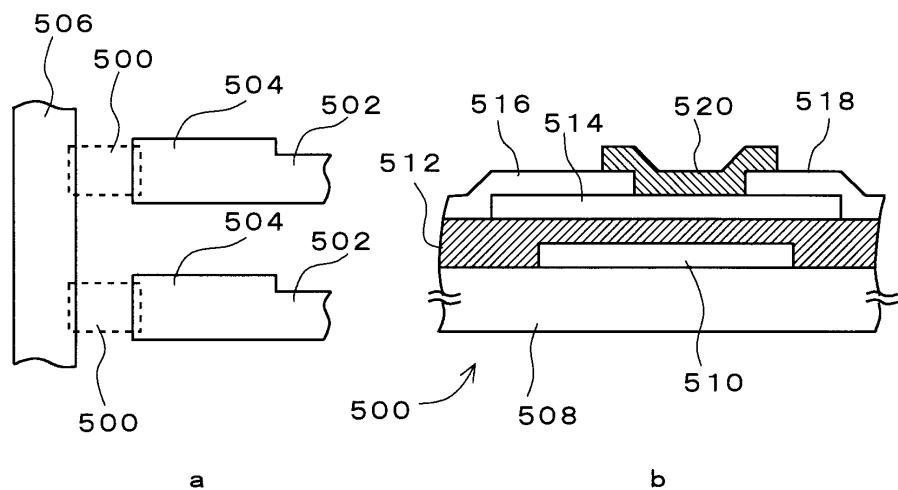

그런데, 쇼트 링과 각 버스라인 사이에 저항 성분을 설치하는 방법이 고안되고 있다. 도 28은 일본국 특개평 8-101397호 공보에 개시된 버스라인과 쇼트 링과의 사이에 저항 성분을 접속한 종래 기술의 설명도이다. 도 28은 어레이측 기판 표면의 일부를 나타내고 있고, 버스라인(504) 단부에는 게이트 메탈 또는 드레인 메탈 위에 형성된 ITO(인듐·탄·옥사이드)를 패터닝하여 사행(蛇行)한 저항층(400)이 형성되어 있다. 사행한 저항층(400)의 선단은 쇼트 링(506)에 접속되어 있다. 이 구조에 의해 어레이 검사가 가능해진다. 통상 이 저항층(400) 및 쇼트 링(506)은 패널 조립시의 패널 스크라이브 공정에 있어서, 도면 중 파선으로 나타낸 스크라이브 라인(SL)을 절단함으로써 제거된다.

그렇지만 이 방법은 ITO로 고 저항화를 도모하기에는 사행 거리를 길게 하기 위한 영역을 확보할 필요가 생기고, 이 때문에 패널 외형 사이즈가 커져 버린다는 문제가 있다.

상기 방법 외에, 버스라인과 셀트 링과의 사이에 트랜지스터 등에 의한 정전기 보호 소자를 삽입한다는 방법이 고안되고 있다. 예를 들면 일본국 특개소 61-79259호 공보에는 게이트 전극을 소스/드레인 전극과 용량 결합하는 방법이 나타나 있다.

도 29는 일본국 특개소 61-79259호에 나타나 있는 종래 기술의 설명도이다.

도 29a는 어레이측 기판의 일부를 기판면을 향해 본 상태를 나타내고 있고, 도 29b는 정전기 보호 소자의 단면을 나타내고 있다. 도 29a에 도시된 바와 같이, 정전기 보호 소자(500)는 버스라인(502) 단부의 외부 인출 전극(504)과 셀트 링(506) 사이에 배치된 TFT구조를 갖고 있다. 정전기 보호 소자(500)는 유리 기판(508)상의 화소 영역에 형성되는 TFT와 동일 공정으로 형성된다. 도 29b에 도시된 바와 같이, 유리 기판(508)상에 게이트 전극(510)이 형성되고, 게이트 전극(510) 상에는 게이트 절연막(512)을 통해서 예를 들면 비정질 실리콘(이하, a-Si로 약기함)으로 이루어지는 동작 반도체층(514)이 형성되어 있다. 동작 반도체층(514) 상에는 보호막(520)이 형성되고, 보호막을 사이에 두어 동작 반도체층(514)의 양측에는, 소스 전극(518)과 드레인 전극(516)이 형성되어 있다. 드레인 전극(516)은 셀트 링(506)에 접속되고, 소스 전극(518)은 외부 인출 전극(504)에 접속되어 있다. 기판면 방향으로 보아, 게이트 전극(510)은 소스/드레인 전극(518, 516)과 평면적 중첩을 갖고 있고, 소스/드레인 전극(518, 516)과 용량 결합에 의해 접속되어 있다. 따라서 소스/드레인 전극(518, 516) 사이에 정전기에 의한 고전압이 발생된 경우에는, 게이트 전극(510)은 소스/드레인 전극(518, 516) 사이에 발생하는 전위차의 중간의 전위가 되기 때문에 동작 반도체층(514)에 채널이 형성되고, 정전기에 의한 전하가 버스라인(502)으로부터 개방된다.

그러나, 이 정전기 보호 소자(500)의 구조는 구성 소자가 한 개이기 때문에 용장성이 부족하다. 즉, 정전기에 의한 고전압을 단지 한 개의 TFT로 막아내기 때문에 파괴되기 쉽고, 파괴에 의해 버스라인(502)과 셀트 링(506) 사이가 절연되어 버리면, 화소 영역의 TFT가 정전기에 노출될 가능성이 높아져 버린다. 또 가령 정전기에 의한 이상이 발생되지 않아도 어떠한 원인으로 정전기 보호 소자(500)가 단락되어 버리면 TFT 시험을 행할 수 없게 된다.

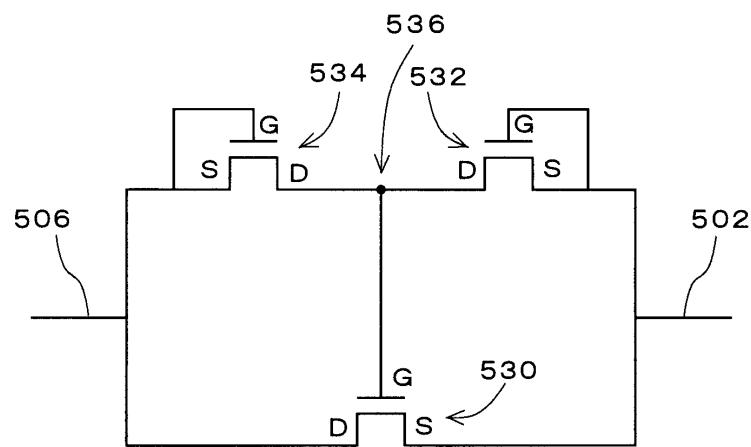

다음에, 도 29에 도시된 구성으로부터 용장성을 갖게 한, 일본국 특개평 10-303431호 공보에 개시된 정전기 보호 회로에 대해서도 30을 이용하여 설명한다. 정전기 보호 소자인 제 1 TFT(530)의 소스 전극(S)은 버스라인의 외부 인출 전극(502)에 접속되어 있고, 다른 쪽의 드레인 전극(D)은 셀트 링(506)에 접속되어 있다. 제 1 TFT(530)의 게이트 전극(G)은 버스라인 외부 인출 전극(502)과 셀트 링(506)의 어느 것과도 전기적으로 절연된 도전체(536)에 접속되고 있다. 한편, 제 2 TFT(532)의 소스 전극(S) 및 게이트 전극(G)은 버스라인의 외부 인출 전극(502)에 접속되어 있고, 다른 쪽의 드레인 전극(D)은 도전체(536)에 접속되고 있다. 또, 제 3 TFT(534)의 드레인 전극(D)은 도전체(536)에 접속되어 있고, 다른 쪽의 소스 전극(S) 및 게이트 전극(G)은 셀트 링(506)에 접속되어 있다. 정전기에 의해서, 셀트 링(506)에 대해서 정(正)의 고전압이 버스라인에 발생한 경우, 제 2 TFT(532)에서는 게이트 전극(G)에 고전압이 인가되어 채널이 형성되기 때문에 도전율이 급격하게 커진다. 한편, 제 3 TFT(534)의 게이트 전극(G)은 셀트 링(506)에 접속되어 있기 때문에, 채널이 형성되는 일이 없이, 도전율은 매우 작은 상태이다. 이 도전율의 차는 매우 크고, 따라서 도전체(536)의 전위는 버스라인의 전위와 거의 동일하게 된다. 이 결과, 정전기 보호 소자인 제 1 TFT(530)의 게이트 전극에는 버스라인과 셀트 링(506) 사이의 전압이 인가되어 채널이 형성되고, 전하를 개방할 수 있다. 또, 제 2 및 제 3 TFT(532, 534)는 기본적으로 전류를 흘리지 않고, 제 1 TFT(530)의 게이트 전위를 제어하기 위해서만 사용된다.

이와 같이 상기 정전기 보호 회로에서는, 제 2 및 제 3 TFT(532, 534)의 게이트 전극(G)이 버스라인의 외부 인출 전극(502) 또는 셀트 링(506)에 접속되어 있기 때문에, 외부 인출 전극(502) 및 셀트 링(506) 사이의 전위차는 즉석에서 해소된다. 그런데, 정전기에 의해 발생된 전압이 시간의 경과와 함께 낮아지면 도전체(536)의 전위도 낮아져 제 1 TFT(530)의 도전율이 저하된다. 이 때문에, 정전기에 의한 전압이 비교적 낮은(~수 볼트) 상태에서는 전하의 해방의 효율이 저하되어 버린다.

또, 지금까지의 제조상의 경험으로부터 정전기에 의한 장해의 발생은 매우 높은 전압 레벨에서 시간적으로는 짧은 날카로운 월스형의 정전기에 의한 경우와, 전압은 비교적 낮아도 장시간에 걸쳐 해당 전압을 각 소자에 계속 인가하는 정전기에 의한 경우가 있음을 알고 있다. 따라서, 일본국 특개평 10-303431호 공보에 기재된 정전기 보호 회로는 전자의 경우에 대해서는 효과를 기대할 수 있지만, 후자의 경우에 대해서는 전압이 어느 정도 낮게 된 시점에서 전류가 빠져나갈 길이 단절되기 때문에 효과를 거의 기대할 수 없다. 또 상기 공보에 기재된 정전기 보호 회로에서는, 정전기에 의한 전류는 모두 제 1 TFT를 흐르기 때문에 용장성이 부족하고, 부하가 너무 커져 제 1 TFT가 파괴되어 버릴 가능성을 갖고 있다. 또, 제 2 TFT(532)의 게이트 전극(G)이 버스라인의 외부 인출 전극(502)과 직접 접속되고, 제 3 TFT(534)의 게이트 전극(G)이 셀트 링(506)과 직접 접속되어 있기 때문에, 단락에 대한 용장성이 낮아져 버리고 있다.

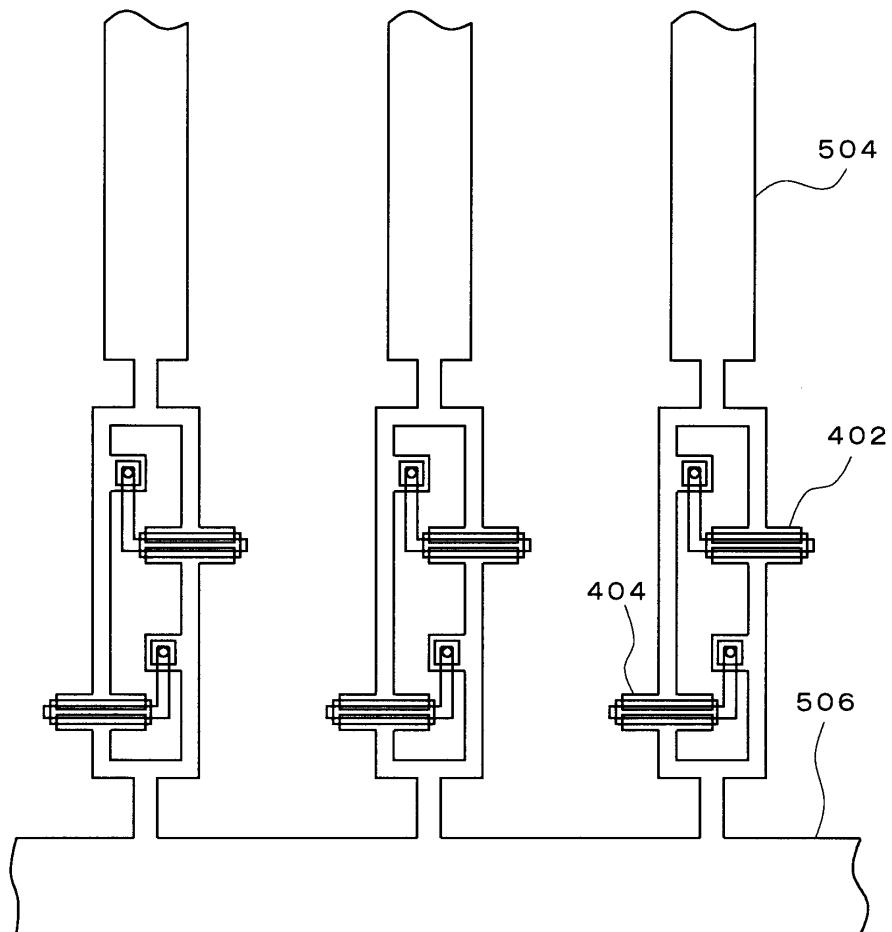

또 다른 종래의 정전기 보호 회로로서, 도 31에 도시된 일본국 특개평 7-60875호 공보에 기재된 구성이 있다. 이것은 각 버스라인(504)과 쇼트 링(506) 사이를 비선형 소자(402, 404)를 사용한 쌍방향 트랜지스터에 의한 저항 성분을 통해서 접속된 정전기 보호 회로이다. 쌍방향 트랜지스터 이외에 저항 성분으로 될 수 있는 쇼트키 다이오드와 같은 비선형 소자를 통한 경우도 있다. 비선형 소자에 의한 저항 성분은 각 버스라인을 구동시키는 경우에 영향을 주지 않도록 충분한 고저항 성분을 갖기 때문에 패널 완성 후에도 잔존시킬 수 있다. 또 정전기에 대해서는 전하 분산이 가능한 정도의 전류는 흐르기 때문에 내정전기 소자로서 기능한다.

쌍방향 트랜지스터와 같은 비선형 소자로 고저항 성분을 설치하는 방식에서는 비교적 좁은 영역에서 고저항 성분을 형성하는 것이 가능하지만 소자 구조가 복잡해지고, 또 비선형 소자이기 때문에 외부 전하(예를 들면 정전기)에 의해 저항 성분이 변화된다는 전류 제어면에서의 문제가 발생한다. 또 유리 단면 근방과 같은 트랜지스터의 동작 반도체막의 동작 보증 영역외에서는 고저항 성분을 형성할 수 없기 때문에, 모(母) 유리에 대해서 패널 사이즈를 크게 할 수 없다는 문제가 있다.

### 발명이 이루고자 하는 기술적 과제

이와 같이 종래의 액정 표시 장치에서는, 패널 공정 또는 패널 완성 이후의 유닛 조립 공정으로 쇼트 링을 제거할 필요가 있지만, 쇼트 링 제거 이후의 공정으로 정전기 대책을 세울 수 없다는 문제가 생긴다.

또, ITO를 사용한 사행 패턴을 마련하는 방식에서는 사행 거리를 길게 취하면 패널 외형 사이즈가 커져 버린다는 문제가 있다.

또 종래의 액정 표시 장치에서는, 정전기에 의한 소자 파괴를 방지시키기 위한 정전기 보호 소자(회로)가 용장성이 부족하여 버스라인 및 쇼트 링 사이가 단락되기 쉽거나, 비교적 낮은 전압이 장시간 발생되는 정전기에 대해서는 보호 회로로서 기능하지 않는다는 문제를 갖고 있다.

또한, 고저항 성분에 쌍방향 트랜지스터와 같은 비선형 소자를 사용하면 소자 구조가 복잡해지는 동시에 전류 제어면에서도 불리해진다. 또 비선형 소자를 유리 단면 근방에 형성할 수 없기 때문에 모 유리에 대해서 패널 사이즈를 크게 할 수 없다는 문제를 갖고 있다.

본 발명의 목적은 용장성이 우수한 정전기 보호 회로를 구비한 액정 표시 장치를 제공하는 것이다.

또 본 발명의 목적은 비교적 낮은 전압이 장시간 발생되는 정전기에 대해서도 충분한 보호 기능을 갖춘 액정 표시 장치를 제공하는 것이다.

또 본 발명의 목적은 기판 조립 공정의 최종 단계까지 정전기 대책을 세울 수 있는 액정 표시 장치를 제공하는 것이다.

또 본 발명의 목적은 정전기 보호 소자부가 패널 사이즈에 영향을 주지 않는 액정 표시 장치를 제공하는 것이다.

또 본 발명의 목적은 소자 구조가 간소하고 전류 제어면에서 불리함이 없는 정전기 보호 소자부를 갖는 액정 표시 장치를 제공하는 것이다.

상기 목적은 복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 상기 버스라인에 접속되는 소스/드레인 전극과, 상기 쇼트 링에 접속되는 드레인/소스 전극을 갖는 박막 트랜지스터와, 상기 박막 트랜지스터의 게이트 전극을 상기 버스라인에 접속하는 제 1 저항체와, 상기 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 제 2 저항체를 구비하고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

상기 본 발명의 액정 표시 장치에 있어서, 상기 제 2 저항체가 복수의 상기 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 공용 저항체여도 좋다.

또 상기 목적은, 복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 인접하는 상기 버스라인의 한쪽에 접속되는 소스/드레인 전극과, 상기 버스라인의 다른 쪽에 접속되는 드레인/소스 전극을 갖는 박막

트랜지스터와, 상기 박막 트랜지스터의 게이트 전극을 상기 버스라인의 한쪽에 접속하는 제 1 저항체와, 상기 박막 트랜지스터의 상기 게이트 전극을 상기 버스라인의 다른 쪽에 접속하는 제 2 저항체를 구비하고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

또 더우기 상기 목적은 복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 상기 버스라인에 접속되는 소스/드레인 전극과, 상기 쇼트 링에 접속되는 드레인/소스 전극을 갖는 제 1 박막 트랜지스터와, 상기 제 1 박막 트랜지스터의 게이트 전극에 접속된 도전체와, 상기 버스라인에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 2 박막 트랜지스터와, 상기 쇼트 링에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 3 박막 트랜지스터를 구비하고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

상기 본 발명의 액정 표시 장치에 있어서, 상기 제 3 박막 트랜지스터가 복수의 상기 제 1 박막 트랜지스터의 상기 게이트 전극을 상기 쇼트 링에 접속하는 공용 트랜지스터여도 좋다.

또 상기 목적은 복수의 버스라인으로 확정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 인접하는 상기 버스라인의 한쪽에 접속되는 소스/드레인 전극과, 상기 버스라인의 다른 쪽에 접속되는 드레인/소스 전극을 갖는 제 1 박막 트랜지스터와, 상기 제 1 박막 트랜지스터의 게이트 전극에 접속된 도전체와, 상기 버스라인의 한쪽에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 2 박막 트랜지스터와, 상기 버스라인의 다른 쪽에 접속된 소스/드레인 전극과, 상기 도전체에 접속된 드레인/소스 전극과, 전기적으로 고립되어 있는 게이트 전극을 갖는 제 3 박막 트랜지스터를 구비하고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

상기 본 발명의 액정 표시 장치에 있어서, 상기 제 1 박막 트랜지스터의 게이트 전극은 상기 도전체와 용량을 통해서 접속되도록 하는 것도 가능하다. 또, 상기 제 2 및 제 3 박막 트랜지스터가 적어도 한쪽의 채널 길이는 상기 제 1 박막 트랜지스터의 채널 길이보다 짧은 것을 특징으로 할 수도 있다.

도 30에 도시된 바와 같은, 제 2 및 제 3 TFT(532, 534)의 게이트 전극(G)을 각각 버스라인(502)과 쇼트 링(506)에 단락 시킨 종래의 정전기 보호 회로에서는, 실질적으로 제 2 및 제 3 TFT(532, 534)에는 전류가 흐르지 않고, 제 1 TFT(530)의 게이트 전위를 제어하기 위해서만 사용되는데 반해, 본 발명의 제 1 및 제 2 저항체, 또는 제 2 및 제 3 TFT는 버스라인과 쇼트 링 사이에서 쌍방향성의 도전성을 나타내어 전류를 흘릴 수 있다. 이 때문에 주로 전류를 흘리기 위한 제 1 TFT가 충분히 도통하기 전부터 제 1 및 제 2 저항체, 또는 제 2 및 제 3 TFT에서 예비적으로 정전기에 의한 전하를 해방하는 기능을 갖고 있다. 즉, 제 2, 제 3 TFT에 예비적으로 전류가 흐르기 때문에 제 1 TFT에 걸리는 부하를 경감할 수 있으므로 정전기 보호 회로의 용장성이 향상된다.

또, 본 발명의 제 1 TFT의 게이트 전극은 용량을 통해서 버스라인, 쇼트 링과 접속되어 있고, 게이트 전극의 전위는 이를 용량의 충방전에 요하는 시간만큼 완만하게 변화한다. 따라서, 본 발명의 구성에 의하면, 완만한 정전기에 대해서도 충분히 대응할 수 있다. 제 1 TFT의 게이트 전극과 제 2, 제 3 TFT 사이의 공통 도전체 사이에 용량을 삽입시킨 경우는 더욱 전체로서의 반응이 완만해져 정전기 보호 소자로서의 효율이 향상된다.

또, 도 30에 도시된 구성은 도 29에 도시된 구성보다 소자수가 많아 용장성이 향상되어 있지만, 예를 들면, 제 2 TFT(532)의 게이트 전극(G)과 드레인 전극(D)이 단락되고, 또한 제 1 TFT(530)의 게이트 전극(G)과 드레인 전극(D)이 단락되면 정전기 보호 회로로서의 기능은 잃게 된다. 마찬가지로, 제 3 TFT(534)의 게이트 전극(G)과 드레인 전극(D)이 단락되고, 또한 제 1 TFT(530)의 게이트 전극(G)과 드레인 전극(D)이 단락된 경우, 또는 제 2 TFT(532)의 게이트 전극(G)과 드레인 전극(D)이 단락되고, 또한 제 3 TFT(534)의 게이트 전극(G)과 드레인 전극(D)이 단락된 경우에도 정전기 보호 회로로서의 기능은 잃게 된다. 결국, 도 30에 도시된 회로에서는 상술한 바와 같이 회로 중의 소자의 2 곳이 단락되면 문제를 일으켜 버린다.

그것에 대해서, 예를 들면 본 실시 형태의 도 3을 참조하여 설명하면, 본 발명에 의한 구성에서는, 제 2 TFT(38)의 게이트 전극(G)과 소스 전극(S)이 단락되고, 또한 제 2 TFT(38)의 게이트 전극(G)과 드레인 전극(D)이 단락되고, 또한 제 1 TFT(32)의 게이트 전극(G)과 드레인 전극(D)이 단락되면 정전기 보호 회로로서의 기능이 상실된다. 마찬가지로, 제 3 TFT(40)의 게이트 전극(G)과 소스 전극(S)이 단락되고, 또한 제 3 TFT(40)의 게이트 전극(G)과 드레인 전극(D)이 단락되고,

또한 제 1 TFT(32)의 게이트 전극(G)과 드레인 전극(D)이 단락된 경우, 또는 제 2 TFT(38)의 게이트 전극(G)과 소스 전극(S)이 단락되고, 또한 제 2 TFT(38)의 게이트 전극(G)과 드레인 전극(D)이 단락되고, 또한 제 3 TFT(40)의 게이트 전극(G)과 소스 전극(S)이 단락되고, 또한 제 3 TFT(40)의 게이트 전극(G)과 드레인 전극(D)이 단락된 경우에 정전기 보호 회로로서의 기능이 상실된다. 결국, 도 3에 도시된 본 발명의 구체적 회로에서는 회로 중의 소자의 3 곳 이상이 단락되어 비로소 정전기 보호 회로로서 기능하지 않게 된다. 이와 같이, 본 발명에 의한 정전기 보호 회로는 게이트가 플로팅이므로 구성 소자의 단락에 대한 용장성에도 우수하다.

또, 상기 목적은 복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 상기 복수의 버스라인에 접속된 쇼트 링과, 상기 복수의 버스라인의 각각과 상기 쇼트 링 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 복수의 금속층과, 상기 복수의 금속층상에 형성된 절연층과, 상기 복수의 금속층상의 상기 절연층을 개구시켜 형성된 컨택트 홀과, 상기 컨택트 홀을 통해서 상기 금속층 사이를 전기적으로 접속하는 접속층을 갖고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

또 상기 목적은 복수의 버스라인으로 획정된 복수의 화소마다 형성된 스위칭 소자와, 인접하는 상기 버스라인 사이에 형성된 정전기 보호 소자부를 갖는 액티브 매트릭스형의 액정 표시 장치에 있어서, 상기 정전기 보호 소자부는 복수의 금속층과, 상기 복수의 금속층상에 형성된 절연층과, 상기 복수의 금속층상의 상기 절연층을 개구시켜 형성된 컨택트 홀과, 상기 컨택트 홀을 통해서 상기 금속층 사이를 전기적으로 접속하는 접속층을 갖고 있는 것을 특징으로 하는 액정 표시 장치에 의해 달성된다.

본 발명에 의하면, 게이트 버스라인 또는 데이터(드레인) 버스라인상의 보호막에 컨택트 홀을 형성하고, 이것을 통해서 쇼트 링과 각 버스라인을 전기적으로 접속한다. 이 구조에서 발생하는 다른 메탈(예를 들면 Ti와 ITO)간의 접촉 저항은 재료를 선택함으로써 오믹 컨택트를 얻을 수 있고, 또한 컨택트 홀수, 사이즈 또는 하층 메탈의 후처리 공정에 의해 저항 성분의 저항값을 제어하는 것이 가능하다. 물론 메탈 컨택트는 오믹 컨택트에 한정하는 것이 아니라, 쇼트키 접속으로 비선형 특성을 갖는 저항 소자를 설치하는 것이 가능하다.

본 발명에 의해 형성된 내정전기 소자는 저항 제어(전류 제어)가 용이하고, 구조도 간단하기 때문에 안정된 저항 성분을 가질 수 있다. 또 상기 설명한 방법에 의해 임의의 저항 성분을 형성하는 것이 가능하기 때문에, 고저항을 만들어 넣음으로써 어레이 검사를 가능하게 하고, 또한 정전기에 대해 충분한 보호 기능을 가질 수 있게 된다.

### 발명의 구성

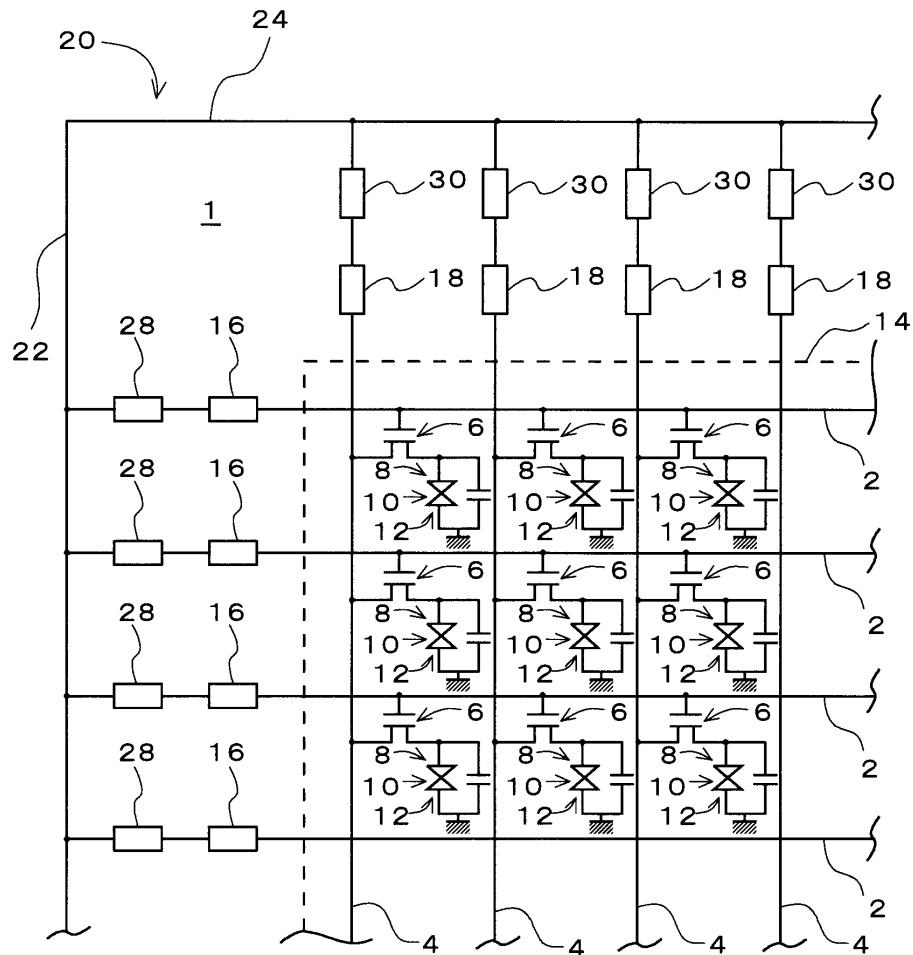

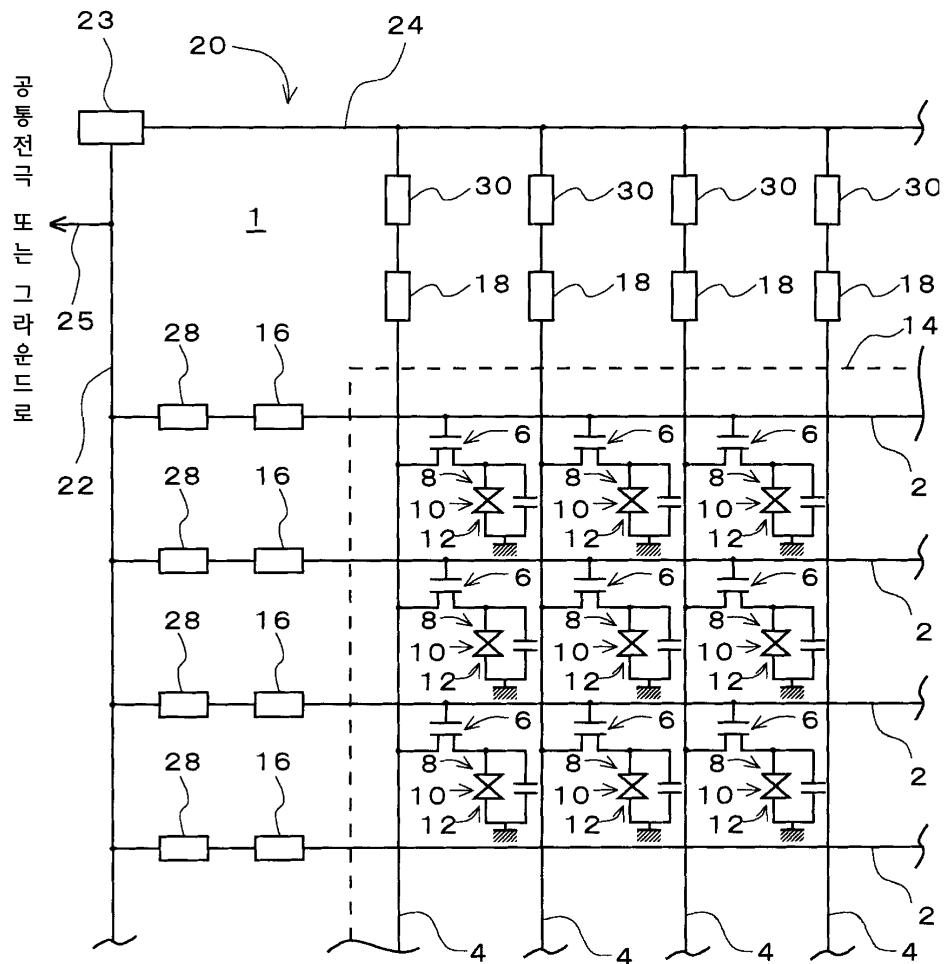

본 발명의 제 1 실시 형태에 의한 액정 표시 장치에 대해서 도 1 및 도 2를 이용하여 설명한다. 먼저, 본 실시 형태에 의한 액정 표시 장치의 개략의 구성을 도 1을 이용하여 설명한다. 도 1은 본 액정 표시 장치의 어레이측 기판(1)측의 일부를 기판면을 향해 본 상태를 나타내고 있다. 또, 화소 영역내는 액정 구동을 위한 등가 회로를 나타내고 있다. 어레이측 기판(1) 상에는, 도면 중 기판 좌우 방향으로 뻗어나가는 게이트 버스라인(2)이 상하 방향으로 평행하게 복수 형성되어 있다. 또, 복수의 게이트 버스라인(2) 상에는 도시를 생략한 절연막이 형성되고, 절연막 상에는 게이트 버스라인(2)에 거의 직교하도록 복수의 데이터 버스라인(4)이 형성되어 있다. 서로 직교하는 복수의 게이트 버스라인(2)과 데이터 버스라인(4)에서 매트릭스 형상으로 획정되는 각 영역이 화소 영역으로 되고, 각 화소 영역 내에는 TFT(6)와 표시 전극(8)이 형성되어 있다. TFT(6)의 게이트 전극은 소정의 게이트 버스라인(2)에 접속되고, 드레인 전극은 소정의 데이터 버스라인(4)에 접속되고, 소스 전극은 화소 영역내의 표시 전극(8)에 접속되어 있다. 도면 중의 파선(14)은 대향 기판의 단부를 나타내고 있다. 대향 기판측에는, 공통 전극(12)이 형성되어 있다. 어레이측 기판(1)과 대향 기판 사이에는 액정(10)이 밀봉되어 있다.

소정의 게이트 버스라인(2)에 출력된 주사 신호에 의해 해당 게이트 버스라인(2)에 게이트 전극이 접속된 TFT(6)는 온 상태가 되고, 데이터 버스라인(4)에 출력된 계조 신호에 의거하는 전압이 화소 전극(8)에 인가된다. 한편, 대향 기판측의 공통 전극(12)에도 소정의 전압이 인가되고, 화소 전극(8)과 공통 전극(12)에 인가된 전압에 의해서, 화소 전극(8)과 공통 전극(12) 사이의 액정이 구동되도록 되어 있다.

각 게이트 버스라인(2)의 단부에는 외부 인출 전극(16)이 형성되고, 각 데이터 버스라인(4)의 단부에도 외부 인출 전극(18)이 형성되어 있다. 외부 인출 전극(16, 18)의 외부 주위에는 정전기 보호 회로의 구성 요소인 쇼트 링(20)이 형성되어 있다. 쇼트 링(20)은 게이트 버스라인측 공통선(22)과 데이터 버스라인측 공통선(24)을 갖고 있다. 게이트 버스라인측 공통선(22)과 각 게이트 버스라인(2)의 외부 인출 전극(16) 사이에는, 정전기 보호 회로의 구성 요소로 되는 정전기 보호 소자부(28)가 형성되어 있다. 한편, 데이터 버스라인측 공통선(24)과 각 데이터 버스라인(4)의 외부 인출 전극(18) 사이에는, 정전기 보호 회로의 구성 요소로 되는 정전기 보호 소자부(30)가 형성되어 있다.

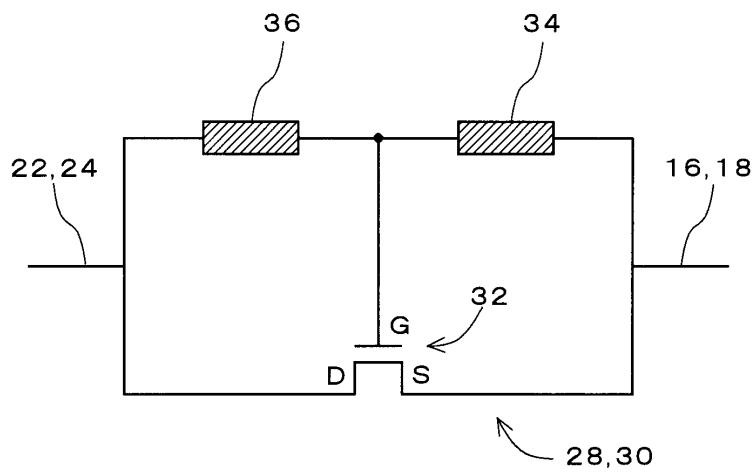

다음에, 본 실시 형태에 의한 정전기 보호 소자부(28, 30)의 회로 구성 및 동작에 대해서 도 2를 이용하여 설명한다. 또, 정전기 보호 소자부(28)와 정전기 보호 소자부(30)의 구성 및 동작은 동일하므로, 이후, 정전기 보호 소자부(28)를 예로서 설명한다. 정전기 보호 소자부(28)는 TFT(32), 제 1 저항체(34), 및 제 2 저항체(36)를 갖고 있다. 정전기 보호 소자인 TFT(32)의 소스 전극(S)은 게이트 버스라인(2)의 외부 인출 전극(16)에 접속되어 있고, 다른 쪽의 드레인 전극(D)은 공통선(22)에 접속되어 있다. TFT(32)의 게이트 전극(G)은 제 1 저항체(34)에 의해 외부 인출 전극(16)에 접속되어 있고, 또, 동시에 TFT(32)의 게이트 전극(G)은 제 2 저항체(36)에 의해 공통선(22)에 접속되어 있다. 정전기에 의해 공통선(22)에 대해 정의 고전압이 버스라인에 발생하면, TFT(32)의 게이트 전극(G)에는 정전기에 의해 발생한 고전압을 제 1 저항체(34)와 제 2 저항체(36)로 분할한 값의 전압이 인가된다. 그 결과, TFT(32)의 도전율이 급격하게 커지기 때문에, TFT(32)를 통해서 정전기에 의한 전하가 해방된다. 이 때, TFT(32)뿐만 아니라, 제 1 및 제 2 저항체(34, 36)를 통해서도 전하는 해방되고, TFT(32)를 흐르는 전류는 도 29에 도시된 바와 같은 TFT가 단일의 경우에 비해 완화되고, 또 도 30에 도시된 보호 회로보다 정전기 보호 소자로서의 용장성이 우수하다. 따라서, 정전기로 용이하게 파괴되지 않고 또한 TFT 시험도 충분히 행할 수 있는 정전기 보호 회로를 탑재한 액정 표시 장치를 제조할 수 있다.

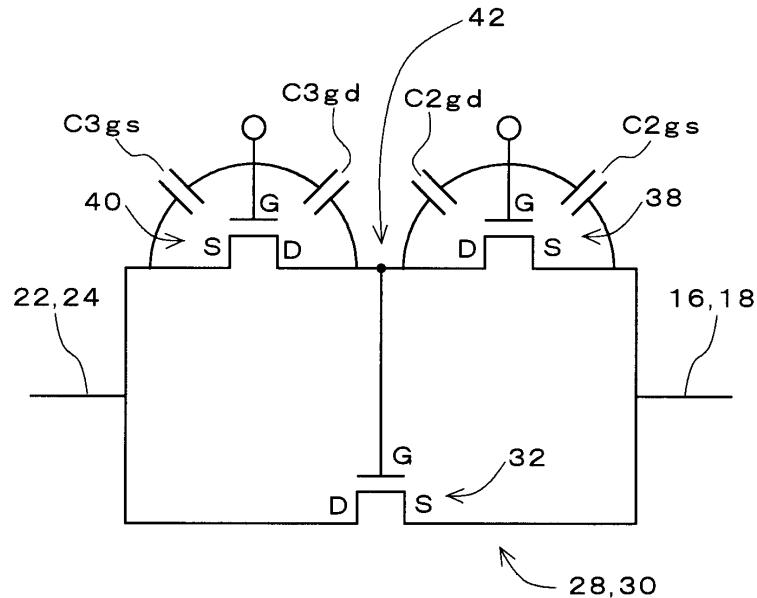

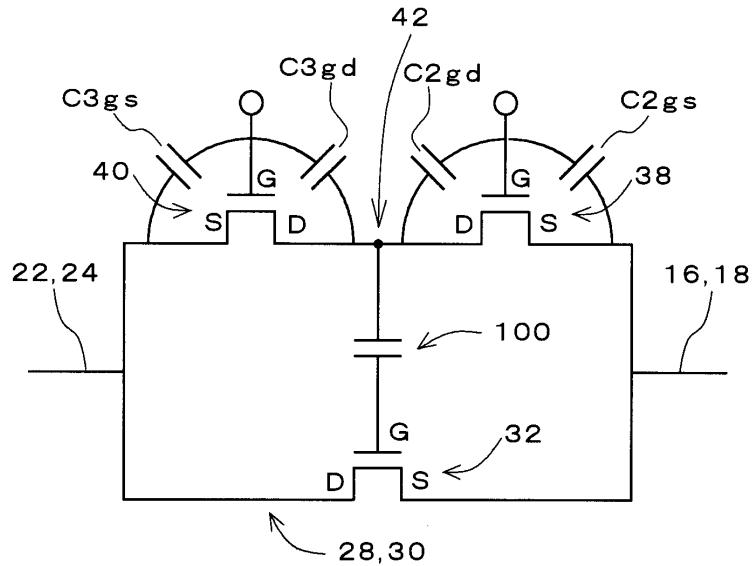

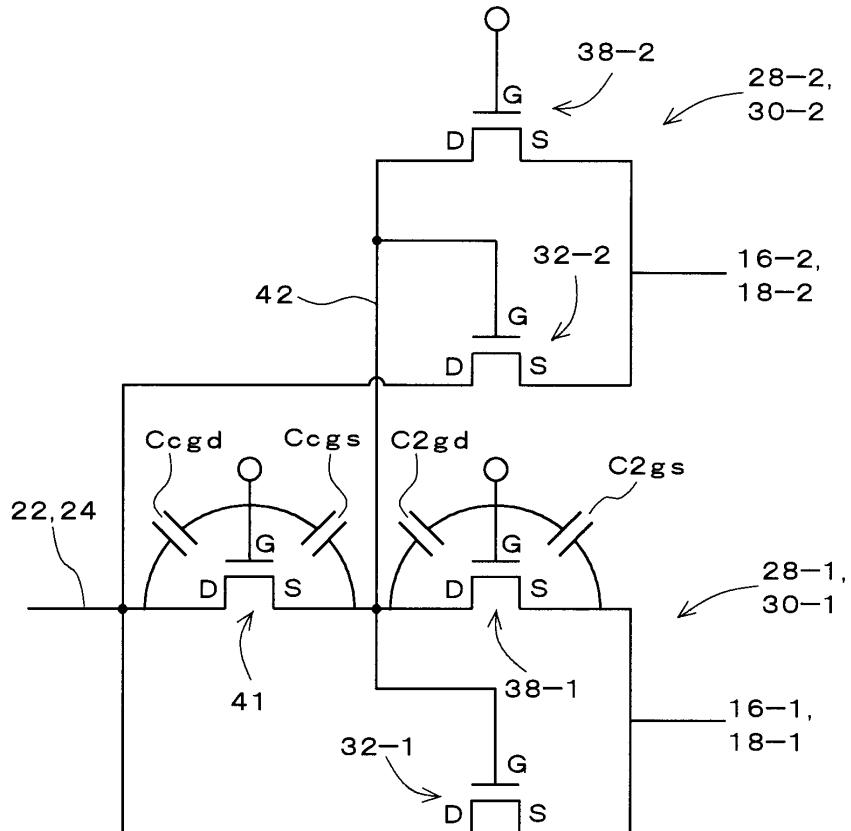

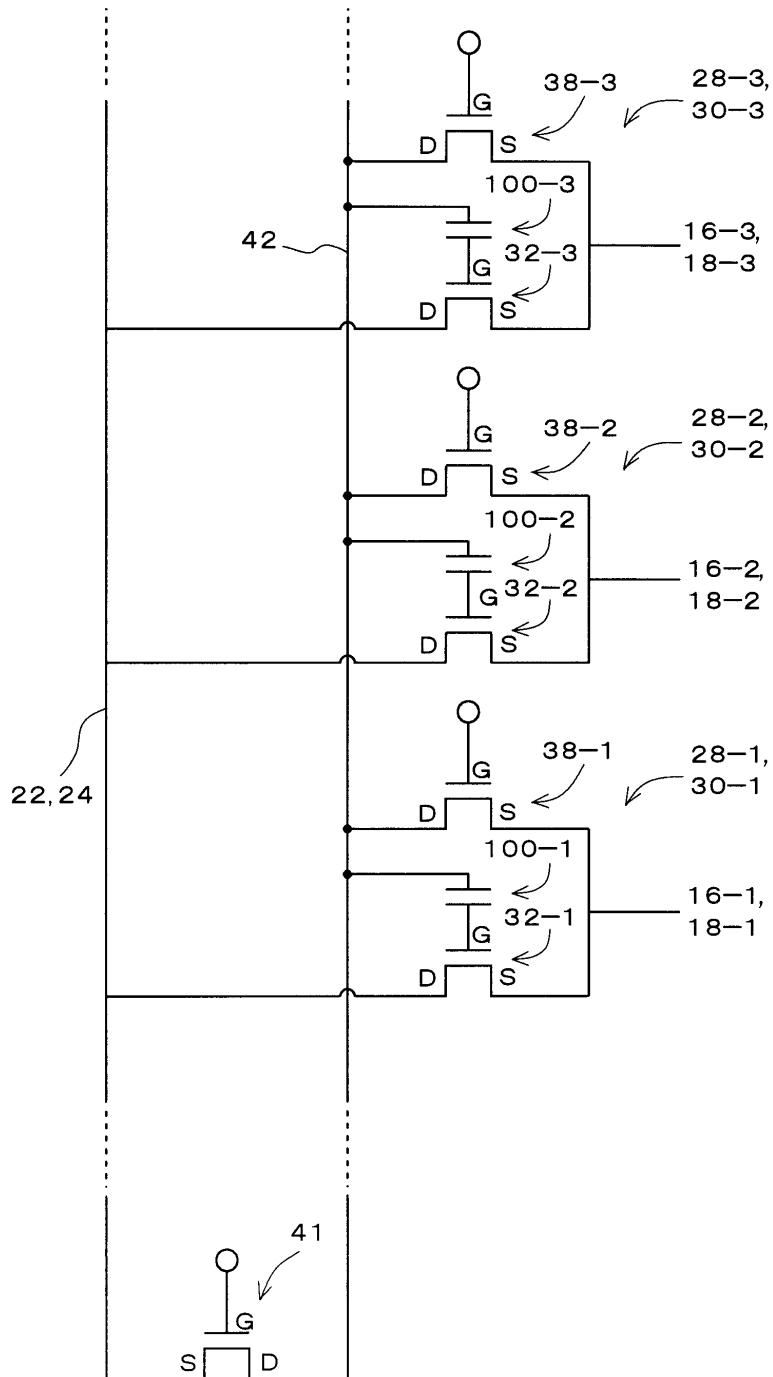

다음에, 본 발명의 제 2 실시 형태에 의한 액정 표시 장치에 대해서 도 3 내지 도 5를 이용하여 설명한다. 본 액정 표시 장치의 개략 구성은 제 1 실시 형태에서 사용한 도 1과 같으므로 설명은 생략하고, 특징적 구성 요소인 정전기 보호 소자부(28, 30)의 회로 구성에 대해서 도 3을 이용하여 설명한다. 정전기 보호 소자부(28)는 제 1 내지 제 3 TFT(32, 38, 40) 및 도전체(42)를 갖고 있다. 정전기 보호 소자인 제 1 TFT(32)의 소스 전극(S)은 버스라인(2)의 외부 인출 전극(16)에 접속되어 있고, 다른 쪽의 드레인 전극(D)은 공통선(22)에 접속되어 있다. 제 1 TFT(32)의 게이트 전극(G)은 버스라인(2)의 외부 인출 전극(16)과 공통선(22)의 어느 것과도 전기적으로 절연된 도전체(42)에 접속되어 있다. 한편, 제 2 TFT(38)의 소스 전극(S)은 외부 인출 전극(16)에 접속되어 있고, 다른 쪽의 드레인 전극(D)은 도전체(42)에 접속되어 있다. 또, 제 3 TFT(40)의 드레인 전극(D)은 도전체(42)에 접속되어 있고, 다른 쪽의 소스 전극(S)은 공통선(22)에 접속되어 있다. 그리고, 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)은 어느 패턴에도 접속되어 있지 않고 고립되어 있다. 정전기에 의해 공통선(22)에 대해 정의 고전압이 버스라인에 발생하면, 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)에는 각각 기생 용량( $C_{2_{gs}}, C_{2_{gd}}, C_{3_{gs}}, C_{3_{gd}}$ )에 의해 내분된 고전압이 인가되어 제 2 및 제 3 TFT(38, 40)에서 채널이 형성된다. 그 결과, 제 2 및 제 3 TFT(38, 40)를 통하여 전류가 흐르고, 도전체(42)의 전위도 상승한다. 그것에 의해 제 1 TFT(32)에 채널이 형성되어 도전율이 커지기 때문에 정전기에 의한 전하가 해방된다. 이와 같이 본 실시 형태에 의하면, 제 2, 제 3 TFT(38, 40)에 예비적으로 전류가 흐르기 때문에 제 1 TFT(32)에 걸리는 부하가 경감되고 정전기 보호 회로의 용장성을 향상시킬 수 있다. 또, 제 1 TFT(32)의 게이트 전극(G)은 용량을 통해서 외부 인출 전극(16, 18), 및 쇼트 링(20)의 공통선(22, 24)과 접속되어 있고, 게이트 전극(G)의 전위는 이들 용량의 충방전에 요하는 시간만큼 완만하게 변화한다. 따라서, 본 실시 형태의 구성에 의하면, 완만한 정전기에 대해서도 충분히 대응할 수 있다.

이와 같이 전하는 복수의 경로에서 해방되기 때문에, TFT가 1개인 종래의 경우에 비해 제 1 TFT로의 부하가 완화되고, 또 정전기 보호 소자로서의 용장성이 증가하므로, 정전기로 용이하게 파괴되지 않고 또한 TFT 시험도 충분히 행할 수 있는 정전기 보호 회로를 탑재한 액정 표시 장치를 제조할 수 있다.

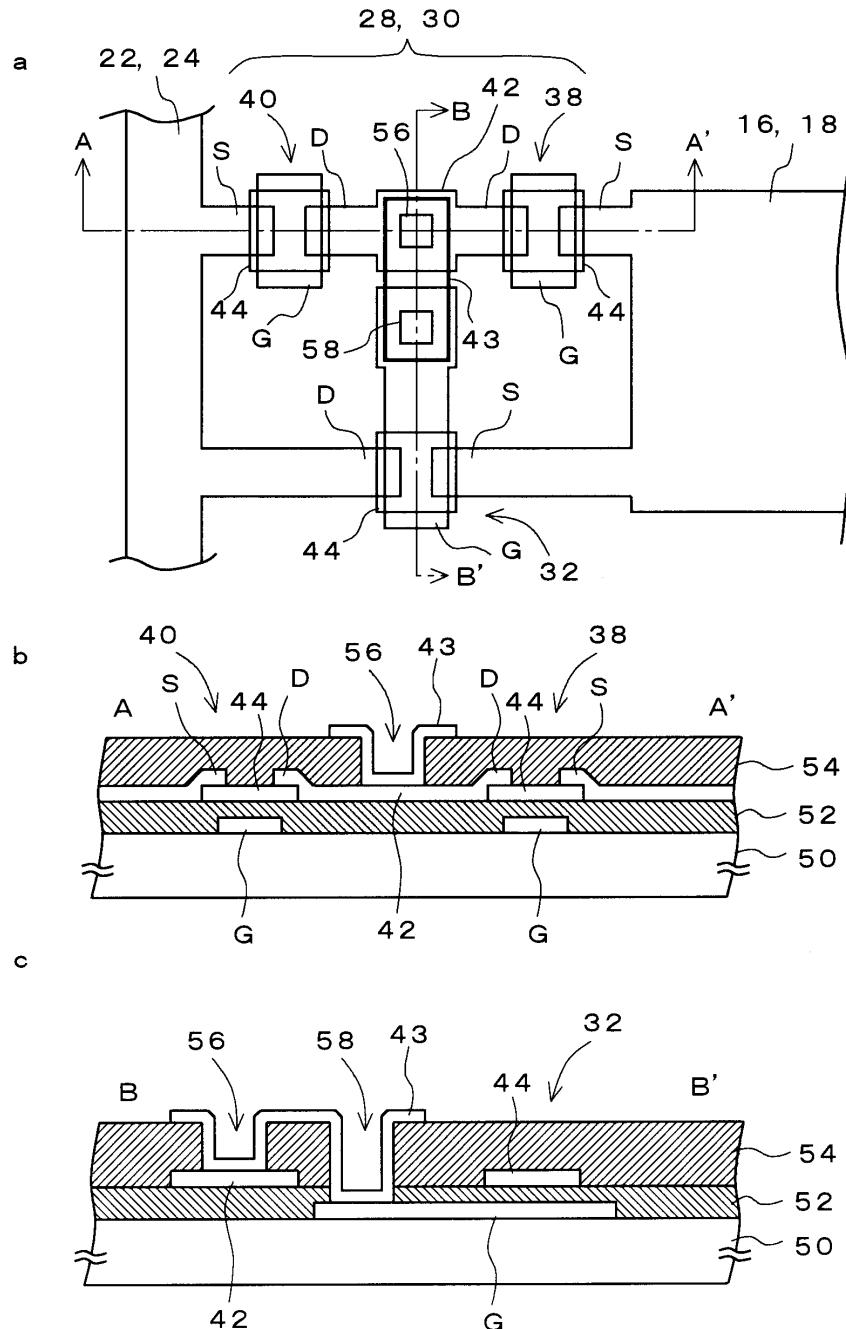

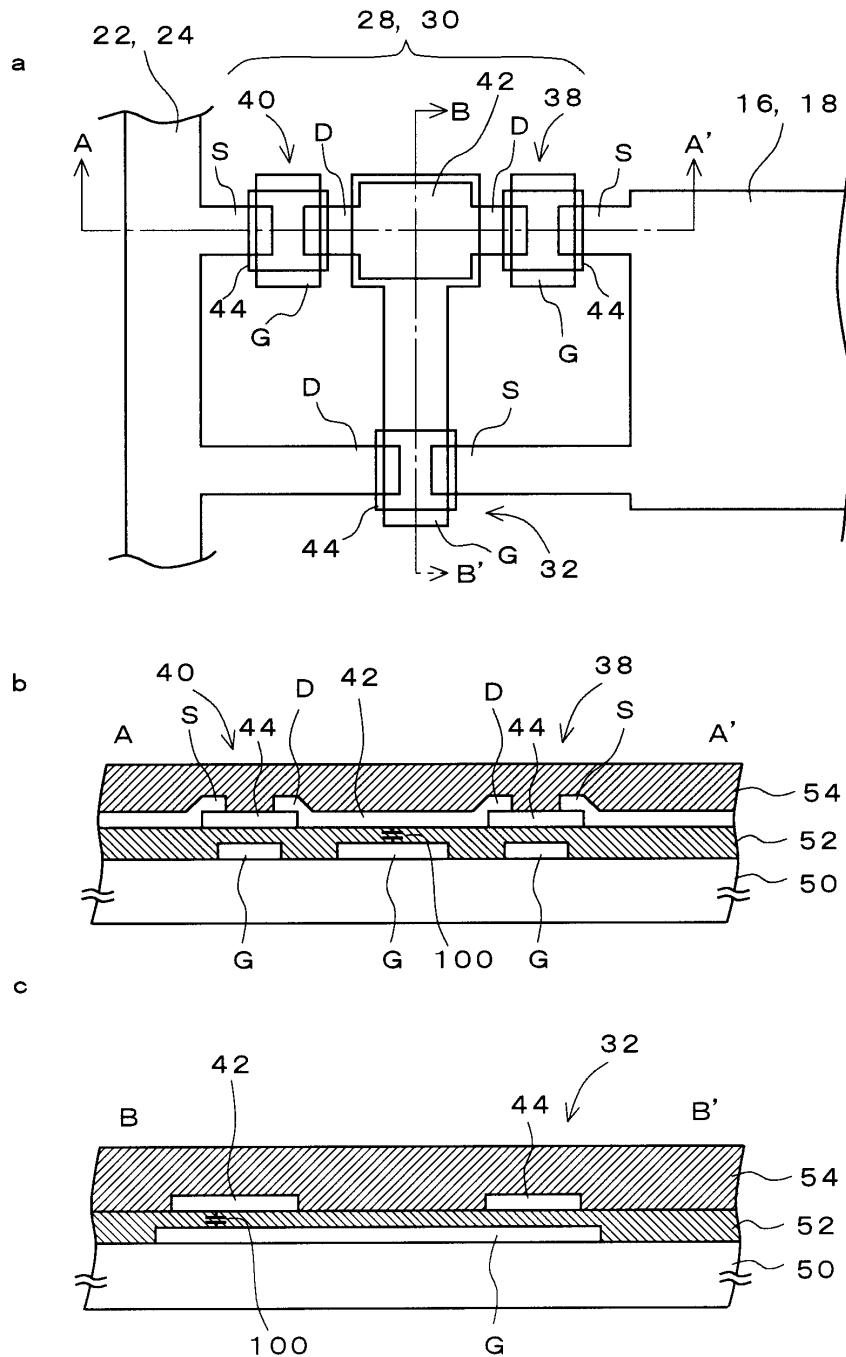

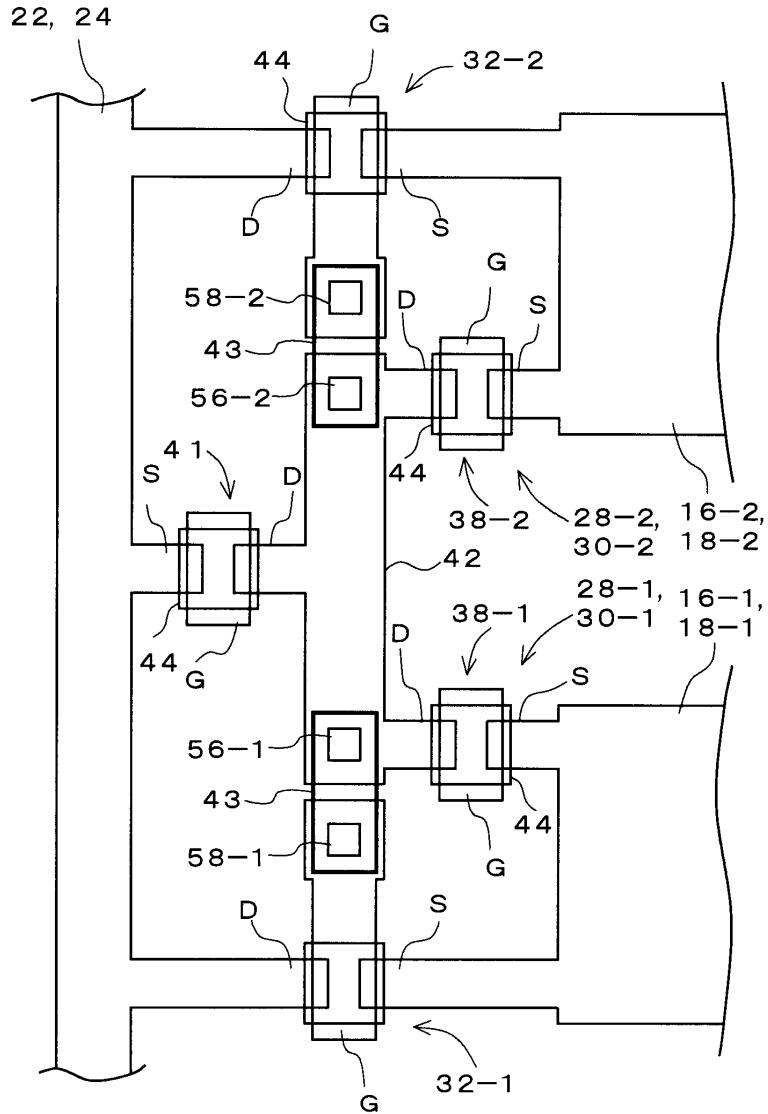

다음에, 본 실시 형태에 의한 정전기 보호 회로의 구조에 대해서 도 4를 이용하여 설명한다. 도 4a는 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 4b는 도 4a의 A-A'선으로 절단한 단면을 나타내고 있다. 도 4c는 도 4a의 B-B'선으로 절단한 단면을 나타내고 있다.

도 4a에 있어서, 도면 중 좌측에서 상하로 뻗어나가는 공통선(22)(또는 24, 이하 기재를 생략함)과 외부 인출 전극(16)(또는 18, 이하 기재를 생략함) 사이에 정전기 보호 소자부(28)(또는 30, 이하 기재를 생략함)가 형성되어 있다. 도 4b, 도 4c에 도시된 바와 같이, 유리 기판(50)상에 게이트 버스라인(2) 및 화소 영역의 TFT(6)(도 1 참조)의 게이트 전극을 형성할 때에 동시에 제 1 내지 제 3 TFT(32, 38, 40)의 게이트 전극(G)도 형성된다. 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)은 다른 배선 구조로부터 전기적으로 고립하여 형성되어 있다. 게이트 전극(G) 및 유리 기판(50) 상에는 게이트 절연막(52)이 형성되어 있다. 제 1 내지 제 3 TFT(32, 38, 40)의 각 게이트 전극(G)상에 형성된 게이트 절연막(52) 상에는 a-Si로 이루어지는 동작 반도체층(44)이 각각 패터닝되어 있다. 각 동작 반도체층(44)을 사이에 두어 양측에는, 데이터(드레인) 버스라인(4) 및 외부 인출 전극(16)의 형성과 동시에 패터닝된 소스/드레인 전극이 형성되어 있다. 각 소스/드레인 전극의 단부는 각 동작 반도체층(44)에 얹혀지고, 기판면 방향으로 보아 각 소스/드레인 전극의 단부와 하층의 게이트 전극(G)이 오버랩하는 영역이 형성되어 있다. 또, 쇼트 링(22)도 데이터 버스라인(4) 형성시에 동시에 형성된다. 소자 형성 영역 전면에 패시베이션막(54)이 형성되어 있다.

제 2 및 제 3 TFT(38, 40) 사이의 소스/드레인 전극의 거의 중앙부상의 패시베이션막(54)을 제거하여 컨택트 홀(56)이 형성되어 있다. 마찬가지로, 제 1 TFT(32)의 게이트 전극의 일단부상의 게이트 절연막(52)과 패시베이션막(54)도 제거되어 컨택트 홀(58)이 형성되어 있다. 2개의 컨택트 홀(56, 58)을 통해서, 제 2 및 제 3 TFT(38, 40) 사이의 소스/드레인 전극의 거의 중앙부와 제 1 TFT(32)의 게이트 전극이 도전체의 일부를 구성하는 ITO층(43)으로 접속되어 있다. 본 예에서는, 도전체(42)의 1구성요소인 ITO층(42)은 각 화소 영역내의 표시 전극을 형성할 때의 투명 전극으로서의 ITO의 패터닝시에 동시에 형성된다.

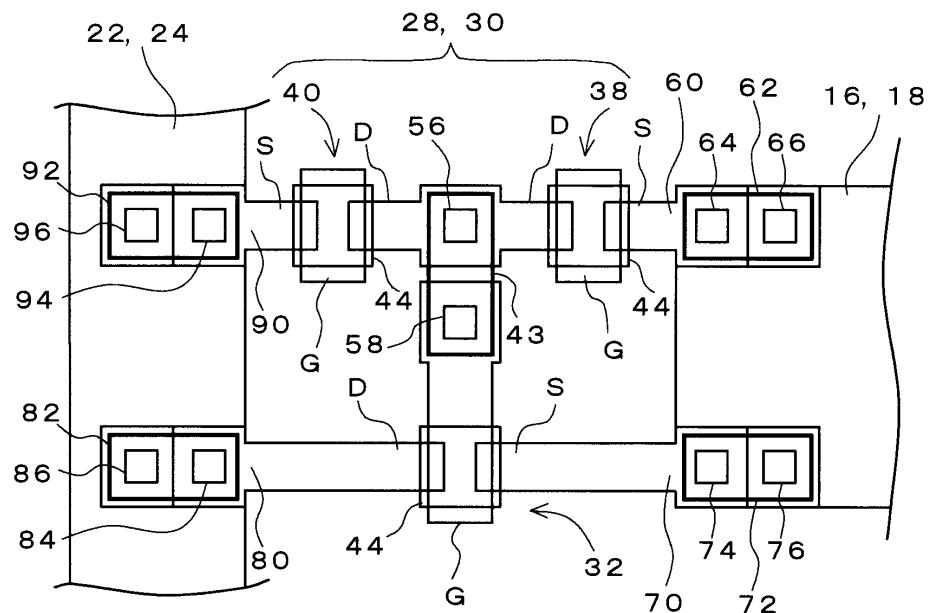

도 4에 도시된 구성에서는, 외부 인출 전극(16, 18) 및 셔트 링(20)의 공통선(22, 24)은 모두 데이터 버스라인(4)의 형성과 동시에 동일 재료로 형성되지만, 이것은 본질적인 것이 아니다. 예를 들면, 도 5에 도시된 바와 같이 게이트 버스라인(2)의 형성시 동시에 게이트 버스라인(2)과 같은 금속층에 의해 외부 인출 전극(16, 18) 및 셔트 링(22, 24)을 형성해도 좋다. 도 5는 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 5에 도시된 바와 같이, 외부 인출 전극(16, 18)과 접속되는 제 1 TFT(32)의 소스 전극(70)은 그 일단부상에 형성된 컨택트 홀(74)과, 외부 인출 전극(16, 18)상에 형성된 컨택트 홀(76)을 통해서, 표시 전극 형성시의 ITO층(72)으로 접속되어 있다. 마찬가지로, 외부 인출 전극(16, 18)과 접속되는 제 2 TFT(38)의 소스 전극(60)은 그 일단부상에 형성된 컨택트 홀(64)과, 외부 인출 전극(16, 18)상에 형성된 컨택트 홀(66)을 통해서, 표시 전극 형성시의 ITO층(62)으로 접속되어 있다. 또 마찬가지로, 셔트 링(20)의 공통선(22, 24)과 접속되는 제 1 TFT(32)의 드레인 전극(80) 및 제 3 TFT(40)의 소스 전극(90)은 그들의 일단부상에 형성된 컨택트 홀(84, 94)과, 공통선(22, 24)상에 형성된 컨택트 홀(86, 96)을 각각 통해서 표시 전극 형성시의 ITO층(82, 92)으로 각각 접속되어 있다.

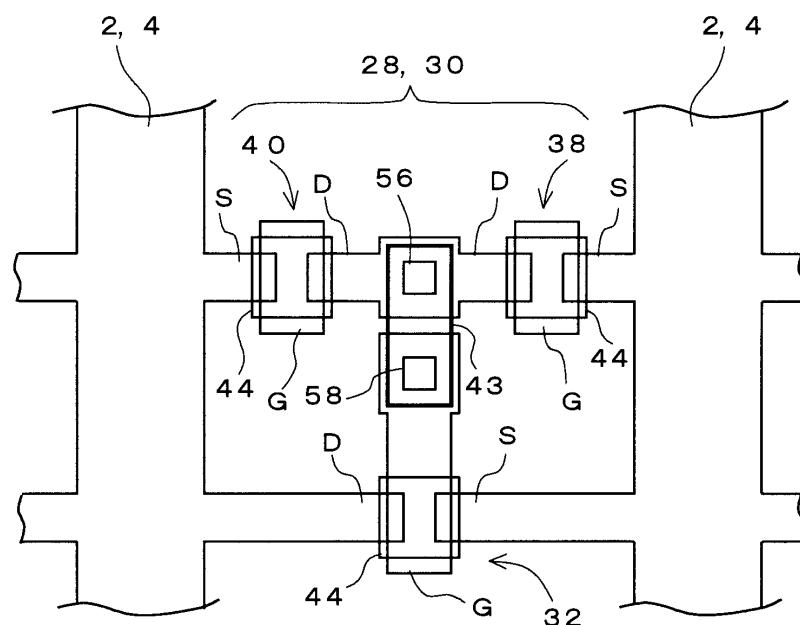

다음에, 본 발명의 제 3 실시 형태에 의한 액정 표시 장치에 대해서 도 6을 이용하여 설명한다. 도 6은 어레이측 기판(1)상의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 본 실시 형태에 의한 액정 표시 장치도 정전기 보호 회로에 특징을 갖고 있고, 다른 구성 요소에 대해서는 제 1 실시 형태에서 도 1을 이용하여 설명한 구성과 동일하므로 그것들의 설명은 생략한다. 또, 정전기 보호소자부에 있어서도, 제 1 및 제 2 실시 형태와 같은 기능 작용을 갖는 구성 요소에는 동일 부호를 붙여 그 설명은 생략한다. 본 실시 형태의 정전기 보호 회로는 도 4를 이용하여 설명한 제 2 실시 형태의 정전기 보호 소자부(28, 30)를 인접하는 버스라인 사이에 형성함으로써, 셔트 링(20)을 형성하지 않는 점에 특징을 갖고 있다. 즉, 제 1 TFT(32)의 소스 전극은 인접하는 2개의 버스라인(2)(또는 4; 이하 기재를 생략함)의 한쪽에 접속되고, 드레인 전극은 인접하는 2개의 버스라인(2)의 다른 쪽에 접속되어 있다. 또, 제 2 TFT(38)의 소스 전극은 인접하는 2개의 버스라인(2)의 한쪽에 접속되고, 제 3 TFT(40)의 소스 전극은 인접하는 2개의 버스라인(2)의 다른 쪽에 접속되어 있다. 이상의 구성의 상위를 제외하고, 본 실시 형태의 정전기 보호 회로에 의해서도 제 2 실시 형태와 같은 효과를 얻을 수 있다.

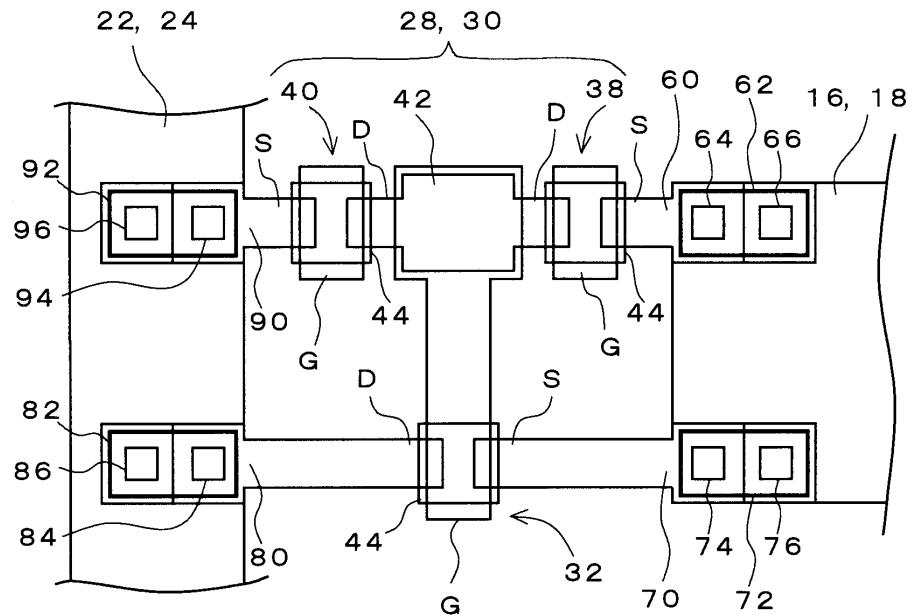

다음에, 본 발명의 제 4 실시 형태에 의한 액정 표시 장치에 대해서 도 7 내지 도 11을 이용하여 설명한다. 본 액정 표시 장치의 개략 구성은 제 1 실시 형태에서 사용한 도 1과 같으므로 설명은 생략하고, 특징적 구성 요소인 정전기 보호 소자부(28, 30)의 회로 구성에 대해서 도 7을 이용하여 설명한다. 단, 도 3 및 도 4에 도시된 구성과 같은 기능 작용을 발휘하는 구성요소에는 동일의 부호를 붙여 그 설명도 생략한다.

본 실시 형태에 의한 정전기 보호 소자부(28)는 제 2 실시 형태와 같이 제 1 내지 제 3 TFT(32, 38, 40) 및 도전체(42)를 갖고 있다. 제 2 실시 형태와 다른 것은 용량(100)을 갖고 있는 점에 있다. 용량(100)은 도전체(42)와 제 1 TFT(32)의 게이트 전극(G) 사이에 형성되어 있다. 정전기가 발생된 경우, 용량(100)에 의해 제 2 및 제 3 TFT(38, 40)에 비해 제 1 TFT(32)의 동작은 완만해진다. 그 때문에, 예리한 멀스형의 전압 변화를 발생하는 정전기의 경우는, 제 2 및 제 3 TFT(38, 40)에 먼저 전류가 흘러 제 1 TFT(32)를 보호할 수 있다. 또, 전압 상승이 완만한 정전기의 경우는, 제 2 및 제 3 TFT(38, 40)에 계속되어 제 1 TFT(32)가 동작하여 전하의 해방에 기여하게 된다. 이와 같이 본 실시 형태에 의하면, 제 2, 제 3 TFT(38, 40)에 예비적으로 전류가 흐르기 때문에, 제 1 TFT(32)에 걸리는 부하가 경감되어 있고 정전기 보호 회로의 용장성을 향상시킬 수 있다. 또, 제 1 TFT(32)의 게이트 전극(G)은 용량을 통해서 외부 인출 전극(16, 18), 및 셔트 링(20)의 공통선(22, 24)과 접속되어 있고, 게이트 전극(G)의 전위는 이들 용량의 충방전에 요하는 시간만큼 완만하게 변화한다. 따라서, 본 실시 형태의 구성에 의하면, 완만한 정전기에 대해서도 충분히 대응할 수 있다. 또 본 실시 형태에서는, 제 1 TFT(32)의 게이트 전극(G)과 제 2, 제 3 TFT(38, 40) 사이의 공통 도전체(42) 사이에 용량(100)을 삽입시키고 있으므로, 외부 인출 전극(16, 18)과 셔트 링(20)의 공통선(22, 24) 사이의 전위차가 낮아져도 용량(100)의 충방전에 요하는 시간만큼 더욱 길게 도통 상태를 유지할 수 있기 때문에 전하 해방의 효율을 보다 향상시킬 수 있다. 또, 용량(100)을 부가함으로써 단락에 의한 문제점에 대한 용장성도 향상되어 있다. 본 실시 형태의 경우도 전하는 복수의 경로로 해방되기 때문에, TFT가 1개인 종래의 경우에 비해 정전기 보호 소자로서의 용장성이 증가하므로, 정전기로 용이하게 파괴되지 않는 보호 회로를 형성할 수 있다.

다음에, 본 실시 형태에 의한 정전기 보호 회로의 구조에 대해서 도 8을 이용하여 설명한다. 도 8a는 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 8b는 도 8a의 A-A'선으로 절단한 단면을 나타내고 있다. 도 8c는 도 8a의 B-B'선으로 절단한 단면을 나타내고 있다.

도 8a에 있어서, 도면 중 좌측에서 상하로 뻗어나가는 공통선(22)과 외부 인출 전극(16) 사이에 정전기 보호 소자부(28)가 형성되어 있다. 도 8b, 도 8c에 도시된 바와 같이, 게이트 버스라인(2) 및 화소 영역의 TFT(6)(도 1 참조)의 게이트 전극을 형성할 때에 유리 기판(50)상에 동시에 제 1 내지 제 3 TFT(32, 38, 40)의 게이트 전극(G)도 형성된다. 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)은 다른 배선 구조로부터 전기적으로 고립하여 형성되어 있다. 게이트 전극(G) 및 유리 기판(50) 상에는 게이트 절연막(52)이 형성되어 있다. 제 1 내지 제 3 TFT의 각 게이트 전극(G)상의 게이트 절연막(52) 상에는 a-Si로 이루어지는 동작 반도체층(44)이 각각 패터닝되어 있다. 각 동작 반도체층(44)을 사이에 두어 양측에는, 데이터(드레인) 버스라인(4) 및 외부 인출 전극(16)의 형성과 동시에 패터닝된 소스/드레인 전극이 형성되어 있다. 각 소스/드레인 전극의 단부는 각 동작 반도체층(44)에 얹혀져 형성되어 있다. 또, 쇼트 링(22)도 데이터 버스라인(4) 형성시 동시에 형성된다. 소자 형성 영역 전면에 패시베이션막(54)이 형성되어 있다.

제 2 및 제 3 TFT(38, 40) 사이의 소스/드레인 전극은 도전체(42)로서 기능하는 동시에, 도전체(42) 아래쪽까지 뻗어난 제 1 TFT(32)의 게이트 전극(G)과의 사이에서 용량(100)을 형성하고 있다.

도 8에 도시된 구성에서는, 외부 인출 전극(16, 18) 및 쇼트 링(22, 24)은 모두 데이터 버스라인(4)의 형성과 동시에 동일 재료로 형성되지만, 이것은 본질적인 것이 아니다. 예를 들면, 도 9에 도시된 바와 같이 게이트 버스라인(2)의 형성시 동시에 게이트 버스라인(2)과 같은 금속층에 의해 외부 인출 전극(16, 18) 및 쇼트 링(22, 24)을 형성해도 좋다. 그리고 도 5를 이용하여 설명한 것과 같은 배선의 연결 교체를 행함으로써 도 9에 도시된 구성을 얻을 수 있다.

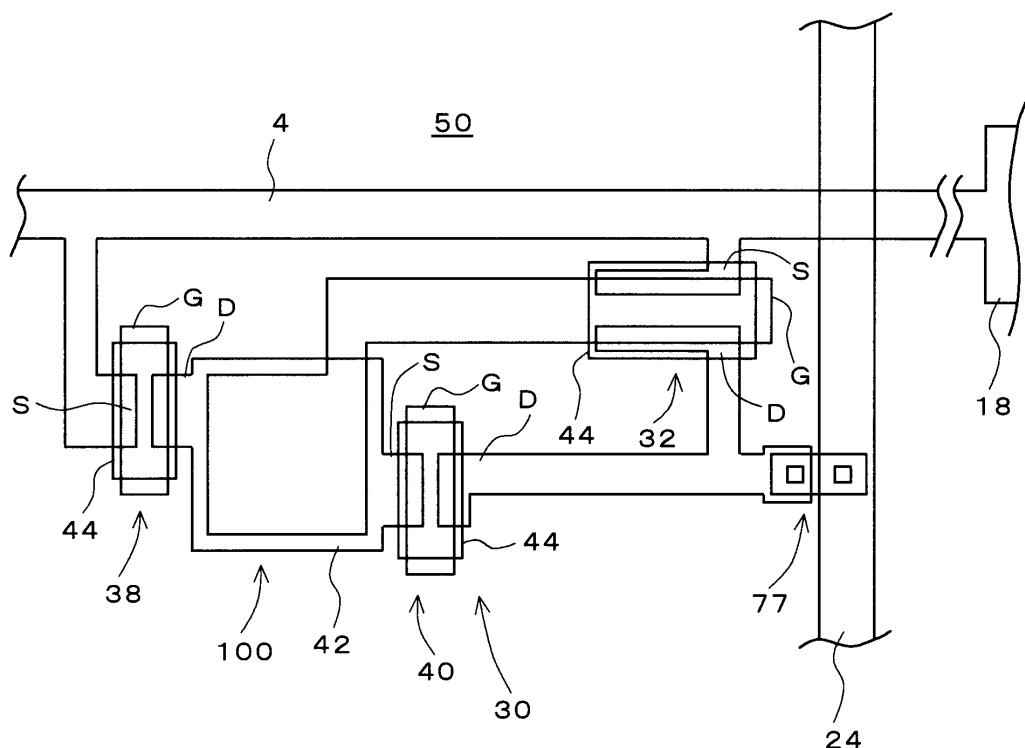

다음에, 본 실시 형태에 의한 정전기 보호 회로의 변형예를 도 10 및 도 11을 이용하여 설명한다. 제 1 및 제 2 실시 형태 및 본 실시 형태에서는, 쇼트 링(20) 및 정전기 보호 소자부(28, 30)는 어레이측 기판 상에서 외부 인출 전극(16, 18)의 외측에 위치하고 있다. 따라서, 패널 스크라이브 후에 면따기 공정에 의해 제거할 수 있다. 한편, 쇼트 링(20)을 외부 인출 전극(16, 18)보다 내측에 배치하면, 유리 기판의 스크라이브 영역을 좁혀 유리 기판을 낭비 없이 유효하게 이용할 수 있다. 이 경우에는 쇼트 링(20) 및 정전기 보호 소자부(28, 30)는 패널 스크라이브 후에도 액정 표시 패널에 잔존하게 되고, 각 버스라인(2, 4)은 정전기 보호 회로를 통해서 단락되지만, 그 저항은 각 버스라인 사이의 간섭을 무시할 수 있을 정도로 크기 때문에, 제품의 품질에는 어떠한 영향도 주지 않는다. 쇼트 링(20)의 형성 위치에 대해서는 이후에 설명하는 실시 형태 모두에 대해서 마찬가지로 생각할 수 있다.

도 10은 데이터 버스라인(4)의 외부 인출 전극(18)보다 내측에 쇼트 링(20)의 공통선(24)이 형성된 정전기 보호 회로의 구조예를 나타내고 있다. 도면 중 상하로 뻗어나가는 공통선(24)과, 도시를 생략한 화소 영역(공통선(24)에 관계되고 외부 인출 전극(18)의 반대측) 사이에 정전기 보호 소자부(30)가 형성되어 있다. 게이트 버스라인(2) 및 화소 영역의 TFT(6)(도 1 참조)의 게이트 전극을 형성할 때에 유리 기판(50)상에 동시에 제 1 내지 제 3 TFT(32, 38, 40)의 게이트 전극(G)이 형성된다. 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)은 다른 배선 구조로부터 전기적으로 고립하여 형성되어 있다. 또, 공통선(24)도 게이트 버스라인(2) 형성시 동시에 형성된다. 제 1 TFT(32)의 드레인 전극(D)과 제 3 TFT(40)의 드레인 전극(D)은 컨택트 홀부(77)를 통해서 공통선(24)에 접속되어 있다.

제 2 및 제 3 TFT(38, 40)간의 소스/드레인 전극은 도전체(42)로서 기능하는 동시에, 도전체(42) 하부에까지 뻗어난 제 1 TFT(32)의 게이트 전극(G) 사이에서, 용량(100)을 형성하고 있다.

또, 본 예에 있어서는, 제 2 및 제 3 TFT(38, 40)의 채널 길이를 제 1 TFT(32)의 채널 길이보다 짧게 형성하고 있다. 이렇게 함으로써, 매우 예리한 펄스 전압으로 정전기가 데이터 라인(4)에 발생한 경우에는, 제 1 TFT(32)가 파괴되기 전에 제 2 또는 제 3 TFT(38, 40)가 먼저 파괴되어 제 1 TFT(32)를 보호할 수 있다. 이 때문에, 제 2 또는 제 3 TFT(38, 40)의 어느 것이 파괴되었다고 해도 데이터 버스라인(4)과 공통선(24)이 직접 단락하는 일이 없으므로, TFT 시험도 포함하여, 그 후의 공정에 지장이 생기는 일은 없다. 또 본 예에서는, 제 2 및 제 3 TFT(38, 40)의 채널 길이를 동일하게 하고, 또한 제 1 TFT(32)의 채널 길이의 약 반의 길이로 하고 있다. 또, 제 2 및 제 3 TFT(38, 40)의 채널 폭을 동일하게 하고, 또한 제 1 TFT(32)의 채널 폭과 동일한 정도의 길이로 하고 있다. 따라서, 제 1 TFT(32)의 도전율과, 제 2 및 제 3 TFT(38, 40)를 직렬로 보았을 때의 도전율이 거의 동일하게 되고, 정전기 보호에 대한 전류의 분담을 제 1 TFT(32)와 제 2 및 제 3 TFT(38, 40)로 거의 반반으로 나눌 수 있다.

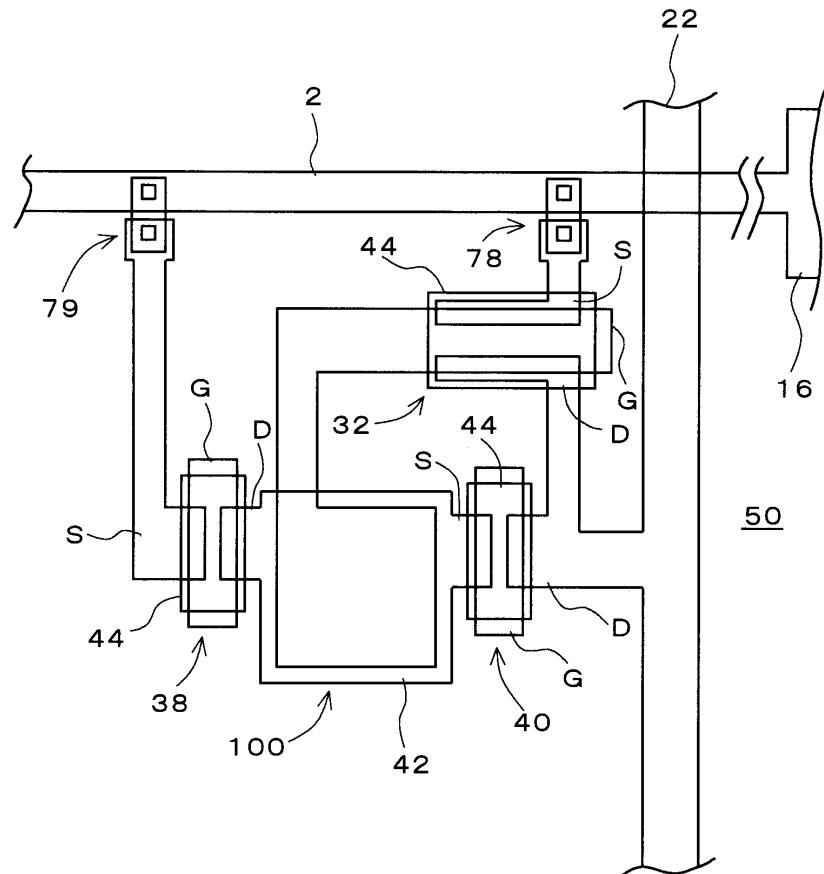

도 11은 게이트 버스라인(2)의 외부 인출 전극(16)보다 내측에 쇼트 링(20)의 공통선(22)이 형성된 정전기 보호 회로의 구조예를 나타내고 있다. 도면 중 상하로 뻗어나가는 공통선(22)과, 도시를 생략한 화소 영역(공통선(22)에 관계되고 외부 인출 전극(16)의 반대측) 사이에 정전기 보호 소자부(28)가 형성되어 있다. 게이트 버스라인(2) 및 화소 영역의 TFT(6) (도 1 참조)의 게이트 전극을 형성할 때에 유리 기판(50)상에 동시에 제 1 내지 제 3 TFT(32, 38, 40)의 게이트 전극(G)이 형성된다. 제 2 및 제 3 TFT(38, 40)의 게이트 전극(G)은 다른 배선 구조로부터 전기적으로 고립하여 형성되어 있다.

제 1 내지 제 3 TFT(32, 38, 40)의 소스/드레인 전극 및 공통선(22)은 데이터 버스라인의 형성과 동시에 동일의 형성 재료로 형성된다. 제 1 TFT(32)의 소스 전극(S)과 제 2 TFT(38)의 소스 전극(S)은 각각 컨택트 홀부(78, 79)를 통해서 게이트 버스라인(2)에 접속되어 있다.

제 2 및 제 3 TFT(38, 40) 사이의 소스/드레인 전극은 도전체(42)로서 기능하는 동시에, 도전체(42) 하부에까지 뻗어난 제 1 TFT의 게이트 전극(G) 사이에서 용량(100)을 형성하고 있다.

또, 본 예에 있어서도, 도 10에 도시된 바와 같이, 제 2 및 제 3 TFT(38, 40)의 채널 길이를 동일하게 하고, 또한 제 1 TFT(32)의 채널 길이의 약 반의 길이로 하고 있다. 또, 제 2 및 제 3 TFT(38, 40)의 채널 폭을 동일하게 하고, 또한 제 1 TFT(32)의 채널 폭과 동일한 정도의 길이로 하고 있다. 따라서, 제 1 TFT(32)의 도전율과, 제 2 및 제 3 TFT(38, 40)를 직렬로 보았을 때의 도전율이 거의 동일하게 되고, 정전기 보호에 대한 전류의 분담을 제 1 TFT(32)와 제 2 및 제 3 TFT(38, 40)로 거의 반반으로 나눌 수 있다.

다음에, 본 발명의 제 5 실시 형태에 의한 액정 표시 장치에 대해서 도 12 및 도 13을 이용하여 설명한다. 상술의 제 1 내지 제 4 실시 형태에서는, 각 버스라인에 각각 1조의 정전기 보호 소자부가 형성되어 있는데 대해서, 본 실시 형태에서는 정전기 보호 소자부에 형성된 소자를 가능한 한 공유화하여, 전체의 소자수를 적게 한 액정 표시 장치를 나타낸다. 구성 소자의 불량 발생율이나 소자가 점유하는 면적 등을 고려하면, 구성 소자수는 가능한 한 적게 하는 편이 바람직하다.

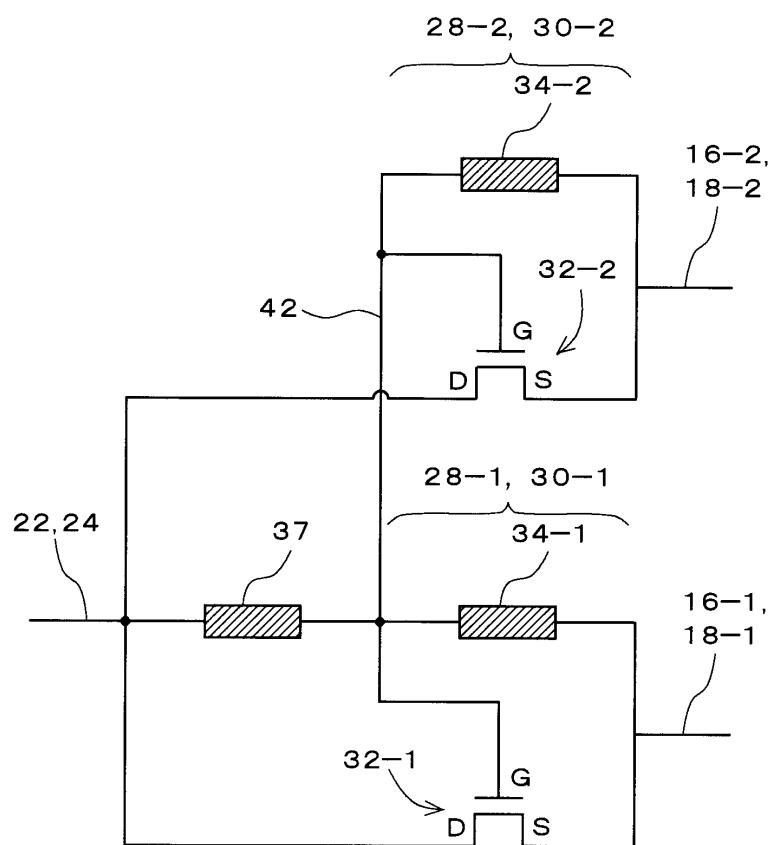

도 12에 본 실시 형태의 정전기 보호 소자부의 회로를 나타낸다. 도 12에 도시된 바와 같이 정전기 보호 소자부(28-1, 28-2)(또는, 30-1, 30-2)는 외부 인출 전극(16-1, 16-2)(또는 18-1, 18-2)마다 TFT(32-1, 32-2) 및 제 1 저항체(34-1, 34-2)가 형성되어 있다. 제 2 저항체(36)는 각 소자부(28-1, 28-2)에 형성되어 있지 않다. 그 대신에, 제 1 TFT(32-1, 32-2)의 게이트 전극(G)이 접속된 도전체(42)와 공통선(22, 24)이 제 2 저항체로서의 1개의 공용 저항체(37)로 접속되어 있다. 공용 저항체(37)를 설치함으로써, 정전기 보호 소자부의 구성 소자수를 제 1 내지 제 4 실시 형태에 비해서 3/4으로 줄일 수 있다.

예를 들면, 정전기에 의해 공통선(22)에 대해 정의 고전압이 외부 인출 전극(16-1)의 버스라인에 발생하면, TFT(32-1, 32-2)의 게이트 전극(G)에는 정전기에 의해 발생된 고전압을 제 1 저항체(34-1)와 공용 저항체(37)로 분할한 값의 전압이 인가된다. 그 결과, TFT(32-1, 32-2)의 도전율이 급격하게 커지기 때문에, TFT(32-1, 32-2)를 통해서 정전기에 의한 전하가 해방된다. 이 때, TFT(32-1, 32-2)뿐만 아니라, 제 1 저항체(34-1, 34-2), 공용 저항체(37)를 통해서도 전하는 해방되고, TFT(32-1)를 흐르는 전류는 완화되므로, 정전기 보호 소자로서의 용장성이 증가하여 정전기로 용이하게는 파괴되지 않는 정전기 보호 회로를 실현할 수 있다.

다음에, 도 13을 이용하여 본 실시 형태의 변형예에 대해서 설명한다. 도 13에 도시된 구성은 정전기 보호 회로의 구성 소자수를 가능한 한 적게 하기 때문에, 도 12에 도시된 구성을 더욱 진전시켜, n(n은 3이상의 정수)개 이상의 버스라인의 정전기 보호 소자부(28-1 ~ 28-n)(또는 30-1 ~ 30-n) 사이에서 1개의 공용 저항체(37)를 공용하고 있는 점에 특징을 갖고 있다.

외부 인출 전극(16-1 ~ 16-n)마다 설치된 정전기 보호 소자부(28-1 ~ 28-n)에는, 각각 TFT(32-1 ~ 32-n) 및 제 1 저항체(34-1 ~ 34-n)가 형성되어 있다. 제 2 저항체(36)는 각 소자부(28-1 ~ 28-n)에 형성되어 있지 않다. 그 대신에, 제 1 TFT(32-1 ~ 32-n)의 게이트 전극(G)이 접속된 도전체(42)와 공통선(22, 24)이 개개의 제 2 저항체에 대신하여 1개의 제 2 저항체로서의 공용 저항체(37)로 접속되어 있다.

모든 버스라인의 정전기 보호 소자부(28, 30)에 대해서 개개의 제 2 저항체에 대신하여 공유 저항체(37)를 사용하는 것으로 하면, 버스라인 1개당의 구성 소자수를 거의 2개로 할 수 있고, 제 1실시 형태에서의 정전기 보호 회로에서 사용되는 소자수를 약 반까지 줄이는 것이 가능하다.

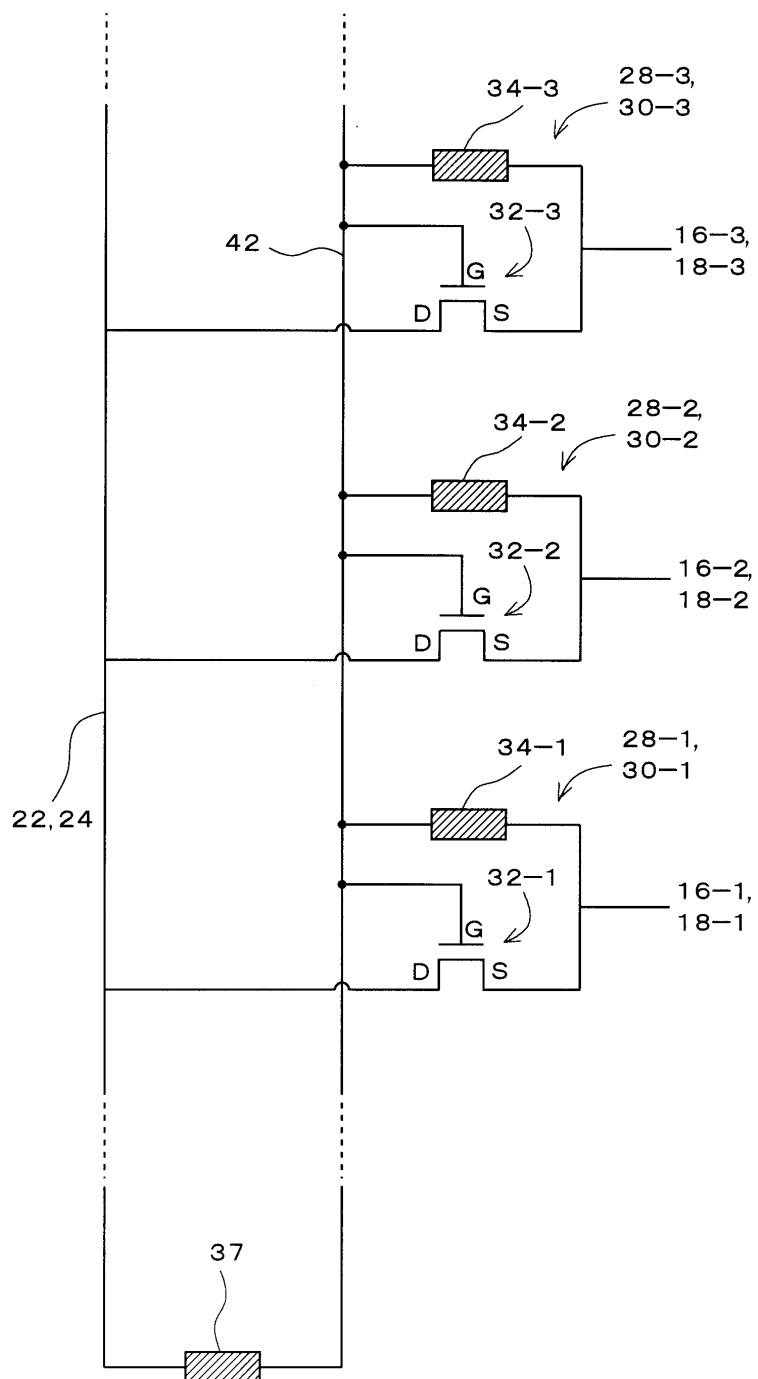

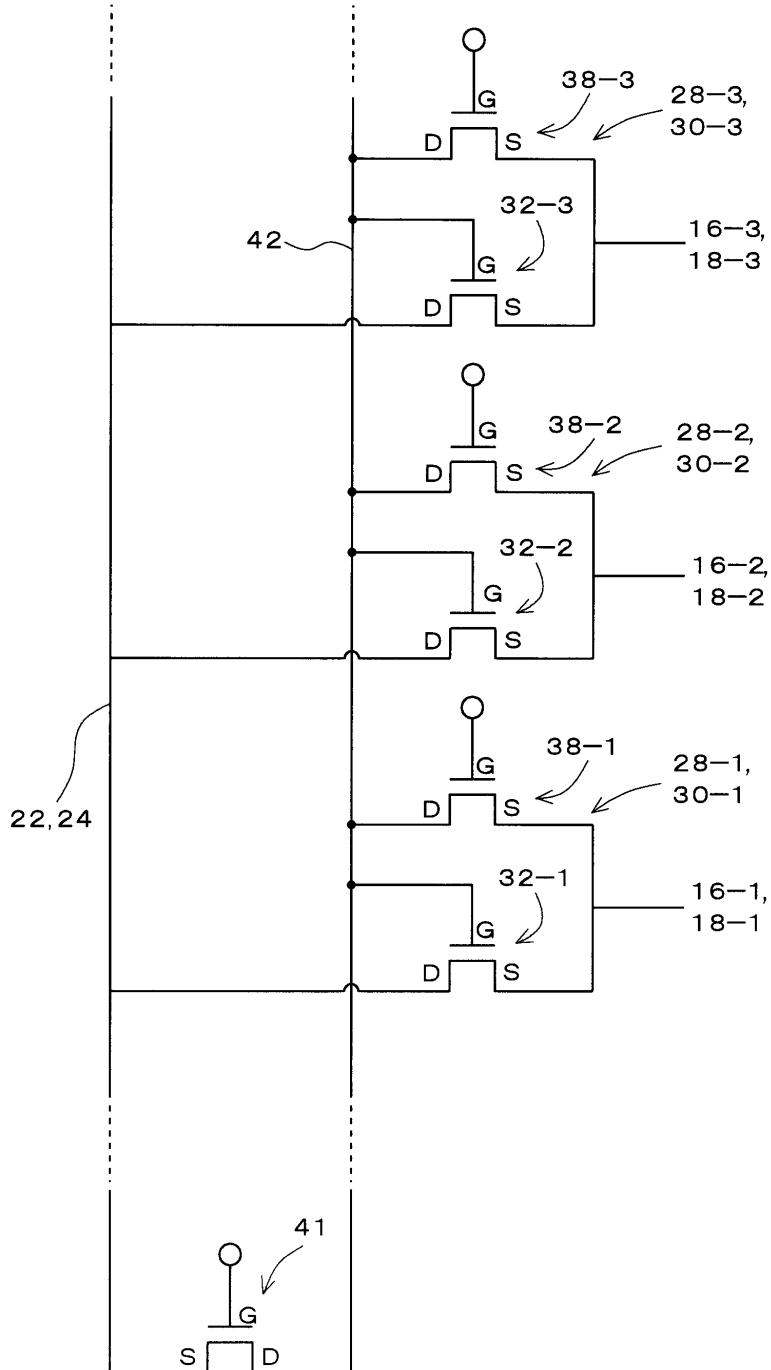

다음에, 본 발명의 제 6 실시 형태에 의한 액정 표시 장치에 대해서 도 14 내지 도 17을 이용하여 설명한다. 상기 제 2 실시 형태에 의한 액정 표시 장치에서는 각 버스라인에 각각 1조의 정전기 보호 소자부가 형성되어 있는데 대해서, 본 실시 형태에서는, 제 5 실시 형태와 같이, 정전기 보호 소자부에 형성된 소자를 가능한 한 공유화하여, 전체의 소자수를 적게 한 액정 표시 장치를 나타낸다.

도 14에 본 실시 형태의 정전기 보호 소자부의 회로를 나타낸다. 도 14에 도시된 바와 같이 정전기 보호 소자부(28-1, 28-2)(또는 30-1, 30-2)는 외부 인출 전극(16-1, 16-2)(또는 18-1, 18-2)마다 제 1 TFT(32-1, 32-2) 및 제 2 TFT(38-1, 38-2)가 형성되어 있다. 제 3 TFT(40)는 각 소자부(28-1, 28-2)에 형성되어 있지 않다. 그 대신에, 제 1 TFT(32-1, 32-2)의 게이트 전극(G)이 접속된 도전체(42)와 공통선(22, 24)이 개개의 제 3 TFT에 대신하여 1개의 제 3 TFT로서의 공용 TFT(41)로 접속되어 있다. 공용 TFT(41)를 설치함으로써, 정전기 보호 소자부의 구성 소자수를 제 1 내지 제 4 실시 형태에 비해서 3/4으로 줄일 수 있다.

예를 들면 정전기에 의해 공통선(22)에 대해 정의 고전압이 외부 인출 전극(16-1)의 버스라인에 발생하면, 제 2 TFT(38-1)와 공용 TFT(41)의 게이트 전극(G)에는 각각 기생 용량( $C_{2gs}$ ,  $C_{2gd}$ ,  $C_{cgs}$ ,  $C_{cgd}$ )에 의해 내분된 고전압이 인가되어 제 2 TFT(38-1), 공용 TFT(41)에서 채널이 형성된다. 그 결과, 제 2 TFT(38-1) 및 공용 TFT(41)를 통과하여 전류가 흐르고, 도전체(42)의 전위도 상승한다. 그것에 의해 제 1 TFT(32-1)에 채널이 형성되어 도전율이 커지기 때문에 정전기에 의한 전하가 해방된다. 이 경우에서도 전하는 복수의 경로로 해방되기 때문에, TFT가 1개인 종래의 경우에 비해 제 1 TFT(32)에 흐르는 전하량이 완화되므로, 정전기 보호 소자로서의 용장성이 증가하여 정전기로 용이하게는 파괴되지 않는 보호 회로를 형성할 수 있다.

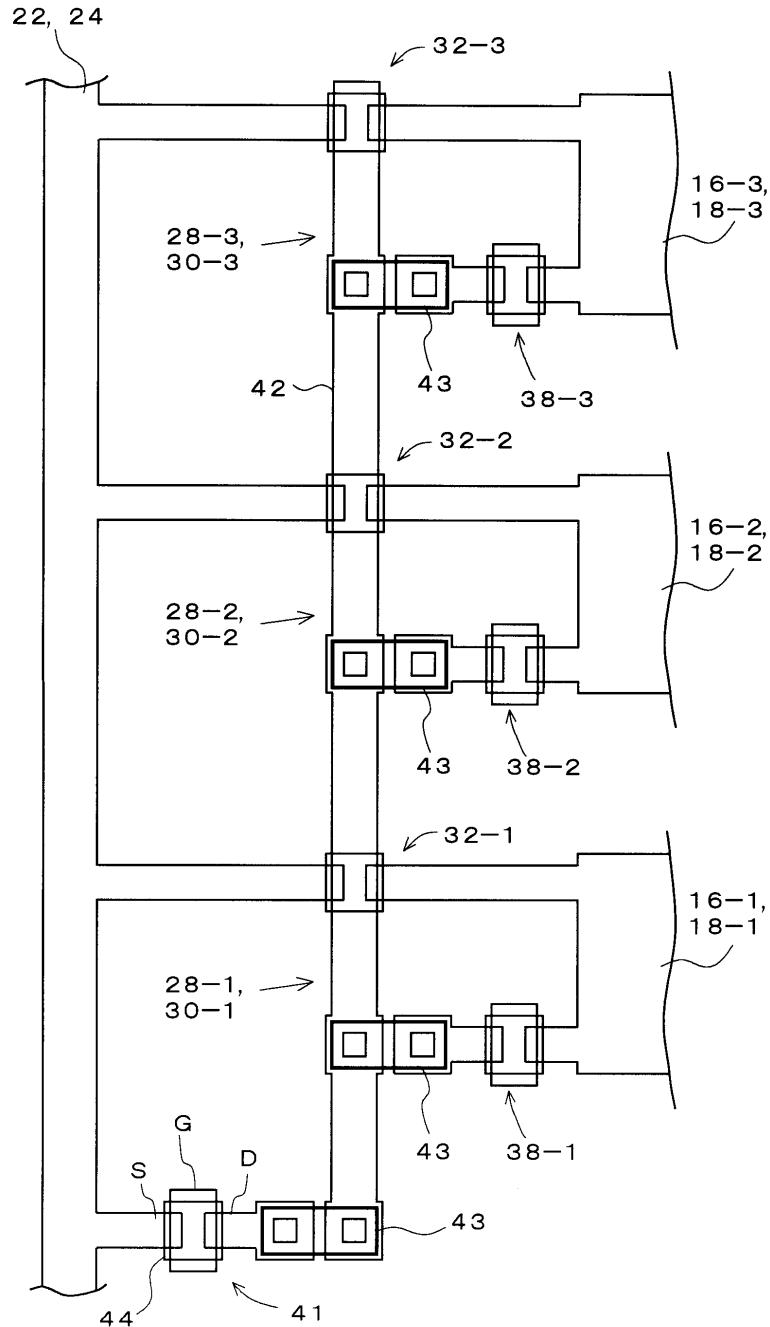

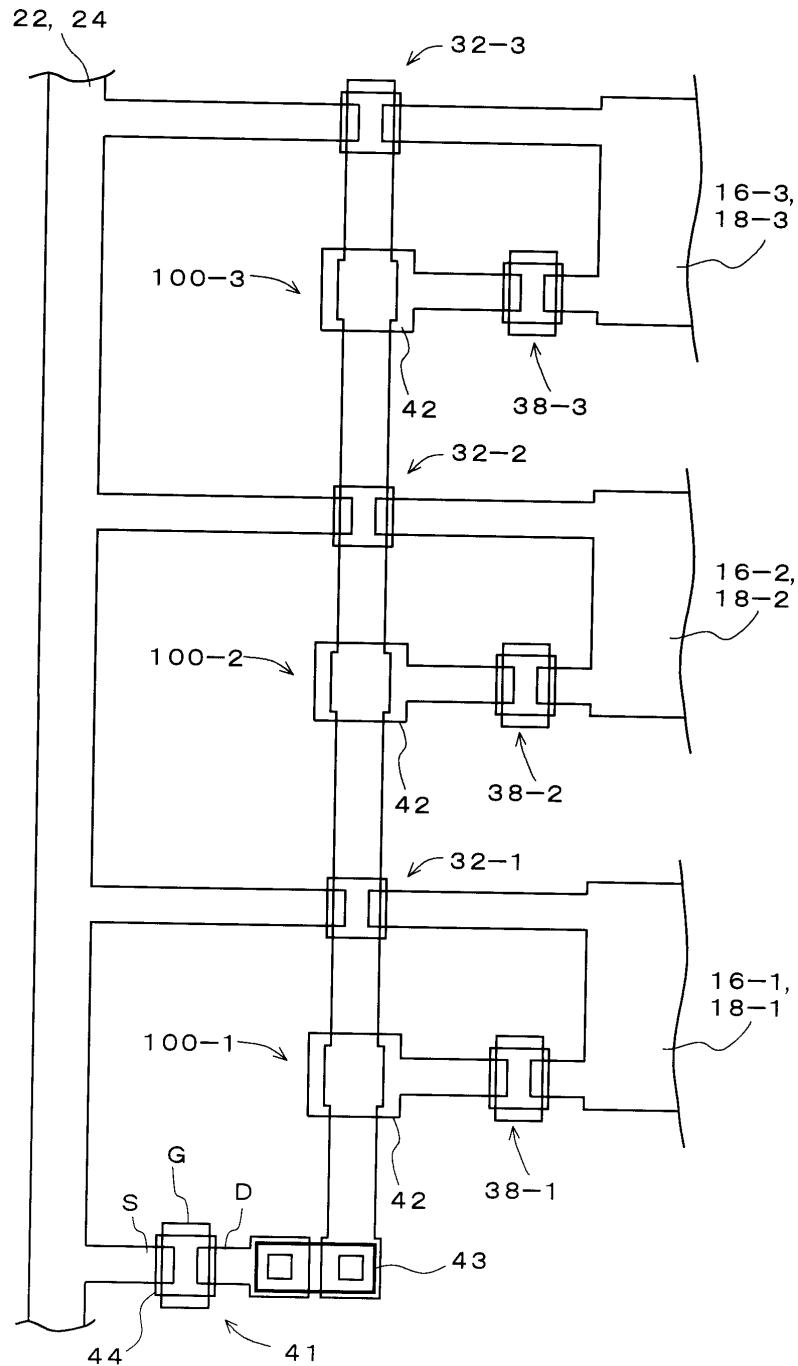

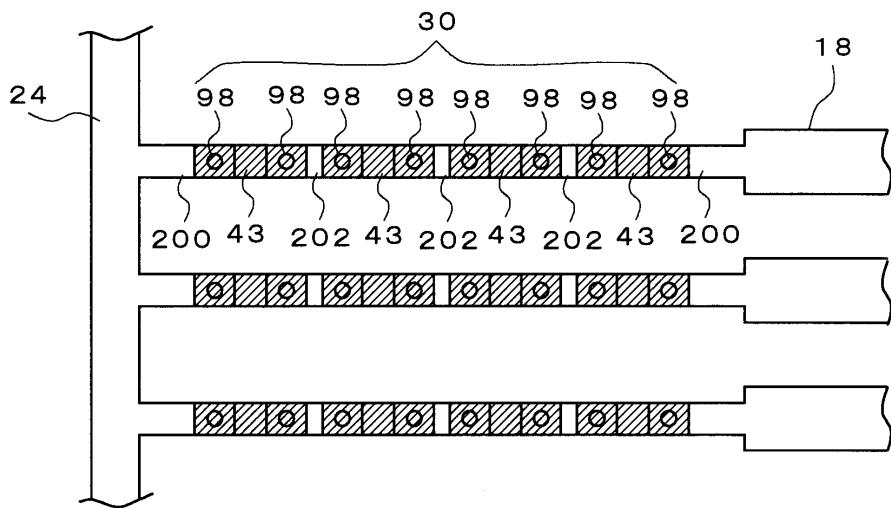

다음에, 본 실시 형태에 의한 정전기 보호 회로의 구조에 대해서 도 15를 이용하여 설명한다. 도 15는 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 15에 있어서, 도면 중 좌측에서 상하로 뻗어나가는 공통선(22)과 외부 인출 전극(16-1, 16-2) 사이에 정전기 보호 소자부(28-1, 28-2)가 형성되어 있다.

본 예에서는, 도전체(42)가 도면 중 상하로 뻗어나가서, 컨택트 홀(56-1, 58-1)을 통해서 정전기 보호 소자부(28-1)측의 제 1 TFT(32-1)와 ITO층(43)에 의해 접속되어 있다. 또, 도전체(42)는 컨택트 홀(56-2, 58-2)을 통해서 정전기 보호 소자부(28-2)측의 제 1 TFT(32-2)와 ITO층(43)에 의해 접속되어 있다.

공용 TFT(41)의 게이트 전극(G)상의 게이트 절연막 상에는 a-Si로 이루어지는 동작 반도체층(44)이 패터닝되어 있다. 동작 반도체층(44)을 사이에 두어 양측에는, 도전체(42)의 거의 중앙부에서 인출된 공용 TFT(41)의 드레인 전극(D)이 접속되어 있다. 공용 TFT(41)의 소스 전극은 공통선(22, 24)에 접속되어 있다. 공용 TFT(41)의 소스/드레인 전극의 단부는 동작 반도체층(44)에 얹혀져, 기판면 방향으로 보아 각 소스/드레인 전극의 단부와 하층의 게이트 전극(G)이 오버랩하는 영역이 형성되어 있다. 도전체(42), 외부 인출 전극(16-1, 16-2), 및 공통선(22, 24)은 데이터 버스라인(4)을 형성할 때 동시에 형성되어 있다.

다음에, 도 16을 이용하여 본 실시 형태의 변형예에 대해서 설명한다. 도 16에 도시된 구성은 정전기 보호 회로의 구성 소자수를 가능한 한 적게 하기 위해, 도 15에 도시된 구성을 더욱 진전시켜서, n(n은 3이상의 정수)개 이상의 버스라인의 정전기 보호 소자부(28-1 ~ 28-n)(또는 30-1 ~ 30-n) 사이에서 1개의 공용 TFT(41)를 사용하고 있는 점에 특징을 갖고 있다.

외부 인출 전극(16-1 ~ 16-n)마다 설치된 정전기 보호 소자부(28-1 ~ 28-n)에는, 각각 제 1 TFT(32-1 ~ 32-n) 및 제 2 TFT(38-1 ~ 38-n)가 형성되어 있다. 제 3 TFT(40)는 각 소자부(28-1 ~ 28-n)에 형성되어 있지 않다. 그 대신에, 제 1 TFT(32-1 ~ 32-n)의 게이트 전극(G)이 접속된 도전체(42)와 공통선(22, 24)이 개개의 제 3 TFT에 대신하여 1개의 제 3 TFT로서의 공용 TFT(41)로 접속되어 있다.

모든 버스라인의 정전기 보호 소자부(28, 30)에 대해서 제 3 TFT(40)에 대신하여 공용 TFT(41)를 사용하는 것으로 하면, 버스라인 1개당의 구성 소자수는 거의 2개로 할 수 있고, 제 2 실시 형태에서의 정전기 보호 회로에서 사용되는 소자수를 약 반까지 줄이는 것이 가능하다.

다음에, 본 실시 형태에 의한 정전기 보호 회로의 구조에 대해서 도 17을 이용하여 설명한다. 도 17은 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 17에 있어서, 도면 중 좌측에서 상하로 뻗어나가는 공통선(22)과 외부 인출 전극(16-1 ~ 16-n) 사이에 정전기 보호 소자부(28-1 ~ 28-n)가 형성되어 있다.

본 예에서는, 도전체(42)가 도면 중 상하로 뻗어나가서, 복수의 제 1 TFT(32-1 ~ 32-n)의 게이트 전극에 접속되어 있다. 또, 도전체(42)에 컨택트 홀을 통해서 제 2 TFT(38-1 ~ 38-n)가 ITO층(43)에 의해 접속되어 있다. 공용 TFT(41)의 구조는 도 15를 이용하여 설명한 것과 동일하므로 설명은 생략한다. 공용 TFT(41)의 드레인 전극은 컨택트 홀을 통해서 ITO층(43)에 의해 도전체(42)에 접속되고, 소스 전극은 공통선(22, 24)에 접속되어 있다.

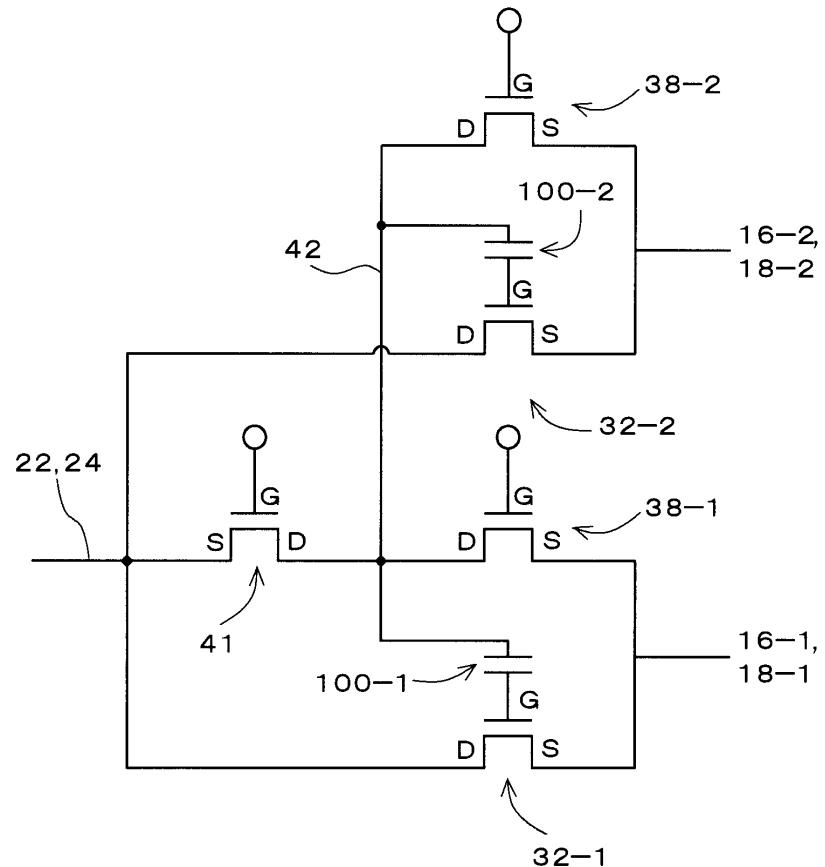

다음에, 본 발명의 제 7 실시 형태에 의한 액정 표시 장치에 대해서 도 18 내지 도 21을 이용하여 설명한다. 상기 제 3 실시 형태에 의한 액정 표시 장치에서는 각 버스라인에 각각 1조의 정전기 보호 소자부가 형성되어 있는데 대해서, 본 실시 형태에서는, 제 5 및 제 6 실시 형태와 같이, 정전기 보호 소자부에 형성된 소자를 가능한 한 공유화하여, 전체의 소자수를 적게 한 액정 표시 장치를 나타낸다.

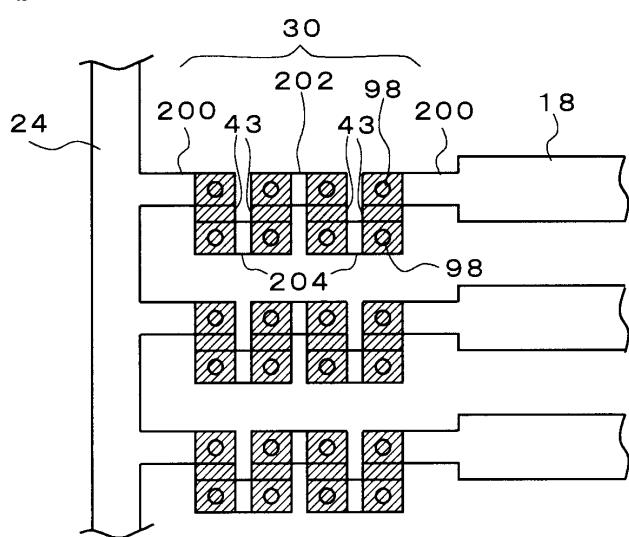

도 18은 본 실시 형태의 정전기 보호 소자부의 회로를 나타낸다. 도 18에 도시된 바와 같이 각 정전기 보호 소자부(28-1, 28-2)에는 용량(100-1, 100-2)이 형성되어 있다. 제 3 TFT(40)는 정전기 보호 소자부(28-1, 28-2)에 형성되어 있지 않다. 그 대신에, 제 1 TFT(32-1, 32-2)의 게이트 전극(G)이 접속된 도전체(42)와 공통선(22, 24)이 개개의 제 3 TFT에 대신하는 1개의 제 3 TFT로서의 공용 TFT(41)로 접속되어 있다. 공용 TFT(41)를 설치함으로써, 정전기 보호 소자부의 구성 소자수를 제 1 내지 제 4 실시 형태에 비하여 3/4으로 줄일 수 있다.

본 실시 형태의 경우도, 용량(100)을 갖고 있음으로써, 정전기가 발생된 경우의 제 1 TFT(32-1, 32-2)의 동작은 제 2 TFT(38-1, 38-2) 및 공용 TFT(41)에 비해 완만해진다. 그 때문에, 예리한 월스형의 전압 변화를 일으키는 정전기의 경우는, 제 2 TFT(38-1, 38-2) 및 공용 TFT(41)에 먼저 전류가 흘러 제 1 TFT(32-1, 32-2)를 보호할 수 있다. 또, 전압 상승이 완만한 정전기의 경우는, 제 2 TFT(38-1, 38-2) 및 공용 TFT(41)에 계속되어 제 1 TFT(32-1, 32-2)가 동작하여 전하의 해방에 기여하게 된다. 본 실시 형태에 의하면, 제 2 TFT(38-1, 38-2) 및 공용 TFT(41)에 예비적으로 전류가 흐르기 때문에, 제 1 TFT(32-1, 32-2)에 걸리는 부하가 경감되어 있고 정전기 보호 회로의 용장성을 늘릴 수 있다. 또, 제 1 TFT(32-1, 32-2)의 게이트 전극(G)은 용량을 통해서 각각 외부 인출 전극(16-1, 18-1, 16-2, 18-2), 및 쇼트 링(20)의 공통선(22, 24)과 접속되어 있고, 게이트 전극(G)의 전위는 이들 용량의 충방전에 요하는 시간만큼 완만하게 변화한다. 따라서, 본 실시 형태의 구성에 의하면, 완만한 정전기여도 충분히 대응할 수 있다. 또 본 실시 형태에서는, 제 1 TFT(32-1, 32-2)의 게이트 전극(G)과 제 2 TFT(38-1, 38-2) 및 공용 TFT(41) 사이의 공통 도전체(42) 사이에 용량(100-1, 100-2)을 삽입시키고 있으므로, 외부 인출 전극(16, 18)과 쇼트 링(20)의 공통선(22, 24) 사이의 전위차가 낮아져도 용량(100-1, 100-2)의 충방전에 요하는 시간만큼 더욱 길게 도통 상태를 유지할 수 있기 때문에 전하 해방의 효율을 보다 향상시킬 수 있다. 또, 용량(100-1, 100-2)을 부가함으로써 단락에 의한 문제점에 대한 용장성도 향상되어 있다. 본 실시 형태의 경우도 전하는 복수의 경로로 해방되기 때문에, TFT가 1개인 종래의 경우에 비해 정전기 보호 소자로서의 용장성이 증가하므로, 정전기에 의한 소자의 파괴가 발생하기 어려워진다.

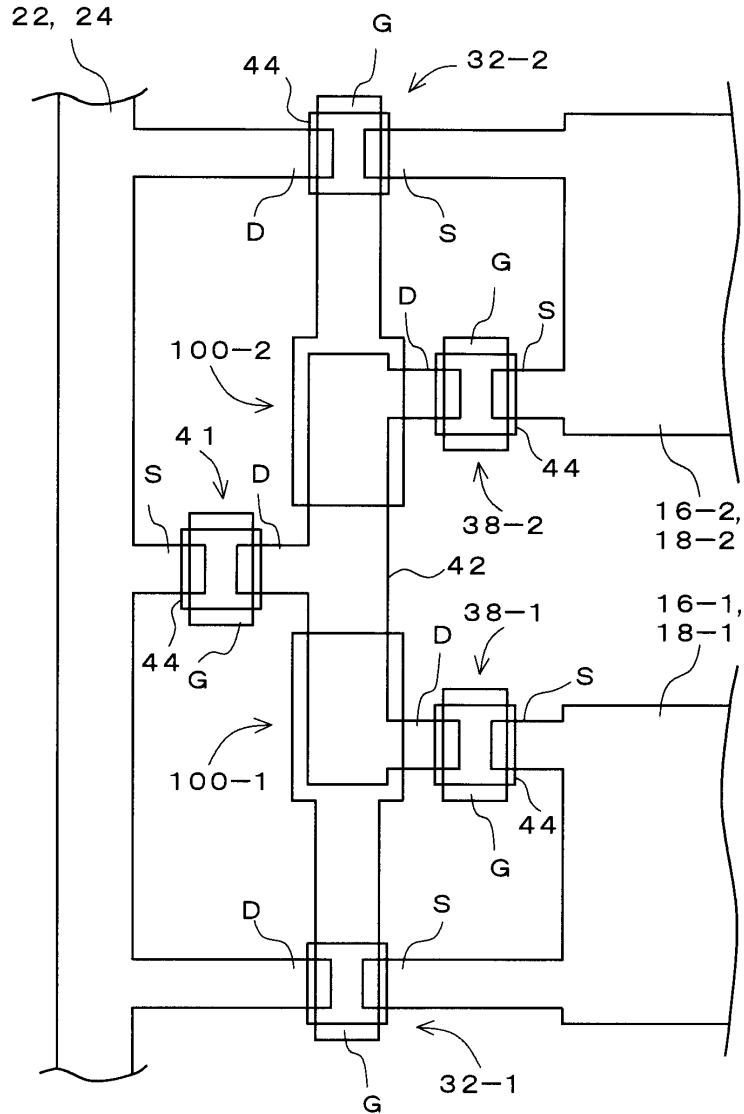

다음에, 본 실시 형태에 의한 정전기 보호 회로의 구조에 대해서 도 19를 이용하여 설명한다. 도 19는 어레이측 기판(1)상의 1개의 정전기 보호 회로를 기판면을 향해 본 상태를 나타내고 있다. 도 19에 도시된 구조는 도 15에 도시된 구조에 대해서, 제 1 TFT(32-1, 32-2)의 게이트 전극이 도전체(42) 하층에 절연막을 통해서 위치함으로써 용량(100-1, 100-2)이 형성되어 있는 점에 있다. 그 이외의 구성은 도 15에 도시된 것과 동일하므로 설명은 생략한다.

다음에, 도 20 및 도 21을 이용하여 본 실시 형태의 변형예에 대해서 설명한다. 도 20 및 도 21에 도시된 구성은 정전기 보호 회로의 구성 소자수를 가능한 한 적게 하기 위해, 도 18에 도시된 구성을 더욱 진전시켜서, n(n은 3이상의 정수)개 이상의 버스라인의 정전기 보호 소자부(28-1 ~ 28-n)(또는 30-1 ~ 30-n) 사이에서 1개의 공용 TFT(41)를 사용하고 있는 점에 특징을 갖고 있다. 도 20, 도 21에 도시된 회로 구성 및 소자 구조는 도 16, 도 17에 대해서, 제 1 TFT(32-1 ~ 32-n)의 게이트 전극이 도전체(42) 하층에 절연막을 통해서 위치함으로써 용량(100-1 ~ 100-n)이 형성되어 있는 점에 있다. 그 이외의 구성은 도 16 및 도 17에 도시된 것과 동일하므로 설명은 생략한다.

이상 설명한 제 1 내지 제 7 실시 형태에 의한 정전기 보호 회로가 형성된 어레이측 기판(1)에 대한 TFT의 제조 공정에 있어서, TFT 검사 없이 단순히 버스라인의 단선/단락을 검출하기 위한 오픈/쇼트 검사(O/S검사)에 의해 패널의 양부(良否) 판단을 하는 경우가 있다. 이 경우, 충간 단락을 검출하기 위해서는, 게이트 버스라인(2)측의 쇼트 링(20)의 공통선(22)과, 데이터 버스라인(4)측의 공통선(24)을 고저항 성분으로 전기적으로 분리할 필요가 있다. 그러므로 일례로서 도 22에 도시된 바와 같은 구성을 취할 수 있다. 도 22에 있어서, 공통선(22)과 공통선(24)의 교차부에는, 예를 들면 제 1 내지 제 4 실시 형태에서 도 2 내지 도 11을 이용하여 설명한 정전기 보호 소자부(28, 30)와 같은 구성을 갖는 충간 분리부(23)가 형성되어 있다.

또, 도 22에 도시된 바와 같이, 쇼트 링(20)의 공통선(22, 24)의 어느 것(도 22에서는 공통선(22))을, 예를 들면 대향 기판 측의 공통 전극(12) 또는 그라운드와 접속하는 접속 단자(25)에 접속하여, 보다 확실하게 TFT나 버스라인을 정전기에 의한 장해로부터 보호하도록 할 수도 있다.

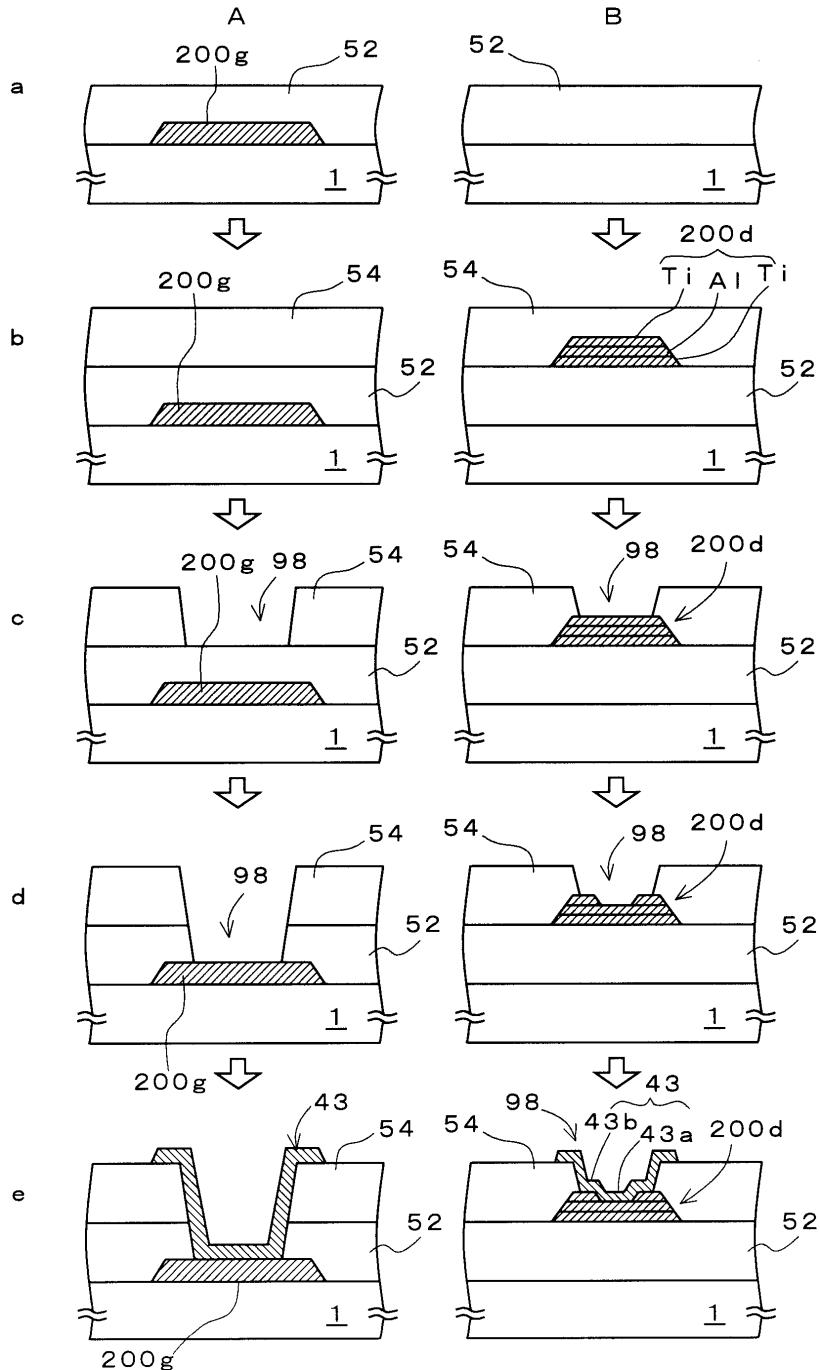

다음에, 본 발명의 제 8 실시 형태에 의한 액정 표시 장치에 대해서 설명한다. 먼저, 본 실시 형태에서 사용하는 TFT-LCD의 어레이측 기판의 제조 프로세스를 간단하게 설명한다. 제 1로, 어레이측 기판상에 게이트 메탈을 성막하여 패터닝하고, 게이트 버스라인 및 각 화소 영역의 TFT의 게이트 전극을 형성한다. 제 2로, 전면에 게이트 절연막을 형성하고, 그 위에 TFT의 동작 반도체막으로 되는 a-Si층, 및 채널 보호막을 형성하기 위한 절연막을 이 순서로 성막한다. 제 3으로, 게이트 버스라인 및 게이트 전극을 마스크로 하는 배면 노광과, 게이트 버스라인상의 a-Si층을 화소 영역으로부터 전기적으로 분리하기 위한 통상의 마스크를 사용한 노광에 의해 상기 절연막을 패터닝하여 채널 보호막을 형성한다. 제 4로, 오믹 컨택트층으로 되는 n<sup>+</sup>층과 드레인/소스 전극 및 데이터 버스라인을 형성하기 위한 드레인 메탈(예를 들면, Ti(티타늄))층을 이 순서로 전면에 성막한다. 제 5로, n<sup>+</sup>층과 드레인 메탈층을 패터닝하여 드레인/소스 전극 및 데이터 버스라인을 형성한다. 제 6으로, 전면에 패시베이션막(예를 들면, SiN막(실리콘 질화막))을 형성하고 나서 패터닝하고, 소정 위치의 패시베이션 막에 컨택트 홀을 형성한다. 제 7로, ITO를 전면에 성막하고 나서 패터닝하고, 화소 전극을 형성한다. 이상의 공정에 있어서, 제 1, 제 3, 제 5, 제 6, 및 제 7 공정에 노광 공정이 포함되어 있고, 전체로 5매의 마스크를 사용하는 5매 마스크 프로세스로 되어 있다.

이상의 공정을 포함하여 형성되는 본 액정 표시 장치에서의 정전기 보호 회로에 대해서 도 23 내지 도 27을 이용하여 상세하게 설명한다. 또한, 본 실시 형태에 있어서, 제 1 내지 제 7 실시 형태와 동일의 기능 작용을 갖는 구성 요소에는 동일의 부호를 붙이고 있다.

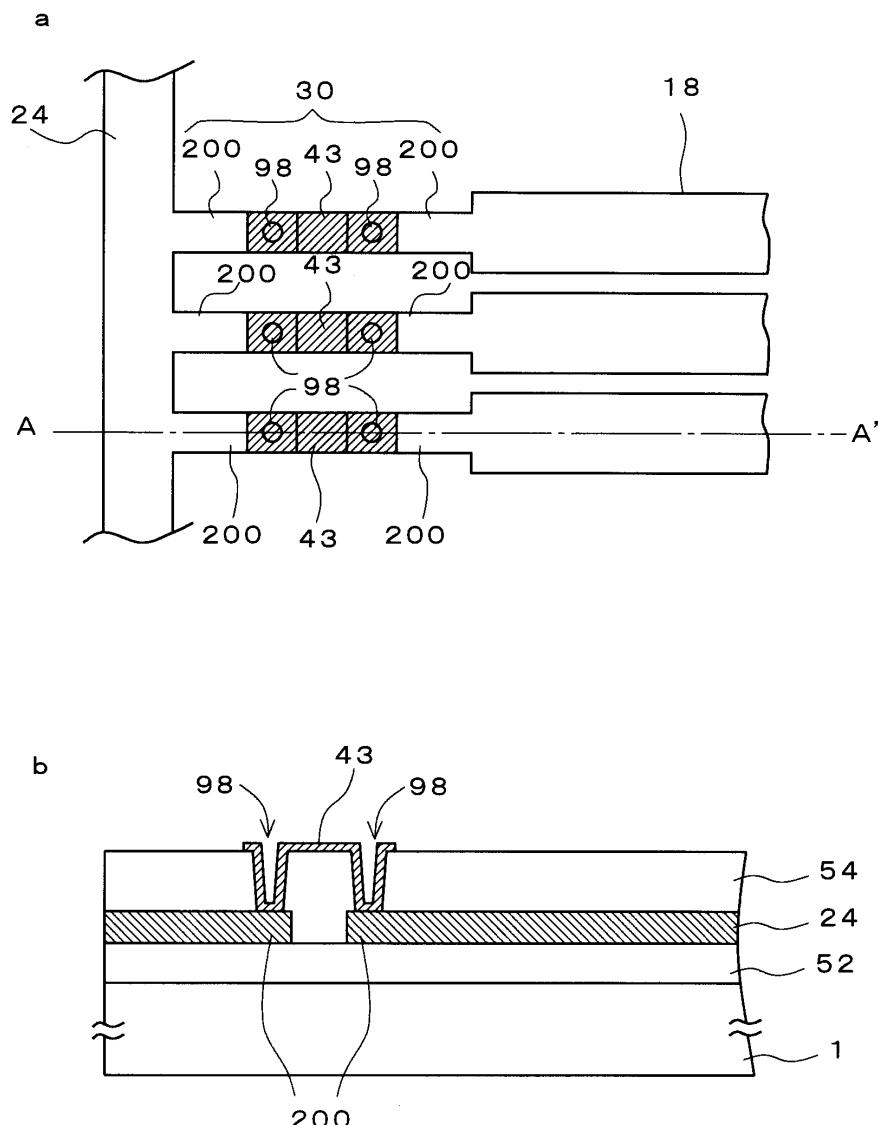

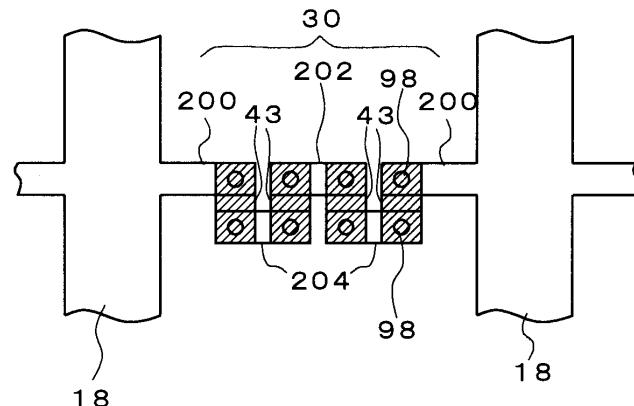

도 23a는 어레이측 기판을 그 기판면을 향해 본 상태를 나타내고 있다. 도 23b는 도 23a의 A-A'선으로 절단한 단면을 나타내고 있다. 도 23은 유리 기판인 어레이측 기판(1)상의 데이터 버스라인(4)(도시되지 않음)으로부터 외부 인출 전극(18)이 인출되어 형성되어 있는 상태를 나타내고 있다. 외부 인출 전극(18) 선단에는 정전기 보호 소자부(30)가 형성되고, 정전기 보호 소자부(30)를 통해서 외부 인출 전극(18)과 쇼트 링(20)의 공통선(24)이 접속되어 있다. 이상의 구성은 게이트 버스라인(2) 및 그 외부 인출 전극(16)에 대해서도 도시를 생략했지만 같은 구성으로 되어 있다.

도 23b에 도시된 바와 같이, 어레이측 기판(1)상에 상기의 제 2 공정에 의한 게이트 절연막(52)이 형성되고, 그 위에 제 4 공정에서의 드레인 메탈층을 패터닝하여 외부 인출 전극(18)과 공통선(24)이 형성되어 있다. 또, 외부 인출 전극(18)과 공통선(24)의 대향측에는, 정전기 보호 소자부(30)의 일부를 구성하는 드레인 메탈층을 패터닝한 금속층(200)이 형성되어 있다. 대향하는 금속층(200) 양단부 사이는 패시베이션막(54)이 매입되어 전기적으로 분리되어 있다. 대향하는 금속층(200) 양단부 상에는 패시베이션막(54)을 개구시킨 컨택트 홀(98)이 각각 형성되어 있다. 2개의 컨택트 홀 내벽 및 양자간에 제 7 공정에서 성막된 도전막의 ITO층(43)이 패터닝되어 있고, 대향하는 2개의 금속층(200)은 ITO층(43)에 의해 전기적으로 접속되어 있다. 이 경우, 하층의 드레인 메탈(Ti)과 상층 메탈(ITO)은 오믹 접속이 되고, 컨택트 홀의 사이즈에 의해 저항 성분이 변화된다. 하층 메탈에 Ti를 사용하고, ITO 성막 전에 열처리(예를 들면, 180°C ~ 215°C 정도)를 하고, 또한 컨택트 홀(98)의 직경이  $\phi=4 \mu\text{m}$ 인 경우에는, 형성되는 저항 성분은 7 ~ 8kΩ로 된다. 컨택트 홀(98)은 상술의 제 6 공정으로 형성되는 것이고, ITO막도 제 7 공정으로 형성되는 것이기 때문에, 종래의 제조 공정을 조금도 변경하지 않고 정전기 보호 회로를 형성할 수 있다.

도 24a 및 24b는 정전기 보호 소자부(30)를 고저항으로 하기 위해서 컨택트 홀(98)을 복수개 직렬 접속한 본 실시 형태의 변형 예를 나타내고 있다. 도 24a에서는, 외부 인출 전극(18)과 공통선(24)의 대향측에 설치되고 선단이 대향되는 2개의 금속층(200) 사이에, 또 섬 형상의 복수의 금속층(202)이 형성되어 있다. 직렬로 정렬한 복수의 금속층(202)의 양단부상의 패시베이션막(54)에는 컨택트 홀(98)이 형성되어 있다. 서로 이웃한 금속층(200, 202)은 컨택트 홀(98)을 통해서 ITO층(43)에 의해 전기적으로 접속되어 있다.

도 24b에 도시된 구조는 직선상으로 정렬한 금속층(200, 202)의 각 대향 단부 근방에, 전기적으로 독립한 섬 형상의 금속층(204)이 설치되고, 그들의 양단부에 컨택트 홀(98)이 형성되어 있다. 그리고, 금속층(200, 202)의 각 대향 단부는 금속층(204)과 컨택트 홀(98)을 통해서 ITO층(43)의 접속층으로 접속되어 있다. 이와 같이 하여, 정전기 보호 소자부(30)를 사행 배치시킴으로써, 공통선(24)과 외부 인출 전극(18) 사이의 거리를 짧게 하는 것이 가능해진다.

어레이 검사 장치에 의해 화소 전극과 공통 전극간에 충전된 전하를 적분 회로에 의해 읽어내는 경우에는, 아이솔레이션 저항으로서 저항값이 100kΩ이상인 것이 바람직하다. 따라서 도 24에 도시된 바와 같은 구성을 채용하여 컨택트 홀(98)의

수를 14개 이상으로 하면, 어레이 검사에 영향을 주지 않는 정전기 보호 회로를 실현할 수 있다. 이와 같이 본 실시 형태에 의하면, 컨택트 홀을 통해서 저항체를 복수단 접속함으로써 임의 값의 저항 성분을 갖는 정전기 보호 회로를 형성할 수 있다.

다음에, 본 실시 형태에 의한 정전기 보호 소자부에 있어서 하층 메탈을 다층 구조로 한 변형 예에 대해서 도 25를 이용하여 설명한다. 도 25는 정전기 보호 소자부의 형성 공정 단면을 나타내고 있고, (A)열은 게이트 버스라인 측을 나타내고, (B)열은 데이터 버스라인 측을 나타내고 있다. 또, (a)행 ~ (e)행은 각 공정에서의 처리를 나타내고 있다. 먼저 도 25a에 있어서, 유리 기판인 어레이 측 기판(1)상에 게이트 버스라인 및 각 화소 영역의 TFT의 게이트 전극을 형성할 때, 게이트 버스라인 (2)측의 정전기 보호 소자부(28)의 금속층(200g)을 게이트 메탈로 동시에 형성한다. 금속층(200g)의 형성과 함께 쇼트 링(20)의 공통선(22)을 게이트 메탈로 동시에 형성할 수도 있다. 그 다음에, 예를 들면 SiN(질화실리콘)을 사용하여 전면에 게이트 절연막(52)을 형성한다.

다음에, 도 25b에 도시된 바와 같이, 데이터 버스라인(4) 및 각 화소 영역의 TFT의 드레인/소스 전극을 형성할 때, 드레인 메탈을 사용하여 동시에, 데이터 버스라인(4)측의 정전기 보호 소자부(30)의 금속층(200d)을 형성한다. 드레인 메탈층은 하층으로부터 차례로 Ti/Al/Ti로 구성되어 있다. 또한, 금속층(200d)의 형성과 함께 쇼트 링(20)의 공통선(24)을 드레인 메탈로 동시에 형성할 수도 있다. 그 다음에, 전면에 패시베이션막(54)을 형성한다.

다음에, 도 25c에 도시된 바와 같이, 금속층(200g, 200d)상의 패시베이션막(54)을 개구시켜 컨택트 홀(98)을 형성한다. 또 도 25d에 도시된 바와 같이, 금속층(200g)상의 게이트 절연막(52)을 에칭하여 금속층(200g) 상부가 노출하는 컨택트 홀(98)을 형성한다. 패시베이션막(54)과 게이트 절연막(52)을 일괄하여 에칭하는 프로세스에서는, 게이트 절연막(42)을 에칭하고 있는 동안은 드레인 메탈 최상층의 Ti층이 에칭 스토퍼로서 기능한다. 이 때 드레인 메탈 최상층의 Ti의 막 두께가 얇으면 하층의 Al층이 노출하는 일이 있다.

다음에, 도 25e에 도시된 바와 같이, 인접하는 소정의 금속층(200, 202) 등이 컨택트 홀(98)을 통해서 전기적으로 접속되도록, 표시 전극 형성 시의 ITO 패터닝하여 ITO층(43)을 형성한다. 이 때, ITO층(43a)과 금속층(200d)의 Al층은 쇼트 키 접속으로 되고, 컨택트 홀(98)내에 링 형상으로 잔존하는 Ti층과 ITO층(43b)은 오믹 접속으로 되기 때문에 전체의 접촉 저항을 높게 할 수 있다. 예를 들면 드레인 메탈을 Ti(20nm)/Al(75nm)/Ti(20nm)로 하면 금속층(200d)상의 컨택트 홀 1개 당의 접촉 저항은 35 ~ 36kΩ이 되고, 금속층(200d)을 3 ~ 4개 직렬 접속하면 어레이 검사가 가능한 상태가 얻어진다.

또한, ITO층(43)의 형성 전으로서 컨택트 홀(98) 저부에 메탈층이 노출한 상태로 열처리 온도를 변화시킴으로써, 메탈/ITO의 접촉 저항을 변화시키는 것이 가능하다. 보다 높은 저항의 소자가 필요한 경우에는, 해당 처리 온도를 높게 하면 좋다.

이와 같이 하여 형성되는 저항 성분은 저항값을 10MΩ 이상으로 하는 것도 가능하고, 패널 완성 후에 있어서 각 버스라인에 주사 신호나 화상 신호 등을 인가해도, 이 고저항 성분에 의해 인접하는 버스라인에 영향을 미치지 않게 하도록 할 수 있다. 따라서, 이들 고저항 성분은 패널 완성 후에도 패널내에 잔존시킬 수 있다. 이 때문에, 패널이 완성되고 나서 유닛 조립 공정에서의 정전기 장해도 방지할 수 있고, 보다 높은 제품 비율로 액정 표시 장치를 제조할 수 있고, 또 장치의 신뢰성을 향상시킬 수 있게 된다.

본 실시 형태에서는, 각 버스라인(2, 4)과 쇼트 링(20)(공통선(22, 24)) 사이에 복수의 컨택트 홀(98)을 직렬 배열하는 것으로 임의 저항값의 저항 성분을 배치할 수 있는 것을 설명했지만, 본 실시 형태는 이에 한정되지 않고, 도 26에 도시된 바와 같이, 인접하는 게이트 버스라인(2) 사이, 또는 인접하는 데이터 버스라인(4) 사이에 본 실시 형태에 의한 구조를 형성하는 것도 가능하다. 이 경우에도, 금속층(200, 202) 등에 설치된 컨택트 홀 사이를 ITO층으로 접속하여 충분한 고저항 소자를 형성함으로써 패널 완성 후도 패널내에 정전기 보호 회로를 잔존시킬 수 있다. 물론 인접하는 버스라인 사이에 한정하지 않고, 고저항 성분이 필요한 임의의 장소에 본 실시 형태에 의한 정전기 보호 소자부를 제조 프로세스의 변경 없이 형성하는 것이 가능하다.

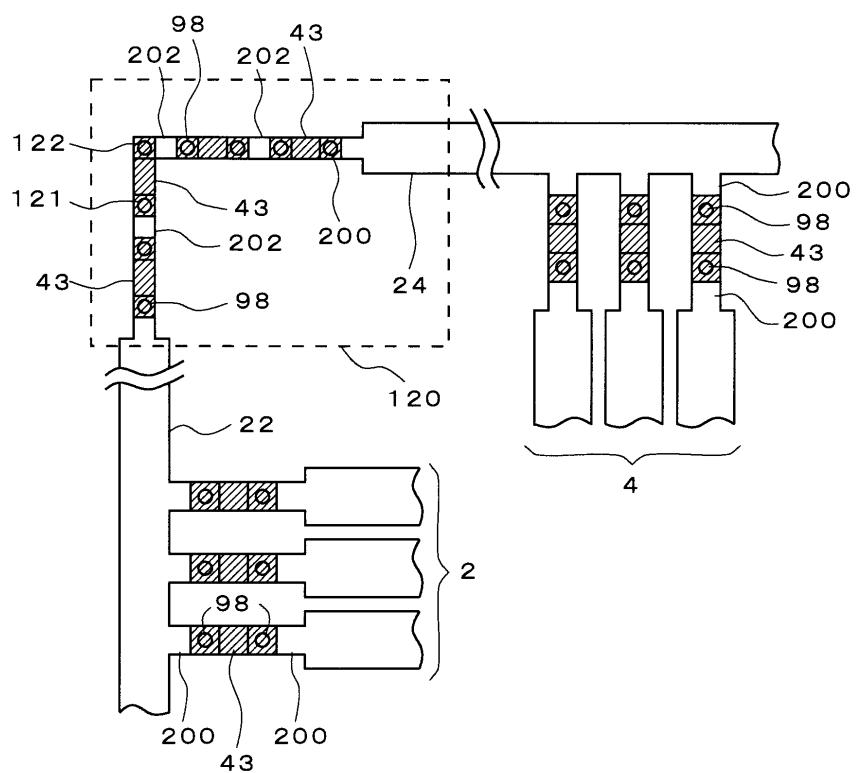

또, TFT 제조 공정에 있어서, 어레이 검사를 사용하지 않고 단지 버스라인의 단선/단락을 검출하기 위한 오픈/쇼트 검사(O/S 검사)에 의해 패널의 양부 판단을 하는 경우가 있다. 이 경우, 충간 단락을 검출하기 위해서는, 게이트 버스라인(2)측의 쇼트 링(20)의 공통선(22)과, 데이터 버스라인(4)측의 공통선(24)을 고저항 성분으로 전기적으로 분리할 필요가 있다. 그러므로 일례로서 도 27에 도시된 바와 같은 구성을 취할 수 있다. 도 27의 파선(120)으로 도시된 블록내는 쇼트 링(20)을 구성하는 공통선(22)과 공통선(24)의 접속 상태를 나타내고 있다. 도 27에 도시된 바와 같이, 게이트 메탈층을 패터닝하여 형성한 공통선(22)의 단부가 노출되는 컨택트 홀(121)과, 드레인 메탈층을 패터닝하여 형성한 공통선(24)의 단부가

노출되는 컨택트 홀(122)을 ITO층(43)으로 접속함으로써 접속 단부에서 용이하게 고저항부를 형성하는 것이 가능하다. 컨택트 홀(122)에서의 고저항부의 형성은 상술의 도 25d, e에 도시된 방식을 채용함으로써 저항값을 임의로 조정하는 것이 가능하다.

또한, 상기 실시 형태에 있어서, 절연막으로서 실리콘 질화막을 사용하고 있지만, 실리콘 산화막( $\text{SiO}_2$ 막)을 사용하는 것도 물론 가능하다. 또, 상기 실시 형태에서는, 컨택트 홀(98)간의 접속층에 ITO를 사용하고 있지만, 본 실시 형태는 이에 한정되지 않고, 다른 비교적 저항값이 높은 재료를 사용하도록 해도 물론 좋다. 또, 드레인 메탈로서 Ti/Al/Ti의 적층 구조를 사용했지만 상층의 금속층은 Ti에 대신하여 몰리브덴(Mo), 텉스텐(W), 또는 탄탈룸(Ta), 및 그것들의 합금, 또는 그것들의 질화산화물을 사용하고, 중간층의 Al에 대신하여, 동(Cu), Al 합금, Cu 합금 등을 사용할 수 있다.

이상 설명한 바와 같이 본 실시 형태에 의하면, 고저항 성분을 용이하게 형성할 수 있고, 또한 저항값의 제어도 가능하므로, 정전기에 의한 소자 파괴를 방지하는 동시에 고정밀도로 어레이 검사를 할 수 있게 된다. 또 패널 완성 후, 유닛 조립 공정에서의 정전기 파괴까지 대처할 수 있게 되므로, 제조 제품 비율의 향상에 의한 생산량의 증가, 또 신뢰성이 높은 장치를 제공할 수 있게 된다.

### 발명의 효과

이상과 같이, 본 발명에 의하면, 용장성이 우수한 정전기 보호 회로를 구비한 액정 표시 장치를 실현할 수 있다. 또 본 발명에 의하면, 비교적 낮은 전압이 장시간 발생되는 정전기에 대해서도 충분한 보호 기능을 갖춘 액정 표시 장치를 실현할 수 있다.

또 본 발명에 의하면, 기판 조립 공정의 최종 단계까지 정전기 대책을 세울 수 있는 액정 표시 장치를 실현할 수 있다. 또 본 발명에 의하면, 정전기 보호 소자부가 패널 사이즈에 영향을 주지 않는 액정 표시 장치를 실현할 수 있다. 또 본 발명에 의하면, 소자 구조가 간소하고 전류 제어면에서 문제점이 없는 정전기 보호 소자부를 갖는 액정 표시 장치를 실현할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 제 1 실시 형태에 의한 액정 표시 장치의 개략의 구성을 나타낸 도면.

도 2는 본 발명의 제 1 실시 형태에 의한 정전기 보호 소자부의 회로 구성 및 동작을 나타낸 도면.

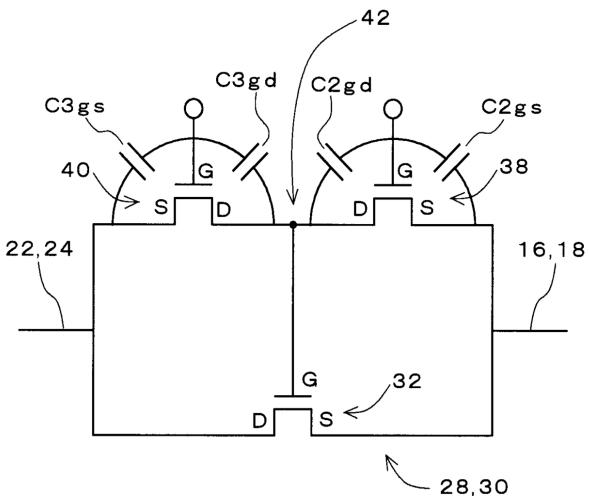

도 3은 본 발명의 제 2 실시 형태에 의한 액정 표시 장치의 특징적 구성요소인 정전기 보호 소자부의 회로 구성을 나타낸 도면.

도 4는 본 발명의 제 2 실시 형태에 의한 정전기 보호 회로의 구조를 나타낸 도면.

도 5는 본 발명의 제 2 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예를 나타낸 도면.

도 6은 본 발명의 제 3 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로를 기판면을 향해 본 상태를 나타낸 도면.

도 7은 본 발명의 제 4 실시 형태에 의한 액정 표시 장치의 특징적 구성요소인 정전기 보호 소자부의 회로의 구성을 나타낸 도면.

도 8은 본 발명의 제 4 실시 형태에 의한 정전기 보호 회로의 구조를 나타낸 도면.

도 9는 본 발명의 제 4 실시 형태에 의한 정전기 보호 회로의 구조의 변형예를 나타낸 도면.

도 10은 본 발명의 제 4 실시 형태에 의한 정전기 보호 회로의 변형예를 나타낸 도면.

도 11은 본 발명의 제 4 실시 형태에 의한 정전기 보호 회로의 다른 변형예를 나타낸 도면.

도 12는 본 발명의 제 5 실시 형태에 의한 액정 표시 장치의 정전기 보호 소자부의 회로를 나타낸 도면.

도 13은 본 발명의 제 5 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예를 나타낸 도면.

도 14는 본 발명의 제 6 실시 형태에 의한 액정 표시 장치의 정전기 보호 소자부의 회로를 나타낸 도면.

도 15는 본 발명의 제 6 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

도 16은 본 발명의 제 6 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예를 나타낸 도면.

도 17은 본 발명의 제 6 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예의 구조를 나타낸 도면.

도 18은 본 발명의 제 7 실시 형태에 의한 액정 표시 장치의 정전기 보호 소자부의 회로를 나타낸 도면.

도 19는 본 발명의 제 7 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

도 20은 본 발명의 제 7 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예를 나타낸 도면.

도 21은 본 발명의 제 7 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예의 구조를 나타낸 도면.

도 22는 본 발명의 제 1 내지 제 7 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예의 구조를 나타낸 도면.

도 23은 본 발명의 제 8 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

도 24는 본 발명의 제 8 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 변형예의 구조를 나타낸 도면.

도 25는 본 발명의 제 8 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 제조 공정을 나타낸 도면.

도 26은 본 발명의 제 8 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 다른 변형예의 구조를 나타낸 도면.

도 27은 본 발명의 제 8 실시 형태에 의한 액정 표시 장치의 정전기 보호 회로의 응용예의 구조를 나타낸 도면.

도 28은 종래의 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

도 29는 종래의 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

도 30은 종래의 액정 표시 장치의 정전기 보호 회로의 구성을 나타낸 도면.

도 31은 종래의 액정 표시 장치의 정전기 보호 회로의 구조를 나타낸 도면.

### 보호의 설명

1 어레이측 기판

2 게이트 버스라인

4 데이터 버스라인

6, 530, 532, 534 TFT

8 표시 전극 화소 전극

10 액정

12 공통 전극

16, 18, 502, 504 외부 인출 전극

20, 506 쇼트 링

22, 24 공통선

28, 30 정전기 보호 소자부

32 제 1 TFT

34 제 1 저항체

36 제 2 저항체

37 공용 저항체

38 제 2 TFT

40 제 3 TFT

41 공용 TFT

42, 536 도전체

43, 62, 72, 82, 92 ITO층

44, 514 동작 반도체층

50, 508 유리 기판

52, 512 게이트 절연막

54 패시베이션막

56, 58, 64, 66, 74, 76, 84, 86, 94, 96, 98 컨택트 홀

60, 70, 90, 518 소스 전극

77, 78, 79 컨택트 홀부

80, 516 드레인 전극

100 용량

120 파선

200, 202, 204 금속층

500 정전기 보호 소자

502 버스라인

510 게이트 전극

520 보호막

도면

도면1

도면2

도면3

도면4

도면5

도면6

## 도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

## 도면17

도면18

도면19

도면20

도면21

도면22

## 도면23

## 도면24

a

b

도면25

도면26

도면27

도면28

도면29

도면30

도면31

|                |                                                                                                               |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">KR100692434B1</a>                                                                                 | 公开(公告)日 | 2007-03-09 |

| 申请号            | KR1020000024573                                                                                               | 申请日     | 2000-05-09 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                        |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                                                        |         |            |

| [标]发明人         | NAGASE YOJI<br>나가세요지<br>TANAKA YOSHINORI<br>다나까요시노리<br>FUJIKAWA TETSUYA<br>후지까와테쓰야<br>NASU YASUHIRO<br>나수야수히로 |         |            |

| 发明人            | 나가세요지<br>다나까요시노리<br>후지까와테쓰야<br>나수야수히로                                                                         |         |            |

| IPC分类号         | G02F1/136 G02F1/1362                                                                                          |         |            |

| CPC分类号         | G02F1/136204                                                                                                  |         |            |

| 代理人(译)         | MOON , KI桑                                                                                                    |         |            |

| 优先权            | 1999244468 1999-08-31 JP                                                                                      |         |            |

| 其他公开文献         | KR1020010020822A                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                     |         |            |

### 摘要(译)

本发明的目的是提供一种液晶显示器，该液晶显示器是配备有保护装置的液晶显示器，其中冗余度极佳并且具有足够的静电保护，其中相对较低的功率产生静电。很长时间。用于保护部件(28,30)的装置包括连接到外部引出电极(16,18)的源电极(S)，具有连接到公共线(22,24)的漏电极(D)的第一薄膜晶体管(32)和具有导体(42)的第二TFT(38)，连接到第一薄膜晶体管(32)的栅电极(G)和连接到外部引出电极(16,18)的源电极(S)和漏电极(D)连接到导体(42)和电隔离栅电极(G)，第三TFT(40)具有源电极(S)，连接到公共线(22,24)和漏电极(D)连接到导体(42)和电隔离的栅电极(G)。TFT，栅极总线，数据总线，标志电极，像素电极，液晶，公共电极，绝缘层，电阻体。