(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2007년11월02일

(11) 등록번호 10-0772617

(24) 등록일자 2007년10월26일

(51) Int. Cl.

G02F 1/1345(2006.01)

(21) 출원번호 10-2002-0000694

(22) 출원일자 2002년01월07일

심사청구일자 2005년11월01일

(65) 공개번호 10-2002-0077033

공개일자 2002년10월11일

(30) 우선권주장

JP-P-2001-00101176 2001년03월30일 일본(JP)

(56) 선행기술조사문현

US 6,064,222

US 6,023,260

US 6,166,713

전체 청구항 수 : 총 10 항

(73) 특허권자

샤프 가부시키가이샤

일본 오사카후 오사카시 아베노구 나가이케조 22

방 22고

(72) 발명자

가이츠토무

일본국가나가와켄가와사키시나가하라구가미고다

나카4-1-1후지쓰가부시끼가이사내

오카자키스스무

일본국가나가와켄가와사키시나가하라구가미고다

나카4-1-1후지쓰가부시끼가이사내

(뒷면에 계속)

(74) 대리인

문기상, 문두현

심사관 : 신영교

(54) 액정 표시 장치

**(57) 요약**

간단하면서 단시간에 검사를 행할 수 있는 액정 표시 장치를 제공하기 위해, 본 발명의 액정 표시 장치는 2차원 매트릭스 형상으로 배선된 데이터 라인 및 주사 라인과 이 데이터 라인 및 주사 라인 사이에 접속되는 스위칭 소자를 포함하는 표시 회로(103)와, 데이터 라인의 한쪽 단부에 제 1 아날로그 스위치를 거쳐서 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력 단자를 포함하는 제 1 검사 회로(101)와, 데이터 라인의 다른쪽 단부에 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력 단자를 포함하는 제 2 검사 회로(102)를 갖는다. 이 표시 회로, 제 1 검사 회로 및 제 2 검사 회로는 1매의 기판 상에 설치되고, 제 1 검사 회로는 표시 회로에 대해서 분리 가능하다.

**대표도 - 도1**

(72) 발명자

장홍용

일본국가나가와켄가와사키시나가하라구가미고다나

카4-1-1후지쓰가부시끼가이샤내

오하시노리유키

일본국가나가와켄가와사키시나가하라구가미고다나

카4-1-1후지쓰가부시끼가이샤내

---

## 특허청구의 범위

### 청구항 1

2차원 매트릭스 형상으로 배선된 데이터 라인 및 주사 라인과 이 데이터 라인 및 주사 라인 사이에 접속되는 스위칭 소자를 포함하는 표시 회로와,

상기 데이터 라인의 한쪽 단부에 제 1 아날로그 스위치를 거쳐서 검사 전압을 출력하기 위한 검사 전압 출력 단자 또는 검사 전압을 입력하기 위한 검사 전압 입력 단자를 포함하는 제 1 검사 회로와,

상기 데이터 라인의 다른쪽 단부에 검사 전압을 입력하기 위한 검사 전압 입력 단자를 포함하는 제 2 검사 회로를 갖고,

상기 표시 회로, 제 1 검사 회로 및 제 2 검사 회로는 1매의 기판 상에 설치되고, 상기 제 1 검사 회로는 상기 표시 회로에 대해서 분리 가능한 액정 표시 장치.

### 청구항 2

제 1 항에 있어서,

상기 제 1 검사 회로는 제어 단자가 시프트 레지스터에 접속된 제 2 아날로그 스위치를 갖고, 이 제 2 아날로그 스위치는 한쪽 단부가 상기 제 1 아날로그 스위치를 거쳐서 상기 데이터 라인에 접속되고, 다른쪽 단부가 상기 검사 전압 출력 단자 또는 검사 전압 입력 단자에 접속되고,

상기 제 2 검사 회로는 제 3 아날로그 스위치를 갖고, 이 제 3 아날로그 스위치는 한쪽 단부가 상기 데이터 라인의 다른쪽 단부에 접속되고, 다른쪽 단부가 상기 검사 전압 입력 단자에 접속되는 액정 표시 장치.

### 청구항 3

제 2 항에 있어서,

상기 각 주사 라인의 단부에 검사용 트랜지스터를 설치하고, 이 검사용 트랜지스터의 게이트 단자에 주사 라인 드라이버를 접속하고, 드레인 또는 소스 단자에 검사 전압 입력 단자를 접속하고, 소스 또는 드레인 단자에 커패시터를 접속한 액정 표시 장치.

### 청구항 4

제 2 항에 있어서,

상기 제 2 검사 회로는 제 1 및 제 2 검사 전압 입력 단자를 갖고, 상기 복수의 제 3 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 입력 단자에 접속되고,

상기 제 1 검사 회로는 제 1 및 제 2 검사 전압 출력 단자를 갖고, 상기 복수의 제 2 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 출력 단자에 접속되는 액정 표시 장치.

### 청구항 5

제 2 항에 있어서,

상기 제 1 검사 회로는 제 1 및 제 2 검사 전압 출력 단자를 갖고, 상기 복수의 제 2 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 출력 단자에 접속되는 액정 표시 장치.

### 청구항 6

각각이 화소 전극을 거쳐서 액정 커패시터에 접속되는 복수의 제 1 스위칭 소자와,

상기 제 1 스위칭 소자에 데이터를 공급하는 데이터 라인과,

상기 제 1 스위칭 소자를 제어하기 위한 주사 라인과,

제어 단자가 상기 데이터 라인 또는 상기 주사 라인에 접속되고, 입출력 단자의 한쪽 단부가 공통의 검사용 입출력 단자에 접속되고, 다른쪽 단부가 커패시터에 접속되는 제 2 스위칭 소자를 갖는 액정 표시 장치.

**청구항 7**

제 6 항에 있어서,

상기 제 2 스위칭 소자는 상기 다른쪽 단부가 화소 전극을 거쳐서 액정 커패시터에 접속되는 액정 표시 장치.

**청구항 8**

제 6 항에 있어서,

상기 제 2 스위칭 소자는 제어 단자가 상기 데이터 라인에 접속되는 스위칭 소자 및 제어 단자가 상기 주사 라인에 접속되는 스위칭 소자를 포함하는 액정 표시 장치.

**청구항 9**

제 6 항에 있어서,

상기 제 2 스위칭 소자는 상기 한쪽 단부가 공통의 검사용 입출력용 단자 및 상기 데이터 라인에 접속되는 액정 표시 장치.

**청구항 10**

제 6 항에 있어서,

상기 제 2 스위칭 소자에 접속되는 커패시터를 리셋 또는 프리셋하기 위한 제 3 스위칭 소자를 더 갖는 액정 표시 장치.

**명세서****발명의 상세한 설명****발명의 목적****발명이 속하는 기술 및 그 분야의 종래기술**

<75> 본 발명은 액정 표시 장치에 관한 것으로, 특히 데이터 라인 및 주사 라인에 접속된 스위칭 소자를 갖는 액정 표시 장치에 관한 것이다.

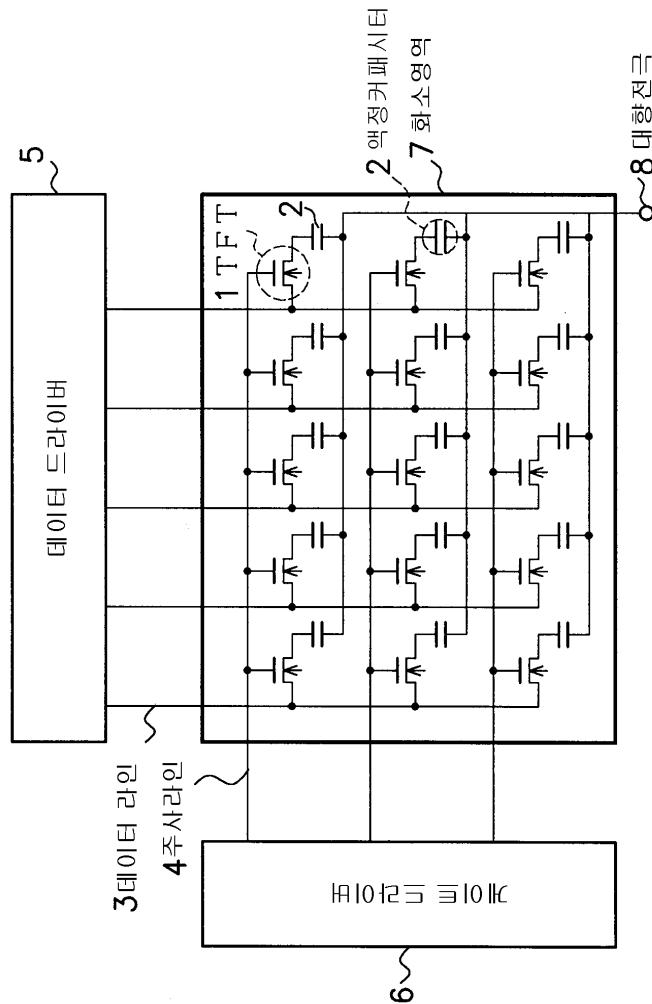

<76> 도 26은 종래 기술에 따른 액정 표시 기판의 구성을 나타낸다. 데이터 드라이버(데이터 라인 드라이버)(5)는 데이터 라인(3)을 거쳐서 화소 영역(7)에 접속된다. 게이트 드라이버(주사 라인 드라이버)(6)는 주사 라인(4)을 거쳐서 화소 영역(7)에 접속된다. 데이터 드라이버(5)는 데이터 라인(3)에 데이터를 공급할 수 있다. 게이트 드라이버(6)는 주사 라인(4)에 주사 신호를 공급할 수 있다.

<77> 화소 영역(7)은 2차원 매트릭스 형상으로 배열된 스위칭 소자(TFT: 박막 트랜지스터)(1) 및 액정 커패시터(2)를 갖는다. TFT(1)는 n채널 MOS 트랜지스터로서, 게이트가 주사 라인(4)에 접속되고, 드레인은 데이터 라인(3)에 접속되고, 소스가 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다.

<78> 이 액정 표시 기판의 검사 방법은 매트릭스의 각 종횡 라인의 단부에 프로브 펀을 닿게 하는 방법이 주된 것이며, 많은 프로브 펀이 필요하기 때문에 검사기가 고가로 된다. 이 검사 방법에서는 다수의 체크 단자를 개별적으로 검사하기 때문에 공정수가 막대하다. 그 때문에, 완전한 검사를 위해서는 액정 표시 기판을 패널로서 완성 상태로 표시하지 않으며 안되어, 수율(yield)을 저해하는 요인으로 되고 있다.

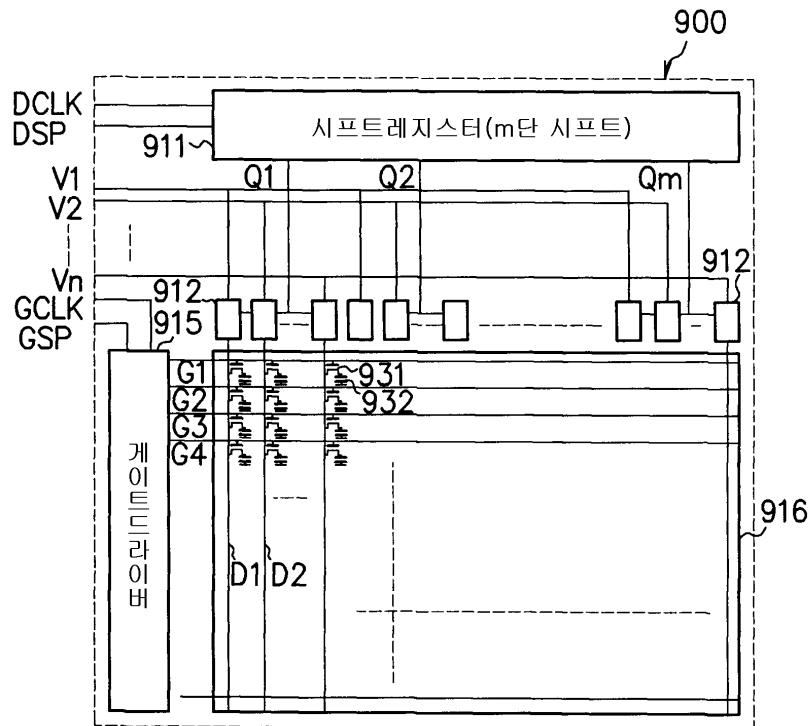

<79> 도 27은 종래 기술에 따른 다른 액정 표시 기판을 나타낸다. 기판(900) 상에는 시프트 레지스터(911), 아날로그 스위치(912), 표시부(916) 및 게이트 드라이버(915)가 설치된다. 게이트 드라이버(915)는 주사 라인(G1~G4) 등을 거쳐서 화소 영역(916)에 접속되어, 게이트 클록(GCLK) 및 게이트 스타트 펄스(GSP)에 따라서 주사 라인(G1~G4) 등에 주사 신호를 공급한다.

<80> 화소 영역(916)은 2차원 매트릭스 형상으로 배열된 TFT(931) 및 액정 커패시터(932)를 갖는다. TFT(931)는 n채널 MOS 트랜지스터로서, 게이트가 주사 라인(G1~G4) 등에 접속되고, 드레인이 데이터 라인(D1, D2) 등에 접속되고, 소스가 액정 커패시터(932)를 거쳐서 대향 기판의 전극에 접속된다.

- <81> 아날로그 스위치(912)는 입출력 단자의 한쪽 단부가 데이터 버스(V1~Vn)에 접속되고, 다른쪽 단부가 데이터 라인(D1, D2) 등에 접속된다. 데이터 버스(V1~Vn)에는 검사 종료 후에 데이터 드라이버가 접속되어 데이터가 공급된다.

- <82> 시프트 레지스터(911)는 m단 시프트가 가능하고, 데이터 클록(DCLK) 및 데이터 스타트 펄스(DSP)에 따라서 제어 선(Q1~Qm)으로 순차 시프트된 펄스를 출력한다. 제어 선(Q1~Qm)은 각각 아날로그 스위치(912)의 제어 단자에 접속된다. 아날로그 스위치(912)는 제어 선(Q1~Qm)이 하이레벨로 되면, 각각 데이터 버스(V1~Vn)와 데이터 라인(D1, D2) 등과의 사이를 접속한다.

- <83> 이 액정 표시 기판의 검사를 행하는 경우에는 데이터 버스(V1~Vn)의 단자에 프로브 핀을 닿게 할 필요가 있다. 그리고, 데이터 버스(V1~Vn)의 수가 많아지면, 액정 표시 기판을 고속 동작시키기 위해 고온의 폴리실리콘을 사용하지 않으면 안되어, 액정 표시 기판이 고가로 되어 버린다.

### 발명이 이루고자 하는 기술적 과제

- <84> 본 발명의 목적은, 검사기에 많은 프로브 핀을 사용하지 않고 간단하면서 단시간에 검사를 행할 수 있는 액정 표시 장치를 제공하는데 있다.

- <85> 본 발명 다른 목적은, 저렴한 액정 표시 장치를 간단하면서 단시간에 검사하는데 있다.

### 발명의 구성 및 작용

- <86> 본 발명의 일 관점에 따르면, 2차원 매트릭스 형상으로 배선된 데이터 라인 및 주사 라인과 이 데이터 라인 및 주사 라인간에 접속되는 스위칭 소자를 포함하는 표시 회로와, 데이터 라인의 한쪽 단부에 제 1 아날로그 스위치를 거쳐서 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력 단자를 포함하는 제 1 검사 회로와, 데이터 라인 다른쪽 단부에 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력 단자를 포함하는 제 2 검사 회로를 갖는 액정 표시 장치가 제공된다. 이 표시 회로, 제 1 검사 회로 및 제 2 검사 회로는 1매의 기판 상에 설치되고, 제 1 검사 회로는 표시 회로에 대해서 분리가 가능하다.

- <87> 액정 표시 기판에 제 1 및 제 2 검사 회로를 설치함으로써, 액정 표시 장치를 유닛화하기 전에, 데이터 라인의 단선, 데이터 라인의 인접 단락(short), 주사 라인의 단선, 인접 화소간의 단락, 다른 신호선과의 단락 등의 검사를 행할 수 있다. 검사 종료 후에 제 1 검사 회로를 분리함으로써, 액정 표시 기판에 데이터 드라이버를 접속하는 것이 가능하게 되어, 더 저비용의 액정 표시 장치를 제공할 수 있다.

<88> [실시형태]

<89> (제 1 실시형태)

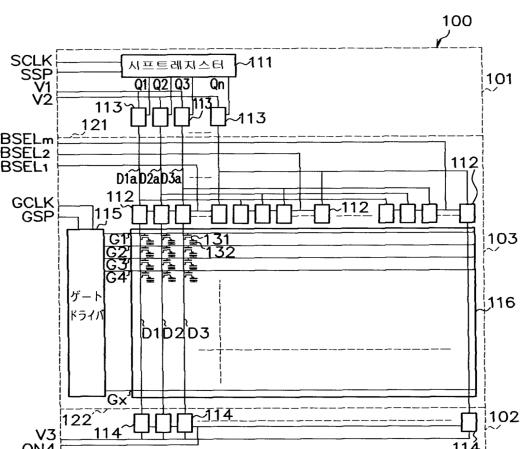

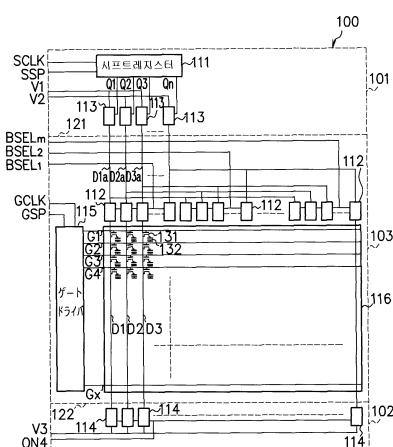

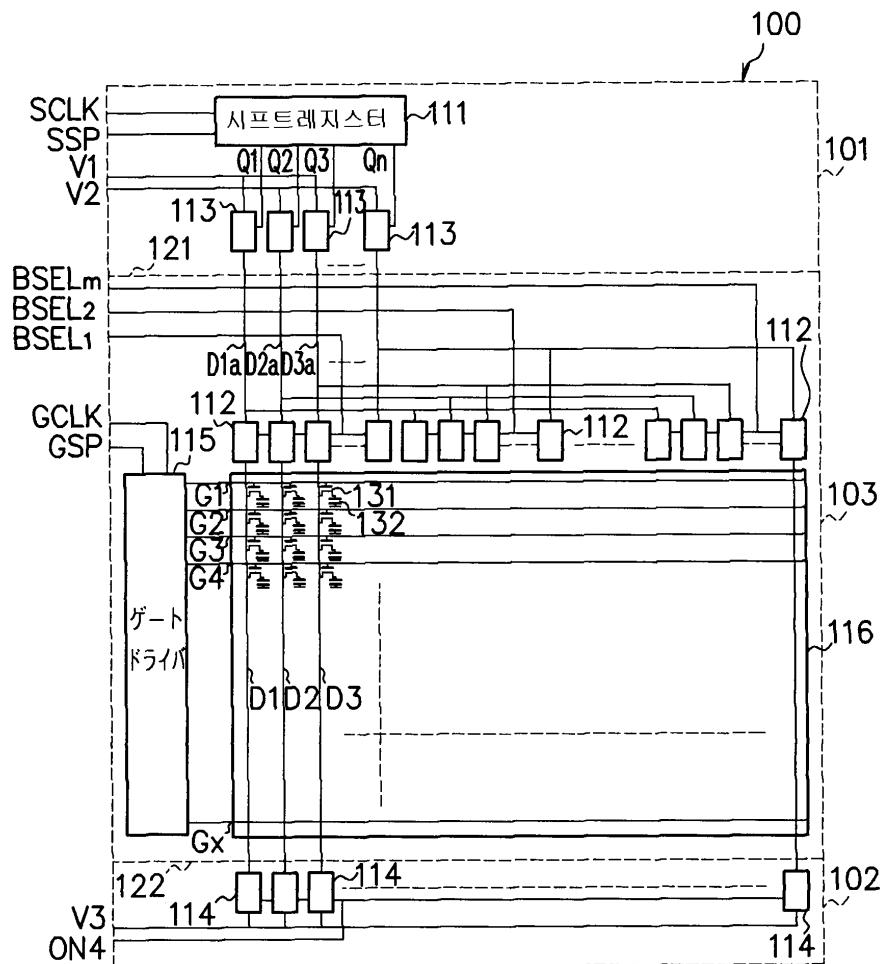

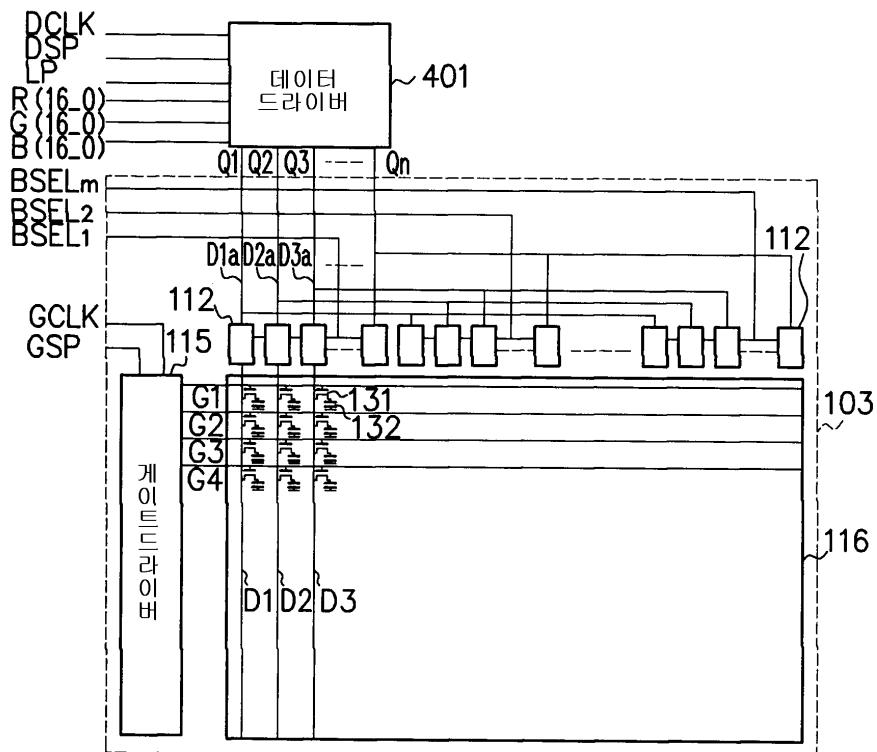

<90> 도 1은 본 발명의 제 1 실시형태에 따른 액정 표시 기판(100)을 나타낸다. 제 1 검사 회로(101), 표시 회로(103) 및 제 2 검사 회로(102)는 1매의 유리 기판(100)상에 설치된다. 제 1 검사 회로(101)는 표시 회로(103)에 대해서 절단 라인(121)으로 분리 가능하다. 제 2 검사 회로(102)는 표시 회로(103)에 대해서 절단 라인(122)으로 분리 가능하다.

<91> 표시 회로(103)는 게이트 드라이버(115), 화소 영역(116) 및 아날로그 스위치(112)를 갖는다. 게이트 드라이버(115)는 주사 라인(G1~Gx)을 거쳐서 화소 영역(116)에 접속되어, 게이트 클록(GCLK) 및 게이트 스타트 펄스(GSP)에 따라서 주사 라인(G1~Gx)에 주사 신호를 공급한다.

<92> 화소 영역(116)은 2차원 매트릭스 형상으로 배열된 TFT(131) 및 액정 커페시터(132)를 갖는다. TFT(131)는 n채널 MOS 트랜지스터로서, 게이트가 주사 라인(G1~Gx)에 접속되고, 드레인은 데이터 라인(D1~D3) 등에 접속되고, 소스(화소 전극)가 액정 커페시터(132)를 거쳐서 대향 기판의 전극에 접속된다.

<93> 아날로그 스위치(112)는 입출력 단자의 한쪽 단부가 데이터 라인(D1a~D3a) 등에 접속되고, 다른쪽 단부가 데이터 라인(D1~D3) 등에 접속된다. 블록 선택 신호선(BSEL1~BSELm)은 각각 아날로그 스위치(112)의 제어 단자에 접속된다. 아날로그 스위치(112)는 블록 선택 신호선(BSEL1~BSELm)이 하이레벨로 되면, 각각 데이터 라인(D1a~D3a) 등과 데이터 라인(D1~D3) 등과의 사이를 접속한다.

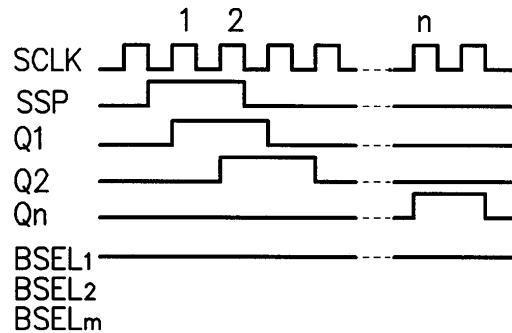

<94> 제 1 검사 회로(101)는 시프트 레지스터(111) 및 아날로그 스위치(113)를 갖는다. 아날로그 스위치(113)는 입출력 단자의 한쪽 단부가 교대로 신호선(V1, V2)에 접속되고, 다른쪽 단부가 데이터 라인(D1a~D3a) 등에 접속된다. 시프트 레지스터(111)는 n단 시프트가 가능하며, 도 2에 나타낸 바와 같이 데이터 클록(DCLK) 및 데이터

스타트 펄스(DSP)에 따라서 제어선(Q1~Qn)으로 순차 시프트된 펄스를 출력한다. 제어선(Q1~Qn)은 각각 아날로그 스위치(113)의 제어 단자에 접속된다. 아날로그 스위치(113)는 제어선(Q1~Qn)이 하이레벨로 되면, 각각 신호선(V1, V2)과 데이터 라인(D1a~D3a) 등과의 사이를 접속한다.

<95> 제 2 검사 회로(102)는 아날로그 스위치(114)를 갖는다. 아날로그 스위치(114)는 입출력 단자의 한쪽 단부가 데이터 라인(D1~D3) 등에 접속되고, 다른쪽 단부가 신호선(V3)에 접속된다. 제어선(ON4)은 아날로그 스위치(114)의 제어 단자에 접속된다. 아날로그 스위치(114)는 제어선(ON4)이 하이레벨로 되면, 각각 데이터 라인(D1~D3) 등과 신호선(V3) 사이를 접속한다.

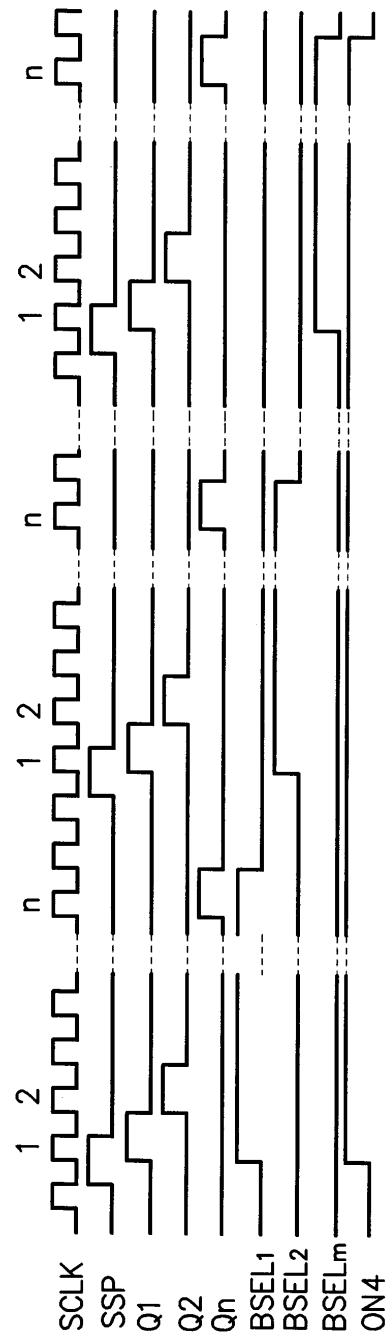

<96> 도 2에 나타낸 바와 같이, 제어선(ON4)이 하이레벨인 동안, 블록 선택 신호선(BSEL1~BSELm)에는 순서대로 펄스가 출력된다. 각 블록 선택 신호선(BSEL1~BSELm)이 하이레벨인 동안, 제어선(Q1~Qn)에는 순서대로 펄스가 출력된다.

<97> 우선, 신호선(V3)에 검사 신호를 입력한다. 제어선(ON4)이 하이레벨로 되면, 아날로그 스위치(114)가 온되어, 데이터 라인(D1~D3)과 신호선(V3) 사이를 접속한다. 블록 선택 신호선 BSEL1이 하이레벨로 되면, 원쪽부터 1 블럭째의 n개의 아날로그 스위치(112)가 온되어, 데이터 라인(D1a~D3a) 등과 데이터 라인(D1~D3)등과의 사이를 접속한다. 제어선(Q1)이 하이레벨로 되면, 좌측단의 아날로그 스위치(113)가 온되어, 신호선(V1)과 데이터 라인(D1a) 사이를 접속한다. 이와 같이, 제어선(Q2~Qn)이 순서대로 하이레벨로 된다.

<98> 신호선(V1 및 V2)의 출력을 검출함으로써, 검사를 행할 수 있다. 제어선(Q1)이 하이레벨로 되었을 때, 신호선(V3)에 입력된 검사 신호를 신호선(V1)으로부터 검출할 수 있으면 데이터 라인(D1 및 D1a)이 단선되어 있지 않다는 것을 확인할 수 있고, 신호선(V1)이 개방 상태이면 데이터 라인(D1 또는 D1a)이 단선되어 있다는 것을 확인할 수 있다. 또한, 제어선(Q2)이 하이레벨로 되었을 때, 신호선(V3)에 입력된 검사 신호를 신호선(V2)으로부터 검출할 수 있으면 데이터 라인(D2 및 D2a)이 단선되어 있지 않다는 것을 확인할 수 있고, 신호선(V2)이 개방 상태이면 데이터 라인(D2 또는 D2a)이 단선되어 있다는 것을 확인할 수 있다. 마찬가지로 하여, 다른 데이터 라인(D3 및 D3a) 등의 단선이 있는지의 여부를 확인할 수 있다. 본 실시형태에 따르면, 상기한 단선을 불량 개소로서 검출할 수 있다.

<99> 다음에, 다른 검사 방법을 설명한다. 도 3에 나타낸 바와 같이, 블록 선택 신호선(BSEL1~BSELm)을 로우 레벨로 하여, 아날로그 스위치(112)를 오프로 한다. 그리고, 스타트 펄스(SSP)의 주기를 클록(SCLK) 주기의 2배로 한다. 그렇게 하면, 제어선(Q1 및 Q2)이 모두 하이레벨로 되는 기간이 있게 된다. 그 기간에, 신호선(V1)으로부터 검사 신호를 입력하고, 신호선(V2)의 출력을 검출한다. 신호선(V1)에 입력된 검사 신호가 신호선(V2)으로부터 검출되면, 데이터 라인(D1a) 및 (D2a) 사이가 단락되어 있다는 것을 확인할 수 있고, 신호선(V2)이 개방 상태이면 데이터 라인(D1a) 및 (D2a) 사이가 단락되어 있지 않다는 것을 확인할 수 있다. 또한, 제어선(Q2 및 Q3)이 모두 하이레벨로 되는 기간에, 마찬가지로 데이터 라인(D2a) 및 (D3a)간의 단락의 유무를 확인할 수 있다. 마찬가지로, 다른 인접하는 데이터 라인간의 단락을 확인할 수 있다. 본 실시형태에 따르면, 상기의 단락을 불량 개소로서 검출할 수 있다.

<100> 본 실시형태는 시프트 레지스터(111)가 1개인 경우를 설명했지만, 시프트 레지스터(111)를 2개 이상 설치해도 좋다. 또한, 제 1 검사 회로(101)에 2개의 신호선(V1, V2)을 설치했지만, 단선 검사만을 행하는 경우에는 1개의 신호선만이라도 좋다. 또한, 2개의 신호선(V1, V2)의 수를 늘림으로써 시프트 레지스터(111)의 시프트 단의 수를 감소시킬 수 있고, 아날로그 스위치(112)와 아날로그 스위치(113) 사이의 데이터 라인(D1a~D3a) 등의 단락을 인접하지 않는 데이터 라인 사이에서도 확인할 수 있다. 또한, 신호선(V2)에 전원이나 접지, 그 밖의 신호선의 신호가 검출된 경우에는 전원 등과의 단락도 확인할 수 있다.

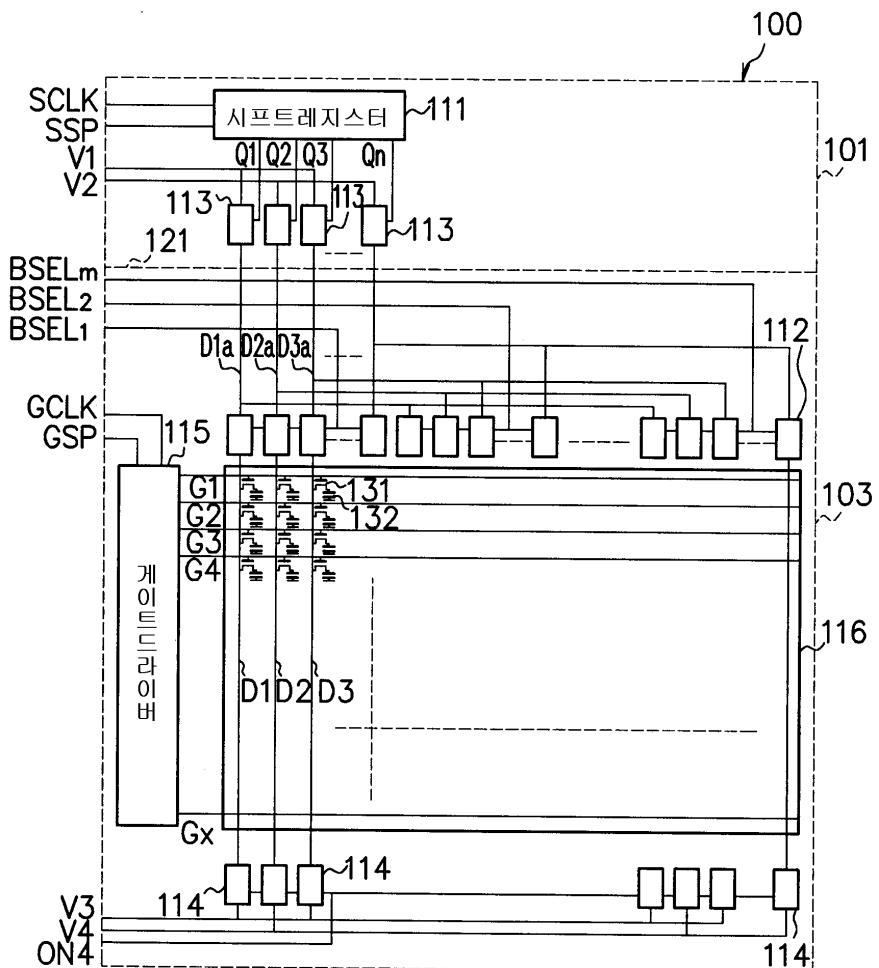

<101> 검사 후, 제 1 검사 회로(101) 및 제 2 검사 회로(102)를 절단 라인(121 및 122)에 의해 표시 회로(102)로부터 분리한다. 그 후, 도 4에 나타낸 바와 같이 액정 표시 장치를 유닛화할 때, 표시 회로(103)의 데이터 라인(D1a~D3a) 등에 데이터 드라이버(401)의 출력선(Q1~Qn)을 접속한다. 데이터 드라이버(401)는 클록(DCLK), 스타트 펄스(DSP), 래치 펄스(LP) 및 데이터(R, G, B)를 입력하고, 출력선(Q1~Qn)으로부터 데이터를 출력한다. 이것에 의해, 액정 표시 장치는 통상의 동작을 행할 수 있다.

<102> 또한, 제 2 검사 회로(102)는 반드시 표시 회로(103)로부터 분리될 필요는 없다. 제 2 검사 회로(102)를 분리하지 않는 경우에는, 통상의 동작시에 아날로그 스위치(114)를 항상 오프로 하면 좋다. 또한, 통상의 동작시에, 제 2 검사 회로(102)를 프리차지 기능으로서 사용할 수 있다. 즉, 데이터 드라이버(401)의 출력선(Q1~Qn)에 데이터를 출력하기 전에, 제 2 검사 회로(102)의 신호선(V3)에 소정의 전압을 입력함으로써, 데이터

라인(D1) 등을 프리차지할 수 있다.

<103> 본 실시형태는 도 27의 종래 기술에 따른 액정 표시 기판에 비해서 고속으로 동작시키지 않고도 표시 가능하므로, 저온 폴리실리콘을 이용하여 저렴한 액정 표시 기판을 제조할 수 있다.

<104> (제 2 실시형태)

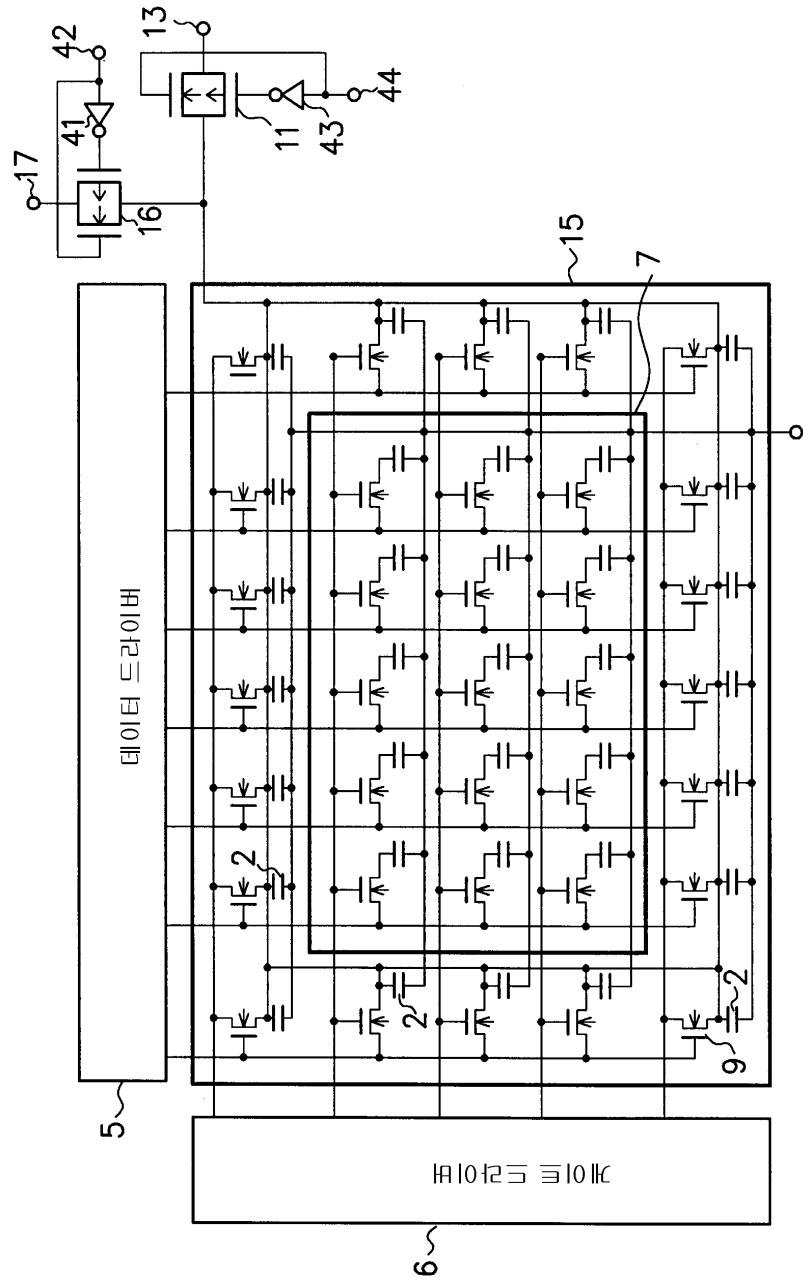

<105> 도 5는 본 발명의 제 2 실시형태에 따른 액정 표시 기판(100)을 나타낸다. 제 2 실시형태는 제 1 실시형태와 비교해서, 제 2 검사 회로가 표시 회로(103)에 포함되고, 아날로그 스위치(114)의 입출력 단자의 다른쪽 단부에 교대로 신호선(V3)과 (V4)가 접속되는 점이 다르며, 그 이외의 점은 동일하다.

<106> 신호선(V3, V4)에 다른 검사 신호를 입력하고, 제 1 실시형태와 마찬가지로 도 3의 타이밍으로 동작시킨다. 이 때, 예를 들면, 데이터 라인(D1)과 (D2) 사이가 단락되어 있는 경우, 또는 데이터 라인(D1a)과 (D2a) 사이가 단락되어 있는 경우에는, 신호선(V1, V2)으로부터 동일한 신호가 검출된다. 한편, 데이터 라인(D1)과 (D2) 사이가 단락되어 있지 않고, 또한 데이터 라인(D1a)과 (D2a) 사이가 단락되어 있지 않은 경우에는, 신호선(V3)으로부터 입력된 검사 신호가 신호선(V1)으로부터 검출되고, 신호선(V4)으로부터 입력된 검사 신호가 신호선(V2)으로부터 검출된다. 이와 같이, 인접하는 데이터 라인간의 단락의 유무를 확인할 수 있다.

<107> 또한, 통상의 동작시에, 신호선(V3, V4)을 프리차지 기능으로서 사용할 수 있다. 데이터 라인(D1~D3) 등은 화상의 깜박거림 방지 등을 위해, 우수 라인과 기수 라인에서 데이터의 정부 극성을 역으로 하는 것이 바람직하다. 이 때, 데이터 드라이버(401)의 출력선(Q1~Qn)으로 데이터를 출력하기 전에, 신호선(V3, V4)에 역극성의 전압을 입력함으로써, 데이터 라인(D1~D3) 등을 프리차지할 수 있다.

<108> (제 3 실시형태)

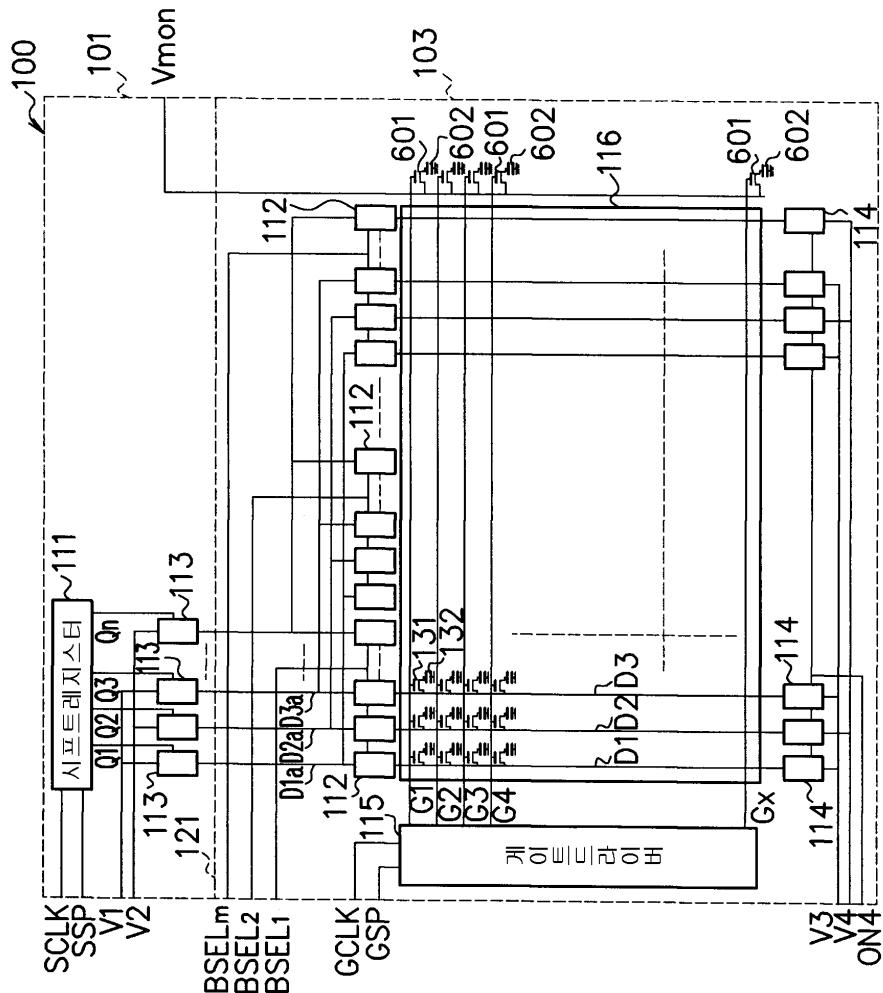

<109> 도 6은 본 발명의 제 3 실시형태에 따른 액정 표시 기판(100)을 나타낸다. 제 3 실시형태는 제 2 실시형태와 비교해서, n채널 MOS 트랜지스터(601) 및 커패시터(콘텐서)(602)를 마련한 점이 다르며, 그 이외의 점은 동일하다.

<110> 트랜지스터(601)는 게이트가 각각 주사 라인(G1~Gx)에 접속되고, 드레인이 공통의 신호선(Vmon)에 접속되고, 소스가 커패시터(602)를 거쳐서 소정의 공통 전압 단자에 접속된다.

<111> 도 7은 검사 방법을 나타내는 타이밍도이다. 게이트 드라이버(115)는 클록(GCLK) 및 스타트 펄스(GSP)에 따라서 주사 라인(G1~Gx)으로 순서대로 주사 신호를 출력한다. 그 동안의 기간(701)에서는 신호선(Vmon)에 검사 전압(Va)을 입력한다. 트랜지스터(601)는 주사 라인(G1~Gx)이 각각 하이레벨로 되면 온되어, 검사 전압(Va)을 커패시터(602)에 축적한다.

<112> 다음에, 재차 스타트 펄스(GSP)를 입력하고, 주사 라인(G1~Gx)으로 순차 주사신호를 출력한다. 그 동안의 기간(702)에, 신호선(Vmon)의 출력을 검출한다. 각 주사 라인(G1~Gx)이 하이레벨일 때, 신호선(Vmon)으로부터 검사 전압(Va)이 검출되면, 모든 주사 라인(G1~Gx)이 단선되어 있지 않다는 것을 확인할 수 있다. 한편, 기간(702) 내에서 신호선(Vmon)으로부터 검사 전압(Va)이 검출되지 않는 기간이 있으면, 그 기간에 대응하는 주사 라인이 단선되어 있다는 것을 확인할 수 있다. 본 실시형태에 따르면, 주사 라인(G1~Gx)의 단선을 결함 개소로서 검출할 수 있다.

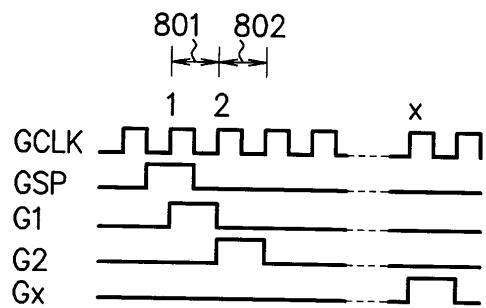

<113> 도 8은 상기한 검사 후에 실행하는 다른 검사 방법의 타이밍도이다. 클록(GCLK), 스타트 펄스(GSP), 주사 라인(G1~Gx)은 도 7과 마찬가지이다. 기간(801 및 802)은 각각 주사 라인(G1 및 G2)이 하이레벨인 기간이다. 그 기간(801 및 802) 내에 각각 도 9에 나타낸 처리를 실행한다. 다른 주사 라인(G3~Gx)이 하이레벨로 되는 기간에서도 마찬가지로 도 9에 나타낸 타이밍으로 처리를 실행한다.

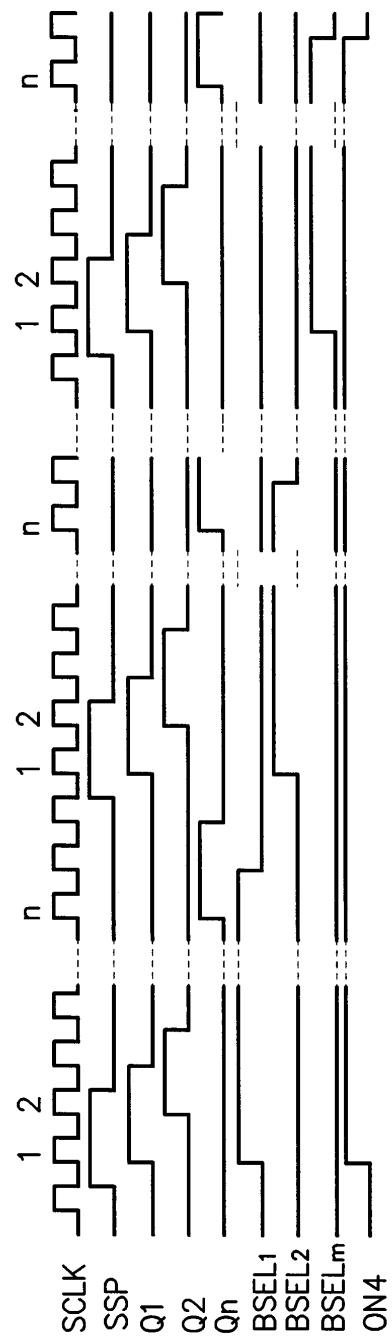

<114> 도 9에서의 클록(SCLK), 스타트 펄스(SSP) 및 제어선(Q1~Qn)은 도 3과 동일하다. 제어선(ON4)이 하이레벨인 동안, 블록 선택 신호선(BSEL1~BSELm)은 순차로 하이레벨로 된다. 각 블록 선택 신호선(BSEL1~BSELm)이 각각 하이레벨인 동안, 제어선(Q1~Qn)은 순차로 하이레벨로 된다.

<115> 예를 들면, 도 8에 나타낸 바와 같이 주사 라인 G1이 하이레벨인 동안, 도 9에 나타낸 바와 같이 제어선(Q1 및 Q2)은 모두 하이레벨로 된다. 아날로그 스위치(113)는 신호선(V1)과 데이터 라인(D1a) 사이를 접속하고, 신호선(V2)과 데이터 라인(D2a) 사이를 접속한다. 그 때, 블록 선택 신호선(BSEL1)은 하이레벨이므로, 아날로그 스위치(112)는 데이터 라인(D1a)과 (D1) 사이를 접속하고, 데이터 라인(D2a)과 (D2) 사이를 접속한다. 제어선(ON4)은 하이레벨이므로, 아날로그 스위치(114)는 데이터 라인(D1)과 신호선(V3) 사이를 접속하고, 데이터 라인

(D2)과 신호선(V4) 사이를 접속한다.

<116> 제 2 실시형태와 마찬가지로, 신호선(V3, V4)에 다른 검사 신호를 입력한다. 라인 (G1)과 (D1) 사이가 단락되어 있지 않고, 또한 라인 (G2)와 (D2) 사이가 단락되어 있지 않으면, 신호선(V3, V4)에 입력된 검사 신호는 각각 신호선(V1 및 V2)으로부터 검출할 수 있다. 한편, 라인 (G1)과 (D1) 사이 또는 라인 (G2)와 (D2) 사이가 단락되어 있으면, 신호선(V1 및 V2)으로부터 주사 라인(G1 또는 G2)의 영향을 받은 전압이 검출된다. 이 때, 인접 화소간의 단락의 유무도 확인할 수 있다. 본 실시형태에 의하면, 주사 라인 및 데이터 라인간의 단락 및 인접 화소간의 단락의 결함을 검출할 수 있다.

<117> 상기한 검사에 의해, 액정 표시 기판의 선 결함을 검사할 수 있다. 그 후, 표시 회로(103)의 각 TFT(스위칭 소자)(131)에 대응하는 화소의 점 결함을 검사한다. 이것에 의해, 선 결함 및 점 결함의 양쪽 모두의 검사를 행할 수 있다.

<118> 이상 설명한 바와 같이, 제 1~제 3 실시형태에 의하면, 액정 표시 기판에 표시 회로와 함께 제 1 및 제 2 검사 회로를 설치함으로써, 액정 표시 장치를 유닛화하기 전에, 데이터 라인의 단선, 데이터 라인의 인접 단락, 아날로그 스위치(112)와 아날로그 스위치(113) 사이의 데이터 라인의 단락, 주사 라인의 단선, 인접 화소간의 단락, 다른 신호선과의 단락 등의 결함의 유무를 검사할 수 있다. 검사 종료 후에 제 1 검사 회로(101)를 분리함으로써, 표시 회로(103)에 데이터 드라이버(401)를 접속하는 것이 가능하게 되어, 더 저비용의 액정 표시 장치를 제공할 수 있다.

<119> (제 4 실시형태)

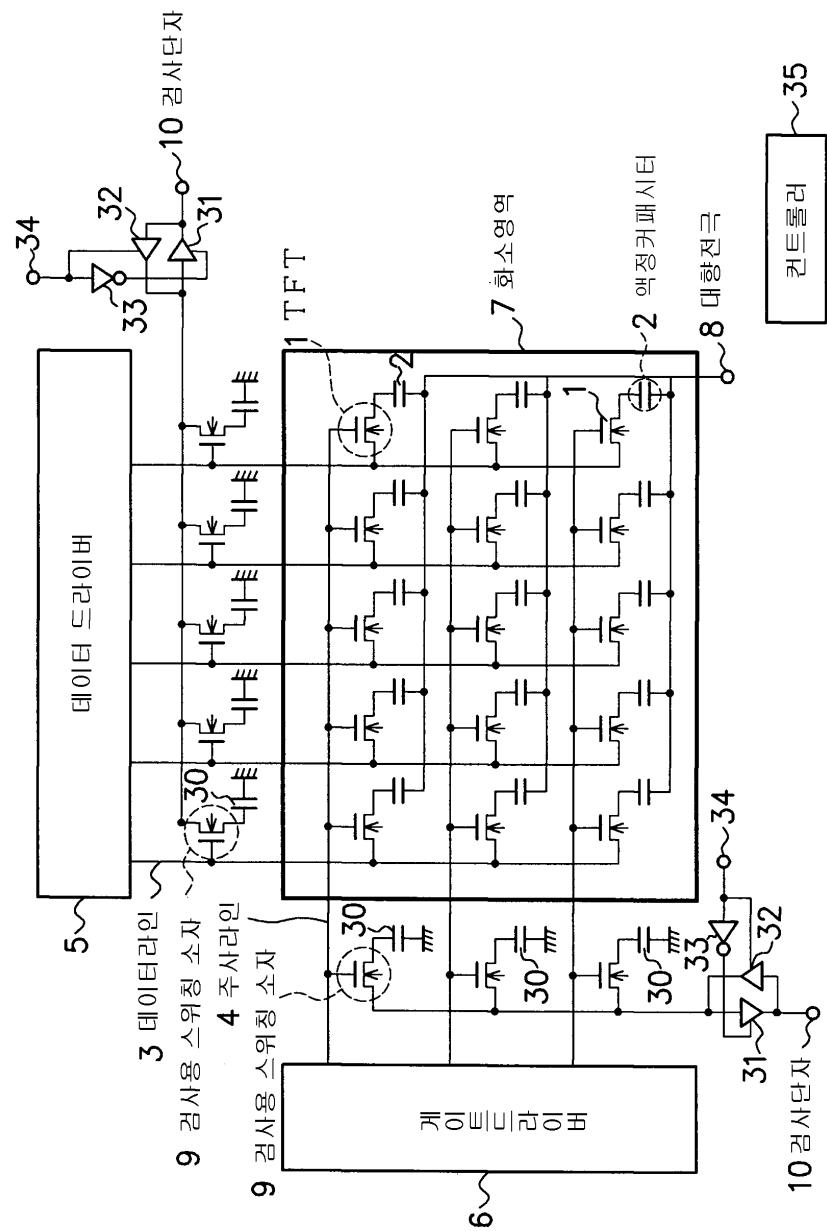

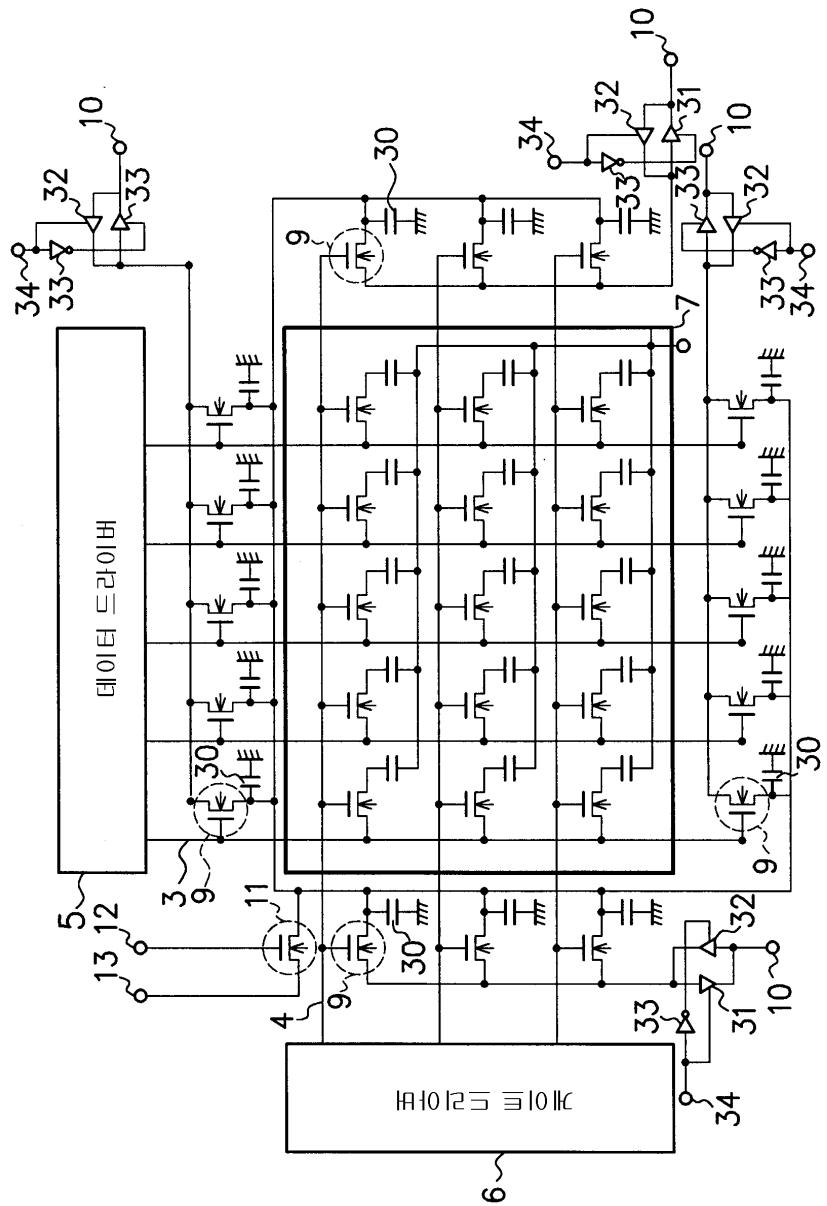

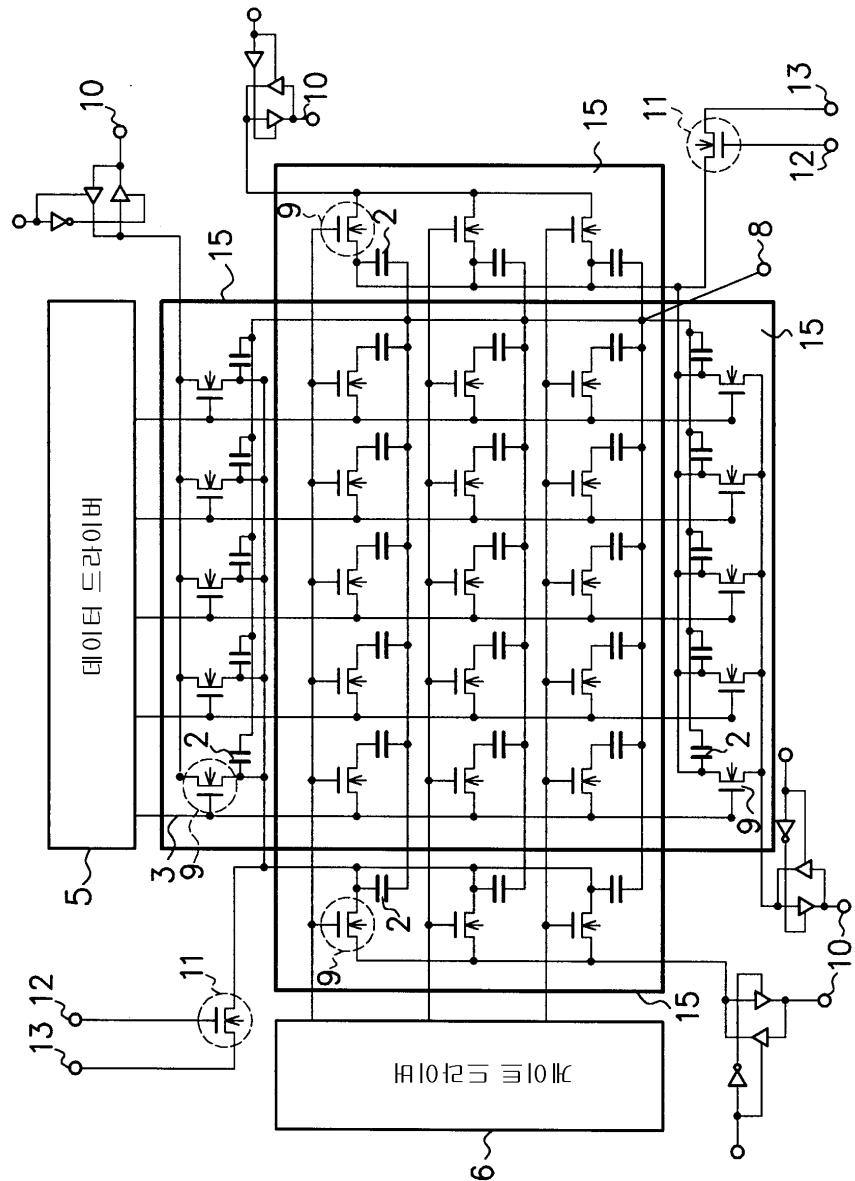

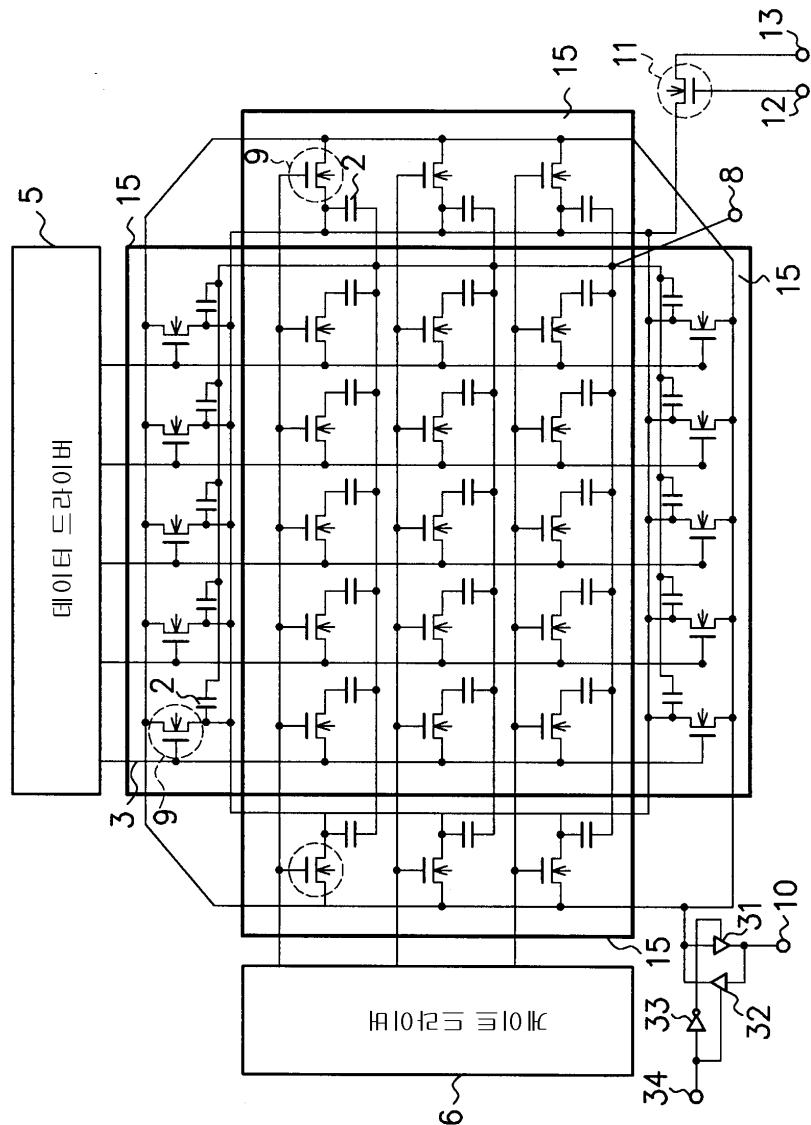

<120> 도 10은 본 발명의 제 4 실시형태에 따른 액정 표시 기판을 나타낸다. 화소 영역(7)에서, TFT(n채널 MOS 트랜지스터)(1)는 게이트가 주사 라인(4)에 접속되고, 드레인이 데이터 라인(3)에 접속되고, 소스(화소 전극)가 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다. 화소 영역(7)과 게이트 드라이버(6) 사이 및 화소 영역(7)과 데이터 드라이버(5) 사이에, 검사용 스위칭 소자(n채널 MOS 트랜지스터)(9)가 설치된다. 이 검사용 스위칭 소자(9)의 게이트는 주사 라인(4) 또는 데이터 라인(3)에 접속된다. 스위칭 소자(9)는 소스가 커패시터(30)를 거쳐서 접지에 접속되고, 드레인이 베퍼(31 또는 32)를 거쳐서 공통의 검사 단자(10)에 접속된다. 베퍼(31 및 32)는 쌍방향 스위치를 구성한다. 베퍼(31)의 제어 단자는 직접 단자(34)에 접속된다. 베퍼(32)의 제어 단자는 인버터(33)를 거쳐서 단자(34)에 접속된다. 컨트롤러(35)가 단자(34)에 하이레벨을 입력하면 검사 단자(10)는 입력 단자로 되고, 단자(34)에 로우 레벨을 입력하면 검사 단자(10)는 출력 단자로 된다.

<121> 데이터 드라이버(5)는 데이터 라인(3)에 데이터를 공급하기 위한 데이터 공급 회로로서, 아날로그 스위치라도 좋다. 게이트 드라이버(6)는 주사 라인(4)에 주사 신호를 공급할 수 있다.

<122> 다음에, 검사 방법을 설명한다. 우선, 게이트 드라이버(6) 또는 데이터 드라이버(5)가 검사용 스위칭 소자(9)를 온시키는 신호를 출력한다. 검사용 스위칭 소자(9)가 온되어 있는 기간에, 컨트롤러(35)가 검사 단자(10)에 검사 신호를 입력하고, 커패시터(30)에 충전(프리셋)한다. 재차, 검사용 스위칭 소자(9)를 온시키고, 검사 단자(10)에서 커패시터(30)로 충전하고 있는 전압을 검출한다. 검사 전압을 검출할 수 있으면, 게이트 드라이버(6) 또는 데이터 드라이버(5)가 정상적으로 구동하고 있고 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 화소 영역(7)까지의 주사 라인(4) 또는 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다. 이 검사를 주사 라인(4) 및 데이터 라인(3)에 대해서 각각 제 1 라인에서 최종 라인까지 반복함으로써, 게이트 드라이버(6) 및 데이터 드라이버(5)의 고장과 주사 라인(4) 및 데이터 라인(3)의 단선 개소와 단선 개수를 검사할 수 있다.

<123> 본 실시형태에서는 검사용 스위칭 소자(9)를 화소 영역(7)의 입력측(좌측 및 상측)에 배치하고 있지만, 출력측(우측 및 하측)에 배치해도 좋다. 출력측에 배치한 경우, 화소 영역(7) 내에서의 주사 라인(4) 및 데이터 라인(3)의 단선도 검사할 수 있다. 상기 커패시터(30)는 각 검사용 스위칭 소자(9)마다 따로 따로 설치해도 좋고, 1개의 커패시터(30)를 복수의 검사용 스위칭 소자(9)에서 공용해도 좋다. 또한, 각 검사용 스위칭 소자(9)마다의 커패시터(30)를 병렬로 접속해도 좋다.

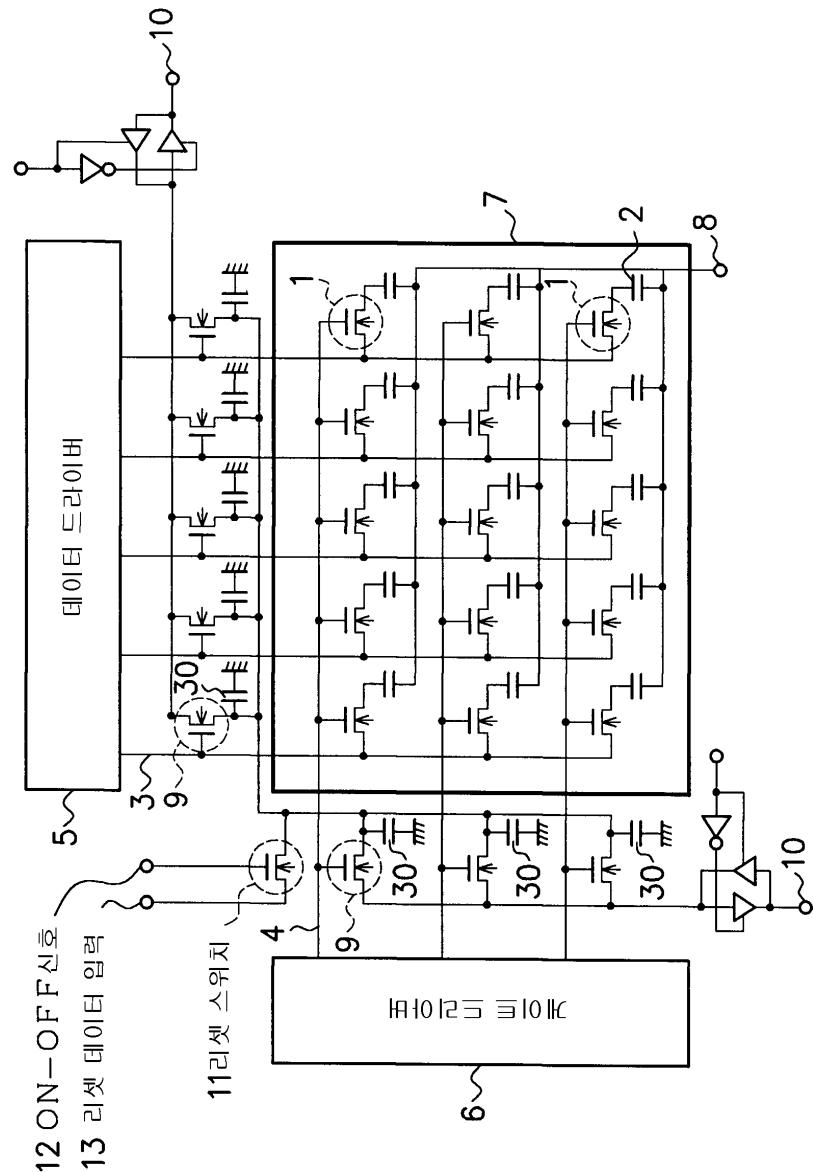

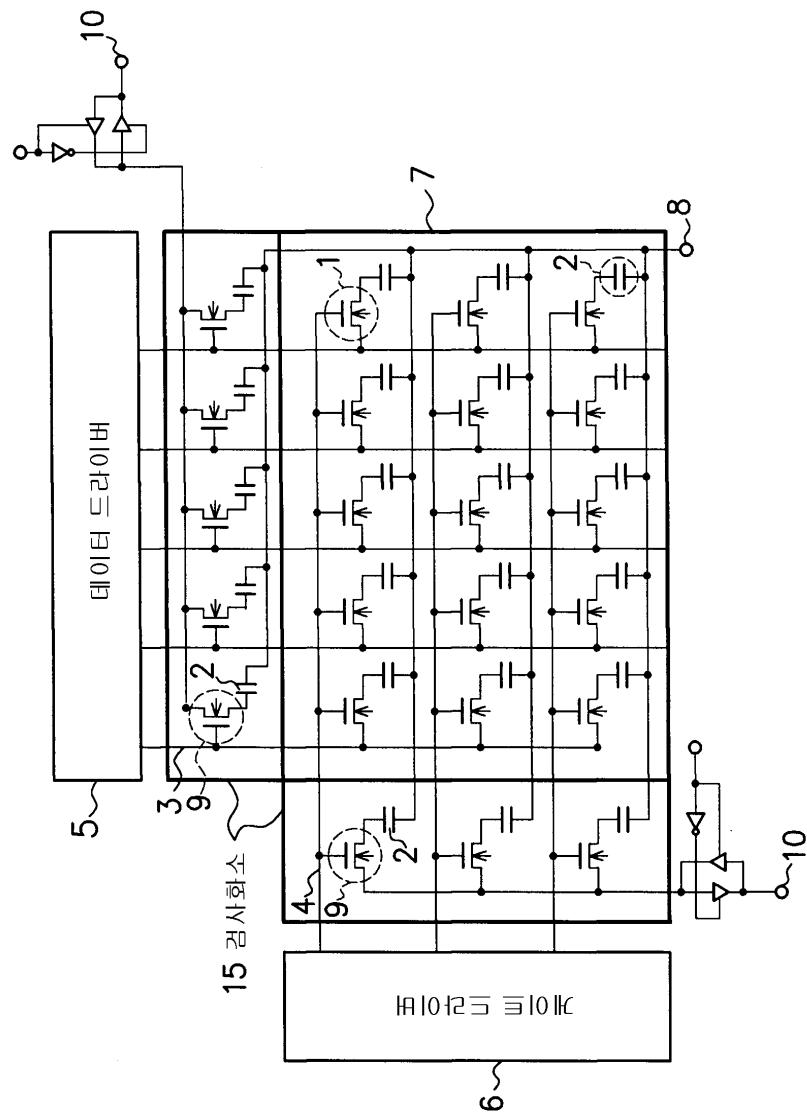

<124> (제 5 실시형태)

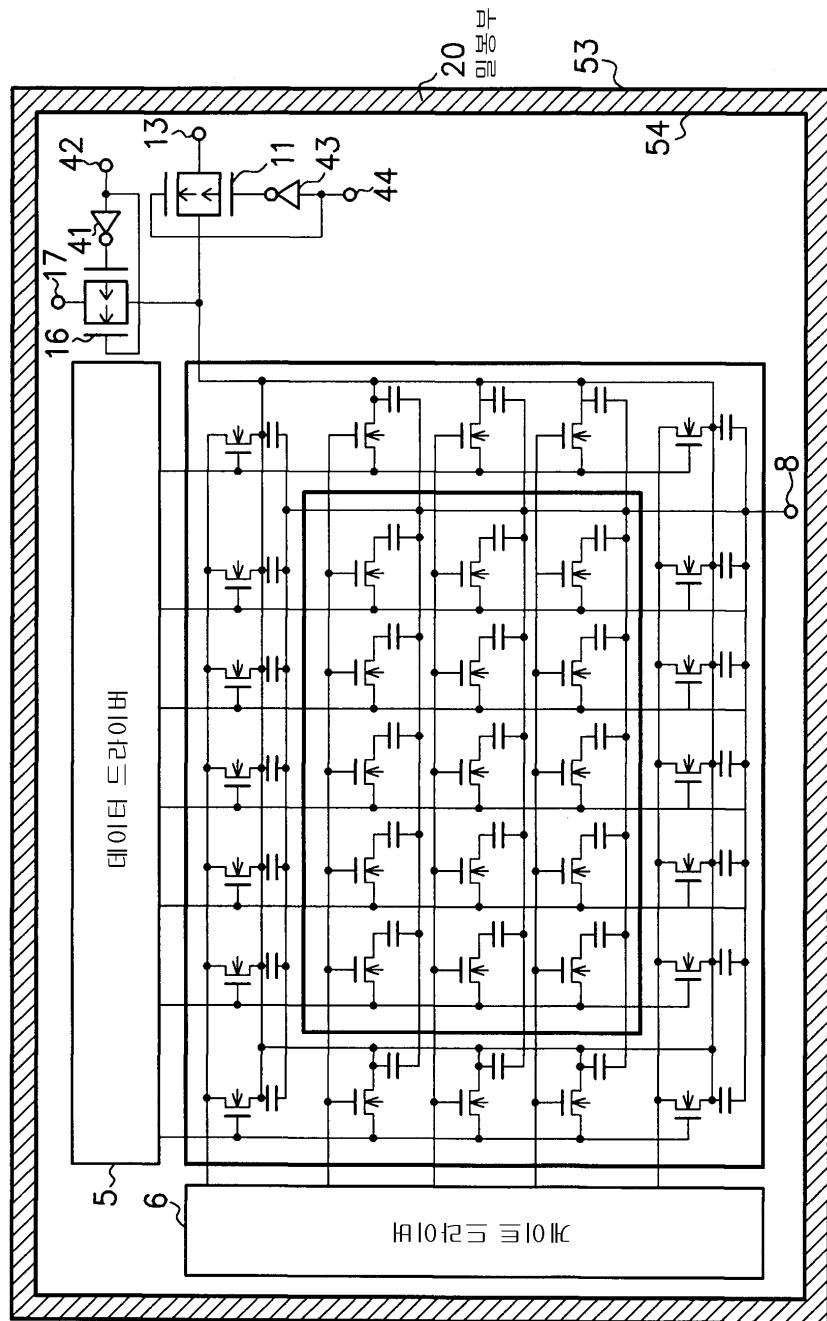

<125> 도 11은 본 발명의 제 5 실시형태에 따른 액정 표시 기판을 나타낸다. 제 5 실시형태는 제 4 실시형태와 비교해서, 리셋 스위치(n채널 MOS 트랜지스터)(11)를 설치한 점이 다르며, 그 이외의 점은 동일하다. 리셋 스위치(11)는 게이트가 온/오프 신호 단자(12)에 접속되고, 드레인은 리셋 데이터 입력 단자(13)에 접속되고, 소스는

검사용 스위칭 소자(9)의 각 소스에 접속된다.

<126> 검사를 행하기 위해서는, 우선 온/오프 신호 단자(12)를 하이레벨로 함으로써 리셋 스위치(11)를 온하고, 리셋 데이터 입력 단자(13)를 접지 레벨로 하여 커패시터(30)의 차지를 없앤다. 그 후, 제 4 실시형태에 나타낸 검사를 실행한다. 커패시터(30)를 리셋함으로써 적절한 검사 전압의 검출이 가능하게 되어, 검사 정밀도가 향상된다.

<127> (제 6 실시형태)

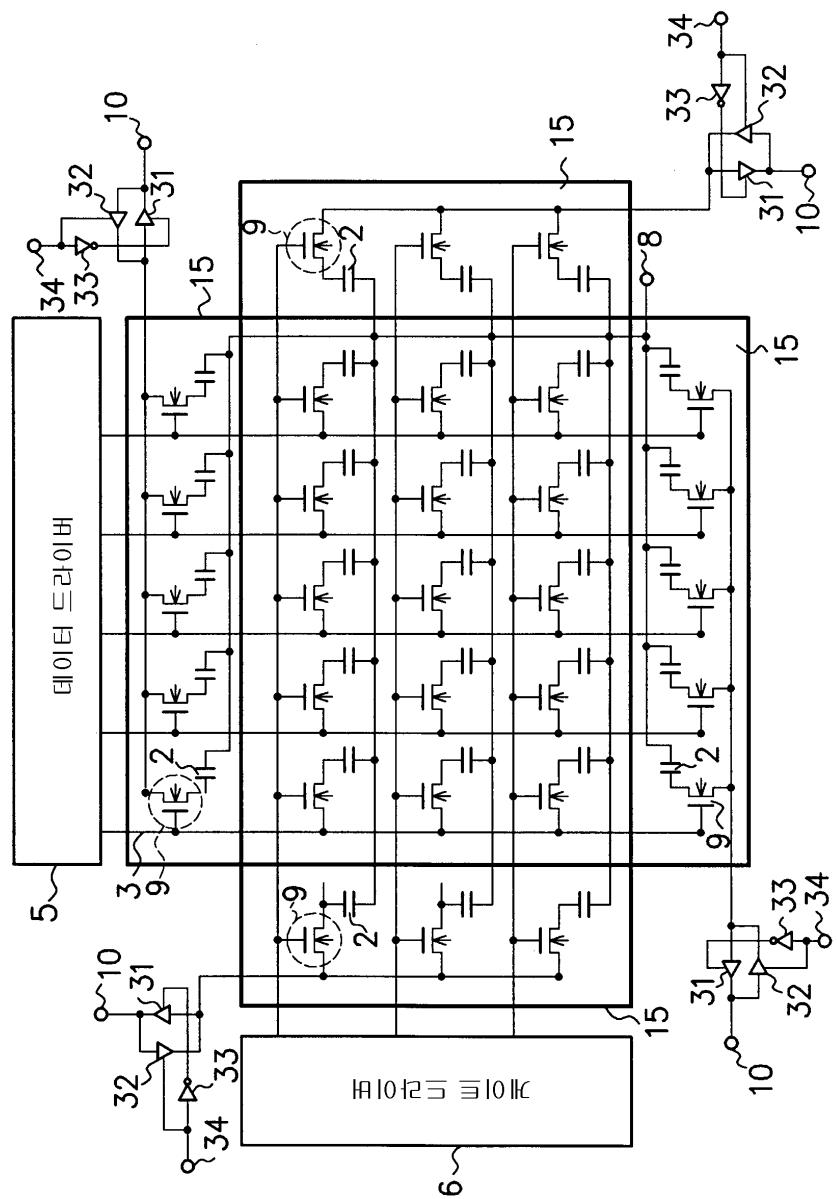

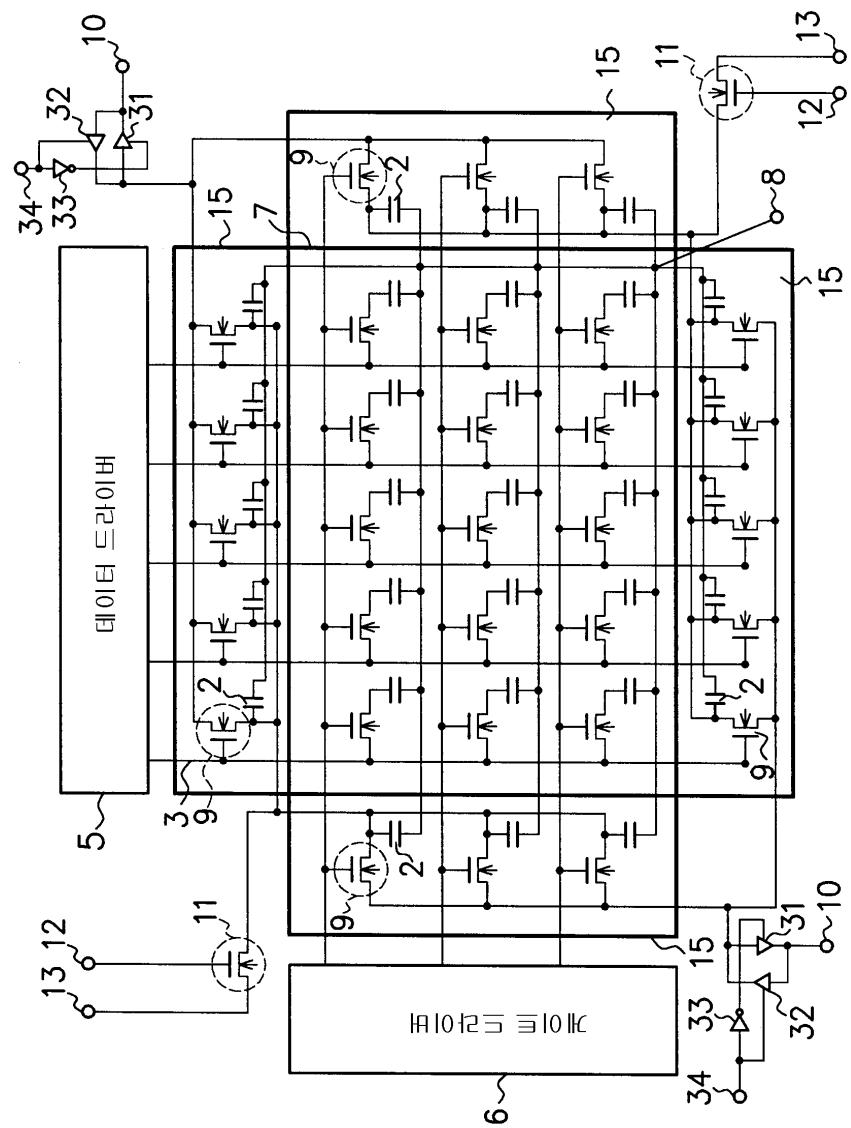

도 12는 본 발명의 제 6 실시형태에 따른 액정 표시 기판을 나타낸다. 제 6 실시형태가 제 5 실시형태와 비교해서 다른 점을 설명한다. 검사용 스위칭 소자(9)가 화소 영역(7)의 상측 및 좌측 뿐만 아니라, 우측 및 하측에도 설치된다. 즉, 검사용 스위칭 소자(9)는 게이트 드라이버(6)에 대해서 화소 영역(7)의 출력단, 및 데이터 드라이버(5)에 대해서 화소 영역(7)의 출력단에 설치된다. 검사용 스위칭 소자(9)는 상기와 마찬가지로 게이트가 주사 라인(4) 또는 데이터 라인(3)에 접속되고, 드레인이 베퍼(31 또는 32)를 거쳐서 검사 단자(10)에 접속되고, 소스가 커패시터(30)를 거쳐서 접지에 접속된다. 리셋 데이터 입력 단자(13)는 리셋 스위치(11)를 거쳐서 검사용 스위칭 소자(9)의 소스에 접속된다.

<129> 제 5 실시형태와 동일한 검사를 실행한다. 화소 영역(7)의 입력측(좌측 및 상측)에서, 커패시터(30)에 축적되어 있는 전하를 정상적으로 검사 단자(10)로부터 검출할 수 있으면, 게이트 드라이버(6) 및 데이터 드라이버(5)가 정상 구동하고 있고, 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 화소 영역(7)까지의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<130> 또한, 화소 영역(7)의 출력측(우측 및 하측)에서, 커패시터(30)에 축적되어 있는 전하를 정상적으로 검사 단자(10)로부터 검출할 수 있으면, 화소 영역(7) 내에서의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<131> 이 검사를 게이트 드라이버(6) 및 데이터 드라이버(5)의 제 1 라인에서 최종 라인까지 반복함으로써, 게이트 드라이버(6) 및/또는 데이터 드라이버(5)의 고장 및 주사 라인(4) 및/또는 데이터 라인(3)의 단선 개소와 개수를 검사할 수 있다.

<132> (제 7 실시형태)

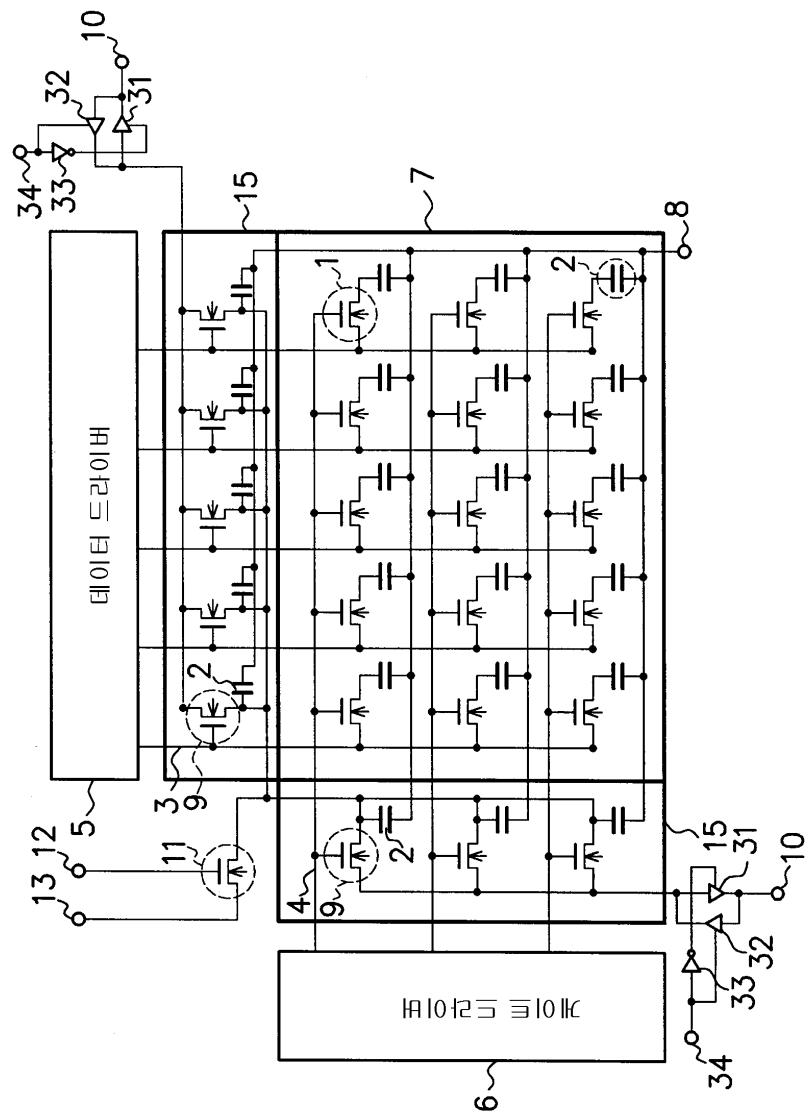

<133> 도 13은 본 발명의 제 7 실시형태에 따른 액정 표시 기판을 나타낸다. 제 7 실시형태는 제 4 실시형태(도 10)에서의 검사용 스위칭 소자(9)가 검사 화소(15)인 경우를 나타낸다. 즉, 검사용 스위칭 소자(9)는 화소 영역(7) 내의 TFT(1)와 마찬가지의 TFT이다. 검사용 스위칭 소자(9)의 소스(화소 전극)는 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다.

<134> 제 4~제 6 실시형태에서는 커패시터(30)에 검사 전압을 충전했지만, 본 실시형태에서는 액정 커패시터(2)에 검사 전압을 충전한다. 액정 커패시터(2)는 커패시터(30)에 비해서 축적 가능 용량이 크기 때문에, 검사시의 판단이 용이하다. 검사 후의 통상 동작시에는 검사 화소(15)에 흑색의 데이터를 기록하지만, 콘트라스트 저하의 원인으로 되므로, 미리 검사 화소(15)를 차광해 두는 것이 바람직하다.

<135> (제 8 실시형태)

<136> 도 14는 본 발명의 제 8 실시형태에 따른 액정 표시 기판을 나타낸다. 제 8 실시형태가 제 7 실시형태와 비교해서 다른 점을 설명한다. 제 6 실시형태(도 12)와 마찬가지로, 검사 화소(15)인 검사용 스위칭 소자(9)가 화소 영역(7)의 입력측(상측 및 좌측) 뿐만 아니라, 출력측(우측 및 하측)에도 설치된다.

<137> 화소 영역(7)의 입력측(좌측 및 상측)에서, 액정 커패시터(2)에 축적되어 있는 전하를 정상적으로 검사 단자(10)로부터 검출할 수 있으면, 게이트 드라이버(6) 및 데이터 드라이버(5)가 정상 구동하고 있고, 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 화소 영역(7)까지의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<138> 또한, 화소 영역(7)의 출력측(우측 및 하측)에서, 액정 커패시터(2)에 축적되어 있는 전하를 정상적으로 검사 단자(10)로부터 검출할 수 있으면, 화소 영역(7) 내에서의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<139> (제 9 실시형태)

<140> 도 15는 본 발명의 제 9 실시형태에 따른 액정 표시 기판을 나타낸다. 제 9 실시형태는 제 7 실시형태와 비교해서, 제 5 실시형태(도 11)와 마찬가지로 리셋 스위치(n채널 MOS 트랜지스터)(11)를 설치한 점이 다르며, 그 이외의 점은 동일하다. 리셋 스위치(11)는 게이트가 온/오프 신호 단자(12)에 접속되고, 드레인이 리셋 데이터 입력 단자(13)에 접속되고, 소스가 검사 화소인 검사용 스위칭 소자(9)의 각 소스에 접속된다.

<141> 검사를 실행하기 위해서는, 우선 온/오프 신호 단자(12)를 하이레벨로 함으로써 리셋 스위치(11)를 온하고, 리셋 데이터 입력 단자(13)를 접지 레벨로 하여 액정 커패시터(2)의 차지를 없앤다. 그 후, 제 4 실시형태에 나타낸 검사를 실행한다. 액정 커패시터(2)를 리셋함으로써 검사 정밀도를 향상시킬 수 있다.

<142> (제 10 실시형태)

<143> 도 16은 본 발명의 제 10 실시형태에 따른 액정 표시 기판을 나타낸다. 제 10 실시형태는 제 8 실시형태(도 14)와 비교해서, 제 9 실시형태(도 15)와 마찬가지로 리셋 스위치(n채널 MOS 트랜지스터)(11)를 설치한 점이 다르며, 그 이외의 점은 동일하다. 검사를 실행하기 위해서는, 우선 온/오프 신호 단자(12)를 하이레벨로 함으로써 리셋 스위치(11)를 온하고, 리셋 데이터 입력 단자(13)를 접지 레벨로 하여 액정 커패시터(2)의 차지를 없앤다. 그 후, 제 4 실시형태에 나타낸 검사를 실행한다.

<144> (제 11 실시형태)

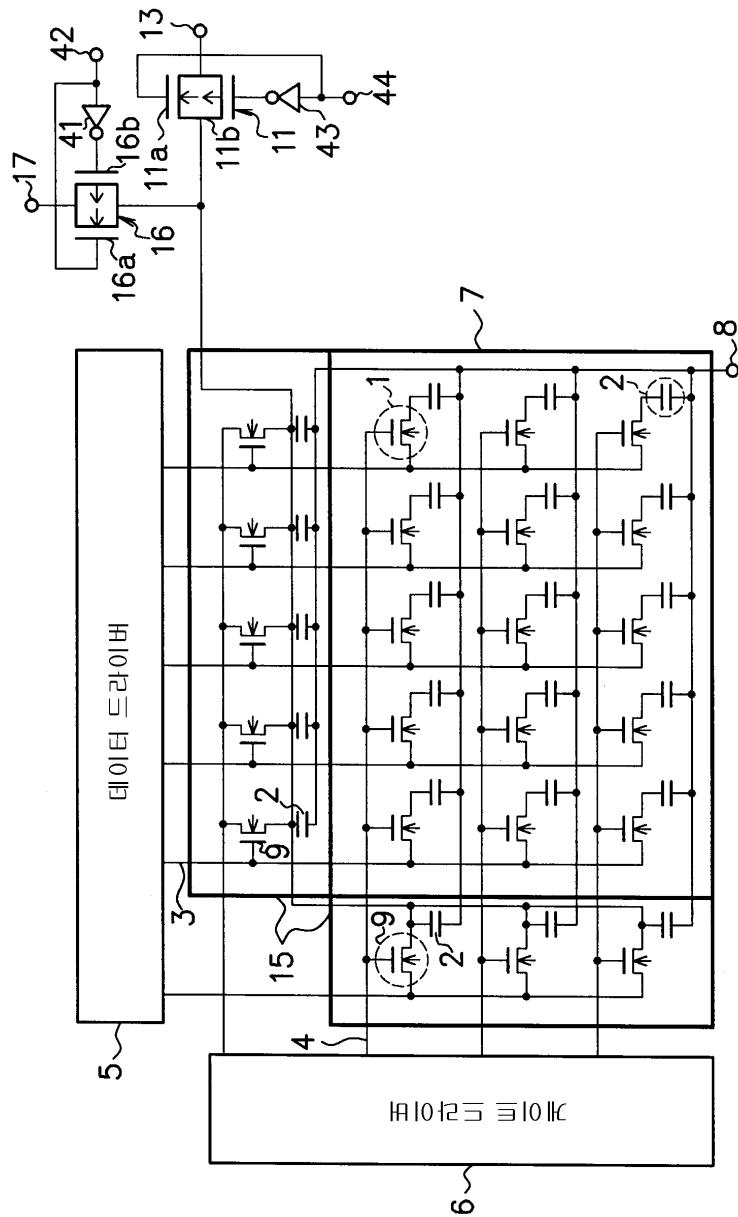

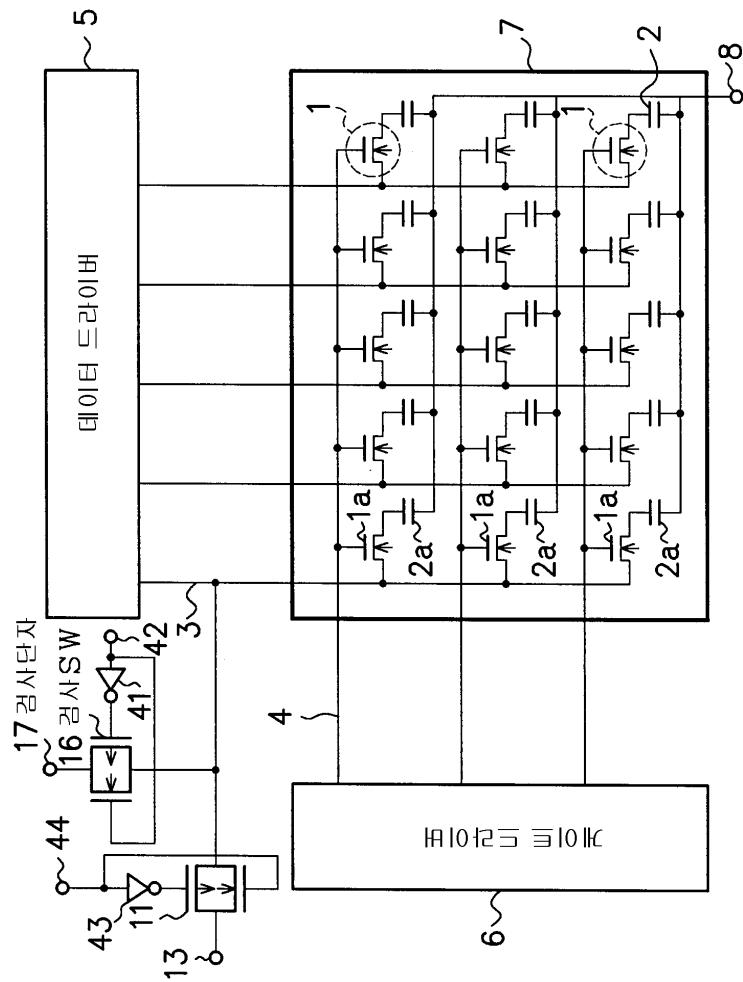

<145> 도 17은 본 발명의 제 11 실시형태에 따른 액정 표시 기판을 나타낸다. 제 11 실시형태가 제 9 실시형태(도 15)에 대해서 다른 점을 설명한다. 화소 영역(7)과 게이트 드라이버(6) 사이 및 화소 영역(7)과 데이터 드라이버(5) 사이에, 검사 화소(15)인 검사용 스위칭 소자(9)를 설치한다. 이 검사용 스위칭 소자(9)는 게이트가 주사 라인(4) 또는 데이터 라인(3)에 접속되고, 드레인이 데이터 라인(3) 또는 주사 라인(4)에 접속되고, 소스가 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다. 즉, 검사용 스위칭 소자(9)는 게이트에 주사 라인(4)이 접속되면 드레인에 데이터 라인(3)이 접속되고, 게이트에 데이터 라인(3)이 접속되면 드레인에 주사 라인(4)이 접속된다.

<146> 검사 화소(15)인 검사용 스위칭 소자(9)의 소스에는 리셋 스위치(11)를 거쳐서 리셋 데이터 입력 단자(13)가 접속되고, 검사 스위치(16)를 거쳐서 검사 단자(17)가 접속된다. 이 검사 스위치(16)는 제 9 실시형태(도 15)의 버퍼(31)에 상당하며, 검사 단자(17)는 제 9 실시형태의 검사 단자(10)에 상당한다.

<147> 리셋 스위치(11)는 제 9 실시형태와 달리 CMOS 구성이며, n채널 MOS 트랜지스터(11a) 및 p채널 MOS 트랜지스터(11b)의 소스 및 드레인을 서로 접속한 것이다. 단자(44)는 인버터(43)를 거쳐서 트랜지스터(11b)의 게이트에 접속됨과 동시에, 직접 트랜지스터(11a)의 게이트에 접속된다. 단자(44)를 하이레벨로 하면 리셋 스위치(11)는 온되고, 로우 레벨로 하면 리셋 스위치(11)는 오프된다.

<148> 검사 스위치(16)는 CMOS 구성이며, n채널 MOS 트랜지스터(16a) 및 p채널 MOS 트랜지스터(16b)의 소스 및 드레인을 서로 접속한 것이다. 단자(42)는 인버터(41)를 거쳐서 트랜지스터(16b)의 게이트에 접속됨과 동시에, 직접 트랜지스터(16a)의 게이트에 접속된다. 단자(42)를 하이레벨로 하면 검사 스위치(16)는 온되고, 로우 레벨로 하면 검사 스위치(16)는 오프된다.

<149> 다음에, 검사 방법을 설명한다. 우선, 리셋 스위치(11)를 온하고, 리셋 데이터 입력 단자(13)를 OV로 하여 액정 커패시터(2)의 차지를 없앤다. 다음에, 게이트 드라이버(6) 또는 데이터 드라이버(5)로부터 검사 화소(15)인 검사용 스위칭 소자(9)의 액정 커패시터(2)에 데이터를 기록한다. 다음에, 검사 스위치(16)를 온하여, 액정 커패시터(2)에 기록된 데이터를 검사 단자(17)로부터 판독한다. 기록 데이터를 검출할 수 있으면, 게이트 드라이버(6) 또는 데이터 드라이버(5)가 정상적으로 구동하고 있고, 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 화소 영역(7)까지의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다. 이 검사를 게이트 드라이버(6) 및 데이터 드라이버(5)의 제 1 라인에서 최종 라인까지 반복함으로써, 게이트 드라이버(6) 및/또는 데이터 드라이버(5)의 고장과 주사 라인(4) 및/또는 데이터 라인(3)의 단선 개소와 개수를 검사할 수 있다.

<150> 또, 액정 커패시터(2)의 리셋 및 검사 전압의 프리셋은 데이터 드라이버(5)로부터 데이터를 공급함으로써 실행해도 좋다.

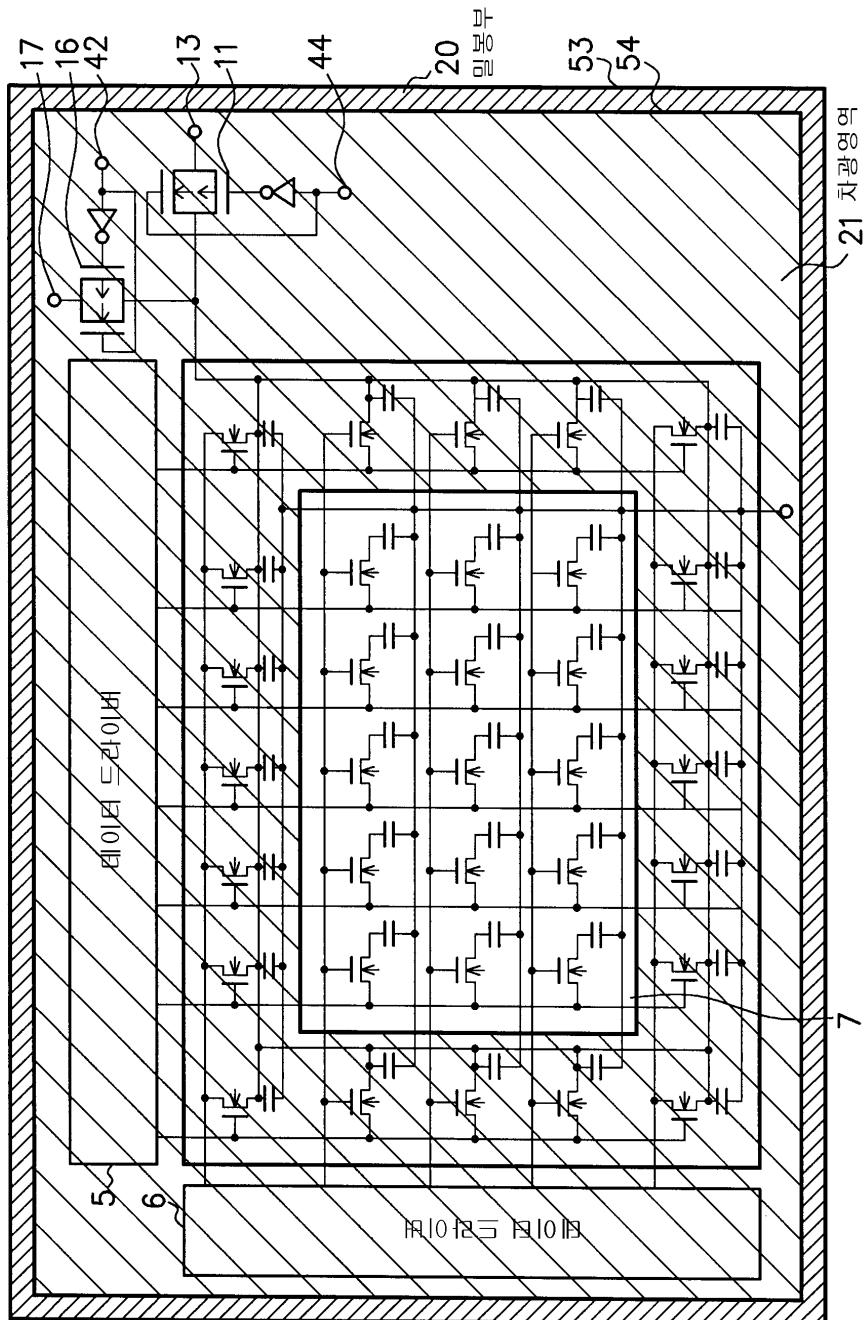

<151> (제 12 실시형태)

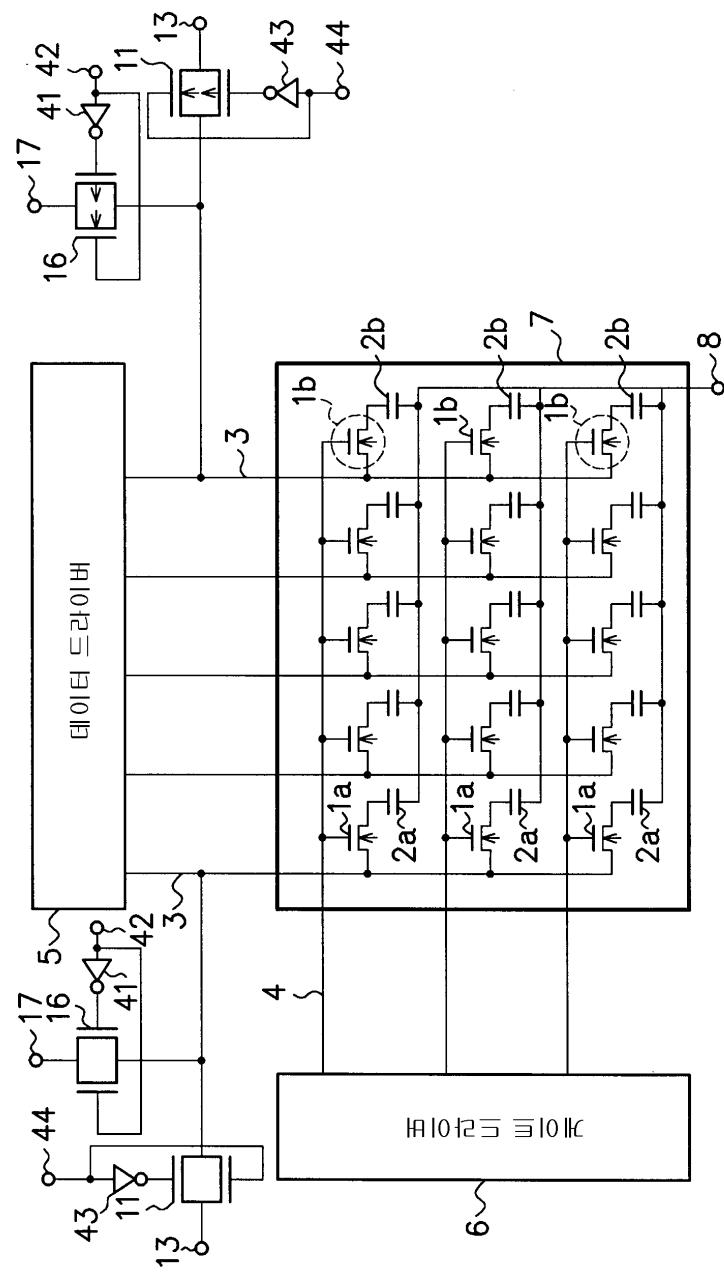

<152> 도 18은 본 발명의 제 12 실시형태에 따른 액정 표시 기판을 나타낸다. 제 12 실시형태가 제 11 실시형태와 비교해서 다른 점을 설명한다. 제 8 실시형태(도 14)와 마찬가지로 검사 화소(15)인 검사용 스위칭 소자(9)가 화

소 영역(7)의 입력측(상측 및 좌측) 뿐만 아니라, 출력측(우측 및 하측)에도 설치된다.

<153> 화소 영역(7)의 입력측(좌측 및 상측)에서, 액정 커패시터(2)에 축적되어 있는 전하를 정상적으로 검사 단자(17)로부터 검출할 수 있으면, 게이트 드라이버(6) 및 데이터 드라이버(5)가 정상 구동하고 있고, 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 화소 영역(7)까지의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<154> 또한, 화소 영역(7)의 출력측(우측 및 하측)에서, 액정 커패시터(2)에 축적되어 있는 전하를 정상적으로 검사 단자(17)로부터 검출할 수 있으면, 화소 영역(7) 내에서의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<155> 또, 액정 커패시터(2)의 리셋 및 검사 전압의 프리셋은 게이트 드라이버(6) 또는 데이터 드라이버(5)로부터 데이터를 기록함으로써 실행해도 좋다.

<156> (제 13 실시형태)

도 19는 본 발명의 제 13 실시형태에 따른 액정 표시 기판을 나타낸다. 제 13 실시형태가 제 10 실시형태(도 16)와 비교해서 다른 점을 설명한다. 제 10 실시형태에서는 화소 영역(7)의 상하 좌우의 4영역의 검사용 스위칭 소자(9)군에 대해서 각각 따로 따로 검사 단자(10)를 설치하고 있지만, 제 13 실시형태에서는 화소 영역(7)의 좌측 및 하측의 2영역의 검사용 스위칭 소자(9)군에 공통의 검사 단자(10)를 설치하고, 화소 영역(7)의 상측 및 우측의 2영역의 검사용 스위칭 소자(9)군에 공통의 검사 단자(10)를 설치하고 있다. 본 실시형태에 의하면, 2영역의 스위칭 소자(9)군을 각 1개의 검사 단자(10) 및 리셋 데이터 입력 단자(13)에 의해 제어할 수 있다.

<158> (제 14 실시형태)

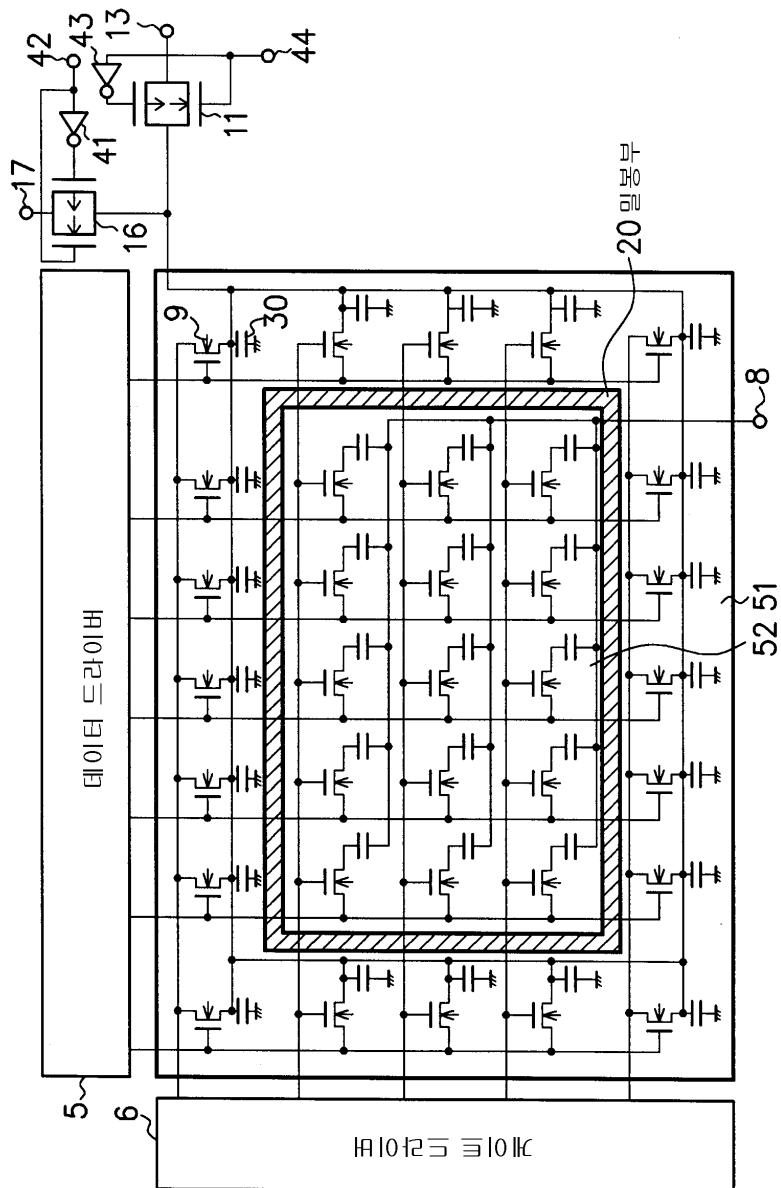

도 20은 본 발명의 제 14 실시형태에 따른 액정 표시 기판을 나타낸다. 제 14 실시형태가 제 13 실시형태(도 19)와 비교해서 다른 점을 설명한다. 제 13 실시형태에서는 화소 영역(7)의 좌측 및 하측의 2영역의 검사용 스위칭 소자(9)군 및 화소 영역(7)의 상측 및 우측의 2영역의 검사용 스위칭 소자(9)군에 각각 공통의 검사 단자(10) 및 리셋 데이터 입력 단자(13)를 설치하고 있다. 제 14 실시형태에서는 화소 영역(7)의 상하 좌우의 4영역의 검사용 스위칭 소자(9)군에 대해서 공통의 검사 단자(10) 및 리셋 데이터 입력 단자(13)를 설치하고 있다. 본 실시형태에 의하면, 4영역의 스위칭 소자(9)군을 1개의 검사 단자(10) 및 리셋 데이터 입력 단자(13)에 의해 제어할 수 있다.

<160> (제 15 실시형태)

도 21은 본 발명의 제 15 실시형태에 따른 액정 표시 기판을 나타낸다. 화소 영역(7)에서, TFT(1)는 게이트가 주사 라인(4)에 접속되고, 드레인은 데이터 라인(3)에 접속되고, 소스(화소 전극)가 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다. 게이트 드라이버(6)는 주사 라인(4)으로 주사 신호를 출력하고, 데이터 드라이버(5)는 데이터 라인(3)으로 데이터를 출력한다.

<162> 본 실시형태에서는 화소 영역(7) 내의 좌측단의 세로 1열의 TFT(1a)를 검사용 스위칭 소자로서 이용한다. TFT(1a)의 소스에는 액정 커패시터(2a)를 거쳐서 대향 기판의 전극(8)이 접속된다. 데이터 드라이버(5)에 접속되는 좌측단의 데이터 라인(3)에는 제 11 실시형태(도 17)와 마찬가지로 리셋 스위치(11)를 거쳐서 리셋 데이터 입력 단자(13)가 접속되고, 검사 스위치(16)를 거쳐서 검사 단자(17)가 접속된다.

<163> 검사 방법을 설명한다. 제 11 실시형태와 마찬가지로, 리셋 스위치(11)에 의해 액정 커패시터(2a)의 차지를 없앤다. 다음에, 게이트 드라이버(6)에 의해 검사할 화소의 TFT(1a)를 온한다. TFT(1a)가 온되어 있는 기간에, 데이터 드라이버(5)로부터 전압을 공급하여 액정 커패시터(2a)에 충전한다. 다음에, 검사 스위치(16)를 열고 액정 커패시터(2a)에 축적되어 있는 전압을 검사 단자(17)로부터 검출한다. 이 때, 전압을 검출할 수 있으면, 게이트 드라이버(6)와 데이터 드라이버(5)가 정상 구동하고 있고 또한 게이트 드라이버(6) 또는 데이터 드라이버(5)에서 TFT(1a)까지의 주사 라인(4) 및 데이터 라인(3)의 단선이 없어 합격이라고 판단할 수 있다.

<164> 또, 리셋 데이터 입력 단자(13)로부터 액정 커패시터(2a)를 리셋하는 대신에, 데이터 드라이버(5)로부터 리셋해도 좋다.

<165> (제 16 실시형태)

도 22는 본 발명의 제 16 실시형태에 따른 액정 표시 기판을 나타낸다. 제 16 실시형태가 제 15 실시형태(도 21)와 비교해서 다른 점을 설명한다. 화소 영역(7) 내의 좌측단(입력단)의 TFT(1a)군 이외에 우측단(출력단)의

TFT(1b)군을 검사용 스위칭 소자로서 이용한다. TFT(1b)의 소스는 액정 커패시터(2b)를 거쳐서 대향 기판의 전극(8)에 접속된다.

<167> 데이터 드라이버(5)의 좌측단의 데이터 라인(3) 이외에 우측단의 데이터 라인(3)에도 검사 스위치(16)를 거쳐서 검사 단자(17)가 접속되고, 리셋 스위치(11)를 거쳐서 리셋 데이터 입력 단자(13)가 접속된다.

{

<168> 검사 방법을 설명한다. 제 15 실시형태와 마찬가지로, 리셋 스위치(11)에 의해 액정 커패시터(2a 또는 2b)의 차지를 없앤다. 다음에, 게이트 드라이버(6)에 의해 검사할 화소의 TFT(1a 및 1b)를 온한다. TFT(1a 및 1b)가 온되어 있는 기간에, 데이터 드라이버(5)로부터 전압을 공급하여 액정 커패시터(2a 및 2b)에 충전한다. 다음에, 검사 스위치(16)를 열고 액정 커패시터(2a 및 2b)에 축적되어 있는 전압을 각 검사 단자(17)로부터 검출한다. 이것이에 의해, 화소 영역(7) 내의 주사 라인(4)의 단선의 검사도 실행할 수 있다.

<169> (제 17 실시형태)

<170> 도 23은 본 발명의 제 17 실시형태에 따른 액정 표시 장치를 나타낸다. 제 17 실시형태는 제 11 실시형태의 액정 표시 기판을 이용한 액정 표시 장치이다. 기판(51)에는 검사용 스위칭 소자(9), 커패시터(30) 및 화소 영역(7)이 마련된다. 대향 기판(52)에는 공통 전극(8)이 설치된다. 기판(51)과 대향 기판(52)은 그 사이에 액정부(커패시터(2))를 끼우고 밀봉부(20)에 의해 밀봉된다. 밀봉부(20)는 화소 영역(7)과 검사용 스위칭 소자(9) 사이에 마련된다. 검사용 스위칭 소자(9)에 접속되는 커패시터(30)는 밀봉부(20)의 밖에 있기 때문에, 액정을 이용할 수 없어, 액정 커패시터가 아니고 새롭게 형성한 커패시터이다.

<171> (제 18 실시형태)

<172> 도 24는 본 발명의 제 18 실시형태에 따른 액정 표시 장치를 나타낸다. 제 18 실시형태가 제 17 실시형태(도 23)와 비교해서 다른 점을 설명한다. 기판(53)에는 공통 전극(8)을 제외한 상기한 모든 소자가 설치된다. 대향 기판(54)에는 공통 전극(8)이 설치된다. 기판(53)과 대향 기판(54)은 그 사이에 액정(커패시터(2))을 끼우고 밀봉부(20)에 의해 밀봉된다. 밀봉부(20)는 액정 표시 장치의 외주에 마련된다. 검사용 스위칭 소자(9)는 밀봉부(20)의 내측에 있기 때문에, 검사용 스위칭 소자(9)로서 검사 화소를 이용할 수 있다. 이 검사용 스위칭 소자(9)의 소스는 액정 커패시터(2)를 거쳐서 대향 기판의 전극(8)에 접속된다.

<173> 제 17 실시형태(도 23)의 경우, 밀봉부(20)의 외측에 게이트 드라이버(6), 데이터 드라이버(5) 및 검사용 스위칭 소자(9)가 설치되므로, 부식이나 그 밖의 외적 요인에 의한 파손의 위험이 있지만, 제 18 실시형태에서는 게이트 드라이버(6), 데이터 드라이버(5) 및 검사용 스위칭 소자(9)가 밀봉부(20)의 내측에 있으므로, 그들을 보호할 수 있다. 또한, 제 17 실시형태에서는 검사용 커패시터(30)의 축적 가능 용량이 작아져 버리지만, 제 18 실시형태에서는 액정을 이용하므로, 액정 커패시터(2)의 축적 가능 용량을 크게 할 수 있다.

<174> (제 19 실시형태)

<175> 도 25는 본 발명의 제 19 실시형태에 따른 액정 표시 장치를 나타낸다. 제 19 실시형태가 제 18 실시형태(도 24)와 비교해서 다른 점을 설명한다. 기판(54) 중, 화소 영역(7)을 제외한 부분에 차광 영역(블랙 매트릭스)(21)을 마련한다.

<176> 검사 화소(15)(검사용 스위칭 소자(9))는 통상의 동작시에는 장해물로 되므로, 통상 동작시에는 검사 화소(15)에 흑색의 데이터를 기록하고, 표시하고 있지 않은 상태로 한다. 그러나, 검사 화소(15)를 완전한 흑표시로 하는 것은 곤란하여, 적지 않게 콘트라스트 저하의 원인이 된다. 본 실시형태와 같이, 검사 화소(15)를 덮는 부분에 차광 영역(21)을 마련함으로써, 검사 화소(15)의 완전한 흑표시가 가능해져, 콘트라스트의 저하를 방지할 수 있다.

<177> 차광 방법은 프로세스에 의해 차광막을 형성하는 방법이 바람직하다. 이 방법은 차광 정밀도가 높다. 그 이외에 기계 구조적인 차광 방법(차광 테이프나 베젤(bezel) 등)이 있다.

<178> 제 1~제 19 실시형태에 의하면, 액정 표시 기판의 상태에서 용이하게 검사의 합격 여부이 판정을 실행할 수 있으므로, 종래의 검사 방법에 비해 시간을 단축할 수 있음과 동시에 패널화 시험에 의한 부대 부재의 폐기가 불필요하게 되기 때문에 비용을 절감할 수 있다.

<179> 또, 상기 실시형태는 모두 본 발명을 실시하기 위한 구체화된 일례를 나타낸 것에 불과하며, 이들에 의해서 본 발명의 기술적 범위가 한정적으로 해석되어서는 않된다. 즉, 본 발명은 그 기술 사상 또는 그 주요한 특징으로

부터 일탈하지 않고 여러 가지 형태로 실시할 수 있다.

<180> 본 발명은 이하의 여러 가지 실시형태에 적용할 수 있다.

<181> (부기 1) 2차원 매트릭스 형상으로 배선된 데이터 라인 및 주사 라인과 그 데이터 라인 및 주사 라인 사이에 접속되는 스위칭 소자를 포함하는 표시 회로와,

<182> 상기 데이터 라인의 한쪽 단부에 제 1 아날로그 스위치를 거쳐서 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력 단자를 포함하는 제 1 검사 회로와,

<183> 상기 데이터 라인의 다른쪽 단부에 검사 전압을 입력 및/또는 출력하기 위한 검사 전압 입력 및/또는 출력단자를 포함하는 제 2 검사 회로를 갖고,

<184> 상기 표시 회로, 제 1 검사 회로 및 제 2 검사 회로는 1매의 기판 상에 설치되고, 상기 제 1 검사 회로는 상기 표시 회로에 대해서 분리 가능한 액정 표시 장치.

<185> (부기 2) 상기 제 1 및 제 2 검사 회로는 상기 표시 회로에 대해서 분리 가능한 부기 1에 기재된 액정 표시 장치.

<186> (부기 3) 상기 제 1 검사 회로는 제어 단자가 시프트 레지스터에 접속된 제 2 아날로그 스위치를 갖고, 그 제 2 아날로그 스위치는 한쪽 단부가 상기 제 1 아날로그 스위치를 거쳐서 상기 데이터 라인에 접속되고, 다른쪽 단부가 상기 검사 전압 입력 및/또는 출력 단자에 접속되고,

<187> 상기 제 2 검사 회로는 제 3 아날로그 스위치를 갖고, 이 제 3 아날로그 스위치는 한쪽 단부가 상기 데이터 라인의 다른쪽 단부에 접속되고, 다른쪽 단부가 상기 검사 전압 입력 및/또는 출력 단자에 접속되는 부기 1에 기재된 액정 표시 장치.

<188> (부기 4) 상기 각 주사 라인의 단부에 검사용 트랜지스터를 설치하고, 그 검사용 트랜지스터의 게이트 단자에 주사 라인 드라이버를 접속하고, 드레인 또는 소스 단자에 검사 전압 입출력 단자를 접속하고, 소스 또는 드레인 단자에 커패시터를 접속한 부기 3에 기재된 액정 표시 장치.

<189> (부기 5) 상기 제 1 검사 회로의 시프트 레지스터가 상기 제 2 아날로그 스위치를 온시키고고, 상기 제 2 검사 회로의 검사 전압 입력 단자로부터 입력한 검사 전압을, 상기 제 1 검사 회로의 검사 전압 출력 단자로부터 확인함으로써, 상기 데이터 라인의 단선 또는 단락을 검사할 수 있는 부기 3에 기재된 액정 표시 장치.

<190> (부기 6) 상기 제 2 검사 회로는 제 1 및 제 2 검사 전압 입력 단자를 갖고, 상기 복수의 제 3 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 입력 단자에 접속되고,

<191> 상기 제 1 검사 회로는 제 1 및 제 2 검사 전압 출력 단자를 갖고, 상기 복수의 제 2 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 출력 단자에 접속되는 액정 표시 장치.

<192> (부기 7) 상기 제 1 검사 회로의 제 1 및 제 2 검사 전압 출력 단자는 상기 제 2 검사 회로의 제 1 및 제 2 검사 전압 입력 단자로부터 입력된 검사 전압의 출력을 확인함으로써, 상기 데이터 라인이 단선 또는 단락되어 있는지의 여부를 확인할 수 있는 부기 6에 기재된 액정 표시 장치.

<193> (부기 8) 상기 제 2 검사 회로의 제 1 및 제 2 검사 전압 입력 단자에는 다른 검사 전압이 입력되는 부기 7에 기재된 액정 표시 장치.

<194> (부기 9) 상기 제 1 검사 회로는 제 1 및 제 2 검사 전압 입출력 단자를 갖고, 상기 복수의 제 2 아날로그 스위치는 교대로 상기 제 1 및 제 2 검사 전압 입출력 단자에 접속되는 부기 3에 기재된 액정 표시 장치.

<195> (부기 10) 상기 제 1 검사 회로는 상기 제 1 아날로그 스위치가 오프되어 있을 때, 상기 제 1 검사 전압 입출력 단자로부터 입력한 검사 전압이 상기 제 2 검사 전압 입출력 단자로부터 출력되는지의 여부를 확인함으로써, 상기 제 1 및 제 2 아날로그 스위치간을 접속하는 선간 단락을 확인할 수 있는 부기 9에 기재된 액정 표시 장치.

<196> (부기 11) 상기 검사용 트랜지스터는 상기 검사 전압 입출력 단자를 거쳐서 드레인 또는 소스 단자에 검사 전압을 입력하고, 상기 주사 라인 드라이버에 의해 상기 검사용 트랜지스터를 온시켰을 때, 소스 또는 드레인 단자에 접속된 커패시터에 상기 검사 전압을 충전하고, 재차 상기 주사 라인 드라이버에 의해 상기 검사용 트랜지스터를 온시켰을 때, 상기 커패시터에 충전되어 있는 검사 전압을 상기 검사 전압 입출력 단자로부터 확인하기 위한 것인 부기 4에 기재된 액정 표시 장치.

- <197> (부기 12) 부기 3에 기재된 액정 표시 장치의 검사 방법으로서,

- <198> (a) 상기 제 1~제 3 아날로그 스위치를 온시키는 단계와,

- <199> (b) 상기 제 2 검사 회로의 검사 전압 입력 단자로부터 입력한 검사 전압을, 상기 제 1 검사 회로의 검사 전압 출력 단자로부터 확인함으로써, 상기 데이터 라인의 단선 또는 단락을 검사하는 단계를 갖는 액정 표시 장치의 검사 방법.

- <200> (부기 13) 부기 6에 기재된 액정 표시 장치의 검사 방법으로서,

- <201> (a) 상기 제 2 검사 회로의 제 1 및 제 2 검사 전압 입력 단자와 상기 제 1 검사 회로의 제 1 및 제 2 검사 전압 출력 단자를 각각 접속하기 위해 상기 제 1~제 3 아날로그 스위치를 온하는 단계와,

- <202> (b) 상기 제 1 검사 회로의 제 1 및 제 2 검사 전압 출력 단자는 상기 제 2 검사 회로의 제 1 및 제 2 검사 전압 입력 단자로부터 입력된 검사 전압이 상기 제 1 검사 회로의 제 1 및 제 2 검사 전압 출력 단자로부터 출력되는지의 여부를 확인함으로써, 상기 데이터 라인이 단선 또는 단락되어 있는지의 여부를 확인하는 단계를 갖는 액정 표시 장치의 검사 방법.

- <203> (부기 14) 부기 9에 기재된 액정 표시 장치의 검사 방법으로서,

- <204> (a) 상기 제 1 검사 회로의 제 1 및 제 2 검사 전압 입력 출력 단자에 대응하는 상기 제 2 아날로그 스위치를 온시키고 상기 제 1 아날로그 스위치를 오프시키는 단계와,

- <205> (b) 상기 제 1 검사 회로의 제 1 검사 전압 입력 출력 단자로부터 입력한 검사 전압이 상기 제 1 검사 회로의 제 2 검사 전압 입력 출력 단자로부터 출력되는지의 여부를 확인함으로써, 상기 제 1 및 제 2 아날로그 스위치 사이를 접속하는 선간 단락을 확인하는 단계를 갖는 액정 표시 장치의 검사 방법.

- <206> (부기 15) 부기 4에 기재된 액정 표시 장치의 검사 방법으로서,

- <207> (a) 상기 주사 라인 드라이버에 의해 상기 검사용 트랜지스터를 온시키는 단계와,

- <208> (b) 상기 검사 전압 입력 출력 단자를 거쳐서 상기 검사용 트랜지스터의 드레인 또는 소스 단자에 검사 전압을 입력하고, 상기 검사용 트랜지스터의 소스 또는 드레인 단자에 접속된 커패시터에 그 검사 전압을 충전시키는 단계와,

- <209> (c) 제자 상기 주사 라인 드라이버에 의해 상기 검사용 트랜지스터를 온시키는 단계와,

- <210> (d) 상기 커패시터에 충전되어 있는 검사 전압이 상기 검사 전압 입력 출력 단자로부터 출력되는지의 여부를 확인하는 단계를 갖는 액정 표시 장치의 검사 방법.

- <211> (부기 16) 각각이 화소 전극을 거쳐서 액정 커패시터에 접속되는 복수의 제 1 스위칭 소자와,

- <212> 상기 제 1 스위칭 소자에 데이터를 공급하는 데이터 라인과,

- <213> 상기 제 1 스위칭 소자를 제어하기 위한 주사 라인과,

- <214> 제어 단자가 상기 데이터 라인 또는 상기 주사 라인에 접속되고, 입력 단자의 한쪽 단부가 공통의 검사용 입력 출력 단자에 접속되고, 다른쪽 단부가 커패시터에 접속되는 제 2 스위칭 소자를 갖는 액정 표시 장치.

- <215> (부기 17) 상기 데이터 라인에 데이터를 공급하기 위한 데이터 라인 드라이버 또는 스위칭 소자를 포함하는 데이터 공급 회로와,

- <216> 상기 주사 라인에 주사 신호를 공급하기 위한 주사 신호 공급 회로를 더 갖는 부기 16에 기재된 액정 표시 장치.

- <217> (부기 18) 상기 커패시터는 한쪽 단부를 상기 제 2 스위칭 소자에 접속하고, 다른쪽 단부를 공통 접속함으로써 축적 가능 용량을 증가시키는 부기 16에 기재된 액정 표시 장치.

- <218> (부기 19) 상기 제 2 스위칭 소자는, 상기 다른쪽 단부가 화소 전극을 거쳐서 액정 커패시터에 접속되는 부기 16에 기재된 액정 표시 장치.

- <219> (부기 20) 상기 제 2 스위칭 소자는, 제어 단자가 상기 데이터 라인에 접속되는 스위칭 소자 및 제어 단자가 상기 주사 라인에 접속되는 스위칭 소자를 포함하는 부기 16에 기재된 액정 표시 장치.

- <220> (부기 21) 상기 제 2 스위칭 소자는, 상기 한쪽 단부가 공통의 검사용 입출력용 단자 및 상기 데이터 라인에 접속되는 부기 16에 기재된 액정 표시 장치.

- <221> (부기 22) 상기 제 2 스위칭 소자에 접속되는 커패시터를 리셋 또는 프리셋하기 위한 제 3 스위칭 소자를 더 갖는 부기 16에 기재된 액정 표시 장치.

- <222> (부기 23) 상기 제 2 스위칭 소자는, 액정 표시 장치에 액정을 밀봉하기 위한 밀봉부의 내측에 설치되는 부기 16에 기재된 액정 표시 장치.

- <223> (부기 24) 상기 제 2 스위칭 소자는, 액정 표시 장치에 액정을 밀봉하기 위한 밀봉부의 외측에 설치되는 부기 16에 기재된 액정 표시 장치.

- <224> (부기 25) 상기 데이터 라인에 접속되는 스위칭 소자 및 상기 주사 라인에 접속되는 스위칭 소자는 공통의 검사용 입출력 단자에 접속되는 부기 20에 기재된 액정 표시 장치.

- <225> (부기 26) 상기 데이터 라인에 접속되는 스위칭 소자 및 상기 주사 라인에 접속되는 스위칭 소자는 다른 검사용 입출력 단자에 접속되는 부기 20에 기재된 액정 표시 장치.

- <226> (부기 27) 상기 제 2 스위칭 소자에 대응하는 화소를 차광하기 위한 차광부를 더 갖는 부기 19에 기재된 액정 표시 장치.

### 발명의 효과

<227> 이상 설명한 바와 같이, 본 발명에 의하면, 액정 표시 기판에 제 1 및 제 2 검사 회로를 설치하는 것에 의해, 액정 표시 장치를 유닛화하기 전에, 데이터 라인의 단선, 데이터 라인의 인접 단락, 주사 라인의 단선, 인접 화소간의 단락, 다른 신호선과의 단락 등의 검사를 실행할 수 있다. 검사 종료 후에 제 1 검사 회로를 분리함으로써, 액정 표시 기판에 데이터 드라이버를 접속하는 것이 가능해져서, 더 저비용의 액정 표시 장치를 제공할 수 있다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 제 1 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <2> 도 2는 제 1 실시형태에 따른 제 1 검사 방법을 나타내는 타이밍도,

- <3> 도 3은 제 1 실시형태에 따른 제 2 검사 방법을 나타내는 타이밍도,

- <4> 도 4는 제 1 실시형태에 따른 액정 표시 기판에 데이터 드라이버를 접속한 도면,

- <5> 도 5는 본 발명의 제 2 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <6> 도 6은 본 발명의 제 3의 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <7> 도 7은 제 3 실시형태에 따른 제 1 검사 방법을 나타내는 타이밍도,

- <8> 도 8은 제 3 실시형태에 따른 제 2 검사 방법을 나타내는 타이밍도,

- <9> 도 9는 제 3 실시형태에 따른 제 2 검사 방법을 나타내는 다른 타이밍도,

- <10> 도 10은 본 발명의 제 4 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <11> 도 11은 본 발명의 제 5 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <12> 도 12는 본 발명의 제 6 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <13> 도 13은 본 발명의 제 7 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <14> 도 14는 본 발명의 제 8 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <15> 도 15는 본 발명의 제 9 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <16> 도 16은 본 발명의 제 10 실시형태에 따른 액정 표시 기판을 나타내는 도면,

- <17> 도 17은 본 발명의 제 11 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<18> 도 18은 본 발명의 제 12 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<19> 도 19는 본 발명의 제 13 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<20> 도 20은 본 발명의 제 14 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<21> 도 21은 본 발명의 제 15 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<22> 도 22는 본 발명의 제 16 실시형태에 따른 액정 표시 기판을 나타내는 도면,

<23> 도 23은 본 발명의 제 17 실시형태에 따른 액정 표시 장치를 나타내는 도면,

<24> 도 24는 본 발명의 제 18 실시형태에 따른 액정 표시 장치를 나타내는 도면,

<25> 도 25는 본 발명의 제 19 실시형태에 따른 액정 표시 장치를 나타내는 도면,

<26> 도 26은 종래 기술에 따른 액정 표시 기판을 나타내는 도면,

<27> 도 27은 종래 기술에 따른 다른 액정 표시 기판을 나타내는 도면.

- <28> <도면의 주요부분에 대한 부호의 설명>

- <29> 1 TFT

<30> 2 액정 커패시터

<31> 3 데이터 라인

<32> 4 게이트 라인

<33> 5 데이터 드라이버

<34> 6 게이트 드라이버

<35> 7 화소 영역

<36> 8 대향 전극

<37> 9 검사용 스위칭 소자

<38> 10 검사 단자

<39> 11 리셋 스위치

<40> 12 온/오프 신호 단자

<41> 13 리셋 데이터 입력 단자

<42> 15 검사 화소

<43> 16 검사 스위치

<44> 17 검사 단자

<45> 20 밀봉부

<46> 21 차광 영역

<47> 30 커패시터

<48> 31, 32 버퍼

<49> 33 인버터

<50> 34 단자

<51> 41, 43 인버터

<52> 42, 44 단자

- <53> 51, 52, 53, 54 기판

<54> 100 액정 표시 기판

<55> 101 제 1 검사 회로

<56> 102 제 2 검사 회로

<57> 103 표시 회로

<58> 111 시프트 레지스터

<59> 112, 113, 114 아날로그 스위치

<60> 115 게이트 드라이버

<61> 116 화소 영역

<62> 121, 122 절단 라인

<63> 131 TFT

<64> 132 액정 커패시터

<65> 401 데이터 드라이버

<66> 601 트랜지스터

<67> 602 커패시터

<68> 900 액정 표시 기판

<69> 911 시프트 레지스터

<70> 912 아날로그 스위치

<71> 915 게이트 드라이버

<72> 916 화소 영역

<73> 931 TFT

<74> 932 액정 커패시터

## 도면

도면1

도면2

도면3

도면4

## 도면5

도면6

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

도면26

도면27

|                |                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">KR100772617B1</a>                                                                            | 公开(公告)日 | 2007-11-02 |

| 申请号            | KR1020020000694                                                                                          | 申请日     | 2002-01-07 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                   |         |            |

| 申请(专利权)人(译)    | 夏普株式会社                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 夏普株式会社                                                                                                   |         |            |

| [标]发明人         | KAI TSUTOMU<br>가이츠토무<br>OKAZAKI SUSUMU<br>오카자키스스무<br>ZHANG HONGYONG<br>장홍용<br>OHASHI NORIYUKI<br>오하시노리유키 |         |            |

| 发明人            | 가이츠토무<br>오카자키스스무<br>장홍용<br>오하시노리유키                                                                       |         |            |

| IPC分类号         | G09G3/36 G02F1/1368 G01R31/02 G09F9/30 G02F1/1345 G09F9/00 G02F1/13                                      |         |            |

| CPC分类号         | G09G2300/0408 G09G3/3688                                                                                 |         |            |

| 代理人(译)         | MOON , KI桑                                                                                               |         |            |

| 优先权            | 2001101176 2001-03-30 JP                                                                                 |         |            |

| 其他公开文献         | KR1020020077033A                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                |         |            |

### 摘要(译)

为了提供能够简单快速检查的液晶显示装置，本发明的液晶显示装置包括以二维矩阵形式布线的数据线和扫描线，以及连接在数据线和扫描线之间的开关元件。第一检查电路101，包括检查电压输入和/或输出端子，用于通过第一模拟开关将检查电压输入和/或输出到数据线的一端；第二检查电路102包括检查电压输入和/或输出端子，用于将检查电压输入和/或输出到数据线的另一端。显示电路，第一检查电路和第二检查电路设置在单个基板上，并且第一检查电路可与显示电路分离。