**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

G02F 1/136

(45) 공고일자 2005년12월28일

(11) 등록번호 10-0539336

(24) 등록일자 2005년12월21일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2002-0051066 | (65) 공개번호 | 10-2003-0040025 |

| (22) 출원일자 | 2002년08월28일     | (43) 공개일자 | 2003년05월22일     |

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2001-00349571 | 2001년11월15일 | 일본(JP) |

|------------|--------------------|-------------|--------|

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 특허권자 | 가부시키가이샤 히타치세이사쿠쇼<br>일本国 도쿄토 치요다쿠 마루노우치 1초메 6반 6고 |

|-----------|--------------------------------------------------|

|          |                              |

|----------|------------------------------|

| (72) 발명자 | 오찌아이다까히로<br>일본지바肯모바라시하야노3550 |

|----------|------------------------------|

|                           |

|---------------------------|

| 오께류따로<br>일본지바肯모바라시하야노3550 |

|---------------------------|

|                                |

|--------------------------------|

| 이마야마히로따까<br>일본지바肯모바라시오시비705-30 |

|--------------------------------|

|                            |

|----------------------------|

| 오노기꾸오<br>일본지바肯모바라시모바라716-1 |

|----------------------------|

|          |            |

|----------|------------|

| (74) 대리인 | 장수길<br>구영창 |

|----------|------------|

심사관 : 임동재

**(54) 액정 표시 장치**

**요약**

액정 표시 장치에 있어서, 반도체층을 한쪽의 전극으로 하고, 절연막을 사이에 끼고 보유 용량 배선 사이에서 용량 소자를 구성하며, 해당 보유 용량 배선에 MOS형 트랜지스터를 항상 온 상태로 하는 전압을 인가한다. 보유 용량치가 커서 안정적으로 표시를 할 수 있는 TFT 표시 장치가 얻어진다.

**대표도**

도 1

**색인어**

액정 표시, 보유 용량, MOS형 트랜지스터, IPS 모드

## 명세서

### 도면의 간단한 설명

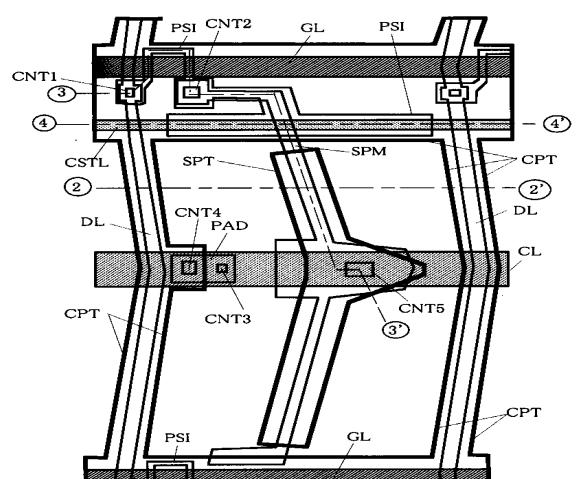

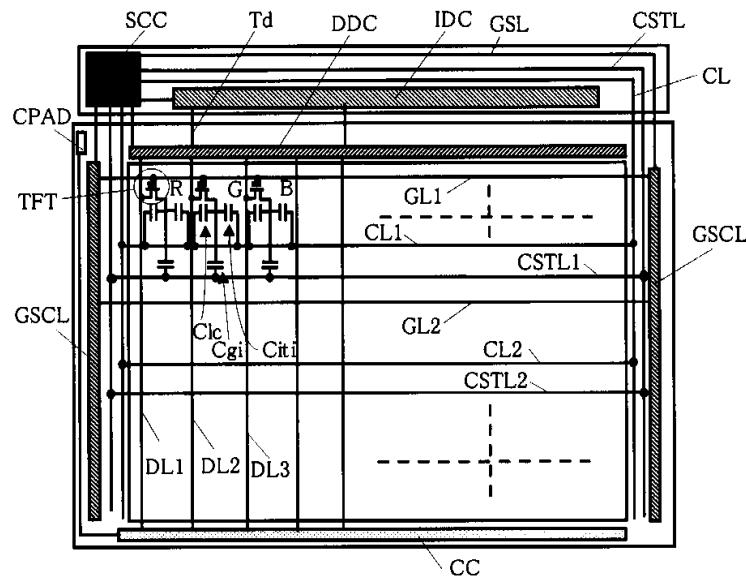

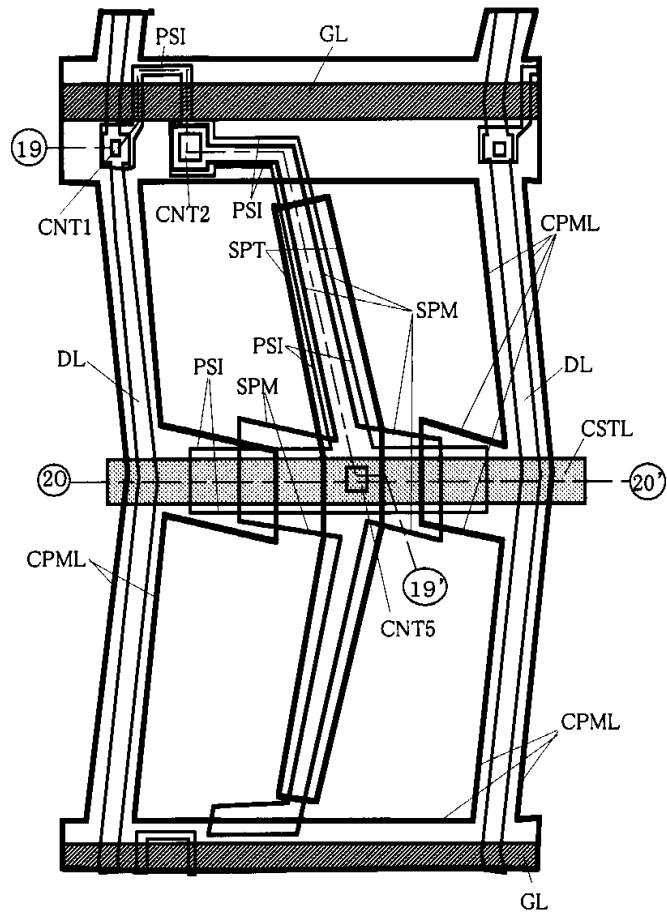

도 1은 본 발명의 일 실시예에 따른 TFT 액정 표시 장치의 화소의 평면도.

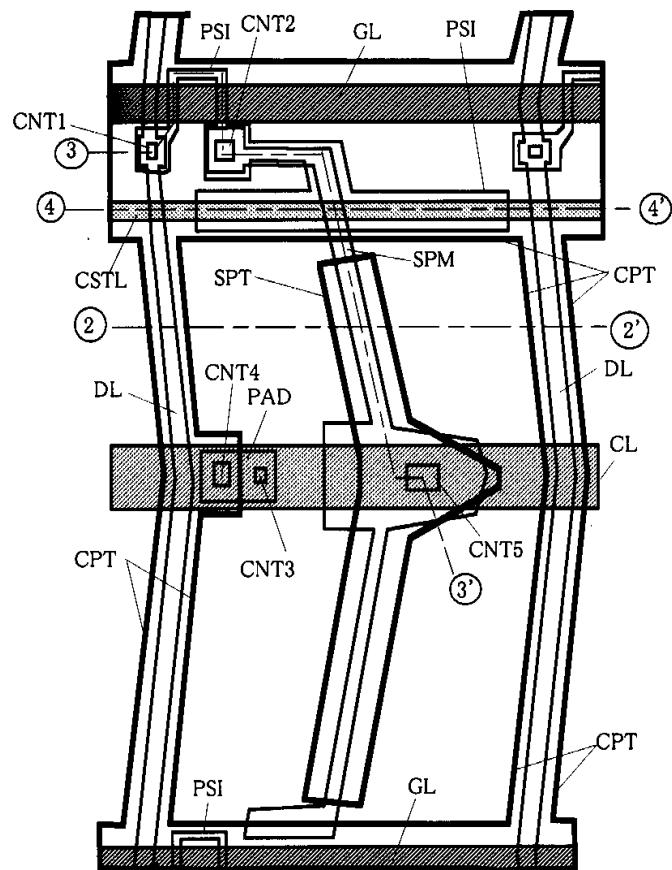

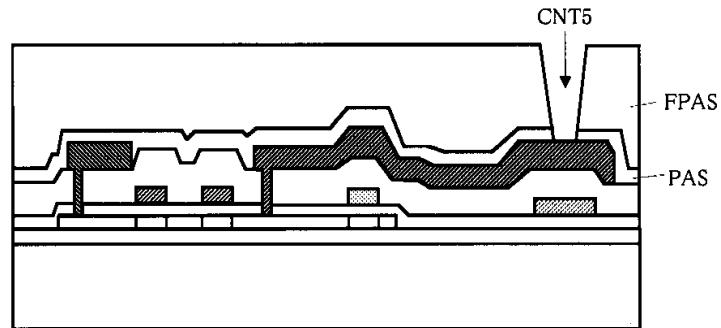

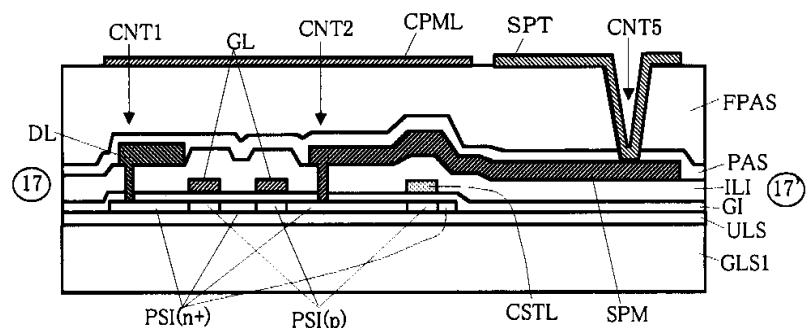

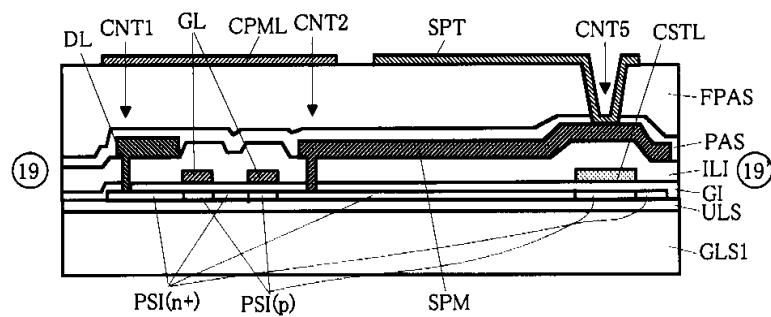

도 2는 도 1의 2-2' 절단선을 따라 취한 모식 단면도.

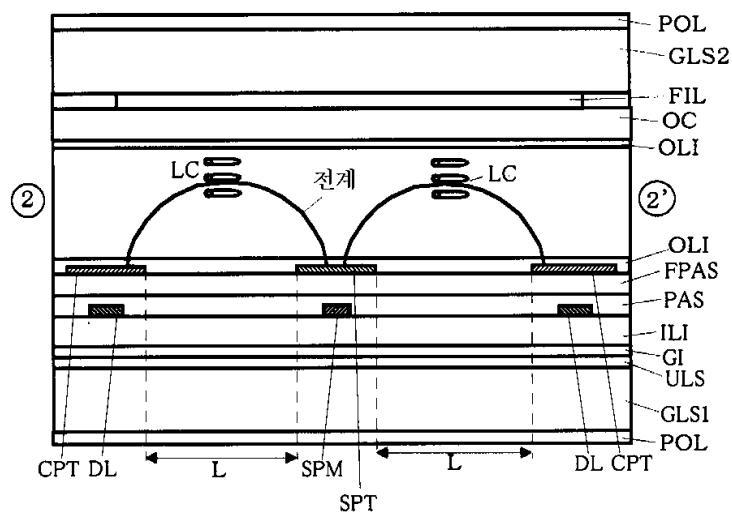

도 3은 도 1의 3-3' 절단선을 따라 취한 모식 단면도.

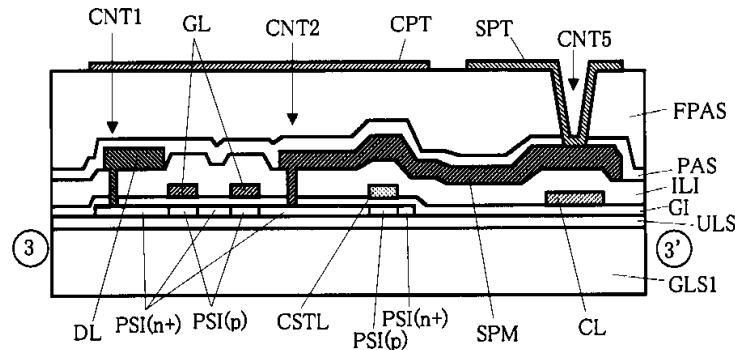

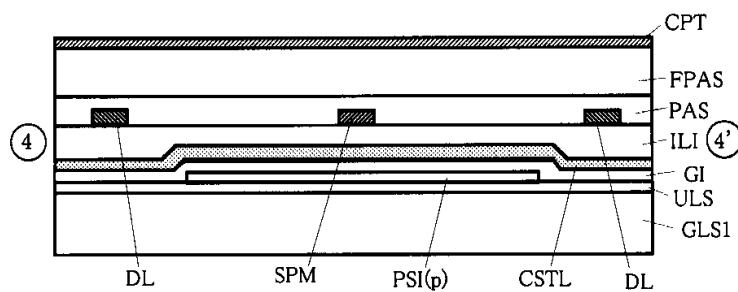

도 4는 도 1의 4-4' 절단선을 따라 취한 모식 단면도.

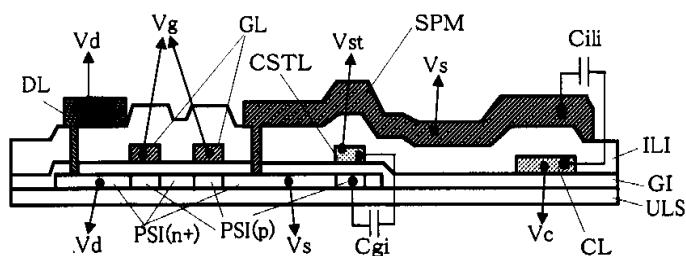

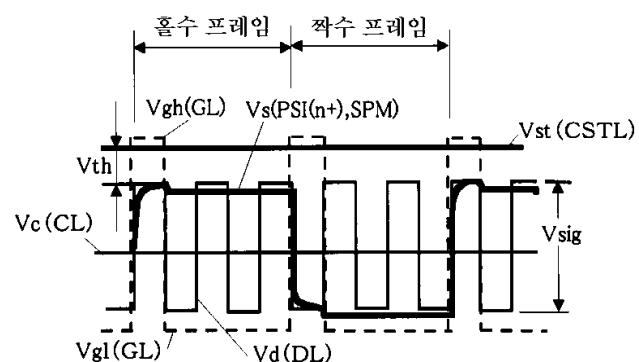

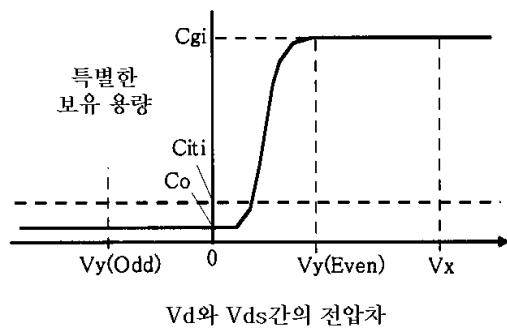

도 5는 본 발명의 일 실시예에 따른 TFT 액정 표시 장치의 보유 용량의 구조 및 그 전기적 동작을 설명하는 단면도, 구동 전압 과형, 특성도.

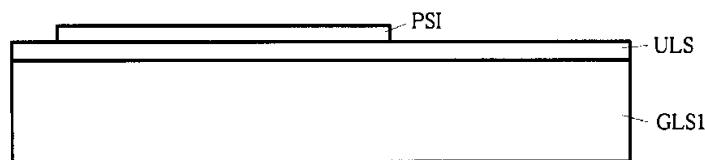

도 6은 본 발명의 일 실시예의 제1 포토 공정 후까지의 모식 단면도.

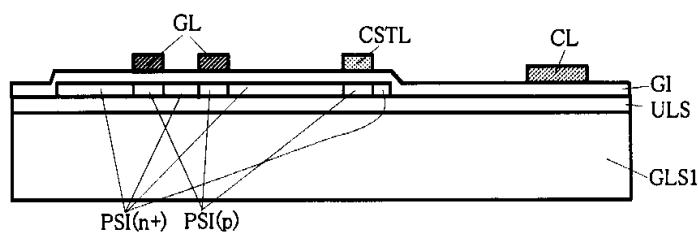

도 7은 본 발명의 일 실시예의 제2 포토 공정 후까지의 모식 단면도.

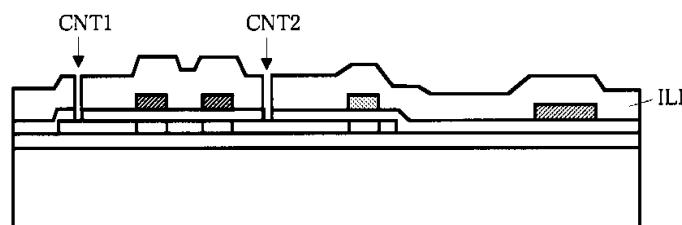

도 8은 본 발명의 일 실시예의 제3 포토 공정 후까지의 모식 단면도.

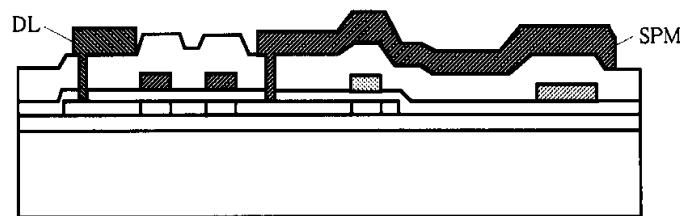

도 9는 본 발명의 일 실시예의 제4 포토 공정 후까지의 모식 단면도.

도 10은 본 발명의 일 실시예의 제5 포토 공정 후까지의 모식 단면도.

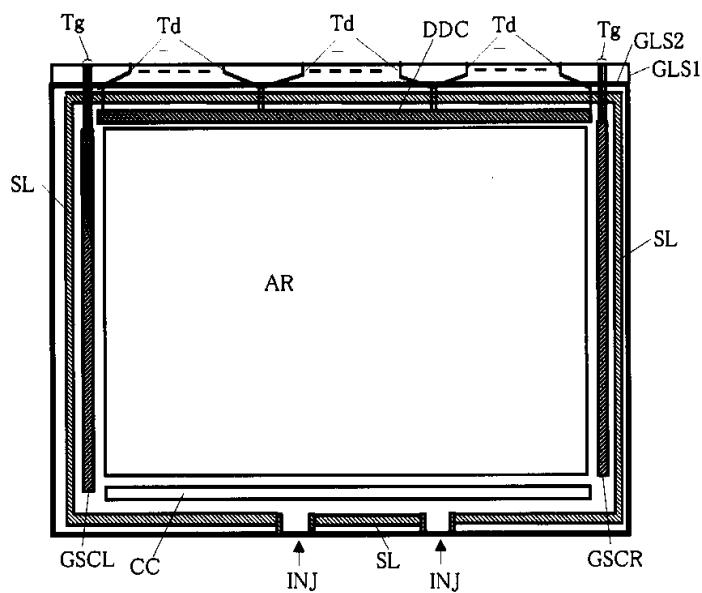

도 11은 LCD 셀의 전체의 평면도.

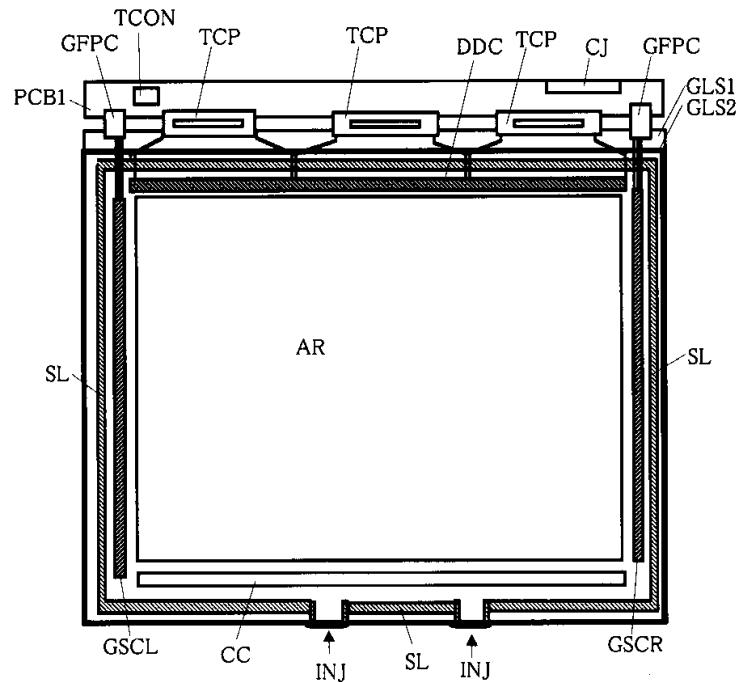

도 12는 LCD 셀에 PCB 기판과 TAB를 접속한 전체 평면도.

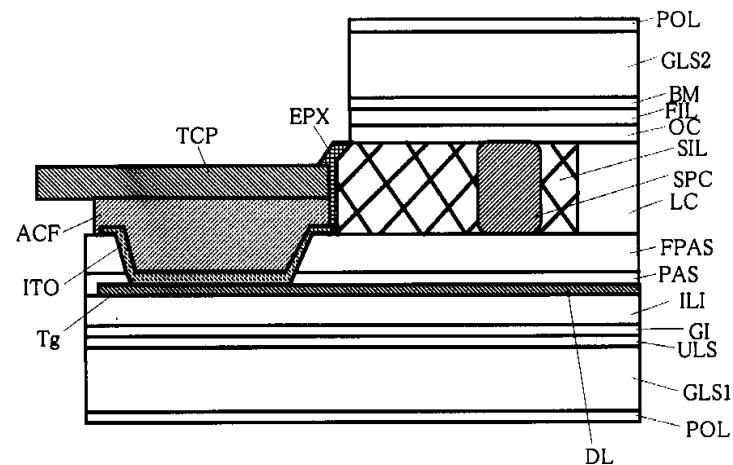

도 13은 LCD 셀의 TAB와 드레인측 인출 단자부 부근의 단면도.

도 14는 TFT-LCD의 개략의 등가 회로를 도시하는 평면도.

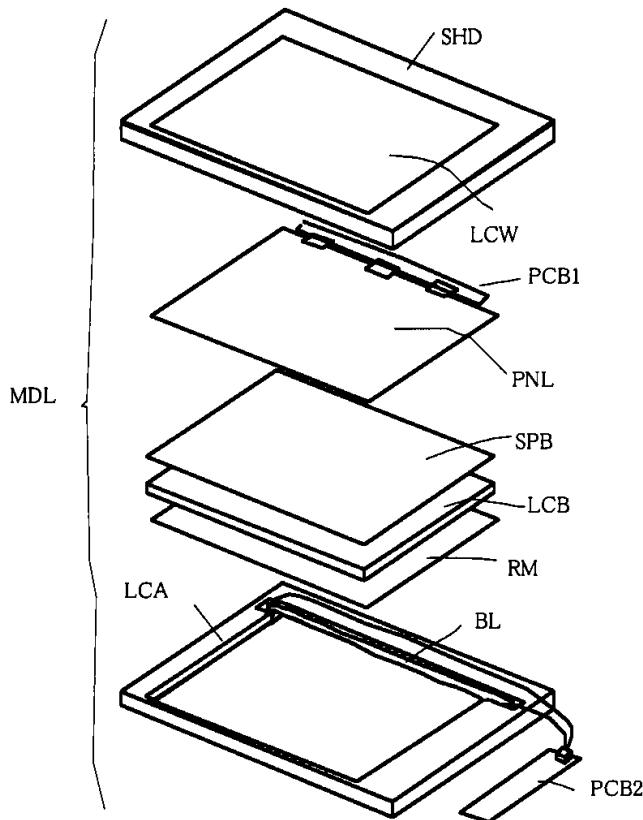

도 15는 TFT-LCD의 모듈의 분해 사시도.

도 16은 본 발명의 다른 실시예에 따른 TFT 액정 표시 장치의 화소의 평면도.

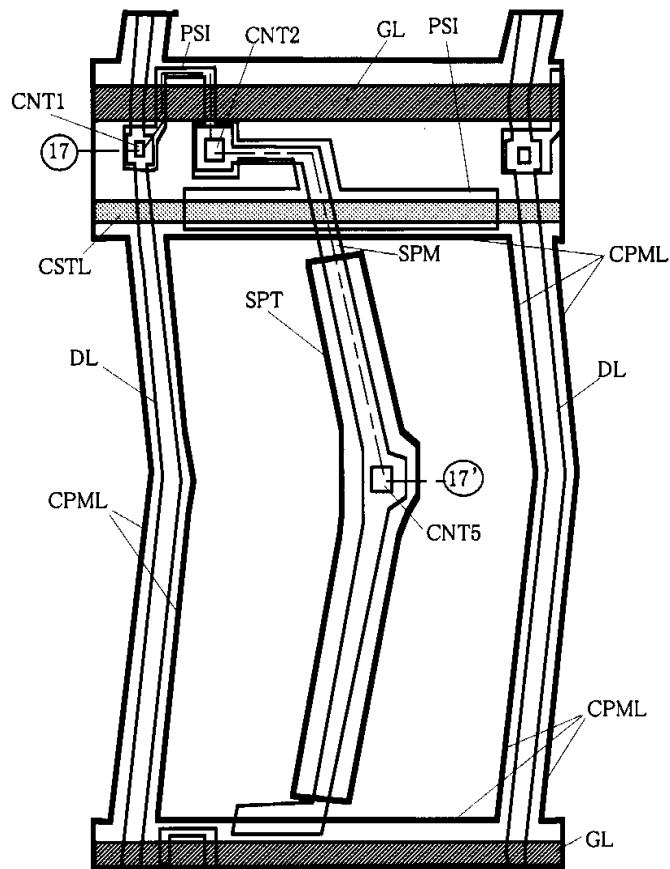

도 17은 도 16의 17-17' 절단선을 따라 취한 모식 단면도.

도 18은 본 발명의 다른 실시예에 따른 TFT 액정 표시 장치의 화소의 평면도.

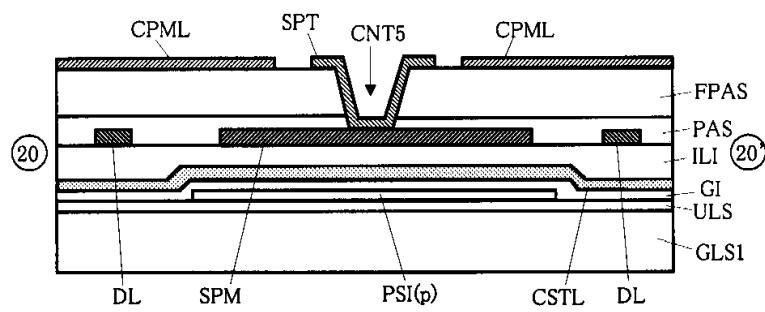

도 19는 도 18의 19-19' 절단선을 따라 취한 모식 단면도.

도 20은 도 18의 20-20' 절단선을 따라 취한 모식 단면도.

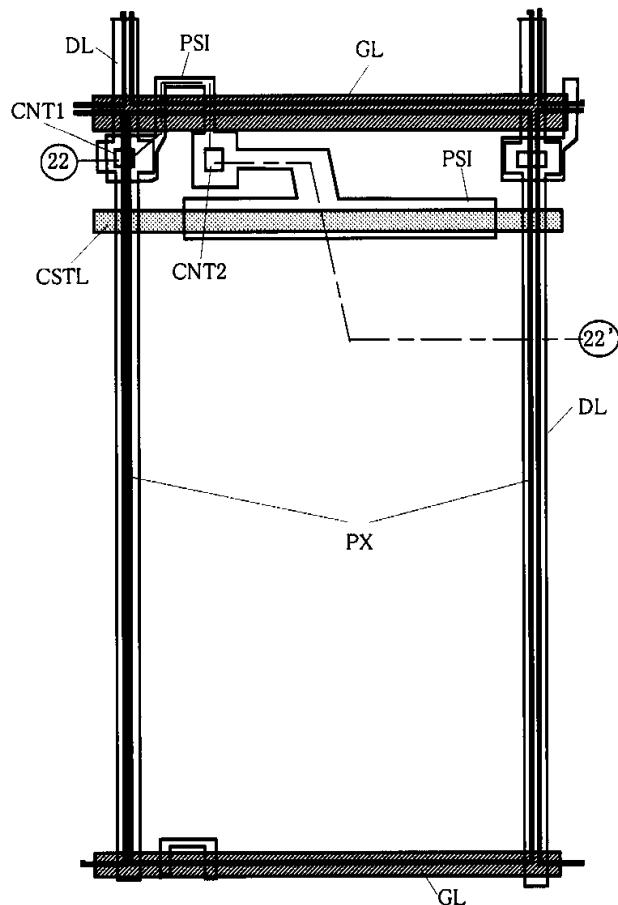

도 21은 본 발명의 다른 실시예에 따른 TFT 액정 표시 장치의 화소의 평면도.

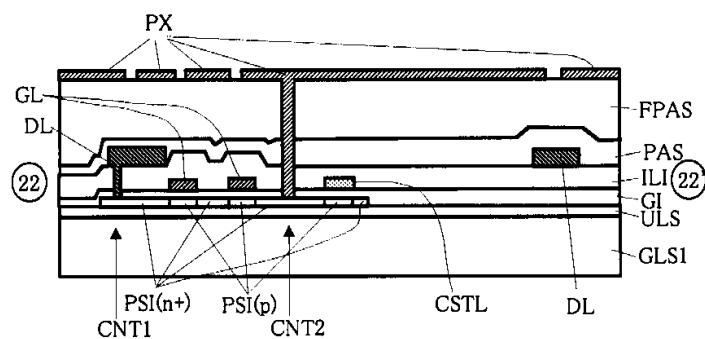

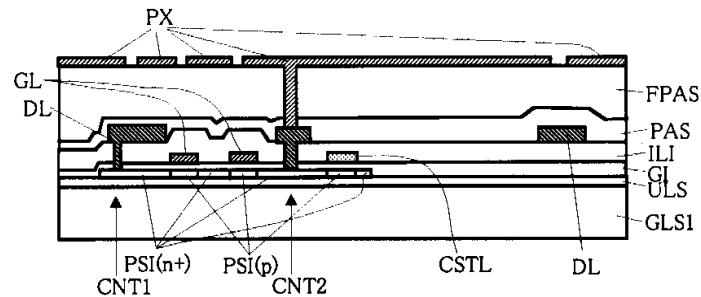

도 22는 도 21의 22-22' 절단선을 따라 취한 모식 단면도.

도 23은 도 21의 변형예.

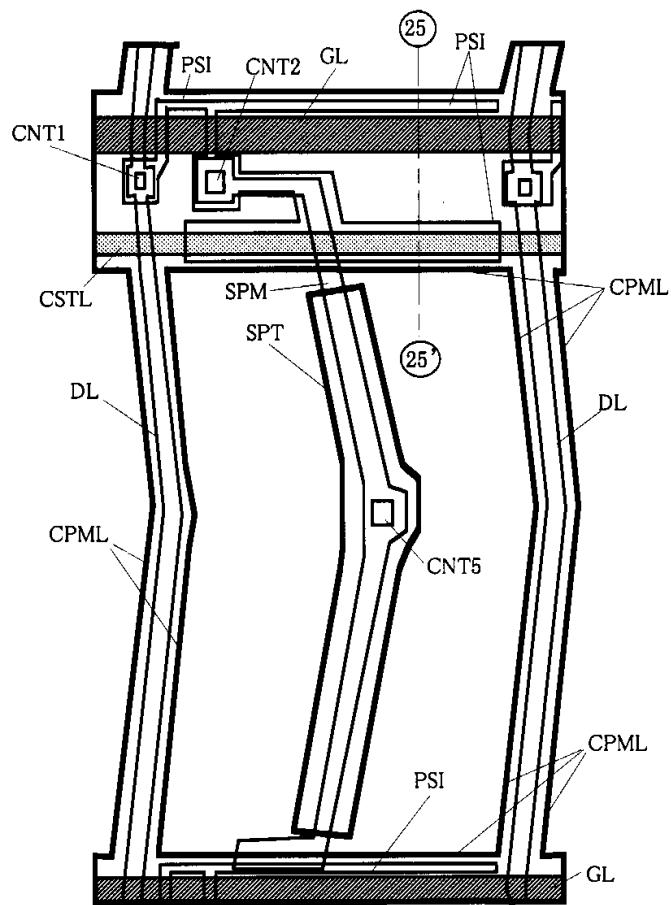

도 24는 본 발명의 다른 실시예에 따른 TFT 액정 표시 장치의 화소의 평면도.

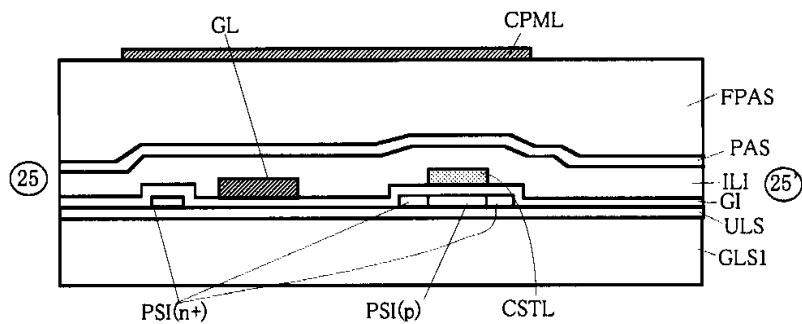

도 25는 도 24의 25-25' 절단선을 따라 취한 모식 단면도.

〈도면의 주요 부분에 대한 부호의 설명〉

BM : 블랙 매트릭스

CJ : 커넥터부

CL : 공통 배선

CPAD : 검사 패드

CPM : 공통 금속 전극

CPT : 공통 투명 전극

CSTL : 보유 용량 배선

CPML : 공통 전극

CNT1 : 드레인 배선과 Si 아일런드를 연결하는 컨택트 홀

CNT2 : 화소 금속 전극과 Si 아일런드를 연결하는 컨택트 홀

CNT3 : 공통 배선과 전극 패드를 연결하는 컨택트 홀

CNT4 : 공통 투명 전극과 전극 패드를 연결하는 컨택트 홀

CNT5 : 화소 금속 전극과 투명 화소 전극을 연결하는 컨택트 홀

CPM : 공통 금속 전극

CPT : 공통 투명 전극

DDC : 유리 기판 위의 드레인 분할 회로

DL : 드레인 배선

EPX : 에폭시 수지

FIL : 컬러 필터층

FPAS : 유기 보호막

GFPC : 게이트 FPC

GI : 게이트 절연막

GL : 게이트 배선

GLS1 : TFT 유리 기판

GLS2 : CF 유리 기판

IDC : 외장 드레인 회로

INJ : 봉입구

ILI : 층간 절연막

LC : 액정(분자)

LCB : 도광판

MDL : 모듈

OC : 컬러 필터의 오버코팅막

OLI : 배향막

PAD : 패드 전극

PAS : 보호 절연막

POL : 편광판

PSI : P-Si 아일런드

PSI(p) : p형 저온 P-Si 반도체층

PSI(n+) : n+ 형 저온 P-Si 반도체층

RM : 반사판

SPB : 확산 필름

SPC : 지주

SHD : 샤프

SPM : 화소 금속 전극

SPT : 화소 투명 전극

SSC : 전원, 컨트롤 회로

TCP : 테이프 캐리어 패키지

ULS : 기초 절연막

**발명의 상세한 설명**

**발명의 목적**

**발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 액정 표시 장치에 관한 것으로, 특히 박막 트랜지스터(TFT) 방식 등의 액티브 매트릭스형 액정 표시 장치에 관한 것이다.

액정 표시 장치는 박형, 경량, 저소비 전력 등의 특징을 살려, 퍼스널 컴퓨터로 대표되는 정보 기기나 휴대형 정보 단말기나 휴대 전화, 디지털 카메라나 카메라 일체형 VTR 기기 등의 비주얼 기기의 화상 정보, 문자 정보의 표시 기기로서 널리 이용되고 있다. 최근, DVD의 등장, 대용량 자기 드라이브의 급속한 진전에 의한 대용량 미디어의 보급이나 BS 디지털 방송의 개시에 따라, 퍼스널 컴퓨터와 영상 디지털 미디어의 융합이 진행되고 있으며, 이러한 용도에 대응할 수 있는 고화질의 화상 표시 장치에 대한 요구가 강해지고 있다. 이들은 TV 용도를 전제로 하고 있기 때문에 보다 밝은 화면 표시가 요구되고 있으며, 그 때문에 사용하는 백 라이트(BL)는 보다 밝은 것으로 되어 있다.

고화질 용도의 액정 표시 장치에는, 기판 상하 방향으로 전계를 인가하는 TN 방식, MVA 방식 등으로 대표되는 종전계형과, 기판 수평 방향으로 전계를 인가하는 획전계형, 소위 인플레인 스위칭(IPS) 모드가 주로 이용되고 있다.

IPS 모드의 액정 표시 장치에서는, 특히 2701698호에 개시되어 있는 바와 같이 TFT가 형성되어 있는 기판 위에서 화소 전극과 대향 전극 사이의 절연막으로 보유 용량을 구성하는 것이 일반적이다.

또한, 종전계 방식에 있어서도, TFT가 형성되어 있는 기판 위에서 화소 전극과 보유 용량 신호선 사이의 절연막으로 보유 용량을 구성하는 것이 알려져 있다.

### 발명이 이루고자 하는 기술적 과제

액정 표시 장치에서 BL의 광량이 증가하면 그 조사 광이 증가되므로 TFT의 광 조사 시의 오프 전류가 커져, 결과적으로 그 동작 안정화를 위해서는 보다 큰 보유 용량이 필요하게 되는 과제가 있다.

발명자들은 큰 보유 용량을 작성하기 위해서, 반도체층을 이용하는 것을 검토하였다. 특히 2682997호에서는 반도체층을 보유 용량의 구성에 사용한 구조가 개시되어 있다. 그러나, 보유 용량으로서, 절연막과 반도체층의 적층 구조를 이용하면, 화소 전극과 대향 전극 사이의 전위차가 교류화되기 때문에, 반도체층이 보유 기간 중에 온, 오프하여 보유 전위를 안정화 할 수 없다는 과제가 있는 것이 판명되었다. 한편, 특개평7-244296호에는 보유 용량으로서 반도체층을 이용하고, 바이어스를 연구하여 항상 오프 상태로 사용하는 방법이 개시되어 있다. 그러나, 이 방법에서는 BL의 광량이 증대하여 반도체층에 강한 광이 조사되고 있는 상태에서는 이 오프 상태가 불안정하게 되어, 보유 용량의 보유 전위가 영향을 받는 것이 판명되었다.

또한, 발명자들은 다음의 새로운 과제도 발견하였다. 액정 표시 장치의 TFT 유리 기판 위에 쳐온 폴리실리콘에 의한 TFT를 형성하고, 화면을 구동하는 주사 회로를 내장한 경우, 가장 얇고, 따라서 가장 큰 보유 용량이 형성 가능한 절연막은 게이트 절연막이다. 플래너형이라고 하는 반도체층 위에 게이트 절연막이 있고 그 절연막 위에 게이트 전극을 구성하는 구조에서는, 해당 절연막의 하부는, 소위 TFT의 채널 영역의 다결정 실리콘이다. 이 때, 해당 반도체층을 이용하여 보유 용량을 구성하면, TFT의 게이트 전압, 소스 전압, 드레인 전압에 의해 더욱 극단적인 전위 변동이 생기는 것이 판명되었다. 즉, TFT가 온 상태일 때에만 게이트 절연막의 두께로 결정되는 큰 보유 용량이 생긴다. 따라서, 구동 상태에 의해 보유 용량의 용량에 큰 변동이 생겨, 보유 전위를 안정화할 수 없다. 또한, TFT가 전자나 홀의 한쪽 극성의 MOS형이므로, 보유 기간의 극성에서도 용량치가 변동한다. TFT의 종류, 즉 n형이나 p형인지에 의해서도 차이가 생긴다. 또한, 이동도가 큰 폴리실리콘에서는 비정질 실리콘보다 전자와 홀의 이동도의 차가 확대되므로, 또한 보유 용량의 용량에 큰 변동이 생겨, 보유 전위를 안정화할 수 없는 것을 발견하였다.

또한, IPS형 표시 장치의 경우, 화소 전극 및 공통 전극을 보유 용량의 전극으로 하면, 화소 전극 전위와 공통 전극 전위는 주기적으로 극성이 반전하도록 구동할 필요가 있기 때문에, 반도체층을 보유 용량 구성의 구성 요소에 이용한 경우, 구동에 의해 보유 용량의 용량에 큰 변동이 생겨, 보유 전위를 안정화할 수 없는 것을 발견하였다.

또한, IPS형 액정 표시 장치의 경우, 플래너형의 TFT 구조에 있어서는 게이트 절연막보다 윗쪽에 화소 전극 및 공통 전극이 배치되기 때문에, 화소 전극 및 공통 전극을 보유 용량의 전극으로 하면, 게이트 절연막을 보유 용량의 절연막으로서 이용할 수 없어, 큰 보유 용량을 구성할 수 없는 문제가 있다.

또한, IPS 표시 장치의 경우, 공통 전극 및 화소 전극 이외의 전위를 액정의 투과부에 가하면 그 전위로 표시가 흐트러져 버리는 문제가 있다. 또한, 큰 보유 용량을 형성하면 동일 평면 내의 전극 또는 배선간의 거리가 줄어들어 전극간 또는 배선간의 쇼트 불량이 증가하는 문제가 있다. 또한, 큰 보유 용량을 형성하게 되면 개구율이 저하되어, 액정 표시 장치의 밝기가 저하되는 문제가 있다.

본 발명은 상기한 여러가지 과제를 해결하는 것을 목적으로 하고, 그 최대의 목적은 보유 용량이 크고, 또한 보유 전위가 안정된 보유 용량을 실현하고, BL의 휘도가 높은 상태에서도 안정된 표시를 실현할 수 있는 액정 표시 장치를 제공하는 데 있다.

또한, 저온 폴리실리콘 TFT를 화소 TFT에 이용한 IPS 방식의 액정 표시 장치에 있어서, 보유 용량을 증가 배치시킨 TFT 액정 표시 장치를 제공하는 데 있다.

또한, IPS 방식의 액정 표시 장치에 있어서, 큰 보유 용량을 형성한 경우에서, 액정의 주 투과부에 화소 전위, 공통 전극 전위 이외의 전위가 인가되지 않아 안정 표시를 할 수 있는 TFT 액정 표시 장치를 제공하는 데 있다.

또한, 큰 보유 용량을 구성해도, 전극 사이의 쇼트 불량율을 저하시키지 않는 TFT 액정 표시 장치를 제공하는 데 있다.

또한, 큰 보유 용량을 구성해도, 개구율을 높여 밝은 TFT 액정 표시 장치를 제공하는 데 있다.

### 발명의 구성 및 작용

본 발명의 과제 중 하나 또는 복수의 과제를 해결하는 수단의 예는 다음과 같다.

#### 〈수단 1〉

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고, 상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고, 상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서, 상기 TFT 소자를 구성하는 반도체층을 갖고, 절연층을 사이에 끼워 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고, 상기 반도체층과 용량 배선간에, 상기 반도체층을 도통 상태로 할 수 있는 극성의 전위차가 거의 항상 인가되도록 구성한다.

#### 〈수단 2〉

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고, 상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고, 상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서, 상기 TFT 소자와 일체로 구성된 반도체층을 갖고, 절연층을 사이에 끼워 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고, 상기 TFT 소자와 일체로 형성된 반도체층은, 상기 TFT 소자의 게이트 전극에 대하여 상기 드레인 배선이 형성된 층과는 반대 층에서 상기 화소 전극과 전기적으로 접속하고, 상기 용량 배선에 상기 반도체층을 도통 상태로 하는 전압을 거의 항상 인가한다.

#### 〈수단 3〉

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고, 상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고, 상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서, 상기 화소 전극은 금속 재료층과 투명 도전체층의 2층으로 구성되고, 상기 TFT 소자와 일체로 구성된 반도체층을

갖고, 절연층을 사이에 끼워 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고, 상기 반도체층은 상기 화소 전극의 금속층과 상기 절연층에 형성된 관통 홀로 접속되고, 상기 화소 전극의 금속층과 상기 화소 전극의 투명 도전체층은 별도의 절연층에 형성된 관통 홀로 접속되고, 상기 용량 배선에 상기 반도체층을 도통 상태로 하는 전압을 거의 항상 인가한다.

#### 〈수단 4〉

수단 1 내지 수단 3 중 어느 하나의 수단에 있어서, 상기 제1 기판 위에 공통 신호선을 갖고, 상기 공통 신호선과 상기 화소 전극이 평면적으로 중첩부를 갖고, 그 공통 신호선과 상기 용량 배선의 전위가 다르다.

#### 〈수단 5〉

수단 1 내지 수단 4 중 어느 하나의 수단에 있어서, 상기 제1 기판 위에 공통 전극을 갖고, 상기 화소 전극과 이격되어 구성되고, 해당 공통 전극과 해당 화소 전극 간에 형성되는 상기 제1 기판과 평행한 방향의 성분을 갖는 전계에 의해 상기 액정 층을 구동한다.

#### 〈수단 6〉

수단 1 내지 수단 5 중 어느 하나의 수단에 있어서, 상기 반도체층과 상기 용량 배선 사이의 절연막의 막 두께를, 상기 화소 전극에 접하는 어느 절연막의 막 두께보다도 얇게 한다.

#### 〈수단 7〉

수단 6에 있어서, 상기 반도체층과 상기 용량 배선 사이의 절연막을  $\text{SiO}_2$ 로 한다.

#### 〈수단 8〉

수단 1 내지 수단 7 중 어느 하나의 수단에 있어서, 상기 용량 배선의 전위가 상기 게이트 배선의 ON 전위와 동일하게 한다.

#### 〈수단 9〉

수단 1 내지 수단 7 중 어느 하나의 수단에 있어서, 상기 용량 배선의 전위가 상기 드레인 배선의 최대 전압에 상기 TFT의 임계치 전압을 더한 값 이상으로 한다.

#### 〈수단 10〉

수단 1 내지 수단 7 중 어느 하나의 수단에 있어서, 상기 용량 배선에 절연막을 사이에 두고 평면적으로 중첩하여 실드 전극을 구성한다.

#### 〈수단 11〉

수단 10에 있어서, 상기 실드 전극을 상기 공통 전극 또는 상기 공통 전극 배선으로 한다.

#### 〈수단 12〉

수단 1 내지 수단 11 중 어느 하나의 수단에 있어서, 상기 반도체층을 폴리실리콘으로 구성한다.

#### 〈수단 13〉

수단 12에 있어서, 상기 반도체층을 p-TFT 또는 n-TFT 중 어느 하나로 구성하고, 화소 영역밖에 설치된 TFT와 동일한 형으로 한다.

#### 〈수단 14〉

수단 1 내지 수단 12 중 어느 하나의 수단에 있어서, 상기 제1 기판의 배면에 백 라이트 유닛을 설치한다.

#### 〈수단 15〉

수단 14에 있어서, 상기 백 라이트 유닛의 휘도를  $8000\text{cd}/\text{m}^2$  이상으로 한다.

#### 〈수단 16〉

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고, 상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고, 상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖고, 각 화소는 복수의 화소에 걸쳐 접속되며 기준 전압을 공급하는 공통 전극 배선과, 해당 공통 전극 배선과 접속된 공통 전극을 갖고, 해당 공통 전극과 해당 화소 전극 사이에 형성되는 상기 제1 기판과 평행한 성분의 전계를 갖는 횡전계에 의해 상기 액정층의 액정 분자를 구동하는 액정 표시 장치에 있어서, 상기 공통 전극 및 공통 전극 배선은 서로 다른 보유 용량 전극 또는 보유 용량 배선을 갖고, 해당 보유 용량 전극 또는 보유 용량 배선과 상기 화소 전극의 전위에 접속된 보유 용량 부재와의 사이에 보유 용량을 형성한다.

#### 〈수단 17〉

수단 16에 있어서, 상기 보유 용량은 한쪽의 전극을 상기 보유 용량 전극 또는 보유 용량 배선으로 하고, 다른 쪽의 전극이 되는 상기 보유 용량 부재를 박막 트랜지스터를 구성하는 반도체막으로 하여, 해당 보유 용량 전극 또는 보유 용량 배선과 해당 보유 용량 부재 사이에 게이트 절연막을 형성한다.

#### 〈수단 18〉

수단 16 또는 수단 17에 있어서, 상기 박막 트랜지스터를 구성하는 반도체막을 폴리실리콘막으로 한다.

#### 〈수단 19〉

수단 17 또는 수단 18에 있어서, 상기 반도체막은, 상기 보유 용량 전극 또는 보유 용량 배선에 전압이 인가되어 상기 반도체막의 상기 게이트 절연막과의 계면에서 전자 또는 정공이 유기됨으로써 저항율이 저하하여 상기 보유 용량을 구성하는 다른 쪽의 전극으로서 기능한다.

#### 〈수단 20〉

수단 16에 있어서, 상기 보유 용량 전극 또는 보유 용량 배선 위에 공통 전극 또는 공통 전극 배선이 절연막을 사이에 두고 중첩한다.

#### 〈수단 21〉

수단 20에 있어서, 상기 공통 전극 또는 공통 전극 배선은 상기 게이트 배선과 평행하게 배치된 제2 공통 전극 배선과 상기 절연막의 개구부로 접속한다.

#### 〈수단 22〉

수단 20에 있어서, 상기 보유 용량 전극 또는 보유 용량 배선은 상기 박막 트랜지스터가 형성된 상기 투명한 제1 기판 위에서, 상기 보유 용량 전극 또는 보유 용량 배선 위에 절연막을 피복하고, 다시 그 상부를 공통 전극 또는 공통 전극 배선 및 화소 전극으로 전기적으로 실드한다.

#### 〈수단 23〉

수단 22에 있어서, 상기 보유 용량 전극 또는 보유 용량 배선 위에는 제1 절연막, 화소 전극, 제2 절연막, 공통 전극을 순차적으로 갖고, 해당 화소 전극과 해당 공통 전극은 해당 제2 절연막을 사이에 두고 상호 중첩되는 구조로 한다.

#### 〈수단 24〉

수단 22 또는 수단 23에 있어서, 상기 보유 용량 전극 또는 보유 용량 배선을 피복하는 상기 화소 전극 및 상기 공통 전극은, 평면 패턴적으로 상호 텁날 형상으로 중첩된다.

#### 〈수단 25〉

IPS형 액정 표시 장치에 있어서, TFT가 형성되는 투명 기판 위의 1 화소를 구성하는 영역에, 액정에 화소 전위를 공급하는 TFT를 구동하는 게이트 전극 및 게이트 배선, 영상 전위를 공급하는 드레인 전극 및 드레인 배선, 공통 전위를 공급하는 공통 전극 및 공통 전극 배선의 어느 것과도 다른 보유 용량을 구성하는 반도체와 게이트 절연막의 적층 구조를 갖고, 상기 적층 구조의 반도체층이 항상 온 상태로 되고, 상기 보유 용량은 상기 반도체층에 대하여 상기 게이트 절연막을 사이에 두고 상기 게이트 배선, 공통 전극 배선, 드레인 배선의 어느 것과도 다른 보유 용량 전극 또는 보유 용량 배선을 설치한다.

#### 〈수단 26〉

수단 25에 있어서, 화소 TFT가 n형 MOS 구조인 경우, 보유 용량 배선의 전위를, 드레인 배선에 인가되는 최고 전압에 화소 TFT의 임계 전압을 가산한 값보다 동등 이상의 전압으로 한다.

#### 〈수단 27〉

수단 25에 있어서, 화소 TFT가 n형 MOS 구조인 경우, 게이트 배선에 인가되는 최고 전압을 적어도 TFT 화소가 선택되는 시간의 3배로 하거나, 또는 직류 전압을 인가한다.

#### 〈수단 28〉

수단 25에 있어서, 화소 TFT가 p형 MOS 구조인 경우, 보유 용량 배선의 전위는, 드레인 배선에 인가되는 최저 전압에 화소 TFT의 임계 전압을 감산한 값보다 동등 이하로 한다.

#### 〈수단 29〉

수단 25에 있어서, 화소 TFT가 p형 MOS 구조인 경우, 게이트 배선에 인가되는 최저 전압을 적어도 TFT 화소가 선택되는 시간의 3배로 하거나, 또는 직류 전압을 인가한다.

#### 〈수단 30〉

수단 25 내지 수단 29 중 어느 하나의 수단에 있어서, 보유 용량 배선을 다른 절연막을 사이에 두고 공통 전극 또는 공통 전극 배선으로 평면적으로 중첩하여, 전기적인 실드 구조로 한다.

#### 〈수단 31〉

수단 25 내지 수단 30 중 어느 하나의 수단에 있어서, 게이트 배선과 동층의 공통 전극 배선을 제거하고, 상기 배선 및 화소 TFT 상부에 저유전률의 절연막을 구성하고, 그 상부에 있는 공통 전극을 저저항화한다.

#### 〈수단 32〉

수단 25 내지 수단 31 중 어느 하나의 수단에 있어서, 보유 용량 배선을 공통 전극 또는 공통 전극 배선과 화소 전극으로 교대로 겹쳐지도록 피복하고, 전기적인 실드 구조로 함으로써 달성된다.

#### 〈수단 33〉

투명한 제1 기판과 제2 기판 사이에 협착되는 액정층을 갖고, 상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선과, 상기 게이트 배선과 상기 드레인 배선의 교점에 대응하여 형성된 박막 트랜지스터를 갖고, 상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 복수의 화소에 걸쳐 접속되며 기준 전압을 공급하는 공통 전극 배선과, 해당 기준 전극 배선과 접속된 공통 전극과, 대응하는 박막 트랜지스터에 접속되어 상기 공통 전극에 대향하여 배치된 화소 전극을 갖고, 해당 공통 전극과 해당 화소 전극 사이에 형성되는 상기 제1 기판과 평행한 성분의 전계를 갖는 횡전계에 의해 상기 액정층의 액정 분자를 구동하는 액정 표시 장치에 있어서, 상기 공통 전극 및 공통 전극 배선과는 다른 보유 용량 또는 보유 용량 배선을 갖고, 해당 보유 용량 전극 또는 보유 용량 배선과 상기 화소 전극의 전위에 접속된 보유 용량 부재와의 사이에 보유 용량이 형성되고, 상기 보유 용량 배선과 상기 게이트 배선은 거의 평행하게 배치되고, 상기 게이트 배선의 단부는 절연막을 피복하고 그 상부에서 공통 전극 또는 공통 전극 배선으로 피복되어 전기적으로 실드되고, 또한 그 단부의 하부는 또한 절연막을 통해 폴리실리콘의 반도체층으로 전기적으로 실드된다.

본 발명의 또 다른 수단 및 효과는 본 명세서에서 분명하게 될 것이다.

본 발명의 실시예의 상세를, 이하 실시예에 있어서 설명한다.

#### 〈제1 실시예〉

도 1은 제1 실시예의 액정 표시 장치의 단위 화소의 모식 평면도이고, 도 2, 도 3, 도 4는 각각 도 1에서의 2-2', 3-3', 4-4'(도면에서는 알기 쉽게 하기 위해서 ○를 붙여 기재하고 있음)부의 모식 단면 구조이다.

도 1의 평면 패턴에서, 1 화소는 인접하는 게이트 배선 GL, 인접하는 드레인 배선 DL에 둘러싸인 영역이다. 게이트 배선 GL은 게이트 배선 GL과 폴리실리콘 PSI의 교차부에서 폴리실리콘 PSI로 구성된 TFT의 게이트 전극으로서도 작용하여, TFT를 온/오프시키는 전압을 공급한다. 드레인 배선 DL은 폴리실리콘 PSI에의 전류를 공급하는, 즉 상기 게이트 전압 GL이 온 전압을 공급한 타이밍에서 인가된 영상 전압(드레인 전압)을 1 화소의 액정 용량에 급전하고, 최종적으로 금속 화소 전극 SPM 및 이에 연결된 투명 화소 전극 SPT의 전위가 영상 전위로 된다. 돌입 전압 등에 관한 설명, 고려는 제외하고 설명한다.

도 1의 평면도에서의 상기 영상 전압의 전류 경로는, 드레인 배선 DL로부터 제1 컨택트 홀 CNT1을 통해 폴리실리콘 PSI에 연결되고, 이 폴리실리콘 내의 전류는 다시 제2 컨택트 홀 CNT2를 통해, 금속 화소 전극 SPM으로 흐른다. 또한, 금속 화소 전극 SPM으로부터 다시 제5 컨택트 홀 CNT5를 통해, 절연막 위의 투명 화소 전극 SPT에 이른다.

투명 화소 전극 SPT와 함께 횡전계를 형성하기 위한 또 한쪽의 전극 CPT의 공통 전극 전위는 이하의 경로로 인가된다. 인접하는 게이트 배선 DL 사이의 거의 중앙에 배치된 공통 전극 배선 CL에, 우선적으로 공통 전위가 인가된다. 이 전위는 프레임별로 교류화되는 화소 전위의 거의 중점 전위가 설정된다(도 5에서 다시 상세를 설명함). 공통 전극 배선 CL의 전위는, 우선 제3 컨택트 홀 CNT3을 통해 전극 패드 PAD에 연결된다. 또한, 상기 전극 패드는 상부의 절연막을 통해, 드레인 배선 DL, 게이트 배선 GL을 피복하는 투명 공통 전극 CPT에 최종적으로 전위를 공급한다.

본 발명의 특징적 구조로서, 영상 표시에 관련된 액정 용량의 전위가 표시 중, 즉 보유 기간 중에 폴리실리콘 PSI로 만들어진 TFT를 통해 백 라이트(BL) 광에 의해 감쇠되는 것을 방지하기 위해서 액정 용량과 등가 회로적으로 병렬로 특별한 보유 용량을 형성한다. 상기 특별한 보유 용량은 보유 용량 배선 CSTL과 반도체층 PSI를 각각 전극으로 하고, 해당 전극 사이에 게이트 절연막을 용량의 유전체막으로 이용하여 구성된다. 도 1에 도시한 바와 같이 보유 용량 배선 CSTL은 게이트 배선 GL 및 공통 전극 배선 CL과 독립적으로 배치되어 있다. CNT2에 의해 PSI와 SPM은 전기적으로 접속되어 있기 때문에, 결과적으로 화소 전극 SPM의 전위와 보유 용량 배선 CSTL의 전위 사이에서 보유 용량이 구성되게 된다. 도 1에서, SPM은 CSTL을 가로지르도록 연장하기 때문에, 해당 교차 영역에서도 용량이 더 형성되어, 보유 용량의 증가가 더욱 도모되고 있다.

도 1에 도시한 바와 같이 IPS형 액정 표시 장치에서는, 보유 용량 배선 CSTL로부터의 누설 전계가 액정에 인가됨으로써 표시가 흐트러지는 것을 방지하기 위해서, 투명 공통 전극 CPT로 보유 용량 배선 CSTL을 덮어 전기적으로 실드하는 것이 바람직하다. 이 투명 공통 전극 CPT는 드레인 배선 DL도 덮고, 또한 본 실시예에서는 게이트 배선 GL도 피복하고 있다. 이에 의해, CPT 아래에 GL, DL, CSTL의 3종의 배선을 갖고, 전계의 난비에도 관계없이, 액정에 대한 영향을 회피할 수 있게 되어 있다.

다음으로, 각부의 구성을 단면도를 이용하여 상세하게 설명한다.

도 2는 도 1의 2-2' 절단선을 따라 취한 단면도로서, 인접하는 드레인선 DL 사이의 1 화소 영역을 가로지르는 부분이다. 2 측의 영역으로부터 설명한다. 왜곡점 약 670°C의 무 알칼리 TFT 유리 기판 GLS1 위에 막 두께 50nm의  $\text{Si}_3\text{N}_4$ 막과 막 두께 120nm의  $\text{SiO}_2$ 막으로 이루어지는 기초 절연막 ULS가 형성되어 있다. 기초 절연막 ULS는 TFT 유리 기판 GLS1로부터의 Na 등의 불순물 확산을 방지하는 역할을 한다. 기초 절연막 ULS 위에는 TFT의 게이트 절연막이 되는  $\text{SiO}_2$ 막으로 이루어지는 게이트 절연막 GI가 성막되어 있다. 게이트 절연막 GI 위에는  $\text{SiO}_2$ 로 이루어지는 층간 절연막 ILI가 형성되고, 층간 절연막 ILI 위에는 Ti/Al/Ti의 3층 금속막으로 이루어지는 드레인 배선 DL 및 드레인 배선 DL과 동일 공정, 재료로 구성된 금속 전극으로서, 도 1의 평면도에서 제2 컨택트 홀 CNT2에 의해 폴리실리콘 PSI와 접속된 금속 화소 전극 SPM이 형성되어 있다.

이들 소자 전체는 막 두께 200nm의  $\text{Si}_3\text{N}_4$ 로 이루어지는 보호 절연막 PAS와 막 두께 2 $\mu\text{m}$ 의 아크릴계 수지를 주성분으로 하는 유기 보호막 FPAS에 의해 피복되어 있다. 유기 보호막 FPAS 위에는 드레인 배선 DL의 폭보다 넓은 투명 공통 전극 CPT가 형성되어 있다. 본 실시예에서는 CPT에는 인듐-주석 산화물(ITO)을 이용했지만, 인듐-아연 산화물(IZO), 인듐-주석-아연 산화물(ITZO) 등이어도 된다. 동일한 공정, 동일한 재료로 제작된 ITO로 이루어지는 투명 화소 전극 SPT도 상기 유기 절연막 FPAS 위에 형성되어 있다. 상기 투명 화소 전극 SPT와 금속 화소 전극 SPM은 도 1의 제5 컨택트 홀 CNT5에 의해 접속되어 있다.

표시에 이용하는 광 투과 영역은, 주로 드레인선 DL 상의 투명 공통 전극 CPT와 투명 화소 전극 SPT 사이이고, 투명 전극의 단부로부터의 일부도 광 투과 영역에 기여한다. 서로 이웃하는 드레인 배선간 DL은 투명 화소 전극 SPT로 구획되어 두 개의 광 투과 영역으로 분할되어 있다.

IPS 방식의 액정 표시 장치는, 액정 LC 중에의 화소 전극 SPT와 공통 전극 CPT 사이에 인가되는 횡전계로 액정을 구동하여 투과 광을 제어한다. 따라서, ITO 등의 투명 전극에서 상기 화소 전극 및 공통 전극으로 구성해도 투명 전극 상의 모든 영역을 투과 영역으로 하는 것은 곤란하지만, 일부를 투과 영역으로서 이용할 수 있다. 일례로서, 포지티브형 액정 재료에서는 투명 전극 단부로부터 전극 상에서 1.5 $\mu\text{m}$  내측, 네가티브형 액정에서 3 $\mu\text{m}$  내측까지가 투과 범위로서 이용 가능하다.

액정 LC를 밀봉하는 대향측의 기판은 컬러 필터(CF) 기판 GLS2이다. GLS2는 액정측에 색 표시를 행하는 안료를 분산한 유기막 재료로 구성된 색 필터(FIL)가 그 화소별로 할당된 색에 따라, 청(B), 적(R), 녹(G)의 투과 광을 표현하는 색 필터(적(R)에서는 FIL(R))로 되어 있다. 그 내측에는 유기 재료로 이루어지는 오버코팅막 OC막을 형성해도 된다. CF로부터의 오염 방지, CF간의 평탄성 향상을 도모할 수 있기 때문이다. GLS2 및 GLS1의 액정 LC에 대하여 접하고 있는 면에는 배향막 OLI가 인쇄되어 소정의 러빙이 실시되어, 초기 배향을 제어하고 있다. 또한, 상기 GLS2 및 GLS1의 외측의 면에는 각각 편광판 POL이 접착된다. 이 편광판은 상호 편광축이 직교하는, 소위 크로스니콜 상태가 형성되어 있다.

도 3은 도 1의 3-3'의 절단선을 따라 취한 단면도이다. 본 단면도는 도 1의 평면도에서 드레인 배선 DL~제1 컨택트 홀 CNT1~TFT의 폴리실리콘층 PSI~제2 컨택트 홀 CNT2를 일부 가로지르고, 또한 게이트 배선 GL과 평행하게 배치된 보유 용량 배선 CSTL을 가로지르며, 또한 금속 화소 전극 SPM 상을 통해, 상기 게이트 배선 GL 및 보유 용량 배선 CSTL과 평행하게 배치된 공통 전극 배선 CL 상의 제5 컨택트 홀 CNT5에 이르는 횡단선 상의 단면도를 도시한다.

도 3의 단면도의 좌측은, 소위 TFT의 단면이다. 드레인 배선 DL, 금속 화소 전극 SPM을 소위 드레인 전극, 소스 전극으로 하고, 또한 게이트 배선 GL을 게이트 전극으로 하여, 게이트 절연막 GI를 갖는, 소위 MOS형 TFT이다. 드레인 배선 DL 및 금속 화소 전극 SPM은 게이트 절연막 GI 및 층간 절연막 ILI에 개방된 제1 컨택트 홀 CNT1, 제2 컨택트 홀 CNT2를 통해, 저온 폴리실리콘 PSI에서, 인을 불순물로 하여 도핑된 고농도 n형층 PSI(n+)에 접속되어 있다. 해당 고농도 영역은 PSI이어도 항상 도전성이 비교적 높은 상태로 되어 있기 때문에, 반도체라기보다 도전층으로서 간주할 수 있다. 이 때문에, 게이트선 GL 아래 이외의 폴리실리콘층 PSI는 도전층으로 간주할 수 있다. 한편, 게이트 배선 GL 하부의, 봉소를 불순물로서 도핑된 p형층 PSI(p)는 게이트 전압에 의해 스위칭 동작을 보이는 반도체 상태로 되어 있다. 게이트 배선 GL에 온 전압이 인가된 경우, p형층 PSI(p)의 게이트 절연막 GI 계면이 반전하여 채널 영역이 형성되어 TFT로 온 전류가 흐르고, 금속 화소 전극 SPM으로 전류가 흘러 액정 용량이 충전된다. 드레인 배선 DL 및 금속 화소 전극 SPM이 접촉하는 폴리실리콘 PSI가 n형인 것을 n형의 MOS 또는 n형의 TFT라고 한다. 반대로, 상기 접속부의 폴리실리콘이 봉소를 도핑한 고농도 p형 반도체층인 것을 p형 MOS 또는 p형의 TFT라고 한다.

도 4의 단면도의 중앙 부근은 특별한 보유 용량을 구성하는 부분의 단면도이다. 게이트 배선 GL과 동일 공정으로 형성된 Mo 또는 MoW으로 구성된 보유 용량 배선 CSTL은 게이트 배선 GL과는 다른 전원 전위가 인가되어 있다. 상기 보유 용량 배선 CSTL 하부에는 게이트 절연막 GI가 있다. 기본적으로 이 보유 용량 부분의 단면 구조는 TFT 형상의 구조로 구성되어 있다. 따라서, 게이트 배선 GL에 온 전압이 인가된 경우, 채널 영역의 p형 반도체층과 게이트 절연막 GI의 계면 부근의 반도체층이 반전되어 온 전류가 흐른다. 이 기간 중에 보유 용량 배선 CSTL에도 온 전압 상당 이상의 전압이 인가되면, 특별한 보유 용량부는 게이트 절연막 GI를 유전체로서, p형 반도체층 PSI(p)를 한쪽의 전극으로서 보유 용량 배선 CSTL을 다른 쪽의 전극으로 하여 용량을 형성할 수 있다. 즉, 보유 용량 CSTL의 전위를 조정하여, 항상 ON 전위 이상으로 함으로써, 신호 극성에 의한 용량 변동이 없는 안정된 보유 용량을 형성할 수 있다. 화소 전극 전위와 공통 전극 전위 사이에 형성하는 경우와 달리, 전위차의 극성을 반전하는 것을 회피할 수 있기 때문이다.

도 3에서는 보유 용량 배선 CSTL은 보호막 PAS 및 유기 보호막 FPAS 상에 배치된 투명 화소 전극 CPT로 피복되고, 그 전위가 액정에 인가되지 않도록 실드되어 있다.

한편, 액정을 구동하는 투명 화소 전극 SPT는 금속 화소 전극 SPM과 보호막 PAS 및 유기 보호막 FPAS에 형성된 제5 컨택트 홀 CNT5를 통해 접속된다.

도 4는 도 1의 4-4'의 절단선을 따라 취한 단면도이다. 본 단면도는 주로 보유 용량을 구성하는 보유 용량 배선 CSTL의 횡단선을 따라 취한 단면도이다. 도 1의 평면 구조적으로는 보유 용량 배선 CSTL보다 폭이 넓은 폴리실리콘 PSI와 게이트 배선 GL과 동일 공정, 재료로 구성된 보유 용량 배선 CSTL을 전극으로서 유전체를 게이트 절연막 GI로 하는 보유 용량이 구성된다. 또한, 이 보유 용량 배선 CSTL은 유기 보호막 FPAS 상에 형성된 투명 공통 전극 CPT에서 서로 이웃하는 드레인 배선 DL, 즉 복수의 화소를 포함해서 완전하게 피복되어 전기적으로 실드되어 있어, 큰 보유 용량치를 형성하면서도, 액정에 보유 용량 배선 CSTL의 전위가 누설되지 않는 구조로 되어 있다.

도 5는 본원의 특별한 보유 용량의 동작을 설명하는 도면이다. 도 5의 (a)는 도 3의 단면 구조도의 일부를 이용하여 보유 용량의 동작을 설명하는 것이다. 도 5의 (b)는 각부의 전극으로 인가되는 구동 전압의 타이밍 흐름도이고, 도 5의 (c)는 보유 용량의 인가 전압과 용량치의 변화를 도시한다.

도 5의 (b)의 구동 파형의 타이밍차트의 시간 축에 따라 그 동작을 설명한다. 홀수 프레임에서 해당하는 TFT의 게이트 배선 GL에 적어도 드레인 배선 DL 전위 Vd의 최고 전위에 TFT의 임계 전압 Vth를 가산한 값 이상의 전압 Vgh가 인가되면, TFT는 온 상태가 되어 폴리실리콘의 p형 폴리실리콘에 n형의 반전층이 형성되어, 소스 전위 Vs가 기본적으로 드레인 전압 Vd와 동일 전위까지 액정 용량을 충전하면서 근접한다.

한편, 보유 용량 배선 CSTL의 전압 Vst는, 적어도 드레인 배선 DL 전위 Vd의 최고 전위에 TFT의 임계 전압 Vth를 가산한 전압 이상으로서 설정한다. 이러한 경우, TFT의 Vgh가 걸려 있는 기간이면, 보유 용량을 구성하는 p형 폴리실리콘이 반전하여, 게이트 절연막 GI를 유전체로 하는 보유 용량치 Cgi가 얻어진다.

또한, TFT의 게이트 전압 Vg이 비선택, 즉 게이트 전압이 Vgl로 되면, 화소의 TFT는 오프 상태로 되어 화소 전위 Vs는 다시 게이트 전압이 Vgh의 값으로 선택될 때까지 유지된다. 보유 용량 배선 CSTL의 전위 Vst는 이 보유 기간 중에도, 적어도 드레인 배선 DL 전위 Vd의 최고 전위에 TFT의 임계 전압 Vth를 가산한 값 이상으로 설정되어 있기 때문에, 보유 용량은 게이트 절연막 GI를 유전체로 하는 값 Cgi로 유지된다. 물론, 공통 전극 또는 공통 전극 배선 CL과 금속 화소 전극 SPM이 교차하는 영역도 보유 용량 Cili를 구성하지만, 게이트 절연막 GI는 통상 100nm 정도인 반면, 층간 절연막 ILI는 두께 200nm 이상의 금속인 게이트 배선 GL이나 보유 용량 배선 CSTL과 드레인 배선 DL 또는 금속 화소 전극 SPM의 절연을 유지하기 위해서 게이트 절연막보다 두껍게 구성되고, 예를 들면 500nm 정도의 두꺼운 값으로 설정되어 있다. 따라서, 게이트 절연막 GI를 유전체로 하는 용량치는 단위 면적당 예를 들면 5배의 용량치를 형성할 수 있고, 금속 불투과 영역의 면적을 삭감할 수 있어 개구율을 높여 밝은 액정 표시 장치를 실현할 수 있다. 또한, 동일한 개구율이면 매우 큰 보유 용량치를 형성할 수 있어, TFT의 하부로부터 광 조사된 오프 전류에 의한 액정 용량 전위의 보유 기간 중의 저하를 작게 할 수 있으므로, 보유가 안정된 액정 표시 장치를 실현할 수 있다.

이에 의해, 백 라이트의 강도가 강한 TV용 액정 표시 장치에 있어서도, 고화질의 표시를 실현할 수 있게 된다.

도 5의 (c)에 보유 용량 배선 CSTL의 인가 전압과 보유 용량의 관계를 도시한다. 도 5의 (c)의 횡축은 설명을 알기 쉽게 하기 위해서 DL의 전압 Vd와 보유 용량 배선 CSTL의 전압 Vst의 전압 차로 나타내고, 우측이 플러스, 좌측이 마이너스이다. 종축은 특별한 보유 용량이다.

도 5의 (c)에서 알 수 있는 바와 같이, 전압 차에 의해 특별한 보유 용량치는 크게 변동한다. 그래서, 본 발명에서는  $V_x$ 의 전위, 즉  $V_d$ 의 최대치보다  $V_{th}$  이상 높은 전압치로서 보유 용량 배선 CSTL의 전위를 항상 설정함으로써, 항상 특별한 보유 용량치를 높은 값으로 안정시킨 것을 특징으로 한다. 도 5의 (c)의  $V_y$ (짝수),  $V_y$ (홀수)는 비교를 위한 예로, 가령 보유 용량 배선 CSTL의 전압  $V_{st}$ 를 드레인 전압  $V_d$ 의 거의 중점 전위로 설정된 공통 전극 배선 CL의 공통 전압  $V_c$ 와 동일 전위로 설정한 경우이다. 홀수 프레임에서는 드레인 전압  $V_d$ 가 보유 용량 배선 CSTL의 전위  $V_{st}$ 보다 크기 때문에, 전압 차는 도 5의 (c)의  $V_y$ (홀수)와 같이 마이너스로 되고, p형 폴리실리콘 PSI(p)는 반전하지 않고 유전체로서 기능하기 때문에, 특별한 보유 용량치는 보유 용량 배선 CSTL과 n+ 형 폴리실리콘 PSI(n+)의 기하학적 형상으로 결정되는 작은 기생 용량치  $C_0$ 밖에 얻을 수 없다. 한편, 짝수 프레임에서는, 보유 용량 배선 CSTL의 전압  $V_{st}$ 는 드레인 전압  $V_d$ 보다 높고, 또한 그 진폭치  $V_{sig}$ 의 1/2 전압이 TFT의  $V_{th}$ 보다 높은 상태에서는 전압 차는 예를 들면 도 5의 (c)의  $V_y$ (짝수)와 같이 되어, 보유 용량치는  $C_{g1}$ 로 큰 값이 된다. 이 결과, 홀수와 짝수 프레임에서 특별한 보유 용량치  $C_{stg}$ 가 크게 다르다. 이 때문에, 보유 기간의 화소 전위  $V_s$ 가 비대칭으로 되어 액정에 직류 전압이 인가되어, 잔상이나 화면의 아른거림인 풀리커가 화면 표시에서 발생하는 문제가 발생한다. 즉, 공통 전극 배선 CL과 화소 전극 SPM 또는 SPT 사이의 보유 용량으로서 공통 전극 전위로 온 오프하는 반도체와 절연막의 적층 구조의 보유 용량은 사용할 수 없는 것도 의미한다.

또한, 본 실시예의 방식은, CSTL에 의해 PSI를 ON 상태로 함으로써 보유 용량을 구성한다. 다시 말하면, 해당 보유 용량 부는 원래 도통 상태로 되도록 구동한 상태에서 사용하기 때문에, 보유 용량부에서의 광 전도에 의한 리크는 원리적으로 해소할 수 있는 현저한 효과를 발휘한다. 즉, 리크는 오프 상태에서의 전하의 누출을 문제로 하는 것으로, 오프 상태로 하지 않으면 생기지 않기 때문이다. 이에 의해, BL로서  $8000\text{cd}/\text{m}^2$ 를 초과하는 고휘도, 나아가서는  $10000\text{cd}/\text{m}^2$ 를 초과하는 초고휘도 백 라이트의 적용을 가능하게 하여, 고휘도로 밝고, 또한 보유 특성이 우수한 액정 표시 장치를 실현할 수 있다.

또한, 보유 용량부에 대하여 말하면, 광 강도가 증가하여 광 캐리어의 증대는 오히려 보유 특성부의 특성 안정화에 기여하기 때문에, 고휘도화에 적합한 구조라고 할 수 있다.

또한, CSTL의 전위는 게이트의 ON 전위와 동일하게 해도 된다. 게이트의 ON 전압과 동일한 전원 회로를 이용할 수 있고, 또한 동일한 급전 라인을 이용할 수 있어, 저비용화에 기여하기 위함이다.

다음으로, 상기 도 3에 도시한 바와 같은 n형 TFT만으로 구성한 액정 표시 소자에 이용하는 TFT 액티브 매트릭스 기판을 예로 들어, 그 제조 공정을 도 6~도 10 및 도 3을 이용하여 설명한다.

우선, 도 6의 제1 포토 공정 완료까지의 제조 방법을 설명한다.

두께 0.7mm, 폭 730mm, 폭 920mm의 왜곡점 약 670°C의 무 알칼리 TFT 유리 기판 GLS1 위를 세정한 후,  $\text{SiH}_4$ 와  $\text{NH}_3$ 와  $\text{N}_2$ 의 혼합 가스를 이용한 플라즈마 CVD법에 의해 막 두께 50nm의  $\text{Si}_3\text{N}_4$ 막, 계속해서, 테트라에톡시실란과 산소의 혼합 가스를 이용한 플라즈마 CVD법에 의해, 막 두께 120nm의  $\text{SiO}_2$ 막의 적층인 기초 절연막 ULS를 형성한다. 본 절연막 ULS는 다결정 실리콘막에의 TFT 유리 기판 GLS1로부터의 Na 확산을 방지하기 위함이다.  $\text{Si}_3\text{N}_4$ ,  $\text{SiO}_2$  모두 형성 온도는 400°C이다.

다음으로,  $\text{SiH}_4$ , Ar의 혼합 가스를 이용한 플라즈마 CVD법에 의해 거의 진성의 수소화 비정질 실리콘막을 50nm 형성한다. 성막 온도는 400°C이고, 성막 직후 수소량은 약 5at%이었다. 다음으로, 기판을 450°C에서 약 30분 어닐링함으로써, 수소화 비정질 실리콘막(300) 중의 수소를 방출시킨다. 어닐링 후의 수소량은 약 1at%이었다.

다음으로, 과장 308nm의 엑시머 레이저 광을 상기 비정질 실리콘막에 플루엔스 400mJ/cm<sup>2</sup>로 조사하여, 비정질 실리콘막을 용융 재결정화시켜, 거의 진성의 다결정 실리콘막 PSI를 얻는다. 이 때, 레이저 빔은 폭 0.3mm, 길이 200mm의 세션 형상으로, 빔의 길이 방향과 거의 수직인 방향으로 기판을 10μm 피치로 이동하면서 조사하였다. 조사 시에는 질소 분위기로 하였다.

다음으로, 통상의 포토리소그래피법에 의해 소정의 레지스트 패턴을 다결정 실리콘막 위에 형성하고  $\text{CF}_4$ 와  $\text{O}_2$ 의 혼합 가스를 이용한 리액티브 이온 에칭법에 의해 다결정 실리콘막 PSI를 소정의 형상으로 가공한다.

계속해서, 도 7의 제2 포토 공정 완료까지의 제조 방법을 설명한다.

테트라에톡시실란과 산소의 혼합 가스를 이용한 플라즈마 CVD법에 의해 막 두께 100nm의  $\text{SiO}_2$ 를 형성하여 게이트 절연막 GI를 얻는다. 이 때의 테트라에톡시실란과  $\text{O}_2$ 의 혼합비는 1:50이고, 형성 온도는 400°C이다. 그 후, 이온 주입법에 의해 B 이온을 가속 전압 33KeV, 도우즈량 1E12( $\text{cm}^{-2}$ )로 주입하여, n형 TFT의 채널 영역의 폴리실리콘막 PSI(p)를 형성한다. 이 단계에서는 폴리실리콘 전체가 PSI(p)로 되어 있다.

다음으로, 스퍼터링법에 의해, Mo 또는 MoW막을 200nm 형성한 후, 통상의 포토리소그래피법에 의해 소정의 레지스트 패턴을 Mo막 상에 형성하고, 혼합산을 이용한 웨트 에칭법에 의해 Mo막을 소정의 형상으로 가공하여 게이트 배선 GL, 보유용량 배선 CSTL 및 공통 전극 배선 CL을 얻는다.

에칭에 이용한 레지스트 패턴을 남긴 채, 이온 주입법에 의해 P 이온을 가속 전압 60KeV, 도우즈량 1E15( $\text{cm}^{-2}$ )로 주입하여, n형 TFT의 소스, 드레인 영역 PSI(n+)를 형성한다. 이 때, GL 아래의 폴리실리콘층에는 GL 및 레지스트가 스토퍼로 되어 P 이온이 주입되지 않아, PSI(p) 상태이다. 한편, 레지스트 및 GL 외부 영역의 폴리실리콘층은 P 이온이 주입되므로 PSI(n+)로 된다.

상기에서 n형 TFT의 소스, 드레인이 n+ 형의 저온 폴리실리콘막 PSI(n+) 및 p형의 채널 영역의 폴리실리콘막 PSI(p)가 생성되지만, 이하와 같이 p형과 n+ 형 사이에 P 이온 농도가 n+ 형보다 적은 n형의 LDD 영역을 형성하여, TFT의 누설 전류를 저감시킬 수 있다(도시 생략).

즉, 에칭에 이용한 레지스트 패턴을 제거한 후, 재차 이온 주입법에 의해 P 이온을 가속 전압 65KeV, 도우즈량 2E13( $\text{cm}^{-2}$ )으로 주입하여, n형 TFT의 LDD 영역을 형성한다. LDD 영역의 길이는, Mo을 웨트 에칭했을 때의 사이드 에칭량으로 정해진다. 일례로서 약 0.8 $\mu\text{m}$ 이다. 이 길이는 Mo의 오버 에칭 시간을 변화시킴으로써 제어할 수 있다.

다음으로, 기판에 엑시머 램프 또는 메탈 할로겐 램프의 광을 조사하는 래피드 서멀 어닐링(RAT)법에 의해 주입한 불순물을 활성화한다. 엑시머 램프 또는 메탈 할로겐 램프 등의 자외광을 많이 포함하는 광을 이용하여 어닐링함으로써, 다결정 실리콘층 PSI만을 선택적으로 가열할 수 있어, 유리 기판이 가열됨으로 인한 손상을 회피할 수 있다. 불순물의 활성화는 기판 수축이나 굴곡 변형 등이 문제가 되지 않는 범위에서, 450°C 정도 이상의 온도에서의 열 처리에 의해서도 가능하다.

계속해서, 도 8의 제3 포토 공정 완료까지의 제조 방법을 설명한다.

테트라에톡시실란과 산소의 혼합 가스를 이용한 플라즈마 CVD법에 의해 막 두께 500nm의  $\text{SiO}_2$ 를 형성하여 층간 절연막 ILI를 얻는다. 이 때의 테트라에톡시실란과  $\text{O}_2$ 의 혼합비는 1:5이고, 형성 온도는 350°C이다.

다음으로, 소정의 레지스트 패턴을 형성한 후, 혼합산을 이용한 웨트 에칭법에 의해 상기 층간 절연막에 제1 컨택트 관통 홀 CNT1, 제2 컨택트 관통 홀 CNT2 및 도 1의 평면도의 제3 컨택트 관통 홀 CNT3을 형성한다.

계속해서, 도 9의 제4 포토 공정 완료까지의 제조 방법을 설명한다.

스퍼터링법에 의해, Ti 50nm, Al-Si 합금 500nm, Ti 50nm를 순차적으로 적층 형성한 후, 소정의 레지스트 패턴을 형성하고,  $\text{BCl}_3$ 과  $\text{Cl}_2$ 의 혼합 가스를 이용한 리액티브 이온 에칭법에 의해 일괄적으로 에칭하여, 드레인 배선 DL과 금속 화소 전극 SPM, 도 1의 평면도의 전극 패드 PAD를 얻는다.

계속해서, 도 10의 제5 포토 공정 완료까지의 제조 방법을 설명한다.

$\text{SiH}_4$ 와  $\text{NH}_3$ 과  $\text{N}_2$ 의 혼합 가스를 이용한 플라즈마 CVD법에 의해 막 두께 300nm의  $\text{Si}_3\text{N}_4$  막인 보호막 PAS를 형성하고, 또한 스핀 도포법에 의해 아크릴계 감광성 수지를 약 3.5 $\mu\text{m}$ 의 막 두께로 도포하고, 소정의 마스크를 이용하여 노광, 현상하여 상기 아크릴계 수지에 관통 홀을 형성한다. 다음으로, 230°C에서 20분 베이킹 함으로써 아크릴 수지를 소성하고, 막 두께 2.0 $\mu\text{m}$ 의 평탄화 유기 보호막 FPAS를 얻는다. 계속해서, 상기 유기 보호막 FPAS에 형성한 관통 홀 패턴을 마스크로 하여 하층의  $\text{Si}_3\text{N}_4$  막을  $\text{CF}_4$ 를 이용한 리액티브 이온 에칭법에 의해 가공하여,  $\text{Si}_3\text{N}_4$  막에 도 1의 제4 컨택트 홀 CNT4, 제5 컨택트 홀 CNT5를 형성한다.

본 실시예에서는 유기 보호막 FPAS를 마스크로 이용하여 하층의 절연막을 가공함으로써, 일회의 포토리소그래피 공정에서 2층의 막을 패터닝하여, 노광 공정을 1회 저감시켜, 공정의 간략화와 저비용화를 실현하였다.

마지막으로, 도 3의 제6 포토 공정 완료까지의 제조 방법을 설명한다.

스퍼터링법에 의해 ITO막을 70nm 형성하고, 혼합산을 이용한 웨트 에칭에 의해 소정의 형상으로 가공하여 투명 공통 전극 CPT 및 도 1의 평면도에 도시한 투명 화소 전극 SPT를 형성하여 액티브 매트릭스 기판이 완성된다(도 3).

이상 6회의 포토리소그래피 공정으로 다결정 실리콘 TFT를 이용한 TFT 기판 GLS1 위의 막 가공이 종료된다.

다음으로, 액정 패널의 개판의 평면 구조에 대하여 설명한다. 도 11은 상하의 유리 기판 GLS1, GLS2를 포함하는 표시 패널의 매트릭스(AR) 주변의 주요부 평면을 도시하는 도면이다. 이 패널의 제조에서는, 작은 사이즈이면 처리량 향상을 위해 1매의 유리 기판으로 복수개분의 디바이스를 동시에 가공하고 나서 분할하고, 큰 사이즈이면 제조 설비의 공용을 위해 어떤 품종이라도 표준화된 크기의 유리 기판을 가공하고 나서 각 품종에 맞는 사이즈로 작게 하여, 어느 경우도 한 가지의 공정을 거치고 나서 유리를 절단한다.

도 11은 상하 기판 GLS1, GLS2의 절단 이후를 도시하고 있다. 도 11의 윗면에는 외부 접속 단자군 Tg, Td가 존재하고, 이들이 노출되도록 상측 기판 GLS2의 크기가 하측 기판 GLS1보다 내측으로 제한되어 있다. 단자군 Tg, Td는 각각 후술하는 TFT 유리 기판 GLS1 상에서 표시부 AR의 좌우에 배치된 저온 폴리실리콘 TFT의 주사 회로 GSCL에 공급하는 전원 및 타이밍 데이터에 관한 접속 단자, 표시 영역 AR의 상부에서 TFT 유리 기판 GLS1 상에 저온 폴리실리콘 TFT의 영상 신호 회로 DDC로의 영상 데이터 또는 전원 데이터를 공급하기 위한 단자군 Td이다. 인출 배선부는 접적 회로 칩 CHI가 탑재된 테이프 캐리어 패키지 TCP(후술)의 단위로 복수개 통합하여 배치한 것이다. 각 군의 매트릭스부로부터 영상 신호 회로 DDC를 거쳐 외부 접속 단자부에 이르기까지의 인출 배선은 양단에 균접함에 따라 경사져 있다. 이것은 패키지 TCP의 배열 피치 및 각 패키지 TCP에서의 접속 단자 피치에 표시 패널의 영상 신호 단자 Td를 맞추기 위함이다.

투명 유리 기판 GLS1, GLS2 사이에는 그 가장자리를 따라, 액정 봉입구 INJ를 제외하고, 액정 LC를 밀봉하도록 시일 패턴 SL이 형성된다. 시일재는, 예를 들면 에폭시 수지로 이루어진다.

도 2의 단면 구조에서 도시한 배향막 ORI층은 시일 패턴 SL의 내측에 형성된다. 액정 LC는 액정 문자의 방향을 설정하는 하부 배향막 ORI와 상부 배향막 ORI 사이에서 시일 패턴 SL로 구획된 영역에 봉입되어 있다.

이 액정 표시 장치는 하부 투명 TFT 유리 기판 GLS1측, 상부 투명 CF 유리 기판 GLS2측에서 별개로 여러가지의 층을 적층하고, 시일 패턴 SL을 기판 GLS2측에 형성하고, 하부 투명 유리 기판 SUB1과 상부 투명 유리 기판 GLS2를 중첩시켜, 시일재 SL의 개구부 INJ로부터 액정 LC를 주입하고, 주입구 INJ를 에폭시 수지 등으로 밀봉하고, 상하 기판을 절단함으로써 조립된다.

도 12는 도 11에 도시한 표시 패널에 영상 신호 구동 IC를 탑재한 TCP와 TFT 기판 GLS1 위에 저온 폴리실리콘 TFT로 형성한 신호 회로 DDC와의 접속 및 TFT 기판 GLS1에 저온 폴리실리콘 TFT로 형성한 주사 회로 GSCL과 외부를 접속한 상태를 도시하는 상면도이다.

TCP는 구동용 IC 칩이 테이프 오토메틱 본딩법(TAB)에 의해 실장된 테이프 캐리어 패키지, PCB1은 상기 TCP나 컨트롤 IC인 TCON, 기타 전원용 증폭기, 저항, 컨덴서 등이 실장된 구동 회로 기판이다. CJ는 퍼스널 컴퓨터 등으로부터의 신호 또는 전원을 도입하는 커넥터 접속 부분이다.

도 13은 테이프 캐리어 패키지 TCP를 액정 표시 패널의, 신호 회로용 단자 Td에 접속한 상태를 나타내는 주요부 단면도이다. 테이프 캐리어 패키지 TCP는 이방성 도전막 ACF에 의해 액정 표시 패널에 접속된다. 패키지 TCP는, 전기적으로는 그 선단부가 패널측의 접속 단자 Td와 접속되면 좋지만, 실제는 TFT의 보호막 PAS, 유기 보호막 FPAS의 개구부를 덮도록 형성된, 투명 공통 전극 CPT와 동일 공정으로 형성된 투명 전극 ITO와 접속되어 있다. 시일 패턴 SL의 외측의 상하 유리 기판의 간극은 세정 후 에폭시 수지 EPX 등에 의해 보호되고, 패키지 TCP와 상측 CF 기판 GLS2 사이에는 또한 실리콘 수지가 충전되어 보호가 다중화되고 있다. 또한, 상하의 유리 기판 GLS2, GLS1의 액정 LC에 대한 캡은 유기막으로 형성된 지주 SPC에 의해 그 높이가 결정되어 있다.

도 14에, 표시 매트릭스부의 등가 회로와 그 주변 회로의 결선도를 도시한다. 도 14는 회로도이기는 하지만, 실제의 기학적 배치에 대응하여 작성되어 있다.

도 14에서 DL은 드레인선을 의미하고, DL1, DL2, DL3으로서 그 숫자가 화면 좌측으로부터의 화면 내의 드레인 배선을 의미하는, 첨자 R, G 및 B가 각각 적, 녹 및 청 화소에 대응하여 부가되어 있다. GL은 게이트 배선을 의미하고, GL1, GL2로서 그 숫자가 화면 상부로부터의 화면 내의 게이트선을 의미한다. 첨자 1, 2는 주사 타이밍의 순서에 따라 부가되어 있다. CL은 공통 전극 배선을 의미하고, CL1, CL2로서 그 숫자가 화면 상부로부터의 화면 내의 공통 전극 배선을 의미한다.

또한, CSDL은 보유 용량 배선을 의미하고, CSDL1, CSDL2로서 그 숫자가 화면 상부로부터의 화면 내의 보유 용량 배선을 의미한다.

게이트 배선 GL(첨자 생략)은 유리 기판 위의 주사 회로 GSCL에 연결되고, 그 주사 회로에의 전원 또는 타이밍 신호는 유리 기판 외부의 PCB 상에 형성된 전원 및 타이밍 회로 SCC로부터 공급된다. 상기에서 저온 폴리실리콘 TFT로 구성된 유리 기판 위의 주사 회로는 용장성을 높이기 위해서 1개의 게이트선(주사선)에 대하여 좌우의 양측으로부터 급전되고 있지만, 화면 사이즈 등에 따라 편측으로부터 급전해도 된다.

한편, 드레인 배선 DL로의 급전은 유리 기판 위의 저온 폴리실리콘 TFT로 구성된 신호 회로 DDC로부터 급전된다. 신호 회로 DDC는 유리 기판의 영상 신호 회로 IC로 구성된 회로로부터의 영상 데이터를 R, G, B의 색 데이터에 따라 분배하는 기능을 갖는다. 따라서, 유리 기판 위의 신호 회로로부터의 접속 단자 수는 화면 내의 드레인 배선 수의 1/3이다.

또한, 공통선 CL은 화면 내의 화소의 공통 전위를 공급하지만, 제1 실시예의 각 전압의 구동 방식에서는 거의 일정한 전위를 공급하기 때문에, 이는 화면의 좌우로 인출되며, 통합하여 결선되고, 전원 및 타이밍 회로 IC의 SCC에 결선된다.

화면 내의 저온 폴리실리콘 TFT은 n형의 TFT이고, 게이트 배선 GL에 게이트 전압을 인가하고, 그 타이밍에서 드레인선 DL에 급전된 드레인 전압(데이터)을 공통 전극 배선 CL 사이의 액정 용량 Clc에 급전함으로써 표시를 행한다. 액정 용량 Clc의 전위를 표시 기간 중에 유지하는 능력을 향상시키기 위해서, 보유 용량 배선 CSDL과 화소 전위인 폴리실리콘층을 전극으로서, 게이트 절연막 GI를 유전체로 하는 보유 용량 Cgi 및 공통 전극 배선 CL과 화소 전극 사이의 층간 절연막 ILI를 유전체로 하는 보유 용량 Cili로 합계하여 전극 보유 용량 Cstg를 형성한다. CC는 드레인 배선 DL의 단선을 검사하는 저온 폴리실리콘 TFT로 형성한 검사 회로이고, CPAD는 검사 단자이다.

도 15는 액정 표시 모듈 MDL의 각 구성 부품을 도시하는 분해 사시도이다. SHD는 금속판으로 이루어지는 프레임 형상의 실드 케이스(메탈 프레임), LCW는 그 표시창, PNL은 액정 표시 패널, SPB는 광 확산판, LCB는 도광체, RM은 반사판, BL은 백 라이트 형광관, LCA는 백 라이트 케이스로, 도 15에 도시한 바와 같은 상하의 배치 관계로 각 부재가 적층되어 모듈 MDL이 조립된다.

모듈 MDL은 실드 케이스 SHD에 설치된 갈고리와 후크에 의해 전체가 고정되도록 되어 있다. 백 라이트 케이스 LCA는 백 라이트 형광관 BL, 광 확산판 SPB, 도광체 LCB, 반사판 RM을 수납하는 형상으로 되어 있으며, 도광체 LCB의 측면에 배치된 백 라이트 형광관 BL의 광을, 도광체 LCB, 반사판 RM, 광 확산판 SPB에 의해 표시 면에서 균일한 백 라이트로 하여, 액정 표시 패널 PNL 측으로 출사한다. 백 라이트 형광관 BL에는 인버터 회로 기판 PCB2가 접속되어 있으며, 백 라이트 형광관 BL의 전원으로 되어 있다.

이상 상세히 설명한 바와 같이 본 실시예의 구조의 최대 특징은, 특별한 보유 용량의 구성에 있고, 본 실시예에 개시 개념을 이용하여 종전계 방식의 액정 표시 장치, TN 방식, VA 방식, MVA 방식, PVA 방식, 또는 OCB 방식이나 FFS 방식의 액정 표시 장치를 구성해도 용량 증가에 의한 효과를 발휘할 수 있다.

## 〈제2 실시예〉

도 16에 본 실시예의 화소의 평면도를 도시하고, 도 17에 도 16의 17-17' 절단선을 따라 취한 단면 구조를 도시한다.

제1 실시예의 구조와의 차이는, 도 1에 임의의 게이트 배선 GL과 거의 평행하게 배치된 화소 중앙부를 가로지르는 공통 전극 배선 CL이 제거되어 있다는 점에 있다. 또한, 이에 수반하여 절연막에 개구된 컨택트 홀이 제1 실시예에서는 1 화소에 5부분인 반면, 본 실시예에서는 1 화소에 3부분으로 저감되어 있다. 이에 의해, 게이트 배선 GL과 동층인 배선이 줄어

들어 쇼트 불량율이 저감되어, 수율이 향상되는 효과를 발휘할 수 있다. 또한, 컨택트 홀 수가 저감되어 컨택트 홀의 형성 불량에 의한 오픈 불량(컨택트 홀에서의 도통으로 발생되지 않는 불량)이 저감되는 특징을 갖는다. 또한, 게이트 전극 배선 GL과 평행 배치된 공통 전극 배선 CL이 제거된 만큼, 개구율이 향상되어, 휘도의 향상을 실현할 수 있다.

본 실시예에서는 공통 전극 CPML은, 예를 들면, Mo, Al, Ti 또는 이들의 합금 등의 금속 재료로 구성하는 것이 바람직하다. 이에 의해, 제1 실시예의 저저항의 금속 재료를 이용한 공통 전극 배선 CL을 제외해도, 공통 신호의 변동을 억제할 수 있다.

또한, 상기 공통 전극 CPML을 Mo, Al, Cr, Ti 등의 금속 재료와 ITO 등의 고저항이면서 투명한 재료의 적층 구조로서, 평면적으로 공통 전극 CPML의 윤곽선보다 저저항 재료의 윤곽선을 공통 전극의 내부를 향해, 액정 재료를 포지티브형의 경우 적어도  $1.5\mu\text{m}$ , 네가티브형 액정의 경우  $3\mu\text{m}$  내측으로 설정하도록 배치하면, 그 투명 전극의 단부는 투과 영역으로 되어 IPS 방식의 액정 표시 장치는 더욱 밝아진다. 이 경우, 투명 화소 전극 SPT는 그 투명 전극 단층이여도 된다.

도 17은 도 16의 17-17'선을 따라 취한 단면도이다. 영상 전압이 인가되는 드레인 배선 DL로부터 고농도의 n+ 형 폴리실리콘 PSI(n+), 게이트 배선 GL에 온 전압이 인가된 경우에 반전하여 도통하는 p형 폴리실리콘 PSI(p), 제2 컨택트 홀 CNT2를 거쳐 금속 화소 전극 SPM에, 다시 제5 컨택트 홀 CNT5를 거쳐 투명 화소 전극 SPT에 이르는 것이 화소 전위의 충전 경로이다. 한편, 보유 용량 배선 CSTL은 TFT가 온 상태로 되는 전압 Vst가 인가되어 있으며, 게이트 절연막 GI를 유전체로 하는 단위 면적당 큰 보유 용량치를 얻을 수 있는 구조로 되어 있다.

공통 전극 CPML은 상술한 바와 같이 저저항 금속 재료나 또는 저저항 금속 재료와 고저항이면서 ITO와 같은 투명 전극의 적층 구조로 구성되어 있다. 그 경우, 투명 화소 전극 SPT도 공통 전극 CPML과 동일 공정, 재료로 구성된 저저항의 금속 재료로 구성해도 된다.

### 〈제3 실시예〉

도 18은 본 실시예에서의 화소의 평면도이고, 도 19는 도 18의 19-19' 절단선을 따라 취한 단면 구조이고, 도 20은 도 18의 20-20' 절단선을 따라 취한 단면 구조이다.

제1 실시예 및 제2 실시예에서는, 보유 용량 배선 CSTL은 게이트 배선 GL과 인접하여 배치되어 있지만, 본 실시예에서는 드레인 배선 DL 사이의 중앙부, 즉 제1 실시예의 도 1의 공통 전극 배선 CL이 배치된 위치에 보유 용량 배선 CSTL이 배치되어 있다. 또한, 이 보유 용량 배선 CSTL은 평면적으로는 공통 전극 CPML 및 금속 화소 전극 SPM이 겹쳐지도록 피복되어 있다. 이에 의해, 단락을 방지하면서 CSTL로부터의 누설 전류의 실드가 실현된다.

본 구조에서는 제1 실시예에 비하여, 보유 용량 배선 CSTL이 점유하는 면적의 개구율이 향상되어, 밝은 액정 표시 장치를 실현할 수 있다.

도 19는 도 18의 19-19' 절단선을 따라 취한 단면도이다. 화소의 액정 용량을 구동하는 TFT 및 보유 용량부의 단면 구조를 도시한다. TFT의 동작은 제1 실시예 및 제2 실시예와 마찬가지이다. TFT의 게이트 배선 GL에 온 전압이 인가되면 드레인 배선 DL로부터의 전류가 흐른다. 그 때에, 보유 용량 배선 CSTL이 온 전압이 인가되어 있기 때문에, 보유 용량 CSTL을 한쪽의 전극으로 하고, p형 폴리실리콘 PSI(p)를 다른 쪽의 전극으로 하여, 유전체를 게이트 절연막 GI로 하는 보유 용량이 동작한다. 액정 분자는 저저항의 금속 또는 저저항의 금속과 ITO 등의 투명 전극의 적층인 공통 전극 CPML과, TFT로부터 전류를 공급하고, 금속 화소 전극에 접속된 투명 화소 전극 SPT 사이에서 형성되는 기판과 평행한 방향의 성분을 갖는 전류, 즉 횡전류로 구동된다.

도 19에서, 보유 용량 배선 CSTL은 금속 화소 전극 SPM과 CPML로 전기적으로 실드된다.

도 20은 도 18의 20-20' 절단선을 따라 취한 단면도로서, 서로 이웃하는 드레인 배선 DL 사이를 가로지르는 보유 용량 배선 CSTL에 관한 단면도이다.

서로 이웃하는 드레인 배선 DL 사이의 하부를 층간 절연막 ILI를 사이에 두고 보유 용량 배선 CSTL이 가로지르고 있다. 보유 용량은, 보유 기간도 포함하여 TFT의 게이트의 온 전압 이상의 전압이 인가되어 있다. 따라서, 게이트 절연막 GI와 접하는 p형 폴리실리콘 PSI(p) 계면에는 전자가 유기되어 p형 폴리실리콘으로 동작한다. 따라서, 게이트 절연막 GI를 유전체로 하는 보유 용량으로서 기능한다.

한편, 상기 보유 용량 배선 CSTL의 전압은 액정에의 구동 전압과는 다르기 때문에, 이것은 전기적으로 실드할 필요가 있다. 제1 실시예 및 제2 실시예에서는 이것을 투명 공통 전극 CPT 또는 공통 전극 CPML의 공통 전위로 행했다.

본 실시예에서는 단면 구조에서 알 수 있는 바와 같이, 유기 보호막 FPAS 상의 공통 전극 CPML과 투명 화소 전극 SPM은, 기본적으로는 동일 공정으로 형성하고 있기 때문에, 예를 들면 공통 전극 CPML만으로의 피복 실드는 전기적으로 쇼트 불량이 되므로 할 수 없다. 그래서, 액정에는 공통 전극의 전위, 화소 전극의 전위이면 전계의 왜란은 발생하지 않기 때문에, 공통 전극 CPML과 금속 화소 전극 SPM, 또한 투명 화소 전극 SPT를 절연막인 충간 절연막 ILI 및 보호막 PAS 및 유기 보호막 FPAS의 적층막으로 끼워, 상호 쇼트되지 않도록 겹쳐 포캡으로써 전기적으로 실드하고 있는 것이 특징으로 되어 있다.

이상의 각 실시예는, 소위 n형의 MOS 구조의 TFT를 이용한 IPS 방식의 TFT 액정 표시 장치로 기재하였지만, 이것을 p형 MOS 구조를 이용한 방식에서 사용할 수 있는 것은 물론이다.

#### 〈제4 실시예〉

도 21은 본 실시예에서의 화소의 평면도이고, 도 22는 도 21의 22-22' 절단선을 따라 취한 단면 구조이고, 도 23은 도 22의 변형 예이다.

본 실시예에서는 PSI와 CSTL에 의한 용량 형성의 개념을 TN 방식에 적용한 것이다. PX는 화소 전극이고, CNT2에 의해 PSI와 접속되어, 화소 전위가 공급된다. PX는 ITO 등의 투명 전극으로 구성되고, 또한 개구율 향상의 관점에서 경계부를 GL 상 및 DL 상에 구성하고 있다. 대향 기판(도시 생략)에는 공통 전극이 ITO 등의 투명 전극으로 형성되고, 해당 공통 전극과 화소 전극 사이의 전위차를 기판과 수직인 방향에 형성하는, 소위 종전계에 의해 액정 문자가 구동된다.

본 실시예에서는 IPS 이외의 방식이라도, 보유 용량의 증대를 실현하였다.

도 22는 도 21의 22-22' 절단선을 따라 취한 단면도이다. 화소의 액정 용량을 구동하는 TFT 및 보유 용량부의 단면 구조를 도시한다. TFT의 동작은 제1 실시예와 마찬가지이다. TFT의 게이트 배선 GL에 온 전압이 인가되면, 드레인 배선 DL로부터의 전류가 흐른다. 그 때에, 보유 용량 배선 CSTL에 온 전압이 인가되어 있기 때문에, 보유 용량 CSTL을 한쪽의 전극으로 하고, p형 폴리실리콘 PSI(p)를 다른 쪽의 전극으로 하며, 유전체를 게이트 절연막 GI로 하는 보유 용량이 동작한다.

도 23은 도 22의 변형 예이다. PX와 PSI의 CNT2에 의한 컨택트 대신에, PSI와 DL층에서 형성된 PAD가 한 번 컨택트하고, 이 PAD와 PX가 컨택트하고 있다. PST는 반도체층으로, 산소의 존재에 의해 산화됨으로써 표면에 산화층이 형성되어, 접속 저항의 증가가 일어날 수 있다. PX는 투명 전극이지만, 이것은 예를 들면 ITO와 같이 대부분 도전성 산화물이기 때문에, 이 현상에 대한 대책을 강구함으로써 신뢰성의 향상과 특성의 향상을 도모할 수 있다.

따라서, PAD를 구성하고, PSI와 접속하는 것은 어디까지나 금속층으로 하고, 해당 금속층인 PAD와 PX를 접속함으로써 전기적인 접속을 행했다.

본 실시예와 같이 종전계 방식의 액정 표시 장치, TN 방식, VA 방식, MVA 방식, PVA 방식, 또는 OCB 방식이나 FFS 방식의 액정 표시 장치를 구성해도 용량 증가에 의한 효과를 발휘할 수 있다.

또한, 본 명세서에 있어서 폴리실리콘은, 비정질에 대향하는 의미로서, 결정성이 부여된 반도체의 의미로 이용되고 있으며, 고온, 저온을 막론하고 폴리실리콘 또는 p-Si는 전부 포함한다. 거대 결정 실리콘, 연속 입계 실리콘, CGS도 포함한다. 또한 단결정이어야 된다. 반도체는 실리콘에 한정되지 않고, 다른 반도체라도 결정성을 부여받은 것이면 어떠한 것이어도 된다.

#### 〈제5 실시예〉

도 24에 본 실시예의 화소의 평면도를 도시하고, 도 25에 도 24의 25-25' 절단선을 따라 취한 단면 구조를 도시한다. 본 실시예 구조 및 그 동작은, 제2 실시예에서의 내용을 기본으로 기재되어 있다.

제1 실시예의 구조와의 차이는, 도 16에 있는 게이트 배선 GL과 거의 평행하게, n+ 형 폴리실리콘 PSI가 연장되도록 배치된 점에 있다. 이에 의해, IPS 표시 장치의 오동작을 저감시키기 위한, 화소 전극 및 공통 전극 전위 이외의 전위인, 게이트 배선 GL 또는 보유 용량 배선 CSTL, 또한, 드레인 배선 DL의 전위를 가능한 한 실드하는 효과가 높아져 화질이 우수한 IPS 액정 표시 장치를 제공할 수 있다.

동작은 거의 평행하게 배치된 게이트 배선 GL 및 보유 용량 배선 CSTL에 대하여, 이것을 상부의 유기 보호막을 통해 피복된 그 공통 전극 배선 CPML의 그 단부의 하부 부근에 화소 전극 전위인 폴리실리콘 PSI를 평행하게 배치하고, 게이트 배선 GL의 전계의 누설을 저감시킨다. 보유 용량 배선 CSTL에 관해서는 그에 가장 가까운 공통 전극 배선 CPML의 단부의 하부는 상기 보유 용량 배선 CSTL의 하부로부터 돌출된 폴리실리콘 PSI로 실드된다.

도 25는 도 24의 25-25'선을 따라 취한 단면도이다. 게이트 배선 GL은 도면 좌측에서의 상부는 유기 보호막 FPAS를 통해 ITO로 구성된 공통 전극 배선 CPML로, 하부는 게이트 절연막 GI 하부의 n+ 형 폴리실리콘 PSI로 실드되어 있다. 한편, 보유 용량 배선 CSTL은 도면 우측에서의 상부는 마찬가지로 공통 전극 배선 CPML로, 하부는 돌출된 n+ 형 폴리실리콘 PSI로 실드되어 있다. 이와 같이 IPS 액정 표시 장치의 오동작의 원인이 되는 게이트 배선 GL 또는 보유 용량 배선 CSTL을 절연막을 끼워 상부로부터 ITO 등의 공통 전극 배선 CSTL, 하부로부터 폴리실리콘 등의 화소 전극으로 끼우도록 실드하여 그 효과가 높아진다.

상기, 공통 전극 배선 단부의 하부에서 절연막을 사이에 두고, 오동작의 원인이 되는 게이트 배선이나 보유 용량 배선의 하부에 배치된 폴리실리콘 PSI의 전위는, 본 실시예에서는 화소 전극 전위를 사용하고 있지만, 전위로서는 공통 전극 배선의 전위와 동일해도 그 실드 효과는 동등 이상이다.

이상 각 실시예를 이용하여 본 발명의 사상을 상세하게 설명했지만, 상기 각 실시예의 사상에 따라 적용해도 되는 것은 물론이다.

### 발명의 효과

이상 상세하게 설명한 바와 같이, 본 발명에 따르면 큰 보유 용량을 안정적으로 실현할 수 있어, 고화질, 고수율, 고성능의 액정 표시 장치를 실현할 수 있다. 특히, 저온 폴리실리콘 TFT로 구성된 IPS 표시 방식의 액정 표시 장치에 있어서, 큰 보유 용량을 안정적으로 동작시키는 구조, 구동이 실현되어, 수율이 높고, 밝고, 신뢰성이 높은 TFT 액정 표시 장치를 제공할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고,

상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고,

상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서,

상기 TFT 소자를 구성하는 반도체층을 갖고,

절연층을 사이에 두고 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고,

상기 반도체층과 용량 배선간에, 상기 반도체층을 도통 상태로 할 수 있는 극성의 전위차가 게이트 배선의 전압이 오프로 되는 유지 기간 중 인가되는 것을 특징으로 하는 액정 표시 장치.

## 청구항 2.

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고,

상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고,

상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서,

상기 TFT 소자와 일체로 구성된 반도체층을 갖고,

절연층을 사이에 두고 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고,

상기 TFT 소자와 일체로 형성된 반도체층은, 상기 TFT 소자의 게이트 전극에 대하여 상기 드레인 배선이 형성된 측과는 반대 측에서 상기 화소 전극과 전기적으로 접속하고,

상기 용량 배선에 상기 반도체층을 도통 상태로 하는 전압을 게이트 배선의 전압이 오프로 되는 유지 기간 중 인가하는 것을 특징으로 하는 액정 표시 장치.

## 청구항 3.

투명한 제1 기판과 제2 기판 사이에 협지되는 액정층을 갖고,

상기 제1 기판 위에는 복수의 게이트 배선과, 그 복수의 게이트 배선과 매트릭스 형상으로 교차하는 복수의 드레인 배선을 갖고,

상기 복수의 게이트 배선 및 드레인 배선으로 둘러싸이는 영역에 의해 화소가 구성되고, 각 화소는 적어도 하나의 TFT 소자를 갖고, 상기 TFT 소자에 의해 상기 드레인 배선으로부터의 신호가 상기 게이트 배선의 신호에 의해 선택되어 전기적으로 공급되는 화소 전극을 갖는 액정 표시 장치에 있어서,

상기 화소 전극은 금속 재료층과 투명 도전체층의 2층으로 구성되고,

상기 TFT 소자와 일체로 구성된 반도체층을 갖고,

절연층을 사이에 두고 상기 반도체층과 용량 소자를 구성하는 용량 배선을 갖고,

상기 반도체층은, 상기 화소 전극의 금속층과 상기 절연층에 형성된 관통 홀에 의해 접속되고, 상기 화소 전극의 금속층과 상기 화소 전극의 투명 도전체층은 별도의 절연층에 형성된 관통 홀에 의해 접속되고,

상기 용량 배선에 상기 반도체층을 도통 상태로 하는 전압을 게이트 배선의 전압이 오프로 되는 유지 기간 중 인가하는 것을 특징으로 하는 액정 표시 장치.

## 청구항 4.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 제1 기판 위에 공통 신호선을 갖고, 상기 공통 신호선과 상기 화소 전극이 평면적으로 중첩부를 갖고,

해당 공통 신호선과 상기 용량 배선의 전위가 서로 다른 것을 특징으로 하는 액정 표시 장치.

### 청구항 5.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 제1 기판 위에 공통 전극을 갖고, 상기 화소 전극과 이격되어 구성되고, 해당 공통 전극과 해당 화소 전극 간에 형성되는 상기 제1 기판과 평행한 방향의 성분을 갖는 전계에 의해 상기 액정층을 구동하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 6.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 반도체층과 상기 용량 배선 사이의 절연막의 막 두께가, 상기 화소 전극에 접하는 어느 절연막의 막 두께보다도 얇은 것을 특징으로 하는 액정 표시 장치.

### 청구항 7.

제6항에 있어서,

상기 반도체층과 상기 용량 배선 사이의 절연막이  $\text{SiO}_2$ 인 것을 특징으로 하는 액정 표시 장치.

### 청구항 8.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 용량 배선의 전위가, 상기 게이트 배선의 ON 전위와 동일한 것을 특징으로 하는 액정 표시 장치.

### 청구항 9.

삭제

### 청구항 10.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 용량 배선에 절연막을 사이에 두고 평면적으로 중첩하여 실드 전극이 구성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 11.

제10항에 있어서,

상기 실드 전극이, 상기 공통 전극 또는 상기 공통 전극 배선인 것을 특징으로 하는 액정 표시 장치.

### 청구항 12.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 반도체층이, 폴리실리콘인 것을 특징으로 하는 액정 표시 장치.

### 청구항 13.

제12항에 있어서,

상기 반도체층이, p-TFT 또는 n-TFT 중 어느 하나로 구성되고, 화소 영역밖에 설치된 TFT와 동일한 형인 것을 특징으로 하는 액정 표시 장치.

### 청구항 14.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 제1 기판의 배면에 백 라이트 유닛을 갖는 액정 표시 장치.

### 청구항 15.

삭제

### 청구항 16.

삭제

### 청구항 17.

삭제

### 청구항 18.

삭제

### 청구항 19.

삭제

### 청구항 20.

삭제

### 청구항 21.

삭제

### 청구항 22.

삭제

### 청구항 23.

삭제

### 청구항 24.

삭제

청구항 25.

삭제

청구항 26.

삭제

청구항 27.

삭제

청구항 28.

삭제

청구항 29.

삭제

청구항 30.

삭제

청구항 31.

삭제

청구항 32.

삭제

도면

도면1

도면2

도면3

도면4

도면5a

도면5b

도면5c

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24

도면25

|                |                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">KR100539336B1</a>                                                                             | 公开(公告)日 | 2005-12-28 |

| 申请号            | KR1020020051066                                                                                           | 申请日     | 2002-08-28 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA                                                                                   |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                                 |         |            |

| [标]发明人         | OCHIAI TAKAHIRO<br>오찌아이다까히로<br>OKE RYUTARO<br>오께류따로<br>IMAYAMA HIROTAKA<br>이마야마히로따까<br>ONO KIKUO<br>오노기꾸오 |         |            |

| 发明人            | 오찌아이다까히로<br>오께류따로<br>이마야마히로따까<br>오노기꾸오                                                                    |         |            |

| IPC分类号         | G02F1/133 G02F1/1343 G02F1/1362 G09F9/30 G02F1/136 G02F1/1368 G09F9/35                                    |         |            |

| CPC分类号         | G02F1/1368 G02F1/134363 G02F1/136213 G02F2202/104                                                         |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                            |         |            |

| 优先权            | 2001349571 2001-11-15 JP                                                                                  |         |            |

| 其他公开文献         | KR1020030040025A                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                 |         |            |

### 摘要(译)

在液晶显示装置中，在存储电容器布线之间形成电容器，其中半导体层作为一个电极，夹在其间的绝缘膜，并且电压施加到存储电容器布线，使得MOS晶体管始终保持导通。可以获得TFT显示装置，其中存储电容器值大并且可以进行稳定的显示。1指数方面 液晶显示，存储容量，MOS晶体管，IPS模式