**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

G02F 1/136

(45) 공고일자 2005년02월21일

(11) 등록번호 10-0471397

(24) 등록일자 2005년02월01일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2001-0030552 | (65) 공개번호 | 10-2002-0091683 |

| (22) 출원일자 | 2001년05월31일     | (43) 공개일자 | 2002년12월06일     |

(73) 특허권자

비오이 하이디스 테크놀로지 주식회사

경기도 이천시 부발읍 아미리 산 136-1

(72) 발명자

노정동

부산광역시영도구봉래동4가134번지11/2

이승희

경기도이천시창전동49-1현대아파트102-1206

(74) 대리인

강성배

심사관 : 임동재

**(54) 프린지 필드 스위칭 액정표시장치 및 그 제조방법**

**요약**

본 발명은 프린지 필드 스위칭 액정표시장치 및 그 제조방법에 관한 것으로, 상부기판과 대향하는 하부기판상에 단위 화소를 한정하도록 배치되어 있는 데이터 버스 라인 및 스토리지 커패시턴스 버스 라인과; 상기 스토리지 커패시턴스 버스 라인에 평행하며 단위 화소를 양분하도록 배치되어 있는 게이트 버스 라인과; 상기 게이트 버스 라인 상에 배치되어 있는 박막트랜지스터와; 상기 단위 화소내에 형성되어 있는 카운터 전극과; 상기 카운터 전극과 오버랩되어 프린지 필드를 형성하며 상기 박막트랜지스터와 비아홀을 통해 전기적으로 콘택되는 화소전극을 포함하여 구성되며, 상기 화소전극은 상기 카운터 전극의 가장자리에 배치되는 틀 형상의 바디부와, 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 게이트 버스 라인과 일정 각도를 이루는 다수의 사선형 슬릿을 포함하고, 상기 화소전극의 사선형 슬릿의 각도는 상기 게이트 버스 라인을 중심으로 상하 대칭을 이루며, 상기 스토리지 커패시턴스 버스 라인은 어느 하나의 단위 화소내 화소전극의 상부 가장자리와 최인접 단위 화소내 화소전극의 하부 가장자리와 일부 중첩되는 것이며, 화소내 구조를 변경하여 빛샘 현상을 제거 또는 최소화시켜 블랙매트릭스 영역을 줄일 수 있고, 개구율과 투과율이 향상되는 것이다.

**대표도**

도 2

**명세서**

**도면의 간단한 설명**

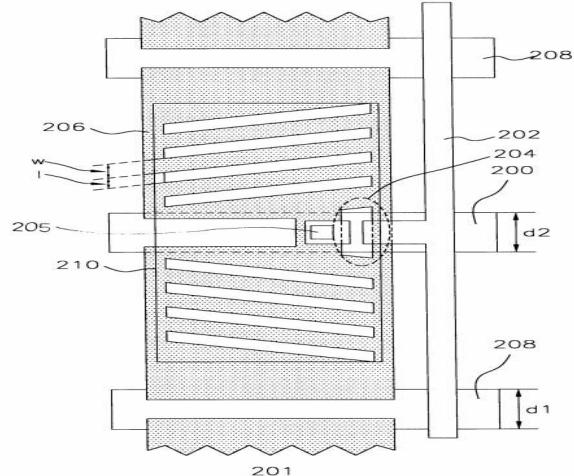

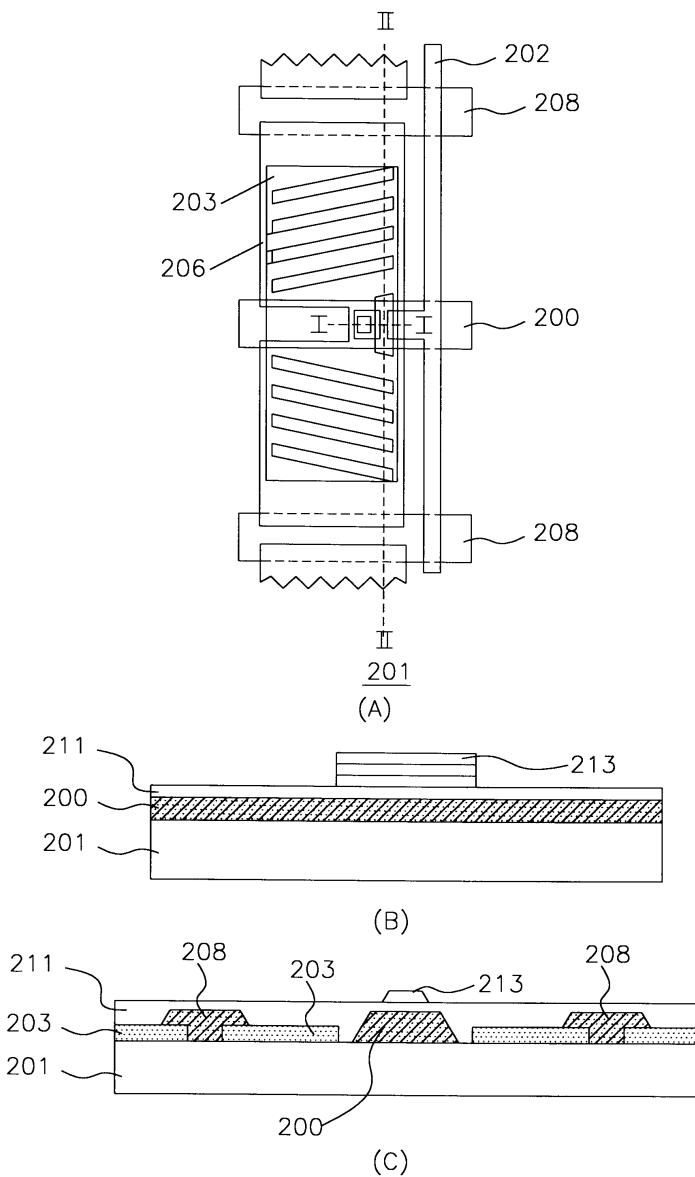

도 1은 종래 기술에 따른 프린지 필드 스위칭 액정표시장치의 단위 화소를 도시한 평면도.

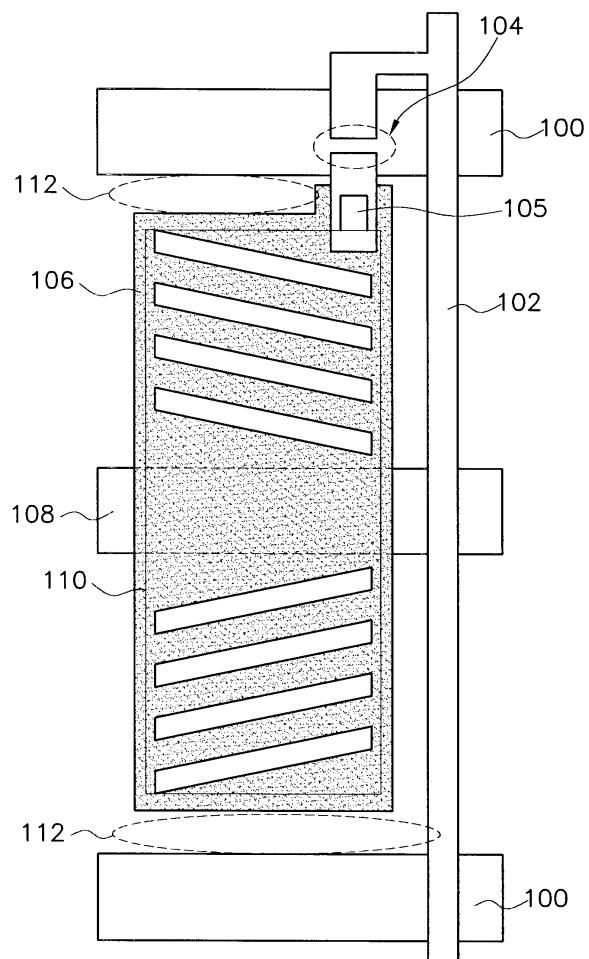

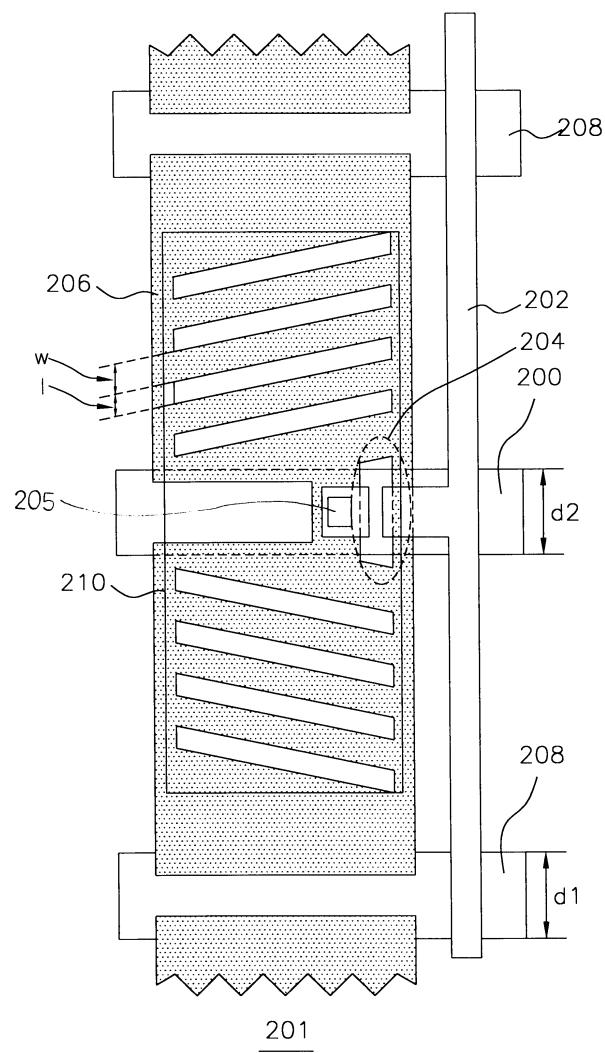

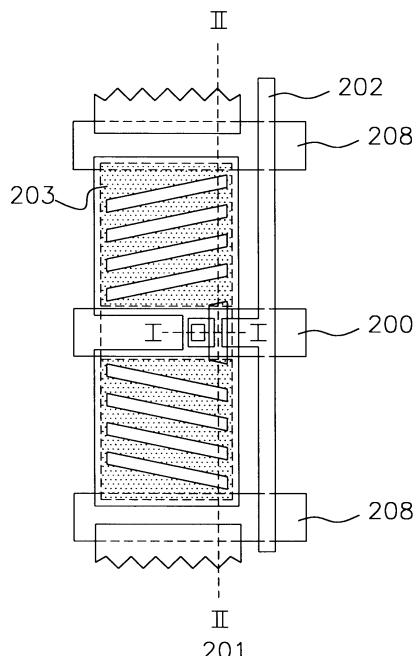

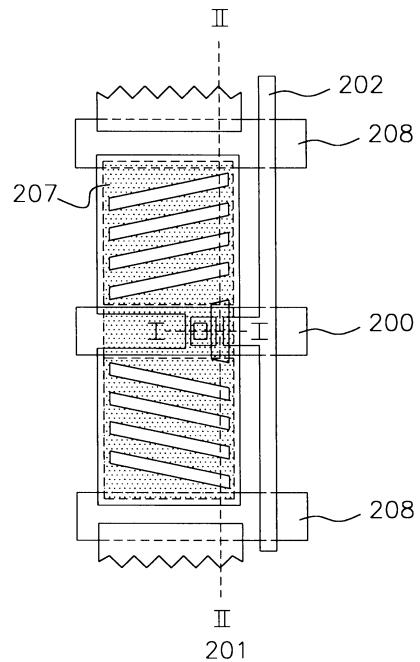

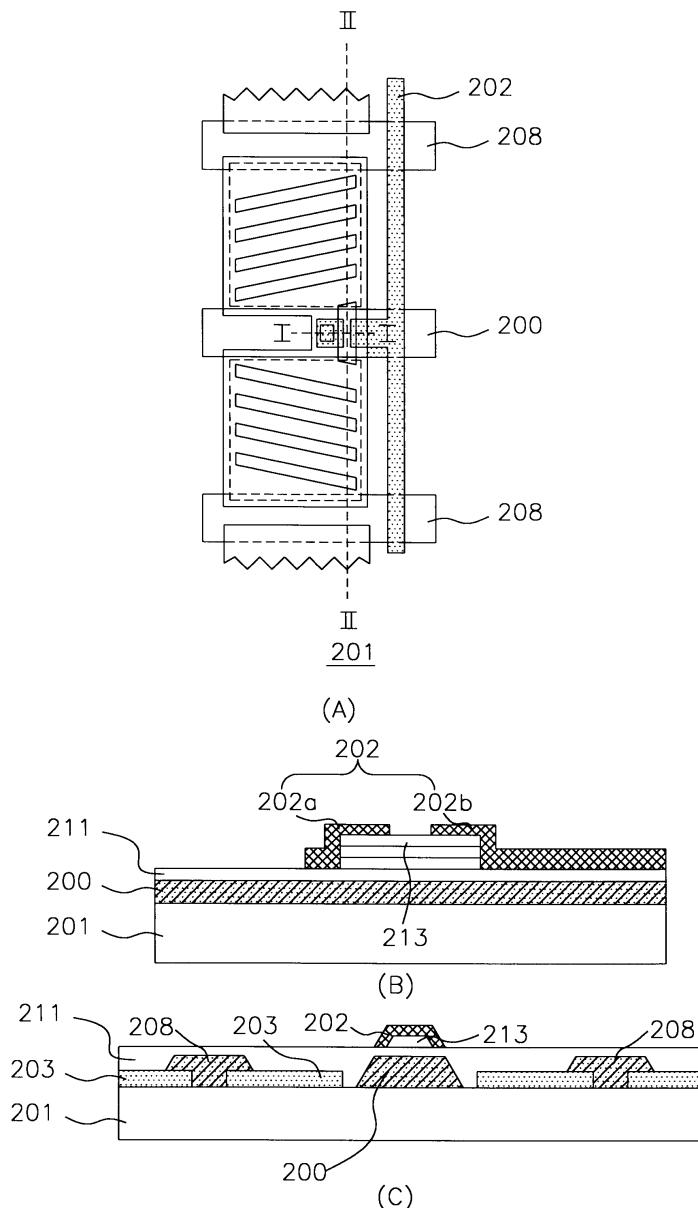

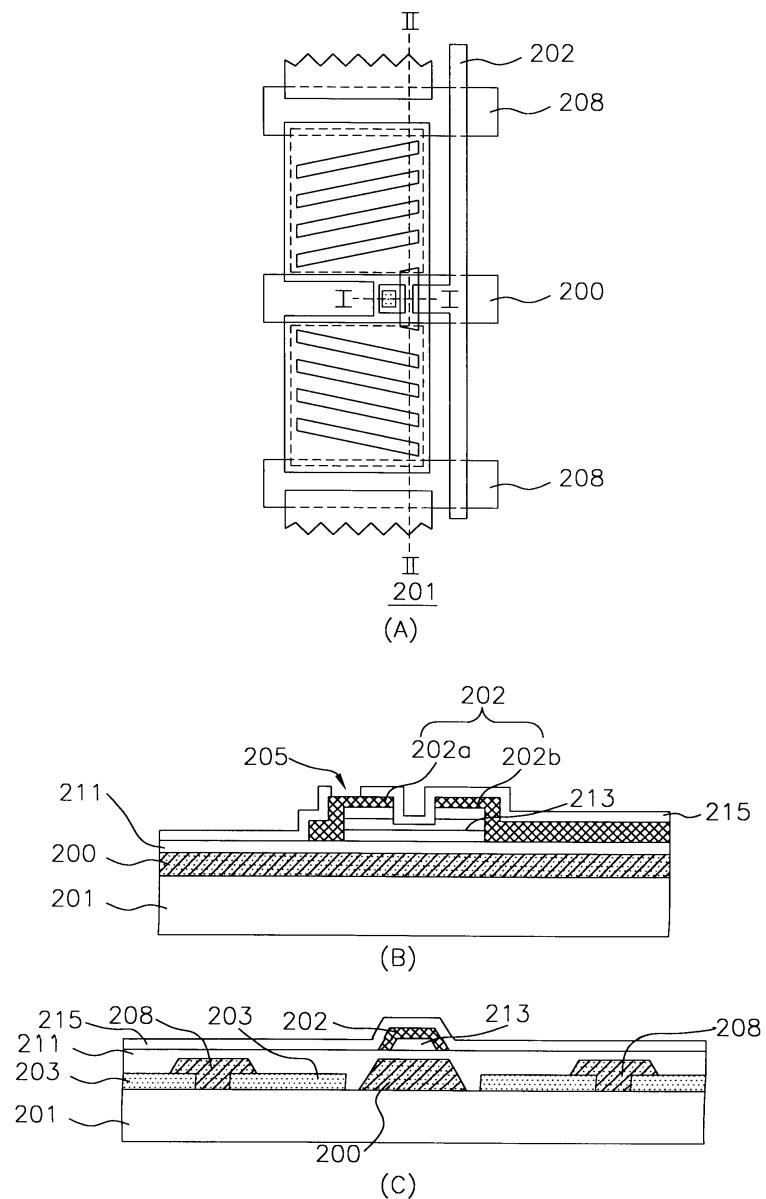

도 2 및 3은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 단위 화소를 도시한 평면도.

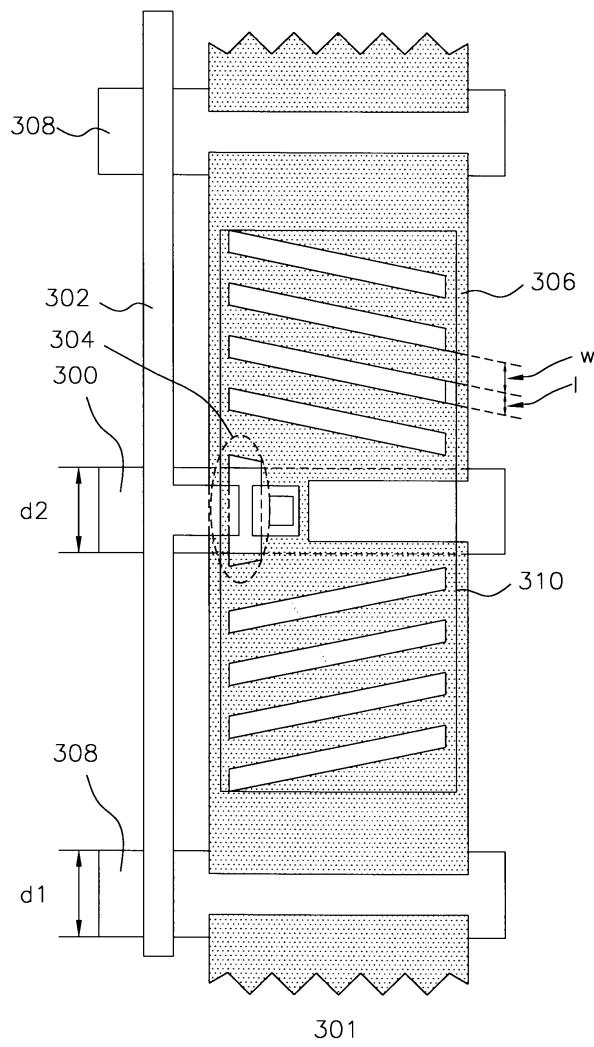

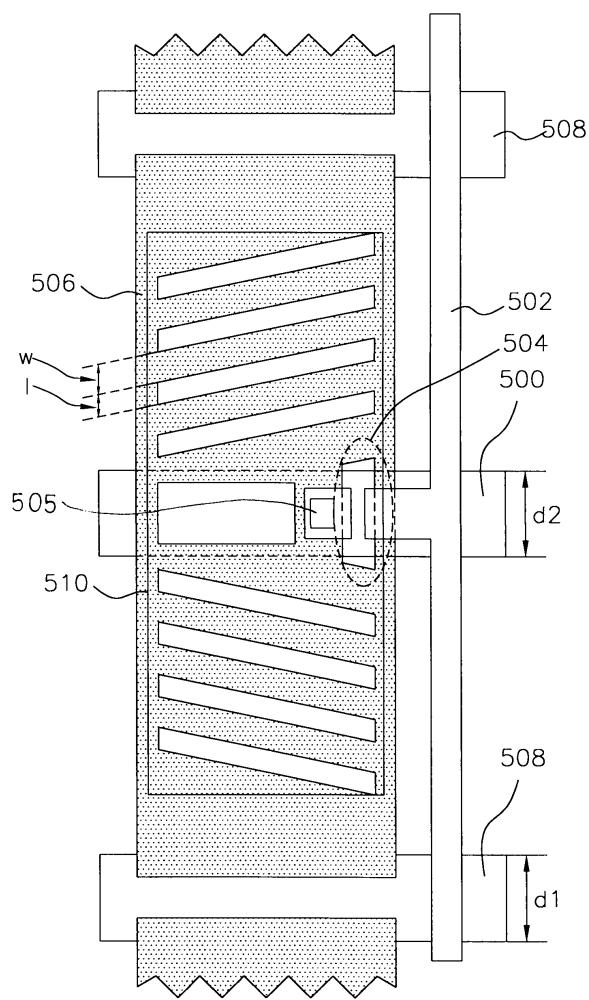

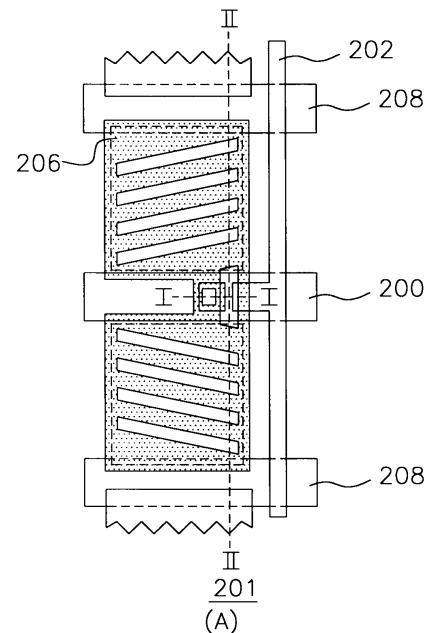

도 4는 본 발명의 변형 실시예에 따른 프린지 필드 스위칭 액정표시장치의 단위 화소를 도시한 평면도.

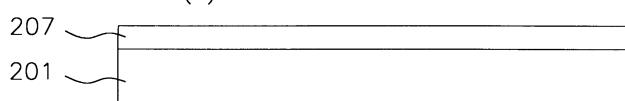

도 5는 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 상대전극 형성을 나타내는 도면.

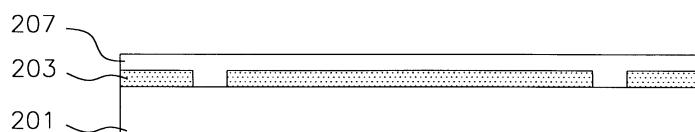

도 6은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 상대전극상의 절연막 형성을 나타내는 도면.

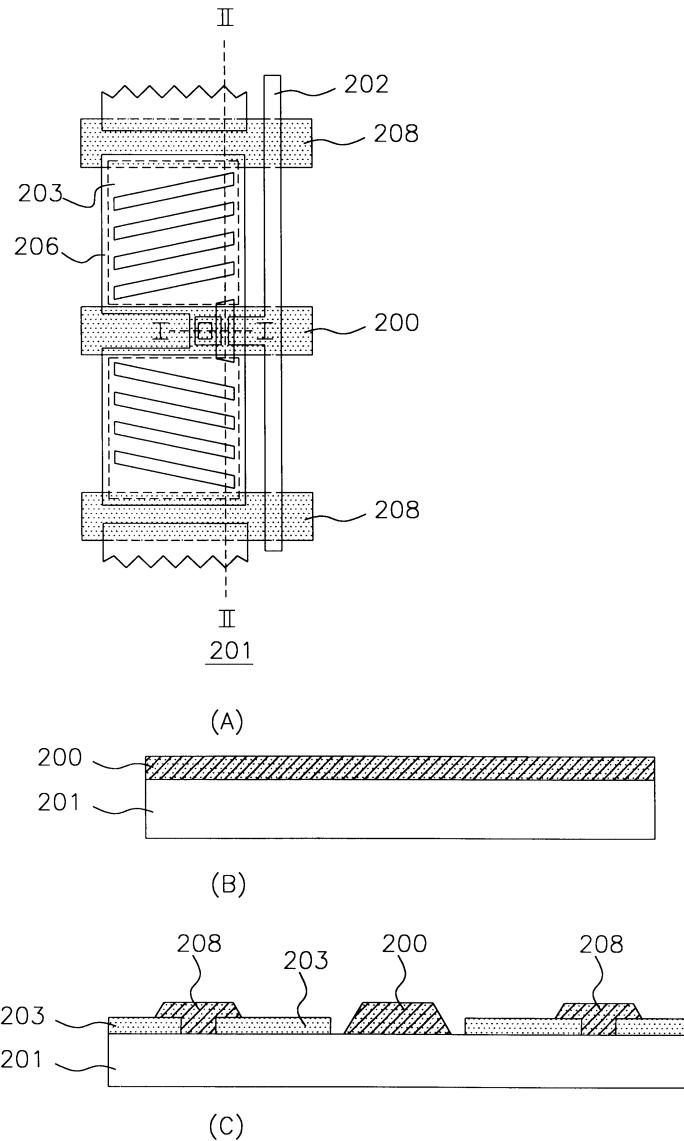

도 7은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 게이트 버스 라인 및 스토리지 커페시턴스 버스 라인 형성을 나타내는 도면.

도 8은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 액티브층 형성을 나타내는 도면.

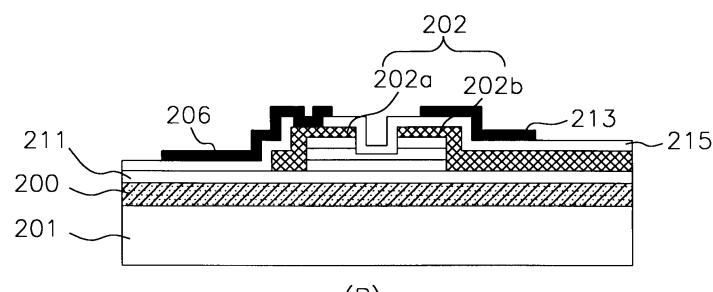

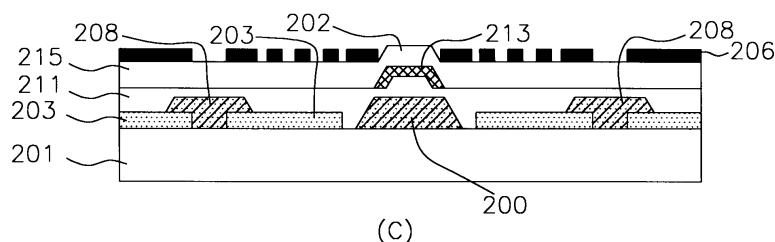

도 9는 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 데이터 버스 라인 및 소오스/드레인 전극 형성을 나타내는 도면.

도 10은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 보호막 및 비아홀 형성을 나타내는 도면.

도 11은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 화소전극 형성을 나타내는 도면.

\* 도면의 주요부분에 대한 부호의 설명 \*

200; 게이트 버스 라인 201; 하부기판

202; 데이터 버스 라인 203; 상대전극

204; 박막트랜지스터 205; 비아홀

206; 화소전극 207; 절연막

208; 스토리지 커페시턴스 버스 라인 210; 블랙매트릭스 애지

211; 절연막 213; 액티브층

215; 보호막

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 프린지 필드 스위칭 액정표시장치 및 그 제조방법에 관한 것으로, 보다 상세하게는 개구율과 투과율이 향상된 프린지 필드 스위칭 액정표시장치 및 그 제조방법에 관한 것이다.

프린지 필드 스위칭 액정표시장치는 인플레이인 스위칭 액정표시장치의 낮은 개구율 및 투과율을 개선시키기 위하여 제안된 것으로, 카운터 전극과 화소전극을 투명 전도체로 형성하면서, 카운터 전극과 화소전극과의 간격을 상, 하기판 사이의 간격보다 좁게 형성하여, 카운터 전극과 화소전극간에 프린지 필드(fringe field)가 형성되도록 하는 것이다.

이와 같은 프린지 필드 스위칭 액정표시장치는 화소 공간에 있는 대부분의 분자들이 모두 동작되어 고개구율 및 고투과율을 얻을 수 있지만, 카운터 전극과 화소전극 사이에 전계가 형성되면 굴절율이 방성을 갖는 액정 분자들이 동일한 방향으로 일제히 동작되므로, 시야각에 따라서는 화이트 상태이어야 함에도 불구하고 소정의 색상이 나타나는 컬러 쉬프트 현상이 나타나는 바, 이의 해결을 위하여 다음과 같은 구조를 갖는 프린지 필드 스위칭 액정표시장치가 제안되었다.

종래 컬러 쉬프트를 방지하기 위한 프린지 필드 스위칭 액정표시장치는, 도 1에 도시된 바와 같이, 게이트 버스 라인(100)과 데이터 버스 라인(102)에 의해 한정되어 지는 단위 화소를 상하로 이동분하도록 스토리지 커페시턴스 버스 라인(108)이 놓여 있으며, 상기 게이트 버스 라인(100)과 데이터 버스 라인(102)의 교차점에는 스위칭 소자인 박막트랜지스터(104)가 배치되어 있으며, 단위 화소내에는 카운터 전극(미도시)과 이와 중첩되는 화소전극(106)이 배치된다.

여기서, 화소전극(106)은 비아홀(105)을 통하여 박막트랜지스터(104)내의 소오스 전극과 콘택되며, 틀 형상의 바디부와 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 게이트 버스 라인(100)과 일정 각도를 이루는 사선형 슬릿을 포함하고 있다. 이때, 사선형 슬릿은 스토리지 커페시턴스 버스 라인(108)을 중심으로 상하로 대칭되어 있다. 이러한 전극 구조를 가지므로 형성되는 프린지 필드 역시 스토리지 커페시턴스 버스 라인(108)을 중심으로 상하로 대칭을 이루고, 이에 따라 액정 분자들도 스토리지 커페시턴스 버스 라인(108)을 중심으로 상하로 대칭되어 배열되므로 화면의 어느 방향에서나 액정 분자의 장축 및 단축이 모두 보여지게 된다. 따라서, 액정 분자의 굴절율이 방성을 갖는 것이다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 종래와 같은 프린지 필드 스위칭 액정표시장치에 있어서는 패널에 크로스 토크(CROSS TALK) 패턴과 같은 신호가 인가되었을 때, 화소전극(106) 및 카운터 전극(미도시)의 애지(EDGE) 부분과 주의의 게이트 버스 라인

(100)과 데이터 버스 라인(102) 사이의 공간(112)에서 전계가 형성되어 원치 않은 빛샘이 발생한다. 한편, 이러한 빛샘을 방지하기 위하여는 종래는 불가피하게 합착 마진이나 시야각 등을 고려하여, 도 1에 도시된 바와 같이, 상부 기판상의 블랙매트릭스(110)를 필요 이상으로 화소 영역내로 형성할 수 밖에 없었던 바, 이로 인하여 패널의 전체적인 개구율이 떨어져서 휙도가 저하되는 문제점이 있었다.

또한, 소비전력 문제로 인하여 적정 휙도를 유지하면서 브라이트(BRIGHT) 상태에서의 휙도를 높이기 위해서는 패널의 개구율을 향상시키는 방법 밖에 없는데 종래 구조는 상부기판상의 블랙매트릭스를 획기적으로 줄이는데 한계가 있었다.

이에, 본 발명에 따른 프린지 필드 스위칭 액정표시장치 및 그 제조방법은 종래 기술의 문제점을 해결하기 위하여 안출된 것으로, 본 발명의 목적은 화소내 구조를 변경하여 빛샘 현상을 제거 또는 최소화시켜 블랙매트릭스 영역을 줄이거나 완전히 제거할 수 있으며, 또한 화소 전체 크기는 유지하면서 화소전극의 크기를 확대하여 투과율을 발생시키는 슬릿을 보다 많이 형성할 수 있어서 개구율과 투과율이 향상된 프린지 필드 스위칭 액정표시장치 및 그 제조방법을 제공함에 있다.

### 발명의 구성 및 작용

상기 목적을 달성하기 위한 본 발명에 따른 프린지 필드 스위칭 액정표시장치는, 상부기판과; 상기 상부기판과 대향하는 하부기판상에 단위 화소를 한정하도록 배치되어 있는 데이터 버스 라인 및 스토리지 커패시턴스 버스 라인과; 상기 스토리지 커패시턴스 버스 라인에 평행하며 단위 화소를 양분하도록 배치되어 있는 게이트 버스 라인과; 상기 게이트 버스 라인 상에 배치되어 있는 박막트랜지스터와; 상기 단위 화소내에 형성되어 있는 카운터 전극과; 상기 카운터 전극과 오버랩되어 프린지 필드를 형성하며 상기 박막트랜지스터와 비아홀을 통해 전기적으로 콘택트되는 화소전극을 포함하여 구성되며, 상기 화소전극은 상기 카운터 전극의 가장자리에 배치되는 틀 형상의 바디부와, 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 게이트 버스 라인과 일정 각도를 이루는 다수의 사선형 슬릿을 포함하고, 상기 화소전극의 사선형 슬릿의 각도는 상기 게이트 버스 라인을 중심으로 상하 대칭을 이루며, 상기 스토리지 커패시턴스 버스 라인은 어느 하나의 단위 화소내 화소전극의 상부 가장자리와 최인접 단위 화소내 화소전극의 하부 가장자리와 일부 중첩하는 것을 특징으로 한다.

또한, 상기 목적을 달성하기 위한 본 발명에 따른 프린지 필드 스위칭 액정 표시장치의 제조방법은, 투명성 절연기판상에 상대전극을 형성하는 단계; 상기 상대전극이 형성된 투명성 절연기판상에 단위화소를 한정하도록 상하 외관에 스토리지 커패시턴스 버스 라인을 각각 형성하는 단계와 상기 단위화소를 상하 이동분하는 게이트 버스 라인을 형성하는 단계; 상기 게이트 버스 라인과 스토리지 커패시턴스 버스 라인이 형성된 투명성 절연기판상에 절연막을 형성한 후 상기 게이트 버스 라인 상면에 상당하는 절연막상에 액티브층을 형성하는 단계; 상기 액티브층이 형성된 절연막상에 데이터 버스 라인과 상기 데이터 버스 라인에서 신장되는 소오스/드레인 전극을 형성하는 단계; 상기 소오스/드레인 전극 및 데이터 버스 라인상에 보호막을 형성한 후, 상기 소오스 전극의 일부를 노출시키는 비아홀을 형성하는 단계; 및 상기 비아홀을 통하여 상기 소오스 전극과 콘택트되며 다수개의 슬릿을 구비하는 화소전극을 형성하는 단계를 포함하는 것을 특징으로 한다.

이하, 본 발명에 따른 프린지 필드 스위칭 액정표시장치 및 그 제조방법을 첨부한 도면을 참조하여 상세히 설명한다.

도 2 및 3은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 단위 화소를 도시한 평면도이고, 도 4는 본 발명의 변형 실시예에 따른 프린지 필드 스위칭 액정표시장치의 단위 화소를 도시한 평면도이고, 도 5는 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 상대전극 형성을 나타내는 도면이고, 도 6은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 상대전극상의 절연막 형성을 나타내는 도면이고, 도 7은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 게이트 버스 라인 및 스토리지 커패시턴스 버스 라인 형성을 나타내는 도면이고, 도 8은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 액티브층 형성을 나타내는 도면이고, 도 9는 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 데이터 버스 라인 및 소오스/드레인 전극 형성을 나타내는 도면이고, 도 10은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 보호막 및 비아홀 형성을 나타내는 도면이고, 도 11은 본 발명에 따른 프린지 필드 스위칭 액정표시장치의 화소전극 형성을 나타내는 도면이다.

본 발명에 따른 프린지 필드 스위칭 액정표시장치는, 도 2에 도시된 바와 같이, 상부기판(미도시)상에 형성되어 있는 블랙매트릭스(210)와, 상기 상부기판(미도시)과 대향하는 하부기판(201)상에 단위 화소를 한정하도록 배치되어 있는 데이터 버스 라인(202) 및 스토리지 커패시턴스 버스 라인(208)과; 상기 스토리지 커패시턴스 버스 라인(208)에 평행하며 단위 화소를 양분하도록 배치되어 있는 게이트 버스 라인(200)과; 상기 게이트 버스 라인(200)상에 배치되어 있는 박막트랜지스터(204)와; 상기 단위 화소내에 형성되어 있는 카운터 전극(미도시)과; 상기 카운터 전극과 오버랩되어 프린지 필드를 형성하며 상기 박막트랜지스터(204)와 비아홀(205)을 통해 전기적으로 콘택트되는 화소전극(206)을 포함하여 구성된다.

여기서, 상기 화소전극(206)은 상기 카운터 전극(미도시)의 가장자리에 배치되는 틀 형상의 바디부와, 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 상기 게이트 버스 라인(200)과 일정 각도를 이루는 다수의 사선형 슬릿을 포함하고, 상기 화소전극(206)의 사선형 슬릿의 각도는 상기 게이트 버스 라인(200)을 중심으로 상하 대칭을 이루고 있다. 이때, 상기 슬릿의 간격(w)과 폭(l)은 최대  $8\mu\text{m}$ 이며, 상기 박막트랜지스터(204)의 소오스 전극(도면부호 미표시)과 상기 게이트 버스 라인(200)간의 기생용량(Cgs)을 줄이기 위해 상기 화소전극(206)의 일부가 제거되어 있다.

한편, 상기 게이트 버스 라인은 그 폭이 약 10 내지  $30\mu\text{m}$ 이고, 상기 스토리지 커패시턴스 버스 라인(200)은 그 폭이 10 내지  $40\mu\text{m}$ 인데, 특히, 상기 스토리지 커패시턴스 버스 라인(200)은 어느 하나의 단위 화소내 화소전극의 상부 가장자리와 최인접 단위 화소내 화소전극의 하부 가장자리와 일부 중첩하여 화소가 충분히 스위칭할 수 있을 만큼의 충전율을 가지게 된다.

또한, 상기 스토리지 커페시턴스 버스 라인(200)과 화소전극(206)이 단위 화소내 상하 가장자리에 오버랩되므로 씨상기 가장자리에서의 원치 않은 전계 형성을 방지할 수 있으며, 이와 더불어 상기 상부기판(미도시)상의 블랙매트릭스를 획기적으로 줄이거나 제거할 수 있다.

도면부호 210은 상기 블랙매트릭스의 에지를 단위 화소내에 가상으로 도시한 것으로, 상기 스토리지 커페시턴스 버스 라인(208) 상부에 해당하는 상부기판(미도시) 및 단위 화소 내부에 해당하는 상부기판(미도시)상에 형성될 필요가 없다. 이때, 상기 블랙매트릭스 에지(210)는 최대 약  $5\mu\text{m}$  길이로 상기 화소전극(206)의 에지 부분과 오버랩되어 빛샘을 막는다.

하지만, 유전율 이방성이 양인 액정을 사용하면 상기 게이트 버스 라인(202)에 평행하게 러빙을 하고, 유전율 이방성이 음인 액정을 사용하면 상기 데이터 버스 라인(202)에 평행하게 러빙하기 때문에 전압 인가시 상기 데이터 버스 라인(202)과 화소전극(206) 사이에 있는 액정들은 움직이지 않는다. 즉, 빛이 새지 않고 블랙 상태를 유지하기 때문에 이 영역의 상부기판의 블랙매트릭스(미도시)의 제거가 가능하다.

본 발명의 구성에 있어서는 스위칭 소자인 박막트랜지스터(204)는 상기 게이트 버스 라인(200)상에 단위 화소내에 위치하도록 형성되어 있는데, 올바른 스위칭 동작을 위해 상기 화소전극(206)과 오버랩되지 않도록 상기 화소전극(206)상에 사각형이나 임의의 모양으로 훌을 형성한다. 한편, 상기 화소전극(206)은 상기 박막트랜지스터(204)와 비아홀(205)을 통해 전기적으로 콘택된다.

상기 화소전극(206)의 사선형 슬릿 패턴은 상기 게이트 버스 라인(200)을 중심으로 그 상부 패턴은 반시계 방향으로 0도를 초과하여 45도 이하의 각도를 이루며, 그 하부 패턴은 상기 상부 패턴과 상하 대칭을 이루도록 시계방향으로 0도를 초과하여 45도 이하의 각도를 이룬다. 상기와 같은 슬릿 패턴에 있어서는 상기 게이트 버스 라인(200)과 교차하는 데이터 버스 라인(202)은 단위 화소의 우측장변에 위치하고, 상기 게이트 버스 라인(200)상의 박막트랜지스터(204)는 단위 화소의 우측장변, 즉 상기 데이터 버스 라인(202)에 근접하여 위치한다.

한편, 도 2에는 도시하지 않았지만, 상기 화소전극(206)의 사선형 슬릿 패턴이 상기 게이트 버스 라인(200)을 중심으로 그 상부 패턴은 시계 방향으로 0도를 초과하여 45도 이하의 각도를 이루며, 그 하부 패턴은 상기 상부 패턴과 상하 대칭을 이루도록 반시계방향으로 0도를 초과하여 45도 이하의 각도를 이를 수도 있다.

이러한 슬릿 패턴에 있어서는 상기 게이트 버스 라인(200)과 교차하는 데이터 버스 라인(202)은 단위 화소의 우측장변에 위치하고, 상기 게이트 버스 라인(200)상의 박막트랜지스터(204)는 단위 화소의 우측장변, 즉 상기 데이터 버스 라인(202)에 근접하여 위치한다.

한편, 도 3에 도시된 바와 같이, 슬릿 패턴에 있어서 상기 게이트 버스 라인(300)과 교차하는 데이터 버스 라인(302)이 단위 화소의 좌측장변에 위치하고, 상기 게이트 버스 라인(300)상의 박막트랜지스터(304)는 단위 화소의 좌측장변, 즉 상기 데이터 버스 라인(302)에 근접하여 위치하는 구조도 가능하다.

한편, 상기 카운터 전극은 도면에는 도시되지는 않았지만 사각 플레이트 형태이거나, 또는 상기 화소전극처럼 바디부와 사선형 슬릿으로 구성될 수도 있으며, 카운터 전극이 후자와 같이 바디부와 사선형 슬릿으로 구성되는 경우에는 그 브랜치가 상기 화소전극의 슬릿 사이에 위치할 수 있으며, 또한 각 슬릿 일부가 최대 약  $4\mu\text{m}$  길이로 중첩하여 위치할 수도 있다.

또한, 도면에는 도시되지는 않았지만, 상기 하부기판 및 상부기판의 배면에는 각각 편광판이 위치하며, 상기 각 편광판의 투과축은 상호 직교하며, 상기 투과축중 어느 하나는 상부기판 또는 하부기판의 러빙 방향과 일치한다.

도 4는 본 발명의 다른 실시예로서, 게이트 라인(500)과 화소전극(506)이 오버랩되는 영역에서 기생정전용량(Cgs)를 줄이기 위해 상기 화소전극(506)의 일부를 제거하는 것만이 다를 뿐 이 이외는 도 2에 도시된 것과 동일하므로 여기서의 상세한 설명은 생략한다.

본 발명에 따른 프린지 필드 스위칭 액정표시장치는 다음과 같이 제조된다.

본 발명에 따른 프린지 필드 스위칭 액정표시장치는, 먼저, 도 5에 도시된 바와 같이, 유리와 같은 투명성 절연기판(201)상에 ITO와 같은 투명성 도전체를 사용하여 상대전극(203)을 형성한다. 이때, 도 5의 B는 도 5의 A에 있어서 I-I 선의 단면을 도시한 것이고, 도 5의 C는 도 5의 A에 있어서 II-II 선의 단면을 도시한 단면도이다(이하 같다.) 여기에서 알 수 있듯이, 상기 상대전극(203)은 후속 공정에서 게이트 라인(200) 형성 예정 영역을 제외한 기판(201)상에 형성된다.

한편, 도 6에 도시된 바와 같이, 상기 상대전극(203)층이 형성된 기판(201) 전면상에 별도의 절연막(207)층을 형성 할 수도 있다.

이어, 도 7에 도시된 바와 같이, 상기 기판(201)상에 게이트 버스 라인(200)과 스토리지 커페시턴스 버스 라인(208)을 형성한다. 한편, 도 7의 C에 도시된 바와 같이, 도 7의 A의 II-II 선의 단면은 상기 기판(201)의 중앙부에는 게이트 버스 라인(200)이 위치하며, 그 양측면에는 상대전극(203)이 위치하며, 상기 상대전극(203) 사이에는 상기 스토리지 커페시턴스 버스 라인(208)이 형성되는데 상기 상대전극(203) 일부를 도포하도록 형성된다.

이때, 상기 게이트 버스 라인(200) 및 스토리지 커페시턴스 버스 라인(208)은 몰리브덴-텅스텐 합금(MoW)이나 알루미늄-네오디뮴 합금(AlNd), 또는 몰리브덴/알루미늄(Mo/Al) 적층구조로 이루어진 불투명 금속을 사용하며, 상기 스토리지 커페시턴스 버스 라인(208)은 단위화소의 상하 외곽에 각각 배치되며, 상기 게이트 버스 라인(200)은 상

기 단위화소를 상하 이등분 하도록 형성한다. 여기서, 단위화소는 상기 상하 2개의 스토리지 커패시턴스 버스 라인(208) 및 후속의 데이터 버스 라인(202)으로 한정되는 영역으로 정의된다.

이어, 도 8에 도시된 바와 같이, 상기 게이트 버스 라인(200) 및 스토리지 커패시턴스 버스 라인(208) 상에 실리콘 산화물(SiON)로써 절연막(211)을 형성하고, 사이 게이트 버스 라인(200) 상에 액티브층(213)을 형성하는데, 상기 액티브층(213)은 실리콘질화물/비정질실리콘/도핑된 비정질실리콘(SiN/a-Si/n+ a-Si)을 연속 층착한 적층구조이다.

이어, 도 9에 도시된 바와 같이, 상기 액티브층(213)이 형성된 절연막(211)상에 데이터 버스 라인(202)을 형성한다. 한편, 상기 액티브층(213)상에는 상기 데이터 버스 라인(202)으로부터 신장된 소오스/드레인 전극(202a)(202b)이 형성된다. 상기 데이터 버스 라인(202)의 경우도 몰리브덴-텅스텐 합금(MoW)이나 몰리브덴/알루미늄(Mo/Al) 적층구조로 이루어진 불투명 금속을 사용한다.

이어, 도 10에 도시된 바와 같이, 상기 데이터 버스 라인(202) 및 소오스/드레인 전극(202a)(202b)을 포함한 절연막(211)상에 실리콘질화물(SiN)을 사용하여 보호막(215)을 형성한 후, 상기 보호막(215)중 하부의 소오스 전극(202a) 일부를 노출시키는 비아홀(205)을 형성한다.

이어, 도 11에 도시된 바와 같이, 상기 보호막(215)상에 투명 도전체인 ITO를 사용하여 슬릿형상의 화소전극(206)을 형성하면, 본 발명에 따른 프린지 필드 스위칭 액정표시장치가 완성된다.

본 발명의 원리와 정신에 위배되지 않는 범위에서 여러 실시예는 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 자명할 뿐만 아니라 용이하게 실시할 수 있다. 따라서, 본원에 첨부된 특허청구범위는 이미 상술된 것에 한정되지 않으며, 하기 특허청구범위는 당해 발명에 내재되어 있는 특허성 있는 신규한 모든 사항을 포함하며, 아울러 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자에 의해서 균등하게 처리되는 모든 특징을 포함한다.

### 발명의 효과

이상에서 살펴 본 바와 같이, 본 발명에 따른 프린지 필드 스위칭 액정표시장치 및 그 제조방법은 다음과 같은 효과가 있다.

본 발명에 있어서는 게이트 버스 라인을 단위 화소내 중앙부에 위치시켜 전극, 게이트 버스 라인 및 데이터 버스 라인 사이에 형성되었던 전계에 의한 빛샘 발생 영역을 제거할 수 있어 컬러 쉬프트 현상을 방지할 뿐만 아니라 빛샘 현상을 제거 또는 최소화시켜 블랙매트릭스 영역을 줄이거나 제거할 수 있어 개구율과 투과율이 향상된다.

### (57) 청구의 범위

#### 청구항 1.

상부기판과; 상기 상부기판과 대향하는 하부기판상에 단위 화소를 한정하도록 배치되어 있는 데이터 버스 라인 및 스토리지 커패시턴스 버스 라인과; 상기 스토리지 커패시턴스 버스 라인에 평행하며 단위 화소를 양분하도록 배치되어 있는 게이트 버스 라인과; 상기 게이트 버스 라인 상에 배치되어 있는 박막트랜지스터와; 상기 단위 화소내에 형성되어 있는 카운터 전극과; 상기 카운터 전극과 오버랩되어 프린지 필드를 형성하며 상기 박막트랜지스터와 비아홀을 통해 전기적으로 콘택되는 화소전극을 포함하여 구성되되,

상기 화소전극은 상기 카운터 전극의 가장자리에 배치되는 틀 형상의 바디부와, 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 게이트 버스 라인과 일정 각도를 이루는 다수의 사선형 슬릿을 포함하고, 상기 화소전극의 사선형 슬릿의 각도는 상기 게이트 버스 라인을 중심으로 상하 대칭을 이루고 있으며, 상기 스토리지 커패시턴스 버스 라인은 어느 하나의 단위 화소내 화소전극의 상부 가장자리와 최인접 단위 화소내 화소전극의 하부 가장자리와 일부 중첩하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

#### 청구항 2.

제 1항에 있어서,

상기 게이트 버스 라인은 그 폭이 10 내지 30  $\mu\text{m}$ 인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

#### 청구항 3.

제 1항에 있어서,

상기 스토리지 커패시턴스 버스 라인은 그 폭이 10 내지 40  $\mu\text{m}$ 인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

#### 청구항 4.

제 1항에 있어서,

상기 상부기판은 그 내측면에 블랙매트릭스가 형성되어 있으며, 상기 블랙매트릭스의 예지부분은 상기 화소전극의 예지부분과 0 내지 5  $\mu\text{m}$  길이로 오버랩되는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 5.

제 4항에 있어서,

상기 블랙매트릭스는 상기 스토리지 커패시턴스 버스 라인 상부에 해당하는 상부기판상 및 단위 화소 내부에 해당하는 상부기판상에 형성되지 않는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 6.

제 1항에 있어서,

상기 상부기판은 그 내측면에 블랙매트릭스가 형성되지 않은 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 7.

제 1항에 있어서,

상기 화소전극은 상기 박막트랜지스터와 오버랩되지 않도록 홀이 형성되어 있는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 8.

제 1항에 있어서,

상기 화소전극의 사선형 슬릿 패턴은 상기 게이트 버스 라인을 중심으로 그 상부 패턴은 반시계 방향으로 0도를 초과하여 45도 이하의 각도를 이루며, 그 하부 패턴은 상기 상부 패턴과 상하 대칭을 이루도록 시계방향으로 0도를 초과하여 45도 이하의 각도를 이루는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 9.

제 8항에 있어서,

상기 게이트 버스 라인과 교차하는 데이터 버스 라인은 단위 화소의 우측장변에 위치하고, 상기 게이트 버스 라인상의 박막트랜지스터는 단위 화소의 우측장변에 위치하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 10.

제 1항에 있어서,

상기 화소전극의 사선형 슬릿 패턴은 상기 게이트 버스 라인을 중심으로 그 상부 패턴은 시계 방향으로 0도를 초과하여 45도 이하의 각도를 이루며, 그 하부 패턴은 상기 상부 패턴과 상하 대칭을 이루도록 반시계방향으로 0도를 초과하여 45도 이하의 각도를 이루는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 11.

제 10항에 있어서,

상기 게이트 버스 라인과 교차하는 데이터 버스 라인은 단위 화소의 좌측장변에 위치하고, 상기 게이트 버스 라인상의 박막트랜지스터는 단위 화소의 좌측장변에 위치하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 12.

제 8항 또는 제 10항에 있어서,

상기 화소전극의 슬릿은 그 폭이 8  $\mu\text{m}$ 이하인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 13.

제 8항 또는 제 10항에 있어서,

상기 화소전극의 슬릿은 그 간격이  $8\mu\text{m}$ 이하인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 14.

제 1항에 있어서,

상기 카운터 전극은 사각 플레이트 형태의 투명전극이거나, 또는 틀 형상의 바디부와 상기 바디부를 다수개의 공간으로 구획하도록 등간격으로 배치되며 게이트 버스 라인과 일정 각도를 이루는 다수의 사선형 슬릿으로 구성된 투명전극인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 15.

제 14항에 있어서,

상기 카운터 전극의 사선형 슬릿은 상기 화소전극의 사선형 슬릿 사이에 위치하거나, 일부 중첩하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 16.

제 15항에 있어서,

상기 카운터 전극의 사선형 슬릿과 화소전극의 사선형 슬릿의 일부 중첩하는 길이는 최대  $4\mu\text{m}$ 인 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치.

### 청구항 17.

투명성 절연기판상에 상대전극을 형성하는 단계;

상기 상대전극이 형성된 투명성 절연기판상에 단위화소를 한정하도록 상하 외곽에 스토리지 커패시턴스 버스 라인을 각각 형성하는 단계와 상기 단위화소를 상하 이등분하는 게이트 버스 라인을 형성하는 단계;

상기 게이트 버스 라인과 스토리지 커패시턴스 버스 라인이 형성된 투명성 절연기판상에 절연막을 형성한 후 상기 게이트 버스 라인 상면에 상당하는 절연막상에 액티브층을 형성하는 단계;

상기 액티브층이 형성된 절연막상에 데이터 버스 라인과 상기 데이터 버스 라인에서 신장되는 소오스/드레인 전극을 형성하는 단계;

상기 소오스/드레인 전극 및 데이터 버스 라인상에 보호막을 형성한 후, 상기 소오스 전극의 일부를 노출시키는 비아홀을 형성하는 단계; 및

상기 비아홀을 통하여 상기 소오스 전극과 콘택하며 다수개의 슬릿을 구비하는 화소전극을 형성하는 단계를 포함하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치의 제조방법.

### 청구항 18.

제 17항에 있어서,

상기 상대전극 형성 단계후 스토리지 커패시턴스 버스 라인 및 게이트 버스 라인 형성단계전에 상기 상대전극이 형성된 투명성 절연기판상에 절연막을 형성하는 것을 특징으로 하는 프린지 필드 스위칭 액정표시장치의 제조방법.

**도면**

도면1

도면2

도면3

도면4

도면5

(A)

(B)

(C)

도면6

(A)

(B)

(C)

도면7

도면8

도면9

도면10

도면11

201

(A)

(B)

(C)

|                |                                             |         |            |

|----------------|---------------------------------------------|---------|------------|

| 专利名称(译)        | 边缘场切换液晶显示装置及其制造方法                           |         |            |

| 公开(公告)号        | <a href="#">KR100471397B1</a>               | 公开(公告)日 | 2005-02-21 |

| 申请号            | KR1020010030552                             | 申请日     | 2001-05-31 |

| [标]申请(专利权)人(译) | HYDIS TECH<br>HYDIS技术有限公司                   |         |            |

| 申请(专利权)人(译)    | 하이디스테크놀로지주식회사                               |         |            |

| 当前申请(专利权)人(译)  | 하이디스테크놀로지주식회사                               |         |            |

| [标]发明人         | NOH JEONGDONG<br>노정동<br>LEE SEUNGHEE<br>이승희 |         |            |

| 发明人            | 노정동<br>이승희                                  |         |            |

| IPC分类号         | G02F1/1362 G02F1/1368 G02F1/1343 G02F1/136  |         |            |

| CPC分类号         | G02F1/136213 G02F1/134363                   |         |            |

| 其他公开文献         | KR1020020091683A                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                   |         |            |

### 摘要(译)

本发明涉及一种边缘场切换液晶显示设备及其制造方法，和上基板的方法;所述上基板和所述数据总线线路被布置成限定在衬底相对较低的存储容量，和总线的单位像素;与存储电容总线平行并将单位像素平分安排了一条门总线;和薄膜晶体管被布置在栅极总线;形成在单位像素中的对电极; Doedoe，包括：像素电极形成边缘场重叠在反电极，并电与所述薄膜晶体管和导通孔接触，像素电极被以相等间隔布置和框架形状的主体部设置在所述反电极的边缘，以便分配到主体部分的多个空间包括多个四个线性狭缝形成一个栅极总线和一个角度的，所述像素电极的四个线性狭缝的角度在垂直方向相对于栅极总线形成一个对称的，存储电容总线线路将在像素电极上边缘和重叠部分中的一个单位像素和在最相邻的单位像素的像素电极的下边缘，消除或通过改变I结构的像素减少漏光现象可以减小黑矩阵区域，并且可以减小孔径比和透射率它会得到改善。度