(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년06월25일

(11) 등록번호 10-1158899

(24) 등록일자 2012년06월15일

- (51) 국제특허분류(Int. C1.)

*G09G 3/36* (2006.01) *G02F 1/13* (2006.01)

- (21) 출원번호 10-2005-0076614

(22) 출원일자 2005년08월22일

심사청구일자 2010년08월10일

(65) 공개번호 10-2007-0022424

(43) 공개일자 2007년02월27일

(56) 선행기술조사문현

JP05265045 A\*

KR1020020017340 A\*

KR1020030056856 A

\*는 심사관에 의하여 인용된 문현

- (73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

이현수

경기도 안양시 동안구 경수대로797번길 12, 한마

음임광아파트 205동 2404호 (호계동)

하재민

경기도 용인시 수지구 진산로66번길 10, 삼성5차

526동 1604호 (풍덕천동)

(74) 대리인

박영우

전체 청구항 수 : 총 16 항

심사관 : 이성현

(54) 발명의 명칭 액정표시장치 및 이의 구동방법

### (57) 요약

표시 특성을 향상하기 위한 액정표시장치 및 이의 구동방법이 개시된다. 액정패널은 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는다. 데이터 구동부는 데이터 신호를 액정패널에 제공한다. 게이트 구동부는 액정패널로 게이트 신호를 제공하여 제1 및 제2 화소부중에서 선충전되는 제1 화소부를 후충전되는 제2 화소부보다 상대적으로 과충전시킨다. 이에 따라, 데이터 라인 반감 구조에서, 선충전되는 제1 화소부에 대해서는 상대적으로 크거나 넓은 펄스 폭의 게이트 신호를 제공하고, 후충전되는 제2 화소부에 대해서는 정상적인 크기나 펄스 폭의 게이트 신호를 제공하므로, 세로줄성 플리커링 현상을 제거할 수 있다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는 액정패널;

데이터 신호를 상기 액정패널에 제공하는 데이터 구동부; 및

상기 액정패널로 게이트 신호를 제공하여 상기 제1 및 제2 화소부중에서 선충전되는 제1 화소부를 후충전되는 제2 화소부보다 상대적으로 과충전시키는 게이트 구동부를 포함하되,

상기 게이트 구동부는

제1 게이트 온 전압에 응답하여 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 레벨의 제1 게이트 신호를 출력하는 제1 게이트 구동부; 및

제2 게이트 온 전압에 응답하여 상기 제2 화소부에 제2 레벨의 제2 게이트 신호를 출력하는 제2 게이트 구동부를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제1항에 있어서, 상기 제1 화소부는 제1 스위칭 소자와, 상기 제1 스위칭 소자에 전기적으로 연결된 제1 액정 캐패시터를 포함하고,

상기 제2 화소부는 제2 스위칭 소자와, 상기 제2 스위칭 소자에 전기적으로 연결된 제2 액정 캐패시터를 포함하며,

상기 제1 및 제2 액정 캐패시터는 스토리지 캐패시터에 공통 연결된 것을 특징으로 하는 액정표시장치.

### 청구항 3

삭제

### 청구항 4

제1항에 있어서, 상기 제1 게이트 온 전압 및 상기 제2 게이트 온 전압을 상기 제1 및 제2 게이트 구동부로 각각 출력하는 타이밍 제어부를 더 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 5

제1항에 있어서, 상기 제1 레벨은 상기 제2 레벨보다 큰 것을 특징으로 하는 액정표시장치.

### 청구항 6

제1항에 있어서, 상기 제1 게이트 구동부와 제2 게이트 구동부는 서로 다른 수직개시신호(STV)에 의해 기동되는 것을 특징으로 하는 액정표시장치.

### 청구항 7

제6항에 있어서, 상기 서로 다른 수직개시신호는 1H 구간만큼 이격된 것을 특징으로 하는 액정표시장치.

### 청구항 8

제1항에 있어서, 상기 게이트 구동부는

제1 출력 인에이블 신호에 응답하여 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 펄스 폭의 제1 게이트 신호를 출력하는 제1 게이트 구동부; 및

제2 출력 인에이블 신호에 응답하여 상기 제2 화소부에 전기적으로 연결된 게이트 라인에 제2 펄스 폭의 제2 게이트 신호를 출력하는 제2 게이트 구동부를 포함하는 것을 특징으로 하는 액정표시장치.

**청구항 9**

제8항에 있어서, 상기 제1 펄스 폭은 상기 제2 펄스 폭 보다 큰 것을 특징으로 하는 액정표시장치.

**청구항 10**

제8항에 있어서, 상기 제1 게이트 구동부와 제2 게이트 구동부는 서로 다른 수직개시신호(STV)에 의해 기동되는 것을 특징으로 하는 액정표시장치.

**청구항 11**

제10항에 있어서, 상기 서로 다른 수직개시신호는 1H 구간만큼 이격된 것을 특징으로 하는 액정표시장치.

**청구항 12**

제8항에 있어서, 상기 제1 출력 인에이블 신호와 상기 제2 출력 인에이블 신호를 상기 제1 및 제2 게이트 구동부로 각각 출력하는 타이밍 제어부를 더 포함하는 것을 특징으로 하는 액정표시장치.

**청구항 13**

서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는 액정패널;

데이터 전압을 상기 액정패널에 제공하는 데이터 구동부;

선충전된 상기 제1 화소부에 상기 제2 화소부의 후충전에 따른 상기 제1 화소부의 충전량 감소를 보상하기 위해, 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 레벨의 제1 게이트 신호를 출력하는 제1 게이트 구동부; 및

상기 제2 화소부에 전기적으로 연결된 게이트 라인에 상기 제1 레벨보다 낮은 제2 레벨의 제2 게이트 신호를 출력하는 제2 게이트 구동부를 포함하는 것을 특징으로 하는 액정표시장치.

**청구항 14**

삭제

**청구항 15**

서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 형성된 제1 화소부 및 제2 화소부를 갖는 액정패널을 포함하는 액정표시장치의 구동방법에서,

상기 데이터 라인들에 데이터 전압을 공급하는 단계;

선충전되는 상기 제1 화소부가 후충전되는 상기 제2 화소부보다 상대적으로 과충전되도록 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 게이트 신호를 출력하는 단계; 및

상기 제2 화소부에 전기적으로 연결된 게이트 라인에 제2 게이트 신호를 출력하는 단계를 포함하되,

상기 제1 게이트 신호의 레벨은 상기 제2 게이트 신호의 레벨보다 큰 것을 특징으로 하는 액정표시장치의 구동방법.

**청구항 16**

삭제

**청구항 17**

제15항에 있어서, 상기 제1 게이트 신호 및 제2 게이트 신호 각각은 서로 다른 게이트 오프 전압과 서로 다른 게이트 온 전압에 의해 정의되는 것을 특징으로 하는 액정표시장치의 구동방법.

**청구항 18**

제15항에 있어서, 상기 제1 게이트 신호 및 제2 게이트 신호 각각은 동일한 게이트 오프 전압과 서로 다른 게

이트 온 전압에 의해 정의된 것을 특징으로 하는 액정표시장치의 구동방법.

## 청구항 19

제15항에 있어서, 상기 제1 게이트 신호의 폴스 폭은 상기 제2 게이트 신호의 폴스 폭보다 넓은 것을 특징으로 하는 액정표시장치의 구동방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- [0016] 본 발명은 액정표시장치 및 이의 구동방법에 관한 것으로, 보다 상세하게는 표시 특성을 향상하기 위한 액정표시장치 및 이의 구동방법에 관한 것이다.

- [0017] 일반적으로 액정표시장치는 두 개의 기판간에 주입된 이방성 유전율을 갖는 액정물질에 세기가 조절된 전계를 인가하여 상기 액정물질을 투과하는 광량을 조절하므로써, 원하는 화상을 얻는 표시장치이다.

- [0018] 상기 액정표시장치는 게이트 전극에 인가되는 게이트 전압에 의해 데이터 라인을 통해 액정에 전달되는 신호 전압의 크기가 제어되며, 이와 같은 가변적인 데이터 전압은 액정의 분극 상태를 단계적으로 바꾸기 때문에 액정표시장치에서 다양한 그레이 레벨을 표현할 수 있다.

- [0019] 상기 액정표시장치는 소스 구동 IC와 이를 구동하는 소스 PCB(Printed Circuit Board), 그리고 게이트 구동 IC와 이를 구동하는 게이트 PCB로 구성된다. 상기 액정표시장치의 사용이 보편화됨에 따라, 제조 업체측에서는 원가 절감 및 효율적인 구동을 위해 소스 구동 IC의 수를 줄이려는 노력들이 진행되고 있다.

- [0020] 이러한 노력들 중의 하나는 데이터 라인 반감 구조를 갖는 액정표시장치를 채용하는 것이다. 상기 데이터 라인 반감 구조는 서로 인접하는 데이터 라인들과 서로 인접하는 게이트 라인들에 의해 구획되는 영역에 형성된 첫 번째 픽셀과 두 번째 픽셀을 포함한다. 상기 첫 번째 픽셀과 두 번째 픽셀은 서로 서로 다른 시간에 충전된다.

- [0021] 하지만, 상기 데이터 라인 반감 구조에서, 상기 첫 번째 픽셀을 충전시킨 후 상기 두 번째 픽셀을 충전시키면, 선충전된 첫 번째 픽셀에는 두 번째 픽셀의 충전에 따라 커플링 캐패시터에 의해 충전량(charge quantity)이 감소한다.

- [0022] 상기한 충전량 감소는 화면 전체적으로 보았을 때, 세로줄로 나타나는 플리커링 현상이 발생되는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

- [0023] 이에 본 발명의 기술적 과제는 이러한 종래의 문제점을 해결하기 위한 것으로, 본 발명의 목적은 데이터 라인 반감 구조에서 충전량 감소에 의한 플리커링 현상을 방지하여 표시 특성을 향상하기 위한 액정표시장치를 제공하는 것이다.

- [0024] 본 발명의 다른 목적은 상기한 액정표시장치의 구동방법을 제공하는 것이다.

#### 발명의 구성 및 작용

- [0025] 상기한 본 발명의 목적을 실현하기 위하여 일실시예에 따른 액정표시장치는 액정패널, 데이터 구동부 및 게이트 구동부를 포함한다. 상기 액정패널은 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는다. 상기 데이터 구동부는 데이터 신호를 상기 액정패널에 제공한다. 상기 게이트 구동부는 상기 액정패널로 게이트 신호를 제공하여 상기 제1 및 제2 화소부중에서 선충전되는 제1 화소부를 후충전되는 제2 화소부보다 상대적으로 과충전시킨다.

- [0026] 상기한 본 발명의 목적을 실현하기 위하여 다른 실시예에 따른 액정표시장치는 액정패널, 데이터 구동부, 제1 게이트 구동부 및 제2 게이트 구동부를 포함한다. 상기 액정패널은 서로 인접하는 게이트 라인들과 서로 인접

하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는다. 상기 데이터 구동부는 데이터 전압을 상기 액정패널에 제공한다. 상기 제1 게이트 구동부는 선충전된 상기 제1 화소부에 상기 제2 화소부의 후충전에 따른 상기 제1 화소부의 충전량 감소를 보상하기 위해, 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 레벨의 제1 게이트 신호를 출력한다. 상기 제2 게이트 구동부는 상기 제2 화소부에 전기적으로 연결된 게이트 라인에 상기 제1 레벨보다 낮은 제2 레벨의 제2 게이트 신호를 출력한다.

[0027] 상기한 본 발명의 목적을 실현하기 위하여 또 다른 실시예에 따른 액정표시장치는 액정패널, 데이터 구동부, 제1 게이트 구동부 및 제2 게이트 구동부를 포함한다. 상기 액정패널은 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 서로 다른 시간 동안 충전되는 제1 화소부 및 제2 화소부를 갖는다. 상기 데이터 구동부는 데이터 전압을 상기 액정패널에 제공한다. 상기 제1 게이트 구동부는 선충전된 상기 제1 화소부에 상기 제2 화소부의 후충전에 따른 상기 제1 화소부의 충전량 감소를 보상하기 위해, 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 펄스 폭의 제1 게이트 신호를 출력한다. 상기 제2 게이트 구동부는 상기 제2 화소부에 전기적으로 연결된 게이트 라인에 상기 제1 펄스 폭보다 좁은 제2 펄스 폭의 제2 게이트 신호를 출력한다.

[0028] 상기한 본 발명의 다른 목적을 실현하기 위하여 일실시예에 따른 액정표시장치의 구동방법은 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 각 영역에 형성된 제1 화소부 및 제2 화소부를 갖는 액정패널을 포함하는 액정표시장치의 구동방법에서, 상기 데이터 라인들에 데이터 전압을 공급하는 단계와, 선충전되는 상기 제1 화소부가 후충전되는 상기 제2 화소부보다 상대적으로 과충전되도록 상기 제1 화소부에 전기적으로 연결된 게이트 라인에 제1 게이트 신호를 출력하는 단계와, 상기 제2 화소부에 전기적으로 연결된 게이트 라인에 제2 게이트 신호를 출력하는 단계를 포함한다.

[0029] 이러한 액정표시장치 및 이의 구동방법에 의하면, 데이터 라인 반감 구조에서, 선충전되는 제1 화소부에 대해서는 상대적으로 크거나 넓은 펄스 폭의 게이트 신호를 제공하고, 후충전되는 제2 화소부에 대해서는 정상적인 크기나 펄스 폭의 게이트 신호를 제공하므로, 세로줄성 플리커링 현상을 제거할 수 있다.

[0030] 이하, 첨부한 도면들을 참조하여, 본 발명을 보다 상세하게 설명하고자 한다.

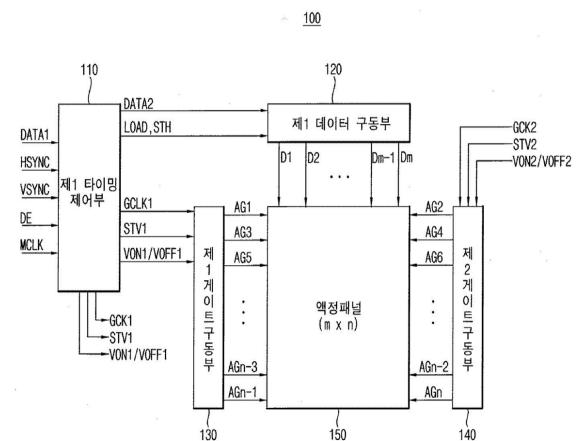

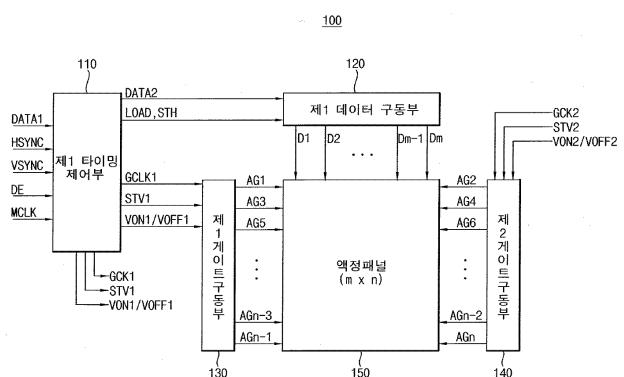

[0031] 도 1은 본 발명의 일실시예에 따른 액정표시장치를 설명하는 블록도이다. 도 2는 도 1에 도시된 제1 및 제2 게이트 구동부에서 액정패널의 화소부에 출력되는 게이트 신호를 설명하는 과형도이다.

[0032] 도 1 및 도 2를 참조하면, 액정표시장치(100)는 제1 타이밍 제어부(110), 제1 데이터 구동부(120), 제1 게이트 구동부(130), 제2 게이트 구동부(140) 및 액정패널(150)을 포함한다.

[0033] 상기 제1 타이밍 제어부(110)는 외부로부터 제1 데이터 신호(DATA1), 각종 동기 신호들(Hsync, Vsync), 데이터 인에이블 신호(DE) 및 메인 클럭(MCLK)을 제공받는다. 상기 제1 타이밍 제어부(110)는 제2 데이터 신호(DATA2)와, 상기 제2 데이터 신호(DATA2)의 출력을 위한 데이터 구동 신호(LOAD, STH)를 상기 제1 데이터 구동부(120)에 출력한다.

[0034] 상기 제1 타이밍 제어부(110)는 제1 게이트 구동 신호(GCK1, STV1) 및 제1 게이트 온/오프 전압(VON1/VOFF1)을 상기 제1 게이트 구동부(130)에 출력하고, 제2 게이트 구동 신호(GCK2, STV2) 및 제2 게이트 온/오프 전압(VON2/VOFF2)을 상기 제2 게이트 구동부(140)에 출력한다. 여기서, 제1 수직개시신호(STV1)는 제2 수직개시신호(STV2)보다 앞선다. 이에 따라 상기 제1 게이트 구동부(130)가 액티브된 후 상기 제2 게이트 구동부(140)가 액티브된다. 상기 제1 수직개시신호(STV1)와 제2 수직개시신호(STV2)는 1H 구간만큼 이격된다.

[0035] 상기 제2 게이트 온/오프 전압(VON2/VOFF2)은 상기 액정패널(150)에 형성된 스위칭 소자를 정상적으로 턠-온/오프시키는 레벨이다. 본 실시예에서 상기 스위칭 소자는 박막 트랜지스터(TFT)이다.

[0036] 일례로, 상기 제1 게이트 오프 전압(VOFF1)과 제2 게이트 오프 전압(VOFF2)은 동일하고, 상기 제1 게이트 온 전압(VON1)은 상기 제2 게이트 온 전압(VON2)보다 크다.

[0037] 다른 예로, 상기 제1 게이트 온 전압(VON1)은 상기 제2 게이트 온 전압(VON2)보다 크고, 상기 제1 게이트 오프 전압(VOFF1)은 상기 제2 게이트 오프 전압(VOFF2)보다 작다. 예를들어, 상기 제2 게이트 오프 전압(VOFF2)이 -6V이면, 상기 제1 게이트 오프 전압(VOFF1)은 -7V이고, 상기 제2 게이트 온 전압(VON2)이 20V이면, 상기 제1 게이트 온 전압(VON1)은 25V이다.

[0038] 상기 제1 데이터 구동부(130)는 상기 제1 타이밍 제어부(110)에서 제2 데이터 신호(DATA2)가 수신됨에 따라,

상기 제2 데이터 신호(DATA2)를 데이터 전압(계조 전압)으로 변경하고, 변경된 데이터 전압(D1, D2, ..., Dm)(여기서, m은 정수 또는 3의 배수)을 상기 액정패널(150)에 인가한다.

[0039] 상기 제1 게이트 구동부(130)는 상기 제1 게이트 구동 신호(GCK1, STV1)에 응답하여 상기 액정패널(150)의 홀수번째 게이트 라인을 활성화하는 홀수번째 게이트 신호(AG1, AG3, ..., AGn-3, AGn-1)(여기서, n은 짝수)를 상기 액정패널(150)에 순차적으로 인가한다.

[0040] 상기 제2 게이트 구동부(140)는 상기 제2 게이트 구동 신호(GCK2, STV2)에 응답하여 상기 액정패널(150)의 짝수번째 게이트 라인을 활성화하는 짝수번째 게이트 신호(AG2, AG4, ..., AGn-2, AGn)를 순차적으로 상기 액정패널(150)에 인가한다. 상기 홀수번째 게이트 신호(AG1, AG3, ..., AGn-3, AGn-1)와 상기 짝수번째 게이트 신호(AG2, AG4, ..., AGn-2, AGn)는 교호로 출력된다.

[0041] 본 실시예에서, 상기 홀수번째 게이트 신호(AG1, AG3, ..., AGn-3, AGn-1)의 레벨은 상기 짝수번째 게이트 신호(AG2, AG4, ..., AGn-2, AGn)의 레벨보다 상대적으로 크다. 이는 상대적으로 선충전되는 홀수번째 게이트 신호(AG1, AG3, ..., AGn-3, AGn-1)에 대응하는 화소부가 상대적으로 후충전되는 짝수번째 게이트 신호(AG2, AG4, ..., AGn-2, AGn)에 대응하는 화소부에 충전량 감소를 방지하기 위함이다.

[0042] 상기 액정패널(150)은 게이트 신호(스캔 신호 또는 주사 신호)(AG1, AG2, ..., AGn-1, AGn)를 전달하는 복수의 게이트 라인(주사 라인 또는 스캔 라인)들과, 상기 데이터 전압(D1, D2, ..., Dm)을 전달하는 복수의 데이터 라인(소스 라인)들을 포함한다. 상기 액정패널(150)은 게이트 라인의 수가 증가되고, 데이터 라인의 수가 감소된 데이터 라인 반감 구조를 갖는다.

[0043] 상기 데이터 라인 반감 구조의 액정패널은 서로 인접하는 게이트 라인들과 서로 인접하는 데이터 라인들에 의해 정의되는 영역에 제1 화소부 및 제2 화소부를 갖는다.

[0044] 일례로, 상기 제1 화소부는 제1 박막 트랜지스터(TFT)와, 상기 제1 박막 트랜지스터(TFT)의 드레인에 전기적으로 연결된 제1 액정 캐패시터(Cl1c)를 포함한다.

[0045] 일례로, 상기 제2 화소부는 제2 박막 트랜지스터(TFT)와, 상기 제2 박막 트랜지스터(TFT)의 드레인 전극에 전기적으로 연결된 제2 액정 캐패시터(Cl1c)를 포함한다. 스토리지 캐패시터(Cst)는 상기 제1 및 제2 액정 캐패시터에 연결되어, 상기 제1 화소부와 제2 화소부가 공유한다.

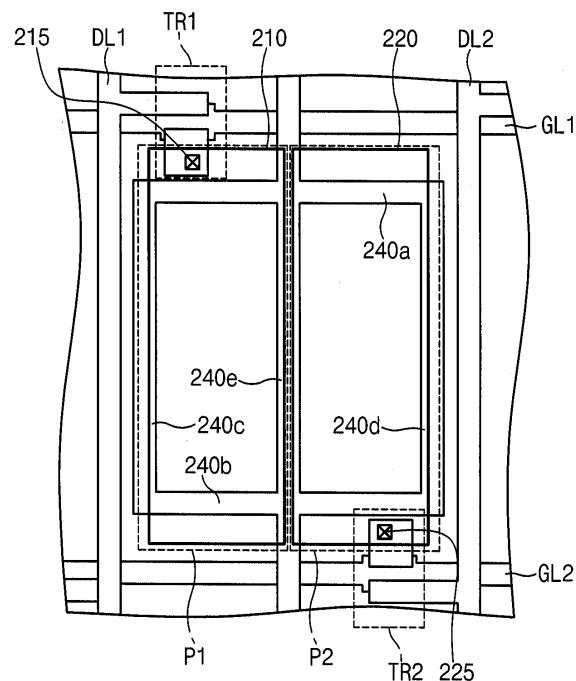

[0046] 도 3은 도 1에 도시된 액정패널에 형성된 화소부를 상세하게 나타낸 레이아웃도이다.

[0047] 도 3을 참조하면, 제1 화소부(P1)는 제1 게이트 라인(GL1)에 전기적으로 연결되고, 제2 화소부(P2)는 제2 게이트 라인(GL2)에 전기적으로 연결된다. 상기 제1 화소부(P1)는 제1 데이터 라인(DL1)에 전기적으로 연결되고, 상기 제2 화소부(P2)는 제2 데이터 라인(DL2)에 전기적으로 연결된다.

[0048] 상기 제1 화소부(P1)에는 상기 제1 게이트 라인(GL2)에서 분기된 게이트 전극, 상기 제1 데이터 라인(DL1)에서 분기된 소스 전극과 드레인 전극으로 이루어진 제1 트랜지스터(TR1) 및 제1 화소전극(210)이 형성된다. 상기 제1 트랜지스터(TR1)의 드레인 전극은 제1 콘택홀(215)을 통해 제1 화소전극(210)과 전기적으로 연결된다.

[0049] 상기 제2 화소부(P2)에는 제2 게이트 라인(GL2)에서 분기된 게이트 전극, 제2 데이터 라인(DL2)에서 분기된 소스 전극과 드레인 전극으로 이루어진 제2 트랜지스터(TR2) 및 제2 화소전극(220)이 형성된다. 상기 제2 트랜지스터(TR2)의 드레인 전극은 제2 콘택홀(225)을 통해 제2 화소전극(220)과 전기적으로 연결된다.

[0050] 한편, 상기 제1 게이트 라인(GL1)에 인접하고, 상기 제1 게이트 라인(GL1)과 평행하도록 연장되어 제1 및 제2 화소부(P1, P2)에 걸쳐서 제1 스토리지 라인(240a)이 형성되며, 제2 게이트 라인(GL2)에 인접하고, 제2 게이트 라인(GL2)과 평행하도록 연장되어 제1 및 제2 화소부(P1, P2)에 걸쳐서 제2 스토리지 라인(240b)이 형성된다.

[0051] 상기 제1 화소부(P1)에는 제1 스토리지 라인(240a)의 일단과 제2 스토리지 라인(240b)의 일단을 연결시키고, 제1 데이터 라인(DL1)과 평행한 제3 스토리지 라인(240c)이 형성된다. 예를들어, 제3 스토리지 라인(240c)은 제1 화소전극(210)과 일부 오버레이되도록 형성된다.

[0052] 또한, 제2 화소부(P1)에는 제1 스토리지 라인(240a)의 타단과 제2 스토리지 라인(240b)의 타단을 연결시키고, 제3 스토리지 라인(240c) 및 제2 데이터 라인(DL2)과 평행한 제4 스토리지 라인(240d)이 형성된다. 예를들어, 제4 스토리지 라인(240d)은 제2 화소전극(220)과 일부 오버레이되도록 형성된다.

[0053] 상기 제1 및 제2 화소부(P1, P2)가 인접하는 영역에서 제1 스토리지 라인(240a)과 제2 스토리지 라인(240b)의 중앙을 서로 연결하고, 제1 및 제2 데이터 라인(DL1, DL2)에 평행하도록 연장되도록 제5 스토리지 라인(240e)

이 형성된다. 예를들어, 제5 스토리지 라인(240e)은 제1 화소전극(210)과 일부 오버레이되고, 제2 화소전극(220)과 일부 오버레이되도록 형성된다. 따라서, 제1 화소부(P1)와 제2 화소부(P2)는 제5 스토리지 라인(240e)을 공유한다.

[0054] 여기서, 제1 및 제2 스토리지 라인(240a, 240b)의 일부, 제3 스토리지 라인(240c) 및 제5 스토리지 라인(240e)의 일부에 의해 스토리지 커패시터(Cst)의 하부전극이 형성된다. 또한, 제1 및 제2 스토리지 라인(240a, 240b)의 일부, 제4 스토리지 라인(240d) 및 제5 스토리지 라인(240e)의 일부에 의해 스토리지 커패시터(Cst)의 하부전극이 형성된다.

[0055] 상기 제1 내지 제5 스토리지 라인(240a~240e)은 제1 및 제2 트랜지스터(TR1, TR2)의 소스 전극 및 드레인 전극을 형성하는 동일 금속물질로 동일 공정에서 형성된다.

[0056] 따라서, 제1 내지 제5 스토리지 라인(240a~240e)은 제1 및 제2 트랜지스터(TR1, TR2)의 게이트 절연막 위에 형성되어 스토리지 커패시터(Cst)의 하부전극을 정의하고, 제1 내지 제5 스토리지 라인(240a~240e) 상부에는 절연막(도시되지 않음)이 형성되어 스토리지 커패시터(Cst)의 유전체를 정의하며, 상기 절연막(도시되지 않음) 위에 형성된 제1 및 제2 화소전극(210, 220)은 스토리지 커패시터(Cst)의 상부전극을 정의한다.

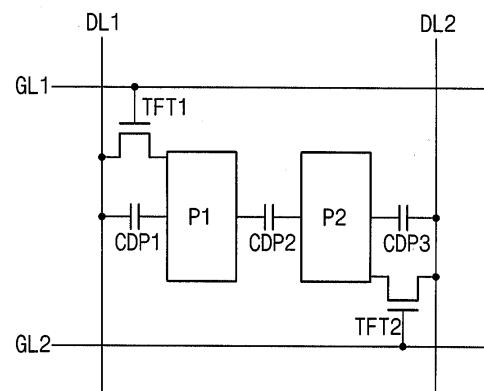

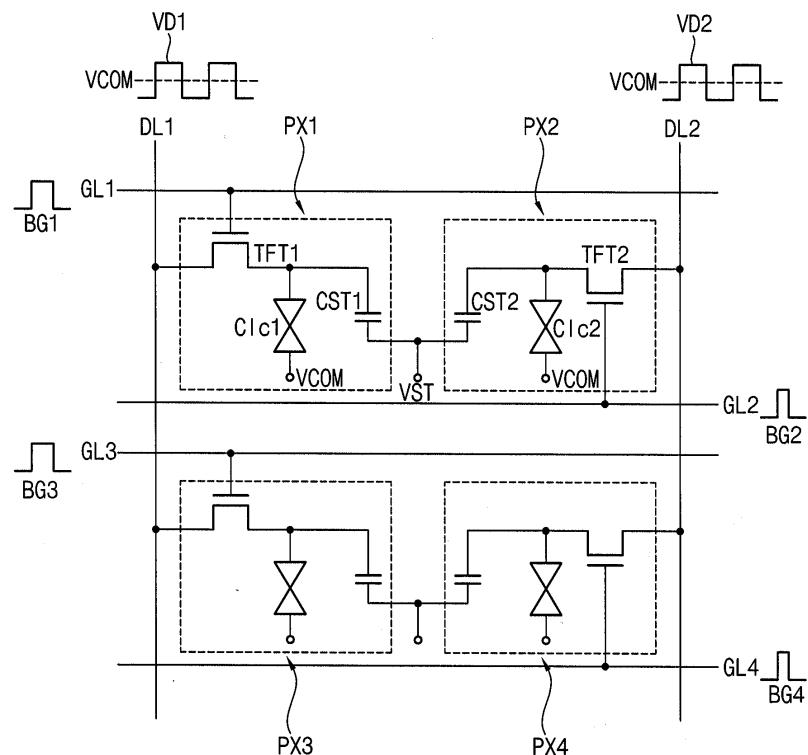

[0057] 도 4는 도 1에 도시된 액정패널의 화소부를 설명하는 등가회로도이다.

[0058] 도 4를 참조하면, 화소부는 제1 및 제2 데이터 라인(DL1, DL2)과 제1 및 제2 게이트 라인(GL1, GL2)에 의해 둘러싸인 영역에 형성된다. 상기 화소부는 제1 박막 트랜지스터(TFT1), 상기 제1 박막 트랜지스터(TFT1)에 전기적으로 연결된 제1 픽셀(P1), 제2 박막 트랜지스터(TFT2), 상기 제2 박막 트랜지스터(TFT2)에 전기적으로 연결된 제2 픽셀(P2)을 포함한다.

[0059] 상기 제1 박막 트랜지스터(TFT1)의 게이트, 소스 및 드레인은 제1 게이트 라인(GL1), 제1 데이터 라인(DL1) 및 제1 픽셀(P1)에 각각 연결되고, 상기 제2 박막 트랜지스터(TFT2)의 게이트 전극, 소스 전극 및 드레인 전극은 제2 게이트 라인(GL2), 제2 데이터 라인(DL2) 및 제2 픽셀(P2)에 각각 연결된다.

[0060] 도 4에 도시된 화소부의 구조는 제1 픽셀(P1)과 제2 픽셀(P2)이 서로 인접하는 제1 및 제2 데이터 라인(DL1, DL2)에 의해 둘러싸이는 데이터 라인 반감 구조이다. 상기 데이터 라인 반감 구조에서, 제1 데이터 라인(DL1)과 제1 픽셀(P1)간에는 제1 커플링 캐패시터(Cdp1)가 존재하고, 제1 픽셀(P1)과 제2 픽셀(P2)간에는 제2 커플링 캐패시터(Cdp2)가 존재하며, 제2 픽셀(P2)과 제2 데이터 라인(DL2)간에는 제3 커플링 캐패시터(Cdp3)가 존재한다.

[0061] 통상적인 구동 방식에 따르면, 제1 게이트 라인(GL1)이 액티브되어 제1 픽셀(P1)이 충전된 후, 제2 게이트 라인(GL2)이 액티브되어 제2 픽셀(P2)이 충전된다.

[0062] 상기 제2 픽셀(P2)이 충전됨에 따라, 선충전된 제1 픽셀(P1)에는 충전량 감소가 발생된다. 상기한 충전량 감소는 주로 상기 제2 커플링 캐패시터(Cdp2)에 기인된다. 화면 전체적으로 홀수번째 데이터 라인에 전기적으로 연결된 픽셀과 짝수번째 데이터 라인에 전기적으로 연결된 픽셀간의 충전량 차이는 세로줄성 플리커링 현상을 발생시킨다.

[0063] 하지만, 본 발명의 제1 실시예에 따르면, 상대적으로 선충전되는 제1 픽셀(P1)에 대해서는 상대적으로 큰 레벨의 제1 게이트 신호를 이용하여 충전 동작을 수행하고, 상대적으로 후충전되는 제2 픽셀(P2)에 대해서는 정상적인 레벨의 제2 게이트 신호를 이용하여 충전 동작을 수행하므로써, 세로줄성 플리커링 현상을 제거할 수 있다.

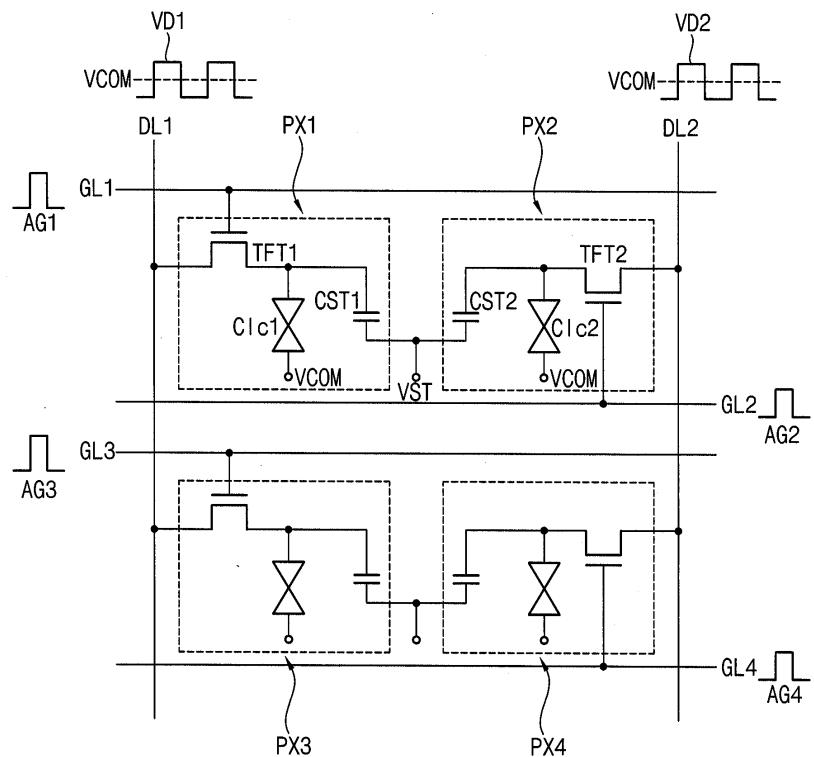

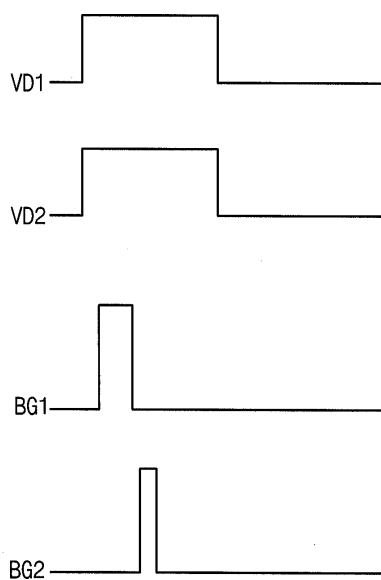

[0064] 도 5는 도 1에 도시된 액정표시장치의 화소부를 설명하는 회로도이다. 도 6은 도 5에 도시된 게이트 전압과 데이터 전압을 설명하는 과정도이다.

[0065] 도 5 및 도 6을 참조하면, 상기 제1 데이터 라인(DL1)에 인가되는 상기 제1 데이터 전압(VD1)은 상기 제1 게이트 신호(AG1)에 따라 상기 제1 픽셀부(PX1)에 충전된다. 상기 제1 픽셀부(PX1)는 제1 박막 트랜지스터(TFT1), 제1 액정 캐패시터(Cl1c1) 및 제1 스토리지 캐패시터(Cst1)를 포함한다.

[0066] 상기 제1 데이터 전압(VD1)은 공통전압(VCOM) 대비 정극성을 갖는다. 상기 제1 게이트 신호(AG1)는 상기 제1 게이트 라인(GL1)에 공급되어 상기 제1 게이트 라인(GL1)에 전기적으로 연결된 상기 제1 박막 트랜지스터(TFT1)를 액티브시킨다. 상기 제1 데이터 전압(VD1)은 상기 제1 박막 트랜지스터(TFT1)를 경유하여, 공통 연결된 상기 제1 액정 캐패시터(Cl1c1) 및 제1 스토리지 캐패시터(Cst1)에 충전된다. 상기 제1 스토리지 캐패시터(Cst1)의 일단은 상기 제1 박막 트랜지스터(TFT1)의 드레인 전극에 전기적으로 연결되고, 타단은 스토리지

전압(VST)에 전기적으로 연결된다.

[0067] 상기 제2 데이터 라인(DL2)에 인가되는 상기 제2 데이터 전압(VD2)은 상기 제2 게이트 신호(AG2)에 따라 상기 제2 픽셀부(PX2)에 충전된다. 상기 제2 픽셀부(PX2)는 제2 박막 트랜지스터(TFT2), 제2 액정 캐패시터(C1c2) 및 제2 스토리지 캐패시터(Cst2)를 포함한다. 상기 제2 스토리지 캐패시터(Cst2)의 일단은 상기 제2 박막 트랜지스터(TFT2)의 드레인 전극에 전기적으로 연결되고, 타단은 상기 제1 스토리지 캐패시터(Cst1)의 타단에 공통 연결된다.

[0068] 상기 제2 데이터 전압(VD2)은 공통전압(VCOM) 대비 정극성을 갖는다. 상기 제2 게이트 신호(AG2)는 상기 제2 게이트 라인(GL2)에 공급되어 상기 제2 게이트 라인(GL2)에 전기적으로 연결된 상기 제2 박막 트랜지스터(TFT2)를 액티브시킨다. 상기 제2 데이터 전압(VD2)은 상기 제2 박막 트랜지스터(TFT2)를 경유하여, 공통 연결된 상기 제2 액정 캐패시터(C1c1) 및 제2 스토리지 캐패시터(Cst2)에 충전된다.

[0069] 상기 제2 게이트 신호(AG2)의 하이레벨은 통상적으로 상기 제2 박막 트랜지스터(TFT2)를 턴-온시키는 정도이다. 이에 반면, 상기 제1 게이트 신호(AG1)의 하이레벨은 상기 제2 게이트 신호(AG2)의 하이레벨보다 상대적으로 높다. 일례로, 상기 제1 게이트 신호(AG1)의 로우레벨 및 하이레벨이 -6V 및 20V에 의해 각각 정의된다면, 상기 제2 게이트 신호(AG2)의 로우레벨 및 하이레벨은 -7V와 25V에 의해 각각 정의된다.

[0070] 도 5 및 도 6에서는 서로 인접하는 데이터 라인에 공통전압 대비 동일 극성의 데이터 전압이 인가되는 것을 도시하였으나, 서로 인접하는 데이터 라인에 공통전압 대비 서로 다른 극성의 데이터 전압이 인가될 수도 있다.

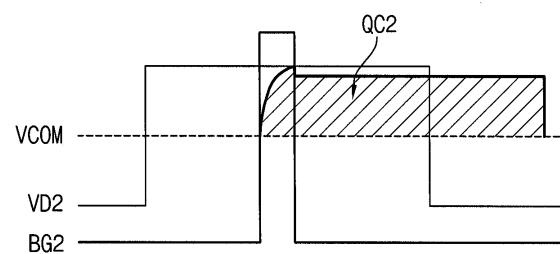

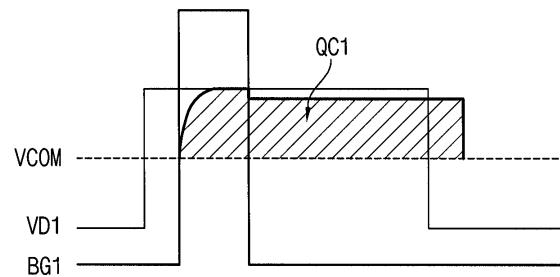

[0071] 그러면, 상기 제1 및 제2 픽셀부(PX1, PX2)에 충전되는 데이터 전압의 충전량 특성을 도 7을 참조하여 설명한다.

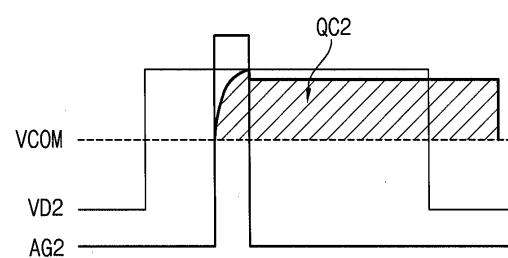

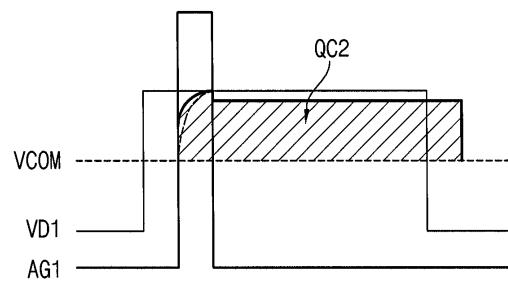

[0072] 도 7은 도 5에 도시된 데이터 전압의 충전량 특성을 설명하는 과정도이다.

[0073] 도 7을 참조하면, 상대적으로 큰 전위차를 갖는 제1 게이트 신호(AG1)가 액티브됨에 따라, 상기 제1 데이터 전압(VD1)이 충전되는 라이즈 타임(risetime)은 기준 라이즈 타임에 비해 줄어든다. 상기 라이즈 타임은 펄스 진폭이 10%값에서 90%값에 이르기까지의 경과 시간이다.

[0074] 상기 기준 라이즈 타임은 박막 트랜지스터의 동작을 제어하는 임계 전위차를 갖는 기준 게이트 신호에 의해 데이터 전압이 충전되는 시간이다. 이에 따라, 선충전되는 상기 제1 픽셀부(PX1)의 실질적인 충전시간은 증가되어 실질적인 충전량은 상기 기준 게이트 신호에 의한 충전량보다 증가한다.

[0075] 이어, 임계 전위차를 갖는 상기 제2 게이트 신호(AG2)가 액티브됨에 따라, 상기 제2 데이터 전압(VD2)은 기준 라이즈 타임을 갖고서 상기 제2 픽셀부(PX2)에 충전된다. 즉, 후충전되는 상기 제2 픽셀부(PX2)에는 정상적인 충전시간에 의해 정상적인 제2 충전량(QC2) 만큼 충전이 이루어지는 반면, 선충전되는 상기 제1 픽셀부(PX1)에는 상기 제2 충전량(QC2)보다 증가된 제1 충전량(QC1) 만큼 충전된다.

[0076] 이에 따라, 커플링 캐패시터를 통해 상기 제1 픽셀부(PX1)에 전기적으로 연결된 상기 제2 픽셀부(PX2)가 충전될 때, 상기 제1 픽셀부(PX1)가 정상적인 충전량보다 낮게되는 것을 방지할 수 있다. 왜냐하면, 상기 제1 픽셀부(PX1)는 충전량 감소가 감안되어 상대적으로 과도하게 충전되기 때문이다.

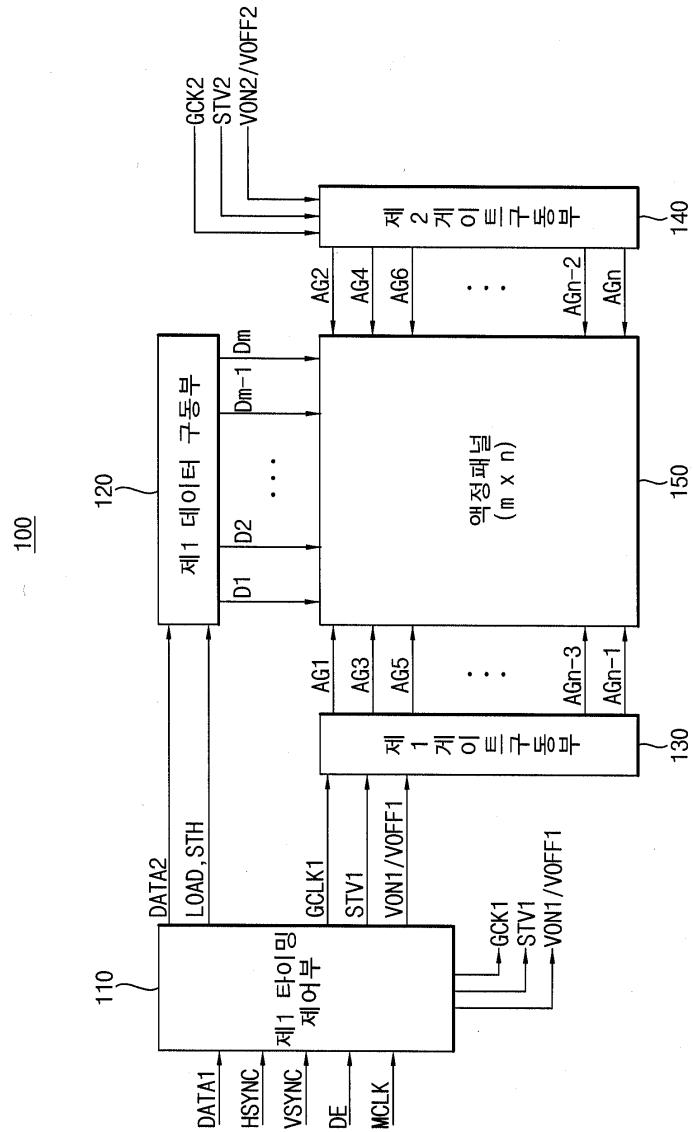

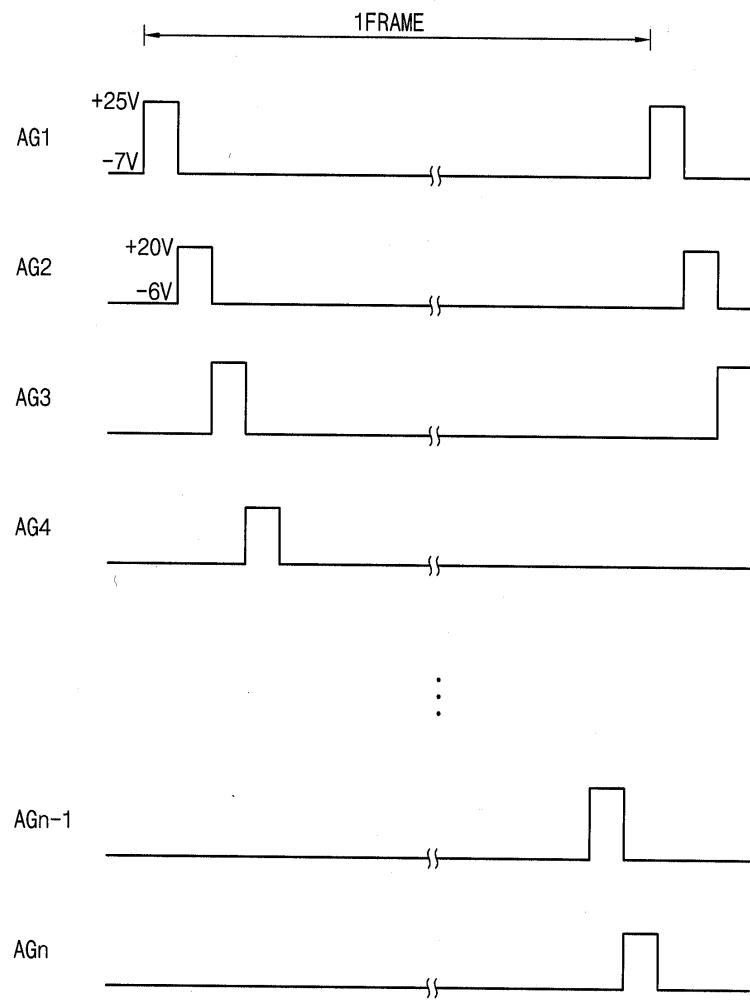

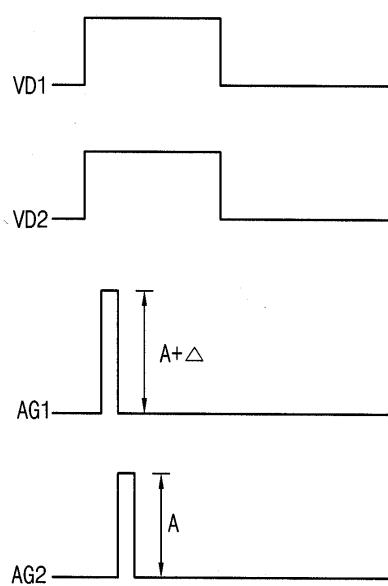

[0077] 도 8은 본 발명의 다른 실시예에 따른 액정표시장치를 설명하는 블록도이다. 도 9는 도 8에 도시된 제3 및 제4 게이트 구동부에서 출력되는 게이트 신호를 설명하는 과정도이다.

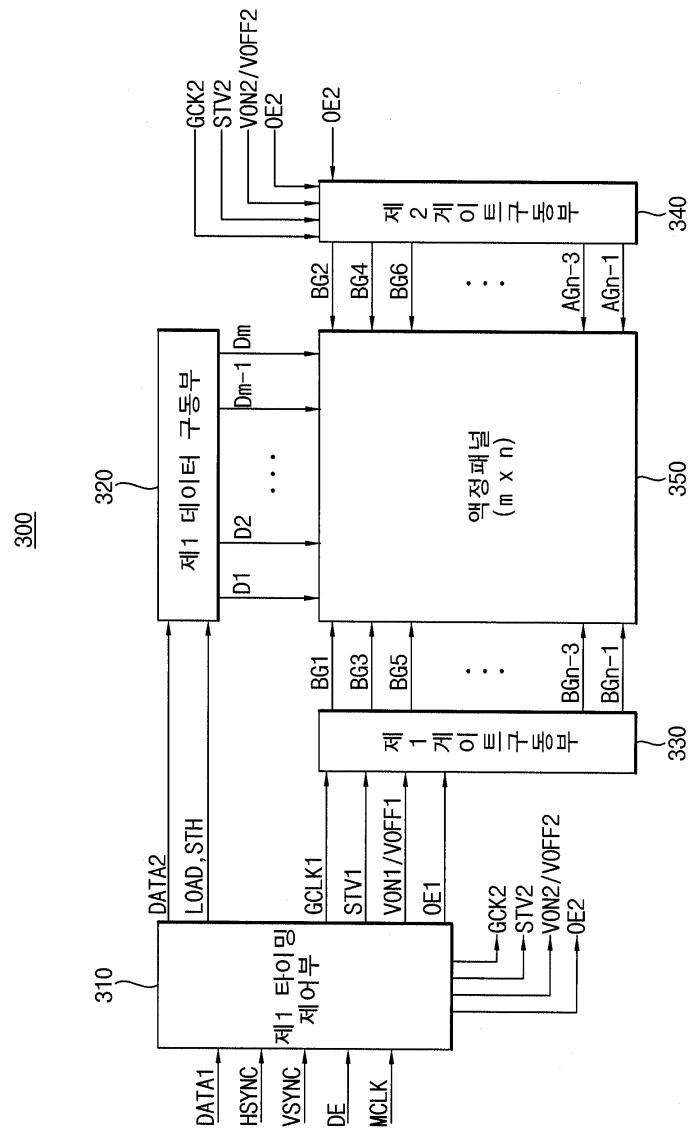

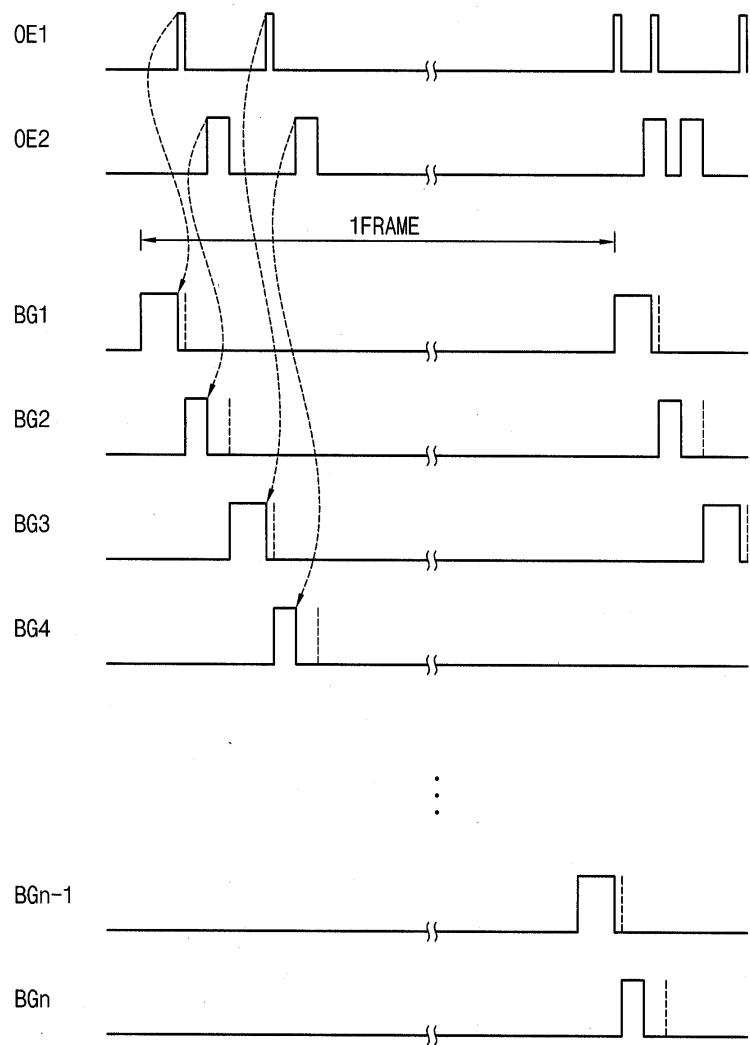

[0078] 도 8 및 도 9를 참조하면, 액정표시장치(300)는 제2 타이밍 제어부(310), 제2 데이터 구동부(320), 제3 게이트 구동부(330), 제4 게이트 구동부(340) 및 액정패널(350)을 포함한다.

[0079] 상기 제2 타이밍 제어부(310)는 외부로부터 제1 데이터 신호(DATA1), 각종 동기 신호들(Hsync, Vsync), 데이터 인에이블 신호(DE) 및 메인 클럭(MCLK)을 제공받아, 제2 데이터 신호(DATA2)와, 상기 제2 데이터 신호(DATA2)의 출력을 위한 데이터 구동 신호(LOAD, STH)를 상기 제2 데이터 구동부(320)에 출력한다. 상기 제2 타이밍 제어부(310)는 제1 게이트 구동 신호(GCK1, STV1, OE1)를 상기 제3 게이트 구동부(330)에 출력하고, 제2 게이트 구동 신호(GCK2, STV2, OE2)를 상기 제4 게이트 구동부(340)에 출력한다.

[0080] 여기서, 제1 수직개시신호(STV1)는 제2 수직개시신호(STV2)보다 앞서고, 이에 따라 상기 제3 게이트 구동부(330)에 액티브된 후 상기 제4 게이트 구동부(340)가 액티브된다.

[0081] 제1 출력 인에이블 신호(OE1)와 제2 출력 인에이블 신호(OE2)는 서로 다른 펄스 폭을 갖는다. 상기 제1 출력

인에이블 신호(OE1)는 홀수번째 게이트 신호(BG1, BG3, ..., BGn-1)(여기서, n은 짝수)가 상대적으로 넓은 펄스 폭을 갖도록 제어하고, 상기 제2 출력 인에이블 신호(OE2)는 짝수번째 게이트 신호(BG2, BG4, ..., BGn)가 정상적인 펄스 폭을 갖도록 제어한다.

[0082] 상기 제2 데이터 구동부(330)는 상기 제2 타이밍 제어부(310)에서 제2 데이터 신호(DATA2)가 수신됨에 따라, 상기 제2 데이터 신호(DATA2)를 데이터 전압(계조 전압)으로 변경하고, 변경된 데이터 전압(D1, D2, ..., Dm)을 상기 액정패널(350)에 인가한다.

[0083] 상기 제3 게이트 구동부(330)는 상기 제1 게이트 구동 신호(GCK1, STV1)에 응답하여 상기 액정패널(350)의 홀수번째 게이트 라인을 활성화하는 홀수번째 게이트 신호(BG1, BG3, ..., BGn-3, BGn-1)를 상기 액정패널(350)에 순차적으로 인가한다.

[0084] 상기 제4 게이트 구동부(340)는 상기 제2 게이트 구동 신호(GCK2, STV2)에 응답하여 상기 액정패널(350)의 짝수번째 게이트 라인을 활성화하는 짝수번째 게이트 신호(BG2, BG4, ..., BGn-2, BGn)를 순차적으로 상기 액정패널(350)에 인가한다. 상기 홀수번째 게이트 신호(BG1, BG3, ..., BGn-3, BGn-1)와 상기 짝수번째 게이트 신호(BG2, BG4, ..., BGn-2, BGn)는 교호로 출력된다.

[0085] 본 실시예에서, 상기 홀수번째 게이트 신호(BG1, BG3, ..., BGn-3, BGn-1)의 펄스 폭은 상기 짝수번째 게이트 신호(BG2, BG4, ..., BGn-2, BGn)의 펄스 폭보다 상대적으로 크다. 이는 상대적으로 선충전되는 홀수번째 게이트 신호(BG1, BG3, ..., BGn-3, BGn-1)에 대응하는 화소부가 상대적으로 후충전되는 짝수번째 게이트 신호(BG2, BG4, ..., BGn-2, BGn)에 대응하는 화소부에 충전량 감소를 방지하기 위함이다.

[0086] 상기 액정패널(350)은 게이트 신호(스캔 신호 또는 주사 신호)(BG1, BG2, ..., BGn-1, BGn)를 전달하는 복수의 게이트 라인(주사 라인 또는 스캔 라인)들과, 상기 데이터 전압(D1, D2, ..., Dm)을 전달하는 복수의 데이터 라인(소스 라인)들을 포함한다. 상기 액정패널(350)은 게이트 라인의 수가 증가되고, 데이터 라인의 수가 감소된 데이터 라인 반감 구조를 갖는다. 상기 데이터 라인 반감 구조는 도 3 및 도 4에서 설명된 바 있다.

[0087] 도 10은 도 8에 도시된 액정표시장치의 화소부를 설명하는 회로도이다. 도 11은 도 10에 도시된 게이트 전압과 데이터 전압을 설명하는 과형도이다. 도 10은 도 5와 비교할 때 동일한 구성 요소에 대해서는 동일한 도면 번호를 부여한다.

[0088] 도 10 및 도 11을 참조하면, 상기 제1 데이터 라인(DL1)에 인가되는 상기 제1 데이터 전압(VD1)은 상기 제1 게이트 신호(BG1)에 따라 상기 제1 픽셀부(PX1)에 충전된다.

[0089] 상기 제1 데이터 전압(VD1)은 공통전압(VCOM) 대비 정극성을 갖는다. 상기 제1 게이트 신호(BG1)는 상기 제1 게이트 라인(GL1)에 공급되어 상기 제1 게이트 라인(GL1)에 전기적으로 연결된 상기 제1 박막 트랜지스터(TFT1)를 액티브시킨다. 상기 제1 데이터 전압(VD1)은 상기 제1 박막 트랜지스터(TFT1)를 경유하여, 공통 연결된 상기 제1 액정 캐패시터(Cl1c1) 및 제1 스토리지 캐패시터(Cst1)에 충전된다.

[0090] 상기 제2 데이터 라인(DL2)에 인가되는 상기 제2 데이터 전압(VD2)은 상기 제2 게이트 신호(BG2)에 따라 상기 제2 픽셀부(PX2)에 충전된다. 상기 제2 데이터 전압(VD2)은 공통전압(VCOM) 대비 정극성을 갖는다. 상기 제2 게이트 신호(BG2)는 상기 제2 게이트 라인(GL2)에 공급되어 상기 제2 게이트 라인(GL2)에 전기적으로 연결된 상기 제2 박막 트랜지스터(TFT2)를 액티브시킨다. 상기 제2 데이터 전압(VD2)은 상기 제2 박막 트랜지스터(TFT2)를 경유하여, 공통 연결된 상기 제2 액정 캐패시터(Cl2c1) 및 제2 스토리지 캐패시터(Cst2)에 충전된다.

[0091] 상기 제2 게이트 신호(BG2)의 펄스 폭은 통상적으로 상기 제2 박막 트랜지스터(TFT2)를 턴-온시키는 정도이다. 이에 반면, 상기 제1 게이트 신호(BG1)의 펄스 폭은 상기 제2 게이트 신호(BG2)의 펄스 폭보다 상대적으로 크다. 상기 제1 및 제2 게이트 신호(BG1, BG2)의 펄스 폭은 서로 다른 제1 및 제2 출력 인에이블 신호(OE1, OE2)에 의해 조절된다.

[0092] 도 10 및 도 11에서는 서로 인접하는 데이터 라인에 공통전압 대비 동일 극성의 데이터 전압이 인가되는 것을 도시하였으나, 서로 인접하는 데이터 라인에 공통전압 대비 서로 다른 극성의 데이터 전압이 인가될 수도 있다.

[0093] 그러면, 상기 제1 및 제2 픽셀부(PX1, PX2)에 충전되는 데이터 전압의 충전량 특성을 도 12를 참조하여 설명한다.

[0094] 도 12는 도 10에 도시된 데이터 전압의 충전량 특성을 설명하는 과형도이다.

[0095] 도 12를 참조하면, 상대적으로 넓은 펠스 폭을 갖는 상기 제1 게이트 신호(BG1)가 액티브됨에 따라, 상기 제1 데이터 전압(VD1)이 충전되는 라이즈 타임은 기준 라이즈 타임에 비해 줄어든다. 상기 기준 라이즈 타임은 박막 트랜지스터의 동작을 제어하는 임계 전위차를 갖는 기준 게이트 신호에 의해 데이터 전압이 충전되는 시간이다. 이에 따라, 상기 제1 핵셀부(PX1)의 실질적인 충전시간은 증가되어 실질적인 충전량은 상기 기준 게이트 신호에 의한 충전량보다 증가한다.

[0096] 이어, 임계 전위차를 갖는 상기 제2 게이트 신호(BG2)가 액티브됨에 따라, 상기 제2 데이터 전압(VD2)은 기준 라이즈 타임을 갖고서 상기 제2 핵셀부(PX2)에 충전된다. 즉, 상기 제2 핵셀부(PX2)에는 정상적인 충전시간에 의해 정상적인 제2 충전량(QC2) 만큼 충전이 이루어지는 반면, 상기 제1 핵셀부(PX1)에는 상기 제2 충전량(QC2)보다 증가된 제1 충전량(QC1) 만큼 충전된다.

[0097] 이에 따라, 커플링 캐패시터를 통해 상기 제1 핵셀부(PX1)에 전기적으로 연결된 상기 제2 핵셀부(PX2)가 충전될 때, 상기 제1 핵셀부(PX1)가 정상적인 충전량보다 낮게되는 것을 방지할 수 있다. 왜냐하면, 상기 제1 핵셀부(PX1)는 충전량 감소가 감안되어 상대적으로 과도하게 충전되기 때문이다.

### 발명의 효과

[0098] 이상에서 설명한 바와 같이, 첫 번째 핵셀과 두 번째 핵셀이 서로 인접하는 데이터 라인에 의해 둘러싸이는 데이터 라인 반감 구조에서, 첫 번째 핵셀이 충전된 후 두 번째 핵셀이 충전된다. 이때, 미리 충전된 첫 번째 핵셀은 두 번째 핵셀의 충전에 따라 커플링 캐패시터에 의해 충전량 감소가 발생되어 세로줄성 플리커링 현상이 발생된다.

[0099] 하지만, 본 발명에 따라 첫 번째 핵셀에 대해서는 상대적으로 큰 레벨 또는 상대적으로 넓은 펠스 폭의 게이트 신호를 이용하여 충전 동작을 수행하고, 두 번째 핵셀에 대해서는 정상적인 레벨 또는 정상적인 펠스 폭의 게이트 신호를 이용하여 충전 동작을 수행하므로써, 세로줄성 플리커링 현상을 제거할 수 있다.

[0100] 이상에서는 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 도면의 간단한 설명

[0001] 도 1은 본 발명의 일실시예에 따른 액정표시장치를 설명하는 블록도이다.

[0002] 도 2는 도 1에 도시된 제1 및 제2 게이트 구동부에서 출력되는 게이트 신호를 설명하는 과정도이다.

[0003] 도 3은 도 1에 도시된 액정패널에 형성된 화소부를 상세하게 나타낸 레이아웃도이다.

[0004] 도 4는 도 1에 도시된 액정패널의 화소부를 설명하는 등가회로도이다.

[0005] 도 5는 도 1에 도시된 액정표시장치의 화소부를 설명하는 회로도이다.

[0006] 도 6은 도 5에 도시된 게이트 전압과 데이터 전압을 설명하는 과정도이다.

[0007] 도 7은 도 5에 도시된 데이터 전압의 충전량 특성을 설명하는 과정도이다.

[0008] 도 8은 본 발명의 다른 실시예에 따른 액정표시장치를 설명하는 블록도이다.

[0009] 도 9는 도 8에 도시된 제3 및 제4 게이트 구동부에서 출력되는 게이트 신호를 설명하는 과정도이다.

[0010] 도 10은 도 9에 도시된 액정표시장치의 화소부를 설명하는 회로도이다.

[0011] 도 11은 도 10에 도시된 게이트 전압과 데이터 전압을 설명하는 과정도이다.

[0012] 도 12는 도 10에 도시된 데이터 전압의 충전량 특성을 설명하는 과정도이다.

[0013] <도면의 주요부분에 대한 부호의 설명>

[0014] 110, 310 : 타이밍 제어부 120, 320 : 데이터 구동부

[0015] 130, 140, 330, 340 : 게이트 구동부 150, 350 : 액정패널

### 도면

## 도면1

## 도면2

도면3

도면4

## 도면5

## 도면6

도면7

## 도면8

## 도면9

도면10

도면11

도면12

|                |                                                                            |         |            |

|----------------|----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 液晶显示装置及其驱动方法                                                          |         |            |

| 公开(公告)号        | <a href="#">KR101158899B1</a>                                              | 公开(公告)日 | 2012-06-25 |

| 申请号            | KR1020050076614                                                            | 申请日     | 2005-08-22 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                   |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                   |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                   |         |            |

| [标]发明人         | LEE HYUN SU<br>이현수<br>HA JAE MIN<br>하재민                                    |         |            |

| 发明人            | 이현수<br>하재민                                                                 |         |            |

| IPC分类号         | G09G3/36 G02F1/13                                                          |         |            |

| CPC分类号         | G09G3/3648 G09G3/3607 G09G3/3677 G09G2300/0426 G09G2300/0852 G09G2320/0247 |         |            |

| 代理人(译)         | 英西湖公园                                                                      |         |            |

| 其他公开文献         | KR1020070022424A                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                  |         |            |

## 摘要(译)

公开了一种用于改善显示特性的液晶显示装置及其驱动方法。液晶面板具有第一像素部分和第二像素部分，第一像素部分和第二像素部分在由相邻的栅极线和彼此相邻的数据线限定的各个区域中被充电不同的时段。数据驱动器将数据信号提供给液晶面板。栅极驱动器向液晶面板提供栅极信号，以相对于要充电的第二像素单元对在第一和第二像素单元中预充电的第一像素单元进行相对充电。因此，在数据线半结构中，具有相对大或宽的脉冲宽度的栅极信号被提供给预充电的第一像素部分，并且具有正常尺寸或脉冲宽度的栅极信号被提供给第二像素部分以被预充电。可以消除垂直条纹闪烁现象。