**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.

*G02F 1/1368* (2006.01)

(11) 공개번호 10-2007-0018032

*G02F 1/136* (2006.01)

(43) 공개일자 2007년02월13일

*H01L 29/786* (2006.01)

*C23C 14/34* (2006.01)

(21) 출원번호 10-2006-7018342

(22) 출원일자 2006년09월08일

심사청구일자 없음

번역문 제출일자 2006년09월08일

(86) 국제출원번호 PCT/JP2005/003489

(87) 국제공개번호 WO 2005/086180

국제출원일자 2005년03월02일

국제공개일자 2005년09월15일

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2004-00065324 | 2004년03월09일 | 일본(JP) |

|            | JP-P-2004-00070113 | 2004년03월12일 | 일본(JP) |

|            | JP-P-2004-00130702 | 2004년04월27일 | 일본(JP) |

|            | JP-P-2004-00132621 | 2004년04월28일 | 일본(JP) |

|            | JP-P-2004-00272951 | 2004년09월21일 | 일본(JP) |

(71) 출원인

이데미쓰 고산 가부시키가이샤

일본 도쿄도 지요다구 마루노우치 3쵸메 1반 1고

(72) 발명자

이노우에, 가즈요시

일본 299-0205 치바肯 소데가우라 가미-이즈미 1280반치 이데미쓰고

산 가부시키가이샤 중앙연구소내

도마이, 시게카즈

일본 299-0205 치바肯 소데가우라 가미-이즈미 1280반치 이데미쓰고

산 가부시키가이샤 중앙연구소내

마쓰바라 마사토

일본 299-0205 치바肯 소데가우라 가미-이즈미 1280반치 이데미쓰고

산 가부시키가이샤 중앙연구소내

(74) 대리인

주성민

위혜숙

전체 청구항 수 : 총 53 항

(54) 박막 트랜지스터, 박막 트랜지스터 기판, 이들의 제조방법, 이를 사용한 액정 표시 장치, 관련된 장치 및 방법, 및 스퍼터링 타깃, 이것을 사용하여 성막한 투명도전막, 투명 전극, 및 관련된 장치 및 방법

(57) 요약

본 발명은 예칭에 의한 잔사 등의 발생이 거의 없는 투명 도전막을 구비하는 박막 트랜지스터형 기판, 그의 제조 방법 및 이 박막 트랜지스터형 기판을 사용한 액정 표시 장치를 제공한다. 투명 기판, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극 및 상기 투명 기판 위에 설치된 투명 화소 전극을 구비하여 이루어지는 박막 트랜지스터형 기판에서, 상기 투명 화소 전극이 산화인듐을 주성분으로서 포함하며, 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막이고, 상기 투명 화소 전극은 상기 소스 전극 또는 상기 드레인 전극과 전기적으로 접속하고 있는 박막 트랜지스터형 기판, 그의 제조 방법 및 이 박막 트랜지스터형 기판을 사용한 액정 표시 장치이다.

## 내용

### 도 1

#### 특허청구의 범위

##### 청구항 1.

투명 기판,

상기 투명 기판 위에 설치된 소스 전극,

상기 투명 기판 위에 설치된 드레인 전극, 및

상기 투명 기판 위에 설치된 투명 화소 전극

을 구비하여 이루어지고, 이때 상기 투명 화소 전극이

산화인듐을 주성분으로서 포함하며 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막이며,

상기 투명 화소 전극이 상기 소스 전극 또는 상기 드레인 전극과 전기적으로 접속하고 있는 것을 특징으로 하는, 박막 트랜지스터형 기판.

##### 청구항 2.

투명 기판, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극 및 상기 투명 기판 위에 설치된 투명 화소 전극을 구비하여 이루어지는 박막 트랜지스터형 기판;

복수색의 착색 패턴이 설치된 컬러 필터 기판; 및

상기 박막 트랜지스터형 기판과 상기 컬러 필터 기판 사이에 끼워진 액정층

을 구비하여 이루어지고, 이때 상기 투명 화소 전극이

산화인듐을 주성분으로서 포함하며 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막이며,

상기 투명 화소 전극이 상기 소스 전극 또는 상기 드레인 전극과 전기적으로 접속하고 있는 것을 특징으로 하는, 박막 트랜지스터형 액정 표시 장치.

### 청구항 3.

투명 기판 위에 투명 도전막을 퇴적하는 단계, 및

상기 퇴적한 투명 도전막을 산성의 에칭제를 사용하여 에칭함으로써 투명 화소 전극을 형성하는 단계

를 포함하는 것을 특징으로 하는, 제1항에 기재된 박막 트랜지스터형 기판의 제조 방법.

### 청구항 4.

제3항에 있어서, 산성의 에칭제가 옥살산, 인산·아세트산·질산을 포함하는 혼합산 및 질산 제2 세륨암모늄 중 1종 또는 2종 이상을 포함하는 것을 특징으로 하는, 박막 트랜지스터형 기판의 제조 방법.

### 청구항 5.

산화인듐을 주성분으로 하며,

W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물, 및

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 것을 특징으로 하는, 스퍼터링 타깃(sputtering target).

### 청구항 6.

제5항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속

산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성

인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 스퍼터링 타깃(여기서, 상기  $[M1]$ 은 상기 제1 금

속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[M2]$ 는 상기 제2 금속군으로부터 선택된

1종 또는 2종 이상의 금속의 원자의 수를 나타내며, 상기  $[In]$ 은 인듐의 원자의 수를 나타낸다).

### 청구항 7.

제5항 또는 제6항에 있어서, 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce,

Ho 및 Er 중으로부터 선택된 1종 이상의 금속의 산화물인 것을 특징으로 하는, 스퍼터링 타깃.

### 청구항 8.

산화인듐을 주성분으로 하며,

W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물, 및

Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 것을 특징으로 하는, 스퍼터링 타깃.

### 청구항 9.

제8항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이며,

Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 스퍼터링 타깃(여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내며, 상기 [M3]은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [In]은 인듐 금속의 원자의 수를 나타낸다).

### 청구항 10.

제8항 또는 제9항에 있어서, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 1종 이상의 금속의 산화물인 것을 특징으로 하는, 스퍼터링 타깃.

### 청구항 11.

산화인듐을 주성분으로 하며,

W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물, 및

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 것을 특징으로 하는, 투명 도전막.

### 청구항 12.

제11항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 투명 도전막(여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내며, 상기 [In]은 인듐의 원자의 수를 나타낸다).

### 청구항 13.

제11항 또는 제12항에 있어서, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 1종 이상의 금속의 산화물인 것을 특징으로 하는, 투명 도전막.

## 청구항 14.

산화인듐을 주성분으로 하며,

W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물, 및

Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 것을 특징으로 하는, 투명 도전막.

## 청구항 15.

제14항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이며,

Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 투명 도전막(여기서, 상기  $[M1]$ 은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[M2]$ 는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내며, 상기  $[M3]$ 은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[In]$ 은 인듐 원자의 수를 나타낸다).

## 청구항 16.

제14항 또는 제15항에 있어서, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 1종 이상의 금속의 산화물인 것을 특징으로 하는, 투명 도전막.

## 청구항 17.

유리 기판;

상기 유리 기판 위에 설치되고, 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물, 및 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 투명 도전막; 및

상기 유리 기판 위에 설치된, Al 또는 Ag을 주성분으로 하는 금속 박막

을 갖는 것을 특징으로 하는, 투명 도전 유리 기판.

## 청구항 18.

제17항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 투명 도전 유리 기판(여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타낸다).

### 청구항 19.

제17항 또는 제18항에 있어서, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 1종 이상의 금속의 산화물인 것을 특징으로 하는, 투명 도전 유리 기판.

### 청구항 20.

유리 기판;

상기 유리 기판 위에 설치되고, 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물, 및 추가로 Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 투명 도전막; 및

상기 유리 기판 위에 설치된, Al 또는 Ag을 주성분으로 하는 금속 박막

을 갖는 것을 특징으로 하는, 투명 도전 유리 기판.

### 청구항 21.

제20항에 있어서, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이며,

Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는, 투명 도전 유리 기판(여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내며, 상기 [M3]은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [In]은 인듐 원자의 수를 나타낸다).

### 청구항 22.

제20항 또는 제21항에 있어서, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 1종 이상의 금속의 산화물인 것을 특징으로 하는, 투명 도전 유리 기판.

### 청구항 23.

W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 사용하여, 게이트, 소스 및 드레인을 포함하는 도체군 E1에 포함되는 어느 하나의 도체인 제1 도체를, 투명 절연성 기판 위에 형성하는 제1 도체 형성 공정;

형성된 상기 제1 도체 및 상기 투명 절연성 기판을 덮도록 절연막을 성막하는 절연막 성막 공정;

성막된 상기 절연막에 콘택트 홀(contact hole)을 형성하는 콘택트 홀 형성 공정; 및

상기 절연막 위에 투명막 전극을 포함하는 제2 도체를 형성하는 공정으로서, 상기 제2 도체와 상기 제1 도체가 상기 콘택트 홀을 통해 전기적으로 접속하는 전극 접속 공정

을 적어도 포함하는 것을 특징으로 하는, 박막 트랜지스터 기판의 제조 방법.

#### 청구항 24.

투명 절연성 기판, 및 상기 투명 절연성 기판 위에 설치된, 게이트, 소스, 및 드레인을 포함하는 도체군 E1에 포함되는 어느 하나의 도체인 제1 도체

를 포함하고, 이때 상기 제1 도체가 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 포함하는 Al층을 포함하며, 상기 제1 도체 위의 절연막에 형성된 콘택트 홀을 통해, 투명막 전극을 포함하는 제2 도체와 접속하는 것을 특징으로 하는, 박막 트랜지스터.

#### 청구항 25.

제24항에 있어서, 제1 도체가 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 0.5 내지 5 중량% 갖는 Al층을 포함하는 것을 특징으로 하는, 박막 트랜지스터.

#### 청구항 26.

투명 절연성 기판; 상기 투명 절연성 기판 위에 형성된, 게이트, 소스 및 드레인을 포함하는 도체군 E1에 포함되는 어느 하나의 도체인 제1 도체; 적어도 상기 투명 절연성 기판을 덮도록 형성된 절연막; 및 상기 절연막 위에 형성된 제2 도체

를 적어도 포함하고, 이때 상기 제1 도체가 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 포함하는 Al층을 포함하며,

상기 절연막이 상기 제1 도체 및 상기 제2 도체 방향으로 관통하고 있는 소정의 콘택트 홀을 구비하고,

상기 제2 도체가 투명막 전극을 포함하며, 상기 콘택트 홀을 통해, 상기 제1 도체의 상기 Al층과 전기적으로 접속하고 있는 것을 특징으로 하는, 박막 트랜지스터 기판.

#### 청구항 27.

제26항에 있어서, 투명막 전극이 산화인듐, 산화주석, 산화인듐주석, 산화인듐아연 및 산화아연 중 어느 하나를 포함하는 것을 특징으로 하는, 박막 트랜지스터 기판.

#### 청구항 28.

제26항 또는 제27항에 있어서, 제1 도체가 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 0.5 내지 5 중량% 갖는 Al층을 포함하는 것을 특징으로 하는, 박막 트랜지스터 기판.

**청구항 29.**

제26항 내지 제28항 중 어느 한 항에 기재된 박막 트랜지스터 기판, 및

상기 박막 트랜지스터 기판에 의해 구동되는 액정층

을 포함하는 것을 특징으로 하는, 액정 표시 장치.

**청구항 30.**

투명 기판,

상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극,

상기 투명 기판 위에 설치된 소스 전극,

상기 투명 기판 위에 설치된 드레인 전극,

상기 투명 기판 위에 설치된 실리콘층, 및

상기 투명 기판 위에 설치된 투명 전극

을 구비하고, 이때 상기 투명 전극이

산화인듐, 및

W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 도전성 산화물이며, 상기 투명 전극이 상기 Al을 주성분으로 하는 게이트 전극, 상기 소스 전극 및 상기 드레

인 전극을 포함하는 군으로부터 선택된 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는, 액정 표시 장치용

TFT(박막 트랜지스터) 기판.

**청구항 31.**

제30항에 있어서, 도전성 산화물 중, 인듐에 대한 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In] + [M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는, TFT 기판(여기서, 상기 식 중의  $[M1]$ 은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 식 중의  $[In]$ 은 인듐의 원자의 수를 나타낸다).

**청구항 32.**

제30항 또는 제31항에 있어서, 도전성 산화물이 산화인듐 이외에, 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로

부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는, TFT 기판.

**청구항 33.**

제32항에 있어서, 도전성 산화물 중, 인듐에 대한 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In] + [M2])$ 이 0.01 내지 0.3의 범위인 것을 특징으로 하는, TFT 기판(여기서, 상기 식 중의  $[M2]$ 는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 1종 또는 2종 이상의 원자의 수를 나타내고, 상기 식 중의  $[In]$ 은 인듐의 원자의 수를 나타낸다).

**청구항 34.**

액정 표시 장치용 TFT 기판에 사용되는 투명 전극으로서 액정을 구동하는 상기 투명 전극을 스퍼터링법으로 제조할 때 사용하는 스퍼터링 타깃에서,

산화인듐, 및

W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속 산화물

을 포함하는 도전성 산화물을 포함하는 것을 특징으로 하는, Al을 주성분으로 하는 전극 또는 배선과 전기적으로 접합 가능한 투명 전극 제조용 스퍼터링 타깃.

**청구항 35.**

제34항에 있어서, 도전성 산화물 중, 인듐에 대한 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In] + [M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는, 스퍼터링 타깃(여기서, 상기 식 중의 [M1]은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

**청구항 36.**

제34항 또는 제35항에 있어서, 도전성 산화물이 산화인듐 이외에, 주석, 아연, 계르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는, 스퍼터링 타깃.

**청구항 37.**

제36항에 있어서, 도전성 산화물 중, 인듐에 대한 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In] + [M2])$ 이 0.01 내지 0.3의 범위인 것을 특징으로 하는, 스퍼터링 타깃(여기서, 상기 식 중의 [M2]는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 계르마늄 및 갈륨 중 1종 또는 2종 이상의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

**청구항 38.**

TFT 기판과 액정을 구비하고, 이때 상기 TFT 기판이

투명 기판,

상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극,

상기 투명 기판 위에 설치된 소스 전극,

상기 투명 기판 위에 설치된 드레인 전극,

상기 투명 기판 위에 설치된 실리콘층,

상기 투명 기판 위에 설치되어, 상기 액정을 구동하는 화소 전극, 및

상기 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 보호하는 투명 전극

을 구비하며, 상기 화소 전극 또는 투명 전극이

산화인듐, 및

W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물

을 포함하는 도전성 산화물이고, 상기 화소 전극 또는 투명 전극이 상기 Al을 주성분으로 하는 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 포함하는 군으로부터 선택된 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는, 액정 표시 장치.

### 청구항 39.

제38항에 있어서, 도전성 산화물 중, 인듐에 대한 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In] + [M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는, 액정 표시 장치(여기서, 상기 식 중의 [M1]은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

### 청구항 40.

제38항 또는 제39항에 있어서, 도전성 산화물이 산화인듐 이외에, 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는, 액정 표시 장치.

### 청구항 41.

제40항에 있어서, 도전성 산화물 중, 인듐에 대한 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In] + [M2])$ 이 0.01 내지 0.3의 범위인 것을 특징으로 하는, 액정 표시 장치(여기서, 상기 식 중의 [M2]는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 1종 또는 2종 이상의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

### 청구항 42.

투명 기판,

상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극,

상기 투명 기판 위에 설치된 소스 전극,

상기 투명 기판 위에 설치된 드레인 전극,

상기 투명 기판 위에 설치된 실리콘층,

상기 투명 기판 위에 설치된 화소 전극, 및

상기 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 보호하는 투명 전극

을 구비한 액정 표시 장치용 TFT 기판에 사용되어 액정을 구동하고;

산화인듐, 및

W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이며;

상기 Al을 주성분으로 하는 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 포함하는 군으로부터 선택되는 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는, 화소 전극.

#### 청구항 43.

제42항에 있어서, 도전성 산화물 중, 인듐에 대한 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In] + [M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는, 화소 전극(여기서, 상기 식 중의 [M1]은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

#### 청구항 44.

제42항 또는 제43항에 있어서, 도전성 산화물이 산화인듐 이외에, 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는, 화소 전극.

#### 청구항 45.

제44항에 있어서, 도전성 산화물 중, 인듐에 대한 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In] + [M2])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는, 화소 전극(여기서, 상기 식 중의 [M2]는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 1종 또는 2종 이상의 원자의 수를 나타내고, 상기 식 중의 [In]은 인듐의 원자의 수를 나타낸다).

#### 청구항 46.

투명 기판,

상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극,

상기 투명 기판 위에 설치된 소스 전극,

상기 투명 기판 위에 설치된 드레인 전극,

상기 투명 기판 위에 설치된 실리콘층,

상기 투명 기판 위에 설치된 화소 전극, 및

상기 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 보호하는 투명 전극

을 구비한 액정 표시 장치용 TFT 기판에 사용되고;

산화인듐, 및

W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이며;

상기 AI을 주성분으로 하는 케이트 전극, 상기 소스 전극 및 상기 드레인 전극을 포함하는 군으로부터 선택되는 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는, 투명 전극.

#### 청구항 47.

제46항에 있어서, 도전성 산화물 중, 인듐에 대한 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In] + [M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는, 투명 전극(여기서, 상기 식 중의  $[M1]$ 은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 식 중의  $[In]$ 은 인듐의 원자의 수를 나타낸다).

#### 청구항 48.

제46항 또는 제47항에 있어서, 도전성 산화물이 산화인듐 이외에, 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는, 투명 전극.

#### 청구항 49.

제48항에 있어서, 도전성 산화물 중, 인듐에 대한 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In] + [M2])$ 이 0.01 내지 0.3의 범위인 것을 특징으로 하는, 투명 전극(여기서, 상기 식 중의  $[M2]$ 는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 1종 또는 2종 이상의 원자의 수를 나타내고, 상기 식 중의  $[In]$ 은 인듐의 원자의 수를 나타낸다).

#### 청구항 50.

투명 기판 위에 도전성 산화물을 퇴적하여, 도전성 산화물의 박막을 형성하는 단계, 및

상기 형성된 도전성 산화물의 박막을 옥살산을 포함하는 수용액으로 예칭함으로써 투명 전극을 형성하는 단계

를 포함하는 것을 특징으로 하는, 제30항 내지 제33항 중 어느 한 항에 기재된 TFT 기판의 제조 방법.

#### 청구항 51.

투명 기판 위에 도전성 산화물을 퇴적하여, 도전성 산화물의 박막을 형성하는 단계, 및

상기 형성된 도전성 산화물의 박막을 인산·아세트산·질산을 포함하는 수용액으로 예칭함으로써 투명 전극을 형성하는 단계

를 포함하는 것을 특징으로 하는, 제30항 내지 제33항 중 어느 한 항에 기재된 TFT 기판의 제조 방법.

#### 청구항 52.

투명 기판 위에 도전성 산화물을 퇴적하여, 도전성 산화물의 박막을 형성하는 단계, 및

상기 형성된 도전성 산화물의 박막을 질산 세륨암모늄염을 포함하는 수용액으로 예칭함으로써 투명 전극을 형성하는 단계

를 포함하는 것을 특징으로 하는, 제30항 내지 제33항 중 어느 한 항에 기재된 TFT 기판의 제조 방법.

## 청구항 53.

제30항 내지 제52항 중 어느 한 항에 있어서, 란타노이드가 Ce, Nd, Er 및 Ho으로부터 선택된 1종 또는 2종 이상의 란타노이드인 것을 특징으로 하는, TFT 기판, 투명 전극 제조용 스퍼터링 타깃, 액정 표시 장치, 화소 전극, 투명 전극, 또는 TFT 기판의 제조 방법.

명세서

### 기술분야

#### 제1 그룹: 분야

제1 그룹의 본 발명은 액정 표시 장치의 액정을 구동하는 박막 트랜지스터형 기판에 관한 것이다. 또한, 본 발명은 이 박막 트랜지스터형 기판을 제조하는 방법에 관한 것이며, 이 박막 트랜지스터형 기판을 사용한 액정 표시 장치에 관한 것이다.

박막 트랜지스터형 기판은, 박막 트랜지스터의 단축된 통칭을 사용하여 TFT 기판이라고 부르는 경우도 있다.

#### 제2 그룹: 분야

또한 제2 그룹의 본 발명은 비정질 실리콘 박막 트랜지스터(a-SiTFT) 또는 폴리실리콘 박막 트랜지스터(p-SiTFT)를 사용한 액정 표시 장치의 제조 방법에 관한 것이다. 더욱 상세하게는, 화소 전극 패턴과 소스·드레인 배선의 접촉 저항 및 게이트 배선 축출부, 소스·드레인 전극 축출부의 배선 금속과 투명 전극의 접촉 저항을 감소시킬 수 있는 액정 표시 장치 및 그의 제조 방법에 관한 것이다.

특히, 스퍼터링 타깃(sputtering target)에 대한 고안, 이 스퍼터링 타깃을 사용한 제조 방법에 따른 투명 도전막, 및 이 투명 도전막을 구비한 투명 도전 유리 기판에 관한 것이다.

#### 제3 그룹: 분야

제3 그룹의 본 발명은 박막 트랜지스터(Thin Film Transistor: 이하, TFT로 기재하는 경우도 있음) 기판, 특히 TFT에 관한 것이다. 또한, 이 TFT 기판의 제조 방법에 관한 것이다. 또한, 이 TFT 기판을 사용한 액정 표시 장치에 관한 것이다.

#### 제4 그룹: 분야

제4 그룹의 본 발명은 비정질 실리콘 박막 트랜지스터(a-SiTFT) 또는 폴리 실리콘 박막 트랜지스터(p-SiTFT)를 사용한 액정 표시 장치의 제조 방법에 관한 것이다. 더욱 상세하게는, 화소 전극 패턴과 배선과 소스·드레인 배선의 접촉 저항 및 게이트 배선 축출부, 소스 드레인 전극 축출부의 배선 금속과 투명 전극의 접촉 저항을 감소시킬 수 있는 액정 표시 장치 및 그의 제조 방법에 관한 것이다.

특히, 제4 그룹의 본 발명은 TFT 기판(TFT를 어레이상(狀)으로 배치한 TFT 어레이 기판을 포함함), 액정 구동용 전극 기판 및 스퍼터링 타깃에 관한 것이기도 하다.

### 배경기술

#### 제1 그룹: 배경

종래부터, 액정 표시 장치는 예의 연구 개발되었다. 특히, 최근 대형 텔레비전용 액정 표시 장치가 등장한 후, 더욱 활발히 연구 개발되고 있다.

이 액정 표시 장치의 화소 전극의 재료에는 일반적으로, ITO(Indium Tin Oxide: 인듐·주석 산화물)이 사용되고 있다. 이 것은 ITO가 도전성 및 투명성이 우수하며, 강산(왕수(王水), 염산계 에칭제)에 의해 용이하게 에칭할 수 있기 때문이다.

그러나, 스퍼터링에 의해 대형 기판으로 성막되는 ITO는 결정질의 막이기 때문에, 기판 온도 또는 분위기 가스 및 플라즈마 밀도의 상태 등에 따라 결정의 상태가 다양하게 변화되며, 동일한 기판 위에 결정질의 막과 비정질의 막이 혼재되는 경우가 있다. 이 혼재가 원인이 되어, 예칭 불량(인접하는 전극과의 도통, 오버 에칭에 의한 화소 전극의 가늘어짐 및 예칭 잔사에 의한 화소 불량 등)의 문제점이 자주 발생하고 있었다.

예칭시에 생기는 문제점을 해결하기 위해, 예를 들면 일본 특허 공개 (소)63-184726호 공보에는, ITO 화소 전극막을 비정질로 함으로써,  $HCl-HNO_3-H_2O$ 계의 예칭액에 대한 ITO/Al 예칭 속도비를 크게 하여, 예칭시에 발생하는 Al의 용출을 개선하는 방법이 개시되어 있다.

또한, 상기 ITO를 포함하는 타깃은 장시간의 연속 성막시에, 타깃 표면에 흑색의 입자(노들: nodule)를 발생시켜 이상 방전을 야기하거나, 이를질을 발생시켜 화소 불량을 야기하는 경우도 자주 있었다.

따라서, ITO를 성막할 때, 스퍼터 가스 중에 물 또는 수소를 첨가함으로써 비정질 상태의 ITO를 성막하며, 이 성막한 ITO를 예칭한 후, 가열하여 결정화하는 방법이 검토되고 있다. 그러나, 성막시에 물 또는 수소를 첨가하면, 바탕 기판에 대한 밀착성이 저하되거나, ITO 표면이 환원되어 노들이 대량으로 발생하는 경우가 자주 있었다.

이들의 문제점을 해결하는 목적으로, 상기 ITO 대신에 IZO(등록 상표: 이데미쯔 코산 가부시끼가이샤, Indium Zinc Oxide: 인듐·아연 산화물)가 사용되고 있다. 이 IZO는 성막시에 거의 완전한 비정질막을 성막할 수 있으며, 약산인 옥살산계 예칭제에 의해 예칭할 수 있고, 인산·아세트산·질산의 혼합산 또는 질산 제2 세륨암모늄 수용액 등으로도 예칭할 수 있는 등, 유용성이 풍부하다. 또한, 이 IZO는 ITO에 비해, 보다 약한 산으로 예칭하는 것이 가능하다. 또한, 이 IZO를 포함하는 타깃은 스퍼터링시에 노들의 발생이 적고, 이를질의 발생도 억제되기 때문에, 유용한 타깃이라고 할 수 있다.

상기 IZO를 포함하는 타깃으로서, 예를 들면 하기 일본 특허 공개 (평)6-234565호 공보에는, 화학식  $In_2O_3(ZnO)_m$  ( $m=2$  내지 20)으로 표시되는 육방정 층상 화합물을 포함하는 산화물의 소결체를 포함하는 타깃이 개시되어 있다. 이 타깃에 따르면, 내습성(내구성)이 우수한 투명 도전막을 성막하는 것이 가능해진다.

또한, 상기 IZO를 포함하는 투명 도전막으로서, 예를 들면 하기 일본 특허 공개 (평)6-187832호 공보에는 인듐 화합물과 아연 화합물을 알칸올아민 존재하에 용해시켜 제조한 코팅 용액을 기판에 도포하여 소성한 후, 환원 처리함으로써 투명 도전막을 제조하는 방법이 개시되어 있다. 이 투명 도전막의 제조 방법에 따르면, 내습성(내구성)이 우수한 투명 도전막을 얻을 수 있다.

또한, 상기 IZO를 포함하는 투명 도전막을 예칭하는 방법으로서, 예를 들면 하기 일본 특허 공개 (평)11-264995호 공보에는,  $In_2O_3-ZnO$ 를 포함하는 투명 도전막을 옥살산 수용액로 예칭함으로써, 화소 전극을 형성하는 액정 표시 장치의 제조 방법이 개시되어 있다. 이 액정 표시 장치의 제조 방법에 따르면, 옥살산 용액을 사용하여 예칭을 행하기 때문에, 화소 전극의 패턴을 용이하게 형성할 수 있다. 이 때문에, 수율을 향상시킬 수 있다.

## 제2 그룹: 배경

액정 표시 장치는 저소비 전력 및 풀 컬러화의 용이 등의 특징을 갖기 때문에 박형 디스플레이 중에서 유망시되며, 최근 표시 화면의 대형화에 대한 개발이 활발하다. 이 중에서도, 각 화소마다  $\alpha$ -SiTFT(TFT: Thin Film Transistor: 박막 트랜지스터) 또는 p-SiTFT를 스위칭 소자로서 매트릭스상으로 배열하여 구동하는 활성 매트릭스 방식 액정 평면 디스플레이인, 800×600 화소 이상의 고정밀화를 행하여도, 콘트라스트비가 열화되지 않기 때문에, 고성능 컬러 표시용 평면 디스플레이로서 주목받고 있다. 이러한 활성 매트릭스 방식 액정 평면 디스플레이에서는, 화소 전극으로서 ITO(Indium Tin Oxide)와 같은 투명 전극, 소스 전극으로서는 Al계 합금 박막을 사용하는 경우가 많은데, 이것은 ITO가 시트 저항이 낮고 투과율이 높으며, Al은 용이하게 패턴화할 수 있을 뿐만 아니라 저저항이고 밀착성이 높기 때문이다.

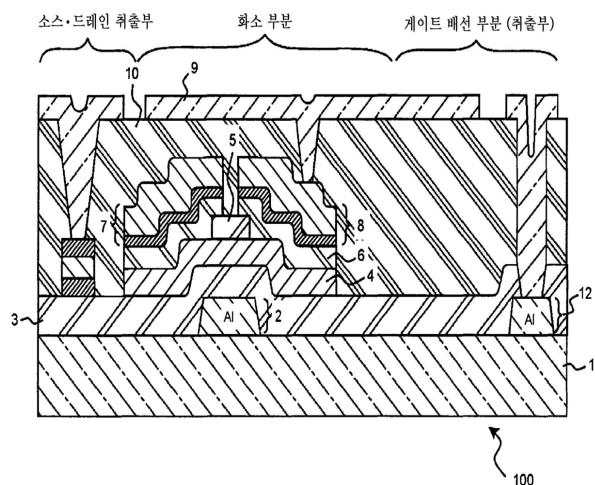

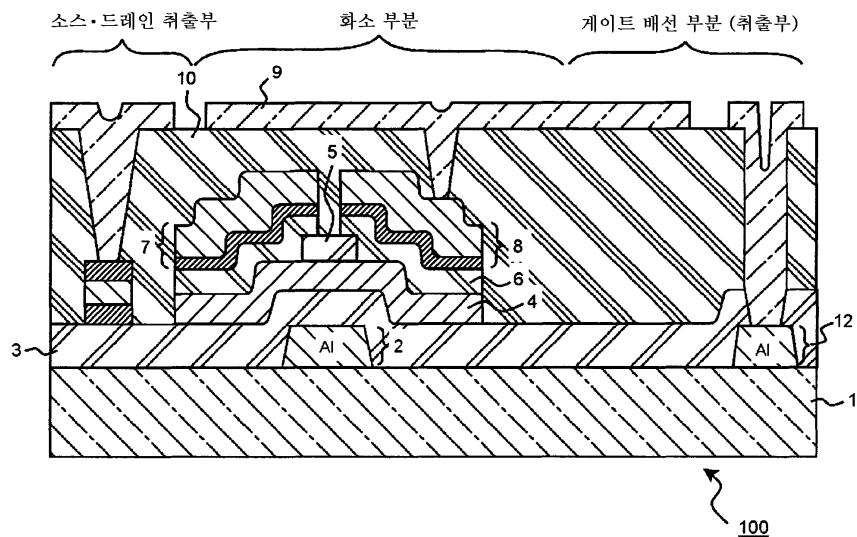

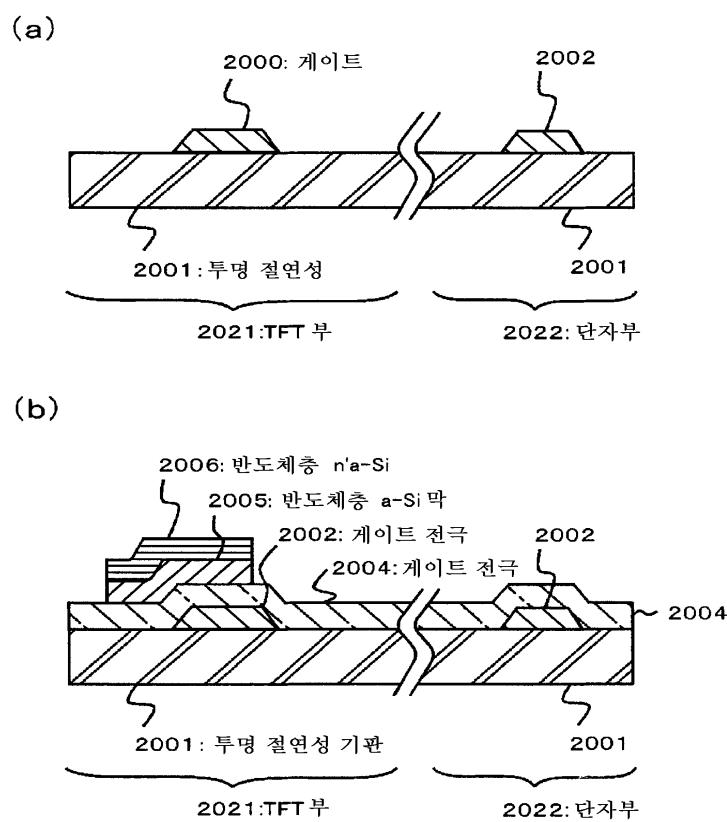

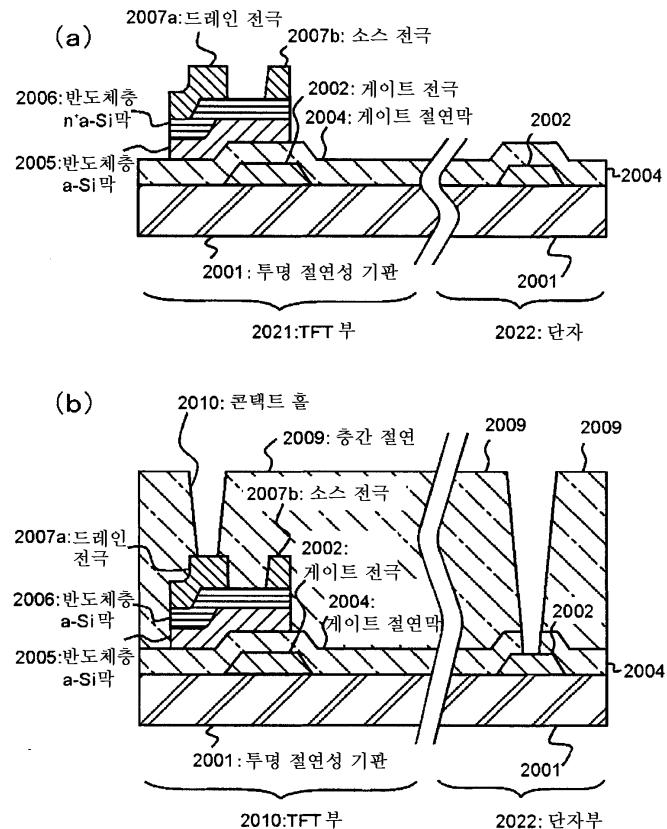

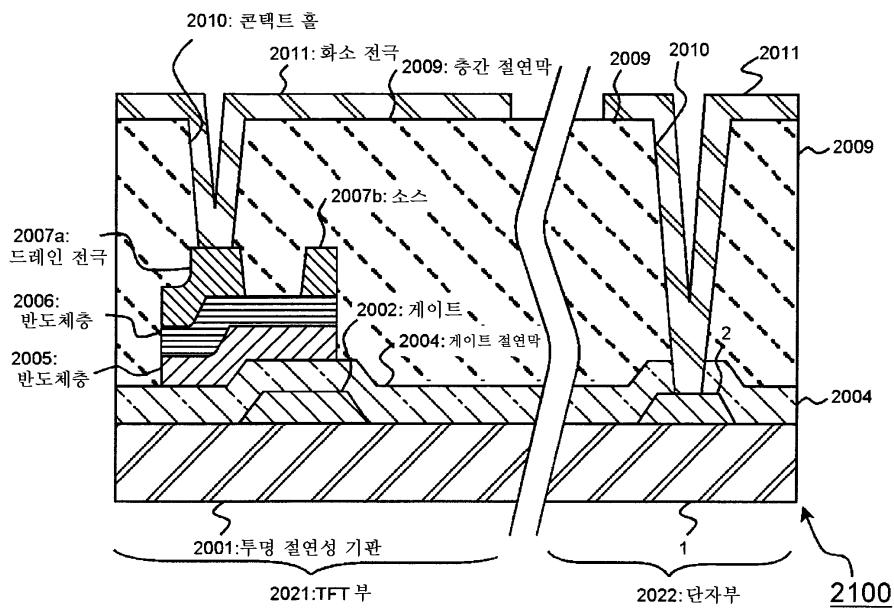

도 1은 본 발명에 따른 액정 평면 디스플레이의 제조 공정에서, 화소 전극의 패턴 형성이 종료된 단계의 비정질-SiTFT 근방의 단면을 도시한 것이지만, 종래의 액정 디스플레이도 화소 전극의 소재를 제외하고, 기본적인 구조는 마찬가지이기 때문에 이것을 이용하여 설명한다.

도 1에서, 투광성 유리 기판(1) 위에 게이트 전극(2)의 패턴을 형성하고, 이어서 플라즈마 CVD(Chemical Vapor Deposition)법을 이용하여, SiN 게이트 절연막(3), 비정질-Si:H(i)막(4), 채널 보호막(5) 및 비정질-Si:H(n)막(6)을 연속적으로 형성하여, 원하는 형상으로 패턴화한다.

또한, Al을 주체로 하는 금속막을 진공 증착법 또는 스퍼터법에 의해 퇴적하고, 포토리소그래피 기술에 의해 소스 전극(7)의 패턴 및 드레인 전극(8)의 패턴(8)을 각각 형성하여, a-SiTFT 소자 부분이 완성된다.

이 위에, ITO막을 스퍼터링법으로 퇴적하여, 포토리소그래피 기술에 의해 소스 전극(7)과 전기적으로 접속된 화소 전극(9)의 패턴이 형성된다. ITO막을 Al막 이후에 퇴적하는 이유는, 비정질-Si:H막(4)(및(6))와 소스 전극(7) 및 드레인 전극(8)의 전기적인 콘택트 특성을 열화시키지 않기 때문이다. 또한, Al은 저렴하고 비저항이 낮으며, 게이트 전극(2) 및 소스 전극(7) · 드레인 전극(8)의 배선의 저항 증대에 따른 액정 디스플레이의 표시 성능의 저하를 방지하는 의미에서 필수적인 재료이다.

상기한 제조 공정에서, Al을 주체로 하는 소스 전극(7) · 드레인 전극(8)의 패턴을 형성한 후, ITO 화소 전극(9)의 패턴을 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계 에칭액으로 가공하면, 가공 종료 시점에 Al 패턴이 용출되는 사태가 자주 발생하는 경우가 있다.

이것은 본래, Al도 ITO 에칭액인 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계 에칭액에 용해되는 성질을 갖고 있는 것에 기인한다. 에칭액 중의 HNO<sub>3</sub>은 Al 표면에 얇은 Al 산화막을 형성하며, Al의 용출을 방지하는 의미로 첨가되어 있지만, ITO막의 에칭 시간이 길거나, Al 퇴적 중에 혼입된 Al막 중의 불순물 및 이물질 등의 결함 부분이 존재하면, 국부 전지 반응에 의해, 상기한 Al의 산화 효과가 충분히 작용하지 않는 것이라고 생각된다.

이러한 Al의 용출을 방지하기 위해 ITO막을 비정질로 함으로써, HCl-HNO<sub>3</sub>-H<sub>2</sub>O계의 에칭액에 대한 ITO/Al 에칭레이트 비를 크게 하는 것이 알려져 있다. 이 것은 예를 들면, 후술하는 일본 특허 공개(소)63-184726호 공보에 기재되어 있다. 또한 에칭레이트비란, 에칭의 속도비를 말한다.

그러나, ITO막을 비정질로 하여도 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계의 에칭액을 사용하기 때문에, Al의 용출은 완전하게는 방지되어 있지 않으므로, 고정밀 액정 디스플레이를 실현하기에는 곤란하였다. 이러한 문제에 감안하여 이루어진 발명으로서 후술하는 일본 특허 공개(평)6-234565호 공보가 알려져 있다. 이 일본 특허 공개(평)6-234565호 공보에는, Al 게이트 전극, 소스 전극 · 드레인 전극의 각 패턴 위에서의 투명 전극, 화소 전극(9)의 패턴화를 옥살산계의 에칭액을 사용함으로써 패턴화를 용이하게 하여, 고정밀 액정 디스플레이의 제조 방법을 제공하는 것을 목적으로 하며, 산화인듐-산화아연을 포함하는 조성의 투명 전극을 사용하는 것이 제안되어 있다.

이러한 구성에서는, Al 게이트선/투명 전극, Al 소스 · 드레인 전극/화소 전극 사이에서 접촉 저항이 발생한다고 알려져 있으며, 통상적으로 Al선을 Ti, Cr 및 Mo 등의 배리어 금속으로 덮는 것이 일반적이다. 이러한 배리어 금속에 대해서는, 후술하는 일본 특허 공개(평)10-65174호 공보, 일본 특허 공개(평)11-184195호 공보, 일본 특허 공개(평)11-258625호 공보 및 일본 특허 공개(평)11-253976호 공보에 기재되어 있다.

### 제3 그룹: 배경

매트릭스형 액정 표시 장치는 통상적으로, TFT 어레이 기판, 대향 기판, 이 TFT 어레이 기판 및 대향 기판에 협지(狹持)된 액정 등의 표시 재료로 구성되어 있다. 매트릭스형 액정 표시 장치는 이 표시 재료에 대하여, 화소마다 선택적으로 전압을 인가함으로써 소정의 화상을 표시한다.

TFT 어레이 기판 위에는 반도체 박막(이하, 간단히 반도체막으로 기재함) 등이 설치되며, 한편, 대향 기판 위에는 대향 전극, 컬러 필터 및 블랙 매트릭스 등이 설치되어 있다. 이러한 TFT 어레이 기판 등을 사용한 액정 표시 장치(Liquid Crystal Display: 이하, LCD로 기재함)를 이하 TFT-LCD라고 부른다.

상기 TFT 어레이 기판에는 유리 등을 포함하는 절연성 기판 위에, 각 소자마다 어레이상으로 게이트 전극, 소스 전극, 드레인 전극 및 반도체막을 포함하는 TFT와 화소 전극이 적어도 설치되어 있다. 또한, 이외에도 배향막 또는 필요에 따라 축

적 용량 등이 설치됨과 동시에, 각 화소 사이에는 게이트 배선 또는 소스 배선 등의 신호선이 설치되어 있다. 이들의 게이트 배선 및 소스 배선은 상기 절연성 기판 위에 각각 서로 직교하도록, 복수개씩 설치되어 표시 영역이 구성되어 있다. 또한, 이 표시 영역의 외측에는 각 신호선에 대응하여, 입력 단자 또는 TFT를 구동하는 구동 회로 등이 각각 설치되어 있다.

또한, 이러한 TFT 어레이 기판을 사용한 액정 표시 장치를 제조하기 위해서는, 유리 기판 위에, TFT에 포함되는 게이트 및 소스/드레인과 그 밖의 공통 배선을 어레이상으로 제조하여, 표시 영역으로 한다. 또한, 이 표시 영역의 주변에 입력 단자, 예비 배선 및 구동 회로 등을 배치한다.

또한 본 특허에서는, 게이트 전극 및 게이트 배선의 총칭을 게이트로 기재하고, 소스 전극 및 소스 배선의 총칭을 소스로 기재한다. 또한, 드레인 전극을 간단히 드레인으로 기재하는 경우도 있다. 또한, 소스 및 드레인의 총칭을 소스/드레인으로 기재한다. 또한 본 특허에서, 제1 도체는 구체적으로 이들의 게이트, 소스 및 드레인이고, 제2 도체는 상기 화소 전극이다.

TFT 어레이 기판의 절연성 기판 위에는 소정의 기능을 발휘시키기 위해, 도전성 박막(이하, 간단히 도전막으로 기재함) 또는 절연성 박막(이하, 간단히 절연막으로 기재함)을 필요에 따라 배치하는 것도 바람직하다. 한편 대향 기판 위에는 상술한 바와 같이, 대향 전극이 설치됨과 동시에, 컬러 필터 또는 블랙 매트릭스가 설치된다.

상술한 바와 같이, TFT 어레이 기판과 대향 전극을 제조한 후, 이들 2매의 기판 사이에 액정 재료를 주입할 수 있도록, 소정의 간극을 설치한다. 이 상태로, 양 기판을 그의 주위에서 접합시킨 후, 이들 기판의 간극에 액정 재료를 주입하여 TFT-LCD를 제조한다.

TFT-LCD에 사용되는 TFT 어레이 기판 또는 대향 기판에는, 공지된 박막 기술을 이용하여 다양한 반도체 소자 등이 설치된다. 예를 들면, TFT 어레이 기판의 반도체 소자를 제조하기 위해서는, 상술한 바와 같이 절연성 기판 위에 게이트, 소스 및 드레인(이하, 이들을 제1 도체로 기재함)과, 반도체막, 절연막 및 화소 전극(이하, 제2 도체로 기재함)을 구성하는 도전막 등이 형성된다. 이때 일반적으로는, 제2 도체는 제1 도체 위에 설치된 절연막의 위에 형성되기 때문에, 제2 도체 및 제1 도체가 직접 접촉하지는 않는다. 이 때문에, 제1 도체와 제2 도체 사이에 전기적인 접속을 취하는 경우에는, 절연막에 콘택트 홀(contact hole)을 형성한다. 즉, 절연막에 형성된 콘택트 홀을 통해, 제1 도체와 제2 도체가 전기적으로 접속하는 것이다.

한편 상기 제1 도체, 특히 게이트 배선 또는 소스 배선의 재료로서는, TFT-LCD의 대형화 또는 고정밀화에 따라, 신호 전달의 지연을 방지하기 위해, 순Al 또는 Al 합금이 그의 특성상 및 공정상의 관점에서 바람직하다고 생각되고 있다. 그 이유는 순Al 또는 Al 합금이 전기적으로 저저항이기 때문이다.

그러나, 투명성의 화소 전극(제2 도체)의 재료로서, ITO(Indium Tin Oxide: 인듐·주석 산화물) 또는 IZO(등록 상표: 이데미쯔 코산 가부시끼가이샤, Indium Zinc Oxide: 인듐·아연 산화물) 등을 사용하는 경우에는, 제1 도체의 재료로서 상기 순Al 또는 Al 합금을 사용하는 것은 반드시 바람직하다고는 생각되지 않았다. 그 이유는, 상기 제2 도체와 제1 도체가 접속(이하, 콘택트로 기재하는 경우도 있음)하면, 이 콘택트 저항은  $1\times E10$  내지  $1\times E12$   $\Omega$ 으로 매우 높아져, 양호한 콘택트 특성을 얻을 수 없기 때문이다.

이 때문에, 절연막에 개구된 콘택트 홀을 통해 순Al 또는 Al 합금을 포함하는 제1 도체와, ITO 또는 IZO 등의 투명 도전막을 포함하는 제2 도체를 직접 콘택트하는 구조의 TFT 어레이 기판에서, 양호한 콘택트 저항을 얻는 것은 곤란하다고 생각되고 있었다.

이 문제를 해결하는 방법으로서, 상기 제1 도체 및 상기 제2 도체가 양호한 콘택트를 얻기 위해, 종래부터 다양한 방법이 검토되었다. 예를 들면, 하기 일본 특허 공개 (평)4-253342호 공보에는, Al을 포함하는 Al층과, 산화되기 어려운 도전성의 금속층을 포함하는 2층 구조의 소스 전극을 갖는 박막 트랜지스터 어레이 기판이며, 화소 전극이 패시베이션막으로 형성된 콘택트 홀을 통해, 소스 전극의 금속층과 접속하고 있는 박막 트랜지스터 어레이 기판이 개시되어 있다. 이와 같이, 화소 전극이 금속층과 접속함으로써, 소스 전극과 화소 전극의 전기적 접촉이 양호해진다.

또한, 하기 일본 특허 공개 (평)4-305627호 공보에는 드레인 전극 위의 콘택트 홀 내에, 원하는 두께로 금속층을 형성하여, 콘택트 홀에 의한 단자를 효과적으로 감소시킴으로써, 제조 공정이 보다 간략화되고, 화소 전극이 절단되기 어려운 활성 매트릭스 기판의 제조 방법이 개시되어 있다.

또한, 하기 일본 특허 공개 (평)8-18058호 공보에는, 실리사이드를 형성하는 금속을 포함하는 하부층과, 구리를 포함하는 상부층을 포함하는 2층 구조의 드레인 전극을 갖는 박막 트랜지스터 어레이이며, 화소 전극이 보호막으로 형성된 콘택트

홀을 통해, 드레인 전극의 상부층과 접속하고 있는 박막 트랜지스터 어레이가 개시되어 있다. 이와 같이, 화소 전극이 구리를 포함하는 상부층과 접속함으로써, 박막 트랜지스터 어레이를 드레인 전극의 저항이 낮고, 양호한 전기적 콘택트를 유지하면서, 높은 효율로 액정에 대하여 전압을 인가할 수 있다.

또한, 하기 일본 특허 공개 (평)11-284195호 공보에는, 순Al 또는 Al 합금을 포함하는 하층과, 순Al 또는 Al 합금에 N, O, Si 및 C 중으로부터 1종 이상의 원소를 첨가하여 이루어지는 상층을 포함하는 2층 구조의 제1 전극을 갖는 박막 트랜지스터이며, 제2 전극과 제1 전극의 상층이 전기적으로 접속하고 있는 박막 트랜지스터가 개시되어 있다.

하기 일본 특허 공개 (평)4-253342호 공보 내지 일본 특허 공개 (평)11-284195호 공보의 기판에서의 소스 전극 또는 게이트 전극에서, 화소 전극과 접속하는 부분은 모두 2층 구조로 되어 있었다(예를 들면, 일본 특허 공개 (평)4-253342호 공보의 소스 전극은 순Al 또는 Al 합금 위에 Cr, Ti, Mo, Cu 및 Ni 등을 성막한 2층 구조로 되어 있음).

#### 제4 그룹: 배경

액정 표시 장치는 저소비 전력 및 풀 컬러화의 용이 등의 특징을 갖기 때문에 박형 디스플레이 중에서 유망시되며, 최근 표시 화면의 대형화에 따른 개발이 활발하다. 이 중에서도, 각 화소마다  $\alpha$ -SiTFT 또는 p-SiTFT를 스위칭 소자로서 매트릭스 위에 배열하여, 각 화소를 구동하는 활성 매트릭스 방식 액정 평면 디스플레이에는  $800 \times 600$  화소 이상의 고정밀화를 행하여도, 콘트라스트비가 열화되지 않기 때문에, 고성능 컬러 표시용 평면 디스플레이로서 주목받고 있다. 이러한 활성 매트릭스 방식 액정 평면 디스플레이에는 화소 전극으로서 ITO(Indium Tin Oxide)와 같은 투명 전극, 소스 전극으로서는 Al계 합금 박막을 사용하는 경우가 많다. 이것은 ITO는 시트 저항이 높고, Al은 용이하게 패턴화할 수 있을 뿐만 아니라 저저항이고 밀착성이 높기 때문이다.

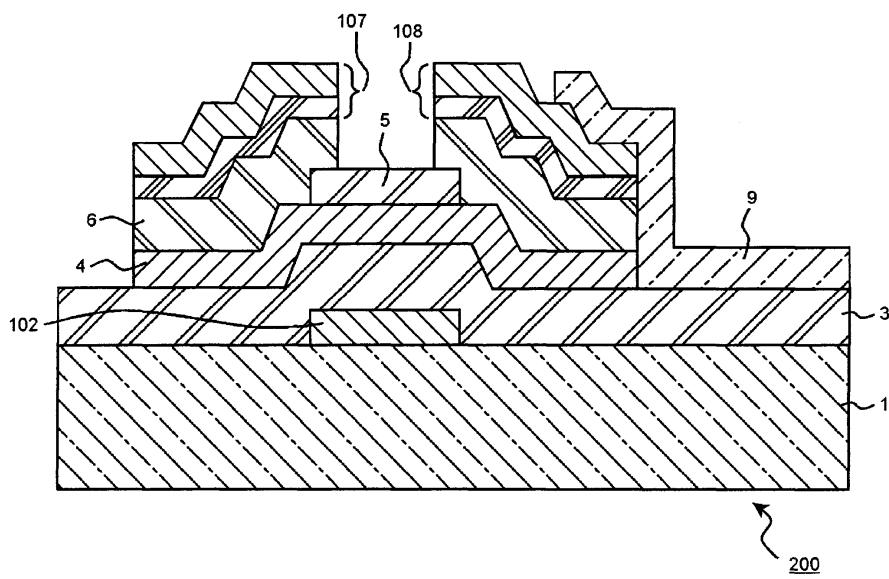

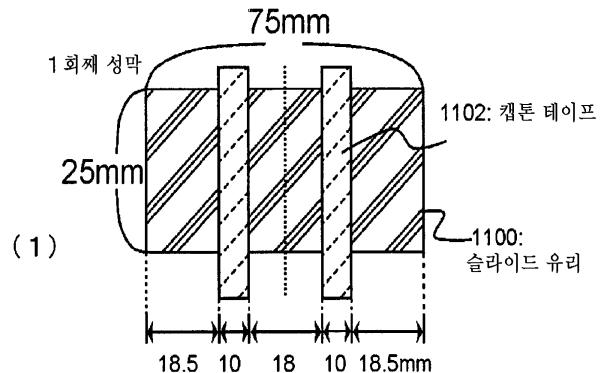

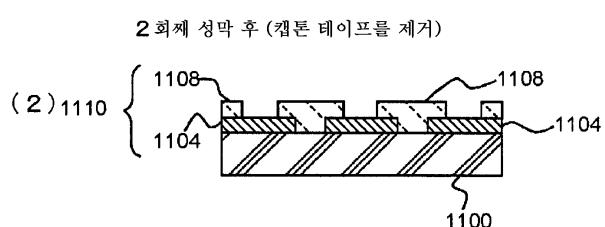

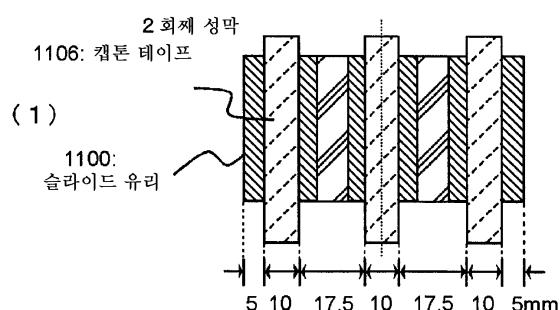

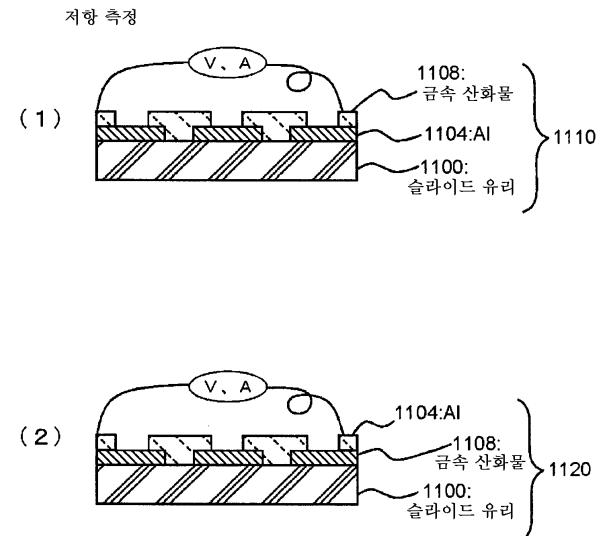

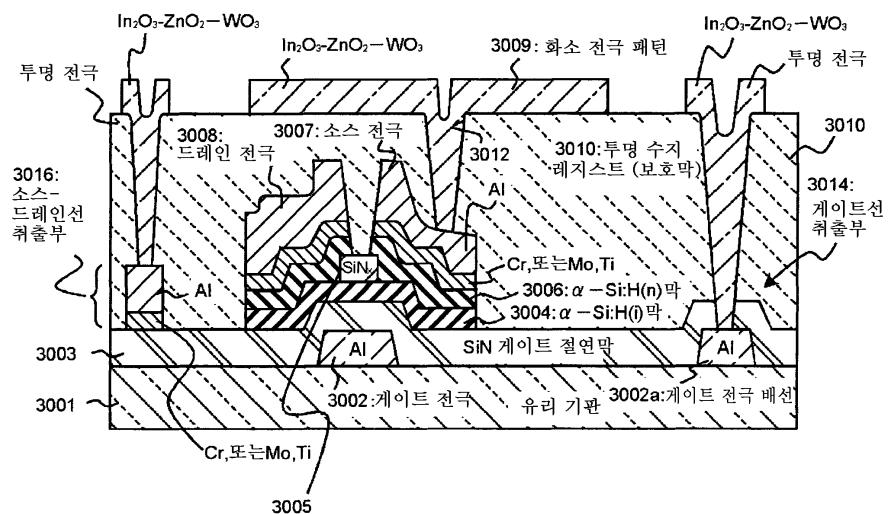

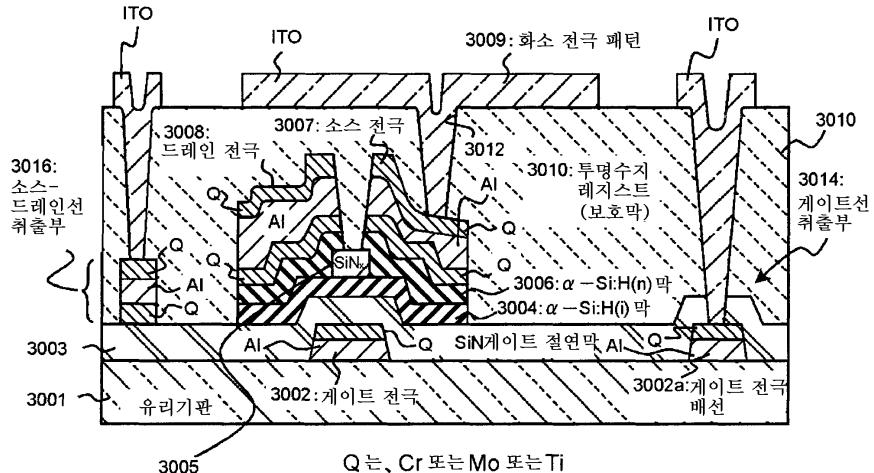

도 10은 본 발명에 따른 액정 평면 디스플레이의 제조 공정에서, 화소 전극의 패턴 형성이 종료된 단계의  $\alpha$ -SiTFT 근방의 단면도를 도시한 것이다. 도 11은 종래의 액정 평면 디스플레이의 제조 공정에서, 화소 전극의 패턴 형성이 종료된 단계의  $\alpha$ -SiTFT 근방의 단면도를 도시한 것이다.

도 11에서, 투광성의 유리 기판 (3001) 위에 게이트 전극 (3002)의 패턴을 형성하고, 이어서 플라즈마 CVD법을 이용하여, SiN을 포함하는 게이트 절연막 (3003),  $\alpha$ -Si:H(i)막 (3004) 및 SiN을 포함하는 채널 보호막 (3005)를 연속적으로 형성한다. 이어서 에칭에 의해, 채널 보호막 (3005)를 원하는 형상으로 패턴화한다. 또한,  $\alpha$ -Si:H(n)막 (3006) 및 Al을 주체로 하는 금속막을 CVD법, 진공 증착법 또는 스퍼터법에 의해 퇴적하여, 포토리소그래피 기술에 의해 소스 전극 (3007)(의 패턴) 및 드레인 전극 (3008)(의 패턴)을 형성하며,  $\alpha$ -Si:H(n)막 (3006) 및  $\alpha$ -Si:H(i)막 (3004)를 형성하여  $\alpha$ -SiTFT 소자 부분이 완성된다. 그리고 필요에 따라, 투명 수지 레지스트 (3010)을 퇴적하여, 콘택트 홀 (3012)를 설치한다.

이 위에 ITO막을 스퍼터링법을 이용하여 퇴적하여, 포토리소그래피 기술에 의해 소스 전극 (3007)과 전기적으로 접속된 화소 전극 패턴 (3009)를 형성한다. 이때, 게이트 전극 (3002)는 Al/Cr(또는 Al/Mo 및 Al/Ti)의 적층막으로 하고, 소스 전극 (3007), 드레인 전극 (3008)은 Cr/Al/Cr(또는 Mo/Al/Mo 및 Ti/Al/Ti)의 3층 적층막으로 한다. 이것은 ITO막과 게이트 전극 (3002), 소스 전극 (3007) 및 드레인 전극 (3008) 사이의 전기적인 콘택트 특성을 열화시키지 않기 때문이다. 또한, Al은 저렴하고 비저항이 낮으며, 게이트 전극 (3002), 소스 전극 (3007) 및 드레인 전극 (3008)의 배선의 저항 증대에 따른 액정 디스플레이의 표시 성능의 저하를 방지하는 의미에서 필수적인 재료이다.

ITO막을 Al막 이후에 퇴적하는 이유는,  $\alpha$ -Si:H(i)막 (3004) 및  $\alpha$ -Si:H(n)막 (3006)과, 소스 전극 (3007) 및 드레인 전극 (3008) 사이의 전기적인 콘택트 특성을 열화시키지 않기 때문이다. 또한, 이 Al이 저렴하고 비저항이 낮은 것은 상술한 바와 같다.

위에서 설명한 제조 공정에서, Al을 주체로 하는 소스 전극 (3007) · 드레인 전극 (3008)의 패턴을 형성한 후, ITO를 포함하는 화소 전극 패턴 (3009)를 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계 에칭액으로 가공하면, 가공 종료 시점에서 Al 패턴이 용출되는 사고가 발생하는 경우가 자주 있다.

이것은 본래, Al도 ITO를 에칭하는 에칭액인 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계 에칭액에 용해되는 성질을 갖고 있는 것에 기인한다. 에칭액 중의 HNO<sub>3</sub>은 Al 표면에 얇은 Al산화막을 형성하여, Al의 용출을 방지하는 의미로 첨가되어 있지만, ITO막의 에칭 시간이 길거나, Al 퇴적 중에 혼입된 Al막 중의 불순물 및 이물질 등의 결함 부분이 존재하면, 국부 전지 반응에 의해 상기한 Al의 산화 효과가 충분히 작용하지 않는다고 생각된다.

이러한 Al의 용출을 방지하기 위해 ITO막을 비정질로 함으로써, HCl-HNO<sub>3</sub>-H<sub>2</sub>O계의 에칭액에 대한 ITO/Al 에칭 속도비를 크게 하는 것이 하기 일본 특허 공개(소)63-184726호 공보에 기재되어 있다.

그러나, ITO막을 비정질로 하여도 HCl-HNO<sub>3</sub>-H<sub>2</sub>O계의 에칭액을 사용하기 때문에, Al의 용출은 완전하게는 방지되지 않으므로, 고정밀 액정 디스플레이를 실현할 수 없었다.

상술한 문제에 감안하여 이루어진 발명이 하기 일본 특허 공개(평)11-264995호 공보에 기재되어 있다. 이 일본 특허 공개(평)11-264995호 공보에는 Al 게이트, 소스·드레인 전극 패턴 위에서의 투명 전극 및 화소 전극의 패턴화를 옥살산계의 에칭액을 사용함으로써 패턴화를 용이하게 하는 것이 기재되어 있다. 또한, 일본 특허 공개(평)11-264995호 공보에는 고정밀 액정 디스플레이의 제조 방법을 제공하는 것을 목적으로서, 산화인듐-산화아연을 포함하는 조성의 투명 전극을 사용하는 것이 제안되어 있다.

일반적으로 이러한 구성을 채용하는 경우, Al 게이트선/투명 전극, Al 소스·드레인 전극/화소 전극 사이에서 접촉 저항이 발생한다고 알려져 있으며, 통상적으로 Al선을 Ti, Cr 및 Mo 등의 배리어 금속으로 덮는 것이 일반적이다. 이러한 구성은 하기 일본 특허 공개(평)10-65174호 공보, 일본 특허 공개(평)11-184195호 공보, 일본 특허 공개(평)11-258625호 공보 및 일본 특허 공개(평)11-253976호 공보 등에 기재되어 있다.

이와 같이 Al 배선을 사용하는 경우, 배리어 금속을 사용하지 않을 수 없기 때문에 이 배리어 금속의 성막 및 에칭이 필요하며, 제조 공정을 복잡하게 할 우려가 있다.

또한, Al에 각종 금속을 첨가한 합금의 이용이 보고되어 있지만, 상기 접촉 저항을 작게 하는 것은 매우 곤란할 것으로 예상된다. 그 이유는, Al 자체 표면에 산화 피막을 형성하기 때문이다. 이 산화 피막은 절연체이며, 이 절연체가 접촉 저항을 크게 하고 있다고 생각되기 때문이다. 이러한 기재는, 예를 들면 하기 일본 특허 공개(평)7-45555호 공보, 일본 특허 공개(평)7-301705호 공보 및 일본 특허 공개(평)1-289140호 공보에 기재되어 있다.

이 산화 피막에 의한 접촉 저항을 감소시키기 위해, Al 박막 위에 In 및 Zn 등의 금속의 박막을 설치하는 방법 등이 제안되어 있다. 이 방법에 따르면 접촉 저항은 작아지지만, 이들의 박막을 성막할 필요가 생기기 때문에, 화소 전극의 투과율이 저하되는 등의 문제점이 있었다. 이러한 기재가 하기 일본 특허 공개 제2003-017706호 공보에 기재되어 있다.

특허 문헌 1: 일본 특허 공개(소)63-184726호 공보

특허 문헌 2: 일본 특허 공개(평)6-234565호 공보

특허 문헌 3: 일본 특허 공개(평)6-187832호 공보

특허 문헌 4: 일본 특허 공개(평)11-264995호 공보

특허 문헌 5: 일본 특허 공개(평)11-264996호 공보

특허 문헌 6: 일본 특허 공개(평)10-65174호 공보

특허 문헌 7: 일본 특허 공개(평)11-184195호 공보

특허 문헌 8: 일본 특허 공개(평)11-258625호 공보

특허 문헌 9: 일본 특허 공개(평)11-253976호 공보

특허 문헌 10: 일본 특허 공개(평)4-253342호 공보

특허 문헌 11: 일본 특허 공개(평)4-305627호 공보

특허 문헌 12: 일본 특허 공개(평)8-18058호 공보

특허 문현 13: 일본 특허 공개 (평)11-284195호 공보

특허 문현 14: 일본 특허 공개 (평)7-45555호 공보

특허 문현 15: 일본 특허 공개 (평)7-301705호 공보

특허 문현 16: 일본 특허 공개 (평)1-289140호 공보

특허 문현 17: 일본 특허 공개 제2003-017706호 공보(일본 특원 2001-200710)

### 발명의 상세한 설명

#### 제1 그룹: 과제

그러나, 투명한 화소 전극의 재료로서 일반적으로 사용되고 있는 ITO는, Al과 접촉하고 있는 경우, 전지 반응을 일으키기 쉽다는 문제점이 있었다. 또한, 결정질의 ITO는, 왕수 또는 염산 등의 강산이 아니면 에칭할 수 없으며, 에칭 중에 예를 들면 TFT의 배선 재료 등을 부식시키는 문제점이 발생하는 경우도 있었다. 한편, 비정질의 ITO인 경우에는, 바탕 기판과의 밀착성의 저하가 종종 관찰되거나, TFT 배선 재료와의 접촉 저항의 증대를 초래한 경우도 있었다. 또한, 에칭시에 잔사를 발생시켜, 전극 간의 쇼트 또는 액정 구동의 문제점이 발생할 우려도 있었다.

이에 대하여, 비정질계의 재료로서 IZO가 고안되어 있지만, 이 재료는 산화인듐과 산화아연으로부터 특수한 육방정 층상화합물을 생성시켜야만 하기 때문에, 제조 공정이 번잡해질 뿐만 아니라, 비용이 비싸지는 것이 과제였다.

제1 그룹의 본 발명은 상기 과제에 감안하여 이루어진 것이며, 에칭에 의한 잔사 등의 발생이 거의 없는 투명 도전막을 구비하는 박막 트랜지스터형 기판을 제공하는 것을 목적으로 한다. 또한, 본 발명의 다른 목적은, 상기 박막 트랜지스터형 기판을 이용한 액정 표시 장치를 제공하는 것이다. 또한, 본 발명의 또 다른 목적은 상기 박막 트랜지스터형 기판이 효율적으로 얻어지는 제조 방법을 제공하는 것이다.

#### 제2 그룹: 과제

본 발명의 제2 그룹은 상기 과제에 감안하여 이루어진 것이며, 특정한 금속을 함유하는 투명 도전 재료를 화소 전극 및 투명 전극에 사용함으로써, TFT(박막 트랜지스터) 기판의 제조 방법을 간략화하는 것이다. 바꾸어 말하면, 배리어 금속 등을 퇴적하기 위한 공정이 불필요한 제조 방법을 제공하는 것이 본 발명의 목적이다.

마찬가지로, 본 발명은 이와 같은 화소 전극 및 투명 전극을 스퍼터법으로 성막하기 위한 스퍼터링 타깃을 제공하는 것을 목적으로 한다.

또한, 본 발명의 다른 목적은 특정한 금속을 함유하는 투명 도전 재료를 화소 전극 및 투명 전극에 사용함으로써, Al 게이트/투명 전극, Al 소스 · 드레인/화소 전극을 (배리어 금속 없이) 직접 접촉시킨 경우에도, 이 사이의 접촉 저항을 작게 하는 것을 목적으로 한다. 이러한 작은 값의 접촉 저항을 실현함으로써, 이 투명 도전 재료를 화소 전극으로서 사용한 기판을 이용한, 중간조(中間調)의 표시가 가능한 액정 표시 장치를 제공하는 것이 본 발명의 목적이다.

#### 제3 그룹: 과제

상술한 바와 같이 종래의 제조 방법에서는, ITO 또는 IZO 등을 포함하는 제2 도체와, 순Al 또는 Al 합금을 포함하는 제1 도체의 콘택트 저항이  $1 \times 10^{-10}$  내지  $1 \times 10^{-12}$  Ω으로 매우 높았기 때문에, 양호한 콘택트 저항이 얻어지지 않았다.

또한, 양호한(낮은) 콘택트 저항을 얻기 위해, 제1 도체의 구조를 상이한 재료를 포함하는 2층 구조로 한 경우에는, 이 제1 도체를 1 종류의 시약(에칭액)으로 1 번에 에칭하는 것은 곤란하였으며, 이 종류의 시약(에칭액)을 사용하여, 2번 에칭하는 것이 필요하였다. 이 때문에, 제조 공정의 복잡화를 초래하고 있었다.

제3 그룹의 본 발명은 상기 과제를 해결하기 위해 이루어진 것이며, 제2 도체와 제1 도체가 전기적으로 접속할 때, 그의 콘택트 저항이 낮은 박막 트랜지스터 및 박막 트랜지스터 기판을 제공하는 것을 목적으로 한다. 또한, 본 발명은 상기 박막 트랜지스터 기판을 보다 간편하고, 보다 저비용으로 제조할 수 있는 박막 트랜지스터 기판의 제조 방법을 제공하는 것을 목적으로 한다. 또한, 제3 그룹의 본 발명의 목적은, 상기 박막 트랜지스터 기판을 포함하는 액정 표시 장치를 제공하는 것을 목적으로 한다.

#### 제4 그룹: 과제

또한, 상기 제4 그룹의 배경 기술에서 상술한 바와 같이, 특정한 금속을 함유하는 투명 도전 재료를 화소 전극 및 투명 전극에 사용함으로써, 제조 공정이 복잡해지지 않는 TFT(박막 트랜지스터) 기판 및 그의 간편한 제조 방법을 실현하는 것이 제4 그룹의 본 발명의 목적이다. 이러한 TFT 기판의 화소 전극 및 이 화소 전극을 형성하는 데 유용한 스퍼터링 타깃을 제공하는 것도 제4 그룹의 본 발명의 목적이다.

또한, 제4 그룹의 본 발명은, AI을 포함하는 케이트/투명 전극, (AI을 포함하는)소스·드레인/화소 전극을 직접 접촉시켜도 그 사이의 접촉 저항을 작게 할 수 있으며, 중간조의 표시가 가능한 액정 표시 장치를 제공하는 것을 목적으로 한다.

#### 제1 그룹: 수단

본 발명의 상기 목적은, 투명 화소 전극으로서 산화인듐을 주성분으로서 포함하며, 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막을 사용함으로써 달성된다. 이 투명 도전막은 산성의 에칭액으로 패턴화함으로써, 투명 화소 전극의 형상으로 형성된다. 구체적으로 설명하면, 본 발명은 하기의 수단을 채용한다.

(1) 우선, 본 발명은 투명 기판, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극 및 상기 투명 기판 위에 설치된 투명 화소 전극을 구비하여 이루어지는 박막 트랜지스터형 기판에서, 상기 투명 화소 전극이 산화인듐을 주성분으로서 포함하며, 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막이고, 상기 투명 화소 전극이 상기 소스 전극 또는 상기 드레인 전극과 전기적으로 접속하고 있는 것을 특징으로 하는 박막 트랜지스터형 기판이다.

또한, 본 특허에서 "산화인듐을 주성분으로서 포함한다"란, 산화인듐을 주요한 성분으로서 포함하는 것을 의미하며, 대체로 원자 조성 비율로 50 % 이상인 경우를 의미한다. 또한, 상기 투명 화소 전극을 성막할 때, 산화인듐을 주성분으로 하며, 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 이루어지는 타깃을 사용하면, 이 타깃에 노ಡ이 거의 발생하지 않는다.

투명 도전막에 산화텅스텐, 산화몰리브덴, 산화니켈 또는 산화니오븀을 첨가함으로써, 비정질의 투명 도전막을 성막한 후, 성막한 비정질의 투명 도전막을 옥살산을 포함하는 에칭제를 사용하여 에칭하는 것이 가능해진다. 성막 기판 온도는 R.T. (실온) 내지 200 °C인 것이 바람직하며, 보다 바람직하게는 80 내지 180 °C이다. 성막시의 기판 온도를 상기 범위로 하는 이유로서는, 기판 온도를 실온 이하로 제어하기 위해서는 냉각이 필요하며, 이것이 에너지의 손실이 되기 때문이고, 한편 기판 온도가 200 °C를 초과하면, 투명 도전막의 결정화 등에 의해, 옥살산을 포함하는 에칭제에서의 에칭을 행할 수 없게 되는 경우가 있기 때문이다. 또한, 성막시의 분위기 가스 중에 물 또는 수소를 첨가할 수도 있다. 이에 따라, 성막된 투명 도전막을, 옥살산을 포함하는 에칭제를 사용하여 에칭하기 쉬워지기 때문에, 잔사를 보다 감소시킬 수 있다.

또한, 상기 금속 산화물의 첨가에 의해 성막된 상기 투명 도전막을 에칭한 후, 기판의 온도를 200 °C 이상으로 가열함으로써, 기판 위의 투명 도전막을 간단하게 결정화할 수 있다. 이 결정화의 온도는 바람직하게는 220 °C이고, 보다 바람직하게는 230 °C 이상이다.

투명 도전막을 결정화시킴으로써, 투명 도전막이 AI과 전기적으로 접속된 상태로 전해질에 접촉하여도, 전지 반응이 억제된다. 이 때문에, AI의 단선 등의 에칭 불량은 거의 발생하지 않는다.

이와 같이 성막된 투명 도전막의 비저항은, ITO와 동일한 정도로 감소되어 있다. 또한, 이 투명 도전막은 투명성이 우수하다.

투명 도전막의 막 두께는 바람직하게는 20 내지 500 nm이고, 보다 바람직하게는 30 내지 300 nm이고, 더욱 바람직하게는 30 내지 200 nm이다. 투명 도전막의 막 두께가 20 nm 미만이면, 투명 도전막의 표면 저항이 상승되는 경우가 있으며, 한편 투명 도전막의 막 두께가 500 nm를 초과하면, 투과율이 저하되거나, 가공 정밀도에 문제점이 발생하는 경우가 있다.

투명 도전막 중의 조성은 원자비로서 In의 조성 비율(이하, 원자비로 기재하는 경우도 있음)이,  $[In]/[전체 금속]$ 의 값이 0.85 내지 0.99인 것이 바람직하다. In의 조성 비율이 0.85 미만이면, 투명 도전막의 저항값이 증대되거나, 투명 도전막이 성막된 기판을 200 °C 이상으로 가열하여도, 투명 도전막이 결정화되지 않게 되는 경우가 있다. 또한, In의 조성 비율이 0.99를 초과하면, 투명 도전막의 성막시에 투명 도전막이 결정화되어, 옥살산을 포함하는 에칭제로 에칭할 수 없거나, 잔사가 대량으로 발생하는 경우가 있기 때문이다. 여기서,  $[In]$ 은 투명 도전막 중의 단위 부피당 인듐 원자의 수를 나타내고,  $[전체 금속]$ 은 투명 도전막 중의 단위 부피당 전체 금속 원자의 수를 나타낸다.

또한, 제3 원자로서 상기 투명 도전막 중에 Sn 및 Zn을 첨가하는 것도 바람직하다.

또한, 제1 원자란 산화인듐 중의 인듐 원자이고, 제2 원자란, 산화텅스텐, 산화니오븀, 산화니켈 및 산화몰리브덴으로부터 선택된 1종 또는 2종 이상의 산화물 중의 텅스텐 원자, 니오븀 원자, 니켈 원자 및 몰리브덴 원자이다.

Sn을 첨가하는 경우, 원자비로서 Sn의 조성 비율은  $[Sn]/[전체 금속] < 0.2$ 인 것이 바람직하며, 보다 바람직하게는  $[Sn]/[전체 금속] < 0.1$ 이다. 투명 도전막 중의  $[Sn]/[전체 금속]$ 의 값이 0.2 이상이면, 에칭시에 잔사가 발생하는 경우가 있다. 여기서,  $[Sn]$ 은 투명 도전막 중의 단위 부피당 주석 원자의 수를 나타낸다.

또한, Zn을 첨가하는 경우, 원자비로서 Zn의 조성 비율은  $[Zn]/[전체 금속] < 0.1$ 인 것이 바람직하며, 보다 바람직하게는  $[Zn]/[전체 금속] < 0.05$ 이다. 여기서,  $[Zn]$ 은 투명 도전막 중의 단위 부피당 아연 원자의 수를 나타낸다.

(2) 또한, 본 발명은 투명 기판, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극 및 상기 투명 기판 위에 설치된 투명 화소 전극을 구비하여 이루어지는 박막 트랜지스터형 기판, 복수색의 착색 패턴이 설치된 컬러 필터 기판 및 상기 박막 트랜지스터형 기판과 상기 컬러 필터 기판 사이에 끼워진 액정층을 구비하여 이루어지는 박막 트랜지스터형 액정 표시 장치에서, 상기 투명 화소 전극이 산화인듐을 주성분으로서 포함하며, 추가로 산화텅스텐, 산화몰리브덴, 산화니켈 및 산화니오븀으로부터 선택된 1종 또는 2종 이상의 산화물을 포함하는 투명 도전막이고, 상기 투명 화소 전극이 상기 소스 전극 또는 상기 드레인 전극과 전기적으로 접속하고 있는 것을 특징으로 하는 박막 트랜지스터형 액정 표시 장치이다.

상기 박막 트랜지스터형 기판은 그의 제조 공정에서, Al 단선 등의 에칭 불량이 거의 발생하지 않는다. 이 때문에, 이러한 박막 트랜지스터형 기판을 사용하면, 표시 결함이 적은 박막 트랜지스터형 액정 표시 장치를 제조할 수 있다.

(3) 또한, 본 발명은 상기 (1)에 기재된 박막 트랜지스터형 기판을 제조하는 방법에서, 상기 투명 기판 위에 상기 투명 도전막을 퇴적하는 단계와, 상기 퇴적한 상기 투명 도전막을 산성의 에칭제를 사용하여 에칭함으로써, 상기 투명 화소 전극을 형성하는 단계를 포함하는 것을 특징으로 하는 박막 트랜지스터형 기판의 제조 방법이다.

산성의 상기 에칭제는 약산인 것이 바람직하다. 상기 투명 도전막은 약산의 에칭제를 사용하여 에칭한 경우에도, 에칭에 의한 잔사가 거의 발생하지 않는다.

옥살산을 포함하는 에칭제의 옥살산 농도는 1 내지 10 중량%인 것이 바람직하며, 보다 바람직하게는 1 내지 5 중량%이다. 옥살산 농도가 1 중량% 미만이면, 투명 도전층의 에칭 속도가 늦어지는 경우가 있으며, 10 중량%를 초과하면, 옥살산의 결정이 옥살산을 포함하는 에칭제의 수용액 중에 석출되는 경우가 있기 때문이다.

(4) 상기 (3)에 있어서, 본 발명은 산성의 상기 에칭제가 옥살산, 인산 · 아세트산 · 질산을 포함하는 혼합산, 또는 질산 제2 세륨암모늄 중 어느 1종 또는 2종 이상을 포함하는 것을 특징으로 하는 박막 트랜지스터형 기판의 제조 방법이다.

## 제2 그룹: 수단

이하, 본 발명의 제2 그룹의 수단이다.

### A. 스퍼터링 타깃

(5) 본 발명은 상기 과제를 해결하기 위해, 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물과, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 스퍼터링 타깃이다.

이와 같이 본 발명에서는, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물과, 제1 금속군 M1의 W, Mo, Nb, Ni, Pt 및 Pd으로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물을 동시에 첨가하고 있는 것이 특징적인 점이다.

이러한 구성에 의해, 본 발명의 스퍼터링 타깃을 사용하여 스퍼터법으로 투명 도전막을 성막하면, 이 투명 도전막과 다른 Al 부재 사이의 접촉 저항을 작은 값으로 유지할 수 있다.

구체적으로 말하면, 본 발명의 스퍼터링 타깃을 사용하여 스퍼터법으로 투명 전극 또는 화소 전극을 형성한 경우,

- Al 게이트선/투명 전극 사이

- Al 소스 · 드레인 전극/화소 전극 사이

- Al 소스 · 드레인 배선/투명 전극 사이

에 발생하는 접촉 저항의 값을, 종래 발생하고 있었던 접촉 저항의 값에 비해 작게 하는 것이 가능하다.

또한, 본 특허에서 "주성분"이란, 그의 재료 중의 주요한 성분을 말하며, 대체로 50 % 이상의 조성 비율을 갖는 성분을 말한다.

(6) 또한, 본 발명은 상기 과제를 해결하기 위해, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고, 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는 청구의 범위 제1항에 기재된 스퍼터링 타깃이다. 여기서, 상기  $[M1]$ 은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[M2]$ 는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[In]$ 은 인듐의 원자의 수를 나타낸다.

#### 란타노이드계 금속 산화물의 조성

이와 같이 본 발명에서는, 란타노이드계 금속 산화물의 조성은 산화인듐에 대하여, 하기 수학식 1이다.

$$[M2]/([M2]+[In])=0.005 \text{ 내지 } 0.2$$

이 값은 바람직하게는 0.01 내지 0.15이다. 또한, 보다 바람직하게는 0.01 내지 0.1이다.

또한 본 특허에서는, 란타노이드계 금속군을 제2 금속군이라 부르며, "M2"로 총칭하고 있다. 또한, 이 M2는 어느 하나의 란타노이드계 금속을 나타내는 기호로서도 사용되고 있다.

또한 본 특허에서는, []의 기호를 그의 원자의 단위 중량 · 부피당 원자의 수를 나타내는 기호로서 사용하고 있다. 예를 들면, [세륨] 또는 [Ce]는 세륨의 원자의 수를 나타낸다. [인듐] 또는 [In]은 인듐의 원자의 수를 나타내는 것이다.

또한, [] 중에 상기 금속군의 총칭인 M2를 삽입한  $[M2]$ 가 되는 기술법도 이용하고 있다.  $[M2]$ 는 제2 금속군 중으로부터 적절하게 선택된 금속의 원자의 수를 나타낸다.

이 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나기 어려우며, 이와 같은 스퍼터링 타깃으로 투명 전극 또는 화소 전극을 제조한 경우, Al과 이 투명 전극 사이, Al과 이 화소 전극 사이에 큰 값의 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 이와 같은 스퍼터링 타깃으로 투명 전극 또는 화소 전극을 제조한 경우, 이 투명 전극·화소 전극 자체의 비저항이 큰 값이 되는 경우가 있다. 또한, 마찬가지로 상기 식의 값이 0.2를 초과하는 경우는, 이 투명 전극 또는 화소 전극 자체의 에칭이 곤란해지는 경우가 있으며, 그 결과, 액정 표시 장치용의 기판의 제조가 곤란해질 가능성이 있다.

W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물의 조성

또한 본 발명에서는, W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물의 조성(비율)이 산화인듐에 대하여, 하기 수학식 2 이다.

$$[M1]/([M1]+[In])=0.005 \text{ 내지 } 0.2$$

이 식의 보다 바람직한 값은 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. 또한, 이들의 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도, 금속 산화물의 상태로 첨가될 수도 있다.

상술한 제2 금속군 M2와 마찬가지로, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 금속군을 제1 금속군 M1로 부르고 있다. 또한, 상기 [M2]와 마찬가지로, [M1]은 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의(단위 부피·단위 중량당) 원자의 수를 나타낸다.

또한, 상기 식 2의 값이 0.005 미만이면, 그의 첨가 효과가 나타나기 어렵다. 즉, Al과 투명 전극 또는 Al과 화소 전극 사이에서 접촉 저항이 커지는 경우가 있다. 한편, 상기 식 2의 값이 0.2를 초과하면, 투명 전극 및 화소 전극의 비저항이 커지는 경우가 있으며, 이들의 투명 전극·화소 전극의 에칭이 곤란해지는 경우가 있다.

(7) 상기 (5) 또는 (6)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중으로부터 선택된 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 스퍼터링 타깃이다.

이와 같이, 란타노이드계 금속 산화물 중에서도, 특히 Ce, Ho 및 Er 중 어느 1종 이상의 금속 산화물을 첨가한 경우, 상술한 작용·효과가 한층 현저해진다. 또한, 1종 이상이기 때문에, 상기 금속으로부터 2종의 금속을 선택할 수도 있으며, 3종 전부의 금속 산화물을 첨가할 수도 있다.

(8) 또한, 본 발명은 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물과, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물과, 추가로 Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 스퍼터링 타깃이다.

이와 같이, 본 발명에서는 란타노이드계 금속을 포함하는 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물과, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물을 동시에 첨가하는 구성을 채용하고 있다.

종래에는, Al 게이트선/투명 전극, Al 소스·드레인 전극/화소 전극 사이 및 Al 소스·드레인 배선/투명 전극 사이에, 큰 접촉 저항이 발생하고 있었다.

이에 대하여, 상기 본 발명에 따르면, 상술한 구성을 의해 종래 발생하고 있었던 큰 접촉 저항의 값을 작게 할 수 있다. 말하자면, 접촉 저항을 사실상 무시할 수 있는 정도까지 작게 할 수 있는 것이다.

또한, Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물을 첨가함으로써, 스퍼터링 타깃 자체의 저항값을 개선하여, 노듈의 발생을 억제할 수 있다. 여기서, 저항값의 개선이란, 저항값의 값을 작은 값으로 하는 것이다. 또한, 이 스퍼터링 타깃을 사용하여 스퍼터법으로 제조한 투명 도전막에도, 하기에 나타낸 바와 같은 유익한 영향을 미친다.

- 제조한 투명 도전막의 저항값을 개선할 수 있음

- 제조한 투명 도전막의 에칭 특성을 개선할 수 있음

- 제조한 투명 도전막의 투명성을 개선할 수 있음

여기서, 비저항의 개선이란 비저항값의 감소를 의미한다. 또한, 예칭 특성의 개선이란, 예칭에 사용하는 예칭제에 의해 보다 용이하게 용해하는 것을 의미한다. 또한, 투명성의 개선이란, 투명도의 향상, 나아가서는 광 투과율의 값이 100 %에 근접하는 것을 의미한다.

(9) 또한, 본 발명은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고, 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이고, Zn, Sn, Zr, Ga 및 Ge을 포함하는 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는 상기 (4)에 기재된 스퍼터링 타깃이다. 여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M3]은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [In]은 인듐 금속의 원자의 수를 나타낸다.

#### 란타노이드계 금속 산화물

이와 같이 본 발명에서는, 란타노이드계 금속 산화물의 조성이 산화인듐에 대하여,  $[In]/([In]+[M2])=0.005$  내지 0.2이다. 여기서, [M2]는 [란타노이드계 금속]으로 기재하는 경우도 있지만, 어느 하나의 란타노이드계 금속 산화물의 원자의 수를 나타낸다.

또한, 본 발명에서 상술한 원자수의 비의 값의 범위 "0.005 내지 0.2"는, 바람직하게는 0.01 내지 0.15이고, 보다 바람직하게는 0.01 내지 0.1이다.

산화인듐에 대한 란타노이드계 금속 산화물의 조성을 나타내는 상기 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나지 않는 경우도 생각된다. 즉, Al과 투명 전극 및 화소 전극 사이에서 무시할 수 없는 접촉 저항이 발생하는 경우도 있다.

#### W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물

또한, 본 발명에서는 W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물의 조성이 산화인듐에 대하여,  $[In]/([In]+[M1])=0.005$  내지 0.2인 구성을 채용하고 있다. 이 식의 값은 보다 바람직하게는 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. [M1]은 제1 금속군 W, Mo, Nb, Ni, Pt 및 Pd 중으로부터 선택된 1종 또는 2종 이상의 금속의 수를 나타낸다.

제1 금속군 M1 중의 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도 있고, 금속 산화물의 상태로 첨가될 수도 있다.

또한, 상기 식의 값이 0.005 미만이면, 상기 W, Mo, Nb, Ni, Pt 및 Pd을 첨가하는 효과가 나타나지 않는 경우가 있다. 구체적으로는, 본 발명의 스퍼터링 타깃을 사용하여 스퍼터법으로 제조한 투명 전극 · 화소 전극에 대하여, Al과 이 투명 전극 사이, Al과 이 화소 전극 사이에 무시할 수 없는 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 투명 전극 · 화소 전극의 비저항이 커지는 경우가 있다. 또한, 제조 공정에서 투명 전극 · 화소 전극의 예칭이 곤란해지는 경우도 있다.

#### Zn, Sn, Zr, Ga 및 Ge 산화물

본 발명에서는 상술한 바와 같이, 제3 금속군 M3 중의 Zn, Sn, Zr, Ga 및 Ge의 산화물로부터 선택된 1종 또는 2종 이상의 금속 산화물의 조성이 산화인듐에 대하여  $[M3]/([In]+[M3])=0.005$  내지 0.2이다. 여기서, [M3]은 제3 금속군으로부

터 선택된 1종 또는 2종 이상의 금속의 단위 부피 · 단위 질량당 수를 나타내고, 상기 식은 인듐에 대한 제3 금속군 중의 금속의 원자 조성비를 나타낸다. 또한, 이 식의 값은 실질적으로는, 산화인듐에 대한 제3 금속군 M3 중의 금속 산화물의 조성비이기도 하다.

이 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나기 어렵다. 구체적으로는, 본 발명의 스퍼터링 타깃을 사용하여 스퍼터법으로 제조한 투명 전극 · 화소 전극에 대하여, Al과 투명 전극 사이, Al과 화소 전극 사이에 무시할 수 없는 크기의 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 투명 전극 및 화소 전극의 비저항이 커지는 경우나, 제조 공정에서 이들의 투명 전극 등의 에칭이 곤란해지는 경우도 있다.

(10) 상기 (8) 또는 (9)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 스퍼터링 타깃이다.

란타노이드계 금속 산화물 중에서도, 특히 Ce, Ho 및 Er을 포함하는 산화물이 바람직하기 때문에, 본 발명에서는 이들의 Ce, Ho 및 Er을 포함하는 산화물을 채용한다.

(11) 또한, 본 발명은 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물과, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 투명 도전막이다.

이와 같이, 본 발명은 이하의 2종의 물질을 산화인듐에 첨가하고 있다.

- 란타노이드계 금속 산화물로부터 선택된 1종 또는 2종 이상의 금속 산화물

- W, Mo, Nb, Ni, Pt 및 Pd으로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물

본 발명에서는 이들을, 투명 도전막에 동시에 첨가하고 있다. 따라서, 본 발명의 투명 도전막을 사용하여 투명 전극 또는 화소 전극을 구성한 경우,

- Al 게이트선/투명 전극 사이

- Al 소스 · 드레인 전극/화소 전극 사이

- Al 소스 · 드레인 배선/투명 전극 사이

등에 발생하는 접촉 저항을 거의 무시할 수 있는 값으로 감소시킬 수 있다.

이에 대하여, 종래의 투명 도전막을 사용하여 투명 전극 · 화소 전극을 구성한 경우, Al 게이트선/투명 전극 사이, Al 소스 · 드레인 전극/화소 전극 사이 및 Al 소스 · 드레인 배선/투명 전극 사이에는, 무시할 수 없는 크기의 접촉 저항이 발생하고 있다.

(12) 상기 (11)에 있어서, 본 발명은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는 투명 도전막이다. 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [In]은 인듐의 원자의 수를 나타낸다.

#### 란타노이드계 금속 산화물

이와 같이, 본 발명에서는 란타노이드계 금속 산화물의 조성이 산화인듐에 대하여,  $[M2]/([In]+[M2])=0.005$  내지 0.2가 되도록 설정하고 있다. [M2]는 란타노이드계 금속을 포함하는 제2 금속군 M2 중의 1종 또는 2종 이상의 금속의 원자

의 수를 나타낸다. 여기서 이 수는, 단위 질량 · 단위 부피당 수이다.  $[In]$ 은 인듐 원자의 단위 부피 · 단위 질량당 수를 나타낸다. 따라서, 상기 식은 원자의 수로부터 본 제2 금속군 M2 중의 금속의 인듐에 대한 조성비이다. 또한, 이 조성비는 제2 금속군 M2 중의 금속 산화물의 산화인듐에 대한 조성비이기도 하다.

또한, 이 값은 바람직하게는 0.01 내지 0.15이고, 보다 바람직하게는 0.01 내지 0.1이다.

산화인듐에 대한 란타노이드계 금속 산화물의 조성을 나타내는 상기 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나지 않는 경우도 생각된다. 즉, 이 투명 도전막을 사용한 투명 전극 또는 화소 전극에 대하여, 다른 배선의 Al과 이 투명 전극 · 화소 전극 사이에서 무시할 수 없는 접촉 저항이 발생하는 경우도 있다.

한편, 상기 값이 0.2를 초과하면, 본 발명의 투명 도전막을 포함하는 투명 전극 · 화소 전극의 비저항이 커지는 경우나, 제조 공정에서 이 투명 전극 · 화소 전극의 에칭이 곤란해지는 경우가 발생할 우려가 있다.

이와 같이, 본 발명에서는 란타노이드계 금속 산화물의 조성이 산화인듐에 대하여,  $[M2]/([In]+[M2])=0.005$  내지 0.2 이지만, 이 조성 비율은 바람직하게는 0.01 내지 0.15이다. 또한, 더욱 바람직하게는 0.01 내지 0.1이다,

#### W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물

또한, 본 발명에서는 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 중의 금속 또는 금속 산화물의 조성이 산화인듐에 대하여,  $[M1]/([In]+[M1])=0.005$  내지 0.2인 구성을 채용하고 있다. 이 식의 값은 보다 바람직하게는 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. 이 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도 있고, 금속 산화물의 상태로 첨가될 수도 있다.

M1은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군의 총칭이고,  $[M1]$ 은 제1 금속군 중의 1종 또는 2종 이상의 금속의 단위 질량 · 단위 부피당 수를 나타낸다.  $[In]$ 은 상술한 바와 같이, 단위 질량 · 단위 부피당 인듐의 원자의 수를 나타낸다.

또한, 상기 식의 값이 0.005 미만이면, 상기 W, Mo, Nb, Ni, Pt 및 Pd을 첨가하는 효과가 나타나지 않는 경우가 있다. 구체적으로는, 본 발명의 투명 도전막을 이용한 투명 전극 · 화소 전극에 대하여, Al과 이 투명 전극 사이, Al과 이 화소 전극과의 사이에 무시할 수 없는 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막을 포함하는 투명 전극 · 화소 전극의 비저항이 커지는 경우가 있다. 또한, 제조 공정에서 이 투명 전극 · 화소 전극의 에칭이 곤란해지는 경우도 있다.

(13) 상기 (11) 또는 (12)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 투명 도전막이다.

이와 같이, 란타노이드계 금속 산화물 중에서도 Ce, Ho 및 Er을 포함하는 산화물을 채용하는 것이 바람직하다.

(14) 또한, 본 발명은 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물과, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물과, 추가로 Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 투명 도전막이다.

이와 같이, 본 발명에서는 란타노이드계 금속군(제2 금속군)으로부터 선택된 1종 또는 2종 이상의 금속의 산화물과, W, Mo, Nb, Ni, Pt 및 Pd(제1 금속군)으로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물을 동시에 첨가하는 구성을 채용하고 있다.

종래의 투명 도전막을 투명 전극 또는 화소 전극으로서 사용하면,

- Al 게이트선/투명 전극 사이

- Al 소스 · 드레인 전극/화소 전극 사이

• Al 소스 • 드레인 배선/투명 전극 사이

등에서 큰 접촉 저항이 발생하고 있었다.

이에 대하여, 상기 본 발명에 따른 투명 도전막을 사용하여 투명 전극 또는 화소 전극을 구성하면, 상술한 구성에 의해, 종래 발생하고 있었던 큰 접촉 저항의 값을 작게 할 수 있다. 말하자면, 접촉 저항을 무시할 수 있는 정도까지 작게 할 수 있는 것이다.

또한, Zn, Sn, Zr, Ga 및 Ge(제3 금속군 M3)으로부터 선택된 1종 또는 2종 이상의 금속 산화물을 첨가함으로써, 하기에 나타낸 바와 같은 유익한 영향을 미친다.

- 제조한 투명 도전막의 비저항을 개선할 수 있음

- 제조한 투명 도전막의 예칭 특성을 개선할 수 있음

- 제조한 투명 도전막의 투명성을 개선할 수 있음

여기서, 비저항의 개선이란, 비저항값의 감소를 의미한다. 또한, 예칭 특성의 개선이란, 예칭에 사용하는 예칭제에 의해 보다 용이하게 용해하는 것을 의미한다. 또한, 투명성의 개선이란, 광 투과율의 값이 100 %에 근접하는 것을 의미한다.

(15) 상기 (14)에 있어서, 본 발명은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고, 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이고, Zn, Sn, Zr, Ga 및 Ge을 포함하는 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는 투명 도전막이다. 여기서, 상기  $[M1]$ 은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[M2]$ 는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[M3]$ 은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기  $[In]$ 은 인듐 원자의 수를 나타낸다.

란타노이드계 금속 산화물

이와 같이, 본 발명에서는 란타노이드계 금속군(제2 금속군)의 산화물의 조성을 산화인듐에 대하여,  $[M2]/([In]+[M2]) = 0.005$  내지 0.2로 설정하고 있다. M2는 란타노이드계 금속을 포함하는 제2 금속군의 총칭이고,  $[M2]$ 는 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 수를 나타낸다. 여기서, 이  $[M2]$ 는 단위 질량 · 단위 중량당 수이다.  $[In]$ 은 상술한 바와 같이, 단위 질량 · 단위 중량당 인듐의 원자의 수이다. 따라서, 상기 식은 제2 금속군 중에 포함되는 금속의 인듐에 대한 원자수의 비를 나타낸다. 또한, 이 식의 값은 동시에 제2 금속군에 포함되는 금속 산화물의 산화인듐에 대한 조성비이기도 하다.

또한, 이값은 바람직하게는 0.01 내지 0.15이고, 보다 바람직하게는 0.01 내지 0.1이다.

산화인듐에 대한 란타노이드계 금속 산화물의 조성을 나타내는 상기 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나지 않는 경우도 생각된다. 즉, Al과 본 발명의 투명 도전막을 포함하는 투명 전극 또는 화소 전극 사이에서 무시할 수 없는 접촉 저항이 발생하는 경우도 있다.

한편, 상기 값이 0.2를 초과하면, 본 발명의 투명 도전막을 포함하는 투명 전극 · 화소 전극의 비저항이 커지는 경우나, 제조 공정에서 이 투명 전극 · 화소 전극의 예칭이 곤란해지는 경우가 발생할 우려가 있다.

W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물

또한, 본 발명에서는 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1에 포함되는 금속 또는 이 금속 산화물의 조성이 산화인듐에 대하여,  $[M1]/([In]+[M1]) = 0.005$  내지 0.2인 구성을 채용하고 있다. 상술한 바와 같이,  $[M1]$ 은 제1 금속군 중의 금속의 원자의 수를 나타낸다. 이 수는 단위 질량 · 단위 부피당 수이다.

이 식의 값은 보다 바람직하게는 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. 이 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도 있고, 금속 산화물의 상태로 첨가될 수도 있다.

또한, 상기 식의 값이 0.005 미만이면, 상기 W, Mo, Nb, Ni, Pt 및 Pd을 첨가하는 효과가 나타나지 않는 경우가 있다. 구체적으로는, 본 발명의 투명 도전막을 포함하는 투명 전극·화소 전극에 대하여, Al과 이 투명 전극 사이, Al과 이 화소 전극 사이에 무시할 수 없는 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막을 포함하는 투명 전극·화소 전극의 비저항이 커지는 경우가 있다. 또한, 제조 공정에서 이 투명 전극·화소 전극의 애칭이 곤란해지는 경우도 있다.

#### Zn, Sn, Zr, Ga 및 Ge 산화물

본 발명에서는 상술한 바와 같이, Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속 산화물의 조성이 산화인듐에 대하여,  $[M3]/([In] + [M3]) = 0.005$  내지 0.2이다. [M3]은 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타낸다. 그 때문에, 이 식은 제3 금속군 M3 중의 1종 또는 2종 이상의 금속의 인듐에 대한 조성비(원자수)이다. 이 값은 동시에, 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의 산화인듐에 대한 조성비도 나타낸다.

이 식의 값(조성비)이 0.005 미만이면, 그의 첨가 효과가 나타나기 어렵다. 구체적으로는, 본 발명의 투명 도전막을 포함하는 투명 전극·화소 전극에 대하여, Al과 이 투명 전극 사이, Al과 이 화소 전극 사이에 무시할 수 없는 크기의 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막을 이용한 투명 전극·화소 전극의 비저항이 커지는 경우나, 제조 공정에서 이들의 투명 전극·화소 전극의 애칭이 곤란해지는 경우도 있다.

(16) 상기 (14) 또는 (15)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 투명 도전막이다.

이와 같이, 란타노이드계 금속 산화물 중에서도, Ce, Ho 및 Er을 포함하는 산화물을 채용하는 것이 바람직하다.

(17) 또한, 본 발명은 유리 기판, 상기 유리 기판 위에 설치되고, 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 투명 도전막 및, 상기 유리 기판 위에 설치된 Al 또는 Ag을 주성분으로 하는 금속 박막을 갖는 것을 특징으로 하는 투명 도전 유리 기판이다.

이와 같이 본 발명에서는, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물과, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물을 동시에 첨가하는 구성(동시 첨가 구성이라고 부름)을 채용하고 있다.

또한, 본 발명의 투명 도전 유리는, 투명 도전막을 투명 전극 또는 화소 전극으로서 이용함으로써, 투명 전극 또는 화소 전극을 구비한 기판으로서 이용하는 것이 가능하다. 또한, 본 발명의 금속 박막은 Al을 채용하는 경우, Al 게이트선, Al 소스·드레인 전극을 구성할 수 있다. 그 때문에, 본 발명의 투명 도전 유리 기판은 배선부의 기판으로서 이용하는 것이 가능하다.

또한, 이러한 경우, 종래의 투명 도전 유리에 따르면,

- Al 게이트선/투명 전극 사이,

- Al 소스·드레인 전극/화소 전극 사이

- Al 소스·드레인 배선/투명 전극 사이

등에 큰 접촉 저항이 발생하고 있었다. 이에 대하여, 본 발명의 투명 도전 유리에 따르면, 큰 접촉 저항이 발생하지 않는다.

또한, 금속 박막에 Ag을 사용하는 경우, Ag 게이트선, Ag 소스·드레인 전극을 구성할 수 있다. 이 경우에도, Al의 경우와 동일한 작용 효과를 발휘한다.

이와 같이, 상기 본 발명에 따르면, 상술한 구성(동시 첨가 구성)에 의해, 종래 발생하고 있었던 큰 접촉 저항의 값을 작게 할 수 있다. 말하자면, 접촉 저항을 사실상 무시할 수 있는 정도까지 작게 할 수 있는 것이다.

또한, Al 또는 Ag으로 적층된 구조를 채용함으로써, 보다 저저항의 투명 도전 유리가 얻어진다. 이러한 투명 도전 유리는 적층 투명 도전 유리라고 불리는 경우도 있다.

### Al 또는 Al 합금의 이용

이 (17) 및 후술하는 (20)에서, 게이트선, 소스·드레인 전극 또는 배선에는 Al 또는 Al 합금이 바람직하게 사용된다. 이 경우, Al 게이트선, Al 소스·드레인 전극으로 부르고 있지만, Al을 주성분으로 하는 합금이 사용되는 경우도 많다. 이들에 사용되는 Al 또는 Al 합금은 Al을 주성분으로 하고 있지만, 주기율표의 IIIa 내지 VIIIa의 중금속 또는 란타노이드계 금속을 포함할 수도 있다. 예를 들면, Nd, Ni, Co 및 Zr 등을 포함하는 것이 바람직하다. 그의 함유량은 요구되는 Al 게이트선, Al 소스·드레인 전극의 성능에 따라 상이하지만, 대체로 0.1 내지 5 중량%의 범위가 바람직하다. 보다 바람직한 함유량은 0.5 내지 2.0 중량%이다.

함유량이 0.1 중량% 미만이면 첨가 효과가 나타나지 않는 경우도 있으며, 0.1 중량%의 함유량에서는 Al 박막 위에 힐록(hillock) 등의 돌기가 발생하는 경우가 있기 때문이다.

한편, 함유량이 0.5 중량%를 초과하면, Al 자체(Al 합금 자체)의 저항값이 커지는 경우가 있다.

또한, 본 발명에서 게이트선, 소스·드레인 전극 또는 배선에는 Ag 또는 Ag 합금도 바람직하게 사용된다. 또한, 빛을 반사하는 반사 전극이 설치되는 경우도 있지만, 이 반사 전극에도 Ag 또는 Ag 합금이 바람직하게 사용되는 경우가 있다.

또한, Ag이 사용되는 경우는, Ag 게이트선, Ag 소스·드레인 전극 등으로 부른다. 이들에 사용되는 Ag 또는 Ag 합금은 Ag을 주성분으로 하며, 주기율표의 IIIa 내지 VIIIa의 중금속 또는 란타노이드계 금속을 포함할 수도 있다. 예를 들면, Nd, Ni, Co 및 Zr 등을 포함하는 것이 바람직하다. 그의 함유량은 요구되는 Al 게이트선, Al 소스·드레인 전극 또는 배선이나 반사 전극의 성능에 따라 상이하지만, 대체로 0.1 내지 5 중량%의 범위가 바람직하다. 보다 바람직한 함유량은 0.5 내지 2.0 중량%이다.

함유량이 0.1 중량% 미만이면 첨가 효과가 나타나지 않는 경우도 있으며, 0.1 중량%의 함유량에서는 Ag 박막 위에 힐록 등의 돌기가 발생하는 경우 또는 Ag 박막의 밀착성이 저하되는 경우가 있기 때문이다.

한편, 함유량이 0.5 중량%를 초과하면, Ag 자체(Ag 합금 자체)의 저항값이 커지는 경우가 있다.

(18) 상기 (17)에 있어서, 본 발명은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고, 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이, 0.005 내지 0.2인 것을 특징으로 하는 투명 도전 유리 기판이다. 여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타낸다.

### 란타노이드계 금속 산화물

이와 같이, 본 발명에서는 란타노이드계 금속 산화물의 조성을 산화인듐에 대하여,  $In/(In+ \text{란타노이드계 금속}) = 0.005$  내지 0.2로 하고 있다.

또한, 이값은 바람직하게는 0.01 내지 0.15이고, 보다 바람직하게는 0.01 내지 0.1이다.

산화인듐에 대한 란타노이드계 금속 산화물의 조성을 나타내는 상기 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나지 않는 경우도 생각된다. 즉, Al 또는 Ag을 주성분으로 하는 금속 박막과, 투명 도전막(예를 들면 투명 전극 또는 화소 전극을 구성하고 있음) 사이에서 무시할 수 없는 접촉 저항이 발생하는 경우도 있다.

한편, 상기 값이 0.2를 초과하면, 본 발명의 투명 도전막(예를 들면, 투명 전극 · 화소 전극을 구성하고 있음)의 비저항이 커지는 경우나, 제조 공정에서 이 투명 도전막의 예칭이 곤란해지는 경우 등이 발생할 우려가 있다.

#### W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물

또한, 본 발명에서는 W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물의 조성이 산화인듐에 대하여,  $In/(In + (W, Mo, Nb, Ni, Pt 및 Pd)) = 0.005$  내지 0.2인 구성을 채용하고 있다. 이 식의 값은 보다 바람직하게는 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. 이 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도 있고, 금속 산화물의 상태로 첨가될 수도 있다.

또한, 상기 식의 값이 0.005 미만이면, 상기 W, Mo, Nb, Ni, Pt 및 Pd를 첨가하는 효과가 나타나지 않는 경우가 있다. 구체적으로는, 본 발명의 투명 도전막(예를 들면 투명 전극 · 화소 전극을 구성하고 있음)과 Al 또는 Ag을 주성분으로 하는 금속 박막 사이에 무시할 수 없는 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막(예를 들면, 투명 전극 · 화소 전극)의 비저항이 커지는 경우가 있다. 또한, 제조 공정에서 이 투명 도전막의 예칭이 곤란해지는 경우도 있다.

#### 적층

이와 같이, 상기한 바와 같은 조성의 투명 도전막과 금속 박막을 적층함으로써, 보다 저저항의 투명 도전 유리를 제공할 수 있다.

(19) 상기 (17) 또는 (18)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이 La, Ce, Ho 및 Er 중 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 투명 도전 유리 기판이다.

이와 같이, 란타노이드계 금속 산화물 중에서도, 특히 Ce, Ho 및 Er 중 어느 1종 이상을 포함하는 산화물을 사용하는 것이 보다 효과적이며, 바람직하게 사용할 수 있다.

(20) 또한, 본 발명은 유리 기판, 상기 유리 기판 위에 설치되고, 산화인듐을 주성분으로 하며, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 이 금속의 산화물과, 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물과, 추가로 Zn, Sn, Zr, Ga 및 Ge을 포함하는 제3 금속군 M3으로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 투명 도전막 및, 상기 유리 기판 위에 설치된 Al 또는 Ag을 주성분으로 하는 금속 박막을 갖는 것을 특징으로 하는 투명 도전 유리 기판이다.

이와 같이, 본 발명에서는 란타노이드계 금속을 포함하는 제2 금속군 M2로부터 선택된 선택된 1종 또는 2종 이상의 금속의 산화물과, W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물을 동시에 첨가하는 구성(동시 첨가 구성이라고 부름)을 채용하고 있다.

또한, 본 발명의 투명 도전 유리는, 투명 도전막을 투명 전극 또는 화소 전극으로서 사용함으로써, 투명 전극 또는 화소 전극을 구비한 기판으로서 이용하는 것이 가능하다. 또한, 본 발명의 금속 박막은 Al을 채용하는 경우, Al 게이트선, Al 소스 · 드레인 전극을 구성할 수 있다. 그 때문에, 본 발명의 투명 도전 유리 기판은 배선이 부착된 기판으로서 이용하는 것이 가능하다.

또한, 이러한 경우, 종래의 투명 도전 유리에 따르면,

- Al 게이트선/투명 전극 사이

- Al 소스 · 드레인 전극/화소 전극 사이

### • Al 소스 · 드레인 배선/투명 전극 사이

등에 큰 접촉 저항이 발생하고 있었다. 이에 대하여, 본 발명의 투명 도전 유리에 따르면, 큰 접촉 저항이 발생하지 않았다.

또한, 금속 박막에 Ag을 사용하는 경우, Ag 게이트선, Ag 소스 · 드레인 전극을 구성할 수 있다. 이 경우도, Al의 경우와 동일한 작용 효과를 발휘한다.

이와 같이, 상기 본 발명에 따르면, 상술한 구성(동시 첨가 구성)에 의해, 종래 발생하고 있었던 큰 접촉 저항의 값을 작게 할 수 있다. 말하자면, 접촉 저항을 사실상 무시할 수 있는 정도까지 작게 할 수 있는 것이다.

또한, Zn, Sn, Zr, Ga 및 Ge으로부터 선택된 1종 또는 2종 이상의 금속 산화물을 첨가함으로써 투명 도전 유리 위의 상기 투명 도전막에, 하기에 나타낸 바와 같은 유익한 영향을 미친다.

- 제조한 투명 도전막의 비저항을 개선할 수 있음

- 제조한 투명 도전막의 에칭 특성을 개선할 수 있음

- 제조한 투명 도전막의 투명성을 개선할 수 있음

여기서, 비저항의 개선이란, 비저항값의 감소를 의미한다. 또한, 에칭 특성의 개선이란, 에칭에 사용하는 에칭제에 의해 보다 용이하게 용해되는 것을 의미한다. 또한, 투명성의 개선이란, 광 투과율의 값이 향상되는 것을 의미한다. 또한, Al 또는 Ag으로 적층된 구조를 채용함으로써, 보다 저저항의 투명 도전 유리가 얻어진다.

이러한 투명 도전 유리는 적층 투명 도전 유리로 부르는 경우도 있다.

또한, 이 (20)에서도 상기 (17)에서 설명한 바와 같이, 게이트선, 소스 · 드레인 전극 또는 배선에는 Al 또는 Al 합금이 바람직하게 사용된다. 그의 내용은 상기 (13)의 경우와 마찬가지이다.

(21) 상기 (20)에 있어서, 본 발명은 W, Mo, Nb, Ni, Pt 및 Pd을 포함하는 상기 제1 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 또는 금속 산화물의, 산화인듐에 대한 조성인  $[M1]/([M1]+[In])$ 의 값이 0.005 내지 0.2이고,

란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M2]/([M2]+[In])$ 의 값이 0.005 내지 0.2이고,

Zn, Sn, Zr, Ga 및 Ge을 포함하는 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속 산화물의, 산화인듐에 대한 조성인  $[M3]/([M3]+[In])$ 의 값이 0.005 내지 0.2인 것을 특징으로 하는 투명 도전 유리 기판이다. 여기서, 상기 [M1]은 상기 제1 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M2]는 상기 제2 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [M3]은 상기 제3 금속군으로부터 선택된 1종 또는 2종 이상의 금속의 원자의 수를 나타내고, 상기 [In]은 인듐 원자의 수를 나타낸다.

### 란타노이드계 금속 산화물

이와 같이, 본 발명에서는 란타노이드계 금속 산화물의 조성을 산화인듐에 대하여,  $In/(In+ \text{란타노이드계 금속}) = 0.005$  내지 0.2로 하고 있다.

또한, 이 값은 바람직하게는 0.01 내지 0.15이고, 보다 바람직하게는 0.01 내지 0.1이다.

산화인듐에 대한 란타노이드계 금속 산화물의 조성을 나타내는 상기 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나지 않는 경우도 생각된다. 즉, Al 또는 Ag을 주성분으로 하는 금속 박막과, 투명 도전막(예를 들면 투명 전극 또는 화소 전극을 구성하고 있음) 사이에서 무시할 수 없는 접촉 저항이 발생하는 경우도 있다.

한편, 상기 값이 0.2를 초과하면, 본 발명의 투명 도전막(예를 들면, 투명 전극 · 화소 전극을 구성하고 있음)의 비저항이 커지는 경우나, 제조 공정에서 이 투명 도전막의 에칭이 곤란해지는 경우 등이 발생할 우려가 있다.

### W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물

또한, 본 발명에서는 W, Mo, Nb, Ni, Pt 및 Pd 금속 또는 금속 산화물의 조성이 산화인듐에 대하여,  $In/(In+ (W, Mo, Nb, Ni, Pt 및 Pd))=0.005$  내지 0.2인 구성을 채용하고 있다. 이 식의 값은 보다 바람직하게는 0.01 내지 0.15이고, 더욱 바람직하게는 0.01 내지 0.1이다. 이 W, Mo, Nb, Ni, Pt 및 Pd는 금속의 상태로 첨가될 수도 있고, 금속 산화물의 상태로 첨가될 수도 있다.

또한, 상기 식의 값이 0.005 미만이면, 상기 W, Mo, Nb, Ni, Pt 및 Pd을 첨가하는 효과가 나타나지 않는 경우가 있다. 구체적으로는, 본 발명의 투명 도전막(예를 들면 투명 전극·화소 전극을 구성하고 있음)과, Al 또는 Ag을 주성분으로 하는 금속 박막 사이에 무시할 수 없는 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막(예를 들면, 투명 전극·화소 전극)의 비저항이 커지는 경우가 있다. 또한, 제조 공정에서 이 투명 도전막의 에칭이 곤란해지는 경우도 있다.

### Zn, Sn, Zr, Ga 및 Ge 산화물

본 발명에서는 상술한 바와 같이, Zn, Sn, Zr, Ga 및 Ge 산화물로부터 선택된 1종 또는 2종 이상의 금속 산화물의 조성이 산화인듐에 대하여  $In/(In+ (Zn, Sn, Zr, Ga 및 Ge))=0.005$  내지 0.2이다.

이 식의 값이 0.005 미만이면, 그의 첨가 효과가 나타나기 어렵다. 구체적으로는, 본 발명의 투명 도전막(예를 들면, 투명 전극·화소 전극을 구성하고 있음)과, Al 또는 Ag을 주성분으로 하는 금속 박막 사이에 무시할 수 없는 크기의 접촉 저항이 발생하는 경우가 있다.

한편, 상기 식의 값이 0.2를 초과하면, 본 발명의 투명 도전막(또는, 투명 도전막을 이용한 투명 전극·화소 전극)의 비저항이 커지는 경우가 있다. 또한, 상기 식의 값이 0.2를 초과하는 경우, 제조 공정에서 이들의 투명 도전막을 에칭하여, 투명 전극 또는 화소 전극을 형성하고자 한 경우에 그의 에칭이 곤란해지는 경우도 있다.

### 적층

이와 같이, 상기한 바와 같은 조성의 투명 도전막과 금속 박막을 적층함으로써, 보다 저저항의 투명 도전 유리를 제공할 수 있다.

(22) 상기 (20) 또는 (21)에 있어서, 본 발명은 란타노이드계 금속을 포함하는 상기 제2 금속군 M2로부터 선택된 금속의 산화물이, La, Ce, Ho 및 Er 중 어느 1종 이상의 금속의 산화물인 것을 특징으로 하는 투명 도전 유리 기판이다.

이와 같이, 란타노이드계 금속 산화물 중에서도, 특히 Ce, Ho 및 Er 중 어느 1종 이상을 포함하는 산화물을 사용하는 것이 보다 효과적이며, 바람직하게 사용할 수 있다.

### 적층의 구체적인 방법

이상 (5) 내지 (22)에서 상술한 바와 같이, 본 발명에서는 금속 산화물 도전막과 금속 박막을 적층하는 구성이 채용되는 경우가 있다. 이하, 이 경우에 대하여 설명한다.

이 금속 산화물 투명 도전막과, Al 또는 Ag을 주성분으로 하는 금속 박막을 적층하는 방법에는 다양한 형태가 있다.

a. 금속 산화물/Al 또는 Ag을 주성분으로 하는 금속 박막/금속 산화물

b. 금속 산화물/Al 또는 Ag을 주성분으로 하는 금속 박막/금속 산화물/Al 또는 Ag을 주성분으로 하는 금속 박막/금속 산화물

상기 a.는 3층이고, 상기 b.는 5층이다. 이외에 7층 등을 채용하는 것도 물론 바람직하다.

이 경우의 Al 또는 Ag을 주성분으로 하는 금속 박막의 막 두께는 1 내지 20 nm이다. 막 두께는 바람직하게는 5 내지 15 nm이고, 보다 바람직하게는 5 내지 10 nm이다. 막 두께가 1 nm 이하이면, 적층된 금속의 막이 "박막"이 되지 않고, 해도(海島) 구조가 되는 경우가 있으며, 본 발명의 효과가 얻어지지 않는 경우도 있다. 한편, 금속 박막의 막 두께가 20 nm 이상인 경우는, 적층된 금속 박막의 광선 투과율이 저하되는 경우가 있다. 그 결과, 중첩하여 설치되어 있는 투명 도전막의 "투명"성에 사실상 영향을 주는 경우도 있다.

또한, 본 발명에서는 종종 금속 산화물을 포함하는 상기 투명 도전막과, Al 또는 Ag을 주성분으로 하는 금속 박막을 적층하고 있지만, 이 "적층"에는 금속 산화물을 포함하는 투명 도전막의(전부가 아님) 일부가 금속 박막과 접촉하고 있는 경우도 포함된다. 이 경우, 전극 구성으로서는 예를 들면 20  $\mu\text{m}$  폭의 금속 박막과 일부가 접촉하고, 금속 박막의 전체를 덮도록 투명 도전막이 접촉하고 있는 경우 등을 들 수 있다. 바꾸어 말하면, 평면적으로 두 막은 중첩하고 있지만, 단면도로부터 보면 일부만이 접촉하고 있는 경우이다.

이러한 경우, 금속 박막의 두께는 20 내지 500 nm, 바람직하게는 30 내지 300 nm, 보다 바람직하게는 50 내지 200 nm이다. 막 두께가 20 nm 이하이면, 저항을 감소시키는 효과가 작은 경우도 있다. 한편, 막 두께가 500 nm 이상이면, 그의 박막의 단차가 크기 때문에, 투명 도전막과의 접촉 불량을 발생시키는 경우도 있다.

금속 박막의 폭은 적절하게 선택할 수 있지만, 예를 들면 1  $\mu\text{m}$  내지 100  $\mu\text{m}$  이다. 이 값은 바람직하게는 5 내지 50  $\mu\text{m}$ 이고, 보다 바람직하게는 10 내지 30  $\mu\text{m}$  이다.

금속 박막의 폭이 1  $\mu\text{m}$  이하이면, 저항 감소의 효과가 지나치게 작아지는 경우가 있다. 한편, 금속 박막의 폭이 100  $\mu\text{m}$  이상이면, 광선 투과율(개구율)이 저하되는 경우가 있다. 단, 금속 박막과 투명 도전막을 적층한 것을 반사 전극으로서 사용하는 경우는, 이것으로 한정되지 않는다.

### 제3 그룹: 수단

#### A. 박막 트랜지스터 기판의 제조 방법의 발명

(23) 따라서, 상기 과제를 해결하기 위해, 본 발명은 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 사용하여, 게이트, 소스 및 드레인을 포함하는 도체군 E1에 포함되는 어느 하나의 도체인 제1 도체를, 투명 절연성 기판 위에 형성하는 제1 도체 형성 공정, 형성된 상기 제1 도체 및 상기 투명 절연성 기판을 덮도록 절연막을 성막하는 절연막 성막 공정, 성막된 상기 절연막에 콘택트 홀을 형성하는 콘택트 홀 형성 공정 및, 상기 절연막 위에 투명막 전극을 포함하는 제2 도체를 형성하는 공정이며, 상기 제2 도체와 상기 제1 도체가 상기 콘택트 홀을 통해 전기적으로 접속하는 전극 접속 공정을 적어도 포함하는 것을 특징으로 하는 박막 트랜지스터 기판의 제조 방법이다.

또한, 본 특허에서는 게이트 전극 및 게이트 배선의 총칭을 게이트라고 부르며, 소스 전극 및 소스 배선의 총칭을 소스라고 부른다. 드레인 전극을 간단히 드레인이라고 부른다. 또한, 제1 도체는 구체적으로 게이트, 소스 및 드레인이고, 제2 도체는 화소 전극이다.

제1 도체는 단층 구조이기 때문에, 1 종류의 에칭액으로 1번에 에칭하는 것이 가능하다.

또한, 제1 도체는 Al을 주성분으로 하며, 이외에 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 층이기 때문에, 제2 도체와의 콘택트 저항이 낮다.

또한, 제1 도체에 대하여, 힐록 발생의 억제 또는 내식성 향상의 관점에서, Al 또는 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 이외에, 제3 금속으로서 Cu, Si 및 희토류 원소 등을 첨가하는 것도 바람직하다. 이때, Al의 전기적 저저항의 특성을 발휘시키기 위해, 제3 금속의 첨가량은 제1 도체의 비저항이  $10 \mu\text{·}\Omega\text{·cm}$ 를 초과하지 않는 정도로 억제하는 것이 바람직하다. 또한, 여기서 제1 금속은 Al이고, 제2 금속은 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속이다. 이들에 대한 3번째의 성분이라는 의미로, 상기 첨가하는 Cu, Si 및 희토류 원소 등을 제3 금속이라고 부른다.

또한, 제1 도체 중에 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 첨가한 경우에도, 상기 제3 금속을 첨가한 경우와 마찬가지로, 힐록 발생의 억제 또는 내식성 향상의 효과가 얻어진다. 이 때문에, 특히 상기 제3 금속을 첨가하지 않은 경우에도, 힐록의 발생 또는 내식을 억제할 수 있는 것이다.

또한, 제2 도체는 절연막에 형성된 콘택트 홀을 통해, 제1 도체와 접속하고 있다. 이 때문에, 화소 전극과 게이트 및 소스의 배선이 직접 접촉하지 않기 때문에, 쇼트 등의 결점이 발생하기 어렵다.

제1 도체는 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er으로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금 타깃을 사용하여, 스퍼터링에 의해 성막된다. 또한, 이 Al 합금 타깃은 진공 용해법 및 스프레이 포밍법 등에 의해 제조된다. 이 Al 합금 타깃을 사용하여 성막한 Al 합금 박막을 인산-아세트산-질산의 혼합산을 사용한 에칭에 의해 패턴화하여, 제1 도체를 형성한다.

### B. 박막 트랜지스터의 발명

(24) 또한, 본 발명은 투명 절연성 기판과, 상기 투명 절연성 기판 위에 설치되어, 게이트, 소스, 및 드레인을 포함하는 도체 군 E1에 포함되는 어느 하나의 도체인 제1 도체를 포함하는 박막 트랜지스터이며, 상기 제1 도체가 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 포함하는 Al 층을 포함하고, 상기 제1 도체 위의 절연막에 형성된 콘택트 홀을 통해, 투명막 전극을 포함하는 제2 도체와 접속하는 것을 특징으로 하는 박막 트랜지스터이다.

또한, 제1 도체는 순Al 또는 Al 합금 이외에 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 층을 포함함으로써, 제2 도체와의 콘택트 저항이 낮다.

또한, 제1 도체에 대하여, 헐록 발생의 억제 또는 내식성 향상의 관점에서, Al 또는 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속 이외에, 제3 금속으로서 Cu, Si 및 희토류 원소 등을 첨가하는 것도 바람직하다. 이때, Al의 비저항이 지나치게 높아지지 않도록, 제3 금속의 첨가량은 제1 도체의 비저항이  $10 \mu \cdot \Omega \cdot \text{cm}$ 를 초과하지 않는 정도로 억제하는 것이 바람직하다. 또한, 여기서 제1 금속은 Al이고, 제2 금속은 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속이다.

제1 도체는 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er으로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금 타깃을 사용하여, 스퍼터링에 의해 성막된다. 또한, 이 Al의 합금 타깃은 진공 용해법 및 스프레이 포밍법 등에 의해 제조된다. 이 Al 합금 타깃을 사용하여 성막한 Al 합금 박막을 인산-아세트산-질산의 혼합산을 사용한 에칭에 의해 패턴화하여, 제1 도체를 형성한다.

(25) 상기 (24)에 있어서, 본 발명은 상기 제1 도체가 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 0.5 내지 5 중량% 갖는 Al층을 포함하는 것을 특징으로 하는 박막 트랜지스터이다.

제1 도체의 Al층에서, 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속의 함유량은 0.5 내지 5 중량%이고, 바람직하게는 1 내지 3 중량%이다. 함유량이 0.5 중량% 미만인 경우에는, 제1 도체 및 제2 도체의 콘택트 저항을 억제하는 것이 곤란해지는 경우가 있으며, 한편 함유량이 5 중량%를 초과하는 경우에는, 제1 도체 전체의 비저항이 높아지는 경우가 있다.

### C. 박막 트랜지스터 기판의 발명

(26) 또한, 본 발명은 투명 절연성 기판과, 상기 투명 절연성 기판 위에 형성되어, 게이트, 소스, 및 드레인을 포함하는 도체 군 E1에 포함되는 어느 하나의 도체인 제1 도체를 포함하며, 적어도 상기 투명 절연성 기판을 덮도록 형성된 절연막과, 상기 절연막 위에 형성된 제2 도체를 적어도 포함하는 박막 트랜지스터 기판이고, 상기 제1 도체는 W, Mo, La, Nb, Fe, Pd, Pt, Ce, Ho 및 Er을 포함하는 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 포함하는 Al 합금을 포함하는 Al층을 포함하며, 상기 절연막은 소정의 상기 제1 도체 및 상기 제2 도체 방향으로 관통하고 있는 콘택트 홀을 구비하고, 상기 제2 도체는 투명막 전극을 포함하여, 상기 제2 도체가 상기 콘택트 홀을 통해, 상기 제1 도체의 상기 Al층과 전기적으로 접속하고 있는 것을 특징으로 하는 박막 트랜지스터 기판이다.

제1 도체는 단층을 포함하기 때문에, 1 종류의 에칭액으로 1 번에 에칭하는 것이 가능하다. 이 때문에, 본 발명의 박막 트랜지스터 기판을 보다 간편하게 제조할 수 있다.

또한, 제2 도체는 절연막에 형성된 콘택트 홀을 통해, 제1 도체와 접속하고 있다. 이 때문에, 화소 전극과 게이트 및 소스의 배선이 직접 접촉하지 않기 때문에, 쇼트 등의 결점이 발생하기 어렵다.

(27) 상기 (26)에 있어서, 본 발명은 상기 투명막 전극이 산화인듐, 산화주석, 산화인듐주석, 산화인듐아연 및 산화아연 중 어느 하나를 포함하는 것을 특징으로 하는 박막 트랜지스터 기판이다.

제2 도체가 산화인듐, 산화주석, 산화인듐주석, 산화인듐아연 및 산화아연 중 어느 하나를 포함하는 경우에도, 제1 도체와의 콘택트 저항은 낮아진다.

(28) 상기 (26) 또는 (27)에 있어서, 본 발명은 상기 제1 도체가 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속을 0.5 내지 5 중량% 갖는 Al층을 포함하는 것을 특징으로 하는 박막 트랜지스터 기판이다.

제1 도체의 Al층에서, 상기 금속군 M1로부터 선택된 1종 또는 2종 이상의 금속의 함유량은 0.5 내지 5 중량%이고, 바람직하게는 1 내지 3 중량%이다. 함유량이 0.5 중량% 미만인 경우에는, 제1 도체 및 제2 도체의 콘택트 저항을 억제하는 것이 곤란해지는 경우가 있으며, 한편 함유량이 5 중량%를 초과하는 경우에는, 제1 도체 전체의 비저항이 높아지는 경우가 있다.

#### D. 액정 표시 장치의 발명

(29) 또한, 본 발명은 상기 (26) 내지 (28) 중 어느 하나에 기재된 박막 트랜지스터 기판과, 상기 박막 트랜지스터 기판에 의해 구동되는 액정층을 포함하는 것을 특징으로 하는 액정 표시 장치이다.

또한, 광 투과율이 낮은 층을 통과하지 않고, 제2 도체는 절연막에 형성된 콘택트 홀을 통해 제1 도체와 직접 접속하고 있기 때문에, 액정 표시 장치는 높은 개구율을 갖는다.

또한, 본 발명의 액정 표시 장치는 상기 (26) 내지 (28)에 기재된 박막 트랜지스터 기판을 구비하기 때문에, 상기 (26) 내지 (28)과 동일한 작용 · 효과를 발휘한다.

#### 제4 그룹: 수단

제4 그룹의 본 발명의 상기 목적은 투명 전극으로서, 산화인듐과 산화아연을 성분으로서 포함하는 비정질 도전성 산화물을 포함하는 투명 도전막을 사용하여, 상기 투명 도전막을 옥살산 수용액 등의 에칭액으로 패턴화함으로써 달성된다. 구체적으로 설명하면, 본 발명은 하기와 같은 수단을 채용한다.

#### A. TFT 기판의 발명

(30) 우선, 본 발명은 투명 기판, 상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극, 상기 투명 기판 위에 설치된 실리콘층 및 상기 투명 기판 위에 설치된 화소 전극을 구비한 액정 표시 장치용 TFT 기판에서, 상기 화소 전극이 산화인듐과 W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이고, 이 상기 화소 전극은 상기 Al을 주성분으로 하는 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 포함하는 군으로부터 선택되는 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는 TFT 기판이다.

Al을 포함하는 게이트선/투명 전극, Al을 포함하는 소스 · 드레인 전극/화소 전극 사이에는 지금까지 접촉 저항이 발생하였지만, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드의 첨가에 의해, 접촉 저항을 감소시킬 수 있다. Al을 포함하는 게이트선, Al을 포함하는 소스 · 드레인 전극에 사용되는 Al 또는 Al 합금은 Al을 주성분으로 하고 있으면, 주기율표의 IIIa 내지 VIIa의 중금속 또는 란타노이드계 금속을 포함할 수도 있다. 이 Al에 포함되는 원소로서는 Nd, Ni, Co 및 Zr 등이 바람직하게 사용된다. 그의 함유량은 요구되는 Al 게이트선, Al 소스 · 드레인 전극의 성능에 따라서도 상이하지만, 0.1 중량% 내지 0.5 중량%의 범위가 바람직하다. 보다 바람직하게는 0.5 중량% 내지 2.0 중량%이다.

0.1 중량% 미만이면 첨가 효과가 거의 나타나지 않으며, Al 박막 위에 힐록 등의 돌기가 발생하는 경우도 있다. 또한, 5 중량%를 초과하면, Al 자체의 저항이 커지는 경우도 있다.

Al을 포함하는 것은 적어도 게이트일 수 있다. 소스 · 드레인의 Al을 포함하고 있는 것도 물론 바람직하며, 게이트와 동일한 작용 · 효과가 얻어지는 것은 위에서 상술한 바와 같다.

또한, 본 특허에서 "Al을 주성분으로 한다"란, Al을 주요한 성분으로서 포함하는 것을 의미하며, 대체로 원자 조성 비율로 50 % 이상인 경우를 의미한다.

(31) 또한, 본 발명은 상기 (30)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In]+[M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는 TFT 기판이다. 여기서, 상기 식 중의  $[M1]$ 은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다. 또한, 상기 식 중의  $[In]$ 은 인듐의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다.

첨가량이 0.005 미만이면 첨가 효과가 작으며, Al을 주성분으로 하는 게이트 전극/투명 전극이 커지는 경우도 있다. 소스 · 드레인이 Al을 포함하는 경우에는, Al 소스 · 드레인 전극/화소 전극 사이의 접촉 저항이 커지는 경우도 있다. 한편, 첨가량이 0.2를 초과하면, 전극 자체의 저항이 커지는 경우나, 전극의 에칭 가공시에 불량이 발생하는 경우도 있기 때문이다.

(32) 또한, 본 발명은 상기 (30) 또는 (31)에 있어서, 상기 도전성 산화물이 산화인듐 이외에 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 함유하는 것을 특징으로 하는 TFT 기판이다.

산화주석, 산화아연, 산화게르마늄 및 산화갈륨을 첨가함으로써, 목적으로 하는 도전성 산화물의 도전성을 개선할 수 있는 경우가 있다. 또한, 이 첨가에 의해, 에칭 가공성을 개선할 수 있는 경우도 있다. 또한, 이 첨가에 의해, 투과율을 개선할 수 있는 경우도 있다.

(33) 또한, 본 발명은 상기 (32)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In]+[M2])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는 TFT 기판이다. 여기서, 상기 식 중의  $[M2]$ 는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 어느 1종 또는 2종 이상의 원자의(단위 부피 · 단위 중량당) 수를 나타낸다. 또한, 상기 식 중의  $[In]$ 은 인듐의(단위 부피 · 단위 중량당) 원자의 수를 나타낸다.

첨가량이 0.01 미만이면, 그의 첨가 효과가 작기 때문에, 오히려 저항이 커지는 경우가 있으며, 한편 첨가량이 0.3을 초과하면, 저항이 커지는 경우나, 목적으로 하는 개선(Al 전극과의 접촉 저항을 작게 함)이 곤란한 경우가 있기 때문이다. 또한, 스퍼터링 타깃 중의 결정 입자의 평균 직경을  $10 \mu\text{m}$  미만의 크기로 함으로써, 노듈의 발생이 적은 스퍼터링 타깃을 구성할 수 있다. 바람직하게는 직경을  $5 \mu\text{m}$  이하의 크기로 함으로써, 노듈이 거의 발생하지 않으며, 이상 방전도 생기기 어려운 스퍼터링 타깃이 얻어진다.

이와 같이, 본 발명의 TFT 기판은 Al을 포함하는 전극과 화소 전극의 접촉 저항을 작게 할 수 있으며, 중간조의 표시를 양호하게 행할 수 있는 액정 표시 장치를 구성하는 데 유용하다. 또한, 후술하는 실시 형태에서 설명하는 TFT 어레이 기판은 TFT 기판의 바람직한 일례에 상당한다. 기판 위에 TFT(박막 트랜지스터)를 어레이상으로 배치한 것이 TFT 어레이 기판이다.

## B. 스퍼터링 타깃의 발명

(34) 본 발명은 액정 표시 장치용 TFT 기판에 사용되는 화소 전극이며, 액정을 구동하는 상기 화소 전극을 스퍼터링법으로 제조할 때 사용하는 스퍼터링 타깃에서, 산화인듐과, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물을 포함하는 것을 특징으로 하는, Al을 주성분으로 하는 전극 또는 배선과 전기적으로 접합 가능한 화소 전극 제조용 스퍼터링 타깃이다.

이러한 스퍼터링 타깃을 사용함으로써, 상기 구성의 TFT 기판을 효율적으로 제조할 수 있다. 또한, 스퍼터링 타깃 중의 결정 입자의 평균 직경을  $10 \mu\text{m}$  미만의 크기로 함으로써, 노듈의 발생이 거의 없는 스퍼터링 타깃을 실현할 수 있다. 또한, 에칭성을 개선하여, 투과율을 향상시킨 화소 전극을 제조할 수 있다. 바람직하게는 결정 입자의 평균 직경을  $5 \mu\text{m}$  이하의 크기로 함으로써, 노듈의 발생도 적고, 이상 방전도 생기기 어려운 스퍼터링 타깃이 얻어진다.

(35) 또한, 본 발명은 상기 (34)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In]+[M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는 스퍼터링 타깃이다. 여기서, 상기 식 중의  $[M1]$ 은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다. 또한, 상기 식 중의  $[In]$ 은 인듐의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다.

첨가량이 0.005 미만이면 첨가 효과가 작으며, Al을 주성분으로 하는 게이트 전극/투명 전극, Al 소스 · 드레인 전극/화소 전극 사이의 접촉 저항이 커지는 경우가 있으며, 0.2를 초과하면, 스퍼터링시에 이상 방전을 일으키는 경우, 전극 자체의 저항이 커지는 경우 또는 전극의 에칭 가공시에 불량이 발생하는 경우도 있기 때문이다.

(36) 또한, 본 발명은 상기 (34) 또는 (35)에 있어서, 상기 도전성 산화물이 산화인듐 이외에 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 스퍼터링 타깃이다.

산화주석, 산화아연, 산화게르마늄 및 산화갈륨을 첨가함으로써, 목적으로 하는 도전성 산화물의 도전성을 개선할 수 있는 경우가 있다. 또한, 이 첨가에 의해, 에칭 가공성을 개선할 수 있는 경우도 있다. 또한, 이 첨가에 의해, 투과율을 개선할 수 있는 경우도 있다.

또한, 스퍼터링 타깃 중의 결정 입자의 평균 직경을  $10 \mu\text{m}$  미만의 크기로 함으로써, 노들의 발생이 거의 없는 스퍼터링 타깃을 실현할 수 있다. 바람직하게는 결정 입자의 평균 직경을  $5 \mu\text{m}$  이하의 크기로 함으로써, 노들의 발생도 적고, 이상 방전도 생기기 어려운 스퍼터링 타깃이 얻어진다.

(37) 또한, 본 발명은 상기 (36)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[\text{M2}] / ([\text{In}] + [\text{M2}])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는 스퍼터링 타깃이다. 여기서, 상기 식 중의  $[\text{M2}]$ 는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 어느 1종 또는 2종 이상의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다. 또한, 상기 식 중의  $[\text{In}]$ 은 인듐의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다.

첨가량이 0.01 미만이면, 그의 첨가 효과가 작기 때문에, 오히려 저항이 커지는 경우가 있으며, 한편 0.3을 초과하면, 저항이 커지는 경우나, 목적으로 하는 개선(Al을 포함하는 전극과의 접촉 저항을 작게 함)이 곤란한 경우가 있기 때문이다.

### C. 액정 표시 장치의 발명

(38) 본 발명은 TFT 기판과 액정을 구비한 액정 표시 장치에서, 상기 TFT 기판은 투명 기판, 상기 투명 기판 위에 설치된 Al을 주성분으로 하는 게이트 전극, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극, 상기 투명 기판 위에 설치된 실리콘층, 상기 투명 기판 위에 설치되어, 상기 액정을 구동하는 화소 전극 및 상기 게이트 전극 및 상기 소스 전극 · 상기 드레인 전극을 보호하는 투명 전극을 구비하고, 상기 화소 전극 또는 상기 투명 전극은 산화인듐과, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이고, 이 상기 화소 전극 또는 상기 투명 전극은 상기 Al을 주성분으로 하는 게이트 전극, 상기 소스 전극 및 상기 드레인 전극을 포함하는 군으로부터 선택되는 하나 이상의 전극과 직접 접합하고 있는 것을 특징으로 하는 액정 표시 장치이다.

Al을 포함하는 게이트선/투명 전극, Al 소스 · 드레인 전극 사이에 종래에는 비교적 큰 접촉 저항이 발생하였지만, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드의 첨가에 의해, 접촉 저항의 값을 작게 할 수 있다. 소스 · 드레인이 Al을 포함하는 경우에는, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드의 첨가에 의해, Al을 포함하는 소스 · 드레인 전극 사이의 접촉 저항의 값을 작게 할 수 있다. 이에 따라, 이 TFT 기판을 사용한 액정 표시 장치는 Al을 포함하는 게이트선/투명 전극, 또는 Al을 포함하는 소스 · 드레인 전극/화소 전극 사이의 접촉 저항이 감소되어, 중간조의 표시 품질이 개선된 액정 표시 장치가 얻어진다.

(39) 또한, 본 발명은 상기 (38)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[\text{M1}] / ([\text{In}] + [\text{M1}])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는 청구의 범위 제13항에 기재된 액정 표시 장치이다. 여기서, 상기 식 중의  $[\text{M1}]$ 은 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다. 또한, 상기 식 중의  $[\text{In}]$ 은 인듐의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다.

첨가량이 0.005 미만이면 첨가 효과가 작기 때문에, Al을 주성분으로 하는 게이트 전극/투명 전극, Al 소스 · 드레인 전극/화소 전극 사이의 접촉 저항이 커지는 경우가 있으며, 첨가량이 0.2를 초과하면, 스퍼터링시에 이상 방전을 일으키는 경우, 전극 자체의 저항이 커지는 경우 또는 전극의 에칭 가공시에 불량이 발생하는 경우도 있기 때문이다. 또한, 첨가량이 0.2를 초과하면, 액정 표시 장치의 구동시에 중간조의 표시 품위가 저하되는 경우가 있기 때문이다.

(40) 또한, 본 발명은 상기 (38) 또는 (39)에 있어서, 상기 도전성 산화물이 산화인듐 이외에 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 액정 표시 장치이다.

산화주석, 산화아연, 산화게르마늄 및 산화갈륨을 첨가함으로써, 목적으로 하는 도전성 산화물의 도전성을 개선할 수 있는 경우가 있다. 또한, 이 첨가에 의해, 에칭 가공성을 개선할 수 있는 경우도 있다. 또한, 이 첨가에 의해, 투과율을 개선할 수 있는 경우도 있다.

또한, 스퍼터링 타깃 중의 결정 입자의 평균 직경을  $10 \mu\text{m}$  미만의 크기로 함으로써, 노들의 발생이 거의 없는 스퍼터링 타깃을 실현할 수 있기 때문에, 이것을 사용하여 액정 표시 장치를 제조하면, 표시 결함이 적은 액정 표시 장치가 얻어진다. 바람직하게는, 결정 입자의 평균 직경을  $5 \mu\text{m}$  이하의 크기로 함으로써, 노들의 발생도 적고, 이상 방전도 생기기 어려운 스퍼터링 타깃이 얻어지며, 이 스퍼터링 타깃을 사용하면, 보다 표시 결함이 적은 액정 표시 장치를 제조할 수 있다.

(41) 또한, 본 발명은 상기 (40)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[\text{M2}] / ([\text{In}] + [\text{M2}])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는 액정 표시 장치이다. 여기서, 상기 식 중의  $[\text{M2}]$ 는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속, 즉 주석, 아연, 게르마늄 및 갈륨 중 어느 1종 또는 2종 이상의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다. 또한, 상기 식 중의  $[\text{In}]$ 은 인듐의 원자의(단위 중량 · 단위 부피당) 수를 나타낸다.

첨가량이 0.01 미만이면, 그의 첨가 효과가 작아지기 때문에, 오히려 저항이 커지는 경우가 있으며, 한편 0.3을 초과하면, 저항이 커지는 경우나, 목적으로 하는 개선(AI 전극과의 접촉 저항을 작게 함)이 곤란한 경우가 있기 때문이다.

#### D-1. 화소 전극의 발명

이어서, 화소 전극의 발명에 대하여 그의 구성을 설명한다. 이하에 나타내는 발명은 상술한 TFT 기판 등에 사용되는 화소 전극이며, 그의 작용 · 효과는 상술한 TFT 기판 등과 마찬가지이다.

(42) 본 발명은 투명 기판, 상기 투명 기판 위에 설치된 AI을 주성분으로 하는 게이트 전극, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극, 상기 투명 기판 위에 설치된 실리콘층, 상기 투명 기판 위에 설치된 화소 전극 및 상기 게이트 전극 및 상기 소스 전극 · 상기 드레인 전극을 보호하는 투명 전극을 구비한 액정 표시 장치용 TFT 기판에 사용되며, 액정을 구동하는 상기 화소 전극에서, 산화인듐과, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이고, 상기 화소 전극은 상기 AI을 주성분으로 하는 게이트 전극 또는 상기 소스 전극 또는 상기 드레인 전극과 직접 접합하고 있는 것을 특징으로 하는 화소 전극이다.

(43) 또한, 본 발명은 상기 (42)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[\text{M1}] / ([\text{In}] + [\text{M1}])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는 화소 전극이다.

여기서, 상기 식 중의  $[\text{M1}]$  또는  $[\text{In}]$ 은 이미 설명한 바와 같다.

(44) 또한, 본 발명은 상기 (42) 또는 (43)에 있어서, 상기 도전성 산화물이 산화인듐 이외에 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 화소 전극이다.

(45) 또한, 본 발명은 상기 (44)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[\text{M2}] / ([\text{In}] + [\text{M2}])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는 화소 전극이다. 여기서, 상기 식 중의  $[\text{M2}]$  또는  $[\text{In}]$ 은 이미 설명한 바와 같다.

#### D-2. 투명 전극의 발명

이어서, 투명 전극의 발명에 대하여 그의 구성을 설명한다.

(46) 본 발명은 투명 기판, 상기 투명 기판 위에 설치된 AI을 주성분으로 하는 게이트 전극, 상기 투명 기판 위에 설치된 소스 전극, 상기 투명 기판 위에 설치된 드레인 전극, 상기 투명 기판 위에 설치된 실리콘층, 상기 투명 기판 위에 설치된 화소

전극 및 상기 게이트 전극 및 상기 소스 전극 · 상기 드레인 전극을 보호하는 투명 전극을 구비한 액정 표시 장치용 TFT 기판에 사용되며, 상기 투명 전극에서 산화인듐과, W, Mo, Ni, Nb, Fe, Pt, Pd 및 란타노이드를 포함하는 제1군 M1로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 도전성 산화물이고, 상기 투명 전극은 상기 Al을 주성분으로 하는 게이트 전극 또는 상기 소스 전극 또는 상기 드레인 전극과 직접 접합하고 있는 것을 특징으로 하는 투명 전극이다.

(47) 또한, 본 발명은 상기 (46)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제1군 M1로부터 선택된 금속 산화물의 원자 조성 비율인  $[M1]/([In]+[M1])$ 이 0.005 내지 0.2의 범위인 것을 특징으로 하는 투명 전극이다. 여기서, 상기 식 중의 [M1] 또는 [In]은 이미 설명한 바와 같다.

(48) 또한, 본 발명은 상기 (46) 또는 (47)에 있어서, 상기 도전성 산화물이 산화인듐 이외에 주석, 아연, 게르마늄 및 갈륨을 포함하는 제2군 M2로부터 선택된 1종 또는 2종 이상의 금속의 산화물을 포함하는 것을 특징으로 하는 투명 전극이다.

(49) 또한, 본 발명은 상기 (48)에 있어서, 상기 도전성 산화물 중, 인듐에 대한 상기 제2군 M2로부터 선택된 금속 산화물의 원자 조성 비율인  $[M2]/([In]+[M2])$ 가 0.01 내지 0.3의 범위인 것을 특징으로 하는 투명 전극이다. 여기서, 상기 식 중의 [M2] 또는 [In]은 이미 설명한 바와 같다.

#### E. TFT 기판의 제조 방법의 발명

(50) 본 발명은 TFT 기판을 제조하는 방법에서, 상기 투명 기판 위에 상기 도전성 산화물을 퇴적하여, 상기 도전성 산화물의 박막을 형성하는 단계와, 상기 형성된 상기 도전성 산화물의 박막을 옥살산을 포함하는 수용액으로 에칭함으로써, 상기 투명 전극을 형성하는 단계를 포함하는 것을 특징으로 하는 TFT 기판의 제조 방법이다.

이러한 구성에 의해, 소스 전극 등이 Al로 구성되어 있는 경우에도, 투명 전극의 성형시(에칭시)에 Al을 포함하는 소스 전극 등이 용출되는 것을 방지할 수 있다. 이러한 작용 · 효과는, 다른 에칭액을 사용한 하기 발명에서도 마찬가지이다.

(51) 또한, 본 발명은 TFT 기판을 제조하는 방법에서, 상기 투명 기판 위에 상기 도전성 산화물을 퇴적하여, 상기 도전성 산화물의 박막을 형성하는 단계와, 상기 형성된 상기 도전성 산화물의 박막을 인산 · 아세트산 · 질산을 포함하는 수용액으로 에칭함으로써, 상기 투명 전극을 형성하는 단계를 포함하는 것을 특징으로 하는 TFT 기판의 제조 방법이다.

(52) 또한, 본 발명은 TFT 기판을 제조하는 방법에서, 상기 투명 기판 위에 상기 도전성 산화물을 퇴적하여, 상기 도전성 산화물의 박막을 형성하는 단계와, 상기 형성된 상기 도전성 산화물의 박막을 질산세륨암모늄염을 포함하는 수용액으로 에칭함으로써, 상기 투명 전극을 형성하는 단계를 포함하는 것을 특징으로 하는 TFT 기판의 제조 방법이다.

또한, 투명 전극(도전성 산화물)의 성막 방법으로서는 증착법, 스퍼터법, CVD법, 분무법 및 디핑법 등을 이용할 수 있다. 특히, 스퍼터법을 채용하는 것이 바람직하다.

#### F. 란타노이드의 종류

(53) 또한, 본 발명은 상기 란타노이드가 Ce, Nd, Er 및 Ho으로부터 선택된 1종 또는 2종 이상의 란타노이드인 것을 특징으로 하는 상기 (30) 내지 (52) 중 어느 하나에 기재된 TFT 기판, 투명 전극 제조용 스퍼터링 타깃, 액정 표시 장치, 화소 전극, 투명 전극 또는 TFT 기판의 제조 방법이다.

#### 제1 그룹: 효과

상기한 바와 같이, 본 발명의 박막 트랜지스터형 기판에서의 투명 도전막은, 제조시에 약산(유기산 등)을 사용한 에칭에 의한 잔사가 거의 발생하지 않는다. 이 때문에, 본 발명의 박막 트랜지스터형 기판은 가공성이 우수하고, 수율이 향상된다. 또한, 본 발명의 박막 트랜지스터형 액정 표시 장치는, 상기 박막 트랜지스터형 기판을 구비하기 때문에, 제조 효율이 향상된다.

또한, 본 발명의 박막 트랜지스터형 기판의 제조 방법에 따르면, 소정의 산성의 에칭제를 사용한 투명 도전막의 에칭에 의한 잔사 등이 거의 발생하지 않기 때문에, 상기 박막 트랜지스터형 기판을 효율적으로 제조하는 것이 가능해진다.

#### 제2 그룹: 효과

제2 그룹의 본 발명은 상술한 종래의 기술이 갖는 문제점에 감안하여 이루어진 것이며, 특정한 금속을 함유하는 투명 도전 재료를 화소 전극·투명 전극에 사용함으로써, 배리어 금속 등을 사용하지 않아도, Al 게이트/투명 전극, Al 소스·드레인/화소 전극 사이의 접촉 저항을 작게 억제할 수 있다.

그 결과, 제조 공정의 수를 감소시킬 수 있기 때문에, TFT(박막 트랜지스터) 기판의 제조 방법을 간략화할 수 있다.

또한, 제2 그룹의 본 발명에 투명 도전(막) 재료를 직접 Al 게이트 또는 Al 소스·드레인 전극에 접촉시켜도, 이곳에 생기는 접촉 저항을 작은 값으로 할 수 있기 때문에, 중간조의 표시를 양호하게 행할 수 있는 액정 표시 장치를 제공할 수 있다.

또한, 지금까지의 제2 그룹의 본 발명의 설명에 있어서, Al과의 관계로부터 본 발명의 설명을 하고 있는 부분이 있다. 이 설명 부분에서의 Al 대신에, Ag를 사용하여도 거의 동일한 작용·효과를 발휘한다. 이 점에 대해서는, 실시예에서 상세히 설명하고 있다.

### 제3 그룹: 효과

상기한 바와 같이, 제3 그룹의 본 발명의 박막 트랜지스터 기판의 제조 방법에 따르면, 제1 도체가 특정한 금속을 포함하는 Al 합금을 포함하기 때문에, 용이하게 에칭할 수 있다. 이 때문에, 박막 트랜지스터 기판을 보다 간편하고, 보다 저비용으로 제조하는 것이 가능해진다.

또한, 제3 그룹의 본 발명의 박막 트랜지스터 및 박막 트랜지스터 기판은, 제1 도체가 특정한 금속을 포함하는 Al 합금을 포함하기 때문에, 제2 도체가 절연막에 형성된 콘택트 홀을 통해, 제1 도체와 접속할 때의 콘택트 저항이 낮다. 또한, 이 제1 도체는 용이하게 에칭 가능하다.

또한, 제3 그룹의 본 발명의 액정 표시 장치는, 제2 도체가 광 투과율이 낮은 층을 통과하지 않고, 절연막에 형성된 콘택트 홀을 통해 제1 도체와 직접 접속하고 있기 때문에, 높은 개구율을 갖는다.

### 제4 그룹: 효과

제4 그룹의 본 발명은 상술한 바와 같이, 종래의 기술이 갖는 문제점에 감안하여 이루어진 것이며, 특정한 금속을 함유하는 투명 도전 재료를 화소 전극 및 투명 전극에 사용함으로써, TFT(박막 트랜지스터) 기판의 제조 방법을 간략화하는 것이 가능하다.

또한, 제4 그룹의 본 발명에 따르면, Al을 포함하는 게이트/투명 전극, 또는 Al을 포함하는 소스·드레인/화소 전극을 직접 접촉·접합시켜도, 이 사이의 접촉 저항을 종래보다 낮은 값으로 억제할 수 있기 때문에, 중간조의 표시가 가능한 액정 표시 장치를 제공할 수 있다.

## 실시예

### 제1 그룹: 실시예

이하, 도면을 이용하여, 제1 그룹의 본 실시 형태의 바람직한 예에 대하여 설명한다.

[실시예 1-1]

도 1에는 본 실시예 1-1에서의  $\alpha$ -SiTFT(비정질 실리콘 박막 트랜지스터) 활성 매트릭스 기판 (100) 근방의 단면도가 도시되어 있다. 투광성의 유리 기판 (1) 위에 고주파 스퍼터링에 의해, 그의 막 두께가 1500 옹스트롬이 되도록 금속 Al을 퇴적하였다. 또한, 이 유리 기판 (1)은 특히 청구의 범위에 기재된 투명 기판의 일례에 상당한다.

이어서, 인산·아세트산·질산·수(그의 부피비는 12:6:1:1임)계 수용액을 에칭액으로서 사용한 포토에칭법에 의해, 상기 퇴적한 금속 Al을 도 1에 도시하는 형상으로 에칭하여, 게이트 전극 (2) 및 게이트 전극 배선 (12)를 형성하였다.

이어서, 글로 방전 CVD법에 의해, 상기 유리 기판 (1), 상기 게이트 전극 (2) 및 상기 게이트 전극 배선 (12) 위에, 게이트 절연막 (3)이 되는 질화 실리콘막(이하, SiN막으로 기재하는 경우도 있음)을 그의 막 두께가 3000 옹스트롬이 되도록 퇴