**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

G02F 1/1343 (2006.01)

|           |             |

|-----------|-------------|

| (45) 공고일자 | 2007년04월20일 |

| (11) 등록번호 | 10-0710164  |

| (24) 등록일자 | 2007년04월16일 |

|           |                 |

|-----------|-----------------|

| (21) 출원번호 | 10-2003-0100857 |

| (22) 출원일자 | 2003년12월30일     |

| 심사청구일자    | 2005년03월07일     |

|           |                 |

|-----------|-----------------|

| (65) 공개번호 | 10-2005-0070709 |

| (43) 공개일자 | 2005년07월07일     |

|           |                                      |

|-----------|--------------------------------------|

| (73) 특허권자 | 엘지.필립스 엘시디 주식회사<br>서울 영등포구 여의도동 20번지 |

|-----------|--------------------------------------|

|          |                               |

|----------|-------------------------------|

| (72) 발명자 | 이재균<br>경기도군포시산본동우륵아파트707-1701 |

|----------|-------------------------------|

|                                  |

|----------------------------------|

| 이동훈<br>경기도안양시동안구호계동샘마을아파트505-105 |

|----------------------------------|

|          |            |

|----------|------------|

| (74) 대리인 | 김용인<br>심창섭 |

|----------|------------|

|                   |                   |

|-------------------|-------------------|

| (56) 선행기술조사문현     | JP2003255907 A    |

| JP2001356356 A *  | KR1020010108997 A |

| KR1019980068682 A | *                 |

| * 심사관에 의하여 인용된 문현 |                   |

심사관 : 윤성주

전체 청구항 수 : 총 5 항

**(54) 횡전계 방식 액정 표시 장치**

**(57) 요약**

본 발명은 구동전압 강하를 위해 공통 전압을 스윙하는 횡전계 방식 액정표시장치의 전압 강하 및 딜레이를 줄이기 위한 것으로, 화소 영역을 정의하기 위해 서로 수직하게 배열되는 복수개의 게이트 라인 및 데이터 라인과, 상기 각 게이트 라인과 데이터 라인이 교차하는 부분에 형성되는 복수개의 박막트랜지스터와, 상기 각 게이트 라인에 평행한 방향으로 형성되는 복수개의 공통 라인 및 상기 각 공통 라인에서 상기 데이터 라인에 평행한 방향으로 돌출되는 복수개의 공통 전극과, 상기 각 박막트랜지스터의 드레인 전극에 연결되고 상기 공통 전극 사이에 상기 공통 전극과 평행하게 각 화소 영역에 형성되는 복수개의 화소 전극과, 상기 복수개의 공통 라인 중 홀수번째 공통 라인을 그룹핑하여 인접한 홀수번째 공통 라인이 폐회로를 구성하도록 하여 제 1 공통 전압 또는 제 2 공통 전압을 인가하는 제 1 공통 전압 인가 라인과, 상기 복수개의 공통 라인 중 짹수번째 공통 라인을 그룹핑하여 인접한 짹수번째 공통 라인이 폐회로를 구성하도록 하여 제 2 공통 전압 또는 제 1 공통 전압을 인가하는 제 2 공통 전압 인가 라인을 구비하여 구성된 것이다.

대표도

도 8

## 특허청구의 범위

### 청구항 1.

화소 영역을 정의하기 위해 서로 교차하는 복수개의 게이트 라인 및 데이터 라인과,

상기 각 게이트 라인과 데이터 라인이 교차하는 부분에 형성되는 복수개의 박막트랜지스터와,

상기 각 게이트 라인에 평행한 방향으로 형성되는 복수개의 공통 라인 및 상기 각 공통 라인에서 돌출되는 복수개의 공통 전극과,

상기 각 박막트랜지스터의 드레인 전극에 연결되고 상기 공통 전극 사이에 상기 공통 전극과 평행하게 각 화소 영역에 형성되는 복수개의 화소 전극과,

상기 복수개의 공통 라인 중 홀수번째 공통 라인들 각각의 양단과 공통 접속되어 폐회로를 구성하고 제 1 공통 전압을 인가하는 제 1 공통 전압 인가 라인과,

상기 복수개의 공통 라인 중 짝수번째 공통 라인들 각각의 양단과 공통 접속되어 폐회로를 구성하고 제 2 공통 전압을 인가하는 제 2 공통 전압 인가 라인을 구비하고,

상기 제1 및 제2 공통 전압 인가 라인은 상기 복수개의 공통 라인과 절연막을 사이에 두고 다른 층에 형성되고 상기 절연막을 관통하는 컨택홀 각각을 통해 해당 공통 라인과 접속된 것을 특징으로 하는 횡전계 방식 액정표시장치.

### 청구항 2.

제 1 항에 있어서,

상기 제 1 공통 전압과 제 2 공통 전압은 서로 다른 위상을 갖고 프레임 단위로 스윙됨을 특징으로 하는 횡전계 방식 액정표시장치.

### 청구항 3.

제 1 항에 있어서,

상기 제 1, 제 2 공통 전압 인가 라인은 상기 데이터 라인과 동일층에 형성되고, 상기 공통 라인은 상기 게이트 라인과 동일 층에 형성된 것을 특징으로 하는 횡전계 방식 액정표시장치.

### 청구항 4.

제 1 항에 있어서,

상기 제 1, 제 2 공통 전압 인가 라인은 상기 데이터 라인과 동일 물질로 형성되고, 상기 공통 라인은 상기 게이트 라인과 동일 물질로 형성된 것을 특징으로 하는 횡전계 방식 액정표시장치.

### 청구항 5.

제 1 항에 있어서,

상기 제 1 공통 전압 인가 라인과 상기 제 2 공통 전압 인가 라인은 서로 동일한 저항값을 갖음을 특징으로 하는 횡전계 방식 액정표시장치.

**명세서**

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 횡전계 방식의 액정 표시 장치에 관한 것으로, 특히 공통 전압의 전압 강하 및 딜레이(delay)를 줄이기 위한 횡전계 방식 액정표시장치에 관한 것이다.

평판표시소자 중 하나인 액정표시장치는 액체의 유동성과 결정의 광학적 성질을 겸비하는 액정에 전계를 가하여 광학적 이방성을 변화시키는 소자로서, 종래 음극선관(Cathode Ray Tube)에 비해 소비전력이 낮고 부피가 작으며 대형화 및 고정세가 가능하여 널리 사용하고 있다.

이와 같은 액정 표시 장치는 화상을 표시하는 액정 패널과 상기 액정 패널에 구동 신호를 인가하기 위한 구동회로부로 크게 구분되며, 상기 액정 패널은 일정 공간을 갖고 합착된 제 1, 제 2 기판과, 상기 제 1, 제 2 기판 사이에 주입된 액정층으로 구성된다.

여기서, 상기 제 1 기판(박막 트랜지스터 어레이 기판)에는 일정 간격을 갖고 일 방향으로 배열되는 복수개의 게이트 라인과, 상기 각 게이트 라인과 수직한 방향으로 일정한 간격으로 배열되는 복수개의 데이터 라인과, 상기 각 게이트 라인과 데이터 라인이 교차되어 정의된 각 화소 영역에 매트릭스 형태로 형성되는 복수개의 화소 전극과 상기 게이트 라인의 신호에 의해 스위칭되어 상기 데이터 라인의 신호를 각 화소 전극에 전달하는 복수개의 박막 트랜지스터가 형성된다.

그리고, 제 2 기판(칼라 필터 어레이 기판)에는, 상기 화소 영역을 제외한 부분의 빛을 차단하기 위한 블랙 매트릭스층과, 칼라 색상을 표현하기 위한 R, G, B 칼라 필터층이 형성된다.

이와 같은 상기 제 1, 제 2 기판은 스페이서(spacer)에 의해 일정 공간을 갖고 실재(sealant)에 의해 합착되고 상기 두 기판 사이에 액정이 주입된다.

한편, 상기 액정표시패널은 액정의 성질과 패턴의 구조에 따라서 여러 가지 다양한 모드가 있다.

구체적으로, 액정 방향자가  $90^{\circ}$  트위스트 되도록 배열한 후 전압을 가하여 액정 방향자를 제어하는 TN 모드(Twisted Nematic Mode)와, 한 화소를 여러 도메인으로 나눠 각각의 도메인의 주시야각 방향을 달리하여 광시야각을 구현하는 멀티도메인 모드(Multi-Domain Mode)와, 보상필름을 기판 외주면에 부착하여 빛의 진행방향에 따른 빛의 위상변화를 보상하는 OCB 모드(Optically Compensated Birefringence Mode)와, 한 기판 상에 두개의 전극을 형성하여 액정의 방향자가 배향막의 나란한 평면에서 꼬이게 하는 횡전계 방식(In-Plane Switching Mode)과, 네가티브형 액정과 수직배향막을 이용하여 액정 분자의 장축이 배향막 평면에 수직 배열되도록 하는 VA 모드(Vertical Alignment) 등 다양하다.

이중, 상기 횡전계 방식은 화소 전극과 공통 전극이 동일 기판상에 형성된 것으로, 제 1 기판상에 단위 화소를 정의하는 게이트 라인 및 데이터 라인과, 상기 게이트 라인 및 데이터 라인의 교차 지점에 형성된 스위칭소자와, 서로 엇갈리게 교차되어 횡전계를 발생시키는 공통전극 및 화소전극이 형성된다.

이하, 도면을 참조하여 일반적인 횡전계 방식 액정표시장치 및 그 제조방법을 설명하면 다음과 같다.

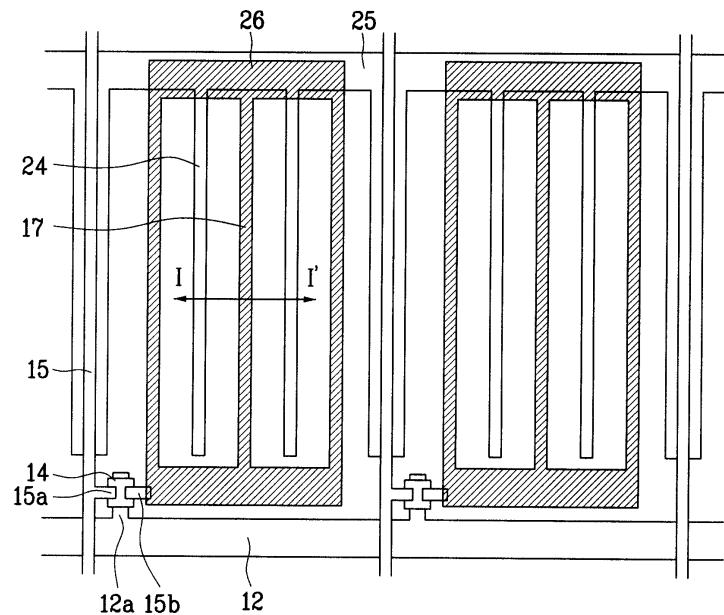

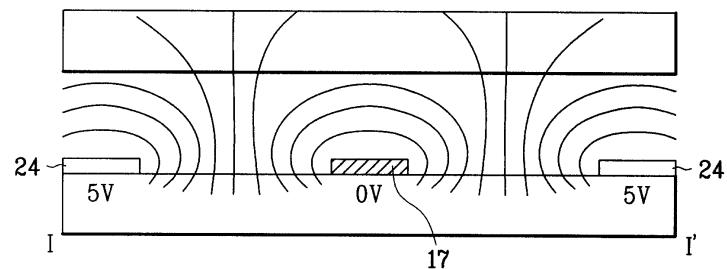

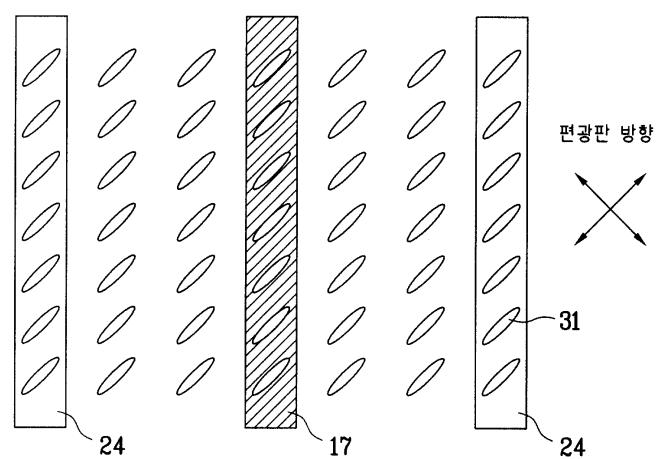

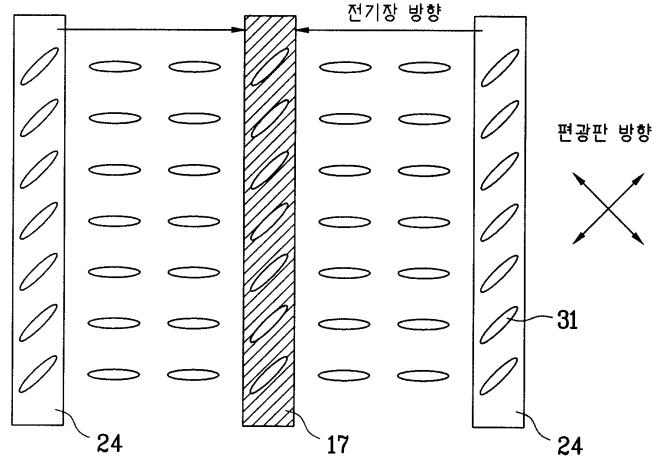

도 1은 일반적인 횡전계 방식 액정표시장치의 단위 화소 평면도이고, 도 2는 도 1의 I - I 선상에서의 횡전계 방식 액정표시장치의 전압분포도이며, 도 3a 및 도 3b는 전압 무인가/인가시에서의 횡전계 방식 액정표시장치의 평면도이다.

즉, 박막 트랜지스터 어레이 기판 상에, 도 2에 도시된 바와 같이, 서로 수직한 방향으로 교차 배치되어 화소를 정의하는 게이트 라인(12) 및 데이터 라인(15)과, 상기 게이트 라인(12) 및 데이터 라인(15)의 교차 부위에 배치된 박막트랜지스터(TFT)와, 상기 게이트 라인(12)과 평행하도록 화소 내에 배치된 공통라인(25)과, 상기 공통라인(25)에서 분기되어 상기 데이터 라인(15)에 평행하도록 상기 화소내에 형성되는 다수개의 공통전극(24)과, 상기 박막트랜지스터(TFT)의 드레인 전극에 연결되어 상기 공통전극(24) 사이에서 상기 공통전극(24)과 평행하게 교차 배치된 다수개의 화소 전극(17)과, 상기 화소 전극(17)에서 연장되어 공통라인(25) 상부에 형성된 커패시터 전극(26)이 구비되어 있다.

상기 박막트랜지스터(TFT)는 상기 게이트 라인(12)에서 분기되는 게이트 전극(12a)과, 상기 게이트 전극(12a)을 포함한 전면에 형성된 게이트 절연막(도시하지 않음)과, 상기 게이트 전극 상부의 게이트 절연막 상에 형성된 반도체층(14)과, 상기 데이터 라인(15)에서 분기되어 상기 반도체층(14) 양 끝에 각각 형성되는 소스 전극(15a) 및 드레인 전극(15b)으로 구성된다.

이 때, 상기 공통라인(25) 및 공통전극(24)은 일체로 형성되고, 상기 게이트 라인(12) 및 게이트 전극도 일체로 형성되며, 상기 공통라인(25) 및 게이트 라인(12)은 저저항 금속을 재료로 하여 동시에 형성할 수 있다.

상기 화소전극(17)은 인듐-틴-옥사이드(indium-tin-oxide : ITO)와 같이 빛의 투과율이 비교적 뛰어난 투명도전성 금속을 재료로 사용하여 상기 공통전극(24)과 엇갈리게 교차할 수 있도록 다수개의 분기 형태로 형성되며, 상기 드레인 전극(15b)에 연결되어 데이터 전압을 인가 받는다.

또한, 상기 공통라인(25) 상부에는 상기 화소전극(17)과 일체형인 커패시터 전극(26)이 형성되어 스토리지 커패시터를 구성한다.

이와 같이 구성된 횡전계 방식 액정표시장치는, 도 2에 도시한 바와 같이, 상기 공통 전극(24)에 5V를 걸어주고 화소 전극(17)에 0V를 걸어주면, 전극 바로 위의 부분에서는 등전위면이 전극에 평행하게 분포하고 두 전극 사이의 영역에서는 오히려 등전위면이 수직에 가깝도록 분포한다.

따라서, 전기장의 방향은 등전위면에 수직하므로 공통전극(24)과 화소 전극(17) 사이에서는 수직 전기장보다는 수평 전기장이, 각 전극 상에서는 수평 전기장보다는 수직전기장이, 그리고 전극 모서리 부분에서는 수평 및 수직전기장이 복합적으로 형성된다.

횡전계방식 액정표시소자는 이러한 전기장을 이용하여 액정분자의 배열을 조절한다.

즉, 어느 한 편광판의 투과축과 동일한 방향으로 초기 배향된 액정분자(31)에 충분한 전압을 걸어주면, 도 3b에 도시된 바와 같이, 액정분자(31)의 장축이 전기장에 나란하도록 배열된다. 만일, 액정의 유전율 이방성이 음이면 액정분자의 단축이 전기장에 나란하게 배열된다.

구체적으로, 대량 합착된 박막 어레이 기판 및 컬러필터 기판의 외주면에 부착된 제 1, 제 2 편광판은 그 투과축이 서로 직교하도록 배치하고, 하부기판 상에 형성된 배향막의 러빙방향은 어느 한 편광판의 투과축과 나란하게 함으로써 흑색바탕 모드(normally black mode)가 되게 한다.

즉, 액정표시패널에 전압을 인가하지 않으면, 액정분자(31)가, 도 3a에 도시된 바와 같이, 배열되어 블랙(black) 상태를 표시하고, 액정표시패널에 전압을 인가하면, 도 3b에 도시된 바와 같이 액정분자(31)가 전기장에 나란하게 배열되어 화이트(white) 상태를 표시한다.

한편, 이와 같은 일반적인 횡전계 방식 액정 표시 장치의 구동 방법을 살펴보면 다음과 같다.

횡전계 방식 액정 표시 장치를 포함한 일반적인 액정 표시 장치는 각 화소가 매트릭스 형태로 배열되어 하나의 게이트 라인에 주사 신호가 입력되었을 때, 그 라인에 해당하는 화소에 영상 신호가 인가되는 방식을 취한다.

그런데, 상기 제 1, 제 2 기판 사이에 주입된 액정은 DC 전압을 오랫동안 인가하면 특성 열화가 일어나므로, 이를 방지하기 위하여 인가 전압의 극성을 주기적으로 바꾸어 구동하며, 이러한 방식을 극성 반전 방식이라 한다.

상기 극성 반전 방식에는 프레임 반전(Frame Inversion), 라인 반전(Line Inversion), 열 반전(Column Inversion) 및 도트 반전(Dot Inversion) 방식 등이 있다.

상기 프레임 반전 방식은, 공통 전극 전압에 대한 액정에 인가되는 데이터 전압의 극성이 프레임 단위로 동일하도록 인가하는 방식이다. 즉, 짝수 프레임(Even Frame)에 정(+) 극성의 데이터 전압이 인가되었다면, 홀수 프레임(Odd Frame)에는 부(-) 극성의 데이터 전압이 인가되는 방식이다. 그러나, 이와 같은 프레임 반전 구동 방법은 스위칭 시 발생하는 소모 전류가 적다는 장점은 가지고 있으나, 정 극성과 부 극성의 투과율 비대칭 현상에 의한 플리커(Flicker) 현상에 민감하고 데이터간 간섭에 의한 크로스토크(Crosstalk)에 매우 취약한 단점을 갖고 있다.

또한, 상기 라인 반전 방식은 일반적으로 저 해상도(VGA, SVGA)에 널리 사용되는 극성 반전 구동 방법으로, 공통 전극 전압에 대한 액정에 인가되는 데이터 전압의 극성이 수평 라인 단위로 달라지도록 데이터 전압이 인가된다. 즉, 홀수 번째 게이트 라인에 정(+) 극성이 인가되고 짝수 번째 게이트 라인에는 부(-) 극성의 데이터 전압이 인가되었다면, 다음 프레임에서는 홀수 번째 게이트 라인에 부(-) 극성의 데이터 전압이 인가되고 짝수 번째 게이트 라인에는 정(+) 극성의 데이터 전압이 인가된다. 이와 같은 라인 반전 방식은 인접 라인간의 반대 극성의 데이터 전압이 인가되므로 라인간 휘도 편차가 공간 평균화법(spatial averaging)에 의해 프레임 반전 대비 플리커 현상이 작아지고, 수직 방향으로는 반대 극성의 전압이 분포하여 데이터간에 발생하는 커플링(coupling) 현상이 상쇄되어 프레임 반전 대비 수직 크로스토크(Vertical Crosstalk)가 작다. 그러나, 수평 방향으로는 동일 극성의 전압이 분포되어 수평 크로스토크(Horizontal Crosstalk)가 발생하고, 프레임 반전 대비 스위칭 반복 횟수가 증가하므로 소비 전류가 증가하는 단점이 있다.

상기 열 반전 방식은 공통 전극 전압에 대한 액정에 인가되는 데이터 전압의 극성이 수직 방향으로 동일하고 수평 방향으로는 반대 극성으로 인가하는 구동 방법이다. 이는, 프레임 반전 방식에 비하여 공간 평균화법에 의해 플리커 현상이 프레임 반전 방식에 비해 작고, 수평 크로스토크가 작다. 그러나, 공통 전극 대비 수직 방향으로 인접 라인간 반대 극성의 데이터 전압을 인가해야 하므로 고전압용 칼럼 드라이버(Column Drive IC)를 사용해야 한다.

마지막으로, 도트 반전 방식은 현재 가장 우수한 화질을 구현하는 극성 반전 구동 방법으로 고해상도(XGA, SXGA, UXGA)에 적용되며, 상하좌우 모든 방향에서 인접 화소간 데이터 전압의 극성이 반대이다. 따라서, 공간 평균화법에 의해 플리커 현상을 최소화시킬 수 있으나, 고 전압용 소오스 드라이버를 사용해야 하고 소비 전류가 크다는 단점을 갖고 있다.

이하, 도트 반전 구동 방식을 취하는 종래의 횡전계 방식 액정 표시 장치에 대해 설명한다.

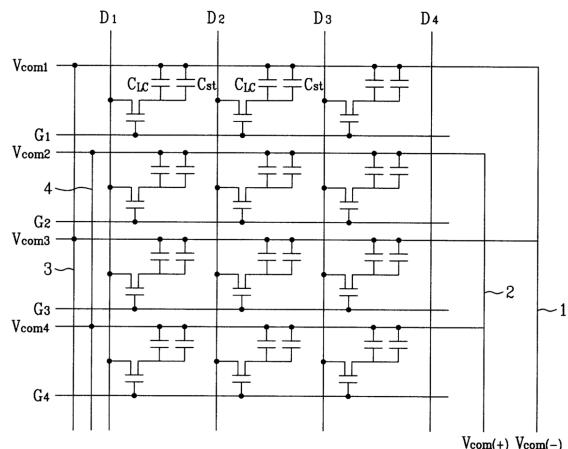

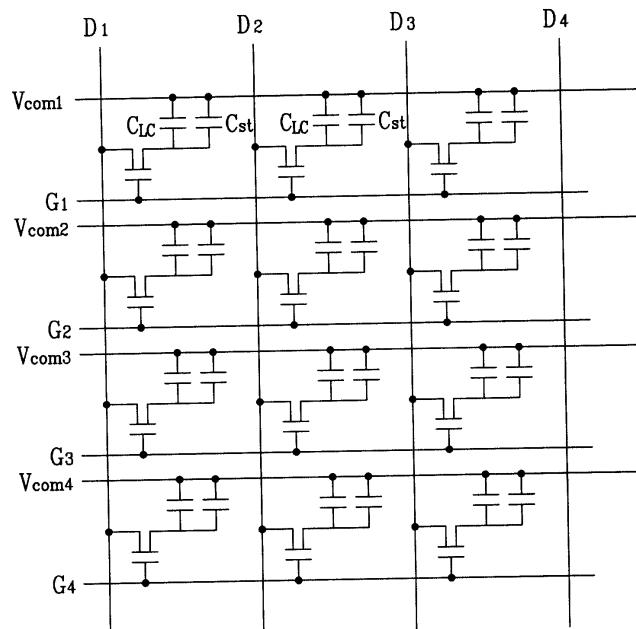

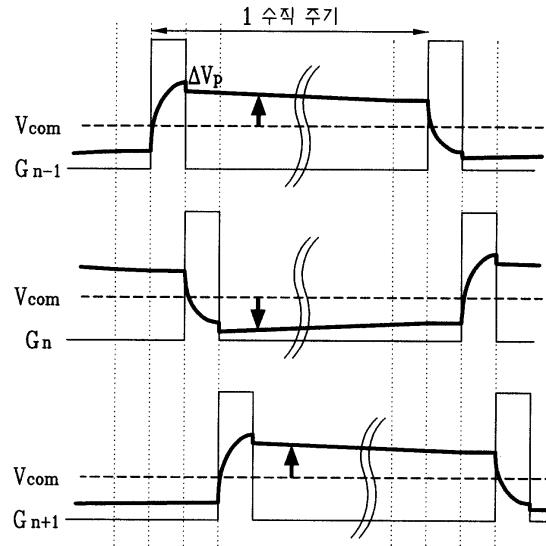

도 4는 일반적인 횡전계 방식 액정표시장치의 등가회로도이고, 도 5는 도 4의 각 게이트 라인별 화소 전압을 나타낸 타이밍도이다.

일반적인 횡전계 방식 표시 장치는 수직으로 교차한 복수개의 게이트 라인( $G_1, G_2, G_3, G_4, \dots$ ) 및 복수개의 데이터 라인( $D_1, D_2, D_3, D_4, \dots$ )과, 각 게이트 라인 사이에 형성된 복수개의 공통 라인( $V_{com1}, V_{com2}, V_{Com3}, \dots$ )과, 상기 각 게이트 라인과 각 데이터 라인이 교차하는 부분에 형성된 박막 트랜지스터와, 상기 박막 트랜지스터의 드레인 전극에 연결된 화소 전극(도 1의 17 참조)과 상기 각 공통 라인 사이에 병렬로 형성되는 스토리지 커패시터( $C_{st}$ ) 및 액정 커패시터( $C_{LC}$ )를 포함하여 이루어진다.

이 때, 상기 각 데이터 라인에 인가되는 데이터 전압은 1수직 주기로 (+)극성 또는 (-)극성을 갖도록 반전되어 인가되며, 화소를 구동하기 위해 해당 게이트 라인에 게이트 펄스를 인가하면, 해당 게이트 라인의 박막트랜지스터가 턴-온 되므로 화소 전극에 데이터 전압이 인가된다. 그리고, 박막 트랜지스터의 드레인 전극과 공통 라인(화소 전극과 공통 라인)사이에 연결된 액정 커패시터( $C_{LC}$ ) 및 스토리지 커패시터( $C_{st}$ )는 박막 트랜지스터가 턴-온되는 동안 충전되고, 상기 박막 트랜지스터가 턴-오프(turn off)되면 이후에 박막 트랜지스터가 턴-온될까지 충전 전하를 유지한다.

이 때, 상기 공통 라인에는, 도 5와 같이, 화소나 게이트 라인 또는 프레임(frame)에 관계없이 상기 데이터 전압의 (+)극성과 (-)극성의 중간 레벨에 해당되는 DC 전압이 인가된다.

따라서, 화소 전압은 게이트 라인에 인가되는 주사 신호의 하강 에지(edge)시 박막 트랜지스터의 게이트 전극과 소오스 전극 사이에 형성되는 기생 커패시터( $C_{gs}$ ) 등에 의해 액정 전압이  $\Delta V_p$ 만큼 변동이 발생하며, 상기  $\Delta V_p$ 만큼 떨어진 값으로, 화소 전극에 유도된다.

그러나, 상기와 같은 일반적인 횡전계 방식 액정 표시 장치의 구동 방법은 공통 전압으로 일정한 DC값을 인가하고, 데이터 라인에 인가하는 데이터 전압은 상기 공통 전압을 기준으로 (+)극성 또는 (-)극성의 전압이 되도록 교대로 인가하여 구동 하므로, 액정에 인가되는 화소 전압(V<sub>p</sub>)은 상기 데이터 전압에 의존하여 극성을 가지므로, 액정에 높은 전압이 형성되기 위해서는 높은 출력 전압차를 갖는 소오스 드라이버를 사용하여야 하므로 코스트가 높아진다.

또한, 횡전계 방식 액정 표시 장치에서는 공통 전극과 화소 전극간에 형성되는 프린지 필드(fringe field)에 의해 액정이 구동되므로, 액정의 원활한 구동을 위해서는 화소 전극과 공통 전극간의 간격을 좁게 하여 두 전극 사이에 유도되는 프린지 필드를 큰 값으로 형성시켜야 한다.

상기 화소 전극과 공통 전극간의 간격을 좁게 하기 위해서는, 화소 전극 및 공통 전극의 패턴을 형성할 때, 단일 라인형의 화소 전극과 공통 전극이 형성되는 것이 아니라, 서로 소정 간격 이격하며 맞물려서 교차한 팩터(finger) 형태의 화소 전극과 공통 전극 패턴을 형성하게 되는데, 이럴 경우 화소 전극과 공통 전극 사이의 간격은 좁아지게 되나, 화소의 개구율은 낮아지는 문제점이 생기게 된다.

물론, 상기 화소 전극 또는 공통 전극의 패턴을 주로 투명한 재질의 ITO 등을 사용하기는 하나, 화소 영역 내에 여러 형상의 패턴이 형성됨으로써, 빛이 고르게 투과되지 못하는 문제가 있다.

이 경우 고개구율을 위하여 화소 전극 및 공통 전극간의 간격을 크게 하면, 두 전극 사이에 형성되는 수평 전계장이 작아지므로, 필요한 휘도를 얻기 위해 고 출력 범위의 데이터 전압이 필요하게 된다.

따라서, 최근에는 전극 간격 증대 및 구동 전압 강하를 위하여, 공통 라인을 홀수/짝수 라인으로 구분하여 각 공통 라인에 독립적으로 데이터 전압과 반대 극성으로 공통 전압을 스윙(swing)하여 고 출력 소오스 드라이버를 사용하지 않고도 공통 전극과 화소 전극 사이의 액정 전압을 크게하여 화질을 향상시킬 수 있는 횡전계 방식 액정 표시 장치 및 그 구동 방법이 제안되었다.

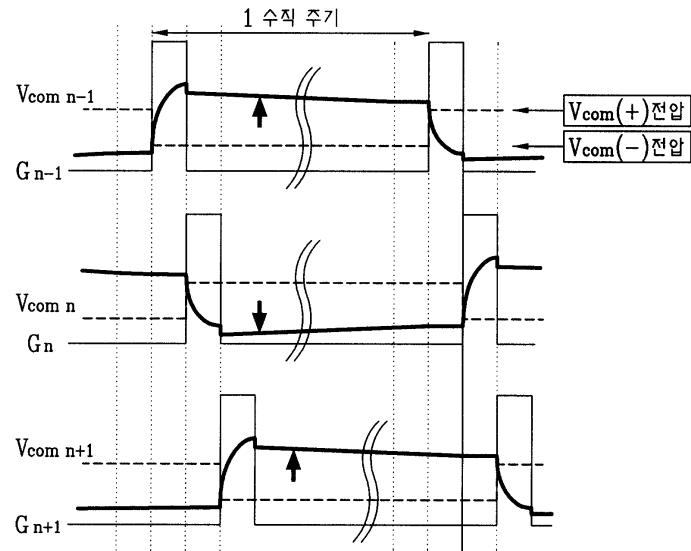

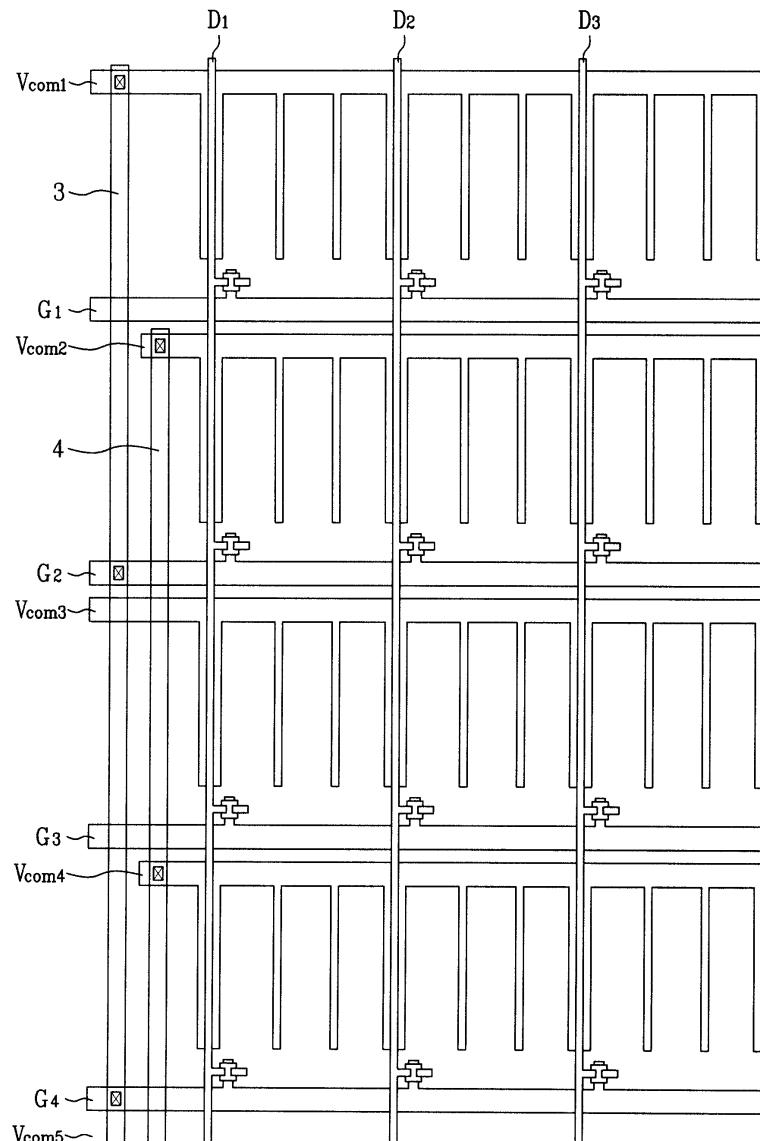

도 6은 전극 간격 증대 및 구동 전압 강하를 위한 종래의 횡전계 방식 액정표시장치의 등가회로도이고, 도 7은 도 6의 각 게이트 라인별 화소 전압을 나타낸 타이밍도이다.

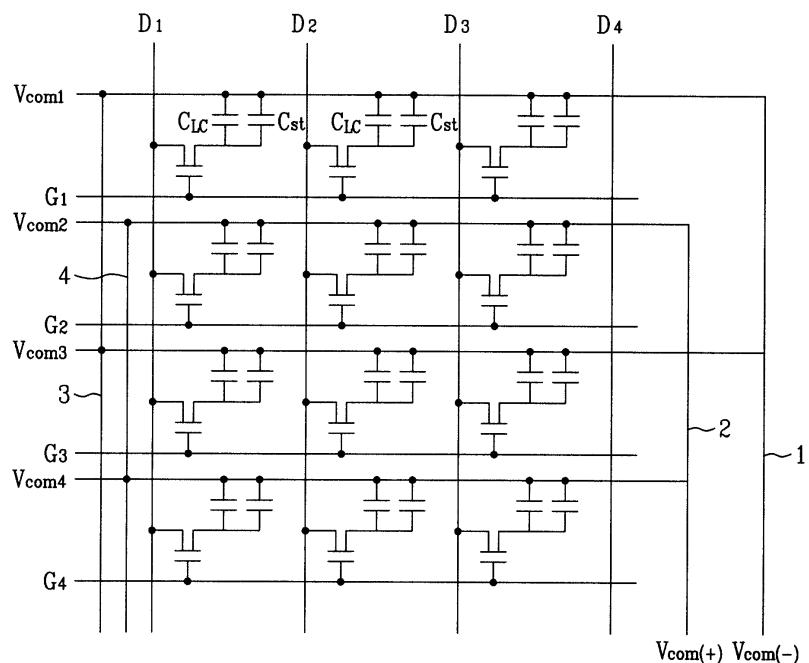

즉, 도 6과 같이, 서로 수직한 방향으로 교차되는 복수개의 게이트 라인(G<sub>1</sub>, G<sub>2</sub>, G<sub>3</sub>, G<sub>4</sub>, ...) 및 복수개의 데이터 라인(D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>, D<sub>4</sub>, ...)과, 각 게이트 라인 사이에 형성된 복수개의 공통 라인(Vcom<sub>1</sub>, Vcom<sub>2</sub>, Vcom<sub>3</sub>, ...)과, 상기 각 게이트 라인과 각 데이터 라인이 교차하는 부분에 형성된 박막 트랜지스터와, 상기 박막 트랜지스터의 드레인 전극에 연결된 화소 전극(도 2의 17 참조)과 상기 각 공통 라인 사이에 병렬로 형성되는 스토리지 커패시터(C<sub>st</sub>) 및 액정 커패시터(C<sub>LC</sub>)를 포함하여 이루어진다.

이 때, 횡전계 방식 액정표시장치의 전극 간격 증대 및 구동 전압 강하를 위하여, 상기 공통 라인 중 홀수 번째 공통 라인(Vcom<sub>1</sub>, Vcom<sub>3</sub>, ...)에는 제 1 공통 전압(또는 제 2 공통 전압)이 인가되며, 짝수 번째 공통 라인(Vcom<sub>2</sub>, Vcom<sub>4</sub>, ...)에는 제 2 공통 전압(또는 제 1 공통 전압)이 인가된다. 이 경우 같은 공통 라인에 연결되어 있는 화소에는 동일한 극성의 데이터 전압이 인가된다.

즉, 도 7과 같이, 임의의 화소에 (+)극성의 데이터 전압이 인가될 때, 해당 공통 라인에는 제 1 공통 전압(Vcom(-))이 인가되고, 임의의 화소에 (-)극성의 데이터 전압이 인가될 때, 해당 공통 라인에는 제 2 공통 전압(Vcom(+))이 인가된다.

따라서, 화소 전극과 공통 전극간의 전압차가 증가하게 된다

상기에서 공통 전압을 일괄적으로 인가하기 위하여, 상기 홀수번재 공통 라인들은 일측에서 각각 제 1 공통 전압 인가 라인(1)에 연결되고, 상기 짝수번재 공통 라인들은 일측에서 각각 제 2 공통 전압 인가 라인(2)에 연결된다. 그리고 상기 각 공통 라인의 타측은 개방되어 있다.

### 발명이 이루고자 하는 기술적 과제

그러나 이와 같은 종래의 공통 전압 스윙을 위한 횡전계 방식 액정표시장치에 있어서는 다음과 같은 문제점이 있었다.

즉, 공통 전압을 홀수번째 라인과 짝수번째 라인으로 구분하여 인가할 때, 홀수번째 공통 라인들은 일측에서 제 1 공통 전압 인가 라인에 연결되고, 짝수번째 공통 라인들은 일측에서 제 2 공통 전압 인가 라인에 연결되지만, 각 타측의 공통 라인들은 개방되어 있으므로, 각 공통 라인의 위치에 따라 각 공통 라인의 저항 차가 발생하고 저항 차로 인해 공통 전압이 강화되고 또한 RC 딜레이가 증가되어 이로 인하여 화질이 저하되는 문제점이 있었다.

본 발명은 이와 같은 문제점을 해결하기 위하여 안출한 것으로, 홀수번째 공통 라인과 짝수번째 공통 라인으로 나누어 공통 전압을 스윙함에 있어, 인접한 홀수번째 공통 라인들끼리 폐회로를 구성하도록 하고, 인접한 짝수번째 공통 라인들끼리 폐회로를 구성하도록 공통 라인을 구성하여 공통 전압의 전압 강화 및 딜레이를 줄일 수 있는 횡전계 방식 액정표시장치를 제공하는데 그 목적이 있다.

### 발명의 구성

상기와 같은 목적을 달성하기 위한 본 발명에 따른 횡전계 방식 액정표시장치는, 화소 영역을 정의하기 위해 서로 수직하게 배열되는 복수개의 게이트 라인 및 데이터 라인과, 상기 각 게이트 라인과 데이터 라인이 교차하는 부분에 형성되는 복수개의 박막트랜지스터와, 상기 각 게이트 라인에 평행한 방향으로 형성되는 복수개의 공통 라인 및 상기 각 공통 라인에서 상기 데이터 라인에 평행한 방향으로 돌출되는 복수개의 공통 전극과, 상기 각 박막트랜지스터의 드레인 전극에 연결되고 상기 공통 전극 사이에 상기 공통 전극과 평행하게 각 화소 영역에 형성되는 복수개의 화소 전극과, 상기 복수개의 공통 라인 중 홀수번째 공통 라인을 그룹핑하여 인접한 홀수번째 공통 라인들이 폐회로를 구성하도록 하여 제 1 공통 전압 또는 제 2 공통 전압을 인가하는 제 1 공통 전압 인가 라인과, 상기 복수개의 공통 라인 중 짝수번째 공통 라인을 그룹핑하여 인접한 짝수번째 공통 라인들이 폐회로를 구성하도록 하여 제 2 공통 전압 또는 제 1 공통 전압을 인가하는 제 2 공통 전압 인가 라인을 구비하여 구성됨에 그 특징이 있다.

상기와 같은 특징을 갖는 본 발명에 따른 횡전계 방식 액정표시장치를 첨부된 도면을 참조하여 보다 상세히 설명하면 다음과 같다.

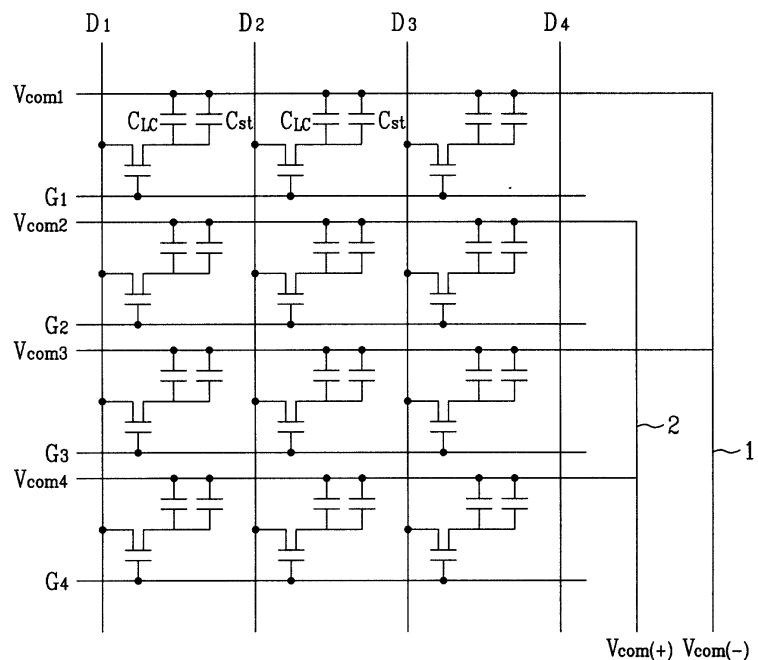

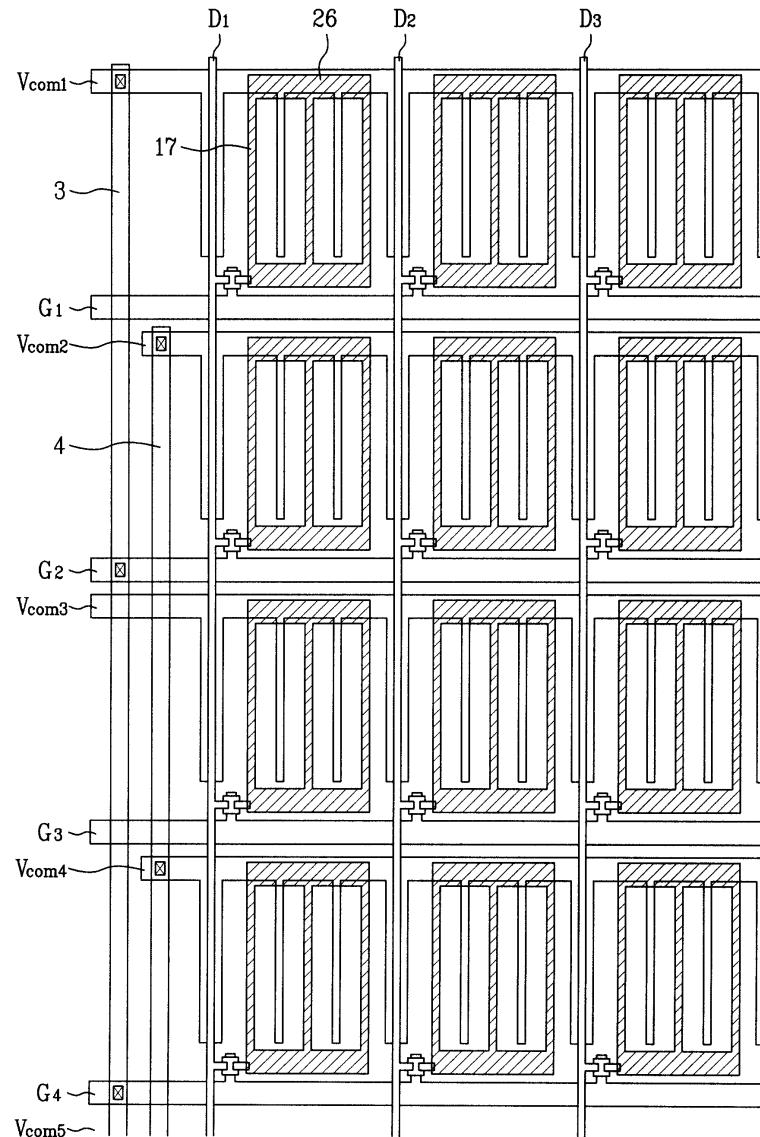

도 8은 본 발명의 실시예에 따른 횡전계 방식 액정표시장치의 등가회로도이다.

본 발명에 따른 횡전계 액정표시장치는, 화소 영역을 정의하기 위해 서로 수직한 방향으로 교차 배열되는 복수개의 게이트 라인( $G_1, G_2, G_3, G_4, \dots$ ) 및 복수개의 데이터 라인( $D_1, D_2, D_3, D_4, \dots$ )과, 각 게이트 라인 사이에 형성된 복수개의 공통 라인( $V_{com1}, V_{com2}, V_{com3}, \dots$ )과, 상기 각 게이트 라인과 각 데이터 라인이 교차하는 부분에 형성된 박막 트랜지스터와, 상기 박막 트랜지스터의 드레인 전극에 연결된 화소 전극(도 2의 17 참조)과, 상기 각 공통 라인 사이에 병렬로 형성되는 스토리지 커퍼시터( $C_{st}$ ) 및 액정 커퍼시터( $C_{LC}$ )를 포함하여 이루어진다.

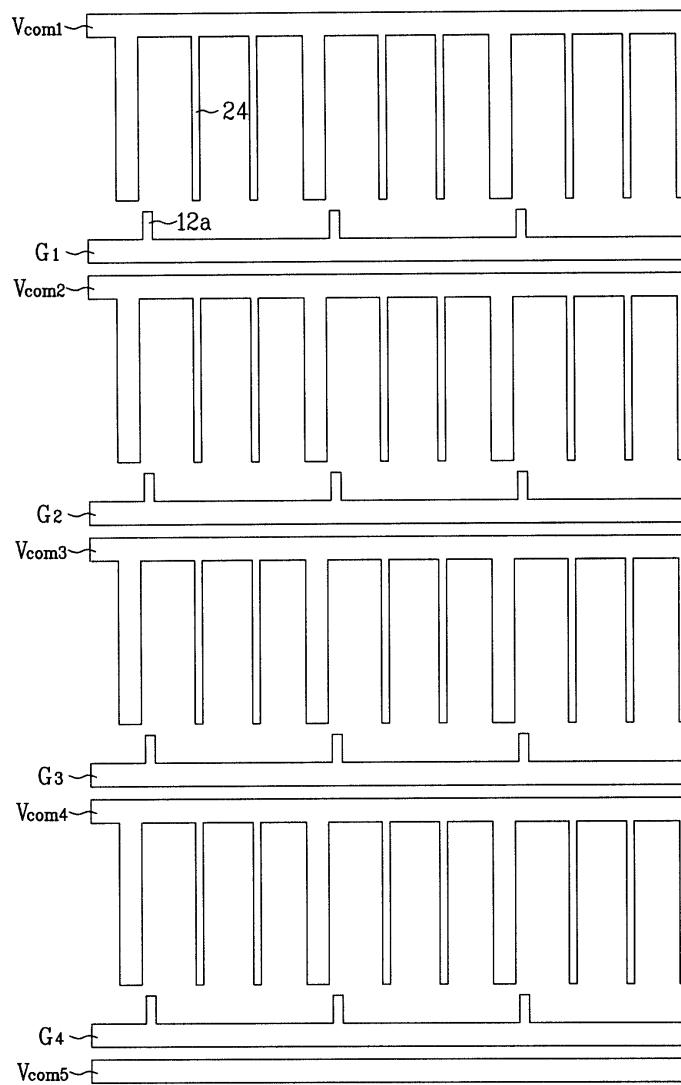

그리고, 상기 복수개의 공통 라인들 중 홀수번째 공통 라인( $V_{com1}, V_{com3}, \dots$ )들은 양측에서 제 1 공통 전압 인가 라인(1, 3)에 의해 연결되어 인접한 홀수번째 공통 라인들끼리 폐회로를 구성하도록 하고, 상기 복수개의 공통 라인들 중 짝수번째 공통 라인( $V_{com2}, V_{com4}, \dots$ )들은 양측에서 제 2 공통 전압 인가 라인(2, 4)에 의해 연결되어 인접한 짝수번째 공통 라인들끼리 폐회로를 구성하도록 한다.

또한, 상기에서 홀수번째 공통 라인에 공통 전압을 인가하기 위한 제 1 공통 전압 인가 라인(1, 3)의 저항값과 상기 짝수번째 공통 라인에 공통 전압을 인가하기 위한 제 2 공통 전압 인가 라인(2, 4)의 저항값은 서로 동일하도록 구성한다.

따라서, 횡전계 방식 액정표시장치의 전극 간격 증대 및 구동 전압 강화를 위하여, 상기 공통 라인 중 홀수 번째 공통 라인( $V_{com1}, V_{com3}, \dots$ )에는 제 1 공통 전압(또는 제 2 공통 전압)이 인가되며, 짝수 번째 공통 라인( $V_{com2}, V_{com4}, \dots$ )에는 제 2 공통 전압(또는 제 1 공통 전압)이 인가된다.

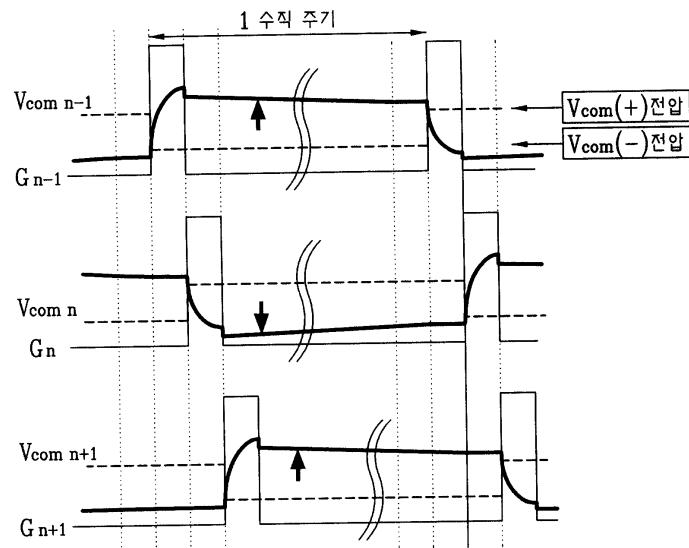

즉, 도 9와 같이, 임의의 화소에 (+)극성의 데이터 전압이 인가될 때, 해당 공통 라인에는 제 1 공통 전압( $V_{com}(-)$ )이 인가되고, 임의의 화소에 (-)극성의 데이터 전압이 인가될 때, 해당 공통 라인에는 제 2 공통 전압( $V_{com}(+)$ )이 인가된다.

따라서, 화소 전극과 공통 전극간의 전압차가 증가하게 된다

이 때, 상기 제 1 공통 전압 인가 라인(1 or 3)을 통해 홀수번째 공통 라인에 공통 전압을 인가하거나, 제 2 공통 전압 인가 라인(2 or 4)을 통해 짹수번째 공통 라인에 공통 전압을 인가하면, 각 공통 라인 양측이 공통 전압 인가 라인에 의해 폐회로를 구성하고 있으므로, 저항으로 인한 RC 딜레이가 줄어들기 때문에 공통 전압의 전압 강하 및 신호 지연(delay)이 발생하지 않는다.

또한, 홀수번째 라인끼리 또는 짹수번째 라인끼리 폐회로를 구성하므로 공통 라인의 단선 불량도 방지할 수 있다.

이와 같이, 홀수번째 공통 라인의 양측에 제 1 공통 전압 인가 라인(1, 3)을 구성하고 짹수번째 공통 라인의 양측에 제 2 공통 전압 인가 라인(2, 4)을 구성함에 있어서, 각 공통 전압 인가 라인(1, 2, 3, 4)은 데이터 라인과 동일한 물질로 데이터 라인 형성 시 동시에 형성한다.

도 10a 내지 10c는 본 발명에 따른 횡전계 방식 액정표시장치의 공정 평면도이다.

먼저, 도 10a에 도시된 바와 같이, 기판 상에 크롬(Cr), 구리(Cu), 알루미늄(Al), 몰리브덴(Mo), Al 합금 등의 저저항 금속을 증착한 후 패터닝하여 복수개의 게이트 라인(G1, G2, G3, G4,...) 및 공통 라인(Vcom1, Vcom2, Vcom3, Vcom4,...)을 동시에 형성한다. 이 때, 각 게이트 라인에는 게이트 전극(12a)이 돌출되어 형성되고, 상기 각 공통 라인(Vcom1, Vcom2, Vcom3, Vcom4,...)에는 공통 전극(24)이 상기 공통 라인에 수직한 방향으로 돌출되도록 형성된다.

상기 게이트 라인 및 공통 라인을 포함한 기판 전면에 실리콘 질화물질(SiNx) 또는 실리콘 산화물질(SiOx) 등의 무기 절연 물질을 적층하여 게이트 절연막(도시하지 않음)을 형성한다.

다음, 도 10b에 도시한 바와 같이, 상기 게이트 전극(12a) 상부의 게이트 절연막위에 섬모양으로 반도체층(14)을 형성한다. 이 때, 상기 반도체층(14)상에 아몰퍼스 실리콘에 불순물을 이온주입한 오믹 콘택층을 더 형성하여도 된다.

그리고, 상기 각 공통 라인(Vcom1, Vcom2, Vcom3, Vcom4,...) 양측 끝단의 게이트 절연막을 선택적으로 제거하여 콘택 홀을 형성한 다음, 상기 게이트 절연막 상부에 Cr, Cu, Al, Mo, Al합금 등의 금속을 증착한 후 패터닝하여, 상기 게이트 라인과 수직 방향으로 교차되어 단위 화소를 정의하는 데이터 라인(D1, D2, D3, D4,...)을 형성하고, 상기 데이터 라인과 동시에 상기 반도체층(14) 양 끝에 각각 배치되는 소스/드레인 전극(15a, 15b)을 형성한다.

그와 동시에, 상기 콘택홀을 통해 홀수번째 공통 라인들끼리 서로 연결되고 짹수번째 공통 라인들끼리 서로 연결되도록 제 1, 제 2, 제 3, 제 4 공통 전압 인가 라인(도 8의 1, 2, 3, 4 참조)을 형성한다.

이어서, 상기 데이터 라인 및 공통 전압 인가 라인을 포함한 전면에 BCB(Benzocyclobutene) 또는 아크릴 수지(acryl resin) 등의 유기 절연물질을 도포하여 보호막을 형성하고, 상기 드레인 전극(15b)이 노출되도록 상기 보호막을 오픈한다.

다음, 도 10c에 도시된 바와 같이, 상기 보호막 상에 ITO 또는 IZO 등의 투명한 도전물질을 증착하고 패터닝하여 상기 공통 전극(24)과 평행하게 교차하는 복수개의 화소 전극(17)을 형성한다.

상기 화소 전극(17)의 일 끝단은 서로 일체형으로 형성되어 드레인 전극(15b)에 연결되도록 하고, 다른 일 끝단은 일체형으로 형성된 형태로 상기 공통 라인에 오버랩시켜 커패시터 전극(26)으로 사용한다.

따라서, 마스크 공정 또는 식각 공정을 더 추가하지 않고 홀수번째 공통 라인들끼리 폐회로를 구성하고, 짹수번째 공통 라인들끼리 폐회로를 구성하도록 횡전계 방식 액정표시장치를 구성할 수 있다.

### **발명의 효과**

상기와 같은 본 발명에 따른 횡전계 방식 액정 표시 장치에 있어서는 다음과 같은 효과가 있다.

첫째, 복수개의 공통 라인 중 홀수번째 공통 라인 그룹과 짹수번째 공통 라인 그룹으로 구분하여 각 화소 영역에 인가되는 데이터 신호의 극성에 반대되는 극성의 공통 전압을 스윙함에 있어서, 홀수번째 공통 라인들끼리 폐회로를 구성하도록 하여, 짹수번째 공통 라인들끼리 폐회로를 구성하도록 하므로, 공통 라인의 저항으로 인한 RC 딜레이가 줄어들기 때문에 공통 전압의 전압 강하 및 신호 지연(delay)이 발생하지 않는다.

둘째, 홀수번째 라인끼리 또는 짝수번째 라인끼리 폐회로를 구성하므로 공통 라인의 단선 불량도 방지할 수 있다.

### 도면의 간단한 설명

도 1은 일반적인 횡전계 방식 액정표시장치의 단위 화소 평면도

도 2는 도 1의 I - I 선상에서의 횡전계 방식 액정표시장치의 전압분포도

도 3a 및 도 3b는 전압 무인가/인가시에서의 횡전계 방식 액정표시장치의 평면도

도 4는 일반적인 횡전계 방식 액정표시장치의 등가회로도

도 5는 도 4의 각 게이트 라인별 화소 전압을 나타낸 타이밍도

도 6은 전극 간격 증대 및 구동 전압 강하를 위한 종래의 횡전계 방식 액정표시장치의 등가회로도

도 7은 도 6의 각 게이트 라인별 화소 전압을 나타낸 타이밍도

도 8은 본 발명의 실시예에 따른 횡전계 방식 액정표시장치의 등가회로도

도 9는 본 발명의 실시예에 따른 각 게이트 라인별 화소 전압을 나타낸 타이밍도

도 10a 내지 10c는 본 발명에 따른 횡전계 방식 액정표시장치의 공정 평면도

도면의 주요 부분에 대한 부호의 설명

G1, G2, G3, G4 : 게이트 라인 D1, D2, D3, D4 : 데이터 라인

Vcom1, Vcom2, Vcom3, Vcom4 : 공통 라인

1, 2, 3, 4 : 공통 전압 인가 라인

도면

도면1

도면2

도면3a

도면3b

도면4

도면5

도면6

도면7

도면8

도면9

도면10a

도면10b

도면10c

|                |                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 横向电场型液晶显示器                                                                       |         |            |

| 公开(公告)号        | <a href="#">KR100710164B1</a>                                                    | 公开(公告)日 | 2007-04-20 |

| 申请号            | KR1020030100857                                                                  | 申请日     | 2003-12-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                        |         |            |

| [标]发明人         | LEE JAEKYUN<br>이재균<br>LEE DONGHOON<br>이동훈                                        |         |            |

| 发明人            | 이재균<br>이동훈                                                                       |         |            |

| IPC分类号         | G02F1/1343 G02F1/133 G02F1/136 G09G3/36 H01L21/00 H01L29/04 H01L29/15 H01L29/786 |         |            |

| CPC分类号         | G09G2300/0434 G09G3/3655 G09G3/3614 G02F1/13439 G02F1/134363                     |         |            |

| 代理人(译)         | 金勇<br>新昌                                                                         |         |            |

| 其他公开文献         | KR1020050070709A                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                        |         |            |

### 摘要(译)

用途：提供一种面内切换模式液晶显示装置，通过减少公共线路电阻引起的RC延迟，防止降低公共电压和信号延迟。