(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년10월17일

(11) 등록번호 10-1074402

(24) 등록일자 2011년10월11일

(51) Int. Cl.

G09G 3/36 (2006.01)

(21) 출원번호 10-2004-0076457

(22) 출원일자 2004년09월23일

심사청구일자 2009년07월09일

(65) 공개번호 10-2006-0027593

(43) 공개일자 2006년03월28일

(56) 선행기술조사문헌

JP05265045 A\*

JP07199154 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

엘지디스플레이 주식회사

서울특별시 용산구 한강로3가 65-228

(72) 발명자

김빈

서울특별시 양천구 신정7동 신시가지11단지아파트

1107동 1307호

문수환

경북 칠곡군 북삼면 인평리 시티타운 301/302

윤수영

경기도 군포시 오금동 율곡아파트 349-1604

(74) 대리인

김용인, 박영복

전체 청구항 수 : 총 8 항

심사관 : 이성현

(54) 액정표시장치 및 그의 구동방법

### (57) 요약

본 발명은 양방향 내장 게이트 구동회로를 이용하여 데이터라인의 수를 반감시킬 수 있는 액정표시장치 및 그의 구동방법을 제공하기 위한 것으로, 이와 같은 목적을 달성하기 위한 본 발명에 따른 액정표시장치는, 하부기판상에 수평방향으로 배열된 인접한 픽셀이 같은 데이터라인을 공유하도록 쌍을 이루고 있는 복수개의 픽셀들을 구비한 픽셀 어레이부와; 상기 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하도록, 제 1 내지 제 n 훌수 쉬프트 레지스터로 구성된 제 1 게이트 구동회로와, 제 1 내지 제 n 짝수 쉬프트 레지스터로 구성된 제 2 게이트 구동회로를 포함함을 특징으로 한다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

하부기판상에 수평방향으로 배열된 인접한 픽셀이 같은 데이터라인을 공유하도록 쌍을 이루고 있는 복수개의 픽셀들을 구비한 픽셀 어레이부와;

상기 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하도록, 상기 하부기판의 좌, 우측에 내장되어 있으며, 제 1 내지 제 n 홀수 쉬프트 레지스터로 구성된 제 1 게이트 구동회로와, 제 1 내지 제 n 짹수 쉬프트 레지스터로 구성된 제 2 게이트 구동회로를 포함하며,

상기 각 쉬프트 레지스터는,

Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되는 제 1 트랜지스터와, 상기 Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되는 제 2 트랜지스터와, Q노드의 신호를 입력받아 턴온 여부가 결정되는 제 3 트랜지스터로 구성된 풀업 구동부와;

상기 Q노드의 신호를 입력받아서 턴온 여부가 결정되는 제 4 트랜지스터로 구성된 풀업부와;

제 1 또는 제 2 클리바신호를 입력받아서 턴온 여부가 결정되는 제 5 트랜지스터와, QB노드의 신호를 입력받아서 턴온 여부가 결정되는 제 6 트랜지스터와, 다음단 출력을 입력받아서 턴온 여부가 결정되는 제 7 트랜지스터로 구성된 풀다운 구동부와;

상기 QB노드 신호를 입력받아서 턴온 여부가 결정되는 제 8 트랜지스터로 구성된 풀다운부로 구성됨을 특징으로 하는 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 픽셀 어레이부는 수평방향(행방향)의 홀수번째 픽셀과 짹수번째 픽셀이 서로 인접하여 한쌍을 이루고 있고, 상기 수평방향으로 인접한 한쌍의 픽셀은 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있으며, 상기 수평방향의 픽셀들 사이에는 홀수번째와 짹수번째의 2개의 게이트라인이 일방향으로 배열되어 있음을 특징으로 하는 액정표시장치.

### 청구항 3

제 2 항에 있어서,

상기 각 픽셀에는 데이터 신호를 인가시키기 위한 스위칭소자(TFT)가 각각 접속되어 있고, 상기 스위칭소자(TFT)의 드레인전극은 데이터라인에 접속되어 있고, 소오스전극은 각 픽셀 전극에 접속되어 있음을 특징으로 하는 액정표시장치.

### 청구항 4

제 1 항에 있어서,

상기 데이터라인의 수는 수평방향의 픽셀수의 절반임을 특징으로 하는 액정표시장치.

### 청구항 5

제 1 항에 있어서,

상기 제 1 내지 제 n 홀수 쉬프트 레지스터는 상기 픽셀 어레이부의 각 홀수번째(Odd) 게이트라인에 게이트 신호를 출력하도록 구성됨을 특징으로 하는 액정표시장치.

### 청구항 6

제 1 항에 있어서,

상기 제 1 내지 제 n 짹수 쉬프트 레지스터는 상기 픽셀 어레이부의 각 짹수번째(Even) 게이트라인에 게이트 신

호를 출력하도록 구성됨을 특징으로 하는 액정표시장치.

### 청구항 7

삭제

### 청구항 8

제 1 항에 있어서,

상기 쉬프트 레지스터의 각 트랜지스터는 비정질 실리콘 트랜지스터로 구성됨을 특징으로 하는 액정표시장치.

### 청구항 9

하부기판 상에 수평방향(행방향)의 홀수번째 픽셀과 짝수번째 픽셀이 서로 인접하여 한쌍을 이루고 있고, 상기 수평방향으로 인접한 한쌍의 픽셀은 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있으며, 상기 수평방향의 픽셀들 사이에는 홀수번째와 짝수번째의 2개의 게이트라인이 일방향으로 배열되어 있는 픽셀 어레이부와, 상기 픽셀 어레이부의 좌, 우 양측에 구성되며, 제 1 내지 제 n 홀수 쉬프트 레지스터로 구성된 제 1 게이트 구동회로와, 제 1 내지 제 n 짝수 쉬프트 레지스터로 구성된 제 2 게이트 구동회로를 포함하며,

상기 각 쉬프트 레지스터는 Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되는 제 1 트랜지스터와, 상기 Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되는 제 2 트랜지스터와, Q노드의 신호를 입력받아 턴온 여부가 결정되는 제 3 트랜지스터로 구성된 풀업 구동부와;

상기 Q노드의 신호를 입력받아서 턴온 여부가 결정되는 제 4 트랜지스터로 구성된 풀업부와;

제 1 또는 제 2 클럭바신호를 입력받아서 턴온 여부가 결정되는 제 5 트랜지스터와, QB노드의 신호를 입력받아서 턴온 여부가 결정되는 제 6 트랜지스터와, 다음단 출력을 입력받아서 턴온 여부가 결정되는 제 7 트랜지스터로 구성된 풀다운 구동부와;

상기 QB노드 신호를 입력받아서 턴온 여부가 결정되는 제 8 트랜지스터로 구성된 풀다운부로 구성된 액정표시장치의 구동방법에 있어서,

상기 제 1, 제 2 게이트 구동회로는 H/2의 시간 차이를 두고 제 1, 제 2 클럭신호를 입력받아서 상기 픽셀 어레이부의 각 짝수번째 및 홀수번째 게이트라인에 각각 H/2의 시간차가 나는 게이트 출력 신호들을 독립적으로 출력시킴을 특징으로 하는 액정표시장치의 구동방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0012] 본 발명은 액정표시장치에 대한 것으로, 특히 양방향 내장 게이트 구동회로를 이용하여 데이터라인의 수를 줄이기 위해 알맞은 액정표시장치에 관한 것이다.

[0013] 정보화 사회가 발전함에 따라 표시장치에 대한 요구도 다양한 형태로 점증하고 있으며, 이에 부응하여 근래에는 LCD(Liquid Crystal Display Device), PDP(Plasma Display Panel), ELD(Electro Luminescent Display), VFD(Vacuum Fluorescent Display)등 여러 가지 평판 표시 장치가 연구되어 왔고 일부는 이미 여러 장비에서 표시장치로 활용되고 있다.

[0014] 그 중에, 현재 화질이 우수하고 경량, 박형, 저소비 전력의 특징 및 장점으로 인하여 이동형 화상 표시장치의 용도로 CRT(Cathode Ray Tube)을 대체하면서 LCD가 가장 많이 사용되고 있으며, 노트북 컴퓨터의 모니터와 같은 이동형의 용도 이외에도 방송신호를 수신하여 디스플레이하는 텔레비전, 및 컴퓨터의 모니터 등으로 다양하게 개발되고 있다.

[0015] 이하, 일반적인 액정표시장치에 대하여 설명하면 다음과 같다.

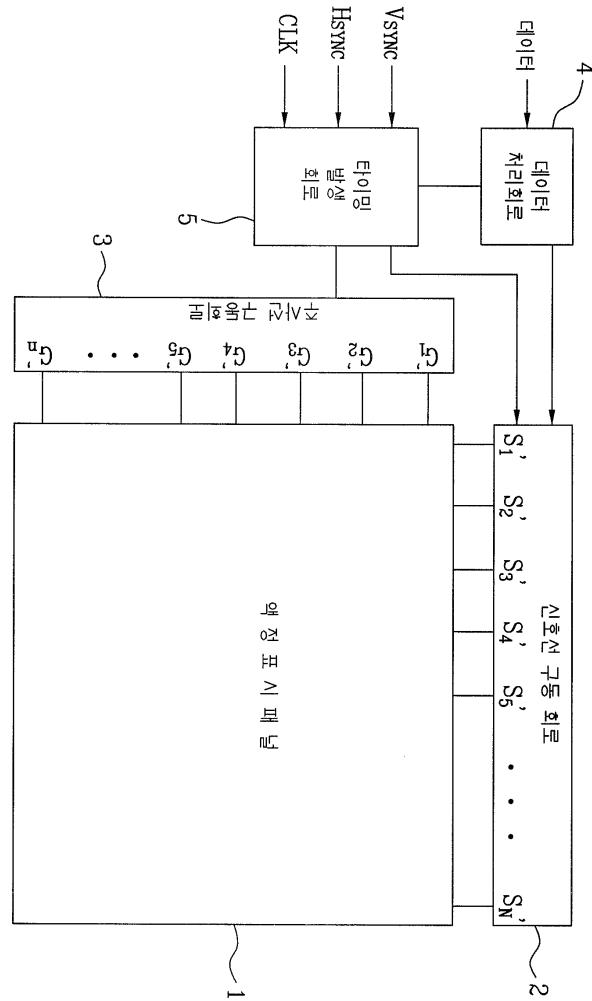

- [0016] 도 1은 일반적인 액티브 매트릭스형 액정표시장치의 블록 구성도이다.

- [0017] 화상을 표시하는 부분이 액정표시패널(1)이다. 이 액정표시패널(1)을 구동하기 위한 회로로서, 상기의 수직방향과 수평방향의 각 단부에 각각 신호선 구동회로(2)와 주사선 구동회로(3)가 배치되어 있다. 이들 신호선 구동회로(2) 및 주사선 구동회로(3)를 제어하는 제어신호는 타이밍 발생회로(5)에서 발생된다. 기본적으로는 외부에서 입력되는 수평 동기신호(HSYNC)와 수직 동기신호(VSYNC)와 도트 클럭(CLK)에서 각종 제어신호가 생성된다. 그리고, 신호선 구동회로(2)의 데이터입력과의 인터페이스 형태에 따라, 지정된 지시대로 정리하는 등의 데이터처리를 실시할 필요가 있으며, 이를 실시하는 것이 데이터 처리회로(4)이며, 이것도 타이밍 발생회로(5)에 의해 제어된다. 통상, 상기의 데이터 처리회로(4)와 타이밍 발생회로(5)는 ASIC에서 하나로 합쳐져 개발되는 일이 많다.

- [0018] 상술한 바와 같은 액정표시장치는 크게 영상신호를 표시하는 액정표시패널과 외부에서 상기 액정표시패널에 구동신호를 인가하는 구동회로로 구분할 수 있다.

- [0019] 상기 액정표시패널(1)은, 도면에는 도시되지 않았지만, 일정한 공간을 갖고 합착된 두 개의 투명 기판(유리 기판) 사이에 액정이 주입된 표시장치로서, 상기 두개의 투명 기판 중 하나에는 일정 간격으로 배열된 복수개의 게이트 라인(G1, G2, G3, …, Gn)과, 게이트 라인에 수직한 방향으로 일정한 간격을 갖고 배열되는 복수개의 데이터 라인(S1, S2, S3, …, Sn)과, 상기 각 게이트 라인과 데이터 라인에 의해 정의된 매트릭스 형태의 각 픽셀 영역에 형성된 복수개의 픽셀전극과, 상기 게이트 라인의 신호에 따라 상기 데이터 라인의 신호를 각 픽셀전극에 인가하는 복수개의 박막트랜지스터가 상기 각 게이트 라인과 데이터 라인이 교차하는 부분에 형성된다. 그리고 나머지 기판에는 칼라필터층, 공통전극(VCOM) 및 블랙 매트릭스층이 형성된다.

- [0020] 따라서, 게이트 라인에 순차적으로 턴온 신호를 인가하면 그 때마다 해당 라인의 픽셀 전극에 데이터 신호가 인가되므로 영상이 표시된다.

- [0021] 상기 구성을 갖는 박막트랜지스터(Thin Film Transistor:TFT)용 LCD는 내부의 픽셀을 온/오프시키는 스위칭소자로서 TFT를 이용하며, 이 TFT가 온/오프됨에 따라 픽셀들이 온/오프된다.

- [0022] 즉, 일반적인 TFT 액정표시장치는 화소를 구성하는 셀들이 어레이 형태로 배열되어 있고, 각 셀들은 스위칭 기능을 하는 TFT와 액정 셀, 스토리지 커패시터(CSTG)로 구성된다. 그리고, 각 TFT의 소스(source)들이 컬럼(column) 방향으로 공통으로 연결되어 데이터라인(D1~DN)을 형성한 후 소스 드라이버에 연결되어 있고, 각 TFT의 게이트(gate)들이 로우(row) 방향으로 공통으로 연결되어 게이트 라인(G1~GM)을 형성한 후 게이트 드라이버에 연결되어 NxM 해상도(예컨대, SVGA는 800x600, XGA는 1024x768, UXGA는 1600x1200)를 갖는 표시장치를 구현하고 있다.

- [0023] 여기서, 소스 드라이버는 데이터 드라이버, 컬럼 드라이버 또는 신호선 구동회로라고도 하고, 게이트 드라이버는 로우(ROW) 드라이버, 스캔(SCAN) 드라이버 또는 주사선 구동회로라고도 한다. 이하, 소스 드라이버는 신호선 구동회로, 게이트 드라이버는 주사선 구동회로라고 명명하여 설명한다.

- [0024] 액정 셀은 TFT의 드레인(drain)과 화소전극을 통해 연결되고, 다른 편은 공통전극으로 연결된다. 화소전극은 투명하고 전기 전도성을 갖는 ITO로 만들어지며 TFT 게이트에 온신호가 인가될 때 신호선 구동회로를 통해 인가되는 신호전압을 액정 셀에 가해주고, 공통전극은 역시 ITO로 만들어져 액정 셀에 공통전압(VCOM)을 인가한다. 그리고, 스토리지 커패시터(CSTG)는 화소전극(픽셀 ITO)에 인가된 신호전압을 일정 시간 유지시켜주는 역할을 하며, 충전 및 방전을 통해 액정 셀의 배열 상태를 변화시켜줌으로써 픽셀의 광투과율을 조절한다. 스토리지 커패시터(CSTG)의 일측은 독립 전극이나 게이트 전극과 연결될 수 있는데, 게이트전극과 연결되는 구조를 스토리지 온 게이트(storage on gate)방식이라 한다.

- [0025] 최근에는 박막 트랜지스터 (이하, TFT 라 함)를 사용한 액정표시장치(LCD)가 노트북 컴퓨터의 디스플레이 등의 용도로 보급되어 가격의 저렴화가 추진되고 있지만, 보다 더 저가격화가 요구되고 있다. 이와 같은 저가격화를 실현하기 위한 하나의 대책으로 부재비의 삭감을 들 수 있는데, 그 중에서도 부재비의 대부분을 차지하는 액정 표시패널의 신호선을 구동하는 회로로 사용되는 드라이버 IC의 비용을 내리는 것이 키포인트가 된다. 이 신호선 층의 드라이버 IC 가 부재비 중에서 대부분을 차지하는 이유는, 고도의 동작 기능이기 때문에 1개 당의 가격이 높고, 게다가 1개 당 240 출력으로 하면 SVGA 패널에서는 10개가 필요하게 되도록 수를 많이 사용하는 점에 있다. 따라서, 이 드라이버 IC의 수를 줄이는 것이 제안되고 있으며, 예컨대, 일본 공개특허공보 평3-38689호 공보, 일본 공개특허공보 평5-265045 호 공보, 일본 공개특허공보 평6-148680 호 공보에 제안된 것이 있다. 이들은 모두, 액정표시패널의 인접하는 표시화소에서 신호선을 공용하여, 신호선 층 드라이버 IC의 개수를 절반으로

하려고 하는 것이다.

[0026] 이하, 첨부 도면을 참조하여 상기 신호선 드라이버 IC를 반감하기 위한 종래 기술에 대하여 설명한다.

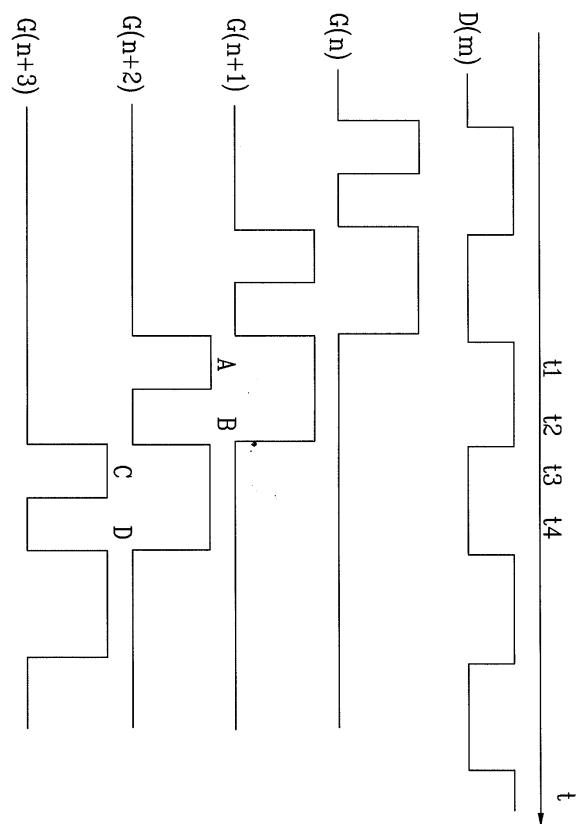

[0027] 도 2와 도 3은 종래 기술에 따른 액정표시장치의 구성도 및 그 구동 파형도이다.

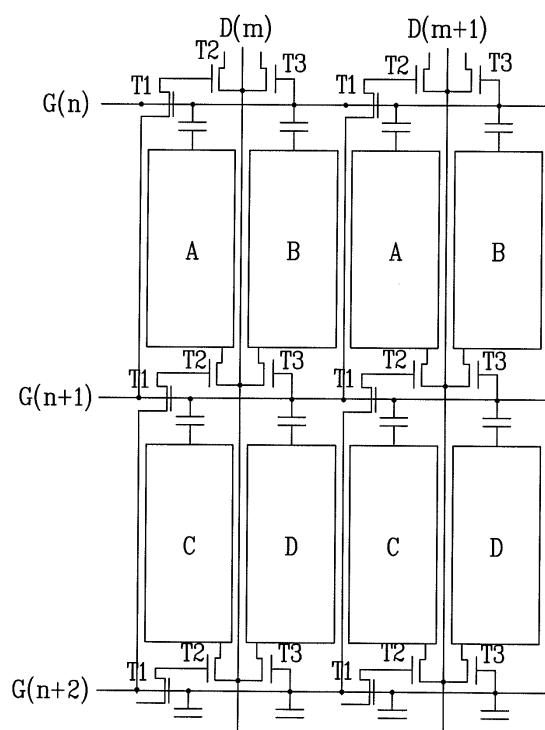

[0028] 먼저, 종래 기술에 따른 액정표시장치는, 도 2에 도시한 바와 같이, 일방향으로 배열된 복수개의 게이트라인과, 1개의 데이터라인에 짹을 이루어 연결된 2개의 이웃하는 픽셀(제 1, 제 2 픽셀(A,B)(C,D))과, 각 게이트라인의 신호를 받아 턴온/턴오프가 결정되는 제 1 트랜지스터(T1)와, 제 1 트랜지스터(T1)가 턴온될 경우 다음단 게이트라인의 신호를 입력받아 턴온되어 데이터라인을 통해 데이터 신호를 제 1 픽셀로 전달하는 제 2 트랜지스터(T2)와, 다음단 게이트라인의 신호를 받아서 턴온/턴오프되어 제 2 픽셀로 데이터라인을 통해 데이터 신호를 전달하는 제 3 트랜지스터(T3)와, 이전단 게이트라인과 각 픽셀 사이에 연결된 스토리지 커패시터(Cst)로 구성되어 있다.

[0029] 상기의 구성은 1개의 데이터라인을 이용하여 인접한 2개의 픽셀을 구동하기 위한 것으로 데이터 라인 쉐어링(Data Line Sharing:DLS) 구동을 위한 구성이다.

[0030] 상기 DLS 구동 방식을 이용한 액정표시장치는, 1개의 데이터라인을 이용하여 인접한 2개의 픽셀에 데이터 신호를 인가할 수 있어 구동 IC의 수를 반으로 절감할 수 있다.

[0031] 상기 액정표시장치의 구동을 위해서는 도 3에 도시한 바와 같이, 1주기의 출력 파형 앞에 반주기의 출력 파형을 갖는 게이트 파형을 이용한다. 즉, DLS 구동을 위해서는 종래의 게이트 구동 파형과는 다른 파형이 필요하며, 1개의 게이트 라인에 인가되는 파형은 2개의 파형으로 구성되어 있고, 앞에 위치하는 파는 뒤따라 오는 파의 반주기의 크기를 갖는다.

[0032] 도면을 참조하여 구동 원리를 설명하면 다음과 같다.

[0033] 도 2, 도 3에 도시한 바와 같이 게이트 신호가 G(n), G(n+1), G(n+2)에 순차적으로 인가될 경우, t1 구간에서는 G(n+1)에 한 주기, G(n+2)에 반주기의 "하이" 신호가 인가되면, G(n+1) 신호를 받아 제 1, 제 3 트랜지스터(T1,T3)가 턴온되고, G(n+1)이 턴온됨에 따라 G(n+2) 신호를 받은 제 2 트랜지스터(T2)도 턴온된다. 이에 따라서 제 1, 제 2 픽셀(A,B)에 동시에 데이터 신호가 인가된다.

[0034] 이후에 반주기 시간이 경과한 t2구간에서는 제 2 트랜지스터(T2)는 턴오프되고, 제 1, 제 3 트랜지스터(T1,T3)는 턴온된 상태이므로 제 1 픽셀(A)에는 이미 인가된 데이터 신호만이 남게 되고, 제 2 픽셀(B)에는 다른 데이터 신호를 인가시킬 수 있다.

[0035] 따라서 1개의 데이터 라인을 이용하여 2개의 이웃하는 픽셀에 순차적으로 서로 다른 2개의 데이터 신호를 인가할 수 있다.

[0036] 상기에서와 같이 반주기의 다음단 게이트 신호를 이용하여 선택적으로 서로 다른 픽셀에 데이터 신호를 인가할 수 있으며, 이러한 방법으로 구동시킬 경우 1개의 데이터라인에 1픽셀을 연결하던 일반적인 데이터 구동 방법에 비하여 데이터 라인의 수를 절반으로 줄일 수 있어 구동을 위한 데이터 IC의 채널 수를 반감할 수 있다.

[0037] 그러나, 데이터 라인 쉐어링(DLS) 방법을 적용하기 위해서는, 일반적인 출력 파형이 아닌 반주기 출력과 한주기 출력이 연속적으로 나오는 특이한 게이트 파형을 출력할 수 있는 별도의 구동 IC를 구비시켜야 한다. 따라서 데이터 라인의 수를 반감하더라도 별도의 게이트 구동 IC를 구비시켜야 하므로 제조 원가를 줄이는데는 한계가 있다.

[0038] 다음에, 종래의 다른 기술에 따른 액정표시장치에 대하여 설명한다.

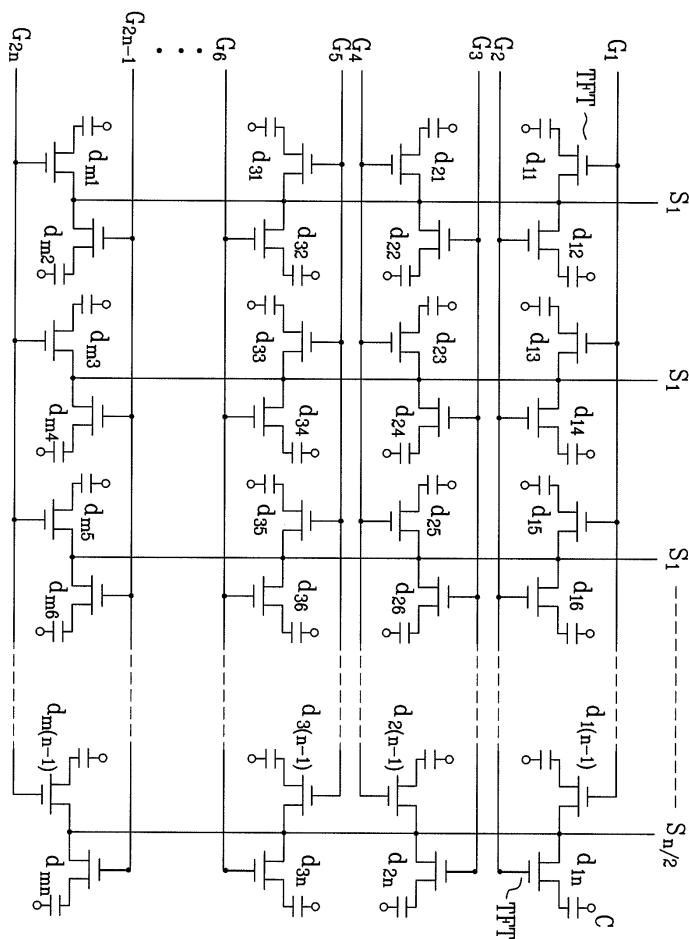

[0039] 도 4와 도 5는 종래의 다른 기술에 따른 액정표시장치의 회로 구성도 및 그 구동 파형도이다.

[0040] 종래의 다른 기술에 따른 액정표시장치는, 도 4에 도시한 바와 같이, 액정표시패널은  $n$  열  $\times$   $m$  행의 화소전극으로 구성된다 ( $n, m$ 은 각각 2 이상의 정수). 그리고, 수평방향(행방향)의 홀수번째 픽셀과 짹수번째 픽셀이 서로 인접하는 픽셀에서, 수직방향(열방향)으로 신장한 1개의 데이터라인을 공용하고 있으며, 각 픽셀에 접속되는 스위칭소자인 TFT의 드레인이 접속되어 있다. 즉, 데이터라인의 수는 수평방향의 픽셀수의 절반( $n/2$  개)이 된다. 상기의 인접하는 2개의 TFT의 게이트는 홀수번째의 TFT와 짹수번째의 TFT로, 수평방향의 1표시라인에 할당된 수평방향으로 신장하는 2개의 게이트라인의 각각 다른 게이트라인에 접속되어 있다. 따라서, 게이트라인의

수는 수직방향의 픽셀수의 배 ( $2m$ 개)가 된다.

[0041] 그러나, 상기 구성에서는, 홀수행째의 표시라인에서는, 수평방향의 홀수번째 픽셀의 TFT의 게이트는 홀수행째의 게이트라인에 접속되고, 수평방향의 짹수번째 픽셀의 TFT의 게이트는 짹수행째의 게이트라인에 접속된다. 또한, 짹수행째의 표시라인에서는, 수평방향의 홀수번째 픽셀의 TFT의 게이트는 짹수행째의 게이트라인에 접속되고, 수평방향의 짹수번째 픽셀의 TFT의 게이트는 홀수행째의 게이트라인에 접속된다. 즉, 수평방향의 임의의 표시라인에 주목한 경우, 그 표시라인에 할당되는 복수개의 게이트라인에서, 수평방향 홀수번째의 TFT의 게이트는 어느 한쪽의 게이트라인에 접속되어 있으며, 짹수번째의 TFT의 게이트는 다른 한쪽의 게이트라인에 접속되어 있다. 그리고, 그 표시라인에 인접하는 표시라인에서는, 상기의 TFT의 게이트와 게이트라인의 접속은 반대관계에 있다. 다시 말하면, 홀수번째의 표시라인과 짹수번째의 표시라인에서, TFT의 게이트와 게이트라인의 접속관계가 반대라는 것이다.

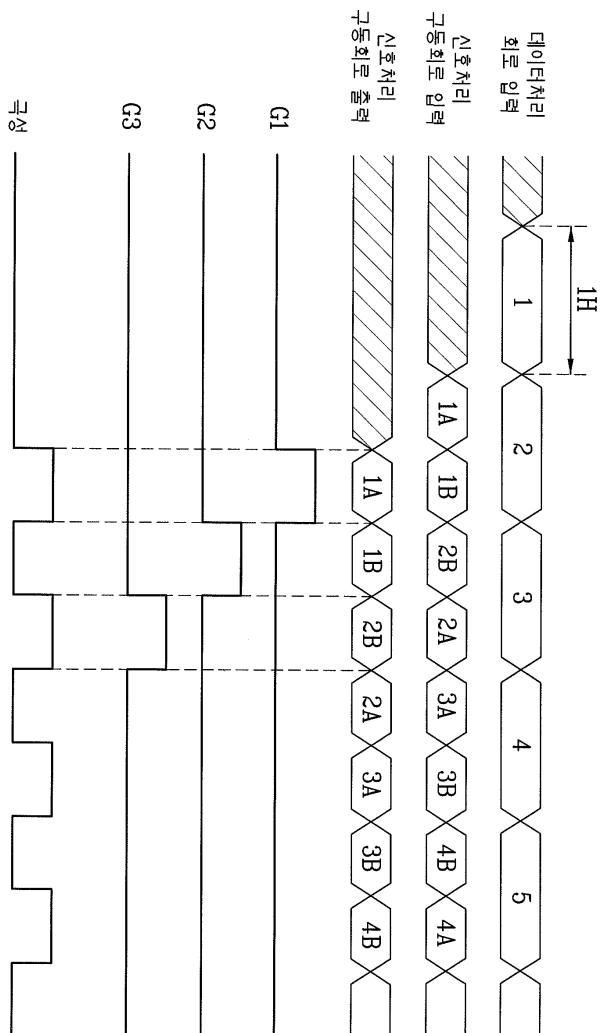

[0042] 상기의 구성을 갖을 때 동작을 도 5의 타이밍도를 참조하여 설명한다.

[0043] 도 5에 도시한 바와 같이, 시리얼로 입력되어 오는 데이터를 데이터 처리회로(미도시)로 받아, 데이터 처리회로에 형성되어 있는 라인메모리에 1 라인 분을 기입하고, 패널의 TFT와 데이터라인, 게이트라인의 접속에 따라, 데이터를 1 수평기간(1H)의 절반으로 전반과 후반으로 나눈다.

[0044] 즉, 패널 1행째의 표시라인( $m=1$ )에서, 전반에 출력되는 데이터는, 홀수번째의 데이터에서 S1, S3, S5, … 가 된다. 이것을 A 패턴이라 한다. 후반에 출력되는 데이터는 짹수번째의 데이터에서 S2, S4, S6, … 이 된다. 이것을 B 패턴이라 한다.

[0045] 2행째의 표시라인( $m=2$ )에서는, 반대로 전반이 B 패턴, 후반이 A 패턴이 된다. 3 행째의 표시라인 이후는, 이 1, 2 행째의 반복으로, 데이터라인에 출력된다. 이와 같이 데이터가 데이터라인에 출력되면, 게이트라인은 순차적으로 G1, G2, G3, … 로 TFT의 ON 전압을 시프트해 가면, 소정의 픽셀에 소정의 데이터가 기입되게 된다.

[0046] 예컨대, 데이터라인(S1)에 주목하면, 게이트라인이 순차적으로 G1부터 ON되면, d11(A), d12(B), d22(B), d21(A) … 로 데이터는 기입된다. 상기에서 (A), (B)는 A 패턴, B 패턴을 의미한다.

[0047] 여기에서 신호선 구동회로에서 출력되는 신호의 극성은, 인접하는 출력끼리가 서로 반대극성으로 1 회의 출력마다 극성반전하는 것을 고려하면, 1 프레임 기입 종료후의 화면상의 극성은 수평방향은 2 픽셀 간격, 수직방향은 1 픽셀 간격으로 극성이 반전한다. 이것은 상기한 모든 인접 픽셀에 대하여 반대극성의 관계가 되는 도트 반전 구동과는 약간 다르지만, 2개를 1조로 하는 인접 픽셀 관계에서 보면 반대극성으로 되어, 양극성과 음극성의 차이에 의한 플리커(flicker, 어른거림)에 강하다고 할 수 있다.

[0048] 상기에서와 같이 종래 다른 기술에 따른 액정표시장치는 2개의 게이트라인을 사용하여 각 라인의 홀수번째 픽셀과 짹수번째 픽셀을 구동하는 것에 특징이 있다.

[0049] 상기와 같이 1표시라인을 2개의 게이트라인을 사용하여 구동하기 위해서는 1개의 게이트라인을 사용하여 구동하는 액정표시장치와 비교하여 2배의 게이트라인이 필요하다. 이에 따라서 1프레임동안 2배의 게이트라인을 모두 구동시키기 위해서는 1픽셀 충전시간이 1H에서 H/2로 감소하게 되므로 충분한 픽셀 유효 충전시간의 확보가 어렵다는 문제가 있다.

### 발명이 이루고자 하는 기술적 과제

[0050] 본 발명은 상기와 같은 문제를 해결하기 위하여 안출한 것으로, 본 발명의 목적은 양방향 내장 게이트 구동회로를 이용하여 픽셀 유효 충전 시간을 줄이지 않으면서 데이터 라인의 수를 반감시킬 수 있는 액정표시장치 및 그의 구동방법을 제공하는데 있다.

### 발명의 구성 및 작용

[0051] 상기와 같은 목적을 달성하기 위한 본 발명에 따른 액정표시장치는 하부기판상에 수평방향으로 배열된 인접한 픽셀이 같은 데이터라인을 공유하도록 쌍을 이루고 있는 복수개의 픽셀들을 구비한 픽셀 어레이부와; 상기 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하도록, 제 1 내지 제 n 홀수 쉬프트 레지스터로 구성된 제 1 게이트 구동회로와, 제 1 내지 제 n 짹수 쉬프트 레지스터로 구성된 제 2 게이트 구동회로를 포함함을 특징으로 한다.

[0052] 상기 픽셀 어레이부는 수평방향(행방향)의 홀수번째 픽셀과 짹수번째 픽셀이 서로 인접하여 한쌍을 이루고 있고, 상기 수평방향으로 인접한 한쌍의 픽셀은 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있

으며, 상기 수평방향의 픽셀들 사이에는 홀수번째와 짝수번째의 2개의 게이트라인이 일방향으로 배열되어 있음을 특징으로 한다.

[0053] 상기 각 픽셀에는 데이터 신호를 인가시키기 위한 스위칭소자(TFT)가 각각 접속되어 있고, 상기 스위칭소자(TFT)의 드레인전극은 데이터라인에 접속되어 있고, 소오스전극은 각 픽셀 전극에 접속되어 있음을 특징으로 한다.

[0054] 상기 데이터라인의 수는 수평방향의 픽셀수의 절반임을 특징으로 한다.

[0055] 상기 제 1 내지 제 n 홀수 쉬프트 레지스터는 상기 픽셀 어레이부의 각 홀수번째(odd) 게이트라인에 게이트 신호를 출력하도록 구성됨을 특징으로 한다.

[0056] 상기 제 1 내지 제 n 짝수 쉬프트 레지스터는 상기 픽셀 어레이부의 각 짝수번째(even) 게이트라인에 게이트 신호를 출력하도록 구성됨을 특징으로 한다.

[0057] 상기 각 쉬프트 레지스터는, Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되며 상기 Vst 또는 이전단 쉬프트 레지스터의 출력 신호와 Q노드 사이에 다이오드 커넥팅된 제 1 트랜지스터와, 상기 Vst 또는 이전단 쉬프트 레지스터의 출력 신호를 입력받아서 턴온 여부가 결정되며 일단이 접지전압단 사이에 연결된 제 2 트랜지스터와, 상기 Q노드의 신호를 입력받아 턴온 여부가 결정되며 일단이 접지전압단 사이에 연결된 제 3 트랜지스터로 구성된 풀업 구동부와; 상기 Q노드의 신호를 입력받아서 턴온 여부가 결정되며 제 1 또는 제 2 클럭 신호 입력단과 게이트 출력 신호단 사이에 연결된 제 4 트랜지스터로 구성된 풀업부와; 제 1 또는 제 2 클럭바신호를 입력받아서 턴온 여부가 결정되며 Vdd와 QB노드 사이에 연결된 제 5 트랜지스터와, 상기 QB노드의 신호를 입력받아서 턴온 여부가 결정되며 상기 Q노드와 접지전압단 사이에 연결된 제 6 트랜지스터와, 다음단 출력을 입력받아서 턴온 여부가 결정되며 상기 Q노드와 접지전압단 사이에 연결된 제 7 트랜지스터로 구성된 풀다운 구동부와; 상기 QB노드 신호를 입력받아서 턴온 여부가 결정되며 상기 게이트 출력 신호단과 접지전압단 사이에 연결된 제 8 트랜지스터로 구성된 풀다운부로 구성됨을 특징으로 한다.

[0058] 상기 쉬프트 레지스터의 각 트랜지스터는 비정질 실리콘 트랜지스터로 구성됨을 특징으로 한다.

[0059] 상기 구성을 갖는 본 발명에 따른 액정표시장치의 구동방법은 하부기판 상에 수평방향(행방향)의 홀수번째 픽셀과 짝수번째 픽셀이 서로 인접하여 한쌍을 이루고 있고, 상기 수평방향으로 인접한 한쌍의 픽셀은 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있으며, 상기 수평방향의 픽셀들 사이에는 홀수번째와 짝수번째의 2개의 게이트라인이 일방향으로 배열되어 있는 픽셀 어레이부와, 상기 픽셀 어레이부의 좌, 우 양측에 구성되며, 제 1 내지 제 n 홀수 쉬프트 레지스터로 구성된 제 1 게이트 구동회로와, 제 1 내지 제 n 짝수 쉬프트 레지스터로 구성된 제 2 게이트 구동회로를 포함하여 구성된 액정표시장치의 구동방법에 있어서, 상기 제 1, 제 2 게이트 구동회로는 H/2의 시간 차이를 두고 제 1, 제 2 클럭신호(C1, C2)를 입력받아서 상기 픽셀 어레이부의 각 짝수번째 및 홀수번째 게이트라인에 각각 H/2의 시간차가 나는 게이트 출력 신호(G1\_odd, G1\_even)(G2\_odd, G2\_even),~, (GN\_odd, GN\_even)들을 독립적으로 출력시킴을 특징으로 한다.

[0060] 이하, 첨부 도면을 참조하여 본 발명의 바람직한 실시예에 따른 액정표시장치 및 그의 구동방법에 대하여 설명하면 다음과 같다.

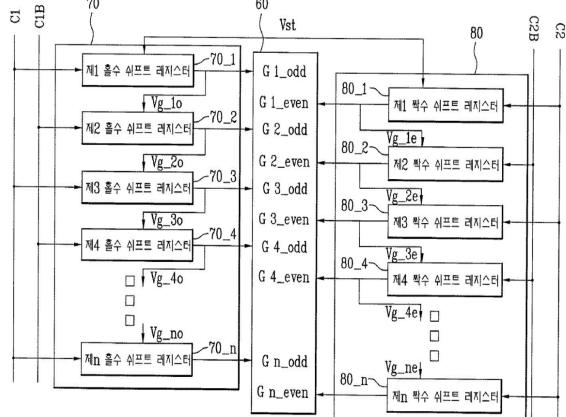

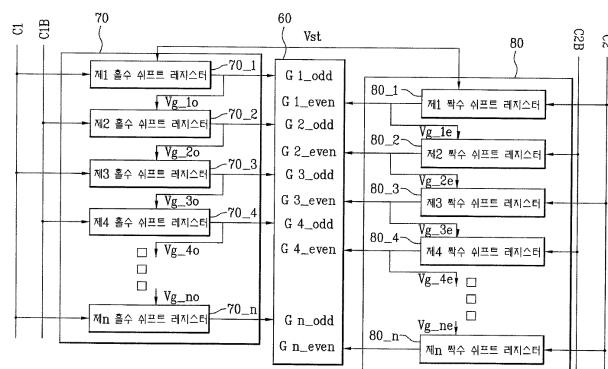

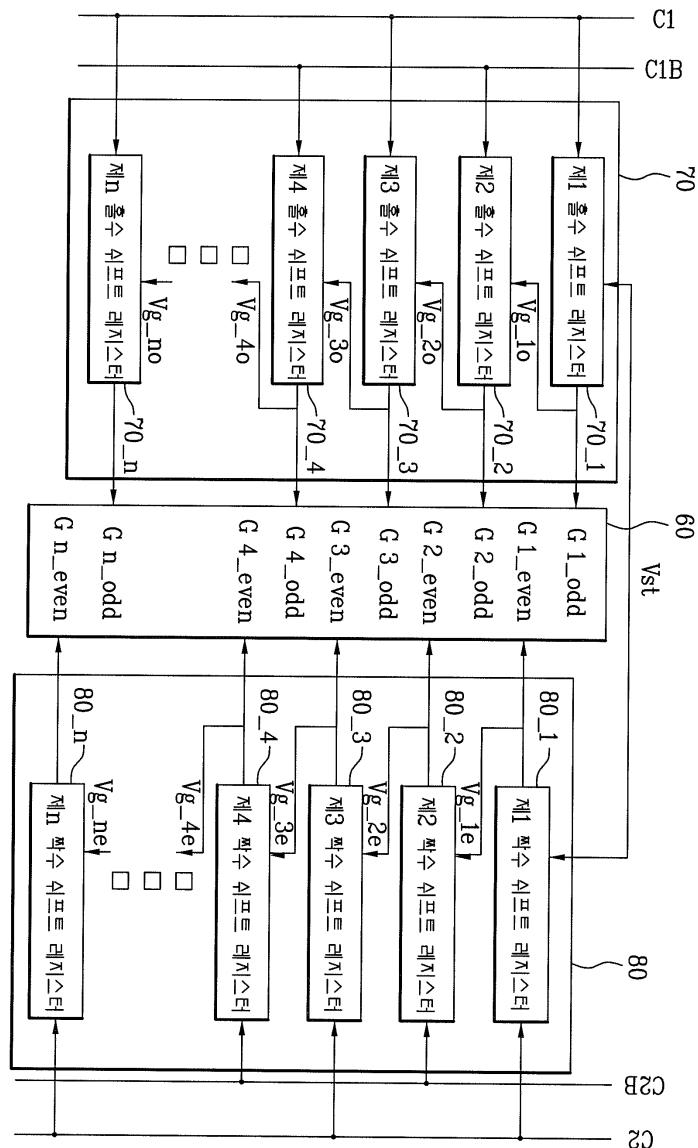

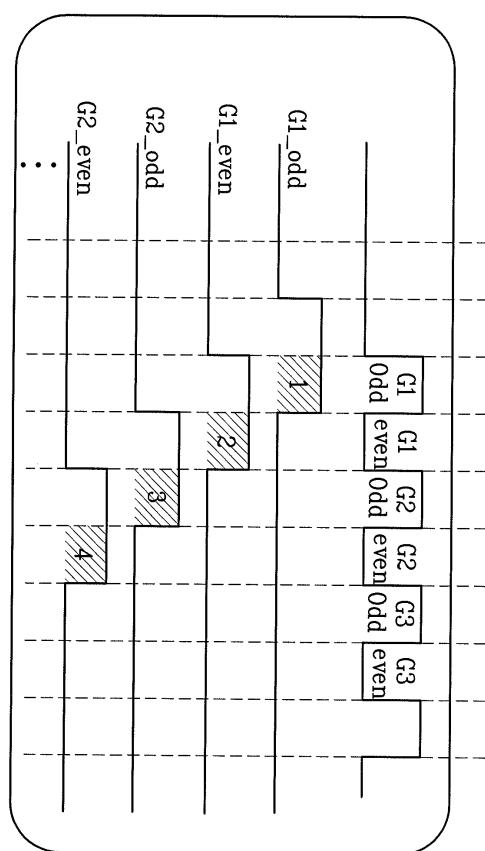

[0061] 도 6은 본 발명의 실시예에 따른 액정표시장치의 구성 블록도이고, 도 7은 도 6의 각 쉬프트 레지스터의 회로 구성도이며, 도 8은 도 6의 셀 어레이 구성 블록도이다.

[0062] 본 발명의 일실시예에 따른 액정표시장치는, 하부기판의 좌우 양측 상부에 게이트 구동회로가 내장되어 있으며, 데이터 라인 쉐어링(Data Line Sharing:DLS) 기술을 구현하기 위한 것으로, 도 6에 도시한 바와 같이, 픽셀 어레이부(60)와, 상기 픽셀 어레이부(60)의 좌우 양측에 각각 배치된 제 1, 제 2 게이트 구동회로(70, 80)로 구성된다.

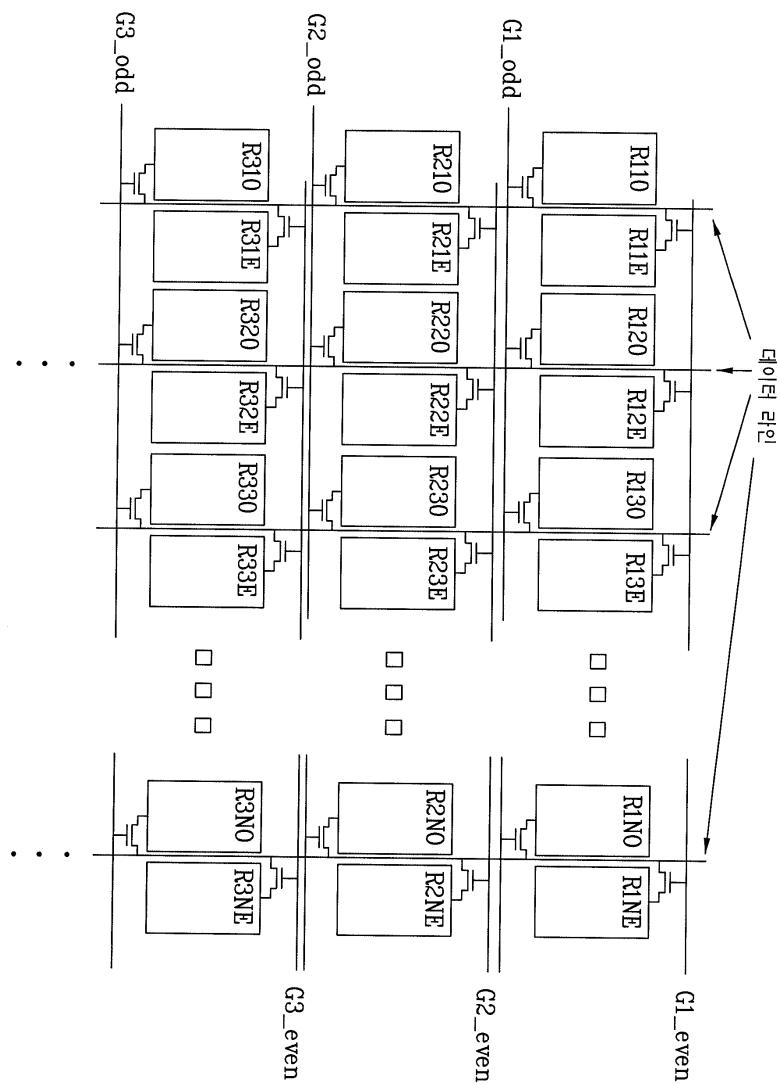

[0063] 상기 픽셀 어레이부(60)는 도 8에 도시된 바와 같이, 수평방향(행방향)의 홀수번째 픽셀과 짝수번째 픽셀이 서로 인접하여 한쌍을 이루고 있고, 상기 수평방향으로 인접한 한쌍의 픽셀은 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있으며, 상기 수평방향의 픽셀들 사이에는 홀수번째와 짝수번째의 2개의 게이트라인이 일방향으로 배열되어 있다.

[0064] 각 픽셀에는 데이터 신호를 인가시키기 위한 스위칭소자(TFT)가 각각 접속되어 있고, 스위칭소자(TFT)의 드레인전극은 데이터라인에 접속되어 있고, 소오스전극은 각 픽셀 전극에 접속되어 있다. 즉, 상기 픽셀에 접속된 각각의 스위칭소자(TFT)는 수평방향의 홀수번째 픽셀의 TFT와 짝수번째 픽셀의 TFT로, 수평방향의 1표시라인에 할

당된 홀수번째와 짝수번째 게이트라인에 각각 접속되어 있다. 따라서, 게이트라인의 수는 수직방향의 핵셀수의 배가 된다.

- [0065] 또한, 상기와 같이 수평방향으로 인접한 한쌍의 핵셀이 수직방향(열방향)으로 배열된 1개의 데이터라인을 공용하고 있으면, 데이터라인의 수는 수평방향의 핵셀수의 절반이 된다.

- [0066] 그리고 제 1, 제 2 게이트 구동회로(70, 80)는 하부기판의 좌, 우측에 내장되어 있으며, 각각 상기 핵셀 어레이부(60)의 홀수번째(Odd)와 짝수번째(Even) 핵셀에 독립적으로 게이트 구동신호를 인가하도록 구성되어 있다.

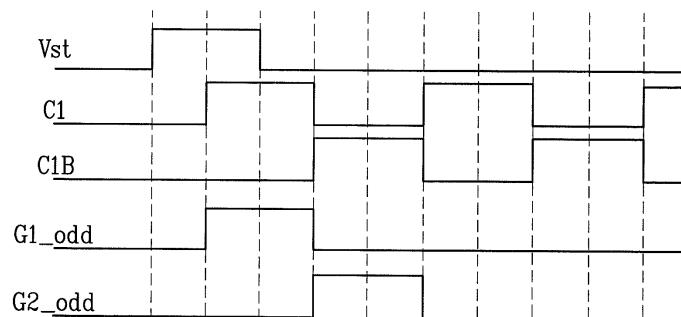

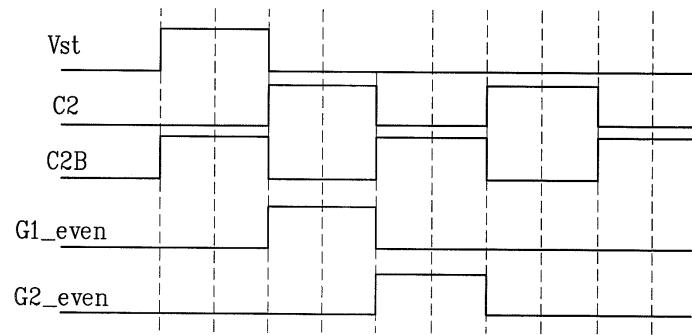

- [0067] 이때 제 1 게이트 구동회로(70)에는 Vst의 스캔 개시 신호와, C1과 C1B의 2상의 클럭신호와, VDD와 VSS 신호가 인가되고, 제 2 게이트 구동회로(80)에는 Vst의 스캔 개시 신호와, C2과 C2B의 2상의 클럭신호와, VDD와 VSS 신호가 인가되어 있다.

- [0068] 상기에서 핵셀 어레이부(60) 좌, 우 양측의 하부기판에 내장된 제 1, 제 2 게이트 구동회로(70, 80)는 각각 제 1 내지 제 n 홀수 쉬프트 레지스터(70\_1, ~, 70\_n)와, 제 1 내지 제 n 짝수 쉬프트 레지스터(80\_1, ~, 80\_n)로 구성되며, 각 게이트 구동회로를 구성하는 각 쉬프트 레지스터는 비정질 실리콘 트랜지스터로 구현된다.

- [0069] 상기 제 1 내지 제 n 홀수 쉬프트 레지스터(70\_1, ~, 70\_n)는 핵셀 어레이부(60)의 각 홀수번째(Odd) 게이트라인에 게이트 신호를 출력하고, 스캔 개시 신호(Vst) 또는 이전단 쉬프트 레지스터의 출력 신호와, C1과 C1B의 2상의 클럭신호와, VDD와 VSS 신호를 받아 동작한다. 이때 상기 제 1 홀수 쉬프트 레지스터(70\_1)는 스캔 개시 신호(Vst)를 받아 구동하도록 구성되었고, 상기 제 2 홀수 쉬프트 레지스터 내지 제 n 홀수 쉬프트 레지스터(70\_2, ~, 70\_n)는 순차적으로 이전단 쉬프트 레지스터의 출력 신호를 받아 구동하도록 구성되어 있다.

- [0070] 그리고 제 1 내지 제 n 짝수 쉬프트 레지스터(80\_1, ~, 80\_n)는 핵셀 어레이부(60)의 각 짝수번째(Even) 게이트라인에 게이트 신호를 출력하고, 스캔 개시 신호(Vst) 또는 이전단의 쉬프트 레지스터의 신호와, C2과 C2B의 2상의 클럭신호와, VDD와 VSS 신호를 받아 동작한다. 이때 상기 제 1 짝수 쉬프트 레지스터(70\_1)는 스캔 개시 신호(Vst)를 받아 구동하도록 구성되었고, 상기 제 2 짝수 쉬프트 레지스터 내지 제 n 짝수 쉬프트 레지스터(80\_2, ~, 80\_n)는 순차적으로 이전단 쉬프트 레지스터의 출력 신호를 받아 구동하도록 구성되어 있다.

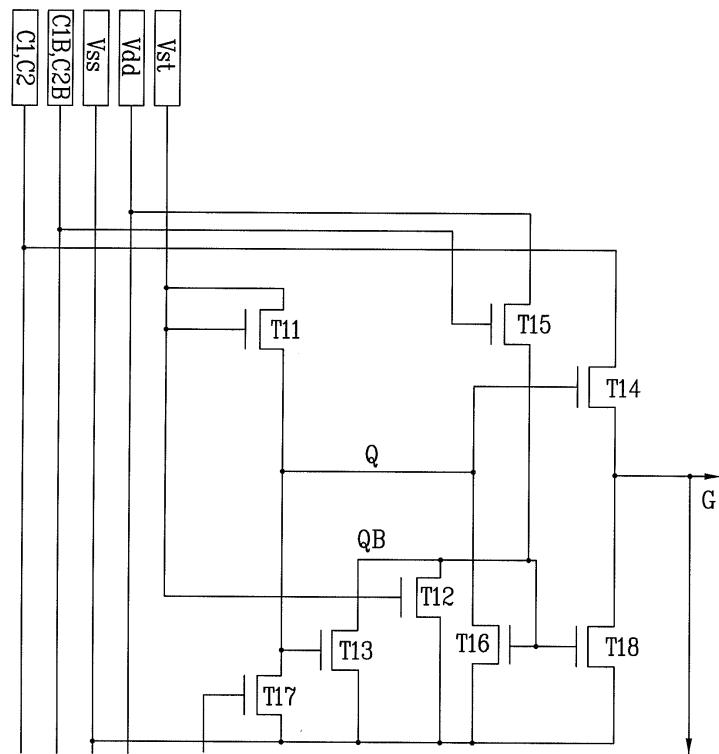

- [0071] 상기 제 1 내지 제 n 홀수 및 짝수 쉬프트 레지스터는, 도 7에 도시된 바와 같이, 제 1 내지 제 8 트랜지스터(T11~T18)로 구성되어 있는데, 각각 풀업 구동부와 풀다운 구동부와 풀업부와 풀다운부로 구성되어 있다. 그리고 제 1 내지 제 8 트랜지스터(T11~T18)은 비정질 실리콘 트랜지스터로 구성되어 있다.

- [0072] 풀업 구동부는 Vst 또는 이전단 쉬프트 레지스터의 출력 신호(이하, Vst를 예로 설명한다.)를 입력받아서 턴온 여부가 결정되며 Vst와 Q노드 사이에 다이오드 커넥팅된 제 1 트랜지스터(T11)와, Vst를 입력받아서 턴온 여부가 결정되며 일단이 접지전압단(Vss) 사이에 연결된 제 2 트랜지스터(T12)와, 상기 Q노드의 신호를 입력받아 턴온 여부가 결정되며 일단이 접지전압단 사이에 연결된 제 3 트랜지스터(T13)로 구성된다.

- [0073] 그리고 풀업부는 Q노드의 신호를 입력받아서 턴온 여부가 결정되며 제 1 또는 제 2 클럭 신호(C1, C2) 입력단과 게이트 출력 신호단(G) 사이에 연결된 제 4 트랜지스터(T14)로 구성된다.

- [0074] 그리고 풀다운 구동부는 제 1 또는 제 2 클럭바신호(C1B, C2B)를 입력받아서 턴온 여부가 결정되며 Vdd와 QB노드 사이에 연결된 제 5 트랜지스터(T15)와, QB노드의 신호를 입력받아서 턴온 여부가 결정되며 Q노드와 접지전압단 사이에 연결된 제 6 트랜지스터(T16)와, 다음단 출력을 입력 받아서 턴온 여부가 결정되며 Q노드와 접지전압단(Vss) 사이에 연결된 제 7 트랜지스터(T17)로 구성된다.

- [0075] 그리고 풀다운부는 QB노드 신호를 입력받아서 턴온 여부가 결정되며 게이트 출력 신호단(G)과 접지전압단 사이에 연결된 제 8 트랜지스터(T18)로 구성된다.

- [0076] 상기에서 제 1, 제 2 게이트 구동회로(70, 80)를 구성하는 도 7에 도시된 각 쉬프트 레지스터의 회로 구성은 일 예로써, 이와 다른 다양한 회로적 구성이 가능하다.

- [0077] 이하, 상기 구성을 갖는 본 발명의 실시예에 따른 액정표시장치의 구동방법에 대하여 설명하기로 한다.

- [0078] 도 9a와 도 9b는 본 발명의 게이트 구동을 위한 양방향으로 내장된 게이트 구동회로의 타이밍도이고, 도 10은 본 발명에 따른 데이터라인 및 게이트라인의 출력 타이밍도이다.

- [0079] 상기 구성을 갖는 본 발명의 실시예에 따른 액정표시장치는, 수평방향으로 배열된 핵셀 사이에 배열된 홀수번째와 짝수번째의 2개의 게이트라인이 내장된 2개의 제 1, 제 2 게이트 구동회로(70, 80)에 의해 순차 구동하는데,

이때 제 1, 제 2 게이트 구동회로(70, 80)는 각각 홀수번째와 짝수번째 픽셀을 독립적으로 구동시킨다.

[0080] 예를 들어 제 1 홀수 쉬프트 레지스터(70\_1)의 출력 신호를 받아서 수평 방향의 첫 번째 라인의 홀수번째 픽셀들이 구동되고, 다음에 제 2 짝수 쉬프트 레지스터(80\_1)의 출력 신호를 받아서 첫 번째 라인의 짝수번째 픽셀들이 구동된다.

[0081] 좀더 자세히 설명하면, 도 9a와 도 9b, 도 10에 도시한 바와 같이, 제 1, 제 2 게이트 구동회로(70, 80)를 구성시키기 위한 제 1, 제 2 클럭신호(C1,C2)는 H/2의 시간 차이를 두고 입력되어 H/2의 시간차가 나는 게이트 출력신호((G1\_odd, G1\_even)(G2\_odd, G2\_even),~, (GN\_odd, GN\_even))를 발생시킨다. 이때 제 1 게이트 구동회로(70)는 Vst, C1, C1B, Vdd, Vss 신호를 받아 구동하고, 제 2 게이트 구동회로(80)는 Vst, C2, C2B, Vdd, Vss의 신호에 의해 구동한다.

[0082] 예를 들어, 제 1 게이트 구동회로(70)로부터 픽셀 어레이부(60)의 제 1 홀수번째 게이트라인에 G1\_odd 신호가 입력되는 경우, 첫 번째 수평 라인의 홀수번째 픽셀들(R110, R120,~,R1NO)에 연결된 스위칭 소자(TFT)들이 턴온되고, 턴온된 스위칭 소자(TFT)를 통해 데이터 신호가 각 홀수번째 픽셀들(R110, R120,~,R1NO)에 기록된다.

[0083] 이후에 H/2 시간 후, 제 2 게이트 구동회로(80)로부터 픽셀 어레이부(60)의 제 1 짝수번째 게이트라인에 G1\_even 신호가 입력되는 경우, 첫 번째 수평 라인의 짝수번째 픽셀들(R11E, R12E,~,R1NE)에 연결된 스위칭 소자(TFT)들이 턴온되고, 턴온된 스위칭 소자들을 통해 데이터 신호가 각 짝수번째 픽셀들(R11E, R12E,~,R1NE)에 기록된다.

[0084] 상기와 같은 방법으로 픽셀 어레이부의 각 픽셀들에 데이터가 기록된다.

[0085] 이와 같이 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하는 제 1, 제 2 게이트 구동회로(70, 80)가 내장되어 있고 이를 이용하여 구동시킬 경우, 데이터 라인 쉐어링(DLS)에 따른 게이트 구동 속도의 증가는 별도로 증가시킬 필요가 없다.

[0086] 부연 설명하면, 종래에는 데이터 라인 쉐어링(DLS) 구동을 할 경우, 게이트 라인이 2배로 증가함에 따라 1프레임동안 구동해야 하는 게이트 구동속도가 2배로 증가해야 했다. 이와 같은 게이트 구동 속도의 증가는 하부기판에 내장된 비정질 실리콘 트랜지스터로 구성된 쉬프트 레지스터를 이용할 경우 그 구동에 어려움이 따르게 된다.

[0087] 그러나, 본 발명에서와 같이 하부기판의 좌, 우 양측에 독립적으로 구동하도록 내장된 제 1, 제 2 게이트 구동회로(70, 80)를 이용하여 데이터 라인 쉐어링(DLS) 구동을 하면, 게이트 구동속도의 증가없이 구동시키는 것이 가능하며, 동시에 도 9a, 도 9b 및 도 10에서와 같이 각 구동회로의 출력을 오버랩시켜 구동시킬 수 있으므로, 구동회로의 출력 파형의 늘어짐에 따른 픽셀 유효 충전시간의 확보가 용이하다. 상기에서 오버랩 영역은 최대 50%까지 조절 가능하다.

[0088] 상기에서 내장 게이트 구동회로는 2상 이상의 모든 구동회로로 구현 가능하다.

[0089] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술 사상을 이탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다.

[0090] 따라서, 본 발명의 기술 범위는 상기 실시예에 기재된 내용으로 한정되는 것이 아니라, 특히 청구의 범위에 의하여 정해져야 한다.

### 발명의 효과

[0091] 상기와 같은 본 발명의 액정표시장치 및 그의 구동방법은 다음과 같은 효과가 있다.

[0092] 첫째, 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하는 제 1, 제 2 게이트 구동회로가 내장되어 있으므로, 게이트 구동속도의 증가없이 픽셀의 구동이 가능하다.

[0093] 둘째, 픽셀 어레이부의 좌, 우 양측에 독립적으로 구동하도록 내장된 제 1, 제 2 게이트 구동회로를 이용하여 데이터 라인 쉐어링(DLS) 기술을 구현할 경우, 게이트 구동을 위한 외부 구동 IC 없이 또한, 픽셀 유효 충전시간을 줄이지 않으면서 데이터라인의 수를 반감시킬 수 있다.

### 도면의 간단한 설명

[0001] 도 1은 일반적인 액정표시장치의 블록 구성도

- [0002] 도 2와 도 3은 종래 기술에 따른 액정표시장치의 구성도 및 그 구동 과정도

- [0003] 도 4와 도 5는 종래의 다른 기술에 따른 액정표시장치의 회로 구성도 및 그 구동 과정도

- [0004] 도 6은 본 발명의 실시예에 따른 액정표시장치의 구성 블록도

- [0005] 도 7은 도 6의 각 쉬프트 레지스터의 회로 구성도

- [0006] 도 8은 도 6의 셀 어레이 구성을 나타낸 구성 블록도

- [0007] 도 9a와 도 9b는 본 발명의 게이트 구동을 위한 양방향으로 내장된 게이트 구동회로의 타이밍도

- [0008] 도 10은 본 발명에 따른 데이터라인 및 게이트라인의 출력 타이밍도

- [0009] \* 도면의 주요 부분에 대한 부호의 설명 \*

- [0010] 60 : 픽셀 어레이부 70 : 제 1 게이트 구동회로

- [0011] 80 : 제 2 게이트 구동회로

### 도면

#### 도면1

## 도면2

દોર્ય 3

도면4

## 도면5

도면6

도면7

도면8

도면9a

도면9b

도면10

|                |                                                                           |         |            |

|----------------|---------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器及其驱动方法                                                               |         |            |

| 公开(公告)号        | <a href="#">KR101074402B1</a>                                             | 公开(公告)日 | 2011-10-17 |

| 申请号            | KR1020040076457                                                           | 申请日     | 2004-09-23 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                  |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                 |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                 |         |            |

| [标]发明人         | KIM BINN<br>김빈<br>MOON SUHWAN<br>문수환<br>YOON SOOYOUNG<br>윤수영              |         |            |

| 发明人            | 김빈<br>문수환<br>윤수영                                                          |         |            |

| IPC分类号         | G09G3/36 G09G                                                             |         |            |

| CPC分类号         | G09G2300/0426 G09G2300/0408 G09G3/3677 G11C19/184 G09G2310/0205 G11C19/28 |         |            |

| 代理人(译)         | 金勇<br>年轻的小公园                                                              |         |            |

| 其他公开文献         | KR1020060027593A                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                 |         |            |

### 摘要(译)

根据本发明的一个方面，提供了一种能够使用双向内置栅极驱动电路将数据线的数量减半的液晶显示装置及其驱动方法，具有多个像素的像素阵列部分配对，使得在基板上沿水平方向排列的相邻像素共享相同的数据线；由第一至第n奇数移位寄存器组成的第一栅极驱动电路和由第一至第n偶数移位寄存器组成的第二栅极驱动电路，以独立驱动像素阵列部分的左右两侧它表征。