**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

G02F 1/133

(45) 공고일자 2005년03월23일

(11) 등록번호 10-0478170

(24) 등록일자 2005년03월11일

---

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2002-0011276 | (65) 공개번호 | 10-2002-0071457 |

| (22) 출원일자 | 2002년03월04일     | (43) 공개일자 | 2002년09월12일     |

---

(30) 우선권주장 JP-P-2001-00059394 2001년03월05일 일본(JP)

(73) 특허권자 히다치디바이스 엔지니어링가부시키가이샤

일본국 지바켄 모바라시 하야노 3681

가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

(72) 발명자 이사미히로노부

일본도쿄도지요다꾸마루노우찌1초메5-1신마루노우찌빌딩가부시

키가이샤히타치세이사쿠쇼지적재산권본부내

다께모또이와오

일본도쿄도지요다꾸마루노우찌1초메5-1신마루노우찌빌딩가부시

키가이샤히타치세이사쿠쇼지적재산권본부내

미야자와도시오

일본도쿄도지요다꾸마루노우찌1초메5-1신마루노우찌빌딩가부시

키가이샤히타치세이사쿠쇼지적재산권본부내

마쓰모또가쓰미

일본지바켄모바라시하야노3681히다치디바이스엔지니어링가부시키

가이샤내

(74) 대리인 장수길

구영창

심사관 : 김정훈

---

**(54) 계조 전압 선택 회로를 구비하는 액정 표시 장치**

---

**요약**

액정 표시 장치는, 표시 데이터에 기초하여, 시간에 따라 주기적으로 변화하는 외부 계조 전압으로부터 전압 레벨을 선택하기 위한 회로를 갖는다. 회로는 복수의 연산 회로의 직렬 결합을 포함한다. 직렬 결합 각각은 화소에 결합된 영상 신호선 중 하나와 연관되고, 상기 복수의 직렬 결합 각각의 연산 회로들 각각은 표시 데이터를 공급하기 위한 N개의 표시 데이터선 각각 및 계조 전압에 동기하여 변하는 시간 제어 신호를 공급하는 복수의 시간 제어 신호선 각각에 연관된다. 연산 회로들 각각은 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 설치된다. 시간 제어 신호는 계조 전압의 하나의 레벨을 유일하게 결정한다.

**대표도**

도 5

색인어

액정 표시 장치, 전압 선택 회로, 계조 전압, 연산 회로, 시간 제어 신호선, 표시 데이터선

## 명세서

### 도면의 간단한 설명

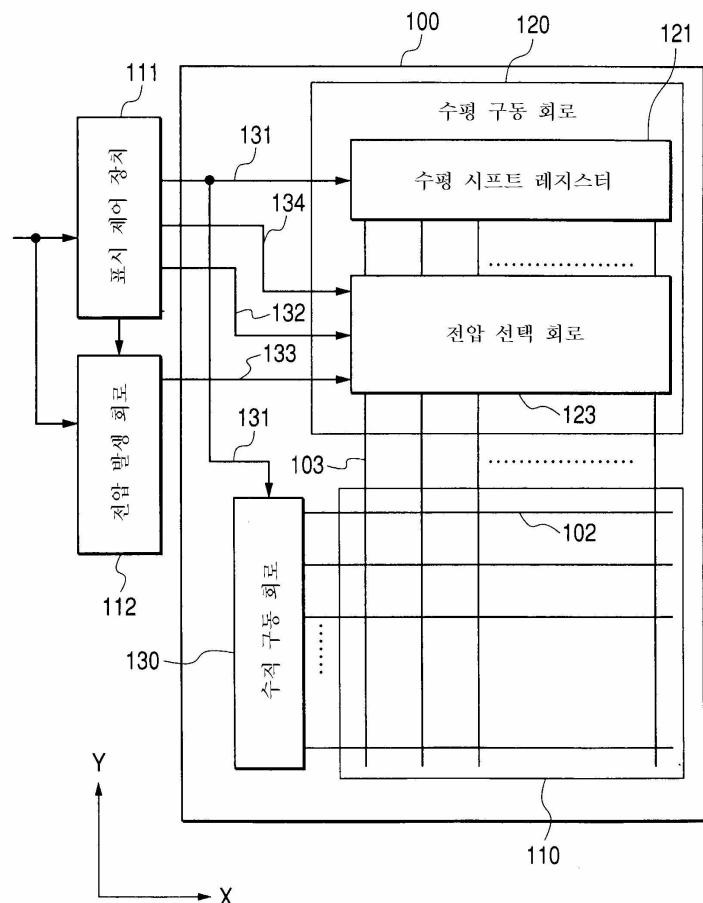

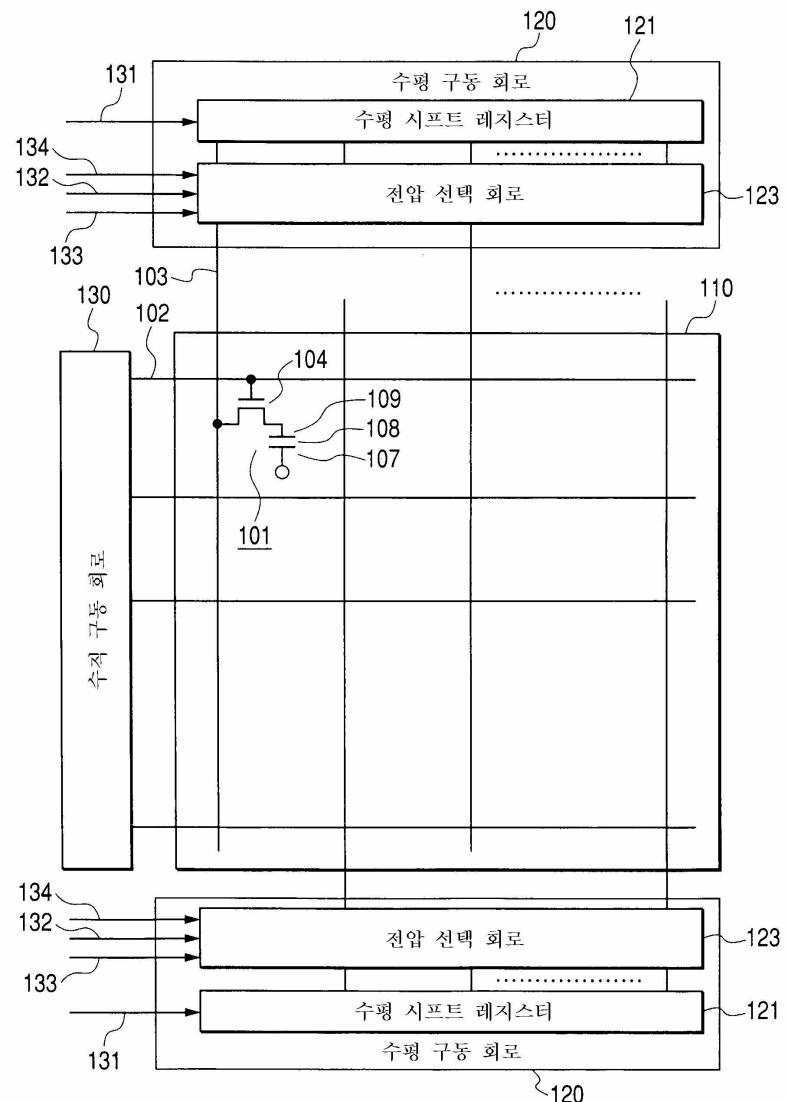

도 1은 본 발명에 따른 액정 표시 장치의 일 실시예의 개략적인 전체 구성을 도시하는 블럭도.

도 2는 본 발명에 따른 액정 표시 장치의 액정 표시 패널의 등가 회로도.

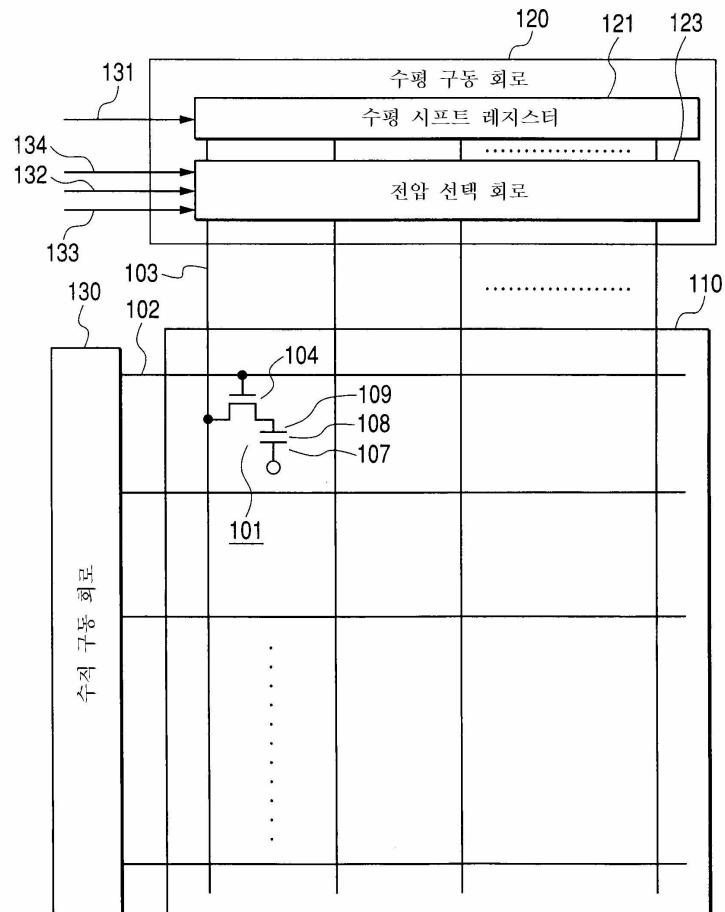

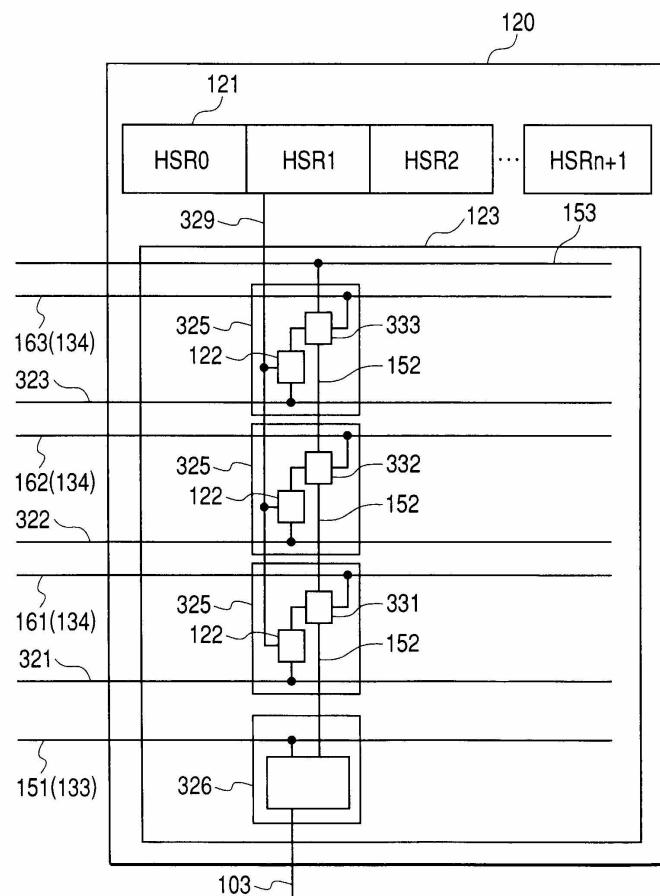

도 3은 본 발명의 일 실시예에 따른 액정 표시 장치의 수평 구동 회로 및 표시부의 개략적인 구성을 설명하기 위한 블럭도.

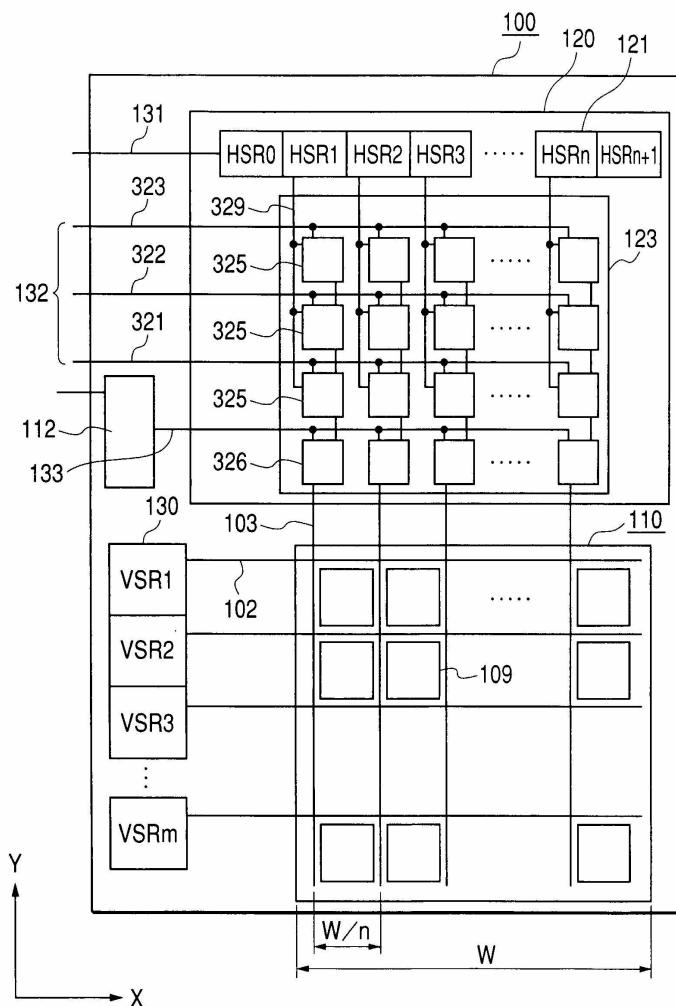

도 4는 본 발명의 일 실시예에 따른 액정 표시 장치의 수평 구동 회로의 개략적인 구성을 설명하기 위한 블럭도.

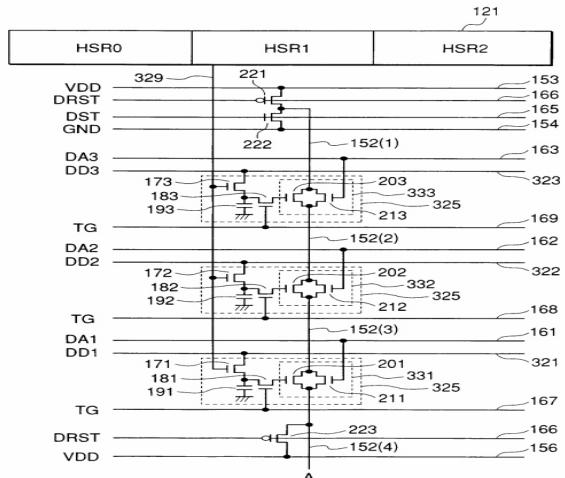

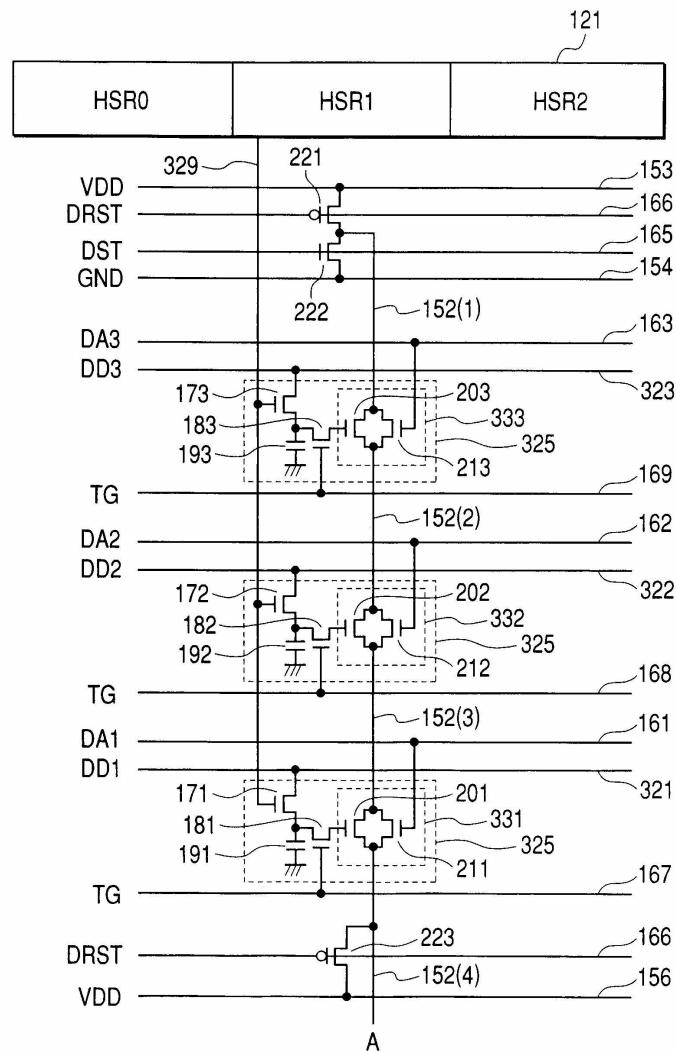

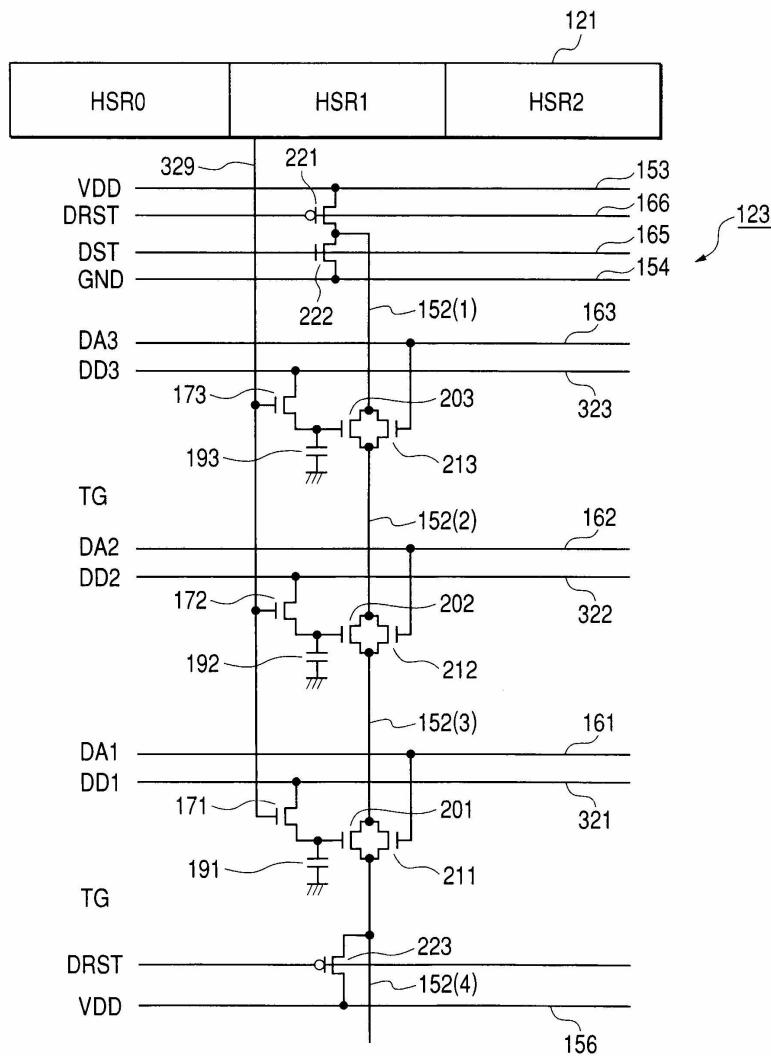

도 5는 본 발명의 일 실시예에 따른 액정 표시 장치의 전압 선택 회로의 개략적인 구성을 설명하기 위한 회로도.

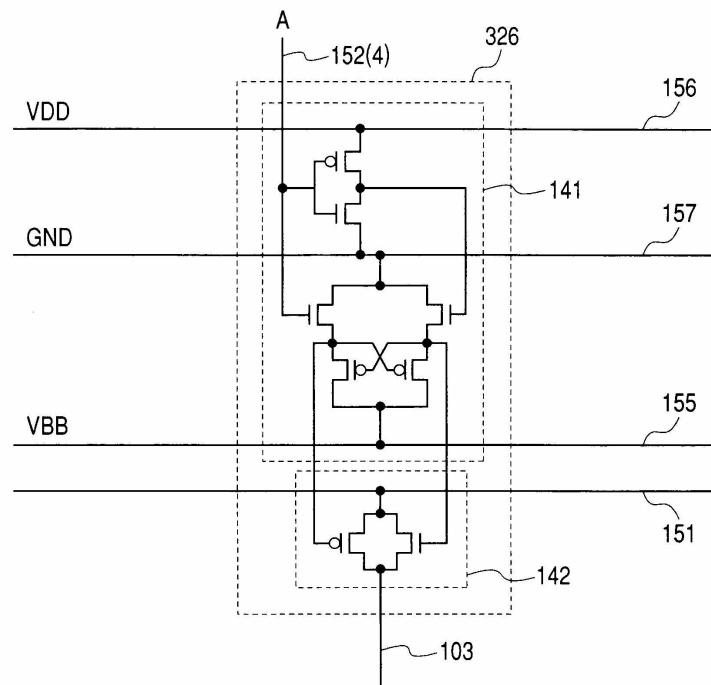

도 6은 본 발명의 일 실시예에 따른 액정 표시 장치의 전압 선택 회로의 개략적인 구성을 설명하기 위한 회로도.

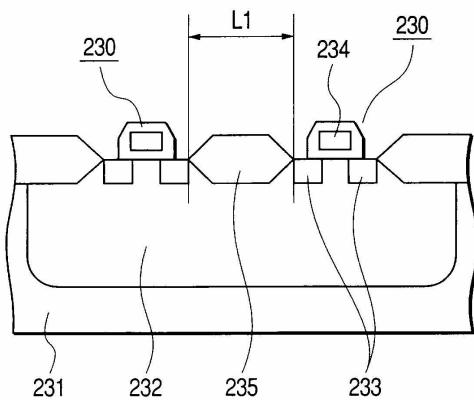

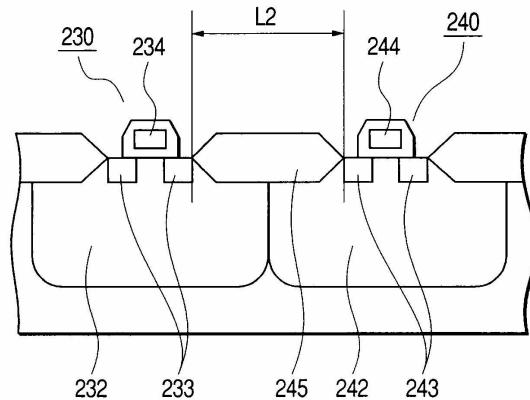

도 7a 및 도 7b는 2개의 트랜지스터가 인접하여 형성되어 있는 2개의 상이한 종래 구조에 대한 개략적인 단면도.

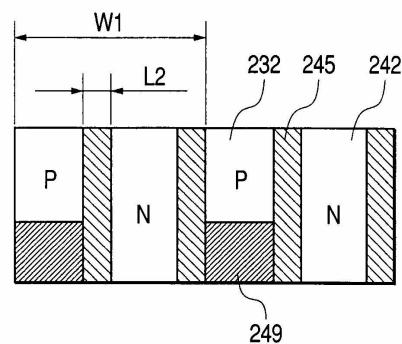

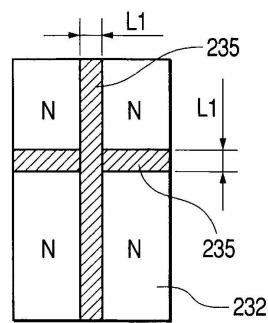

도 8a~8c는 2개의 트랜지스터에 대한 3가지의 상이한 배열과 트랜지스터들에 의해 점유되는 영역을 각각 도시한 개략적인 평면도.

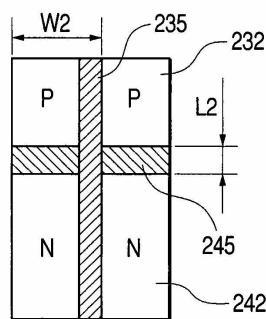

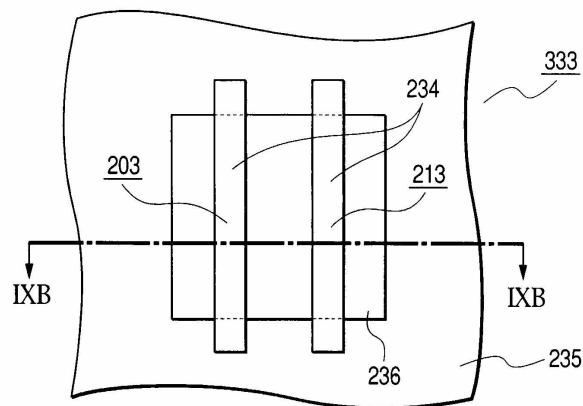

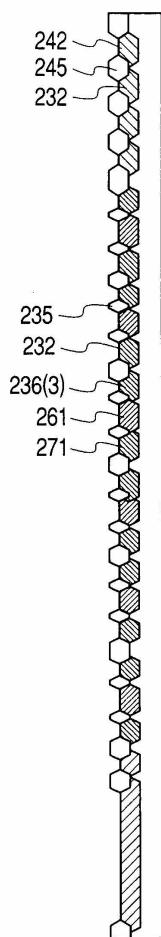

도 9a는 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 2개의 소자의 레이아웃을 나타내는 개략적인 평면도이고, 도 9b는 도 9a의 IXB-IXB선을 따른 개략적인 단면도.

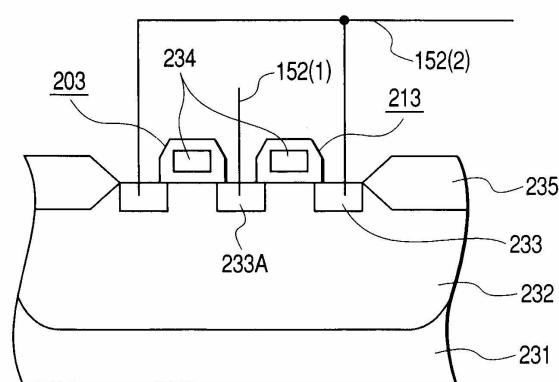

도 10은 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 연산 회로의 레이아웃을 나타내는 개략적인 평면도.

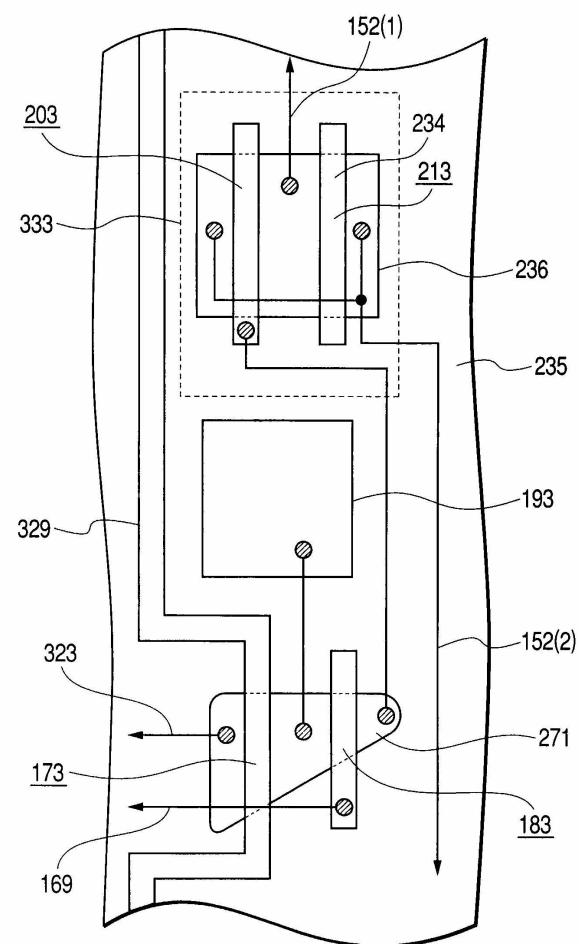

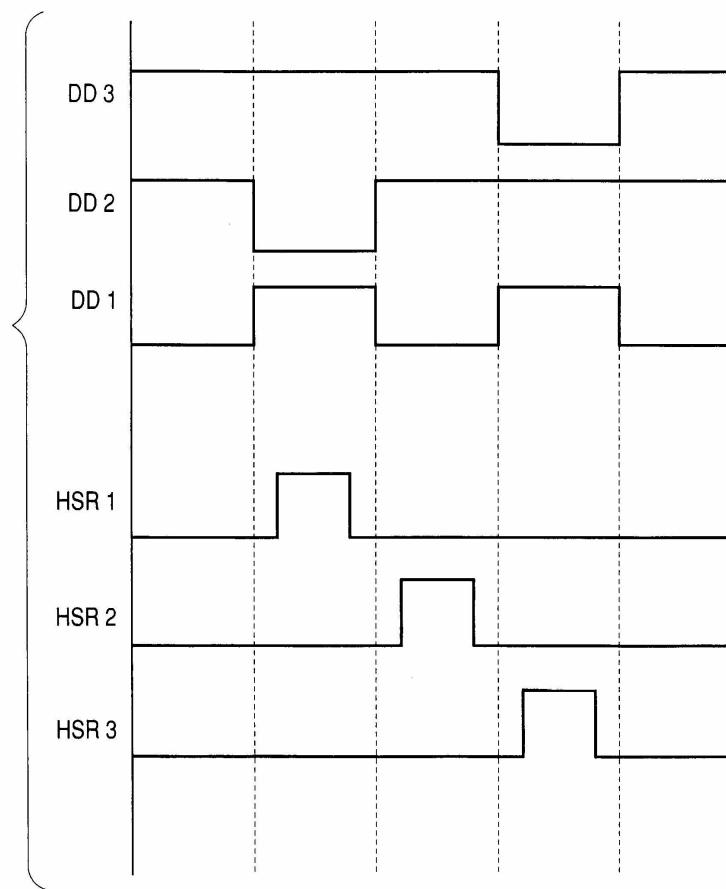

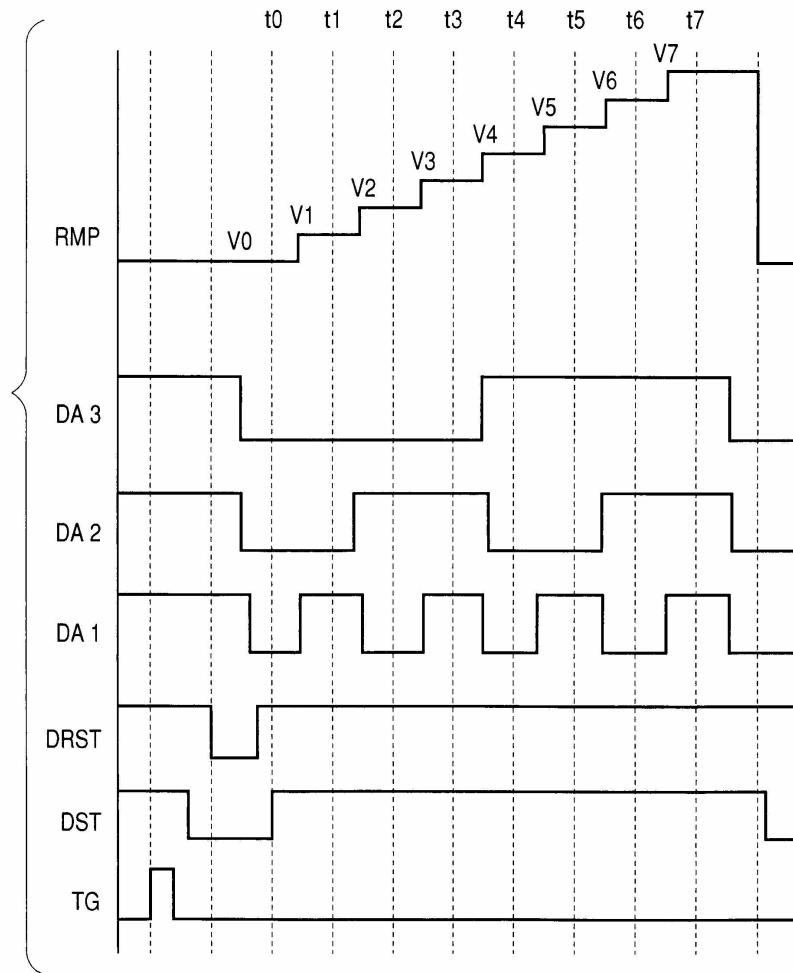

도 11은 본 발명의 일 실시예에 따른 액정 표시 장치의 동작을 설명하기 위해 표시 데이터 및 타이밍 신호의 파형을 나타내는 도면.

도 12는 본 발명의 일 실시예에 따른 액정 표시 장치의 동작을 설명하기 위해 계조 전압, 시간 제어 신호 및 타이밍 신호의 파형을 도시하는 도면.

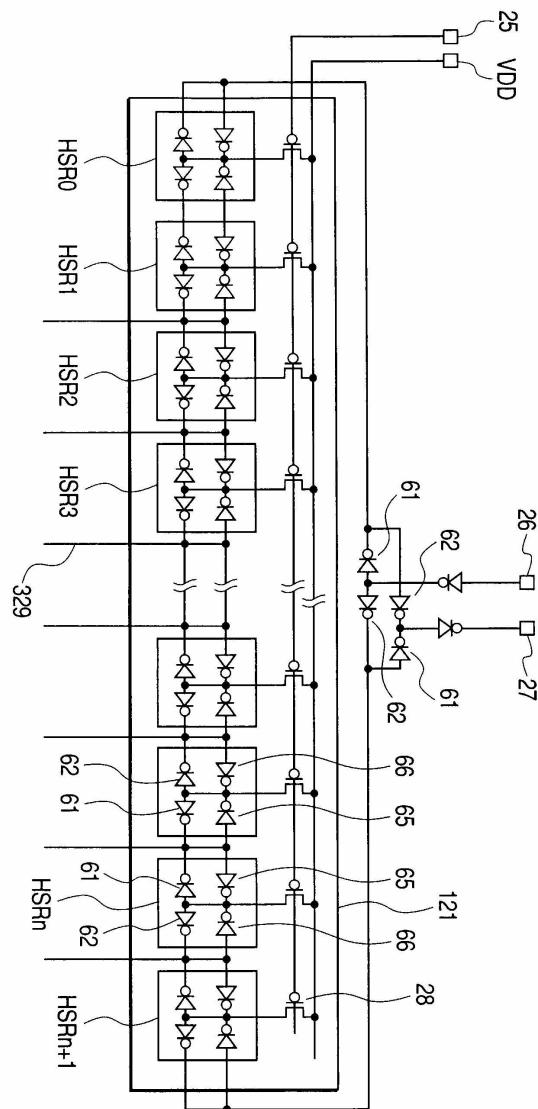

도 13은 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 시프트 레지스터의 개략적인 회로도.

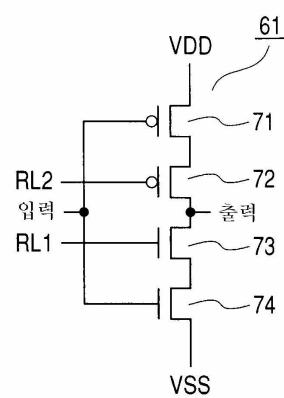

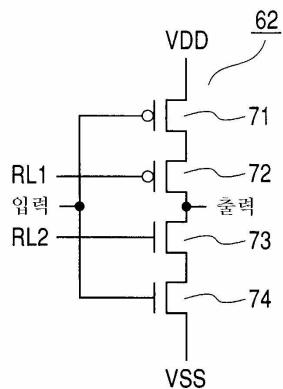

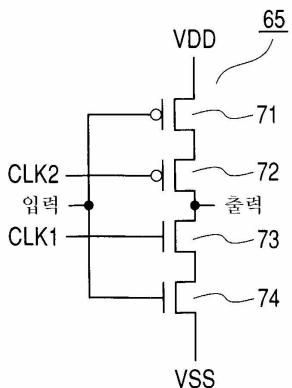

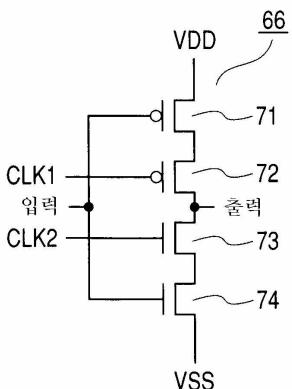

도 14a~14d는 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 4개의 클럭드 인버터의 개략적인 회로도.

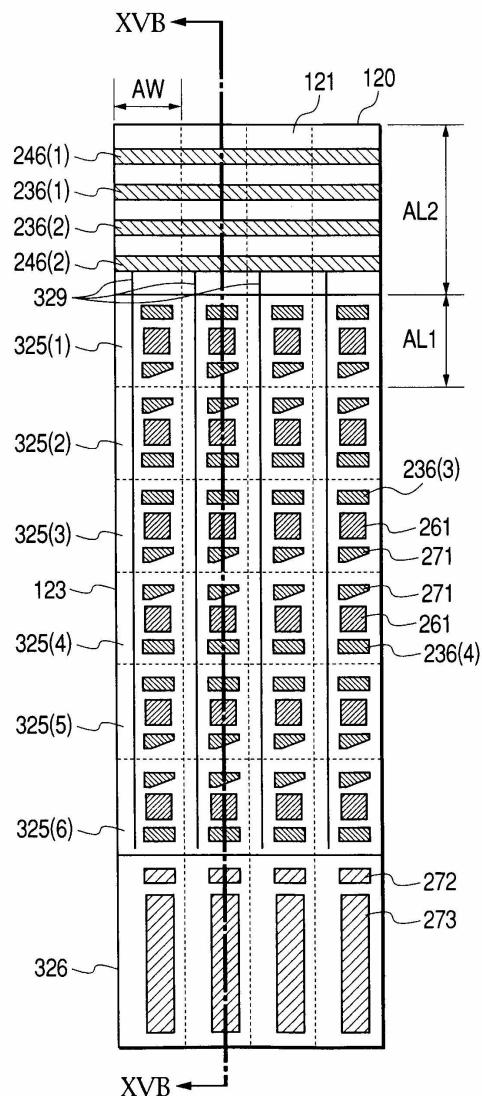

도 15a는 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 수평 구동 회로를 형성하는 트랜지스터의 레이아웃을 나타내는 개략적인 평면도이고, 도 15b는 XVB-XVB선을 따른 개략적인 단면도.

도 16은 본 발명의 실시예에 따른 액정 표시 장치에 이용되는 2 시스템 수평 구동 회로의 개략적인 구성을 설명하기 위한 블럭도.

도 17은 본 발명의 일 실시예에 따른 액정 표시 장치에 이용되는 수평 구동 회로의 개략적인 회로도.

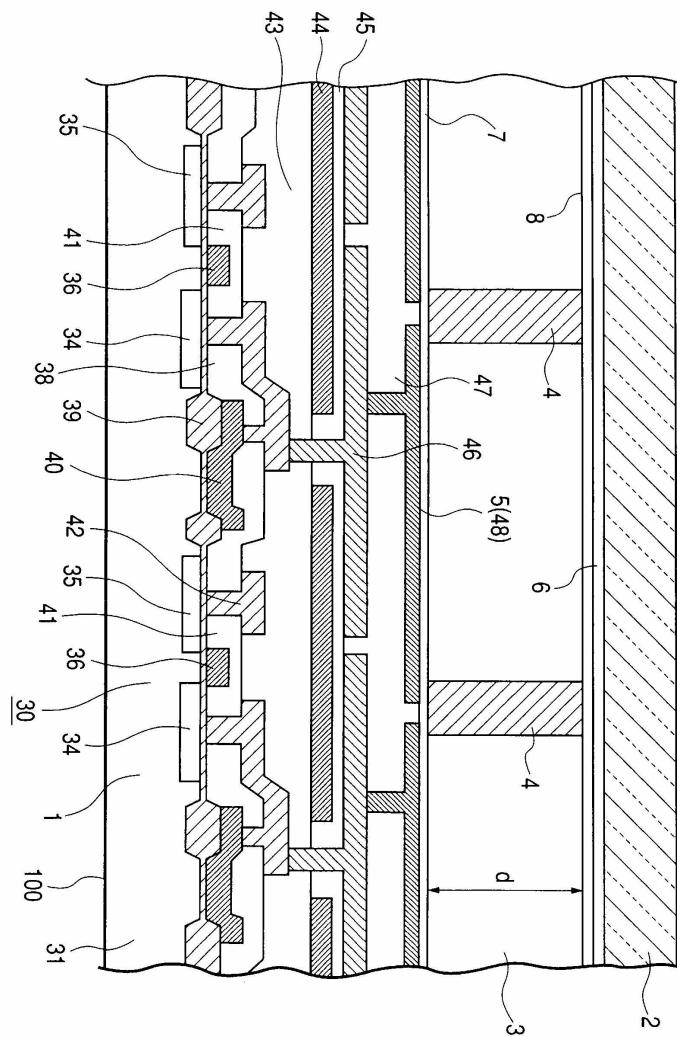

도 18은 본 발명의 일 실시예에 따른 액정 표시 장치 내의 화소부의 개략적인 단면도.

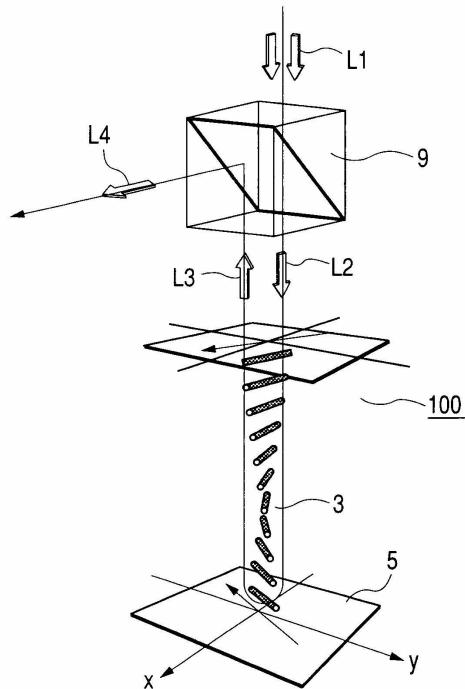

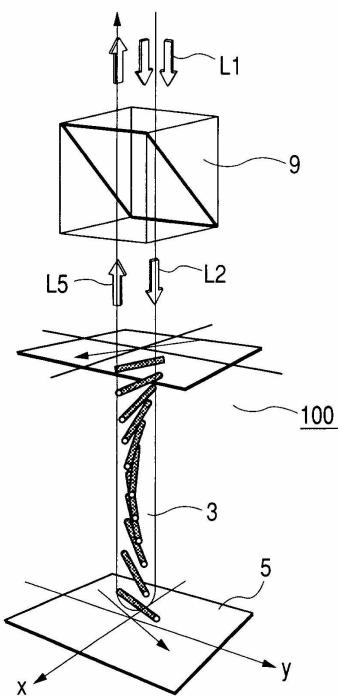

도 19a 및 19b는 본 발명의 일 실시예에 따른 액정 표시 장치에 공급되는 단일 편광판 트위스티드 네마틱 모드의 필드-오프 및 필드-오프 상태를 도시한 도면.

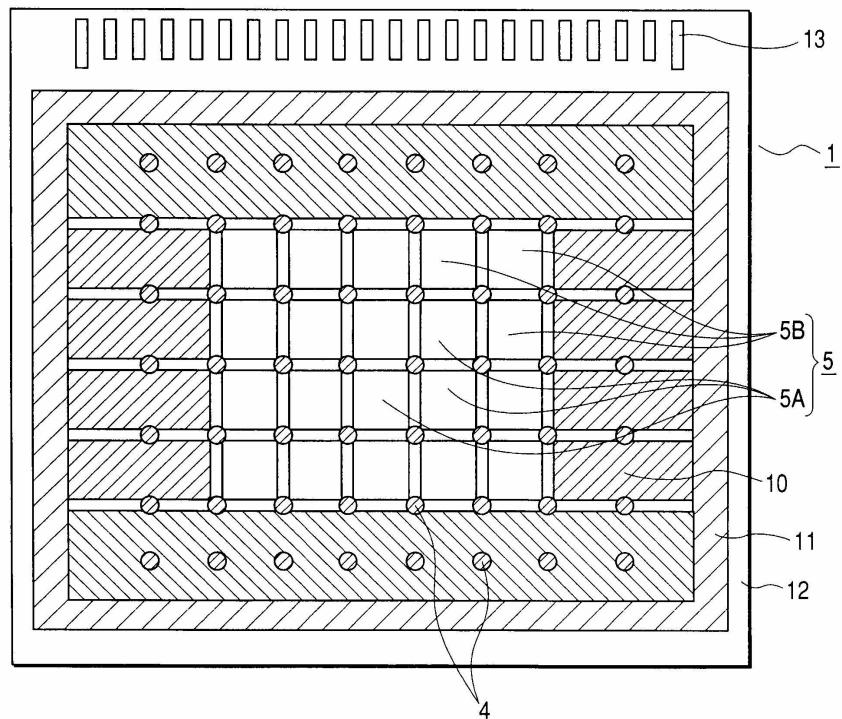

도 20은 본 발명의 일 실시예에 따른 액정 표시 장치의 구동 회로 기판 상에 배치되는 반사 전극 및 스페이서의 배열을 도시하는 개략적인 평면도.

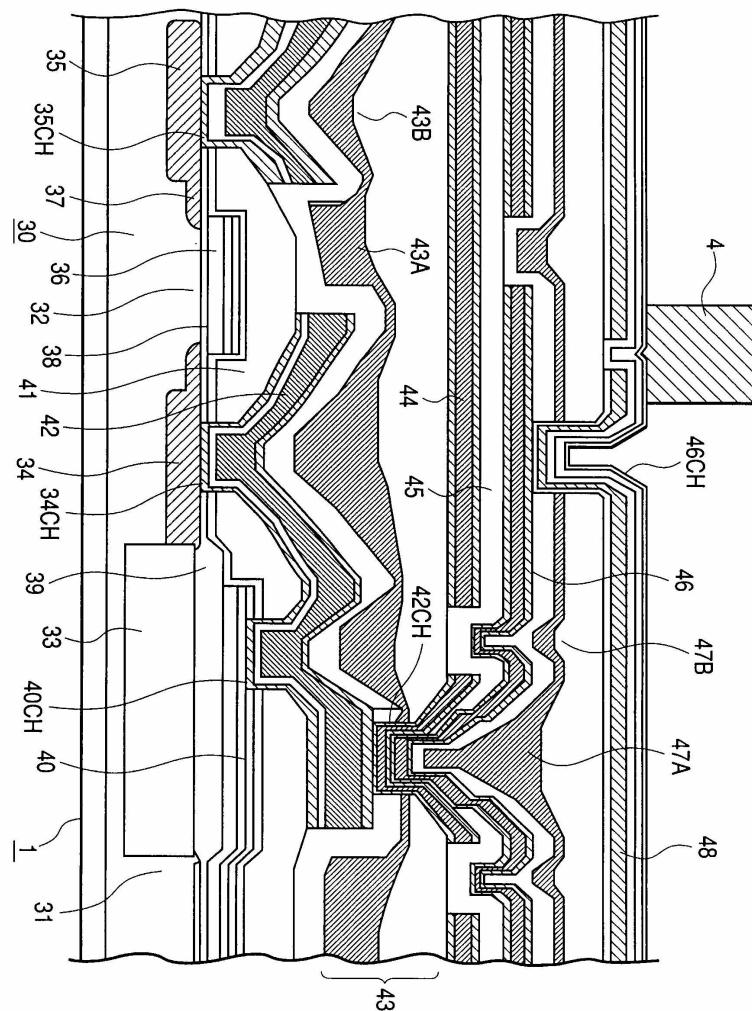

도 21은 본 발명의 일 실시예에 따른 액정 표시 장치의 능동 소자와 그 부근을 도 20의 XXI-XXI선을 따라 나타낸 개략적인 단면도.

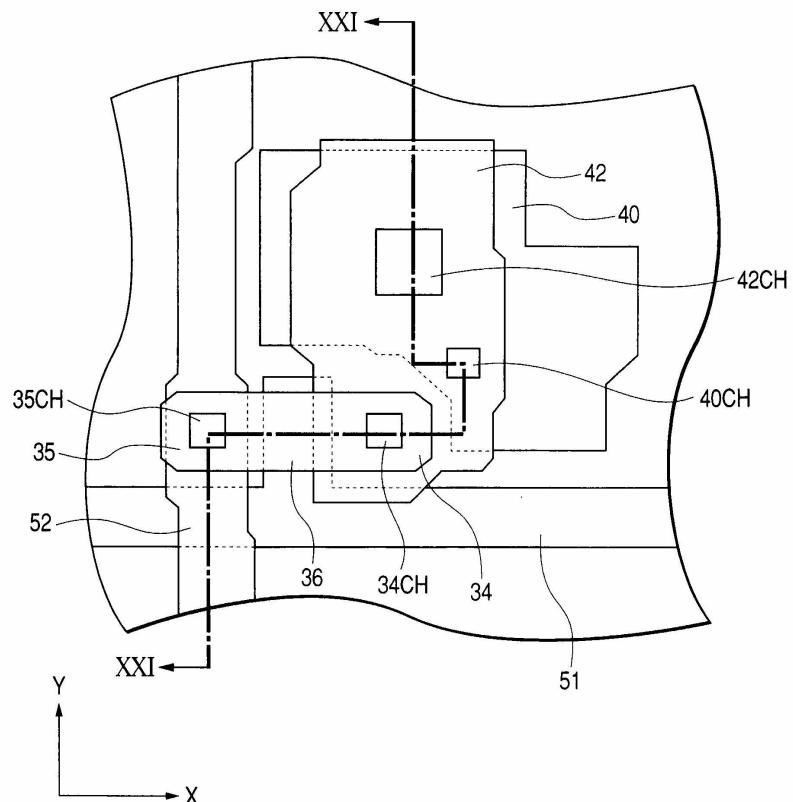

도 22는 본 발명의 일 실시예에 따른 액정 표시 장치의 능동 소자 및 그 부근의 개략적인 평면도.

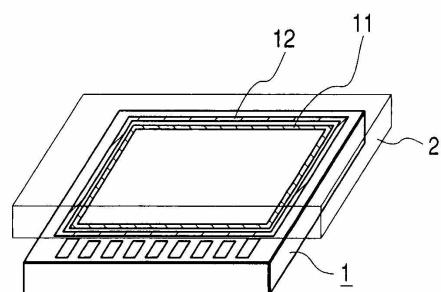

도 23은 본 발명의 일 실시예에 따른 액정 표시 장치의 투명 기판에 정합된 구동 회로 기판의 개략적인 사시도.

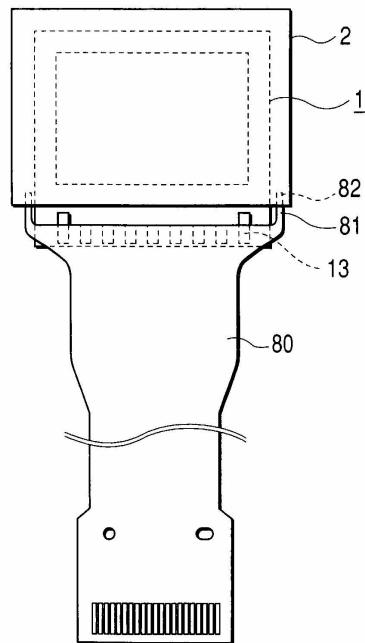

도 24는 본 발명의 일 실시예에 따른 액정 표시 장치의 플렉시블 배선판이 결합된 액정 표시 패널의 개략적인 평면도.

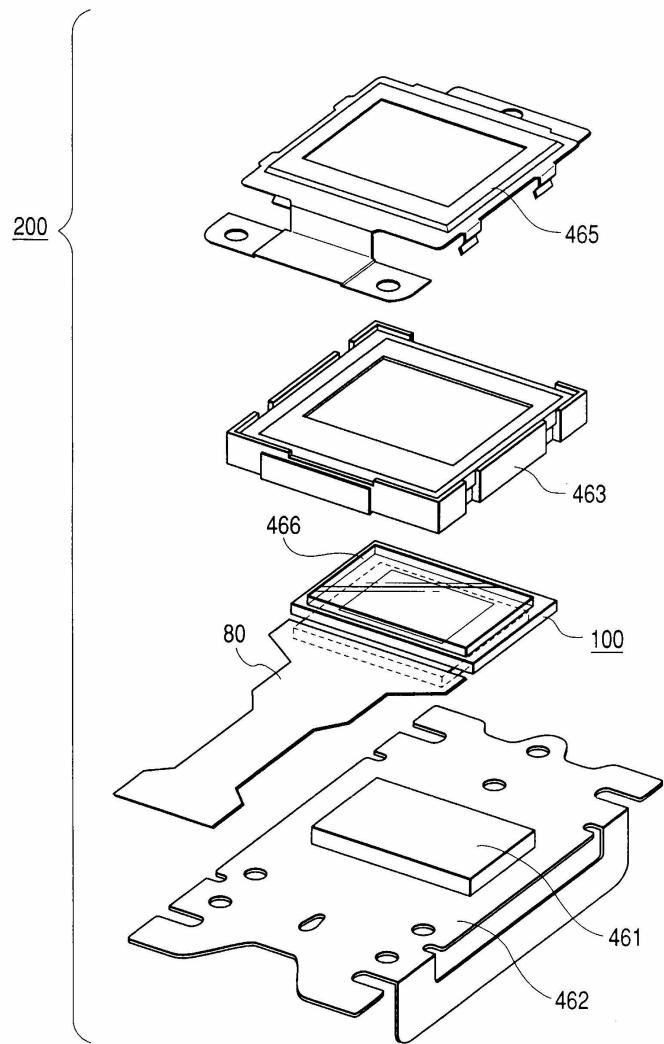

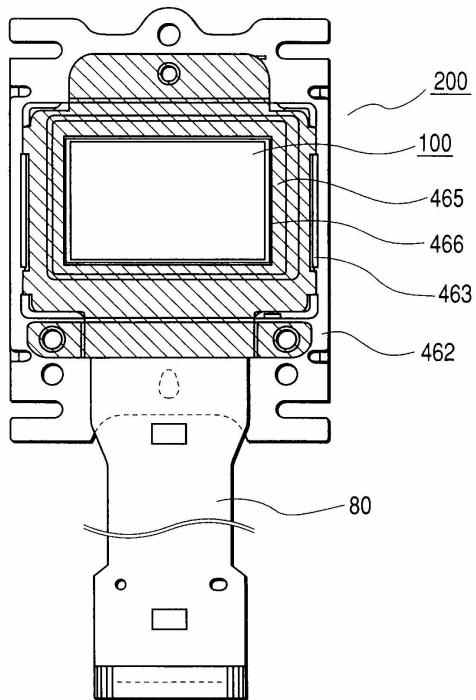

도 25는 본 발명의 일 실시예에 따른 액정 표시 장치의 주요 부분의 개략적인 분해 사시도.

도 26은 본 발명의 일 실시예에 따른 액정 표시 장치의 개략적인 평면도.

<도면의 주요 부분에 대한 부호의 설명>

10 : 더미 화소

11 : 주변 프레임

12 : 밀봉 부재

13 : 외부 접속 단자

25 : 수평 주사 리세트 신호 입력 단자

26 : 수평 주사 개시 신호 입력 단자

27 : 수평 주사 종료 신호 출력 단자

28 : 리세트용 트랜지스터

30 : 능동 소자

34 : 드레인 영역

35 : 소스 영역

36 : 게이트 영역

38 : 절연막

39 : 필드 산화막

61, 62, 65, 66 : 클럭드 인버터

100 : 액정 패널

102 : 주사 신호선

103 : 영상 신호선

104 : 스위칭 소자

107 : 대향 전극

108 : 액정 용량

109 : 화소 전극

110 : 표시부

111 : 표시 제어 장치

112 : 전압 발생 회로

120 : 수평 구동 회로

121 : 수평 시프트 레지스터

122 : 표시 데이터 보유 회로

123 : 전압 선택 회로

130 : 수직 구동 회로

131 : 타이밍 제어 신호선

132 : 표시 데이터선

133 : 계조 전압선

134 : 시간 제어 신호선

141 : 레벨 시프트 회로

142 : 게이트 회로

151 : 전압 버스 라인

152 : 연산 결과 신호선

153~157 : 정전압선

161~163 : 시간 제어 신호선

165 : 연산 결과 신호선 세트 신호선

166 : 연산 결과 신호선 리세트 신호선

167~169 : 전송 신호선

171~173 : 데이터 취득 소자

181~183 : 표시 데이터 전송 소자

191~193 : 메모리 용량

201~203 : 표시 데이터 연산 소자

211~213 : 시간 데이터 연산 소자

221, 223 : 연산 결과 신호선 리세트 소자

222 : 연산 결과 신호선 세트 소자

230 : n형 트랜지스터

231 : 반도체 기판

232, 242 : p형 웨

233 : n형 반도체층

234, 244 : 게이트 전극

235, 245 : 소자 분리 영역

236, 246, 271~273 : 액티브 영역

240 : p형 트랜지스터

243 : p형 반도체층

249 : 비사용 영역

321~323 : 표시 데이터선

325 : 표시 데이터 연산 회로

326 : 주사 전압 출력 회로

328 : 표시 데이터 보유 회로

329 : 타이밍 신호선

331~333 : 연산 전달 회로

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시 장치에 관한 것으로, 특히 각 화소에 영상 신호 전압을 공급하는 회로에 유용한 기술에 관한 것이다.

화소마다 능동 소자(예를 들면, 박막 트랜지스터)를 지니고, 이 능동 소자를 스위칭 구동하는 액티브 매트릭스형 액정 표시 장치는, 노트북 컴퓨터 등의 표시 장치로서 널리 사용되고 있다.

이 액티브 매트릭스형 액정 표시 장치의 하나로서, TFT(Thin Film Transistor) 방식의 액정 표시 모듈이 알려져 있다. TFT 방식의 액정 표시 모듈에서는, 박막 트랜지스터(TFT)를 통해 화소 전극에 영상 신호 전압(계조 전압)을 인가하기 때문에, 각 화소 사이의 크로스토크가 없으므로, 단순 매트릭스형 액정 표시 장치와는 달리, 크로스토크를 방지하기 위한 특수한 구동 방법을 이용하지 않고서도 다계조 표시를 제공할 수 있다.

그러나, 계조 전압을 화소 전극에 공급하는 방법으로서, 디지털 형태의 표시 데이터에 대응하는 계조 전압을 선택하는 D/A 변환의 방법을 이용하는 경우에, 계조 수가 증가할수록 표시 데이터의 비트 수가 증가하여, 그 결과 회로 규모가 대형화하고 회로의 동작 속도가 불충분해진다는 문제가 발생한다. 또한, 상기 문제는 구동 회로를 표시부와 동일 기판 상에 형성하는 구동 회로 일체형의 액정 표시 장치에서는, 유효 표시 면적 이외의 구동 회로부의 면적이 커져 버리기 때문에, 특히 심각해진다.

영상 기기로부터의 출력 신호가 아날로그 신호보다는 디지털 신호로 공급되는 경향에 따라, 구동 회로 일체형의 액정 표시 장치에서도, 액정 표시 장치에 디지털 신호를 입력하여, 액정 표시 패널 상에 형성한 구동 회로에서, 디지털 신호를 다계조의 영상 신호 전압으로 변환하는 구동 방법이 요구되고 있다.

액티브 매트릭스형 액정 표시 장치에서, 디지털 신호 입력에 의한 다계조 표시를 가능하게 하기 위해서, 각 화소에 다계조의 영상 신호 전압을 인가하는 구동 방법으로서, 일본 특개평 5-35200호 공보(미국 특허 제5,337,070호)에 기재되어 있는 방법이 알려져 있다.

상기 일본 특개평 5-35200호 공보에 기재되어 있는 방법은,  $2^m$ 개의 전압 버스 라인을 설치하여, 이  $2^m$ 개의 전압 버스 라인에서 공급되는 계조 전압을, 1 주사 기간(1 주사 라인)의 사이에  $2^K$ 개의 계단 형상으로 변화시킨다.

$n$  비트의 표시 데이터의 상위  $m$  비트의 값에 기초하여, 상기  $2^m$ 개의 전압 버스 라인 중 어느 하나를 선택하고,  $n$  비트의 표시 데이터의 하위  $k$  ( $k = n - m$ ) 비트의 값에 기초하여, 그 선택된 전압 버스 라인 상의 계단 형상으로 변화하는 계조 전압 중 하나를 선택하고, 그 선택된 전압 레벨을 각 화소의 화소 전극에 인가한다.

예를 들면, 표시 데이터가 3 비트( $n = 3$ )이고,  $m = 1$ ,  $k = 2$ 인 경우를 가정하도록 하자. 2개의 전압 버스 라인을 설치하고, 1 주사 기간동안 4 단계의 계단 형상으로 변화하는 계조 전압을 각 전압 버스 라인에 제공한다. 3 비트 표시 데이터의 상위 1 비트에 기초하여 2개의 전압 버스 라인 중 어느 하나의 전압 버스 라인 상의 계조 전압을 선택하고, 3 비트 표시 데이터의 하위 2 비트에 기초하여 그 선택된 전압 버스 라인 상의 4 단계의 계단 형상으로 변화하는 계조 전압을 선택하고, 그 선택된 전압 레벨을 화소의 화소 전극에 인가한다.

상기 일본 특개평 5-35200호 공보에 기재된 구동 방법에 따르면, 각 화소에 영상 신호 전압을 인가하는 회로의 동작 속도를 감소시킬 수 있고, 표시 영역 전체에서 D/A 변환에 의해 유발되는 영상 신호 전압의 변동을 적게 할 수 있으며, 전압 버스 라인의 개수를 감소시킬 수 있다.

그러나, 화질을 개선하기 위해 계조 수가 증가하면, 계단 형상으로 변화하는 전압 레벨을 선택하는 선택 회로의 회로 규모가 대형화하고, 해당 선택 회로를 액정 표시 패널 내에 내장하는 경우에는, 해당 선택 회로의 점유 면적이 커져서, 액정 표시 패널이 대형화한다고 하는 문제가 생긴다. 상기 문제점을 해결하는 액정 표시 장치로서, 일본 특개평 2000-194330호 공보에 기재되어 있는 선택 회로의 폭을 감소시키는 기술이 공지되어 있다.

### 발명이 이루고자 하는 기술적 과제

최근, 액정 표시 장치에서는, 계조 전압의 수가 64 또는 256로 더 증가되고 있다. 그리고, 상기 일본 특개평 2000-194330호 공보에 기재된 구동 회로에서는, 64 계조 또는 그 이상의 계조 레벨을 실현하는 경우에, 구동 회로가 길어지는 것에 따르는 문제점에 대해서는 고려되어 있지 않다.

또한, 액정 표시 장치에서는, 표시 해상도가 증가하고 있지만, 구동 회로를 형성하는 영역, 즉 구동 회로의 점유 면적이나 필요 최소한의 소자 수에 대해서도 고려되어 있지 않다.

본 발명은 상기 종래 기술의 문제점을 해결하기 위해서 이루어진 것으로, 액정 표시 장치에서, 구동 회로의 회로 규모를 작게 하여, 회로의 점유 면적을 작게 하는 것이 가능해지는 기술을 제공하는 것에 있다.

본 발명의 상기 목적과 신규인 특징은, 본 명세서의 기술 및 첨부 도면에 의해서 더 명확해질 것이다.

아래에서, 본 발명의 대표적인 개요를 간단히 설명한다.

본 발명의 일 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 설치된 복수의 화소, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아, 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 레벨을 복수의 영상 신호선에 출력하는 전압 선택 회로를 포함하고, 전압 선택 회로는, 복수의 연산 회로의 직렬 결합을 포함하며, 복수의 직렬 결합들 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합 각각의 연산 회로들 각각은, N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며, 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고, 표시 데이터는, 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합들 각각에서 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,  $2^N$ 개의 상이한 조합들 각각은 계조 전압의 하나의 레벨에만 동기하고, 시간 제어 신호는, 오프된 표시 데이터용 스위칭 소자와 함께 병렬 결합을 구성하는 시간 제어 신호용 스위칭 소자를 온시킴으로써, 계조 전압의 레벨을 유일하게 결정하는 액정 표시 장치가 제공된다.

본 발명의 다른 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 매트릭스 어레이로 정렬된 복수의 화소, 매트릭스 어레이의 열 방향으로 연장하고 행 방향으로 배열되어, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 행 방향으로 연장하고 열 방향으로 배열되어, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 행 방향으로 연장하고 열 방향으로 배열되어, 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 선택 회로에 타이밍 신호를 공급하는 시프트 레지스터, 및 타이밍 신호를 시프트 레지스터로부터 전압 선택 회로로 공급하는 복수의 타이밍 신호선을 포함하고, 전압 선택 회로는, 복수의 연산 회로의 직렬 결합, 및 타이밍 신호에 동기하여 표시 데이터를 취득하는 복수의 데이터 취득 소자를 포함하며, 복수의 데이터 취득 소자 각각은 연산 회로들 각각에 대응하고 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 연산 회로들 각각과 함께 배치되고, 복수의 타이밍 신호선은 시프트 레지스터로부터 열 방향으로 연장되고, 데이터 취득 소자 중 대응하는 데이터 취득 소자에 접속되며, 데이터 취득 소자의 제어 전극을 형성하는 도전막의 레벨과 동일한 레벨의 도전막으로 이루어지고, 복수의 직렬 결합들 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합들 각각의 연산 회로들 각각은 N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고, 표시 데이터는, 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합들 각각에서 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온시킴으로써,  $2^N$ 개의 상이한 조합을 만들며,  $2^N$ 개의 상이한 조합 각각은 계조 전압의 하나의 레벨에만 동기하여, 시간 제어 신호는, 오프된 표시 데이터용 스위칭 소자와 함께 병렬 결합을 구성하는 시간 제어 신호용 스위칭 소자를 온시키는 것에 의해, 계조 전압의 한 레벨을 유일하게 결정하는 액정 표시 장치가 제공된다.

본 발명의 다른 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 설치된 복수의 화소, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아, 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 레벨을 복수의 영상 신호선에 출력하는 전압 선택 회로를 포함하고, 전압 선택 회로는, 복수의 연산 회로의 직렬 결합, 및 복수의 직렬 결합으로부터의 출력에 기초하여 전압 레벨을 복수의 영상 신호선에 출력하

는 출력 회로를 포함하며, 복수의 출력 회로 각각은 복수의 직렬 결합 중 대응하는 직렬 결합에 직렬로 접속되며, 복수의 직렬 결합들 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합 각각의 연산 회로들 각각은, N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며, 연산 회로들 각각은, 결합되어 OR 회로를 형성하는 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고, 표시 데이터는, 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합들 각각에서 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,  $2^N$ 개의 상이한 조합들 각각은 계조 전압의 하나의 레벨에만 동기하고, 복수의 출력 회로 각각에는, 복수의 직렬 결합 중 대응하는 직렬 결합의 연산 회로들 전부가 온된 경우에, 표시 데이터에 대응하는 계조 전압의 하나의 레벨을 유일하게 결정하는 제어 신호가 공급되는 액정 표시 장치가 제공된다.

본 발명의 다른 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 설치된 복수의 화소, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아, 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 레벨을 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합을 포함하며, 복수의 직렬 결합들 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합 각각의 연산 회로들 각각은, N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며, 연산 회로들 각각은 표시 데이터용 스위칭 소자의 병렬 결합을 포함하고, 시간 제어 신호는, 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합들 각각에서 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,  $2^N$ 개의 상이한 조합들 각각은 계조 전압의 하나의 레벨에만 동기하고, 표시 데이터는, 오프된 시간 제어 신호용 스위칭 소자와 함께 병렬 결합을 구성하는 표시 데이터용 스위칭 소자를 온시킴으로써, 계조 전압의 레벨을 유일하게 결정하는 액정 표시 장치가 제공된다.

본 발명의 다른 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 매트릭스 어레이로 정렬된 복수의 화소, 매트릭스 어레이의 열 방향으로 연장하고 행 방향으로 배열되어, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 행 방향으로 연장하고 열 방향으로 배열되어, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 행 방향으로 연장하고 열 방향으로 배열되어, 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 레벨을 복수의 영상 신호선에 출력하는 전압 선택 회로, 전압 선택 회로에 타이밍 신호를 공급하는 시프트 레지스터, 및 타이밍 신호를 시프트 레지스터로부터 전압 선택 회로로 공급하는 복수의 타이밍 신호선을 포함하고, 전압 선택 회로는 복수의 연산 회로의 직렬 결합, 및 타이밍 신호에 동기하여 표시 데이터를 취득하는 복수의 데이터 취득 소자를 포함하며, 복수의 데이터 취득 소자 각각은 연산 회로들 각각에 대응하고 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 연산 회로들 각각과 함께 배치되고, 복수의 타이밍 신호선은 시프트 레지스터로부터 열 방향으로 연장되고, 데이터 취득 소자 중 대응하는 데이터 취득 소자에 접속되며, 데이터 취득 소자의 제어 전극을 형성하는 도전막의 레벨과 동일한 레벨의 도전막으로 이루어지고, 복수의 직렬 결합 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합 각각의 연산 회로들 각각은 N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고, 시간 제어 신호는, 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합 각각에서 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시키는 것에 의해,  $2^N$ 개의 상이한 조합을 만들며,  $2^N$ 개의 상이한 조합 각각은 계조 전압의 하나의 레벨에만 동기하며, 표시 데이터는, 오프된 시간 제어 신호용 스위칭 소자와 함께 병렬 결합을 구성하는 표시 데이터용 스위칭 소자를 온시키는 것에 의해, 계조 전압의 한 레벨을 유일하게 결정하는 액정 표시 장치가 제공된다.

본 발명의 다른 실시예에 따르면, 제1 기판, 제2 기판, 제1 기판과 제2 기판 사이에 협지된 액정 조성물, 제1 기판 상에 설치된 복수의 화소, 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선, 주기적으로 변화하는 계조 전압을 공급받아, 복수의 영상 신호선에 영상 신호 전압을 출력하는 구동 회로, 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및 계조 전압에 동기하여 변화하는 시간 제어 신호를 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하는 액정 표시 장치에 있어서, 구동 회로는, 표시 데이터에 기초하여 계조 전압으로부터 전압 레벨을 선택하고, 전압 레벨을 복수의 영상 신호선에 출력하는 전압 선택 회로를 포함하고, 전압 선택 회로는 복수의 연산 회로의 직렬 결합, 및 복수의 직렬 결합으로부터의 출력에 기초하여 전압 레벨을 복수의 영상 신호선에 출력하는 출력 회로를 포함하며, 복수의 출력 회로 각각은 복수의 직렬 결합 중 대응하는 직렬 결합에 직렬로 접속되며, 복수의 직렬 결합 각각은 복수의 영상 신호선 중 하나와 연관되고, 복수의 직렬 결합 각각의 연산 회로들 각각은, N개의 표시 데이터선 각각 및 N개의 시간 제어 신호선 각각과 연관되고, N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며, 연산 회로들 각각은, 결합되어 OR 회로를 형성하는 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고, 시간 제어 신호는, 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 복수의 직렬 결합 각각에서 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,  $2^N$ 개의 상이한 조합들 각각은 계조 전압의 하나의 레벨에만 동기하고, 복수의 출력 회로 각각에는, 복수의 직렬 결합 중 해당 직렬 결합의 연산 회로들 전부가 온된 경우에, 표시 데이터에 대응하는 계조 전압의 하나의 레벨을 유일하게 결정하는 제어 신호가 공급되는 액정 표시 장치가 제공된다.

## 발명의 구성 및 작용

이하, 본 발명 실시예를 도면을 참조하여 설명한다. 또, 발명의 실시예를 설명하기 위한 도면들에 있어서, 기능적으로 동일한 부분들은 동일한 참조 번호를 부여하고, 반복적으로 설명하지 않기로 한다.

도 1은, 본 발명의 실시예에 따른 액정 표시 모듈의 개략적인 전체 구성을 나타내는 블록도이다. 본 실시예의 액정 표시 모듈은, 액정 표시 패널(액정 표시 소자)(100), 표시 제어 장치(111), 전압 발생 회로(112)를 포함한다.

액정 표시 패널(100)은, 표시부(110), 수평 구동 회로(영상 신호선 구동 회로)(120) 및 수직 구동 회로(주사 신호선 구동 회로)(130)를 포함한다. 또한, 표시부(110), 수평 구동 회로(120), 수직 구동 회로(130)는 동일 기판 상에 설치되어 있다. 또한, 표시 제어 장치(111)와 전압 발생 회로(112)를, 액정 표시 패널(100)과 분리하여 도시하고 있지만, 액정 표시 패널(100)과 동일 기판 상에 설치하는 것도 가능하다.

표시 제어 장치(111)는 외부로부터 송신되어 오는 클럭 신호, 표시 타이밍 신호, 수평 동기 신호, 수직 동기 신호 등의 제어 신호에 기초하여, 수평 구동 회로(120) 및 수직 구동 회로(130)를 제어한다. 표시 제어 장치(111)는 액정 표시 패널(100)에 표시하여야 할 화상 데이터인 표시 데이터를 수평 구동 회로(120)에 공급한다. 전압 발생 회로(112)는 액정 표시 패널(100)이 표시를 행하는 데에 필요한 전압을 발생한다. 수평 구동 회로(120)는 표시 데이터에 따라 전압 발생 회로(112)로부터 공급되는 계조 전압을 표시부(110)에 선택 출력하고, 표시부(110)는 수직 구동 회로(130)로부터 출력되는 주사 신호에 동기하여 계조 전압을 화소(도시하지 않음)에 입력한다.

복수의 영상 신호선(드레인 신호선 또는 수직 신호선으로 칭함)(103)이, 수평 구동 회로(120)로부터 수직 방향(도 1의 Y 방향)으로 표시부(110)까지 연장되어 있고, 이들은 수평 방향(도 1의 X 방향)으로 정렬되어 있다. 계조 전압은 영상 신호선(103)을 통해 표시부(110)에 공급된다. 복수의 주사 신호선(게이트 신호선 또는 수평 신호선으로도 칭함)(102)이 수직 구동 회로(130)로부터 수평 방향(도 1의 X 방향)으로 표시부(110)까지 연장되고 있고, 이들은 수직 방향(도 1의 Y 방향)으로 정렬되어 있다. 주사 신호는 주사 신호선(102)을 통해 표시부(110)에 공급된다.

수평 구동 회로(120)는 수평 시프트 레지스터(121) 및 전압 선택 회로(123)를 포함한다. 표시 제어 장치(111)로부터의 타이밍 제어 신호선(131)이 수평 시프트 레지스터(121) 및 수직 구동 회로(130)에 접속되고, 표시 제어 장치(111)로부터의 표시 데이터선(132)과 시간 제어 신호선(134)이 전압 선택 회로(123)에 접속되어 있다. 또한, 전압 발생 회로(112)로부터의 계조 전압선(133)이 전압 선택 회로(123)에 접속되고, 계조 전압이 공급되고 있다. 편의상, 도 1에서 각 회로의 전원 전압선에 대해서는 표시를 생략하였지만, 각 회로에 필요한 전압이 공급되고 있는 것으로 한다.

표시 제어 장치(111)는, 수직 동기 신호 입력 직후에 입력되는 최초의 디스플레이 타이밍 신호를 최초의 표시 라인에 대응하는 것이라고 판단하여, 타이밍 제어 신호선(131)을 통해 수직 구동 회로(130)에 타이밍 제어 신호의 하나인 개시 펄스를 출력한다. 다음으로, 표시 제어 장치(111)는, 수평 동기 신호에 기초하여, 1 수평 주사 시간마다 주사 신호선(102)을 순차 선택하도록 하는 시프트 클럭을 수직 구동 회로(130)에 출력한다. 수직 구동 회로(130)는, 시프트 클럭에 따라 주사 신호선(102)을 선택하여, 선택된 주사 신호선(102)에 주사 신호를 출력한다.

또한, 표시 제어 장치(111)는, 표시 타이밍 신호가 입력되면, 이것을 표시 개시에 대응하는 것으로 판단하여, 표시 데이터를 수평 구동 회로(120)에 출력한다. 표시 데이터는 표시 제어 장치(111)로부터 순차 출력되지만, 수평 시프트 레지스터(121)는 표시 제어 장치(111)로부터 전송되는 타이밍 제어 신호 중의 하나인 시프트 클럭에 기초하여, 각 영상 신호선(103)에 공급될 표시 데이터를 선택하는 타이밍 신호를 전압 선택 회로(123)에 출력한다.

전압 선택 회로(123)는 타이밍 신호에 따라 표시 데이터를 취득하여, 전압 발생 회로(112)가 공급하는 계조 전압 중에서 그 표시 데이터의 각각에 대응하는 전압을 선택하여 영상 신호선(103)에 출력한다. 전압 선택 회로(123)에 대해서는 나중에 상세하게 설명할 것이다.

도 2는 본 발명의 실시예인 액정 표시 패널(100)의 등가 회로도를 나타낸다. 도 2에 도시된 회로도는, 실제의 기하학적 배치도 나타내고 있다. 표시부(110)는, 매트릭스 형상으로 배치된 화소부(101)를 갖고 있다. 도 2에서는 편의상 하나의 화소부만을 나타내고 있다. 각 화소부(101)는 스위칭 소자(104)와 화소 전극(109)을 가지며, 인접하는 2개의 주사 신호선(102)과 인접하는 2개의 영상 신호선(103)으로 둘러싸인 영역에 배치된다.

전술한 바와 같이, 수직 구동 회로(130)는 1 수평 주사 기간마다 주사 신호선(102)에 주사 신호를 순차 출력하고, 이 주사 신호는 스위칭 소자(104)의 온·오프 제어에 이용된다.

영상 신호선(103)에 계조 전압이 공급되고, 스위칭 소자(104)가 온되면, 영상 신호선(103)으로부터 화소 전극(109)에 계조 전압이 공급된다. 화소 전극(109)에 대향하도록 대향 전극(공통 전극)(107)이 배치되어 있고, 화소 전극(109)과 대향 전극(107) 사이에는 액정정중(도시하지 않음)이 설치되어 있다. 도 2에 도시된 회로도에서, 액정정중에 의한 등가 액정 용량(108)은 화소 전극(109)과 대향 전극(107) 사이에 접속되어 있는 것으로 나타내었다.

화소 전극(109)과 대향 전극(107) 간에 전압을 인가하여, 액정정중의 광에 특성을 변화시킴으로써 표시가 행해진다. 액정 표시 패널 상에 표시되는 화상을 구성하는 각 화소의 계조는, 화소 전극(109)에 공급되는 전압에 의존한다. 따라서, 액정 표시 패널 상에 표시되는 계조 수의 증가에 따라, 화소 전극(109)에 공급되는 계조 전압의 수도 증가한다.

표시부(110)에서, 전체의 면적에 대하여 화소 전극(109)이 차지하는 면적의 비율에 따라, 표시부(110)의 밝기가 결정되며, 화소부(101)의 화소 전극(109)은 가능한 한 크게 형성된다. 즉, 액정 표시 패널에서는 화소 전극(109) 이외의 구성이 차지하는 면적은 가능한 한 좁아지도록 설계되어 있다.

전술한 바와 같이, 화소 전극(109)에 공급되는 계조 전압은 전압 선택 회로(123)로부터 출력된다. 액정 표시 패널(100) 상에 표시되는 계조 레벨의 수가 증가한 경우에, 전압 선택 회로(123)는 다수의 계조 전압 레벨 중에서 영상 신호선(103)에 출력되는 전압을 선택해야 하며, 표시 제어 장치(111)와 전압 선택 회로(123) 사이에 접속되어 있는

표시 데이터선(132)을 통해 전해지는 데이터량도 증가한다. 따라서, 액정 표시 패널(100) 상에 표시되는 계조 레벨의 수가 증가한 경우에, 표시 데이터선(132)의 개수가 증가하고, 그에 따라 전압 선택 회로(123)의 회로 규모가 커져 버린다고 하는 문제가 생긴다. 본 발명에서는, 전압 선택 회로(123)를 가능한한 작은 회로로 구성하여, 액정 표시 패널 내에 효율적으로 배치한다.

또한, 본 발명은, 특히 구동 회로와 표시부가 동일 기판 상에 형성되는 소위 구동 회로 일체형의 액정 표시 장치에서, 액정 표시 장치의 소형화가 진행하고 계조 레벨의 수가 증가하는 경우의 문제점에 대해서도 해결한다.

이하, 도 3을 이용하여 전압 선택 회로(123)에 대하여 설명한다. 도 3은 전압 선택 회로(123)의 내부 회로의 폭과, 인접하는 2개의 영상 신호선(103)의 중심간의 간격과의 관계를 설명하는 블록도이다. 전압 선택 회로(123)는 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)를 포함한다. 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)는, 대응하는 영상 신호선(103)의 연장선 상에 정렬된다.

수평 구동 회로(120)에는, 표시 제어 회로(111)(도시하지 않음)로부터의 표시 데이터선(321~323)이 접속되어 있다. 표시 데이터선(321~323) 각각은, 도 1 및 도 2과 관련하여 설명한 표시 데이터를 디지털 데이터로 한 경우에, 디지털 형식의 표시 데이터의 1비트에 대응한다. 표시 데이터선(321~323)은 도 1 및 도 2의 표시 데이터선(132)을 비트 단위로 표시한 것이다. 또한, 표시 제어 회로(111)로부터의 시간 제어 신호선(134)이 전압 선택 회로(123)에 접속되어 있지만, 도 3에서는 생략되어 있다.

표시 데이터선(321~323)에는 표시 데이터가 순차적으로 출력되고, 수평 시프트 레지스터(121)는 표시 데이터가 동기하여 취득되는 타이밍 신호를 출력한다. 수평 시프트 레지스터(121)로부터의 타이밍 신호선(329)은 전압 선택 회로(123)에 접속되어 있고, 이 타이밍 신호선(329)에 의해 타이밍 신호가 전압 선택 회로(123)에 전해진다. 참조 기호 HSR1 내지 HSRn은 쌍방향 시프트 레지스터이다. 수평 시프트 레지스터(121)는 쌍방향 시프트 레지스터 HSR1 내지 HSRn으로 구성되어 있다. 쌍방향 시프트 레지스터 HSR1 내지 HSRn은 타이밍 제어 신호선(131)으로 부터의 신호(시프트 클럭)에 따라 타이밍 신호를 출력한다.

각 영상 신호선(103)에 대한 표시 데이터는 표시 데이터 신호선(321~323)에 출력되고, 표시 데이터 연산 회로(325)는 대응 타이밍 신호에 동기하여 표시 데이터를 취득한다. 또, 쌍방향 시프트 레지스터 HSR0와 HSRn+1은 더미의 쌍방향 시프트 레지스터이다.

도 3에서, 액정 표시 패널(100)을 형성하는 기판 중 하나에 전압 발생 회로(112)가 설치되고 있고, 전압 발생 회로(112)로부터의 계조 전압선(133)이 계조 전압 출력 회로(326)에 접속되어 있다. 표시부(110)에는 영상 신호선(103)이 거의 등간격으로 복수개(n개) 설치되어 있다. 인접 영상 신호선(103)들 간의 간격은, 표시부(110)에 설치된 화소 전극(109)의 폭과 거의 동일하다. 일정한 면적의 표시부(110) 내에서, 설치되는 화소 수는 관련 규격으로 정해지고 있다. 따라서, 표시부(110)의 면적과 화소 수에 의해, 하나의 화소가 설치되는 영역의 크기가 정해진다. 인접하는 2개의 영상 신호선(103) 간의 간격도 화소를 설치하는 영역의 크기에 따라 선택되고 있다. 예를 들면, 도 3에서 표시부(110)의 수평 방향(X 방향)으로 n개의 화소가 설치되고, 표시부(110)의 폭이 W라고 가정한다. 그러면, 화소 피치는 W/n으로 되고, 영상 신호선(103)들의 중심 대 중심 간격은 화소 피치 W/n과 거의 동일하게 된다. 또한, 영상 신호선(103)의 연장선 상에 설치되는 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)의 폭도 화소 피치 W/n과 거의 동일하게 되도록 설치된다.

각각의 영상 신호선(103)의 연장선 상에는, 해당 영상 신호선(103)에 계조 전압을 출력하기 위한 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)가 설치된다. 임의의 1개의 영상 신호선 연장선에 인접하는 2개의 영상 신호선(103)의 연장선 상에도, 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)의 조합이 설치된다. 따라서, 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)의 폭이 수평 화소 피치 내로 제한되지 않으면, 인접하는 표시 데이터 연산 회로(325) 및 계조 전압 출력 회로(326)와 중첩되어 버린다고 하는 문제가 생긴다. 따라서, 표시부를 작게 하거나 화소 수를 증가시킨 경우에, 화소 피치 내에 구동 회로를 형성하기 위해서는, 회로의 폭도 고려하지 않으면 안된다고 하는 문제가 생긴다.

본 실시예에서는, 표시 데이터 연산 회로(325)와 계조 전압 출력 회로(326)를 수평 화소 피치 범위 내로 효율적으로 제한하기 위해서, 복수의 표시 데이터 연산 회로(325)를 제공하며, 표시 데이터 연산 회로(325) 각각은 표시 데이터선(321~323) 중 해당 표시 데이터선에 대응하며, 해당 영상 신호선(103)의 연장선 상에 설치된다.

도 3에 도시한 바와 같이, 표시 데이터선(321~323)은 표시 제어 회로(111)로부터 연장되어, 표시 데이터 연산 회로(325)에 접속하고 있다. 본 실시예에서는 8 계조 레벨을 나타내는 3비트가 이용되고, 표시 데이터선(321~323)은 3개이다. 또한, 본 실시예에서는 편의상 표시 데이터선 수가 3개인 경우에 대해 진술하지만, 표시 데이터선 수는 표시 데이터에 따라 임의로 선택하는 것이 가능하다.

표시 데이터 연산 회로(325)는 각 표시 데이터선(321~323)마다 설치되고 있고, 표시 데이터의 대응 비트를 이용하여 디지털 연산을 행하고, 연산 결과를 계조 전압 출력 회로(326)에 전달한다. 계조 전압 출력 회로(326)는 표시 데이터 연산 회로(325)로부터의 연산 결과에 기초하여 표시 데이터에 따른 계조 전압을 출력한다.

전술한 바와 같이 영상 신호선(103) 간의 간격은, 표시부(110)에 설치된 화소 전극(109)의 크기로 제한된다. 한편, 인접하는 2개의 표시 데이터선(321~323)의 간격은, 각각의 표시 데이터 연산 회로(325)가 설치되도록 충분히 넓게 하는 것이 가능하다. 도 3에 도시한 바와 같이, 영상 신호선(103) 중 하나에 대응하는 3개의 표시 데이터 연산 회로(325)를, 그 영상 신호선(103)의 연장선 상(도 3의 Y 방향)으로 표시 데이터선(321~323)의 각각에 대응시켜 정렬함으로써, 3개의 표시 데이터 연산 회로(325) 각각은 표시 데이터선(321~323) 중 해당 표시 데이터선의 부근에 정렬된다. 따라서, 표시 데이터 연산 회로(325)는 인접하는 2개의 영상 신호선(103)의 간격 내에 배치될 수 있다.

그러나, 본 발명자들은, 표시 데이터선(321~323)의 간격이 무제한으로 넓어질 수는 없고, 가능한 한 작게 할 필요가 있다는 것을 발견하였다. 표시 데이터 연산 회로(325)의 폭만이 아니라 길이도 짧게 하는 것에 대해서는 후술한다.

다음에 도 4를 이용하여 전압 선택 회로(123)에 대하여 상세히 설명한다. 도 4는, 전압 선택 회로(123)의 회로 구성을 나타내는 개략 블록도이다. 도 4에서는, 도면이 복잡하게 되는 것을 피하여, 1개의 영상 신호선(103)과 관련한 전압 선택 회로(123)의 구성만을 도시하고 있다.

전술한 바와 같이, 전압 선택 회로(123)에는, 표시 데이터선(321~323)의 각각에 대응하여 표시 데이터 연산 회로(325)가 설치되어 있다. 각 표시 데이터 연산 회로(325)에는, 시간 제어 신호선(161~163)이 접속되어 있다.

시간 제어 신호선(161~163)은 도 1 및 도 2에 나타낸 제어 신호선(134)에 포함되며, 표시 제어 장치(111)(도 4에는 도시되지 않음)에 접속된다.

도 4에서, 참조 번호 122는 표시 데이터 보유 회로로서, 수평 시프트 레지스터(121)로부터 타이밍 신호선(329)을 통해 공급되는 신호에 동기하여, 표시 데이터선(321~323)으로부터의 표시 데이터를 저장한다. 참조 번호 331, 332, 333은 연산 결과 전달 회로이며, 이들 각각은 표시 데이터 보유 회로(122)로부터의 출력과 해당 시간 제어 신호선(161~163)의 신호 간에 연산을 행하여, 연산 결과를 연산 결과 신호선(152)에 출력한다. 연산 결과 전달 회로(331~333)는, 연산 결과 신호선(152)에 의해 직렬로 접속되어 있다. 또한, 계조 전압 출력 회로(326)도 연산 결과 신호선(152)에 의해 연산 결과 전달 회로(331~333)와 직렬로 접속되어 있다. 계조 전압 출력 회로(326)는 연산 결과 전달 회로(331~333)가 전달하는 연산 결과에 따라, 전압 버스 라인(151) 상의 계조 전압 중 하나를 선택하여 영상 신호선(103)에 출력한다. 또한, 전압 버스 라인(151)은 도 1~도 3에 있어서 계조 전압선(133)으로 도시한 신호선에 포함되어, 시간에 따라 변화하는 전압이 인가되어 있는 것을 나타내고 있다. 도 4에서는 전압 버스 라인을 1개의 배선으로 나타내었지만, 복수개의 배선으로 구성하는 것도 가능하다.

본 실시예에서는, 연산 결과 전달 회로(331~333)와 계조 전압 출력 회로(326)는, 표시 데이터선의 개수보다 적은 수의 연산 결과 신호선(152)에 의해 접속되어 있기 때문에, 배선에 필요한 영역이 감소될 수 있다. 즉, 3개의 표시 데이터선(321~323)에 의해 전달되는 데이터를 3개의 연산 결과 전달 회로(331~333)에서 연산하여, 그 연산 결과를 1개의 연산 결과 신호선(152)을 통해 수직 방향으로 전달하고, 그 결과 배선 수가 감소된다. 또한, 3개의 연산 결과 전달 회로(331~333)를 수직 방향으로 정렬함으로써, 영상 신호선(103)에 계조 전압을 출력하는 구성의 폭이 감소될 수 있다.

이하에서는, 계조 전압 출력 회로(326)를 이용하여 계조 전압이 선택되고 영상 신호선(103)에 출력되는 방법에 대하여 설명한다. 계조 전압 출력 회로(326)에는, 전압 버스 라인(151)이 접속되어 있다. 전압 버스 라인(151)의 전압 값은 시간에 따라 주기적으로 변화한다. 시간에 따라 변화하는 전압 버스 라인(151) 상의 전압이 원하는 전압 값으로 되면, 계조 전압 출력 회로(326)는 전압 버스 라인(151)을 영상 신호선(103)에 전기적으로 접속하지만, 전압 버스 라인(151) 상의 전압이 원하는 전압 값이 아닌 경우에는, 전압 버스 라인(151)과 영상 신호선(103)을 전기적으로 차단함으로써, 원하는 전압을 영상 신호선 상에 계조 전압으로서 출력할 수 있다.

이하, 전압 선택 회로(123)의 동작에 대하여 간단하게 설명한다. 우선, 표시 데이터 보유 회로(122)에, 수평 시프트 레지스터(121)가 출력하는 타이밍 신호에 동기하여 표시 데이터가 보유된다. 다음에, 표시 데이터 보유 회로(122)에 저장된 표시 데이터가 연산 결과 전달 회로(331~333)에 전해진다. 시간 제어 신호선(161~163)의 시간 제어 신호는 시간에 따라 변화하고 있고, 연산 결과 전달 회로(331~333)는 표시 데이터 보유 회로(122)의 값과 시간 제어 신호선(161~163)의 시간 제어 신호의 값 간에 디지털 연산을 행한다. 연산 결과 전달 회로(331~333)의 연산 결과는 계조 전압 출력 회로(326)에 전달된다. 전압 버스 라인(151)의 전압이 표시 데이터가 나타내는 계조 전압과 일치했을 때에, 연산 결과 전달 회로(331~333)의 연산 결과가 출력되어, 계조 전압 출력 회로(326)는 전압 버스 라인(151)으로부터의 계조 전압을 영상 신호선(103)에 출력한다.

이하에서는, 계속해서 도 4를 참조하여, 각 연산 결과 전달 회로(331~333)를 스위칭 회로로 구성하고, 정전압선(153)의 전위를 연산 결과 신호선(152)에 출력한 후, 계조 전압 출력 회로(326)에 전하여, 계조 전압 출력 회로(326)가 원하는 계조 전압을 출력하는 방법에 대하여 설명한다.

여기서, 3개의 연산 결과 전달 회로(331~333)는 연산 결과 신호선(152)에 의해 직렬로 접속되어 있기 때문에, 연산 결과 전달 회로(331~333)에 의해 표현할 수 있는 상태는 다음과 같은 2 상태뿐이다.

(i) 모든 연산 결과 전달 회로(331~333)가 온되어, 정전압선(153)의 전압이 계조 전압 출력 회로(326)에 전해지는 상태; 및

(ii) 연산 결과 전달 회로(331~333) 중 적어도 하나가 오프되어, 계조 전압 출력 회로(326)에 정전압선(153)의 전압이 전해지지 않은 상태.

계조 전압 출력 회로(326)에 전해지는 상태의 수가 2개뿐인 경우, 복수 계조의 전압을 출력하는 것은 어렵다.

이러한 문제를 해결하기 위해, 본 실시예에서, 표시 데이터 연산 회로(325)는, m개(본 실시예에서는 3개)의 연산 결과 전달 회로(331~333) 중에서 특정 개수의 연산 결과 전달 회로를 선택하여 연산 스위칭 회로로서 기능하게 하는 구성으로 되어 있다. 이러한 구성을 이용하면, m개의 연산 결과 전달 회로(331~333)가 연산 결과 신호선(152)에 의해 직렬로 접속되어 있더라도,  $2^m$ 의 상태를 나타내는 것이 가능하다.

표 1은, 3개의 연산 결과 전달 회로(331~333)를 스위칭 회로로 할당하는 것의 여러가지 변경 예를 나타내고 있다.

표 1.

| 연산 결과<br>전달 회로 | 케이스<br>1 | 케이스<br>2 | 케이스<br>3 | 케이스<br>4 | 케이스<br>5 | 케이스<br>6 | 케이스<br>7 | 케이스<br>8 |

|----------------|----------|----------|----------|----------|----------|----------|----------|----------|

| 333            | -        | -        | -        | -        | SW       | SW       | SW       | SW       |

| 332            | -        | -        | SW       | SW       | -        | -        | SW       | SW       |

| 331            | -        | SW       | -        | SW       | -        | SW       | -        | SW       |

표 1에서, "-"는 연산 결과 전달 회로(331~333)가 항상 ON(도통)인 상태를 나타내는 것이고, "SW"는 연산 결과 전달 회로(331~333)가 스위칭 회로로서 기능하는 것임을 나타내고 있다. 3개의 연산 결과 전달 회로(331~333)는 스위칭 회로로서 구성되지만, 연산 결과 전달 회로(331~333)가 항상 ON이도록 설정한다면, 스위칭 회로가 없고 도통 상태인 것으로 생각된다.

전술한 바와 같이, 스위칭 회로가 직렬로 접속된 경우에는, 스위칭 회로가 전부 ON인 상태와 적어도 하나의 스위칭 회로가 OFF인 상태의 두가지 상태 밖에 선택할 수 없다. 그러나, 표 1에 나타낸 바와 같이, m개의 스위칭 회로(표 1에서는 3개)가, 각 경우에서 m개의 스위칭 회로 중에서 일정 수의 스위칭 회로만이 스위칭 동작용으로 선택되도록 구성되면,  $2^m$  개의 상이한 상태를 선택할 수 있다.

반복 주기가  $2^m$  간격으로 분할되고,  $2^m$  개의 간격 각각에서, 복수의 시간 제어 신호선(161~163)으로부터 주기적으로 시간에 따라 변하는 데이터의 상이한 조합들이 상이한  $2^m$  개의 상태를 표현할 수 있도록 설정하는 경우, 시간 제어 신호선(161~163)으로부터의 데이터와 표시 데이터에 기초하여, 그 표시 데이터에 대응하는  $2^m$  개의 간격 중 하나에서, 모든 연산 결과 전달 회로(331~333)는 도전 상태로 될 수 있으며, 따라서 정전압선(153)의 전압을 제어 전압 출력 회로(326)에 전할 수 있게 된다.

도 5 및 도 6은, 본 실시예에 있어서, 전압 선택 회로(123)의 회로 구성의 제1 및 제2 부분을 각각 나타내는 회로도 있고, 도 5에서 A로 표시된 선의 끝은 도 6에서 A로 표시된 부분에 연결된다. 도 5 및 도 6에 있어서도, 편의상, 표시 데이터가 3 비트인 경우를 보이고 있다. 도 5에 있어서, 신호선들 일부에서는, 전달되는 신호를 나타내는 참조 부호를 그 좌단에 표시하고, 각 신호선에 할당되는 참조 번호를 그 우단에 표시한다.

도 5에 도시한 바와 같이, 도 4의 연산 결과 전달 회로(331~333) 각각은 표시 데이터 연산 소자(201~203)와 시간 데이터 연산 소자(211~213)로서 각각 기능하는 2개의 n형 트랜지스터로 구성되어 있다.

도 4의 표시 데이터 연산 회로(325)는 표시 데이터 연산 소자(201~203)와 시간 데이터 연산 소자(211~213) 외에, 데이터 취득 소자(171~173), 메모리 용량(191~193) 및 표시 데이터 전송 소자(181~183)를 포함한다. 표시 데이터 연산 회로(325)에는 표시 데이터 DD1~DD3를 공급하는 표시 데이터선(321~323), 시간 제어 신호 DA1~DA3를 공급하는 시간 제어 신호선(161~163), 표시 데이터 전송 소자(181~183)를 제어하는 전송 신호 TG를 공급하는 전송 신호선(167~169)이 접속되어 있다.

메모리 용량(191~193)에 보유된 표시 데이터가, 전송 신호 TG에 따라 표시 데이터 전송 소자(181~183)를 통해 표시 데이터 연산 소자(201~203)에 전해진다. 참조 번호 153, 156은 전원 전압 VDD를 공급하기 위한 정전압선이다. 참조 번호 154는 전원 전압 GND를 공급하는 정전압선이다. 참조 번호 165는 연산 결과 신호선 세트 신호선이고, 참조 번호 166은 연산-결과-신호선 리세트 신호선이다. 도 6에서, 참조 번호 141은 레벨 시프트 회로이고, 참조 번호 142는 게이트 회로이며, 참조 번호 151은 전압 버스 라인이다.

도 5에 도시한 바와 같이, 표시 데이터 연산 회로(325)를 표시 데이터선(321~323)마다 설치하고, 동일한 도전형의 트랜지스터로 구성함으로써, 액정 표시 장치에서 전압 선택 회로(123)가 차지하는 영역의 폭뿐만 아니라, 길이도 짧게 하는 것이 가능하다.

우선, 도 5의 회로에 대하여 설명하기 전에, 도 7a, 7b, 도 8a~8c, 도 9a~9b를 참조하여 표시 데이터 연산 회로(325) 등의 회로를 형성하는 소자의 형성에 요구되는 영역의 크기에 대하여 설명한다.

도 7a 및 7b는, 2개의 트랜지스터를 인접하여 형성한 구성을 나타내는 개략적인 단면도이다. 도 7a 및 7b는 일반적인 트랜지스터의 구성을 나타내는 종래의 예이다. 도 7a는 동일한 도전형의 트랜지스터 2개를 인접하여 형성한 경우로서, 2개의 n형 트랜지스터(230)가 인접하여 정렬되어 있다. 도 7b는 상이한 도전형의 트랜지스터 2개를 인접하여 형성한 경우로서, 좌측에는 n형 트랜지스터(230)가 있고, 우측에는 p형 트랜지스터(240)가 있다.

도 7a에서, 참조 번호 232는 p형 웨이로, 반도체 기판(231)에 이온 주입 등의 방법에 의해 형성되며, p형 웨이(232)에는 소스/드레인 영역을 형성하기 위한 n형 반도체층(233)이 이온 주입 등에 의해 형성되어 있다. 참조 번호 234는 게이트 전극으로서, 게이트 절연막을 통해 p형 웨이(232) 상에 형성된다. 2개의 트랜지스터(230)는 LOCOS(Local Oxidation of Silicon) 등으로 형성된 소자 분리 영역(235)으로 분리되어 있다. 소자 분리 영역(235)은 동일 기판 상에 다수개의 소자를 형성하는 경우에, 각 소자를 전기적으로 절연하여 배치하기 위한 것이고, 각 n형 트랜지스터(230)는 소자 분리 영역(235)에 의해 분리된 영역에 형성되어 있다. 도 7a에서, L1은 소자 분리 영역(235)의 길이를 나타내는 것이다.

도 7b는 상이한 도전형의 트랜지스터 2개를 인접하여 형성한 경우를 나타내고 있는 것으로, 참조 번호 240은 p형 트랜지스터, 참조 번호 242는 n형 웨爾, 참조 번호 243은 P형 반도체층, 참조 번호 244는 게이트 전극이다. 이 경우에는, 동일한 도전형의 트랜지스터를 인접하여 형성하는 경우에 비교하여, 인접 소자들 간의 전위차가 커지고, p형 웨爾(232)과 n형 웨爾(242)이 서로 인접하게 되어, 기생 트랜지스터가 발생하기 쉬워지므로, 소자 분리 영역(245)의 길이 L2는 소자 분리 영역(235)의 길이 L1보다 길게 할 필요가 있다.

전술한 바와 같이, 동일 기판 상에 복수의 트랜지스터를 형성하는 경우에, 반대되는 도전형의 2개의 트랜지스터를 인접하여 배열하면, 소자 분리 영역의 면적이 넓게 되어, 형성 영역의 면적에 낭비가 생기는 문제가 있다.

도 8a~8c를 참조하여, 트랜지스터의 배열 방법과 그 형성 영역의 면적에 대하여 설명한다. 도 8a~8c는 3개의 다른 경우를 나타내고 있으며, 각 경우에서는 한쌍의 트랜지스터로 이루어진 2개의 회로를 설치하고 있다.

도 8a는 2개의 회로가 수평 방향으로 정렬되어 있는 경우를 나타내고 있으며, 상기 2개의 회로는 반대되는 도전형(n형 및 p형)을 가지며 수평 방향으로 정렬되어 있는 트랜지스터쌍으로 이루어진다. 도 8a의 W1은 각각의 회로에 요구되는 면적의 폭을 나타내는 것이다. 도 8a에 도시한 바와 같이, 각 회로의 폭 W1은 소자 분리 영역(245)의 길이 L2를 포함한다. 또한, p형 웨爾(232)의 면적과 n형 웨爾(242)의 면적이 동일하지 않은 경우에는, 이용되지 않은 영역(249)이 발생한다.

도 8b는 동일한 구성의 2개의 회로가 수평 방향으로 정렬된 경우를 도시하는 것으로서, 2개의 회로 각각은 반대되는 도전형(n형 및 p형)을 가지며 수직 방향으로 정렬되는 트랜지스터쌍으로 이루어진다. 2개의 회로 각각이 점유하는 폭은 W2이다. 폭 W2는 폭 W1보다 좁기 때문에, 이 구성은 전술한 바와 같이 화소 피치의 범위 내에 회로를 형성하는 경우에는 유효하다. 그러나, 길이 L2의 소자 분리 영역(245)이, 수직 방향으로 정렬된 P형 웨爾과 n형 웨爾 사이에 배치되기 때문에, 도 8b의 구성의 길이는 동일 도전형의 트랜지스터를 수직으로 배열하는 경우보다 길다.

도 8c는 동일한 구성의 2개의 회로를 수평 방향으로 정렬한 경우를 도시하는 것으로, 2개의 회로 각각은 동일한 도전형을 가지며 수직 방향으로 정렬된 트랜지스터쌍으로 이루어진다. 소자 분리 영역(235)의 길이는 L1이고, 이것은 도 8b의 길이 L2보다 짧다. 길이 L1과 L2의 차는 최대 수  $\mu\text{m}$  정도이지만, 각각 한쌍의 트랜지스터로 구성되는 복수의 회로가 수직 방향으로 연속하여 설치되는 경우에, 길이의 차는 그 합이 되기 때문에 무시할 수 없게 된다. 예를 들면, 회로가 도 3의 표시 데이터 연산 회로(325)에 이용되는 경우에는, 하나의 표시 데이터가 3 비트로 표현되기 때문에, 총 길이의 차는 길이 L1과 길이 L2의 차의 3배가 된다. 액정 표시 패널에 표시되는 계조 레벨의 수가 증가하여, 표시 데이터의 비트 수가 8 또는 16 비트로 증가하는 경우, 트랜지스터의 정렬 방식을 개선하여, 쓸모없는 영역을 감소시키는 일이 유효하게 된다.

본 실시예에서는, 도 5에 도시한 바와 같이, 데이터 취득 소자(171~173), 표시 데이터 전송 소자(181~183), 표시 데이터 연산 소자(201~203), 시간 데이터 연산 소자(211~213)를 동일한 도전형의 트랜지스터로 구성하고 있고, 따라서 트랜지스터를 인접하여 설치하는 데에 요구되는 소자 분리 영역의 면적이 더 감소될 수 있다. 도 5에서는, n형 트랜지스터를 이용하여 설명하고 있지만, n형 트랜지스터와 마찬가지로 P형 트랜지스터를 이용하여 동일한 도전형의 트랜지스터를 인접하여 설치하는 구성으로 하는 것도 물론 가능하다.

도 9a~9b는, 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)의 레이아웃을 나타내는 도면으로, 도 9a는 레이아웃을 나타내는 개략 평면도이고, 도 9b는 도 9a의 IXB-IXB 선을 따른 개략 단면도이다. 도 9a에서, 소자 분리 영역(235)은 LOCOS 공정에 의해 형성되고, 웨ルド 산화막으로서 반도체 기판(231)을 덮고 있다. 참조 번호 236은 소자 분리 영역(웨ルド 산화막)(235)에 설치된 액티브 영역이다. 액티브 영역(236)에는, 트랜지스터로 이루어진 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)가 형성되어 있다. 참조 번호 234는 게이트 전극이다. 도 9a 및 9b를 간명히 하기 위해서, 도 9a에서는 배선을 생략하고, 도 9b에서는 전기적 접속을 선으로 나타내었다.

도 5에 나타난 바와 같이, 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)에는, 연산 결과 신호선(152)이 접속되어 있고, 표시 데이터 연산 소자(201~203)와 시간 데이터 연산 소자(211~213)는 동일 기판 상에 형성 가능하고, 소스/드레인 영역의 공유화가 가능하기 때문에, 소스/드레인 영역은 동일한 전위가 되도록 접속된다. 도 9b에 도시한 바와 같이, 소스/드레인 영역(233A)은 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)에 의해 공유되도록 형성되므로, 2개의 소자(203 및 213)의 소스 또는 드레인 영역 사이에 다층 배선은 불필요하다. 표시 데이터 연산 소자(201~203) 및 시간 데이터 연산 소자(211~213)의 각 쌍은 소스/드레인 영역(233A)을 공유하기 때문에, 표시 데이터 연산 소자(201~203)와 시간 데이터 연산 소자(211~213)의 사이에는, 소자 분리 영역(235)을 설치할 필요가 없다.

도 9a 및 9b에 도시한 바와 같이, 연산 결과 전달 회로(333)는 표시 데이터 연산 소자(203)를 위한 하나의 트랜지스터와 시간 데이터 연산 소자(213)를 위한 하나의 트랜지스터의 2개의 트랜지스터로 구성되고, 그 2개의 트랜지스터를 동일한 도전형의 트랜지스터로 함으로써 소자 분리 영역(235) 및 배선 영역이 생략 가능하기 때문에, 반대되는 도전형을 가지며 인접하여 배열된 2개의 트랜지스터에 의해 점유되는 면적에 비해 점유 면적이 작다. 그 때문에, 표시 데이터 연산 회로(325)를 조밀한 구성으로 하는 것이 가능하다. 또한, 표시 데이터 연산 소자(201~203)와 시간 데이터 연산 소자(211~213)의 사이의 다층 배선도 생략되므로, 배선에 의해 발생하는 용량이 감소하여, 고속 동작이 가능해진다.

또한, 도 5, 도 9a 및 9b에 도시한 바와 같이, 연산 결과 전달 회로(331~333)에서, 표시 데이터 연산 소자(201~203) 각각은 1개의 트랜지스터로 구성되고, 시간 데이터 연산 소자(211~213) 각각도 1개의 트랜지스터로 구성되어 있다. 연산 결과 전달 회로(331~333)는 표시 데이터와 시간 제어 신호를 이용하여 디지털 연산을 행하는 것이므로, 표시 데이터를 위한 소자와 시간 제어 신호를 위한 소자를 필요로 하고, 따라서 연산 결과 전달 회로

(331~333) 각각은 적어도 2개의 소자를 필요로 한다. 그 때문에, 도 5에 도시된 연산 결과 전달 회로(331~333) 각각은 최소 개수의 소자로 형성된다. 전술한 바와 같이, 연산 결과 전달 회로(331~333) 각각에 의해 접유되는 면적은, 최소 개수인 2개의 종래의 트랜지스터를 사용하여 형성하는 경우보다도 작아질 수 있다.

도 10은 표시 데이터 연산 회로(325)의 레이아웃을 나타낸다. 도 10을 간단히 하기 위해서, 타이밍 신호선(329) 이외의 배선 도전체를 생략하여, 접속 상태를 선으로 도시하고 있다. 도 9a 및 9b와 관련하여 설명한 바와 같이, 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)는 연산 결과 전달 회로(333)를 구성하는 트랜지스터이다. 데이터 취득 소자(173)와 표시 데이터 전송 소자(183)는, 메모리 용량(193)을 구성하는 2개의 전극 중 하나와 동일한 전위의 소스/드레인 영역을 공유한다. 그 때문에, 데이터 취득 소자(173)와 표시 데이터 전송 소자(183)가 동일한 환경상에 형성될 수가 있고, 데이터 취득 소자(173)와 표시 데이터 전송 소자(183) 사이의 소자 분리 영역 및 배선 영역을 생략하는 것이 가능하다.

도 10에 도시한 바와 같이, 타이밍 신호선(329)은 데이터 취득 소자(173)의 게이트 전극과 동일한 도전층으로 형성되어 있다. 또한, 타이밍 신호선(329)은 연산 결과 전달 회로(333) 및 메모리 용량(193)에 인접하여 형성되고, 데이터 취득 소자(173)의 게이트 전극으로서는 타이밍 신호선(329)의 일부가 이용된다.

데이터 취득 소자(173)와 표시 데이터 전송 소자(183)의 액티브 영역(271)은 이들의 게이트 전극과 중첩되는 영역의 형상이 사다리꼴이 되도록 형성된다. 이 형상에 의하면, 게이트 전극의 아래에 나타나는 전하가 이동하기 쉬운 방향이 발생한다. 트랜지스터가 온 상태이고 게이트 전극에 전압이 인가되는 때에는 게이트 전극 아래의 액티브 영역에 전하가 발생되고, 트랜지스터가 오프 상태로 변하는 때에는 소스/드레인 영역 중 하나가 전하로 유입된다. 도 10에 도시된 바와 같이, 액티브 영역(271)과 중첩되는 하나의 게이트 전극의 일부의 2개의 대향하는 긴 변의 길이에 차이가 있으면, 전하는 2개의 긴 변 중 더 긴 쪽으로 쉽게 유입된다.

데이터 취득 소자(173)의 경우, 메모리 용량(193)에 정극성의 신호를 수신하면, 메모리 용량(193)으로부터 표시 데이터 신호선(323)으로 유입되는 부극성 전하의 양은 매우 적다. 그 때문에, 트랜지스터(데이터 취득 소자(173))가 오프되면, 게이트 전극 아래의 전하가 메모리 용량(193) 측으로 유입되어 버리는 경우, 메모리 용량(193)에 충분한 신호가 기입될 수 없게 된다. 이 문제를 해결하기 위해, 액티브 영역(271)은 도 10에 도시한 것과 같은 형상을 갖고, 그 결과 전하는 표시 데이터 신호선(323)으로 쉽게 유입한다. 또한, 표시 데이터 전송 소자(183)도 동일한 이점을 가지므로, 신호는 후속 회로에 쉽게 전달될 수 있다.

이하에서는, 도 11 및 도 12에 나타내는 신호의 타이밍 차트를 참조하여, 도 5 및 도 6에 나타내는 회로의 동작에 대하여 설명한다.

도 11은, 표시 데이터선(321~323) 각각에 출력되는 표시 데이터 DD1~DD3와, 수평 시프트 레지스터(121)로부터 출력되는 타이밍 신호 HSR1~HSR3를 나타낸다. 도 5에서, 표시 데이터선(321~323)에는 표시 데이터 DD1~DD3이 각각 출력되고, 수평 시프트 레지스터(121)는 타이밍 신호 HSR1~HSR3를 순차적으로 출력한다. 도 11에서는, 단 3개의 타이밍 신호 HSR1~HSR3만을 나타내었지만, 영상 신호선의 수에 따라, 필요한 수의 타이밍 신호가 수평 시프트 레지스터로부터 출력될 수 있음에 유의한다.

표시 데이터 DD1~DD3는 DD1을 최하위 비트로 하는 3 비트의 데이터를 나타내고 있다. 타이밍 신호 HSR1이 출력되는 때에, 표시 데이터 DD1은 하이 레벨이고, 표시 데이터 DD2는 로우 레벨이고, 표시 데이터 DD3는 하이 레벨이다. 본 실시예의 표시 데이터 DD1~DD3에서, 하이 레벨과 로우 레벨은 각각 "1"과 "0"으로 표현되므로, 타이밍 신호 HSR1이 출력되는 기간동안의 표시 데이터는 하위 비트측으로부터 (1, 0, 1)로 된다.

도 11에서, 표시 데이터 DD1~DD3이 (1, 0, 1)인 상태에서, 타이밍 신호선(329)에 타이밍 신호 HSR1이 출력되면, 데이터 취득 소자(171~173)가 온되고, 표시 데이터 DD1~DD3는 각각 메모리 용량(191~193)에 취득된다. 표시 데이터 DD1~DD3는 (1, 0, 1)인 경우, 메모리 용량(191)은 하이 레벨의 전압을, 메모리 용량(192)은 로우 레벨의 전압을, 메모리 용량(193)은 하이 레벨의 전압을 취득한다.

다음에, 메모리 용량(191~193)에 표시 데이터가 취득된 후의 동작에 대하여, 도 12를 참조하여 설명한다. 도 12에서, 참조 기호 RMP는 계조 전압으로서, 전압 발생 회로(112)(도시하지 않음)로부터 도 6에 도시된 버스 라인(151)에 공급되는 것이다. 계조 전압 RMP는 도 12에 도시한 바와 같이, 시간에 따라 전압이 계단 형상으로 변화하며, 표시 데이터 (1, 1, 1)의 경우에는 계조 전압 V0가 화소 전극에 기입되고, 표시 데이터 (0, 0, 0)의 경우에는 계조 전압 V7이 화소 전극에 기입되는 방식으로 할당이 이루어진다.

도 12에서, 우선 전송 신호 TG가 하이 레벨로 변하면, 표시 데이터 전송 소자(181~183)는 온되므로, 메모리 용량(191~193)에 보유되는 표시 데이터는 표시 데이터 연산 소자(201~203)에 전송된다. 여기서, 표시 데이터에 대응하는 전위가 표시 데이터 연산 소자(201~203) 각각의 게이트 전극에 전해지긴 하지만, 표시 데이터 연산 소자(201~203)의 게이트 전극에는 1 수평 주사 기간 전의 전하가 저장되기 때문에, 각 메모리 용량(191~193)에 저장된 전위와 1 수평 주사 기간 전의 게이트 전극과 그 배선의 용량에 기초한 분압에 의해, 게이트 전극의 전위가 결정된다. 도 11에 도시한 바와 같이, 표시 데이터 DD1~DD3가 (1, 0, 1)인 경우에서, 표시 데이터 연산 소자(201 및 203)는 온되고, 표시 데이터 연산 소자(202)는 오프된다.

다음으로, 시간 제어 펄스 DA1~DA3가 하이 레벨인 상태에서, 연산 결과 신호선 세트 신호 DST를 로우 레벨로 하여, 연산 결과 신호선 세트 소자(222)를 오프시킨다. 다음으로, 연산 결과 신호선 리세트 신호 DRST를 로우 레벨로 하여, 2개의 연산 결과 신호선 리세트 소자(221, 223)를 오프시키고, 그 결과 연산 결과 신호선(152(1) 및 152(4))은 각각 정전압선(153, 156)에 접속되어 하이 레벨이 된다.

연산 결과 신호선(152)이 하이 레벨이 되면, 계조 전압 출력 회로(326)의 레벨 시프터 회로(141)는 게이트 회로(142)에 게이트 전압을 인가하여, 게이트 회로(142)가 전압 버스선(151)을 영상 신호선(103)에 전기적으로 접속하

게 한다. 즉, 연산 결과 신호선(152)이 하이 레벨인 기간동안, 영상 신호선(103)에는 전압 버스 라인(151)으로부터 계조 전압 RMP가 공급된다. 전술한 바와 같이, 도 12의 계조 전압 RMP는 시간에 따라 계단 형상으로 변화한다. 연산 결과 신호선(152)이 하이 레벨인 기간동안, 영상 신호선(103)에는 도 12의 계조 전압 RMP이 출력된다.

다음으로, 시간 제어 펄스 DA1~DA3는 시간 제어 신호선(161~163) 각각에 출력되기 시작한다. 그 다음, 연산 결과 신호선 리세트 신호 DRST를 하이 레벨로 한 다음, 연산 결과 신호선 세트 신호 DST를 하이 레벨로 한다. 연산 결과 신호선 세트 신호 DST가 하이 레벨이 되면, 연산 결과 신호선 세트 소자(222)가 혼되고, 연산 결과 신호선(152(1))은 GND 레벨의 선(154)에 접속되어 로우 레벨로 된다.

도 12에서, t0의 타이밍에서는, 모든 시간 제어 펄스 DA1~DA3가 로우 레벨이기 때문에, 시간 데이터 연산 소자(211~213)는 모두 온된다. 그 결과, 표시 데이터 연산 소자(201~203) 전부가 온되지 않으면, 즉 표시 데이터(201~203)가 (1, 1, 1)이 아니면, 연산 결과 신호선(152(4))의 전위는 VDD로 유지되어, 게이트 회로(142)는 온 상태로 유지된다.

예를 들어, 도 5, 6, 11, 12에서, 타이밍 신호 HSR1이 출력되는 기간동안 표시 데이터가 (1, 0, 1)인 경우를 고려해보자.

타이밍 t0에서, 표시 데이터 연산 소자(202)는 오프되고, 연산 결과 신호선(152(4))은 VDD로 유지된다.

그 다음, 타이밍 t2에서는 시간 제어 펄스 DA1~DA3가 (0, 1, 0)으로 되기 때문에, 시간 데이터 연산 소자(212)는 온된다. 한편, 표시 데이터가 (1, 0, 1)이기 때문에, 표시 데이터 연산 소자(203, 201)는 온 상태에 있다. 그 결과, 연산 결과 신호선((152)(1)~(4)) 전부가 GND 선(154)에 접속되고, 연산 결과 신호선((152)(4))이 로우 레벨로 되어, 게이트 회로(142)는 전압 버스 라인(151)과 영상 신호선(103)의 전기적 접속을 차단한다. 그 결과, 영상 신호선(103)은, 전압 버스선(151)으로부터 차단되는 순간에서의 전압 버스 라인(151)의 전압 V2로 유지된다. 그 다음, 연산 결과 신호선 리세트 신호 DRST가 로우 레벨이 되어, 연산 결과 신호선(152)을 하이 레벨로 할 때까지, 영상 신호선(103)과 전압 버스 라인(151)은 전기적으로 접속되지 않는다.

이하에서는, 도 13을 참조하여, 수평 시프트 레지스터(121)의 회로 구성을 설명한다. 참조 기호 HSR은 쌍방향 시프트 레지스터이고, 좌우 쌍방향으로 신호를 시프트할 수 있다. 쌍방향 시프트 레지스터 HSR은 클럭드(clocked) 인버터(61, 62, 65, 66)로 구성되어 있다.

참조 번호 25는 수평 주사 리세트 신호의 입력 단자이고, 참조 번호 26은 수평 주사 개시 신호의 입력 단자이다. 클럭드 인버터(61)는, 도 13의 좌측으로부터 우측으로 주사를 행하는 개시 신호를 수평 시프트 레지스터(121)에 공급하고, 클럭드 인버터(62)는 도 13의 우측으로부터 좌측으로 주사를 행하기 위한 개시 신호를 수평 시프트 레지스터(121)에 공급한다. 참조 번호 27은 수평 주사 종료 신호의 출력 단자이다.

이하에서는, 도 14a 및 14b를 참조하여, 쌍방향 시프트 레지스터 HSR에 이용되는 클럭드 인버터(61, 62)를 설명한다. 참조 기호 RL1 및 RL2는 각각 제1 및 제2 수평 방향 설정선을 나타낸다. 제1 수평 방향 설정선 RL1은 도 13의 좌측으로부터 우측으로 주사를 행하기 위한 H 레벨을 제공하고, 제2 수평 방향 설정선 RL2는 도 13의 우측으로부터 좌측으로 주사를 행하기 위한 H 레벨을 제공한다. 도 13에서는 도면을 보기 쉽게 하기 위해서 배선을 생략하고 있지만, 제1 수평 방향 설정선 RL1과 제2 수평 방향 설정선 RL2는 쌍방향 시프트 레지스터 HSR을 구성하는 클럭드 인버터들(61, 62)에 접속되어 있다.

클럭드 인버터(61)는 도 14a에 도시한 바와 같이 p형 트랜지스터(71, 72)와 n형 트랜지스터(73, 74)로 이루어진다. p형 트랜지스터(72)는 제2 수평 방향 설정선 RL2에 접속되어 있고, n형 트랜지스터(73)는 제1 수평 방향 설정선 RL1에 접속되어 있다. 제1 수평 방향 설정선 RL1이 H 레벨이고, 제2 수평 방향 설정선 RL2이 L 레벨인 경우, 클럭드 인버터(61)는 인버터로서 기능하지만, 제2 수평 방향 설정선 RL2가 H 레벨이고 제1 수평 방향 설정선 RL1이 L 레벨인 경우, 클럭드 인버터(62)는 하이 임피던스로 기능한다.

한편, 클럭드 인버터(62)에서, p형 트랜지스터(72)는 제1 수평 방향 설정선 RL1에 접속되고, n형 트랜지스터(73)는 제2 수평 방향 설정선 RL2에 접속된다. 클럭드 인버터(62)는, 제2 수평 방향 설정선 RL2가 H 레벨인 경우에는 인버터로서 기능하고, 제1 수평 방향 설정선 RL1이 H 레벨인 경우에는 하이 임피던스로서 기능한다.

도 14c는 클럭드 인버터(65)의 회로 구성을 나타낸 것이다. 클럭드 인버터(65)는, 클럭 신호선 CLK1이 H 레벨이고 클럭 신호선 CLK2가 L 레벨인 경우에는 반전된 입력을 출력하고, 클럭 신호선 CLK1이 L 레벨이고 클럭 신호선 CLK2가 H 레벨인 경우에는 하이 임피던스로 기능한다.

도 14d는 클럭드 인버터(66)의 회로 구성을 나타낸 것이다. 클럭드 인버터(66)는, 클럭 신호선 CLK2가 H 레벨이고 클럭 신호선 CLK1이 L 레벨인 경우에는 반전된 입력을 출력하고, 클럭 신호선 CLK2가 L 레벨이고 클럭 신호선 CLK1이 H 레벨인 경우에는 하이 임피던스로서 기능한다. 도 13에서는, 도면을 간단하게 하기 위해, 클럭 신호선 CLK1, CLK2의 접속을 생략하고 있지만, 클럭드 인버터들(65, 66)에는 클럭 신호선 CLK1, CLK2가 접속되어 있다.

도 15a 및 15b는 수평 구동 회로(120)를 구성하는 트랜지스터의 레이아웃을 나타낸 것이다. 도 15a는 수평 구동 회로(120)의 개략적인 평면도로서, 도면을 간단하게 하기 위해서, 도 15a 및 15b는 4개의 영상 신호선(103)(도시하지 않음)에 대응하는 수평 구동 회로(120)만을 보이고 있다. 영상 신호선(103)마다 설치되는 수평 구동 회로(120)의 폭 AW는, 전술한 바와 같이 화소 피치에 의해 결정된다. 도 15b는 도 15a의 XVB-XVB 선을 따라 절취한 개략 단면도이다.

참조 번호 121은 수평 시프트 레지스터로서, 도 14a~14d에 도시한 바와 같이, n형 트랜지스터와 p형 트랜지스터가 인접하여 정렬되어 있는 것이다. 참조 번호 246 및 236은 각각 p형 및 n형 트랜지스터의 액티브 영역이다. 액티브 영역(246(1))에는 예를 들면 도 13, 도 14a~14b의 클럭드 인버터(61)와 클럭드 인버터(62)의 p형 트랜지스터가 폭 AW에 포함되도록 인접하여 설치된다. 동일하게, 액티브 영역(236(1))에는 클럭드 인버터(61)와 클럭드 인버터(62)의 n형 트랜지스터가 설치되고, 액티브 영역(246(2))에는 클럭드 인버터(65)와 클럭드 인버터(66)의 p형 트랜지스터가 설치되며, 액티브 영역(236(2))에는 클럭드 인버터(65)와 클럭드 인버터(66)의 n형 트랜지스터가 설치된다. 도 15b에서, 참조 번호 242는 n형 웨일이고, 참조 번호 232는 p형 웨일이며, 참조 번호 245는 n형 웨일과 p형 웨일 사이에 설치되는 소자 분리 영역이다. 참조 기호 AL2는 수평 시프트 레지스터(121)가 형성될 영역의 길이를 나타내고 있다. 참조 번호 325는 표시 데이터 연산 회로이다. 도 15a 및 15b에서, 6개의 데이터 연산 회로(523(1)~(6))이 수직 방향으로 배열된다. 표시 데이터 연산 회로들(325(1)~(6)) 각각은 각 영상 데이터 선(103)마다 설치되기 때문에, 표시 데이터의 비트 수가 증가하면, 표시 데이터 연산 회로의 형성 영역도 수직 방향으로 길어져 버린다. 이러한 문제점을 해결하기 위해, 표시 데이터 연산 회로(325)는 도 5에 도시한 바와 같이 n형의 트랜지스터로 구성되어 있다.

도 15a, 15b의 참조 번호 236은, 도 5의 표시 데이터 연산 소자(도 5 중 201~203)와 시간 데이터 연산 소자(도 5 중 211~213)가 형성되는 액티브 영역을 나타낸 것이다. 표시 데이터 연산 소자(203)와 시간 데이터 연산 소자(213)는 도 9a 및 9b에 도시한 바와 같이 액티브 영역(236)에 가로 방향으로 정렬된다. 도 15b에서, 참조 번호 232는 n형 웨일이고, 참조 번호 235는 2개의 n형 웨일 사이에 설치되는 소자 분리 영역이다. 참조 기호 AL1은 표시 데이터 연산 회로(325(1)~325(6)) 각각이 형성되는 영역의 길이를 나타낸다. 도 15a 및 15b에서, 참조 번호 261은 도 5의 메모리 용량(191~193)이 설치되는 영역이고, 참조 번호 271은 도 5의 데이터 취득 소자(도 5의 171~173)와 표시 데이터 전송 소자(도 5의 181~183)가 형성되는 액티브 영역이다. 데이터 취득 소자와 표시 데이터 전송 소자는, 표시 데이터 연산 소자 및 시간 데이터 연산 소자와 마찬가지로, 액티브 영역(271)에 가로 방향으로 정렬되어 설치된다.

도 15a의 참조 번호 329는 타이밍 신호선(예를 들어 폴리실리콘으로 형성됨)으로서, 수평 시프트 레지스터(121)로부터 연장되어, 각 데이터 취득 소자에 접속된다(도 15a 및 15b에서, 데이터 취득 소자로의 배선은 생략함). 타이밍 신호선(329)은 표시 데이터 연산 회로(325(1)~325(6))에 타이밍 신호를 전하도록, 표시 데이터 연산 회로(325(1)~325(6))를 따라 형성된다. 따라서, 표시 데이터의 비트 수가 증가하여, 표시 데이터 연산 회로(325(1), 325(2), ...)의 수가 증가한 경우에, 타이밍 신호선(329)은 수직 방향으로 길어진다.

타이밍 신호선(329)이 길어지면, 배선 저항이 커진다. 타이밍 신호는 고주파수의 펄스이기 때문에, 배선 저항이 커지면, 타이밍 신호의 파형에 왜곡이 발생한다. 타이밍 신호의 파형에 왜곡이 발생하면, 데이터 취득 소자(171~173)에서 표시 데이터를 취득하는 타이밍에 에러가 발생한다. 예를 들어, 표시 데이터 연산 회로(325(1))는 주어진 타이밍에서 표시 데이터를 취득하고 있는 반면, 표시 데이터 연산 회로(325(6))는 표시 데이터를 취득하고 있지 않고, 그 결과 표시 품질이 저하된다.

타이밍 신호선(329)의 배선 저항 및 용량을 고려하면, 표시 데이터 연산 회로(325)의 길이 AL1은 가능한 한 짧은 것이 바람직하다. 수평 시프트 레지스터(121)의 길이 AL2가 표시 데이터 연산 회로(325(1), 325(2), 325(3), ...)의 길이 AL1보다 긴 경우, 표시 데이터 연산 회로(325(1), 325(2), 325(3), ...)의 전체 길이는 길이 AL1과 표시 데이터 비트 수의 곱이기 때문에, 표시 데이터 비트수를 증가시키면, 표시 데이터 연산 회로(325(1), 325(2), 325(3), ...)의 길이 AL1을 짧게 하는 것이, 회로 전체와 타이밍 신호선(329)의 길이를 짧게 하는 것에 유효하다. 이러한 점에서, 표시 데이터 연산 회로(325(1), 325(2), 325(3), ...)는, n형의 트랜지스터를 이용하여 회로(325(1), 325(2), 325(3), ...)를 형성하여, 소자 분리 영역(235)의 길이를 짧게 함으로써, 표시 데이터 연산 회로(325)의 길이 AL1을 짧게 하고 있다.

도 15a에서, 참조 번호 326은 계조 전압 출력 회로이고, 참조 번호 272 및 273은 각각 레벨 시프터 회로(141)의 p형 및 n형 트랜지스터의 액티브 영역이다. 액티브 영역(273)은 트랜지스터의 온/오프 속도를 증가시키기 위해서, 다른 액티브 영역에 비교해 크게 형성된다.

이상 설명한 바와 같이, 수평 구동 회로(120)를 구성하는 트랜지스터의 레이아웃의 설계에서, 동일한 도전형의 트랜지스터를 이용하여 구동 회로를 형성하고, 그 회로를 화소 퍼치의 폭 내에 배치하는 것에 의해, 구동 회로의 길이를 감소시킬 수 있다. 또한, 액정 표시 패널의 표시부의 면적은 감소되지만, 계조 레벨 또는 화소의 수가 증가하더라도, 표시부보다 작은 면적을 갖는 구동 회로를 실현할 수 있다. 또한, 구동 회로의 길이를 짧게 함으로써, 계조 수가 증가해도 표시 데이터를 취득하는 타이밍 신호선의 배선 저항을 낮게 억제할 수 있어, 표시 데이터 취득 에러를 감소시키는 것이 가능하다.

도 16은 2 시스템의 수평 구동 회로(120)를 설치한 경우의 구성을 도시한 것이다. 도 16에서, 2 시스템의 수평 구동 회로(120)는 표시부(110)의 상측과 하측에 나누어 배치된 것으로 도시되어 있지만, 2 시스템의 수평 구동 회로(120)를 상측과 하측 중 어느 한 쪽에 배치하는 것도 가능하다. 도 17은 2 시스템의 수평 구동 회로(120)를 설치한 경우에 가능해지는 전압 선택 회로(123)의 회로 구성을 나타낸 것이다. 도 16에 도시된 수평 구동 회로(120)에서, 2 시스템 중 하나의 전압 선택 회로(123)가 표시 데이터를 취득하는 기간동안, 2 시스템 중 다른 하나의 전압 선택 회로(123)는 계조 전압을 선택하고, 그 결과 도 17에 도시한 바와 같이 표시 데이터 전송 소자가 생략될 수 있다.

이하에서는, 도 18을 이용하여, 본 발명에 따른 액정 표시 장치의 화소부를 설명한다. 도 18은 본 발명에 따른 일 실시예의 개략적인 단면도이다.

도 18에서, 참조 번호 100은 액정 표시 패널, 참조 번호 1은 구동 회로 기판으로서 기능하는 제1 기판, 참조 번호 2는 투명 기판으로서 기능하는 제2 기판, 참조 번호 3은 액정 조성물, 참조 번호 4는 스페이서이다. 스페이서(4)는 구동 회로 기판(1)과 투명 기판(2) 사이에 액정 조성물(3)이 협지된 고정 셀 갭 d를 형성한다. 참조 번호 5는 구동 회

로 기판(1) 상에 형성된 반사 전극이고, 참조 번호 6은 반사 전극(5)과 함께 액정 조성물(3)을 통해 전압을 인가하기 위한 대향 전극이고, 참조 번호 7, 8은 액정 조성물(3)의 액정 분자를 지정된 방향으로 배향시키는 배향막이며, 참조 번호 30은 반사 전극(5)에 전압을 공급하는 능동 소자이다.

참조 번호 34는 드레인 영역, 참조 번호 35는 소스 영역, 참조 번호 36은 게이트 전극, 참조 번호 38은 절연막, 참조 번호 39는 트랜지스터들 사이를 전기적으로 분리하는 필드 산화막, 참조 번호 40은 절연막(38)을 사이에 두고 구동 회로 기판(1)과의 사이에서 용량을 형성하는 저장 용량 형성용 전극, 참조 번호 41은 제1 충간 절연막, 참조 번호 42는 제1 도전막, 참조 번호 43은 제2 충간 절연막, 참조 번호 44는 제1 차광막, 참조 번호 45는 제3 충간 절연막, 참조 번호 46은 제2 차광막, 참조 번호 47은 제4 충간 절연막, 참조 번호 48은 반사 전극(5)을 형성하는 제2 도전막이다.

본 실시예의 액정 표시 패널은 반사형이다. 액정 표시 패널(100)에 조사된 광은, 투명 기판(2)측(도 18의 상단)으로부터 입사한 후, 액정 조성물(3)을 투과하여 반사 전극(5)으로 반사한 다음, 다시 액정 조성물(3), 투명 기판(2)을 투과하여 액정 표시 패널(100)로부터 출사한다.

반사형의 액정 표시 패널에서, 구동 회로 기판(1)의 액정 조성물(3)측 면에 반사 전극(5)을 형성한 경우, 구동 회로 기판(1)에 불투명한 실리콘 기판 등을 이용할 수 있다. 또한, 이러한 구성은, 능동 소자(30)나 배선을 반사 전극(5) 아래에 설치할 수 있어, 화소가 되는 반사 전극(5)을 넓게 하여, 고개구울을 실현할 수 있는 이점이 있다. 또한, 액정 표시 패널(100)에 조사되는 광에 의한 열을 구동 회로 기판(1)의 배면에서 방열할 수 있다는 이점도 있다.

이하에서는, 액정 표시 패널에 전계 제어 복굴절 모드(electrically controlled birefringence mode)를 이용한 경우의 동작을 설명한다. 액정 표시 패널(100)에는 편광 소자에 의해 직선 편광된 광이 입사한다. 반사 전극(5)과 대향 전극(6) 사이에 전압을 인가하면, 액정 조성물(3)의 액정 분자들은 그 유전 이방성에 의해 배열이 변화하고, 그 결과 액정층의 복굴절율이 변화한다. 전계 제어 복굴절 모드는, 복굴절율의 변화를 광 투과율의 변화로 변환하여 상을 형성하는 것이다.

다음으로, 도 19a 및 19b를 이용하여, 전계 제어 복굴절 모드의 하나인 단 편광판 트위스티드 네마티(Single-Polarizer Twisted Nematic, SPTN) 모드에 대하여 설명한다.

참조 번호 9는 광원(도시하지 않음)으로부터의 입사광 L1을 두개의 편광으로 분할하여, 직선 편광된 광 L2을 출사하는 편광 빔 분할기이다.

도 19a 및 19b에서는 편광 빔 분할기(9)를 투과한 P 편광된 광이 액정 표시 패널(100)에 입사되는 경우를 나타내고 있지만, 편광 빔 분할기(9)에 의해 반사된 S 편광된 광도 액정 표시 패널(100)에 입사될 수 있다.

액정 조성물(3)은 유전 이방성이 플러스인 네마티 액정 재료이다. 액정 분자의 장축은 구동 회로 기판(1)과 투명 기판(2)의 주면에 대하여 거의 평행하게 배향되고, 액정 분자는 배향막(7, 8)에 의해 약 90°트위스트된 상태로 배향된다.

도 19a는 액정 조성물(3)의 층에 전압이 인가되지 않는 경우를 나타낸다. 액정 표시 패널(100)에 입사한 광 L2는 액정 조성물(3)의 복굴절성에 의해 타원 편광된 후, 반사 전극(5) 상에서 원 편광된다. 반사 전극(5)에 의해 반사된 광은 액정 조성물(3)을 통과하여 다시 타원 편광된 다음, 액정 표시 패널(100)로부터 출사될 때에는 직선 편광으로 되돌아간다. 직선 편광된 출사광 L3은 편광 방향이 입사광 L2에 대하여 90°회전한 S 편광된 광이며, 편광 빔 분할기(9)에 다시 입사한 후, 편광 빔 분할기(9)의 내부 계면에 의해 반사되어, 출사광 L4로 된 다음, 표시를 행하기 위해 스크린 등에 조사된다. 이러한 구성은, 액정 조성물(3)의 층에 전압을 인가하지 않은 경우에 광이 출사되는 소위 노멀 화이트(노멀 오픈) 타입이다.

도 19b는 액정 조성물(3)에 전압이 인가되는 경우를 나타낸 것이다. 액정 조성물(3)의 층에 전계가 인가되면, 액정 분자가 전계 방향으로 배열되기 때문에, 액정 분자의 복굴절은 발생하지 않는다. 따라서, 직선 편광으로 액정 표시 패널(100)에 입사한 광 L2는 반사 전극(5)에 의해 그대로 반사되며, 액정 표시 패널(100)로부터의 출사광 L5는 입사광 L2와 동일한 편광 방향을 갖는다. 출사광 L5는 편광 빔 분할기(9)를 투과하여 광원으로 되돌아가서, 스크린 등에 광이 조사되지 않기 때문에, 화면 상에는 흑 표시가 제공된다.

단일 편광판 트위스티드 네마티 모드에서는, 액정 분자의 배향 방향이 기판의 주면과 평행하기 때문에, 일반적인 액정 분자의 배향 방법이 이용될 수 있고, 프로세스의 안정성이 높다. 노멀 화이트 모드 동작에 의해, 저전압 레벨에서 표시 불량이 발생하는 것을 방지한다. 이는, 노멀 화이트 방식에서, 액정층에 고전압이 인가되는 때에 암(暗) 레벨(흑 표시)이 제공되고, 이러한 상태에서는 대부분의 액정 분자가 기판의 주면에 수직인 전계 방향으로 배향되므로, 암 레벨의 표시가 저전압 인가시의 액정 분자의 초기 배향 상태에 지나치게 의존하지 않기 때문이다.

인간의 눈은, 휙도의 비율에 의해 휙도 불균일을 인식하고, 휙도에 대하여 대수 스케일에 가까운 반응을 가지며, 암 레벨의 변동에는 민감하다.

이러한 이유로 인해, 노멀 화이트 방식은, 액정 분자의 초기 배향 상태에 의해 유발되는 불균일의 방지에 대하여 이점을 갖는다.

전술한 전계 제어 복굴절 모드에서는, 액정 표시 패널의 기판들 간에 높은 셀 갭의 정밀도가 요구된다. 전계 제어 복굴절 모드는, 광이 액정층을 통과하는 동안 발생하는 이상 광과 정상 광 간의 위상차를 이용하기 때문에, 액정층을 통과한 투과광의 강도는 이상 광과 정상 광 간의 지연  $\Delta n \cdot d$ 에 의존한다. 여기서,  $\Delta n$ 은 굴절율 이방성이고,  $d$ 는 스페이스(4)에 의해 형성되는 투명 기판(2)과 구동 회로 기판(1) 사이의 셀 갭이다.

본 실시예에서는, 표시 불균일을 고려하여, 셀 캡은  $\pm 0.05\mu\text{m}$  내의 정확도로 제어되었다. 반사형 액정 표시 패널에서, 액정층에 입사한 광은 반사 전극에 의해 반사된 다음 재차 액정층을 통과하기 때문에, 투과형 액정 표시 패널에서 이용되는 액정 조성물과 동일한 굴절율 이방성  $\Delta n$ 을 갖는 액정 조성물을 이용하는 경우, 셀 캡 d는 투과형 액정 표시 패널에 비하여 절반으로 된다. 일반적으로, 투과형 액정 표시 패널의 셀 캡 d는  $5\sim 6\mu\text{m}$  정도인 데 대하여, 본 실시예에서는 약  $2\mu\text{m}$ 이다.

본 실시예에서, 높은 셀 캡 정밀도와, 종래의 액정 표시 패널보다 좁은 셀 캡을 보장하기 위해서, 비즈 분산법을 이용하는 대신에, 기둥형의 스페이서를 구동 회로 기판(1) 상에 형성하는 방법을 이용하였다.

도 20은 구동 회로 기판(1) 상에 설치된 반사 전극(5)과 스페이서(4)의 배치를 설명하는 개략적인 평면도를 나타낸다. 다수의 스페이서(4)가 일정한 간격을 유지하도록 구동 회로 기판 전면에 매트릭스 형상으로 형성되어 있다. 반사 전극들(5) 각각은 액정 표시 패널에 의해 형성되는 최소 회소(picture element)로서 기능하는 화소이다. 도 20에서는 간략화를 위해, 5열  $\times$  4행의 화소 어레이로 도시하고 있으며, 최외곽의 열/행에 있는 화소들은 참조 부호 5A로 표시되고, 최외곽의 열/행 내부에 있는 화소들은 참조 부호 5B로 표시된다.

도 20에서, 5열  $\times$  4행의 어레이가 표시 영역을 형성하며, 그 영역 내에 액정 표시 패널에 의한 표시가 형성된다. 표시 영역의 외측에는 더미 화소(10)가 설치되어 있고, 이 더미 화소(10)의 주변에는 스페이서(4)와 동일한 재료로 주변 프레임(11)이 설치되어 있으며, 구동 회로 기판(1) 상의 주변 프레임(11)의 외측에는 밀봉 부재(12)가 도포된다. 참조 번호 13은 액정 표시 패널(100)에 외부 신호를 공급하는 데 이용되는 외부 접속 단자이다.

스페이서(4)와 주변 프레임(11)은 수지 재료를 이용하였다. 수지 재료로는, 예를 들면, 주식회사 JSR(일본, 도쿄)의 학화 증폭형 네가티브 타입 레지스트 "BPR-113" (상품명)을 이용할 수 있다. 반사 전극(5)이 형성되어 있는 구동 회로 기판(1) 상에 스펀 코트법 등으로 포토레지스트 재료를 도포한 후, 스페이서(4) 및 주변 프레임(11) 형태의 패턴을 갖는 마스크를 통해 레지스트를 노광한 다음, 제거제를 이용하여 현상함으로써 스페이서(4)와 주변 프레임(11)을 형성한다.

스페이서(4) 및 주변 프레임(11)이 포토레지스트 등의 재료를 이용하여 형성되는 경우, 스페이서(4) 및 주변 프레임(11)의 높이는 재료의 도포 두께에 의해 제어할 수 있으므로, 스페이서(4)와 주변 프레임(11)을 높은 정밀도로 형성하는 것이 가능하다. 또한, 스페이서(4)의 위치는 마스크 패턴에 의해 결정될 수 있으므로, 원하는 위치에 정확하게 스페이서(4)를 설치하는 것이 가능하다.

액정 프로젝터에서 이용되는 액정 표시 패널에서, 스페이서들(4) 중 하나가 화소 상에 존재하는 경우, 스페이서의 그림자가 확대 투영되어 보이는 문제가 발생할 수 있다. 마스크 패턴을 통한 노출 및 그에 따른 현상에 의해 스페이서(4)를 형성함으로써, 표시되는 영상의 품질을 저하시키지 않도록 하는 위치에 스페이서(4)를 설치할 수 있다.

또한, 스페이서(4)와 주변 프레임(11)을 동시에 형성하고 있기 때문에, 먼저 소량의 액정 조성물(3)을 구동 회로 기판(1)에 적하한 후, 액정층을 협진한 채로 투명 기판(2)을 구동 회로 기판(1)에 중첩시킨 다음, 투명 기판(2)을 구동 회로 기판(1)에 접합함으로써, 액정 조성물(3)이 구동 회로 기판(1)과 투명 기판(2) 사이에 밀봉될 수 있다.

구동 회로 기판(1)과 투명 기판(2)의 사이에 액정 조성물(3)을 삽입한 후, 액정 표시 패널(100)을 조립하는 때에, 주변 프레임(11)에 의해 둘러싸인 영역 내에 액정 조성물(3)이 보유된다.

또한, 주변 프레임(11)의 외측에는 밀봉 부재(12)가 도포되어, 액정 조성물(3)을 액정 표시 패널(100) 내에 봉입한다.

전술한 바와 같이, 주변 프레임(11)은 마스크 패턴을 이용하여 형성되기 때문에, 높은 위치 정밀도로 구동 회로 기판(1) 상에 형성할 수 있으며, 따라서 액정 조성물(3)의 경계를 높은 정밀도로 정하는 것이 가능하다. 또한, 주변 프레임(11)은 밀봉 부재(12)의 경계를 높은 정밀도로 정할 수 있다.

밀봉 부재(12)는 구동 회로 기판(1)과 투명 기판(2)을 고정하는 역할과, 액정 조성물(3)에 유해한 물질이 침입하는 것을 저지하는 역할을 한다. 유동성이 있는 밀봉 부재(12)를 도포한 경우에, 주변 프레임(11)은 밀봉 부재(12)의 스토퍼로서 기능한다. 밀봉 부재(12)에 대한 스토퍼로서, 주변 프레임(11)을 설치함으로써, 액정 조성물(3)의 경계나 밀봉 부재(12)의 경계를 고정밀도로 설정할 수 있고, 따라서 액정 표시 패널(100)의 외주변에서 표시 영역까지의 영역을 좁게 할 수 있으며, 그 결과 표시 영역 둘레의 주변 경계를 감소시킬 수 있다.

주변 프레임(11)과 표시 영역 사이에는, 최외부 화소(5B)에 의해 생성되는 표시의 품질과, 최외부 화소(5B)의 내측에 설치된 내부 화소(5A)에 의해 생성되는 표시의 품질을 균일하게 하기 위한 더미 화소(10)가 설치되어 있다. 내부 화소(5A)는 인접하는 화소를 갖기 때문에, 내부 화소(5A)와 그 인접 화소들 간에서 불필요한 전계가 발생하고, 그 결과, 내부 화소(5A)에 의해 생성되는 표시의 품질은 인접 화소가 없는 경우에 비교하여 저하된다.

한편, 더미 화소(10)가 제공되지 않는 경우를 고려하면, 표시 품질을 저하시키는 불필요한 전계가 최외부 화소(5B)에서는 생성되지 않기 때문에, 최외부 화소(5B)에 의한 표시 품질은 내부 화소(5A)에 비해 양호하다. 일부의 화소에 표시 품질의 차가 생기면 표시 불균일이 발생한다. 이러한 문제를 해결하기 위해, 더미 화소(10)를 설치하고, 화소(5A, 5B)와 동일한 신호 전압을 공급하여, 최외부 화소(5B)와 내부 화소(5A)의 표시 품질을 동등하게 하고 있다.

또한, 표시 영역을 둘러싸도록 주변 프레임(11)이 형성되어 있기 때문에, 액정 조성물(3)의 액정 분자를 일정한 방향으로 배향하기 위해서, 구동 회로 기판(1)의 표면을 러빙 처리(rubbing treatment)할 때에, 주변 프레임(11)으로 인해 그 부근을 잘 러빙 할 수 없는 문제가 있다. 본 실시예에서는, 구동 회로 기판(1)에 스페이서(4) 및 주변 프레임

(11)이 형성된 후에 액정 분자 배향막(7)(도 18 참조)이 도포되고, 그 다음 액정 조성물(3)의 액정 분자들이 일정 방향으로 배향하도록, 배향막(7)을 천 등을 이용하여 액정 분자 배향막을 문지르는 것에 의해 리빙 처리가 행하여진다.

리빙 처리에 있어서, 주변 프레임(11)이 구동 회로 기판(1)보다 둘출하여 있기 때문에, 주변 프레임(11) 근방에 있는 배향막(7)은, 주변 프레임(11)에 의해 형성된 단자로 인해 충분히 리빙되지 않으며, 따라서 주변 프레임(11)의 근방에서는 액정 분자들의 배향에 불균일이 발생하기 쉽다. 액정 조성물(3)의 액정 분자들의 배향 불량에 의한 표시 불균일을 눈에 띠지 않게 하기 위해서, 주변 프레임(11)의 바로 내측에 있는 화소의 일부를, 표시에 기여하지 않는 더미 화소(10)로서 형성한다.

그러나, 더미 화소(10)에 화소(5A, 5B)와 동일한 신호가 공급되는 경우, 더미 화소(10)와 투명 기판(2) 사이에 액정 조성물(3)이 존재하기 때문에, 더미 화소(10)에 의한 표시도 관찰된다고 하는 문제가 생긴다. 노멀 화이트 모드의 액정 표시 패널을 사용하는 경우, 액정 조성물(3)의 층에 전압을 인가하지 않으면, 더미 화소(10)가 희게 표시되고, 그 결과 표시 영역의 경계가 불명확하게 되어, 표시 품질이 저하된다. 더미 화소(10)를 차광하는 것도 생각되지만, 화소들 간의 간격은 수  $\mu m$ 이기 때문에, 표시 영역의 경계에 정밀도 좋게 차광 프레임을 형성하기는 어렵고, 따라서, 더미 화소(10)에는 표시 영역을 둘러싸는 흑색의 테로서 흑색의 상이 관찰되도록 하였다.

다음에, 도 21 및 도 22를 이용하여 구동 회로 기판(1) 상에 설치되는 능동 소자(30)와 그 주변의 구성을 설명한다. 도 21 및 도 22에서, 도 18과 동일한 부호는 동일한 구성을 나타낸다. 도 22는 능동 소자(30)와 그 주변을 나타내는 개략 평면도이고, 도 21은 도 22의 XXI-XXI 선에서의 단면도이다. 편의상, 도 21의 구성 요소들 간의 거리는 도 22에 대응하는 것과 동일하게 표시되지는 않으며, 도 22는 주사 신호선(51), 게이트 전극(36), 영상 신호선(52), 드레인 영역(35), 소스 영역(34), 저장 용량 형성용 전극(40), 제1 도전층(42), 컨택트홀(35CH, 34CH, 40CH, 42CH) 간의 위치 관계를 나타내는 것으로, 그 밖의 구성은 생략하였다. 도 21에서, 참조 번호 31은 구동 회로 기판인 실리콘 기판, 참조 번호 32는 구동 회로 기판(31)에 이온 주입으로 형성한 반도체 영역( $n$ 형 웨이), 참조 번호 33은 채널 스토퍼, 참조 번호 34는  $n$ 형 웨이(32)에 이온 주입에 의해 전기적으로 도전성이 되도록 형성한 소스 영역, 참조 번호 35는  $n$ 형 웨이(32)에 이온 주입으로 형성한 드레인 영역이다. 또한, 소스 및 드레인 영역은 본래 그들 간의 바이어스 극성에 대해서 결정되는 것이지만, 액정 표시 패널의 동작 중에 전압의 극성을 주기적으로 반전하므로, 드레인 영역과 소스 영역은 동작 중에 교체하게 된다. 이하의 설명에서는, 편의상, 바이어스 전압의 극성과는 무관하게, 2개의 영역 중 한쪽을 드레인 영역으로, 다른쪽을 소스 영역으로 고정하여 표현한다.

도 21에서, 참조 번호 36은 게이트 전극, 참조 번호 37은 게이트 전극 단부의 전계 강도를 완화하는 오프셋 영역, 참조 번호 38은 절연막, 참조 번호 39는 트랜지스터들을 전기적으로 절연시키는 필드 산화막, 참조 번호 40은 절연막(38)을 사이에 두고 실리콘 기판(31)과 용량을 형성하는 저장 용량 형성용 전극이다. 게이트 전극(36)과 저장 용량 형성용 전극(40)은, 절연막(38)에 능동 소자(30)의 임계치를 낮게 하기 위한 도전층과 저저항의 도전층을 적층한 2층막으로 이루어져 있다. 2층막으로서는 예를 들면 폴리실리콘과 텅스텐 실리사이드의 막을 이용할 수 있다. 참조 번호 41은 제1 층간 절연막, 참조 번호 42는 제1 도전막이다. 제1 도전막(42)은 접촉 불량을 방지하는 배리어 메탈과 저저항의 도전막의 다층막으로 이루어지고 있다. 제1 도전막으로서, 예를 들면 티탄 텅스텐(TiW)과 알루미늄의 다층 금속막을 스팍터로 형성하여 이용할 수 있다.

도 22에서, 참조 번호 51은 주사 신호선이다. 주사 신호선(51)은, 도 22의 X 방향으로 연장하여 Y 방향으로 정렬되어 있고, 능동 소자(30)를 온·오프하는 주사 신호가 공급된다. 주사 신호선(51)은 게이트 전극(36)과 동일한 2층막으로 이루어져 있다. 예를 들면, 폴리실리콘과 텅스텐 실리사이드를 적층한 2층막이 주사 신호선(51)으로서 이용될 수 있다. 영상 신호선(52)은 Y 방향으로 연장하여 X 방향으로 정렬되어 있고, 반사 전극(5)에 기입되는 영상 신호가 공급된다. 영상 신호선(52)은 제1 도전막(42)과 동일한 다층 금속막으로 이루어지고 있다. 예를 들면, 티탄 텅스텐(TiW)과 알루미늄의 다층 금속막이 영상 신호선(52)으로서 이용될 수 있다.

영상 신호는 절연막(38)과 제1 층간 절연막(41)에 형성된 컨택트홀(35CH)을 통하여 제1 도전막(42)에 의해 드레인 영역(35)으로 전해진다. 주사 신호선(51)에 주사 신호가 공급되면, 능동 소자(30)가 온되어, 영상 신호가 반도체 영역( $n$ 형 웨이)(32)으로부터 소스 영역(34)으로 전해진 후, 컨택트홀(34CH)을 통하여 제1 도전막(42)으로 전해진다. 그 다음, 영상 신호는, 컨택트홀(40CH)을 통하여 저장 용량 형성용 전극(40)에 전해진 다음, 도 21에 도시한 바와 같이 컨택트홀(42CH)을 통하여 반사 전극(5)으로 전해져 간다. 컨택트홀(42CH)은 필드 산화막(39) 상에 형성되어 있다. 필드 산화막(39)은 두껍기 때문에, 필드 산화막(39)의 상부 표면은 다른 구성 요소에 비교하여 높은 위치에 있다. 필드 산화막(39)에 컨택트홀(42CH)을 설치함으로써, 컨택트홀(42CH)이 상층의 도전막에 가까운 위치에 설치될 수 있으므로, 컨택트홀(42CH)의 접속부의 길이가 짧아질 수 있다.

제2 층간 절연막(43)은, 제1 도전막(42)과 제2 도전막(44)을 절연하고 있다. 제2 층간 절연막(43)은, 그 아래의 구성 요소들에 의해 발생하는 요철을 막기 위해 형성되는 평탄화막(43A)과 그 위의 절연막(43B)의 2층으로 형성되어 있다. 평탄화막(43A)은 SOG(Spin On Glass)를 도포하여 형성되며, 절연막(43B)은 반응 가스로서 TEOS(Tetraethylorthosilicate)를 이용하여 CVD에 의해 형성한  $SiO_2$ 막이다. 제2 층간 절연막(43)은 실리콘 기판(31) 상에 괴착된 후, CMP(화학기계적 폴리싱)에 의해 염마되어 평탄화된다. 평탄화된 제2 층간 절연막(43) 상에 제1 차광막(44)이 형성된다. 제1 차광막(44)은 제1 도전막(42)과 동일한 티탄 텅스텐(TiW)과 알루미늄의 다층 금속막으로 형성하고 있다.

제1 차광막(44)은 구동 회로 기판(1)의 거의 전면을 덮고 있고, 개구는 도 21에 도시된 컨택트홀(42CH)의 부분에만 형성된다. 제1 차광막(44) 상에 제3 층간 절연막(45)이 반응 가스로서 TEOS(Tetraethylorthosilicate)를 이용하는 CVD 공정에 의해 형성되어 있다. 또한, 제3 층간 절연막(45) 상에 제2 차광막(46)이 형성되어 있다. 제2 차광막(46)은 제1 도전막(42)과 동일한 티탄 텅스텐(TiW)과 알루미늄의 다층 금속막으로 형성하고 있다. 제2 차광막(46)은 컨택트홀(42CH)을 통해 제1 도전막(42)과 접속되어 있다. 컨택트홀(42CH)에서는, 전기적 접속을 위해, 제1 차광막(44)을 형성하는 금속막과 제2 차광막(46)을 형성하는 금속막이 적층되어 있다.

제1 차광막(44)과 제2 차광막(46)을 도전막으로 형성하여, 그 사이에 절연막(유전막)으로 이루어진 제3 층간막(45)을 형성하고, 제1 차광막(44)에 전압을 공급하면, 제1 차광막(44)과 제2 차광막(46) 사이에 저장 용량이 형성된다. 또한, 구동 전압에 대한 제3 층간 절연막(45)의 내압과, 절연막(45)의 두께 감소로 인한 용량 증가를 고려하면, 제3 층간 절연막(45)의 두께는 150nm 내지 450nm가 바람직하며, 보다 바람직하게는 약 300nm다.

도 23은 구동 회로 기판(1)에 투명 기판(2)을 정합시킨 것을 나타낸 도면이다. 구동 회로 기판(1)의 주변부에는 주변 프레임(11)이 형성되어 있고, 액정 조성물(3)은 주변 프레임(11), 구동 회로 기판(1) 및 투명 기판(2)에 의해 둘러싸인 공간에 보유된다. 정합된 구동 회로 기판(1)과 투명 기판(2) 사이의 주변 프레임(11)의 외측에는, 밀봉 부재(12)가 도포된다. 밀봉 부재(12)에 의해 구동 회로 기판(1)과 투명 기판(2)이 접착 고정되어 액정 표시 패널(100)이 형성된다.

다음으로, 도 24에 도시한 바와 같이, 액정 표시 패널(100)에 외부 신호를 공급하는 플렉시블 프린트 배선판(80)이 외부 접속 단자(13)에 접속된다. 플렉시블 프린트 배선판(80)의 양 외측의 단자는 다른 단자에 비해 길게 형성되고, 투명 기판(2)에 형성된 대향 전극(5)에 접속되어, 대향 전극용 단자(81)를 형성하고 있다. 즉, 플렉시블 프린트 배선판(80)은, 구동 회로 기판(1)과 투명 기판(2)의 양방에 접속되어 있다.

종래에서, 플렉시블 프린트 배선판은 구동 회로 기판(1)에 설치된 외부 접속 단자에만 접속되었으므로, 플렉시블 프린트 배선판으로부터 대향 전극(5)으로의 배선은 구동 회로 기판(1)을 경유하였다.

본 발명의 실시예의 투명 기판(2)에는 플렉시블 프린트 배선판(80)에 접속될 접속부(82)가 설치되어, 플렉시블 프린트 배선판(80)이 대향 전극(5)에 직접 접속된다. 즉, 액정 표시 패널(100)은 투명 기판(2)을 구동 회로 기판(1) 상에 중첩시켜 형성된다. 투명 기판(2)은, 그 주변부가 구동 회로 기판(1)의 외주부보다 외측으로 연장되고, 플렉시블 프린트 배선판(80)을 대향 전극(5)에 접속시킬 접속부(82)를 제공하도록 형성된다.

도 25 및 도 26은 액정 표시 장치(200)의 구성을 나타낸다. 도 25는 액정 표시 장치(200)의 주요 구성 요소에 대한 분해 조립 도면이고, 도 26은 액정 표시 장치(200)의 평면도이다.

도 25에 도시한 바와 같이, 플렉시블 프린트 배선판(80)이 접속된 액정 표시 패널(100)은, 쿠션 부재(461)를 사이에 두고 방열판(462) 상에 배치된다. 쿠션 부재(461)는 열전도성이 높고, 방열판(462)과 액정 표시 패널(100)과의 간극을 매립하여, 액정 표시 패널(100)의 열이 방열판(462)에 쉽게 전해지게 한다. 참조 번호 463은 몰드로서, 방열판(462)에 접착 고정되어 있다.

도 26에 도시한 바와 같이, 플렉시블 프린트 배선판(80)은 몰드(463)와 방열판(462) 사이를 통과하여, 몰드(463)의 외측으로 추출되고 있다. 참조 번호 465는 광원으로부터의 광이 액정 표시 장치(200)의 원하지 않는 부분에 입사하는 것을 방지하기 위한 차광판이고, 참조 번호 466은 액정 표시 장치(200)의 표시 영역을 한정하기 위한 외부 프레임이다.

이상, 본 발명자에 의해서 이루어진 발명을 실시예들에 기초하여 구체적으로 설명하였지만, 본 발명은 상기 실시예들로 한정되는 것이 아니고, 그 요지를 벗어나지 않은 범위에서 여러가지 변경 가능한 것은 물론이다.

### 발명의 효과

본 명세서에 개시된 발명 중 대표적인 것에 의해서 얻어지는 효과를 간단히 설명하면 다음과 같다.

본 발명에 따르면, 액정 표시 패널 내에 내장되는 수평 구동 회로의 접유 면적을 감소시킬 수 있으며, 액정 표시 패널을 소형화할 수 있다.

### (57) 청구의 범위

#### 청구항 1.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협지된 액정 조성물,

상기 제1 기판 상에 설치된 복수의 화소,

상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아, 상기 영상 신호 전압을 상기 복수의 영상 신호선에 출력하는 구동 회로,

상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선

을 포함하고,

상기 구동 회로에는 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고, 상기 전압 레벨을

상기 복수의 영상 신호선에 출력하는 전압 선택 회로가 제공되고,

상기 전압 선택 회로는 복수의 연산 회로의 직렬 결합을 포함하며,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합의 개개의 결합에 대한 상기 연산 회로들 각각은, 상기 N개의 표시 데이터선 각

각 및 상기 N개의 시간 제어 신호선 각각과 연관되고, 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선

사이에 배치되며,

상기 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 표시 데이터는 상기 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결

합 각각에서, 상기 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온

시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합들 각각은 상기 계조 전압의 하나의 레벨에만 동기하고,

상기 시간 제어 신호는, 상기 오프된 표시 데이터용 스위칭 소자와 함께 상기 병렬 결합을 구성하는 시간 제어 신호

용 스위칭 소자를 온시킴으로써, 상기 계조 전압의 한 레벨을 유일하게 결정하며,

상기 표시 데이터용 스위칭 소자 및 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 이루어지

는 액정 표시 장치.

## 청구항 2. 삭제

## 청구항 3.

제1항에 있어서, 상기 제1 기판은 실리콘으로 이루어지는 액정 표시 장치.

## 청구항 4.

제1항에 있어서, 상기 계조 전압은 계단 형상으로 변화하는 액정 표시 장치.

## 청구항 5.

제1항에 있어서, 상기 N개의 표시 데이터선 각각에는 상기 표시 데이터를 2진법으로 표현하는 N비트 중의 각각의

비트가 공급되는 액정 표시 장치.

## 청구항 6.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협진된 액정 조성물,

상기 제1 기판 상에 매트릭스 어레이로 정렬된 복수의 화소,

상기 매트릭스 어레이의 열 방향으로 연장하고 행 방향으로 배열되어, 상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아 상기 복수의 영상 신호선에 상기 영상 신호 전압을 출력하는 구동 회로,

상기 행 방향으로 연장하고 상기 열 방향으로 배열되어, 상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 행 방향으로 연장하고 상기 열 방향으로 배열되어, 상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하고,

상기 구동 회로는, 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 전압 선택 회로, 상기 전압 선택 회로에 타이밍 신호를 공급하는 시프트 레지스터, 및 상기 타이밍 신호를 상기 시프트 레지스터로부터 상기 전압 선택 회로로 공급하는 복수의 타이밍 신호선을 포함하고,

상기 전압 선택 회로는, 복수의 연산 회로의 직렬 결합, 및 상기 타이밍 신호에 동기하여 상기 표시 데이터를 취득하는 복수의 데이터 취득 소자를 포함하며, 상기 복수의 데이터 취득 소자 각각은 상기 연산 회로들 각각에 대응하고 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 상기 연산 회로들 각각과 함께 배치되고,

상기 복수의 타이밍 신호선은 상기 시프트 레지스터로부터 상기 열 방향으로 연장되고, 상기 데이터 취득 소자 중 대응하는 데이터 취득 소자에 접속되며, 상기 데이터 취득 소자의 제어 전극을 형성하는 도전막의 레벨과 동일한 레벨의 도전막으로 이루어지고,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합의 개개의 결합에 대한 상기 연산 회로들 각각은 상기 N개의 표시 데이터선 각각 및 상기 N개의 시간 제어 신호선 각각과 연관되고,

상기 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 표시 데이터는, 상기 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결합 각각에서 상기 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합 각각은 상기 계조 전압의 하나의 레벨에만 동기하며,

상기 시간 제어 신호는, 상기 오프된 표시 데이터용 스위칭 소자와 함께 상기 병렬 결합을 구성하는 시간 제어 신호 용 스위칭 소자를 온시킴으로써, 상기 계조 전압의 한 레벨을 유일하게 결정하며,

상기 표시 데이터용 스위칭 소자 및 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 형성되는 액정 표시 장치.

## 청구항 7. 삭제

## 청구항 8.

제6항에 있어서, 상기 제1 기판은 실리콘으로 이루어지는 액정 표시 장치.

## 청구항 9.

제6항에 있어서, 상기 계조 전압은 계단 형상으로 변화하는 액정 표시 장치.

## 청구항 10.

제6항에 있어서, 상기 N개의 표시 데이터선 각각에는 상기 표시 데이터를 2진법으로 표현하는 N 비트 중의 각각의 비트가 공급되는 액정 표시 장치.

## 청구항 11.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협지된 액정 조성물,

상기 제1 기판 상에 설치된 복수의 화소,

상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아, 상기 복수의 영상 신호선에 상기 영상 신호 전압을 출력하는 구동 회로,

상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선

을 포함하고,

상기 구동 회로에는 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고, 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 전압 선택 회로가 제공되고,

상기 전압 선택 회로는 복수의 연산 회로의 직렬 결합, 및 상기 복수의 연산 회로의 직렬 결합으로부터의 출력에 기초하여 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 복수의 출력 회로를 포함하며, 상기 전압 레벨을 상기 영상 신호선에 출력하는 상기 복수의 출력 회로 각각은 상기 복수의 연산 회로의 직렬 결합 중 대응하는 것에 직렬로 접속되며,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합의 개개의 결합에 대한 상기 연산 회로들 각각은, 상기 N개의 표시 데이터선 각각 및 상기 N개의 시간 제어 신호선 각각과 연관되고, 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며,

상기 연산 회로들 각각은, 결합되어 OR 회로를 형성하는 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 표시 데이터는, 상기 표시 데이터용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결합 각각에서 상기 선택된 수의 표시 데이터용 스위칭 소자를 오프시키고, 그 외의 표시 데이터용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합들 각각은 상기 계조 전압의 하나의 레벨에만 동기하고,

상기 전압 레벨을 상기 영상 신호선에 출력하는 상기 복수의 출력 회로 각각에는, 상기 복수의 연산 회로의 직렬 결합 중 대응하는 것의 상기 연산 회로들 전부가 온된 경우에, 상기 표시 데이터에 대응하는 상기 계조 전압의 하나의 레벨을 유일하게 결정하는 제어 신호가 공급되며,

상기 표시 데이터용 스위칭 소자 및 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 이루어지는 액정 표시 장치.

## 청구항 12. 삭제

## 청구항 13.

제11항에 있어서, 상기 제1 기판은 실리콘으로 이루어지는 액정 표시 장치.

## 청구항 14.

제11항에 있어서, 상기 계조 전압은 계단 형상으로 변화하는 액정 표시 장치.

### 청구항 15.

제11항에 있어서, 상기 N개의 표시 데이터선 각각에는 상기 표시 데이터를 2진법으로 표현하는 N비트 각각이 공급되는 액정 표시 장치.

### 청구항 16.

제1항에 있어서, 상기 연산 회로들 각각은 상기 복수의 영상 신호선 중 인접하는 2개의 영상 신호선 사이에 설치되는 액정 표시 장치.

### 청구항 17.

제6항에 있어서, 상기 연산 회로들 각각은 상기 복수의 영상 신호선 중 인접하는 2개의 영상 신호선 사이에 설치되는 액정 표시 장치.

### 청구항 18.

제11항에 있어서, 상기 연산 회로들 각각은 상기 복수의 영상 신호선 중 인접하는 2개의 영상 신호선 사이에 설치되는 액정 표시 장치.

### 청구항 19.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협지된 액정 조성물,

상기 제1 기판 상에 설치된 복수의 화소,

상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아, 상기 복수의 영상 신호선에 상기 영상 신호 전압을 출력하는 구동 회로,

상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선

을 포함하고,

상기 구동 회로는, 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고, 상기 전압 레벨을

상기 복수의 영상 신호선에 출력하는 전압 선택 회로를 포함하고,

상기 전압 선택 회로는 복수의 연산 회로의 직렬 결합을 포함하며,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합의 개개의 결합에 대한 상기 연산 회로들 각각은, 상기 N개의 표시 데이터선 각각 및 상기 N개의 시간 제어 신호선 각각과 연관되고, 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며,

상기 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 시간 제어 신호는, 상기 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결합 각각에서 상기 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합들 각각은 상기 계조 전압의 하나의 레벨에만 동기하고,

상기 표시 데이터는, 상기 오프된 시간 제어 신호용 스위칭 소자와 함께 상기 병렬 결합을 구성하는 표시 데이터용 스위칭 소자를 온시킴으로써, 상기 계조 전압의 한 레벨을 유일하게 결정하며,

상기 표시 데이터용 스위칭 소자와 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 이루어지는 액정 표시 장치.

## 청구항 20.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협지된 액정 조성물,

상기 제1 기판 상에 매트릭스 어레이로 정렬된 복수의 화소,

상기 매트릭스 어레이의 열 방향으로 연장하고 행 방향으로 배열되어, 상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아 상기 복수의 영상 신호선에 상기 영상 신호 전압을 출력하는 구동 회로,

상기 행 방향으로 연장하고 상기 열 방향으로 배열되어, 상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 행 방향으로 연장하고 상기 열 방향으로 배열되어, 상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선을 포함하고,

상기 구동 회로는, 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 전압 선택 회로, 상기 전압 선택 회로에 타이밍 신호를 공급하는 시프트 레지스터, 및 상기 타이밍 신호를 상기 시프트 레지스터로부터 상기 전압 선택 회로로 공급하는 복수의 타이밍 신호선을 포함하고,

상기 전압 선택 회로는, 복수의 연산 회로의 직렬 결합, 및 상기 타이밍 신호에 동기하여 상기 표시 데이터를 취득하는 복수의 데이터 취득 소자를 포함하며, 상기 복수의 데이터 취득 소자 각각은 상기 연산 회로들 각각에 대응하고 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 상기 연산 회로들 각각과 함께 배치되고,

상기 복수의 타이밍 신호선은, 상기 시프트 레지스터로부터 상기 열 방향으로 연장되고, 상기 데이터 취득 소자 중 대응하는 데이터 취득 소자에 접속되며, 상기 데이터 취득 소자의 제어 전극을 형성하는 도전막의 레벨과 동일한 레벨의 도전막으로 이루어지고,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합 개개의 결합에 대한 상기 연산 회로들 각각은 상기 N개의 표시 데이터선 각각 및 상기 N개의 시간 제어 신호선 각각과 연관되고,

상기 연산 회로들 각각은 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 시간 제어 신호는, 상기 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결합 각각에서 상기 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합 각각은 상기 계조 전압의 하나의 레벨에만 동기하고,

상기 표시 데이터는, 상기 오프된 시간 제어 신호용 스위칭 소자와 함께 상기 병렬 결합을 구성하는 표시 데이터용 스위칭 소자를 온시킴으로써, 상기 계조 전압의 한 레벨을 유일하게 결정하며,

상기 표시 데이터용 스위칭 소자와 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 이루어지는 액정 표시 장치.

## 청구항 21.

액정 표시 장치에 있어서,

제1 기판,

제2 기판,

상기 제1 기판과 상기 제2 기판 사이에 협지된 액정 조성물,

상기 제1 기판 상에 설치된 복수의 화소,

상기 복수의 화소에 영상 신호 전압을 공급하는 복수의 영상 신호선,

주기적으로 변화하는 계조 전압을 공급받아, 상기 복수의 영상 신호선에 상기 영상 신호 전압을 출력하는 구동 회로,

상기 구동 회로에 표시 데이터를 공급하는 N개의 표시 데이터선, 및

상기 계조 전압에 동기하여 변화하는 시간 제어 신호를 상기 구동 회로에 공급하는 N개의 시간 제어 신호선

을 포함하고,

상기 구동 회로에는 상기 표시 데이터에 기초하여 상기 계조 전압으로부터 전압 레벨을 선택하고, 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 전압 선택 회로가 제공되고,

상기 전압 선택 회로는 복수의 연산 회로의 직렬 결합, 및 상기 복수의 직렬 결합으로부터의 출력에 기초하여 상기 전압 레벨을 상기 복수의 영상 신호선에 출력하는 출력 회로를 포함하고, 상기 전압 레벨을 상기 영상 신호선에 출력하는 상기 복수의 출력 회로 각각은 상기 복수의 연산 회로의 직렬 결합 중 대응하는 직렬 결합에 직렬로 접속되며,

상기 복수의 연산 회로의 직렬 결합 각각은 상기 복수의 영상 신호선 중 하나와 연관되고,

상기 복수의 연산 회로의 직렬 결합의 개개의 결합에 대한 상기 연산 회로들 각각은, 상기 N개의 표시 데이터선 각각 및 상기 N개의 시간 제어 신호선 각각과 연관되고, 상기 N개의 표시 데이터선 중 인접하는 2개의 표시 데이터선 사이에 배치되며,

상기 연산 회로들 각각은, 결합되어 OR 회로를 형성하는 표시 데이터용 스위칭 소자 및 시간 제어 신호용 스위칭 소자의 병렬 결합을 포함하고,

상기 시간 제어 신호는, 상기 시간 제어 신호용 스위칭 소자 중 0 내지 N개를 선택하고, 상기 복수의 연산 회로의 직렬 결합 각각에서 상기 선택된 수의 시간 제어 신호용 스위칭 소자를 오프시키고, 그 외의 시간 제어 신호용 스위칭 소자를 온시킴으로써  $2^N$ 개의 상이한 조합을 만들고,

상기  $2^N$ 개의 상이한 조합들 각각은 상기 계조 전압의 하나의 레벨에만 동기하고,

상기 전압 레벨을 상기 영상 신호선에 출력하는 상기 복수의 출력 회로 각각에는, 상기 복수의 연산 회로의 직렬 결합 중 대응하는 직렬 결합의 상기 연산 회로들 전부가 온된 경우에, 상기 표시 데이터에 대응하는 상기 계조 전압의 하나의 레벨을 유일하게 결정하는 제어 신호가 공급되며,

상기 표시 데이터용 스위칭 소자와 상기 시간 제어 신호용 스위칭 소자는 동일한 도전형의 트랜지스터로 이루어지는 액정 표시 장치.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7a

(종래 기술)

도면7b

(종래 기술)

도면8a

도면8b

도면8c

도면9a

도면9b

도면10

도면11

도면12

도면13

도면14a

도면14b

도면14c

도면14d

도면15a

도면15b

도면16

## 도면17

도면18

도면19a

도면19b

도면20

도면21

도면22

도면23

도면24

도면25

도면26

|                |                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种具有灰度电压选择电路的液晶显示装置                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">KR100478170B1</a>                                                                                                     | 公开(公告)日 | 2005-03-23 |

| 申请号            | KR1020020011276                                                                                                                   | 申请日     | 2002-03-04 |

| [标]申请(专利权)人(译) | 日立HITACHI SEISAKUSHODBA<br>日立器件工程株式会社                                                                                             |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>地伤装置工程可否让这个夏                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所<br>地伤装置工程可否让这个夏                                                                                                         |         |            |

| [标]发明人         | ISAMI HIRONOBU<br>이사미히로노부<br>TAKEMOTO IWAO<br>다께모또이와오<br>MIYAZAWA TOSHIO<br>미야자와도시오<br>MATSUMOTO KATSUMI<br>마쓰모또가쓰미               |         |            |

| 发明人            | 이사미히로노부<br>다께모또이와오<br>미야자와도시오<br>마쓰모또가쓰미                                                                                          |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133                                                                                                       |         |            |

| CPC分类号         | G09G2310/0259 G09G2300/0408 G09G3/3688 G09G2310/027 G09G3/2011 G09G2320/0233 G09G3/3611 G09G2310/0232 G09G2310/0283 G09G2300/0426 |         |            |

| 代理人(译)         | CHANG, SOO KIL                                                                                                                    |         |            |

| 优先权            | 2001059394 2001-03-05 JP                                                                                                          |         |            |

| 其他公开文献         | KR1020020071457A                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                         |         |            |

## 摘要(译)

液晶显示器具有用于来自外部灰度电压的电压电平的电路，该电路根据选择的时间基于显示数据周期性地改变。该电路包括多个计算电路的串联组合。与串联组合的图像信号线中的一个相关的是像素。它分别与指示数据线的各个灰度电压N相关，其中多个时间控制信号线提供时间控制信号的同步和变化。多个系列组合每个计算电路提供显示数据。它安装在N的指示数据线中的计算电路相邻的指示数据线之间。时间控制信号唯一地确定灰度电压的一个电平。液晶显示器，电压选择电路，灰度电压，计算电路，时间控制信号线，指示数据线。