(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년01월30일

(11) 등록번호 10-0799440

(24) 등록일자 2008년01월23일

(51) Int. C1.

G02F 1/1335 (2006.01)

(21) 출원번호 10-2005-0037574

(22) 출원일자 2005년05월04일

심사청구일자 2005년05월04일

(65) 공개번호 10-2006-0047724

(43) 공개일자 2006년05월18일

(30) 우선권주장

JP-P-2004-00165320 2004년06월03일 일본(JP)

(56) 선행기술조사문현

KR1020010031885NUL

KR1019950033585NUL

(73) 특허권자

**후지쯔 가부시끼가이샤**일본국 가나가와Ken 가와사키시 나카하라구 가미고

다나카 4초메 1-1**우 익트로닉스 코포레이션**대만 신츄 300, 사이언스-베이스드 인더스트리얼

파크, 리-신 로드. 2, 넘버. 1

(72) 벌명자

**다사까 야스또시**일본 가나가와Ken 가와사끼시 나카하라구 가미꼬다

나카 4초메 1-1후지쯔 디스플레이 테크놀로지스

코포레이션 내**요시다, 히데후미**일본 가나가와Ken 가와사끼시 나카하라구 가미꼬다

나카 4초메 1-1후지쯔 디스플레이 테크놀로지스

코포레이션 내

(뒷면에 계속)

(74) 대리인

구영창, 이중희, 장수길, 주성민

심사관 : 김연호

전체 청구항 수 : 총 14 항

(54) 액정 표시 장치 및 그 제조 방법

**(57) 요약**

표면에 미세하고 고밀도인 요철을 갖는 반사막을 구비한 액정 표시 장치 및 그 제조 방법을 제공한다. 반사 전극(33)의 하방의 제1 금속막 패턴(14a), 제1 반도체막(17), 제2 금속막 패턴(24a) 및 제3 절연막(27) 등에, 각각 상이한 배열 패치 및 크기로 개구부(개구 패턴)를 형성한다. 이를 개구부가 복잡하게 서로 겹쳐, 반사 전극(33)의 표면에 미세한 요철이 형성된다. 또한, TFT의 형성과 동시에 제1 금속막 패턴(14a), 제1 반도체막(17) 및 제2 금속막 패턴(24a)에 개구부를 형성하면 되어, 공정수의 증가가 회피된다.

**대표도 - 도1**

(72) 발명자

다시로 구니히로

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1후지쓰 디스플레이 테크놀로지스 코

포레이션 내

다나까 요시노리

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1후지쓰 디스플레이 테크놀로지스 코

포레이션 내

도이 세이지

일본 미에쿄 아게군 나카베면 294-1 가와게초 레베

우르 룸 102

---

오다 도모시게

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1후지쓰 디스플레이 테크놀로지스 코

포레이션 내

쓰시마 이사오

일본 가나가와쿄 가와사끼시 나카하라구 가미꼬다

나카 4조메 1-1후지쓰 디스플레이 테크놀로지스 코

포레이션 내

## 특허청구의 범위

### 청구항 1

삭제

### 청구항 2

제1 기판과,

상기 제1 기판에 대향하여 배치되어 광을 투과하는 제2 기판과,

상기 제1 기판 위에 형성되고, 제2 기판을 투과한 광을 반사하는 반사막과,

상기 제2 기판 위에 형성되고, 상기 반사막에 대향하는 위치에 개구부가 형성된 컬러 필터와,

상기 제1 기판과 상기 반사막 사이에 금속막, 절연막 및 반도체막 중 2 이상을 적층하여 형성된 복수의 막과,

상기 제1 기판과 상기 제2 기판 사이에 봉입된 액정을 갖고,

1 화소 영역 내에, 상기 반사막에서 반사하는 광에 의해 표시를 행하는 반사 영역과, 상기 제1 및 제2 기판을 투과하는 광에 의해 표시를 행하는 투과 영역을 갖고,

상기 복수의 막에는 막마다 배열 피치가 상이한 패턴이 형성되고, 상기 반사막의 표면에는 상기 복수의 막의 상기 패턴에 따른 요철이 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 3

화소마다 박막 트랜지스터 및 반사 전극이 설치된 제1 기판과, 상기 제1 기판에 대향하여 배치되는 제2 기판과, 상기 제1 기판 및 상기 제2 기판 사이에 봉입된 액정을 갖고, 1 화소 영역 내에, 상기 반사 전극에서 반사하는 광에 의해 표시를 행하는 반사 영역과, 상기 제1 및 제2 기판을 투과하는 광에 의해 표시를 행하는 투과 영역을 갖는 액정 표시 장치의 제조 방법으로서,

상기 제1 기판의 상기 반사 전극을 형성하는 영역 위에 상기 박막 트랜지스터의 형성과 동시에, 막마다 배열 피치가 상이한 패턴을 갖는 금속막, 절연막 및 반도체막 중 2 이상을 적층하여 복수의 막을 형성하고, 그 후, 상기 복수의 막 위에, 상기 복수의 막의 패턴에 따른 요철을 표면에 갖는 반사막을 형성하여 상기 반사 전극으로 하고,

상기 제2 기판 위에, 상기 반사막에 대향하는 위치에 개구부가 형성된 컬러 필터를 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

### 청구항 4

제1 기판 위에 제1 금속막을 형성하는 공정과,

상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

상기 제1 절연막 위에 제1 반도체막을 형성하는 공정과,

상기 제1 반도체막 위에 제2 절연막을 형성하는 공정과,

상기 제2 절연막을 패터닝하여 적어도 박막 트랜지스터의 채널을 보호하는 채널 보호막을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제2 반도체막을 형성하는 공정과,

상기 제2 반도체막 위에 제2 금속막을 형성하는 공정과,

상기 제2 금속막, 상기 제1 반도체막 및 상기 제2 반도체막을 패터닝하여, 상기 박막 트랜지스터의 활성층의 형상을 확정함과 함께, 데이터 버스 라인과, 상기 박막 트랜지스터의 소스 전극 및 드레인 전극과, 상기 제1 절연막을 통하여 상기 보조 용량 버스 라인에 대향하는 보조 용량 전극을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제3 절연막을 형성하는 공정과,

상기 제3 절연막 위에, 상기 제3 절연막에 형성된 컨택트 홀을 통하여 상기 박막 트랜지스터의 소스 전극 및 상기 보조 용량 전극과 전기적으로 접속되는 반사 전극을 형성하는 공정과,

상기 제1 기판에 제2 기판을 대향시켜 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고, 상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 제1 반도체막, 상기 제2 반도체막, 상기 제2 절연막 및 상기 제3 절연막 중 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

## 청구항 5

제1 기판 위에 제1 금속막을 형성하는 공정과,

상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

상기 제1 절연막 위에 제1 반도체막을 형성하는 공정과,

상기 제1 반도체막 위에 제2 절연막을 형성하는 공정과,

상기 제2 절연막을 패터닝하여 적어도 박막 트랜지스터의 채널을 보호하는 채널 보호막을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제2 반도체막을 형성하는 공정과,

상기 제2 반도체막 위에 제2 금속막을 형성하는 공정과,

상기 제2 금속막, 상기 제1 반도체막 및 상기 제2 반도체막을 패터닝하여, 상기 박막 트랜지스터의 활성층의 형상을 확정함과 함께, 데이터 버스 라인과, 상기 박막 트랜지스터의 소스 전극 및 드레인 전극과, 반사 전극을 형성하는 공정과,

상기 기판의 상측 전면에 제3 절연막을 형성하는 공정과,

상기 제3 절연막에 개구부를 형성하여 상기 반사 전극을 노출시키는 공정과,

상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 제1 반도체막 및 상기 제2 절연막 중 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

## 청구항 6

제1 기판 위에 제1 금속막을 형성하는 공정과,

상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

상기 제1 절연막 위에 반도체막을 형성하는 공정과,

상기 반도체막을 패터닝하는 공정과,

상기 제1 기판의 상측 전면에 제2 금속막을 형성하는 공정과,

상기 제2 금속막을 패터닝하여, 데이터 버스 라인과, 박막 트랜지스터의 소스 전극 및 드레인 전극과, 상기 제1 절연막을 통하여 상기 보조 용량 버스 라인에 대향하는 보조 용량 전극을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제2 절연막을 형성하는 공정과,

상기 제2 절연막에 개구부를 형성하는 공정과,

상기 제1 기판의 상측 전면에 제3 금속막을 형성하는 공정과,

상기 제3 금속막을 패터닝하여 반사 전극을 형성하는 공정과,

상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 반도체막 및 상기 제2 절연막 중 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

### 청구항 7

제1 기판 위에 제1 금속막을 형성하는 공정과,

상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

상기 제1 절연막 위에 반도체막을 형성하는 공정과,

상기 반도체막을 패터닝하는 공정과,

상기 제1 기판의 상측 전면에 제2 금속막을 형성하는 공정과,

상기 제2 금속막을 패터닝하여, 데이터 버스 라인과, 박막 트랜지스터의 소스 전극 및 드레인 전극과, 반사 전극을 형성하는 공정과,

상기 기판의 상측 전면에 제2 절연막을 형성하는 공정과,

상기 제2 절연막에 개구부를 형성하여 상기 반사 전극을 노출시키는 공정과,

상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

상기 반사 전극의 하방의 상기 보조 용량 버스 라인 및 상기 반도체막에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

### 청구항 8

제2항에 있어서,

상기 컬러 필터의 개구부의 크기는, 상기 반사막의 크기보다도 작은 것을 특징으로 하는 액정 표시 장치.

### 청구항 9

제8항에 있어서,

상기 컬러 필터의 개구부 및 그 주위에는 투명 수지막이 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 10

제9항에 있어서,

상기 투명 수지막에는 광학적 확산성이 부여되어 있는 것을 특징으로 하는 액정 표시 장치.

### 청구항 11

제9항에 있어서,

상기 투명 수지막의 막 두께가, 상기 컬러 필터의 막 두께보다도 두꺼운 것을 특징으로 하는 액정 표시 장치.

### 청구항 12

제3항에 있어서,

상기 컬러 필터의 개구부의 크기를, 상기 반사막의 크기보다도 작게 하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

### 청구항 13

제12항에 있어서,

상기 컬러 필터의 개구부 및 그 주위에 투명 수지막을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

**청구항 14**

제13항에 있어서,

상기 투명 수지막에 광학적 확산성을 부여하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

**청구항 15**

제13항에 있어서,

상기 투명 수지막의 막 두께를, 상기 컬러 필터의 막 두께보다도 두껍게 하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

**명세서****발명의 상세한 설명****발명의 목적****종래기술의 문헌 정보**

<45> [특허문헌1] 특개평5-173158호 공보

<46> [특허문헌2] 특허 제2990046호 명세서

**발명이 속하는 기술 및 그 분야의 종래기술**

<47> 본 발명은, 외광을 이용하여 영상의 표시를 행하는 반사형 또는 반투과형 액정 표시 장치에 관한 것으로, 특히 반사막의 표면에 미세한 요철을 형성한 액정 표시 장치 및 그 제조 방법에 관한 것이다.

<48> 액정 표시 장치는, 얇고 경량임과 더불어 저전압으로 구동할 수 있어 소비 전력이 적다고 하는 장점이 있어서, 각종 전자 기기에 널리 이용되고 있다. 특히, 화소마다 스위칭 소자로서 TFT(Thin Film Transistor: 박막 트랜지스터)가 형성된 액티브 매트릭스 방식의 액정 표시 장치는, 표시 품질에 있어서도 CRT(Cathode-Ray Tube)에 필적할 정도로 우수하기 때문에, 텔레비전이나 퍼스널 컴퓨터 등의 디스플레이에 널리 사용되고 있다.

<49> 일반적인 액정 표시 장치는, 서로 대향하여 배치된 2매의 기판 사이에 액정을 봉입한 구조를 갖고 있다. 한쪽 기판에는 TFT 및 화소 전극 등이 형성되고, 다른쪽 기판에는 컬러 필터 및 커먼(공통) 전극 등이 형성되어 있다. 이하, TFT 및 화소 전극 등이 형성된 기판을 TFT 기판이라 칭하고, TFT 기판에 대향하여 배치되는 기판을 대향 기판이라 칭한다.

<50> 액정 표시 장치에는, 백 라이트를 광원으로 하여 액정 패널을 투과하는 광에 의해 영상을 표시하는 투과형 액정 표시 장치와, 외광(자연광 또는 전등광)의 반사를 이용하여 영상을 표시하는 반사형 액정 표시 장치와, 어두운 곳에서는 백 라이트를 사용하고, 밝은 곳에서는 외광의 반사를 이용하여 영상을 표시하는 반투과형 액정 표시 장치가 있다.

<51> 반사형 액정 표시 장치는, 백 라이트가 불필요하기 때문에, 투과형 액정 표시 장치보다도 소비 전력이 작다고 하는 이점이 있다. 또한, 주위가 밝은 장소에서는, 백 라이트를 이용하는 투과형 액정 표시 장치보다도, 외광을 이용하는 반사형 액정 표시 장치 또는 반투과형 액정 표시 장치가 영상이 깨끗하게 보이는 경우가 많다.

<52> 그런데, 반사형 액정 표시 장치 및 반투과형 액정 표시 장치에서는, 광을 반사시키는 막(반사막)의 표면이 평탄하면, 영상을 깨끗하게 볼 수 있는 범위(시야각)가 극단적으로 좁아짐과 더불어, 비쳐들어감 등의 문제가 발생한다. 따라서, 반사막의 표면에 미세한 요철을 형성하여, 광을 산란시키는 것이 필요로 된다.

<53> 종래부터, 반사판의 표면에 미세한 요철을 형성하는 방법이 제안되어 있다. 예를 들면 특개평5-173158호 공보에는, 포토리소그래피법 및 드라이 에칭법을 이용하여 유기 절연막(폴리이미드막)의 표면에 요철을 형성하고, 그 위에 반사막을 형성하는 것이 기재되어 있다. 또한, 특허 제2990046호 명세서에는, 스위칭 소자(TFT)의 형성에 사용하는 금속막, 절연막 및 반도체막 중 적어도 1개의 막을 이용하여 요철을 형성하고, 그 위에 절연막을 통하여 반사막을 형성하는 것이 기재되어 있다.

<54> 그러나, 본원 발명자들은, 전술한 종래 기술에는 이하에 나타내는 문제점이 있다고 생각한다. 즉, 특개평5-

173158호 공보에 개시된 기술에서는, 유기 절연막 위에 감광성 수지(포토레지스트)를 도포하는 공정이나, 노광 및 현상공정이나, 드라이 에칭 공정이 필요로 된다. 이 때문에, 공정수의 증가에 수반하여 제조 코스트가 증가함과 더불어, 수율이 저하한다.

<55> 특히 제2990046호 명세서에 기재된 기술에서는, 금속막, 절연막 및 반도체막을 적층하여, 포토리소그래피법에 의해 이들 막을 에칭하여, TFT와 동시에 요철을 형성한 후, 전면에 절연막을 형성하고, 또한 그 위에 반사막을 형성하고 있다. 이와 같이 TFT와 동시에 요철을 형성함으로써, 제조 공정의 증가를 회피할 수 있다. 그러나, 이 기술에서는, 요철의 밀도가 포토리소그래피의 해상도에 의존하기 때문에, 요철을 고밀도로 형성하는 것이 곤란하다.

<56> 또한, 특히 제2990046호 명세서에 기재된 실시예의 일부에서는, 글래스 기판을 에칭하고 있다. 그러나, 글래스 기판을 에칭하면, 글래스 기판에 함유되어 있는 불순물이 용출하여 액정을 오염시켜, 표시 품질을 현저히 손상 시킬 우려가 있다.

### 발명이 이루고자 하는 기술적 과제

<57> 이상으로부터, 본 발명의 목적은, 표면에 미세하고 고밀도인 요철을 갖는 반사막을 구비한 액정 표시 장치이다.

<58> 본 발명의 다른 목적은, 표면에 미세하고 고밀도인 요철을 구비한 반사막을 적은 공정으로 형성할 수 있는 액정 표시 장치의 제조 방법을 제공하는 것이다.

### 발명의 구성 및 작용

<59> 상기의 과제는, 제1 기판과, 상기 제1 기판에 대향하여 배치되어 광을 투과하는 제2 기판과, 상기 제1 기판 위에 형성되고, 상기 제2 기판을 투과한 광을 반사하는 반사막과, 상기 제1 기판과 상기 반사막 사이에 적층하여 형성된 복수의 막과, 상기 제1 기판과 상기 제2 기판 사이에 봉입된 액정을 갖고, 상기 복수의 막에는 막마다 배열 피치가 상이한 패턴이 형성되고, 상기 반사막의 표면에는 상기 복수의 막의 상기 패턴에 따른 요철이 형성되어 있는 것을 특징으로 하는 액정 표시 장치에 의해 해결한다.

<60> 또한, 상기의 과제는, 화소마다 박막 트랜지스터 및 반사 전극이 형성된 제1 기판과, 상기 제1 기판에 대향하여 배치되는 제2 기판과, 상기 제1 기판 및 상기 제2 기판 사이에 봉입된 액정을 갖는 액정 표시 장치의 제조 방법으로서, 상기 제1 기판의 상기 반사 전극을 형성하는 영역위에 상기 박막 트랜지스터의 형성과 동시에, 막마다 배열 피치가 상이한 패턴을 갖는 복수의 막을 적층하여 형성하고, 그 후, 상기 복수의 막 위에, 상기 복수의 막의 패턴에 따른 요철을 표면에 갖는 반사막을 형성하여 상기 반사 전극으로 하는 것을 특징으로 하는 액정 표시 장치의 제조 방법에 의해 해결한다.

<61> 본 실시예에서는, 반사 전극의 하방에 배치된 복수의 막 중의 적어도 2 이상의 막에, 막마다 배열 피치가 상이한 패턴을 형성한다. 이에 의해, 각막의 패턴이 복잡하게 서로 중첩되어, 미세하고 랜덤한 요철이 형성된다. 이 미세하고 랜덤한 요철이 형성된 막 위에 예를 들면 Al(알루미늄) 또는 Ag(은)를 주성분으로 하는 반사율이 높은 막을 형성하여 반사 전극으로 한다. 따라서, 반사 전극의 표면에는, 하층의 막에 형성된 패턴을 모방한 미세한 요철이 형성된다. 이 요철의 밀도는 포토리소그래피의 해상도에 의존하지 않는다. 이에 의해, 반사형 액정 표시 장치로서 사용했을 때에, 양호한 표시 특성이 얻어진다.

<62> 이하, 본 발명에 대하여 첨부의 도면을 참조하여 설명한다.

<63> (제1 실시예)

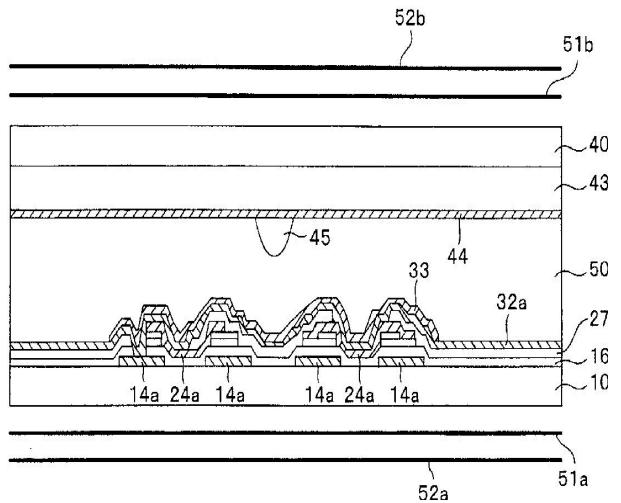

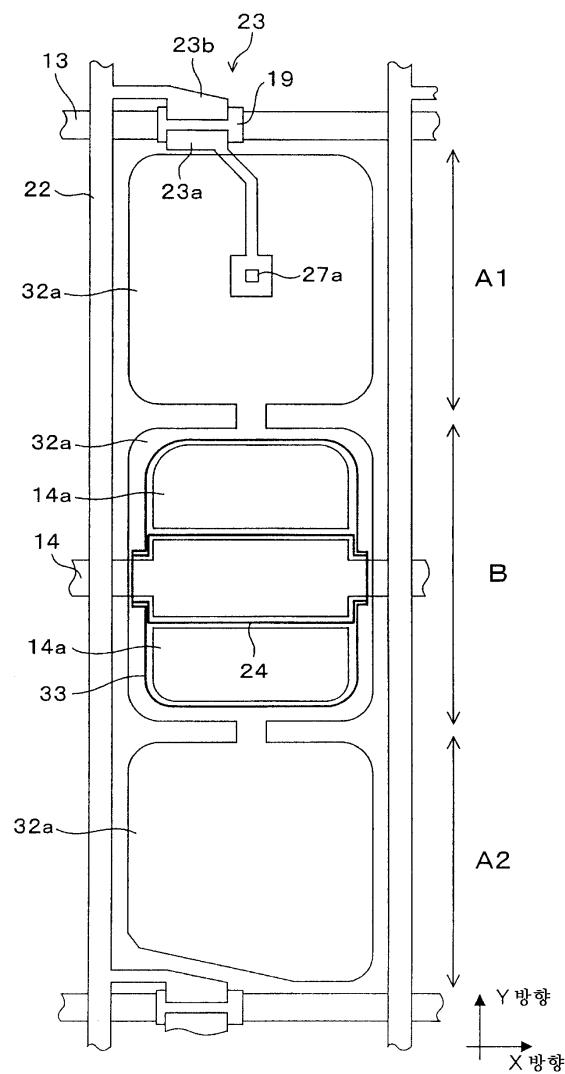

<64> 도 1은 본 발명의 제1 실시예의 액정 표시 장치를 도시하는 단면도, 도 2는 동일한 그 평면도이다. 본 실시예는 본 발명을 채널 보호 타입의 TFT를 갖는 반투과형 액정 표시 장치에 적용한 예를 나타내고 있다.

<65> 본 실시예의 액정 표시 장치는, 도 1에 도시한 바와 같이, 서로 대향하여 배치된 TFT 기판(10) 및 대향 기판(40)과, 이들 TFT 기판(10) 및 대향 기판(40) 사이에 봉입된 수직 배향형 액정(유전율 이방성이 마이너스인 액정)(50)에 의해 구성되어 있다. TFT 기판(10)의 하측에는  $\lambda/4$  과장판(위상차판)(51a) 및 편광판(52a)이 배치되고, 또한 하방에는 백 라이트(도시 생략)가 배치된다. 한편, 대향 기판(40)의 상측에는  $\lambda/4$  과장판(위상차판)(51b) 및 편광판(52b)이 배치된다.  $\lambda/4$  과장판(51a, 51b)은 지상축이 서로 직교하도록 배치되고, 편광판(52a, 52b)은 투과축이 서로 직교하도록 배치된다.

<66> TFT 기판(10)에는, 도 2에 도시한 바와 같이, X 방향(수평방향)으로 연장되는 복수의 게이트 버스 라인(13)과,

Y 방향(수직방향)으로 연장되는 복수의 데이터 버스 라인(22)이 형성되어 있다. 게이트 버스 라인(13)은 Y 방향으로 예를 들면 약  $300\text{ }\mu\text{m}$ 의 피치로 나란히 배열되어 있고, 데이터 버스 라인(22)은 X 방향으로 예를 들면 약  $100\text{ }\mu\text{m}$ 의 피치로 나란히 배열되어 있다. 이들 게이트 버스 라인(13) 및 데이터 버스 라인(22)에 의해 구획되는 직사각형의 영역이 각각 화소 영역이다.

<67> TFT 기판(10)에는, 게이트 버스 라인(13)과 평행하게 배치되어 화소 영역의 중앙을 획단하는 보조 용량 버스 라인(14)이 형성되어 있다. 게이트 버스 라인(13) 및 보조 용량 버스 라인(14)과 데이터 버스 라인(22)과의 사이에는 제1 절연막(게이트 절연막)(16)이 형성되어 있고, 이 제1 절연막(16)에 의해 게이트 버스 라인(13)과 데이터 버스 라인(22) 사이, 및 보조 용량 버스 라인(14)과 데이터 버스 라인(22) 사이가 전기적으로 분리되어 있다.

<68> 또한, TFT 기판(10)에는, 각 화소 영역마다 TFT(23)가 형성되어 있다. 이 TFT(23)는, 도 2에 도시한 바와 같이, 게이트 버스 라인(13)의 일부를 게이트 전극으로 하고 있고, 게이트 버스 라인(13) 위에 제1 절연막(16)을 통하여 형성된 소정의 크기의 반도체막(도시 생략)을 활성층으로 하고 있다. 또한, 게이트 버스 라인(13)의 상방에는 채널 보호막(19)이 선택적으로 형성되어 있고, 게이트 버스 라인(13)의 꼭 방향의 양측에는 소스 전극(23a) 및 드레인 전극(23b)이 서로 대향하여 배치되어 있다. TFT(23)의 드레인 전극(23b)은 데이터 버스 라인(22)에 접속하고 있다.

<69> 1개의 화소 영역은, 데이터 버스 라인(22)을 따라 나란히 배열되는 3개의 영역으로 분할되어 있다. 이하, 이들 3개의 영역중의 중앙의 영역을 반사 영역 B라고 칭하고, 반사 영역 B를 사이에 두는 2개의 영역을 제1 투과 영역 A1 및 제2 투과 영역 A2라고 칭한다. 이들 제1 투과 영역 A1, 제2 투과 영역 A2 및 반사 영역 B에는, 각각 각부가 만곡한 대략 직사각형의 투명 화소 전극(32a)이 형성되어 있다. 이들 투명 화소 전극(32a)은 모두 ITO(Indium-Tin Oxide) 등의 투명 도전체에 의해 형성되고, 투명 화소 전극(32a)과 동시에 형성된 투명 도전체로 이루어지는 접속부를 통하여 서로 전기적으로 접속되어 있다.

<70> 또한, 반사 영역 B의 투명 화소 전극(32d) 위에는, 각부가 만곡한 대략 직사각형의 반사 전극(반사판)(33)이 형성되어 있다. 이 반사 전극(33)의 표면에는, 미세하고 랜덤한 요철이, 후술하는 방법에 의해 고밀도로 형성되어 있다. 또한, 반사 전극(33)의 하방에는, 후술하는 바와 같이, 보조 용량 버스 라인(14) 및 제1 절연막(16)과 함께 보조 용량을 구성하는 보조 용량 전극(24)과, 반사 전극(33)의 표면에 요철을 형성하기 위한 개구부가 형성된 제1 및 제2 금속막 패턴(14a, 24a), 반도체막(도시 생략) 및 절연막(27) 등이 형성되어 있다.

<71> TFT(23)의 소스 전극(23a)은 투과 영역 A1의 투명 화소 전극(32a)의 중앙부의 하방까지 연장되어, 컨택트홀(27a)을 통하여 투명 화소 전극(32a)과 전기적으로 접속되어 있다.

<72> 투명 화소 전극(32a) 및 반사 전극(33)의 표면은, 예를 들면 폴리이미드로 이루어지는 수직 배향막(도시 생략)에 괴복되어 있다.

<73> 한편, 도 1에 도시한 바와 같이, 대향 기판(40)의 한쪽 면상(도 1에서는 하측)에는, 블랙 매트릭스(도시 생략) 및 컬러 필터(43)가 형성되어 있다. 블랙 매트릭스는 예를 들면 Cr(크롬) 등의 차광성 재료로 이루어지고, TFT 기판(10)측의 게이트 버스 라인(13), 데이터 버스 라인(22) 및 TFT(23)에 대향하는 위치에 배치되어 있다. 컬러 필터(43)에는 적색, 녹색 및 청색의 3종류가 있고, 각 화소마다 적색, 녹색 및 청색 중 어느 한 색의 컬러 필터가 배치된다. 본 실시예에서는, X 방향으로 서로 인접하여 배치된 적색, 녹색 및 청색의 3개의 화소에 의해 1개의 꼭 셀이 구성된다.

<74> 컬러 필터(43) 아래에는, ITO 등의 투명 도전체로 이루어지는 커먼 전극(44)이 형성되어 있다. 이 커먼 전극(44) 아래에는, 예를 들면 수지 등의 유전체로 이루어지는 원추형상의 배향 규제용 돌기(45)가 형성되어 있다. 이 배향 규제용 돌기(45)는, 투과 영역 A1, A2 및 반사 영역 B의 중앙의 위치에 각각 배치되어 있다. 또한, 커먼 전극(44) 및 도메인 규제용 돌기(45)의 표면은, 예를 들면 폴리이미드로 이루어지는 수직 배향막(도시 생략)에 괴복되어 있다.

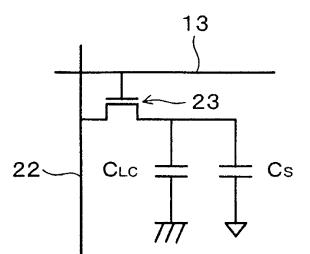

<75> 도 3은 본 실시예의 액정 표시 장치의 1 화소의 등가 회로도이다. 이 도 3에 도시한 바와 같이, 화소 전극(투명 화소 전극(32a) 및 반사 전극(33))과, 커먼 전극(44)과, 그들 사이의 액정(50)에 의해 구성되는 용량  $C_{LC}$ 에 대하여, 보조 용량 버스 라인(14)과 보조 용량 전극(24)에 의해 구성되는 보조 용량  $C_S$ 가 병렬 접속되어, TFT(23)를 통하여 화소 전극에 기입되는 표시 전압의 저하를 억제하고 있다.

<76> 전술한 바와 같이 구성된 본 실시예의 액정 표시 장치에 있어서, 실내 등에서 사용할 때에는 TFT 기판(10)의 하

방에 배치된 백 라이트를 점등하여 액정 패널을 투과하는 광에 의해 영상을 표시한다. 또한, 밝은 장소에서 사용할 때에는 백 라이트를 소등하여, 반사 전극(33)에 의해 반사된 광에 의해 영상의 표시를 행한다. 이 경우, 반사 전극(33)의 표면에는 미세한 요철이 고밀도로 형성되어 있기 때문에, 시야각 특성이 양호하여, 비교적 넓은 범위에서 양호한 영상을 감상할 수 있다.

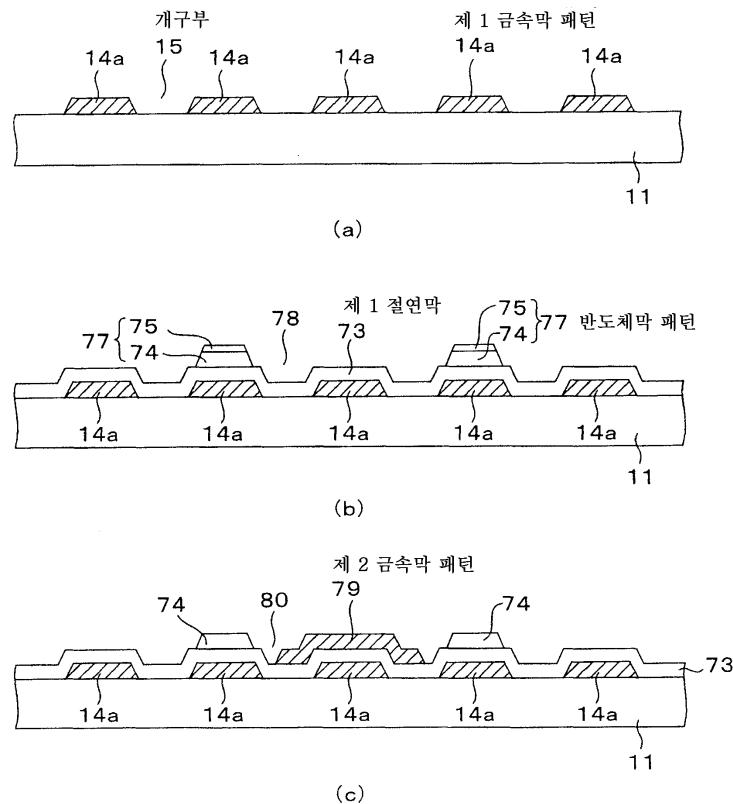

<77> 이하, 본 실시예의 액정 표시 장치의 제조 방법에 대하여 설명한다. 우선, TFT 기판(10)의 제조 방법에 대하여, 도 4 내지 도 8을 참조하여 설명한다. 단, 도 4 내지 도 6은 반사 영역 B에 있어서의 단면도이고, 도 7, 도 8은 반사 영역 B에 있어서의 평면도이다.

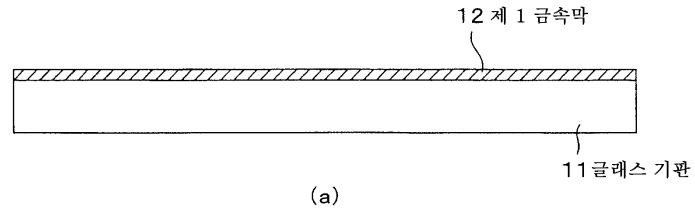

<78> 우선, 도 4a에 도시하는 바와 같이, TFT 기판(10)의 베이스로 되는 글래스 기판(11)의 상측 전면에, 예를 들면 스퍼터법에 의해 Al(알루미늄)막(약 150nm), MoN(질화 몰리브덴)막(약 70nm) 및 Mo(몰리브덴)막(약 15nm)을 순차적으로 형성하여, Al막/MoN막/Mo막의 3층 구조의 제1 금속막(12)을 형성한다.

<79> 또한, 제1 금속막(12)은, 상기의 구성에 한정하는 것은 아니지만, Al 또는 Ag 등의 저저항 금속막을 Ti(티탄) 및 Mo 등의 고용접 금속을 주성분으로 하는 금속막으로 피복한 구성으로 하는 것이 바람직하다.

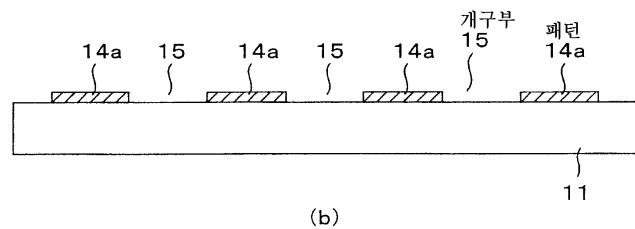

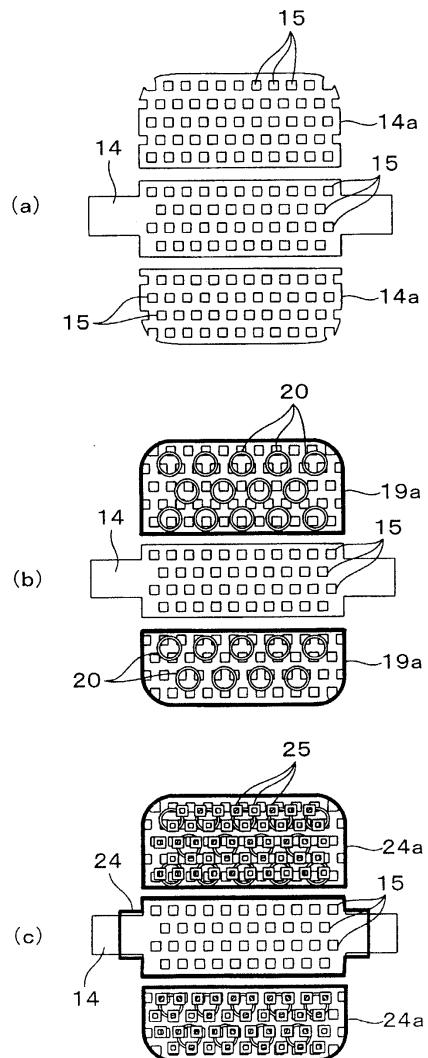

<80> 그 후, 포토리소그래피법에 의해 제1 금속막(12)을 패터닝하여, 게이트 버스 라인(13) 및 보조 용량 버스 라인(14)을 형성함과 더불어, 도 7a에 도시하는 바와 같이, 보조 용량 버스 라인(14)을 Y 방향의 양측으로부터 끼우는 위치에 각각 제1 금속막 패턴(14a)을 형성한다. 게이트 버스 라인(13)의 폭은 예를 들면 10  $\mu\text{m}$ 로 한다. 또한, 보조 용량 버스 라인(14) 중 인접하는 화소간을 연락하는 부분의 폭을 예를 들면 약 12  $\mu\text{m}$ 로 하고, 화소내에서 보조 용량을 형성하는 부분(이하, 폭광부라고 함)의 폭을 그것보다도 넓게(예를 들면 25  $\mu\text{m}$ ) 한다. 또한, 제1 금속막(12)은, 상기의 구조에 한정되는 것은 아니고, 여러가지의 금속 재료를 이용하여 형성할 수 있다.

<81> 제1 금속막 패턴(14a)은, 예를 들면 Y 방향의 길이가 약 30  $\mu\text{m}$ , X 방향의 길이가 약 55  $\mu\text{m}$ 로 한다. 도 7a에 도시한 바와 같이, 제1 금속막 패턴(14a)은 보조 용량 버스 라인(14)으로부터 떨어진 위치에 배치되어, 보조 용량 버스 라인(14)과 전기적으로 분리된다. 또한, 보조 용량 버스 라인(14)의 폭광부 및 제1 금속막 패턴(14a)에는, 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)의 형성과 동시에, 도 4b의 단면도 및 도 7a의 평면도에 도시한 바와 같이, 복수의 개구부(개구 패턴)(15)를 형성한다. 이들 개구부(15)는, 예를 들면 한 변이 약 4  $\mu\text{m}$ 인 정방형(또는, 직경이 4  $\mu\text{m}$ 인 원형)으로 하고, 각각의 개구부(15)의 중심점이, 한 변이 5.5  $\mu\text{m}$ 인 정삼각형의 정점 위치에 중첩되도록 한다.

<82> 또한, 개구부(15)의 단면은 15 ~ 70° 정도의 순테이퍼 형상으로 하는 것이 바람직하다. 이 개구부(15)의 단면 형상은, 제1 금속막(12)의 구조(각층의 재질 및 두께)와 에친트의 조성 및 에칭 조건(오버 에칭 조건)에 의존한다. 제1 금속막(12)이 전술한 구조를 갖는 경우, 에친트로서, 예를 들면 인산, 질산 및 초산의 혼산을 사용하여, 30~75%의 오버 에칭을 행하면 무방하다.

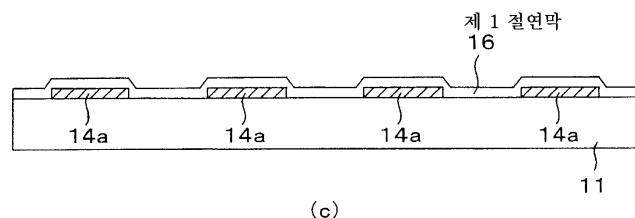

<83> 다음으로, 도 4c에 도시한 바와 같이 글래스 기판(11)의 상측 전면에, 예를 들면 SiN(질화 실리콘)으로 이루어지는 제1 절연막(게이트 절연막)(16)을 약 350nm의 두께로 형성한다. 이 제1 절연막(16)에 의해 게이트 버스 라인(13), 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)이 피복된다.

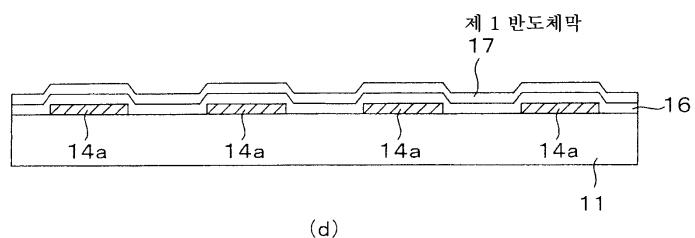

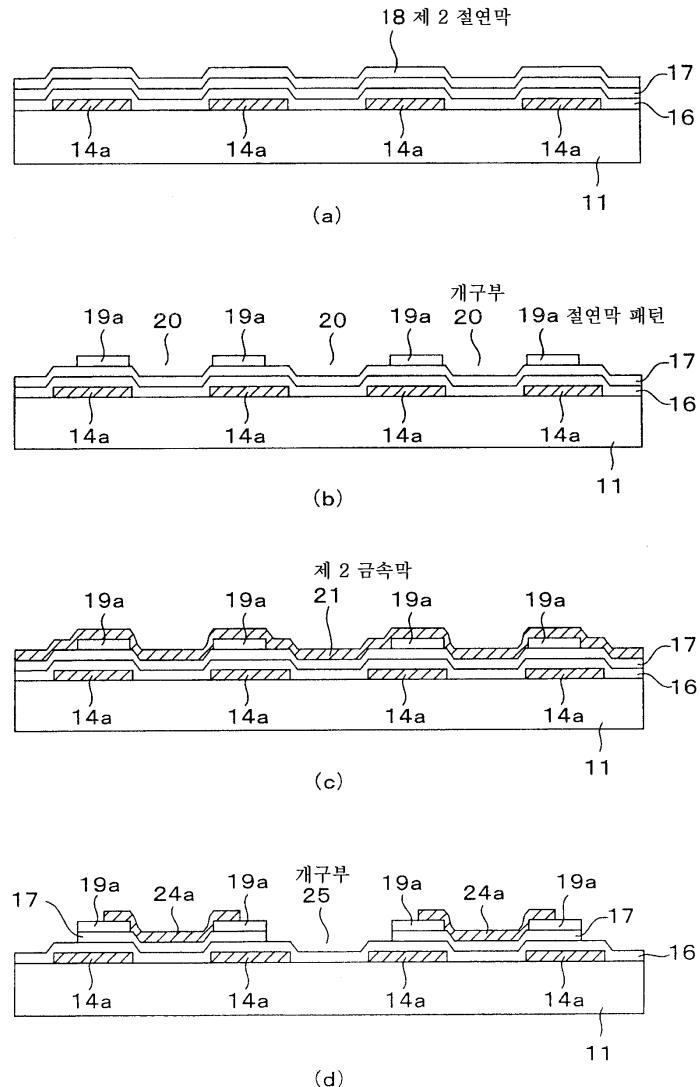

<84> 다음으로, 도 4d에 도시한 바와 같이, 제1 절연막(16) 위에, 예를 들면 CVD(Chemical Vapor Deposition)법에 의해 두께가 30nm인 비정질 실리콘으로 이루어지는 제1 반도체막(17)을 형성하고, 계속하여 도 5a에 도시한 바와 같이 예를 들면 SiN(질화 실리콘)으로 이루어지는 제2 절연막(18)을 약 120nm의 두께로 형성한다. 그리고, 포토리소그래피법에 의해 제2 절연막(18)을 패터닝하여, 도 2의 평면도에 도시한 바와 같이, 게이트 버스 라인(13)의 상방에, Y 방향의 길이가 예를 들면 10  $\mu\text{m}$ , X 방향의 길이가 예를 들면 40  $\mu\text{m}$ 인 채널 보호막(19)을 형성한다. 또한, 이 때 동시에, 도 5b 및 도 7b에 도시한 바와 같이, 제1 금속막 패턴(14a)의 상방에 절연막 패턴(19a)을 형성한다. 이 때, 절연막 패턴(19a)에는, 직경이 약 7  $\mu\text{m}$ 인 복수의 제2 개구부(20)를 형성한다. 이들 개구부(20)는, 그 중심점이, 한 변이 10  $\mu\text{m}$ 인 정삼각형의 정점과 겹쳐지는 위치에 배치된다.

<85> 또한, 본 실시예에서는, 보조 용량 버스 라인(14) 상의 제2 절연막(18)은 제거하고 있다. 이것은, 보조 용량 버스 라인(14) 위에 제2 절연막(18)이 존재하면, 보조 용량 버스 라인(14)과 보조 용량 전극(24) 사이의 간격이 커져서, 보조 용량 Cs의 용량값을 설계값대로 하는 것이 어렵게 되기 때문이다.

<86> 또한, 개구부(20)의 단면은 15 ~ 70° 정도의 순테이퍼 형상으로 하는 것이 바람직하다. 예를 들면, RIE(Reactive Ion Etching)법에 의해 제2 절연막(18)을 드라이 에칭하는 경우, 챔버내의 압력을 37.5Pa, 가스의 종류 및 유량을 SF<sub>6</sub>/O<sub>2</sub>=70/430sccm(standard cc/min), 파워를 600W로 한다. 이 조건에서는 SiN의 에칭레이

트가 약 100nm/min, 레지스트막(감광성 수지막)의 에칭 레이트가 300 ~ 500nm/min으로 되고, 레지스트막을 제2 절연막(18)보다도 후퇴시킴으로써, 개구부(20)를, 상측의 직경이 하측의 직경보다도 큰 순테이퍼 형상으로 할 수 있다.

<87> 다음으로, 클래스 기판(11)의 상측 전면에, 오믹 컨택트층으로 되는 고밀도의 n형 불순물 비정질 실리콘으로 이루어지는 제2 반도체막(도시 생략)을 예를 들면 30nm의 두께로 형성한다. 계속하여, 도 5c에 도시한 바와 같이, 제2 반도체막 위에, 예를 들면 Ti(티탄)막(두께 20nm), Al막(두께 75nm) 및 Ti막(두께 40nm)을 순차적으로 형성하여, 이들의 적층 구조의 제2 금속막(21)을 형성한다. 제2 금속막(21)의 층 구조는 상기의 예에 한정되는 것은 아니고, 예를 들면, Ti막(두께 20nm)/Al막(두께 75nm)/MoN막(두께 70nm)/Mo막(두께 15nm)의 4층 구조이어도 무방하고, MoN막(두께 50nm)/Al막(두께 75nm)/MoN막(두께 70nm)/Mo막(두께 15nm)의 4층 구조이어도 무방하다.

<88> 또한, 제2 금속막도 상기의 구성에 한정하는 것은 아니지만, Al 또는 Ag 등을 주성분으로 하는 저저항 금속막을, Ti 및 Mo를 주성분으로 하는 고용접 금속막에 의해 끼운 구성으로 하는 것이 바람직하다.

<89> 다음으로, 포토리소그래피법에 의해 제2 금속막(21), 제2 반도체막 및 제1 반도체막(17)을 패터닝하여, 데이터 버스 라인(22), 소스 전극(23a), 드레인 전극(23b), 보조 용량 전극(24) 및 제2 금속막 패턴(24a)을 동시에 형성한다. 데이터 버스 라인(22)의 폭은 예를 들면 7μm로 한다. 또한, 소스 전극(23a)은, 도 2에 도시한 바와 같이, 제1 투과 영역 A1의 중앙부까지 인출하여, 그 선단부에 예를 들면 한 변이 15μm인 정방형의 접속부를 형성한다.

<90> 보조 용량 전극(24)은, 예를 들면 보조 용량 버스 라인(14)의 폭광부보다도 Y 방향으로 각각 약 2μm씩 폭을 넓게 한 크기로 형성한다. 이 보조 용량 전극(24)에는 요철 패턴은 형성하지 않는다. 제1 절연막(16)을 사이에 두고 대향하는 보조 용량 전극(24) 및 보조 용량 버스 라인(14)에 의해, 도 3의 등가 회로에 도시한 보조 용량 Cs가 구성된다.

<91> 제2 금속막 패턴(24a)은, 제2 절연막(18)을 사이에 두고 제1 금속막 패턴(14a)과 대향하는 위치에 형성한다. 도 5d, 도 7c에 도시한 바와 같이, 이 제2 금속막 패턴(24a)에는, 제2 금속막 패턴(24a)의 형성과 동시에, 예를 들면 한 변이 약 4μm인 대략 정방형의 복수의 개구부(25)를 형성한다. 이를 개구부(25)는, 그 중심점이, 한 변이 6μm인 정삼각형의 정점과 겹쳐지는 위치에 배치된다.

<92> 다음으로, 도 6a에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에, 예를 들면 SiN으로 이루어지는 제3 절연막(27)을 약 330nm의 두께로 형성하고, 이 제3 절연막(27)에 의해 데이터 버스 라인(22), TFT(23), 보조 용량 전극(24) 및 제2 금속막 패턴(24a)을 피복한다. 그리고, 포토리소그래피법에 의해 제3 절연막(27)을 패터닝하여, 소스 전극(22a)의 접속부로 통하는 컨택트 홀(27a)을 형성함과 더불어, 도 6b의 단면도 및 도 8a의 평면도에 도시한 바와 같이, 보조 용량 전극(24) 또는 제2 금속막 패턴(24a)로 통하는 복수의 제4 개구부(28)와, 제1 금속막 패턴(14a)로 통하는 컨택트 홀(28a)을 형성한다. 개구부(28)는, 그 중심점이, 한 변이 7μm인 정삼각형의 정점과 겹쳐지는 위치에 배치된다.

<93> 여기서, 제3 절연막(SiN막)(27)의 드라이 에칭 조건은, 예를 들면 캠버내의 압력이 6.7Pa, 에칭 가스의 종류 및 유량이 SF<sub>6</sub>/O<sub>2</sub>=200/200(sccm), 파워를 600W로 한다. 제3 절연막(27)은, 상층이 에칭 레이트가 높은 SiN으로 이루어지고, 하층이 에칭 레이트가 낮은 SiN으로 이루어지는 2층 이상의 적층 구조로 하고, 에칭 형상이 15 ~ 70° 인 순테이퍼 형상으로 되도록 하는 것이 바람직하다. 또한, 미리 제3 절연막(27)을 구성하는 2개의 SiN층의 에칭 레이트가 제1 절연막(16)의 에칭 레이트보다도 높아지는 막 구조으로 함으로써, 제1 및 제3 절연막(16, 27)의 에칭 형상은 각각 15 내지 70° 의 순테이퍼 형상으로 되고, 두께 방향의 중앙에 단차를 갖는 컨택트 홀이 형성된다.

<94> 상기의 에칭 조건에서, 제1 절연막(16)의 에칭 레이트는 약 200nm/min, 제3 절연막(27)의 하층막의 에칭 레이트가 약 300~400nm/min, 제3 절연막(27)의 상층막의 에칭 레이트가 400~500nm/min, 레지스트막의 에칭 레이트가 200~300nm/min으로 된다. 에칭 직후의 형상은 제3 절연막(27)이 제1 절연막(16)보다도 후퇴하고 있고, 레지스트막의 후퇴량과 제1 절연막(16)의 후퇴량은 거의 동일하며, 차양(지붕) 형상으로 된다.

<95> 다음으로, 도 6c에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에, ITO 등의 투명 도전체에 의해 제3 금속막(29)을 형성한다. 이 제3 금속막(29)의 막 두께는 예를 들면 70nm으로 한다. 이 제3 금속막(29)을 포토리소그래피법에 의해 패터닝하여, 도 2, 도 8b에 도시하는 투명 화소 전극(32a)을 형성한다. 이를 투명 화소 전극(32a)의 사이즈는, 예를 들면 한 변이 80μm인 대략 정방형으로 한다. 또한, 각 투명 화소 전극(32a)간의 간격

은, 예를 들면  $8\text{ }\mu\text{m}$ 로 한다. 이를 투명 화소 전극(32a)은, 제3 절연막(27)에 형성된 컨택트 홀(27a)을 통하여 소스 전극(22a)에 전기적으로 접속됨과 더불어, 개구부(28)를 통하여 보조 용량 전극(24)과 전기적으로 접속된다.

<96> 계속해서, 클래스 기판(11)의 상측 전면에 제4 금속막을 형성한다. 이 제4 금속막은, 적어도 최상층이 Al 또는 Ag 등을 주성분으로 하는 고반사율의 금속에 의해 형성한다. 그 후, 제4 금속막을 포토리소그래피법에 의해 패터닝하여, 도 6d, 도 8c에 도시한 바와 같이, 반사 영역 B의 투명 화소 전극(32a) 위에 반사 전극(33)을 형성한다.

<97> 본 실시예에서는, 전술한 바와 같이, 보조 용량 버스 라인(14) 또는 제1 금속막(14a)의 개구부(15), 제2 절연 패턴(19a)의 개구부(20), 제2 금속막 패턴(24a)의 개구부(25) 및 제3 절연막(27)의 개구부(28)의 크기 및 배열 피치가 각각 상이하기 때문에, 이를 개구부(15, 20, 25, 28)의 중첩이 균일하지 않고, 그 결과 반사 전극(33)의 표면에 요철이 형성된다. 이 요철의 밀도는 포토리소그래피의 해상도에 의존하지 않으며, 미세하고 랜덤 또한 고밀도이다. 이와 같이 하여 반사 전극(33)의 표면에 미세하고 랜덤한 요철을 고밀도로 형성한 후, 클래스 기판(11)의 상측 전면에 폴리이미드를 도포하여, 수직 배향막을 형성한다. 이와 같이 하여 TFT 기판(10)이 완성된다.

<98> 이하, 대향 기판(40)의 제조 방법에 대하여, 도 1을 참조하여 설명한다.

<99> 우선, 대향 기판(40)의 베이스로 되는 클래스 기판 위(도 1에서는 하측의 면)에, 예를 들면 Cr 등의 금속막을 형성하고, 이 금속막을 패터닝하여 블랙 매트릭스를 형성한다. 그 후, 적색 감광성 수지, 녹색 감광성 수지 및 청색 감광성 수지를 사용하여, 적색, 녹색 및 청색의 컬러 필터(43)를 형성한다. 또한, 블랙 매트릭스는 흑색의 수지에 의해 형성하여도 무방하고, 적색, 녹색 및 청색의 컬러 필터 중의 2색 이상의 컬러 필터를 겹쳐 블랙 매트릭스로 하여도 무방하다.

<100> 다음으로, 클래스 기판의 상측 전면에 예를 들면 ITO 등의 투명 도전체를 스퍼터링하여, 커먼 전극(44)을 형성한다. 그 후, 커먼 전극(44) 위에 감광성 수지를 도포하여, 노광 및 현상 처리를 행하여, 배향 규제용 돌기(45)를 형성한다. 배향 규제용 돌기(45)는, 투과 영역 A1, A2 및 반사 영역 B의 중심 위치에 형성한다. 이를 배향 규제용 돌기(45)는, 예를 들면 직경이  $10\text{ }\mu\text{m}$ , 높이가  $2.5\text{ }\mu\text{m}$ 으로 한다.

<101> 계속해서, 커먼 전극(44) 및 배향 규제용 돌기(45)의 표면에 예를 들면 폴리이미드를 도포하여, 수직 배향막(도시 생략)을 형성한다. 이와 같이 하여, 대향 기판(40)이 완성된다.

<102> 전술된 바와 같이 하여 TFT 기판(10) 및 대향 기판(40)을 형성한 후, 진공 주입법 또는 적하 주입법에 의해 TFT 기판(10)과 대향 기판(40) 사이에 유전율 이방성이 마이너스( $\Delta \varepsilon < 0$ )인 액정(50)을 봉입하여, 액정 패널을 형성한다. 그 후, 액정 패널의 양면에 각각  $\lambda/4$  과장판(51a, 51b) 및 편광판(52a, 52b)을 배치하여, 백 라이트 유닛을 부착한다. 이와 같이 하여, 본 실시예의 액정 표시 장치가 완성된다.

<103> 본 실시예에서는, TFT의 형성과 동시에 반사 영역 B에 절연막, 반도체막 및 금속막을 형성하고, 이를 절연막, 반도체막 및 금속막에 각각 상이한 크기 및 배열 피치로 개구부를 형성함으로써, 반사 전극의 표면에 요철을 형성한다. 이에 의해, 공정수를 증가시키지 않고, 미세하고 고밀도의 요철을 표면에 갖는 반사 전극을 비교적 용이하게 형성할 수 있다.

<104> (변형 예)

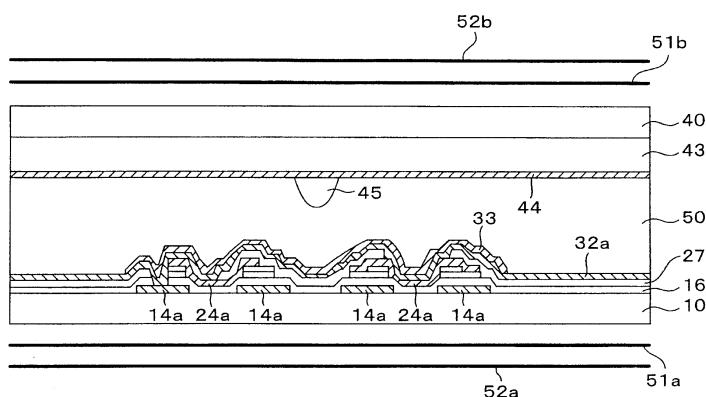

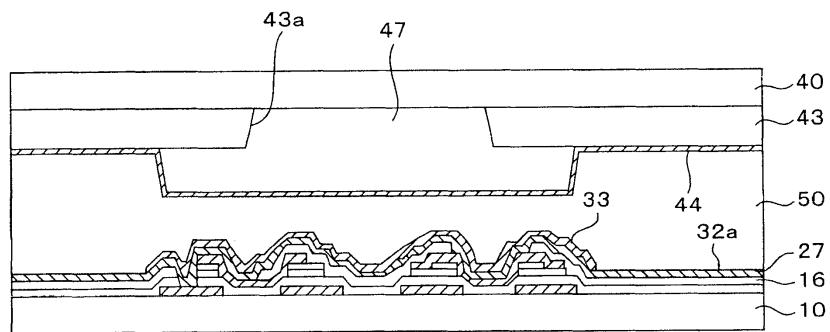

<105> 도 9는 제1 실시예의 변형 예의 액정 표시 장치를 도시한 단면도이다. 또한, 도 9에서, 도 1과 동일물에는 동일 부호를 붙이고 그 상세한 설명을 생략한다. 또한, 도 9에서는, 배향 규제용 돌기,  $\lambda/4$  과장판 및 편광판의 도시를 생략하고 있다.

<106> 도 1에 도시하는 액정 표시 장치에서는, 투과형 액정 표시 장치로서 사용할 때에는 광이 컬러 필터(43)를 1회만 통과하는 것에 반하여, 반사형 액정 표시 장치로서 사용할 때에는 광이 컬러 필터(43)를 2회 통과하기 때문에, 화면이 어두워진다.

<107> 따라서, 도 9에 도시하는 액정 표시 장치에서는, 반사 영역 B의 컬러 필터(43)에 개구부(43a)를 형성하여, 그 개구부(43a)의 부분에 투명 수지막(47)을 형성하고 있다. 이와 같이, 반사 영역 B의 부분에 투명 수지막(47)을 형성하면, 컬러 필터(43)에 의해 감쇄되는 광량이 적어지기 때문에, 화면을 밝게 할 수 있다.

<108> 이 경우에, 컬러 필터(43)의 개구부(43a)가 지나치게 크면, 컬러 필터(43)를 통과하는 광의 비율이 감소하게 되

어, 색 표시 특성이 열화한다. 그러나, 칼라 필터(43)의 개구부(43a)의 사이즈를 작게 함으로써, 투명 수지막(47)을 통과하는 대부분의 광은 액정 패널내에 입사할 때 또는 액정 패널로부터 출사할 때에 컬러 필터(43)를 통과하도록 되어, 색 표시 특성의 열화가 회피된다.

<109> 또한, 도 9에 도시한 바와 같이, 투명 수지막(47)에 의해 반사 영역 B의 셀 캡을 투과 영역 A1, A2의 셀 캡과 개별적으로 조정하는 것이 가능하게 된다. 즉, 투과 영역 A1, A2의 셀 캡을 투과형 액정 표시 장치에 최적화한 값으로 하고, 반사 영역 B의 셀 캡을 반사형 액정 표시 장치에 최적화한 값으로 할 수 있다. 이에 의해, 투과형 액정 표시 장치로서 사용했을 때, 및 반사형 액정 표시 장치로서 사용했을 때의 어느 경우에도, 우수한 표시 성능이 얻어진다.

<110> 투명 수지막(47)에는, 광의 산란성을 높이기 위해, 광학적 확산성을 부여하는 처리를 실시하는 것이 바람직하다. 예를 들면, 투명 수지중에 광을 확산시키는 재료(굴절율이 투명 수지와 상이한 비즈 등)를 첨가하여 투명 수지막을 형성하면 된다.

<111> (제2 실시예)

<112> 이하, 본 발명의 제2 실시예에 대하여 설명한다.

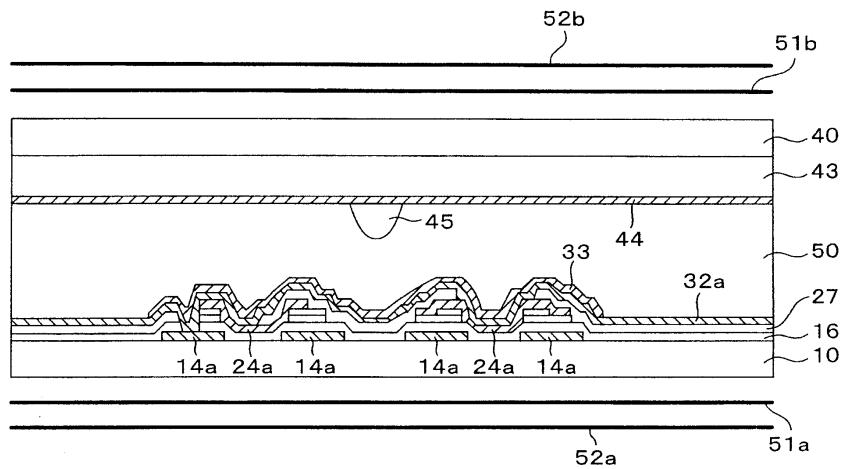

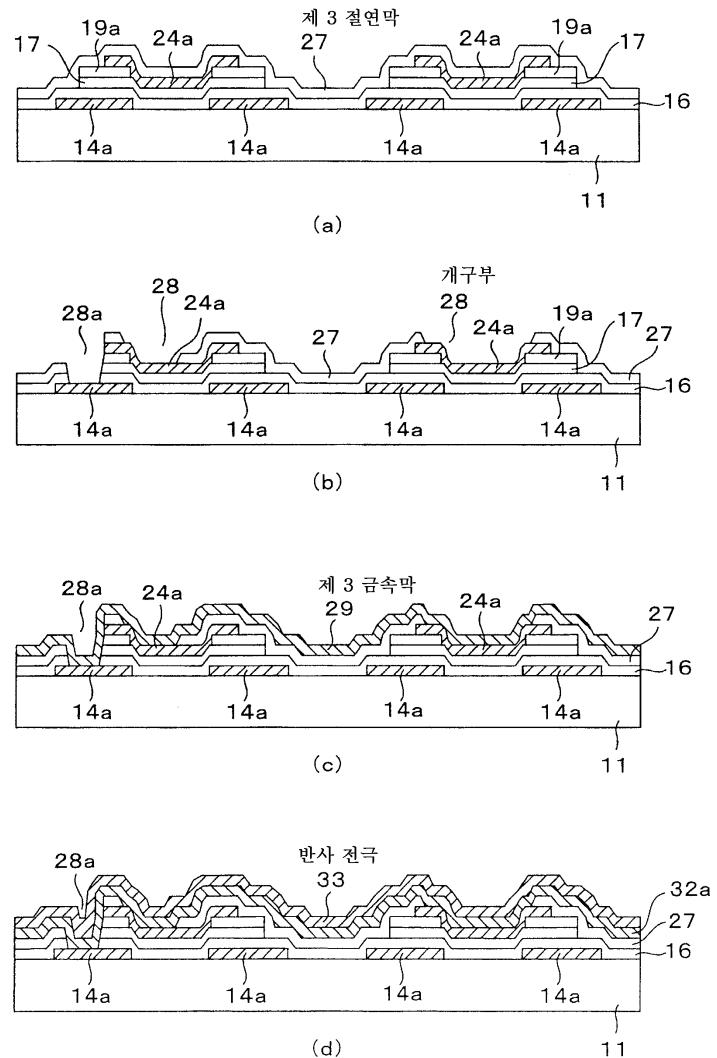

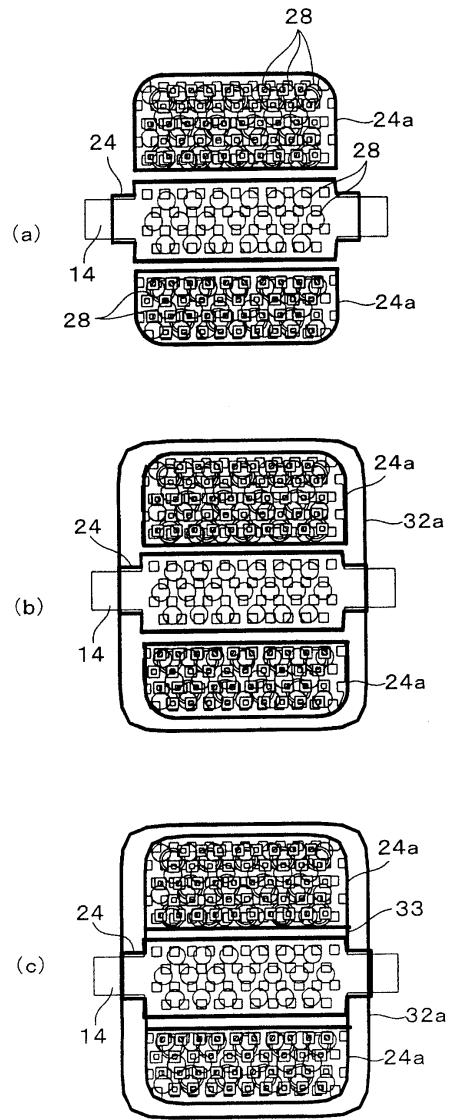

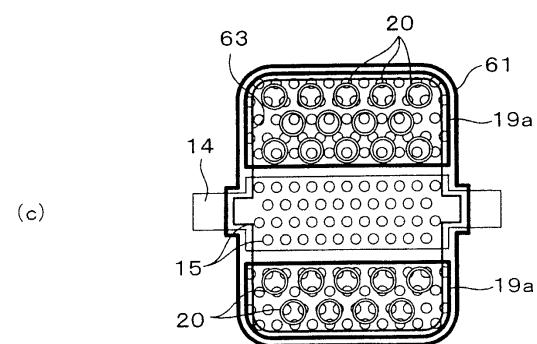

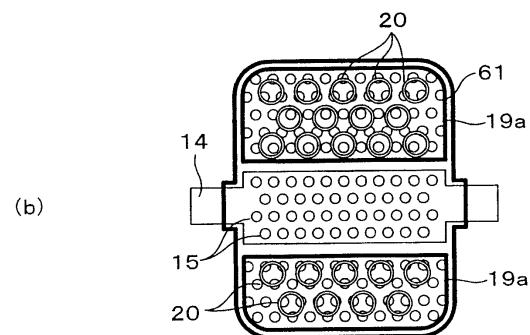

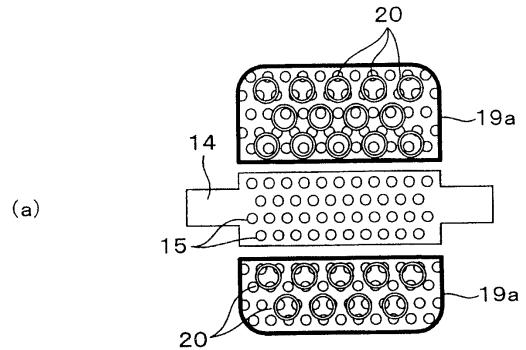

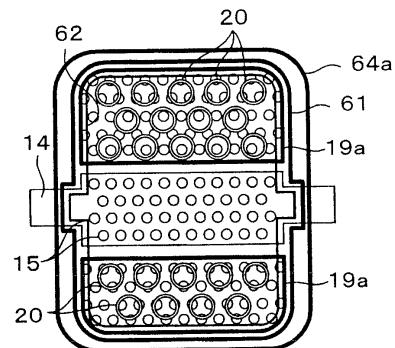

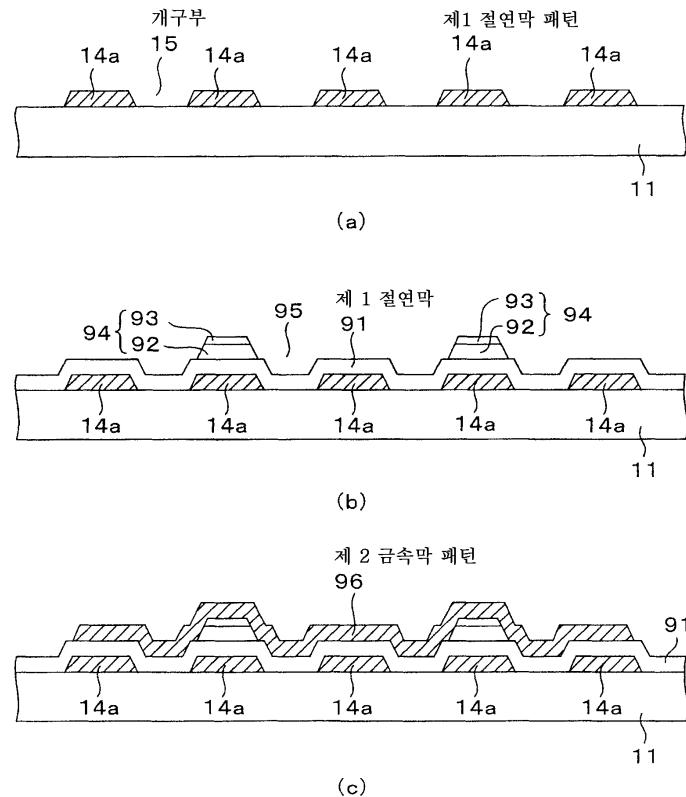

<113> 도 10, 도 11은 본 발명의 제2 실시예의 액정 표시 장치의 제조 방법을 나타내는 단면도, 도 12, 도 13은 동일한 그 평면도이다. 또한, 도 10, 도 11은 반사 영역에 있어서의 단면도이고, 도 12, 도 13은 반사 영역에 있어서의 평면도이다. 또한, 본 실시예가 제1 실시예와 상이한 점은 반사 전극의 형성 방법이 상이한 것에 있고, 그 밖의 구성은 기본적으로 제1 실시예와 마찬가지이기 때문에, 제1 실시예와 동일 부분에 대해서는 도 2를 참조하여 설명한다. 단, 도 12, 도 13에 있어서는, 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)의 개구부(개구 패턴)(15)의 형상을 원형으로 하고 있다. 또한, 대향 기판의 구성은 제1 실시예와 마찬가지이기 때문에, 여기서는 대향 기판의 설명을 생략한다.

<114> 우선, 제1 실시예와 동일한 방법에 의해, 도 10a, 도 12a에 도시한 바와 같이 클래스 기판(11) 위에 게이트 버스 라인(13), 보조 용량 버스 라인(14), 제1 금속막 패턴(14a), 제1 절연막(16), 제1 반도체막(17) 및 절연막 패턴(19a)을 형성하고, 또한 그 위에 제2 금속막(21)을 형성한다. 이 제2 금속막(21)은, 예를 들면 두께가 20nm인 Ti막과, 두께가 75nm인 Al막과, 두께가 40nm인 Ti막을 아래로부터 이 순서로 적층하여 형성한다. 제2 금속막(21)을, 예를 들면 Ti막(두께 20nm)/Al막(두께 75nm)/MoN막(두께 70nm)/Mo막(두께 15nm)의 4층 구조이어도 무방하고, MoN막(두께 50nm)/Al막(두께 75nm)/MoN막(두께 70nm)/Mo막(두께 15nm)의 4층 구조로 하여도 무방하다.

<115> 또한, 제1 실시예와 마찬가지로, 보조 용량 버스 라인(14)의 폭광부 및 제1 금속 패턴(14a)에는 개구부(15)를 형성하고, 절연막 패턴(19a)에는 개구부(20)를 형성해 놓는다. 이를 개구부(15, 20)는 크기 및 배열 위치가 서로 상이하다.

<116> 다음으로, 포토리소그래피법에 의해 제2 금속막(21)을 패터닝하여, 데이터 버스 라인(22), 소스 전극(23a) 및 드레인 전극(23b)을 형성함과 더불어, 도 10b, 도 12b에 도시한 바와 같이, 반사 영역 B에 보조 용량 전극을 겸용하는 반사 전극(61)을 형성한다.

<117> 다음으로, 도 10c에 도시한 바와 같이 클래스 기판(11)의 상측 전면에, 예를 들면 SiN에 의해 제3 절연막(62)을 형성하고, 데이터 버스 라인(22), TFT(23) 및 반사 전극(61)을 이 제3 절연막(62)에 의해 피복한다.

<118> 다음으로, 도 11a, 도 12c에 도시한 바와 같이, 포토리소그래피법에 의해 제3 절연막(62)을 패터닝하여, 반사 전극(61)이 노출하는 개구부(63)를 형성한다. 단, 개구부(63)는, 반사 전극(61)보다도 포토리소그래피의 마진 분만큼 작게 하고, 반사 전극(61)의 연부가 제3 절연막(62)에 의해 피복된 채로 한다. 또한, 제3 절연막(62)의 에칭은, 예를 들면 SF<sub>6</sub>/O<sub>2</sub> 가스를 이용한 드라이 에칭에 의해 행한다.

<119> 이 포토리소그래피 공정에서는, 소스 전극(23a) 위에 컨택트 홀(27a)을 개구함과 더불어, 데이터 버스 라인(22)의 단부(접속 단자부) 위의 제3 절연막(62) 및 게이트 버스 라인(13)의 단부(접속 단자부) 위의 제1 및 제3 절연막(16, 62)을 에칭하여 개구부를 형성한다. 이 에칭 동안에 제2 금속막(21)의 최상층의 Ti막(또는 MoN막/Mo막)이 에칭 제거되어, Ti막 아래의 Al막이 노출된다. 이와 같이 제2 금속막(21)의 중간층인 Al막을 노출시킴으로써, Ti막, MoN막 또는 Mo막 등이 표면에 노출되어 있는 경우와 비교하여 반사 전극의 반사율이 높아져서, 밝은 표시가 가능하게 된다.

- <120> 또한, 통상의  $SF_6/O_2$  가스를 이용한 SiN막의 드라이 에칭에서는, Ti막, MoN막 및 Mo막은 용이하게 에칭되지만 Al막은 에칭되지 않기 때문에, Al막을 에칭 스토퍼로서 잔존시키는 것이 가능하다. 이 공정에 있어서의 SiN막의 드라이 에칭 조건으로서는, 예를 들면 챔버내의 압력이 0.7Pa, 가스의 종류 및 유량이  $SF_6/O_2=200/200$ (sccm), 파워가 600W로 한다.

- <121> 다음으로, 도 11b에 도시한 바와 같이 글래스 기판(11)의 상측 전면에 ITO 등의 투명 도전체를 스퍼터링하여, 제3 금속막(64)을 형성한다.

- <122> 다음으로, 포토리소그래피법에 의해 제3 금속막(64)을 패터닝하여, 도 11c, 도 13에 도시한 바와 같이, 제1 및 제2 투과 영역 A1, A2 및 반사 영역 B에 각각 투명 화소 전극(64a)을 형성한다.

- <123> 계속해서, 제1 실시예와 마찬가지로 하여, 투명 화소 전극(64a)의 표면을 피복하는 수직 배향막(도시 생략)을 형성한다. 이와 같이 하여, TFT 기판이 완성된다. 그 후, TFT 기판과 대향 기판을 대향시켜 배치하고, 이들 TFT 기판과 대향 기판 사이에 액정을 봉입한다. 이와 같이 하여, 본 실시예의 액정 표시 장치가 완성된다.

- <124> 본 실시예에 있어서도, 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)에 형성한 개구부(15)와, 절연막 패턴(19a)에 형성한 개구부(20)와의 크기 및 배열 피치가 상이하기 때문에, 제조 공정을 추가하지 않고, 반사 전극(61)의 표면에 미세하고 고밀도의 요철을 형성할 수 있다. 또한, 본 실시예에서는, 제1 실시예와 비교하여 금속막을 형성하는 공정이 1개 감소하기 때문에, 제조 코스트를 저감할 수 있다고 하는 이점이 있다.

- <125> (제3 실시예)

- <126> 이하, 본 발명의 제3 실시예에 대하여 설명한다. 본 실시예는, 본 발명을 채널 에칭 타입의 TFT를 갖는 액정 표시 장치의 제조 방법에 적용한 예에 대하여 설명하고 있다.

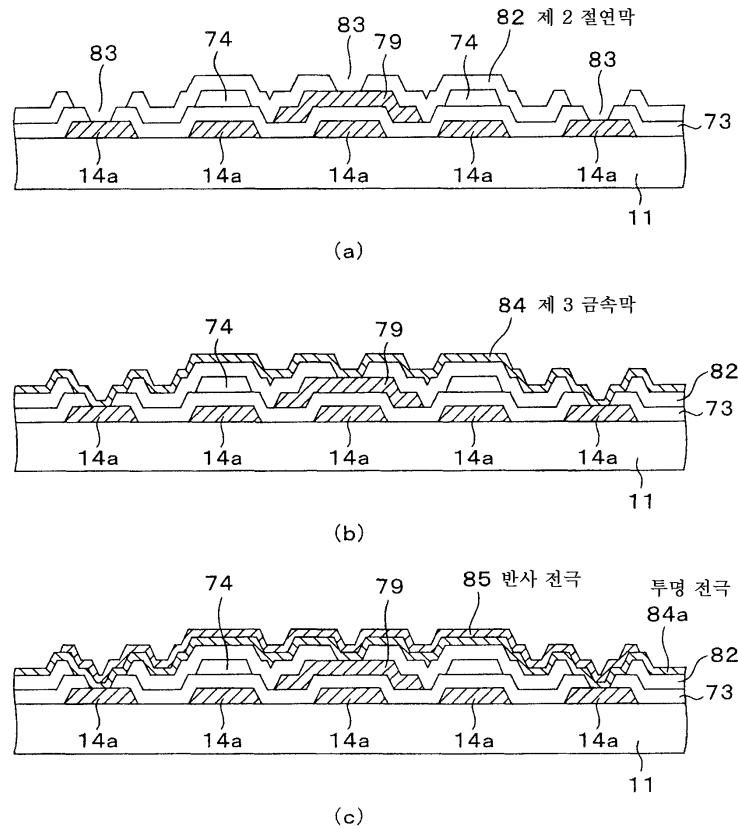

- <127> 도 14 내지 도 16은, 본 발명의 제3 실시예의 액정 표시 장치의 제조 방법을 나타내는 단면도이다. 도 14, 도 15는 반사 영역 B에 있어서의 단면도이고, 도 16은 TFT 형성부에 있어서의 단면도이다. 또한, 본 실시예에 있어서도, 제1 실시예와 동일 부분에 대해서는 도 2를 참조하여 설명한다. 또한, 대향 기판의 구조는 제1 실시예와 동일하기 때문에, 여기서는 대향 기판의 설명을 생략한다.

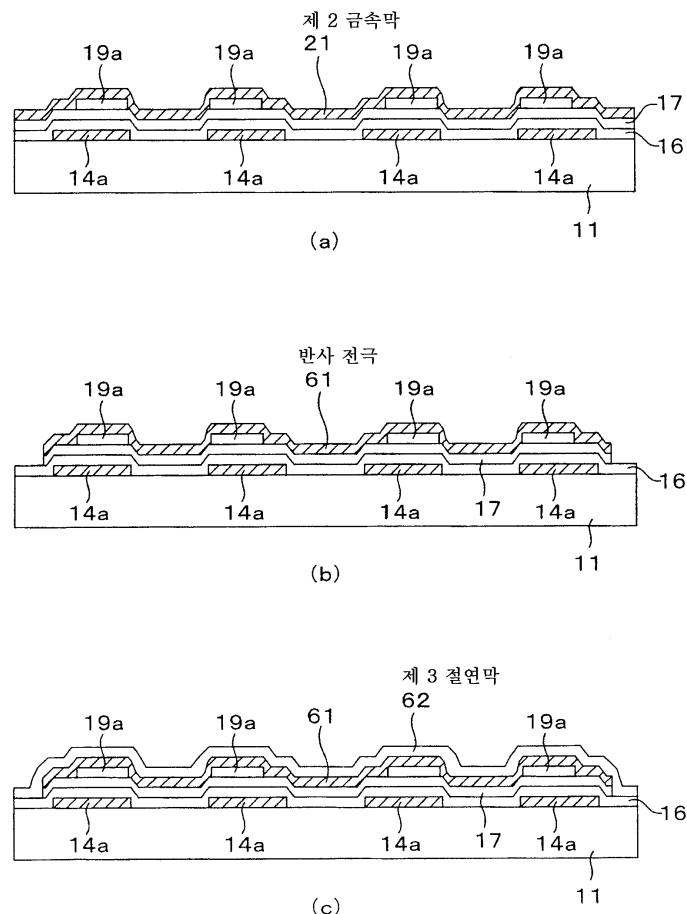

- <128> 우선, 도 14a, 도 16a에 도시한 바와 같이, TFT 기판(10)의 베이스로 되는 글래스 기판(11)의 상측에, 예를 들면 스퍼터법에 의해 Al막, MoN막 및 Mo막을 순차적으로 형성하여, Al막/MoN막/Mo막의 3층 구조의 제1 금속막을 형성한 후, 포토리소그래피법에 의해 이 제1 금속막을 패터닝하여, 게이트 버스 라인(13), 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)을 형성한다. 이 때, 제1 실시예와 마찬가지로, 보조 용량 버스 라인(14)의 폭광부 및 제1 금속막 패턴(14a)에는, 각각 복수의 개구부(15)를 형성한다. 또한, 도 16a에 있어서, 참조부호 71은 게이트 버스 라인(13)을 형성할 때의 레지스트막을 나타내고 있다.

- <129> 다음으로, 도 14b, 도 16b에 도시한 바와 같이, CVD법에 의해, 글래스 기판(11)의 상측 전면에 SiN을 퇴적시켜 제1 절연막(73)을 형성하고, 이 제1 절연막(73)에 의해 게이트 버스 라인(13), 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)을 피복한다. 그리고, 이 제1 절연막(73) 위에, TFT(23)의 활성층으로 되는 제1 반도체막(74)을 비도팽의 비정질 실리콘 또는 다결정 실리콘에 의해 형성하고, 또한 그 위에 오믹 컨택트층으로 되는 제2 반도체막(75)을 n형 불순물이 고농도로 도입된 비정질 실리콘에 의해 형성한다. 그리고, 포토리소그래피법에 의해 이들 제1 및 제2 반도체막(74, 75)을 패터닝하여, 도 16b에 도시한 바와 같이 TFT 형성 영역에 섬 형상 반도체막을 형성한다. 또한, 도 16b에 있어서, 참조부호 76은 TFT 형성 영역에 섬 형상 반도체막을 형성할 때의 레지스트막을 나타내고 있다.

- <130> 또한, 이 때 동시에, 도 14b에 도시한 바와 같이, 제1 금속막 패턴(14a)의 상방의 제1 절연막(73) 위에 제1 및 제2 반도체막(74, 75)으로 이루어지는 반도체막 패턴(77)을 형성함과 더불어, 이 반도체막 패턴(77)에 제2 개구부(78)를 형성한다. 이 제2 개구부(78)는, 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)에 형성된 제1 개구부(15)와 상이한 크기 및 배열 피치로 형성한다.

- <131> 다음으로, 글래스 기판(11)의 상측 전면에 제2 금속막을 형성한다. 이 제2 금속막은, 예를 들면 Ti막(두께 20nm), Al막(두께 75nm) 및 Ti막(두께 40nm)의 3층 구조로 한다. 그리고, 도 14c, 도 16c에 도시한 바와 같이, 포토리소그래피법에 의해 제2 금속막을 패터닝하여, 데이터 버스 라인(22), 소스 전극(23a), 드레인 전극(23b) 및 제2 금속막 패턴(79)을 형성한다. 이 때, 도 16c에 도시한 바와 같이, 소스 전극(23a) 및 드레인 전극(23b)간의 제1 및 제2 반도체막(74, 75)을 제1 반도체막(74)의 두께 방향의 도중까지 에칭하여, 소스 전극

(23a)의 하방의 제2 반도체막(75)과 드레인 전극(23b)의 하방의 제2 반도체막(75)을 전기적으로 분리한다. 또한, 제2 금속막 패턴(79)은, 제1 금속막 패턴(14a)의 상방에 형성한다. 이 제2 금속막 패턴(79)에는, 제1 및 제2 개구부(15, 78)와 상이한 크기 및 배열 편치로 제3 개구부(80)를 형성한다. 또한, 도 16c에 있어서의 참조 부호 81은, 소스 전극(23a) 및 드레인 전극(23b)을 형성할 때의 레지스트막을 나타내고 있다.

<132> 다음으로, 도 15a에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에 예를 들면 SiN으로 이루어지는 제2 절연 막(82)을 형성하고, 이 제2 절연막(82)에 의해 데이터 버스 라인(22), TFT(27) 및 제2 금속막 패턴(79)을 피복 한다. 그리고, 포토리소그래피법에 의해, 소스 전극(23a)으로 통하는 컨택트 홀(27a)을 형성함과 더불어, 보조 용량 전극(14), 제1 금속 패턴(14a) 및 제2 금속막 패턴(79)으로 통하는 복수의 제4 개구부(83)를 형성한다.

<133> 다음으로, 도 15b에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에, ITO 등의 투명 도전체로 이루어지는 제3 금속막(84)을 형성한다.

<134> 계속해서, 도 15c, 도 16d에 도시한 바와 같이, 제3 금속막(84)을 패터닝하여 투명 화소 전극(84a)을 형성한다. 그 후, 클래스 기판(11)의 상측 전면에, 적어도 최상층이 Al 또는 Ag 등을 주성분으로 하는 고 반사율의 금속으로 이루어지는 제4 금속막을 형성하고, 이 제4 금속막을 패터닝하여, 반사 전극(85)을 형성한다. 그리고, 예를 들면 폴리이미드에 의해, 투명 화소 전극(84a) 및 반사 전극(85)의 표면을 피복하는 수직 배향막을 형성한다. 이와 같이 하여 TFT 기판이 완성된다. 그 후, TFT 기판과 대향 기판을 대향시켜 배치하고, 이들 TFT 기판과 대향 기판 사이에 액정을 봉입한다. 이와 같이 하여, 본 실시예의 액정 표시 장치가 완성된다.

<135> 본 실시예에서는, 제1 실시예와 마찬가지의 효과를 얻을 수 있는 것에 부가하여, 절연막의 성막 공정이 제1 실시예보다도 적기 때문에, 제1 실시예의 액정 표시 장치보다도 제조 코스트가 저감된다고 하는 효과를 발휘한다.

<136> (제4 실시예)

<137> 이하, 본 발명의 제4 실시예에 대하여 설명한다. 본 실시예에 있어서도, 본 발명을 채널 에칭 타입의 TFT를 갖는 액정 표시 장치의 제조 방법에 적용한 예에 대하여 설명하고 있다.

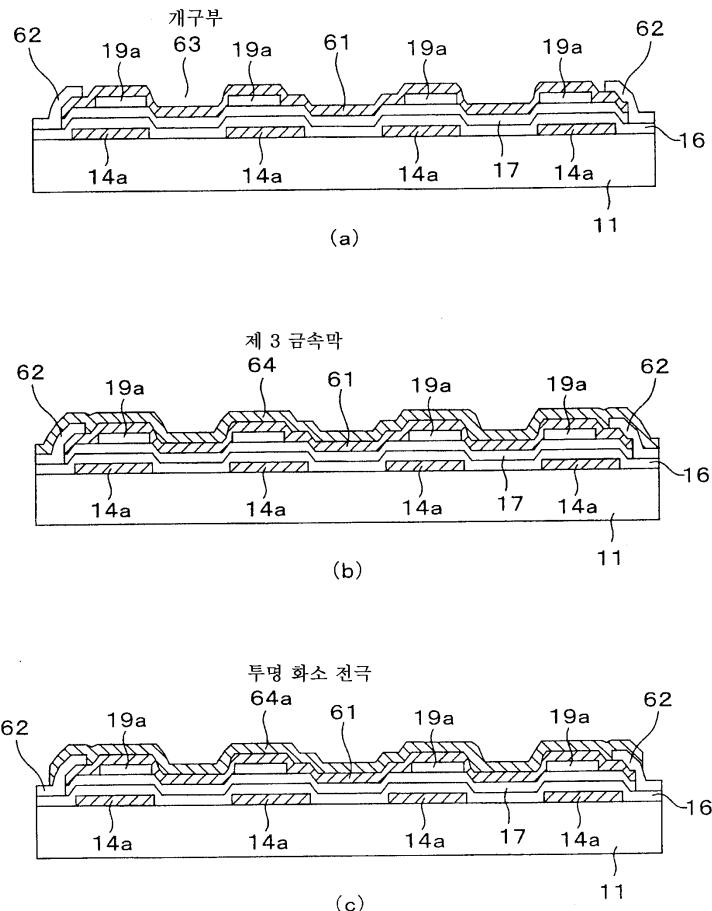

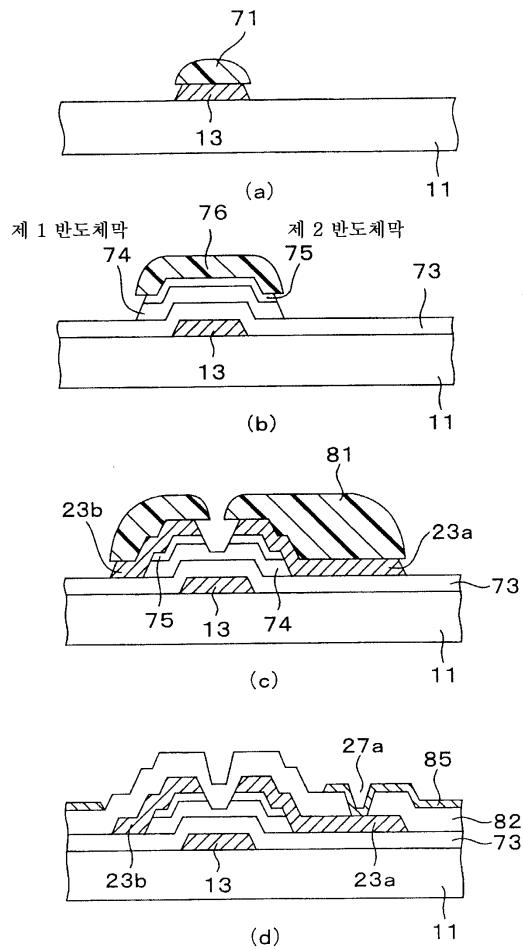

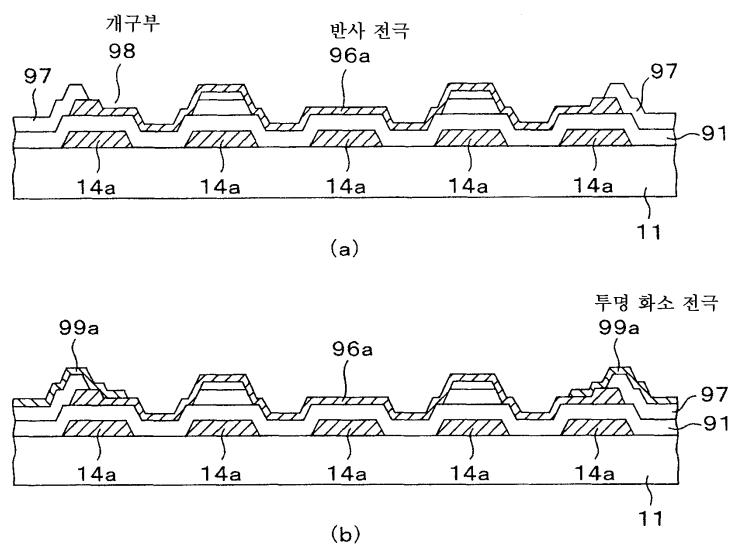

<138> 도 17, 도 18은 본 발명의 제4 실시예의 제조 방법을 나타내는 단면도이다. 이들 도 17, 도 18은, 반사 영역 B에 있어서의 단면도이다. 또한, 본 실시예에 있어서도, 제1 실시예와 동일 부분에 대해서는 도 2를 참조하여 설명한다. 또한, 대향 기판의 구조는 제1 실시예와 마찬가지이기 때문에, 여기서는 대향 기판의 설명을 생략한다.

<139> 우선, 도 17a에 도시한 바와 같이, TFT 기판(10)의 베이스로 되는 클래스 기판(11)의 상측에, 예를 들면 스퍼터 법에 의해 Al막, MoN막 및 Mo막을 순차적으로 형성하고, 이들 Al막, MoN막 및 Mo막의 3층 구조의 제1 금속막을 형성한 후, 포토리소그래피법에 의해 제1 금속막을 패터닝하여, 게이트 버스 라인(13), 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)을 형성한다. 이 때, 제1 실시예와 마찬가지로, 보조 용량 버스 라인(14)의 폭광부 및 제1 금속막 패턴(14a)에는, 각각 복수의 제1 개구부(15)를 형성한다.

<140> 다음으로, 도 17b에 도시한 바와 같이, CVD법에 의해, 클래스 기판(11)의 상측 전면에 SiN을 퇴적시켜 제1 절연 막(91)을 형성하고, 이 제1 절연막(91)에 의해 게이트 버스 라인(13), 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)을 피복한다. 그리고, 이 제1 절연막(91) 위에, TFT(23)의 활성층으로 되는 제1 반도체막(92)을 비도 평의 비정질 실리콘막 또는 다결정 실리콘막에 의해 형성하고, 또한 그 위에 오믹 컨택트층으로 되는 제2 반도체막(93)을 n형 불순물이 고농도로 도입된 비정질 실리콘에 의해 형성한다. 그리고, 포토리소그래피법에 의해 이들 제1 및 제2 반도체막(92, 93)을 패터닝하여, TFT 형성 영역에 삼 형상 반도체막을 형성한다. 또한, 이 때 동시에, 도 17b에 도시한 바와 같이 제1 금속막 패턴(14a)의 상방의 제1 절연막(91) 위에 제1 및 제2 반도체막(92, 93)으로 이루어지는 반도체막 패턴(94)을 형성함과 더불어, 이 반도체막 패턴(94)에 제2 개구부(95)를 형성한다. 이 제2 개구부(95)는 보조 용량 버스 라인(14) 및 제1 금속막 패턴(14a)에 형성된 제1 개구부(15)와 상이한 크기 및 배열 편치로 형성한다.

<141> 다음으로, 도 17c에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에, 예를 들면 Ti막(두께 20nm), Al막(두께 75nm) 및 Ti막(두께 40nm)의 3층 구조의 제2 금속막을 형성한다. 그리고, 이 제2 금속막을 패터닝하여, 데이터 버스 라인(22), 소스 전극(23a) 및 드레인 전극(23b)을 형성한다. 이 때 동시에, 제1 금속막 패턴(14a)에 대향하는 위치에, 제2 금속막 패턴(96)을 형성한다.

<142> 다음으로, 도 18a에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에 제2 절연막(97)을 형성하고, 이 제2 절연막(97)에, 소스 전극(23a)으로 통하는 컨택트 홀(27a)을 형성함과 더불어, 제2 금속막 패턴(96)이 노출되는

개구부(98)를 형성한다. 이 때, 금속막 패턴(96)의 표면을 에칭하여 중간층의 Al막을 노출시켜, 반사 전극(96a)으로 한다.

<143> 또한, 중간층은 Al 또는 Ag 등을 주성분으로 하는 고 반사율의 금속에 의해 형성하면 되고, 또한 피복층은 Ti 또는 Mo 등의 고응집 금속을 주성분으로 하는 금속에 의해 형성하면 된다.

<144> 다음으로, 도 18b에 도시한 바와 같이, 클래스 기판(11)의 상측 전면에 ITO 등의 투명 도전체로 이루어지는 제3 금속막을 형성하고, 이 제3 금속막을 패터닝하여, 투명 화소 전극(99a)을 형성한다. 그리고, 예를 들면 폴리이미드에 의해, 투명 화소 전극(99a) 및 반사 전극(96a)의 표면을 피복하는 수직 배향막을 형성한다. 이와 같이 하여 TFT 기판이 완성된다. 그 후, TFT 기판과 대향 기판을 대향시켜 배치하고, 이들 TFT 기판과 대향 기판과의 사이에 액정을 봉입한다. 이와 같이 하여, 본 실시예의 액정 표시 장치가 완성된다.

<145> 본 실시예에서는, 제1 실시예와 마찬가지의 효과를 얻을 수 있는 것에 부가하여, 절연막의 성막 공정 및 금속막의 성막 공정이 제1 실시예보다도 적기 때문에, 제1 실시예와 비교하여 제조 코스트가 저감된다고 하는 효과를 발휘한다.

<146> 또한, 상기 제1 내지 제4 실시예에서는, 본 발명을 반 투과형 액정 표시 장치에 적용한 예에 대하여 설명했지만, 본 발명은 반사형 액정 표시 장치에 적용할 수 있는 것은 물론이다. 또한, 본 발명은, 제1 내지 제4 실시예에서 설명한 구조의 액정 표시 장치에 한정되지 않고, 그 밖의 반사판을 갖는 액정 표시 장치에 적용할 수 있다.

<147> 이하, 본 발명의 여러 가지 양태를, 부기로서 요약하여 기재한다.

<148> (부기 1) 제1 기판과,

상기 제1 기판에 대향하여 배치되어 광을 투과하는 제2 기판과,

상기 제1 기판 위에 형성되고, 상기 제2 기판을 투과한 광을 반사하는 반사막과,

상기 제1 기판과 상기 반사막 사이에 적층하여 형성된 복수의 막과,

상기 제1 기판과 상기 제2 기판 사이에 봉입된 액정을 갖고,

상기 복수의 막에는 막마다 배열 피치가 상이한 패턴이 형성되고, 상기 반사막의 표면에는 상기 복수의 막의 상기 패턴에 따른 요철이 형성되어 있는 것을 특징으로 하는 액정 표시 장치.

<154> (부기 2) 1 화소 영역내에, 상기 반사막에 의해 반사하는 광에 의해 표시를 행하는 반사 영역과, 상기 제1 및 제2 기판을 투과하는 광에 의해 표시를 행하는 투과 영역을 갖는 것을 특징으로 하는 부기 1에 기재된 액정 표시 장치.

<155> (부기 3) 상기 제2 기판에는, 상기 제1 기판의 반사막에 대향하는 위치에 개구부가 형성된 컬러 필터를 갖는 것을 특징으로 하는 부기 1 또는 2에 기재된 액정 표시 장치.

<156> (부기 4) 상기 컬러 필터의 개구부의 크기는, 상기 반사막의 크기보다도 작은 것을 특징으로 하는 부기 3에 기재된 액정 표시 장치.

<157> (부기 5) 상기 컬러 필터의 개구부 및 그 주위에는 투명 수지막이 형성되어 있는 것을 특징으로 하는 부기 4에 기재된 액정 표시 장치.

<158> (부기 6) 상기 투명 수지막에는 광학적 확산성이 부여되어 있는 것을 특징으로 하는 부기 5에 기재된 액정 표시 장치.

<159> (부기 7) 상기 투명 수지막의 막 두께가, 상기 컬러 필터의 막 두께보다도 두꺼운 것을 특징으로 하는 부기 5 또는 6에 기재된 액정 표시 장치.

<160> (부기 8) 상기 복수의 막 중 적어도 1개의 막에 형성된 패턴의 단면 형상이,  $15^\circ$  내지  $70^\circ$  의 순테이퍼 형상인 것을 특징으로 하는 부기 1 또는 2에 기재된 액정 표시 장치.

<161> (부기 9) 화소마다 박막 트랜지스터 및 반사 전극이 형성된 제1 기판과, 상기 제1 기판에 대향하여 배치되는 제2 기판과, 상기 제1 기판 및 상기 제2 기판 사이에 봉입된 액정을 갖는 액정 표시 장치의 제조 방법으로서,

<162> 상기 제1 기판의 상기 반사 전극을 형성하는 영역위에 상기 박막 트랜지스터의 형성과 동시에, 막마다 배열 피

치가 상이한 패턴을 갖는 복수의 막을 적층하여 형성하고, 그 후, 상기 복수의 막 위에, 상기 복수의 막의 패턴에 따른 요철을 표면에 갖는 반사막을 형성하여 상기 반사 전극으로 하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

- <163> (부기 10) 제1 기판 위에 제1 금속막을 형성하는 공정과,

- <164> 상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

- <165> 상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

- <166> 상기 제1 절연막위에 제1 반도체막을 형성하는 공정과,

- <167> 상기 제1 반도체막위에 제2 절연막을 형성하는 공정과,

- <168> 상기 제2 절연막을 패터닝하여 적어도 박막 트랜지스터의 채널을 보호하는 채널 보호막을 형성하는 공정과,

- <169> 상기 제1 기판의 상측 전면에 제2 반도체막을 형성하는 공정과,

- <170> 상기 제2 반도체막 위에 제2 금속막을 형성하는 공정과,

- <171> 상기 제2 금속막, 상기 제1 반도체막 및 상기 제2 반도체막을 패터닝하여, 상기 박막 트랜지스터의 활성층의 형상을 확정함과 더불어, 데이터 버스 라인과, 상기 박막 트랜지스터의 소스 전극 및 드레인 전극과, 제1 절연막을 통하여 상기 보조 용량 버스 라인에 대향하는 보조 용량 전극을 형성하는 공정과,

- <172> 상기 제1 기판의 상측 전면에 제3 절연막을 형성하는 공정과,

- <173> 상기 제3 절연막위에, 상기 제3 절연막에 형성된 컨택트 홀을 통하여 상기 박막 트랜지스터의 소스 전극 및 상기 보조 용량 전극과 전기적으로 접속되는 반사 전극을 형성하는 공정과,

- <174> 상기 제1 기판에 제2 기판을 대향시켜 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

- <175> 상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 제1 반도체막, 상기 제2 반도체막, 상기 제2 절연막 및 상기 제3 절연막 중 적어도 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

- <176> (부기 11) 상기 보조 용량 버스 라인의 형성과 동시에, 상기 보조 용량 버스 라인 근방에 제1 금속막 패턴을 형성하고, 상기 보조 용량 전극의 형성과 동시에, 상기 보조 용량 전극 근방에 제2 금속막 패턴을 형성하며, 이들 제1 및 제2 금속막 패턴에, 패턴마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 부기 10에 기재된 액정 표시 장치의 제조 방법.

- <177> (부기 12) 상기 제3 절연막과 상기 반사 전극 사이에, 투명 도전체로 이루어지는 제4 금속막을 형성하는 것을 특징으로 하는 부기 10에 기재된 액정 표시 장치의 제조 방법.

- <178> (부기 13) 제1 기판 위에 제1 금속막을 형성하는 공정과,

- <179> 상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

- <180> 상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

- <181> 상기 제1 절연막위에 제1 반도체막을 형성하는 공정과,

- <182> 상기 제1 반도체막위에 제2 절연막을 형성하는 공정과,

- <183> 상기 제2 절연막을 패터닝하여 적어도 박막 트랜지스터의 채널을 보호하는 채널 보호막을 형성하는 공정과,

- <184> 상기 제1 기판의 상측 전면에 제2 반도체막을 형성하는 공정과,

- <185> 상기 제2 반도체막 위에 제2 금속막을 형성하는 공정과,

- <186> 상기 제2 금속막, 상기 제1 반도체막 및 상기 제2 반도체막을 패터닝하여, 상기 박막 트랜지스터의 활성층의 형상을 확정함과 더불어, 데이터 버스 라인과, 상기 박막 트랜지스터의 소스 전극 및 드레인 전극과, 반사전극을 형성하는 전극과,

- <187> 상기 기판의 상측 전면에 제3 절연막을 형성하는 공정과,

- <188> 상기 제3 절연막에 개구부를 형성하여 상기 반사 전극을 노출시키는 공정과,

- <189> 상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

- <190> 상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 제1 반도체막 및 상기 제2 절연막 중 적어도 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

- <191> (부기 14) 상기 보조 용량 버스 라인의 형성과 동시에, 상기 보조 용량 버스 라인 근방에, 개구부를 갖는 금속막 패턴을 형성하는 것을 특징으로 하는 부기 13에 기재된 액정 표시 장치의 제조 방법.

- <192> (부기 15) 상기 제3 절연막과 상기 반사 전극 사이에, 투명 도전체로 이루어지는 제4 금속막을 형성하는 것을 특징으로 하는 부기 13에 기재된 액정 표시 장치의 제조 방법.

- <193> (부기 16) 제1 기판 위에 제1 금속막을 형성하는 공정과,

- <194> 상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

- <195> 상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

- <196> 상기 제1 절연막위에 반도체막을 형성하는 공정과,

- <197> 상기 반도체막을 패터닝하는 공정과,

- <198> 상기 제1 기판의 상측 전면에 제2 금속막을 형성하는 공정과,

- <199> 상기 제2 금속막을 패터닝하여, 데이터 버스 라인과, 박막 트랜지스터의 소스 전극 및 드레인 전극과, 상기 제1 절연막을 통하여 상기 보조 용량 버스 라인에 대향하는 보조 용량 전극을 형성하는 공정과,

- <200> 상기 제1 기판의 상측 전면에 제2 절연막을 형성하는 공정과,

- <201> 상기 제2 절연막에 개구부를 형성하는 공정과,

- <202> 상기 제1 기판의 상측 전면에 제3 금속막을 형성하는 공정과,

- <203> 상기 제3 금속막을 패터닝하여 반사 전극을 형성하는 공정과,

- <204> 상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

- <205> 상기 반사 전극의 하방의 상기 보조 용량 버스 라인, 상기 반도체막 및 상기 제2 절연막 중 적어도 2 이상에, 막마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

- <206> (부기 17) 상기 보조 용량 버스 라인의 형성과 동시에, 상기 보조 용량 버스 라인 근방에 제1 금속막 패턴을 형성하고, 상기 보조 용량 전극의 형성과 동시에, 상기 보조 용량 전극 근방에 제2 금속막 패턴을 형성하고, 이들 제1 및 제2 금속막 패턴에, 패턴마다 배열 피치가 상이한 패턴을 형성하는 것을 특징으로 하는 부기 16에 기재된 액정 표시 장치의 제조 방법.

- <207> (부기 18) 상기 제3 절연막과 상기 반사 전극 사이에, 투명 도전체로 이루어지는 제4 금속막이 형성되어 있는 것을 특징으로 하는 부기 16에 기재된 액정 표시 장치의 제조 방법.

- <208> (부기 19) 제1 기판 위에 제1 금속막을 형성하는 공정과,

- <209> 상기 제1 금속막을 패터닝하여, 게이트 버스 라인 및 보조 용량 버스 라인을 형성하는 공정과,

- <210> 상기 제1 기판의 상측 전면에 제1 절연막을 형성하는 공정과,

- <211> 상기 제1 절연막위에 반도체막을 형성하는 공정과,

- <212> 상기 반도체막을 패터닝하는 공정과,

- <213> 상기 제1 기판의 상측 전면에 제2 금속막을 형성하는 공정과,

- <214> 상기 제2 금속막을 패터닝하여, 데이터 버스 라인과, 박막 트랜지스터의 소스 전극 및 드레인 전극과, 반사 전극을 형성하는 공정과,

- <215> 상기 기판의 상측 전면에 제2 절연막을 형성하는 공정과,

- <216> 상기 제2 절연막에 개구부를 형성하여 상기 반사 전극을 노출시키는 공정과,

- <217> 상기 제1 기판에 대향시켜 제2 기판을 배치하고, 이들 제1 및 제2 기판 사이에 액정을 봉입하는 공정을 갖고,

- <218> 상기 반사 전극의 하방의 상기 보조 용량 버스 라인 및 상기 반도체막에, 막마다 배열 퍼치가 상이한 패턴을 형성하는 것을 특징으로 하는 액정 표시 장치의 제조 방법.

- <219> (부기 20) 상기 제2 금속막이, 중간층과, 그 중간층을 피복하는 피복층에 의해 구성되고, 상기 제2 절연막을 패터닝하는 공정에서는, 상기 피복층을 에칭하여 상기 중간층을 노출시키는 것을 특징으로 하는 부기 19에 기재된 액정 표시 장치의 제조 방법.

- <220> (부기 21) 상기 중간층이 Al 및 Ag 중 적어도 한쪽을 주성분으로 하는 금속으로 이루어지고, 상기 피복층이 Ti 및 Mo 중 적어도 한쪽을 주성분으로 하는 금속으로 이루어지는 것을 특징으로 하는 부기 20에 기재된 액정 표시 장치의 제조 방법.

- <221> (부기 22) 상기 보조 용량 버스 라인의 형성과 동시에, 상기 보조 용량 버스 라인 근방에, 복수의 개구부를 갖는 금속막 패턴을 형성하는 것을 특징으로 하는 부기 19에 기재된 액정 표시 장치의 제조 방법.

- <222> (부기 23) 상기 제1 및 제2 기판 위에는 수직 배향막이 형성되고, 또한 상기 액정은 마이너스의 유전율 이방성을 갖는 것을 특징으로 하는 부기 1 내지 8 중 어느 한 항에 기재된 액정 표시 장치.

- <223> (부기 24) 상기 액정을 봉입한 제1 및 제2 기판으로 이루어지는 액정 패널의 한쪽 면측에 제1 위상차판 및 제1 편광판이 배치되고, 상기 액정 패널의 다른쪽 면측에 제2 위상차판 및 제2 편광판이 배치되어 있는 것을 특징으로 하는 부기 23에 기재된 액정 표시 장치.

### 발명의 효과

<224> 따라서, 본 발명에 따르면, 반사 전극의 표면에 미세한 요철을 고밀도로 형성함으로써, 시야각 특성이 양호하여, 비교적 넓은 범위에서 양호한 영상을 감상할 수 있다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 제1 실시예의 액정 표시 장치를 도시하는 단면도.

- <2> 도 2는 제1 실시예의 액정 표시 장치의 평면도.

- <3> 도 3은 제1 실시예의 액정 표시 장치의 1 화소의 등가 회로도.

- <4> 도 4는 제1 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 1).

- <5> 도 5는 제1 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 2).

- <6> 도 6은 제1 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 3).

- <7> 도 7은 제1 실시예의 액정 표시 장치의 제조 방법을 도시하는 평면도(그 1).

- <8> 도 8은 제1 실시예의 액정 표시 장치의 제조 방법을 도시하는 평면도(그 2).

- <9> 도 9는 제1 실시예의 변형예의 액정 표시 장치를 도시하는 단면도.

- <10> 도 10은 본 발명의 제2 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 1).

- <11> 도 11은 본 발명의 제2 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 2).

- <12> 도 12는 본 발명의 제2 실시예의 액정 표시 장치의 제조 방법을 도시하는 평면도(그 1).

- <13> 도 13은 본 발명의 제2 실시예의 액정 표시 장치의 제조 방법을 도시하는 평면도(그 2).

- <14> 도 14는 본 발명의 제3 실시예의 액정 표시 장치의 제조 방법을 나타내는 반사 영역에 있어서의 단면도(그 1).

- <15> 도 15는 본 발명의 제3 실시예의 액정 표시 장치의 제조 방법을 나타내는 반사 영역에 있어서의 단면도(그 2).

- <16> 도 16은 본 발명의 제3 실시예의 액정 표시 장치의 제조 방법을 나타내는 TFT 형성부에 있어서의 단면도.

- <17> 도 17은 본 발명의 제4 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 1).

- <18> 도 18은 본 발명의 제4 실시예의 액정 표시 장치의 제조 방법을 도시하는 단면도(그 2).

- <19> <도면의 주요 부분에 대한 부호의 설명>

- <20> 10: TFT 기판

- <21> 12, 21, 29, 64, 84 : 금속막

- <22> 13 : 게이트 버스 라인

- <23> 14 : 보조 용량 버스 라인

- <24> 14a, 24a, 79, 96 : 금속막 패턴

- <25> 15, 20, 25, 28, 78, 83, 95 : 개구부

- <26> 16, 18, 27, 62, 73, 82, 91, 97 : 절연막

- <27> 17, 74, 75, 92, 93 : 반도체막

- <28> 19 : 채널 보호막

- <29> 19a : 절연막 패턴

- <30> 22 : 데이터 버스 라인

- <31> 23 : TFT

- <32> 23a : 소스 전극

- <33> 23b : 드레인 전극

- <34> 24 : 보조 용량 전극

- <35> 32a, 64a, 84a, 99a : 투명 화소 전극

- <36> 33, 61, 85 : 반사 전극

- <37> 40 : 대향 기판

- <38> 43 : 컬러 필터

- <39> 44 : 커먼 전극

- <40> 45 : 도메인 규제용 돌기

- <41> 47 : 투명 수지막

- <42> 50 : 액정

- <43> 51a, 51b :  $\lambda/4$  과장판

- <44> 52a, 52b : 편광판

도면

도면1

## 도면2

## 도면3

도면4

## 도면5

## 도면6

## 도면7

도면8

도면9

## 도면10

도면11

## 도면12

## 도면13

## 도면14

## 도면15

도면16

도면17

도면18

|                |                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">KR100799440B1</a>                                                                                                                                                                        | 公开(公告)日 | 2008-01-30 |

| 申请号            | KR1020050037574                                                                                                                                                                                      | 申请日     | 2005-05-04 |

| [标]申请(专利权)人(译) | 富士通株式会社<br>友达光电股份有限公司                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 富士sikki有限公司<br>我们用鼻子来尼克斯捕法                                                                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 富士sikki有限公司<br>我们用鼻子来尼克斯捕法                                                                                                                                                                           |         |            |

| [标]发明人         | TASAKA YASUTOSHI<br>다사까야스또시<br>YOSHIDA HIDEFUMI<br>요시다히데후미<br>TASHIRO KUNIHIRO<br>다시로구니히로<br>TANAKA YOSHINORI<br>다나까요시노리<br>DOI SEIJI<br>도이세이지<br>ODA TOMOSHIGE<br>오다도모시게<br>TSUSHIMA ISAO<br>쯔시마이사오 |         |            |

| 发明人            | 다사까야스또시<br>요시다, 히데후미<br>다시로구니히로<br>다나까요시노리<br>도이세이지<br>오다도모시게<br>쯔시마이사오                                                                                                                              |         |            |

| IPC分类号         | G02F1/1335 G02B5/02 G02F1/1333 G02F1/1343                                                                                                                                                            |         |            |

| CPC分类号         | G02F1/133553 G02F1/133345                                                                                                                                                                            |         |            |

| 代理人(译)         | Jangsugil<br>Yijunghui<br>Juseongmin                                                                                                                                                                 |         |            |

| 优先权            | 2004165320 2004-06-03 JP                                                                                                                                                                             |         |            |

| 其他公开文献         | <a href="#">KR1020060047724A</a>                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                            |         |            |

**摘要(译)**

本发明提供一种液晶显示装置及其制造方法，该液晶显示装置具有在其表面上具有细微且致密的凹凸的反射膜。在反射电极33下面的第一金属膜图案14a，第一半导体膜17，第二金属膜图案24a和第三绝缘膜27设置有开口(开放模式)形成。这些开口彼此复杂地重叠，