**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

G02F 1/136 (2006.01)

|           |             |

|-----------|-------------|

| (45) 공고일자 | 2007년03월27일 |

| (11) 등록번호 | 10-0699208  |

| (24) 등록일자 | 2007년03월19일 |

|           |                 |

|-----------|-----------------|

| (21) 출원번호 | 10-2003-0016891 |

| (22) 출원일자 | 2003년03월18일     |

| 심사청구일자    | 2004년12월01일     |

|           |                 |

|-----------|-----------------|

| (65) 공개번호 | 10-2003-0079683 |

| (43) 공개일자 | 2003년10월10일     |

(30) 우선권주장 JP-P-2002-00099990 2002년04월02일 일본(JP)

(73) 특허권자 어드밴스트 디스플레이 인코포레이티드

일본국 구마모토케이 키쿠치군 니시고시마찌 미요시 997(72) 발명자 모리따히로마사

일본구마모토케이꾸찌군니시고시마찌미요시997반찌어드밴스트디스플

레이인코포레이티드나이

나카시마겐

일본구마모토케이꾸찌군니시고시마찌미요시997반찌어드밴스트디스플

레이인코포레이티드나이

(74) 대리인 특허법인코리아나

(56) 선행기술조사문현

KR1019990066664 A \*

KR1020020089810 A \*

\* 심사관에 의하여 인용된 문현

**심사관 : 임동재**

전체 청구항 수 : 총 11 항

**(54) 박막 트랜지스터 어레이 및 그 제조방법 그리고 이를 이용한 액정표시장치****(57) 요약**

(과제) 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판 및 그 제조방법 그리고 이를 이용한 액정표시장치를 제공하는 것을 목적으로 한다.

(해결수단) 본 발명과 관련된 TFT 어레이 기판의 제조방법은, 게이트 배선 (1) 이 형성된 기판 위에 게이트 절연막 (3), 반도체층 (4a) 과 오믹층 (4b) 및 금속막 (16) 을 형성하는 공정과, 사진 제판에 의하여 금속막 (16) 위의 레지스트 패턴 (17) 을 반도체 활성층 (8) 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 형성하는 공정과, 금속막 (16) 을 에칭하여 소스 배선 (6), 소스 전극 (5) 및 드레인 전극 (7) 을 형성하는 공정과, 반도체 활성층 (8) 해당부 위의 레지스트를 제거한 후에 오믹층 (4b) 및 반도체층 (4a) 을 제거하는 공정과, 금속막 (16) 을 제거하는 공정과, 오믹층 (4b) 을 제거하는 공정을 구비한 TFT 어레이 기판의 제조방법이다.

**대표도**

도 15

**특허청구의 범위****청구항 1.**

절연성 기판 위에 게이트 배선을 형성하는 공정과,

상기 게이트 배선이 형성된 절연성 기판 위에 게이트 절연막, 반도체층과 오믹층 및 금속막을 형성하는 공정과,

사진 제판에 의하여 상기 금속막 위의 레지스트 패턴을, 적어도 후공정에서 상기 오믹층 위에 형성되는 박막 트랜지스터의 소스 배선, 소스 전극, 드레인 전극과 반도체 활성층 해당부가 덮이고, 또한 해당 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 형성하는 공정과,

상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 상기 드레인 전극을 형성하는 공정과,

상기 금속막을 에칭한 후에, 상기 레지스트를 박막화함으로써 상기 반도체 활성층 해당부 위의 레지스트를 제거하는 공정과,

상기 반도체 활성층 해당부 위의 레지스트를 제거한 후에, 상기 소스 배선, 상기 소스 전극, 상기 드레인 전극 및 상기 반도체 활성층 해당부 이외의 오믹층 및 반도체층을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 금속막을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 상기 오믹층을 에칭에 의하여 제거하는 공정을 포함하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

**청구항 2.**

절연성 기판 위에 게이트 배선을 형성하는 공정과,

상기 게이트 배선이 형성된 절연성 기판 위에 게이트 절연막, 반도체층과 오믹층 및 금속막을 형성하는 공정과,

사진 제판에 의하여 상기 금속막 위의 레지스트 패턴을, 적어도 후공정에서 상기 오믹층 위에 형성되는 박막 트랜지스터의 소스 배선, 소스 전극, 드레인 전극과 반도체 활성층 해당부가 덮이고, 또한 해당 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 형성하는 공정과,

상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 상기 드레인 전극을 형성하는 공정과,

상기 금속막을 에칭한 후에, 상기 레지스트를 박막화함으로써 상기 반도체 활성층 해당부 위의 레지스트를 제거하는 공정과,

상기 반도체 활성층 해당부 위의 레지스트를 제거한 후에, 상기 소스 배선, 상기 소스 전극, 상기 드레인 전극 및 상기 반도체 활성층 해당부 이외의 오믹층 및 반도체층을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 금속막을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 상기 오믹층을 에칭에 의하여 제거하는 공정과,

충간절연막을 성막하는 공정과,

제 3 사진 제판 및 에칭으로 상기 게이트 절연막 및 충간절연막에 상기 드레인 전극에 도달하는 드레인 전극 컨택트홀, 상기 소스 전극에 도달하는 소스 단자부 컨택트홀 및 게이트 배선에 도달하는 게이트 단자부 컨택트홀을 형성하는 공정과,

도전막을 형성하는 공정과,

제 4 사진 제판 및 에칭으로 상기 드레인 전극 컨택트홀, 상기 소스 단자부 컨택트홀 및 상기 게이트 단자부 컨택트홀을 덮는 화소 전극을 형성하는 공정을 포함하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

### 청구항 3.

제 1 항 또는 제 2 항에 있어서,

상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 드레인 전극을 형성하는 공정에서는, 사이드 에칭을 실시하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

### 청구항 4.

제 3 항에 있어서,

상기 사이드 에칭에 의하여, 금속막은  $0.5\mu m$  내지  $1.3\mu m$  정도 제거되는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

### 청구항 5.

제 1 항 또는 제 2 항에 있어서,

상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 레지스트 패턴을 형성하는 공정에서는, 하프톤 마스크를 사용하여 사진 제판하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

### 청구항 6.

제 1 항 또는 제 2 항에 있어서,

상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 레지스트 패턴을 형성하는 공정에서는, 복수의 마스크를 사용하여 사진 제판하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

### 청구항 7.

제 1 항 또는 제 2 항에 있어서,

상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 레지스트 패턴을 형성하는 공정에서는, 해당 레지스트 패턴의 단부가 상기 금속막의 단부와 거의 동등해지도록 해당 레지스트를 제거하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

**청구항 8.**

제 1 항 또는 제 2 항에 있어서,

상기 소스 배선, 상기 소스 전극, 상기 드레인 전극이 Cr, Mo, Ti, W, Al 또는 이들 중 하나 이상을 포함하는 금속을 주성분으로 하는 합금임을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

**청구항 9.**

제 1 항 또는 제 2 항에 있어서,

상기 반도체 활성층 해당부 위에서의 레지스트를 제거하는 애싱을 RIE 모드에서 실시하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

**청구항 10.**

제 1 항 또는 제 2 항에 기재된 제조방법을 이용하여 제조된 박막 트랜지스터 어레이 기판.

**청구항 11.**

제 10 항에 기재된 박막 트랜지스터 어레이 기판을 구비하는 액정표시장치.

**명세서**

**발명의 상세한 설명****발명의 목적****발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 박막 트랜지스터 어레이 기판 및 그 제조방법에 관한 것이다. 예를 들면, 액정표시장치에 사용되는 박막 트랜지스터 기판에 관한 것이다.

액정을 사용한 전기광학소자는 디스플레이에 활발히 응용되고 있다. 그 중에서도, 박막 트랜지스터 (이하, TFT 라 함) 를 스위칭 소자로서 사용하는 TFT-LCD 는 휴대성, 저소비 전력, 표시품위면에서 우수하여 폭넓게 이용되고 있다. 보다 광범위한 보급을 위해서는, 더욱 저가격화가 요구되고 있으며, 그 수단의 하나로서 생산성 향상을 위한 TFT 어레이 제조공정 수의 삭감이 검토되어 왔다.

그 중, 사진 제판 공정 즉, 마스크를 삭감하는 시도가 일본 공개특허공보 2000-111958 호에 나타나 있다. 도 2a 에 4 회의 사진 제판 공정에 의하여 제조되는 TFT 어레이 기판의 화소부의 단면도를 나타내고, 이를 이용하여 설명한다.

본 종래기술에서는, 투명기판 위에 100nm 정도의 두께로 도전막을 형성한 후, 제 1 사진 제판 공정에서는, 제 1 마스크를 사용하여 레지스트 패턴을 형성하고, 예칭에 의하여 게이트 배선 (1) 을 형성한다. 다음으로, 게이트 배선 (1) 이 형성된 투명기판 위에 게이트 절연막 (3), 반도체층 (4a) 및 오믹층 (4b) (일본 공개특허공보 2000-111958 호에서는 접촉층이라 기재) 을 각각 150~500nm, 50~150nm, 30~60nm 의 두께로 성막한다. 다음으로, 금속막 (16) 을 150~300nm 의 두께로 성막한다.

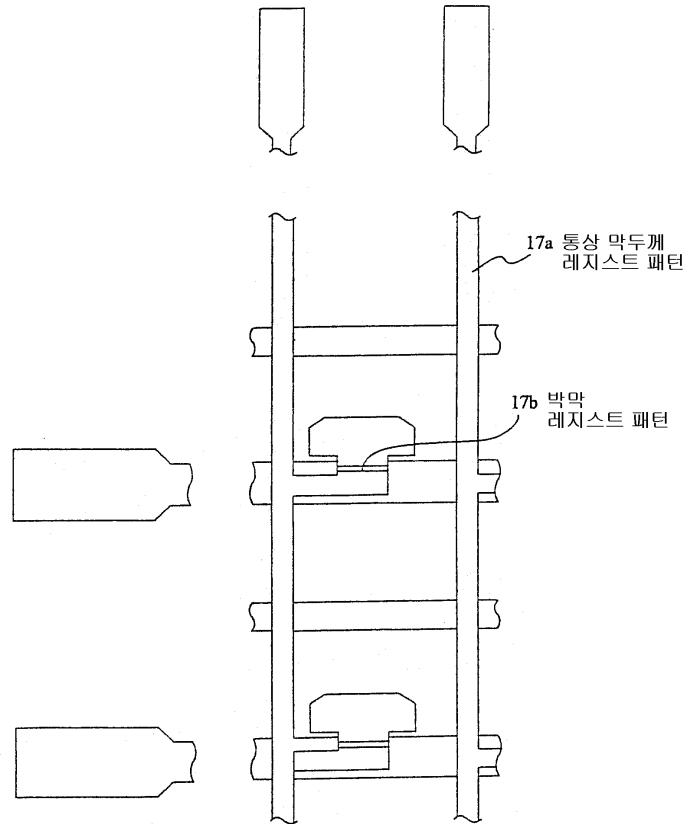

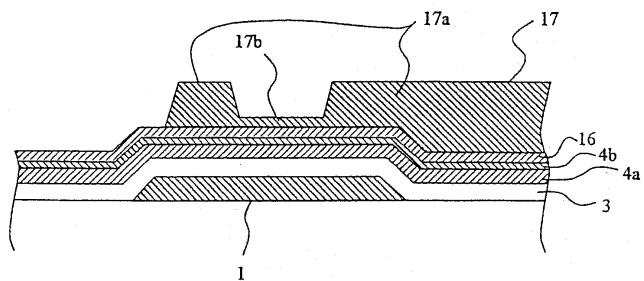

제 2 사진 제판 공정에서는, 제 2 마스크를 사용하여 레지스트 패턴 (17) (일본 공개특허공보 2000-111958 호에서는 감광막이라 기재) 을 소스 전극 (5), 소스 배선 (6) (일본 공개특허공보 2000-111958 호에서는 데이터선이라 기재), 드레인 전극 (7) 위에는 두껍게, 반도체 활성층 (8) 해당부 (일본 공개특허공보 2000-111958 호에서는 채널부라 기재) 에는 얇게

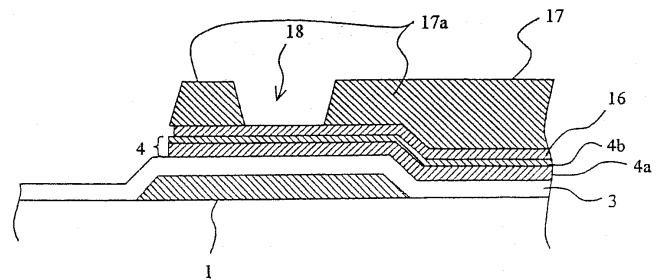

형성한다. 이하, 상기 소스 전극(5), 소스 배선(6) 및 드레인 전극(7) 위의 두꺼운 레지스트 패턴을 통상 막두께 레지스트 패턴(17a)이라 칭하고, 반도체 활성층(8) 해당부의 얇은 레지스트 패턴을 박막 레지스트 패턴(17b)이라 칭한다. 그 후, 금속막을 습식 에칭 등에 의하여 제거한다. 그 후, 박막 레지스트 패턴(17b), 오믹층(4b) 및 오믹층(4b)의 하층인 반도체층(4a)을 건식 에칭에 의하여 동시에 제거한다. 이들 처리에 의하여, 반도체 활성층(8) 해당부에 있어서 금속막(16)이 노출된다. 그리고, 습식 에칭에 의하여 반도체 활성층(8) 해당부의 금속막(16)을 제거하여 하층인 오믹층(4b)을 노출시킨다. 다시 반도체 활성층(8) 해당부의 오믹층(4b)과 반도체층(4a)의 일부를 건식 에칭으로 제거하고, 그 후 레지스트를 박리한다. 다음으로, 층간절연막(9) 인  $\text{SiN}_x$  를 300nm 이상 적층한다. 제 3 사진 제판 공정에서는 제 3 마스크를 사용하여 패터닝하고, 층간절연막(9) 및 게이트 절연막을 에칭한다. 다시 40~50nm 의 도전층을 적층한다. 마지막으로, 제 4 사진 제판 공정에서 제 4 마스크를 사용하여 패터닝하고, 도전막을 에칭하여 TFT를 완성한다. 상기 제조방법에 있어서는, 제 2 마스크에 있어서의 레지스트의 두께를 장소에 따라 변경함으로써, 마스크 매수의 저감을 달성하고 있다.

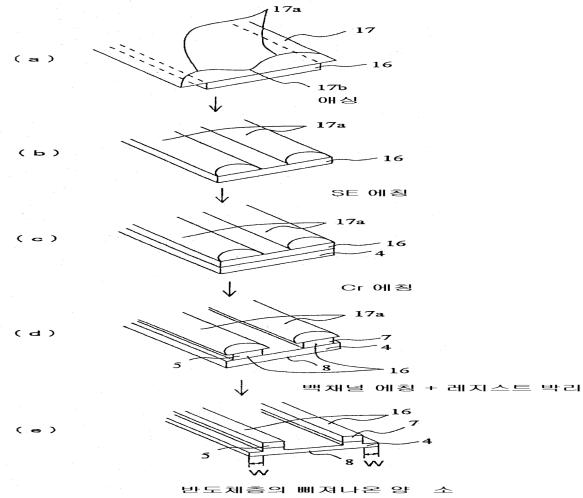

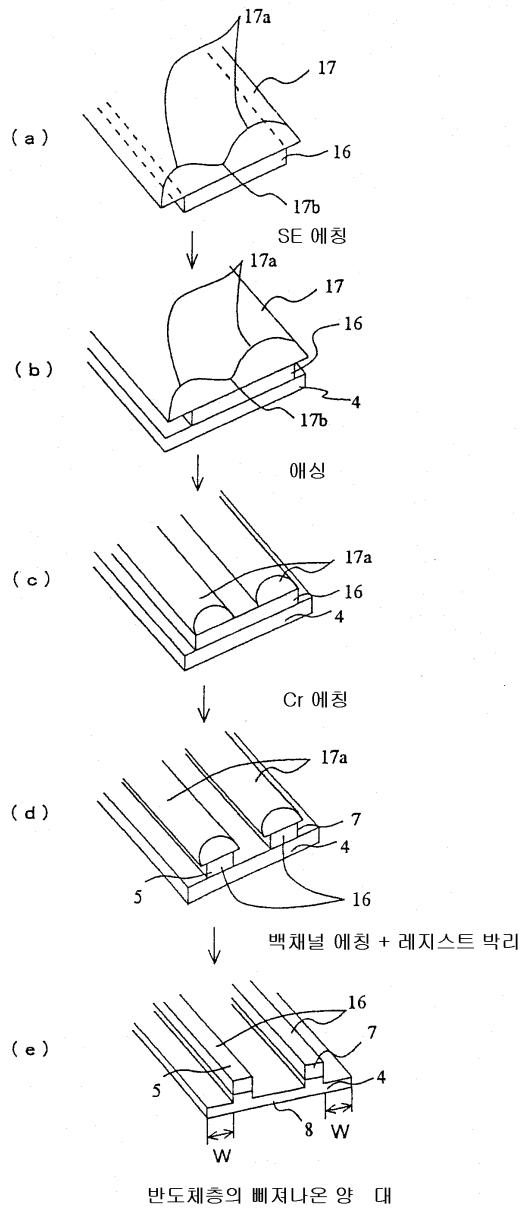

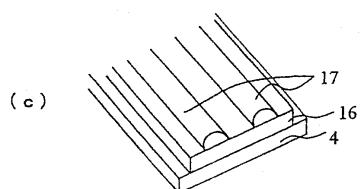

도 16a~16e에 종래기술에 의하여 형성되는 TFT 어레이 기판의 제조과정 중, 제 2 사진 제판 공정에 있어서의 상세한 공정을 나타낸다. 일본 공개특허공보 2000-111958 호에 나타내는 종래기술에서는 박막 레지스트 패턴(17b), 오믹층(4b) 및 오믹층(4b)의 하층인 반도체층(4a)을 건식 에칭에 의하여 동시에 제거하고 있다. 또한, 일본 공개특허공보 2001-339072 호에 나타내는 종래기술에서는 오믹층(4b) 및 반도체층(4a)을 건식 에칭에 의하여 제거한 후, 박막 레지스트 패턴(17b)을 애싱에 의하여 제거하고 있다.

도 16a 는 소스 전극(5), 소스 배선(6), 드레인 전극(7) 위에는 두꺼운 통상 막두께 레지스트 패턴(17a)을, 반도체 활성층(8) 해당부에는 얇은 박막 레지스트 패턴(17b)으로 이루어지는 레지스트 패턴(17)을 형성하고 금속막(16)을 습식 에칭 등에 의하여 제거한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 여기서 금속막(16)은 사이드 에칭에 의하여 레지스트 패턴(17) 단부보다 내측으로 들어간 구조가 된다. 도 16b 는 그 다음 공정인 오믹층(4b) 및 반도체층(4a)을 건식 에칭에 의하여 제거한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 도 16c 는 다시 그 다음 공정인 박막 레지스트 패턴을 애싱에 의하여 제거한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 도 16d 는 반도체 활성층(8) 해당부의 금속막(16)을 제거하여, 하층인 오믹층(4b)을 노출시킨 단계인 TFT 어레이 기판의 구조를 나타내는 도면이며, 도 16e 는 반도체 활성층(8) 해당부의 오믹층(4b)과 반도체층(4a)의 일부를 건식 에칭으로 제거하고, 그 후 레지스트를 박리한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 이 단계에서 소스 전극(5), 드레인 전극(7) 및 반도체 활성층(8)이 노출된다.

### 발명이 이루고자 하는 기술적 과제

전술한 일본 공개특허공보 2000-111958 호의 제 8 실시예에서는 제 2 사진 제판 공정에서의 레지스트 패턴 형성후, 금속막의 에칭을 실시하고, 그 후 채널 상부의 얇은 레지스트, 오믹층 및 반도체층을 동시에 제거하고 있다. 또한, 일본 공개특허공보 2001-339072 호에서는 오믹층 및 반도체층을 에칭에 의하여 제거한 후, 박막 레지스트 패턴을 애싱에 의하여 제거하고 있다. 이러한 종래기술에서는 이하와 같은 문제가 발생한다.

제 2 마스크에서 사용한 레지스트용 감광제는 점성 및 유동성을 가지므로 레지스트 패턴의 단부는 테이퍼각을 갖는 형상이 된다. 금속막의 에칭전에 레지스트와 금속막의 밀착력을 향상시키기 위하여 베이킹을 실시한 경우, 그 경향이 현저해진다. 이로 인하여, 채널 상부의 얇은 레지스트를 제거할 때, 다른 장소의 두꺼운 레지스트 부분도 테이퍼 형상을 가지므로, 레지스트 패턴 단부는 후퇴하여 레지스트 패턴 면적이 감소하게 된다. 그 후퇴의 정도는 레지스트 패턴의 테이퍼 각도가 작을수록 커진다.

한편, 반도체층은 박막 레지스트 패턴을 제거하기 전 또는 동시에 제거하므로, 레지스트 패턴 면적 즉 테이퍼 각도에 그다지 영향을 받지 않는다. 따라서, 박막 레지스트 패턴의 제거후에 있어서 반도체층의 패턴 단부는 레지스트 패턴 단부로부터 빠져나오게 된다. 반도체층과 박막 레지스트 패턴을 동시에 제거하는 경우에도 반도체층의 단부는 테이퍼 형상을 이루지만, 레지스트 패턴 단부로부터 빠져나오는 것은 동일하다. 이 빠져나오는 폭은 레지스트의 두께를 얇게 한 채널 상부의 레지스트의 두께와 패턴 단부의 테이퍼 각도에 따라 결정된다.

그 후, 반도체 활성층 해당부의 금속막을 에칭으로 제거할 때, 금속막의 단부는 사이드 에칭에 의하여 레지스트 단부의 내측에 내포되는 구조가 된다. 따라서, 반도체층은 금속막으로부터 현저히 빠져나온 구조가 된다(예를 들면, 도 16e에 있어서의 반도체층의 빠져나온 양(W)이 큰 구조가 된다).

이러한 구조를 갖는 TFT 트랜지스터 어레이 기판은 빠져나온 반도체층의 광전도 효과에 의하여 광휘도의 변동에 매우 민감한 특성을 보일 가능성이 있다. 그로 인하여, 광조사에 기인하여 TFT 특성이 열화되는 문제점이 발생하였다. 예를 들면, 이 TFT 어레이 기판을 액정표시장치에 사용한 경우, 화질 향상을 위하여 광휘도를 변동시킨 경우, 화질의 안정성에 현저한 악영향을 미치는 경우가 있었다.

본 발명은 이러한 문제점을 해결하기 위하여 이루어진 것으로, 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판 및 그 제조방법 및 이를 이용한 액정표시장치를 제공하는 것을 목적으로 한다.

## 발명의 구성

### 과제를 해결하기 위한 수단

본 발명과 관련된 TFT 어레이 기판의 제조방법은,

절연성 기판 위에 게이트 배선을 형성하는 공정과,

상기 게이트 배선이 형성된 절연성 기판 위에 게이트 절연막, 반도체층과 오믹층 및 금속막을 형성하는 공정과,

사진 제판에 의하여 상기 금속막 위의 레지스트 패턴을, 적어도 후공정에서 상기 오믹층 위에 형성되는 박막 트랜지스터의 소스 배선, 소스 전극, 드레인 전극과 반도체 활성층 해당부가 덮이고, 또한 해당 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 형성하는 공정과,

상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 상기 드레인 전극을 형성하는 공정과,

상기 레지스트를 박막화함으로써 상기 반도체 활성층 해당부 위의 레지스트를 제거하는 공정과,

상기 반도체 활성층 해당부 위의 레지스트를 제거한 후에, 상기 소스 전극, 상기 소스 배선, 상기 드레인 전극 및 상기 반도체 활성층 해당부 이외의 오믹층 및 반도체층을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 금속막을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 상기 오믹층을 에칭에 의하여 제거하는 공정을 구비한 박막 트랜지스터 어레이 기판의 제조방법이다. 이러한 제조방법에 의하여 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판을 제조할 수 있다.

또한, 본 발명과 관련된 TFT 어레이 기판의 제조방법은,

절연성 기판 위에 게이트 배선을 형성하는 공정과,

상기 게이트 배선이 형성된 절연성 기판 위에 게이트 절연막, 반도체층과 오믹층 및 금속막을 형성하는 공정과,

사진 제판에 의하여 상기 금속막 위의 레지스트 패턴을, 적어도 후공정에서 상기 오믹층 위에 형성되는 박막 트랜지스터의 소스 배선, 소스 전극, 드레인 전극과 반도체 활성층 해당부가 덮이고, 또한 해당 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아지도록 형성하는 공정과,

상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 상기 드레인 전극을 형성하는 공정과,

상기 레지스트를 박막화함으로써 상기 반도체 활성층 해당부 위의 레지스트를 제거하는 공정과,

상기 반도체 활성층 해당부 위의 레지스트를 제거한 후에, 상기 소스 전극, 상기 소스 배선, 상기 드레인 전극 및 상기 반도체 활성층 해당부 이외의 오믹층 및 반도체층을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 금속막을 에칭에 의하여 제거하는 공정과,

상기 반도체 활성층 해당부 위의 상기 오믹층을 에칭에 의하여 제거하는 공정과,

충간절연막을 성막하는 공정과,

제 3 사진 제판 및 에칭으로 상기 게이트 절연막 및 충간절연막에 상기 드레인 전극에 도달하는 드레인 전극 컨택트홀, 상기 소스 전극에 도달하는 소스 단자부 컨택트홀 및 게이트 배선에 도달하는 게이트 단자부 컨택트홀을 형성하는 공정과,

도전막을 형성하는 공정과,

제 4 사진 제판 및 에칭으로 상기 드레인 전극 컨택트홀, 상기 소스 단자부 컨택트홀 및 상기 게이트 단자부 컨택트홀을 덮는 화소 전극을 형성하는 공정을 구비한 TFT 어레이 기판의 제조방법이다. 이러한 제조방법에 의하여 4 회의 사진 제판 공정으로 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판을 제조할 수 있다.

전술한 상기 금속막을 에칭하여 상기 소스 배선, 상기 소스 전극 및 상기 드레인 전극을 형성하는 공정에서는, 사이드 에칭 되는 것이 바람직하다. TFT 특성의 열화가 억제된 TFT 어레이 기판을 제조할 수 있다.

또한, 전술한 상기 사이드 에칭에 의하여, 금속막은  $0.5\mu\text{m}$  내지  $1.3\mu\text{m}$  정도 제거하는 것이 바람직하다. 이로써, TFT 특성의 열화가 더욱 억제된 TFT 어레이 기판을 제조할 수 있다.

전술한 상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아진 레지스트 패턴은 하프톤 마스크를 사용하는 사진 제판에 의하여 형성하는 것이 바람직하다. 이로써, 4 회의 사진 제판으로 TFT 어레이 기판을 제조할 수 있다.

또한, 전술한 상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아진 레지스트 패턴은 복수의 마스크를 사용하는 사진 제판에 의하여 형성할 수도 있다. 이로써, 4 회의 사진 제판으로 TFT 어레이 기판을 제조할 수 있다.

전술한 상기 반도체 활성층 해당부 위에서의 막두께가 다른 부분보다 얇아진 레지스트 패턴은 해당 레지스트 패턴의 단부가 상기 금속막의 단부와 거의 동등해지도록 해당 레지스트를 제거하는 것이 바람직하다. 이로써, TFT 특성의 열화가 더욱 억제된 TFT 어레이 기판을 제조할 수 있다.

상기 소스 배선, 상기 소스 전극, 상기 드레인 전극은 Cr, Mo, Ti, W, Al 또는 이를 중 적어도 하나를 포함하는 합금을 이용하여 형성할 수 있다.

상기 반도체 활성층 해당부 위에서의 레지스트를 제거하는 애싱을 RIE 모드에서 실시하는 것이 바람직하다. 이로써, 더욱 생산성을 향상시킬 수 있다.

전술한 TFT 어레이 기판의 제조방법에 의하여 TFT 특성의 열화가 억제된 TFT 어레이 기판을 제공할 수 있다.

전술한 TFT 어레이 기판은 액정표시장치에 사용되는 것이 바람직하다. 이로써, 광휘도의 변동에 대하여 화질이 안정된 액정표시장치를 제공할 수 있다.

### 발명의 실시형태

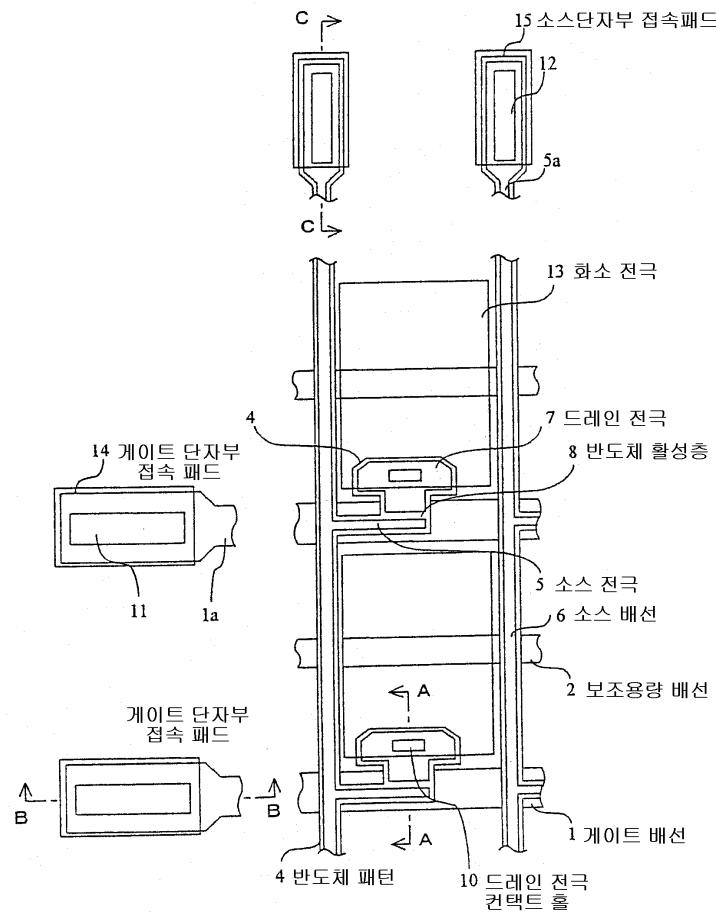

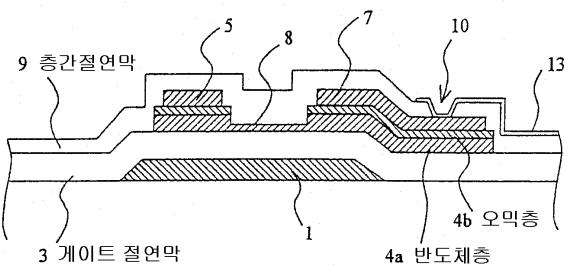

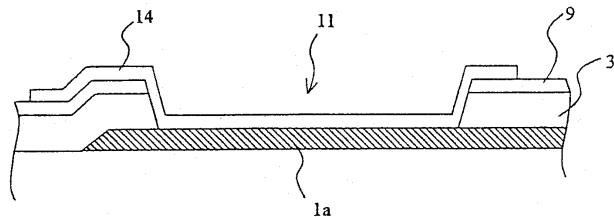

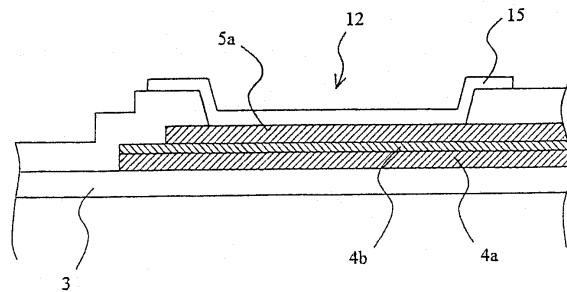

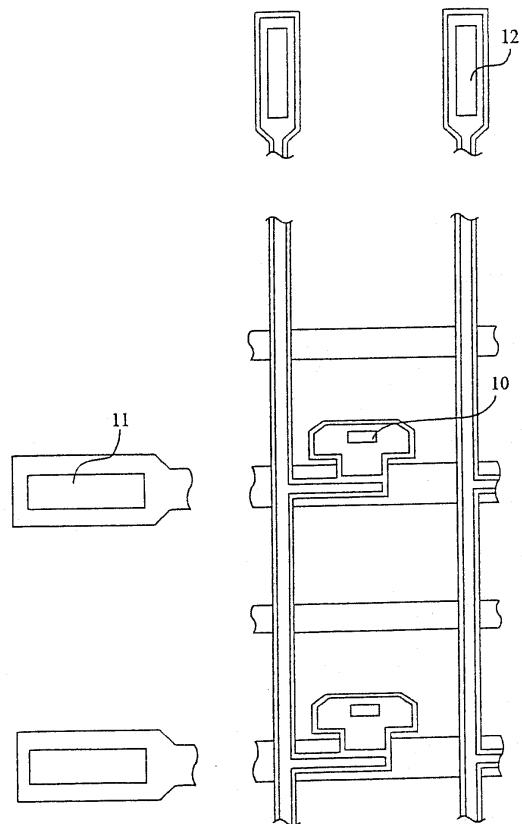

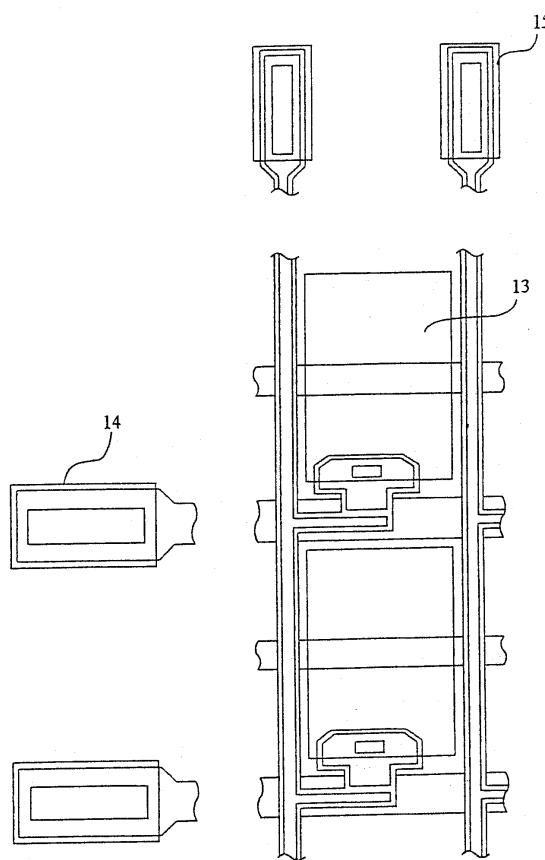

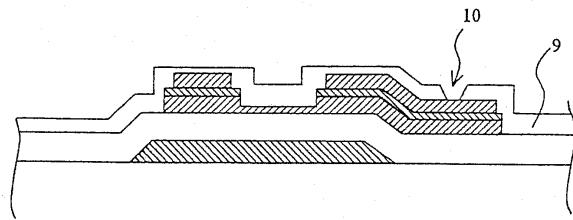

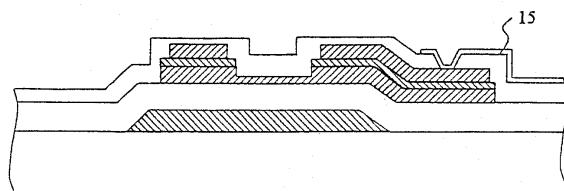

도 1, 도 2 는 본 발명의 실시형태에 의하여 제조된 TFT 어레이 기판을 나타내는 도면으로, 도 1 은 그 평면도, 도 2a 는 도 1 에 있어서의 A-A 에서의 단면도, 도 2b 는 도 1 에 있어서의 B-B 에서의 단면도, 도 2c 는 도 1 에 있어서의 C-C 에서의 단면도이다. 도 1, 2 에 있어서, 1 은 게이트 배선, 1a 는 게이트 단자부 금속패드, 2 는 보조용량 배선, 3 은 게이트 절연막, 4 는 반도체 패턴, 4a 는 반도체층 (반도체 능동막), 4b 는 오믹층 (오믹 컨택트막), 5 는 소스 전극, 5a 는 소스 단자부 금속패드, 6 은 소스 배선, 7 은 드레인 전극, 8 은 박막 트랜지스터의 반도체 활성층, 9 는 충간절연막, 10 은 드레인 전극 컨택트홀, 11 은 게이트 단자부 컨택트홀, 12 는 소스 단자부 컨택트홀, 13 은 화소 전극, 14 는 게이트 단자부 접속패드, 15 는 소스 단자부 접속패드이다.

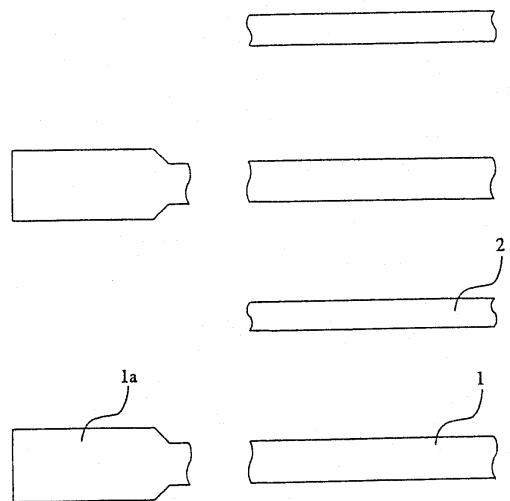

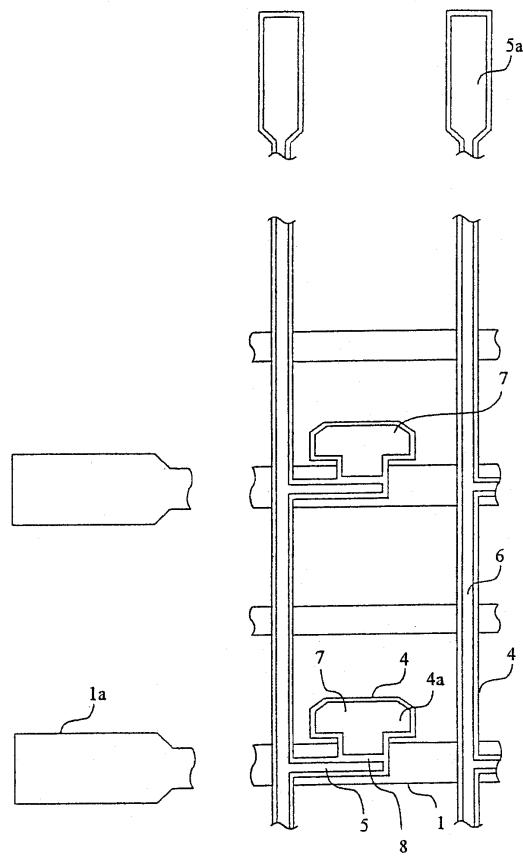

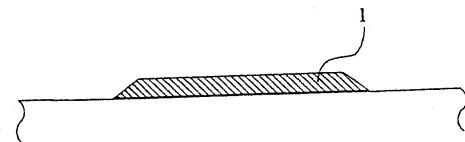

다음으로 구체적인 제조방법에 대하여 설명한다. 도 3 에서 도 7 까지가 각 공정에서의 평면도이며, 도 8 에서 도 14 까지가 각 공정에서의 도 1 에 있어서의 A-A 단면에 상당하는 지점의 단면을 나타내고 있다. 먼저, 투명한 절연성 기판 위에  $400\text{nm}$  정도의 두께로 Cr, Mo, Ti, W, Al 등의 도전막이 형성된다. 다음으로 제 1 사진 제판 공정에서 도전막을 패터닝하

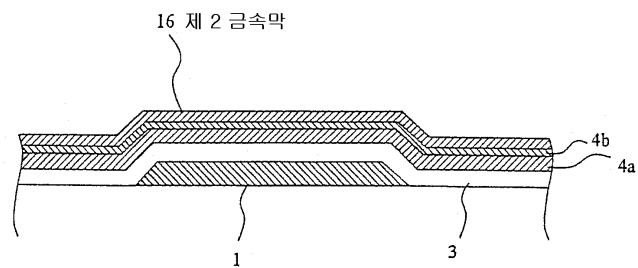

여, 도 3, 도 8 과 같이 게이트 배선 (1), 게이트 단자부 금속패드 (1a), 보조용량 배선 (2)을 형성한다. 이 때, 도전막이 Cr인 경우에는 예를 들면,  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  액을 이용하여 습식 에칭 처리된다. 다음으로 도 9에 나타내는 바와 같이, 도전막이 패터닝된 절연성 기판 위에 게이트 절연막 (3)으로서  $\text{SiN}_x$  막, 반도체 능동막 (4a)으로서 a-Si막, 오믹 컨택트막 (4b)으로서  $n^+ \text{a-Si}$  막, 금속막 (16)으로서 Cr을 각각 400nm, 150nm, 30nm, 400nm 정도의 막두께로 적층한다.  $\text{SiN}_x$ , a-Si,  $n^+ \text{a-Si}$  막은 플라스마 CVD 장치를 사용하여 형성한다. 오믹층 성막시에는  $\text{PH}_3$ 를 도프하여  $n^+ \text{a-Si}$ 를 형성한다. Cr 성막에 대해서는 DC 마그네트론형 스퍼터 장치를 사용하여 성막한다.

다음으로 제 2 사진 제판 공정에서 도 4에 나타내는 바와 같이 소스 전극 (5), 소스 단자부 금속패드 (5a), 소스 배선 (6), 드레인 전극 (7)을 형성하기 위한 통상 막두께 레지스트 패턴 (17a) 및 박막 트랜지스터의 반도체 활성층 (8)을 형성하기 위한 박막 레지스트 패턴 (17b)을 형성한다. 여기서 레지스트는 노볼락 수지계의 포지티브형 레지스트를 사용하고, 레지스트 도포는 스판코터에 의하여  $1.5\mu\text{m}$ 로 한다. 레지스트 도포후에는  $120^\circ\text{C}$ 에서 90초 프리베이크를 실시하고, 그 후 통상 막두께 레지스트 패턴 (17a) 및 박막 레지스트 패턴 (17b)이 노광되지 않은 마스크 패턴으로 1000msec 노광을 실시하고, 그 후 통상 막두께 레지스트 패턴 (17a)이외의 부분을 노광할 수 있는 마스크 패턴을 사용하여 400msec 추가 노광을 실시하였다. 이 2 단계의 노광을 실시함으로써, 통상 막두께 레지스트 패턴 (17a)과 박막 레지스트 패턴 (17b)의 막두께를 다르게 하고 있다. 노광기는 스텝퍼 또는 미러 프로젝션 타입의 노광기이고, 광원에는 고압 수은램프의 g 선, h 선을 이용하였다. 이어서, 유기 알칼리계 현상액을 이용하여 현상한 후,  $100^\circ\text{C}$  내지  $120^\circ\text{C}$ 에서 포스트베이크를 180초 실시하고, 레지스트 중의 용매를 휘발시키는 동시에 레지스트와 Cr의 밀착력을 높인다. 이들 프로세스에 의하여, TFT 부의 레지스트 형상은 도 10에 나타내는 바와 같이 다른 막두께를 갖는 형상이 된다. 여기서 통상 막두께 레지스트 패턴 (17a)의 레지스트 막두께는  $1.4\mu\text{m}$  정도, 박막 레지스트 패턴 (17b)의 레지스트 막두께는  $0.4\mu\text{m}$  정도가 된다.

그 후, 다시  $120^\circ\text{C}$  내지  $130^\circ\text{C}$ 에서 오븐 베이크를 실시하여 더욱 레지스트-Cr 간의 밀착력을 높인다. 이 때, 베이크 온도가 너무 높은 경우에는 레지스트 단면이 늘어지므로 주의를 요한다. 그 후, 금속막 (16)의 에칭을 실시하여, 소스 전극 (5), 소스 배선 (6), 소스 단자부 금속패드 (5a), 드레인 전극 (7)에 해당하는 이외의 부분을 제거한다. 금속막 (16)이 Cr 막인 경우에는, 예를 들면  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  액을 이용하여 습식 에칭 처리된다. 이 때, 사이드 에칭에 의하여 금속막 (16)은 레지스트 패턴 (17) 보다 내측으로 들어간 형상이 된다.

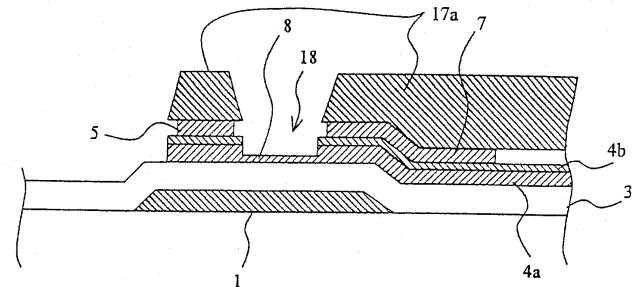

그 후, 산소 플라스마를 이용한 애싱에 의하여 박막 레지스트 패턴 (17b)을 제거하여, 박막 레지스트 패턴 (17b) 하부의 금속막 (16)이 노출되도록 한다. 본 실시형태에서는, 애싱은 압력이 40Pa에서 60초 실시하였다. 또한, 애싱할 때에는 RIE 모드 쪽이 PE 모드에 비하여, 도 11의 18에 나타내는 레지스트 개구부의 크기를 제어하기 쉽다. 이것은 RIE 모드 쪽이 이방성, 균일성 모두 양호하기 때문이다. 그 밖에도, RIE 모드에는 PE 모드에 비하여, 레지스트의 제거 속도를 빠르게 할 수 있다는 이점이 있다. 이 애싱 공정에서는 레지스트 패턴 (17)의 단부와 금속막 (16) 단부는 거의 동등하게 하는 것이 바람직하다. 다음으로, 통상 막두께 레지스트 패턴 (17a) 및 박막 레지스트 패턴 (17b)이외의 부분인 오믹층 (4b) 및 반도체층 (4a)을 건식 에칭에 의하여 제거하고, 반도체 패턴 (4)을 형성한다. 이 에칭을 SE 에칭이라 한다. 이러한 제조공정에 의하여 도 11에 나타내는 구조가 된다.

다시  $130^\circ\text{C}$  내지  $140^\circ\text{C}$ 에서 오븐 베이크를 실시한 후, 그 노출된 반도체 활성층 (8) 해당부의 금속막 (16)을 에칭에 의하여 제거한다. 오버 에칭의 양은 50% 정도가 바람직하다. 그 후, 레지스트 패턴 개구부 (18)의 오믹층 (4b) 및 반도체층 (4a)의 일부를 에칭에 의하여 제거한다. 본 실시형태에서는  $\text{HCl} + \text{SF}_6 + \text{He}$  가스를 이용한 에칭에 의하여 오믹층 (4b) 및 반도체층 (4a)의 일부를 합계 100nm 정도 제거하였다. 이 에칭을 백채널 에칭이라 한다. 이러한 제조공정에 의하여 도 12에 나타내는 형상이 된다. 그 후, 레지스트를 박리하면 반도체 패턴 (4), 소스 전극 (5), 소스 배선 (6), 드레인 전극 (7), 소스 단자부 금속패드 (5a) 및 반도체 활성층 (8)이 노출되어, 도 5에 나타내는 구조가 된다.

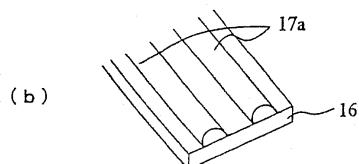

도 15a~15e에 제 2 사진 제판 공정후에 있어서의 제조과정의 상세한 공정을 나타낸다. 도 15a는 소스 전극 (5), 소스 배선 (6), 드레인 전극 (7) 위에는 두꺼운 통상 막두께 레지스트 패턴 (17a)을, 반도체 활성층 (8) 해당부에는 얇은 박막 레지스트 패턴 (17b)을 형성한 후, 금속막 (16)을 에칭에 의하여 제거한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 여기서, 금속막 (16)은 사이드 에칭에 의하여 레지스트 단부보다 내측으로 들어간 형상이 된다. 도 15b는 그 다음의 박막 레지스트 패턴 (17b)을 애싱에 의하여 제거한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 여기서, 애싱에 의하여 반도체 활성층 (8) 해당부 위의 레지스트가 제거되는 동시에, 레지스트 패턴 단부에서 가로방향으로도 삭제되어 레지스트 패턴 면적이 감소한다. 도 15c는 그 다음의 SE 에칭을 실시한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. SE 에칭에 의하여 반도체 패턴 (4)과 금속막 (16)의 단부가 거의 동등해진다. 도 15d는 그 다음의 반도체 활성층 해당부의 금속막 (16)에 침을 실시한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 이 에칭에 의하여 소스 전극 (5), 드레인 전극 (7)이 형성된다. 여기서 사이드 에칭에 의하여 금속막 (16)은 통상 막두께 레지스트 패턴 (17a) 보다 내

측으로 들어간 형상이 된다. 도 15e 는 그 다음의 백채널 에칭과 레지스트 박리를 실시한 단계인 TFT 어레이 기판의 구조를 나타내는 도면이다. 레지스트 박리에 의하여, 소스 전극 (5) 및 드레인 전극 (7) 이 노출되는 동시에, 반도체 패턴 (4) 의 일부가 에칭되어 반도체 활성층 (8) 이 노출된다.

본 실시형태에서는 반도체 패턴 (4) 보다 박막 레지스트 패턴이 먼저 제거되므로, 종래기술보다 에칭되는 반도체 패턴 (4) 의 영역이 넓어져, 도 15e 에 나타내는 빼져나오는 양 (W) 이 적어진다. 이 제조방법에 의하여, 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판을 제조할 수 있다.

이 후, 다시 PCVD 장치를 사용하여 충간절연막 (9) 인  $\text{SiN}_x$  를 300nm 형성하고, 이 충간절연막 (9) 을 제 3 사진 제판 공정에서 패터닝한다. 그리고, 충간절연막 (9) 및 게이트 절연막 (3) 을 에칭함으로써, 도 2a, 도 6 및 도 13 에 나타내는 드레인 전극 (7) 으로 통하는 드레인 컨택트홀 (10) 을 형성한다. 또한, 도 2b 및 도 6 에 나타내는 게이트 단자부 금속패드 (1a) 로 통하는 게이트 단자부 컨택트홀 (11) 도 형성한다. 또한, 도 2c 및 도 6 에 소스 단자부 금속패드 (5a) 로 통하는 소스 단자부 컨택트홀 (12) 도 형성한다. 본 실시형태에서는,  $\text{CF}_4 + \text{O}_2$  를 이용한 건식 에칭으로 충간절연막 (9) 및 게이트 절연막 (3) 인  $\text{SiN}_x$  를 제거하였다. 또한, 투명도전막 (19) 을 형성하고, 드레인 전극 컨택트홀 (10), 게이트 단자부 컨택트홀 (11) 및 소스 단자부 컨택트홀 (12) 에 매몰하여, 각각 드레인 전극 (7), 게이트 단자부 금속패드 (1a), 소스 단자부 금속패드 (5a) 에 접촉된다. 본 실시형태에서는, 투명도전막 (19) 을 두께가 약 100nm 인 ITO 막으로 하고, DC 마그네트론형 스팍터장치를 사용하여 성막하였다. 다음으로, 제 4 사진 제판 공정에서 투명도전막 (19) 을 패터닝한다. 그리고 에칭에 의하여 투명 화소 전극 (13), 게이트 단자부 접속패드 (14) 및 소스 단자부 접속패드 (15) 를 형성한다. 본 실시형태에서는  $\text{HCl} + \text{HNO}_3 + \text{H}_2\text{O}$  액을 이용한 습식 에칭에 의하여 ITO 막을 제거하였다. 이렇게 하여 도 7 에 나타내는 바와 같은 구조가 된다.

전술한 제조방법에서는 TFT 어레이 기판을 4 회의 사진 제판 공정으로 제조할 수 있다. 또한, 이렇게 제조된 구조에서는 소스 배선 (6) 하에 반도체층 (4a) 과의 단차가 존재하지 않으므로, 소스 배선 (6) 의 단선이 잘 발생하지 않는다. 또한, 소스 전극 (5), 드레인 전극 (7) 의 패턴이 반도체층 (4a) 의 내측에 내포되어 교차되지 않으므로, TFT 의 리크 전류도 낮게 억제된다. 또한, 반도체층 (4a) 이 금속막 (16) 으로부터 빼져나와 있는 양 (W) 이 적기 때문에 광조사에 기인하는 TFT 특성의 열화를 방지할 수 있다. 또한, 금속막 (16) 을 Cr 로 함으로써, 투명도전막 (19) 의 에칭액에 의한 소스 배선 등의 부식을 방지할 수 있다. 이로써 수율을 향상시킬 수 있다.

전술한 제 2 사진 제판 공정에서 막두께가 다른 통상 막두께 레지스트 패턴 및 박막 레지스트 패턴을 형성하는 공정에서는 하프톤 마스크를 사용하여 사진 제판할 수 있다. 예를 들면, 네거티브형 레지스트를 사용한 경우, 통상 막두께 레지스트 패턴 (17a) 에 해당하는 부분에 투광부를, 박막 레지스트 패턴 (17b) 에 해당하는 부분에는 반투과부를, 그 이외의 부분에는 차광부를 구비하는 포토마스크 (하프톤 마스크라 함) 를 사용하여 노광함으로써 사진 제판할 수 있다. 또한, 포지티브형 레지스트를 사용한 경우에는, 통상 막두께 레지스트 패턴 (17a) 에 해당하는 부분에 차광부를, 박막 레지스트 패턴 (17b) 에 해당하는 부분에는 반투과부를, 그 이외의 부분에는 투광부를 구비하는 하프톤 마스크를 사용하여 노광한다. 이로써 막두께가 다른 레지스트 패턴을 1 회의 사진 제판으로 형성할 수 있으며, 4 회의 사진 제판 공정으로 TFT 어레이 기판을 제조할 수 있다.

또한, 제 2 사진 제판 공정에서 막두께가 다른 통상 막두께 레지스트 패턴 (17a) 및 박막 레지스트 패턴 (17b) 을 형성하는 공정에서는 2 장의 마스크를 사용하여 사진 제판할 수 있다. 예를 들면, 네거티브형 레지스트를 사용한 경우, 통상 막두께 레지스트 패턴 (17a) 에 해당하는 부분에 투광부를, 박막 레지스트 패턴 (17b) 에 해당하는 부분을 포함한 그 이외의 부분에는 차광부를 갖는 제 1 포토마스크와, 통상 막두께 레지스트 패턴 (17a) 및 박막 레지스트 패턴 (17b) 에 해당하는 부분에 투광부, 그 이외의 부분에는 차광부를 구비하는 제 2 포토마스크의 2 장의 마스크를 사용하여 노광함으로써 사진 제판할 수 있다. 또한, 포지티브형 레지스트를 사용한 경우, 통상 막두께 레지스트 패턴 (17a) 에 해당하는 부분에 차광부를, 박막 레지스트 패턴 (17b) 에 해당하는 부분을 포함한 그 이외의 부분에는 투광부를 구비하는 제 1 포토마스크와, 통상 막두께 레지스트 패턴 (17a) 및 박막 레지스트 패턴 (17b) 에 해당하는 부분에 차광부, 그 이외의 부분에는 투광부를 구비하는 제 2 포토마스크의 2 장의 마스크를 사용하여 노광한다. 이로써, 막두께가 다른 레지스트 패턴을 1 회의 사진 제판으로 형성할 수 있고, 4 회의 사진 제판 공정으로 TFT 어레이 기판을 제조할 수 있다.

전술한 금속막 (16) 을 에칭하여 소스 전극 (5), 소스 배선 (6), 드레인 전극 (7) 및 반도체 활성층 (8) 해당부 이외를 에칭하는 공정에서는 사이드 에칭되는 것이 바람직하다. 즉, 도 15a 와 같이 금속막 (16) 이 레지스트 패턴 (17) 단부의 내측으로 들어가는 구조가 된다. 이로써 소스 배선 (6) 하에 반도체층 (4a) 과의 단차가 존재하지 않으므로, 소스 배선 (6) 의 단선이 잘 발생하지 않게 된다. 또한, 소스 전극 (5), 드레인 전극 (7) 의 패턴이 반도체 패턴 (4) 의 내측에 내포되어 교차되

지 않으므로, TFT의 리크 전류도 낮게 억제된다. 또한, 사이드 에칭량은 레지스트 패턴 (17) 단부로부터 금속막 (16) 단부의 거리가  $0.5\mu\text{m} \sim 1.3\mu\text{m}$ 인 것이 바람직하다. 이 구조에서는 빠져나오는 양 (W)이 적으므로, TFT 특성이 더욱 양호한 TFT 어레이 기판을 제조할 수 있다.

또한, 전술한 박막 레지스트 패턴 (17b)을 애싱에 의하여 제거하는 공정에서는, 통상 막두께 레지스트 패턴 (17a)의 단부가 사이드 에칭되어 내측으로 들어간 금속막 (16) 단부와 거의 동등해지도록 형성되는 것이 바람직하다. 이로써, 반도체층이 빠져나오는 양 (W)이 적어져 TFT 특성이 더욱 양호한 TFT 어레이 기판을 제조할 수 있다.

본 실시형태에서는 금속막에 Cr을 사용하였는데, Al, Ti, Mo, W, Ta 또는 이들 중 적어도 하나를 포함하는 합금이어도 된다. 또한, 금속막이 이들 금속과 그 금속의 질화막과의 다층구조, 예를 들면 AlN/Al/AlN과 같은 3층 구조로 되어 있어도 된다. 이 구조로 함으로써, 소스 전극 (5), 소스 배선 (6) 및 드레인 전극 (7)의 형성과 반도체 활성층 (8)의 형성이 각각 1회의 에칭으로 가능하며, 합계 2회의 에칭 공정으로 금속막 (16)의 에칭이 가능하다. 이로써 제조공정을 간략화할 수 있어 생산성을 향상시킬 수 있다. 나아가서는, 이 중 2종류 이상의 금속으로 다층구조로 되어 있어도 된다. 예를 들면, Al/Mo와 같은 2층 구조나 Cr/Al/Cr과 같은 3층 구조로 되어 있어도 된다. 또한, 애싱시에 산소 플라스마를 사용하는 것으로 되어 있는데,  $\text{CF}_4$ 나  $\text{SF}_6$  등의 불소를 포함한 가스를 산소가스에 첨가해도 된다. 이 경우, 애싱시의 레지스트 제거속도를 빠르게 할 수 있어, 생산성이 향상된다는 이점을 갖는다.

본 실시형태 및 종래기술에 의한 구체적인 반도체층 (4a)은 빠져나오는 양을 표 1에 나타낸다. Case 1은 본 실시형태에서 소스 전극 (5), 소스 배선 (6), 드레인 전극 (7) 및 반도체 활성층 (8) 해당부 이외를 에칭하는 단계(도 15a의 단계)에서의 사이드 에칭량을 200nm로 하였다. Case 2는 본 실시형태에서 오버 에칭시켜, 동일한 단계(도 15a의 단계)에서의 금속막 (16)의 사이드 에칭량을 1000nm로 하였다. Case 3은 종래기술에서 동일한 단계(도 16a의 단계)에서의 금속막 (16)의 사이드 에칭량을 200nm로 하였다. 여기서 금속막 (16)을 Cr, 막두께 200nm로 하였다. 또한, Cr을 에칭하여 반도체 활성층 (8)을 형성하는 단계(도 15d 또는 도 16d의 단계)에서의 사이드 에칭량은 200nm, 애싱에 의한 레지스트 패턴 (17)의 가로방향의 후퇴량은 1000nm, 수직방향 제거량은 800nm였다.

**[표 1]**

**빠져나오는 양 (W)**

|                                 | 빠져나오는 양 (W) |

|---------------------------------|-------------|

| Case 1 본 실시형태<br>사이드 에칭량 200nm  | 1000nm      |

| Case 2 본 실시형태<br>사이드 에칭량 1000nm | 200nm       |

| Case 3 종래기술<br>사이드 에칭량 200nm    | 1200nm      |

Case 1에서는 도 15a의 단계에서 Cr의 사이드 에칭량이 200nm이다. 다음의 애싱으로 가로방향으로 레지스트 패턴 (17)이 1000nm 후퇴하므로, 도 17b와 같이 Cr의 단부는 레지스트 패턴의 단부의 800nm 외측으로 빠져나와 있다. 그 후, Se에칭이 있어, Cr막과 반도체 패턴 (4)의 단부는 거의 동등해진다. 그 다음으로 반도체 활성층 (8) 해당부의 Cr의 에칭이 있어, Cr의 가로방향의 후퇴량은 레지스트 패턴 (17)으로부터 빠져나와 있는 800nm와 사이드 에칭에 의한 200nm로 합계 1000nm가 된다. 이 빠져나와 있는 부분은 상부에 레지스트가 있으므로 백채널 에칭으로는 에칭되지 않는다. 따라서, 이 빠져나오는 양 1000nm가 반도체층 (4a)의 빠져나오는 양 (W)이 된다.

Case 2에서는 도 15a의 단계에서 Cr의 사이드 에칭량이 1000nm이다. 다음의 애싱으로 가로방향으로 레지스트 패턴 (17)이 1000nm 후퇴하므로, 도 15b와 같이 Cr의 단부와 레지스트 패턴의 단부는 거의 동등해진다. 그 다음으로 반도체 활성층 (8) 해당부의 Cr의 에칭이 있어, 이 사이드 에칭량 200nm가 반도체층 (4a)의 빠져나오는 양 (W)이 된다. 매우 양호한 결과가 얻어진다.

Case 3에서는 도 16a의 단계에서 Cr에칭량이 200nm이다. 다음의 도 16b의 Se에칭으로 반도체 패턴 (4)이 레지스트 패턴 (17) 단부와 동등해진다. 다음으로 애싱을 실시하므로 레지스트 패턴 (17) 단부는 1000nm 가로방향으로 제거되어,

도 18c 와 같이 Cr 단부로부터 800nm, 반도체 패턴 (4a) 으로부터 1000nm 내측으로 들어가 있다. 그 후, 반도체 활성층 (8) 해당부의 Cr 의 에칭이 있어, 다시 Cr 이 200nm 사이드 에칭되므로, 빠져나오는 양 (W) 의 합계는  $1000 + 200 = 1200\text{nm}$  가 된다.

본 실시형태의 표 1 에서 나타낸 조건은 대표적인 조건으로 Cr 의 막두께, 사이드 에칭량, 에칭 조건, 레지스트 막두께, 레지스트의 테이퍼 각도, 애칭 조건 등의 조건이 변경되어도, 본 발명의 효과를 얻을 수 있다. 또한, 레지스트 패턴 (17) 의 가로방향의 삭제량과 반도체 활성층 (8) 을 에칭할 때, 금속막 (16) 의 사이드 에칭량을 조정하여, 금속막 (16) 단부와 레지스트 패턴 (17) 단부를 거의 동등하게 함으로써, 반도체층 (4a) 의 빠져나오는 양 (W) 을 적게 할 수 있어, TFT 특성의 열화가 억제된 TFT 어레이 기판을 제조할 수 있다.

### 발명의 효과

본 발명에 의하면, 광조사에 기인하는 TFT 특성의 열화가 억제된 TFT 어레이 기판 및 그 제조방법 및 이를 이용한 액정표시장치를 제공할 수 있다.

### 도면의 간단한 설명

도 1 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 평면도.

도 2a 는 도 1 의 A-A 단면도.

도 2b 는 도 1 의 B-B 단면도.

도 2c 는 도 1 의 C-C 단면도.

도 3 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에서의 평면도.

도 4 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에서의 평면도.

도 5 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에서의 평면도.

도 6 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에서의 평면도.

도 7 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에서의 평면도.

도 8 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 9 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 10 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 11 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 12 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 13 은 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 14 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 도 1 의 A-A 단면도.

도 15 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정을 설명하는 공정도(a~e).

도 16 은 종래기술에 의한 박막 트랜지스터 어레이 기판의 제조과정을 설명하는 공정도(a~e).

도 17 는 본 발명과 관련된 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 TFT 부의 확대도(b).

도 18 는 종래기술에 의한 박막 트랜지스터 어레이 기판의 제조과정에 있어서의 TFT 부의 확대도(c).

※ 도면의 주요부분에 대한 부호의 설명

1 : 게이트 배선

1a : 게이트 단자부 금속패드 2 : 보조용량 배선

3 : 게이트 절연막 4 : 반도체 패턴

4a : 반도체층 4b : 오믹층

5 : 소스 전극 5a : 소스 단자부 금속패드

6 : 소스 배선 7 : 드레인 전극

8 : 반도체 활성층 9 : 층간절연막

10 : 드레인 전극 컨택트홀 11 : 게이트 단자부 컨택트홀

12 : 소스 단자부 컨택트홀 13 : 화소 전극

14 : 게이트 단자부 접속패드 15 : 소스 단자부 접속패드

16 : 금속막 17 : 레지스트 패턴

17a : 통상 막두께 레지스트 패턴 17b : 박막 레지스트 패턴

18 : 레지스트 패턴 개구부 19 : 투명도전막

도면

도면1

도면2a

도면2b

도면2c

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

## 도면15

도면16

도면17

도면18

|               |                                                                                                              |         |            |

|---------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 薄膜晶体管阵列，其制造方法以及使用其的液晶显示装置                                                                                    |         |            |

| 公开(公告)号       | <a href="#">KR100699208B1</a>                                                                                | 公开(公告)日 | 2007-03-27 |

| 申请号           | KR1020030016891                                                                                              | 申请日     | 2003-03-18 |

| 申请(专利权)人(译)   | 提升者显示的激光炮的鼻子                                                                                                 |         |            |

| 当前申请(专利权)人(译) | 提升者显示的激光炮的鼻子                                                                                                 |         |            |

| [标]发明人        | MORITA HIROMASA<br>모리따히로마사<br>NAKASHIMA KEN<br>나까시마겐                                                         |         |            |

| 发明人           | 모리따히로마사<br>나까시마겐                                                                                             |         |            |

| IPC分类号        | G02F1/136 G02F1/1368 H01L21/28 H01L21/3213 H01L21/336 H01L21/77 H01L21/84 H01L27/12<br>H01L29/417 H01L29/786 |         |            |

| CPC分类号        | H01L27/1288 H01L27/1214 Y10S438/945                                                                          |         |            |

| 代理人(译)        | 韩国专利公司                                                                                                       |         |            |

| 优先权           | 2002099990 2002-04-02 JP                                                                                     |         |            |

| 其他公开文献        | KR1020030079683A                                                                                             |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                                    |         |            |

### 摘要(译)

(对象) 本发明的目的是提供一种TFT阵列基板及其制造方法和使用该TFT阵列基板的液晶显示器，该TFT阵列基板中抑制了由光照射引起的TFT特性的劣化。(用于解决问题的手段) 基板上的栅极绝缘层(3)，其与本发明相关的制造阵列基板的TFT方法形成有栅极布线(1)，以及半导体层(4a)，欧姆层(4b)和金属层(16)可以参考制造阵列基板的TFT方法，该阵列基板配备有形成工艺的工艺，形成以便减薄和源极布线(6)，以及源电极(5)通过形成工艺，在金属层(16)上方的抗蚀剂图案(17)的适当部分处，蚀刻金属层(7)的金属层(16)被蚀刻而不是具有不同膜厚的部分。和光机械工艺，在去除半导体有源层(8)靶上方的抗蚀剂之后去除欧姆层(4b)和半导体层(4a)的过程，去除金属层(16)的过程，以及该过程去除欧姆层(4b)。阵列的薄膜晶体管。