(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2010년03월05일

(11) 등록번호 10-0945442

(24) 등록일자 2010년02월25일

(51) Int. Cl.

G02F 1/1335 (2006.01)

(21) 출원번호 10-2003-0012615

(22) 출원일자 2003년02월28일

심사청구일자 2008년01월23일

(65) 공개번호 10-2004-0077161

(43) 공개일자 2004년09월04일

(56) 선행기술조사문현

KR1020010087657 A\*

KR1019990080631 A

JP09146124 A

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

김옹권

경기도군포시산본동1145세종아파트640-1204

김세준

서울특별시용산구동빙고동32-15

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 31 항

심사관 : 김효우

(54) 씨오티 구조 반투과형 액정표시장치

### (57) 요 약

본 발명에 따른 COT 구조 반투과형 액정표시장치에 의하면, 첫째 별도의 공정추가없이 박막트랜지스터를 이루는 전극 물질과 동일 공정에서 반사판을 형성하기 때문에, 별도의 반사판 제조 공정을 생략할 수 있고, 둘째 박막트랜지스터의 제조 공정에서, 반사판의 벼파 패턴을 동시에 형성함에 따라, 반사부 컬러필터와 투과부 컬러필터 간의 색재현율 차이를 최소화함에 따라, 화질 특성을 향상시킬 수 있으며, 셋째 상기 반사판의 디자인을 다양하게 변경할 수 있어, 반사부와 투과부의 면적비를 원하는 비율로 조절하는 것이 용이하다.

### 대 표 도 - 도9

## 특허청구의 범위

### 청구항 1

기판 상에 화면을 구현하는 최소 단위인 화소 영역별로 형성되며, 게이트 전극, 반도체층, 소스 전극, 드레인 전극으로 이루어진 박막트랜지스터와;

상기 화소 영역 내에서, 상기 기판 상에 박막트랜지스터의 전극물질과 동일 공정에서 동일 물질로 이루어진 반사판과;

상기 박막트랜지스터를 덮는 위치에 형성된 블랙매트릭스와;

상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와;

상기 컬러필터 상부에서, 상기 드레인 전극과 연결되며, 투명 도전성 물질로 이루어진 화소 전극

을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 화소 영역의 평면적인 구조는 상기 투과부 내에 반사부가 위치하여, 상기 투과부에 의해 반사부가 둘러싸인 구조를 가지는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 반사판은, 상기 게이트 전극 물질로 이루어진 반투과형 액정표시장치.

### 청구항 3

제 2 항에 있어서,

상기 게이트 전극 물질은 알루미늄을 포함하는 금속층을 하부층으로 포함하는 이중층 구조 금속층으로 이루어지고, 상기 반사판의 상부층 금속물질은 제거되어, 상기 알루미늄을 포함하는 금속층이 실질적인 반사판을 이루는 반투과형 액정표시장치.

### 청구항 4

제 3 항에 있어서,

상기 게이트 전극 및 반사판 물질은, 알루미늄/몰리브덴인 반투과형 액정표시장치.

### 청구항 5

제 1 항에 있어서,

상기 반사판은, 상기 소스 전극 및 드레인 전극 물질로 이루어진 반투과형 액정표시장치.

### 청구항 6

제 5 항에 있어서,

상기 소스 전극 및 드레인 전극 물질은 알루미늄을 포함하는 금속층을 중간층으로 포함하는 삼중층 구조 금속층으로 이루어지고, 상기 반사판의 상부층 금속물질은 제거되어, 상기 알루미늄을 포함하는 금속층이 실질적인 반사판을 이루는 반투과형 액정표시장치.

### 청구항 7

제 5 항에 있어서,

상기 소스 전극 및 드레인 전극 그리고, 반사판 물질은 몰리브덴/알루미늄/몰리브덴인 반투과형 액정표시장치.

### 청구항 8

삭제

### 청구항 9

제 1 항에 있어서,

상기 반사부의 4면이 투과부에 둘러싸여 있으며, 상기 투과부와 반사부는 각각의 대각선 방향이 서로 일치되어 있는 반투과형 액정표시장치.

### 청구항 10

제 1 항에 있어서,

상기 반사부의 4면이 투과부에 둘러싸여 있으며, 상기 투과부와 반사부 각각의 대각선 방향이 서로 직교되게 위치하여, 상기 반사부는 마름모꼴을 가지는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 11

제 1 항에 있어서,

상기 반사부는, 6면이 투과부에 둘러싸여 있는 육각형상을 이루는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 12

제 1 항에 있어서,

상기 반사부는, 8면이 투과부에 둘러싸여 있는 팔각형상을 이루는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 13

제 1 항에 있어서,

상기 투과부의 한 모서리부에 반사부가 위치하며, 상기 반사부의 2면이 투과부에 의해 둘러싸여 있는 구조를 가지는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 14

제 1 항에 있어서,

상기 투과부의 일측 중앙부에 반사부가 위치하여, 상기 반사부의 3면이 투과부에 의해 둘러싸여 있는 구조를 가지는 반투과형 액정표시장치.

### 청구항 15

제 1 항에 있어서,

상기 반사부는 직각삼각형상을 가지고, 상기 반사부의 두면이 투과부의 두면과 대응되게 위치하는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 16

제 1 항에 있어서,

상기 반사부는 직각삼각형상을 가지고, 상기 투과부의 일측부에서, 상기 반사부의 2면이 투과부에 의해 둘러싸여 있는 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 17

제 9 항에 있어서,

상기 반사부와 투과부의 두면이 서로 일치되게 배치되어 있는 반투과형 액정표시장치.

### 청구항 18

제 1 항에 있어서,

상기 반사부는 이등변삼각형상을 가지는 것을 특징으로 하며, 상기 투과부의 일측부에 반사부가 위치하여, 상기

반사부의 2면이 투과부에 의해 둘러싸여 있는 구조를 가지는 반투과형 액정표시장치.

### 청구항 19

제 1 항에 있어서,

상기 블랙매트릭스와 컬러필터 사이에는 또 하나의 보호층을 추가로 포함하는 반투과형 액정표시장치.

### 청구항 20

제 1 항에 있어서,

상기 화소 전극은, 상기 블랙매트릭스와 컬러필터 사이에 형성되며, 상기 드레인 전극과 실질적으로 연결되는 또 하나의 투명 도전성 물질로 이루어진 투명 전극을 추가로 포함하는 반투과형 액정표시장치.

### 청구항 21

제 1 항에 있어서,

상기 박막트랜지스터와 반사판 사이에는, 상기 박막트랜지스터를 포함한 기판 전면을 덮는 보호층을 추가로 포함하는 반투과형 액정표시장치.

### 청구항 22

기판 상에 형성된 게이트 전극과;

상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과;

상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과;

상기 반도체층과 동일한 공정에서 동일 물질로 형성되며, 화면을 구현하는 최소 단위인 화소 영역에 위치하는 제 1 베퍼페틴과;

상기 반도체층 상부에서 서로 이격되게 형성된 소스 전극 및 드레인 전극과;

상기 소스 전극 및 드레인 전극과 동일 공정에서 동일 물질로 이루어진 반사판과;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에 형성된 블랙매트릭스와;

상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와;

상기 컬러필터 상부에서, 상기 드레인 전극과 연결된 투명 도전성 물질로 이루어진 화소 전극

을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치.

### 청구항 23

기판 상에 형성된 게이트 전극과;

상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과;

상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과;

상기 반도체층 상부에서, 상기 반도체층과 동일한 패턴 구조를 가지며, 서로 이격되게 위치하는 소스 전극 및 드레인 전극과;

상기 반도체층 및 소스 전극, 드레인 전극과 동일 공정에서 동일 물질로 이루어지며, 서로 대응된 패턴 구조를 가지는 제 1 베퍼페틴 및 반사판과;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 위치에 형성되며, 상기 드레인 전극을 노출시키는 제 1 오픈부와, 상기 제 1 오픈부와 연결되며, 상기 반사판 형성부를 제외한 화소 영역 상의 기판을 노출시키는 제 2 오픈부를 가지는 보호층과;

상기 박막트랜지스터를 덮는 영역에 형성된 블랙매트릭스와;

상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와;

상기 컬러필터 상부에서, 상기 드레인 전극과 연결된 투명 도전성 물질로 이루어진 화소 전극

을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치.

#### 청구항 24

제 22 항 또는 제 23 항 중 어느 하나의 항에 있어서,

상기 제 1 버퍼패턴과 대응된 하부에는, 상기 게이트 전극과 동일 공정에서 동일 물질로 이루어진 또 하나의 버퍼패턴을 추가로 포함하는 반투과형 액정표시장치.

#### 청구항 25

제 23 항에 있어서,

상기 블랙매트릭스와 컬러필터 사이에는 또 하나의 보호층을 추가로 포함하는 반투과형 액정표시장치.

#### 청구항 26

제 25 항에 있어서,

상기 또 하나의 보호층에는, 상기 제 1, 2 오픈부와 대응된 오픈부를 가지는 것을 특징으로 하는 반투과형 액정표시장치.

#### 청구항 27

기판 상에 형성된 게이트 전극과;

상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과;

상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과;

상기 반도체층 상부에서, 상기 반도체층과 동일한 패턴 구조를 가지며, 서로 이격되게 위치하는 소스 전극 및 드레인 전극과;

상기 반도체층 및 소스 전극, 드레인 전극과 동일 공정에서 동일 물질로 이루어지며, 서로 대응된 패턴 구조를 가지는 제 1 버퍼패턴 및 반사판과;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 위치에 형성되며, 상기 드레인 전극을 노출시키는 제 1 오픈부와, 상기 제 1 오픈부와 연결되며, 상기 반사판 형성부를 제외한 화소 영역 상의 기판을 노출시키는 제 2 오픈부를 가지는 보호층과;

상기 보호층 상부에서, 적, 녹, 청 컬러순으로 차례대로 형성되며, 상기 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 컬러필터와;

상기 컬러필터 상부에서, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되며, 투명 도전성 물질로 이루어진 화소 전극

을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치.

#### 청구항 28

제 27 항에 있어서,

상기 화소 전극 상부에는, 상기 박막트랜지스터를 덮는 위치에 형성되는 블랙매트릭스를 추가로 포함하는 반투과형 액정표시장치.

#### 청구항 29

제 27 항에 있어서,

상기 박막트랜지스터와 대응된 위치의 컬러필터의 컬러별 경계부에는 블랙매트릭스를 추가로 포함하는 반투과형 액정표시장치.

### 청구항 30

제 27 항에 있어서,

상기 컬러필터와 화소 전극 사이에는, 상기 드레인 콘택홀과 대응된 위치에서 콘택홀을 가지는 평탄화막을 추가로 포함하고, 상기 화소 전극 상부의 상기 박막트랜지스터를 덮는 위치에는 블랙매트릭스를 추가로 포함하는 반투과형 액정표시장치.

### 청구항 31

제 27 항에 있어서,

상기 박막트랜지스터와 대응된 위치의 컬러필터의 컬러별 경계부에는 블랙매트릭스를 추가로 포함하고, 상기 컬러필터와 화소 전극 사이에는, 상기 드레인 콘택홀과 대응된 위치에서 콘택홀을 가지는 평탄화막 추가로 포함하는 반투과형 액정표시장치.

### 청구항 32

기판 상에 제 1 금속물질을 이용한 제 1 마스크 공정에 의해 게이트 전극을 형성하는 단계와;

상기 게이트 전극을 덮는 영역에, 제 1 절연물질, 비정질 실리콘 물질, 불순물 비정질 실리콘 물질, 제 2 금속 물질을 차례대로 형성한 다음, 상기 제 1 절연물질은 게이트 절연막으로 삼고, 제 2 마스크 공정에 의해, 서로 대응된 패턴 구조를 가지는 반도체층과, 소스 전극 및 드레인 전극 그리고, 화소 영역 내에 제 1 버퍼패턴 및 반사판을 형성하는 단계와;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에 제 1 보호층을 형성하는 단계와;

상기 제 1 보호층 상부의 박막트랜지스터를 덮는 위치에 블랙매트릭스를 형성하는 단계와;

상기 블랙매트릭스를 덮는 영역에 제 2 보호층을 형성하고, 상기 제 1 보호층과 함께 상기 드레인 전극을 일부 노출시키는 제 1 오픈부 및 상기 제 1 오픈부와 연결되며, 상기 게이트 절연막 및 제 1 보호층과 함께 반사판 형성부 이외의 화소 영역의 기판을 노출시키는 제 2 오픈부를 가지는 제 2 보호층을 형성하는 단계와;

상기 제 2 보호층 상부에, 상기 제 1 오픈부를 통해 드레인 전극과 연결되는 제 1 투명 전극 물질층을 형성하는 단계와;

상기 제 1 투명 전극 상부에, 상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와;

상기 컬러필터 상부에서, 상기 제 1 투명 전극 물질층과 접촉되며, 상기 제 1 투명 전극 물질층과 동일한 물질로 이루어진 제 2 투명 전극 물질층을 형성하고, 상기 제 1, 2 투명 전극 물질층을 화소 영역별로 패터닝하여, 제 1, 2 투명 전극으로 이루어지는 화소 전극을 형성하는 단계

를 포함하는 반투과형 액정표시장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0026] 본 발명은 액정표시장치에 관한 것이며, 특히 공정이 단순화된 반투과형 액정표시장치에 관한 것이다.

[0027] 최근에, 액정표시장치는 소비전력이 낮고 휴대성이 양호한 기술집약적이며 부가가치가 높은 차세대 첨단 표시장

치 소자로 각광받고 있다.

[0028] 상기 액정표시장치는 투명 전극이 형성된 두 기판 사이에 액정을 주입하고, 상부 및 하부 기판 외부에 상부 및 하부 편광판을 위치시켜 형성되며, 액정분자의 이방성에 따른 빛의 편광특성을 변화시켜 영상효과를 얻는 비발광 소자에 해당된다.

[0029] 현재에는, 각 화소를 개폐하는 스위칭 소자인 박막트랜지스터(Thin Film Transistor ; TFT)가 화소마다 배치되는 능동행렬방식 액정표시장치(AM-LCD ; Active Matrix Liquid Crystal Display)가 해상도 및 동영상 구현능력이 우수하여 가장 주목받고 있다.

[0030] 이러한 액정표시장치에서는 별도의 광원인 백라이트를 포함한다. 그러나, 상기 백라이트에서 생성된 빛은 액정표시장치의 각 셀을 통과하면서 실제로 화면 상으로는 7% 정도만 투과되므로, 고휘도의 액정표시장치를 제공하기 위해서는 백라이트를 더욱 밝게 해야 하므로, 전력 소모량이 커지게 된다.

[0031] 그러므로, 충분한 백라이트의 전원 공급용으로 무게가 많이 나가는 배터리(battery)를 사용해왔으나, 이 또한 사용시간에 제한이 있다.

[0032] 이러한 문제점을 해결하기 위해, 최근에는 백라이트 광원외에 외부광을 광원으로 이용하여 반사모드 및 투과모드로의 전환이 용이한 반투과형 액정표시장치가 연구/개발되었다.

[0033] 반투과형 액정표시장치에서는, 투명전극으로 형성된 화소부에 반사특성을 가지는 금속물질로 이루어진 반사판이 추가로 구비되는 것을 구조적 특징으로 한다.

[0034] 상기 화소부에서 반사판의 형성위치는 투명 전극의 상, 하부 어느쪽에 배치되도 무방하지만, 액정배열을 용이하게 유도하기 위하여 투명 전극을 반사판 상부에 배치하는 구조가 주류를 이루며, 상기 반사판과 투명 전극을 단락시키고, 반사판을 보호하기 위한 목적으로 하는 다중층 구조 절연막을 가지는 반사투과형 액정표시장치가 제작되고 있다.

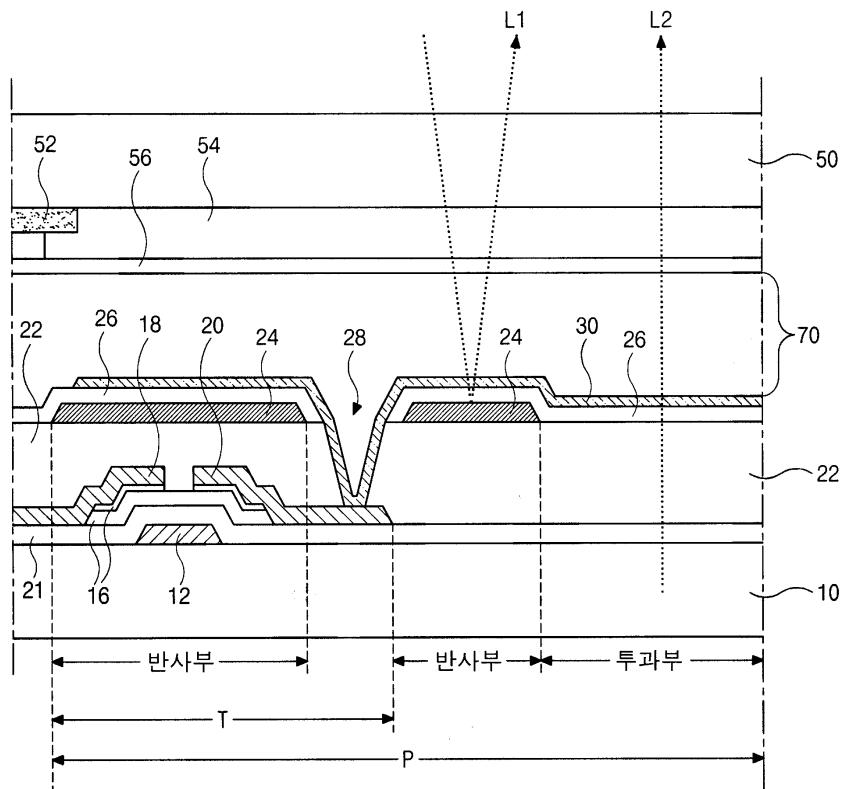

[0035] 이하, 도 1은 종래의 반투과형 액정표시장치용 어레이 기판에 대한 단면도이다.

[0036] 도시한 바와 같이, 서로 대향되게 제 1, 2 기판(10, 50)이 배치되어 있고, 제 1 기판(10)의 내부면에는 게이트 전극(12), 반도체층(16), 소스 전극(18) 및 드레인 전극(20)으로 이루어진 박막트랜지스터(T)가 형성되어 있으며, 박막트랜지스터(T)를 덮는 영역에는 제 1 보호층(22)이 차례대로 적층되어 있고, 제 1 보호층(22) 상부에는 화면을 구현하는 최소 단위로 정의되는 화소 영역(P) 일부를 덮는 영역에 반사판(24)이 형성되어 있으며, 상기 반사판(24)을 덮는 기판 전면에는 제 2 보호층(26)이 형성되어 있다. 상기 제 1 보호층(22), 반사판(24), 제 2 보호층(26)에는 드레인 전극(20)을 일부 노출시키는 드레인 콘택홀(28)이 공통적으로 형성되어 있으며, 제 2 보호층(26) 상부에는 드레인 콘택홀(28)을 통해 드레인 전극(20)과 연결되는 투명 도전성 물질로 이루어진 화소 전극(30)이 형성되어 있다.

[0037] 한편, 상기 소스 전극(18)과 연결되어 데이터 배선(21)이 형성되어 있고, 도면으로 제시하지는 않았지만, 상기 게이트 전극(12)과 연결되어 게이트 배선이 형성되며, 상기 게이트 배선과 데이터 배선(21)은 서로 교차되게 배열된다.

[0038] 상기 제 2 기판(50)의 내부면에는 데이터 배선(21)으로 대표되는 배선부를 덮는 영역에 블랙매트릭스(52)가 형성되어 있고, 블랙매트릭스(52)를 덮는 위치에는 컬러필터(54)가 형성되어 있으며, 컬러필터(54) 하부에는 전술한 화소 전극(30)과 동일 물질로 이루어진 공통 전극(56)이 형성되어 있다.

[0039] 상기 화소 전극(30)과 공통 전극(56) 사이 구간에는 액정층(70)이 개재되어 있다.

[0040] 상기 반사판(24)과 대응된 화소 영역(P)은 반사부를 이루고, 그외 화소 전극(30)과 대응된 화소 영역(P)은 투과부를 이룬다.

[0041] 이러한 종래의 반투과형 액정표시장치는, 게이트 공정(게이트 전극, 게이트 배선) →액티브 공정(반도체층) →소스/드레인 공정(소스 전극, 드레인 전극, 데이터 배선) →제 1 콘택홀 공정(제 1 보호층) →반사부 공정(반사판) →제 2 콘택홀 공정(제 2 보호층) →투과부 공정(화소 전극)을 포함하는 어레이 공정과, 블랙매트릭스 공정 →컬러필터 공정(적, 녹, 청 컬러필터) →공통 전극 공정으로 이루어지는 복잡한 공정순서를 거쳐야 하고, 특히 반사판과 화소 전극을 격리시키기 위한 절연막 공정은 반사판 물질과 화소 전극 물질 간의 화학적 반응을 방지하기 위해 추가된 공정에 해당된다.

- [0042] 좀 더 상세히 설명하면, 상기 반사판을 이루는 물질은 알루미늄(Al), 알루미늄합금(Al alloy), 은(Ag)과 같이 반사성이 우수한 금속물질에서 선택되는데, 이러한 금속물질들은 화소 전극을 이루는 대표적인 투명 도전성 물질인 ITO(indium tin oxide)와의 전기화학적 반응에 의해 손상(damage)을 입게 되고, 화소 전극 물질 또한 산화막을 형성하여 투명성을 잃고 검게 변하는 현상인 흑화현상이 발생되므로, 전술한 바와 같이 별도의 절연막 삽입을 통한 격리가 필요하며, 이에 따라 추가되는 절연막의 콘택홀 공정이 추가된다.

- [0043] 또한, 투과부와 반사부 간의 색재현율을 맞추기 위한 공정이 추가로 요구되기도 한다.

- [0044] 상기 도 1에서 반사부와 투과부에서의 빛의 경로 차이(L1, L2)는 투과부 대비 반사부에서 약 2배의 경로차이를 보이게 된다. 이로 인해, 반사부에서와 투과부에서의 동일 컬러필터를 적용한 색재현율 차이가 나타나게 된다.

- [0045] 이러한 차이를 개선하기 위한 방법으로, 반사부 컬러필터의 두께를 투과부 컬러필터 두께보다 얇게 형성하여, 컬러필터를 통과하는 전체경로 차이를 최소한 감소시키는 방법이 제안되고 있다.

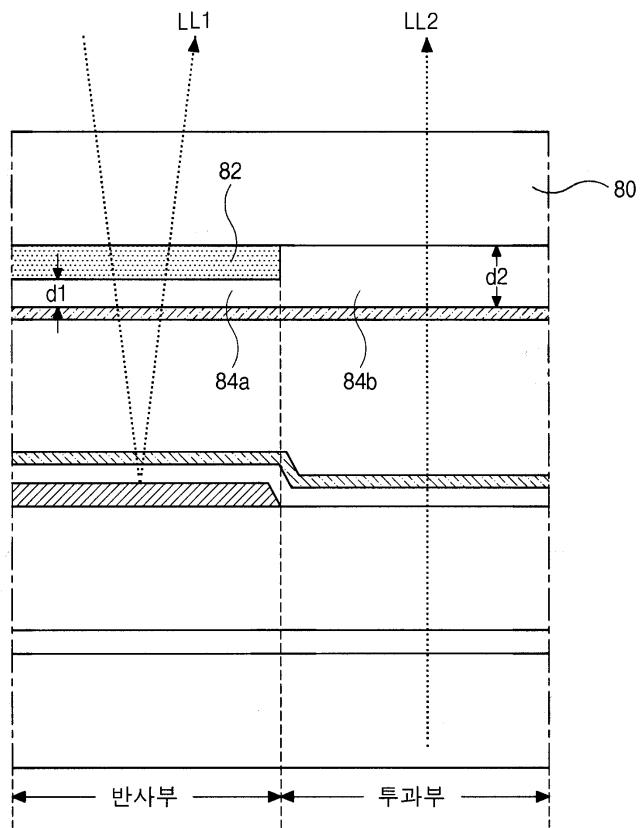

- [0046] 도 2는 기존의 색재현율 조절용 투명막을 가지는 반투과형 액정표시장치에 대한 개략적인 단면도로서, 투과부 대비 반사부에서의 빛의 진행상태를 중심으로 도시한 것으로, 상기 도 1의 기본 구조는 그대로 적용한 구조에서, 제 2 기판(80)의 내부면의 반사부 영역에는 투명막(82)이 형성되어 있어, 상기 투명막(82)에 의해 반사부 컬러필터(84a)의 두께(d1)는 투과부 컬러필터(84b) 두께보다 얇아져, 상기 반사부 컬러필터(84a)에서의 빛의 진행경로(LL1)는 투과부 컬러필터(84b)에서의 빛의 진행경로(LL2)와 비슷하게 되어, 이러한 효과에 의해 색재현율을 조절할 수 있다.

- [0047] 그러나, 이러한 구조에서는 별도의 투명막 제조 공정 및 컬러평탄화 공정이 추가되는 단점을 갖게 된다.

### 발명이 이루고자 하는 기술적 과제

- [0048] 상기 문제점을 해결하기 위하여, 본 발명에서는 제조 공정이 단순화된 반투과형 액정표시장치를 제공하는 것을 목적으로 한다.

- [0049] 이를 위하여, 본 발명에서는 박막트랜지스터가 형성된 기판 상에 컬러필터를 동시에 형성하는 COT(Color Filter on Transistor)구조를 적용하며, 반사판을 게이트 공정 또는 소스/드레인 공정에서 동시에 형성하여 공정추가가 발생하지 않도록 한다.

- [0050] 본 발명의 또 다른 목적에서는, 상기 목적에 더하여 색재현율을 향상시키고자 함이며, 이를 위하여 본 발명에서는 반사부 컬러필터의 두께치를 투과부 컬러필터 두께치보다 얇게 하기 위하여, 박막트랜지스터의 제조 공정에서 반사판 베퍼페턴들을 동시에 형성하고자 한다.

### 발명의 구성 및 작용

- [0051] 상기 목적을 달성하기 위하여, 본 발명의 제 1 특징에서는 기판 상에 화면을 구현하는 최소 단위인 화소 영역별로 형성되며, 게이트 전극, 반도체층, 소스 전극, 드레인 전극으로 이루어진 박막트랜지스터와; 상기 화소 영역 내에서, 상기 기판 상에 박막트랜지스터의 전극물질과 동일 공정에서 동일 물질로 이루어진 반사판과; 상기 박막트랜지스터를 덮는 위치에 형성된 블랙매트릭스와; 상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와; 상기 컬러필터 상부에서, 상기 드레인 전극과 연결되며, 투명 도전성 물질로 이루어진 화소 전극을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 화소 영역의 평면적인 구조는 상기 투과부 내에 반사부가 위치하여, 상기 투과부에 의해 반사부가 둘러싸인 구조를 가지는 것을 특징으로 하는 반투과형 액정표시장치를 제공한다.

- [0052] 상기 반사판은, 상기 게이트 전극 물질로 이루어지고, 상기 게이트 전극 물질은 알루미늄을 포함하는 금속층을 하부층으로 포함하는 이중층 구조 금속층으로 이루어지고, 상기 반사판의 상부층 금속물질은 제거되어, 상기 알루미늄을 포함하는 금속층이 실질적인 반사판을 이루고, 상기 게이트 전극 및 반사판 물질은, 알루미늄/몰리브덴인 것을 특징으로 한다.

- [0053] 상기 반사판은, 상기 소스 전극 및 드레인 전극 물질로 이루어지고, 상기 소스 전극 및 드레인 전극 물질은 알루미늄을 포함하는 금속층을 중간층으로 포함하는 삼중층 구조 금속층으로 이루어지고, 상기 반사판의 상부층 금속물질은 제거되어, 상기 알루미늄을 포함하는 금속층이 실질적인 반사판을 이루며, 상기 소스 전극 및 드레

인 전극 그리고, 반사판 물질은 몰리브덴/알루미늄/몰리브덴인 것을 특징으로 한다.

[0054] 상기 반사부의 4면이 투과부에 둘러싸여 있으며, 상기 투과부와 반사부는 각각의 대각선 방향이 서로 일치되어 있거나, 상기 투과부와 반사부 각각의 대각선 방향이 서로 직교되게 위치하여, 상기 반사부는 마름모꼴을 가지는 것을 특징으로 한다.

[0055] 그리고, 상기 반사부는, 6면이 투과부에 둘러싸여 있는 육각형상을 이루는 것을 특징으로 하거나, 상기 반사부는, 8면이 투과부에 둘러싸여 있는 팔각형상을 이루는 것을 특징으로 한다.

[0056] 또한, 상기 투과부의 한 모서리부에 반사부가 위치하며, 상기 반사부의 2면이 투과부에 의해 둘러싸여 있는 구조를 가지거나, 상기 투과부의 일측 중앙부에 반사부가 위치하여, 상기 반사부의 3면이 투과부에 의해 둘러싸여 있는 구조를 가지는 것을 특징으로 하거나, 상기 반사부는 직각삼각형상을 가지고, 상기 반사부의 두변이 투과부의 두변과 대응되게 위치하는 것을 특징으로 한다.

[0057] 또한, 상기 반사부는 직각삼각형상을 가지고, 상기 투과부의 일측부에서, 상기 반사부의 2면이 투과부에 의해 둘러싸여 있는 것을 특징으로 한다.

[0058] 상기 반사부와 투과부의 두변이 서로 일치되게 배치되어 있거나, 또는 상기 반사부는 이등변삼각형상을 가지는 것을 특징으로 하며, 상기 투과부의 일측부에 반사부가 위치하여, 상기 반사부의 2면이 투과부에 의해 둘러싸여 있는 구조를 가지는 것을 특징으로 한다.

[0059] 상기 블랙매트릭스와 컬러필터 사이에는 또 하나의 보호층을 추가로 포함하며, 상기 화소 전극은, 상기 블랙매트릭스와 컬러필터 사이에 형성되며, 상기 드레인 전극과 실질적으로 연결되는 또 하나의 투명 도전성 물질로 이루어진 투명 전극을 추가로 포함하는 것을 특징으로 한다.

[0060] 상기 박막트랜지스터와 반사판 사이에는, 상기 박막트랜지스터를 포함한 기판 전면을 덮는 보호층을 추가로 포함하는 것을 특징으로 한다.

[0061] 본 발명의 제 2 특징에서는, 기판 상에 형성된 게이트 전극과; 상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과; 상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과; 상기 반도체층과 동일한 공정에서 동일 물질로 형성되며, 화면을 구현하는 최소 단위인 화소 영역에 위치하는 제 1 베틀페인과; 상기 반도체층 상부에서 서로 이격되게 형성된 소스 전극 및 드레인 전극과; 상기 소스 전극 및 드레인 전극과 동일 공정에서 동일 물질로 이루어진 반사판과; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에 형성된 블랙매트릭스와; 상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와; 상기 컬러필터 상부에서, 상기 드레인 전극과 연결된 투명 도전성 물질로 이루어진 화소 전극을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치를 제공한다.

[0062] 본 발명의 제 3 특징에서는, 기판 상에 형성된 게이트 전극과; 상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과; 상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과; 상기 반도체층 상부에서, 상기 반도체층과 동일한 패턴 구조를 가지며, 서로 이격되게 위치하는 소스 전극 및 드레인 전극과; 상기 반도체층 및 소스 전극, 드레인 전극과 동일 공정에서 동일 물질로 이루어지며, 서로 대응된 패턴 구조를 가지는 제 1 베틀페인 및 반사판과; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 위치에 형성되며, 상기 드레인 전극을 노출시키는 제 1 오픈부와, 상기 제 1 오픈부와 연결되며, 상기 반사판 형성부를 제외한 화소 영역 상의 기판을 노출시키는 제 2 오픈부를 가지는 보호층과; 상기 박막트랜지스터를 덮는 영역에 형성된 블랙매트릭스와; 상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와; 상기 컬러필터 상부에서, 상기 드레인 전극과 연결된 투명 도전성 물질로 이루어진 화소 전극을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치를 제공한다.

[0063] 본 발명의 제 2, 3 특징에 따른 상기 제 1 베틀페인과 대응된 하부에는, 상기 게이트 전극과 동일 공정에서 동일 물질로 이루어진 또 하나의 베틀페인을 추가로 포함하는 것을 특징으로 한다.

[0064] 본 발명의 제 3 특징에 따른 상기 블랙매트릭스와 컬러필터 사이에는 또 하나의 보호층을 추가로 포함하고, 상기 또 하나의 보호층에는, 상기 제 1, 2 오픈부와 대응된 오픈부를 가지는 것을 특징으로 한다.

- [0065] 본 발명의 제 4 특징에 따른 기판 상에 형성된 게이트 전극과; 상기 게이트 전극을 덮는 영역에 형성된 게이트 절연막과; 상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 형성된 반도체층과; 상기 반도체층 상부에서, 상기 반도체층과 동일한 패턴 구조를 가지며, 서로 이격되게 위치하는 소스 전극 및 드레인 전극과; 상기 반도체층 및 소스 전극, 드레인 전극과 동일 공정에서 동일 물질로 이루어지며, 서로 대응된 패턴 구조를 가지는 제 1 베퍼패턴 및 반사판과; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 위치에 형성되며, 상기 드레인 전극을 노출시키는 제 1 오픈부와, 상기 제 1 오픈부와 연결되며, 상기 반사판 형성부를 제외한 화소 영역 상의 기판을 노출시키는 제 2 오픈부를 가지는 보호층과; 상기 보호층 상부에서, 적, 녹, 청 컬러순으로 차례대로 형성되며, 상기 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 컬러필터와; 상기 컬러필터 상부에서, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되며, 투명 도전성 물질로 이루어진 화소 전극을 포함하며, 상기 반사판과 대응된 화소 영역은 반사부를 이루고, 그외 화소 영역은 투과부를 이루며, 상기 반사부 컬러필터의 두께는 투과부 컬러필터의 두께보다 얇은 것을 특징으로 하는 반투과형 액정표시장치를 제공한다.

- [0066] 상기 화소 전극 상부에는, 상기 박막트랜지스터를 덮는 위치에 형성되는 블랙매트릭스를 추가로 포함하거나, 상기 박막트랜지스터와 대응된 위치의 컬러필터의 컬러별 경계부에는 블랙매트릭스를 추가로 포함하거나, 상기 컬러필터와 화소 전극 사이에는, 상기 드레인 콘택홀과 대응된 위치에서 콘택홀을 가지는 평탄화막을 추가로 포함하고, 상기 화소 전극 상부의 상기 박막트랜지스터를 덮는 위치에는 블랙매트릭스를 추가로 포함하거나, 상기 박막트랜지스터와 대응된 위치의 컬러필터의 컬러별 경계부에는 블랙매트릭스를 추가로 포함하고, 상기 컬러필터와 화소 전극 사이에는, 상기 드레인 콘택홀과 대응된 위치에서 콘택홀을 가지는 평탄화막 추가로 포함하는 것을 특징으로 한다.

- [0067] 본 발명의 제 5 특징에 따른 기판 상에 제 1 금속물질을 이용한 제 1 마스크 공정에 의해 게이트 전극을 형성하는 단계와; 상기 게이트 전극을 덮는 영역에, 제 1 절연물질, 비정질 실리콘 물질, 불순물 비정질 실리콘 물질, 제 2 금속물질을 차례대로 형성한 다음, 상기 제 1 절연물질은 게이트 절연막으로 삼고, 제 2 마스크 공정에 의해, 서로 대응된 패턴 구조를 가지는 반도체층과, 소스 전극 및 드레인 전극 그리고, 화소 영역 내에 제 1 베퍼패턴 및 반사판을 형성하는 단계와; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에 제 1 보호층을 형성하는 단계와; 상기 제 1 보호층 상부의 박막트랜지스터를 덮는 위치에 블랙매트릭스를 형성하는 단계와; 상기 블랙매트릭스를 덮는 영역에 제 2 보호층을 형성하고, 상기 제 1 보호층과 함께 상기 드레인 전극을 일부 노출시키는 제 1 오픈부 및 상기 제 1 오픈부와 연결되며, 상기 게이트 절연막 및 제 1 보호층과 함께 반사판 형성부 이외의 화소 영역의 기판을 노출시키는 제 2 오픈부를 가지는 제 2 보호층을 형성하는 단계와; 상기 제 2 보호층 상부에, 상기 제 1 오픈부를 통해 드레인 전극과 연결되는 제 1 투명 전극 물질층을 형성하는 단계와; 상기 제 1 투명 전극 상부에, 상기 블랙매트릭스를 컬러별 경계부로 하여, 적, 녹, 청 컬러순으로 차례대로 형성된 컬러필터와; 상기 컬러필터 상부에서, 상기 제 1 투명 전극 물질층과 접촉되며, 상기 제 1 투명 전극 물질층과 동일한 물질로 이루어진 제 2 투명 전극 물질층을 형성하고, 상기 제 1, 2 투명 전극 물질층을 화소 영역별로 패터닝하여, 제 1, 2 투명 전극으로 이루어지는 화소 전극을 형성하는 단계를 포함하는 반투과형 액정표시장치를 제공한다.

- [0068] 이하, 본 발명에 따른 바람직한 실시예를 도면을 참조하여 상세히 설명한다.

- [0069] -- 제 1 실시예 --

- [0070] 본 실시예는 반투과형 액정표시장치를 COT 방식으로 동일 기판에 박막트랜지스터를 포함한 어레이 소자와 컬러필터를 구성한 것으로, 특히 일 예로 게이트 전극 물질을 반사판으로 이용하는 것을 특징으로 한다.

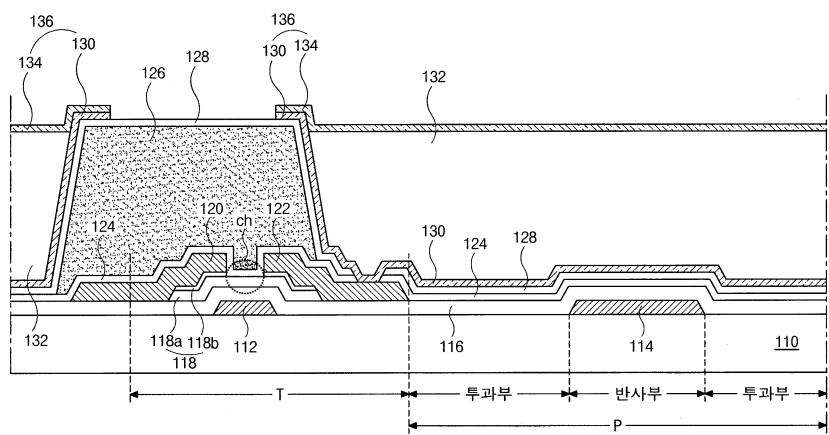

- [0071] 도 3은 본 발명의 제 1 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도이다.

- [0072] 도시한 바와 같이, 기판(110) 상에 게이트 전극(112) 및 게이트 전극(112)과 일정간격 이격되며, 상기 게이트 전극(112)과 동일 물질로 이루어진 반사판(114)이 형성되어 있고, 게이트 전극(112) 및 반사판(114)을 덮는 기판 전면에는 게이트 절연막(116)이 형성되어 있으며, 게이트 절연막(116) 상부의 게이트 전극(112)을 덮는 위치에는 반도체층(118)이 형성되어 있고, 반도체층(118) 상부에는 서로 이격되게 소스 전극(120) 및 드레인 전극(122)이 형성되어 있다.

- [0073] 상기 반도체층(118)은 비정질 실리콘 물질(a-Si)로 이루어진 액티브층(118a)과, 액티브층(118a)을 덮는 영역에 형성된 불순물 비정질 실리콘 물질(n+ a-Si)로 이루어진 오믹콘택층(118b)으로 이루어지고, 상기 소스 전극

(120) 및 드레인 전극(122) 사이 이격구간에는 액티브층(118a)이 노출되어, 노출된 액티브층(118a) 영역은 채널(ch)을 이룬다.

[0074] 상기 게이트 전극(112), 반도체층(118), 소스 전극(120) 및 드레인 전극(122)은 박막트랜지스터(T)를 이루고, 상기 박막트랜지스터(T)를 덮는 영역에는 제 1 보호층(124)이 형성되어 있으며, 제 1 보호층(124) 상부의 박막트랜지스터(T)를 덮는 영역에는 블랙매트릭스(126)가 형성되어 있고, 블랙매트릭스(126)를 덮는 영역에는 제 2 보호층(128)이 기판 전면에 형성되어 있으며, 제 2 보호층(128)을 덮는 영역에는 화면을 구현하는 최소단위인 화소 영역(P)별로 제 1 투명 전극(130)이 형성되어 있다. 도면으로 상세히 제시하지는 않았지만, 상기 블랙매트릭스(126)는 박막트랜지스터(T)를 덮는 영역외에 미도시한 컬러필터의 컬러별 경계부를 이루는 영역에 형성된다.

[0075] 또한, 상기 제 2 보호층(128)은 공정방법 및 물질개발 정도에 따라 생략가능하다.

[0076] 통상적으로, 본 실시예서와 같이 제 2 보호층이 구비된 경우, 상기 블랙매트릭스 물질은 블랙 레진에서 선택되는 것이 바람직하다.

[0077] 상기 제 1 투명 전극(130) 상부에는 블랙매트릭스(126)를 컬러별 경계부로 하여 컬러필터(132)가 화소 영역(P) 별로 형성되어 있고, 컬러필터(132) 상부에는 상기 제 1 투명 전극(130)과 연결되어 제 2 투명 전극(134)이 형성되어 있다.

[0078] 도면으로 상세히 제시하지는 않았지만, 상기 컬러필터(132)는 적, 녹, 청 컬러필터를 차례대로 형성하는 방법으로 이루어진다.

[0079] 상기 제 1, 2 투명 전극(130, 134)은 화소 전극(136)을 이루며, 상기 화소 영역(P)은 반사판(114)과 대응된 영역으로 정의되는 반사부와, 그외 절연층(116, 124, 128)과 화소 전극(136)의 적층 구조로 이루어진 투과부로 이루어진다.

[0080] 이와 같이, 본 실시예에 따른 COT구조 반투과형 액정표시장치에 의하면, COT 방식으로 반투과형 액정표시장치를 구성함에 따라 박막트랜지스터를 포함하는 어레이 소자와 컬러필터 소자(컬러필터+블랙매트릭스) 간의 합착마진을 제거할 수 있어 개구율을 향상시킬 수 있으며, 반사판 공정을 별도로 추가하지 않고, 어레이 소자 제조 공정 중 금속 패턴의 제조 공정에서 동시에 형성함에 따라, 공정을 보다 단순화시킬 수 있으며, 반사판과 투명 전극 간의 격리를 위한 별도의 절연막 공정이 생략가능한 잇점을 가진다.

[0081] -- 제 2 실시예 --

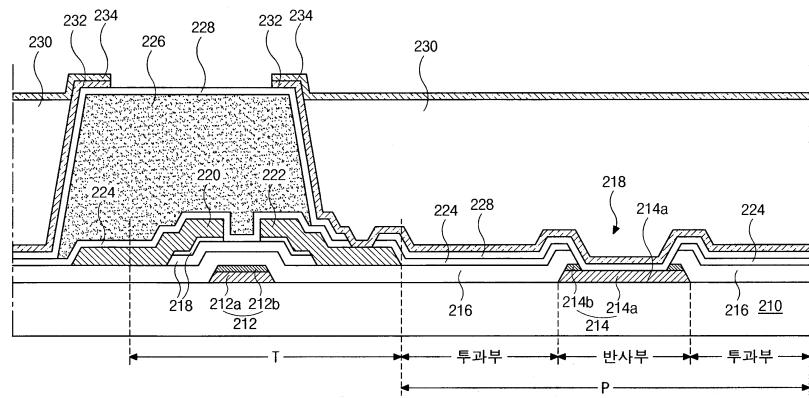

[0082] 본 실시예는, COT 구조 반투과형 액정표시장치에 관한 것이며, 특히 이중층 구조 게이트 전극과 동일 공정에서 이루어진 반사판을 포함하는 실시예이다.

[0083] 도 4는 본 발명의 제 2 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도로서, 상기 도 3의 적층 구조를 기본 구조로 삼아, 특징적인 부분을 중심으로 설명하며, 기판(210) 상에 제 1 게이트 물질층(212a), 제 2 게이트 물질층(212b)이 차례대로 적층된 구조의 게이트 전극(212)이 형성되어 있고, 게이트 전극(212)과 일정간격 이격되게 위치하며, 게이트 전극(212)과 동일 물질로 이루어진 제 1 반사판 물질층(214a), 제 2 반사판 물질층(214b)으로 이루어진 반사판(214)이 형성되어 있다.

[0084] 상기 제 1 게이트 물질층(212a), 제 1 반사판 물질층(214a)은 비저항값이 낮은 금속물질에서 선택되고, 제 2 게이트 물질층(212b), 제 2 반사판 물질층(214b)은 화학적 내식성이 강한 금속물질에서 선택되는 것을 특징으로 한다. 바람직하게는, 상기 제 1 게이트 물질층(212a), 제 1 반사판 물질층(214a)은 알루미늄(Al)으로 이루어지고, 제 2 게이트 물질층(212b), 제 2 반사판 물질층(214b)은 몰리브덴(Mo)으로 이루어지는 것이다.

[0085] 상기 게이트 전극(212) 및 반사판(214)을 덮는 위치에는 게이트 절연막(216)이 형성되어 있고, 게이트 절연막(216) 상부의 게이트 전극(212)을 덮는 위치에는 반도체층(218)이 형성되어 있으며, 반도체층(218) 상부에는 서로 이격되게 소스 전극(220) 및 드레인 전극(222)이 형성되어 있고, 상기 게이트 전극(212), 반도체층(218), 소스 전극(220) 및 드레인 전극(222)은 박막트랜지스터(T)를 이룬다.

[0086] 상기 박막트랜지스터(T) 및 반사판(214)을 덮는 위치에는 제 1 보호층(224)이 형성되어 있다. 이때, 상기 반사판(214)을 덮는 영역의 게이트 절연막(216), 제 1 보호층(224)에는 반사판(214)의 주영역을 노출시키는 반사판 오픈부(218)가 형성되어 있는 것을 특징으로 하고, 상기 반사판 오픈부(218)를 통해 노출된 제 2 반사판 물질층

(214b)은 제거되어 있고, 그 하부층을 이루는 제 1 반사판 물질층(214a)이 노출되어 있는 것을 특징으로 한다.

[0087] 이러한 구조적 특징은, 제 2 반사판 물질층(214b)을 이루는 몰리브덴과 같은 금속물질보다 제 1 반사판 물질층(214a)을 이루는 알루미늄과 같은 금속물질의 반사성이 높기 때문에, 상기 게이트 절연막(216), 제 1 보호층(224)의 오픈부 공정을 통해 제 1 반사판 물질층(214a)을 노출시키는 것이다.

[0088] 전술한 오픈부 공정은, 상기 제 1 보호층(224)의 콘택홀 공정에서 동시에 진행할 수 있다.

[0089] 또한, 상기 제 2 반사판 물질층(214b)을 몰리브덴으로 할 경우, 몰리브덴은 절연막의 건식식각(dry etching) 공정을 통해 동시에 식각되므로 별도의 식각 공정이 추가하지 않아도 된다.

[0090] 이후, 상기 제 1 보호층(224) 상부에 블랙매트릭스(226), 제 2 보호층(228), 컬러필터(230), 제 1, 2 투명 전극(232, 234)의 적층구조는 상기 제 1 실시예 구조를 동일하게 적용할 수 있다.

[0091] -- 제 3 실시예 --

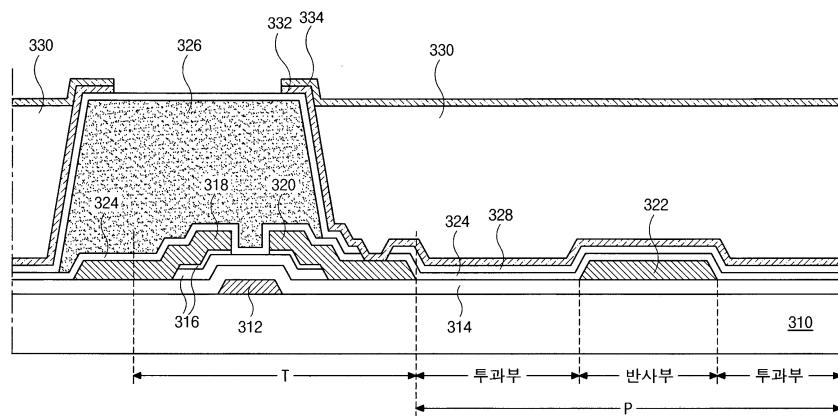

[0092] 본 실시예는, COT 구조 반투과형 액정표시장치에 관한 것이며, 특히 소스 전극 및 드레인 전극과 동일 공정에서 이루어진 반사판을 포함하는 실시예이다.

[0093] 도 5는 본 발명의 제 3 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도로서, 상기 도 3의 적층 구조를 기본 구조로 삼아, 특징적인 부분을 중심으로 설명해보면, 기판(310) 상에 게이트 전극(312), 게이트 절연막(314), 반도체층(316)이 차례대로 형성되어 있고, 반도체층(316) 상부에는 서로 이격되게 소스 전극(318) 및 드레인 전극(320)이 형성되어 있으며, 상기 소스 전극(318) 및 드레인 전극(320)과 이격되게 위치하며, 상기 소스 전극(318) 및 드레인 전극(320)과 동일공정에서 동일물질로 이루어진 반사판(322)이 형성되어 있다.

[0094] 상기 게이트 전극(312), 반도체층(316), 소스 전극(318) 및 드레인 전극(320)은 박막트랜지스터(T)를 이루고, 박막트랜지스터(T) 및 반사판(322)을 덮는 영역에는 제 1 보호층(324), 블랙매트릭스(326), 제 2 보호층(328), 컬러필터(330), 제 1, 2 투명 전극(332, 334)이 상기 도 3과 같은 적층 구조를 가지며 차례대로 형성되어 있다.

[0095] -- 제 4 실시예 --

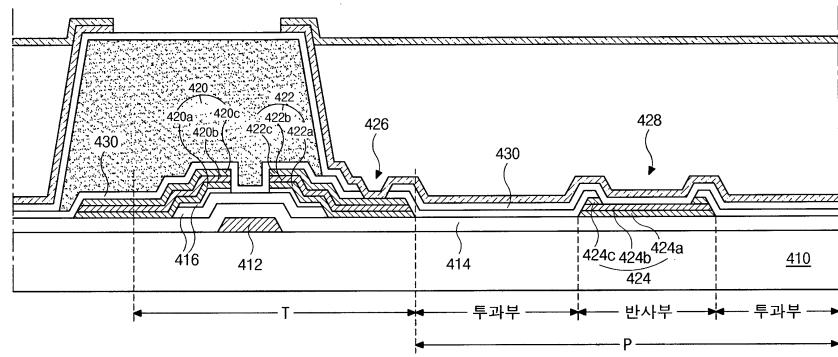

[0096] 본 실시예는, COT 구조 반투과형 액정표시장치에 관한 것이며, 특히 삼중층 구조 소스 전극 및 드레인 전극과 동일 공정에서 이루어진 반사판을 포함하는 실시예이다.

[0097] 도 6은 본 발명의 제 4 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도로서, 상기 도 5의 적층 구조를 기본 구조로 삼아, 특징적인 부분을 중심으로 설명하며, 기판(410) 상에 게이트 전극(412), 게이트 절연막(414), 반도체층(416)이 차례대로 적층되어 있고, 반도체층(416) 상부에는 서로 이격되게 삼중층 구조의 소스 전극(420) 및 드레인 전극(422)이 형성되어 있으며, 상기 소스 전극(420) 및 드레인 전극(422)과 이격되게 위치하며, 상기 소스 전극(420) 및 드레인 전극(422)과 동일 공정에서 동일 물질로 이루어진 반사판(424)이 형성되어 있다.

[0098] 상기 소스 전극(420) 및 드레인 전극(422)은 제 1, 2, 3 소스 전극 물질층(420a, 420b, 420c) 및 제 1, 2, 3 드레인 전극 물질층(422a, 422b, 422c)이 차례대로 적층된 구조로 이루어지고, 상기 반사판(424)은 제 1, 2, 3 반사판 물질층(424a, 424b, 424c)이 차례대로 적층된 구조로 이루어진다.

[0099] 상기 제 1, 3 소스 전극 물질층(420a, 420c) 및 제 1, 3 드레인 전극 물질층(422a, 422c)은 화학적 내식성이 강한 금속물질에서 선택되고, 제 2 소스 전극 물질층(420b) 및 제 2 드레인 전극 물질층(422b)은 비저항값이 낮은 금속물질에서 선택되는 것으로, 한 예로 몰리브덴/알루미늄/몰리브덴으로 구성되는 삼중층 구조로 이루어질 수 있다. 상기 알루미늄을 기준으로 하부층에 위치하는 몰리브덴층은 알루미늄층의 공정 중 스파이크(spike) 발생에 의해 반도체층에 손상이 가해지는 것을 방지하는 역할을 하며, 상부층을 이루는 몰리브덴층은 알루미늄층과 투명 전극간의 화학적 반응을 방지하는 역할을 한다.

[0100] 상기 게이트 전극(412), 반도체층(416), 소스 전극(420) 및 드레인 전극(422)은 박막트랜지스터(T)를 이루고, 박막트랜지스터(T) 및 반사판(424)을 덮는 영역에는 위치하며, 상기 드레인 전극(422) 및 반사판(424)의 주영역을 노출시키는 영역에는 드레인 콘택홀(426) 및 반사판 오픈부(428)를 가지는 제 1 보호층(430)이 형성되어 있

다.

[0101] 상기 반사판 오픈부(428)를 통해 제 3 반사판 물질층(424c)이 제거되고, 그 하부층을 이루는 제 2 반사판 물질층(424b)이 노출되는 것을 특징으로 하며, 상기 제 3 반사판 물질층(424c)의 제거 공정은 제 1 보호층(430)의 콘택홀 공정 중 같이 제거가능하여, 별도의 공정을 추가하지 않아도 된다.

[0102] -- 제 5 실시예 --

[0103] 도 7a 내지 7k는 본 발명의 제 5 실시예에 따른 COT 방식 반투과형 액정표시장치용 화소부에 대한 개략적인 평면도로서, 하나의 화소부 기준 반사부와 투과부의 배치 구조에 대해서 도시한 것으로, 반사부 패턴의 다양한 디자인(design) 변경을 통해 반사부와 투과부간의 면적비율을 조정하는 일예들에 대한 것이다.

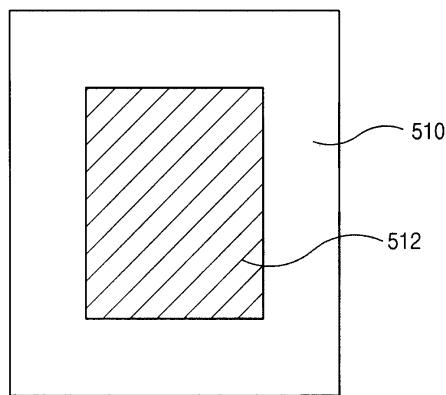

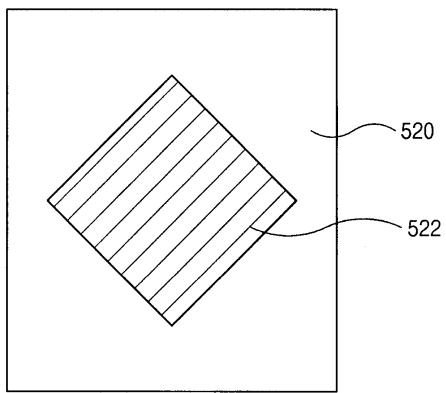

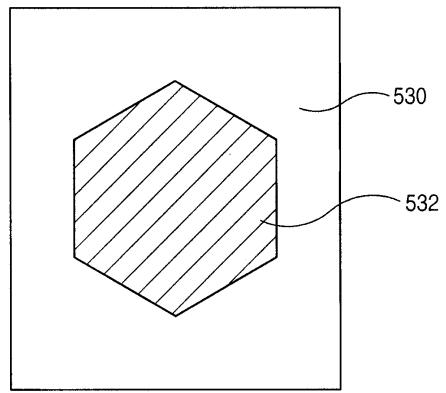

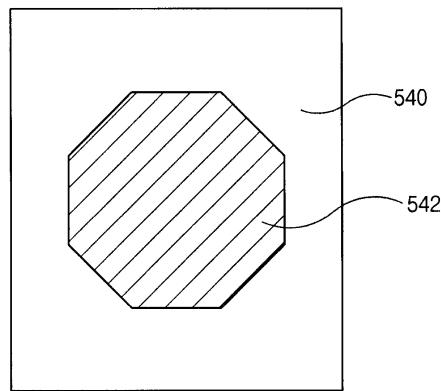

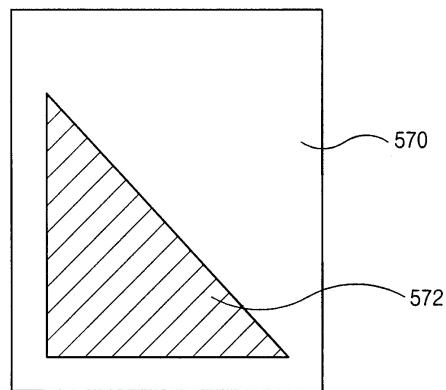

[0104] 도 7a 내지 7d는, 투과부(510, 520, 530, 540) 영역 내에 반사부(512, 522, 532, 542)가 위치하며, 특히 도 7a, 7b에서는 반사부(512, 522)의 4면이 투과부(510, 520)에 둘러싸여 있으며, 이때 도 7a에서는 투과부(510)와 반사부(512)는 서로의 대각선 방향이 서로 일치되게 배치되어 있고, 도 7b에서는 투과부(520)와 반사부(522) 각각의 대각선 방향이 서로 직교되게 위치하는 즉, 반사부(522)가 마름모꼴을 이루는 것을 특징으로 한다.

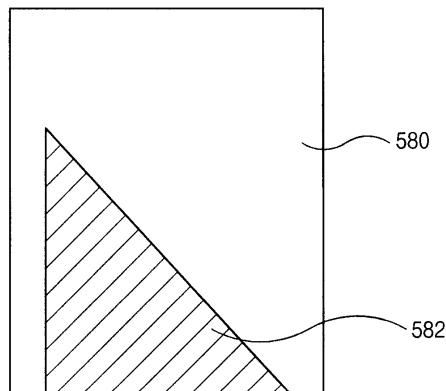

[0105] 도 7c에 따른 반사부(532)는, 6면이 투과부(530)에 둘러싸여 있는 육각형상을 이루며, 도 7d에 따른 반사부(542)는, 8면이 투과부(540)에 둘러싸여 있는 팔각형상을 이룬다.

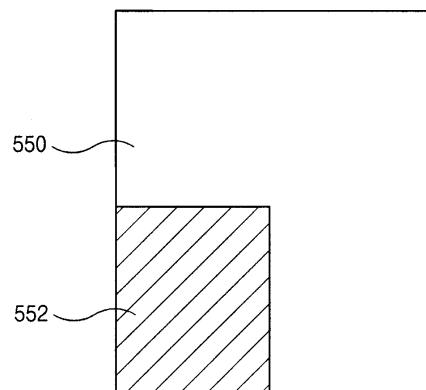

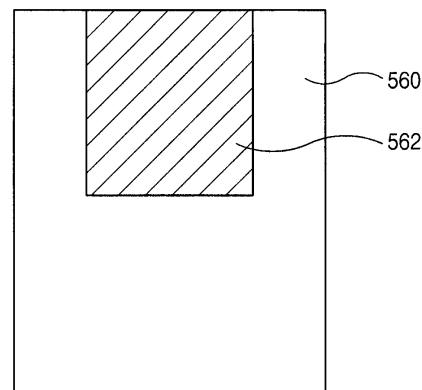

[0106] 그리고, 도 7e, 7f는 상기 도 7a와 같은 형상의 반사부(512) 형상의 위치를 변형한 예로서, 도 7e는 투과부(550)의 한 모서리부에 반사부(552)가 위치하며, 상기 반사부(552)의 2면이 투과부(550)에 의해 둘러싸여 있는 구조를 가지고, 도 7f는 투과부(560)의 일측 중앙부에 반사부(562)가 위치하여, 상기 반사부(562)의 3면이 투과부(560)에 의해 둘러싸여 있는 구조를 가진다.

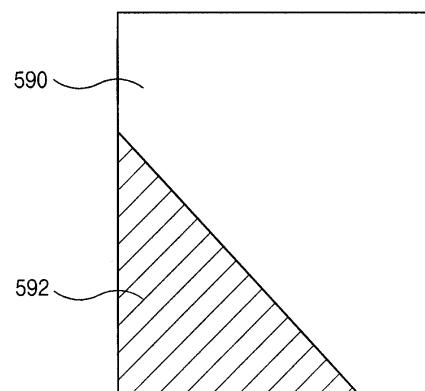

[0107] 도 7g 내지 7i는 반사부(572, 582, 592, 612, 622)가 직각삼각형상을 가지는 것을 특징으로 하며, 상기 도 7g는 투과부(570) 영역 내에서, 반사부(572)의 두변이 투과부(570)의 두변과 대응되게 위치하는 것을 특징으로 하고, 도 7h는 투과부(580)의 일측부에서, 반사부(582)의 2면이 투과부(580)에 의해 둘러싸여 있는 것을 특징으로 하고, 도 7i에서는 상기 도 7g를 기준으로 봤을 때, 반사부(590)와 투과부(592)의 두변이 서로 일치되게 배치되어 있다.

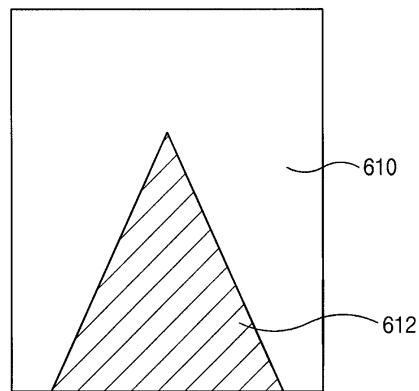

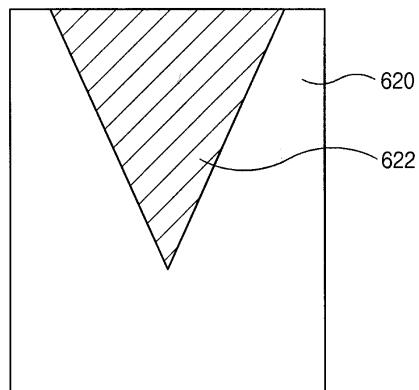

[0108] 그리고, 도 7j, 7k에 따른 반사부(612, 622)는 이등변삼각형상을 가지는 것을 특징으로 하며, 도 7j는 투과부(610)의 일측부에 반사부(612)가 위치하여, 반사부(612)의 2면이 투과부(610)에 의해 둘러싸여 있는 예이고, 도 7k는, 상기 도 7j에서 언급한 일측부와 마주보는 일측부에 반사부(622)가 위치하여, 반사부(622)의 2면이 투과부(620)에 의해 둘러싸여 있는 구조에 대한 예이다.

[0109] -- 제 6 실시예 --

[0110] 본 실시예는, COT 구조 반투과형 액정표시장치에 있어서, 별도의 공정추가없이 반사부와 투과부간의 색재현율 특성을 일정하게 유지할 수 있는 베피패턴을 반사부에 추가로 가지는 것을 특징으로 한다.

[0111] 도 8은 본 발명의 제 6 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도로서, 상기 제 1 실시예의 기본 구조를 적용하며, 본 실시예의 핵심적인 구조인 반사부의 적층구조를 중심으로 설명한다.

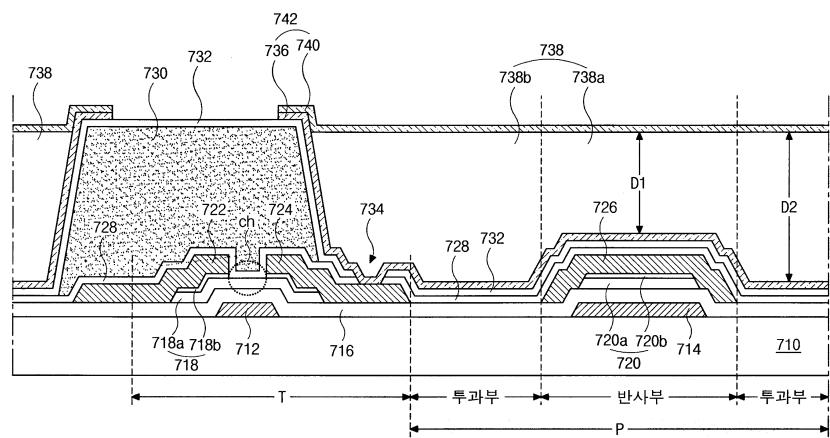

[0112] 도시한 바와 같이, 기판(710) 상에는 게이트 전극(712)과, 게이트 전극(712)과 일정간격 이격되어, 상기 게이트 전극(712)과 동일 물질로 이루어진 제 1 베피패턴(714)이 형성되어 있고, 게이트 전극(712) 및 제 1 베피패턴(714)을 덮는 기판 전면에는 게이트 절연막(716)이 형성되어 있다.

[0113] 그리고, 상기 게이트 절연막(716) 상부의 게이트 전극(712)을 덮는 위치에는 반도체층(718)이 형성되어 있고, 상기 제 1 베피패턴(714)을 덮는 위치에는 상기 반도체층(718)과 동일 물질로 이루어진 제 2 베피패턴(720)이 형성되어 있다.

[0114] 상기 반도체층(718)은 비정질 실리콘 물질로 이루어진 액티브층(718a)과, 불순물 비정질 실리콘 물질로 이루어진 오믹콘택층(718b)이 차례대로 적층된 구조로 이루어지며, 상기 제 2 베피패턴(720)은 비정질 실리콘 물질로 이루어진 제 2a 베피패턴(720a)과, 불순물 비정질 실리콘 물질로 이루어진 제 2b 베피패턴(720b)으로 이루어진 것을 특징으로 한다.

- [0115] 상기 반도체층(718) 상부에는 서로 이격되게 소스 전극(722) 및 드레인 전극(724)이 형성되어 있고, 상기 제 2 베피패턴(720) 상부에는 소스 전극(722) 및 드레인 전극(724)과 동일 물질로 이루어진 반사판(726)이 형성되어 있다.

- [0116] 상기 소스 전극(722)과 드레인 전극(724) 사이 이격구간에는 액티브층(718a)이 노출되어, 노출된 액티브층(718a) 영역은 채널(ch ; channel)을 이룬다.

- [0117] 상기 게이트 전극(712), 반도체층(718), 소스 전극(722) 및 드레인 전극(724)은 박막트랜지스터(T)를 이루며, 상기 박막트랜지스터(T) 및 반사판(726)을 덮는 기판 전면에는 제 1 보호층(728)이 형성되어 있고, 상기 제 1 보호층(728) 상부의 박막트랜지스터(T)를 덮는 위치에는 블랙매트릭스(730)가 형성되어 있으며, 블랙매트릭스(730)를 덮는 기판 전면에는 제 2 보호층(732)이 형성되어 있다.

- [0118] 상기 제 1, 2 보호층(728, 732)에는, 상기 드레인 전극(724)을 일부 노출시키는 드레인 콘택홀(734)이 형성되어 있고, 상기 제 2 보호층(732) 상부에는 드레인 콘택홀(734)을 통해 드레인 전극(724)과 연결되는 제 1 투명 전극(736)이 형성되어 있고, 제 1 투명 전극(736) 상부에는 블랙매트릭스(730)를 컬러별 경계부로 하여 컬러필터(738)가 형성되어 있고, 상기 컬러필터(738) 상부에는 상기 제 1 투명 전극(736)과 접촉되는 제 2 투명 전극(740)이 형성되어 있으며, 상기 제 1, 2 투명 전극(736, 740)은 화소 영역별로 패터닝되어 있으며, 상기 제 1, 2 투명 전극(736, 740)은 화소 전극(742)을 이룬다.

- [0119] 상기 반사판(726)과 대응된 화소 영역(P)은 반사부를 이루고, 그외 제 1, 2 투명 전극(736, 740)과 컬러필터(738)와 절연층(716, 728, 732)만의 적층구조로 이루어지는 화소 영역(P)은 투과부를 이룬다.

- [0120] 본 실시예에서는, 소스 전극(722) 및 드레인 전극(724)과 동일공정에서 동일 물질을 이용하여 형성된 반사판(726)을 포함함에 있어서, 게이트 공정 및 반도체 공정과 동일공정에서 동일물질로 형성된 형성된 제 1, 2 베피패턴(714, 720)을 반사판 하부에 형성함에 따라, 반사부 컬러필터(738a)의 두께(D1)를 투과부 컬러필터(738b)의 두께(D2)보다 일정 두께 얇게 형성함에 따라, 빛의 진행경로 차이에 따른 반사부 컬러필터(738a)와 투과부 컬러필터(738b)간의 색재현율 차이를 최소화할 수 있다. 더욱이, 본 실시예에서는 별도의 공정추가없이 색재현율을 보정용 베피 패턴(714, 720)을 형성할 수 있는 것을 특징으로 한다.

- [0121] -- 제 7 실시예 --

- [0122] 본 실시예는, 상기 제 6 실시예보다 저마스크 COT 구조 반투과형 액정표시장치에서의 색재현율을 보정용 베피패턴을 구비한 반사판을 포함한 것을 특징으로 한다.

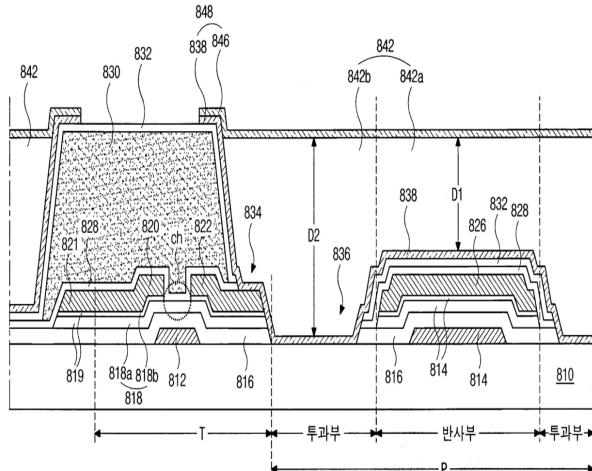

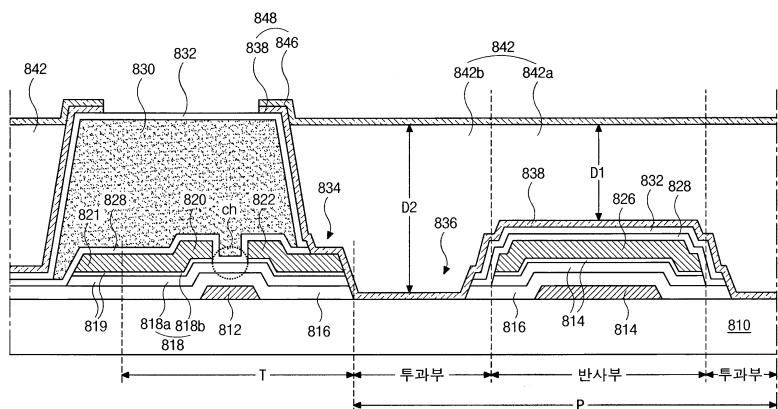

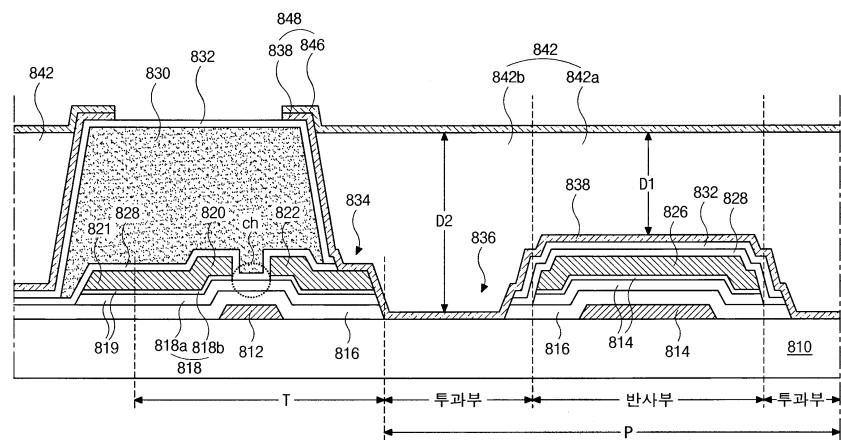

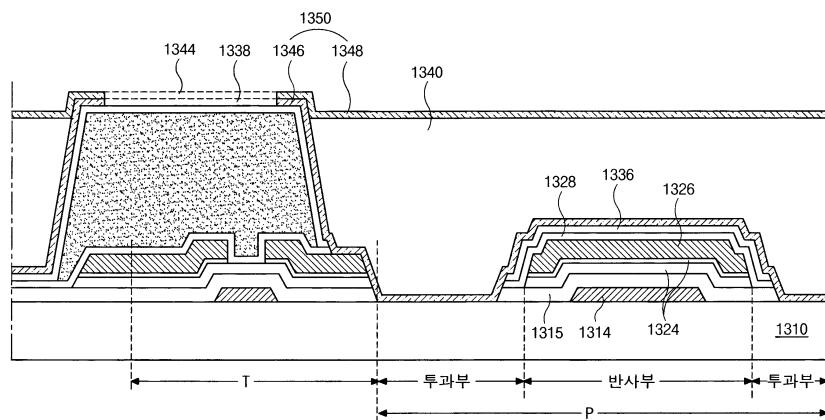

- [0123] 도 9는 본 발명의 제 7 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도이다.

- [0124] 도시한 바와 같이, 기판(810) 상에는 게이트 전극(812)과, 게이트 전극(812)과 일정간격 이격되어, 상기 게이트 전극(812)과 동일 물질로 이루어진 제 1 베피패턴(814)이 형성되어 있고, 게이트 전극(812) 및 제 1 베피패턴(814)을 덮는 영역에는 게이트 절연막(816)이 형성되어 있다.

- [0125] 그리고, 상기 게이트 절연막(816) 상부의 게이트 전극(812)을 덮는 위치에는 반도체층(818)과, 반도체층(818)과 대응된 패턴 구조로 서로 이격되게 소스 전극(820) 및 드레인 전극(822)이 형성되어 있고, 상기 제 1 베피패턴(814)을 덮는 위치에는 상기 반도체층(818), 소스 전극(820) 및 드레인 전극(822)과 동일 물질로 이루어지며, 서로 대응된 패턴 구조를 가지는 제 2 베피패턴(824), 반사판(826)이 차례대로 형성되어 있다.

- [0126] 그리고, 상기 소스 전극(820)과 연결되어 데이터 배선(821)이 형성되어 있고, 데이터 배선(821)의 하부에는 대응된 패턴 구조를 이루며, 상기 반도체층(818)과 동일한 물질로 이루어진 반도체 물질층(819)이 형성되어 있다.

- [0127] 상기 반도체층(818)은 액티브층(818a), 오믹콘택층(818b)이 차례대로 적층된 구조로 이루어지고, 상기 소스 전극(820) 및 드레인 전극(822) 사이구간에는 액티브층(818a)이 노출되어 노출된 액티브층(818a) 영역은 채널(channel)을 이룬다.

- [0128] 상기 게이트 전극(812), 반도체층(818), 소스 전극(820), 드레인 전극(822)은 박막트랜지스터(T)를 이룬다.

- [0129] 상기 박막트랜지스터(T) 및 반사판(826)을 덮는 영역에는 제 1 보호층(828)이 형성되어 있고, 제 1 보호층(828) 상부의 박막트랜지스터(T)를 덮는 영역에는 블랙매트릭스(830)가 형성되어 있으며, 상기 블랙매트릭스(830)를 덮는 영역에는 제 2 보호층(832)이 형성되어 있다.

- [0130] 상기 제 1, 2 보호층(828, 832)에는 드레인 전극(822)을 일부 노출시키는 제 1 오픈부(834)가 형성되어 있고, 상기 제 1 오픈부(834)는 화소 영역(P)에서 반사판(826) 형성부를 제외한 투과부에서 기판을 노출시키는 제 2 오픈부(836)와 연결되게 형성되어 있다.

- [0131] 상기 제 2 보호층(832) 및 제 1 오픈부(834)를 통해 드레인 전극(822)과 접촉된 영역에는 제 1 투명 전극(838)이 형성되어 있고, 제 1 투명 전극(838)을 덮는 영역에는 블랙매트릭스(830)를 컬러별 경계부로 하여 컬러필터(842)가 형성되어 있고, 컬러필터(842) 상부에는 제 1 투명 전극(838)과 접촉되어 제 2 투명 전극(846)이 형성되어 있다.

- [0132] 상기 제 1, 2 투명 전극(838, 846)은 화소 전극(848)을 이룬다.

- [0133] 상기 반사판(826)과 대응된 화소 영역(P)은 반사부를 이루고, 그외 화소 영역(P)은 투과부를 이룬다.

- [0134] 본 실시예에서는, 소스 전극(820) 및 드레인 전극(822)과 동일공정에서 동일 물질을 이용하여 형성된 반사판(826)을 포함함에 있어서, 게이트 공정에서 형성된 제 1 베퍼페蹲(814)과 반도체 및 소스/드레인 일체 공정에서 형성된 제 2 베퍼페蹲(824) 그리고, 제 2 오픈부(836) 공정에 의해 반사부 컬러필터(842a)와 투과부 컬러필터(842b)의 두께차(D2-D1)는 상기 제 6 실시예보다 큰 값을 가진다.

- [0135] 또한, 본 실시예에서는 게이트 공정에서 형성되는 제 1 베퍼페蹲(814)을 생략한 구조를 포함할 수 있다.

- [0136] -- 제 8 실시예 --

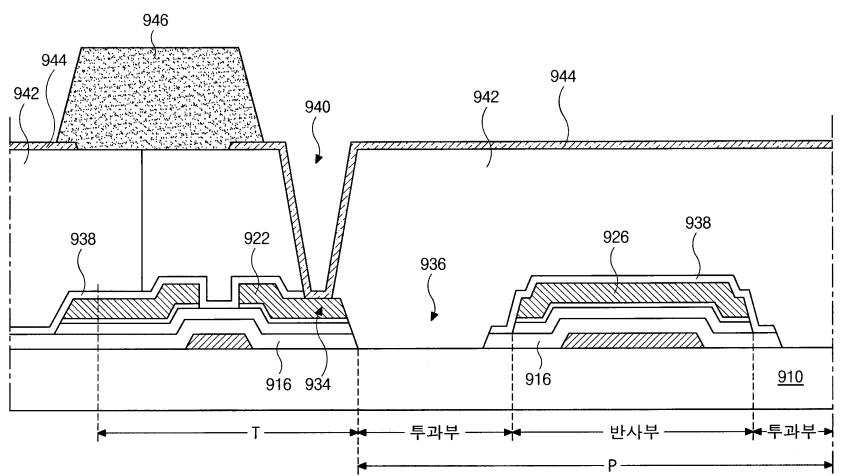

- [0137] 도 10a 내지 10e는 본 발명의 제 8 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도로서, 컬러필터 및 블랙매트릭스의 배치 구조를 다양하게 변형한 예에 대한 것이다.

- [0138] 도 10a 내지 10d의 박막트랜지스터 및 반사판의 적층 구조는 상기 제 7 실시예에 따른 구조를 동일하게 적용할 수 있으므로, 이에 대한 구체적인 설명은 생략한다.

- [0139] 도 10a는, 기판(910) 상에 형성된 박막트랜지스터(T) 및 반사판(926)을 덮는 위치에 형성되며, 드레인 전극(922)을 일부 노출시키는 제 1 오픈부(934)와, 게이트 절연막(916)과 함께 반사판(926) 형성부를 제외한 투과부 영역에서 기판(910)을 노출시키는 제 2 오픈부(936)를 가지는 제 1 보호층(938)이 형성되어 있다.

- [0140] 상기 제 1 보호층(938) 상부에는 화소 영역(P)별로 형성되며, 상기 제 1 오픈부(934)와 대응되는 위치에서 콘택홀(940)을 가지는 컬러별 컬러필터(942 ; 적, 녹, 청)가 형성되어 있고, 상기 컬러필터(942) 상부에는 콘택홀(940) 및 제 1 오픈부(934)를 통해 드레인 전극(922)과 연결되는 화소 전극(944)이 화소 영역(P)별로 형성되어 있고, 화소 전극(944) 상부의 박막트랜지스터(T)를 덮는 영역에는 블랙매트릭스(946)가 형성되어 있다.

- [0141] 상기 제 7 실시예 도면과 비교시, 블랙매트릭스용 보호층인 제 2 보호층 및 하나의 투명 전극 공정을 생략할 수 있어, 보다 단순화된 공정을 제공할 수 있는 잇점을 가진다.

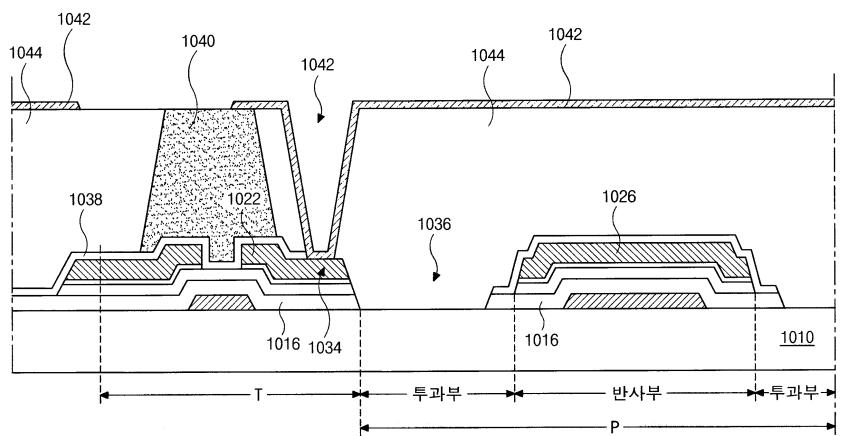

- [0142] 도 10b에서는, 박막트랜지스터(T) 및 반사판(1026)을 덮는 영역에 위치하며, 드레인 전극(1022)을 일부 노출시키는 제 1 오픈부(1034) 및 게이트 절연막(1016)과 함께 반사부를 제외한 투과부에서 기판(1010)을 노출시키는 제 2 오픈부(1036)를 일체형으로 가지는 제 1 보호층(1038)이 형성되어 있고, 제 1 보호층(1038) 상부의 박막트랜지스터(T)를 덮는 영역에는 블랙매트릭스(1040)가 형성되어 있고, 상기 블랙매트릭스(1040)를 컬러별 경계부로 하여 별도의 보호층없이 블랙매트릭스(1040)와 측면접촉되게 형성되며, 상기 제 1 오픈부(1034)와 대응된 위치에서 콘택홀(1042)을 가지는 컬러필터(1044 ; 적, 녹, 청)가 형성되어 있고, 컬러필터(1044) 및 블랙매트릭스(1040) 상부에는 상기 콘택홀(1042)을 통해 드레인 전극(1022)과 연결되는 화소 전극(1042)이 형성되어 있다.

- [0143] 상기 블랙매트릭스(1040) 물질은 크롭게 금속물질에서 선택됨에 따라 별도의 보호층을 구비하지 않는 것을 특징으로 하며, 이에 따라 별도의 블랙매트릭스용 보호층 공정이 생략되고, 또한 컬러필터에 콘택홀을 형성하는 방법으로 또 하나의 투명 전극 공정을 생략함에 따라, 공정을 보다 단순화시키는 잇점을 가진다.

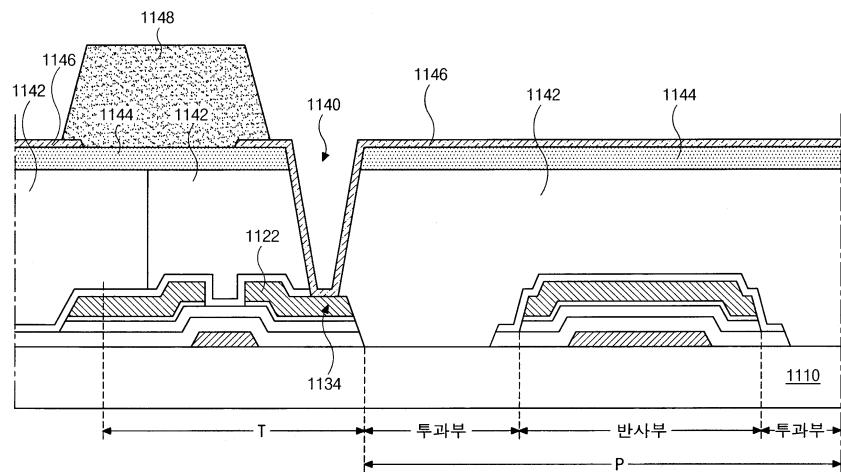

- [0144] 도 10c는, 상기 도 10a에 대한 변형예로서, 컬러필터(1142)와 화소 전극(1146) 사이에 평탄화를 위한 목적으로 평탄화막(1144)이 개재된 것을 특징으로 하며, 상기 평탄화막(1144)은 컬러필터(1142)와 함께 제 1 오픈부

(1134)와 대응된 위치에서 콘택홀(1140)을 가지고, 상기 평탄화막(1144) 상부에 콘택홀(1140)을 통해 드레인 전극(1122)과 연결되는 화소 전극(1146)이 형성되어 있고, 상기 화소 전극(1146) 상부의 박막트랜지스터(T)를 덮는 위치에는 블랙매트릭스(1148)가 형성되어 있다.

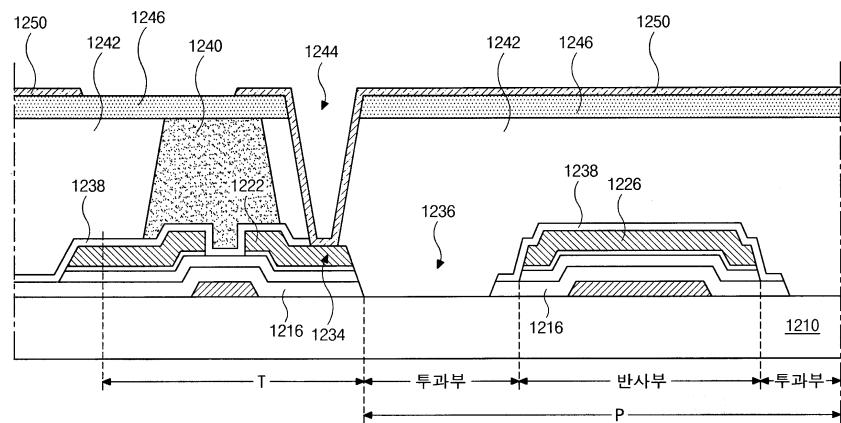

[0145] 도 10d는, 상기 10a 내지 10c를 병합한 예로서, 박막트랜지스터(T) 및 반사판(1226)을 덮는 위치에는 드레인 전극(1222)을 일부 노출시키는 제 1 오픈부(1234) 및 게이트 절연막(1216)과 함께 투과부에서 기판(1210)을 노출시키는 제 2 오픈부(1236)를 일체형으로 가지는 보호층(1238)이 형성되어 있고, 보호층(1238) 상부의 박막트랜지스터(T)를 덮는 위치에는 블랙매트릭스(1240)가 형성되어 있으며, 블랙매트릭스(1240)를 컬러별 경계부로 하여 컬러필터(1242 ; 적, 녹, 청)가 형성되어 있고, 컬러필터(1242) 및 블랙매트릭스(1240)를 덮는 위치에는, 상기 컬러필터(1242)와 함께 제 1 오픈부(1234)와 대응된 위치에서 콘택홀(1244)을 가지는 평탄화막(1246)이 형성되어 있고, 평탄화막(1248) 상부에는 콘택홀(1244) 및 제 1 오픈부(1234)를 통해 드레인 전극(1222)과 연결되는 화소 전극(1250)이 형성되어 있다.

[0146] -- 제 9 실시예 --

[0147] 본 실시예는, 본 발명의 대표적인 실시예라고 할 수 있는 제 7 실시예에 따른 COT 구조 반투과형 액정표시장치의 제조 공정에 대한 것이다.

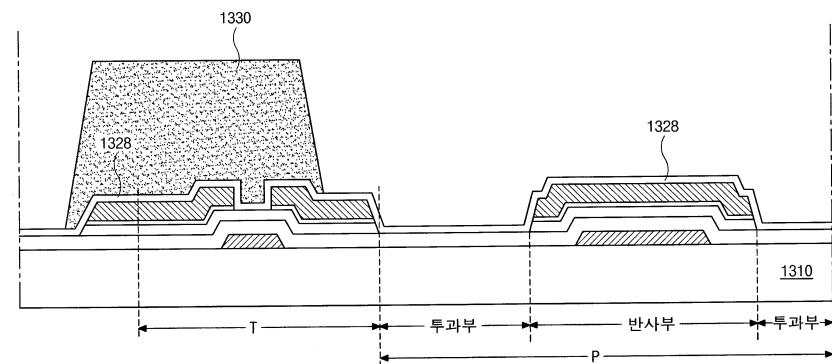

[0148] 도 11a 내지 11h는 본 발명의 제 9 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 제조 공정을 단계별로 나타낸 단면도로서, 마스크 공정을 중심으로 도시하였다.

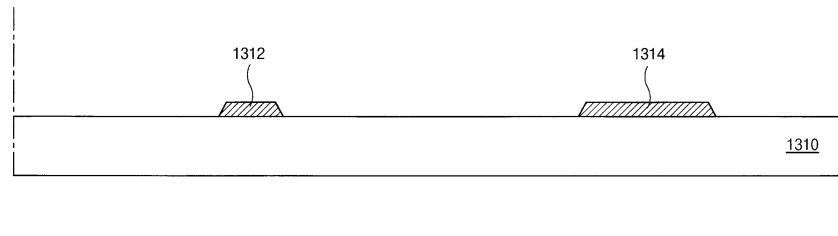

[0149] 도 11a는, 기판(1310) 상에 제 1 금속물질을 이용한 제 1 마스크 공정에 의해, 게이트 전극(1312) 및 게이트 전극(1312)과 일정간격 이격된 제 1 베퍼페蹲(1314)을 형성하는 단계이다.

[0150] 상기 제 1 금속물질은 비저항값이 낮은 금속물질에서 선택되며, 바람직하게는 알루미늄을 포함하는 금속물질에서 선택되는 것이다.

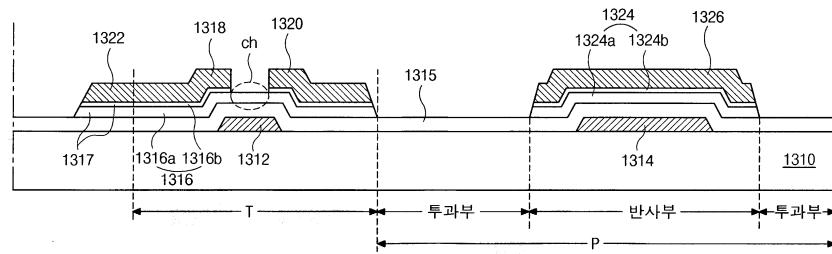

[0151] 도 11b는, 상기 게이트 전극(1312) 및 제 1 베퍼페蹲(1314)을 덮는 영역에 제 1 절연물질, 비정질 실리콘 물질, 불순물 비정질 실리콘 물질, 제 2 금속물질을 연속적으로 형성한 다음, 상기 제 1 절연물질은 게이트 절연막(1315)으로 삼고, 제 2 마스크 공정에 의해, 비정질 실리콘 물질, 불순물 비정질 실리콘 물질, 제 2 금속물질을 일괄식각하여, 비정질 실리콘 물질, 불순물 비정질 실리콘 물질로 이루어진 반도체층(1316)과, 반도체층(1316)과 대응되는 패턴 구조를 가지는 소스 전극(1318) 및 드레인 전극(1320) 그리고, 소스 전극(1318)과 연결되는 데이터 배선(1322) 그리고, 상기 제 1 베퍼페蹲(1314)을 덮는 위치에 제 2 베퍼페蹲(1324) 및 제 2 베퍼페蹲(1324)과 대응되는 패턴 구조를 가지는 반사판(1326)을 형성하는 단계이다.

[0152] 상기 제 2 금속물질은, 상기 소스 전극(1318) 및 드레인 전극(1320)외에 반사판(1326) 겸용으로 이용되기 때문에, 화학성 내식성이 강한 특성뿐만 아니라 반사특성이 우수한 금속물질에서 선택되는 것이 바람직하며, 이러한 금속물질로는 알루미늄을 다중층 금속물질(몰리브덴(Mo), 텉스텐(W), 니켈(Ni), 티탄(Ti) 등)을 들 수 있다.

[0153] 상기 비정질 실리콘 물질은 반도체층(1316)의 액티브층(1316a)과, 제 2 베퍼페蹲(1324)의 제 2a 베퍼페蹲(1324a)을 이루고, 상기 불순물 비정질 실리콘 물질은 반도체층(1316)의 오믹콘택층(1316b)과, 제 2 베퍼페蹲(1324)의 제 2b 베퍼페蹲(1324b)을 이룬다. 그외, 상기 비정질 실리콘 물질 및 불순물 실리콘 물질은 데이터 배선(1322)의 하부에서 데이터 배선(1322)과 대응된 패턴구조를 이루는 반도체 물질층(1317)을 이룬다.

[0154] 이 단계에서는, 상기 소스 전극(1318)과 드레인 전극(1320) 이격구간에서, 마스크 공정에 이용되는 감광성 물질인 포토레지스트(photoresist)의 두께치를 선택적으로 조절할 수 있는 슬릿(slit)패턴 또는 하프톤(half tone) 마스크를 배치하여, 상기 소스 전극(1318) 및 드레인 전극(1320) 사이 이격구간의 오믹콘택층(1316b) 만을 선택적으로 제거하여, 그 하부층을 이루는 액티브층(1316a)을 노출하여, 노출된 액티브층(1316a) 영역을 채널(ch)로 형성하는 단계를 포함한다.

[0155] 상기 게이트 전극(1312), 반도체층(1316), 소스 전극(1318) 및 드레인 전극(1320)은 박막트랜지스터(T)를 이루고, 박막트랜지스터(T)와 인접하여 화면을 구현하는 최소단위인 화소 영역(P)이 정의되어 있으며, 화소 영역(P)은 반사판(1326)과 대응된 영역으로 정의되는 반사부와 그외 화소 영역(P)인 투과부로 이루어진다.

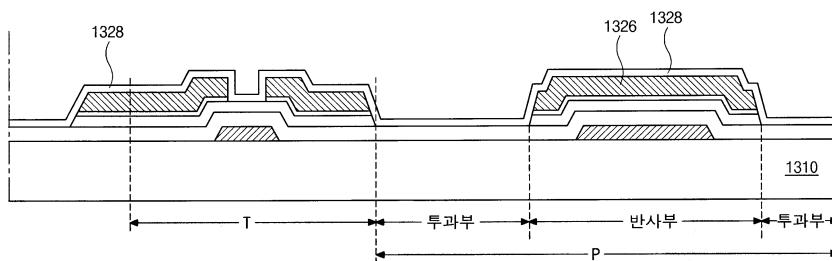

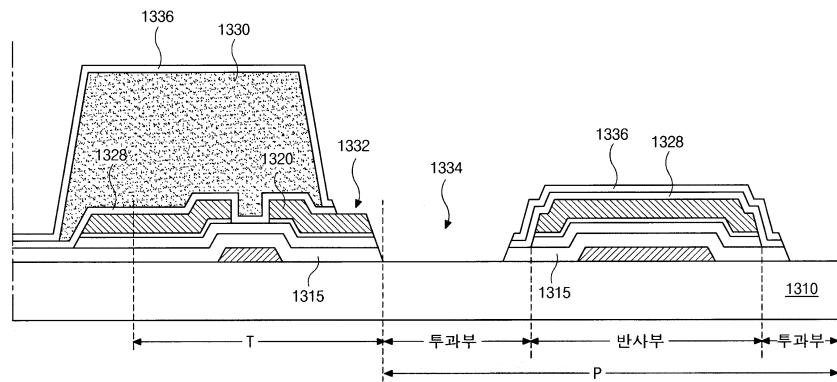

[0156] 도 11c에서는, 상기 박막트랜지스터(T) 및 반사판(1326)을 덮는 영역에 제 2 절연물질을 이용하여 제 1 보호층

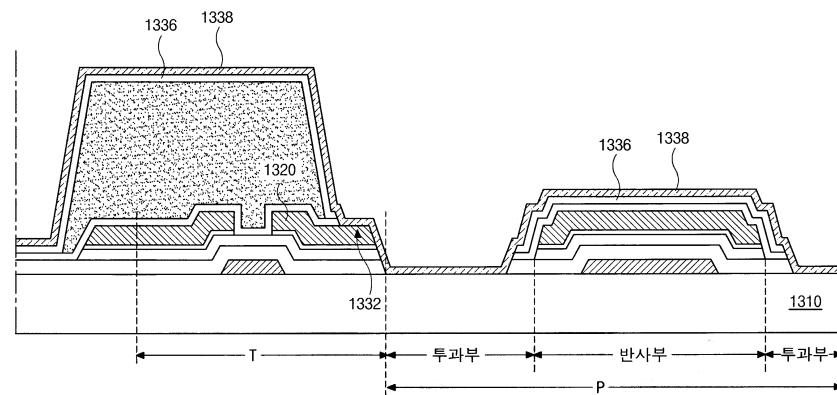

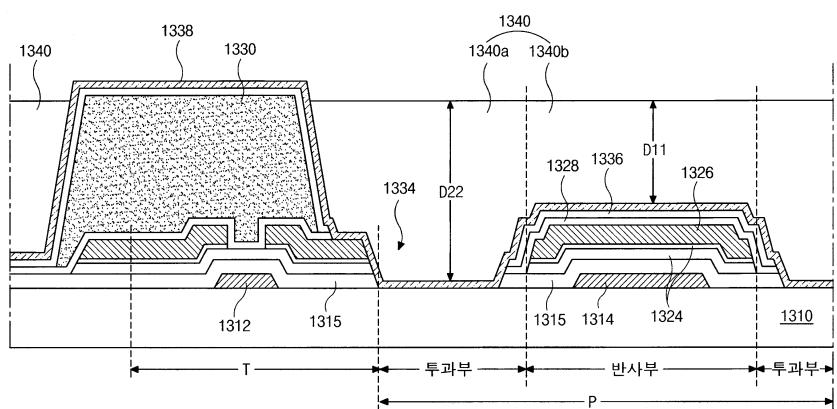

(1328)을 형성하는 단계이고, 도 11d는 제 1 보호층(1328) 상부의 박막트랜지스터(T)를 덮는 위치에 광차단성 물질을 이용한 제 3 마스크 공정에 의해 블랙매트릭스(1330)를 형성하는 단계이고, 도 11e는 상기 블랙매트릭스(1330)를 덮는 기판 전면에 제 3 절연물질을 이용한 제 4 마스크 공정에 의해, 상기 제 1 보호층(1328)과 함께 드레인 전극(1320)을 일부 노출시키는 제 1 오픈부(1332) 및 상기 제 1 오픈부(1332)와 일체형을 이루며, 상기 제 1 보호층(1328), 게이트 절연막(1315)과 함께 전술한 화소 영역(P)의 투과부 영역의 기판(1310)을 노출시키는 제 2 오픈부(1334)를 가지는 제 2 보호층(1336)을 형성하는 단계이다.

[0157] 도 11f에서는, 상기 제 2 보호층(1336) 상부에 투명 전도성 물질을 이용하여, 상기 제 1 오픈부(1332)를 통해 드레인 전극(1320)과 연결되는 제 1 투명 전극 물질층(1338)을 형성하는 단계이고, 도 11g에서는, 상기 제 1 투명 전극 물질층(1338) 상부에 컬러 안료를 이용한 제 5 마스크 공정에 의해 블랙매트릭스(1330)를 컬러별 경계부로 하여 컬러필터(1340)를 형성하는 단계이다.

[0158] 도면으로 상세히 제시하지는 않았지만, 상기 컬러필터(1340)를 화소 영역(P)별로 적, 녹, 청 컬러필터를 순서대로 형성하는 방법에 의해 이루어진다.

[0159] 본 실시예에서는, 상기 반사부에는 제 1 베퍼패턴(1314), 게이트 절연막(1315), 제 2 베퍼패턴(1324), 반사판(1326), 제 1, 2 보호층(1328, 1336)이 차례대로 적층된 구조물 상에 컬러필터(1340)가 형성되지만, 상기 투과부는 전술한 패턴들을 모두 제거한 제 2 오픈부(1334) 상에 컬러필터(1340)를 형성하기 때문에, 반사부 컬러필터(1340a)의 두께(D11)를 투과부 컬러필터(1340b)의 두께(D22)보다 선택적으로 얇게 형성함에 따라, 반사부 컬러필터(1340a)와 투과부 컬러필터(1340b)의 빛의 경로차이에 의한 색재현을 차이를 최소화할 수 있다.

[0160] 도 11h에서는, 상기 컬러필터(1340) 상부에 제 1 투명 전극 물질층(1338)과 접촉되게 투명 도전성 물질을 이용하여 제 2 투명 전극 물질층(1344)을 형성한 다음, 제 6 마스크 공정에 의해 상기 제 1, 2 투명 전극 물질층(1338, 1344)을 화소 영역(P)별로 패터닝하여 제 1, 2 투명 전극(1346, 1348)으로 형성하는 단계이고, 상기 제 1, 2 투명 전극(1346, 1348)은 화소 전극(1350)을 이룬다.

[0161] 상기 제 1, 2 투명 전극(1346, 1348)을 이루는 투명 도전성 물질은 ITO(indium tin oxide)에서 선택되는 것이 바람직하다.

[0162] 그러나, 본 발명은 상기 실시예들로 한정되지 않고, 본 발명의 취지를 벗어나지 않는 한도 내에서 다양하게 변경가능하다.

### 발명의 효과

[0163] 이와 같이, 본 발명에 따른 COT 구조 반투과형 액정표시장치에 의하면, 첫째 별도의 공정추가없이 박막트랜지스터를 이루는 전극 물질과 동일 공정에서 반사판을 형성하기 때문에, 별도의 반사판 제조 공정을 생략할 수 있고, 둘째 박막트랜지스터의 제조 공정에서, 반사판의 베퍼 패턴을 동시에 형성함에 따라, 반사부 컬러필터와 투과부 컬러필터 간의 색재현을 차이를 최소화함에 따라, 화질 특성을 향상시킬 수 있으며, 셋째 상기 반사판의 디자인을 다양하게 변경할 수 있어, 반사부와 투과부의 면적비를 원하는 비율로 조절하는 것이 용이하다.

### 도면의 간단한 설명

[0001] 도 1은 종래의 반투과형 액정표시장치용 어레이 기판에 대한 단면도.

[0002] 도 2는 기존의 색재현율 조절용 투명막을 가지는 반투과형 액정표시장치에 대한 개략적인 단면도.

[0003] 도 3은 본 발명의 제 1 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도.

[0004] 도 4는 본 발명의 제 2 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도.

[0005] 도 5는 본 발명의 제 3 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도.

[0006] 도 6은 본 발명의 제 4 실시예에 따른 COT 구조 반투과형 액정표시장치용 기판에 대한 단면도.

[0007] 도 7a 내지 7k는 본 발명의 제 5 실시예에 따른 COT 방식 반투과형 액정표시장치용 화소부에 대한 개략적인 평

면도.

[0008] 도 8은 본 발명의 제 6 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도.

[0009] 도 9는 본 발명의 제 7 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도.

[0010] 도 10a 내지 10e는 본 발명의 제 8 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 단면도.

[0011] 도 11a 내지 11h는 본 발명의 제 9 실시예에 따른 COT 구조 반투과형 액정표시장치에 대한 제조 공정을 단계별로 나타낸 단면도.

[0012] <도면의 주요부분에 대한 간단한 설명>

[0013] 810 : 기판 812 : 게이트 전극

[0014] 814 : 제 1 벼퍼패턴 816 : 게이트 절연막

[0015] 818 : 반도체층 819 : 반도체 물질층

[0016] 820 : 소스 전극 821 : 데이터 배선

[0017] 822 : 드레인 전극 824 : 제 2 벼퍼패턴

[0018] 826 : 반사판 828 : 제 1 보호층

[0019] 830 : 블랙매트릭스 832 : 제 2 보호층

[0020] 834 : 제 1 오픈부 836 : 제 2 오픈부

[0021] 838 : 제 1 투명 전극 842 : 컬러필터

[0022] 842a : 반사부 컬러필터 842b : 투과부 컬러필터

[0023] 846 : 제 2 투명 전극 848 : 화소 전극

[0024] ch : 채널 T : 박막트랜지스터

[0025] D1 : 반사부 컬러필터의 두께 D2 : 투과부 컬러필터의 두께

도면

도면1

## 도면2

## 도면3

도면4

도면5

도면6

도면7a

도면7b

도면7c

도면7d

도면7e

도면7f

도면7g

도면7h

도면7i

도면7j

도면7k

도면8

도면9

도면10a

도면10b

### 도면 10c

도면 10d

## 도면11a

도면11b

도면11c

도면11d

도면11e

도면11f

도면11g

도면11h

|                |                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 透反液晶显示器                                                                                             |         |            |

| 公开(公告)号        | <a href="#">KR100945442B1</a>                                                                       | 公开(公告)日 | 2010-03-05 |

| 申请号            | KR1020030012615                                                                                     | 申请日     | 2003-02-28 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                            |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                           |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                           |         |            |

| [标]发明人         | KIM WOONGKWON<br>김용권<br>KIM SEJUNE<br>김세준                                                           |         |            |

| 发明人            | 김용권<br>김세준                                                                                          |         |            |

| IPC分类号         | G02F1/1335 G02F1/1333 G02F1/1343 G02F1/1362 G02F1/1368                                              |         |            |

| CPC分类号         | G02F1/1343 G02F1/1335 G02F1/1333 G02F1/1362 G02F2001/136222 G02F1/136227 G02F1/1368<br>G02F1/136209 |         |            |

| 其他公开文献         | KR1020040077161A                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                           |         |            |

## 摘要(译)

根据本发明的COT结构半透射型液晶显示装置，反射器在与包含薄膜晶体管的电极材料相同的工艺中形成，而没有第一次单独处理添加。因此，可以省略单独的反射器制造工艺。同时，由于在第二薄膜晶体管的制造过程中形成反射器的缓冲图案，因为穿透滤色器和反射体滤色器之间的色域差异被最小化，所以可以改善图像质量特性。第三，反射器的设计可以进行各种改变。便于以期望的速率控制透射部分和反射体的纵横比。