(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0050851

(43) 공개일자 2008년06월10일

(51) Int. Cl.

G02F 1/1343 (2006.01)

(21) 출원번호 10-2006-0121674

(22) 출원일자 2006년12월04일

심사청구일자 없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 범명자

유혜란

인천 서구 당하동 탑스빌아파트 115동 602호

유승후

경기 성남시 분당구 수내동 로얄팰리스 하우스빌

B-1202

(뒷면에 계속)

(74) 대리인

권혁수, 송윤호, 오세준

전체 청구항 수 : 총 13 항

#### (54) 액정표시패널

#### (57) 요 약

액정표시패널은 제1 화소전극과 제1 공통전극을 갖는 어레이 기판, 제2 화소전극과 제2 공통전극을 갖는 대향기판, 및 어레이 기판과 대향기판과의 사이에 개재된 액정층으로 이루어진다. 여기서, 제1 화소전극과 제1 공통전극과의 사이 및 제2 화소전극과 제2 공통전극과의 사이에는 서로 동일한 크기의 전계가 형성된다. 이에 따라, 액정표시패널의 구동 전압이 감소되고, 액정층의 굴절률 조절이 용이하며, 표시 품질이 향상된다.

**대표도** - 도1

(72) 발명자

강성민

경기 수원시 영통구 영통동 벽적골9단지아파트 90

3동 2005호

도희옥

경기 수원시 팔달구 매교동 179-99 수연아트빌 30

2호

김훈

경기 안산시 상록구 사동 대우푸르지오 7차 701동

1604호

문현철

서울 영등포구 당산동 삼성아파트 105동 903호

## 특허청구의 범위

### 청구항 1

영상을 표시하는 화소영역이 정의된 제1 베이스 기판과, 상기 화소영역에 형성되어 화소전압을 입력받는 제1 화소전극, 및 상기 화소영역에 형성되고 상기 제1 화소전극과 이격되어 위치하며 공통전압을 입력받는 제1 공통전극을 포함하는 어레이 기판;

상기 제1 베이스 기판과 마주하는 제2 베이스 기판과, 상기 제2 베이스 기판 상에서 상기 화소영역에 형성되고 상기 화소전압을 입력받는 제2 화소전극, 및 상기 제2 베이스 기판상에서 상기 화소영역에 형성되고 상기 제2 화소전극과 이격되어 위치하며 상기 공통전압을 입력받는 제2 공통전극을 포함하는 대향기판; 및

상기 어레이 기판과 상기 대향기판과의 사이에 개재된 액정층을 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 2

제1항에 있어서, 상기 제1 화소전극과 상기 제2 화소전극과의 사이에 개재되고, 상기 제1 화소전극과 상기 제2 화소전극을 전기적으로 연결하는 도전성 스페이서를 더 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 3

제1항에 있어서, 상기 제2 화소전극은 상기 제1 화소전극이 형성된 영역과 대응하는 영역에 형성된 것을 특징으로 하는 액정표시패널.

### 청구항 4

제3항에 있어서, 상기 제1 화소전극은,

제1 방향으로 연장되어 형성된 메인 화소전극; 및

상기 메인 화소전극으로부터 상기 제1 방향과 서로 다른 제2 방향으로 분기되어 형성되고, 서로 이격되어 위치하는 다수의 서브 화소전극을 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 5

제4항에 있어서, 상기 제2 화소전극은 상기 제1 화소전극과 동일한 형상을 갖는 것을 특징으로 하는 액정표시패널.

### 청구항 6

제4항에 있어서, 상기 제2 공통전극은 상기 제1 공통전극이 형성된 영역과 대응하는 영역에 형성된 것을 특징으로 하는 액정표시패널.

### 청구항 7

제6항에 있어서, 상기 제1 공통전극은,

상기 제1 방향으로 연장되어 형성되고, 상기 메인 화소전극과 마주하는 메인 공통전극; 및

상기 메인 공통전극으로부터 상기 제2 방향으로 분기되어 형성되고, 서로 이격되어 위치하는 다수의 서브 공통전극을 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 8

제7항에 있어서, 상기 서브 화소전극들과 상기 서브 공통전극들은 서로 교대로 위치하는 것을 특징으로 하는 액정표시패널.

### 청구항 9

제8항에 있어서,

상기 서브 화소전극들은 각각 제1 폭을 갖고,

상기 서브 공통전극들은 각각 제2 폭을 가지며,

서로 인접한 서브 화소전극과 서브 공통전극은 상기 제1 폭 또는 제2 폭과 실질적으로 동일한 거리로 이격된 것을 특징으로 하는 액정표시패널.

### 청구항 10

제9항에 있어서, 상기 제2 폭은 실질적으로 상기 제1 폭과 동일한 것을 특징으로 하는 액정표시패널.

### 청구항 11

제1항에 있어서, 상기 액정층은 블루상(Blue phase) 액정들을 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 12

제1항에 있어서, 상기 어레이 기판은,

상기 제1 베이스 기판상에 형성되고, 게이트 신호를 전송하는 게이트 라인;

상기 게이트 라인과 절연되어 교차하고, 상기 게이트 라인과 함께 상기 화소영역을 정의하며, 데이터 신호를 전송하는 데이터 라인; 및

상기 화소영역에 형성되고, 상기 게이트 라인과 상기 데이터 라인 및 상기 제1 화소전극과 전기적으로 연결된 스위칭 소자를 더 포함하는 것을 특징으로 하는 액정표시패널.

### 청구항 13

제12항에 있어서, 상기 어레이 기판은,

상기 게이트 라인과 동일한 방향으로 연장되어 형성되고, 상기 공통전압을 전송하며, 상기 제1 공통전극과 전기적으로 연결된 공통전압 라인을 더 포함하는 것을 특징으로 하는 액정표시패널.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<12>

본 발명은 액정표시패널에 관한 것으로, 더욱 상세하게는 고속 응답이 가능한 액정표시패널에 관한 것이다.

<13>

일반적으로, 액정표시장치는 영상을 표시하는 액정표시패널 및 액정표시패널에 광을 제공하는 백라이트 어셈블리를 포함한다.

<14>

액정표시패널은 어레이 기판, 어레이 기판과 마주보는 대향 기판 및 어레이 기판과 대향 기판과의 사이에 개재된 액정층으로 이루어지고, 어레이 기판에는 화소전극이 형성되며, 대향 기판에는 공통전극이 형성된다.

<15>

액정표시패널에 이용되는 액정으로는 네마틱(Nematic) 액정, 스멕틱 액정(smectic) 및 콜레스테릭(Cholesteric) 액정 등이 있으며, 네마틱 액정이 주로 이용된다. 이러한 네마틱 액정은 화소전극과 공통전극 사이에 형성된 전계에 따라 경사각이 조절되고, 액정층은 네마틱 액정의 경사각에 따라 광 투과율을 조절한다. 이에 따라, 액정표시패널의 휘도는 액정층의 두께의 두께, 즉, 액정표시패널의 셀 캡과 액정의 이방성 굴절률에 의해 결정된다. 이로 인해, 액정표시패널의 균일한 셀 캡이 요구되고, 액정의 이방성 굴절률로 인해 시야각이 저하된다.

<16>

이러한 시야각 저하 및 셀 캡 의존도를 극복하기 위해 블루상(Blue phase) 액정을 갖는 액정표시패널이 제안되고 있으며, 그 일례가 미국특허 4,767,149호에 개시되어 있다. 블루상 액정은 인가 전압의 크기에 따라 이방성 굴절률이 등방성으로 변하는 특성을 가지므로, 액정표시패널의 시야각 및 응답 속도를 향상시킬 수 있다. 그러나, 블루상 액정은 높은 구동 전압을 필요로 하는 단점이 있다.

#### 발명이 이루고자 하는 기술적 과제

<17> 본 발명의 목적은 구동 전압을 감소시킬 수 있는 액정표시패널을 제공하는 것이다.

### 발명의 구성 및 작용

<18> 상기한 본 발명의 목적을 실현하기 위한 하나의 특징에 따른 액정표시패널은, 어레이 기판, 대향기판 및 액정층으로 이루어진다.

<19> 어레이 기판은 제1 베이스 기판, 제1 화소전극 및 제1 공통전극을 구비한다. 제1 베이스 기판은 영상을 표시하는 적어도 하나의 화소영역이 어레이 형태로 정의된다. 제1 화소전극은 화소영역에 형성되어 화소전압을 입력받는다. 제1 공통전극은 화소영역에 형성되고, 제1 화소전극과 이격되어 위치하며, 공통전압을 입력받는다. 대향기판은 제2 베이스 기판, 제2 화소전극 및 제2 공통전극을 구비한다. 제2 베이스 기판은 상기 제1 베이스 기판과 마주한다. 제2 화소전극은 제2 베이스 기판상에 형성되고 화소영역에 위치하며, 화소전압을 입력받는다. 제2 공통전극은 상기 제2 베이스 기판상에 형성되고, 상기 화소영역에 위치한다. 제2 공통전극은 제2 화소전극과 이격되어 위치하고, 공통전압을 입력받는다. 한편, 액정층은 상기 어레이 기판과 상기 대향기판과의 사이에 개재된다.

<20> 또한, 액정표시패널은, 제1 화소전극과 제2 화소전극과의 사이에 개재되고, 제1 화소전극과 제2 화소전극을 전기적으로 연결하는 도전성 스페이서를 더 포함한다.

<21> 한편, 액정층은 블루상(Blue phase) 액정들을 포함한다.

<22> 이러한 액정표시패널에 따르면, 어레이 기판과 대향기판 각각 액정층을 제어하는 전극을 구비하므로, 액정층을 제어하기 위한 전계가 어레이 기판으로부터 대향기판까지 균일한 세기로 형성된다. 이에 따라, 액정표시패널의 구동 전압을 감소시키고, 액정층의 굴절률을 제어가 용이하며, 표시 품질을 향상시킬 수 있다.

<23> 이하, 첨부한 도면을 참조하여, 본 발명을 보다 상세하게 설명하고자 한다.

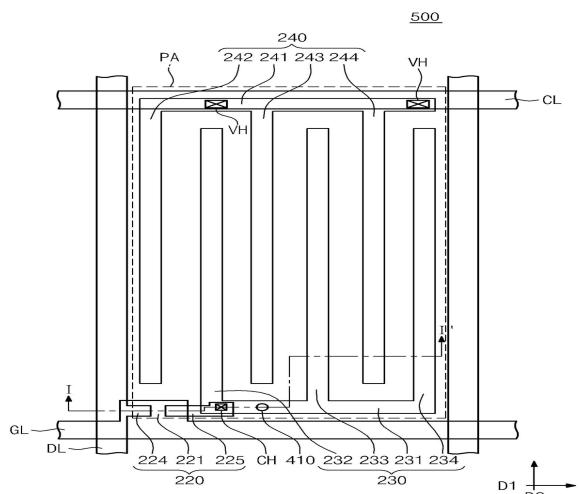

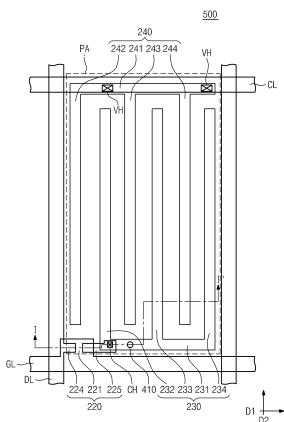

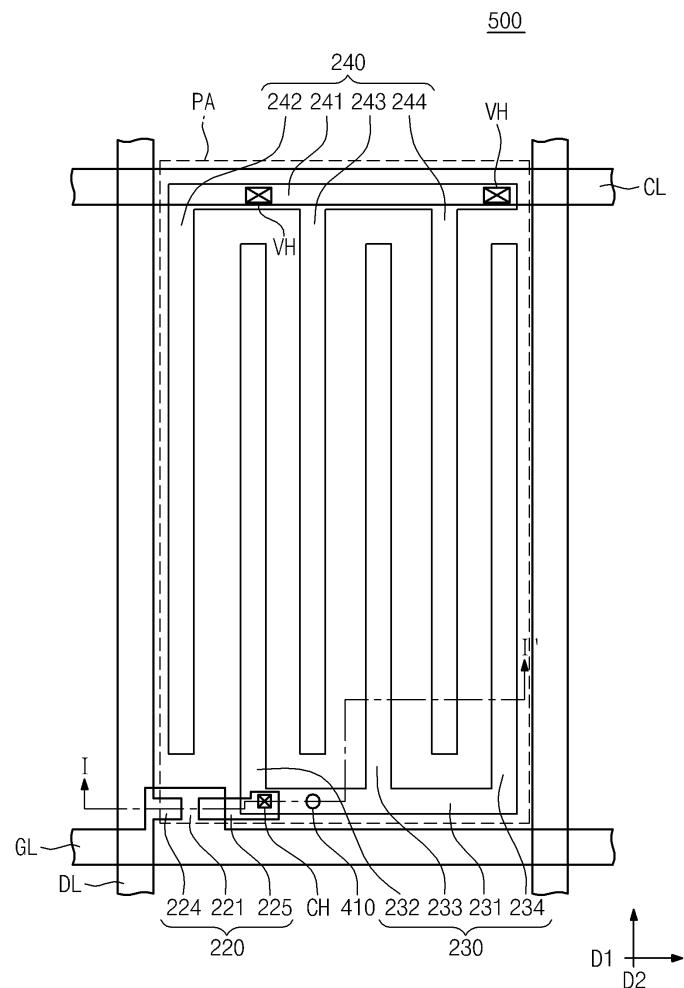

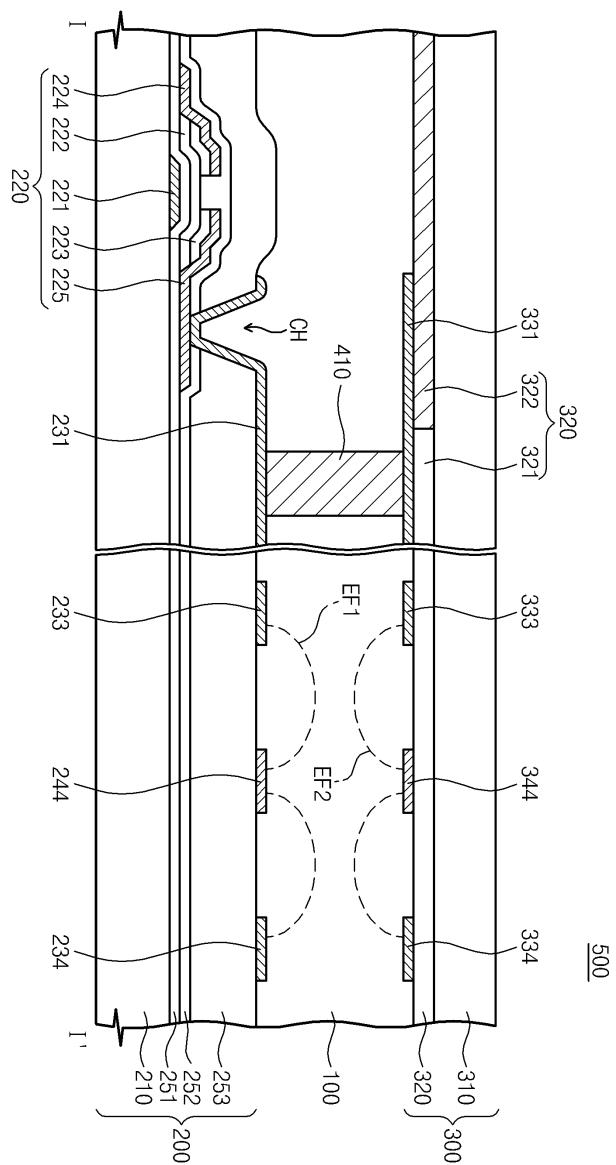

<24> 도 1은 본 발명의 일 실시예에 따른 액정표시패널을 나타낸 평면도이고, 도 2는 도 1의 절단선 I-I'에 따른 단면도이다.

<25> 도 1 및 도 2를 참조하면, 본 발명의 액정표시패널(500)은 액정층(100), 상기 액정층(100)의 아래에 구비된 어레이 기판(200), 및 상기 액정층(100)의 상부에 구비된 대향기판(300)을 포함한다.

<26> 상기 액정층(100)은 상기 어레이 기판(200)과 상기 대향기판(300)에 각각 입력된 공통전압과 화소전압에 의해 형성된 전계(EF1, EF2)에 따라 광 투과율을 조절한다. 즉, 상기 액정층(100)은 블루상(Blue Phase : BP) 액정들로 이루어지고, 상기 블루상 액정은 키랄 네마티상(chiral nematic phase)과 등방상(isotropic phase) 사이의 온도 영역에서 나타나는 액정상이다.

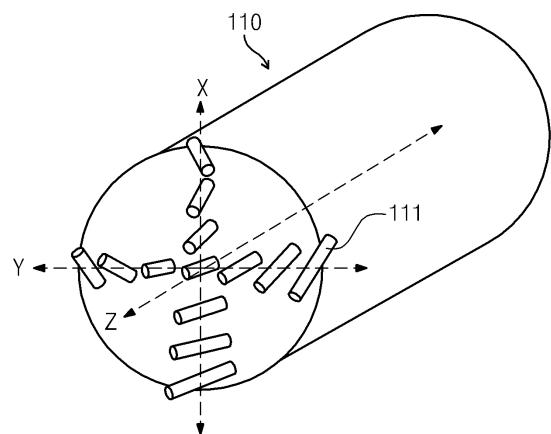

<27> 도 3은 블루상 액정의 구조를 나타낸 도면이다.

<28> 도 3을 참조하면, 상기 블루상 액정들은 원기둥 형상으로 배향되고, 이러한 배향 구조를 더블 트위스트 실린더(Double Twist Cylinder : 이하, DTC)(110) 구조라 한다. 상기 블루상 액정들은 상기 DTC(110)의 중심축(z 축)으로부터 외측 방향으로 갈수록 점점 꼬이게 배치된다. 즉, 상기 블루상 액정들은 상기 DTC(110) 내에서 서로 직교하는 두 개의 트위스트 축(x축, y축)을 따라 꼬이도록 배치된다. 이와 같이, 상기 블루상 액정들은 상기 DTC(110)의 중심축을 기준으로 상기 DTC(110) 내에서 방향성을 갖는다.

<29> 상기 블루상의 종류로는 제1 블루상(BP I)과 제2 블루상(BP II) 및 제3 블루상(BP III)이 있으며, 상기 DTC(110)는 상기 블루상의 종류에 따라 그 배치 구조가 달라진다.

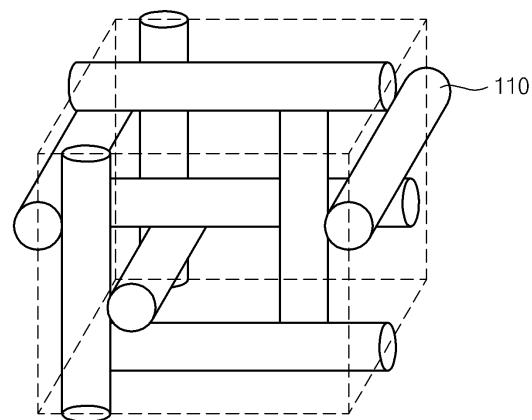

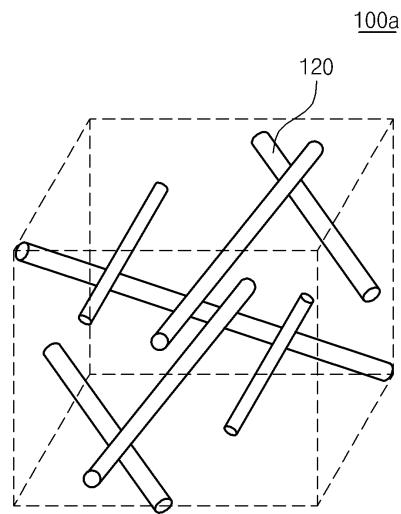

<30> 도 4는 제1 블루상의 구조를 나타낸 사시도이고, 도 5는 도 4에 도시된 제1 블루상의 선결함 라인을 나타낸 사시도이다.

<31> 도 4 및 도 5를 참조하면, 상기 제1 블루상(100a)은 DTC들이 격자 구조의 하나인 체심입방(Body-Centred Cubic : BCC) 구조로 배치된다. 도면에는 도시하지 않았으나, 상기 제2 블루상은 상기 DTC들이 단순입방(Simple-cubic) 구조로 배치된다. 이와 같이, 상기 블루상은 상기 DTC들이 격자 구조로 배치되므로, 서로 인접한 세 개의 DTC들이 만나는 부분에서 선결함(Disclination)이 발생한다. 상기 선결함은 액정들이 규칙적인 방향성을 갖지 않아서 불규칙하게 배열되는 부분으로서, 선결함 라인(120)을 형성한다.

<32> 본 발명의 일례로, 상기 액정층(100)은 고분자와 결합되어 안정화된 고분자 안정화 블루상(Polymer-Stabilized Blue Phase) 액정으로 이루어진다. 상기 고분자 안정화 블루상 액정은 고분자가 혼합된 블루상 액정으로서, 상

기 DTC들의 격자 구조가 안정된다. 즉, 블루상 액정에 고분자를 혼합하면, 고분자는 상기 DTC(110)를 이루는 액정들, 즉 방향성을 갖는 액정들보다 상기 선결함 라인(120)을 이루는 액정들, 즉, 방향성을 갖지 않는 액정들과 더 잘 결합한다. 이에 따라, 상기 선결함 라인(120)을 고정되어 상기 DTC들이 격자 구조가 안정화되고, 상기 블루상이 발현되는 온도 대역이 약 1°C 내지 약 5°C에서 약 60°C 이하로 확대된다.

<33> 이러한, 상기 블루상 액정은 인가된 전압의 크기에 따라 이방성 굴절률이 상기 인가 전압의 제곱에 비례하여 변한다. 이와 같이, 등방성 유극성 물질에 전계를 인가하였을 때 굴절률이 인가 전압의 제곱에 비례하는 광학 효과를 커 효과(Kerr effect)라 하고, 상기 액정표시패널(500)은 상기 블루상 액정의 커 효과를 이용하여 영상을 표시한다. 이에 따라, 상기 액정표시패널(500)은 응답 속도가 향상된다. 또한, 블루상 액정은 상기 전계가 형성되는 영역별로 굴절율이 결정된다. 따라서, 상기 전계가 형성되는 영역이 일정하게 형성되면, 셀 갭 균일도에 상관없이 균일한 휘도를 가지므로, 상기 액정표시패널(100)의 표시 특성을 향상시킬 수 있다. 또한, 상기 블루상 액정은 배향할 필요가 없으므로, 상기 액정표시패널(100)의 배향막을 구비할 필요가 없다.

<34> 다시, 도 1 및 도 2를 참조하면, 상기 어레이 기판(200)은 제1 베이스 기판(210), 상기 데이터 라인(DL), 게이트 라인(GL), 박막 트랜지스터(220), 제1 화소전극(230) 및 제1 공통전극(240)을 포함한다.

<35> 상기 제1 베이스 기판(210)은 상기 영상을 표시하는 적어도 하나의 화소영역(PA)이 어레이 형태로 정의된다. 상기 게이트 라인(GL)은 상기 제1 베이스 기판(210)의 상면에서 상기 제1 방향(D1)으로 연장되어 형성되고, 게이트 신호를 전송한다. 상기 데이터 라인(DL)은 상기 제1 방향(D1)과 직교하는 제2 방향(D2)으로 연장되어 형성되고, 데이터 신호를 전송한다. 상기 데이터 라인(DL)은 상기 게이트 라인(GL)과 절연되어 교차하고, 상기 게이트 라인(GL)과 함께 상기 화소영역(PA)을 정의한다.

<36> 상기 박막 트랜지스터(220)는 상기 화소영역(PA)에 형성되고, 상기 화소전압을 스위칭한다. 구체적으로, 상기 박막 트랜지스터(220)는 상기 게이트 라인(GL)으로부터 분기된 게이트 전극(221), 상기 게이트 전극(221)에 상부에 순차적으로 형성된 액티브층(222)과 오믹 콘택층(223), 상기 데이터 라인(DL)으로부터 분기되어 상기 오믹 콘택층(223)의 상면에 형성된 소오스 전극(224), 및 상기 오믹 콘택층(223)의 상면에 형성된 드레인 전극(225)을 포함한다.

<37> 상기 제1 화소전극(230)은 상기 화소영역(PA)에 형성되고, 인듐 틴 옥사이드(Indium Tin Oxide: ITO) 또는 인듐 징크 옥사이드(Indium Zinc Oxide: IZO)와 같은 투명한 도전성 물질로 이루어진다. 상기 제1 화소전극(230)은 상기 드레인 전극(225)과 전기적으로 연결되고, 상기 드레인 전극(225)을 통해 상기 화소전압을 입력받는다.

<38> 상기 제1 화소전극(230)은 상기 제1 방향(D1)으로 연장되어 형성된 메인 화소전극(230), 및 상기 메인 화소전극(231)으로부터 분기되어 형성된 제1 내지 제3 서브 화소전극(232, 233, 234)을 포함한다. 본 실시예에 있어서, 상기 제1 화소전극(230)은 세 개의 서브 화소전극(232, 233, 234)을 구비하나, 상기 서브 화소전극(232, 233, 234)의 개수는 증가하거나 감소될 수도 있다.

<39> 상기 메인 화소전극(231)은 상기 게이트 라인(GL)과 인접하게 위치한다. 본 발명의 일례로, 상기 제1 내지 제3 서브 화소전극(232, 233, 234)은 상기 제2 방향(D2)으로 연장되어 상기 데이터 라인(DL)과 평행하게 배치되고, 상기 제1 방향(D1)으로 서로 이격되어 위치한다. 또한, 본 발명의 일례로, 상기 제1 내지 제3 서브 화소전극(232, 233, 234)은 실질적으로 서로 동일한 폭을 갖고, 상기 제1 내지 제3 서브 화소전극(232, 233, 234) 각각의 폭은 상기 메인 화소전극(231)의 폭과 실질적으로 동일하다.

<40> 본 실시예에 있어서, 상기 드레인 전극(225)은 상기 메인 화소전극(231)과 전기적으로 연결되나, 상기 제1 화소전극(230)의 형상 및 그 배치 구조에 따라 제1 내지 제3 서브 화소전극(232, 233, 234) 중 어느 하나와 전기적으로 연결될 수도 있다.

<41> 한편, 상기 제1 공통전극(240)은 상기 화소영역(PA)에 형성되어 상기 공통전압을 입력받고, 상기 제1 화소전극(230)과 서로 이격되어 형성된다. 본 발명의 일례로, 상기 제1 공통전극(240)은 상기 제1 화소전극(230)과 동일한 재질로 이루어진다. 구체적으로, 상기 제1 공통전극(240)은 상기 제1 방향(D1)으로 연장되어 형성된 메인 공통전극(241), 및 상기 메인 공통전극(241)으로부터 분기되어 형성된 제1 내지 제3 서브 공통전극(242, 243, 244)을 포함한다. 본 실시예에 있어서, 상기 제1 공통전극(240)은 세개의 서브 공통전극(242, 243, 244)을 구비하나, 상기 서브 공통전극(242, 243, 244)의 개수는 증가하거나 감소할 수도 있다.

<42> 상기 메인 공통전극(241)은 상기 제1 화소전극(230)의 메인 화소전극(231)과 대향하게 배치된다. 본 발명의 일례로, 상기 메인 공통전극(241)은 상기 메인 화소전극(231)과 실질적으로 동일한 폭을 갖는다. 또한, 본 발명의 일례로, 상기 제1 내지 제3 서브 공통전극(242, 243, 244)은 상기 제2 방향(D2)으로 연장되어 형성되고, 상기

제1 방향(D1)으로 서로 이격된다. 상기 제1 상기 제1 내지 제3 서브 공통전극(242, 243, 244)은 실질적으로 서로 동일한 폭을 갖고, 상기 제1 상기 제1 내지 제3 서브 공통전극(242, 243, 244) 각각의 폭은 상기 메인 공통전극(241)의 폭과 실질적으로 동일하다.

<43> 상기 제1 내지 제3 서브 공통전극(242, 243, 244)은 상기 제1 화소전극(230)의 제1 내지 제3 서브 화소전극(232, 233, 234)과 교대로 배치된다. 예컨대, 상기 제1 방향(D1)으로 상기 제1 서브 공통전극(242), 상기 제1 서브 화소전극(232), 상기 제2 서브 공통전극(243), 상기 제2 서브 화소전극(233), 상기 제3 서브 공통전극(244) 및 상기 제3 서브 화소전극(234) 순으로 배치된다.

<44> 본 발명의 일례로, 상기 제1 화소전극(230)과 상기 제1 공통전극(240)은 상기 제1 내지 제3 서브 화소전극(232, 233, 234) 각각의 폭 또는 상기 제1 내지 제3 서브 공통전극(242, 243, 244) 각각의 폭과 실질적으로 동일한 거리로 이격된다. 예컨대, 서로 인접한 상기 제2 서브 화소전극(232)과 상기 제2 서브 공통전극(242)은 실질적으로 서로 동일한 폭을 갖고, 상기 제2 서브 화소전극(232)의 폭 또는 상기 제2 서브 공통전극(242)의 폭과 실질적으로 동일한 거리로 이격된다.

<45> 한편, 상기 어레이 기판(200)은 상기 제1 베이스 기판(210)의 상면에 형성된 공통전압 라인(CL)을 더 포함한다. 상기 공통전압 라인(CL)은 상기 제1 방향(D1)으로 연장되어 형성되고, 상기 공통전압을 전송한다. 평면상에서 볼 때, 상기 공통전압 라인(CL)은 상기 제1 공통전극(240)의 상기 메인 공통전극(241)과 부분적으로 오버랩되고, 상기 메인 공통전극(241)과 전기적으로 연결되어 상기 메인 공통전극(241)에 상기 공통전압을 인가한다.

<46> 또한, 상기 어레이 기판(100)은 게이트 절연막(251), 보호막(252) 및 유기 절연막(253)을 더 포함한다. 상기 게이트 절연막(251)은 상기 제1 베이스 기판(210)의 상부에 형성되어 상기 게이트 라인(GL), 상기 게이트 전극(221) 및 상기 공통전압 라인(CL)을 커버한다. 상기 보호막(252)은 상기 게이트 절연막(251)의 상부에 형성되어 상기 데이터 라인(DL)과 소오스 및 드레인 전극(224, 225)을 커버한다. 상기 유기 절연막(253)의 상기 보호막(252)의 상부에 형성되고, 상기 제1 화소전극(230)과 상기 제1 공통전극(240)은 상기 유기 절연막(253)의 상면에 형성된다.

<47> 상기 보호막(252)과 상기 유기 절연막(253)은 상기 드레인 전극(255)을 부분적으로 노출하는 콘택홀(CH)이 형성되고, 상기 제1 화소전극(230)은 상기 콘택홀(CH)을 통해 상기 드레인 전극(255)과 전기적으로 연결된다.

<48> 상기 게이트 절연막(251)과 상기 보호막(252) 및 상기 유기 절연막(253)은 상기 공통전압 라인(CL)을 부분적으로 노출하는 적어도 하나의 비아홀(VH)이 형성된다. 상기 제1 공통전극(240)은 상기 비아홀(VH)을 통해 상기 공통전압 라인(CL)과 전기적으로 연결된다.

<49> 상기 어레이 기판(200)은 상기 액정층(100)을 사이에 두고 상기 대향기판(300)과 마주한다. 상기 대향기판(300)은 제2 베이스 기판(310), 컬러필터 층(320), 제2 화소전극(330) 및 제2 공통전극(340)을 포함한다.

<50> 상기 제2 베이스 기판(310)은 상기 제1 베이스 기판(210)과 마주하여 결합한다. 상기 컬러필터 층(320)은 상기 제2 베이스 기판(320)의 상면에 형성되고, 색화소(321)와 블랙 매트릭스(322)를 포함한다. 상기 색화소(321)는 상기 화소영역(PA)에 형성되고, 상기 액정층(100)으로부터 제공된 광을 이용하여 소정의 색을 발현한다. 상기 블랙 매트릭스(322)는 상기 색화소(321)를 둘러싸고, 광을 차단한다.

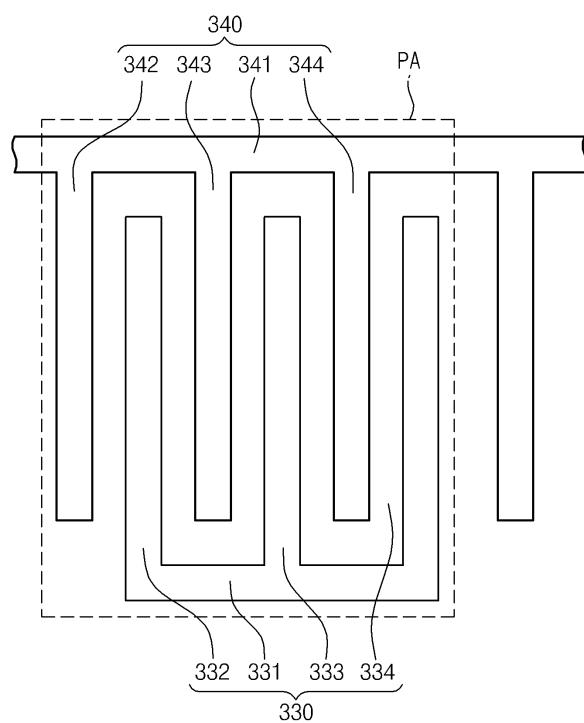

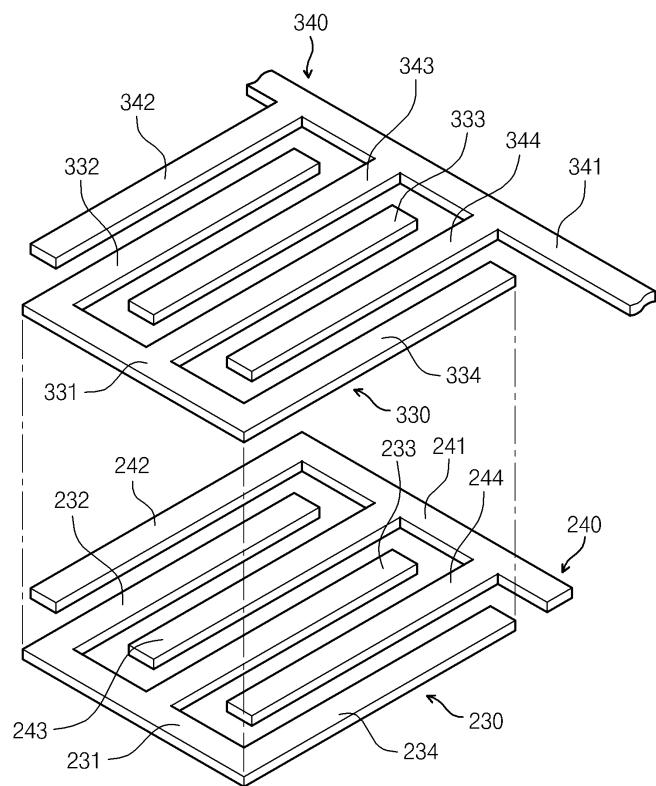

<51> 도 6은 도 2에 도시된 제2 화소전극 및 제2 공통전극을 나타낸 평면도이고, 도 7은 도 2에 도시된 제1 화소전극 및 제1 공통전극과 제2 화소전극 및 제2 공통전극 간의 위치 관계를 나타낸 사시도이다.

<52> 도 2 및 도 6을 참조하면, 상기 제2 화소전극(330)과 상기 제2 공통전극(340)은 상기 컬러필터 층(320)의 상면에 형성된다. 상기 제2 화소전극(330)은 인듐 턴 옥사이드 또는 인듐 징크 옥사이드와 같은 투명한 도전성 물질로 이루어지고, 상기 제1 화소전극(230)으로부터 상기 화소전압을 입력받는다.

<53> 도 2 및 도 7을 참조하면, 상기 제2 화소전극(330)은 상기 제1 화소전극(230)이 형성된 영역과 대응하는 영역에 형성되어 상기 제1 화소전극(230)과 오버랩되고, 상기 제1 화소전극(230)과 동일한 형상을 갖는다. 본 실시예에 있어서, 상기 제2 화소전극(330)은 상기 제1 화소전극(230)과 동일한 구성을 가지므로, 상기 제2 화소전극(330)의 구성에 대한 구체적인 설명은 생략한다.

<54> 상기 제2 화소전극(330)의 메인 화소전극(331)은 상기 제1 화소전극(230)의 메인 화소전극(231)과 실질적으로 동일한 폭을 갖는다. 상기 제2 화소전극(330)의 제1 내지 제3 서브 화소전극(332, 333, 334)은 서로 대응하는

상기 제1 화소전극(230)의 제1 내지 제3 서브 화소전극(332, 333, 334)과 실질적으로 동일한 폭을 갖는다.

<55> 도 6 및 도 7을 참조하면, 상기 제2 공통전극(340)은 ITO 또는 IZO와 같이 투명한 도전성 물질로 이루어지고, 외부로부터 상기 공통전압을 입력받는다. 상기 제2 공통전극(340)은 상기 화소영역(PA) 안에서 상기 제1 공통전극(240)이 형성된 영역과 대응하는 영역에 형성되어 상기 제1 공통전극(240)과 오버랩되고, 상기 제1 공통전극(240)과 동일한 형상을 갖는다. 본 실시예에 있어서, 상기 제2 공통전극(330)은 상기 제2 공통전극(330)과 동일한 구성을 가지므로, 상기 제2 공통전극(330)의 구성에 대한 구체적인 설명은 생략한다.

<56> 단, 각 화소영역(PA)에 형성된 제1 공통전극(240)은 서로 절연되나, 상기 각 화소영역(PA)에 형성된 제2 공통전극(340)은 서로 도전된다. 즉, 서로 인접한 두개의 화소영역에 형성된 제1 공통전극들의 메인 공통전극들은 서로 이격되어 위치한다. 그러나, 상기 서로 인접한 두 개의 화소영역에 각각 형성된 제2 공통전극들의 메인 공통전극들은 서로 연결된다.

<57> 상기 제2 공통전극(340)의 메인 공통전극(341)은 상기 제2 화소전극(330)의 메인 화소전극(331)과 서로 대향하게 위치하고, 상기 제1 공통전극(240)의 메인 공통전극(241)과 실질적으로 동일한 폭을 갖는다. 상기 제2 공통전극(340)의 메인 공통전극(341)과 상기 제2 화소전극(330)의 메인 화소전극(331)과의 사이에는 상기 제2 공통전극(340)의 제1 내지 제3 서브 공통전극(342, 342, 344)과 상기 제2 화소전극(330)의 제1 내지 제3 서브 화소전극(332, 333, 334)이 위치한다. 상기 제2 공통전극(340)의 제1 내지 제3 서브 공통전극(332, 333, 334)은 서로 대응하는 상기 제1 공통전극(240)의 제1 내지 제3 서브 공통전극(242, 243, 244)과 실질적으로 동일한 폭을 갖는다.

<58> 상기 제2 공통전극(340)의 제1 내지 제3 서브 공통전극(342, 342, 344)과 상기 제2 화소전극(330)의 제1 내지 제3 서브 화소전극(332, 333, 334)은 서로 교대로 위치한다. 상기 제2 공통전극(340)과 상기 제2 화소전극(330) 간의 이격 거리는 상기 제1 공통전극(240)과 상기 제1 화소전극(230) 간의 이격 거리와 실질적으로 동일하다.

<59> 상기 액정표시패널(500)은 상기 제1 화소전극(230)과 상기 제1 공통전극(240)에 의해 제1 전계(EF1)가 형성되고, 상기 제2 화소전극(330)과 상기 제2 공통전극(340)에 의해 제2 전계(EF2)가 형성된다. 즉, 상기 제1 전계(EF1)는 상기 어레이 기판(200)에 입력된 화소전압과 공통전압에 의해 형성되고, 상기 제2 전계(EF2)는 상기 대향기판(300)에 입력된 화소전압과 공통전압에 의해 형성된다. 따라서, 상기 어레이 기판(200)과 상기 대향기판(300)의 사이에는 상기 제1 및 제2 전계(EF1, EF2)가 서로 동일한 영역에 형성된다. 상기 제1 화소전극(230)과 상기 제2 화소전극(330) 각각 동일한 화소전압이 인가되고, 상기 제1 공통전극(240)과 상기 제2 공통전극(340) 각각 동일한 공통전압이 인가된다. 이에 따라, 상기 제1 전계(EF1)와 상기 제2 전계(EF2)는 서로 동일한 세기를 갖는다.

<60> 상기 액정층(300)의 상기 블루상 액정들은 상기 제1 및 제2 전계(EF1, EF2)에 따라 이방성 굴절율이 변경되어 광 투과율을 조절한다. 즉, 상기 블루상 액정들 중 상기 어레이 기판(200)과 인접하게 위치한 블루상 액정들은 상기 제1 전계(EF1)에 의해 이방성 굴절률이 변경되고, 상기 대향기판(300)과 인접하게 위치한 블루상 액정들은 상기 제2 전계(EF2)에 의해 이방성 굴절률이 변경된다.

<61> 이와 같이, 상기 액정표시패널(500)은 상기 블루상 액정들의 이방성 굴절율을 제어하기 위한 전계(EF1, EF2)가 복층으로 형성되므로, 상기 블루상 액정들의 이방성 굴절률을 종래보다 낮은 전압으로 조절한다. 따라서, 상기 액정표시패널(500)의 구동 전압을 감소시킬 수 있다. 또한, 상기 화소영역(PA) 내에 위치하는 블루상 액정들이 상기 제1 전계(EF1) 또는 상기 제2 전계(EF1)의 영향권 안에 위치하므로, 상기 블루상 액정들의 이방성 굴절률을 제어가 용이하고, 표시 품질을 향상시킬 수 있다.

<62> 한편, 상기 액정표시패널(500)은 상기 제1 화소전극(230)과 상기 제2 화소전극(330)과의 사이에 개재된 도전성 스페이서(410)를 더 포함한다. 상기 도전성 스페이서(410)는 상기 제1 및 제2 화소전극(230, 330)을 전기적으로 연결시키고, 상기 제1 화소전극(230)으로부터 인가된 상기 화소전압을 상기 제2 화소전극(330)에 제공한다. 본 실시예에 있어서, 상기 도전성 스페이서(410)는 상기 제1 화소전극(230)의 메인 화소전극(231)과 상기 제2 화소전극(330)의 메인 화소전극(331)과의 사이에 개재된다. 그러나, 상기 도전성 스페이서(410)는 상기 제1 화소전극(230)의 서브 화소전극들(232, 233, 234) 중 어느 하나와 이와 대응하는 상기 제2 화소전극(330)의 서브 화소전극과의 사이에 개재될 수도 있다.

### 발명의 효과

<63> 상술한 본 발명에 따르면, 어레이 기판과 대향기판 각각은 화소전압을 입력받는 화소전극과 공통전압을 입력받

는 공통전극을 구비한다. 이에 따라, 액정층을 제어하기 위한 수평 전계가 어레이 기판으로부터 대향기판까지 균일하게 세기로 형성된다. 따라서, 액정표시패널의 구동전압이 감소되고, 액정층의 굴절률 제어가 용이하며, 표시 품질이 향상된다.

<64> 이상 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 일 실시예에 따른 액정표시패널을 나타낸 평면도이다.

- <2> 도 2는 도 1의 절단선 I-I'에 따른 단면도이다.

- <3> 도 3은 블루상 액정의 구조를 나타낸 도면이다.

- <4> 도 4는 제1 블루상의 구조를 나타낸 사시도이다.

- <5> 도 5는 도 4에 도시된 제1 블루상의 선결합 라인을 나타낸 사시도이다.

- <6> 도 6은 도 2에 도시된 제2 화소전극 및 제2 공통전극을 나타낸 평면도이다.

- <7> 도 7은 도 2에 도시된 제1 화소전극 및 제1 공통전극과 제2 화소전극 및 제2 공통전극 간의 위치 관계를 나타낸 사시도이다.

<8> \*도면의 주요 부분에 대한 부호의 설명\*

- |                    |                 |

|--------------------|-----------------|

| <9> 100 -- 액정층     | 200 -- 어레이 기판   |

| <10> 300 -- 대향기판   | 410 -- 도전성 스페이서 |

| <11> 500 -- 액정표시패널 |                 |

## 도면

## 도면1

도면2

도면3

도면4

100a

도면5

도면6

도면7

|                |                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">KR1020080050851A</a>                                                                                                     | 公开(公告)日 | 2008-06-10 |

| 申请号            | KR1020060121674                                                                                                                      | 申请日     | 2006-12-04 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 三星显示器有限公司                                                                                                                            |         |            |

| [标]发明人         | YOU HYE RAN<br>유혜란<br>YOO SEUNG HOO<br>유승후<br>KANG SUNG MIN<br>강성민<br>DO HEE WOOK<br>도희욱<br>KIM HOON<br>김훈<br>MOON HYUN CHEOL<br>문현철 |         |            |

| 发明人            | 유혜란<br>유승후<br>강성민<br>도희욱<br>김훈<br>문현철                                                                                                |         |            |

| IPC分类号         | G02F1/1343                                                                                                                           |         |            |

| CPC分类号         | G02F1/13718 G02F2001/13793 G02F1/134363                                                                                              |         |            |

| 代理人(译)         | KWON , HYUK SOO<br>SE JUN OH<br>宋 , 云何                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                            |         |            |

#### 摘要(译)

液晶显示面板包括具有第一像素电极和第一公共电极的阵列基板，具有第二像素电极和第二公共电极的对向基板，以及夹在阵列基板和对向基板之间的液晶层。在第一像素电极和第一公共电极之间以及第二像素电极和第二公共电极之间形成相同大小的电场。因此，降低了液晶显示面板的驱动电压，容易调节液晶层的折射率，并且提高了显示质量。