(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년02월18일

(11) 등록번호 10-0884541

(24) 등록일자 2009년02월12일

(51) Int. Cl.

G02F 1/136 (2006.01)

(21) 출원번호 10-2002-0078106

(22) 출원일자 2002년12월10일

심사청구일자 2007년10월22일

(65) 공개번호 10-2004-0050311

(43) 공개일자 2004년06월16일

(56) 선행기술조사문헌

JP09311327 A\*

KR1020020058628 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

김세준

서울특별시 용산구 동빙고동 32-15

박승렬

인천광역시 연수구 청학동 469-325/2

(74) 대리인

특허법인 네이트

전체 청구항 수 : 총 6 항

심사관 : 임동재

(54) 액정표시장치 및 그 제조방법

**(57) 요약**

본 발명에 따른 TOC 액정표시장치 및 그 제조방법에 의하면, 컬러필터 소자와 어레이 소자를 동일 기판에 형성하기 때문에 합착 마진을 최소화하여 개구율을 높일 수 있고, 블랙매트릭스와 게이트 패턴(한 예로, 게이트 배선)을 동일 공정에서 동일 물질을 이용하여 형성하기 때문에, 공정을 단순화시킬 수 있고 원가 절감을 통해 생산수율을 높일 수 있고, 또한, 블랙매트릭스와 게이트 패턴을 동일 공정에서 형성하기 때문에, 게이트 패턴 형성부에서 블랙매트릭스 패턴을 생략할 수 있어, 개구율 향상효과를 보다 높일 수 있는 장점을 가진다.

**대 표 도 - 도3**

## 특허청구의 범위

### 청구항 1

기판의 동일층 상에, 광차단성 금속물질로 이루어지며, 서로 이격되게 형성된 게이트 전극을 가지는 게이트 배선 및 블랙매트릭스와;

상기 블랙매트릭스 및 게이트 배선을 덮는 영역에서, 상기 블랙매트릭스를 컬러별 경계부로 하여 형성된 컬러 필터층과;

상기 컬러필터층을 덮는 영역에 형성된 오버코트층과;

상기 오버코트층 및 컬러필터층에는 상기 게이트 전극을 노출시키는 오픈부가 형성되어 있으며, 상기 오버코트 층 및 오픈부를 덮는 영역에 형성된 게이트 절연막과;

상기 게이트 절연막 상부에서, 상기 게이트 전극을 덮는 영역에 형성된 반도체층과;

상기 반도체층 상부에서 서로 이격되게 위치하는 소스 전극 및 드레인 전극과, 상기 소스 전극과 연결되어, 상기 게이트 절연막 상에 형성되고 상기 블랙매트릭스와 대응되게 위치하며 상기 블랙매트릭스와 전기적으로 절연되어 있는 데이터 배선과;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터 및 상기 데이터 배선을 덮으며 형성되고 상기 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 보호층과;

상기 보호층 상부에서, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되는 화소 전극

을 포함하는 TOC 액정표시장치용 기판.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서,

상기 광차단성 금속물질은, 알루미늄을 포함하는 금속층을 하부층으로 하고, 크롬을 포함하는 금속층을 상부층으로 하는 구조로 이루어지는 TOC 액정표시장치용 기판.

### 청구항 4

제 1 항에 있어서,

상기 블랙매트릭스 및 게이트 배선과 동일 공정에서 동일 물질로 이루어진 제 1 캐패시터 전극을 포함하고, 상기 컬러필터층 및 오버코트층에는 상기 제 1 캐패시터 전극을 노출시키는 또 하나의 오픈부를 추가로 포함하며, 상기 게이트 절연막 상부에서 상기 제 1 캐패시터 전극을 덮는 위치에는 상기 데이터 배선과 동일 공정에서 동일 물질로 이루어진 제 2 캐패시터 전극이 형성되어 있고, 상기 보호층에는 상기 제 2 캐패시터 전극을 일부 노출시키는 캐패시터 콘택홀이 형성되어 있으며, 상기 캐패시터 콘택홀을 통해 화소 전극은 제 2 캐패시터 전극과 연결되고, 상기 제 1, 2 캐패시터 전극 중첩 영역은 스토리지 캐패시턴스를 이루는 TOC 액정표시장치용 기판.

### 청구항 5

기판의 동일층 상에 광차단성 금속물질을 이용하여 게이트 전극을 가지는 게이트 배선 및 블랙매트릭스를 동일 공정으로 형성하는 단계와;

상기 게이트 배선 및 블랙매트릭스를 덮는 영역에 컬러필터층 및 오버코트층을 차례대로 형성하고, 상기 컬러 필터층 및 오버코트층에 게이트 전극을 노출시키는 오픈부를 형성하는 단계와;

상기 오버코트층 및 오픈부를 덮는 영역에 게이트 절연막과, 상기 게이트 절연막 상부에서 게이트 전극을 덮는 영역에 반도체층을 차례대로 형성하는 단계와;

상기 반도체층 상부에서 서로 이격되게 위치하는 소스 전극 및 드레인 전극과, 상기 소스 전극과 연결되어, 상

기 게이트 절연막 상에 형성되고 상기 블랙매트릭스와 대응되게 위치하며 상기 블랙매트릭스와 전기적으로 절연되어 있는 데이터 배선을 형성하는 단계와;

상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터 및 상기 데이터 배선을 덮으며 형성되고 상기 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 보호층을 형성하는 단계와;

상기 보호층 상부에, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되는 화소 전극을 형성하는 단계를 포함하는 TOC 액정표시장치용 기판의 제조방법.

## 청구항 6

삭제

## 청구항 7

제 5 항에 있어서,

상기 광차단성 금속물질은, 알루미늄을 포함하는 금속층을 하부층으로 하고, 크롬을 포함하는 금속층을 상부층으로 하는 금속물질에서 선택되는 TOC 액정표시장치용 기판의 제조방법.

## 청구항 8

제 5 항에 있어서,

상기 블랙매트릭스 및 게이트 배선 형성단계에서는, 제 1 캐패시터 전극을 형성하는 단계를 포함하고, 상기 컬러필터층 및 오버코트층에 오픈부를 형성하는 단계에서는, 상기 제 1 캐패시터 전극을 노출시키는 또 하나의 오픈부를 형성하는 단계를 포함하며, 상기 소스 전극 및 드레인 전극을 형성하는 단계에서는, 상기 게이트 절연막 상부에서 제 1 캐패시터 전극을 덮는 영역에 위치하는 제 2 캐패시터 전극을 형성하는 단계를 포함하며, 상기 보호층 형성단계에서는, 상기 제 2 캐패시터 전극을 일부 노출시키는 캐패시터 콘택홀을 형성하는 단계를 포함하고, 상기 화소 전극 형성단계에서는, 상기 캐패시터 콘택홀을 통해 제 2 캐패시터 전극과 화소 전극을 연결시키는 단계를 포함하는 TOC 액정표시장치용 기판의 제조방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <16> 본 발명은 액정표시장치에 관한 것이며, 특히 컬러필터 기판 상에 박막트랜지스터를 포함하는 어레이 소자를 형성하는 TOC(Thin Film Transistor on Color Filter) 액정표시장치 및 그 제조방법에 관한 것이다.

- <17> 일반적으로, 액정표시장치는 액정분자의 광학적 이방성과 복굴절 특성을 이용하여 화상을 표현하는 것으로, 전계가 인가되면 액정의 배열이 달라지고 달라진 액정의 배열 방향에 따라 빛이 투과되는 특성 또한 달라진다.

- <18> 일반적으로, 액정표시장치는 전계 생성 전극이 각각 형성되어 있는 두 기판을 두 전극이 형성되어 있는 면이 마주 대하도록 배치하고 두 기판 사이에 액정 물질을 주입한 다음, 두 전극에 전압을 인가하여 생성되는 전기장에 의해 액정 분자를 움직이게 함으로써, 이에 따라 달라지는 빛의 투과율에 의해 화상을 표현하는 장치이다.

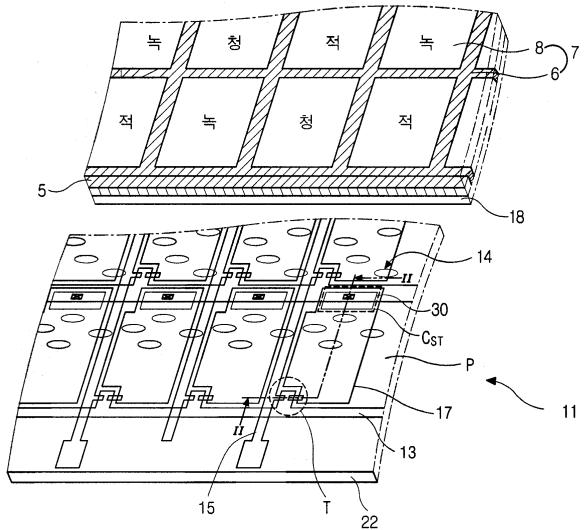

- <19> 도 1은 일반적인 액정표시장치를 개략적으로 나타낸 도면이다.

- <20> 도시한 바와 같이, 일반적인 컬러 액정표시장치(11)는 서브 컬러필터(8)와 각 서브 컬러필터(8)사이에 구성된 블랙매트릭스(6)를 포함하는 컬러필터(7)와 상기 컬러필터(8)의 상부에 증착된 공통전극(18)이 형성된 상부기판(5)과, 화소영역(P)이 정의되고 화소영역에는 화소전극(17)과 스위칭소자(T)가 구성되며, 화소영역(P)의 주변으로 어레이배선이 형성된 하부기판(22)과, 상부기판(5)과 하부기판(22) 사이에는 액정(14)이 충진되어 있다.

- <21> 상기 하부기판(22)은 어레이기판(array substrate)이라고도 하며, 스위칭 소자인 박막트랜지스터(T)가 매트릭스 형태(matrix type)로 위치하고, 이러한 다수의 박막트랜지스터(TFT)를 교차하여 지나가는 게이트배선(13)과 테

이터배선(15)이 형성된다.

- <22> 이때, 상기 화소영역(P)은 상기 게이트배선(13)과 데이터배선(15)이 교차하여 정의되는 영역이며, 상기 화소영역(P)상에는 전술한 바와 같이 투명한 화소전극(17)이 형성된다.

- <23> 상기 화소전극(17)은 ITO(indium-tin-oxide)와 같이 빛의 투과율이 비교적 뛰어난 투명 도전성금속을 사용한다.

- <24> 상기 화소전극(17)과 병렬로 연결된 스토리지 캐패시터(C<sub>ST</sub>)가 게이트 배선(13)의 상부에 구성되며, 스토리지 캐패시터(C<sub>ST</sub>)의 제 1 전극으로 게이트 배선(13)의 일부를 사용하고, 제 2 전극으로 소스 및 드레인 전극과 동일층 동일물질로 형성된 아일랜드 형상의 소스/드레인 금속층(30)을 사용한다.

- <25> 이때, 상기 소스/드레인 금속층(30)은 화소전극(17)과 접촉되어 화소전극의 신호를 받도록 구성된다.

- <26> 전술한 바와 같이 상부 컬러필터 기판(5)과 하부 어레이기판(22)을 합착하여 액정패널을 제작하는 경우에는, 컬러필터 기판(5)과 어레이기판(22)의 합착 오차에 의한 빛샘 불량 등이 발생할 확률이 매우 높다.

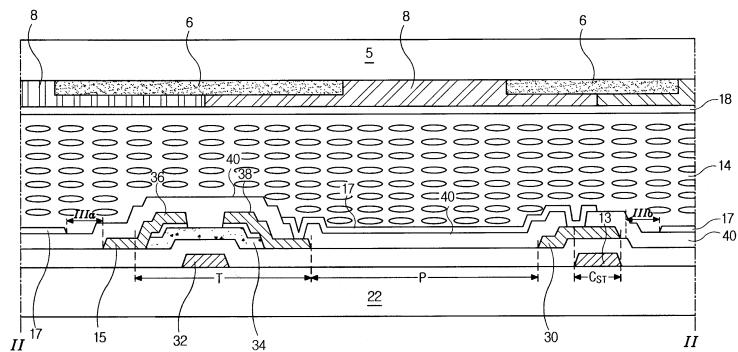

- <27> 이하, 도 2를 참조하여 설명한다.

- <28> 도 2는 도 1의 II-II를 따라 절단한 단면도이다.

- <29> 앞서 설명한 바와 같이, 어레이기판인 제 1 기판(22)과 컬러필터 기판인 제 2 기판(5)이 이격되어 구성되고, 제 1 및 제 2 기판(22,5)의 사이에는 액정층(14)이 위치한다.

- <30> 어레이기판(22)의 상부에는 게이트 전극(32)과 액티브층(34)과 소스 전극(36)과 드레인 전극(38)을 포함하는 박막트랜지스터(T)와, 상기 박막트랜지스터(T)의 상부에는 이를 보호하는 보호막(40)이 구성된다.

- <31> 화소영역(P)에는 상기 박막트랜지스터(T)의 드레인 전극(38)과 접촉하는 투명 화소전극(17)이 구성되고, 화소전극(17)과 병렬로 연결된 스토리지 캐패시터(C<sub>ST</sub>)가 게이트 배선(13)의 상부에 구성된다.

- <32> 상기 상부 기판(5)에는 상기 게이트 배선(13)과 데이터 배선(15)과 박막트랜지스터(T)에 대응하여 블랙매트릭스(6)가 구성되고, 하부 기판(22)의 화소영역(P)에 대응하여 컬러필터(8)가 구성된다.

- <33> 이때, 일반적인 어레이기판의 구성은 수직 크로스토크(cross talk)를 방지하기 위해 데이터 배선(15)과 화소 전극(17)을 일정 간격(IIIa) 이격하여 구성하게 되고, 게이트 배선(13)과 화소 전극 또한 일정간격(IIIb) 이격하여 구성하게 된다.

- <34> 데이터 배선(15) 및 게이트 배선(13)과 화소 전극(17) 사이의 이격된 공간(A,B)은 빛샘 현상이 발생하는 영역이기 때문에, 상부 컬러필터기판(5)에 구성한 블랙 매트릭스(black matrix)(6)가 이 부분을 가려주는 역할을 하게 된다.

- <35> 또한, 상기 박막트랜지스터(T)의 상부에 구성된 블랙매트릭스(6)는 외부에서 조사된 빛이 보호막(40)을 지나 액티브층(34)에 영향을 주지 않도록 하기 위해 빛을 차단하는 역할을 하게 된다.

- <36> 그런데, 상기 상부 기판(5)과 하부 기판(22)을 합착하는 공정 중 합착 오차(misalign)가 발생하는 경우가 있는데, 이를 감안하여 상기 블랙매트릭스(6)를 설계할 때 일정한 값의 마진(margin)을 두고 설계하기 때문에 그 만큼 개구율이 저하된다.

- <37> 또한, 마진을 넘어서 합착오차가 발생할 경우, 빛샘 영역(IIIa, IIIb)이 블랙매트릭스(6)에 모두 가려지지 않는 빛샘 불량이 발생하는 경우가 종종 있다.

- <38> 이러한 경우에는 상기 빛샘이 외부로 나타나기 때문에 화질이 저하되는 문제가 있다.

### 발명이 이루고자 하는 기술적 과제

- <39> 본 발명은 상기 문제점을 해결하기 위하여, 합착 마진을 최소화하여 투과율을 높일 수 있는 구조의 액정표시장치를 제공하는 것을 목적으로 한다.

- <40> 이를 위하여, 본 발명에서는 컬러필터 기판 상에 박막트랜지스터를 포함하는 어레이 소자를 함께 형성하는 TOC 구조 액정표시장치에 대한 것이다.

<41> 특히, 본 발명에서는 공정을 단순화하기 위하여, 블랙매트릭스와 게이트 금속을 동일 공정에서 형성하고자 한다.

### 발명의 구성 및 작용

<42> 상기 목적을 달성하기 위하여, 본 발명의 제 1 특징에서는 기판 상에, 광차단성 금속물질로 이루어지며, 서로 이격되게 형성된 게이트 전극을 가지는 게이트 배선 및 블랙매트릭스와; 상기 블랙매트릭스 및 게이트 배선을 덮는 영역에서, 상기 블랙매트릭스를 컬러별 경계부로 하여 형성된 컬러필터층과; 상기 컬러필터층을 덮는 영역에 형성된 오버코트층과; 상기 오버코트층 및 컬러필터층에는 상기 게이트 전극을 노출시키는 오픈부가 형성되어 있으며, 상기 오버코트층 및 오픈부를 덮는 영역에 형성된 게이트 절연막과; 상기 게이트 절연막 상부에서, 상기 게이트 전극을 덮는 영역에 형성된 반도체층과; 상기 반도체층 상부에서 서로 이격되게 위치하는 소스 전극 및 드레인 전극과, 상기 소스 전극과 연결되며, 상기 블랙매트릭스와 대응되게 위치하는 데이터 배선과; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에서 상기 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 보호층과; 상기 보호층 상부에서, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되는 화소 전극을 포함하는 TOC 액정표시장치용 기판을 제공한다.

<43> 상기 광차단성 금속물질은 비저항값이 낮은 물질에서 선택되고, 상기 비저항값이 낮은 광차단성 금속물질은, 알루미늄을 포함하는 금속층을 하부층으로 하고, 크롬을 포함하는 금속층을 상부층으로 하는 구조로 이루어지는 것을 특징으로 한다.

<44> 그리고, 상기 블랙매트릭스 및 게이트 배선과 동일 공정에서 동일 물질로 이루어진 제 1 캐패시터 전극을 포함하고, 상기 컬러필터층 및 오버코트층에는 상기 제 1 캐패시터 전극을 노출시키는 또 하나의 오픈부를 추가로 포함하며, 상기 게이트 절연막 상부에서 상기 제 1 캐패시터 전극을 덮는 위치에는 상기 데이터 배선과 동일 공정에서 동일 물질로 이루어진 제 2 캐패시터 전극이 형성되어 있고, 상기 보호층에는 상기 제 2 캐패시터 전극을 일부 노출시키는 캐패시터 콘택홀이 형성되어 있으며, 상기 캐패시터 콘택홀을 통해 화소 전극은 제 2 캐패시터 전극과 연결되고, 상기 제 1, 2 캐패시터 전극 중첩 영역은 스토리지 캐패시턴스를 이루는 것을 특징으로 한다.

<45> 본 발명의 제 2 특징에서는, 기판 상에 광차단성 금속물질을 이용하여 게이트 전극을 가지는 게이트 배선 및 블랙매트릭스를 형성하는 단계와; 상기 게이트 배선 및 블랙매트릭스를 덮는 영역에 컬러필터층 및 오버코트층을 차례대로 형성하고, 상기 컬러필터층 및 오버코트층에 게이트 전극을 노출시키는 오픈부를 형성하는 단계와; 상기 오버코트층 및 오픈부를 덮는 영역에 게이트 절연막과, 상기 게이트 절연막 상부에서 게이트 전극을 덮는 영역에 반도체층을 차례대로 형성하는 단계와; 상기 반도체층 상부에서 서로 이격되게 위치하는 소스 전극 및 드레인 전극과, 상기 소스 전극과 연결되고, 상기 블랙매트릭스와 대응되게 위치하는 데이터 배선을 형성하는 단계와; 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이루고, 상기 박막트랜지스터를 덮는 영역에 드레인 전극을 일부 노출시키는 드레인 콘택홀을 가지는 보호층을 형성하는 단계와; 상기 보호층 상부에, 상기 드레인 콘택홀을 통해 드레인 전극과 연결되는 화소 전극을 형성하는 단계를 포함하는 TOC 액정표시장치용 기판의 제조방법을 제공한다.

<46> 상기 광차단성 금속물질은 비저항값이 낮은 금속물질에서 선택되고, 상기 비저항값이 낮은 금속물질은, 알루미늄을 포함하는 금속층을 하부층으로 하고, 크롬을 포함하는 금속층을 상부층으로 하는 금속물질에서 선택되며, 상기 블랙매트릭스 및 게이트 배선 형성단계에서는, 제 1 캐패시터 전극을 형성하는 단계를 포함하고, 상기 컬러필터층 및 오버코트층에 오픈부를 형성하는 단계에서는, 상기 제 1 캐패시터 전극을 노출시키는 또 하나의 오픈부를 형성하는 단계를 포함하며, 상기 소스 전극 및 드레인 전극을 형성하는 단계에서는, 상기 게이트 절연막 상부에서 제 1 캐패시터 전극을 덮는 영역에 위치하는 제 2 캐패시터 전극을 형성하는 단계를 포함하며, 상기 보호층 형성단계에서는, 상기 제 2 캐패시터 전극을 일부 노출시키는 캐패시터 콘택홀을 형성하는 단계를 포함하고, 상기 화소 전극 형성단계에서는, 상기 캐패시터 콘택홀을 통해 제 2 캐패시터 전극과 화소 전극을 연결시키는 단계를 포함하는 것을 특징으로 한다.

<47> 본 발명은 액정표시장치에 관한 것이며, 특히 TOC 액정표시장치 및 그 제조방법에 관한 것으로서, 블랙매트릭스와 게이트 금속(예를 들어, 게이트 전극, 게이트 배선)을 게이트 배선 겹용으로 이용함으로써 공정을 단순화시

키는 것을 특징으로 한다.

-- 제 1 실시예 --

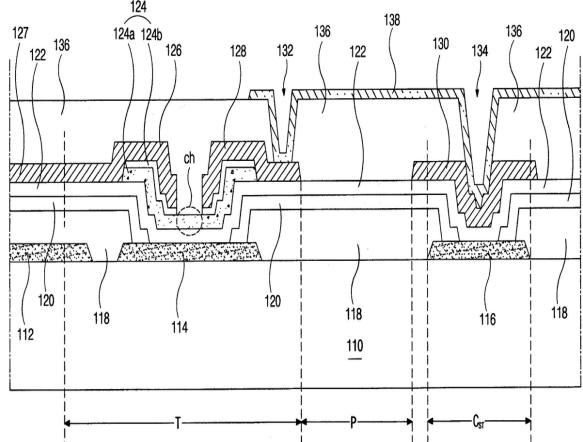

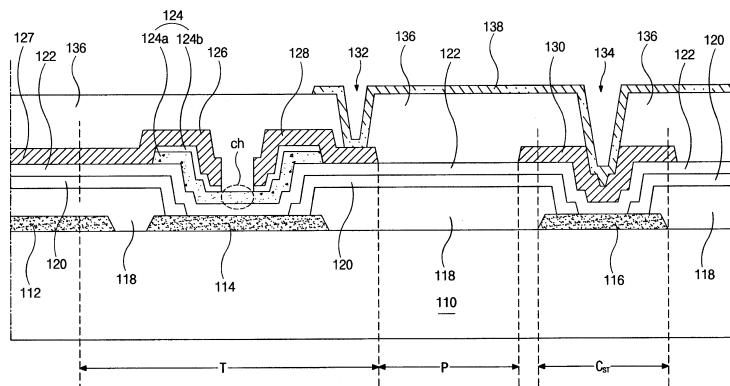

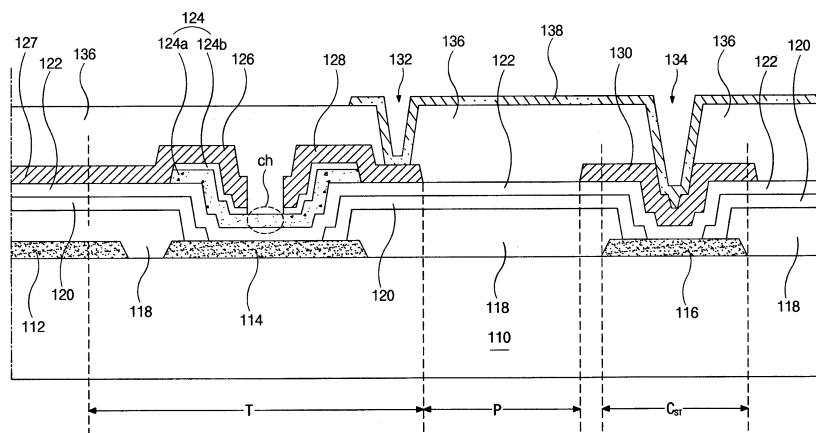

<49> 도 3은 본 발명의 제 1 실시예에 따른 TOC 구조 액정표시장치에 대한 단면도이다.

<50> 도시한 바와 같이, 기판(110) 상에 블랙매트릭스(112), 게이트 전극(114) 및 제 1 캐패시터 전극(116)이 서로 이격되게 형성되어 있고, 블랙매트릭스(112), 게이트 전극(114) 및 제 1 캐패시터 전극(116)을 덮는 영역에는 컬러필터층(118)가 형성되어 있다.

<51> 이때, 상기 게이트 전극(114) 및 제 1 캐패시터 전극(116)의 주영역을 노출시키며, 상기 컬러필터층(118)은 게이트 전극(114) 및 제 1 캐패시터 전극(116)의 양측과 일정간격 중첩되게 위치한다.

<52> 상기 게이트 전극(114) 및 제 1 캐패시터 전극(116)은 블랙매트릭스(112)와 동일 공정에서 동일 물질로 이루어지므로, 광차단성 및 비저항값이 낮은 금속물질에서 선택되는 것으로, 즉 상기 게이트 전극(114) 및 제 1 캐패시터 전극(116)은 블랙매트릭스 역할을 겸하는 패턴에 해당된다. 그리고, 상기 컬러필터층(118)은 화면이 구현되는 최소 단위 영역으로 정의되는 화소 영역(P)별로 적, 녹, 청 컬러필터가 차례대로 배열되어 이루어지며, 컬러별 경계부에는 블랙매트릭스(112)가 위치하며, 게이트 패턴(게이트 전극, 게이트 배선, 게이트 패드, 제 1 캐패시터 전극)이 형성된 부분에서는 별도의 블랙매트릭스 패턴은 생략된다.

<53> 상기 컬러필터층(118)를 덮는 기판 전면에 위치하며, 게이트 전극(114) 및 제 1 캐패시터 전극(116)을 노출시키는 영역을 포함하여 오버코트층(120)이 형성되어 있고, 오버코트층(120) 상부의 게이트 전극(114) 및 제 1 캐패시터 전극(116)을 덮는 위치에 게이트 절연막(122)이 형성되어 있으며, 게이트 절연막(122) 상부의 게이트 전극(112)과 중첩되는 위치에는 반도체층(124)이 형성되어 있다.

<54> 좀 더 상세히 설명하면, 상기 반도체층(124)은 비정질 실리콘(a-Si) 물질로 이루어진 액티브층(124a)과, 불순물 비정질 실리콘(n+ a-Si) 물질로 이루어진 오믹 콘택층(124b)으로 이루어진다.

<55> 상기 반도체층(124) 상부에서 서로 일정간격 이격되게 소스 전극(126) 및 드레인 전극(128)이 형성되어 있고, 제 1 캐패시터 전극(114)을 덮는 게이트 절연막(122) 상부에는 제 2 캐패시터 전극(130)이 형성되어 있다. 그리고, 상기 소스 전극(126)과 연결되며, 상기 블랙매트릭스(112)와 대응되는 위치에 데이터 배선(127)이 형성되어 있다.

<56> 상기 게이트 전극(114), 반도체층(124), 소스 전극(126) 및 드레인 전극(128)은 박막트랜지스터(T)를 이룬다.

<57> 그리고, 상기 소스 전극(126) 및 드레인 전극(128) 사이 이격구간에는 오믹콘택층(124b)이 제거되고, 그 하부층을 이루는 액티브층(124a)이 노출되어, 노출된 액티브층(124a) 영역은 채널(ch)을 이룬다.

<58> 상기 박막트랜지스터(T) 및 제 2 캐패시터 전극(130)을 덮는 위치에는 드레인 전극(128) 및 제 2 캐패시터 전극(130)의 일부를 각각 노출시키는 드레인 콘택홀(132) 및 캐패시터 콘택홀(134)을 가지는 보호층(136)이 형성되어 있고, 보호층(136) 상부에는 드레인 콘택홀(132) 및 캐패시터 콘택홀(134)을 통해 드레인 전극(128) 및 제 2 캐패시터 전극(130)을 덮는 위치에 화소 전극(138)이 형성되어 있다.

<59> 상기 제 2 캐패시터 전극(130)은 화소 전극(138)을 통해 전기적으로 연결되어 전도체를 이루어, 게이트 절연막(122)이 개재된 상태에서 제 1, 2 캐패시터 전극(116, 130) 중첩 영역은 스토리지 캐패시턴스(C<sub>ST</sub>)를 이룬다.

<60> 본 발명에 따른 TOC 구조 액정표시장치는, 게이트 패턴(게이트 전극, 게이트 배선, 게이트 패드, 제 1 캐패시터 전극)과 블랙매트릭스를 동일 공정에서 형성하기 때문에, 공정 수를 줄일 수 있고, 기존의 블랙매트릭스 게이트 패턴부를 덮는 영역에 형성되는 블랙매트릭스 영역을 생략할 수 있으며, 블랙매트릭스와 게이트 패턴 간의 중첩 마진을 제거할 수 있다.

<61> 상기 블랙매트릭스 및 게이트 패턴을 이루는 물질은 광차단성 및 비저항값이 낮은 금속물질에서 선택되는 것이 바람직하며, 한 예로 알루미늄을 포함하는 금속을 하부층으로 하고, 크롬계(Cr) 금속물질을 상부층으로 포함하는 구조의 복수층으로 구성할 수 있다.

-- 제 2 실시예 --

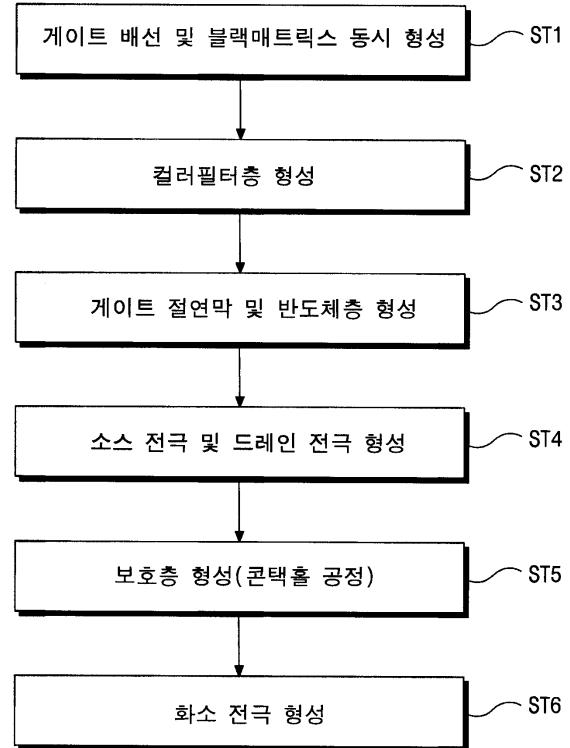

<63> 도 4는 본 발명의 제 2 실시예에 따른 TOC 액정표시장치용 기판의 제조 방법을 단계별로 나타낸

공정흐름도이다.

- <64> ST1에서는, 제 1 금속물질을 이용하여 서로 이격되게 게이트 배선 및 블랙매트릭스를 동시에 형성하는 단계이다.

- <65> 상기 게이트 배선 형성 단계에서는, 게이트 배선에서 분기되는 게이트 전극 및 제 1 캐패시터 전극 그리고, 게이트 배선의 일끝단에 게이트 패드를 형성하는 단계를 포함한다.

- <66> 상기 제 1 금속물질은, 비저항값이 낮은 광차단성 금속물질에서 선택되는 것이 바람직하며, 한 예로 알루미늄을 포함하는 금속층을 하부층으로 하고, 크롬계 금속물질을 상부층으로 하는 복수층 구조로 구성할 수 있다.

- <67> 본 발명에서는, 게이트 배선과 블랙매트릭스를 동일 공정에서 동일 물질로 형성하기 때문에, 공정을 단순화시킬 수 있고, 블랙매트릭스의 형성폭을 줄일 수 있어 개구율 향상을 꾀할 수 있다.

- <68> 상기 블랙매트릭스는 데이터 배선 형성부에 위치하여, 상기 게이트 배선 및 블랙매트릭스는 서로 교차되어 교차되는 영역은 화소 영역을 이룬다.

- <69> ST2에서는, 상기 게이트 배선 및 블랙매트릭스를 덮는 영역에 컬러필터층 및 오버코트층을 형성하는 단계이다.

- <70> 상기 컬러필터층은, 상기 블랙매트릭스를 컬러별 경계부로 하여 적, 녹, 청 컬러필터가 차례대로 형성되어 이루어지고, 상기 오버코트층은 평탄화 및 컬러필터용 보호층 역할을 하며, 이 단계에서는 상기 컬러필터층 및 오버코트층에 게이트 전극 및 제 1 캐패시터 전극을 노출시키는 오픈부를 형성하는 단계를 포함한다.

- <71> ST3에서는, 상기 오버코트층 상부를 덮는 영역에 게이트 절연막을 형성하는 단계와, 상기 게이트 절연막 상부의 게이트 전극을 덮는 영역에 반도체층을 형성하는 단계를 포함한다.

- <72> 상기 게이트 절연막은, 컬러필터 및 오버코트층의 오픈부를 통해 게이트 전극 및 제 1 캐패시터 전극과 연접되게 위치하는 것이 중요하며, 상기 반도체층은 비정질 실리콘 물질로 이루어진 액티브층과, 불순물 비정질 실리콘 물질로 이루어진 오믹콘택층으로 이루어진다.

- <73> ST4에서는, 상기 반도체층 상부에서 서로 일정간격 이격되게 위치하는 소스 전극 및 드레인 전극과, 게이트 절연막 상부의 제 1 캐패시터 전극을 덮는 제 2 캐패시터 전극과, 상기 소스 전극과 연결되며, 전술한 블랙매트릭스와 대응되는 위치에 데이터 배선을 형성하는 단계이다.

- <74> 상기 제 2 캐패시터 전극은 아일랜드 패턴으로 형성된다.

- <75> 상기 게이트 전극, 반도체층, 소스 전극 및 드레인 전극은 박막트랜지스터를 이룬다.

- <76> ST5에서는, 상기 박막트랜지스터를 덮는 영역에 위치하며, 상기 드레인 전극 및 제 2 캐패시터 전극을 일부 노출시키는 드레인 콘택홀 및 캐패시터 콘택홀을 가지는 보호층을 형성하는 단계이다.

- <77> ST6에서는, 상기 보호층 상부에서, 드레인 콘택홀 및 캐패시터 콘택홀을 통해 드레인 전극 및 제 2 캐패시터 전극과 연결되는 화소 전극을 형성하는 단계이다.

- <78> 상기 제 2 캐패시터 전극은 화소 전극을 통해 전도체를 이루어, 게이트 절연막이 개재된 상태에서 제 1, 2 캐패시터 전극이 중첩된 영역은 스토리지 캐패시턴스를 이룬다.

- <79> 이와 같이, 본 발명에 따른 TOC 액정표시장치의 제조방법에 의하면, 게이트 공정과 블랙매트릭스 공정을 동시에 진행하기 때문에 공정을 단순화시킬 수 있어 원가를 절감할 수 있는 효과를 얻게 된다.

### 발명의 효과

- <80> 본 발명에 따른 TOC 액정표시장치 및 그 제조방법에 의하면, 컬러필터 소자와 어레이 소자를 동일 기판에 형성하기 때문에 합착 마진을 최소화하여 개구율을 높일 수 있고, 블랙매트릭스와 게이트 패턴(한 예로, 게이트 배선)을 동일 공정에서 동일 물질을 이용하여 형성하기 때문에, 공정을 단순화시킬 수 있고 원가 절감을 통해 생산수율을 높일 수 있다.

- <81> 또한, 블랙매트릭스와 게이트 패턴을 동일 공정에서 형성하기 때문에, 게이트 패턴 형성부에서 블랙매트릭스 패턴을 생략할 수 있어, 개구율 향상효과를 보다 높일 수 있다.

## 도면의 간단한 설명

- <1> 도 1은 일반적인 액정표시장치를 개략적으로 나타낸 도면.

- <2> 도 2는 도 1의 II-II를 따라 절단한 단면도.

- <3> 도 3은 본 발명의 제 1 실시예에 따른 TOC 구조 액정표시장치에 대한 단면도.

- <4> 도 4는 본 발명의 제 2 실시예에 따른 TOC 액정표시장치용 기판의 제조 방법을 단계별로 나타낸 공정흐름도.

### <5> <도면의 주요부분에 대한 간단한 설명>

|                        |                              |

|------------------------|------------------------------|

| <6> 110 : 기판           | 112 : 블랙매트릭스                 |

| <7> 114 : 게이트 전극       | 116 : 제 1 캐패시터 전극            |

| <8> 118 : 컬러필터층        | 120 : 오버코트층                  |

| <9> 122 : 게이트 절연막      | 124a : 액티브층                  |

| <10> 124b : 오믹콘택층      | 124 : 반도체층                   |

| <11> 126 : 소스 전극       | 128 : 드레인 전극                 |

| <12> 130 : 제 2 캐패시터 전극 | 132 : 드레인 콘택홀                |

| <13> 134 : 캐패시터 콘택홀    | 136 : 보호층                    |

| <14> 138 : 화소 전극       | C <sub>ST</sub> : 스토리지 캐패시턴스 |

| <15> P : 화소 영역         | T : 박막트랜지스터                  |

## 도면

### 도면1

도면2

도면3

도면4

|                |                                            |         |            |

|----------------|--------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                               |         |            |

| 公开(公告)号        | <a href="#">KR100884541B1</a>              | 公开(公告)日 | 2009-02-18 |

| 申请号            | KR1020020078106                            | 申请日     | 2002-12-10 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                   |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                  |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                  |         |            |

| [标]发明人         | KIM SEJUNE<br>김세준<br>PARK SEUNGRYUL<br>박승렬 |         |            |

| 发明人            | 김세준<br>박승렬                                 |         |            |

| IPC分类号         | G02F1/136 G02F1/1362                       |         |            |

| CPC分类号         | G02F1/1362 G02F2001/136222 G02F1/136227    |         |            |

| 其他公开文献         | KR1020040050311A                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                  |         |            |

## 摘要(译)

根据TOC液晶显示装置及其制造根据本发明的相同的方法，颜色，因为它们形成具有相同底物，可以通过最小化渗碳的余量，黑矩阵和栅极图案（例如，栅极布线，以增加孔径比在阵列元件的过滤器元件）在相同的过程中使用相同的材料黑矩阵图案和栅极图案可以在相同的工艺中形成，因此，在栅极图案形成部分中可以省略黑矩阵图案，更高孔径比的优点我有。