(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl. (11) 공개번호 10-2007-0065626

G02F 1/1333 (2006.01) (43) 공개일자 2007년06월25일

(21) 출원번호 10-2005-0126256

(22) 출원일자 2005년12월20일

심사청구일자 없음

(71) 출원인 엘지.필립스 엘시디 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자 박성일

대구 북구 동천동 화성센트럴파크 205-805

이건희

경북 구미시 고아읍 449 원호대우아파트 105-202

(74) 대리인 김영호

전체 청구항 수 : 총 10 항

**(54) 액정 표시 장치 및 그 제조방법**

**(57) 요약**

본 발명은 액정 표시장치 및 그 제조방법에 관한 것으로, 특히 구동 회로가 실장된 액정 표시장치의 공정 시간을 단축함과 아울러 칼라 필터 어레이 기판의 공통전극과 박막트랜지터 어레이 기판의 구동회로부간의 단락을 방지하기 위한 액정 표시장치 및 그 제조방법에 관한 것이다.

이 액정 표시장치는 상부기판 상에 형성된 공통전극과; 상기 상부 기판과 대향하는 하부기판 상에 형성된 게이트 구동부와; 상기 게이트 구동부와 대면하는 상기 공통전극 상부에 형성된 절연패턴과; 상기 상부기판과 상기 하부기판을 합착시키기 위한 도전성 실링재를 구비하는 것을 특징으로 한다.

**대표도**

도 11

**특허청구의 범위**

**청구항 1.**

상부기판 상에 형성된 공통전극과;

상기 상부 기판과 대향하는 하부기판 상에 형성된 게이트 구동부와;

상기 게이트 구동부와 대면하는 상기 공통전극 상부에 형성된 절연패턴과;

상기 상부기판과 상기 하부기판을 합착시키기 위한 도전성 실링재를 구비하는 것을 특징으로 하는 액정 표시장치.

### 청구항 2.

제 1 항에 있어서,

상기 절연 패턴은,

상기 상부 기판과 상기 하부 기판 사이의 셀 갭 이하로 형성되는 것을 특징으로 하는 액정 표시장치.

### 청구항 3.

제 1 항에 있어서,

상기 게이트 구동부는,

전원신호들 및 게이트 제어 신호들을 공급하기 위해 상기 하부 기판상에 형성된 신호 라인군과;

상기 신호 라인군 중 적어도 어느 하나와 접속된 다수의 박막트랜지스터들을 구비하는 것을 특징으로 하는 액정 표시장치.

### 청구항 4.

제 3 항에 있어서,

상기 신호 라인군을 덮는 게이트 절연막과;

상기 게이트 절연막 및 상기 박막트랜지스터를 덮는 보호막과;

상기 게이트 절연막 및 상기 보호막을 관통하여 상기 신호 라인군을 노출시키는 제1 접촉홀과;

상기 보호막을 관통하여 상기 박막트랜지스터를 노출시키는 제2 접촉홀과;

상기 보호막 상부에 형성되어 상기 제1 접촉홀 및 상기 제2 접촉홀을 통해 상기 신호 라인군 및 상기 박막트랜지스터를 접속시키는 접속 패턴을 더 구비하는 것을 특징으로 하는 액정 표시장치.

### 청구항 5.

제 4 항에 있어서,

상기 절연패턴은 상기 접속 패턴과 중첩되는 것을 특징으로 하는 액정 표시장치.

### 청구항 6.

제 3 항에 있어서,

상기 신호 라인군을 덮는 게이트 절연막과;

상기 게이트 절연막 상에 형성된 추가 접속패턴과;

상기 게이트 절연막 및 상기 박막트랜지스터를 덮는 보호막과;

상기 게이트 절연막 및 상기 보호막을 관통하여 상기 신호 라인군을 노출시키는 제1 접촉홀과;

상기 보호막을 관통하여 상기 박막트랜지스터를 노출시키는 제2 접촉홀과;

상기 보호막을 관통하여 상기 추가 접속패턴을 노출시키는 제3 및 제4 접촉홀과;

상기 보호막 상부에 형성됨과 아울러 상기 제1 접촉홀 및 제3 접촉홀을 통해 상기 신호 라인군과 상기 추가 접속패턴을 접속시키는 제1 접속 패턴과;

상기 보호막 상부에 형성됨과 아울러 상기 제2 접촉홀 및 제4 접촉홀을 통해 상기 박막트랜지스터와 상기 추가 접속패턴을 접속시키는 제2 접속 패턴을 추가로 구비하는 것을 특징으로 하는 액정 표시장치.

## 청구항 7.

제 6 항에 있어서,

상기 절연패턴은 상기 제1 및 제2 접속 패턴과 중첩되는 것을 특징으로 하는 액정 표시장치.

## 청구항 8.

하부 기판상에 다수의 게이트 라인과, 상기 게이트 라인에 전원신호들 및 게이트 제어 신호들을 공급하는 게이트 구동부를 구비하는 박막 트랜지스터 어레이 기판을 마련하는 단계와;

상부 기판상에 공통 전압을 공급받는 공통전극과, 상기 공통 전극 상에 형성된 절연패턴을 포함하는 칼라필터 어레이 기판을 마련하는 단계와;

상기 박막 트랜지스터 어레이 기판 및 상기 칼라 필터 어레이 기판을 도전성 실링재로 합착시키는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 제조 방법.

## 청구항 9.

제 8 항에 있어서,

상기 절연패턴은,

상기 박막 트랜지스터 어레이 기판과 상기 칼라 필터 어레이 기판 사이의 셀캡을 유지하기 위한 스페이서와 상기 절연패턴을 동시에 형성하는 것을 특징으로 하는 액정표시장치의 제조 방법.

## 청구항 10.

제 9 항에 있어서,

상기 절연 패턴은,

상기 셀 캡 이하로 형성되는 것을 특징으로 하는 액정 표시장치의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시장치 및 그 제조방법에 관한 것으로, 특히 구동 회로가 실장된 액정 표시장치의 공정 시간을 단축함과 아울러 상판의 공통전극과 하판의 구동회로부간의 단락을 방지하기 위한 액정 표시장치 및 그 제조방법에 관한 것이다.

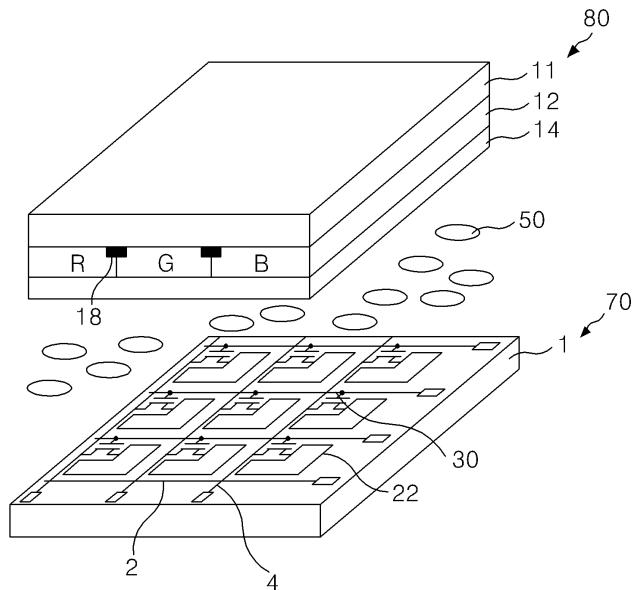

액정 표시 장치는 전계를 이용하여 액정의 광투과율을 조절함으로써 화상을 표시하게 된다. 이러한 액정 표시 장치는 도 1 및 도 2에 도시된 바와 같이 액정(50)을 사이에 두고 서로 대향하는 박막 트랜지스터 어레이 기판(70) 및 컬러 필터 어레이 기판(80)을 구비한다.

박막 트랜지스터 어레이 기판(70)은 하부기판(1) 상에 서로 교차되게 형성된 게이트라인(2) 및 데이터라인(4)과, 그들 (2,4)의 교차부에 형성된 박막트랜지스터(30)와, 박막트랜지스터(30)와 접속된 화소전극(22)과, 그들 위에 액정 배향을 위해 도포된 하부 배향막을 포함한다.

컬러 필터 어레이 기판(80)은 상부기판(11) 상에 형성되어 빛샘 방지를 위한 블랙 매트릭스(18)와, 컬러 구현을 위한 컬러 필터(12), 화소전극(22)과 수직전계를 이루는 공통전극(14)과, 그들 위에 액정 배향을 위해 도포된 상부 배향막을 포함한다.

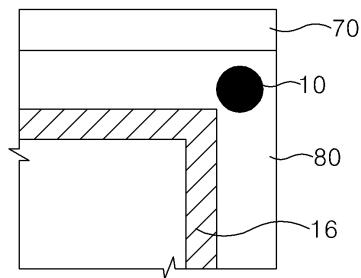

한편, 컬러필터 어레이 기판(80)의 공통전극(14)에 공통전압을 인가하기 위해서 도 2에 도시된 바와 같이 실링재(16) 바깥 쪽으로 형성된 은 도트(10)를 구비한다. 이 은 도트(10)는 페이스트 상태로 박막트랜지스터 어레이 기판(70)과 컬러 필터 어레이 기판(80) 사이에 도팅된 후 두 기판(70,80)은 실링재를 이용하여 합착된다. 합착시 기판(1,11)에 가해지는 압력에 의해 은 도트(10)가 인접영역으로 퍼지게 된다. 이 때, 인접영역으로 확장된 은 도트(6)가 스크라이빙 공정에 의해 손상되지 않기 위해서는 스크라이빙 라인 양쪽으로 상대적으로 많은 은 도트 영역이 필요로 한다. 이러한 은 도트(6)를 형성하기 위해 액정패널을 형성한 후 모든 패널 영역에 은 도트 공정을 진행해야 하므로 공정이 복잡함과 아울러 공정시간이 많이 필요로 하는 문제점이 있다.

또한 박막 트랜지스터 어레이 기판(70)에 구비된 게이트 라인(2) 및 데이터 라인(4)에 신호를 공급하기 위해 액정표시장치는 게이트 구동부 및 데이터 구동부를 추가로 구비해야 한다.

게이트 구동부와 데이터 구동부는 다수개의 집적회로(Integrated Circuit; 이하, IC라 함)들로 분리되어 칩 형태로 제작된다. 집적화된 구동IC들 각각은 TCP(Tape Carrier Package)상에 오픈된 IC영역에 실장되거나 COF(Chip On Film)방식으로 TCP베이스 필름 상에 실장되고, TAB(Tape Automated Bonding)방식으로 액정 패널과 전기적으로 접속된다. 이와 같이 종래 액정표시장치의 제조방법은 구동IC를 별도로 제작하여 TCP를 통해 액정패널에 접착하는 과정을 포함함으로써 제조 공정이 복잡하고, 액정표시장치의 제조 비용 증가의 요인이 된다.

#### 발명이 이루고자 하는 기술적 과제

따라서 본 발명의 목적은 공정을 단순화할 수 있는 액정표시장치 및 그 제조 방법을 제공함에 있다.

#### 발명의 구성

상기 목적을 달성하기 위하여 본 발명에 따른 액정표시장치는 상부기판 상에 형성된 공통전극과; 상기 상부 기판과 대향하는 하부기판 상에 형성된 게이트 구동부와; 상기 게이트 구동부와 대면하는 상기 공통전극 상부에 형성된 절연패턴과; 상기 상부기판과 상기 하부기판을 합착시키기 위한 도전성 실링재를 구비하는 것을 특징으로 한다.

상기 절연 패턴은, 상기 상부 기판과 상기 하부 기판 사이의 셀 갭 이하로 형성되는 것을 특징으로 한다.

상기 게이트 구동부는, 전원신호들 및 게이트 제어 신호들을 공급하기 위해 상기 하부 기판상에 형성된 신호 라인군과; 상기 신호 라인군 중 적어도 어느 하나와 접속된 다수의 박막트랜지스터들을 구비한다.

상기 신호 라인군을 덮는 게이트 절연막과; 상기 게이트 절연막 및 상기 박막트랜지스터를 덮는 보호막과; 상기 게이트 절연막 및 상기 보호막을 관통하여 상기 신호 라인군을 노출시키는 제1 접촉홀과; 상기 보호막을 관통하여 상기 박막트랜지스터를 노출시키는 제2 접촉홀과; 상기 보호막 상부에 형성되어 상기 제1 접촉홀 및 상기 제2 접촉홀을 통해 상기 신호 라인군 및 상기 박막트랜지스터를 접속시키는 접속 패턴을 더 구비하는 것을 특징으로 한다.

상기 절연패턴은 상기 접속 패턴과 중첩되는 것을 특징으로 한다.

상기 신호 라인군을 덮는 게이트 절연막과; 상기 게이트 절연막 상에 형성된 추가 접속패턴과; 상기 게이트 절연막 및 상기 박막트랜지스터를 덮는 보호막과; 상기 게이트 절연막 및 상기 보호막을 관통하여 상기 신호 라인군을 노출시키는 제1 접촉홀과; 상기 보호막을 관통하여 상기 박막트랜지스터를 노출시키는 제2 접촉홀과; 상기 보호막을 관통하여 상기 추가 접속패턴을 노출시키는 제3 및 제4 접촉홀과; 상기 보호막 상부에 형성됨과 아울러 상기 제1 접촉홀 및 제3 접촉홀을 통해 상기 신호 라인군과 상기 추가 접속패턴을 접속시키는 제1 접속 패턴과; 상기 보호막 상부에 형성됨과 아울러 상기 제2 접촉홀 및 제4 접촉홀을 통해 상기 박막트랜지스터와 상기 추가 접속패턴을 접속시키는 제2 접속 패턴을 추가로 구비하는 것을 특징으로 한다.

상기 절연패턴은 상기 제1 및 제2 접속 패턴과 중첩되는 것을 특징으로 한다.

또한 본 발명에 따른 액정표시장치의 제조 방법은 하부 기판상에 다수의 게이트 라인과, 상기 게이트 라인에 전원신호들 및 게이트 제어 신호들을 공급하는 게이트 구동부를 구비하는 박막 트랜지스터 어레이 기판을 마련하는 단계와; 상부 기판상에 공통 전압을 공급받는 공통전극과, 상기 공통 전극 상에 형성된 절연패턴을 포함하는 칼라필터 어레이 기판을 마련하는 단계와; 상기 박막 트랜지스터 어레이 기판 및 상기 칼라 필터 어레이 기판을 도전성 실링재로 합착시키는 단계를 포함한다.

상기 절연패턴은, 상기 박막 트랜지스터 어레이 기판과 상기 칼라 필터 어레이 기판 사이의 셀 갭을 유지하기 위한 스페이서와 상기 절연패턴을 동시에 형성하는 것을 특징으로 한다.

상기 절연 패턴은, 상기 셀 갭 이하로 형성되는 것을 특징으로 한다.

상기 목적 외에 본 발명의 다른 목적 및 이점들은 첨부 도면을 참조한 본 발명의 바람직한 실시 예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

이하, 본 발명의 바람직한 실시 예들을 도 3 내지 도 13c를 참조하여 상세하게 설명하기로 한다.

액정 표시장치는 전계를 이용하여 유전 이방성을 갖는 액정의 광 투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여 액정 표시장치는 액정 셀들이 매트릭스형으로 배열된 액정 표시패널과 액정표시패널을 구동하기 위한 구동부를 구비한다.

액정표시패널은 액정 셀들이 화소 신호에 따라 광 투과율을 조절함으로써 화상을 표시한다.

구동부는 액정 표시패널의 게이트 라인들을 구동하기 위한 게이트 구동부와, 데이터 라인들을 구동하기 위한 데이터 구동부와, 게이트 구동부 및 데이터 구동부의 구동 타이밍을 제어하기 위한 타이밍 제어부와, 상기 액정표시패널과 상기 구동부들의 구동에 필요한 전원 신호를 공급하는 전원부를 구비한다.

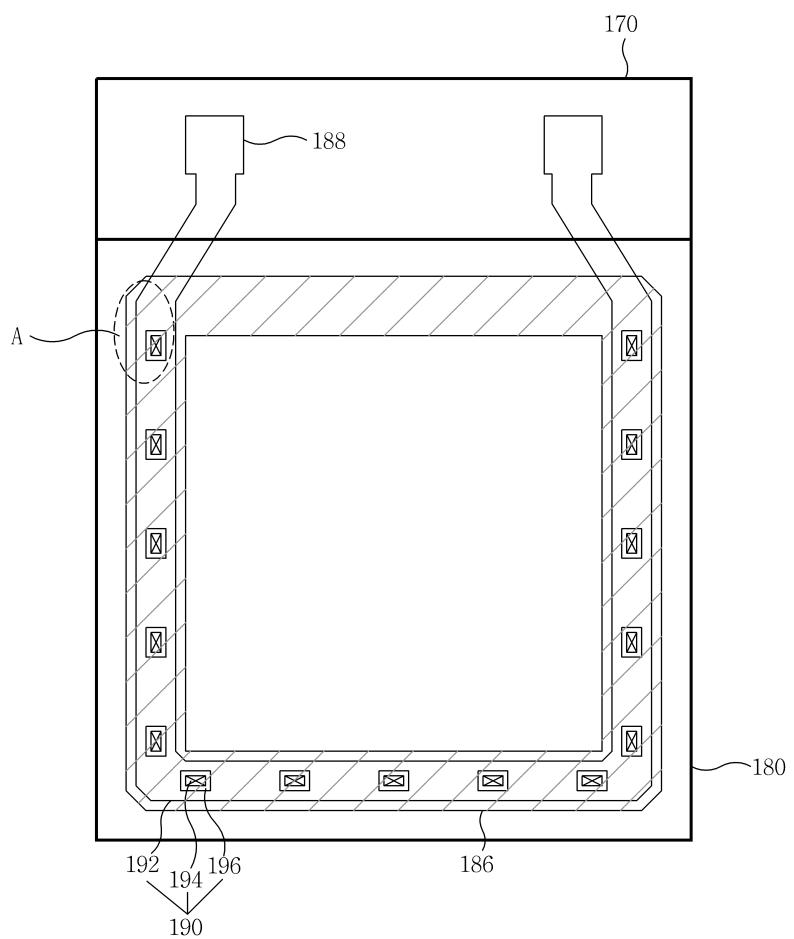

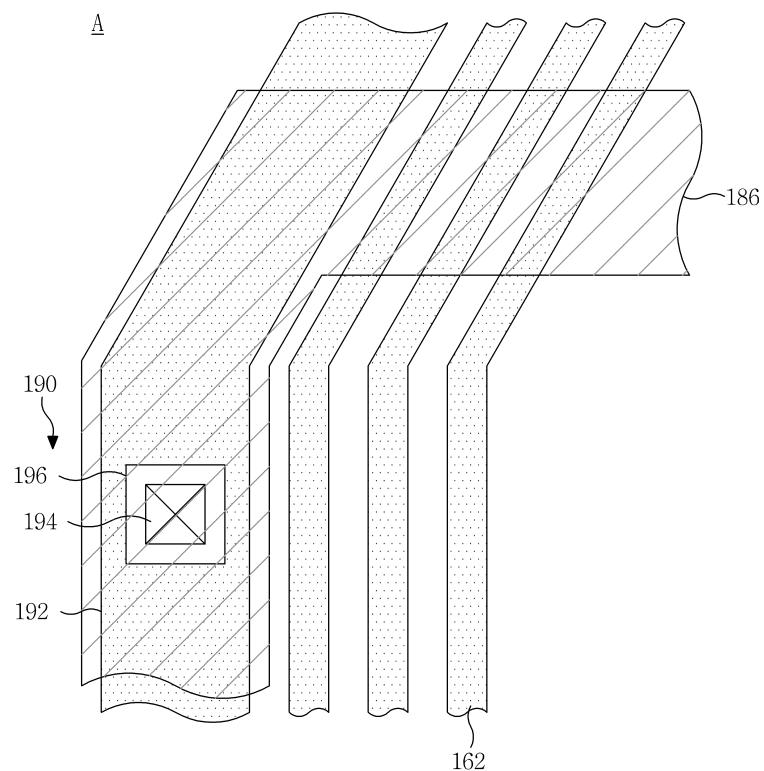

도 3은 본 발명의 제1 실시 예에 따른 액정 표시 패널을 나타내는 평면도다.

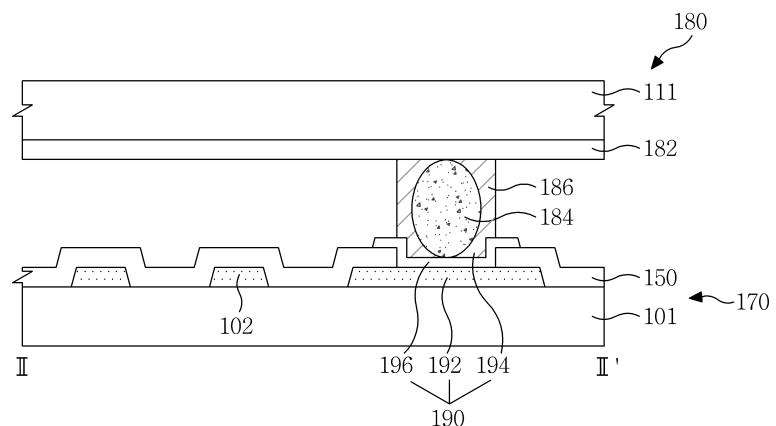

도 3에 도시된 액정 표시 패널은 박막트랜지스터 어레이가 형성된 박막트랜지스터 기판(170)과; 컬러필터 어레이가 형성된 칼라필터 기판(180)과, 박막트랜지스터 기판(170)과 컬러필터 기판(180)을 합착하기 위한 도전성 실링재(186)를 구비한다.

박막 트랜지스터 어레이 기판(170)은 서로 교차되게 형성된 게이트라인 및 데이터라인과, 그들의 교차부에 형성된 박막트랜지스터와, 박막트랜지스터와 접속된 화소전극과, 그들 위에 액정 배향을 위해 도포된 하부 배향막을 포함하는 박막트랜지스터 어레이가 하부 기판 상에 형성된다.

칼라 필터 어레이 기판(180)에는 도 5에 도시된 바와 같이 빛샘 방지를 위한 블랙 매트릭스와, 칼라 구현을 위한 칼라 필터, 화소전극과 수직전계를 이루는 공통전극(182)과, 그들 위에 액정 배향을 위해 도포된 상부 배향막을 포함하는 컬러필터 어레이가 상부기판(111) 상에 형성된다.

공통 전극(182)에 공통전압을 인가하기 위해서 도전성 실링재(186)를 통해 공통전극(182)과 접속되는 연결부(190)가 하부기판(101) 상에 형성된다. 연결부(190)는 도 4 및 도 5에 도시된 바와 같이 도전성 실링재(186)를 따라서 도전성 실링재(186)와 중첩되는 영역에 형성되는 제1 공급패턴(192)과, 그 제1 공급패턴(192)과 적어도 한 층의 절연막(150)을 관통하는 공급 콘택홀(194)을 통해 접속되는 제2 공급패턴(196)과, 제2 공급패턴(196)과 공통전극(182)을 연결하기 위한 도전체(184)를 구비한다. 본 발명의 제1 실시예에서 도전성 실링재(186)는 상기의 도전체(184)를 포함함으로써 도전성을 가진다.

제1 공급패턴(192)은 게이트라인과 접속된 게이트 링크(102)와 동일 금속으로 동일 평면 상에 형성되므로 게이트 링크(102)와 소정 간격 이격되어 형성된다. 이 제1 공급패턴(192)은 전원 공급부(도시하지 않음)와 접속된 공급패드(188)로부터 신장되어 형성된다.

제2 공급패턴(196)은 화소전극(도시하지 않음)과 동일 물질로 동일 평면 상에 형성된다. 이 제2 공급패턴(196)은 라인 형태로 형성되는 제1 공급패턴(192)을 따라 라인 형태로 형성되거나 제1 공급패턴(192)과 부분적으로 중첩되도록 도트 형태로 형성된다.

공급 콘택홀(194)은 게이트 절연막 및 보호막을 포함하는 절연막(150)을 관통하여 제1 공급패턴(192)을 노출시킨다.

도전체(184)는 도전성 클래스 파이버 및 도전성 볼 중 적어도 어느 하나가 이용된다. 여기서, 도전성 볼은 도전성을 가짐과 아울러 높이를 유지할 수 있도록 볼 스페이셔의 외측에 은(Ag), 금(Au) 등의 도전성 물질이 덮혀져 형성된다. 이 도전성 볼은 이방성 도전 필름(Anisotropic Conductive Film ; ACF)에 포함된 도전성 볼과 달리 소정 압력에도 높이를 유지할 수 있다.

이러한 도전체(184)는 도전성 실링재(186)와 혼합되어 기판 상에 도포된다.

이와 같이 본 발명의 제1 실시예는 도전체(184)를 포함하는 도전성 실링재(186)를 구비함으로써 별도의 은 도팅 공정 없이 컬러필터 어레이 기판(180)의 공통 전극에 공통전압을 인가할 수 있게 된다. 이 경우, 별도의 은 도팅 공정이 불필요하여 공정이 단순화된다.

한편, 본 발명의 제1 실시 예를 게이트 구동부가 패널상에 직접 실장된 액정표시장치에 적용할 경우, 상부 기판에 형성된 공통전극과 하부 기판에 실장된 게이트 구동부 간에 단락이 발생할 수 있다. 이와 같은 단락 발생을 도 6내지 도 9를 참조하여 상세히 하기로 한다.

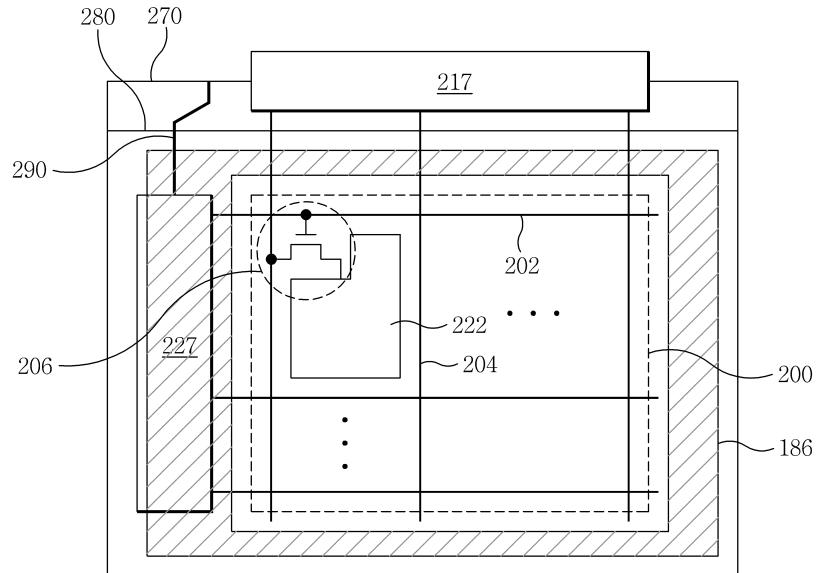

도 6은 본 발명의 제2 실시예에 따른 액정표시장치를 도시한 것이다. 도 6을 참조하면, 본 발명의 제2 실시예에 따른 액정표시장치는 게이트 구동부(227)가 패널상에 실장되고, 제2 실시예에 따른 박막 트랜지스터 어레이 기판(270)과 칼라 필터 어레이 기판(280)의 합착을 위해 본 발명의 제1 실시예에서와 마찬가지로 도전성 실링재(186)를 이용한다. 또한, 도전성 실링재(186)에는 제1 실시예에서와 마찬가지로 도전체(184)를 포함함으로써 도전성을 가진다. 도전성 실링재(186)에 포함된 도전체(184)를 통하여 공통전압이 공급되는 경로는 본 발명의 제1 실시예에서와 동일하므로 이에 대한 설명은 생략한다.

본 발명의 제2 실시예에서 게이트 구동부를 패널상에 직접 실장하는 이유는 액정표시장치의 가격 경쟁력 확보 및 모듈 공정의 단순화를 위해서이다. 이와 같이 게이트 구동부를 게이트 라인 및 데이터 라인의 형성과 함께 패널상에 직접 실장하면, 게이트 구동부의 접적회로를 별도로 제작하여 TCP를 통해 패널부에 접착하는 과정이 필요하지 않으므로 액정표시장치의 공정이 단순화되고, 가격이 저렴해지는 장점이 있다.

본 발명의 제2 실시예에 따른 액정 표시장치는 박막트랜지스터 어레이가 형성된 박막트랜지스터 어레이 기판(270)과, 컬러필터 어레이가 형성된 컬러필터 어레이 기판(280)과, 박막트랜지스터 어레이 기판(270)과 컬러필터 어레이 기판(280)을 합착하기 위한 도전성 실링재(186)를 구비한다. 또한, 도전성 실링재(186)에는 제1 실시예에서와 마찬가지로 도전체(184)가 혼합되어 있다.

박막 트랜지스터 어레이 기판(270)은 서로 교차되게 형성된 게이트 라인(202) 및 데이터 라인(204)과, 그들의 교차부에 형성된 박막 트랜지스터(206)와, 박막트랜지스터(206)와 접속된 화소전극(222)과, 그들 위에 액정 배향을 위해 도포된 하부 배향막을 포함하는 박막트랜지스터 어레이가 하부 기판 상에 구비됨으로써 형성된다. 그리고 본 발명의 제1 실시예에서 상술한 바와 같이 공통 전극(미도시)에 공통전압을 인가하기 위해서 도전성 실링재(186)에 포함된 도전체(184)를 통해 공통전극(미도시)과 접속되는 연결부(미도시)가 하부기판 상에 형성된다. 또한 하부 기판상에는 타이밍 제어부로부터의 게이트 제어 신호들과 전원부로부터의 전원신호들을 공급받는 LOG(Line On Glass)형 라인군(290)이 형성된다. LOG형 라인군(290)은 하부 기판상에 미세 패턴으로 형성된 신호라인군으로써 게이트 구동부(227)와 접속된다.

도전성 실링재(186)는 도 6에 도시된 바와 같이 박막 트랜지스터(206)가 배열된 액티브 어레이 영역(200)을 제외한 액정 패널의 외곽부를 감싸면서 도포됨과 아울러 패널상에 실장된 게이트 구동부(227)와 중첩되어 도포될 수 있다.

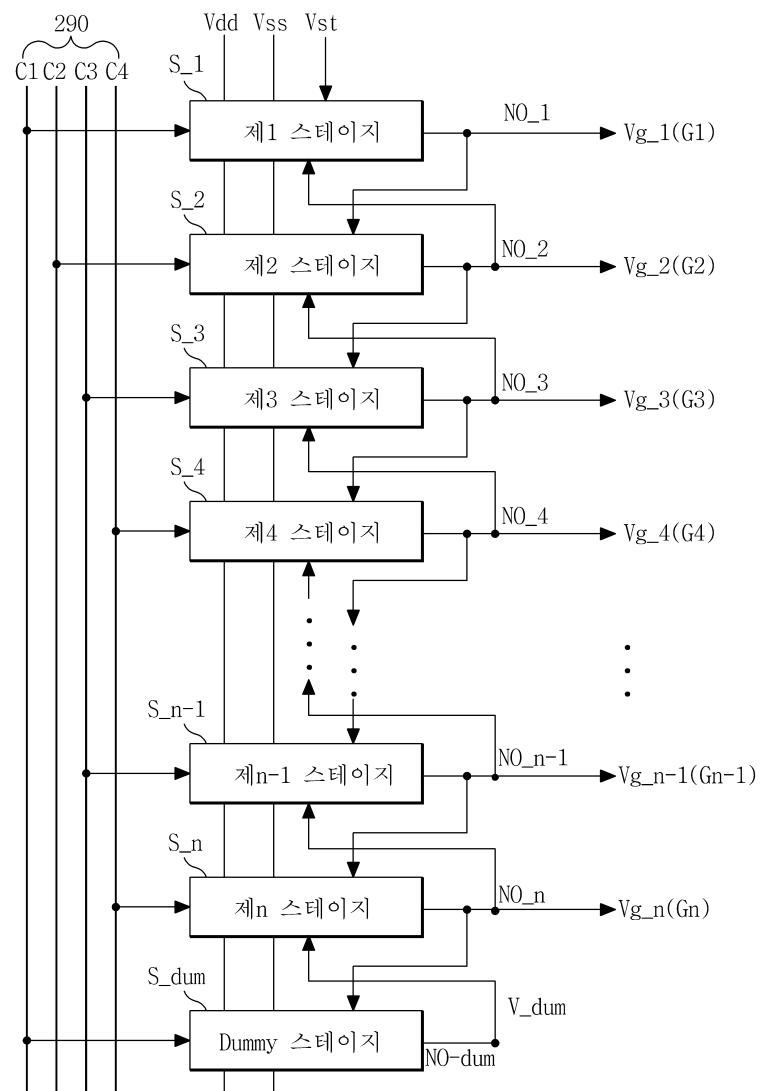

도 7을 참조하여 도 6에 도시된 게이트 구동부(227)를 상세히 설명하면, 게이트 구동부(227)는 1 수평주기마다 스타트 펄스를 순차적으로 쉬프트시켜 스캔펄스를 발생하는 쉬프트 레지스터, 쉬프트 레지스터의 출력신호를 액정셀의 구동에 적합한 스윙폭으로 변환하기 위한 레벨 쉬프터 및 레벨 쉬프터와 게이트 라인(G1 내지 Gn) 사이에 접속되는 출력 버퍼를 각각 포함하는 다수의 게이트 드라이브 집적회로들로 구성된다. 이 게이트 구동부(227)는 스캔 펄스를 게이트 라인들(G1 내지 Gn)에 순차적으로 공급하여 데이터가 공급되는 액정표시패널의 수평 라인을 선택한다.

도 7은 게이트 구동부(227)의 쉬프트 레지스터 회로 구성의 일례이며, 쉬프트 레지스터는 종속적으로 접속된 n 개의 스텝 이지들(S\_1 내지 S\_n) 및 더미 스테이지(S\_dum)을 구비한다. 스텝이지들(S\_1 내지 S\_n)과 게이트 라인들(G1 내지 Gn) 사이에는 도시하지 않은 레벨 쉬프터와 출력 버퍼가 설치된다.

이러한 쉬프트 레지스터에서 제1 스텝이지(S\_1)에는 스타트 신호로서 스타트펄스(Vst)가 입력되고 제2 내지 제n 스텝이지들(S\_2 내지 S\_n)에는 스타트 신호로서 이전 단 출력신호(Vg\_1 내지 Vg\_n-1)가 입력된다. 그리고, 제1 내지 제n-1 스텝이지들(S\_1 내지 S\_n-1)에는 리셋 신호로서 다음 단 출력신호(Vg\_2 내지 Vg\_n)가 입력되고, 제n 스텝이지에는 더미 스텝이지(Dummy Stage)의 출력신호(V\_dum)가 리셋 신호로서 입력된다.

또한, 각 스텝이지(S\_1 내지 S\_n)는 동일한 회로구성을 가지며 LOG 라인군(290)을 통해 인가되는 4 개의 클럭신호(C1 내지 C4) 중 어느 하나의 클럭 신호에 응답하여 스타트펄스(Vst) 또는 이전 단 출력신호(Vg\_1 내지 Vg\_n-1)를 쉬프트 시킴으로써 1 수평기간의 펄스 폭을 가지는 스캔펄스를 발생한다.

상기 각 스텝이지(S\_1 내지 S\_n)의 회로 구성과 상기 클럭 신호의 개수는 다양하게 설계될 수 있다.

또한 각 스텝이지(S\_1 내지 S\_n)는 다수의 박막 트랜지스터를 구비함으로써 스타트펄스 또는 이전 단 스텝이지의 출력신호와 클럭 신호에 응답하여 각 게이트 라인에 스캔 펄스를 순차적으로 공급한다.

각 스텝이지(S\_1 내지 S\_n)에 구비되는 박막 트랜지스터의 개수와 형태는 설계 방법에 따라 다양하게 형성될 수 있다.

또한 각 스텝이지(S\_1 내지 S\_n) 내에 형성된 박막 트랜지스터는 게이트 전극, 소스 전극 및 드레인 전극을 구비한다.

상기 각 스텝이지(S\_1 내지 S\_n)에 형성된 박막 트랜지스터의 게이트 전극, 소스 전극 및 드레인 전극 중 어느 하나는 클럭 신호를 공급하는 LOG 라인군(290)과 접속되어 상기 각 스텝이지(S\_1 내지 S\_n)에 클럭 신호를 공급한다.

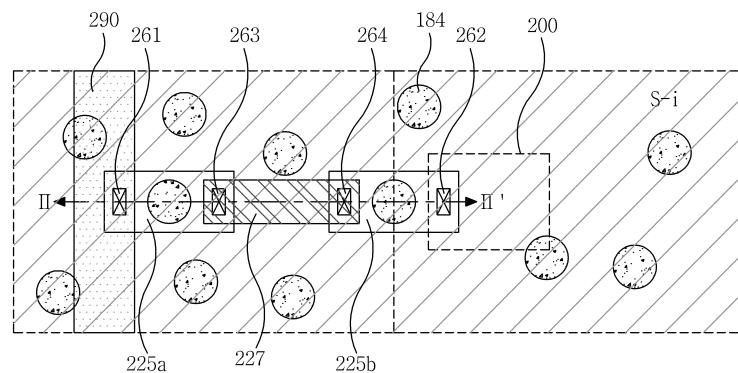

도 8은 도 6에 도시된 액정표시장치의 일부 영역으로서, 그 일부 영역은 도 7에 도시된 쉬프트 레지스터에서 제i 스텝이지(S\_i ; 단, i 는 n 보다 작거나 같은 양의 정수)와 제i 스텝이지(S\_i)에 접속된 LOG 라인군(290)을 나타낸 것이다.

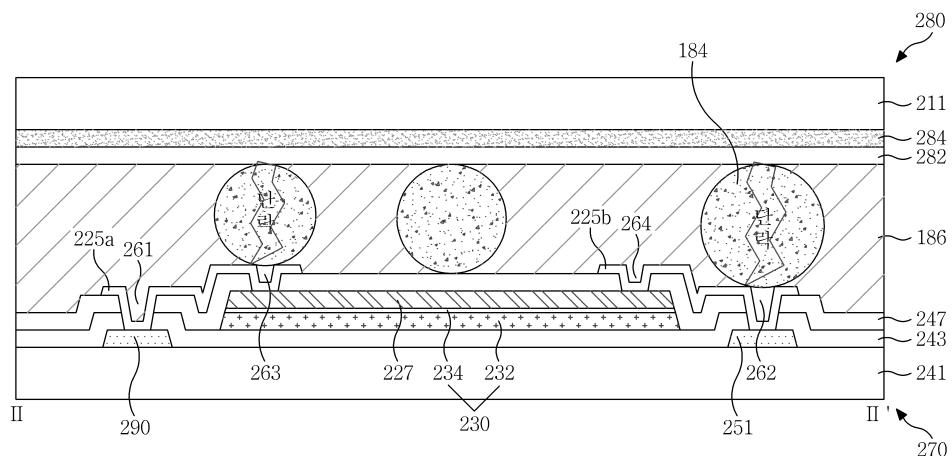

도 9는 도 8에 도시된 II - II'선을 따라 절취한 단면을 도시한 것이다.

도 8 및 도 9를 참조하면, 본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판(270)은 하부 기판(241) 위에 제i 스테이지(S\_i)와 LOG 라인군(290)을 구비한다.

LOG 라인군(290)은 게이트 로우 전압(VGL), 게이트 하이 전압(VGH), 공통 전압(VCOM), 그라운드 전압(GND), 베이스 구동 전압(VCC)과 같이 전원 신호들과; 게게이트 스타트 펄스(GSP), 게이트 쉬프트 클럭 신호(GSC), 게이트 이네이블 신호(GOE)와 같은 게이트 제어 신호들 각각을 공급하는 신호 라인들로 구성된다.

제i 스테이지(S\_i)는 상기 LOG 라인군(290) 중 어느 하나와 접속되어 상기 전원 신호들(VGL, VGH, VCOM, GND, VCC) 및 게이트 제어 신호들(GSP, GSC, GOE)을 게이트 라인에 공급하는 다수의 박막 트랜지스터(200)들로 구성된다. 이와 같이 제i 스테이지(S\_i)를 구성하는 다수의 박막 트랜지스터(200)들은 제i 스테이지(S\_i)의 회로 구성에 따라 다양한 방법으로 형성될 수 있다. 따라서 제i 스테이지(S\_i)의 회로 구성에 따라 상기 LOG 라인군(290) 중 어느 하나는 제i 스테이지(S\_i)에 구비된 박막 트랜지스터(200)의 게이트 전극, 소스 전극, 드레인 전극 중 어느 하나와 접속된다.

LOG 라인군(290)과 박막 트랜지스터(200)의 접속은 제1 접속 패턴(225a) 및 제2 접속 패턴(225b)을 통해 이루어진다.

참고로 도 9는 박막 트랜지스터(200)의 게이트 전극(251)과 LOG 라인군(290)의 접속을 일례로 도시한 것이다.

상기의 게이트 전극(251)과 LOG 라인군(290)의 접속관계를 상세히 하면, LOG 라인군(290)은 하부 기판(241) 위에 게이트 금속으로 형성되며, 게이트 전극(251)은 하부 기판(241) 위에 LOG 라인군(290)과 이격되게 형성됨과 아울러 게이트 금속으로 형성된다.

상기의 LOG 라인군(290) 및 게이트 전극(251)은 게이트 절연막(243)을 통해 절연되며, 게이트 절연막(243) 상부에는 추가 접속패턴(227)이 형성된다. 추가 접속 패턴(227)과 게이트 절연막(243) 상부에는 추가 접속 패턴(227) 등을 외부로부터 보호하기 위한 보호막(247)이 형성된다. 또한 박막 트랜지스터 어레이 기판(270)에는 게이트 절연막(243) 및 보호막(247) 중 적어도 어느 하나를 관통하는 제1 접촉홀 내지 제4 접촉홀(261, 262, 263, 264)이 형성된다. 추가 접속 패턴(227)의 하부에는 활성층(232) 및 오믹 접촉층(234)을 포함하는 반도체 패턴(230)이 중첩될 수 있다.

그리고 제1 접촉홀 및 제3 접촉홀(261, 263)은 제1 접속 패턴(225a)에 의해 덮히고, 제2 접촉홀 및 제4 접촉홀(262, 264)은 제2 접속 패턴(225b)에 의해 덮힌다.

한편, 제1 접촉홀(261)은 LOG 라인군(290)을 노출시키고, 제3 접촉홀(263) 및 제4 접촉홀(264)은 추가 접속 패턴(227)을 노출시키며, 제2 접촉홀(262)은 게이트 전극(251)을 노출시킨다. 이에 따라 LOG 라인군(290)은 제1 접촉홀 및 제3 접촉홀(261, 263)과 제1 접속 패턴(225a)을 통해 추가 접속 패턴(227)과 접속되고, 게이트 전극(251)은 제2 접촉홀 및 제4 접촉홀(262, 264)과 제2 접속 패턴(225b)을 통해 추가 접속 패턴(227)과 접속된다. 이에 따라 LOG 라인군(290)을 통해 공급되는 신호들은 제1 접속 패턴(225a) -> 추가 접속 패턴(227) -> 제2 접속 패턴(225b)을 경유하여 제i 스테이지(S\_i)의 게이트 전극(251)에 전달된다.

상기의 추가 접속 패턴(227)과, 제3 및 제4 접촉홀(263, 264)이 없더라도, LOG 라인군(290)과 게이트 전극(251)은 제1 접촉홀(261) 및 제2 접촉홀(264)을 덮는 한 라인의 접속 패턴을 통해 접속될 수 있다. 그러나 제1 및 제2 접속 패턴(225a, 225b)이 ITO등과 같이 저항이 큰 투명도전성 금속으로 형성되고, 저항은 금속의 길이에 비례한다. 따라서 제1 및 제2 접속 패턴(225a, 225b)으로 각각 형성할 경우는 하나의 라인으로 접속 패턴을 형성할 경우에 비해 접속 패턴을 형성하는 금속의 길이가 짧아짐에 따라 접속 패턴의 저항이 감소하므로 보다 안정적으로 신호를 전달할 수 있게 된다.

상술한 제2 실시예에 따른 박막 트랜지스터 어레이 기판(270)에 합착되는 칼라 필터 어레이 기판(280)은 상부 기판(211) 위에 빛샘 방지를 위한 블랙 매트릭스(284)와 공통 전압을 인가받기 위한 공통 전극(282)을 구비한다.

그리고 상기의 칼라 필터 어레이 기판(280)과 박막 트랜지스터 어레이 기판(270)은 도전성 실재(186)를 통해 합착된다. 도전성 실재(186)는 도전체(184)를 포함하므로 도전체(184)를 통해 칼라 필터 어레이 기판(280)의 공통 전극(282)과 박막 트랜지스터 어레이 기판(270)의 접속 패턴(225a, 225b) 사이에 단락이 발생할 수 있다.

상기의 접속 패턴(225a, 225b)을 통해 공통 전압이 공급될 경우에 발생하는 단락은 칼라 필터 어레이 기판(280)의 공통 전극(282)에 공통 전압을 공급해주는 역할을 하므로 액정표시장치의 구동에 문제를 일으키지 않는다.

그러나 상기의 접속 패턴(225a, 225b)을 통해 게이트 로우 전압, 게이트 하이 전압, 그라운드 전압, 베이스 구동 전압과 같은 전원신호들과 게이트 제어신호들(GSP, GSC, GOE)이 공급될 경우 발생하는 단락은 본 발명의 제2 실시예에 따른 액정표시장치의 구동에 문제를 일으킨다.

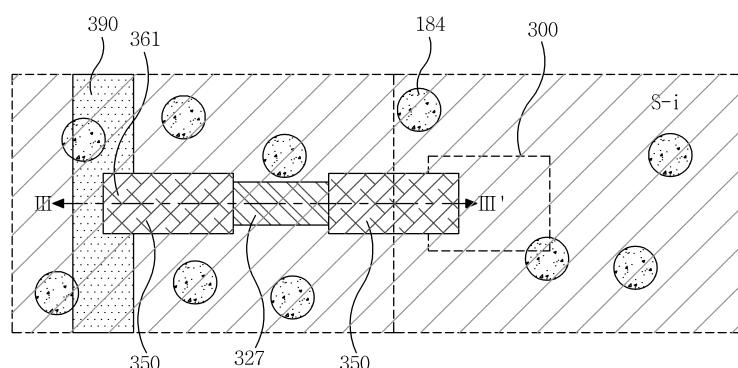

도 10 및 도 11에서는 상기 제2 실시예에 따른 액정표시장치의 문제를 해결하기 위해 본 발명의 제3 실시예에 따른 액정표시장치의 일부 영역을 도시한 것이다.

본 발명의 제3 실시예에 따른 액정표시장치는 본 발명의 제2 실시예에서와 마찬가지로 구동부가 패널상에 실장된 것이고, 칼라 필터 어레이 기판(380)과 박막 트랜지스터 어레이 기판(370)의 합착을 위해 본 발명의 제1 실시예에서와 마찬가지로 도전성 실링재(186)를 이용한다. 도전성 실링재(186)를 통하여 공통전압이 공급되는 경로는 본 발명의 제1 실시예에서와 동일하므로 이에 대한 설명은 생략한다.

도 10 및 도 11에 도시된 액정표시장치의 일부 영역은 쉬프트 레지스터에서 제i 스테이지(S\_i ; 단, i 는 n 보다 작거나 같은 양의 정수)와 제i 스테이지(S\_i)에 접속된 LOG 라인군(390)을 나타낸 것이다.

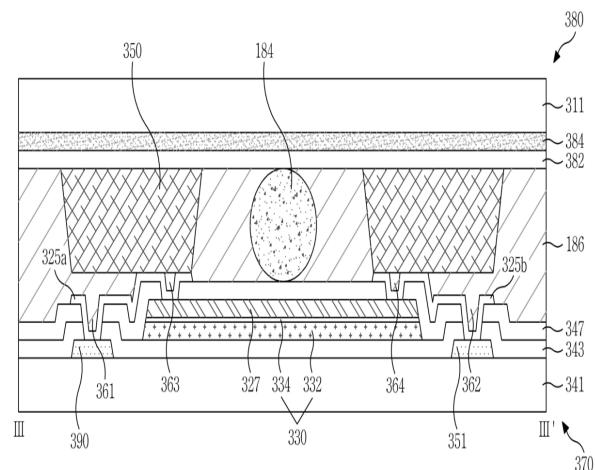

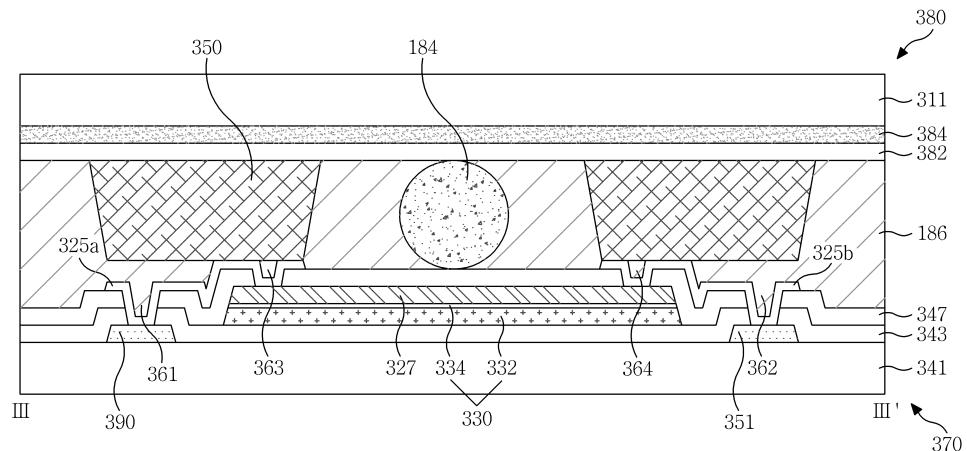

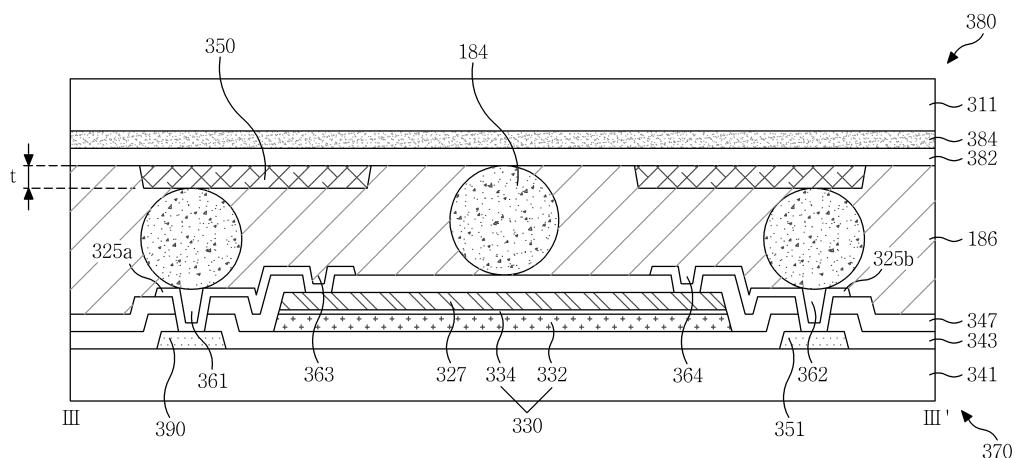

도 11은 도 10에 도시된 III-III'선을 따라 절취한 단면을 도시한 것이다.

도 10 및 도 11을 참조하면, 본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판(370)은 하부 기판(341) 위에 제i 스테이지(S\_i)와 LOG 라인군(390)을 구비한다.

LOG 라인군(390)은 게이트 로우 전압(VGL), 게이트 하이 전압(VGH), 공통 전압(VCOM), 그라운드 전압(GND), 베이스 구동 전압(VCC)과 같이 전원 신호들과; 게게이트 스타트 펄스(GSP), 게이트 쉬프트 클럭 신호(GSC), 게이트 이네이블 신호(GOE)와 같은 게이트 제어 신호들 각각을 공급하는 신호 라인들로 구성된다.

제i 스테이지(S\_i)는 상기 LOG 라인군(390) 중 어느 하나와 접속되어 상기 전원 신호들(VGL, VGH, VCOM, GND, VCC) 및 게이트 제어 신호들(GSP, GSC, GOE)을 게이트 라인에 공급하는 다수의 박막 트랜지스터(300)들로 구성된다. 이와 같이 제i 스테이지(S\_i)를 구성하는 다수의 박막 트랜지스터(300)들은 제i 스테이지(S\_i)의 회로 구성에 따라 다양한 방법으로 형성될 수 있다. 따라서 제i 스테이지(S\_i)의 회로 구성에 따라 상기 LOG 라인군(390) 중 어느 하나는 제i 스테이지(S\_i)에 구비된 박막 트랜지스터(300)의 게이트 전극, 소스 전극, 드레인 전극 중 어느 하나와 접속된다.

LOG 라인군(390)과 박막 트랜지스터(300)의 접속은 제1 접속 패턴(325a) 및 제2 접속 패턴(325b)을 통해 이루어진다.

참고로 도 11은 박막 트랜지스터(300)의 게이트 전극(351)과 LOG 라인군(390)의 접속을 일례로 도시한 것이다.

상기의 게이트 전극(351)과 LOG 라인군(390)의 접속관계를 상세히 하면, LOG 라인군(390)은 하부 기판(341) 위에 게이트 금속으로 형성되며, 게이트 전극(351)은 하부 기판(341) 위에 LOG 라인군(390)과 이격되게 형성됨과 아울러 게이트 금속으로 형성된다.

상기의 LOG 라인군(390) 및 게이트 전극(351)은 게이트 절연막(343)을 통해 절연되며, 게이트 절연막(343) 상부에는 추가 접속패턴(327)이 형성된다. 추가 접속 패턴(327)과 게이트 절연막(343) 상부에는 추가 접속 패턴(327) 등을 외부로부터 보호하기 위한 보호막(347)이 형성된다. 또한 박막 트랜지스터 어레이 기판(370)에는 게이트 절연막(343) 및 보호막(347) 중 적어도 어느 하나를 관통하는 제1 접촉홀 내지 제4 접촉홀(361, 362, 363, 364)이 형성된다. 추가 접속 패턴(327)의 하부에는 활성층(332) 및 오믹 접촉층(334)을 포함하는 반도체 패턴(330)이 중첩될 수 있다.

그리고 제1 접촉홀 및 제3 접촉홀(361, 363)은 제1 접속 패턴(325a)에 의해 덮히고, 제2 접촉홀 및 제4 접촉홀(362, 364)은 제2 접속 패턴(325b)에 의해 덮힌다.

한편, 제1 접촉홀(361)은 LOG 라인군(390)을 노출시키고, 제3 접촉홀(363) 및 제4 접촉홀(364)은 추가 접속 패턴(327)을 노출시키고, 제2 접촉홀(362)은 게이트 전극(351)을 노출시킨다. 이에 따라 LOG 라인군(390)은 제1 접촉홀 및 제3 접촉홀(361, 363)과 제1 접속 패턴(325a)을 통해 추가 접속 패턴(327)과 접속되고, 게이트 전극(351)은 제2 접촉홀 및 제4 접촉홀(362, 364)과 제2 접속 패턴(325b)을 통해 추가 접속 패턴(327)과 접속된다. 이에 따라 LOG 라인군(390)을 통해 공급되는 신호들은 제1 접속 패턴(325a)-> 추가 접속 패턴(327)-> 제2 접속 패턴(325b)을 경유하여 제i 스테이지(S\_i)의 게이트 전극(351)에 전달된다.

상기의 추가 접속 패턴(327)과, 제3 및 제4 접촉홀(363, 364)이 없더라도, LOG 라인군(390)과 게이트 전극(351)은 제1 접촉홀(361) 및 제2 접촉홀(364)을 덮는 한 라인의 접속 패턴을 통해 접속될 수 있다. 그러나 제1 및 제2 접속 패턴(325a, 325b)이 ITO등과 같이 저항이 큰 투명도전성 금속으로 형성되고, 저항은 금속의 길이에 비례한다. 따라서 제1 및 제2 접속 패턴(325a, 325b)으로 각각 형성할 경우는 하나의 라인으로 접속 패턴을 형성할 경우에 비해 접속 패턴을 형성하는 금속의 길이가 짧아짐에 따라 접속 패턴의 저항이 감소하므로 보다 안정적으로 신호를 전달할 수 있게 된다.

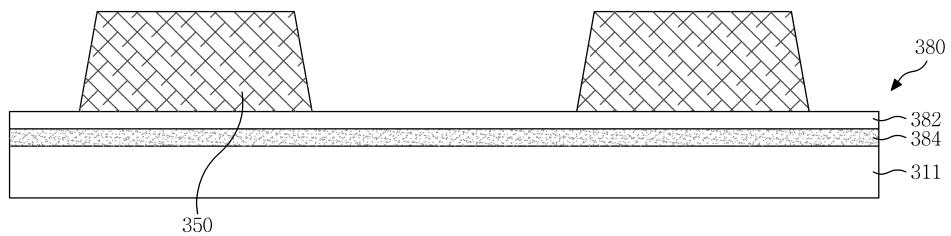

상술한 제3 실시예에 따른 박막 트랜지스터 어레이 기판(370)에 합착되는 칼라 필터 어레이 기판(380)은 상부 기판(311) 위에 빛샘 방지를 위한 블랙 매트릭스(384)와 공통 전압을 인가받기 위한 공통 전극(382)을 구비한다. 또한 칼라 필터 어레이 기판(380)은 박막 트랜지스터 어레이 기판(270)의 제1 및 제2 접속 패턴(325a, 325b)과 대응되는 영역에 절연패턴(350)을 추가로 구비한다. 이 절연패턴(350)은 상기의 칼라 필터 어레이 기판(380)의 공통 전극(382)과 박막 트랜지스터 어레이 기판(370)의 접속 패턴(325a, 325b) 사이에 단락이 발생하는 현상을 막아준다.

단락 현상을 막아주는 절연패턴(350)에 대해 상세히 하면, 상기의 칼라 필터 어레이 기판(380)과 박막 트랜지스터 어레이 기판(370)이 도전성 실재(186)를 통해 합착될 때, 공통 전극(382)과 접속 패턴(325a, 325b) 사이에는 절연 물질로 이루어진 절연패턴(350)이 배치되어 있으므로 공통 전극(382)과 접속 패턴(325a, 325b) 사이가 전기적으로 절연된다. 이와 같이 공통 전극(382)과 접속 패턴(325a, 325b) 사이가 절연됨으로써 액정표시장치의 제조 공정이 안정화 될 수 있다.

또한 상기의 절연패턴(350)의 두께(t1)는 도 12에 도시된 바와 같이 칼라 필터 어레이 기판(380)과 박막 트랜지스터 어레이 기판(370) 사이에서 셀 캡을 유지하기 위해 형성되는 스페이서의 두께 이하로 형성될 수 있다. 즉, 절연패턴(350)의 두께(t1)는 셀 캡 보다 작게 형성될 수 있다. 이와 같이 절연패턴(350)의 두께(t1)가 셀 캡 보다 작게 형성되더라도 공통 전극(282)과 도전성 스페이서(184) 사이는 절연패턴(350)에 의해 절연된다. 따라서 절연패턴(350)의 두께(t1)는 셀 캡 이하로 형성되어도 무관하다.

그리고 절연패턴(350)은 칼라 필터 어레이 기판(380) 뿐 아니라 박막 트랜지스터 어레이 기판(370)의 접속 패턴(325a, 325b) 상부에 형성될 수 있다.

도 13a 내지 도 13c는 도 11 및 도 12에 도시된 본 발명의 제3 실시예에 따른 칼라 필터 어레이 기판(380)의 제조 방법을 설명하기 위한 도면이다.

도 13a를 참조하면, 상부 기판(311) 상에 빛샘 방지를 위한 블랙 매트릭스(384)를 형성한다.

블랙 매트릭스(384)는 불투명 금속물질 또는 불투명 수지가 증착된 후 마스크를 이용한 포토리쏘그래피 공정과 식각공정을 이용하여 패터닝됨으로써 형성된다.

도 13b를 참조하면, 블랙 매트릭스가 형성된 상부 기판(311) 상에 액정의 움직임을 제어하기 위한 공통 전극(382)이 형성된다.

공통 전극(382)은 ITO와 같은 투명 도전물질이 증착됨으로 형성된다.

또한 도시되진 않았으나, 액티브 어레이 영역에는 블랙 매트릭스가 형성된 상부 기판(311) 상에 적색, 녹색, 청색의 컬러필터 어레이가 형성된 후 공통전극(382)이 형성된다.

도 13c를 참조하면, 공통 전극(382)이 형성된 상부 기판(311) 상에 칼라 필터 어레이 기판(380)과 박막 트랜지스터 어레이 기판(370)의 단락을 방지하기 위한 절연 패턴(325a, 325b)이 형성된다.

절연 패턴(325a, 325b)은 폴리 아크릴레이트(polyacrylate) 등을 포함하는 유기 절연물질이 전면 도포된 후 마스크를 이용한 포토리쏘그래피공정과 식각공정에 의해 형성된다. 또한 절연 패턴(325a, 325b)은 액정표시장치의 셀 캡을 유지하기 위해 액티브 어레이 영역에 형성되는 스페이서와 함께 형성될 수 있다.

셀 캡 유지를 위해 형성되는 스페이서보다 절연 패턴(325a, 325b)의 두께를 작게 형성하기 위해서는 회절 노광 마스크 또는 하프 톤 마스크를 적용한다.

회절 노광 마스크 또는 하프 톤 마스크를 적용하여 스페이서 보다 낮은 높이의 절연패턴을 형성하는 방법은 다음과 같다. 회절 노광 마스크 또는 하프 톤 마스크를 적용하여 제1 높이 및 제1 높이보다 낮은 제2 높이의 포토레지스트 패턴을 형성할 수 있다. 제1 높이의 포토레지스트 패턴에 대응되는 영역에서는 스페이서가 형성되고, 제1 높이의 포토레지스트 패턴에 대응되는 영역에서는 절연패턴이 형성된다. 스페이서와 절연패턴이 형성되는 과정을 상세히 하면, 먼저 상기 제1 및 제2 포토레지스트 패턴을 이용하여 폴리 아크릴레이트를 식각한다. 이 후, 제1 및 제2 높이의 포토레지스트 패턴을 애싱하여 제2 높이의 포토레지스트 패턴을 제거한다. 제2 높이의 포토레지스트 패턴이 제거됨으로써 제2 높이의 포토레지스트 패턴 하부에 있던 폴리 아크릴레이트가 노출되고, 이 노출된 폴리 아크릴레이트를 일부식각하여 절연패턴을 형성한다. 그리고 애싱 공정으로 높이가 낮아진 제1 높이의 포토레지스트 패턴은 절연패턴 형성 후, 스트립 공정으로 제거됨으로써 스페이서와 스페이서 보다 낮은 높이의 절연패턴이 모두 완성된다.

도 13a 내지 도 13c에 도시된 바와 같은 방법으로 칼라 필터 어레이 기판(380)을 마련하고, 본 발명의 제3 실시예와 같은 박막 트랜지스터 어레이 기판(370)을 마련한 후, 도전성 실링재(186)를 도포하여 상기 칼라 필터 어레이 기판(380) 및 상기 박막 트랜지스터 어레이 기판(370)을 합착한다.

### 발명의 효과

상술한 바와 같이 본 발명의 제1 실시예에 따른 액정표시장치는 도전체를 포함하는 도전성 실링재를 통해 공통전극과 공통 라인을 접속시킴으로써 은 도팅 공정이 필요없이 공통전압을 인가할수 있게 되어 공정이 단순화 될 수 있다.

또한 본 발명의 제2 실시예에 따른 액정표시장치는 상기와 같은 도전성 실링재를 이용함과 아울러 게이트 구동부를 패널 상에 실장함으로써 게이트 구동부의 접적회로를 별도로 제작하여 TCP를 통해 패널부에 접착하는 과정이 필요하지 않으므로 액정표시장치의 공정이 단순화되고, 가격이 저렴해지는 장점이 있다.

그리고 본 발명의 제3 실시예에 따른 액정표시장치는 상기와 같은 도전성 실링재를 이용하고 게이트 구동부를 패널상에 실장함과 아울러 게이트 구동부와 대면하는 칼라 필터 어레이 기판에 절연 패턴을 구비함으로써 액정표시장치의 구동부와 칼라 필터 어레이 기판간의 단락 현상을 방지할 수 있다. 이러한 단락 현상을 방지 함으로써 액정 표시장치의 제조 공정을 안정화시킬 수 있다.

이상 설명한 내용을 통해 당업자라면 본 발명의 기술 사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 도면의 간단한 설명

도 1은 종래 액정 표시장치를 나타내는 평면도.

도 2는 도 1에 도시된 공통전극에 공통전압을 공급하기 위한 은 도트를 나타내는 평면도.

도 3은 본 발명의 제1 실시 예에 따른 액정 표시장치를 나타내는 평면도.

도 4는 도 3에서 A영역을 확대한 평면도.

도 5는 도 4에서 I-I' 선을 따라 절취한 액정 표시장치를 나타내는 단면도.

도 6은 본 발명의 제2 실시 예에 따른 액정 표시장치를 나타내는 도면.

도 7은 도 6에 도시된 액정 표시장치의 게이트 구동부를 상세히 설명하기 위한 도면.

도 8은 도 7에 도시된 스테이지와 LOG 라인군의 접속관계를 설명하기 위한 도면.

도 9는 도 8에 도시된 II-II' 선을 따라 절취한 액정표시장치의 단면도.

도 10은 본 발명의 제3 실시 예에 따른 액정표시장치를 나타내는 도면.

도 11은 도 10에 도시된 III-III' 선을 따라 절취한 액정표시장치의 단면도.

도 12는 도 10에 도시된 III-III' 선을 따라 절취한 액정표시장치의 다른 단면도.

도 13a 내지 도 13c는 본 발명의 제3 실시예에 따른 액정표시장치의 컬러필터 어레이 기판을 제조하는 과정을 설명하기 위한 도면.

<도면의 주요부분에 대한 부호의 설명>

80, 180, 280, 380 : 칼라 필터 어레이 기판

70, 170, 280, 370 : 박막 트랜지스터 어레이 기판

186 : 도전성 실링재 182, 282, 382 : 공통 전극

227 : 게이트 구동부 200, 300 : 구동부의 박막트랜지스터

350 : 절연 패턴 184 : 도전체

225a, 225b, 325a, 325b, 227, 327 : 접속 패턴

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13a

도면13b

도면13c

|                |                                           |         |            |

|----------------|-------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                              |         |            |

| 公开(公告)号        | <a href="#">KR1020070065626A</a>          | 公开(公告)日 | 2007-06-25 |

| 申请号            | KR1020050126256                           | 申请日     | 2005-12-20 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                  |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                 |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                 |         |            |

| [标]发明人         | PARK SUNG IL<br>박성일<br>LEE GUN HEE<br>이건희 |         |            |

| 发明人            | 박성일<br>이건희                                |         |            |

| IPC分类号         | G02F1/1333                                |         |            |

| CPC分类号         | G02F1/13454 G02F1/1339 G09G3/3677         |         |            |

| 其他公开文献         | KR101201068B1                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                 |         |            |

### 摘要(译)

本发明涉及液晶显示器及其制造方法，用于防止滤色器阵列基板的公共电极的驱动电路部分与薄膜晶体管阵列面板之间的短路，缩短液晶显示器的处理时间特别地，驱动电路作为液晶显示器安装，以及制造该驱动电路的方法。该液晶显示器包括形成在上板上的公共电极;栅极驱动单元形成在下板上，面向上板;门驱动单元;以及用于粘附安装氧化物的导电密封材料，在上部形成面向上板和下板的公共电极。