(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년06월01일

(11) 등록번호 10-1151799

(24) 등록일자 2012년05월24일

(51) 국제특허분류(Int. Cl.)

*G02F 1/136* (2006.01)

(21) 출원번호 10-2005-0106840

(22) 출원일자 2005년11월09일

심사청구일자 2010년11월09일

(65) 공개번호 10-2007-0049743

(43) 공개일자 2007년05월14일

(56) 선행기술조사문현

JP2000312006 A\*

JP2000312006 A\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 14 항

심사관 : 신창우

(54) 발명의 명칭 액정표시장치용 어레이기판과 그 제조방법

(57) 요약

본 발명은 액정표시장치에 관한 것으로 특히, 구동회로 일체형 액정표시장치용 어레이 기판과 그 제조방법에 관한 것이다.

특히, 제 1 마스크 공정으로, 구동회로부와 화소영역에 구성하는 P형 및 N형 다결정 박막트랜지스터의 다결정 반도체층을 형성하고, 다결정 반도체층과 보조전극이 적층된 스토리지 제 1 전극을 형성하는 것을 특징으로 한다.

또한, 제 2 마스크 공정 및 제 3 마스크 공정으로, P형 및 N형 다결정 박막트랜지스터의 게이트 전극을 형성하고, 상기 각 다결정 박막트랜지스터의 다결정 반도체층에  $p^+$ 이온과,  $n^+$ 이온 도핑공정 및  $n^-$ 이온 도핑공정을 진행하고, 스토리지 제 2 전극을 형성하는 것을 특점으로 한다.

또한, 상기 각 다결정 박막트랜지스터의 소스 및 드레인 전극과 화소 전극을 단일 마스크 공정으로 형성하는 것을 특징으로 한다.

본 발명은 전술한 마스크 공정을 포함하는 5마스크 공정으로 구동회로 일체형 액정표시장치용 어레이기판을 제작함으로써, 공정시간 단축 및 공정 단순화를 통해 공정수율을 개선할 수 있는 장점이 있다.

대표도 - 도7

## 특허청구의 범위

### 청구항 1

화소영역을 포함하는 표시부와, 비표시부로 정의된 기판과;

상기 기판의 비표시부에 구성되며, n형 다결정 박막트랜지스터와 p형 다결정 박막트랜지스터로 구성된 CMOS소자의 조합으로 이루어진 구동회로와;

상기 화소영역의 일 측에 구성되며 n형 다결정 박막트랜지스터로 이루어진 스위칭 소자와;

상기 화소영역의 일부에 구성되고, 상기 n형 다결정 박막트랜지스터를 구성하는 다결정 반도체층과 이의 상부로 제 1 금속전극이 적층된 이중층 구조의 스토리지 제 1 전극과, 상기 스토리지 제 1 전극과 중첩하며 형성된 스토리지 제 2 전극과, 상기 스토리지 제 2 전극과 중첩하며 투명전극과 제 2 금속 전극으로 이루어진 이중층 구조의 스토리지 제 3 전극으로 구성된 스토리지 캐패시터와;

상기 스위칭 소자의 드레인 전극과 접촉하고, 상기 화소영역에 위치한 화소 전극

을 포함하며, 상기 n형 다결정 박막트랜지스터와 p형 다결정 박막트랜지스터 각각은 다결정의 반도체층과, 게이트 절연막과, 게이트 전극과, 상기 다결정의 반도체층을 각각 노출시키는 콘택홀을 구비한 총간접연막과, 상기 콘택홀을 통해 각각 상기 다결정의 반도체층과 접촉하는 소스 전극 및 드레인 전극의 적층 구조를 이루는 것이 특징이며, 상기 스토리지 제 3 전극을 이루는 투명전극은 상기 화소전극이 연장되어 이루어지며, 상기 소스 전극 및 드레인 전극은 투명 도전성 물질과 불투명 금속물질의 이중층 구조를 이루는 것이 특징인 구동회로 일체형 액정표시장치용 어레이기판.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서,

상기 p형 다결정 박막트랜지스터는 상기 소스 및 드레인 전극과 접촉하는 상기 다결정 반도체층의 표면에 p+이온이 도핑되고,

상기 n형 다결정 박막트랜지스터는 상기 소스 및 드레인 전극과 접촉하는 상기 다결정 반도체층의 표면에 n+이온이 도핑되고, 상기 다결정 반도체층은 상기 n+이온의 도핑영역과 상기 게이트 전극의 사이에는 n-이온이 도핑된 저농도 도핑영역을 포함하는 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판.

### 청구항 4

삭제

### 청구항 5

기판에 스위칭 영역과 스토리지 영역을 포함하는 다수의 화소영역으로 구성된 표시영역과, 구동회로부를 포함하는 비표시영역을 정의하는 단계와;

상기 구동회로부에 제 1 다결정 반도체층과 제 2 다결정 반도체층을 형성하고, 상기 스위칭 영역과 스토리지 영역에 제 3 다결정 반도체층과 제 4 다결정 반도체층을 형성하고, 상기 제 4 다결정 반도체층의 상부에 보조전극을 형성하여 이중층 구조의 스토리지 제 1 전극을 형성하는 제 1 마스크 공정 단계와;

상기 제 1, 2, 3 다결정 반도체층 및 상기 스토리지 제 1 전극 위로 전면에 게이트 절연막을 형성하는 단계와;

상기 게이트 절연막 위로 상기 제 1 다결정 반도체층의 중앙부에 대응하여 제 1 게이트 전극을 형성하고, 상기 제 2 다결정 반도체층과 제 3 다결정 반도체층 및 상기 보조전극의 상부에 각각 이들을 덮는 금속패턴을 형성하고, 상기 게이트 전극 외측으로 노출된 상기 제 1 다결정 반도체층의 표면에 p+이온을 도핑하는 제 2 마스크 공정 단계와;

상기 금속패턴 패터닝하여 상기 게이트 절연막 위로 상기 각 제 2 및 제 3 다결정 반도체층의 중앙부에 대응

하여에 제 2 및 제 3 게이트 전극을 형성하고, 상기 제 2 및 제 3 게이트 전극 각각의 외측으로 노출된 제 2 및 제 3 다결정 반도체층의 표면에 부분적으로 n+이온과 n-이온을 각각 도핑하고 동시에, 상기 보조 전극 주변의 제 4 다결정 반도체층 표면에 n+이온을 도핑하고, 상기 보조 전극에 대응하여 스토리지 제 2 전극을 형성하는 제 3 마스크 공정 단계와;

상기 기판의 전면에 상기 제 1 내지 제 3 다결정 반도체층을 각각 노출하는 제 1 및 제 2 콘택홀을 갖는 제 1 충간 절연막과 제 2 충간절연막을 형성하는 제 4 마스크 공정 단계와;

상기 제 2 충간절연막 상부에 상기 제 1 내지 제 3 다결정 반도체층 각각에 대응하여 상기 제 1 및 제 2 콘택홀을 통해 상기 제 1 내지 제 3 다결정 반도체층과 각각 접촉하고 서로 이격하는 형태로 투명전극과 불투명전극이 적층되어 구성된 제 1 내지 제 3 소스 및 드레인 전극을 형성하고, 상기 스토리지 제 2 전극에 대응하여 상기 투명전극과 불투명전극으로 이루어진 스토리지 제 3 전극을 형성하고, 상기 스토리지 영역 및 스위칭 영역을 제외한 화소 영역에 상기 투명전극으로 이루어진 화소 전극을 형성하는 제 5 마스크 공정 단계

를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 6

제 5 항에 있어서,

상기 제 1 마스크 공정 단계는,

상기 기판 상에 다결정 실리콘층과, 제 1 금속층을 적층하는 단계와;

상기 제 1 금속층의 상부에 포토레지스트를 도포하여 감광층을 형성하는 단계와;

상기 감광층의 이격된 상부에 투과부와 차단부와 반투과부로 구성된 제 1 마스크를 위치시키는 단계와;

상기 제 1 마스크의 상부로 빛을 조사하여 하부의 상기 감광층을 노광하고 현상하여, 상기 구동회로부에 상부로부터 일부가 제거된 상태로 패턴된 제 1 높이의 제 1 포토패턴과 제 2 포토패턴을 형성하고, 상기 스위칭 영역에 상기 제 1 내지 제 2 포토패턴과 동일한 제 1 높이의 제 3 포토패턴을 형성하고, 상기 스토리지 영역에 상기 제 1 높이보다 큰 제 2 높이로 패턴된 제 4 포토패턴을 형성하는 단계와;

상기 제 1 내지 제 4 포토패턴의 주변으로 노출된 상기 제 1 금속층을 제거하여, 상기 제 1 내지 제 4 포토패턴의 하부에 제 1 내지 제 4 금속패턴을 형성하는 단계와;

상기 제 1 높이를 갖는 상기 제 1 내지 제 3 포토패턴을 애싱공정으로 제거하여, 상기 제 1 내지 제 3 금속패턴을 노출하는 단계와;

상기 노출된 제 1 내지 제 3 금속패턴을 제거하여, 상기 구동회로부에 제 1 다결정 반도체층과 제 2 다결정 반도체층과, 상기 스위칭 영역에 제 3 다결정 반도체층을 형성하고, 동시에 상기 스토리지 영역에 제 4 다결정 반도체층과 이것의 상부에 제 4 금속패턴으로 이루어진 상기 보조전극의 이중층 구조를 갖는 상기 스토리지 제 1 전극을 형성하는 단계

를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 7

제 6 항에 있어서,

상기 제 1 내지 제 4 다결정 반도체층과 상기 기판 사이에 절연성 버퍼층을 더욱 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 8

제 5 항에 있어서,

상기 제 2 마스크 공정 단계는,

상기 게이트 절연막 위로 제 2 금속층을 적층하는 단계와;

상기 제 2 금속층을 제 2 마스크 공정으로 패턴하여, 상기 게이트 절연막 위로 상기 제 1 다결정 반도체층의

중심에 대응하여 상기 제 1 게이트 전극을 형성하고, 상기 제 2 다결정 반도체층 내지 제 4 다결정 반도체층의 상부에 각각 이들을 덮는 상기 금속패턴을 형성하는 단계

를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

### 청구항 9

제 5 항에 있어서,

상기 제 3 마스크 공정 단계는,

상기 제 1 다결정 반도체층의 상부에 상기 제 1 게이트 전극이 형성되고, 상기 제 2 다결정 반도체층과 제 3 다결정 반도체층과 제 4 다결정 반도체층의 상부에 이들을 덮는 상기 금속패턴이 형성된 기판의 전면에 포토레지스트를 도포하여 감광층을 형성하는 단계와;

상기 제 2 다결정 반도체층과 제 3 다결정 반도체층에 제 1 액티브 영역과, 제 1 액티브 영역의 양측에 제 2 액티브 영역과, 상기 제 1 및 제 2 액티브 영역 사이에 제 3 액티브 영역을 정의하는 단계와;

상기 감광층을 제 3 마스크로 노광한 후 현상하여, 상기 제 1 다결정 반도체층을 덮는 제 1 포토패턴과, 상기 제 2 및 제 3 다결정 반도체층 중 상기 제 1 및 제 3 액티브 영역을 덮는 제 2 포토패턴과 제 3 포토패턴과, 상기 제 4 다결정 반도체층을 덮는 제 4 포토패턴을 형성하는 단계와;

상기 제 1 내지 제 4 포토패턴 사이로 노출된 상기 금속패턴을 제거하여, 상기 제 2 및 제 3 포토패턴의 하부에 각각 상기 제 2 및 제 3 게이트 전극을 형성하고, 상기 제 4 포토패턴의 하부에 상기 스토리지 제 2 전극을 형성하는 단계와;

상기 제 2 및 제 3 다결정 반도체층의 제 2 액티브 영역에 n+이온을 도핑하여 오믹영역을 형성하고 동시에, 상기 보조전극 주변의 제 4 반도체층에 n+이온을 도핑하는 단계와;

상기 제 2 내지 제 3 포토패턴을 애싱하여, 상기 제 2 및 제 3 다결정 반도체층의 제 3 액티브 영역에 대응하는 제 2 및 제 3 게이트 전극의 양측단을 각각 노출하는 단계와;

상기 노출된 제 2 및 제 3 게이트 전극의 양측단을 제거하는 단계와;

상기 제 2 및 제 3 다결정 반도체층의 상기 제 3 액티브 영역에 n-이온을 도핑하여 저농도 도핑영역을 형성하는 단계

를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

### 청구항 10

제 9 항에 있어서,

상기 제 2 및 제 3 다결정 반도체층의 제 2 액티브 영역에 상기 제 2 및 제 3 소스 및 드레인 전극이 각각 접촉하는 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

### 청구항 11

제 5 항에 있어서,

상기 제 5 마스크 공정 단계는,

상기 제 1 및 제 2 층간절연막 위로 전면에 투명전극층과 불투명 금속층과 감광층을 적층하는 단계와;

상기 감광층의 이격된 상부에 투과부와 차단부와 반투과부로 구성된 제 5 마스크를 위치시키는 단계와;

상기 제 5 마스크의 상부로 부터 빛을 조사하여 상기 감광층을 노광한 후에 현상하여, 상기 구동회로 영역에 각각 이격된 제 1 포토패턴과 제 2 포토 패턴과, 상기 스위칭 영역에 이격된 제 3 포토패턴과, 상기 스토리지 영역과 화소영역에 걸쳐 제 4 포토패턴을 형성하는 단계와;

상기 제 1 내지 제 4 포토패턴의 주변으로 노출된 상기 불투명 금속층과 하부의 상기 투명전극층을 제거하여, 상기 제 1 내지 제 3 포토패턴의 하부에 상기 제 1 내지 제 3 반도체층과 각각 접촉하고 상기 투명전극과 불투명 금속이 적층되어 구성된 제 1 내지 제 3 소스 전극과 드레인 전극과, 상기 제 4 포토패턴의 하부에 상기

스토리지 영역 및 화소 영역에 걸쳐 패턴된 투명전극패턴과 불투명 금속패턴을 형성하는 단계와;

상기 제 1 내지 제 4 포토패턴을 애싱(ashing)하여, 상기 제 4 포토패턴을 제거하여 패턴된 상기 불투명 금속 패턴을 노출하는 단계와;

상기 노출된 불투명 금속패턴을 제거하여, 상기 스토리지 영역에 대응하여 적층된 투명전극층과 불투명전극의 이중층 구조의 상기 스토리지 제 3 전극과, 상기 스위칭 영역 및 스토리지 영역을 제외한 화소 영역에 대응하여 투명한 상기 화소전극을 형성하는 단계

를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 12

제 11 항에 있어서,

상기 제 3 및 제 4 다결정 반도체층은 일체로 형성되고, 상기 제 3 다결정 반도체층과 접촉하는 상기 제 3 드레인 전극을 구성하는 불투명 전극과 상기 스토리지 영역의 상기 불투명 전극 또한 일체로 구성된 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 13

제 12 항에 있어서,

상기 화소전극은 상기 제 3 다결정 반도체층과 접촉하는 상기 제 3 드레인 전극 또는 상기 스토리지 영역의 상기 불투명 전극과 접촉하는 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 14

제 5 항에 있어서,

상기 스토리지 영역의 적층된 상기 이중층 구조의 스토리지 제 1 전극과 게이트 절연막과 스토리지 제 2 전극과 제 1, 2 층간절연막과 스토리지 제 3 전극은 스토리지 캐페시터를 이루는 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 15

제 5 항에 있어서,

상기 제 1 층간 절연막을 형성한 후에, 기판을 열처리 하여 상기 제 4 다결정 반도체층의 표면에 도핑된 n+ 이온이 상기 보조 전극의 하부로 확산되도록 하여, 상기 보조 전극과 상기 제 4 다결정 반도체층이 오믹 콘택을 이루도록 하는 단계를 포함하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 청구항 16

제 5 항에 있어서,

상기 제 1 층간 절연막은 산화 실리콘( $\text{SiO}_2$ )을 증착하여 형성하고, 상기 제 2 층간 절연막은 질화 실리콘( $\text{SiN}_x$ )을 증착하여 형성하는 것을 특징으로 하는 구동회로 일체형 액정표시장치용 어레이기판 제조방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0019] 본 발명은 액정표시장치에 관한 것으로, 특히 구동회로 일체형 액정표시장치용 어레이기판과 그 제조방법에 관한 것이다.

[0020] 일반적으로, 액정표시장치는 박막 트랜지스터(Thin Film Transistor ; TFT)를 포함하는 어레이기판과 컬러필터(color filter)기판 사이에 액정을 주입하여, 이 액정의 이방성에 따른 빛의 굴절률 차이를 이용해 이미지

를 얻는 표시장치이다.

[0021] 이러한 표시장치의 스위칭 소자로 사용되는 박막트랜지스터는, 어레이부의 설계에 따라 다양한 형태로 구성 가능하며 특히, 액티브층으로 사용되는 반도체층으로는 비정질 실리콘 또는 다결정 실리콘(폴리 실리콘)을 사용하게 된다.

[0022] 이때, 일반적인 스위칭 소자로는 수소화된 비정질 실리콘(a-Si:H)이 주로 이용되는데, 이는 저온공정이 가능하여 저가의 절연기판을 사용할 수 있기 때문이다.

[0023] 그러나, 수소화된 비정질 실리콘은 원자 배열이 무질서하기 때문에 약한 결합(weak Si-Si bond) 및 맹클링 본드(dangling bond)가 존재하여 빛 조사나 전기장 인가 시 준 안정상태로 변화되어 박막 트랜지스터 소자로 활용시 안정성이 문제로 대두되고 있으며, 전기적 특성(낮은 전계효과 이동도 :  $0.1 \sim 1.0 \text{cm}^2/\text{V}\cdot\text{s}$ )이 좋지 않아 구동회로로는 쓰기 어렵다.

[0024] 반면, 폴리 실리콘은 비정질 실리콘에 비하여 전계효과 이동도가 크기 때문에 기판 위에 구동회로를 만들 수 있으며, 폴리 실리콘을 이용하여 기판에 직접 구동회로를 만들면 실장이 매우 간단해지고 액정패널을 더욱 컴팩트(compact)하게 제작할 수 있는 장점이 있다.

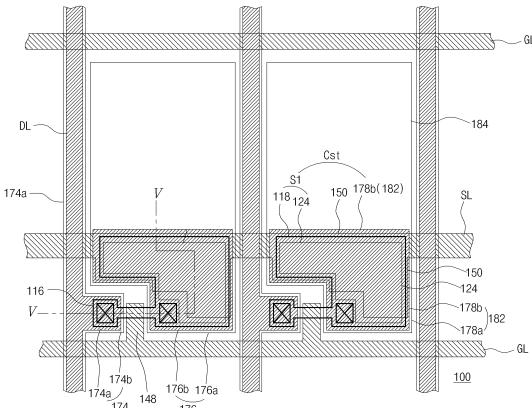

[0025] 도 1은 일반적인 구동회로 일체형 액정표시장치용 어레이기판의 개략도이다.

[0026] 도시한 바와 같이, 절연 기판(10)은 크게 표시부(D1)와 비표시부(D2)로 정의될 수 있으며, 상기 표시부(D1)에는 다수의 화소(P)가 매트릭스 형태로 위치하고 각 화소마다 스위칭 소자(T) 및 이와 연결된 화소 전극(17)이 구성된다.

[0027] 또한, 상기 화소(P)의 일 측을 따라 연장된 게이트 배선(12)과 이와는 수직하게 교차하는 데이터 배선(14)이 구성된다.

[0028] 상기 비표시부(D2)에는 구동회로부(16, 18)가 구성되는데, 구동 회로부(16, 18)는 기판(10)의 일 측에 위치하여 상기 게이트 배선(12)에 신호를 인가하는 게이트 구동회로부(16)와, 이와는 평행하지 않은 기판(10)의 타 측에 위치하여 상기 데이터 배선(14)에 신호를 인가하는 데이터 구동회로부(18)를 포함한다.

[0029] 상기 게이트 및 데이터 구동회로부(16, 18)는 외부로부터 입력된 신호를 조절하여 각각 게이트 및 데이터 배선(12, 14)을 통해 화소부(P)로 디스플레이 컨트롤 신호 및 데이터 신호를 공급하기 위한 장치이다.

[0030] 따라서, 상기 게이트 및 데이터 구동회로부(16, 18)는 입력되는 신호를 적절하게 출력시키기 위하여 일반적으로는 인버터(inverter)인 CMOS(complementary metal-oxide semiconductor)구조의 박막트랜지스터로 구성된다.

[0031] 상기 CMOS는 고속 신호처리가 요구되는 구동회로부 박막 트랜지스터에 사용되는 반도체 기술의 일종으로서, 음전기로 충전된 여분의 전자들(n형 반도체)과 양전기로 충전된 정공들(p형 반도체)을 이용하여 하나의 전도체를 형성하고, 상기 두 종류의 반도체들의 효과적인 전기제어에 의해 전류 게이트를 이루기 위한 상호 보완적인 방법으로 사용된다.

[0032] 이와 같이, 비표시부의 구동회로부를 이루는 CMOS 소자는 n형 및 p형 다결정 박막트랜지스터의 조합으로 이루어지고, 상기 표시부의 스위칭 소자는 n형 또는 p형 다결정 박막트랜지스터로 이루어진다.

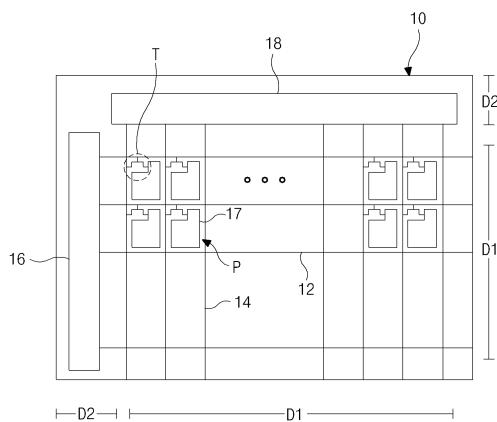

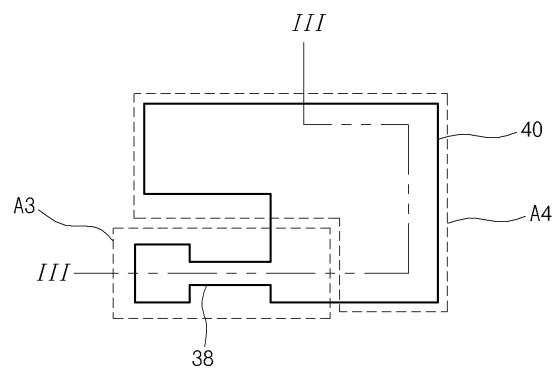

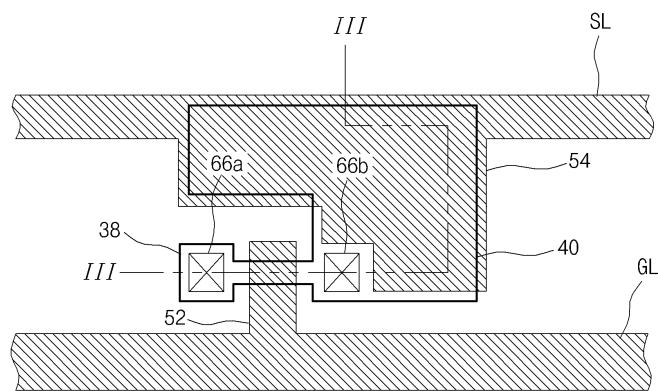

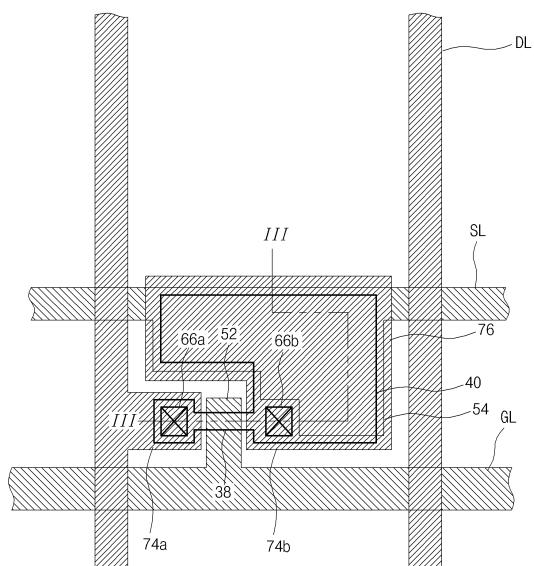

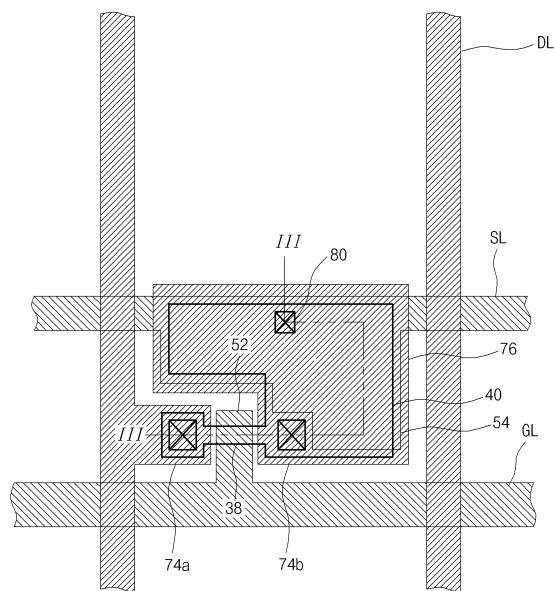

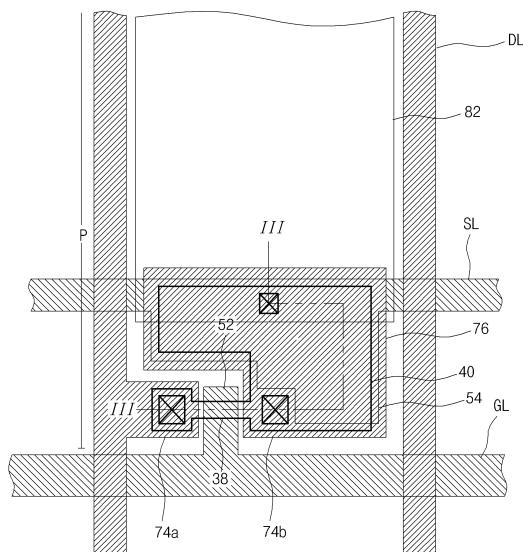

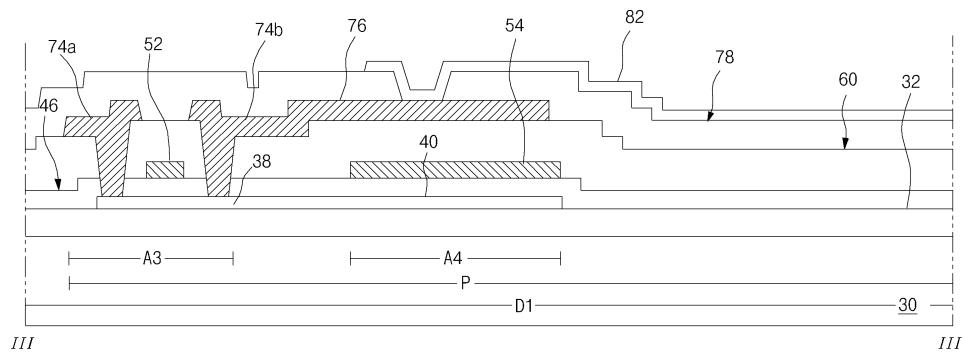

[0033] 이하, 도 2를 참조하여, 구동회로 일체형 액정표시장치용 어레이기판의 표시부의 구성을 설명한다.

[0034] 도시한 바와 같이, 기판(30)의 일면에 제 1 방향으로 게이트 배선(GL)이 구성되고, 상기 게이트 배선(GL)과 교차하여 화소 영역(P)을 정의하는 데이터 배선(DL)이 구성된다.

[0035] 상기 두 배선(SL, GL)의 교차부에는 게이트 전극(52)과 액티브층(38, 다결정 실리콘층)과 소스 전극(74a)과 드레인 전극(74b)으로 구성된 다결정 박막트랜지스터(T)가 구성되고, 상기 화소 영역(P)에는 상기 드레인 전극(74b)과 접촉하는 화소 전극(82)이 구성된다.

[0036] 또한, 상기 화소 영역(P)의 일부에는 제 1, 제 2, 제 3 스토리지 전극(40, 54, 76)으로 형성된 스토리지 캐퍼시터(Cst)가 구성된다.

[0037] 전술한 구성은, 액정패널의 표시영역을 일부 도시한 것이며 이러한 형상이 연속되어 표시영역을 이루게 된다.

[0038] 전술한 표시영역의 주변으로는 구동회로부(미도시)를 형성하게 되며, 구동회로부(미도시)에는 상기 데이터 배선 및 게이트 배선(DL, GL)에 신호를 전달하기 위한 구동회로(미도시)가 형성된다.

- [0039] 상기 구동회로(미도시)는 다결정 박막트랜지스터의 조합으로 이루어지며, 구동 특성이 빠르고 누설전류 특성이 낮아야 하기 때문에 N형 다결정 박막트랜지스터 또는, 앞서 언급한 바와 같이 CMOS 트랜지스터의 조합으로 형성할 수 있다.

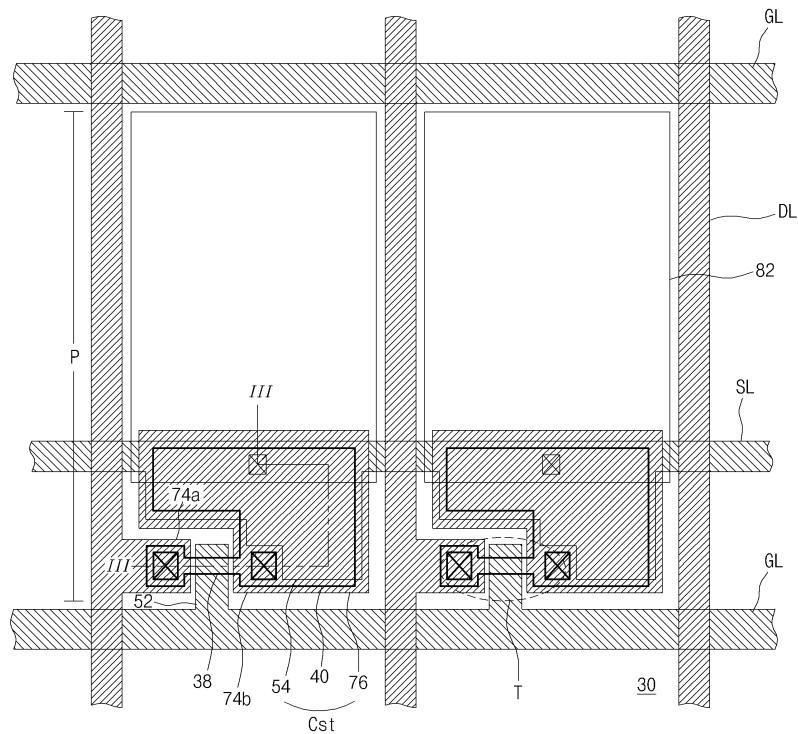

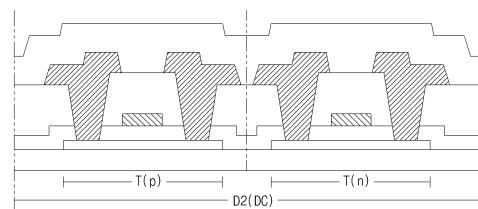

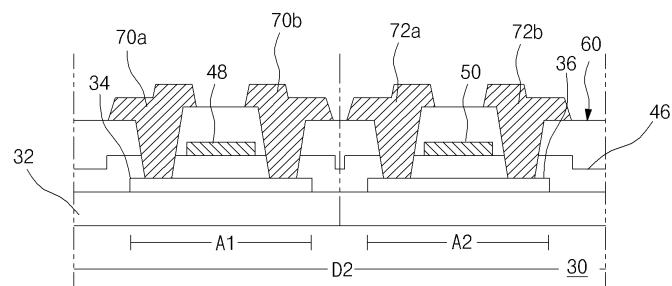

- [0040] 이하, 도 3a와 도 3b를 참조하여, 종래에 따른 구동회로 일체형 액정표시장치의 단면 구성을 설명한다.

- [0041] (도 3a는 구동 회로부를 나타낸 단면도이고, 도 3b는 도 2의 II-II를 따라 절단한 단면도이다.)

- [0042] 도시한 바와 같이, 비표시 영역(D2)에 구성한 구동회로(DC)는 CMOS 트랜지스터의 조합으로 이루어지며, 상기 CMOS트랜지스터는 N형 박막트랜지스터(T(n))와 P형 박막트랜지스터(P(n))의 조합으로 이루어진다.

- [0043] 표시 영역(D1)에 구성된 단일 화소 영역(P)은, 스위칭 소자(Ts)와 이와 접촉하면서 화소 영역(P)의 전면에 형성된 화소 전극(82)과, 보조 용량부인 스토리지 캐퍼시터가(Cst) 형성된다.

- [0044] 이때, 상기 표시영역(P)에 사용하는 스위칭 소자로(Ts)는 P형 또는 N형 다결정 박막트랜지스터를 사용하게 되는데, 일반적으로는 N형 다결정 박막트랜지스터를 사용한다.

- [0045] 상기 스토리지 캐퍼시터(Cst)는, 스토리지 제 1 전극(40)과 스토리지 제 2 전극(54)과 스토리지 제 3 전극(76)으로 구성되며, 등가회로적으로는 두 개의 캐퍼시터(C1,C2)터가 직렬 연결된 상태이다.

- [0046] 이와 같은 구성은, 영역을 확대하지 않고도 보조 용량을 더욱 확보할 수 있는 장점이 있다.

- [0047] 전술한 바와 같은 구성의 구동회로 일체형 액정표시장치용 어레이기판은, 일반적으로 스토리지 캐퍼시터(Cs t)를 형성하기 위한 도핑 공정과, N형 박막트랜지스터(T(n))를 형성하기 위한 n+이온 도핑공정 그리고, P형 박막트랜지스터(T(p))를 형성하기 위한 p+이온 도핑공정을 포함하여 9마스크 공정을 필요로 한다.

- [0048] 이에 대해, 이하 공정도면을 참조하여 종래에 따른 구동회로 일체형 액정표시장치용 어레이기판의 제조공정을 설명한다.

- [0049] 도 4a 내지 도 4i는 종래에 따른 구동회로를 제작하는 공정을 순서대로 도시한 공정 단면도이다.

- [0050] 도 5a 내지 도 5i는 종래에 따른 구동회로 일체형 액정표시장치용 어레이기판의 표시부 형성공정을 순서대로 도시한 공정 평면도이다.

- [0051] 도 6a 내지 도 6i는 각각 도 5a 내지 도 5i의 III-III을 따라 절단한 공정 단면도이다.

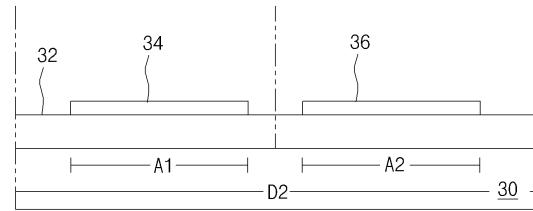

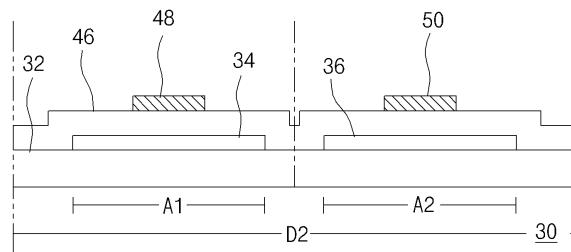

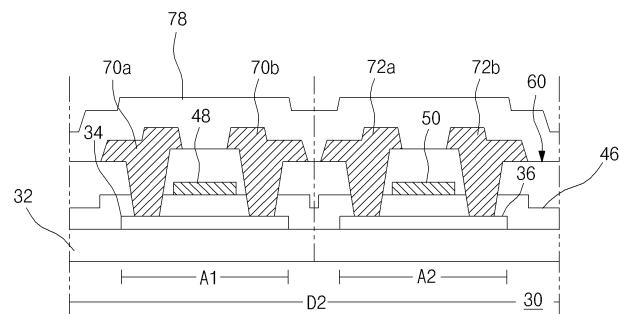

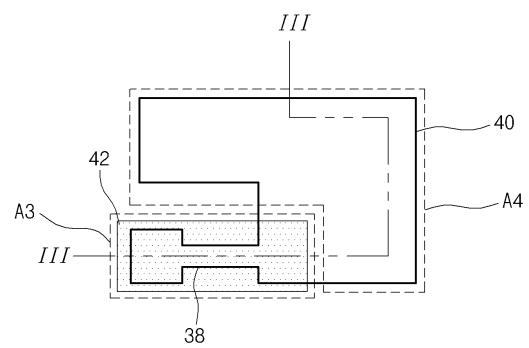

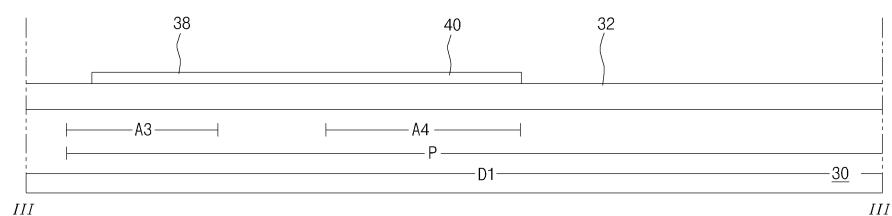

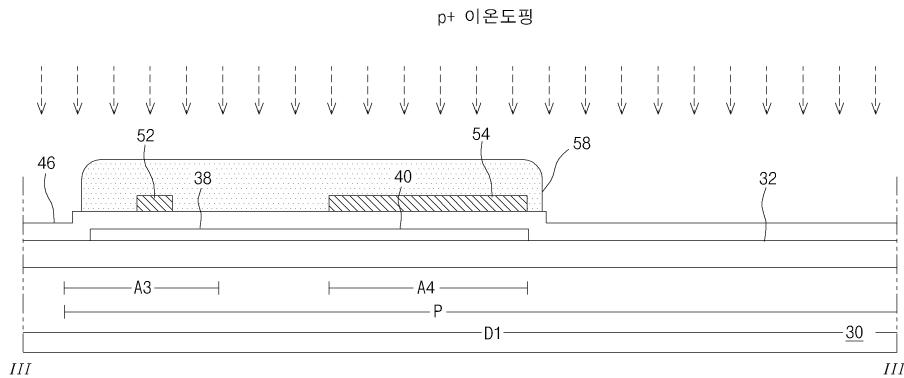

- [0052] 도 4a와 도 5a와 도 6a는 제 1 마스크 공정을 나타낸 도면이다.

- [0053] 도시한 바와 같이, 기판(30)을 표시부(D1)와 비표시부(D2)로 정의하고, 표시부(D1)는 다시 다수의 화소영역(P)으로 정의 한다.

- [0054] 이때, 비표시부(D2)에 편의상 P영역(A1)과 N영역(A2)을 정의하고, 상기 화소영역(P)에 스위칭 영역(A3)과 스토리지 영역(A4)을 정의한다.

- [0055] 전술한 바와 같이, 다수의 영역(A1,A2,A3,A4)이 정의된 기판(30)의 일면에 절연물질을 증착하여 베퍼층(32)을 형성하고, 상기 베퍼층(32)의 상부에 비정질 실리콘(a-Si:H)을 증착한 후 결정화 하는 공정을 진행한다.

- [0056] 상기 결정화를 위해 다양한 열전달 수단이 이용될 수 있지만, 일반적으로는 레이저(laser)를 이용하여 결정화를 진행한다.

- [0057] 결정화 공정으로 결정화된 층을 패턴하여, 상기 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 액티브층(active layer)으로서 기능을 하는 제 1 내지 제 3 다결정 반도체층(34,36,38)을 형성하고, 상기 스토리지 영역(A4)에 전극으로서 기능을 하는 제 4 다결정 반도체층(40)을 형성한다.

- [0058] 이때, 제 3 다결정 반도체층(38)과 제 4 다결정 반도체층(40)은 일체로 형성할 수 있다.

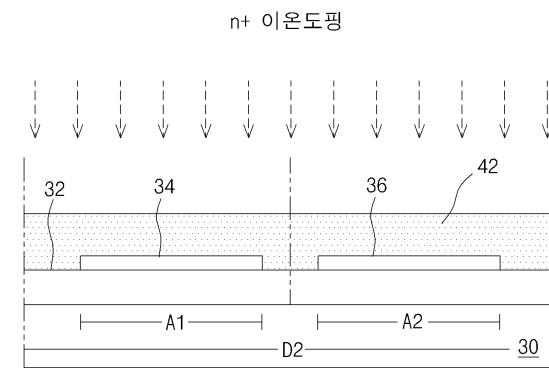

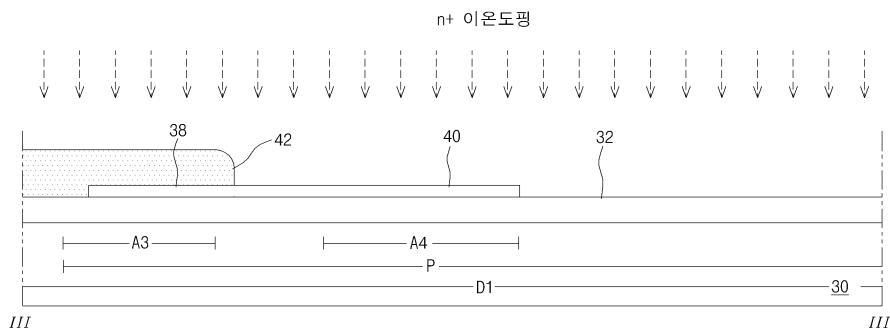

- [0059] 도 4b와 도 5b와 도 6b는 제 2 마스크 공정을 나타내며, 상기 스토리지 영역(A4)의 제 4 다결정 반도체층(40)에 이온을 도핑(doping)하는 공정을 도시한 도면이다.

- [0060] 도시한 바와 같이, 상기 제 1 내지 제 4 다결정 반도체층(34,36,38,40)이 형성된 기판(30)의 전면에 포토레지스트(photoresist)를 도포한 후, 제 2 마스크 공정으로 패턴하여, 상기 P영역(A1)과 N영역(A2)및 스위칭 영역(A3)을 차폐하는 포토패턴(42)을 형성한다.

- [0061] 다음으로, 포토패턴(42)으로 차폐되지 않은 스토리지 영역(A4)의 제 4 다결정 반도체층(40) 표면에 이온(ion,

$n^+$ 이온)을 도핑하는 공정을 진행한다.

[0062] 상기 제 4 다결정 반도체층(40)은 전극의 역할을 해야 하기 때문에 저항을 낮추기 위해 전술한 바와 같이 이온( $n$ 또는  $p$ 형 이온)을 도핑하는 공정을 진행하는 것이며, 이온 도핑공정이 완료되면 상기 포토패턴(42)을 제거하는 공정을 진행한다.

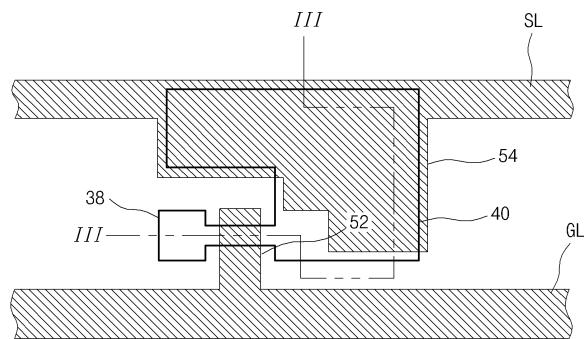

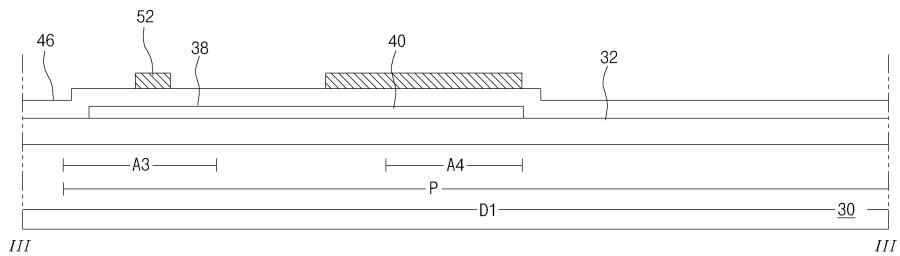

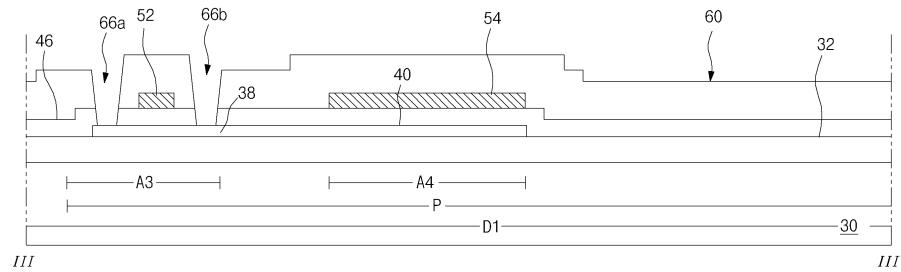

[0063] 도 4c와 도 5c와 도 6c는 제 3 마스크 공정을 나타낸 단면도이다.

[0064] 도시한 바와 같이, 상기 스토리지 영역(A4)의 제 4 다결정 반도체층(40)에 이온(ion)을 도핑하여 스토리지 제 1 전극으로 형성하는 공정 후, 상기 제 1 및 제 4 다결정 반도체층(34,36,38,40)이 형성된 기판(30)의 전면에 게이트 절연막(46)을 형성한다.

[0065] 상기 게이트 절연막(46)은 질화 실리콘( $\text{SiN}_x$ )과 산화 실리콘( $\text{SiO}_2$ )을 포함하는 무기절연물질 그룹 중 선택된 하나 이상의 물질을 증착하여 형성할 수 있다.

[0066] 다음으로, 상기 게이트 절연막(46)이 형성된 기판(30)의 전면에 도전성 금속을 증착하고 제 3 마스크 공정으로 패턴하여, 상기 제 1 내지 제 3 다결정 반도체층(34,36,38)의 중심에 대응하는 상부에 제 1 내지 제 3 게이트 전극(48,50,52)을 형성하고, 상기 스토리지 영역(A4)의 제 4 다결정 반도체층(40)에 대응하는 상부에 스토리지 제 2 전극(54)을 형성한다.

[0067] 동시에, 상기 스위칭 영역(A3)에 구성한 게이트 전극(52)에서 연장되고 화소 영역(P)의 일 측에 위치하도록 게이트 배선(GL)을 형성하고, 상기 스토리지 제 2 전극(54)에서 연장되어 화소 영역(P)을 가로지르는 스토리지 배선(SL)을 형성한다.

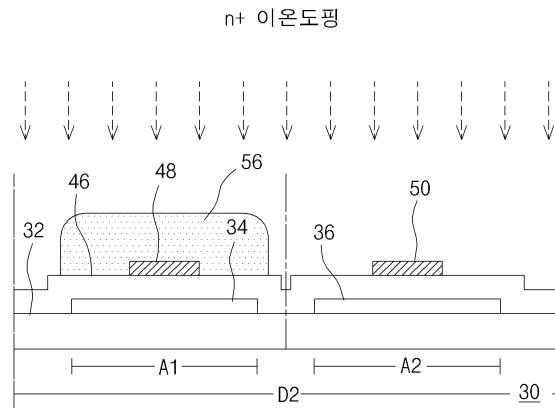

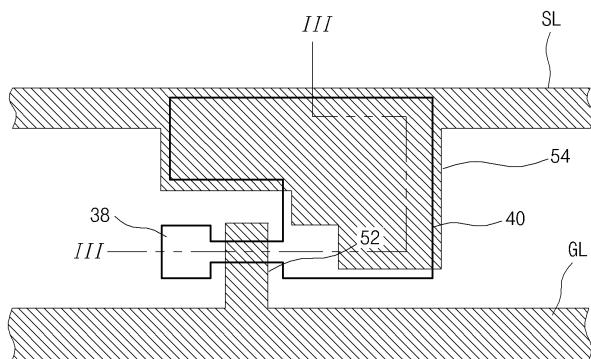

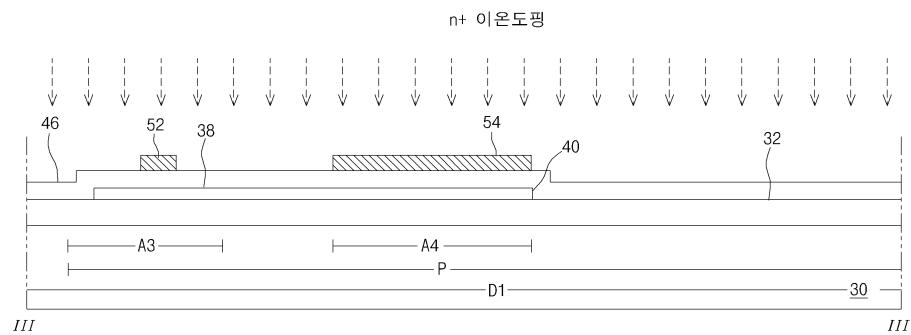

[0068] 도 4d와 도 5d와 도 6d는 제 4 마스크 공정을 나타내며, N영역(A2)과 스위칭 영역(A3)의 제 2 및 제 3 다결정 반도체층(36,38)에  $n^+$ 이온을 도핑하기 위한 공정 단면도이다.

[0069] 도시한 바와 같이, 상기 제 1 내지 제 3 게이트 전극(48,50,52)과 스토리지 제 2 전극(54)과 게이트 배선(미도시)이 형성된 기판(30)의 전면에 포토레지스트(photo-resist)를 도포한 후 제 4 마스크 공정으로 패턴하여, 상기 P영역(A1)을 덮는 포토패턴(56)을 형성한다.

[0070] 다음으로, 상기 포토패턴(56)사이로 노출된 N영역(A2)과 스위칭 영역(A3)에  $n^+$ 이온을 도핑(doping)하는 공정을 진행한다.

[0071] 이와 같이 하면, 상기 N영역(A2)과 스위칭 영역(A3)의 제 2 다결정 반도체층(36)과 제 3 다결정 반도체층(38)영역 중 상기 제 2 게이트 전극(50)과 제 3 게이트 전극(52)의 주변으로 노출된 표면에  $n^+$ 이온이 도핑되며, 이온이 도핑된 영역은 저항성 접촉(ohmic contact)특성을 갖는다.

[0072] 전술한 바와 같은 제 4 마스크 공정이 완료되면, 상기 포토패턴(56)을 제거하는 공정을 진행한다.

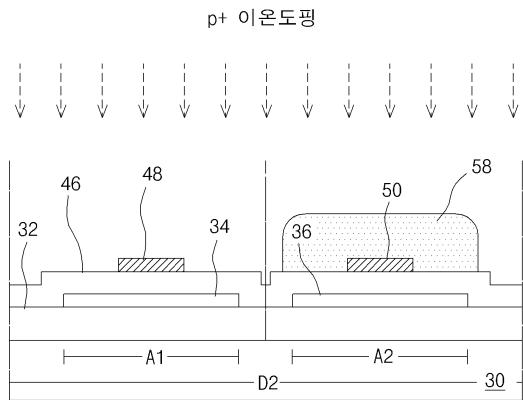

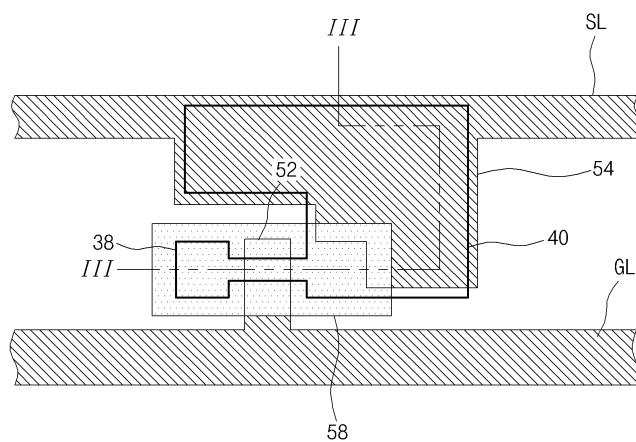

[0073] 도 4e와 도 5e와 도 6e는 제 5 마스크 공정을 나타내며, P영역(A1)의 다결정 반도체층에  $p^+$ 이온을 도핑하기 위한 공정 단면도이다.

[0074] 도시한 바와 같이, 제 1 내지 제 3 게이트 전극(48,50,52)과 스토리지 제 2 전극(54)이 형성된 기판(30)의 전면에 포토레지스트(photoresist)를 도포한 후 제 5 마스크 공정으로 패턴하여, N영역(A2)과 스위칭 영역(A3)과 스토리지 영역(A4)을 덮는 포토패턴(58)을 형성한다.

[0075] 이때, 상기 스토리지 영역(A4)은 이미 제 2 스토리지 전극(54)이 형성된 상태이므로 포토패턴을 형성하지 않아도 좋다.

[0076] 다음으로, P영역(A1)의 노출된 제 1 다결정 반도체층(34)중 게이트 전극(48)의 주변으로 노출된 표면에  $p^+$ 이온을 도핑하는 공정을 진행한다.

[0077] 이때, 이온이 도핑된 영역은 앞서 언급한 바와 같이 저항성 접촉(ohmic contact)특성을 갖는다.

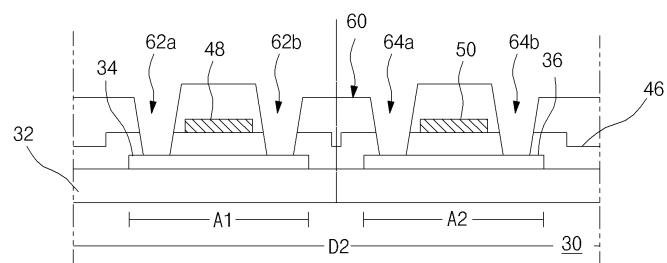

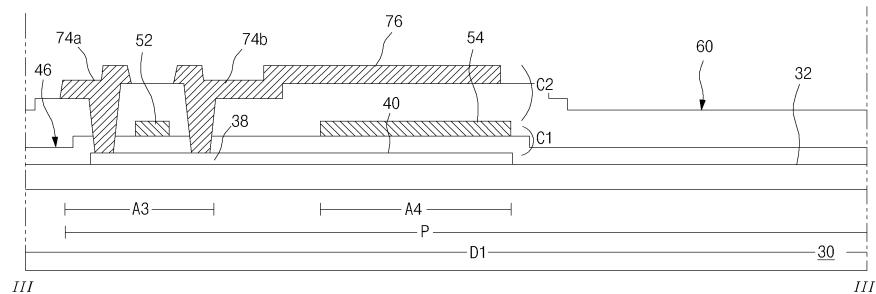

[0078] 도 4f와 도 5f와 도 6f는 제 6 마스크 공정을 나타낸 공정 단면도이다.

[0079] 전술한 바와 같이, 제 1 내지 제 3 다결정 반도체층(34,36,38)에 이온을 도핑하여 저항성 접촉영역(이하, 오믹영역 이라함) 형성공정이 진행된 기판(30)의 전면에 질화 실리콘( $\text{SiN}_x$ )과 산화 실리콘( $\text{SiO}_2$ )을 포함하는 무기절연물질그룹 중 선택된 하나를 증착하여 충간 절연막(interlayer, 60)을 형성한다.

[0080] 다음으로, 상기 충간 절연막(60)과 하부의 게이트 절연막(46)을 제 6 마스크 공정으로 패턴하여, 상기 제 1

내지 제 3 다결정 반도체층(34,36,38)의 이온도핑 영역(오믹콘택영역)을 노출하는 콘택홀을 형성한다.

[0081] 상세히는, 상기 제 1 내지 제 3 게이트 전극(48,50,52)을 중심으로 양측의 다결정 반도체층(34,36,38)즉, 오믹영역을 각각 노출하는 제 1 콘택홀(62a,64a,66a)과 제 2 콘택홀(62b,64b,66b)을 형성한다.

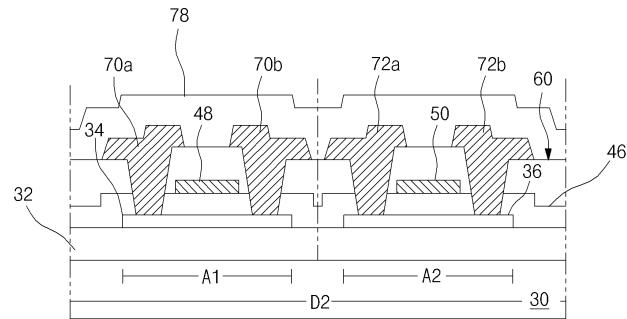

[0082] 도 4g와 도 5g와 도 6g는 제 7 마스크 공정을 나타낸 공정 단면도이다.

[0083] 상기 제 1 내지 제 3 다결정 반도체층(34,36,38)의 오믹영역(이온 도핑영역)일부를 노출하는 중간 절연막(60)이 형성된 기판(30)의 전면에 크롬(Cr), 몰리브덴(Mo), 텅스텐(W), 구리(Cu), 알루미늄합금(AlNd)등을 포함하는 도전성 금속 그룹 중 선택된 하나를 증착하고 패턴하여, 상기 노출된 오믹영역과 접촉하는 소스 전극(70a,72a,74a)과 드레인 전극(70b,72b,74b)을 형성한다.

[0084] 이때, 상기 스위칭 영역(A3)에 구성한 드레인 전극(74b)에서 스토리지 영역(A3)으로 연장된 연장부를 더욱 형성하며, 이는 스토리지 제 3 전극(76)으로서의 역할을 하게 된다.

[0085] 또한, 상기 표시영역(D1)의 스위칭 영역(A3)에 형성한 소스 전극(74a)에서 연장되고, 상기 게이트 배선(GL)과 교차하여 화소 영역(P)의 일 측으로 연장된 데이터 배선(DL)을 형성한다.

[0086] 전술한 제 1 내지 제 7 마스크 공정을 통해, 비표시부(D2)에는 p형 다결정 박막트랜지스터와 n형 다결정 박막트랜지스터의 조합인 CMOS소자가 형성되고, 상기 표시 영역(D1)의 스위칭 영역(A3)에는 n형 다결정 박막트랜지스터가 형성되고, 상기 스토리지 영역(A4)에는 스토리지 제 1 전극(40)과 스토리지 제 2 전극(54)과 스토리지 제 3 전극(76, 소스 드레인 금속층)으로 구성된 제 1 및 제 2 스토리지 캐패시터(C1,C2)가 형성된다.

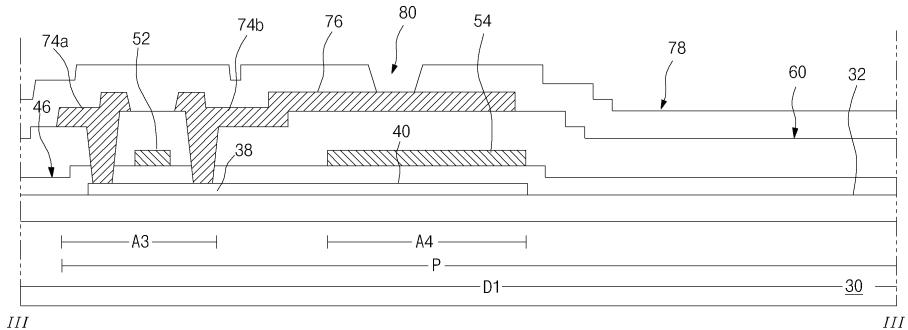

[0087] 도 4h와 도 5h와 도 6h는 제 8 마스크 공정을 나타낸 공정 단면도이다.

[0088] 도시한 바와 같이, 상기 각 영역(A1,A2,A3)마다 소스전극(70a,72a,74a)과 드레인 전극(70b,72b,74b)이 형성된 기판(30)의 전면에 앞서 언급한 절연물질 그룹 중 선택된 하나 이상의 물질을 증착하여 보호층(78)을 형성한다.

[0089] 상기 보호층(78)을 제 8 마스크 공정으로 패턴하여, 상기 스위칭 영역(A3)의 드레인 전극(74b) 또는 스토리지 제 3 전극(76)을 노출하는 드레인 콘택홀(80)을 형성한다.

[0090] 도 4i와 도 5i와 도 6i는 제 9 마스크 공정을 나타낸 공정 단면도이다.

[0091] 도시한 바와 같이, 보호층(78)이 형성된 기판(30)의 전면에 인듐-틴-옥사이드(ITO)와 인듐-징크-옥사이드(IZO)를 포함하는 투명한 도전성 금속 그룹 중 선택된 하나를 증착하고 제 9 마스크 공정으로 패턴하여, 상기 드레인 전극(74b)또는 이에 연장된 상기 스토리지 제 3 전극과 접촉하면서 상기 화소 영역(P)에 위치하는 화소 전극(82)을 형성한다.

[0092] 이상으로, 전술한 바와 같은 제 1 내지 제 9 마스크공정을 통해 종래에 따른 구동회로 일체형 액정패널의 박막트랜지스터 어레이기판을 제작할 수 있다.

[0093] 따라서, 종래에는 다수의 공정으로 구동회로 일체형 어레이기판을 제작하기 때문에, 공정시간 지연과 생산비용 증가에 의해 공정수율이 저하되는 문제점이 있다.

[0094] 또한, 다수의 공정에 따른 불량 발생률을 높이는 단점이 있다.

### 발명이 이루고자 하는 기술적 과제

[0095] 본 발명은 전술한 문제를 해결하기 위해 제안된 것으로, 공정수를 줄여 공정 시간을 단축하고, 공정비용을 낮추는 동시에, 불량 발생률을 낮춰 생산수율을 높이는 것을 목적으로 한다.

### 발명의 구성 및 작용

[0096] 상기 목적을 달성하기 위한 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판은 화소영역을 포함하는 표시부와, 비표시부로 정의된 기판과; 상기 기판의 비표시부에 구성된 구동회로와; 상기 화소영역의 일측에 구성된 스위칭 소자와; 상기 화소 영역의 일부에 구성되고, 다결정 반도체층과 제 1 금속전극이 적층된 스토리지 제 1 전극과, 스토리지 제 2 전극과, 투명전극과 제 2 금속 전극이 적층된 스토리지 제 3 전극으로

구성된 스토리지 캐패시터와; 상기 스위칭 소자와 접촉하고, 상기 화소 영역에 위치한 화소 전극을 포함한다.

[0097] 상기 구동회로는 n형 다결정 박막트랜지스터와 p형 다결정 박막트랜지스터로 구성된 CMOS소자의 조합으로 이루어지고, 상기 스위칭 소자는 n형 다결정 박막트랜지스터인 것을 특징으로 한다.

[0098] 상기 p형 다결정 박막트랜지스터와 상기 n형 다결정 박막트랜지스터는 다결정 액티브층과, 상기 액티브층 상부의 게이트 전극과 소스및 드레인 전극을 포함하고, 상기 p형 다결정 박막트랜지스터는 상기 소스 및 드레인 전극과 접촉하는 액티브층의 표면에 p+이온이 도핑되고, 상기 n형 다결정 박막트랜지스터는 상기 소스 및 드레인 전극과 접촉하는 액티브층의 표면에 n+이온이 도핑되고, 상기 n+이온의 도핑영역과 게이트 전극의 사이에는 n-이온이 도핑된 저농도 도핑영역을 포함하는 것을 특징으로 한다.

[0099] 상기 소스 및 드레인 전극은 투명전극과 불투명전극이 적층되어 구성된 것을 특징으로 한다.

[0100] 본 발명의 특징에 따른 구동회로 일체형 액정표시장치용 어레이기판 제조방법은 기판에 스위칭 영역과 스토리지 영역을 포함하는 다수의 화소 영역으로 구성된 표시영역과, 구동 회로부를 포함하는 비표시 영역을 정의하는 단계와; 상기 구동회로부에 제 1 다결정 반도체층과 제 2 다결정 반도체층을 형성하고, 상기 스위칭 영역과 스토리지 영역에 제 3 다결정 반도체층과 제 4 다결정 반도체층과, 상기 제 4 다결정 반도체층의 상부에 보조 전극을 형성하고, 상기 제 2 다결정 반도체층과 제 3 다결정 반도체층 및 상기 보조전극의 상부에 각각 이들을 덮는 금속패턴을 형성하고, 상기 게이트 전극이 덮히지 않은 제 1 다결정 반도체층의 표면에 p+이온을 도핑하는 제 2 마스크 공정 단계와; 상기 제 2 및 제 3 다결정 반도체층의 일부 상부에 게이트 전극을 형성하고, 상기 게이트 전극에 대응하지 않는 제 2 및 제 3 다결정 반도체층의 표면에 부분적으로 n+이온과 n-이온을 각각 도핑하고 동시에, 상기 보조 전극 주변의 제 4 다결정 반도체층 표면에 n+이온을 도핑하고, 상기 보조 전극의 상부에 제 1 금속전극을 형성하는 제 3 마스크 공정 단계와; 상기 기판의 전면에 상기 제 1 내지 제 3 다결정 반도체층을 노출하는 제 1 제 2 충간 절연막을 형성하는 제 4 마스크 공정 단계와; 상기 노출된 제 1 내지 제 3 다결정 반도체층마다 이와 접촉하고 투명전극과 불투명 전극이 적층되어 구성된 소스 및 드레인 전극을 형성하고, 상기 제 1 금속전극의 상부에 투명전극과 제 2 금속전극을 적층 형성하고, 상기 스토리지 영역 및 스위칭 영역을 제외한 화소 영역에 투명한 화소 전극을 형성하는 제 5 마스크 공정 단계를 포함한다.

[0101] 상기 제 1 마스크 공정 단계는, 기판 상에 다결정 실리콘층과, 제 1 도전성 금속층을 적층하는 단계와; 상기 제 1 도전성 금속층의 상부에 포토레지스트를 도포하여 감광층을 형성하는 단계와; 상기 감광층의 이격된 상부에 투과부와 차단부와 반투과부로 구성된 제 1 마스크를 위치시키는 단계와; 상기 마스크의 상부로 빛을 조사하여 하부의 감광층을 노광하고 현상하여, 상기 구동회로부에 상부로 부터 일부가 제거된 상태로 패턴된 제 1 포토패턴과 제 2 포토 패턴을 형성하고, 상기 스위칭 영역에 상기 제 1 내지 제 2 포토패턴과 동일한 높이의 제 3 포토 패턴을 형성하고, 상기 스토리지 영역에 원래 높이로 패턴된 제 4 포토패턴을 형성하는 단계와; 상기 제 1 내지 제 4 포토 패턴의 주변으로 노출된 상기 제 1 도전성 금속층을 제거하여, 상기 제 1 내지 제 4 포토 패턴의 하부에 제 1 내지 제 4 금속패턴을 형성하는 단계와; 상기 제 1 내지 제 3 포토패턴을 애싱공정으로 제거하여, 상기 제 1 내지 제 3 금속패턴을 노출하는 단계와; 상기 노출된 제 1 내지 제 3 금속패턴을 제거하여, 상기 구동 회로부에 제 1 다결정 반도체층과 제 2 다결정 반도체층과, 상기 스위칭 영역에 제 3 다결정 반도체층과 상기 스토리지 영역에 제 4 다결정 반도체층과 이것의 상부에 제 4 금속패턴(보조 전극)을 형성하는 단계를 포함한다.

[0102] 상기 제 1 내지 제 4 다결정 반도체층과 상기 기판 사이에 절연성 베퍼층을 더욱 포함한다.

[0103] 상기 제 2 마스크 공정 단계는, 상기 제 1 내지 제 4 다결정 반도체층과, 상기 제 4 다결정 반도체층의 상부에 보조전극이 형성된 기판의 전면에 절연막과 제 2 도전성 금속층을 적층하는 단계와; 상기 제 2 도전성 금속층을 제 2 마스크 공정으로 패턴하여, 상기 제 1 다결정 반도체층의 중심에 대응하여 게이트 전극을 형성하고, 상기 제 2 다결정 반도체층 내지 제 4 다결정 반도체층의 상부에 각각 이들을 덮는 금속패턴을 형성하는 단계를 포함한다.

[0104] 상기 제 3 마스크 공정 단계는, 상기 제 1 다결정 반도체층의 상부에 게이트 전극이 형성되고, 상기 제 2 다결정 반도체층과 제 3 다결정 반도체층과 제 4 다결정 반도체층의 상부에 이들을 덮는 금속패턴이 형성된 기판의 전면에 포토레지스트를 도포하여 감광층을 형성하는 단계와; 상기 제 2 다결정 반도체층과 제 3 다결정 반도체층에 제 1 액티브 영역과, 제 1 액티브 영역의 양측에 제 2 액티브 영역과, 상기 제 1 및 제 2 액티브

영역 사이에 제 3 액티브 영역을 정의하는 단계와; 상기 감광층을 제 3 마스크로 노광한 후 현상하여, 상기 제 1 다결정 반도체층을 덮는 제 1 포토패턴과, 상기 제 2 및 제 3 다결정 반도체층 중 제 1 및 제 3 액티브 영역을 덮는 제 2 포토패턴과 제 3 포토패턴과, 상기 제 4 다결정 반도체층을 덮는 제 4 포토패턴을 형성하는 단계와; 상기 제 1 내지 제 4 포토패턴 사이로 노출된 상기 금속패턴을 제거하여, 상기 제 2 및 제 3 포토패턴의 하부에 각각 게이트 전극을 형성하고, 상기 제 4 포토 패턴의 하부에 제 1 금속전극을 형성하는 단계와; 상기 제 2 및 제 3 다결정 반도체층의 제 2 액티브 영역에  $n+$ 이온을 도핑하여 오믹영역을 형성하고 동시에, 상기 보조 전극 주변의 제 4 반도체층에  $n+$ 이온을 도핑하는 단계와; 상기 제 2 내지 제 3 포토 패턴을 애싱하여, 상기 제 2 및 제 3 다결정 반도체층의 제 3 액티브 영역에 대응하는 게이트 전극을 노출하는 단계와; 상기 노출된 게이트 전극을 제거하는 단계와; 상기 제 2 및 제 3 다결정 반도체층의 제 3 액티브 영역에  $n-$ 이온을 도핑하여 저농도 도핑영역을 형성하는 단계를 포함한다.

[0105] 상기 제 2 및 제 3 다결정 반도체층의 제 2 액티브 영역에 상기 소스 및 드레인 전극이 접촉하는 것을 특징으로 한다.

[0106] 상기 제 5 마스크 공정 단계는, 상기 제 1 및 제 2 층간 절연막이 형성된 기판의 전면에 투명 전극층과 도전성 금속층과 감광층을 적층하는 단계와; 상기 감광층의 이격된 상부에 투과부와 차단부와 반투과부로 구성된 제 5 마스크를 위치시키는 단계;

[0107] 상기 마스크의 상부로 부터 빛을 조사하여 상기 감광층을 노광한 후에 현상하여, 상기 구동회로 영역에 각각 이격된 제 1 포토 패턴과 제 2 포토 패턴과, 상기 스위칭 영역에 이격된 제 3 포토 패턴과, 상기 스토리지 영역과 화소 영역에 걸쳐 제 4 포토 패턴을 형성하는 단계와; 상기 제 1 내지 제 4 포토 패턴의 주변으로 노출된 도전성 금속층과 하부의 투명 전극층을 제거하여, 상기 제 1 내지 제 3 포토 패턴의 하부에 상기 제 1 내지 제 3 반도체층과 각각 접촉하고 투명전극층과 도전성 금속층이 적층되어 구성된 소스 전극과 드레인 전극과, 상기 제 4 포토 패턴의 하부에 상기 스토리지 영역 및 화소 영역에 걸쳐 패턴된 투명전극층과 도전성 금속층을 형성하는 단계와; 상기 제 1 내지 제 4 포토 패턴을 애싱(ashing)하여, 제 4 포토 패턴을 제거하여 하부의 패턴된 도전성 금속층을 노출하는 단계와; 상기 노출된 도전성 금속층을 제거하여, 상기 스토리지 영역에 대응하여 적층된 투명 전극층과 도전성 금속층(제 2 금속전극)과, 상기 스위칭 영역 및 스토리지 영역을 제외한 화소 영역에 대응하여 투명한 화소 전극을 형성하는 단계를 포함한다.

[0108] 상기 제 3 및 제 4 다결정 반도체층은 일체로 형성되고, 상기 제 3 다결정 반도체층과 접촉하는 드레인 전극을 구성하는 도전성 금속층과 상기 스토리지 영역의 도전성 금속층(제 2 금속전극)또한 일체로 구성된 것을 특징하며, 상기 화소 전극은 상기 제 3 다결정 반도체층과 접촉하는 드레인 전극 또는 상기 스토리지 영역의 도전성 금속층(제 2 금속전극)과 접촉하는 것을 특징으로 한다.

[0109] 상기 층간 절연막을 형성하는 제 4 마스크 공정 후에, 기판을 열처리 하여 상기 제 4 다결정 반도체층의 표면에 도핑된  $n+$  이온이 상기 보조 전극의 하부로 확산되도록 하여, 상기 보조 전극과 상기 제 4 다결정 반도체층이 오믹 콘택을 이루도록 하는 단계를 포함한다.

[0110] 상기 스토리지 영역의 적층된 제 4 다결정 반도체층과 보조 전극은 스토리지 제 1 전극의 기능을 하고, 상기 제 1 금속 전극은 스토리지 제 2 전극의 기능을 하고, 상기 적층된 투명전극층과 제 2 금속전극(도전성 금속층)은 스토리지 제 3 전극의 기능을 하여 스토리지 캐페시터를 이루는 것을 특징으로 한다.

[0111] 상기 제 1 층간 절연막은 산화 실리콘( $\text{SiO}_2$ )을 증착하여 형성하고, 상기 제 2 층간 절연막은 질화 실리콘( $\text{SiN}_x$ )을 증착하여 형성하는 것을 특징으로 한다.

[0112] 이하, 본 발명의 실시예에 따른 구동회로 일체형 액정표시장치용 어레이기판의 제조방법을 설명한다.

-- 실시예 --

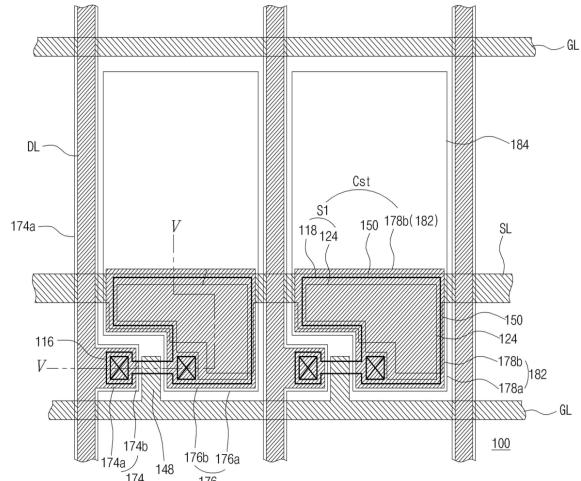

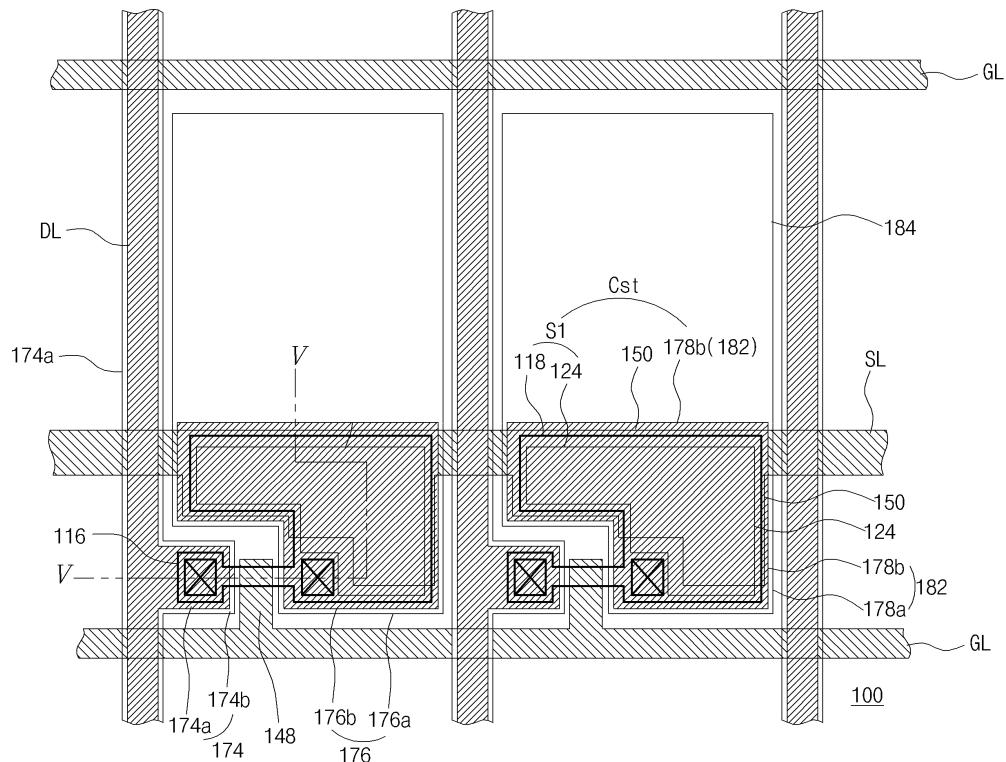

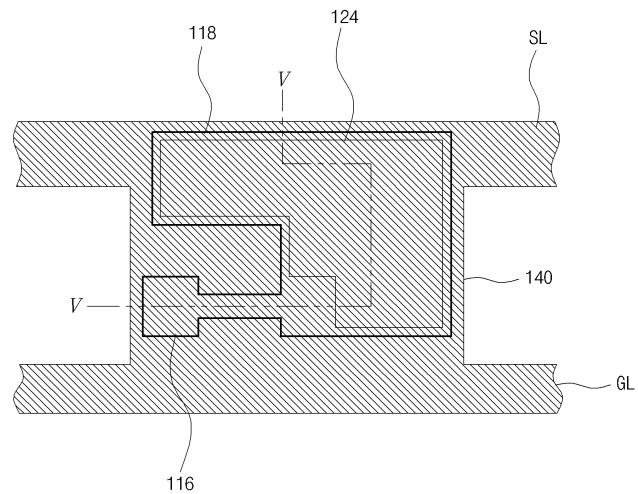

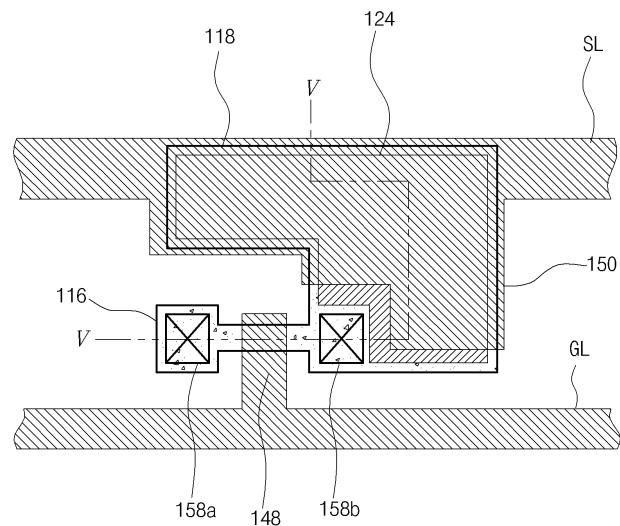

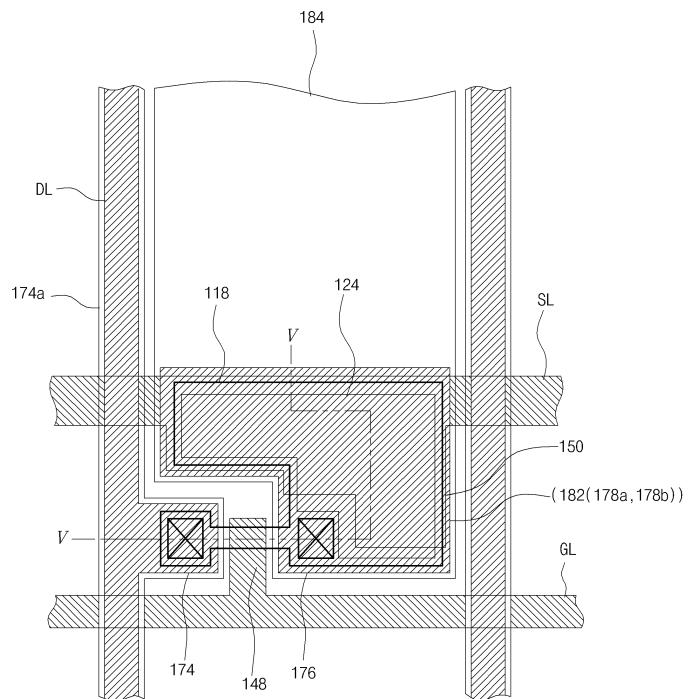

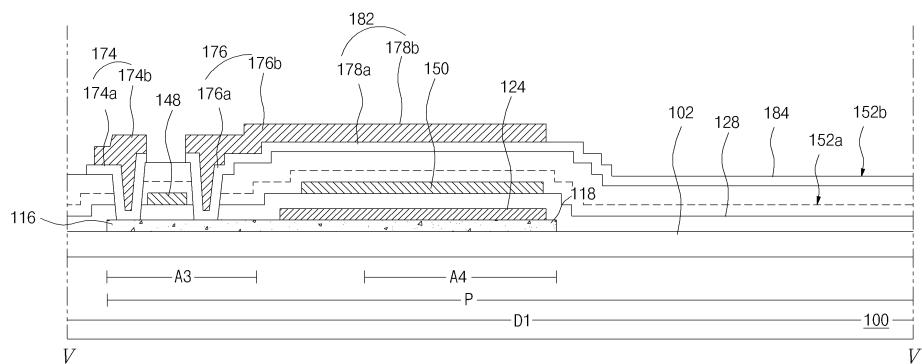

[0114] 도 7은 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이 기판의 표시영역 일부를 확대한 평면도이다.

[0115] 도시한 바와 같이, 기판(100)상에 일 방향으로 연장된 게이트 배선(GL)과, 상기 게이트 배선(GL)과 수직하게 교차하여 화소 영역(P)을 정의하는 데이터 배선(DL)을 구성한다.

[0116] 상기 게이트 배선(GL)과 데이터 배선(DL)의 교차점에는 스위칭 소자인 다결정 박막트랜지스터(Ts)를 구성하며, 상기 화소 영역(P)에는 화소 전극(184)을 구성한다.

[0117] 상기 다결정 박막트랜지스터(Ts)는 다결정 실리콘층인 액티브층(116)과, 게이트 전극(148)과 소스 전극(174)

과 드레인 전극(176)을 포함하며, 상기 화소 전극(184)은 상기 드레인 전극(176)과 접촉하도록 구성한다.

[0118] 상기 화소 영역(P)의 일부에는, 보조 용량부인 스토리지 캐패시터(Cst)를 구성하는데 이때, 상기 스토리지 캐패시터(Cst)는 다결정 반도체층(120)과 보조전극(124)이 적층된 스토리지 제 1 전극(S1)과, 스토리지 배선(SL)에서 상기 스토리지 제 1 전극(S1)의 상부로 연장된 스토리지 제 2 전극(150)과, 상기 드레인 전극(176)에서 상기 스토리지 제 2 전극(150)의 상부로 연장된 스토리지 제 3 전극(182)으로 이루어진다.

[0119] 이때, 특징적인 것은 상기 보조 전극(124)과 그 하부의 다결정 반도체층(118)은 오믹 콘택을 이루어 동일 신호가 흐르도록 한다.

[0120] 또한, 상기 소스 및 드레인 전극(174, 176)은 투명 전극층(174a, 176a)과 도전성 금속층(174b, 176b)이 적층된 형상이고 동시에, 상기 스토리지 제 3 전극(182) 또한 투명 전극층(178a)과 도전성 금속층(178b)된 형상이며 이때, 상기 스토리지 제 3 전극의 투명 전극층(178a)은 상기 화소 전극(184)과 일체로 구성되는 것을 특징으로 한다.

[0121] 이하, 단면 구성을 참조하여 전술한 구성을 포함하는 구동회로 일체형 액정표시장치용 어레이기판의 구성을 알아본다.

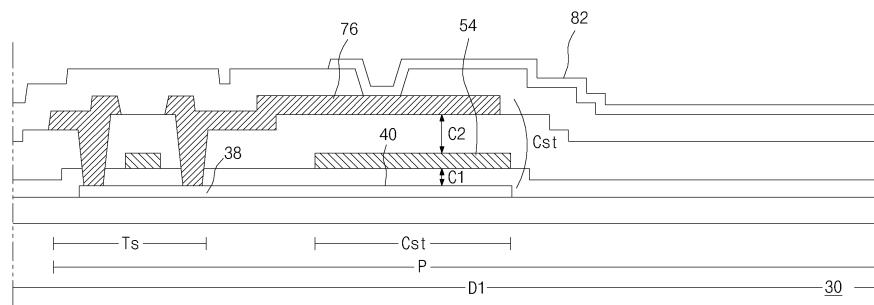

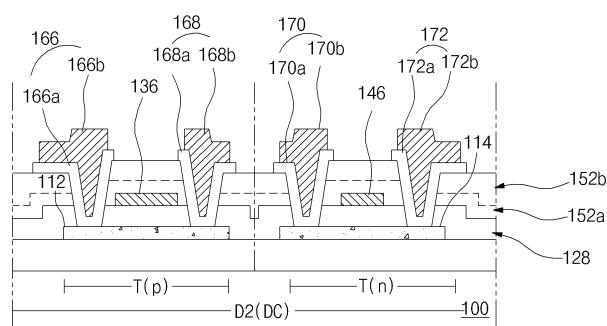

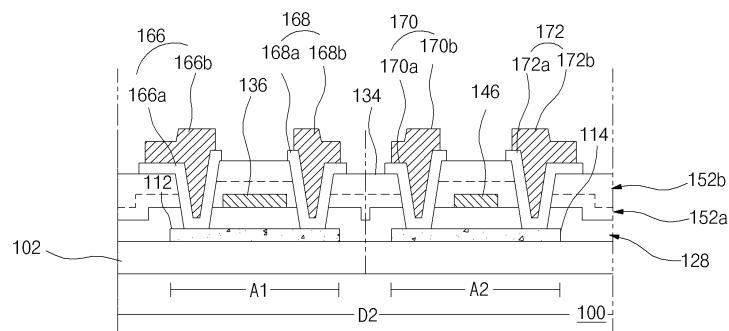

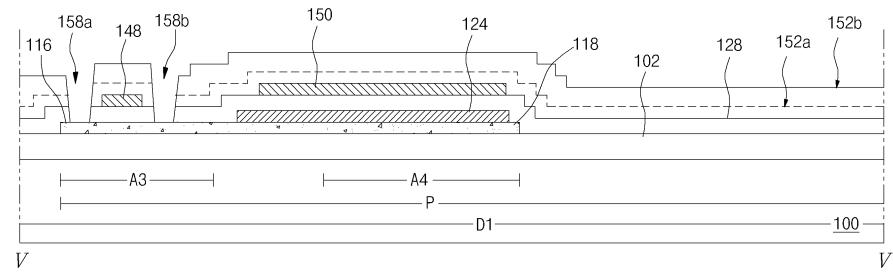

[0122] 이하, 도 8a와 도 8b본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판의 단면 구성을 도시한 단면도이다.(도 8b는 도 7의 V-V를 따라 절단한 단면도이다. )

[0123] 도시한 바와 같이, 구동회로 일체형 액정표시장치용 어레이기판(100)은 표시부(D1)와 비표시부(D2)로 나눌 수 있다.

[0124] 상기 비표시부(D2)에는 n형 다결정 박막트랜지스터(T(n))와 p형 다결정 박막트랜지스터(T(p))로 이루어진 CMOS조합으로 구성된 구동회로를 형성한다.

[0125] 상기 표시부(D1)에는 스위칭 소자(Ts)와, 다결정 반도체층과(118)과 보조전극(124)이 적층된 제 1 스토리지 전극(S1)과, 제 2 스토리지 전극(150)과 투명 전극층(178a)과 도전성 금속층(178b)이 적층된 스토리지 제 3 전극(182)을 포함하는 스토리지 캐패시터(Cst)와, 화소 영역(P)마다 상기 스위칭 소자(Ts)와 접촉하는 화소 전극(184)을 형성한다.

[0126] 상기 스위칭 소자(Ts)로 보통 n형 다결정 박막트랜지스터를 구성하고, 상기 스토리지 캐패시터(Cst)는 스토리지 제 1 전극 및 제 2 전극(S1, 150)으로 구성된 제 1 스토리지 캐패시터(C1)와, 상기 스토리지 제 2 전극 및 제 3 전극(150, 182)으로 이루어진 제 2 스토리지 캐패시터(C2)를 등가 회로적으로 직렬 연결한 구성을이다.

[0127] 전술한 구성을 특징적인 것은, 상기 구동회로 및 스위칭 소자(DC, Ts)로 사용되는 n형 및 p형 다결정 박막트랜지스터(T(n), Ts, T(p))의 다결정 반도체층(112, 114, 116)과, 상기 스토리지 캐패시터(Cst)의 다결정 반도체층(118)과 그 상부의 보조전극(124)을 단일 마스크 공정으로 구성하는 것이다.

[0128] 또 다른 특징은, n형 및 p형 다결정 박막트랜지스터(T(n), Ts, T(p))의 게이트 전극(136, 146, 148)과, n형 다결정 박막트랜지스터(T(n), Ts)의 다결정 반도체층(114, 116)의 표면에 부분적으로 n+ 이온 도핑과, n-이온도핑을 진행하고, 상기 p형 다결정 박막트랜지스터(T(p))의 반도체층(112)에 p+이온을 도핑하는 공정과, 상기 스토리지 캐패시터(Cst)의 스토리지 제 2 전극(150)을 형성하는 공정을 두 번의 마스크 공정으로 진행하는 것을 특징으로 한다.

[0129] 또한, 상기 소스 및 드레인 전극(174, 176)과 스토리지 제 3 전극(182)과 상기 화소 전극(184)을 단일 마스크 공정으로 형성하는 것을 특징으로 한다.

[0130] 이때, 상기 화소전극(184)과 접촉하는 충간 절연막(152a, 152b)은 산화 실리콘막(152a, SiO<sub>2</sub>)과 질화 실리콘막(152b, SiN<sub>x</sub>)을 적층하여 형성하며 특히, 상기 화소 전극(184)과의 계면특성이 좋은 질화 실리콘막(152b)이 상기 화소 전극과 직접 접촉하도록 구성한다.

[0131] 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판은 전술한 마스크 공정을 포함해 5마스크 공정으로 제작할 수 있는 것을 특징으로 한다.

[0132] 이하, 공정도면을 참조하여, 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판의 제조공정을 설명한다.

[0133] 도 9a 내지 도 9p는 본 발명에 따른 구동회로 제조공정을 순서대로 도시한 공정 단면도이다.

- [0134] 도 10a 내지 도 10p는 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판의 표시부 제조공정을 순서대로 도시한 공정 평면도이다.

- [0135] 도 11a 내지 도 11p는 각각 도 10a 내지 도 10p의 V-V를 따라 절단한 공정 단면도이다.

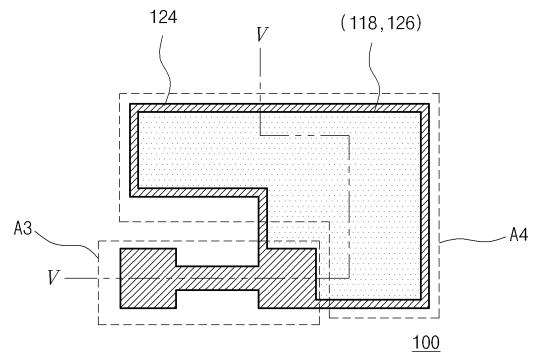

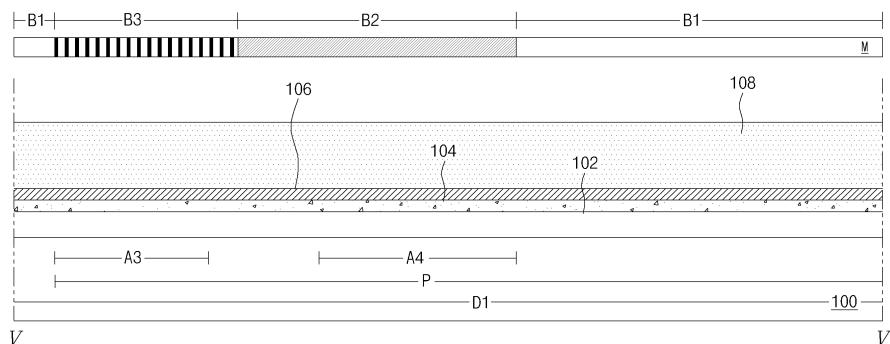

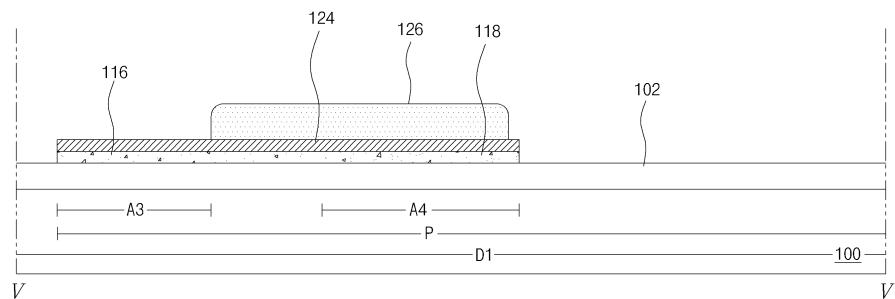

- [0136] 이하, 도 9a 내지 도 9e와 도 10a 내지 도 10e와 도 11a 내지 도 11e는 제 1 마스크 공정을 나타낸 도면이다.

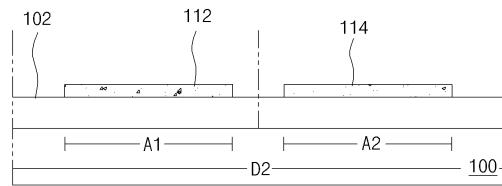

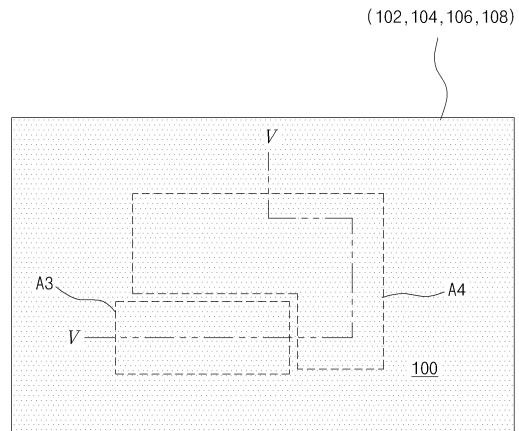

- [0137] 도 9a와 도 10a와 도 11a에 도시한 바와 같이, 기판(100)을 표시부(D1)와 비표시부(D2)로 정의하고, 표시부(D1)는 다시 다수의 화소영역(P)으로 정의 한다.

- [0138] 이때, 비표시부(D2)에 편의상 P영역(A1)과 N영역(A2)을 정의하고, 상기 화소영역(P)에 스위칭 영역(A3)과 스토리지 영역(A4)을 정의한다.

- [0139] 이때, P영역(A1)은 p형 다결정 박막트랜지스터(T(p))가 형성될 영역이고, N영역(A2)은 n형 다결정 박막트랜지스터(T(n))가 형성될 영역이고, 상기 스위칭 영역(A3)은 스위칭 소자로 n형 다결정 박막트랜지스터가 형성될 영역이고, 상기 스토리지 영역(A4)은 스토리지 캐패시터가 형성될 영역이다.

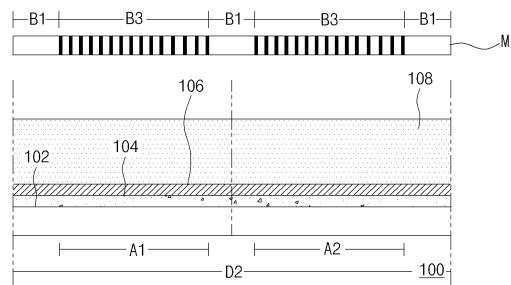

- [0140] 전술한 바와 같이, 다수의 영역(A1,A2,A3,A4)이 정의된 기판(100)의 전면에 베퍼층(102)과 다결정 실리콘층(104)과 제 1 도전성 금속층(106)을 적층 형성한다.

- [0141] 상기 베퍼층(102)은 질화 실리콘( $\text{SiN}_2$ )과 산화 실리콘( $\text{SiN}_x$ )을 포함하는 무기질연물질 그룹 중 선택된 하나 또는 그 이상의 물질을 증착하여 형성한다.

- [0142] 상기 다결정 실리콘층(104)은 불순물이 포함되지 않은 순수한 ( $a\text{-Si : H}$ )을 비정질 실리콘을 증착한 후, 탈수소 공정 및 결정화 공정을 진행하여 형성한다.

- [0143] 상기 도전성 금속층(106)은 텅스텐(W), 몰리브덴(Mo), 크롬(Cr), 몰리 텅스텐(MoW)등을 포함하는 도전성 금속 그룹 중 선택된 하나를 증착하여 형성한다.

- [0144] 다음으로, 상기 제 1 도전성 금속층(106)이 형성된 기판(100)의 전면에 포토레지스트(photoresist)를 도포하여 감광층(108)을 형성한다.

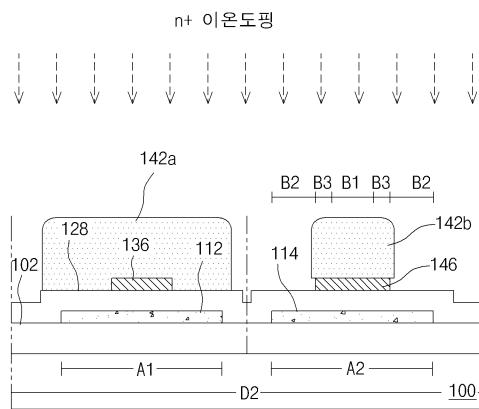

- [0145] 다음으로, 상기 감광층(108)과 이격된 상부에 투과부(B1)와 차단부(B2)와 반투과부(B3, slit area)로 구성된 마스크(mask, m)를 위치시킨다.

- [0146] 상기 차단부(B2)는 스토리지 영역(A4)에 대응되도록 하고, 상기 반투과부(B3)는 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 대응되도록 하고, 상기 투과부(B1)는 그 외 영역에 대응되도록 한다.

- [0147] 이때, 상기 마스크(M)는 감광층(108)의 위치에 따라 강도가 다른 빛이 조사되도록 하여 부분적으로 감광층을 노광하도록 하는 것으로 특히, 상기 반투과부(slit area, B3)는 빛의 회절에 따른 광강도 감소를 이용해 하부 감광층이 표면으로부터 일부만 노광되도록 하는 특징을 가진다.

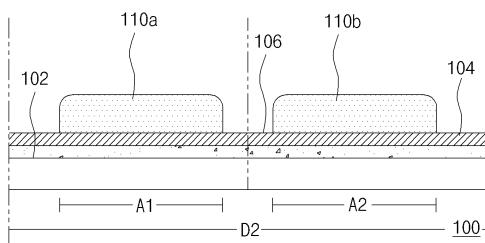

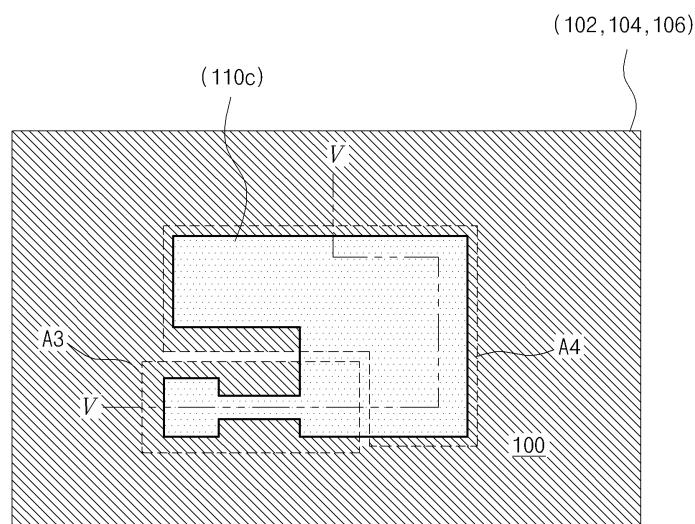

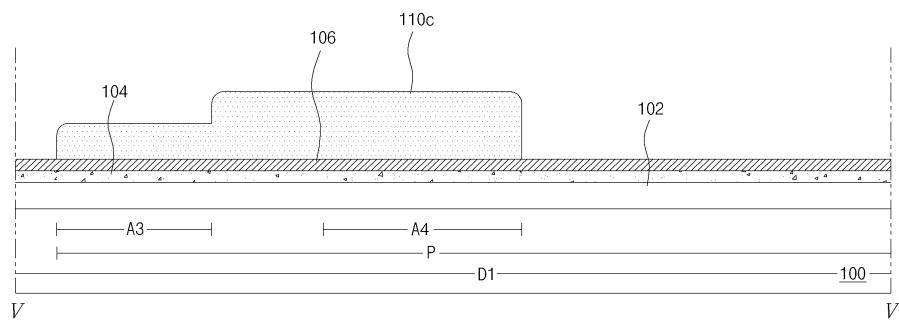

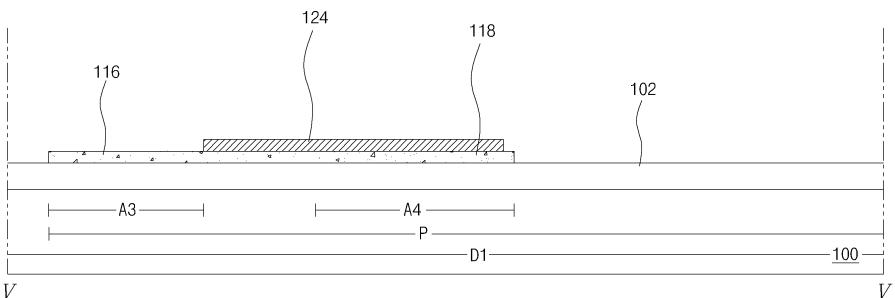

- [0148] 따라서, 도 9b와 도 10b와 도 11b에 도시한 바와 같이, 상기 마스크의 상부로 빛을 조사한 후 현상하게 되면, 상기 P영역(A1)과 N영역(A2)에는 처음 높이보다 일부 제거되어 낮아진 제 1 포토패턴(110a)과 제 2 포토패턴(110b)이 형성되고, 상기 스위칭 영역 및 스토리지 영역(A3,A4)은 높이에 차이가 존재하는 제 3 포토패턴(110c)이 존재한다.

- [0149] 즉, 상기 스위칭 영역(A3)과 스토리지 영역(A4)에 걸쳐 제 3 포토패턴(110c)이 형성되나, 상기 마스크의 반투과부(도 9a,11a의 B3)가 위치했던 상기 스위칭 영역(A3)에 대응하는 부분은 낮은 높이로 형성된다.

- [0150] 연속하여, 상기 제 1 내지 제 3 포토패턴(110a,110b,110c)의 주변으로 노출된 도전성 금속층(106)및 그 하부의 다결정 실리콘층(104)을 제거하는 공정을 진행한다.

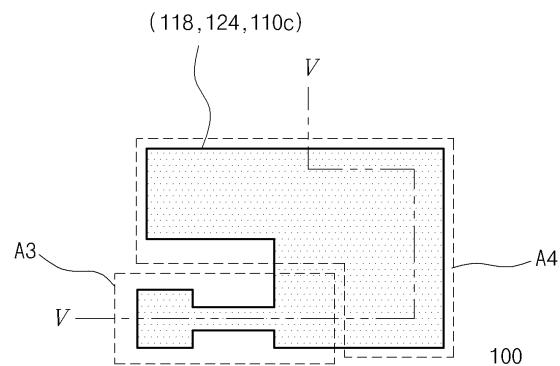

- [0151] 이와 같이 하면, 도 9c와 도 10c와 도 11c에 도시한 바와 같이, 제 1 내지 제 3 포토 패턴(110a,110b,110c)의 하부에는 제 1 내지 제 3 금속패턴(120,122,124)과 그 하부에 제 1 내지 제 4 다결정 반도체층(112,114,116,118)이 남게 된다.

- [0152] 이때, 상기 제 3 및 제 4 다결정 반도체층(116,118)은 일체로 패턴된다.

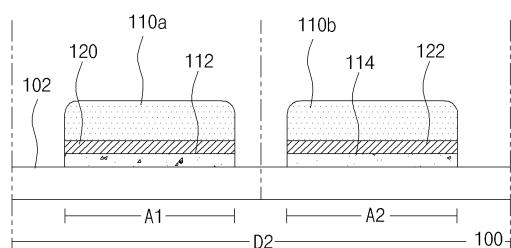

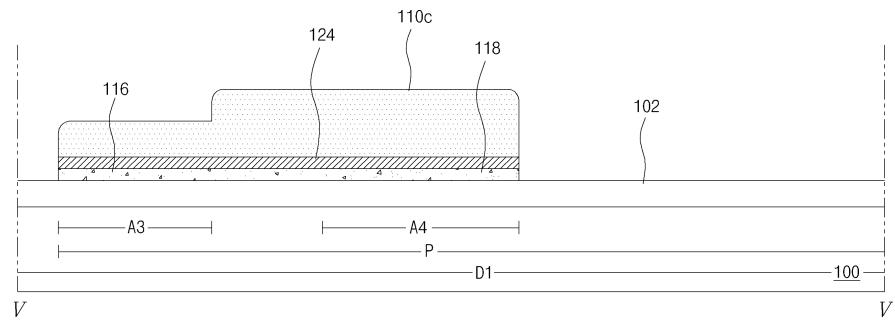

- [0153] 다음으로, 상기 제 1 내지 제 3 포토 패턴(110a,110b,110c)을 애싱하는 공정을 진행한다.

- [0154] 이와 같이 하면, 도 9d와 도 10d와 도 11d에 도시한 바와 같이, 상기 P영역(A1)과 N영역(A2)과 스위칭 영역

(A3)에 대응하는 포토패턴(미도시)이 제거되고, 상기 스토리지 영역(A4)에 대응하는 포토패턴(126)만이 남게 된다.

[0155] 다음으로, 상기 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 대응하여 노출된 제 1 내지 제 3 금속패턴(120, 122, 124)를 제거하는 공정을 진행한다.

[0156] 이와 같이 하면, 도 9e와 도 10e와 11e에 도시한 바와 같이, P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 제 1 내지 제 3 다결정 반도체층(112, 114, 116)이 노출되고, 상기 스토리지 영역의 제 4 반도체층(118)상부에는 상기 제 3 다결정 반도체층(116)에 대응하는 부분이 식각된 제 3 금속패턴(124, 이하, 보조 전극이라 함)이 남게 된다.

[0157] 이상으로 전술한 제 1 마스크 공정을 통해, P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 제 1 내지 제 3 다결정 반도체층(112, 114, 116)을 형성할 수 있었고, 상기 스토리지 영역(A4)에 상기 제 3 다결정 반도체층(116)과 일체로 구성된 제 4 다결정 반도체층(118)과, 보조 전극(124)을 적층하여 형성할 수 있었다.

[0158] 이때, 상기 제 4 다결정 반도체층(118)과 이에 적층된 보조 전극(124)은 스토리지 제 1 전극으로서의 역할을 하게 된다.

[0159] 전술한 공정에서, 상기 제 4 다결정 반도체층(118)에 보조 전극(124)을 형성함으로써, 상기 제 4 다결정 반도체층을 전극으로 사용하기 위한 별도의 불순물 이온도핑 공정을 생략할 수 있다.

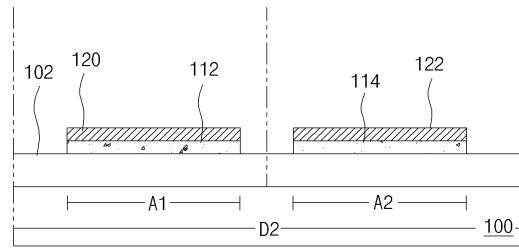

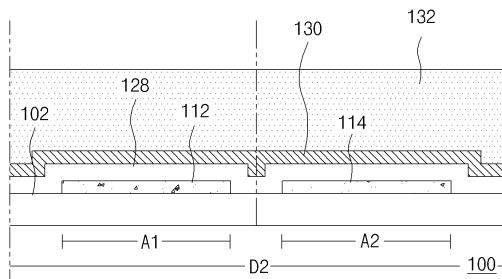

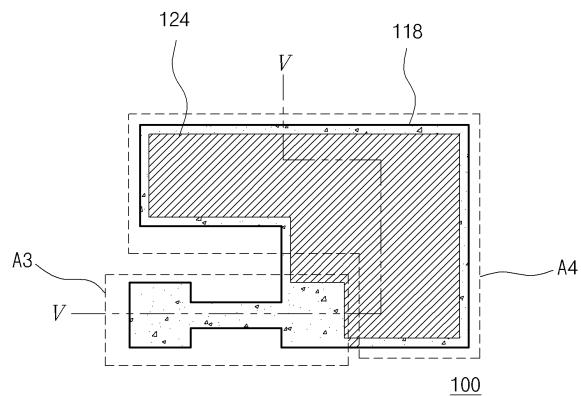

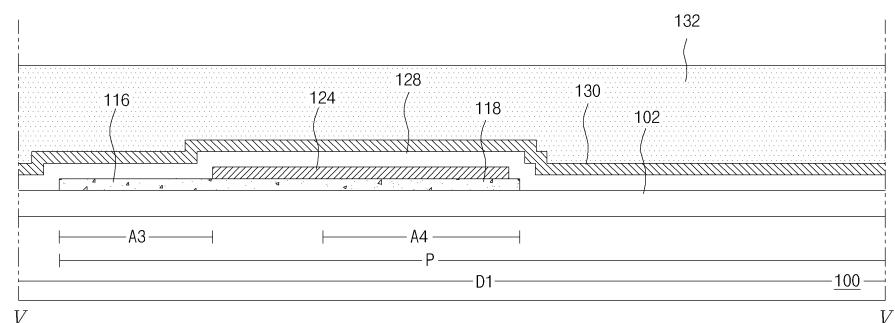

[0160] 이하, 도 9f 내지 도 9g와 도 10f 내지 도 10g와 도 11f 내지 도 11g는 제 2 마스크 공정을 나타낸 도면이다.

[0161] 도 9f와 도 10f와 도 11f에 도시한 바와 같이, 상기 스토리지 영역(A4)에 보조 전극(124)이 형성된 기판(100)의 전면에 게이트 절연막(128)과 제 2 도전성 금속층(130)을 적층한다.

[0162] 다음으로, 상기 제 2 도전성 금속층(130)이 형성된 기판(100)의 전면에 포토레지스트(photoresist)를 도포하여 감광층(132)을 형성한다.

[0163] 다음으로, 제 2 마스크로 상기 감광층(132)을 노광하고 현상하는 공정을 진행한다.

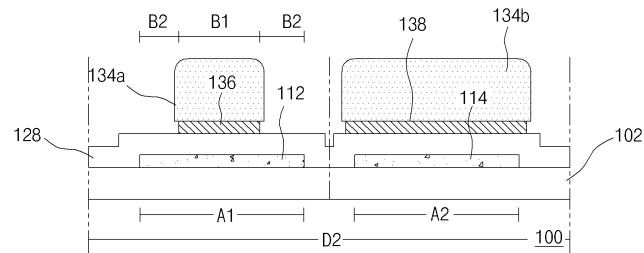

[0164] 도 9g와 도 10g와 도 11g에 도시한 바와 같이, P영역(A1)과 N영역(A2)에 남겨진 제 1 및 제 2 포토 패턴(134a, 134b)과, 상기 스위칭 영역(S)과 상기 스토리지 영역(A4)에 남겨진 제 3 포토 패턴(134c)의 주변으로 노출된 도전성 제 2 금속층(도 9f와 도 11f의 130)을 제거하는 공정을 진행한다.

[0165] 이와 같이 하면, 상기 P영역(A1)의 제 1 포토패턴(134a) 하부에는 게이트 전극(136)이 형성되고, 상기 N영역(A2)과 스위칭 영역 및 스토리지 영역(A3, A4)에는 제 1 금속패턴(138)과 제 2 금속패턴(140)이 남게 된다.

[0166] 이때, 상기 P영역(A1)의 제 1 다결정 반도체층(112)을 제 1 액티브 영역(B1)과, 제 1 액티브 영역(B1)양측의 제 2 액티브 영역(B2)으로 정의한다면, 상기 게이트 전극(136)은 상기 제 1 액티브 영역(B1)에 대응하도록 형성한다.

[0167] 전술한 공정에서, 상기 제 2 금속패턴(140)의 일측과 타측에 연결된 게이트 배선(GL)과 스토리지 배선(SL)을 형성한다.

[0168] 다음으로, 상기 제 1 내지 제 3 포토패턴(134a, 134b, 134c)을 제거하는 공정을 진행한다.

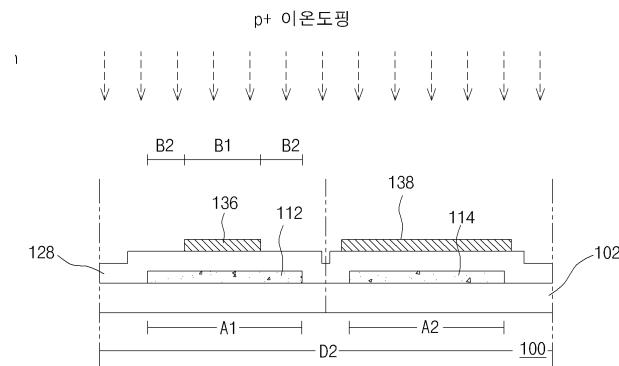

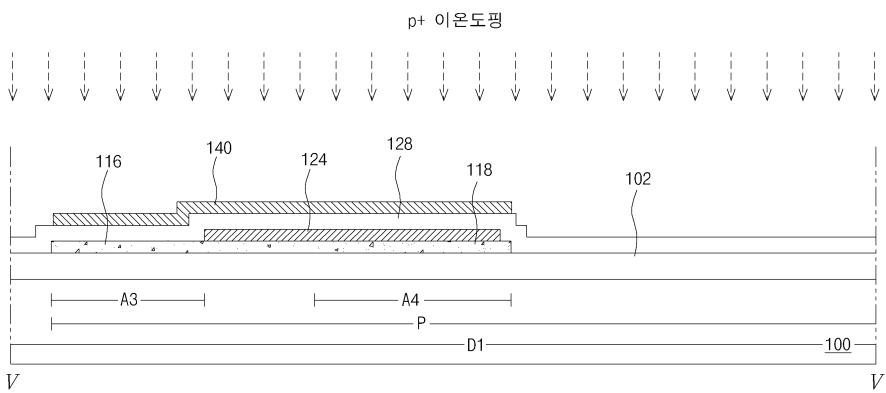

[0169] 도 9h와 도 10h와 도 11h는 P영역의 제 1 다결정 반도체층에 p+이온을 도핑하는 공정을 나타낸 도면이다.

[0170] 도시한 바와 같이, 상기 P영역(A1)에 게이트 전극(136)과, 상기 N영역(A2)에 제 1 금속패턴(138)과, 상기 스위칭 영역 및 스토리지 영역(A3, A4)에 제 3 금속패턴(140)이 형성된 기판(100)의 전면에 p+이온을 도핑하는 공정을 진행한다.

[0171] 이와 같이 하면, 상기 P영역(A1)에 구성한 제 1 다결정 반도체층(112)의 제 2 액티브 영역(B2)에 p+이온이 도핑되어 오믹영역이 형성된다.

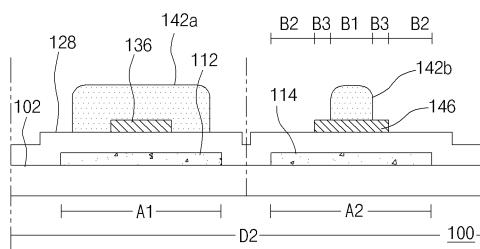

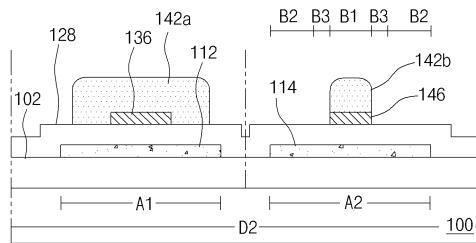

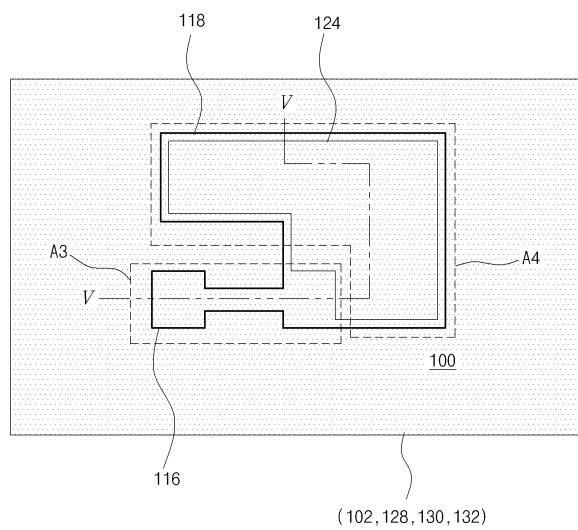

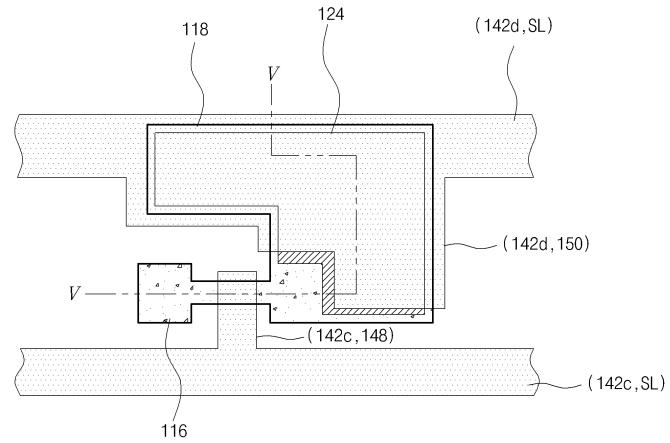

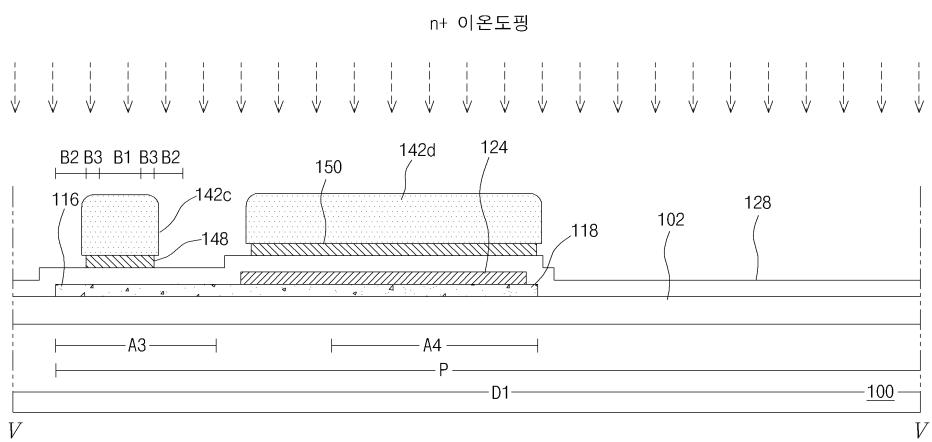

[0172] 도 9i 내지 도 9k와 도 10i 내지 도 10k와 도 11i 내지 도 11k는 제 3 마스크 공정을 나타낸 도면이다.

[0173] 도 9i와 도 10i와 도 11i에 도시한 바와 같이, 상기 게이트 전극(136)과 제 1 내지 제 2 금속패턴(도 9h와 도 11h의 140)이 형성된 기판(SL)의 전면에 감광층형성하고 제 3 마스크 공정으로 패턴하여, 상기 P영역(A1)에는 이를 덮는 제 1 포토패턴(142a)과, 상기 N영역(A2)은 제 2 포토패턴(142b)과 그 하부의 게이트 전극(146)과, 상기 스위칭 영역(A3)은 제 3 포토 패턴(142c)과 그 하부의 게이트 전극(148)과, 상기 스토리지 영역(A4)은

제 4 포토 패턴(142d)과 그 하부의 스토리지 제 2 전극(150)을 형성한다.

[0174] 상기 스위칭 영역(A3)의 게이트 전극(148)은 게이트 배선(GL)에서 돌출된 형상이고, 상기 스토리지 제 2 전극(150)은 상기 스토리지 배선(SL)에서 돌출 연장된 형상이다.

[0175] 이때, 상기 N영역(A2)과 스위칭 영역(A3)의 제 2 내지 제 3 다결정 반도체층(114, 116)을 제 1 액티브 영역(B1)과, 제 1 액티브 영역(B1) 양측의 제 2 액티브 영역(B2)과, 상기 제 2 액티브 영역(B2)과 제 1 액티브 영역(B1)의 사이를 제 3 액티브 영역(B3)으로 정의한다면, 상기 각 게이트 전극(146, 148)은 상기 제 1 액티브 영역 및 제 3 액티브 영역(B1, B3)에 대응하여 위치하도록 형성한다.

[0176] 다음으로, 상기 제 1 내지 제 4 포토 패턴(142a, 142b, 142c, 142d)을 그대로 둔 상태에서 기판(100)의 전면에 n+이온을 도핑하는 공정을 진행한다.

[0177] 이와 같이 하면, 상기 제 2 포토 패턴(142b)과 제 3 포토 패턴(142c)에 의해 가려지지 않은 제 2 및 제 3 다결정 반도체층(114, 116)의 제 2 액티브 영역(B2)에 n+이온이 도핑되고 이 부분은 오믹 영역이 된다.

[0178] 이때, 상기 보조 전극(124)의 주변으로 노출된 상기 제 4 다결정 반도체층의 표면에도 n+이온이 도핑된다.

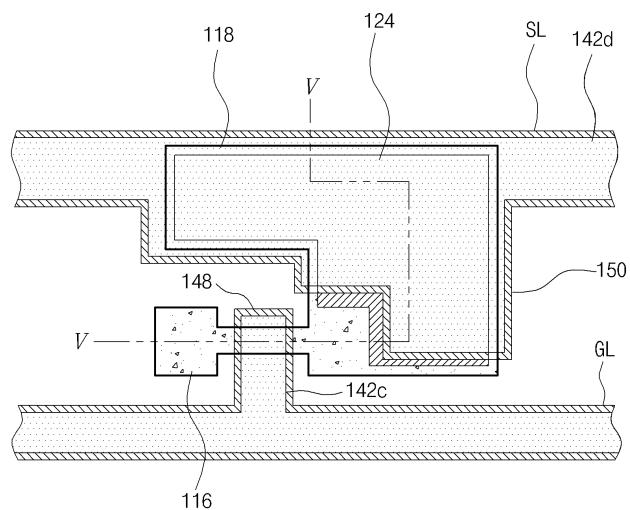

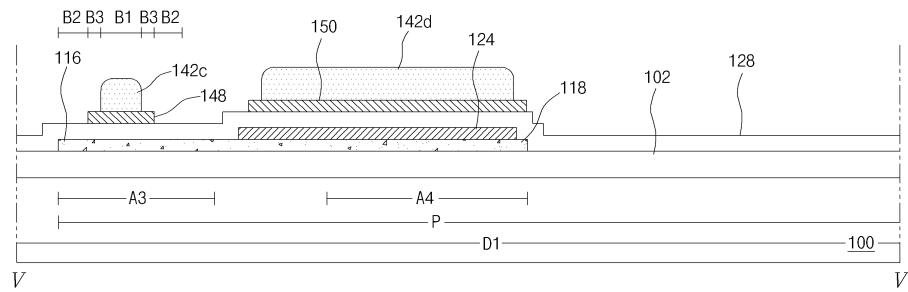

[0179] 도9j 내지 도 9k와 도 10j 내지 도10k와 도11j 내지 도11k N영역과 스위칭영역의 다결정 반도체층에 저농도 도핑영역인 LDD영역을 형성하기 위한 공정이다.

[0180] 도 9j와 도 10j와 도 11j는 상기 제 1 내지 제 4 포토패턴을 애싱(ashing)한 결과를 도시한 도면이다.

[0181] 도시한 바와 같이, 상기 P영역(A1)과 N영역 및 스위칭 영역(A2, A3)과 스토리지 영역(A4)에 남겨진 제 1 내지 제 4 포토패턴(142a, 142b, 142c, 142d)을 애싱(ashing)하는 공정을 진행한다.

[0182] 상기 애싱공정은 건식식각 공정과 유사하며, 상기 제 1 내지 제 4 포토패턴(142a, 142b, 142c, 142d)을 완전히 제거하는 목적 보다는, 주변의 일부만을 제거하여 하부 금속층 일부를 노출하기 위한 것이다.

[0183] 따라서, 본 공정에서는 포토패턴 애싱을 통해, 제 2 및 제 3 다결정 반도체층(114, 116)의 제 3 액티브 영역(B3)에 대응하는 상부 게이트 전극(146, 148)을 노출한다. 이때, 상기 스토리지 제 2 전극 및 게이트 배선(150, GL)과 스토리지 배선(SL)의 주변도 일부 노출된다.

[0184] 이후, 상기 노출된 부분의 게이트 전극(146, 148)을 제거하는 공정을 진행한다.

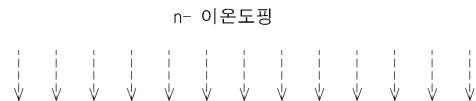

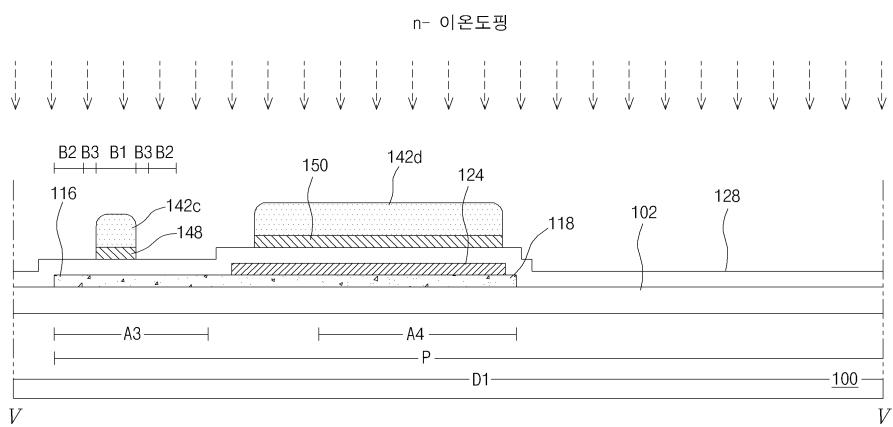

[0185] 도 9k와 도 10k와 도 11k는 LDD영역을 형성하기 위한 n-도핑공정을 나타낸 도면이다.

[0186] 도시한 바와 같이, 전술한 공정에서 N영역(A2)과 스위칭 영역(A2)에 위치한 게이트 전극(146, 148)둘레의 일부가 제거된 부분에 대응하는 제 2 및 제 3 다결정 반도체층(114, 116)의 제 3 액티브영역(B3)에 n-이온을 도핑하는 공정을 진행하여, 저농도 도핑영역(드레인 영역)(lightly doped drain, LDD)을 형성한다.

[0187] 저농도 도핑영역을 형성하는 이유는, 채널(제 1 액티브 영역)에 근접한 영역에서 열전자 효과에 의해 발생하는 누설전류 특성을 최소화하기 위한 것이다.

[0188] 상기 제 2 및 제 3 다결정 반도체층(114, 116)에 LDD영역을 형성한 후, 상기 P영역(A1)과 상기 N영역(A2)과 스위칭 영역(A3)과 스토리지 영역(A4)의 제 1 내지 제 4 포토패턴(142a, 142b, 142c, 142d)을 제거하는 공정을 진행한다.

[0189] 이상으로, 전술한 제 2 내지 제 3 마스크 공정을 통해, P영역(A1)의 제 1 다결정 반도체층(112)의 상부에 게이트 전극(118)을 형성하고, 상기 게이트 전극(118)이 위치하지 않은 제 1 다결정 반도체층(112)의 표면에 p+이온을 도핑하여 오믹 영역을 형성하고, 상기 N영역(A2)과 스위칭 영역(A3)의 제 2 내지 제 3 다결정 반도체층(114, 116)에는 n+이온과 n-이온을 각각 도핑하여 오믹 영역과 저농도 도핑영역을 형성함과 동시에 각각 게이트 전극(146, 148)을 형성하고, 상기 스토리지 영역(A4)에는 스토리지 제 2 전극(150)을 형성하는 공정을 진행하였다.

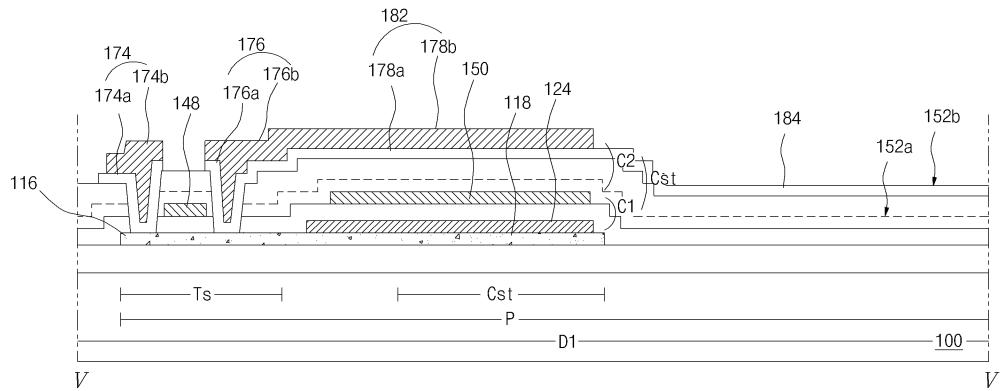

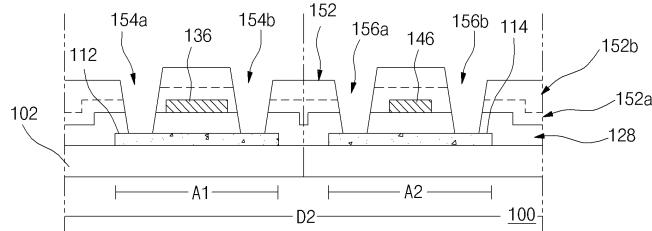

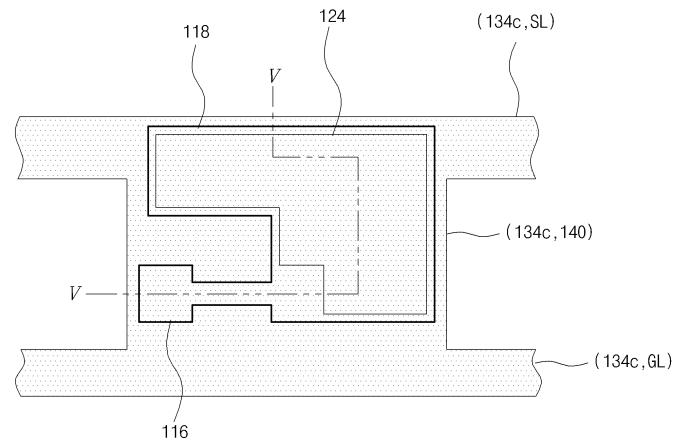

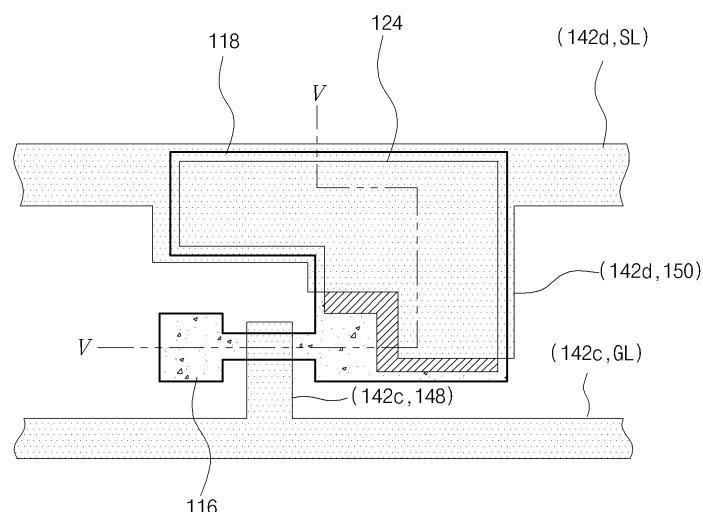

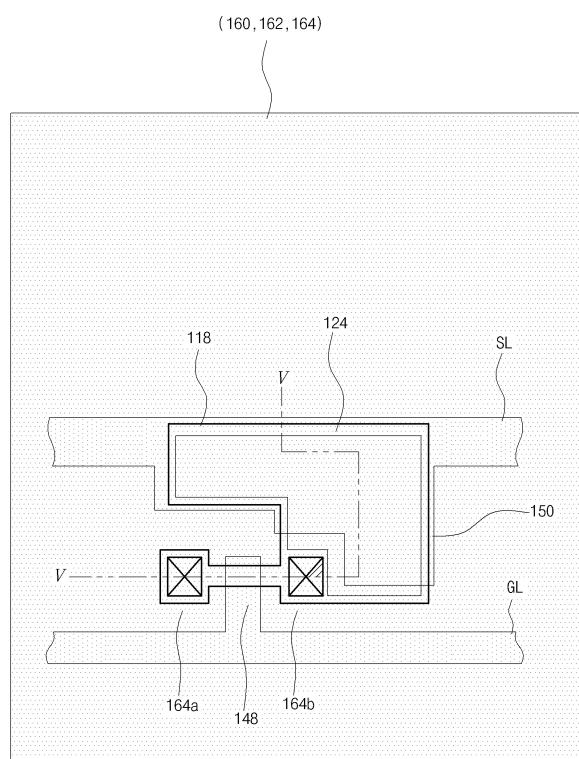

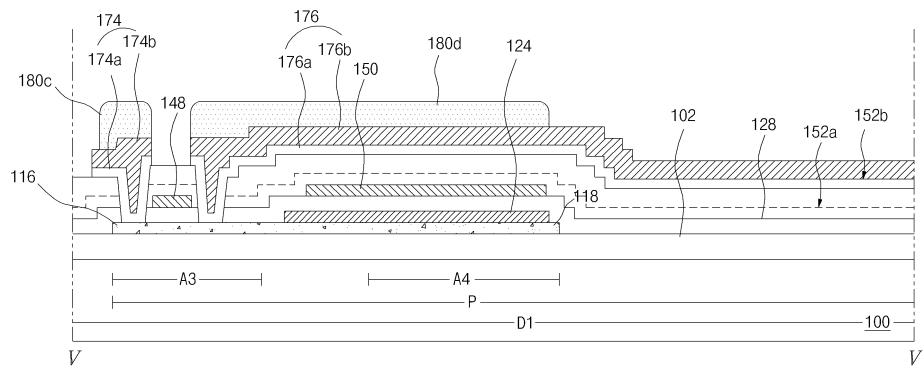

[0190] 도 91과 도 101과 도 111은 제 4 마스크 공정을 나타낸 도면이다.

[0191] 도시한 바와 같이, N영역(A1)과 P영역(A2)과 스위칭 영역(A3)에 각각 게이트 전극(136, 146, 148)이 형성되고, 상기 스토리지 영역(A4)에 스토리지 제 2 전극(150)이 형성된 기판(100)의 전면에, 산화 실리콘( $\text{SiO}_2$ )을 증착한 실리콘 산화막(152a)과 상기 실리콘 산화막(152a)의 상부에 질화 실리콘( $\text{SiN}_x$ )을 증착하여 형성한 실리콘 질화막(152a)을 적층하여 제 1 및 제 2 층간 절연막(152a, 152b)을 형성한다.

- [0192] 다음으로, 상기 제 1 및 제 2 층간 절연막(152a, 152b)이 형성된 기판(100)의 전면에 포토레지스트(photoresist)를 도포한 후 제 4 마스크 공정으로 패턴하여, 상기 제 1 다결정 반도체층(112)과 제 2 다결정 반도체층(114)과 제 3 다결정 반도체층(116)의 이온도핑영역(오믹 영역)을 각각 노출하는 콘택홀을 형성한다.

- [0193] 상세히는, 상기 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 형성한 각 게이트 전극(136, 146, 148)을 중심으로 양측의 다결정 반도체층(112, 114, 116)즉, 이온이 도핑된 영역을 각각 노출하는 제 1 콘택홀(154a, 156a, 158a)과 제 2 콘택홀(154b, 156b, 158b)을 형성한다.

- [0194] 전술한 공정에서, 상기 제 1 층간 절연막(152a)을 형성한 후, 기판(100)을 열처리 하는 공정을 진행한다.

- [0195] 이와 같이 하면, 상기 보조 전극(124) 주변으로 노출된 상기 제 4 반도체층(118)의 표면에 도핑된 이온( $n+i$ 온)이 상기 보조 전극(124)의 하부로 확산되는 현상이 일어난다. 이와 같은 현상으로, 상기 보조 전극(124)과 그 하부의 제 4 반도체층(118)은 오믹 콘택을 이루어 서로 신호가 흐를 수 있게 된다.

- [0196] 또한, 상기 제 2 층간 절연막(152b)을 형성한 후, 수소화 열처리를 진행한다.

- [0197] 또한, 전술한 공정에서 콘택홀을 형성하면서, 상기 제 3 반도체층(118)의 제 2 콘택홀(158b)대신, 상기 보조 전극(124)의 주변으로 노출된 제 4 반도체층(118) 또는 상기 보조 전극(124)을 노출하여 콘택홀을 형성할 수도 있다.

- [0198] 이것이 가능한 이유는, 상기 제 3 반도체층(116)과 제 4 반도체층(118)이 일체로 형성되어 동일한 신호가 흐르는 구조로 형성되었기 때문이다.

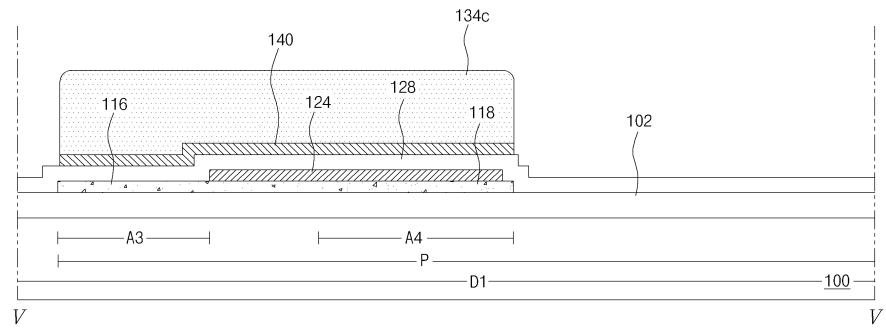

- [0199] 이하, 도 9m 내지 도 9p와 도 10m 내지 도 10p와 도 11m 내지 도 11p는 제 5 마스크 공정을 나타낸 도면이다.

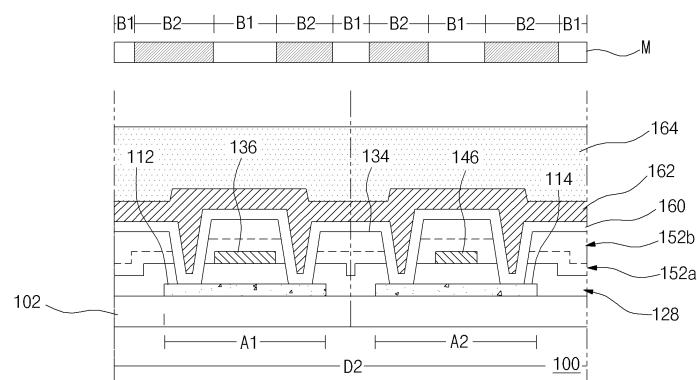

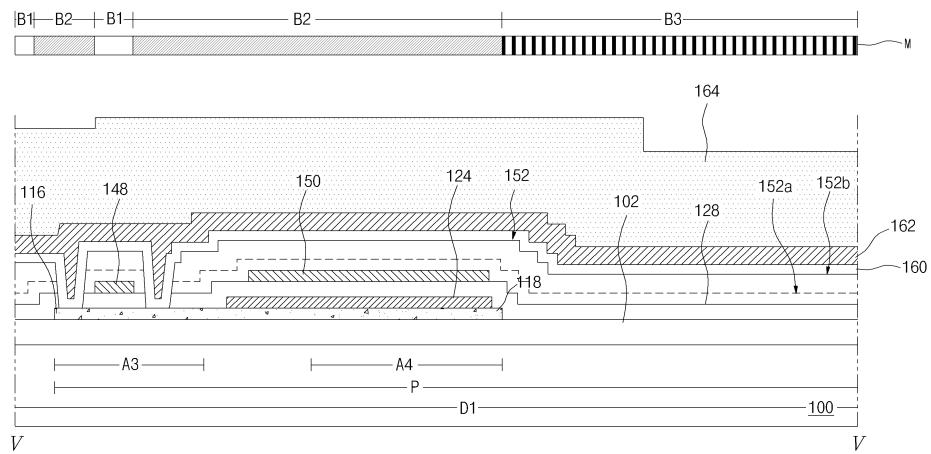

- [0200] 도 9m과 도 10m과 도 11m에 도시한 바와 같이, 상기 층간 절연막이 형성된 기판의 전면에 투명 전극층(160)과 제 3 도전성 금속층(162)과 감광층(164)을 적층하여 형성한다.

- [0201] 상기 투명 전극층(160)은 인듐-텅-옥사이드(ITO)와 인듐-징크-옥사이드(IZO)를 포함하는 투명한 물질 그룹 중 선택된 하나 또는 그 이상을 증착하여 형성하고, 상기 제 3 도전성 금속층(162)은 앞서 언급한 도전성 금속물질 그룹 중 선택된 하나 또는 그 이상의 물질을 증착하여 형성한다.

- [0202] 상기 감광층(164)은 포토레지스트(포지티브형, positive type)를 도포하여 형성한다.

- [0203] 상기 감광층(164)이 형성된 기판(100)과 이격된 상부에 투과부(B1)와 반투과부(B3)와 차단부(B2)로 구성된 마스크(M)를 위치시킨다.

- [0204] 이때, 상기 투과부(B1)는 P영역(A1)과 N영역 및 스위칭 영역(A2, A3)에 구성한 게이트 전극(136, 146, 148)에 대응한 부분과, 상기 P영역(A1)과 N영역 및 스위칭 영역(A2, A3) 및 스토리지 영역(A4)이외의 영역에 대응하도록 구성한다.

- [0205] 상기 반투과부(B3)는 상기 스위칭 영역 및 스토리지 영역(A3, A4)을 제외한 화소 영역(P)에 대응하여 위치하도록 하고,

- [0206] 상기 차단부(B2)는 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)중 각 게이트 전극(136, 146, 148)으로 덮히지 않은 영역과, 상기 스토리지 영역(A4)에 대응하여 위치하도록 한다.

- [0207] 다음으로, 상기 마스크(M)의 상부로 빛(자외선)을 조사하여, 하부의 감광층(164)을 부분적으로 노광하는 공정을 진행한다.

- [0208] 앞에서도 언급하였지만, 상기 투과부(B1)에 대응하는 부분은 완전히 노광되고 상기 반투과부(B3)에 대응하는 부분은 표면으로부터 일부만이 노광되고, 상기 차단부(B2)에 대응하는 부분은 노광되지 않고 남게 된다.

- [0209] 다음으로, 상기 노광된 부분을 현상한 후, 상기 노출된 하부의 제 3 금속층(162)과 투명 전극층(160)을 제거하는 공정을 진행한다.

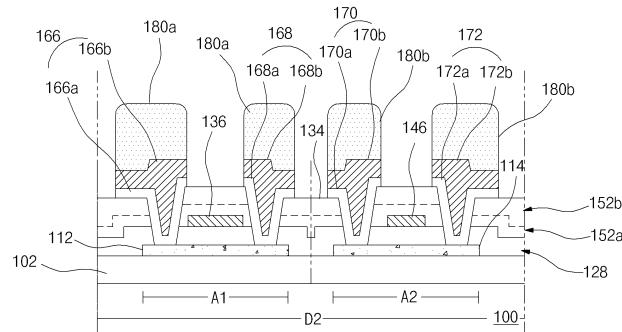

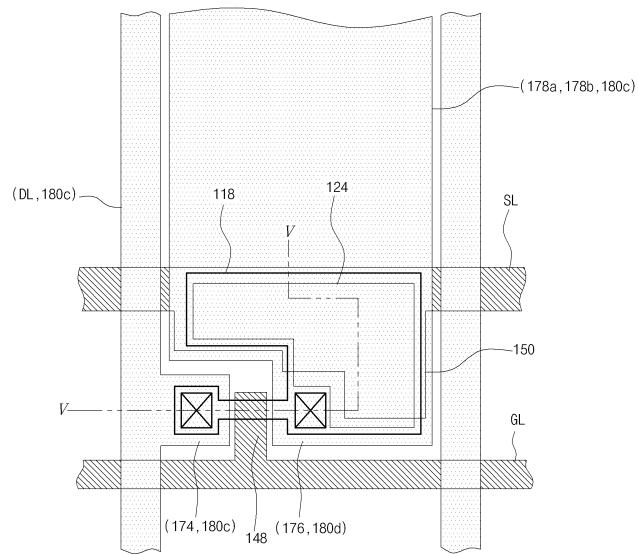

- [0210] 이와 같이 하면, 도 9n과 도 10n과 도 11n에 도시한 바와 같이, 상기 P영역(A1)과 N영역(A2)과 스위칭 영역(A3)에 투명 전극(166a, 168a, 170a, 172a, 174a, 176a)과 불투명 전극(166b, 168b, 170b, 172b, 173b, 176b)이 적층된 소스 전극(166, 170, 174)과 드레인 전극(168, 172, 176)이 형성되고, 상기 스토리지 영역 및 화소 영역(A4, P)에 걸쳐 투명전극 패턴과 불투명 전극패턴(178a, 178b(패턴된 제 3 도전성 금속층))이 남게 된다.

- [0211] 또한 상기 각 영역에 형성한 소스 및 드레인 전극((166, 170, 174), (168, 172, 176))의 상부에 제 1 내지 제 4 포

토 패턴(180a, 180b, 180c, 180d)이 남게 된다.(이때, 스위칭 영역(A3)을 제외하고 동일한 영역(A1,A2)의 포토 패턴을 하나로 봄)

- [0212] 전술한 공정에서, 상기 스위칭 영역(A1)의 소스 전극(174)에서 화소 영역(P)의 일 측을 따라 연장된 데이터 배선(DL)을 형성한다.

- [0213] 상기 데이터 배선(DL)또한, 투명전극 패턴과 불투명 전극 패턴이 적층된 형상이며, 소스 전극(174)의 투명전극 패턴과 불투명 전극 패턴(174a, 174b)에서 연장된 형상이므로 이후, 동일 기호를 사용한다.

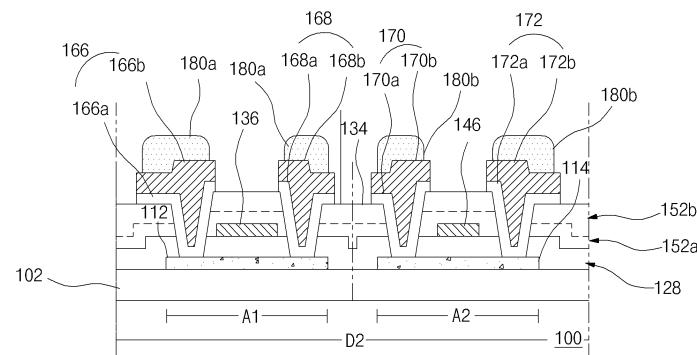

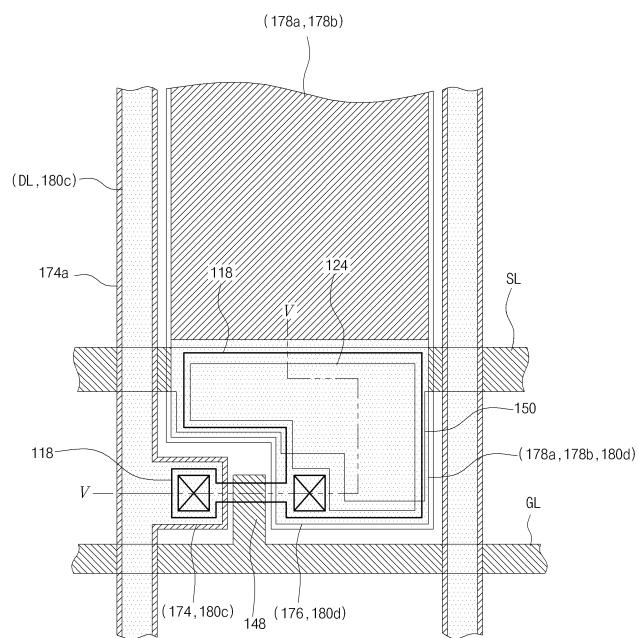

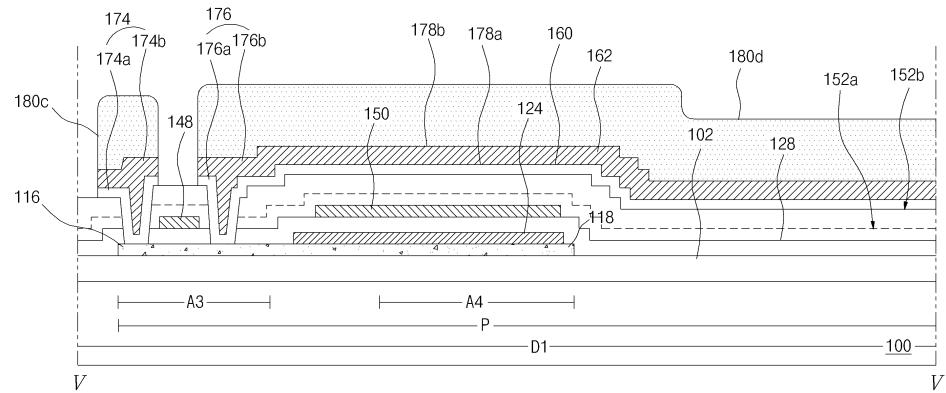

- [0214] 도 90와 도 100와 도 110는 상기 제 1 내지 제 4 포토패턴을 애싱하여 식각한 후를 나타낸 도면이다.

- [0215] 도 90와 도 100와 도 110에 도시한 바와 같이, 애싱 공정 후 상기 제 1 내지 제 3 포토 패턴(180a, 180b, 180c)은 표면으로부터 일부만이 제거된 상태로 남게 된다. 동시에 주변이 제거되어 하부의 소스전극(166, 170, 174)과 드레인 전극(168, 172, 176)의 불투명 전극패턴(166b, 168b, 170b, 172b, 174b, 176b)이 일부 노출된다.

- [0216] 동시에, 상기 제 4 포토 패턴(180d)중 앞서 마스크 공정에서 반투과부에 대응하는 부분 즉, 스위칭 영역 및 스토리지 영역(A3,A4)을 제외한 화소 영역(P)에 대응하는 부분은 완전히 제거되어 하부의 불투명 전극패턴(178b)이 노출된다.

- [0217] 다음으로, 상기 노출된 불투명 전극패턴(166b, 168b, 170b, 172b, 174b, 176b, 178b)을 제거하는 공정을 진행한다.

- [0218] 다음으로, 상기 제 1 내지 제 4 포토 패턴(180a, 180b, 180c, 180d)을 제거하는 공정을 진행한다.

- [0219] 이와 같이 하면, 도 9p와 도 10p와 도 11p에 도시한 바와 같이, 상기 제 1 내지 제 4 포토 패턴(180a, 180b, 180c, 180d)이 제거된 만큼, 상기 각 영역(A1,A2,A3)의 소스 전극(166, 170, 174)과 드레인 전극(168, 172, 176)을 이루는 불투명 전극 패턴(166b, 168b, 170b, 172b, 174b)이 일부 제거되고 주변으로 하부의 투명전극 패턴(166a, 168b, 170c, 172d, 174e)이 노출된 형상이 된다.

- [0220] 또한, 상기 스토리지 영역(A4)에는 투명전극 패턴(178a)과 불투명 전극 패턴(178b)이 적층된 스토리지 제 3 전극(182)이 형성되고, 상기 스위칭 영역 및 스토리지 영역(A3,A4)을 제외한 화소 영역(P)에는 투명한 화소전극(184)이 형성된다.

- [0221] 이상과 같이, 단일 마스크 공정으로, 각 영역(A1,A2,A3)의 소스 및 드레인 전극((166, 170, 174), (168, 172, 176))과 스토리지 전극(182)과 화소 전극(184)을 형성할 수 있다.

- [0222] 전술한 바와 같이, 5 마스크 공정으로 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판을 제작할 수 있다.

- [0223]

### 발명의 효과

- [0224] 따라서, 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판 제조방법(5마스크 제조방법)은, 종래에 비해 공정이 단순화되어 공정비용을 절감하고 공정 시간을 단축할 수 있는 효과가 있다.

- [0225] 또한, 공정이 단순화됨으로써, 불량 발생률을 낮출 수 있어 생산수율을 개선하는 효과가 있다.

### 도면의 간단한 설명

- [0001] 도 1은 일반적인 구동회로 일체형 액정패널을 개략적으로 도시한 평면도이고,

- [0002] 도 2는 종래에 따른 구동회로 일체형 액정표시장치용 어레이기판의 일부를 도시한 확대 평면도이고,

- [0003] 도 3a와 도 3b는 종래에 따른 구동회로 일체형 액정표시장치의 구성을 개략적으로 도시한 단면도이고,

- [0004] 도 4a 내지 도 4i는 종래에 따른 구동회로를 제작하는 공정을 순서대로 도시한 공정 단면도이고,

- [0005] 도 5a 내지 도 5i는 종래에 따른 구동회로 일체형 액정표시장치용 어레이기판의 표시영역에 대응하는 공정을 순서대로 도시한 공정 평면도이고,

- [0006] 도 6a 내지 도 6i는 도 5a 내지 도 5i의 III-III을 따라 절단한 공정 단면도이고,

- [0007] 도 7은 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이 기판의 표시영역 일부를 확대한 평면도이고,

- [0008] 도 8a와 도 8b는 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판의 단면 구성을 도시한 단면도이고,

- [0009] 도 9a 내지 도 9p는 본 발명에 따른 구동회로를 제작하는 공정을 순서대로 도시한 공정 단면도이고,

- [0010] 도 10a 내지 도 10p는 본 발명에 따른 구동회로 일체형 액정표시장치용 어레이기판의 표시영역에 대응하는 공정을 순서대로 도시한 공정 평면도이고,

- [0011] 도 11a 내지 도 11p는 각각 도 10a 내지 도 10p의 V-V를 따라 절단한 공정 단면도이다.

- [0012] < 도면의 주요 부분에 대한 부호의 설명 >

- |                          |                   |

|--------------------------|-------------------|

| [0013] 100 : 기판          | 116 : 액티브층        |

| [0014] 118 : 제 4 반도체층    | 124 : 보조 전극       |

| [0015] 148 : 게이트 전극      | 174 : 소스 전극       |

| [0016] 176 : 드레인 전극      | 150 : 스토리지 제 2 전극 |

| [0017] 182 : 스토리지 제 3 전극 | 184 : 화소 전극       |

- [0018]

## 도면

### 도면1

도면2

도면3a

도면3b

도면4a

도면4b

도면4c

도면4d

## 도면4e

## 도면4f

## 도면4g

## 도면4h

도면4i

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면5g

도면5h

도면5i

도면6a

## 도면6b

## 도면6c

## 도면6d

## 도면6e

## 도면6f

## 도면6g

## 도면6h

## 도면6i

## 도면7

도면8a

## 도면8b

## 도면9a

## 도면9b

## 도면9c

## 도면9d

## 도면9e

## 도면9f

## 도면9g

## 도면9h

## 도면9i

## 도면9j

## 도면9k

## 도면9l

## 도면9m

## 도면9n

## 도면9o

## 도면9p

## 도면10a

## 도면10b

## 도면10c

## 도면10d

## 도면10e

## 도면10f

## 도면10g

## 도면10h

## 도면10i

도면10j

도면10k

## 도면101

## 도면10m

## 도면10n

## 도면10o

## 도면10p

## 도면11a

## 도면11b

도면11c

도면11d

도면11e

도면11f

## 도면11g

## 도면11h

## 도면11i

## 도면11j

## 도면11k

## 도면11l

## 도면11m

## 도면11n

## 도면11o

## 도면11p

|                |                                            |         |            |

|----------------|--------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 用于液晶显示装置的阵列基板及其制造方法                   |         |            |

| 公开(公告)号        | <a href="#">KR101151799B1</a>              | 公开(公告)日 | 2012-06-01 |

| 申请号            | KR1020050106840                            | 申请日     | 2005-11-09 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                   |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                  |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                  |         |            |

| [标]发明人         | LEE SEOK WOO<br>이석우<br>PARK YONG IN<br>박용인 |         |            |

| 发明人            | 이석우<br>박용인                                 |         |            |

| IPC分类号         | G02F1/136                                  |         |            |

| CPC分类号         | G02F1/136213 G02F1/13454 G02F2001/136231   |         |            |

| 其他公开文献         | KR1020070049743A                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                  |         |            |

## 摘要(译)

目的 : 提供一种用于LCD ( 液晶显示器 ) 的阵列基板及其制造方法 , 通过五个掩模工艺制造用于驱动电路集成型LCD的阵列基板 , 从而缩短工艺时间并简化工艺。组成 : A基板 ( 100 ) 包括显示区域和非显示区域 , 显示区域包括像素区域。驱动电路配置在基板的非显示区域。开关装置配置在像素区域的一侧。存储电容器 ( Cst ) 配置在像素区域的一部分处 , 并且包括用于存储的第一电极 , 包括堆叠的多晶半导体层和第一金属电极 , 用于存储的第二电极 ( 150 ) 和第三电极用于存储 ( 182 ) 的包括透明电极和第二金属电极的堆叠 , 像素电极 ( 184 ) 与开关装置接触 , 并放置在像素区域。©KIPO 2007