## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G02F 1/1343 (2006.01)

(11) 공개번호

10-2007-0034145

(43) 공개일자

2007년03월28일

(21) 출원번호 10-2005-0088460

(22) 출원일자 2005년09월23일

심사청구일자 없음

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

창학선

경기 용인시 풍덕천동 동부아파트 103동 203호

유승후

경기 성남시 분당구 수내동 로얄팰리스하우스빌 B-1202

김현옥

경기 용인시 기흥읍 삼성전자(주)기흥공장 LCD총괄 LCD연구소 액정기

술그룹

김연주

경기 수원시 영통구 매탄동 111-74번지 202호

도희욱

경기 수원시 팔달구 인계동 1007-5번지 1층

신경주

경기 용인시 기흥읍 보라리 289-12 삼정선비마을 102-504

(74) 대리인 조희원

전체 청구항 수 : 총 38 항

(54) 액정 표시 패널과 그의 구동 방법 및 그를 이용한 액정표시 장치

**(57) 요약**

본 발명은 멀티-도메인 VA 모드에서 시인성 및 투과율을 향상시킬 수 있는 액정 패널과 그의 구동 방법 및 그를 이용한 액정 표시 장치에 관한 것이다.

본 발명의 한 특징에 따른 액정 패널은 상하로 분할되고 면적이 서로 다른 제1 및 제2 계조 영역을 갖으며, 인접한 서브 화소와 상기 제1 및 제2 계조 영역이 상하로 엇갈려 배열된 다수의 서브 화소; 상기 제1 및 제2 계조 영역을 독립적으로 구동하는 다수의 박막 트랜지스터와; 상기 박막 트랜지스터와 접속되어 상기 제1 및 제2 계조 영역 각각에 공급될 제1 및 제2 데이터 신호를 공급하는 다수의 데이터 라인과; 상기 다수의 박막 트랜지스터를 수평 기간 단위로 구동하는 다수의 게이트 라인을 구비하고; 상기 박막 트랜지스터는 다수의 게이트 라인 중 한 게이트 라인이 구동될 때 상기 제1 계조 영역들이 구동되고, 다른 게이트 라인이 구동될 때 상기 제2 계조 영역들이 구동되도록 상기 제1 및 제2 계조 영역 각각과 접속된 것을 특징으로 한다.

**대표도**

도 9

### 특허청구의 범위

#### 청구항 1.

제1 및 제2 계조의 조합으로 원하는 계조를 표시하는 서브 화소를 포함하는 액정 패널에 있어서,

상하로 분할되고 면적이 서로 다른 제1 및 제2 계조 영역을 갖으며, 인접한 서브 화소와 상기 제1 및 제2 계조 영역이 상하로 엇갈려 배열된 다수의 서브 화소;

상기 제1 및 제2 계조 영역을 독립적으로 구동하는 다수의 박막 트랜지스터와;

상기 박막 트랜지스터와 접속되어 상기 제1 및 제2 계조 영역 각각에 공급될 제1 및 제2 데이터 신호를 공급하는 다수의 데이터 라인과;

상기 다수의 박막 트랜지스터를 수평 기간 단위로 구동하는 다수의 게이트 라인을 구비하는 것을 특징으로 하는 액정 패널.

#### 청구항 2.

제 1 항에 있어서,

상기 제1 및 제2 계조 영역은 수평 및 수직 방향을 따라 교변적으로 배열된 것을 특징으로 하는 액정 패널.

#### 청구항 3.

제 1 항에 있어서,

상기 제1 및 제2 계조 영역 각각의 양측면은 수평축을 기준으로 꺽여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된 것을 특징으로 하는 액정 패널.

#### 청구항 4.

제 3 항에 있어서,

상기 게이트 라인 중 한 게이트 라인은 상기 제1 및 제2 계조 영역의 꺽인 부분과 중첩되게 형성되고, 다른 게이트 라인은 상하로 인접한 상기 서브 화소의 경계부와 중첩되게 형성된 것을 특징으로 하는 액정 패널.

#### 청구항 5.

제 4 항에 있어서,

상기 상하로 인접한 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비하는 것을 특징으로 하는 액정 패널.

## 청구항 6.

제 5 항에 있어서,

상기 박막 트랜지스터는 상기 스토리지 라인과 근접하거나, 중첩된 접속부에 의해 상기 제1 및 제2 계조 영역 각각의 화소 전극과 접속된 것을 특징으로 하는 액정 패널.

## 청구항 7.

제 1 항 내지 제 6 항 중 어느 한 항에 기재된 액정 패널을 구동하는 방법에 있어서,

입력 데이터 신호를 툭-업 테이블을 이용하여 상기 제1 및 제2 데이터 신호로 변조하는 단계와;

상기 제1 및 제2 데이터 신호가 교변적으로 배열되게 정렬하는 단계와;

상기 제1 및 제2 데이터 신호가 교변되게 정렬된 데이터 신호를 감마 전압을 이용하여 아날로그 데이터 신호로 변환하는 단계와;

상기 게이트 라인이 구동되는 수평 기간마다 교변적으로 배열된 상기 제1 및 제2 데이터 신호를 상기 다수의 데이터 라인에 동시에 공급하는 단계를 포함하는 것을 특징으로 하는 액정 패널의 구동 방법.

## 청구항 8.

제 1 항 내지 제 6 항 중 어느 한 항에 기재된 액정 패널과;

상기 액정 패널의 게이트 라인을 구동하는 게이트 드라이버와;

상기 액정 패널의 데이터 라인을 구동하는 데이터 드라이버와;

상기 게이트 드라이버 및 데이터 드라이버를 제어하고 외부로부터 입력된 데이터 신호를 상기 제1 및 제2 데이터 신호로 변조하여 상기 데이터 드라이버로 공급하는 타이밍 컨트롤러를 구비하는 것을 특징으로 하는 액정 표시 장치.

## 청구항 9.

제 8 항에 있어서,

상기 타이밍 컨트롤러는 상기 입력 데이터 신호에 대응된 상기 제1 및 제2 데이터 신호가 미리 저장된 툭-업 테이블을 이용하여 상기 입력 데이터 신호를 상기 제1 및 제2 데이터 신호로 변조하는 것을 특징으로 하는 액정 표시 장치.

## 청구항 10.

제 9 항에 있어서,

상기 수평 기간마다 상기 제1 및 제2 데이터 신호의 배열 순서가 바뀌게 되는 것을 특징으로 하는 액정 패널의 구동 방법.

## 청구항 11.

제1 및 제2 계조의 조합으로 원하는 계조를 표시하는 서브 화소를 포함하는 액정 패널에 있어서,

상하로 분할되고 면적이 서로 다른 제1 및 제2 계조 영역을 갖으며, 인접한 서브 화소와 상기 제1 및 제2 계조 영역이 상하로 엇갈려 배열된 다수의 서브 화소와;

상기 제1 및 제2 계조 영역을 독립적으로 구동하는 다수의 박막 트랜지스터와;

상기 박막 트랜지스터와 접속되어 상기 제1 및 제2 계조 영역 각각에 공급될 제1 및 제2 데이터 신호를 공급하는 다수의 데이터 라인과;

상기 다수의 박막 트랜지스터를 수평 기간 단위로 구동하는 다수의 게이트 라인을 구비하고;

상기 박막 트랜지스터는 다수의 게이트 라인 중 한 게이트 라인이 구동될 때 상기 제1 계조 영역들이 구동되고, 다른 게이트 라인이 구동될 때 상기 제2 계조 영역들이 구동되도록 상기 제1 및 제2 계조 영역 각각과 접속된 것을 특징으로 하는 액정 패널.

## 청구항 12.

제 11 항에 있어서,

상기 제1 및 제2 계조 영역은 수평 및 수직 방향을 따라 교번적으로 배열된 것을 특징으로 하는 액정 패널.

## 청구항 13.

제 11 항에 있어서,

상기 제1 및 제2 계조 영역 각각의 양측면은 수평축을 기준으로 꺽여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된 것을 특징으로 하는 액정 패널.

## 청구항 14.

제 3 항에 있어서,

상기 게이트 라인 중 제1 게이트 라인은 상기 제1 및 제2 계조 영역의 꺽인 부분과 중첩되게 형성되고, 제2 게이트 라인은 상하로 인접한 상기 서브 화소의 경계부와 중첩되게 형성된 것을 특징으로 하는 액정 패널.

## 청구항 15.

제 14 항에 있어서,

상기 상하로 인접한 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비하는 것을 특징으로 하는 액정 패널.

## 청구항 16.

제 14 항에 있어서,

상기 제1 게이트 라인과 접속된 박막 트랜지스터는 상기 스토리지 라인을 기준으로 상단 및 하단에 위치한 제1 계조 영역 각각과 접속되고,

상기 제2 게이트 라인과 접속된 박막 트랜지스터는 상기 스토리지 라인을 기준으로 상단 및 하단에 위치한 제2 계조 영역 각각과 접속된 것을 특징으로 하는 액정 패널.

### 청구항 17.

제 16 항에 있어서,

상기 박막 트랜지스터는 그의 드레인 전극이 상기 스토리지 라인 쪽으로 신장되어 그 스토리지 라인과 근접하거나, 중첩된 컨택부를 통해 해당 계조 영역과 접속된 것을 특징으로 하는 액정 패널.

### 청구항 18.

제 16 항에 있어서,

상기 제1 게이트 라인과 접속된 박막 트랜지스터와 상기 제1 계조 영역과의 컨택부는 상기 스토리지 라인 방향을 따라 그 스토리지 라인의 상단 및 하단에 교변적으로 위치하는 것을 특징으로 하는 액정 패널.

### 청구항 19.

제 16 항에 있어서,

상기 제2 게이트 라인과 접속된 박막 트랜지스터와 상기 제2 계조 영역과의 컨택부는 상기 스토리지 라인 방향을 따라 그 스토리지 라인의 상단 및 하단에 교변적으로 위치하는 것을 특징으로 하는 액정 패널.

### 청구항 20.

제 16 항에 있어서,

한 서브 화소에 포함된 상기 제1 계조 영역과 접속된 박막 트랜지스터와, 상기 제2 계조 영역과 접속된 박막 트랜지스터가 인접한 서로 다른 데이터 라인과 접속된 것을 특징으로 하는 액정 패널.

### 청구항 21.

제 16 항에 있어서,

상기 제1 게이트 라인과 접속된 박막 트랜지스터는 제1 측으로 인접한 데이터 라인과 접속되고, 상기 제2 게이트 라인과 접속된 박막 트랜지스터는 제2 측으로 인접한 데이터 라인과 접속된 것을 특징으로 하는 액정 패널.

### 청구항 22.

제 3 항에 있어서,

상기 게이트 라인은 상하로 인접한 상기 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된 것을 특징으로 하는 액정 패널.

### 청구항 23.

제 22 항에 있어서,

상기 제1 및 제2 계조 영역 각각의 격인 부분과 중첩된 스토리지 라인을 추가로 구비하는 것을 특징으로 하는 액정 패널.

### 청구항 24.

제 23 항에 있어서,

상기 게이트 라인 중 제1 게이트 라인과 접속된 박막 트랜지스터는 그 제1 게이트 라인을 기준으로 상부 및 하부에 위치하는 제1 계조 영역과 각각 접속되고,

제2 게이트 라인과 접속된 박막 트랜지스터는 그 제2 게이트 라인을 기준으로 상부 및 하부에 위치하는 제2 계조 영역과 각각 접속된 것을 특징으로 하는 액정 패널.

### 청구항 25.

제 24 항에 있어서,

상기 제1 계조 영역은 상기 제1 게이트 라인을 따라 상기 상부 및 하부에 교번적으로 배열되고, 상기 제2 계조 영역은 상기 제2 게이트 라인을 따라 상기 상부 및 하부에 교번적으로 배열된 것을 특징으로 하는 액정 패널.

### 청구항 26.

제 24 항에 있어서,

상기 제1 게이트 라인 및 제2 게이트 라인과 각각 접속된 박막 트랜지스터의 데이터 신호 인가 방향이 제1 및 제2 계조 영역의 위치에 따라 교번적으로 바뀌게 되는 것을 특징으로 하는 액정 패널.

### 청구항 27.

제 24 항에 있어서,

상기 제1 게이트 라인과 접속된 박막 트랜지스터와 상기 제1 계조 영역과의 컨택부 위치가 상기 제1 계조 영역의 위치에 따라 교번적으로 바뀌게 되고,

상기 제2 게이트 라인과 접속된 박막 트랜지스터와 상기 제2 계조 영역과의 컨택부 위치가 상기 제2 계조 영역의 위치에 따라 교번적으로 바뀌게 되는 것을 특징으로 하는 액정 패널.

### 청구항 28.

제 27 항에 있어서,

상기 컨택부는 상기 스토리지 라인과 중첩되게 형성된 것을 특징으로 하는 액정 패널.

**청구항 29.**

제 24 항에 있어서,

한 서브 화소에 포함된 상기 제1 계조 영역과 접속된 박막 트랜지스터와, 상기 제2 계조 영역과 접속된 박막 트랜지스터가 인접한 서로 다른 데이터 라인과 접속된 것을 특징으로 하는 액정 패널.

**청구항 30.**

제1 및 제2 계조의 조합으로 원하는 계조를 표시하는 서브 화소를 포함하는 액정 패널에 있어서,

제1 감마 곡선에 따른 제1 데이터 신호가 공급되는 제1 계조 영역과, 제2 감마 곡선에 따른 제2 데이터 신호가 공급되는 제2 계조 영역과, 상기 제2 계조 영역과 접속된 제3 계조 영역을 구비하는 각 서브 화소와;

상기 제1 계조 영역을 구동하는 제1 박막 트랜지스터와;

상기 제2 및 제3 계조 영역을 구동하는 제2 박막 트랜지스터와;

상기 제1 및 제2 박막 트랜지스터와 접속되어 상기 제1 및 제2 데이터 신호를 공급하는 데이터 라인과;

상기 제1 박막 트랜지스터를 구동하는 제1 게이트 라인과;

상기 제2 박막 트랜지스터를 구동하는 제2 게이트 라인을 구비하는 것을 특징으로 하는 액정 패널.

**청구항 31.**

제 30 항에 있어서,

상기 제1 박막 트랜지스터와 접속된 상기 제1 계조 영역은 상기 제1 게이트 라인을 기준으로 상부에 배열되고,

상기 제2 박막 트랜지스터와 접속된 상기 제2 및 제3 계조 영역은 상기 제1 게이트 라인을 기준으로 하부에 배열되거나, 상기 제2 및 제3 계조 영역 중 어느 한 계조 영역이 상기 상부에 배열된 것을 특징으로 하는 액정 패널.

**청구항 32.**

제 31 항에 있어서,

상기 제2 및 제3 계조 영역은 한 서브 화소에는 상기 하부에 배열되고, 양측으로 인접한 서브 화소에는 상기 제2 및 제3 계조 영역 각각이 상기 상하부에 각각 배열된 것을 특징으로 하는 액정 패널.

**청구항 33.**

제 30 항에 있어서,

상기 제1 내지 제3 계조 영역 각각의 양측면은 수평축을 기준으로 꺽여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된 것을 특징으로 하는 액정 패널.

**청구항 34.**

제 33 항에 있어서,

상기 상하로 인접한 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비하는 것을 특징으로 하는 액정 패널.

### 청구항 35.

제 34 항에 있어서,

상기 박막 트랜지스터와 상기 계조 영역의 컨택부는 상기 스토리지 라인과 중첩된 것을 특징으로 하는 액정 패널.

### 청구항 36.

제 11 항 내지 제 35 항 중 어느 한 항에 기재된 액정 패널을 구동하는 방법에 있어서,

제1 감마 곡선에 따른 제1 감마 전압 세트를 생성하는 단계와;

제2 감마 곡선에 따른 제2 감마 전압 세트를 생성하는 단계와;

상기 게이트 라인이 구동되는 수평 기간 단위로 상기 제1 및 제2 감마 전압 세트 중 어느 하나의 감마 전압 세트를 선택하여 출력하는 단계와;

외부로부터 입력된 데이터 신호를 상기 수평 기간 단위로 상기 어느 하나의 감마 전압 세트를 이용하여 상기 제1 계조 영역에 각각 공급될 제1 데이터 신호 또는 상기 제2 계조 영역에 공급될 제2 데이터로 변환하여 상기 데이터 라인으로 공급하는 단계를 포함하는 것을 특징으로 하는 액정 패널의 구동 방법.

### 청구항 37.

제 11 항 내지 제 35 항 중 어느 한 항에 기재된 액정 패널과;

상기 액정 패널의 게이트 라인을 구동하는 게이트 드라이버와;

제1 감마 곡선에 따른 제1 감마 전압 세트를 생성하는 제1 감마 전압 생성부와;

제2 감마 곡선에 따른 제2 감마 전압 세트를 생성하는 제2 감마 전압 생성부와;

상기 게이트 라인이 구동되는 수평 기간 단위로 상기 제1 및 제2 감마 전압 세트 중 어느 하나의 감마 전압 세트를 선택하여 출력하는 스위치와;

외부로부터 입력된 데이터 신호를 상기 수평 기간 단위로 상기 스위치를 통해 공급된 어느 하나의 감마 전압 세트를 이용하여 상기 제1 계조 영역에 각각 공급될 제1 데이터 신호 또는 상기 제2 계조 영역에 공급될 제2 데이터로 변환하여 상기 데이터 라인으로 공급하는 데이터 드라이버와;

상기 게이트 드라이버 및 데이터 드라이버를 제어하는 타이밍 컨트롤러를 구비하는 것을 특징으로 하는 액정 표시 장치.

### 청구항 38.

제 37 항에 있어서,

상기 스위치는 상기 데이터 드라이버에 내장된 것을 특징으로 하는 액정 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정 표시 장치에 관한 것으로, 특히 멀티-도메인의 계조 조합으로 광시야각을 구현하면서 투과율 및 시인성을 향상시킬 수 있는 액정 표시 패널과, 그의 구동 방법 및 그를 이용한 액정 표시 장치에 관한 것이다.

액정 표시 장치는 전계에 따라 액정 분자를 구동시켜 광투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여, 액정 표시 장치는 액정셀 매트릭스를 통해 화상을 표시하는 액정 표시 패널(이하, 액정 패널)과, 그 액정 패널을 구동하는 구동 회로를 구비한다. 이러한 액정 표시 장치는 화면을 바라보는 위치에 따라 이미지가 왜곡되어 보이는 시야각 한계점을 극복하기 위하여 광시야각 기술로 발전하고 있다.

액정 표시 장치의 대표적인 광시야각 기술로는 멀티-도메인 VA(Multi-domain Vertical Alignment) 모드가 이용된다. VA 모드는 음의 유전율이 방향을 갖는 액정 분자들이 수직으로 배향되고 전계 방향에 수직하게 구동되어 광투과율을 조절하게 된다. 이러한 VA 모드는 전압 미인가시 액정 분자들의 배향 방향과 직교하는 편광자에 의해 빛의 투과가 차단되므로 노멀리 블랙 모드(Normally Black Mode)가 된다. 특히, 멀티-도메인 VA 모드는 각 서브 화소를 멀티-도메인으로 분할하여 액정 분자를 대칭적으로 배열시킴으로써 투과율 변화가 대칭적으로 발생하여 광시야각을 얻게 된다. 멀티-도메인은 돌기 또는 슬릿을 이용하여 형성된다.

돌기를 이용한 VA 모드는 상하판에 돌기를 형성하여 액정 분자들이 그 돌기를 기준으로 대칭된 프리-틸트(Pre-tilt)를 형성한 상태에서 전압을 인가하여 프리-틸트된 방향으로 구동되게 함으로써 멀티-도메인을 형성하게 된다. 그런데, 돌기를 이용한 VA 모드는 돌기에 의한 액정 분자들의 규제력이 약하여 돌기 주변에서 빛샘이 발생함으로써 시인성이 낮은 단점이 있다.

슬릿 패턴을 이용한 VA 모드, 즉 PVA(Patterned Vertical Alignment) 모드는 상하판의 공통 전극 및 화소 전극에 슬릿을 형성하여 그 슬릿에 의해 발생된 프린지 전계(Fringe Field)를 이용하여 액정 분자들이 슬릿을 기준으로 대칭적으로 구동되게 함으로써 멀티-도메인을 형성하게 된다. 그런데, PVA 모드는 직사각형 형상을 갖는 서브 화소의 가장자리에서 발생되는 측면 전계(Lateral Filed)로 인하여 액정 배향이 흐트러지면서 에지 텍스처(Edge Texture)와 같은 현상이 발생함으로써 측면 시인성이 나쁘고 투과율이 낮은 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명의 목적은 멀티-도메인 VA 모드에서 시인성 및 투과율을 향상시킬 수 있는 액정 패널과 그의 구동 방법 및 그를 이용한 액정 표시 장치를 제공하는 것이다.

#### 발명의 구성

상기 목적을 달성하기 위하여, 본 발명의 제1 특징에 따른 액정 패널은 상하로 분할되고 면적이 서로 다른 제1 및 제2 계조 영역을 갖으며, 인접한 서브 화소와 상기 제1 및 제2 계조 영역이 상하로 엇갈려 배열된 다수의 서브 화소와; 상기 제1 및 제2 계조 영역을 독립적으로 구동하는 다수의 박막 트랜지스터와; 상기 박막 트랜지스터와 접속되어 상기 제1 및 제2 계조 영역 각각에 공급될 제1 및 제2 데이터 신호를 공급하는 다수의 데이터 라인과; 상기 다수의 박막 트랜지스터를 수평 기간 단위로 구동하는 다수의 게이트 라인을 구비한다.

상기 제1 및 제2 계조 영역은 수평 및 수직 방향을 따라 교번적으로 배열된다.

상기 제1 및 제2 계조 영역 각각의 양측면은 수평축을 기준으로 격여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된다.

상기 게이트 라인 중 한 게이트 라인은 상기 제1 및 제2 계조 영역의 꺽인 부분과 중첩되게 형성되고, 다른 게이트 라인은 상하로 인접한 상기 서브 화소의 경계부와 중첩되게 형성된다.

그리고, 본 발명의 제1 특징에 따른 액정 패널은 상기 상하로 인접한 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비한다.

상기 박막 트랜지스터는 상기 스토리지 라인과 근접하거나, 중첩된 접속부에 의해 상기 제1 및 제2 계조 영역 각각의 화소 전극과 접속된다.

상기 목적을 달성하기 위하여, 본 발명의 제1 특징에 따른 액정 패널의 구동 방법은 입력 데이터 신호를 툭-업 테이블을 이용하여 상기 제1 및 제2 데이터 신호로 변조하는 단계와; 상기 제1 및 제2 데이터 신호가 교번적으로 배열되게 정렬하는 단계와; 상기 제1 및 제2 데이터 신호가 교번되게 정렬된 데이터 신호를 감마 전압을 이용하여 아날로그 데이터 신호로 변환하는 단계와; 상기 게이트 라인이 구동되는 수평 기간마다 교번적으로 배열된 상기 제1 및 제2 데이터 신호를 상기 다수의 데이터 라인에 동시에 공급하는 단계를 포함한다.

상기 목적을 달성하기 위하여, 본 발명의 제1 특징에 따른 액정 표시 장치는 상기 제1 특징에 따른 액정 패널과; 상기 액정 패널의 게이트 라인을 구동하는 게이트 드라이버와; 상기 액정 패널의 데이터 라인을 구동하는 데이터 드라이버와; 상기 게이트 드라이버 및 데이터 드라이버를 제어하고 외부로부터 입력된 데이터 신호를 상기 제1 및 제2 데이터 신호로 변조하여 상기 데이터 드라이버로 공급하는 타이밍 컨트롤러를 구비한다.

상기 타이밍 컨트롤러는 상기 입력 데이터 신호에 대응된 상기 제1 및 제2 데이터 신호가 미리 저장된 툭-업 테이블을 이용하여 상기 입력 데이터 신호를 상기 제1 및 제2 데이터 신호로 변조한다.

상기 수평 기간마다 상기 제1 및 제2 데이터 신호의 배열 순서가 바뀌게 된다.

상기 목적을 달성하기 위하여, 본 발명의 제2 특징에 따른 액정 패널은 상하로 분할되고 면적이 서로 다른 제1 및 제2 계조 영역을 갖으며, 인접한 서브 화소와 상기 제1 및 제2 계조 영역이 상하로 엇갈려 배열된 다수의 서브 화소와; 상기 제1 및 제2 계조 영역을 독립적으로 구동하는 다수의 박막 트랜지스터와; 상기 박막 트랜지스터와 접속되어 상기 제1 및 제2 계조 영역 각각에 공급될 제1 및 제2 데이터 신호를 공급하는 다수의 데이터 라인과; 상기 다수의 박막 트랜지스터를 수평 기간 단위로 구동하는 다수의 게이트 라인을 구비하고; 상기 박막 트랜지스터는 다수의 게이트 라인 중 한 게이트 라인이 구동될 때 상기 제1 계조 영역들이 구동되고, 다른 게이트 라인이 구동될 때 상기 제2 계조 영역들이 구동되도록 상기 제1 및 제2 계조 영역 각각과 접속된 것을 특징으로 한다.

상기 제1 및 제2 계조 영역은 수평 및 수직 방향을 따라 교번적으로 배열된다.

상기 제1 및 제2 계조 영역 각각의 양측면은 수평축을 기준으로 꺾여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된다.

상기 게이트 라인 중 제1 게이트 라인은 상기 제1 및 제2 계조 영역의 꺽인 부분과 중첩되게 형성되고, 제2 게이트 라인은 상하로 인접한 상기 서브 화소의 경계부와 중첩되게 형성된다.

그리고, 본 발명의 제2 특징에 따른 액정 패널은 상기 상하로 인접한 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비한다.

상기 제1 게이트 라인과 접속된 박막 트랜지스터는 상기 스토리지 라인을 기준으로 상단 및 하단에 위치한 제1 계조 영역 각각과 접속되고, 상기 제2 게이트 라인과 접속된 박막 트랜지스터는 상기 스토리지 라인을 기준으로 상단 및 하단에 위치한 제2 계조 영역 각각과 접속된다.

상기 박막 트랜지스터는 그의 드레인 전극이 상기 스토리지 라인 쪽으로 신장되어 그 스토리지 라인과 근접하거나, 중첩된 컨택부를 통해 해당 계조 영역과 접속된다.

상기 제1 게이트 라인과 접속된 박막 트랜지스터와 상기 제1 계조 영역과의 컨택부는 상기 스토리지 라인 방향을 따라 그 스토리지 라인의 상단 및 하단에 교번적으로 위치하게 된다.

상기 제2 게이트 라인과 접속된 박막 트랜지스터와 상기 제2 계조 영역과의 컨택부는 상기 스토리지 라인 방향을 따라 그 스토리지 라인의 상단 및 하단에 교번적으로 위치하게 된다.

한 서브 화소에 포함된 상기 제1 계조 영역과 접속된 박막 트랜지스터와, 상기 제2 계조 영역과 접속된 박막 트랜지스터가 인접한 서로 다른 데이터 라인과 접속된다.

상기 제1 게이트 라인과 접속된 박막 트랜지스터는 제1 측으로 인접한 데이터 라인과 접속되고, 상기 제2 게이트 라인과 접속된 박막 트랜지스터는 제2 측으로 인접한 데이터 라인과 접속된다.

상기 게이트 라인은 상하로 인접한 상기 제1 및 제2 계조 영역의 경계부와 중첩되게 형성된다.

또한, 본 발명의 제2 특징에 따른 액정 패널은 상기 제1 및 제2 계조 영역 각각의 격인 부분과 중첩된 스토리지 라인을 추가로 구비한다.

상기 게이트 라인 중 제1 게이트 라인과 접속된 박막 트랜지스터는 그 제1 게이트 라인을 기준으로 상부 및 하부에 위치하는 제1 계조 영역과 각각 접속되고, 제2 게이트 라인과 접속된 박막 트랜지스터는 그 제2 게이트 라인을 기준으로 상부 및 하부에 위치하는 제2 계조 영역과 각각 접속된다.

상기 제1 계조 영역은 상기 제1 게이트 라인을 따라 상기 상부 및 하부에 교번적으로 배열되고, 상기 제2 계조 영역은 상기 제2 게이트 라인을 따라 상기 상부 및 하부에 교번적으로 배열된다.

상기 제1 게이트 라인 및 제2 게이트 라인과 각각 접속된 박막 트랜지스터의 데이터 신호 인가 방향이 제1 및 제2 계조 영역의 위치에 따라 교번적으로 바뀌게 된다.

상기 제1 게이트 라인과 접속된 박막 트랜지스터와 상기 제1 계조 영역과의 컨택부 위치가 상기 제1 계조 영역의 위치에 따라 교번적으로 바뀌게 되고, 상기 제2 게이트 라인과 접속된 박막 트랜지스터와 상기 제2 계조 영역과의 컨택부 위치가 상기 제2 계조 영역의 위치에 따라 교번적으로 바뀌게 된다.

상기 컨택부는 상기 스토리지 라인과 중첩되게 형성된다.

한 서브 화소에 포함된 상기 제1 계조 영역과 접속된 박막 트랜지스터와, 상기 제2 계조 영역과 접속된 박막 트랜지스터가 인접한 서로 다른 데이터 라인과 접속된다.

상기 목적을 달성하기 위하여, 본 발명의 제3 특징에 따른 액정 패널은 제1 감마 콕선에 따른 제1 데이터 신호가 공급되는 제1 계조 영역과, 제2 감마 콕선에 따른 제2 데이터 신호가 공급되는 제2 계조 영역과, 상기 제2 계조 영역과 접속된 제3 계조 영역을 구비하는 각 서브 화소와; 상기 제1 계조 영역을 구동하는 제1 박막 트랜지스터와; 상기 제2 및 제3 계조 영역을 구동하는 제2 박막 트랜지스터와; 상기 제1 및 제2 박막 트랜지스터와 접속되어 상기 제1 및 제2 데이터 신호를 공급하는 데이터 라인과; 상기 제1 박막 트랜지스터를 구동하는 제1 게이트 라인과; 상기 제2 박막 트랜지스터를 구동하는 제2 게이트 라인을 구비한다.

상기 제1 박막 트랜지스터와 접속된 상기 제1 계조 영역은 상기 제1 게이트 라인을 기준으로 상부에 배열되고, 상기 제2 박막 트랜지스터와 접속된 상기 제2 및 제3 계조 영역은 상기 제1 게이트 라인을 기준으로 하부에 배열되거나, 상기 제2 및 제3 계조 영역 중 어느 한 계조 영역이 상기 상부에 배열된다.

상기 제2 및 제3 계조 영역은 한 서브 화소에는 상기 하부에 배열되고, 양측으로 인접한 서브 화소에는 상기 제2 및 제3 계조 영역 각각이 상기 상하부에 각각 배열된다.

상기 제1 내지 제3 계조 영역 각각의 양측면은 수평축을 기준으로 격여서 대칭된 경사각을 갖는 지그-재그 구조로 형성된다.

그리고, 본 발명의 제3 특징에 따른 액정 패널은 상기 상하로 인접한 계조 영역의 경계부와 중첩되게 형성된 스토리지 라인을 추가로 구비한다.

상기 박막 트랜지스터와 상기 계조 영역의 컨택부는 상기 스토리지 라인과 중첩된다.

상기 목적을 달성하기 위하여, 본 발명의 제2 및 제3 특징에 따른 액정 패널의 구동 방법은 제1 감마 곡선에 따른 제1 감마 전압 세트를 생성하는 단계와; 제2 감마 곡선에 따른 제2 감마 전압 세트를 생성하는 단계와; 상기 게이트 라인이 구동되는 수평 기간 단위로 상기 제1 및 제2 감마 전압 세트 중 어느 하나의 감마 전압 세트를 선택하여 출력하는 단계와; 외부로부터 입력된 데이터 신호를 상기 수평 기간 단위로 상기 어느 하나의 감마 전압 세트를 이용하여 상기 제1 계조 영역에 각각 공급될 제1 데이터 신호 또는 상기 제2 계조 영역에 공급될 제2 데이터로 변환하여 상기 데이터 라인으로 공급하는 단계를 포함한다.

상기 목적을 달성하기 위하여, 본 발명의 제2 특징에 따른 액정 표시 장치는 상기 제2 및 제3 특징에 따른 액정 패널과; 상기 액정 패널의 게이트 라인을 구동하는 게이트 드라이버와; 제1 감마 곡선에 따른 제1 감마 전압 세트를 생성하는 제1 감마 전압 생성부와; 제2 감마 곡선에 따른 제2 감마 전압 세트를 생성하는 제2 감마 전압 생성부와; 상기 게이트 라인이 구동되는 수평 기간 단위로 상기 제1 및 제2 감마 전압 세트 중 어느 하나의 감마 전압 세트를 선택하여 출력하는 스위치와; 외부로부터 입력된 데이터 신호를 상기 수평 기간 단위로 상기 스위치를 통해 공급된 어느 하나의 감마 전압 세트를 이용하여 상기 제1 계조 영역에 각각 공급될 제1 데이터 신호 또는 상기 제2 계조 영역에 공급될 제2 데이터로 변환하여 상기 데이터 라인으로 공급하는 데이터 드라이버와; 상기 게이트 드라이버 및 데이터 드라이버를 제어하는 타이밍 컨트롤러를 구비한다.

상기 스위치는 상기 데이터 드라이버에 내장된다.

상기 목적 외에 본 발명의 다른 목적 및 이점들은 첨부 도면을 참조한 본 발명의 바람직한 실시 예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

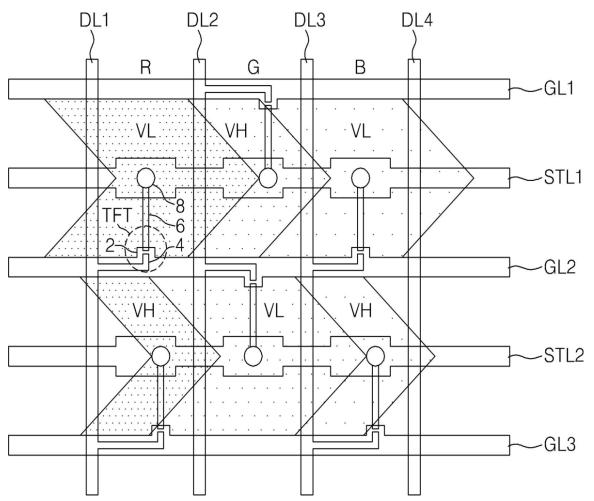

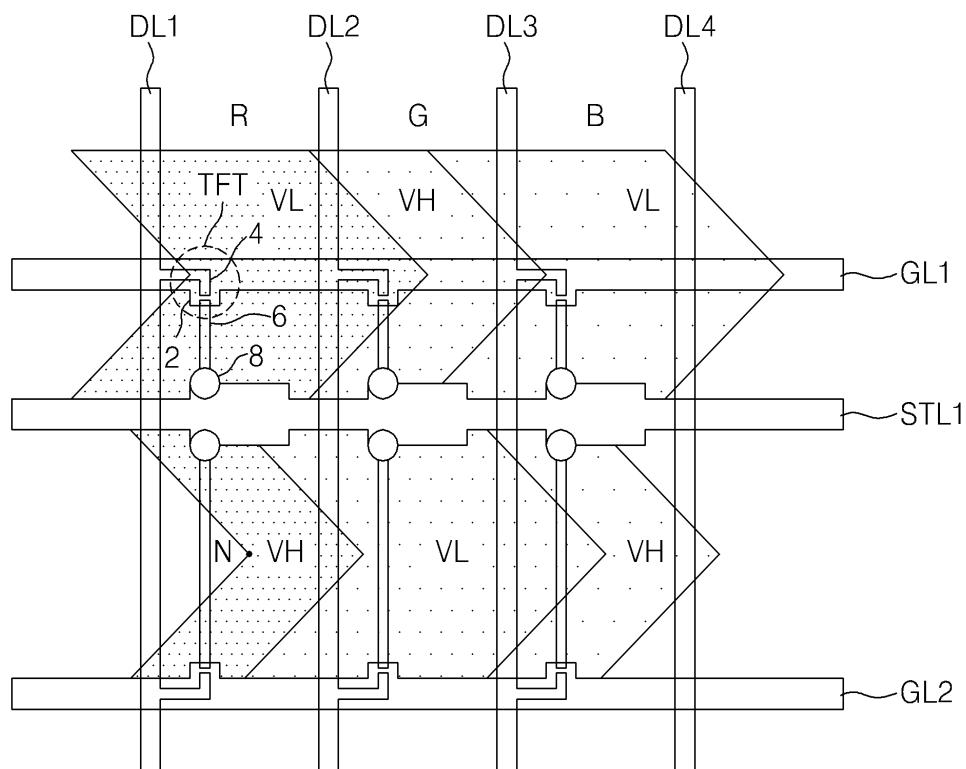

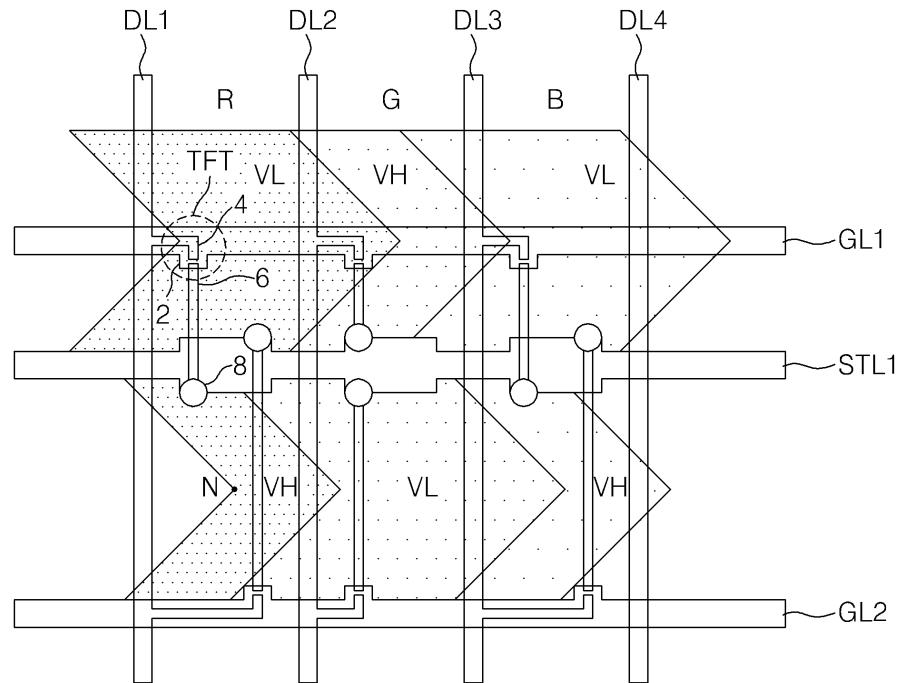

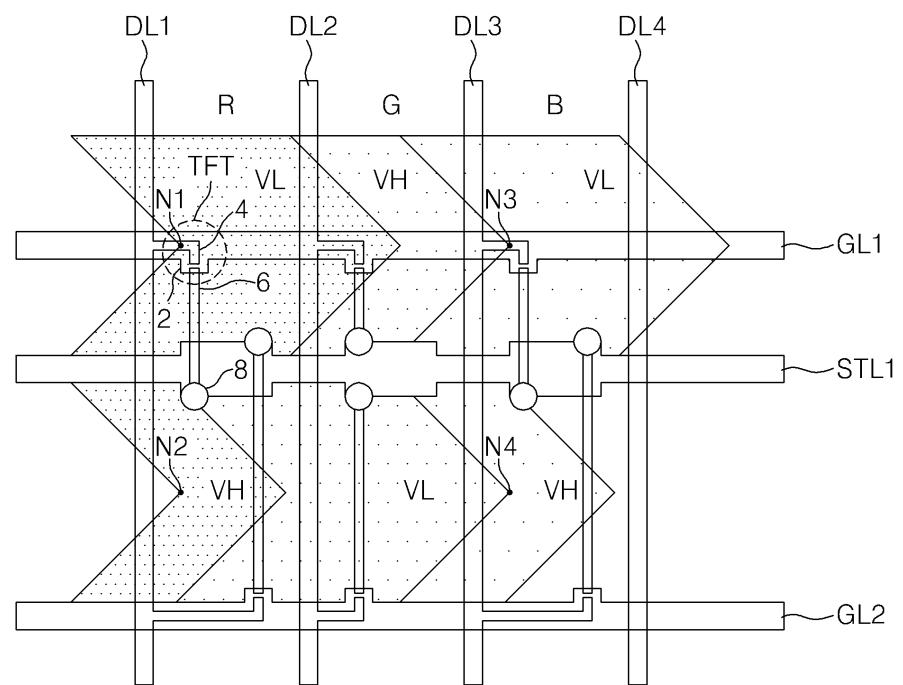

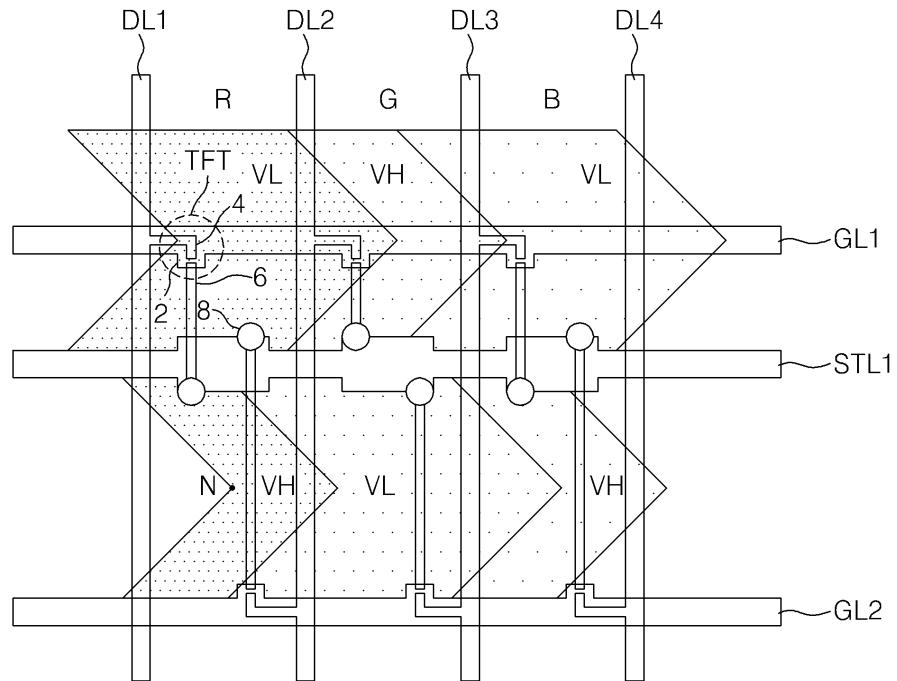

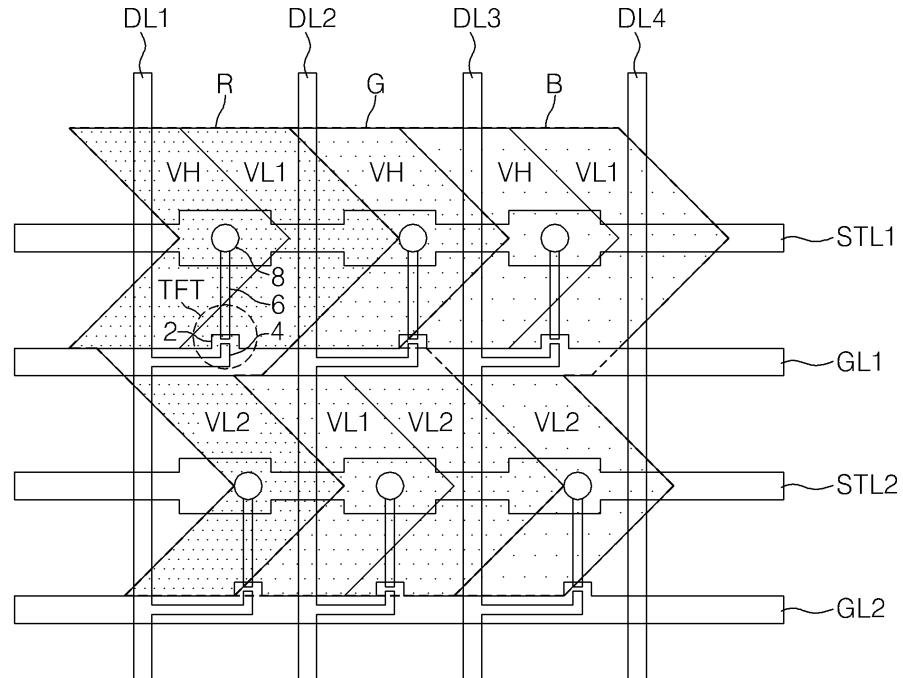

도 1은 본 발명의 제1 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이고, 도 2는 본 발명의 제2 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 1 및 도 2에 도시된 액정 패널의 각 화소는 지그-재그(Zig-zag) 구조의 R, G, B 서브 화소를 구비한다.

R, G, B 서브 화소 각각은 시인성 향상을 위하여 서로 다른 감마 곡선에 따라 구동되는 고계조 영역(VH)과, 저계조 영역(VL)으로 분할된다. 이러한 고계조 영역(VH)과 저계조 영역(VL)은 서로 다른 박막 트랜지스터(TFT)에 의해 독립적으로 구동된다.

특히, 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 시인성 향상을 위한 최적 비율인 1:2로 분할된다. 또한, 투과율 향상을 위하여 2개의 서브 화소 영역을 3분할하여 1분할 영역인 고계조 영역(VH)과, 2분할 영역인 저계조 영역(VL)이 상하로 배치되고, 인접한 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)과는 상하로 엇갈리게 배치된다. 이에 따라, 수평 방향 및 수직 방향으로 진행할 수록 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)이 교번적으로 배치된다.

또한, 상하로 분리된 각 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)은 지그-재그 구조로 경사진 좌우 측면(Side)을 갖도록 형성된다. 예를 들면, 도 1 및 도 2에 도시된 바와 같이 고계조 영역(VH) 및 저계조 영역(VL) 각각의 좌우 측면은 중앙부의 접점을 기준으로 대칭된 45도의 경사각을 갖도록 형성된다. 이에 따라, 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)의 좌우 측면이 그 고계조 영역(VH) 및 저계조 영역(VL) 각각에서 좌우 도메인 분할을 위하여 화소 전극 및 공통 전극에 서로 엇갈리게 형성된 슬릿과 나란하게 된다. 이 결과, 각 서브 화소의 좌우 측면 전계가 액정 제어에 도움을 줌으로써 투과율을 향상시킬 수 있게 된다.

이러한 지그-재그 구조를 갖는 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 도 1에 도시된 바와 같이 센터 얼라인드(Center Aligned) 구조로 정렬되거나, 도 2에 도시된 바와 같이 에지 얼라인드(Edge Aligned) 구조로 정렬된다.

도 1에 도시된 센터 얼라인드 구조는 고계조 영역(VH)의 대칭된 좌측면의 접점(N)이 인접한 두 데이터 라인(DL) 사이의 중심점과 일치하도록 고계조 영역(VH) 및 저계조 영역(VL)을 정렬시킨 구조이다.

도 2에 도시된 에지 얼라인드 구조는 수평 방향으로 인접한 2개의 서브 화소 중 그의 좌측면 상에 위치하는 저계조 영역(VL)의 접점(N1)과 고계조 영역(VH)의 접점(N2)이 같은 수직선상에 위치하고, 그의 우측면 상에 위치하는 다른 고계조 영역(VH)의 접점(N3)과 저계조 영역(VL)의 접점(N4)이 같은 수직선상에 위치하도록 고계조 영역(VH) 및 저계조 영역(VL)을 정렬시킨 구조이다.

이러한 지그-재그 구조의 서브 화소는 고계조 영역(VH) 및 저계조 영역(VL)에 형성된 화소 전극과, 그 화소 전극과 정렬되어 중첩된 R, G, B 칼라 필터의 형상에 의해 결정된다. 다시 말하여, 각 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)에 형성된 화소 전극과 R, G, B 칼라 필터가 전술한 지그-재그 구조를 갖게 된다.

화소 전극은 각 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL) 각각에 독립적으로 형성되고 서로 다른 박막 트랜지스터(TFT)에 의해 구동된다. 이러한 화소 전극은 박막 트랜지스터(TFT)와 함께 하판에 형성되고, 상판에 형성된 공통 전극과 전계를 형성하여 상하판 사이에 수직 배향된 액정 분자들을 구동하게 된다. 이때, 고계조 영역(VH) 및 저계조 영역(VL) 각각에 멀티-도메인을 형성하기 위하여 화소 전극과 공통 전극은 서로 엇갈린 구조의 슬릿을 구비한다. 예를 들면, 고계조 영역(VH)은 공통 전극 및 화소 전극에 서로 엇갈리게 형성된 슬릿에 의해 상하좌우 4개의 도메인으로 분할되고, 저계조 영역(VL)은 8개의 도메인으로 분할된다.

박막 트랜지스터(TFT)는 게이트 라인(GL)의 스캔 신호에 응답하여 데이터 라인(DL)의 데이터 신호를 화소 전극에 공급한다. 이를 위하여, 박막 트랜지스터(TFT)는 게이트 라인(GL)과 접속된 게이트 전극(2), 데이터 라인(DL)과 접속된 소스 전극(4)과, 컨택부(8)를 통해 화소 전극과 접속된 드레인 전극(6)과, 소스 및 드레인 전극(4, 6) 사이에 채널을 형성하는 반도체층을 구비한다.

특히, 각 서브 화소에서 상하로 분리된 고계조 영역(VH) 및 저계조 영역(VL)은 서로 다른 게이트 라인(GL)과 접속된 박막 트랜지스터(TFT)를 통해 독립적으로 구동된다.

예를 들면, 도 1 및 도 2에 도시된 바와 같이 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 각각과 제1 게이트 라인(GL1) 사이에 접속된 박막 트랜지스터(TFT)에 의해 제1 게이트 라인(GL1)이 구동될 때 R 저계조 영역(VL), G 고계조 영역(VH), B 저계조 영역(VL)이 구동된다. 그리고, 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 각각과 제2 게이트 라인(GL2) 사이에 접속된 박막 트랜지스터(TFT)에 의해 제2 게이트 라인(GL2)이 구동될 때 R 고계조 영역(VH), G 저계조 영역(VL), B 고계조 영역(VH)이 구동된다. 이에 따라 R, G, B 서브 화소의 계조가 고계조 영역(VH)에 표현된 고계조와 저계조 영역(VL)에 표현된 저계조의 조합으로 표현되므로 시인성이 향상된다.

여기서, 투과율 향상을 위하여 제1 게이트 라인(GL1)은 각 서브 화소 중 상부에 위치하는 저계조 영역(VL) 또는 고계조 영역(VH)의 격인 부분과 중첩되도록 형성되고, 제2 게이트 라인(GL2)은 상하로 인접한 서브 화소의 경계부와 중첩되도록 형성된다. 제1 내지 제4 데이터 라인(DL1 내지 DL4)은 제1 및 제2 게이트 라인(GL1, GL2)과 절연막을 사이에 두고 교차하게 형성된다. 그리고, 제1 및 제2 게이트 라인(GL1, GL2) 사이에 제1 스토리지 라인(STL1)이 각 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)의 경계부와 중첩되도록 형성된다.

제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 제1 스토리지 라인(STL1) 위에 위치하는 고계조 영역(VH) 또는 저계조 영역(VL)의 화소 전극과 접속된다. 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 제1 스토리지 라인(STL1) 아래에 위치하는 고계조 영역(VH) 또는 저계조 영역(VL)의 화소 전극과 접속된다.

이를 위하여, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 아래쪽의 제1 스토리지 라인(STL1)까지 신장되고 그 스토리지 라인(STL1)의 상부와 중첩되거나 근접한 컨택부(8)를 통해 저계조 영역(VL) 또는 고계조 영역(VH)의 화소 전극과 접속된다. 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 위쪽의 제1 스토리지 라인(STL1)까지 신장되고 그 스토리지 라인(STL1)의 하부와 중첩되거나 근접한 컨택부(8)를 통해 고계조 영역(VH) 또는 저계조 영역(VL)의 화소 전극과 접속된다. 그리고, 컨택부(8)를 통해 고계조 영역(VH) 또는 저계조 영역(VL)의 화소 전극과 접속된 드레인 전극(6)은 스토리지 라인(STL)과 중첩되어 스토리지 캐패시터를 형성하게 된다.

이와 같이, 본 발명의 제1 및 제2 실시 예에 따른 액정 패널의 각 서브 화소는 지그-재그 구조로 1:2 면적비를 갖고 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)을 구비함으로써 투과율 및 시인성을 향상시킬 수 있게 된다.

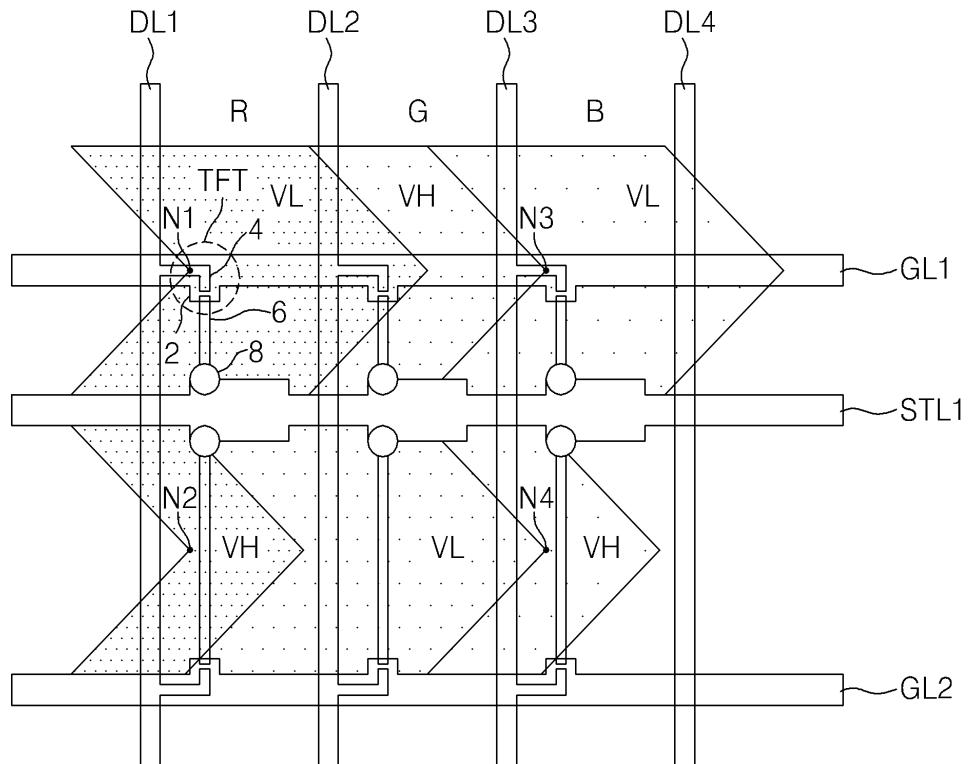

도 3은 도 1 및 도 2에 도시된 액정 패널이 적용된 본 발명의 제1 실시 예에 따른 액정 표시 장치를 도시한 블록도이다.

도 3에 도시된 액정 표시 장치는 액정 패널(12)과, 액정 패널(12)의 게이트 라인(GL)을 구동하는 게이트 드라이버(14)와, 액정 패널(12)의 데이터 라인(DL)을 구동하는 데이터 드라이버(16)와, 게이트 드라이버(14) 및 데이터 드라이버(16)를 제어하는 타이밍 컨트롤러(20)를 구비한다.

액정 패널(12)은 도 1 및 도 2에 도시된 바와 같이 지그-재그 구조로 1:2 면적비를 갖고 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)으로 구성된 R, G, B 서브 화소를 구비하지만, 도 3에서는 R, G, B 서브 화소를 단순화하여 도시하기로 한다. 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 서로 다른 박막 트랜지스터(TFT)에 의해 구동되고, 인접한 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)과 상하로 엇갈리게 배치된다.

예를 들면, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)에 의해 R 저계조 영역(VL), G 고계조 영역(VH), B 저계조 영역(VL)이 구동되고, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)에 의해 R 고계조 영역(VH), G 저계조 영역(VL), B 고계조 영역(VH)이 구동된다.

타이밍 컨트롤러(20)는 외부로부터 입력된 동기 신호 및 클럭 신호를 이용하여 게이트 드라이버(14)를 제어하는 게이트 제어 신호와, 데이터 드라이버(16)를 제어하는 데이터 제어 신호를 발생한다. 또한, 타이밍 컨트롤러(20)는 외부로부터의 R, G, B 데이터 신호를 입력하여 미리 저장된 루-업 테이블(LUT)을 통해 고계조의 RH, GH, BH 데이터 신호와 저계조의 RL, GL, BL 데이터 신호로 분리, 즉 변조하여 메모리에 저장하게 된다. 그 다음, 타이밍 컨트롤러(20)는 메모리에 저장된 고계조 및 저계조 데이터 신호를 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)의 배치 구조에 맞게 데이터 드라이버(16)로 공급되게 한다. 예를 들면, 타이밍 컨트롤러(20)는 1H 기간에서는 RL, GH, BL 데이터 신호를, 2H 기간에서는 RH, GL, BH 데이터 신호를 데이터 드라이버(16)로 공급한다. 이 때, 타이밍 컨트롤러(20)는 R, G, B 데이터 신호를 고계조 및 저계조 데이터 신호로 분할하여 데이터 드라이버(16)로 공급해야 하므로 고속 동작이 필요하게 된다.

게이트 드라이버(14)는 타이밍 컨트롤러(20)로부터의 게이트 제어 신호에 응답하여 액정 패널(12)의 게이트 라인(GL)을 순차적으로 구동한다.

데이터 드라이버(16)는 타이밍 컨트롤러(20)로부터의 데이터 신호를 감마 전압부(18)로부터의 감마 전압을 이용하여 아날로그 데이터 신호로 변환하여 액정 패널(12)의 게이트 라인(GL)이 구동될 때마다 데이터 라인(DL)으로 공급한다.

예를 들면, 데이터 드라이버(16)는 제1 게이트 라인(GL1)이 구동될 때 타이밍 컨트롤러(20)로부터의 RL, GH, BL 데이터 신호를 아날로그 데이터 신호로 변환하여 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 각각으로 공급한다. 이에 따라, 제1 게이트 라인(GL1)과 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 사이에 접속된 박막 트랜지스터(TFT)를 통해 R 저계조 영역(VL)에 RL 데이터 신호가, G 고계조 영역(VH)에 GH 데이터 신호가, B 저계조 영역(VL)에 BL 데이터 신호가 충전된다.

이어서, 데이터 드라이버(16)는 제2 게이트 라인(GL2)이 구동될 때 타이밍 컨트롤러(20)로부터의 RH, GL, BH 데이터 신호를 아날로그 데이터 신호로 변환하여 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 각각으로 공급한다. 이에 따라, 제2 게이트 라인(GL2)과 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 사이에 접속된 박막 트랜지스터(TFT)를 통해 R 고계조 영역(VH)에 RH 데이터 신호가, G 저계조 영역(VL)에 GL 데이터 신호가, B 고계조 영역(VH)에 BH 데이터 신호가 충전된다.

따라서 R, G, B 서브 화소 각각은 고계조 영역(VH)과 저계조 영역(VL) 각각에 충전된 데이터 신호에 따른 고계조 및 저계조의 조합으로 계조를 표현하게 된다.

이와 같이, 본 발명의 제1 실시 예에 따른 액정 표시 장치는 타이밍 컨트롤러(20)의 루-업 테이블(LUT)을 이용한 데이터 변조 방법, 즉 디지털 방법으로 R, G, B 데이터를 고계조 및 저계조 데이터로 분리하여 액정 패널(12)에서 상하로 분할된 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL) 각각에 공급하게 된다.

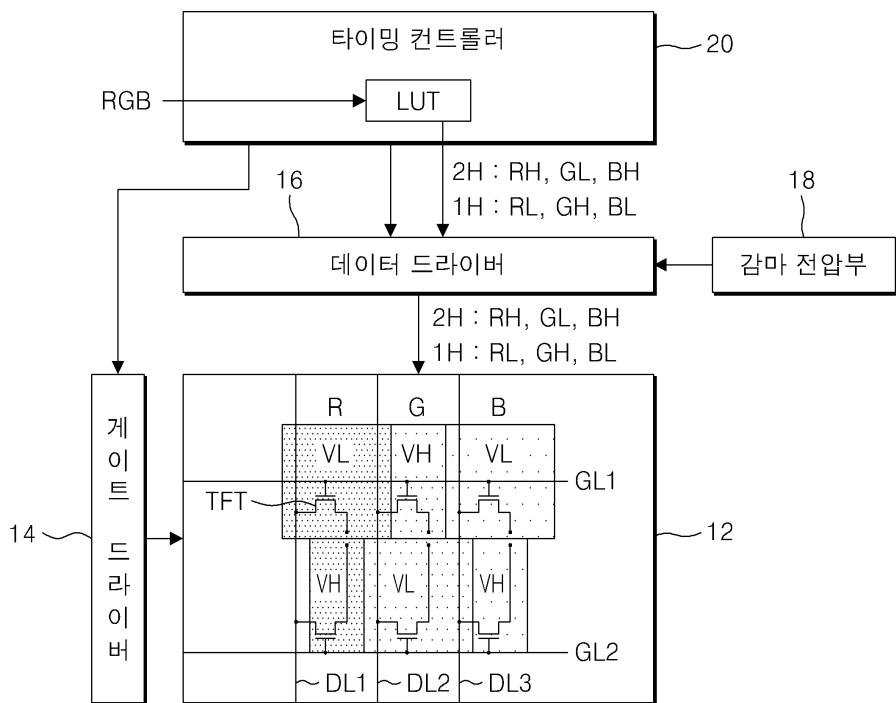

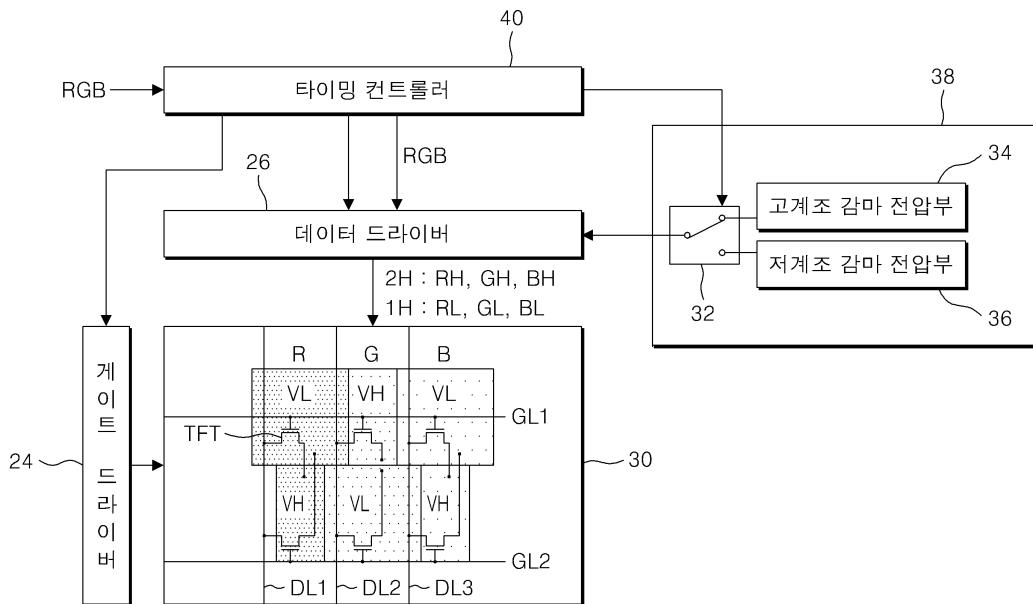

도 4는 본 발명의 제2 실시 예에 따른 액정 표시 장치를 도시한 블록도이다.

도 4에 도시된 액정 표시 장치는 고계조 감마 전압과 저계조 감마 전압을 이용하여 R, G, B 데이터를 고계조 및 저계조 데이터로 분리하는 공급하는 아날로그 방법으로 상하로 분할된 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)을 독립적으로 구동하게 된다.

이를 위하여, 도 4에 도시된 액정 표시 장치는 액정 패널(30)과, 액정 패널(30)의 게이트 라인(GL)을 구동하는 게이트 드라이버(24)와, 액정 패널(30)의 데이터 라인(DL)을 구동하는 데이터 드라이버(26)와, 게이트 드라이버(24) 및 데이터 드라이버(26)를 제어하는 타이밍 컨트롤러(40)와, 데이터 드라이버(26)로 고계조 및 저계조 감마 전압을 선택적으로 공급하는 감마 전압부(38)를 구비한다.

타이밍 컨트롤러(40)는 외부로부터 입력된 동기 신호 및 클럭 신호를 이용하여 게이트 드라이버(24)를 제어하는 게이트 제어 신호와, 데이터 드라이버(26)를 제어하는 데이터 제어 신호를 발생한다. 또한, 타이밍 컨트롤러(40)는 외부로부터 입력된 R, G, B 데이터 신호를 재정렬하여 데이터 드라이버(26)로 공급한다.

게이트 드라이버(24)는 타이밍 컨트롤러(40)로부터의 게이트 제어 신호에 응답하여 액정 패널(30)의 게이트 라인(GL)을 순차적으로 구동한다.

데이터 드라이버(26)는 타이밍 컨트롤러(40)로부터의 데이터 신호를 아날로그 데이터 신호로 변환하게 된다. 이때, 데이터 드라이버(26)는 데이터 신호를 감마 전압부(38)에서 발생된 고계조 감마 전압과 저계조 감마 전압을 이용하여 고계조 데이터 신호와 저계조 데이터 신호로 각각 변환하여 액정 패널(30)로 공급하게 된다.

구체적으로, 감마 전압부(38)는 다수의 고계조 감마 전압을 생성하는 고계조 감마 전압부(34)와, 다수의 저계조 감마 전압을 생성하는 저계조 감마 전압부(36)와, 고계조 감마 전압부(34) 및 저계조 감마 전압부(36)의 출력을 스위칭하는 아날로그 스위치(32)를 구비한다.

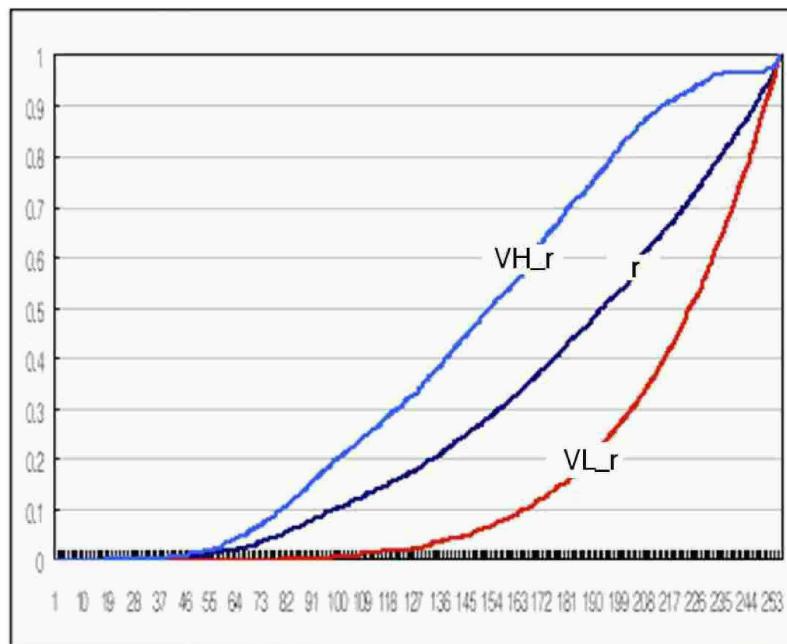

고계조 감마 전압부(34)는 도 5에 도시된 고계조 감마 곡선(VH\_r)에 따라 설계된 저항 스트링에 의해 다수의 고계조 감마 전압들을 생성한다.

저계조 감마 전압부(36)은 도 5에 도시된 저계조 감마 곡선(VL\_r)에 따라 설계된 저항 스트링에 의해 다수의 저계조 감마 전압들을 생성한다.

아날로그 스위치(32)는 한 수평 동기 기간에서는 고계조 감마 전압부(34)로부터의 고계조 감마 전압들을, 다음 수평 동기 기간에서는 저계조 감마 전압부(36)로부터의 저계조 감마 전압들을 데이터 드라이버(26)로 공급하고, 이러한 스위칭 동작을 수평 기간마다 반복하게 된다. 이때 아날로그 스위치(32)는 타이밍 컨트롤러(40)의 제어로 데이터 드라이버(26)에서 데이터 신호가 액정 패널(30)로 출력되는 기간과 동기되어 구동된다. 이러한 아날로그 스위치(32)는 데이터 드라이버(26)에 내장되기도 한다.

이에 따라, 데이터 드라이버(26)는 타이밍 컨트롤러(40)로부터의 R, G, B 데이터 신호를 한 수평 기간에서는 고계조 감마 전압을 이용하여 고계조 데이터 신호로 변환하여 액정 패널(30)로 공급하고, 다음 수평 기간에서는 저계조 감마 전압을 이용하여 저계조 데이터 신호로 변환하여 액정 패널(30)로 공급하게 된다.

액정 패널(30)은 지그-재그 구조로 1:2 면적비를 갖고 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)으로 구성된 R, G, B 서브 화소를 구비하지만, 도 4에서는 R, G, B 서브 화소를 단순화하여 도시하기로 한다. 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 각각의 박막 트랜지스터(TFT)에 의해 구동되고, 인접한 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)과는 상하로 엇갈려 배치된다. 특히, 감마 전압부(38)를 이용한 아날로그 방법에 의해 R, G, B 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 고계조 데이터 신호가 공급되는 수평 기간과 저계조 데이터 신호가 공급되는 수평 기간으로 구분되어 구동된다.

예를 들면, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 R, G, B 서브 화소의 고계조 영역(VH)과 접속되고, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 R, G, B 서브 화소의 저계조 영역(VL)과 접속된다.

구체적으로, 제1 게이트 라인(GL1)과 접속되고 상단의 R 및 B 저계조 영역(VL)에 위치하는 각각의 박막 트랜지스터(TFT)는 그의 드레인 전극이 아래쪽으로 신장되어 하단에 위치하는 R 및 B 고계조 영역(VH) 각각과 접속된다. 또한, 제2 게이트 라인(GL2)과 접속되고 하단의 R 및 G 고계조 영역(VH)에 위치하는 각각의 박막 트랜지스터(TFT)는 그의 드레인 전극이 위쪽으로 신장되어 상단의 R 및 B 저계조 영역(VL) 각각과 접속된다. 그리고, 제1 게이트 라인(GL1)과 접속되어 상단의 G 고계조 영역(VH)에 위치하는 박막 트랜지스터(TFT)는 그 G 고계조 영역(VH)과 접속되고, 제2 게이트 라인(GL2)과 접속되어 하단의 G 저계조 영역(VL)에 위치하는 박막 트랜지스터(TFT)는 그 G 저계조 영역(VL)과 접속된다.

이에 따라, 제1 게이트 라인(GL1)이 구동되는 1H 기간에서 데이터 드라이버(26)로부터 제1 내지 제3 데이터 라인(DL1, DL2, DL3)으로 공급된 고계조의 RH, GH, BH 데이터 신호가 R, G, B 고계조 영역(VH)에 각각 충전된다. 이어서, 제2 게이트 라인(GL2)이 구동되는 2H 기간에서 데이터 드라이버(26)로부터 제1 내지 제3 데이터 라인(DL1, DL2, DL3)으로 공급된 저계조의 RL, GL, BL 데이터 신호가 R, G, B 저계조 영역(VH)에 각각 충전된다. 이에 따라 R, G, B 서브 화소 각각은 고계조 영역(VH)과 저계조 영역(VL) 각각에 충전된 데이터 신호에 따른 고계조 및 저계조의 조합으로 도 5에 도시된 바와 같은 감마 곡선(r)을 따르는 계조를 표현하게 된다.

이와 같이, 본 발명의 제2 실시 예에 따른 액정 표시 장치는 고계조 감마 전압과 저계조 감마 전압을 이용한 아날로그 방법으로 R, G, B 데이터를 고계조 및 저계조 데이터로 분리하여 서브 화소에서 상하로 분할된 고계조 영역(VH) 및 저계조 영역(VL)에 각각 공급하게 된다. 이러한 아날로그 방법은 룩-업 테이블(LUT)을 이용한 디지털 방법을 위한 타이밍 컨트롤러의 고속 동작이 필요치 않으므로 고속 동작의 노이즈로 인한 화질 저하 문제를 방지할 수 있게 된다. 또한, 디지털 방법은 하나의 감마 스트링으로 고계조 및 저계조를 표현해 하므로 세밀한 계조 표현이 어려운 반면 아날로그 방법은 고계조 및 저계조 각각의 감마 스트링을 조정하여 세밀한 계조를 표현할 수 있는 장점이 있다.

따라서, 이하에서는 도 4에 도시된 아날로그 방법에 적용될 수 있는 VA 모드의 액정 패널들을 구체적으로 살펴보기로 한다.

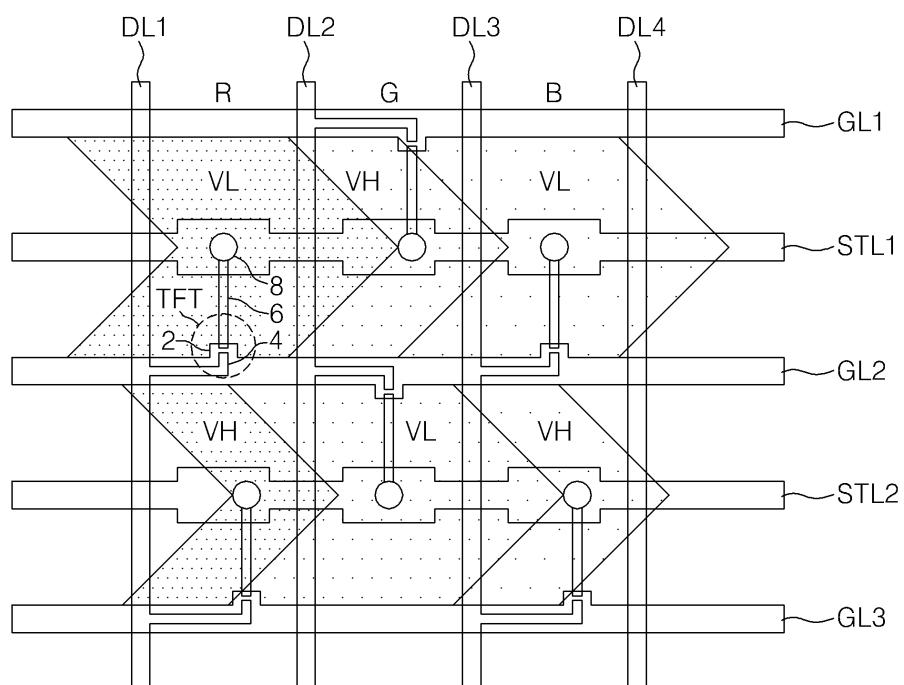

도 6은 본 발명의 제3 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이고, 도 7은 본 발명의 제4 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 6 및 도 7에 도시된 액정 패널은 도 4에 도시된 액정 패널(30)의 R, G, B 서브 화소를 지그-재그 구조로 도시한 것으로, 도 1 및 도 2에 도시된 액정 패널과 대비하여 인접 서브 화소와 상하로 엇갈려 배치된 고계조 영역(VH) 및 저계조 영역(VL)과 마찬가지로 박막 트랜지스터(TFT)의 컨택부(8)도 인접 서브 화소와 상하로 엇갈려 배치된 것을 제외하고는 동일한 구성 요소들을 구비하므로, 중복된 구성 요소들에 대한 상세한 설명은 생략하기로 한다.

도 6 및 도 7에 도시된 R, G, B 서브 화소는 1:2의 면적비를 갖는 고계조 영역(VH) 및 저계조 영역(VL)이 상하로 분할된다. 분할된 고계조 영역(VH)과 저계조 영역(VL)은 도 6에 도시된 바와 같이 센터 얼라인드 구조로 정렬되거나, 도 7에 도시된 바와 같이 에지 얼라인드 구조로 정렬된다. 또한, 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)은 인접 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)과 상하로 엇갈리게 배치된다. 이러한 각 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)에 도 4에 도시된 아날로그 방법으로 분리된 고계조 데이터 신호 및 저계조 데이터 신호를 공급하기 위하여 한 수평 기간에서 R, G, B 서브 화소의 고계조 영역(VH)이 동시에 구동되고, 다음 수평 기간에서 R, G, B 서브 화소의 저계조 영역(VL)이 동시에 구동된다.

예를 들면, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 R, G, B 서브 화소의 고계조 영역(VH)을 각각 구동하고, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 R, G, B 서브 화소의 저계조 영역(VL)을 각각 구동한다.

구체적으로, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 그 제1 게이트 라인(GL1)과 함께 상단 저계조 영역(VL) 또는 고계조 영역(VH)의 꺽인 부분과 중첩되게 형성된다. 이들 중 R 및 B 고계조 영역(VH) 각각을 구동하기 위한 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 아래쪽으로 신장되어 제1 스토리지 라인(STL1) 하단에 위치하는 컨택부(8)를 통해 하단의 R 및 B 고계조 영역(VH) 각각과 접속되고, G 고계조 영역(VH)을 구동하기 위한 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 아래쪽으로 신장되어 제1 스토리지 라인(STL1) 상단에 위치하는 컨택부(8)를 통해 상단의 G 고계조 영역(VH)과 접속된다. 다시 말하여, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)와 저계조 영역(VL) 또는 고계조 영역(VH)의 접속을 위한 컨택부(8)는 제1 스토리지 라인(STL1)을 따라 하단과 상단에 교번적으로 위치하게 된다.

제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 그 제2 게이트 라인(GL2)과 함께 각 서브 화소의 상하 경계부와 중첩되게 형성된다. 이들 중 R 및 B 저계조 영역(VL) 각각을 구동하기 위한 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 위쪽으로 신장되어 스토리지 라인(STL) 상단에 위치하는 컨택부(8)를 통해 상단 R 및 B 저계조 영역(VL) 각각과 접속되고, G 저계조 영역(VL)을 구동하기 위한 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 위쪽으로 신장되어 스토리지 라인(STL) 하단에 위치하는 컨택부(8)를 통해 하단 G 저계조 영역(VL)과 접속된다. 다시 말하여, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)와 고계조 영역(VH) 또는 저계조 영역(VL)의 접속을 위한 컨택부(8)는 제1 스토리지 라인(STL1)을 따라 상단과 하단에 교번적으로 위치하게 된다.

이에 따라, 제1 게이트 라인(GL1)이 구동되는 수평 기간에서는 고계조 감마 전압을 이용한 고계조 데이터 신호가 R, G, B 서브 화소의 고계조 영역(VH) 각각에 충전된다. 그리고, 제2 게이트 라인(GL2)이 구동되는 수평 기간에서는 저계조 감마 전압을 이용한 저계조 데이터 신호가 R, G, B 서브 화소의 저계조 영역(VL) 각각에 충전된다. 이 결과 R, G, B 서브 화소는 고계조 영역(VH)과 저계조 영역(VL)에 구현되는 고계조 및 저계조의 조합으로 해당 계조를 표현하게 된다.

도 8은 본 발명의 제5 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 8에 도시된 액정 패널은 도 6에 도시된 액정 패널과 대비하여 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 박막 트랜지스터(TFT)가 서로 다른 데이터 라인(DL)과 접속된 것을 제외하고는 동일한 구성 요소들을 구비하므로 중복된 구성 요소들에 대한 설명은 생략하기로 한다.

도 8에 도시된 한 서브 화소에서 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)는 서로 다른 게이트 라인(GL)과 접속됨과 아울러 서로 다른 데이터 라인(DL)과 접속된다. 이는 도 6과 같이 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)가 동일한 데이터 라인(DL)과 접속되면 둘 중 어느 한 박막 트랜지스터(TFT)의 소스 전극(4)과 게이트 라인(GL)과의 중첩 길이가 증가하여 기생 캐패시턴스가 증가하기 때문이다. 이를 방지하기 위하여, 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)를 양측의 서로 다른 데이터 라인(DL)과 접속시킴으로써 소스 전극(4)과 게이트 라인(GL)의 중첩 길이를 감소시킬 수 있게 된다.

예를 들면, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)는 좌측으로 인접한 데이터 라인(DL)과 접속되고, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)는 우측 데이터 라인(DL)과 접속된다.

구체적으로, 제1 게이트 라인(GL1)과 접속되어 R, G, B 각각의 고계조 영역(VH)을 구동하기 위한 박막 트랜지스터들(TFT)은 좌측으로 인접한 제1 내지 제3 데이터 라인(DL1 내지 DL3) 각각과 접속된다. 이에 따라, 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터들(TFT) 각각은 좌측의 데이터 라인(DL1 내지 DL3) 각각과 접속된 소스 전극(4), 아래쪽으로 신장되어 R, G, B 각각의 고계조 영역(VH)과 접속된 드레인 전극(6)을 구비한다.

그리고, 제2 게이트 라인(GL2)과 접속되어 R, G, B 각각의 저계조 영역(VL)을 구동하기 위한 박막 트랜지스터들(TFT)은 우측으로 인접한 제2 내지 제4 데이터 라인(DL2 내지 DL4) 각각과 접속된다. 이에 따라, 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터들(TFT) 각각은 우측의 데이터 라인(DL2 내지 DL4) 각각과 접속된 소스 전극(4), 위쪽으로 신장되어 R, G, B 각각의 저계조 영역(VL)과 접속된 드레인 전극(6)을 구비한다.

이에 따라, 제2 게이트 라인(GL2)과 접속되고 우측의 데이터 라인(DL)과 접속된 박막 트랜지스터(TFT)는 도 6과 같이 좌측의 데이터 라인(DL)과 접속된 경우 보다 소스 전극(4)과 게이트 라인(GL2)과 중첩 길이를 감소시킬 수 있게 된다. 이 결과, 게이트 라인(GL2)과 소스 전극(4)과의 중첩으로 인한 기생 캐패시턴스가 감소하게 됨으로써 기생 캐패시티로 인한 신호 왜곡을 방지할 수 있게 된다.

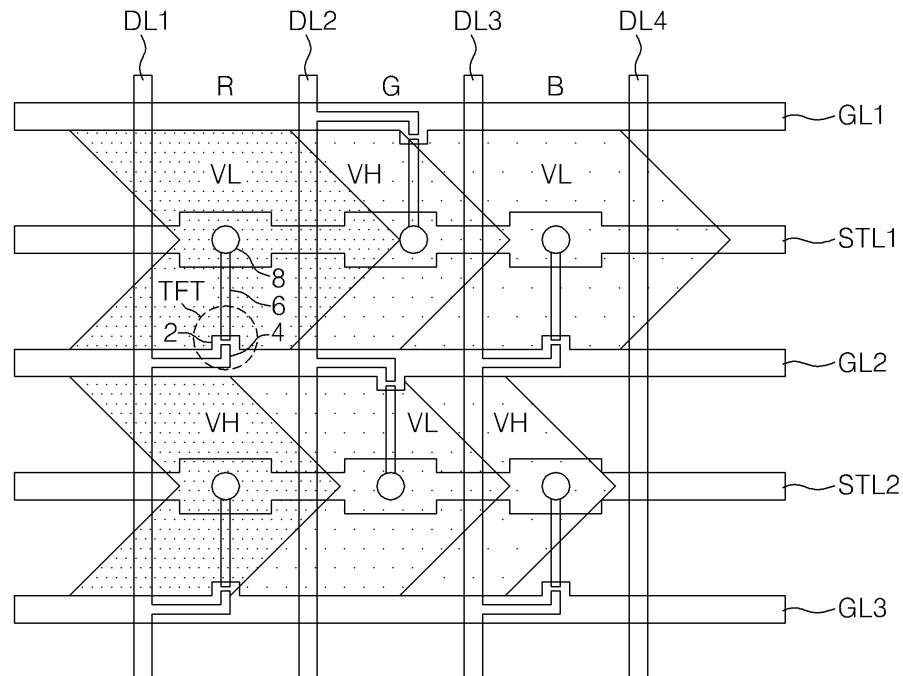

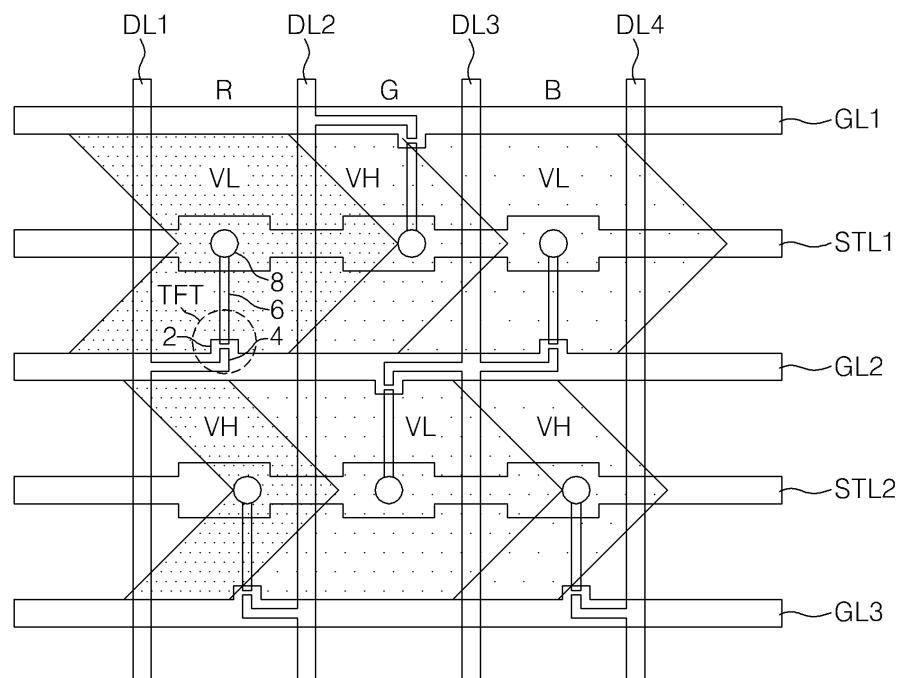

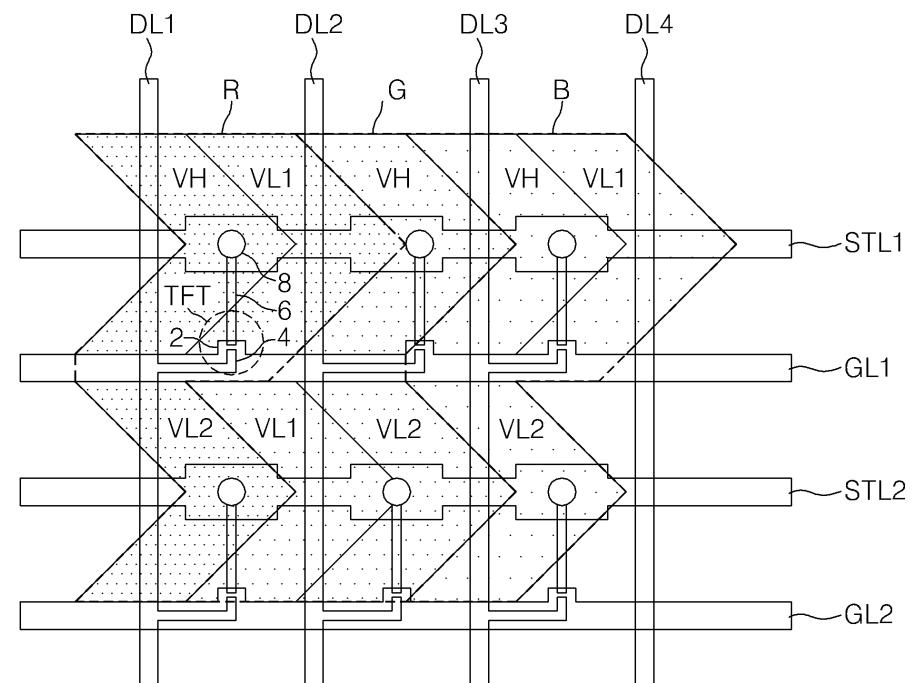

도 9는 본 발명의 제6 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이고, 도 10은 본 발명의 제7 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 9 및 도 10에 도시된 액정 패널은 도 6 및 도 7에 도시된 액정 패널과 대비하여 게이트 라인(GL) 및 스토리지 라인(STL)을 추가하고 박막 트랜지스터(TFT)의 데이터 신호 인가 방향이 인접한 서브 화소와 상반된 것을 제외하고는 동일한 구성 요소들을 구비하므로, 중복된 구성 요소들에 대한 설명은 생략하기로 한다.

도 9 및 도 10에 도시된 R, G, B 서브 화소 각각은 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)이 수평 방향으로 인접한 서브 화소와 상하로 엇갈려 배치된다. 이러한 R, G, B 서브 화소는 도 9에 도시된 바와 같이 센터 얼라인드 구조로 정렬되거나, 도 10에 도시된 바와 같이 에지 얼라인드 구조로 정렬된다.

그리고, 각 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)는 수평 방향으로 인접한 서브 화소를 구동하기 위한 2개의 박막 트랜지스터(TFT)의 데이터 신호 인가 방향과 상반된다.

예를 들면, R 서브 화소의 저계조 영역(VL) 및 고계조 영역(VH)을 각각 구동하는 2개의 박막 트랜지스터(TFT)는 그의 위쪽에 위치하는 컨택부(8)를 통해 저계조 영역(VL) 및 고계조 영역(VH)과 접속된다. 반면에, G 서브 화소의 고계조 영역(VH) 및 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)는 그의 아래쪽에 위치하는 컨택부(8)를 통해 고계조 영역(VH) 및 저계조 영역(VL)과 접속된다.

구체적으로, 제1 게이트 라인(GL1)은 상측으로 인접한 서브 화소간의 경계부와 중첩되도록, 제2 게이트 라인(GL2)은 각 서브 화소 고계조 영역(VH)과 저계조 영역(VL)과의 경계부와 중첩되도록, 제3 게이트 라인(GL3)은 하측으로 인접한 서브 화소간의 경계부와 중첩되도록 형성된다.

제1 스토리지 라인(STL1)은 제2 게이트 라인(GL2)을 기준으로 상단에 위치하는 고계조 영역(VH) 및 저계조 영역(VL)의 격인 부분과 중첩되도록, 제2 스토리지 라인(STL2)은 하단에 위치하는 고계조 영역(VH) 및 저계조 영역(VL)의 격인 부분과 중첩되도록 형성된다.

R 및 G 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하기 위한 박막 트랜지스터들(TFT)은 그 고계조 영역(VH)과 저계조 영역(VL) 하단에 각각 위치하는 제2 및 제3 게이트 라인(GL2, GL3)에 의해 구동된다. 다시 말하여, 제2 게이트 라인(GL2)과 접속되어 R 및 B 저계조 영역(VL) 각각을 구동하는 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 위쪽으로 신장되어 상단의 제1 스토리지 라인(STL1)과 중첩된 컨택부(8)를 통해 R 및 B 저계조 영역(VL) 각각과 접속된다. 제3 게이트 라인(GL3)과 접속되어 R 및 B 고계조 영역(VH) 각각을 구동하는 박막 트랜지스터(TFT)도 그의 드레인 전극(6)이 위쪽으로 신장되어 상단의 제2 스토리지 라인(STL2)과 중첩된 컨택부(8)를 통해 R 및 G 고계조 영역(VH) 각각과 접속된다.

반면에, G 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하기 위한 박막 트랜지스터들(TFT)은 그 고계조 영역(VH)과 저계조 영역(VL) 상단에 각각 위치하는 제1 및 제2 게이트 라인(GL1, GL2)에 의해 구동된다. 다시 말하여, 제1 게이트 라인(GL1)과 접속되어 G 고계조 영역(VH)을 구동하는 박막 트랜지스터(TFT)는 그의 드레인 전극(6)이 아래쪽으로 신장되어 하단의 제1 스토리지 라인(STL1)과 중첩된 컨택부(8)를 통해 G 고계조 영역(VH)과 접속된다. 제2 게이트 라인(GL2)과 접속되어 G 저계조 영역(VL)을 구동하는 박막 트랜지스터(TFT)도 그의 드레인 전극(6)이 아래쪽으로 신장되어 하단의 제2 스토리지 라인(STL2)과 중첩된 컨택부(8)를 통해 G 저계조 영역(VL)과 접속된다.

이에 따라, 제1 게이트 라인(GL1)이 구동되는 수평 기간에서는 G 저계조 영역(VL)에 저계조 데이터가 충전되고, 제2 게이트 라인(GL2)이 구동되는 수평 기간에서는 R, G, B 저계조 영역(VL) 각각에 저계조 데이터가 충전된다. 그리고, 제3 게이트 라인(GL3)이 구동되는 수평 기간에서 R 및 B 고계조 영역(VH) 각각에 고계조 데이터가 충전된다. 이때, 제3 게이트 라인(GL3)이 구동되는 수평 기간에 다음 화소의 G 고계조 영역(VH)에도 고계조 데이터가 충전된다. 이에 따라, 한 수평 기간에서는 2개의 수평 라인 분에 해당되는 데이터가 공급되어야 하는데, 이는 타이밍 컨트롤러가 2개의 수평 라인 분의 데이터를 조합하여 공급함으로써 가능하게 된다. 이때, 타이밍 컨트롤러는 그 내부에 필수적으로 구비된 프레임 메모리를 이용하거나, 라인 메모리를 추가로 구비하여 2개의 수평 라인 분의 데이터를 조합하게 된다.

이 결과 R, G, B 서브 화소는 고계조 영역(VH)과 저계조 영역(VL)에 구현되는 고계조 및 저계조의 조합으로 해당 계조를 표현하게 된다.

이와 같이, 도 9 및 도 10에 도시된 액정 패널은 고계조 영역(VH) 및 저계조 영역(VL)의 상하 경계부마다 게이트 라인(GL)을 형성하고, 박막 트랜지스터(TFT)의 데이터 신호 인가 방향이 게이트 라인(GL)을 따라 교번적으로 바뀌게 한다. 이에 따라, 박막 트랜지스터(TFT)의 드레인 전극(6)의 길이가 도 6 및 도 7에 도시된 액정 패널 보다 감소하게 되어 개구율이 증가하게 된다.

또한, 도 6 및 도 7에 도시된 액정 패널은 박막 트랜지스터(TFT)의 드레인 전극(6)이 다른 데이터 신호가 공급되는 계조 영역을 경유함에 따라 기생 캐패시터(Cpp)로 인한 커플링 편차가 발생되는 단점이 있는 반면, 도 9 및 도 10에 도시된 액정 패널은 박막 트랜지스터(TFT)의 드레인 전극이 다른 데이터 신호가 공급되는 계조 영역과 중첩되지 않으므로 커플링 편차를 방지할 수 있게 된다.

예를 들면, 도 6 및 도 7에 도시된 R 고계조 영역(TFT)을 구동하는 박막 트랜지스터(TFT)의 드레인 전극(6)은 R 저계조 영역(VL)을 경유하고, R 저계조 영역(TFT)을 구동하는 박막 트랜지스터(TFT)의 드레인 전극(6)은 R 고계조 영역(VH)을 경유하게 된다. 반면에, G 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 박막 트랜지스터(TFT)의 드레인 전극(6)은 해당 계조 영역만 경유하게 된다. 이때, R 및 G 고계조 영역(VH)과 저계조 영역(VL)은 도트 인버전 구동에 따라 상하좌

우로 데이터 신호의 극성이 상반된다. 이에 따라, R 고계조 영역(VH)과 저계조 영역(VL)간의 기생 캐패시턴스(Cpp)가 G 고계조 영역(VH)과 저계조 영역(VL)간의 기생 캐패시턴스(Cpp) 보다 증가하여 커플링 편차가 발생하게 됨으로써 세로줄 얼룩이 발생할 수 있는 단점이 있다.

이러한 단점을 해결하기 위하여, 도 9 및 도 10에 도시된 액정 패널은 박막 트랜지스터(TFT)의 데이터 신호 인가 방향을 전환하여 드레인 전극(6)이 다른 계조 영역과는 중첩되지 않고 해당 계조 영역에만 중첩되게 한다. 따라서, 전술한 기생 캐패시턴스(Cpp)의 차이로 인한 커플링 편차를 방지할 수 있게 된다.

도 11은 본 발명의 제8 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 11에 도시된 액정 패널은 도 9에 도시된 액정 패널과 대비하여 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 박막 트랜지스터(TFT)가 서로 다른 데이터 라인(DL)과 접속된 것을 제외하고는 동일한 구성 요소들을 구비하므로 중복된 구성 요소들에 대한 설명은 생략하기로 한다.

도 11에 도시된 한 서브 화소에서 상하로 분할된 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)는 서로 다른 게이트 라인(GL)과 접속됨과 아울러 서로 다른 데이터 라인(DL)과 접속된다. 이는 도 9와 같이 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)가 동일한 데이터 라인(DL)과 접속되면 둘 중 어느 한 박막 트랜지스터(TFT)의 소스 전극(4)과 게이트 라인(GL)과의 중첩 길이가 증가하여 기생 캐패시턴스가 증가하기 때문이다. 이를 방지하기 위하여, 한 서브 화소의 고계조 영역(VH)과 저계조 영역(VL)을 각각 구동하는 2개의 박막 트랜지스터(TFT)를 양측의 서로 다른 데이터 라인(DL)과 접속시킴으로써 소스 전극(4)과 게이트 라인(GL)의 중첩 길이를 감소시켜 기생 캐패시턴스를 감소시킬 수 있게 된다.

도 12은 본 발명의 제9 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이고, 도 13은 본 발명의 제10 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도이다.

도 12 및 도 13에 도시된 액정 패널의 R, G, B 서브 화소는 1:2의 면적비를 갖는 고계조 영역(VH) 및 저계조 영역(VL)으로 분할되고, 저계조 영역(VL) 다시 같은 면적비를 갖는 제1 및 제2 저계조 영역(VL1, VL2)으로 2분할된다. 이러한 R, G, B 서브 화소는 도 12에 도시된 바와 같이 센터 얼라인드 구조로 정렬되거나, 도 13에 도시된 바와 같이 에지 얼라인드 구조로 정렬된다.

이러한 R, G, B 서브 화소에서 한 서브 화소는 그의 고계조 영역(VH)과 저계조 영역(VL)이 상하로 분리되어 형성된 반면, 양측으로 인접한 다른 두 서브 화소는 고계조 영역(VH)과 제1 저계조 영역(VL1)은 상단에 분리되어 형성되고 제2 저계조 영역(VL2)은 상단의 제1 저계조 영역(VL1)과 접속되어 하단에 형성된다. 다시 말하여, 각 서브 화소의 고계조 영역(VH)은 상단에 위치하게 되고, 제1 및 제2 저계조 영역(VL1, VL2)은 모두 하단에 위치하거나 상하단에 위치하게 된다.

예를 들면, G 서브 화소는 그의 고계조 영역(VH)과 저계조 영역(VL)이 상하로 분리되어 형성된 반면, G 서브 화소와 양측으로 인접한 R 및 B 서브 화소는 고계조 영역(VH)과 제1 저계조 영역(VL1)은 상단에 분리되어 형성되고 제2 저계조 영역(VL2)은 상단의 제1 저계조 영역(VL1)과 접속되어 하단에 형성된다. 다시 말하여 R, G, B 고계조 영역(VH)은 모두 상단에 위치하게 되고, G의 제1 및 제2 저계조 영역(VL)은 하단에 위치하며, R 및 B의 제1 및 제2 저계조 영역은 상하단에 각각 위치하게 된다. 이러한 R, G, B 고계조 영역(VH)은 제1 게이트 라인(GL1)과 접속된 박막 트랜지스터(TFT)에 의해 구동되고, 저계조 영역(VL)은 제2 게이트 라인(GL2)과 접속된 박막 트랜지스터(TFT)에 의해 구동된다.

구체적으로, 제1 게이트 라인(GL1)은 각 서브 화소에서 상하로 분할된 계조 영역의 경계부와 중첩되도록, 제2 게이트 라인(GL3)은 하측으로 인접한 서브 화소간의 경계부와 중첩되도록 형성된다. 제1 스토리지 라인(STL1)은 제1 게이트 라인(GL1)을 기준으로 상단에 위치하는 계조 영역의 격인 부분과 중첩되도록, 제2 스토리지 라인(STL2)은 하단에 위치하는 계조 영역의 격인 부분과 중첩되도록 형성된다.

R, G, B 고계조 영역(VH)은 제1 게이트 라인(GL1)과 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 사이에 각각 형성된 박막 트랜지스터(TFT)에 의해 구동된다. 이러한 박막 트랜지스터(TFT)는 제1 스토리지 라인(STL1)과 중첩된 컨택부(8)를 통해 고계조 영역(VH)과 접속된다.

그리고 R, G, B 저계조 영역(VL)은 제2 게이트 라인(GL2)과 제1 내지 제3 데이터 라인(DL1, DL2, DL3) 사이에 각각 형성된 박막 트랜지스터(TFT)에 의해 구동된다. 이러한 박막 트랜지스터(TFT)는 제2 스토리지 라인(STL2)과 중첩된 컨택부(8)를 컨택부(8)를 제2 저계조 영역(VL1, VL2) 중 어느 하나와 접속된다.

이에 따라, 제1 게이트 라인(GL1)이 구동되는 수평 기간에서는 R, G, B 고계조 영역(VH) 각각에 고계조 데이터가 충전되고, 제2 게이트 라인(GL2)이 구동되는 수평 기간에서는 R, G, B 저계조 영역 각각에 저계조 데이터가 충전된다. 이 결과 R, G, B 서브 화소는 고계조 영역(VH)과 저계조 영역(VL)에 구현되는 고계조 및 저계조의 조합으로 해당 계조를 표현하게 된다.

이와 같이, 도 12 및 도 13에 도시된 액정 패널은 각 서브 화소의 고계조 영역(VH)은 동일한 수평 라인에 형성하고, 제1 및 제2 저계조 영역(VL1, VL2) 중 적어도 어느 하나가 다른 수평 라인에 형성함으로써 도 4에 도시된 아날로그 방법으로 고계조 및 저계조 데이터를 분할하여 구동할 수 있게 된다. 이때, 박막 트랜지스터(TFT)의 돌출 방향이 모두 동일하므로 박막 트랜지스터(TFT)의 돌출 방향이 상하로 전환되는 경우 보다 개구율을 향상시킬 수 있게 된다.

### **발명의 효과**

상술한 바와 같이, 본 발명에 따른 액정 표시 장치는 지그-재그 구조의 R, G, B 서브 화소가 1:2의 면적비를 갖고 상하로 분할되고 인접 서브 화소와 엇갈리게 배치된 고계조 영역(VH) 및 저계조 영역(VL)을 구비함으로써 시인성 및 투과율이 향상된다.

아울러, 본 발명에 따른 액정 표시 장치는 지그-재그 구조의 R, G, B 서브 화소를 고계조와 저계조 데이터를 분리하는 디지털 방법을 이용하거나, 아날로그 방법을 적용하여 구동할 수 있게 된다.

이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허청구의 범위에 의해 정하여져야만 할 것이다.

### **도면의 간단한 설명**

도 1은 본 발명의 제1 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 2는 본 발명의 제2 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 3은 도 1 및 도 2에 도시된 액정 패널을 이용한 본 발명의 제1 실시 예에 따른 액정 표시 장치를 도시한 블록도.

도 4는 본 발명의 제2 실시 예에 따른 액정 표시 장치를 도시한 블록도.

도 5는 도 4에 도시된 감마 전압부에 적용된 감마 곡선을 도시한 그래프.

도 6은 본 발명의 제3 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 7은 본 발명의 제4 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 8은 본 발명의 제5 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 9는 본 발명의 제6 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 10은 본 발명의 제7 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 11은 본 발명의 제8 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 12는 본 발명의 제9 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

도 13은 본 발명의 제10 실시 예에 따른 VA 모드 액정 패널의 한 화소의 구조를 도시한 평면도.

< 도면의 주요 부분에 대한 부호의 설명 >

VH : 고계조 영역 VL : 저계조 영역

2 : 게이트 전극 4 : 소스 전극

6 : 드레인 전극 8 : 컨택부

12, 30 : 액정 패널 14, 24 : 게이트 드라이버

16, 26 : 데이터 드라이버 18, 38 : 감마 전압부

32 : 스위치 20, 40 : 타이밍 컨트롤러

34 : 고계조 감마 전압부 36 : 저계조 감마 전압부

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

|                |                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板，其驱动方法以及使用其的液晶显示装置                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">KR1020070034145A</a>                                                                                                         | 公开(公告)日 | 2007-03-28 |

| 申请号            | KR1020050088460                                                                                                                          | 申请日     | 2005-09-23 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                                                                 |         |            |

| [标]发明人         | CHANG HAK SUN<br>창학선<br>YOO SEUNG HOO<br>유승후<br>KIM HYUN WUK<br>김현욱<br>KIM YEON JU<br>김연주<br>DO HEE WOOK<br>도희욱<br>SHIN KYOUNG JU<br>신경주 |         |            |

| 发明人            | 창학선<br>유승후<br>김현욱<br>김연주<br>도희욱<br>신경주                                                                                                   |         |            |

| IPC分类号         | G02F1/1343                                                                                                                               |         |            |

| CPC分类号         | G02F2001/134345 G09G2300/0443 G09G3/3648 G09G2320/0673 G09G3/3696 G09G2300/0447                                                          |         |            |

| 代理人(译)         | KWON , HYUK SOO<br>SE JUN OH<br>宋，云何                                                                                                     |         |            |

| 其他公开文献         | KR101182771B1                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                |         |            |

#### 摘要(译)

本发明涉及提高多域垂直配向模式下的可见度和透射率的液晶面板及其驱动方法和使用该液晶面板的液晶显示器。根据本发明的一个特征的液晶面板具有第一和第二灰度级区域，其具有不同的面积，它被分成顶部和底部。并且，以水平周期为单位包括当前驱动倍数的栅极线，并且当在薄膜晶体管中，在多条栅极线中驱动一条栅极线，第一灰度级区域是独立驱动的数据线和多个薄膜晶体管。提供连接的第一和第二数据信号的倍数分别提供有第一和第二灰度级区域，其中薄膜晶体管和当前驱动的多个薄膜晶体管。其中第一和第二灰度级区域在顶部和底部不同并且布置栅极线连接到第一和第二灰度级区域，使得当驱动另一栅极线时驱动第二灰度级区域。多域VA，之字形和。