**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.

*G02F 1/136* (2006.01)

(11) 공개번호 10-2007-0050612

(43) 공개일자 2007년05월16일

(21) 출원번호 10-2005-0108016

(22) 출원일자 2005년11월11일

심사청구일자 2005년11월11일

(71) 출원인 비오이 하이디스 테크놀로지 주식회사

경기도 이천시 부발읍 아미리 산 136-1

(72) 발명자 김병훈

경기 부천시 소사구 범박동 현대홈타운아파트 406동 1503호

임삼호

서울 강동구 암사동 선사현대아파트 105-1501

(74) 대리인 최태창

정태훈

오용수

전체 청구항 수 : 총 14 항

**(54) 반투과형 액정표시장치의 어레이기판 제조방법**

**(57) 요약**

본 발명은 반투과형 액정표시장치의 어레이기판 제조방법을 개시한다. 개시된 본 발명의 방법은, 화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 하프톤 노광 기술을 적용한 제1마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인 및 공통전극라인을 형성함과 아울러 투과 영역에 배치되는 ITO의 플레이트형 카운터전극 및 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계와, 상기 유리기판의 전면 상에 게이트절연막과 비정질실리콘막 및 도팽된 비정질실리콘막을 차례로 형성하는 단계와, 하프톤 노광 기술을 적용한 제2마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 액티브 패턴을 형성하는 단계와, 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 AI막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성함과 아울러 반사 영역에 바텀-Mo막과 AI막의 2층막으로 이루어진 반사전극을 형성하는 단계와, 상기 결과물 상에 보호막을 형성하는 단계와, 제4마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계와, 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트되는 ITO의 슬릿형 화소전극을 형성하는 단계를 포함하는 것을 특징으로 한다.

**내포도**

도 41

**특허청구의 범위**

청구항 1.

화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 ITO막과 게이트용 금속막을 차례로 형성하는 단계;

상기 게이트용 금속막과 ITO막에 대해 하프톤 노광 기술을 적용한 제1마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인 및 공통전극라인을 형성함과 아울러 투과 영역에 배치되는 ITO의 플레이트형 카운터전극 및 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계;

상기 게이트전극을 포함한 게이트라인, 공통전극라인, 카운터전극 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트 절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계;

상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제2마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계;

상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계;

상기 3층막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 Al막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계;

상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계;

상기 보호막에 대해 제4마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계;

상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및

상기 ITO막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트와 아울러 투과 영역 및 반사 영역 모두에 배치되는 슬릿형의 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 아래 이기판 제조방법.

## 청구항 2.

제 1 항에 있어서, 상기 게이트전극을 포함한 게이트라인 및 공통전극라인과 엠보싱 패턴을 형성하는 단계는,

상기 게이트용 금속막 상에 하프톤 노광 공정을 적용해서 카운터전극 형성 영역을 가리는 부분이 게이트전극을 포함한 게이트라인 형성 영역과 공통전극라인 형성 영역 및 엠보싱 패턴 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제1감광막패턴을 형성하는 단계;

상기 제1감광막패턴을 식각마스크로 이용해서 게이트용 금속막과 ITO막을 식각하여 게이트전극을 포함한 게이트라인과 공통전극라인 및 엠보싱 패턴을 형성하는 단계;

상기 제1감광막패턴에 대해 카운터전극 형성 영역을 가리는 부분이 제거되도록 예상하는 단계;

상기 예상된 제1감광막패턴을 식각마스크로 이용해서 카운터전극 상의 게이트용 금속막을 제거하는 단계; 및

상기 잔류된 제1감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 하는 반투과형 액정표시장치의 아래이기판 제조방법.

### 청구항 3.

제 1 항에 있어서, 상기 제1비아홀 및 액티브 패턴을 형성하는 단계는,

상기 도핑된 비정질실리콘막 상에 하프톤 노광 공정을 적용해서 투과 영역을 가리는 부분이 액티브 패턴 형성 영역 및 반사전극 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제2감광막패턴을 형성하는 단계;

상기 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막을 식각하여 공통전극라인을 노출시키는 제1비아홀을 형성하는 단계;

상기 제2감광막패턴에 대해 투과 영역 상에 형성된 부분이 제거되도록 에칭하는 단계;

상기 에칭된 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막을 식각하여 액티브 패턴을 형성하는 단계; 및

상기 잔류된 제2감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 4.

제 1 항에 있어서, 상기 소오스/드레인전극을 포함한 데이터라인과 반사전극을 형성하는 단계는,

상기 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막 상에 하프톤 노광 공정을 적용해서 반사전극 형성 영역을 가리는 부분이 소오스/드레인전극을 포함한 데이터라인 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제3감광막패턴을 형성하는 단계;

상기 제3감광막패턴을 식각마스크로 이용해서 3층막을 식각하여 소오스/드레인전극을 포함한 데이터라인을 형성하는 단계;

상기 제3감광막패턴에 대해 반사전극 형성 영역에 형성된 제3감광막패턴이 제거되도록 에칭하는 단계;

상기 에칭된 제3감광막패턴을 식각마스크로 이용해서 반사 영역의 탑-Mo막을 식각하여 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계; 및

상기 잔류된 제3감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 5.

제 1 항에 있어서, 상기 바텀-Mo막은 500~700Å 두께로 형성하고, 상기 Al막은 1400~1600Å 두께로 형성하며, 그리고, 상기 탑-Mo막은 100~200Å 두께로 형성하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 6.

제 1 항에 있어서, 상기 반사전극은 상기 엠보싱 패턴에 의해 엠보싱을 갖도록 형성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 7.

제 1 항에 있어서, 상기 투과 영역 및 반사 영역은 각각 카운터전극과 화소전극 및 반사전극과 화소전극 사이의 수평 전계에 의한 FFS 모드로 구동되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 8.

화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 ITO막과 게이트용 금속막을 차례로 형성하는 단계;

상기 게이트용 금속막 상에 ITO막을 형성하는 단계;

상기 ITO막에 대해 제1마스크 공정 및 식각 공정을 진행해서 투과 영역에 ITO의 플레이형 카운터전극을 형성하는 단계;

상기 카운터전극이 형성된 유리기판 상에 게이트용 금속막을 형성하는 단계;

상기 게이트용 금속막에 대해 제2마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인과 공통전극라인 및 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계;

상기 게이트전극을 포함한 게이트라인, 공통전극라인, 카운터전극 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트 절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계;

상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계;

상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계;

상기 3층막에 대해 하프톤 노광 기술을 적용한 제4마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 Al막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계;

상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계;

상기 보호막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계;

상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및

상기 ITO막에 대해 제6마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트되는 슬릿형의 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

### 청구항 9.

화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 게이트용 금속막을 형성하는 단계;

상기 게이트용 금속막에 대해 제1마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인 및 공통전극라인을 형성함과 아울러 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계;

상기 게이트전극을 포함한 게이트라인과 공통전극라인 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계;

상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제2마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계;

상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계;

상기 3층막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 Al막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계;

상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계;

상기 보호막에 대해 제4마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계;

상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및

상기 ITO막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트와 아울러 투과 영역에 배치되는 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

## 청구항 10.

제 9 항에 있어서, 상기 제1비아홀 및 액티브 패턴을 형성하는 단계는,

상기 도핑된 비정질실리콘막 상에 하프톤 노광 공정을 적용해서 투과 영역을 가리는 부분이 액티브 패턴 형성 영역 및 반사전극 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제2감광막패턴을 형성하는 단계;

상기 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막을 식각하여 공통전극라인을 노출시키는 제1비아홀을 형성하는 단계;

상기 제2감광막패턴에 대해 투과 영역 상에 형성된 부분이 제거되도록 에칭하는 단계;

상기 에칭된 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막을 식각하여 액티브 패턴을 형성하는 단계; 및

상기 잔류된 제2감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

## 청구항 11.

제 9 항에 있어서, 상기 소오스/드레인전극을 포함한 데이터라인과 반사전극을 형성하는 단계는,

상기 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막 상에 하프톤 노광 공정을 적용해서 반사전극 형성 영역을 가리는 부분이 소오스/드레인전극을 포함한 데이터라인 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제3감광막패턴을 형성하는 단계;

상기 제3감광막패턴을 식각마스크로 이용해서 3층막을 식각하여 소오스/드레인전극을 포함한 데이터라인을 형성하는 단계;

상기 제3감광막패턴에 대해 반사전극 형성 영역에 형성된 제3감광막패턴이 제거되도록 예상하는 단계;

상기 예상된 제3감광막패턴을 식각마스크로 이용해서 반사 영역의 탑-Mo막을 식각하여 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계; 및

상기 잔류된 제3감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

## 청구항 12.

제 9 항에 있어서, 상기 바텀-Mo막은 500~700Å 두께로 형성하고, 상기 Al막은 1400~1600Å 두께로 형성하며, 그리고, 상기 탑-Mo막은 100~200Å 두께로 형성하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

## 청구항 13.

제 9 항에 있어서, 상기 반사전극은 상기 엠보싱 패턴에 의해 엠보싱을 갖도록 형성되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

## 청구항 14.

제 9 항에 있어서, 상기 투과 영역 및 반사 영역은 TN 모드로 구동되는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법.

**명세서**

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반투과형 액정표시장치의 제조방법에 관한 것으로, 보다 상세하게는, 투과 영역에서의 콘택저항을 낮춤과 아울러 반사 영역에서의 고반사율 특성을 갖도록 하면서 공정 단순화를 이룬 반투과형 액정표시장치의 어레이기판 제조방법에 관한 것이다.

액정표시장치는 전극이 형성되어 있는 두 장의 기판과 그 사이에 개재되어 있는 액정층을 포함하며, 전극에 전압을 인가해서 액정층의 액정분자들을 재배열시키는 것에 의해 투과되는 빛의 양을 조절해서 소정의 화상을 구현한다.

이러한 액정표시장치는 백라이트와 같은 광원을 이용하여 화상을 표시하는 투과형 액정표시장치와 자연광을 광원으로 이용하는 반사형 액정표시장치로 분류할 수 있다. 상기 투과형 액정표시장치는 백라이트를 광원으로 이용하므로 어두운 주변환경에서도 밝은 화상을 구현할 수 있지만, 백라이트 사용에 의해 소비전력이 높다는 단점이 있다. 반면, 상기 반사형 액정표시장치는 백라이트를 사용하지 않고 주변환경의 자연광을 이용하기 때문에 소비전력은 작지만, 주변환경이 어두울 때에는 사용이 불가능하다는 단점이 있다.

이에, 화소부를 투과 영역과 반사 영역으로 나눔으로써, 실내나 외부 광원이 존재하지 않는 어두운 곳에서는 자체의 내장 광원을 이용하여 화상을 표시하는 투과형으로 작동하고, 실외의 고조도 환경에서는 외부의 입사광을 반사시켜 화상을 표시하는 반사형으로 작동하는 반투과형 액정표시장치가 제안되었다.

도 1은 대한민국 특허공개 2004-0070716에 제안된 종래 반투과형 TN 모드 액정표시장치의 어레이기판을 도시한 단면도로서, 이를 참조하여 그 제조방법을 설명하면 다음과 같다.

도시된 바와 같이, 화소부가 박막트랜지스터 영역(TFT), 반사 영역(R) 및 투과 영역(T)으로 구획된 유리기판(1) 상에 게이트용 금속막을 증착한 후, 이를 패터닝해서 박막트랜지스터 영역(TFT)에 배치되는 게이트전극(2)을 포함하여 화소부의 경계에 횡방향으로 배열되는 다수의 게이트라인(도시안됨)을 형성한다. 그런 다음, 상기 게이트전극(2)을 포함한 게이트라인들을 덮도록 기판(1)의 전면 상에 게이트절연막(3)을 형성한다.

다음으로, 상기 게이트절연막(3) 상에 비도핑된 비정질실리콘막과 도핑된 비정질실리콘막을 차례로 형성한 후, 이들을 패터닝하여 박막트랜지스터 영역(TFT)에 배치되는 액티브 패턴을 형성한다. 그런 다음, 박막트랜지스터 영역(TFT) 및 투과 영역(T)을 제외한 반사 영역(R)의 게이트절연막 부분 상에 그 표면에 다수의 요철을 포함하는 유기절연막(6)을 선택적으로 형성한다. 이때, 상기 투과 영역(T)에는 유기절연막(6)의 패터닝 과정에서 상기 유기절연막(6)을 관통하는 제1개구부(7)가 형성된다.

계속해서, 액티브 패턴 및 유기절연막(6)이 형성된 기판 결과물 상에 소오스/드레인용 금속막을 증착한 후, 이를 패터닝해서 화소부의 경계에 실질적으로 게이트라인과 직교하는 종방향으로 배열되는 다수의 데이터라인(도시안됨)을 형성함과 아울러 박막트랜지스터 영역(TFT)에 배치되는 소오스/드레인 전극(8a, 8b)을 형성한다. 연이어, 소오스전극(8a)과 드레인전극(8b) 사이의 도핑된 비정질실리콘층 부분을 식각하여 오믹층(5)을 형성함과 아울러 비도핑된 비정질실리콘층으로 이루어진 채널층(4)을 형성하며, 이 결과로서, 박막트랜지스터 영역(TFT)에 박막트랜지스터(10)를 구성한다. 여기서, 상기 데이터라인의 형성시에는 반사 영역(R)의 유기절연막(6) 상에, 예컨대, 박막트랜지스터(10)의 소오스전극(8a)과 일체형으로 이루어진 반사전극(11)을 함께 형성한다.

다음으로, 박막트랜지스터(10) 및 반사전극(11)을 덮도록 기판 결과물 상에 보호막(12)을 형성한 후, 상기 보호막(12)을 식각하여 소오스전극(8a)을 노출시키는 비아홀(13)을 형성함과 아울러 투과 영역(T) 상에 형성된 보호막 부분을 제거하여 제2개구부(14)를 형성한다. 그런 다음, 상기 보호막(12) 상에 ITO막을 증착한 후, 이를 패터닝하여 비아홀(13)을 통해 소오스전극(8a)과 콘택트되는 화소전극(15)을 형성하고, 이 결과로서, 어레이기판의 제조를 완성한다.

상기에서, 전술한 종래의 반투과형 액정표시장치는 반사전극을 소오스/드레인용 금속막을 사용하여 형성하므로 상기 소오스/드레인용 금속막으로서 반사율이 높은 금속을 채택하고 있다. 예컨대, 종래에는 Al, Al 합금, Ag, Ag 합금 중 어느 하나의 단일층이나, Cr, Ti, MoW 중 어느 하나의 하부층과 Al, Ag 중 어느 하나의 상부층으로 구성되는 이중층으로 소오스/드레인 전극 및 반사전극을 형성하고 있다.

그런데, Al 계열의 금속은 화소전극 물질인 ITO와 콘택트저항이 높기 때문에 점등이 되지 않거나 점등이 되더라도 무라(Mura) 및 휘도 저하가 발생되는 등 화면품위 저하를 유발하게 된다. 반면, Ag 계열의 금속은 ITO와의 콘택트저항이 낮아서 Al 계열 금속을 적용하는 경우에서의 문제는 해결할 수 있겠지만, 고가이므로 제품의 생산단가를 고려할 때 그 이용이 실질적으로 곤란하다.

결국, 소오스/드레인용 금속막으로 반사전극을 형성하는 종래의 반투과형 액정표시장치는 ITO막과의 콘택트저항 문제 및 비용 문제로 인해 실질적으로 원하는 제품을 구현함에 어려움이 있다.

한편, 종래의 반투과형 액정표시장치는 그의 어레이기판 제작시 일반적으로 8~11장의 마스크를 필요로 한다. 이는 5~8장의 마스크를 필요로 하는 투과 영역의 형성에 비해 반사 영역의 형성이 레진막에의 비아 형성, 엠보싱 형성 및 반사전극 형성이 더 수행되어야 하는 것과 관련해서 최소 3장의 마스크를 더 필요로하기 때문이다.

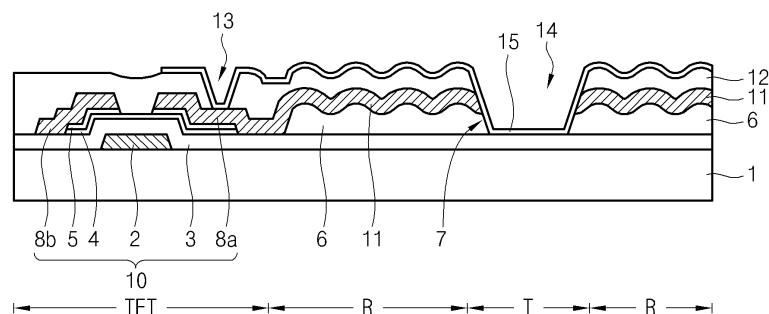

구체적으로, 도 2는 종래 반투과형 TN 모드 액정표시장치의 어레이기판을 도시한 단면도로서, 이 구조의 경우는 게이트전극(2)을 포함한 게이트라인 및 공통전극라인을 형성하기 위한 제1마스크 공정, 액티브 패턴을 형성하기 위한 제2마스크 공정, 소오스/드레인전극(8a, 8b)을 포함한 데이터라인을 형성하기 위한 제3마스크 공정, 소오스/드레인전극(8a, 8b)을 노출시키는 비아 형성을 위한 제4마스크 공정, ITO의 화소전극(15)을 형성하기 위한 제5마스크 공정, 레진막(6)에의 비아(13) 형성을 위한 제6마스크 공정, 반사 영역(R)에의 엠보싱(16) 형성을 위한 제7마스크 공정, 그리고, 상기 반사 영역(R)에의 반사전극(11) 형성을 위한 제8마스크 공정이 차례로 수행되는 것에 의해 제조된다.

여기서, 상기 반사 영역(R)의 형성은 레진막(6)에의 비아(13) 형성, 엠보싱(16) 형성, 그리고, 반사전극(11) 형성으로 인해 투과 영역(T)의 형성에 비해 적어도 3장의 마스크를 더 필요로 한다.

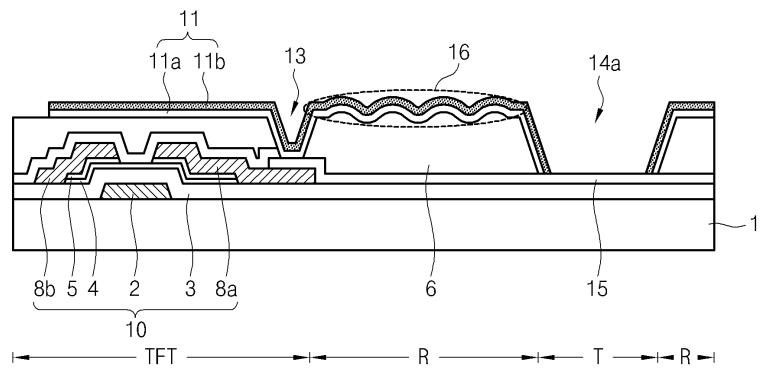

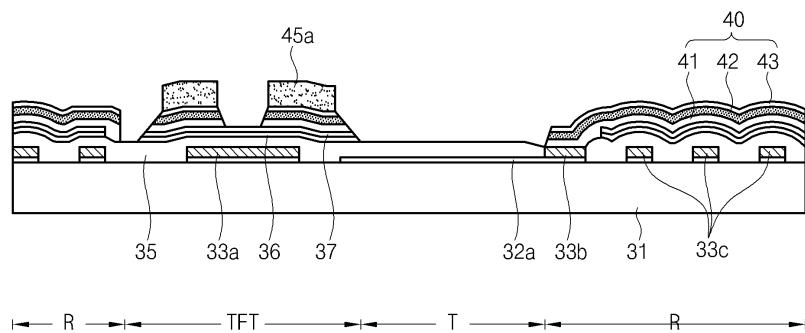

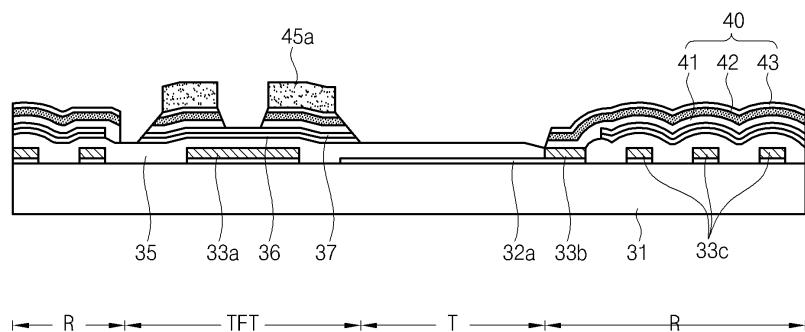

도 3은 종래 반투과형 FFS 모드 액정표시장치의 어레이기판을 도시한 단면도로서, 이 구조의 경우는 게이트전극(2)을 포함한 게이트라인과 공통전극라인(2a) 및 반사 영역(R)에의 엠보싱 패턴(2b)을 형성하기 위한 제1마스크 공정, 액티브 패턴을 형성하기 위한 제2마스크 공정, 소오스/드레인전극(8a, 8b)을 포함한 데이터라인을 형성하기 위한 제3마스크 공정, 공통전극라인(2a)을 노출시키는 비아(9) 형성을 위한 제4마스크 공정, 투과 영역(T)에의 플레이트형 카운터전극(17)을 형성하기 위한 제5마스크 공정, 반사 영역(R)에의 반사전극(11)을 형성하기 위한 제6마스크 공정, 소오스/드레인전극(8a, 8b)을 노출시키는 비아(13) 형성을 위한 제7마스크 공정, 그리고, 투과 영역(T) 및 반사 영역(R)에의 슬릿형 화소전극(15)을 형성하기 위한 제8마스크 공정이 차례로 수행되는 것에 의해 제조된다.

여기서, FFS 모드의 경우에 반사 영역(R)의 형성은 투과 영역(T)의 형성에 비해 공통전극라인(2a)을 노출시키는 레진막(6)에의 비아(9) 형성 및 반사전극(11) 형성을 위해 최소한 2장의 마스크가 더 필요하며, 그래서, 기판 전체로는 8장 이상의 마스크를 필요로 한다.

그러므로, 종래의 반투과형 액정표시장치는 그의 어레이기판 제작시에 최소한 8장 이상의 마스크를 필요로 하며, 주지된 바와 같이, 각 마스크 공정은 그 자체로 감광막 도포 공정, 기 도포된 감광막에 대한 마스크를 이용한 노광 공정 및 노광된 감광막에 대한 현상 공정, 그리고, 소프트 베이크, 하드 베이크 등의 열공정을 포함하므로, 결과적으로, 8장 이상의 마스크를 필요로 하는 종래 반투과형 액정표시장치의 어레이기판 제조방법은 매우 복잡할 뿐만 아니라, 비용 측면에서도 바람직하지 못하다.

도 2 및 도 3에서, 미설명된 도면부호 1은 유리기판, 3은 게이트절연막, 4는 채널층, 5는 오믹층, 10은 박막트랜지스터, 11a는 Al금속막, 11b는 Mo금속막, 12는 보호막, 그리고, 14a는 개구부를 각각 나타낸다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기한 바와 같은 종래의 제반 문제점을 해결하기 위해 안출된 것으로, 소오스/드레인용 금속막으로 반사전극을 함께 형성하면서도 투과 영역에서의 콘택저항을 개선시킴과 아울러 반사 영역에서의 반사율 특성을 개선시킬 수 있는 반투과형 액정표시장치의 어레이기판 제조방법을 제공함에 그 목적이 있다.

또한, 본 발명은 투과 영역에서의 콘택저항을 개선시킴과 아울러 반사 영역에서의 반사율 특성을 개선시킴으로써 안정적인 동작이 이루어지도록 함과 아울러 우수한 화면품위를 확보할 수 있는 반투과형 액정표시장치의 어레이기판 제조방법을 제공함에 그 다른 목적이 있다.

계다가, 본 발명은 마스크 공정 수를 줄임으로써 공정 단순화를 이룸과 아울러 제조비용을 절감할 수 있는 반투과형 액정표시장치의 어레이기판 제조방법을 제공함에 그 또 다른 목적이 있다.

### 발명의 구성

상기와 같은 목적을 달성하기 위하여, 본 발명은, 화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 ITO막과 게이트용 금속막을 차례로 형성하는 단계; 상기 게이트용 금속막과 ITO막에 대해 하프톤 노광 기술을 적용한 제1마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인 및 공통전극라인을 형성함과 아울러 투과 영역에 배치되는 ITO의 플레이트형 카운터전극 및 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계; 상기 게이트전극을 포함한 게이트라인, 공통전극라인, 카운터전극 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계; 상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제2마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계; 상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계; 상기 3층막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 Al막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계; 상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계; 상기 보호막에 대해 제4마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계; 상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및 상기 ITO막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택됨과 아울러 투과 영역 및 반사 영역 모두에 배치되는 슬릿형의 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법을 제공한다.

여기서, 상기 게이트전극을 포함한 게이트라인 및 공통전극라인과 엠보싱 패턴을 형성하는 단계는, 상기 게이트용 금속막 상에 하프톤 노광 공정을 적용해서 카운터전극 형성 영역을 가리는 부분이 게이트전극을 포함한 게이트라인 형성 영역과 공통전극라인 형성 영역 및 엠보싱 패턴 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제1감광막패턴을 형성하는 단계; 상기 제1감광막패턴을 식각마스크로 이용해서 게이트용 금속막과 ITO막을 식각하여 게이트전극을 포함한 게이트라인과 공통전극라인 및 엠보싱 패턴을 형성하는 단계; 상기 제1감광막패턴에 대해 카운터전극 형성 영역을 가리는 부분이 제거되도록 예상하는 단계; 상기 예상된 제1감광막패턴을 식각마스크로 이용해서 카운터전극 상의 게이트용 금속막을 제거하는 단계; 및 상기 잔류된 제1감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 한다.

상기 제1비아홀 및 액티브 패턴을 형성하는 단계는, 상기 도핑된 비정질실리콘막 상에 하프톤 노광 공정을 적용해서 투과 영역을 가리는 부분이 액티브 패턴 형성 영역 및 반사전극 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제2감광막패턴을 형성하는 단계; 상기 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막을 식각하여 공통전극라인을 노출시키는 제1비아홀을 형성하는 단계; 상기 제2감광막패턴에 대해 투과 영역 상에 형성된 부분이 제거되도록 예상하는 단계; 상기 예상된 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막을 식각하여 액티브 패턴을 형성하는 단계; 및 상기 잔류된 제2감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 한다.

상기 소오스/드레인전극을 포함한 데이터라인과 반사전극을 형성하는 단계는, 상기 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막 상에 하프톤 노광 공정을 적용해서 반사전극 형성 영역을 가리는 부분이 소오스/드레인전극을 포함한 데이터라인 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제3감광막패턴을 형성하는 단계; 상기 제3감광막패턴을 식각마스크로 이용해서 3층막을 식각하여 소오스/드레인전극을 포함한 데이터라인을 형성하는 단계; 상기 제3감광막패턴에 대해 반사전극 형성 영역에 형성된 제3감광막패턴이 제거되도록 예상하는 단계; 상기 예상된 제3감광막패턴을 식각마스크로 이용해서 반사 영역의 탑-Mo막을 식각하여 바텀-Mo막과 AI막의 2층막으로 이루어진 반사전극을 형성하는 단계; 및 상기 잔류된 제3감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 한다.

상기 바텀-Mo막은 500~700Å 두께로 형성하고, 상기 AI막은 1400~1600Å 두께로 형성하며, 그리고, 상기 탑-Mo막은 100~200Å 두께로 형성하는 것을 특징으로 한다.

상기 반사전극은 상기 엠보싱 패턴에 의해 엠보싱을 갖도록 형성되는 것을 특징으로 한다.

상기 투과 영역 및 반사 영역은 각각 카운터전극과 화소전극 및 반사전극과 화소전극 사이의 수평 전계에 의한 FFS 모드로 구동되는 것을 특징으로 한다.

또한, 상기와 같은 목적을 달성하기 위하여, 본 발명은, 화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 ITO막과 게이트용 금속막을 차례로 형성하는 단계; 상기 게이트용 금속막 상에 ITO막을 형성하는 단계; 상기 ITO막에 대해 제1마스크 공정 및 식각 공정을 진행해서 투과 영역에 ITO의 플레이형 카운터전극을 형성하는 단계; 상기 카운터전극이 형성된 유리기판 상에 게이트용 금속막을 형성하는 단계; 상기 게이트용 금속막에 대해 제2마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인과 공통전극라인 및 반사 영역에 배치되는 엠보싱 패턴을 형성하는 단계; 상기 게이트전극을 포함한 게이트라인, 공통전극라인, 카운터전극 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계; 상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계; 상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계; 상기 3층막에 대해 하프톤 노광 기술을 적용한 제4마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 AI막 및 탑-Mo막의 3층 막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 AI막의 2층막으로 이루어진 반사전극을 형성하는 단계; 상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계; 상기 보호막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계; 상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및 상기 ITO막에 대해 제6마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트되는 슬릿형의 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법을 제공한다.

게다가, 상기와 같은 목적을 달성하기 위하여, 본 발명은, 화소부가 박막트랜지스터 영역, 반사 영역 및 투과 영역으로 구획된 유리기판 상에 게이트용 금속막을 형성하는 단계; 상기 게이트용 금속막에 대해 제1마스크 공정 및 식각 공정을 진행해서 게이트전극을 포함한 게이트라인 및 공통전극라인을 형성함과 아울러 반사 영역에 배치되는 엠보싱 패턴을 형성하는

단계; 상기 게이트전극을 포함한 게이트라인과 공통전극라인 및 엠보싱 패턴이 형성된 유리기판의 전면 상에 게이트절연막과 비정질실리콘막 및 도핑된 비정질실리콘막을 차례로 형성하는 단계; 상기 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막에 대해 하프톤 노광 기술을 적용한 제2마스크 공정 및 식각 공정을 진행해서 공통전극라인을 노출시키는 제1비아홀을 형성함과 아울러 박막트랜지스터 영역에 액티브 패턴을 형성하는 단계; 상기 제1비아홀 및 액티브 패턴을 포함한 게이트절연막 상에 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막을 형성하는 단계; 상기 3층막에 대해 하프톤 노광 기술을 적용한 제3마스크 공정 및 식각 공정을 진행해서 바텀-Mo막과 Al막 및 탑-Mo막의 3층막으로 이루어진 소오스/드레인전극을 포함한 데이터라인을 형성하여 박막트랜지스터를 구성함과 아울러 반사 영역에 배치되는 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계; 상기 소오스/드레인전극 및 반사전극이 형성된 결과물의 전면 상에 보호막을 형성하는 단계; 상기 보호막에 대해 제4마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극을 노출시키는 제2비아홀을 형성하는 단계; 상기 제2비아홀을 포함한 보호막 상에 ITO막을 형성하는 단계; 및 상기 ITO막에 대해 제5마스크 공정 및 식각 공정을 진행해서 소오스/드레인전극과 콘택트와 아울러 투과 영역에 배치되는 화소전극을 형성하는 단계;를 포함하는 것을 특징으로 하는 반투과형 액정표시장치의 어레이기판 제조방법을 제공한다.

여기서, 상기 제1비아홀 및 액티브 패턴을 형성하는 단계는, 상기 도핑된 비정질실리콘막 상에 하프톤 노광 공정을 적용해서 투과 영역을 가리는 부분이 액티브 패턴 형성 영역 및 반사전극 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제2감광막패턴을 형성하는 단계; 상기 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막 및 게이트절연막을 식각하여 공통전극라인을 노출시키는 제1비아홀을 형성하는 단계; 상기 제2감광막패턴에 대해 투과 영역 상에 형성된 부분이 제거되도록 예상하는 단계; 상기 예상된 제2감광막패턴을 식각마스크로 이용해서 도핑된 비정질실리콘막과 비정질실리콘막을 식각하여 액티브 패턴을 형성하는 단계; 및 상기 잔류된 제2감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 한다.

상기 소오스/드레인전극을 포함한 데이터라인과 반사전극을 형성하는 단계는, 상기 바텀-Mo막과 Al막 및 탑-Mo막이 차례로 형성된 3층막 상에 하프톤 노광 공정을 적용해서 반사전극 형성 영역을 가리는 부분이 소오스/드레인전극을 포함한 데이터라인 형성 영역을 가리는 부분 보다 상대적으로 얇은 두께를 갖는 제3감광막패턴을 형성하는 단계; 상기 제3감광막패턴을 식각마스크로 이용해서 3층막을 식각하여 소오스/드레인전극을 포함한 데이터라인을 형성하는 단계; 상기 제3감광막패턴에 대해 반사전극 형성 영역에 형성된 제3감광막패턴이 제거되도록 예상하는 단계; 상기 예상된 제3감광막패턴을 식각마스크로 이용해서 반사 영역의 탑-Mo막을 식각하여 바텀-Mo막과 Al막의 2층막으로 이루어진 반사전극을 형성하는 단계; 및 상기 잔류된 제3감광막패턴을 제거하는 단계;로 구성되는 것을 특징으로 한다.

상기 바텀-Mo막은 500~700Å 두께로 형성하고, 상기 Al막은 1400~1600Å 두께로 형성하며, 그리고, 상기 탑-Mo막은 100~200Å 두께로 형성하는 것을 특징으로 한다.

상기 반사전극은 상기 엠보싱 패턴에 의해 엠보싱을 갖도록 형성되는 것을 특징으로 한다.

상기 투과 영역 및 반사 영역은 TN 모드로 구동되는 것을 특징으로 한다.

(실시예)

이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세하게 설명하도록 한다.

먼저, 본 발명은 소오스/드레인 및 반사전극을 형성하기 위한 물질로서 Mo-Al-Mo의 3층막을 적용하되, 반사 영역에서는 탑-Mo를 제거해서 반사도가 높은 Al금속막이 노출되도록 하고, 박막트랜지스터 영역에서는 상기 탑-Mo가 그대로 존재 토록 한다. 이렇게 하면, 본 발명은 반사 영역에서의 우수한 반사도를 확보할 수 있음은 물론 박막트랜지스터 영역에서의 양호한 전기적 콘택트가 이루어지도록 할 수 있으며, 그래서, 제품의 화면품위를 향상시킬 수 있을 뿐만 아니라 저가의 Mo와 Al을 사용하는 것으로부터 생산 원가의 증가 또한 방지할 수 있다.

또한, 본 발명은 하프톤(Half Tone) 노광 기술을 이용해서 반투과형 액정표시장치의 어레이기판을 제작한다. 이렇게 하면, 본 발명은 대략 5~6장의 마스크 공정을 이용하는 것만으로도 어레이기판의 제작이 가능하므로, 감소된 마스크 수 및 공정 수 만큼 제조비용을 절감할 수 있음은 물론 공정 단순화를 이룰 수 있다.

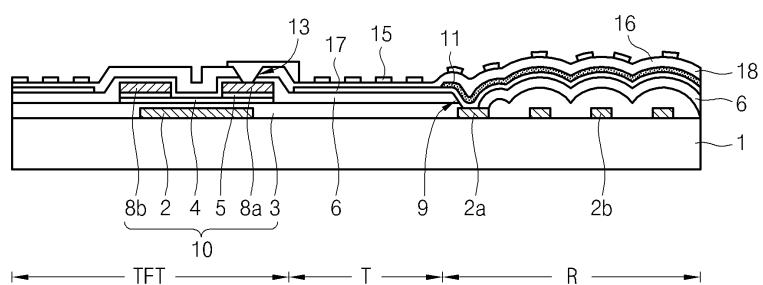

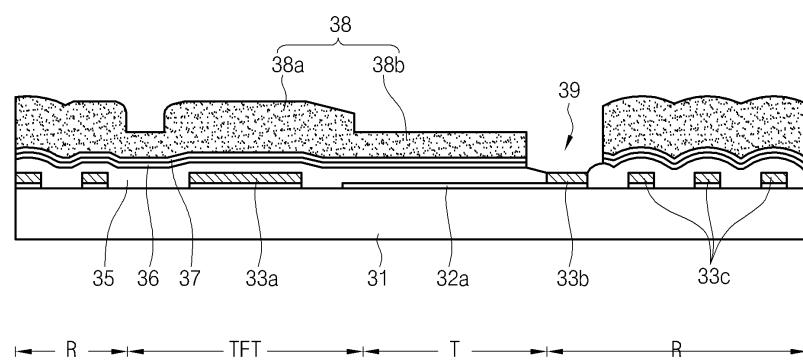

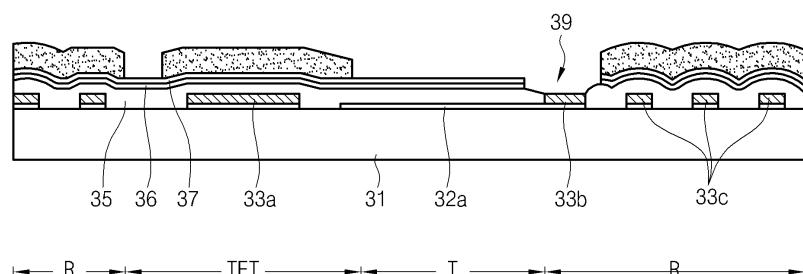

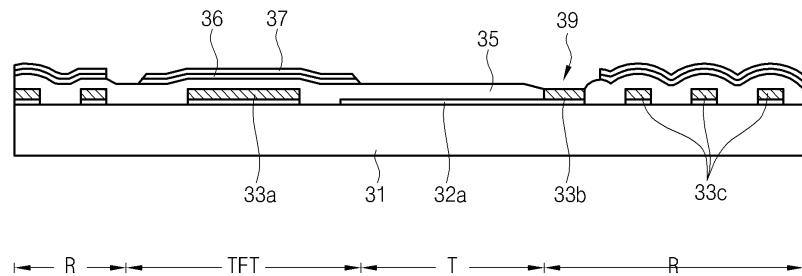

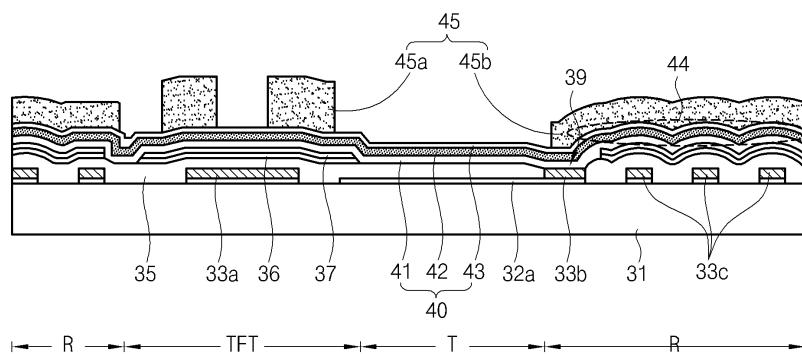

자세하게, 도 4a 내지 도 4l은 본 발명의 일실시예에 따른 반투과형 FFS 모드 액정표시장치의 어레이기판 제조방법을 도시한 공정별 단면도로서, 이를 설명하면 다음과 같다.

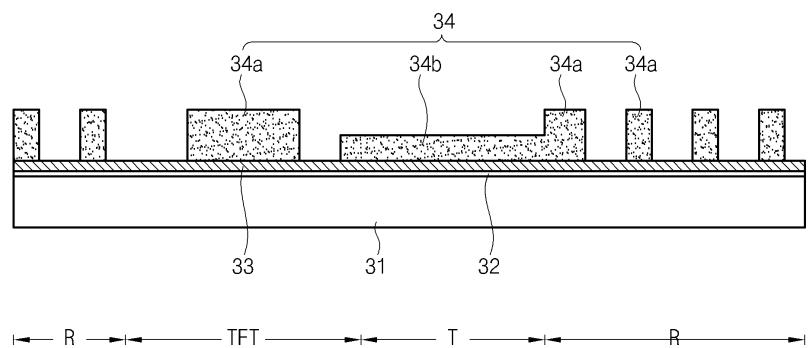

도 4a를 참조하면, 화소부가 박막트랜지스터 영역(TFT), 반사 영역(R) 및 투과 영역(T)으로 구획된 유리기판(31) 상에 ITO막(32)과 게이트용 금속막(33)을 차례로 증착한다. 그런 다음, 도시하지는 않았으나 제1마스크를 이용해서 상기 게이트용 금속막(33) 상에 게이트전극을 포함한 게이트라인 형성 영역 및 공통전극라인 형성 영역과 반사 영역(R)에서의 엠보싱 형성을 위한 엠보싱 패턴 형성 영역을 가리면서 투과 영역(R)에서의 카운터전극 형성 영역을 가리는 제1감광막패턴(34)을 형성한다. 이때, 상기 제1감광막패턴(34)은 하프톤 노광 공정을 적용해서 카운터전극 형성 영역을 가리는 제1감광막패턴 부분(34b)이 그 이외 부분, 즉, 게이트전극을 포함한 게이트라인 형성 영역과 공통전극라인 형성 영역 및 엠보싱 패턴 형성 영역을 가리는 제1감광막패턴 부분(34a) 보다 상대적으로 얇은 두께를 갖도록 형성한다.

도 4b를 참조하면, 식각마스크로서 제1감광막패턴을 이용해서 게이트용 금속막 및 ITO막을 식각하고, 이를 통해, 게이트전극(33a)을 포함한 게이트라인(도시안됨) 및 공통전극라인(33b)을 형성함과 아울러 반사 영역(R)에 엠보싱 패턴(33c)을 형성한다. 그런 다음, 상기 결과물에 대해 애싱(ashing) 공정을 진행해서 투과 영역(R)에 형성된 제1감광막패턴 부분을 제거한다. 이때, 상기 게이트전극(33a)을 포함한 게이트라인과 공통전극라인(33b) 및 엠보싱 패턴(33c) 상의 제1감광막패턴 부분(34a)은 투과 영역(T)의 카운터전극 형성 영역 상에 형성된 제1감광막패턴 부분 보다 상대적으로 두껍게 형성되었기 때문에 완전히 제거되지 않고 일부 두께가 잔류된다.

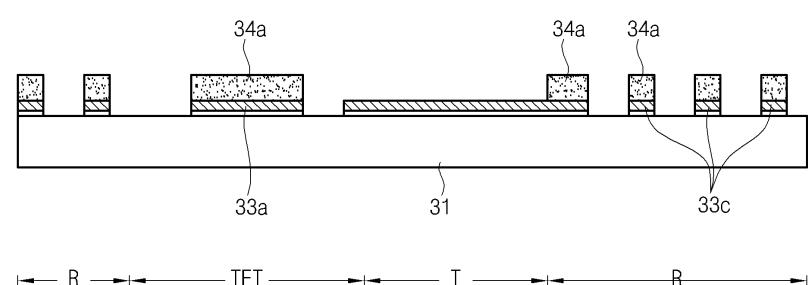

도 4c를 참조하면, 잔류된 제1감광막패턴(34a)을 식각마스크로 이용해서 노출된 투과 영역(T) 상의 게이트용 금속막을 제거하고, 이를 통해, 상기 투과 영역(T)에 ITO막으로 이루어진 플레이트형의 카운터전극(32a)을 형성한다.

도 4d를 참조하면, 공지의 공정에 따라 잔류된 제1감광막패턴을 제거한다. 그런 다음, 게이트전극(33a)을 포함한 게이트라인, 공통전극라인(33b), 엠보싱 패턴(33c) 및 카운터전극(32a)이 형성된 유리기판(31)의 전면 상에 게이트절연막(35)과 액티브층, 즉, 비정질실리콘층(36)과 도핑된 비정질실리콘층(37)을 차례로 형성한다. 이때, 반사 영역(R)에 엠보싱 패턴(33c)이 형성되어 있는 것과 관련해서 상기 반사 영역(R)에 형성된 게이트절연막(35) 및 액티브층(36, 37)은 그 표면이 굽곡지게 된다.

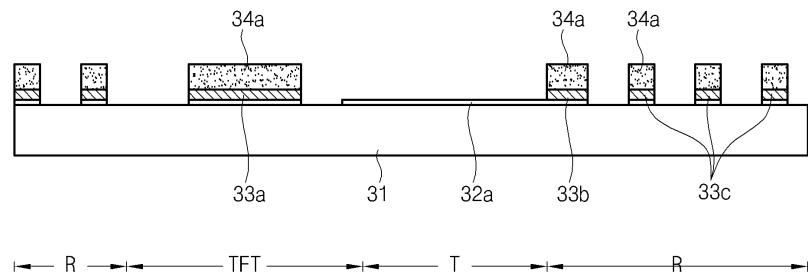

도 4e를 참조하면, 제2마스크를 이용해서 도핑된 비정질실리콘층(37) 상에 공통전극라인(33b) 상부 영역을 노출시키는 제2감광막패턴(38)을 형성한다. 이때, 상기 제2감광막패턴(38)은 하프톤 노광 기술을 적용해서 투과 영역(T)을 가리도록 형성된 부분(38b)이 액티브 패턴 형성 영역 및 반사전극 형성 영역을 가리는 부분(38a) 보다 상대적으로 얇은 두께를 갖도록 형성한다. 그런 다음, 식각마스크로서 상기 제2감광막패턴(38)을 이용해서 액티브층(37, 36) 및 게이트절연막(35)을 식각하여 공통전극라인(33b)을 노출시키는 제1비아홀(39)을 형성한다.

도 4f를 참조하면, 상기 제1비아홀(39)이 형성된 결과물에 대해 애싱 공정을 진행해서 투과 영역(T) 상에 형성된 제2감광막패턴 부분을 제거한다. 이때, 상기 투과 영역(T) 이외의 지역에 형성된 제2감광막패턴은 상대적으로 두껍게 형성되어 있었기 때문에 완전히 제거되지 않고 일부 두께가 잔류된다.

도 4g를 참조하면, 잔류된 제2감광막패턴를 식각마스크로 이용해서 도핑된 비정질실리콘막과 그 아래의 비정질실리콘막을 식각해서 액티브 패턴을 형성한다. 그런 다음, 상기 식각마스크로 이용된 제2감광막패턴을 제거한다.

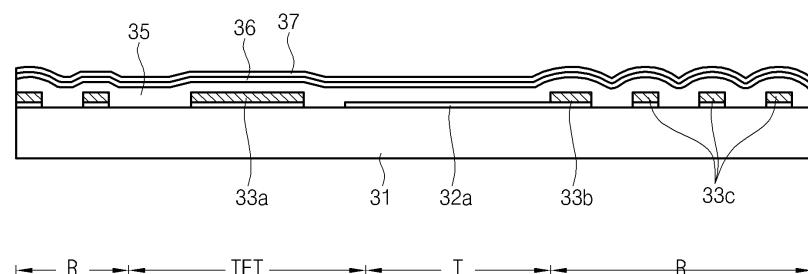

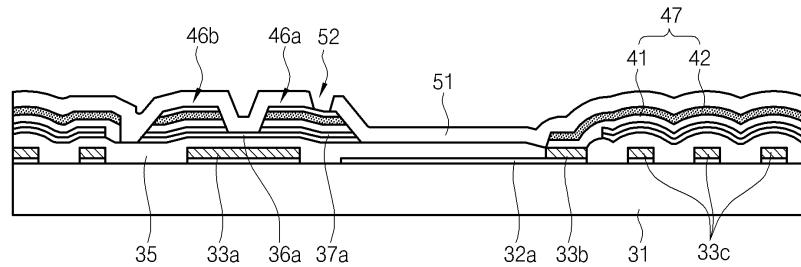

도 4h를 참조하면, 액티브 패턴 및 제1비아홀(39)이 형성된 결과물의 전면 상에 소오스/드레인용 금속막(40)을 형성한다. 여기서, 상기 소오스/드레인용 금속막(40)은 3층막 구조로 형성하며, 실질적인 배선 물질인 제2층막으로는 전기전도도가 우수할 뿐만 아니라 반사율이 우수한 Al 계열의 막을 적용하여, 상기 Al계 금속막 아래에 배치되는 제1층막은 상기 Al계 금속막이 게이트절연막(35)과 불필요한 반응이 일어나는 것이 억제되도록 Mo 계열의 금속막을 이용하여, 그리고, Al계 금속막 위에 배치되는 제3층막은 화소전극 물질인 ITO와의 전기적 연결이 용이하도록 Mo 계열의 금속막을 이용한다. 예컨데, Mo-Al-Mo의 3층 구조에서 바텀-Mo막(41)은 500~700Å, 바람직하게, 600Å의 두께로, Al막(42)은 1400~1600Å, 바람직하게, 1500Å의 두께, 그리고, 탑-Mo막(43)은 후속 공정에서의 그 제거가 용이하도록 100~200Å의 두께로 형성한다.

이때, 상기 3층 구조의 소오스/드레인용 금속막(40)은 제1비아홀(39)을 통해 공통전극라인(33b)과 연결된다. 또한, 반사 영역(R)에 형성된 소오스/드레인용 금속막 부분은 하지층이 표면 굽곡을 가지고 있는 것과 관련해서 그 자신 또한 표면 굽곡, 즉, 엠보싱(44)을 갖게 된다.

계속해서, 제3마스크를 이용해서 상기 소오스/드레인용 금속막(40) 상에 소오스/드레인전극을 포함한 데이터라인 형성 영역 및 반사전극 형성 영역을 노출시키는 제3감광막패턴(45)을 형성한다. 이때, 상기 제3감광막패턴(45)은 하프톤 노광 기술을 적용해서 반사전극 형성 영역에 부분(45b)이 그 이외 지역에 형성된 부분(45a) 보다 상대적으로 얇은 두께를 갖도록 형성한다.

도 4i를 참조하면, 식각마스크로서 상기 제3감광막패턴을 이용해서 3층 구조의 소오스/드레인용 금속막을 습식식각하여 소오스/드레인전극(46a, 46b)을 포함한 데이터라인(도시안됨)을 형성한다. 이때, 반사 영역(R)에는 3층 구조의 소오스/드레인용 금속막이 잔류된다. 그 다음, 상기 소오스/드레인전극(46a, 46b)이 형성된 결과물에 대해 예상 공정을 진행해서 투과 영역(T) 상에 형성된 제3감광막패턴 부분을 제거한다. 이때, 상기 투과 영역(T) 이외의 지역에 형성된 제3감광막패턴은 상대적으로 두껍게 형성되어 있었기 때문에 완전히 제거되지 않고 일부 두께가 잔류된다.

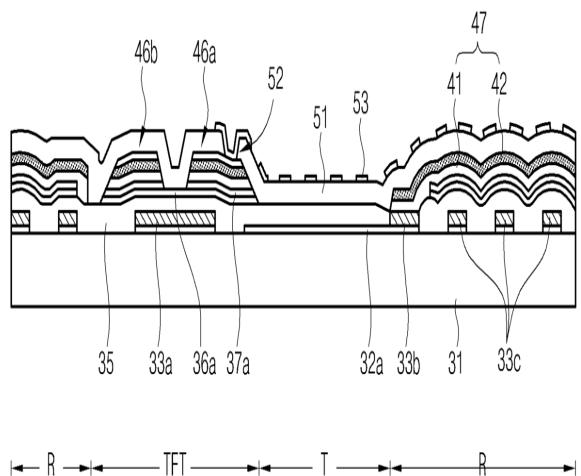

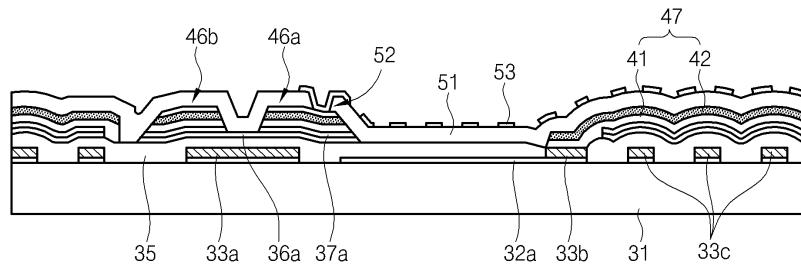

도 4j를 참조하면, 국부적으로 잔류된 제3감광막패턴을 식각마스크로 이용해서 결과물에 대해 건식식각을 진행하고, 이를 통해, 반사 영역(R)에서의 탑-Mo를 제거해서 바텀-Mo막(41)과 Al막(42)의 2층막으로 이루어진 반사전극(47)을 형성하고, 이와 동시에, 박막트랜지스터 영역(TFT)에서의 도핑된 비정질실리콘층을 식각하여 오믹층(37a)과 채널층(36a)을 형성하여 박막트랜지스터(50)를 구성한다. 그런 다음, 상기 국부적으로 잔류된 제3감광막패턴을 제거한다.

여기서, 본 발명에 따른 반사 영역(R)에서의 반사전극(47)은 바텀-Mo막(41)과 Al막(42)의 2층막으로 이루어지며, 특히, 상부에 Al막(42)이 배치되기 때문에 우수한 반사율 특성을 갖는다. 또한, 본 발명에 따른 박막트랜지스터 영역(TFT)에서의 소오스/드레인전극(46a, 46b)은 바텀-Mo막(41)과 Al막(42) 및 탑-Mo막(43)의 3층막으로 이루어지며, 특히, 상부에 Mo막이 배치되기 때문에 후속에서 형성될 ITO 화소전극과 양호한 전기적 콘택을 이룰 수 있다.

도 4k를 참조하면, 반사전극(47) 및 박막트랜지스터(50)가 형성된 결과물의 전면 상에 실리콘질화막과 같은 무기절연물질로 이루어진 보호막(51)을 약 2000Å의 두께로 형성한다. 그런 다음, 제4마스크를 이용해서 상기 보호막(51)을 식각하여, 예컨대, 박막트랜지스터(50)의 소오스전극(46a) 상부를 노출시키는 제4감광막패턴(도시안됨)을 형성한 후, 상기 제4감광막패턴을 식각마스크로 이용해서 상기 보호막(51)을 식각하고, 이를 통해, 상기 박막트랜지스터(50)의 소오스전극(46a)을 노출시키는 제2비아홀(52)를 형성한다. 이어서, 상기 식각마스크로 이용된 제4감광막패턴을 제거한다.

도 4l를 참조하면, 제2비아홀(52)을 포함한 보호막(51) 상에 ITO막을 증착한다. 그런 다음, 상기 ITO막 상에 제5마스크를 이용해서 투과 영역(T)에서의 제1화소전극 형성 영역 및 반사 영역(R)에서의 제2화소전극 형성 영역을 가리는 제5감광막패턴을 형성한 후, 이러한 제5감광막패턴을 식각마스크로 이용해서 ITO막을 식각하여 투과 영역(T) 및 반사 영역(R)에 슬릿형의 화소전극(53)을 형성한다.

그리고나서, 상기 제5감광막패턴을 제거하여 본 발명의 일실시예에 따른 반투과형 FFS 모드 액정표시장치의 어레이기판 제조를 완성한다.

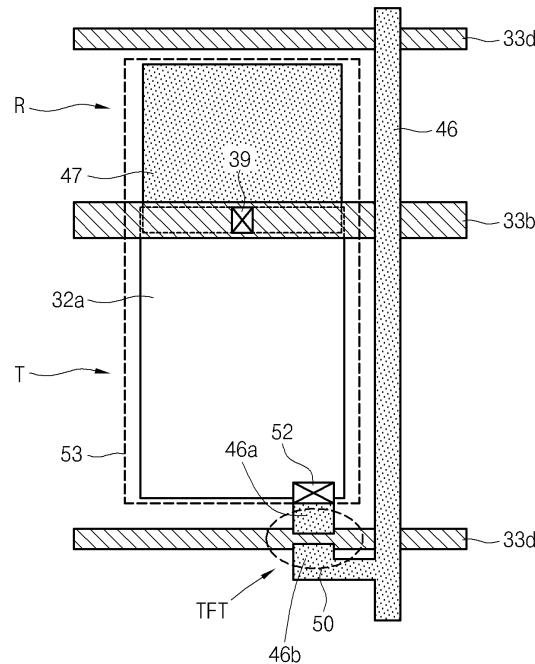

도 5는 도 4l에 대응하는 평면도로서, 도시된 바와 같이, 게이트라인(33d)과 데이터라인(46)이 교차하도록 배열되어 있고, 공통전극라인(33b)이 상기 게이트라인(33d)과 평행하도록 배열되어 있으며, 상기 게이트라인(33d)과 데이터라인(46)의 교차부에는 박막트랜지스터(50)가 배치되어져 있고, 투과 영역(T)에는 ITO의 카운터전극(32a)이 배치되어져 있으며, 반사 영역(R)에는 제1비아홀(39)을 통해 공통전극라인(33b)과 콘택되게 반사전극(47)이 배치되어져 있다.

그리고, 게이트라인(33d)과 데이터라인(46)에 의해 구획된 화소영역 내에는 ITO의 화소전극(53)이 배치되어져 있다.

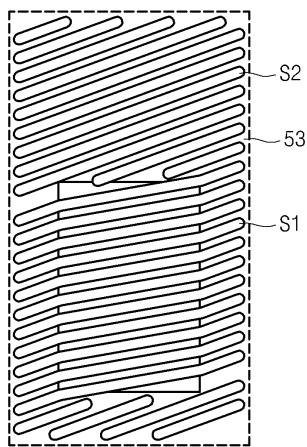

여기서, 상기 화소전극(53)은, 도 6에 도시된 바와 같이, 반사 영역(R) 및 투과 영역(T) 모두에서 일정 기울기를 갖는 다수의 슬릿들(S1, S2)을 구비한 슬릿형 구조로 이루어지며, 특별히, 투과 영역(T)에서의 슬릿(S1)은 꺾여지면서 반사 영역(R)에서의 슬릿(S2) 보다 수평면에 대해 낮은 기울기를 갖도록 구비된다.

전술한 바와 같은 본 발명의 일실시예에 따른 반투과형 FFS 모드 액정표시장치의 어레이기판 제조방법에 따르면, 반사전극(47)을 소오스/드레인용 금속막으로 형성하면서도 반사 영역(R)에서의 반사전극(47)은 Mo와 Al의 2층막으로 이루어지도록 함으로써 우수한 반사율 특성을 나타내도록 할 수 있고, 또한, 박막트랜지스터 영역(TFT)에서는 Mo-Al-Mo의 3층막으로 이루어지도록 함으로써 ITO의 화소전극과 양호한 콘택이 이루어지도록 할 수 있다.

아울러, 본 발명의 방법에 따르면, 5장의 마스크를 사용해서 어레이기판을 제조하므로, 최소 8장의 마스크를 사용해야 하는 종래 기술과 비교해 적어도 3장 이상의 마스크를 줄일 수 있으며, 이에 따라, 제조비용을 절감할 수 있음은 물론 공정 단순화를 이룰 수 있다.

한편, 전술한 본 발명의 일실시예에서는 게이트전극을 포함한 게이트라인, 공통전극라인, 엠보싱패턴 및 ITO의 카운터전극을 하프톤 기술을 적용한 제1마스크 공정을 통해 형성하였지만, 본 발명의 다른 실시예로서 하나의 마스크를 이용해 ITO의 카운터전극을 형성한 후, 또 다른 마스크를 이용해 나머지 게이트전극을 포함한 게이트전극, 공통전극라인 및 엠보싱 패턴을 형성하고, 이후, 전술한 본 발명의 일실시예와 동일한 후속 공정들을 진행하여 어레이기판을 제작할 수 있다.

이 경우, 본 발명의 다른 실시예는 총 6장의 마스크를 필요로 하게 되며, 따라서, 종래 기술과 비교해서 2장의 마스크를 줄일 수 있으므로, 여전히 제조비용을 절감할 수 있음은 물론 공정 단순화를 이룰 수 있다.

또한, 전술한 실시예들은 투과 영역 및 반사 영역이 각각 카운터전극과 화소전극 사이 및 반사전극과 화소전극 사이의 수평 전계에 의한 구동되는 FFS 모드에 대해 설명한 것이지만, 본 발명은 반투과형 TN 모드 액정표시장치의 어레이기판 제조방법에도 적용 가능하다.

즉, 자세하게 도시하고 설명하지는 않지만, TN 모드는 FFS 모드와 달리 ITO의 카운터전극 형성이 필요치 않으므로, 전술한 일실시예에서의 제1마스크를 이용한 공정 진행시, 하프톤 노광 기술을 적용하지 않아도 되며, 아울러, 제5마스크를 이용한 공정 진행시, 화소전극은 반사 영역에는 형성함이 없이 투과 영역에만 형성하면 된다. 그 이외에, 나머지 제2마스크 공정, 제3마스크 공정 및 제4마스크 공정은 일실시예와 동일한 방법으로 진행한다.

게다가, 전술한 본 발명의 일실시예에서는 소오스/드레인전극을 포함한 데이터라인 및 반사전극을 형성하기 위한 제3마스크 공정시 하프톤 노광 기술을 적용해서 반사 영역에서의 탑-Mo를 선택적으로 제거하였으나, 전형적인 노광 기술을 적용해서 반사 영역에서의 탑-Mo를 제거함은 물론 박막트랜지스터 영역에서의 탑-Mo 또한 제거하는 것도 가능하다. 이것은 순수 AI의 경우는 ITO와의 콘택저항이 높아서 문제를 일으킬 수 있지만, 순수 AI 상에 Mo를 증착한 후에 상기 Mo를 제거하게 되면, 스퍼터에 의해 AI의 표면에 박힌 Mo 입자는 완전히 제거되고 잔류되는 바, 이와같은 AI에 ITO를 콘택시키는 경우에는 표면 Mo 입자에 의해 콘택저항을 낮출 수 있기 때문이다.

### 발명의 효과

이상에서와 같이, 본 발명은 소오스/드레인용 금속막으로 반사전극을 형성하되 상기 소오스/드레인용 금속으로서 Mo-Al-Mo의 3층막을 적용하면서 선택적으로 반사 영역에서의 탑-Mo를 제거해줌으로써 반사 영역에서의 우수한 반사율 특성을 확보할 수 있음은 물론 박막트랜지스터 영역에서 양호한 전기적 콘택이 이루어지도록 할 수 있으며, 그래서, 제품의 화면품위를 향상시킬 수 있다.

또한, 본 발명은 하프톤 노광 기술을 이용해 대략 5~6장의 마스크 공정을 이용하는 것으로 어레이기판을 제작함으로써 8~11장의 마스크를 필요로 하는 종래와 비교해 마스크 수를 줄일 수 있으며, 그에 따라, 절감된 마스크 수 및 공정 수 만큼 제조비용을 줄일 수 있음은 물론 공정 단순화를 이룰 수 있다.

이상, 여기에서는 본 발명을 특정 실시예에 관련하여 도시하고 설명하였지만, 본 발명이 그에 한정되는 것은 아니며, 이하의 특허청구의 범위는 본 발명의 정신과 분야를 이탈하지 않는 한도 내에서 본 발명이 다양하게 개조 및 변형될 수 있다는 것을 당업계에서 통상의 지식을 가진 자가 용이하게 알 수 있다.

### 도면의 간단한 설명

도 1은 종래 반투과형 TN(Twisted Nematic) 모드 액정표시장치의 어레이기판을 도시한 단면도.

도 2는 종래 다른 반투과형 TN 모드 액정표시장치의 어레이기판을 도시한 단면도.

도 3은 종래 반투과형 FFS(Fringe Field Switching) 모드 액정표시장치의 어레이기판을 도시한 단면도.

도 4a 내지 도 4l는 본 발명의 일실시예에 따른 반투과형 FFS 모드 액정표시장치의 어레이기판 제조방법을 설명하기 위한 공정별 단면도.

도 5는 도 4l에 대응하는 평면도.

도 6은 도 5에서의 화소전극을 도시한 평면도.

\* 도면의 주요 부분에 대한 부호의 설명 \*

31 : 유리기판 32 : ITO막

32a : 카운터전극 33 : 게이트용 금속막

33a : 게이트전극 33b : 공통전극라인

33c : 엠보싱 패턴 33d : 게이트라인

34 : 제1감광막패턴 35 : 게이트절연막

36 : 비정질실리콘막 37 : 도핑된 비정질실리콘막

38 : 제2감광막패턴 39 : 제1비아홀

40 : 소오스/드레인용 금속막 41 : 제1층막

42 : 제2층막 43 : 제3층막

44 : 엠보싱 45 : 제3감광막패턴

46 : 데이터라인 46a : 소오스전극

46b : 드레인전극 47 : 반사전극

50 : 박막트랜지스터 51 : 보호막

52 : 비아홀 53 : 화소전극

## 도면

도면1

도면2

도면3

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면4g

도면4h

도면4i

도면4j

도면4k

← R → TFT → T → R →

도면4l

← R → TFT → T → R →

도면5

도면6

|                |                                            |         |            |

|----------------|--------------------------------------------|---------|------------|

| 专利名称(译)        | 半透射型液晶显示装置的阵列基板的制造方法                       |         |            |

| 公开(公告)号        | <a href="#">KR1020070050612A</a>           | 公开(公告)日 | 2007-05-16 |

| 申请号            | KR1020050108016                            | 申请日     | 2005-11-11 |

| [标]申请(专利权)人(译) | HYDIS TECH<br>HYDIS技术有限公司                  |         |            |

| 申请(专利权)人(译)    | 하이디스테크놀로지주식회사                              |         |            |

| 当前申请(专利权)人(译)  | 하이디스테크놀로지주식회사                              |         |            |

| [标]发明人         | KIM BYUNG HOON<br>김병훈<br>IHM SAM HO<br>임삼호 |         |            |

| 发明人            | 김병훈<br>임삼호                                 |         |            |

| IPC分类号         | G02F1/136                                  |         |            |

| CPC分类号         | G02F2001/136231 G02F1/134309 G02F1/133555  |         |            |

| 代理人(译)         | OH YONG SOO<br>郑某 , TAE HOON               |         |            |

| 其他公开文献         | KR100792300B1                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                  |         |            |

### 摘要(译)

本发明公开了一种半透半反型液晶显示装置的阵列基板的制作方法。形成布置在板型对电极中的压花图案的步骤和布置在透射区域中的ITO的反射区域形成栅极线和公共电极线，形成有源图案的步骤是应用第二掩模工艺的步骤。在玻璃基板的前侧依次形成栅极绝缘层和非晶硅膜以及掺杂的非晶硅膜的步骤，以及进行蚀刻处理并暴露公共电极线的半色调光刻和内部通孔形成，形成反射电极的步骤，该反射电极包括Al膜的2层反射区和底部-Mo膜，形成应用半色调光刻和数据线进行蚀刻处理的第三掩模工艺，包括由底部-Mo膜，Al膜和顶部-Mo膜的3层组成的源/漏电极，形成保护膜的步骤结果，形成第四掩模工艺和第二通孔的步骤进行蚀刻工艺并暴露出包括在本发明方法中的源/漏电极，像素，TFT区域，反射区域和在由透射区域和栅电极分割的玻璃基板上应用半色调光刻的第一掩模工艺，进行蚀刻工艺。包括形成ITO的滑动像素电极的步骤，进行蚀刻工艺并与源/接触漏电极和第五掩模处理。