#### US009488880B2

# (12) United States Patent

Nakayoshi et al.

#### (54) LIQUID CRYSTAL DISPLAY DEVICE, DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

(71) Applicants: Japan Display Inc., Tokyo (JP); Panasonic Liquid Crystal Display Co., Ltd., Himeji-shi, Hyogo-ken (JP)

(72) Inventors: **Yoshiaki Nakayoshi**, Ooamishirasato (JP); **Kazuhiko Yanagawa**, Mobara

(73) Assignees: Japan Display Inc., Tokyo (JP);

Panasonic Liquid Crystal Display Co.,

Ltd., Himeji-Shi, Hyogo-ken (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 14/942,120

(22) Filed: Nov. 16, 2015

#### (65) **Prior Publication Data**

US 2016/0077391 A1 Mar. 17, 2016

#### Related U.S. Application Data

(60) Continuation of application No. 14/708,348, filed on May 11, 2015, now Pat. No. 9,213,204, which is a continuation of application No. 14/285,006, filed on May 22, 2014, now Pat. No. 9,086,600, which is a

(Continued)

# (30) Foreign Application Priority Data

Oct. 15, 2001 (JP) ...... 2001-317147

(51) **Int. Cl.** *G02F 1/136* (2006.01) *G02F 1/1343* (2006.01)

(Continued)

# (10) Patent No.: US 9,488,880 B2

(45) **Date of Patent:** \*Nov. 8, 2016

(52) **U.S. Cl.** CPC ...... *G02F 1/134309* (2013.01); *G02F 1/1343* (2013.01); *G02F 1/1368* (2013.01); (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,060,036 A 5,185,601 A 10/1991 Choi 2/1993 Takeda et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1242854 A 3/1999 JP 2000-08408 9/1998 (Continued)

#### OTHER PUBLICATIONS

JPO Office Action dated Apr. 8, 2008, in Japanese. (Continued)

Primary Examiner — Lucy Chien (74) Attorney, Agent, or Firm — Juan Carlos A. Marquez; Marquez IP Law Office

# (57) ABSTRACT

Image display device having an electrode forming layer which includes a plurality of gate lines, a plurality of drain lines, a plurality of switching elements and the a plurality of pixel electrodes, and having reference electrode layer between the electrode forming layer and a substrate where the electrode forming layer formed thereon, and the reference electrode layer and the electrode forming layer are insulated by insulating layer.

#### 4 Claims, 63 Drawing Sheets

### Related U.S. Application Data

continuation of application No. 13/927,539, filed on Jun. 26, 2013, now Pat. No. 8,760,609, which is a continuation of application No. 13/650,203, filed on Oct. 12, 2012, now Pat. No. 8,493,522, which is a continuation of application No. 13/364,092, filed on Feb. 1, 2012, now Pat. No. 8,310,641, which is a continuation of application No. 12/926,735, filed on Dec. 7, 2010, now Pat. No. 8,248,549, which is a continuation of application No. 12/292,728, filed on Nov. 25, 2008, now Pat. No. 7,872,696, which is a division of application No. 11/976,884, filed on Oct. 29, 2007, now Pat. No. 7,605,876, which is a division of application No. 11/409,076, filed on Apr. 24, 2006, now Pat. No. 7,307,673, which is a division of application No. 11/211,574, filed on Aug. 26, 2005, now Pat. No. 7,423,701, which is a division of application No. 10/237,911, filed on Sep. 10, 2002, now Pat. No. 6,970,222.

# (51) **Int. Cl. G02F 1/1362** (2006.01) **G02F 1/1333** (2006.01) **G02F 1/1368** (2006.01) **G02F 1/13** (2006.01)

#### (52) U.S. Cl.

CPC ..... *G02F1/13439* (2013.01); *G02F 1/133345* (2013.01); *G02F 1/136213* (2013.01); *G02F 1/136286* (2013.01); *G02F 1/13* (2013.01); *G02F 2201/40* (2013.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,668,379 A  | 9/1997  | Ono et al.      |

|--------------|---------|-----------------|

| 5,686,980 A  | 11/1997 | Hirayama et al. |

| 5,742,365 A  | 4/1998  | Seo             |

| 5,745,207 A  | 4/1998  | Asada et al.    |

| 5,771,082 A  | 6/1998  | Chaudet et al.  |

| 5,892,562 A  | 4/1999  | Yamazaki et al. |

| 5,914,762 A  | 6/1999  | Lee et al.      |

| 5,946,066 A  | 8/1999  | Lee et al.      |

| 6,069,678 A  | 5/2000  | Sakamoto et al. |

| 6,233,034 B1 | 5/2001  | Lee et al.      |

| 6,256,081    | В1            | 7/2001  | Lee et al.       |  |

|--------------|---------------|---------|------------------|--|

| 6,259,502    | B1            | 7/2001  | Komatsu          |  |

| 6,266,116    | B1            | 7/2001  | Ohta et al.      |  |

| 6,285,429    | B1            | 9/2001  | Nishida et al.   |  |

| 6,335,148    | B2            | 1/2002  | Lee et al.       |  |

| 6,337,726    | B1            | 1/2002  | Kawano et al.    |  |

| 6,356,330    | B1            | 3/2002  | Ando et al.      |  |

| 6,362,858    | В1            | 3/2002  | Jeon et al.      |  |

| 6,380,672    | B1            | 4/2002  | Yudasaka         |  |

| 6,404,470    | B1            | 6/2002  | Kim et al.       |  |

| 6,456,351    | В1            | 9/2002  | Kim et al.       |  |

| 6,462,800    | В1            | 10/2002 | Kim et al.       |  |

| 6,469,765    | В1            | 10/2002 | Matsuyama et al. |  |

| 6,493,046    | B1            | 12/2002 | Ueda             |  |

| 6,552,770    | B2            | 4/2003  | Yanagawa et al.  |  |

| 6,556,265    | В1            | 4/2003  | Murade           |  |

| 6,580,487    | В1            | 6/2003  | Kim et al.       |  |

| 6,587,162    | B1            | 7/2003  | Kaneko et al.    |  |

| 6,597,413    | B2            | 7/2003  | Kurashina        |  |

| 6,600,541    | B2            | 7/2003  | Kurahashi et al. |  |

| 6,600,542    | B2            | 7/2003  | Kim et al.       |  |

| 6,611,310    | B2            | 8/2003  | Kurahashi et al. |  |

| 6,621,545    | B2            | 9/2003  | Park et al.      |  |

| 6,633,360    | B2            | 10/2003 | Okada et al.     |  |

| 6,639,640    | В1            | 10/2003 | Matsuoka et al.  |  |

| 6,646,707    | B2            | 11/2003 | Noh et al.       |  |

| 6,650,389    | B1            | 11/2003 | Sakamoto         |  |

| 6,661,476    | В1            | 12/2003 | Abe et al.       |  |

| 6,667,790    | B2            | 12/2003 | Yanagawa et al.  |  |

| 6,671,019    | B1            | 12/2003 | Petschek et al.  |  |

| 6,721,028    | B2            | 4/2004  | Kim et al.       |  |

| 6,724,444    | B2            | 4/2004  | Ashizawa et al.  |  |

| 6,771,342    | В1            | 8/2004  | Hirakata et al.  |  |

| 6,784,964    | B2            | 8/2004  | Nakayoshi et al. |  |

| 6,985,194    | B2            | 1/2006  | Kawano et al.    |  |

| 2002/0041354 | $\mathbf{A}1$ | 4/2002  | Noh et al.       |  |

| 2002/0048500 | $\mathbf{A}1$ | 4/2002  | Hermann et al.   |  |

| 2003/0071952 | $\mathbf{A}1$ | 4/2003  | Yoshida et al.   |  |

| 2003/0086045 | $\mathbf{A}1$ | 5/2003  | Ono et al.       |  |

| 2005/0105034 | $\mathbf{A}1$ | 5/2005  | Ono et al.       |  |

| 2007/0153203 | A1            | 7/2007  | Kim et al.       |  |

|              |               |         |                  |  |

# FOREIGN PATENT DOCUMENTS

| JP | 3591513     | 4/2001 |

|----|-------------|--------|

| JP | 2001-228493 | 8/2001 |

#### OTHER PUBLICATIONS

Chinese Office action dated May 9, 2008 regarding Chinese Patent Application No. 2007100057283, in Chinese.

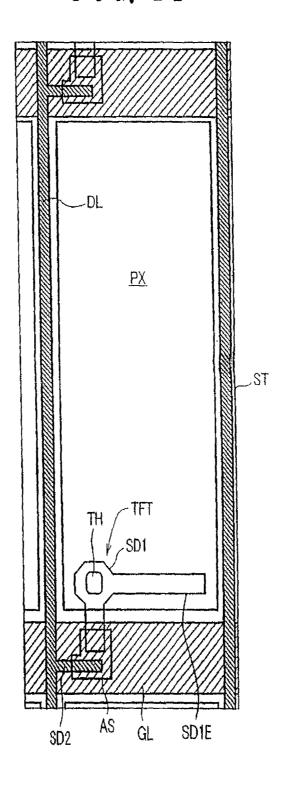

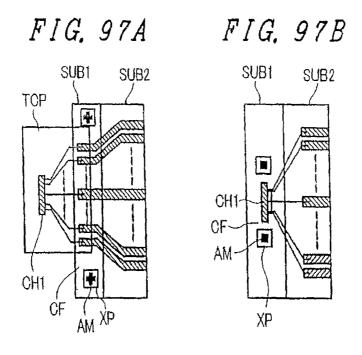

FIG. 1

F I G. 4

F I G. 7

FIG. 10

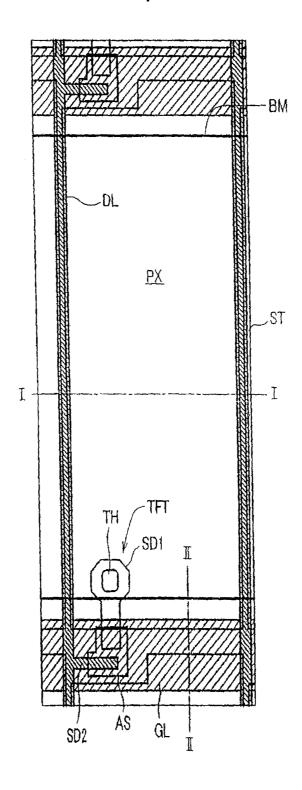

FIG. 11

FIG. 12

FIG. 15

FIG. 16

FIG. 18 SUB2 I Ι -CT LC > AL - PX O-PAS - PAS DL: 7117. \_GI 00-~ CF -ST SÚB1

FIG. 20

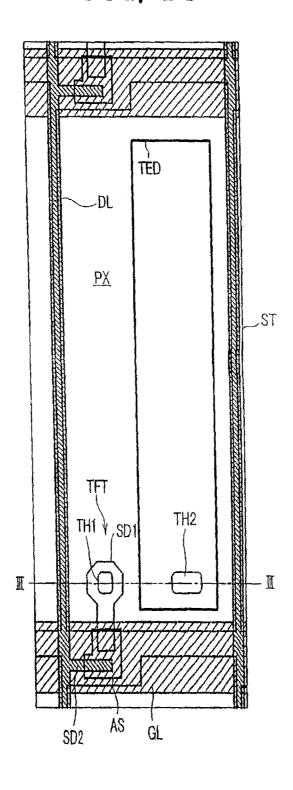

FIG. 24

FIG. 28

FIG. 29

FIG. 30

FIG. 32

FIG. 33

FIG. 34

FIG. 38

FIG. 39

FIG. 40

FIG. 41

FIG. 42

FIG. 43

FIG. 44

FIG. 45

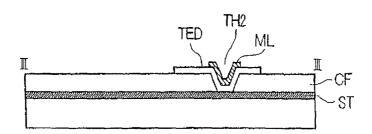

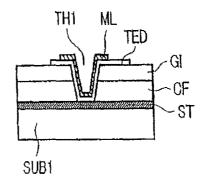

FIG. 46B

FIG. 46C

FIG. 46D

FIG. 48

FIG. 49

FIG. 50

FIG. 52

FIG. 53

FIG. 54

FIG. 55

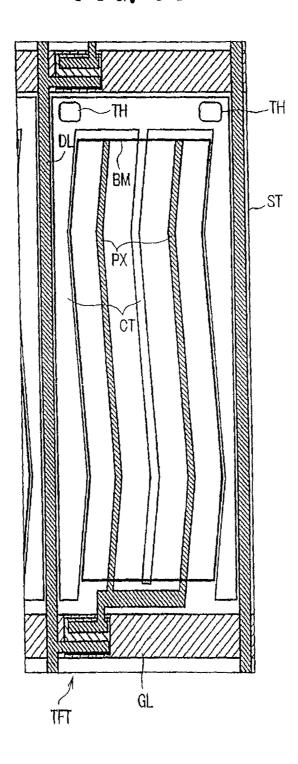

FIG. 56

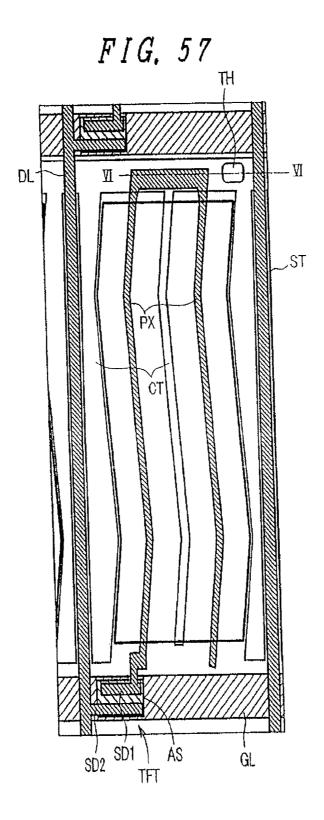

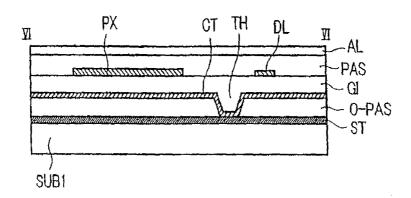

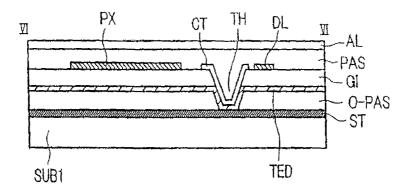

FIG. 58

FIG. 59

FIG. 60

FIG. 61

FIG. 62

FIG. 64 SD1 TFT AS SD2  $\operatorname{GL}$

FIG. 65

FIG. 66

FIG. 67

FIG. 68

FIG. 69

FIG. 70

FIG. 71

FIG. 72

FIG. 73

FIG. 75

FIG. 76

FIG. 77

FIG. 78

FIG. 79

FIG. 80

FIG. 82

TMG SUB1

SUB2

AR

SL

FIG. 84

FIG. 88

FIG. 89

FIG. 90

FIG. 91

FIG. 92

FIG. 94

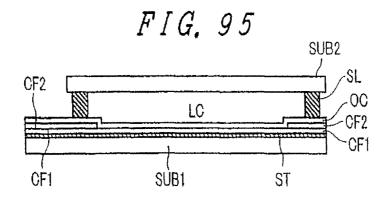

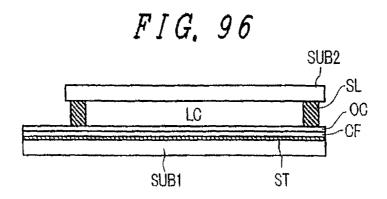

SUB2

CF2

LC

CF2

CF1

SUB1

ST

FIG. 98 SUB2 SLN O-PAS LC ST SÙB1

FIG. 104

FIG. 105

FIG. 106

FIG. 107 ∃~ SUB2 ST SÚB1 ĊF

FIG. 108

FIG. 109

FIG. 110

FIG. 111

### LIQUID CRYSTAL DISPLAY DEVICE, DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

# CROSS-REFERENCE TO RELATED APPLICATION

This application is a Continuation of U.S. application Ser. No. 14/708,348 filed May 11, 2015, which is a Continuation of U.S. application Ser. No. 14/285,006 filed May 22, 2014, 10 which is a Continuation of U.S. application Ser. No. 13/927, 539 filed Jun. 26, 2013, which is a Continuation of U.S. application Ser. No. 13/650,203 filed Oct. 12, 2012, which is a Continuation of U.S. application Ser. No. 13/364,092 filed Feb. 1, 2012, which is a Continuation of U.S. appli- 15 cation Ser. No. 12/926,735 filed Dec. 7, 2010, which is a Continuation of U.S. application Ser. No. 12/292,728 filed Nov. 25, 2008, which is a Divisional of U.S. application Ser. No. 11/976,884 filed Oct. 29, 2007, which is a Divisional of U.S. application Ser. No. 11/409,076 filed Apr. 24, 2006, 20 which is a Divisional of U.S. application Ser. No. 11/211, 574 filed Aug. 26, 2005, which is a Divisional of U.S. application Ser. No. 10/237,911 filed Sep. 10, 2002. Priority is claimed based on U.S. application Ser. No. 14/708,348 filed May 11, 2015, which claims priority of U.S. application 25 Ser. No. 14/285,006 filed May 22, 2014, which claims priority of U.S. application Ser. No. 13/927,539 filed Jun. 26, 2013, which claims priority of U.S. application Ser. No. 13/650,203 filed Oct. 12, 2012, which claims priority of U.S. application Ser. No. 13/364,092 filed Feb. 1, 2012, which 30 claims priority of U.S. application Ser. No. 12/926,735 filed Dec. 7, 2010, which claims priority of U.S. application Ser. No. 12/292,728 filed Nov. 25, 2008, which claims priority of U.S. application Ser. No. 11/976,884 filed Oct. 29, 2007, which claims priority of U.S. application Ser. No. 11/409, 35 076 filed on Apr. 24, 2006, which claims priority to U.S. application Ser. No. 11/211,574 filed Aug. 26, 2005, which claims priority to U.S. application Ser. No. 10/237,911 filed Sep. 10, 2002, which claims priority to Japanese Patent Application No. 2001-317147 filed on Oct. 15, 2001, and 40 which is hereby incorporated by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display device, and more particularly to an active matrix type liquid crystal display device which can reduce holding capacity for holding lighting of pixels for a given time and feeding resistance thereof thus enhancing numerical aperture.

## 2. Description of the Related Art

An active matrix type liquid crystal display device generally adopts a system in which liquid crystal is sandwiched between a pair of substrates which face each other in an opposed manner and pixels are selected by pixel electrodes 55 which are driven by a large number of switching elements represented by thin film transistors formed on one of the above-mentioned pair of substrates. One type of the liquid crystal display device adopting such a system is a so-called vertical field type in which on the other substrate (second 60 substrate) which faces one substrate (first substrate) of the above-mentioned pair of substrates, color filters and common electrodes are formed or the color filters are also formed on the first substrate.

As another system, there exists a so-called IPS system in 65 which counter electrodes which correspond to the common electrodes are formed on the above-mentioned first substrate

2

side. Also with respect to this system, there has been known a system which forms color filters on either the first substrate side or the second substrate side.

The vertical field type liquid crystal display device includes a plurality of gate lines which extend in the first direction (usually horizontal scanning direction) and are arranged parallel to each other and a plurality of drain lines which extend in the second direction which crosses the gate lines (usually vertical scanning direction) and are arranged parallel to each other. The liquid crystal display device further includes switching elements such as thin film transistors or the like in the vicinity of respective crossing portions of the gate lines and drain lines and pixel electrodes which are driven by the switching elements.

In this vertical field type liquid crystal display device, the common electrodes are formed on the second substrate such that the common electrodes face the pixel electrodes in an opposed manner, an electric field is generated between the common electrodes and the selected pixel electrodes in the direction which approximately crosses a surface of the substrate at a right angle, and lighting of the pixels is performed by changing the orientation of liquid crystal molecules sandwiched between the pixel electrode and the common electrodes.

On the other hand, in the IPS type liquid crystal display device, gate lines, drain lines, and switching elements similar to those of the vertical field type liquid crystal display device are formed on an inner surface of the above-mentioned first substrate, comb-shaped pixel electrodes are formed on the same substrate, and counter electrodes are formed close to the pixel electrodes on the same substrate. Then, an electric field is generated between the selected pixel electrodes and the counter electrodes in the direction approximately parallel to a surface of the substrate, and lighting of the pixels is performed by changing the orientation direction of liquid crystal molecules arranged between the pixel electrodes and the counter electrodes. As a liquid crystal display device which has developed this type, there exists a liquid crystal display device which adopts a matted electrode as the counter electrodes and forms comb-shaped pixel electrodes as a layer above or below the counter

In both of the above-mentioned type liquid crystal display devices, the charge storing capacity for holding the lighting time of the pixels which are lit due to selection at a given value (hereinafter, simply referred to as "holding capacity") is formed in regions where the pixel electrodes and the gate lines are overlapped or regions where other electrode lines which are formed such that the other electrode lines transverse the pixel electrode forming region and the pixel electrodes, and feeding paths for storing charge in the holding capacity is formed of either the gate lines or the above-mentioned electrode lines.

### SUMMARY OF INVENTION

In this manner, one electrode which forms the holding capacity is a linear electrode and the feeding is limited to one direction (extending direction of the electrode) and hence, the feeding resistance is large. Further, corresponding to the increase of the distance between the electrode and a feeding end, the voltage drop is remarkably increased so that there arises a case that the required charge cannot be fed. Further, since the above-mentioned gate line usually crosses the drain line, a crossing capacity is increased. As a result, this has been one of causes which make the rapid driving of liquid crystal display device difficult. As a countermeasure

to cope with such a problem, there has been proposed a liquid crystal display device which uses the above-mentioned other electrode line. However, when the holding capacity is formed in the pixel electrode forming region, numerical aperture is reduced as a matter of course.

Further, along with the demand for high definition, the size of pixels per one pixel is reduced so that there has been a task that it is difficult to form the sufficient holding capacity.

Further, although it is effective to reduce the size of the holding capacity to enhance the numerical aperture, this brings about the reduction of the holding capacity. That is, there has been a task that there exists a trade-off relationship between the enhancement of numerical aperture and the assurance of holding capacity.

Accordingly, it is an object of the present invention to provide an active matrix liquid crystal display device which can reduce resistance of feeding electrodes which constitute holding capacities. It is another object of the present invention to provide a rapid driving active matrix type liquid crystal display device having high brightness by obviating the reduction of numerical aperture of pixels.

It is still another object of the present invention to realize an active matrix type liquid crystal display device which can 25 satisfy both of the assurance of holding capacity and the enhancement of numerical aperture simultaneously.

Other objects and advantages of the present invention will be apparent from the explanation made hereinafter.

The typical constitution of the present invention lies in 30 that on a switching element forming substrate of the liquid crystal display device, a transparent conductive layer (reference layer) having a large area which covers at least a major portion or a whole area of a pixel electrode forming region is formed, and switching elements (active elements), 35 other electrodes and lines are formed over the transparent conductive layer by way of an insulation layer. Due to such a constitution, the feeding resistance with respect to the holding capacity can be largely reduced. Further, a trade-off between the enhancement of numerical aperture and the 40 increase of holding capacity can be eliminated. Representative constitutions of the present invention are described hereinafter.

1):

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate which face each other in an opposed manner, and at least a plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes which are driven by the switching elements are formed on an inner surface of the first substrate,

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel electrodes,

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first 60 insulation layer between the reference electrode layer and the electrode forming layer, and

holding capacities of the pixels are formed between the pixel electrodes and the reference electrode layer.

Due to such a constitution, the feeding resistance with 65 respect to the storage capacity is largely reduced so that it is possible to realize the liquid crystal display device which

4

can realize both of the enhancement of numerical aperture of pixels and the assurance of holding capacity.

(2):

In the constitution (1), the electrode forming layer includes the gate lines, a gate insulation layer, the semiconductor layers, the drain lines, a passivation layer and the pixel electrodes in this order over the first insulation layer, and the holding capacity of the pixel is formed between the pixel electrodes and the reference electrode layer.

Since the holding capacity is constituted of the passivation layer, the gate insulation layer and the first insulation layer which are formed between the pixel electrode and the reference electrode layer, the distance to the reference electrode layer as viewed from the liquid crystal layer can be largely increased so that the influence of the electric field of the reference electrode layer on the electric field for driving liquid crystal can be attenuated.

3):

In the constitution (1), the reference electrode layer is arranged in the extension direction of the gate lines such that the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are formed.

Due to such a constitution, the parasitic capacity between the gate line and the reference electrode layer can be reduced and the potential can be made stable.

(4):

In the constitution (1), the reference electrode layer is provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated.

(5):

In the constitution (1), the passivation layer is formed over the gate insulation layer, the pixel electrodes are formed over the passivation layer, and the whole or a. portion of the pixel electrodes penetrate the passivation layer and are brought into contact with the gate insulation layer.

Due to such a constitution, holding capacity formed between the conductive layers and the pixel electrodes can be adjusted by changing the area that the pixel electrodes penetrate the passivation layer.

(6):

In the constitution (1), the passivation layer is formed over the gate insulation layer, the pixel electrodes are formed over the passivation layer, and the whole or a portion of the pixel electrodes in the pixel regions penetrate the passivation layer and the gate insulation layer and are brought into contact with the first insulation layer.

Due to such a constitution, holding capacity formed between the reference electrode layer and the pixel electrodes can be adjusted by changing the area that the pixel electrodes penetrate the passivation layer and the gate insulation layer.

(7):

In the constitution (1), the passivation layer is formed over the gate insulation layer, the pixel electrodes are formed over the passivation layer, and the switching elements include source electrodes on the gate insulation layer which are connected to the pixel electrodes via through holes formed in the passivation layer and extension portions which extend along the gate lines or the drain lines at one portions of the source electrodes.

Due to such a constitution, holding capacity can be adjusted by changing the length or the width of the extension portions of the source electrodes, that is, by changing the area that the source electrodes overlap the pixel electrodes. (8):

In the constitution (1), the first insulation layer is formed of an organic insulation layer.

Due to such a constitution, the electric distance between the reference electrode layer and the electrode forming layer can be increased compared to a case in which the insulation 10 layer is provided. Further, parasitic capacity between the reference electrode layer and the gate lines as well as the drain lines can be reduced.

(9):

In the constitution (1), the liquid crystal display device 15 includes a light shielding layer which perform light shielding of gaps defined between the vicinities in the extension direction of the drain lines and the pixel electrodes.

Due to such a constitution, leaking of light can be prevented.

(10):

In the constitution (1), common electrodes which constitute pixels together with the pixel electrodes are formed on an inner surface of the second substrate.

(11):

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate which face each other in an opposed manner, and at least a plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes which are driven by the switching elements are formed on an inner surface of the first substrate,

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel electrodes,

having a reference electrode layer arranged between the 40 first substrate and the electrode forming layer with first insulation layer between the reference electrode layer and the electrode forming layer, and

the electrode forming layer includes the gate insulation layer, the passivation layer, a second insulation layer and the 45 pixel electrodes in this order over the first insulation layer, and

holding capacities of the pixels are formed between the pixel electrodes and the reference electrode layer.

Due to such a constitution, the numerical aperture of the 50 pixels can be enhanced. Since the area of the conductive layers is large, the feeding resistance can be reduced. Further, since the holding capacity is formed by the passivation layer, the gate insulation layer and the first insulation layer which are formed between the pixel electrodes and the 55 reference electrode layer, the holding capacity can be easily controlled. Further, since the organic insulation layer is also formed over the switching elements, the pixel electrodes and the drain lines can overlap each other so that the numerical aperture is further enhanced. When the pixel electrodes and 60 the drain lines overlap each other, it is possible to eliminate light shielding layers between the vicinities of the extension direction of the drain lines and the pixel electrodes so that the numerical aperture is further enhanced.

In the constitution (11), the reference electrode layer is arranged in the extension direction of the gate lines such that

6

the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are formed

Due to such a constitution, the capacity between the gate lines and the reference electrode layers can be reduced so that the increase of holding capacity can be suppressed and the potential can be made stable.

(13):

In the constitution (11), the reference electrode layer is provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated. (14):

In the constitution (11), the first organic insulation layer  $_{20}$  is formed of color filters.

Due to such a constitution, the numerical aperture of the pixels is enhanced. Since the area of the conductive layers is large, the feeding resistance can be reduced. Further, since the holding capacity is formed by the passivation layer, the gate insulation layer and the color filter layer which is made of organic material and exhibits small dielectric constant between the pixel electrodes and the reference electrode layer, the increase of parasitic capacity between lines can be suppressed. Still further, since the color filter layer is formed over the first substrate, the tolerance of alignment of the first substrate with the second substrate is increased. (15):

In the constitution (14), the reference electrode layer is arranged in the extension direction of the gate lines such that the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are formed

Due to such a constitution, the capacity between the gate lines and the conductive layer can be reduced and the potential can be made stable.

(16):

In the constitution (14), the reference electrode layer is provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated.

(17)

In the constitution (11), the first insulation layer is an organic insulation layer.

Due to such a constitution, the electric distance between the reference electrode layer and the electrode forming layer can be increased compared to a case in which the insulation layer is provided. Further, the parasitic capacity between the reference electrode layer and the gate line as well as the drain line can be reduced.

(18):

In the constitution (11), the liquid crystal display device includes a light shielding layer which performs light shielding of gaps defined between the vicinities in the extension direction of the drain lines and the pixel electrodes.

Due to such a constitution, leaking of light can be prevented.

(23):

7

(19):

In the constitution (11), common electrodes which constitute pixels together with the pixel electrodes are formed on an inner surface of the second substrate.

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate which face each other in an opposed manner, and at least a plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes 15 which are driven by the switching elements are formed on an inner surface of the first substrate, and pixel regions are formed of a plurality of pixel electrodes,

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel 20 (25):

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first insulation layer between the reference electrode layer and the electrode forming layer, and

the electrode forming layer includes the gate insulation layer, the passivation layer and the pixel electrode in this order over the first insulation layer and further includes a capacitive electrode layer which is formed over the first insulation layer and is connected to the pixel electrodes, and 30

holding capacities of the pixels are formed among the pixel electrodes, the reference electrode layer and the capacitive electrode layer.

Due to such a constitution, the numerical aperture of the pixels can be enhanced. Since the area of the conductive 35 layers is large, the feeding resistance can be reduced. Further, since the holding capacity can be adjusted by changing the area and size of the capacitive electrode layer, it is possible to realize both of the enhancement of numerical aperture and the assurance of holding capacity. Still further, 40 when the organic insulation layer is formed between the passivation layer and the pixel electrodes, it is possible to make the pixel electrodes and the drain lines overlap each other and hence, the numerical aperture is further enhanced. When the pixel electrodes and the drain lines overlap each 45 other, it is possible to eliminate light shielding layers between the vicinities of the extension direction of the drain lines and the pixel electrodes so that the numerical aperture is further enhanced.

(21):

In the constitution (20), the reference electrode layer is arranged in the extension direction of the gate lines such that the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are

Due to such a constitution, the capacity between the gate lines and the reference electrode layer can be reduced and the potential can be made stable.

In the constitution (20), the reference electrode layer is 60 provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding 65 resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated.

In the constitution (20), the switching elements include source electrodes over the gate insulation layer which are connected to the pixel electrodes via through holes formed in the passivation layer, and the capacitive electrode layer is connected to the source electrodes and is provided to regions of the pixel electrodes.

Due to such a constitution, the holding capacity can be adjusted by changing the size of the capacitive electrode

(24):

In the constitution (20), the first insulation layer is formed of color filters.

Due to such a constitution, the numerical aperture of the pixels can be enhanced. Since the area of the conductive layers is large, the feeding resistance can be reduced. Further, since the color filter layer is formed over the first substrate, the tolerance of alignment of the first substrate with the second substrate can be increased.

In the constitution (20), the capacitive electrode layer is formed over the passivation layer, the organic insulation layer is formed over the passivation layer, the pixel electrodes are formed over the organic insulation layer and are 25 connected to the capacitive electrode layer via through holes formed in the organic insulation layer.

Due to such a constitution, the holding capacity can be adjusted by changing the size of the capacitive electrode layer.

(26):

In the constitution (20), the capacitive electrode layer is formed over the gate insulation layer, and the pixel electrodes are connected to the capacitive electrode layer via through holes formed in the passivation layer.

Due to such a constitution, the holding capacity can be adjusted by changing the size of the capacitive electrode layer.

(27):

In the constitution (20), the capacitive electrode layer is formed over the first insulation layer, and the pixel electrodes penetrate the passivation layer and are connected to the capacitive electrode layer via through holes formed in the gate insulation layer.

Due to such a constitution, the holding capacity formed between the conductive layer and the pixel electrodes can be adjusted by changing the area that the pixel electrodes penetrate the passivation layer and the gate insulation layer.

In the constitution (20), the first insulation layer is formed 50 of an organic insulation layer.

Due to such a constitution, the electric distance between the reference electrode layer and the electrode forming layer can be increased compared to a case in which the insulation layer is provided. Further, parasitic capacity between the 55 reference electrode layer and the gate lines as well as the drain lines can be reduced.

In the constitution (20), the liquid crystal display device includes a light shielding layer which performs light shielding of gaps defined between the vicinities in the extension direction of the drain lines and the pixel electrodes.

Due to such a constitution, leaking of light can be prevented.

(30):

In the constitution (20), common electrodes which constitute pixels together with the pixel electrodes are formed on an inner surface of the second substrate.

8

(31):

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate which face each other in an opposed manner, and at least a plurality of gate lines which extend in the first direction and 5 are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes 10 which are driven by the switching elements are formed on an inner surface of the first substrate, and pixel regions are formed of a plurality of pixel electrodes,

the improvement is characterized in that between an electrode forming layer which is constituted of the gate 15 lines, the drain lines, the switching elements and the pixel electrodes including the pixel regions of the first substrate and the first substrate side, a reference electrode layer which is insulated by a first insulation layer with respect to the electrode forming layer is formed,

wherein having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first 25 insulation layer between the reference electrode layer and the electrode forming layer, and

the electrode forming layer includes the gate insulation layer, the passivation layer and the pixel electrode in this order over the first insulation layer and further includes a 30 capacitive electrode layer which is connected to the pixel electrodes between the first insulation layer and the passivation layer, and

holding capacities of the pixels are formed among the pixel electrodes, the reference electrode layer and the 35 capacitive electrode layer.

Due to such a constitution, the numerical aperture of pixels can be enhanced. Further, since the area of the reference electrode layer is large, the feeding resistance can be reduced. Still further, the holding capacity can be 40 adjusted by changing the area and the shape of the capacitive electrode layer.

(32):

In the constitution (31), the reference electrode layer is arranged in the extension direction of the gate lines such that 45 the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are formed.

Due to such a constitution, the capacity between the gate lines and the reference electrode layer can be reduced. The 50 increase of parasitic capacity between lines can be suppressed. Further, the potential can be made stable.

In the constitution (31), the reference electrode layer is provided to a region of the first substrate which includes 55 regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed 60 easily adjusted by changing the areas of the capacitive on the feeding direction can be eliminated. (34):

In the constitution (31), the organic insulation layer is formed of color filters.

Due to such a constitution, the numerical aperture of the 65 of an organic insulation layer. pixels is enhanced. Since the area of the reference electrode layers is large, the feeding resistance can be reduced. Fur-

10

ther, since the color filters are formed of organic films, the parasitic capacitance between lines can be reduced. Still further, since the color filter layer is formed over the first substrate, the tolerance of alignment of the first substrate with the second substrate is increased.

In the constitution (31), the first insulation layer is formed of an organic insulation layer.

Due to such a constitution, the electric distance between the reference electrode layer and the electrode forming layer can be increased compared to a case in which the insulation layer is provided. Further, the parasitic capacity between the reference electrode layer and the gate lines as well as the drain lines can be reduced.

In the constitution (31), the liquid crystal display device includes a light shielding layer which performs light shielding of gaps defined between the vicinities in the extension direction of the drain lines and the pixel electrodes.

Due to such a constitution, leaking of light can be prevented.

(37):

In the constitution (31), the capacitive electrode layer is formed over the first insulation layer, and the capacitive electrode layer is connected to the reference electrode layer via through holes which penetrate the first insulation layer.

Due to such a constitution, the holding capacity formed between the reference electrode layer and the pixel electrodes can be adjusted by changing the area of the capacitive electrode layer connected to the reference electrode layer. (38):

In the constitution (31), the capacitive electrode layer is formed over the gate insulation layer, and the capacitive electrode layer is connected to the reference electrode layer via through holes which penetrate the gate insulation layer.

Due to such a constitution, the holding capacity formed between the reference electrode layer and the pixel electrodes can be adjusted by changing the area of the capacitive electrode layer connected to the reference electrode layer.

In the constitution (31), the capacitive electrode layer is formed over the passivation layer, and the capacitive electrode layer is connected to the reference electrode layer via through holes which penetrate the passivation layer, the gate insulation layer and the first insulation layer.

Due to such a constitution, the holding capacity formed between the reference electrode layer and the pixel electrodes can be adjusted by changing the area of the capacitive electrode layer connected to the reference electrode layer. (40):

In the constitution (31), the capacitive electrode layer is formed over the gate insulation layer, a second capacitive electrode layer is formed over the first insulation layer, the pixel electrode is connected to the capacitive electrode layer via through holes formed in the passivation layer, and the second capacitive electrode layer is connected to the reference electrode layer via through holes formed in the first insulation layer.

Due to such a constitution, the holding capacity can be electrode layer and the second capacitive electrode layer. Further, the holding capacity can be further increased.

In the constitution (31), the first insulation layer is formed

Due to such a constitution, the electric distance between the reference electrode layer and the electrode forming layer

can be increased compared to a case that the insulation layer is provided. Further, the parasitic capacity among the reference electrode layer, the gate lines and the drain lines can

(42):

In the constitution (31), the liquid crystal display device includes a light shielding layer which performs light shielding of gaps defined between the vicinities in the extension direction of the drain lines and the pixel electrodes.

Due to such a constitution, leaking of light can be  $^{10}$ prevented.

(43):

In the constitution (31), common electrodes which constitute pixels together with the pixel electrodes are formed 15 be reduced and the potential can be made stable. on an inner surface of the second substrate.

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate which face each other in an opposed manner, and at least a 20 plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions 25 of the gate lines and the drain lines, pixel electrodes which are driven by the switching elements, and counter electrodes which generate an electric field for driving pixels between the pixel electrodes and the counter electrodes are formed on an inner surface of the first substrate,

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel electrodes.

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first 35 insulation layer between the reference electrode layer and the electrode forming layer, and

holding capacities of the pixels are formed among the pixel electrodes and the reference electrode layer.

Due to such a constitution, the liquid crystal display 40 device can achieve both of the large numerical aperture and the large holding capacity. Further, since it is unnecessary to increase the areas of the pixel electrodes and the lines for forming the holding capacity, the numerical aperture is enhanced. Still further, since the area of the reference 45 electrode layer is large, the feeding resistance can be reduced.

(45):

In the constitution (44), the counter electrodes are formed over the organic insulation layer, and the counter electrodes 50 are connected to the reference electrode layer via through holes formed in the first insulation layer.

Due to such a constitution, the area of the reference electrode layer can be increased and hence, the feeding resistance to the counter electrodes can be reduced. (46):

In the constitution (44), the counter electrodes are formed over the gate insulation layer, and the counter electrodes are connected to the reference electrode layer via through holes formed in the gate insulation layer and the first insulation 60

Due to such a constitution, the area of the reference electrode layer can be increased and hence, the feeding resistance can be reduced.

In the constitution (44), the counter electrodes are formed over the passivation layer, and the counter electrodes are 12

connected to the reference electrode layer via through holes formed in the passivation layer, the gate insulation layer and the first insulation layer.

Due to such a constitution, the area of the reference electrode layer can be increased and hence, the feeding resistance can be reduced.

(48)

In the constitution (44), the reference electrode layer is arranged in the extension direction of the gate lines such that the reference electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are formed.

Due to such a constitution, the parasitic capacity formed between the gate lines and the reference electrode layer can (49):

In the constitution (44), the reference electrode layer is provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the reference electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated.

In the constitution (44), the counter electrodes are formed over the first insulation layer, the counter electrodes extend to the neighboring pixel regions by crossing the drain lines and are connected to the reference electrode layers of the neighboring pixel regions via through holes formed in the first insulation layer.

Due to such a constitution, even when the through holes are formed insufficiently, the feeding of electricity is performed through the counter electrodes from the neighboring pixel sides. Further, when the through holes which connect each counter electrode and each reference electrode are formed in a plural number for every pixel, the reliability of connection between the electrode layers can be enhanced. (51):

In the constitution (44), the counter electrodes are formed over an organic insulation layer, conductive layers which extend to the neighboring pixel regions by crossing the drain lines are formed over the gate insulation layer, the counter electrodes are connected to the conductive layers via through holes formed in the gate insulation layer, and the conductive layers are connected to the reference electrode layer via through holes formed in the first insulation layer.

Due to such a constitution, even when the through holes are formed insufficiently, the feeding of electricity is performed through the conductive layers from the neighboring pixel sides. Further, when the through holes which connect each counter electrode and each reference electrode are formed in a plural number for every pixel, the reliability of connection between the electrode layers can be enhanced. 55 (52):

In the constitution (44), the counter electrodes are formed over a passivation layer, conductive layers which extend to the neighboring pixel regions by crossing the drain lines are formed over the gate insulation layer, the counter electrodes are connected to the conductive layers via through holes formed in the passivation layer and the gate insulation layer, and the conductive layers are connected to the reference electrode layer via through holes formed in the first insulation layer.

Due to such a constitution, even when the through holes are formed insufficiently, the feeding of electricity is performed through the conductive layers from the neighboring

pixel sides. Further, when the through holes which connect each counter electrode and each reference electrode are formed in a plural number for every pixel, the reliability of connection between the electrode layers can be enhanced.

In the constitution (44), a color filter layer is formed between the reference electrode which is formed below the first insulation layer and the first substrate.

Due to such a constitution, it is possible to isolate the color filter layer from the liquid crystal layer with the use of 10 the reference electrodes and hence, it is possible to prevent the liquid crystal from being contaminated by constituent materials of the color filter layer.

(54):

In the constitution (44), the counter electrodes are formed 15 over the first insulation layer parallel to the extension direction of the gate lines, the counter electrodes extends over the pixel region, and the counter electrodes are connected to the reference electrodes in respective pixel regions via through holes formed in the first insulation layer.

Due to such a constitution, holding capacity is formed at portions where the counter electrodes and the pixel electrodes overlap each other, and the gate insulation layer functions as a dielectric of the holding capacity and hence, the constitution is suitable for increasing the holding capac- 25 (62): ity.

(55):

In the constitution (44), the counter electrodes are connected to the reference electrodes in respective pixel regions via through holes formed in the first insulation layer and the 30 gate insulation layer in a penetrating manner, and holding capacities are formed at overlapping portions of the counter electrodes and the pixel electrodes.

In the constitution (44), the pixel electrodes are formed 35 over the gate insulation layer, the counter electrodes are formed below the gate insulation layers, the counter electrodes are connected to the reference electrodes via through holes formed in the first insulation layer, and holding capacities are formed by the counter electrodes and the pixel 40 electrodes.

(57):

In the constitution (44), the pixel electrodes and the counter electrodes are formed on the same layer.

In the constitution (44), the counter electrodes are formed over the pixel electrodes and are connected to the reference electrodes by way of through holes formed in a gate insulation film and a first insulation film.

(59):

In the constitution (44), the first insulation layer is formed of an organic insulation layer.

In a liquid crystal display device in which liquid crystal is sandwiched between a first substrate and a second substrate 55 which face each other in an opposed manner, and at least a plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of 60 switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes which are driven by the switching elements are formed on an inner surface of the first substrate,

having an electrode forming layer which include the gate 65 lines, the drain lines, the switching elements and the pixel electrodes,

14

having a counter electrode layer arranged between the first substrate and the electrode forming layer with first insulation layer between the reference electrode layer and the electrode forming layer, and the reference electrode layer overlapped substantially all region of the pixel electrode and function as a counter electrode, and

holding capacities of the pixels are formed between the pixel electrodes and the counter electrode layer.

Due to such a constitution, the feeding resistance with respect to the holding capacity can be largely reduced so that the image quality is enhanced. Further, it is possible to realize both of the enhancement of numerical aperture and the assurance of holding capacity.

(61):

In the constitution (60), the counter electrode layer is arranged in the extension direction of the gate lines such that the counter electrode layer is arranged parallel to the gate lines and overlaps regions where the pixel electrodes are 20 formed.

Due to such a constitution, an independent reference electrode layer is unnecessary, the parasitic capacity between the gate lines and the conductive layers can be reduced, and the potential can be made stable.

In the constitution (60), the counter electrode layer is provided to a region of the first substrate which includes regions in which the gate lines, the drain lines and the pixel electrodes are formed.

Due to such a constitution, the counter electrode layer forms a so-called matted electrode so that the feeding resistance can be further reduced and the limitation imposed on the feeding direction can be eliminated. (63):

In the constitution (60), the whole or a portion of the layer constitution of insulation layers below the pixel electrodes and the whole or a portion of the region are removed.

Due to such a constitution, the strength of electric field generated between the pixel electrodes and the counter electrodes is increased so that the driving voltage can be reduced.

(64):

In the constitution (60), over the counter electrode layer, connection lines which are arranged parallel to the extension direction of the gate lines and are connected to counter electrodes which are disposed close to the counter electrode are formed.

(65):

In the constitution (60), below the counter electrode layer, connection lines which are arranged parallel to the extension direction of the gate lines and are connected to counter electrodes which are disposed close to the counter electrode are formed.

Due to the above-mentioned constitution (64) or (65), even when the through holes are formed insufficiently, the feeding of electricity is performed through the connection lines from the neighboring pixel sides. Further, when the through holes which connect each counter electrode with each reference electrode are formed in a plural number for every pixel, the reliability of connection of the electrode layers can be enhanced.

(66):

In the constitution (60), the first insulation layer is removed at portions of the pixel regions.

Due to such a constitution, a plurality of regions which differ in driving voltage can be formed in the pixel region so that the multi-domain effect can be obtained.

(67):

In the constitution (60), a color filter layer is formed between the reference electrodes which are arranged below the first insulation layer and the first substrate.

In the constitution (60), the first insulation layer is formed of an organic insulation layer.

(69):

In the constitution (68), the organic insulation layer is formed of color filters.

(70):

In a liquid crystal display device, liquid crystal sandwiched between a first substrate and a second substrate which face each other in an opposed manner;

a plurality of gate lines which extend in the first direction and are arranged parallel to each other;

a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other;

a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines;

pixel electrodes which are driven by the switching elements are formed on an inner surface of the first substrate,

counter electrodes which generate an electric field for 25 driving pixels between the pixel electrodes formed on an inner surface of the first;

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel electrodes,

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first insulation layer between the reference electrode layer and the electrode forming layer,

the electrode forming layer is formed by laminating the 35 gate insulation layer, the passivation layer, an organic insulation layer and counter electrodes in this order over the first insulation layer,

the counter electrode layer is shared by a pixel region which is arranged close to the pixel region in the extension 40 direction of the gate lines and a pixel region which is arranged close to the pixel region in the extension direction of the drain lines,

the counter electrode layer is connected to the reference electrode layer via through holes which electrically penetrate the organic insulation layer, the passivation layer, the gate insulation layer and the first insulation layer, and

holding capacities of the pixels are formed between the pixel electrodes and the reference electrode layer. (71):

In the constitution (70), the liquid crystal display device includes a capacitive electrode layer which is disposed below the pixel electrodes and is formed between the first insulation layer and the gate insulation layer, and the capacitive electrode layer is connected to the reference electrode 55 layer via through holes.

Due to such a constitution, the holding capacity can be increased and adjusted by the capacitive electrode layer. (72):

In the constitution (70), removing regions are formed in 60 the first insulation layer disposed below the pixel electrodes.

Due to such a constitution, the holding capacity formed between the pixel electrode and the reference electrode layer can be increased.

(73):

In the constitution (70), the first insulation layer is formed of an organic insulation layer. 16

74):

In the constitution (73), the organic insulation layer is formed of color filters.

(75)

In an image display device in which at least a plurality of gate lines which extend in the first direction and are arranged parallel to each other, a plurality of drain lines which extend in the second direction which crosses the gate lines and are arranged parallel to each other, a plurality of switching elements which are arranged at crossing portions of the gate lines and the drain lines, and pixel electrodes which are driven by the switching elements are formed on an inner surface of the first substrate,

having an electrode forming layer which include the gate lines, the drain lines, the switching elements and the pixel electrodes.

having a reference electrode layer arranged between the first substrate and the electrode forming layer with first 20 insulation layer between the reference electrode layer and the electrode forming layer, and

the reference electrode layer is substantially formed over the whole surface of the pixel regions and shared by a plurality of pixels.

(76)

In the constitution (75), a semiconductor layer which constitutes the switching element has crystalline property. (77):

An image display device being characterized in that a reference electrode layer formed between a substrate and a semiconductor having crystalline property, and having insulation layer between the reference electrode layer and the semiconductor, and the reference electrode layer is formed over substantially the whole surface of a pixel region and is shared by a plurality of pixels.

(78):

In the constitution (77), the reference electrode layer is formed of a transparent electrode. (79):

A manufacturing method of an image display device comprises at least a first step in which a reference electrode layer which is shared by a plurality of pixels is formed on a substantially whole surface of a pixel region on a substrate, a second step in which an insulation layer is formed, and a third step in which a semiconductor layer is formed in this order, and thereafter, further comprise a fourth step in which laser beams are irradiated to the semiconductor layer. (80):

A manufacturing method of an image display device comprises at least a first step in which a reference electrode layer which is shared by a plurality of pixels is formed on a substantially whole surface of a pixel region on a substrate, a second step in which an insulation layer is formed, and a third step in which a semiconductor layer is formed in this order, and thereafter, further comprises a fourth step in which ions are implanted into the semiconductor layer.

The present invention is not limited to the above-mentioned respective constitutions and the constitutions of embodiments which will be explained later and various modifications are considered without departing from the technical concept of the present invention.

## BRIEF DESCRIPTION OF THE DRAWINGS

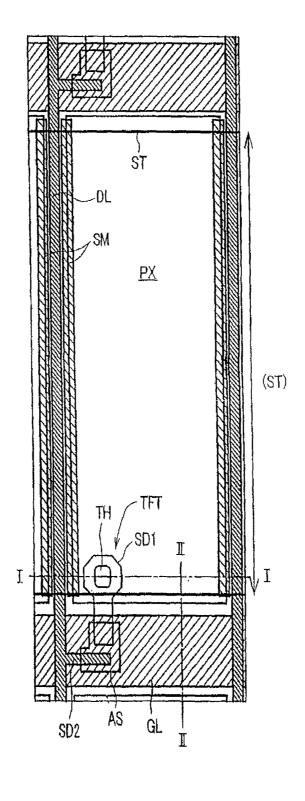

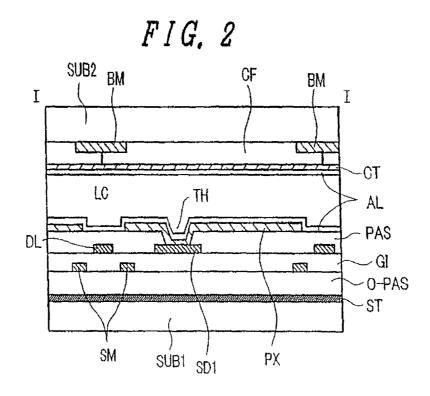

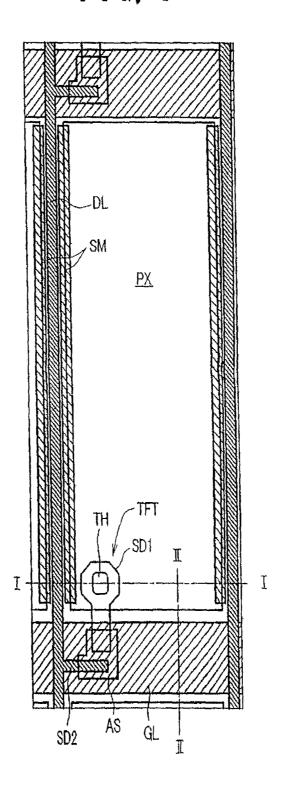

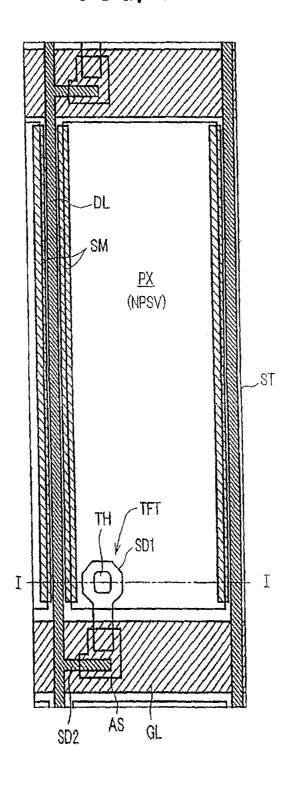

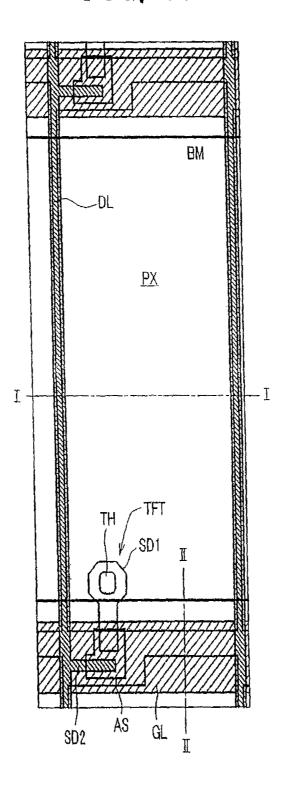

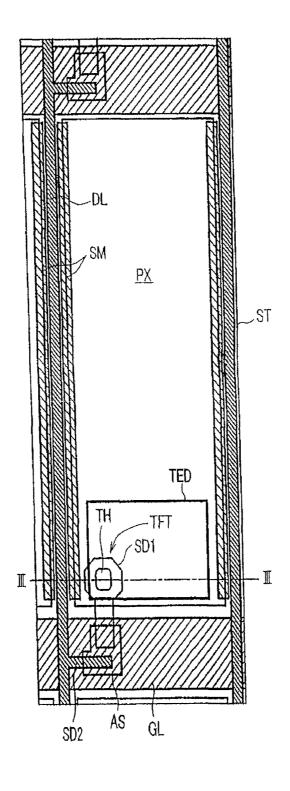

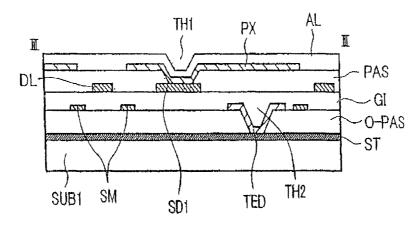

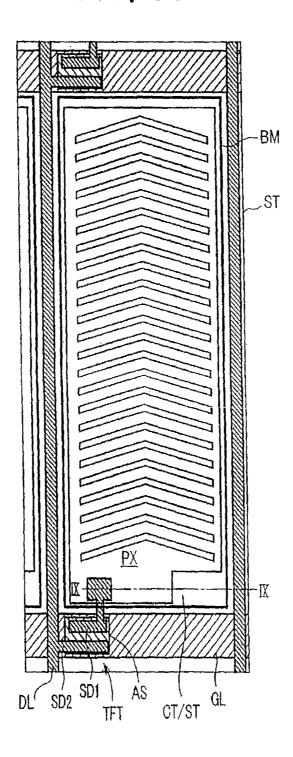

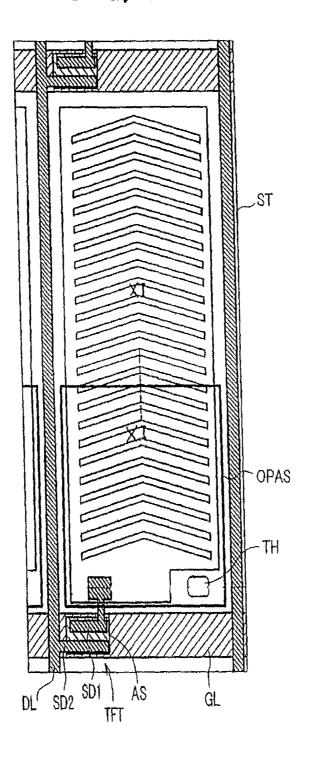

FIG. 1 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of one embodiment of the present invention.

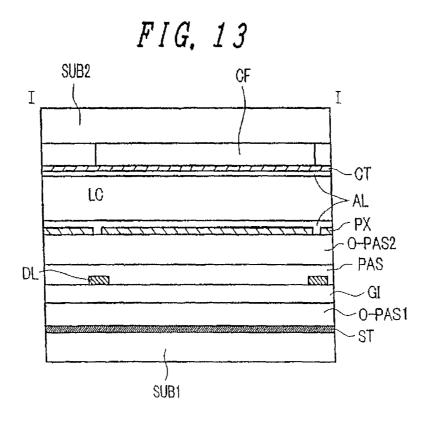

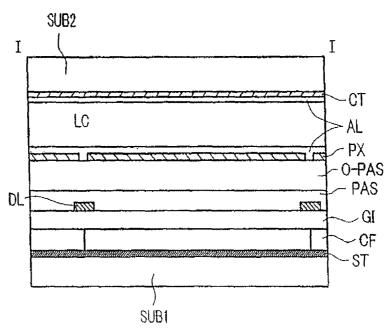

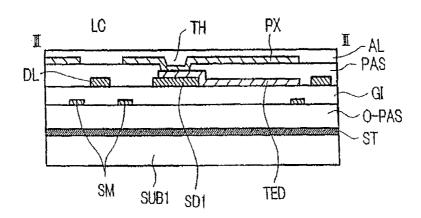

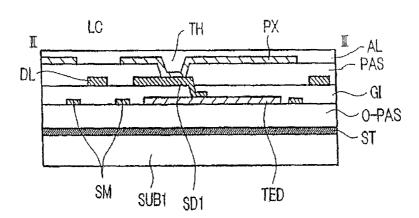

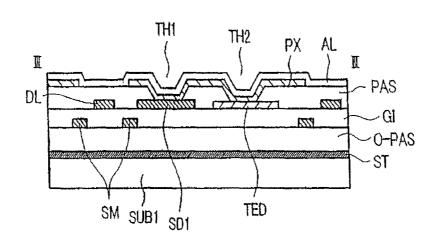

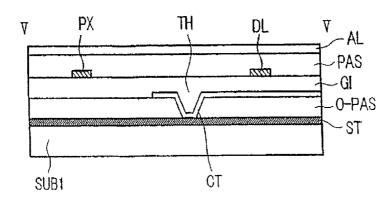

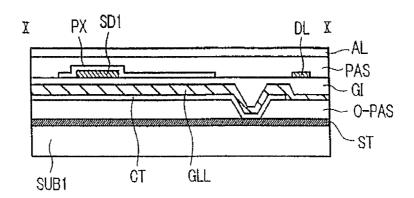

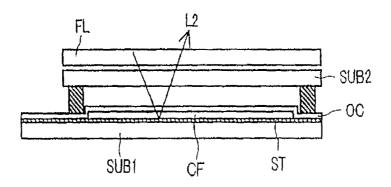

FIG.  ${\bf 2}$  is a cross-sectional view taken along a line I-I in FIG.  ${\bf 1}$ .

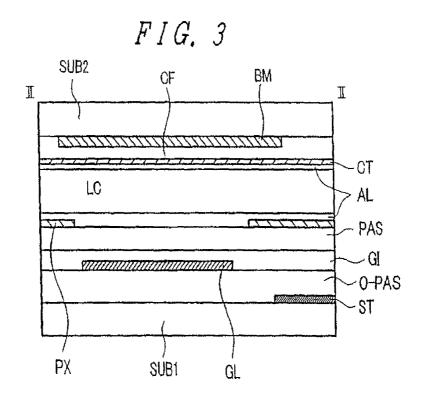

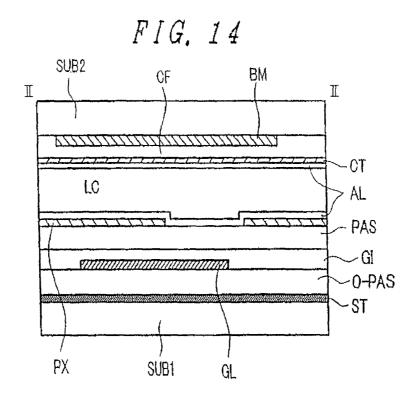

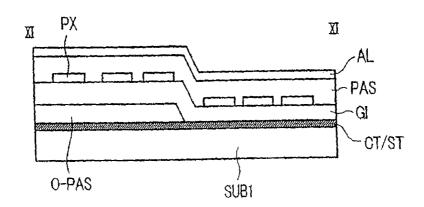

FIG. 3 is a cross-sectional view taken along a line II-II in FIG. 1.

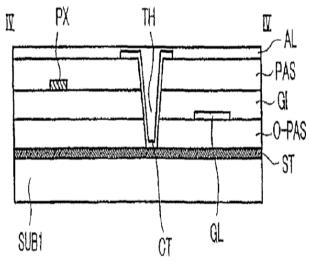

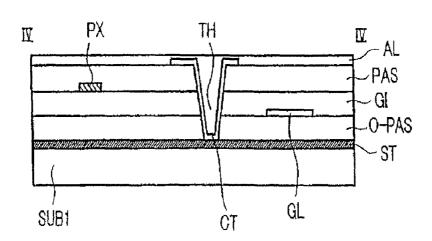

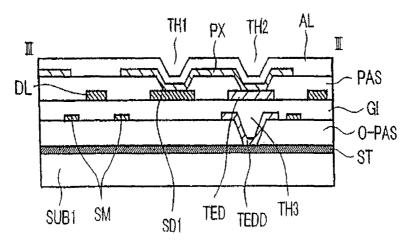

FIG. **4** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of another embodiment of the present invention.

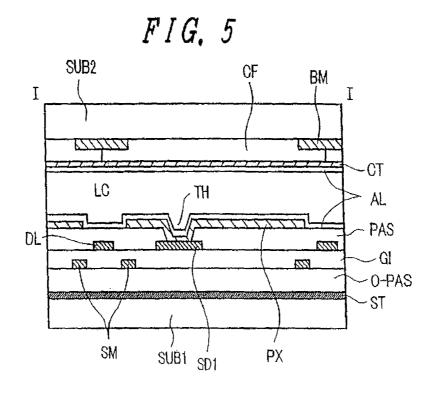

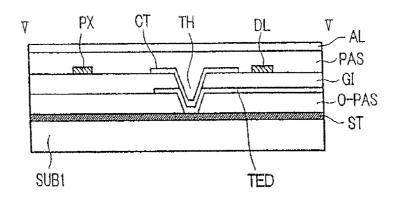

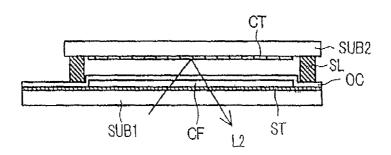

FIG. 5 is a cross-sectional view taken along a line I-I in FIG. 4.

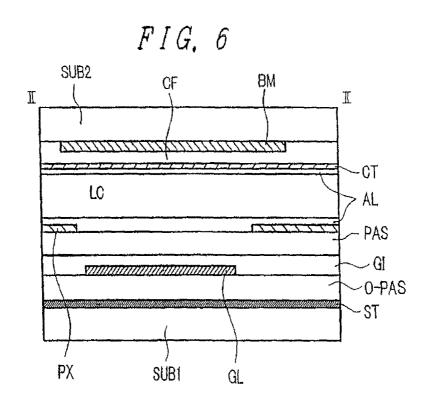

FIG. **6** is a cross-sectional view taken along a line II-II in FIG. **4**.

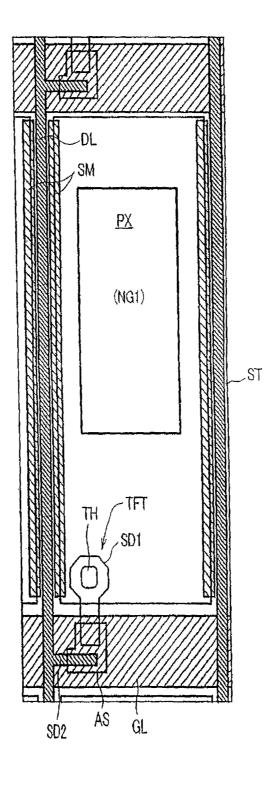

FIG. 7 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

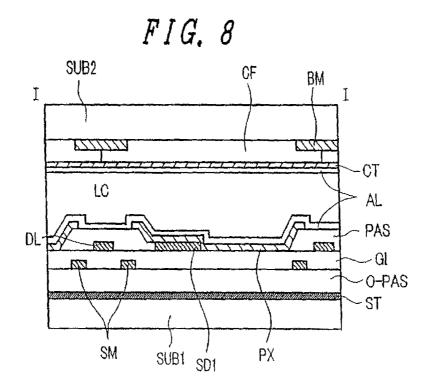

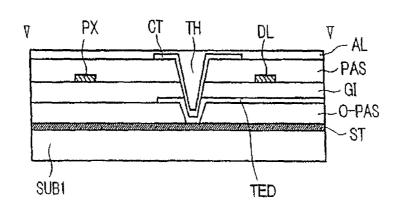

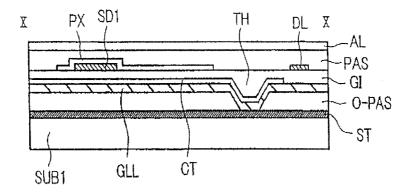

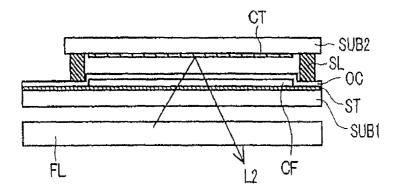

FIG.  $\bf 8$  is a cross-sectional view taken along a line I-I in FIG.  $\bf 7$ .

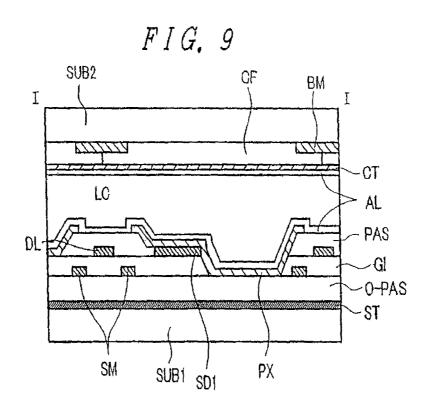

FIG. **9** is a cross-sectional view taken along a line I-I in FIG. **8** showing the vicinity of one pixel of a liquid crystal 20 display device for schematically explaining the pixel constitution of still another embodiment of the present invention

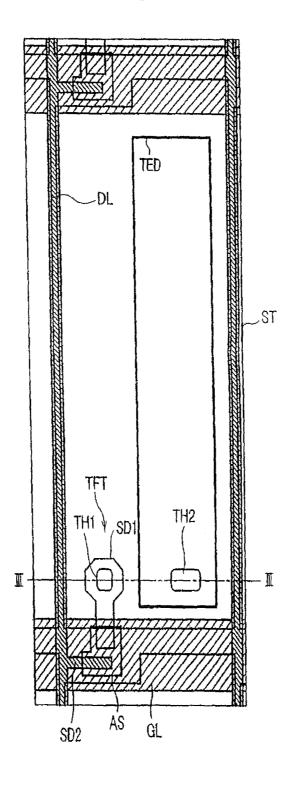

FIG. **10** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the <sup>25</sup> pixel constitution of still another embodiment of the present invention.

FIG. 11 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 12 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

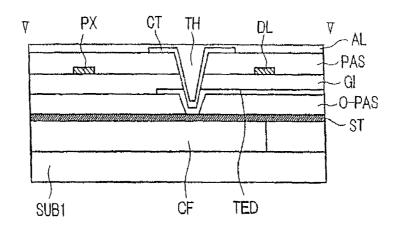

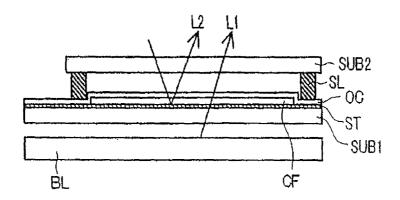

FIG. 13 is a cross-sectional view taken along a line I-I in FIG. 12.

FIG. 14 is across-sectional view taken along a line II-II in FIG. 12.

FIG. 15 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 16 is a cross-sectional view taken along a line I-I in  $\ ^{45}$  FIG. 15.

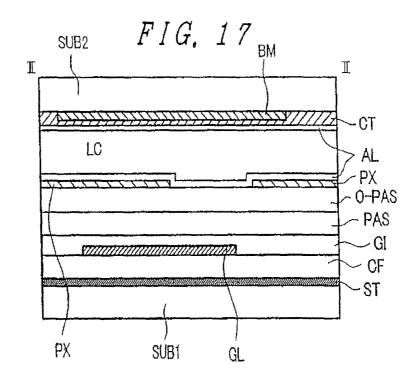

FIG. 17 is across-sectional view taken along a line II-II in FIG. 15.

FIG. **18** is a cross-sectional view taken along a line I-I in FIG. **15** of a liquid crystal display device for schematically explaining the pixel constitution of another embodiment of the present invention.

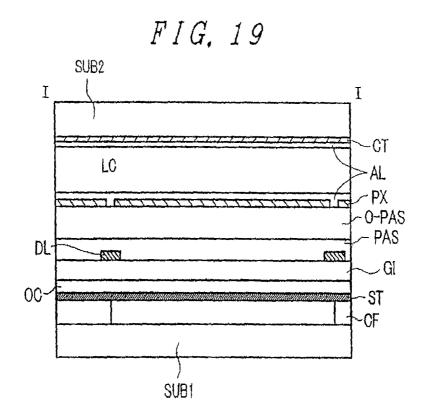

FIG. 19 is across-sectional view taken along a line II-II in FIG. 18

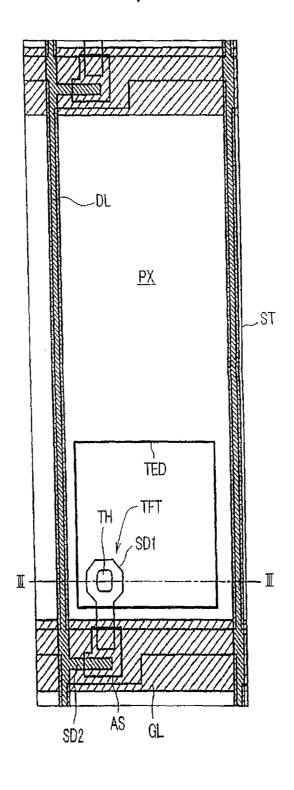

FIG. 20 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

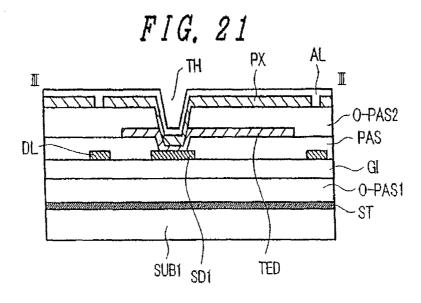

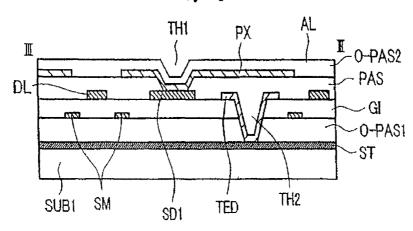

FIG. 21 is a cross-sectional view taken along a line III-III 60 in FIG. 38. in FIG. 20.

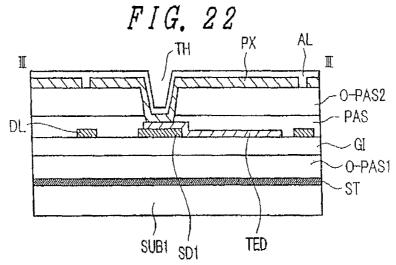

FIG. 22 is a cross-sectional view taken along the line III-III in FIG. 20 for schematically explaining the pixel constitution of another embodiment of the present invention.

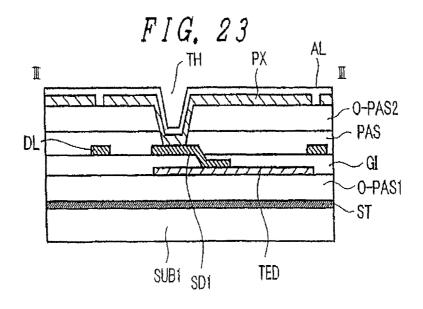

FIG. 23 is a cross-sectional view taken along the line 65 III-III in FIG. 20 for schematically explaining the pixel constitution of another embodiment of the present invention.

18

FIG. 24 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

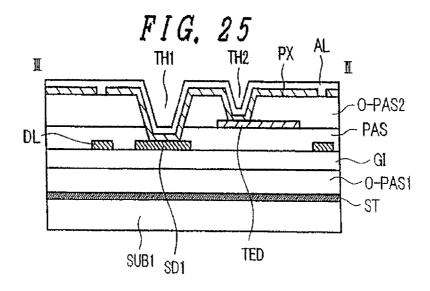

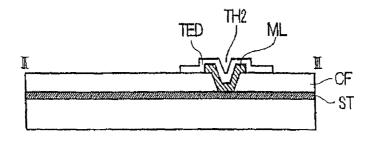

FIG. 25 is a cross-sectional view taken along a line III-III in FIG. 24

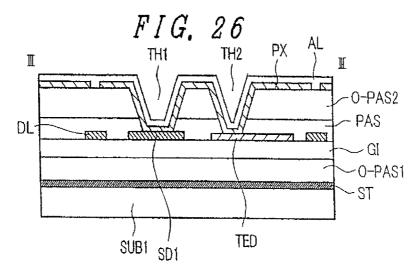

FIG. 26 is a cross-sectional view taken along a line III-III in FIG. 24 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention

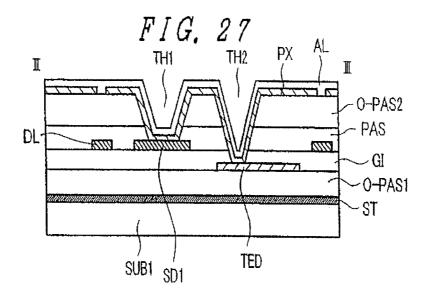

FIG. 27 is a cross-sectional view taken along a line III-III in FIG. 24 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 28 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 29 is a cross-sectional view taken along a line III-III in FIG. 28.

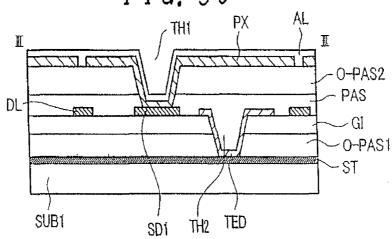

FIG. 30 is a cross-sectional view taken along a line III-III in FIG. 28 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention

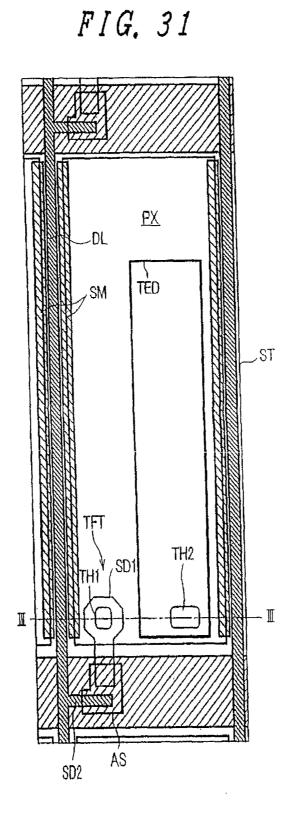

FIG. 31 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 32 is a cross-sectional view taken along a line III-III in FIG. 31.

FIG. 33 is a cross-sectional view taken along a line III-III in FIG. 31 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention

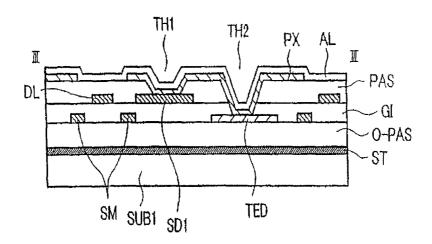

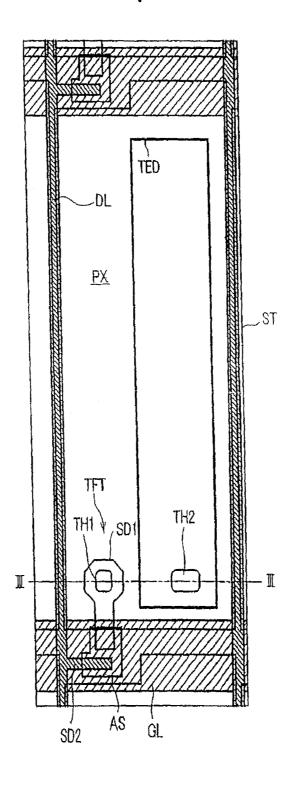

FIG. **34** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

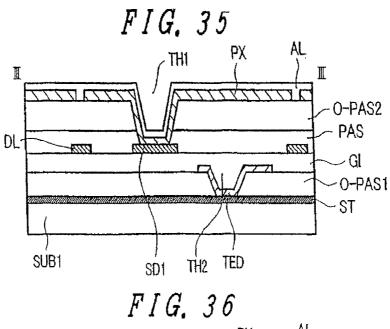

FIG. 35 is a cross-sectional view taken along a line III-III in FIG. 34.

FIG. 36 is a cross-sectional view taken along a line III-III in FIG. 34 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

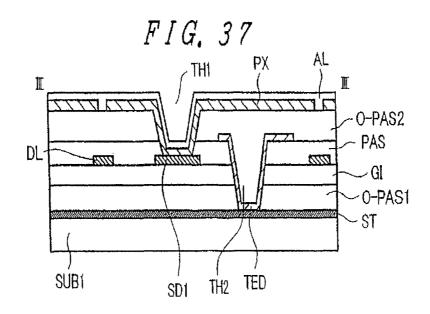

FIG. 37 is a cross-sectional view taken along a line III-III in FIG. 34 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

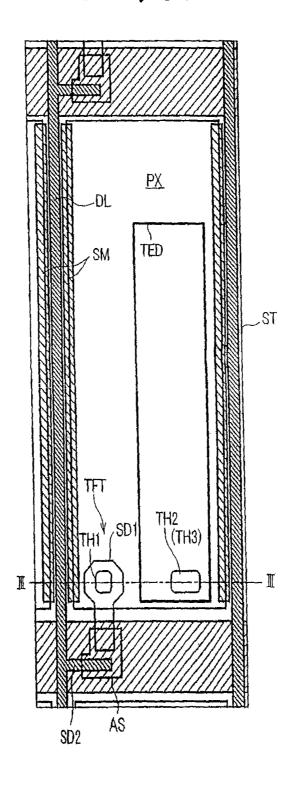

FIG. 38 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention

FIG. 39 is a cross-sectional view taken along a line III-III in FIG. 38.

FIG. 40 is a cross-sectional view taken along a line III-III in FIG. 38 of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **41** is a cross-sectional view taken along a line III-III in FIG. **38** of the vicinity of one pixel of the liquid crystal

display device for schematically explaining the pixel constitution of still another embodiment of the present invention

FIG. **42** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the <sup>5</sup> pixel constitution of still another embodiment of the present invention.

FIG. 43 is a cross-sectional view taken along a line III-III in FIG. 38.

FIG. **44** is a cross-sectional view taken along a line III-III in FIG. **42** of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention

FIG. **45** is a plan view of a through hole and a metal light shielding film in still another embodiment of the present invention.

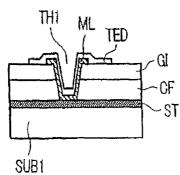

FIGS. **46**A-**46**D are cross-sectional views of an essential part for explaining still another embodiment of the present 20 invention.

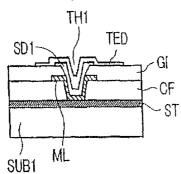

FIG. 47 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. 48 is a cross-sectional view taken along a line III-III in FIG. 47.

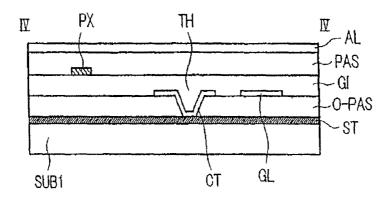

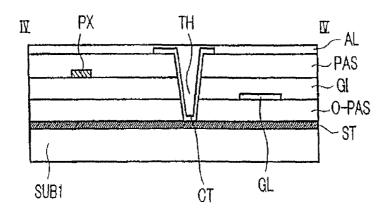

FIG. **49** is a cross-sectional view taken along a line IV-IV in FIG. **47** of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **50** is across-sectional view taken along a line IV-IV in FIG. **47** of the vicinity of one pixel of the liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

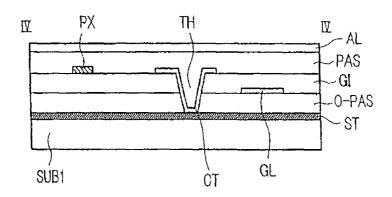

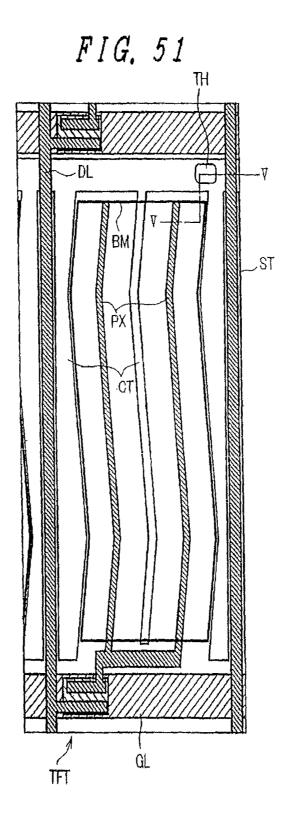

FIG. 51 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present of the present in FIG. 69 in FIG. 68.

FIG. **52** is a cross-sectional view taken along a line V-V in FIG. **51**.

FIG. **53** is a cross-sectional view taken along a line V-V in FIG. **51** showing the vicinity of one pixel of a liquid 45 crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **54** is a cross-sectional view taken along a line V-V in FIG. **51** showing the vicinity of one pixel of a liquid 50 crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **55** is a cross-sectional view taken along a line V-V in FIG. **51** showing the vicinity of one pixel of a liquid 55 crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **56** is a plan view of the vicinity of one pixel of a liquid crystal display device for explaining a modification of 60 the embodiments shown in FIG. **47** to FIG. **55**.

FIG. 57 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG.  $\bf 58$  is a cross-sectional view taken along a line VI-VI in FIG.  $\bf 57$ .

20

FIG. **59** is a cross-sectional view taken along a line VI-VI in FIG. **57** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

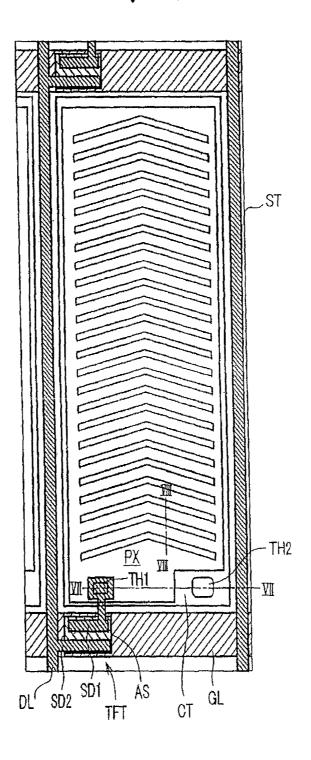

FIG. **60** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

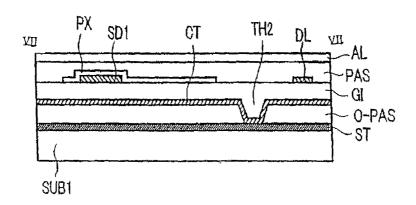

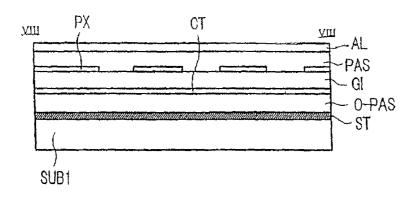

FIG. **61** is a cross-sectional view taken along a line VII-VII in FIG. **60**.

FIG. **62** is a cross-sectional view taken along a line VIII-VIII in FIG. **60**.

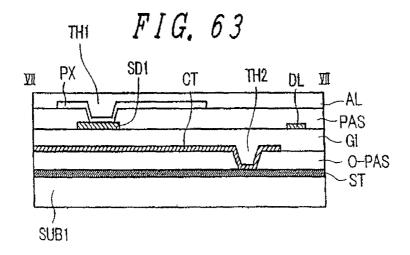

FIG. **63** is a cross-sectional view taken along a line VII-VII in FIG. **60** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining the pixel constitution of still another embodiment of the present invention.

FIG. **64** is a plan view of a portion of a thin film transistor TFT of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

FIG. **65** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

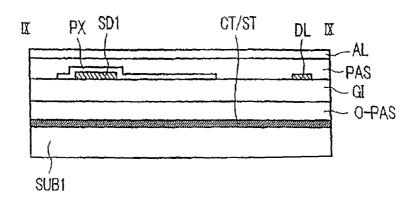

FIG. **66** is a cross sectional view taken along a line IX-IX in FIG. **65**.

FIG. 67 is a cross-sectional view taken along a line IX-IX in FIG. 65 showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

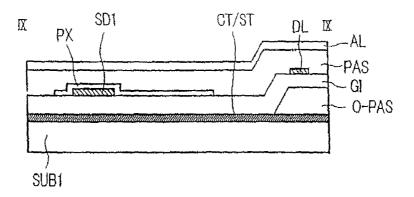

FIG. **68** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

FIG. **69** is a cross sectional view taken along a line X-X in FIG. **68**.

FIG. **70** is a cross-sectional view taken along a line X-X in FIG. **68** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

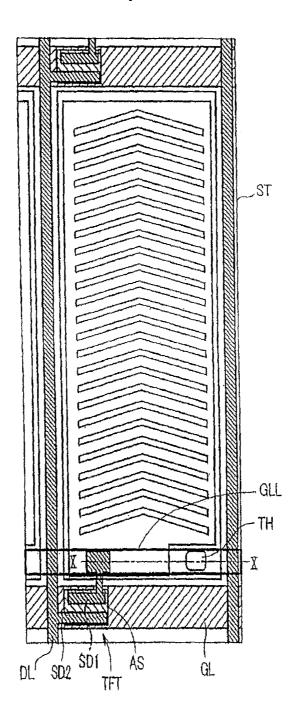

FIG. 71 is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

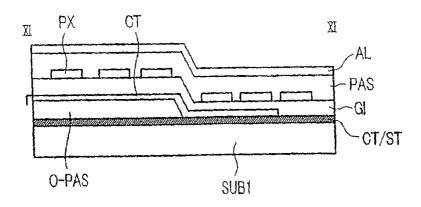

FIG. **72** is a cross sectional view taken along a line XI-XI in FIG. **71**.

FIG. **73** is a cross-sectional view taken along a line XI-XI in FIG. **68** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

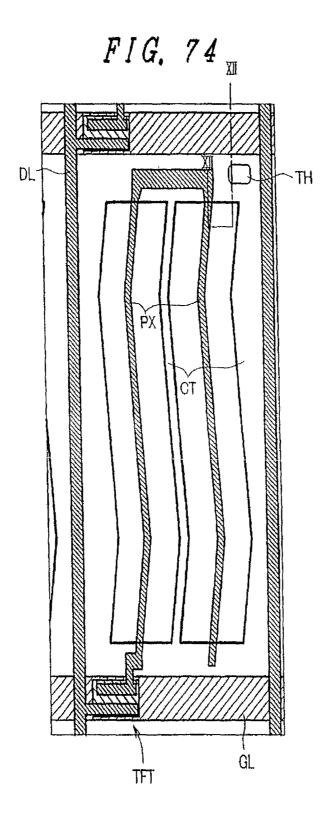

FIG. **74** is a plan view of the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

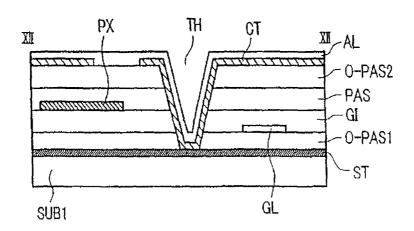

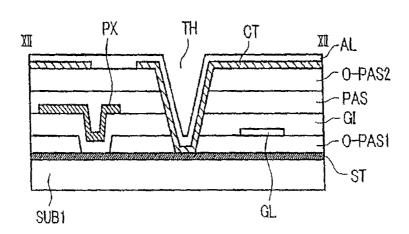

FIG. 75 is a cross sectional view taken along a line XII-XII in FIG. 74.

FIG. **76** is across-sectional view taken along a line XII-XII in FIG. **74** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

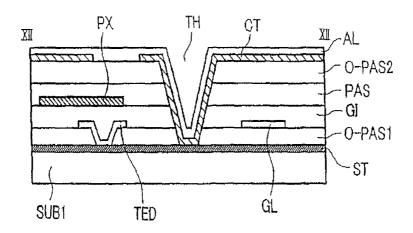

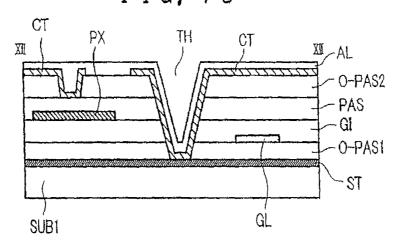

FIG. 77 is a cross-sectional view taken along a line XII-XII in FIG. 74 showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

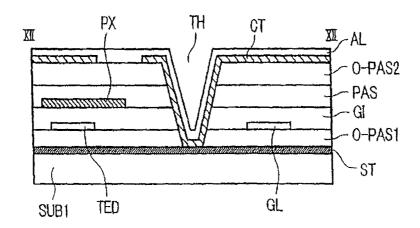

FIG. **78** is a cross-sectional view taken along a line XII-XII in FIG. **74** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

FIG. **79** is a cross-sectional view taken along a line XII-XII in FIG. **74** showing the vicinity of one pixel of a liquid crystal display device for schematically explaining an essential part of the pixel constitution of still another embodiment of the present invention.

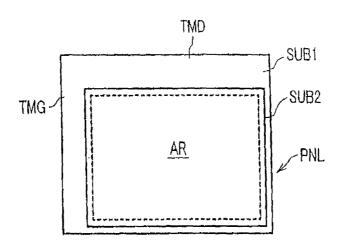

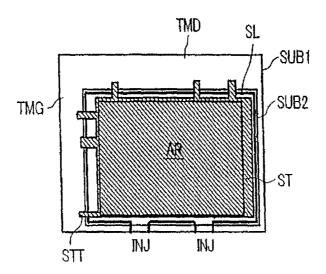

FIG. **80** is an explanatory view for explaining the constitution of a substrate of the liquid crystal display device of the present invention.

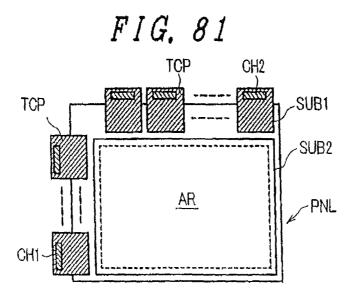

FIG. **81** is an explanatory view showing a state in which a tape carrier package on which a driving circuit is formed 20 is mounted on the first substrate at a terminal region.

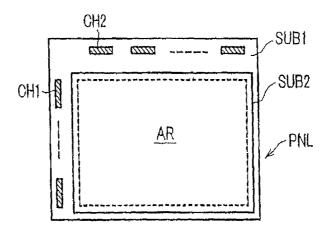

FIG. 82 is an explanatory view showing a state in which a driving circuit chip is directly mounted on the first substrate at the terminal region.

FIG. **83** is an explanatory view of an example of layout of 25 a liquid crystal filling port for allowing liquid crystal to be filled and sealed between two substrates.

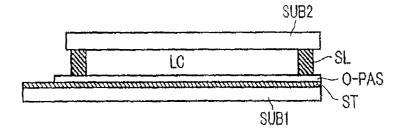

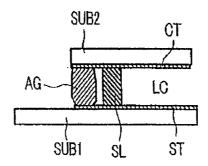

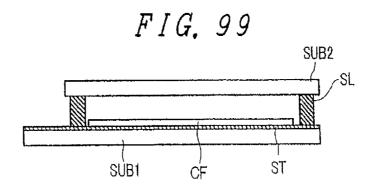

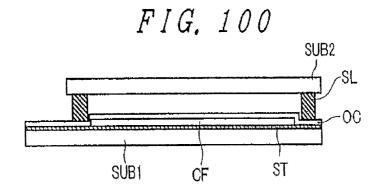

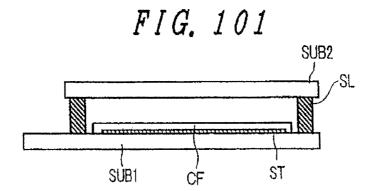

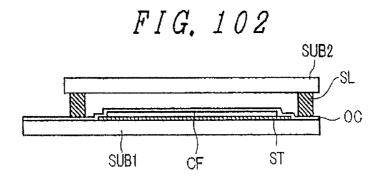

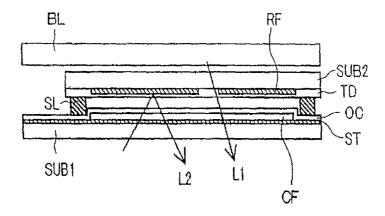

FIG. **84** is a schematic cross-sectional view of the liquid crystal display device of the present invention.

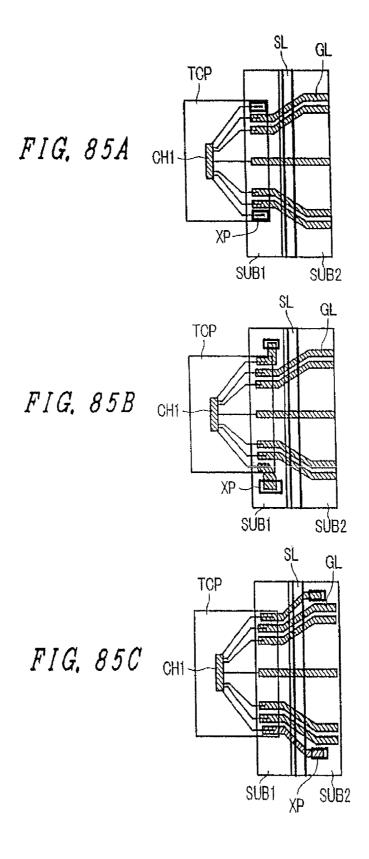

FIGS. **85**A-**85**C are plan views for schematically explaining a terminal region of a gate driving circuit mounted in a tape carrier package method

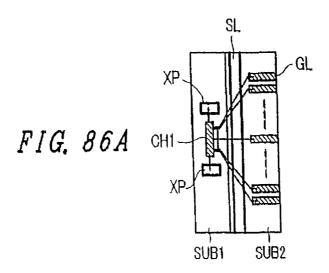

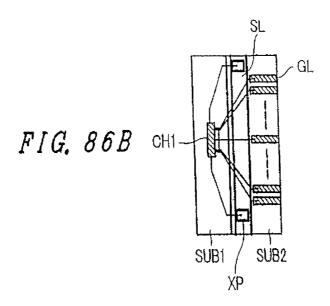

FIGS. **86**A-**86**B are plan views for schematically explaining a terminal region on which a driving circuit chip is mounted in a FCA method.

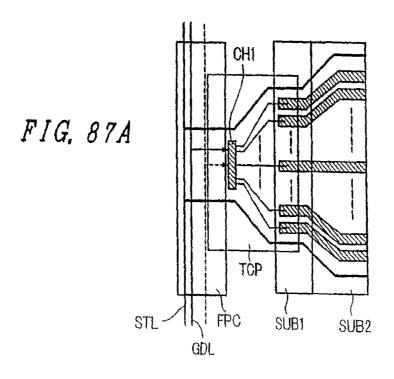

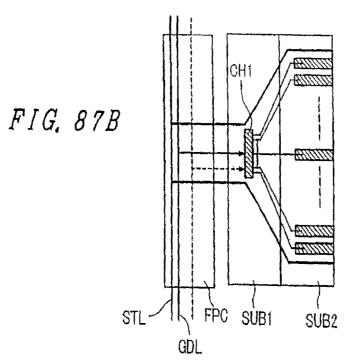

FIGS. **87**A-**87**B are plan views for schematically explaining a terminal region when a method in which electricity is supplied to a flexible printed circuit board or the like from a reference potential generation circuit disposed in a control circuit of the liquid crystal display device is adopted.

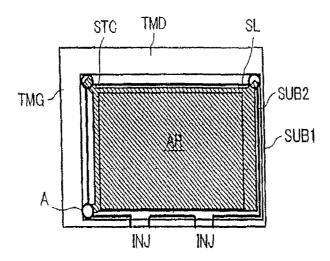

FIG. **88** is a schematic plan view of the liquid crystal display device for explaining a first example in which a feeding terminal to a reference electrode is formed.

FIG. **89** is a schematic plan view of the liquid crystal display device for explaining a second example in which 45 feeding terminal to a reference electrode is formed.

FIG. **90** is a cross-sectional view of an essential part showing a portion A of FIG. **89** in an enlarged manner.

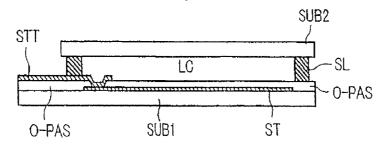

FIG. **91** is a schematic cross-sectional view of the liquid crystal display device for explaining a third example in 50 which a feeding terminal to a reference electrode is formed.

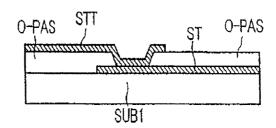

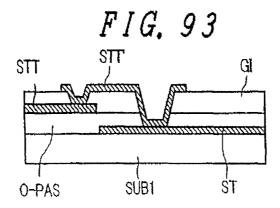

FIG. 92 is a cross-sectional view of an essential part showing the feeding terminal portion of FIG. 91 in an enlarged manner.