US 20110227887A1

### (19) United States

# (12) Patent Application Publication DALLAS et al.

### (10) Pub. No.: US 2011/0227887 A1

(43) **Pub. Date:** Sep. 22, 2011

# (54) ADJUSTMENT OF LIQUID CRYSTAL DISPLAY VOLTAGE

(75) Inventors: **JAMES M. DALLAS**, SUPERIOR,

CO (US); **DAVID B.**

HOLLENBECK, FREDERICK, CO (US); PER HAROLD LARSEN, BOULDER, CO (US); RAINER M. MALZBENDER, NIWOT, CO (US); EARLE R. VICKERY, III, HENDERSON, NV (US); MICHAEL WAYNE YEE, BROOMFIELD, CO (US)

(73) Assignee: MICRON TECHNOLOGY, INC.,

BOISE, ID (US)

(21) Appl. No.: 13/117,966

(22) Filed: May 27, 2011

#### Related U.S. Application Data

(63) Continuation of application No. 13/051,899, filed on Mar. 18, 2011, which is a continuation of application No. 12/815,108, filed on Jun. 14, 2010, now Pat. No. 7,932,875, which is a continuation of application No. 11/873,309, filed on Oct. 16, 2007, now Pat. No. 7,755, 570, which is a continuation of application No. 10/831, 545, filed on Apr. 23, 2004, now Pat. No. 7,283,105.

(60) Provisional application No. 60/465,364, filed on Apr. 24, 2003.

#### **Publication Classification**

(51) Int. Cl. G09G 3/36 (2006.01) G06F 3/038 (2006.01)

(57) ABSTRACT

Drive voltages of a liquid crystal display are adjusted based on one or more environmental conditions. The pixel drive voltages may be adjusted based on temperature. A pixel voltage may be varied such that it is a higher voltage at relatively lower temperatures and a lower voltage at relatively higher temperatures. The window voltage may be varied based on temperature. The window voltage may be stepped through different values within a display phase. The window voltage may be varied during a blanking period of the display phase such that the pixel sees a relatively larger voltage to obtain a desired initial state more quickly. Then, during a light modulating time period, the window voltage may be stepped such that there is a lower voltage field for holding the state of the pixel.

FIG.1

FIG.2

FIG.4

FIG.5

FIG.6

FIG.9

FIG.7

FIG.8

FIG.12

FIG.13

FIG.14

FIG.15a

FIG.15b

FIG.17

FIG.20

FIG.21

FIG.22

FIG.23

FIG.24

FIG.25

FIG.26

FIG.27

FIG.28

FIG.29a

FIG.29b

FIG.31

### ADJUSTMENT OF LIQUID CRYSTAL DISPLAY VOLTAGE

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. patent application Ser. No. 13/051,899, filed Mar. 18, 2011, entitled "Adjustment of Display Illumination Timing," which is a continuation of U.S. patent application Ser. No. 12/815,108, filed Jun. 4, 2010, entitled "Microdisplay and Interface on a Single Chip," which is a continuation of U.S. patent application Ser. No. 11/873,309, filed Oct. 16, 2007, entitled "Microdisplay and Interface on a Single Chip," now issued as U.S. Pat. No. 7,755,570, which is a continuation of U.S. patent application Ser. No. 10/831,545, filed Apr. 23, 2004, entitled "Microdisplay and Interface on Single Chip," now issued as U.S. Pat. No. 7,283,105, which claims priority from U.S. Provisional Patent Application No. 60/465,364, filed Apr. 24, 2003, entitled "Microdisplay and Interface on a Single Chip," the contents of each of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] In the past several years, microdisplays have begun to displace cathode ray tubes (CRT) in various consumer product applications and to be a desirable near-eye display in certain newer product applications. These applications may include video camcorders, digital still cameras, and the emerging area of head-mounted displays. These microdisplays include miniature display panels made from a silicon integrated circuit "backplane" that can be viewed by a user via a lens system or any optical magnifier. Many microdisplays produce full color images, monochrome images, or black and white images by acting as a spatial light modulator on light provided by a separate light source. Spatial light modulator microdisplays may employ liquid crystal materials, such as ferroelectric or nematic liquid crystal materials, or may utilize other technologies such as miniature mechanical mirrors or other suitable light modulation technology. Alternatively, microdisplays may emit their own light by employing miniature light emitting arrays made from emitters such as electroluminescent phosphors or organic lightemitting diodes (OLED). In the case of liquid crystal spatial light modulators, they may be transmissive or reflective in nature. In the case of reflective spatial light modulators utilizing liquid crystals, one suitable arrangement is known as reflective LCOS (liquid crystal on silicon). Other arrangements, with liquid-crystal modulators that are frequently transmissive, include active-matrix backplanes made from thin-film transistors (TFT) of either polysilicon or amorphous silicon, or made from single-crystal silicon that has been "lifted off" of a bulk-silicon wafer, as exemplified by the microdisplay products of Kopin Corporation.

[0003] The different microdisplay technologies differ significantly in their drive voltage requirements. For example, the electroluminescent (EL) phosphor displays require pixel drive varying over approximately an 80 V range to switch a pixel from fully OFF to fully ON. EL microdisplays have achieved such drive voltages with backplanes fabricated with doubly-diffused MOS (DMOS) high-voltage transistors as pixel drivers. The nematic LCOS displays do not usually require voltages as high, typically needing voltage swings in the range of 9-18 V, or even as low as 5 V. In the case of LCOS

using ferroelectric liquid crystals (FLCs), microdisplay products with pixels switching through only 3.3 V are currently in commercial production by the applicant. The 5 V and 3.3 V LCOS microdisplays have been made with backplanes fabricated in standard-logic CMOS processes having ground rules of 0.5  $\mu m$  and 0.35  $\mu m$ , respectively, where the standard CMOS logic provides adequate pixel drive voltage.

[0004] The different microdisplay technologies also differ in how they produce color. They may generate color in a field sequential fashion or via simultaneous generation of each of the three color fields using pixels with color triads. Field sequential color means displaying color images one color field at a time. For example, a red field may be displayed, followed by a green field, followed by a blue field. If these separate color fields are sequenced at a sufficiently high rate, the human eye/brain will integrate them together into a perceived full color image.

[0005] A further issue with microdisplays is generation of gray-scale images. It is advantageous to fabricate microdisplay backplanes as conventional silicon integrated circuits (ICs). Producing gray scale requires each display pixel to be capable of displaying multiple brightness levels. This can be accomplished by driving an analog-responding pixel emitter or modulator with analog circuitry. Silicon fabrication processes specialized for analog circuitry are known, but again typically cost more than baseline digital processes. Further, design of analog circuitry is more difficult and requires greater effort than design of similar digital circuitry. Analog circuitry is susceptible to a variety of noise and offset effects which can produce unwanted image artifacts if not carefully managed. Thus, it is desirable to provide gray-scale through purely digital circuitry.

[0006] A number of techniques capable of producing gray scale through digital drive that are suitable for microdisplays are known in the art. For example, fast-responding emitters and modulators such as those found in plasma displays, electroluminescent displays, light-emitting diodes, the Texas Instruments Digital Micromirror Device and other microelectromechanical (MEMS) devices, and ferroelectric liquid crystals (FLCs) can be driven with two-level drive in such a way that variations in the bright/dark duty cycle are used to produce apparent gray scale. In one class of such techniques, the image data is typically separated into "bit planes," ranging from the most-significant bit (MSB) plane down to the leastsignificant bit (LSB) plane, and the image data in the bit planes is written onto the display and held for an interval of duration proportional to the significance. Thus, in a very simple exemplary implementation, a pixel displaying an eight-bit monochrome gray scale would be written to eight times during a video frame, and might change state as many times. In fact, such gray scale techniques are known to produce severe visual artifacts, especially with moving pictures. One class of such artifacts is known as dynamic false contouring. Reduction of such artifacts requires complex variations of the simple example given above, with increased data processing, and more pixel state changes. Furthermore, production of a large number of gray shades, such as 256 gray shades usually required for high-quality video images, results in short LSB intervals during which the pixel emitter or modulator must be able to change states. Production of 60 Hz color images from three sequential color fields, each of which fields comprises an image with the abovementioned 256 levels may require switching in intervals as short as 1/(3×60× 255) of a second, which is about 22 μs. For some types of modulators, such as ferroelectric liquid crystal modulators, maintaining response times this fast can be difficult, especially in the lower-temperature portions of the ranges most displays are expected to operate over.

[0007] The bit-plane family of gray scale techniques can also be used with more slowly responding display materials such as nematic liquid crystals. In this case the pixel has an analog response to the RMS (root-mean-square) value of an underlying two-level electrical drive. In this case, the slow, averaging nature of the liquid crystal material prevents the occurrence of dynamic false contouring, but another class of artifacts occurs instead. Neighboring pixels driven to adjacent gray values may experience very different drive waveforms. For example, in an eight-bit gray-scale scheme, a pixel driven to gray value 128 (binary 10000000) might be driven high for approximately the first half of a video frame and low for the remainder, while another pixel driven to gray value 127 (binary 01111111) might be driven low for approximately the first half of a video frame and high for the remainder. If these two pixels are physically adjacent to each other, as would be the case if they were part of an image with a smoothly varying brightness, a strong lateral electrical field would be produced at the boundary between the two pixels. This lateral or fringing electrical field often produces in nematic liquid crystals a defect called a disclination. Such disclinations have a visual contrast to the adjacent liquid crystal material, often appearing much darker, and, once formed, are slow to disappear even when the electrical drive conditions that produced them are removed. Thus, brightness variations in the images produced on nematic microdisplays driven with bit-plane type digital drive become "decorated" with undesirable dark lines, which can persist momentarily even when the image content is changed.

[0008] Many of the above disadvantages of bit-plane type digital gray scale drive can be overcome by alternative twostate drive schemes that reduce the number of drive transitions per video frame. For example, pulse-width modulation (PWM) drive schemes have previously been used, for example as taught in U.S. Pat. Nos. 5,977,940, 6,249,269, 6,329,974, and 6,525,709. In these examples, each pixel has its own driver, which is typically "reset" to a chosen digital value at the beginning of the video field, and are then switched once (and only once) to the other digital value at a time proportionate to the desired gray value. However, the previous implementations referenced above, while utilizing digital pixel drive, have all relied on underlying analog pixel circuitry to perform a comparison between an analog image value, stored on a pixel capacitor, and a global analog ramp voltage, with each pixel having a analog voltage comparator in it. Analog storage of the image value was chosen to reduce achievable pixel size, since a single capacitor can store an 8-bit image value, replacing the function of eight digital memory registers. These analog implementations, while avoiding the image-artifact issues described above with respect to bit-plane type digital gray scale, all suffer from the practical difficulties previously described for analog cir-

[0009] It is against this background and with a desire to improve on the prior art that the present invention has been developed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

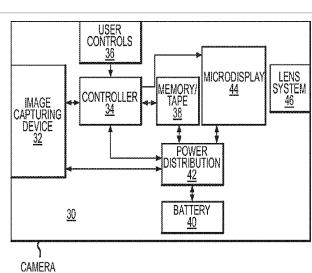

[0010] FIG. 1. is a block diagram of a camera in which the microdisplay of the present invention could be employed.

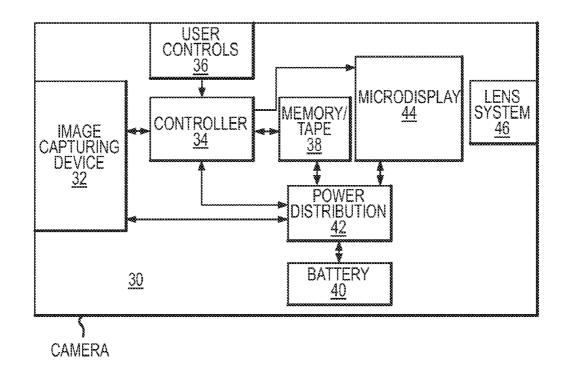

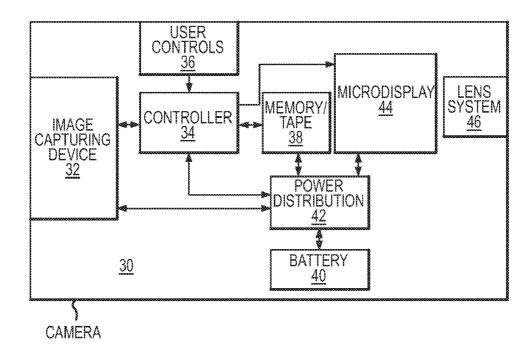

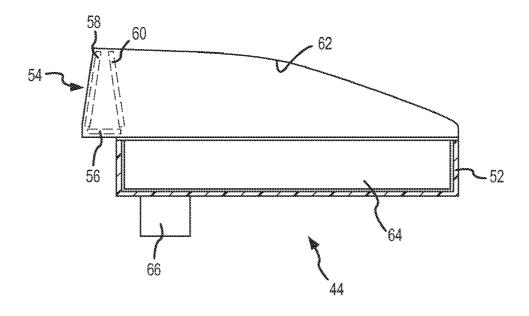

[0011] FIG. 2 is a side view of the microdisplay of the present invention showing a portion of the plastic packaging cut away to reveal an LCOS unit of the microdisplay of the present invention.

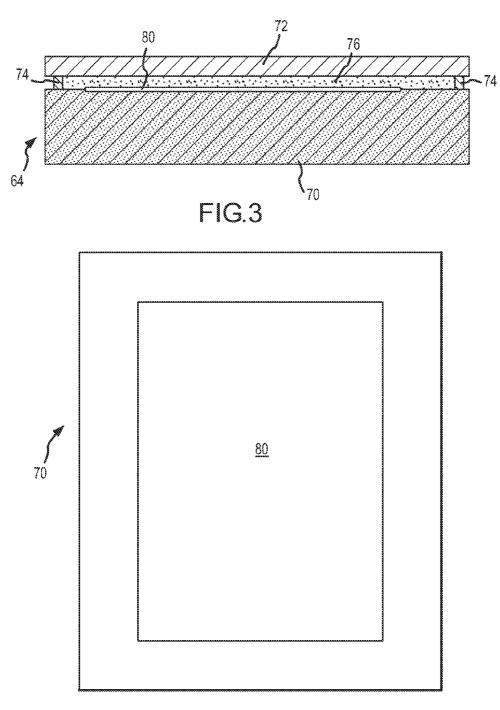

[0012] FIG. 3 is a cross-sectional view of the LCOS unit of FIG. 2.

[0013] FIG. 4 is top view of the silicon backplane of the LCOS unit of FIG. 2.

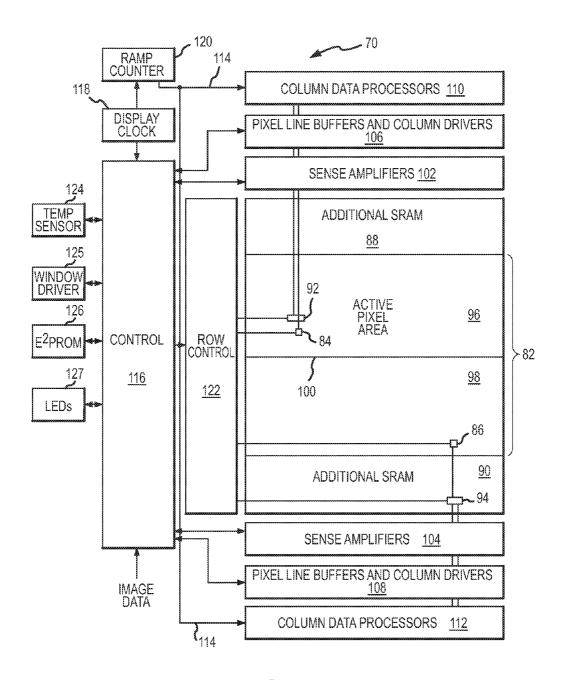

[0014] FIG. 5 is a block diagram of portions of the silicon backplane of FIG. 4.

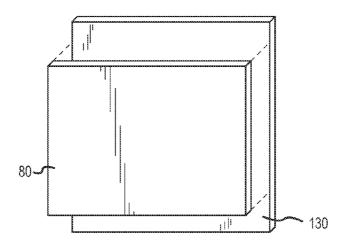

[0015] FIG. 6 is a perspective view of portions of the silicon backplane showing the size relationship between the pixel array and the layer of boost circuits and SRAM memory cells.

[0016] FIG. 7 is a functional representation of a portion of the silicon backplane of the present invention.

[0017] FIG. 8 is a larger-scale functional representation of a portion of the silicon backplane of the present invention.

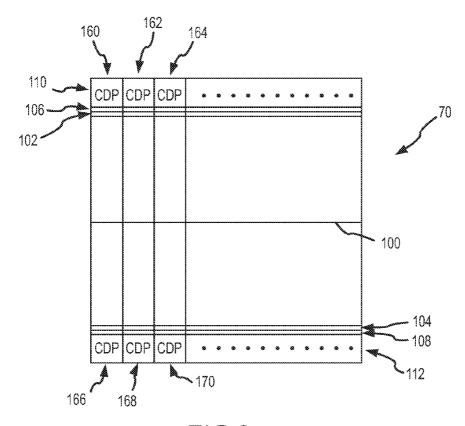

[0018] FIG. 9 is a functional representation of a portion of the silicon backplane of the present invention, showing the CDP slices.

[0019] FIG. 10 is a functional view of a single CDP slice of the silicon backplane of the present invention.

[0020] FIG. 11 is a more detailed functional view of a single CDP slice of the silicon backplane of the present invention.

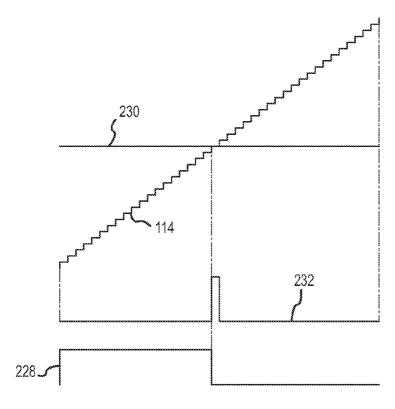

[0021] FIG. 12 is a representation of the input signals to a comparator and a resulting pixel electrical drive signal in a CDP slice of the microdisplay of the present invention.

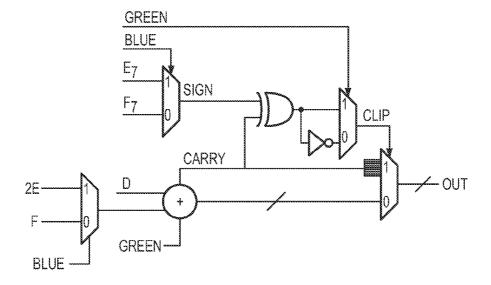

[0022] FIG. 13 is a logic diagram of a circuit of the present invention that is utilized in transforming between coordinate systems while decoding from DEF to RGB color-space.

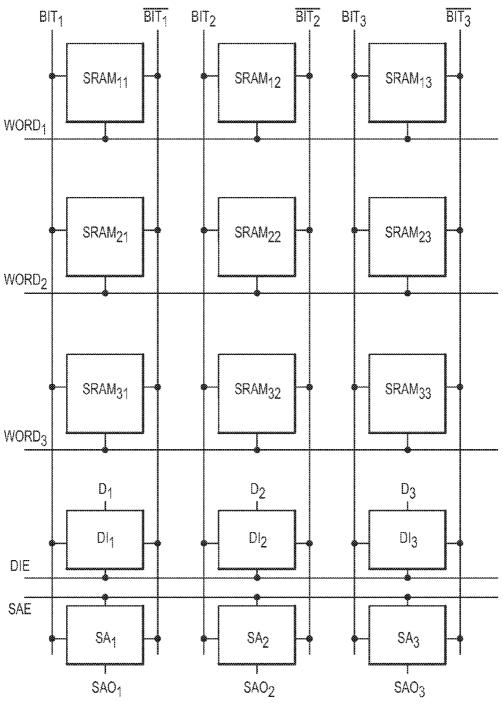

[0023] FIG. 14 is a simplified representation of a portion of the SRAM memory array and its connection to data-in circuits and sense amplifier circuits.

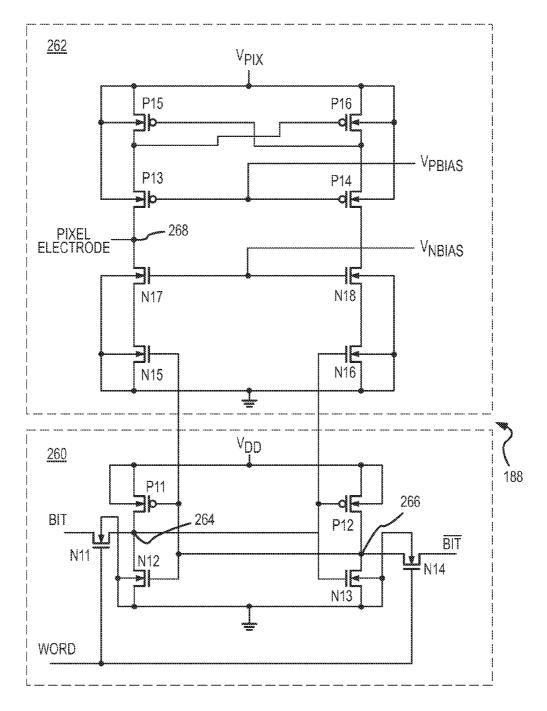

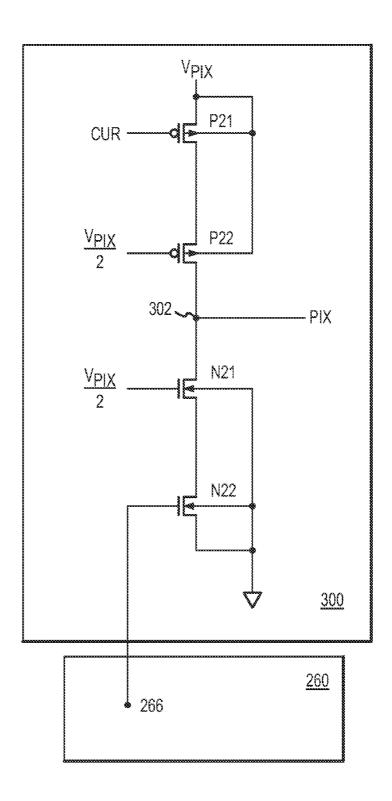

[0024] FIGS. 15a, 15b, and 15c are schematic diagrams of boost circuits for an associated SRAM memory cell that is associated with each pixel of the microdisplay of the present invention.

[0025] FIG. 16 is a schematic diagram of a circuit used to regulate the voltage supplied by a voltage supply of the present invention as well as to generate a voltage signal representative of the operating temperature of the microdisplay of the present invention.

[0026] FIG. 17 is an illustration of a visual artifact known as tearing that is visible in some displays of moving images.

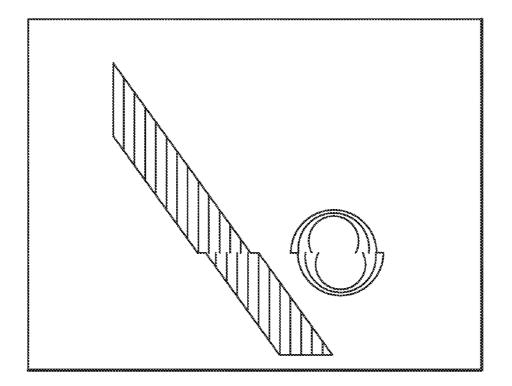

[0027] FIG. 18 is an illustration of portions of logic for implementing PWM gray scale in digital hardware.

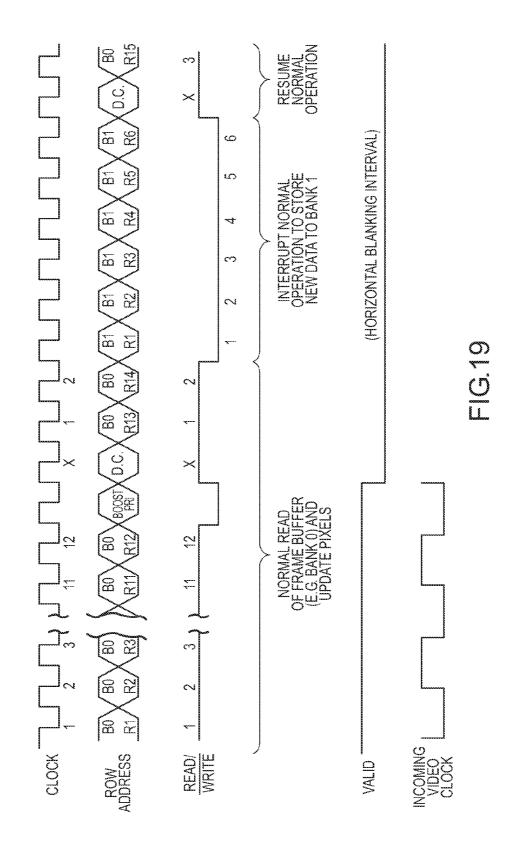

[0028] FIG. 19 is a timing diagram showing the interleaving of reading and writing operations in the present invention.

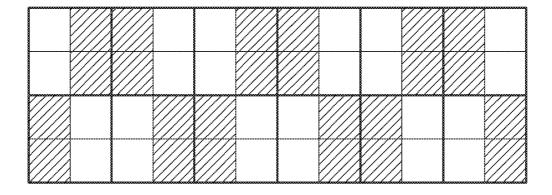

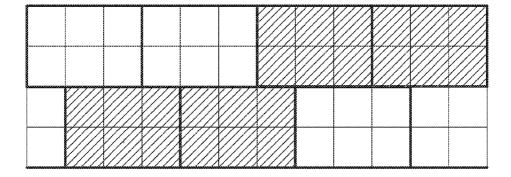

[0029] FIG. 20 is a representation of a sampling technique for image data.

[0030] FIG. 21 is a representation of a sampling technique for compressed image data.

[0031] FIG. 22 is a representation of a sampling technique for compressed image data.

[0032] FIG. 23 is a representation of a first sampling technique of the present invention for compressed image data.

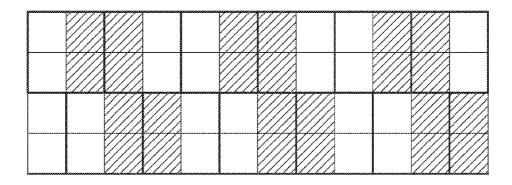

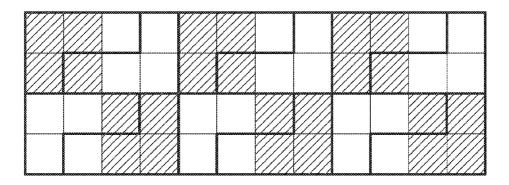

[0033] FIG. 24 is a representation of a second sampling technique of the present invention for compressed image data.

[0034] FIG. 25 is a representation of a third sampling tech-

nique of the present invention for compressed image data.

[0035] FIG. 26 is a representation of a fourth sampling technique of the present invention for compressed image data.

[0036] FIG. 27 is a representation of a fifth sampling technique of the present invention for compressed image data.

[0037] FIG. 28 is a representation of a sixth sampling technique of the present invention for compressed image data.

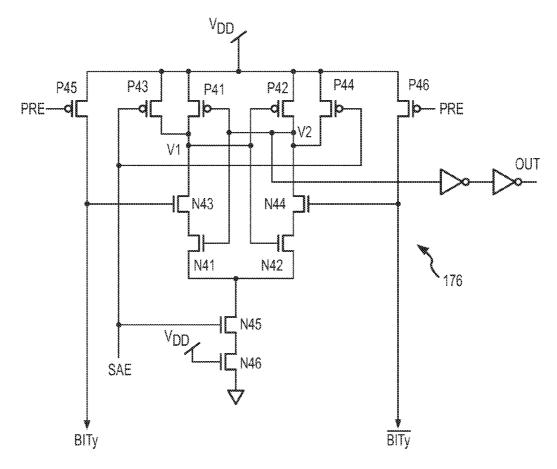

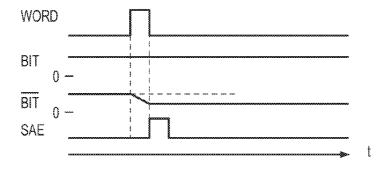

[0038] FIGS. 29a and 29b are a schematic and a timing diagram, respectively, for a sense amplifier for an SRAM circuit of the present invention.

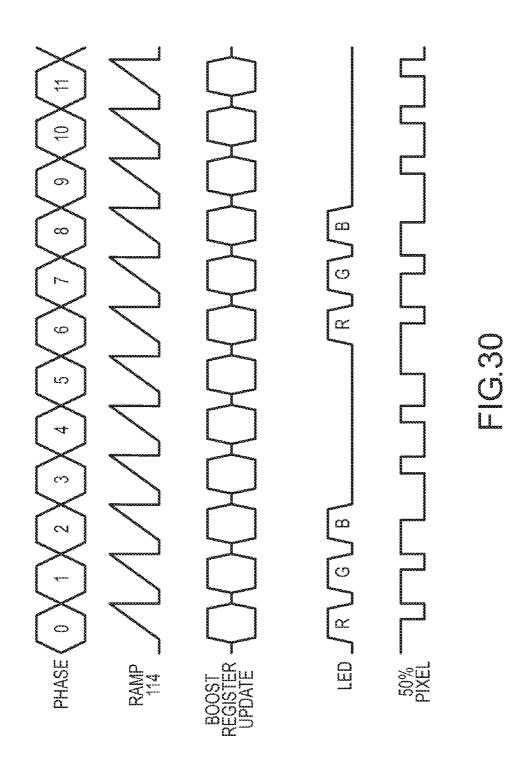

[0039] FIG. 30 is a timing diagram showing the various phases of sequential color operation of the present invention.

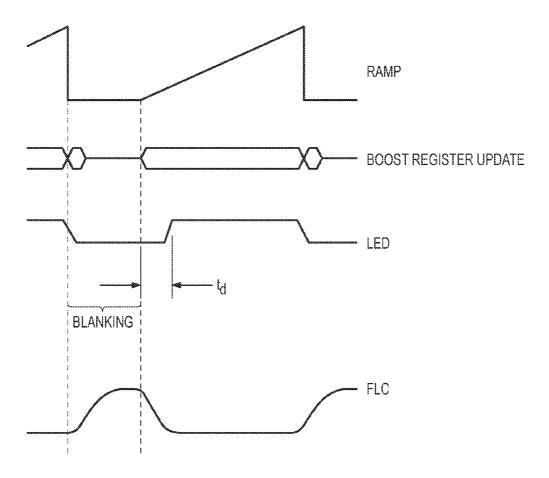

[0040] FIG. 31 is a timing diagram illustrating the temperature variation of the timing of the LED illumination according to the present invention.

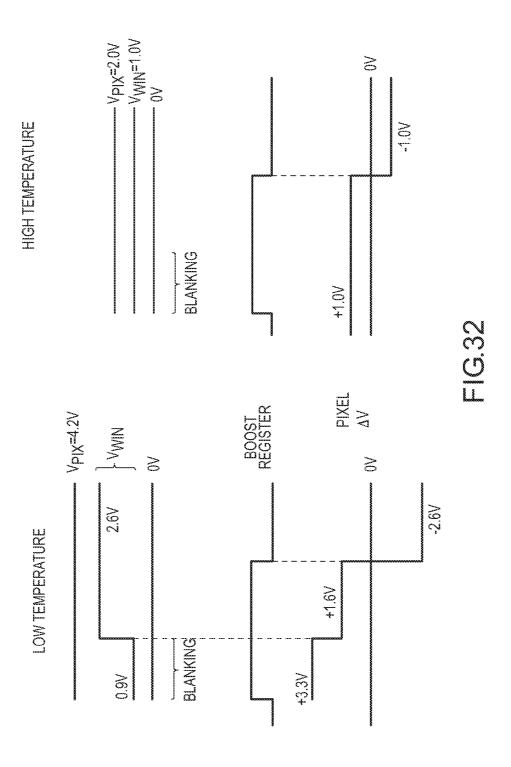

[0041] FIG. 32 is a timing diagram illustrating the varying of display characteristics for low-temperature and high-temperature operation according to the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0042] Reference will now be made to the accompanying drawings, which assist in illustrating the various pertinent features of the present invention. Although the present invention will now be described primarily in conjunction with microdisplays based on spatial light modulators, it should be expressly understood that the present invention may be applicable to other applications where digital interfaces to image display systems, image compression, low power SRAM, and many other features of the present invention are required/ desired. In this regard, the following description of a microdisplay system is presented for purposes of illustration and description only. Furthermore, the description is not intended to limit the invention to the form disclosed herein. Consequently, variations and modifications commensurate with the following teachings, and skill and knowledge of the relevant art, are within the scope of the present invention. The embodiments described herein are further intended to explain best modes known of practicing the invention and to enable others skilled in the art to utilize the invention in such, or other embodiments and with various modifications required by the particular application(s) or use(s) of the present invention.

[0043] As can be appreciated from the background of the invention, it is desirable to implement PWM gray scale in digital architecture. Before describing how this has been done by the inventors, we first have set out below why a straightforward implementation of a digital PWM technique is likely to suffer from a high degree of pixel complexity. The complexity of digital implementations of microdisplays depend on the total number of image bits needed per pixel, which in turn depends on a display's gamma characteristic. Gamma (γ) is the exponent of a power-law relationship between display brightness and input image value. The abovementioned "bitplane" type digital gray scale techniques produce a linear relationship between image data value and display brightness, and thus have  $\gamma=1$ , as do most PWM schemes. On the other hand, typical CRT displays have γ≥2, which, it turns out, better matches the characteristics of human perception. Gamma values of about two result in brightness steps between numerically adjacent input data that have more nearly even perceptual spacing, while for γ=1, the perceived brightness steps are large at the low-brightness end of the scale and small at the high-brightness end of the gray scale. It is generally thought that the image-quality penalty for  $\gamma=1$  is about two bits per color; that is, to display an image equal in quality to a standard 24-bit image on a CRT requires 30 bits on a  $\gamma=1$  display. Thus, a  $\gamma=1$  display operating directly from a standard 8-bit/color input signal produces a color palette most similar in perceptible quality to a CRT with a palette of  $2^{18}$ =262,144 colors, instead of the desired 16.7 million-color palette.

[0044] In the case of microdisplays generating field sequential color images, current products typically include a separate interface chip upstream of the microdisplay to convert the incoming standard video image data into an acceptable format for the microdisplay. For example, a standard digital video image signal may provide red data for a first pixel (picture element), green data for that same pixel, and then blue data for the same pixel. This will be followed by red, green, and blue data (RGB data) for the next pixel and so forth. This is continued for each of the pixels in a particular line in the image, followed by the next subsequent line in the image, and so forth. The data is typically delivered at an almost even rate throughout the time allotted for the display of a frame, except for short horizontal blanking intervals at the end of each line and a short vertical blanking period at the end of each frame. For example, in the CCIR 601 and CCIR 656 standard video signals, the horizontal blanking occupies approximately 17% of the time allotted to each line (which time is on the order of 60 µs), while the vertical blanking occupies approximately 8% of the frame time. The remainder of the time, data is being delivered for display. Field sequential color displays, on the other hand, typically require first the red data for each of the pixels in the image, followed by the green data for each of the pixels in the image, followed by the blue data for each of the pixels in the image. In the simplest sequential-color display illumination schemes, the entire display is illuminated with a single primary color at one time. In this case, all the data for a given primary color must be written to the pixels before the illumination can commence, which further aggravates the data-supply problem, requiring that the data be provided to the display at a high rate for a short interval of time, to avoid unduly reducing the illumination duty factor. For these reasons, field sequential color microdisplay systems require additional circuitry to receive the data in one format and supply it to the microdisplay in a different format. This format conversion necessarily requires a considerable amount of buffer memory—at least the substantial fraction of a memory capable of storing all the red, green, and blue data for all the pixels in the displayed image. With moving images, additional buffer memory is required to prevent the "tearing" artifact illustrated in FIG. 17. The figure illustrates the image on a sequential-color display, the display being refreshed from a single frame buffer that is simultaneously being updated with a new incoming frame. The depicted object is moving (horizontally, in this example), which causes its position to change from frame to frame. Since the display refresh rate is different (i.e. three or more times higher) than the update rate, the refresh and the update cannot be entirely synchronized, and it is therefore unavoidable that portions of the image data corresponding to a present frame and to a previous frame appear simultaneously on different regions of the display. Horizontal lines along which there is a mismatch in the position of the displayed object separate these regions. The object's details or texture will appear to be "torn" along these lines. This artifact is quite obvious and objectionable to the average viewer. Avoiding it requires double buffering the image data, i.e., using one buffer memory to store and display the previous frame, while a second buffer memory is updated with incoming image data. The role of the two buffers is reversed between incoming [0045] One way to provide the needed additional data reformatting or reordering and image buffer circuitry practiced in the art is to supply it on semiconductor chips separate from the microdisplay. A disadvantage of this separate interface chip approach is the increased cost due to the need for the microdisplay system to have additional chips, for example one extra chip for the data format conversion and another dedicated to image buffering memory. A further disadvantage is the increased size of a multiple-chip display system. Finally, off-chip buffering further requires high-bandwidth communication between the buffer chip and the microdisplay, which invariably produces increased power consumption

[0046] An alternative location for the needed circuitry and buffer memory is on the microdisplay backplane itself, perhaps within the pixel array. However, the large amount of backplane circuitry required to effect image buffering prevents practical implementations, since the resulting backplane would be so large and hence expensive. If the frame buffer was simply a memory block separate from the pixels, but still on the microdisplay backplane, the ratio of pixel array area to total backplane area would be undesirably reduced, since it would be impractical for the pixels to cover the memory block area. Alternatively, the circuit architecture of the microdisplay pixels could be designed so that the needed buffer memory for a given pixel was part of the circuitry physically associated with and underneath that pixel. Although this doesn't solve the overall backplane size problem, it does avoid the unfavorable active-area ratio problem of a separate memory block, since the pixels now cover the memory circuits. However, this benefit comes at the price of introducing another substantial problem. The failure of any of the memory registers produces visible pixel defects. Redundancy techniques used in the semiconductor memory art to improve yield by "mapping" around the address of defective registers cannot easily be used to compensate for such pixel failures, since a defective pixel at one location cannot be replaced by a functioning pixel at a different location.

[0047] The backplane size problem could be addressed by specialized CMOS silicon fabrication processes, such as embedded DRAM processes, but these processes are more expensive to fabricate. Further, DRAM requires constant refreshing, which adds substantial unwanted power consumption.

The impracticality of prior-art techniques for providing the desired fully digital sequential-color format conversion entirely within a microdisplay backplane can best be illustrated by an example. For purposes of illustration, consider a microdisplay capable of displaying sequential full color, with eight bits of gray scale per color. Consider further that the microdisplay utilizes a double image buffer, with the buffer circuitry located within the pixel, to eliminate visual artifacts and to allow high color field rates. Although the layout size of an arbitrary pixel circuit cannot be determined exactly without carrying out a complete design, its lower bound can be estimated by assuming that its transistors are laid out with the same density as transistors in a standard six-transistor SRAM cell. Given that the design rules and layout for standard SRAM cells are highly optimized, it is very unlikely that arbitrary pixel circuits could be laid out with higher density. In a survey of leading CMOS silicon foundries performed by the applicant, it was found that the area of optimized six-transistor SRAM cells offered by the foundries was generally larger than 130 f<sup>2</sup>, where f designates the CMOS process ground rule (usually the finest feasible half-pitch for polysilicon lines in the specified process). For example, in a 0.35  $\mu m$  CMOS process, six-transistor SRAM cells generally had areas of about  $16~\mu m^2$ . The formula a=130  $f^2$  produces an SRAM area estimate slightly larger than that estimated for future processes and future years in the "International Technology Roadmap for Semiconductors 2002 Update", sponsored by (among others) the United States' Semiconductor Industry Association.

[0049] In-pixel buffering and re-ordering of image data could conveniently be accomplished with shift registers, as is known in the sequential-color display art. Standard CMOS shift register cells comprising two static latches (each latch further comprising four transistors in the form of crosscoupled inverters) and two transmission gates (each transmission gate comprising two transistors) require twelve transistors per stored bit. Thus, double-buffering 24 bits of image information requires 48×12=576 transistors. If these transistors could be laid out with a density matching that of the highly optimized standard SRAM cells, they would occupy 1536 μm<sup>2</sup> in a 0.35 μm CMOS process. Thus, just the transistors associated with the image buffer would limit the minimum achievable pitch of square microdisplay pixels to 39.2 μm for this candidate CMOS process. It is known in the sequential color display art that a stored digital image value can be converted to a pixel-duration signal (in effect, a PWM drive signal) by using a down counter. Each stage of the counter can be conventionally implemented using a halfadder and a master/slave flip-flop, with a NAND gate to detect the zero condition, as shown in FIG. 18. The half-adder includes an eight-transistor XOR gate plus a four-transistor AND gate, the master stage includes four transistors arranged as cross-coupled inverters plus a load transistor and an enable transistor; the slave stage is the same, minus the load transistor. The NAND gate requires two transistors per input. Thus, the counter requires 25 transistors per bit, which, for an eightbit gray scale translates into a total of 196 transistors, after four transistors in the unused AND gate at the zeroth stage of the counter are discarded. In total, then, this double-buffered PWM implementation of 24-bit color display requires 576+ 196=772 transistors. This estimate ignores miscellaneous transistors needed for pixel selection, and so on. In the aforementioned 0.35 μm CMOS process, this 772-transistor pixel would require more than 2050 µm<sup>2</sup>, which would limit achievable square-pixel pitch to 45 µm. This pixel size estimate can be contrasted with pixel pitches found in current commercial microdisplays, which range around 12 µm. Thus, straightforward implementation of digital sequential-color format conversion results in pixels with areas more than 10 times larger than commercially competitive. For a given display resolution, a large pixel size results in a large backplane die size, which correspondingly results in few backplane die per silicon wafer and low backplane die yield, compounding to give an undesirably high backplane die cost.

[0050] It may be appreciated that techniques for reducing the number of bits needed for an image might reduce the complexity and size of a microdisplay backplane. For example, image compression techniques such as JPEG compression can be used to reduce the amount of memory needed to store an image. However, these techniques typically require complex numerical processing logic, whose additional size offsets any savings in required memory.

[0051] The number of image-data bits that must be stored can also be reduced through the technique of constraining the

number of colors the display is capable of showing to a "palette" smaller than the full 16.7 million shades available at the full twenty-four bits per pixel. For example, if the number of shades were restricted to 65,536 shades, then the number of bits needed to be stored could be reduced from twenty-four per pixel to sixteen per pixel, with a consequent reduction in backplane complexity. Palettizing the image, though, produces undesirable image artifacts of its own, particularly for continuous-tone image content such as is found in photographs or videos of natural scenes, since it makes it difficult to portray smooth color and brightness variations. This problem is greatly exacerbated for PWM pixel modulators, which produce a linear relationship between display brightness and input image value. Further reduction of the input-value palette to 16 bits would result in a palette displayed at  $\gamma=1$ equivalent to 2<sup>10</sup>=1024 colors on a γ=2 display, unsuitable for almost any application.

#### System Elements

[0052] With this in mind, we can now discuss the present invention. One example of an application in which the present invention may be employed is a camera 30, as shown in FIG. 1. The camera 30 may be a video camera, a digital still camera, or another type of camera. The camera 30 may include an image-capturing device 32 that is capable of creating electrical signals representative of an image that a user may desire to record. The electrical signals are passed from the image-capturing device 32 to a controller 34 which controls the function of the camera 30. The camera 30 also includes user controls 36 that the user may use to select modes of operation of the camera 30. The controller 34 has the ability to store the electronic signals representative of the images in a storage device such as memory/tape unit 38. In the case of a video camera, this may typically be a videotape, while in the case of a digital still camera, this may typically be some type of electronic, non-volatile memory. The camera 30 also includes a battery 40 that supplies power to the components of the camera 30 via a power distribution unit 42. The stored electronic representation of the images can be converted to visual images by a microdisplay 44 that may be viewed by the user via a lens system 46 or reflective magnifier. While this is one example of an application in which the microdisplay of the present invention may be utilized, it is only exemplary in nature and is not intended to limit in any fashion the scope of the invention.

[0053] The microdisplay 44 is shown in FIG. 2 to illustrate its major components. The microdisplay 44 includes a plastic package housing 52 to which an illuminator housing 54 is attached. The illuminator housing 54 houses a tri-color LED 56 and a reflector 58 that collects light emitted by the LED 56. The light then passes through a pre-polarizer and diffuser 60 to minimize stray light of unwanted polarization and to create even illumination. The diffuse, polarized light is directed toward a polarizing beam splitter (PBS) 62, which reflects light of one linear polarization while rejecting light of an orthogonal linear polarization. The reflected light is directed down toward a liquid crystal on silicon (LCOS) display panel 64 that resides in the package housing 52. As will be described in further detail below, the display panel includes an array of pixels that can be electronically controlled into one of two different light-modulating states. In one lightmodulating state, the incoming polarized light is reflected back toward the PBS 62 with the same polarization. In another light-modulating state, the light is reflected back toward the PBS 62 with its linear polarization rotated by 90°. As can be appreciated, the PBS 62 will reflect the reflected light that has not had its polarization rotated, while the light that has been rotated in polarization will pass through the PBS 62 for viewing by the user via the lens system 46. A connector 66 depends downward from the package housing 52 for electrical connection to the camera 30 such as via a flex cable.

[0054] The above discussion of the operation of the display panel 64 is not intended to limit the present invention, as other types of spatial light modulators could also be utilized in the present invention, such as spatial light modulators depending on miniature mechanical mirrors, for example. Also, display panels that emit their own light could be used. In addition, while the discussion involves linearly polarized light of two different orthogonal directions, it is also possible to utilize the present invention in a system in which unpolarized light or different types of polarization are used. Further details on the operation of liquid crystal spatial light modulators can be found in U.S. Pat. Nos. 5,748,164, 5,808,800, 5,977,940, 6,100,945,6,507,330,6,525,709, and 6,633,301, the contents of each of which are incorporated herein by reference.

#### Display Panel Detail

[0055] The display panel 64 is shown in greater detail in FIGS. 3 and 4. As shown in FIG. 3, the display panel 64 includes a silicon backplane 70 to which a sheet of glass 72 has been affixed via glue seal 74. Sandwiched between the silicon backplane 70 and the sheet of glass 72 is a layer of liquid crystal material 76. When viewed from a different side, it may become clear that the glass 72 and the backplane 70 are offset slightly in one direction to allow there to be a slight overhang of glass on one side and a slight overhang of silicon on the opposite side. The liquid crystal material 76 may include any of several types of liquid crystals including, but not limited to, ferroelectric, nematic, or other types of liquid crystals. In this embodiment, ferroelectric liquid crystals are utilized. Alternatively, other types of display devices such as digital micromirror and other microelectromechanical devices, plasma displays, electroluminescent displays, lightemitting diodes, and the like could be employed as part of the display panel. As can be appreciated, these alternatives may either be spatial light modulators that modulate light from a light source or they may be light emissive devices that do not require a separate light source.

[0056] The silicon backplane 70 includes an area on a top surface thereof where an array 80 of reflective pixel electrodes is located. As can be appreciated, the image is formed in this area of the display panel 64, which is known as the "active area" of the display panel. The silicon backplane 70 is shown in FIG. 3 to be formed of solid silicon material solely for ease of illustration of the major components of the display panel 64. In actuality, a plurality of circuits, conductors, and so forth exist within the silicon backplane 70, as will be discussed in further detail below.

[0057] FIG. 5 is intended to represent certain significant portions of the silicon backplane 70 in a functional manner and components that interface with the backplane 70, rather than in a positional manner. The silicon backplane 70 has an active pixel area 82 that includes a plurality of rows and columns of pixels. Two pixels are shown in the active pixel area 82, a first pixel 84 and a second pixel 86. Located within the silicon backplane under the array 80 of reflective pixel electrodes is circuitry (that will be discussed in further detail below), a major component of which is a plurality of memory

cells underneath the active pixel area 82 and optionally extending beyond the boundary of the active pixel area 82 vertically as viewed in FIG. 5, where additional regions 88 and 90 of memory cells are shown. In the present embodiment, these memory cells are implemented as conventional six-transistor SRAM, although other types of memory registers, including dynamic registers, could be used as well. Two particular areas of memory cells are illustrated in FIG. 5, a first area 92 of SRAM and a second area 94 of SRAM. As will be seen, the first area of SRAM 92 is functionally associated with the first pixel 84 and the second area of SRAM 94 is functionally associated with the second pixel 86, although the areas of SRAM 92 and 94 are not located next to the first and second pixels 84 and 86. A second major component is a plurality of boost circuits which are capable of storing data as an SRAM cell as well as being able to drive a particular voltage onto a pixel electrode as commanded by the data stored in the boost cell.

[0058] In this embodiment, an upper-half 96 of the active pixel area 82 is associated with one set of circuitry shown in FIG. 5 above the active pixel area 82, while a lower-half 98 of the active pixel area 82 is associated with circuitry shown in FIG. 5 below the active pixel area 82. In this case, the upper half 96 and lower half 98 are divided along a dividing line 100 shown in FIG. 5. As will be discussed in further detail below, the additional circuitry above and below the active pixel area 82 that is associated with the upper and lower halves 96 and 98 are a pair of banks of sense amplifiers 102 and 104 respectively, a pair of banks of pixel line-buffers and column drivers 106 and 108 respectively, and a pair of banks of column data processors (CDPs) 110 and 112, respectively. The sense amplifiers in the banks 102 and 104 read the contents of the SRAM memory cells for use by the column data processors of the banks 110 and 112. The pixel line-buffers of the banks 106and 108 temporarily store data on the way to the SRAM, include a circuit to drive the columns of the SRAM, and provide a mechanism to selectively drive only particular columns of the SRAM. The column data processors of the banks 110 and 112 receive data read back by the sense amplifiers from the SRAM, decompress and compare the data to a ramp signal 114, to determine when and how pixel electrodes of pixel array 82 should be driven so as to generate a displayed image.

[0059] A control unit 116 in the silicon backplane 70 receives image data provided to the microdisplay 44 such as image data that may come from controller 34 of the camera 30 in any one of various formats. The control unit 116 is operative to accept image data in at least three different standard video formats, including RGB serial, CCIR-601, and CCIR-656. In each of these standard formats, the image data associated with all three primary colors is transmitted for a given pixel before any image data is transmitted for the next pixel. The timing for each of these video formats can be NTSC or PAL and the vertical frequency can be either 50 Hz or 60 Hz. The resolution of the RGB serial data may be 432×240 while the resolution for the CCIR video formats may be either 720×242 or 720×288. The invention is not limited to any particular format, timing, vertical frequency, resolution, or geometry. The invention can further provide an analog to digital converter in the input data path, to allow the display to accept standard analog video signals, and provide digital data to the remainder of the display. The control unit is operative to perform gamma correction, dither, and scaling on the received images as may be necessary and appropriate. For example, if the column data processors and SRAM array were acting together to produce a PWM gray-scale with γ=1, as will be described in more detail below, and the received image data were provided from a standard source designed to drive a  $\gamma$ =2 display, the control unit could transform the incoming digital values to new values such that when displayed a viewer would perceive a correct gamma characteristic. In the present embodiment, this is accomplished by transforming the incoming 8-bit/color data to 10-bit/color data with the desired gamma correction. In order to display this data within an 8-bit/color limitation of one embodiment of the present invention, the 10-bit/color data is converted to 8-bit/color data using a Floyd-Steinberg error-diffusion algorithm carried out within control block 116 to minimize the visibility of any errors resulting from lack of precision with which the 10-bit values can be represented. Additionally, the control block 116 can horizontally and vertically scale the incoming image data (which might have, for example, 720×242 or 720×288 formats) using bilinear interpolation to a 432×240 format matching the format of the pixel array.

[0060] The control unit 116 receives a clock signal from a display clock 118. The clock signal from the display clock also drives a ramp counter 120 that supplies the afore-mentioned ramp signal 114. The control unit 116 controls row control logic 122, which selects which row of the pixels and which SRAM cells will be accessed. The control unit 116 also communicates with a variety of peripheral circuit elements, some of which may be located separately from the backplane 70. These elements include a temperature sensor 124, a window driver 125, a pixel-voltage generator, one or more LED drivers, one or more digital-to-analog converters (DACs), one or more analog-to-digital converters (ADCs), a non-volatile memory such as an EEPROM 126, and a set of LEDs 127.

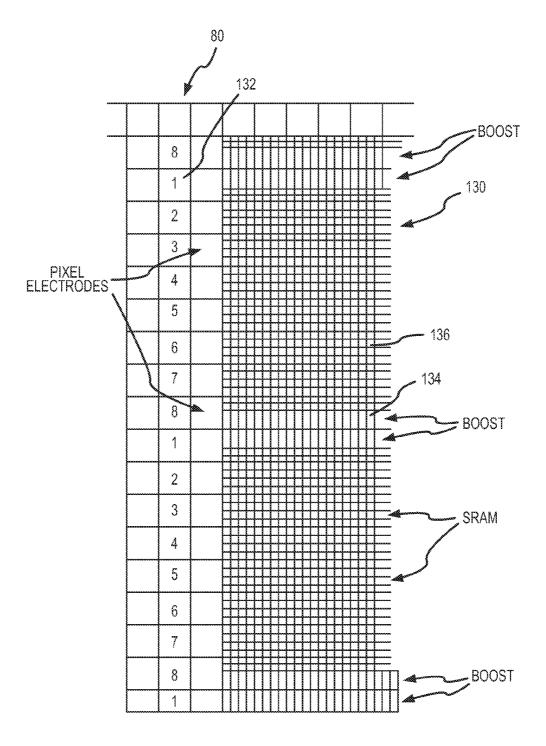

[0061] FIG. 6 shows the size relationship between the array of pixel electrodes 80 in the layer 130 of SRAM memory cells and the pixel-driving boost circuits lying therebeneath. As can be appreciated, in one dimension, the pixel array 80 and the layer 130 underneath are the same width, while in another dimension, the layer 130 is significantly taller than the pixel array 80. As illustrated in FIG. 5, this is because of the additional SRAM 88 and 90 that is utilized in this particular embodiment.

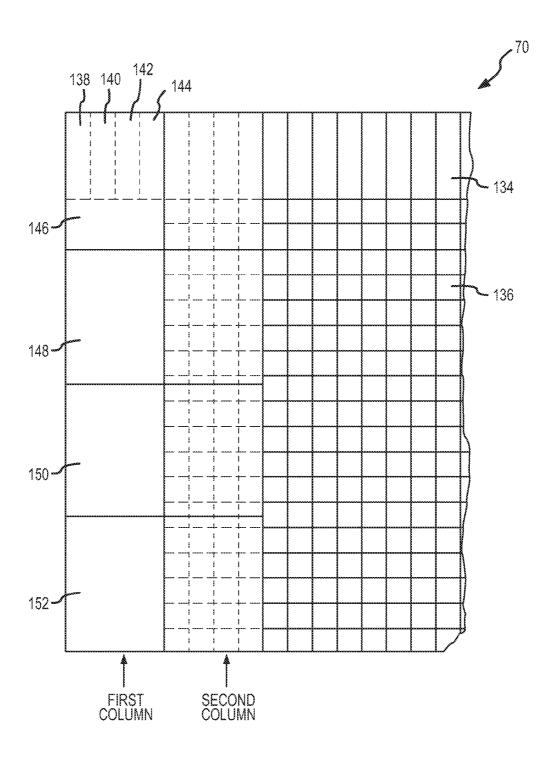

[0062] FIG. 7 illustrates the positional relationship between the pixel array 80 and the layer 130. For purposes of illustration, portions of the pixel array 80 have been removed to expose portions of the layer 130 therebeneath. In this embodiment, each of the pixel electrodes 132 is one of a group of eight adjacent pixel electrodes in a single column, as shown in FIG. 7. The layer 130 underneath the pixel array 80 includes a plurality of rows of boost circuits 134 and a plurality of SRAM memory cells 136. As can be seen, the boost circuits 134 are grouped together in pairs of adjacent rows, separated by approximately thirty rows of SRAM memory cells 136. Further, the boost circuits 134 are located in this embodiment in a particular position relative to each of the pixel electrodes 132, while SRAM occupies the remaining area between boost circuits. The location of data in SRAM cells relative to boost circuits and pixels in which that data will be eventually displayed is essentially arbitrary. These relationships, or lack thereof, can be better appreciated in FIG. 8. On the left side of FIG. 8, eight pixel electrodes, of which four 146, 148, 150, and 152 are in a first vertical column and another four are in a second vertical column, can be seen with a plurality of boost circuits 138, 140, 142, and

144 shown in phantom underneath the pixel electrode 146. Additional boost circuits and SRAM memory cells are shown in phantom underneath the second vertical column of pixel electrodes. At the right side of FIG. 8, the silicon backplane 70 is seen with the pixel electrodes removed to directly expose a plurality of pixel boost circuits 134 and SRAM memory cells 136.

[0063] In this embodiment, a group of four particular boost circuits 138, 140, 142, and 144 in a particular row are associated with four particular pixel electrodes 146, 148, 150, and 152 in a particular column. Since the boost circuits occupy a space that is approximately 1/4 of the width of a pixel electrode, the four boost circuits 138, 140, 142, and 144 lie underneath a single one 146 of the pixel electrodes. In this embodiment, boost circuit 138 is associated with and drives pixel electrode 146, boost circuit 140 is associated with and drives pixel electrode 148, boost circuit 142 is associated with and drives pixel electrode 150, and boost circuit 144 is associated with and drives pixel electrode 152. As can be appreciated, the remaining space under pixel electrode 146 and all of the space under pixel electrodes 148, 150, and 152 is occupied by a plurality of SRAM memory cells 136. With this particular sizing of the pixel electrodes 132, however, and the particular semiconductor fabrication process used, the remaining space under particular pixel electrodes 146, 148, 150, and 152 is not sufficient for the buffered storage required by this design for those four pixel electrodes. For this reason, additional space vertically above and below the pixel array 80 is used for additional SRAM 88 and 90 in the layer 130 as shown in FIGS. 5 and 6.

[0064] Referring back to FIG. 7, it can be appreciated that the bottom row of each adjacent two rows of boost circuits 134 is associated with and drives four pixel electrodes—the pixel electrode in that same column that is located directly on top of the bottom row of boost circuits and the three adjacent pixel electrodes lying therebeneath in the same column. Similarly, the upper row of each pair of boost circuits 134 is associated with and drives four pixel electrodes—the pixel electrode in that same column that is located directly on top of the upper row of boost circuits and the three adjacent pixel electrodes vertically above in the same column.

[0065] As previously described, in this embodiment more SRAM storage is required than will fit beneath the active pixel array, in the space between the boost circuits. For this reason, the SRAM extends beyond the active pixel array 80 as indicated in FIG. 6. It can be appreciated then, that there exists no specific relationship between a pixel electrode of the active pixel array and the SRAM locations where data for that pixel is stored, other than that the SRAM used must reside in the same vertical slice as the pixel electrode, which will be explained further on.

[0066] It can be appreciated that the lack of a specific relationship between the location of the particular SRAM memory cells 136 and a particular pixel electrode 132 is advantageous because it allows the microdisplay 44 to utilize SRAM memory cells that are in the additional SRAM areas 88 and 90 as a memory buffer for image data to be displayed on a pixel electrode anywhere in the pixel array 80. In addition, should it be determined that particular SRAM memory cells 136 or rows of SRAM memory cells are defective, spare SRAM memory cells or rows of SRAM memory cells located elsewhere in the silicon backplane 70 can be utilized as a memory buffer for that particular pixel electrode 132. The address location of the bad cells or rows can be stored at the

time of an external die test in the EEPROM non-volatile memory associated with the microdisplay, or determined by a built-in self-test function that launches when the microdisplay is powered up and stored in volatile registers in the microdisplay. Logic within the control block 116 can retrieve and interpret the addresses of the bad cells or rows, and automatically substitute the addresses of suitable spare cells or rows.

#### Column Data Processor and its Functions

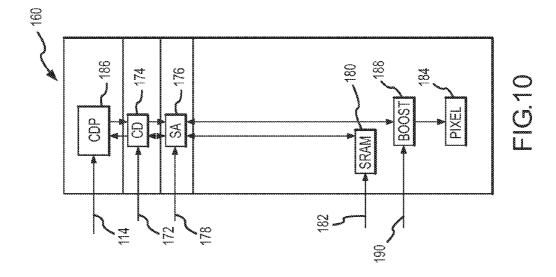

[0067] Portions of the silicon backplane 70 are illustrated in FIG. 9. As has been previously discussed, the silicon backplane 70 is divided into an upper half and a lower half by a dividing line 100. The upper half includes a horizontal bank 102 of sense amplifiers, a horizontal bank 106 of pixel line buffers and column drivers, and a horizontal bank 110 of column data processors (CDPs). Further, it can be seen that this portion of the silicon backplane is divided into vertical slices, of which three of the slices, 160, 162, and 164 are shown. Each vertical slice has its own CDP and associated pixel line buffers and column drivers from the bank 106 as well as associated sense amplifiers from the bank 102. The CDP of a particular slice performs the data processing for each of the pixel electrodes in that given slice. On the other side of the dividing line 100, similar CDP slices 166, 168, and 170 are shown. Each of these slices 166, 168, and 170 include a single CDP and associated pixel line buffers and column drivers from the bank 108 and associated sense amplifiers from the bank 104.

#### SRAM Reading and Writing

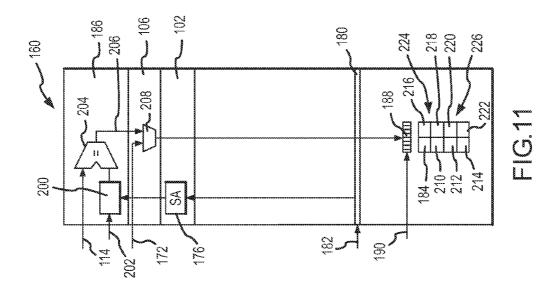

[0068] FIG. 10 shows a functional representation of the CDP slice 160. Encoded image data 172 from the control unit 116 is provided to a column driver 174 in the slice 160. The column driver 174 passes data past a sense amplifier 176 (which is deselected via a signal 178 for this write operation) to a plurality of SRAM memory cells 180. The particular SRAM memory cell in which the data is stored is determined by the particular column driver 174 and a row enable signal 182 from the row control unit 122. Later, the control unit 116 will command the row control unit 122 to drive the row enable signal 182 for the row of SRAM cells 180 where the pixel electrode's data is stored and enable sense amplifier 176 by activating the sense amp enable signal 178. The sense amplifiers 176 will determine the contents of the selected SRAM cells 180 and pass the data to the CDP 186 of slice 160. The CDP 186 decompresses the data and compares selected portions of the decompressed value to the ramp signal 114, the result of which is then stored temporarily and then later written to the boost circuit 188 that is associated with pixel 184, by disabling the sense amp 176, enabling the column driver 174, and causing the row control unit 122 to drive row enable signal 190.

#### Digital Pulse-Width-Modulation Gray Scale

[0069] FIG. 11 shows more detail about the operation of reading data from SRAM, performing a comparison and using the result of the comparison to determine when to change the state of the pixel. In this case, the SRAM memory cells are represented as an entire row of memory cells that may include 48 different memory cells in this CDP slice 160. The particular row 180 is selected by the row enable signal 182. The data from particular memory cells in the SRAM

memory 180 is read by the sense amplifiers 176 and supplied to a decode block 200, which will be discussed in further detail below. The decode block 200 receives a decode signal 202 from the control unit 116. The decode signal 202 indicates which portion of the result decoded from stored encoded image data should be provided to a first input of a digital comparator 204. The comparator 204 compares this decoded portion of the encoded image value to the digital ramp signal 114 (which is provided to its second input) and provides (via logic described below in conjunction with FIG. 12) a pixel control signal 206 to a multiplexer 208 that can be controlled to enable writing of either the pixel control signal 206 or the encoded image signal to storage locations below. In this case, the pixel control signal 206 is provided to the selected boost circuit 188 that is in a group of four boost circuits in a column underneath four pixels, 184, 210, 212, and 214 (for ease of illustration, the boost circuits are not shown underneath one of the pixels in this case). Boost circuit 188 is associated with and is in electrical communication with the pixel electrode 184, whose state the pixel control signal 206 is intended to control. In this embodiment, each boost circuit functions as a one-bit storage register for the desired state of the pixel. It can be seen that eight boost circuits are shown in the row including boost circuit 188. These are grouped into 2 groups of four boost circuits, with the leftmost group of four boost circuits storing the intended display value for the four pixels shown therebelow 184, 210, 212, and 214, and the right-most group of four boost circuits storing the intended display value for the four pixels 216, 218, 220, and 222 shown therebelow. For ease of later discussion, a two-by-two array of pixels 184, 210, 216, and 218 is indicated in FIG. 11 as pixel group 224 while another group of four pixels 212, 214, 220, and 222 is shown in FIG. 11 as pixel group **226**.

[0070] In this particular embodiment, the pixel array 80 includes 240 pixels vertically and 432 pixels horizontally. The dividing line 100 separates this 240×432 array into two arrays of 120 pixels vertically and 432 pixels horizontally. Each of these two arrays is sliced vertically, as has been previously described, into 36 CDP slices. Each of these CDP slices includes a sub-array of 120 pixels vertically and 12 pixels horizontally. Underneath these pixels are rows of boost circuits, with 48 boost circuits in each particular row of a CDP slice, or 4 boost circuits for each column of pixels. In between the double rows of boost circuits, there are approximately 30 rows of SRAM memory cells, with there being 48 memory cells in each row of each CDP slice. This is intended as but one embodiment of the present invention, and none of the sizes or numbers discussed herein are intended to limit the invention.

[0071] FIG. 12 shows the signals input to the comparator 204 in the CDP slice 160, the output 232 of the comparator 204 that helps to create the pixel control signal 206, and also the resulting pixel electrical drive signal 228 that represents the state of the pixel electrode. The ramp signal 114 is one of the inputs to the comparator, while the other input is a decoded pixel value 230. The pixel electrical drive signal 228 is shown just below, on the same time scale. Both comparator input signals are digital, although they are shown pictorially in this figure in a way where vertical direction in the figure indicates value. The ramp signal 114, output by ramp counter 120, might be the output of an eight-bit counter, progressing from binary value 00000000 (digital 0) to binary value 1111111 (digital 255). Schemes other than simple counting,

such as gray codes, can also be used. Further, the count can proceed in descending order as well as ascending order. As can be appreciated from the figure, when the ramp signal 114 begins, the pixel electrical drive signal 228 transitions from, for example, a low to a high state, as signaled by the pixel control signal 206. Once the ramp signal 114 reaches the same digital value as the decoded pixel value 230, the comparator output 232 goes high. This output enables column driver 174 to write to a pixel selected by row enable signal 182, thereby providing pixel control signal 206. In this case, the value of pixel control signal 206 has been selected so that the pixel electrical drive signal 228 transitions from a high state to a low state in response to the detection of equality by comparator 204. Of course, the length of time the pixel electrical drive signal 228 is in a high state relative to in a low state is a function of the magnitude of the decoded pixel value 230. In other words, for small magnitudes of the decoded pixel value 230, the high state of the pixel electrical drive signal 228 will be relatively short, while for relatively large magnitudes of the decoded pixel value 230, the pixel electrical drive signal 228 will be in a high state for a substantial majority of the time. In this way, the microdisplay 44 implements pulsewidth modulation pixel drive. Of course, the sense of the PWM can be reversed (i.e. relatively long durations of pixel electrical drive signal 228 for small magnitudes of decoded pixel value 230, and so on, by simple changes to the logic circuitry). The functionality of the column data processors is accomplished via combinatorial logic such as adders, shifters, and the like.

[0072] It may be preferable for the pixel control signal 206 to be written to the boost circuits for each pixel in a different order for the top half of the display versus the bottom half of the display. For example if the signal were written to each half in the same manner, updating the image from top row to bottom row in each half, the portion of the image near the dividing lines 100 between the two halves would have portions of an old image next to a portion of the new image a substantial majority of the time. This may cause visible image artifacts. In order to avoid this, it is possible to update the top half from top row to bottom row, while updating the bottom half from bottom row to top row. This may also be called updating from outside to inside. Alternatively, the updating could be done in exactly the opposite fashion, from inside to outside, or from bottom row to top row in the top half and from top row to bottom row in the bottom half. Another alternative would be to go from outside to inside in one frame of data, from inside to outside in the next succeeding frame, and repeating in this alternating fashion. Any variations on these alternatives or any other that eliminates the visual artifacts would be acceptable.

[0073] An important feature of the microdisplay disclosed here is its ability to accept and simultaneously display standard video signals. This is accomplished by the aforementioned banks of pixel line buffers 106 and 108, in conjunction with the action of column data processors 110 and 112, as is now described with respect to FIG. 19. This figure shows the timing relationship between elements of the input video signal, namely the encoded input video data and a VALID signal, and elements of the gray-scale action of the CDP and pixel line buffers, namely the display clock 118, a READ signal supplied by the control block 116 to the pixel line buffers 106 and 108 and the sense amplifiers 102 and 104, and a sequence of row addresses supplied by control block 116 to row control 122. The READ signal has one state (e.g., high) when it is

desired for the sense amplifiers to be reading the data from a row of SRAM registers selected by row control 122, and the opposite state (e.g., low) when it is desired to write encoded image data to selected rows of the SRAM registers. As previously described, the SRAM array provides double buffering of the encoded image data so that while data corresponding to an incoming image may be written to one buffer, data corresponding to a previous image can be read without being corrupted from a second buffer. For the purposes of FIG. 19, row addresses in one image buffer are denoted B0Ri, where i denotes the row number, while row addresses in the other buffer are denoted B1Ri. Row addresses corresponding to pixel boost circuit registers are denoted PRi. At the time depicted at the left of FIG. 19, VALID is high indicating that valid image data is being supplied as this data is supplied it is temporarily written to the registers in pixel line buffers 106 and 108. Meanwhile, READ is high and the CDPs are processing stored encoded image data for gray-scale display on the pixel array. In the example depicted in FIG. 19, encoded image data is being read from buffer bank B0, starting with row B0R1 at the left of the figure. After twelve clocks, data has been read from rows B0R1 through B0R12, after which time the CDP has accumulated enough comparison results to write back pixel control signal 206 to registers in the boost cells. To effect this, READ goes low at this point, completing a cycle of reading frame buffer registers and updating pixels. As depicted in the figure, VALID might go low during this cycle, marking the end of a line of incoming video data. Control block 116 thus recognizes that the pixel line-buffers are full. Even though the next cycle of reading of image data from the frame buffer has already begun (reading from lines B0R13 and B0R14 in the example portrayed in this figure), the buffer-full signal causes the cycle to be interrupted, READ goes low, and the data stored in the pixel line-buffers is written to the other frame-buffer bank (to rows B1R1 through B1R6 in this example). After this writing completes, READ goes high, and the normal cycle of reading followed eventually by writing to the boost registers continues. In this way, by interleaving the reading of data from one frame buffer with occasional writing of data to the other frame buffer, the display can simultaneously accept standard video data while displaying an artifact-free image. Given that a new line of incoming video data starts every 60 ms or so, and that the horizontal blanking portion of this period occupies about 11 ms, and that the time required to empty the pixel line-buffers is equal to six display clock periods, or about 100 ns (for the 60 MHz display clock typically used by the applicant), the requirement to write incoming data occurs relatively infrequently, and can be caused to occur anywhere in a relatively wide interval, and causes only minimal perturbation of the gray scale scheme.

#### Image Compression/Decompression

[0074] One of the features of the present invention is that the incoming image data provided to the control unit 116 can be compressed for storage purposes in the SRAM image buffer distributed throughout the silicon backplane 70 and decompressed for eventual display by the pixels. Any of several different types of compression algorithms are available to accomplish this. One approach is to first convert RGB data from red, green, and blue values for each pixel to the conventional YUV system or a variant thereof. The YUV system includes a luminance component (Y) and two color-difference signals (U and V). In one common version, denoted

$\mathrm{YC}_{\mathcal{B}}\mathrm{C}_{\mathcal{R}}$ , the color difference signals store largely red  $(\mathrm{C}_{\mathcal{B}})$  and blue  $(\mathrm{C}_{\mathcal{B}})$  information where luminance (which also contains most of the green) has been subtracted out. The following matrix transformation generates standard  $\mathrm{YC}_{\mathcal{B}}\mathrm{C}_{\mathcal{R}}$  signals from RGB signals:

$$\begin{bmatrix} Y \\ C_B \\ C_R \end{bmatrix} = \begin{bmatrix} 16 \\ 128 \\ 128 \end{bmatrix} + \frac{1}{256} \begin{bmatrix} 65.738 & 129.057 & 25.064 \\ -37.945 & -74.494 & 112.439 \\ 112.439 & -94.154 & 18.285 \end{bmatrix} \cdot \begin{bmatrix} R \\ G \\ B \end{bmatrix}$$

(1)

**[0075]** In this representation R, G, and B take on values from 0 to 255 (unsigned 8-bit numbers). Y ranges from 16 to 235, and  $C_B$  and  $C_R$  range from 16 to 240. In some implementations, the  $YC_BC_R$  values are restricted to a subset of the 8-bit range (0-255) to permit the insertion of special codes for synchronization and to allow processing headroom in video electronics.

[0076] One can invert this transformation to restore RGB values (which are required to actually view an image, on a CRT monitor, for example):

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \frac{1}{256} \begin{bmatrix} 298.082 & 0 & 408.583 \\ 298.082 & -100.291 & -208.120 \\ 298.082 & 516.411 & 0 \end{bmatrix} \cdot \begin{bmatrix} Y - 16 \\ C_B - 128 \\ C_R - 128 \end{bmatrix}$$

(2)

[0077] One motivation for using the YUV system rather than other similar systems is that the human visual system has different responses to different wavelengths of light. The ability to discriminate fine spatial detail, for example, is higher for images where the detail is in the luminance than it is for images where the luminance is more constant and the detail is in color variations. Spatial resolving power is also lower for blue than it is for red or green. The compression algorithm of the present invention takes advantage of this difference in spatial resolving power based on color. The algorithm converts the RGB data to a variant of the YUV system.

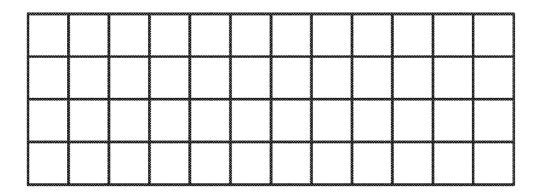

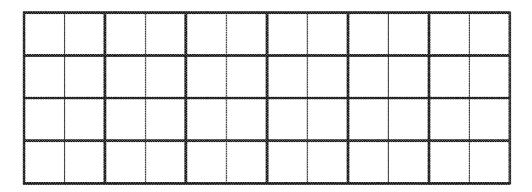

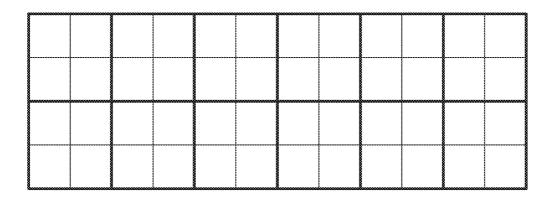

[0078] Existing standard sampling techniques are denoted by terms such as 4:4:4 (illustrated in FIG. 20), 4:2:2 (FIG. 21), and 4:1:1 (FIGS. 22 and 23). In YUV-type systems having a first component containing luminance information and the next two components containing color difference or some other type of chroma information, the three numbers in the term 4:2:2 express the rate at which each of those components is sampled. In FIGS. 20 and 21, each square represents a separate pixel with a separate luminance sample for each pixel. In FIG. 20, these squares also represent separate U and V values for each pixel. In FIG. 21, each rectangle with thick-lined borders represents two adjacent pixels that together have a single U value and a single V value. Thus, in 4:2:2 the Y component is sampled twice as often as the color difference components, and in 4:1:1, the Y component is sampled four times as often (as demonstrated by the thicklined rectangles that each include four pixels as shown in FIGS. 22 and 23). The phrase 4:2:2 is often called "broadcast video" and is considered a fairly high quality image compression format. Modern-day consumer digital video camcorders use 4:1:1 almost exclusively. This reduced sampling normally occurs within a given horizontal line of image data. Thus, for a scan line including 720 pixels, a 4:1:1 sampling technique would imply 720 luminance (Y) samples, 180 C<sub>R</sub> samples, and  $180 \, C_B$  samples, as shown in FIG. 22. This is the NTSC version of 4:1:1. PAL systems typically also include vertical sub-sampling. Instead of four horizontal pixels sharing a single  $C_R$  sample, for example, a 2×2 region of pixels shares a single  $C_R$  sample, as shown in FIG. 23. This requires the addition of a line buffer and digital video systems to store previous scan lines, but it produces slightly more pleasing images. Thus, the PAL version of 4:1:1 is sometimes denoted as 4:2:0 to emphasize this difference in sampling geometry.

[0079] The present invention receives 24-bit RGB data (8 bits each for red, green, and blue) for each pixel and converts it to a format to be discussed further below that can be stored as an average of 12 bits per pixel. As will be seen, the pixels are grouped into 2×2 pixel groups, such as pixel group 224 and 226, so for each pixel group, 48 bits of data are stored for each image. Because of double buffering, two 48-bit rows of data are required for each pixel group.

[0080] Furthermore, in order to simplify the data processing at the encoding stage performed by the control unit 116 and at the decoding stage performed by decode blocks in the CDPs, such as decode block 200, a new variant on the YUV system, called DEF, has been created. The coordinate transformations are

$$D_i = (\frac{1}{2})R_i + (\frac{1}{2})G_i$$

$$E{=}({}^{-1}\!/\!4)R_{ave}{+}({}^{-1}\!/\!4)G_{ave}{+}({}^{1}\!/\!2)B_{ave}$$

$$F = (\frac{1}{2})R_{ave} + (-\frac{1}{2})G_{ave}$$

(3)

for the forward transformation and

$R_i = D_i + F$

$G_i=D_i-F$

$$B_i = D_i + 2E \tag{4}$$

for the reverse transformation. Here the i subscript denotes values for single pixels while E and F are based on  $R_{ave}$ ,  $G_{ave}$ , and  $R_{ave}$  values averaged over several pixels

and  $B_{ave}$  values averaged over several pixels. [0081] D, E, and F are three letters arbitrarily selected to represent this new color-space that is a variant of the YUV system. The letters have no particular meaning other than they seek to avoid use of letters common to other color-space schemes such as RGB, YUV,  $C_R$ , and  $C_B$ . Note that the coordinate transformations can be performed with integer arithmetic rather than the floating-point arithmetic that would be required to convert between the RGB and YUV formats as shown in Equations 1 and 2 above. Since the DEF color space is intended only as an interim color-space for the purpose of storage of images internal to the microdisplay, the meaning of what D, E, and F represent is somewhat arbitrary, unlike the YUV system.

[0082] As an alternative to the sampling described above, that requires a frame buffer of effectively 12 bits per pixel, it would also be possible to sample at a 12:2:1 format to effectively require a frame buffer of 10 bits per pixel.

[0083] As will be understood, referring back to FIGS. 5 and 11, the image data provided to the control unit 116 may be 24 bit RGB data while the encoded image data 172 provided from the control unit 116 to the line buffer and column driver banks 106 and 108 is in DEF format (with 48 bits coding the image content associated with four pixels, for an average of 12 bits per pixel). The data in this DEF format is then stored in the SRAM memory cells 180 in the vertical slices and later read by the sense amplifiers 176 and provided to the decode

blocks **200** of the vertical slices where the DEF data is converted back to RGB data, prior to the aforementioned comparison operations.

[0084] There are many alternatives to the type of sampling that could be utilized in the present invention. This may also include many variants to the 4:1:1-equivalent coding, such as one in which each of the 2×2 pixel groups is aligned with the 2×2 pixel group therebeneath (FIG. 23), or the 2×2 pixel group in the next adjacent pair of rows to the first 2×2 pixel group could be offset horizontally by one pixel (FIG. 24) so that the 2×2 pixel groups are not vertically aligned. Another variant (shown in FIG. 25) would be to define different 2×2 pixel groups for one of the chroma components (e.g., the E or the F component) (signified by the thick-lined borders) and define a different 2×2 pixel group for the other of the two chroma components (signified by the absence or presence of cross-hatching). In other words, the pixel group for the E component would share only two pixels with a pixel group for the F component. Otherwise, the E component pixel groups would be aligned with each other vertically and the F component pixel groups could be aligned with each other vertically. As a further variation on this variation, there could be an offset by one pixel horizontally in every other pair of adjacent rows (FIG. 26) so that the E component pixel groups were not aligned vertically, nor are the F component pixel groups aligned vertically. Another variation would be to define a four-pixel group that is not a  $2\times2$  array (FIG. 27). For example, a pixel group could consist of three pixels on one row and one pixel in an adjacent row, to achieve an L shape. The next adjacent pixel group could have three pixels on the adjacent row and one pixel on the original row to also achieve an L shape and make the two L shapes mate together into a combination of the pixel groups which is two pixels high and four pixels wide. This arrangement could be done for both of the chroma components, or only one with the other chroma components having the original 2×2 configuration, for example. As can be seen, there are nearly endless variations of chroma combinations. There are several methods to these variations, one is to stagger the starting positions of the color difference samples in the vertical direction. This is intended to address the appearance of vertical striping that can occur in the image if there is too much vertical correlation of samples in the compression technique. Another method is to displace the two chroma samples relative to each other. Yet another method is to vary the type of sampling geometries. Also, since the human visual system is relatively less sensitive to blue light, the E component that has the blue light as a sub-component could be sampled at an even lower rate that the F component. One approach would be a 12:2:1 sampling technique that would require an average 10 bits per pixel. In this case (shown in FIG. 28), every pixel would have its own D value, while a 3×2 pixel group would share an F value and a 6×2 pixel group would share an E value.

[0085] Thus, it can be understood that since each row of SRAM within a particular vertical slice contains 48 bits of data, which represents the encoded luminance and chroma information (in the defined DEF format) for a 2×2 pixel array or pixel group, and that it is desired to write an entire row or rows of pixels at the same time (actually it is desired to write to one row of boost circuits which corresponds to four rows of pixels), there needs to be 12 different reads, each of a different 48-bit row to get all the information needed to decode, compare, and write the desired state to four of the rows of pixels. As the comparisons are performed, their results are gradually

stored in a 48-bit register. After this register is full (of 48 comparison results), the accumulated values are used to enable (in the case that the result of a particular comparison was equality) or not enable (in the case that the result of a different particular comparison was inequality) the writing of a change to the boost circuit register in a single write operation.

[0086] A power-saving feature of the microdisplay 44 is that the data in the register acts as a write enable to the boost circuits and thus only causes a change to the bit lines in one of the 0 or 1 conditions. Because of this, the number of times that the bit lines need to be charged/discharged is reduced.

[0087] Since E and F are signed numbers between -127 and 128 and D is an unsigned number between 0 and 255, it is possible to have valid DEF values that transform (via Equation 4) to invalid RGB values (e.g., R, G, or B has a value less than 0 or greater than 255). Performing clipping in the traditional manner by comparing the transformed values to 0 and 255 and taking action if they exceed the acceptable range is possible, but it is likely to consume too much silicon real estate. FIG. 13 shows a simplified clipping circuit that is included as part of each decode block 200 to prevent the generation of any values outside of the range of 0 to 255 by the DEF to RGB conversion. As can be seen from Equation 4, the DEF to RGB conversion requires as inputs D<sub>i</sub>, 2E, and F. A decode signal 202 is provided in, for example, on two lines called GREEN and BLUE. When the CDP is providing green decoded image data to the comparator, GREEN is active and BLUE is inactive. When the CDP is providing blue decoded image data, BLUE is active and GREEN is inactive. When the CDP is providing red decoded image data, both GREEN and BLUE are inactive. GREEN and BLUE both being simultaneously active is avoided. A first multiplexer selects between 2E and F depending on the state of BLUE, with the multiplexer output being provided as a first input to a summer. The signal D is provided as the other input to the summer, which also accepts the signal GREEN at its carry input. The output of the summer is provided to a second multiplexer. A carry output of the summer is provided as an input to an exclusive OR gate. The other input to the exclusive OR gate is provided from a third multiplexer that receives the sign bits from E and F (the MSB of each). The third multiplexer is controlled by the BLUE decode signal so that when blue is to be decoded, the sign bit of E is used and otherwise, the sign bit of F is used. Thus, the selected sign bit and the carry bit from the summer are inputs to the exclusive OR gate and the output will be a logical 1 if the inputs are different and a logical 0 if the inputs are the same. This output and its inverse are provided as the two inputs to a fourth multiplexer. The fourth multiplexer is controlled by the GREEN decode signal so that when green is to be decoded, the inverted output of the exclusive OR is used and otherwise the inverted output of the exclusive OR is used. If the output of the fourth multiplexer is a logical 0, it means no clipping is necessary and the 8-bit output of the summer is used. If the output is a logical 1, however, it means clipping is necessary and instead of the output of the summer, the carry bit is selected (expanded to 8 bits of the same value of the carry bit, of course). Thus, either a 255 (binary 11111111) or a 0 (binary 00000000) is provided.

[0088] One aspect of the present invention is the logical separation of data storage in the distributed frame buffer from the storage register to control the display of the pixel. These two storage locations are logically separated while a common