US 20130107151A1

(19) **United States**

(12) **Patent Application Publication**

Sasaki et al.

(10) **Pub. No.: US 2013/0107151 A1**

(43) **Pub. Date: May 2, 2013**

(54) **LIQUID CRYSTAL DISPLAY DEVICE HAVING FIRST, SECOND, AND THIRD TRANSPARENT ELECTRODES WHEREIN A SECOND REGION OF THE SECOND ELECTRODE PROTRUDES FROM A FIRST REGION**

(71) Applicants: **Tohru Sasaki**, Mobera (JP); **Takahiro Ochiai**, Chiba (JP)

(72) Inventors: **Tohru Sasaki**, Mobera (JP); **Takahiro Ochiai**, Chiba (JP)

(21) Appl. No.: **13/718,467**

(22) Filed: **Dec. 18, 2012**

**Related U.S. Application Data**

(63) Continuation of application No. 13/550,330, filed on Jul. 16, 2012, now Pat. No. 8,368,830, which is a continuation of application No. 12/230,417, filed on Aug. 28, 2008, now Pat. No. 8,253,873.

(30) **Foreign Application Priority Data**

Sep. 4, 2007 (JP) ..... 2007-228412

**Publication Classification**

(51) **Int. Cl.**

**G02F 1/1362** (2006.01)

(52) **U.S. Cl.**

CPC .... **G02F 1/136213** (2013.01); **G02F 1/136286** (2013.01)

USPC ..... **349/38; 349/43; 349/46**

(57) **ABSTRACT**

To form a sufficiently large storage capacitor, a liquid crystal display device includes a liquid crystal display panel having a first substrate, a second substrate, and a liquid crystal held between the first substrate and the second substrate, the liquid crystal display panel having multiple pixels arranged in matrix. The first substrate has, in a transmissive display area provided in each of the pixels, a laminated structure containing a first transparent electrode, a first insulating film, a second transparent electrode, a second insulating film, and a third transparent electrode which are laminated in this order. The first transparent electrode and the second transparent electrode are electrically insulated from each other and together form a first storage capacitor through the first insulating film, and the second transparent electrode and the third transparent electrode are electrically insulated from each other and together form a second storage capacitor through the second insulating film.

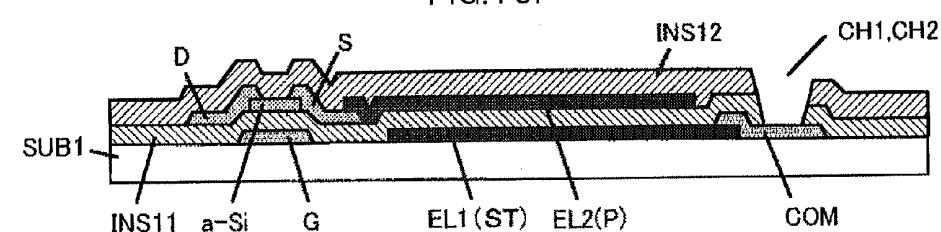

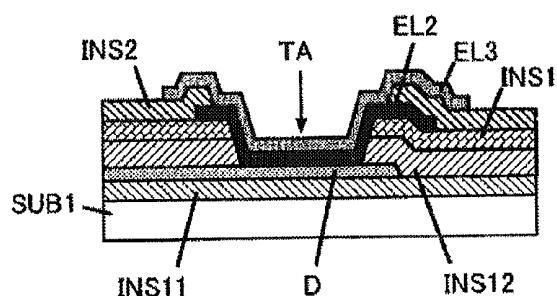

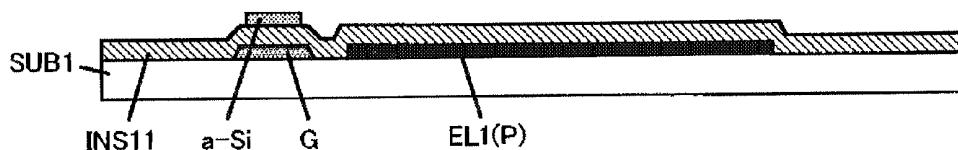

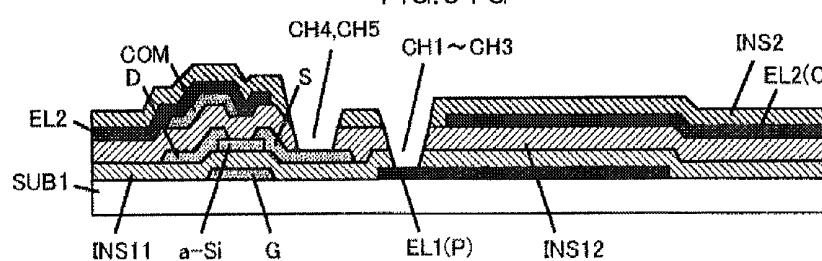

FIG.1A

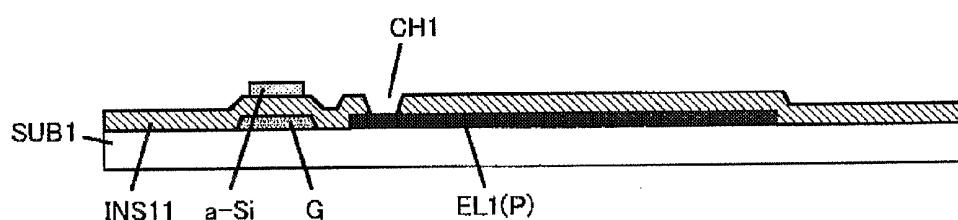

FIG.1B

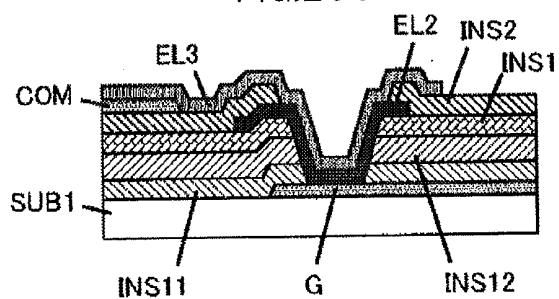

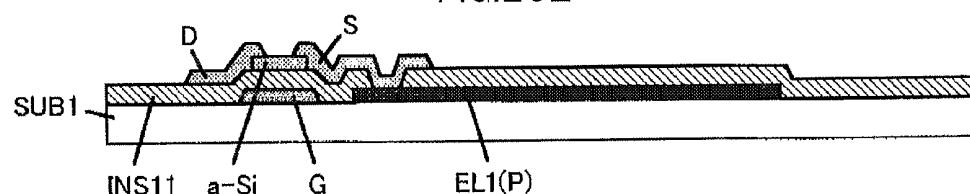

FIG.2A

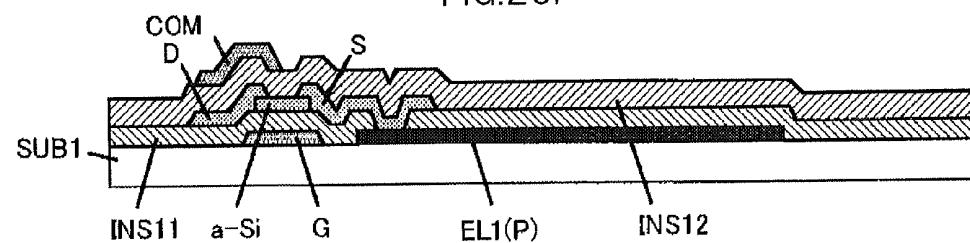

FIG.2B

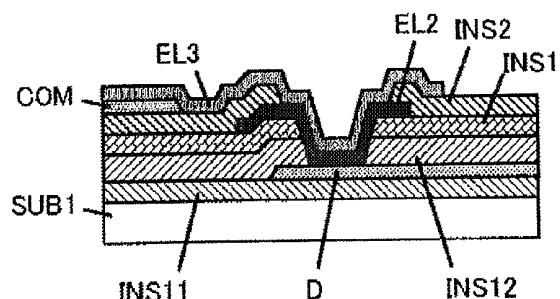

FIG.3

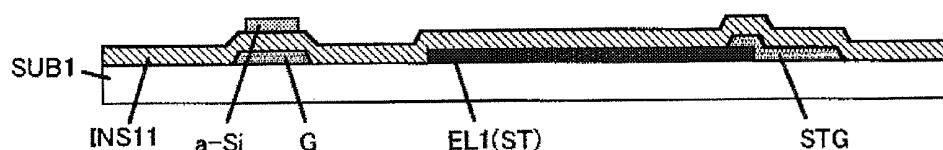

FIG.4A

FIG.4B

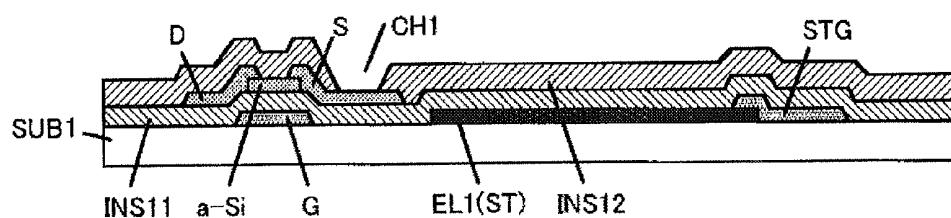

FIG.4C

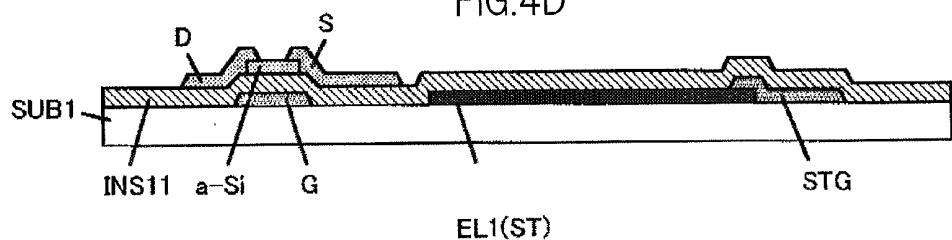

FIG.4D

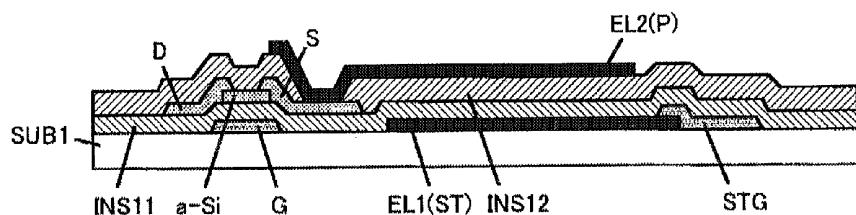

FIG.4E

FIG.4F

FIG.4G

FIG.4H

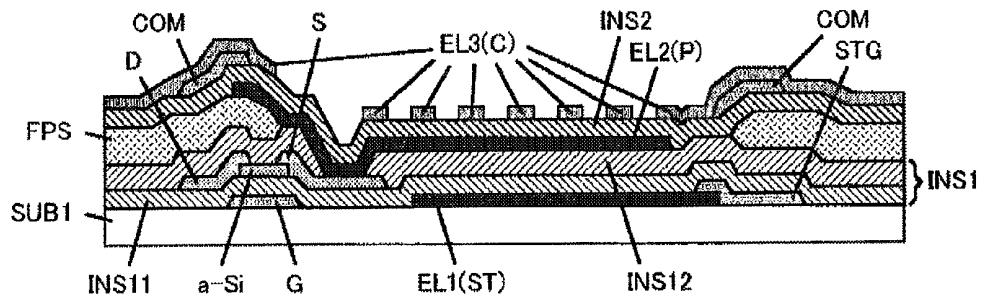

FIG.5A

FIG.5B

FIG.5C

FIG.5D

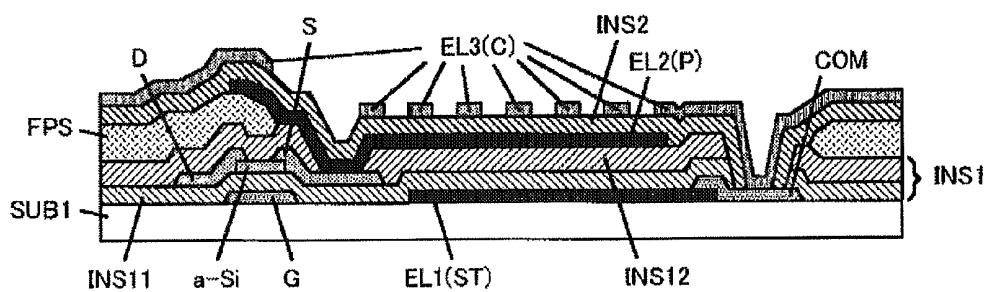

FIG.6A

FIG.6B

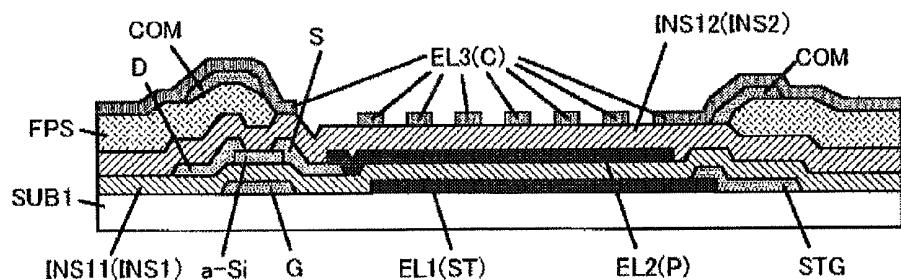

FIG.7

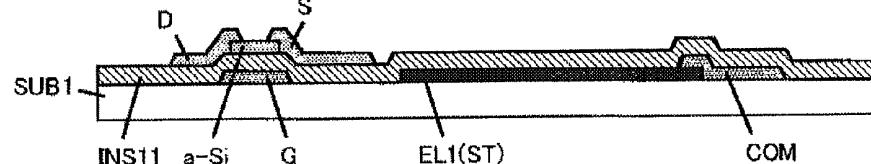

FIG.8A

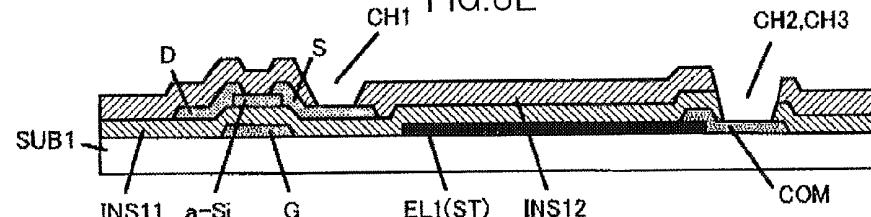

FIG.8B

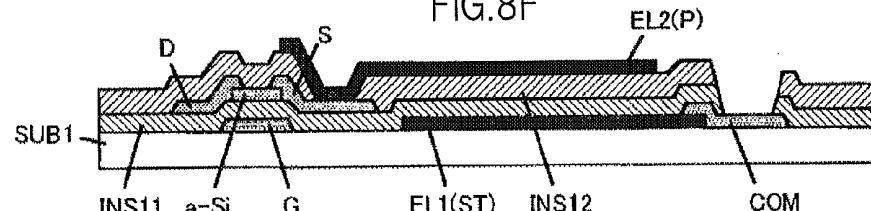

FIG.8C

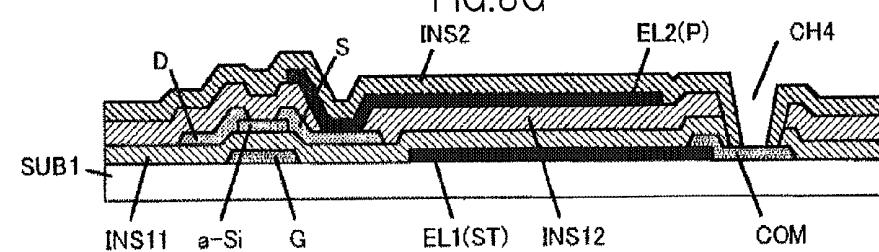

FIG.8D

FIG.8E

FIG.8F

FIG.8G

FIG.9A

FIG.9B

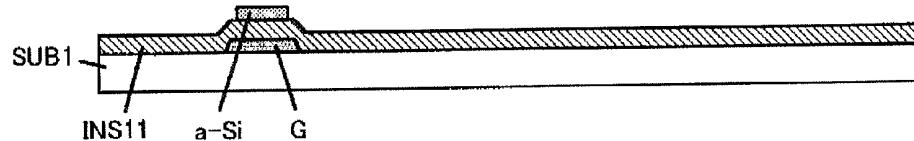

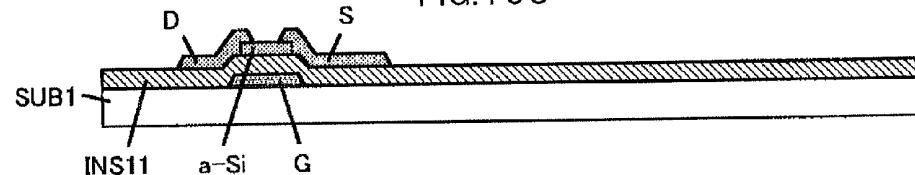

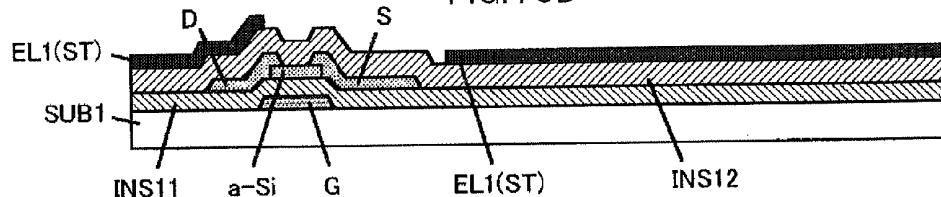

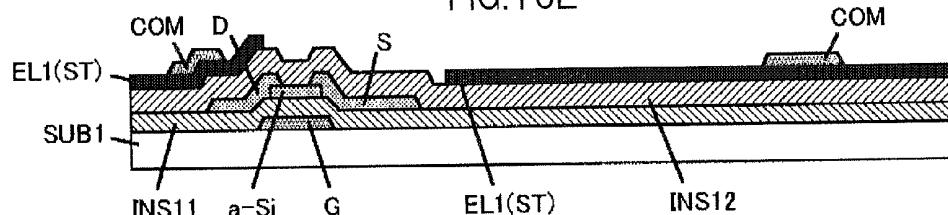

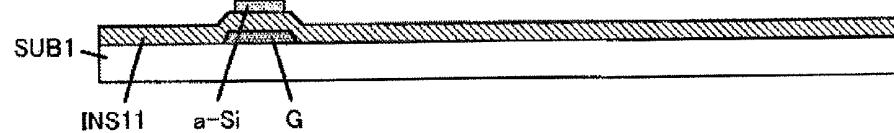

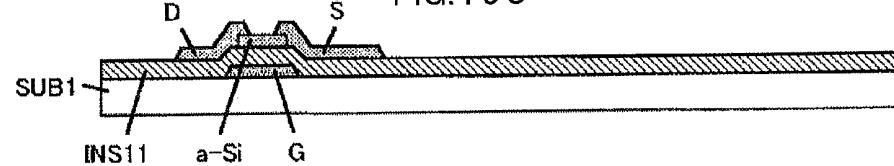

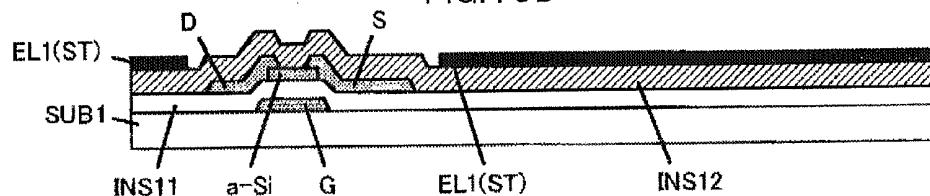

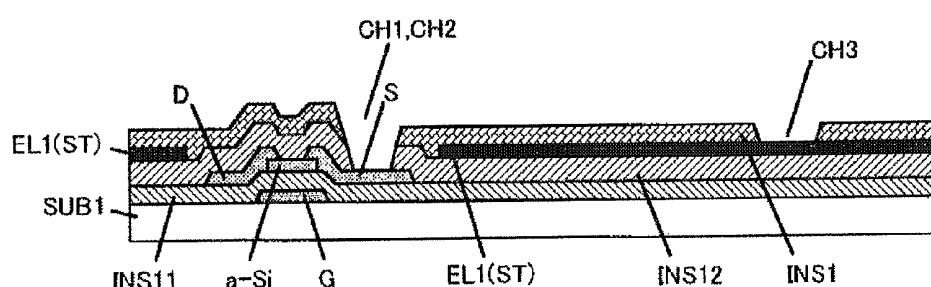

FIG.10A

FIG.10B

FIG.10C

FIG.10D

FIG.10E

FIG.10F

FIG.10G

FIG.11A

FIG.11B

FIG.11C

FIG.11D

FIG.12A

FIG.12B

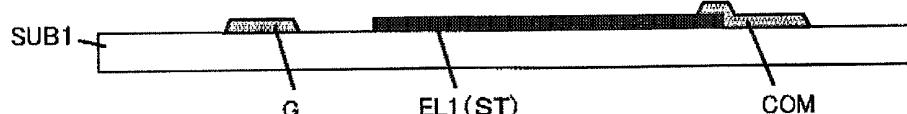

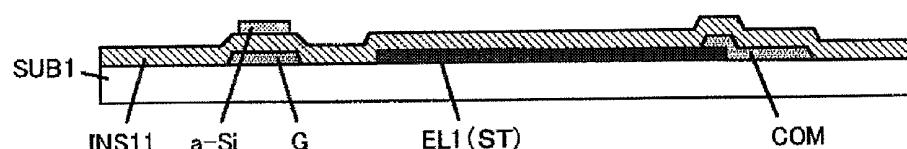

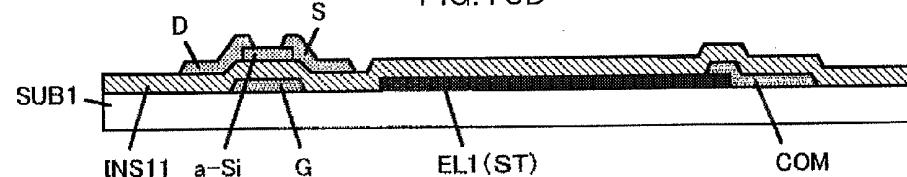

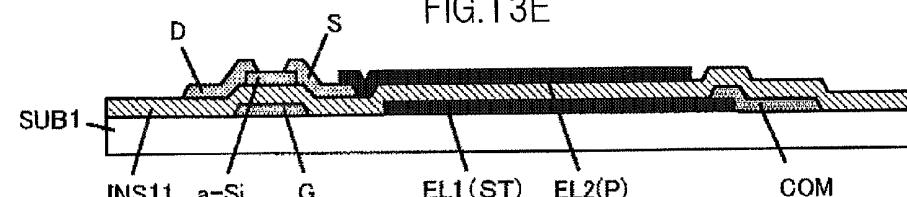

FIG.13A

FIG.13B

FIG.13C

FIG.13D

FIG.13E

FIG.13F

FIG.14A

FIG.14B

FIG.14C

FIG.14D

FIG.15A

FIG.15B

FIG.16A

FIG.16B

FIG.16C

FIG.16D

FIG.16E

FIG.16F

FIG.16G

FIG.16H

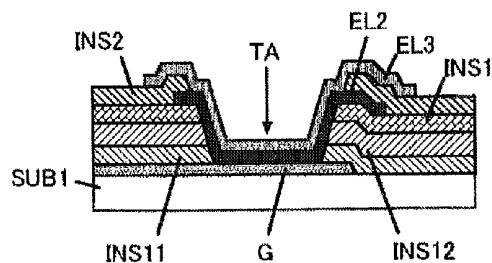

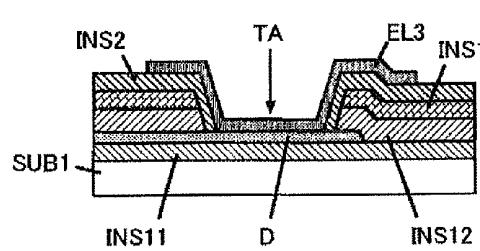

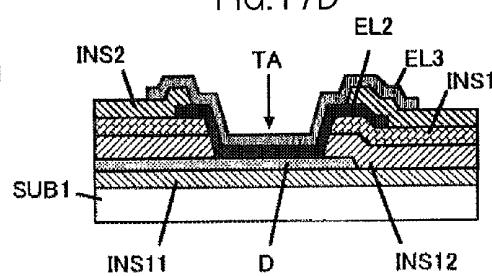

FIG.17A

FIG.17B

FIG.17C

FIG.17D

FIG.17E

FIG.17F

FIG.18A

FIG.18B

FIG.19A

FIG.19B

FIG.19C

FIG.19D

FIG.19E

FIG.19F

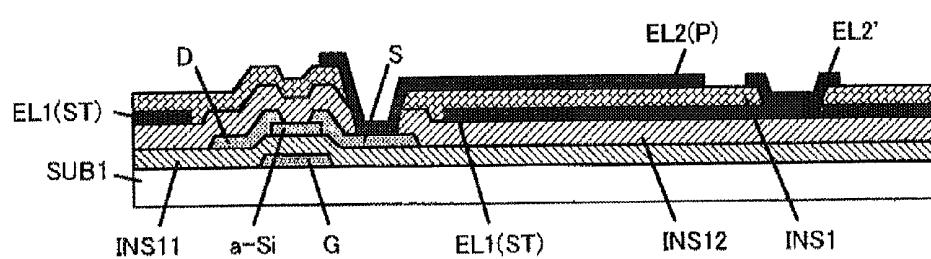

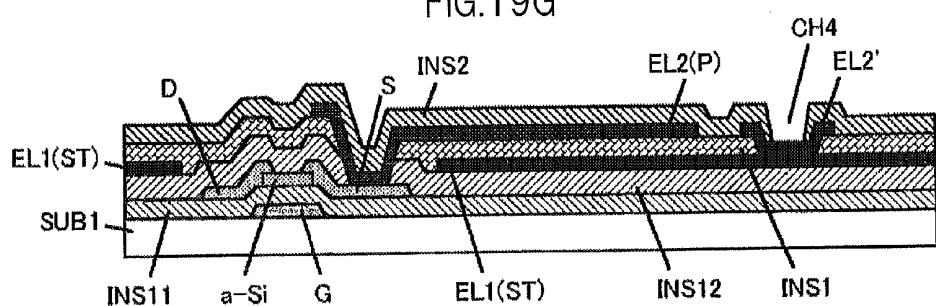

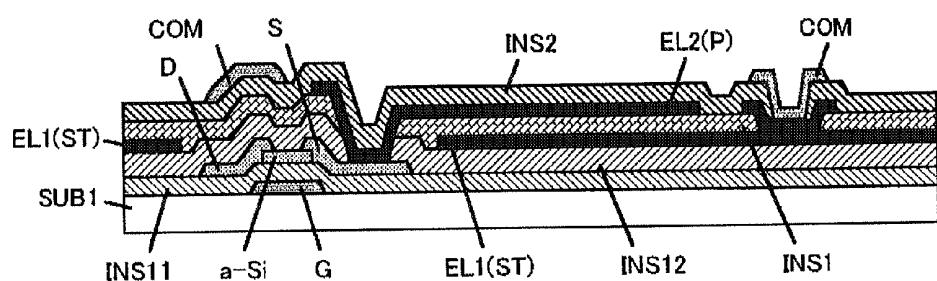

FIG.19G

FIG.19H

FIG.20A

FIG.20B

FIG.20C

FIG.20D

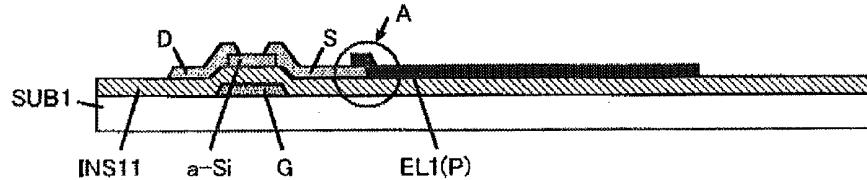

FIG.21A

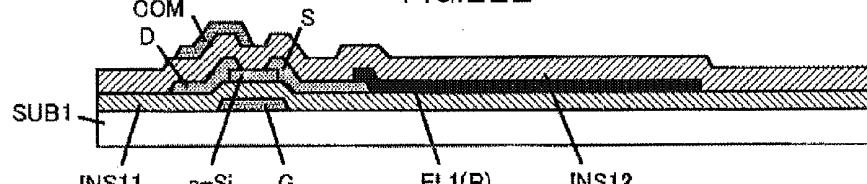

FIG.21B

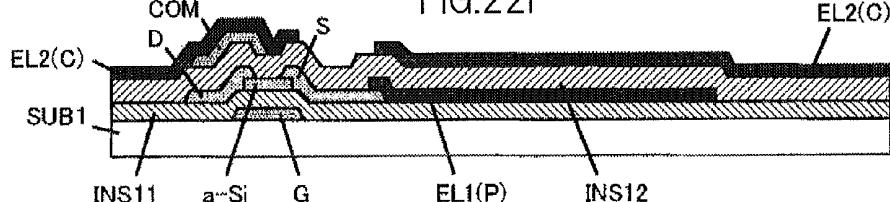

FIG.22A

FIG.22B

FIG.22C

FIG.22D

FIG.22E

FIG.22F

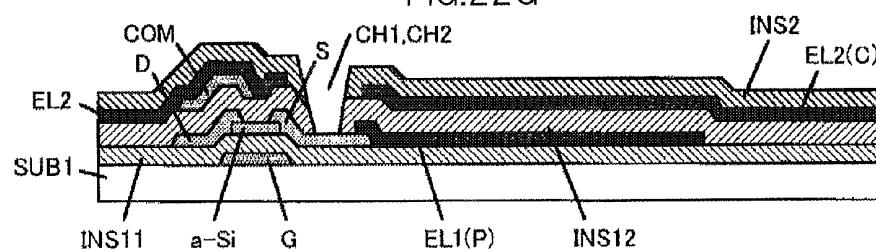

FIG.22G

FIG.23A

FIG.23B

FIG.23C

FIG.23D

FIG.24A

FIG.24B

FIG.25A

FIG.25B

FIG.25C

FIG.25D

FIG.25E

FIG.25F

FIG.25G

FIG.25H

FIG.26A

FIG.26B

FIG.26C

FIG.26D

FIG.27A

FIG.27B

FIG.28A

FIG.28B

FIG.28C

FIG.28D

FIG.28E

FIG.28F

FIG.28G

FIG.28H

FIG.29A

FIG.29B

FIG.29C

FIG.29D

FIG.30A

FIG.30B

FIG.31A

FIG.31B

FIG.31C

FIG.31D

FIG.31E

FIG.31F

FIG.31G

FIG.32A

FIG.32B

FIG.32C

FIG.32D

FIG.32E

FIG.32F

FIG.32G

FIG.32H

FIG.32I

FIG.32J

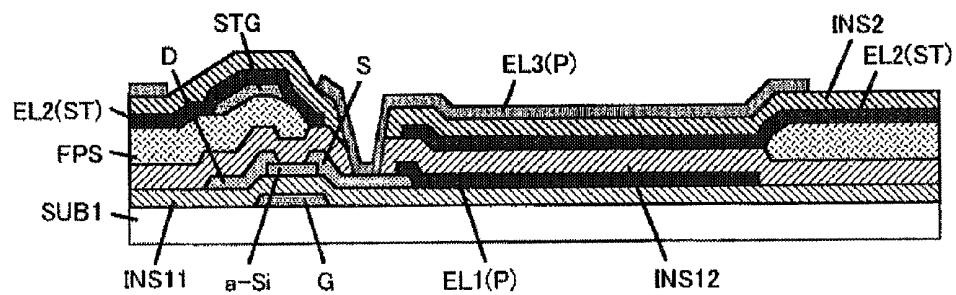

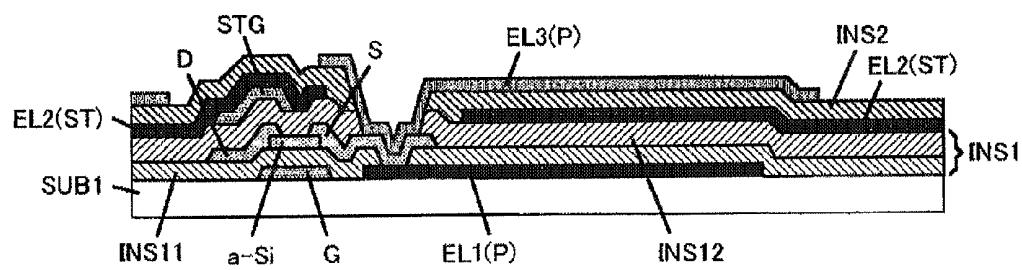

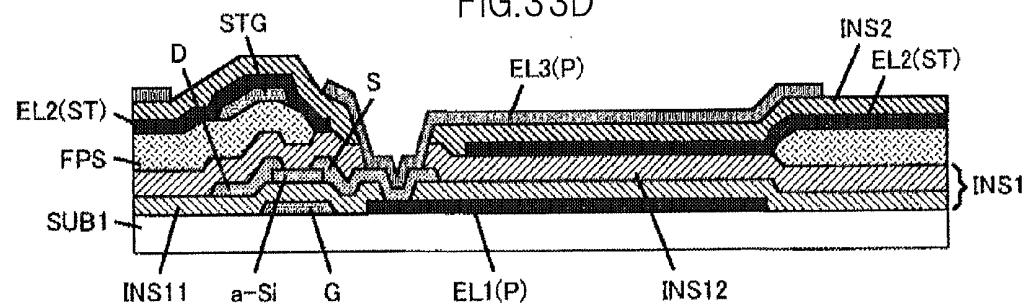

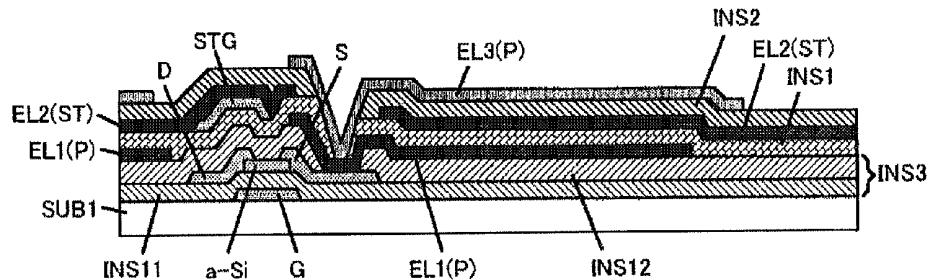

FIG.33A

FIG.33B

FIG.33C

FIG.33D

FIG.33E

FIG.33F

FIG.33G

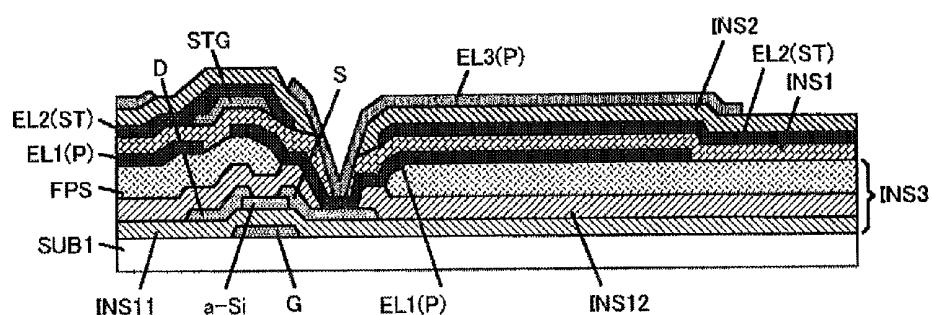

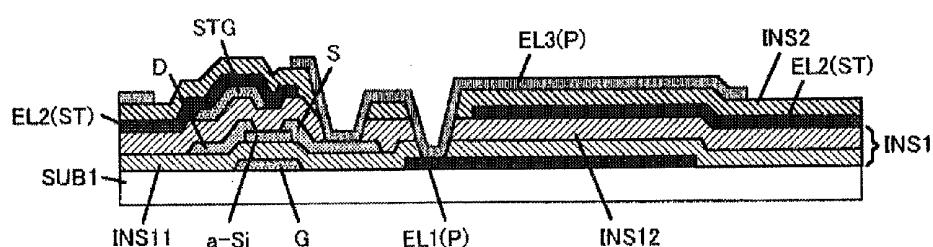

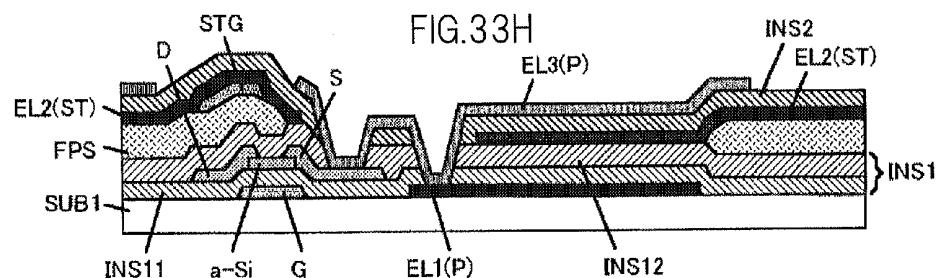

FIG.33H

FIG.34A

FIG.34B

FIG.35A

FIG.35B

FIG.35C

**LIQUID CRYSTAL DISPLAY DEVICE

HAVING FIRST, SECOND, AND THIRD

TRANSPARENT ELECTRODES WHEREIN A

SECOND REGION OF THE SECOND

ELECTRODE PROTRUDES FROM A FIRST

REGION**

**CROSS-REFERENCE TO RELATED

APPLICATION**

[0001] This application is a Continuation of U.S. application Ser. No. 13/550,330 filed on Jul. 16, 2012, which is a Continuation of U.S. application Ser. No. 12/230,417 filed on Aug. 28, 2008. Priority is claimed based on U.S. application Ser. No. 13/550,330 filed on Jul. 16, 2012, which claims priority from U.S. application Ser. No. 12/230,417 filed on Aug. 28, 2008, which claims priority from Japanese application JP 2007-228412 filed on Sep. 4, 2007, the content of which is hereby incorporated by reference into this application.

**BACKGROUND OF THE INVENTION**

[0002] 1. Field of the Invention

[0003] The present invention relates to a liquid crystal display device, and more particularly, to a technology effectively applied to a liquid crystal display device that has a liquid crystal display panel with fine pixel dimensions.

[0004] 2. Description of the Related Art

[0005] A liquid crystal display device is composed of a pair of substrates (for example, glass substrates) and a liquid crystal composition sealed in a gap between the substrates. Specifically, in the case of an in-plane switching (IPS) liquid crystal display device, for example, thin film transistors with amorphous silicon or other semiconductor layers, pixel electrodes, signal lines, scanning lines, gate electrodes, counter electrodes, and the like are formed on one of the substrates (hereinafter, referred to as TFT substrate), whereas a light shielding film, a color filter, and the like are formed on the other substrate (hereinafter, referred to as CF substrate). The TFT substrate and the CF substrate are arranged to face each other across a predetermined interval, which is kept by a spacer, and are sealed with a sealant. A liquid crystal composition is sealed between the substrates.

[0006] Pixels in a common liquid crystal display device each have a storage capacitor. The storage capacitor is used mainly to prevent feed-through voltage caused by a voltage change in the scanning line or the signal line from affecting the voltage of the pixel electrode during a hold period in which the thin film transistor is off.

[0007] The storage capacitor is implemented by, for example, the following four structures:

[0008] (1) Upper layer transparent pixel electrode/insulating film/lower layer transparent storage capacitor electrode.

[0009] (2) Upper layer transparent pixel electrode/insulating film/lower layer metal storage capacitor electrode.

[0010] (3) Upper layer metal source (or drain) electrode/insulating film/lower layer metal storage capacitor electrode.

[0011] (4) Upper layer metal source (or drain) electrode/insulating film/intermediate metal storage capacitor electrode/insulating film/lower layer polycrystalline silicon source (or drain) electrode.

[0012] The above-mentioned structure (1) is described in, for example, JP 08-179363 A, and the above-mentioned structure (4) is described in, for example, JP 2000-180900 A.

**SUMMARY OF THE INVENTION**

[0013] When one of the electrodes that constitute the storage capacitor is metal as in the above-mentioned structures (2) to (4), the non-transparent metal part makes it difficult to raise the aperture ratio, particularly in the case of a transmissive liquid crystal display device. It is therefore preferred to employ transparent conductive materials for both of the electrodes of the storage capacitor as in the above-mentioned structure (1).

[0014] However, reducing the pixel dimensions for the purpose of obtaining an ultra-high definition liquid crystal display panel, such as one for portable terminal that have a VGA-level resolution, accordingly reduces the area per pixel that can be used to form the electrodes of the storage capacitor.

[0015] The insulating film that forms the storage capacitor can be thinned in response to the reduction in electrode area only to a limited degree, because the insulating film needs to retain a certain thickness in consideration of manufacture yield. Then allocating the entire transmissive display area in a single pixel to the electrodes of the storage capacitor that has the structure (1) is not enough to prevent the storage capacitor from being smaller.

[0016] The reduction in capacitance of the storage capacitor is more prominent in IPS liquid crystal display panels, where one of the electrodes is a planar transparent electrode and the other electrode is a comb-shaped transparent electrode which is formed above the former electrode with an insulating film sandwiched between the two. This structure (comb-shaped transparent electrode/insulating film/flat board-like transparent electrode) also functions as the storage capacitor but, since a reduction in dimensions per pixel reduces the comb teeth of the upper layer transparent electrode in length and number, the capacitance of the storage capacitor is made even smaller.

[0017] A parasitic capacitor, which is formed between the pixel electrode and the scanning line or the signal line, is also made smaller by a reduction in per-pixel dimensions due to the coupling length being shortened by the reduction. However, compared to the way the capacitance of the storage capacitor, which is almost dependent on the per-pixel area, is reduced the reduction in capacitance of the parasitic capacitor is more gradual. Rather, the parasitic capacitor is hardly reduced in capacitance since obtaining a sufficient aperture ratio requires closing the planar gap between the pixel electrode and the scanning line or the signal line (or increasing the overlapping area), which reduces the coupling interval of the parasitic capacitor. This makes it difficult to form a sufficiently large storage capacitor balanced with the parasitic capacitor even in the conventional structure (1).

[0018] If the storage capacitor is not large enough in relation to the parasitic capacitor, the voltage of the pixel electrode is easily affected by feed-through voltage, which is caused by a voltage change in the scanning line or the signal line, during a hold period in which the thin film transistor is off. The resultant problem resides in that the image quality is degraded from such phenomena as smearing and cross talk.

[0019] The present invention has been made to solve the aforementioned problems of prior art, and an object of the present invention is therefore to provide a technology with which a sufficiently large storage capacitor can be formed in a display device that has a liquid crystal display panel with fine pixel dimensions.

[0020] The above-mentioned and other objects and novel characteristics of the present invention will be clarified by the descriptions herein and the accompanying drawings.

[0021] Representative aspects of the present invention are summarized as follows.

[0022] (1) A liquid crystal display device including: a liquid crystal display panel having a first substrate, a second substrate, and a liquid crystal held between the first substrate and the second substrate, the liquid crystal display panel having multiple pixels arranged in matrix; and a transmissive display area provided in at least part of each of the pixels, having a laminated structure containing a first transparent electrode, a first insulating film, a second transparent electrode, a second insulating film, and a third transparent electrode which are laminated in this order with the first transparent electrode closest to the first substrate. The first transparent electrode and the second transparent electrode are electrically insulated from each other and together form a first storage capacitor through the first insulating film, and the second transparent electrode and the third transparent electrode are electrically insulated from each other and together form a second storage capacitor through the second insulating film.

[0023] (2) In the aspect (1), at least one of the first insulating film and the second insulating film is a laminate of multiple insulating films.

[0024] (3) In the aspect (1), the first insulating film and the second insulating film are formed from one of the same material and different materials.

[0025] (4) In the aspect (1), the first insulating film and the second insulating film have one of the same refractive index and different refractive indices.

[0026] (5) In the aspect (1), the transmissive display area provided in at least part of each of the multiple pixels has a third insulating film, which is placed on the first substrate side of the first transparent electrode.

[0027] (6) In the aspect (5), the third insulating film has a dielectric constant equal to or lower than a dielectric constant of one of the first insulating film and the second insulating film.

[0028] (7) In the aspect (5), the third insulating film is a laminate of multiple insulating films.

[0029] (8) In the aspect (5), the first insulating film, the second insulating film, and the third insulating film are formed from one of the same material and different materials.

[0030] (9) In the aspect (1), the first transparent electrode, the second transparent electrode, and the third transparent electrode are formed from one of the same material and different materials.

[0031] (10) In the aspect (1), the first transparent electrode, the second transparent electrode, and the third transparent electrode have one of the same refractive index and different refractive indices.

[0032] (11) In the aspect (1), the first transparent electrode, the second transparent electrode, and the third transparent electrode have one of the same thickness and different thicknesses.

[0033] (12) In the aspect (1), the first transparent electrode, the second transparent electrode, the third transparent electrode, the first insulating film, and the second insulating film are respectively set to such refractive indices and thicknesses that, when combined, provide a no-reflection condition with respect to at least a part of light whose wavelength is within the visible light range.

[0034] (13) In the aspect (5), the first transparent electrode, the second transparent electrode, the third transparent electrode, the first insulating film, the second insulating film, and the third insulating film are set respectively to such refractive indices and thicknesses that, when combined, provide a no-reflection condition with respect to at least a part of light whose wavelength is within the visible light range.

[0035] (14) In the aspect (1), the first transparent electrode, the second transparent electrode, and the third transparent electrode have one of the same area and different areas.

[0036] (15) In the aspect (1), an overlap between the first transparent electrode and the second transparent electrode which is measured by area is the same as, or differs from, an overlap between the second transparent electrode and the third transparent electrode which is measured by area.

[0037] (16) In the aspect (1), the first substrate has a reflective electrode in a reflective display area, which is provided in at least part of each of the multiple pixels, and the reflective electrode is electrically connected to at least one of the first transparent electrode, the second transparent electrode, and the third transparent electrode.

[0038] (17) In the aspect (1), the third transparent electrode has multiple comb-teeth electrodes, and the liquid crystal display device generates an electric field that has a component parallel to a surface of the first substrate between the third transparent electrode and the second transparent electrode, and uses the electric field to drive a liquid crystal on the surface side of the third transparent electrode.

[0039] (18) In the aspect (1), the third transparent electrode has a shape of a flat board with a slit, and the liquid crystal display device generates an electric field that has a component parallel to a surface of the first substrate between the third transparent electrode and the second transparent electrode, and uses the electric field to drive a liquid crystal on the surface side of the third transparent electrode.

[0040] (19) In the aspect (1), each of the multiple pixels has a fourth transparent electrode, which is placed on the second substrate side, and the liquid crystal display device generates an electric field between the fourth transparent electrode and the third transparent electrode, and uses the electric field to drive a liquid crystal on the surface side of the third transparent electrode.

[0041] (20) In any one of the aspects (1) to (18), each of the multiple pixels has a thin film transistor, the third transparent electrode is a counter electrode, the second transparent electrode is a pixel electrode, and the first transparent electrode is a storage capacitor electrode.

[0042] (21) In the aspect (20), the first insulating film is a laminate of a gate insulating layer and an interlayer insulating layer with the gate insulating layer placed closer to the first substrate, the third transparent electrode is connected to a common electrode wiring line, the second transparent electrode is connected to a first electrode of the thin film transistor through an opening formed in the interlayer insulating layer, and the first transparent electrode is connected to a storage capacitor wiring line.

[0043] (22) In the aspect (20), the first insulating film is a laminate of a gate insulating layer and an interlayer insulating layer with the gate insulating layer placed closer to the first substrate, the first transparent electrode is connected to a common electrode wiring line, the second transparent electrode is connected to a first electrode of the thin film transistor through an opening formed in the interlayer insulating layer, and the third transparent electrode is connected to one of the

first transparent electrode and the common electrode wiring line through openings formed in the gate insulating layer, the interlayer insulating layer, and the second insulating film.

[0044] (23) In the aspect (20), the first transparent electrode is connected to a storage capacitor wiring line, the second transparent electrode is connected to a first electrode of the thin film transistor, and the third transparent electrode is connected to a common electrode wiring line.

[0045] (24) In the aspect (20), the first transparent electrode is connected to a common electrode wiring line, the second transparent electrode is connected to a first electrode of the thin film transistor, and the third transparent electrode is connected to one of the first transparent electrode and the common electrode wiring line through openings formed in the first insulating film and the second insulating film.

[0046] (25) In the aspect (20), the liquid crystal display device has an interlayer insulating layer formed above a first electrode of the thin film transistor, the first transparent electrode is formed above the interlayer insulating layer, the first transparent electrode is connected to a common electrode wiring line, the second transparent electrode is connected to the first electrode of the thin film transistor through openings formed in the interlayer insulating layer and the first insulating film, and the third transparent electrode is connected to one of the first transparent electrode and the common electrode wiring line through openings formed in the first insulating film and the second insulating film.

[0047] (26) In the aspect (20), the liquid crystal display device has an interlayer insulating layer formed above a first electrode of the thin film transistor, the first transparent electrode is formed above the interlayer insulating layer, the third transparent electrode is connected to a common electrode wiring line, the second transparent electrode is connected to the first electrode of the thin film transistor through openings formed in the interlayer insulating layer and the first insulating film, the first transparent electrode is connected to an insular transparent electrode pattern which is formed within an opening in the first insulating film, and the insular transparent electrode pattern is connected to the common electrode wiring line through an opening formed in the second insulating film.

[0048] (27) In the aspect (21) or (23), the common electrode wiring line and the storage capacitor wiring line have one of the same voltage and different voltages.

[0049] (28) In the aspect (20), the first transparent electrode in one pixel is separated from the first transparent electrode in another pixel.

[0050] (29) In the aspect (20), the first transparent electrode is one of common on a pixel row basis to be shared by pixels in one pixel row, common on a pixel column basis to be shared by pixels in one pixel column, and shared by all pixels.

[0051] (30) In the aspect (20), the third transparent electrode in one pixel is separated from the third transparent electrode in another pixel.

[0052] (31) In the aspect (20), the third transparent electrode is one of common on a pixel row basis to be shared by pixels in one pixel row, common on a pixel column basis to be shared by pixels in one pixel column, and shared by all pixels.

[0053] (32) In the aspect (20), one of the first transparent electrode and the second transparent electrode is connected to a common electrode wiring line, the common electrode wiring line is provided for each pixel row, and the common electrode wiring line in each pixel row is shared.

[0054] (33) In the aspect (20), one of the first transparent electrode and the second transparent electrode is connected to a common electrode wiring line, the common electrode wiring line is provided for each pixel row, and the common electrode wiring line in one pixel row is independent from the common electrode wiring line in another pixel row.

[0055] (34) In the aspect (21) or (23), the storage capacitor wiring line is provided for each pixel row, and the storage capacitor wiring line in each pixel row is shared.

[0056] (35) In the aspect (21) or (23), the storage capacitor wiring line is provided for each pixel row, and the storage capacitor wiring line in one pixel row is independent from the storage capacitor wiring line in another pixel row.

[0057] (36) In the aspect (20), the first transparent electrode and at least part of the first electrode of the thin film transistor form a third storage capacitor through an insulating film that is inserted between the first transparent electrode and the at least part of the first electrode of the thin film transistor.

[0058] (37) In the aspect (21) or (23), part of the capacitor storage wiring line and at least part of the first electrode of the thin film transistor form a third storage capacitor through an insulating film that is inserted between the part of the storage capacitor wiring line and the at least part of the first electrode of the thin film transistor.

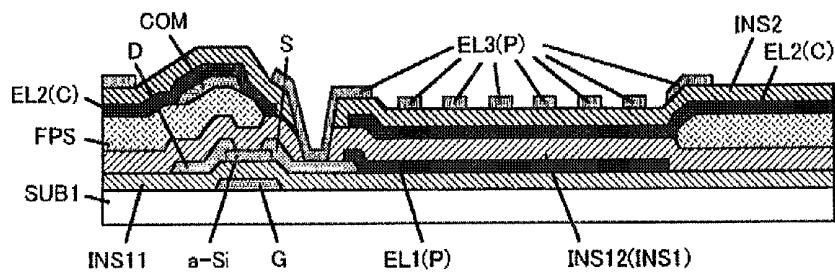

[0059] (38) In any one of the aspects (1) to (19), each of the multiple pixels has a thin film transistor, the first transparent electrode and the third transparent electrode are pixel electrodes, and the second transparent electrode is a counter electrode.

[0060] (39) In the aspect (38), the first transparent electrode is connected to a first electrode of the thin film transistor, the second transparent electrode is connected to a common electrode wiring line, and the third transparent electrode is connected to the first electrode of the thin film transistor through openings formed in the first insulating film and the second insulating film.

[0061] (40) In the aspect (38), the first insulating film is a laminate of a gate insulating layer and an interlayer insulating layer with the gate insulating layer placed closer to the first substrate, the first transparent electrode is connected to a first electrode of the thin film transistor through an opening formed in the gate insulating layer, the second transparent electrode is connected to a common electrode wiring line, and the third transparent electrode is connected to the first electrode of the thin film transistor through openings formed in the interlayer insulating layer and the second insulating film.

[0062] (41) In the aspect (38), the liquid crystal display device has an interlayer insulating layer formed above a first electrode of the thin film transistor, the first transparent electrode is formed above the interlayer insulating layer, the first transparent electrode is connected to the first electrode of the thin film transistor through an opening formed in the interlayer insulating layer, the second transparent electrode is connected to a common electrode wiring line, and the third transparent electrode is connected to the first transparent electrode through openings formed in the first insulating film and the second insulating film.

[0063] (42) In the aspect (38), the first insulating film is a laminate of a gate insulating layer and an interlayer insulating layer with the gate insulating layer placed closer to the first substrate, the first transparent electrode is connected to the third transparent electrode through openings formed in the gate insulating layer, the interlayer insulating layer, and the second insulating film, the second transparent electrode is

connected to a common electrode wiring line, and the third transparent electrode is connected to a first electrode of the thin film transistor through openings formed in the interlayer insulating layer and the second insulating film.

[0064] (43) In the aspect (38), the second transparent electrode in one pixel is separated from the second transparent electrode in another pixel.

[0065] (44) In the aspect (38), the second transparent electrode is one of common on a pixel row basis to be shared by pixels in one pixel row, common on a pixel column basis to be shared by pixels in one pixel column, and shared by all pixels.

[0066] (45) In the aspect (38), the second transparent electrode is connected to a common electrode wiring line, the common electrode wiring line is provided for each pixel row, and the common electrode wiring line in each pixel row is shared.

[0067] (46) In the aspect (38), the second transparent electrode is connected to a common electrode wiring line, the common electrode wiring line is provided for each pixel row, and the common electrode wiring line in one pixel row is independent from the common electrode wiring line in another pixel row.

[0068] (47) In the aspect (38), the liquid crystal display device has a storage capacitor wiring line formed on the first substrate side of the first electrode of the thin film transistor, and part of the capacitor storage wiring line and at least part of the first electrode of the thin film transistor form a third storage capacitor through an insulating film that is inserted between the part of the storage capacitor wiring line and the at least part of the first electrode of the thin film transistor.

[0069] An effect obtained from the representative embodiments of the present invention disclosed in this application is summarized as follows.

[0070] According to the present invention, a sufficiently large storage capacitor can be formed in a liquid crystal display device that has a liquid crystal display panel with fine pixel dimensions.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0071] In the accompanying drawings:

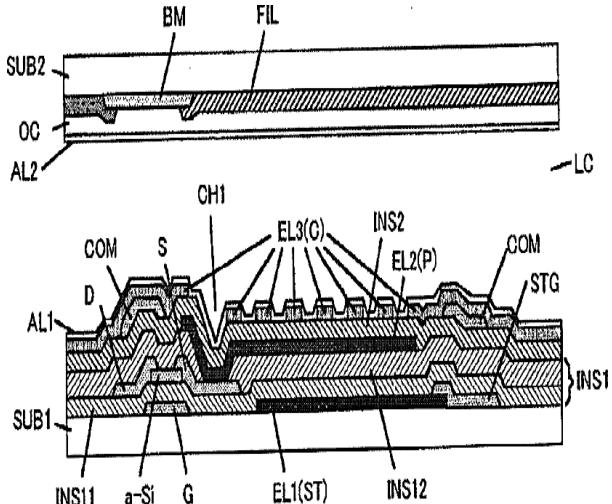

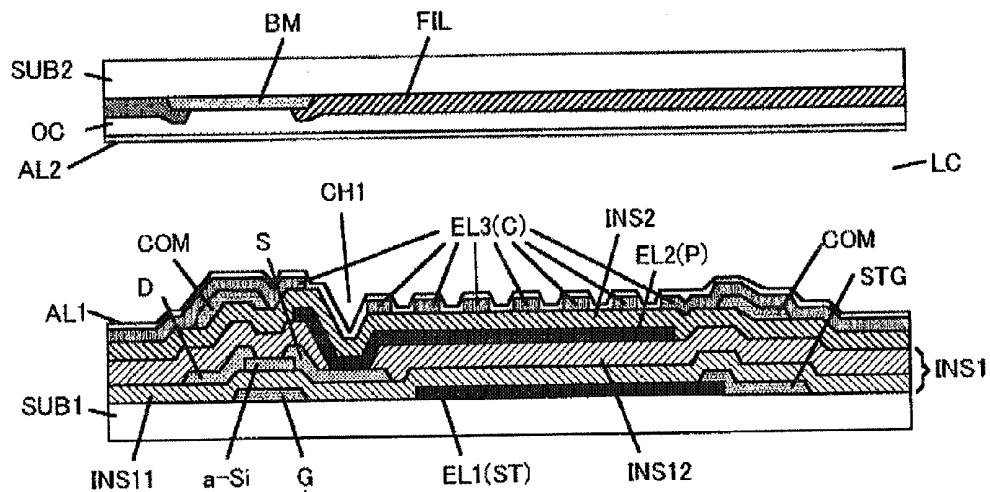

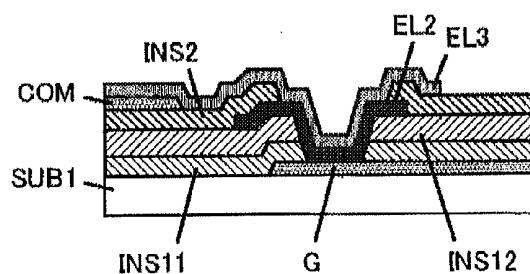

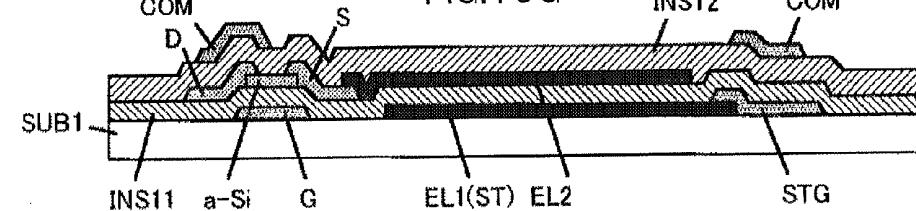

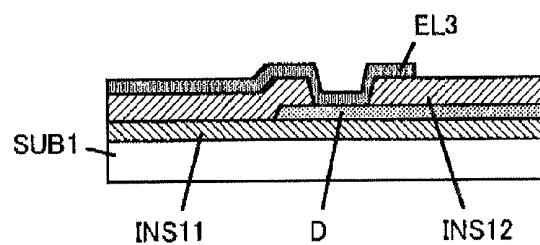

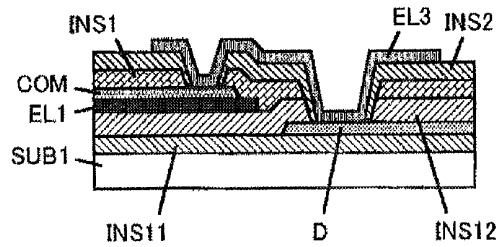

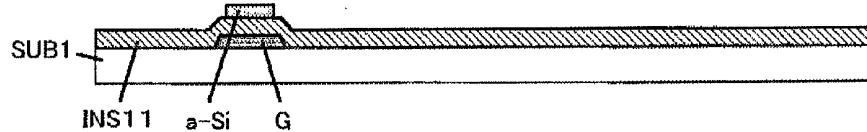

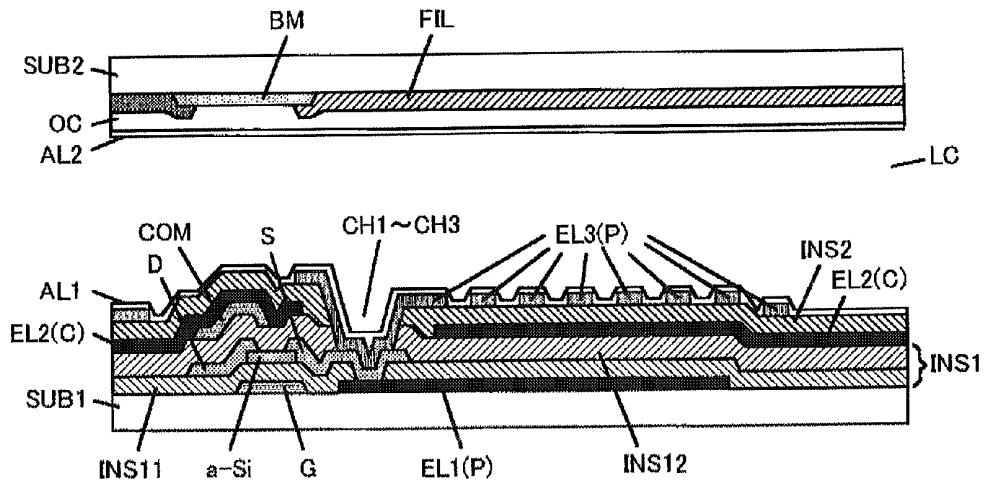

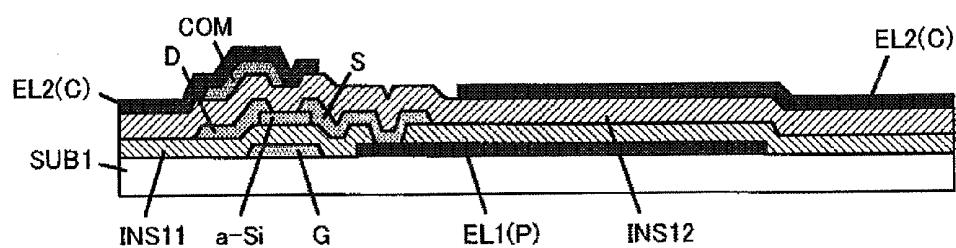

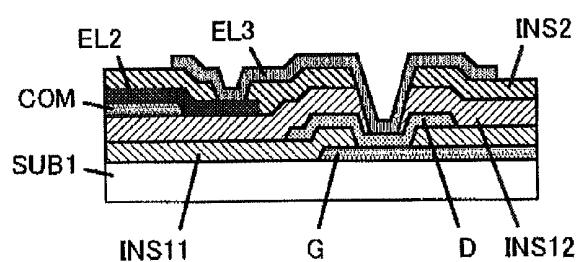

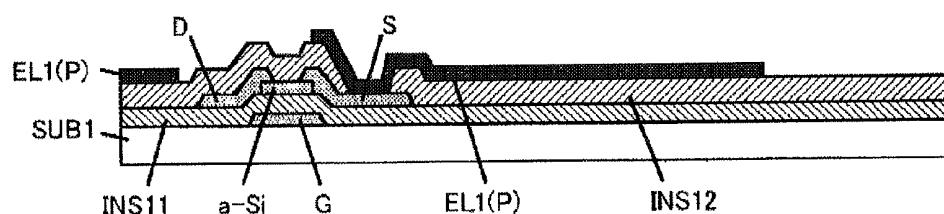

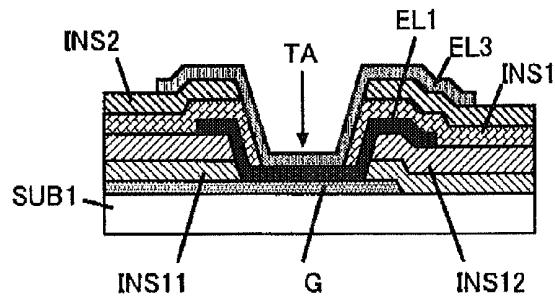

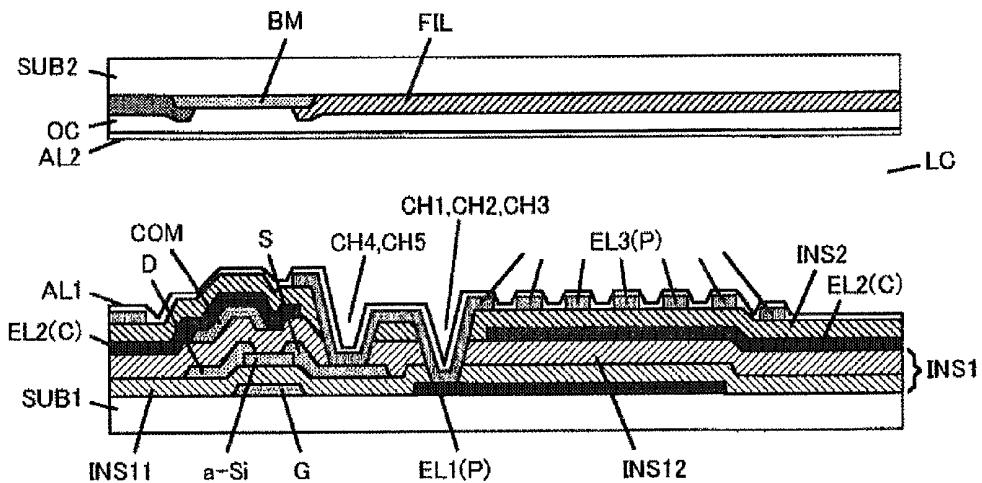

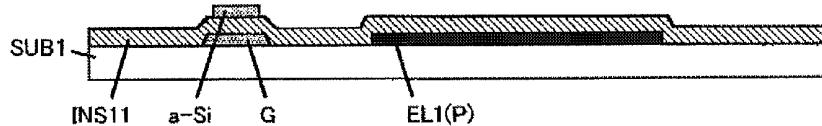

[0072] FIGS. 1A and 1B are sectional views showing a basic sectional structure of a main part of a pixel in a liquid crystal display device according to a mode of carrying out the present invention;

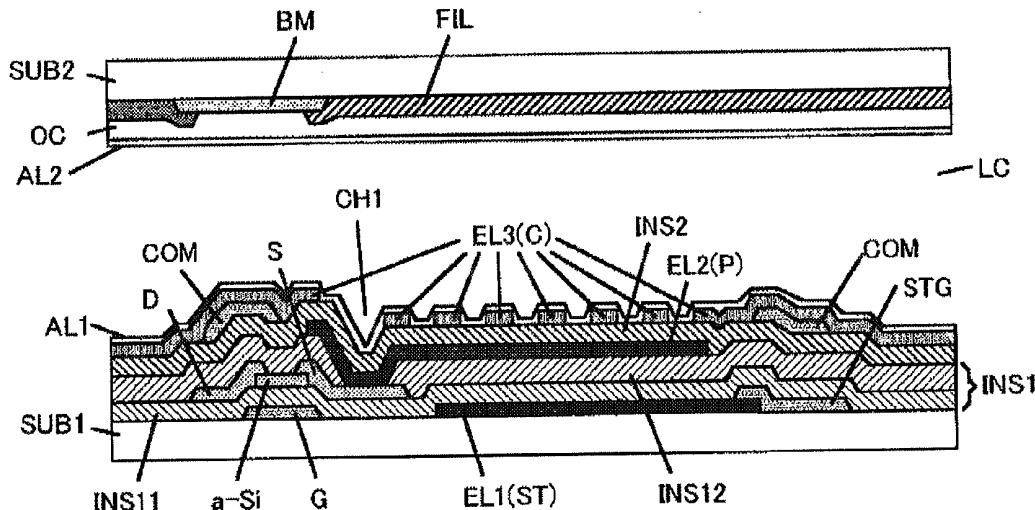

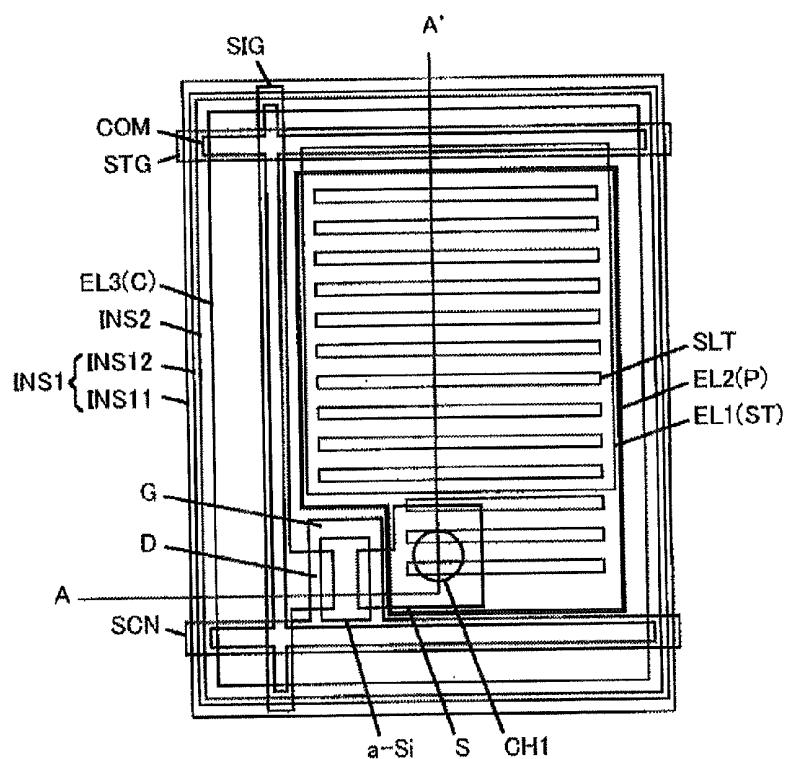

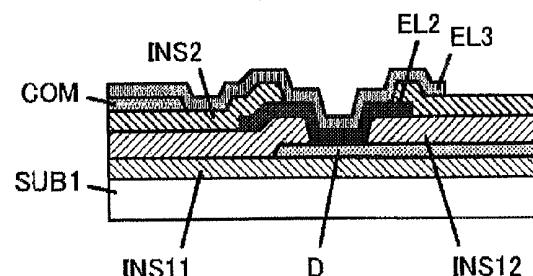

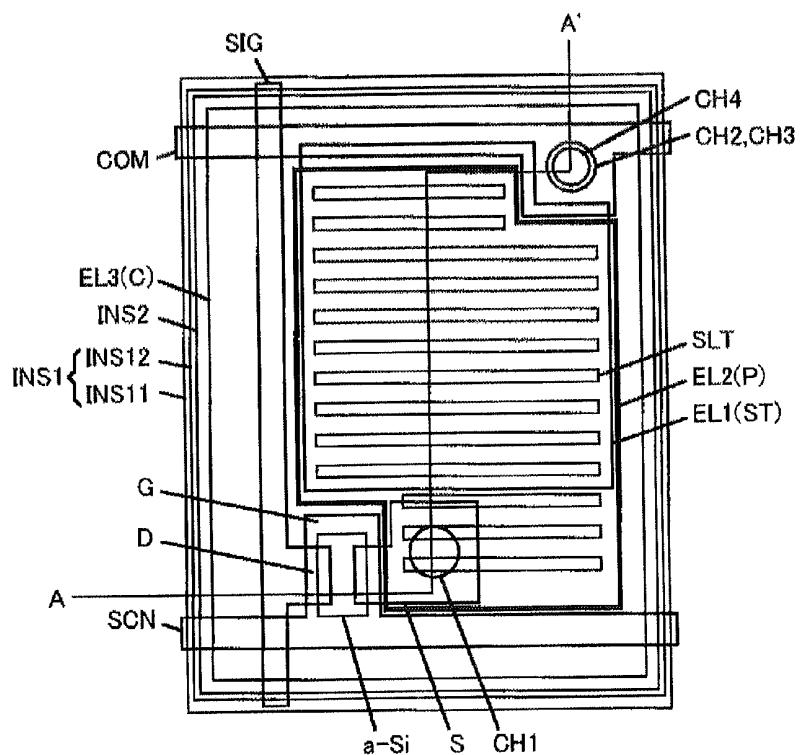

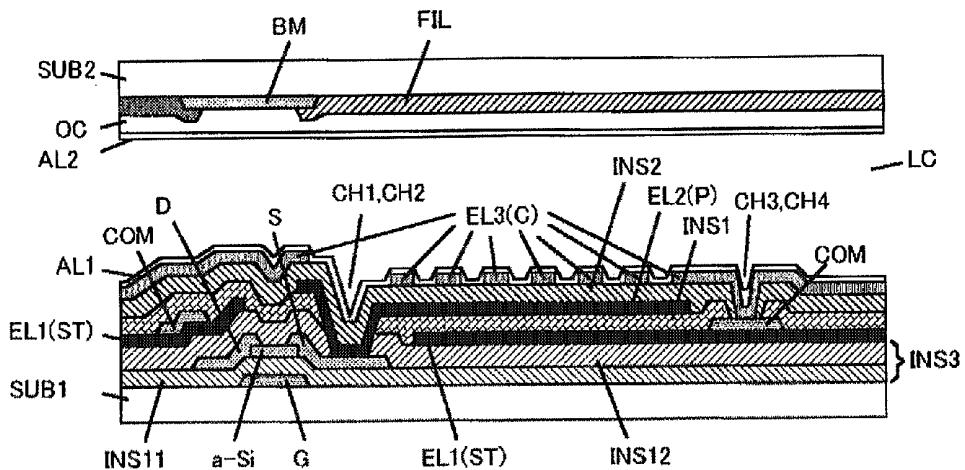

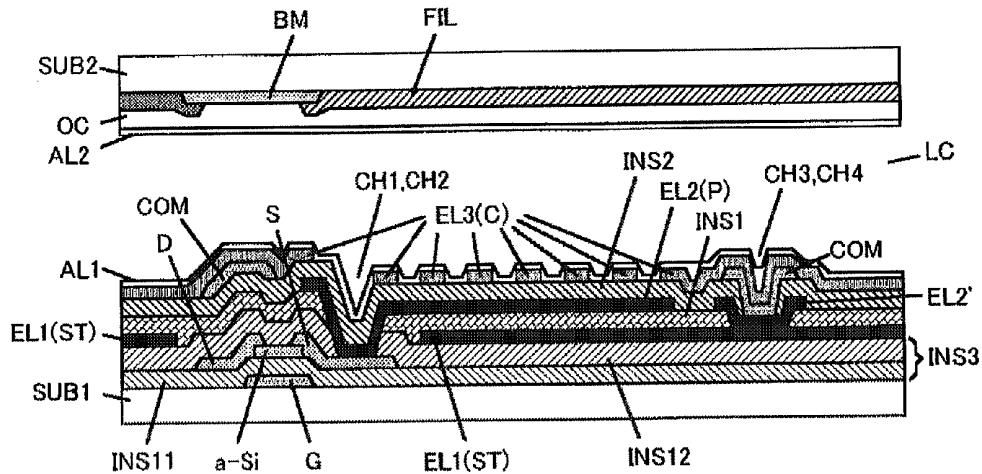

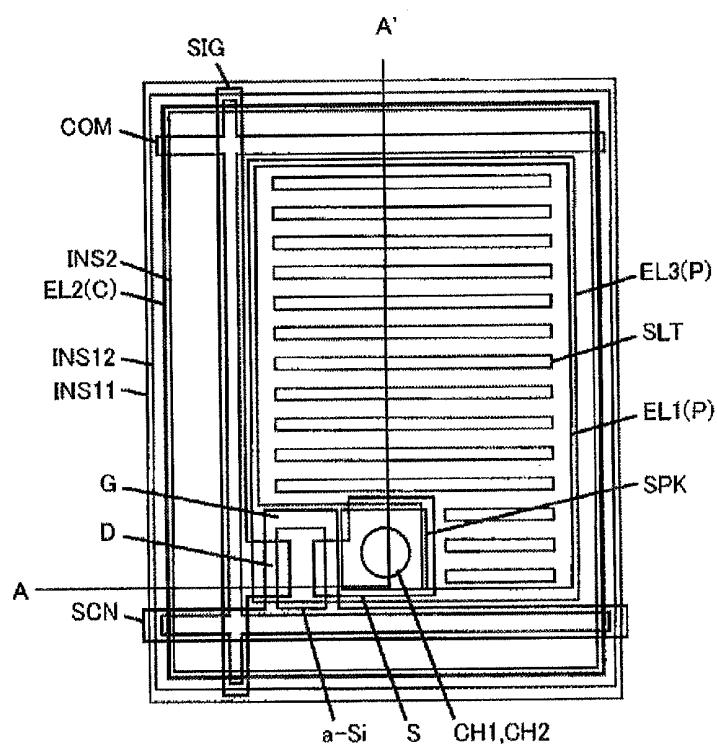

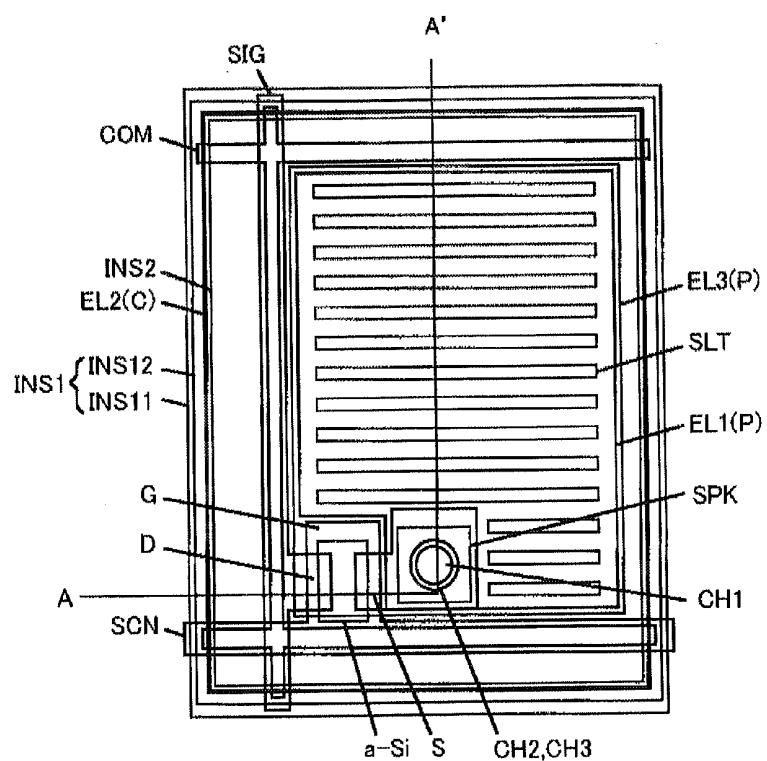

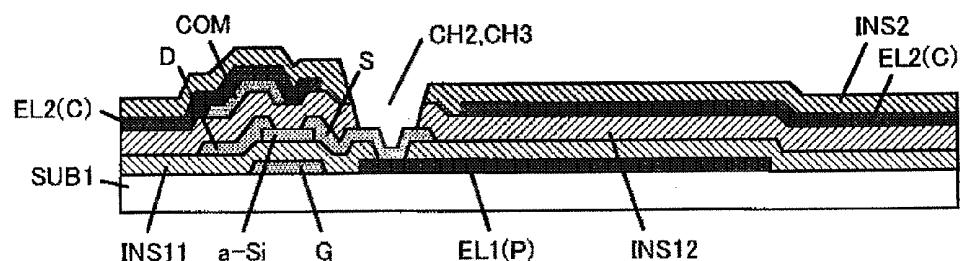

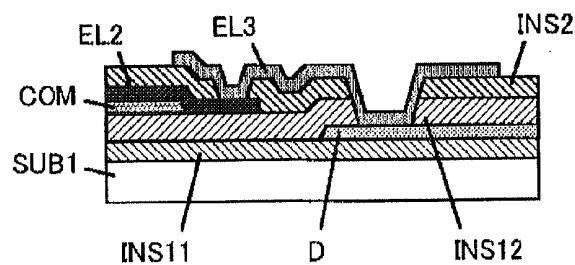

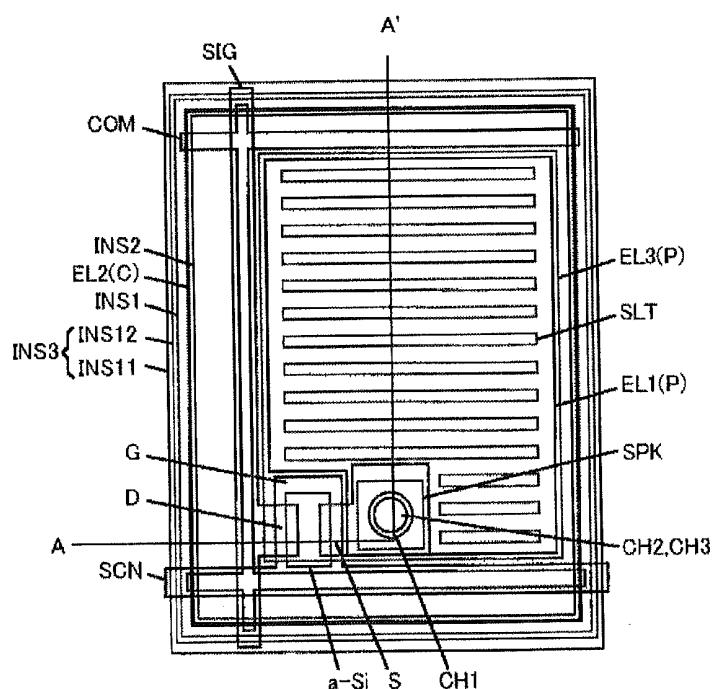

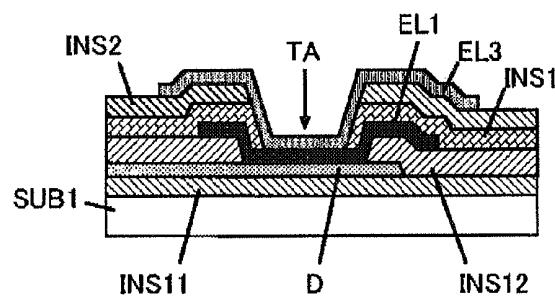

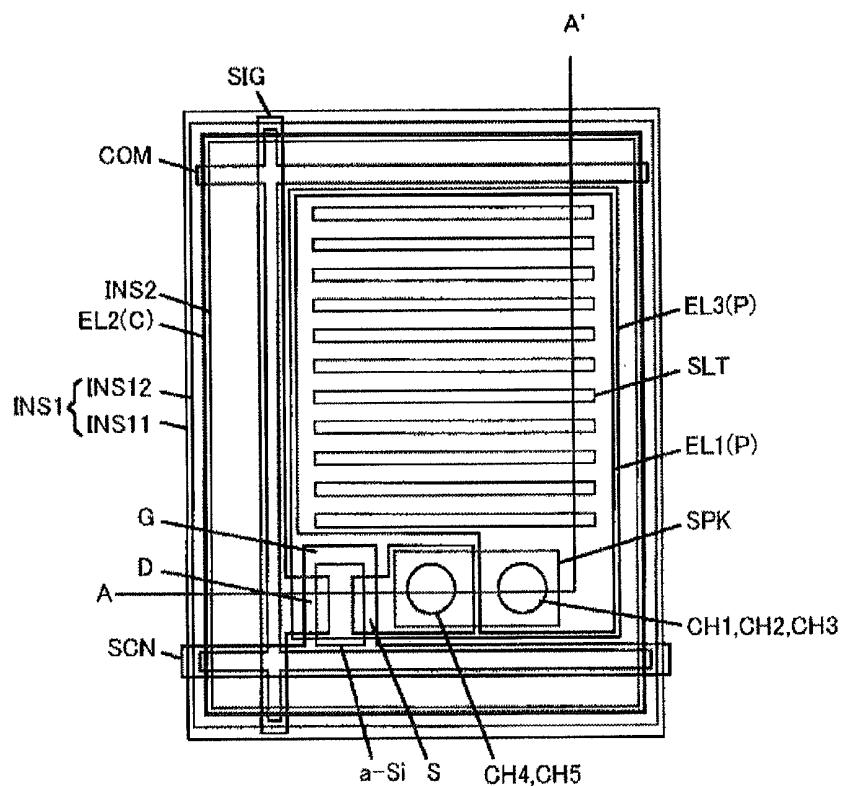

[0073] FIGS. 2A and 2B are schematic diagrams showing a pixel structure in a liquid crystal display device according to a first embodiment of the present invention;

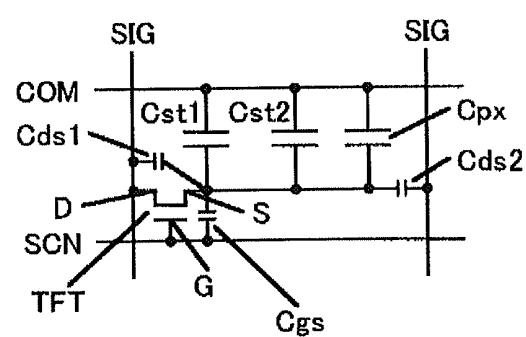

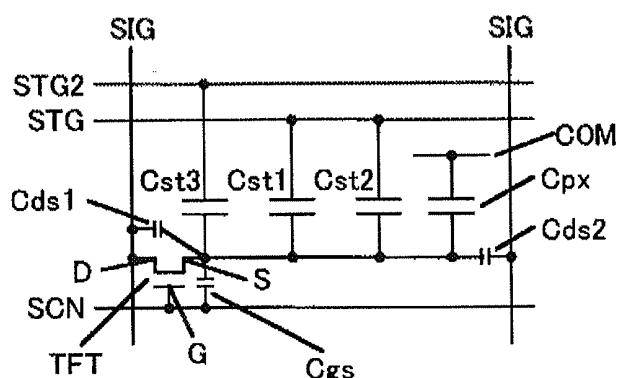

[0074] FIG. 3 is a circuit diagram showing an equivalent circuit that represents a single pixel in the liquid crystal display device according to the first embodiment and in a liquid crystal display device according to a third embodiment of the present invention;

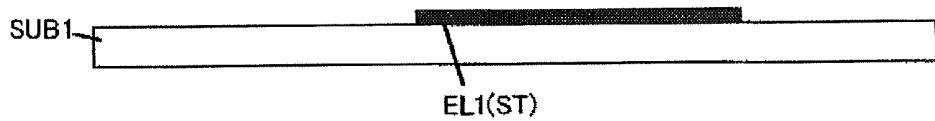

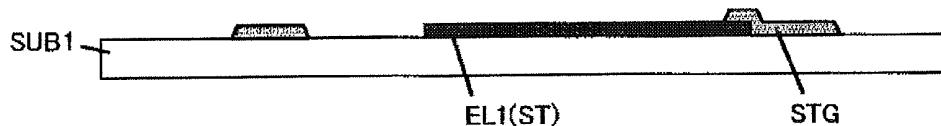

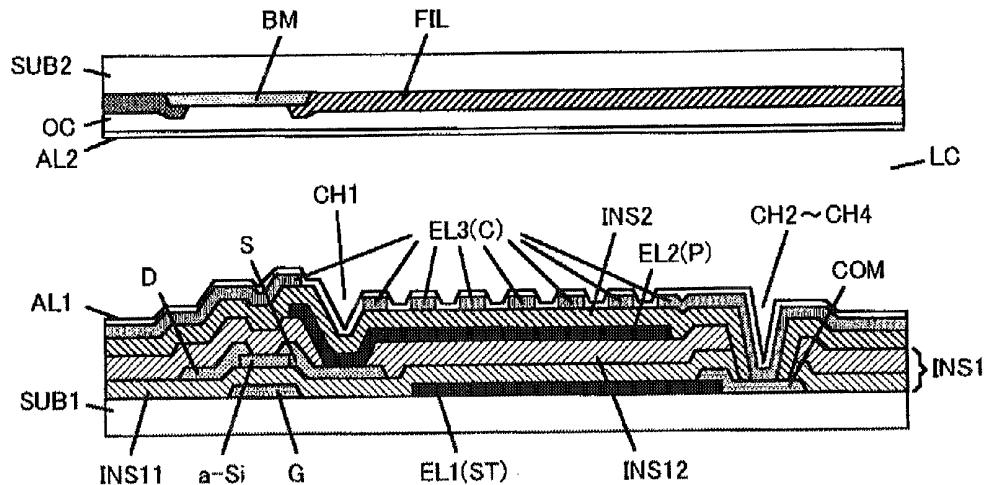

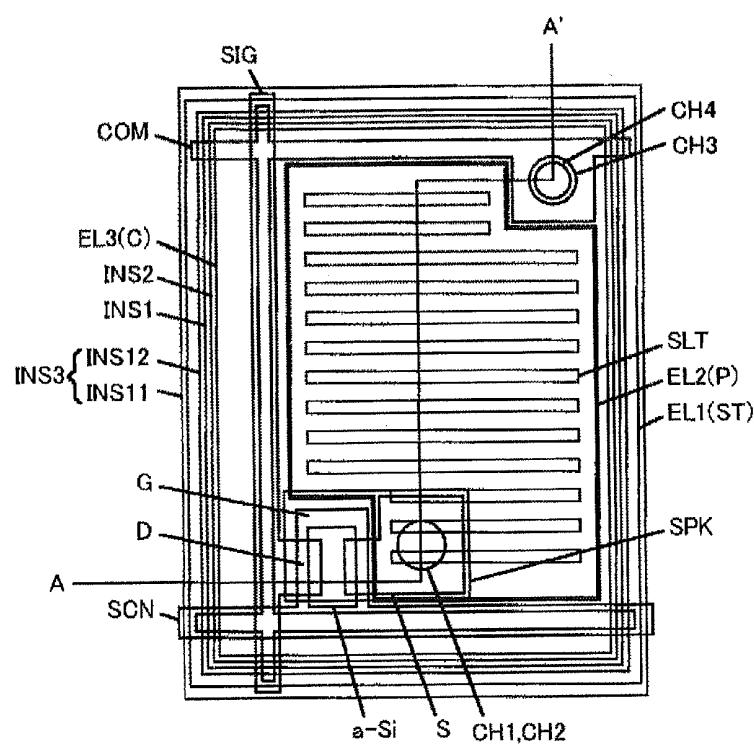

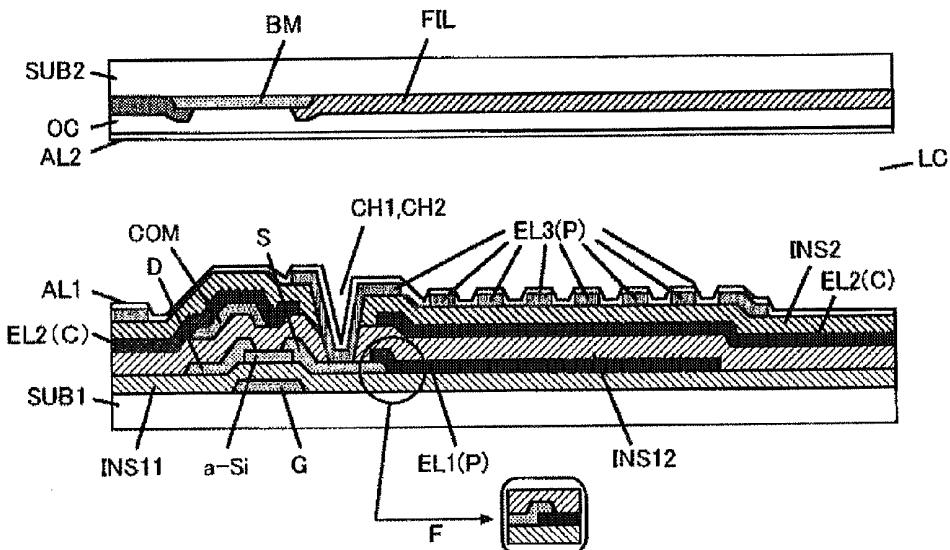

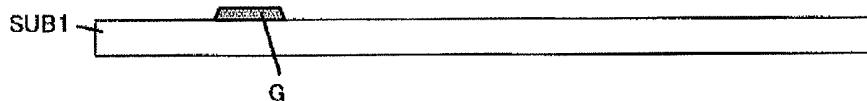

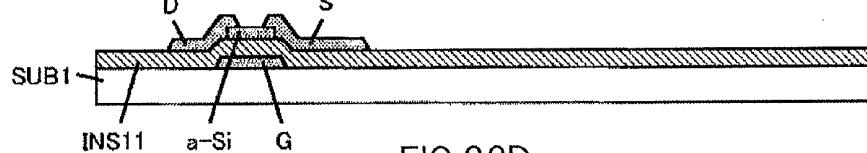

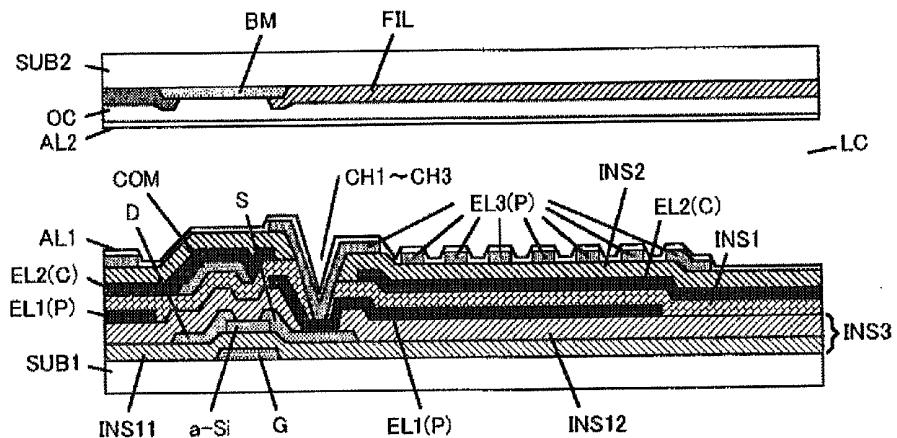

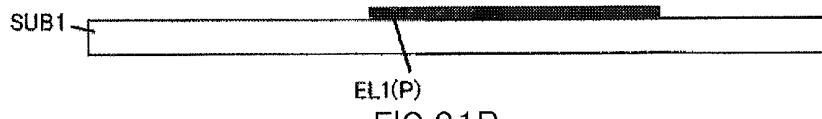

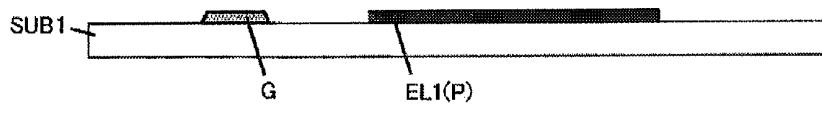

[0075] FIGS. 4A to 4H are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the first embodiment of the present invention;

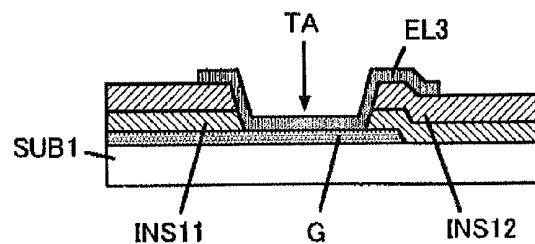

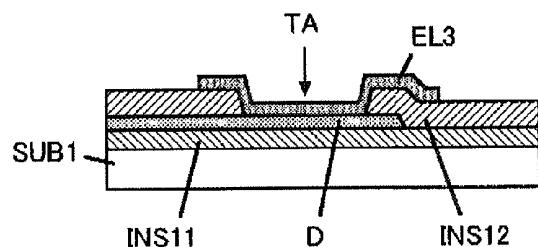

[0076] FIGS. 5A to 5D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the first embodiment of the present invention;

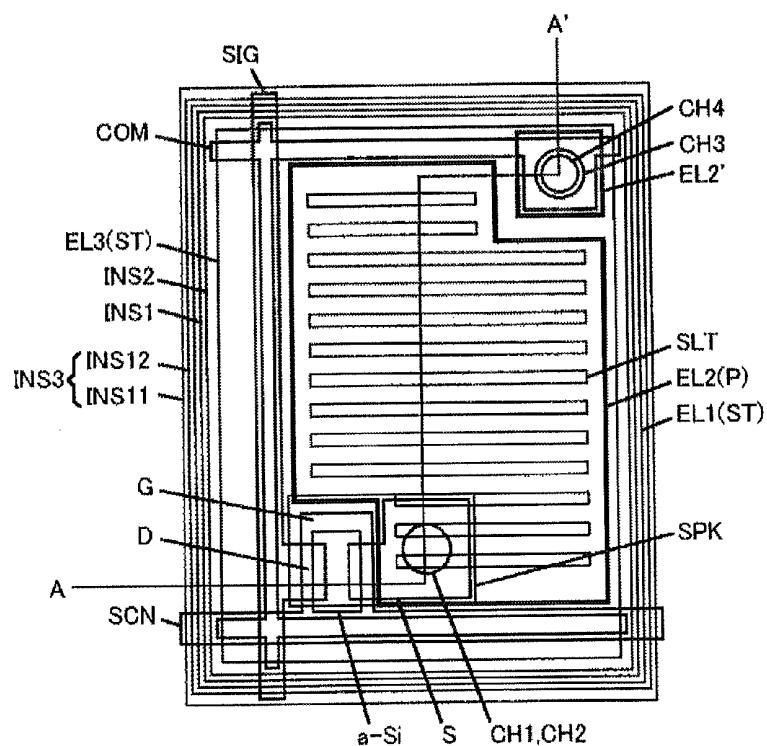

[0077] FIGS. 6A and 6B are schematic diagrams showing a pixel structure in a liquid crystal display device according to a second embodiment of the present invention;

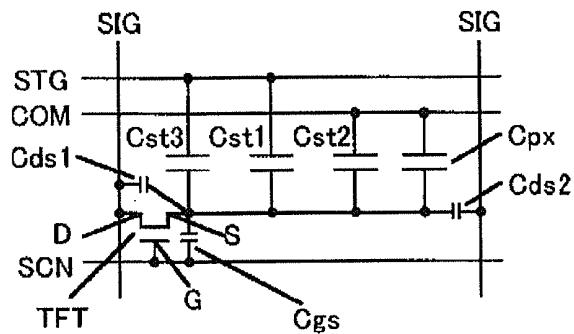

[0078] FIG. 7 is a circuit diagram showing an equivalent circuit that represents a single pixel in the liquid crystal display device according to the second embodiment and in liquid crystal display devices according to a fourth, fifth, sixth, seventh, eighth, ninth, and tenth embodiments of the present invention;

[0079] FIGS. 8A to 8G are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the second embodiment of the present invention;

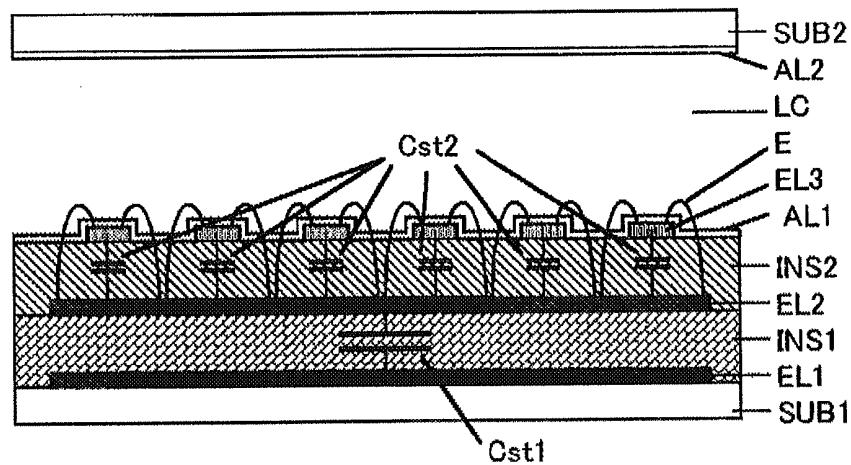

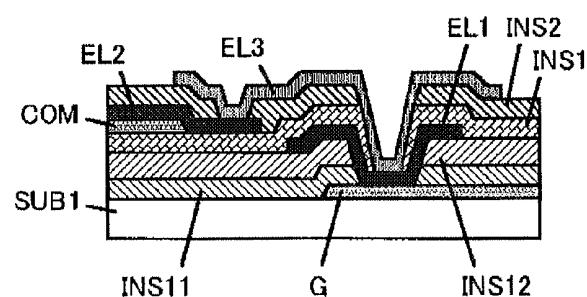

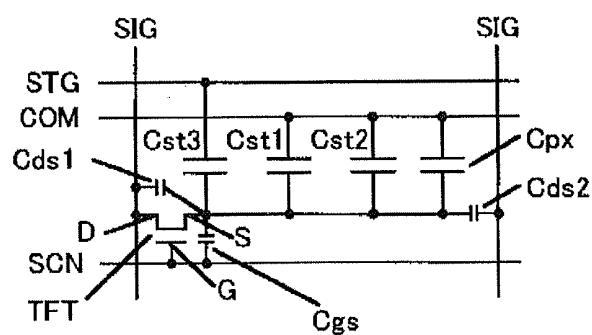

[0080] FIGS. 9A and 9B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the third embodiment of the present invention;

[0081] FIGS. 10A to 10G are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the third embodiment of the present invention;

[0082] FIGS. 11A to 11D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the third embodiment of the present invention;

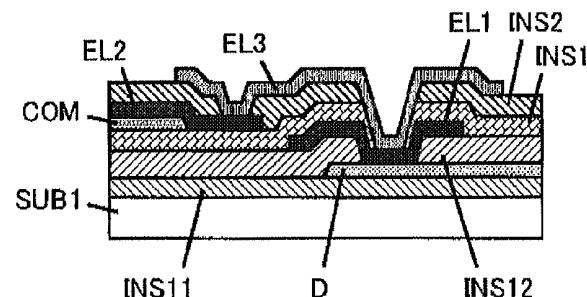

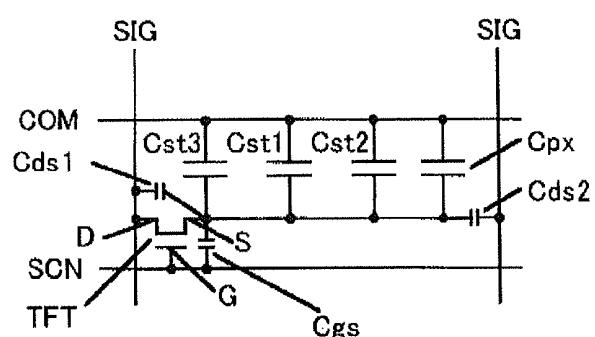

[0083] FIGS. 12A and 12B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the fourth embodiment of the present invention;

[0084] FIGS. 13A to 13F are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the fourth embodiment of the present invention;

[0085] FIGS. 14A to 14D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the fourth embodiment of the present invention;

[0086] FIGS. 15A and 15B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the fifth embodiment of the present invention;

[0087] FIGS. 16A to 16H are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the fifth embodiment of the present invention;

[0088] FIGS. 17A to 17F are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the fifth embodiment of the present invention;

[0089] FIGS. 18A and 18B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the sixth embodiment of the present invention;

[0090] FIGS. 19A to 19H are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the sixth embodiment of the present invention;

[0091] FIGS. 20A to 20D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the sixth embodiment of the present invention;

[0092] FIGS. 21A and 21B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the seventh embodiment of the present invention;

[0093] FIGS. 22A to 22G are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the seventh embodiment of the present invention;

[0094] FIGS. 23A to 23D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display devices according to the seventh and tenth embodiments of the present invention;

[0095] FIGS. 24A and 24B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the eighth embodiment of the present invention;

[0096] FIGS. 25A to 25H are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the eighth embodiment of the present invention;

[0097] FIGS. 26A to 26D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the eighth embodiment of the present invention;

[0098] FIGS. 27A and 27B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the ninth embodiment of the present invention;

[0099] FIGS. 28A to 28H are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the ninth embodiment of the present invention;

[0100] FIGS. 29A to 29D are sectional views showing the sectional structures of terminal portions and interlayer connection portions of the TFT substrate in the liquid crystal display device according to the ninth embodiment of the present invention;

[0101] FIGS. 30A and 30B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the tenth embodiment of the present invention;

[0102] FIGS. 31A to 31G are diagrams showing steps of manufacturing a TFT substrate in the liquid crystal display device according to the tenth embodiment of the present invention;

[0103] FIGS. 32A to 32J are schematic diagrams showing modification examples of the pixel structures in the liquid crystal display devices according to the first to tenth embodiments of the present invention;

[0104] FIGS. 33A to 33H are schematic diagrams showing examples of a pixel structure in a liquid crystal display device according to a twelfth embodiment of the present invention;

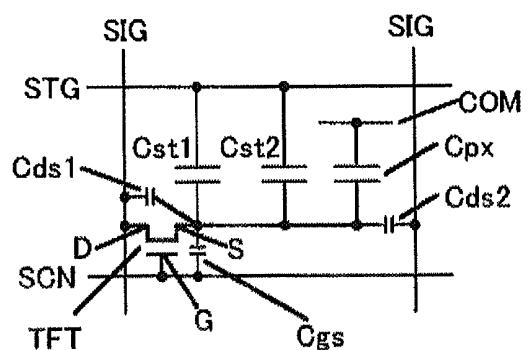

[0105] FIG. 34A is a circuit diagram showing an equivalent circuit that represents a single pixel in the liquid crystal display device according to the twelfth embodiment of the present invention, and FIG. 34B is a circuit diagram showing a modification example of the equivalent circuit that represents a single pixel in the liquid crystal display device according to the twelfth embodiment of the present invention; and

[0106] FIGS. 35A to 35C are circuit diagrams showing modification examples of the equivalent circuits that represent a single pixel in the liquid crystal display devices according to the first to tenth embodiments of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

[0107] Embodiments of the present invention will be described below in detail with reference to the accompanying drawings.

[0108] Throughout the drawings illustrating the embodiments, components that have an identical function are denoted by the same reference symbol in order to avoid repetitive descriptions.

#### [Basic Structure]

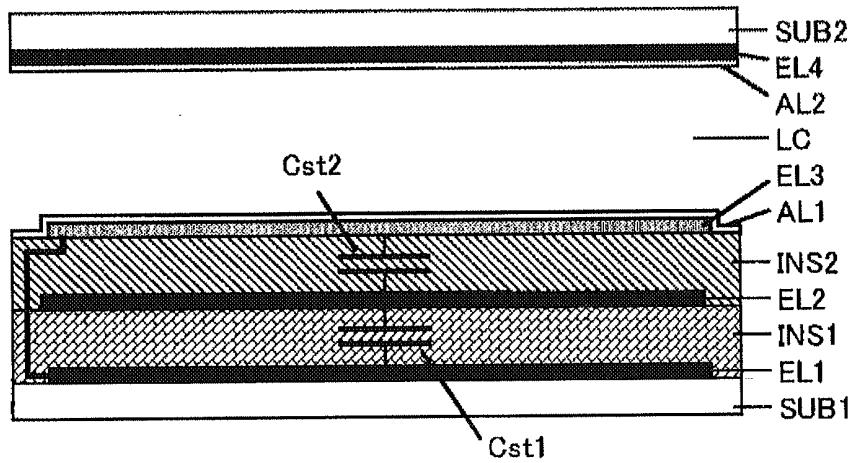

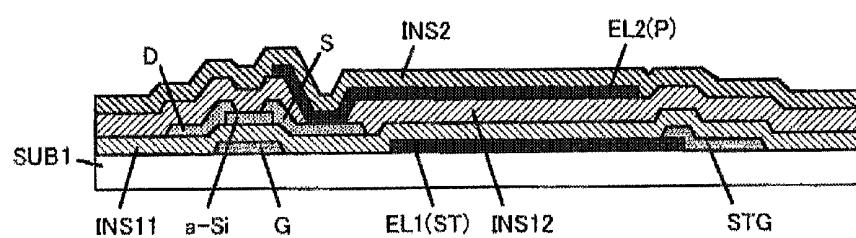

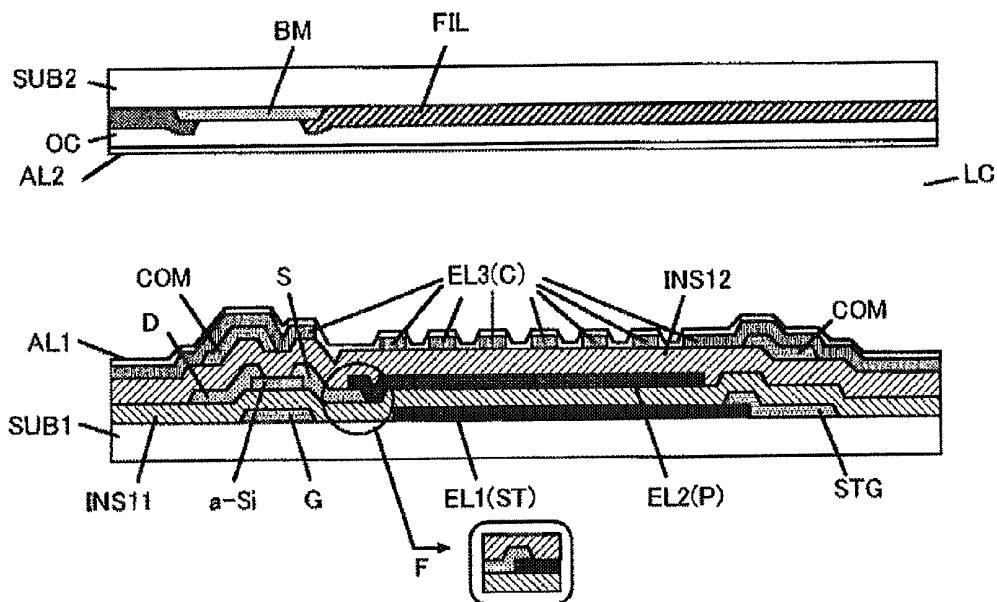

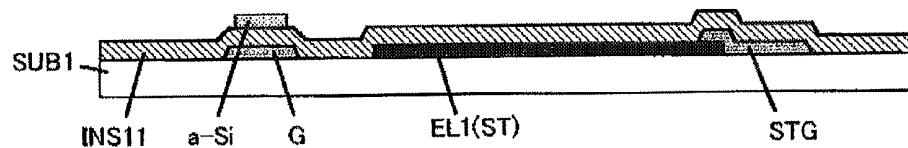

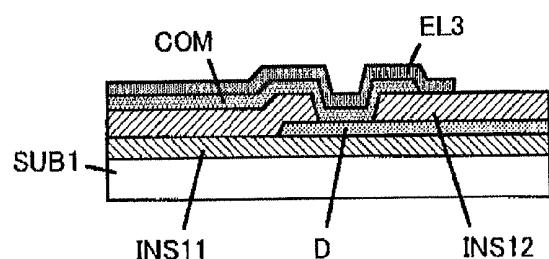

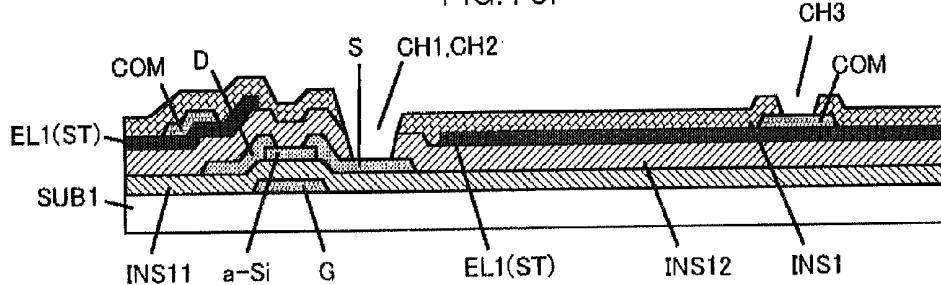

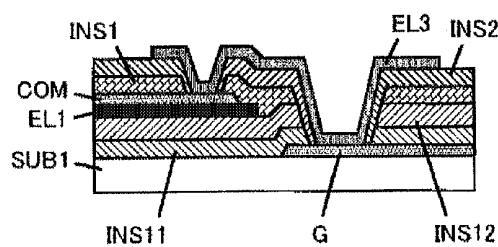

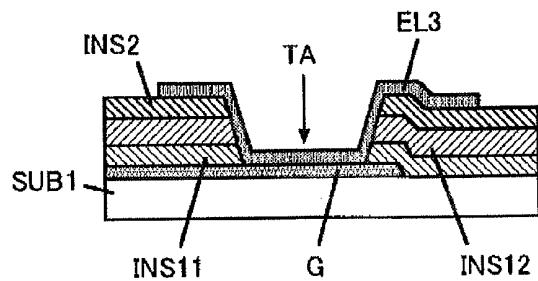

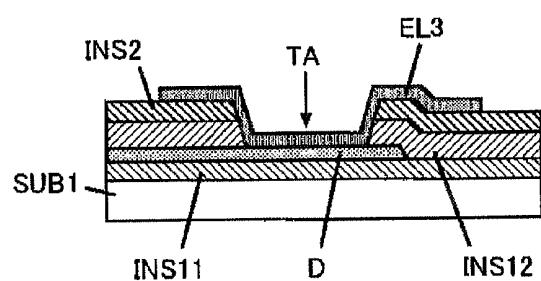

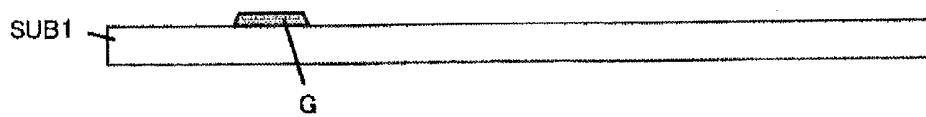

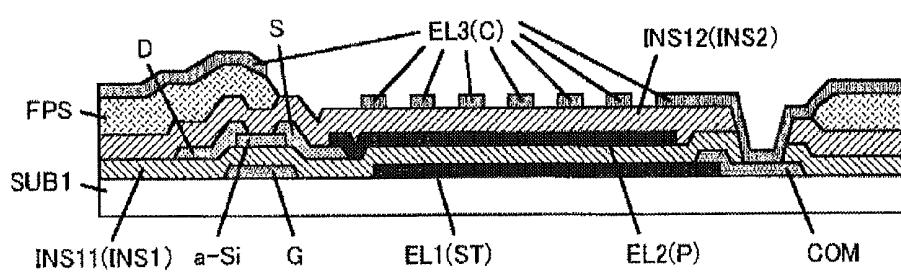

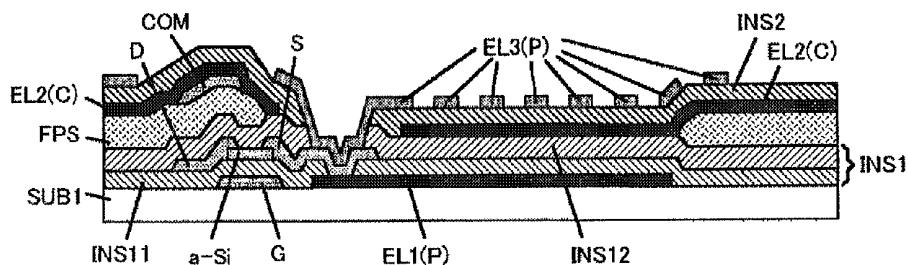

[0109] FIGS. 1A and 1B show a basic sectional structure of a main part of a pixel in a liquid crystal display device according to a mode of carrying out the present invention. Shown in FIG. 1A is a case where the present invention is applied to an IPS liquid crystal display device, and shown in FIG. 1B is a case where the present invention is applied to a vertical-field driven liquid crystal display device. In either case, a transmissive display area provided in at least a part of each pixel has a laminated structure in which a first transparent electrode EL1 is put on a first substrate SUB1 and then a first insulating film INS1, a second transparent electrode EL2, a second insulating film INS2, a third transparent electrode EL3, a first alignment film AL1, a liquid crystal layer LC, a second alignment film AL2, and a second substrate SUB2 are laminated on top of the first transparent electrode EL1 in the order stated.

[0110] In the case where the liquid crystal display device displays color images, the above-mentioned pixels correspond to sub-pixels. In the following description, one subpixel in the case of color image display is treated as one pixel.

[0111] The first transparent electrode EL1 and the second transparent electrode EL2 are electrically insulated from each other, and together form a first storage capacitor Cst1 through the first insulating film INS1. The second transparent electrode EL2 and the third transparent electrode EL3 are electrically insulated from each other, and together form a second storage capacitor Cst2 through the second insulating film INS2.

[0112] As described in the following embodiments, the first storage capacitor Cst1 and the second storage capacitor Cst2 may have the same capacitance or different capacitances. The transmissive display area may further have a third insulating film INS3, which is placed below the first transparent electrode EL1, though not shown in FIGS. 1A and 1B.

[0113] The first, second, and third insulating films (INS1 to INS3) may each be a laminate constituted of multiple insulating films. The first, second, and third insulating films (INS1 to INS3) may have the same material, dielectric constant, refractive index, and thickness, or may have different materials, dielectric constants, refractive indices, and thicknesses. The dielectric constant of the third insulating film INS3 is desirably equal to or lower than the dielectric constant of the first insulating film INS1 or of the second insulating film INS2.

[0114] The first, second, and third transparent electrodes (EL1 to EL3) may have the same material, refractive index, thickness, and area or may have different materials, refractive indices, thicknesses, and areas. Desirably, the refractive indices and thicknesses of the first, second, and third transparent electrodes (EL1 to EL3) and the first, second, and third insulating films (INS1 to INS3) are set so as to, when combined, provide a no-reflection condition with respect to at least some of light whose wavelength is within the visible light range, respectively.

[0115] In the IPS liquid crystal display device of FIG. 1A, the third transparent electrode EL3 has a comb teeth shape in plan view, and the liquid crystal layer LC is driven by an electric field E, which is generated between the third transparent electrode EL3 and the second transparent electrode

EL2. The shape of the third transparent electrode EL3 may instead be like a slip, or a flat board with a slit, or a flat board with an opening. In the case of a reflective or transflective liquid crystal display device that employs an IPS display mode, a reflective electrode provided in a reflective display area, which is provided in at least a part of each pixel, is electrically connected to at least one of the first transparent electrode EL1 and the second transparent electrode EL2. The first to third transparent electrodes (EL1 to EL3) can be used in the following two ways:

[0116] (1) The second transparent electrode EL2 in one pixel is separated from the second transparent electrode EL2 in another pixel to serve as a pixel electrode, whereas the first transparent electrode EL1 serves as a storage capacitor electrode and the third transparent electrode EL3 serves as a counter electrode. The first transparent electrode EL1 and the third transparent electrode EL3 may be electrically connected to or electrically insulated from each other. In the case where the first transparent electrode EL1 and the third transparent electrode EL3 are electrically insulated from each other, the first transparent electrode EL1 and the third transparent electrode EL3 may have the same voltage or different voltages. In the case of a reflective or transflective liquid crystal display device that employs an IPS display mode, particularly when the reflective electrode is connected to the first transparent electrode EL1, the reflective electrode may double as a storage capacitor wiring line.

[0117] (2) The first transparent electrode EL1 and the third transparent electrode EL3 in one pixel are separated from the first and third transparent electrodes EL1 and EL3 in another pixel, and are electrically connected to each other to serve as pixel electrodes, whereas the second transparent electrode EL2 serves as a counter electrode. The second transparent electrode EL2 in this case doubles as a storage capacitor electrode. In the case of a reflective or transflective liquid crystal display device that employs an IPS display mode, particularly when the reflective electrode is connected to the second transparent electrode EL2, the reflective electrode may double as a storage capacitor wiring line.

[0118] The vertical-field driven liquid crystal display device of FIG. 1B has a fourth transparent electrode EL4, which is shaped like a flat board in plan view, between the second alignment film AL2 and the second substrate SUB2 as a counter electrode. The first transparent electrode EL1 and the third transparent electrode EL3 in one pixel are separated from the first and third transparent electrodes EL1 and EL3 in another pixel, and are electrically connected to each other. The third transparent electrode EL3 serves as a pixel electrode that is shaped like a flat board in plan view. The liquid crystal layer LC is driven by an electric field generated between the third transparent electrode EL3 and the fourth transparent electrode EL4. The shapes of the third transparent electrode EL3 and the fourth transparent electrode EL4 in plan view may be like a flat board with a slit or a flat board with an opening.

[0119] In the vertical-field driven liquid crystal display device, the second transparent electrode EL2 serves as a storage capacitor electrode, and the second transparent electrode EL2 and the fourth transparent electrode EL4 may have the same voltage or different voltages. In the case of a reflective or transflective liquid crystal display device that employs a vertical-field driven liquid crystal display mode, a reflective electrode provided in a reflective display area, which is provided in at least part of each pixel, is electrically connected to

at least one of the first to third transparent electrodes EL1 to EL3. The reflective electrode may double as a storage capacitor wiring line, particularly when connected to the second transparent electrode EL2. The vertical-field driven liquid crystal display mode discussed here may be a known technology such as the VA mode, the TN mode, the ECB mode, the OCB mode, and the polymer dispersed type.

[0120] Embodiments in which the above-mentioned basic structure is applied to an active matrix liquid crystal display device with thin film transistors will now be described.

#### First Embodiment

[0121] A first embodiment of the present invention, as well as second to sixth embodiments of the present invention which will be described later, deals with an IPS liquid crystal display device in which the second transparent electrode EL2 serves as a pixel electrode, whereas the first transparent electrode EL1 and the third transparent electrode EL3 serve as a storage capacitor electrode and as a counter electrode, respectively.

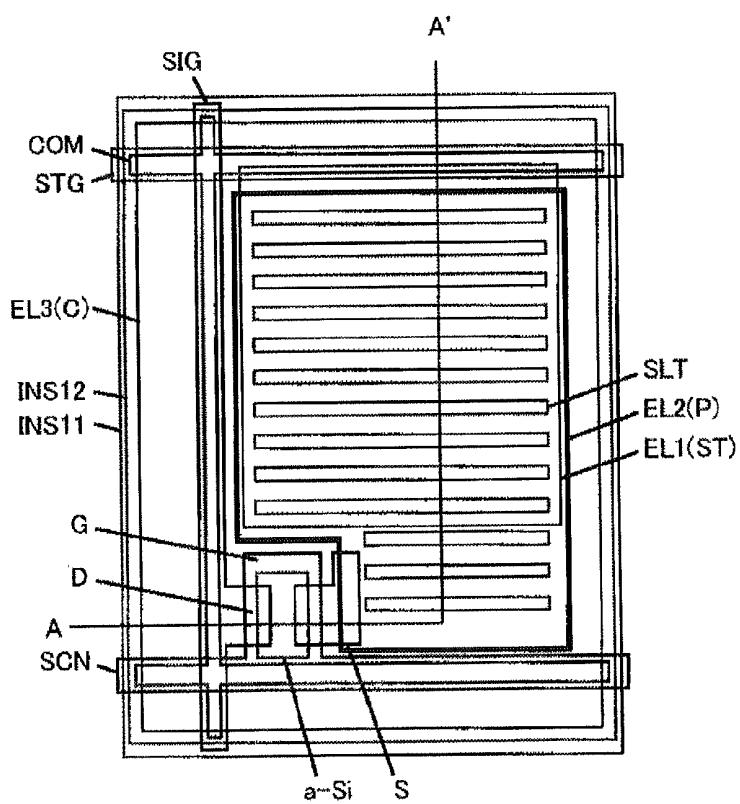

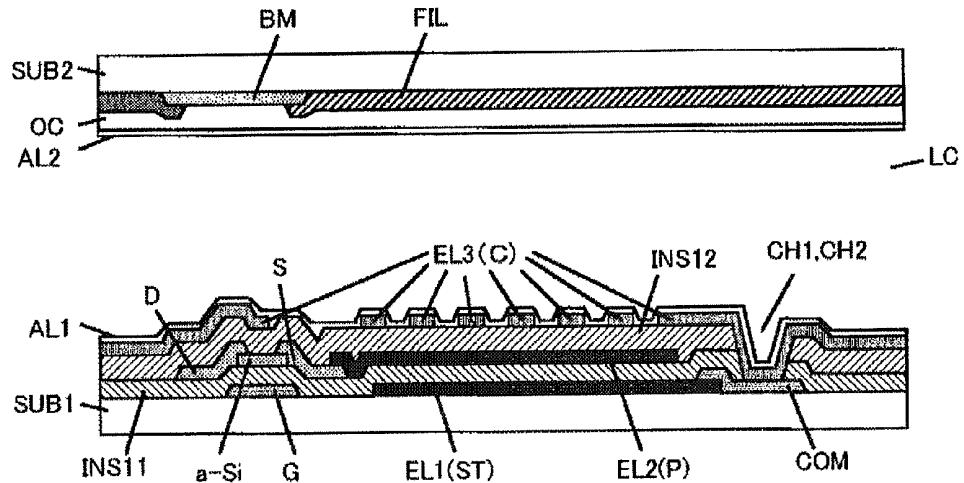

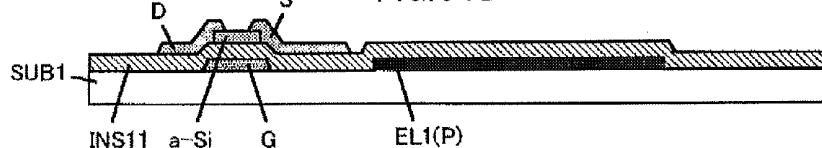

[0122] FIGS. 2A and 2B are schematic diagrams showing a pixel structure in the liquid crystal display device according to the first embodiment of the present invention. FIG. 2A shows the sectional structure of a pixel and FIG. 2B shows the plan view structure of the pixel on the TFT substrate side. The sectional structure shown in FIG. 2A corresponds to a view taken along the line A-A' shown in FIG. 2B.

[0123] On the first substrate SUB1, scanning lines SCN and as many storage capacitor wiring lines STG are provided so that the former and the latter are associated with each other on a one-on-one basis. Signal lines SIG intersect with the scanning lines SCN and the storage capacitor wiring lines STG with a gate insulating film INS11 interposed therebetween. Each pixel defined by the intersecting scanning lines SCN and signal lines SIG is provided with a thin film transistor TFT, a transparent storage capacitor electrode EL1 (ST), which functions as the first transparent electrode, and a transparent pixel electrode EL2 (P), which functions as the second transparent electrode. The transparent storage capacitor electrode EL1 (ST) and the transparent pixel electrode EL2 (P) have different areas as shown in FIG. 2B.

[0124] The storage capacitor wiring line STG and the transparent storage capacitor electrode EL1 (ST) partially overlap each other to be electrically connected to each other. A gate electrode G of the thin film transistor TFT is connected to the scanning line SCN, a drain electrode D of the thin film transistor TFT is connected to the signal line SIG, and a source electrode S of the thin film transistor TFT is connected to the transparent pixel electrode EL2 (P) through an opening (contact hole) CH1 formed in a passivation film INS12.

[0125] A laminate constituted of the passivation film INS12 and the gate insulating film INS11 is used as the first insulating film INS1. Through the first insulating film INS1, the first storage capacitor Cst1 is formed between the transparent storage capacitor electrode EL1 (ST) and the transparent pixel electrode EL2 (P).

[0126] Formed above those electrodes are the second insulating film INS2, which serves as an interlayer insulating film, a common electrode wiring line COM, which is shaped after the shape of the storage capacitor wiring line STG and the signal line SIG, and a transparent counter electrode EL3 (C), which functions as the third transparent electrode. The second storage capacitor Cst2 is formed between the transparent

pixel electrode EL<sub>2</sub> (P) and the transparent counter electrode EL<sub>3</sub> (C) through the second insulating film INS<sub>2</sub>, whereby the TFT substrate is obtained.

[0127] The transparent counter electrode EL<sub>3</sub> (C) and the common wiring line COM directly overlap each other to be electrically connected to each other and thereby lower the overall resistance of the counter electrode. The first alignment film AL<sub>1</sub> for aligning the liquid crystal layer LC in a given direction is formed in the topmost layer on the TFT substrate.

[0128] On the second substrate SUB<sub>2</sub>, a light shielding film (black matrix) BM, a color filter FIL whose color varies from one pixel to another, a protective film (overcoat) OC, and the second alignment film AL<sub>2</sub> are formed to obtain a counter substrate.

[0129] The first alignment film AL<sub>1</sub> and the second alignment film AL<sub>2</sub> are each processed in advance so that liquid crystal molecules are aligned in a given direction. The first substrate SUB<sub>1</sub> and the second substrate SUB<sub>2</sub> are arranged such that their alignment film formation faces are opposed to each other across a predetermined interval, and the gap between the two is filled with a nematic liquid crystal composition having a positive dielectric anisotropy to form the liquid crystal layer LC.

[0130] The transparent counter electrode EL<sub>3</sub> (C) above the transparent pixel electrode EL<sub>2</sub> (P) has multiple slit-like openings SLT which run parallel to one another, and hence an electric field having a component parallel to the surface of the first substrate SUB<sub>1</sub> is generated between the transparent pixel electrode EL<sub>2</sub> (P) and the transparent counter electrode EL<sub>3</sub> (C) through the liquid crystal layer LC. The liquid crystal layer LC is driven by this electric field.

[0131] A retardation plate and polarization plate (not shown) are disposed outside of the first substrate SUB<sub>1</sub> and the second substrate SUB<sub>2</sub> to obtain a normally black (NB) display mode liquid crystal display device. Drive circuits (not shown) are connected to the scanning lines SCN, the storage capacitor wiring lines STG, the signal lines SIG, and the common electrode wiring lines COM.

[0132] FIG. 3 shows an equivalent circuit that represents a single pixel in the liquid crystal display device according to the first embodiment. The transparent pixel electrode EL<sub>2</sub> (P), or the source electrode S, is provided with a parasitic capacitor C<sub>gs</sub>, which is formed between the gate (G) and source (S) of the thin film transistor TFT, and parasitic capacitors C<sub>ds1</sub> and C<sub>ds2</sub>, which are formed by the transparent pixel electrode EL<sub>2</sub> (P) and the signal lines SIG, in addition to the first storage capacitor C<sub>s1</sub>, the second storage capacitor C<sub>s2</sub>, and a pixel capacitor C<sub>p</sub>.

[0133] When the pixel dimensions are reduced to obtain fine pixels, an equivalent storage capacitor sufficiently large in relation to the parasitic capacitors including C<sub>gs</sub>, C<sub>ds1</sub>, C<sub>ds2</sub>, and the like can be formed from the parallel capacitance of the first storage capacitor C<sub>s1</sub> and the second storage capacitor C<sub>s2</sub>. This makes the voltage of the transparent pixel electrode EL<sub>2</sub> (P) less susceptible to feed-through voltage, which is caused by a voltage change in the scanning line SCN or the signal line SIG, during a hold period in which the thin film transistor TFT is off. Phenomena called smearing and cross talk can thus be reduced.

[0134] It also reduces the leakage of electric charges accumulated in the transparent pixel electrode EL<sub>2</sub> (P) and the source electrode (S) during a hold period. Accordingly, the electric field applied to the liquid crystal layer LC drops less and degradation in image quality can be prevented.

[0135] Furthermore, since the first storage capacitor C<sub>s1</sub> and the second storage capacitor C<sub>s2</sub> are constituted of the transparent storage capacitor electrode EL<sub>1</sub> (ST), the first insulating film INS<sub>1</sub>, the transparent pixel electrode EL<sub>2</sub> (P), the second insulating film INS<sub>2</sub>, and the transparent counter electrode EL<sub>3</sub> (C), which are all transparent, forming a storage capacitor that is sufficiently large in relation to the parasitic capacitor does not lower the aperture ratio of the transmissive display portion. The formation of a sufficiently large storage capacitor and the securing of a sufficiently high aperture ratio are thus accomplished simultaneously. Those effects of the first embodiment are shared by the second to sixth embodiments and an eleventh embodiment which will be described later.

[0136] In this embodiment and the third embodiment described later, the storage capacitor wiring line STG in one pixel row and the storage capacitor wiring line STG in another pixel row may receive voltage application independently of each other or commonly. The common electrode wiring line COM and the transparent counter electrode EL<sub>3</sub> (C) in one pixel row may receive voltage application independently of those in another pixel row, or the common electrode wiring line COM and the transparent counter electrode EL<sub>3</sub> (C) in one pixel column may receive voltage application independently of those in another pixel column, though, from the standpoint of reducing the resistance of the counter electrode, it is preferred to connect the common electrode wiring line COM and the transparent counter electrode EL<sub>3</sub> (C) in one pixel to those in adjacent pixels so that a voltage is applied commonly to all pixels. The voltage of the storage capacitor wiring line STG and the voltage of the common electrode wiring line COM may be the same, which does not mean that the two always need to match.

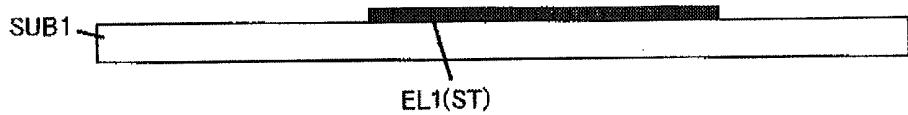

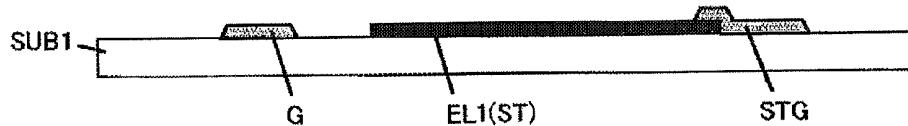

[0137] FIGS. 4A to 4H show steps of manufacturing the TFT substrate in the liquid crystal display device according to the first embodiment.

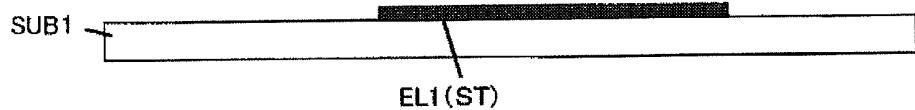

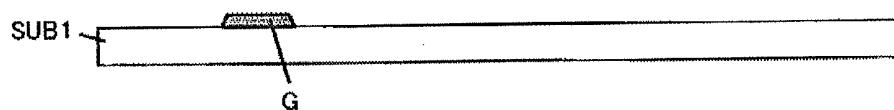

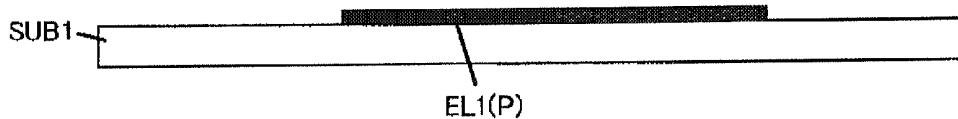

[0138] In FIG. 4A, a film is formed from a transparent conductive material such as ITO on the first substrate SUB<sub>1</sub>, which is a transparent insulating member such as a glass substrate. The film is treated by a photolithography process to form the transparent storage capacitor electrode EL<sub>1</sub> (ST).

[0139] In FIG. 4B, a film is formed from a metal material to form the gate electrode G, the scanning line SCN (not shown), and the storage capacitor wiring line STG simultaneously by a photolithography process. This layer is called a gate layer. Part of the transparent storage capacitor electrode EL<sub>1</sub> (ST) is overlapped with part of the storage capacitor wiring line STG, and hence the transparent storage capacitor electrode EL<sub>1</sub> (ST) and the storage capacitor wiring line STG are electrically connected to each other.

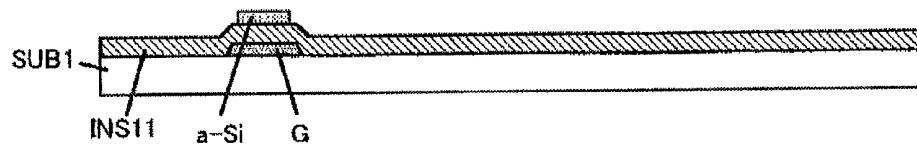

[0140] In FIG. 4C, the gate insulating film INS<sub>11</sub>, which is made of a transparent insulating material such as SiN, SiO, or TaO, and a semiconductor layer a-Si, which is made of amorphous silicon, are formed in succession, and only the semiconductor layer a-Si is treated by a photolithography process. A heavily doped n-type thin film (not shown) is present on the top face of the semiconductor layer a-Si.

[0141] In FIG. 4D, a film is formed from a metal material to form the source electrode S, the drain electrode D, and the signal line SIG (not shown) simultaneously by a photolithography process. This layer is called a drain layer. The heavily doped n-type layer which is not covered with the drain layer is removed at the same time when the drain layer is treated.

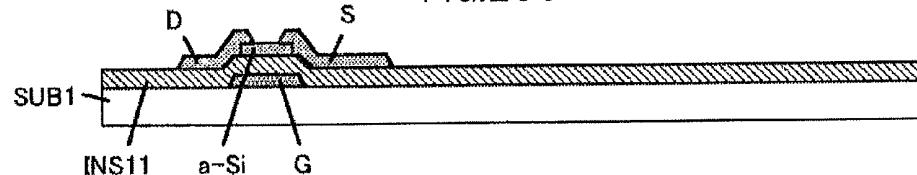

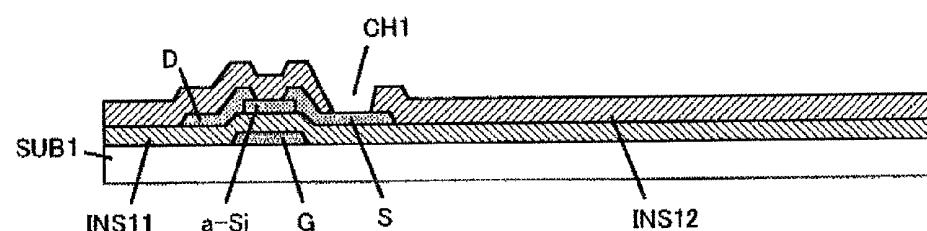

[0142] In FIG. 4E, the passivation film INS12 is formed from SiN. The passivation film INS12 and the gate insulating film INS11 are treated at once by a photolithography process. The opening CH1 is formed in a portion of the passivation film INS12 that is located above the source electrode S.

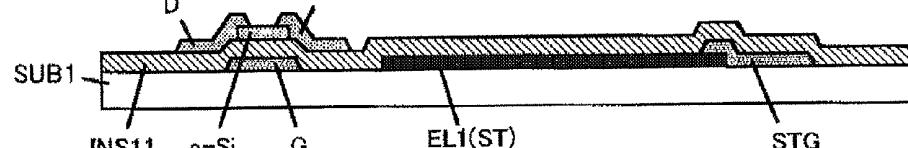

[0143] In FIG. 4F, a film is formed from a transparent conductive material such as ITO and is treated by a photolithography process to form the transparent pixel electrode EL2 (P). The transparent pixel electrode EL2 (P) is electrically connected to the source electrode S through the opening CH1 in the passivation film INS12. A region in which the transparent storage capacitor electrode EL1 (ST) and the transparent pixel electrode EL2 (P) overlap each other through the laminate constituted of the gate insulating film INS11 and the passivation film INS12 serves as the first storage capacitor Cst1.

[0144] In FIG. 4G, the second insulating film INS2 is formed from SiN and is treated by a photolithography process. By this photolithography process, a pixel portion is not patterned, whereas openings are opened in terminal portions and interlayer connection portions.

[0145] In FIG. 4H, a film is formed from a metal material and is treated by a photolithography process to form the common electrode wiring line COM.

[0146] Lastly, a film is formed from a transparent conductive material such as ITO to cover the common electrode wiring line COM, and is treated by a photolithography process to form the transparent counter electrode EL3 (C) as the one shown in FIG. 2A. The TFT substrate is thus manufactured by conducting a photolithography process nine times in total.

[0147] The steps of FIGS. 4A to 4F can be adopted from, for example, a manufacturing process of an IPS liquid crystal display device in which a comb-like pixel electrode, or a pixel electrode having a slit, is formed on a planar counter electrode (C) with an interlayer insulating film interposed between the electrodes. Then, three subsequent steps are added to the steps of FIGS. 4A to 4F.

[0148] The order in which the steps of FIGS. 4A and 4B are executed may be reversed as long as the transparent storage capacitor electrode EL1 (ST) and the storage capacitor wiring line STG are electrically connected to each other.

[0149] In the first embodiment and the third embodiment described later, a third storage capacitor Cst3 may be formed in a region where the transparent storage capacitor electrode EL1 (ST), or the storage capacitor wiring line STG formed in the gate layer, overlaps with the source electrode S with the gate insulating film INS11 interposed between the two by letting the transparent storage capacitor electrode EL1 (ST) or the storage capacitor wiring line STG slip in under the source electrode S. In this case, the third storage capacitor Cst3 constitutes an equivalent circuit connected in parallel to the first storage capacitor Cst1 as shown in FIG. 35A.

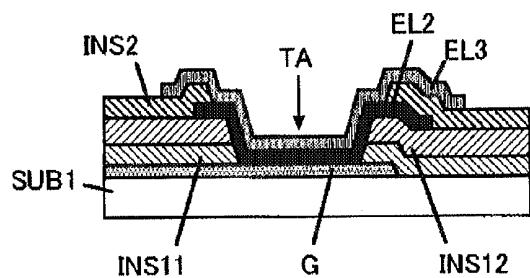

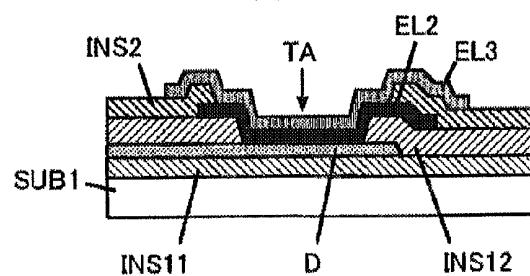

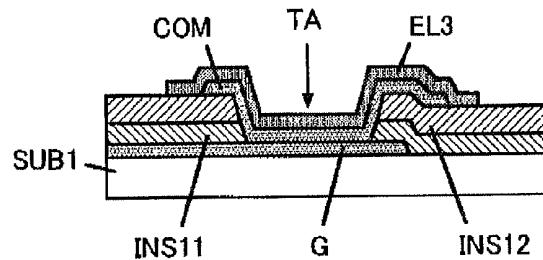

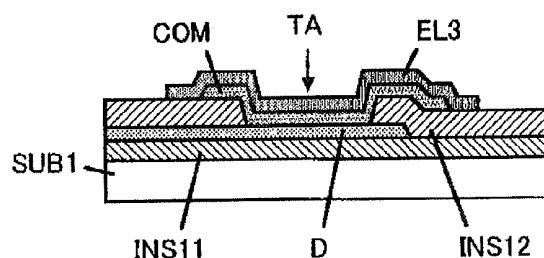

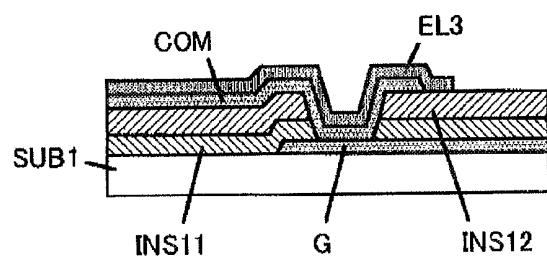

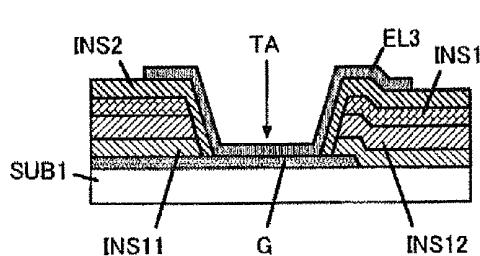

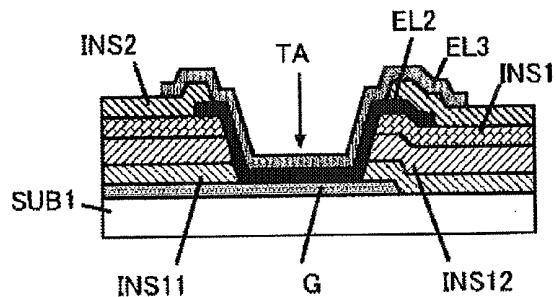

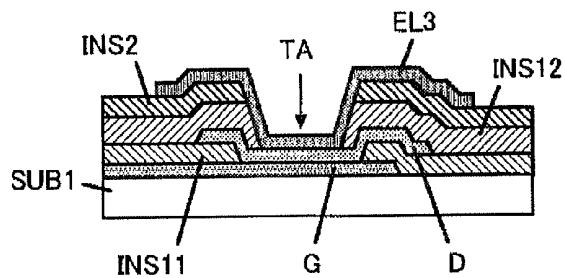

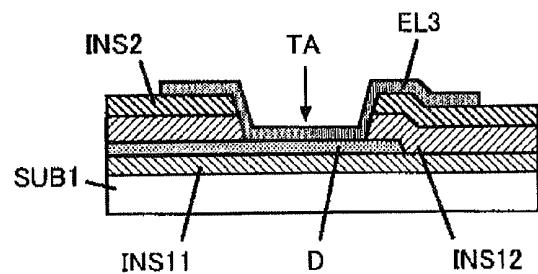

[0150] The sectional structures of the terminal portions and the interlayer connection portions that are formed by the manufacturing steps of the first embodiment are shown in FIGS. 5A to 5D. FIG. 5A shows terminal portions of the scanning line SCN and the storage capacitor wiring line STG which are formed in the gate layer. FIG. 5B shows a terminal portion of the signal line SIG which is formed in the drain layer. FIG. 5C shows a connection portion between the common electrode wiring line COM and the gate layer. FIG. 5D shows a connection portion between the common electrode wiring line COM and the drain layer. In FIGS. 5A and 5B, TA

represents a terminal portion as in FIGS. 11A and 11B, FIGS. 14A and 14B, FIGS. 17A to 17D, FIGS. 20A and 20B, FIGS. 23A and 23B, FIGS. 26A and 26B, and FIGS. 29A and 29B, which will be described later.

[0151] The transparent electrode EL2 is formed as shown in the drawings in order to prevent the treatment of the second insulating film INS2 from disturbing the gate insulating film INS11 and the passivation film INS12 and in order to prevent the treatment of the common electrode wiring line COM from disturbing the gate layer and the drain layer.

[0152] The structure of the first embodiment and the structures of the second to eleventh embodiments described later can also be applied to a reflective or transflective liquid crystal display device of IPS display mode. In that case, a reflective electrode is formed in part of the transparent storage capacitor electrode EL1 (ST) or part of the transparent pixel electrode EL2 (P) to be used as a reflective display portion, which may be provided with a liquid crystal layer thickness adjusting layer. Using a part of the storage capacitor wiring line STG and a part of the common electrode wiring line COM for the reflective electrode is particularly preferred because it does not increase the number of the manufacturing steps.

[0153] The structures of those embodiments are also applicable to a liquid crystal display device that has both, within one pixel, an IPS display mode transmissive display portion of NB display mode and an IPS display mode reflective display portion of normally white (NW) display mode.

[0154] In this embodiment and all the embodiments described later, the transparent conductive material employed may be SnO, InZnO, ZnO, or the like instead of ITO. The transparent storage capacitor electrode EL1 (ST), the transparent pixel electrode EL2 (P), and the transparent counter electrode EL3 (C) are desirably set to thicknesses that are appropriate in terms of manufacture yield and that are appropriate in terms of optical design.

[0155] The gate layer, the drain layer, and the common electrode wiring line COM may also employ Al, Cr, Cu, Mo, Nd, Ta, Ti, W, Zr and other similar metal materials, or an alloy of those materials.

[0156] The gate insulating film INS11, the passivation film INS12, and the second insulating film INS2 may be formed from SiO or TaO instead of SiN, or may also be a laminate of SiO and TaO layers, or may partially contain an organic insulating material such as photosensitive acrylic resin.

[0157] The gate insulating film INS11, the passivation film INS12, and the second insulating film INS2 are desirably set to thicknesses that are appropriate in terms of manufacture yield as well as characteristics and reliability for a thin film transistor TFT and a liquid crystal display device, and that are appropriate in terms of optical design.

[0158] The semiconductor layer may be formed from polycrystalline silicon, an organic semiconductor, crystalline silicon, or the like instead of amorphous silicon.

[0159] The shape in plan view of the transparent counter electrode EL3 (C), which is located closest to the liquid crystal layer LC, may be like a slip or comb-teeth instead of a shape with multiple slit-like openings SLT which are parallel to one another. The transparent counter electrode EL3 (C) may also have a shape in plan view that makes it possible to generate an electric field in multiple different field directions, and hence the liquid crystal layer LC can change to multiple domains having different alignment directions upon application of an electric field to the liquid crystal layer LC.

[0160] How the layers are treated does not need to be limited to a photolithography process, and printing, ink jet, or the like may be employed. The dielectric anisotropy of the liquid crystal composition may also be negative, and the liquid crystal composition does not always need to be a nematic liquid crystal, depending on the display mode.

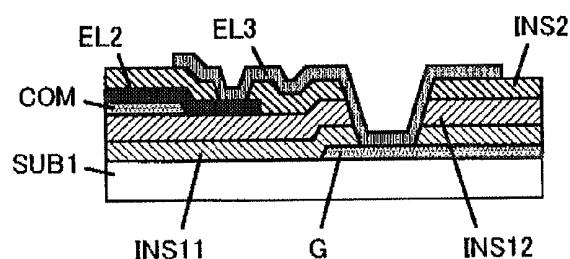

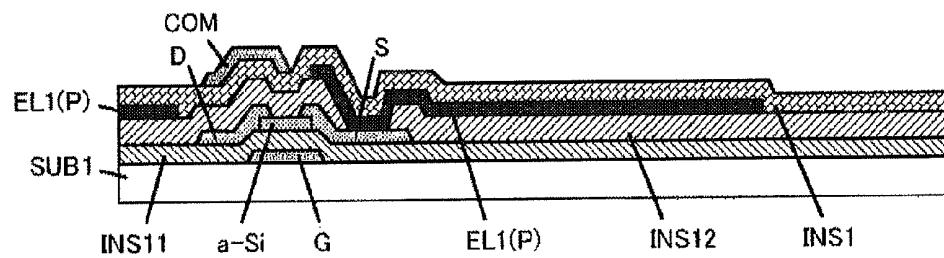

#### Second Embodiment

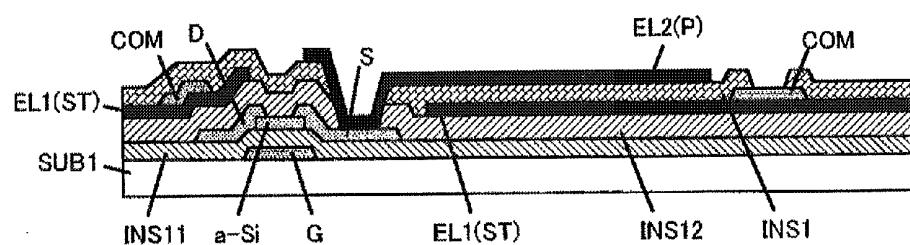

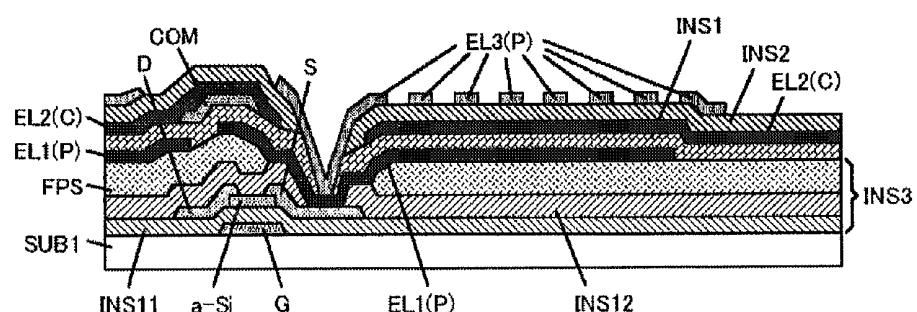

[0161] FIGS. 6A and 6B are schematic diagrams showing a pixel structure in a liquid crystal display device according to the second embodiment of the present invention. Shown in FIG. 6A is the sectional structure of a pixel, and shown in FIG. 6B is the plan view structure of the pixel on the TFT substrate side. The sectional structure of FIG. 6A corresponds to a view taken along the line A-A' shown in FIG. 6B.

[0162] The difference from the first embodiment is that, instead of using the common electrode wiring line COM between the transparent counter electrode EL3 (C) and the second insulating film INS2, the second embodiment makes the storage capacitor wiring line STG formed in the gate layer double as the common electrode wiring line COM.

[0163] The transparent counter electrode EL3 (C) in the second embodiment is reduced in resistance as in the first embodiment by forming openings (contact holes CH2 to CH4) in a portion of the gate insulating film INS11, a portion of the passivation film INS12, and a portion of the second insulating film INS2 that are located above the common electrode wiring line formed in the gate layer, and by connecting the transparent counter electrode EL3 (C) to the common electrode wiring line COM through the openings (CH2 to CH4).

[0164] An equivalent circuit per pixel in the second embodiment, where the storage capacitor wiring line STG doubles as the common electrode wiring line COM, is as shown in FIG. 7.

[0165] In the second embodiment, an equivalent storage capacitor sufficiently large in relation to the parasitic capacitors including Cgs, Cds1, and Cds2 can also be formed from the parallel capacitance of the first storage capacitor Cst1 and the second storage capacitor Cst2, and the same effects as in the first embodiment can be attained.

[0166] In this embodiment and the fourth embodiment described later, a voltage may be applied commonly to the common electrode wiring line COM in one pixel row and the common electrode wiring line COM in another pixel row, or the common electrode wiring line COM and the transparent counter electrode EL3 (C) in one pixel row may be separated from those in another pixel row to receive voltage application independently of the other pixel row.

[0167] In FIG. 6B, the openings (CH2 to CH4) are formed in the gate insulating film INS11, the passivation film INS12, and the second insulating film INS2 as a connection portion between the transparent counter electrode EL3 (C) and the common electrode wiring line COM. The transparent counter electrode EL3 (C) accordingly has a smaller region where the slit-like openings SLT are provided to apply an electric field to the liquid crystal layer LC, and the aperture ratio is lowered compared to FIG. 2B. However, the structure of FIG. 6B has an advantage over the structure of FIG. 2B in that the number of TFT substrate manufacturing steps in the second embodiment is one step less than in the first embodiment as described below.

[0168] FIGS. 8A to 8G show steps of manufacturing the TFT substrate in the liquid crystal display device according to

the second embodiment. FIGS. 8A to 8D are the same as FIGS. 4A to 4D described in the first embodiment.

[0169] FIG. 8E is similar to FIG. 4E except that the openings (CH2 and CH3) are formed in a portion of the gate insulating film INS11 and a portion of the passivation film INS12 that are located above the common electrode wiring line COM, in addition to forming the opening CH1 in a portion of the passivation film INS12 that is located above the source electrode S, by treating the gate insulating film INS11 and the passivation film INS12 at once.

[0170] The step of FIG. 8F is the same as the step of FIG. 4F.

[0171] FIG. 8G is similar to FIG. 4G except that, when the second insulating film INS2 is treated, an opening CH4 is formed in a portion of the second insulating film INS2 that is within the openings (CH2 and CH3) of the gate insulating film INS11 and the passivation film INS12, thereby exposing the surface of the common electrode wiring line COM in the gate layer. Thereafter, a step corresponding to FIG. 4H is skipped, and a film is formed from a transparent conductive material such as ITO and treated by a photolithography process to form the transparent counter electrode EL3 (C) as the one shown in FIG. 6A.

[0172] The transparent counter electrode EL3 (C) and the common electrode wiring line COM are electrically connected to each other through the openings (CH2 to CH4) in the gate insulating film INS11, the passivation film INS12, and the second insulating film INS2.

[0173] The TFT substrate is thus manufactured by conducting a photolithography process eight times in total.

[0174] As in the first embodiment, the steps of FIGS. 8A to 8F can be adopted from a manufacturing process of an IPS liquid crystal display device in which a comb-like pixel electrode (P), or a pixel electrode (P) having a slit, is formed on a planar counter electrode (C) with an interlayer insulating film interposed between the electrodes. Then, two subsequent steps are added to the steps of FIGS. 8A to 8F.

[0175] As in the first embodiment, the order in which the steps of FIGS. 8A and 8B are executed may be reversed as long as the transparent storage capacitor electrode EL1 (ST) and the common electrode wiring line COM are electrically connected to each other.

[0176] In this embodiment and the fourth embodiment described later, a third storage capacitor Cst3 may also be formed in a region where the transparent storage capacitor electrode EL1 (ST), or the common electrode wiring line COM formed in the gate layer, overlaps the source electrode S with the gate insulating film INS11 interposed between the two by letting the transparent storage capacitor electrode EL1 (ST) or the common electrode wiring line COM slip in under the source electrode S. In this case, the third storage capacitor Cst3 constitutes an equivalent circuit connected in parallel to the first storage capacitor Cst1, the second storage capacitor Cst2, and the pixel capacitor Cpx as shown in FIG. 35C.

[0177] The sectional structures of terminal portions that are formed by the manufacturing steps of the second embodiment are the same as those in FIGS. 5A and 5B. The sectional structures of interlayer connection portions that are formed by the manufacturing steps of the second embodiment are the same as those in FIGS. 5C and 5D except for the following points.

[0178] In other words, in the second embodiment where the common electrode wiring line COM between the transparent counter electrode EL3 (C) and the second insulating film

INS2 is not used, the sectional structures of the interlayer connection portions do not have the common electrode wiring line COM between the transparent counter electrode EL3 (C) and the second insulating film INS2 unlike those in FIGS. 5C and 5D.

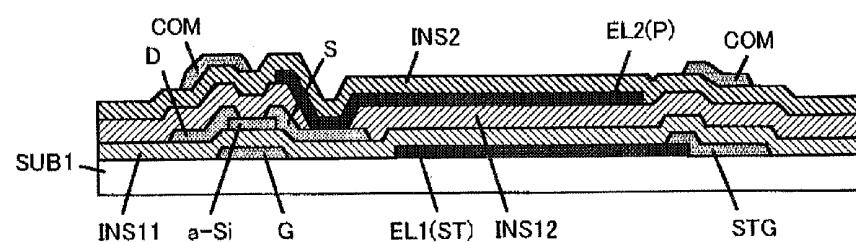

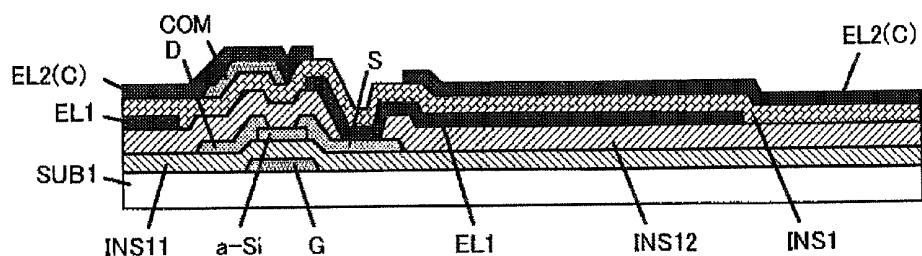

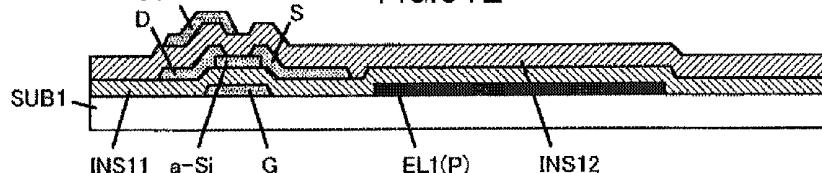

### Third Embodiment

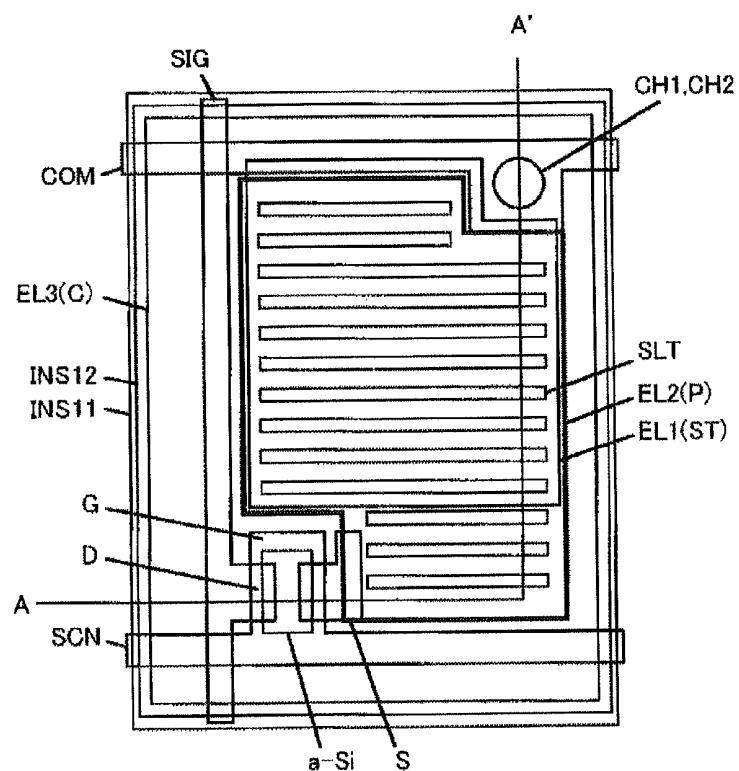

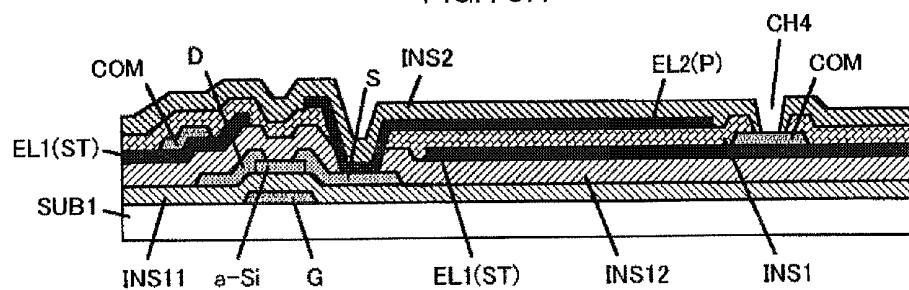

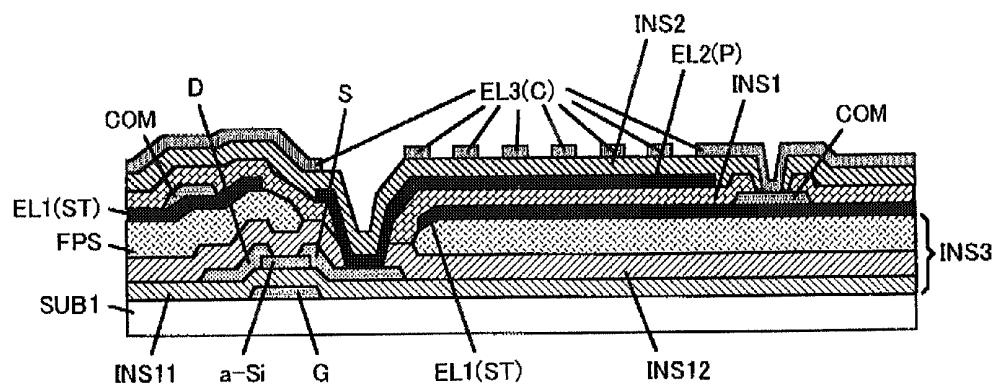

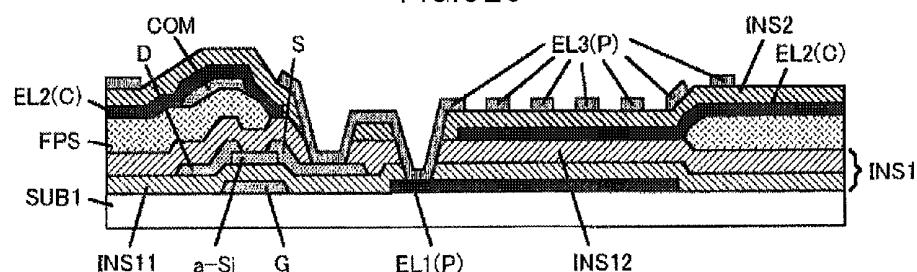

[0179] FIGS. 9A and 9B are schematic diagrams showing a pixel structure in a liquid crystal display device according to the third embodiment of the present invention. Shown in FIG. 9A is the sectional structure of a pixel, and shown in FIG. 9B is the plan view structure of the pixel on the TFT substrate side. The sectional structure of FIG. 9A corresponds to a view taken along the line A-A' shown in FIG. 9B.

[0180] The difference from the first embodiment is that the third embodiment uses the passivation film INS12 as the second insulating film INS2 by moving the transparent pixel electrode EL2 (P) to a place between the gate insulating film INS11 and the passivation film INS12 and constituting the first insulating film INS1 solely from the gate insulating film INS11.

[0181] Accordingly, this embodiment can reduce one insulating film and, in addition, can easily form a sufficiently large storage capacitor in a pixel having reduced pixel dimensions because the capacitance per unit area of the first insulating film INS1 which constitutes the first storage capacitor Cst1 is increased.

[0182] In the first embodiment, the source electrode S of the thin film transistor TFT and the transparent pixel electrode EL2 (P) are connected to each other through an opening formed in the passivation film INS12. In the third embodiment, the source electrode S and the transparent pixel electrode EL2 (P) are electrically connected each other by an overlapping portion between the two.

[0183] With the need to form the opening of the passivation film INS12 in the pixel region eliminated, the area that can be used to display increases and the aperture ratio is improved. An equivalent circuit that represents a single pixel in the third embodiment is the same as the one in the first embodiment which is shown in FIG. 3.

[0184] In FIG. 9B where only one insulating film is formed between the drain layer and the common electrode wiring line COM and between the drain layer and the transparent counter electrode EL3 (C), the parasitic capacitance between the signal line SIG and the common electrode wiring line COM tends to be larger than the parasitic capacitance of FIG. 2B. However, the structure of FIG. 9B has an advantage over the structure of FIG. 2B in that the number of TFT substrate manufacturing steps in the third embodiment is one step less than in the first embodiment as described below.

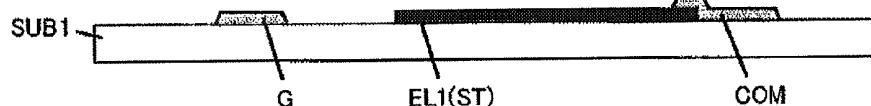

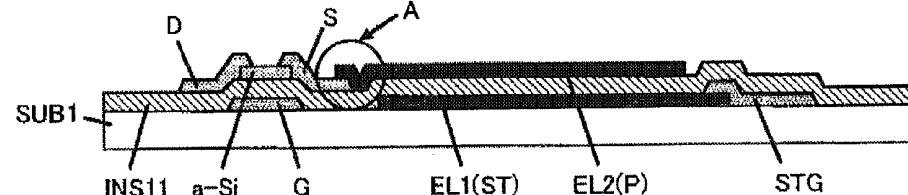

[0185] FIGS. 10A to 10G show steps of manufacturing the TFT substrate in the liquid crystal display device according to the third embodiment. FIGS. 10A to 10D are the same as FIGS. 4A to 4D described in the first embodiment.

[0186] In FIG. 10E, a film is formed from a transparent conductive material such as ITO and treated by a photolithography process to form the transparent pixel electrode EL2 (P). The transparent pixel electrode EL2 (P) and the source electrode S are electrically connected to each other by an overlapping portion between the two (the circled portion indicated by an arrow A). A region where the transparent storage capacitor electrode EL1 (ST) and the transparent pixel elec-

trode EL2 (P) overlap each other with the gate insulating film INS11 interposed between the electrodes serves as the first storage capacitor Cst1.

[0187] In FIG. 10F, the passivation film INS12 is formed from SiN, and the gate insulating film INS11 and the passivation film INS12 are treated by a photolithography process at once. By this photolithography process, a pixel portion is not patterned, whereas openings are opened in terminal portions and interlayer connection portions.

[0188] In FIG. 10G, a film is formed from a metal material and is treated by a photolithography process to form the common electrode wiring line COM.

[0189] Lastly, a film is formed from a transparent conductive material such as ITO to cover the common electrode wiring line COM, and is treated by a photolithography process to form the transparent counter electrode EL3 (C) as the one shown in FIG. 9A. The TFT substrate is thus manufactured by conducting a photolithography process eight times in total.

[0190] As in the first embodiment, the order in which the steps of FIGS. 10A and 10B are executed may be reversed as long as the transparent storage capacitor electrode EL1 (ST) and the common electrode wiring line COM are electrically connected to each other.

[0191] A third storage capacitor Cst3 may also be formed in a region where the transparent storage capacitor electrode EL1 (ST) and the source electrode S overlap each other with the gate insulating film INS11 interposed between the two by letting the transparent storage capacitor electrode EL1 (ST) slip in under the source electrode S. In this case, the third storage capacitor Cst3 constitutes an equivalent circuit as the one shown in FIG. 35A.

[0192] The connection portion between the transparent pixel electrode EL2 (P) and the source electrode S may also have a structure reverse to the one shown in FIG. 9A, and hence the source electrode S is laid on top of the transparent pixel electrode EL2 (P) (see a structure indicated by an arrow F shown in FIG. 9A), because the connection portion is merely required to establish an electric connection between the transparent pixel electrode EL2 (P) and the source electrode S. This structure can be formed by reversing the order in which the steps of FIG. 10D and FIG. 10E are executed.

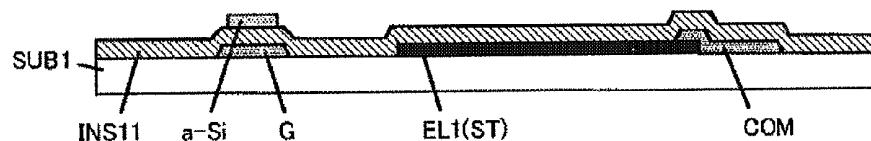

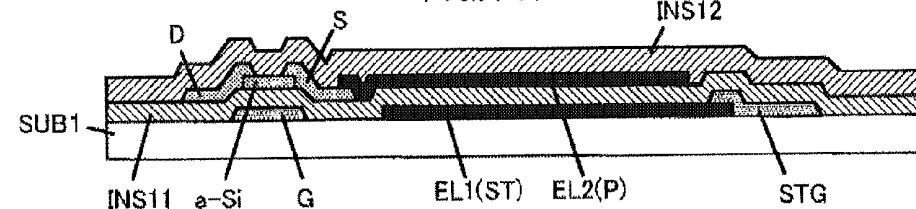

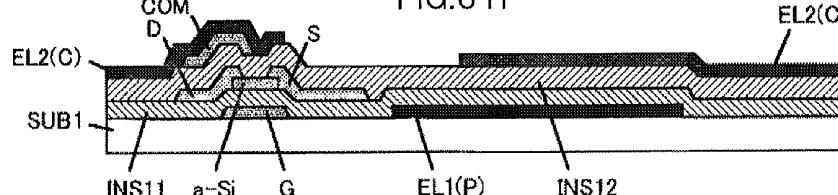

[0193] The sectional structures of the terminal portions and the interlayer connection portions that are formed by the manufacturing steps of the third embodiment are shown in FIGS. 11A to 11D. FIG. 11A shows terminal portions of the scanning line SCN and the storage capacitor wiring line STG which are formed in the gate layer. FIG. 11B shows a terminal portion of the signal line SIG which is formed in the drain layer. FIG. 11C shows a connection portion between the common electrode wiring line COM and the gate layer. FIG. 11D shows a connection portion between the common electrode wiring line COM and the drain layer.

[0194] The common electrode wiring line COM is formed as shown in the drawings in order to prevent the treatment of the common electrode wiring line COM from disturbing the gate layer and the drain layer.

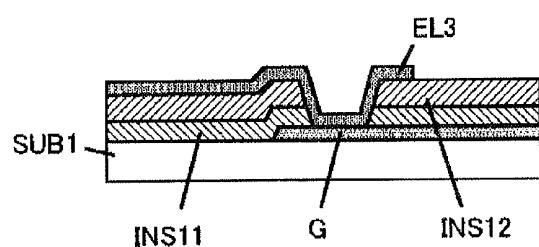

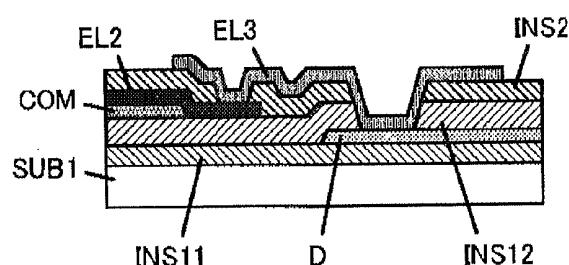

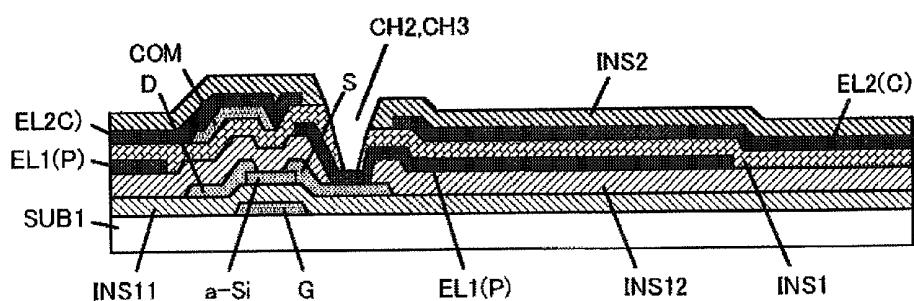

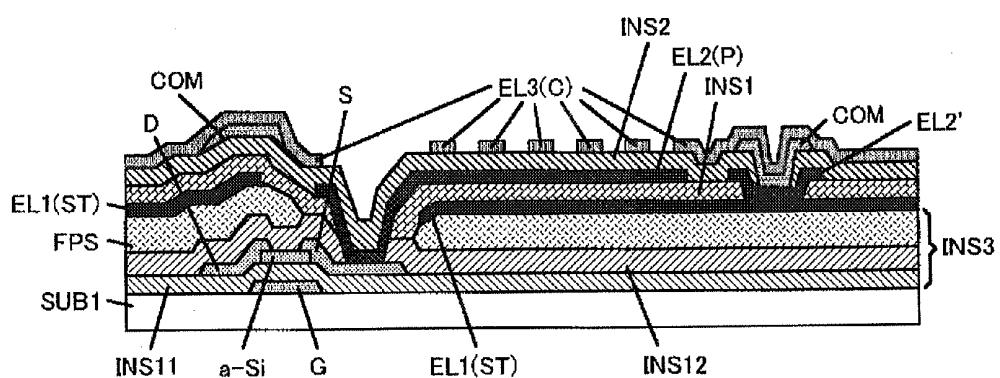

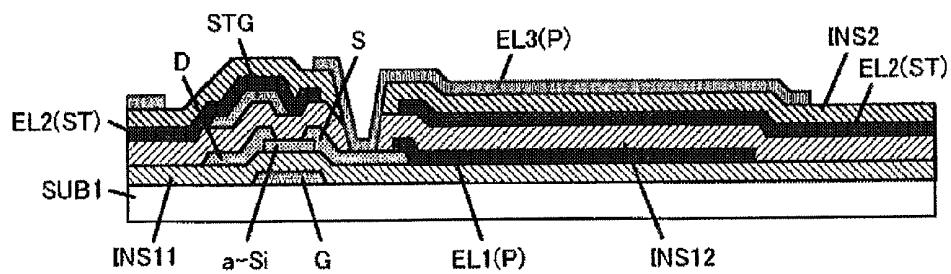

### Fourth Embodiment

[0195] FIGS. 12A and 12B are schematic diagrams showing a pixel structure in a liquid crystal display device according to the fourth embodiment of the present invention. Shown in FIG. 12A is the sectional structure of a pixel, and shown in FIG. 12B is the plan view structure of the pixel on the TFT

substrate side. The sectional structure of FIG. 12A corresponds to a view taken along the line A-A' shown in FIG. 12B. [0196] The difference from the third embodiment is that, instead of using the common electrode wiring line COM between the transparent counter electrode EL3 (C) and the passivation film INS12, the fourth embodiment makes the storage capacitor wiring line STG formed in the gate layer double as the common electrode wiring line COM as in the second embodiment.

[0197] The transparent counter electrode EL3 (C) in the fourth embodiment is reduced in resistance as in the third embodiment by forming openings (contact holes CH1 and CH2) in a portion of the gate insulating film INS11 and a portion of the passivation film INS12 that are located above the common electrode wiring line COM formed in the gate layer, and by connecting the transparent counter electrode EL3 (C) to the common electrode wiring line COM through the openings (CH1 and CH2).

[0198] An equivalent circuit per pixel in the fourth embodiment, where the storage capacitor wiring line STG doubles as the common electrode wiring line COM, is the same as the one described in the second embodiment with reference to FIG. 7.

[0199] In FIG. 12B, the openings (CH1 and CH2) are formed in the gate insulating film INS11 and the passivation film INS12 as a connection portion between the transparent counter electrode EL3 (C) and the common electrode wiring line COM. The transparent counter electrode EL3 (C) accordingly has a smaller region where the slit-like openings SLT are provided to apply an electric field to the liquid crystal layer LC, and the aperture ratio is lowered compared to FIG. 9B. However, the structure of FIG. 12B has an advantage over the structure of FIG. 9B in that the number of TFT substrate manufacturing steps in the fourth embodiment is even smaller (by one step) than in the third embodiment as described below.

[0200] FIGS. 13A to 13F show steps of manufacturing the TFT substrate in the liquid crystal display device according to the fourth embodiment. FIGS. 13A to 13E are the same as FIGS. 10A to 10E described in the third embodiment.

[0201] FIG. 13F is similar to FIG. 10F except that the openings (CH1 and CH2) are formed in a portion of the gate insulating film INS11 and a portion of the passivation film INS12 that are located above the common electrode wiring line COM, in addition to forming openings in terminal portions and interlayer connection portions, by treating the gate insulating film INS11 and the passivation film INS12 at once, thus exposing the surface of the common electrode wiring line COM formed in the gate layer.

[0202] Thereafter, a step corresponding to FIG. 10G is skipped, and a film is formed from a transparent conductive material such as ITO and treated by a photolithography process to form the transparent counter electrode EL3 (C) as the one shown in FIG. 12A. The transparent counter electrode EL3 (C) and the common electrode wiring line COM are electrically connected to each other through the openings (CH1 and CH2) in the gate insulating film INS11 and the passivation film INS12. The TFT substrate is thus manufactured by conducting a photolithography process seven times in total.

[0203] As in the third embodiment, the order in which the steps of FIGS. 13A and 13B are executed may be reversed as

long as the transparent storage capacitor electrode EL1 (ST) and the common electrode wiring line COM are electrically connected to each other.