US 20140184993A1

### (19) United States

# (12) Patent Application Publication SONG

(10) Pub. No.: US 2014/0184993 A1

(43) **Pub. Date:** Jul. 3, 2014

### (54) LIQUID CRYSTAL DISPLAY AND THIN FILM TRANSISTOR ARRAY PANEL THEREFOR

(71) Applicant: Samsung Display Co., Ltd.,

Yongin-City (KR)

(72) Inventor: **JANG-KUN SONG**, Seoul (KR)

(73) Assignee: SAMSUNG DISPLAY CO., LTD.,

Yongin-City (KR)

(21) Appl. No.: 14/197,781

(22) Filed: Mar. 5, 2014

### Related U.S. Application Data

(63) Continuation of application No. 13/655,651, filed on Oct. 19, 2012, now Pat. No. 8,698,990, Continuation of application No. 12/820,687, filed on Jun. 22, 2010, now Pat. No. 8,310,643, Continuation of application No. 11/845,438, filed on Aug. 27, 2007, Continuation of application No. 11/043,157, filed on Jan. 27, 2005, now Pat. No. 7,280,177, Continuation of application No. 10/602,710, filed on Jun. 25, 2003, now Pat. No. 6,850,302.

### (30) Foreign Application Priority Data

Jun. 28, 2002 (KR) ...... 10-2002-0036979

#### **Publication Classification**

(51) Int. Cl.

**G02F 1/1343** (2006.01)

(52) U.S. Cl.

### (57) ABSTRACT

A liquid crystal display (LCD) is provided, which includes: first and second gate lines, a data line intersecting the gate lines, first to fourth drain electrodes located near the intersections between the first and second gate lines and the data line, and a coupling electrode. First to fourth pixel electrodes respectively connected to the first to fourth drain electrodes are also provided, and the first pixel electrode is connected to the coupling electrode while the fourth pixel electrode overlaps the coupling electrode. The LCD further includes a common electrode opposite the pixel electrodes, a liquid crystal layer interposed between the pixel electrodes and the common electrode, and a domain partitioning member formed on at least one of the pixel electrode and the common electrode. Two long edges of the domains are angled with respect to the first and the second gate lines or the data line substantially by about 45°.

FIG.1

FIG.2 ШC'← -171 271 -91 272-171 --190a Polarization axes 93 MB' -273 V 131 177 -190b -274 -187 175b 154 IIIC <del>-1</del>85b 173 121 175a 181 <del>-1</del>85a

FIG.3A

FIG.3B

FIG.3C

FIG.4

## FIG.5(PRIOR ART)

FIG.6

## FIG.7(PRIOR ART)

FIG.8

## LIQUID CRYSTAL DISPLAY AND THIN FILM TRANSISTOR ARRAY PANEL THEREFOR

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. patent application Ser. No. 13/655,651, filed Oct. 19, 2012, which is a continuation of U.S. patent application Ser. No. 12/820,687, filed Jun. 22, 2010, issued as U.S. Pat. No. 8,310,643 on Nov. 13, 2012, which is a continuation of U.S. patent application Ser. No. 11/845,438, filed Aug. 27, 2007, which is a continuation of U.S. patent application Ser. No. 11/043,157, filed Jan. 27, 2005, issued as U.S. Pat. No. 7,280,177 on Oct. 9, 2007, which is a continuation of U.S. patent application Ser. No. 10/602,710, filed on Jun. 25, 2003, issued as U.S. Pat. No. 6,850,302 on Feb. 1, 2005, which claims priority to Korean Patent Application No. 10-2002-0036979, filed Jun. 28, 2002. The disclosures of the above-cited applications are incorporated by reference herein in their entireties.

### BACKGROUND OF THE INVENTION

[0002] (a) Field of the Invention

[0003] The present invention relates to a liquid crystal display, and in particular, to a panel for the liquid crystal display.

[0004] (b) Description of Related Art

[0005] Generally, a liquid crystal display (LCD) includes a liquid crystal (LC) panel assembly including two panels provided with two kinds of field generating electrodes such as pixel electrodes and a common electrode and a LC layer with dielectric anisotropy interposed therebetween. The variation of the voltage difference between the field generating electrodes, i.e., the variation in the strength of an electric field generated by the electrodes changes the transmittance of the light passing through the LCD, and thus desired images are obtained by controlling the voltage difference between the electrodes.

[0006] However, the LCD involves a critical shortcoming of the narrow viewing angle. In order to overcome such a problem, various techniques for widen the viewing angle have been developed, and among them, a technique of forming cutouts or protrusions at the pixel electrodes and the common electrode while aligning the LC molecules vertical to the upper and lower panels is the strongest candidate for the wide viewing angle technique.

[0007] The cutouts provided at the respective pixel electrodes and the common electrode generate fringe fields, which control the tilt directions of the LC molecules are controlled to thereby widen the viewing angle.

[0008] The protrusions provided on the respective pixel electrodes and the common electrode deform the electric field, and the tilt directions of the LC molecules are controlled due to the deformed electric field to thereby widen the viewing angle.

[0009] Alternatively, the cutouts are provided at the pixel electrodes of a lower panel while protrusions are provided at the common electrode of an upper panel. Fringe fields generated by the cutouts and the protrusions controls the tilt directions of the LC molecules to thereby form multiple domains.

[0010] The multi-domain LCD involves a very excellent contrast-based viewing angle or gray inversion-based viewing angle of up to  $80^\circ$  or more in all directions. The contrast-based viewing angle is defined as a viewing angle showing the

contrast ratio of 1:10, and the gray inversion-based viewing angle is defined by the limit angle of the inter-gray luminance inversion. However, the multi-domain LCD shows a lateral gamma curve distortion that the front gamma curve and the lateral gamma curve do not agree to each other is made to exhibit deteriorated left and right visibility even compared with the twisted nematic (TN) mode LCD. For instance, the patterned vertically aligned (PVA) mode LCD having cutouts for partitioning domains becomes brighter and color-shifts to white as it goes to the lateral sides. In a serious case, the difference between the bright grays is eradicated, and hence, the images become conglomerated. However, it becomes a critical matter to improve the visibility more and more as the LCD has been recently used for the multimedia purpose to display still or moving picture images.

### SUMMARY OF THE INVENTION

[0011] A liquid crystal display is provided, which includes: a first insulating substrate; first and second signal lines formed on the first insulating substrate; a third signal line formed on the first insulating substrate and crossing the first and the second signal lines; a first thin film transistor connected to the first and the third signal lines; a second thin film transistor connected to the second and the third signal lines; a first pixel electrode connected to the first thin film transistor; a second pixel electrode connected to the second thin film transistor; a second insulating substrate facing the first insulating substrate; a common electrode formed on the second insulating substrate; a liquid crystal layer interposed between the first and the second insulating substrates and including a first liquid crystal region on the first pixel electrode and a second liquid crystal region on the second pixel electrode; and a domain partitioning member formed on at least one of the first and the second insulating substrates for partitioning the first and the second liquid crystal regions into a plurality of domains, respectively, wherein the domains of each of the first and the second liquid crystal regions includes a first directional domain and a second directional domain, the average directors of liquid crystal molecules in the first and the second directional domains are angled with respect to the first or the second signal line by a predetermined degree of about 0-90°, and the first pixel electrode and the second pixel electrode are capacitively coupled.

[0012] It is preferable that the first pixel electrode occupies about 50-80% of an entire area of the first and the second pixel electrodes, and the second thin film transistor is activated after the first thin film transistor is activated.

[0013] The threshold voltage of the first pixel electrode is preferably lower than the threshold voltage of the second pixel electrode by about 0.4-1.0V.

[0014] The liquid crystal display may further includes a storage electrode line formed on the first substrate and forming storage capacitors along with the first and the second pixel electrodes.

[0015] The average director of the liquid crystal molecules in the fist and the second directional domains are preferably angled with respect to the first or the second signal line by about  $45^{\circ}$ .

[0016] Preferably, the liquid crystal display further includes a first polarizer placed on an outer surface of the first substrate and having a polarizing axis parallel to the first or the second signal line, and a second polarizer placed on an outer surface of the second substrate and having a polarizing axis crossing the polarizing axis of the first polarizing plate.

[0017] A thin film transistor array panel is provided, which includes: an insulating substrate; first and second gate lines formed on the substrate; a gate insulating layer formed on the first and the second gate lines; a semiconductor layer formed on the gate insulating layer; a data line formed at least on the semiconductor layer and intersecting the gate lines; first and second drain electrodes formed at least on the semiconductor layer and located near the intersection between the first gate line and the data line; third and fourth drain electrodes formed at least on the semiconductor layer and located near the intersection between the second gate line and the data line; a coupling electrode formed on the gate insulating layer; a passivation layer formed on the data line, the first to the fourth drain electrodes, and the coupling electrode and having a plurality of contact holes exposing the first to the fourth drain electrodes and the coupling electrode; a first pixel electrode formed on the passivation layer and connected to the first drain electrode and the coupling electrode; a second pixel electrode formed on the passivation layer and connected to the second drain electrode; a third pixel electrode formed on the passivation layer and connected to the third drain electrode; and a fourth pixel electrode formed on the passivation layer and connected to the fourth drain electrode and partially overlapping the coupling electrode, wherein at least one of the first and the fourth pixel electrodes has an oblique cutout.

[0018] A liquid crystal display is provided, which includes: a first insulating substrate; first and second gate lines formed on the first substrate; a gate insulating layer formed on the first and the second gate lines; a semiconductor layer formed on the gate insulating layer; a data line formed at least on the semiconductor layer and intersecting the gate lines; first and second drain electrodes formed at least on the semiconductor layer and located near the intersection between the first gate line and the data line; third and fourth drain electrodes formed at least on the semiconductor layer and located near the intersection between the second gate line and the data line; a coupling electrode formed on the gate insulating layer; a passivation layer formed on the data line, the first to the fourth drain electrodes, and the coupling electrode and having a plurality of contact holes exposing the first to the fourth drain electrodes and the coupling electrode; a first pixel electrode formed on the passivation layer and connected to the first drain electrode and the coupling electrode; a second pixel electrode formed on the passivation layer and connected to the second drain electrode; a third pixel electrode formed on the passivation layer and connected to the third drain electrode; a fourth pixel electrode formed on the passivation layer and connected to the fourth drain electrode and partially overlapping the coupling electrode; a second insulating substrate facing the first insulating substrate; a common electrode formed on the second insulating substrate; a liquid crystal layer interposed between the first and the second insulating substrates; and a domain partitioning member formed on at least one of the first and the second insulating substrates and partitioning the liquid crystal layer into a plurality of domains, wherein two long edges of the domains are angled with respect to the gate line or the data line substantially by about 45°.

[0019] Preferably, the first pixel electrode occupies about 50-80% of an entire area of the first and the fourth pixel electrodes and the fourth pixel electrode is supplied with a voltage after the first pixel electrode is supplied with a voltage.

The threshold voltage of the first pixel electrode is preferably lower than the threshold voltage of the fourth pixel electrode by about 0.4-1.0V.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0020] The above and other advantages of the present invention will become more apparent by describing preferred embodiments thereof in detail with reference to the accompanying drawings in which:

[0021] FIG. 1 is a circuit diagram of an LCD according to an embodiment of the present invention;

[0022] FIG. 2 is a layout view of an LCD according to an embodiment of the present invention;

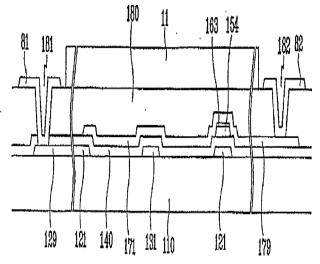

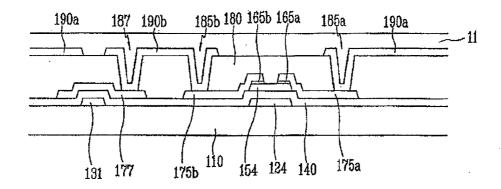

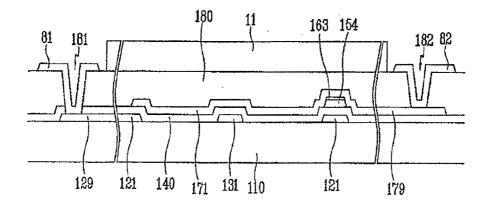

[0023] FIG. 3A is a sectional view of the LC panel assembly shown in FIG. 2 taken along the line IIIB-IIIB';

[0024] FIG. 3B is a sectional view of a TFT array panel shown in FIG. 3A, which is a portion of the LC panel assembly shown in FIG. 3A except for a color filter array panel and polarization films;

[0025] FIG. 3C is a sectional view of a TFT array panel shown in FIG. 2 taken along the line IIIC-IIIC';

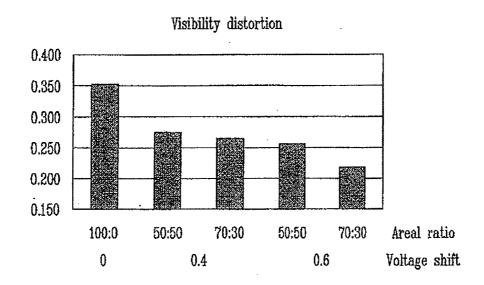

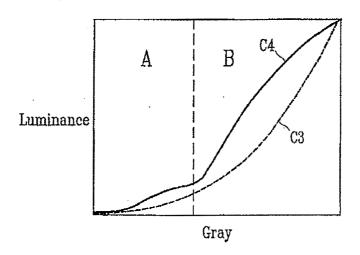

[0026] FIG. 4 is a graph illustrating the distortion in the visibility as a function of the voltage shift and the domain ratio;

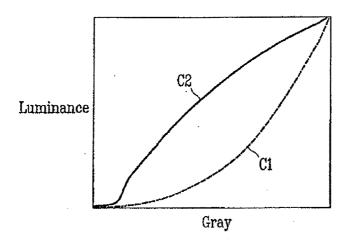

[0027] FIG. 5 is a graph illustrating gamma curves for a front view and a lateral view of a conventional patterned-vertically-aligned (PVA) LCD;

[0028] FIG. 6 is a graph illustrating gamma curves for a front view and a lateral view of an LCD according to an embodiment of the present invention;

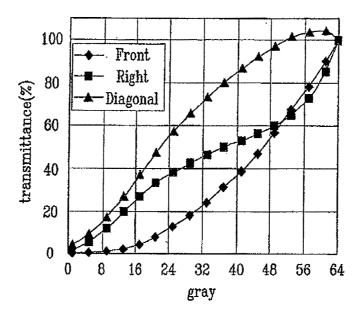

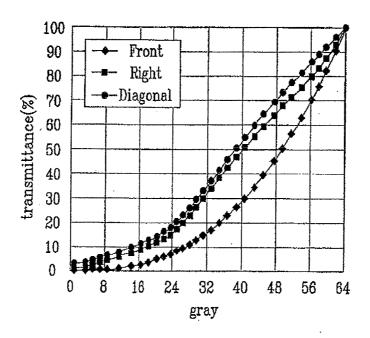

[0029] FIG. 7 illustrates measured gamma curves of a conventional PVA mode LCD; and

[0030] FIG. 8 illustrates measured gamma curves of an LCD according to an embodiment of the present invention.

## DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

[0031] The present invention now will be described more fully hereinafter with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The present invention may, however, be embodied in many different forms and should not be construed as limited to the embodiments set forth herein.

[0032] In the drawings, the thickness of layers, films and regions are exaggerated for clarity. Like numerals refer to like elements throughout. It will be understood that when an element such as a layer, film, region or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present. In contrast, when an element is referred to as being "directly on" another element, there are no intervening elements present.

[0033] Now, LCDs according to embodiments of this invention will be described in detail with reference to the accompanying drawings.

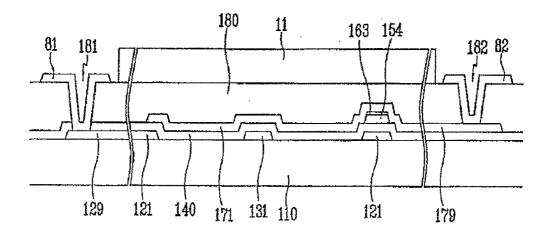

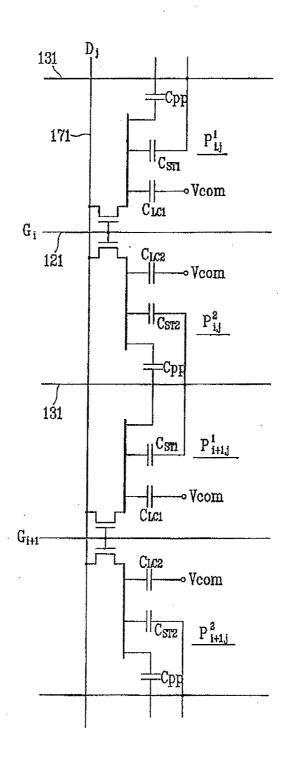

[0034] FIG. 1 is an equivalent circuit diagram of a pixel of an LCD according to an embodiment of the present invention. [0035] Referring to FIG. 1, an LCD according to an embodiment includes a plurality of display signal lines  $G_i$ ,  $D_j$  and 131 and a plurality of pixels connected thereto and arranged substantially in a matrix.

[0036] The display signal lines  $G_i$  and  $D_j$  include a plurality of gate lines  $G_i$  transmitting gate signals (called scanning signals) and a plurality of data lines  $D_i$  transmitting data

signals. The gate lines  $G_i$  extend substantially in a row direction and are substantially parallel to each other, and the data lines  $D_j$  extend substantially in a column direction and are substantially parallel to each other.

[0037] The display signal lines 131 further includes a plurality of storage electrode lines 131 located between the gate lines  $G_i$  and between the pixels and supplied with a common voltage Vcom.

**[0038]** Each pixel  $P_{ij}(i=1, 2, \ldots, n \text{ and } j=1, 2, \ldots, m)$  includes a pair of subpixels  $P_{ij}^{-1}$  and  $P_{i,j}^{-2}$ , and each subpixel  $P_{i,j}^{-1}$  or  $P_{i,j}^{-2}$  includes a switching element Q1 or Q2 connected to a pair of one of the gate lines  $G_i$  and one of the data lines  $D_j$ , and an LC capacitor  $C_{LC1}$  or  $C_{LC2}$  and a storage capacitor  $C_{ST1}$  or  $C_{ST2}$  that are connected to the switching element Q1 or Q2.

**[0039]** Two adjacent pixels in the column direction are capacitively coupled by a coupling capacitor Cpp. For example, an upper subpixel  $P_{i,j}^{\ 1}$  of a pixel  $P_{ij}$  is capacitively coupled with a lower subpixel  $P_{i,j}^{\ 2}$  of an upper pixel  $P_{i-1,j}$ , and a lower subpixel  $P_{i,j}^{\ 2}$  of a pixel  $P_{ij}$  is capacitively coupled with an upper subpixel  $P_{i+1,j}^{\ 1}$  of a lower pixel  $P_{i+1,j}$ .

**[0040]** The switching element Q1 or Q2 has three terminals: a control terminal connected to one of the gate lines  $G_1$ - $G_n$ ; an input terminal connected to one of the data lines  $D_0$ - $D_m$ ; and an output terminal connected to the LC capacitor  $C_{LC1}$  or  $C_{LC2}$ , the storage capacitor  $C_{ST1}$  or  $C_{ST2}$ , and the coupling capacitor Cpp.

**[0041]** The LC capacitor  $C_{LC1}$  or  $C_{LC2}$  is connected between the switching element Q1 or Q2 and a common voltage Vcom. The storage capacitor  $C_{ST1}$  or  $C_{ST2}$  is connected between the switching element Q1 or Q2 and the storage electrode line **131**.

[0042] Now, an LC panel assembly for an LCD according to an embodiment of the present invention is described in detail with reference to FIGS. 2 to 3C.

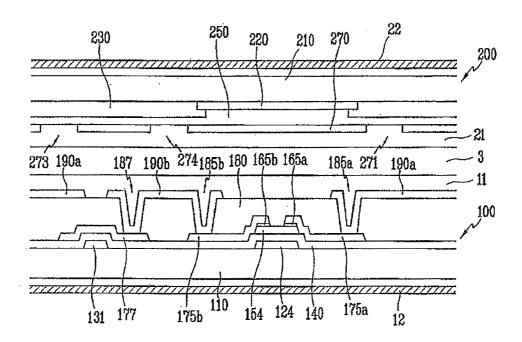

[0043] FIG. 2 is a layout view of an LC panel assembly according to an embodiment of the present invention, FIG. 3A is a sectional view of the LC panel assembly shown in FIG. 2 taken along the line IIIB-IIIB', and FIG. 3B is a sectional view of a TFT array panel shown in FIG. 3A, which is a portion of the LC panel assembly shown in FIG. 3A except for a color filter array panel and polarization films. FIG. 3C is a sectional view of a TFT array panel shown in FIG. 2 taken along the line IIIC-IIIC'.

[0044] Referring to FIG. 3A, an LC panel assembly according to this embodiment includes a TFT array panel 100, a color filter array panel 200 facing the TFT array panel 100, and an LC layer 3 interposed therebetween.

[0045] Referring to FIGS. 2 to 3C, the TFT array panel 100 includes a plurality of gate lines 121 and a plurality of storage electrode lines 131 formed on an insulating substrate 110 preferable made of transparent glass. Each gate line 121 extends substantially in a row direction and includes a plurality of gate electrodes 124. The storage electrode lines 131 extend substantially in the row direction and are partially curved.

[0046] A gate insulating layer 140 is formed on the gate lines 121 and the storage electrode lines 131, and a plurality of semiconductor islands 154 is formed on the gate insulating layer 140 opposite the gate electrodes 124. Each semiconductor island 154 is preferably made of amorphous silicon ("a-Si") and forms a channel of a TFT. A plurality of ohmic contacts 163, 165a and 165b preferably made of a-Si heavily

doped with N type impurity such as phosphorous (P) are formed on the semiconductor islands 154.

[0047] A plurality of data lines 171, a plurality of pairs of drain electrodes 175*a* and 175*b*, and a plurality of coupling electrodes 177 are formed on the ohmic contacts 163, 165*a* and 165*b* and the gate insulating layer 140.

[0048] Each data line 171 extends substantially in a column direction and includes a plurality of source electrodes 173, and each source electrode 173 is located opposite a pair of drain electrodes 175a and 175b separated therefrom with respect to the gate electrode 124.

[0049] Each pair of drain electrodes 175a and 175b extends opposite directions with respect to the gate line 124.

[0050] Each coupling electrode 177 extends in the column direction across the storage electrode line 131.

[0051] The portions of the semiconductor islands 154 located between the source electrode 173 and the drain electrodes 175a and 175b are exposed, and the ohmic contacts 163, 165a and 165b are disposed only between the semiconductor islands 154 and the data lines 171 and the drain electrodes 175a and 175b.

[0052] A passivation layer 180 is formed on the data lines 171, the drain electrodes 175a and 175b, and the coupling electrodes 177. The passivation layer 180 has a plurality of contact holes 185a and 185b exposing end portions of the drain electrodes 175a and 175b and a plurality of contact holes 187 exposing end portions of the coupling electrodes 177. The passivation layer 180 further has a plurality of contact holes 182 exposing end portions 179 of the data lines 171, and the passivation layer 180 and the gate insulating layer 140 have a plurality of contact holes 181 exposing end portions 129 of the gate lines 121.

[0053] A plurality of pairs of pixel electrodes 190a and 190b and a plurality of contact assistants 81 and 92 are formed on the passivation layer 180. The pixel electrodes 190a and 190b and the contact assistants 81 and 92 are preferably made of a transparent conductive material such as indium-tin-oxide (ITO) and indium-zinc-oxide (IZO) or a reflective material.

[0054] Each pair of pixel electrodes 190a and 190b includes a lower pixel electrode 190a and an upper pixel electrode 190b connected to the drain electrodes 175a and 175b through the contact holes 185a and 185b, respectively. The upper electrode 190b is connected to the coupling electrode 177 through the contact hole 187 and the lower electrode 190a overlaps the coupling electrode 177 such that the lower pixel electrode 190a of an upper pixel and the upper pixel electrode 190b of a lower pixel are capacitively coupled. In addition, the lower pixel electrode 190a of an upper pixel and the upper pixel electrode 190b of a lower pixel are located opposite across the storage electrodes line 131 and overlap the storage electrode line 131 to form a plurality of storage capacitors. The edges of the pixel electrodes 190a and 190b opposite across the storage electrode line 131 are curved to form V shapes, and the V-shaped edge of the pixel electrode 190a is convex, while that of the pixel electrode 190b is concave.

[0055] Each lower pixel electrode 190a has upper, lower and central linear cutouts 91-93. The central cutout 93 is located at the middle portion in the column direction and enters into the pixel electrode 190a from the left to the right, thereby partitioning the pixel electrode 190a into upper and lower partitions. The upper and the lower cutouts 91 and 92

obliquely extend in the upper and the lower partitions, respectively, and are located symmetrically with respect to the central cutout 93.

[0056] The contact assistants 81 and 82 are connected to the exposed end portions 129 and 179 of the gate lines 121 and the data lines 171 through the contact holes 181 and 182, respectively, and provided for protecting the exposed end portions 129 and 179 but is optional.

[0057] An alignment layer 11 is coated on the entire surface of the TFT array panel 100 except for the contact assistants 81 and 82.

[0058] One gate electrode 124, one source electrode 173, and a pair of drain electrodes 175*a* and 175*b* along with one semiconductor island 154 form a pair of TFTs respectively connected to the pixel electrodes 190*a* and 190*b*.

[0059] Referring to FIGS. 2 and 3B, the color filter array panel 200 includes a black matrix 220 formed on an insulating substrate 210 preferably made of transparent glass. The black matrix 220 defines a plurality of windows where a plurality of red, green and blue color filters 230 are formed. An overcoat is formed on the color filters and a common electrode 270 is formed thereon. The common electrode 270 is preferably made of a transparent conductive material such as ITO and IZO, and has a plurality of sets of four linear cutouts 271-274. Three 271-273 of the cutouts 271-274 overlap the lower pixel electrode 190a to partition the pixel electrode 190a along with the cutouts 91-93 into a plurality of subareas. The cutout 274 having a V shape overlap the upper electrode 190b to bisect the upper pixel electrode 190b into two subareas. An alignment layer 21 is coated on the entire surface of the color filter array panel 200.

[0060] Each subarea defined by the cutouts 91-93 and 271-273 has substantially a shape of a tetragon having two major edges making an angle of about 45 degrees with the gate lines 121 and the data lines 171. The subareas defined by edges of the upper pixel electrode 190b and the cutout 274 have V shapes, which are combinations of two tetragons.

[0061] A pair of polarizers 12 and 22 are attached to outer surfaces of the panels 100 and 200, respectively. The polarization, axes of the polarizers 12 and 22 are crossed and substantially parallel to the gate lines 121 or the data lines 171.

[0062] The molecules of the LC layer 3 are aligned such that their major axes are substantially perpendicular to the surfaces of the panels 100 and 200 in absence of electric field.

[0063] Referring back to FIG. 1, the difference between the data voltage and the common voltage Vcom applied to a pixel is expressed as a charged voltage of the LC capacitor  $C_{LC1}$  or  $C_{LC2}$ , i.e., a pixel voltage. The LC molecules have orientations depending on the magnitude of the pixel voltage and the orientations determine the polarization of light passing through the LC capacitor  $C_{LC1}$  or  $C_{LC2}$ . The polarizers 11 and 21 convert the light polarization into the light transmittance.

[0064] In the meantime, it is assumed that the difference between a data voltage for a pixel Pup and the common voltage Vcom is  $d_{up}$ , and pixel voltages charged in LC capacitors  $C_{LC1}$  and  $C_{LC2}$  of the upper and the lower subpixels  $P_{up}^{-1}$  and  $P_{up}^{-2}$  of the pixel Pup are V  $(P_{up}^{-1})$  and V  $(P_{up}^{-2})$ , respectively. In addition, let us assume that the lower subpixel  $P_{up}^{-2}$  of the pixel Pup and the upper subpixel  $P_{down}^{-1}$  of the pixel Pdown are coupled with a coupling capacitor Cpp, and the difference between the data voltage for the pixel Pdown and the common voltage Vcom is  $d_{down}$ . Furthermore, after the

pixel Pup is supplied with the data voltage, the pixel Pdown is supplied with the data voltage. Then, the following relations are satisfied:

$$V(P_{up}^1) = d_{up}$$

; and (1)

$$V(P_{up}^2) = d_{up} + \frac{Cpp}{C_{LC2} + C_{ST2} + Cpp} \cdot (d_{down} - d'_{down}). \tag{2}$$

[0065] In Equations 1 and 2,  $C_{LC2}$  and  $C_{ST2}$  are the capacitances of the LC capacitor and the storage capacitor of the lower subpixel  $P_{up}^{\ \ 2}$ , Cpp is the capacitance of the coupling capacitor, and  $d'_{down}$  is the difference between the data voltage applied to subpixel  $P_{down}^{\ \ 1}$  in a previous frame and the common voltage Vcom. For descriptive convenience, the wire resistance and the signal delay of the data lines  $D_j$  are ignored.

**[0066]** In Equation 2, if  $d_{down}$  and  $d'_{down}$  have opposite polarity since  $d_{up}$  and  $d_{down}$  have the same polarity, the pixel Pdown displays the same gray as the pixel Pup, and the displayed images are still images,  $d_{up} = d_{down} = -d_{down}$  and thus Equation 2 becomes:

$$\begin{split} V(P_{up}^2) = & (3) \\ d_{up} + \frac{2d_{up}\,Cpp}{C_{LC2} + C_{ST2} + Cpp} = \frac{C_{LC2} + C_{ST2} + 3Cpp}{C_{LC2} + C_{ST2} + Cpp} d_{up} = T_1 d_{up}, \\ & \text{where } T1 = \frac{C_{LC2} + C_{ST2} + Cpp}{C_{LC2} + C_{ST2} + Cpp} > 1. \end{split}$$

[0067] On the contrary, if  $d_{up}$  and  $d_{down}$  have opposite polarities, the pixel Pdown displays the same gray as the pixel Pup, and the displayed images are still images, Equation 2 becomes:

$$V(P_{up}^{2}) =$$

$$d_{up} - \frac{2d_{up} Cpp}{C_{LC2} + C_{ST2} + Cpp} = \frac{C_{LC2} + C_{ST2} - Cpp}{C_{LC2} + C_{ST2} + Cpp} d_{up} = T_{2}d_{up},$$

$$\text{where } T_{2} = \frac{C_{LC2} + C_{ST2} - Cpp}{C_{LC2} + C_{ST2} + Cpp} < 1.$$

[0068] According to Equations 3 and 4, if a lower subpixel  $P_{up}^{-2}$  of a pixel Pup is capacitively coupled with a upper subpixel  $P_{down}^{-1}$  of a pixel Pdown, the lower subpixel  $P_{up}^{-2}$  of the pixel Pup is charged with a voltage higher than that charged in the upper subpixel  $P_{up}^{-1}$  of the pixel Pup when the polarity of the data voltages applied to the two subpixels  $P_{up}^{-2}$  and  $P_{down}^{-1}$  is the same, and vice versa when the polarity is opposite.

[0069] This pixel structure that a pixel includes two switching elements and two LC capacitors and adjacent pixels are capacitively coupled by a coupling capacitor prevents gray inversion at a bottom view and improves visibility at all directions.

[0070] FIG. 4 is a graph illustrating the distortion in the visibility as function of the voltage shift and the areal ratio of the pixel electrodes.

[0071] The vertical axis shown in FIG. 4 indicates the value of quantifying the distortion in the visibility, and the horizon-

tal axis indicates the areal ratio between lower and upper pixel electrodes 190a and 190b for the voltage shifts 0, 0.4V and 0.6V.

[0072] The visibility distortion in a range of 0.1-0.2 means that the visibility is exceptionally excellent, which is equal to the level of the cathode ray tube (CRT), and the visibility distortion in a range of 0.2-0.25 means that the visibility is very excellent. The visibility distortion in a range of 0.25-0.3 means that the visibility is excellent, and the visibility distortion in a range of 0.3-0.35 means that the visibility is good. However, the visibility distortion less than about 0.35 means that the visibility is bad, which results in the poor display quality.

[0073] It is known from FIG. 4 that an excellent visibility is obtained when the areal ratio of the lower pixel electrode to the upper pixel electrode is in a range of 50:50-80:20, and when the voltage shift is in a range of 0.4-1.0V close to a threshold voltage Vth. That is, the lower pixel electrode is preferably designed to be larger than the upper pixel electrode. However, when the lower pixel electrode is equal to or larger than 80%, various problems such as a flicker phenomenon may be made due to the kick-back voltage or other factors. Furthermore, when the threshold voltage Vth of the lower pixel electrode is lower than the threshold voltage Vth of the upper pixel electrode by 0.4-1.0V, the visibility is improved. The voltage difference between the lower and the upper pixel electrodes for the higher grays may be greater.

[0074] Then, the reason why the visibility is improved with the LCD according to the present invention will be now described with reference to FIGS. 5 and 6.

[0075] FIG. 5 is a graph illustrating gamma curves C1 and C2 respectively for a front view and a lateral view of a conventional patterned-vertically-aligned (PVA) LCD, and FIG. 6 is a graph illustrating gamma curves C3 and C4 respectively for a front view and a lateral view of an LCD according to an embodiment of the present invention.

[0076] As shown in FIG. 5, the lateral gamma curve C2 of a conventional PVA LCD having one pixel electrode for a pixel is largely deformed upward compared with the front gamma curve C1.

[0077] However, according to an embodiment of the present invention, when the data voltage is established such that the pixel voltage applied to the lower subpixel is lower than the usual data voltage, the voltage of the lower subpixel may be kept to be lower than a threshold voltage Vth for some lower grays. Accordingly, the lower subpixel is kept to be in a black state, while the upper subpixel exhibits a transmitting state as indicated by reference character A in FIG. 6. However, since the area of the upper pixel electrode is small, the total luminance is small than that of a conventional LCD. For the gray equal to or larger than a predetermined value (indicated by reference character B), the voltage of the lower subpixel exceeds the threshold voltage Vth, and hence, the lower subpixel also contributes to the total luminance. There-

fore, the increase of the luminance depending on the gray increase is enlarged. Accordingly, as shown in FIG. 6, the distortion in the gamma curve becomes decreased.

[0078] FIG. 7 illustrates measured gamma curves of a conventional PVA mode LCD, and FIG. 8 illustrates measured gamma curves of an LCD according to an embodiment of the present invention.

[0079] Comparing the gamma curves illustrated in FIGS. 7 and 8, it can be known that the gamma curve distortion for all directions of the LCD according to the embodiment of the present invention be smaller than that of the conventional LCD for all directions.

[0080] As described above, two pixel electrodes and two TFTs are assigned to one pixel, and the two pixel electrodes of adjacent two pixels are capacitively coupled, thereby improving the visibility in all directions. Furthermore, as the domain partitioning is made such that the average director of the liquid crystal molecules is angled with respect to the gate line or the data line by 45°, polarizers having polarizing axes parallel to the gate line or the data line can be used. Consequently, the production cost for the polarizing plate can be reduced.

[0081] Although preferred embodiments of the present invention have been described in detail hereinabove, it should be clearly understood that many variations and/or modifications of the basic inventive concepts herein taught which may appear to those skilled in the present art will still fall within the spirit and scope of the present invention, as defined in the appended claims.

What is claimed:

- 1. A liquid crystal display, comprising:

- a first substrate comprising:

- a pixel electrode comprising a first subpixel electrode and a second subpixel electrode, the first and the second subpixel electrodes being located at a same layer; and

- a first polarizer having a first polarizing axis;

- a second substrate facing the first substrate, and comprising a second polarizer having a second polarizing axis crossing the first polarizing axis; and

- a liquid crystal layer interposed between the first substrate and the second substrate,

- wherein the liquid crystal layer on each of the first subpixel electrode and the second subpixel electrode is divided into a plurality of domains, at least one of the plurality of domains being defined by a direction of liquid crystal molecules when an electric field is applied, and a value of an electric field on the second subpixel electrode is weaker than a value of an electric field on the first subpixel electrode, and

- wherein the directions of the liquid crystal molecules of the domains are angled with respect to the first and the second polarizing axes in a plan view.

\* \* \* \* \*

| 专利名称(译)        | 液晶显示器及其薄膜晶体管阵列面板                                                                                                                                                                                          |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | US20140184993A1                                                                                                                                                                                           | 公开(公告)日 | 2014-07-03 |

| 申请号            | US14/197781                                                                                                                                                                                               | 申请日     | 2014-03-05 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 三星DISPLAY CO., LTD.                                                                                                                                                                                       |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO., LTD.                                                                                                                                                                                       |         |            |

| [标]发明人         | SONG JANG KUN                                                                                                                                                                                             |         |            |

| 发明人            | SONG, JANG-KUN                                                                                                                                                                                            |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/1333 G02F1/1362                                                                                                                                                               |         |            |

| CPC分类号         | G02F1/13439 G02F1/133707 G02F1/136213 G02F1/13624 G02F2001/134318 G02F1/133345 G02F1 /133514 G02F1/133528 G02F1/134309 G02F1/136286 G02F1/1368 G02F2001/133531 G02F2001 /134345 G02F2201/121 G02F2201/123 |         |            |

| 优先权            | 1020020036979 2002-06-28 KR                                                                                                                                                                               |         |            |

| 其他公开文献         | US9477121                                                                                                                                                                                                 |         |            |

| 外部链接           | Espacenet USPTO                                                                                                                                                                                           |         |            |

|                |                                                                                                                                                                                                           |         |            |

### 摘要(译)

提供一种液晶显示器(LCD),包括:第一和第二栅极线,与栅极线交叉的数据线,位于第一和第二栅极线与数据线之间的交叉点附近的第一至第四漏极电极,以及耦合电极。还提供分别连接到第一至第四漏电极的第一至第四像素电极,并且第一像素电极连接至耦合电极,而第四像素电极与耦合电极重叠。 LCD还包括与像素电极相对的公共电极,插入在像素电极和公共电极之间的液晶层,以及形成在像素电极和公共电极中的至少一个上的畴分隔构件。畴的两个长边相对于第一和第二栅极线或数据线成角度大致为45°。