US 20140247409A1

(19) **United States**

(12) **Patent Application Publication**

SHIN et al.

(10) **Pub. No.: US 2014/0247409 A1**

(43) **Pub. Date: Sep. 4, 2014**

(54) **LIQUID CRYSTAL DISPLAY**

**Publication Classification**

(71) **Applicant: SAMSUNG DISPLAY CO., LTD., YONGIN-CITY (KR)**

(51) **Int. Cl.**

**G02F 1/1362** (2006.01)

(72) **Inventors: Yong-Hwan SHIN, Yongin-si (KR); Hwa-Sung WOO, Suwon-si (KR); Kwang-Chul JUNG, Seongnam-si (KR); Chong-Chul CHAI, Seoul (KR); Mee-Hye JUNG, Suwon-si (KR)**

(52) **U.S. Cl.**

CPC ..... **G02F 1/136286** (2013.01)

USPC ..... **349/41**

(73) **Assignee: SAMSUNG DISPLAY CO., LTD., YONGIN-CITY (KR)**

(57) **ABSTRACT**

(21) **Appl. No.: 14/273,188**

(22) **Filed: May 8, 2014**

**Related U.S. Application Data**

(62) **Division of application No. 12/350,698, filed on Jan. 8, 2009, now Pat. No. 8,760,479.**

(30) **Foreign Application Priority Data**

Jun. 16, 2008 (KR) ..... 10-2008-0056321

Jun. 17, 2008 (KR) ..... 10-2008-0057043

A liquid crystal display according to an embodiment of the present invention includes: first and second substrates opposed to each other; a liquid crystal layer including liquid crystal molecules interposed between the first and second substrates; a gate line formed on the first substrate and transmitting a gate signal; first and second data lines formed on the first substrate and transmitting first and second data voltages having different polarities; a first switching element connected to the gate line and the first data line; a second switching element connected to the gate line and the second data line; and first and second pixel electrodes that are connected to the first and second switching elements, respectively, and separated from each other, wherein the liquid crystal layer has positive dielectric anisotropy.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28A

FIG. 28B

FIG. 29

FIG. 30

FIG. 31

FIG. 32

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 38

$V_{com} = 7V$

FIG. 39

$V_{com} = 7V$

FIG. 40

FIG. 41

FIG. 42

FIG. 43

FIG. 44

FIG. 45

FIG. 46

FIG. 47

FIG. 48

FIG. 49

FIG. 50

FIG. 51

FIG. 52

FIG. 53

FIG. 54

FIG. 55

FIG. 56

FIG. 57

FIG. 58

## LIQUID CRYSTAL DISPLAY

### CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a divisional application of U.S. patent application Ser. No. 12/350,698 filed on Jan. 8, 2009, which claims the benefit of Korean Patent Application Nos. 10-2008-0057043 and 10-2008-0056321 filed in the Korean Intellectual Property Office on Jun. 17, 2008 and Jun. 16, 2008, and all the benefits accruing therefrom under 35 U.S.C. §119, the contents of the prior applications being herein incorporated by reference.

### BACKGROUND OF THE INVENTION

[0002] (a) Field of the Invention

[0003] The present invention relates to a liquid crystal display.

[0004] (b) Description of the Related Art

[0005] A liquid crystal display is one of the most commonly used flat panel displays. The liquid crystal display includes two display panels respectively having electric field generating electrodes such as pixel electrodes and common electrodes formed thereon, and a liquid crystal layer interposed between the two display panels. An electric field is generated in the liquid crystal layer by applying a voltage to the electric field generating electrodes to determine the alignment of liquid crystal molecules of the liquid crystal layer and control the polarization of incident light, thereby displaying an image.

[0006] The liquid crystal display also includes a switching element connected to each pixel electrode and a plurality of signal lines such as gate lines, data lines, and the like for applying the voltage to the pixel electrodes by controlling the switching element.

[0007] Such a liquid crystal display receives an input image signal from an external graphics controller. The input image signal contains luminance information of each pixel, and each luminance level has a predetermined number. Each luminance level is represented by a data voltage corresponding to desired luminance information. The data voltage applied to the pixel is displayed with a pixel voltage according to a difference of a common voltage. Each pixel displays luminance indicated by the gray of the image signal according to the pixel voltage. At this time, a pixel voltage range that the liquid crystal display can use is determined according to a driver.

[0008] Meanwhile, the driver of the liquid crystal display is mounted directly on a display panel in the form of a plurality of integrated circuit chips or is attached to the display panel while being mounted on a flexible circuit membrane. The integrated circuit chips represent a high ratio of the manufacturing cost of the liquid crystal display.

[0009] In addition, as the number of wires such as the gate lines or the data lines forming a liquid crystal panel assembly increases, the aperture ratio of the liquid crystal display is remarkably reduced.

[0010] The above information disclosed in this Background section is only for enhancement of understanding of the background of the invention and therefore it may contain information that does not form the prior art that is already known in this country to a person of ordinary skill in the art.

### SUMMARY OF THE INVENTION

[0011] A liquid crystal display according to an embodiment of the present invention includes: first and second substrates opposed to each other; a liquid crystal layer including liquid crystal molecules interposed between the first and second substrates; a gate line formed on the first substrate and transmitting a gate signal; first and second data lines formed on the first substrate and respectively transmitting first and second data voltages having different polarities; a first switching element connected to the gate line and the first data line; a second switching element connected to the gate line and the second data line; and first and second pixel electrodes that connected to the first and second switching elements, respectively, and separated from each other, wherein the liquid crystal layer has positive dielectric anisotropy.

[0012] The liquid crystal molecules may be aligned substantially vertical to the first and second substrates.

[0013] The liquid crystal molecules may be aligned substantially parallel to surfaces of the first and second substrates.

[0014] The liquid crystal display may further include: third and fourth data lines formed on the first substrate and respectively transmitting third and fourth data voltages having different polarities; a third switching element connected to the gate line and the third data line; a fourth switching element connected to the gate line and the fourth data line; a third pixel electrode connected to the third switching element; and a fourth pixel electrode separated from the third pixel electrode and connected to the fourth switching element.

[0015] The liquid crystal display may further include: a third data line formed on the first substrate and transmitting a third data voltage; a third switching element connected to the gate line and the second data line; a fourth switching element connected to the gate line and the third data line; the third pixel electrode connected to the third switching element; and a fourth pixel electrode separated from the third pixel electrode and connected to the fourth switching element, wherein the second data voltage and the third data voltage have different polarities.

[0016] A polarity of each of the first and second data voltages may change for every frame.

[0017] The first and second pixel electrodes may be formed in the same layer.

[0018] The first and second pixel electrodes may be formed in different layers.

[0019] The liquid crystal display may further include a common electrode that is formed on the first substrate and applied with a common voltage.

[0020] The liquid crystal display may further include a common electrode that is formed on the second substrate and applied with a common voltage.

[0021] The first and second pixel electrodes may include a plurality of branch electrodes, and the branch electrodes of the first pixel electrode and the branch electrodes of the second pixel electrode may be alternately disposed.

[0022] Distances between adjacent branch electrodes of the first pixel electrode and the second pixel electrode may be uniform over their positions.

[0023] Distances between the adjacent branch electrodes of the first pixel electrode and the second pixel electrode may be different according to their positions.

[0024] The branch electrodes of the first and second pixel electrodes may be bent one or more times.

[0025] The plurality of branch electrodes of the first and second pixel electrodes may be obliquely inclined with respect to the gate line.

[0026] The first and second data lines may be bent one or more times.

[0027] The liquid crystal display may further include a storage electrode line formed on the first substrate, wherein the first switching element includes a first drain electrode connected to the first pixel electrode, the second switching element includes a second drain electrode connected to the second pixel electrode, and at least one of the first pixel electrode, the second pixel electrode, the first drain electrode, and the second drain electrode overlaps the storage electrode line.

[0028] The first pixel electrode or an electrode connected to the first pixel electrode may overlap the second pixel electrode.

[0029] A liquid crystal display according to another embodiment of the present invention includes: first and second substrates opposing each other; a liquid crystal layer including liquid crystal molecules and interposed between the first and second substrates; a gate line formed on the first substrate and transmitting a gate signal; first and second data lines formed on the first substrate and respectively transmitting first and second data voltages that are different from each other; first and second switching elements connected to the gate line and the first data line; third and fourth switching elements connected to the gate line and the second data line; and first, second, third, and fourth pixel electrodes connected to the first, second, third, and fourth switching elements, respectively, wherein the liquid crystal layer has positive dielectric anisotropy.

[0030] Polarities of the first data voltage and the second data voltage may be opposite to each other.

[0031] The liquid crystal molecules may be aligned substantially vertical or parallel to the first and second substrates.

[0032] The liquid crystal display may further include: third and fourth data lines formed on the first substrate and respectively transmitting third and fourth data voltages that are different from each other; fifth and sixth switching elements connected to the gate line and the third data line; seventh and eighth switching elements connected to the gate line and the fourth data line; and fifth, sixth, seventh, and eighth pixel electrodes connected to the fifth, sixth, seventh, and eighth switching elements, respectively.

[0033] The liquid crystal display may further include: a third data line formed on the first substrate and transmitting a third data voltage; fifth and sixth switching elements connected to the gate line and the second data line; seventh and eighth switching elements connected to the gate line and the third data line; and fifth, sixth, seventh, and eighth pixel electrodes connected to the fifth, sixth, seventh, and eighth switching elements, respectively, wherein the second data voltage and the third data voltage are different from each other.

[0034] The first, second, third, and fourth switching elements have first, second, third, and fourth gate electrodes and first, second, third, and fourth drain electrodes, respectively; the first, second, third, and fourth drain electrodes are connected to the first, second, third, and fourth pixel electrodes, respectively; and when an overlapping area of the first gate electrode and the first drain electrode is represented as a first area, an overlapping area of the second gate electrode and the second drain electrode is represented as a second area, an

overlapping area of the third gate electrode and the third drain electrode is represented as a third area, and an overlapping area of the fourth gate electrode and the fourth drain electrode is represented as a fourth area, at least one among the first to fourth areas may be different from the other areas.

[0035] The first area may be greater than the third area, or the fourth area may be greater than the third area.

[0036] Each of the first to fourth pixel electrodes may include a plurality of branch electrodes, the branch electrodes of the first pixel electrode and the branch electrodes of the third pixel electrode may be alternately disposed, and the branch electrodes of the second pixel electrode and the branch electrodes of the fourth pixel electrode may be alternately disposed.

[0037] The branch electrodes of the first to fourth pixel electrodes may be obliquely inclined with respect to the gate line.

[0038] The liquid crystal display may further include a storage electrode line formed on the first substrate.

[0039] A liquid crystal display according to another embodiment of the present invention includes: first and second substrates opposing each other; a liquid crystal layer including liquid crystal molecules and interposed between the first and second substrates; a gate line formed on the first substrate and transmitting a gate signal; first, second, third, and fourth data lines formed on the first substrate and respectively transmitting first, second, third, and fourth data voltages that are different from each other; a first switching element connected to the gate line and the first data line; a second switching element connected to the gate line and the second data line; a third switching element connected to the gate line and the third data line; a fourth switching element connected to the gate line and the fourth data line; and first, second, third, and fourth subpixel electrodes connected to the first, second, third, and fourth switching elements, respectively, wherein the first to fourth subpixel electrodes are applied with different voltages acquired from information for an image, and the liquid crystal layer has positive dielectric anisotropy.

[0040] Polarities of the first data voltage and the second data voltage may be opposite to each other, and polarities of the third data voltage and the fourth data voltage are opposite to each other.

[0041] The liquid crystal molecules may be aligned substantially vertical or parallel to the first and second substrates.

[0042] The liquid crystal display may further include a storage electrode line formed on the first substrate.

[0043] A liquid crystal display according to another embodiment of the present invention includes: first and second substrates opposing each other; a liquid crystal layer including liquid crystal molecules and interposed between the first and second substrates; first and second gate lines formed on the first substrate; first and second data lines formed on the first substrate and respectively transmitting first and second data voltages that are different from each other; a first switching element connected to the first gate line and the first data line; a second switching element connected to the first gate line and the second data line; a third switching element connected to the second gate line and the first data line; a fourth switching element connected to the second gate line and the second data line; and first, second, third, and fourth subpixel electrodes connected to the first, second, third, and fourth switching elements, respectively, wherein the first to fourth subpixel electrodes are applied with differ-

ent voltages acquired from information for an image, and the liquid crystal layer has positive dielectric anisotropy.

[0044] Polarities of the first data voltage and the second data voltage may be opposite to each other.

[0045] The liquid crystal molecules may be aligned vertical or parallel to the first and second substrates.

[0046] The liquid crystal display may further include a storage electrode line formed on the first substrate.

[0047] A liquid crystal display according to another embodiment of the present invention includes: a pixel including first and second subpixels and a coupling capacitor; a gate line formed on a substrate and transmitting a gate signal; and first and second data lines formed on the substrate and respectively transmitting first and second data voltages that are different from each other, wherein the first subpixel includes a first switching element connected to the gate line and the first data line, a second switching element connected to the gate line and the second data line, and a first liquid crystal capacitor connected to the first and second switching elements, the coupling capacitor is connected to the first switching element, the second subpixel includes the second switching element, the coupling capacitor, and a second liquid crystal capacitor connected to the second switching element, and the first and second liquid crystal capacitors include a liquid crystal layer having positive dielectric anisotropy.

[0048] Polarities of the first data voltage and the second data voltage may be opposite to each other.

[0049] The liquid crystal layer may include liquid crystal molecules that are aligned substantially vertical or parallel to the substrate.

[0050] The liquid crystal display may further include a storage electrode line formed on the first substrate.

[0051] A liquid crystal display according to another embodiment of the present invention includes: a plurality of pixels including first and second subpixels and a boost-up unit; first and second gate lines formed on a substrate and transmitting a gate signal; and first and second data lines formed on the substrate and respectively transmitting first and second data voltages that are different from each other. The first subpixel includes a first switching element connected to the first gate line and the first data line, a second switching element connected to the first gate line and the second data line, and a first liquid crystal capacitor connected to the first and second switching elements, the second subpixel includes a third switching element connected to the first gate line and the first data line, the second switching element, and a second liquid crystal capacitor connected to the second and third switching elements. The boost-up unit includes a boost-up capacitor connected to the first switching element, a fourth switching element controlled by the gate signal of the first gate line and connected between the boost-up capacitor and a common voltage, and a fifth switching element controlled by the gate signal of the second gate line and connected between the boost-up capacitor and the second liquid crystal capacitor, and the second gate line is applied with a gate-on voltage later than the first gate line and the first and second liquid crystal capacitors include a liquid crystal layer having positive dielectric anisotropy.

[0052] Polarities of the first data voltage and the second data voltage may be opposite to each other.

[0053] The liquid crystal layer may include liquid crystal molecules that are aligned substantially vertical or parallel to the substrate.

[0054] When two adjacent pixels are represented as a first pixel and a second pixel, the second data voltage transmitted by the second data line of the first pixel may be the same as the second data voltage transmitted by the second data line of the second pixel.

[0055] The first subpixel may further include a first storage capacitor connected to the first switching element and a second storage capacitor connected to the second switching element, and the second subpixel may further include a third storage capacitor connected to the third switching element and the second storage capacitor.

[0056] The first subpixel may further include a first storage capacitor connected to the first and second switching elements, and the second subpixel may further include a second storage capacitor connected to the second and third switching elements.

[0057] A liquid crystal display according to another embodiment of the present invention includes: first and second substrates opposing each other; a liquid crystal layer including liquid crystal molecules and interposed between the first and second substrates; a gate line formed on the first substrate and transmitting a gate signal; first, second, and third data lines formed on the first substrate and respectively transmitting first, second, and third data voltages; a first switching element connected to the gate line and the first data line; a second switching element connected to the gate line and the second data line; a third switching element connected to the gate line and the third data line; a fourth switching element connected to the gate line and the third data line; and first, second, third, and fourth pixel electrodes connected to the first, second, third, and fourth switching elements, respectively.

[0058] The liquid crystal layer may have positive dielectric anisotropy.

[0059] The liquid crystal molecules may be aligned substantially vertical or parallel to the first and second substrates.

[0060] The second data voltage may vary between a first level and a second level by a predetermined period.

[0061] The first level may be the highest voltage that is usable in the liquid crystal display, and the second level may be the lowest voltage that is usable in the liquid crystal display.

[0062] The predetermined period may be one frame.

[0063] The first to third data lines may be formed in the same layer.

[0064] The second data line may be formed in the same layer as the gate line.

[0065] The liquid crystal display may further include a storage electrode line formed on the first substrate.

[0066] The first and second pixel electrodes may include a plurality of branch electrodes, and the branch electrodes of the first pixel electrode and the branch electrodes of the second pixel electrode may be alternately disposed.

[0067] Distances between adjacent branch electrodes of the first pixel electrode and the second pixel electrode may be different according to their positions.

[0068] A liquid crystal display according to another embodiment of the present invention includes: a pixel including a first subpixel and a second subpixel; a gate line formed on a substrate; and first, second, and third data lines formed on the substrate, wherein the first subpixel includes a first switching element connected to the gate line and the first data line, a second switching element connected to the gate line and the second data line, and a liquid crystal capacitor con-

nected to the first and second switching elements, the second subpixel includes a third switching element connected to the gate line and the second data line, a fourth switching element connected to the gate line and the third data line, and a liquid crystal capacitor connected to the third and fourth switching elements, and the first and second subpixels are applied with different data voltages acquired from information for an image.

[0069] The liquid crystal capacitor may have positive dielectric anisotropy.

[0070] The liquid crystal layer may include liquid crystal molecules that are aligned substantially vertical or parallel to the substrate.

[0071] A voltage applied to the second data line may vary between a first level and a second level by a predetermined period.

[0072] The first to third data lines may be formed in the same layer.

[0073] The second data line may be formed in the same layer as the gate line.

[0074] The liquid crystal display may further include a storage electrode line formed on the substrate.

[0075] A liquid crystal display according to another embodiment of the present invention includes: a plurality of pixels arranged in a matrix, each including a first subpixel and a second subpixel; a plurality of first and second gate lines formed on a substrate; and a plurality of first and second data lines formed on the substrate, wherein the first subpixel includes a first switching element connected to the first gate line and the first data line, a second switching element connected to the first gate line and the second data line, and a first liquid crystal capacitor connected to the first and second switching elements, the second subpixel includes a third switching element connected to the second gate line and the first data line, a fourth switching element connected to the second gate line and the second data line, and a second liquid crystal capacitor connected to the third and fourth switching elements, and the first and second subpixels are applied with different data voltages acquired from information for an image.

[0076] The liquid crystal capacitor may include a liquid crystal layer having positive dielectric anisotropy.

[0077] The liquid crystal layer may include liquid crystal molecules that are aligned substantially vertical or parallel to the substrate.

[0078] A voltage applied to the second data line may be varied between a first level and a second level in a predetermined cycle.

[0079] The second data line may be formed in the same layer as the first and second gate lines.

[0080] The liquid crystal display may further include a plurality of third data lines formed on the substrate, wherein when two adjacent pixels among the plurality of pixels represent a first pixel and a second pixel, the first subpixel of the second pixel includes a fifth switching element connected to the first gate line and the third data line, a sixth switching element connected to the first gate line and the second data line, and a third liquid crystal capacitor connected to the fifth and sixth switching elements, the second subpixel of the second pixel includes a seventh switching element connected to the second gate line and the third data line, an eighth switching element connected to the second gate line and the second data line, and a fourth liquid crystal capacitor connected to the seventh and eighth switching elements, and the

first and second subpixels of the second pixel are applied with different data voltages acquired from one set of image information.

[0081] The liquid crystal display may further include a storage electrode line formed on the substrate.

[0082] A liquid crystal display according to another embodiment of the present invention includes: first and second pixels adjacent to each other, each including a first subpixel and a second subpixel; a gate line formed on a substrate; and first, second, and third data lines formed on the substrate, wherein the first subpixel of the first pixel includes a first switching element connected to the first gate line and the first data line, a second switching element connected to the first gate line and the second data line, and a first liquid crystal capacitor connected to the first and second switching elements, the coupling capacitor of the first pixel is connected to the first switching element, the second subpixel of the first pixel includes the second switching element and a second liquid crystal capacitor connected between the coupling capacitor and the second switching element, the first subpixel of the second pixel includes a third switching element connected to the first gate line and the second data line, a fourth switching element connected to the first gate line and the third data line, and a third liquid crystal capacitor connected to the third and fourth switching elements, the coupling capacitor of the second pixel is connected to the fourth switching element, and the second subpixel of the second pixel includes the third switching element and a fourth liquid crystal capacitor connected between the coupling capacitor and the third switching element.

[0083] The first to fourth liquid crystal capacitors may include a liquid crystal layer having positive dielectric anisotropy.

[0084] The liquid crystal layer may be a vertical or horizontal alignment layer.

[0085] A voltage applied to the second data line may be varied between a first level and a second level in a predetermined cycle.

[0086] The first to third data lines may be formed in the same layer.

[0087] The second data line may be formed in the same layer as the gate line.

[0088] A liquid crystal display according to another embodiment of the present invention includes: a plurality of pixels arranged in a matrix; a plurality of gate lines formed on a substrate and transmitting a gate signal; and a plurality of the first and second data lines formed on the substrate and respectively transmitting first and second data voltages, wherein each pixel includes a first switching element connected to the gate line and the first data line, a second switching element connected to the gate line and the second data line, and a liquid crystal capacitor connected to the first and second switching elements, the liquid crystal capacitor includes a first pixel electrode, a second pixel electrode, and a liquid crystal layer having positive dielectric anisotropy and positioned between the first and second pixel electrodes, the liquid crystal layer is a vertical alignment layer, and each pixel displays a low-gray image for at least one frame after displaying an image for one or more frames.

[0089] The plurality of pixels may display the low-gray image for the same frame.

[0090] The low-gray image may be displayed for one frame.

[0091] At least one pixel row or at least one pixel column among the plurality of pixels may display the low-gray image and the remaining pixels may display the image for the same frame.

[0092] Two adjacent pixel rows or two adjacent pixel columns may sequentially display the low-gray image for two successive frames.

[0093] At least one pixel row displaying the low-gray image may simultaneously display the low-gray image for the same frame.

[0094] A data voltage of the low-gray image may be equal to  $\frac{2}{3}$  or less than a data voltage of the image.

#### BRIEF DESCRIPTION OF THE DRAWINGS

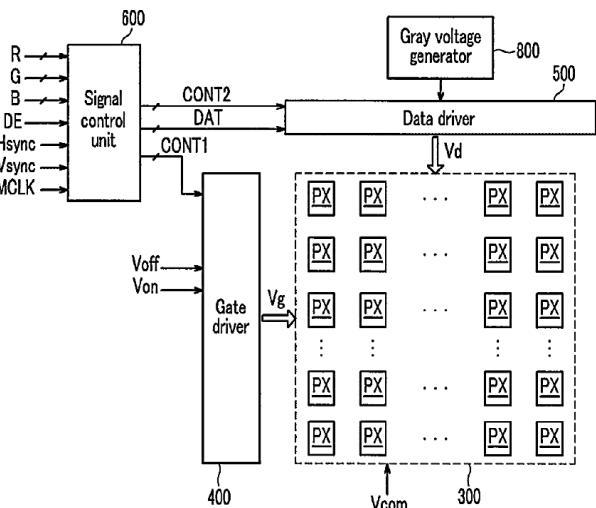

[0095] FIG. 1 is a block diagram of a liquid crystal display according to an embodiment of the present invention;

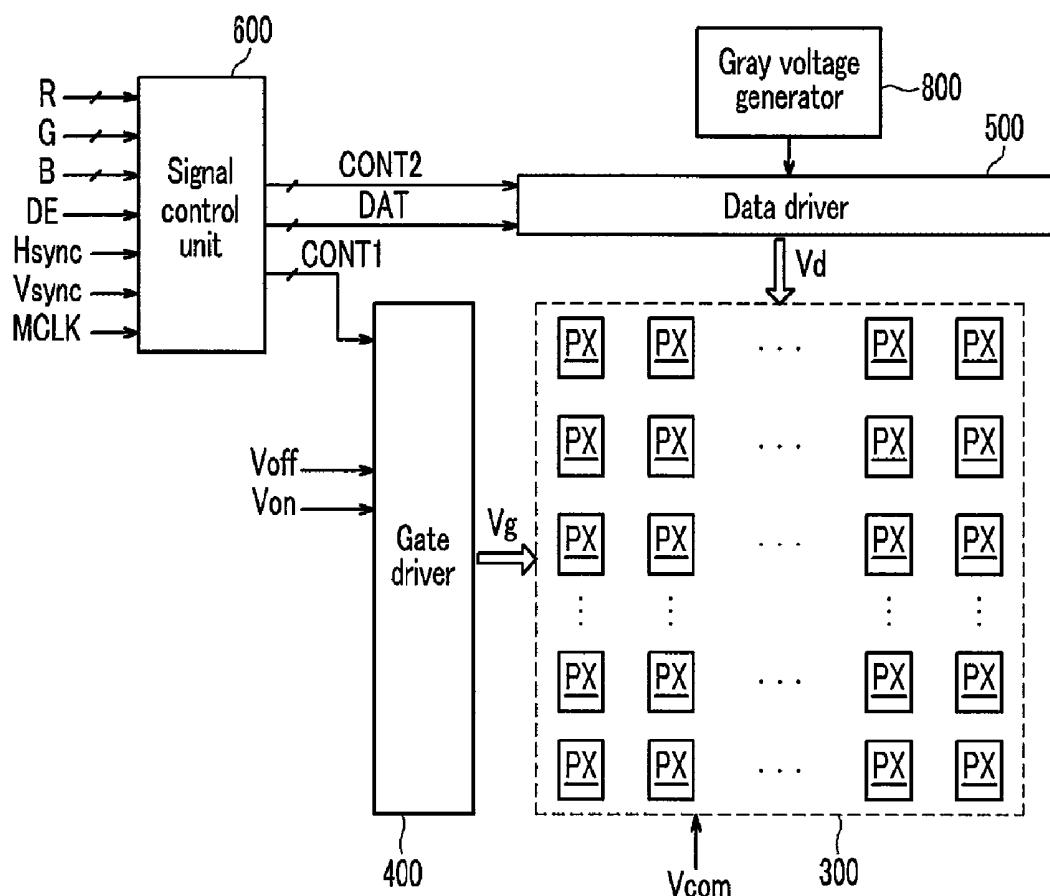

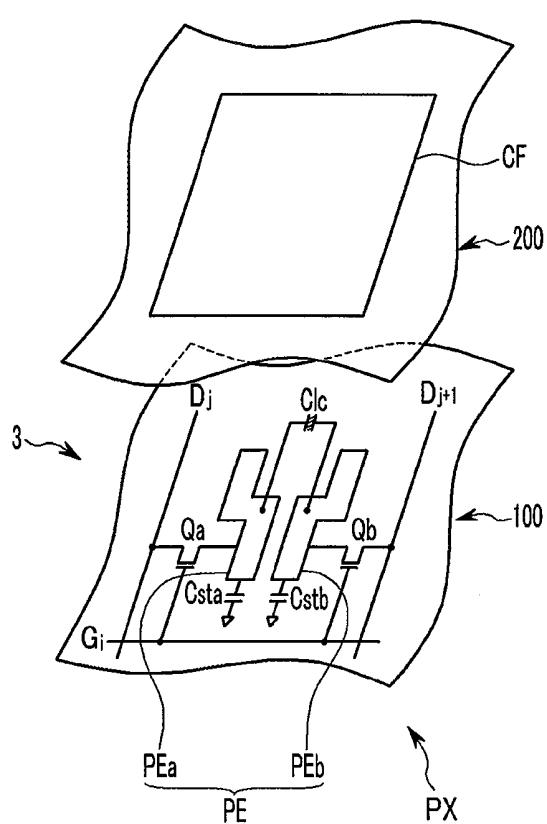

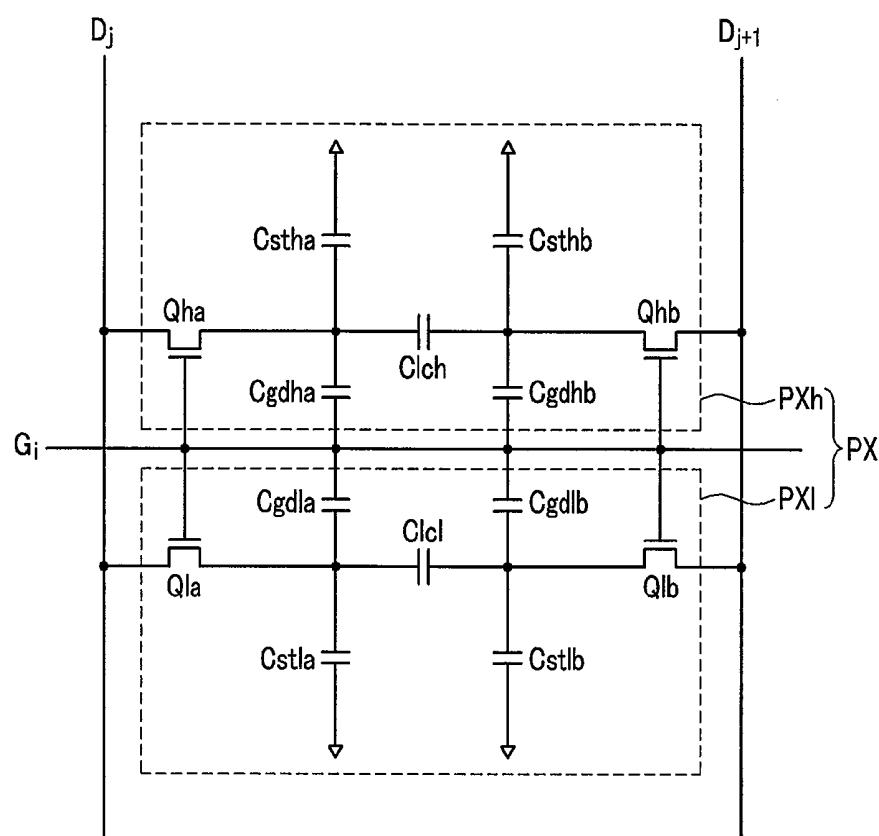

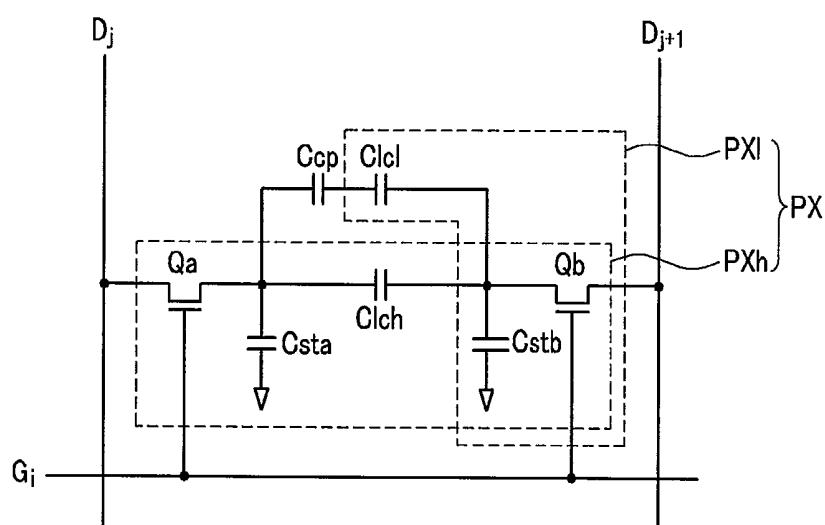

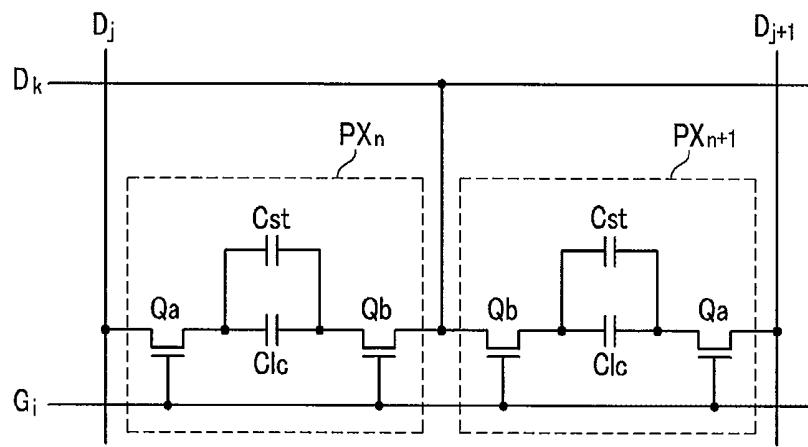

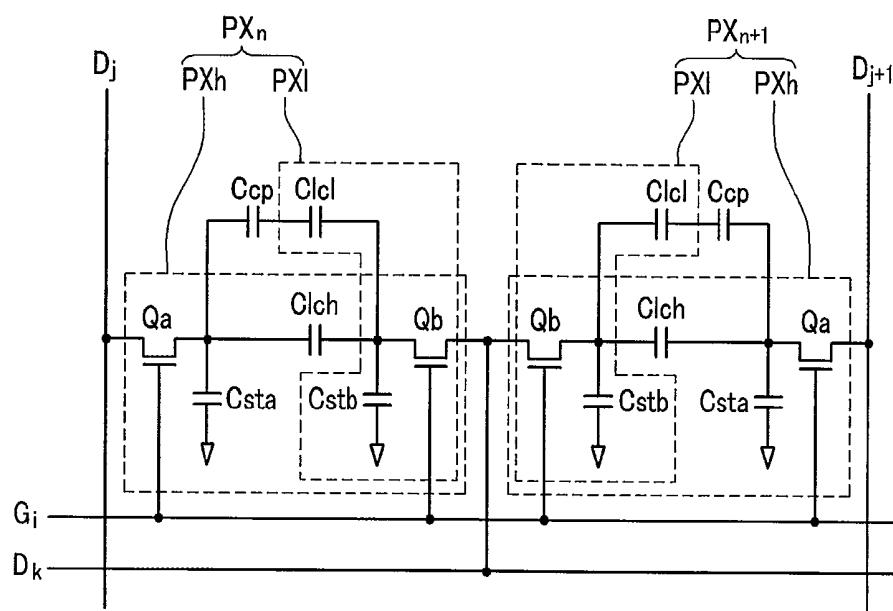

[0096] FIG. 2 is an equivalent circuit diagram of a structure of a liquid crystal display and one pixel according to an embodiment of the present invention;

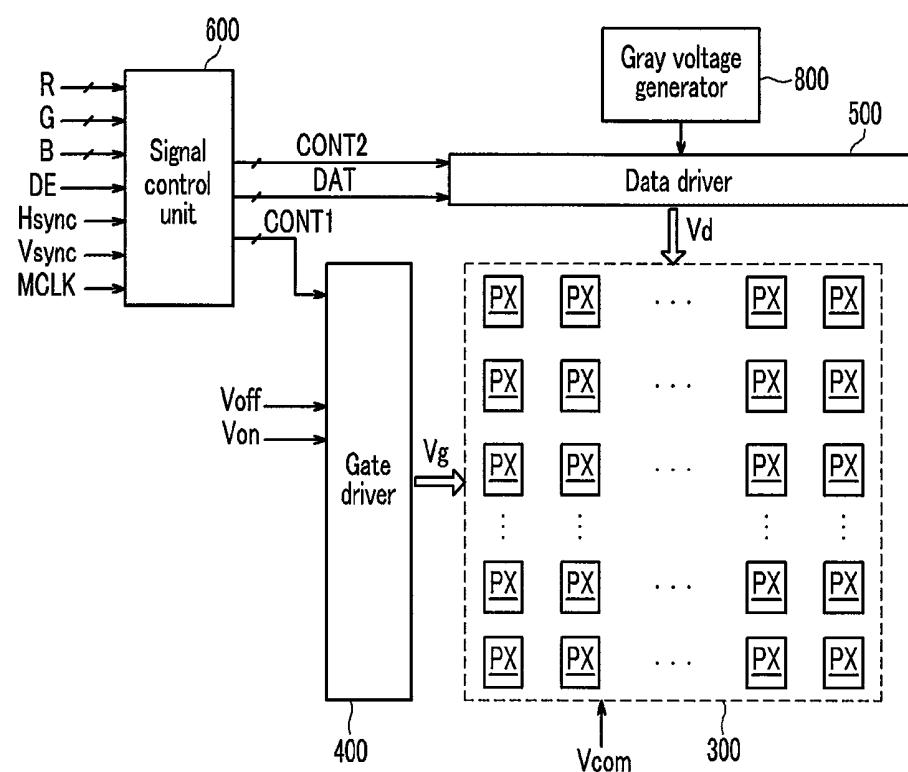

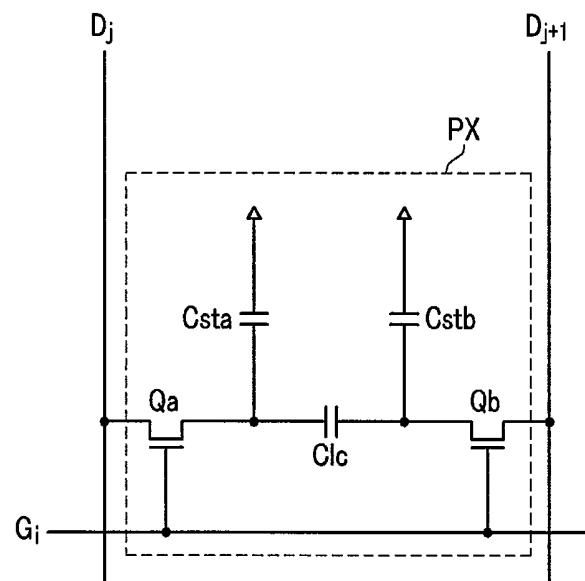

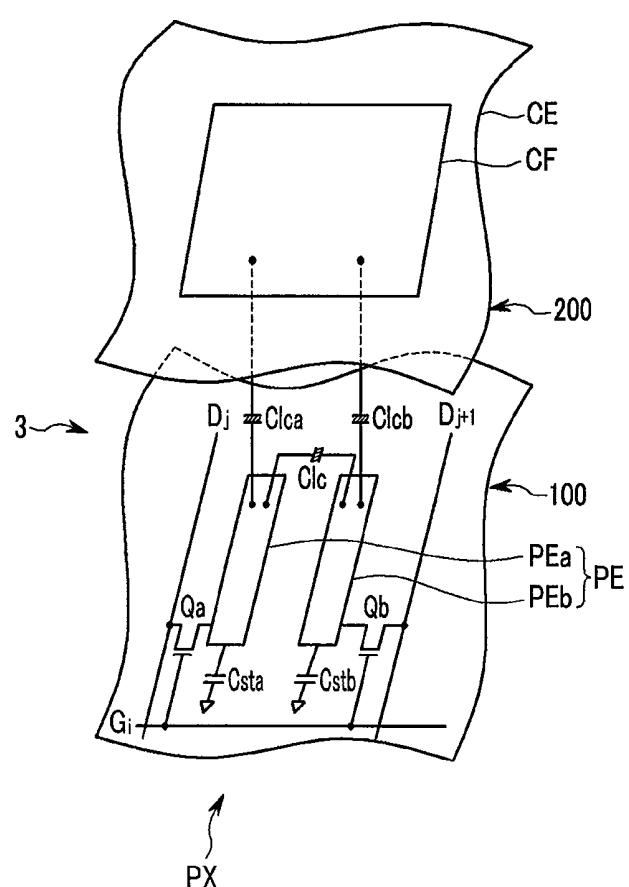

[0097] FIG. 3 is an equivalent circuit diagram illustrating one pixel of a liquid crystal display according to an embodiment of the present invention;

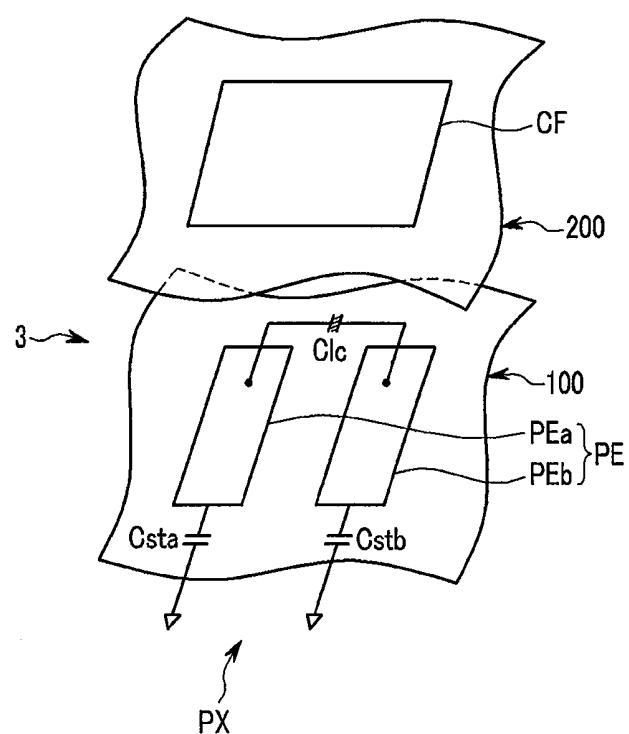

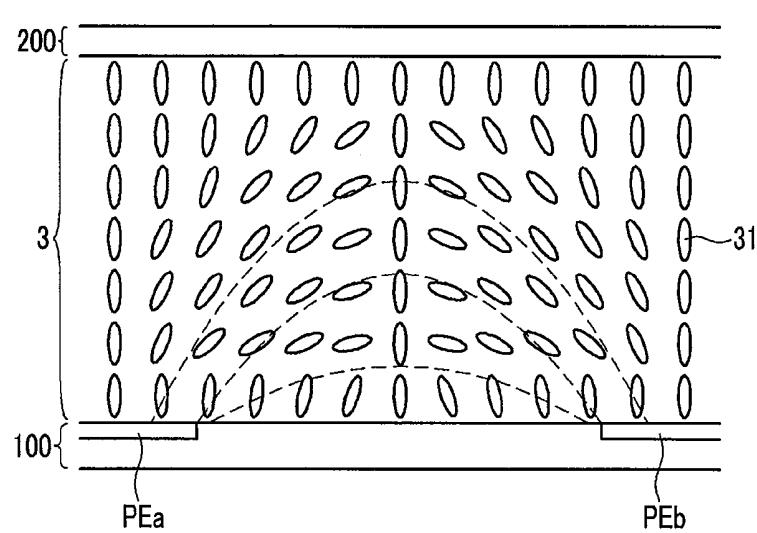

[0098] FIG. 4 is a schematic cross-sectional view of a liquid crystal display according to an embodiment of the present invention;

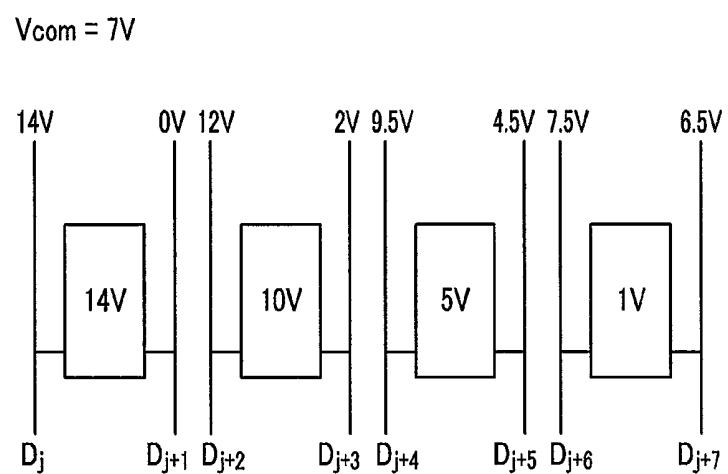

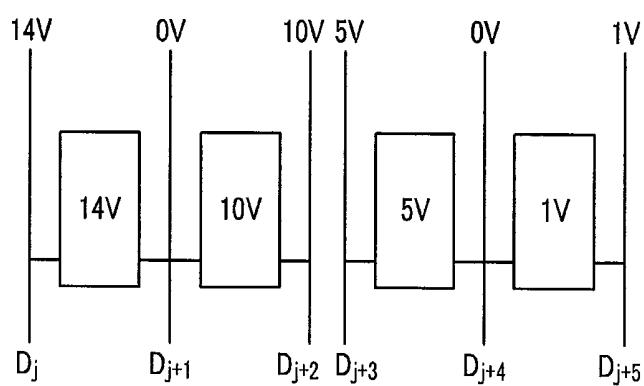

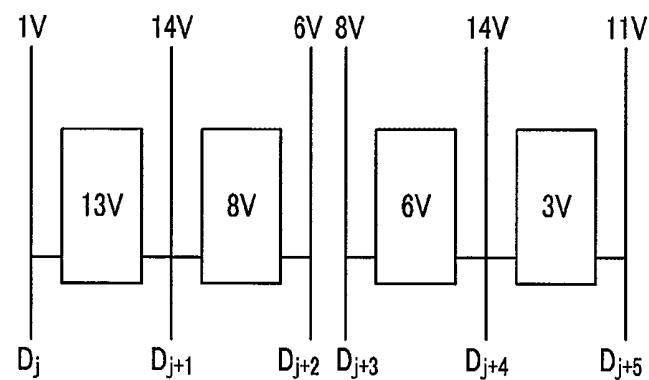

[0099] FIG. 5 is a diagram illustrating voltages of data lines and pixels of a liquid crystal display according to an embodiment of the present invention;

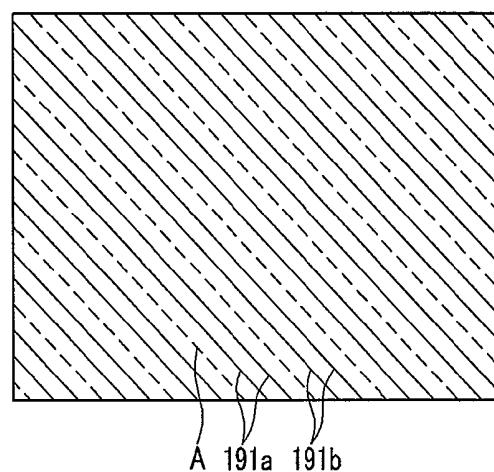

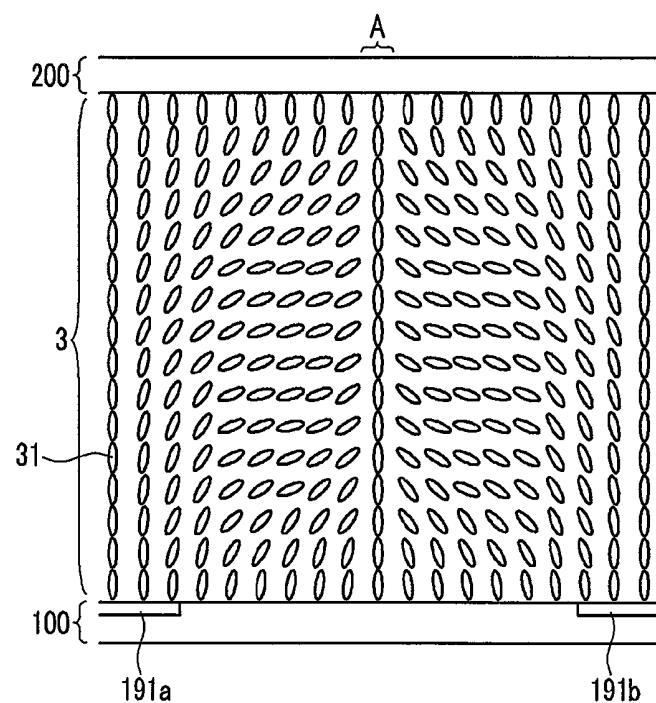

[0100] FIG. 6 is a diagram illustrating the pixel electrode and a texture region of a liquid crystal display according to an embodiment of the present invention;

[0101] FIG. 7 is a schematic cross-sectional view of a liquid crystal display according to an embodiment of the present invention;

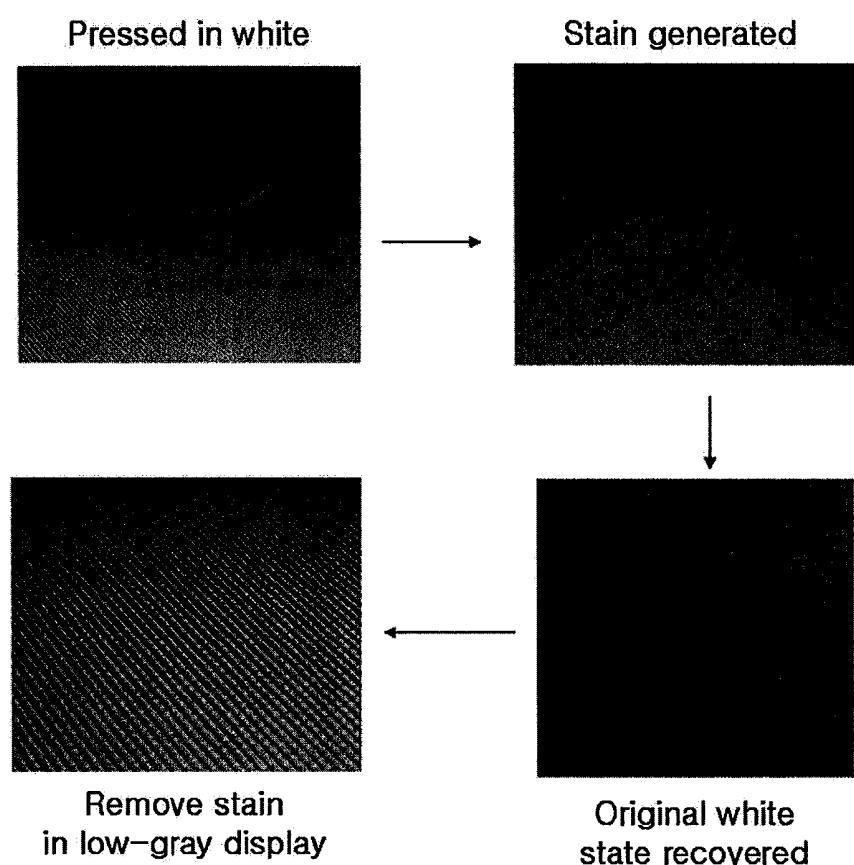

[0102] FIG. 8 is a diagram illustrating a sequence of a driving method of a liquid crystal display according to an embodiment of the present invention;

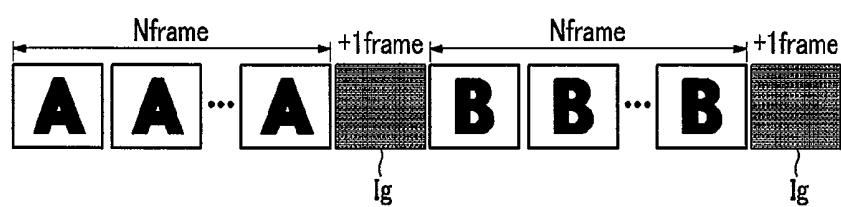

[0103] FIG. 9 is a diagram illustrating a driving method according to an embodiment of the present invention;

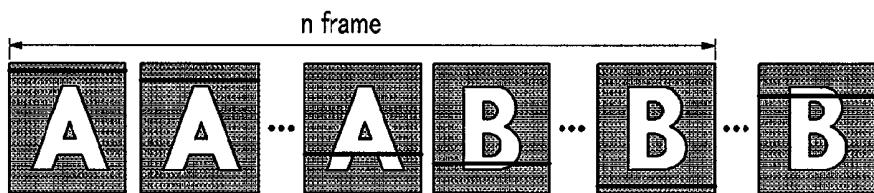

[0104] FIG. 10 is a diagram illustrating a driving method according to another embodiment of the present invention;

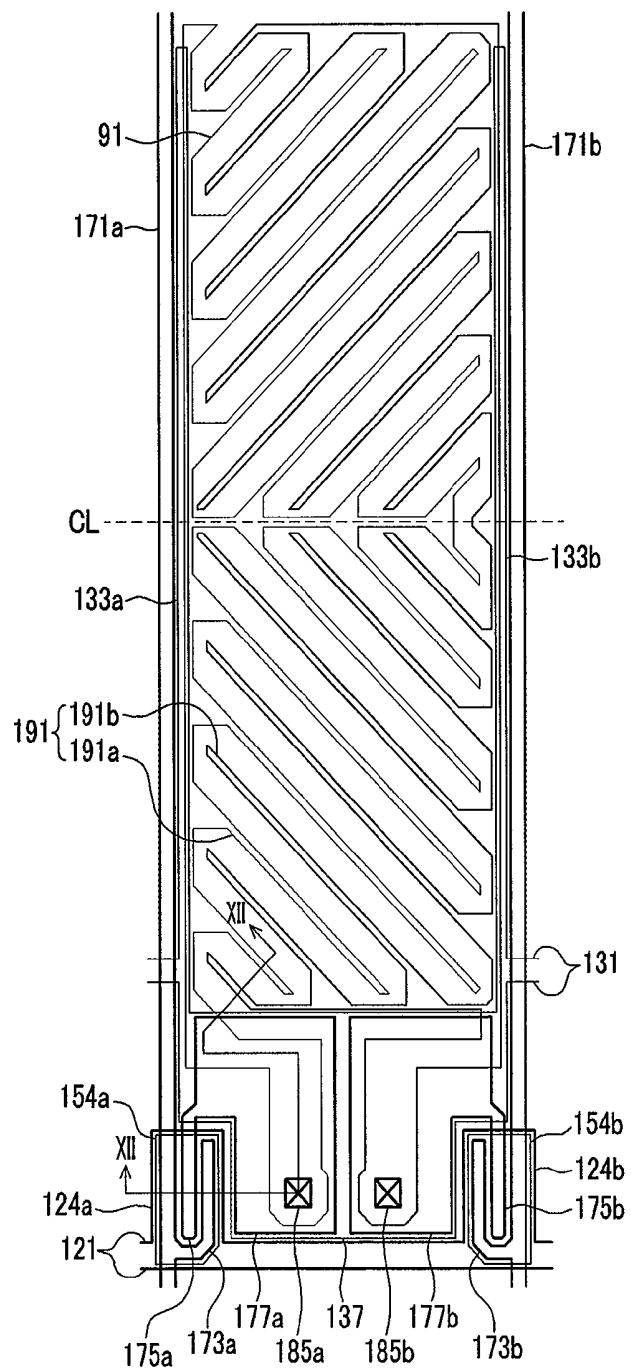

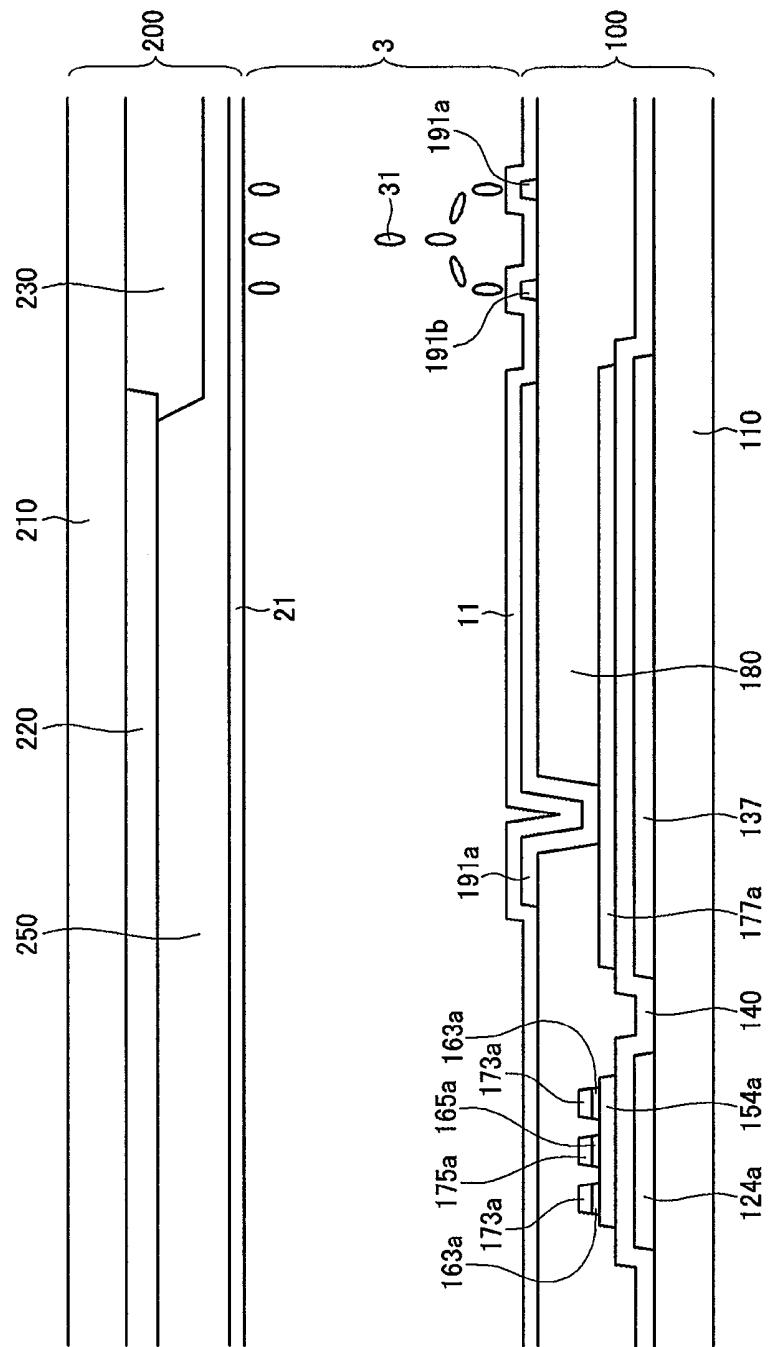

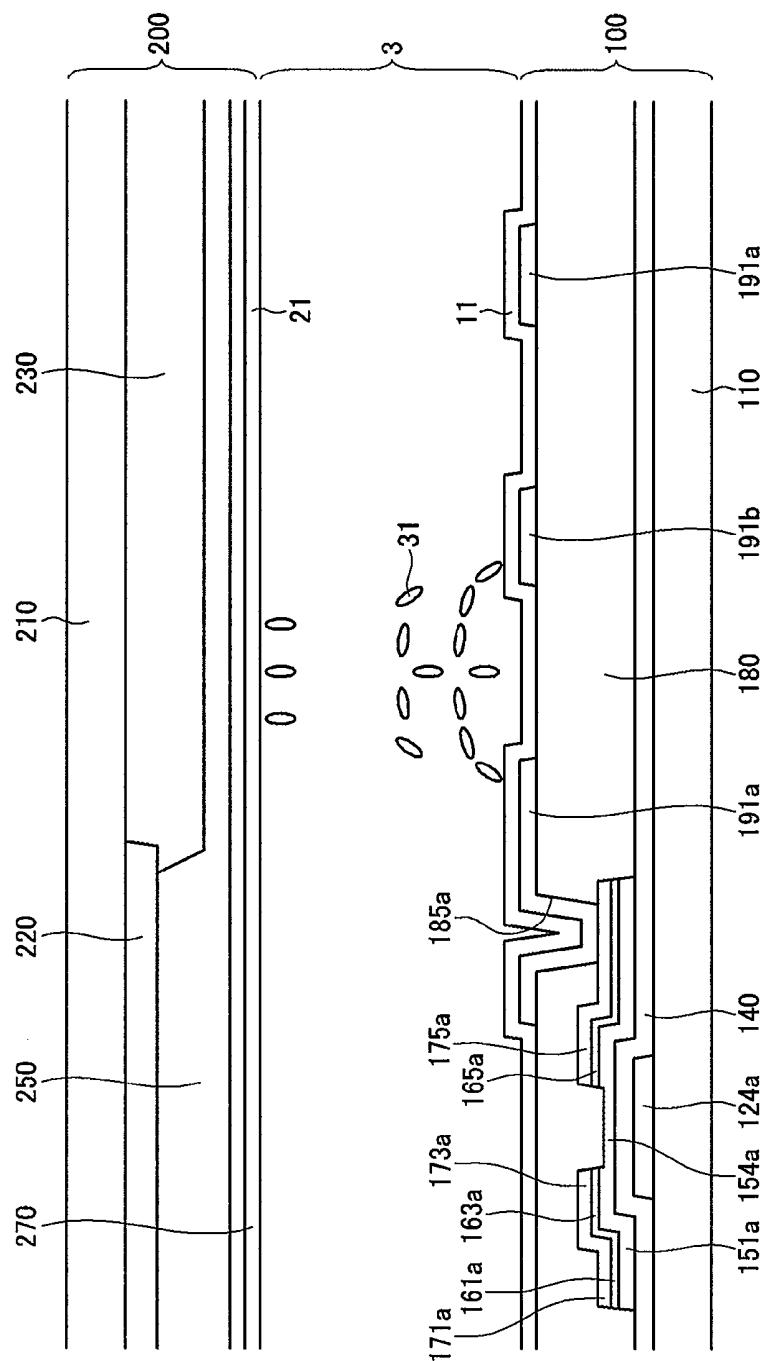

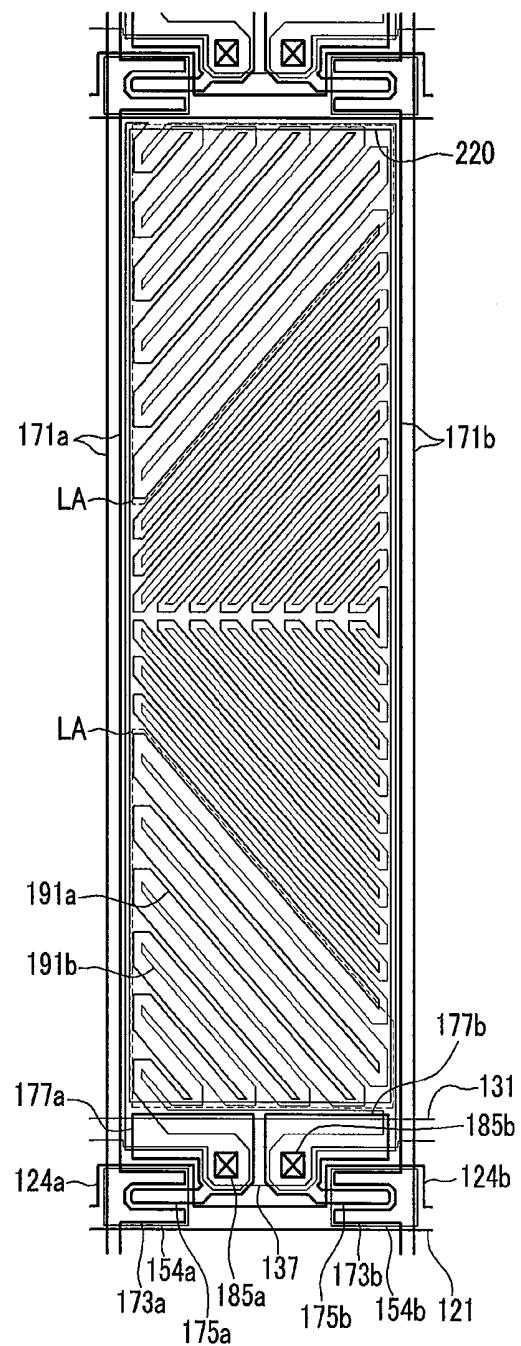

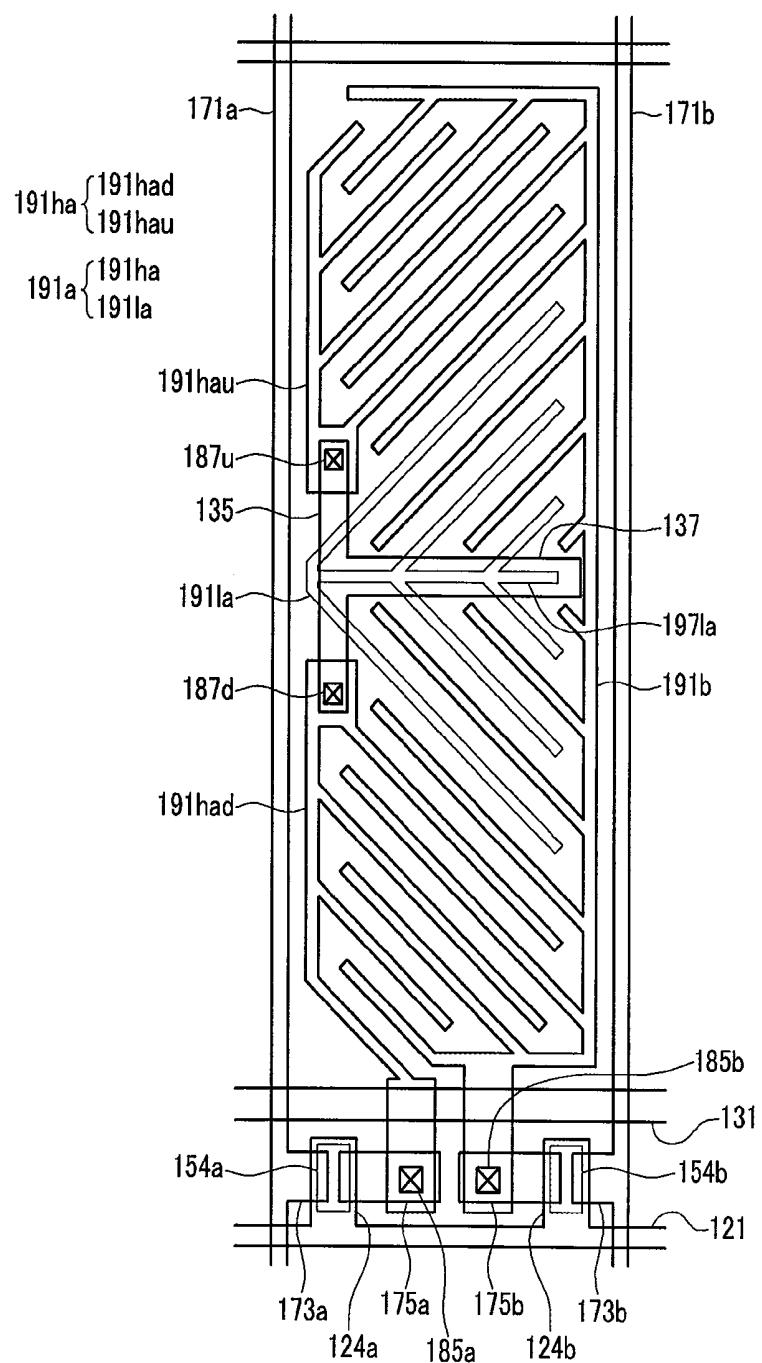

[0105] FIG. 11 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

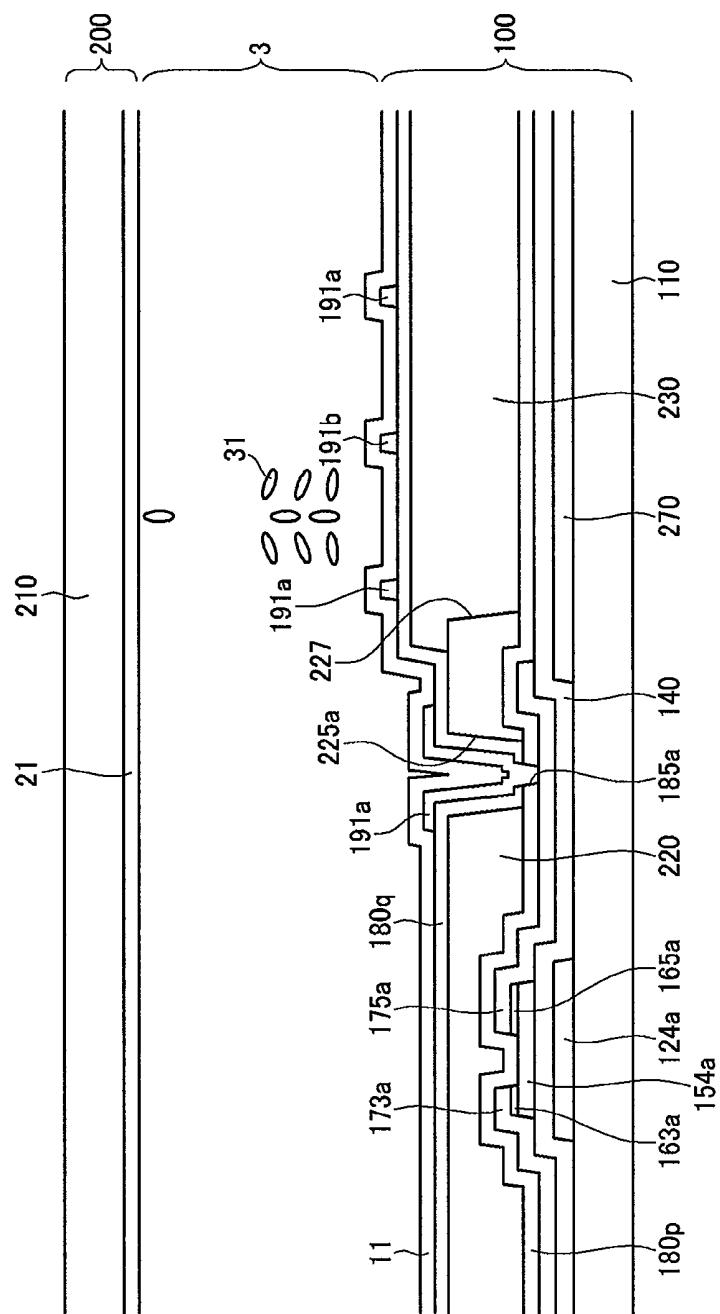

[0106] FIG. 12 is a cross-sectional view of the liquid crystal panel assembly taken along line XII-XII of FIG. 11;

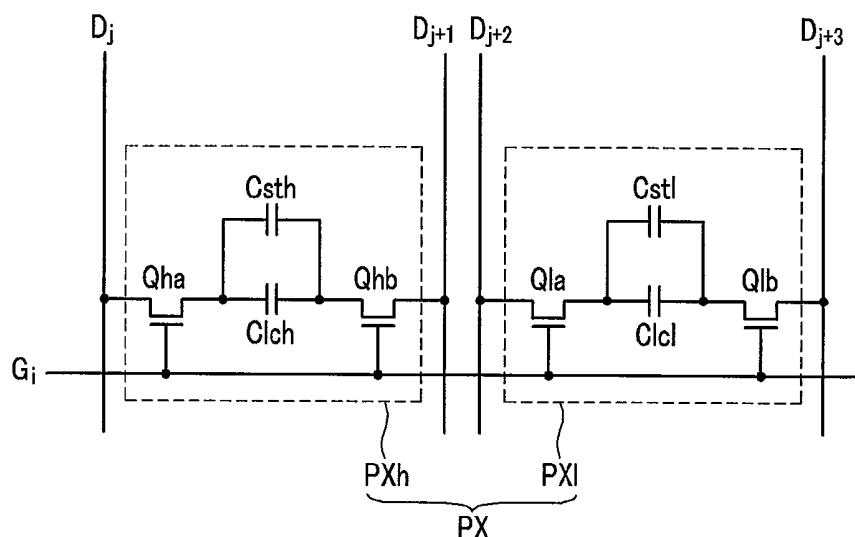

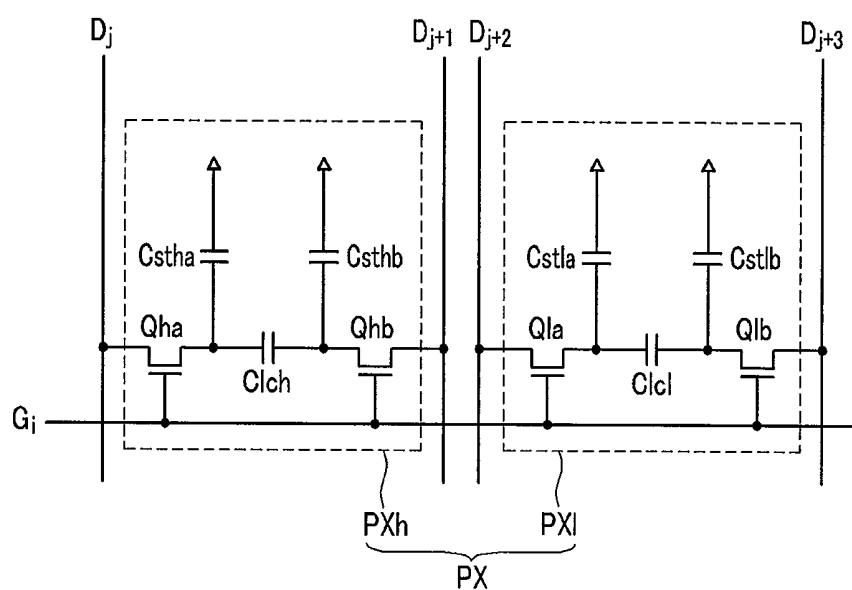

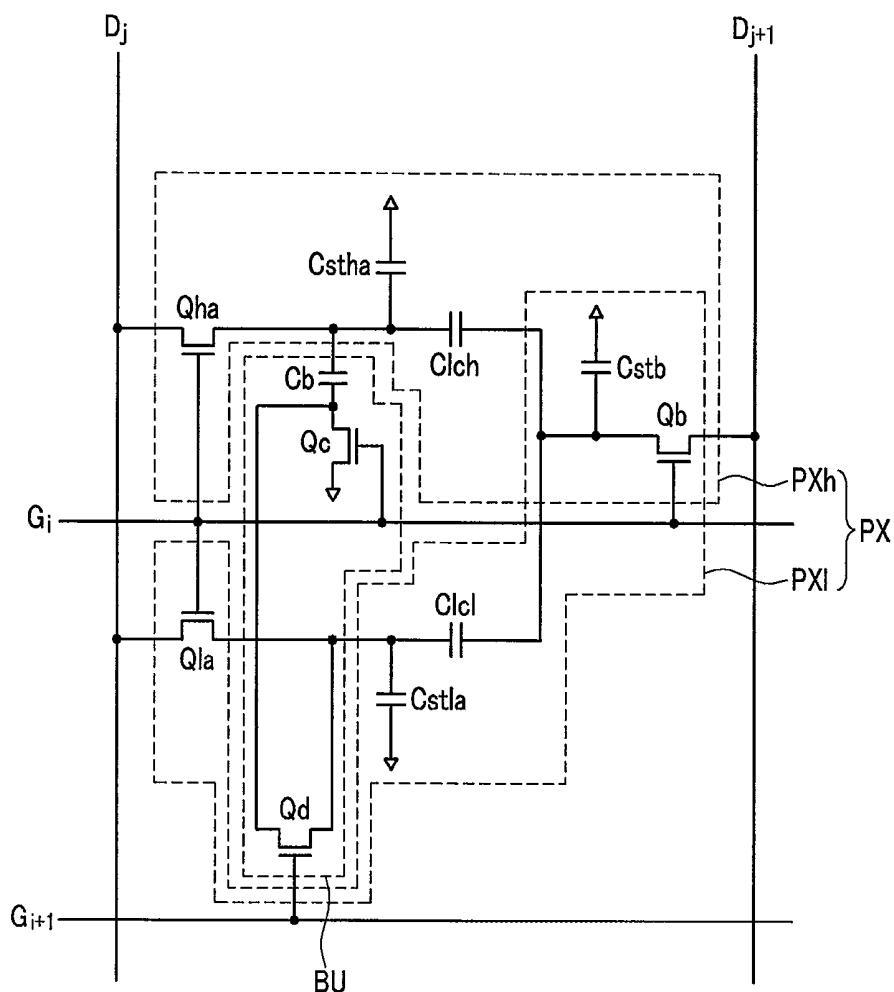

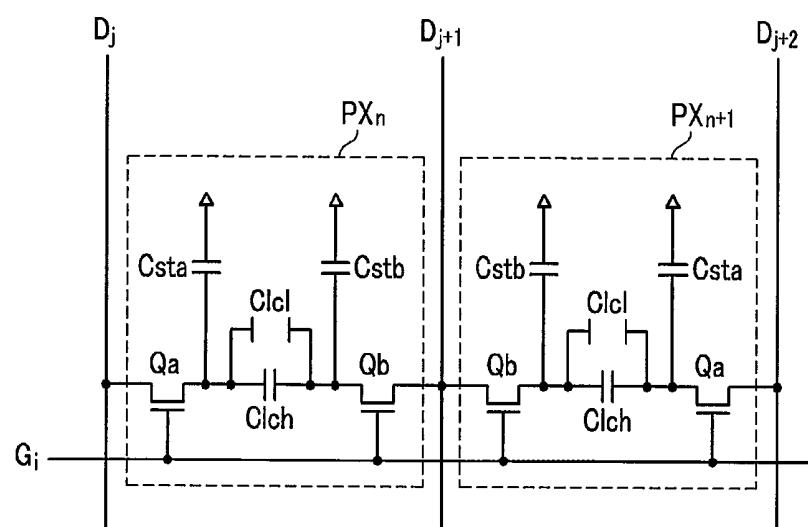

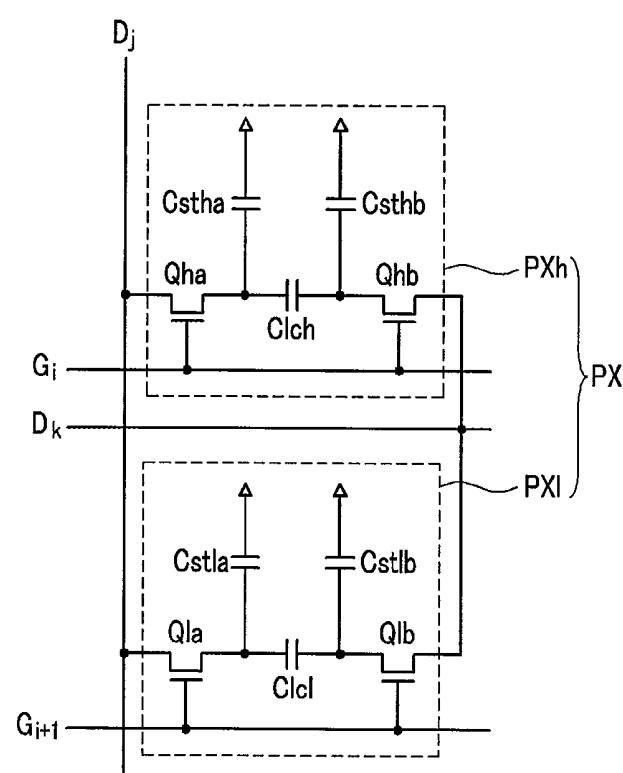

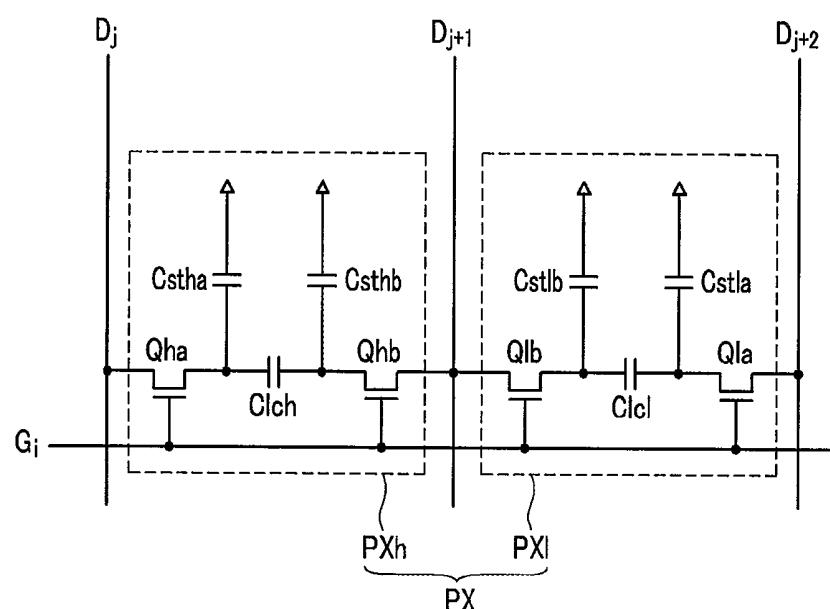

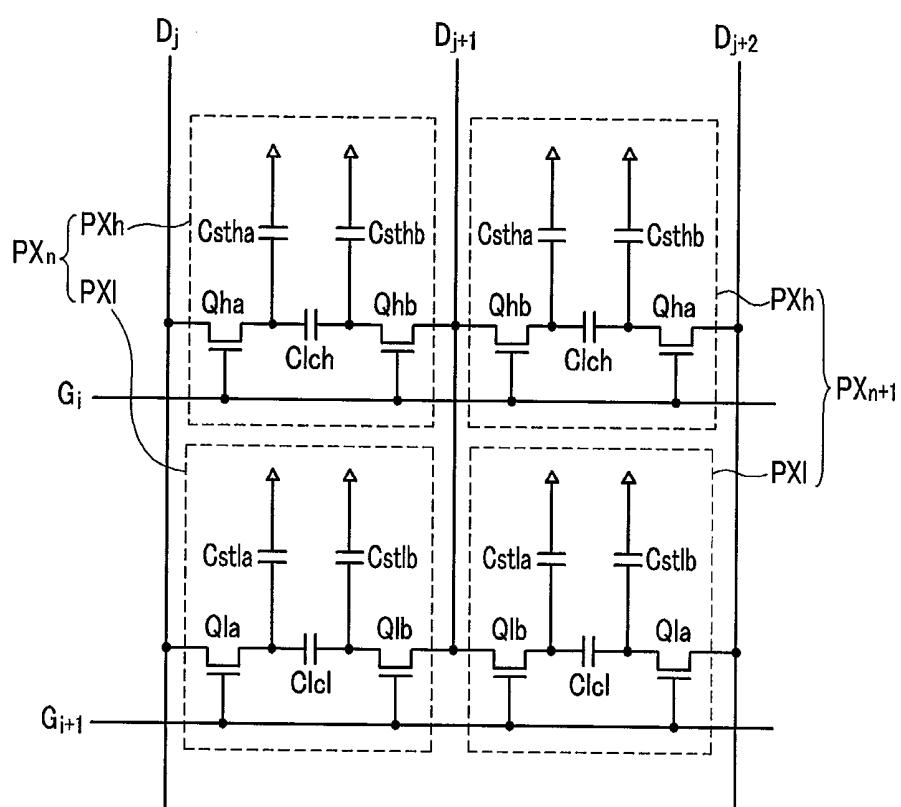

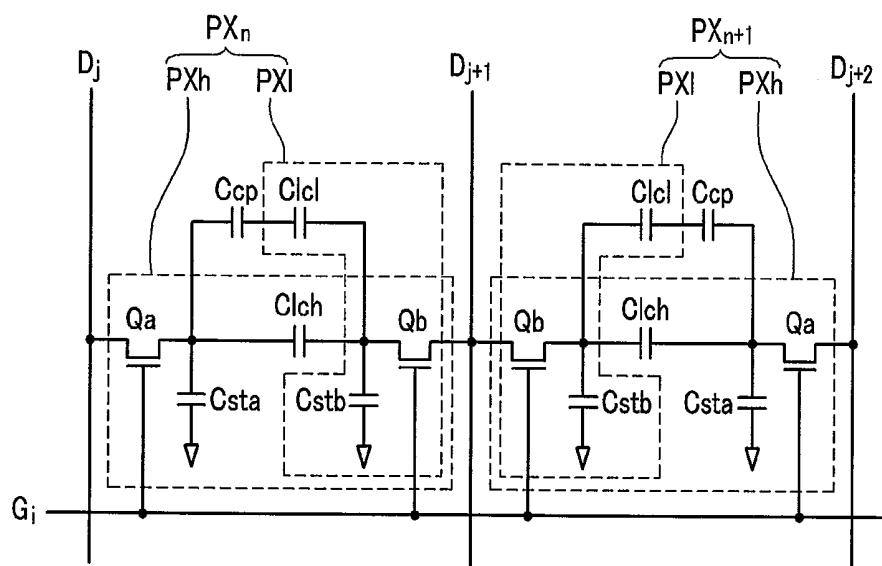

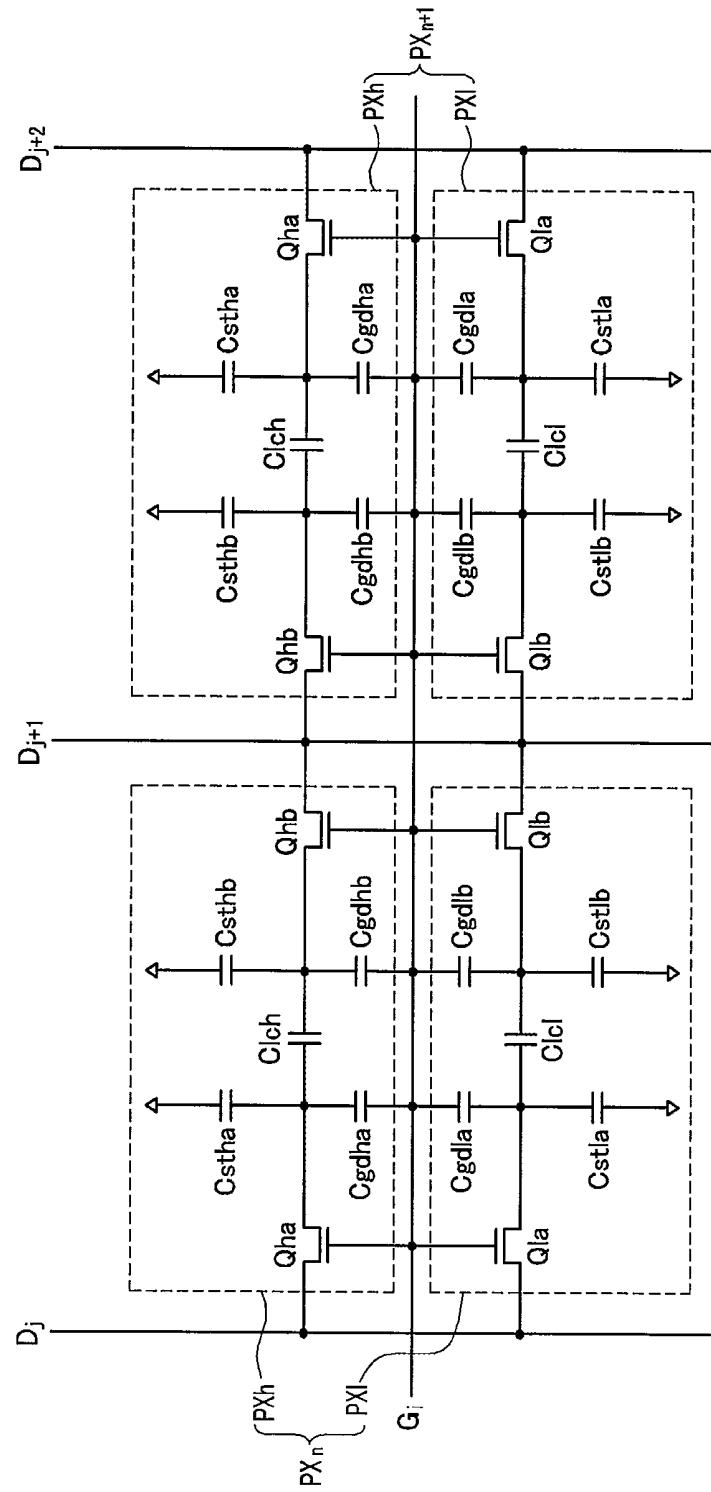

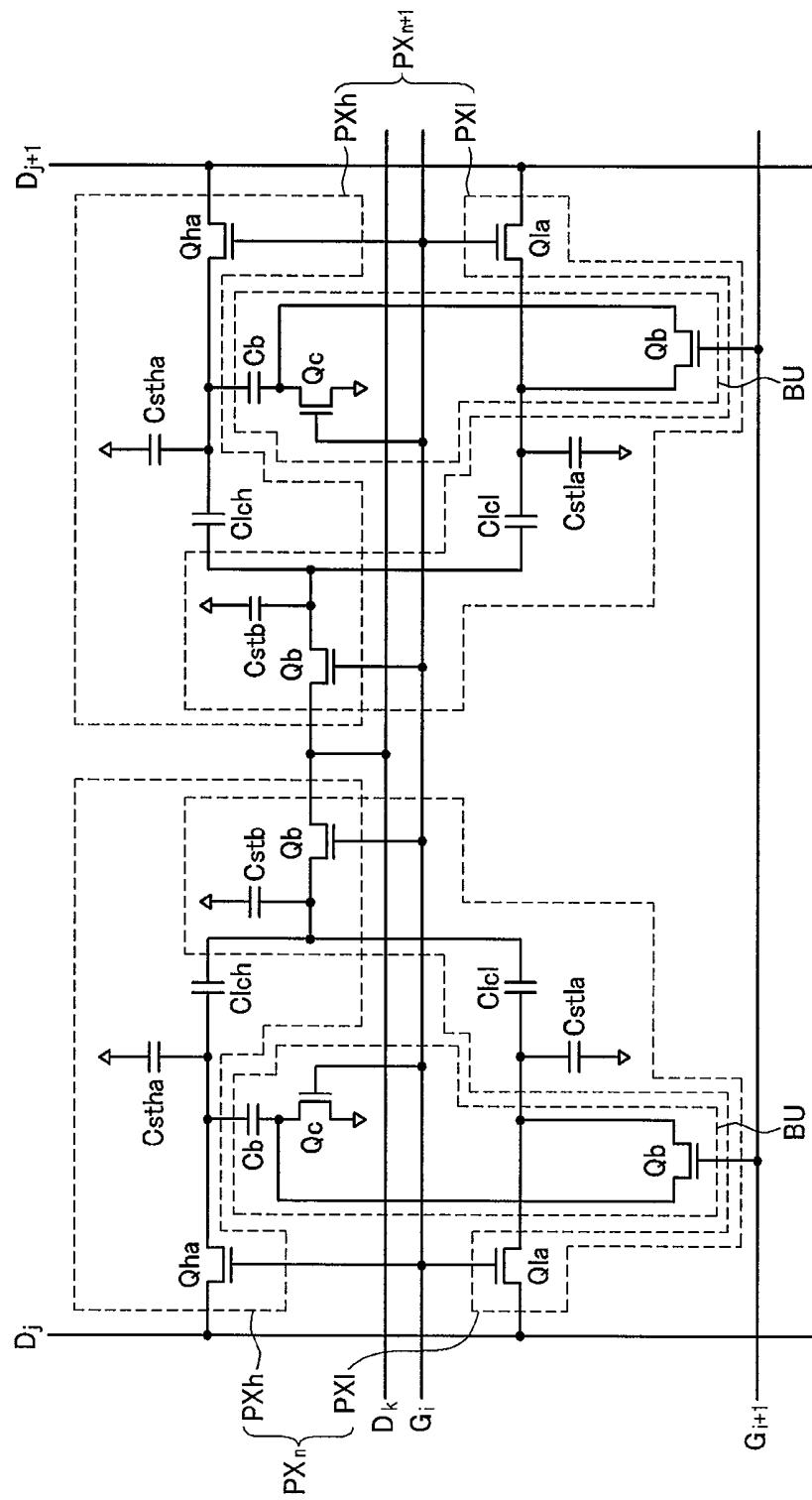

[0107] FIG. 13 and FIG. 14 are equivalent circuit diagrams each illustrating one pixel and a structure of a liquid crystal display panel according to another embodiment of the present invention;

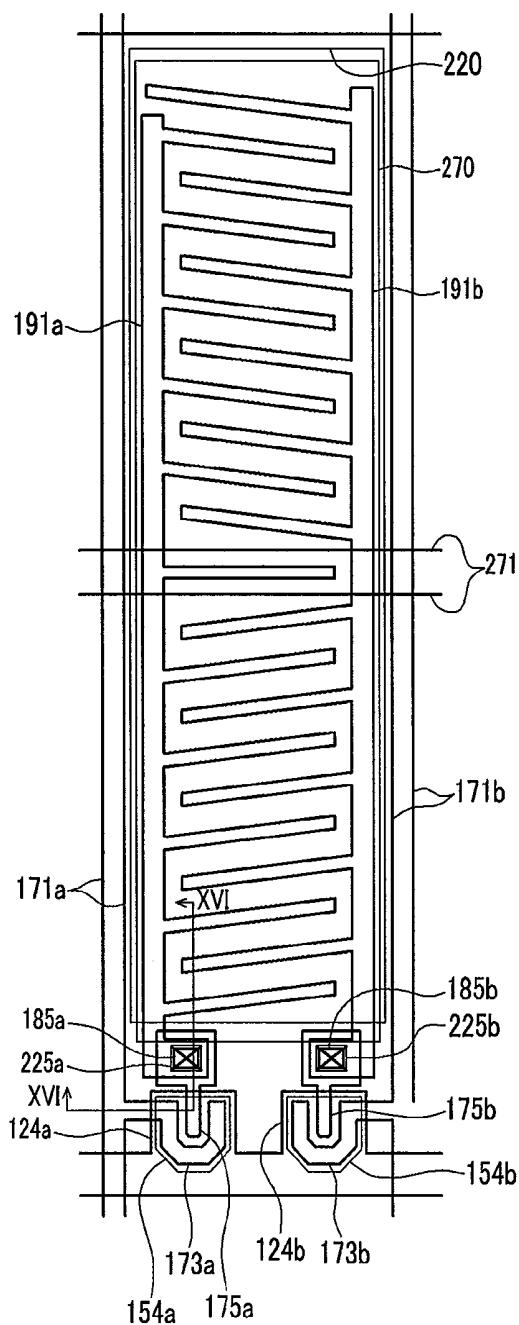

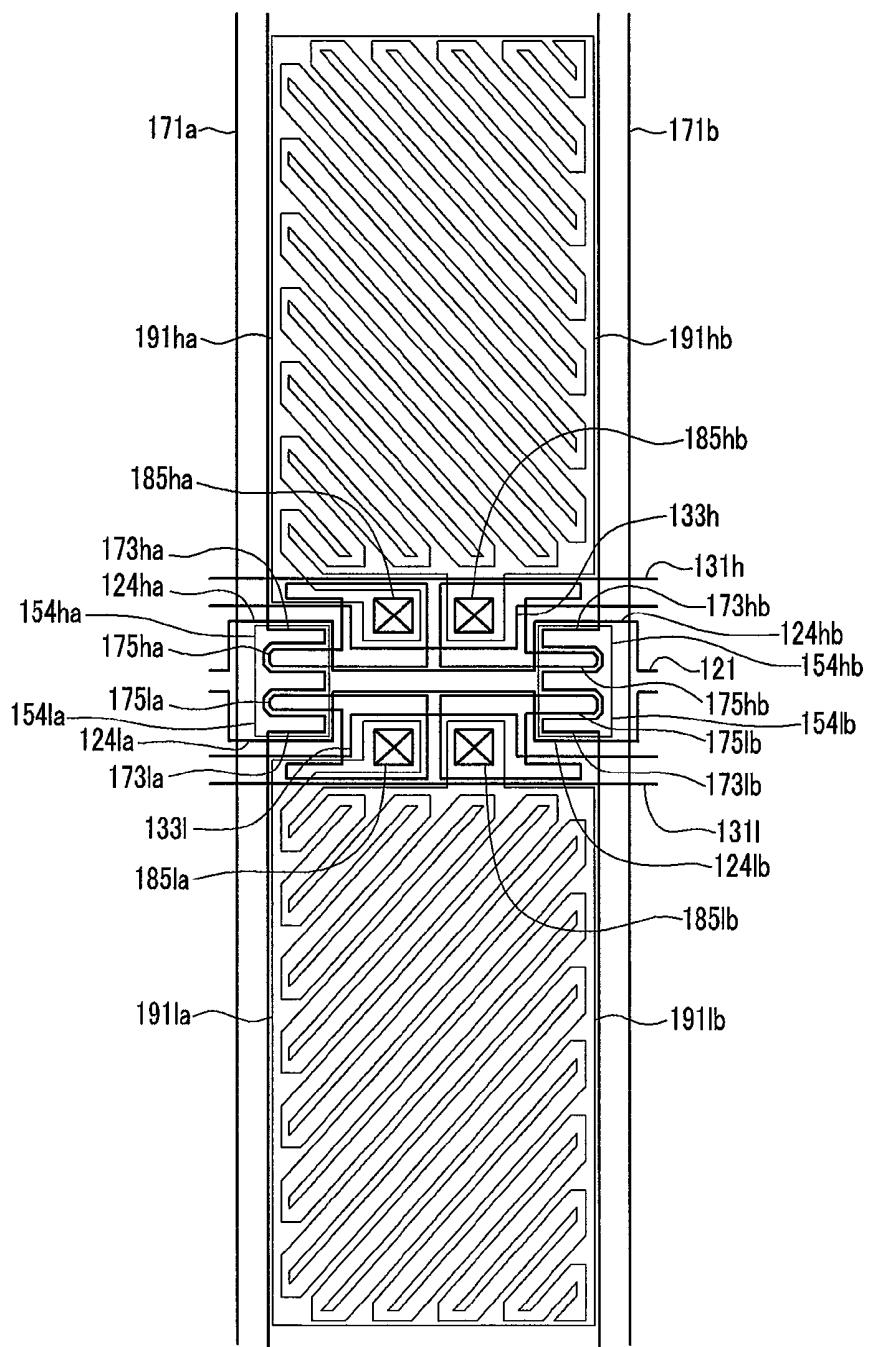

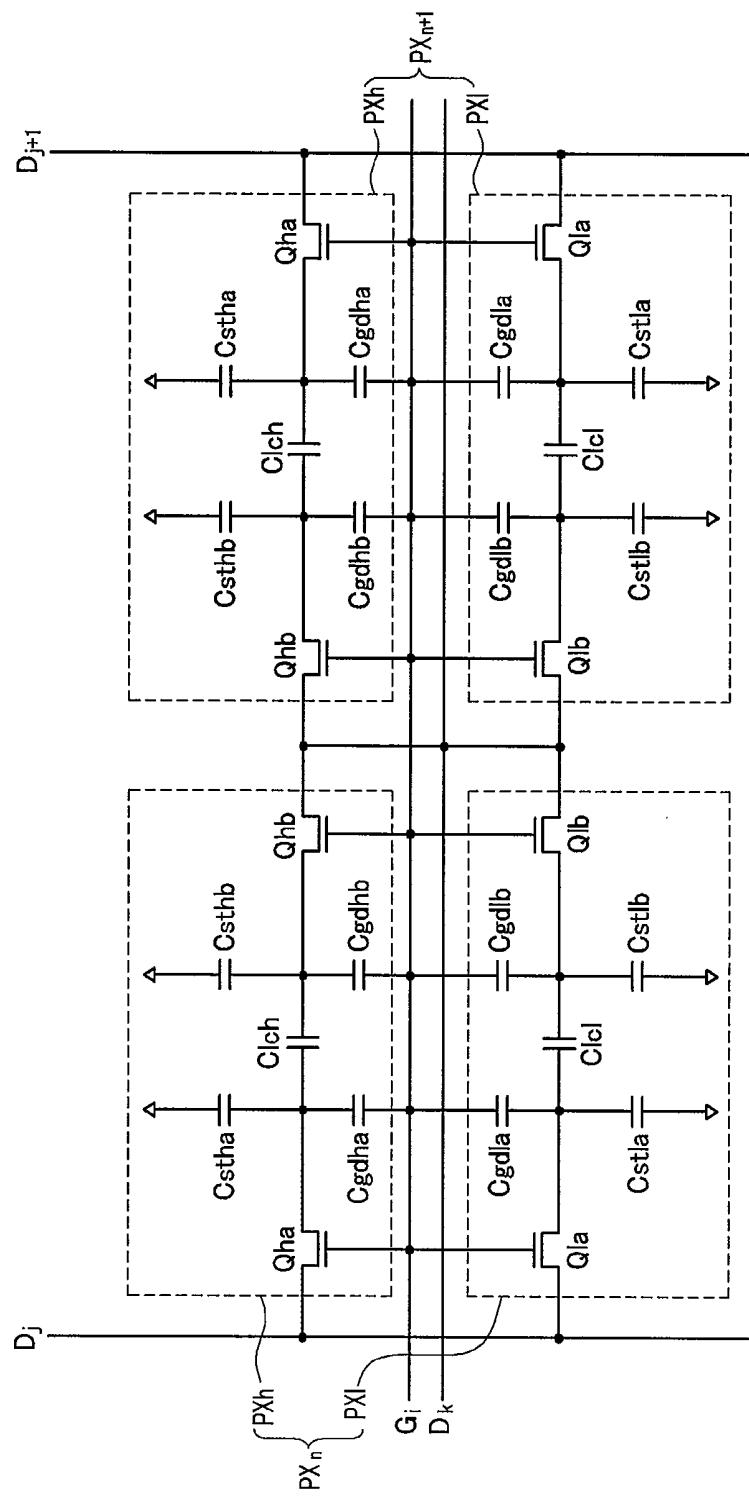

[0108] FIG. 15 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

[0109] FIG. 16 is a cross-sectional view of the liquid crystal panel assembly taken along line XVI-XVI of FIG. 15;

[0110] FIG. 17 is an equivalent circuit diagram illustrating a structure of a liquid crystal panel assembly and one pixel according to an embodiment of the present invention;

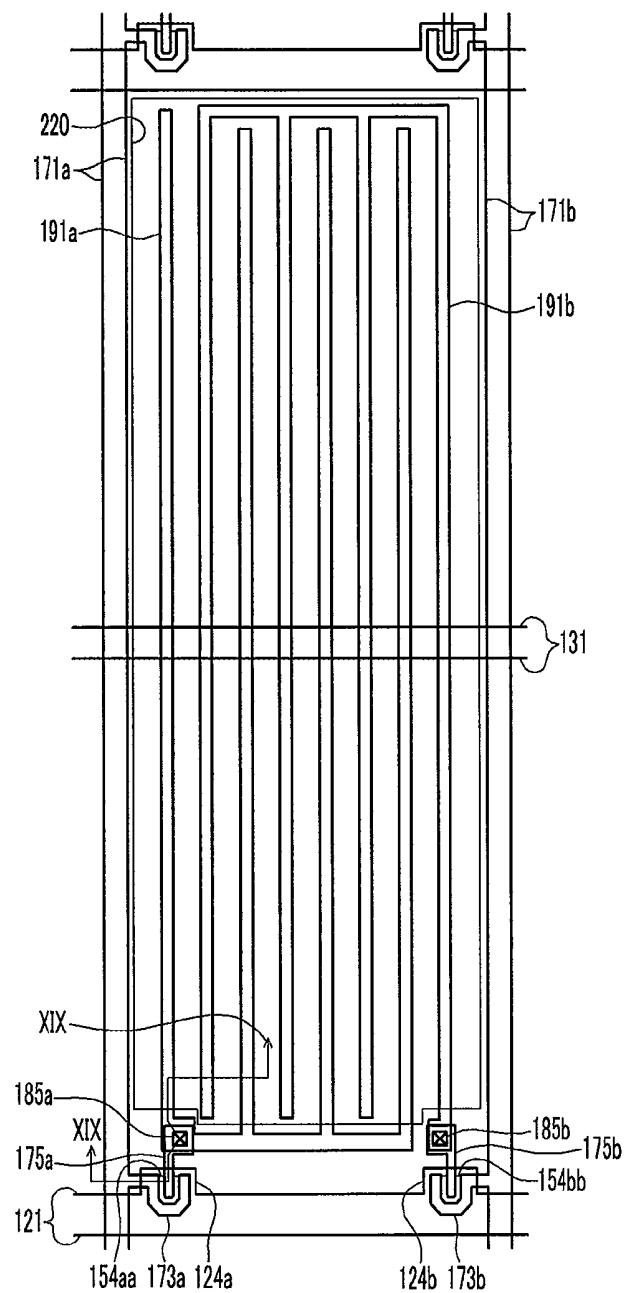

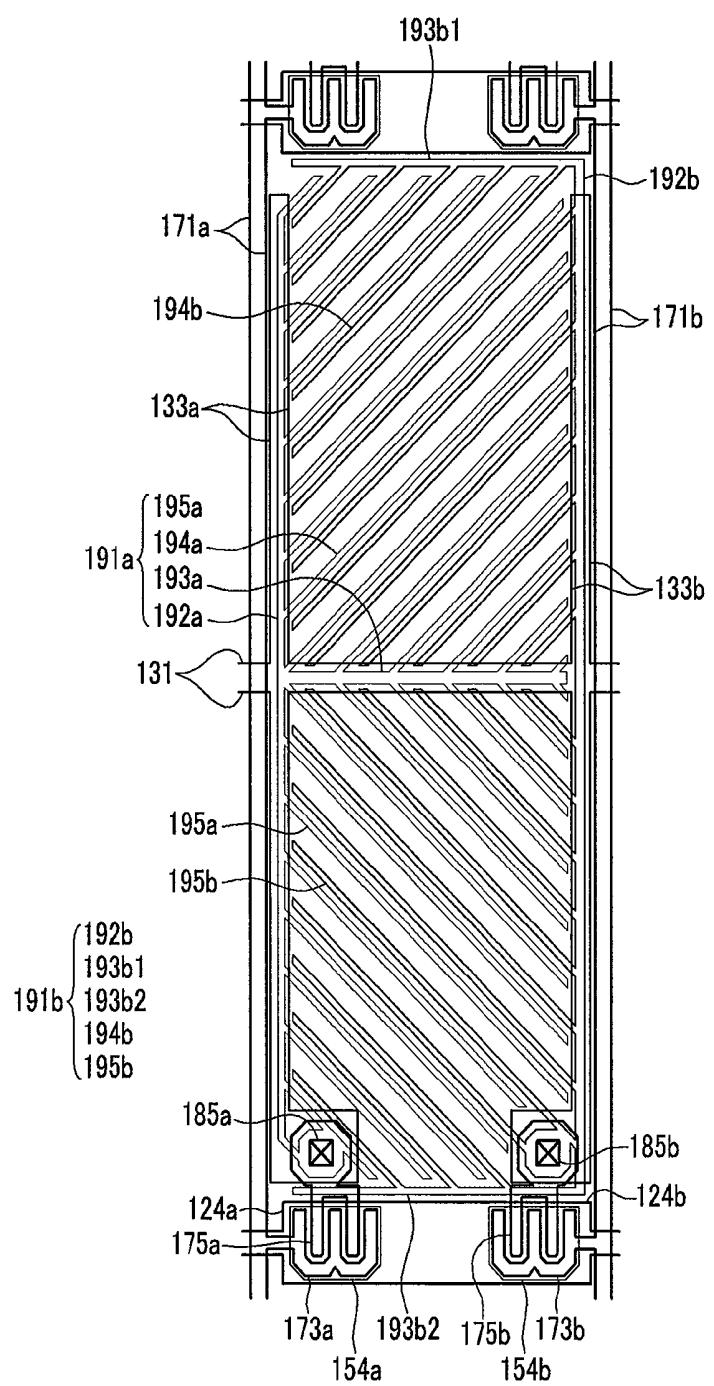

[0111] FIG. 18 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

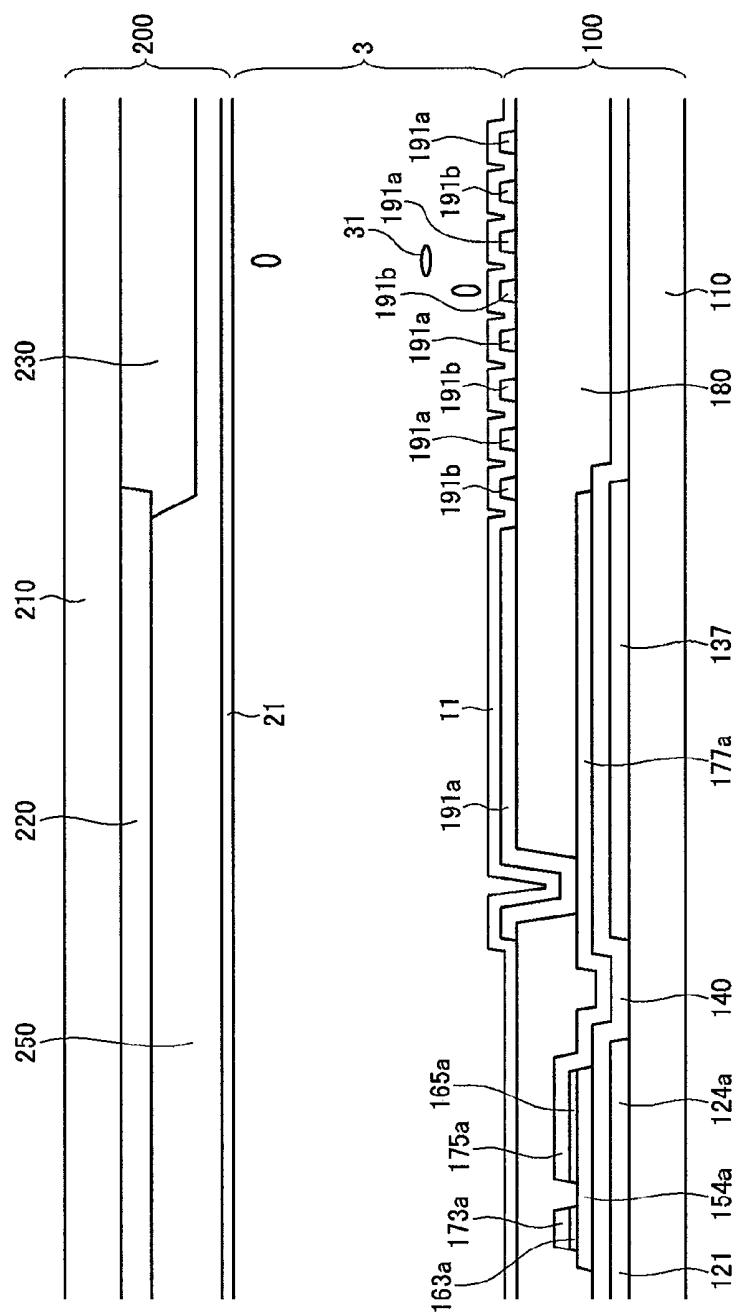

[0112] FIG. 19 is a cross-sectional view of the liquid crystal panel assembly taken along line XIX-XIX in FIG. 18;

[0113] FIG. 20 is an equivalent circuit diagram illustrating a structure of a liquid crystal panel assembly and one pixel according to an embodiment of the present invention;

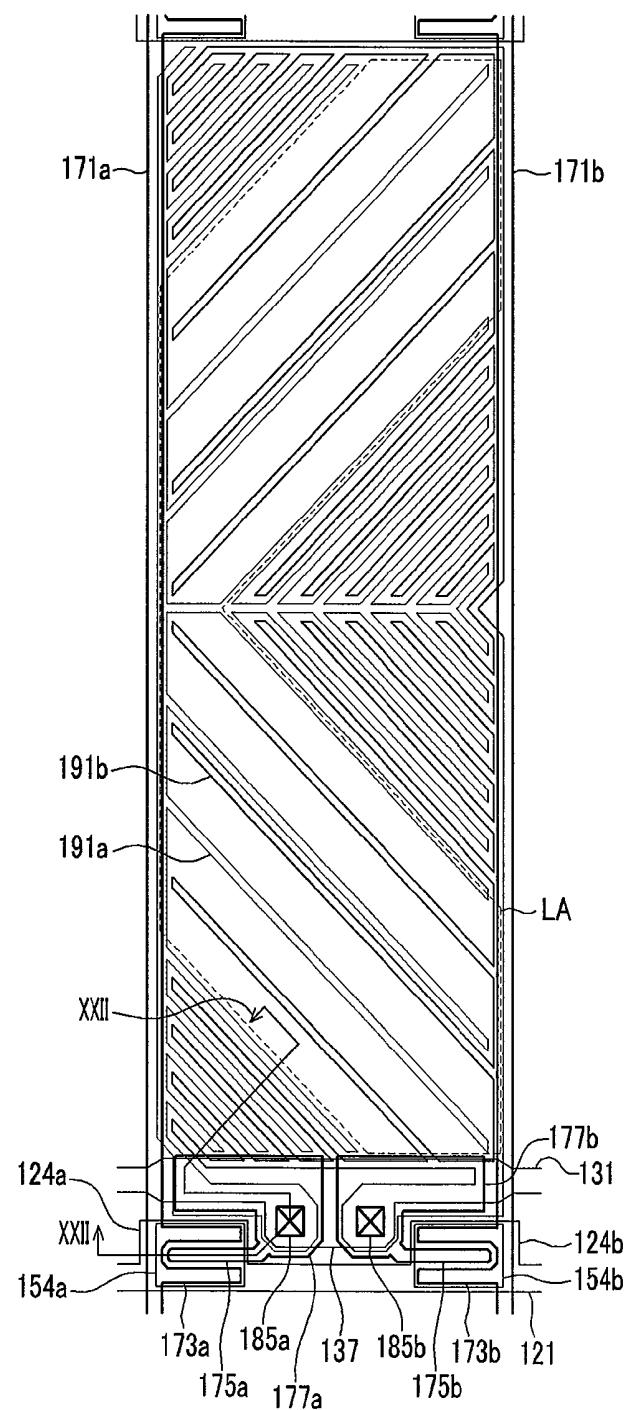

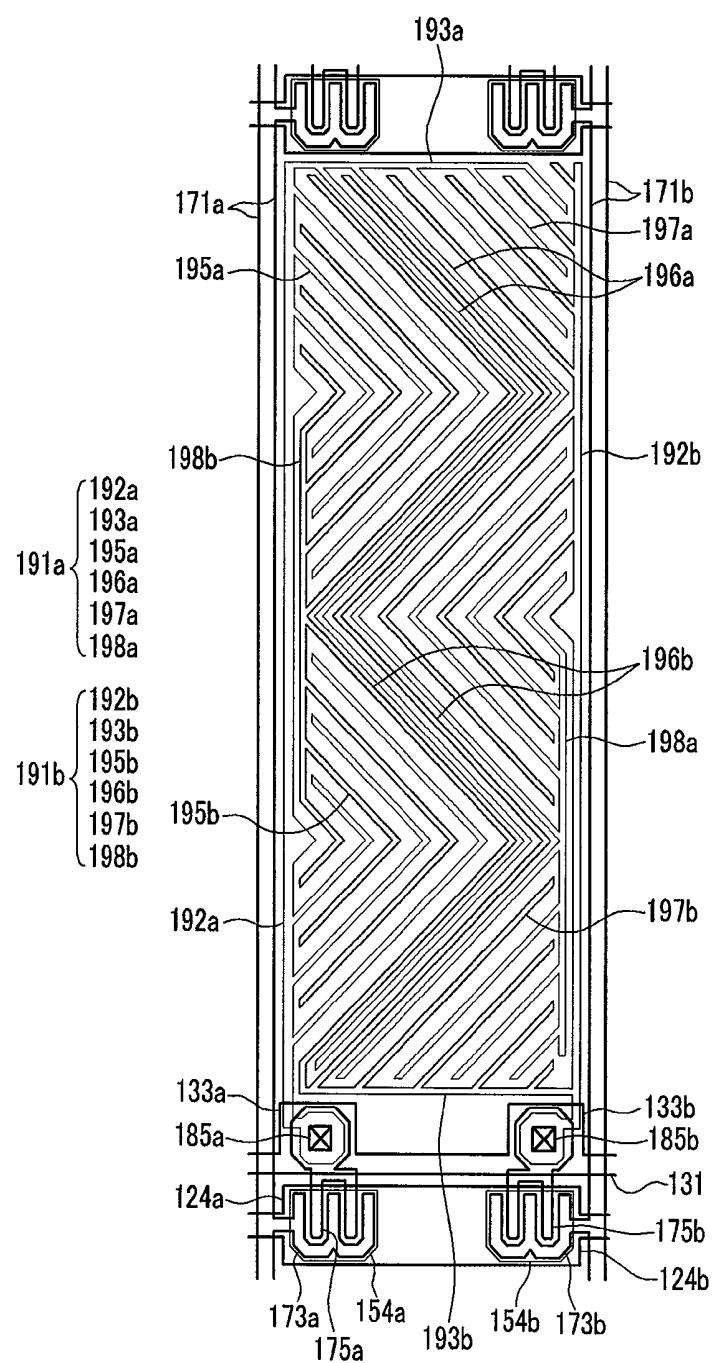

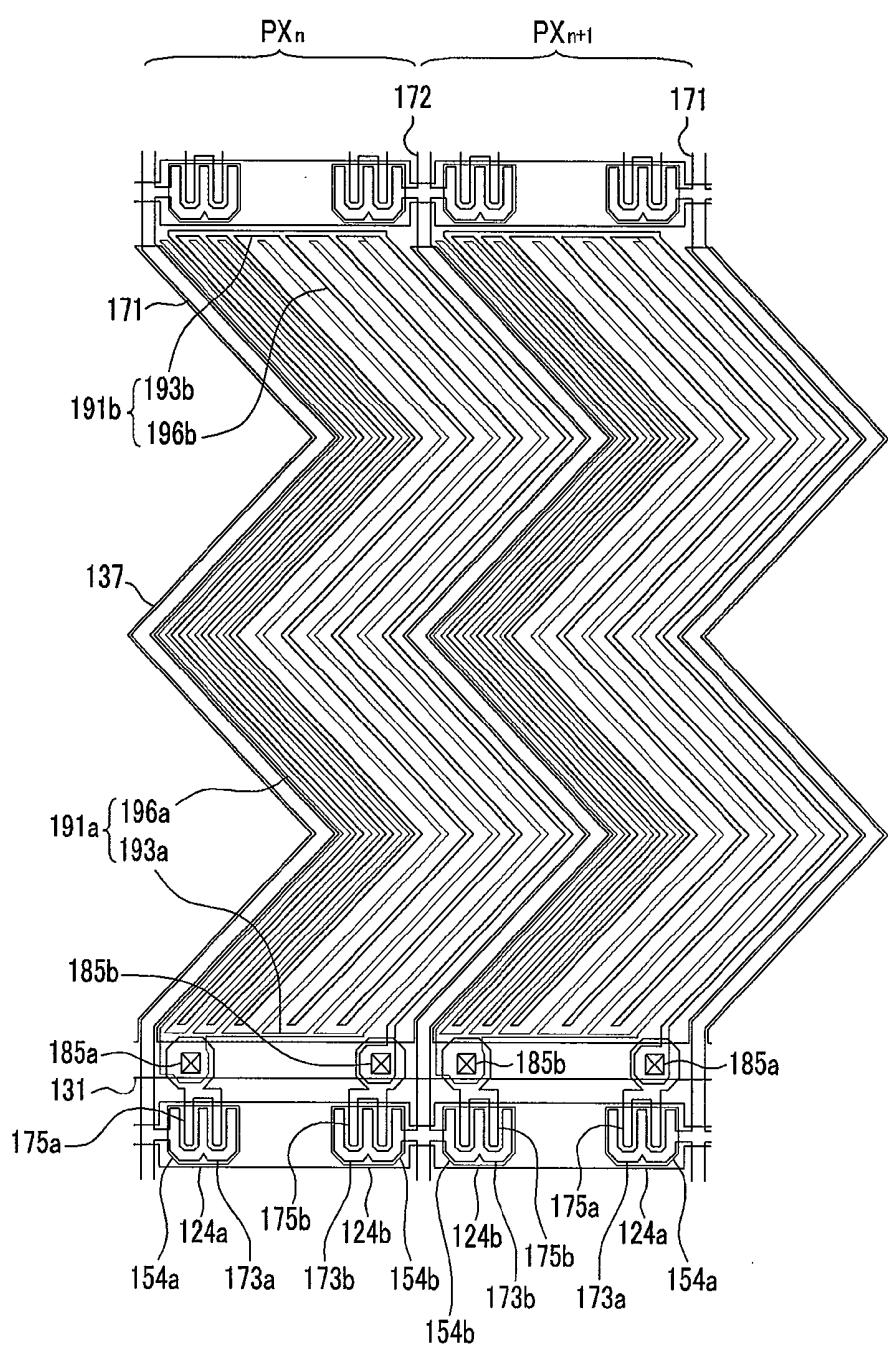

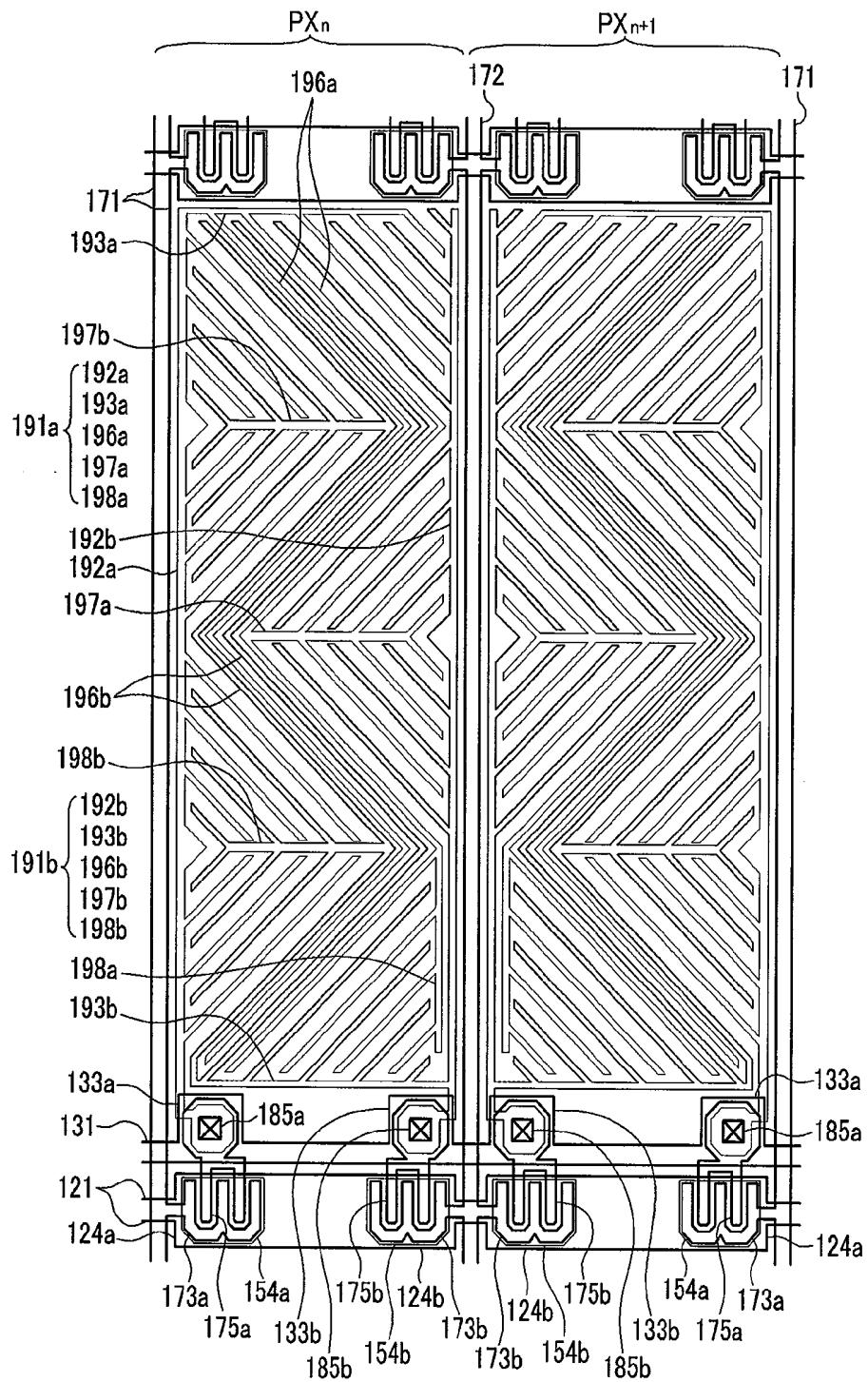

[0114] FIG. 21 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

[0115] FIG. 22 is a cross-sectional view of the liquid crystal panel assembly taken along line XXII-XXII in FIG. 21;

[0116] FIG. 23 to FIG. 25 are layout views of a liquid crystal panel assembly according to an embodiment of the present invention;

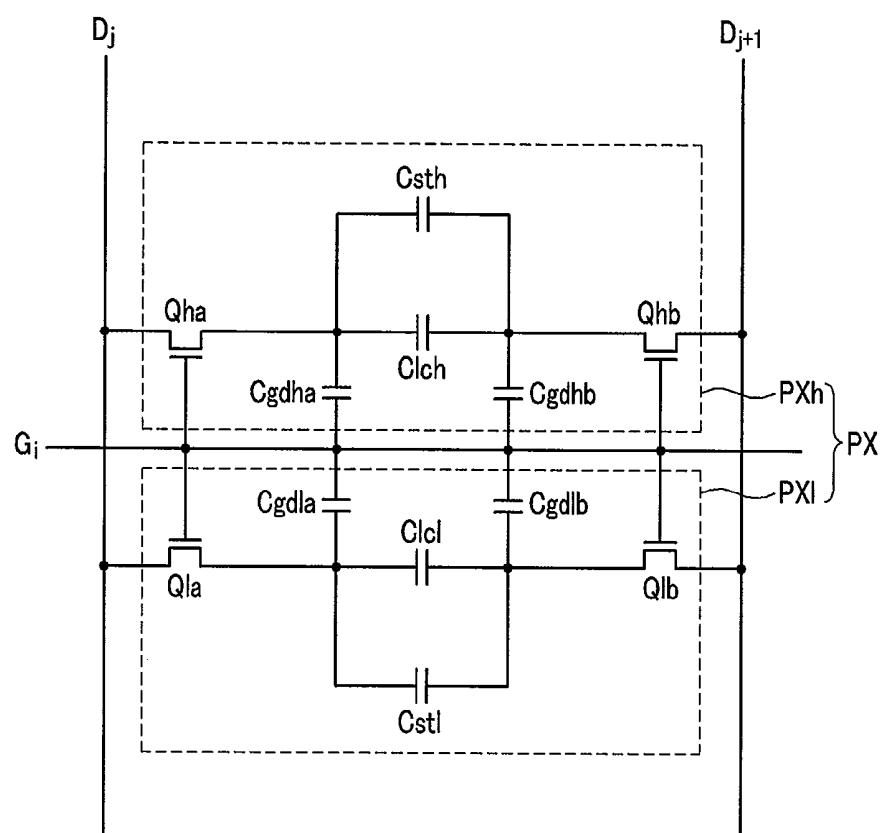

[0117] FIG. 26 is an equivalent circuit diagram illustrating a structure of a liquid crystal panel assembly and one pixel according to an embodiment of the present invention;

[0118] FIG. 27 is an equivalent circuit diagram illustrating two subpixels of a liquid crystal panel assembly according to another embodiment of the present invention;

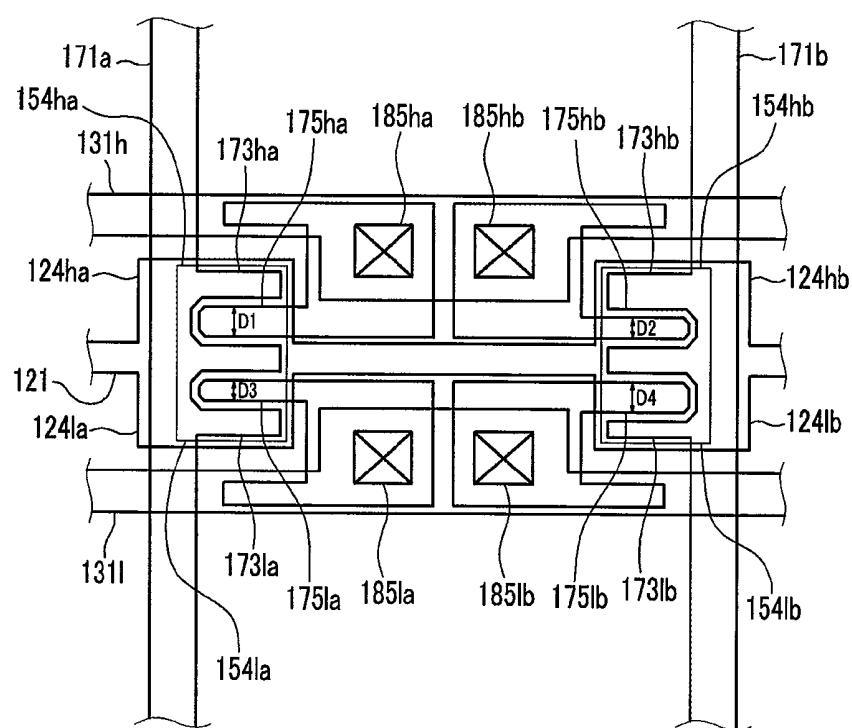

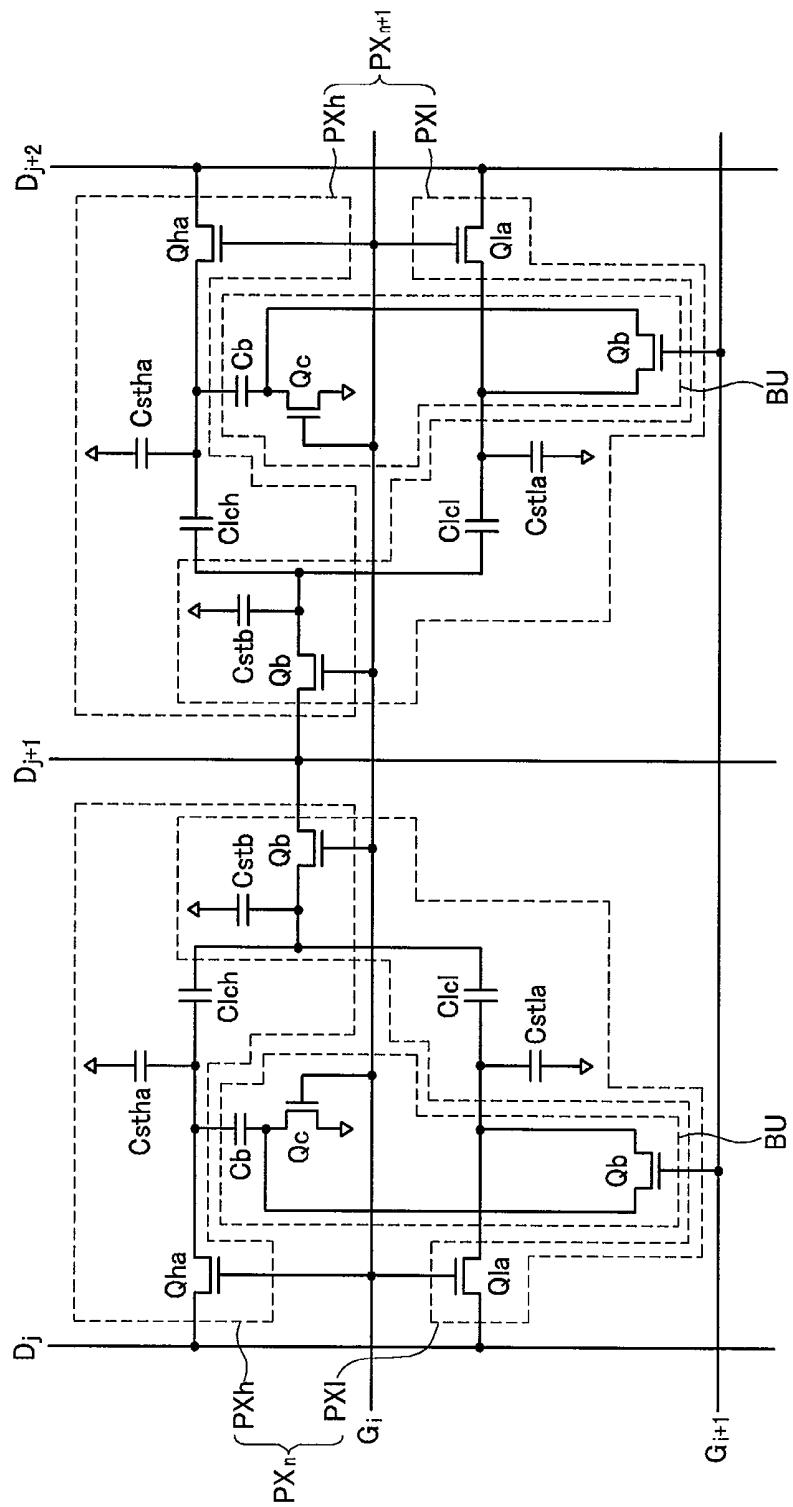

[0119] FIG. 28A is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

[0120] FIG. 28B is an enlarged layout view of switching elements of the liquid crystal panel assembly shown in FIG. 28A;

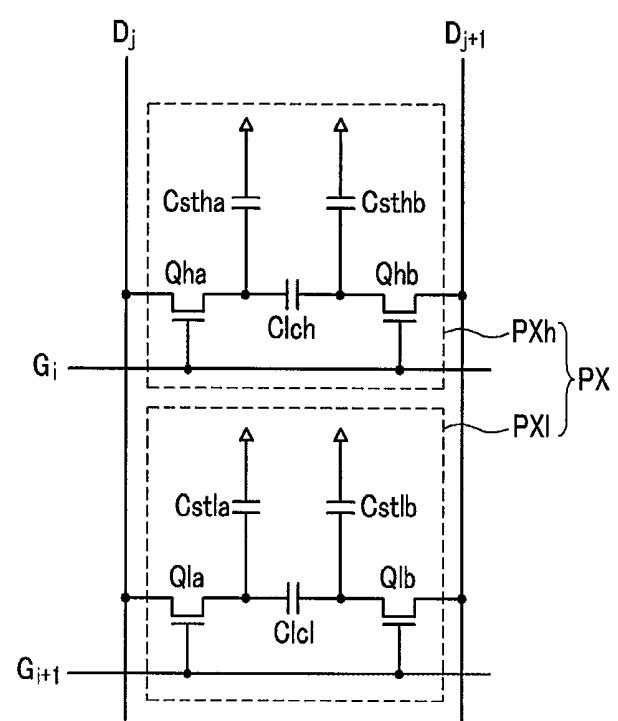

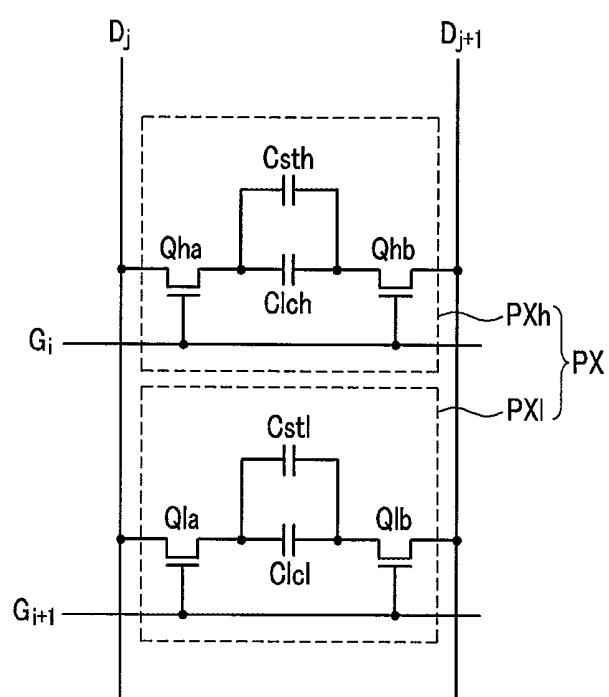

[0121] FIG. 29 to FIG. 34 are equivalent circuit diagrams of two subpixels of a liquid crystal panel assembly according to another embodiment of the present invention;

[0122] FIG. 35 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention;

[0123] FIG. 36 is an equivalent circuit diagram of two subpixels of a liquid crystal panel assembly according to another embodiment of the present invention;

[0124] FIG. 37 is an equivalent circuit diagram of two pixels of a liquid crystal panel assembly according to an embodiment of the present invention;

[0125] FIG. 38 and FIG. 39 are diagrams illustrating charging voltages of liquid crystal capacitors of four adjacent pixels in two successive frames and voltages applied to data lines in a case where the highest voltage and the lowest voltage that are usable by a liquid crystal display are 0V and 7V, and a common voltage Vcom is 7V according to an embodiment of the present invention;

[0126] FIG. 40 to FIG. 43 are equivalent circuit diagrams of two pixels of a liquid crystal panel assembly according to another embodiment of the present invention;

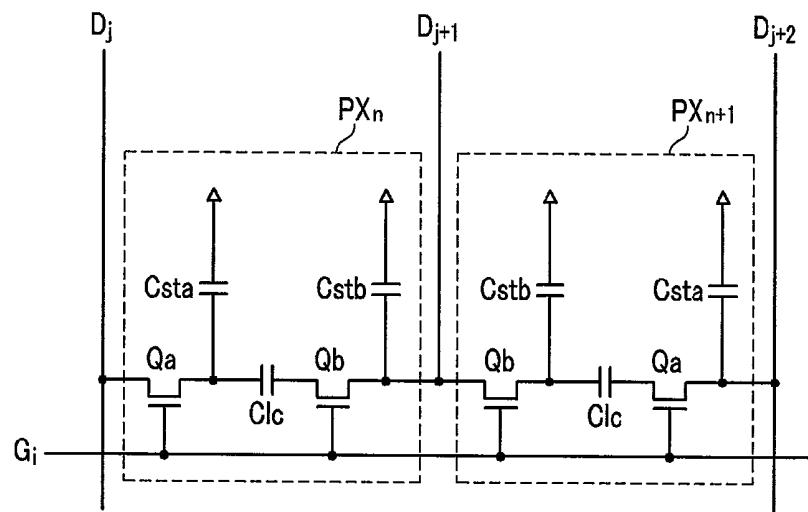

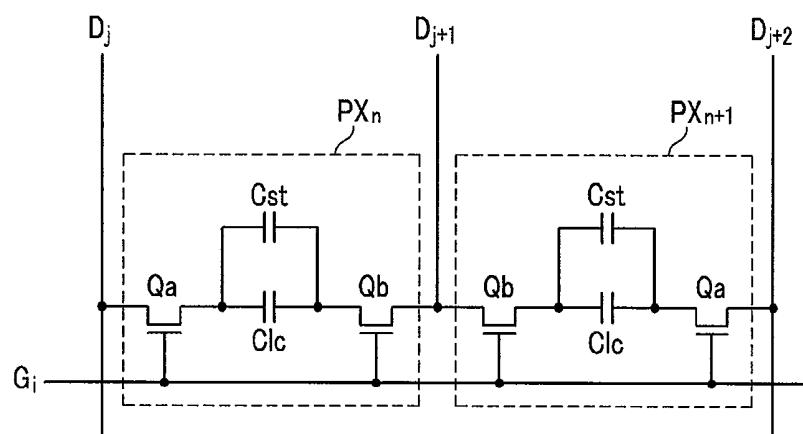

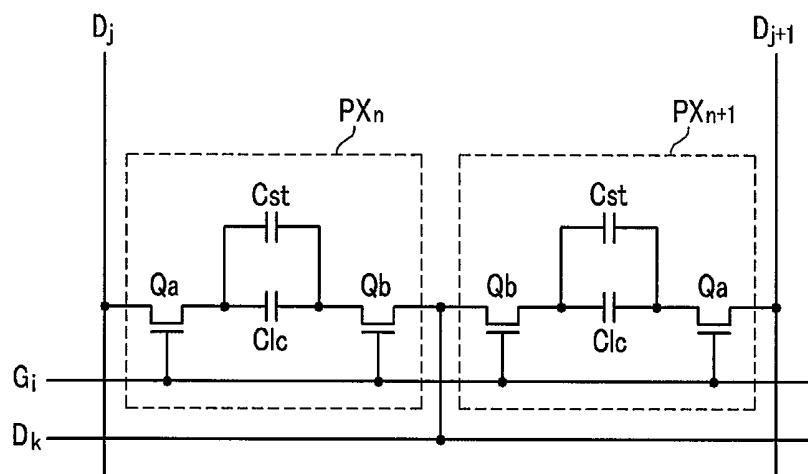

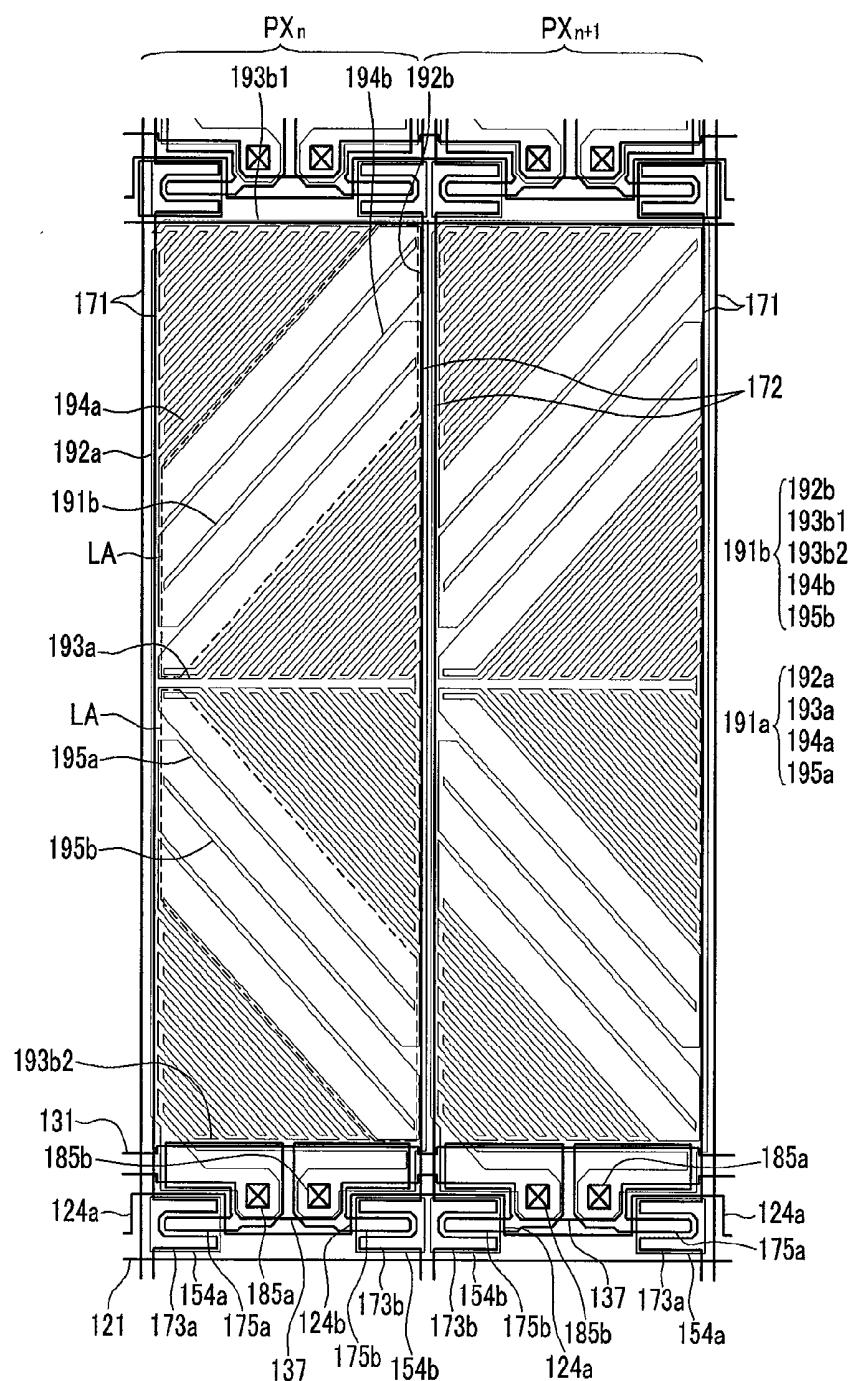

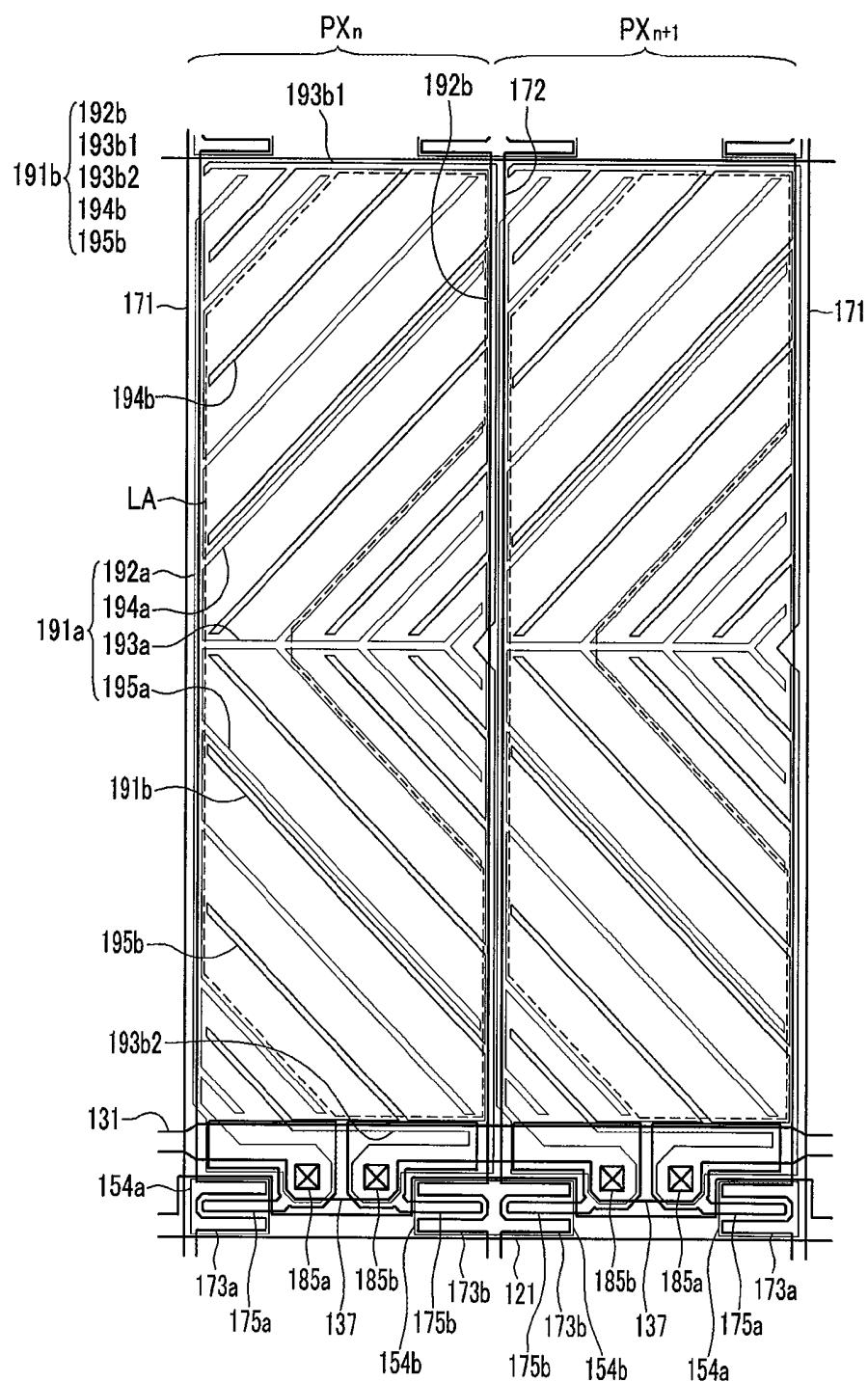

[0127] FIG. 44 to FIG. 47 are layout views of two pixels  $PX_n$  and  $PX_{n+1}$  of a liquid crystal panel assembly according to an embodiment of the present invention;

[0128] FIG. 48 is an equivalent circuit diagram illustrating a structure of a liquid crystal panel assembly and one pixel according to another embodiment of the present invention;

[0129] FIG. 49 to FIG. 51 are equivalent circuit diagrams of two subpixels of a liquid crystal panel assembly according to another embodiment of the present invention; and

[0130] FIG. 52 to FIG. 58 are equivalent circuit diagrams of two pixels of a liquid crystal panel assembly according to another embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

[0131] The present invention will be described more fully hereinafter with reference to the accompanying drawings, in which embodiments of the invention are shown. As those skilled in the art would realize, the described embodiments

may be modified in various different ways, all without departing from the spirit or scope of the present invention.

[0132] In the drawings, the thickness of layers, films, panels, regions, etc., are exaggerated for clarity. Like reference numerals designate like elements throughout the specification. It will be understood that when an element such as a layer, film, region, or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present. In contrast, when an element is referred to as being "directly on" another element, there are no intervening elements present.

[0133] Hereinafter, a liquid crystal display according to an embodiment of the present invention will be described in detail with reference to the accompanying drawings.

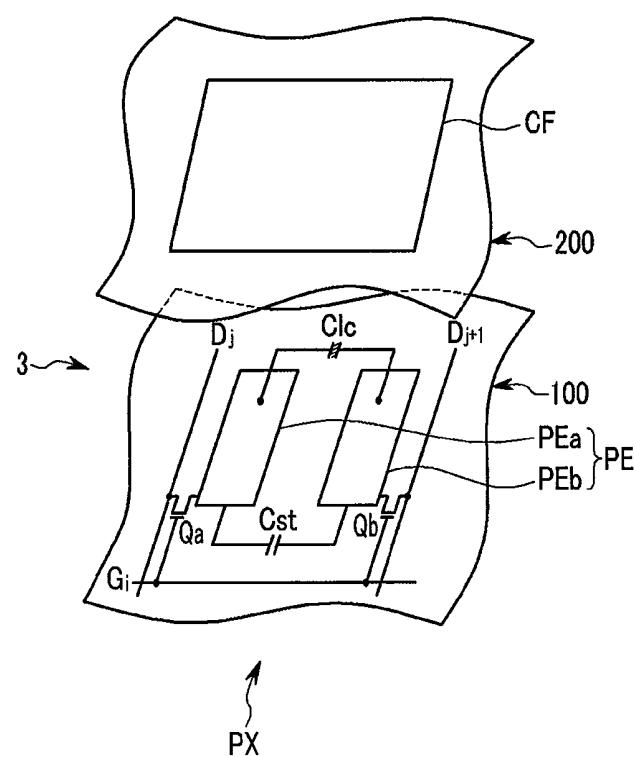

[0134] FIG. 1 is a block diagram of a liquid crystal display according to an embodiment of the present invention, FIG. 2 is an equivalent circuit diagram illustrating a structure of a liquid crystal display according to an embodiment of the present invention and one pixel, and FIG. 3 is an equivalent circuit diagram illustrating one pixel of a liquid crystal display according to an embodiment of the present invention.

[0135] Referring to FIG. 1, a liquid crystal display according to an embodiment of the present invention includes a liquid crystal panel assembly 300, a gate driver 400, a data driver 500, a gray voltage generator 800, and a signal controller 600.

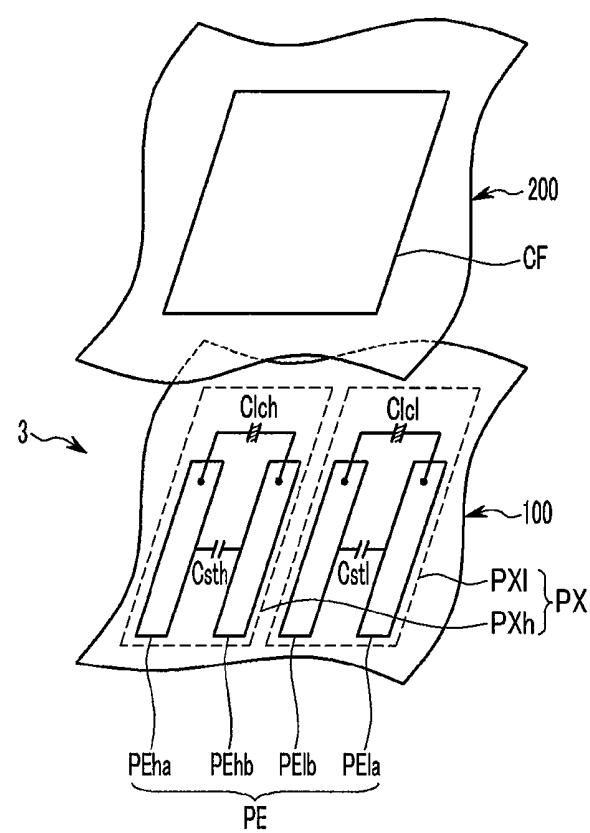

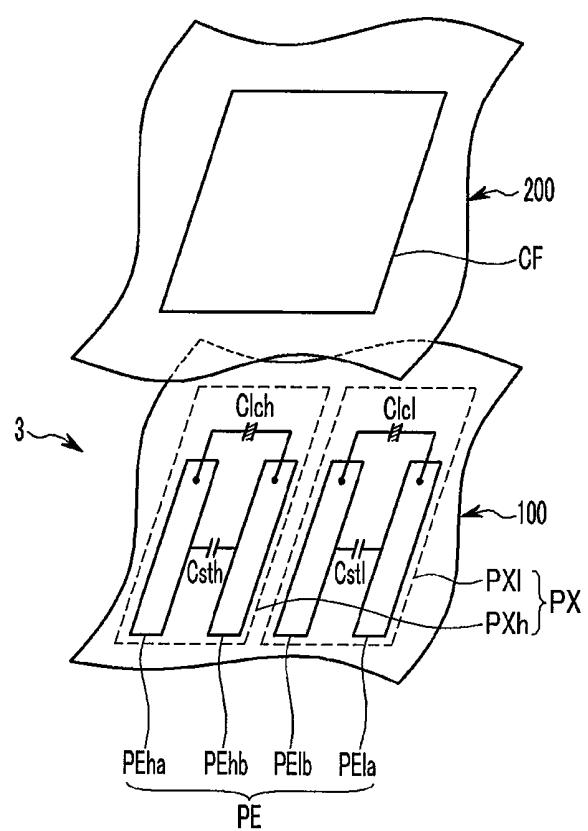

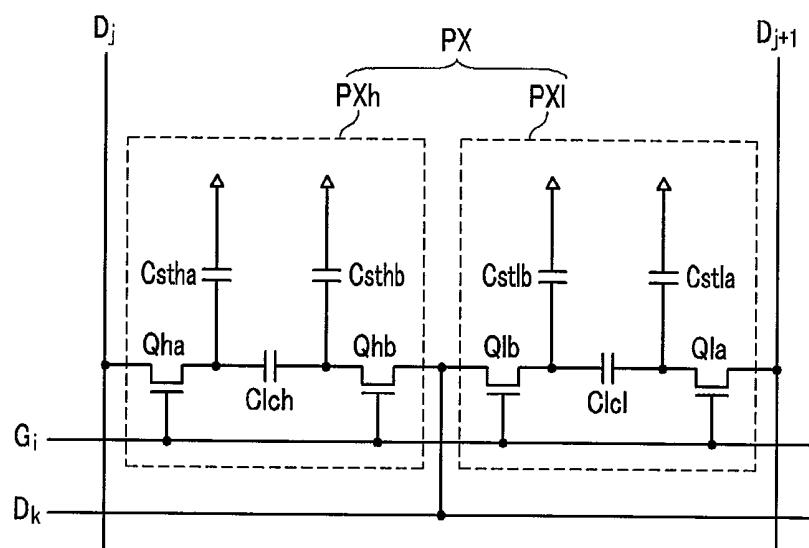

[0136] Referring to FIG. 1 and FIG. 3, the liquid crystal panel assembly 300 includes a plurality of signal lines  $G_i$ ,  $D_j$ , and  $D_{j+1}$  and a plurality of pixels PX that are connected thereto and arranged substantially in a matrix in view of an equivalent circuit. In contrast, in view of a structure shown in FIG. 2, the liquid crystal panel assembly 300 includes upper and lower panels 100 and 200 that are opposed to each other, and a liquid crystal layer 3 interposed therebetween.

[0137] The signal lines  $G_i$ ,  $D_j$ , and  $D_{j+1}$  include a plurality of gate lines  $G_i$  transmitting a gate signal (also referred to as "a scanning signal") and a plurality of pairs of data lines  $D_j$  and  $D_{j+1}$  transmitting a data voltage. The gate lines  $G_i$  extend substantially in a row direction and are substantially parallel to each other. The data lines  $D_j$  and  $D_{j+1}$  extend substantially in a column direction and are substantially parallel to each other.

[0138] Each pixel PX, for example a pixel PX that is connected to the  $i$ -th ( $i=1, 2, \dots, n$ ) gate line  $G_i$  and the  $j$ -th and ( $j+1$ )-th ( $j=1, 2, \dots, m$ ) data lines  $D_j$  and  $D_{j+1}$  includes first and second switching devices  $Qa$  and  $Qb$  connected to the signal lines  $G_i$ ,  $D_j$ , and  $D_{j+1}$ , a liquid crystal capacitor  $Clc$  connected thereto, and first and second storage capacitors  $Csta$  and  $Cstb$ . The first and second storage capacitors  $Csta$  and  $Cstb$  may be omitted as necessary.

[0139] The first/second switching device  $Qa/Qb$  is a three-terminal device such as a thin-film transistor provided in the lower panel 100. A control terminal thereof is connected to the gate line  $G_i$ , an input terminal thereof is connected to the data line  $D_j/D_{j+1}$ , and an output terminal thereof is connected to the liquid crystal capacitor  $Clc$  and the first and second storage capacitors  $Csta$  and  $Cstb$ .

[0140] Referring to FIG. 2 and FIG. 3, the liquid crystal capacitor  $Clc$  adopts the first pixel electrode  $PEa$  and the second pixel electrode  $PEb$  of the lower panel 100 as two terminals, and the liquid crystal layer 3 between the first and second pixel electrodes  $PEa$  and  $PEb$  and the upper panel 200 serves as a dielectric material.

[0141] The first pixel electrode  $PEa$  is connected to the first switching element  $Qa$  and the second pixel electrode  $PEb$  is connected to the second switching element  $Qb$ .

[0142] Alternatively to FIG. 2, the second pixel electrode  $PEb$  may be provided on the upper panel 200. In this case, the second pixel electrode  $PEb$  is not connected to a switching element and receives a separate common voltage  $Vcom$ .

[0143] The liquid crystal layer 3 has dielectric anisotropy, and liquid crystal molecules of the liquid crystal layer 3 have their long axes aligned to be vertical to surfaces of the two panels 100 and 200 without an electric field.

[0144] A pixel electrode  $PE$  including the first and second pixel electrodes  $PEa$  and  $PEb$ , and a common electrode  $CE$ , may be formed in different layers or in the same layer. The first and second storage capacitors  $Csta$  and  $Cstb$  serving as assistants of the liquid crystal capacitor  $Clc$  may be formed by superimposing separate electrodes (not shown) provided on the lower panel 100 with being interposed between the first and second pixel electrodes  $PEa$  and  $PEb$ , and insulators.

[0145] Meanwhile, in order to implement color display, a desired color is recognized by a spatial or temporal sum of primary colors by allowing pixels  $PX$  to uniquely display one of the primary colors (spatial division) or the pixels  $PX$  to alternately display the primary colors (temporal division).

[0146] The primary colors include three primary colors such as red, green, and blue.

[0147] FIG. 2 shows that each pixel  $PX$  includes a color filter  $CF$  displaying one of the primary colors in an area of the upper panel 200 corresponding to the first and second pixel electrodes  $PEa$  and  $PEb$  as one example of the spatial division.

[0148] Alternatively to FIG. 2, the color filter  $CF$  may be disposed above or below the first and second pixel electrodes  $PEa$  and  $PEb$  of the lower panel 100.

[0149] At least one polarizer (not shown) is provided in the liquid crystal panel assembly 300.

[0150] Referring back to FIG. 1, the gray voltage generator 800 generates all gray voltages or gray voltages of a limited number (hereinafter referred to as "reference gray voltages") related to transmittance of the pixel  $PX$ .

[0151] The reference gray voltages may include a gray voltage having a positive value and another gray voltage having a negative value with respect to the common voltage  $Vcom$ .

[0152] The gate driver 400 is connected to the gate lines of the liquid crystal panel assembly 300, and applies a gate signal configured of a combination of a gate-on voltage  $Von$  and a gate-off voltage  $Voff$  to the gate lines.

[0153] The data driver 500 is connected to the data lines of the liquid crystal panel assembly 300, and selects a gray voltage applied from the gray voltage generator 800 and applies the selected gray voltage as a data voltage to the data line.

[0154] However, in a case in which the gray voltage generator 800 provides reference gray voltages of a limited number instead of all the gray voltages, the data driver 500 may generate desired data voltages by dividing the reference gray voltages.

[0155] The signal controller 600 controls the gate driver 400 and the data driver 500.

[0156] Each of the drivers 400, 500, 600, and 800 is mounted directly on the liquid crystal panel assembly in the form of at least one IC chip, is mounted on a flexible printed circuit film (not shown) to be attached onto the liquid crystal

panel assembly 300 in the form of a tape carrier package (TCP), or is mounted on a separate printed circuit board (PCB) (not shown).

[0157] Alternatively, the drivers 400, 500, 600, and 800 may be integrated on the liquid crystal panel assembly 300 with signal lines and a thin-film transistor switching element.

[0158] Further, the drivers 400, 500, 600, and 800 may be integrated in the form of a single chip. In this case, at least one of them or at least one circuit element constituting them may be positioned outside the single chip.

[0159] Hereinafter, referring to FIG. 4 and FIG. 5, and FIG. 1 to FIG. 3, an example of a driving method of a liquid crystal display according to an embodiment of the present invention will be described in detail.

[0160] FIG. 4 is a schematic cross-sectional view of a liquid crystal display according to an embodiment of the present invention, and FIG. 5 is a diagram illustrating voltages applied to data lines and pixels of a liquid crystal display according to an embodiment of the present invention.

[0161] First, referring to FIG. 1, the signal controller 600 receives input image signals R, G, and B and input control signals controlling display of the input image signals R, G, and B from an external graphics controller (not shown).

[0162] The input image signals R, G, and B contain luminance information of each pixel, and the luminance has a predetermined number, for example 1024 (=2<sup>10</sup>), 256 (=2<sup>8</sup>) or 64 (=2<sup>6</sup>), of grays.

[0163] The input control signals may include a vertical synchronization signal (Vsync), a horizontal synchronization signal (Hsync), a main clock signal (MCLK), a data enable signal (DE), and the like.

[0164] The signal controller 600 appropriately processes the input image signals R, G, and B according to an operating condition of the liquid crystal panel assembly 300 on the basis of the input image signals R, G, and B and the input control signals. The signal controller 600 generates a gate control signal CONT1 and a data control signal CONT2, and outputs the gate control signal CONT1 to the gate driver 400 and outputs the data control signal CONT2 and processed image signals DAT to the data driver 500.

[0165] According to the data control signal from the signal controller 600, the data driver 500 receives digital image signals DAT for a pixel of one row and converts each digital image signal DAT into an analog data voltage by selecting a gray voltage corresponding to each digital image signal DAT, and then applies the analog data voltages to the corresponding data lines.

[0166] The gate driver 400 applies the gate-on voltage Von to the gate line G<sub>i</sub> according to the gate control signal CONT1 from the signal controller 600 to turn on the first and second switching elements Qa and Qb connected to the gate line G<sub>i</sub>.

[0167] Then, the data voltages applied to the data lines D<sub>j</sub> and D<sub>j+1</sub> are applied to the corresponding pixels PX through the first and second switching elements Qa and Qb.

[0168] That is, the data voltage flowing in the first data line D<sub>j</sub> is applied to the first pixel electrode PEa through the first switching element Qa, and the data voltage flowing in the second data line D<sub>j+1</sub> is applied to the second pixel electrode PEb through the second switching element Qb.

[0169] At this time, the data voltages applied to the first and second pixel electrodes PEa and PEb are data voltages corresponding to luminance displayed by the pixels PX, and have polarities opposite to each other with respect to the common voltage Vcom.

[0170] A difference between the two data voltages having different polarities, which are applied to the first and second pixel electrodes PEa and PEb, is indicated by a charging voltage of the liquid crystal capacitor Clc, that is, a pixel voltage.

[0171] When a potential difference is generated between both terminals of the liquid crystal capacitor Clc, an electric field parallel to the surfaces of the panels 100 and 200 is generated in the liquid crystal layer 3 between the first and second pixel electrodes PEa and PEb, as shown in FIG. 4.

[0172] In a case in which liquid crystal molecules 31 have positive dielectric anisotropy, the liquid crystal molecules 31 are inclined so that their long axes are aligned to be vertical to the direction of the electric field and the inclination degree depends on the amplitude of the pixel voltage.

[0173] Such a liquid crystal layer 3 is referred to as an electrically-induced optical compensation (EOC) mode.

[0174] The degree of variation of polarization of light passing through the liquid crystal layer 3 depends on the inclination degree of the liquid crystal molecules 31.

[0175] The variation of polarization is expressed by variation in transmittance of light through the polarizers, through which the pixel PX displays luminance indicated by the gray of the image signal DAT.

[0176] By repeating such a process by one horizontal period (also referred to as "1H", equal to one period of the horizontal synchronization signal (Hsync) and the data enable signal DE), the gate-on signal Von is sequentially applied to all the gate lines and the data voltages are applied to all the pixels PX thereby to display an image of one frame.

[0177] After one frame is terminated, the next frame starts. A state of an inversion signal RVS applied to the data driver 500 is controlled so that the polarity of the data voltage applied to each pixel PX is reversed to be opposite to that of the previous frame ("frame inversion").

[0178] At this time, the polarity of the data voltage flowing in one data line may be periodically changed during one frame according to characteristics of the inversion signal RVS (for example, row inversion and dot inversion) or the polarities of the data voltages applied to one pixel row may be alternately different from each other (for example, column inversion and the dot inversion).

[0179] FIG. 5 is a diagram illustrating voltages applied to each of the data lines when charging voltages of the liquid crystal capacitors of four adjacent pixels are 14V, 10V, 5V, and 1V, respectively, and a minimum voltage and a maximum voltage which the liquid crystal display can use are 0V and 14V, respectively, in the liquid crystal display according to an embodiment of the present invention.

[0180] Referring to FIG. 5, each pixel is connected to two data lines D<sub>j</sub>, D<sub>j+1</sub>/D<sub>j+2</sub>, D<sub>j+3</sub>/D<sub>j+4</sub>, D<sub>j+5</sub>/D<sub>j+6</sub>, D<sub>j+7</sub>. Different data voltages having different polarities with respect to the common voltage Vcom are applied to the two data lines D<sub>j</sub>, D<sub>j+1</sub>/D<sub>j+2</sub>, D<sub>j+3</sub>/D<sub>j+4</sub>, D<sub>j+5</sub>/D<sub>j+6</sub>, D<sub>j+7</sub> connected to one pixel. A difference between the two data lines is a pixel voltage in each pixel PX. For example, when the common voltage Vcom is 7V, 14V and 0V may be applied to the first and second data lines D<sub>j</sub> and D<sub>j+1</sub> respectively with a target pixel voltage, 14V, of the first pixel, 12V and 2V may be applied to the third and fourth data lines D<sub>j+2</sub> and D<sub>j+3</sub> respectively with a target pixel voltage, 5V, of the second pixel, 9.5V and 4.5V may be applied to the fifth and sixth data lines D<sub>j+4</sub> and D<sub>j+5</sub> respectively with a target pixel voltage, 5V, of the third pixel, and 7.5V and 6.5V may be applied to the seventh

and eighth data lines  $D_{j+6}$  and  $D_{j+7}$  respectively with a target pixel voltage, 1V, of the fourth pixel.

[0181] As described above, by applying two data voltages having different polarities with respect to the common voltage  $V_{com}$  to one pixel  $PX$ , a driving voltage may be increased, the response speed of the liquid crystal molecules may be improved, and the transmittance of the liquid crystal display may be improved. Further, since the two data voltages applied to the one pixel  $PX$  have polarities that are opposite to each other, it is possible to prevent deterioration of image quality due to flickers even in a case where the inversion type in the data driver **500** is the column inversion or the row inversion advantageously like the dot inversion.

[0182] In addition, when the first and second switching elements  $Qa$  and  $Qb$  are turned off in one pixel, the voltages applied to the first and second pixel electrodes  $PEa$  and  $PEb$  drop simultaneously by respective kickback voltages, whereby there is little variation in the charging voltage of the pixel  $PX$ . Accordingly, it is possible to improve display characteristics of the liquid crystal display.

[0183] Furthermore, in a case of using liquid crystal molecules **31** aligned vertical to the surfaces of the display panels **100** and **200**, it is possible to improve the contrast ratio of a liquid crystal display and implement a good optical viewing angle. Since the liquid crystal molecules **31** having positive dielectric anisotropy have dielectric anisotropy that is larger and rotational viscosity that is lower compared to liquid crystal molecules **31** having negative dielectric anisotropy, it is possible to increase the response speed of the liquid crystal molecules **31**. Also, since the tilt directions of the liquid crystal molecules **31** are easily set to the direction of a generated electric field, it is possible to acquire excellent display characteristics even when the alignment of the liquid crystal molecules **31** is scattered due to an external influence.

[0184] Next, referring to FIG. 6 to FIG. 10 and FIG. 1 to FIG. 5 described above, another example of the driving method of the liquid crystal display according to an embodiment of the present invention will be described in detail.

[0185] FIG. 6 is a diagram illustrating the pixel electrode and a texture region of a liquid crystal display according to an embodiment of the present invention. FIG. 7 is a schematic cross-sectional view of a liquid crystal display according to an embodiment of the present invention, FIG. 8 is a diagram illustrating a sequence of a driving method of a liquid crystal display according to an embodiment of the present invention, and FIG. 9 is a diagram illustrating a driving method according to an embodiment of the present invention. FIG. 10 is a diagram illustrating a driving method according to another embodiment of the present invention.

[0186] First, referring to FIG. 6 and FIG. 7, a liquid crystal panel assembly according to the embodiment also includes lower and upper panels **100** and **200** opposing each other and a liquid crystal layer **3** interposed therebetween, and first and second pixel electrodes **191a** and **191b** are provided on the lower panel **100** like the liquid crystal panel assembly shown in FIG. 2.

[0187] The liquid crystal molecules **31** of the liquid crystal layer **3** have their long axes aligned to be vertical to the surfaces of the two panels **100** and **200** without the electric field.

[0188] When two data voltages having different polarities with respect to the common voltage  $V_{com}$  are applied to the first and second pixel electrodes **191a** and **191b**, the liquid crystal molecules **31** of the liquid crystal layer **3** are tilted to

be parallel to the panels **100** and **200** as shown in FIG. 7. However, the liquid crystal molecules **31** spaced at the same distance from the first and second pixel electrodes **191a** and **191b** may not be tilted to any one side and maintain their initial orientation that is vertical to the panes **100** and **200**. Then, texture A having lower luminance than the circumference thereof may be generated between the two pixel electrodes **191a** and **191b** as shown in FIG. 6 and FIG. 7.

[0189] Referring to FIG. 9, a driving method of the liquid crystal display according to an embodiment also includes displaying images of  $N$  frames to be displayed for a predetermined time in the same manner as the driving method of the liquid crystal display shown in FIG. 1 to FIG. 5 as described above (e.g., images of 60 frames are displayed per second in a 60 Hz driving). After images of  $N$  frames are displayed, a low gray image  $Ig$  of one frame is additionally displayed as shown in FIG. 9, and then, images of  $N$  frames to be displayed are displayed.

[0190] In a case where the liquid crystal display displays high-gray luminance such as white, the liquid crystal molecules **31** in the texture region between the two pixel electrodes **191a** and **191b** may be arranged horizontally to the display panels **100** and **200** when the liquid crystal molecules **31** receive pressure from the outside. The texture region A where the liquid crystal molecules **31** are horizontally arranged may be recognized as yellowish bruising since the horizontally arranged liquid crystal molecules **31** contribute to the transmittance of the liquid crystal display. The horizontally arranged liquid crystal molecules **31** in the texture region A maintain the state by the strong electric field in the liquid crystal layer **3** even though the pressure from the outside is removed, whereby such bruising may not be removed even when time passes by.

[0191] When an image  $Ig$  for a frame having a low-gray is displayed after displaying images for a predetermined number of frames as in the embodiment, the liquid crystal molecules **31** that were maintained to be arranged horizontally to the panels **100** and **200** by the strong electric field recover their original inclination state to be vertical to the panels **100** and **200** when the influence from the outside is removed. Accordingly, the bruising is removed and a white image may be displayed. At this time, the gray of the low-gray image  $Ig$  may be equal or less than a gray with which the bruising appearing in the high-gray image may be removed after the influence such as an external pressure is removed. Alternatively, the gray may be a gray corresponding to a data voltage equal to or less than  $\frac{1}{3}$  of the data voltage for a high gray.

[0192] Alternatively to the above embodiment, the number of added frames of low-gray images  $Ig$  may be one or more.

[0193] Next, referring to FIG. 10, a driving method of a liquid crystal display according to another embodiment of the present invention will be described.

[0194] Referring to FIG. 10, one row or a plurality of rows of pixels display a low gray in respective frames and the one row or the plurality of rows of pixels having a low gray may scroll the display screen from one end to the other end of the screen while the liquid crystal display displays images during  $n$  frames. At this time, the gray of the one or the plurality of rows of pixels having a low gray may be equal to or less than a gray with which the bruising can be removed in the high-gray image after the influence such as an external pressure is removed, or may be a gray corresponding to a data voltage equal to or less than  $\frac{1}{3}$  of the data voltage corresponding to the high gray in one example.

[0195] Unlike FIG. 10, the low-gray row may be scrolled bottom to top, left to right, or right to left.

[0196] In this way, one row or a plurality of rows of a low gray, which are difficult to be recognized, are added to each frame and are scrolled in the same manner as the above embodiment, then it is possible to release the liquid crystal molecules 31 that are laid due to the influence such as an external pressure from the strong electric field and return back the liquid crystal molecules 31 to their initial orientation after the external pressure is removed. Accordingly, it is possible to remove display defects such as a yellowish bruising, etc.

[0197] As described above, by adding an image or at least one row of a low gray when displaying a high-gray image in the liquid crystal display including vertically aligned liquid crystal molecules 31, it is possible to recover the liquid crystal molecules 31, which are laid horizontally to the panels 100 and 200 due to the influence such as the external force and trapped by the strong electric field even though the external influence is removed, back to initial orientation.

[0198] Hereinafter, referring to FIG. 11 and FIG. 12, an example of the liquid crystal panel assembly described above will be described in detail.

[0199] FIG. 11 is a layout view of a liquid crystal panel assembly according to an embodiment of the present invention, and FIG. 12 is a cross-sectional view of the liquid crystal panel assembly taken along line XII-XII of FIG. 11.

[0200] Referring to FIG. 11 and FIG. 12, the liquid crystal panel assembly according to an embodiment of the present invention includes a lower panel 100 and an upper panel 200, and a liquid crystal layer 3 interposed therebetween.

[0201] First, the lower panel 100 will be described.

[0202] A plurality of gate conductors including a plurality of gate lines 121 and a plurality of storage electrode lines 131 are formed on an insulation substrate 110.

[0203] The gate lines 121 transmit gate signals and extend mainly in a horizontal direction. Each of the gate lines 121 includes plural pairs of first and second gate electrodes 124a and 124b projecting upward.

[0204] Each of the storage electrode lines 131 receives a predetermined voltage such as the common voltage Vcom, and extends mainly in the horizontal direction. Each of the storage electrode lines 131 is positioned between two neighboring gate lines 121 and is closer to the gate line 121 positioned below the storage electrode line 131. Each storage electrode line 131 includes plural pairs of first and second storage electrodes 133a and 133b elongated vertically, and a storage extension part 137 having a wide area. The first and second storage electrodes 133a and 133b are formed in a rod shape from the vicinity of the first and second gate electrodes 124a and 124b of the lower gate line 121 to the vicinity of the upper gate line 121. The storage extension part 137 has a substantially quadrangle shape in which two corners formed in a lower part of the storage extension part 137 are cut, and connects lower ends of the first and second storage electrodes 133a and 133b to each other. However, the shape and arrangement of the storage electrode line 131 including the storage electrodes 133a and 133b and the storage extension part 137 may be changed in various forms.

[0205] The gate conductors 121 and 131 may have a single layered structure or a multilayered structure.

[0206] A gate insulating layer 140 made of silicon nitride (SiNx), silicon oxide (SiOx), or the like is formed on the gate conductors 121 and 131.

[0207] Plural pairs of first and second island-type semiconductors 154a and 154b made of hydrogenated amorphous silicon, polysilicon, or the like are formed on the gate insulating layer 140. The first and second semiconductors 154a and 154b are positioned above the first and second gate electrodes 124a and 124b, respectively.

[0208] A pair of island-type ohmic contacts 163a and 165a are formed on each of the first semiconductors 154a, and a pair of island-type ohmic contacts (not shown) are formed on each of the second semiconductors 154b. The ohmic contacts 163a and 165a may be made of a material such as n+ hydrogenated amorphous silicon doped with n-type impurities at a high concentration, etc., or of silicide.

[0209] A data conductor including plural pairs of first and second data lines 171a and 171b and plural pairs of first and second drain electrodes 175a and 175b is formed on the ohmic contacts 163a and 165a and the gate insulating layer 140.

[0210] The first and second data lines 171a and 171b transmit the data signals and intersect the gate lines 121 and the storage electrode lines 131 while extending mainly in a vertical direction. The first and second data lines 171a and 171b include plural pairs of first and second source electrodes 173a and 173b bent in a U shape toward the first and second gate electrodes 124a and 124b.

[0211] The first and second drain electrodes 175a and 175b include first and second extension parts 177a and 177b of which ends have a rod shape and a large area. The ends of the first and second drain electrodes 175a and 175b are partially surrounded by the first and second source electrodes 173a and 173b that are bent while facing each other around the first and second gate electrodes 124a and 124b. Outer contours of the first and second extension parts 177a and 177b are substantially similar to those of the storage extension part 137 positioned below the first and second extension parts 177a and 177b. The first extension part 177a overlaps the left half of the storage extension part 137, and the second extension part 177b overlaps the right half of the storage extension part 137.

[0212] The first/second gate electrode 124a/124b, the first/second source electrode 173a/173b, and the first/second drain electrodes 175a/175b respectively constitute the first/second thin film transistors Qa/Qb together with the first/second semiconductor 154a/154b. Channels of the first/second thin film transistor Qa/Qb is respectively formed in the first/second semiconductor 154a/154b between the first/second source electrode 173a/173b and the first/second drain electrode 175a/175b.

[0213] The data conductors 171a, 171b, 175a, and 175b may have a single layered structure or a multilayered structure.

[0214] The ohmic contacts 163a and 165a are formed only between the semiconductors 154a and 154b below the ohmic contacts 163a and 165a and the data conductors 171a, 171b, 175a, and 175b above the ohmic contacts 163a and 165a. The ohmic contacts 163a and 165a lower contact resistance between the semiconductors 154a and 154b and the data conductors 171a, 171b, 175a, and 175b. The semiconductors 154a and 154b are exposed between the source electrodes 173a and 173b and the drain electrodes 175a and 175b. In addition, the semiconductors 154a and 154b are exposed to the data conductors 171a, 171b, 175a, and 175b.

[0215] A passivation layer 180 that is may be made of an inorganic insulator, an organic insulator, or the like is formed

on the data conductors **171a**, **171b**, **175a**, and **175b** and the exposed parts of the semiconductors **154a** and **154b**.

[0216] A plurality of contact holes **185a** and **185b** for exposing the first and second extension parts **177a** and **177b** are formed on the passivation layer **180**.

[0217] A plurality of pixel electrodes **191** including plural pairs of first and second pixel electrodes **191a** and **191b** that are may be made of a transparent material such as indium tin oxide (ITO), indium zinc oxide (IZO), or the like, or a reflective metal such as aluminum, silver, chromium, or an alloy thereof, are formed on the passivation layer **180**.

[0218] As shown in FIG. 11, the overall contour of the one pixel electrode **191** has a quadrangular shape. The first and second pixel electrodes **191a** and **191b** engage with each other with a gap **91** therebetween. The first and second pixel electrodes **191a** and **191b** are generally vertically symmetrical with respect to a virtual horizontal center line **CL** and are divided into upper and lower regions.

[0219] The first pixel electrode **191a** includes a lower projection portion, a left longitudinal stem portion, a horizontal stem portion extending to the right from a center of the longitudinal stem portion, and a plurality of branch portions. A branch portion positioned above the horizontal center line **CL** extends obliquely in an upper right direction from the longitudinal stem portion or the horizontal stem portion. The other branch portion positioned below the horizontal center line **CL** extends obliquely in a lower right direction from the longitudinal stem portion or the horizontal stem portion. An angle between the branch portions and the gate line **121** or the horizontal center line **CL** may be approximately 45 degrees.

[0220] The second pixel electrode **191b** includes a lower projection portion, a right longitudinal stem portion, upper and lower horizontal stem portions, and a plurality of branch portions. The upper and lower horizontal stem portions extend horizontally to the left from a lower end and an upper end of the longitudinal stem portion, respectively. A branch portion positioned above the horizontal center line **CL** extends obliquely in a lower left direction from the longitudinal stem portion or the upper horizontal stem portion. The other branch portion positioned below the horizontal center line **CL** extends obliquely in an upper left direction from the longitudinal stem portion or the lower horizontal stem portion. An angle between the branch portions of the second pixel electrode **191b** and the gate line **121** or the horizontal center line **CL** may also be approximately 45 degrees. The upper and lower branch portions may be at right angles to each other around the horizontal center line **CL**.

[0221] The branch portions of the first and second pixel electrodes **191a** and **191b** engage with each other with a predetermined gap and are alternately disposed, thereby forming a pectinated pattern.

[0222] The first and second pixel electrodes **191a** and **191b** are physically and electrically connected to the first and second drain electrodes **175a** and **175b** through the contact holes **185a** and **185b**, respectively. The first and second pixel electrodes **191a** and **191b** receive data voltages from the first and second drain electrodes **175a** and **175b**. The first and second pixel electrodes **191a** and **191b** constitute the liquid crystal capacitor **Clc** together with the liquid crystal layer **3**. The first and second pixel electrodes **191a** and **191b** maintain the applied voltage even after the first and second thin film transistors **Qa** and **Qb** are turned off.

[0223] The first and second extension parts **177a** and **177b** of the first and second drain electrode **175a** and **175b** con-

nected to the first and second pixel electrodes **191a** and **191b** overlap the storage extension part **137** with the gate insulating layer **140** interposed therebetween, thereby constituting the first and second storage capacitors **Csta** and **Cstb**. The first and second storage capacitors **Csta** and **Cstb** strengthen voltage storage capacitance of the liquid crystal capacitor **Clc**.

[0224] Next, the upper panel **200** will be described.

[0225] A light blocking member **220** is formed on an insulation substrate **210** made of transparent glass, plastic, or the like. The light blocking member **220** prevents light from being leaked between the pixel electrodes **191** and defines an opening region facing the pixel electrodes **191**.

[0226] A plurality of colors filter **230** are formed on the insulation substrate **210** and the light blocking member **220**. Most of the color filters **230** exist within a region surrounded by the light blocking member **220**. The color filters **230** may be elongated on a row of the pixel electrodes **191**. Each of the color filters **230** may display one of primary colors including three primary colors such as red, green, and blue.

[0227] An overcoat **250** is formed on the color filters **230** and the light blocking member **220**. The overcoat **250** may be made of the (organic) insulator. The overcoat **250** prevents the color filters **230** from being exposed and provides a flat surface. The overcoat **250** may be omitted.

[0228] Alignment layers **11** and **21** are applied on inner surfaces of the panels **100** and **200**. The alignment layers **11** and **21** may be vertical alignment layers.

[0229] A polarizer (not shown) may be provided on outer surfaces of the panels **100** and **200**.

[0230] The liquid crystal layer **3** interposed between the lower panel **100** and the upper panel **200** has positive dielectric anisotropy. The liquid crystal molecules **31** may have their long axes aligned to be vertical to the surfaces of two panels **100** and **200** without the electric field.

[0231] When data voltages having different polarities are applied to the first and second pixel electrodes **191a** and **191b**, an electric field substantially parallel to the surfaces of the panels **100** and **200** is generated. The liquid crystal molecules of the liquid crystal layer **3**, which are initially aligned to be vertical to the surfaces of the panels **100** and **200**, respond to the electric field and the long axes of the liquid crystal molecules are aligned to be parallel to the electric field. A variation degree of polarization of light incident in the liquid crystal layer **3** is changed depending on the inclination degree of the liquid crystal molecules. The variation of the polarization is represented by variation of transmittance by the polarizers, whereby the liquid crystal display displays an image.

[0232] In this way, it is possible to increase the contrast ratio of the liquid crystal display and implement a wide viewing angle by using liquid crystal molecules **31** that are aligned vertically to the surfaces of the panels **100** and **200**. Also, it is possible to increase the driving voltage and improve response speed by applying two data voltages having different polarities with respect to the common voltage **Vcom** to one pixel **PX**. Further, as described above, influences by the kickback voltage may be removed, thereby preventing flickering and the like.

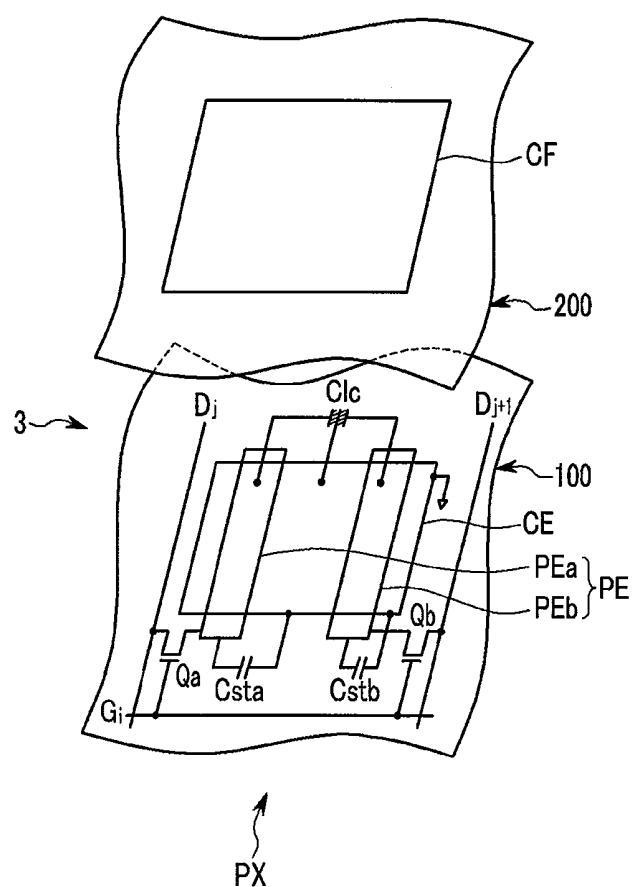

[0233] Next, referring to FIG. 13, a liquid crystal panel assembly according to another embodiment of the present invention will be described.

[0234] FIG. 13 is an equivalent circuit diagram illustrating one pixel and a structure of a liquid crystal display panel according to another embodiment of the present invention.

[0235] Referring to FIG. 13, the liquid crystal panel assembly according to the present embodiment also includes a signal line including a plurality of gate lines  $G_i$  and plural pairs of data lines  $D_j$  and  $D_{j+1}$ , and a plurality of pixels PX connected thereto. With regard to a structure of the liquid crystal display, the liquid crystal display includes lower and upper panels 100 and 200 opposed to each other, and a liquid crystal layer 3 interposed therebetween. Each pixel PX includes first and second switching elements Qa and Qb that are connected to the signal line  $G_i$ ,  $D_j$ , and  $D_{j+1}$ , a liquid crystal capacitor Clc, and a storage capacitor Cst.

[0236] Unlike the embodiment shown in FIG. 2 and FIG. 3, in the present embodiment, first and second pixel electrodes PEa and PEb are superimposed on each other with an insulator interposed therebetween to form a storage capacitor Cst. In this way, by forming a storage capacitor Cst in each pixel PX, additional wiring for transmitting a common voltage Vcom is not required, thereby increasing the aperture ratio.

[0237] Description of the operation and effect of a liquid crystal display including the first and second switching elements Qa and Qb, the liquid crystal capacitor Clc, a color filter CF, a polarizer (not shown), and the liquid crystal panel assembly refers to the description of the same components shown in FIG. 1 to FIG. 5. Therefore, a detailed description thereof will be omitted.

[0238] Next, referring to FIG. 14, a liquid crystal panel assembly according to another embodiment of the present invention will be described.

[0239] FIG. 14 is an equivalent circuit diagram illustrating one pixel as well as a structure of a liquid crystal display panel according to another embodiment of the present invention.

[0240] Referring to FIG. 14, the liquid crystal panel assembly according to the present embodiment also includes a signal line including a plurality of gate lines  $G_i$  and plural pairs of data lines  $D_j$  and  $D_{j+1}$ , and a plurality of pixels PX connected thereto. With regard to a structure of the liquid crystal display, the liquid crystal display includes lower and upper panels 100 and 200 opposed to each other, and a liquid crystal layer 3 interposed therebetween.

[0241] Each pixel PX includes first and second switching elements Qa and Qb that are connected to the signal line  $G_i$ ,  $D_j$ , and  $D_{j+1}$ , a liquid crystal capacitor Clc, and first and second storage capacitors Csta and Cstb.

[0242] The first and second switching elements Qa and Qb are three-terminal elements such as a thin film transistor provided in the lower panel 100. A control terminal thereof is connected to the gate lines  $G_i$ , an input terminal thereof is connected to the data lines  $D_j$  and  $D_{j+1}$ , and an output terminal thereof is connected to the liquid crystal capacitor Clc and the first and second storage capacitors Csta and Cstb.

[0243] The liquid crystal capacitor Clc may adopt first and second pixel electrodes PEa and PEb of the lower panel 100 as two terminals, or may adopt the first pixel electrode PEa or the second pixel electrode PEb and a common electrode CE as the two terminals. The first and second pixel electrodes PEa and PEb are connected to the first and second switching elements Qa and Qb. The common electrode CE is formed on a front surface within a region of one pixel PX of the lower panel 100, and is formed on a layer different from a layer where a pixel electrode PE including the first and second pixel electrodes PEa and PEb is formed. A predetermined voltage such as a common voltage Vcom or the like is applied to the common electrode CE. Data voltages having different polarities with respect to the common voltage Vcom are applied to

the first and second pixel electrodes PEa and PEb, respectively. Meanwhile, the liquid crystal layer 3 has positive dielectric anisotropy. Liquid crystal molecules of the liquid crystal layer 3 have their long axes aligned to be vertical to horizontal surfaces of the panels 100 and 200 without an electric field.