US 20120062811A1

(19) **United States**

(12) **Patent Application Publication**

**MIYAKE**

(10) **Pub. No.: US 2012/0062811 A1**

(43) **Pub. Date: Mar. 15, 2012**

(54) **LIQUID CRYSTAL DISPLAY DEVICE**

(52) **U.S. Cl. .... 349/39; 257/296; 257/E27.016**

(75) Inventor: **Hiroyuki MIYAKE, Atsugi (JP)**

(73) Assignee: **SEMICONDUCTOR ENERGY

LABORATORY CO., LTD.,**

Kanagawa-ken (JP)

(21) Appl. No.: **13/212,510**

(22) Filed: **Aug. 18, 2011**

(30) **Foreign Application Priority Data**

Sep. 15, 2010 (JP) ..... 2010-206282

(57) **ABSTRACT**

An object of the present invention is to provide a liquid crystal display device which allows a desirable storage capacitor to be ensured in a pixel without decreasing the aperture ratio in response to changes in frame frequency. In a liquid crystal display device including a pixel transistor and two capacitive elements using an oxide semiconductor material in each pixel, one of the capacitive elements comprises a light-transmitting material to improve the aperture ratio of the pixel. Furthermore, through the use of characteristics of the light-transmitting capacitive element, the size of the storage capacitor in the pixel is varied by adjusting the voltage value of a capacitance value in response to the frame frequency varied depending on images displayed.

**Publication Classification**

(51) **Int. Cl.**

**G02F 1/1343** (2006.01)

**H01L 27/06** (2006.01)

FIG. 1

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6

FIG. 7

FIG. 8

## LIQUID CRYSTAL DISPLAY DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to liquid a crystal display device.

[0003] 2. Description of the Related Art

[0004] In recent years, flat panel displays such as liquid crystal displays (LCDs) have been becoming widespread. While materials using amorphous silicon or polycrystalline silicon have been commonly used as semiconductor layer materials for thin film transistors, light-transmitting metal oxides have been also attracting attention. For example, techniques for improving the aperture ratio have been examined through the application of an In—Ga—Zn—O-based oxide or the like to a channel layer of a thin film transistor. In addition, Patent Document 1 discloses a technique for manufacturing a thin film transistor which has parasitic capacitance reduced and prevents defects caused by peeling of a thin film.

[0005] Non-Patent Document 1 discloses a structure for varying a frame frequency between in the case of displaying a moving image and in the case of displaying a still image in order to achieve a reduction in the power consumption of a liquid crystal display device.

### REFERENCES

[0006] [Patent Document 1] Japanese Published Patent Application No. 2010-098305

[0007] [Non-Patent Document 1] Kazuhiko Tsuda et al., IDW'02, pp. 295-298

### SUMMARY OF THE INVENTION

[0008] In the case of a lower frame frequency (1/60 Hz to 1 Hz) for displaying a still image, the storage capacitor in a pixel is advantageously larger in order to make the holding time of electric signals such as image signals longer and maintain more favorable still image display. However, when a design is made so as to increase the storage capacitor in a pixel, problems such as a decrease in the aperture ratio of the pixel and a need to increase the channel width of a pixel transistor will be caused. In addition, in order to prevent flicker noises (flickers) and achieve smoother moving image display, the frame frequency is increased for moving image display (60 Hz to 180 Hz). In the case of carrying out color display by a sequential method, the frame frequency is further increased (180 Hz to 480 Hz). In this case, there is no need to increase the storage capacitor in a pixel, because electric signals such as image signals are switched quickly. More specifically, it is extremely difficult to ensure an appropriate storage capacitor in a small-area pixel at the same time in both cases of still image display and moving image display.

[0009] In view of the problems described above, an object in an embodiment of the present invention disclosed herein is to provide a liquid crystal device which allows a desirable storage capacitor to be ensured in a pixel without decreasing the aperture ratio in response to changes in frame frequency. In addition, another object in an embodiment of the present invention disclosed herein is to provide a liquid crystal display device which allows for lower power consumption and higher-definition image display.

[0010] An embodiment of the present invention is a semiconductor device comprising: a pixel transistor including a gate electrode electrically connected to a scan line, a first

electrode electrically connected to a signal line, the first electrode serving as one of a source electrode and a drain electrode, and a second electrode electrically connected to a pixel electrode, the second electrode serving as the other of the source electrode and the drain electrode; a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to the capacitance line, wherein the second capacitive element has the one electrode formed from the same layer as the pixel electrode, has the other electrode formed from the same semiconductor material as the semiconductor layer of the pixel transistor, and thus has a MOS capacitor structure of a dielectric layer interposed between the one electrode and the other electrode, and the second capacitive element has a capacitance value varied in response to a time interval of a gate pulse by adjusting an electric potential of the capacitance line.

[0011] In addition, an embodiment of the present invention is a semiconductor device comprising: a pixel transistor including a gate electrode electrically connected to a scan line, a first electrode electrically connected to a signal line, the first electrode serving as one of a source electrode and a drain electrode, and a second electrode electrically connected to a pixel electrode, the second electrode serving as the other of the source electrode and the drain electrode; a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a wiring for shielding; and a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and a transistor including a gate electrode electrically connected to the wiring for shielding, a first electrode electrically connected to the one electrode of the first capacitive element, the first electrode serving as one of a source electrode and a drain electrode, and a second electrode electrically connected to the capacitance line, the second electrode serving as the other of the source electrode and the drain electrode, wherein the second capacitive element has the one electrode formed from the same layer as the pixel electrode, has the other electrode formed from the same semiconductor material as the semiconductor layer of the pixel transistor, and thus has a MOS capacitor structure of a dielectric layer interposed between the one electrode and the other electrode, and the second capacitive element has a capacitance value varied in response to a time interval of a gate pulse by adjusting an electric potential of the capacitance line and supplying, to the wiring for shielding, such an electric field that turns off the transistor at least during image display.

[0012] In addition, in an embodiment of the present invention, the liquid crystal display device is provided wherein the pixel electrode and the semiconductor layer have a light-transmitting property.

[0013] In addition, in an embodiment of the present invention, the semiconductor layer may be composed of an oxide semiconductor.

[0014] It is to be noted that in this specification, etc., the term such as "over" or "below" does not necessarily mean that a component is placed "directly on" or "directly under" another component. For example, the expression "a gate electrode over a gate insulating layer" can mean the case where there is an additional component between the gate insulating

layer and the gate electrode. Further, the terms “over” and “below” are used simply for convenience of explanation.

[0015] In addition, in this specification and the like, the term such as “electrode” or “wiring” does not limit a function of a component. For example, an “electrode” is sometimes used as part of a “wiring”, and vice versa. Furthermore, the term “electrode” or “wiring” can include the case where a plurality of “electrodes” or “wirings” is formed in an integrated manner.

[0016] Functions of a “source” and a “drain” are sometimes replaced with each other when a transistor of opposite polarity is used or when the direction of current flowing is changed in circuit operation, for example. Therefore, the terms “source” and “drain” can be used to denote the drain and the source, respectively, in this specification.

[0017] It is to be noted that in this specification, etc., the term “electrically connected” includes the case where components are connected through “an object which has any “electric action.” There is no particular limitation on “the object which has any electric action” as long as electric signals can be transmitted and received between components that are connected through the object.

[0018] Examples of the “object which has any electric action” include a switching element such as a transistor, a resistor, an inductor, a capacitor, and other elements with a variety of functions as well as an electrode and a wiring.

[0019] According to an embodiment of the present invention, a liquid crystal display device can be achieved which allows a desirable storage capacitor to be ensured in a pixel without decreasing the aperture ratio in response to changes in frame frequency. In addition, a liquid crystal display device can be achieved which allows for lower power consumption and higher-definition image display.

#### BRIEF DESCRIPTION OF THE DRAWINGS

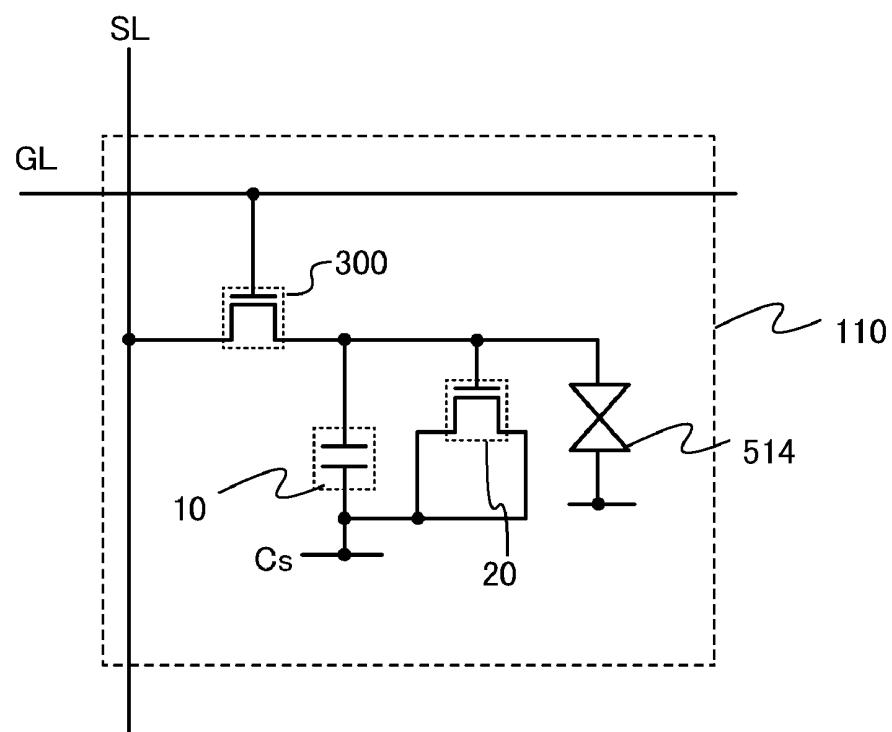

[0020] FIG. 1 is a circuit diagram illustrating a pixel structure of a liquid crystal display device;

[0021] FIG. 2 is a top view illustrating a pixel structure of the liquid crystal display device;

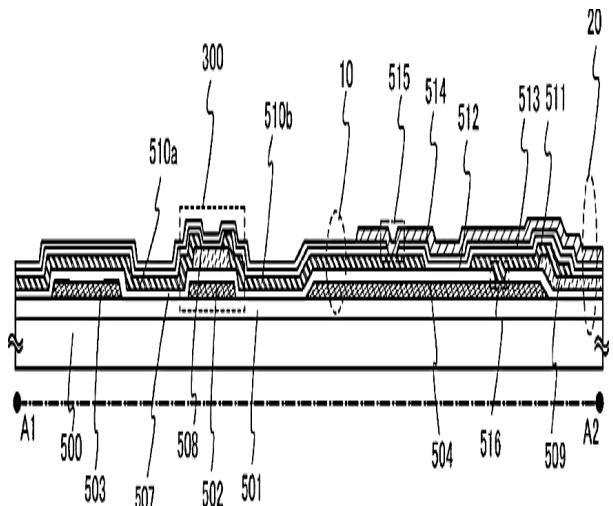

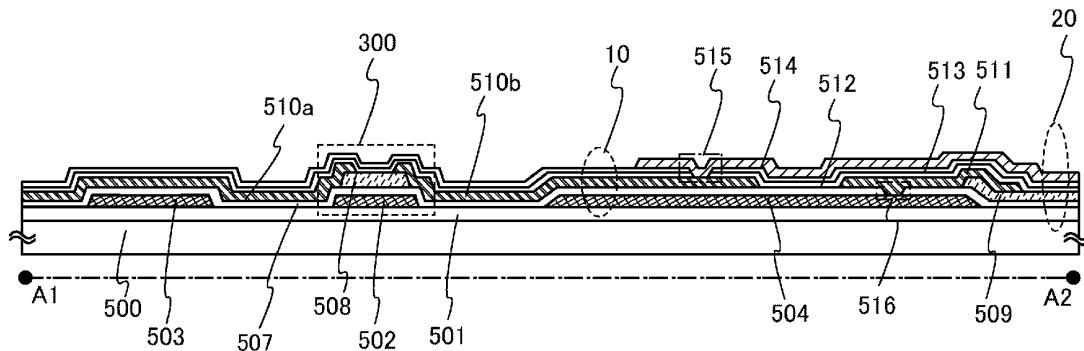

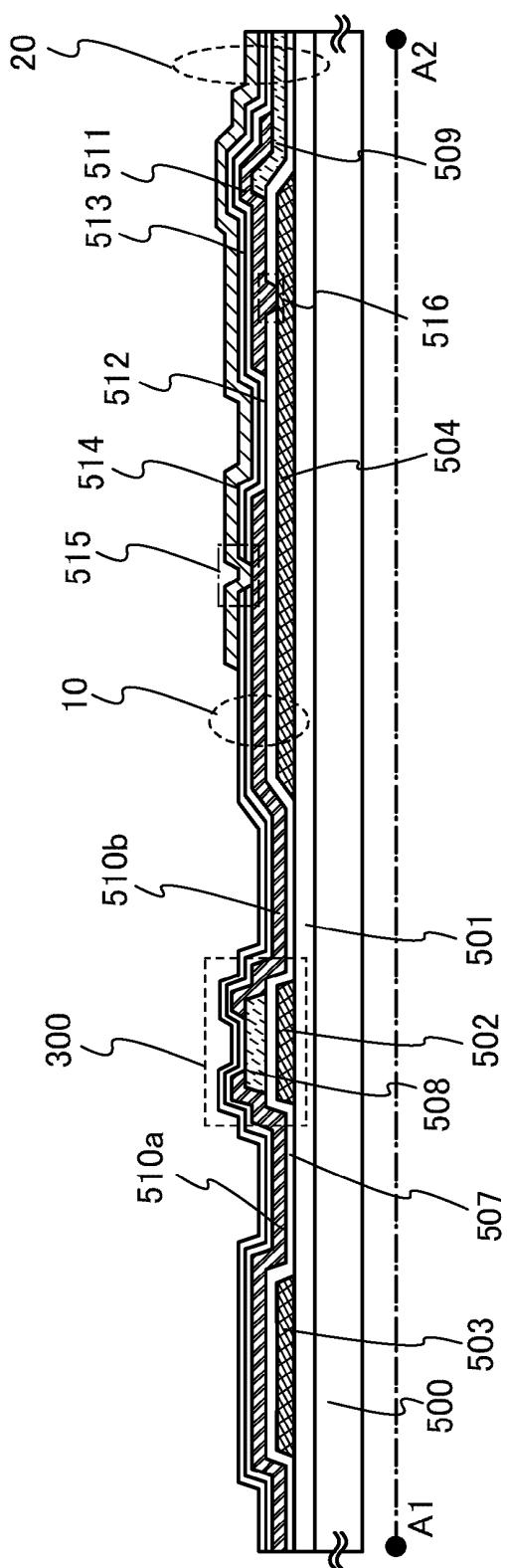

[0022] FIG. 3 is a cross-sectional view illustrating a pixel structure of the liquid crystal display device;

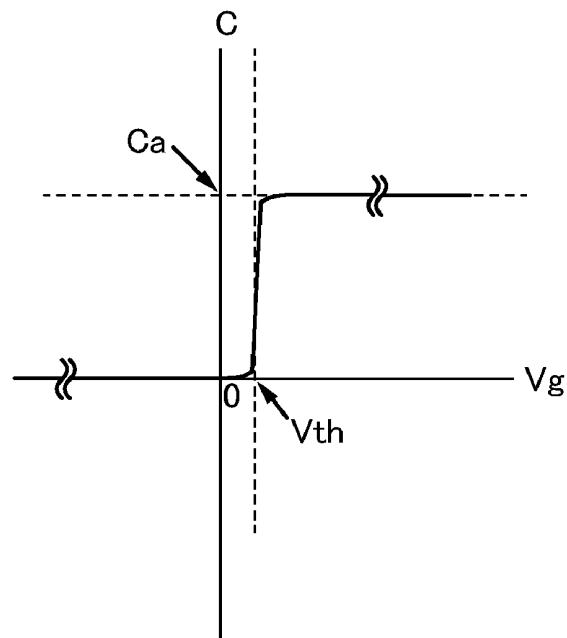

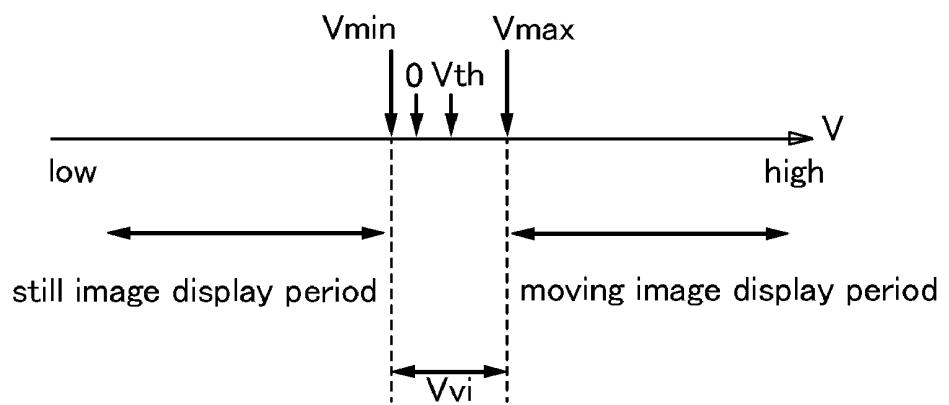

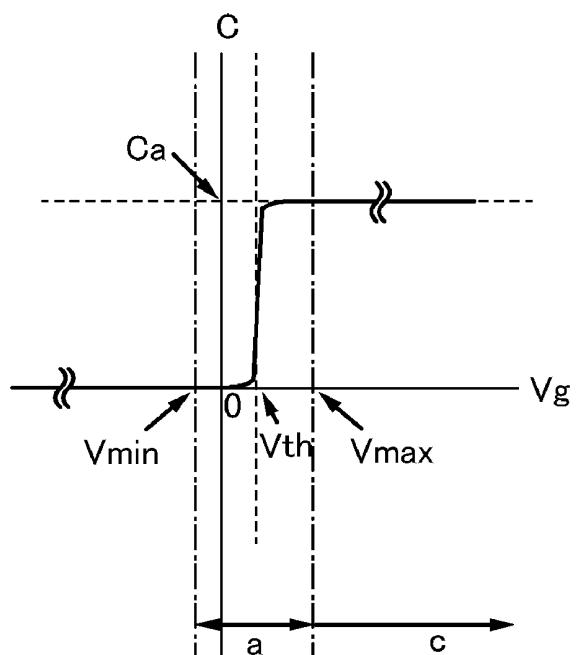

[0023] FIGS. 4A and 4B are respectively a diagram showing capacitance-voltage characteristics and a relationship diagram of voltage;

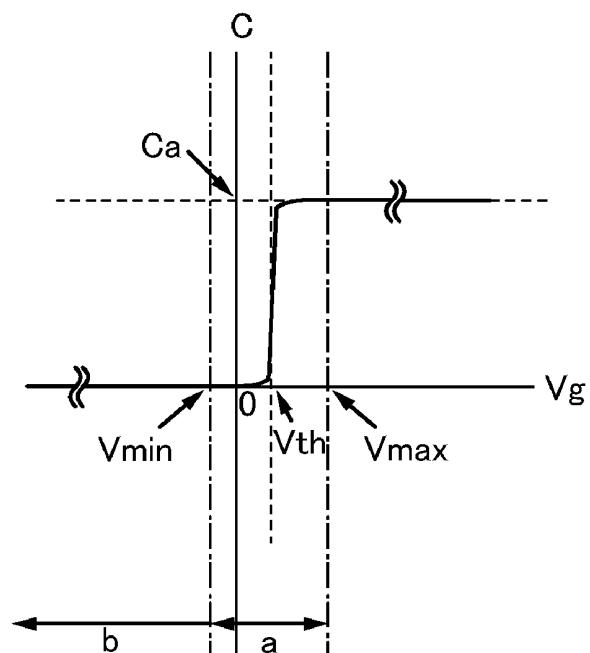

[0024] FIGS. 5A and 5B are diagrams showing capacitance-voltage characteristics;

[0025] FIG. 6 is a circuit diagram illustrating a pixel structure of a liquid crystal display device;

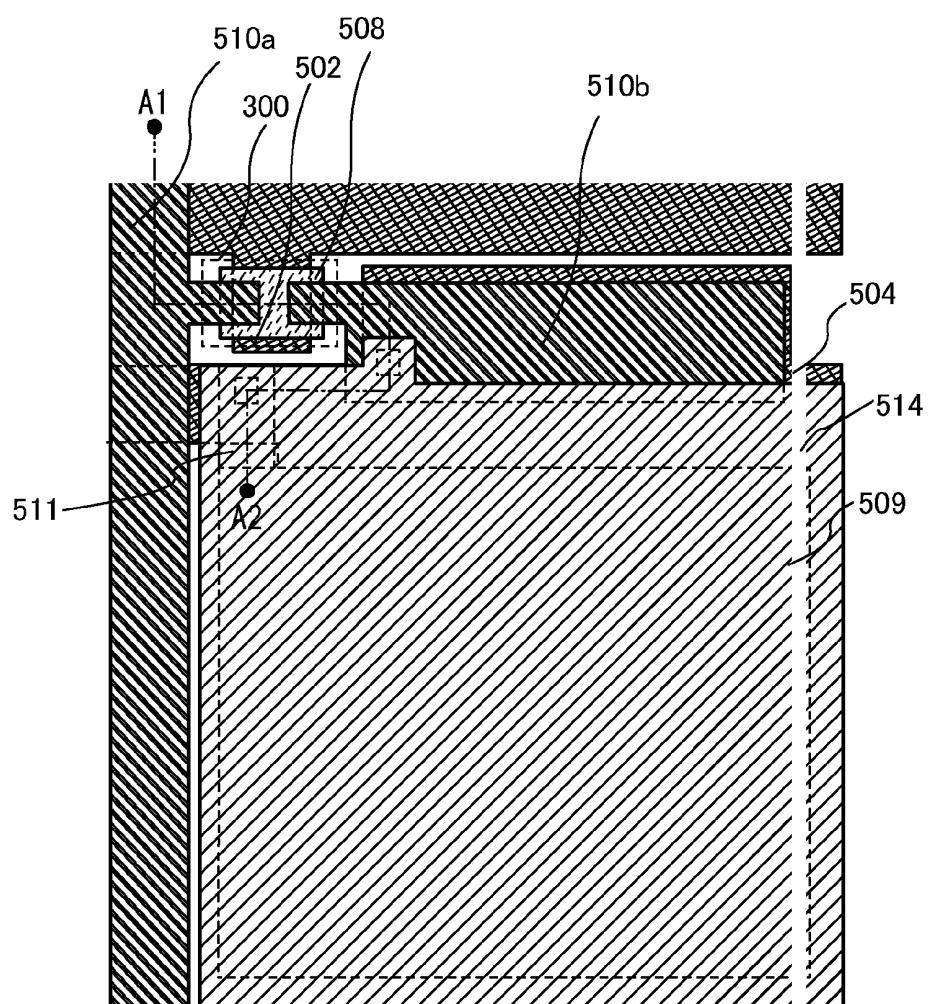

[0026] FIG. 7 is a top view illustrating a pixel structure of the liquid crystal display device; and

[0027] FIG. 8 is a cross-sectional view illustrating a pixel structure of the liquid crystal display device.

#### DETAILED DESCRIPTION OF THE INVENTION

[0028] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. However, the present invention is not limited to the description below, and it is easily understood by those skilled in the art that modes and details disclosed herein can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention is not construed as being limited to description of the embodiments.

[0029] It is to be noted that the position, the size, the range, or the like of each structure illustrated in drawings and the like is not accurately represented in some cases for easy understanding. Therefore, the disclosed invention is not necessarily limited to the position, size, range, or the like as disclosed in the drawings and the like.

[0030] In this specification and the like, ordinal numbers such as “first”, “second”, and “third” are used in order to avoid confusion among components, and the terms do not mean limitation of the number of components.

#### Embodiment 1

[0031] In the present embodiment, a pixel structure and a method for switching the storage capacitors will be described in a liquid crystal display device according to an embodiment of the present invention disclosed herein. It is to be noted that the liquid crystal display device described in the present embodiment includes pixels each with a variable capacitance value in response to images displayed.

[0032] FIG. 1 is a diagram illustrating a circuit example of a pixel included in the liquid crystal display device.

[0033] A pixel 110 includes a pixel transistor 300, a first capacitive element 10, and a second capacitive element 20. The pixel transistor 300 has a gate electrode electrically connected to a scan line GL, and a first electrode electrically connected to a signal line SL, which serves as one of a source electrode and a drain electrode of the pixel transistor 300. Furthermore, one electrode of the first capacitive element 10 is electrically connected to one electrode of the second capacitive element 20, and a second electrode which serves as the other of the source electrode and the drain electrode of the pixel transistor 300, the other electrode of the first capacitive element 10, and the other electrode of the second capacitive element 20 are electrically connected to each other. Further, the one electrode of the first capacitive element 10 and the one electrode of the second capacitive element 20 are electrically connected to a capacitance line Cs.

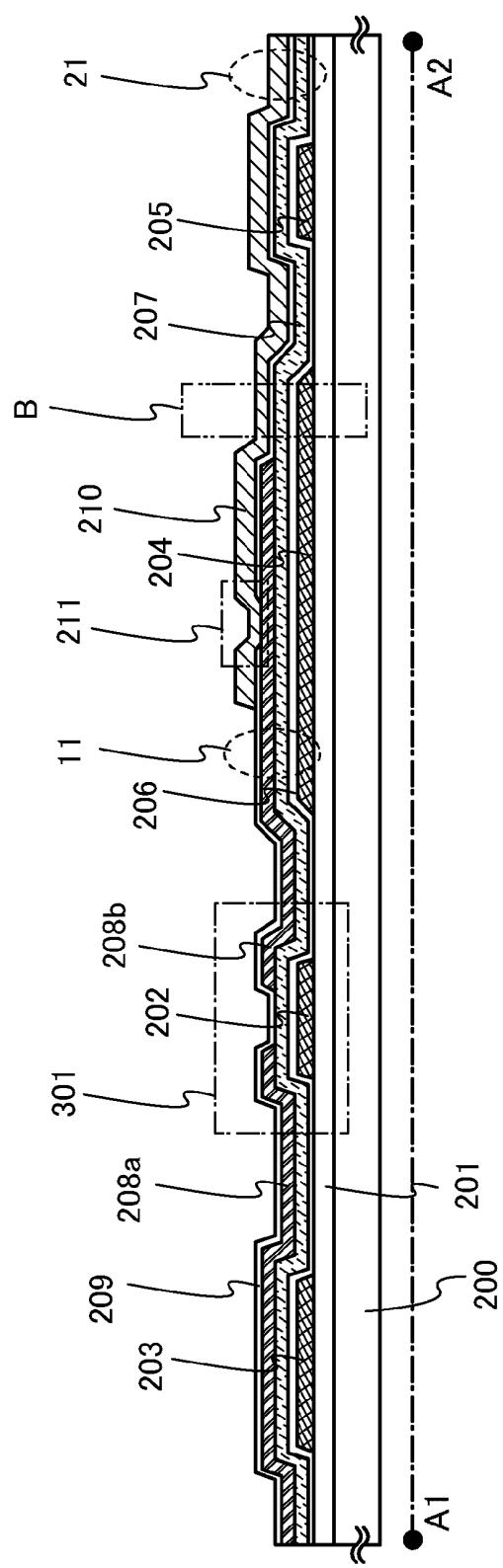

[0034] Next, an example of the specific structure of the pixel shown in FIG. 1 will be described with reference to FIGS. 2 and 3. FIG. 2 shows a top view of the pixel. In addition, FIG. 3 shows a cross-sectional view of the pixel along the chain line A1-A2 in FIG. 2.

[0035] In the cross section A1-A2, a base layer 501 is formed on a substrate 500, and a gate electrode 502, a wiring 503, and a wiring 504 are formed on the base layer 501. In addition, a gate insulating layer 507 is formed to cover the gate electrode 502, the wiring 503, and the wiring 504. Furthermore, a semiconductor layer 508 is formed on the gate insulating layer 507 so as to overlap with the gate electrode 502, and a semiconductor layer 509 is formed on the gate insulating layer 507. In addition, a source electrode 510a and a drain electrode 510b are formed on the semiconductor layer 508 so as to overlap with end portions of the gate electrode 502, and a wiring 511 is formed on the gate insulating layer 507 and the semiconductor layer 509 so as to be in partial contact with the wiring 504. It is to be noted that the wiring 511 is electrically connected to the wiring 504 through a contact hole 516 formed in the gate insulating layer 507. In addition, an insulating layer 512 and an insulating layer 513 are formed sequentially on the source electrode 510a, the drain electrode 510b, and the wiring 511 so as to be in partial contact with the semiconductor layer 508, and a pixel electrode 514 is formed on the insulating layer 513. It is to be noted that the pixel electrode 514 is electrically connected to

the drain electrode **510b** through a contact hole **515** formed in the insulating layer **512** and the insulating layer **513**.

[0036] A section in which the wiring **504** and the drain electrode **510b** are overlapped with the gate insulating layer **507** interposed therebetween functions as the first capacitive element **10**. The gate insulating layer **507** functions as a dielectric layer. In addition, a section in which the semiconductor layer **509** and the pixel electrode **514** are overlapped with the insulating layer **512** and the insulating layer **513** interposed therebetween functions as the second capacitive element **20**. The insulating layer **512** and the insulating layer **513** function as a dielectric layer.

[0037] The multilayer structure of the dielectric layer can prevent interlayer short circuit caused by pinholes, etc. formed in the insulating layers. More specifically, even when a pinhole is caused in one of the dielectric layers, the pinhole is covered with the other dielectric layer, and the function of the second capacitive element **20** can be thus improved.

[0038] The semiconductor layer **508** and the semiconductor layer **509** can be formed with the use of amorphous silicon, microcrystalline silicon, and polycrystalline silicon. However, in the case of driving the pixels at a lower frame frequency, it is preferable to use a semiconductor material which has a wider energy gap than those of the above-mentioned silicon-based semiconductor materials. As the semiconductor material which has a wider energy gap, preferably, oxide semiconductors can be used. For example, zinc-oxide-based oxide semiconductors have an energy gap of approximately 3 eV, which are excellent in a light-transmitting property in a visible light range. While many of these oxide semiconductors exhibits an n-type conductivity, the oxide semiconductors can be brought closer to intrinsic semiconductors by reducing impurities acting as donors, such as hydrogen, and reducing defects caused by oxygen vacancies. This type of highly purified oxide semiconductor can reduce the off-state current of the transistor sufficiently in combination with the wide energy gap.

[0039] The pixel transistor **300** configured with the use of the oxide semiconductor for the semiconductor layer **508** can reduce the off-state current, and reduce the ratio of electric charges disappearing from the storage capacitor provided in the pixel. More specifically, even when the frame frequency is lowered, the pixel transistor **300** makes it possible to keep electric charges held in the storage capacitor until the next writing period.

[0040] The oxide semiconductor to be used preferably contains at least indium (In) or zinc (Zn). In particular, the oxide semiconductor preferably contains In and Zn. In addition, as a stabilizer for reducing the variation in electric characteristics of a transistor using the oxide, the oxide semiconductor preferably gallium (Ga) in addition to In and Zn. In addition, the oxide semiconductor preferably contains tin (Sn) as a stabilizer. In addition, the oxide semiconductor preferably contains hafnium (Hf) as a stabilizer. In addition, the oxide semiconductor preferably contains aluminum (Al) as a stabilizer.

[0041] In addition, as other stabilizer(s), the oxide semiconductor may contain one or more of lanthanoid such as lanthanum (La), cerium (Ce), praseodymium (Pr), neodymium (Nd), samarium (Sm), europium (Eu), gadolinium (Gd), terbium (Tb), dysprosium (Dy), holmium (Ho), erbium (Er), thulium (Tm), ytterbium (Yb), or lutetium (Lu).

[0042] For example, an indium oxide, a tin oxide, a zinc oxide, a two-component metal oxide such as an In—Zn-based

oxide, a Sn—Zn-based oxide, an Al—Zn-based oxide, a Zn—Mg-based oxide, a Sn—Mg-based oxide, an In—Mg-based oxide, or an In—Ga-based oxide, a three-component metal oxide such as an In—Ga—Zn-based oxide (also referred to as IGZO), an In—Al—Zn-based oxide, an In—Sn—Zn-based oxide, a Sn—Ga—Zn-based oxide, an Al—Ga—Zn-based oxide, a Sn—Al—Zn-based oxide, an In—Hf—Zn-based oxide, an In—La—Zn-based oxide, an In—Ce—Zn-based oxide, an In—Pr—Zn-based oxide, an In—Nd—Zn-based oxide, an In—Sm—Zn-based oxide, an In—Eu—Zn-based oxide, an In—Gd—Zn-based oxide, an In—Tb—Zn-based oxide, an In—Dy—Zn-based oxide, an In—Ho—Zn-based oxide, an In—Er—Zn-based oxide, an In—Tm—Zn-based oxide, an In—Yb—Zn-based oxide, or an In—Lu—Zn-based oxide, a four-component metal oxide such as an In—Sn—Ga—Zn-based oxide, an In—Hf—Ga—Zn-based oxide, an In—Al—Ga—Zn-based oxide, an In—Sn—Al—Zn-based oxide, an In—Sn—Hf—Zn-based oxide, or an In—Hf—Al—Zn-based oxide can be used as the oxide semiconductor.

[0043] It is to be noted in this case that, for example, an In—Ga—Zn-based oxide refers to an oxide containing In, Ga, and Zn, and there is no limitation on the ratio of In:Ga:Zn. The In—Ga—Zn-based oxide may contain a metal element besides the In, Ga, and Zn.

[0044] Alternatively, a material represented by  $\text{InMO}_3$  ( $\text{ZnO})_m$  ( $m > 0$ , and  $m$  is not an integer) may be used as an oxide semiconductor. It is to be noted that M represents one or more metal elements selected from Ga, Fe, Mn, and Co. Alternatively, a material represented by  $\text{In}_n\text{SnO}_5(\text{ZnO})_n$  ( $n > 0$ ,  $n$  is a natural number) may be used as the oxide semiconductor.

[0045] For example, an In—Ga—Zn-based oxide with an atomic ratio of  $\text{In:Ga:Zn}=1:1:1$  ( $=1/3:1/3:1/3$ ) or  $\text{In:Ga:Zn}=2:2:1$  ( $=2/5:2/5:1/5$ ), or an oxide whose composition is in the neighborhood of the In—Ga—Zn-based oxide can be used. Alternatively, an In—Sn—Zn-based oxide with an atomic ratio of  $\text{In:Sn:Zn}=1:1:1$  ( $=1/3:1/3:1/3$ ),  $\text{In:Sn:Zn}=2:1:3$  ( $=1/3:1/6:1/2$ ), or  $\text{In:Sn:Zn}=2:1:5$  ( $=1/4:1/8:5/8$ ), or an oxide whose composition is in the neighborhood of the In—Sn—Zn-based oxide may be used.

[0046] However, the oxide semiconductor is not limited to those described above, and a material which has an appropriate composition may be used depending on required semiconductor characteristics (e.g., mobility, threshold voltage, and variation). In addition, in order to obtain the required semiconductor characteristics, it is preferable to make the carrier concentration, the impurity concentration, the defect density, the atomic ratio of a metal element to oxygen, the interatomic distance, the density, etc. appropriate.

[0047] In addition, a configuration is desirably used in which the semiconductor layer **508** of the pixel transistor **300** is overlapped with the gate electrode **502**. The adoption of this configuration can prevent the oxide semiconductor in the semiconductor layer **508** from being deteriorated due to incident light from the substrate **500** side. Thus, characteristic degradation such as the shifted threshold voltage of the pixel transistor **300** can be prevented from being caused.

[0048] For the pixel electrode **514**, a light-transmitting conductive material is preferably used. As the light-transmitting conductive material, materials can be used such as an indium tin oxide containing a silicon oxide (ITSO), an indium tin oxide (ITO), a zinc oxide (ZnO), an indium zinc oxide (IZO), and a gallium-doped zinc oxide (GZO). It is to be noted that

the light-transmitting conductive material refers to a material which has a visible light transmittance of 75% to 100% in the specification.

[0049] The use of the oxide semiconductor for the semiconductor layer 509 and the use of the light-transmitting conductive material for the pixel electrode 514 make it possible to form the light-transmitting second capacitive element 20. Therefore, the aperture ratio of the pixel 110 can be improved. When the area of the second capacitive element 20 accounts for 70 percent or more or 80 percent or more of the pixel pitch, a liquid crystal display device can be achieved which has a further improved aperture ratio.

[0050] Next, a specific method for varying the value of the storage capacitor will be described for the pixel shown in FIGS. 1 through 3.

[0051] FIG. 4A shows capacitance (C)-voltage (Vg) characteristics of a MOS capacitor, where the horizontal axis indicates a gate voltage Vg, whereas the vertical axis indicates a capacitance C. The second capacitive element 20 formed of the semiconductor layer 509 and the pixel electrode 514 overlapped with the insulating layer 512 and the insulating layer 513 interposed therebetween constitutes a MOS capacitor. The MOS capacitor has the characteristics of, as shown in FIG. 4A, failing to function as a capacitive element when the voltage value is lower than a certain threshold voltage Vth, and functioning as a capacitive element only when the voltage value is the certain threshold voltage Vth or more.

[0052] FIG. 4B shows a schematic diagram of the ranges of voltage values which can be taken by the capacitance line Cs when the voltage value of the capacitance line Cs is varied in a moving image display period and a still image display period. The video data voltage Vvi takes a value within a certain range from a maximum value Vmax to a minimum value Vmin, as shown in FIG. 4B. Therefore, the voltage value of the capacitance line Cs is adjusted to not less than the maximum value Vmax of the video data voltage Vvi in the moving image display period, and adjusted to not more than the maximum value Vmin of the video data voltage Vvi in the still image display period.

[0053] In FIGS. 5A and 5B, ranges are referred to as a, b, and c respectively when the voltage Vg of the gate electrode of the second capacitive element 20 takes a value from the maximum value Vmax of the video data voltage Vvi to the minimum value Vmin thereof, takes a value not more than the minimum value Vmin of the video data voltage Vvi, and takes a value not less than the maximum value Vmax of the video data voltage Vvi.

[0054] When the voltage value of the capacitance line Cs is adjusted to not less than the maximum value Vmax of the video data voltage Vvi, the voltage value Vg of the gate electrode of the second capacitive element 20 takes a value not more than the minimum value Vmin of the video data voltage Vvi. From FIG. 5A, it is determined that when the voltage value Vg of the gate electrode of the second capacitive element 20 takes any value within the range b, the capacitance value of the second capacitive element 20 fails to take any value.

[0055] More specifically, in the moving image display period, the voltage value of the capacitance line Cs electrically connected to the one electrode of the first capacitive element 10 and the one electrode of the second capacitive element 20 takes a value not less than the maximum value Vmax of the video data voltage Vvi, and the second capacitive

element 20 as a MOS capacitor thus fails to function at all. Therefore, only the first capacitive element 10 functions in the pixel 110.

[0056] When the voltage value of the capacitance line Cs is adjusted to not more than the minimum value Vmin of the video data voltage Vvi, the voltage value Vg of the gate electrode of the second capacitive element 20 takes a value not less than the maximum value Vmax of the video data voltage Vvi. From FIG. 5B, it is determined that when the voltage value Vg of the gate electrode of the second capacitive element 20 takes any value within the range c, the capacitance value of the second capacitive element 20 takes a certain value Ca.

[0057] More specifically, in the still image display period, the voltage value of the capacitance line Cs electrically connected to the one electrode of the first capacitive element 10 and the one electrode of the second capacitive element 20 takes a value not more than the minimum value Vmin of the video data voltage Vvi, and the second capacitive element 20 as a MOS capacitor thus does function. Therefore, the first capacitive element 10 and the second capacitive element 20 do function in the pixel 110.

[0058] Thus, the above-described configuration allows switching of the capacitance value between the both periods of the moving image display period and the still image display periods by adjusting the voltage value of the capacitance line Cs. More specifically, depending on images displayed, the capacitance value in the pixel can be varied so as to be most suitable for each pixel accordingly in response to the value of the drastically varying frame frequency. In particular, in the case of driving the pixel at an extremely high frame frequency as in color display by a sequential method, the capacitance value in the pixel can be further reduced, thus achieving high integration and downsizing of the liquid crystal display device. More specifically, a desirable capacitance value can be set efficiently for the pixel, thus allowing the power consumption of the entire liquid crystal display device to be reduced.

[0059] In addition, the above-described configuration can control the capacitance value of all the pixels independently by adjusting the voltage value of the capacitance line Cs electrically connected to the one electrode of the first capacitive element 10 and the one electrode of the second capacitive element 20, thus eliminating the need to install wiring uselessly. For this reason, the parasitic capacitance caused by an overlap between adjacent wirings can be reduced to obtain a higher-definition liquid crystal display device. In addition, independently of the channel width of the pixel transistor 300, an appropriate storage capacitor can be ensured in the pixel, thus making it easy to achieve high integration in the liquid crystal display device.

## Embodiment 2

[0060] In the present embodiment, another pixel structure and a method for switching the storage capacitors will be described in a liquid crystal display device according to an embodiment of the present invention disclosed herein. It is to be noted that the liquid crystal display device described in the present embodiment includes pixels each with a variable capacitance value in response to images displayed.

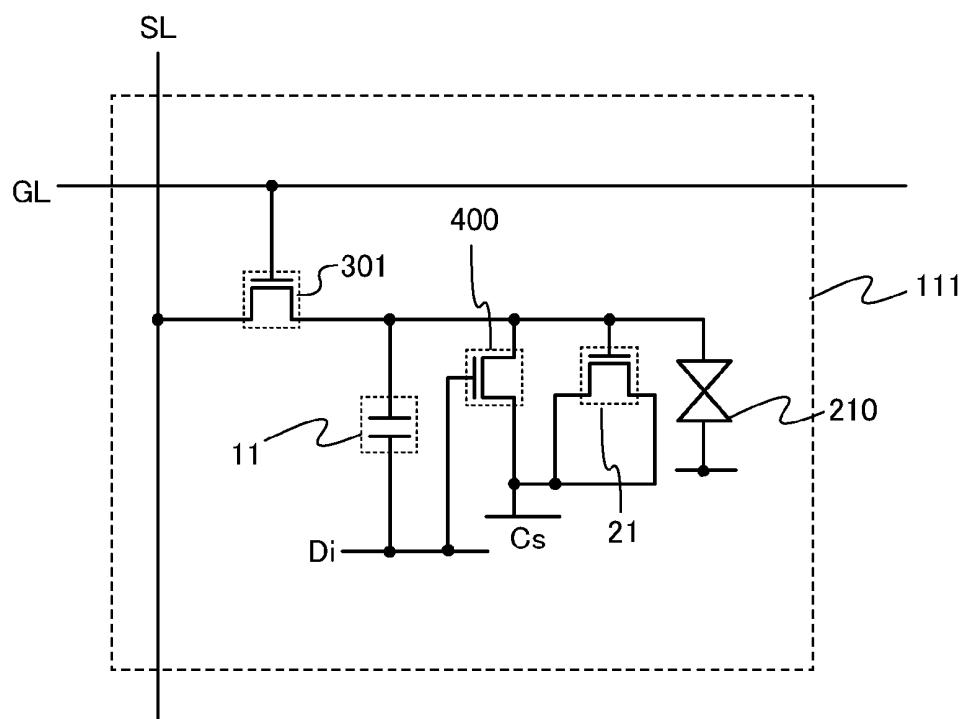

[0061] FIG. 6 is a diagram illustrating a circuit example of a pixel included in the liquid crystal display device.

[0062] A pixel 111 includes a pixel transistor 301, a transistor 400, a first capacitive element 11, and a second capaci-

tive element 21. The pixel transistor 301 has a gate electrode electrically connected to a scan line GL, and a first electrode electrically connected to a signal line SL, which serves as one of a source electrode and a drain electrode of the pixel transistor 301. Furthermore, one electrode of the first capacitive element 11 is electrically connected to a gate electrode of the transistor 400, a first electrode which serves as one of a source electrode and a drain electrode of the transistor 400 is electrically connected to one electrode of the second capacitive element 21, and a second electrode which serve as the other of the source electrode and the drain electrode of the pixel transistor 301, the other electrode of the first capacitive element 11, a second electrode which serve as the other of the source electrode and the drain electrode of the transistor 400, and the other electrode of the second capacitive element 21 are electrically connected to each other.

[0063] Further, the gate electrode of the transistor 400 and the one electrode of the first capacitive element 11 are electrically connected to a wiring Di for shielding, and the first electrode which serves as one of the source electrode and the drain electrode of the transistor 400 and the one electrode of the second capacitive element 21 are electrically connected to the capacitance line Cs. Furthermore, such an electric potential that turns off the transistor 400 at least during image display is supplied to the wiring Di for shielding.

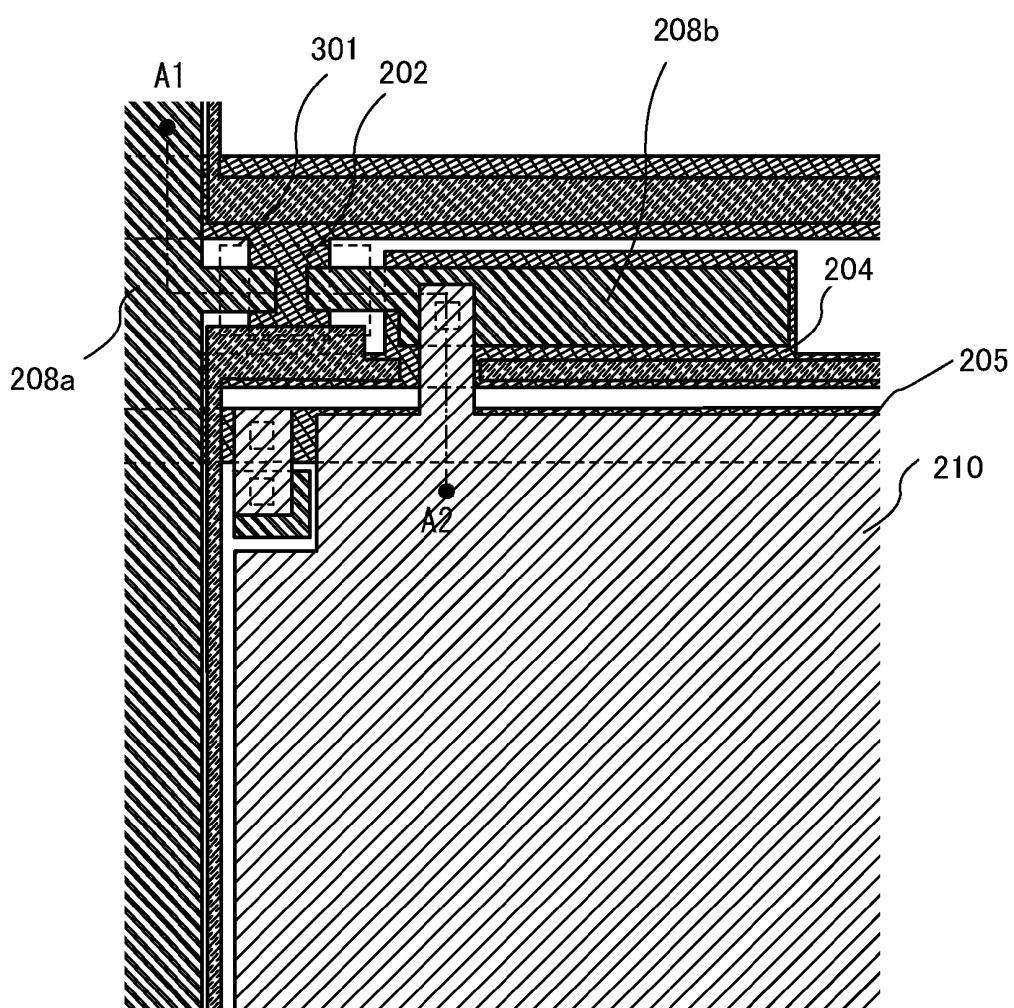

[0064] Next, an example of the specific structure of the pixel shown in FIG. 6 will be described with reference to FIGS. 7 and 8. FIG. 7 shows a top view of the pixel. In addition, FIG. 8 shows a cross-sectional view of the pixel along the chain line A1-A2 in FIG. 7.

[0065] In the cross section A1-A2, a base layer 201 is formed on a substrate 200, and a gate electrode 202, a wiring 203, a wiring 204, and a wiring 205 are formed on the base layer 201. In addition, a gate insulating layer 206 and a semiconductor layer 207 is formed to cover the gate electrode 202, the wiring 203, the wiring 204, and the wiring 205. In addition, a source electrode 208a and a drain electrode 208b on the semiconductor layer 207. In addition, an insulating layer 209 is formed on the source electrode 208a and the drain electrode 208b so as to be in partial contact with the semiconductor layer 207. A pixel electrode 210 is formed on the insulating layer 209. Further, the pixel electrode 210 is electrically connected to the drain electrode 208b through a contact hole 211 formed in the insulating layer 209.

[0066] A section in which the wiring 204 and the drain electrode 208b are overlapped with the gate insulating layer 206 and the semiconductor layer 207 interposed therebetween functions as the first capacitive element 11. The gate insulating layer 206 and the semiconductor layer 207 function as dielectric layers. In addition, a section in which the semiconductor layer 207 and the pixel electrode 210 are overlapped with the gate insulating layer 209 interposed therebetween functions as the second capacitive element 21. The insulating layer 209 functions as a dielectric layer.

[0067] The multilayer structure of the dielectric layer can prevent interlayer short circuit caused by pinholes, etc. formed in the insulating layers. More specifically, even when a pinhole is caused in one of the dielectric layers, the pinhole is covered with the other dielectric layer, and the function of the first capacitive element 11 can be thus improved.

[0068] The pixel transistor 301 configured with the use of the oxide semiconductor for the semiconductor layer 207 can reduce the off-state current, and reduce the ratio of electric charges disappearing from the storage capacitor provided in

the pixel. More specifically, even when the frame frequency is lowered, the pixel transistor 301 makes it possible to keep electric charges held in the storage capacitor until the next writing period.

[0069] For the pixel electrode 210, a light-transmitting conductive material is preferably used. As the light-transmitting conductive material, materials can be used such as an indium tin oxide containing a silicon oxide (ITSO), an indium tin oxide (ITO), a zinc oxide (ZnO), an indium zinc oxide (IZO), and a gallium-doped zinc oxide (GZO). It is to be noted that the light-transmitting conductive material refers to a material which has a visible light transmittance of 75% to 100% in the specification.

[0070] The use of the oxide semiconductor for the semiconductor layer 207 and the use of the light-transmitting conductive material for the pixel electrode 210 make it possible to form the light-transmitting second capacitive element 21. Therefore, the aperture ratio of the pixel 111 can be improved. When the area of the second capacitive element 21 accounts for 70 percent or more or 80 percent or more of the pixel pitch, a liquid crystal display device can be achieved which has a further improved aperture ratio. It is to be noted the pixel pitch refers to the area of a region surrounded by both the distance between adjacent signal lines as a side and the distance between adjacent scan lines as another side.

[0071] Next, a specific method for varying the value of the storage capacitor will be described for the pixel shown in FIGS. 6 through 8.

[0072] The second capacitive element 21 formed of the semiconductor layer 207 and the pixel electrode 210 overlapped with the insulating layer 209 interposed therebetween constitutes a MOS capacitor. The MOS capacitor has the characteristics of, as shown in FIG. 4A, failing to function as a capacitive element when the voltage value is lower than a certain threshold voltage  $V_{th}$ , and functioning as a capacitive element only when the voltage value is the certain threshold voltage  $V_{th}$  or more.

[0073] FIG. 4B shows a schematic diagram of the ranges of voltage values which can be taken by the capacitance line Cs when the voltage value of the capacitance line Cs is varied in a moving image display period and a still image display period. The video data voltage  $V_{vi}$  takes a value within a certain range from a maximum value  $V_{max}$  to a minimum value  $V_{min}$ , as shown in FIG. 4B. Therefore, the voltage value of the capacitance line Cs is adjusted to not less than the maximum value  $V_{max}$  of the video data voltage  $V_{vi}$  in the moving image display period, and adjusted to not more than the maximum value  $V_{min}$  of the video data voltage  $V_{vi}$  in the still image display period.

[0074] It is to be noted that the wiring Di for shielding is placed in the pixel 111 for preventing conduction in a region B in FIG. 8. Therefore, there is a need to supply such an electric potential that turns off the transistor 400 at least during image display, to the wiring Di for shielding, which is electrically connected to the gate electrode of the transistor 400.

[0075] When the voltage value of the capacitance line Cs is adjusted to not less than the maximum value  $V_{max}$  of the video data voltage  $V_{vi}$ , the voltage value  $V_g$  of the gate electrode of the second capacitive element 21 takes a value not more than the minimum value  $V_{min}$  of the video data voltage  $V_{vi}$ . From FIG. 5A, it is determined that when the voltage value  $V_g$  of the gate electrode of the second capacitive

element 21 takes any value within the range b, the capacitance value of the second capacitive element 21 fails to take any value.

[0076] More specifically, in the moving image display period, the voltage value of the capacitance line Cs electrically connected to the one electrode of the second capacitive element 21 and the first electrode which serves as one of the source electrode and the drain electrode of the transistor 400 takes a value not less than the maximum value Vmax of the video data voltage Vvi, and the second capacitive element 21 as a MOS capacitor thus fails to function at all. Therefore, only the first capacitive element 11 functions in the pixel 111.

[0077] When the voltage value of the capacitance line Cs is adjusted to not more than the minimum value Vmin of the video data voltage Vvi, the voltage value Vg of the gate electrode of the second capacitive element 21 takes a value not less than the maximum value Vmax of the video data voltage Vvi. From FIG. 5B, it is determined that when the voltage value Vg of the gate electrode of the second capacitive element 21 takes any value within the range c, the capacitance value of the second capacitive element 21 takes a certain value Ca.

[0078] More specifically, in the still image display period, the voltage value of the capacitance line Cs electrically connected to the one electrode of the second capacitive element 21 and the first electrode which serves as one of the source electrode and the drain electrode of the transistor 400 takes a value not more than the minimum value Vmin of the video data voltage Vvi, and the second capacitive element 21 as a MOS capacitor thus does function. Therefore, the first capacitive element 11 and the second capacitive element 21 do function in the pixel 111.

[0079] Thus, the above-described configuration allows switching of the capacitance value between the both periods of the moving image display period and the still image display periods by adjusting the voltage value of the capacitance line Cs. More specifically, depending on images displayed, the capacitance value in the pixel can be varied so as to be most suitable for each pixel accordingly in response to the value of the drastically varying frame frequency. In particular, in the case of driving the pixel at an extremely high frame frequency as in color display by a sequential method, the capacitance value in the pixel can be further reduced, thus achieving high integration and downsizing of the liquid crystal display device. More specifically, a desirable capacitance value can be set efficiently for the pixel, thus allowing the power consumption of the entire liquid crystal display device to be reduced.

[0080] In addition, the above-described configuration can control the capacitance value of the entire pixel independently by adjusting the voltage value of the capacitance line Cs electrically connected to the one electrode of the second capacitive element 21 and the first electrode which serves as one of the source electrode and the drain electrode of the transistor 400, thus eliminating the need to install wiring uselessly. For this reason, the parasitic capacitance caused by an overlap between adjacent wirings can be reduced to obtain a higher-definition liquid crystal display device. In addition, independently of the channel width of the pixel transistor 301, an appropriate storage capacitor can be ensured in the pixel, thus making it easy to increase the integration in the liquid crystal display device.

[0081] This application is based on Japanese Patent Application serial no. 2010-206282 filed with Japan Patent Office on Sep. 15, 2010, the entire contents of which are hereby incorporated by reference.

What is claimed is:

1. A semiconductor device comprising:

a transistor including a gate electrode electrically connected to a scan line, a first electrode electrically connected to a signal line, and a second electrode electrically connected to a pixel electrode;

- a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and

- a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to the capacitance line, wherein the second capacitive element has a capacitance value variable in response to a time interval of a gate pulse by adjusting an electric potential of the capacitance line.

2. The liquid crystal display device according to claim 1, wherein the pixel electrode and the semiconductor layer have a light-transmitting property.

3. The liquid crystal display device according to claim 1, wherein the semiconductor layer comprises an oxide semiconductor.

4. The liquid crystal display device according to claim 1, wherein the second capacitive element has a MOS capacitor structure with a dielectric layer interposed between the one electrode and the other electrode.

5. The liquid crystal display device according to claim 1, wherein the one electrode of the second capacitive element is formed from the same layer as the pixel electrode, and wherein the other electrode of the second capacitive element is formed from the same semiconductor material as the semiconductor layer of the transistor.

6. The liquid crystal display device according to claim 1, wherein a dielectric layer of the first capacitive element or the second capacitive element has a multilayer structure.

7. A method for driving a display device comprising:

a transistor including a gate electrode electrically connected to a scan line, a first electrode electrically connected to a signal line, and a second electrode electrically connected to a pixel electrode;

- a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and

- a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to the capacitance line, the method comprising a step of:

adjusting an electric potential of the capacitance line, and varying a capacitance value of the second capacitive element in response to a time interval of a gate pulse.

8. A semiconductor device comprising:

a first transistor including a gate electrode electrically connected to a scan line, a first electrode electrically connected to a signal line, and a second electrode electrically connected to a pixel electrode;

- a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a wiring for shielding;

- a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and

- a second transistor including a gate electrode electrically connected to the wiring for shielding, a first electrode electrically connected to the one electrode of the first capacitive element, and a second electrode electrically connected to the capacitance line,

- wherein the second capacitive element has a capacitance value variable in response to a time interval of a gate pulse by adjusting an electric potential of the capacitance line and supplying, to the wiring for shielding, an electric potential that turns off the second transistor at least during image display.

9. The liquid crystal display device according to claim 8, wherein the pixel electrode and the semiconductor layer have a light-transmitting property.

10. The liquid crystal display device according to claim 8, wherein the semiconductor layer comprises an oxide semiconductor.

11. The liquid crystal display device according to claim 8, wherein the second capacitive element has a MOS capacitor structure with a dielectric layer interposed between the one electrode and the other electrode.

12. The liquid crystal display device according to claim 8, wherein the one electrode of the second capacitive element is formed from the same layer as the pixel electrode, and

wherein the other electrode of the second capacitive element is formed from the same semiconductor material as the semiconductor layer of the first transistor.

13. The liquid crystal display device according to claim 8, wherein a dielectric layer of the first capacitive element or the second capacitive element has a multilayer structure.

14. A method for driving a display device comprising:

a first transistor including a gate electrode electrically connected to a scan line, a first electrode electrically connected to a signal line, and a second electrode electrically connected to a pixel electrode;

a first capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a wiring for shielding;

a second capacitive element including one electrode electrically connected to the second electrode, and the other electrode electrically connected to a capacitance line; and

a second transistor including a gate electrode electrically connected to the wiring for shielding, a first electrode electrically connected to the one electrode of the first capacitive element, and a second electrode electrically connected to the capacitance line,

the method comprising a step of:

adjusting an electric potential of the capacitance line, supplying, to the wiring for shielding, an electric potential that turns off the second transistor at least during image display, and

varying a capacitance value of the second capacitive element in response to a time interval of a gate pulse.

\* \* \* \* \*

|                |                                                 |         |            |

|----------------|-------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置                                          |         |            |

| 公开(公告)号        | <a href="#">US20120062811A1</a>                 | 公开(公告)日 | 2012-03-15 |

| 申请号            | US13/212510                                     | 申请日     | 2011-08-18 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                    |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司.                                   |         |            |

| 当前申请(专利权)人(译)  | 半导体能源研究所有限公司.                                   |         |            |

| [标]发明人         | MIYAKE HIROYUKI                                 |         |            |

| 发明人            | MIYAKE, HIROYUKI                                |         |            |

| IPC分类号         | G02F1/1343 H01L27/06                            |         |            |

| CPC分类号         | G02F1/136213 H01L27/1255 H01L27/1225            |         |            |

| 优先权            | 2010206282 2010-09-15 JP                        |         |            |

| 其他公开文献         | US9230994                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a> |         |            |

### 摘要(译)

本发明的一个目的是提供一种液晶显示装置，该液晶显示装置允许在像素中确保所需的存储电容器，而不会响应于帧频的变化而降低孔径比。在包括像素晶体管和在每个像素中使用氧化物半导体材料的两个电容元件的液晶显示装置中，一个电容元件包括透光材料以改善像素的孔径比。此外，通过使用透光电容元件的特性，通过响应于根据所显示的图像而变化的帧频调节电容值的电压值，改变像素中的存储电容器的尺寸。