US 20150221270A1

(19) United States

(12) Patent Application Publication

Lee et al.

(10) Pub. No.: US 2015/0221270 A1

(43) Pub. Date: Aug. 6, 2015

(54) LIQUID CRYSTAL DISPLAY PANEL, LIQUID CRYSTAL DISPLAY DEVICE, AND METHOD OF DRIVING A LIQUID CRYSTAL DISPLAY DEVICE

(71) Applicant: SAMSUNG DISPLAY CO., LTD.,

Yongin-City (KR)

(72) Inventors: Seung-Kyu Lee, Yongin-si (KR);

Dong-Hoon Lee, Yongin-si (KR);

Chul-Ho Kim, Yongin-si (KR); Jin-Woo

Park, Yongin-si (KR)

(21) Appl. No.: 14/690,368

(22) Filed: Apr. 17, 2015

#### Related U.S. Application Data

(62) Division of application No. 13/103,348, filed on May 9, 2011, now Pat. No. 9,024,979.

#### Foreign Application Priority Data

Oct. 28, 2010 (KR) ..... 10-2010-0105654

#### Publication Classification

(51) Int. Cl.

*G09G 3/36* (2006.01)

(52) U.S. Cl.

CPC ..... *G09G 3/3614* (2013.01); *G09G 3/3688* (2013.01); *G09G 3/3659* (2013.01); *G09G 2300/0426* (2013.01); *G09G 2310/0248* (2013.01); *G09G 2320/0209* (2013.01); *G09G 2320/0247* (2013.01); *G09G 2330/023* (2013.01)

#### (57) ABSTRACT

A liquid crystal display (LCD) panel is disclosed. The LCD panel includes a plurality of pixels arranged in rows and columns, a first sub gate-line coupled to first row-pixels that are adjacent to a lower side of the first sub gate-line, a second sub gate-line coupled to second row-pixels that are adjacent to an upper side of the second sub gate-line, a plurality of gate-lines between the first sub gate-line and the second sub gate-line, a plurality of even data-lines coupled to first column-pixels that are adjacent to the even data-lines, and a plurality of odd data-lines coupled to second column-pixels that are adjacent to the odd data-lines. Here, each gate-line of the plurality of gate lines is coupled to first row-pixels that are adjacent to a lower side of the gate-line and second row-pixels that are adjacent to an upper side of the gate-line.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 5D

FIG. 5E

FIG. 6

|     | 140_1 | 150_1 | 140_2 | 150_2 | 140_3 | 150_3 | 140_4 | 150_4 |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| DL1 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL2 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL3 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL4 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL5 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL6 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL7 | -     | +     | -     | +     | -     | +     | -     | +     |

| DL8 | -     | +     | -     | +     | -     | +     | -     | +     |

| 2F  | {     | 1H    | -     | +     | -     | +     | -     | +     |

|     | 2H    | -     | +     | -     | +     | -     | +     | -     |

|     | 3H    | -     | +     | -     | +     | -     | +     | -     |

|     | 4H    | -     | +     | -     | +     | -     | +     | -     |

|     | 5H    | -     | +     | -     | +     | -     | +     | -     |

|     | 6H    | -     | +     | -     | +     | -     | +     | -     |

|     | 7H    | -     | +     | -     | +     | -     | +     | -     |

|     | 8H    | -     | +     | -     | +     | -     | +     | -     |

|     | :     | :     | :     | :     | :     | :     | :     | :     |

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 7D

FIG. 7E

FIG. 8

FIG. 9

FIG. 10

FIG. 11

1100

## LIQUID CRYSTAL DISPLAY PANEL, LIQUID CRYSTAL DISPLAY DEVICE, AND METHOD OF DRIVING A LIQUID CRYSTAL DISPLAY DEVICE

### CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a divisional of U.S. patent application Ser. No. 13/103,348, filed May 9, 2011, which claims priority to and the benefit of Korean Patent Application No. 10-2010-0105654, filed on Oct. 28, 2010 in the Korean Intellectual Property Office, the entire contents of all of which are incorporated herein by reference.

### BACKGROUND

#### [0002] 1. Field

[0003] Aspects of embodiments according to the present invention relate to a display device. More particularly, aspects of embodiments according to the present invention relate to a liquid crystal display (LCD) panel, an LCD device, and a method of driving an LCD device.

#### [0004] 2. Description of Related Art

[0005] A liquid crystal display (LCD) device displays an image by forming an electric field (i.e., an electric potential difference) between a pixel electrode and a common electrode of a liquid crystal capacitor included in each pixel. In the liquid crystal capacitor, a liquid crystal layer is placed between the pixel electrode and the common electrode so that light transmittance of the liquid crystal layer is controlled by an intensity of the electric field formed between the pixel electrode and the common electrode. Recently, an LCD device having a thin film transistor (TFT) as a switching element included in each pixel has been in widespread use. This type of LCD device has been referred to as a TFT LCD device.

[0006] An LCD device may periodically invert polarities of data signals to reduce or prevent deterioration of the liquid crystal capacitor included in each pixel due to polarization. For example, the LCD device may employ inversion methods such as a dot inversion method, a line inversion method, a column inversion method, a frame inversion method, a Z-inversion method, an active level shift (ALS) inversion method, etc. However, these inversion methods may cause various problems, such as horizontal crosstalk, vertical crosstalk, unnecessary power consumption, etc.

### SUMMARY

[0007] Example embodiments provide for a liquid crystal display (LCD) panel capable of reducing or preventing horizontal crosstalk and vertical crosstalk while efficiently reducing power consumption. Further, example embodiments provide for an LCD device capable of generating a high quality image by reducing or preventing horizontal crosstalk and vertical crosstalk while efficiently reducing power consumption. In addition, example embodiments provide for a method of driving an LCD device capable of reducing or preventing horizontal crosstalk and vertical crosstalk while efficiently reducing power consumption.

[0008] In an exemplary embodiment according to the present invention, a liquid crystal display (LCD) panel is disclosed. The LCD panel includes a plurality of pixels, a first sub gate-line, a second sub gate-line, a plurality of gate lines, a plurality of even data lines, and a plurality of odd data-lines.

The plurality of pixels is arranged in rows and columns. The first sub gate-line is coupled to first row-pixels that are adjacent to a lower side of the first sub gate-line. The second sub gate-line is coupled to second row-pixels that are adjacent to an upper side of the second sub gate-line. The plurality of gate-lines is between the first sub gate-line and the second sub gate-line. Each gate-line of the plurality of gate-lines is coupled to first row-pixels that are adjacent to a lower side of the gate-line and second row-pixels that are adjacent to an upper side of the gate-line. The plurality of even data-lines is coupled to first column-pixels that are adjacent to the even data-lines. The plurality of odd data-lines is coupled to second column-pixels that are adjacent to the odd data-lines.

[0009] The first row-pixels may include odd column row-pixels and the second row-pixels may include even column row-pixels.

[0010] The first column-pixels may include odd row column-pixels and the second column-pixels may include even row column-pixels.

[0011] The first column-pixels may include even row column-pixels and the second column-pixels may include odd row column-pixels.

[0012] The first row-pixels may include even column row-pixels and the second row-pixels may include odd column row-pixels.

[0013] The first column-pixels may include odd row column-pixels and the second column-pixels may include even row column-pixels.

[0014] The first column-pixels may include even row column-pixels and the second column-pixels may include odd row column-pixels.

[0015] In an odd frame, the odd data-lines may be configured to receive data signals of a first polarity and the even data-lines may be configured to receive data signals of a second polarity, the second polarity being opposite to the first polarity.

[0016] In an even frame, the odd data-lines may be configured to receive data signals of the second polarity and the even data-lines may be configured to receive data signals of the first polarity.

[0017] The first polarity may be positive polarity relative to a common voltage and the second polarity may be negative polarity relative to the common voltage.

[0018] The first polarity may be negative polarity relative to a common voltage and the second polarity may be positive polarity relative to the common voltage.

[0019] The LCD panel may further include a charge-sharing control circuit configured to control the odd data-lines to share electric charges in accordance with a charge-sharing control signal and to control the even data-lines to share electric charges in accordance with the charge-sharing control signal.

[0020] The charge-sharing control circuit may include a plurality of first switches and a plurality of second switches. The plurality of first switches is configured to couple the odd data-lines to each other in accordance with the charge-sharing control signal. The plurality of second switches is configured to couple the even data-lines to each other in accordance with the charge-sharing control signal.

[0021] The charge-sharing control signal may be a pre charge-sharing (PCS) signal. The first switches and the second switches may be configured to turn on before row-pixels coupled to the first sub gate-line, the second sub gate-line, and the plurality of gate-lines are charged.

[0022] The charge-sharing control signal may be a pre charge-sharing (PCS) signal. The first switches and the second switches may be configured to turn on after row-pixels coupled to the first sub gate-line, the second sub gate-line, and the plurality of gate-lines are charged.

[0023] Each of the pixels may include a switching element and a liquid crystal capacitor. The switching element is configured to perform switching operations in accordance with a gate signal output from the first sub gate-line, the second sub gate-line, or one of the gate-lines. The liquid crystal capacitor may be configured to control light transmittance of a liquid crystal layer in accordance with a data signal output from one of the odd data-lines or one of the even data-lines.

[0024] The switching element may be a thin film transistor (TFT) that includes a gate terminal for receiving the gate signal, a source terminal for receiving the data signal, and a drain terminal for outputting the data signal to the liquid crystal capacitor.

[0025] Each of the pixels may further include a storage capacitor configured to maintain a charged voltage of the liquid crystal capacitor.

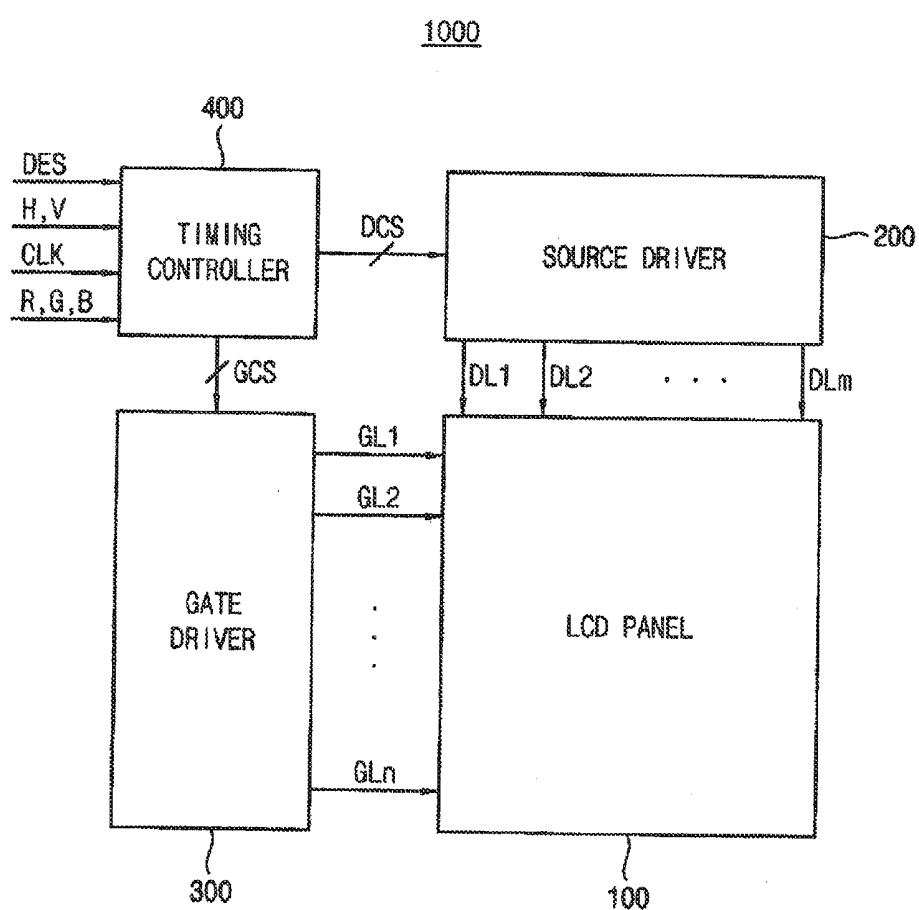

[0026] According to another exemplary embodiment of the present invention, a liquid crystal display (LCD) device is disclosed. The LCD device includes an LCD panel, a source driver, a gate driver, and a timing controller. The LCD panel is configured to apply data signals of a same polarity to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, and to sequentially apply data signals of alternate polarities to column-pixels with an interval of one horizontal period in a column direction. The source driver is configured to provide data signals to the LCD panel in accordance with a data control signal. The gate driver is configured to provide gate signals corresponding to a scan pulse to the LCD panel in accordance with a gate control signal. The timing controller is configured to generate the data control signal and the gate control signal.

[0027] The LCD panel may include a plurality of pixels, a first sub gate-line, a second sub gate-line, a plurality of gate-lines, a plurality of even data-lines, and a plurality of odd data-lines. The plurality of pixels is arranged in rows and columns. The first sub gate-line is coupled to first row-pixels that are adjacent to a lower side of the first sub gate-line. The second sub gate-line is coupled to second row-pixels that are adjacent to an upper side of the second sub gate-line. The plurality of gate-lines is between the first sub gate-line and the second sub gate-line. Each gate-line of the plurality of gate-lines is coupled to first row-pixels that are adjacent to a lower side of the gate-line and second row-pixels that are adjacent to an upper side of the gate-line. The plurality of even data-lines is coupled to first column-pixels that are adjacent to the even data-lines. The plurality of odd data-lines is coupled to second column-pixels that are adjacent to the odd data-lines.

[0028] The LCD panel may further include a charge-sharing control circuit configured to control the odd data-lines to share electric charges in accordance with a charge-sharing control signal and to control the even data-lines to share electric charges in accordance with the charge-sharing control signal.

[0029] The first row-pixels may include odd column row-pixels and the second row-pixels may include even column row-pixels.

[0030] The first column-pixels may include odd row column-pixels and the second column-pixels may include even row column-pixels.

[0031] The first column-pixels may include even row column-pixels and the second column-pixels may include odd row column-pixels.

[0032] The first row-pixels may include even column row-pixels and the second row-pixels may include odd column row-pixels.

[0033] The first column-pixels may include odd row column-pixels and the second column-pixels may include even row column-pixels.

[0034] The first column-pixels may include even row column-pixels and the second column-pixels may include odd row column-pixels.

[0035] In an odd frame, the odd data-lines may be configured to receive data signals of a first polarity and the even data-lines may be configured to receive data signals of a second polarity, the second polarity being opposite to the first polarity.

[0036] In an even frame, the odd data-lines may be configured to receive data signals of the second polarity and the even data-lines may be configured to receive data signals of the first polarity.

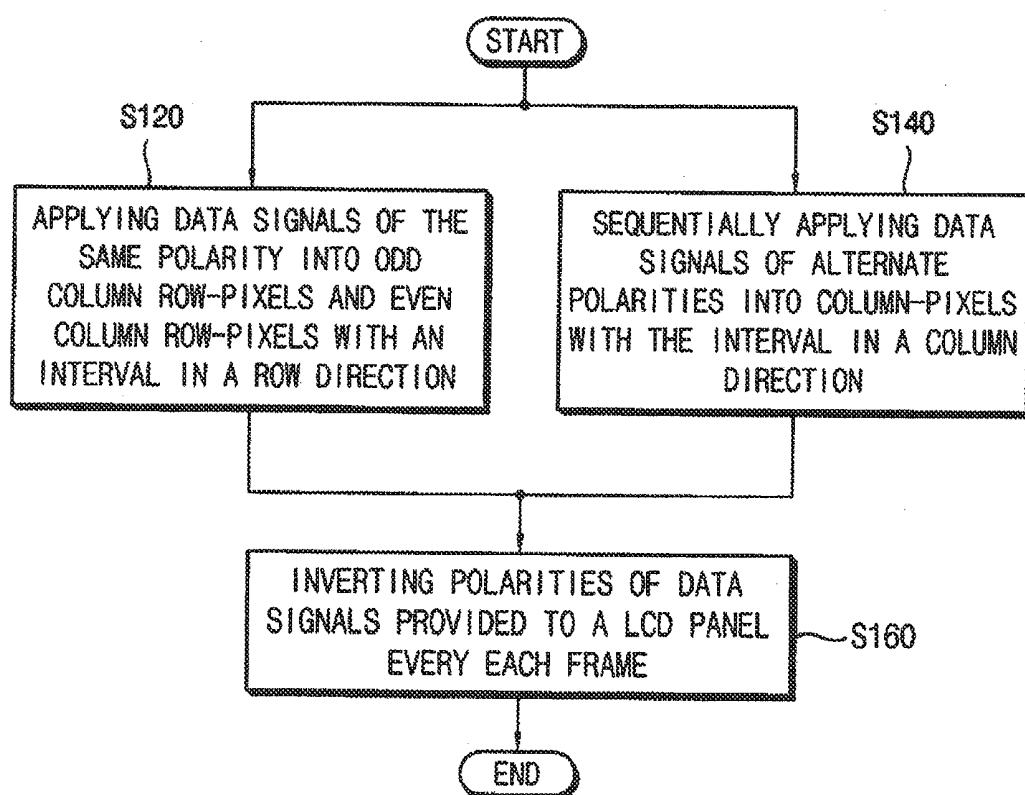

[0037] According to yet another exemplary embodiment of the present invention, a method of driving a liquid crystal display (LCD) device is disclosed. The method includes: applying data signals of a same polarity to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction; sequentially applying data signals of alternate polarities to column-pixels with an interval of one horizontal period in a column direction; and inverting polarities of data signals provided to an LCD panel with each frame.

[0038] According to example embodiments, an LCD panel may reduce power consumption by decreasing a pulse repetition frequency of data signals (i.e., variance of data signals) provided to data-lines in each frame, may reduce or prevent horizontal crosstalk by applying data signals of the same polarity to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, and may reduce or prevent vertical crosstalk by sequentially applying data signals of alternate polarities to column-pixels with an interval of one horizontal period in a column direction. Here, row-pixels describe a plurality of pixels that are common to one row (including a subset of the pixels of one row, such as every other pixel), and column-pixels describe a plurality of pixels that are common to one column (including a subset of the pixels of one column, such as every other pixel).

[0039] Additionally, an LCD device having the LCD panel may generate a high quality image by reducing or preventing horizontal crosstalk and vertical crosstalk while efficiently reducing power consumption. Furthermore, a method of driving an LCD device may reduce or prevent horizontal crosstalk and vertical crosstalk while efficiently reducing power consumption.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0040] Example embodiments can be understood in more detail from the following description taken in conjunction with the accompanying drawings.

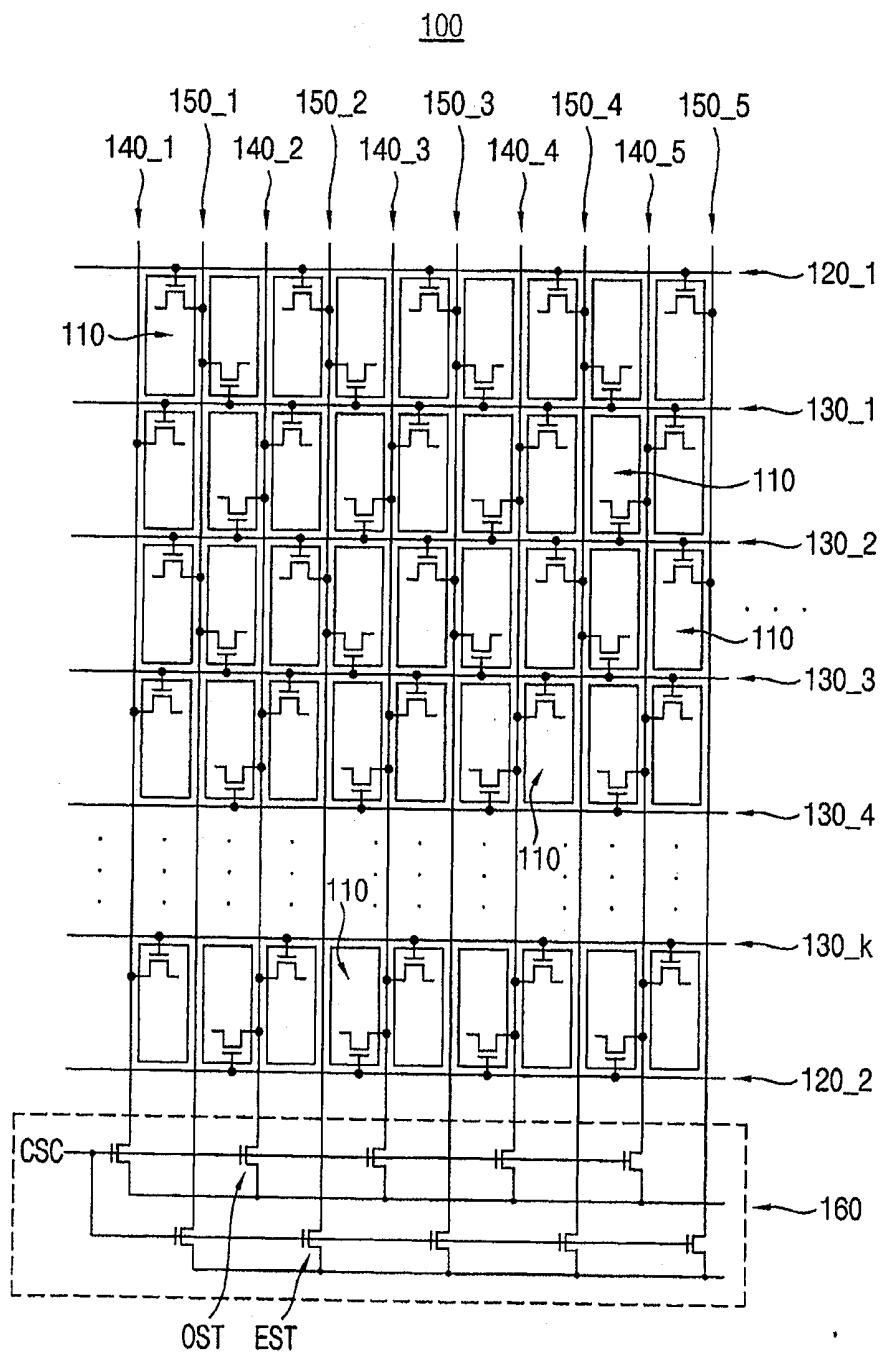

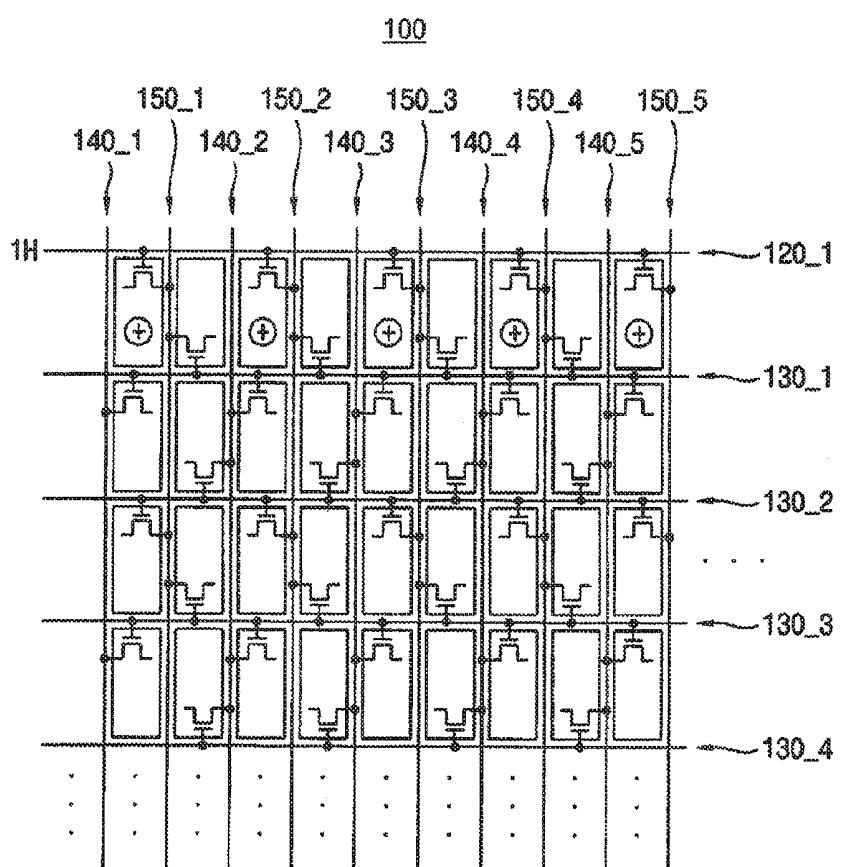

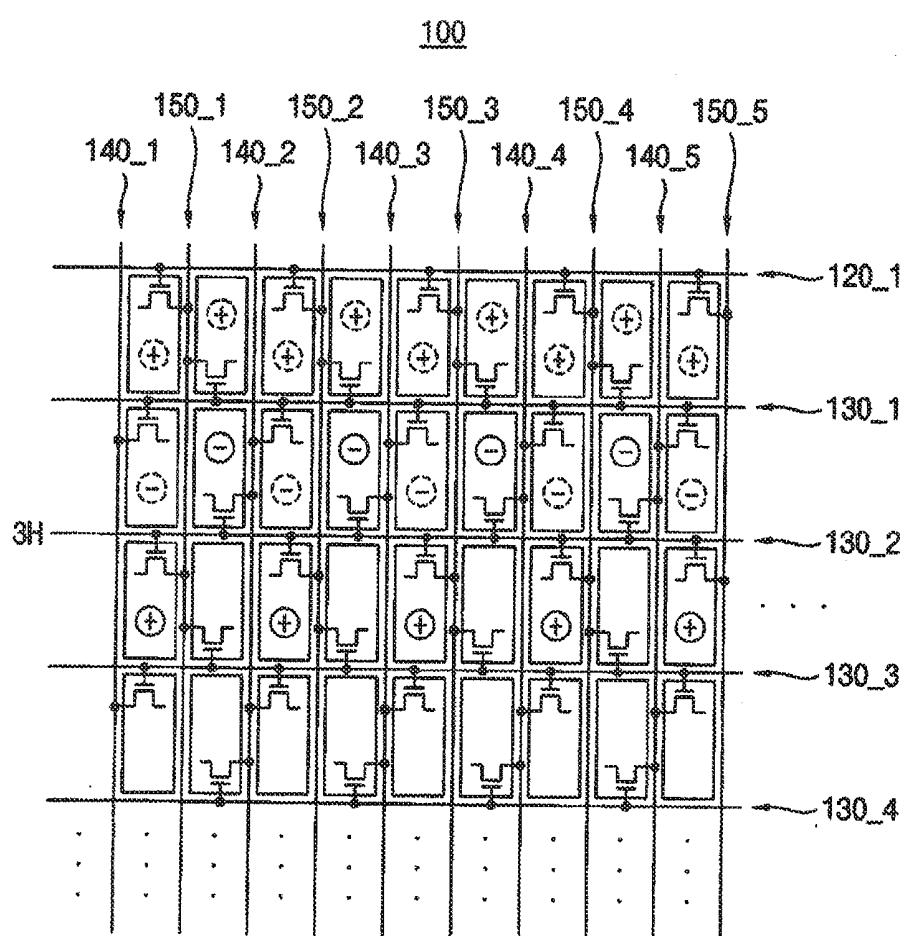

[0041] FIG. 1 is a diagram illustrating a liquid crystal display (LCD) panel in accordance with example embodiments.

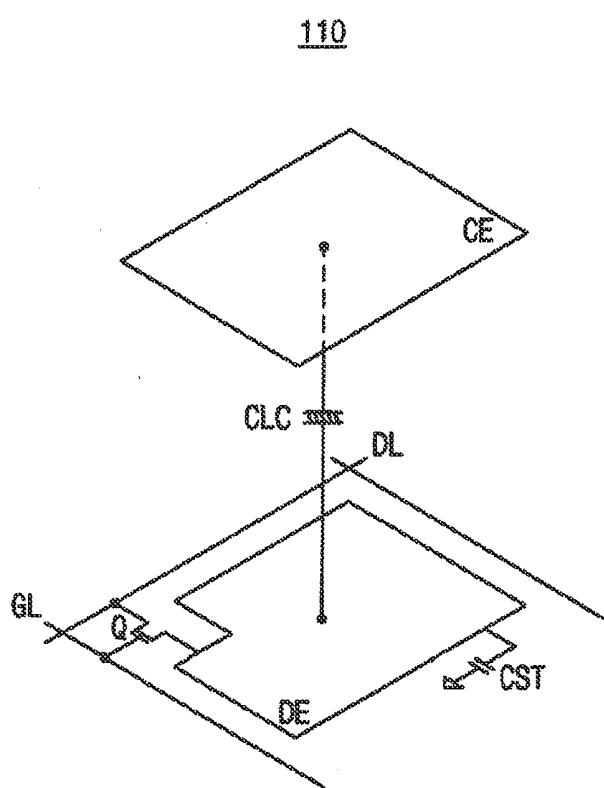

[0042] FIG. 2 is a diagram illustrating a structure of each pixel in the LCD panel of FIG. 1.

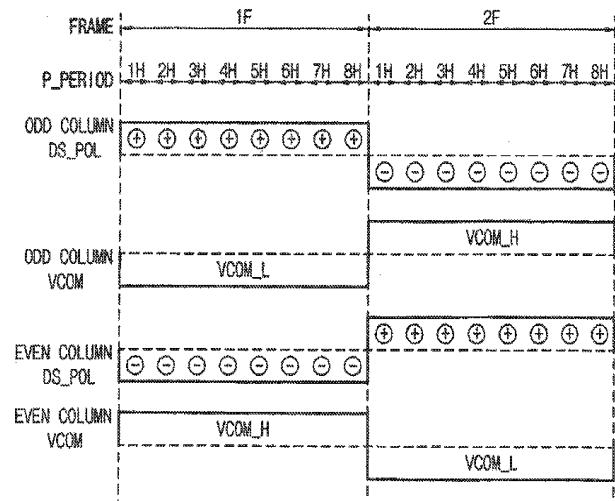

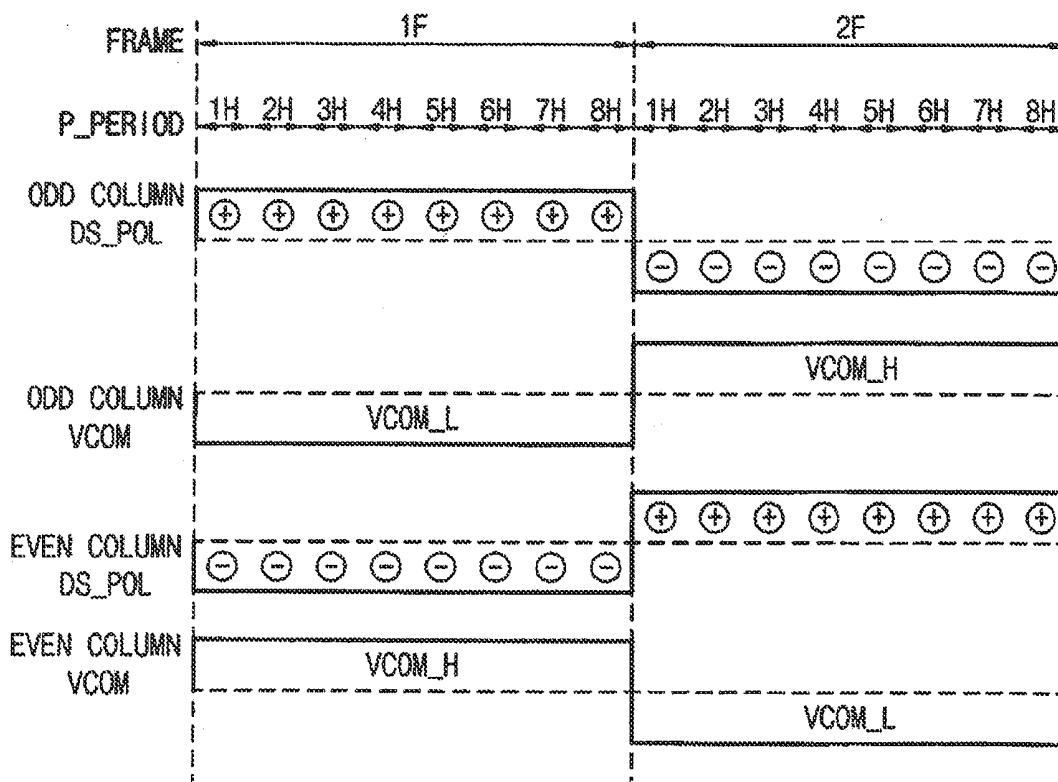

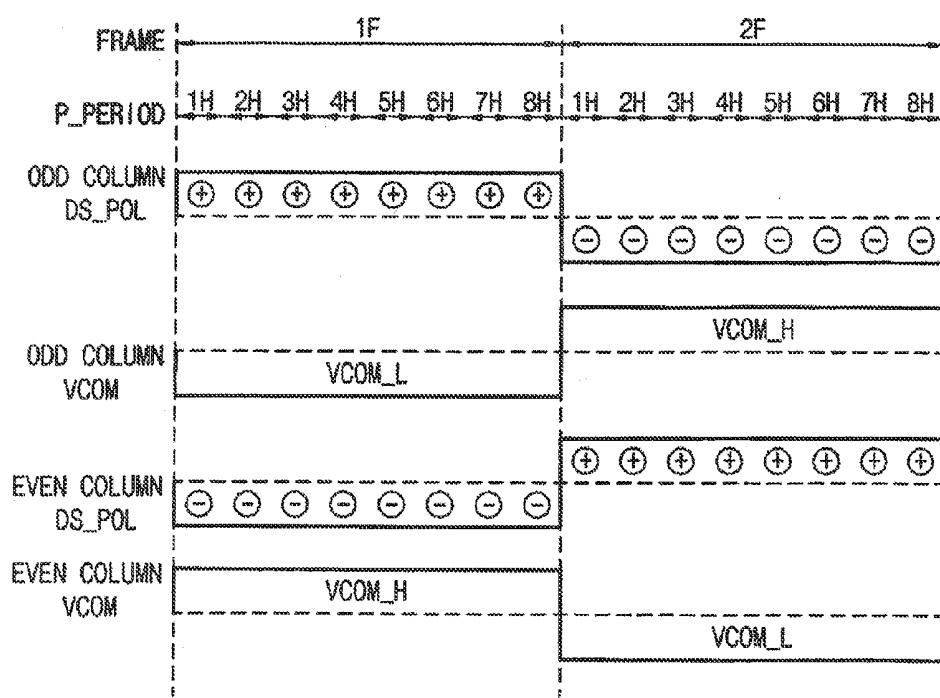

[0043] FIG. 3 is a timing diagram illustrating an example of providing common voltages in accordance with polarities of data signals provided to the LCD panel of FIG. 1.

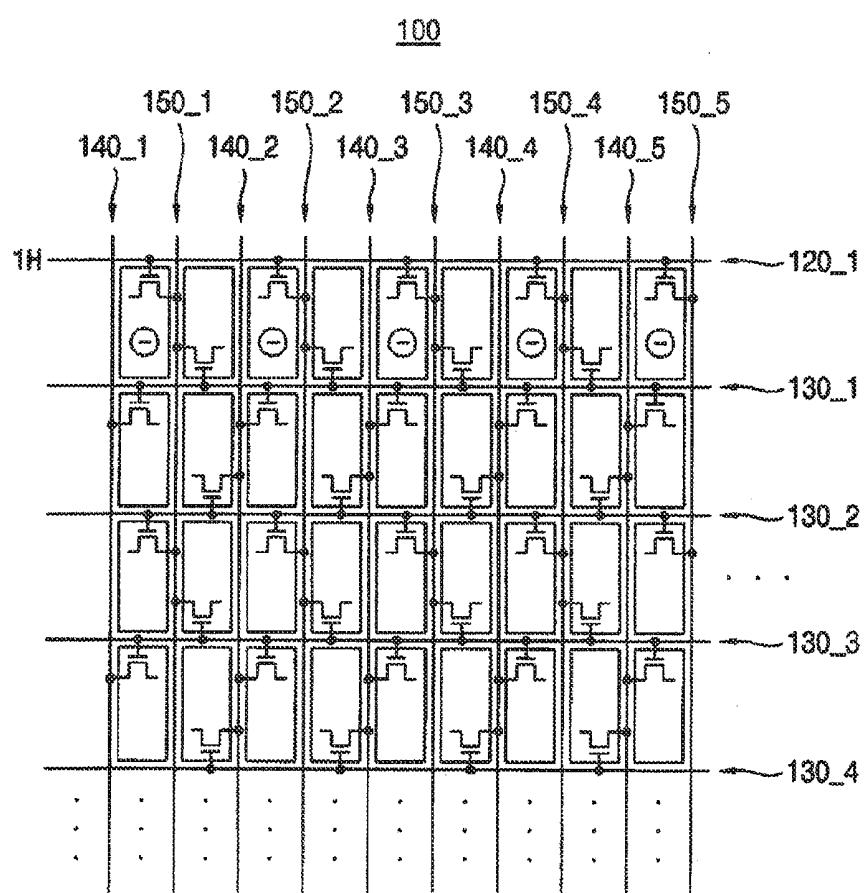

[0044] FIG. 4 is a diagram illustrating an example of providing data signals to the LCD panel of FIG. 1 in an odd frame.

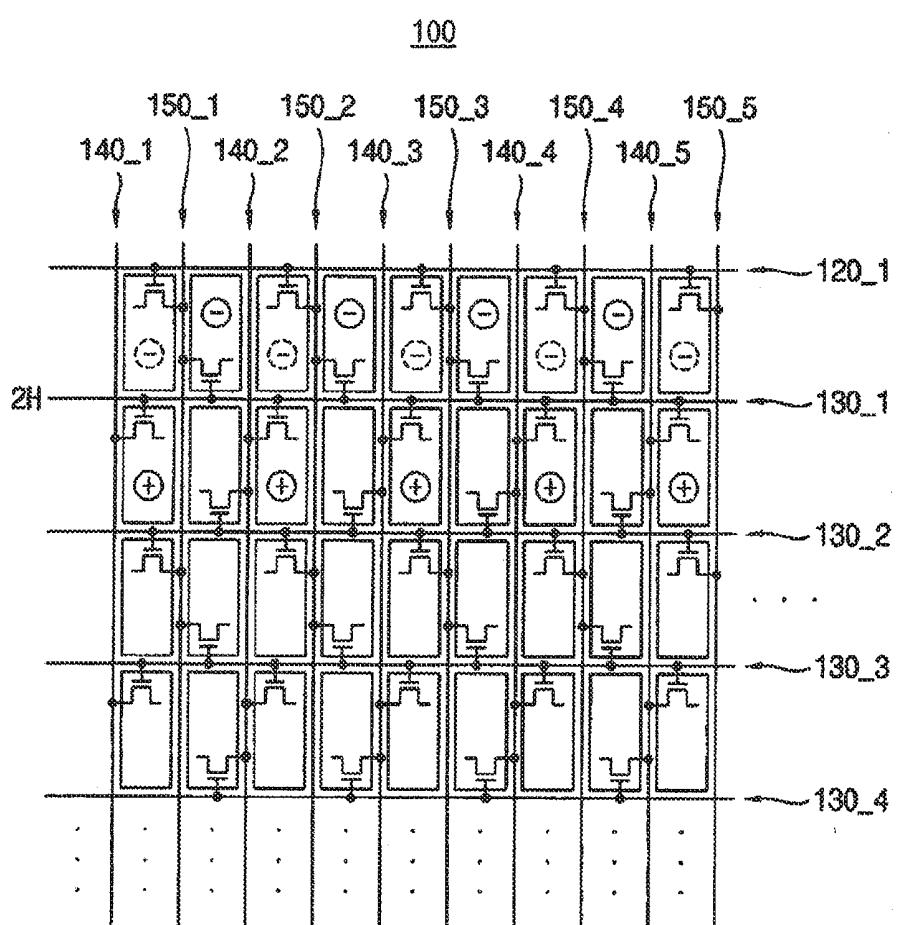

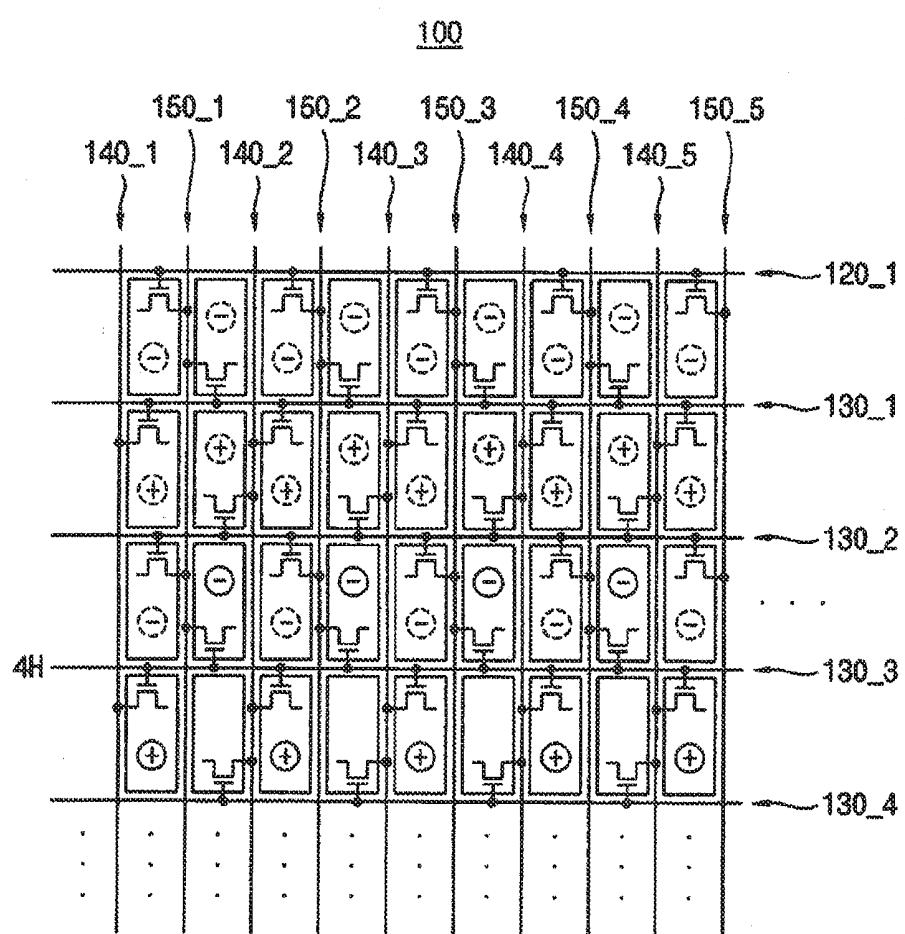

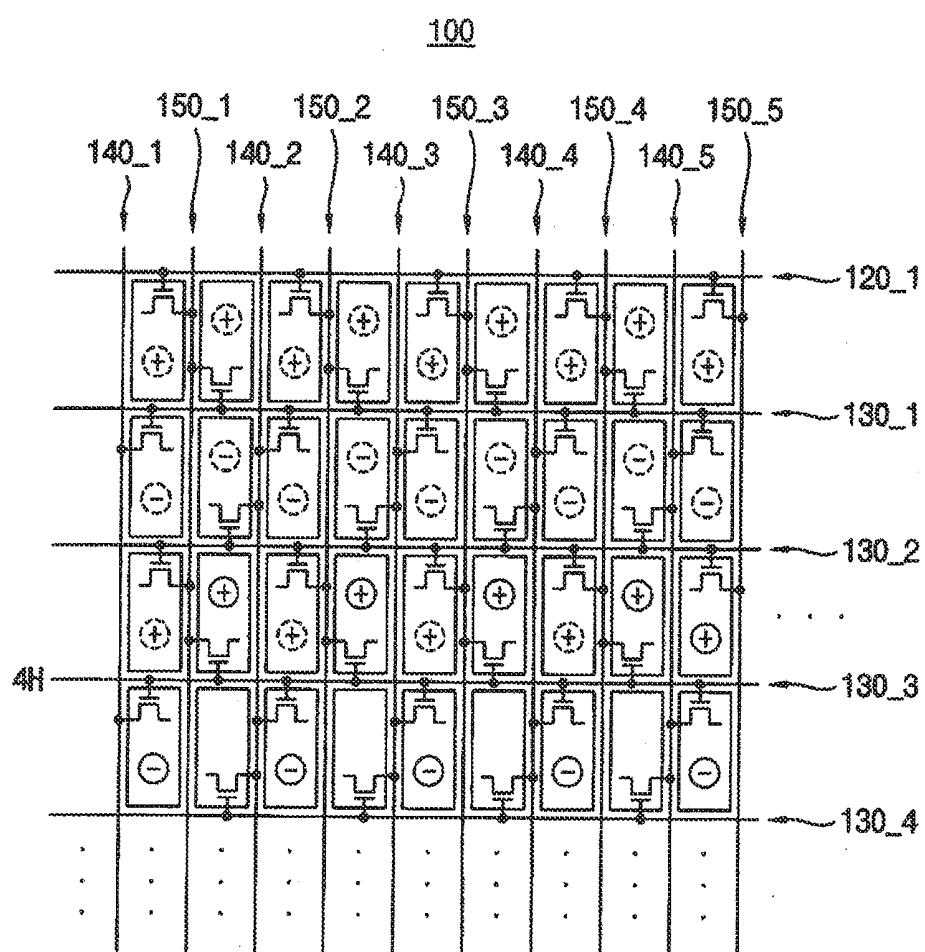

[0045] FIGS. 5A through 5E are diagrams illustrating an example of applying data signals to pixels of the LCD panel of FIG. 1 in a first five horizontal periods of an odd frame.

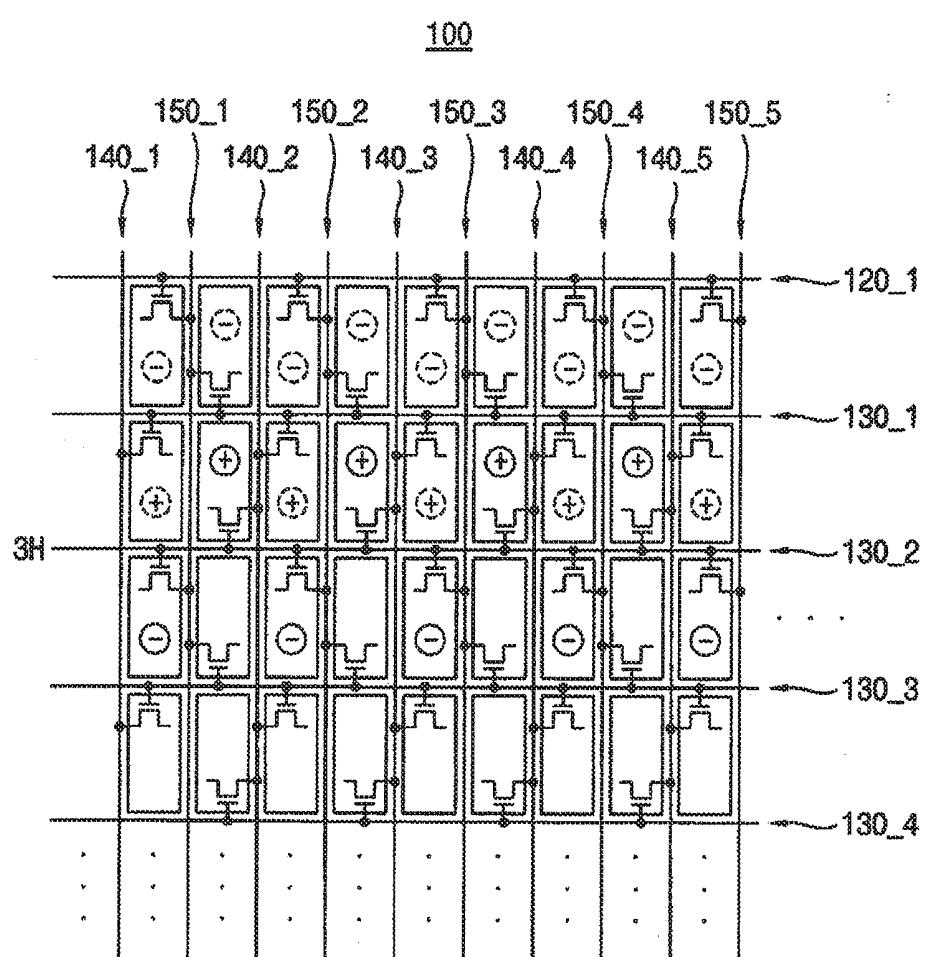

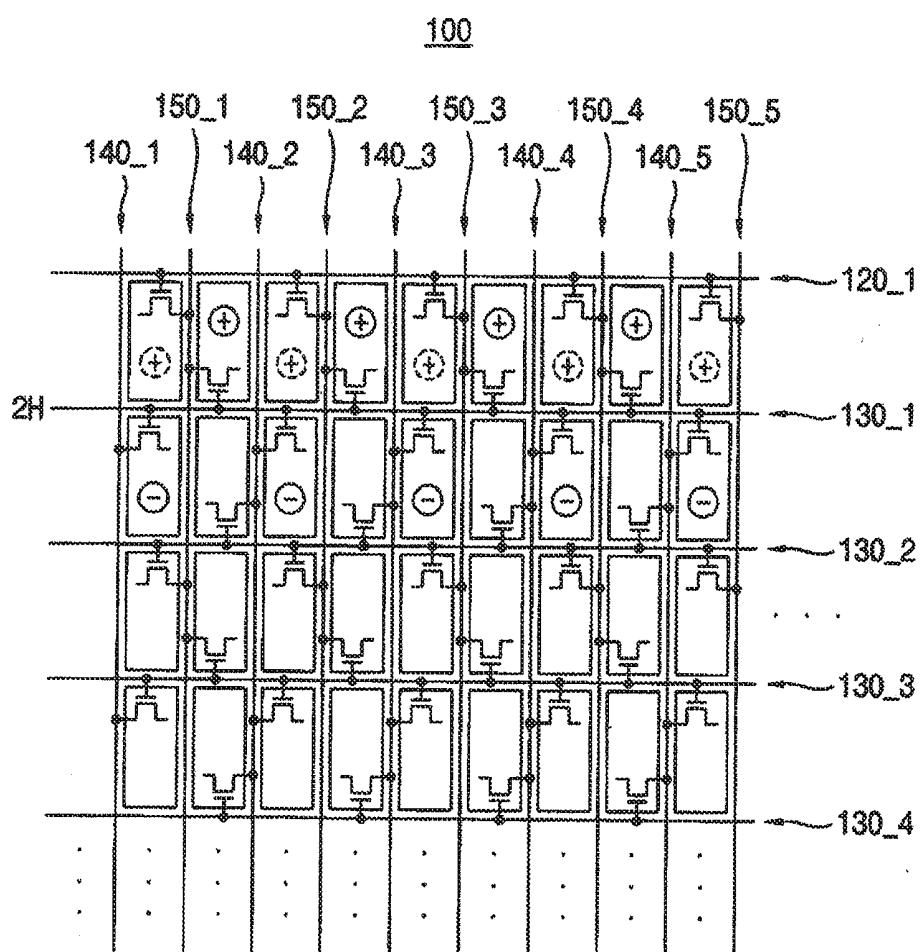

[0046] FIG. 6 is a diagram illustrating an example of providing data signals to the LCD panel of FIG. 1 in an even frame.

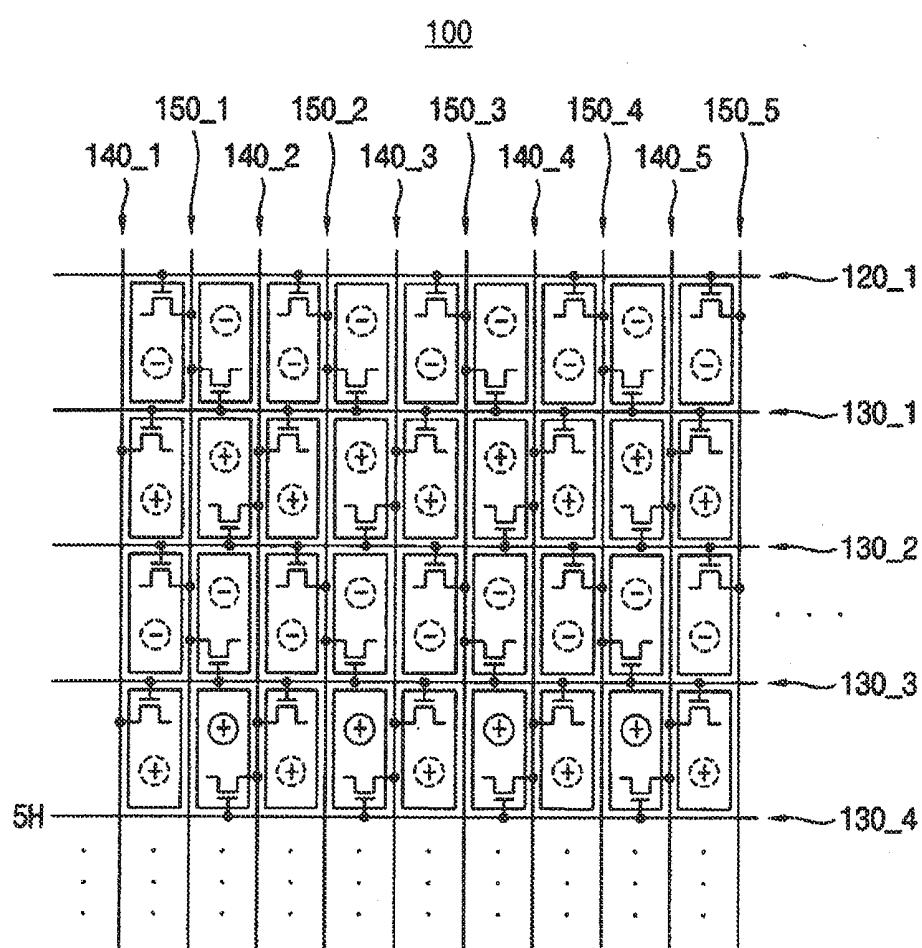

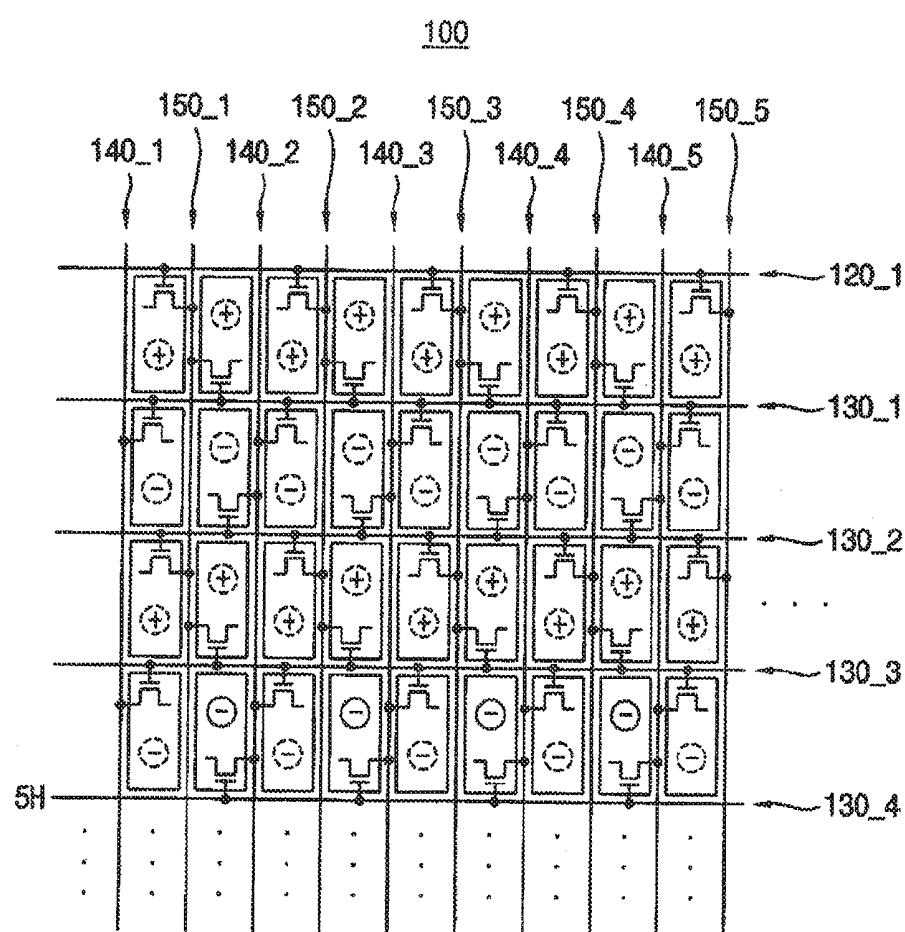

[0047] FIGS. 7A through 7E are diagrams illustrating an example of applying data signals to pixels of the LCD panel of FIG. 1 in a first five horizontal periods of an even frame.

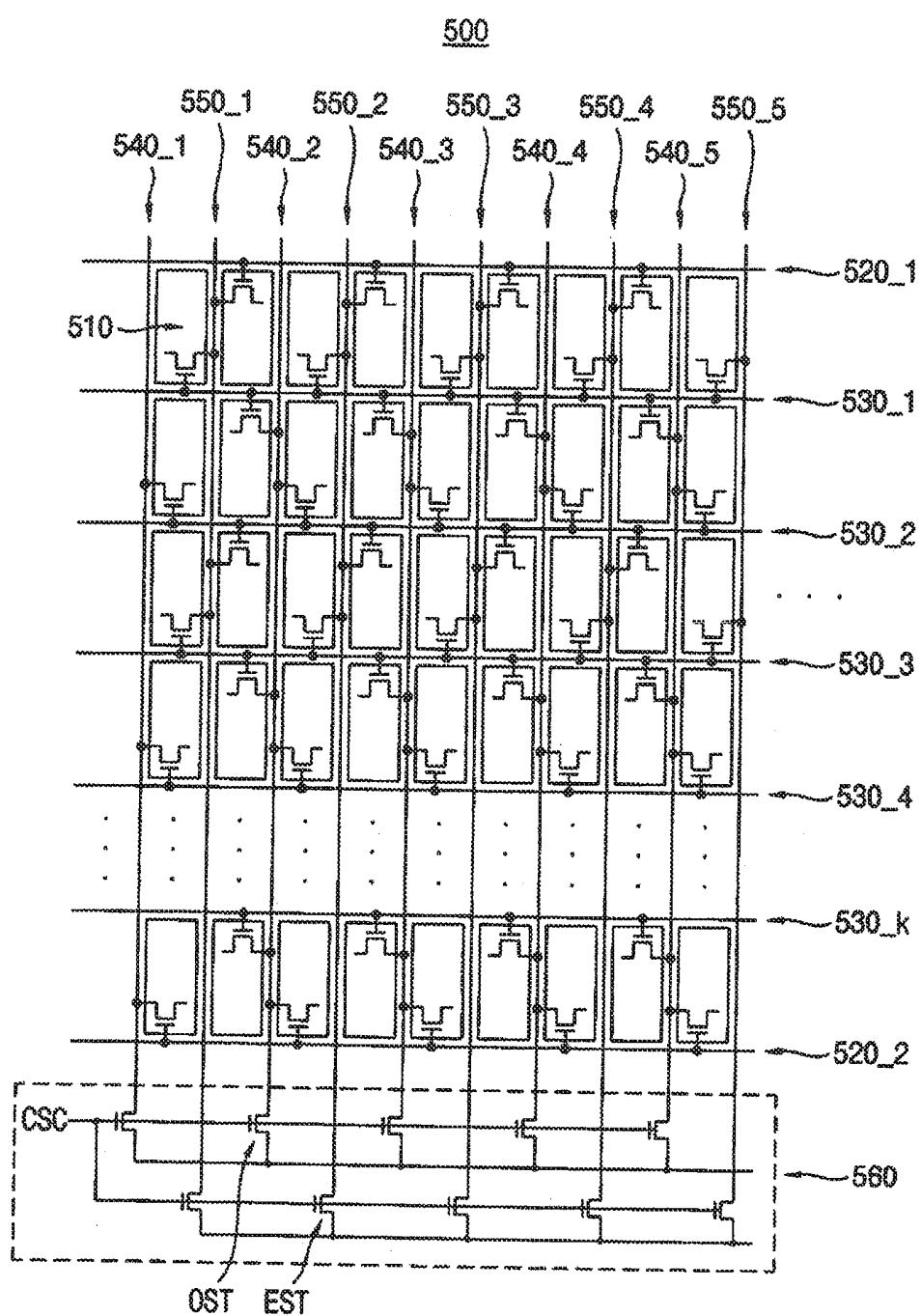

[0048] FIG. 8 is a diagram illustrating another LCD panel in accordance with example embodiments.

[0049] FIG. 9 is a block diagram illustrating an LCD device in accordance with example embodiments.

[0050] FIG. 10 is a flow chart illustrating a method of driving the LCD device of FIG. 9.

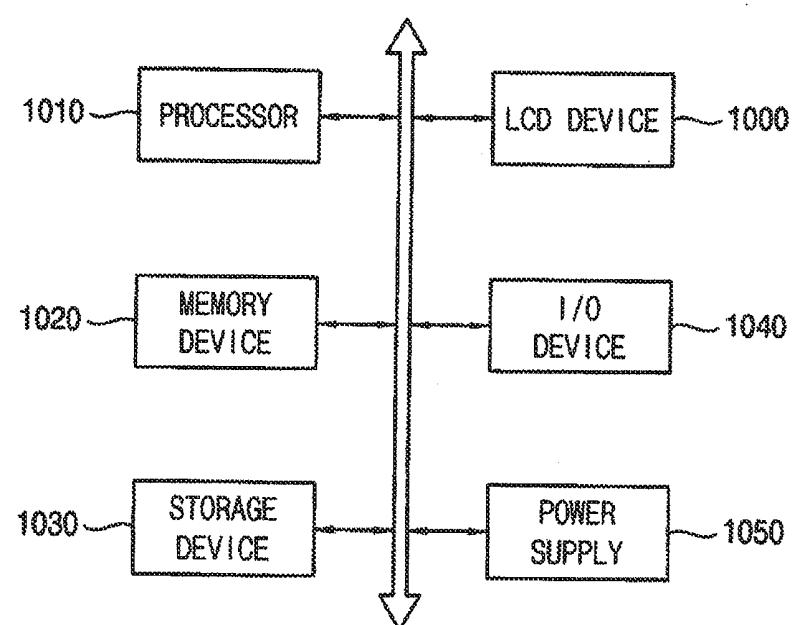

[0051] FIG. 11 is a block diagram illustrating an electric device having the LCD device of FIG. 9.

#### DETAILED DESCRIPTION

[0052] The example embodiments are described more fully hereinafter with reference to the accompanying drawings. The present invention may, however, be embodied in many different forms and should not be construed as limited to the example embodiments set forth herein. In the drawings, the sizes and relative sizes of layers and regions may be exaggerated for clarity.

[0053] It will be understood that when an element or layer is referred to as being “on,” “connected to,” or “coupled to” another element or layer, it can be directly on, directly connected, or directly coupled to the other element or layer, or intervening elements or layers may also be present. In contrast, when an element is referred to as being “directly on,” “directly connected to,” or “directly coupled to” another element or layer, there are no intervening elements or layers present. Like or similar reference numerals refer to like or similar elements throughout. As used herein, the term “and/or” includes any combination of one or more of the associated listed items.

[0054] It will be understood that, although the terms first, second, third, etc., may be used herein to describe various elements, components, regions, layers, patterns, and/or sections, these elements, components, regions, layers, patterns, and/or sections should not be limited by these terms. These terms are only used to distinguish one element, component, region, layer, pattern, or section from another element, component, region, layer, pattern, or section. Thus, a first element, component, region, layer, pattern, or section discussed below could be termed a second element, component, region, layer, pattern, or section without departing from the teachings of example embodiments.

[0055] Spatially relative terms, such as “beneath,” “below,” “lower,” “above,” “upper,” and the like, may be used herein for ease of description to describe one element or feature’s relationship to another element(s) or feature(s) as illustrated in the figures. It will be understood that the spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the

figures is turned over, elements described as “below” or “beneath” other elements or features would then be oriented “above” the other elements or features. Thus, the exemplary term “below” can encompass both an orientation of above and below. The device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein interpreted accordingly.

[0056] The terminology used herein is for describing particular example embodiments only and is not intended to be limiting of the present invention. As used herein, the singular forms “a,” “an,” and “the” are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms “comprises” and/or “comprising,” when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof.

[0057] Example embodiments are described herein with reference to cross sectional illustrations that are schematic illustrations of illustratively idealized example embodiments (and intermediate structures) of the present invention. As such, variations from the shapes of the illustrations because of, for example, manufacturing techniques and/or tolerances, are to be expected. Thus, example embodiments should not be construed as limited to the particular shapes of regions illustrated herein but are to include variations in shapes that result, for example, from manufacturing. The regions illustrated in the figures are schematic in nature and their shapes are not intended to illustrate the actual shape of a region of a device and are not intended to limit the scope of the present invention.

[0058] Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which the present invention belongs. It will be further understood that terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and will not be interpreted in an idealized or overly formal sense unless expressly so defined herein.

[0059] FIG. 1 is a diagram illustrating a liquid crystal display (LCD) panel 100 in accordance with example embodiments.

[0060] Referring to FIG. 1, the LCD panel 100 includes a plurality of pixels 110, a first sub gate-line 120\_1, a second sub gate-line 120\_2, a plurality of gate-lines 130\_1 through 130\_k, a plurality of odd data-lines 140\_1 through 140\_5, and a plurality of even data-lines 150\_1 through 150\_5. The first sub gate-line 120\_1, the second sub gate-line 120\_2, and the plurality of gate-lines 130\_1 through 130\_k are collectively referred to as row-lines. In some example embodiments, the LCD panel 100 further includes a charge-sharing control circuit 160. In the embodiment of FIG. 1, for ease of illustration, five odd data lines 140\_1 through 140\_5 and five even data lines 150\_1 through 150\_5 are shown and described. However, the LCD panel 100 may contain another number of data lines without departing from the spirit or scope of the present invention.

[0061] An LCD device displays an image by forming an electric field (i.e., an electric potential difference) between a pixel electrode and a common electrode of a liquid crystal capacitor included in each pixel. In the liquid crystal capacitor, a liquid crystal layer is placed between the pixel electrode

and the common electrode so that light transmittance of the liquid crystal layer is controlled by an intensity of the electric field formed between the pixel electrode and the common electrode.

[0062] Here, if the electric field is formed between the pixel electrode and the common electrode in one direction for a long time, the liquid crystal capacitor may deteriorate due to polarization. Hence, the LCD device may periodically invert polarities of data signals to reduce or prevent the deterioration of the liquid crystal capacitor included in each pixel. For example, the LCD device may employ inversion methods such as a dot inversion method, a line inversion method, a column inversion method, a frame inversion method, a Z-inversion method, an active level shift (ALS) inversion method, etc.

[0063] The dot inversion method inverts polarities of data signals with respect to alternating dots. Namely, a certain pixel receives a data signal having a polarity opposite to data signals received by its adjacent pixels in both a vertical direction (i.e., a column direction) and a horizontal direction (i.e., a row direction). The line inversion method inverts polarities of data signals with respect to alternating gate-lines (for example, rows). The column inversion method inverts polarities of data signals with respect to alternating data-lines (for example, columns). The frame inversion method inverts polarities of data signals with respect to alternating frames (for example, odd frames and even frames).

[0064] The Z-inversion method arranges a plurality of pixels in zigzags of a column direction. Thus, the Z-inversion method substantially performs the dot inversion when data signals are applied to the pixels in a similar way to the column inversion method. The ALS inversion method substantially inverts polarities of data signals in a similar way to the line inversion method. Here, the ALS inversion method may reduce a voltage displacement applied to a common electrode compared to the line inversion method.

[0065] However, these inversion methods may result in various problems. For example, the dot inversion method may reduce or prevent vertical crosstalk and/or horizontal crosstalk because a certain pixel receives a data signal having a polarity opposite to data signals received by its adjacent pixels in a vertical direction (i.e., a column direction) and a horizontal direction (i.e., a row direction). However, the dot inversion method may consume high power because a pulse repetition frequency of data signals (i.e., variance of data signals) is relatively high as the dot inversion method inverts polarities of data signals with respect to alternating dots.

[0066] In comparison, the line inversion method may reduce power consumption compared to the dot inversion method because a pulse repetition frequency of data signals (i.e., variance of data signals) is decreased. However, the line inversion method may cause horizontal crosstalk because the line inversion method inverts polarities of data signals with respect to alternating gate-lines. The column inversion method may also reduce power consumption compared to the dot inversion method because a pulse repetition frequency of data signals (i.e., variance of data signals) is decreased. However, the column inversion method may cause vertical crosstalk because the column inversion method inverts polarities of data signals with respect to alternating data-lines.

[0067] As for the other inversion methods mentioned above, the frame inversion method may cause flickers when frames are changed because the frame inversion method inverts polarities of data signals with respect to alternating

frames. By contrast, the Z-inversion method may reduce power consumption compared to the dot inversion method because the Z-inversion method applies data signals to the pixels in a similar way to the column inversion method. However, the Z-inversion method may cause vertical stripes in case that data signals have specific patterns. Finally, the ALS inversion method may reduce power consumption compared to the line inversion method because a voltage displacement applied to a common electrode is small compared to the line inversion method. However, the ALS inversion method may cause horizontal crosstalk because the ALS inversion method inverts polarities of data signals with respect to alternating gate-lines.

[0068] For overcoming various problems of these inversion methods, the LCD panel 100 includes the pixels 110, the first sub gate-line 120\_1, the second sub gate-line 120\_2, the gate-lines 130\_1 through 130\_k, the odd data-lines 140\_1 through 140\_5, and the even data-lines 150\_1 through 150\_5. The pixels 110 are arranged in a matrix manner (that is, in rows and columns) at portions corresponding to crossing regions of the first sub gate-line 120\_1, the second sub gate-line 120\_2, the gate-lines 130\_1 through 130\_k, the odd data-lines 140\_1 through 140\_5, and the even data-lines 150\_1 through 150\_5.

[0069] Here, each of the pixels 110 is coupled to the first sub gate-line 120\_1, the second sub gate-line 120\_2, or one of the gate-lines 130\_1 through 130\_k via a gate terminal of its switching element (e.g., a TFT). Additionally, each of the pixels 110 is coupled to one of the odd data-lines 140\_1 through 140\_5 or one of the even data-lines 150\_1 through 150\_5 via a source terminal of its switching element. As a result, each of the pixels 110 receives a gate signal (i.e., a scan pulse) output from the first sub gate-line 120\_1, the second sub gate-line 120\_2, or one of the gate-lines 130\_1 through 130\_k via the gate terminal of its switching element and receives a data signal output from one of the odd data-lines 140\_1 through 140\_5 or one of the even data-lines 150\_1 through 150\_5 via the source terminal of its switching element.

[0070] In some example embodiments, each of the pixels 110 includes a thin film transistor (TFT, i.e., the switching element), a liquid crystal capacitor, and a storage capacitor. Here, the liquid crystal capacitor includes a pixel electrode for receiving the data signal, a common electrode for receiving the common voltage, and a liquid crystal layer placed between the pixel electrode and the common electrode. See, for example, the representative pixel in FIG. 2. The liquid crystal layer includes a dielectric anisotropy material.

[0071] In the embodiment of FIG. 1, the first sub gate-line 120\_1 and the second sub gate-line 120\_2 are placed at peripheries of the display area, with the gate-lines 130\_1 through 130\_k therebetween. In one example embodiment, the first sub gate-line 120\_1 is coupled to first row-pixels that are adjacent to a lower side of the first sub gate-line 120\_1. Here, “row-pixels” describe a plurality of pixels that are common to one row, including a subset of the pixels of one row (such as every other pixel). For example, in one embodiment, first row-pixels correspond to (for example, are or include) the odd column row-pixels (that is, those pixels in one row that are also in the odd columns). Likewise, the second sub gate-line 120\_2 is coupled to second row-pixels that are adjacent to an upper side of the second sub gate-line 120\_2. For example, in one embodiment, second row-pixels

correspond to (for example, are or include) even column row-pixels (that is, those pixels in one row that are also in the even columns).

[0072] The gate-lines 130\_1 through 130\_k are located (for example, placed) between the first sub gate-line 120\_1 and the second sub gate-line 120\_2. Further, each gate-line of the gate-lines 130\_1 through 130\_k is coupled to second row-pixels that are adjacent to an upper side of the gate-line and to first row-pixels that are adjacent to a lower side of the gate-line.

[0073] In other words, each gate-line of the gate-lines 130\_1 through 130\_k is coupled to the pixels 110 in zigzag fashion proceeding in the row direction along the gate-line (that is, the gate-line is alternately coupled to a pixel 110 above the gate-line and to a pixel 110 below the gate-line). Here, as described above, first row-pixels correspond to (for example, are or include) odd column row-pixels and second row-pixels correspond to (for example, are or include) even column row-pixels.

[0074] That is, the first sub gate-line 120\_1 is coupled to odd column row-pixels that are adjacent to a lower side of the first sub gate-line 120\_1, the second sub gate-line 120\_2 is coupled to even column row-pixels that are adjacent to an upper side of the second sub gate-line 120\_2, and each gate-line of the gate-lines 130\_1 through 130\_k is coupled to even column row-pixels that are adjacent to an upper side of the gate-line and to odd column row-pixels that are adjacent to a lower side of the gate-line.

[0075] In the embodiment of FIG. 1, the pixels 110 coupled to the odd data-lines 140\_1 through 140\_5 are different from the pixels 110 coupled to the even data-lines 150\_1 through 150\_5. In other words, when the odd data-lines 140\_1 through 140\_5 are coupled to second column-pixels, then the even data-lines 150\_1 through 150\_5 are coupled to first column-pixels. Here, “column-pixels” describe a plurality of pixels that are common to one column, including a subset of the pixels of one column. For example, in one embodiment, first column-pixels correspond to (for example, are or include) odd row column-pixels (that is, those pixels in one column that are also in the odd rows) while second column-pixels correspond to (for example, are or include) even row column-pixels (that is, those pixels in one column that are also in the even rows).

[0076] In other embodiments, first column-pixels correspond to (for example, are or include) even row column-pixels while second column-pixels correspond to (for example, are or include) odd row column-pixels. In FIG. 1, it is illustrated that the odd data-lines 140\_1 through 140\_5 are coupled to even row column-pixels and that the even data-lines 150\_1 through 150\_5 are coupled to odd row column-pixels.

[0077] As described above, each of the pixels 110 is coupled to the first sub gate-line 120\_1, the second sub gate-line 120\_2, or one of the gate-lines 130\_1 through 130\_k via a gate terminal of its switching element (e.g., a TFT). In addition, each of the pixels 110 is coupled to one of the odd data-lines 140\_1 through 140\_5 or one of the even data-lines 150\_1 through 150\_5 via a source terminal of its switching element (e.g., a TFT).

[0078] In each frame, data signals of a first polarity are applied to the odd data-lines 140\_1 through 140\_5 and data signals of a second polarity (i.e., opposite to the first polarity) are applied to the even data-lines 150\_1 through 150\_5. As a result, data signals of the same polarity are applied to odd

column row-pixels and even column row-pixels with an interval of one horizontal period in the row direction.

[0079] In addition, data signals of alternate polarities are sequentially applied to column-pixels with an interval of one horizontal period in a column direction. That is, the LCD panel 100 substantially receives data signals in a similar way to the column inversion method. For example, in an odd frame, the odd data-lines 140\_1 through 140\_5 receive data signals of a first polarity while the even data-lines 150\_1 through 150\_5 receive data signals of a second polarity. Subsequently, in an even frame, the odd data-lines 140\_1 through 140\_5 receive data signals of the second polarity while the even data-lines 150\_1 through 150\_5 receive data signals of the first polarity.

[0080] The LCD panel 100 may further include the charge-sharing control circuit 160. The charge-sharing control circuit 160 controls the odd data-lines 140\_1 through 140\_5 to share electric charges and controls the even data-lines 150\_1 through 150\_5 to share electric charges. In one example embodiment, the charge-sharing control circuit 160 includes a plurality of first switches OST and a plurality of second switches EST. The first switches OST couple the odd data-lines 140\_1 through 140\_5 to each other in accordance with a charge-sharing control signal CSC. Likewise, the second switches EST couple the even data-lines 150\_1 through 150\_5 to each other in accordance with the charge-sharing control signal CSC.

[0081] For example, in one example embodiment, the charge-sharing control signal CSC is a pre charge-sharing (PCS) signal. In addition, the first switches OST and the second switches EST turn on before the pixels 110 coupled to the row-lines (i.e., the first sub gate-line 120\_1, the second sub gate-line 120\_2, and the gate-lines 130\_1 through 130\_k) are charged. In another example embodiment, the first switches OST and the second switches EST turn on after the pixels 110 coupled to the row-lines are charged. Thus, the odd data-lines 140\_1 through 140\_5 share electric charges and the even data-lines 150\_1 through 150\_5 share electric charges.

[0082] In one example embodiment, the first switches OST and the second switches EST are implemented by n-channel metal oxide semiconductor (NMOS) transistors. In this case, when the charge-sharing control signal CSC has a logic “high” voltage level, the first switches OST and the second switches EST turn on. Accordingly, the odd data-lines 140\_1 through 140\_5 are coupled to each other and the even data-lines 150\_1 through 150\_5 are coupled to each other.

[0083] In another example embodiment, the first switches OST and the second switches EST are implemented by p-channel metal oxide semiconductor (PMOS) transistors. In this case, when the charge-sharing control signal CSC has a logic “low” level, the first switches OST and the second switches EST turn on. Accordingly, the odd data-lines 140\_1 through 140\_5 are coupled to each other and the even data-lines 150\_1 through 150\_5 are coupled to each other.

[0084] The LCD panel 100 having the charge-sharing control circuit 160 may reduce power consumption in cases such as when data signals have fickle patterns and may enhance charging-characteristics of the pixels 110 to have high performance. In FIG. 1, it is illustrated that the LCD panel 100 includes the charge-sharing control circuit 160. However, the charge-sharing control circuit 160 may be embedded in an integrated circuit (IC) in other embodiments.

[0085] As described above, an LCD device may periodically invert polarities of data signals to reduce or prevent

deterioration of a liquid crystal capacitor included in each of the pixels 110. Here, since the LCD panel 100 has a unique structure as illustrated in FIG. 1, the LCD panel 100 may reduce power consumption by applying data signals of a first polarity to odd data-lines and by applying data signals of a second polarity (i.e., opposite to the first polarity) to even data-lines in each frame.

[0086] In addition, the LCD panel 100 may reduce or prevent horizontal crosstalk by applying data signals of the same polarity to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction. Further, the LCD panel 100 may reduce or prevent vertical crosstalk by sequentially applying data signals of alternate polarities to column-pixels with an interval of one horizontal period in a column direction.

[0087] In one example embodiment, each of the pixels 110 generates one of a red color, a green color, a blue color, etc. In this case, the LCD panel 100 further includes a plurality of red filters, a plurality of green filters, a plurality of blue filters, etc., on the pixels 110. In another example embodiment, each of the pixels 110 generates one of a yellow color, a cyan color, a magenta color, etc. In this case, the LCD panel 100 further includes a plurality of yellow filters, a plurality of cyan filters, a plurality of magenta filters, etc., on the pixels 110. Hence, the LCD panel 100 may display an image by generating various colors in accordance with a space-division method or a time-division method.

[0088] FIG. 2 is a diagram illustrating a structure of each pixel 110 in the LCD panel 100 of FIG. 1.

[0089] Referring to FIG. 2, each of the pixels 110 includes a switching element Q, a liquid crystal capacitor CLC, and a storage capacitor CST. In some example embodiments, the switching element Q may correspond to (for example, be) a thin film transistor (TFT) using amorphous silicon.

[0090] In the embodiment of FIG. 2, the switching element Q is placed on a lower display substrate. The switching element Q (e.g., a TFT) provides a data signal to the liquid crystal capacitor CLC in response to a gate signal.

[0091] As illustrated in FIG. 2, the gate signal is input from a gate-line GL and the data signal is input from a data-line DL. The switching element Q is coupled to the gate-line GL via its gate terminal, to the data-line DL via its source terminal, and to the liquid crystal capacitor CLC via its drain terminal.

[0092] The liquid crystal capacitor CLC is charged by a voltage difference between the data signal and a common voltage. The data signal is applied to a pixel electrode DE of the liquid crystal capacitor CLC. The common voltage is applied to a common electrode CE of the liquid crystal capacitor CLC.

[0093] As described above, a liquid crystal layer is placed between the pixel electrode DE and the common electrode CE. Hence, the light transmittance of the liquid crystal layer is controlled by an intensity of the electric field formed between the pixel electrode DE and the common electrode CE. This electric field intensity is also referred to as a charged voltage.

[0094] In case of a normally black mode, for example, the light transmittance of the liquid crystal layer may increase as the intensity of the electric field formed between the pixel electrode DE and the common electrode CE increases. On the other hand, the light transmittance of the liquid crystal layer may decrease as the intensity of the electric field formed between the pixel electrode DE and the common electrode CE decreases.

[0095] In some example embodiments, the liquid crystal capacitor CLC includes the pixel electrode DE formed on the lower display substrate, the common electrode CE formed on an upper display substrate, and the liquid crystal layer placed between the pixel electrode DE and the common electrode CE. However, the structure of the liquid crystal capacitor CLC is not limited thereto.

[0096] For example, the common electrode CE of the liquid crystal capacitor CLC may be formed on the lower display substrate. In this case, the common electrode CE may receive the common voltage from a signal line formed on the lower display substrate. In addition, the pixel electrode DE is coupled to the drain terminal of the switching element Q so that the pixel electrode DE receives the data signal from the data-line DL coupled to the source terminal of the switching element Q.

[0097] In one example embodiment, a low common voltage is applied to the pixels 110 when a data signal of positive polarity is applied to the pixels 110. On the other hand, a high common voltage is applied to the pixels 110 when a data signal of negative polarity is applied to the pixels 110. As a result, the charged voltage (i.e., the intensity of the electric field formed between the pixel electrode DE and the common electrode CE) is greater than a voltage level of the data signal so that power consumption may be substantially reduced.

[0098] The storage capacitor CST maintains the charged voltage of the liquid crystal capacitor CLC. That is, the storage capacitor CST assists the liquid crystal capacitor CLC. The storage capacitor CST may be formed by placing an insulator between the pixel electrode DE and the signal line.

[0099] In some example embodiments, the pixels 110 do not include the storage capacitor CST. The color filters may be arranged on the upper display substrate. Polarizing plates may be attached to the upper display substrate and/or the lower display substrate.

[0100] FIG. 3 is a timing diagram illustrating an example of providing common voltages in accordance with polarities of data signals provided to the LCD panel 100 of FIG. 1.

[0101] Referring to FIG. 3, a frame (i.e., a first frame 1F and a second frame 2F following the first frame 1F) includes a plurality of horizontal periods 1H through 8H. For ease of illustration, in each of the exemplary frames 1F and 2F of FIG. 3, eight horizontal periods are shown and described. However, the frame may contain another number of horizontal periods without departing from the spirit or scope of the present invention. Here, the first frame 1F corresponds to an odd frame and the second frame 2F corresponds to an even frame. As described above, the LCD panel 100 displays an image in a frame unit. Hence, the LCD panel 100 generates an image by sequentially displaying a plurality of frames.

[0102] The first frame 1F includes eight horizontal periods 1H through 8H. When gate signals (i.e., a scan pulse) are applied to the first sub gate-line 120\_1, the gate-lines 130\_1 through 130\_k, and the second sub gate-line 120\_2 in the first frame 1F, data signals output from the odd data-lines 140\_1 through 140\_5 and the even data-lines 150\_1 through 150\_5 are applied to odd column row-pixels and even column row-pixels, as illustrated in FIG. 1.

[0103] Here, a low common voltage VCOM\_L is applied to the pixels 110 when data signals of positive polarity are applied to the pixels 110. On the other hand, a high common voltage VCOM\_H is applied to the pixels 110 when data signals of negative polarity are applied to the pixels 110.

[0104] In detail, when data signals of positive polarity are applied to the odd data-lines 140\_1 through 140\_5 in the first frame 1F, the low common voltage VCOM\_L is applied to the common electrodes of the pixels 110 coupled to the odd data-lines 140\_1 through 140\_5 (that is, the pixels in even rows, as illustrated in the LCD panel 100 of FIG. 1). On the other hand, when data signals of negative polarity are applied to the even data-lines 150\_1 through 150\_5 in the first frame 1F, the high common voltage VCOM\_H is applied to the common electrodes of the pixels 110 coupled to the even data-lines 150\_1 through 150\_5 (that is, the pixels in odd rows, as illustrated in FIG. 1).

[0105] Similarly, when data signals of negative polarity are applied to the odd data-lines 140\_1 through 140\_5 in the second frame 2F, the high common voltage VCOM\_H is applied to the common electrodes of the pixels 110 coupled to the odd data-lines 140\_1 through 140\_5 (the pixels in even rows). On the other hand, when data signals of positive polarity are applied to the even data-lines 150\_1 through 150\_5 in the second frame 2F, the low common voltage VCOM\_L is applied to the common electrodes of the pixels 110 coupled to the even data-lines 150\_1 through 150\_5 (the pixels in odd rows).

[0106] Therefore, charged voltages of the liquid crystal capacitors CLC in the pixels 110 may be greater than voltage levels of data signals provided to the pixels 110. As described above, the LCD panel 100 may substantially receive the low common voltage VCOM\_L and the high common voltage VCOM\_H in a similar way to the ALS inversion method (i.e., common voltages applied to the odd data-lines 140\_1 through 140\_5 and the even data-lines 150\_1 through 150\_5 may be inverted with each frame). Thus, power consumption of the LCD panel 100 may be reduced compared to the earlier described inversion methods.

[0107] FIG. 4 is a diagram illustrating an example of providing data signals to the LCD panel 100 of FIG. 1 in an odd frame 1F.

[0108] Referring to FIG. 4, when an LCD device provides data signals to the data-lines DL1 through DL8 of the LCD panel 100 in the odd frame 1F, the LCD device provides data signals of a first polarity (e.g., positive polarity) to the odd data-lines 140\_1 through 140\_4 and provides data signals of a second polarity (e.g., negative polarity) to the even data-lines 150\_1 through 150\_4. In FIG. 4, for ease of illustration, the first eight data lines DL1 through DL8 (corresponding to odd data-lines 140\_1 through 140\_4 and even data lines 150\_1 through 150\_4) and the first eight horizontal periods 1H through 8H are shown and described. However, there may be another number of data lines and horizontal periods without departing from the spirit or scope of the present invention.

[0109] In other words, the data-lines DL1 through DL8 are divided into the odd data-lines 140\_1 through 140\_4 and the even data-lines 150\_1 through 150\_4 in terms of operations. For example, in the odd frame 1F, the LCD device provides data signals of positive polarity to the odd data-lines 140\_1 through 140\_4 and provides data signals of negative polarity to the even data-lines 150\_1 through 150\_4.

[0110] As described above, the LCD device inverts polarities of data signals with each frame. Therefore, in the even frame 2F following the odd frame 1F, the LCD device provides data signals of negative polarity to the odd data-lines 140\_1 through 140\_4 and provides data signals of positive polarity to the even data-lines 150\_1 through 150\_4.

[0111] However, a polarity pattern as displayed on the LCD panel 100 may be different from a polarity pattern as applied to the data-lines DL1 through DL8. Here, a driver polarity pattern indicates the polarity pattern as applied to the data-lines DL1 through DL8 (for example, odd data-lines receiving data signals of positive polarity and even data-lines receiving data signals of negative polarity), and an apparent polarity pattern indicates the polarity pattern as displayed on the LCD panel 100 (for example, pixels in odd rows receiving data signals of negative polarity and pixels in even rows receiving data signals of positive polarity, which is both rotated and inverted from the driver polarity pattern shown in FIG. 4).

[0112] For example, a driver polarity pattern of the embodiment of the present invention shown in FIGS. 3 (odd frame 1F) and 4 is similar to a driver polarity pattern of the column inversion method (as illustrated in FIG. 4). On the other hand, because of the characteristics of this embodiment of the present invention, namely that data signals are applied to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, an apparent polarity pattern of the embodiment of FIGS. 3 (odd frame 1F) and 4 of the present invention is similar to an apparent polarity pattern of the ALS inversion method and the line inversion method (as illustrated in FIGS. 5A through 5E).

[0113] FIGS. 5A through 5E are diagrams illustrating an example of applying data signals to pixels of the LCD panel 100 of FIG. 1 in a first five horizontal periods 1H through 5H, respectively, of an odd frame 1F.

[0114] Referring to FIG. 5A, a gate signal for turning on TFTs of the pixels 110 coupled to the first sub gate-line 120\_1 is provided during a first horizontal period 1H. Since the first sub gate-line 120\_1 is coupled to odd column row-pixels among the pixels 110 that constitute a first row, data signals are applied to the odd column row-pixels among the pixels 110 that constitute the first row.

[0115] As illustrated in FIG. 5A, the odd column row-pixels among the pixels 110 that constitute the first row are coupled to the even data-lines 150\_1 through 150\_5. In the odd frame 1F, data signals applied to the even data-lines 150\_1 through 150\_5 have negative polarity. Thus, the odd column row-pixels among the pixels 110 that constitute the first row receive data signals of negative polarity during the first horizontal period 1H. As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the first horizontal period 1H.

[0116] Referring to FIG. 5B, a gate signal for turning on TFTs of the pixels 110 coupled to the first gate-line 130\_1 is provided during a second horizontal period 2H. Since the first gate-line 130\_1 is coupled to even column row-pixels among the pixels 110 that constitute the first row and to odd column row-pixels among the pixels 110 that constitute a second row, data signals are applied to the even column row-pixels among the pixels 110 that constitute the first row and to the odd column row-pixels among the pixels 110 that constitute the second row.

[0117] As illustrated in FIG. 5B, the even column row-pixels among the pixels 110 that constitute the first row are coupled to the even data-lines 150\_1 through 150\_4. In the odd frame 1F, data signals applied to the even data-lines 150\_1 through 150\_4 have negative polarity. Thus, the even

column row-pixels among the pixels **110** that constitute the first row receive data signals of negative polarity during the second horizontal period **2H**.

[0118] Further, as illustrated in FIG. 5B, the odd column row-pixels among the pixels **110** that constitute the second row are coupled to the odd data-lines **140\_1** through **140\_5**. In the odd frame 1F, data signals applied to the odd data-lines **140\_1** through **140\_5** have positive polarity. Thus, the odd column row-pixels among the pixels **110** that constitute the second row receive data signals of positive polarity during the second horizontal period **2H**.

[0119] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the second horizontal period **2H** (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the first row of pixels in FIG. 5B). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0120] Referring to FIG. 5C, a gate signal for turning on TFTs of the pixels **110** coupled to the second gate-line **130\_2** is provided during a third horizontal period **3H**. Since the second gate-line **130\_2** is coupled to even column row-pixels among the pixels **110** that constitute the second row to and odd column row-pixels among the pixels **110** that constitute a third row, data signals are applied to the even column row-pixels among the pixels **110** that constitute the second row and to the odd column row-pixels among the pixels **110** that constitute the third row.

[0121] As illustrated in FIG. 5C, the even column row-pixels among the pixels **110** that constitute the second row are coupled to the odd data-lines **140\_2** through **140\_5**. In the odd frame 1F, data signals applied to the odd data-lines **140\_2** through **140\_5** have positive polarity. Thus, the even column row-pixels among the pixels **110** that constitute the second row receive data signals of positive polarity during the third horizontal period **3H**.

[0122] Further, as illustrated in FIG. 5C, the odd column row-pixels among the pixels **110** that constitute the third row are coupled to the even data-lines **150\_1** through **150\_5**. In the odd frame 1F, data signals applied to the even data-lines **150\_1** through **150\_5** have negative polarity. Thus, the odd column row-pixels among the pixels **110** that constitute the third row receive data signals of negative polarity during the third horizontal period **3H**.

[0123] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the third horizontal period **3H** (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the second row of pixels in FIG. 5C). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0124] Referring to FIG. 5D, a gate signal for turning on TFTs of the pixels **110** coupled to the third gate-line **130\_3** is provided during a fourth horizontal period **4H**. Since the third gate-line **130\_3** is coupled to even column row-pixels among the pixels **110** that constitute the third row and to odd column row-pixels among the pixels **110** that constitute a fourth row, data signals are applied to the even column row-pixels among

the pixels **110** that constitute the third row and to the odd column row-pixels among the pixels **110** that constitute the fourth row.

[0125] As illustrated in FIG. 5D, the even column row-pixels among the pixels **110** that constitute the third row are coupled to the even data-lines **150\_1** through **150\_4**. In the odd frame 1F, data signals applied to the even data-lines **150\_1** through **150\_4** have negative polarity. Thus, the even column row-pixels among the pixels **110** that constitute the third row receive data signals of negative polarity during the fourth horizontal period **4H**.

[0126] Further, as illustrated in FIG. 5D, the odd column row-pixels among the pixels **110** that constitute the fourth row are coupled to the odd data-lines **140\_1** through **140\_5**. In the odd frame 1F, data signals applied to the odd data-lines **140\_1** through **140\_5** have positive polarity. Thus, the odd column row-pixels among the pixels **110** that constitute the fourth row receive data signals of positive polarity during the fourth horizontal period **4H**.

[0127] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the fourth horizontal period **4H** (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the third row of pixels in FIG. 5D). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0128] Referring to FIG. 5E, a gate signal for turning on TFTs of the pixels **110** coupled to the fourth gate-line **130\_4** is provided during a fifth horizontal period **5H**. Since the fourth gate-line **130\_4** is coupled to even column row-pixels among the pixels **110** that constitute the fourth row, data signals are applied to the even column row-pixels among the pixels **110** that constitute the fourth row.

[0129] As illustrated in FIG. 5E, the even column row-pixels among the pixels **110** that constitute the fourth row are coupled to the odd data-lines **140\_2** through **140\_5**. As described above, even column row-pixels among the pixels **110** that constitute the fourth row receive data signals of positive polarity during the fifth horizontal period **5H** of the odd frame 1F. Further, though not specifically illustrated in FIG. 5E, odd column row-pixels among the pixels **110** that constitute a fifth row receive data signals of negative polarity during the fifth horizontal period **5H**.

[0130] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the fifth horizontal period **5H** (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the fourth row of pixels in FIG. 5E). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0131] This process continues until the odd frame 1F is finished by applying a gate signal for turning on TFTs of the pixels **110** coupled to the second sub gate-line **120\_2**. Then, polarities of data signals are inverted when the LCD device changes a display frame from the odd frame 1F to the even frame 2F. Hence, polarities of data signals in the odd frame 1F are opposite to polarities of data signals in the even frame 2F following the odd frame 1F.

[0132] As illustrated in FIGS. 5A through 5E, a driver polarity pattern of the embodiment of the present invention

shown in FIGS. 3 (odd frame 1F) and 4 is similar to a driver polarity pattern of the column inversion method (as displayed in FIG. 4). In addition, because of the characteristics of this embodiment of the present invention, namely that data signals are applied to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, an apparent polarity pattern of the embodiment of FIGS. 3 (odd frame 1F) and 4 of the present invention is similar to an apparent polarity pattern of the ALS inversion method and the line inversion method.

[0133] FIG. 6 is a diagram illustrating an example of providing data signals to the LCD panel 100 of FIG. 1 in an even frame 2F.

[0134] Referring to FIG. 6, when an LCD device provides data signals to the data-lines DL1 through DL8 of the LCD panel 100 in the even frame 2F, the LCD device provides data signals of a second polarity (e.g., negative polarity) to the odd data-lines 140\_1 through 140\_4 and provides data signals of a first polarity (e.g., positive polarity) to the even data-lines 150\_1 through 150\_4. In FIG. 6, for ease of illustration, the first eight data lines DL1 through DL8 (corresponding to odd data-lines 140\_1 through 140\_4 and even data lines 150\_1 through 150\_4) and the first eight horizontal periods 1H through 8H are shown and described. However, there may be another number of data lines and horizontal periods without departing from the spirit or scope of the present invention.

[0135] In other words, the data-lines DL1 through DL8 are divided into the odd data-lines 140\_1 through 140\_4 and the even data-lines 150\_1 through 150\_4 in terms of operations. For example, in the even frame 2F, the LCD device provides data signals of negative polarity to the odd data-lines 140\_1 through 140\_4 and provides data signals of positive polarity to the even data-lines 150\_1 through 150\_4.

[0136] As described above, the LCD device inverts polarities of data signals with each frame. Therefore, in the first frame 1F following the second frame 2F, the LCD device provides data signals of positive polarity to the odd data-lines 140\_1 through 140\_4 and provides data signals of negative polarity to the even data-lines 150\_1 through 150\_4.

[0137] However, a polarity pattern as displayed on the LCD panel 100 may be different from a polarity pattern as applied to the data-lines DL1 through DL8. Here, a driver polarity pattern indicates the polarity pattern as applied to the data-lines DL1 through DL8 (for example, odd data-lines receiving data signals of negative polarity and even data-lines receiving data signals of positive polarity), and an apparent polarity pattern indicates the polarity pattern as displayed on the LCD panel 100 (for example, pixels in odd rows receiving data signals of positive polarity and pixels in even rows receiving data signals of negative polarity, which is both rotated and inverted from the driver polarity pattern shown in FIG. 6).

[0138] For example, a driver polarity pattern of an embodiment of the present invention shown in FIGS. 3 (even frame 2F) and 6 is similar to a driver polarity pattern of the column inversion method (as illustrated in FIG. 6). On the other hand, because of the characteristics of this embodiment of the present invention, namely that data signals are applied to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, an apparent polarity pattern of the embodiment of FIGS. 3 (even frame 2F) and 6 of the present invention is similar to an apparent polarity pattern of the ALS inversion method and the line inversion method (as illustrated in FIGS. 7A through 7E).

[0139] FIGS. 7A through 7E are diagrams illustrating an example of applying data signals to pixels of the LCD panel 100 of FIG. 1 in a first five horizontal periods 1H through 5H, respectively, of an even frame 2F.

[0140] Referring to FIG. 7A, a gate signal for turning on TFTs of the pixels 110 coupled to the first sub gate-line 120\_1 is provided during a first horizontal period 1H. Since the first sub gate-line 120\_1 is coupled to odd column row-pixels among the pixels 110 that constitute a first row, data signals are applied to the odd column row-pixels among the pixels 110 that constitute the first row.

[0141] As illustrated in FIG. 7A, the odd column row-pixels among the pixels 110 that constitute the first row are coupled to the even data-lines 150\_1 through 150\_5. In the even frame 2F, data signals applied to the even data-lines 150\_1 through 150\_5 have positive polarity. Thus, the odd column row-pixels among the pixels 110 that constitute the first row receive data signals of positive polarity during the first horizontal period 1H. As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the first horizontal period 1H.

[0142] Referring to FIG. 7B, a gate signal for turning on TFTs of the pixels 110 coupled to the first gate-line 130\_1 is provided during a second horizontal period 2H. Since the first gate-line 130\_1 is coupled to even column row-pixels among the pixels 110 that constitute the first row and to odd column row-pixels among the pixels 110 that constitute a second row, data signals are applied to the even column row-pixels among the pixels 110 that constitute the first row and to the odd column row-pixels among the pixels 110 that constitute the second row.

[0143] As illustrated in FIG. 7B, the even column row-pixels among the pixels 110 that constitute the first row are coupled to the even data-lines 150\_1 through 150\_4. In the even frame 2F, data signals applied to the even data-lines 150\_1 through 150\_4 have positive polarity. Thus, the even column row-pixels among the pixels 110 that constitute the first row receive data signals of positive polarity during the second horizontal period 2H.

[0144] Further, as illustrated in FIG. 7B, the odd column row-pixels among the pixels 110 that constitute the second row are coupled to the odd data-lines 140\_1 through 140\_5. In the even frame 2F, data signals applied to the odd data-lines 140\_1 through 140\_5 have negative polarity. Thus, the odd column row-pixels among the pixels 110 that constitute the second row receive data signals of negative polarity during the second horizontal period 2H.

[0145] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the second horizontal period 2H (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the first row of pixels in FIG. 7B). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0146] Referring to FIG. 7C, a gate signal for turning on TFTs of the pixels 110 coupled to the second gate-line 130\_2 is provided during a third horizontal period 3H. Since the second gate-line 130\_2 is coupled to even column row-pixels among the pixels 110 that constitute the second row and to odd column row-pixels among the pixels 110 that constitute a third row, data signals are applied to the even column row-

pixels among the pixels **110** that constitute the second row and to the odd column row-pixels among the pixels **110** that constitute the third row.

[0147] As illustrated in FIG. 7C, the even column row-pixels among the pixels **110** that constitute the second row are coupled to the odd data-lines **140\_2** through **140\_5**. In the even frame 2F, data signals applied to the odd data-lines **140\_2** through **140\_5** have negative polarity. Thus, the even column row-pixels among the pixels **110** that constitute the second row receive data signals of negative polarity during the third horizontal period 3H.

[0148] Further, as illustrated in FIG. 7C, the odd column row-pixels among the pixels **110** that constitute the third row are coupled to the even data-lines **150\_1** through **150\_5**. In the even frame 2F, data signals applied to the even data-lines **150\_1** through **150\_5** have positive polarity. Thus, the odd column row-pixels among the pixels **110** that constitute the third row receive data signals of positive polarity during the third horizontal period 3H.

[0149] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the third horizontal period 3H (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the second row of pixels in FIG. 7C). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0150] Referring to FIG. 7D, a gate signal for turning on TFTs of the pixels **110** coupled to the third gate-line **130\_3** is provided during a fourth horizontal period 4H. Since the third gate-line **130\_3** is coupled to even column row-pixels among the pixels **110** that constitute the third row and to odd column row-pixels among the pixels **110** that constitute a fourth row, data signals are applied to the even column row-pixels among the pixels **110** that constitute the third row and to the odd column row-pixels among the pixels **110** that constitute the fourth row.

[0151] As illustrated in FIG. 7D, the even column row-pixels among the pixels **110** that constitute the third row are coupled to the even data-lines **150\_1** through **150\_4**. In the even frame 2F, data signals applied to the even data-lines **150\_1** through **150\_4** have positive polarity. Thus, the even column row-pixels among the pixels **110** that constitute the third row receive data signals of positive polarity during the fourth horizontal period 4H.

[0152] Further, as illustrated in FIG. 7D, the odd column row-pixels among the pixels **110** that constitute the fourth row are coupled to the odd data-lines **140\_1** through **140\_5**. In the even frame 2F, data signals applied to the odd data-lines **140\_1** through **140\_5** have negative polarity. Thus, the odd column row-pixels among the pixels **110** that constitute the fourth row receive data signals of negative polarity during the fourth horizontal period 4H.

[0153] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the fourth horizontal period 4H (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the third row of pixels in FIG. 7D). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0154] Referring to FIG. 7E, a gate signal for turning on TFTs of the pixels **110** coupled to the fourth gate-line **130\_4** is provided during a fifth horizontal period 5H. Since the fourth gate-line **130\_4** is coupled to even column row-pixels among the pixels **110** that constitute the fourth row, data signals are applied to the even column row-pixels among the pixels **110** that constitute the fourth row.

[0155] As illustrated in FIG. 7E, the even column row-pixels among the pixels **110** that constitute the fourth row are coupled to the odd data-lines **140\_2** through **140\_5**. As described above, even column row-pixels among the pixels **110** that constitute the fourth row receive data signals of negative polarity during the fifth horizontal period 5H of the even frame 2F. Further, though not specifically illustrated in FIG. 5E, odd column row-pixels among the pixels **110** that constitute a fifth row receive data signals of positive polarity during the fifth horizontal period 5H.

[0156] As a result, horizontal crosstalk may be reduced or prevented because data signals of the same polarity are not applied to adjacent row-pixels at the same time during the fifth horizontal period 5H (that is, adjacent row-pixels receiving data signals of the same polarity do so during different horizontal periods, as illustrated in the fourth row of pixels in FIG. 7E). Further, vertical crosstalk may be reduced or prevented because data signals of opposite polarities are applied to adjacent column-pixels.

[0157] This process continues until the even frame 2F is finished by applying a gate signal for turning on TFTs of the pixels **110** coupled to the second sub gate-line **120\_2**. Then, polarities of data signals are inverted when the LCD device changes a display frame from the even frame 2F to the odd frame 1F. Hence, polarities of data signals in the even frame 2F are opposite to polarities of data signals in the odd frame 1F following the even frame 2F.

[0158] As illustrated in FIGS. 7A through 7E, a driver polarity pattern of the embodiment of the present invention shown in FIGS. 3 (even frame 2F) and 6 is similar to a driver polarity pattern of the column inversion method (as displayed in FIG. 6). In addition, because of the characteristics of this embodiment of the present invention, namely that data signals are applied to odd column row-pixels and even column row-pixels with an interval of one horizontal period in a row direction, an apparent polarity pattern of the embodiment of FIGS. 3 (even frame 2F) and 6 of the present invention is similar to an apparent polarity pattern of the ALS inversion method and the line inversion method.

[0159] FIG. 8 is a diagram illustrating another LCD panel **500** in accordance with example embodiments.

[0160] Referring to FIG. 8, the LCD panel **500** includes a plurality of pixels **510**, a first sub gate-line **520\_1**, a second sub gate-line **520\_2**, a plurality of gate-lines **530\_1** through **530\_k**, a plurality of odd data-lines **540\_1** through **540\_5**, and a plurality of even data-lines **550\_1** through **550\_5**. The first sub gate-line **520\_1**, the second sub gate-line **520\_2**, and the plurality of gate-lines **530\_1** through **530\_k** are collectively referred to as row-lines. According to some example embodiments, the LCD panel **500** further includes a charge-sharing control circuit **560**. In the embodiment of FIG. 8, for ease of illustration, five odd data lines **540\_1** through **540\_5** and five even data lines **550\_1** through **550\_5** are shown and described. However, the LCD panel **500** may contain another number of data lines without departing from the spirit or scope of the present invention.

[0161] The pixels **510** are arranged in a matrix manner (that is, in rows and columns) at portions corresponding to crossing regions of the first sub gate-line **520\_1**, the second sub gate-line **520\_2**, the gate-lines **530\_1** through **530\_k**, the odd data-lines **540\_1** through **540\_5**, and the even data-lines **550\_1** through **550\_5**. Here, each of the pixels **510** is coupled to the first sub gate-line **520\_1**, the second sub gate-line **520\_2**, or one of the gate-lines **530\_1** through **530\_k** via a gate terminal of its switching element (e.g., a TFT). Additionally, each of the pixels **510** is coupled to one of the odd data-lines **540\_1** through **540\_5** or one of the even data-lines **550\_1** through **550\_5** via a source terminal of its switching element (e.g., a TFT). As a result, each of the pixels **510** receives a gate signal (i.e., a scan pulse) output from the first sub gate-line **520\_1**, the second sub gate-line **520\_2**, or one of the gate-lines **530\_1** through **530\_k** via the gate terminal of its switching element (e.g., a TFT) and receives a data signal output from one of the odd data-lines **540\_1** through **540\_5** or one of the even data-lines **550\_1** through **550\_5** via the source terminal of its switching element (e.g., a TFT).

[0162] In the embodiment of FIG. 8, the first sub gate-line **520\_1** and the second sub gate-line **520\_2** are placed at peripheries of the display area, with the gate-lines **530\_1** through **530\_k** therebetween. In one example embodiment, the first sub gate-line **520\_1** is coupled to first row-pixels (for example, even column row-pixels) that are adjacent to a lower side of the first sub gate-line **520\_1**. Likewise, the second sub gate-line **520\_2** is coupled to second row-pixels (for example, odd column row-pixels) that are adjacent to an upper side of the second sub gate-line **520\_2**.

[0163] The gate-lines **530\_1** through **530\_k** are located (for example, placed) between the first sub gate-line **520\_1** and the second sub gate-line **520\_2**. Further, each gate-line of the gate-lines **530\_1** through **530\_k** is coupled to second row-pixels that are adjacent to an upper side of the gate-line and to first row-pixels that are adjacent to a lower side of the gate-line.

[0164] In other words, each gate-line of the gate-lines **530\_1** through **530\_k** is coupled to the pixels **510** in zigzag fashion proceeding in the row direction along the gate-line (that is, the gate-line is alternately coupled to a pixel **110** above the gate-line and to a pixel **110** below the gate-line). Here, as described above, first row-pixels correspond to (for example, are or include) even column row-pixels and second row-pixels correspond to (for example, are or include) odd column row-pixels.

[0165] That is, the first sub gate-line **520\_1** is coupled to even column row-pixels that are adjacent to a lower side of the first sub gate-line **520\_1**, the second sub gate-line **520\_2** is coupled to odd column row-pixels that are adjacent to an upper side of the second sub gate-line **520\_2**, and each gate-line of the gate-lines **530\_1** through **530\_k** is coupled to odd column row-pixels that are adjacent to an upper side of the gate-line and even column row-pixels that are adjacent to a lower side of the gate-line.