# (12) United States Patent

# Numao

#### US 6,937,222 B2 (10) Patent No.:

#### (45) Date of Patent: Aug. 30, 2005

| (54) | DISPLAY, PORTABLE DEVICE, AND SUBSTRATE |                                                                                       |               |  |  |

|------|-----------------------------------------|---------------------------------------------------------------------------------------|---------------|--|--|

| (75) | Inventor:                               | Takaji Numao, Nara (JP)                                                               |               |  |  |

| (73) | Assignee:                               | Sharp Kabushiki Kaisha,                                                               | Osaka (JP)    |  |  |

| (*)  | Notice:                                 | Subject to any disclaimer, the patent is extended or adjust U.S.C. 154(b) by 333 days | sted under 35 |  |  |

| (21) | Appl. No.: 10/034,251                   |                                                                                       |               |  |  |

| (22) | Filed:                                  | Jan. 3, 2002                                                                          |               |  |  |

| (65) |                                         | Prior Publication Data                                                                |               |  |  |

|      | US 2002/0093472 A1 Jul. 18, 2002        |                                                                                       |               |  |  |

| (30) | Foreign Application Priority Data       |                                                                                       |               |  |  |

| Ian  | 18 2001                                 | (IP)                                                                                  | 2001-010866   |  |  |

| (*)  | Notice:    | Subject to any disclaimer, the term of t patent is extended or adjusted under U.S.C. 154(b) by 333 days. |

|------|------------|----------------------------------------------------------------------------------------------------------|

| (21) | Appl. No.: | 10/034,251                                                                                               |

| (22) | Filed:     | Jan. 3, 2002                                                                                             |

| (65) |            | Prior Publication Data                                                                                   |

|      | US 2002/00 | 93472 A1 Jul. 18, 2002                                                                                   |

|      |            |                                                                                                          |

| (30) | Foreign | Application | <b>Priority</b> | Data |

|------|---------|-------------|-----------------|------|

|------|---------|-------------|-----------------|------|

| Jun. | 29, 2001 (JP)         | 2001-200074            |

|------|-----------------------|------------------------|

| (51) | Int. Cl. <sup>7</sup> | G09G 3/36              |

| (52) | U.S. Cl               |                        |

| (58) | Field of Search       | 345/90, 91, 92,        |

| . ,  | 345/96, 97, 204, 2    | 205, 206, 207, 76, 82, |

|      |                       | 98. 89                 |

#### (56)References Cited

## U.S. PATENT DOCUMENTS

| 4,996,523    | Α          |   | 2/1991  | Bell et al.      |       |

|--------------|------------|---|---------|------------------|-------|

| 5,798,746    | Α          |   | 8/1998  | Koyama           |       |

| 5,945,194    | Α          | * | 8/1999  | Pester 428       | 3/120 |

| 5,945,972    | Α          | * | 8/1999  | Okumura et al 34 | 45/98 |

| 5,952,991    | Α          | * | 9/1999  | Akiyama 34       | 45/98 |

| 6,157,356    | Α          | * | 12/2000 | Troutman 34      | 45/82 |

| 6,636,194    | B2         | * | 10/2003 | Ishii 34         | 45/98 |

| 2003/0058200 | <b>A</b> 1 | * | 3/2003  | Numao 34         | 45/76 |

|              |            |   |         |                  |       |

#### FOREIGN PATENT DOCUMENTS

| JP | 63-226178  | 9/1988  |

|----|------------|---------|

| JP | 02-148687  | 6/1990  |

| JP | 5-289635 A | 11/1993 |

| ΙP | 06-067151  | 3/1994  |

| JP | 07-056143   | 3/1995  |

|----|-------------|---------|

| JP | 07-253764   | 10/1995 |

| JP | 08-194205   | 7/1996  |

| JP | 08-237578   | 9/1996  |

| JP | 08-250749   | 9/1996  |

| JP | 08-286170   | 11/1996 |

| JP | 09-212140   | 8/1997  |

| JP | 11-002797   | 1/1999  |

| JP | 11-295700   | 10/1999 |

| JP | 2000-221942 | 8/2000  |

| JP | 2000-227608 | 8/2000  |

| JP | 2000-227782 | 8/2000  |

| JP | 2000-347623 | 12/2000 |

| JP | 2001-147676 | 5/2001  |

| JP | 2002-132217 | 5/2002  |

| JP | 2002-175040 | 6/2002  |

| JP | 2002-202755 | 7/2002  |

| JP | 2002-278499 | 9/2002  |

| WO | WO 00/08625 | 2/2000  |

|    |             |         |

### OTHER PUBLICATIONS

Chinese Office Action mailed Oct. 10, 2003 in corresponding Chinese patent application No. 02102329.8 and English translation thereof.

Korean Office Action mailed Jul. 28, 2004 (w/English translation thereof).

Japanese Office Action mailed Oct. 5, 2004 (w/English translation thereof).

Primary Examiner—Xiao Wu Assistant Examiner-Kevin M. Nguyen (74) Attorney, Agent, or Firm—Nixon & Vanderhye P.C.

### **ABSTRACT**

A memory circuit is caused to retain a voltage corresponding to largest tone data, then a voltage corresponding to tone data except for the largest tone data is applied to a liquid crystal element, and the voltage corresponding to the largest tone data is supplied from the memory circuit to the liquid crystal element. The development of moving picture breakups can be suppressed with a display producing a timedivision gray-scale display, without having to carry out a display scanning operation for every display.

#### 16 Claims, 34 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 3

FIG. 6

FIG. 7

Aug. 30, 2005

FIG. 9 (b)

16T1 16T1 16T1 Cibit1

FIG. 11

РО 54 COLUMN DECODER ADDRESS BUFFER MEMORY ARRAY SELECTOR Ϋ́ 56 58 DECODEK KOM 51 **09**~ -59 52 BCFFER ADDRESS SOEN -SI/O CSN Pbit Α

FIG. 14

FIG. 19

C1 Cibit1 Cibit2 Cibit3 C2 C3 C3 C4 C5 C6 C6 C7 C6 C7 TIME B

FIG. 21

26 VDD -62 Ąij -61 FIG. 22 S 9 ö Voff

FIG. 24

FIG. 25

224 MEMORY CELL = = = = = B<sub>n-2</sub> مء

] [ .228 7000 FIG. 27

FIG. 29

Aug. 30, 2005

FIG. 30

FIG. 31

Aug. 30, 2005

FIG. 32

FIG. 33

2

FIG. 35

1

# DISPLAY, PORTABLE DEVICE, AND SUBSTRATE

#### FIELD OF THE INVENTION

The present invention relates to displays, portable devices, and substrates in or on which every pixel has a memory element and a light-emitting element.

#### BACKGROUND OF THE INVENTION

The organic LED (light-emitting diode) display, a type of flat panel display, is a recent focus of attention as a competitor of the liquid crystal display. A great deal of efforts are put into the development of display circuits and driving 15 methods for the organic LED display.

Drive circuits and methods for use with the organic LED display are divided into two major categories: passive and active. To apply the active drive technology to organic LED displays, those TFT which drive the pixels have to be made 20 of polysilicon.

This is because when self-luminous elements are to be driven by TFTs as in the organic LED display, sufficient movement is required with electric charges in the silicon forming the TFTs to ensure an amount of current flow 25 through the self-luminous elements. This explains why polysilicon is needed in the organic LED display, while amorphous silicon is sufficient in the non-light-emitting shutter element, such as liquid crystal.

U.S. Pat. No. 4,996,523 (issued Feb. 26, 1991) discloses a pixel configuration of the organic LED display based on monocrystalline silicon TFTs instead of polysilicon TFTs, in particular, a configuration using memory elements.

FIG. 26 shows a circuit configuration in a single pixel (precisely, should be termed "a single dot" because 1 pixel=1 dot in a black & white display and 1 pixel=RGB 3 dots in a color display; however, no strict restrictions are made here).

According to U.S. Pat. No. 4,996,523, as shown in FIG. 26, each pixel is formed by: multiple memory cells 221 or  $C_n$  to  $C_{n-3}$ ; transistors 222 or  $D_n$  to  $D_{n-3}$ ; to select from those memory cells; a constant current circuit 225; and an organic LED element 226.

The constant current circuit **225** is a current mirror circuit including FETs **223**, **224**. Therefore, the current through the organic LED element **226** is determined by the total current flow in the FETs  $D_n$  to  $D_{n-3}$ . The current flow in the FETs  $D_n$  to  $D_{n-3}$  is specified by the gate voltages of the FETs  $D_n$  to  $D_{n-3}$  which are determined by the data stored in the memory cells  $C_n$  to  $C_{n-3}$ .

The configuration of the memory cells 221 is shown in FIG. 27. Specifically, a CMOS inverter 228 and MOS transmission gates 227, 229 are controlled by means of a LOW control signal. When the LOW control signal is in a 55 selection state, the MOS transmission gate 227 is in a conducting state, and the MOS transmission gate 229 is in a non-conducting state; therefore, a column input signal Bn is fed to the gate of a CMOS inverter 230 via the MOS transmission gate 227. When the LOW control signal is in a 60 non-selection state, the MOS transmission gate 227 becomes non-conducting, and the MOS transmission gate 229 becomes conducting; therefore, the output from a CMOS inverter 231 is fed back to the CMOS inverter 230 via the MOS transmission gate 229. In the memory cell 221, the 65 output from the CMOS inverter 230 is fed back to the gate of the CMOS inverter 230 via the CMOS inverter 231 and

2

the MOS transmission gate 229; the circuit can be therefore regarded as being a static memory circuit with two-stage inverters

This way, U.S. Pat. No. 4,996,523 discloses a memory structure including monocrystalline silicon TFTs, as a pixel-TFT configuration for use with the organic LED display.

The aforementioned pixel memory structure disclosed in U.S. Pat. No. 4,996,523 (see FIG. 26) includes multiple memory cells  $C_n$  to  $C_{n-3}$ , as well as a current mirror circuit 225, in each pixel to convert a digital signal to an analog signal (current value) by means of the current mirror circuit.

The structure including a current mirror circuit requires its components, the FETs 223, 224, to have identical characteristics; however, fabricating the FETs by a polysilicon process, which is used for fabrication of liquid crystal displays for example, does not guarantee identical characteristics between neighboring FETs.

As a result, the circuit for an analog gray-scale method in FIG. 26 entails a problem of irregular characteristics in polysilicon TFTs and can produce a homogeneous gray-scale display across the entire screen only with difficulties.

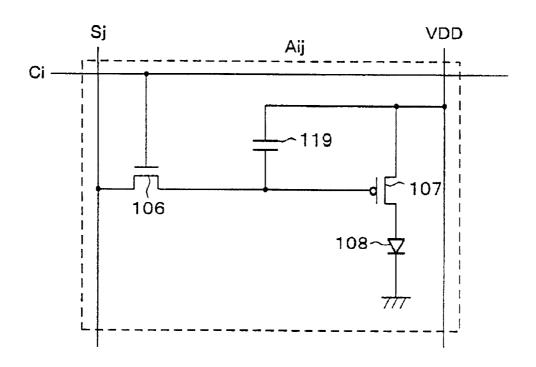

Accordingly, it is suggested to restrain irregularities in polysilicon TFT characteristics by the adoption of digital gray-scale techniques. FIG. 33 shows a pixel circuit structure for use in a time-ratio gray-scale method, a kind of those digital gray-scale method techniques. Specifically, the structure includes a TFT 107 which drives an organic LED display 108, a capacitor 119 which builds voltage accumulation to control the conduction of the TFT 107, and a TFT 106 to control the voltage applied to the capacitor 119. In this structure, the method rewrites the voltage applied to the capacitor 119 in the pixel several times in a single frame period TF as shown in FIG. 34 and produces a gray-scale display by setting the voltage to either such a value that causes the TFT 107 to conduct.

Japanese Unexamined Patent Application 8-194205 (Tokukaihei 8-194205/1996; published on Jul. 30, 1996) discloses a configuration of a liquid crystal display, in which a static memory structure is incorporated in every pixel by means of a polysilicon TFT.

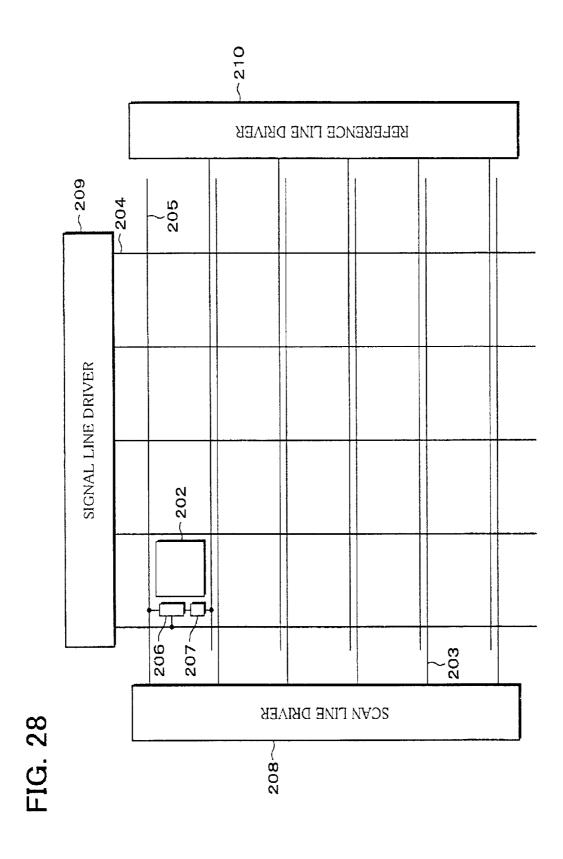

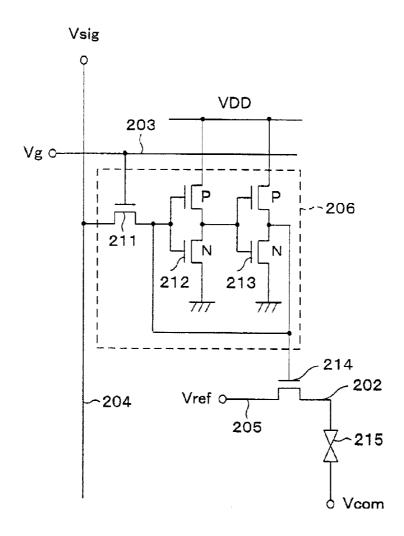

Referring to FIG. 28, in Tokukaihei 8-194205, there are pixel electrodes 202 arranged in a matrix on a first glass substrate, and a scan line 203 running horizontally and a signal lines 204 running vertically between every pair of adjacent pixel electrodes 202. Also, reference lines 205 are provided in parallel to the scan lines 203. At every crossing of the scan lines 203 and the signal lines 204, a memory element 206 (detailed later) is provided, and a switching element 207 is provided between the memory element 206 and the pixel electrode 202.

A second glass substrate is provided to oppose the first glass substrate at a predetermined distance. The second glass substrate has opposite electrodes on a side facing the first glass substrate. A liquid crystal layer as a display material layer is sealed between the two glass substrates. In FIG. 28, 208 is a scan line driver, 209 is a signal line driver, and 210 is a reference line driver.

FIG. 29 is a circuit diagram showing the structure of a pixel portion in FIG. 28. A binary data recording memory element 206 is connected to each of the crossings, of the scan lines 203 and the signal lines 204, arranged in a matrix. The memory element 206 has an output section for outputing stored information. A TFT 214, as a three-terminal switching element 207, is connected to the output section. The switching element 207 controls the resistance between

the reference lines 205 and the pixel electrodes 202 to adjust the bias applied to the liquid crystal layer 215.

In FIG. 29, a static memory element is used as the memory element 206. The static memory element is a memory circuit which delivers a positive feedback by means of two-stage inverters. Consequently, the data fed through the signal lines 204 is supplied to the gate terminal of the inverter 212 when the TFT 211 is conducting. The output from the inverter 212 is resupplied to the gate terminal of the inverter 212 via the inverter 213; therefore, when the TFT 211 conducts, the data supplied to the inverter 212 is fed back to the inverter 212 without changing the polarity thereof and stored until the TFT 211 conducts next time.

This way, Tokukaihei 8-194205 discloses a memory structure including polysilicon TFTs, as a pixel-TFT configuration for use with the liquid crystal display. The TFT substrate structure disclosed in the Tokukaihei as shown in FIG. 29 includes a static memory 206 for every pixel and produces a binary display from data stored in the pixel memory.

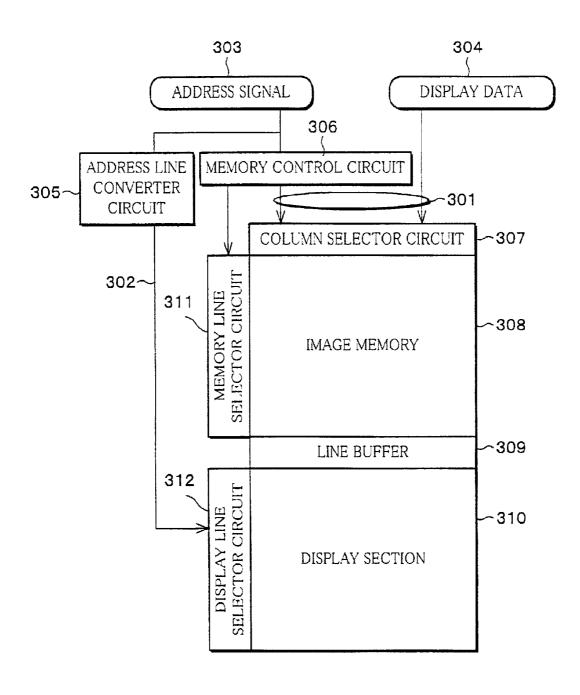

Japanese Unexamined Patent Application 2000-227608 <sup>20</sup> (Tokukai 2000-227608; published on Aug. 15, 2000) discloses a circuit structure for a liquid crystal display in which an exterior of a display section has a memory function.

FIG. 30 is a block diagram showing the structure of a display substrate disclosed in the document.

According to Tokukai 2000-227608, a display section 310 on the display substrate is connected to an image memory 308 via line buffer 309. The image memory 308 includes memory cells arranged in a matrix and has a bitmap structure sharing a common address space with those pixels in the display section 310. An address signal 303 is supplied via a memory control circuit 306 to a memory line selector circuit 311 and a column selector circuit 307. The memory cell address by the address signal 303 is selected by a column line and a line wire (not shown) so that display data 304 is written to the memory cell. After the writing, data for a single line including the selected pixel is transmitted to the line buffer 309 by an address signal supplied to the memory line selector circuit 311. Since the line buffer 309 is connected to signal wiring (not shown) of the display section, the read-out data is transmitted to the signal wiring.

The address signal is also supplied to an address line converter circuit **305** so as to apply the selected voltage to line selector wiring (not shown) by means of a display line 45 selector circuit **312**

This operation results in the writing of the data in the image memory 308 to the display section 310.

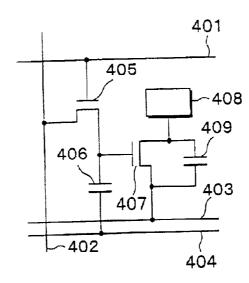

The pixel circuit structure of the display section 310 is shown in FIG. 31. A control TFT 405 is controlled with a 50 line selector wire 401, the data supplied from a signal wire 402 is stored in a capacitor 406 located between a common wire 404 and the control TFT 405, conduction (and non-conduction) of a drive TFT 409 is controlled by the voltage across the capacitor 406, and it is determined whether to 55 apply a voltage supplied to a display electrode 408 from a liquid crystal standard wire 403. A correction capacitor 409 is connected between the source and drain terminals.

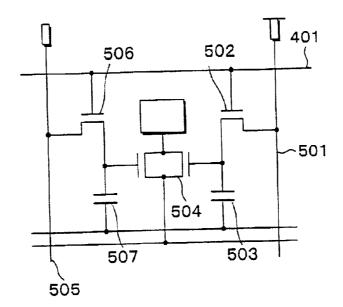

FIG. 32 shows another pixel circuit structure of the display section 310. The TFT drives liquid crystal using an 60 analog switch 504. To drive the analog switch, which is composed of a pch TFT and a nch TFT, two sets of memory circuits are provided, each set including a sampling capacitor 503, 507 and a sampling TFT 502, 506. Data items of different polarities are supplied via two data wires 501, 505, 65 connected to a common line selector wire 401, and simultaneously sample to produce a display.

4

The document also discloses that the data items with different polarities which drive the analog switch can be produced by an inverter circuit built inside a pixel, instead of the provision of two sets of memory circuits, and that the memory circuit used for semiconductor as a memory circuit is constructed around a TFT.

This way, Tokukai 2000-227608 discloses the configuration of a polysilicon TFT substrate for a liquid crystal display. The configuration is such that the TFT substrate structure shown in FIG. 30 includes, outside the display section 310 the image memory 308 composed of an SRAM, the display section 310 includes pixel memories constructed around a capacitor as shown in FIGS. 31 and 32, and a display is produced from binary data stored in the pixel memories.

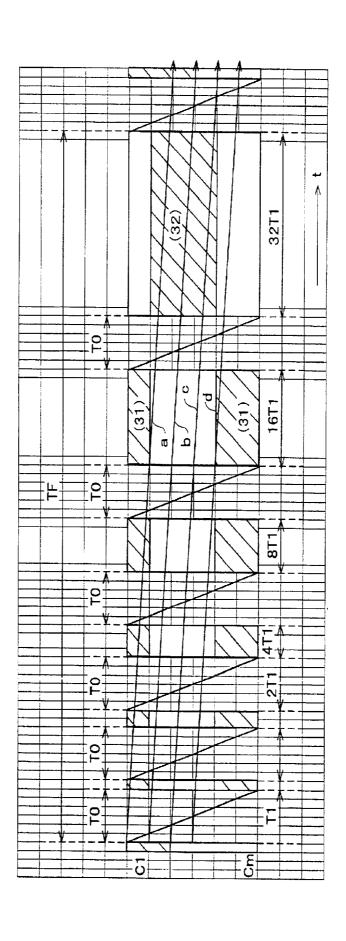

As mentioned in the foregoing, it is suggested to restrain irregularities in polysilicon TFT characteristics by the adoption of digital gray-scale method techniques. However, the time-ratio gray-scale method could probably entail the development of moving picture breakup (dynamic false contours) as is the case with PDPs (plasma display panels). The moving picture breakups develop according to the following mechanism (see FIG. 35). The eye moves as indicated by broken lines (a)-(d) when the pattern of tone level 32 moves on the background of tone level 31 and can recognize a tonal pattern formed by those pixels on the lines at the time of the eye passing over them. For example, along broken line (a), the eye movement coincides with a light-on timing of tones 1, 2, 4, 8, 32 so that the eye can see tone level 47. Along broken line (d), the eye movement coincides only with the light-on timing of tone 16 so that the eye can see tone level 16.

Accordingly, in the PDP and other pieces of apparatus, the animated-image moving picture breakup is improved by dividing large bit-weight data into several sets and displaying those sets before or after small bit-weight data. In other words, the moving picture breakup is reduced by large bit-weight data which appears several times in a cycle of a certain frame period.

However, to produce a display from that large bit-weight data several times on a PDP, etc. scanning is necessary for every display.

Further, U.S. Pat. No. 4,996,523 mentions that the circuit shown in FIG. 26 is provided to each pixel. To compete with recent developments of liquid crystal displays which have achieved a 64 gray-scale method, the PDP requires a 6-bit memory for each pixel. However, in a normal display, three (RGB) pixels are accommodated in a limited space of about  $150 \ [\mu m] \times 150 \ [\mu m] - 300 \ [\mu m] \times 300 \ [\mu m]$ , in which there must be further provided a gate wire, source wire, power source wire, etc, as well as a 6-bit memory circuit arranged as shown in FIG. 26. This is not easy even with a present low-temperature polysilicon process. Building more than 3-bit memory wold be impossible. When this is the case, the device can produce a maximum of only 8 tones and lacks appeal as a commercial product.

Meanwhile, according to Tokukaihei 8-194205, each pixel is provided with only 1-bit memory. Although this is feasible with a present low-temperature polysilicon process, a resultant still image is only binary (of multicolor owing to RGB colors), because the device relies on the 1-bit memory in producing a still image display.

Note that Tokukai 2000-227608 is free from these problems, since the memory is located outside the pixel (display region). Nevertheless, locating the memory outside the display region requires an additional area on the display

substrate, which means a smaller number of substrates fabricated from a glass substrate (of an equal display area) in a TFT process and an increased manufacturing cost for a substrate of an equal display area.

We presume that the biggest advantage in imparting a 5 memory function to the substrate is power saving, which would give the device the most competitive edge in the portable device market than in other markets. However, the above technique is not still preferable in the portable device market where miniaturization and light weight are the key factors, since a larger substrate size is required to produce an equal display area.

### SUMMARY OF THE INVENTION

An objective of the present invention is to offer a display, portable device, and substrate as means for dividing a display period for a bit without new scanning.

Another objective of the present invention is to offer a display, portable device, substrate as a structure of a circuit 20 a pixel used in embodiment 5. for a display substrate which can produce more tones than memories provided to a single pixel.

A further objective of the present invention is to offer, in a display substrate structure in which memories are arranged as a structure of a circuit for a display substrate which is smaller in size with less memories arranged outside display regions, but still capable of producing more or less the same number of tones.

To achieve the objectives, a display in accordance with 30 the present invention includes multiple electro-optic elements and is characterized in that the display includes memory means and potential maintaining means both provided for each of the electro-optic element, wherein a display operation by the electro-optic elements is controlled 35 using outputs from the memory means and the potential maintaining means.

To achieve the objectives, a display in accordance with the present invention includes multiple electro-optic elements and is characterized in that the display includes memory means provided for each of the electro-optic elements, wherein the electro-optic elements and the memory means have individual power source lines.

To achieve the objectives, a portable device in accordance with the present invention is characterized in that the portable device includes the above display.

To achieve the objectives, a substrate in accordance with the present invention includes multiple electrodes and is characterized in that the substrate includes: memory means 50 and potential maintaining means both provided for each of the electrodes; and means for controlling either voltage or current applied to the electrodes using outputs from the memory means and the potential maintaining means.

Consequently, with the arrangement in which each pixel 55 has memory means (memory) and potential maintaining means (capacitor), more tones than memories provided to the pixels can be displayed. Further, by switching between the memories provided to the pixels, a video image is switchably selected to produce a display without externally receiving further data. Moreover, the first memory element can be caused to retain a voltage corresponding to the largest tone data, a voltage application time for that data can be divided in the application of voltage, so as to suppress moving picture breakups.

For a fuller understanding of the nature and advantages of the invention, reference should be made to the ensuing

detailed description taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

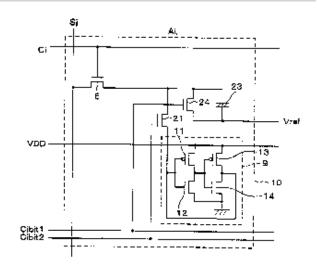

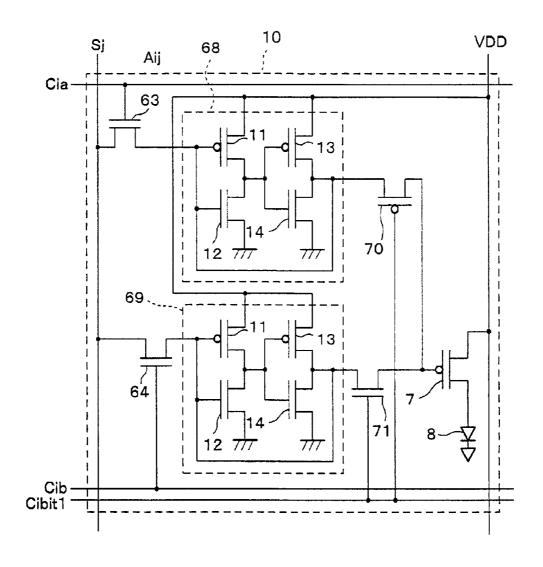

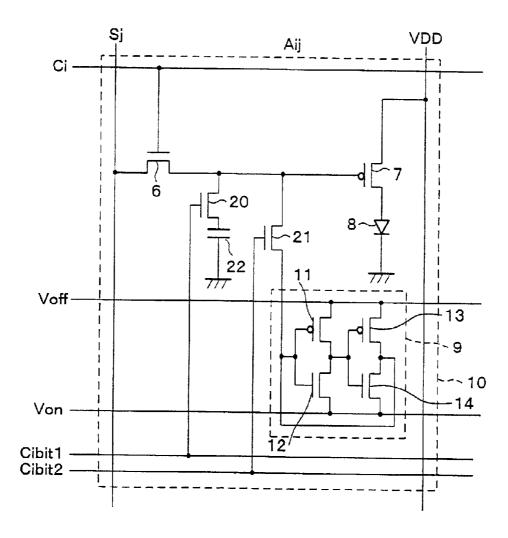

- FIG. 1 is a circuit diagram showing a circuit structure of a pixel used in embodiment 1.

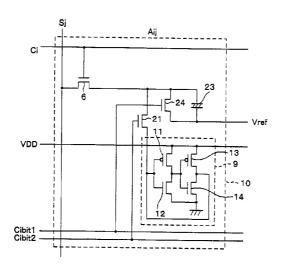

- FIG. 2 is an equivalent circuit diagram showing a circuit structure of a pixel used in embodiment 2.

- FIG. 3 is an equivalent circuit diagram showing a circuit structure of a pixel used in embodiment 3.

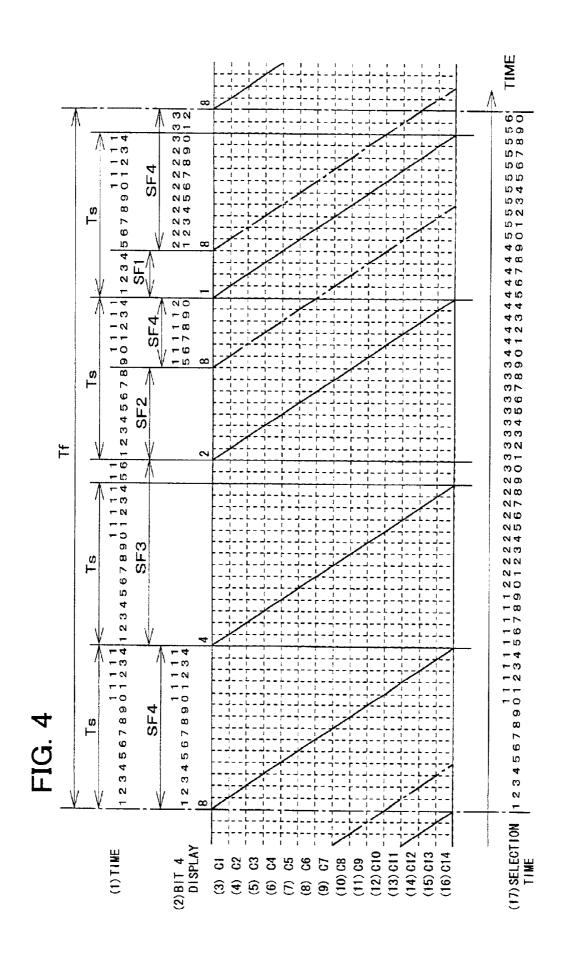

- FIG. 4 is a timing diagram of a time-division tone scan method used in embodiment 3.

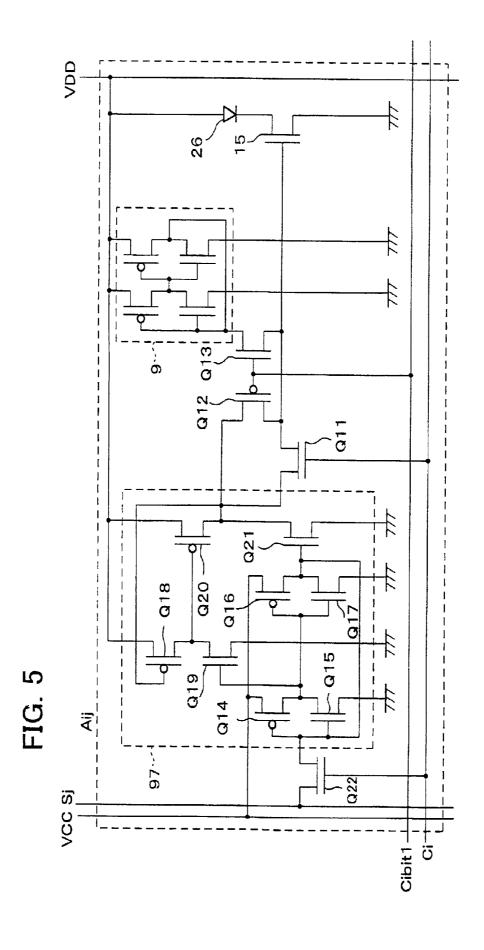

- FIG. 5 is an equivalent circuit diagram showing a circuit structure of a voltage converter circuit described in embodi-

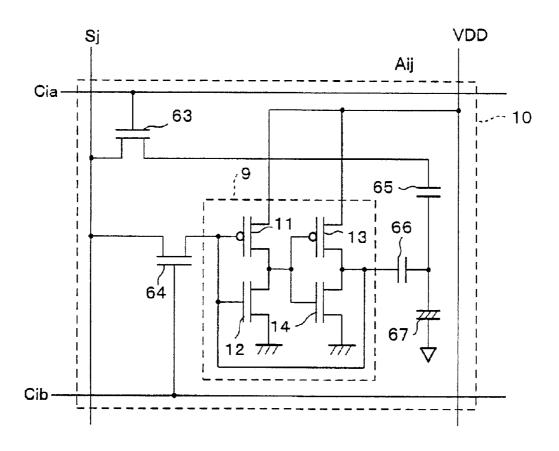

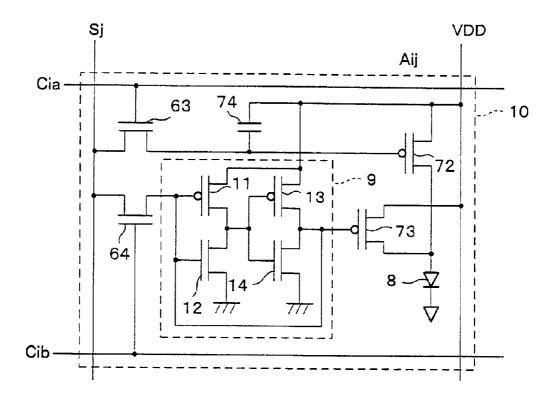

- FIG. 6 is an equivalent circuit diagram showing a circuit structure of a pixel used in embodiment 4.

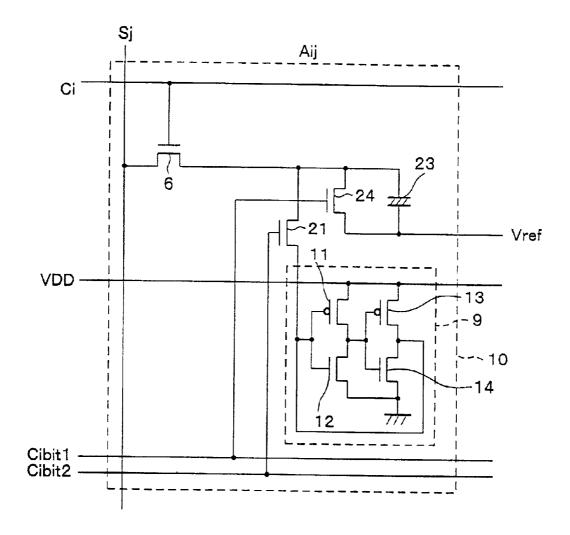

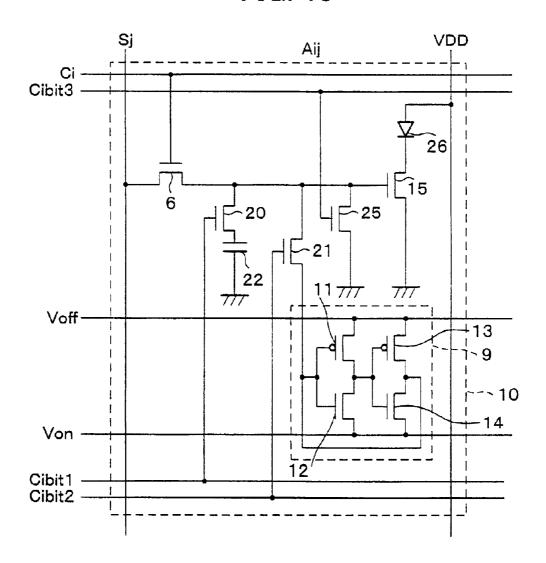

- FIG. 7 is a circuit diagram showing a circuit structure of

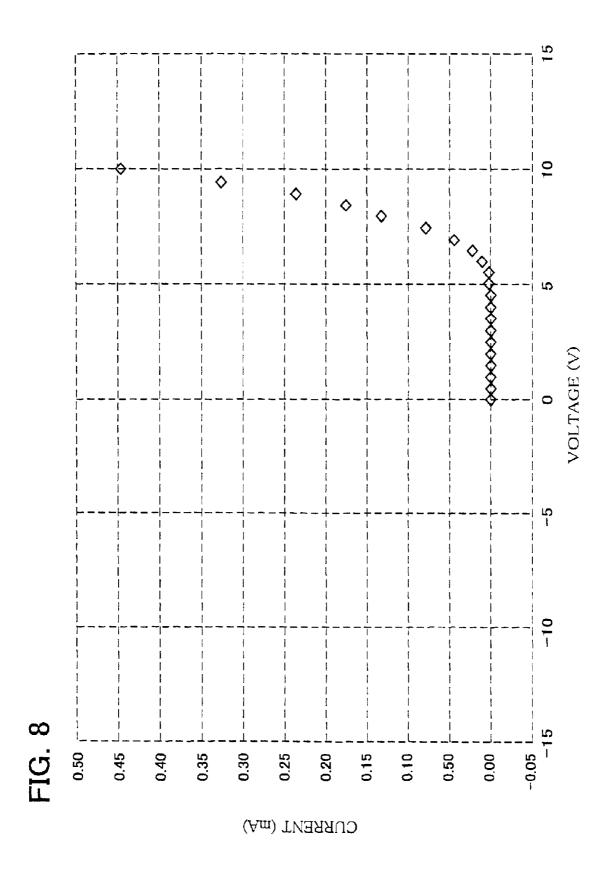

- FIG. 8 is a graph showing an applied voltage versus organic LED display light-emitting current of an organic LED display used in an embodiment.

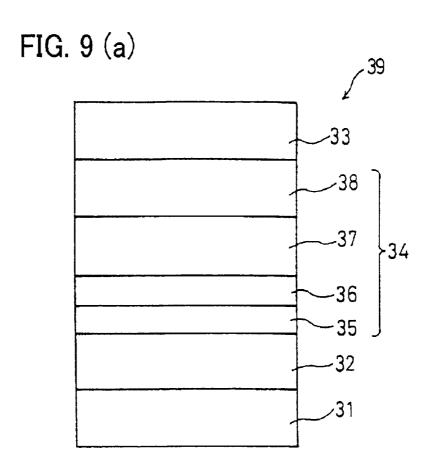

- FIGS. 9(a) and 9(b) show a concept of an organic LED outside display regions, a display, portable device, substrate 25 display used in an embodiment, FIG. 9(a) being an explanatory drawing showing a layer structure, FIG. 9(b) being an explanatory drawing a chemical structure.

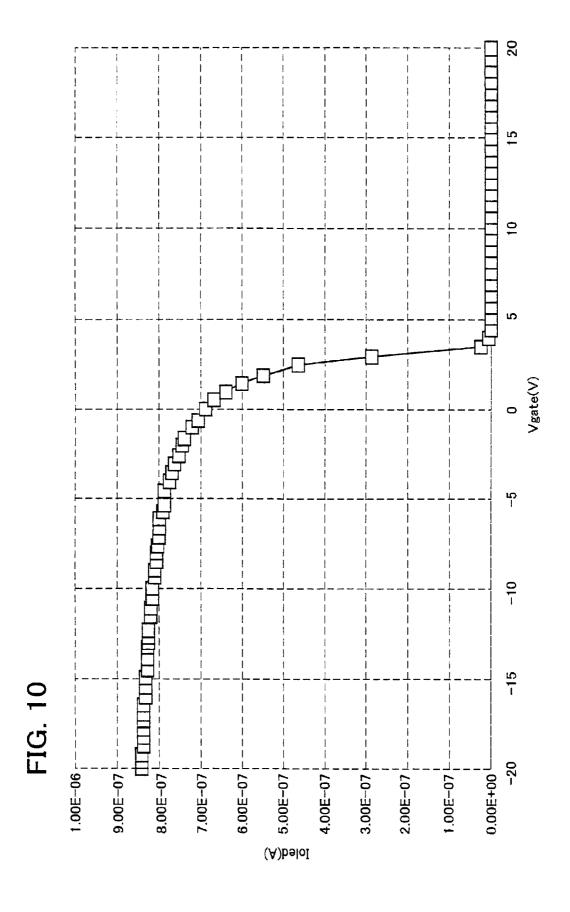

- FIG. 10 is a graph showing a gate voltage and organic LED display light-emitting current of a TFT for used in an organic LED display drive used in embodiment 1.

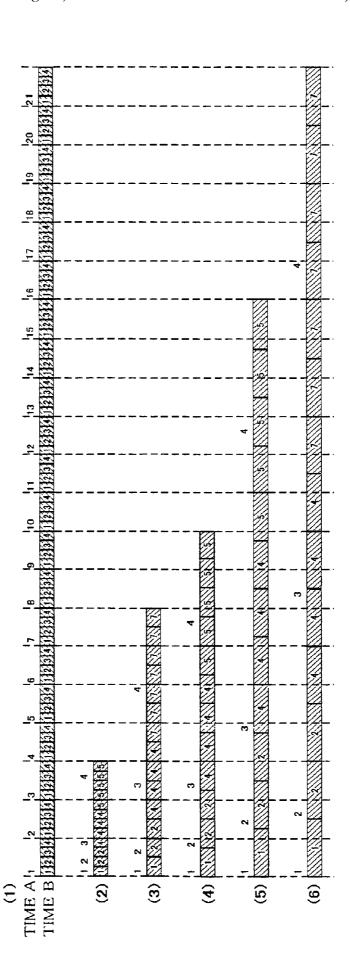

- FIG. 11 is an explanatory drawing showing effects of a moving picture breakup, in accordance with the present invention, used in embodiment 5.

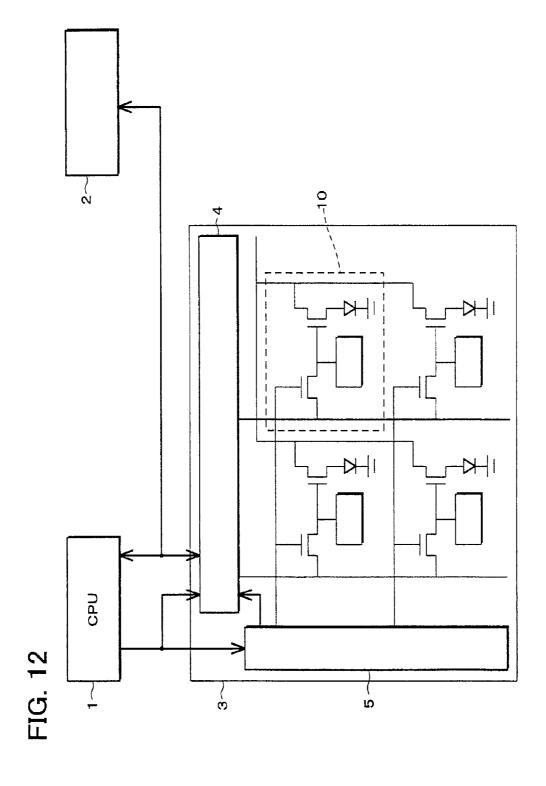

- FIG. 12 is a block diagram showing a system configuration of a display, used in embodiment 5, which includes a memory for each pixel.

- FIG. 13 is a block diagram showing a circuit structure of a SRAM in FIG. 12.

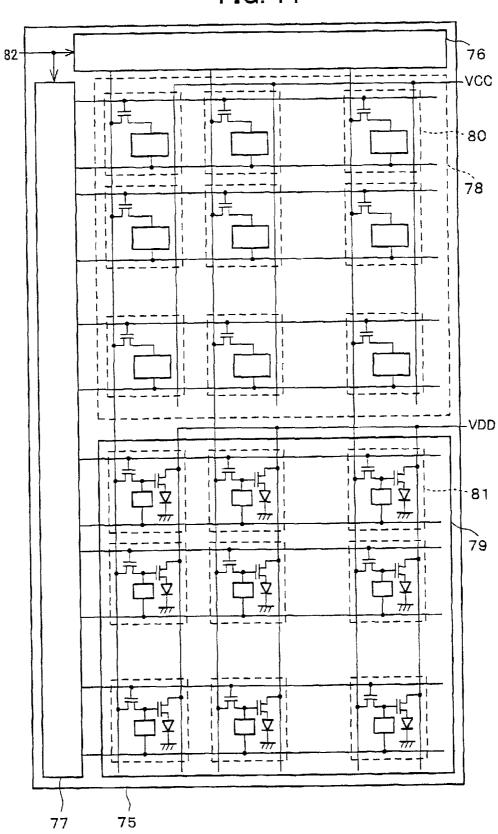

- FIG. 14 is a block diagram showing a system configuration of a display, used in embodiment 6, which includes a memory for each pixel.

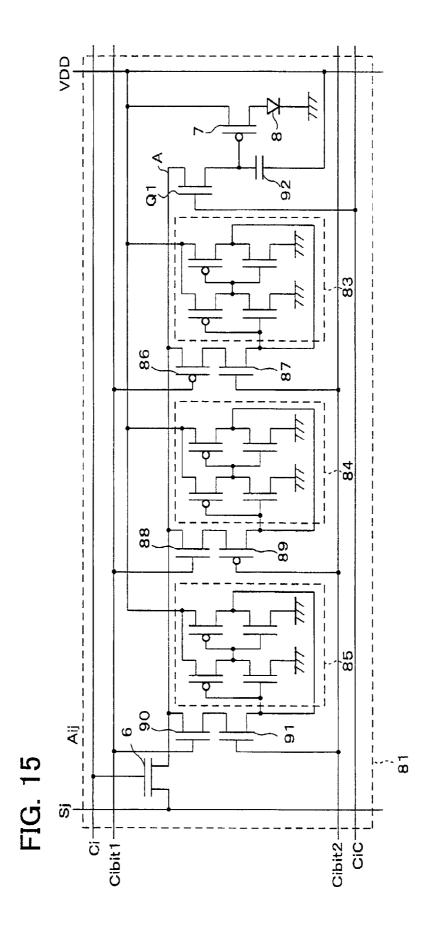

- FIG. 15 is an equivalent circuit diagram showing a circuit structure of a pixel used in embodiment 6.

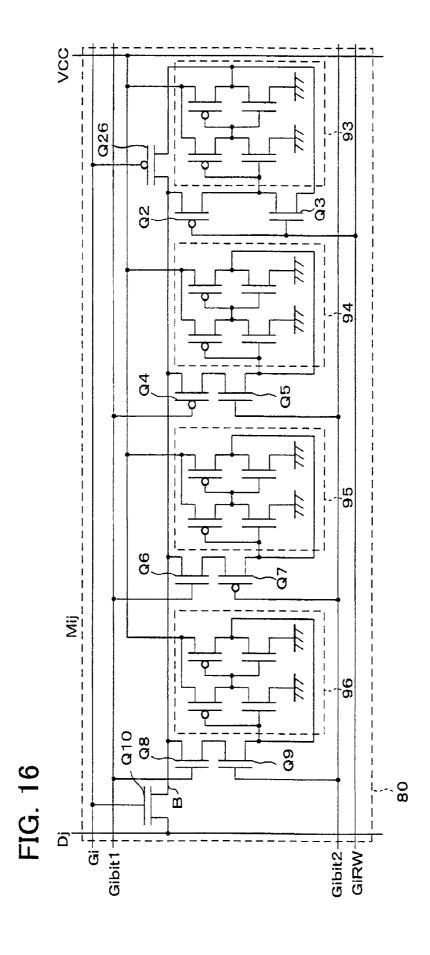

- FIG. 16 is an equivalent circuit diagram showing a circuit structure of a memory cell used in embodiment 6.

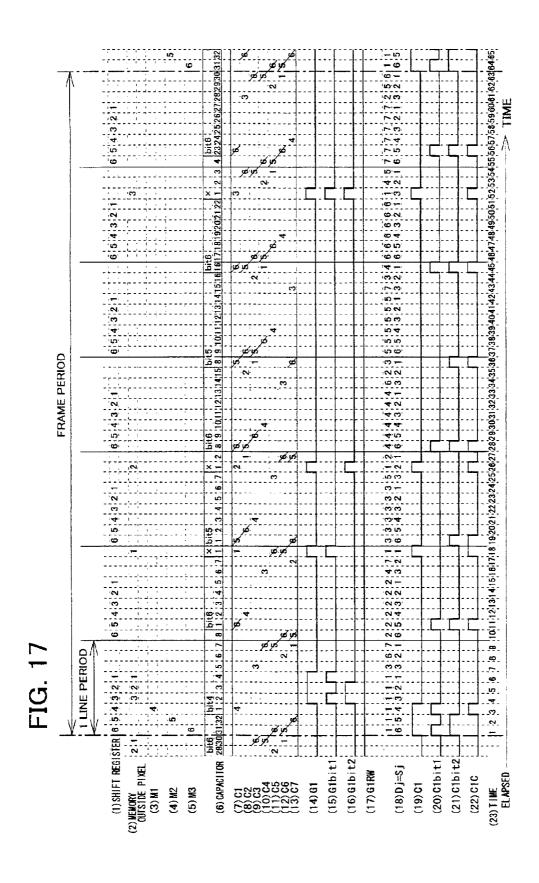

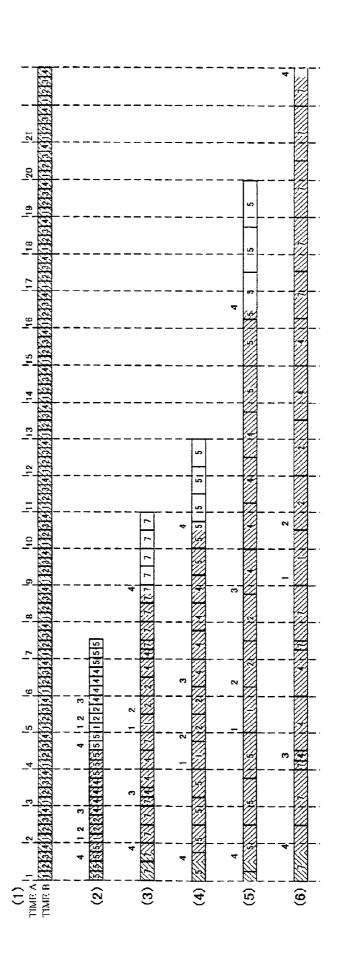

- FIG. 17 is a timing diagram of a time-division tone scan method used in embodiment 6.

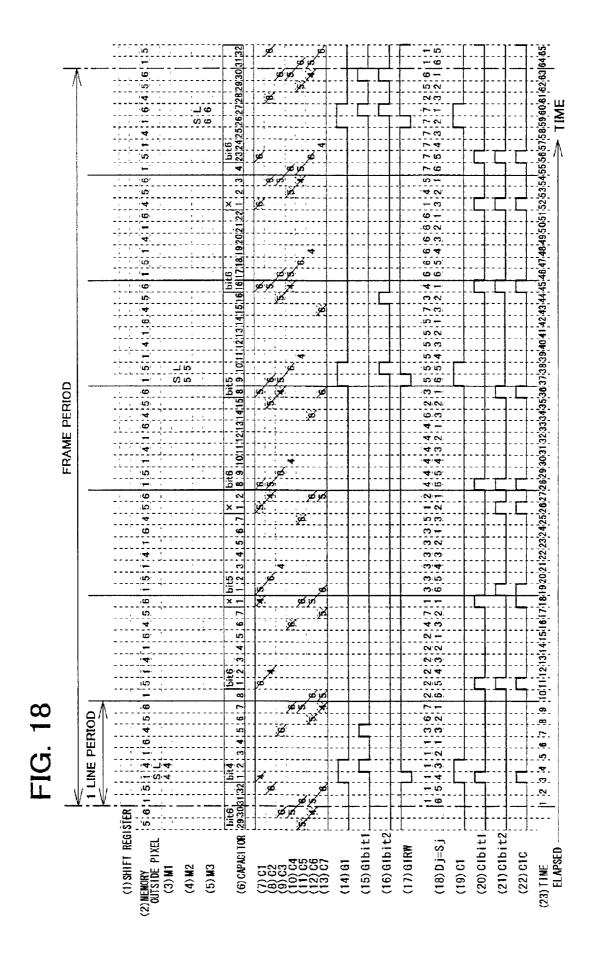

- FIG. 18 is a timing diagram of a video switching scan method used in embodiment 6.

- FIG. 19 is a circuit diagram showing a circuit structure of a pixel used in embodiment 7.

- FIG. 20 is an explanatory drawing showing a timedivision scan method, in accordance with the present invention, used in embodiment 7.

- FIG. 21 is an equivalent circuit diagram showing a circuit structure of a pixel described in embodiment 7.

- FIG. 22 is a circuit diagram showing a circuit structure of a pixel used in embodiment 8.

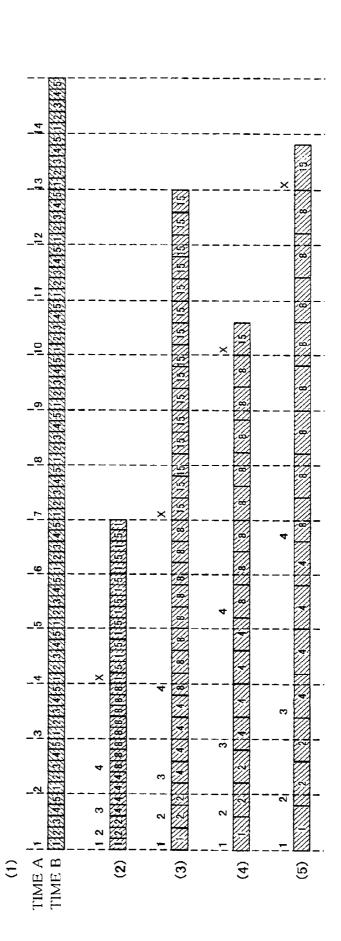

- FIG. 23 is an explanatory drawing showing the acquisition of timings by a time-division scan method, in accordance with the present invention, used in embodiment 8.

- FIG. 24 is an explanatory drawing showing the acquisition of other timings by the time-division scan method, in accordance with the present invention, used in embodiment

FIG. 25 is an explanatory drawing showing the acquisition of other timings by the time-division scan method, in accordance with the present invention, used in embodiment

FIG. 26 is a circuit diagram showing a circuit structure of 5 a pixel in a conventional organic LED display which includes a memory for each pixel.

FIG. 27 is circuit diagram showing a circuit structure of the pixel memory cell in FIG. 26.

FIG. 28 is an explanatory drawing showing a system 10 configuration of a conventional liquid crystal display which includes a memory for each pixel.

FIG. 29 is a circuit diagram showing a circuit structure of the pixel memory in FIG. 28.

FIG. 30 is an explanatory drawing showing a system 15 configuration of a conventional liquid crystal display which includes a memory for each pixel.

FIG. 31 is a circuit diagram showing a circuit structure of the pixel memory in FIG. 30.

FIG. 32 is a circuit diagram showing another circuit 20 structure of the pixel memory in FIG. 30.

FIG. 33 is a circuit diagram showing a conventional circuit structure.

FIG. 34 is an explanatory drawing illustrating a conventional time-ratio gray-scale method.

FIG. 35 is an explanatory drawing showing principles of the development of a moving picture breakup.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[Embodiment 1]

The following will describe an embodiment in accordance with the present invention in reference to FIG. 1.

FIG. 1 shows an equivalent circuit of a pixel Aij which is a first arrangement of first means in accordance with the 35 present invention. The equivalent circuit is adapted so that a data wire Sj, as a signal line, is connected to the source terminal of a TFT (thin film transistor, first switching means) 6 and that the source terminal of a TFT (second switching (electro-optic element) 23 which doubles as potential maintaining means are connected to the drain terminal of the TFT 6. A memory circuit (first memory element) 9, which is a static memory element, is connected to the drain terminal of the TFT **21**.

The TFT 6 is needed, because the data wire Si does not make a one-to-one correspondence to the electro-optic element. If the data wire Si is arranged to make such a correspondence to the electro-optic element, the TFT 6 is dispensable.

To form such a memory circuit 9, the present embodiment employs a CGS (Continuous Grain Silicon) TFT fabrication process. For more details about the process, see Japanese Unexamined Patent Application 8-250749, for example; here, detailed description is omitted.

To control the display state of the liquid crystal element 23, while keeping the potential, Vref, of the opposite electrode of the liquid crystal element 23 at GND, the TFT 6 and the TFT 21 are switched on, i.e., source-to-drain current is caused to flow therein, and the highest-order bit data is 60 applied to the pixel electrode and memory circuit 9 of the liquid crystal element 23. The highest-order bit data here is binary: VDD or GND. To switch on the TFT 6, a selector voltage is applied to a scan line connected to the gate terminal of the TFT 6. To switch on the TFT 21, a selector 65 voltage is applied to a control line Cibit2 connected to the gate terminal of the TFT 21.

In the present embodiment, the source and drain terminals of the TFT are exchangeable since there are not clear distinctions between these two terminals.

Now, while keeping the TFT 6 on and the TFT 21 off, a voltage for a tone equivalent to a low-order bit is applied to the pixel electrode of the liquid crystal element 23.

Thereafter, the TFT 6 is switched off, and the TFT 21 is switched on, to apply the highest-order bit data built up in the memory circuit 9 to the liquid crystal element 23.

Once retained in the memory circuit 9 by the foregoing driving, the highest-order bit data can be applied to the liquid crystal element 23 several times per frame, even with intervening bits.

Note that an a.c. potential can be applied to the liquid crystal element 23 in a frame period which differs from the display period by applying a VDD potential as the potential Vref and switching the voltage applied to the liquid crystal element 23 between VDD and GND via the TFT 6, the TFT

To produce a still image display, the bit data which cannot be arranged in a pixel is also supplied to the liquid crystal (potential maintaining means) from the outside of the pixel. This has an useful effect: 2-bit or more tones are produced even when the memory means in the pixel is capable of handling only a 1-bit gray-scale method.

By the benefit the foregoing driving, the liquid crystal has a time-division gray-scale method capability too. The response of liquid crystal however is so slow that moving picture breakups are rarely visible (they are clearly visible 30 on a high-speed liquid crystal, such as a ferromagnetic liquid crystal). With a high-speed liquid crystal, the driving is useful in restraining moving picture breakups.

Incidentally, in FIG. 1, a TFT 24 (sixth switching element) which enters parallel to the liquid crystal display element 23 and a control line Cibit1 which switches the TFT 24 on and off are provided for the purpose of setting the voltage applied to the liquid crystal element 23 to zero, adjusting the duration of the gray-scale period, and improve tone linearity.

Incidentally, In FIG. 1, the memory circuit 9 has a static element) 21 and a pixel electrode of a liquid crystal element 40 memory structure in which a first inverter circuit formed by a p-type TFT 11 and an n-type TFT 12 is connected to a second inverter circuit formed by a p-type TFT 13 and an n-type TFT 14 so that the output of one is the input of the

> Therefore, as the memory circuit 9, are there included the TFT 13 for controlling the connection to the VDD potential and the TFT 14 for controlling the connection to the GND

Incidentally, a new p-type TFTx may be interposed between the output terminal of the second inverter circuit and the input terminal of the first inverter circuit, with the gate terminal of the p-type TFTx connected to a scan line Ci (the source terminal thereof connected to the output terminal of the second inverter circuit and the drain terminal thereof 55 connected to the input terminal of the first inverter circuit).

When this is the case, when the data on the data wire Si is acquired to the memory circuit 9 with the TFT 6 in a conductive state, the p-type TFT x changes into a nonconductive state, and the output of the second inverter circuit does not affect the input of the first inverter circuit, which makes data setting to the memory circuit 9 easy. When the TFT 6 is in a non-conductive state, the p-type TFT changes into a conductive state, and the output of the second inverter circuit is fed to the input of the first inverter circuit, and the data in the memory circuit 9 is held.

Incidentally, either of the VDD potential and the GND potential can be designated an ON brightness setting

potential, while the remaining one is an OFF brightness setting potential: the designation varies depending on whether the liquid crystal element 23 operates in normally white mode or normally black mode, i.e., whether the transmissive condition or the opaque condition is designated 5 "ON."

## [Embodiment 2]

FIG. 2 shows an equivalent circuit of a pixel Aij which is a second arrangement of the first means in accordance with the present invention. The equivalent circuit includes a TFT 10 (first switching means) 63 so that a data wire Sj, as a signal line, is connected to the source terminal of the TFT 63 and that a capacitor (potential maintaining means) 65 is connected to the drain terminal of the TFT 63. The equivalent circuit further includes a TFT (fourth switching means) 64 15 so that a data wire Si, as a signal line, is connected to the source terminal of the TFT 64 and that an input terminal of a memory element (memory means) 9 is connected to the drain terminal of the TFT 64. A scan line Cia is connected to the gate terminal of the TFT 63, and a scan line Cib is 20 connected to the gate terminal of the TFT 64.

This memory element 9 is identical to that in FIG. 1 and has a static memory structure in which an inverter formed by a p-type TFT 11 and an n-type TFT 12 is connected to another inverter formed by a p-type TFT 13 and an n-type 25 TFT 14 so that the output of one is the input of the other.

A capacitor 66 is connected to an output terminal (which doubles as an input terminal in FIG. 2) of the memory element 9.

A liquid crystal element, which is an electro-optic 30 element, is commonly connected to the other terminals of the capacitors 65, 66. To the remaining terminal of the liquid crystal element is connected a potential Vref of the opposite

to simply as Vref=GND. Assume that the capacitor 65 has a capacitance of C65, the capacitor 66 a capacitance of C66, and the liquid crystal a capacitance of Clc. When the output from the memory means 9 is GND potential, if the voltage applied to the capacitor 65 from the data wire Sj is GND 40 to possible conduction between the TFTs caused by irregular potential, the voltage applied to the liquid crystal is 0 [V]. If the voltage applied to the capacitor 65 from the data wire Sj is VDD, the voltage applied to the liquid crystal is given by  $VDD \times C65/(Clc + C66 + C65)$  [V]. When the output from the memory means 9 is VDD potential, when the voltage 45 applied to the capacitor 65 from the data wire Si is GND potential, the voltage applied to the liquid crystal is given by  $VDD \times C66/(Clc + C66 + C65)[V]$ . If the voltage applied to the capacitor 65 from the data wire Sj is VDD, the voltage applied to the liquid crystal is given by VDD×(C65+C66)/ 50 (Clc+C66+C65) [V].

Accordingly, by setting C65 and C66 to large values relative to Clc and the power source voltage VDD to an appropriate value, a gray-scale method can be produced using the liquid crystal 67. That is, the present embodiment 55 is equivalent to a case where the electro-optic element is driven to produce a display by the application of a voltage created corresponding to the weight of the data stored in the memory means or the potential maintaining means. In such a case, if the data wire Sj makes a one-to-one correspon- 60 dence to the memory means 9 and the potential maintaining means 65, the TFTs 63, 64 are again dispensable. In such a case, the bit data that cannot be arranged in the pixel is fed to the liquid crystal 65, which is the potential maintaining means, from the outside of the pixel in a time-division 65 manner. This is advantageous in that even if the memory means arranged in a pixel is only for a single bit of a memory

10

circuit 9, 2-bit or more tones can be produced (second objective in accordance with the present invention). [Embodiment 3]

FIG. 3 shows an equivalent circuit of a pixel Aij which is a second arrangement of first means in accordance with the present invention. The equivalent circuit is adapted so that a data wire Sj, as a signal line, is connected to the source terminal of a TFT (first switching means) 63, that an input terminal of a static memory (potential maintaining means) 68 is connected to the drain terminal of the TFT 63, that a data wire Sj, as a signal line, is connected to the source terminal of a TFT (fourth switching means) 64, and that the input terminal of a static memory (memory means) 69 is connected to the drain terminal of the TFT 64. A scan line Cia is connected to the gate terminal of the TFT 63, and a scan line Cib is connected to the gate terminal of the TFT 64.

An output terminal of the potential maintaining means 68 is connected to the source terminal of a p-type TFT (fifth switching element) 70, and the drain terminal of the TFT 70 is connected to a gate terminal of a TFT 7 which, in combination with an organic LED display 8, forms an electro-optic element. An output terminal of the memory means 69 is connected to the source terminal of an n-type TFT (fifth switching element) 71. The drain terminal of the TFT 71 is connected to the gate terminal of the TFT 7 which, in combination with the organic LED display 8 (will be described later in detail), forms an electro-optic element.

Either one of the TFTs 70 and 71 is an n-type TFT, while the other is a p-type TFT. Therefore, with the gate terminals thereof connected to a common control line Cibit1, if a control line Cibit1 is HIGH, the TFT 71 is in a conducting state; if the control line Cibit1 is LOW, the TFT 70 is in a conducting state.

Incidentally, if both the TFTs 70, 71 in FIG. 3 are n-type The voltage applied to the liquid crystal will be referred 35 TFTs, the control line connected to the gate terminal of the TFT 71 differs from the control line Cibit1 connected to the gate terminal of the TFT 70.

Therefore, the former case (the example shown in FIG. 3) is advantageous in the use of less control lines, but risky due threshold characteristics of the TFTs 70, 71.

Conversely, in the latter case, the TFTs 70, 71 are separately controlled. Separate control of the TFTs is possible so that they will not conduct simultaneously even when the threshold characteristics of the TFTs 70, 71 are irregular.

Also, in this case, the electro-optic element is formed by the p-type TFT 7 and the organic LED display 8, and the source terminal of the TFT 7 is connected to a power source line at VDD. The drain terminal of the TFT 7 is connected to the anode of the organic LED display 8 (will be described later in detail in terms of its structure). The cathode of the organic LED display 8 is connected to GND.

Accordingly, scanning is done as shown in FIG. 4. Incidentally, in FIG. 4, 3) to 16) represent scan lines, the scanning represented by solid lines is data acquisition from the data wire Si, and the scanning represented by broken lines is data acquisition from the memory means.

Specifically, a single frame period Tf is divided into multiple scanning periods Ts, and first, the highest-order bit data is written to the memory means 69, which switches the control line Cibit1 to HIGH and puts the TFT 71 in a conducting state; the output of the memory means 69 is hence fed to the gate electrode of the TFT 7. Consequently, during this period, a current in accordance with the highestorder bit data runs through the organic LED display 8.

Next, the low-order bit data is written to the potential maintaining means 68, which switches the control line

Cibit 1 to LOW and turns the TFT 70 into a conducting state; the output of the potential maintaining means 68 is hence fed to the gate electrode of the TFT 7. Consequently, during this period, a current in accordance with the low-order bit data runs through the organic LED display 8.

However, with a low-order bit, the display period of a low-order bit may be shorter than the scanning period Ts. Accordingly, during the remaining time, the control line Cibit1 is switched to HIGH and the TFT 71 to a conducting state, so as to feed the output from the memory means 69 to 10 the gate electrode of the TFT 7.

As a result, the period in which current flows through the organic LED display 8 in accordance with the highest-order bit data is divided into subperiods. The sum of the subperiods is made proportional to the weight of the highest-order 15 bit

This driving is effective in restraining the moving picture breakup which is observed when the organic LED display 8 is used to produce a time-ratio gray-scale method.

Incidentally, the present embodiment is equivalent to a 20 case where the output from the memory means or the potential maintaining means is fed to the electro-optic element during a period which corresponds to the weight of the data stored in the memory means or the potential maintaining means.

Another effect is that even if the memory means 69 arranged in a pixel is only for a single bit, 2-bit or more tones can be produced as a result of the supply of the bit data from the outside of the pixel to the static memory 68 which is the potential maintaining means.

Incidentally, when data is transmitted to a pixel as digital data as in the present embodiment, a problem arises that the number of data transmissions is multiplied by the number of bits in comparison to a case where an analog-like voltage is transmitted to the pixel.

However, when an analog-like voltage is transmitted to the pixel, a voltage may be needed to be transmitted to a signal wire Sj to drive the electro-optic element. To this end, a voltage amplitude of, for example, 10 V is needed.

Meanwhile, when binary digital data is transmitted to the 40 pixel, a simple voltage level converter circuit can be provided to the pixel. This means that for example, the voltage transmitted to the signal wire Sj can be maintained as low as about 3 V even when a voltage amplitude of 10 V is applied to the electro-optic element.

Taking the power consumption to transmitted a 10-V voltage once by an analog tone to  $10\times10\times1=100$ , since power consumption is proportional to the voltage squared, the power consumption when a 3-V voltage is transmitted 8 times by a digital tone is reduced to  $3\times3\times8=76$ .

FIG. 5 shows an example of such a voltage converter circuit. In FIG. 5, in a voltage converter circuit 97, a static memory structure is employed including a first inverter formed by a p-type TFT Q14 and an n-type TFT Q15 and a second inverter formed by a p-type TFT Q16 and an n-type 55 TFT Q17; that positive polarity data and reverse polarity data are produced from the data input through the signal wire Sj. One of the two data sets is applied to the gate electrode of an n-type TFT Q19 of a third inverter formed by a p-type TFT Q18 and the n-type TFT Q1, and the other data set is applied to the gate electrode of an n-type TFT Q21 of a fourth inverter formed by a p-type TFT Q20 and the n-type TFT Q21. The p-type TFTs 18 and 20 are connected so that the output of one is supplied to the gate electrode of the other.

Accordingly, as the gate electrode of the n-type TFT Q19 or 21 comes to have a voltage of VCC and turns into a

12

conducting state, the output of the conducting inverter is GND potential. As a result of this, the gate terminal of either the p-type TFT Q18 or 20 becomes equal to GND potential, and a p-type TFT, situated on the side of an n-type TFT, which has been in a non-conducting state now turns into a conducting state. The output from the inverter on that side is VDD. Accordingly, the voltage conversion is completed from VCC to VDD.

This data, converted in terms of voltage, is written to a memory 9 when a scan wire Ci is in a selection state and a control wire Cibit1 is HIGH. The voltage converter circuit 97 doubles as potential maintaining means. This is because new data can be written to the memory circuit 9 only after it is passed through the voltage converter circuit 97, and therefore the voltage converter circuit 97 should be regarded as being potential maintaining means, rather than memory means. Incidentally, the scan wire Ci is in a non-selection state, and the control wire Cibit1 is LOW, the output from the voltage converter circuit 97 which is potential maintaining means is applied to the TFT 15 which is an electro-optic element. The control wire Cibit1 is HIGH, the output from the memory circuit 9 which is memory means is applied to the TFT 15 which is an electro-optic element.

in this manner, by providing a voltage converter circuit to 25 each pixel, power consumption is lowered in a time-ratio gray-scale method.

[Embodiment 4]

FIG. 6 shows an equivalent circuit of a pixel Aij which is a second arrangement of first means in accordance with the present invention. The equivalent circuit is adapted so that a data wire Sj, as a signal line, is connected to the source terminal of a TFT (first switching means) 63 and that a capacitor (potential maintaining means) 74 and the gate terminal of a TFT 72 forming an electro-optic element are connected to the drain terminal of the TFT 63. Further, the data wire Sj, as a signal line, is connected to the source terminal of a TFT (fourth switching means) 64, and the input terminal of a static memory (memory means) 9 is connected to the drain terminal of the TFT 64. A scan line Cia is connected to the gate terminal of the TFT 63, and a scan line Cib is connected to the gate terminal of the TFT 64.

An output terminal of the memory means 9 is connected to the gate terminal a TFT 73 forming an electro-optic element. In this case, the electro-optic element is formed by the p-type TFTs 72, 73 and the organic LED display 8, the source terminals of the TFTs 72, 73 are connected to a power source line VDD, and the drain terminals of the TFTs 72, 73 are connected to an anode of the organic LED display 8 (the organic LED display will be described later in detail in terms of its structure). The cathode of the organic LED display 8 is connected to GND.

Accordingly, while the highest-order bit data of the pixel Aij is being supplied to the signal line Sj in FIG. 6, by turning the scan line Cib to a selection state, the data is acquired to memory means 9. The low-order bit data of the pixel Aij is supplied to the signal line Sj in a time-ratio manner, during that period, by turning the scan line Cia to a selection state, the data is acquired to the capacitor 74.

The TFT 72 ceases to conduct when the capacitor 74 is HIGH and starts to conduct when LOW. The TFT 73 ceases to conduct when the memory means 9 is HIGH and starts to conduct when LOW. The TFTs 72, 73 are fabricated to share the same arrangement (size); if both of them are in a conducting state, the current doubles in comparison to a case where only one of them is in a conducting state.

Accordingly, a gray-scale method can be produced by control the interval at which the low-order data of the pixel

Aij is applied to the capacitor 74 in accordance with the weight of that bit. In this case, the present embodiment is equivalent to a case where a current is generated in accordance with the weight of the data stored in the memory means or the potential maintaining means to display an 5 electro-optic element. In such a case, if the data wire Sj makes a one-to-one correspondence to the memory means 9 and the potential maintaining means 65, the TFTs 63, 64 are again dispensable. Again In this case, the bit data that cannot be arranged in a pixel can be supplied from the outside of the pixel to the capacitor (potential maintaining means) 74, which is effective in producing 2-bit or more tones even when the memory means in the pixel is capable of handling only a 1-bit gray-scale method.

FIG. 7 shows an equivalent circuit of a pixel Aij which is a first arrangement in first means in accordance with the present invention. FIG. 12 shows a block circuit structure including a second memory element (memory array) outside of a display region (pixel) which is second means in accordance with the present invention. Here, for convenience, those members of the present embodiment that have the same arrangement and function as members of any one of the foregoing embodiments, and that are mentioned in that embodiment are indicated by the same reference numerals 25 and description thereof is omitted.

Here, since a self-luminous element, such as an organic LED display, is used, a TFT for use with a self-luminous element drive is fabricated by a silicon process with a large electric charge mobility. That is, to fabricated a TFT for use 30 in the present embodiment, a CGS TFT fabrication process is employed as in embodiments 1–4.

FIG. 7 shows an equivalent circuit of the pixel Aij. The equivalent circuit is adapted so that a data wire Sj is connected to the source terminal of a TFT (first switching 35 element) 6 and that the source terminal of a TFT (second switching element) 21, the source terminal of a TFT (third switching element) 20, and the gate terminal of a TFT 7 forming an electro-optic element are connected to the drain terminal of the TFT 6. Incidentally, a static memory circuit 40 (memory means) 9 is connected to the drain terminal of the TFT 21, and a capacitor (potential maintaining means) 22 is connected to the drain terminal of the TFT 20.

Incidentally, in the structure of FIG. 7, the TFT 20 which is the third switching element is dispensable. The TFT 20 is 45 provided to maintain the potential of the capacitor 22 when the output from the memory element 9 is applied to the gate electrode of the TFT 7. Further, the TFT 20 provided so that the memory state of the memory element 9 does not change due to electric charge of the capacitor 22 when the output of 50 the memory element 9 is fed to the gate terminal of the TFT 7. On account of this, the information stored in the capacitor 22 is retained, and the capacitor 22 works as if it was memory means adopting a dynamic memory, and the stray capacitance of the gate electrode of the TFT 7 works as if it 55 is potential maintaining means.

Therefore, if the TFT 20 is provided, the capacitor 22 is not potential maintaining means of means 1 in accordance with the present invention in a strict sense.

Nevertheless, considering that the stray capacitance of the 60 gate electrode of the TFT 7 is not sufficient and is affected by surrounding wires, resulting in variable potential and that electric power is consumed due to exchange of electric charges in the capacitor 22 too when the capacitor (potential maintaining means) 22 is charged up from the memory 65 means, to prevent development of such problems, the TFT 20 as the third switching element is inserted in series with

14

the capacitor 22 as potential maintaining means to form a potential maintaining means in accordance with the present invention.

With this objective in mind, the third switching element may be situated between the gate electrode of the TFT 7 and the capacitor 22 as in FIG. 7 or between the capacitor 22 and GND. Either way, when the TFT 20 is in a non-conducting state, the electric charge of the capacitor 22 does not vary.

A control line Cibit is connected to the gate terminal of the TFT 20, and a control line Cibit 2 is connected to the gate terminal of the TFT 21.

In the present embodiment, an organic LED display is used as an electro-optic element driven by the TFT 7. FIG. 8 shows characteristics of the element in terms of applied voltage V and current I. FIG. 8 is I-V static characteristics (linear) of an organic LED element. Incidentally, a typical structure of the organic LED display is shown in FIG. 9(a).

As shown in FIG. 9(a), a layered structure 39 is used in which an anode 32, an organic multilayered film 34 (hole entering layer 35, hole transport layer 36, light-emitting layer 37, electron transport layer 38), and a cathode 33 are stacked in this order on a substrate 31.

Incidentally, FIG. 9(b) shows biphenyl (DPVBi available from Idemitsu Kosan Co., Ltd) which is an example of the structure of the light-emitting layer 37.

Incidentally, since the present embodiment is described in a preferred combination, it is also an embodiment in a case when the power source line for the electro-optic element in accordance with the present invention and the power source line for the memory means are separate wires. In other words, in FIG. 7, as the memory circuit 9, an arrangement is made so that a gate ON power source wire (voltage Von) and a gate OFF power source wire (voltage Voff) are power source wires and that a voltage can be specified independently from a power source VDD which drives an organic LED display.

The following will describe how the voltage is specified in the present embodiment. According to a grayscale method in accordance with the present invention, an arrangement in which each pixel has a separate static memory or an arrangement in which an SRAM (static random access memory) is included outside the pixel is preferably used.

Tokukai 2000-227608 introduced in the Background of the Invention is one example of such an arrangement that includes an SRAM (static random access memory) outside the pixel. FIG. 30 shows a TFT substrate structure disclosed by the laid-out patent application: as mentioned earlier, an SRAM-based image memory 308 is provided outside the display section 310, and a display section 310 has a pixel memory formed by the capacitors shown in FIG. 31 and FIG. 32 to produce a display from binary data stored in this pixel memory.

In the foregoing arrangement in which each pixel includes a different memory, the output voltage of the memory is applied to the gate electrode of the TFT for driving the organic LED display. Now, what kind of gate voltage is required to stabilize the display will be described.

FIG. 10 shows a result of simulation of relationship of characteristics, Ioled, of a current running through a gate voltage Vgate of a driver TFT and an organic LED display in an arrangement in which an organic LED display whose applied-voltage-versus-current characteristics are shown in FIG. 8 is connected in series with a driver TFT.

As would be understood from FIG. 10, a self-luminous element, such as the organic LED display, changes the value of the current running in the organic LED display depending on whether the gate voltage of the driver TFT is -5 V or -2 V

In other words, it would be understood that even if the memory outputs normal logic output voltages (VDD, GND), it is insufficient as a voltage to be applied to the gate electrode of a TFT to drive the organic LED display.

Worse than that, we have found out that with the circuit 5 structure disclosed in Tokukai 2000-227608 (see FIG. 31), a change in the electric charges stored in the capacitor 406 causes a change in the gate voltage of the driver TFT 407 and a change in brightness of emitted light. The same holds true with FIG. 32.

Tokukaihei 8-194205 introduced in the Background of the Invention is one example of such an arrangement that include a different static memory for each pixel; as mentioned earlier, the TFT substrate structure disclosed in the laid-open patent application (see FIG. 29) includes a different static memory 206 for each pixel to produce a binary display from the data stored in the pixel memory. In this structure, as the gate voltage of the driver TFT 214, the power source voltage VDD for the logic circuit or the GND voltage is directly used. To drive an self-luminous element, 20 such as the organic LED display, voltage and current are preferably selected so that the V-I characteristics changes little in the relationship between the gate voltage V of the driver TFT in FIG. 10 and the characteristics I of the current running through the organic LED display.

This is because in a driver TFT for use with an selfluminous element, such as an organic LED display, a change in the gate voltage results in a change in brightness of emitted light. However, in a structure in which the power source voltage VDD or GND is directly used, suitable 30 selection of voltage is impossible.

In contrast, according to the arrangement of the present embodiment, as will be described below, a pixel memory circuit can be obtained which is suitable to a display device including different memories for different pixels and also 35 which has stable brightness characteristics when used in a self-luminous element, such as an organic LED display.

FIG. 10 shows V-I characteristics obtained by simulation of the relationship of the gate voltage V of the p-type TFT 7 and the current I running through the organic LED display 40 8 in a combination of a p-type TFT 7 which is used to drive an organic LED display shown in FIG. 7 and an organic LED display 8 whose V-I characteristics are shown in FIG. 8 when the power source voltage VDD is approximately 6 V.

As would be understood from FIG. 10, the gate OFF voltage of the p-type TFT 7 of about 4 V or greater will generate a satisfactory 0  $\mu$ A; however, a gate ON voltage of 0 V is still insufficient, and that of about -5 V or lower will generate a stable, approximate 0.8  $\mu$ A.

For example, taking the gate OFF voltage to Voff=5 V and the variation of the gate ON voltage Von, to (Gate ON Voltage: Von–Gate OFF Voltage: Voff)× $(1\pm0.1)$ , a 0-V gate ON voltage results in a brightness deviation of about  $\pm3\%$ , but a -5 V gate ON voltage results in a small brightness 55 deviation of about  $\pm1\%$ .

The gate voltage of the TFT used to drive the organic LED display is variable due to stray capacitances with surrounding wiring; therefore, setting the gate ON voltage of the organic LED display driver TFT to such a voltage that 60 produces smaller brightness deviations is effective.

By thus connecting a source terminal of one of the two TFTs (transistors) in the inverter circuit which is an output end of the static memory element provided to each pixel which is means 2 in accordance with the present invention 65 to an ON brightness setting wire and the drain terminal of the other TFT (transistor) to an OFF brightness setting wire,

16

the output potential of the static memory element can be rendered a suitable ON potential or OFF potential.

The structure is effective not only with means 1 in accordance with the present invention, but generally with a structure including a static memory element in each pixel.

Accordingly, in the present embodiment, the organic LED display drive voltage is set to +6 V, the gate ON voltage Von is set to -5 V, and the gate OFF voltage Voff is set to +5 V.

In other words, in FIG. 7, the gate OFF power source wire (voltage Voff) is a power source wire at about 5 V, and the gate ON power source wire (voltage Von) is a power source wire at about –5 V. The gate OFF voltage wire (voltage Voff) is connected to the gate wire of the driver TFT 7 via the p-type TFT 13, and the gate ON voltage wire (voltage Von) is connected to the gate wire of the driver TFT 7 via the n-type TFT 14.

Using such a circuit structure, suitable ON and OFF voltages can be supplied to the gate wire of the organic LED display driver TFT. Incidentally, the p-type TFT 13 and the n-type TFT 14 in FIG. 7 forms an inverter circuit. Accordingly, by adding forming another inverter circuit stage with a p-type TFT 11 and a n-type TFT 12 and connecting the gate electrode of one to the output electrode of the other and vice versa, a static memory can be formed based on the memory circuit 9.

FIG. 11 shows a method of controlling the display state of the organic LED element 8.

Specifically, by rendering the power source VDD GND potential (or below GND potential, for example, -6 V) and the control line Cibit2 to a selection state within a first part, TO, of a single frame period TF, the TFT 21 is turned to a conducting state, the TFT 6 (or the source-drain thereof) is turned to a conducting state sequentially for each scan line, and the highest-order bit data is recorded in the memory circuits in the pixels of all the scan lines.

Thereafter, within a period 16T1, the power source VDD is set to +6 V, and a voltage Von or a voltage Voff corresponding to the data stored in the memory circuit 9 is applied to the gate electrode of the organic LED display driver TFT 7

Thereafter, the TFT 21 is turned to a non-conducting state by turning the control line Cibit2 to a non-selection state and the TFT 20 is turned to a conducting state by turning the control line Cibit1 to a selection state.

During this moment, within the period T0, the TFT 6 (or the source-drain thereof) is turned to a conducting state sequentially, the power source VDD is rendered GND potential, a potential which is equivalent to a low-order bit is built up in the capacitor 22, then the power source VDD is rendered +6 V only for a period corresponding to the weight of the bit, and either the voltage Von or the voltage Vof f corresponding to the data stored in the capacitor 22 is applied to the gate electrode of the organic LED display driver TET 7

After completing the display corresponding to the last, low-order bit, the TFT 20 is turned to a non-conducting state by turning the control line Cibit1 to a non-selection state, and the TFT 21 is turned to a conducting state by turning the control line Cibit2 to a selection state, and either the voltage Von or the voltage Voff, stored in the memory circuit 9, which corresponds to the highest-order bit data is applied to the gate electrode of the organic LED display driver TFT 7.

By such scanning, as shown in FIG. 11, when a pattern drawn by the tone level 32 moves on a background drawn by the tone level 31, even if the eye moves along the broken lines (a) to (d) in FIG. 11, there are fewer errors in a tone pattern upon eye movement over a pixel over which the eye moves than the conventional example in FIG. 35.

For example, as to the broken line (a), the eye movement comes across tones 1, 2, 4 and a light-on timing 32/2, and the tone level 23 (=1+2+4+32/2) is visible. As to the broken line (d), the eye movement comes across light-on timings of tones 32/2, 8, 16, and the tone level 40 (=32/2+8+16) is 5 visible. The errors of these values with respect to the original tone levels 31, 32 are reduced by about a half, when compared to the case of FIG. 35.

in this manner, by providing a memory and a capacitor to each pixel and controlling the capacitor independently from 10 the value of the memory, the driving method of the present embodiment becomes possible. The present embodiment is effective in restraining moving picture breakups as shown in FIG. 11, without having to change the required number of

Incidentally, the pixel memory circuit 9 in FIG. 7 operates as follows:

- (1) To update the data in the memory circuit 9, the TFT 6 is turned to a conducting state using the scan line Ci, as a 20 control line, and the TFT 21 is turned to a conducting state using the control line Cibit2, from the data wire Si, as a signal line, the voltage Von or Voff corresponding to the data is supplied to an input end of the first inverter circuit (circuit of the p-type TFT 11 and the n-type TFT 12), and the value 25 of the memory circuit 9 is updated.

- (2) To record data in the memory circuit 9, the TFT 6 or the TFT 21 is turned to a non-conducting state using the scan line (control line) Ci or the control line Cibit2, the output from the second inverter circuit (circuit of the p-type TFT 13 30 and the n-type TFT 14) is supplied to an input end of the first inverter circuit, and the value of the memory circuit 9 is retained.

- (3) Throughout updating and recording of the data in the memory circuit 9, while the TFT 21 is being kept in a 35 conducting state by turning the control line Cibit2 to a selection state, if the p-type TFT 13 in the second inverter circuit is in a conducting state, (regardless whether the TFT 20 is in a conducting or non-conducting state) the gate display becomes Voff, and the organic LED display 8 turns to a non-light-emitting state.

- (4) Throughout updating and recording of the data in the memory circuit 9, while the TFT 21 is being kept in a conducting state by turning the control line Cibit2 to a 45 selection state, if the n-type TFT 14 in the second inverter circuit is in a conducting state, (regardless whether the TFT 20 is in a conducting or non-conducting state) the gate voltage of the p-type TFT 7 used to drive the organic LED display becomes Von, and the organic LED display 8 turns 50 wire. to a light-emitting state.

By doing this, the voltage Von or Voff which binary-drives the organic LED display suitably is supplied to the gate terminal of the organic LED display driver TFT 7 from the result, moving picture breakups are restrained and a display which boasts superior tone linearity becomes possible.

Incidentally, in the present embodiment, the second means in accordance with the present invention is used. Therefore, no data/voltage converter circuit, such as a signal 60 line driver, needs to be inserted as shown in FIG. 28 in association to a conventional technique. Instead, the data in the SRAM located outside the pixel is transmitted to a static memory in the pixel with no modification at all. Accordingly, in FIG. 12, a system configuration is suggested 65 which is suitable as the pixel TFT circuit of the present embodiment.

18

In other words, FIG. 12 shows a structure in which the display incorporates, as an integral part therefor, the SRAM 4 (second memory element) to which the CPU (Central Processing Unit) 1 writes image (additionally, text and the like) data from which a display is produced on the display 3. The SRAM 4 per se may be either built integrally in the display by the aforementioned CGS TFT fabrication process or fabricated as a separate IC by a monocrystalline semiconductor process for mounting to the display 3. In the latter case, the IC may be either directly mounted to the display 3 or mounted to a tape having copper foil wiring thereon by TAB (Tape Automated Bonding) so that the resultant TCP (Tape Carrier Package) is bonded to the display substrate.

Incidentally, 2 is a flash memory located externally to the scans when compared to the conventional example shown in 15 display. 5 is a controller/driver circuit which writes the data in the SRAM 4 to the pixel 10. The pixel 10 has a circuit structure identical to the pixel TFT circuit structure in FIG.

> Apart from a serial I/O port (serial IN control circuit 55 and serial OUT control circuit 54) to the CPU 1, the SRAM 4, as shown in FIG. 13, has a port (parallel OUT control circuit 53) for parallel outputs of data, for the display 3, corresponding to one column (pixel Ail to pixel Aim) on the side of the SEG (signal line driver). Otherwise, the SRAM 4 is identical to a typical SRAM circuit and has address buffers 50, 58, a row decoder 51, a column decoder 57, a selector 56, and a memory array 52. 59, 60 are AND circuits.

> Using this SRAM, the externally input data for each pixel is converted to data for each bit described earlier in association with the driving method and written directly from the SRAM to the pixel memory; as a result, the data does not need to be transmitted serially from the SRAM to the SEG driver. Energy is saved and the display overall consumes less electric power. Also, the user can use the display without paying attention to the employment of such a driving method.

In such a display including a memory element provided to a pixel, the disposition of the second memory element (memory array) outside the pixel (display region) which is voltage of the p-type TFT 7 used to drive the organic LED 40 the second means in accordance with the present invention is greatly effective.

> Incidentally, in the pixel TFT circuit structure in FIG. 7, the gate ON voltage wire (voltage Von) and the power source VDD used to drive the organic LED display are provided as separate wires; however, the V-I characteristics in FIG. 10 tells that a Von of 4 V or higher is all required, and the 6-V VDD can be used. In this case, the gate ON voltage wire (voltage Von) and the power source VDD used to drive the organic LED display can be provided as a single, common

[Embodiment 6]

FIGS. 14-18 show another embodiment of means 1 and means 2 in accordance with the present invention.

FIG. 14 shows a case where the bit data for a pixel is capacitor 22 as well as from the memory circuit 9. As a 55 transmitted line by line similarly to conventional liquid crystal displays. In this case, on a substrate 75 are there provided a serial/parallel converter circuit 76, a controller 77, pixels 81 in display regions 79, and memory cells 80 in memory areas 78 situated external to the pixels.

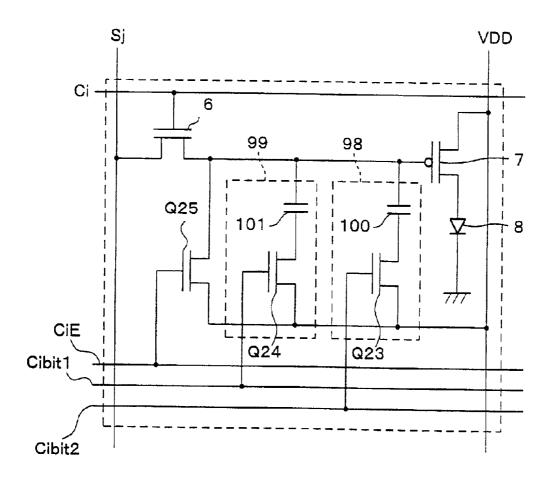

> FIG. 15 shows, as an example, an equivalent circuit structure of the display pixel, and FIG. 16 shows, as an example, an equivalent circuit structure of the memory cell.

Specifically, FIG. 15 is an embodiment of the first arrangement of the first means in accordance with the present invention. The pixel 81 includes a TFT (first switching element) 6, an organic LED display (an electro-optic element) 8, a capacitor (TFT 7, potential maintaining means)

92 which drives the organic LED display 8, and memories (memory means) 83–85. The TFT 6 is connected at the source electrode thereof to a signal wire Sj, at the gate electrode thereof to a scan wire Ci, and at the drain electrode thereof to a wire A. Between each of the memories 83–85 5 and the wire A are there interposed TFTs (second switching elements) 86–91 whose gate electrodes are connected to control lines Cibit1 and Cibit2.

In this case, when the TFT 6 is in a non-conducting state, since the memory 83 is connected to the p-type TFT 86 and 10 the n-type TFT 87, if the control line Cibit1 is LOW and the control line Cibit2 is HIGH, the data in the memory 83 is output to the wire A. Further, since the memory 84 is connected to the n-type TFT 88 and the p-type TFT 89, if the control line Cibit1 is HIGH and the control line Cibit2 is 15 LOW, the data in the memory 84 is output to the wire A. Further, since the memory 85 is connected to the n-type TFT 90 and the n-type TFT 91, if the control lines Cibit1 and Cibit2 are both HIGH, the data in the memory 85 is output to the wire A.

When the TFT 6 is in a conducting state, if the control line Cibit1 is LOW and the control line Cibit2 is HIGH, the data in the signal wire Sj is written to the memory 83. Further, if the control line Cibit1 is HIGH and the control line Cibit2 is LOW, the data in the signal wire Sj is written to the 25 memory 84. Further, if the control lines Cibit1 and Cibit2 are both HIGH, the data in the signal wire Sj is written to the memory 85.

A TFT Q1 is connected between the capacitor 92 and the wire A. A control line CiC is connected to the gate electrode 30 of the TFT Q1. Accordingly, when the TFT Q1 is in a conducting state, the potential of the capacitor 92 is the potential given to the wire A. When the TFT Q1 is in a non-conducting state, the potential of the capacitor 92 is retained. The driver TFT 7 used to drive the organic LED 35 display 8 is controlled through the potential of the capacitor 92.

FIG. 16 shows the memory cell 80 which is another embodiment of the first means in accordance with the present invention. In the memory cell 80 are there provided 40 a TFT (first switching element) Q10 and memories (memory means) 93–96. The TFT Q10 is connected at the source electrode thereof to a signal wire Dj, at the gate electrode thereof to a wire B. The memories 94–96 are connected to TFTs 45 (second switching elements) Q4–Q9 whose gate electrodes are connected to control lines Gibit1, Gibit2.

In this case, when the TFT Q1 is in a conducting state and there is no output from the serial/parallel converter circuit 76, since the memory 94 is connected to the p-type TFT Q4 50 and the n-type TFT Q5, if the control line Gibit1 is LOW and the control line Gibit2 is HIGH, the data in the memory 94 is output to the wire B. Further, since the memory 95 is connected to the n-type TFT Q6 and the p-type TFT Q7, if the control line Gibit1 is HIGH and the control line Gibit2 55 is LOW, the data in the memory 95 is output to the wire B. Further, since the memory 96 is connected to the n-type TFT Q8 and the n-type TFT Q9, if the control lines Gibit1 and Gibit2 are both HIGH, the data in the memory 96 is output to the wire B.

When the TFT Q1 is in a conducting state and there is an output from the serial/parallel converter circuit 76, if the control line Gibit1 is LOW and the control line Gibit2 is HIGH, the data in the signal wire Dj is written to the memory 94. Further, if the control line Gibit1 is HIGH and 65 the control line Gibit2 is LOW, the data in the signal wire Dj is written to the memory 95. Further, if the control lines

20

Gibit1 and Gibit2 are both HIGH, the data in the signal wire Dj is written to the memory 96.

Further, a p-type TFT Q2 is interposed between the input terminal of the memory 93 and the wire B. To the gate electrode thereof is connected a control line GiRW. An n-type TFT Q3 is interposed between the second inverter output terminal (output terminal) of the memory 93 and the first inverter input terminal (input terminal) thereof. To the gate electrode thereof is connected a control line GiRW. Further, a p-type TFT Q26 is interposed between the second inverter output terminal and the wire B. To the gate electrode thereof is connected a gate wire Gi.

As a result, if the gate wire Gi is HIGH and the control line GiRW is LOW, the data in the signal line Dj is written to the memory 93. Further, if the gate wire Gi is HIGH and the control line GiRW is HIGH, the data in the memory 93 is retained. Further, if the gate wire Gi is LOW, the data in the memory 93 is output to the wire B.

Since the output impedance of the memory 93 is specified 20 lower than the other memories 94–96, if the gate wire Gi is LOW, and the other memories 94–96 turns into a conducting state with the wire B, the data in the memories is replaced with the data in the memory 93.

In FIG. 14, the input bit data 82 is temporarily stored in a shift register (not shown) in the serial/parallel converter circuit 76 and thereafter stored in a latch (not shown) where data for one line is retained.

From the latch, data for one line is sequentially output for each bit. For example, in a case of a 6-bit tone, as shown in (1) of FIG. 17, data is output line by line for each bit from the 6th bit through the 1st bit.

Part of the output bit data is acquired to a memory located in the pixel **81** in the display region **79** through the control by the control circuit **77** and the rest is acquired to a memory in the memory cell **80** located in the area **78** outside the pixel (display region).

For example, the 3rd- through 1st-bit data is written to a memory (memories 94–96 in FIG. 16) outside the pixel as shown in (2) of FIG. 17, and the 6th-through 4th-bit data is written to memories M3-M1 (memories 83–85 in FIG. 15) inside the pixel as shown in (3)–(5) of FIG. 17.

Incidentally, the 4th-bit data is simultaneously written also to the capacitor 92 which controls the TFT 7 for driving the organic LED display 8.

FIG. 17(14)–(22) shows the behavior of a control signal for that purpose.