US006862021B2

# (12) United States Patent

Kudo et al.

(10) Patent No.: US 6,862,021 B2

(45) **Date of Patent:** Mar. 1, 2005

### (54) LIQUID CRYSTAL DISPLAY CONTROL APPARATUS AND LIQUID CRYSTAL DISPLAY APPARATUS

(75) Inventors: Yasuyuki Kudo, Fujisawa (JP);

Tsutomu Furuhashi, Yokohama (JP); Hiroyuki Mano, Sagamihara (JP); Shinji Uchida, Chiba-ken (JP); Tatsuhiro Inuzuka, Odawara (JP); Takeshi Maeda, Yokosuka (JP); Satoshi Konuma, Fujisawa (JP)

(73) Assignees: Hitachi, Ltd., Tokyo (JP); Hitachi Video & Information System, Inc.,

Yokohama (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 205 days.

(21) Appl. No.: 10/087,785

(22) Filed: Mar. 5, 2002

(65) **Prior Publication Data**

US 2002/0130881 A1 Sep. 19, 2002

## Related U.S. Application Data

(62) Division of application No. 09/059,363, filed on Apr. 14, 1998, now Pat. No. 6,353,435.

(30) Foreign Application Priority Data

| Apr. 15, 1997 | (JP) | <br>09-097216 |

|---------------|------|---------------|

| Sep. 25, 1997 | (JP) | <br>09-260530 |

(52) **U.S. Cl.** ...... **345/204**; 345/87; 345/89; 345/690

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,347,294 A | *            | 9/1994 | Usui et al 345/89    |

|-------------|--------------|--------|----------------------|

| 5,491,496 A | o <b>ķ</b> c | 2/1996 | Tomiyasu 345/690     |

| 5,534,883 A |              | 7/1996 | Koh 345/3            |

| 5,900,857 A |              | 5/1999 | Kuwata et al 345/100 |

| 5,953,002 A |              | 9/1999 | Hirai et al 345/204  |

| 6,014,126 A |              | 1/2000 | Nishihara            |

| 6,084,561 A | *            | 7/2000 | Kudo et al 345/89    |

#### FOREIGN PATENT DOCUMENTS

| JP | 8-87247  | 4/1996 |

|----|----------|--------|

| JP | 8-194451 | 7/1996 |

<sup>\*</sup> cited by examiner

Primary Examiner—Jimmy H. Nguyen (74) Attorney, Agent, or Firm—Antonelli, Terry, Stout & Kraus, LLP

### (57) ABSTRACT

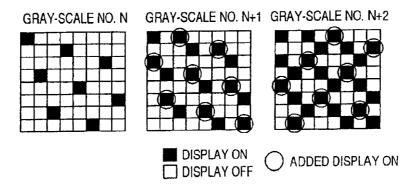

A display apparatus includes a display having a plurality of pixels, and a controller which selects a pattern corresponding to a gradation of gradation data. On-state pixels are added to a pattern corresponding to one gradation of the gradation data to obtain a pattern corresponding to another gradation of the gradation data higher than the one gradation of the gradation data while maintaining unchanged an arrangement of on-state pixels in the pattern corresponding to the one gradation of the gradation data.

15 Claims, 40 Drawing Sheets

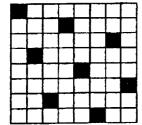

## GRAY-SCALE NO. N GRAY-SCALE NO. N+1 GRAY-SCALE NO. N+2

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

FIG.10

FIG.11

## FIG.12A

## FIG.12B

FRAME MEMORY 8B

| _       | FRAME MEMORY 8A   |         |

|---------|-------------------|---------|

| 1MBit { | UPPER DISPLAY 1ST | ]]      |

| •       | UPPER DISPLAY 2ND | 1       |

|         | UPPER DISPLAY 3RD | ]       |

|         | UPPER DISPLAY 4TH | ] [     |

|         | UPPER DISPLAY 5TH | 1       |

|         | UPPER DISPLAY 6TH |         |

|         |                   |         |

|         |                   | >16MBit |

|         | LOWER DISPLAY 1ST | TOMBIL  |

|         | LOWER DISPLAY 2ND |         |

| Į       | LOWER DISPLAY 3RD |         |

|         | LOWER DISPLAY 4TH |         |

| 1       | LOWER DISPLAY 5TH | ,       |

|         | LOWER DISPLAY 6TH |         |

| Ĺ       |                   |         |

| [       |                   | J       |

|         |                   |         |

| UPPER DISPLAY 1ST |

|-------------------|

| UPPER DISPLAY 2ND |

| UPPER DISPLAY 3RD |

| UPPER DISPLAY 4TH |

| UPPER DISPLAY 5TH |

| UPPER DISPLAY 6TH |

|                   |

|                   |

| LOWER DISPLAY 1ST |

| LOWER DISPLAY 2ND |

| LOWER DISPLAY 3RD |

| LOWER DISPLAY 4TH |

| LOWER DISPLAY 5TH |

| LOWER DISPLAY 6TH |

|                   |

|                   |

VSYNC COUNT VALUE : 0 OR 1→

DATA WRITE

VSYNC COUNT VALUE : 2 OR 3→

DATA READ

US 6,862,021 B2

FIG.14

FIG.15

**FIG.17**

**FIG.18**

FIG. 19

FIG.21

FIG.22

**FIG.23**

FIG.24

**FIG.25**

FIG.26

FIG.27

FIG.28

FIG.29

FIG.30 (PRIOR ART)

DISPLAY OFF DISPLAY ON

FIG.32 (PRIOR ART) 311 312 314 INPUT **INTERFACE** LIQUID GRAYm CRYSTAL SCALE OUTPUT **PROCESSOR** INTERFACE ոխոխոխ FRAME MEMORY 313

FIG.33A

FIG.33B

OUTLVDSPP FIG.41 418 --414 512 ding. LINEEMPP д В +384 OUTPUT VERTICAL COUNTER LSIVDSPCNT 412 INPUT VALID

DISPLAY LINE

NUBER COUNTER LIVDSPCNT 1600 (+768 413 1/2 XGAMODEP IDCLK OUTVCLKP LCHKMODEP LCHKMODEP OVCNTCLRP

**FIG.43**

FIG. 44

FIG.45

FIG.46

LIQUID CRYSTAL DISPLAY INTERFACE STN **ω** } LIQUÍD CRYSTAL CONTROLLER FRC ESTABLISH MEMORY (5 FRAME MEMORY 9 INTERFACE FIG.47 Ø 旧 TFT INTERFACE CONTROLLER 470 472 A/D CONVERTER 251 471 SYSTEM REALITY

# LIQUID CRYSTAL DISPLAY CONTROL APPARATUS AND LIQUID CRYSTAL **DISPLAY APPARATUS**

### CROSS-REFERENCE TO RELATED APPLICATION

This application is a division of application Ser. No. 09/059,363 filed on Apr. 14, 1998 now U.S. Pat. No. 6,353,435, the contents of which are incorporated herein by reference in their entirety.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display control apparatus and a liquid crystal display apparatus and more particularly, to a liquid crystal display control apparatus of a passive matrix type and a liquid crystal display

# 2. Description of the Related Art

In a liquid crystal display apparatus of a so-called passive matrix display type as a super-twisted nematic (STN) type wherein pixels are positioned at intersections between scan and data electrodes perpendicular to each other so that the 25 light transmission factor of the pixel varies with a mean square of a difference between voltages applied to the scan and data electrodes; a drive frame frequency for obtaining the optimum contrast varies with the response time of liquid

It is generally believed that the optimum contrast can be obtained when the response time of liquid crystal material (corresponding to an addition of a rise time until display on and a fall time until display off) is 300 ms and a drive frame frequency is between 90 and 120 Hz.

It is also believed that the optimum contrast can be obtained when the response time is 150 ms and the drive frame frequency is 150 Hz or when the response time is 100 ms and the drive frame frequency is 180 Hz or more.

frame frequencies of 60 to 75 Hz of a cathode-ray tube (CRT) display or thin film transistor (TFT) liquid crystal display.

Accordingly, in order to convert a display signal for the CRT display or TFT liquid crystal display to a display signal for an STN liquid crystal display, it is required to use a frame memory for saving of display data to convert it to a drive frame frequency.

In liquid crystal displays, predominant ones of driving methods for applying binary information (one bit data) of display on and off to the respective pixels of the liquid crystal display.

In order to provide a gray-scale for the liquid crystal systems for implementing this special processing, there is a frame rate control (FRC) system which provides a gravscale display by setting several frame periods as a unit period and setting the display on/off rate of each pixel in the unit period in terms of unit periods of frame periods.

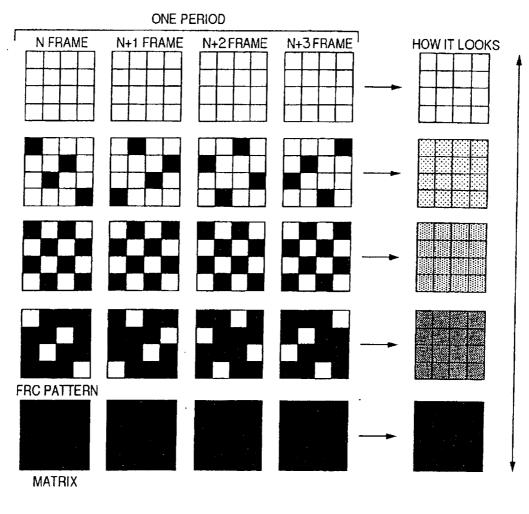

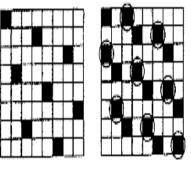

FIG. 30 is a diagram for explaining an example of gray-scale processing of the FRC system.

In the example shown in FIG. 30, 4 frame periods are set as a unit period, and a pattern of display on and off (referred to as the FRC pattern, hereinafter) is switched on every unit 65 period basis with respect to each certain size of matrix on the display screen.

In a liquid crystal display apparatus of an STN type, a means for implementing the drive frame frequency converting operation and the gray-scale processing operation of the FRC system is generally called liquid crystal controller.

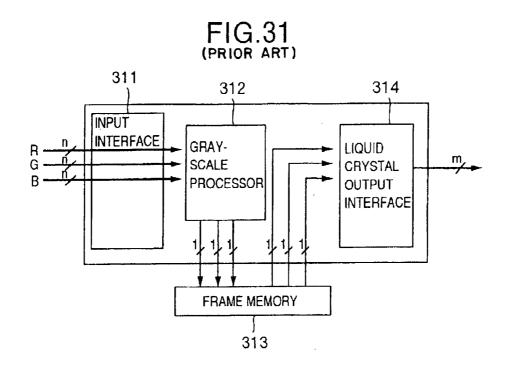

FIGS. 31 and 32 schematically show block diagrams of liquid crystal controllers.

The liquid crystal controller shown in FIG. 31 is of such a type that executes the gray-scale processing operation prior to the drive frame frequency converting operation.

First, for each of colors of red (R), green (G) and blue (B), an input interface 311 accepts gray-scale data (usually, 6-to-8 bit data) of n bits per pixel.

A gray-scale processor 312 then executes the gray-scale processing operation of the FRC system according to the gray-scale data received from the input interface 311 to generate of one bit of indicate on/off data, and writes it into a frame memory 313.

Thereafter, the indicate on/off data are read out from the frame memory 313 in synchronism with the drive frame frequency of the liquid crystal output display data to be converted to a frame frequency, and then output to an STN liquid crystal display (not shown) through a liquid crystal output interface 314.

The liquid crystal controller shown in FIG. 32, on the other hand, is such a type that executes the frame frequency converting operation prior to the gray-scale processing

First, for each of the colors R, G and B, an input interface 311 accepts gray-scale data (usually, 6-to-8 bit data) of n bits per pixel. After that, the gray-scale data are written into a frame memory 313.

Next, the gray-scale data are read out from the frame memory 313 in synchronism with the drive frame frequency 35 of the liquid crystal output display data to be converted to a frame frequency, and thereafter a gray-scale processor 312 executes the gray-scale processing operation of the read gray-scale data to generate one bit of indicate on/off data.

And the gray-scale processor 312 outputs the indicate These drive frame frequencies are higher than the drive 40 on/off data to an STN liquid crystal display (not shown) through a liquid crystal output interface 314.

> Disclosed in Japanese Laid-Open Publication No. 8-87247 is a technique for displaying a video signal not conforming to a liquid crystal display of the passive matrix type.

# SUMMARY OF THE INVENTION

It is therefore a first object of the present invention to provide a liquid crystal display control apparatus and liquid crystal display apparatus which can suppress moving and flickering of a gray-scale display portion and also can avoid increase in the number of pins when the apparatus is made in the form of a large scale integrated (LSI) circuit.

A second object of the present invention is to provide a display, special processing becomes necessary. As one of 55 liquid crystal display control apparatus and liquid crystal display apparatus which can prevent interference fringes generated when gray-scale display is carried out over upper and lower screens of an STN liquid crystal display of a so-called dual scan type.

A third object of the present invention is to provide a liquid crystal display control apparatus and liquid crystal display apparatus which, when digital gray-scale data generated from analog display data for a CRT display is used as an input signal, can suppress deterioration of quality of the gray-scale display due to an quantum error caused by conversion of the analog display data to the digital grayscale data.

A fourth object of the present invention is to provide a liquid crystal display control apparatus and liquid crystal display apparatus which can display on a liquid crystal display a video signal with retrace lines removed therefrom.

In accordance with a first aspect of the present invention, 5 there is provided a liquid crystal controller wherein, in accordance with gray-scale data of pixel units included in a video input signal, a display on/off rate at which pixels of units included in a video output signal to a liquid crystal display are indicated during a plurality of frame periods of the video output signal, is set in the pixel units of the video output signal in its one display scan period on a unit pixel basis to provide intermediate gray-scale display to the liquid crystal display, and which controller comprises:

- a display on/off data generation circuit, in accordance 15 with the gray-scale data of pixel units included in the video input signal, for generating display on/off data corresponding to M (M>N) frame periods of the video output signal in N frame periods of the video input signal on a unit pixel basis:

- a write control circuit for writing display on/off data corresponding to M frames of the video output signal generated by the display on/off data generation circuit into a frame memory during N frame periods of the video input signal; and

a read control circuit for sequentially reading out, from the frame memory, display on/off data corresponding to M frames of the video output signal written in the frame memory in synchronism with frame period of the video output signal.

In this case, the gray-scale data refer to, e.g., display data for a liquid crystal display of a thin film transistor (TFT) type.

The above arrangement, display on/off data corresponding to M (M>N) frames of the video output signal are written into the frame memory during an N frame period of the video input signal, and the written display on/off data of the M frames are sequentially read out from the frame memory in synchronism with the frame period of the video output signal.

In this way, since the data written in the frame memory is not gray-scale data but display on/off data of one bit, a data bus width at the time of accessing the frame memory can be reduced. Accordingly, an increase in the number of pins involved when it is desired to make the controller in the form of an LSI can be suppressed.

Further, since the frame period of the video output signal can be set faster than the frame period of the video input signal, the flow or flickering of the intermediate gray-scale display part can be lightened.

In addition, gray-scale data is data of usually 6 to 8 bits per pixel, whereas display on/off data is data of one bit per pixel.

Therefore, the total number of bits in the data written in the frame memory with one frame period of the video input signal as a unit is:

- (1) When gray-scale data is written in the frame memory, [(the number of pixels in one frame)×6 to 8 bits].

- (2) When display on/off data is written in the frame 60 memory, [(the number of pixels in one frame)×1 bit×M/N bits].

Accordingly, by setting M/N to be smaller than 6 to 8, the memory capacity can be saved when compared with that when gray-scale data is written in the frame memory.

In accordance with a second aspect of the present invention, there is provided a liquid crystal controller 4

wherein, in accordance with gray-scale data of units each having a plurality of pixels and included in a video input signal, display on/off change-over patterns of pixels during a plurality of frame periods of the video output signal to be output to a liquid crystal display, are set to provide intermediate gray-scale display for the liquid crystal display, the liquid crystal display is of a dual scan type in which the liquid crystal display is divided into upper and lower display to be simultaneously driven, and which comprises:

- a first setting circuit for setting a display on/off changeover pattern of pixels during a plurality of frame periods of the video output signal according to gray-scale data of the pixel units located in the upper display and included in the video input signal; and

- a second setting circuit for setting a display on/off changeover pattern of pixels during a plurality of frame periods of the video output signal according to gray-scale data of the pixel units located in the upper display and included in the video input signal;

and wherein the second setting circuit sets the display on/off change-over data in such a manner that the display on/off change-over pattern of pixels located in the lower display is delayed by one frame of the video output signal with respect to the display on/off change-over pattern of pixels located in the upper display.

In the second aspect of the present invention having the above arrangement, the display on/off pattern of the lower display can be output as delayed by one frame with respect to that of the upper display.

In this way, since the display on/off data of pixels in the vicinity of a boundary between the upper and lower displays can be set to be included in the same frame, it can be prevented that interference fringes look like moving in the vicinity of the boundary between the upper and lower displays.

In accordance with a third aspect of the present invention, there is provided a liquid crystal controller wherein, in accordance with gray-scale data of pixel units generated by quantizing an analog gray-scale signal, display on/off change-over patterns of pixels during a plurality of frame periods of a video output signal to be output to a liquid crystal display are set to provide intermediate gray-scale display for the liquid crystal display, and the display on/off change-over patterns are previously set so that gray-scale data of pixels having adjacent values have a nearly common frame to be mutually turned on or off.

In this case, analog gray-scale signal refers to, e.g., display data for a cathode ray tube (CRT) type of display.

In the third aspect of the present invention having the above arrangement, with respect to display on/off data corresponding to one frame of the video output signal, change-over of display on/off of pixels caused by changes in the values of the gray-scale data can be smoothly made without providing an extreme change in the positional relationship between the pixel turned on and the pixel turned off

Thus, when digital gray-scale data generated from such an analog gray-scale signal as analog display data for a CRT display are used as a video input signal, a quantization error generated a the time of converting the analog gray-scale signal to the digital gray-scale data enables suppression of image quality deterioration of intermediate gray-scale display.

In accordance with a fourth aspect of the present invention, there is provided a liquid crystal controller which

comprises a vertical synchronous signal control circuit for converting a vertical synchronous signal inputted to the controller into a vertical synchronous signal having a frequency corresponding to Y (Y being a real number of 2 or more) times the frequency of the input vertical synchronous 5 signal and supplying the converted vertical synchronous signal commonly to two scan driving circuits, and a data drive control circuit for reading out, from the frame memory, data of the video input signal stored in the memory at such a speed as readable by one frame during one period of the converted vertical synchronous signal with respect to each of 2 liquid crystal displays and supplying it to the associated data drive circuit.

Thereby a video signal corresponding to the video input the liquid crystal displays.

## BRIEF DESCRIPTION OF THE DRAWINGS

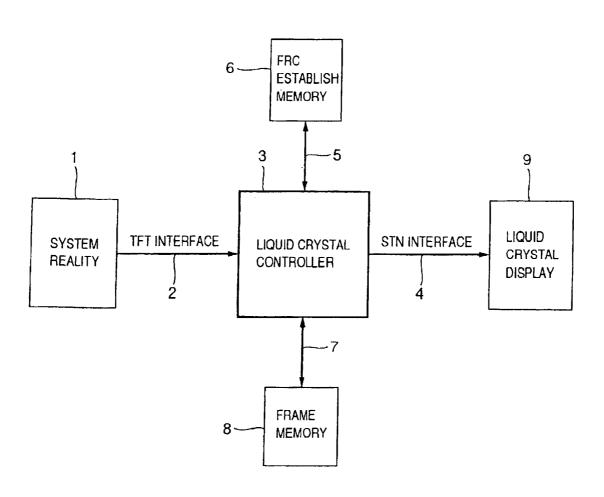

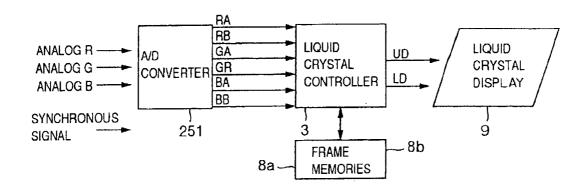

- FIG. 1 is a block diagram of a general liquid crystal display apparatus in accordance with a first embodiment of the present invention;

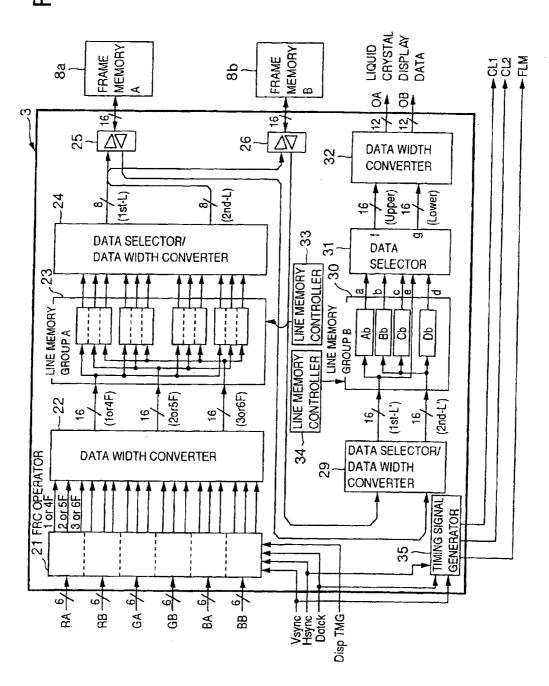

- FIG. 2 is a block diagram of a liquid crystal controller in the embodiment of the present invention;

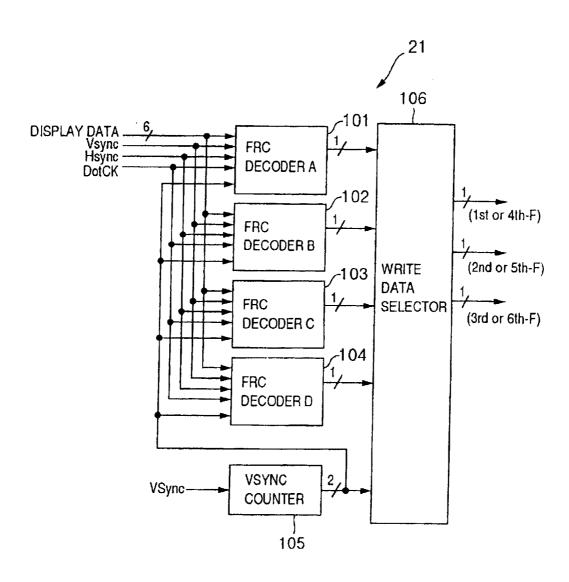

- FIG. 3 schematically shows a block diagram of a circuit used in an FRC operator processor in FIG. 2;

- FIG. 4 schematically shows a block diagram of a circuit used in an FRC decoder in FIG. 3:

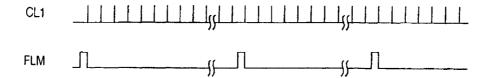

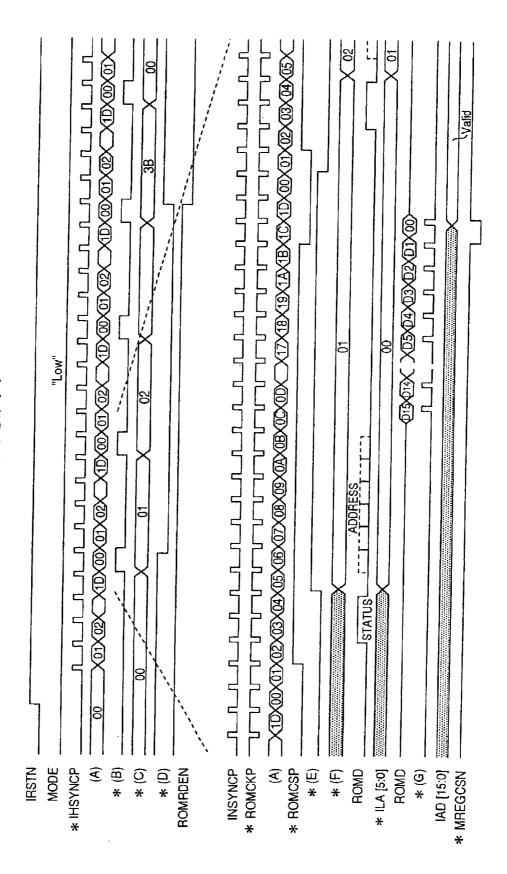

- FIG. 5 is a timing chart for explaining indicate on/off data issued from the FRC decoder of FIG. 4 and read/write control of frame memories in FIG. 2;

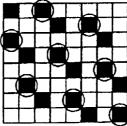

- FIG. 6 is a diagram showing a relationship between indicate on/off data outputted from the FRC decoder of FIG. 4 for more easier understanding of the invention, showing an example of FRC patterns to be displayed on a liquid crystal display;

- FIG. 7 shows FRC patterns constituted by the indicate on/off data generated by the FRC decoder in order to form such FRC patterns as shown in FIG. 6;

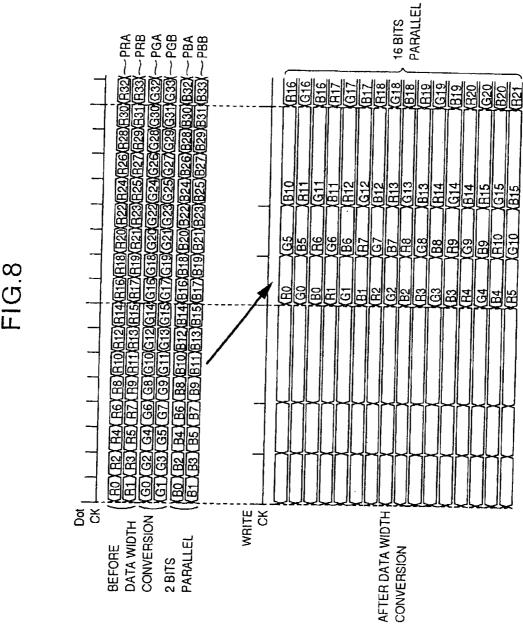

- FIG. 8 is a timing chart for explaining the operation of an indicate data width converter shown in FIG. 2;

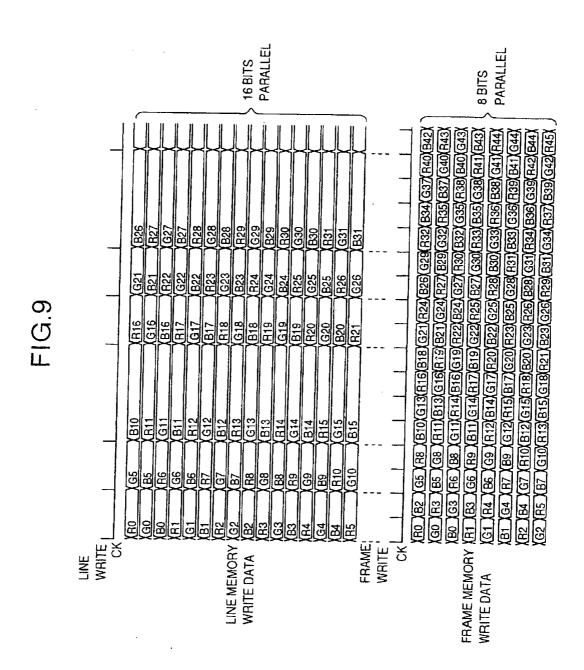

- FIG. 9 is a timing chart for explaining the output bus width converting operation of he indicate on/off data of a data selector/data width converter;

- FIG. 10 is a timing chart for explaining the order re-arranging operation of the indicate on/off data of the data selector/data width converter of FIG. 2;

- FIG. 11 is another timing chart for explaining the order re-arranging operation of the indicate on/off data of the data selector/data width converter of FIG. 2;

- FIGS. 12A and 12B show examples of storage locations of indicate on/off data in the frame memories shown in FIG.

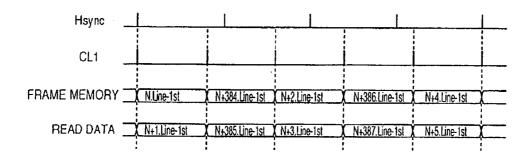

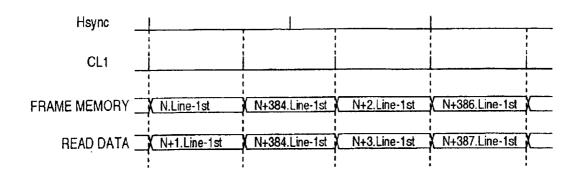

- FIG. 13 is a timing chart showing read timing of the indicate on/off data from the frame memories in FIG. 2, with 55 write and read clocks to and from the frame memories as its

- FIG. 14 is a timing chart showing read timing of the indicate on/off data from either one of the frame memories of FIG. 2, with signals Hsync and CL1 as its time axis;

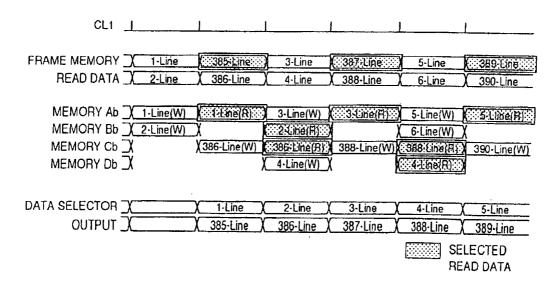

- FIG. 15 is a timing chart showing timing between write and read operation of the indicate on/off data to and from a group of line memories and the indicate on/off data outputted to a data selector shown in FIG. 2;

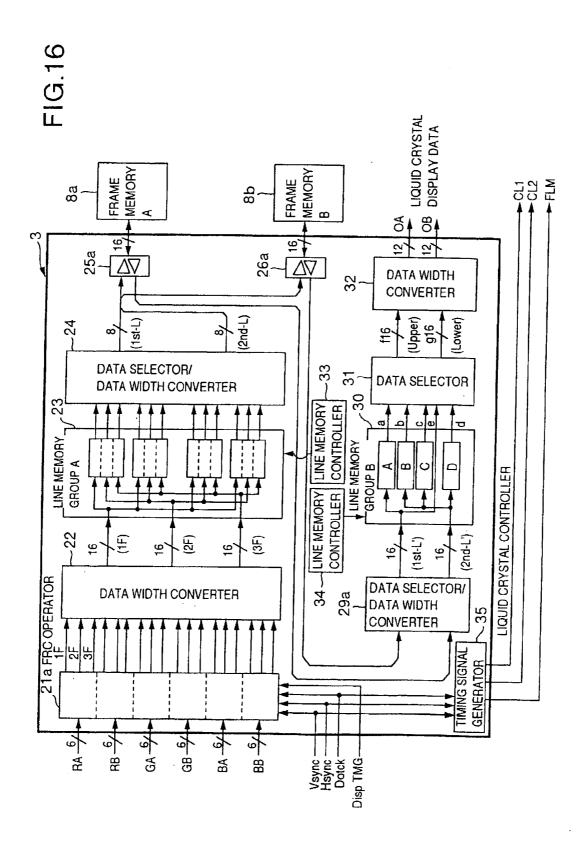

- FIG. 16 is a schematic block diagram of a liquid crystal 65 controller in accordance with a second embodiment of the present invention;

- FIG. 17 is a schematic block diagram of an FRC operator for use in FIG. 16;

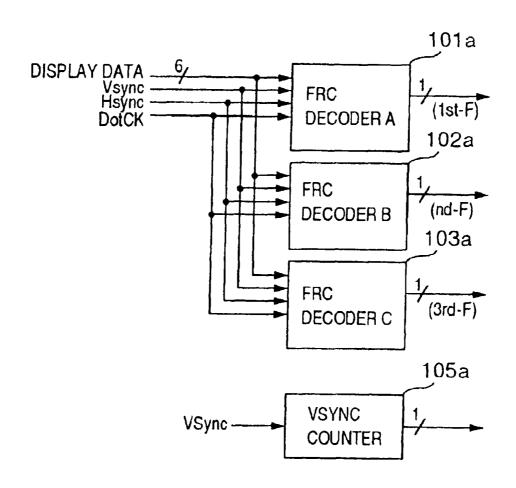

- FIG. 18 is a schematic block diagram of FRC decoders in FIG. 17;

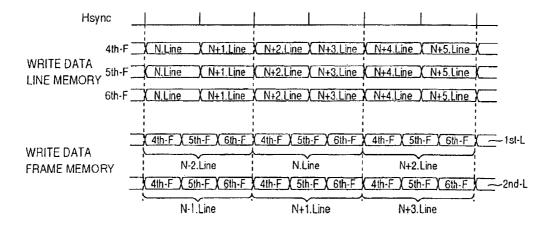

- FIG. 19 is a timing chart for explaining indicate on/off data outputted from the FRC decoders of FIG. 18 and read/write control of frame memories in FIG. 16;

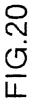

- FIG. 20 is a timing chart showing read timing of indicate on/off data from the frame memories shown in FIG. 16, with write and read clocks of the frame memories as its time axis;

- FIG. 21 is a timing chart showing read timing of indicate on/off data from either one of the frame memories shown in FIG. 16, with read timing signals Hsync and CL1 from either signal but its retrace periods removed can be displayed on 15 one of the frame memories as its time axis as its time axis;

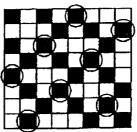

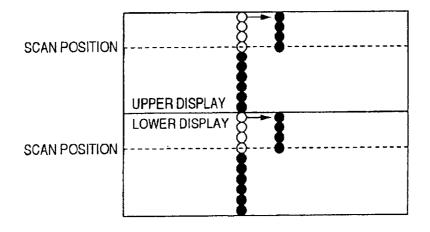

- FIG. 22 is a diagram for explaining interference fringes generated when the FRC patterns are displayed over upper and lower screens of an STN liquid crystal display of a dual scan type under control of a liquid crystal controller;

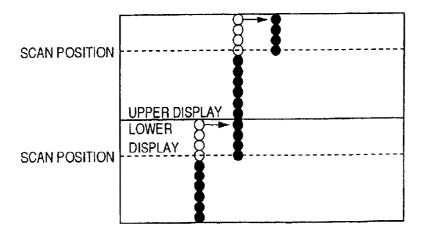

- FIG. 23 is a diagram for explaining changes in FRC patterns in a third embodiment of the present invention;

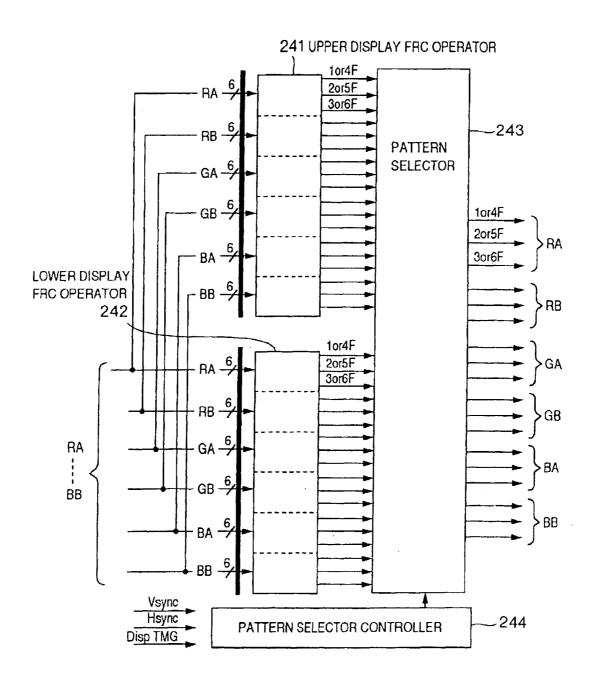

- FIG. 24 is a block diagram of a major structure of the liquid crystal controller in the third embodiment of the present invention;

- FIG. 25 schematically shows an arrangement of a liquid crystal display apparatus in accordance with a fourth embodiment of the present invention;

- FIG. 26 is a diagram for explaining FRC patterns generated in the fourth embodiment of the present invention;

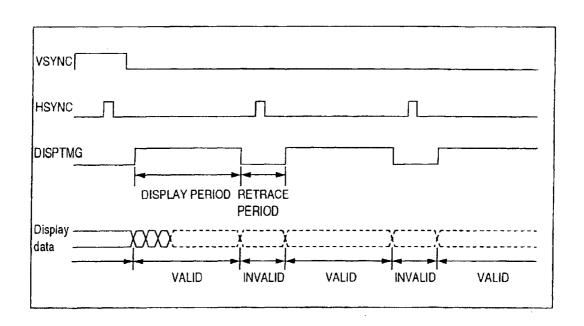

- FIG. 27 is a timing chart for explaining exemplary timing of input signals DotCK, Hsync, Vsync and DispTMG of a liquid crystal controller;

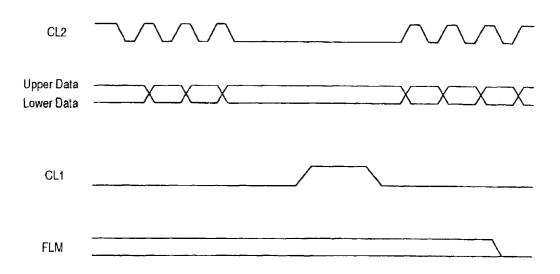

- FIG. 28 is a timing chart for explaining exemplary timing 35 of signals CL2, CL1 and FIM generated in a timing signal generator in FIGS. 2 and 16;

- FIG. 29 is a timing chart for explaining exemplary timing of the signals CL2, CL1 and FLM generated in the timing signal generator in FIGS. 2 and 16;

- FIG. 30 is a diagram for explaining a related art of gray-scale operation of the FRC system;

- FIG. 31 is a schematic block diagram of a liquid crystal controller for explaining its related art;

- FIG. 32 is a schematic block diagram of a liquid crystal controller for explaining its another related art;

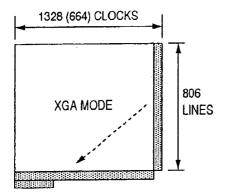

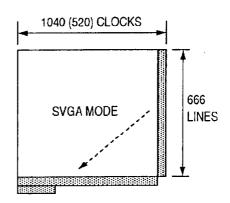

- FIGS. 33A and 33B schematically show a relationship between a total sum of horizontal clocks and a total sum of vertical lines with respect to XGA and SVG mode displays;

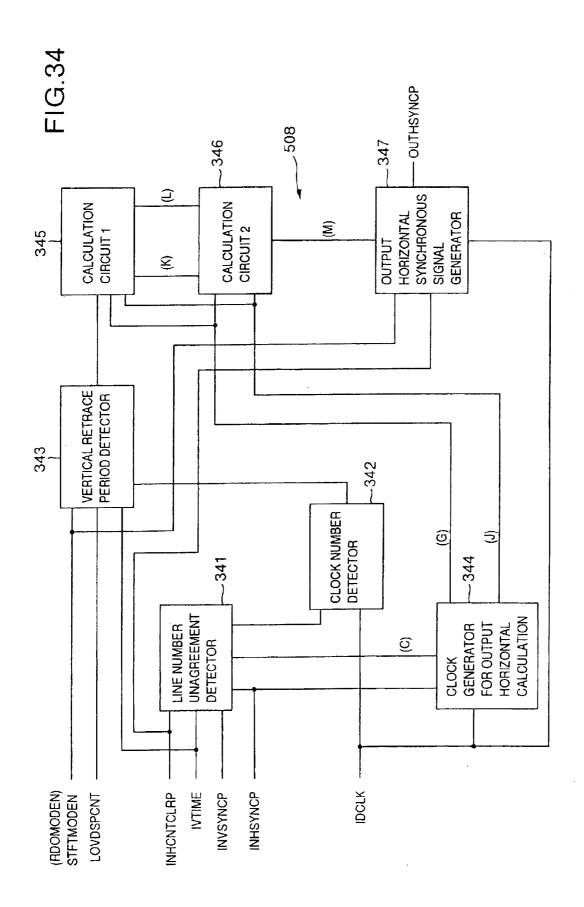

- FIG. 34 schematically shows an arrangement of a horizontal synchronous control circuit;

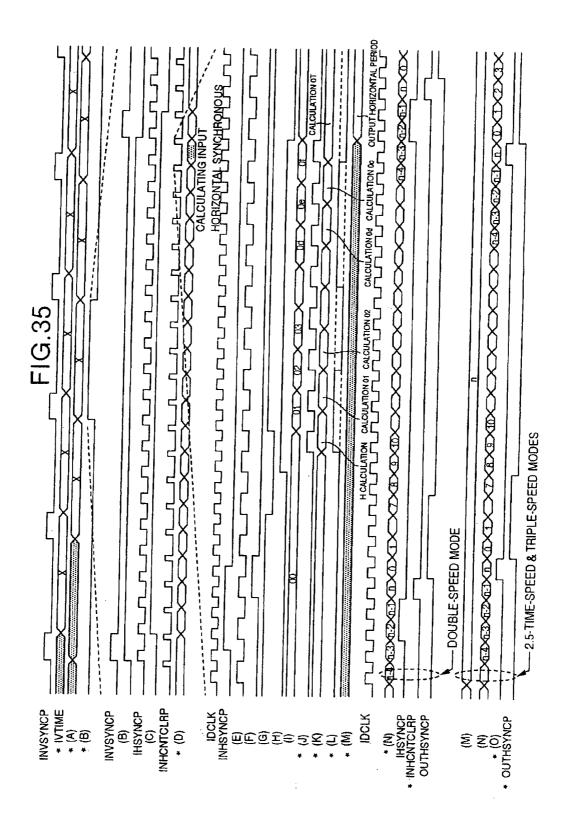

- FIG. 35 is a timing chart of operation of the horizontal synchronous control circuit;

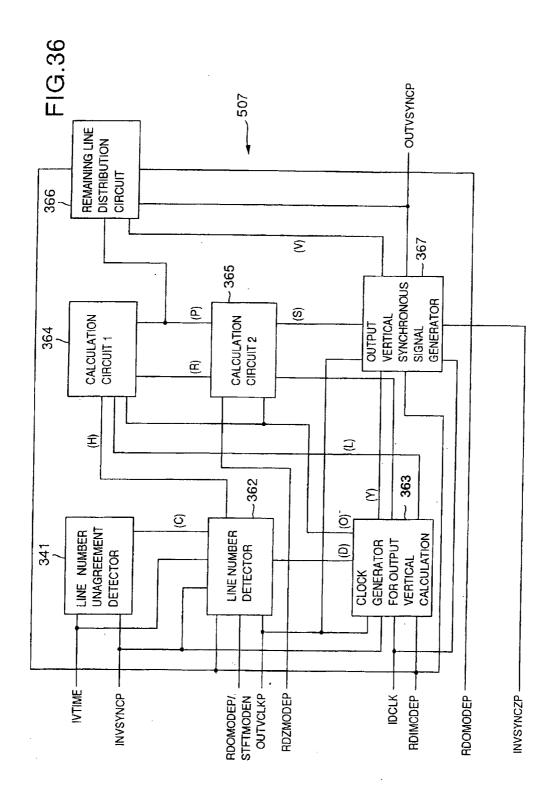

- FIG. 36 schematically shows an arrangement of a vertical synchronous control circuit;

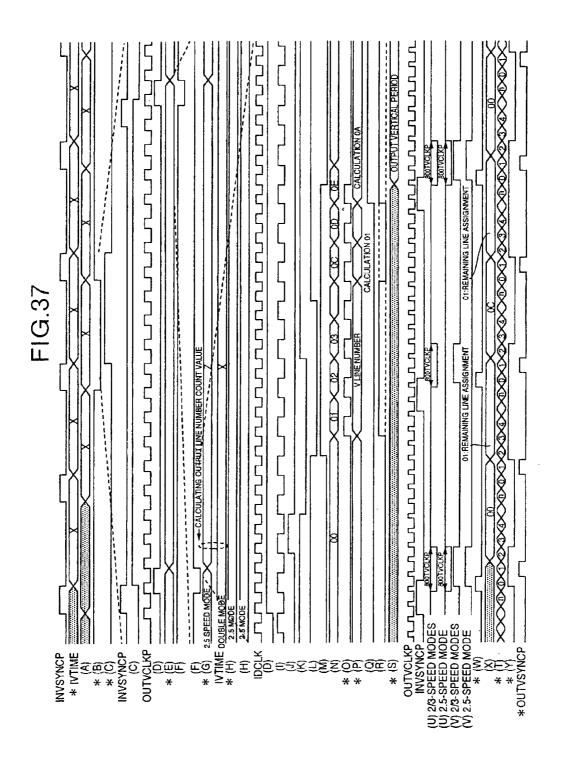

- FIG. 37 is a timing chart of operation of the vertical synchronous control circuit in its double-speed mode;

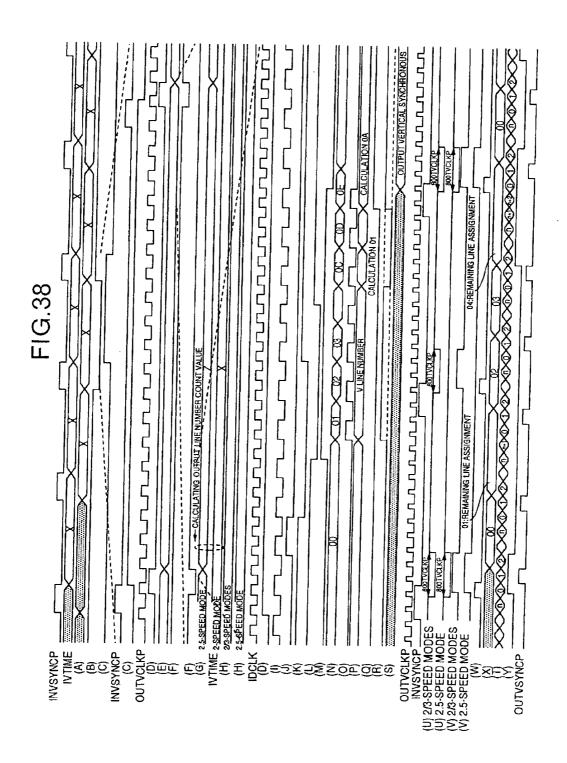

- FIG. 38 is a timing chart of operation of the vertical synchronous control circuit in its 2.5-time-speed mode;

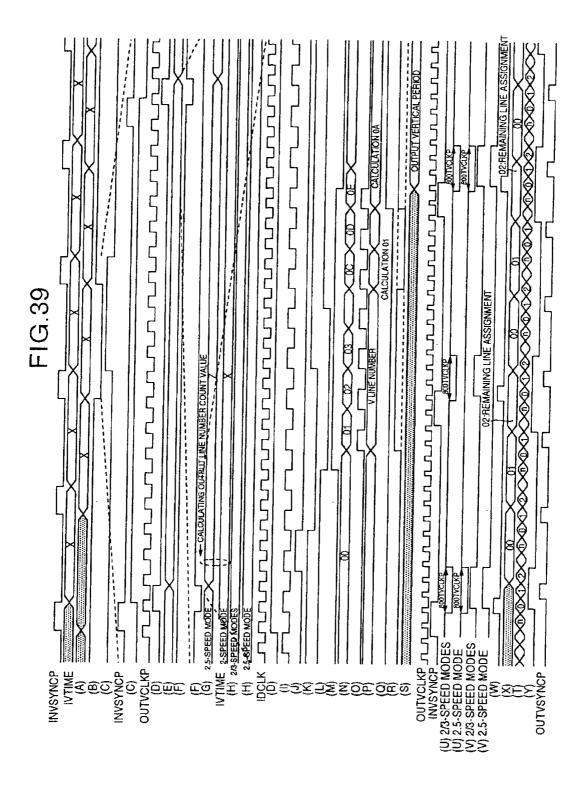

- FIG. 39 is a timing chart of operation of the vertical synchronous control circuit in its triple-speed mode;

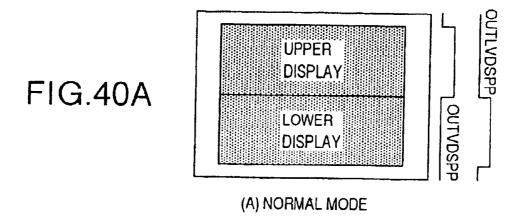

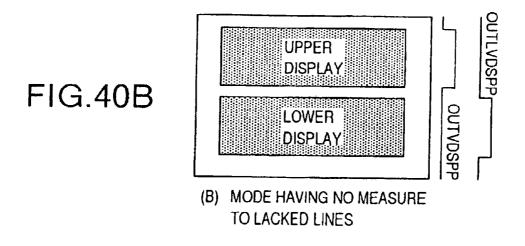

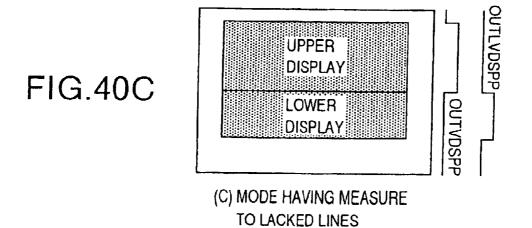

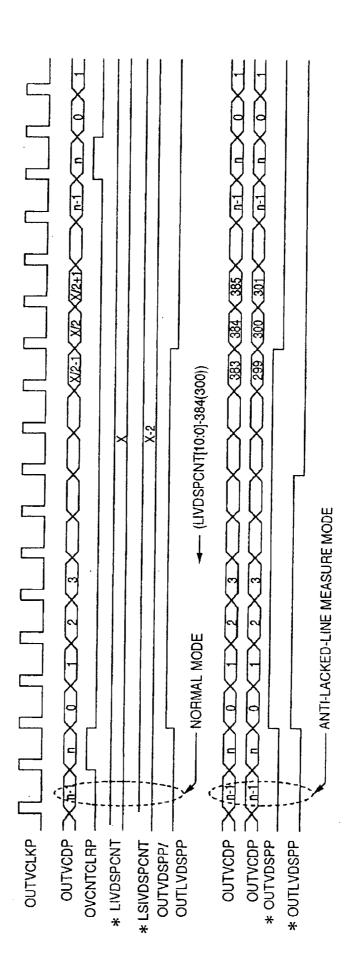

- FIGS. 40A, 40B and 40C are display images of an input video signal on a liquid panel of a passive matrix type with respect to the number of display lines;

- FIG. 41 is a schematic configuration of an upper/lower display separation prevention control circuit;

FIG. 42 is a timing chart of operation of a display division control circuit;

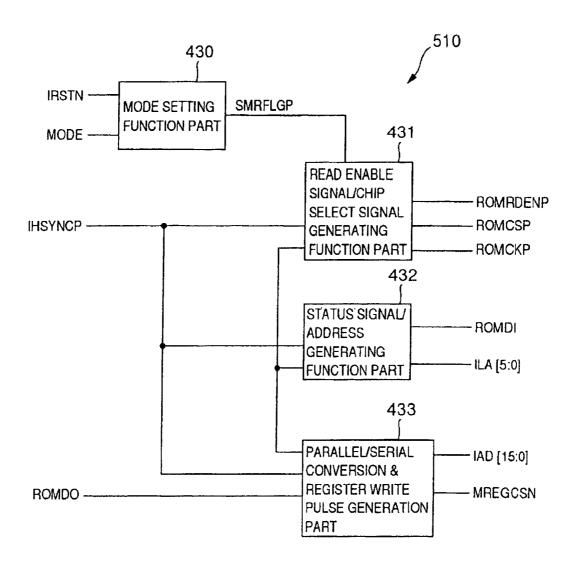

FIG. 43 schematically shows a configuration of a serial memory control circuit for setting of an FRC controller register;

FIG. 44 is a timing chart of operation of the serial memory control circuit of the FRC controller register;

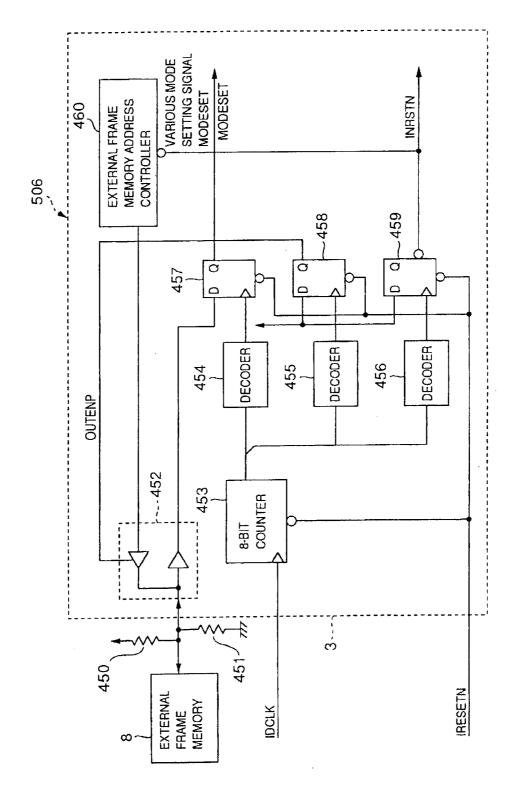

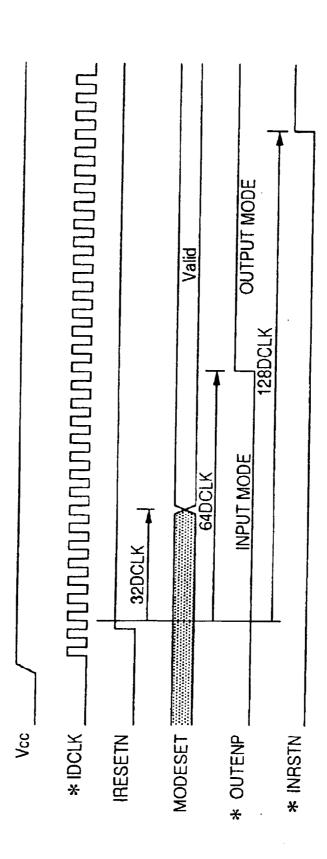

FIG. 45 is a schematic configuration of an LSI-mode setting function control circuit;

FIG. 46 is a timing chart of operation of the LSI-mode setting function control circuit;

FIG. 47 is a general arrangement of another embodiment of the present invention; and

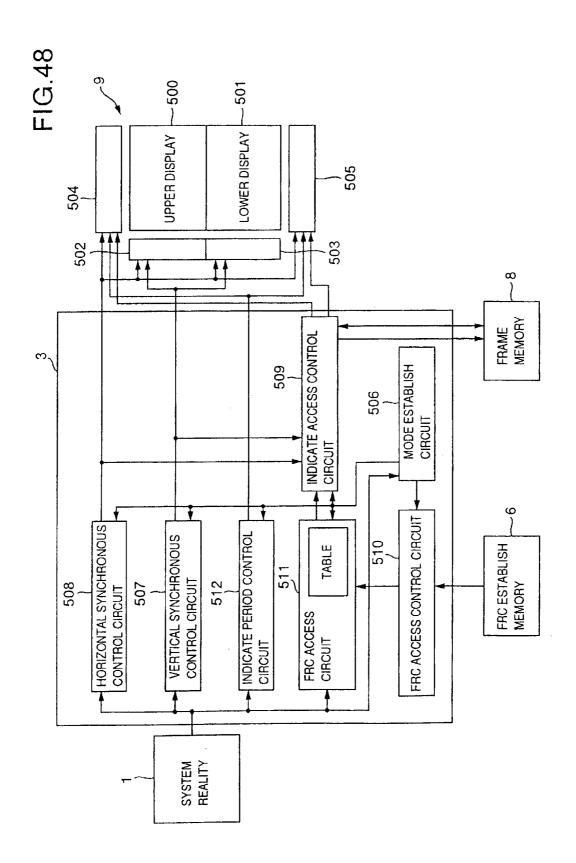

FIG. 48 is a schematic arrangement of a liquid crystal 15 display system.

# DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Embodiments of the present invention will be described  $^{20}$ with reference to the accompanying drawings.

FIG. 1 is a block diagram of a liquid crystal display system in accordance with the present invention. The illustrated liquid crystal display system enhances its image quality by converting a digital video signal 2 of an active 25 matrix type to show it on a super twisted nematic (STN) liquid crystal display 9 of 2-reflection composition type. More specifically, the image quality is improved by setting a frame rate (repetition rate of display corresponding to one display screen) in a display mode to be twice that of the digital video signal 2 or more.

Referring to FIG. 1, reference numeral 1 denotes a system reality, numeral 3 denotes an STN liquid crystal controller control (FRC) establish memory for storing therein grayscale data for gray-scale control, 8 denotes a frame memory for storing therein indicate data included in the digital video signal, and 9 denotes a liquid panel of a 2 reflection composition type (of upper and lower reflections).

The above constituent elements other than the system reality 1 constitutes a liquid crystal display control apparatus. Of these elements, the STN liquid crystal controller 3 is implemented in the form of a one-chip large scale integrated circuit (LSI). The FRC establish memory 6 is implemented in the form of a flash memory. Of course, the above constituent elements including the system reality 1 may be disposed within a single casing.

The system reality 1 outputs the TFT digital video signal 2 of an active matrix type. Also contained in the TFT digital 50 video signal 2 is, in addition to the indicate data, an input synchronous signals (vertical synchronous signal, horizontal synchronous signal and data synchronous signal.

The STN liquid crystal controller 3 inputs the TFT digital video signal 2, converts it to a digital video signal 4 55 conforming to the liquid panel or display 9 of the 2 reflection composition type, and outputs it. The digital video signal 4 contains output synchronous signals (vertical synchronous signal, horizontal synchronous signal and data synchronous signal) as well as indicate data and an indicate period signal 60 compatible with the respective reflections of the liquid crystal display 9. The STN liquid crystal controller 3 can display, as shown in FIG. 33 (to be explained later), both a video signal (1024×768 pixels) of an extended graphics array (XGA) mode and a video signal (800×600 pixels) of 65 a super video graphics array (SVGA), as the TFT digital video signal 2.

Shown in FIG. 2 is a schematic block diagram of the liquid crystal controller 3 in the first embodiment of the present invention.

The STN liquid crystal controller 3 shown in FIG. 2 is designed for such a super twisted nematic (STN) liquid crystal display of a passive matrix display, dual scan type wherein a pixel is positioned at each of intersections between scan and data electrodes perpendicular to each other, the light transmission factor of the pixel varies with a mean square of differences between voltages applied to the scan and data electrodes, a display screen is divided into upper and lower screens to be driven at the same time. It is assumed that the display screen is of an extended graphics array (XGA) type having a resolution of 1024×768 dots.

In FIG. 2, reference numeral 21 denotes an FRC operator for performing intermediate gray-scale operation based on the FRC system, 22 and 32 data width converters, 23 and 30 groups of line memories, 24 and 29 data selector/data width converters, 25 and 26 frame memory read/write controllers, 8a and 8b frame memories for conversion of drive frame frequency, 31 a data selector, 33 and 34 line memory controllers, 35 a timing signal generator.

In FIG. 2, reference symbols RA and RB denote red (R) gray-scale data of 6 bits per pixel, GA and GB denote green (G) gray-scale data of 6 bits per pixel, and BA and BB denote blue (B) gray-scale data of 6 bits per pixel. It is assumed here that RA, GA and BA indicate gray-scale data of the respective colors with respect to the odd-numbered pixels, while RB, GB and GB indicate gray-scale data of the respective colors with respect to the even-numbered pixels. In this connection, in FIG. 2, output signals of the respective circuits are illustrated to have 6, 16, 8 and 12 bits.

Reference symbol DotCK denotes a synchronous signal for converting a digital video signal, 6 denotes a frame rate 35 synchronized with the gray-scale data, Hsync denotes a horizontal synchronous signal indicative of a change-over of the horizontal period, Vsync denotes a vertical synchronous signal (frame period signal) indicative of a change-over of the vertical (frame) period, and DispTMG denotes a signal DispTMG indicative of an effective indicate period.

> Reference symbol OA denotes liquid crystal display data of 12 bits in parallel associated with the upper display screen of the liquid crystal display 9, while symbol OB denotes liquid crystal display data of 12 bits in parallel associated with the lower display screen of the liquid crystal display 9.

> Reference symbol CL2 denotes a synchronous signal CL2 synchronized with the liquid crystal display data, CL1 denotes a horizontal synchronous signal indicative of a change-over of the horizontal period, and FLM denotes a frame period signal (vertical synchronous signal) indicative of a change-over of the frame period (vertical period).

> In the present embodiment, the frequency of the frame period signal FLM to be output to the liquid crystal display 9 is set to be 2.5 times the frequency of the frame period signal Vsync of the input signals. Accordingly, 5 frame periods in the output signal are completed with 2 frame periods in the input signal.

> In the present embodiment, access control to the frame memories 8a and 8b is carried out with 2 frame periods of the input signal as a unit.

The respective parts of FIG. 2 will be explained in detail. Explanation will first be made as to the timing signal generator 35.

The timing signal generator 35, on the basis of the synchronous signals DotCK, Hsync, Vsync and DispTMG applied to the liquid crystal controller 3, generates the

signals FLM, CL1, CL2 and other control signals (such as read/write clocks).

In this connection, the signals DotCK, Hsync, Vsync and DispTMG as the input signals of the STN liquid crystal controller 3 may have timing as that of signals shown in Hitachi LCD controller/driver LSI data book, p. 1001, published by Hitachi Ltd. as shown in FIG. 27.

Further, the signals CL2, CL1 and FLM generated by the timing signal generator 35 may have timing as that of signals CL2, CL1 and FLM shown in the same data book as the above, p. 1028. The timing signal generator 35 will be explained later in more detail.

Explanation will next be made as to the FRC operator 21.

The FRC operator **21** generates 3 types of indicate on/off data per pixel for the gray-scale data RA, RB, GA, GB, BA and BB. This causes the indicate on/off data corresponding, to 3 frames of the video output signal, i.e., 3 FRC patterns to be generated from the gray-scale data corresponding one frame of the video input signal.

The FRC operator 21 has FRC processing circuits provided as associated with the respective gray-scale data RA, RB, GA, GB, BA and BB.

Each of the FRC processing circuits generates 3 types of indicate on/off data per pixel for the associated gray-scale <sup>25</sup> data.

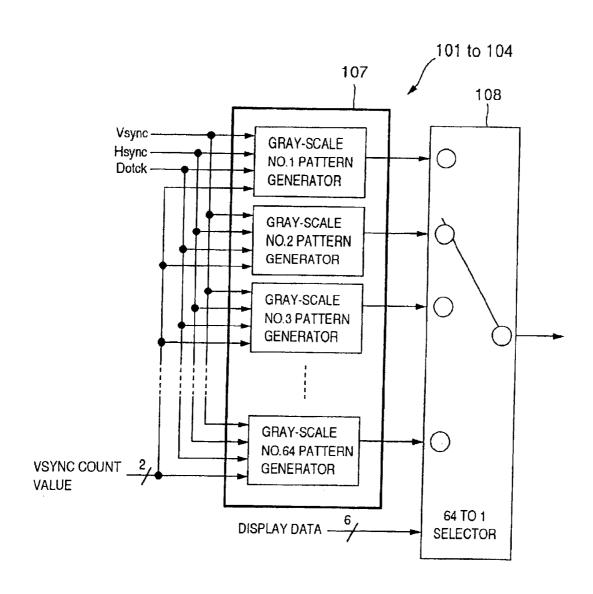

FIG. 3 is a schematic block diagram of FRC processing circuits or decoders 101 to 104.

Reference numeral 105 denotes a Vsync counter and numeral 106 denotes a write data selector.

The Vsync counter 105 counts the vertical synchronous signal Vsync and outputs a Vsync count value of 2 bits. Thus Vsync count value can take a value of 0 to 3.

The FRC decoders 101 to 104, with respect to the input 35 gray-scale data of a pixel, generate indicate on/off data associated with the value of the gray-scale data.

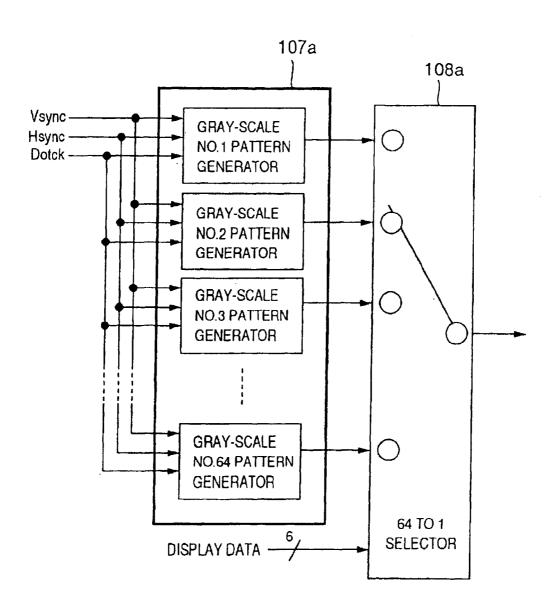

Shown in FIG. 4 is a schematic block diagram of other FRC decoders 101 to 104.

The FRC decoders 101 to 104 include an FRC pattern generator 107 for generating indicate on/off data for generation of 64 types of FRC patterns associated with bits (6 bits) of the gray-scale data per pixel, and a selector 108 for selecting one of the 64 types of indicate on/off data generated by the FRC pattern generator 107.

Explanation will be directed to a relationship between the indicate on/off data generated by the FRC decoders 101 to 104

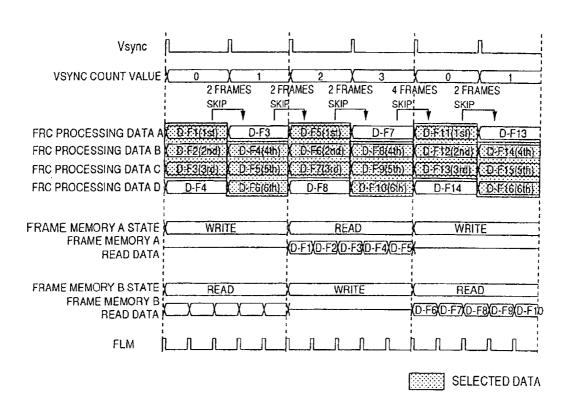

FIG. 5 is a timing chart for explaining the output indicate on/off data of the FRC decoders 101 to 104 as well as read/write control of the frame memories 8a and 8b.

Referring to FIG. 5, FRC processing data A is illustrated therein as the indicate on/off data issued from the FRC decoder 101, FRC processing data B is as the indicate on/off data issued from the FRC decoder 102, FRC processing data C is as the indicate on/off data issued from the FRC decoder 103, and FRC processing data D is as the indicate on/off data issued from the FRC decoder 104. A plurality of D-FNs (N being an integer) mean indicate on/off data of the FRC pattern to be output at the N-th frame.

As shown in FIG. 5, assuming that the indicate on/off data generated by the FRC decoder 101 form an FRC pattern to be output at the N-th frame, then the FRC decoder 102 generates indicate on/off data for formation of an FRC 65 pattern to be output at the (N+1)-th frame, the FRC decoder 103 generates indicate on/off data for formation of an FRC

10

pattern to be output at the (N+2)-th frame, and the FRC decoder 104 generates indicate on/off data for formation of an FRC pattern to be output at the (N+3)-th frame.

As shown in FIG. 3, further, the FRC decoders 101 to 104 generates indicate on/off data for formation of an FRC pattern to be output at a frame previous by 2 frames each time the Vsync count value issued from the Vsync counter 105 is incremented by 1; and generates indicate on/off data for formation of an FRC pattern to be output at a frame previous by 4 frames each time the Vsync count value is reset, i.e., is switched from "3" to "0".

The present embodiment is designed to FRC patterns corresponding in number to the number of frames (Vsync) included in one period (sometimes referred to as the FRC period) of the FRC operation.

This is realized, for example, when 10 frames are included in the FRC period, by setting the FRC decoders 101 to 104 in such a manner as to be explained below.

That is, the 64 types of gray-scale pattern generators of the FRC pattern generator 107 (see FIG. 4) of the FRC decoder 101 corresponding in number to the gray-scale data bits are set to generate, according to the Vsync count value, indicate on/off data for formation of FRC patterns to be output at the first (Vsync count value=0), third (Vsync count value=1), fifth (Vsync count value=2) and seventh (Vsync count value=3) ones of frames included in the FRC period, with respect to pixels specified by the signals Vsync, Hsync and DotCK applied to the FRC decoder 101.

The 64 types of gray-scale pattern generators of the FRC pattern generator 107 (see FIG. 4) of the FRC decoder 102 corresponding in number to the gray-scale data bits are set to generate, according to the Vsync count value, indicate on/off data for formation of FRC patterns to be output at the second (Vsync count value=0), fourth (Vsync count value=1), sixth (Vsync count value=2) and eighth (Vsync count value=3) ones of frames included in the FRC period, with respect to pixels specified by the signals Vsync, Hsync and DotCK applied to the FRC decoder 101.

The 64 types of gray-scale pattern generators of the FRC pattern generator 107 (see FIG. 4) of the FRC decoder 103 corresponding in number to the gray-scale data bits are set to generate, according to the Vsync count value, indicate on/off data for formation of FRC patterns to be output at the third (Vsync count value=0), fifth (Vsync count value=1), seventh (Vsync count value=2) and ninth (Vsync count value=3) ones of frames included in the FRC period, with respect to pixels specified by the signals Vsync, Hsync and DotCK applied to the FRC decoder 101.

The 64 types of gray-scale pattern generators of the FRC pattern generator 107 (see FIG. 4) of the FRC decoder 104 corresponding in number to the gray-scale data bits are set to generate, according to the Vsync count value, indicate on/off data for formation of FRC patterns to be output at the fourth (Vsync count value=0), sixth (Vsync count value=1), eighth (Vsync count value=2) and tenth (Vsync count value=3) ones of frames included in the FRC period, with respect to pixels specified by the signals Vsync, Hsync and DotCK applied to the FRC decoder 101.

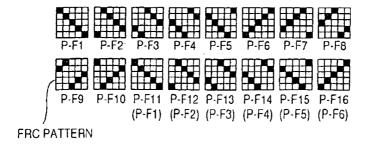

For more understanding of the relationship between the indicate on/off data issued from the FRC decoders 101 to 104, consider a case that gray-scale data of pixels of the display screen form such matrix-like FRC patterns as shown in FIG. 6.

In the drawing, a plurality of P-FNs denote the FRC patterns to be output at the N-th frame.

The FRC patterns shown in FIG. 6 are arranged to be switched on a frame basis with use of 10 frames as one FRC

period. Accordingly, the FRC patterns shown by P-F11 to P-F16 are the same as the FRC patterns shown by P-F1 to P-F6

In this case, the FRC decoders 101 to 104 (see FIG. 3) are set to generate indicate on/off data for formation of such 5 FRC patterns as shown in FIG. 7, with respect to input pixels.

As shown in FIG. 7, the FRC pattern A is made up of indicate on/off data issued from the FRC decoder 101, the FRC pattern B is made up of indicate on/off data issued from 10 the FRC decoder 102, the FRC pattern C is made up of indicate on/off data issued from the FRC decoder 103, and the FRC pattern D is made up of indicate on/off data issued from the FRC decoder 104.

Turning back to FIG. 3, explanation will be continued.

The write data selector **106**, according to the Vsync count value issued from the Vsync counter **105**, selects indicate on/off data corresponding to 3 of 4 FRC patterns issued from the FRC decoders **101** to **104**.

More in detail, as shown in FIG. 5, when the Vsync count value is even ("0" or "2"), the write data selector **106** selects the indicate on/off data (which form the first FRC pattern denoted by D-F1 (1st)) issued from the FRC decoder **101**, selects the indicate on/off data (which form the second FRC pattern denoted by D-F2 (2nd)) issued from the FRC <sup>25</sup> decoder **102**, and selects the indicate on/off data (which form the first FRC pattern denoted by D-F3 (3rd)) issued from the FRC decoder **103**.

When the Vsync count value is odd ("1" or "3"), on the other hand, the write data selector 106 selects the indicate on/off data (which form the fourth FRC pattern denoted by D-F4 (4th)) issued from the FRC decoder 102, selects the indicate on/off data (which form the fifth FRC pattern denoted by D-F5 (5th)) issued from the FRC decoder 103, and selects the indicate on/off data (which form the sixth FRC pattern denoted by D-F6 (6th)) issued from the FRC decoder 104. The respective indicate on/off data will be also denoted by 1st to 6th.

As has been mentioned above, FRC operator 21 (refer to FIG. 2) in the present embodiment has such FRC processing circuits as shown in FIG. 3, with respect to the respective gray-scale data (RA, RB, GA, GB, BA, BB) applied to the liquid crystal controller 3.

Therefore, with respect to the respective gray-scale data (RA, RB, GA, GB, BA, BB), the FRC operator 21 can generate indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) corresponding to 3 frames on the basis of gray-scale data corresponding to one frame.

More specifically, within one frame period, the indicate on/off data of 3 types of FRC patterns are output in 2-bit parallel, for each color R, G or B.

Explanation will then be made as to the data width converter 22.

The data width converter **22** converts 3 types of indicate 55 on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) of 2-bit parallel issued from the FRC operator **21** for each color R, G or B into indicate on/off data of 16-bit parallel.

FIG. 8 shows a timing chart for explaining the operation of the data width converter 22 shown in FIG. 2.

Reference symbol PRA denotes indicate on/off data corresponding to the gray-scale data RA, symbol PGA denotes indicate on/off data corresponding to the gray-scale data GA, PGB denotes indicate on/off data corresponding to the gray-scale data GB, PBA denotes indicate on/off data corresponding to the gray-scale data BA, PBB denotes indicate on/off data corresponding to the gray-scale data BB.

12

Further, symbols RN, GN and BN (N being integer) denote indicate on/off data corresponding to the gray-scale data of the N-th pixel.

In FIG. 8, for the convenience of explanation, only any one of the 3 types of indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) of 2-bit parallel issued for each color R, G or B will be illustrated as processed.

The data width converter 22 rearranges the indicate on/off data of the respective colors issued from the FRC operator 21 in such a manner that the pixels are in order and the colors in the pixels are in the order of R, G and B, e.g., in such an order as R0, G0, B0, R1, G1, B1, R2, ..., as shown in FIG. 8. And the data width converter 22 outputs a plurality of pieces of data (corresponding to 16 data in the illustrated example) on a parallel basis.

Such operation as mentioned above can be realized, for example, by using a plurality of buffers or the like and controlling writing and reading operations of the indicate on/off data to and from the buffers.

Next the line memory group 23 and line memory controller 33 will be explained.

The line memory group 23 is arranged as shown in FIG. 2, so that a plurality of line memories having a 16-bit bus width are connected in parallel.

The line memory controller 33 writes therein the 3 types of indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) of 16-bit parallel issued from the data width converter 22 sequentially by an amount corresponding to every 2 lines, and reads out it after a time corresponding to twice that of the write signal Hsync.

In this case, a read clock from the line memory group 23 is controlled to be faster than a write clock to the line memories.

Explanation will next be made as to the data selector/data width converter 24.

FIG. 9 is a timing chart for explaining the indicate on/off data output bus width converting operation of the data selector/data width converter 24, and FIGS. 10 and 11 are timing charts for explaining the indicate on/off data order rearranging operation of the data selector/data width converter 24.

The data selector/data width converter 24, as shown in FIG. 9, converts the indicate on/off data of 16-bit parallel read out from the line memory group 23 to indicate on/off data of 8-bit parallel.

In the present embodiment, as mentioned above, the line memory controller 33 controls the line memory group 23 in such a manner that the read clock of the indicate on/off data from the line memory group 23 is faster than the write clock into the line memory group 23.

As a result, as shown in FIG. 9, the transmission rate of indicate on/off data subjected to the data width conversion by the data selector/data width converter 24 is set to be 4/3 times the transmission rate of the indicate on/off data applied to the line memory group 23.

Illustrated in FIG. 9, for the convenience of explanation, is the operation of only the indicate on/off data of any one of the 3 types of indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) read out on a 2-line basis from the line memory group 23.

The data selector/data width converter 24, as shown in FIGS. 10 and 11, reads out the indicate on/off data from the line memory group 23 on every 2-line basis, rearranges the order of the 3 types of indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) having a data width converted to 8-bit parallel,

and then converts them to indicate even-number-th lines of on/off data 1st-L and odd-number-th lines of indicate on-off data 2nd-L. And the data selector/data width converter 24 outputs the converted indicate on/off data during a period corresponding to twice that of the signal Hsync.

FIG. 10 shows an example when 3 types of indicate on/off data read out from the line memory group 23 on every 2-line basis are 1st, 2nd and 3rd indicate on/off data, are converted to even-numbered lines of indicate on/off data 1st-L and odd-number-th lines of indicate on-off data 2nd-L, and then output during a next period corresponding to twice that of the horizontal synchronous signal Hsync.

FIG. 11 shows an example when 3 types of indicate on/off data read out from the line memory group 23 on every 2-line basis are 4th, 5th and 6th indicate on/off data, are converted 15 to even-numbered lines of indicate on/off data 1st-L and odd-number-th lines of indicate on-off data 2nd-L, and then output during a next period corresponding to twice that of the horizontal synchronous signal Hsync.

As shown in FIGS. 10 and 11, the transmission rate of the <sup>20</sup> indicate on/off data 1st-L and 2nd-L issued from the data selector/data width converter 24 are 3/2 times the transmission rate of the indicate on/off data applied to the line memory group 23.

That is, the transmission rate of the indicate on/off data <sup>25</sup> applied to the line memory group **23** shown in FIG. **9** is faster than 4/3 times of the transmission rate of the indicate on/off data subjected to the data width conversion.

This is because so-called horizontal retrace (blanking) periods as periods other than non-transmission periods of input effective indicate data are intended to be present.

For example, in the case where a liquid crystal display is of a so-called extended graphics array (XGA) type wherein the display has a screen resolution of  $1024 \times 768$  dots, a horizontal retrace period corresponding to 64 or more signals DotCK is set to be provided in the input signals, while no horizontal retrace period is to be provided in write data to the frame memories 8a and 8b.

In this case, there is satisfied a relationship which follows.  $_{40}$

(512+horizontal retrace period of 64 dots)×2×signal Hsync×4/  $3\!\ge\!512\times3\times$  signal Hsync

In this case, **512** is obtained by dividing the number 1024 of clocks in the signal Dot during the signal Hsync by the number 2 of bits of the indicate on/off data. Meanwhile 4/3 45 indicates a ratio of the transmission rate of the indicate on/off data applied to the line memory group **23** with respect to the transmission rate of the indicate on/off data subjected to the data width conversion.

It will be seen from the above relationship that 3 lines of 50 indicate on/off data can be read out during a period corresponding to twice that of the signal Hsync.

Explanation will next be made as to the frame memory controllers 25 and 26.

The frame memory controllers 25 and 26 perform alter- 55 nate switching between the read and write operations from and to the frame memories 8a and 8b on every unit time basis of twice the period of the signal Vsync.

More concretely, as shown in FIG. 5, the frame memory 8a is controlled to be put in its write state and the frame 60 memory 8b is controlled to be put in its read state when the Vsync count value is "0" or "1"; whereas, the frame memory 8a is controlled to be put in its read state and the frame memory 8b is controlled to be put in its write state when the Vsync count value is "2" or "3".

As has been explained above, the data selector/data width converter 24, as shown in FIGS. 10 and 11, rearranges the

14

order of 3 types of indicate on/off data (1st, 2nd, 3rd or 4th, 5th, 6th) of 8-bit parallel, converts them to even-number-th lines of indicate on/off data 1st-L and odd-number-th lines of indicate on/off data 2nd-L, and then outputs the even-number-th lines of indicate on/off data 1-st-L and the odd-number-th lines of indicate on/off data 2nd-L during a period corresponding to twice the period of the signal Hsync.

Accordingly, even-number-th lines of indicate on/off data 1-st-L of 8-bit parallel and odd-number-th lines of indicate on/off data 2nd-L of 8-bit parallel are written into the frame memory 8a when the Vsync count value is "0" or "1", and are written into the frame memory 8b when the Vsync count value is "2" or "3".

This results in that indicate on/off data corresponding to 6 frames are written into the frame memories 8a and 8b during a period corresponding to twice that of the signal Vsync.

Shown in FIGS. 12A and 12B is an example of storage locations of the indicate on/off data in the frame memories 8a and 8b.

As has been explained above, in the present embodiment, the liquid crystal controller 3 is supposed to be used for the STN liquid crystal display 9 of a so called dual scan type wherein upper and lower divisions of a display screen are driven at the same time.

In the example of FIGS. 12A and 12B, the indicate on/off data of pixels forming the display screen are stored in the frame memories 8a and 8b as divided into two pieces of data for the upper and lower display screens.

With respect to the upper and lower display screens, the indicate on/off data are stored on a frame basis. In FIGS. 12A and 12B, for example, '1st' denotes a group of indicate on/off data forming the first display frame, and '2nd' denotes a group of indicate on/off data forming the second display frame.

Such allocation of storage locations to the frame memories 8a and 8b can be realized by referring to the signals Vsync and Hsync.

Usable as the frame memories **8***a* and **8***b* is, for example, HM5216165 (manufactured by Hitachi Ltd. and explained in a book entitled "IC memory data book", pp. 1023-1071).

The data selector/data width converter  $\overline{29}$  will next be explained.

The data selector/data width converter 29 adjusts read timing of the indicate on/off data from the frame memories 8a and 8b so that the indicate on/off data can be transmitted at a transmission rate corresponding to 4/5 times the transmission rate when the indicate on/off data were written into the frame memories 8a and 8b.

FIG. 13 is a timing chart showing the read timing of the indicate on/off data from the frame memories 8a and 8b, with write and read clocks to the frame memories 8a and 8b used as its time axis.

In reality, indicate on/off data of 2 lines (one line being 8-bit parallel) are alternately read from the frame memories 8a and 8b at intervals of a period corresponding to twice the period of the signal Vsync. In the drawing, for easy understanding, however, timing of only indicate on/off data of one line is illustrated.

The data selector/data width converter 29 reads the indicate on/off data of the upper display and the indicate on/off data of the lower display from the frame memories 8a and 8b.

FIG. 14 is a timing chart showing read timing of the indicate on/off data from either one of the frame memories 8a and 8b, with the signals Hsync and CL1 used as its time axis. In the drawing, N+384.LINE and subsequent data indicate the indicate on/off data of lines for the lower display.

In this connection, as has been explained above, indicate on/off data of 6 frames are written in the frame memories 8a and 8b during a period corresponding to twice the period of the signal Vsync by the data selector/data width converter 24. And the indicate on/off data read out during a next period 5 corresponding to twice the period of the signal Vsync by the data selector/data width converter 29 correspond to 5 frames in the timing chart of FIG. 5.

More in detail, as shown in FIG. 5, when the Vsync count value is "0" or "1", frame indicate on/off data are read out 10 from the frame memory 8b in the order of 2nd, 3rd, 4th, 5th and 6th. When the Vsync count value is "2" or "3", frame indicate on/off data are read out from the frame memory 8a in the order of 1st, 2nd, 3rd, 4th and 5th.

horizontal period of the horizontal synchronous signal Hsync and the horizontal period of the horizontal synchronous signal CL1 of liquid crystal output data in the input signals is 5 times the period of the signal CL1 to 4 times the period of the signal Hsync. This is because, as shown in FIG. 20 13, the transmission rate of indicate on/off data read out from the frame memories 8a and 8b is set to be 4/5 times the transmission rate (corresponding to twice the period of the signal Vsync and thus to 6 frames) when the indicate on/off result, the drive frame frequency FLM of liquid crystal output data becomes;

Vsync×5/4×2 (for driving of two upper and lower displays)=2.5

Accordingly, the drive frame frequency to be output to the STN liquid crystal display is 2.5 times the drive frame frequency of the input signal.

Further, the data selector/data width converter 29 converts the data width of the respective indicate on/off data of the 35 upper and lower displays read out alternately from the frame memories 8a and 8b on every 2-line basis, from 8-bit parallel to 16-bit parallel.

In FIG. 2, reference symbol 1st-L' denotes 16-bit parallel indicate on/off data associated with the indicate on/off data 40 of the upper and lower displays read out from the frame memory 8a; reference symbol 2nd-L' denotes 16-bit parallel indicate on/off data associated with the indicate on/off data of the upper and lower displays read out from the frame memory 8b.

Explanation will then be made as to the line memory group 30 and line memory controller 34.

The line memory group 30, as shown in FIG. 2, is made up of line memories Ab to Db of a 16-bit bus width.

The line memory controller **34** controls write and read 50 operations of the 16-bit parallel indicate on/off data 1st-L' and 2nd-L' issued from the data selector/data width con-

Of the 16-bit parallel indicate on/off data 1st-L' and 2nd-L' issued from the data selector/data width converter 29, 55 indicate on/off data corresponding to predetermined lines are passed through the line memory group 30 and then sent to the data selector 31.

FIG. 15 is a timing chart showing write and read operations of indicate on/off data to and from the line memory 60 group 30 as well as timing of indicate on/off data issued to the data selector 31.

As shown in FIG. 15, the data selector/data width converter 29 alternately outputs 2 lines of 16-bit parallel indicate on/off data with respect to the upper and lower displays. 65

The line memory controller 34 controls the write and read operations of 2 lines of 16-bit parallel indicate on/off data 16

sequentially issued from the data selector/data width converter 29 with respect to the line memory group 30, to thereby output the indicate on/off data of lines of the upper and lower displays from any two of output terminals a to e of the line memory group 30 simultaneously.

The aforementioned operation will be explained in detail with use of FIG. 15.

- (1) First of all, the first Line of indicate on/off data 1-Line of the upper display as well as the second Line of indicate on/off data 2-Line of the upper display, simultaneously sent from the data selector/data width converter 29, are written into the respective Line memories Ab and Bb.

- (2) With respect to the 385-th and 386-th Lines of indicate on/off data 385-Line and 386-Line of the lower display, In this case, as shown in FIG. 14, a ratio between the 15 simultaneously sent from the data selector/data width converter 29; the data 385-Line is passed through

the Line memories and output from its output terminal e, while the data 386-Line is written into the Line memory Cb.

Further, the data 1-Line written in the Line memory Ab is read out therefrom and output from the output terminal a, in synchronism with the output of the data 385-Line from the output terminal e.

(3) The 3-rd and 4-th Lines of indicate on/off data 3-Line 4-Line of the upper display simultaneously sent from the data were written in the frame memories 8a and 8b. As a 25 data selector/data width converter 29 are written into the Line memories Ab and Db respectively.

> Simultaneously with the above, the data 2-Line written in the Line memory Bb as well as the data 386-Line written in the line memory Cb are read out therefrom and output simultaneously from the respective output terminals b and c.

> Through the repetition of the operations similar to those of (1) to (3), the indicate on/off data of lines of the upper display as well as the indicate on/off data of lines of the lower display are output at the same time.

> Explanation will next be made as to the data selector 31. The data selector 31 controls, as shown in FIG. 2, the indicate on/off data of lines of the upper and lower displays simultaneously issued from any two of the output terminals a to e of the line memory group 30 in such a manner that the indicate on/off data of lines of the upper display is output from the output terminal f and the indicate on/off data of lines of the lower display is output from the output terminal

The data width converter 32 will then be explained.

The data width converter 32 converts the data width of the indicate on/off data of lines of the upper and lower displays issued from the data selector 31, to 12-bit parallel data for the liquid crystal display 9, respectively.

The 12-bit parallel data (24 bits in total) of the upper and lower displays are output to the liquid crystal display 9, together with the signals CL1, CL2 and FLM generated in the timing signal generator 35.

In this embodiment of the present invention, indicate on/off data of 6 frames of the output signal are written in the frame memories 8a and 8b during a period corresponding to twice the period of the signal Vsync, and the 6 frames of indicate on/off data written therein are sequentially read out therefrom in synchronism with the frame period FLM of the output signal.

In this manner, the data written in the frame memories 8a and 8b are one bit of indicate on/off data subjected to the FRC operation, whereby the data bus width at the time of accessing the frame memories can be reduced to 16 lines per one frame memory.

Since 3 frames of indicate on/off data are sequentially written within one-frame period of the input signal, the FRC patterns can be switched for every frame period FLM of the

output signal having a frame frequency corresponding to 2.5 times the input frame frequency.

Therefore, the object of the present invention, that is, the reduction of flow of the intermediate gray-scale display portion and increase in the number of pins caused by 5 formation of it in the form of an LSI can be suppressed.

Further, when one frame period in the input signal is used as a unit, the total number of bits in the data written in the frame memories 8a and 8b becomes (number of pixels of one frame)×(3 frames)×(one bit).

Meanwhile, when 6-bit gray-scale data are written directly into the frame memories 8a and 8b, the total number of bits in the data written in the frame memories 8a and 8b during one frame period of the input signal becomes (the number of pixels in one frame)×(6 bits).

Accordingly, when compared to the case of writing the gray-scale data directly in the frame memories 8a and 8b, the memory capacity can be saved.

Next, a second embodiment of the present invention will be explained.

Referring to FIG. 16, there is shown a schematic block diagram of a liquid crystal controller in the second embodiment of the present invention.

The liquid crystal controller 3 shown in FIG. 16, similar to that of the first embodiment shown in FIG. 2, is intended 25 read/write control of the frame memories 8a and 8b. for use with an STN liquid crystal display of a so-called dual scan type wherein upper and lower screens of a display are driven simultaneously. The display screen is of a so-called XGA type having a resolution of 1024×768 dots.

In FIG. 16, reference symbol 21a denotes an FRC opera- 30 tor for performing the intermediate gray-scale operation of an FRC system, symbols 25a and 26a denote frame memory controllers, symbol 29a denotes a data selector/data width

The other arrangement is the same as that of the first 35 embodiment of FIG. 2 and thus detailed explanation thereof is omitted with the same reference numbers or symbols attached thereto.

In the liquid crystal controller 3 in the first embodiment of FIG. 2, the drive frame frequency FLM of liquid crystal 40 output data is set to be 2.5 times the frame frequency Vsync of the input signal (gray-scale data); whereas, in the liquid crystal controller 3 of the present embodiment of FIG. 16, the drive frame frequency FLM of the liquid crystal output data is set to be 3 times the frame frequency Vsync of the 45 input signal (liquid crystal data).

Accordingly, one frame period of the input signal corresponds to 3-frame period of the output signal.

In the present embodiment, access control to the frame memories 8a and 8b is carried out with use of one frame 50 period of the input signal as a unit.

Explanation will next be made in detail as to an arrangement of the liquid crystal controller 3 of the present embodiment different from that of the first embodiment of FIG. 2.

The FRC operator 21a will first be explained.

With respect to gray-scale data RA, RB, GA, GB, BA and BB applied to the liquid crystal controller 3; the FRC operator 21a generates 3 types of indicate on/off data per pixel. This causes 3 frames of indicate on/off data, i.e., 3 FRC patterns to be generated from one frame of gray-scale 60

The FRC operator 21a has FRC processing circuits provided for the respective gray-scale data RA, RB, GA, GB, BA and BB.

The FRC processing circuits generate 3 types of indicate 65 on/off data per pixel, with respect to the corresponding gray-scale data.

18

Shown in FIG. 17 is a schematic block diagram of the FRC processing circuits.

In the drawing, reference symbols 101a to 103a denote FRC decoders, and symbol 105a denotes a Vsync counter.

The Vsync counter 105a counts the signal Vsync and outputs one bit of Vsync count value. Accordingly, the Vsync count value can take "0" or "1".

With respect to the input gray-scale data of a pixel, the FRC decoders 101a to 103a generate indicate on/off data corresponding to the value of the gray-scale data.

FIG. 18 is another schematic block diagram of the FRC decoders 101a to 103a.

The FRC decoders 101a to 103a include an FRC pattern generator 107a for generating indicate on/off data for formation of 64 types of FRC patterns associated with bits (6 bits) of gray-scale data per pixel and also include a selector **108***a* for selecting indicate on/off data of one of the 64 types of indicate on/off data generated by the FRC pattern generator 107a according to the value of the input gray-scale data of a pixel.

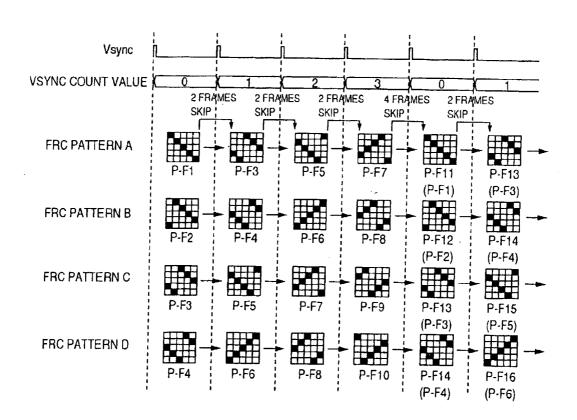

Now explanation will be made as to relationships between indicate on/off data issued from the FRC decoders 101a to

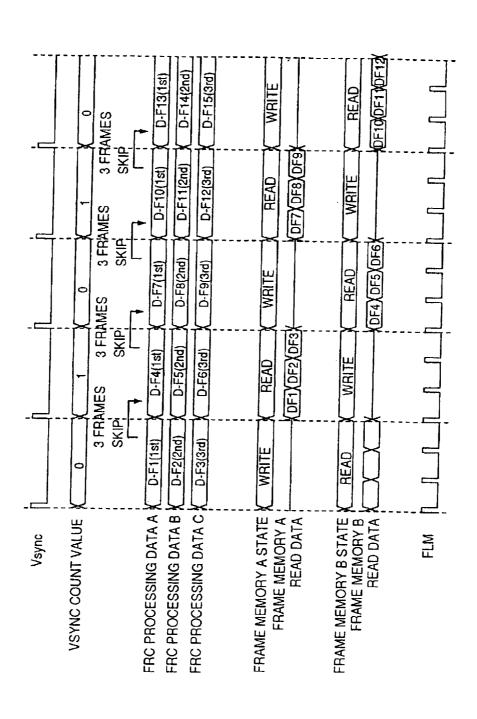

FIG. 19 is a timing chart for explaining indicate on/off data issued from the FRC decoders 101a to 103a as well as

In the drawing, FRC processing data A is indicate on/off data issued from the FRC decoder 101a, FRC processing data B is indicate on/off data issued from the FRC decoder 102a, and FRC processing data C is indicate on/off data issued from the FRC decoder 103a. Reference symbol D-FN (N being an integer) denotes indicate on/off data forming FRC patterns to be issued at the N-th frame.

As shown in FIG. 19, assuming that indicate on/off data generated by the FRC decoder 101a form FRC patterns to be output at the N-th frame, then the FRC decoder 102a generates indicate on/off data for formation of FRC patterns to be output at (N+1)-th frame, and the FRC decoder 103a generates indicate on/off data for formation of FRC patterns to be output at the (N+2)-th frame.

Each of the FRC decoders 101a to 103a generates indicate on/off data to be output at a frame previous by 3 frames each time the Vsync count value issued from the Vsync counter 105a varies.

As has been explained above, the FRC operator 21a of the present embodiment has such FRC processing circuits as shown in FIG. 17 provided for the respective gray-scale data RA, RB, GA, GB, BA and BB applied to the liquid crystal controller 3.

Accordingly, the FRC operator 21a generates indicate on/off data of 3 frame, that is, 3 FRC patterns, from the gray-scale data of one frame for each of the gray-scale data RA, RB, GA, GB, BA and BB.

That is, during one frame period, the indicate on/off data of the 3 types of FRC patterns are respectively output in a 55 2-bit parallel manner for each color of R, G or B.

Explanation will next be made as to the frame memory controllers 25a and 26a.

The frame memory controllers 25a and 26a alternately switch the read/write operations from and to the frame memories 8a and 8b for every signal Vsync.

More specifically, as shown in FIG. 19, the frame memory controllers 25a and 26a control the frame memories 8a and 8b in such a manner that the frame memory 8a is put in its write state and the frame memory 8b is put in its read state when the Vsync count value is "0", and that the frame memory 8a is put in its read state and the frame memory 8bis put in its write state when the Vsync count value is "1".

Next the data selector/data width converter 29a will be explained.

The data selector/data width converter 29a controls read timing of the indicate on/off data from the frame memories 8a and 8b in such a manner that the indicate on/off data can 5 be transmitted at the same transmission rate as that at the time of writing the indicate on/off data in the frame memories 8a and 8b.

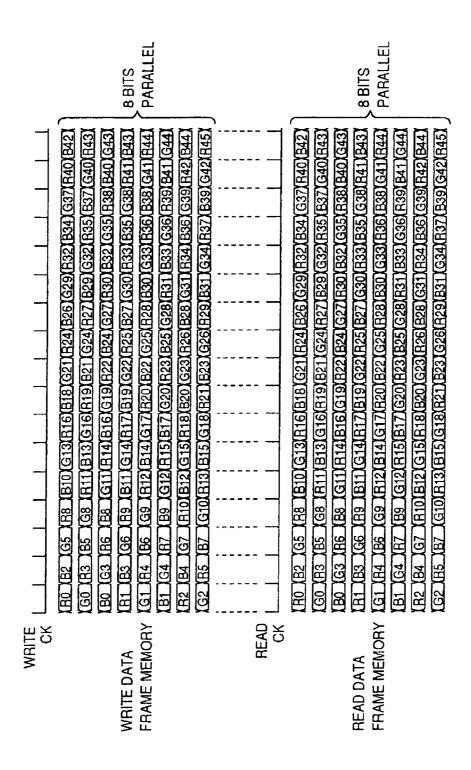

FIG. 20 is a timing chart showing the read timing of the indicate on/off data from the frame memories 8a and 8b, 10 with use of write and read clocks to the frame memories 8a and 8b as its time axis.

In reality, indicate on/off data of 2 lines (one line being 8-bit parallel) at the same time are alternately read out from the frame memories 8a and 8b for every period corresponding to twice the period of the signal Vsync. In the illustrated example, however, for easy understanding, the timing of the indicate on/off data of only one line is illustrated.

The data selector/data width converter **29***a* alternately reads out 2 lines of indicate on/off data of the upper and 20 lower displays from the frame memories **8***a* and **8***b*.

FIG. 21 is a timing chart showing read timing of the indicate on/off data from either one of the frame memories 8a and 8b, with use of the signals Hsync and CL1 as its time axis. In this case, data (N+384.LINE) and subsequent data 25 correspond to the indicate on/off data of lines of the lower display.

In the illustrated example, a ratio between the horizontal period of the horizontal synchronous signal Hsync and the horizontal period of the horizontal synchronous signal CL1 30 of liquid crystal output data in the input signal is 4 times the period of the signal Hsync and 6 times the period of the signal CL1. This results from the fact that, as shown in FIG. 20, the transmission rate at the time of reading the indicate on/off data from the frame memories 8a and 8b is set to be 35 equal to the transmission rate (corresponding to 3 frames of the signal Vsync) at the time of writing the indicate on/off data in the frame memories 8a and 8b. As a result, the drive frame frequency FLM of the liquid crystal output data becomes:

Vsync×6/4×2 (for driving of upper and lower displays)=3×Vsync

Accordingly, the drive frame frequency to be output to the liquid crystal display 9 becomes 3 times the drive frame frequency of the input signal.

Further, the data selector/data width converter **29***a* converts the data width of the respective indicate on/off data of the upper and lower displays from 8-bit parallel to 16-bit parallel

In FIG. 16, symbol "1st-L" denotes 16-bit parallel indicate on/off data corresponding to the indicate on/off data of the upper and lower displays read out from the frame memory 8a, while symbol "2nd-L" denotes 16-bit parallel liquid cry display ov of the upper and lower displays read out from the frame 55 appears the memory 8b.

In the second embodiment of the present invention, during one frame period of the input signal, 3 frames of indicate on/off data are written in the frame memories 8a and 8b, and the 3 frames of indicate on/off data written are sequentially 60 read out therefrom in synchronism with the frame period FLM of the output signal.

In this manner, data to be written in the frame memories 8a and 8b is subjected to the FRC processing to form one bit of indicate on/off data, whereby the data bus width at the 65 time of accessing the frame memories can be reduced to 16 per frame memory.

20

By sequentially writing 3 frames of indicate on/off data during one frame period of the input signal, the FRC pattern can be switched for every frame period FLM of the output signal having a frequency corresponding to 3 times the frequency of the input frame frequency.

Further, data stored in the frame memories 8a and 8b has 3 bits per pixel.

Accordingly, the flow of the intermediate gray-scale display part can be lightened and an increase in pins caused by the formation of an LSI can be suppressed.

When compared to the case where all gray-scale display data of 6 bits are written in the frame memories 8a and 8b, the memory capacity can be made smaller.

In the above first and second embodiments, the foregoing explanation has been made in connection with the case where the frame frequency of the liquid crystal output data is 2.5 times and 3 times the frame frequency of the input signal. However, the present invention is not limited to the specific example, but the same concept as in the above first and second embodiments may be realized, for example, even when the frame frequency of the liquid crystal output data is set to be twice the frame frequency of the input signal.

Further, although the liquid crystal controller for the STN liquid crystal display of a so-called dual scan type has been explained, the present invention may be widely applied as the liquid crystal controller for a liquid crystal display of a passive matrix type.

By the way, the liquid crystal controller 3 in the first and second embodiments may be made in the form of an LSI. In this case, the liquid crystal controller 3 in the form of an LSI is disposed, together with the frame memories 8a and 8b, within a liquid crystal module, e.g., on a printed circuit board having a liquid crystal driver mounted thereon or on a rear side thereof.

In this manner, the interface of the liquid crystal module can be made to be the same as the interface of a digital RGB or TFT liquid crystal having a plurality of bits of gray-scale information. Further, the liquid crystal controller 3 in the first and second embodiments of the present invention may be arranged to incorporate the frame memories 8a and 8b, in which case additional space saving can be realized.

In the first and second embodiments, by sharing constituent elements having the same functions, the single liquid crystal controller 3 can be commonly used to the first and second embodiments. In this case, mode change-over between the first and second embodiments can be implemented, e.g., with use of signal input terminals or the like.

A third embodiment of the present invention will next be explained.

As has been explained above, when the liquid crystal controller 3 is used for the so-called dual scan type of STN liquid crystal display to provide intermediate gray-scale display over the upper and lower displays, it sometimes appears that the interference fringes of the FRC display look like moving at a boundary between the upper and lower displays.

The cause of such interference fringes will be explained in connection with FIG. 22.

FIG. 22 is a diagram for explaining interference fringes generated when the liquid crystal controller 3 is used to display FRC patterns over the upper and lower display screens of a dual scan type of STN liquid crystal display 9.

The illustrated example shows a manner in which vertical FRC patterns move for each frame.

As shown in FIG. 22, scanning is carried out on line-after-line basis on the STN liquid crystal display 9, so that,

even the leading line of the lower display is already scanned, the last line of the upper display is not scanned yet, still leaving the pattern of the previous line.

As a result, the vertical line of the lower display looks like moving somewhat forwardly and thus the upper and lower 5 displays lose the continuity in its looking manner of the display data.

This is the cause of such a phenomenon that interference fringes look like moving at the boundary between the upper and lower displays.

For the purpose of solving the above problem, the liquid crystal controller 3 of the present embodiment is arranged, as shown in FIG. 23, to output the FRC patterns of the lower display as delayed by one frame when compared with those of the upper display.

Shown in FIG. 24 is a block diagram of a major arrangement of the liquid crystal controller 3 in the third embodiment of the present invention.

In the drawing, reference numeral 241 denotes an FRC operator for the upper display, numeral 242 denotes an FRC operator for the lower display, 243 denotes a pattern selector, 20 and 244 denotes a pattern selector controller.

The liquid crystal controller 3 of the present embodiment corresponds to the liquid crystal controller 3 of the first embodiment of the present invention but the FRC operator 21 is replaced by such an arrangement as shown in FIG. 24. 25

Accordingly, arrangements other than the arrangement of the present embodiment shown in FIG. 24 are substantially the same as those shown in FIG. 2 and thus detailed explanation thereof is omitted.

The FRC operator **241** for the upper display and the FRC 30 operator **242** for the lower display are basically the same as those in the first embodiment of FIG. **2**, except that the FRC operator **242** for the lower display is set to generate indicate on/off data delayed by one frame with respect to the FRC operator **21** for the upper display.

The pattern selector controller 244 counts the number of clocks in the input signal Hsync immediately after the input signal DispTMG becomes active. And the pattern selector controller 244 controls the pattern selector 243 to cause the pattern selector 243 to select outputs of the FRC operator 40 241 for the upper display until the count value becomes half of the resolution of the gray-scale data (e.g., 0–384 counts for an XGA type having a resolution of 1024×768 dots).

After the count number became half of the resolution (e.g., 385 to 768 counts for XGA of a resolution of 1024× 45 768 dots), on the other hand, the pattern selector **243** selects the output of the FRC operator 242 for the lower display.

The count value of the signal Hsync is reset by the signal Vsync.

In the present embodiment, the FRC patterns of the lower 50 display can be output as delayed by one frame with respect to those of the upper display with the aforementioned arrangement. This enables prevention of such a phenomenon that interference fringes look like moving at the boundary between the upper and lower displays.

Although the arrangement shown in FIG. 24 has been explained in the present embodiment in connection with the case of applied to the first embodiment of the present invention, this arrangement can be applied to a liquid crystal controller for the ordinary dual type of STN display.

Explanation will next be made as to a liquid crystal display apparatus as a fourth embodiment of the present invention using the liquid crystal controller 3 of the above first to third embodiments.

FIG. 25 schematically shows an arrangement of the liquid 65 crystal display apparatus in accordance with the fourth embodiment of the present invention.

22