US 20030189541A1

(19) United States

(12) Patent Application Publication (10) Pub. No.: US 2003/0189541 A1

Hashimoto (43) Pub. Date: Oct. 9, 2003

(54) DRIVER CIRCUIT OF DISPLAY DEVICE

(52) U.S. Cl. .... 345/89; 345/690

(75) Inventor: Yoshiharu Hashimoto, Tokyo (JP)

(57) ABSTRACT

Correspondence Address:

FOLEY AND LARDNER

SUITE 500

3000 K STREET NW

WASHINGTON, DC 20007 (US)

(73) Assignee: NEC Electronics Corporation

(21) Appl. No.: 10/402,979

(22) Filed: Apr. 1, 2003

(30) Foreign Application Priority Data

Apr. 8, 2002 (JP) ..... 2002-104738

## Publication Classification

(51) Int. Cl.<sup>7</sup> ..... G09G 5/10; G09G 3/36

It has a gradation voltage generation circuit 1 for generating a plurality of voltage values suited to gamma characteristics of a liquid crystal and so on, a digital image data storage circuit 3 for storing digital image data displayed on a display device, a gradation voltage selection circuit 2 for selecting one value according to digital data stored by the digital image data storage circuit 3 from the plurality of voltage values generated by the gradation voltage generation circuit 1, an amplifier 4 for receiving a voltage selected according to the digital image data and driving a data line of the liquid crystal and so on at a predetermined voltage, a voltage detection circuit 7 for detecting voltage variations of the amplifier 4, a correction data storage circuit 6 for storing a state of the voltage variations of the amplifier 4, and a voltage correction circuit 5 for correcting output voltage variations of the amplifier 4.

Fig. 1

PRIOR ART

Fig. 2

PRIOR ART

Fig. 3

PRIOR ART

Fig. 4

PRIOR ART

Fig. 5

PRIOR ART

Fig. 6

PRIOR ART

Fig. 7

PRIOR ART

Fig. 8

PRIOR ART

Fig. 9

PRIOR ART

Fig. 10

PRIOR ART

Fig. 11

Fig. 12A

Fig. 12B

Fig. 13

Fig. 14A

Fig. 14B

**Fig. 15**

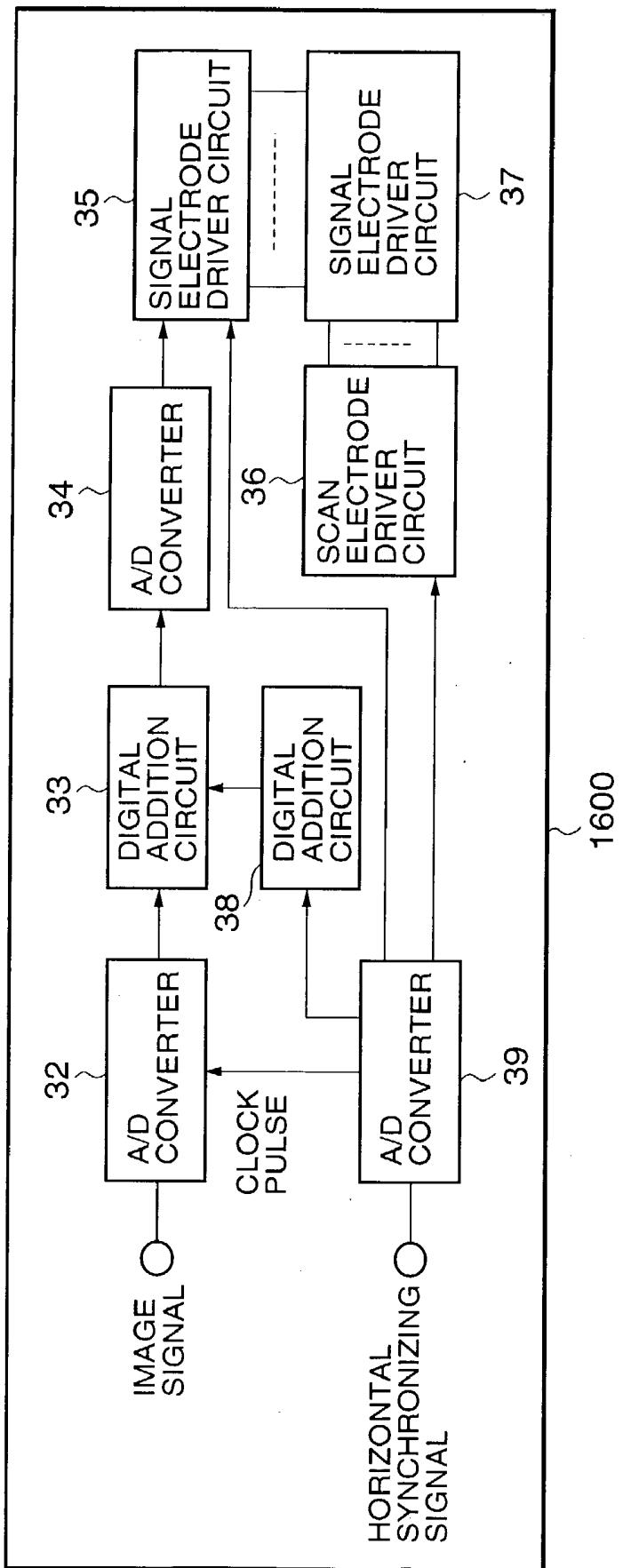

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 20

Fig. 21

Fig. 22

## DRIVER CIRCUIT OF DISPLAY DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to a driver circuit of a display device, and in particular, to the driver circuit of the display device of a self-luminous type such as an organic EL (Electro Luminescence) of which output precision is required.

[0003] 2. Description of the Prior Art

[0004] It is a known fact in recent years that an information electronics device such as a portable telephone is widely used in the world. It is also well known that the information electronics device has a self-luminous type display device such as an organic EL as its display apparatus. A matrix type display device is also well known as one of the representatives of the self-luminous type display devices such as the organic EL.

[0005] The display device shown in FIG. 1 or FIG. 2 is also known as such a matrix type display device, for instance.

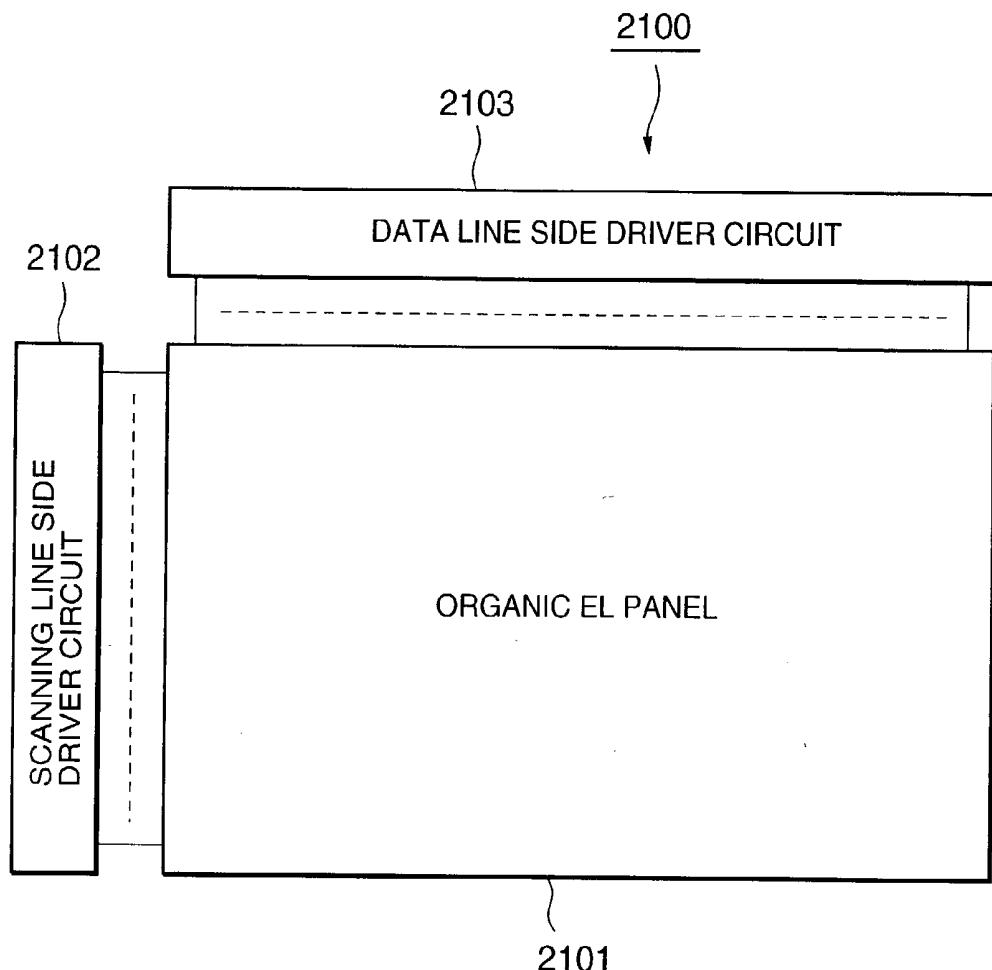

[0006] The matrix type display device in the past 2100 shown in FIG. 1 has a configuration wherein a plurality of data lines (not shown) connected to a data line driver circuit 2103 and a plurality of scanning lines connected to a scanning line side driver circuit 2102 are provided, and a display panel 2101 having a liquid crystal, the organic EL and so on is provided at each intersection thereof.

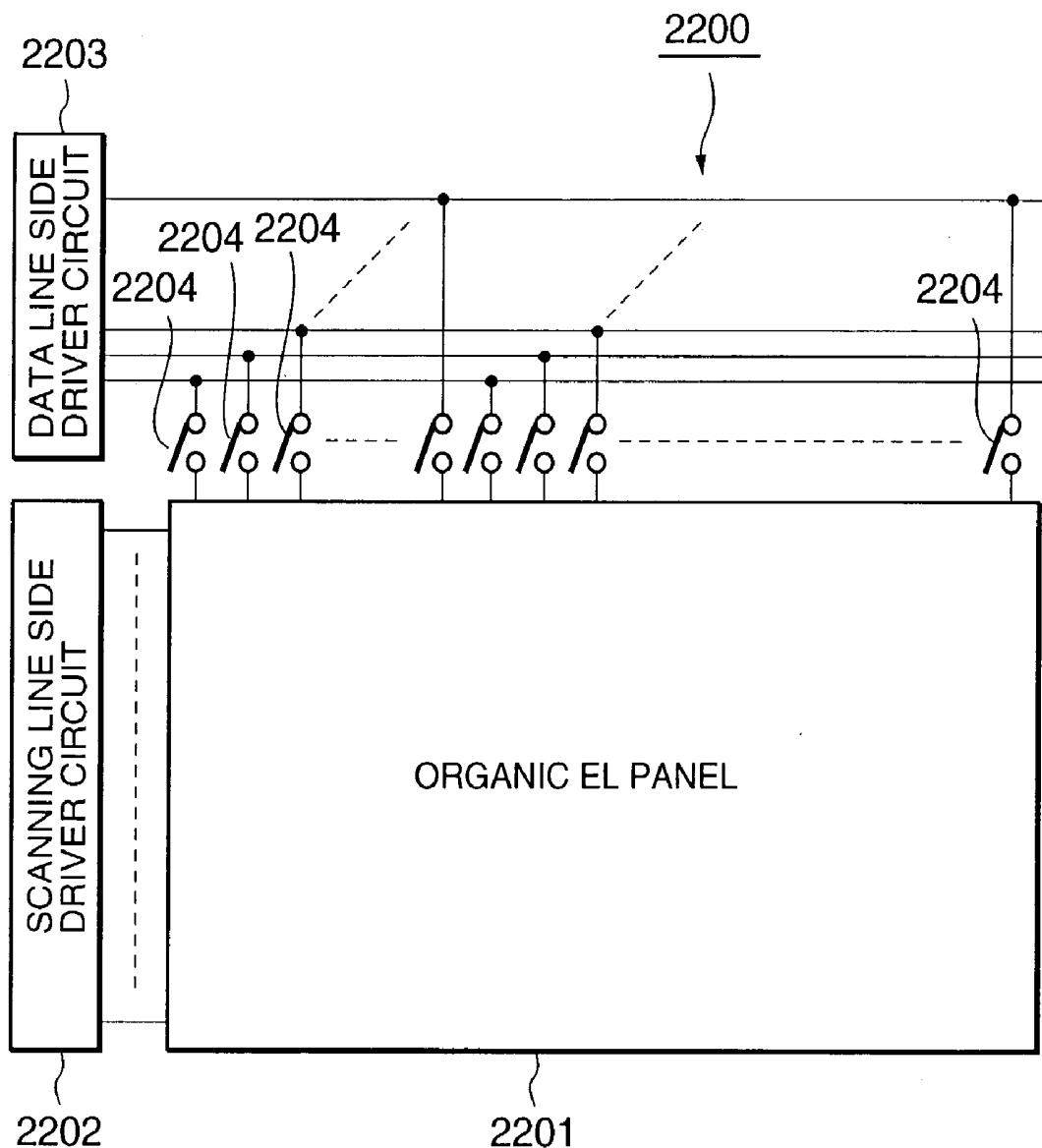

[0007] The matrix type display device in the past 2200 shown in FIG. 2 has a configuration wherein a plurality of data lines (not shown) connected to a data line driver circuit 2203 and a plurality of scanning lines connected to a scanning line side driver circuit 2202 are provided, and a display panel 2201 having the liquid crystal, organic EL and soon is provided at each intersection thereof.

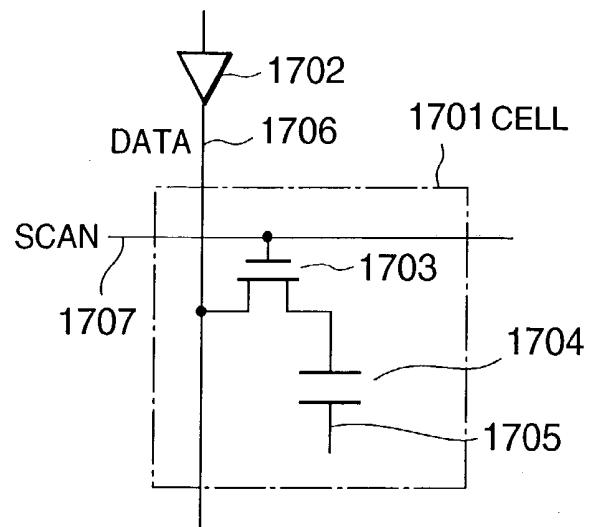

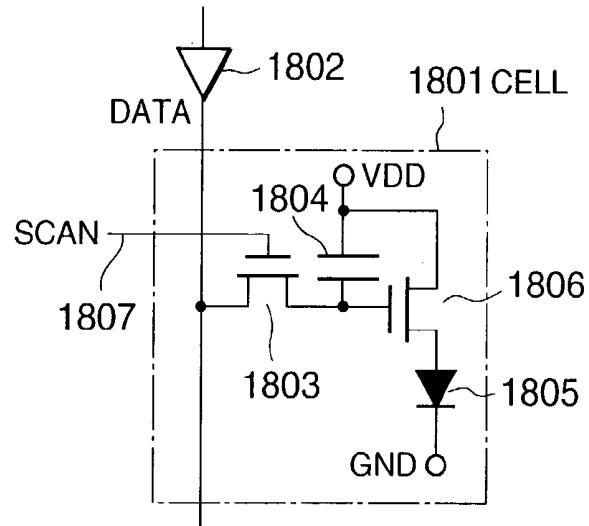

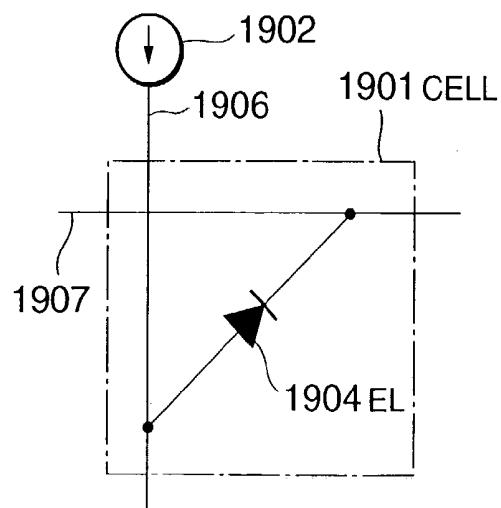

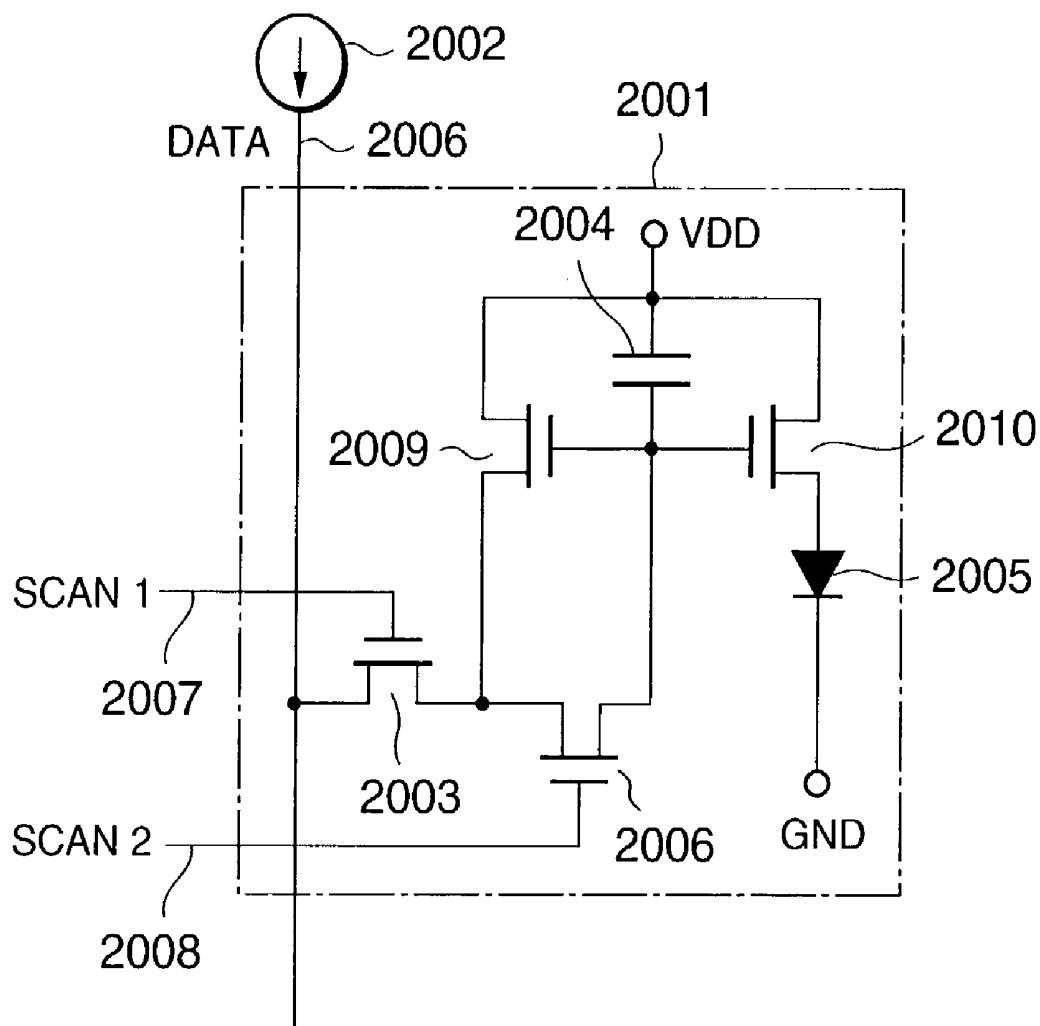

[0008] FIG. 3 is an equivalent circuit diagram of a TFT (Thin Film Transistor) liquid crystal cell 1701 using a TFT 1703 as an active element, wherein transmittance is controlled by voltage. FIG. 4 is an equivalent circuit diagram of an organic EL cell 1801 using two TFTs (1803, 1806), wherein luminance is controlled by voltage. FIG. 5 is an equivalent circuit diagram of a simple matrix type organic EL cell 1901, and FIG. 6 is an equivalent circuit diagram of an organic EL cell 2001 using four TFTs (2003, 2006, 2008, 2009), wherein luminance is controlled by currents.

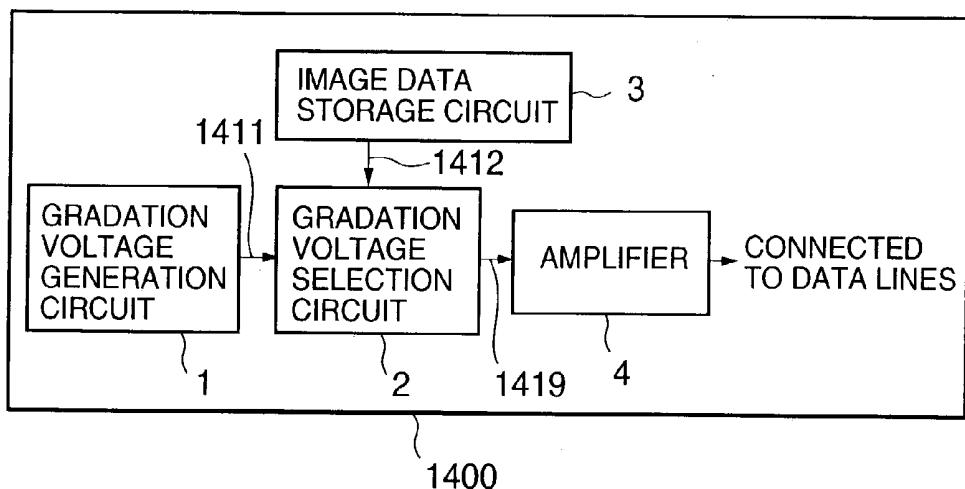

[0009] A voltage-control type data driver circuit 1400 of the matrix type display device in the past selects on a gradation voltage selection circuit 2 one voltage value, according to digital image data, of a plurality of voltages generated on a gradation voltage generation circuit 1 (refer to FIG. 7) so as to drive the data lines via an amplifier 4.

[0010] When the number of bits of the digital image data increases, the gradation voltage selection circuit 2 increases impedance in order to reduce the area of constituting elements because a chip-occupied space thereof becomes larger in proportion to the number of bits. For that reason, the data lines are driven by having the voltage selected on the gradation voltage selection circuit 2 impedance-converted by an amplifier 4.

[0011] In general, a liquid crystal display has a driving voltage range of 3 to 5V, and the digital image data is 4 to 6 bits in the case of the portable telephone and so on.

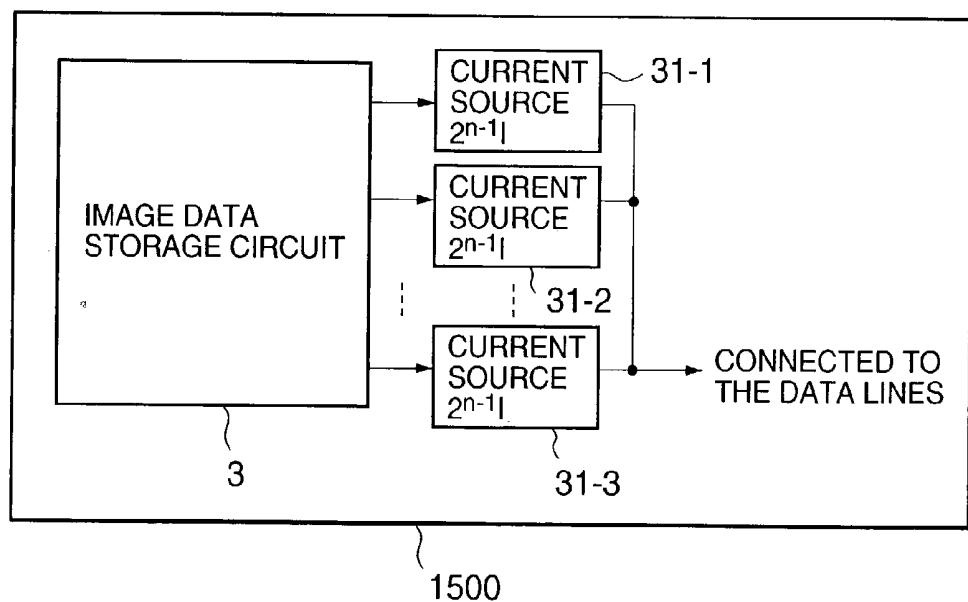

[0012] And a current-control type data driver circuit drives the data lines with a plurality of weighted current sources 31 as shown in FIG. 8.

[0013] The data driver circuit of the display device is generally integrated, and has the same number of output terminals as the number of horizontal data lines of the display device. Or in the case where a plurality of data lines are connected to one driver circuit in parallel as shown in FIG. 2, the data driver circuit of the display device has the number of output terminals which is the number of pixels/the number of parallels added thereto, so that the number of the output terminals thereof becomes a few tens to a few thousands or more. As for semiconductor equipment and so on, manufacturing variations cause voltage variations and current variations.

[0014] For that reason, Japanese Patent Laid-Open No. 4-142591 proposes a method of, in order to reduce output voltage variations of the data driver circuits of the liquid crystal display device, having the data of which output voltage variations are to be corrected stored by storage circuit in advance and driving the liquid crystal with a signal wherein the data of the storage circuit in synchronization with a clock signal is added to a picture signal.

[0015] However, the following problem arises as to the method of adding the digital image data and correction data as with the data driver circuit of the liquid crystal display described in Japanese Patent Laid-Open No. 4-142591.

[0016] In the case of the liquid crystal display, a voltage difference capable of recognizing display variations of the liquid crystal is approximately 5 mV or so. In the case where the driving voltage range of the liquid crystal is 3V, it is  $3000 \text{ mV}/5 \text{ mV} = 600$  and precision of 9 bits (512-value) or higher is required. To be more specific, 9-bit or more correction data is necessary to correct the voltage variations of the driver circuits.

[0017] Even in the case where the digital image data is 6 bits, the circuits from an addition circuit onward are 9 bits or more, and so the circuit scale of the data driver circuit becomes larger.

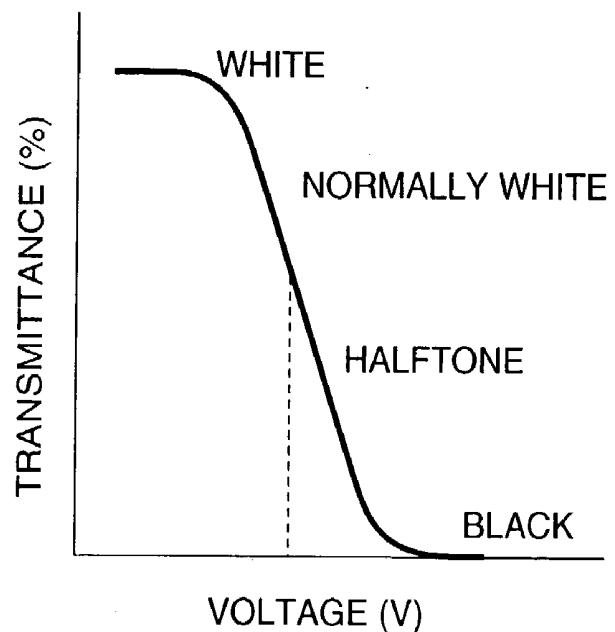

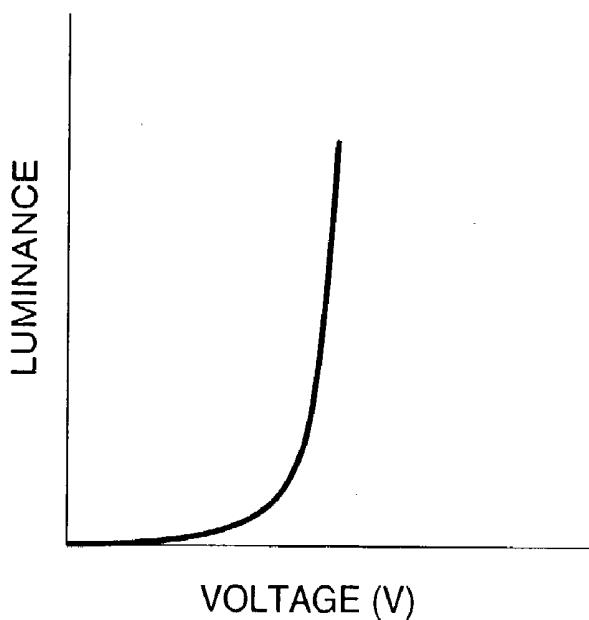

[0018] In addition, a voltage-to-transmittance property of the liquid crystal (FIG. 9) and a voltage-to-luminance property of the organic EL (FIG. 10) are nonlinear and so a correction amount is different according to the voltage. Therefore, as the digital image data cannot be simply added to the correction data, the correction data for each piece of the digital image data is required and thus a correction data storage circuit becomes even larger.

[0019] An organic EL display device has a luminance-to-current property which is linear, and so it is driven by the plurality of weighted current sources. In this case, as can be easily presumed from Japanese Patent Laid-Open No. 4-142591, there is a thinkable method of correcting the current value by storing the data for correcting output current variations in advance. However, there are the cases where, as each of the weighted current sources varies independently, a monotone increase property is lost, and the

correction data storage circuit becomes enormous because each bit of the digital image data requires the correction data.

[0020] Furthermore, the variations at the time of manufacturing are stored in an ROM or the like in order to store the variations in the driver circuits as the correction data in advance, so that the variations cannot be corrected against the change in use conditions (change in temperature and change over time)

#### SUMMARY OF THE INVENTION

[0021] As for a driver circuit of a display device according to the present invention, a matrix type display device having a plurality of scanning lines and a plurality of data lines placed like a matrix thereon has first storage circuit for storing digital image data, first voltage generation circuit for generating a plurality of voltages, first selection circuit for selecting one of the plurality of voltages according to the digital image data, first driving circuit including at least an amplifier for driving the data lines, first detection circuit for detecting output voltage variations of the first driving circuit, second storage circuit for storing a state of the output voltage variations of the first driving circuit, and first correction circuit for correcting an output voltage of the first driving circuit.

[0022] In addition, the first correction circuit of the driver circuit of the display device according to the present invention changes a value of a current running in one of a pair of difference input stages constituting the amplifier according to the correction data stored by the second storage circuit so as to change an offset voltage value of the amplifier.

[0023] In addition, the first correction circuit of the driver circuit of the display device according to the present invention connects one terminals of a first switch and a second switch to a second transistor connected in parallel with a first transistor of the difference input stages of the amplifier and a gate electrode of the second transistor, connects the other terminal of the first switch to an output terminal of the first selection circuit or the output terminal of the amplifier, connects the other terminal of the second switch to a source electrode of the second transistor, and opens and closes the first switch and the second switch according to the correction data so as to render the second transistor active or inactive and thereby change the value of the current running in one of the pair of difference input stages of the amplifier.

[0024] A driving method of the driver circuit of the display device according to the present invention has a third storage step of storing the digital image data inputted to the display device in a third storage circuit, a second driving step of driving data lines with the driving circuit including at least a current source based on the value of the current according to the digital image data, a second detection step of detecting the output current variations of the second driving step, a fourth storage step of storing the state of the output current variations of the second driving step in fourth storage circuit, and a second correction step of correcting an output current of the second driving step.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0025] This above-mentioned and other objects, features and advantages of this invention will become more apparent

by reference to the following detailed description of the invention taken in conjunction with the accompanying drawings, wherein:

[0026] FIG. 1 is a schematic view of a first matrix type display device as a display device in the past;

[0027] FIG. 2 is a schematic view of a second matrix type display device as the display device in the past;

[0028] FIG. 3 is an equivalent circuit diagram of a TFT liquid crystal cell;

[0029] FIG. 4 is a first equivalent circuit diagram of an organic EL cell;

[0030] FIG. 5 is a second equivalent circuit diagram of the organic EL cell;

[0031] FIG. 6 is a third equivalent circuit diagram of the organic EL cell;

[0032] FIG. 7 is a block diagram of a data line driver circuit (voltage-driven type) in the past;

[0033] FIG. 8 is a block diagram of a data line driver circuit (current-driven type) in the past;

[0034] FIG. 9 is a diagram of a transmittance-to-voltage property of a liquid crystal;

[0035] FIG. 10 is a diagram of a luminance-to-voltage property of an organic EL liquid crystal;

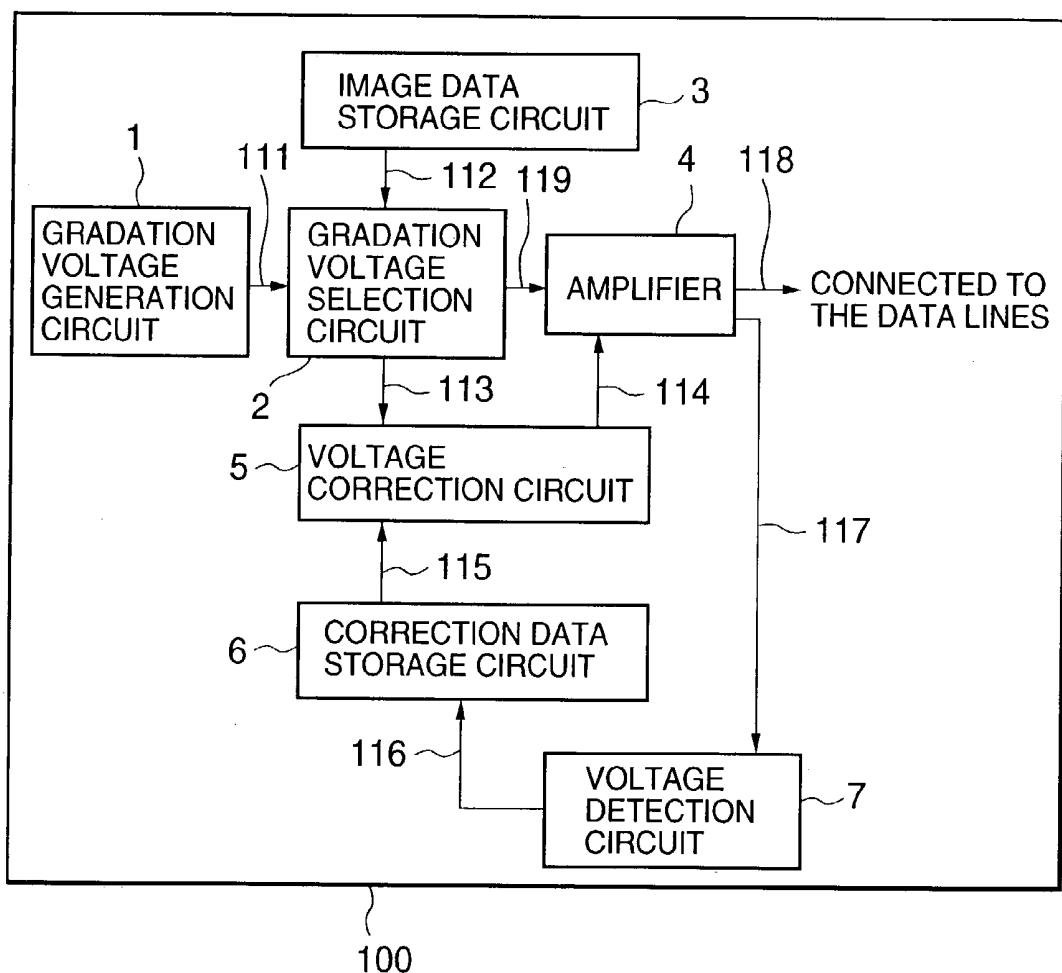

[0036] FIG. 11 is a block diagram showing a configuration of a first data driver circuit of the display device according to a first embodiment of the present invention;

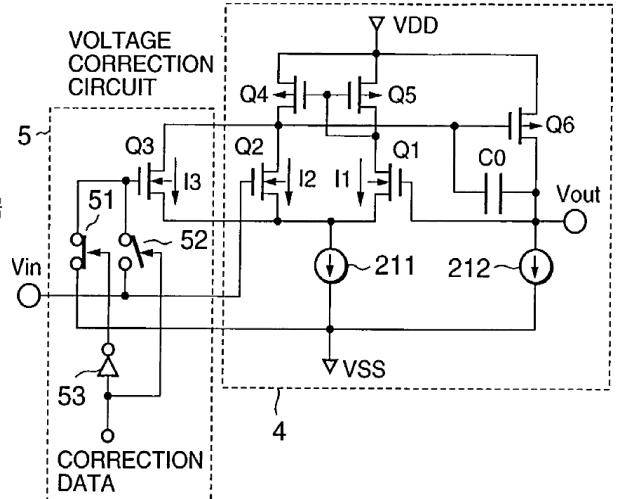

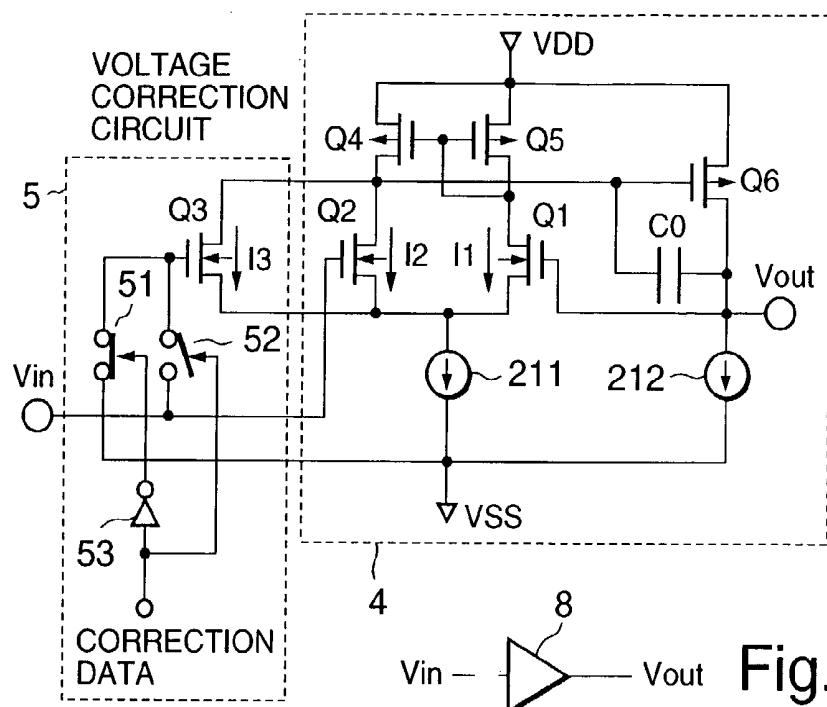

[0037] FIG. 12A is a detailed view of a voltage correction circuit of the first data driver circuit of the display device according to the first embodiment of the present invention shown in FIG. 11;

[0038] FIG. 12B is an equivalent circuit diagram of the voltage correction circuit of the first data driver circuit shown in FIG. 12A;

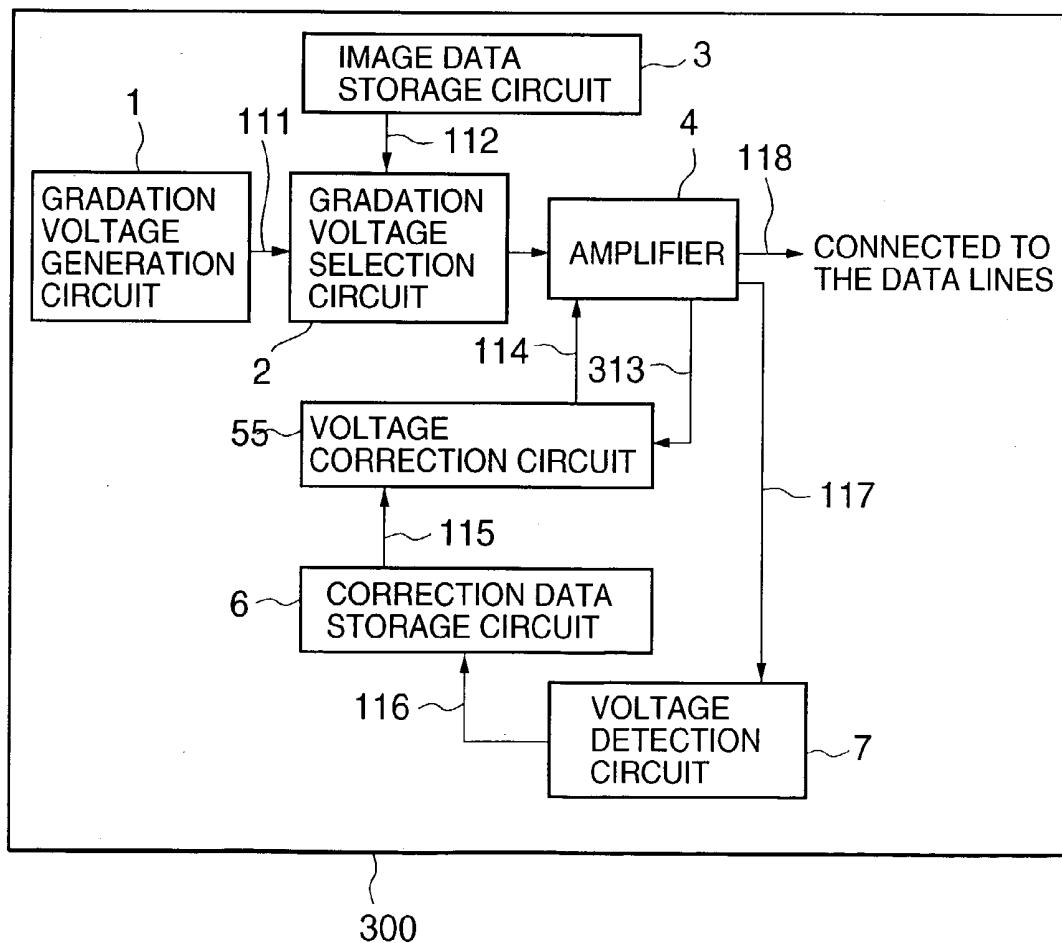

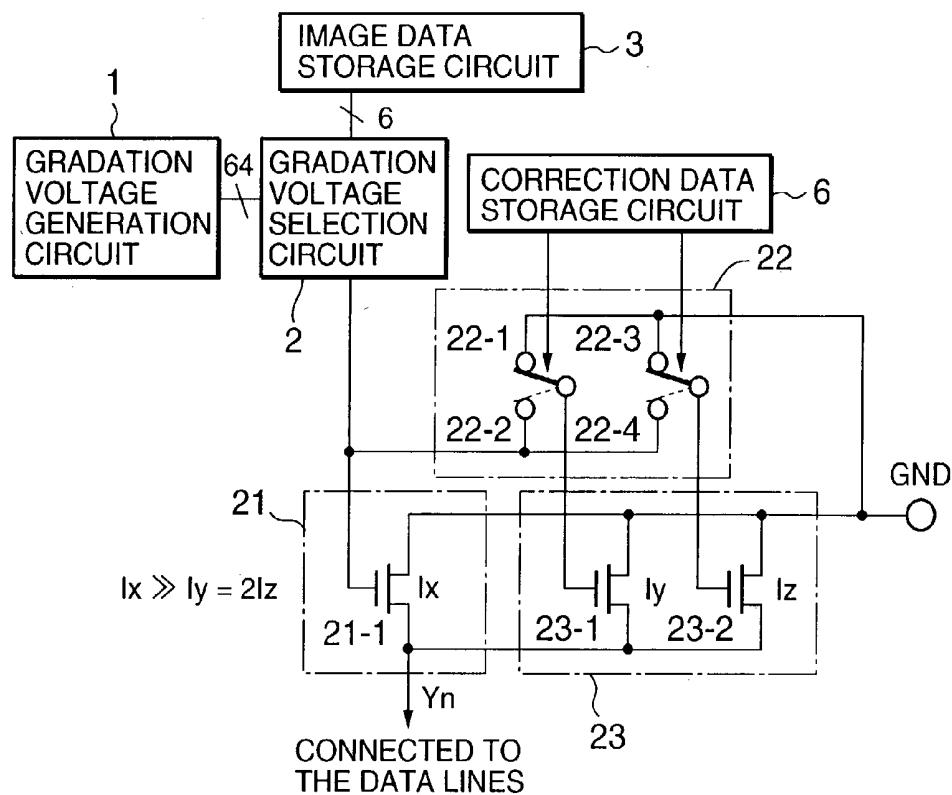

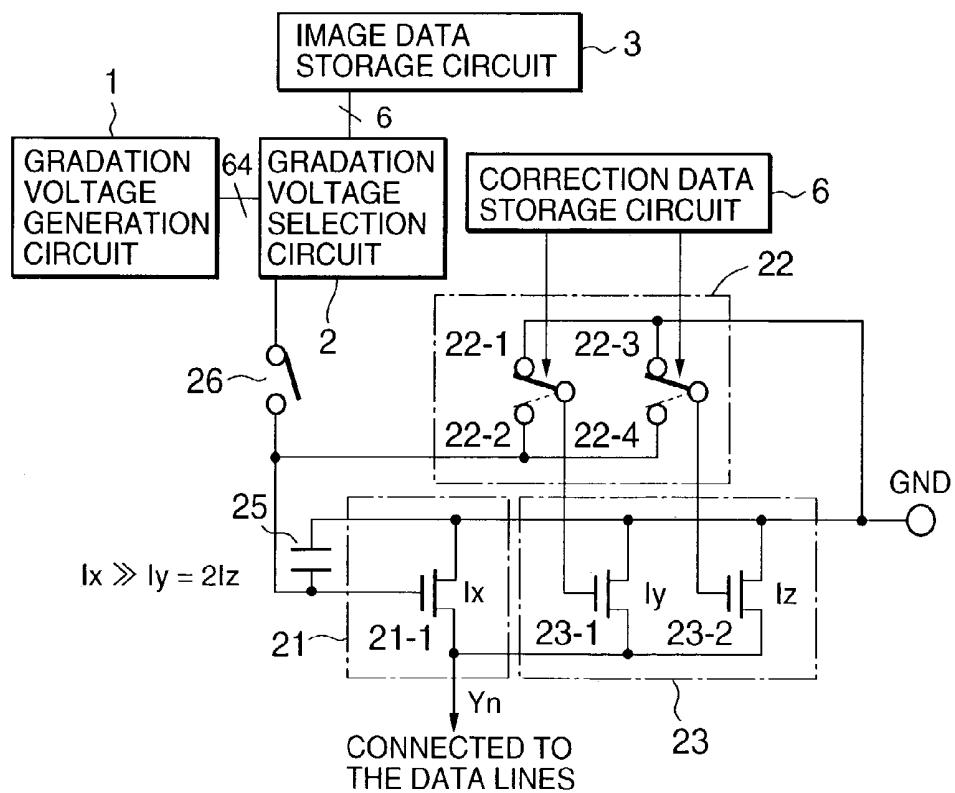

[0039] FIG. 13 is a block diagram showing the configuration of a second data driver circuit of the display device according to the first embodiment of the present invention;

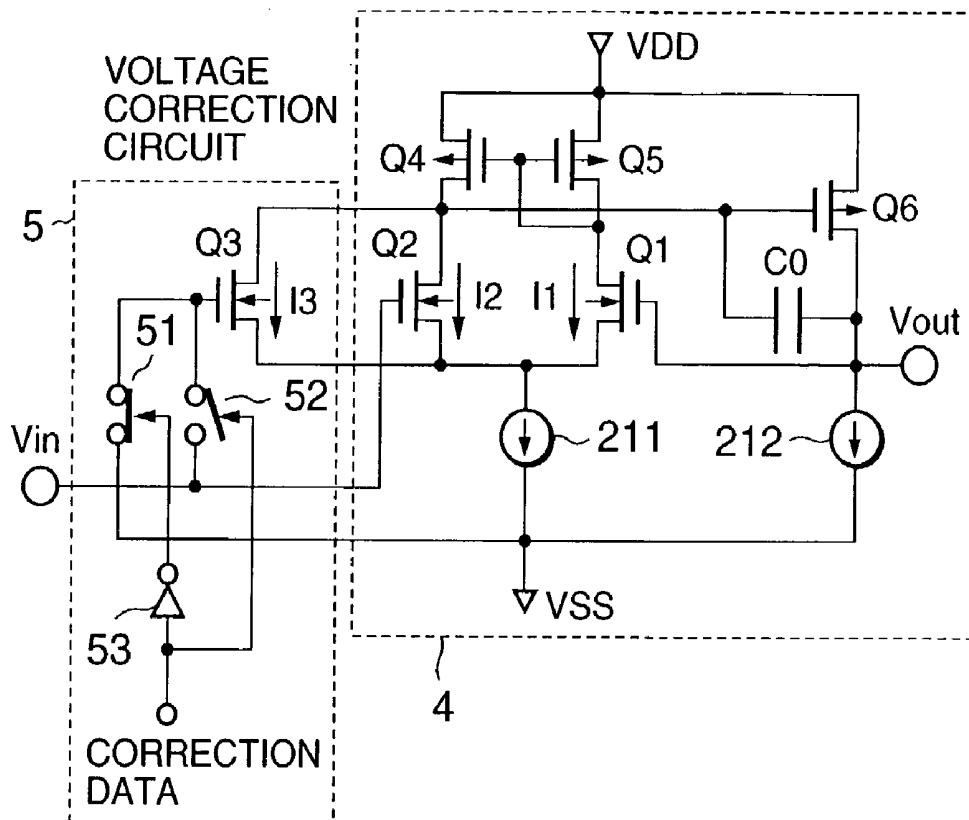

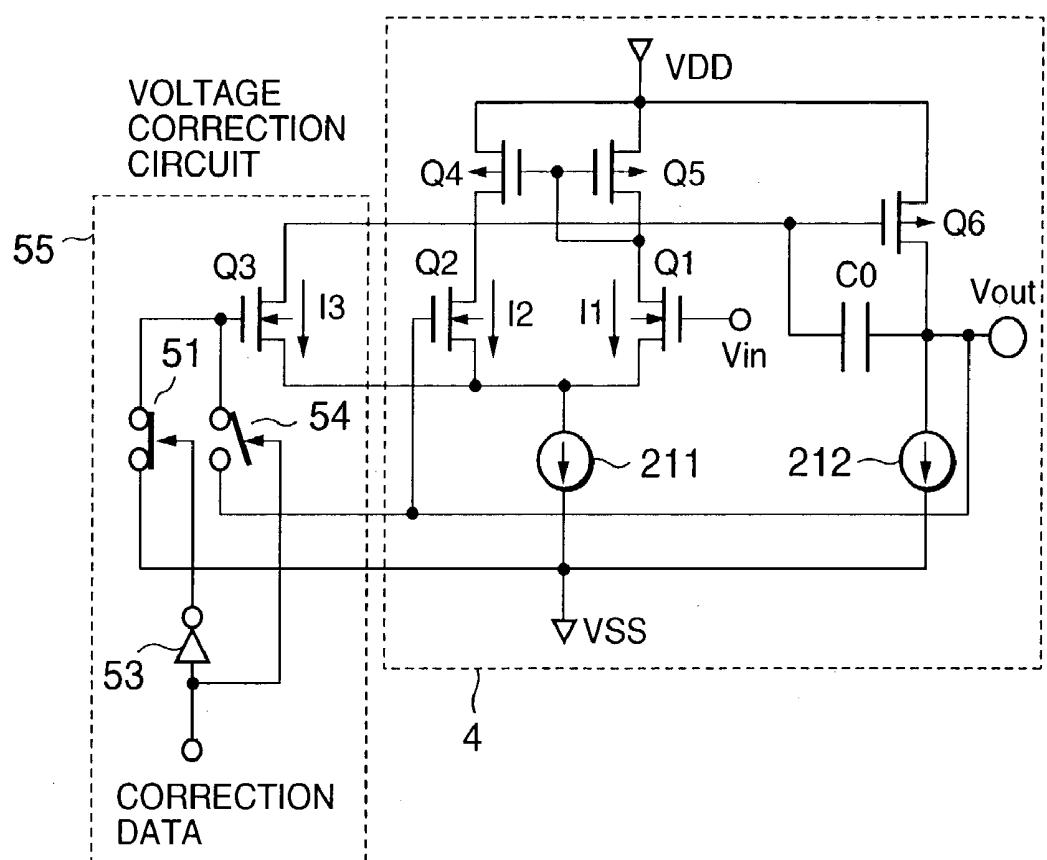

[0040] FIG. 14A is a detailed view of the voltage correction circuit of the second data driver circuit of the display device according to the first embodiment of the present invention shown in FIG. 13;

[0041] FIG. 14B is an equivalent circuit diagram of the voltage correction circuit of the second data driver circuit shown in FIG. 14A;

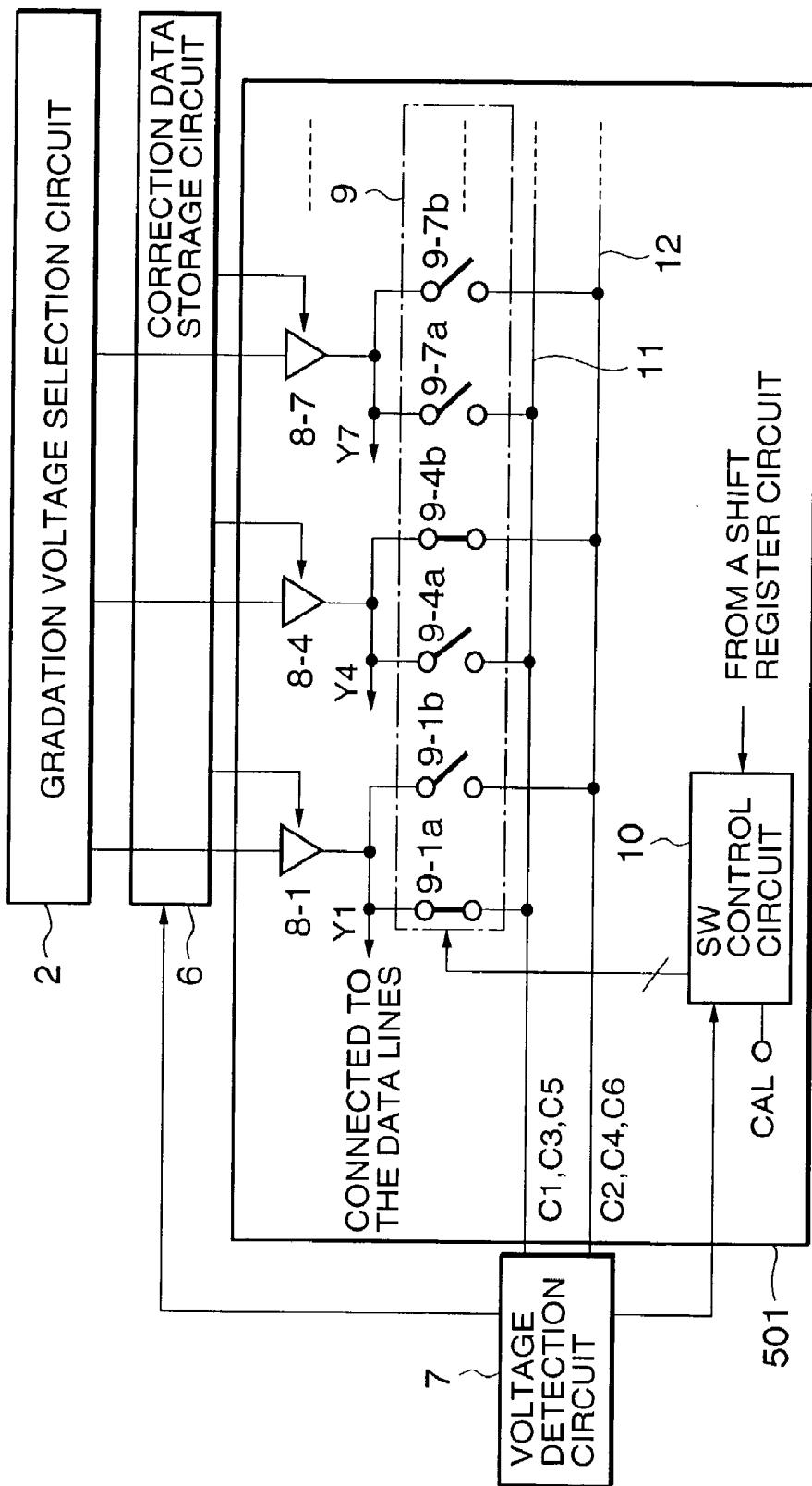

[0042] FIG. 15 is a circuit diagram for detecting voltage variations of an amplifier of the data driver circuit of the display device according to the first embodiment of the present invention;

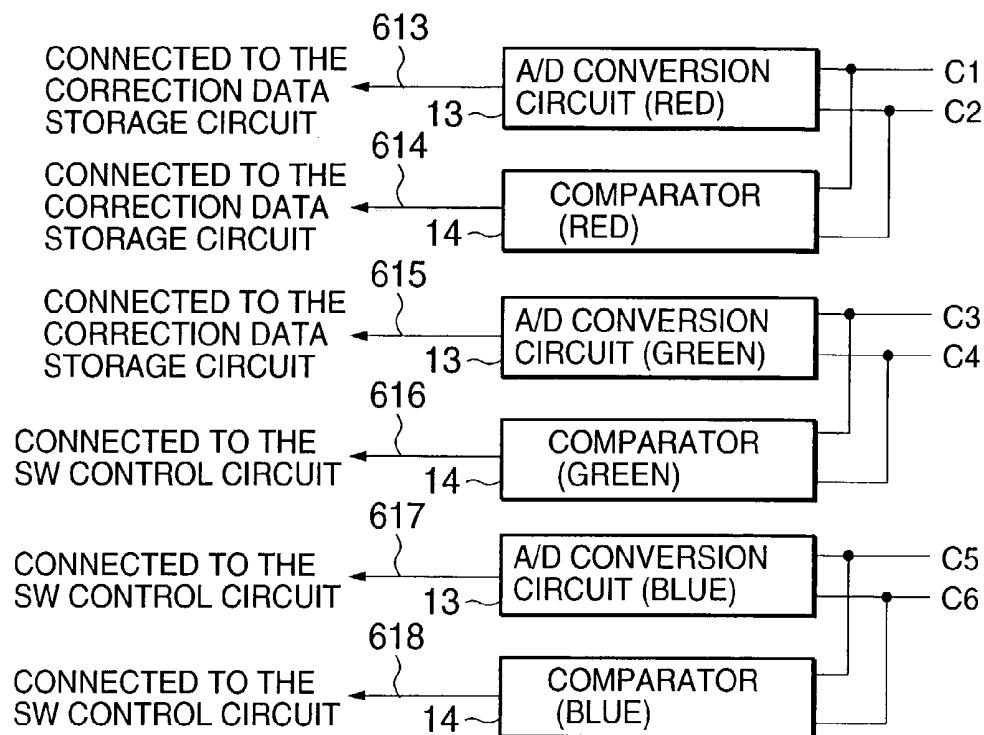

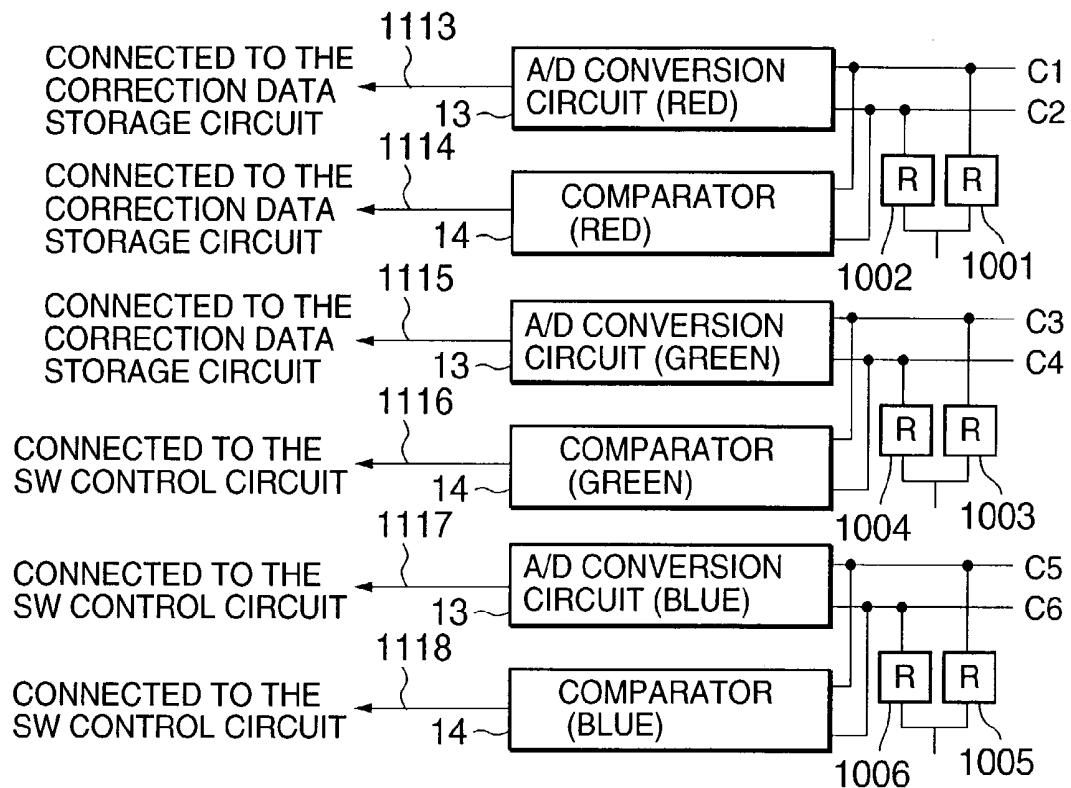

[0043] FIG. 16 is a detailed view of a voltage detection circuit of the data driver circuit of the display device according to the first embodiment of the present invention;

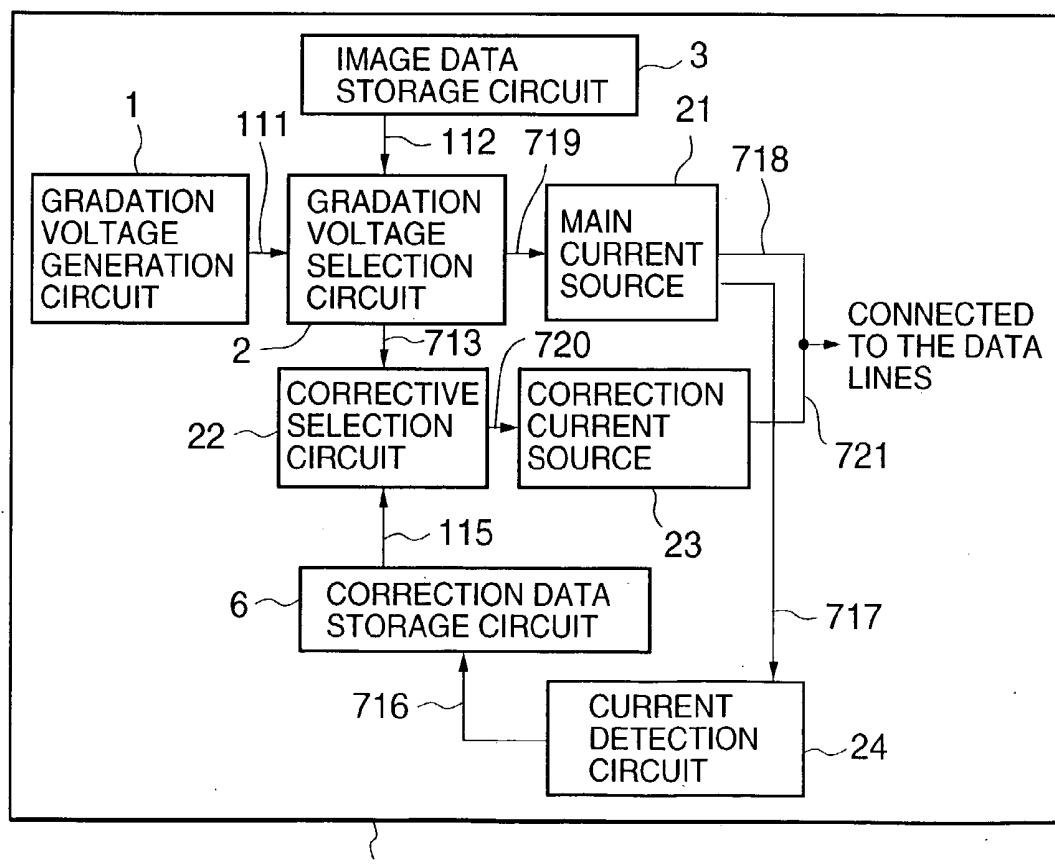

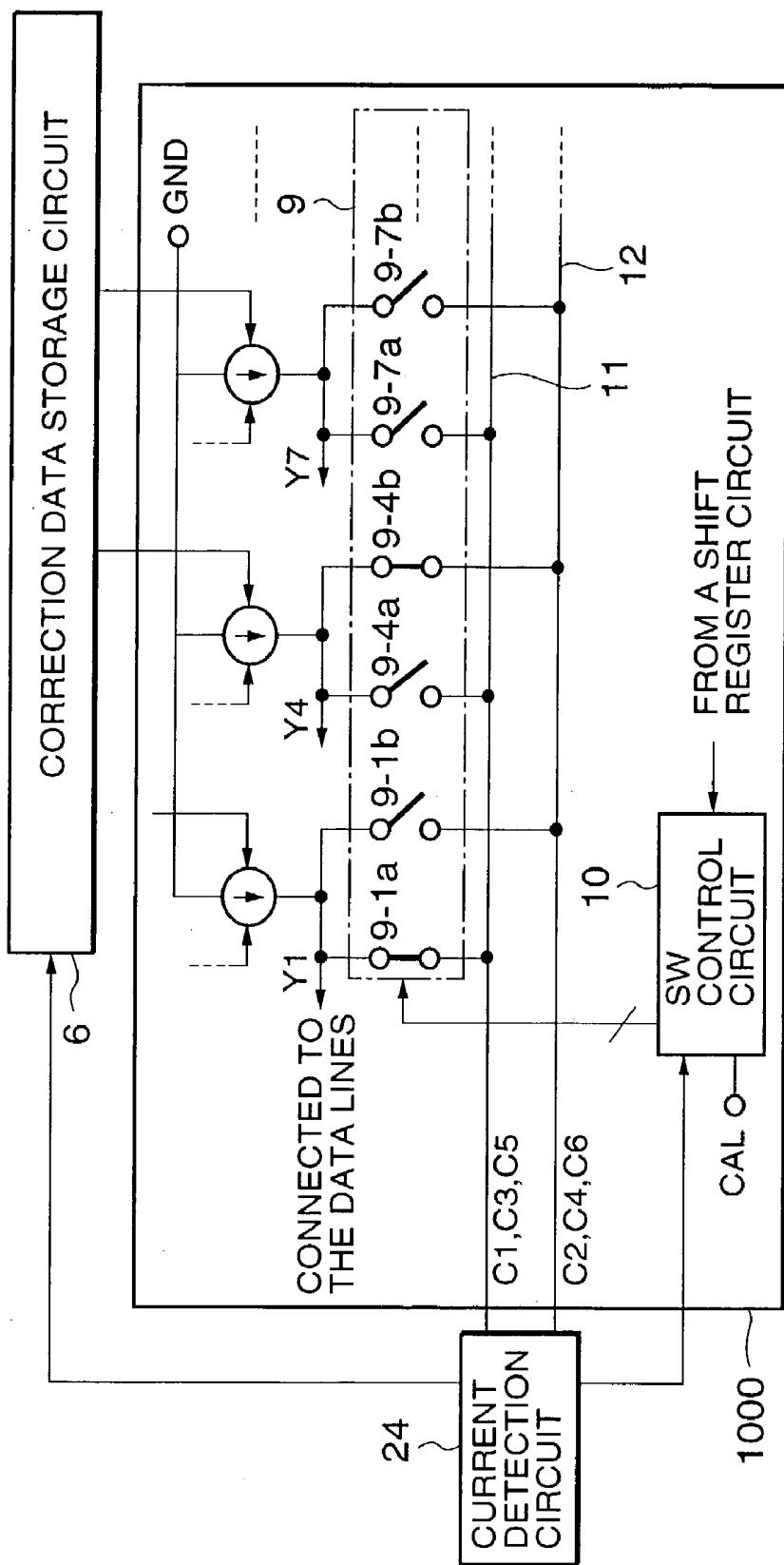

[0044] FIG. 17 is a block diagram showing the configuration of the data driver circuit of the display device according to a second embodiment of the present invention;

[0045] FIG. 18 is a detailed view of the block diagram showing the configuration of the data driver circuit of the display device according to the second embodiment of the present invention;

[0046] FIG. 19 is a detailed view of the block diagram showing the configuration of the data driver circuit of the display device according to a third embodiment of the present invention;

[0047] FIG. 20 is a current detection circuit diagram for detecting current variations of a current source of the data driver circuit of the display device according to the embodiment of the present invention;

[0048] FIG. 21 is a detailed view of the current detection circuit of the current source of the data driver circuit of the display device according to the embodiment of the present invention; and

[0049] FIG. 22 is a block diagram of correction circuit of a liquid crystal display data line driver circuit.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0050] Next, an embodiment of a data driver circuit of a display device according to the present invention will be described in detail by referring to the drawings.

[0051] (First Embodiment)

[0052] FIG. 11 is a block diagram schematically showing a data driver circuit of the display device according to a first embodiment of the present invention.

[0053] A data driver circuit 100 of the display device according to the first embodiment of the present invention has a gradation voltage generation circuit 1, comprised of a resistance string circuit (not shown) having a plurality of resistances serially connected, for generating a plurality of voltage values according to gamma characteristics of a liquid crystal and so on, a digital image data storage circuit 3 for storing digital image data displayed on the display device, a gradation voltage selection circuit 2, comprised of a plurality of analog switches (not shown), for selecting one value according to digital data stored by the digital image data storage circuit 3 from the plurality of voltage values generated by the gradation voltage generation circuit 1, an amplifier 4 for receiving the voltage selected according to the digital image data and driving a data line of the liquid crystal and so on at a predetermined voltage, a voltage detection circuit 7 for detecting voltage variations of the amplifier 4, a correction data storage circuit 6 for storing a state of the voltage variations of the amplifier 4, and a voltage correction circuit 5 for correcting output voltage variations of the amplifier 4.

[0054] To describe it further in detail, the gradation voltage generation circuit 1 of the data driver circuit 100 of the display device according to the first embodiment of the present invention is a circuit for generating a plurality of voltage values according to gamma characteristics of the liquid crystal and so on, and is comprised of the resistance string circuit (not shown) having the plurality of resistances serially connected. As a color organic EL display device has different driving voltages for red, green and blue, it requires the gradation voltage generation circuits 1 for the respective colors.

[0055] The gradation voltage selection circuit 2 of the data driver circuit 100 of the display device according to the first embodiment of the present invention is a circuit for selecting one value according to the digital data stored by the digital image data storage circuit 3 from the plurality of voltage values generated by the gradation voltage generation circuit 1, and is comprised of a plurality of analog switches (not shown). The digital image data storage circuit 3 is comprised of a known latch circuit, an RAM and so on.

[0056] The digital image data is synchronized to a clock signal and so on by a shift register circuit (not shown) or the like so as to be sequentially stored by the digital image data storage circuit 3.

[0057] The voltage selected according to the digital image data is inputted to the amplifier 4, and the data lines of the liquid crystal and so on are driven at the predetermined voltage.

[0058] In the case of 176×240 pixels, a matrix type display device has 528 data lines of 176 lines×3 (RGB) for color display, and requires a plurality of circuits for driving the data lines. Thus, in the case where the circuits are manufactured on a glass substrate such as semiconductor integrated circuits and low-temperature polysilicon, output voltage values of the amplifier 4 vary due to manufacturing variations.

[0059] The present invention further has the voltage detection circuit 7 for detecting the voltage variations of the amplifier 4, and has the state of the voltage variations of the amplifier 4 stored by the correction data storage circuit 6 (latch circuit and so on) and has the output voltage variations of the amplifier corrected by the voltage correction circuit 5.

[0060] Next, a description will be given to an example of the case where correction data is 1 bit, by referring to FIGS. 12A and 12B or FIGS. 14A and 14B, as to a method of correcting the voltages of the amplifiers of the data driver circuit 100 of the display device according to the first embodiment of the present invention.

[0061] The voltage correction circuit 5 has a correction transistor Q3 connected in parallel with one of difference input transistors Q2, and controls a gate voltage of the correction transistor Q3 according to the correction data so as to correct an offset voltage of the amplifier 4. The correction in this case is not rendering the offset voltage of the amplifier as an ideal value, but rendering it closer to that of the amplifier having the highest offset voltage.

[0062] In the case where the correction data is 0, a source voltage of the correction transistor Q3 is applied to the gate electrode and the correction transistor becomes inactive with no current running. In the case where the correction data is 1, the voltage selected by the gradation voltage selection circuit is applied to the gate electrode of the correction transistor Q3, and the correction transistor becomes active with a current I3 running. It is thus possible to control the offset voltage of the amplifier by changing the value of the current running in a differential stage of the amplifier. While the example of the case of one correction transistor was described here, it is also feasible to connect a plurality of weighted correction transistors in parallel with the transistor Q2.

[0063] Next, FIG. 15 shows the circuit on detecting the voltage variations of the amplifier 4. Output terminals of the

amplifiers are connected to the data lines and two switches. One of the switches is connected to a reference line 11 (C1, C3, C5) and the other to a comparison line 12 (C2, C4, C6). As shown in FIG. 16, the reference line 11 and comparison line 12 are connected to an A/D conversion circuit 13 and a comparator 14.

[0064] As for detection of relative voltage variations of the amplifiers, the same digital image data (gray display in the case of the liquid crystal, all white display in the case of the organic EL and so on) is transferred to the digital image data storage circuit so that all the amplifiers will output the same voltage.

[0065] Next, the comparator 14 makes a comparison between the voltage values of the two amplifiers, and a switch control circuit 10 exerts control so as to connect the amplifier of a higher voltage to the reference line 11. The amplifier of the highest offset voltage is selected by repeating this (the number of amplifiers -1) times. The reason for having the amplifier of the highest offset voltage or the lowest offset voltage selected by the comparator 14 is to simplify the configuration of the voltage correction circuit 5.

[0066] The output voltage values of the amplifiers vary in a direction plus or minus to an ideal voltage value (offset voltage is 0). To render the voltage variations of the amplifiers closer to the ideal voltage value, both the values of the currents running in two difference input stages must be changed, so that both the difference input stages require the voltage correction circuits.

[0067] Thus, it is possible, by selecting the amplifier of the highest offset voltage before detecting the correction data, to simplify the voltage correction circuits because it is sufficient to adjust only the current running in one of the difference input stages.

[0068] Next, the A/D conversion circuit 13 detects differences in the output voltages of the amplifiers in reference to the amplifier of the highest offset voltage value, and stores the detected digital data on the correction data storage circuit 6. The number of bits of the correction data is determined by real values of the voltage variations of the amplifier and the values of voltage differences of which display variations are recognizable by human eyes.

[0069] As for a liquid crystal display, the display variations cannot be recognized in the case of the voltage difference of approximately 5 mV or less, and so resolution should be 5 mV or so. In the case where the offset voltage of the amplifier varies by 20 mV at the maximum due to the manufacturing variations and so on, the number of correction bits may be 2 bits (correction amount of the four stages of 0, 5, 10 and 15 mV).

[0070] In the case where manufacturing variations are significant, the number of bits of the correction data should be further increased. Thus, it is possible, even if the correction data is 2 bits, to sufficiently correct the voltage variations of the amplifiers. The organic EL requires approximately 3 bits for the correction bits because the voltage differences of which display variations are recognizable by human eyes are smaller than those of the liquid crystal display.

[0071] As for the time for detecting the correction data per output, at least the time until the output of the amplifier

becomes stable is necessary, which is approximately  $10 \mu s$  or so as to the one for a small liquid crystal panel.

[0072] The time for detecting the correction data of all the outputs is (time for comparison by the comparator+time for A/D conversion)×number of outputs so that it is  $(10 \mu s + 10 \mu s) \times$ number of outputs. In the case where there are one comparator and one A/D conversion circuit, it takes  $20 \mu s \times 528 = 10.56$  ms. However, it can be reduced to 3.52 ms or so by providing the comparators and A/D conversion circuits for the respective colors of red, blue and green.

[0073] It is possible to correct the timing of detecting the correction data against the change in use conditions (such as temperature) by automatically inputting a signal to a correction signal (cal signal in FIG. 15) at power-on.

[0074] In the case of a self-luminous type such as the organic EL, it is possible to avoid a display error during detection of the correction data by delaying application time of a plate voltage. In the case of a transmissive liquid crystal display, lighting of a back light should be delayed.

[0075] In the case of a reflective liquid crystal display, there is a possibility of the display error occurring during the detection of the correction data. However, it will not be displayed if all the scanning lines stop the driving of the scanning lines in a non-selection state, and so it is possible to avoid the display error by stopping the driving of the scanning lines in the non-selection state from the power-on to completion of the detection. The detection of the correction data can be performed not only at power-on but at any time.

#### [0076] (Second Embodiment)

[0077] Next, the data driver circuit of the display device according to a second embodiment of the present invention will be described by referring to the drawings.

[0078] An example of the case where the correction data is 2 bits will be described by referring to FIG. 17 which is a block diagram of the data driver circuit of the current-driven type display device such as the organic EL of the present invention and FIG. 18 which is a detailed view of FIG. 17.

[0079] The data driver circuit of the display device according to the second embodiment of the present invention is different from the prior art in that it has just one current source for driving the data lines (hereafter, it is referred to as a main current source).

[0080] A main current source 21 of the data driver circuit of the display device according to the second embodiment of the present invention is comprised of one transistor (21-1) as shown in FIG. 18, where a current value  $I_x$  of the main current source 21 is controlled by the gate voltage applied to the transistor (21-1). Although it was difficult in the past to secure a monotone increase property because of the driving by a plurality of current sources, it is possible to secure the monotone increase property by having just one current source.

[0081] As for the organic EL, the luminance and currents are linear but the luminance and voltages are nonlinear, and so it has a plurality of voltage values generated by the gradation voltage generation circuit 1 to suit to a luminance

property of the organic EL, and has the value selected by the gradation voltage selection circuit 2 so as to apply it to the current source.

[0082] The present invention has a plurality of correction current sources 23 which are weighted in order to correct current variations of the main current source. While the current variations of the main current source are detected by a current detection circuit 24, the correction current sources 23 are controlled by the correction data so as to correct the value of the current running in the data lines.

[0083] In the case where the correction data is 0, a connection is made to a switch terminal (22-1, 22-3) side of a corrective selection circuit 22 in FIG. 18 so that the source voltage is applied to a transistor (23-1) of the correction current sources 23 and each gate of the transistor (23-1) and the current sources become inactive. In the case where the correction data is 1, a connection is made to a switch terminal (22-2, 22-4) side of the corrective selection circuit 22 in FIG. 18 so that the voltage selected by the gradation voltage selection circuit 2 is applied to the transistor (23-1) of the correction current sources 23 and each gate of the transistor (23-1) and the correction current sources 23 become active with the value of the current at a predetermined rate running to the main current source 21.

[0084] The value of the current of the correction current sources 23 is set to be several percent of the value of the current of the main current source 21. A drain of the main current source 21 and the drain of the correction current sources 23 are connected to the data lines respectively, which drive the data lines with a corrected value of the current by adding the current of the main current source 21 to the current of the correction current sources 23.

[0085] Next, the method of detecting the correction data will be described. Here, as with the first embodiment, the main current source having the largest value of the current is selected by the comparator 14, and the state of current variations of each main current source is stored as the correction data against the main current source having the largest value of the current.

[0086] Thus, it only adds the values of the currents of the correction current sources to the values of the currents of the main current sources by correcting the values of the currents of the other main current sources in reference to the main current source having the largest value of the current (no circuit for subtraction is necessary) so as to simplify a circuit configuration of the correction current sources. In the case where an anode and a cathode of the organic EL are reversed, the values of the currents should be subtracted as to the correction current sources in reference to the main current source having the smallest value of the current.

[0087] Next, the number of bits of the correction data will be described. In the case of passing 20 nA or so per gray scale in a current-driven type organic EL display device, the resolution should be at least 10 nA or so in order to correct the values of the currents to the extent that the display variations are not recognizable by human eyes.

[0088] If the digital image data is 6 bits (64 intensity levels assigned), the currents up to the maximum current of 20 nA $\times$ 64=1,280 nA are to be passed, where the current variations may be 5 percent or more.

[0089] It is possible to correct this in the range of 0 to 7 percent (8 stages) by setting the resolution at 1 percent (12.8 nA) or so of the value of the current of the main current

source while the correction data is 3 bits. In the case where the current variations are 7 percent or more, a modification should be made, such as increasing the number of bits of the correction data or setting the resolution at more than 1 percent.

[0090] There is a possibility that, as the correction current source is comprised of a plurality of transistors, the monotone increase property thereof is lost. However, it will not be a problem because the amount of the current variations of the correction current source (1,280 nA $\times$ 7% $\times$ 5%=4.48 nA) is much smaller than that of the main current source (1,280 nA $\times$ 5%=64 nA) so that it is the value of the current at which the display variations are not recognizable by human eyes.

[0091] (Third Embodiment)

[0092] Next, the liquid crystal display according to a third embodiment of the present invention will be described by referring to the drawings.

[0093] FIG. 19 is a detailed view of another data driver circuit of the current-driven display device such as the organic EL according to the present invention.

[0094] The data driver circuit of the display device according to the third embodiment of the present invention is different from that according to the second embodiment in that it holds the gate voltages of the main current source and the correction current source in a sample hold circuit comprised of a switch 26 and a condenser 25.

[0095] While the data driver circuit of the display device according to the second embodiment of the present invention had the voltages selected by the gradation voltage selection circuit applied to the gates of the current sources on each driver circuit, it is possible, by adopting the sample hold circuit, to hold the gradation voltage and reduce the digital image data storage circuits and the gradation voltage selection circuits of each driver circuit.

[0096] Compared to the data driver circuit of the display device according to the second embodiment of the present invention, the data driver circuit of the display device according to the third embodiment of the present invention has more significant current variations because the voltage variations of the sample hold circuit itself arise. However, it is also possible, according to the present invention, to simultaneously correct the current variations of the main current source caused by those of the sample hold circuit. In this case, the number of bits of the correction data should be 4 bits or so.

[0097] As described above, according to the present invention, it is possible to correct with a small amount of the correction data of 2 to 4 bits or so the voltage variations and current variations of the data driver circuit, which are the causes of vertical line variations of the display device, including not only the manufacturing variations but also the variations due to the changes over time and in temperature so as to allow a good display with no display variations to be obtained.

What is claimed is:

1. A driver circuit of a display device having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, comprising:

a first storage circuit for storing digital image data inputted to the display device;

- a first voltage generation circuit for generating a plurality of voltages to be used on said display device when driving said display device;

- a first selection circuit for selecting one voltage of said plurality of voltages according to said digital image data;

- a first driving circuit including at least an amplifier for driving said data lines;

- a first detection circuit for detecting variations in output voltages of said first driving circuit;

- a second storage circuit for storing a state of the variations in the output voltages of said first driving circuit; and

- a first correction circuit for correcting the output voltages of said first driving circuit.

- 2.** The driver circuit of a display device according to claim 1 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein:

- said first correction circuit changes a value of a current running in one of a pair of difference input stages constituting said amplifier according to correction data stored by said second storage circuit so as to change an offset voltage value of said amplifier.

- 3.** The driver circuit of a display device according to claim 1 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein:

- said first correction circuit connects one terminals of a first switch and a second switch to a second transistor connected in parallel with a first transistor of the difference input stage of said amplifier and a gate electrode of said second transistor, connects the other terminal of said first switch to an output terminal of said first selection circuit or to the output terminal of said amplifier, connects the other terminal of said second switch to a source electrode of said second transistor, opens and closes said first switch and said second switch according to said correction data, and renders said second transistor either active or inactive so as to change the value of the current running in one of the difference input stages of the amplifier.

- 4.** The driver circuit of a display device according to claim 1 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein said first detection circuit further comprises:

- a first comparator for comparing the output voltages of two amplifiers; and

- a first A/D conversion circuit for converting an output voltage difference between the two amplifiers into digital data.

- 5.** The driver circuit of a display device according to claim 1 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, further comprising a first switch control circuit for connecting a third switch and a fourth switch in parallel with the output terminal of said amplifier and controlling said third and fourth switches when detecting the variations in said output voltages.

- 6.** The driver circuit of a display device according to claim 1 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein one piece or three pieces each of said first comparator and said first A/D conversion circuit are provided.

- 7.** A driver circuit of a display device having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, comprising:

- a third storage circuit for storing digital image data inputted to the display device;

- a second driving circuit including at least a current source for driving said data lines at a value of a current according to said digital image data;

- a second detection circuit for detecting variations in output currents of said second driving circuit;

- a fourth storage circuit for storing a state of the variations in the output currents of said second driving circuit; and

- a second correction circuit for correcting the output currents of said second driving circuit.

- 8.** The driver circuit of a display device according to claim 7 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein:

- said second driving circuit further comprises a first current source to be controlled according to said digital image data and a second current source for correcting current variations of the first current source; and

- said second current source is controlled to be active or inactive according to the correction data stored by said third storage circuit.

- 9.** The driver circuit of a display device according to claim 7 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein said second current source is comprised of a plurality of weighted current sources.

- 10.** The driver circuit of a display device according to claim 7 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein said second detection circuit further comprises a second comparator for comparing the output currents of two current sources and a second A/D conversion circuit for converting an output current difference between the two current sources into digital data.

- 11.** The driver circuit of a display device according to claim 7 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, further comprising a second switch control circuit for connecting a fifth switch and a sixth switch in parallel with the output terminal of said first current source and controlling said fifth and sixth switches when detecting the variations in the output currents.

- 12.** The driver circuit of a display device according to claim 7 having a plurality of scanning lines and a plurality of data lines placed like a matrix therein, wherein either one piece or three pieces each of said second comparator and said second A/D conversion circuit are provided.

\* \* \* \* \*

|                |                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的驱动电路                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">US20030189541A1</a>                                                                                                          | 公开(公告)日 | 2003-10-09 |

| 申请号            | US10/402979                                                                                                                              | 申请日     | 2003-04-01 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                                                                                              |         |            |

| 申请(专利权)人(译)    | NEC电子公司                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 瑞萨电子公司                                                                                                                                   |         |            |

| [标]发明人         | HASHIMOTO YOSHIHARU                                                                                                                      |         |            |

| 发明人            | HASHIMOTO, YOSHIHARU                                                                                                                     |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/32 G09G3/36 G09G5/02 H01L51/50 G09G5/10                                                                          |         |            |

| CPC分类号         | G09G3/3283 G09G3/3291 G09G3/3688 G09G5/02 G09G2300/0417 G09G2320/043 G09G2310/0291 G09G2320/0276 G09G2320/0285 G09G2320/029 G09G2310/027 |         |            |

| 优先权            | 2002104738 2002-04-08 JP                                                                                                                 |         |            |

| 其他公开文献         | US7113156                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>                                                                                          |         |            |

#### 摘要(译)

它具有用于产生适合于液晶等伽马特性的多个电压值的灰度电压产生电路1，用于存储显示在显示装置上的数字图像数据的数字图像数据存储电路3，灰度电压选择电路用于根据由数字图像数据存储电路3存储的数字数据从由灰度电压产生电路1产生的多个电压值中选择一个值的放大器4，用于接收根据数字图像数据选择的电压并驱动a的放大器4液晶的数据线等在预定电压下，用于检测放大器4的电压变化的电压检测电路7，用于存储放大器4的电压变化状态的校正数据存储电路6和电压校正电路5，用于校正放大器4的输出电压变化。