US 20010011988A1

### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2001/0011988 A1 Ikeda et al. (43) Pub. Date: Aug. 9, 2001

#### (54) LIQUID CRYSTAL DISPLAY WITH LIQUID CRYSTAL DRIVER HAVING DISPLAY MEMORY

(76) Inventors: Makiko Ikeda, Yokohama-shi (JP);

Tsutomu Furuhashi, Yokohama-shi

(JP); Hiroyuki Nitta, Fujisawa-shi (JP);

Isao Takita, Fujisawa-shi (JP);

Naruhiko Kasai, Fujisawa-shi (JP);

Satoru Tsunekawa,

Higashimurayama-shi (JP); **Tatsuhiro Inuzuka**, Yokohama-shi (JP)

Correspondence Address:

ANTONELLI TERRY STOUT AND KRAUS SUITE 1800 1300 NORTH SEVENTEENTH STREET ARLINGTON, VA 22209

(21) Appl. No.: **09/813,888**

(22) Filed: Mar. 22, 2001

#### Related U.S. Application Data

(60) Division of application No. 08/972,972, filed on Nov. 19, 1997, now Pat. No. 6,222,518, which is a con

tinuation of application No. 08/297,058, filed on Aug. 29, 1994, now Pat. No. 5,815,136.

#### (30) Foreign Application Priority Data

| Aug. 30, 1993 | (JP) | 5-213733 |

|---------------|------|----------|

| Dec. 20, 1993 | (JP) | 5-320074 |

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57) ABSTRACT

An information processing system includes a bus, a display data generating circuit coupled to the bus, and a display apparatus coupled to the bus. The display apparatus includes a display panel capable of displaying a grayscale image in accordance with display data in a form of a plurality of bits for each of a plurality of pixels of a display panel generated by the display data generating circuit, and a signal driver which supplies driving voltages corresponding to the display data to at least a part of the plurality of data lines to display a grayscale image on the display panel. The signal driver includes a display memory which stores the display data, and is embodied in an integrated circuit. The display data generating circuit transfers the display data to the display memory via the bus.

FIG.2 PRIOR ART

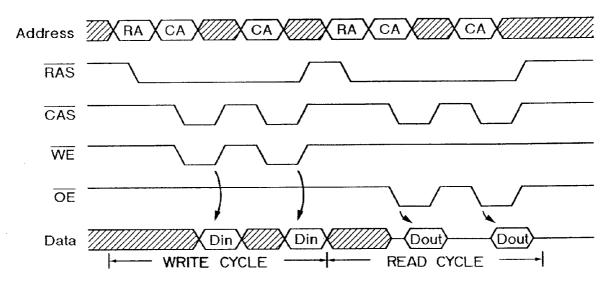

FIG.4 PRIOR ART

### ACCESS TO DISPLAY MEMORY 307

FIG.5 PRIOR ART

### **OPERATION OF DRIVER 203**

FIG.6 PRIOR ART

FIG.7

#### RANDOM ACCESS

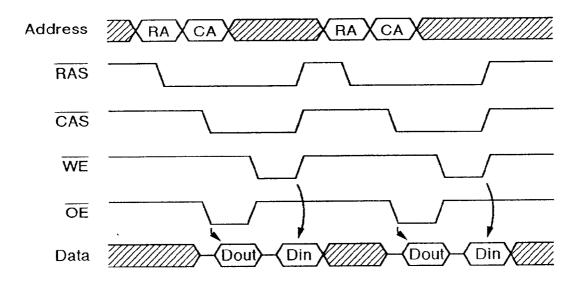

FIG.8

### PAGE ACCESS

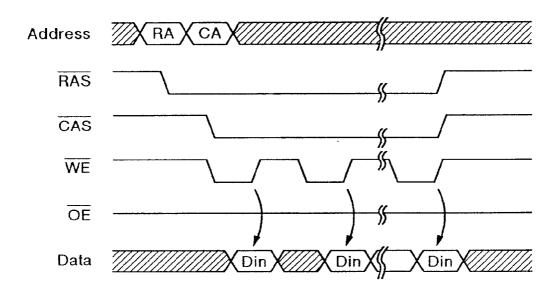

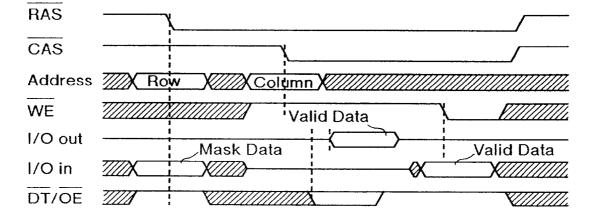

FIG.9 READ-MODIFIED WRITE ACCESS

**FIG.10**

BURST ACCESS WRITE CYCLE

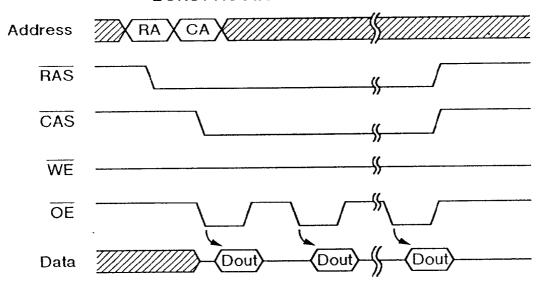

**FIG.11**

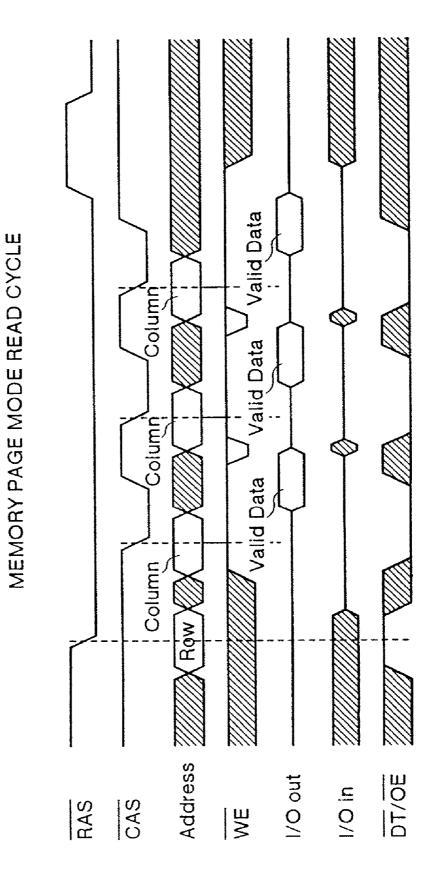

**BURST ACCESS READ CYCLE**

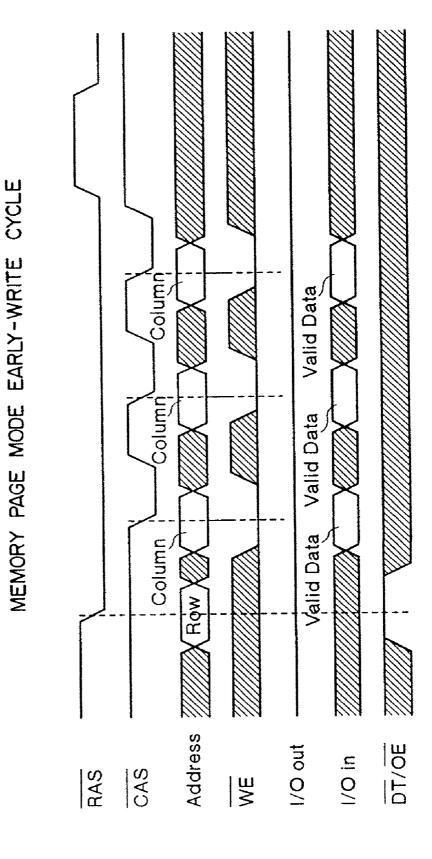

**FIG.12**

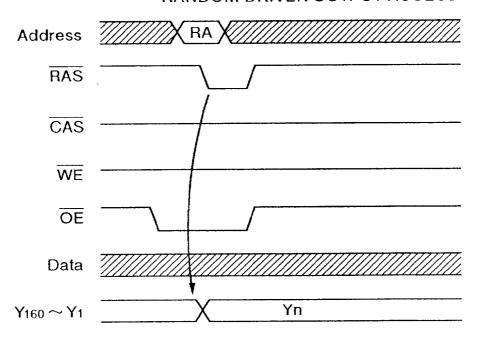

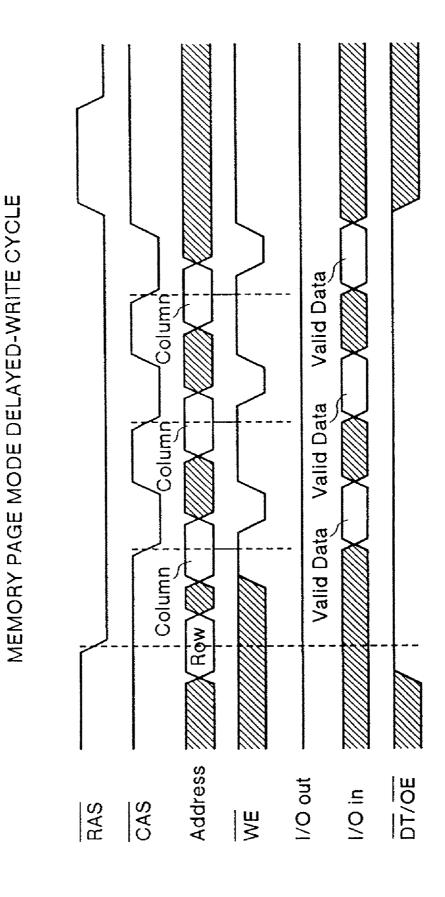

### RANDOM DRIVER OUTPUT ACCESS

# **FIG.13**

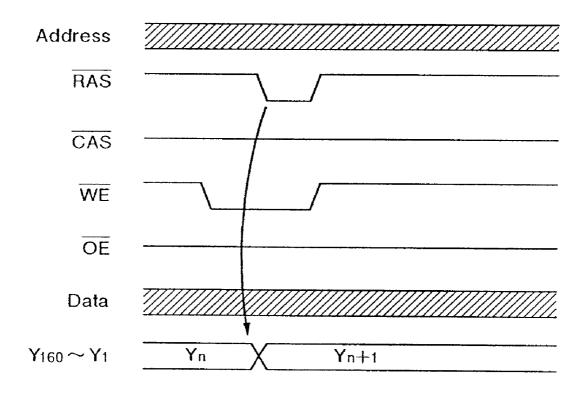

### SEQUENTIAL DRIVER OUTPUT ACCESS

FIG.14

# FIG.15

### MEMORY MAP OF MEMORY CELL 120

| СО | LUMN LOW     | •            |   |               |                  |

|----|--------------|--------------|---|---------------|------------------|

| [  | (hex0,hex0)  | (hex1,hex0)  |   | (hex12,hex0)  | (hex13,hex0)     |

|    | (hex0,hex1)  | (hex1,hex1)  |   | (hex12,hex1)  | (hex13,hex1)     |

|    | :            | 1            | - | 1             | ļ.               |

|    |              | f<br>5<br>1  |   | 1<br>1<br>1   |                  |

|    | ;<br>;       | 1            |   | <br>          | †<br>3<br>5<br>9 |

|    | i            | i            | 1 | ·             | 1                |

|    | (hex0,hexEE) | (hex1,hexEE) |   | (hex12,hexEE) | (hex13,hexEE)    |

|    | (hex0,hexEF) | (hex1,hexEF) | ] | (hex13,hexEF) | (hex13,hexEF)    |

**FIG.16**

## FIG.17A

#### SCREEN MEMORY MAP

| (hex0,hex0)                                              | (hex13,hex0)                    | (hex14,hex0)  | (hex27,hex0)                              |

|----------------------------------------------------------|---------------------------------|---------------|-------------------------------------------|

| (hex0,hex1)                                              | (hex13,hex1)                    | (hex14,hex1)  | (hex27,hex1)                              |

| 1<br>1<br>1<br>1<br>1<br>2<br>1<br>1<br>1<br>3<br>3<br>5 | !<br>!<br>!<br>!<br>!<br>!<br>! | <br>          | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| (hex0,hexEE)                                             | (hex13,hexEE)                   | (hex14,hexEE) | (hex27,hexEE)                             |

| (hex0,hexEF)                                             | (hex13,hexEF)                   | (hex14,hexEF) | (hex27,hexEF)                             |

## FIG.17B

-125-2VOLTAGE SELECTER LEVEL SHIFTER 1/0 PORT DECODER MEMORY CELL LATCH **(4)** 110-2 111-2 COL. ADDR. **DECODER** 109-2 117-2 08-1 TIMING CON-TROLLER 16-2 128-3 LATCH COUNT 107-2 BUFFER UNIT 125-1 1802 -124-1 RAS -122-1 -123-1 -121-1 127-1 115-1 -120-1VOLTAGE SELECTER LEVEL SHIFTER 1/0 PORT DECODER MEMORY CELL LATCH **@** LATCH COUNTER 18-**DECODER** COL. ADDR. 108-1 109-1 117-1 **TROLLER** TIMING 28-1 16-1 LATCH COUNT 07-1 BUFFER UNIT 0

1807 0 **(4)** LIQUID CRYSTAL PANEL <u>(ii)</u> <u>@</u> SCANNING CIRCUIT 134 <u>(L)</u> POWER SUPPLY 133

FIG.19

# FIG.20A

#### SCREEN MEMORY MAP

| (hex0,hex0)  |          | (hex13,hex0)  | (hex14,hex0)  | <b></b> | (hex27,hex0)  |

|--------------|----------|---------------|---------------|---------|---------------|

| ;<br>;<br>;  |          | ;<br>;<br>;   |               |         | ļ             |

| (hex0,hex77) | ][       | (hex13,hex77) | (hex14,hex77) | ][      | (hex27,hex77) |

| (hex0,hex78) |          | (hex13,hex78) | (hex14,hex78) |         | (hex27,hex78) |

| t<br>t<br>1  |          | ;<br>;<br>;   | !             |         | 1<br>1<br>1   |

| (hex0,hexEF) | <b>]</b> | (hex13,hexEF) | (hex14,hexEF) | ][      | (hex27,hexEF) |

## FIG.20B

FIG.21B

FIG.22

# **FIG.23**

\_2314-2 \_2315-2 \_2312-2 \_2313-2 **(4)** LEVEL SHIFTER **@** 2317-2-2316-2 FIG.24B TIMING CONTROL CIRCUIT 128-2 132 LIQUID CRYSTAL PANEL 0 -2314-1 -2313-1-2315-1 <u>(ii)</u> VOLTAGE SELECTOR (L) 135 2316-1-2317-1-TIMING CONTROL CIRCUIT **—134** POWER SUPPLY 131 **(** 130 SCANNING CIRCUIT 1

# FIG.25A

## FIG.25B

## FIG.25C

FIG.25D

**FIG.27**

**FIG.28**

FIG.29A

FIG.29B

# FIG.32A

#### SCREEN MEMORY MAP SEEN FROM CPU

| Г           | <b>-</b> | X-DIREC   | CTION           |    |               |        |        |          |          |                  |     |        |        |

|-------------|----------|-----------|-----------------|----|---------------|--------|--------|----------|----------|------------------|-----|--------|--------|

| Y ♥<br>DIRE | C~       | C- DRIVER |                 |    |               |        |        | DRIVER   |          |                  |     |        |        |

| TION        |          |           |                 |    |               |        |        |          |          |                  |     |        |        |

| F           | $I \cap$ | 00000Н    | 000 <b>01</b> H |    |               | 00026H | 00027H | 00028H   | 00029H   | li               | 1   | 0004EH | 0004FH |

| 13          | H        | 00100H    | 00001H          |    | -             | 00126H | 00127H | 00128H   | 00129H   |                  |     | 0014EH | 0014FH |

| CIRCU       |          |           |                 |    | † †<br>† †    |        |        |          | <u> </u> |                  | j . |        |        |

| _           | ł        |           |                 |    | <u> </u>      |        |        | <u> </u> | <b>!</b> | - <del>i</del> - | Ė.  |        |        |

| ž           |          |           |                 |    | _             |        |        | <b> </b> | <u> </u> |                  | Ŀ.  |        |        |

| ON N        | $  \  $  | 0EE00H    | 0EE01H          | 7- | + -<br>1      | 0EE26H | 0EE27F | 0EE281   | 0EE291   | <b> </b>         |     | 0EE4EH | 0EE4FH |

| SCA         | П        | 0EF00H    | 0EF01H          |    | † -<br>1<br>1 | 0EF26H | 0EF27F | 0EF28H   | 0EF29F   |                  | 1   | 0EF4EH | 0EF4FH |

# FIG.32B

#### DRIVER MEMORY MAP SEEN FROM DRIVER

| Γ        | <b>→</b> ( | COLUMN | j     |      |           |       |       |           |                |         |       |

|----------|------------|--------|-------|------|-----------|-------|-------|-----------|----------------|---------|-------|

| LO\      | Ν          |        | D     | RIVE | R         |       |       | DRIVER    |                |         |       |

|          |            |        |       |      |           |       |       |           |                |         |       |

| 느        | 11         | 0000H  | 0001H |      | 0026H     | 0027H | 0000H | 0001H     |                | 0026H   | 0027H |

| 딍        | П          | 0040H  | 0041H |      | 0066H     | 0067H | 0040H | 0041H     |                | 0066H   | 0067H |

| S.R.     |            |        |       |      |           |       |       |           |                |         | L     |

| ပြ       |            |        |       |      | <br> <br> |       |       | <br> <br> | ┝┪╼┢╺<br>┍┪╼┢╸ | <b></b> |       |

| Z        |            |        |       |      |           |       |       |           | - 4            |         |       |

| Z        | 1/         | 3B80H  | 3B81H |      | 3ВА6Н     | 3ВА7Н | 3B80H | 3B81H     | - +            | 3BA6H   | зва7Н |

| OS<br>OS | Π          | 3ВС0Н  | 3BC1H |      | 3BE6H     | 3BE7H | 3BC0H | 3BC1H     | !!!            | 3BE6H   | 3BE7H |

| S        | '          |        |       |      |           |       |       |           |                |         |       |

**FIG.33**

| DRIVER | <b>ADDRESS</b> | MODE |

|--------|----------------|------|

| MODEA2 | MODEA1 | MODEA0 | DRIVER 1D |

|--------|--------|--------|-----------|

| 0      | 0      | 0      | 0         |

| 0      | 0      | 1      | 1         |

| 0      | 1      | 0      | 2         |

| 0      | 1      | 1      | 3         |

| 1      | 0      | 0      | 4         |

| 1      | 0      | 1      | 5         |

| 1      | 1      | 0      | 6         |

| 1      | 1      | 1      | 7         |

FIG.34

**FIG.35**

**FIG.36**

**FIG.37**

**FIG.38**

## MEMORY READ CYCLE

**FIG.39**

### MEMORY EARLY-WRITE CYCLE

**FIG.40**

### MEMORY DELAYED-WRITE CYCLE

**FIG.41**

## MEMORY READ-MODIFIED WRITE CYCLE

FIG.42

FIG.43

FIG.44

FIG.45

FIG.47A

FIG.47B

**FIG.48**

FIG.49

FIG.50A

FIG.50B

**FIG.51**

FIG.52

FIG.53

**FIG.54**

**FIG.55**

FIG.56

**FIG.57**

FIG.58

FIG.59

FIG.60

**FIG.61**

# **FIG.62**

# MEMORY READ CYCLE

| Address |            |

|---------|------------|

| CS      |            |

| OE      |            |

| WE      |            |

| I/O out | Valid Data |

| I/O in  |            |

# **FIG.63**

## MEMORY WRITE CYCLE

| Address |            |

|---------|------------|

| CS      |            |

| ŌĒ      |            |

| WE      |            |

| I/O out | Valid Data |

| 1/0 in  |            |

# LIQUID CRYSTAL DISPLAY WITH LIQUID CRYSTAL DRIVER HAVING DISPLAY MEMORY

#### BACKGROUND OF THE INVENTION

[0001] The present invention relates to a liquid crystal driver which has an internal memory and a liquid crystal display which uses such a driver.

[0002] In a liquid crystal display connected to a computer, there is performed an operation in which an image is always displayed on a display screen. The image display operation is performed in such a manner that a liquid crystal driver on the liquid crystal display side successively reads display data from a display memory (or makes a display access) and supplies the read data to a liquid crystal panel at a predetermined period. In the case where there is a command from a computer side for rewriting or change and addition of display data (hereinafter referred to as updating), it is necessary to update data of the display memory (or make an updating access). Since the display data updating operation (or updating access) is not synchronous with the display operation on the liquid crystal display side and is not periodical, there may be the case where an access to the display memory for the display operation and an access to the display memory for the updating of data conflict with each other. In general, the display operation cannot be interrupted and has a preference to the updating operation. Therefore, it is necessary to change the contents of the display memory so that the updating operation does not obstruct the display operation.

[0003] The conventional liquid crystal display is constructed using, for example, a liquid crystal driver HD66107 disclosed on pages 787 to 806 of Hitachi LCD Controller/Driver LSI Data Book published by Semiconductor Group, Hitachi Ltd. Such conventional liquid crystal driver will be explained by use of FIGS. 2 to 5.

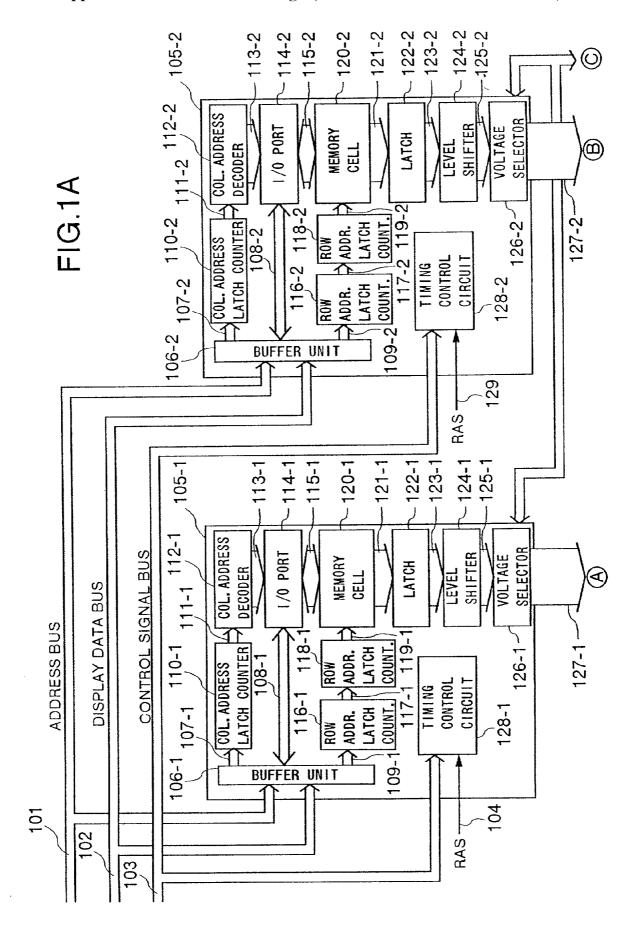

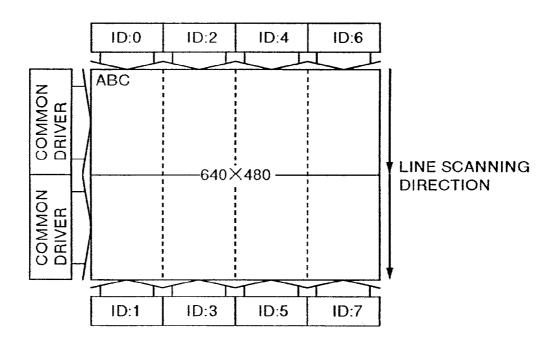

[0004] In FIG. 2, reference numeral 201 denotes a control signal bus for transferring a control signal, and numeral 202 denotes a data bus for transferring display data. Numerals 203-1 and 203-2 denote liquid crystal drivers. In the shown example, two liquid crystal drivers are used in conformity with the width of a liquid crystal panel 219 in an X (or horizontal) direction. The liquid crystal drivers 203-1 and 203-2 will hereinafter be represented generically as "liquid crystal driver 203". (Similar representation will be used for other reference numerals.) Numeral 204 denotes a timing control circuit for controlling the operation of the liquid crystal driver 203, and numeral 205 denotes a shift register for generating a signal which latches display data transferred by the data bus 202. Numeral 206 denotes a signal line for transferring latch clocks outputted from the shift register 205, numeral 207 a latch for successively taking in display data, numeral 208 a data bus for transferring data outputted from the latch 207, numeral 209 a latch for simultaneously taking in data transferred by the data bus 208, and numeral 210 a data bus for transferring data outputted from the latch 209. Numeral 211 denotes a level shifter for shifting display data transferred by the data bus 210 into a voltage level corresponding to a liquid crystal applied voltage (or a voltage to be applied to the liquid crystal of a liquid crystal panel). Numeral 212 denotes a data bus for transferring the level-shifted data, and numeral 213 denotes a voltage selector. Numeral 214 denotes an output voltage line for transferring a liquid crystal applied voltage which is selected by the voltage selector 213 in accordance with display data transferred through the data bus 212. Numeral 215 denotes a CL2 clock signal for controlling the shift register 205, and numeral 216 denotes a CL1 clock signal for taking data into the latch 209. Numeral 217 denotes a scanning circuit for selecting a line on which display is to be made. Numeral 218 denotes a scanning signal line for transferring a scanning signal generated by the scanning circuit 217, and numeral 219 denotes the display panel. Numeral 220 denotes a power supply circuit, and numerals 221 and 222 denote driving voltage lines for transferring driving voltages which drive the scanning circuit 217 and the liquid crystal driver 203, respectively.

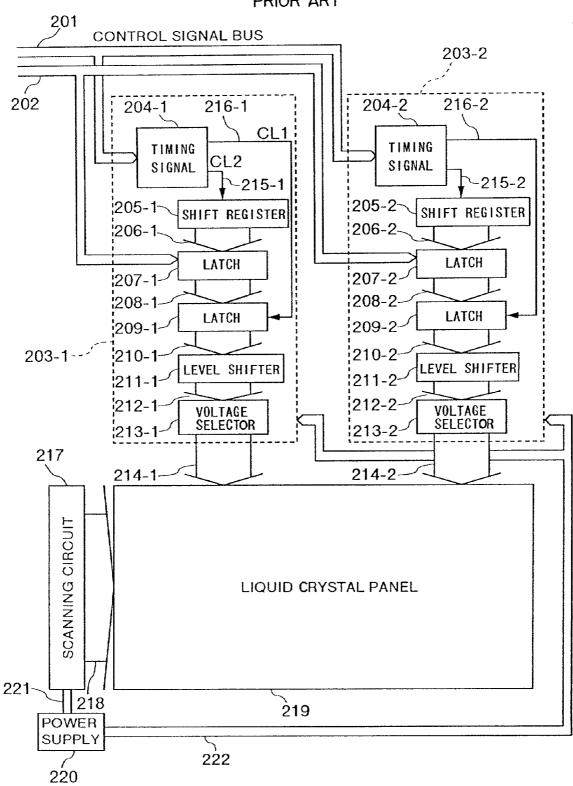

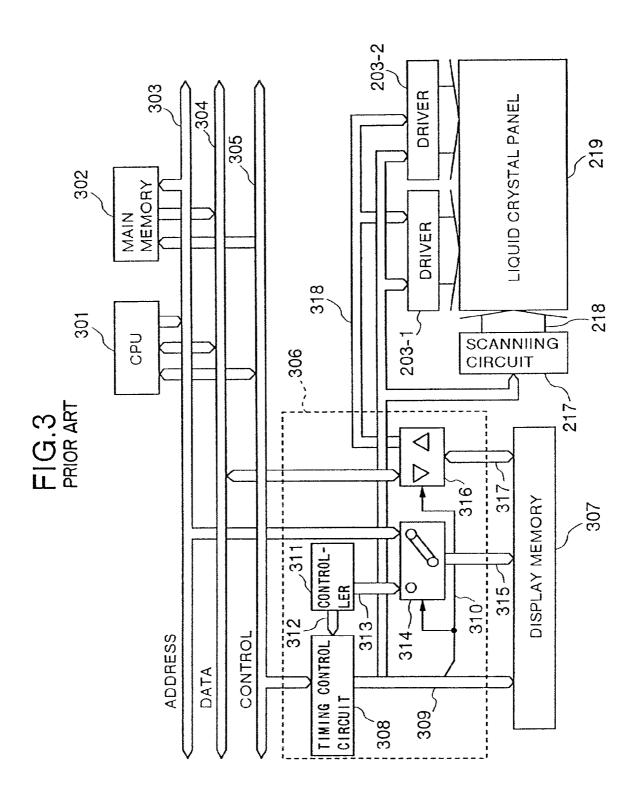

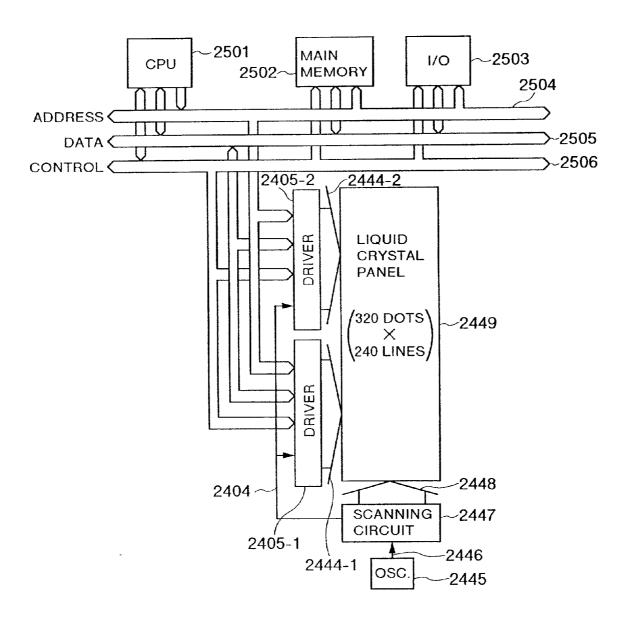

[0005] FIG. 3 shows a block diagram of an example of a personal computer system using the liquid crystal display shown in FIG. 2. In the shown example, a display memory 307 is arranged at the exterior of the liquid crystal driver 203.

[0006] In FIG. 3, reference numeral 301 denotes a CPU, numeral 302 a main memory, numeral 303 an address bus for transferring an address, numeral 304 a data bus for transferring data, and numeral 305 a control signal bus for transferring a control signal. Numeral 306 denotes a display controller, and numeral 307 denotes the display memory for storing display data therein. Numeral 308 denotes a timing control circuit, and numeral 309 denotes a timing signal which includes a signal for accessing the display memory 307 and a signal for operating the liquid crystal driver 208. Numeral 310 denotes a selection signal for making a change-over between a display address (or address for display) and an updating address (or address for updating). Numeral 311 denotes a controller for generating a timing signal to be transferred to a signal bus 312 and an address to be transferred to a display address bus 313. Numeral 314 denotes a selector for selecting a display address and an updating address, numeral 315 an address bus for transferring an address selected by the selector 314 for accessing the display memory 307, and numeral 316 a data buffer. Numeral 317 denotes a data bus for transferring data for accessing the display memory 307, and numeral 318 denotes a data bus for transferring display data for the liquid crystal display.

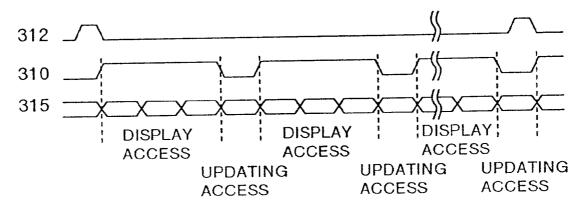

[0007] FIG. 4 is a timing chart showing an access to the display memory 307 in the system shown in FIG. 3.

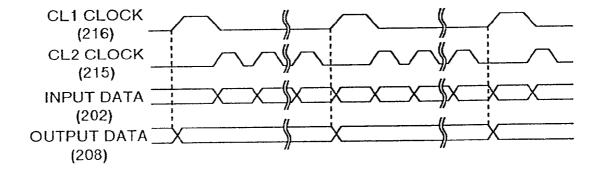

[0008] FIG. 5 is a timing chart showing the operation of the liquid crystal driver 203.

[0009] The liquid crystal display using the conventional liquid crystal driver will be explained using FIG. 2 again.

[0010] A control signal transferred through the signal bus 201 is inputted to the timing control circuit 204. A generated CL2 clock signal 215 is transferred to the shift register 205 which in turn generates a latch clock. The generated latch clock signal is outputted to the signal line 206. On the other hand, display data transferred through the data bus 202 to the driver 203 is successively latched by the latch 207 in accordance with the latch clock signal transferred through the signal line 206. The display data latched by the latch 207 is simultaneously stored into the latch 209 through the data bus 208 in accordance with a CL1 clock signal 216. This operation is shown in FIG. 5. Also, display data outputted

from the latch 209 by the CL1 clock signal is inputted through the data bus 210 to the level shifter 211 for conversion thereof into a voltage level corresponding to a liquid crystal applied voltage. The level-shifted display data is transferred through the data bus 212 to the voltage selector 213 which in turn selects a liquid crystal applied voltage. The selected liquid crystal applied voltage is supplied through the output voltage line 214 to the liquid crystal panel 219

[0011] Thus, the conventional liquid crystal driver has only a function of latching display data and outputting it after conversion into a liquid crystal applied voltage. This point will be explained in detail by use of FIG. 3 in conjunction with the system using the liquid crystal display driven by the conventional liquid crystal driver 203.

[0012] In the conventional system, it is necessary to transfer display data to the liquid crystal display at a fixed period. Therefore, the system requires the display memory 307 for storing display data for one screen, means for reading display data from the display memory 307 to output the read display data to the liquid crystal display, and means for updating display data to be stored in the display memory **307**. Since only one system is provided for the address bus 317, the data bus 317 and the control signal 309 for the display memory 307, it is necessary that a display access for reading display data to output the read display data to the liquid crystal display and an updating access for updating display data should be made to the display memory 307 in a time division or multiplexing manner, as shown in FIG. 4. Therefore, the conventional system is constructed as follows.

[0013] The address bus 315 is constructed such that a display address or updating address is transferred to the address bus 315 in such a manner that the address bus 313 for transferring an address for the display access and the address bus 303 for transferring an address for the updating access are changed over by the selector 314. The changeover control is performed by the timing control circuit 308. The timing control circuit 308 is inputted with a control signal from the CPU 301 through the control signal bus 305 and a control signal from the controller 311 through the control signal bus 312. The two control signals perform an arbitration control which determines whether the display access or the updating access is to be made to the display memory 307. The similar holds for the data bus. Namely, in the case of the display access, the data bus 317 is constructed such that data on the data bus 317 is transferred to the data bus 318 through the buffer 316. In the case of the updating access, data on the data bus 304 is transferred to the data bus 317 through the buffer 316.

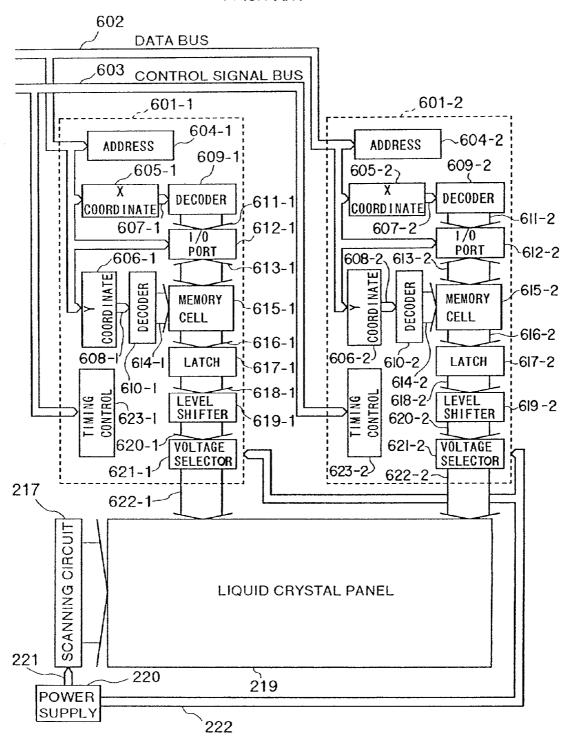

[0014] A liquid crystal driver with internal display memory, in which a display memory is incorporated in the liquid crystal driver, has been disclosed on pages 638 to 690 of "Hitachi IC Memory Data Book, No. 2" published by Semiconductor Group, Hitachi Ltd. A liquid crystal display system using such a liquid crystal driver with internal memory will now be explained by use of a block diagram shown in FIG. 6.

[0015] In FIG. 6, reference numeral 601 denotes a liquid crystal driver, numeral 602 a data bus, and numeral 603 a control signal. Numeral 604 denotes an address register, numeral 605 an X coordinate value register, numeral 606 a

Y coordinate value register, numeral 607 a data bus for outputting an X coordinate value, and numeral 608 a data bus for outputting a Y coordinate value. Numeral 609 denotes an X coordinate value decoder, numeral 610 a Y coordinate value decoder, and numeral 611 an X coordinate value decode signal. Numeral 612 denotes an I/O port for controlling the input/output of display data, numeral 613 a data bus for transferring display data, and numeral 614 a Y coordinate value decode signal. Numeral 615 denotes a memory cell (which may be a static RAM), and numeral 616 denotes a data bus for transferring data for display. Numeral 617 denotes a latch, numeral 618 a data bus for transferring display data outputted from the latch 617, numeral 619 a level shifter, numeral 620 a data bus for transferring the level-shifted data, numeral 621 a voltage selector, and numeral 622 an output voltage line for transferring a liquid crystal applied voltage. Numeral 623 denotes a timing control circuit.

[0016] Next, explanation will be made of the operation of the liquid crystal driver 601.

[0017] Since the liquid crystal driver 601 uses access based on an I/O interface, the address of a register to be accessed is set into the address register 604 through the data bus 602 and the register of the address set in the address register 604 is accessed through the data bus 602. Accordingly, the updating access to the display memory is as follows. First, the address of the X coordinate value register 605 is set into the address register 604. Next, X coordinate value data to be subjected to updating is set into the X coordinate value register 605 through the data bus 602 in accordance with the address set in the address register 604. Next, the address of the Y coordinate value register 606 is set into the address register 604 and Y coordinate value data to be subjected to updating is set into the Y coordinate value register 606 through the data bus 602 in accordance with the address set in the address register 604. Next, the I/O port 612 is accessed, thereby making it possible to update data at any position in the memory cell 615. Data in the memory cell 615 for data lines of each liquid crystal driver 601 is read by the timing control circuit 623 and is stored into the latch 617. Thereafter, a voltage conversion is made by the level shifter 619 and a liquid crystal applied voltage is selected by the voltage selector 621 which in turn outputs the selected liquid crystal applied voltage. This control for reading of data from the memory cell 615 is made for every one horizontal period, thereby enabling the display on the liquid crystal display 219.

[0018] Thus, it becomes possible to update data of the memory cell 615 at any position by setting data of each register of the liquid crystal driver 601.

[0019] In the prior art shown in FIG. 3, the liquid crystal driver always takes in serialized display data, converts the data into a liquid crystal applied voltage after taking-in of display data for one horizontal line, and outputs the liquid crystal applied voltage to effect the display. Therefore, means for transferring the serialized display data to the liquid crystal driver is needed. In the prior art shown in FIG. 3, display data for one frame is stored in the display memory. Provided that the operating conditions of the liquid crystal panel are such that the frame frequency is 70 Hz, the resolving power of the liquid crystal panel is 240 in the number of vertical lines and 320 in the number of horizontal

dots and the data bus width of the liquid crystal driver and the display memory is a 8-bit bus, it is necessary to always read 8-bit data from the display memory at a period of about 0.7 MHz (=70 (Hz)×240 (lines)×320 (dots)+8 (bits)). Accordingly, the display controller, the display memory and the liquid crystal driver must operate at the period of about 0.7 MHz and this operation muse be repeated for each frame even if a displayed image is a still picture.

[0020] The power consumption of the liquid crystal display and system increases in proportion to the operating frequency. Therefore, in order to attain a reduction in power consumption, it is necessary to reduce the operating frequency without deteriorating the operating efficiency of the system.

[0021] In the prior art shown in FIG. 3, the display access and the updating access are made to the display memory in a multiplexing manner. Since the display access has a preference to the updating access, it is necessary to perform the updating access in the intervals of the display access. Therefore, even in the case where it is desired to perform an updating processing at a high speed, the display access imposes a restriction on a processing speed for the updating

[0022] In the prior art shown in FIG. 6, when the display access is made to the display memory, a "BUSY" is given to the CPU to take a wait. In actual, the address register 604 has a "BUSY" bit and the CPU reads the "BUSY" bit (or makes a busy check) to make arbitration between the display access and the updating access. Thereby, in the case where the display and updating accesses to the display memory conflict with each other, the speed of the updating access becomes low. Also, when display data at any position is to be updated, the updating of display data becomes possible after the register data setting has been made four times, as mentioned above. Therefore, a considerable time is required for the updating access, thereby deteriorating the operating efficiency of the system.

[0023] In the prior art shown in FIG. 3, no consideration is taken to grayscale display and the case where the liquid crystal driver is provided in a Y-axis direction of the liquid crystal panel.

#### SUMMARY OF THE INVENTION

[0024] An object of the present invention is to attain a reduction in power consumption by making the operating frequency of a liquid crystal driver without deteriorating the operating efficiency of a liquid crystal display system.

[0025] Another object of the present invention is to provide a liquid crystal driver having a function with conveniences in use taken into consideration which function includes the realization of multi-grayscale display and the arrangement of the liquid crystal driver in the Y-axis direction of a liquid crystal panel.

[0026] A liquid crystal display according to the present invention comprises a liquid crystal panel having a plurality of data lines and a plurality of scanning lines arranged in a matrix form with pixels being formed at intersections of the data and scanning lines, a scanning circuit for successively applying a voltage to the scanning lines, and a liquid crystal driver for receiving display data from an external device to apply a voltage corresponding to the display data to the data

lines. The scanning circuit includes a synchronizing signal generating circuit for generating a frame display synchronizing signal indicative of a frame period for display of image on the liquid crystal panel and a line display synchronizing signal indicative of a line period for image display on the liquid crystal panel. The liquid crystal driver includes a display memory accessed through a memory interface for reading and writing of data, the display memory storing therein display data corresponding to the pixels, an address converter for converting, when the external device performs a read/write operation for the reading/writing of display data for the display memory, an address of display data on a display screen designated by the external device into a corresponding address of the display memory, a reading unit for reading display data of the display memory on each of successive lines in synchronism with the line display synchronizing signal, a holding unit for simultaneously holding display data for output data lines of the liquid crystal driver read by the reading unit, a voltage output circuit for outputting the display data held by the holding unit after conversion thereof into a voltage to be applied to the liquid crystal of the liquid crystal panel, and a timing control circuit for arbitrating between a display operation in which the voltage is applied to the data lines at a predetermined period on the basis of the display data stored in the display memory and the read/write operation which is performed by the external device for the display memory asynchronism with the display operation.

[0027] Since the liquid crystal driver of the present invention has the display memory incorporated therein, the periodic high-speed transfer of display data through a CPU bus becomes unnecessary and hence the operating frequency of the liquid crystal driver can be decreased (or a display access of once in one horizontal period suffices), thereby making it possible to attain a reduction in power consumption. Also, since the liquid crystal driver of the present invention can be accessed through a general purpose memory interface, a CPU can access the liquid crystal driver itself as it is a general purpose memory. Thereby, the updating speed can be improved as compared with that in the case of the conventional access through an I/O interface.

[0028] With the use of the address converter for converting an address designated by the system (or a CPU address) into an address of the internal display memory, an address including the combination of an X-direction address and a Y-direction address of the display screen of the liquid crystal panel can be used as the CPU address, thereby facilitating address determination at the time of updating.

[0029] The address converter is also effective in the case where a liquid crystal driver having a larger size is formed by combining liquid crystal driver elements which have the same construction. Namely, each of the liquid crystal driver elements receives a liquid crystal driver ID indicative of its own arrangement position externally supplied so that the conversion into an address of its own internal display memory can be made in accordance with the arrangement position. With this construction, the plurality of combined liquid crystal driver elements seem to be equivalent to a single liquid crystal driver when seen from the CPU.

[0030] With the use of two stages of holding circuits (or latch circuits) for holding read data from the display

memory at the time of display, an updating access at any point of time is performable without obstructing a display access.

[0031] In the case where the liquid crystal driver is arranged in a Y-axis direction (or on the left or right side) of a liquid crystal panel, selecting mean for successively selecting different pixels one by one from display data of plural pixels on the same address simultaneously read when outputted from the display memory to the liquid crystal panel is provided in the liquid crystal driver. Thereby, at the time of updating from the CPU, simultaneous access to plural continuous pixels arranged in a horizontal direction of the display panel becomes possible as in the case where the liquid crystal drivers are arranged in an X-axis direction (or the upper or lower side) of the liquid crystal panel.

#### BRIEF DESCRIPTION OF THE DRAWINGS

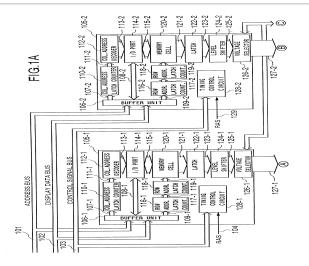

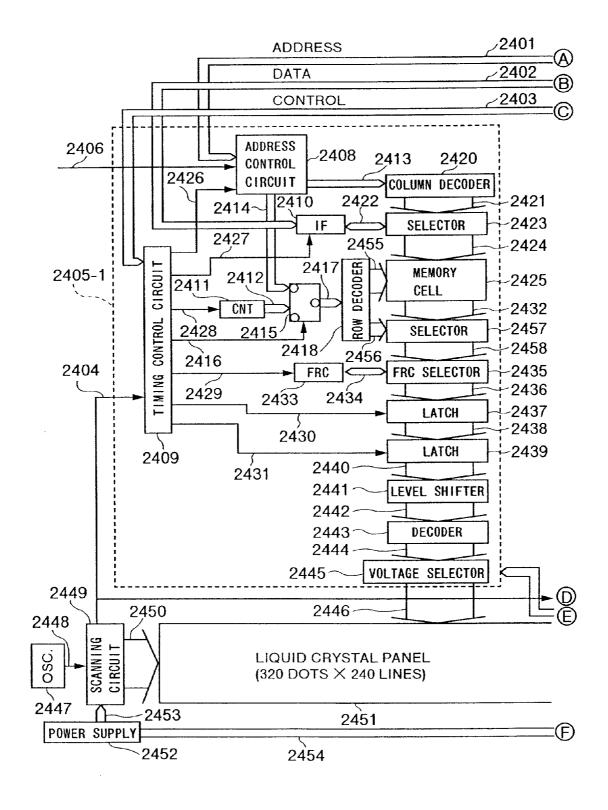

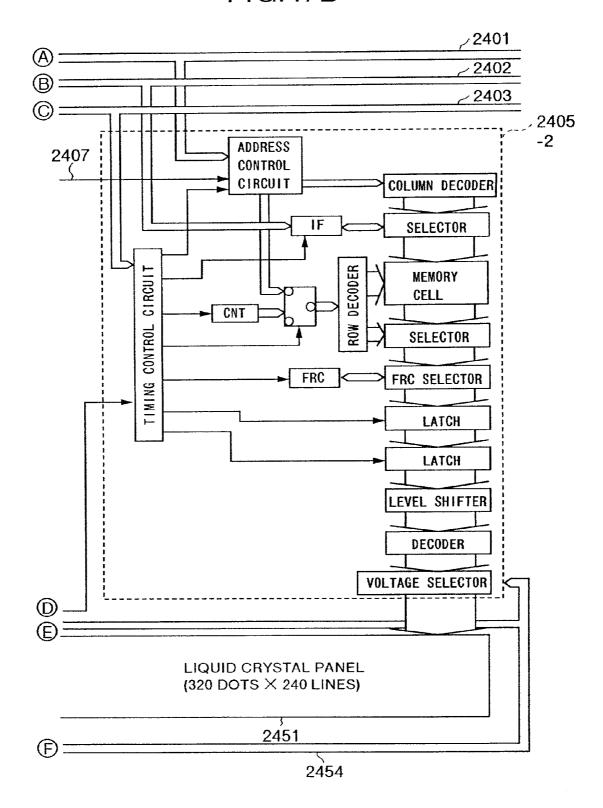

[0032] FIGS. 1A and 1B show a block diagram of a liquid crystal display according to the present invention;

[0033] FIG. 2 is a block diagram of the conventional liquid crystal display;

[0034] FIG. 3 is a block diagram of a personal computer system using the liquid crystal display shown in FIG. 2;

[0035] FIG. 4 is a timing chart showing the access to a display memory in the system shown in FIG. 3;

[0036] FIG. 5 is a timing chart showing the operation of the conventional liquid crystal driver;

[0037] FIG. 6 is a block diagram of a liquid crystal display using the conventional liquid crystal driver with internal memory;

[0038] FIG. 7 is a timing chart of a random access of a liquid crystal driver in the liquid crystal display of the present invention shown in FIG. 1;

[0039] FIG. 8 is a timing chart of a page access of the liquid crystal driver in the liquid crystal display of the present invention shown in FIG. 1;

[0040] FIG. 9 is a timing chart of a read-modified write access of the liquid crystal driver in the liquid crystal display shown in FIG. 1;

[0041] FIG. 10 is a timing chart of a write cycle in a burst access of the liquid crystal driver in the liquid crystal display shown in FIG. 1;

[0042] FIG. 11 is a timing chart of a read cycle in the burst access of the liquid crystal driver in the liquid crystal display shown in FIG. 1;

[0043] FIG. 12 is a timing chart of a random driver output access of the liquid crystal driver in the liquid crystal display shown in FIG. 1;

[0044] FIG. 13 is a timing chart of a sequential driver output access of the liquid crystal driver in the liquid crystal display shown in FIG. 1;

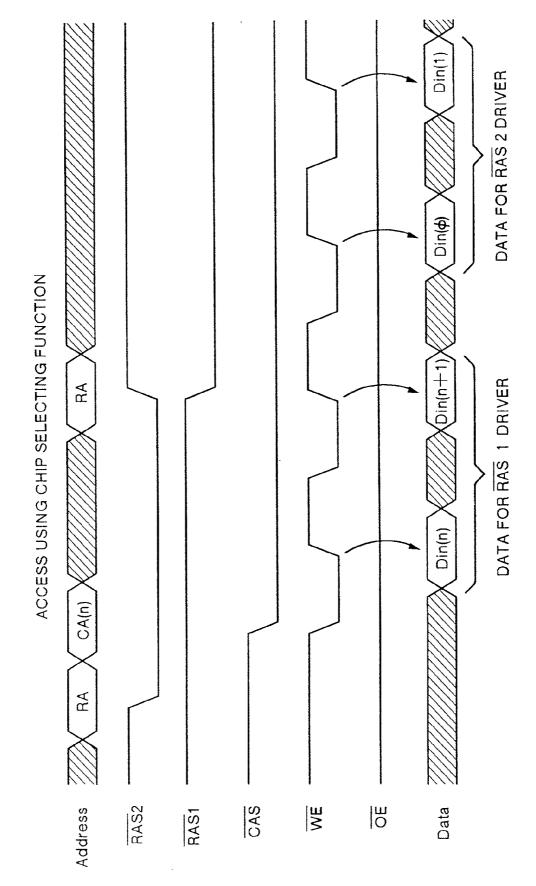

[0045] FIG. 14 is a timing chart in the case where a continuous access using a plurality of liquid crystal drivers is made by use of a chip selecting function in the liquid crystal display shown in FIG. 1;

[0046] FIG. 15 shows a memory map of the liquid crystal driver with internal memory shown in FIG. 1;

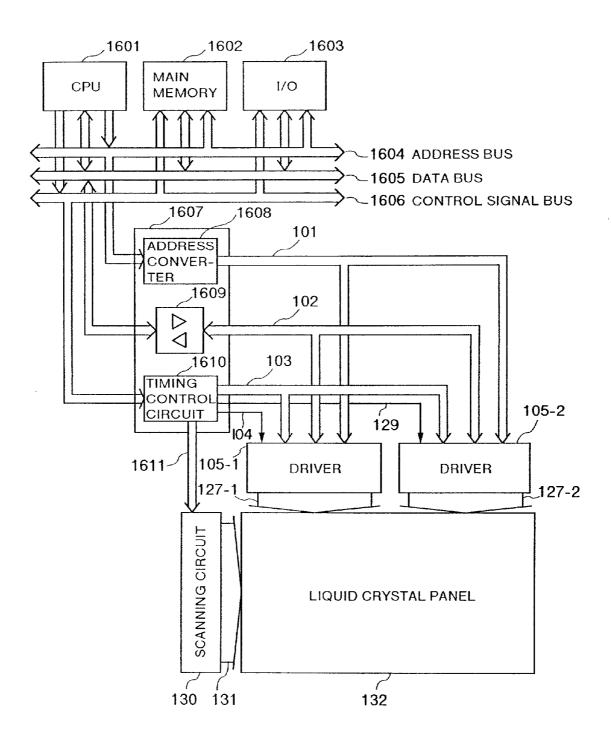

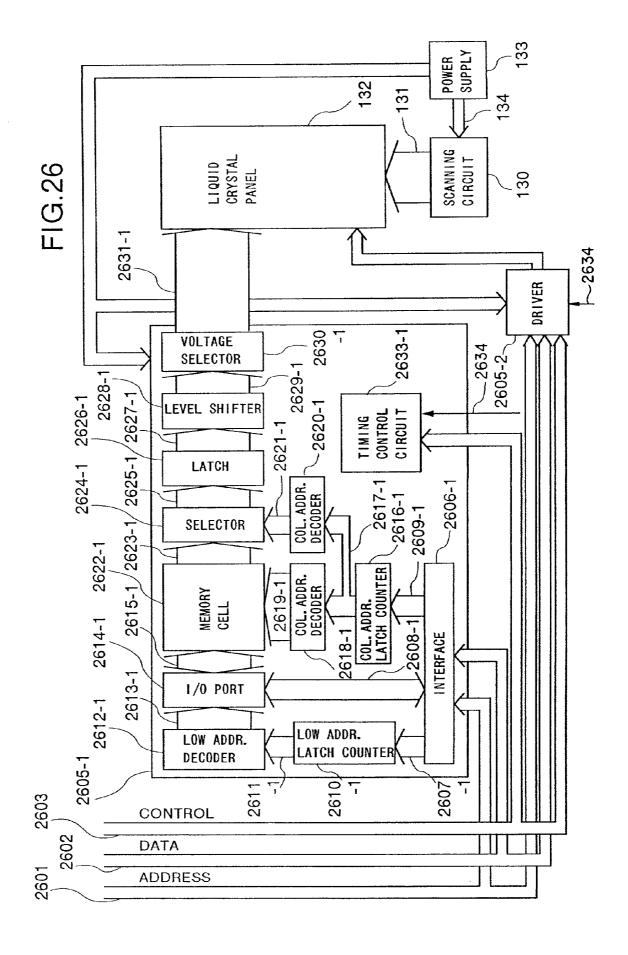

[0047] FIG. 16 is a block diagram of a liquid crystal display system according to a first embodiment in which the liquid crystal driver of the present invention is used;

[0048] FIG. 17A is a screen memory map of the liquid crystal display system of FIG. 16 when seen from the CPU, and

[0049] FIG. 17B is a driver memory map thereof when seen from the driver;

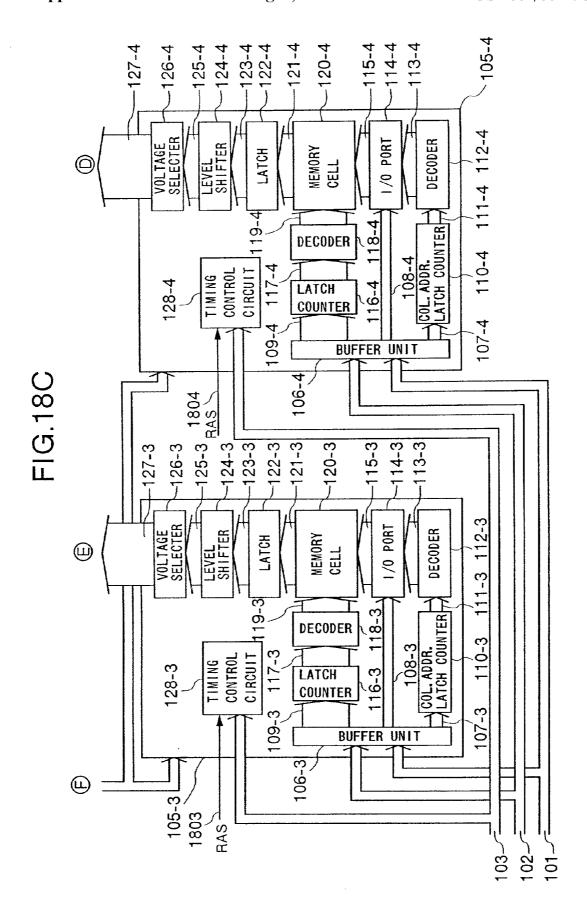

[0050] FIGS. 18A, 18B and 18C show a block diagram of a liquid crystal display according to a second embodiment in which the liquid crystal driver of the present invention is used and two-screen driving is made;

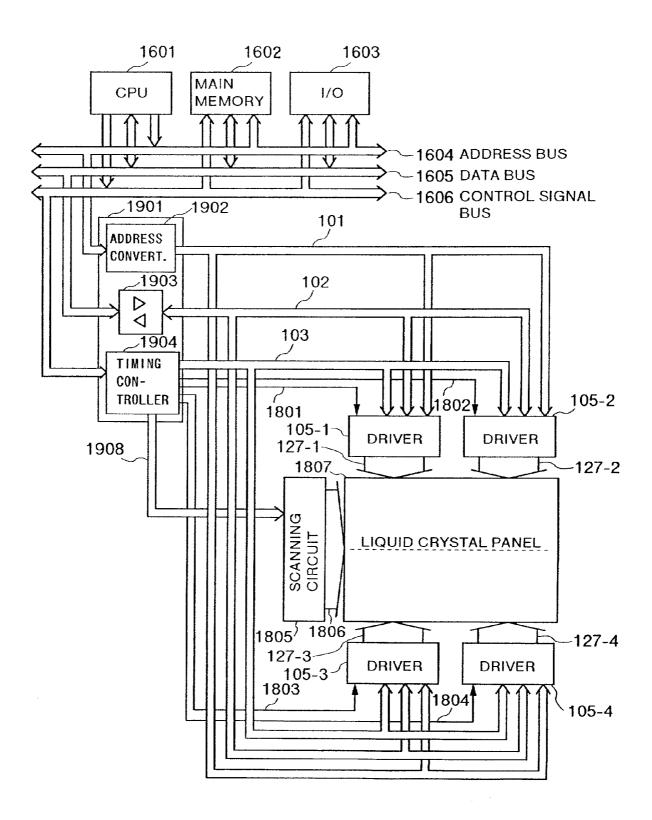

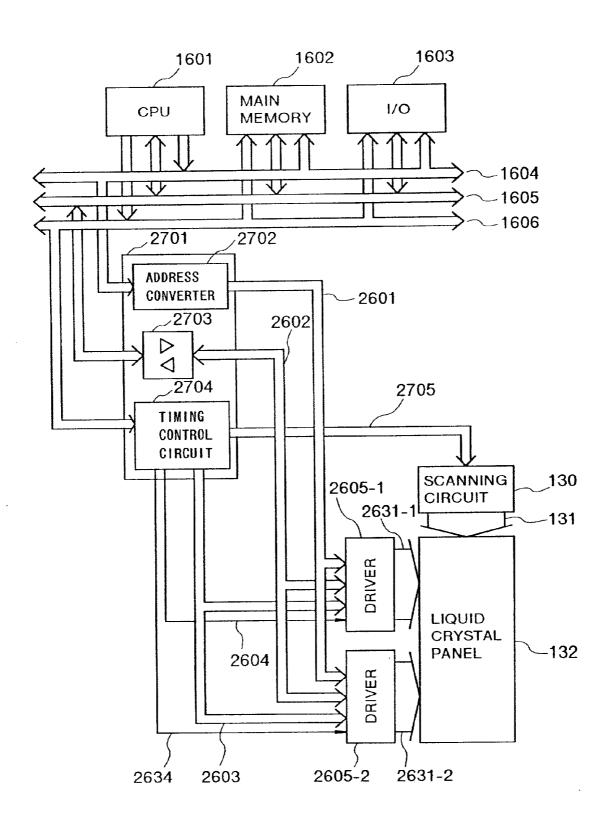

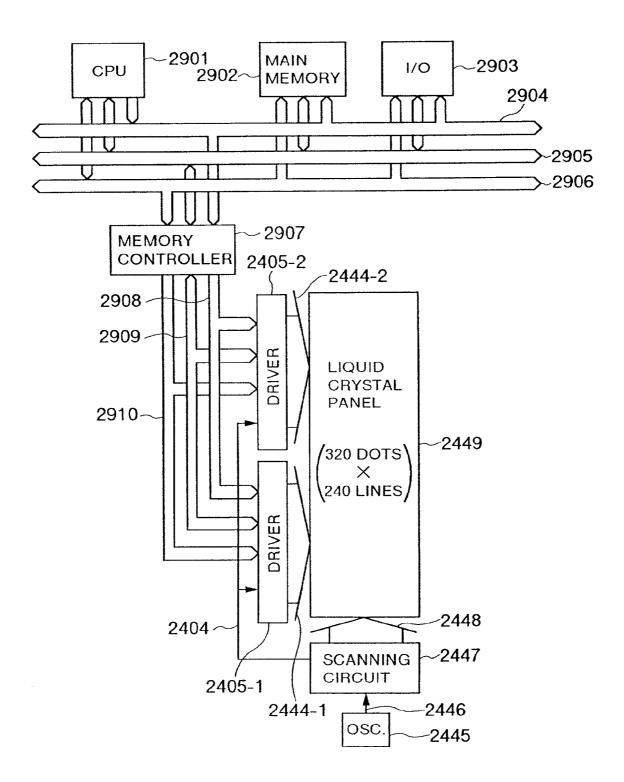

[0051] FIG. 19 is a block diagram of a system using the liquid crystal display shown in FIG. 18;

[0052] FIG. 20A is a screen memory map of the liquid crystal display system of FIG. 18 when seen from the CPU, and

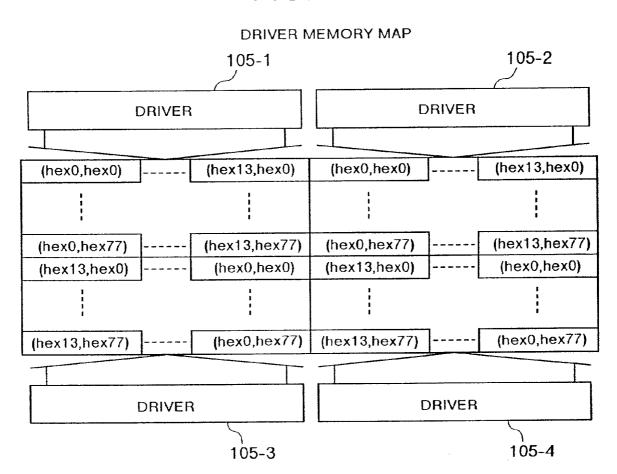

[0053] FIG. 20B is a driver memory map thereof when seen from the liquid crystal driver;

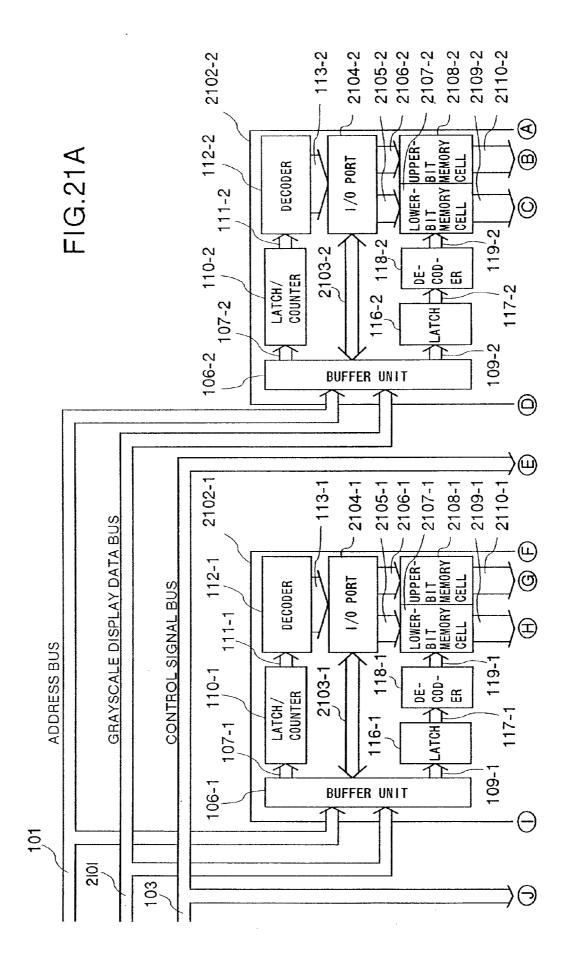

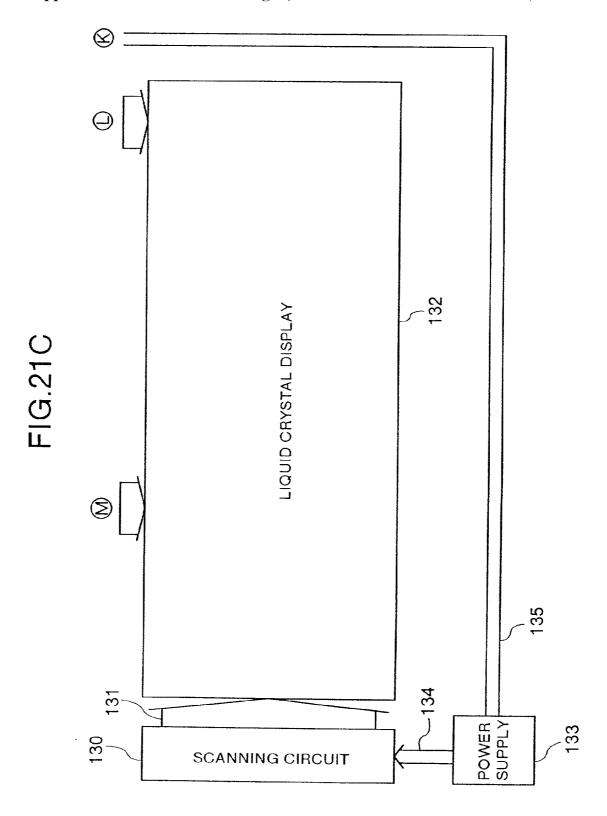

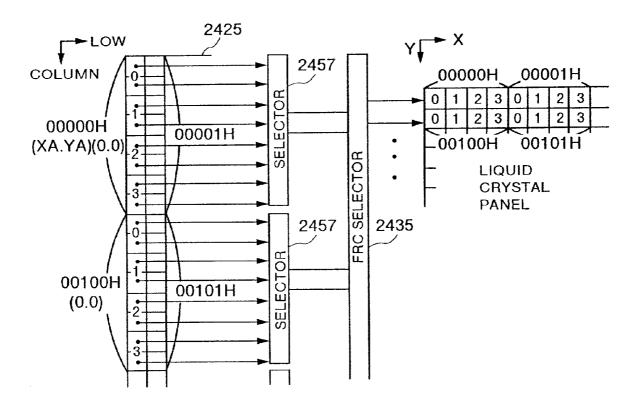

[0054] FIGS. 21A, 21B and 21C show a block diagram of a liquid crystal display according to a third embodiment in which the liquid crystal driver of the present invention using an FRC as a grayscale system is used;

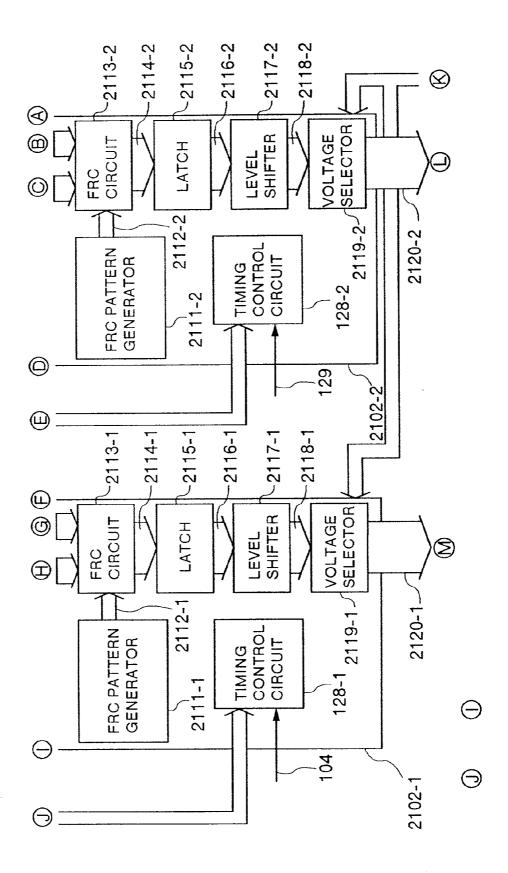

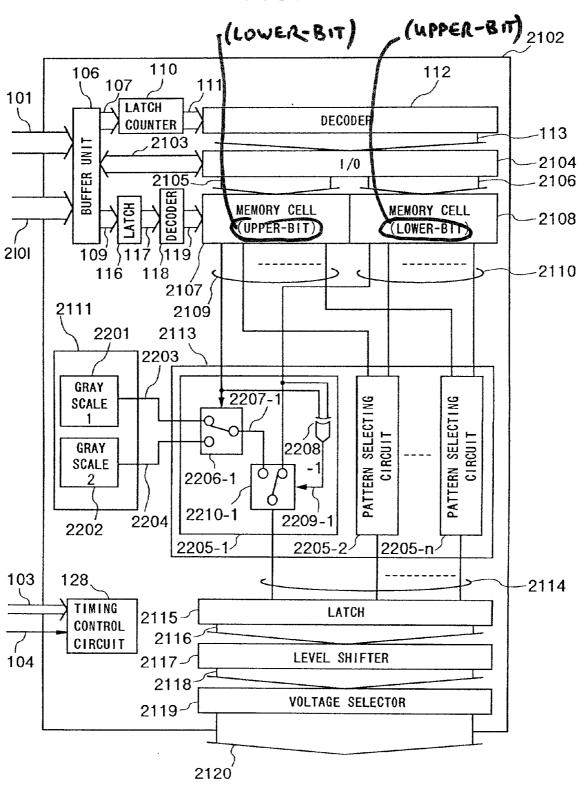

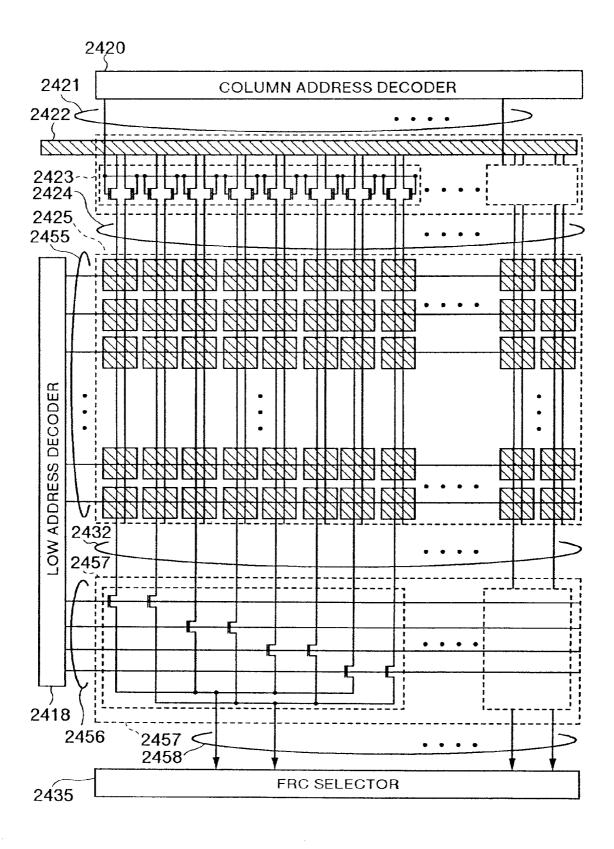

[0055] FIG. 22 is a detailed block diagram of the liquid crystal driver shown in FIG. 21;

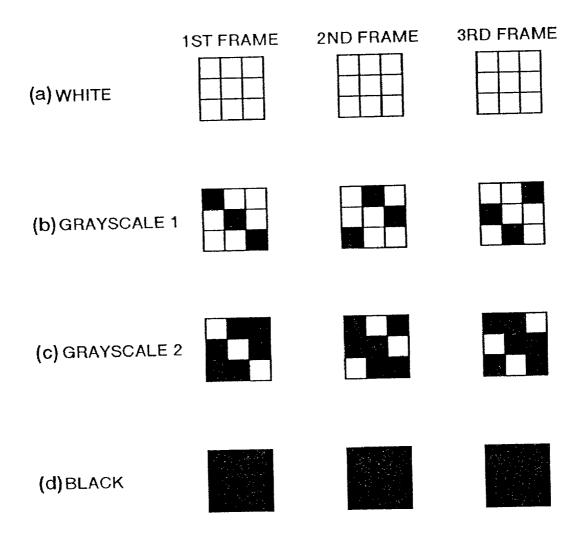

[0056] FIG. 23 shows display patterns in the case where the FRC is used;

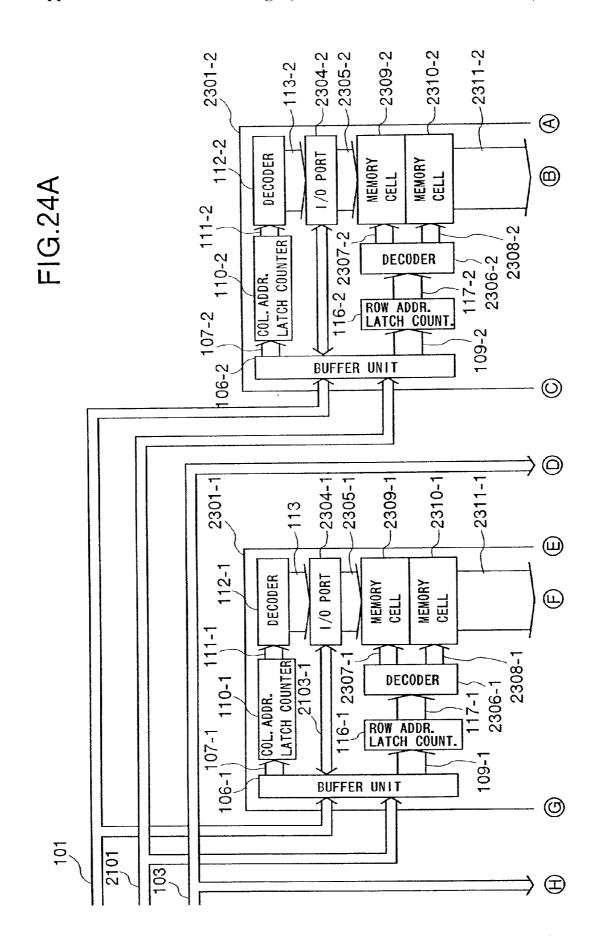

[0057] FIGS. 24A and 24B show a block diagram of a liquid crystal display according to a fourth embodiment in which the liquid crystal driver of the present invention using a PWM the grayscale system is used;

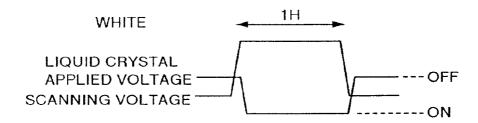

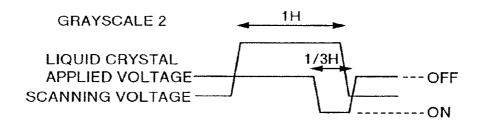

[0058] FIGS. 25A to 25D are timing charts of a liquid crystal applied voltage and a scanning voltage in each grayscale in the case where the PWM is used;

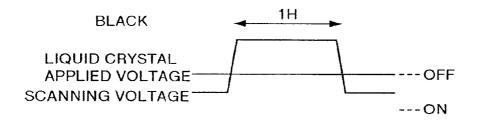

[0059] FIG. 26 is a block diagram of a liquid crystal display according to a fifth embodiment in which the liquid crystal driver of the present invention is used;

[0060] FIG. 27 is a block diagram of a system using the liquid crystal display of the fifth embodiment shown in FIG. 26:

[0061] FIG. 28 shows a memory map of a liquid crystal driver shown in FIG. 26;

[0062] FIGS. 29A and 29B show a block diagram of a liquid crystal display according to a sixth embodiment of the present invention in which the liquid crystal driver of the present invention is used;

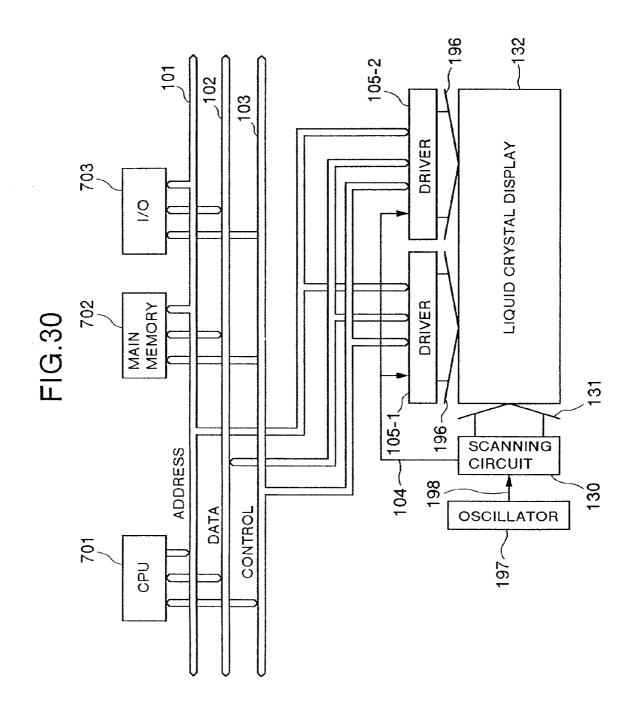

[0063] FIG. 30 is a block diagram showing one example of the construction of a liquid crystal display system using the liquid crystal display of the sixth embodiment shown in FIG. 29;

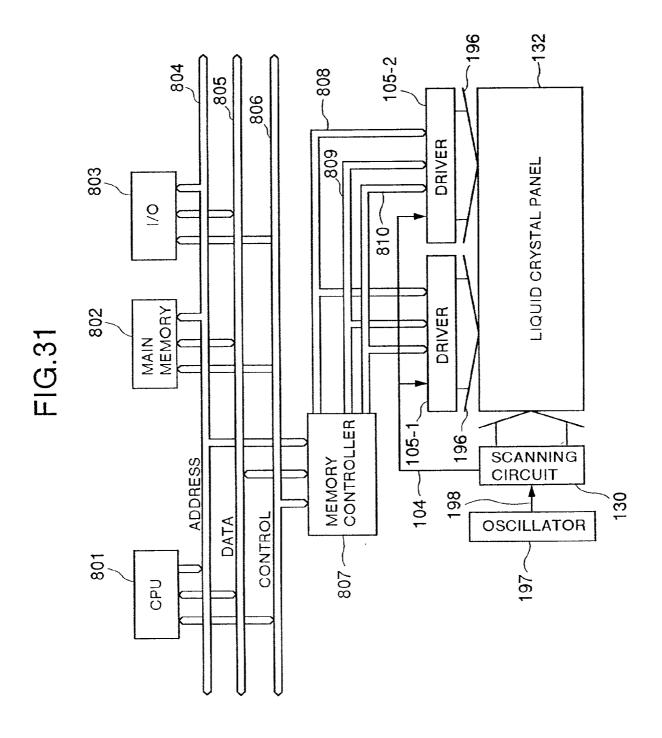

[0064] FIG. 31 is a block diagram showing another example of the construction of a liquid crystal display system using the liquid crystal display of the sixth embodiment shown in FIG. 29;

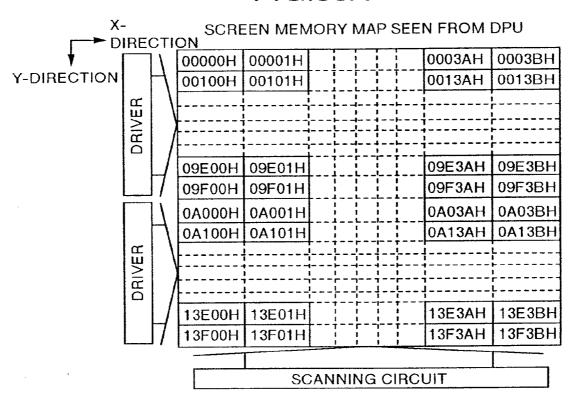

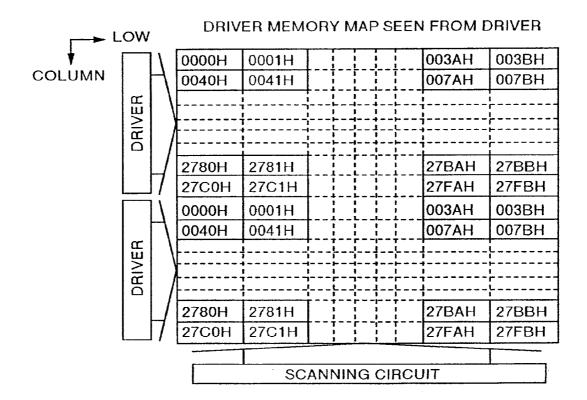

[0065] FIG. 32A is a screen memory map of the liquid crystal display system in the sixth embodiment when seen from the CPU, and

[0066] FIG. 32B is a driver memory map thereof when seen from the liquid crystal driver;

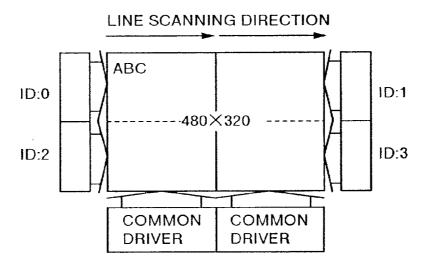

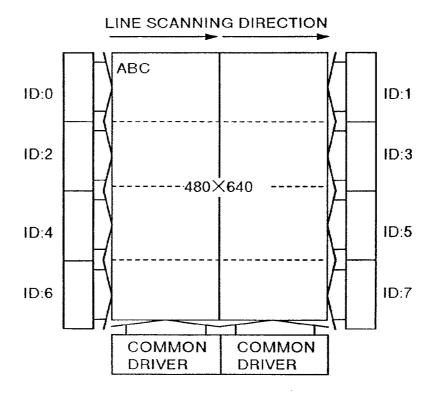

[0067] FIG. 33 is a diagram for explaining an address mode of the liquid crystal driver;

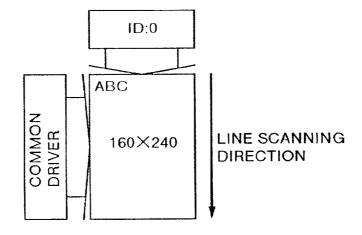

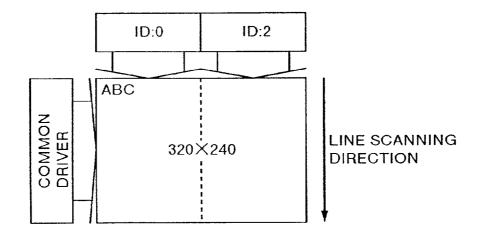

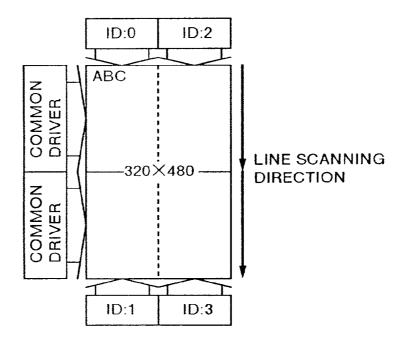

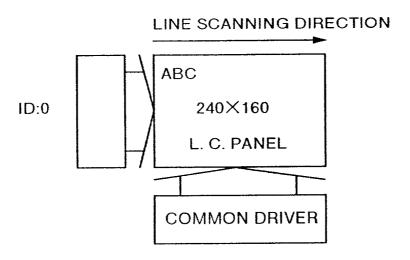

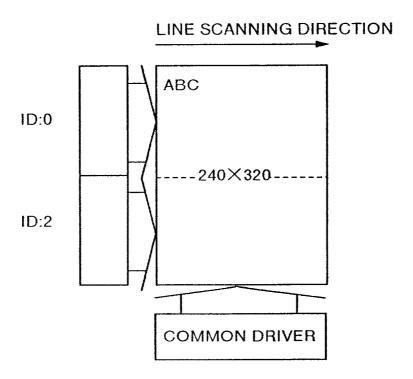

[0068] FIGS. 34 to 37 are diagrams showing the respective liquid crystal driver arrangements in the liquid crystal display of the sixth embodiment for different resolving powers of the liquid crystal panel;

[0069] FIG. 38 is a timing chart showing a memory read cycle;

[0070] FIG. 39 is a timing chart showing a memory early-write cycle;

[0071] FIG. 40 is a timing chart showing a memory delayed-write cycle;

[0072] FIG. 41 is a timing chart showing a memory read-modified write cycle;

[0073] FIG. 42 is a timing chart showing a memory page mode read cycle;

[0074] FIG. 43 is a timing chart showing a memory page mode early-write cycle;

[0075] FIG. 44 is a timing chart showing a memory page mode delayed-write cycle;

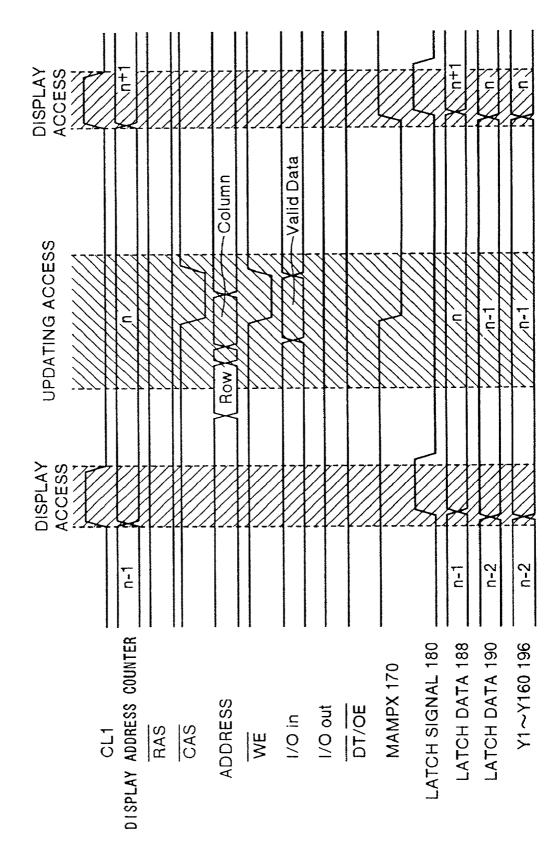

[0076] FIG. 45 is a timing chart showing a display access and an updating access;

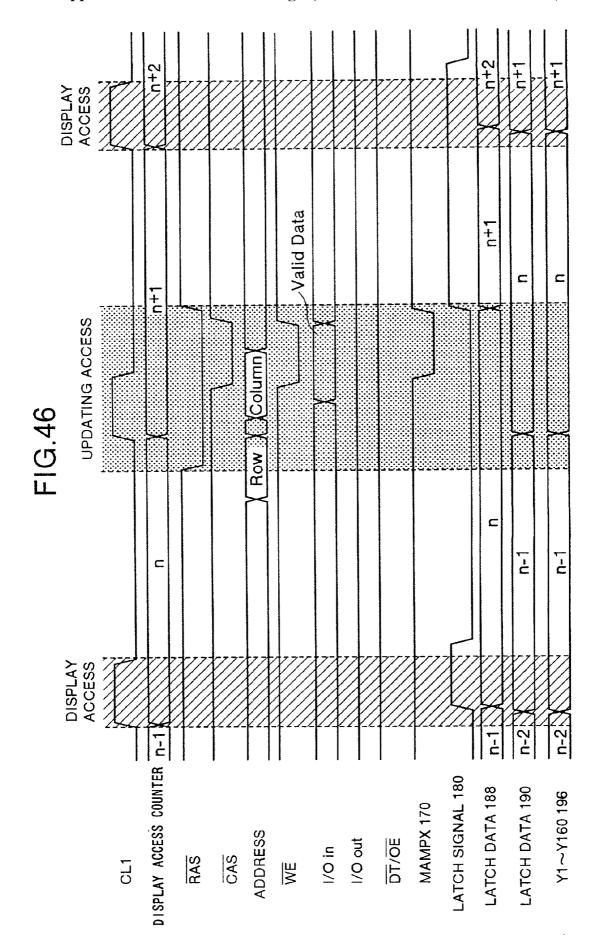

[0077] FIG. 46 is a timing chart similar to FIG. 45 in the case where the display access and the updating access overlap;

[0078] FIGS. 47A and 47B show a block diagram of a liquid crystal display according to a seventh embodiment of the present invention in which the liquid crystal driver with internal memory of the present invention is used;

[0079] FIG. 48 is a block diagram showing one example of the construction of a liquid crystal display system using the liquid crystal display of the seventh embodiment;

[0080] FIG. 49 is a block diagram showing another example of the construction of a liquid crystal display system using the liquid crystal display of the seventh embodiment;

[0081] FIG. 50A is a screen memory map of the liquid crystal display system in the seventh embodiment when seen from the CPU, and FIG. 50B is a driver memory map thereof when seen from the liquid crystal driver;

[0082] FIGS. 51 to 54 are diagrams showing the respective liquid crystal driver arrangements in the liquid crystal display of the seventh embodiment for different resolving powers of the liquid crystal panel;

[0083] FIG. 55 is a detailed block diagram of a memory cell in the seventh embodiment;

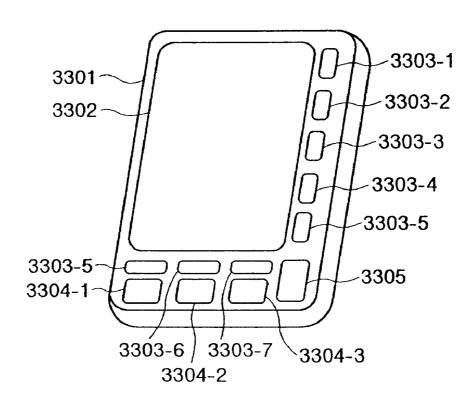

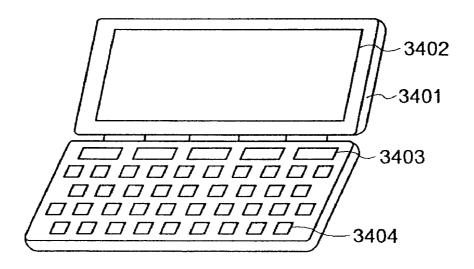

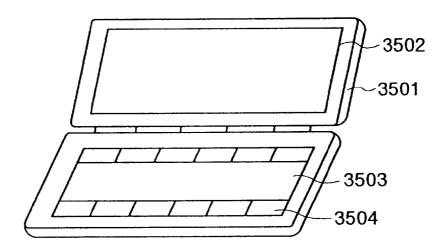

[0084] FIGS. 56 to 60 are sketchy views of portable information equipments in which the liquid crystal driver with internal memory of the present invention is used;

[0085] FIG. 61 is an explanatory view showing a relationship between a memory address and a bit map in he case where the liquid crystal driver is arranged in a Y direction;

[0086] FIG. 62 is a timing chart showing a memory read cycle in another embodiment of the present invention in which an SRAM interface is used; and

[0087] FIG. 63 is a timing chart showing a memory write cycle in the other embodiment of the present invention in which the SRAM interface is used.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0088] A first embodiment of the present invention will be explained in connection with a liquid crystal driver of the present invention by use of FIGS. 1 and 7 to 17.

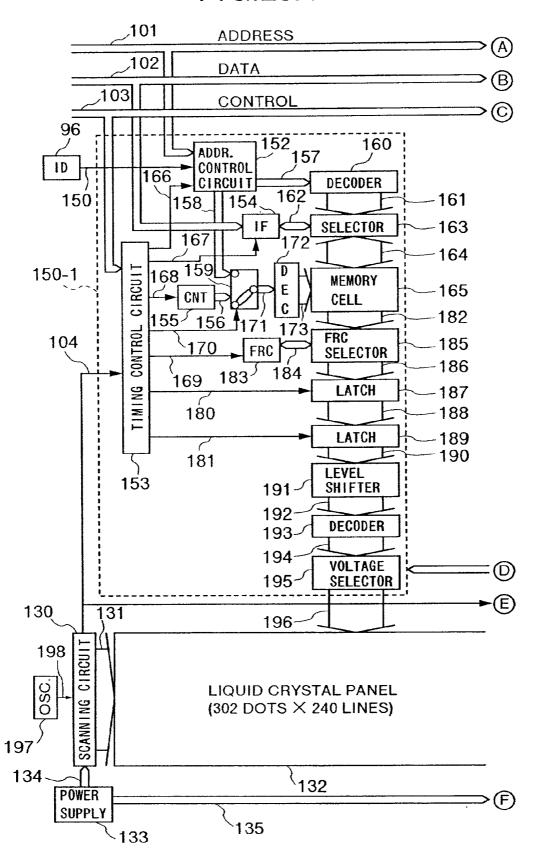

[0089] FIG. 1 is a block diagram of a liquid crystal display using a liquid crystal driver of the present invention.

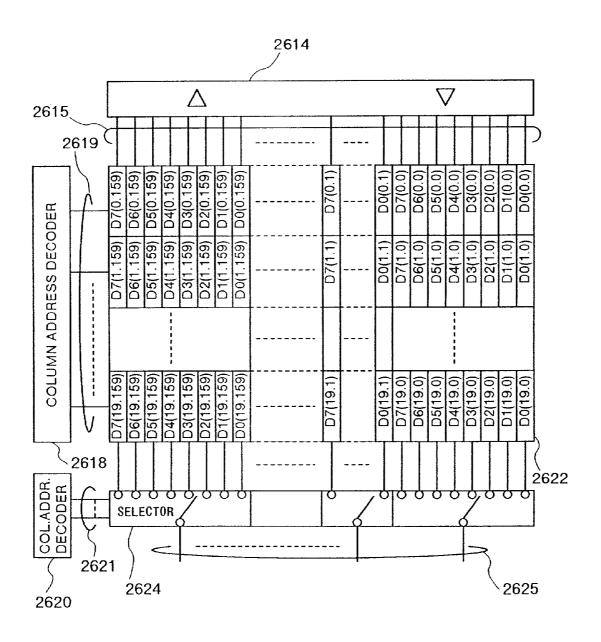

[0090] In FIG. 1, reference numeral 101 denotes an address bus for transferring an address, numeral 102 a data bus for transferring display data, numeral 103 a control signal bus for transferring a control signal, and numeral 104 a RAS signal. Numeral 105 denotes a liquid crystal driver of the present invention which has 160 bits as the number of outputs. Numeral 106 denotes a buffer unit (or a bi-directional buffer) for the address bus 101 and the data bus 102, numeral 107 a column address bus for transferring a column address designating a column address of a memory cell, numeral 108 a data bus for transferring display data, and numeral 109 a row address bus for transferring a row address designating a row address of the memory cell. Numeral 110 denotes a column address latch/counter, and numeral 111 denotes a column address bus for transferring a column address latched or counted by the column address latch/ counter 110. Numeral 112 denotes a column address decoder, and numeral 113 denotes a signal bus for transferring a decode signal decoded by the column address decoder 112. Numeral 114 denotes an I/O port for controlling the input/output of display data. Numeral 115 denotes a data bus for transferring display data. Numeral 116 denotes a row address latch/counter, numeral 117 a row address bus for transferring a row address latched or counted by the row address latch/counter 116, numeral 118 a row address decoder, and numeral 119 denotes a signal bus for transferring a decode signal decoded by the row address decoder 118. Numeral 120 denotes a memory cell, and numeral 121 denotes a data bus for transferring display data of 160 bits outputted from the memory cell 120 in accordance with a display instruction. Numeral 122 denotes a latch for simultaneously latching the display data of 160 bits transferred by the data bus 121. Numeral 123 denotes a data bus for transferring display data latched by the latch 122, and numeral 124 denotes a level shifter for converting a voltage level of display data into a level corresponding to a liquid crystal applied voltage. Numeral 125 denotes a data bus for transferring the level-shifted display data, numeral 126 a voltage selector, and numeral 127 an output voltage line for transferring a liquid crystal applied voltage selected by the voltage selector 126 in accordance with display data. Numeral 128 denotes a timing control circuit, and numeral 129 denotes a RAS signal inputted to a liquid crystal driver 105-2. Numeral 130 denotes a scanning circuit, numeral 131 a scanning signal line for transferring a scanning signal

generated by the scanning circuit 130, and numeral 132 a liquid crystal panel which has a resolving power of (320 dots)×(240 lines). Numeral 133 denotes a power supply circuit, numeral 134 a driving voltage line for transferring a voltage for driving the scanning circuit, and numeral 135 a voltage line for transferring a liquid crystal driving voltage.

[0091] The liquid crystal panel 132 includes 320 data lines 136 which are connected to the output voltage line 127 and 240 scanning lines 137 which are connected to the scanning signal line 131. The data lines 136 and the scanning lines 137 are arranged in a matrix form so that 320×240 pixels are formed at the intersections of the lines 136 and 137.

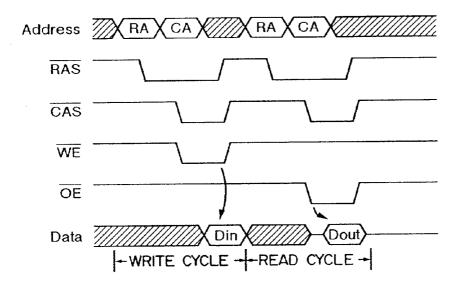

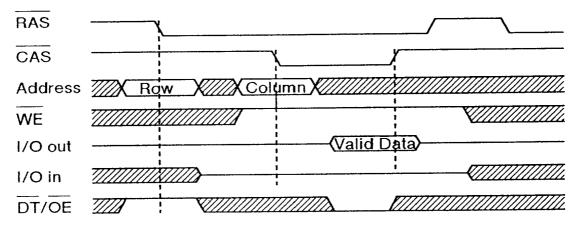

[0092] FIGS. 7 to 14 show timing charts of the access to the memory cell 120. More particularly, FIG. 7 is a timing chart of a random access. A row address and a column address are multiplex-transferred to the address bus. RAS is a row address signal for taking in a row address, and CAS is a column address signal for taking in a column address. WE is a write enable signal, and the writing into the memory cell 120 is made when WE is "L". OE is an output enable signal, and the reading from the memory cell is made when OE is "L". Data to be written in the memory cell 120 and data read from the memory cell 120 are transferred to the data bus.

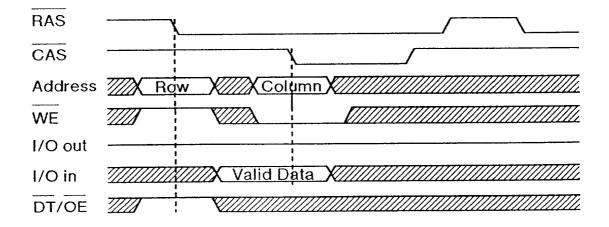

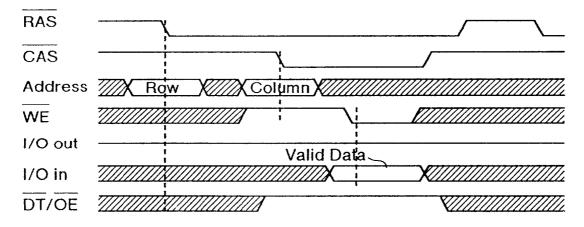

[0093] FIG. 8 is a timing chart of a page access. FIG. 9 is a timing chart of a read-modified write access. FIG. 10 is a timing chart of a write cycle in a burst access. FIG. 11 is a timing chart of a read cycle in the burst access. FIG. 12 is a timing chart of a random driver output access.

[0094] FIG. 13 is a timing chart of a sequential driver output access. A timing chart of the leading line of the sequential driver output access is similar to the timing chart of the random driver output access shown in FIG. 12.

[0095] FIG. 14 is a timing chart in the case where a continuous access using a plurality of liquid crystal drivers 105 is made by use of a chip selecting function. The timing chart shows a burst access write mode as one example.

[0096] In FIG. 14, RAS1 is a RAS (Raw Address Strobe) signal of the liquid crystal driver 105-1, and RAS2 is a RAS signal of the liquid crystal driver 105-2. Each of the RAS signals has a chip selecting function.

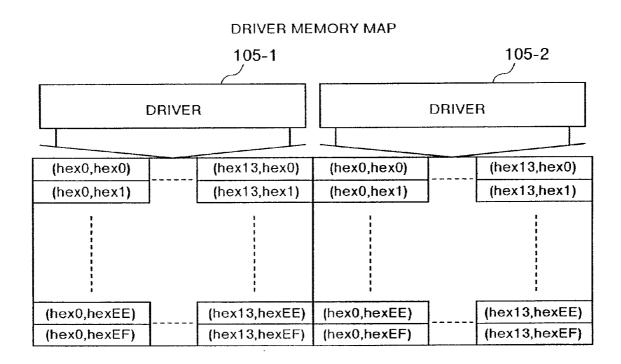

[0097] FIG. 15 shows a memory map of the memory cell 120 of the driver 105. An X coordinate value represents a column address, and a Y coordinate value represents a row address. Since one address includes 8-bit data, the X coordinate value takes hex0 to hex13. Since there are 240 lines in a vertical direction, the Y coordinate value takes hex0 to hexEF.

[0098] FIG. 16 is a block diagram of a liquid crystal display system according to a first embodiment in which the liquid crystal driver 105 of the present invention is used.

[0099] In FIG. 16, reference numeral 1601 denotes a CPU, numeral 1602 a main memory, and numeral 1603 an I/O device. Numeral 1604 denotes an address bus for transferring an address outputted from the CPU 1601, numeral 1605 a data bus for transferring data, and numeral 1606 a control signal bus for transferring a control signal outputted from the CPU 1601. Numeral 1607 denotes a liquid crystal controller, and numeral 1608 denotes an address converter by which an address transferred through

the address bus 1604 is converted into an X coordinate value (or column address) and a Y coordinate value (or row address) corresponding to the driver memory map (or memory cell 120) of the liquid crystal driver 105. Numeral 1609 denotes a buffer for display data, numeral 1610 a timing control circuit, and numeral 1611 a control signal bus for transferring a control signal for the scanning circuit 130.

[0100] FIG. 17A is a screen memory map when seen from the CPU, and FIG. 17B is a driver memory map when seen from the driver. In the screen memory map when seen from the CPU, the X coordinate value takes hex0 to hex27 since the horizontal resolving power is 320 dots, and the Y coordinate value takes hex0 to hexEF since the vertical resolving power is 240 lines.

[0101] The operation of the present invention will be explained by use of the block diagram of the liquid crystal display shown in FIG. 1.

[0102] An address transferred from the CPU 1601 through the address bus 101 is transferred to the buffer unit 106 of the liquid crystal driver 105. A row address is transferred from the buffer unit 106 to the row address latch/counter 116 through the address bus 109, and a column address is transferred from the buffer unit 106 to the column address latch/counter 110 through the address bus 107. A timing control signal and a RAS signal are transferred to the timing control circuit 128 through the control signal bus 103. The timing control circuit 128 generates a control signal for controlling an updating access to the memory cell 120 (for the updating of data) and a display access to the memory cell 120 (for the display of data). The RAS signal of control signals has a chip selecting function and therefore differs for each liquid crystal driver so that RAS signals 104 and 129 are inputted to the liquid crystal drivers 105-1 and 105-2, respectively. However, the drivers has a similar operation. The column address is transferred from the column address latch/counter 110 to the column address decoder 112 through the column address bus 111 and is decoded by the column address decoder 112. A decode signal outputted from the column address decoder 112 through the signal line 113 controls the I/O port 114. A row address outputted from the row address latch/counter 116 through the row address bus 117 is transferred to the row address decoder 118 and is decoded thereby. A decode signal outputted from the row address decoder 118 is transferred to the memory cell 120 through the signal line 119. Data inputted/outputted from the data bus 102 through the buffer unit 106 is transferred through the data bus 108 to the I/O port 114 so that the writing/reading at a coordinate designated by the row address and the column address is performed in accordance with the control signal outputted from the timing control circuit 128.

[0103] When a control signal for effecting a display access is outputted from the timing control circuit 128, display data of 160 bits having a designated row address is simultaneously transferred through the data bus 121 to the latch 122 which in turn latches the display data of 160 bits simultaneously. The display data latched by the latch 122 is transferred through the data bus 123 to the level shifter 124 for shift to a voltage level corresponding to a liquid crystal applied voltage. The level-shifted display data is transferred through the data bus 125 to the voltage selector 126 which in turn selects a liquid crystal applied voltage corresponding

to the data. The selected liquid crystal applied voltage is supplied from the output voltage line 127 to the liquid crystal panel 132.

[0104] Next, the timing of the updating access and the display access will be explained in detail for various modes by use of FIGS. 7 to 17.

[0105] First, a random access, which is one mode of the updating access, will be explained using the timing chart shown in FIG. 7.

[0106] A row address RA transferred from the address bus 101 is read upon falling of a RAS signal to designate a row address at which access to the memory cell 120 is to be made. Similarly, a column address CA is read upon falling of a CAS (Column Address Strobe) signal to designate a column address at which access is to be made. In the case where the access is a write cycle, input data Din transferred from the data bus 115 is written into the designated address of the memory cell 120 upon rising of a write enable signal WE. In the case where the access is a read cycle, data Dout stored at the designated address of the memory cell 120 is read upon falling of an output enable signal OE and is transferred to the data bus 102 through the data bus 115. The access cycle is completed when RAS is turned to "H" (high level).

[0107] Next, a page access, which is another mode of the updating access, will be explained using the timing chart shown in FIG. 8.

[0108] In the page access, in the case where the first designation of a row address is followed by access to data having the same row address, the access can be made continuously by merely designating column addresses. In the leading or first cycle, a row address and a column address are designated upon falling of RAS and upon falling of CAS, respectively, as in the random access, as shown in FIG. 8. In the subsequent cycle, a row address is not designated but only a column address is designated upon falling of CAS, thereby making the access to data having the same row address. Accordingly, it becomes possible to perform a processing for the subsequent cycle inclusive of the second cycle in a short time as compared with the random access, thereby realizing a high-speed access.

[0109] Next, a read-modified write access, which is a mode of the updating access, will be explained using the timing chart shown in FIG. 9.

[0110] The read-modified write access is an access in which the reading and writing at the same address are continuously performed. As shown in FIG. 9, an address at which access is to be made is designated and OE is thereafter rised to read the stored data. After a read cycle with OE rised has been completed, WE is turned to "L" (low level) so that input data Din on the data bus 115 is written upon rising of WE into the address subjected to the reading.

[0111] Next, a burst access, which is a mode of the updating access, will be explained using the timing charts shown in FIGS. 10 and 11.

[0112] The burst access is used in the case where data subjected to access has the same row address and the column addresses are continuous. After an address for the leading or first access cycle has been designated, a sequential access becomes possible in the subsequent cycles inclusive of the

second cycle by making the sequential addition of a column address in the column address latch/counter 110 with no address designation by RAS and CAS.

[0113] First, a write cycle of the burst access will be explained using the timing chart shown in FIG. 10. In the leading cycle, the taking-in of addresses is made upon falling of RAS and CAS, as in the random access, to designate an address of the memory cell 120 at which access is to be made. Upon rising of WE, input data Din is written from the data bus 115 into the designated address. Next, upon falling of WE, 1 (one) is added to the column address latch/counter 110. In the second cycle, input data Din is written upon rising of WE into an address obtained by adding 1 to the column address of the leading cycle. Subsequently, the writing of data is performed at the same cycle as the second cycle. The access is completed when RAS is turned to "H".

[0114] Next, a read cycle of the burst access will be explained using FIG. 11. In the leading cycle, an address of the memory cell 120, at which access is to be made, is designated and output data Dout is thereafter read upon falling of OE. The reading is completed by rising OE. In the second cycle, 1 is added to the column address latch/counter 110 upon falling of OE and data having an address obtained by adding 1 to the leading address is read. Subsequently, the reading of data is performed at the same cycle as the second cycle. The access is completed when RAS is turned to "H". The burst access has an advantage over the page access in the aspect of reduction in power consumption since the address value transferred through the address bus is not changed.

[0115] Next, a random driver output access, which is one mode of the display access, will be explained using the timing chart shown in FIG. 12.

[0116] When the taking-in of a row address RA is made upon falling of RAS, data Yn of one row at the designated row address is simultaneously outputted to the latch 122 through the data bus 121 in the case where OE is "L" and WE is "H".

[0117] Next, a sequential driver output access, which is another mode of the display access, will be explained using the timing chart shown in FIG. 13.

[0118] The leading output cycle is the same as the random output access. Next, in the OE takes "H" and the WE takes "L" upon falling of RAS, data  $Y_{n+1}$  of one row at an address obtained by adding 1 to the row address latch/counter 116 is simultaneously outputted to the latch 122 through the data bus 121. Similarly, the output of data is sequentially performed.

[0119] Thus, the output of data from the memory cell 120 is performed only once in one horizontal period. Namely, the most time of one horizontal period can be used for an updating access, thereby enabling high-speed updating.

[0120] In the case where a plurality of liquid crystal drivers 105 are used in order to drive the liquid crystal panel 132, it is necessary to select a driver which is to make updating access. This liquid crystal driver selecting method will be explained by use of FIG. 14 showing a timing chart of a burst access write cycle in the case where two liquid crystal drivers are used.

[0121] A control signal RAS is used as a chip selection signal for selecting a driver which is to make updating access. It is assumed that the liquid crystal driver is in a non-selected condition when RAS is "H" and a selected condition when RAS is "L". As shown in FIG. 14, the liquid crystal driver 105-1 takes a selected condition when RAS1 inputted to the liquid crystal driver 105-1 is "L". The operation of the liquid crystal driver 105-1 in the selected condition is similar to the burst access write cycle shown by the timing chart in FIG. 10. Namely, input data Din(n) and Din(n+1) corresponding to the liquid crystal driver 1051 are written. At this time, RAS2 inputted to the liquid crystal driver 105-2 is "H" and hence the liquid crystal driver 105-2 takes a non-selected condition. Therefore, even if the other control signals for updating access are inputted, the liquid crystal driver 105-2 does not make access

[0122] Next, when RAS1 is turned to "H", RAS2 is turned to "L" so that the liquid crystal driver 105-1 takes a non-selected condition and the liquid crystal driver 105-2 takes a selected condition. Input data Din(0), Din(1), - - - are written into the liquid crystal driver 105-2 in the selected condition.

[0123] Thus, a driver, which is to make updating access, can be selected by changing over the chip selection signals RAS.

[0124] A memory map of the memory cell 120 will be explained by use of FIG. 15.

[0125] An address map of the memory cell 120 is such that the X coordinate is a column address and the Y coordinate is a row address. Since the resolving power of the liquid crystal panel 132 is 320 (dots)×240 (lines) and the number of outputs of the liquid crystal driver 105 is 160 bits, the X coordinate of the memory map takes hex0 to hex13 and the Y coordinate thereof takes hex0 to hexEF. Thus, the memory map depends upon the number of output signals of the liquid crystal driver 105 and the resolving power of the liquid crystal panel 132.

[0126] Next, a liquid crystal display system using the liquid crystal driver of the present invention will be explained by use of FIGS. 16, 17A and 17B.

[0127] First, the explanation will be made using a block diagram of a liquid crystal display system in a first embodiment shown in FIG. 16.

[0128] An address outputted from a CPU 1601 is transferred through an address bus 1604 to a main memory 1602, an I/O device 1603 and a liquid crystal controller 1607. The address transferred to the liquid crystal controller 1607 is inputted to an address converter 1608 and is converted thereby into an address corresponding to a memory map of the liquid crystal driver 105. The memory map and the address conversion will now be explained using FIGS. 17A and 17B.

[0129] Since the resolving power of the liquid crystal panel is 320 (dots)×240 (lines), a screen memory map when seen from the CPU 1601 is such that the X coordinate of the memory map takes hex0 to hex27 and the Y coordinate thereof takes hex0 to hexEF, as shown in FIG. 17A. On the other hand, since a driver memory map when seen from the liquid crystal driver 105-1 and 105-2 takes a memory map of the internal memory cell 120 of each driver, the driver

memory map is in a form in which two memory maps shown in FIG. 15 lie side by side, as shown in FIG. 17B. Therefore, the driver memory map when seen from the liquid crystal drivers 105-1 and 1052 is different from the screen memory map when seen from the CPU 1601. Therefore, if an address transferred from the CPU 1601 is used as it is, a correct address designation for the memory cell 120 of the liquid crystal driver cannot be performed. Accordingly, the address converter 1608 converts an address transferred from the CPU 1601. In the case where RAS104 inputted to the liquid crystal driver 105-1 is "L", the address transferred from the CPU 1601 is not subjected by the address converter 1608 to address conversion or is outputted therefrom to the address bus 101 as it is. In the case where RAS129 inputted to the liquid crystal driver 105-2 is "L", the X coordinate values hex14 to hex27 of the memory map when seen from the CPU 1601 are converted into hex0 to hex13 which are in turn outputted to the address bus 101. With such address conversion, it is possible to make correspondence to the driver memory map, thereby performing correct address designation.

[0130] Returning to FIG. 16 again, a control signal transferred to the liquid crystal controller is inputted to a timing control circuit 1610. The timing control circuit 1610 generates a control signal for controlling the timing of an updating access performed by the CPU 1601 and a display access of the liquid crystal driver 105. The control signal is outputted to the control signal bus 103. The timing control circuit 1610 also outputs a control signal for the scanning circuit 130 to a control signal bus 1611.

[0131] Display data inputted to or outputted from the CPU 1601 is transferred through a data bus 1605 from or to the main memory 1602, the I/O device 1603 and the liquid crystal controller 1607. The display data transferred to the liquid crystal controller 1607 is transferred through a buffer 1609 to the data bus 102 so that the input/output of data between the CPU 1601 and the liquid crystal driver 105 is made.

[0132] Thus, the liquid crystal display system using the liquid crystal driver of the present invention requires the liquid crystal controller having an address converting function. The address converting function may be provided in the liquid crystal driver 105. In such a case, the liquid crystal controller having no address conversion function can be used. The operations of the liquid crystal driver 105 having the address conversion function and the address conversion function in the driver are same with the operation described above. Since a display access is made once in one horizontal period, high-speed updating access is possible. As a result, the power consumption can be reduced as compared with a liquid crystal display system using the conventional liquid crystal driver.

[0133] Next, a second embodiment of a liquid crystal display system, in which the liquid crystal driver is used and two-screen driving is made, will be explained using FIGS. 18 to 20.

[0134] FIG. 18 is a block diagram of the liquid crystal display according to the second embodiment.

[0135] In FIG. 18, reference numerals 1801 to 1804 denote RSA signals which are inputted to liquid crystal drivers 105-1 to 105-4. Numeral 1805 denote a scanning

circuit, and numeral **1806** denotes a scanning signal line for transferring a scanning signal. Numeral **1807** denotes a liquid crystal panel which has a two-screen construction. The resolving power of an upper display screen portion is 320 (dots)×120 (lines) and that of a lower display screen portion is 320 (dots)×120 (lines). The total resolving power is 320 (dots)×240 (lines).

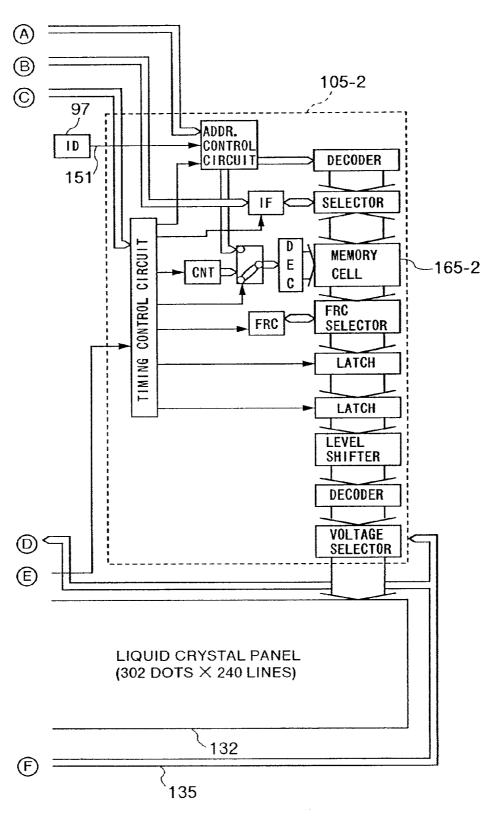

[0136] FIG. 19 is a block diagram of a system when the liquid crystal display shown in FIG. 18 is used.

[0137] In FIG. 19, reference numeral 1901 denotes a liquid crystal controller. Numeral 1902 denotes an address converter by which an address transferred from the CPU 1601 is converted into an address corresponding to a memory map of the liquid crystal driver 105. Numeral 1903 denotes to a buffer, and numeral 1904 denotes a timing control circuit. Numeral 1908 denotes to a control signal bus for transferring a control signal for scanning circuit 1805.

[0138] FIG. 20A is a screen memory map of the twoscreen driving liquid crystal display system of FIG. 18 when seen from the CPU 1601, and FIG. 20B is a driver memory map thereof when seen from the liquid crystal driver 105.

[0139] The second embodiment will now be explained using the system block diagram shown in FIG. 18.

[0140] The scanning circuit 1805 generates a scanning signal for simultaneously driving the upper and lower display screen portions of the liquid crystal panel 1807 and supplies it through the scanning signal line 1806 to the upper and lower display screen portions of the liquid crystal panel 1807. The liquid crystal drivers 105-1 and 105-2 output liquid crystal applied voltages corresponding to display data for the upper display screen portion of the liquid crystal panel 1807 through output voltage lines 127-1 and 127-2 in accordance with the RAS signals 1801 and 1802. Similarly, the liquid crystal drivers 105-3 and 105-4 output liquid crystal applied voltages corresponding to display data for the lower display screen portion of the liquid crystal panel 1807 through output voltage lines 127-3 and 127-4 in accordance with the RAS signals 1803 and 1804. The operation of the liquid crystal driver is similar to the first embodiment.

[0141] Next, the two-screen driving liquid crystal display system will be explained using FIG. 19.

[0142] An address, data and a control signal outputted from the CPU 1601 are transferred to the address converter 1902, the buffer 1903 and the timing control circuit 1904 of the liquid crystal controller 1901 through the address bus 1604, the data bus 1605 and the control signal bus 1606, respectively. The address transferred to the address converter 1902 is converted into an address corresponding to a memory map of the liquid crystal drivers 105-1 to 150-4. A screen memory map when seen from the CPU 1601 and a driver memory map when seen from the liquid crystal drivers 105-1 to 105-4 will be explained using FIG. 20.

[0143] The screen memory map when seen the CPU 1601 is such that the X coordinate of the upper display screen portion includes hex0 to hex27 and the Y coordinate thereof includes hex0 to hex77. Similarly, the X coordinate of the lower display screen portion includes hex0 to hex27 and the Y coordinate thereof includes hex78 to hexEF. On the other hand, the driver memory map when seen from the liquid crystal driver is such that the upper display screen portion

takes a state in which two driver maps each including the X coordinate values of hex0 to hex13 and the Y coordinate values of hex0 to hex77 are arranged side by side. Since the scanning circuit 1805 scans the liquid crystal panel 1807 from up to down in order, the lower display screen portion takes a state of the driver memory map which has the reversed X coordinate values for the driver memory map of the upper display screen portion. Therefore, the address converter 1902 performs no address conversion in the case where RAS1801 is "L" and converts the X coordinate values hex14 to hex27 of the screen memory map into hex0 to hex13 when RAS1802 is "L". In the case where RAS1803 is "L", the X coordinate values hex0 to hex13 of the screen memory map are converted into hex13 to hex0 and the Y coordinate values hex78 to hexEF are converted into hex0 to hex77. In the case where RAS1804 is "L", the X coordinate values hex14 to hex27 of the screen memory map are converted into hex13 to hex0 and the Y coordinate values hex78 to hexEF are converted into hex0 to hex77. With such address conversion, it is possible to make correspondence to the driver memory map of the liquid crystal driver, thereby performing correct address designation.

[0144] The other operation of the liquid crystal display system shown in **FIG. 19** is similar to the first embodiment.

[0145] By thus providing the address converter corresponding to the two-screen driving, the two-screen driving becomes possible even if the liquid crystal driver of the present invention is used.

[0146] The first and second embodiments concern the case where binary display is made. Next, explanation will be made of the case where grayscale display is made.

[0147] First, a third embodiment, in which a frame rate control system (hereinafter abbreviated to FRC) is used and four-grayscale display is made, will be explained by use of FIGS. 21 to 23.

[0148] FIG. 21 is a block diagram of a liquid crystal display in the third embodiment using the liquid crystal driver of the present invention in which the FRC is used.

[0149] In FIG. 21, reference numeral 2101 denotes a data bus for transferring grayscale display data, and numeral 2102 denotes a liquid crystal driver in which the FRC is used as a grayscale system. Numeral 2103 denotes a data bus for transferring grayscale display data, and numeral 2104 denotes an I/O port for performing the input/output control of the grayscale display data. Numeral 2105 denotes a lower-bit data bus for transforming lower-bit data of the grayscale display data, and numeral 2106 denotes an upperbit data bus for transforming upper-bit data thereof. Numerals 2107 and 2108 denote memory cells for storing therein the lower-bit data and the upper-bit data, respectively, and numerals 2109 and 2110 denote a lower-bit data bus and an upper-bit data bus for transferring data outputted from the memory cells 2107 and 2108, respectively. Numeral 2111 denotes an FRC pattern generator, numeral 2112 a signal line for transferring an FRC display pattern, and numeral 2113 an FRC circuit for selects an FRC pattern corresponding to the grayscale display data and outputs the selected FRC pattern as FRC display data. Numeral 2114 denotes a data bus for transferring the FRC display data for one horizontal line selected by the FRC circuit 2113, and numeral 2115 denotes a latch for simultaneously latching the FRC display data for

one horizontal line. Numeral 2116 denotes a data bus for transferring FRC display data outputted from the latch 2115, numeral 2117 a level shifter, numeral 2118 a data bus for transferring the FRC display data voltage subjected to voltage level shift by the level shifter 2117, numeral 2119 a voltage selector, and numeral 2120 an output voltage line for supplying a liquid crystal applied voltage selected by the voltage selector 2119 to the liquid crystal panel 132.

[0150] FIG. 22 is a detailed block diagram of the liquid crystal driver 2102 in which the FRC in the present embodiment is used.

[0151] In FIG. 22, reference numerals 2201 and 2202 denote FRC patterns incorporated in the FRC pattern generating circuit 2111. The pattern 2201 is a grayscale 1 indicative of light gray and the pattern 2202 is a grayscale 2 indicative of dark gray. Numerals 2203 and 2204 denote signal lines for transferring the FRC patterns 2201 and 2202, respectively, and numerals 2205-1 to 2205-n FRC pattern selecting circuits. Numeral 2206 denotes a switch for selecting the FRC patterns 2201 and 2202 in accordance with the lower-bit data. Numeral 2207 denotes a signal line for transferring an FRC pattern selected by the switch 2206, numeral 2208 an EOR element, numeral 2209 a control signal, and numeral 2210 a switch for selecting the FRC pattern and the upper-bit data in accordance with the control signal 2209.

[0152] FIG. 23 shows display patterns in the case where the FRC is used.

[0153] The third embodiment using the FRC will be explained using FIG. 21.

[0154] A row address and a column address transferred through the address bus 101 are decoded by the row address decoder 118 and the column address decoder 112 as in the first embodiment. The decoded row address is transferred as a decode signal through the signal line 119 to the memory cells 2107 and 2108. Similarly, the decoded column address is transferred as a decode signal from the signal lines 2105 and 2106 to the memory cells 2107 and 2108, respectively, so that the same address is designated for the memory cells 2107 and 2108. Lower-bit data and upper-bit data of display data transferred from the data bus 2101 to the I/O port 2104 through the bus 2103 are respectively outputted to the lower-bit bus 2105 and the upper-bit bus 2106, respectively, so that the lower-bit data and the upper-bit data are stored into the same address of the memory cells 2107 and 2108, respectively. Display data transferred from the memory cells 2107 and 2108 respectively through the lower-bit data bus 2109 and the upper-bit data bus 2110 is supplied to the FRC circuit 2113 which in turn selects an FRC pattern and outputs FRC display data to the data bus 2114. The FRC pattern generating circuit 2111 and the FRC circuit 2113 will now be explained using FIG. 22.

[0155] In the FRC pattern generating circuit 2111, FRC patterns for displaying the grayscale 1 (light grayscale) and the grayscale 2 (dark grayscale) of four grayscales of white to black are stored as the FRC patterns 2201 and 2202. The FRC pattern will now be explained using FIG. 23.

[0156] In the present embodiment, black, grayscale 1, grayscale 2 and white as shown by (d), (b), (c) and (a) of FIG. 23 are displayed when the upper and lower bits of the display data are "00", "01", "10" and "11", respectively. The

FRC pattern includes 3×3 dots as one unit. In the case where the grayscale 1 is displayed, three dots of the 3×3 dots are subjected to non-illumination and the other dots are subjected to illumination. Dots to be subjected to non-illumination are the first pixel of the first column, the second pixel of the second column and the third pixel of the third column in the first frame. In the second frame, shift by one pixel to the left is made for each column, that is, the third pixel of the first column, the first pixel of the second column and the second pixel of the third column are subjected to nonillumination. Similarly, in the third frame, the second pixel of the first column, the third pixel of the second column and the first pixel of the third column are subjected to nonillumination. In the subsequent frames, the above is repeated. In the case where the grayscale 2 is displayed, the pixels subjected to illumination and non-illumination are subjected to non-illumination and illumination, respectively. In the case where white or black is displayed, all pixels are subjected to illumination or non-illumination. Accordingly, four-grayscale display is made in such a manner that the number of pixels subjected to illumination is 9, 6, 3 and 0 for white, grayscale 1, grayscale 2 and black, respectively.

[0157] Explanation will be made returning to FIG. 22 again.

[0158] The EOR element 2208 of each FRC pattern selecting circuit 2205 is inputted with lower-bit data and upper-bit data corresponding to that FRC pattern selecting circuit through the lower-bit data bus 2109 and the upper-bit data bus 2110 and outputs a control signal as an output signal to the switch 2210 through the signal line 2209. The control signal takes "0" when the upper-bit data and the lower-bit data are "00" or "11" and takes "1" when they are "01" or "10". The switch 2210 selects the upper-bit data when the control signal transferred from the signal line 2209 is "0" and selects the FRC pattern inputted through the signal line 2207 when it is "1". With the above operation, in the case where the upper and lower bits of the display data are "11", the switch 2210 selects the upper-bit data so that white is displayed. In the case of "00", the upper-bit data is similarly selected so that black is displayed. In the case of "10", the switch 2206 selects the FRC pattern 2203 and the switch 2210 selects the FRC pattern so that the grayscale 1 is displayed. In the case of "01", the switch 2206 selects the FRC pattern **2204** so that the grayscale 2 is displayed.

[0159] With the FRC pattern generating circuit 2111 and the FRC circuit 2113 provided in the liquid crystal driver with internal memory, grayscale display based on the FRC can be made. Also, it is possible to cope with an increase in number of grayscales by increasing the number of FRC patterns.

[0160] Next, a fourth embodiment, in which a four-gray-scale pulse width modulation system (hereinafter abbreviated to PWM) is used as the grayscale system, will be explained by use of FIGS. 24 and 25.

[0161] FIG. 24 is a block diagram of a liquid crystal display system using a liquid crystal driver in which the PWM is used as the grayscale system.

[0162] In FIG. 24, reference numeral 2301 denotes a liquid crystal display in which the PWM is used as the grayscale system. Numeral 2306 denotes a row address decoder, numerals 2307 and 2308 signal buses for transferring decode signals, and numerals 2309 and 2310 memory cells.

[0163] FIGS. 25A to 25D are timing charts for explaining a relationship between a scanning voltage and a liquid crystal applied voltage outputted from the liquid crystal driver 2301 in each grayscale in the case where the PWM is used

[0164] The fourth embodiment will be explained using FIG. 24.

[0165] The row address decoder 2306 decodes a transferred row address and outputs a decode signal the memory cells 2309 and 2310 through the signal lines 2307 and 2308, respectively. Upper-bit data and lower-bit data of grayscale display data transferred to the liquid crystal driver 2301 are stored into the memory cells 2309 and 2310, respectively. In one horizontal period, the upper-bit data stored in the memory cell 2309 and the lower-bit data stored in the memory cell 2310 are outputted to a data bus 2311 in a change-over manner. When the outputted grayscale display data is "1", a voltage selector 2316 selects as a liquid crystal applied voltage an ON voltage for displaying white. When the data is "0", the voltage selector 2316 selects an OFF voltage for displaying black. This operation will now be explained using the timing charts shown in FIGS. 25A to 25D.