US007932884B2

(12) **United States Patent**

Song et al.

(10) **Patent No.:** US 7,932,884 B2

(45) **Date of Patent:** Apr. 26, 2011

(54) **LIQUID CRYSTAL DISPLAY AND DRIVING METHOD THEREOF**

(75) Inventors: **Hong Sung Song**, Gyeongsangbuk-do (KR); **Woong Ki Min**, Daegu (KR); **Byung Jin Choi**, Gyeongsangbuk-do (KR); **Dong Il Kim**, Gyeonggi-do (KR); **Su Hyuk Jang**, Daegu (KR)

(73) Assignee: **LG Display Co., Ltd.**, Seoul (KR)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 741 days.

(21) Appl. No.: 12/003,585

(22) Filed: Dec. 28, 2007

(65) **Prior Publication Data**

US 2008/0170024 A1 Jul. 17, 2008

(30) **Foreign Application Priority Data**

Jan. 15, 2007 (KR) ..... 10-2007-0004255

Feb. 27, 2007 (KR) ..... 10-2007-0019587

Mar. 22, 2007 (KR) ..... 10-2007-0028228

Apr. 10, 2007 (KR) ..... 10-2007-0035126

Apr. 18, 2007 (KR) ..... 10-2007-0037936

(51) **Int. Cl.**

G09G 3/36 (2006.01)

(52) **U.S. Cl.** ..... 345/96; 345/54; 345/209

(58) **Field of Classification Search** ..... 345/50, 345/53, 54, 87, 94, 95, 96, 204, 209

See application file for complete search history.

(56) **References Cited**

**U.S. PATENT DOCUMENTS**

|                   |         |                      |         |

|-------------------|---------|----------------------|---------|

| 7,403,185 B2 *    | 7/2008  | Song et al. ....     | 345/100 |

| 7,764,258 B2 *    | 7/2010  | Kitamura et al. .... | 345/96  |

| 2002/0186193 A1 * | 12/2002 | Lee et al. ....      | 345/96  |

| 2004/0104873 A1 * | 6/2004  | Kang et al. ....     | 345/87  |

| 2004/0263466 A1 * | 12/2004 | Song et al. ....     | 345/100 |

| 2007/0152942 A1 * | 7/2007  | Yamagishi ....       | 345/96  |

| 2007/0242019 A1 * | 10/2007 | Jung et al. ....     | 345/98  |

| 2007/0296680 A1 * | 12/2007 | Lee et al. ....      | 345/100 |

| 2008/0001888 A1 * | 1/2008  | Lee ....             | 345/96  |

| 2008/0001893 A1 * | 1/2008  | Moon et al. ....     | 345/98  |

**FOREIGN PATENT DOCUMENTS**

JP 2008170994 A \* 7/2008

\* cited by examiner

*Primary Examiner* — Amare Mengistu

*Assistant Examiner* — Dmitriy Bolotin

(74) *Attorney, Agent, or Firm* — Morgan, Lewis & Bockius LLP

(57) **ABSTRACT**

A liquid crystal display device includes a liquid crystal display panel including a plurality of data lines to which a data voltage is supplied, a plurality of gate lines to which a gate pulse is supplied, and a plurality of liquid crystal cells, a data drive circuit to invert a polarity of the data voltage in response to a polarity control signal and to output the data voltage to the data lines in response to a source output enable signal, a gate drive circuit to supply the gate pulse to the gate lines, and a POL/SOE logic circuit to invert the polarity control signal for every frame period except at Nth-multiple frame period (where N is a positive integer), wherein the POL/SOE logic circuit controls the polarity control signal at every Nth-multiple frame period such that the polarity of the data voltage is the same as the previous frame period and controls a pulse width of the source output enable signal at every Nth-multiple frame period to be longer than for the other frame periods.

**6 Claims, 50 Drawing Sheets**

**Fig. 1****[Related Art]**

**Fig. 2****[Related Art]**

Fig. 4

[Related Art]

DC IMAGE STICKING

**Fig. 5**

**Fig. 6**

**Fig. 7**

| Frame | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 |

|-------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| POL   | + | - | + | - | + | - | + | + | - | +  | -  | +  | -  | +  | -  | +  | -  | +  | -  | +  | -  | +  | +  | -  | +  | -  | +  | -  | +  |    |

| Frame | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| POL   | -  | -  | +  | -  | +  | -  | +  | +  | -  | +  | -  | +  | -  | +  | -  | +  | -  | -  |

Fig. 8

Frame

Fig. 9

**Fig. 10**

Fig. 11

Fig. 12

**Fig. 13**

**Fig. 14**

**Fig. 15**131.231

**Fig. 16**

**Fig. 17**

Fig. 18

**Fig. 19**

Fig. 20

Fig. 21

**Fig. 22**

Fig. 23

**Fig. 24**

**Fig. 25**

**Fig. 26A**

**Fig. 26B**

**Fig. 27**

Fig. 28

Fig. 29

Fig. 30

**Fig. 31**

Fig. 32

**Fig. 33**

**Fig. 34**

**Fig. 35**

Fig. 36

267,323

Fig. 37

Fig. 38

**Fig. 39A**

Fig. 39B

**Fig. 40**

**Fig. 41A**

Fig. 41B

**Fig. 42**412

**Fig. 43**421

Fig. 44

**Fig. 45**

**Fig. 46**

**Fig. 47**

## LIQUID CRYSTAL DISPLAY AND DRIVING METHOD THEREOF

This application claims the benefit of the Korean Patent Application Nos. P2007-0004255 filed Jan. 15, 2007, P2007-0019587 filed Feb. 27, 2007, P2007-0028228 filed Mar. 22, 2007, P2007-0035126 filed Apr. 10, 2007, and P2007-0037936 filed Apr. 18, 2007, which are hereby incorporated by reference.

### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display device, and more particularly to a liquid crystal display device that is adaptive for increasing display quality by preventing flickers and DC image sticking, and a driving method thereof.

#### 2. Discussion of the Related Art

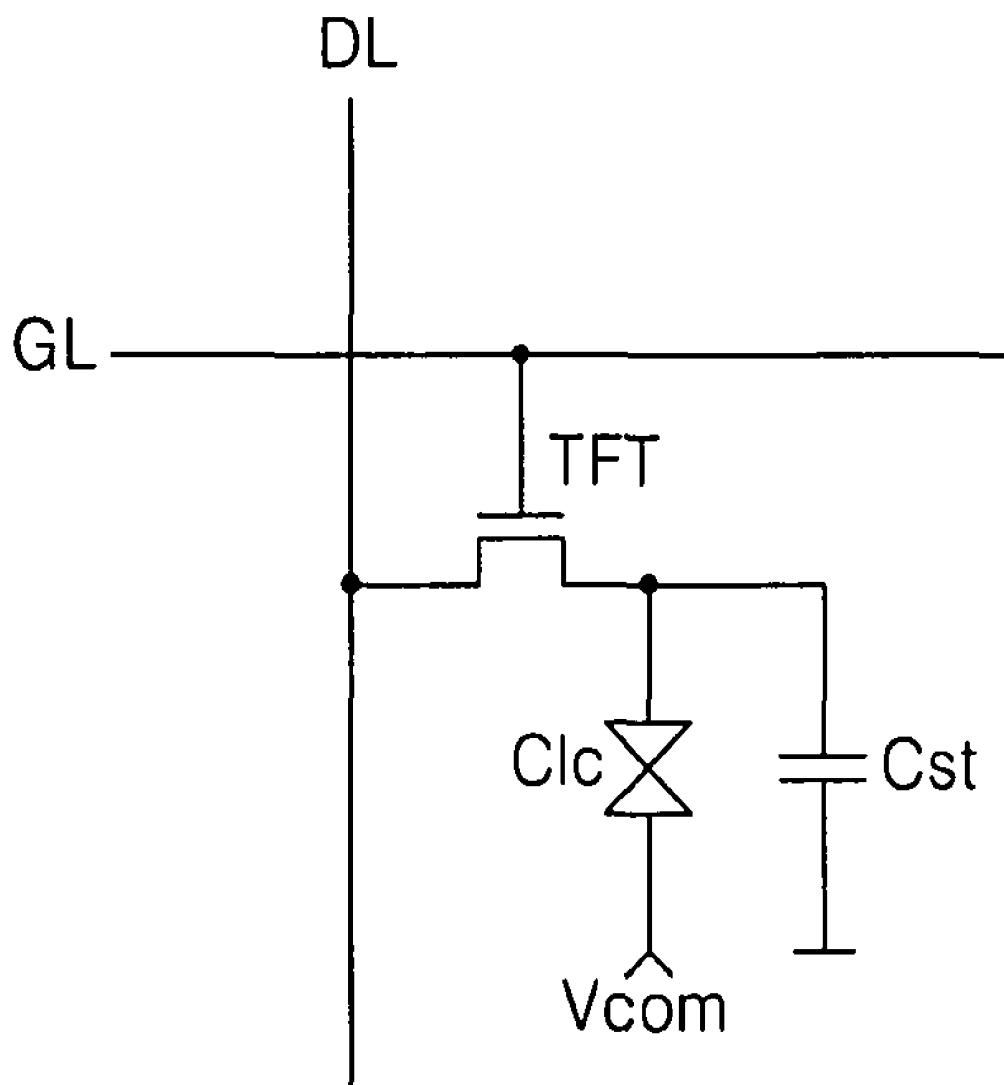

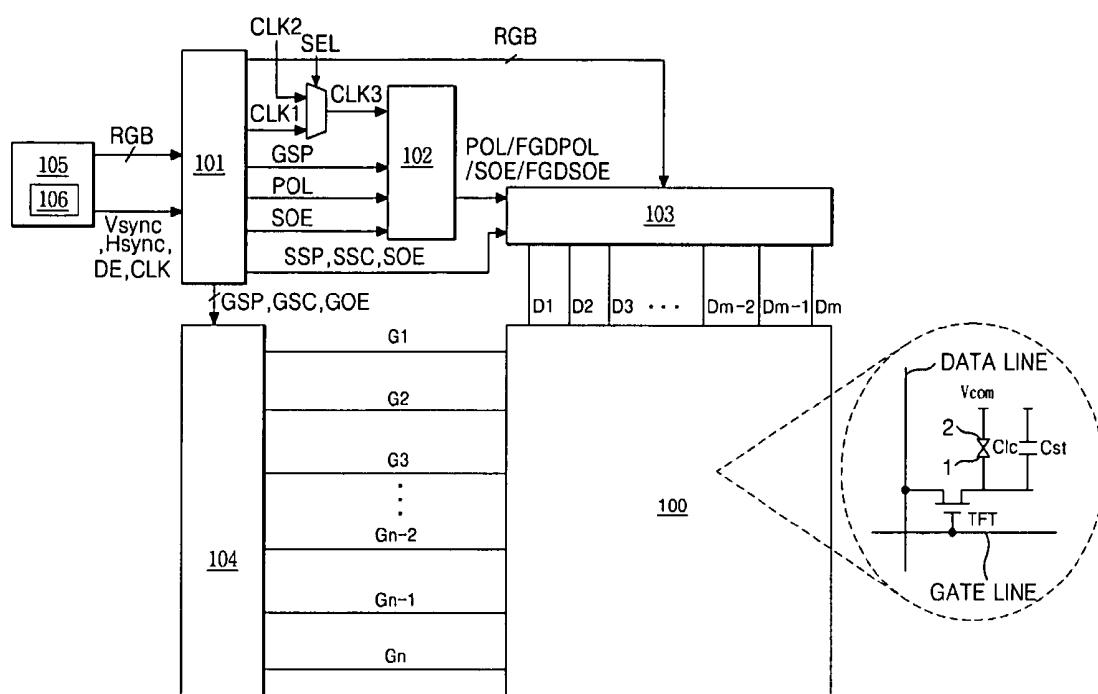

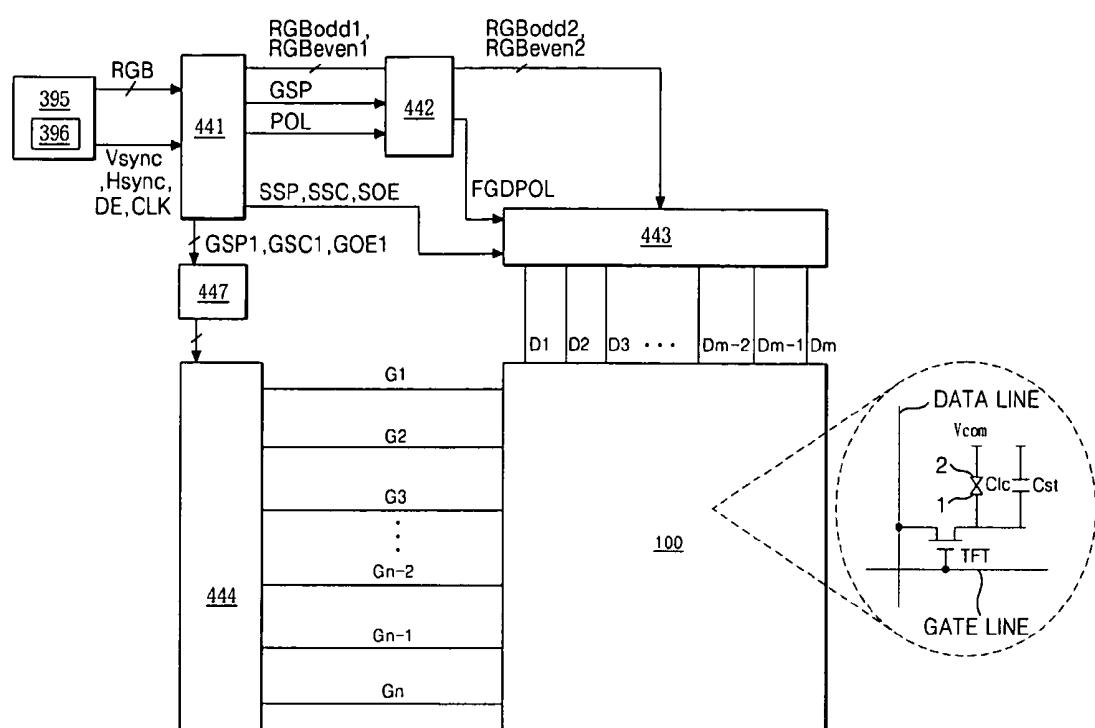

A liquid crystal display device controls the light transmission of liquid crystal cells in accordance with video signals, thereby displaying a picture. An active matrix type liquid crystal display device actively controls the displayed images by switching data voltages supplied to a thin film transistor TFT formed at each liquid crystal cell Clc, as shown in FIG. 1, thus increasing the display quality of motion pictures. As shown in FIG. 1, a reference numeral "Cst" represents a storage capacitor for keeping data voltages charged in the liquid crystal cell Clc. "DL" represents a data line to which the data voltages are supplied, and "GL" represents a gate line to which scan voltages are supplied to activate the thin film transistor TFT.

The liquid crystal display device is driven by an inversion method where polarities are inverted between adjacent liquid crystal cells and between successive frame periods, in order to reduce the deterioration of liquid crystals and to decrease DC offset components. If any one polarity between two polarities of the data voltage is dominantly supplied for a long time, a residual image is generated. Such a residual image, referred to as "DC image sticking," is created because a voltage of the same polarity is repeatedly charged in the liquid crystal cell.

An example of when DC image sticking occurs is when interlaced data voltages are supplied to the liquid crystal display device. An interlace method applies odd-numbered line data voltages to liquid crystal cells in odd-numbered horizontal lines during odd-numbered frame periods and even-numbered line data voltages to liquid crystal cells in even-numbered horizontal line during even-numbered frame periods.

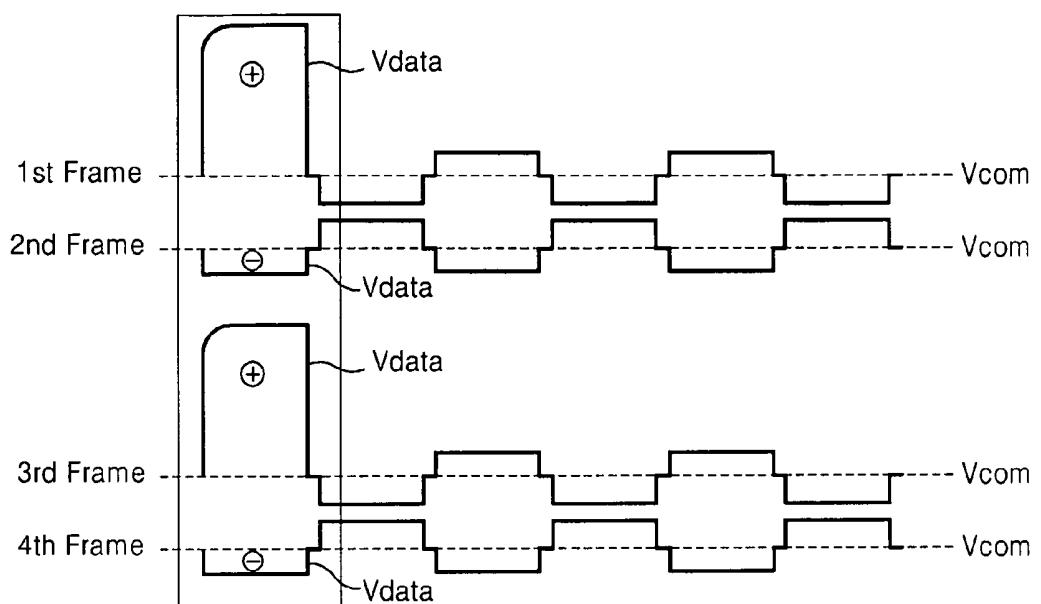

FIG. 2 illustrates a waveform diagram representing an example of data voltages supplied to a liquid crystal cell Clc using an interlace method. The data voltages of FIG. 2 represent data voltages supplied to any one of the liquid crystal cells disposed on an odd-numbered horizontal line.

As shown in FIG. 2, using the interlace method, high data voltages (i.e., image data) are supplied to a liquid crystal cell Clc (not shown) disposed on an odd-numbered horizontal lines only during odd-numbered frame periods. In addition, because the polarity of the data voltages alternate every frame period, the liquid crystal cell Clc is supplied with high voltages that are positive only during odd-numbered frame periods and with low voltages (i.e., no image data) during even-numbered frame periods. Because of this, the positive data voltage, like the waveform shown in the box of FIG. 2, becomes more dominant than the negative data voltage over a four-frame period, for example, thus creating a DC image sticking phenomenon.

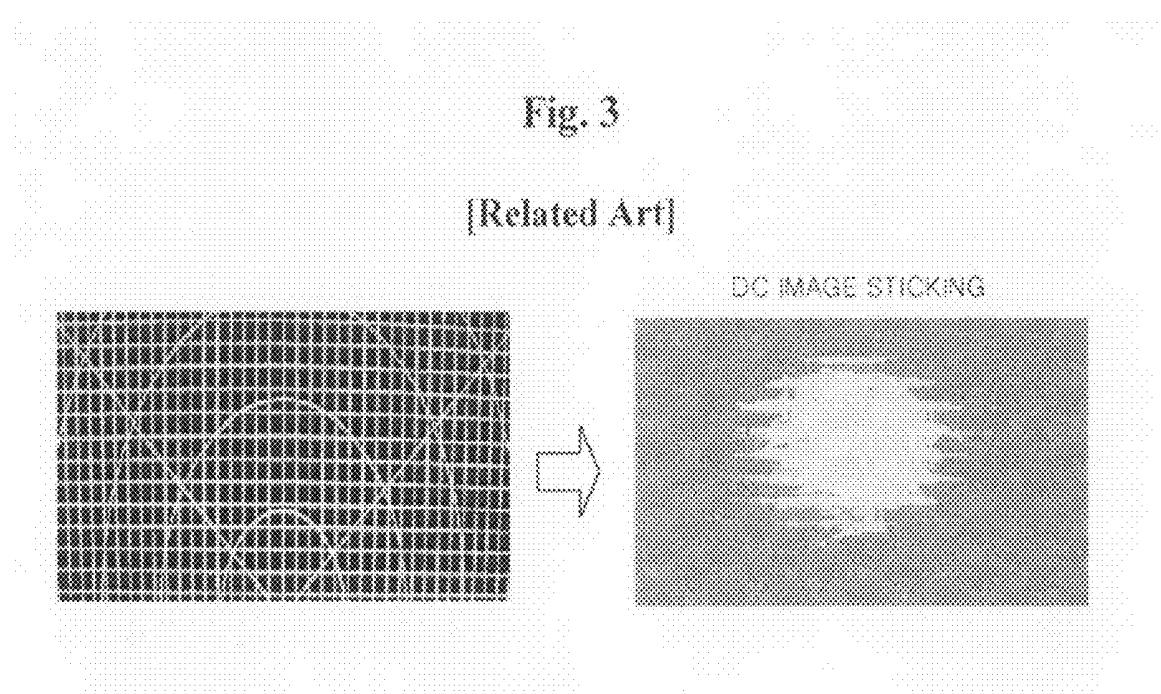

FIG. 3 shows exemplary images of an experimental result of a DC image sticking phenomenon generated due to interlace data. For example, if an original picture (e.g., left image of FIG. 3) is displayed on a liquid crystal display panel using the interlace method for a fixed period of time, a DC image sticking pattern of the original picture (e.g., right image of FIG. 3) dimly appears when a data voltage of an intermediate gray level (e.g., gray level of 127) is supplied to all of the liquid crystal cells Clc of the liquid crystal display panel after the original picture.

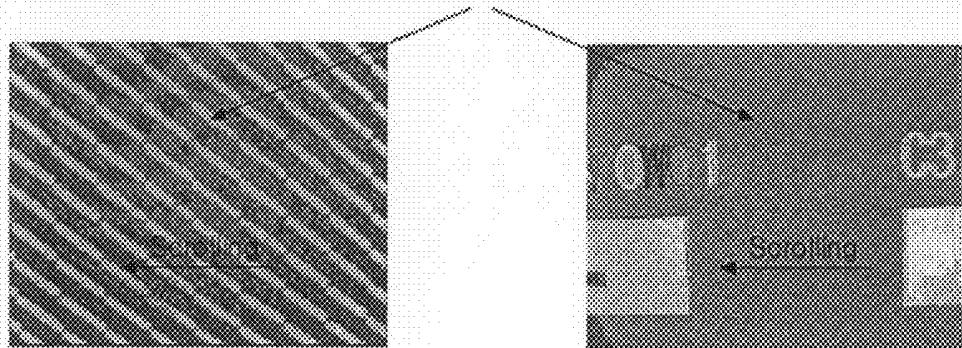

As another example of when the DC image sticking occurs is when an image is moved or scrolled at a fixed speed because the image data voltage of the same polarity is repeatedly accumulated in the liquid crystal cell Clc based on the scroll speed (or moving speed) and the size of a picture which is scrolled (or moved). FIG. 4 shows exemplary images of an experimental result of a DC image sticking phenomenon generated when moving an oblique line or character pattern at a fixed speed.

In a liquid crystal display device, the display quality of motion pictures is degraded not only because of the DC image sticking, but also because of a flicker phenomenon caused by a visual perception of difference in brightness. Accordingly, in order to improve the display quality of a liquid crystal display device, the DC image sticking phenomenon and the flicker phenomenon need to be prevented or minimized.

### SUMMARY OF THE INVENTION

Accordingly, the present invention is directed to a liquid crystal device and a driving method thereof that substantially obviates one or more problems due to limitations and disadvantages of the related art.

An object of the present invention is to provide a liquid crystal device and a driving method thereof for improving display quality by preventing DC image sticking and flicker.

Additional features and advantages of the invention will be set forth in the description which follows, and in part will be apparent from the description, or may be learned by practice of the invention. The objectives and other advantages of the invention will be realized and attained by the structure particularly pointed out in the written description and claims hereof as well as the appended drawings.

To achieve these and other advantages and in accordance with the purpose of the present invention, as embodied and broadly described, a liquid crystal display device includes a liquid crystal display panel including a plurality of data lines to which a data voltage is supplied, a plurality of gate lines to which a gate pulse is supplied, and a plurality of liquid crystal cells, a data drive circuit to invert a polarity of the data voltage in response to a polarity control signal and to output the data voltage to the data lines in response to a source output enable signal, a gate drive circuit to supply the gate pulse to the gate lines, and a POL/SOE logic circuit to invert the polarity control signal for every frame period except at Nth-multiple frame period (where N is a positive integer), wherein the POL/SOE logic circuit controls the polarity control signal at every Nth-multiple frame period such that the polarity of the data voltage is the same as the previous frame period and controls a pulse width of the source output enable signal at every Nth-multiple frame period to be longer than for the other frame periods.

In another aspect, a liquid crystal display device includes a liquid crystal display panel including a plurality of data lines to which a data voltage is supplied, a plurality of gate lines to which a gate pulse is supplied, and a plurality of liquid crystal cells, an image analyzing circuit to detect any one of interlace

data and scroll data in an input image, a data drive circuit to invert a polarity of the data voltage in response to a polarity control signal and to output the data voltage to the data lines in response to a source output enable signal, a gate drive circuit to supply the gate pulse to the gate lines, and a POL/SOE logic circuit to invert the polarity control signal for every frame period except at Nth-multiple frame period (where N is a positive integer), wherein the POL/SOE logic circuit controls the polarity control signal at every Nth-multiple frame period such that the polarity of the data voltage is the same as the previous frame period and controls a pulse width of the source output enable signal at every Nth-multiple frame period to be longer than for the other frame periods when the image analyzing circuit detects that the input image data is any one of the interlace data and the scroll data.

In yet another aspect, a liquid crystal display device includes liquid crystal display panel including a plurality of data lines, a plurality of gate lines, and a plurality of liquid crystal cells, a data drive circuit to invert a polarity of the data voltage in response to a polarity control signal and supplies the data voltage to the data lines in response to a source output enable signal, a gate drive circuit to supply a scan pulse to the gate lines, an image analyzing circuit to detect any one of interlace data and scroll data in an input image, a first controller to increase a data charge amount of the liquid crystal cell during an aging period, the aging period beginning from the time when power to drive the drive circuits is generated to a predetermined time thereafter, and to decrease the data charge amount of the liquid crystal cell at every Nth-multiple frame period (wherein N is a positive integer) using the source output enable signal when any one of the interlace data and the scroll data is detected by the image analyzing circuit during a normal drive period after the aging period, and a second controller to control the polarity of the data supplied to the liquid crystal cell at every Nth-multiple frame period to be the same as the previous frame period when any one of the interlace data and the scroll data is detected by the image analyzing circuit during the normal drive period, and to invert the polarity of the data supplied to the liquid crystal cell at all other frame periods using the polarity control signal.

It is to be understood that both the foregoing general description and the following detailed description are exemplary and explanatory and are intended to provide further explanation of the invention as claimed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are included to provide a further understanding of the invention and are incorporated in and constitute a part of this specification, illustrate embodiments of the invention and together with the description serve to explain the principles of the invention. In the drawings:

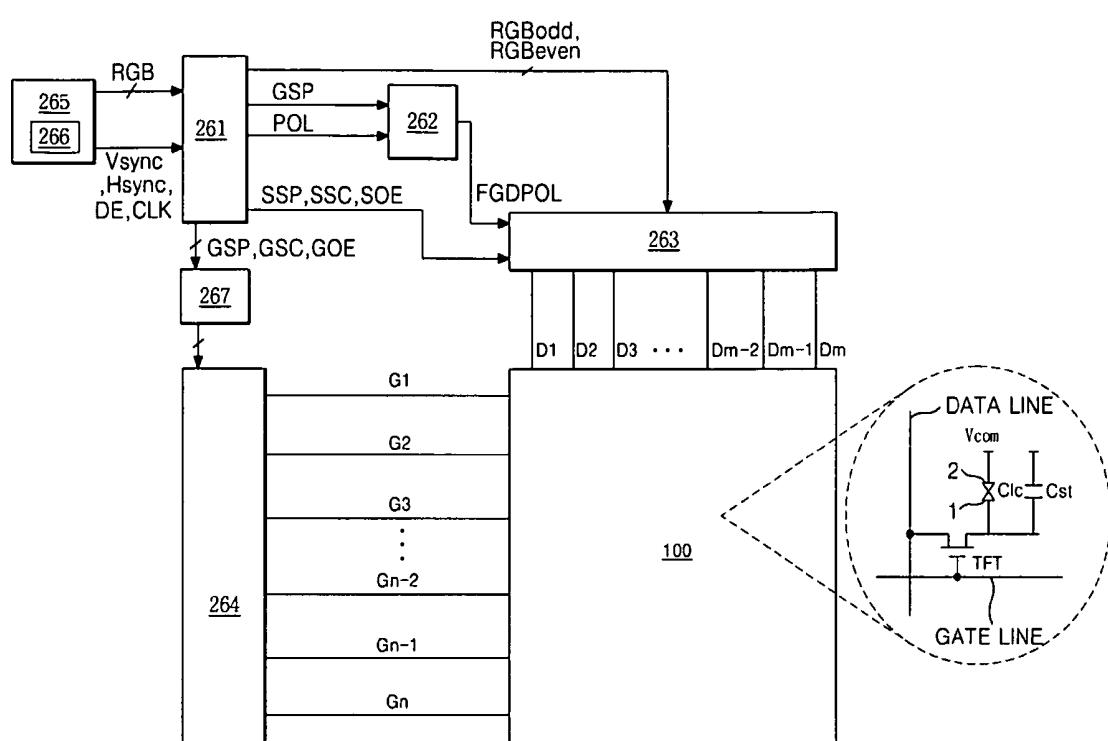

FIG. 1 is a circuit diagram showing a liquid crystal cell of a liquid crystal display device;

FIG. 2 is a waveform diagram showing an example of interlace data;

FIG. 3 is an experimental result screen showing DC image sticking caused by the interlace data;

FIG. 4 is an experimental result screen showing DC image sticking caused by scroll data;

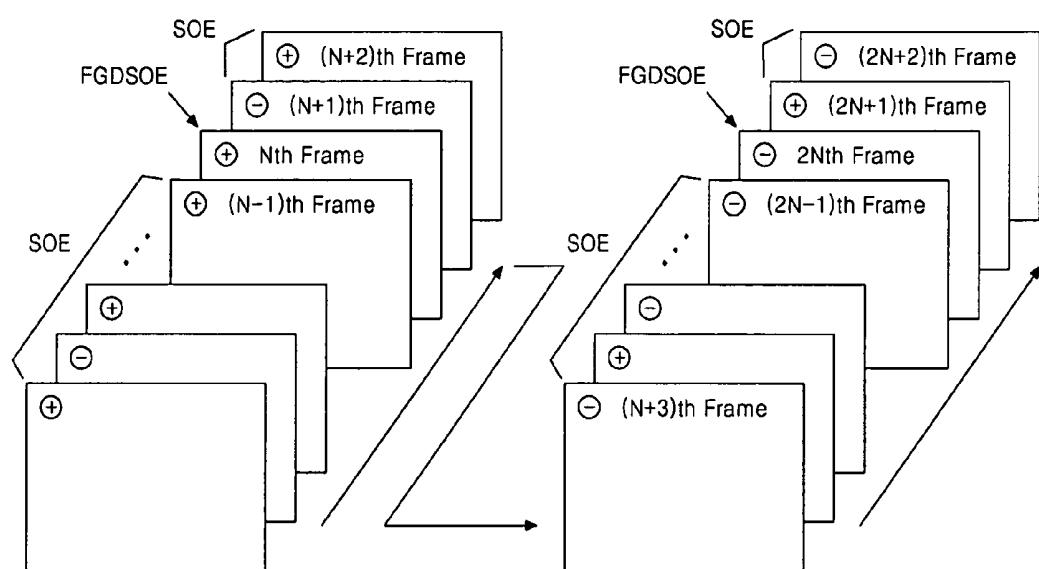

FIG. 5 is a diagram illustrating an exemplary driving method of a liquid crystal display device according to a first embodiment of the present invention;

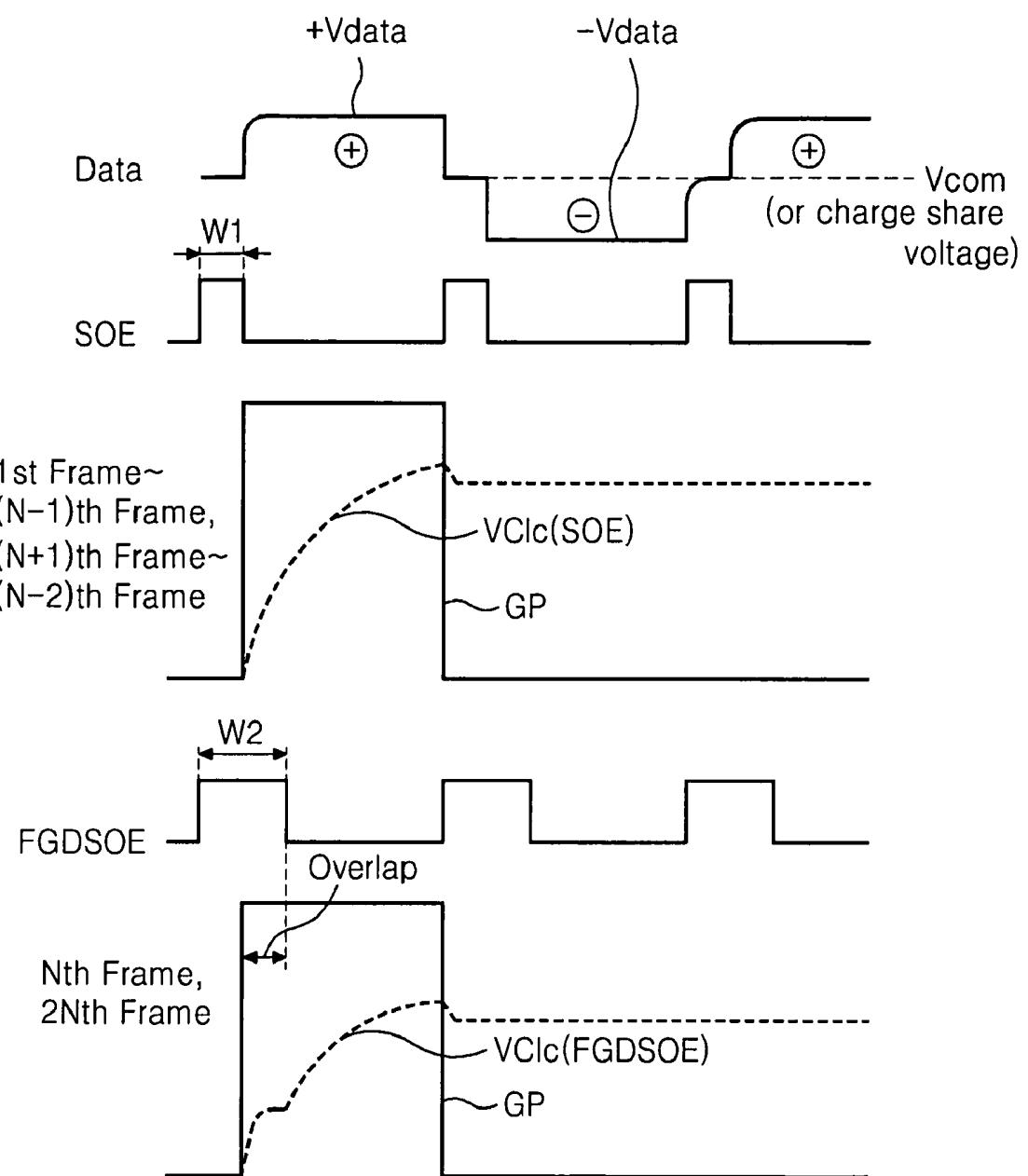

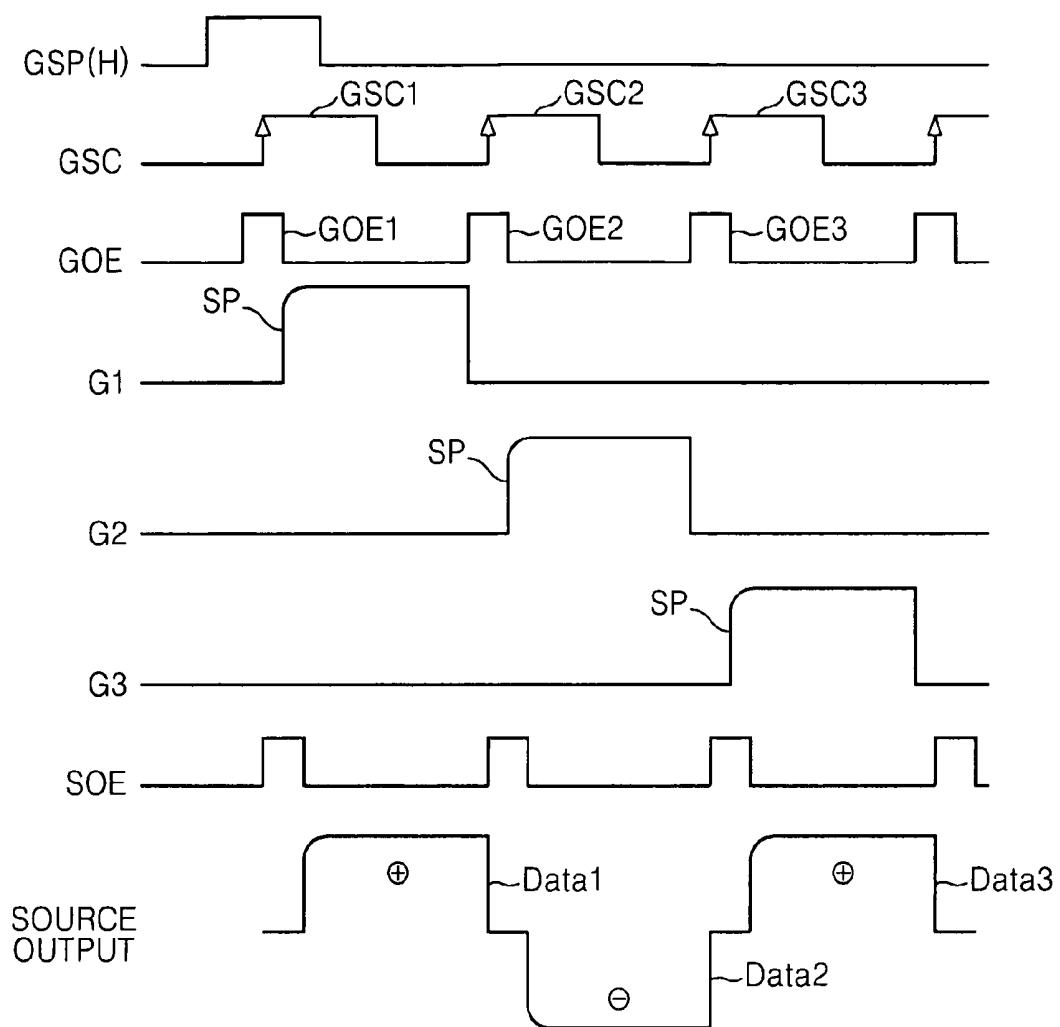

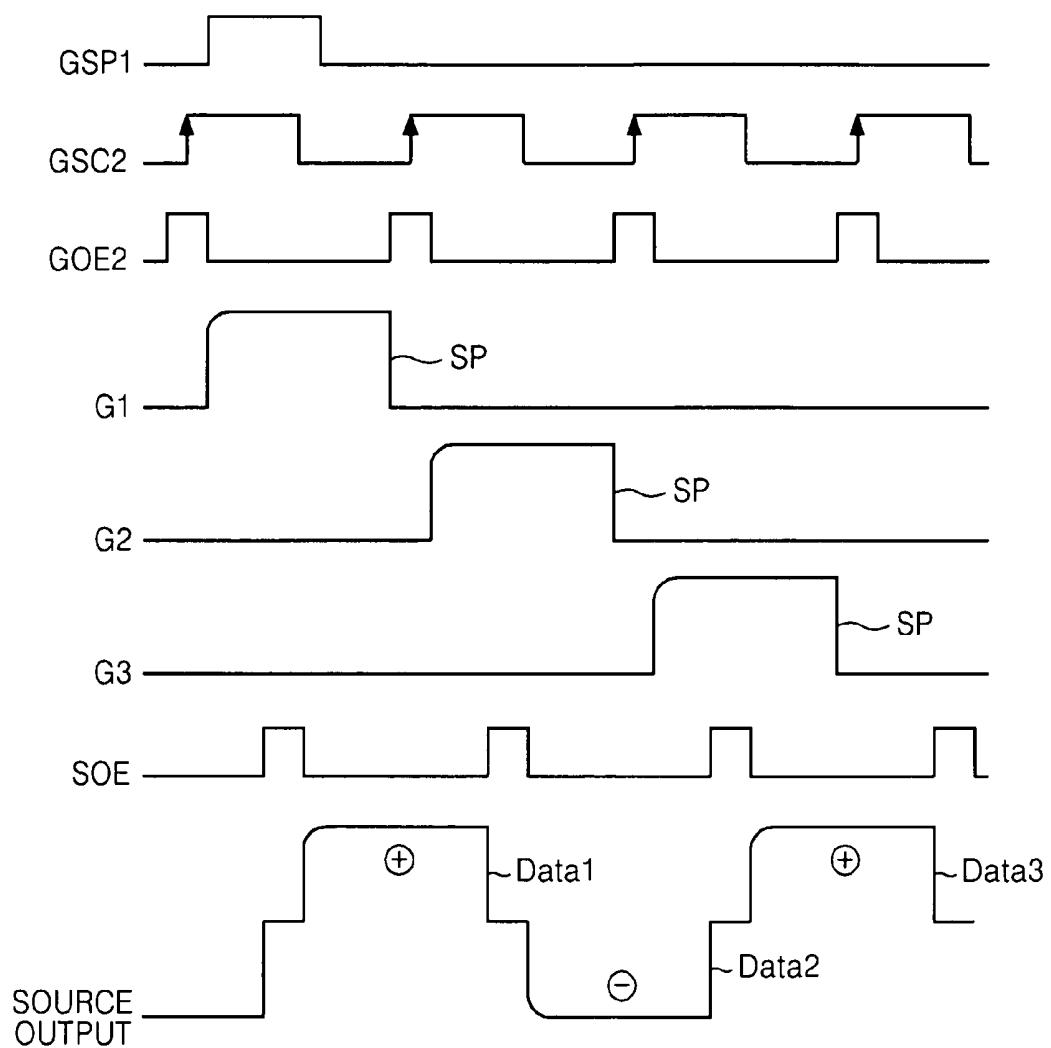

FIG. 6 is a waveform diagram illustrating source output enable signals shown in FIG. 5;

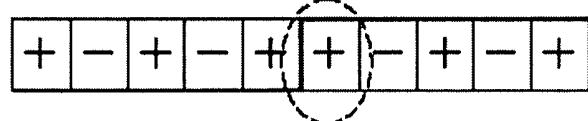

FIG. 7 is a diagram illustrating DC image sticking not generated in scroll data;

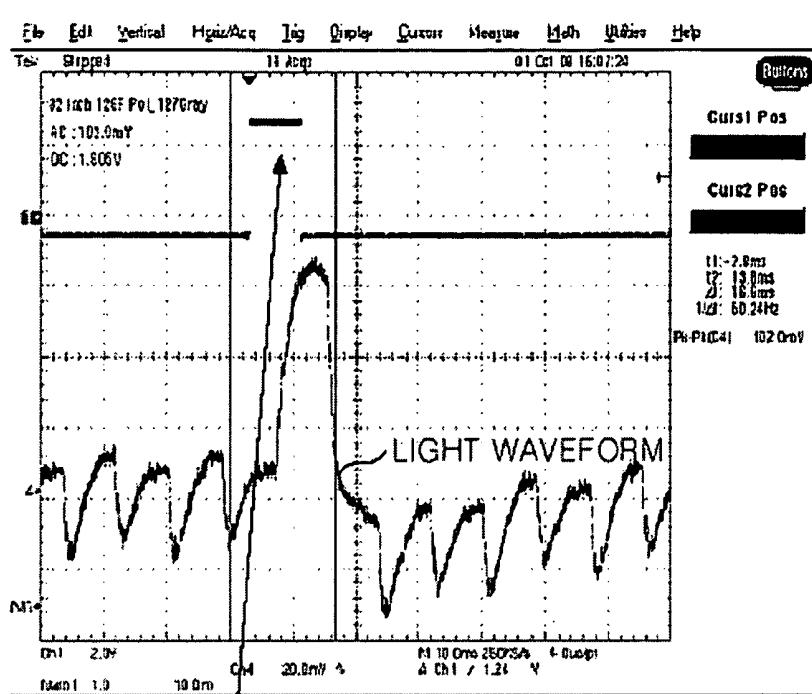

FIG. 8 is a waveform diagram illustrating an experimental result of increased light in Nth-multiple frame period;

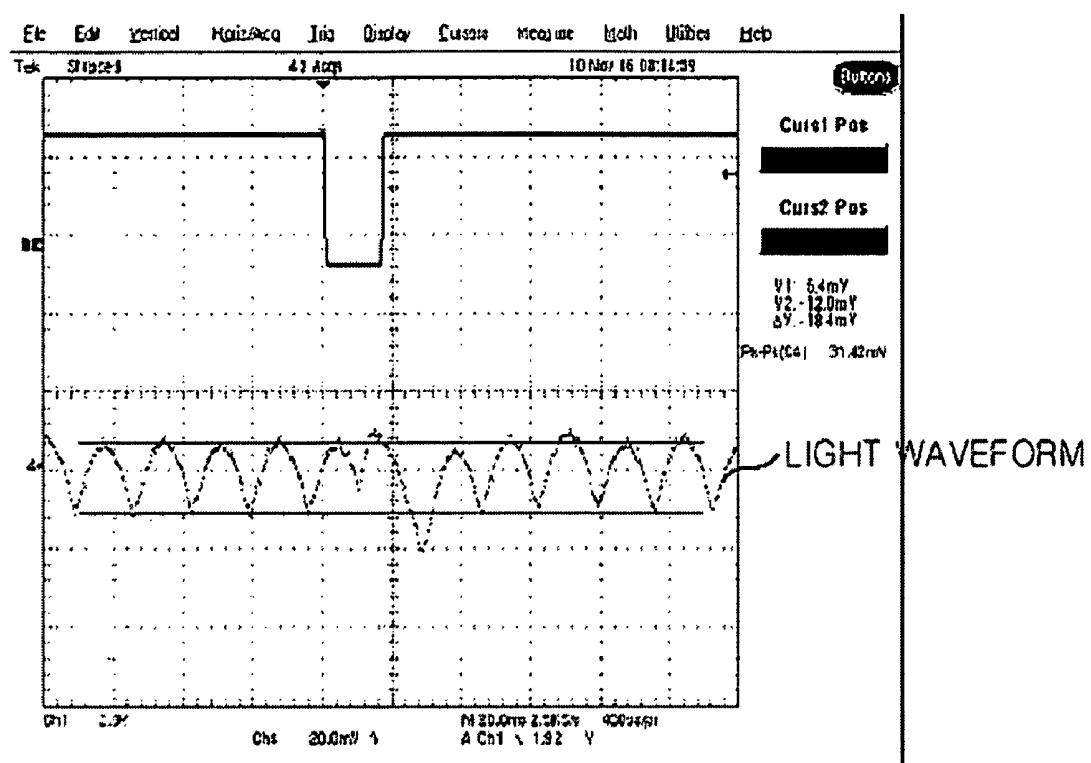

FIG. 9 is a waveform diagram illustrating an experimental result of decreased light in Nth-multiple frame period a second source enable signal;

FIG. 10 is a diagram illustrating DC image sticking not generated in interlace data;

FIG. 11 is a block diagram illustrating an exemplary liquid crystal display device according to a first embodiment of the present invention;

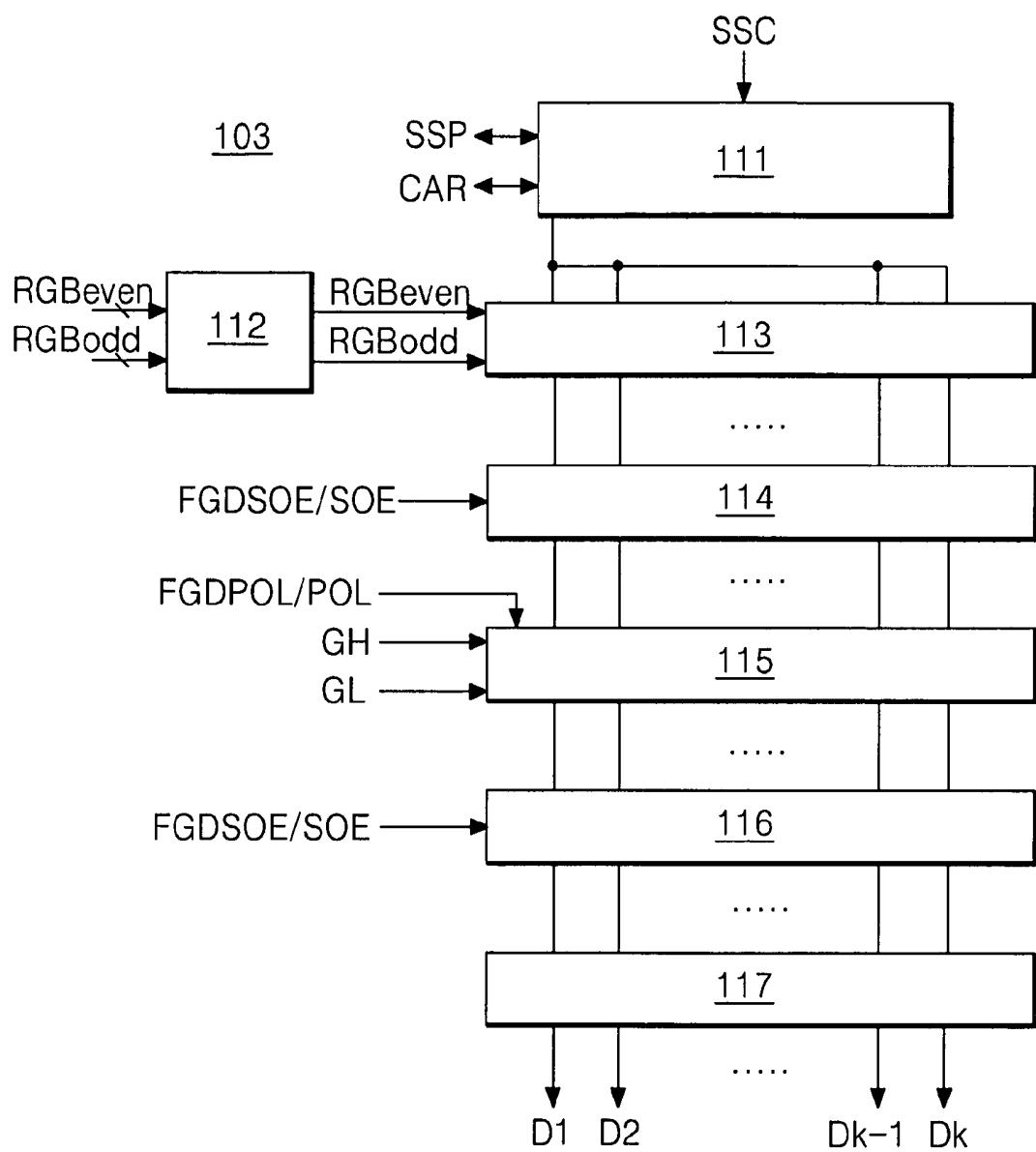

FIG. 12 is a block diagram illustrating an exemplary data drive circuit shown in FIG. 11;

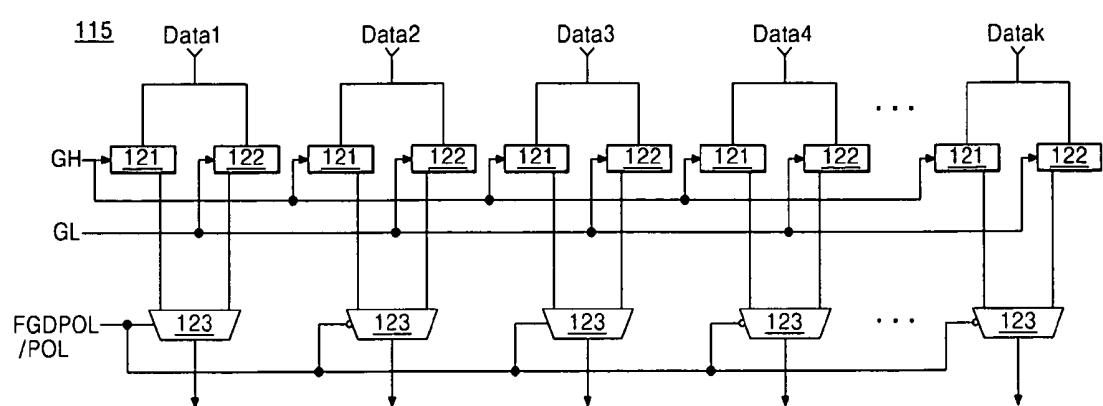

FIG. 13 is a circuit diagram illustrating an exemplary digital/analog converter shown in FIG. 12;

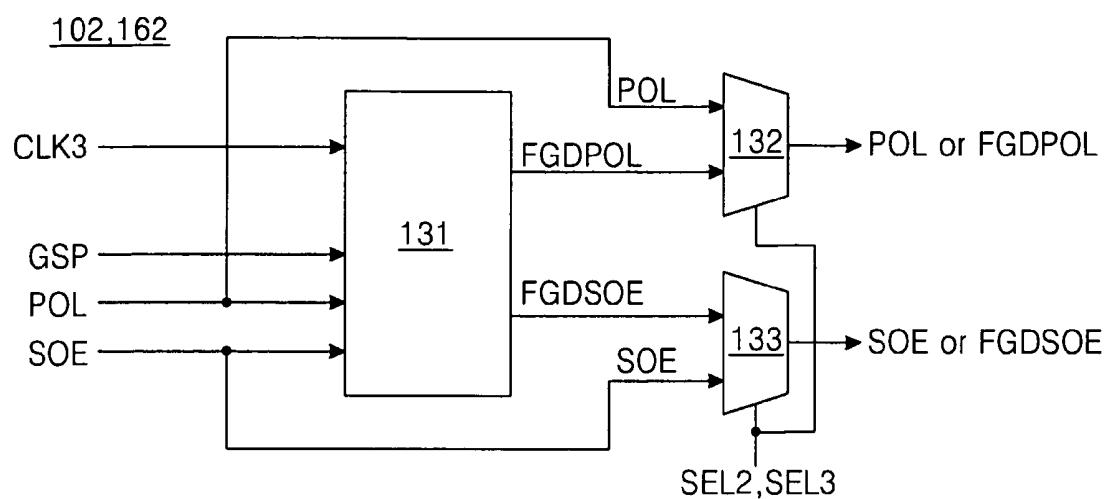

FIG. 14 is a block diagram illustrating an exemplary POL/SOE logic circuit shown in FIG. 11;

FIG. 15 is a block diagram illustrating an exemplary logic part shown in FIG. 14;

FIG. 16 is a waveform diagram illustrating an exemplary POL inversion signal and first and second polarity control signals shown in FIG. 15;

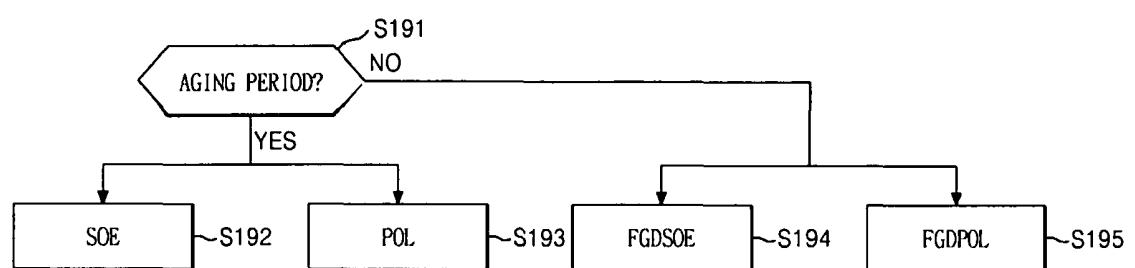

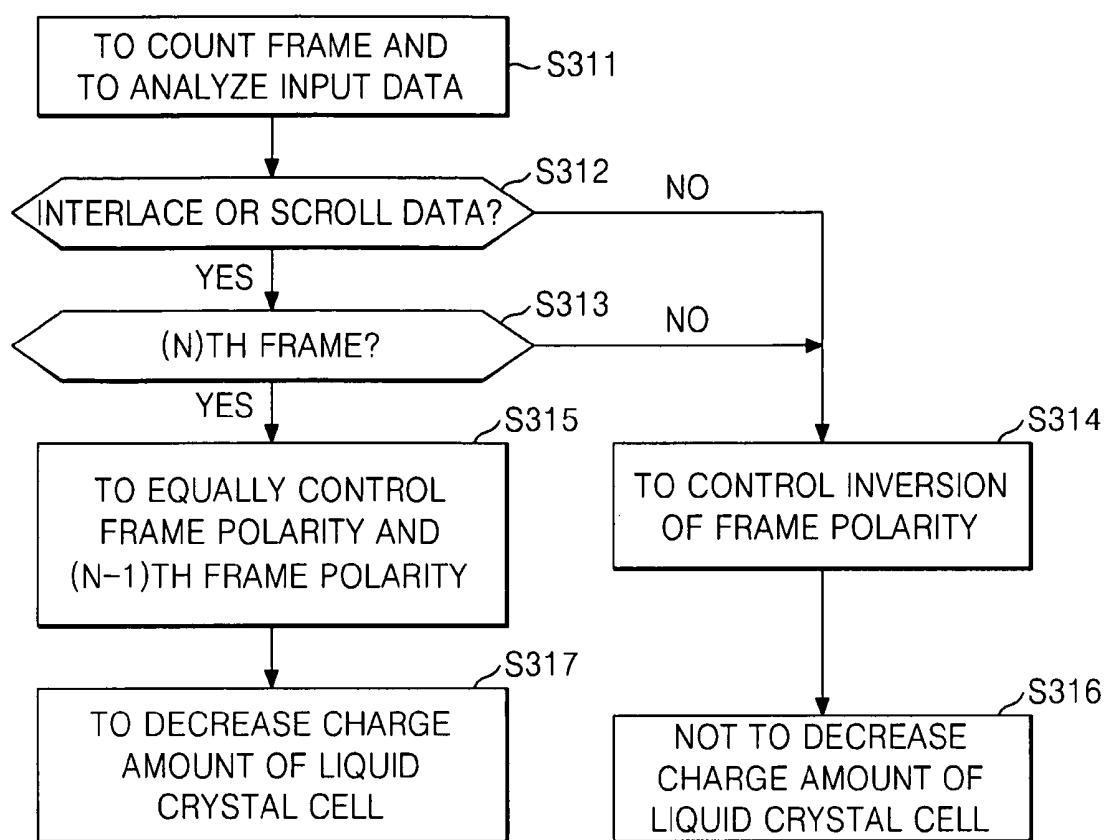

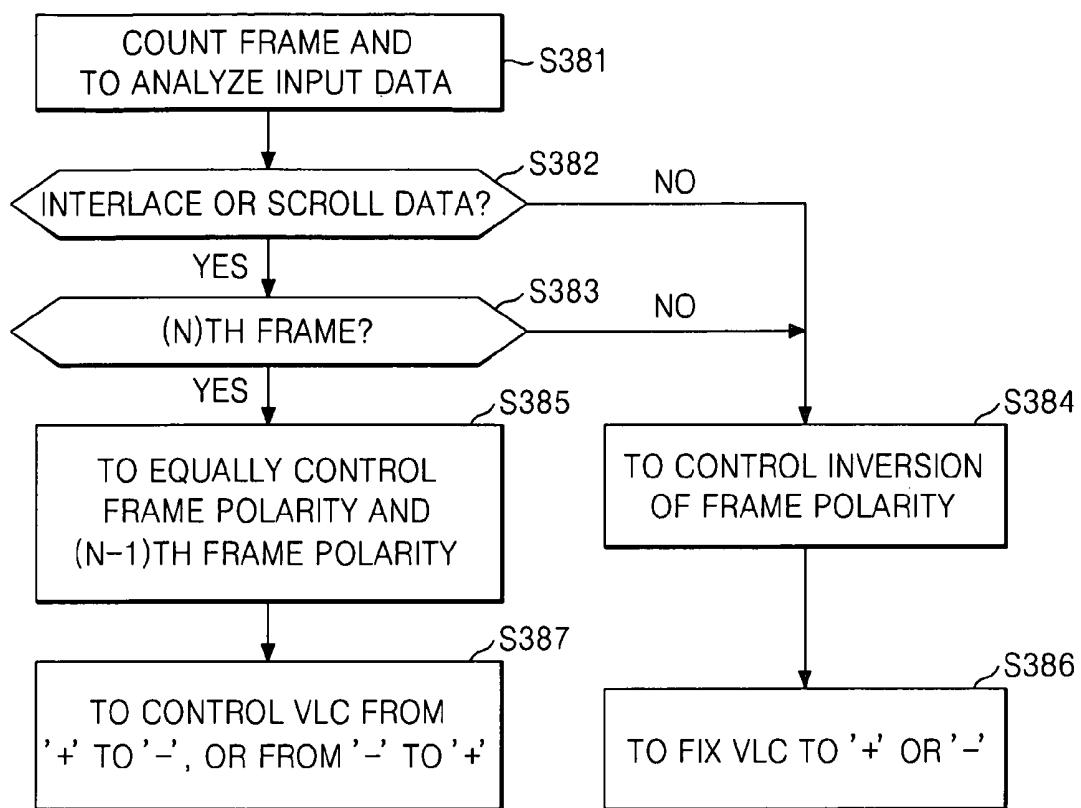

FIG. 17 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a second embodiment of the present invention;

FIG. 18 is a block diagram illustrating an exemplary liquid crystal display device according to the second embodiment of the present invention;

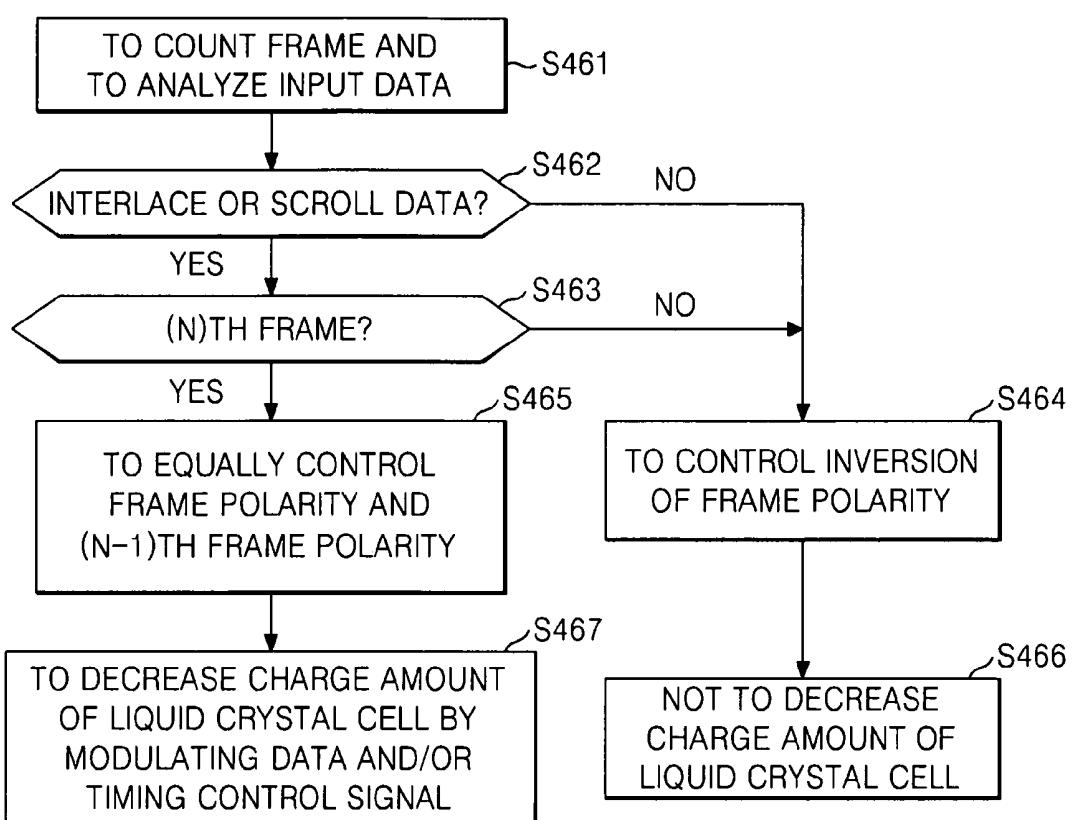

FIG. 19 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a third embodiment of the present invention;

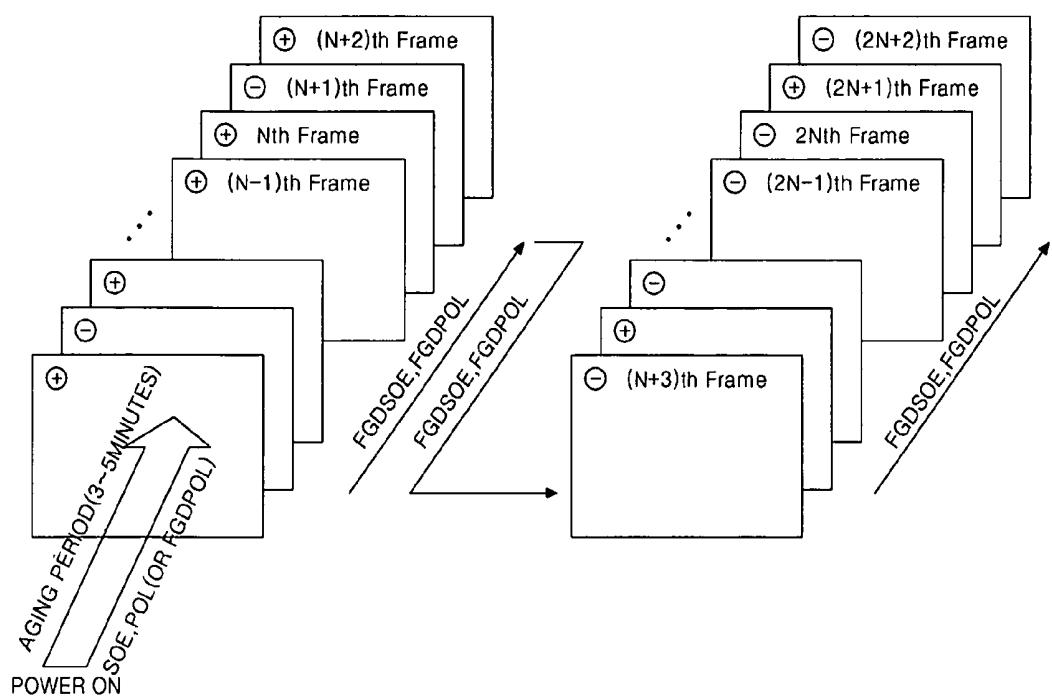

FIG. 20 is an exemplary frame configuration diagram illustrating the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention;

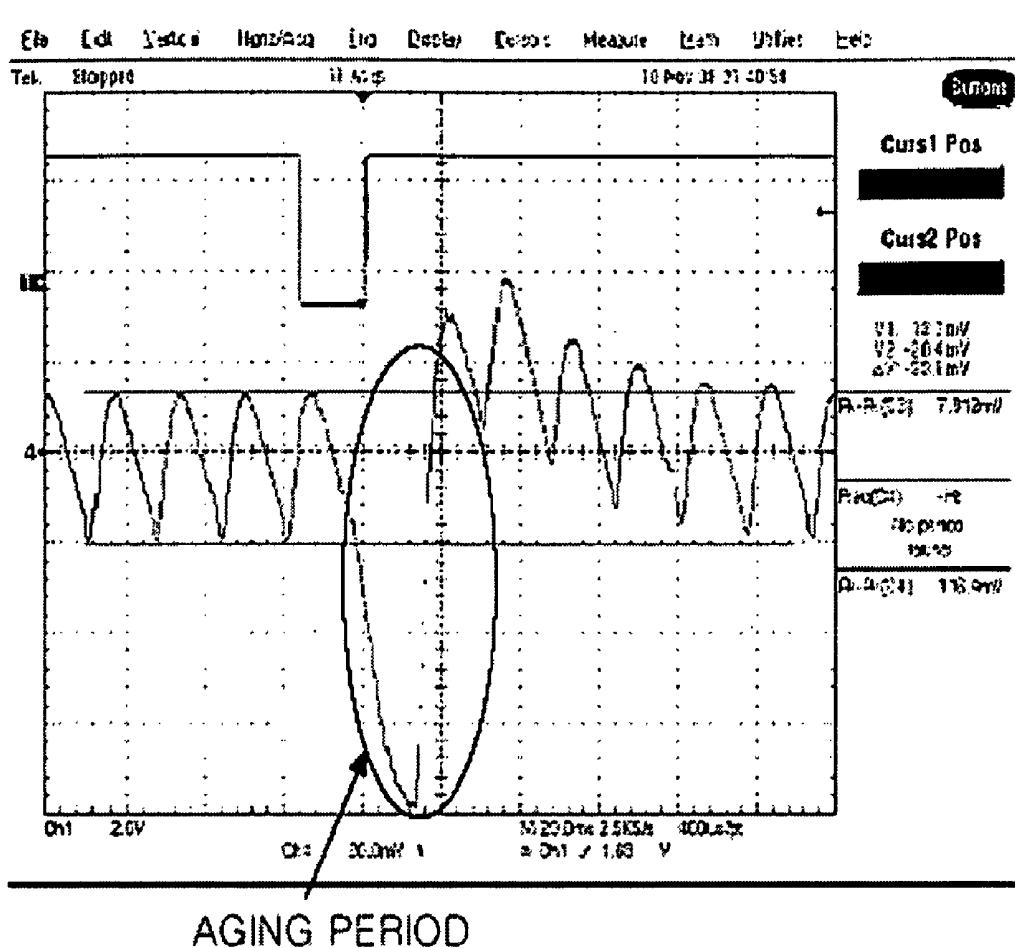

FIG. 21 is a waveform diagram illustrating an exemplary light waveform of a liquid crystal cell during an aging period;

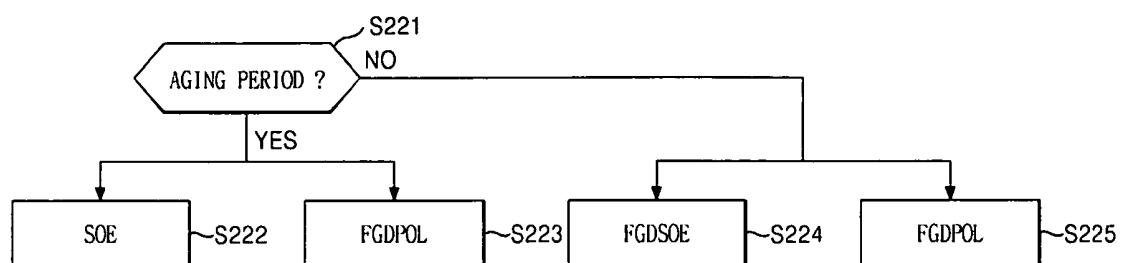

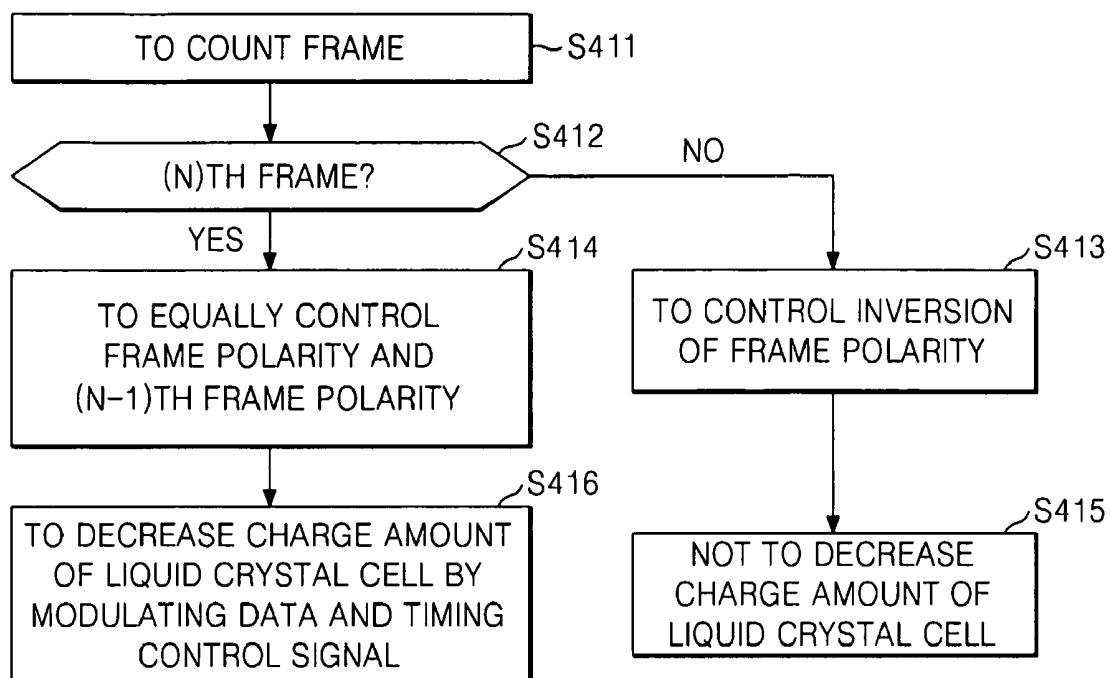

FIG. 22 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a fourth embodiment of the present invention;

FIG. 23 is a block diagram illustrating another exemplary embodiment of a POL/SOE logic circuit shown in FIG. 14;

FIG. 24 is a waveform illustrating an exemplary power supply voltage and a gate start pulse shown in FIG. 23;

FIG. 25 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a fifth embodiment of the present invention;

FIG. 26A is a flow chart illustrating an exemplary method of driving the liquid crystal display according to a sixth embodiment of the present invention;

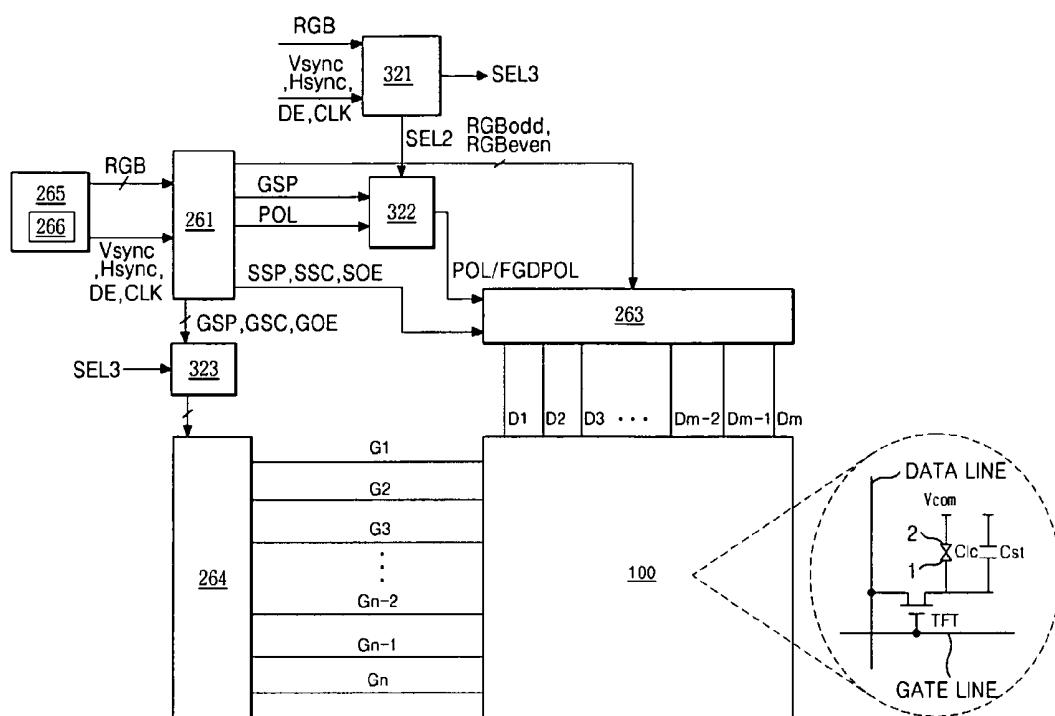

FIG. 26B is a block diagram showing an exemplary liquid crystal display according to the sixth embodiment of the present invention;

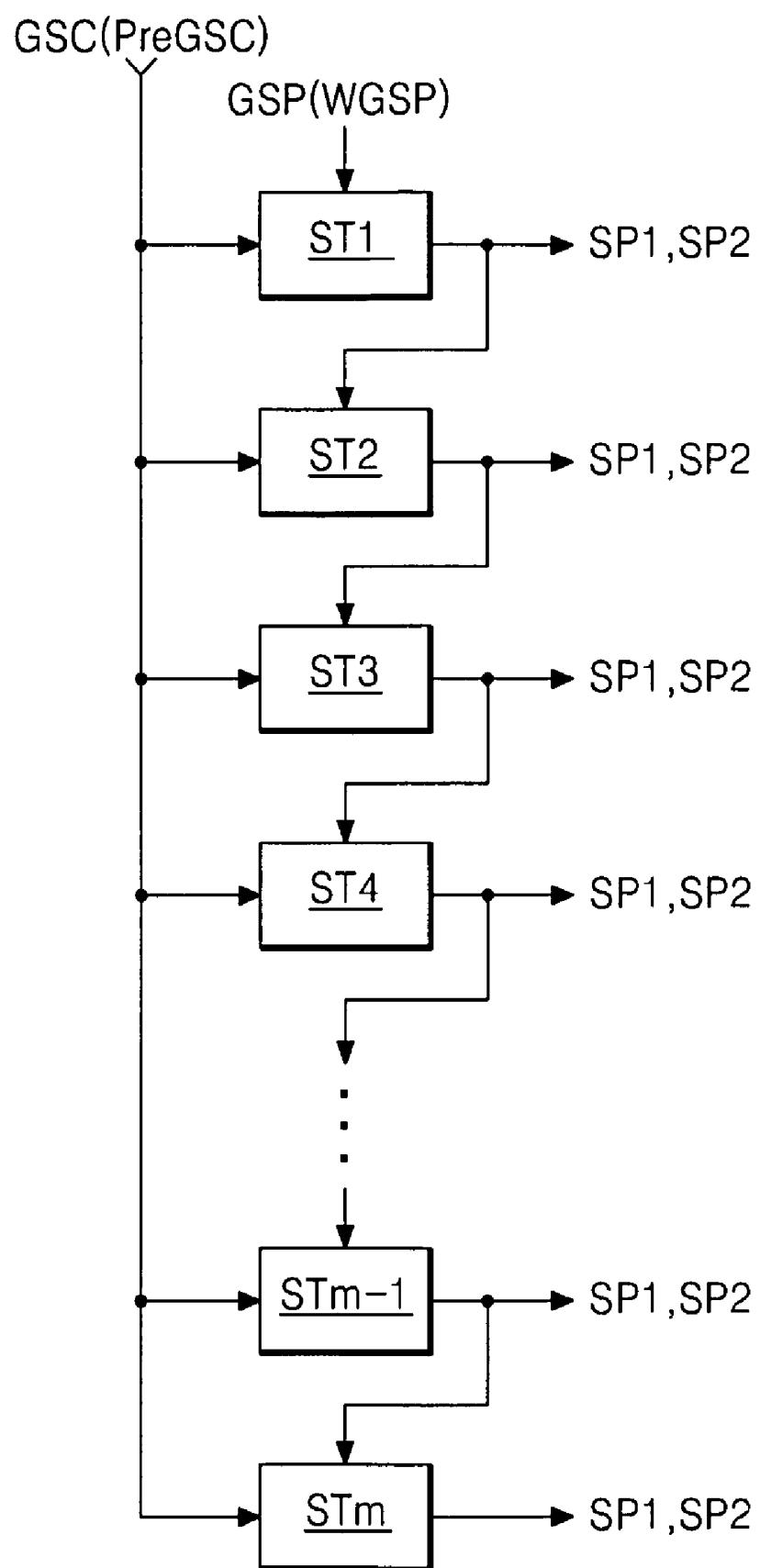

FIG. 27 is a block diagram illustrating an exemplary shift register of a gate driving circuit according to the sixth embodiment of the present invention;

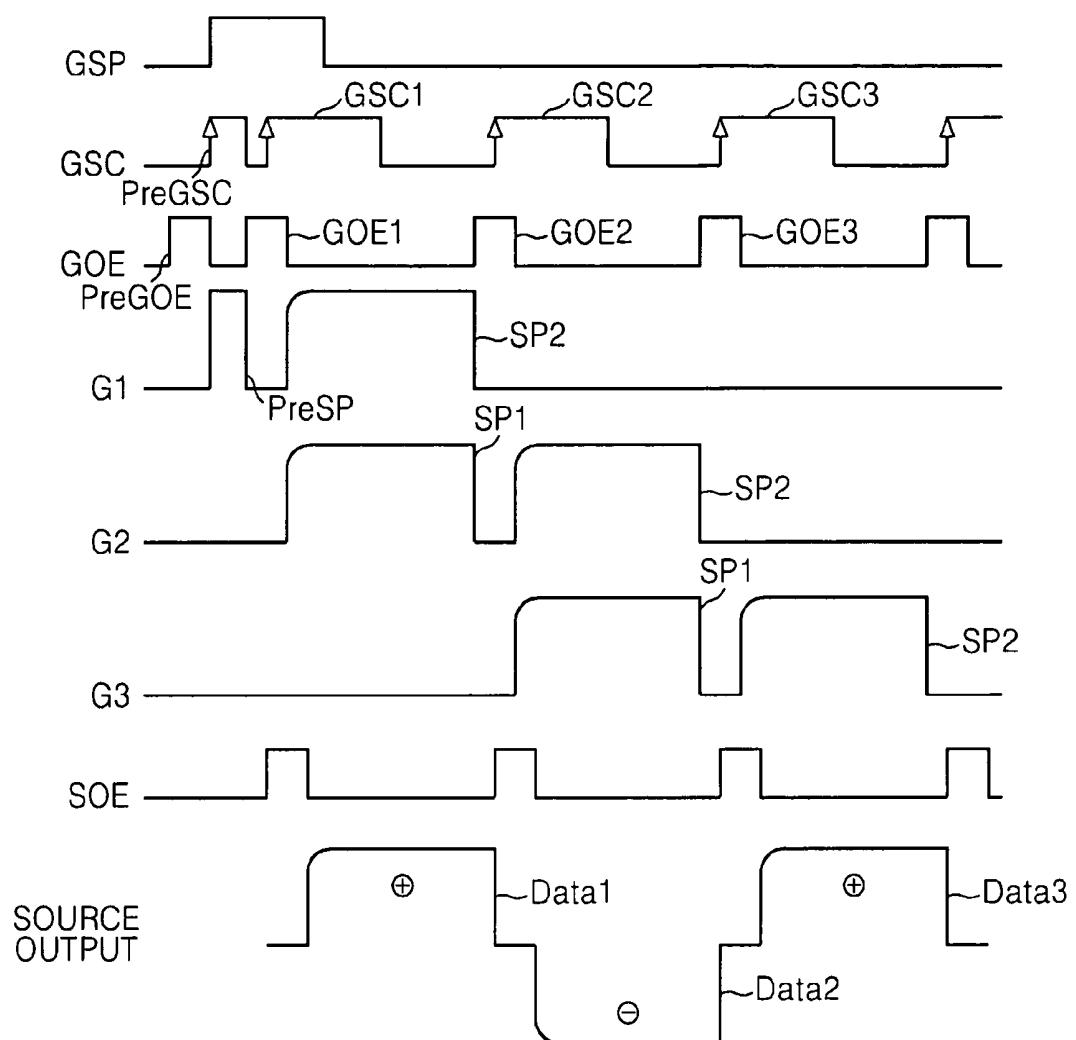

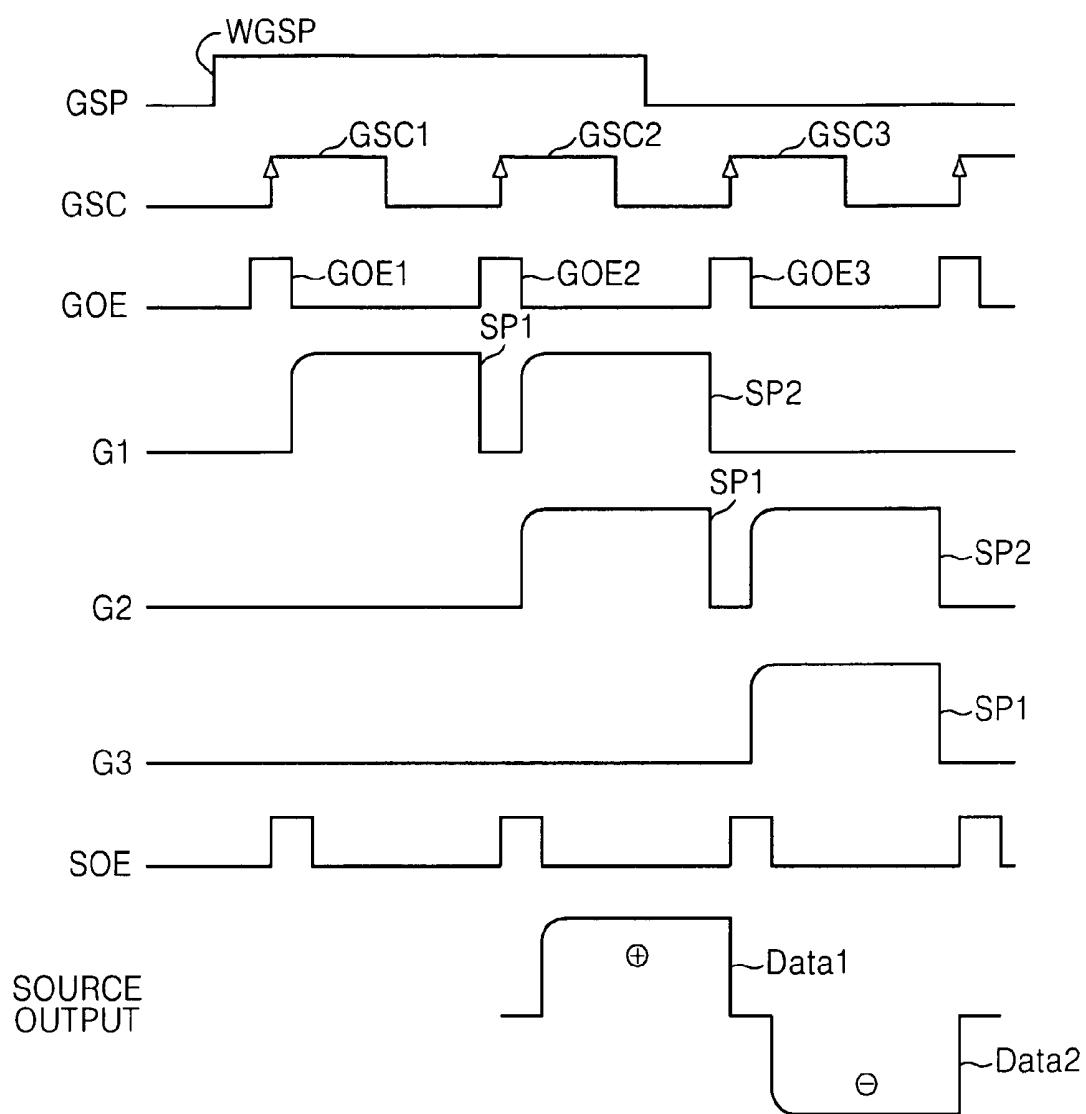

FIGS. 28 and 29 are exemplary waveform diagrams showing a timing signal and a scanning pulse generated in Nth-multiple frame periods;

FIG. 30 is an exemplary waveform diagram showing a gate timing signal and a scanning pulse which are generated at frame periods other than Nth-multiple frame periods;

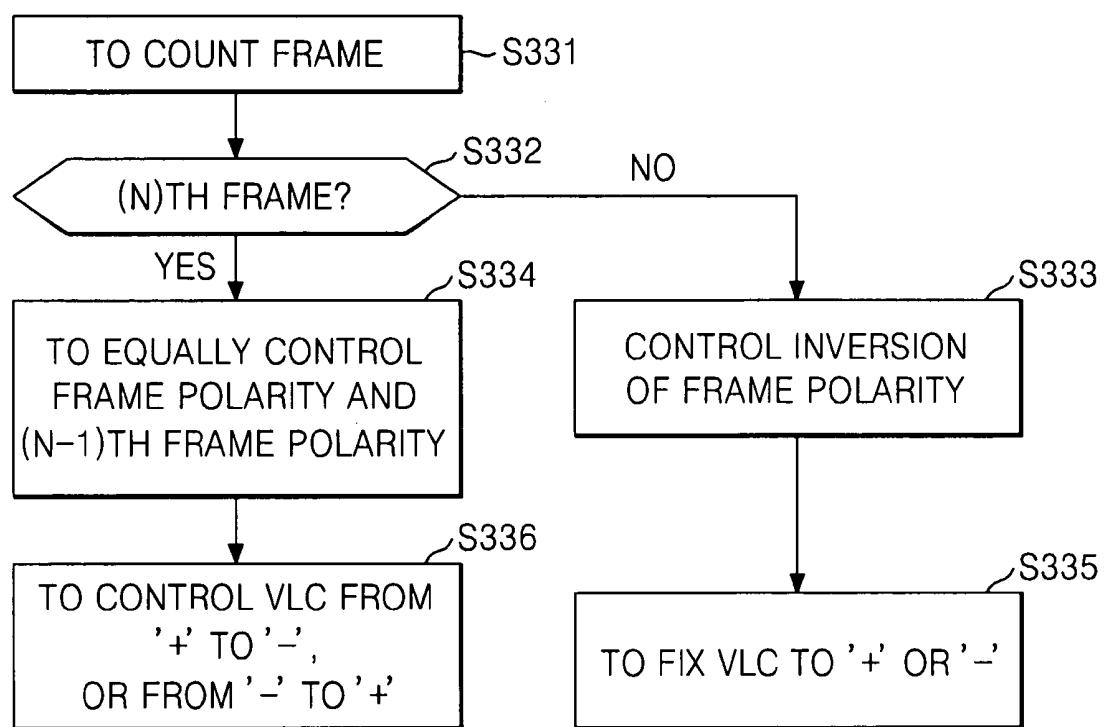

FIG. 31 is a flow chart illustrating an exemplary method of driving a liquid crystal display according to a seventh embodiment of the present invention;

FIG. 32 is a block diagram illustrating an exemplary liquid crystal display according to the seventh embodiment of the present invention;

FIG. 33 is a flow chart illustrating an exemplary method of driving a liquid crystal display according to a eighth embodiment of the present invention;

FIG. 34 is an exemplary waveform diagram showing a data voltage and a scanning pulse at frame periods other than Nth-multiple frame periods;

FIG. 35 an exemplary waveform diagram showing a data voltage and a scanning pulse during the Nth-multiple frame period in the exemplary method of driving the liquid crystal display according to the eighth embodiment of the present invention;

FIG. 36 is a block diagram illustrating an exemplary second logic circuit shown in FIG. 26 and FIG. 32;

FIG. 37 is an exemplary waveform diagram showing data timing control signals and gate timing control signals during Nth-multiple frame periods in the exemplary method of driving the liquid crystal display according to the eighth embodiment of the present invention;

FIG. 38 is flow chart illustrating an exemplary method of driving a liquid crystal display according to a ninth embodiment of the present invention;

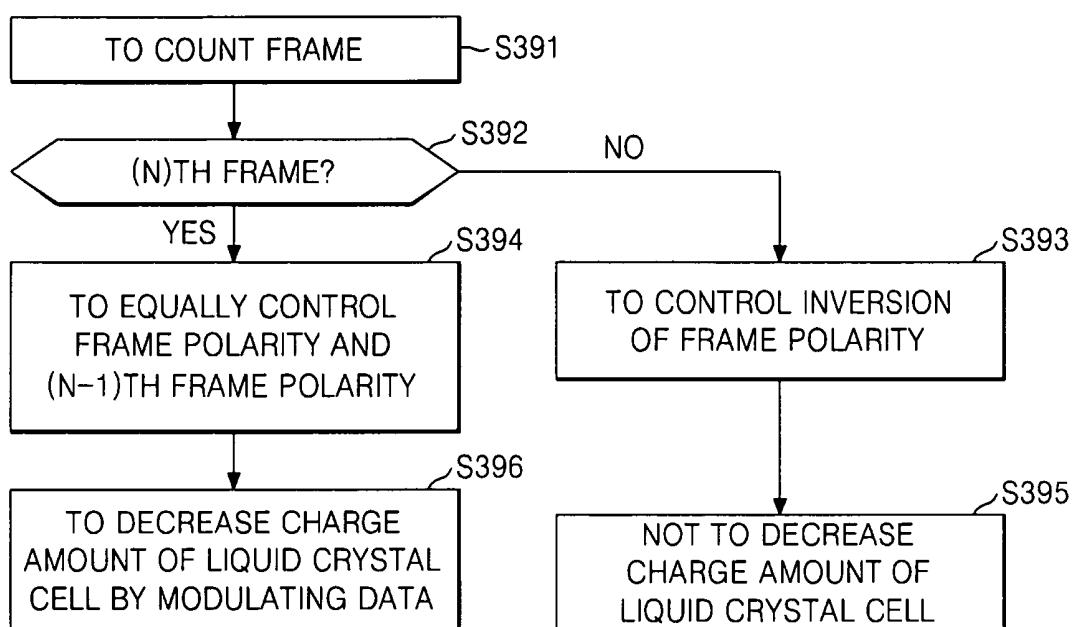

FIG. 39A is a flow chart illustrating an exemplary method of driving a liquid crystal display according to a tenth embodiment of the present invention;

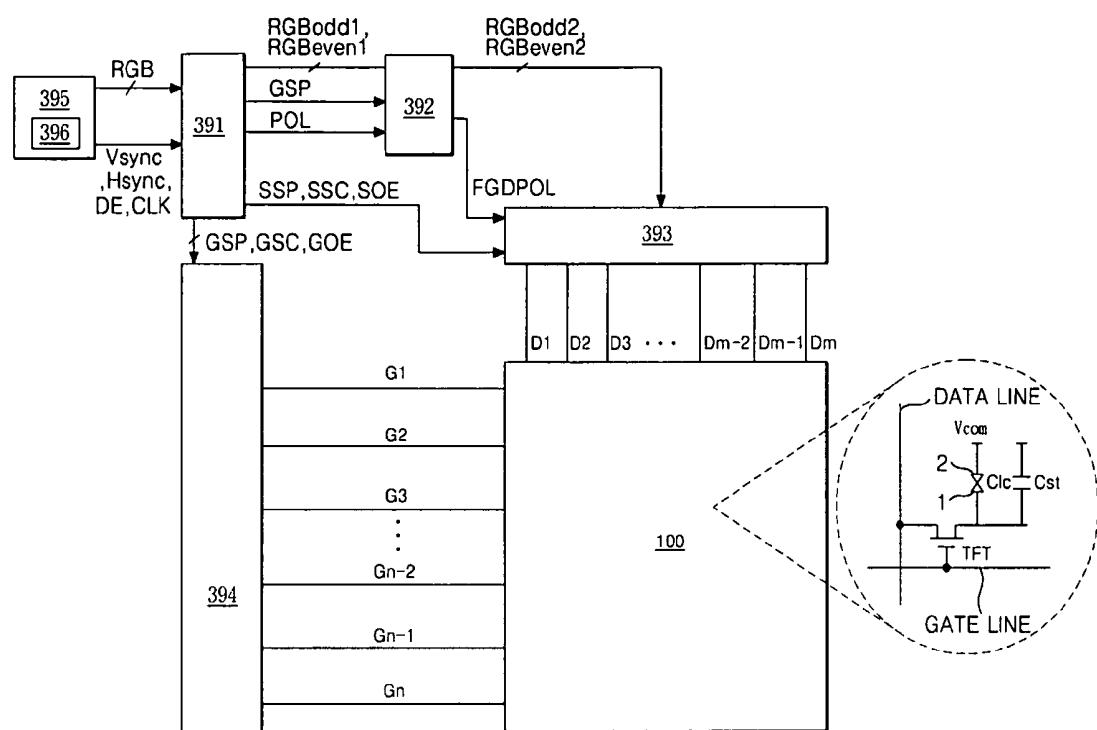

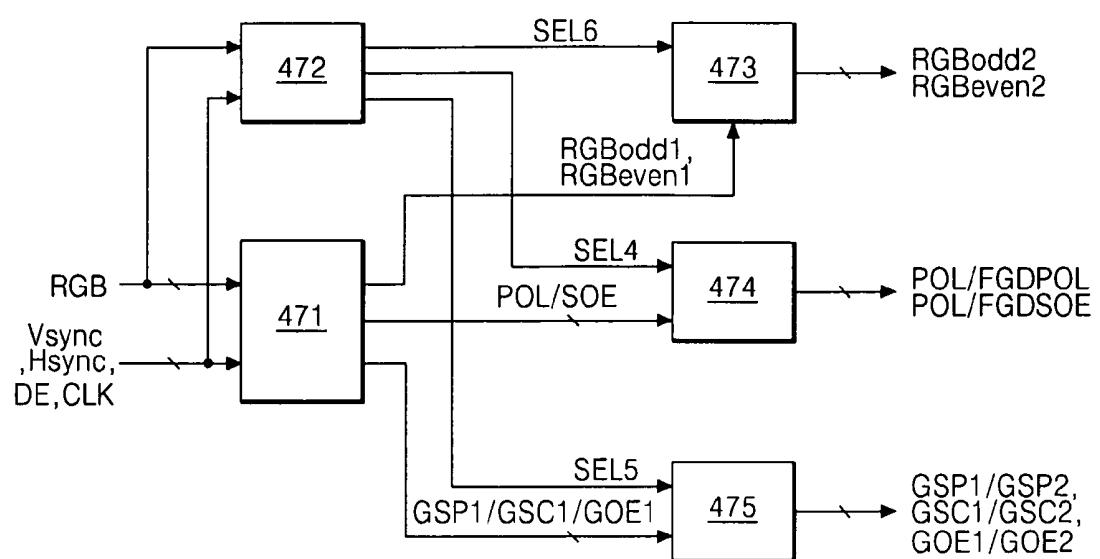

FIG. 39B is a block diagram illustrating an exemplary liquid crystal display according to the tenth embodiment of the present invention;

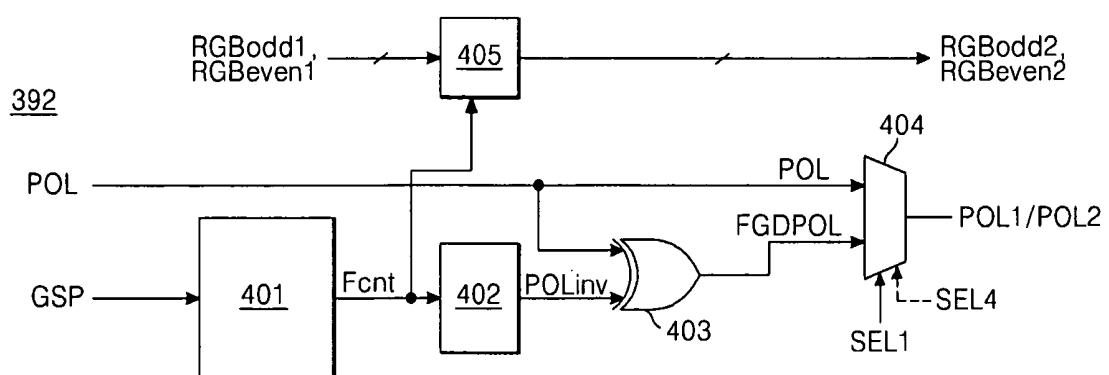

FIG. 40 is a block diagram illustrating an exemplary logic circuit according to the tenth embodiment of the present invention;

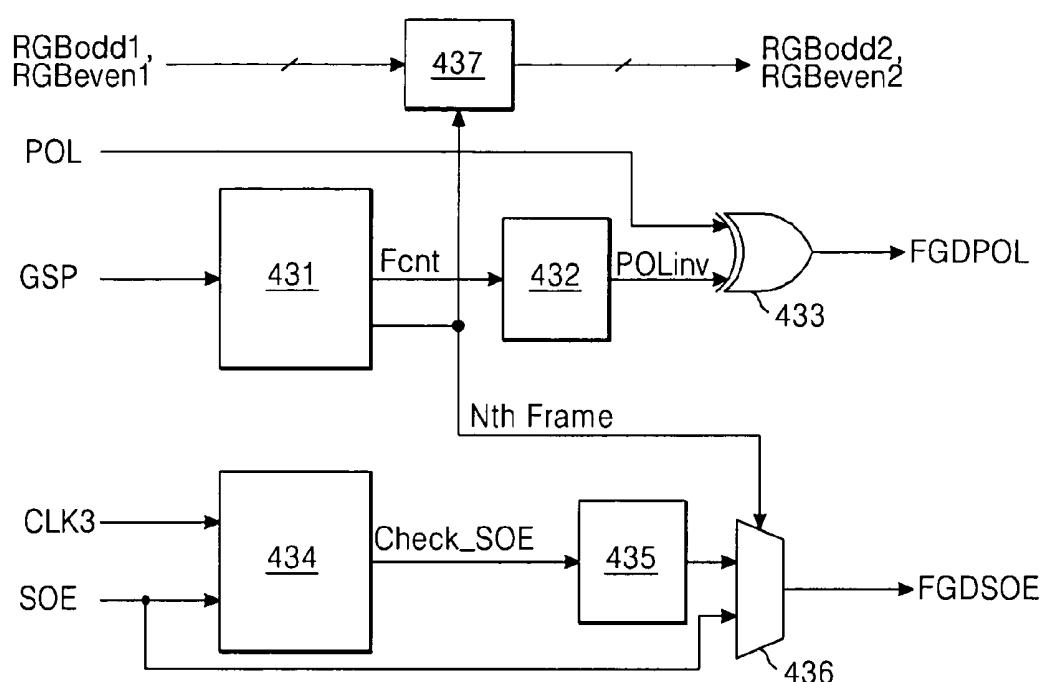

FIG. 41A is a flow chart illustrating an exemplary method of driving a liquid crystal display according to an eleventh embodiment of the present invention;

FIG. 41B is a block diagram illustrating an exemplary liquid crystal display according to the eleventh embodiment of the present invention;

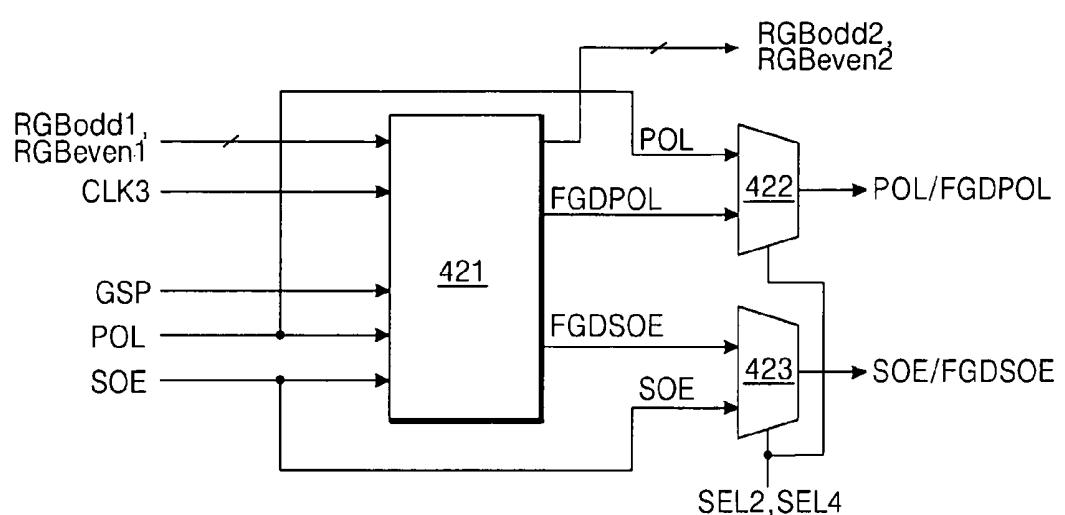

FIG. 42 is a block diagram showing an exemplary logic circuit according to the eleventh embodiment of the present invention;

FIG. 43 is a block diagram illustrating an exemplary logic part shown in FIG. 42;

FIG. 44 is a block diagram illustrating an exemplary liquid crystal display according to a twelfth embodiment of the present invention;

FIG. 45 is a waveform diagram illustrating an exemplary method of modulating gate timing control signals according to the twelfth embodiment of the present invention;

FIG. 46 is a flow chart illustrating an exemplary method of driving a liquid crystal display according to a thirteenth embodiment of the present invention; and

FIG. 47 is a block diagram illustrating an exemplary liquid crystal display according to the thirteenth embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

Reference will now be made in detail to the embodiments of the present invention, examples of which are illustrated in the accompanying drawings.

As shown in FIG. 5, an exemplary method for driving a liquid crystal display device according to a first embodiment of the present invention inverts the polarity of a data voltage supplied to a liquid crystal cell Clc every frame period and

then maintains the same polarity as the previous frame period at each Nth-multiple frame period.

'N' is preferably an integer of not less than 8 because it has been found experimentally that DC image sticking does not seem to appear either in interlace data or scroll data when N is an integer of not less than 8. However, other values of 'N' may be used without departing from the scope of the present invention.

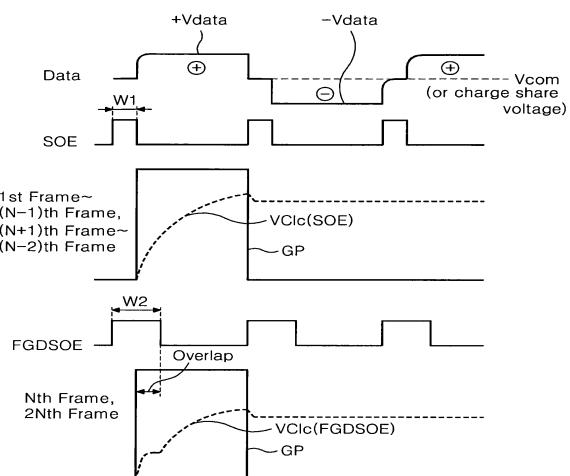

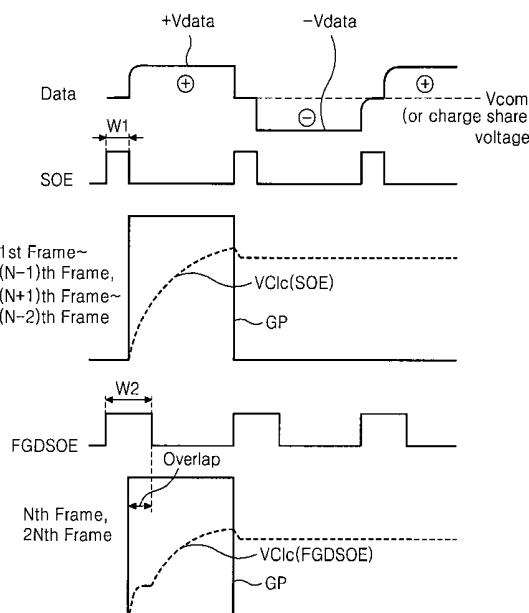

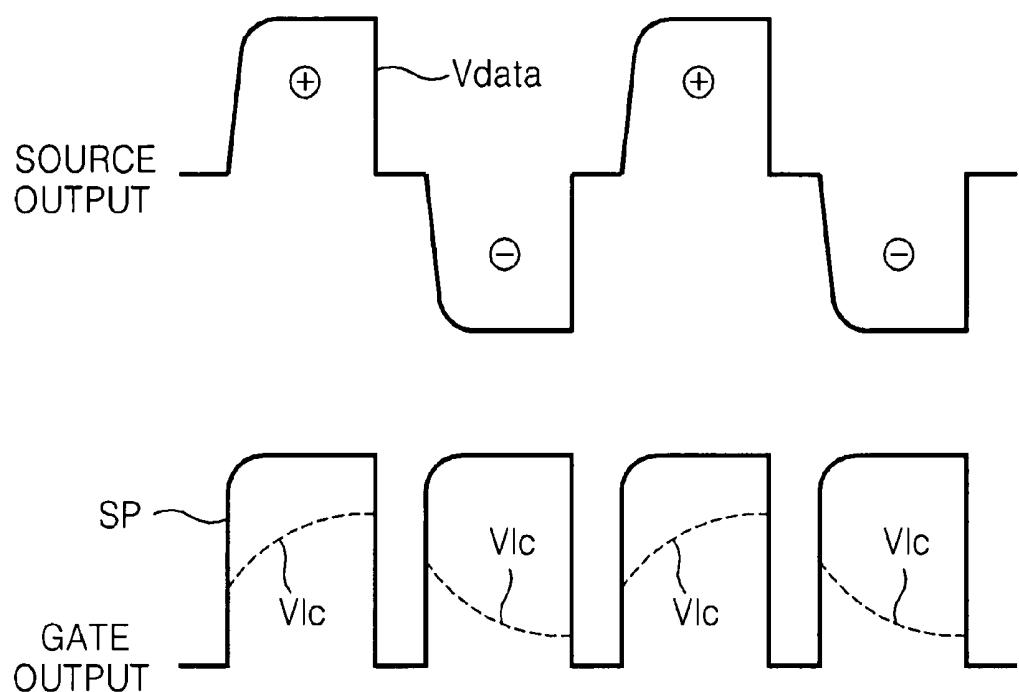

Furthermore, as shown in FIG. 6, the exemplary driving method according to the first embodiment of the present invention generates a first source output enable signal SOE having a first pulse width W1 during the first to (N-1)th frame periods, and a second source output enable signal FGDSOE having a second pulse width W2, which is wider than the first pulse width W1, at the Nth frame period. The first and second source output enable signals SOE, FGDSOE are a timing control signal which indicates the output of a data drive circuit. Subsequently, the exemplary driving method according to the first embodiment of the present invention generates the first source output enable signal SOE having the first pulse width W1 during (N+1)th to (2N-1)th frame periods, and the second source output enable signal FGDSOE having the second pulse width W2 during 2Nth frame period, and so on. In other words, the second source output enable signal FGDSOE having the second pulse width W2 is generated at every Nth-multiple frame period while the first source output enable signal SOE having the first pulse width W1 is generated at all other frame periods.

During a high logic section of the first and second source output enable signals SOE, FGDSOE, a data drive circuit generates a common voltage Vcom or a charge share voltage. The common voltage Vcom is an intermediate voltage between a positive data voltage and a negative data voltage. The charge share voltage is a voltage which is generated to be an average value of the positive data voltage and the negative data voltage by a short circuit between adjacent data lines, one of which the positive data voltage is supplied during the high logic section of the source output enable signal SOE and the other of which is disposed to be close thereto and to which the negative data voltage is supplied. During a low logic period of the first and second source output enable signal SOE, FGDSOE, the data drive circuit generates a positive data voltage +Vdata or a negative data voltage -Vdata.

During the first to (N-1)th frame periods and the (N+1)th to (2N-1)th frame periods, the high logic section of the first source output enable signal SOE and a gate pulse GP are generated not to overlap, or may overlap for a very short time. Accordingly, during the first to (N-1)th frame periods and the (N+1)th to (2N-1)th frame periods, a liquid crystal cell Clc is charged with the positive data voltage +Vdata or the negative data voltage -Vdata while a TFT connected to the liquid crystal cell Clc is turned on by the gate pulse GP. Thereafter, the data voltages +Vdata or -Vdata are maintained by a storage capacitor Cst after the TFT is turned off. The amount of voltage charged by the first source output enable signal SOE is indicated by the dotted line VClc (SOE).

However, for each of the Nth-multiple frame period (e.g., the Nth and 2Nth frame periods), the high logic section of the second source output enable signal FGDSOE and the gate pulse GP are generated to overlap for a relatively long time. Accordingly, at each Nth-multiple frame period (e.g., the Nth and 2Nth frame periods), the liquid crystal cell Clc is charged with the data voltages +Vdata and -Vdata after being charged with the common voltage Vcom or the charge share voltage while the TFT is turned on by the gate pulse GP. Subsequently, the liquid crystal cell Clc maintains the data voltages +Vdata and -Vdata by the storage capacitor Cst after the TFT

is turned off. The amount of voltage charged by the second source output enable signal FGDSOE is indicated by the dotted line V<sub>Clc</sub> (FGDSOE).

Therefore, when the liquid crystal cell Clc is supplied with the data voltages +V<sub>data</sub> and -V<sub>data</sub> of the same gray level at every frame period, the charge amount of the liquid crystal cell Clc at each Nth-multiple frame period (e.g., the Nth and 2Nth frame periods) will be less than the charge amount during the first to (N-1)th frame periods and the (N+1)th to (2N-1)th frame periods because at each Nth-multiple frame period, the liquid crystal cell Clc is charged with the data voltages +V<sub>data</sub> and -V<sub>data</sub> after being charged with the common voltage V<sub>com</sub> or the charge share voltage due to the overlapping of the second source output enable signal FGDSOE and the gate pulse GP.

For purposes of example, if the first pulse width W1 of the first source output enable signal SOE is set to '1,' then the second pulse width W2 of the second source output enable signal FGDSOE should be set to about 1.36-1.71. While these values were found to be the optimum second pulse width values through experimentation at which neither DC image sticking nor flicker was generated during interlace method and scrolling, other proportions between the first pulse width W1 and second pulse width W2 may be used without departing from the scope of the invention.

The experiment included taking 2.24  $\mu$ s as the first pulse width W1 of the first source output enable signal SOE, driving a liquid crystal display panel by controlling the data voltage to have the same polarity as the previous frame for N frame periods, adjusting the second pulse width W2 of the second source output enable signal FGDSOE, and checking for the presence or absence of the DC image sticking and flicker during both of the interlace method and scrolling. Using this experiment, the second pulse width W2 of the second source output enable signal with which neither DC image sticking nor flicker was generated during both the interlace method and scrolling was confirmed to be about 3.04  $\mu$ s-3.8  $\mu$ s. It was found that if the second pulse width W2 of the second source output enable signal FGDSOE was narrower than 3.04  $\mu$ s, the charge amount of the liquid crystal cell Clc was not decreased enough at the Nth frame period and 2Nth frame period. Thus, flicker was visually perceived on the screen. On the other hand, if the second pulse width W2 of the second source output enable signal FGDSOE was wider than 3.84  $\mu$ s, the charge amount of the liquid crystal cell Clc was decreased too much at the Nth frame period and 2Nth frame period. Thus, flicker and reduction of brightness was visually perceived on the screen.

As described above, the principle of the exemplary driving method of the liquid crystal display device according to the first embodiment of the present invention is to prevent DC image sticking and flicker by inverting the polarity of the data voltage during each frame period except at every Nth-multiple frame period, and increasing the pulse width of the source output enable signal SOE at every Nth-multiple frame period, thereby decreasing the charge amount of the liquid crystal cell Clc.

FIGS. 7 to 9 are diagrams illustrating an explanation of DC image sticking and flicker prevention effects when scroll data are supplied to an arbitrary liquid crystal cell Clc. As shown in FIG. 7, if symbols and characters are moved at a speed of 8 pixels per frame, for example, and the data voltage is controlled with the same polarity as the previous frame by 8 frame period units (i.e., every 8th frame period) using a polarity control signal POL, then the arbitrary liquid crystal cell Clc is charged with the data voltage of the symbols and characters in the shaded frame periods shown in FIG. 7.

Looking at the polarity pattern, then, the data voltages are changed in the order of "+" to "—" to "+" to "--" and so on. Accordingly, the present invention prevents the DC image sticking, which is generated because the polarity of the voltage charged in the liquid crystal cell Clc is periodically inverted in the scroll data, of which the symbols and characters are moved at a fixed speed.

As can be seen in a light waveform shown in FIG. 8, an output waveform of a photo diode disposed on top of a liquid crystal display panel shows that when the data voltage of the same polarity is repeated for two frame periods at each 8th frame period, the data voltage of the same polarity is accumulated in the liquid crystal cell, thereby increasing the accumulated voltage. Due to the accumulated voltage of the same polarity, the brightness of the liquid crystal cell Clc increases rapidly between the two frame periods in which the polarity stays the same. This occurs every 8th frame period as shown in FIG. 7, thereby creating a flickering effect. In order to prevent such a flicker phenomenon, the driving method of the liquid crystal display device according to an embodiment of the present invention reduces the charge amount of the liquid crystal cell Clc using the second source output enable signal FGDSOE at every Nth-multiple frame period when the polarity stays the same, thereby preventing a rapid change of the brightness. FIG. 9 shows a light waveform showing that a drastic change in brightness is prevented.

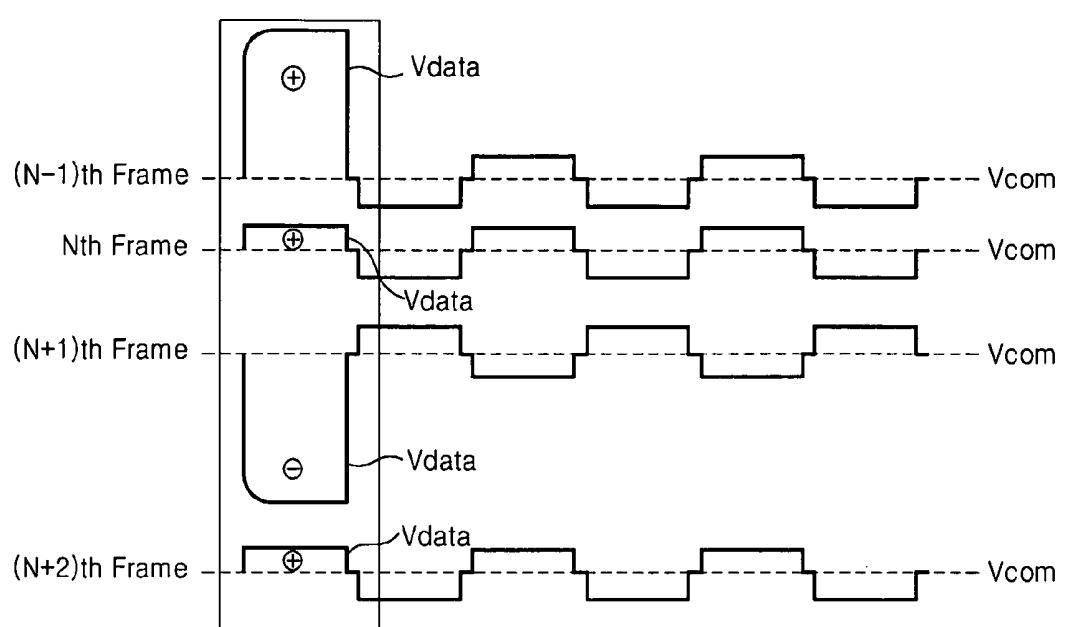

FIG. 10 is a diagram illustrating DC image sticking and flicker prevention effect when interlace data are supplied to an arbitrary liquid crystal cell Clc. As shown in FIG. 10, if interlace data are supplied to an arbitrary liquid crystal cell Clc, a high data voltage is supplied to the liquid crystal cell Clc only in the (N-1)th frame period and the (N+1)th frame period (i.e., odd-numbered frame periods) and a relatively low black voltage or an average voltage is supplied thereto in the Nth frame period and the (N+2)th frame period (i.e., even-numbered frame periods). As a result, the positive data voltage supplied in the (N-1)th frame period and the negative data voltage supplied in the (N+1)th frame period cancel each other so that a voltage charge of the biased polarity is not accumulated in the liquid crystal cell Clc. Accordingly, the liquid crystal display device according to the present invention does not generate the DC image sticking and flicker even when the interlace data are supplied thereto.

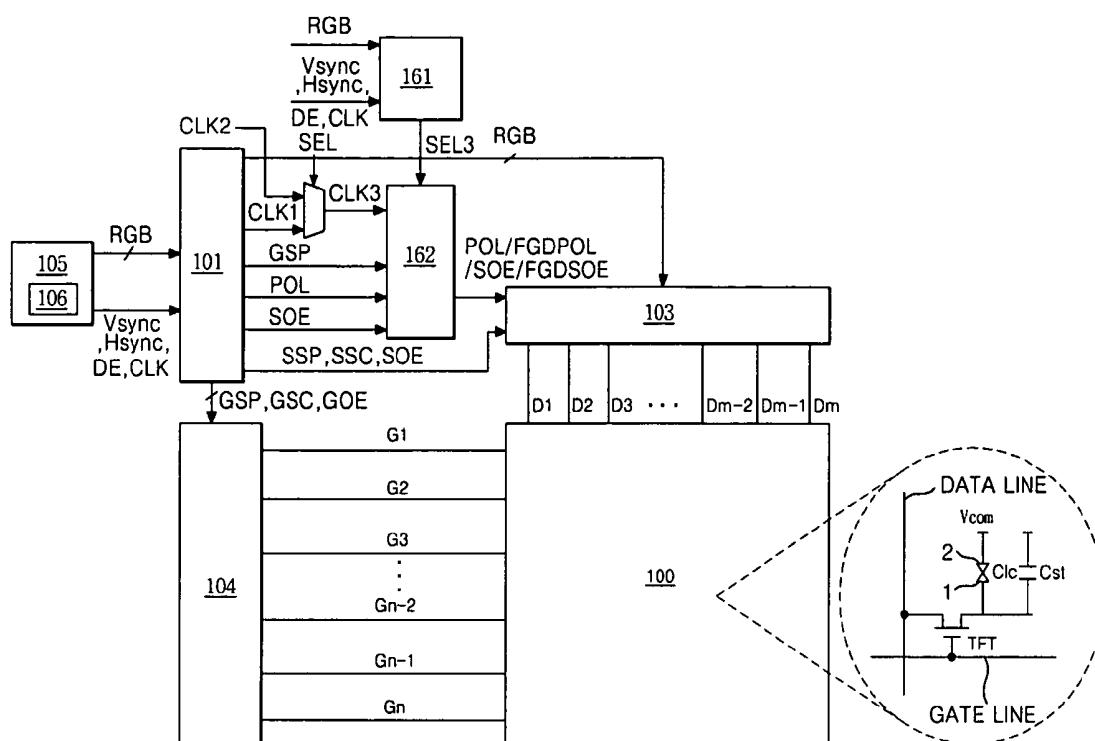

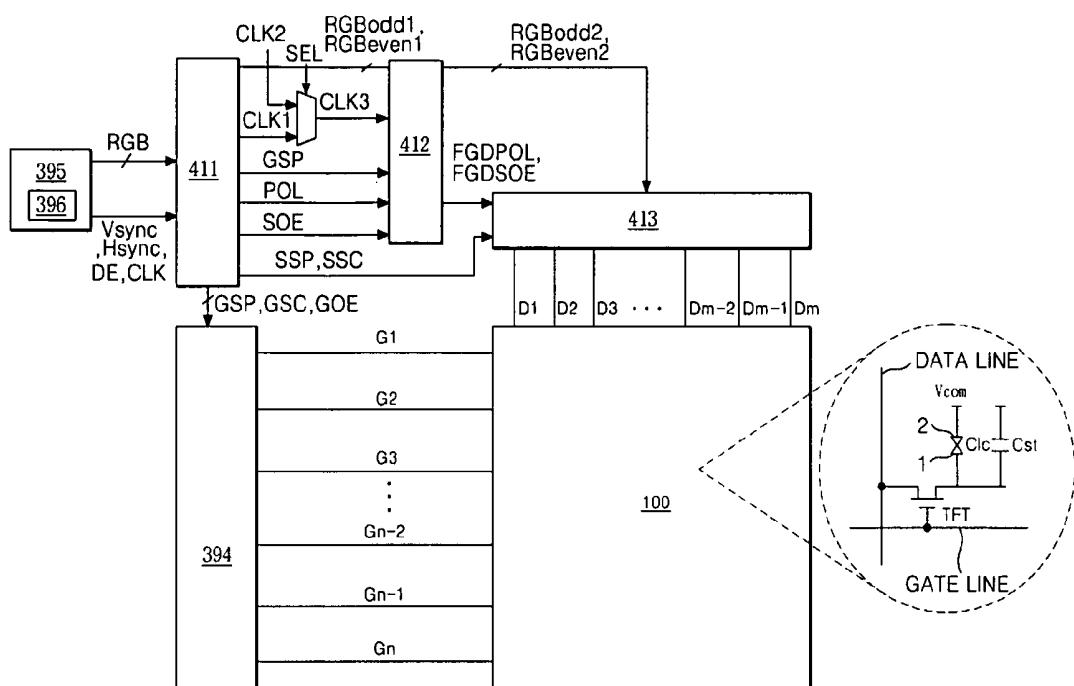

FIGS. 11 to 15 illustrate an exemplary a liquid crystal display device according to a first embodiment of the present invention. As shown in FIG. 11, a liquid crystal display device according to a first embodiment of the present invention includes a liquid crystal display panel 100, a timing controller 101, a POL/SOE logic circuit 102, a data drive circuit 103, and a gate drive circuit 104.

In the liquid crystal display panel 100, liquid crystal molecules are injected between two glass substrates. The liquid crystal display panel 100 includes mxn number of liquid crystal cells Clc where m number of data lines D1 to Dm and n number of gate lines G1 to Gn are arranged in a matrix pattern crossing each other. On one glass substrate of the liquid crystal display panel 100, there are formed data lines D1 to Dm, gate lines G1 to Gn, TFT's, pixel electrodes 1 of the liquid crystal cells Clc connected to the TFTs, storage capacitors Cst, as well as other components. On the other glass substrate of the liquid crystal display panel 100, there are formed a black matrix, color filters, a common electrode 2, as well as other components.

In one alternative, the common electrode 2 is formed on a glass substrate opposing the pixel electrode 1 in a vertical electric field driving configuration such as a TN (Twisted Nematic) mode and a VA (Vertical Alignment) mode. In

another alternative, the common electrode **2** is formed together with the pixel electrode **1** on the same glass substrate in a horizontal electric field driving configuration such as an IPS (In-Plane Switching) mode and an FFS (Fringe Field Switching) mode. The common electrode **2** is supplied with common voltage  $V_{com}$  between the positive data voltage and the negative data voltage. Polarizers with optical axes perpendicularly crossing each other are formed on the upper glass substrate and the lower glass substrate of the liquid crystal display panel **100**, and alignment films for setting the pre-tilt angle of the liquid crystals are formed on the internal surfaces thereof which face the liquid crystals.

The timing controller **101** receives timing signals such as vertical/horizontal synchronization signals  $V_{sync}$ ,  $H_{sync}$ , data enable signals, clock signals, and other control signals to control the operation timing of the POL/SOE logic circuit **102**, the gate drive circuit **104**, and the data drive circuit **103**. The control signals include a gate start pulse  $GSP$ , a gate shift clock signal  $GSC$ , a gate output enable  $GOE$ , a source start pulse  $SSP$ , a source sampling clock  $SSC$ , a source output enable signal  $SOE$ , and a first polarity control signal  $POL$ . The gate start pulse  $GSP$  indicates a start horizontal line from which a scan starts among a first vertical period when a screen is to be displayed. The gate shift clock signal  $GSC$  is input to a shift register within the gate drive circuit and has a pulse that corresponds to the on-period of the TFT as a timing control signal for sequentially shifting the gate start pulse  $GSP$ . The gate output signal  $GOE$  indicates the output of the gate drive circuit **104**. The source start pulse  $SSP$  is a data control signal  $DDC$  and indicates a start pixel in a first horizontal line where data are to be displayed. The source sampling clock  $SSC$  indicates a latch operation of the data within the data drive circuit **103** on the basis of a rising or falling edge. The source output enable signal  $SOE$  indicates the output of the data drive circuit **103**. The first polarity control signal  $POL$  indicates the polarity of the data voltages which are to be supplied to the liquid crystal cells  $Clc$  of the liquid crystal display panel **100**. The first polarity control signal  $POL$  may be generated as any type of 1-dot inversion polarity control signal of which the logic is inverted for each horizontal period and 2-dot inversion polarity control signal of which the logic is inverted for each two horizontal periods.

The timing controller **101** generates timing control signals at a frame frequency of 120 Hz or 60 Hz to control the operation timing of the POL/SOE logic circuit **102**, the data drive circuit **103**, and the gate drive circuit **104** on the basis of 120 Hz or 60 Hz. The frame frequency is a frequency corresponding to the vertical synchronization signal  $V_{sync}$  and indicates the number of screens per second. The 120 Hz frame frequency generates 120 screens per second displayed on the liquid crystal display panel **100**, and 60 Hz frame frequency generates 60 screens per second displayed on the liquid crystal display panel **100**. The flicker is less noticeable when the liquid crystal display device is driven at the 120 Hz frame frequency in comparison with the 60 Hz frame frequency.

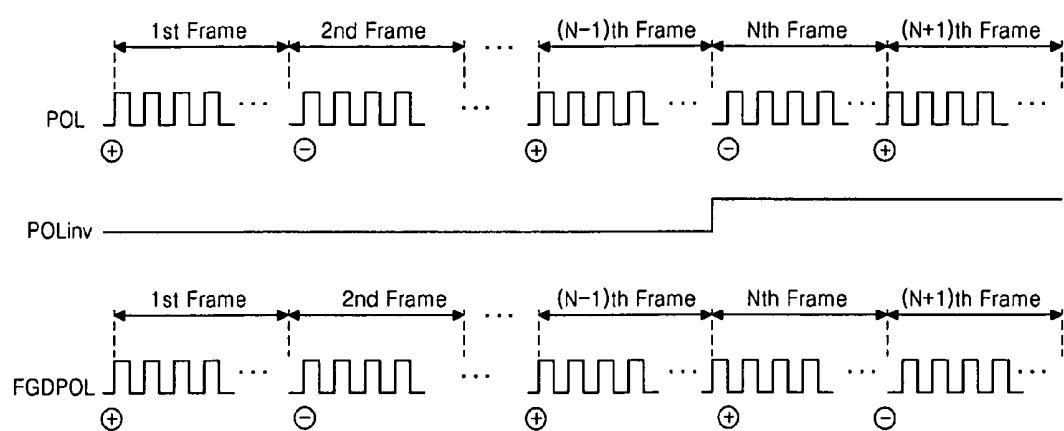

The POL/SOE logic circuit **102** receives the gate start pulse  $GSP$  and the first polarity control signal  $POL$  and, in order to prevent the residual image and flicker as described above, generates the second polarity control signal  $FGDPOL$  in the frame period of a multiple of  $N$  (i.e., in the  $N$ th,  $2N$ th frame periods, and so on) to selectively supply either the first polarity control signal  $POL$  or the second polarity control signal  $FGDPOL$  to the data drive circuit **103**. The first polarity control signal  $POL$  has its logic inverted for each horizontal period (i.e., 1-dot) or for each two horizontal periods (i.e., 2-dot), and the logic is also inverted for each frame period in order to invert the polarity of the data voltage for each frame

period, as shown in FIG. 16. At each  $N$ th-multiple frame period, the second polarity control signal  $FGDPOL$  is generated in the same phase as in the previous frame period and has its logic inverted for each horizontal period or for each two horizontal periods in order to control the polarity of the data voltage in the same polarity pattern as in the previous frame period, as shown in FIG. 16.

The POL/SOE logic circuit **102** also receives a first source output enable signal  $SOE$  and a third clock signal  $CLK3$  so that the POL/SOE logic circuit **102** generates the second source output enable signal  $FGDSOE$  adjusted to have a wider pulse signal at every  $N$ th-multiple frame period. The POL/SOE logic circuit **102** selectively either the first source output enable signal  $SOE$  or the second source output enable signal  $FGDSOE$  to the data drive circuit **103**. The first source output enable signal  $SOE$  is generated to have a first pulse width  $W1$ . The second source output enable signal  $FGDSOE$  is generated to have a second pulse width  $W2$ , which is wider than the first pulse width  $W1$ . The second source output enable signal  $FGDSOE$  is supplied to the data drive circuit **103** at every  $N$ th-multiple frame period, and the first source output enable signal  $SOE$  is supplied at all other frame periods.

The exemplary liquid crystal display device according to the first embodiment of the present invention further includes a multiplexer which is connected between the timing controller **101** and the POL/SOE logic circuit **102** to supply the third clock signal  $CLK3$ . The multiplexer chooses from a first clock signal  $CLK1$ , which is generated from an internal oscillator of the timing controller, or a second clock signal  $CLK2$ , which is supplied from an external oscillator, in accordance with a control signal  $SEL$  supplied to its own control terminal. Based on the control signal  $SEL$ , the multiplexer supplies the selected clock signal  $CLK1$  or  $CLK2$  as the third clock signal  $CLK3$  to the POL/SOE logic circuit **102**. The control terminal of the multiplexer is connected to an option pin. The option pin is connected to the control terminal of the multiplexer and might be selectively connected to a ground voltage source  $GND$  or a power supply voltage  $Vcc$  by the manufacturer. For example, if the option pin is connected to the ground voltage source  $GND$ , the multiplexer has the control terminal supplied with a selection control signal  $SEL$  of “0” to output the first clock signal  $CLK1$  as the third clock signal  $CLK3$ , and if the option pin is connected to the power supply voltage  $Vcc$ , the multiplexer has the control terminal supplied with the selection control signal  $SEL$  of “1” to output the second clock signal  $CLK2$  as the third clock signal  $CLK3$ .

The data drive circuit **103** latches the digital video data  $RGB$  under control of the timing controller **101**. The data drive circuit **103** converts the digital video data into an analog positive/negative gamma compensation voltage in accordance with the polarity control signal  $POL/FGDPOL$  to generate a positive/negative analog data voltage, thereby supplying the data voltage to the data lines  $D1$  to  $Dm$ .

The gate drive circuit **104** is composed of a plurality of gate drive integrated circuits (hereinafter, referred to as “IC”) of which each includes a shift register, a level shifter for converting the swing width of the output signal of the shift register into a swing width that is suitable for driving the TFT of the liquid crystal cell, and an output buffer connected between the level shifter and the gate line  $G1$  to  $Gn$ . The gate drive circuit **104** sequentially outputs gate pulses which have a pulse width of about one horizontal period. The POL/SOE logic circuit **102** may be embedded within the timing controller **101**.

The exemplary liquid crystal display device according to the first embodiment of the present invention further includes

a video signal source 105 for supplying the digital video data RGB and the timing signals Vsync, Hsync, DE, CLK to the timing controller 101. The video signal source 105 includes a broadcasting signal, an external device interface circuit, a graphic processing circuit, a line memory 106 and the like. The video signal source 105 extracts the video data from an external device or a broadcasting signal and converts the video data into the digital data to supply to the timing controller 101. An interlaced broadcasting signal received by the video signal source 105 is stored in the line memory 106 before being output. As described above, the video data of an interlaced broadcasting signal exist only in the odd-numbered lines in the odd-numbered frame period and only in even-numbered lines in the even-numbered frame. Accordingly, if the interlaced broadcasting signal is received, the video signal source 105 generates a black data value or an average value of the effective data stored in the line memory 106 as the even-numbered line data in the odd-numbered frame period and as the odd-numbered line data in the even-numbered frame.

The video signal source 105 supplies the timing signals Vsync, Hsync, DE, CLK together with the digital video data to the timing controller 101. Further, the video signal source 105 supplies power to circuits such as the timing controller 101, the POL/SOE logic circuit 102, the data drive circuit 103, the gate drive circuit 104, a DC-DC converter for generating a drive voltage of the liquid crystal display panel, an inverter for lighting the light source of a backlight unit, and the like.

FIGS. 12 and 13 are circuit diagrams representing an exemplary data drive circuit 103 in detail. Referring to FIGS. 12 and 13, the data drive circuit 103 includes a plurality of source IC's of which each drives k (k is an integer less than m) number of data lines D1 to Dk. The source IC includes a shift register 111, a data register 112, a first latch 113, a second latch 114, a digital/analog converter (hereinafter, referred to as "DAC") 115, a charge share circuit 116, and an output circuit 117.

The shift register 111 shifts the source start pulse SSP from the timing controller 101 in accordance with the source sampling clock SSC to generate a sampling signal. Further, the shift register 111 shifts the source start pulse SSP to transmit a carry signal CAR to the shift register 111 of the next stage. The data register 112 temporarily stores the digital video data RGBodd of odd-numbered pixels and the digital video data RGBeven of even-numbered pixels divided by the timing controller 101 and supplies the stored digital video data RGBodd, RGBeven to the first latch 113. The first latch 113 samples the digital video data RGBodd, RGBeven from the data register 112 in response to the sampling signal sequentially input from the shift register 111, latches the digital video data RGBodd, RGBeven, and outputs them. The second latch 114 latches the latched data input from the first latch 113 and outputs the digital video data simultaneously with the other second latches 114 of other ICs during the low logic period of the source output enable signal SOE, FGDSOE.

As shown in FIG. 13, the DAC 115 of FIG. 12 includes a P-decoder PDEC 121 to which a positive gamma reference voltage GH is supplied, an N-decoder NDEC 122 to which a negative gamma reference voltage GL is supplied, and a multiplexer 123 to select either the output of the P-decoder 121 or the output of the N-decoder 122 in response to the polarity control signals FGDPOL, POL. The P-decoder 121 decodes the digital video data input from the second latch 114 and outputs a positive gamma compensation voltage corresponding to the gray level value of the data. The N-decoder 122 decodes the digital video data input from the second latch 114 and outputs a negative gamma compensation voltage

corresponding to the gray level value of the data. The multiplexer 123 selects between the positive gamma compensation voltage and the negative gamma compensation voltage in response to the polarity control signal FGDPOL, POL, and outputs the selected positive/negative gamma compensation voltage as an analog data voltage.

The charge share circuit 116 shorts adjacent data output channels during the high logic period of the source output enable signal SOE, FGDSOE to output the average value of the data voltages in adjacent data output channels as a charge share voltage. Alternatively, the charge share circuit 116 supplies the common voltage Vcom to the data output channels during the high logic period of the source output enable signal SOE, FGDSOE. As explained above, the charge share circuit 116 generates either the charge share voltage or the common voltage to thereby reduce a rapid change of the positive data voltage and the negative data voltage. The output circuit 117 includes a buffer to minimize signal attenuation of the analog data voltages supplied to the data lines D1 to Dk.

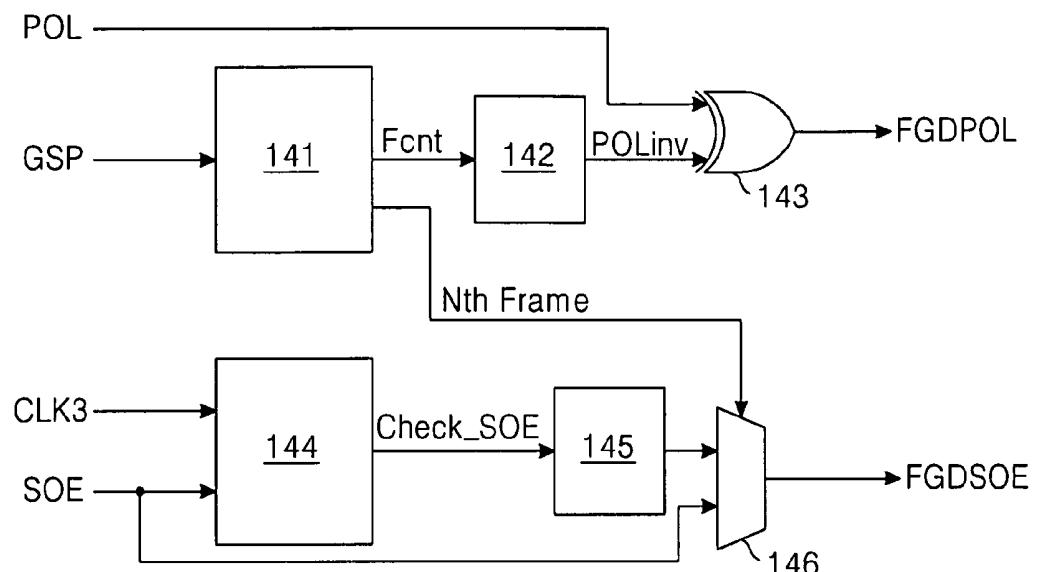

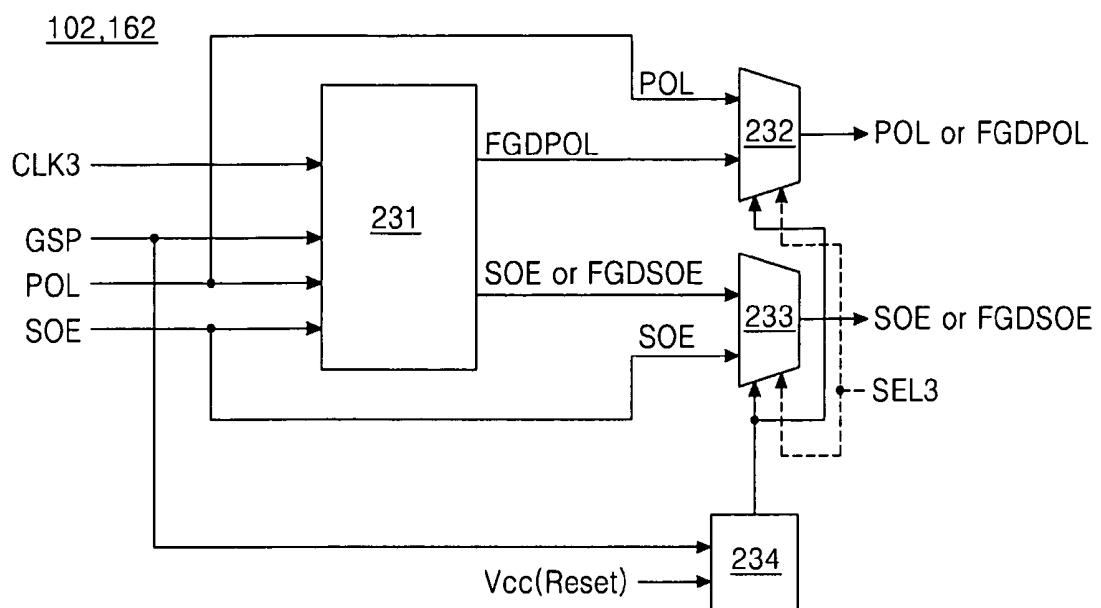

FIGS. 14 and 15 are circuit diagrams representing an exemplary POL/SOE logic circuit 102 in detail. As shown in FIG. 14, the POL/SOE logic circuit 102 includes a logic part 131, a first multiplexer 132, and a second multiplexer 133. The logic part 131 receives the gate start pulse GSP, the first polarity control signal POL, the first source output enable signal SOE, and the clock signal CLK3 from the timing controller 101, and generates the second polarity control signal FGDPOL and the second source output enable signal FGDSOE at every Nth-multiple frame period.

The first multiplexer 132 selects between the first polarity control signal POL and the second polarity control signal FGDPOL in accordance with the logic value of the control signal (SEL2 or SEL3, to be described below) applied to its control terminal. The second multiplexer 133 selects between the first source output enable signal SOE and the second output enable signal FGDSOE in accordance with the logic value of the control signal applied to its own control terminal.

The control terminal of the first and second multiplexers 132, 133 is connected to an option pin. The option pin is connected to the control terminals of the first and second multiplexers 132, 133 and may be selectively connected to a ground voltage source GND or a power supply voltage Vcc by a manufacturer. For example, if the option pin is connected to the ground voltage source GND, the first multiplexer 132 has the control terminal supplied with a selection control signal SEL2 of "0" to output the second polarity control signal FGDPOL, and the second multiplexer 133 has the control terminal supplied with the selection control signal SEL2 of "0" to output the second source output enable signal FGDSOE. If the option pin is connected to the power supply voltage Vcc, the first multiplexer 132 has the control terminal supplied with a selection control signal SEL2 of "1" to output the first polarity control signal POL, and the second multiplexer 133 has the control terminal supplied with the selection control signal SEL2 of "1" to output the first source output enable signal SOE.

As shown in FIGS. 15 and 16, the logic part 131 includes a frame counter 141, a POL inverter 142, an exclusive OR gate (hereinafter, referred to as "XOR") 143, a SOE timing analyzer 144, a SOE adjuster 145, and a third multiplexer 146.

The frame counter 141 outputs a frame count information Fcnt, which indicates the number of frames of a picture that is to be displayed on the liquid crystal display panel 100, in response to the gate start pulse GSP, which is generated one time during one frame period and which is generated at the same time as the start of the frame period. Further, the frame counter 141 generates the value of "N" to indicate the mul-

tuple of the N frame period at which the second polarity control signal FGDPOL and the second source output enable signal FGDSOE are to be generated.

The POL inverter 142 receives the frame count information Fcnt from the frame counter 141 and performs a modulus division on the frame count information Fcnt with N, thereby generating an inverted output signal when the remainder from the operation results in a "0". The output signal is a POL inversion signal POLinv. Therefore, as shown in FIG. 16, the logic (i.e., high or low logic) of the output signal POLinv is maintained for (N-1) number of frame periods and the logic of the output signal POLinv inverts when the frame period is a multiple of N. Accordingly, the POL inversion signal POLinv output from the POL inverter 142 indicates a start time for each Nth-multiple frame period. XOR 143 performs exclusive OR operation on the first polarity control signal POL and the POL inversion signal POLinv to generate the second polarity control signal FGDPOL in order to keep the polarity pattern the same in the Nth frame as the polarity pattern in the previous frame period (e.g., (N-1) frame period).

The SOE timing analyzer 144 analyzes the first source output enable signal SOE by the unit of the clock signal CLK3 and detects a rising edge, a pulse width, and a falling edge of the first source output enable signal SOE. The SOE adjuster 145 generates the second source output enable signal FGDSOE having the second pulse width W2 at every Nth-multiple frame period by using an SOE information Check\_SOE from the SOE timing analyzer 144. The third multiplexer 146 selects the output of the SOE adjuster 145 at every Nth-multiple frame period, and for all other frame periods, the third multiplexer 146 selects the first source output enable signal SOE in accordance with the N frame information from the frame counter 141, thereby generating the second source output enable signal FGDSOE.

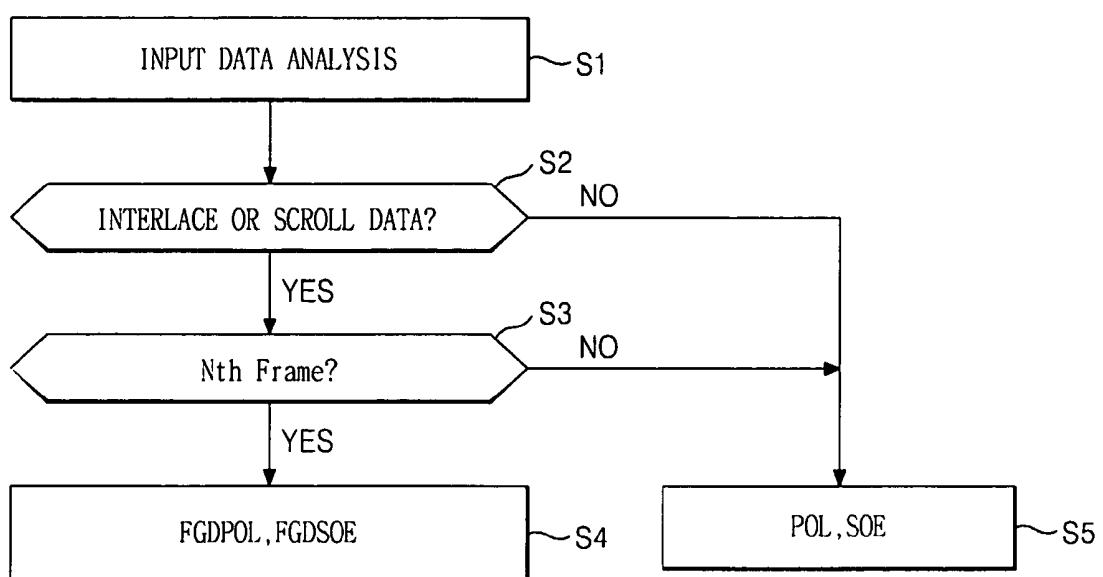

FIG. 17 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a second embodiment of the present invention. As shown in FIG. 17, the exemplary driving method of the liquid crystal display device according to the second embodiment of the present invention includes an analysis of the input data to judge whether the input data is data with which the DC image sticking may likely occur (e.g., the input data is interlace data or the scroll data). (S1, S2) If the input data is determined not to likely cause DC image sticking, then the liquid crystal display device is configured to operate normally using the polarity signal POL and source output signal SOE. (S5)

However, if the currently input data is determined to likely cause DC image sticking (S2), a judgment is made as to whether the current frame is a multiple of N. (S3) If the current frame is an Nth-multiple frame period, the polarity of the data voltage to be displayed on the liquid crystal display panel is controlled using of the second polarity control signal FGDPOL and the second source output enable signal FGDSOE. (S4)

FIG. 18 illustrates an exemplary liquid crystal display device according to the second embodiment of the present invention. As shown in FIG. 18, the liquid crystal display device according to the second embodiment of the present invention include a video signal source 105, a liquid crystal display panel 100, an imaging analyzing circuit 161, a timing controller 101, a POL/SOE logic circuit 162, a data drive circuit 103, and a gate drive circuit 104. In this embodiment, the video signal source 105, the liquid crystal display panel 100, the timing controller 101, the data drive circuit 103, and the gate drive circuit 104 are equivalent to the foregoing description of the first embodiment. Thus, the same reference

numerals are given to the same components and a detail description thereof will be omitted.

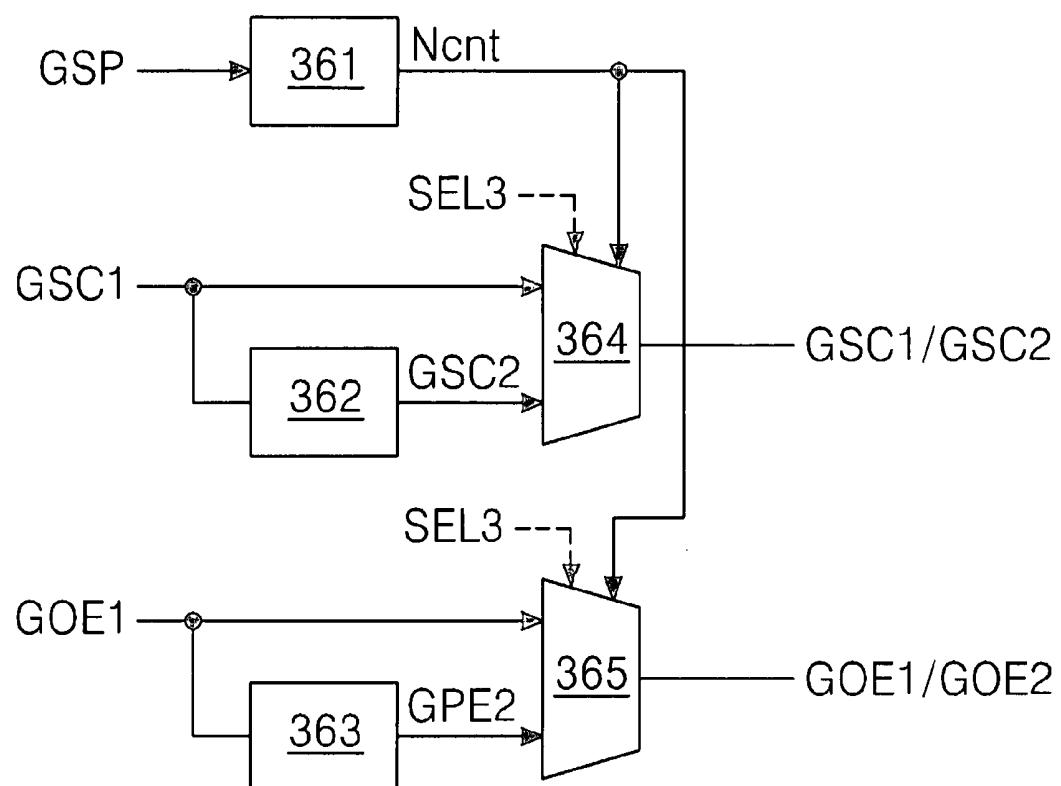

The image analyzing circuit 161 judges whether the digital video data of the currently input image is data with which the DC image sticking will likely occur. For example, the image analyzing circuit 161 compares the data between adjacent lines in one frame image and determines whether the currently input data is interlace data. The currently input data is deemed to be interlace data if the data between the lines is not less than a predetermined threshold value. In addition, the image analyzing circuit 161 compares the data of each pixel in a frame with another frame to detect a moving picture in a display image and the speed of the moving picture. If the moving picture moves at a pre-set speed, the frame data having the moving picture is deemed to be scroll data. Based on the result of the image analysis, the image analyzing circuit 161 generates a selection signal SEL3 which indicates that the currently input data is either interlace data or scroll data. The selection signal SEL3 is then used to control the POL/SOE logic circuit 162.

The POL/SOE logic circuit 162 generates the second polarity control signal FGDPOL and the second source output enable signal FGDSOE in the Nth-multiple frame period in response to the first logic value of the selection signal SEL3 generated by the image analyzing circuit 161 when the input data likely to cause DC image sticking is detected. Otherwise, the POL/SOE logic circuit 162 generates the first polarity control signal POL and the first source output enable signal SOE in response to the second logic value of the selection signal SEL3 from the image analyzing circuit 161. The timing controller 101, the image analyzing circuit 161, and the POL/SOE logic circuit 162 may be integrated into one chip.

FIGS. 19 and 20 represent an exemplary driving method of a liquid crystal display device according to a third embodiment of the present invention. As shown in FIGS. 19 and 20, in addition to controlling the generation of the second source output enable signal FGDSOE and the second polarity control signal FGDPOL, the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention increases the charge amount of the liquid crystal cell by controlling pulse width of the source output enable signal during an aging period and inverts the polarity of the data voltage charged in the liquid crystal cell for each frame period. The "aging period" is a period when the response characteristic of the liquid crystal cell does not reach a satisfactory level and is defined to be a period between when power is supplied to the liquid crystal display device and the liquid crystal cell reaches full response characteristic. The aging period may be about 3 to 5 minutes from the time of the power up. However, the aging period may be changed in accordance with the liquid crystal characteristic of the display panel without departing from the scope of the present invention.

Specifically, the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention increases the data charge amount of the liquid crystal cell by controlling the pulse width of the source output enable signal SOE supplied to the data drive circuit for the aging period. (S191 and S192) As described above, the amount of data voltage charged in the liquid crystal cell may be controlled by the width of the source output enable signal SOE. Accordingly, by generating a source output enable signal SOE to have a narrow pulse width, the amount of data voltage charged in the liquid crystal cell may be increased. Further, the present invention generates the polarity control signal, which is supplied to the data drive circuit for the aging

period, as the first polarity control signal POL shown in FIG. 16, thereby inverting the polarity of the data voltage for each frame period. (S193)

Through experimentation, it has been found that if the liquid crystal display device is driven using the second source output enable signal FGDSOE and the second polarity control signal FGDPOL as described above during the aging period, the light waveform of the liquid crystal cell includes an undershoot and the brightness is noticeably reduced during the aging period as shown in FIG. 21. This phenomenon occurs because the response characteristic of the liquid crystal is low during the aging period (i.e., warm-up period after power up). Accordingly, the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention increases the data charge amount of the liquid crystal cell by making the pulse width of the source output enable signal SOE relatively narrow and inverts the polarity of the data voltage at every frame period during the aging period, thereby increasing the brightness and the response speed of the liquid crystal cell during the aging period.

After the aging period has passed (i.e., during the normal driving period), the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention controls the polarity of the data voltage charged in the liquid crystal cell and the amount of data voltage charged in the liquid crystal cell using the second polarity control signal FGDPOL and the second source output enable signal FGDSOE as described above. For example, the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention decreases the charge amount of the data voltage charged in the liquid crystal cell at every Nth-multiple frame period during the normal drive period using the second source output enable signal FGDSOE in the manner described above. That is to say, the present invention increases the data charge amount of the liquid crystal cell by using the source output enable signal SOE, which has a pulse width that is relatively narrow, at every frame period other than the Nth-multiple frame period during the normal driving period (i.e., after the aging period has passed). At every Nth-multiple frame period, the first source output enable signal SOE is converted into the second source output enable signal FGDSOE, which has a pulse width that is relatively wide, thereby reducing the data charge amount of the liquid crystal cell. (S194) In addition, the exemplary driving method of the liquid crystal display device according to the third embodiment of the present invention also converts the polarity control signal POL into the second polarity control signal FGDPOL, as shown in FIG. 16, during the normal driving period (i.e., after the aging period) to control the polarity of the data voltage charged in the liquid crystal cell at every Nth multiple of the frame period to be the same as the previous frame period and to invert the polarity of the data voltage charged in the liquid crystal cell at each frame period for the remaining frame period. (S195)

FIG. 22 is a flow chart illustrating an exemplary control sequence of a driving method of a liquid crystal display device according to a fourth embodiment of a present invention. As shown in FIGS. 20 and 22, the exemplary driving method of the liquid crystal display device according to the fourth embodiment of the present invention increases the charge amount of the liquid crystal cell during an aging period, controls the polarity of the data voltage charged in the liquid crystal cell at the Nth-multiple frame period to be the same as the previous frame period, and inverts the polarity of

the data voltage charged in the liquid crystal cell at each frame period for the remaining frame period.

Specifically, the present invention increases the data charge amount of the liquid crystal cell by controlling the pulse width of the source output enable signal SOE supplied to the data drive circuit during the aging period to be narrow. (S221 and S222) Further, the present invention controls the polarity of the data voltage output from the data drive circuit using the second polarity control signal FGDPOL during the aging period to control the polarity of the data voltage charged in the liquid crystal cell at each Nth-multiple frame period to be the same as the previous frame period and inverts the polarity of the data voltage charged in the liquid crystal cell at each frame period for the remaining frame periods. (S223)

After the aging period has passed (i.e., during the normal driving period), the driving method of the liquid crystal display device according to the fourth embodiment of the present invention follows the same steps described for the normal driving period of the third embodiment above. That is to say, the present invention decreases the data charge amount of the liquid crystal cell using the second source output enable signal FGDSOE, which has a pulse width that is wider than the first source output enable signal SOE, at every Nth-multiple frame period after the aging period has passed. (S224) In addition, after the aging period, the polarity of the data voltage charged in the liquid crystal cell at every Nth-multiple frame period is kept the same as the previous frame period by using the second polarity control signal FGDPOL and inverts the polarity of the data voltage charged in the liquid crystal cell at each frame period for the remaining frame period. (S225)

The exemplary driving method of the liquid crystal display device according to the third and fourth embodiments of the present invention may be implemented in accordance with the liquid crystal display device shown in FIG. 11 with the addition of an aging stabilization circuit 234 shown in FIG. 23. As shown in FIG. 23, a POL/SOE logic circuit (e.g., 102 in FIG. 11, 162 in FIG. 18) receives the gate start pulse GSP and the first polarity control signal POL during or after the aging period and outputs the second polarity control signal FGDPOL (e.g., as shown in FIG. 16). Further, the POL/SOE logic circuit (102, 162) receives the first source output enable signal SOE and the third clock signal CLK3 after the aging period and outputs the second source output enable signal FGDSOE, which has a pulse width adjusted to be wider than the first source output enable signal SOE, at every Nth-multiple frame period and the first source output enable signal SOE, which has a narrow pulse width, at all the other frame periods in order to prevent the generation of residual images and flicker. The POL/SOE logic circuit (102, 162) can selectively supply any one of the first and second polarity control signals POL, FGDPOL and the first and second source output enable signals SOE, FGDSOE to the data drive circuit 103 based on the selection signal SEL2 determined by the manufacturer.

In accordance with the third and fourth embodiments of the present invention, the POL/SOE logic circuit (102, 162) includes a logic part 231, first and second multiplexers 232, 233, and an aging stabilization circuit 234. The logic part 231 generates the second source output enable signal FGDSOE based on the clock signal CLK3, the gate start pulse GSP, and the first source output enable signal SOE and also outputs the second polarity control signal FGDPOL. The logic part 231 may be implemented by the circuit shown in FIG. 15.

The first multiplexer 232 selects between the first polarity control signal POL and the second polarity control signal FGDPOL based on the control signal from the aging stabilization circuit 234. The second multiplexer 233 selects

between the first source output enable signal SOE and the second source output enable signal FGDSOE based on the control signal from the aging stabilization circuit 234.

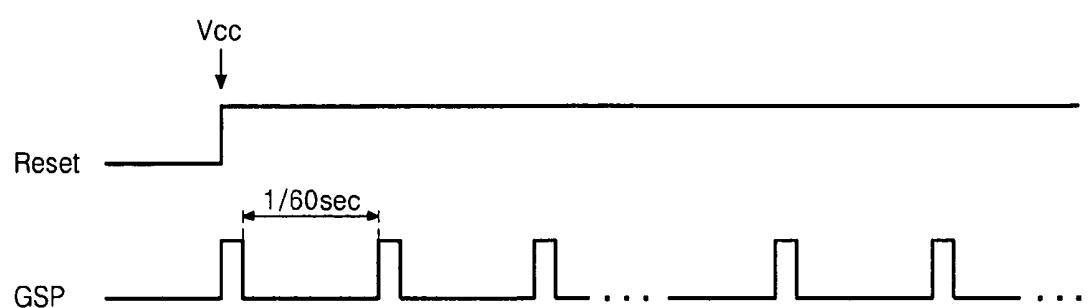

When a user turns on the power supply source of the liquid crystal display device or the video signal source 105, a reset signal Reset, as shown in FIG. 24, and a power supply voltage Vcc is generated. The aging stabilization circuit 234 determines the aging period by counting the supply period of the power supply voltage Vcc with the gate start pulse GSP, as shown in FIG. 24, and controls the second multiplexer 233 to output the first source output enable signal SOE during the aging period. The aging stabilization circuit 234 controls the first multiplexer 232 to output either the first polarity control signal POL or the second polarity control signal FGDPOL during the aging period.

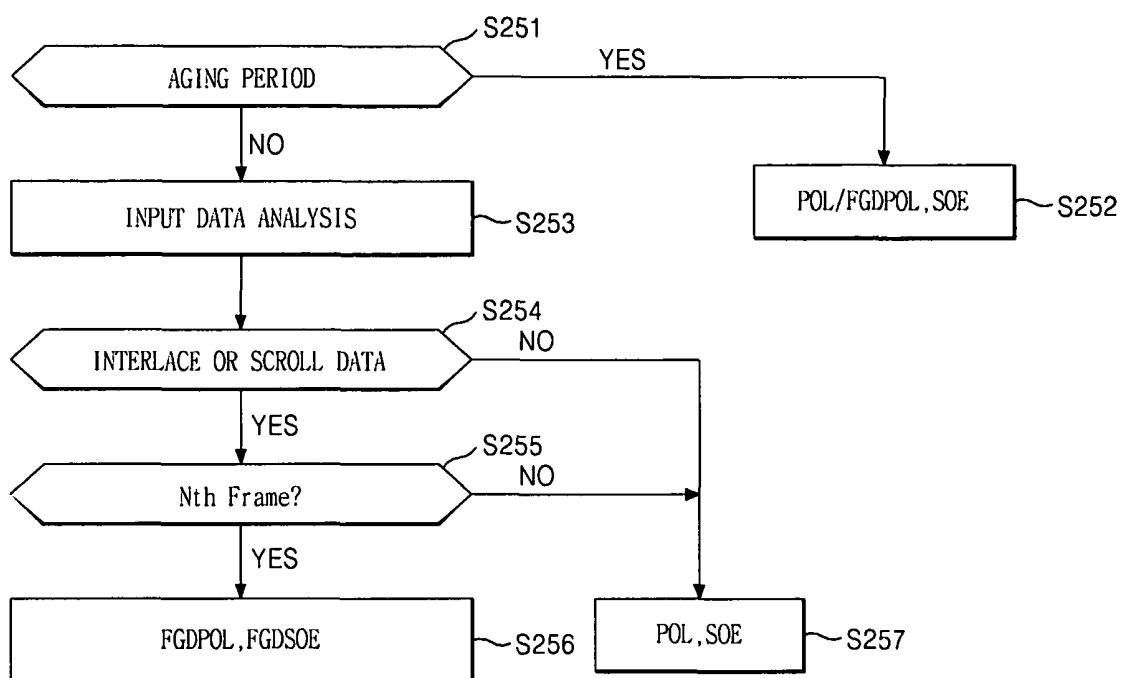

FIG. 25 is a flow chart illustrating an exemplary driving method of a liquid crystal display device according to a fifth embodiment of the present invention. As shown in FIG. 25, the exemplary driving method of the liquid crystal display device according to the fifth embodiment of the present invention is a combination of the first through fourth embodiment as described above. That is to say, the exemplary driving method according to the fifth embodiment of the present invention controls the data drive circuit using the first source output enable signal SOE during the aging period, thereby increasing the data charge amount of the liquid crystal cell. Further, the present invention inverts the polarity of the data voltage supplied to the liquid crystal cell for each frame period using the first polarity control signal POL during the aging period, or controls the polarity of the data voltage charged in the liquid crystal cell at the Nth-multiple frame period to be the same as the previous frame period using the second polarity control signal FGDPOL and inverts the polarity of the data voltage charged in the liquid crystal cell at every frame period for the remaining frame periods. (S251, S252)

Once the liquid crystal display device is operating during the normal driving period (i.e., after the aging period has passed), the present invention analyzes the input data after and judges whether the input data is data that would likely cause DC image sticking, such as interlace data or the scroll data. (S253, S254) In the step S254, if the currently input data is data which is likely to cause DC image sticking, then a determination is made as to whether the current frame period is an Nth-multiple frame period. If the current frame period is an Nth-multiple frame period, the polarity of the data voltage to be displayed in the liquid crystal display panel is controlled using the second polarity control signal FGDPOL and the data charge amount of the liquid crystal cell is controlled to be reduced using the second source output enable signal FGDSOE. (S255, S256) If the currently input data is not data that is likely to cause DC image sticking, the polarity of the data voltage to be displayed in the liquid crystal display panel is controlled using the first polarity control signal POL and the data charge amount of the liquid crystal cell is controlled to be increased using of the first source output enable signal SOE. (S257)

The exemplary driving method of the liquid crystal display device according to the fifth embodiment of the present invention may be implemented according to the liquid crystal display device shown in FIG. 18 with the addition of an aging stabilization circuit 234, as shown in FIG. 23, in combination with the POL/SOE logic circuit of the liquid crystal display device shown in FIG. 18. As shown in FIGS. 18 to 25, the POL/SOE logic circuit 162 determines the aging period by counting the supply period of the power supply voltage Vcc, generates either the first or second polarity control signals POL, FGDPOL during the aging period, and outputs the first

source output enable signal SOE during the aging period. The POL/SOE logic circuit 162 outputs the second polarity control signal FGDPOL and the second source output enable signal FGDSOE in response to the first logic value of the selection signal SEL3 from the image analyzing circuit 161 after the aging period when data that is likely to generate DC image sticking are input. On the other hand, the POL/SOE logic circuit 162 generates the first polarity control signal POL and the first source output enable signal SOE in response to the second logic value of the selection signal SEL3 from the image analyzing circuit 161 after aging period if the input data is not likely to cause DC image sticking.

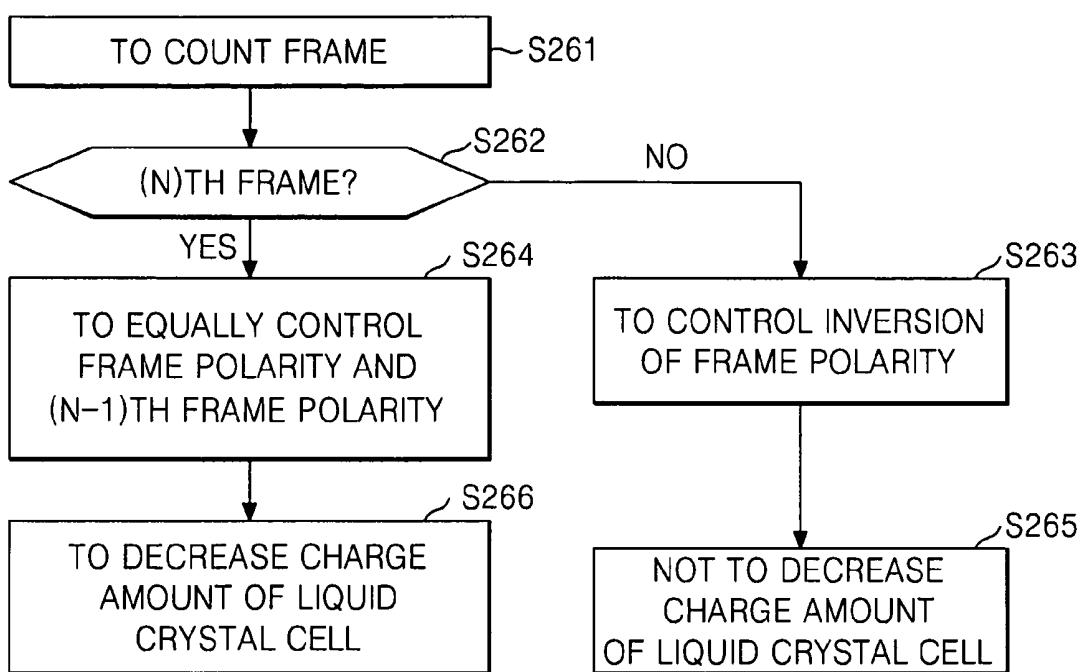

FIG. 26A illustrates an exemplary method of driving the liquid crystal display according to a sixth embodiment of the present invention. As shown in FIG. 26A, the exemplary method of driving the liquid crystal display according to the sixth embodiment of the present invention counts a timing signal input with digital video data to count frame periods. (S261) Next, the exemplary method of driving the liquid crystal display according to the sixth embodiment of the present invention inverts a frame polarity at each frame period to invert the polarity of a data voltage charged in the liquid crystal cell Clc at each frame period (S262 and S263), and maintains a frame polarity of the Nth-multiple frame period to be the same as a frame polarity of the previous frame period. (S262 and S264)

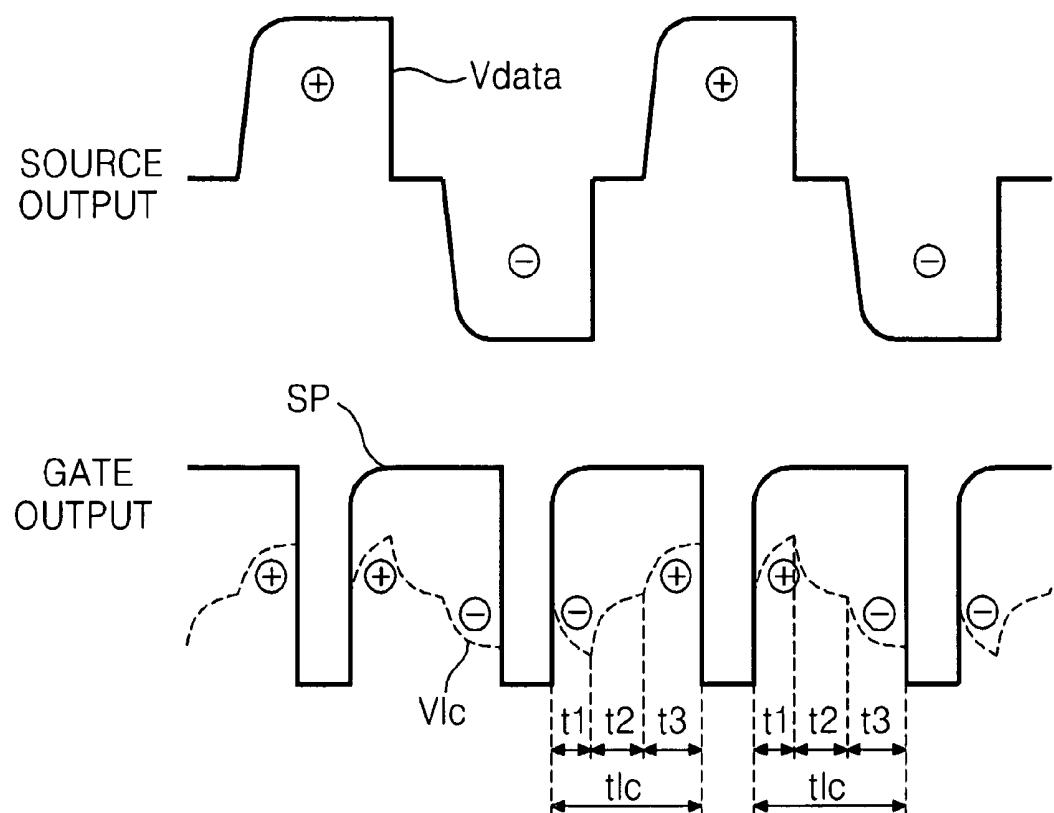

A frame polarity refers to a polarity of a data voltage in liquid crystal cells that are determined by a polarity control signal POL within each frame period. The polarity control signal POL is generated from a timing controller. The present invention generates a second polarity control signal FGDPOL to control a polarity of a data voltage supplied to the liquid crystal cell at an Nth-multiple frame period to be the same as a data voltage supplied to the liquid crystal cell in the previous frame period. The present invention inverts a polarity of a data voltage supplied to the liquid crystal cell at all other frame periods. The second polarity control signal FGDPOL is generated to have the same phase in the Nth-multiple frame period as the previous frame period and is inverted at all other frame periods. In addition, the logic of the second polarity control signal FGDPOL is inverted at each horizontal period (e.g., 1-dot) or every two horizontal periods (e.g., 2-dot) within a first frame period. Accordingly, a polarity of a data voltage charged in the liquid crystal cell at a frame period prior to the Nth-multiple frame period is inverted for each frame period (S262 and S263), and polarities of a data voltage charged in the liquid crystal cell at the Nth-multiple frame period and the previous frame period are controlled to be the same. (S262 and S264) The exemplary method of driving the liquid crystal display according to the sixth embodiment of the present invention does not reduce an amount of voltage charged in the liquid crystal cell except during the Nth-multiple frame period. (S265)

In order to compensate an overcharge of the liquid crystal cell during the Nth-multiple frame periods by applying data voltages having the same polarity for two frame periods, the exemplary method of driving the liquid crystal display according to the sixth embodiment of the present invention temporarily supplies a voltage having a different polarity to the liquid crystal cell to decrease the amount of voltage charged in the liquid crystal cell during the Nth-multiple time periods. (S266) To decrease an amount of voltage charged in the liquid crystal cell during the Nth-multiple frame periods, the present invention applies a different gate timing control signal, which controls a timing of when the gate driving circuit is operation, during the Nth-multiple frame periods to

continuously generate two scan pulses for each gate line to overlap a portion of scanning pulses supplied to adjacent gate lines.

FIG. 26B shows an exemplary liquid crystal display device according to the sixth embodiment of the present invention. As shown in FIG. 26B, the exemplary liquid crystal display device according to the sixth embodiment of the present invention includes a liquid crystal display panel 100, a timing controller 261, a first logic circuit 262, a data driving circuit 263, a gate driving circuit 264, and a second logic circuit 267. The liquid crystal display panel of FIG. 26B may be implemented in accordance with the liquid crystal display panel 100 as described above in reference to the first embodiment. Accordingly, a detailed description of the liquid crystal display panel 100 is not repeated here.

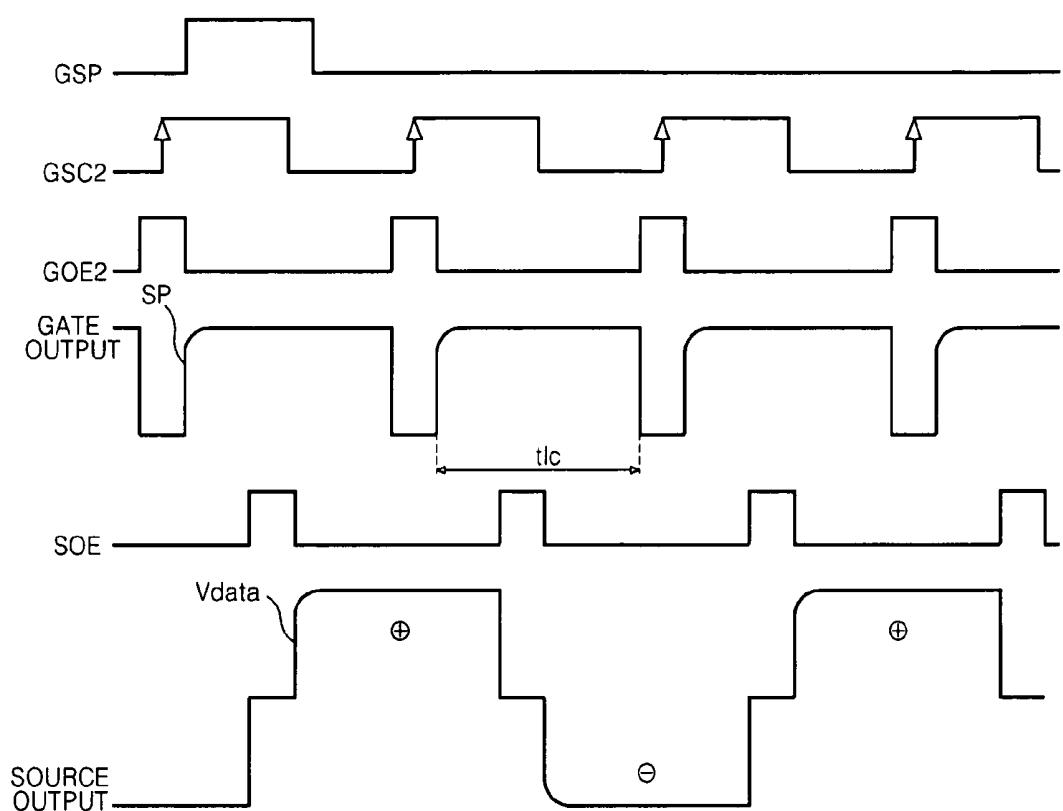

The timing controller 261 receives timing signals such as vertical/horizontal synchronization signals Vsync and Hsync, data enable signals, clock signals, and other signals to generate control signals that controls the operation timing of the data driving circuit 263, the gate driving circuit 264, and the first and second logic circuits 262 and 267. The control signals include a gate timing control signal having a gate start pulse GSP, a gate shift clock signal GSC, and a gate output enable signal GOE, etc. Furthermore, the control signals include a data timing control signal having a source start pulse SSP, a source sampling clock SSC, a source output enable signal SOE, and a first polarity control signal POL, etc. The gate start pulse GSP is a timing control signal that indicates a start horizontal line from which a scan starts among a first vertical period when a screen is displayed. That is, the gate start pulse GSP is a first scanning pulse with which the first gate line is supplied. The gate shift clock signal GSC is input to a shift register within the gate driving circuit to sequentially shift the gate start pulse GSP. The source start pulse SSP indicates a start pixel in a first horizontal line where image data are to be displayed. The source sampling clock SSC indicates a latch operation of the data within the data driving circuit 263 on the basis of a rising or falling edge. The source output enable signal SOE indicates the output of the data driving circuit 263.

The first polarity control signal POL indicates the polarity of the data voltages which are to be supplied to the liquid crystal cells Clc of the liquid crystal display panel 100. The first polarity control signal POL may be generated in any type of 1-dot inversion polarity control signal of which the logic is inverted for each horizontal period and 2-dot inversion polarity control signal of which the logic is inverted for each two horizontal periods. The timing controller 261 generates timing control signals at a frame frequency of 120 Hz or 60 Hz to control the operation timing of the first logic circuit 262, the data driving circuit 263, and the gate driving circuit 264 on the basis of 120 Hz or 60 Hz.

The frame frequency is a frequency corresponding to the vertical synchronization signal Vsync and indicates the number of screen per second. The 120 Hz frame frequency makes 120 screens per second displayed on the liquid crystal display panel 100, and 60 Hz frame frequency makes 60 screens per second displayed on the liquid crystal display panel 100. Flicker is generally not perceivable when the liquid crystal display is driven at the 120 Hz frame frequency compared to the 60 Hz frame frequency. Accordingly, the timing controller 261 generates the control signals on the basis of the 120 Hz frame frequency in order to improve reduction of the flicker effect. However, other frame frequencies may be used without departing from the scope of the present invention. The timing controller 261 divides input digital video data RGB into the digital video data RGBodd of an odd-numbered pixel

and the digital video data RGBeven of an even-numbered pixel to reduce by half a transmission frequency of data transmitted to the data driving circuit 263.

In order to prevent a residual image (i.e., DC image sticking) and flicker, the first logic circuit 262 receives the gate start pulse GSP and the first polarity control signal POL to generate the second polarity control signal FGDPOL such that the polarity of the data voltage is inverted at every frame period except at the Nth-multiple frame period, at which the polarity of the data voltage is kept the same as the polarity of the previous frame period. Herein, the first logic circuit 262 may selectively supply either the first polarity control signal POL or the second polarity control signal FGDPOL to the data driving circuit 263. As shown in FIG. 16, the first polarity control signal POL has its logic inverted for each horizontal period or for each two horizontal periods, and the logic is also inverted for each frame period in order to invert the polarity of the data voltage for each frame period.