US 20050083285A1

(19) **United States**

(12) **Patent Application Publication**

**Yeon et al.**

(10) **Pub. No.: US 2005/0083285 A1**

(43) **Pub. Date: Apr. 21, 2005**

(54) **GRAY VOLTAGE GENERATION CIRCUIT FOR DRIVING A LIQUID CRYSTAL DISPLAY RAPIDLY**

**Publication Classification**

(51) **Int. Cl. 7** ..... G09G 3/36

(52) **U.S. Cl.** ..... 345/89

(76) Inventors: **Yeon-Mo Yeon**, Seoul (KR); **Kun-Bin Lee**, Seoul (KR)

**(57) ABSTRACT**

Correspondence Address:

McGuireWoods LLP

Suite 1800

1750 Tysons Boulevard

McLean, VA 22102 (US)

(21) Appl. No.: **10/747,665**

(22) Filed: **Dec. 30, 2003**

**Related U.S. Application Data**

(63) Continuation of application No. 09/956,146, filed on Sep. 20, 2001, now Pat. No. 6,670,935.

**(30) Foreign Application Priority Data**

Dec. 21, 2000 (KR) ..... 2000-79698

A gray voltage generation circuit for driving a liquid crystal display rapidly outputs an altered gray voltage so that a source driving circuit can charge liquid crystal capacitors constructed in a liquid crystal panel in a short period of time. In response to the gray voltages from the gray voltage generation circuit, while driving a positive polarity, the source driving circuit generates a liquid crystal driving voltage of higher level than the existing liquid crystal driving voltage when applying a gate clock signal of high level, and generates a liquid crystal driving voltage of a level similar to the existing liquid crystal driving voltage when applying a gate clock signal of low level. And, while driving a negative polarity, the source driving circuit generates a liquid crystal driving voltage of lower level than an existing liquid crystal driving voltage when applying a gate clock signal of high level, and generates a liquid crystal driving voltage of a level similar to the existing liquid crystal driving voltage when applying a gate clock signal of low level.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

52

Fig. 5

Fig. 6

56

Fig. 7A

Fig. 7B

Fig. 8

Fig. 9

Fig. 10A

Fig. 10B

Fig. 11A

Fig. 11B

Fig. 12A

Fig. 12B

Fig. 13A

Fig. 13B

## GRAY VOLTAGE GENERATION CIRCUIT FOR DRIVING A LIQUID CRYSTAL DISPLAY RAPIDLY

### FIELD OF THE INVENTION

[0001] The present invention relates to a liquid crystal display and, more particularly, to a gray voltage generation circuit for driving a liquid crystal display and such a liquid crystal display.

### BACKGROUND OF THE INVENTION

[0002] Generally, a liquid crystal is an organic compound having a neutral property between liquid and crystal, and changes in its color or transparency by voltage or temperature. A liquid crystal display (LCD), which expresses information using the liquid crystal, occupies a smaller volume and has a lower power consumption than a conventional display device. Therefore, lots of attentions are paid to the LCD as a novel display device.

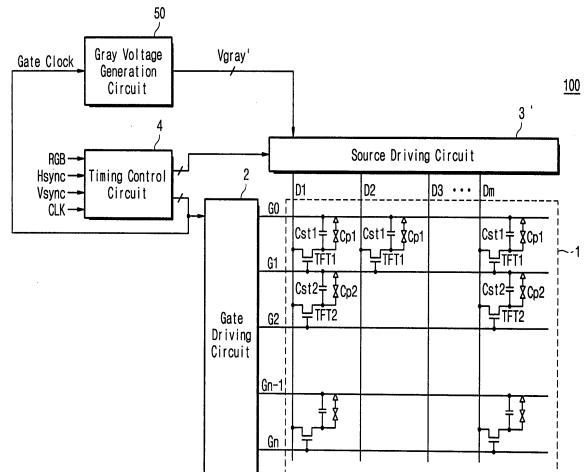

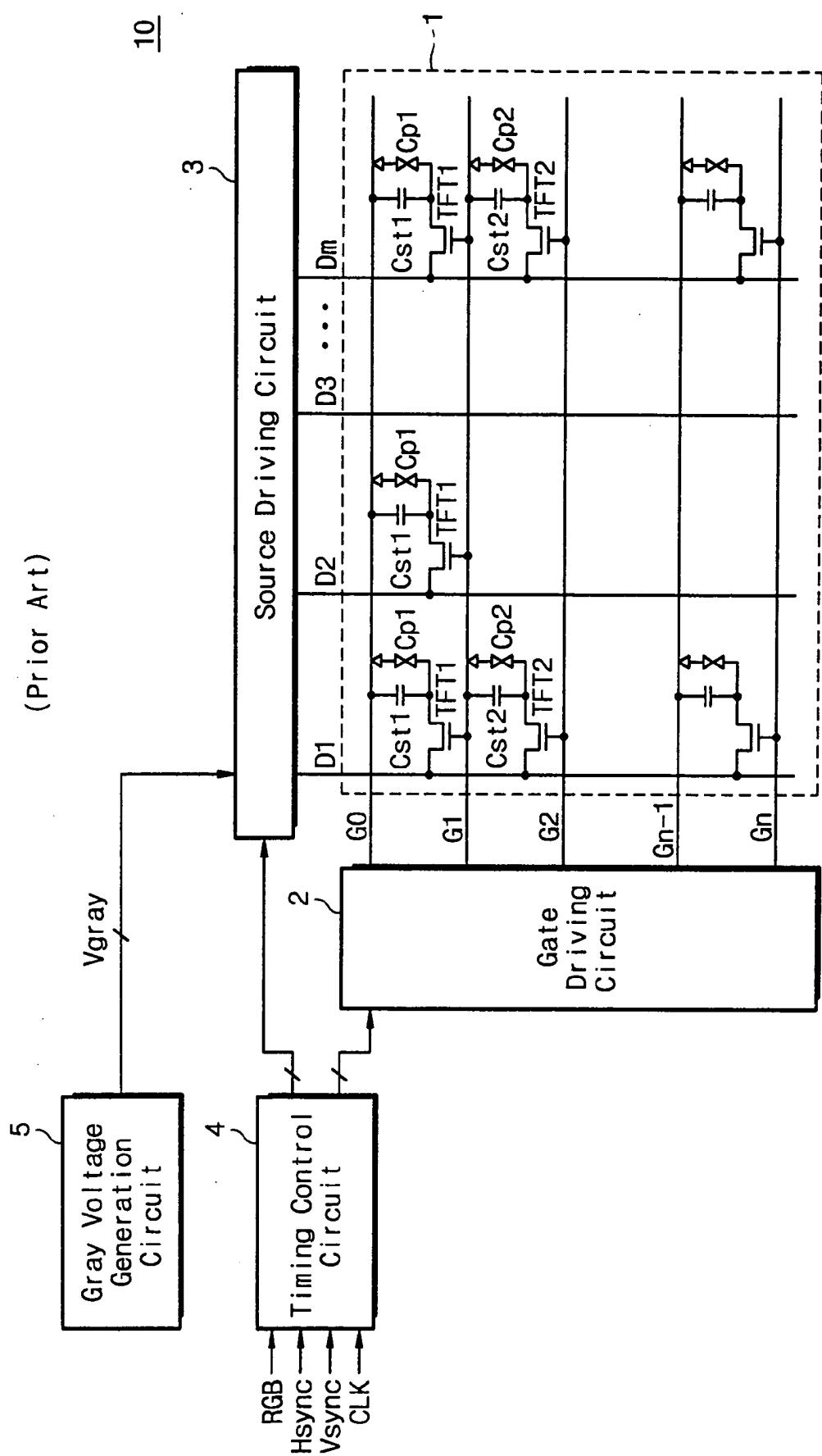

[0003] FIG. 1 schematically illustrates a configuration of a conventional liquid crystal display. A liquid crystal display 10 includes a liquid crystal panel 1, a gate driving circuit 2 coupled to the liquid crystal panel 1, a source driving circuit 3, a timing control circuit 4, and a gray voltage generation circuit (or gamma reference voltage generation circuit) 5.

[0004] The liquid crystal panel 1 is made of a plurality of gate lines G0 through Gn and a plurality of data lines D1 through Dm that are vertically interconnected with the gate lines, respectively. The gate driving circuit 2 is connected to each of the gate lines G0 through Gn, and the source driving circuit 3 is connected to each of the data lines D1 through Dm. One pixel is composed in each interconnection of the gate lines and the data lines. Each pixel is made of one thin film transistor (TFT), one storing capacitor Cst, and one liquid crystal capacitor Cp. Each of pixels composing the liquid crystal panel 1 further includes three sub-pixels corresponding to red (R), green (G), and blue (B). A pixel displayed via the liquid crystal panel 1 is obtained by combination of R, G, and B color filters. The liquid crystal display 10 can display not only color pictures but also pure red, green, blue, and gray scales by combining those pixels.

[0005] The timing control circuit 4 issues control signals (e.g., gate clock and gate on signals) required in the gate driving circuit 2 and the source driving circuit 3 in response to color signals R, G, and B, horizontal and vertical sync signals HSync and Vsync, and a clock signal CLK. The gray voltage generation circuit 5 is connected to the source driving circuit 3, generating a gray voltage Vgray or a gamma reference voltage that is a reference to generate a liquid crystal driving voltage Vdrive. One example of the gray voltage generation circuit 5 is disclosed in U.S. Pat. No. 6,067,063 entitled "LIQUID CRYSTAL DISPLAY HAVING A WIDE VIEW ANGLE AND METHOD FOR DRIVING THE SAME", issued to Kim et al., issued on May 23, 2000. A gray voltage generation circuit 5 disclosed therein includes a plurality of resistors R1 through Rn+1 that are directly coupled between a power supply voltage (Vcc) and a ground (GND). Each of the resistors R1 through Rn+1 distributes the power supply voltage (Vcc) with a predetermined ratio, generating n-bit gray voltages VG1 through V Gn.

[0006] Now, operations of the liquid crystal display 10 having such a configuration will be described in detail. If the

gate driving circuit 2 sequentially scans pixels of the panel row by row, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive based upon the color signals R, G, and B inputted through the timing control circuit 4, in response to the reference voltage Vgray outputted from the gray voltage generation circuit 5. And then, the source drive 3 applies the generated voltage Vdrive to the panel 1 each time of scanning.

[0007] In such an operation, the TFT acts as a switch. For example, when the TFT is turned on, the liquid crystal capacitor Cp is charged by the liquid crystal driving voltage Vdrive generated from the source driving circuit 3. When the TFT is turned off, the capacitor Cp prevents the charged voltage from leaking. This shows that the liquid crystal driving voltage Vdrive applied from the source driving circuit 3 has a great influence upon driving each TFT composing the panel 1.

[0008] As the liquid crystal display tends to implement high speed response, it is required to enhance a response speed of such a liquid crystal display Cp in order to speed up the device. This is because if the voltage Vdrive applied from the source driving circuit 3 has a high value, the capacitor Cp would quickly be charged to enhance a total driving speed of a liquid crystal display.

[0009] There are many methods of boosting a liquid crystal driving voltage Vdrive applied from the source driving circuit 3 in order to enhance a driving speed of the liquid crystal display. For example, it requires a design change of the gate driving circuit 2 or the source driving circuit to generate a liquid crystal driving voltage Vdrive of high level, or a design change of the timing control circuit 4 for issuing a control signal to the driving circuits 2 and 3. Unfortunately, changing designs of such high-priced circuits causes higher costs in a production unit. Furthermore, the increased liquid crystal driving voltage Vdrive also increases power consumption of the liquid crystal display in proportion to the voltage Vdrive rise.

[0010] Accordingly, the object of the present invention is to overcome the foregoing drawbacks, and to provide a gray voltage generation circuit that can enhance a driving speed of a liquid crystal display with low cost and power consumption.

### SUMMARY OF THE INVENTION

[0011] To attain this object, there is provided a liquid crystal display that includes a liquid crystal panel having a plurality of pixels, a gray voltage generation circuit for generating a plurality of gray voltages corresponding to data to be displayed in the liquid crystal panel, a timing control circuit for issuing a gate clock signal and a plurality of control signals, a gate driving circuit for sequentially scanning the pixels row by row in response to the gate clock signal, and a source driving circuit for generating a liquid crystal driving voltage in response to the data and applying the generated liquid crystal driving voltage to the panel each time of scanning. In response to the gray voltage, the source driving circuit generates a liquid crystal driving voltage that has different values in high and low level intervals.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0012] FIG. 1 is a block diagram showing a configuration of a conventional liquid crystal display.

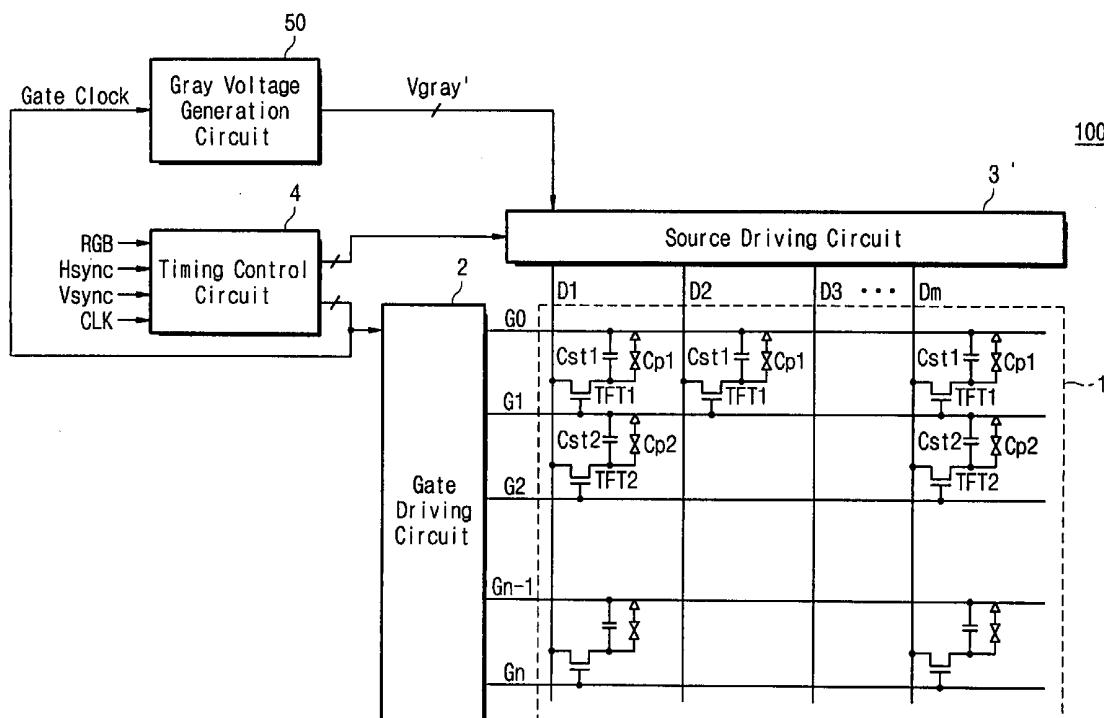

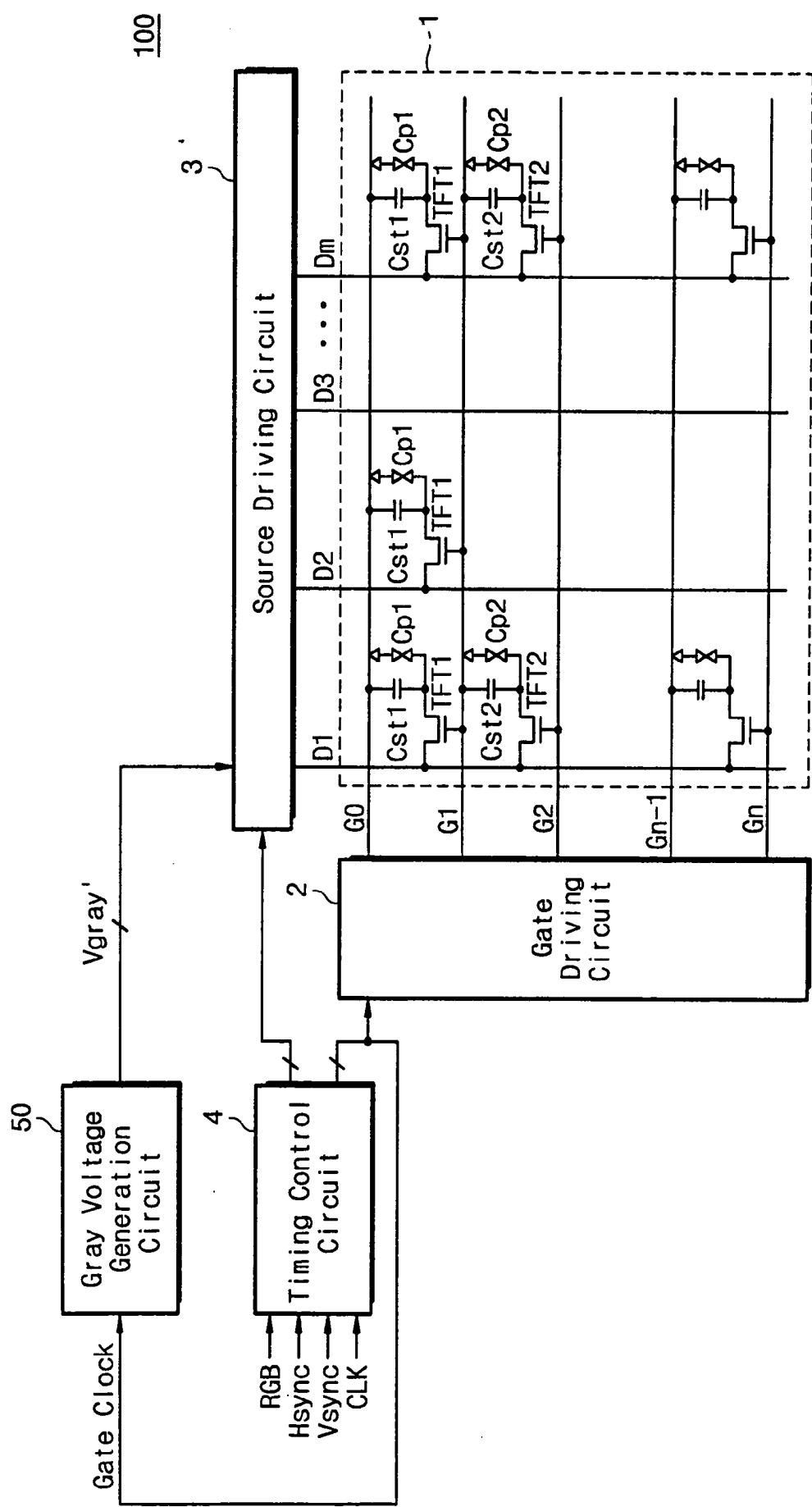

[0013] FIG. 2 is a block diagram showing a configuration of a liquid crystal display in accordance with the present invention.

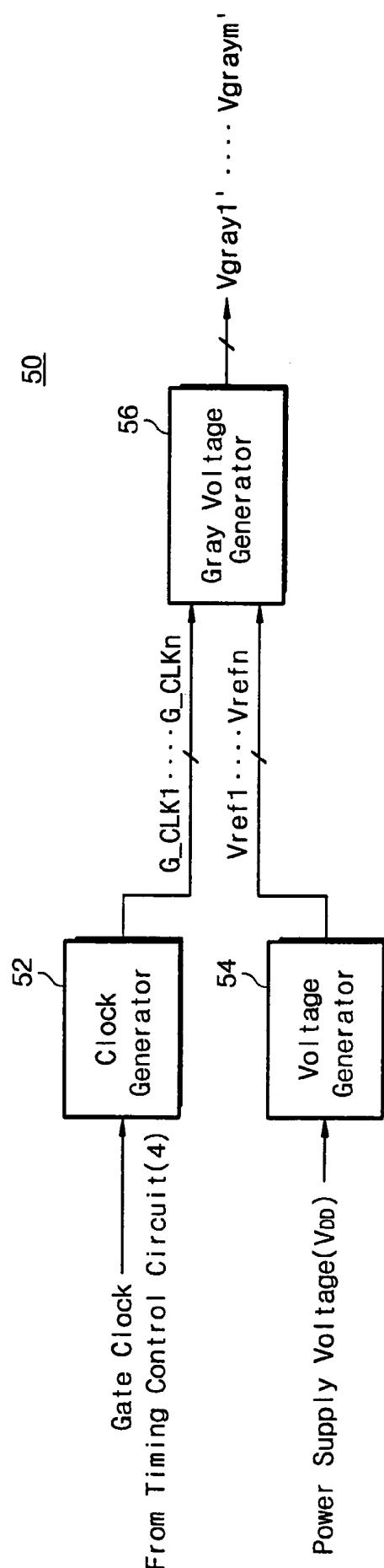

[0014] FIG. 3 is a block diagram showing a configuration of a gray voltage generation circuit in accordance with the present invention.

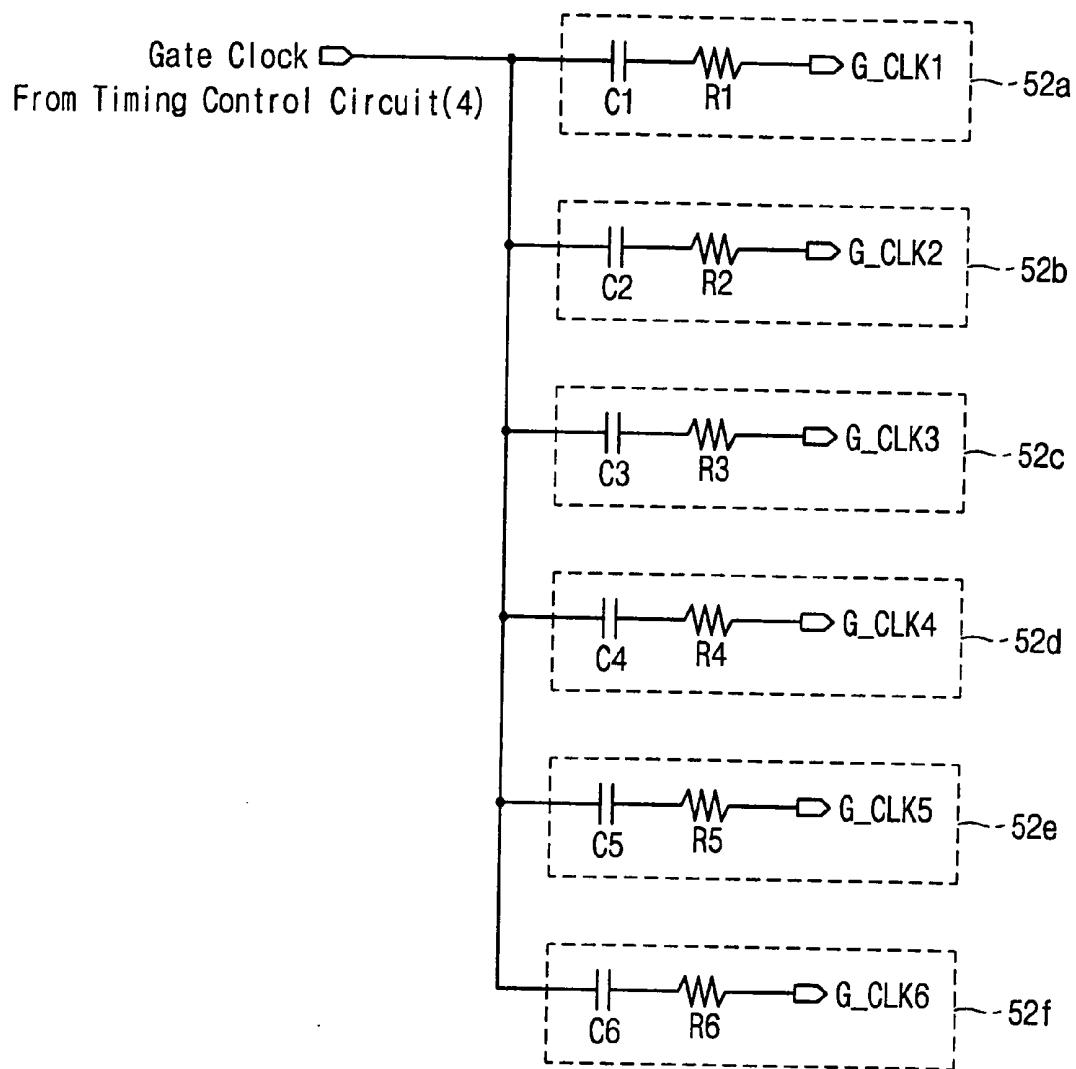

[0015] FIG. 4 is a circuit diagram showing a detailed configuration of a clock generator shown in FIG. 3.

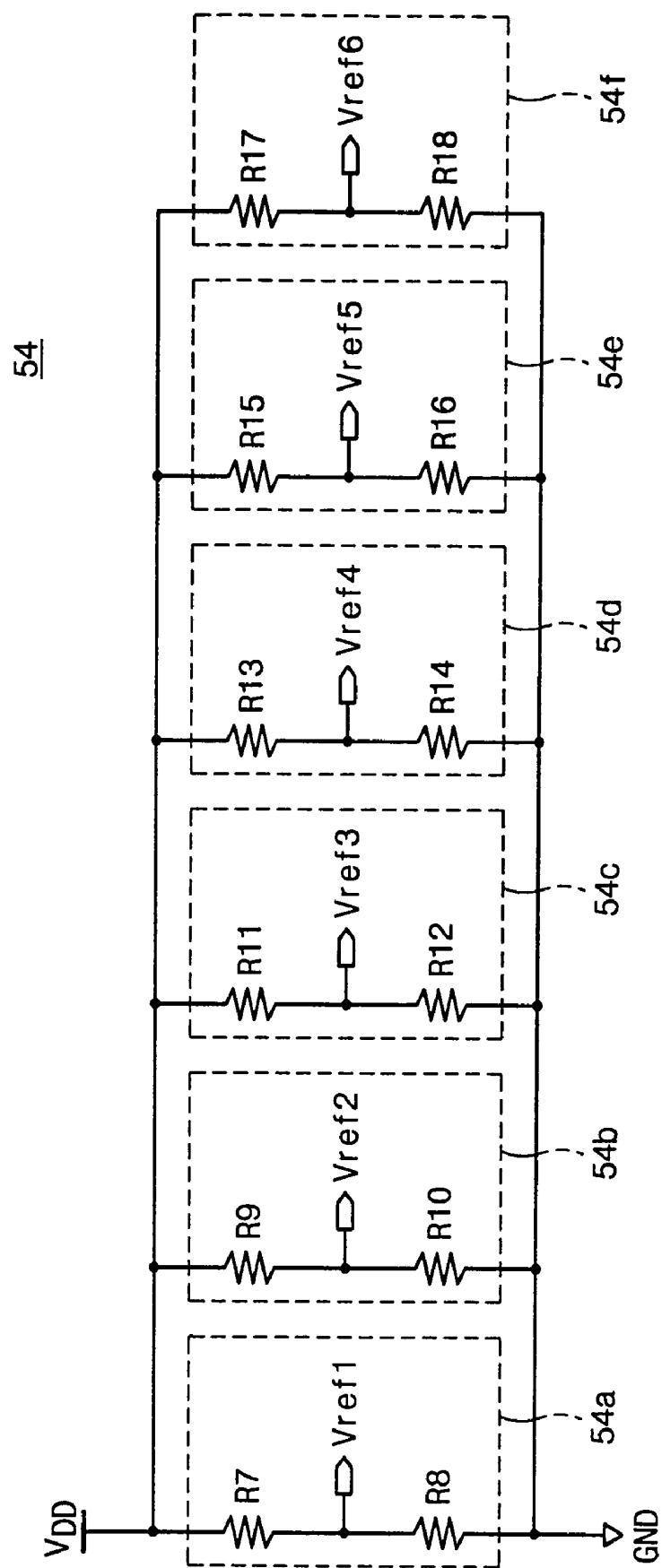

[0016] FIG. 5 is a circuit diagram showing a detailed configuration of a voltage generator shown in FIG. 3.

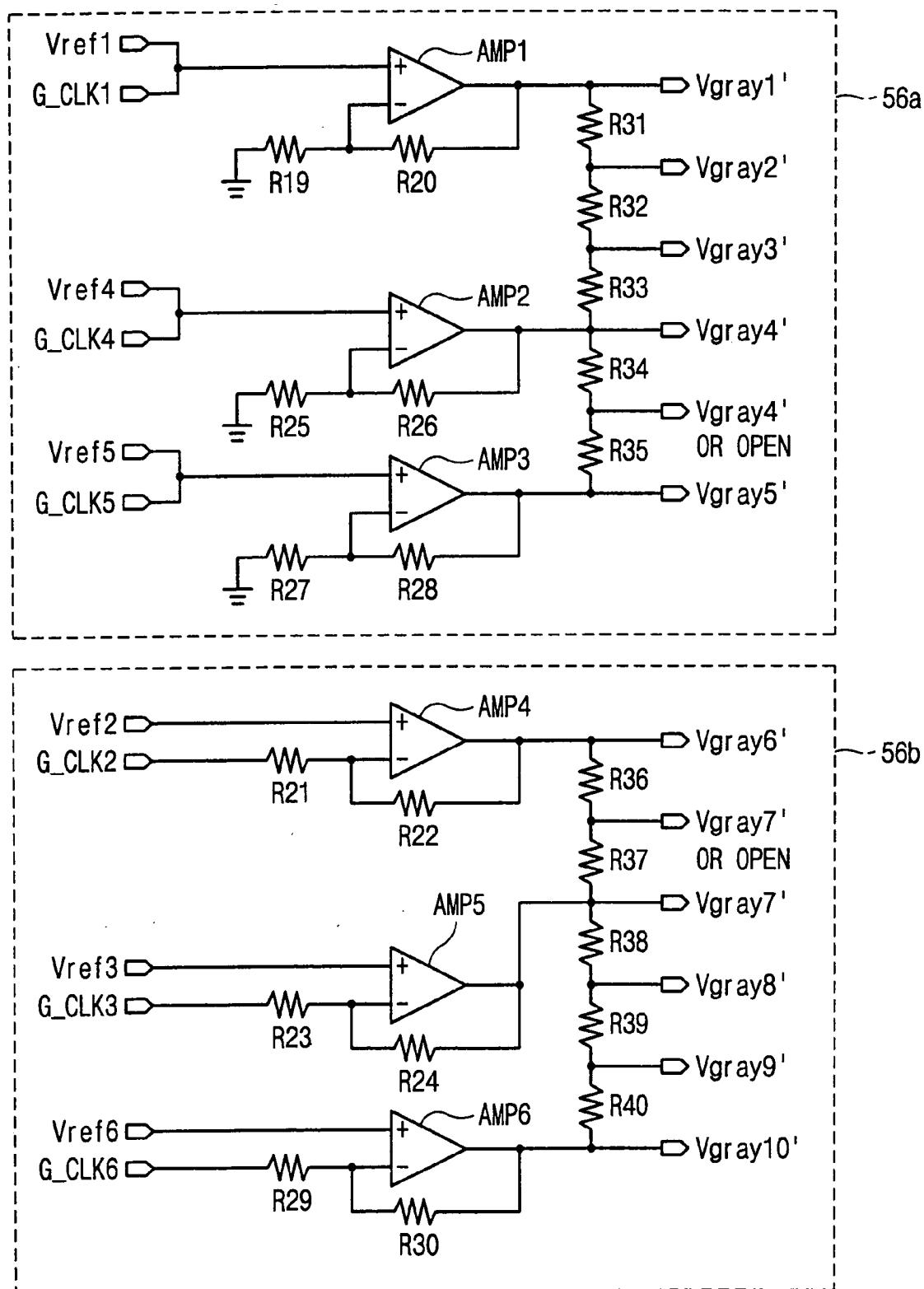

[0017] FIG. 6 is a circuit diagram showing a detailed configuration of a gray voltage generation circuit shown in FIG. 3.

[0018] FIGS. 7A and 7B are waveform diagrams showing one example of waveforms of gray voltages that are generated from a gray voltage generation circuit in accordance with the present invention.

[0019] FIGS. 8 and 9 are waveform diagrams showing one example of waveforms of outputs of a source driving circuit, which are generated by applying the gray voltage shown in FIGS. 7A and 7B.

[0020] FIGS. 10A, 10B, 11A, 11B, 12A, 12B, 13A and 13B are timing diagrams showing response speed measuring results of 0-32, 048, 0-64, and 32-84 grays of the source driving circuits by means of the gray voltage shown in FIGS. 7A and 7B.

#### DESCRIPTION OF THE PREFERRED EMBODIMENT

[0021] A new and improved gray voltage generation circuit of a liquid crystal display is provided to the present invention. The gray voltage generation circuit generates a high-potential liquid crystal driving voltage for a predetermined interval so that liquid crystal capacitors may be charged in a short time, and alters and outputs a gray voltage after the predetermined interval in order to generate a normal liquid crystal driving voltage. As a result, a driving speed of the liquid crystal display can be enhanced.

[0022] FIG. 2 schematically illustrates a configuration of a liquid crystal display 100 according to the present invention. The liquid crystal display 100 includes a liquid display panel 1, a plurality of gate driving circuits 2 coupled to the panel 1, a plurality of source driving circuits 3, a timing control circuit 4, and a gray voltage generation circuit 50. Such a configuration is identical to the configuration of the conventional liquid crystal display shown in FIG. 1, except for a gray voltage generation circuit 50 for generating a gray voltage Vgray' in response to a gate clock signal Gate Clock issued from a timing control circuit. Same numerals denote same elements throughout the drawings, and their description will be skipped herein so as to avoid duplicate description.

[0023] It is well known that the source driving circuit 3 selects one of a plurality of gray voltages according to color signals (R, G, and B), and applies a liquid crystal driving voltage Vdrive to a liquid crystal panel in response to the selected one gray voltage. A function of the source driving circuit 3 is closely bound up with a charging speed of the liquid crystal display Cp constructed in the liquid crystal

panel 1. The liquid crystal driving voltage Vdrive is dependent upon the gray voltage Vgray' generated from the gray voltage generation circuit 50. Therefore, a liquid crystal display 100 of the invention changes a liquid crystal driving voltage Vdrive generated from the source driving circuit 3 so as to enhance a charging speed of the liquid crystal capacitor Cp constructed in the panel 1. Without modifying designs of expensive and complex circuits such as the gate driving circuit 2, the source driving circuit 3, and the timing control circuit 4, a gray voltage generation circuit 50 of much lower price than the above circuits is made to enhance a driving speed of the liquid crystal display 100.

[0024] FIG. 3 schematically illustrates a configuration of a gray voltage generation circuit according to the present invention. A gray voltage generation circuit 50 includes a clock generator 52, a voltage generator 54, and a gray voltage generator 56. The clock generator 52 generates n-bit clock signals G\_CLK1, . . . , and G\_CLKn that are not overlapped with each other, in response to a gate clock signal GATE CLOCK. The voltage generator 54 generates n-bit reference voltages Vref1, . . . , and Vrefn each having different level, in response to a power supply voltage VDD that is an analog signal and is used as a power supply voltage of a source driving circuit 3.

[0025] If the n-bit clock signals G\_CLK1, . . . , and G\_CLKn and the n-bit reference voltages Vref1, . . . , and Vrefn are inputted to the gray voltage generator 56, the gray voltage generator 56 generates m-bit gray voltages Vgray1', . . . , and Vgraym' that are synchronized with the clock signals G\_CLK1, . . . , and G\_CLKn to have different potentials based upon levels of the reference voltages Vref, . . . , and Vrefn. Although described in detail hereinbelow, the gray voltages Vgray1', . . . , and Vgraym' makes the source driving circuit 3 generate a liquid crystal driving voltage Vdrive' that has different values in high and low intervals of the clock signal CLOCK during one period of the gate clock GATE CLOCK. The liquid driving voltage Vdrive' of the source driving circuit 3 having such a characteristic can enhance a driving speed of a liquid crystal display 100.

[0026] FIGS. 4, 5 and 6 illustrate the clock generator 52, the voltage generator 54, and the gray voltage generator 56 that are shown in FIG. 3, respectively. The clock generator 52 issues six clock signals C\_CLK1, . . . , and C\_CLK6. The voltage generator 54 generates six reference voltages Vref1, . . . , and Vref6. And, the gray voltage generator 56 generates ten clock signals G\_CLK1', . . . , and G\_CLK10' in response to the six clock signals C\_CLK1, . . . , and C\_CLK6 and the six reference voltages Vref1, and Vref6. According to a circuit configuration, the number of generated signals can be changed. The circuits shown in the drawings are merely one example of the circuit configuration.

[0027] Referring now to FIG. 4, the clock generator 52 consists of an input terminal for receiving a gate clock signal GATE CLOCK generated from the timing control circuit 4, first and sixth clock generation units 52a-52f each being coupled to the input terminal in parallel, and first and sixth output terminals each being coupled to the units 52a-52f. Each of the units 52a-52f has a capacitor C1, . . . , or C6 and a resistor R1, . . . , or R6 that are serially connected between the input terminal and the output terminal. And, each of the units 52a-52f outputs first and sixth clock signals G\_CLK1,

..., and G\_CLK6 not to be overlapped with each other. A period of the clock signals G\_CLK1, ..., and G\_CLK6 is identical to that of the gate clock signal GATE CLOCK generated from the timing control circuit 4.

[0028] Referring to FIG. 5, the voltage generator 54 consists of six voltage generation units 54a-54f for generating six reference voltages Vref1, ..., and Vref6 by dividing a power supply voltage VDD at a predetermined ratio to generate six reference voltages of different levels. The units 54a-54f are connected between the power supply voltage VDD and a ground voltage GND in parallel. Each of the units 54a-54f includes two resistors serially connected between VDD and GND, and an output terminal coupled to a contact point between the resistors.

[0029] Referring to FIG. 6, the gray voltage generator 56 consists of first and second gray voltage generation units 56a and 56b. The first gray voltage unit 56a generates first to fifth gray voltages Vgray1', ..., and Vgray5' that are used to drive a positive polarity of a liquid crystal. The second gray voltage unit 56b generates sixth to tenth gray voltages Vgray6', ..., and Vgray10' that are used to drive a negative polarity of a liquid crystal.

[0030] The first gray voltage unit 56a includes first to sixth input terminals for receiving clock signals G\_CLK1, G\_CLK4, and G\_CLK5 generated from a clock generator 52 and reference voltages Vref1, Vref4, and Vref5 generated from a voltage generator 54. It also includes a first amplifier AMP1, a second amplifier AMP2 and a third amplifier AMP3 for respectively adding and amplifying G\_CLK1, G\_CLK4, and G\_CLK5 to a predetermined ratio to generate gray voltages Vgray1', Vgray4', and Vgray5', and output terminals for outputting Vgray1', Vgray4', and Vgray5'. The first amplifier circuit AMP1 adds G\_CLK1 to Vref1, and amplifies it to a predetermined ratio to generate Vgray1'. The second amplifier circuit AMP2 adds G\_CLK4 to Vref4, and amplifies it to a predetermined ratio to generate Vgray4'. And, the third amplifier circuit AMP3 adds G\_CLK5 to Vref5, and amplifies it to a predetermined ratio to generate Vgray5'.

[0031] The gray voltages Vgray1', Vgray4', and Vgray5' are given by the following equations;

$$V_{gray1'} = \frac{R19 + R20}{R19} \left[ V_{ref1} + \frac{R1}{R1 + R19} V_{G\_CLK1} \right] \quad <\text{Equation 1}>$$

$$V_{gray4'} = \frac{R25 + R26}{R25} \left[ V_{ref4} + \frac{R4}{R4 + R25} V_{G\_CLK4} \right] \quad <\text{Equation 2}>$$

$$V_{gray5'} = \frac{R27 + R28}{R27} \left[ V_{ref5} + \frac{R5}{R5 + R27} V_{G\_CLK5} \right] \quad <\text{Equation 3}>$$

[0032] wherein  $V_{G\_CLKn}$  represents an alternative element of a gate clock signal GATE CLOCK.

[0033] The first gray voltage generation unit 56a generates second and third gray voltages Vgray2' and Vgray3', as well as Vgray1', Vgray4', and Vgray5'. These gray voltages Vgray2' and Vgray3' have the level of a voltage that is divided by resistors R31, R32, and R33 that are serially connected between output terminals of the first and second amplifier circuit AMP1 and AMP2.

[0034] The second gray voltage generation unit 56b includes seventh to twelfth input terminals for receiving

clock signals G\_CLK2, G\_CLK3, and G\_CLK6 generated from the clock generator 52 and reference voltages Vref2, Vref3, and Vref6 generated from the voltage generator 54. It also has a fourth amplifier AMP4, a fifth amplifier AMP5, and a sixth amplifier AMP6 for subtracting G\_CLK2, G\_CLK3, and G\_CLK6 from Vref2, Vref3, and Vref6 to generate gray voltages Vgray6', Vgray8', and Vgray10', and output terminals for outputting Vgray6', Vgray8', and Vgray10' generated from AMP4, AMP5 and AMP6. The fourth amplifier circuit AMP4 subtracts G\_CLK2 from Vref2, and amplifies it to a predetermined ratio to generate Vgray6'. The fifth amplifier circuit AMP5 subtracts G\_CLK3 from Vref3, and amplifies it to a predetermined ratio to generate Vgray8'. And, the sixth amplifier circuit AMP6 subtracts G\_CLK6 from Vref6, and amplifies it to a predetermined ratio to generate Vgray10'.

[0035] The gray voltages Vgray6', Vgray8', and Vgray10' are given by the following equations;

$$V_{gray6'} = \frac{R2 + R21 + R22}{R22} \left[ V_{ref2} - \frac{R22}{R2 + R21} V_{G\_CLK2} \right] \quad <\text{Equation 4}>$$

$$V_{gray8'} = \frac{R3 + R2 + R24}{R24} \left[ V_{ref3} - \frac{R24}{R3 + R23} V_{G\_CLK3} \right] \quad <\text{Equation 5}>$$

$$V_{gray10'} = \frac{R6 + R29 + R30}{R30} \left[ V_{ref6} - \frac{R30}{R6 + R29} V_{G\_CLK6} \right] \quad <\text{Equation 6}>$$

[0036] wherein  $V_{G\_CLKn}$  represents an alternative element of the gate clock signal GATE CLOCK.

[0037] The second gray voltage generation unit 56b generates eighth and ninth gray voltages Vgray8' and Vgray9', as well as Vgray6', Vgray7', and Vgray10'. These gray voltages Vgray8' and Vgray9' have the level of a voltage that is divided by resistors R38, R39, and R40 that are serially connected between output terminals of the fifth and the sixth amplifier circuit AMP5 and AMP6.

[0038] In the drawings, the fourth and seventh gray voltages Vgray4' and Vgray7' can be outputted through one or two terminals. For example, the fourth gray voltage Vgray4' generated through a fourth output terminal indicates that it uses an output of the second amplifier circuit AMP2 naturally. And, the fourth gray voltage Vgray4' generated through a fifth output terminal indicates that it divides the output of the second amplifier circuit AMP2 through a resistor to a predetermined ratio for output. Based upon a circuit configuration, the gray voltages Vgray1', ..., and Vgray10' generated from the gray voltage generator 56 may use an output of an amplifier circuit naturally, or may divide and use the output of the amplifier circuit to a predetermined rate. Although Vgray4' and Vgray7' are illustrated in the drawing, they are simply examples. This can be applied to any other gray voltages.

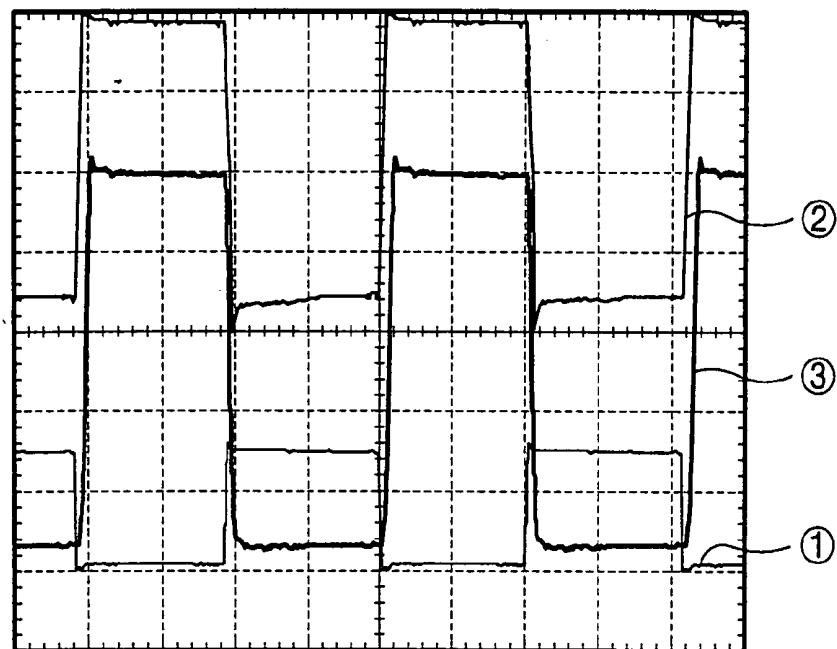

[0039] FIGS. 7A and 7B exemplarily illustrate waveforms of gray voltages generated from a gray voltage generation according to the present invention. In particular, FIG. 7A shows a waveform of a gray voltage of a positive polarity, and FIG. 7B shows a waveform of a gray voltage of a negative polarity. Waveforms (1) and (1)', (2) and (2)', and (3) and (3)' denote a gate clock signal GATE CLOCK issued from a timing control circuit 4, a 48-gray voltage, and a 64-gray voltage, respectively.

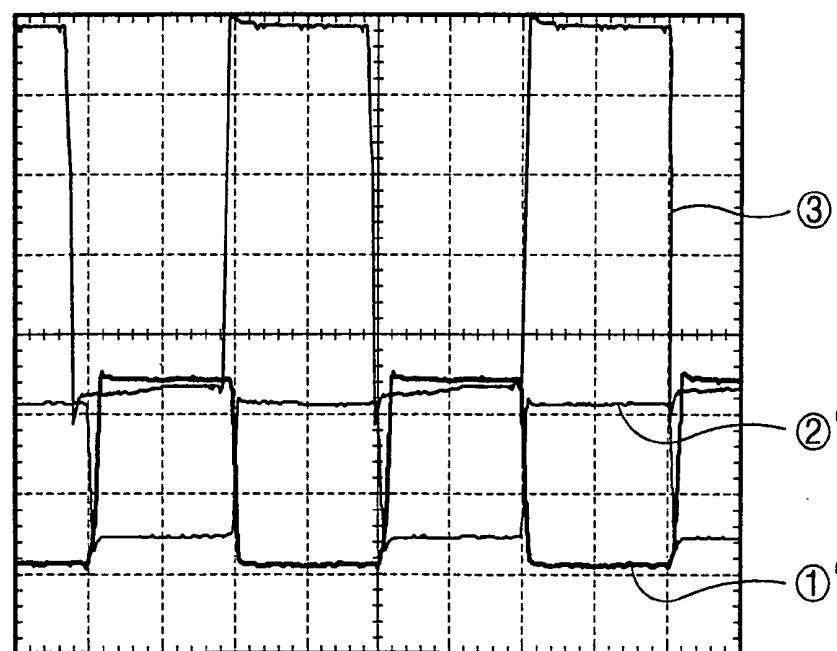

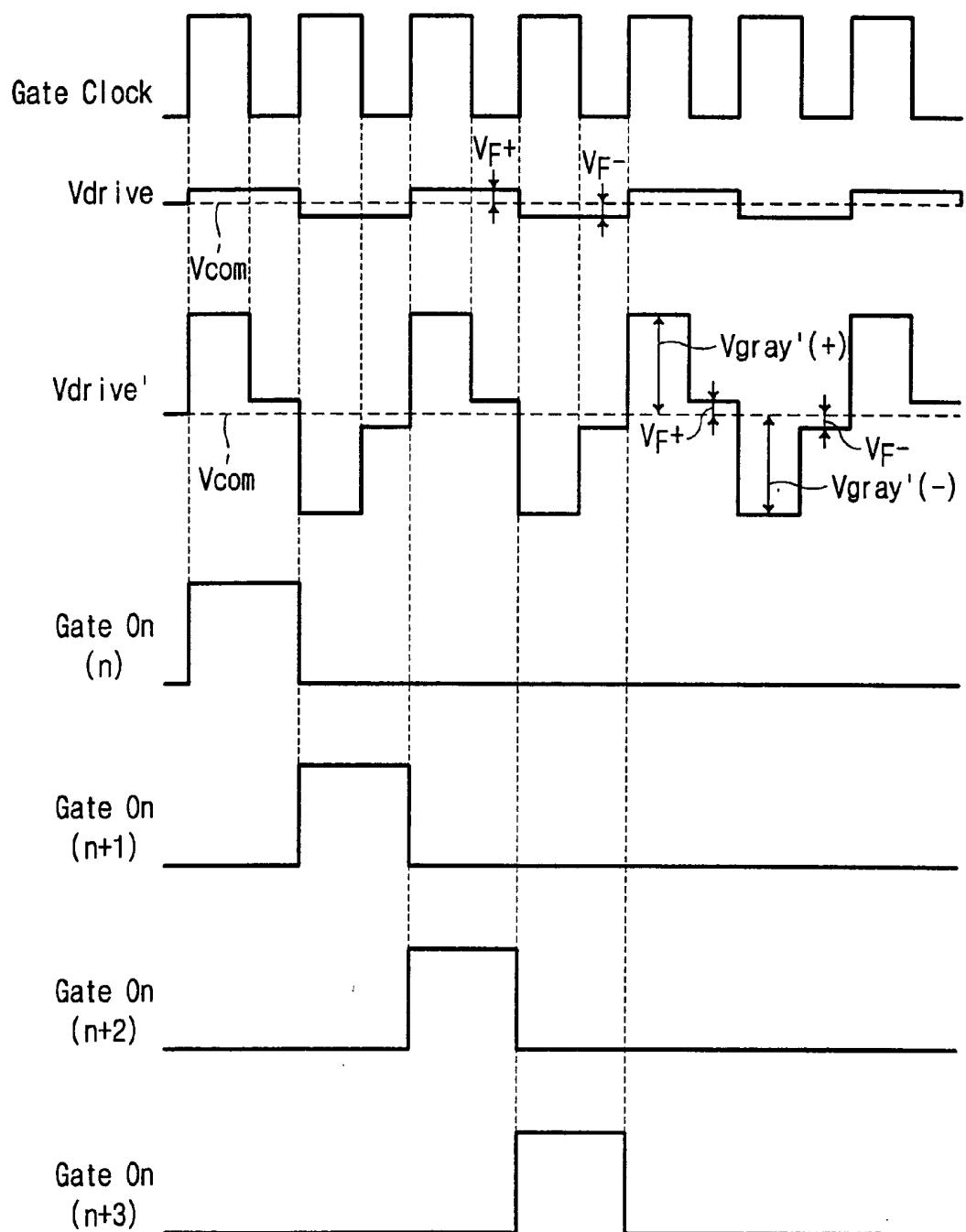

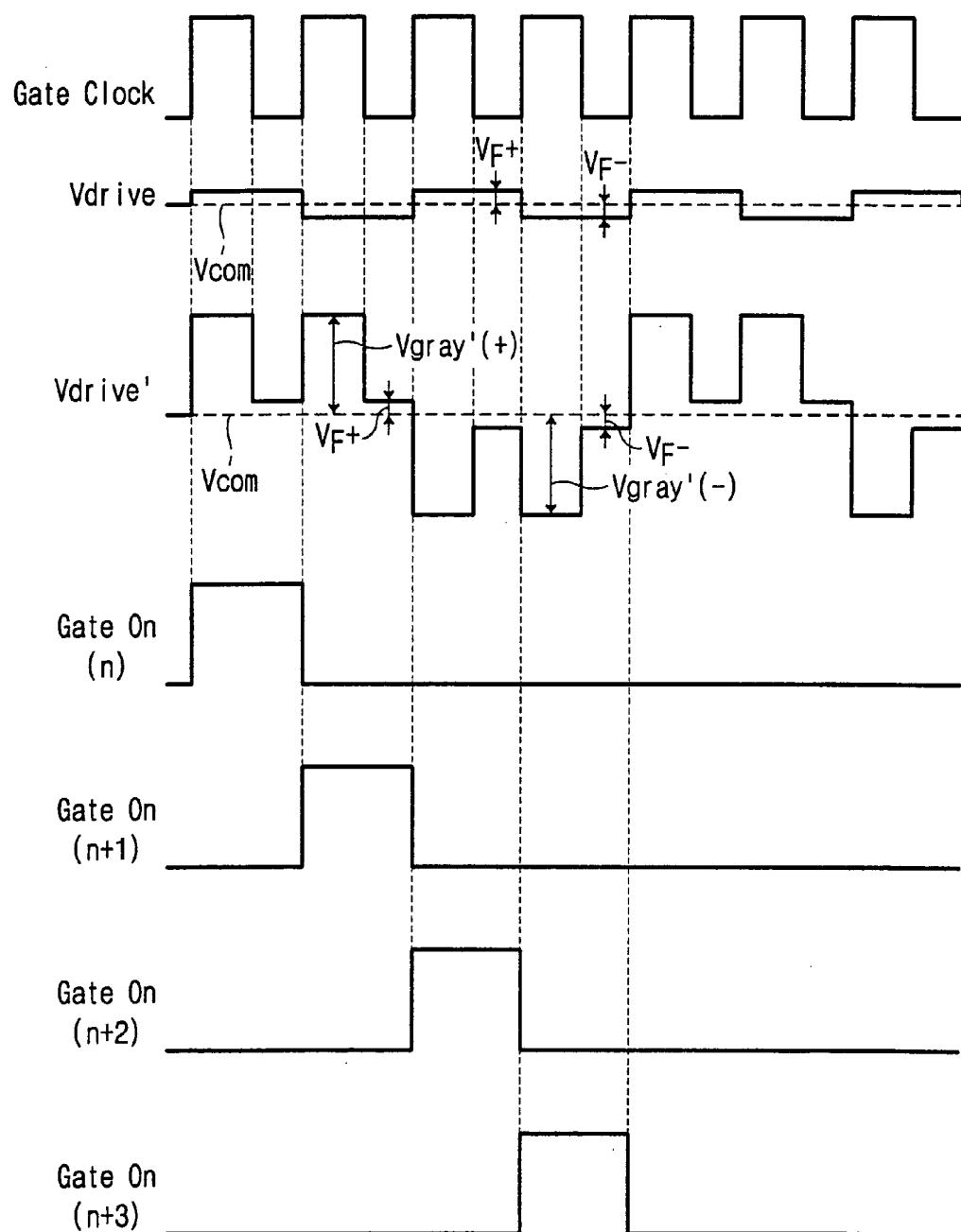

[0040] FIGS. 8 and 9 exemplarily illustrate waveforms of outputs of a source driving circuit, which are generated by applying the gray voltage shown in FIGS. 7A and 7B. In particular, FIG. 8 shows a waveform in driving dot inversion, and FIG. 9 shows a waveform in driving 2-line inversion (i.e., normally white mode that white presents when a power is not applied).

[0041] In the drawings, illustrated elements are a gate clock signal GATE CLOCK outputted from a timing control circuit 4, an output signal Vdrive of a source driving circuit in a conventional liquid crystal display, an output signal of a source driving circuit 3 in a liquid crystal display according to the present invention, and gate on signals GATE ON(n), GATE ON(n+1), GATE ON(n+2) and GATE ON(n+3) that are outputted from the timing control circuit 4 in order to drive (n)th, (n+1)th, (n+2)th and (n+3)th lines.

[0042] The source driving circuit in the conventional liquid crystal display generates a liquid crystal driving voltage Vdrive having voltage level of  $V_{F+}$  and  $V_{F-}$  in each period of the gate clock GATE CLOCK. The voltage Vdrive is symmetric to positive and negative directions on the basis of a common voltage Vcom.

[0043] The source driving circuit 3 in the liquid crystal display 100 according to the present invention generates a liquid crystal driving voltage Vdrive' = Vgray(t) that is changed by a gray voltage in each period of the gate clock signal GATE CLOCK. In each period of the gate clock signal GATE CLOCK, the voltage Vdrive' generates a liquid crystal driving voltage Vdrive' having different levels in high and low level intervals. That is, the liquid crystal driving voltage Vdrive' = Vgray(t) generates positive and negative high voltage that are enough to rapidly charge liquid crystal capacitors Cp constructed in a liquid crystal panel 1. In this case, the liquid crystal driving voltage Vdrive' = Vgray(t) generates the high voltages only for a predetermined interval, in order to prevent power consumption caused by generating such high voltages.

[0044] With reference to FIG. 8, in driving dot inversion, how to drive a positive polarity when applying a gate on signal Gate On(n) for driving an (n)th line, is now explained. If a gate clock signal Gate Clock is laid to high level, a source driving circuit 3 generates a liquid crystal driving voltage Vdrive' having first voltage level that is still higher than that of an existing liquid crystal driving voltage Vdrive. If Gate Clock is laid to low level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' having a second voltage level of  $V_{F+}$  with the same polarity as Vdrive. In this case, both the first voltage level and the second voltage level are higher than a common voltage Vcom. And, the first voltage level is higher than the second voltage level.

[0045] When a gate-on signal Gate On(n) for driving an (n+1)th line is applied, driving a negative polarity is explained. If the gate clock signal Gate Clock is laid to high level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' having third voltage level is still lower than that of the existing liquid crystal driving voltage Vdrive. If Gate Clock is laid to low level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' having fourth voltage level of  $V_{F-}$  with the same polarity as Vdrive. In this case, both values of the third voltage level

and the fourth voltage level are lower than the common voltage Vcom And, the third voltage level is lower than the fourth voltage level.

[0046] With reference to FIG. 9, in driving 2-line inversion, when a gate on signal Gate On(n) for driving (n)th and (n+1)th lines is applied, driving a positive polarity is explained. If a gate clock signal Gate Clock is laid to high level, a source driving circuit 3 generates a liquid crystal driving voltage Vdrive' whose level is still higher than that of an existing liquid crystal driving voltage Vdrive. If Gate Clock is laid to low level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' having voltage level of  $V_{F+}$  the same as Vdrive.

[0047] When a gate on signal Gate On(n) for driving (n+2)th and (n+3)th lines is applied, driving a negative polarity is explained. If the gate clock signal Gate Clock is laid to high level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' whose level is still lower than that of the existing liquid crystal driving voltage Vdrive. If Gate Clock is laid to low level, the source driving circuit 3 generates a liquid crystal driving voltage Vdrive' of  $V_{F-}$  with the same polarity as Vdrive.

[0048] In FIGS. 7 and 8, output waveforms of the source driving circuit 3 can be changed according to a kind of line driving methods, and are applicable to various kinds of line driving methods (e.g., n-line inversion driving method).

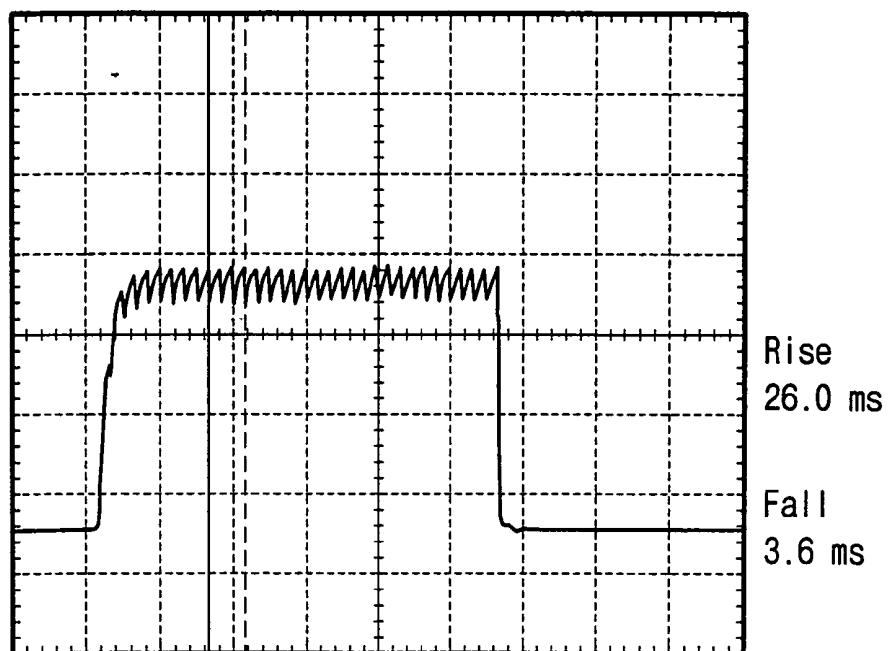

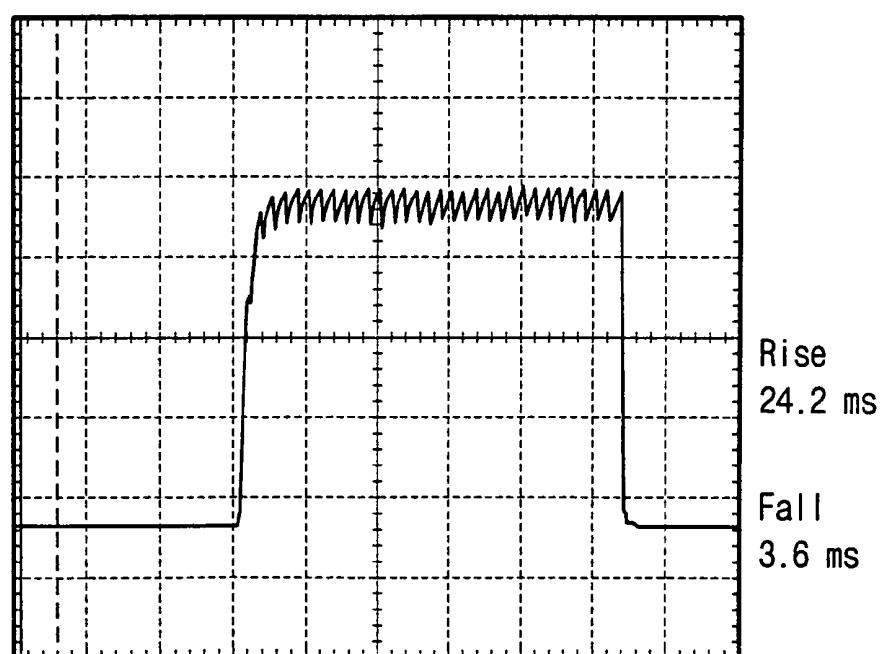

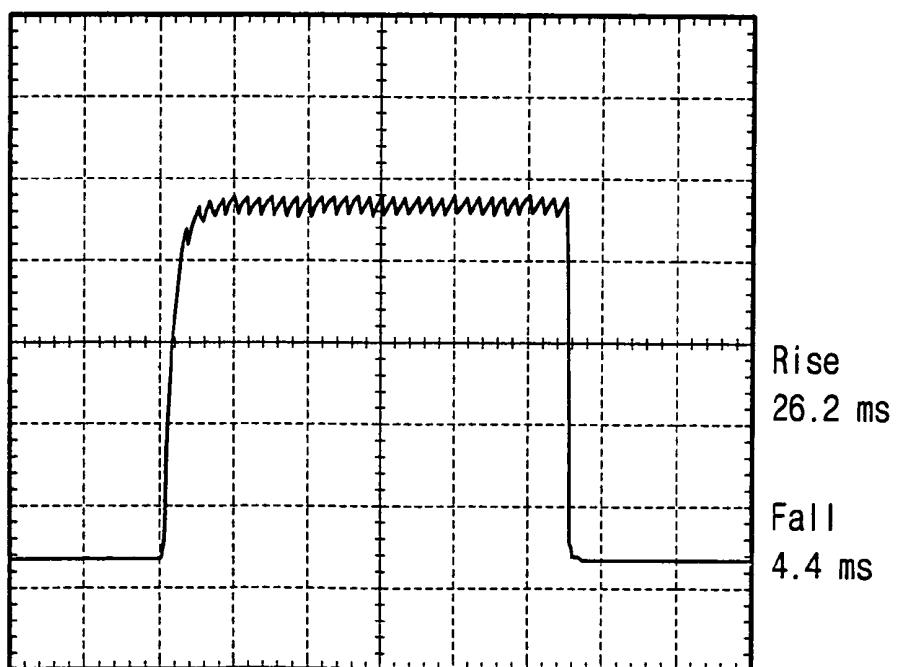

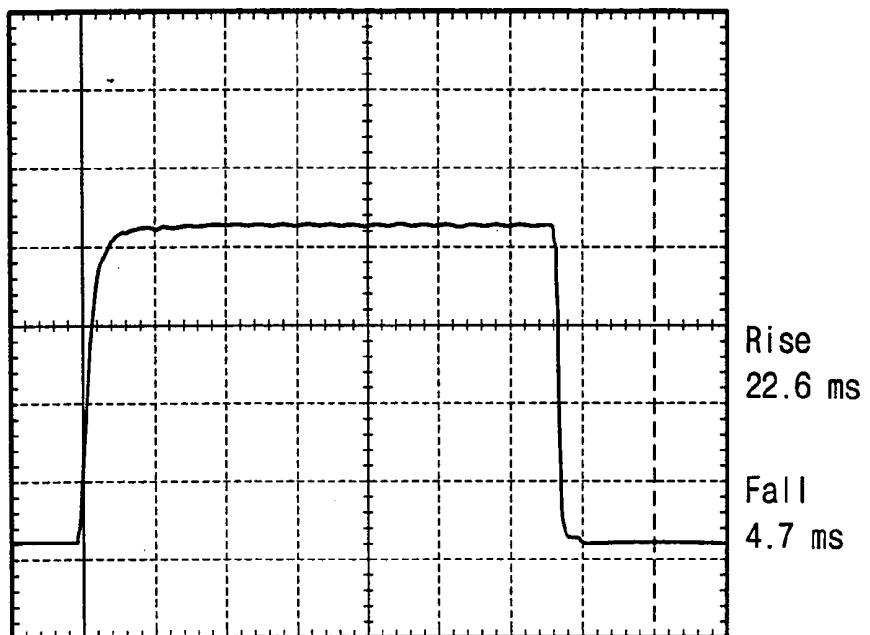

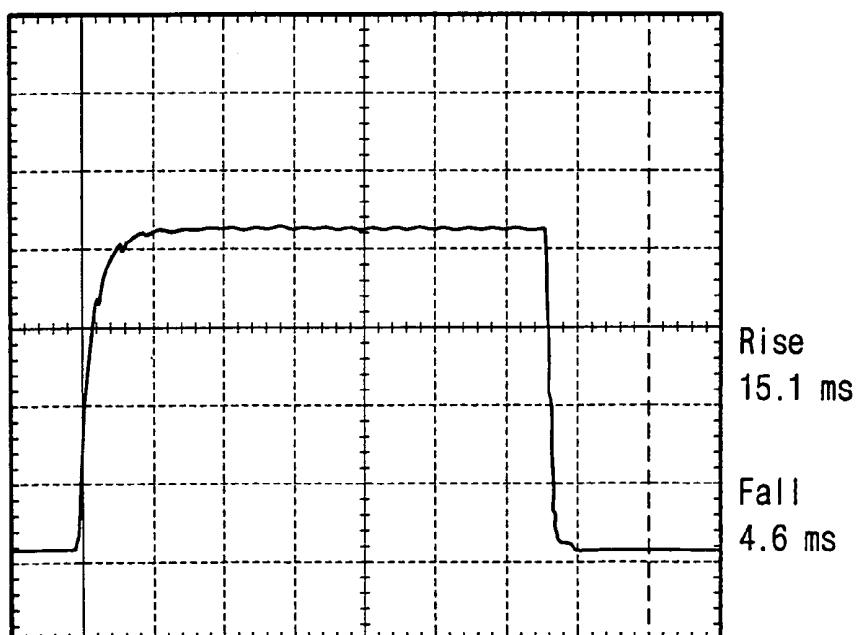

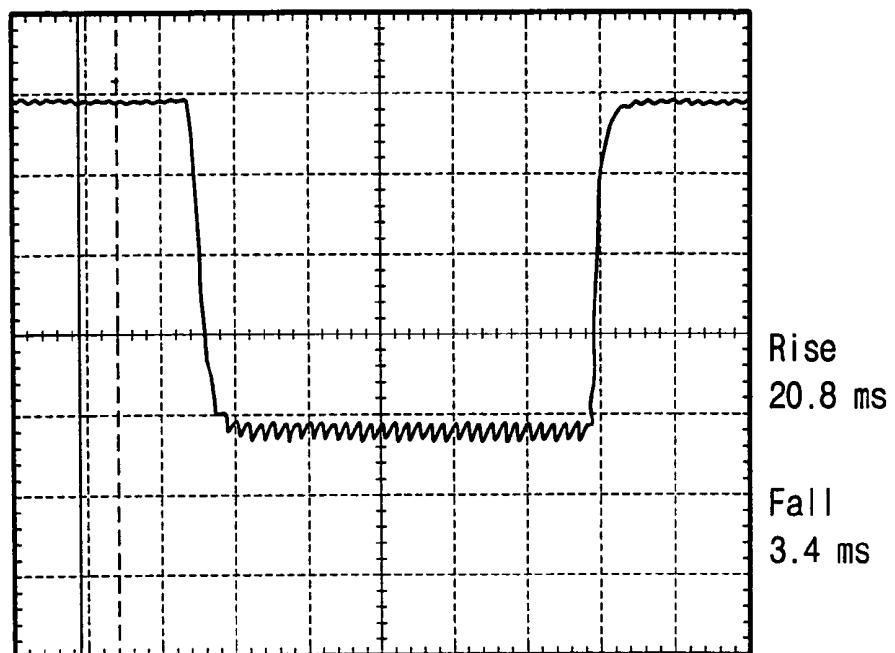

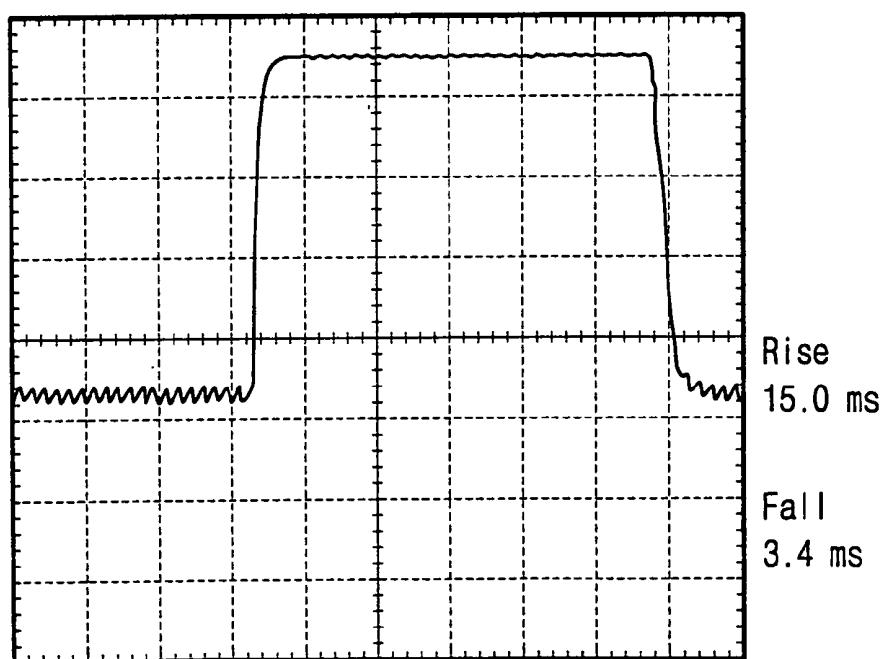

[0049] FIGS. 10A, 10B, 11A, 11B, 12A, 12B, 13A and 13B show response speed measuring results of 0 through 32, 0 through 48, 0 through 64, and 32 through 84 gray levels of the source driving circuits by means of the gray voltage shown in FIGS. 7A and 7B. In particular, FIG. 10A, FIG. 10B, FIG. 11A, and FIG. 11B show a response speed of 0 through 32 gray levels of a conventional source driving circuit, a response speed of 0 through 32 gray levels of a source driving circuit according to the invention, a response speed of 0 through 48 gray levels of the conventional source driving circuit, and a response speed of 0 through 48 gray levels of the source driving circuit according to the invention, respectively. FIG. 12A, FIG. 12B, FIG. 13A, and FIG. 13B show a response speed of 0 through 64 gray levels of the conventional source driving circuit, a response speed of 0 through 64 gray levels of the source driving speed according to the invention, a response speed of 32 through 64 gray levels of the conventional source driving circuit, and a response speed of 32 through 64 gray levels of the source driving circuit according to the invention, respectively.

[0050] The result can be obtained by measuring the 48-gray voltages ② and ②' and the 64-gray voltages ③ and ③' (see FIGS. 7A and 7B) that were changed and applied with respect to five source driving circuits each having positive and negative polarities. A rising time of each waveform is denoted on the basis of a luminance, and corresponds to a falling time of a liquid crystal based on its movement.

[0051] Referring to FIGS. 10A and 10B, in response speeds of a source driving circuit with respect to 0 through 32 gray levels, a conventional rising time (i.e., a falling time of a liquid crystal) is 26.0 ms and a conventional falling time (i.e., a rising time of the liquid crystal) is 3.6 ms. According to the present invention, a rising time (i.e., a falling time of a liquid crystal) is 24.2 ms and a falling time (i.e., a rising

time of the liquid crystal) is 3.6 ms. In this case, a luminance-based falling time is not changed, while a luminance-based rising time is reduced from 26 ms to 24.2 ms by 1.8 ms.

[0052] Referring to **FIGS. 11A and 11B**, in response speeds of a source driving circuit with respect to 0 through 48 gray levels, a conventional rising time (i.e., a falling time of a liquid crystal) is 36.8 ms and a conventional falling time (i.e., a falling time (i.e., a rising time of the liquid crystal) is 3.6 ms. According to the invention, a rising time (i.e., a falling time of a liquid crystal) is 26.2 ms and a falling time (i.e., a rising time of the liquid crystal) is 4.4 ms. In this case, a luminance-based falling time increases in 0.8 ms, while a luminance-based rising is reduced from 36.8 ms to 26.2 ms by 10.6 ms.

[0053] Referring to **FIGS. 12A and 12B**, in response speeds of a source driving circuit with respect to 0 through 64 gray levels, a conventional rising time (i.e., a falling time of a liquid crystal) is 22.6 ms, and a conventional falling time (i.e., a rising time of the liquid crystal) is 4.7 ms. According to the invention, a rising time (i.e., a falling time of a liquid crystal) is 15.1 ms, and a falling time (i.e., a rising time of the liquid crystal) is 4.6 ms. In this case, a luminance-based falling time is reduced by 0.1 ms, and a luminance-based rising time is reduced from 22.6 ms to 15.1 ms by 7.5 ms.

[0054] Referring to **FIGS. 13A and 13B**, in response speeds of 32 through 64 gray levels with respect to a source driving circuit, a conventional rising time (i.e., a falling time of a liquid crystal) is 20.8 ms, and a falling time (i.e., a rising time of the liquid crystal) is 3.4 ms. According to the invention, a rising time (i.e., a falling time of a liquid crystal) is 15.0 ms, and a falling time (i.e., a rising time of the liquid crystal) is 3.4 ms. In this case, a luminance-based falling time is not changed, and a luminance-based rising time is reduced from 20.8 ms to 15.0 ms by 5.8 ms.

[0055] In **FIGS. 10A through 13B**, response speeds of a source driving circuit **3** according to the present invention change as follows. In 0 through 32 gray levels, a response speed is reduced from 26 ms to 24.2 ms by 1.8 ms. In 0 through 48 gray levels, a response speed is reduced from 36.8 ms to 26.2 ms by 10.6 ms. In 0 through 64 gray levels, a response speed is reduced from 22.6 ms to 15.1 ms by 7.5 ms. And, in 32 through 64 gray levels, a response speed is reduced from 20.8 ms to 15.0 ms by 5.8 ms. The following table [TABLE 1] represents these response speeds.

TABLE 1

| <u>Falling Times of Liquid Crystal</u> |                |                   |

|----------------------------------------|----------------|-------------------|

|                                        | Prior Art      | Present Invention |

| 0-32 Gray Levels                       | 26.0 ms (1.00) | 24.2 ms (0.96)    |

| 0-48 Gray Levels                       | 36.8 ms (1.00) | 26.2 ms (0.71)    |

| 0-64 Gray Levels                       | 22.6 ms (1.00) | 15.1 ms (0.67)    |

| 32-64 Gray Levels                      | 20.8 ms (1.00) | 15.0 ms (0.72)    |

[0056] wherein these falling times are results of simulation that is carried out in the same condition,

and numerals in parentheses denote normalized results on the basis of falling times of a conventional liquid crystal, respectively.

[0057] Referring to the normalized results in TABLE 1, in 0 through 32 gray levels, the failing time of the liquid crystal is improved by 7%. In 0 through 48 gray levels, the falling time is improved by 29%. In 0 through 64 gray levels, the falling time is improved by 33%. And, in 32 through 64 gray levels, the falling time is improved by 28%. In other words, the speed of the falling time of the liquid crystal is improved in proportion to the gray values.

[0058] As described above, a gray voltage generation circuit of this invention outputs an altered gray voltage  $V_{gray}'$  so that a source driving circuit can generate a liquid crystal driving voltage  $V_{drive}'$  having a voltage level as shown in **FIGS. 7 and 8**. Thus, the source driving circuit **3** generates a liquid crystal driving voltage  $V_{drive}'=V_{gray}'(t)$  that changes according to a gray voltage in each period of a gate clock signal Gate Clock. Liquid crystal capacitors  $C_p$  constructed in a liquid crystal panel **1** are rapidly charged by the liquid crystal driving voltage  $V_{drive}'$  applied from the source driving circuit **3**. As a result, a falling time of the liquid crystal is reduced to improve a driving speed of a liquid crystal display.

[0059] While an illustrative embodiment of the present invention has been shown and described, numerous variations and alternate embodiments will occur to those skilled in the art, without departing from the spirit and scope of the invention. Accordingly, it is intended that the present invention not be limited solely to the specifically described illustrative embodiment. Various modifications are contemplated and can be made without departing from the spirit and scope of the invention as defined by the appended claims.

1-23. (canceled)

24. A liquid crystal display comprising:

a liquid crystal panel having a plurality of pixels;

a timing control circuit issuing a gate clock signal and a plurality of control signals;

a gray voltage generation circuit generating a plurality of gray voltages corresponding to data to be displayed in the panel in response to the gate clock signal;

a gate driving circuit sequentially scanning the pixels of the panel row by row in response to the gate clock signal; and

a source driving circuit generating a liquid crystal driving voltage corresponding to data in response to the gray voltage and the control signals and applying the generated liquid crystal driving voltage to the panel each of scanning.

25. The liquid crystal display claim 24, wherein the source driving circuit generates a liquid crystal voltage having different values in high and low level intervals of the gate clock signal in response to the gray voltage.

|                |                                                 |         |            |

|----------------|-------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于快速驱动液晶显示器的灰度电压产生电路                            |         |            |

| 公开(公告)号        | <a href="#">US20050083285A1</a>                 | 公开(公告)日 | 2005-04-21 |

| 申请号            | US10/747665                                     | 申请日     | 2003-12-30 |

| [标]申请(专利权)人(译) | YEON允MO<br>李健熙BIN                               |         |            |

| 申请(专利权)人(译)    | YEON允-MO<br>李健熙-BIN                             |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO. , LTD.                            |         |            |

| [标]发明人         | YEON YEUN MO<br>LEE KUN BIN                     |         |            |

| 发明人            | YEON, YEUN-MO<br>LEE, KUN-BIN                   |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                     |         |            |

| CPC分类号         | G09G3/3648 G09G2310/0251 G09G3/3696             |         |            |

| 优先权            | 1020000079698 2000-12-21 KR                     |         |            |

| 其他公开文献         | US7129921                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a> |         |            |

### 摘要(译)

用于驱动液晶显示器的灰度电压产生电路快速输出改变的灰度电压，使得源极驱动电路可以在短时间内对液晶面板中构造的液晶电容器充电。响应于来自灰度电压产生电路的灰度电压，在驱动正极性的同时，当施加高电平的栅极时钟信号时，源极驱动电路产生比现有液晶驱动电压更高电平的液晶驱动电压，并且当施加低电平的栅极时钟信号时，产生与现有液晶驱动电压相似的电平的液晶驱动电压。并且，在驱动负极性时，源极驱动电路在施加高电平的栅极时钟信号时产生比现有液晶驱动电压低的液晶驱动电压，并产生与以下相似的电平的液晶驱动电压。当施加低电平的栅极时钟信号时，现有的液晶驱动电压。