#### US007796221B2

### (12) United States Patent

#### Kamada et al.

# (54) LIQUID CRYSTAL DISPLAY DEVICE AND METHOD OF PREVENTING IMAGE STICKING THEREON

(75) Inventors: Tsuyoshi Kamada, Kawasaki (JP);

Takashi Sasabayashi, Kawasaki (JP);

Kazuya Ueda, Kawasaki (JP); Hidefumi

Yoshida, Kawasaki (JP)

(73) Assignees: Fujitsu Limited, Kawasaki (JP); Au

Optronics Corporation, Hsinchu (TW)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 740 days.

(21) Appl. No.: 11/046,145

(22) Filed: Jan. 28, 2005

(65) Prior Publication Data

US 2006/0023137 A1 Feb. 2, 2006

#### (30) Foreign Application Priority Data

Jul. 28, 2004 (JP) ...... 2004-220263

(51) **Int. Cl.** *G02F 1/1343* (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,840,460 A 6/1989 Bernot et al. ...... 349/144

### (10) Patent No.: US 7,796,221 B2

### (45) **Date of Patent: Sep. 14, 2010**

| 5,126,865 | Α   | 6/1992  | Sarma 349/85          |

|-----------|-----|---------|-----------------------|

| 5,459,596 | A * | 10/1995 | Ueda et al 349/39     |

| 5,521,729 | A * | 5/1996  | Ukai et al 349/42     |

| 5,786,876 | A   | 7/1998  | Ota et al 349/42      |

| 6,040,886 | A   | 3/2000  | Ota et al 349/141     |

| 6,400,427 | B1  | 6/2002  | Hanazawa et al 349/44 |

| 6,563,561 | B1  | 5/2003  | Ota et al 349/141     |

| 6,980,273 | B2  | 12/2005 | Ota et al 349/141     |

| 7,136,116 | B2  | 11/2006 | Sakamoto et al 349/43 |

#### FOREIGN PATENT DOCUMENTS

| CN | 1129035   | 8/1996 |

|----|-----------|--------|

| CN | 1470924   | 1/2004 |

| JP | 02-000012 | 1/1990 |

| JP | 3076938   | 6/2000 |

<sup>\*</sup> cited by examiner

Primary Examiner—David Nelms Assistant Examiner—W. Patty Chen (74) Attorney, Agent, or Firm—Kratz, Quintos & Hanson, LLP

#### (57) ABSTRACT

A sub picture element electrode directly connected to a thin film transistor is disposed between a floating sub picture element electrode capacitively coupled to a control electrode and a gate bus line in order to prevent injection of electric charges from the gate bus line to the floating sub picture element electrode. Moreover, a shield pattern electrically connected to an auxiliary capacitance bus line is formed between the floating sub picture element electrode and a data bus line. This shield pattern avoids injection of electric charges from the data bus line to the floating sub picture element electrode.

#### 1 Claim, 37 Drawing Sheets

# FIG. 1A (PRIOR ART)

FIG. 1B (PRIOR ART)

FIG. 2 (PRIOR ART)

FIG. 3 (PRIOR ART)

## FIG. 4 (PRIOR ART)

FIG. 5 (PRIOR ART)

$$V_{px2} = \frac{C_c}{C_c + C_{LC2}} \times V_{px1}$$

FIG. 6 (PRIOR ART)

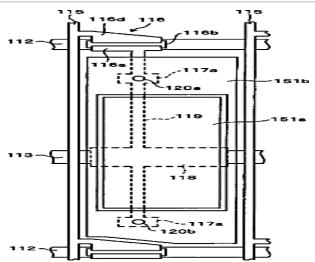

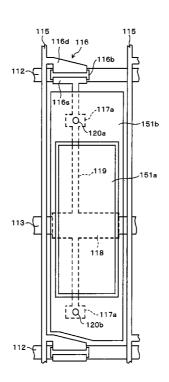

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 8

FIG. 9

### FIG. 11

Q AT A STATIONARY STATE AFTER TERMINATION OF A TRANSIENT STATE  $Q_1 = (R_{LC2}/(R_{LC2}+R_C)) \times \Delta V_S \times C_{LC2}$  $Q_2 = (R_c/(R_{Lc2}+R_c)) \times \Delta V_s \times C_c$  $Q = Q_2 - Q_1$  $= -(R_{LC2} \times C_{LC2}) + (R_C \times C_C)) / R_{LC2} + R_C) \times \Delta Vs$

DIRECT-CURRENT VOLTAGE WHICH REMAINS IN THE LIQUID CRYSTAL LAYER EVEN IF  $\Delta$  Vs IS REMOVED  $\Delta V_{LC2} = -Q/C_{LC2}$

$$\Delta V_{LC2} = \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta V_S$$

### FIG. 12

FIG. 13

FIG. 14A

FIG. 14B

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

FIG. 29

FIG. 30

|                  | 0.9   | 0.8   | 0.72  | 0.7   | 0.6   | 0.5   |

|------------------|-------|-------|-------|-------|-------|-------|

|                  | 9.00  | 4.00  | 2.57  | 2.33  | 1.50  | 1.00  |

| 10 <sup>-5</sup> | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10 <sup>-4</sup> | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10 <sup>-3</sup> | 0.99  | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  |

| 10-2             | 0.90  | 0.95  | 0.97  | 0.98  | 0.98  | 0.99  |

| 10 <sup>-1</sup> | 0.09  | 0.55  | 0.70  | 0.77  | 0.82  | 0.88  |

| 1                | -4.00 | -1.50 | -0.67 | -0.25 | 0.00  | 0.25  |

| 10 <sup>1</sup>  | -8.09 | -3.55 | -2.03 | -1.27 | -0.82 | -0.36 |

| 10 <sup>2</sup>  | -8.90 | -3.95 | -2.30 | -1.48 | -0.98 | -0.49 |

| 10 <sup>3</sup>  | -8.99 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 10 <sup>4</sup>  | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

| 10 <sup>5</sup>  | -9.00 | -4.00 | -2.33 | -1.50 | -1.00 | -0.50 |

FIG. 31

FIG. 32

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 38

FIG. 39

FIG. 40

FIG. 41

FIG. 42

## FIG. 43

$$\Delta V_{LC2} = \frac{(1 - (Rc/R_{LC2} \times Cc/(C_{LC2} + C_{S2})))}{(1 + Rc/R_{LC2})} \times \Delta V_S$$

## FIG. 44

FIG. 45

FIG. 46

## LIQUID CRYSTAL DISPLAY DEVICE AND METHOD OF PREVENTING IMAGE STICKING THEREON

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is based on and claims priority of Japanese Patent Application No. 2004-220263, filed on Jul. 28, 2004, the entire contents of which are being incorporated herein by 10 reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal display device including a plurality of sub picture element electrodes in one picture element region, and to a method of preventing image sticking thereon. More specifically, the present invention relates to such a liquid crystal display device in which at least one of the sub picture element electrodes is capacitively coupled with a control electrode to which a display voltage is applied, and to a method of preventing image sticking thereon.

## 2. Description of the Prior Art

As compared to a cathode ray tube (CRT), liquid crystal display devices have advantages that they are thin, light-weight, as well as have low voltage drive capability and low power consumption. For this reason, liquid crystal display devices are applied to various electronic devices including 30 televisions, notebook personal computers (PCs), desktop PCs, personal digital assistants (PDAs), cellular telephones, and the like. In particular, an active matrix liquid crystal display device provided with thin film transistors (TFTs) as switching elements for respective picture elements (sub pixels) exerts excellent display characteristics almost equal to a CRT owing to high driving performances. Accordingly, active matrix liquid crystal display devices are now used in various fields, such as desktop PCs and televisions, where CRTs have been conventionally applied.

In general, a liquid crystal display device includes two substrates and liquid crystal which is sealed between these substrates. Picture element electrodes, TFTs, and the like are formed for respective picture elements on one of the substrates. Meanwhile, color filters opposed to the picture ele- 45 ment electrodes, and a common electrode common to the respective picture elements are formed on the other substrate. The color filters include three types of red (R), green (G), and blue (B), and a color filter in one of these colors is disposed at each of the picture elements. The three picture elements in red 50 (R), green (G), and blue (B), which are disposed adjacently to one another, collectively constitute one pixel. In this specification, the substrate including formation of the picture element electrodes and the TFTs will be hereinafter referred to as a TFT substrate, and the substrate to be disposed opposite to 55 the TFT substrate will be hereinafter referred to as a counter substrate. Moreover, a structure formed by sealing the liquid crystal between the TFT substrate and the counter substrate will be hereinafter referred to as a liquid crystal panel.

Conventionally, a twisted nematic (TN) liquid crystal display device, which is configured to seal horizontal alignment type liquid crystal (liquid crystal having positive dielectric constant anisotropy) between two substrates and to subject liquid crystal molecules to twisted alignment, has been widely used. However, the twisted nematic liquid crystal 65 display device has a disadvantage of a poor view angle characteristic where contrast and color tone vary largely when a

2

screen is viewed from an inclined angle. For this reason, a multi-domain vertical alignment (MVA) liquid crystal display device having a fine view angle characteristic has been developed and put into practical use.

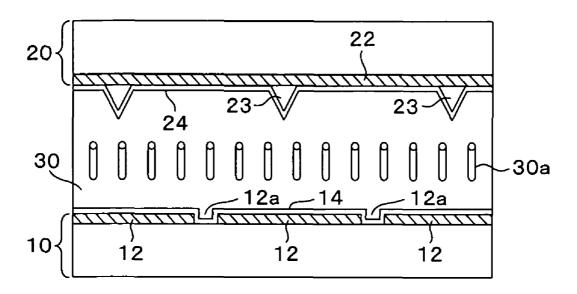

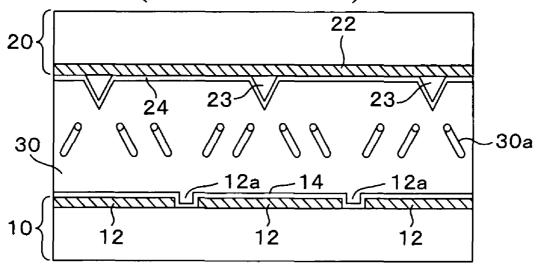

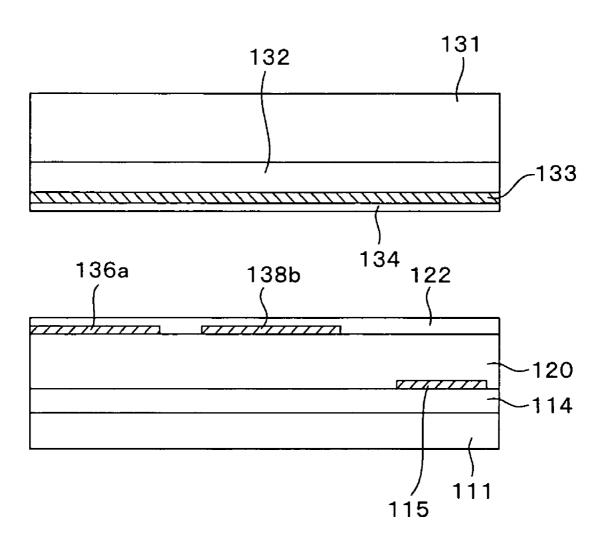

FIG. 1A and FIG. 1B are schematic cross-sectional views showing an example of a MVA liquid crystal display device. A TFT substrate 10 and a counter substrate 20 are disposed opposite to each other while sandwiching spacers (not shown), and vertical alignment type liquid crystal (liquid crystal having negative dielectric constant anisotropy) 30 is sealed between these substrates 10 and 20. Picture element electrodes 12 on the TFT substrate 10 are provided with slits 12a serving as domain regulating structures to determine directions of inclinations of liquid crystal molecules upon application of a voltage. Surfaces of the picture element electrodes 12 are covered with a vertical alignment film 14 made of polyimide, for example.

A plurality of protrusions 23 in the shape of mounds are formed below a common electrode 22 of the counter substrate 20 as domain regulating structures. As shown in FIG. 1A, these protrusions 23 are disposed in positions which are shifted in oblique directions relative to the slits 12a on the substrate 10. Surfaces of the common electrode 22 and the protrusions 23 are also covered with a vertical alignment film 24 made of polyimide, for example.

Polarizing plates (not shown) are disposed below the TFT substrate 10 and above the counter substrate 20, respectively. These polarizing plates are disposed so as to set absorptions axes orthogonal to each other.

In the MVA liquid crystal display device having the abovedescribed configuration, when a voltage is not applied between the picture element electrodes 12 and the common electrode 22, most of liquid crystal molecules 30a are aligned perpendicularly to the surfaces of the substrates. However, the liquid crystal molecules 30a in the vicinity of the protrusions 23 are aligned perpendicularly to inclined surfaces of the protrusions 23. In this case, light entering a liquid crystal layer from a bottom of the TFT substrate 10 through the polarizing plate is transmitted through the liquid crystal layer while not changing the direction of polarization, and is then shielded by the other polarizing plate above the counter substrate 20. In short, a black display is achieved in this case.

When a given voltage is applied between the picture element electrodes 12 and the common electrode 22, the liquid crystal molecules 30a are aligned obliquely to the surfaces of the substrates due to an influence of an electric field. In this case, as shown in FIG. 1B, the directions of inclination of the liquid crystal molecules 30a are different on two sides of each slit 12a or each protrusion 23. In this way, so-called alignment division (or multi-domains) is achieved. When the liquid crystal molecules 30a are aligned obliquely to the surfaces of the substrates as shown in FIG. 1B, the light which enters the liquid crystal layer from the bottom of the TFT substrate 10 through the polarizing plate changes the direction of polarization and is transmitted through the polarizing plate above the counter substrate 20. The amount of the light transmitted through the polarizing plates depends on the voltage applied between the picture element electrodes 12 and the common electrode 22.

In the MVA liquid crystal display device, since the directions of inclination of the liquid crystal molecules 30a are different on the two sides of each slit 12a or each protrusion 23 upon application of the voltage as shown in FIG. 1B. Accordingly, leakage of the light in oblique directions is suppressed and an excellent view angle characteristic is obtained.

Although the above example explains the case where the protrusions and the slits constitute the domain regulating structures, there is also a case where recesses (grooves) on the surface of the substrate are used as the domain regulating structures. Moreover, although FIG. 1A and FIG. 1B describes the example in which the domain regulating structures are formed on both of the TFT substrate 10 and the counter substrate 20, it is also possible to form the domain regulating structures only on one of the TFT substrate 10 and the counter substrate 20.

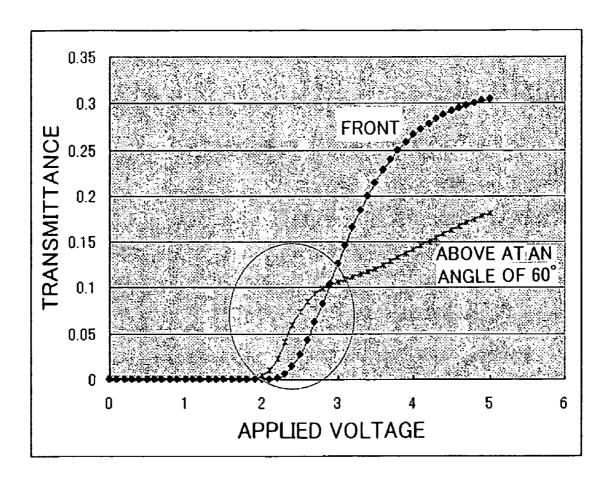

Incidentally, the conventional MVA liquid crystal display device causes a phenomenon in which a screen seems slightly whiter when viewed from an oblique angle. FIG. 2 is a graph showing transmittance-applied voltage (T-V) characteristic when viewing a screen from front and T-V characteristic when viewing the screen from above at an angle of 60°, in which the lateral axis indicates the applied voltage (V) and the longitudinal axis indicates the transmittance. As shown in FIG. 2, when a voltage slightly higher than a threshold voltage is applied (a region surrounded by a circle in the graph), 20 the transmittance when viewing the screen obliquely becomes higher than the transmittance when viewing the screen from front. On the contrary, when the applied voltage is increased to a certain level, the transmittance when viewing the screen obliquely becomes lower than the transmittance 25 when viewing the screen from front. For this reason, differences in luminance among a red picture element, a green picture element, and a blue picture element are reduced when viewing the screen from obliquely, and resultantly, the phenomenon of the whiter screen occurs as described previously. 30 This phenomenon is called wash out. Wash out occurs not only in the MVA liquid crystal display device but also in the TN liquid crystal display device.

The U.S. Pat. No. 4,840,460 Specification disclosed a technique to divide one picture element into a plurality of sub 35 picture elements and to subject the sub picture element to capacitive coupling. In such a liquid crystal display device, electric potential is divided depending on capacity ratios among the respective sub picture elements. Accordingly, it is possible to apply different amounts of voltages to the respec- 40 tive sub picture elements. Therefore, one picture element appears to include a plurality of regions having different threshold values in terms of the T-V characteristic. When one picture element includes the plurality of regions having different threshold values in terms of the T-V characteristic, it is 45 possible to suppress the phenomenon that the transmittance when viewing the screen obliquely becomes higher than the transmittance when viewing the screen from front, and thereby to suppress the phenomenon of the whiter screen (wash out). The above-described method of improving a dis- 50 play characteristic by means of dividing one picture element into the plurality of capacitively coupled sub picture elements is called a halftone gray scale (HT) method applying capacitive coupling. Note that the liquid crystal display device disclosed in U.S. Pat. No. 4,840,460 is a TN liquid crystal 55 display device.

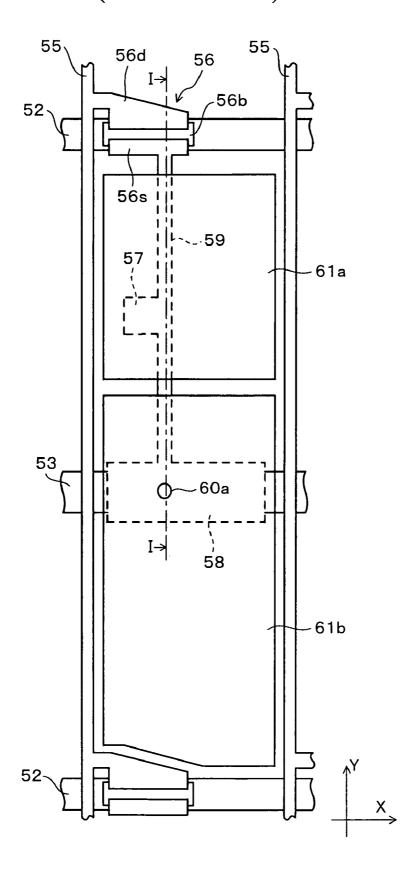

FIG. 3 is a plan view showing an example of a TFT substrate in a liquid crystal display device configured to achieve the HT method applying capacitive coupling, and FIG. 4 is a cross-sectional view taken along the I-I line in FIG. 3.

On a glass substrate **51** constituting a base of the TFT substrate, there are formed a plurality of gate bus lines **52** extending in a horizontal direction (an X direction) and a plurality of data bus lines (drain bus lines) **55** extending in a vertical direction (a Y direction). A rectangular region defined 65 by the gate bus lines **52** and the data bus lines **55** constitutes each picture element region. Meanwhile, on the glass sub-

4

strate 51, there are formed auxiliary capacitance bus lines 53 disposed parallel to the gate bus lines 52 and intersecting the center of the respective picture element regions.

A first insulating film **54** is formed in a space between each of the gate bus lines **52** and each of the data bus lines **55** and in a space between each of the auxiliary capacitance bus lines **53** and each of the data bus lines **55**. By using this first insulating film **54**, the gate bus lines **52** and the data bus lines **55**, and, the auxiliary capacitance bus lines **53** and the data bus lines **55** are electrically insulated, respectively.

A thin film transistor (TFT) 56, a control electrode 57, an auxiliary capacitance electrode 58, and sub picture element electrodes 61a and 61b are formed in each picture element region. As shown in FIG. 3, the TFT 56 applies part of the gate bus line 52 as a gate electrode. Moreover, as shown in FIG. 4, a semiconductor film 56a constituting an active layer for the TFT 56 is formed above the gate bus line 52, and a channel protection film 56b is formed on this semiconductor film 56a.

A drain electrode **56***d* of the TFT **56** is connected to the data bus line **55**, and a source electrode **56***s* thereof is disposed in a position opposed to the drain electrode **56***d* while sandwiching the gate bus line **52**. Moreover, the auxiliary capacitance electrode **58** is formed in a position opposed to the auxiliary capacitance bus line **53** while sandwiching the first insulating film **54**. Furthermore, as shown in FIG. **3**, the control electrode **57** is electrically connected to the source electrode **56***s* and to the auxiliary capacitance electrode **58** through a line **59**

The data bus lines 55, the TFT 56, the control electrode 57, the auxiliary capacitance electrode 58, and the line 59 are covered with a second insulating film 60, and the sub picture element electrodes 61a and 61b are formed on the second insulating film 60. The sub picture element electrode 61a is capacitively coupled to the control electrode 57 while sandwiching the second insulating film 60. Meanwhile, the sub picture element electrode 61b is electrically connected to the auxiliary capacitance electrode 58 through a contact hole 60a which is formed on the second insulating film 60. Surfaces of the sub picture element electrodes 61a and 61b are covered with an alignment film 62.

In the meantime, as shown in FIG. 4, the counter substrate includes a color filter 72 formed on one of surfaces (which is on the lower side in FIG. 4) of a glass substrate 71 constituting a base, a common electrode 73 formed on the color filter 72, and an alignment film 74 covering a surface of the common electrode 73.

The TFT substrate and the counter electrode are disposed opposite to each other while sandwiching spacers (not shown). Then, liquid crystal **80** is sealed between the TFT substrate and the counter substrate.

In a case of a transmissive liquid crystal display device, the sub picture element electrodes 61a and 61b are made of a transparent conductive material such as indium-tin oxide (ITO). On the other hand, in a case of a reflective liquid crystal display device, the sub picture element electrodes 61a and 61b are made of a highly reflective material such as aluminum.

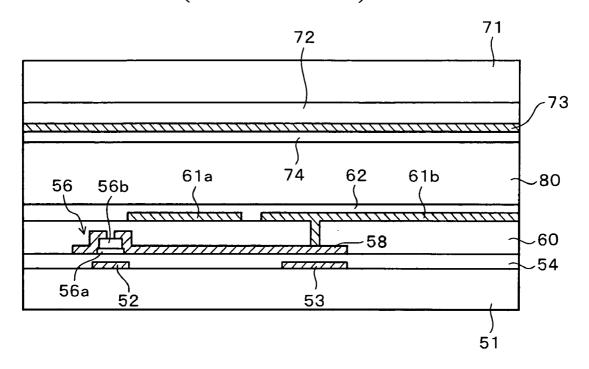

FIG. 5 is an equivalent circuit diagram showing one picture element in a liquid crystal display device including the above60 described TFT substrate. In FIG. 5, reference code C<sub>LC1</sub> denotes a capacitance composed of the sub picture element electrode 61b and the common electrode 73, reference code C<sub>S</sub> denotes a capacitance composed of the auxiliary capacitance electrode 58 and the auxiliary capacitance bus line 53, reference code C<sub>C</sub> denotes a capacitance composed of the sub picture element electrode 61a and the control electrode 57, and reference code C<sub>LC2</sub> denotes a capacitance composed of

the sub picture element electrode  $\mathbf{61}a$  and the common electrode  $\mathbf{73}$ . As shown in FIG. 5, a voltage is divided by the capacitance  $C_{LC2}$ , which is formed between the sub picture element electrode  $\mathbf{61}a$  and the common electrode  $\mathbf{73}$ , and the control capacitance  $C_C$ . Accordingly, when a voltage applied to the sub picture element electrode  $\mathbf{61}b$  is  $V_{px1}$ , a voltage  $V_{px2}$  to be applied to the sub picture element electrode  $\mathbf{61}a$  will be calculated by the following formula (1):

$$V_{px2} = \frac{C_C}{C_C + C_{LC2}} \times V_{pxI} \tag{1}$$

Although an actual voltage ratio  $(V_{px2}/V_{px1})$  is a design item for a display characteristic of a liquid crystal display device, it is considered ideal that the voltage ratio is in a range approximately from 0.6 to 0.8.

A sub picture element electrode to which a display voltage is applied through capacitive coupling, such as the sub picture element electrode 61a, will be hereinafter referred to as a floating sub picture element electrode. Meanwhile, a sub picture element electrode electrically connected to a TFT through a low-resistance conductive body (a line, for example), such as the sub picture element electrode 61b, will be hereinafter referred to as a sub picture element electrode directly connected to the TFT.

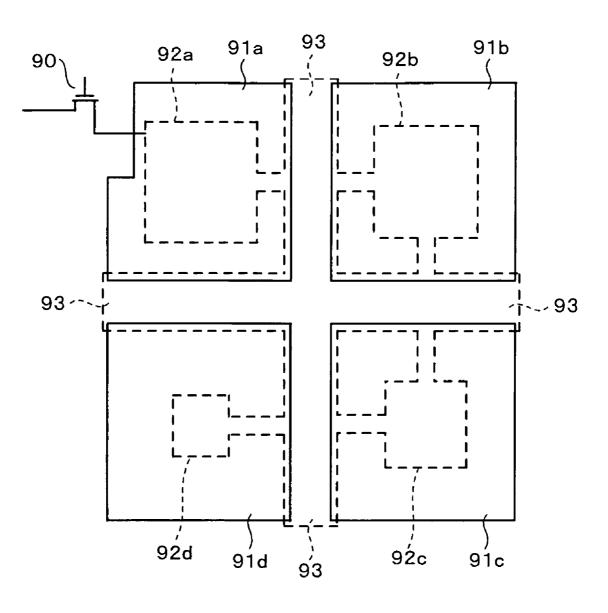

As shown in FIG. 6, Japanese Patent No. 3076938 Specification (equivalent to Japanese Unexamined Patent Publication No. 5(1993)-66412) discloses a TN liquid crystal display 30 device in which a picture element electrode is divided into a plurality (which is equal to four in FIG. 6) of sub picture element electrodes 91a to 91d and control electrodes 92a to 92d are respectively disposed below the sub picture element electrodes 91a to 91d through an insulating film. In this liquid 35 crystal display device, display voltages are applied to the control electrodes 92a to 92d through a TFT 90. Since the sizes of the respective control electrodes 92a to 92d are different from one another, the voltages to be applied to the sub picture element electrodes 91a to 91d are also mutually dif- $_{40}$ ferent. Accordingly, it is possible to obtain an effect attributable to the HT method, namely, an effect to suppress wash out. Here, to avoid leakage of light from a space between any of the sub picture element electrodes 91a to 91d, another control electrode 93 is also disposed in the space between any 45 of the sub picture element electrodes 91a to 91d.

However, the inventors of the present invention have carried out experiments and researches and have found out that a liquid crystal display device including the above-described conventional floating sub picture element electrodes caused 50 deterioration in the display characteristic attributable to image sticking.

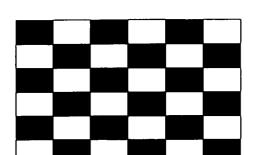

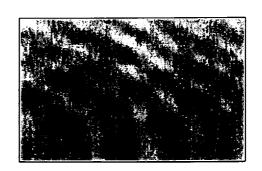

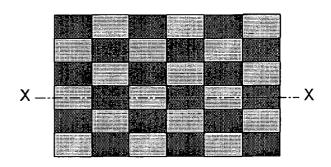

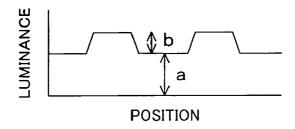

FIG. 7A to FIG. 7C and FIG. 8 are schematic diagrams showing a testing method for measuring a degree of image sticking. Firstly, a black and white checker pattern as shown 55 in FIG. 7A is displayed on a liquid crystal display device continuously for a certain period. Thereafter, a halftone pattern as shown in FIG. 7B is displayed on the entire screen of the liquid crystal display device. In this case, when image sticking occurs on the screen, the checker pattern becomes 60 dimly visible as shown in FIG. 7C. After switching from the checker pattern display to the halftone display, luminance is measured along the X-X line in FIG. 7C, for example. Then, assuming that luminance in a dark portion is "a" and a difference in luminance between the dark portion and a bright 65 portion is "b" as shown in FIG. 8, an image sticking ratio defined as  $100 \times b/(a+b)$  will be calculated.

6

An image sticking ratio of a liquid crystal display device not including the floating sub picture element electrodes and an image sticking ratio of a liquid crystal display device including the floating sub picture element electrodes were measured in accordance with the above-described method. As a result, the image sticking ratio of the liquid crystal display device not including the sub picture element electrodes was equal to or less than 5%. On the contrary, the image sticking ratio of the liquid crystal display device including the sub picture element electrodes was equal to or more than 10%.

### SUMMARY OF THE INVENTION

In consideration of the foregoing problem, it is an object of the present invention to provide a liquid crystal display device applying the capacitive coupling HT method for suppressing wash out, which is capable of preventing occurrence of image sticking, and to provide a method of preventing the image sticking.

The above-described problem will be solved by a liquid crystal display device having first and second substrates disposed opposite to each other, a liquid crystal sealed between the first and second substrates, a gate bus line and a data bus line formed on the first substrate, a thin film transistor connected to the gate bus line and the data bus line, a plurality of sub picture element electrodes formed in a picture element region defined by the gate bus line and the data bus line, and a control electrode capacitively coupled to at least one of the plurality of sub picture element electrodes and to which a display voltage is applied from the data bus line through the thin film transistor. Here, the liquid crystal display device includes a shield member for electrically shielding connection between the sub picture element electrode capacitively coupled to the control electrode and at least any of the gate bus line and the data bus line.

In the present invention, connection between the sub picture element electrode, which is capacitively coupled to the control electrode, and at least any of the gate bus line and the data bus line is electrically shielded by the shield member connected to an auxiliary capacitance bus line that is maintained at constant electric potential, for example. In this way, by shielding the sub picture element electrode capacitively coupled to the control electrode by use of the shield member, it is possible to avoid injection of charges either from the gate bus line or from the data bus line to the sub picture element electrode. As a result, image sticking is prevented.

It is also possible to use a sub picture element which is directly connected to the TFT as the shield member. For example, by disposing the sub picture element electrode directly connected to the TFT between the sub picture element electrode capacitively coupled to the control electrode and the gate bus line, it is possible to avoid injection of electric charges from the gate bus line to the sub picture element electrode capacitively coupled to the control electrode.

The above-described problem will be solved by a method of preventing image sticking on a liquid crystal display device, which has first and second substrates disposed opposite to each other, a liquid crystal sealed between the first and second substrates, a gate bus line and a data bus line formed on the first substrate, a thin film transistor connected to the gate bus line and the data bus line, a plurality of sub picture element electrodes formed in a picture element region defined by the gate bus line and the data bus line, a control electrode capacitively coupled to at least one of the plurality of sub picture element electrodes and to which a display voltage is applied from the data bus line through the thin film transistor, and a common electrode formed on the second substrate and

opposed to the plurality of sub picture element electrodes on the first substrate. Here, assuming that central electric potential of the data bus line relative to electric potential of the common electrode is  $V_{ddc}$ , that central electric potential of the gate bus line relative to the electric potential of the common electrode is  $V_{gdc}$ , that a resistance between the sub picture element electrode capacitively coupled to the control electrode and the data bus line is  $R_D$ , and that a resistance between the sub picture element electrode capacitively coupled to the control electrode and the gate bus line is  $R_G$ , the method includes the step of setting a position and a shape of the sub picture element electrode capacitively coupled to the control electrode so as to satisfy that  $V_{ddc}$ – $V_{gdc}$ × $R_D$ / $R_G$  is approximately equal to zero.

To maintain the TFT to an off state, a negative voltage is 15 applied to the gate bus line in the majority of a frame period. Meanwhile, a positive direct-current voltage is superposed with a signal flowing on the data bus line in order to compensate a feed through voltage. Therefore, it is possible to prevent image sticking by setting the position and the shape of the sub 20 picture element electrode (the sub picture element electrode capacitively coupled to the control electrode) such that an influence of a direct-current voltage component of the signal flowing on the data bus line (that is, the central electric potential of the data bus line relative to the electric potential of the 25 common electrode) and an influence of a direct-current voltage component of a signal flowing on the gate bus line (that is, the central electric potential of the gate bus line relative to the electric potential of the common electrode) cancel each other, i.e., so as to satisfy that  $V_{ddc}$ - $V_{gdc}$ × $R_D$ / $R_G$  is approximately 30 equal to zero.

The above-described problem will be solved by a liquid crystal display device having first and second substrates disposed opposite to each other, a liquid crystal sealed between the first and second substrates, a gate bus line and a data bus 35 line formed on the first substrate, a thin film transistor connected to the gate bus line and the data bus line, a plurality of sub picture element electrodes formed in a picture element region defined by the gate bus line and the data bus line, a control electrode capacitively coupled to at least one of the 40 plurality of sub picture element electrodes and to which a display voltage is applied from the data bus line through the thin film transistor, and a common electrode formed on the second substrate and opposed to the plurality of sub picture element electrodes on the first substrate. Here, the sub picture 45 element electrode capacitively coupled to the control electrode is connected to the sub picture element electrode connected to the thin film transistor through a resistor.

In the present invention, the sub picture element electrode capacitively coupled to the control electrode (the floating sub picture element electrode) is connected to the sub picture element electrode directly connected to the thin film transistor through the high-resistance resistor made of amorphous silicon, for example. In this way, a value of resistance between the floating sub picture element electrode and the control electrode is reduced and a direct-current voltage remaining in a liquid crystal layer is reduced, whereby occurrence of image sticking is prevented. However, if the value of resistance of the resistor is too low, an electric current will flow between the floating sub picture element electrode and the sub picture element electrode directly connected to the TFT and an electric potential difference is reduced. Accordingly, the effect of preventing wash out will be reduced.

The above-described problem will be solved by a liquid crystal display device having first and second substrates disposed opposite to each other, a liquid crystal sealed between the first and second substrates, a gate bus line and a data bus 8

line formed on the first substrate, a thin film transistor connected to the gate bus line and the data bus line, a plurality of sub picture element electrodes formed in a picture element region defined by the gate bus line and the data bus line, a control electrode capacitively coupled to at least one of the plurality of sub picture element electrodes and to which a display voltage is applied from the data bus line through the thin film transistor, and an auxiliary capacitance bus line maintained at constant electric potential and constituting an auxiliary capacitance together with the control electrode. Here, the liquid crystal display device includes a switching element to be driven by a signal flowing on a different gate bus line from the gate bus line to which the thin film transistor is connected, the switching element being provided in any of a location between the sub picture element electrode capacitively coupled to the control electrode and the auxiliary capacitance bus line or a location between the sub picture element electrode capacitively coupled to the control electrode and the sub picture element electrode connected to the thin film transistor.

In the present invention, the switching element is disposed either between the floating sub picture element electrode and the auxiliary capacitance bus line or between the floating sub picture element electrode and the sub picture element electrode directly connected to the thin film transistor, and the switching element is driven by the signal flowing on the different gate bus line from the gate bus line connected to the thin film transistor. In this way, electric charges charged in the floating sub picture element electrode at given timing flow either on the auxiliary capacitance bus line or on the sub picture element electrode directly connected to the TFT, and occurrence of image sticking is thereby prevented.

The above-described problem will be solved by a method of preventing image sticking on a liquid crystal display device having first and second substrates disposed opposite to each other, a liquid crystal sealed between the first and second substrates, a gate bus line and a data bus line formed on the first substrate, a thin film transistor connected to the gate bus line and the data bus line, a plurality of sub picture element electrodes formed in a picture element region defined by the gate bus line and the data bus line, a control electrode capacitively coupled to at least one of the plurality of sub picture element electrodes and to which a display voltage is applied from the data bus line through the thin film transistor, an auxiliary capacitance bus line maintained at constant electric potential and constituting an auxiliary capacitance together with the control electrode, and a common electrode formed on the second substrate and opposed to the plurality of sub picture element electrodes on the first substrate. Here, the method includes the step of forming a second auxiliary capacitance parallel to a capacitance between the sub picture element electrode capacitively coupled to the control electrode and the common electrode.

One of the reasons why the electric potential difference occurs between the floating sub picture element electrodes in a white display portion and in a black display portion is variation in a liquid crystal capacitance. Accordingly, in the present invention, the second auxiliary capacitance is formed parallel to the liquid crystal capacitance to reduce an influence by the variation in the liquid crystal capacitance.

Normally, the auxiliary capacitance bus line is maintained either at the same electric potential as that of the common electrode or at constant electric potential relative to the common electrode. Therefore, when an auxiliary capacitance electrode is formed between the floating sub picture element electrode and the auxiliary capacitance bus line and this auxiliary capacitance electrode is connected to the floating sub

picture element electrode, for example, it is equivalent to formation of the second auxiliary capacitance parallel to the liquid crystal capacitance. In this way, it is possible to avoid occurrence of image sticking.

## BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1A and FIG. 1B are schematic cross-sectional views showing an example of a MVA liquid crystal display device.

FIG. **2** is a graph showing transmittance-applied voltage <sub>10</sub> (T-V) characteristic when viewing a screen of a liquid crystal display device from front and T-V characteristic when viewing the screen from above at an angle of 60°.

FIG. **3** is a plan view showing an example of a TFT substrate in a liquid crystal display device configured to achieve 15 the HT method applying capacitive coupling.

FIG. 4 is a cross-sectional view taken along the I-I line in FIG. 3.

FIG. 5 is an equivalent circuit diagram showing one picture element in the liquid crystal display device shown in FIG. 3. 20

FIG. 6 is a plan view showing a liquid crystal display device disclosed in Japanese Patent No. 3076938 Specification

FIG. 7A to FIG. 7C are schematic diagrams (No. 1) showing a testing method for measuring a degree of image sticking.

FIG. 8 is a schematic diagram (No. 2) showing the testing method for measuring the degree of image sticking.

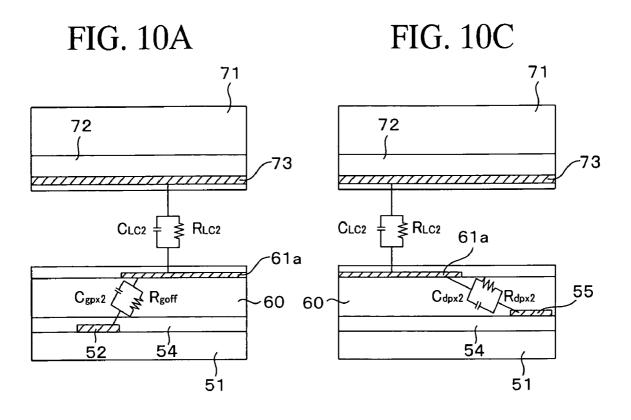

FIG. **9** is a plan view showing one picture element in a liquid crystal display device including a floating sub picture 30 element electrode.

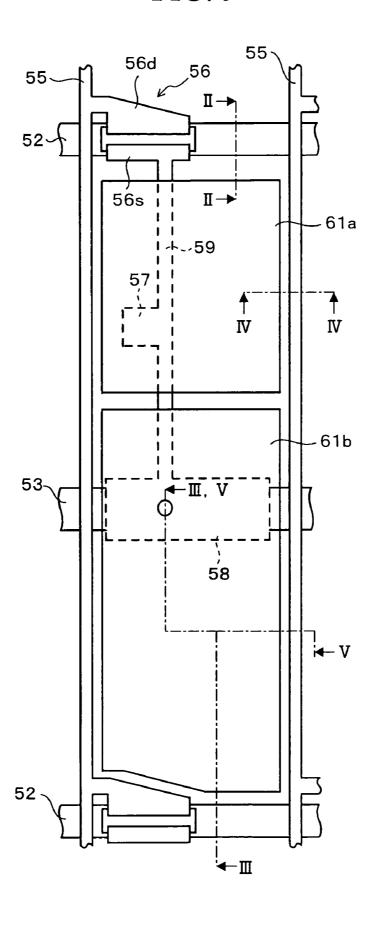

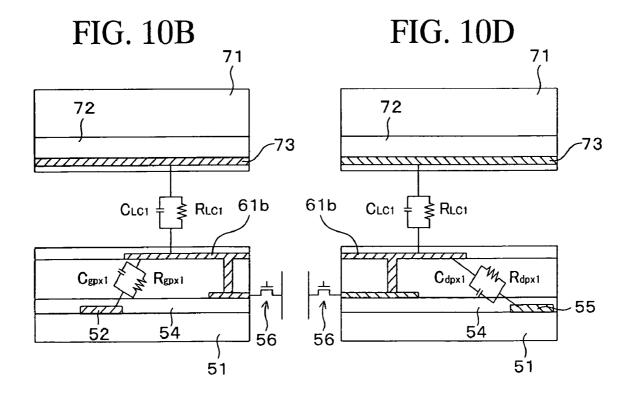

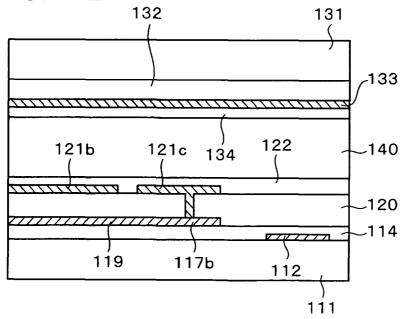

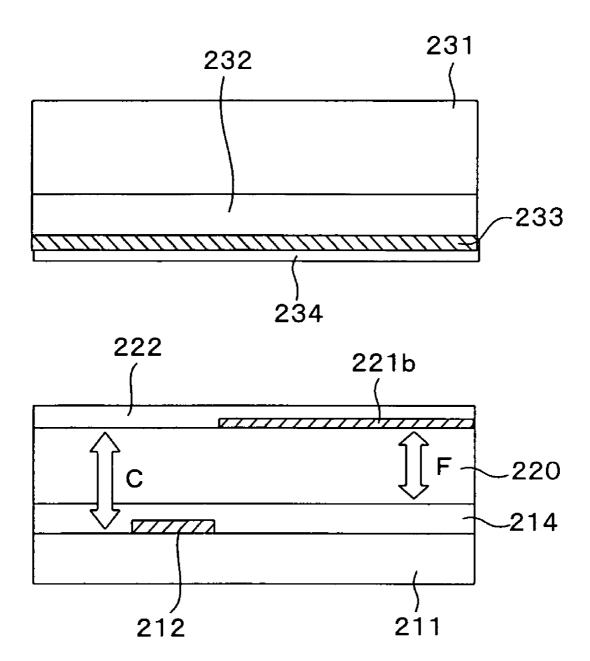

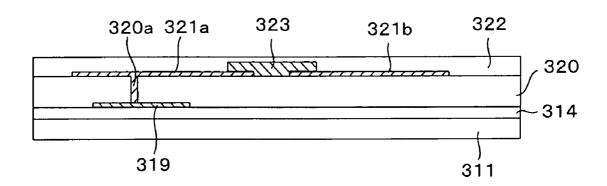

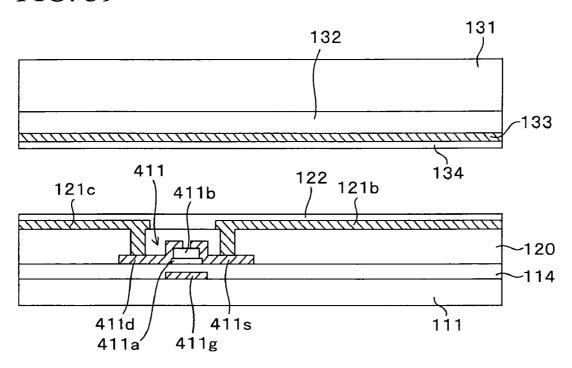

FIG. 10A is a schematic cross-sectional view taken along the II-II line in FIG. 9, FIG. 10B is a schematic cross-sectional view taken along the III-III III line in FIG. 9, FIG. 10C is a schematic cross-sectional view taken along the IV-IV line in 35 FIG. 9, and FIG. 10D is a schematic cross-sectional view taken along the V-V line in FIG. 9.

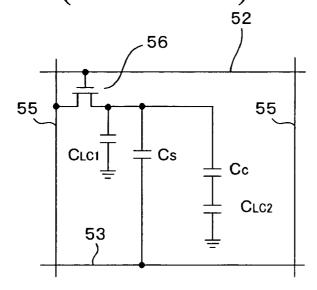

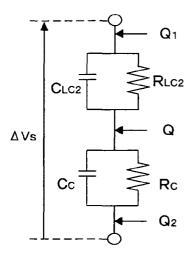

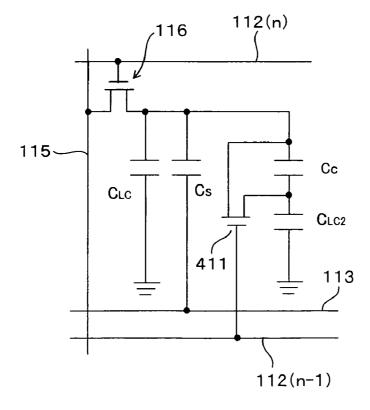

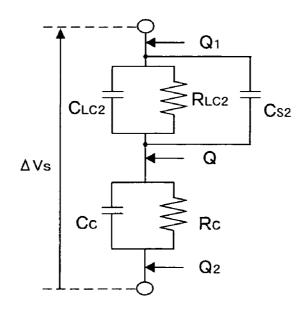

FIG. 11 is an equivalent circuit diagram showing a sub picture element electrode including a floating sub picture element electrode.

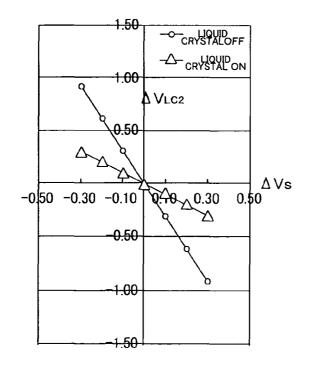

FIG. 12 is a graph showing a relation between  $\Delta V_s$  and  $\Delta V_{LC2}$  when a display voltage is applied to a liquid crystal layer (when liquid crystal is turned on), and a relation between  $\Delta V_s$  and  $\Delta V_{LC2}$  when the display voltage is not applied to the liquid crystal layer (when the liquid crystal is 45 turned off).

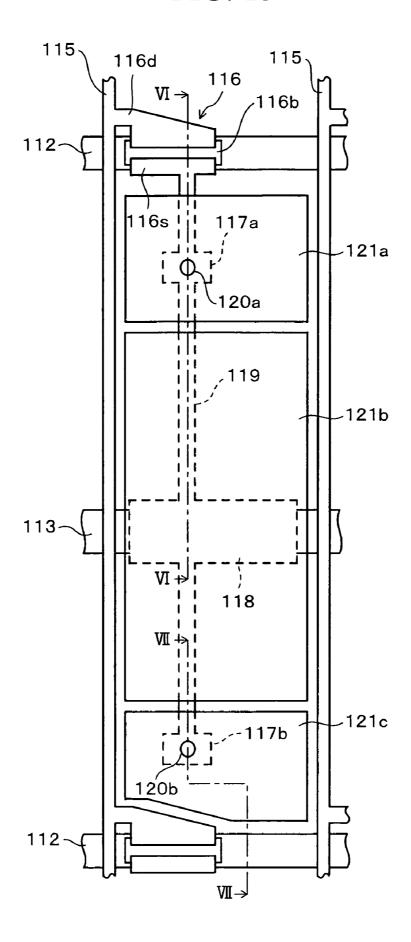

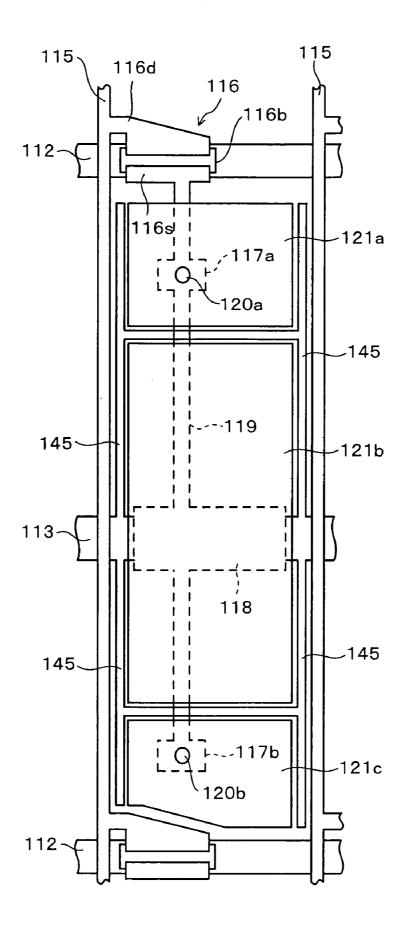

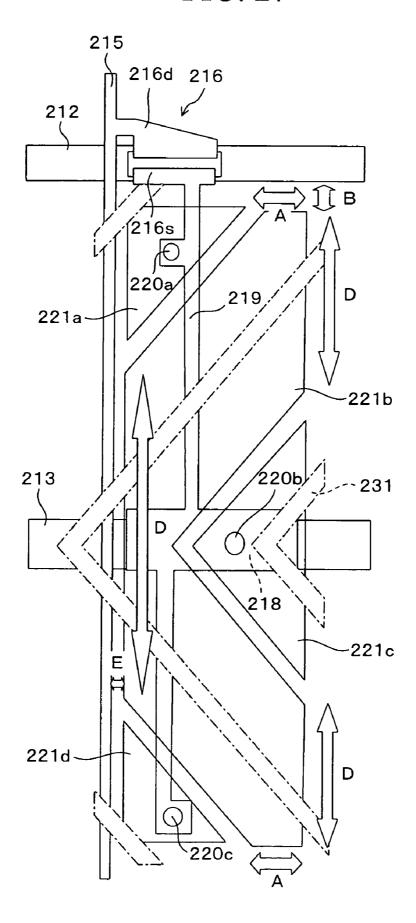

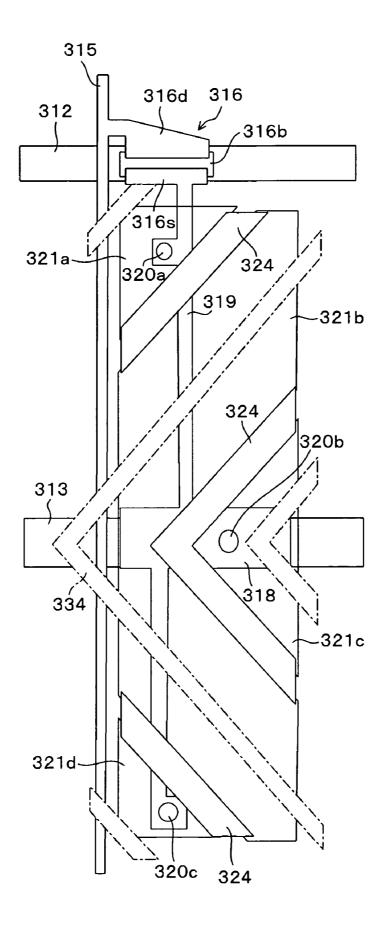

FIG. 13 is a plan view showing a liquid crystal display device according to a first embodiment of the present invention

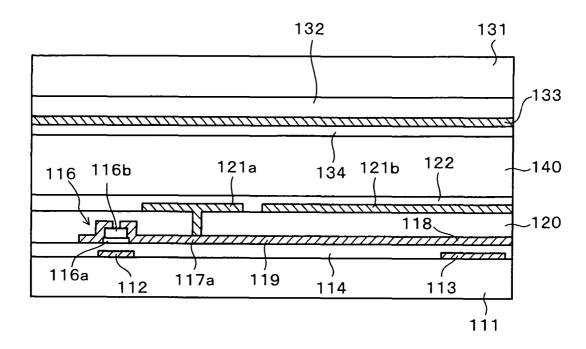

FIG. 14A is a cross-sectional view taken along the VI-VI  $_{50}$  line in FIG. 13, and FIG. 14B is a cross-sectional view taken along the VII-VII line in FIG. 13.

FIG. 15 is a plan view showing a liquid crystal display device according to a first modified example of the first embodiment.

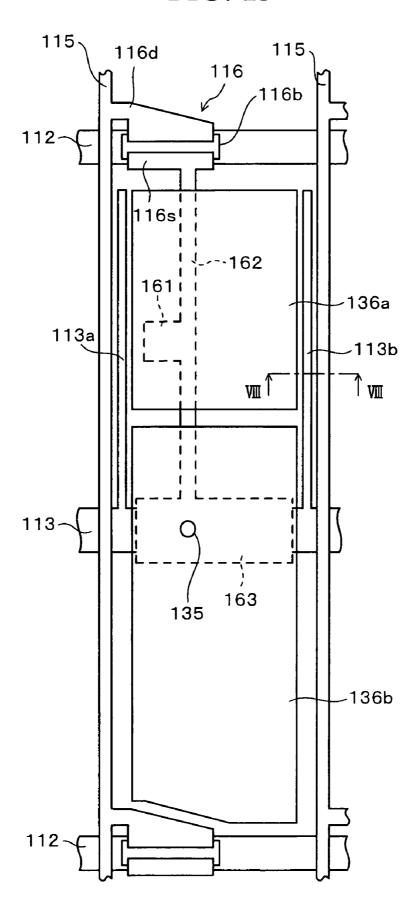

FIG. **16** is a cross-sectional view taken along the VIII-VIII line in FIG. **15**.

FIG. 17 is a plan view showing a liquid crystal display device according to a second modified example of the first embodiment.

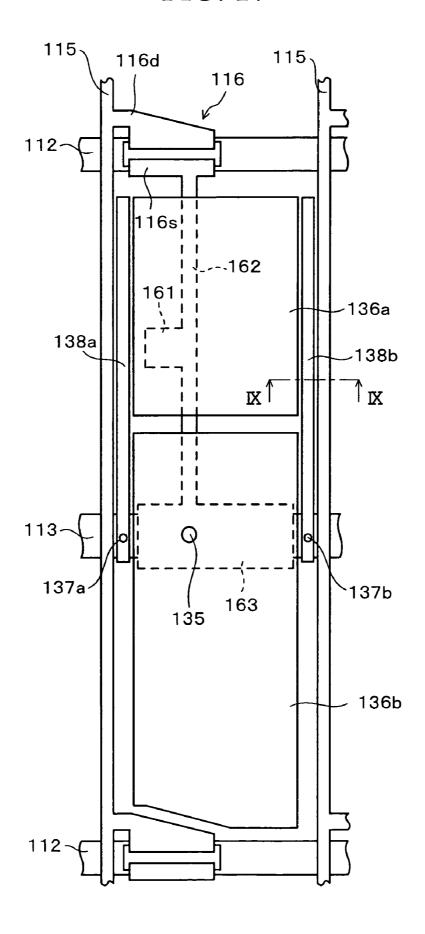

$FIG.\,18$  is a cross-sectional view taken along the IX-IX line in  $FIG.\,17$ .

FIG. 19 is a plan view showing a liquid crystal display device according to a third modified example of the first embodiment.

FIG. 20 is a cross-sectional view taken along the X-X line in FIG. 19.

10

FIG. 21 is a plan view showing a liquid crystal display device according to a fourth modified example of the first embodiment

FIG. 22 is a plan view showing a liquid crystal displaydevice according to a fifth modified example of the first embodiment.

FIG. 23 is a plan view showing a liquid crystal display device according to a sixth modified example of the first embodiment.

FIG. 24 is a plan view showing a liquid crystal display device according to a seventh modified example of the first embodiment.

FIG. 25 is a view showing the principle of a second embodiment of the present invention.

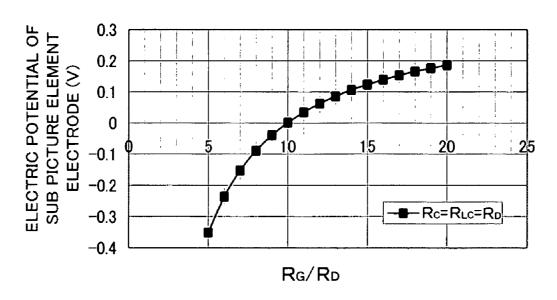

FIG. 26 is a graph showing a relation between  $R_G/R_D$  and final attainment electric potential of a floating sub picture element electrode.

FIG. 27 is a schematic plan view showing a picture element portion of a liquid crystal display device showing a method of adjusting resistance between a floating sub picture element electrode and a gate bus line and resistance between the floating sub picture element electrode and a data bus line.

FIG. 28 is a schematic cross-sectional view showing the picture element of FIG. 27.

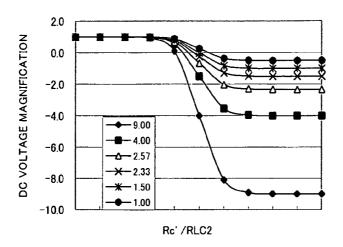

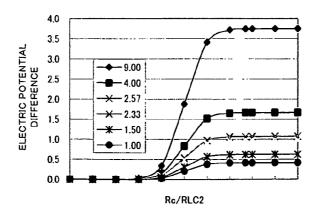

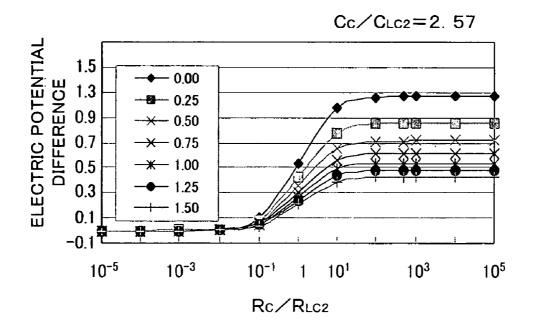

FIG. 29 is a graph showing results of calculations of dependencies (DC voltage magnifications) of image sticking voltages on a resistor  $R_C$  between a control electrode and a floating sub picture element electrode and on a resistor  $R_{LC2}$  between the floating sub picture element electrode and a common electrode.

FIG. 30 is a table showing the results illustrated in FIG. 29.

FIG. 31 is a graph showing relations between  $R_{c}/R_{LC2}$  and electric potential differences of sub picture element electrodes at a white display portion and at a black display portion.

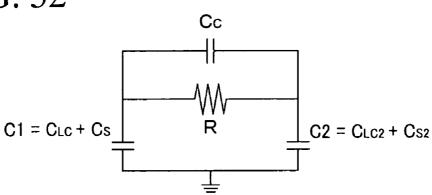

FIG. **32** is an equivalent circuit diagram showing a floating sub picture element electrode and a sub picture element directly connected to a TFT.

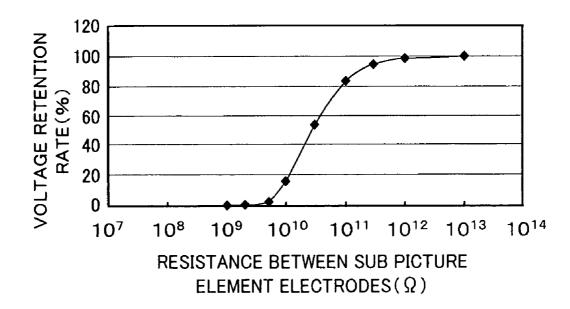

FIG. **33** is a graph showing a relation between a resistor R, which is located between the floating sub picture element electrode and the sub picture element directly connected to the TFT, and a voltage retention rate in one frame period (t=16.6 msec).

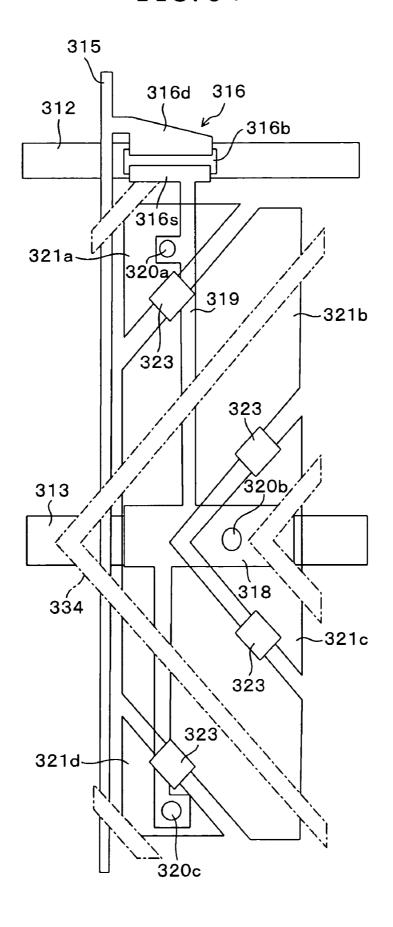

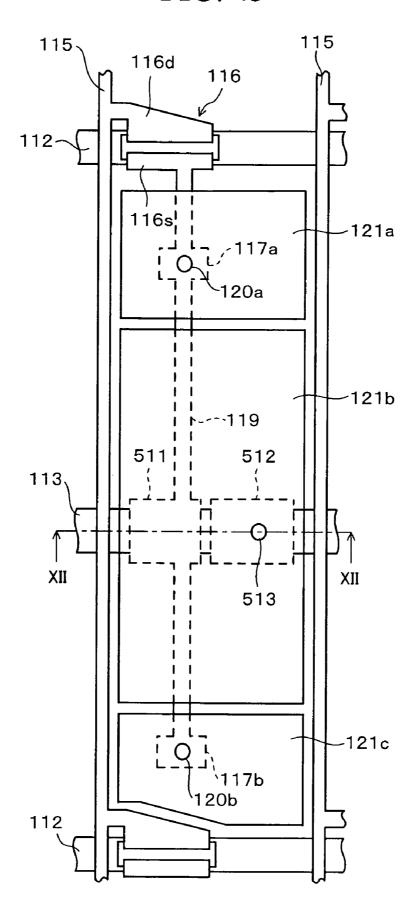

FIG. 34 is a plan view showing a TFT substrate in a liquid crystal display device according to a third embodiment of the present invention.

FIG. 35 is a cross-sectional view of the TFT substrate shown in FIG. 34.

FIG. 36 is a plan view showing a liquid crystal display device according to a first modified example of the third embodiment.

FIG. 37 is a cross-sectional view showing the liquid crystal display device of FIG. 36.

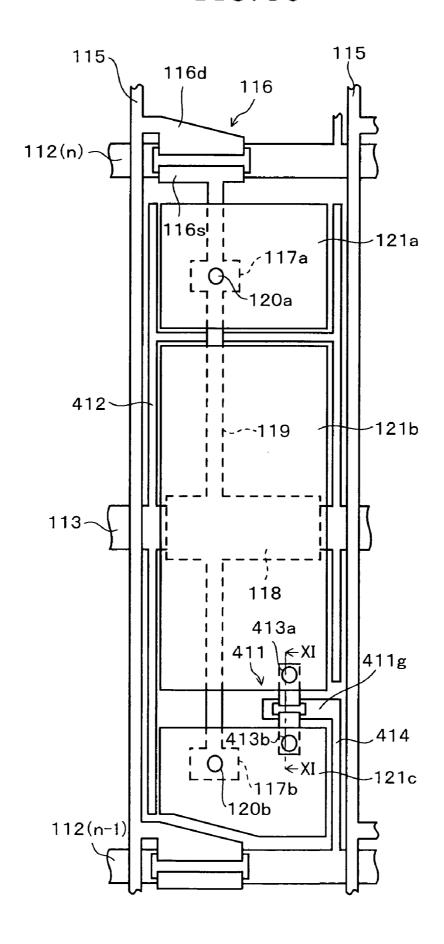

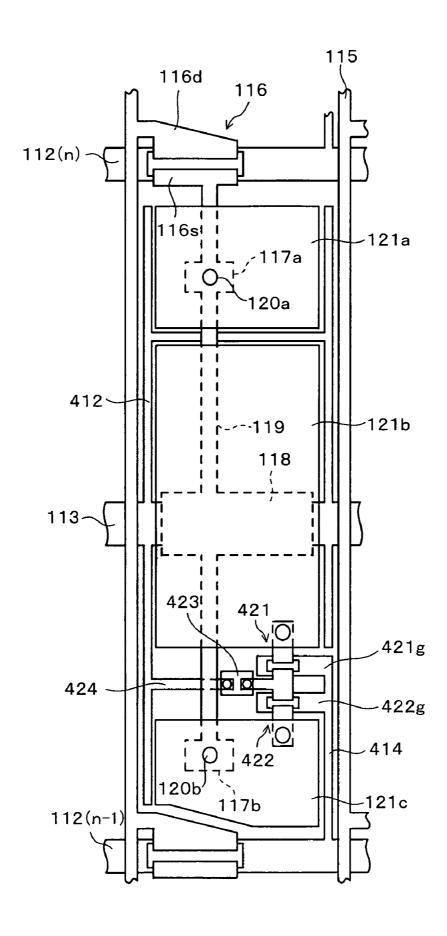

FIG. 38 is a plan view showing a liquid crystal display 55 device according to a fourth embodiment of the present invention

${\rm FIG.\,39}$  is a cross-sectional view taken along the XI-XI line in FIG. 38.

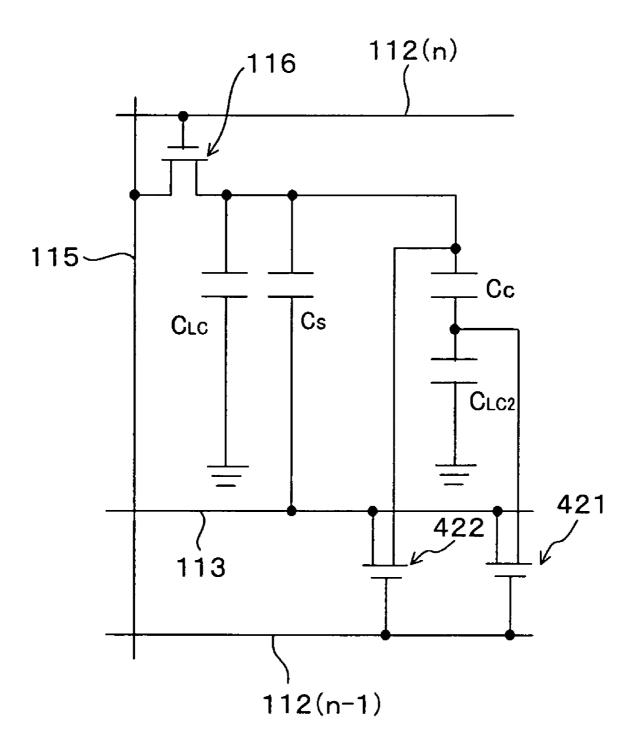

FIG. **40** is an equivalent circuit diagram showing one pic-60 ture element in the liquid crystal display device according to the fourth embodiment.

FIG. 41 is a plan view showing a liquid crystal display device according to a first modified example of the fourth embodiment.

FIG. **42** is an equivalent circuit diagram showing one picture element in the liquid crystal display device according to the first modified example of the fourth embodiment.

FIG. 43 is a circuit diagram of a picture element showing the principle of a fifth embodiment of the present invention.

FIG. 44 is a graph showing relations between  $R_{C}/R_{LC2}$  and electric potential differences of floating sub picture element electrodes at a white display portion and at a black display portion.

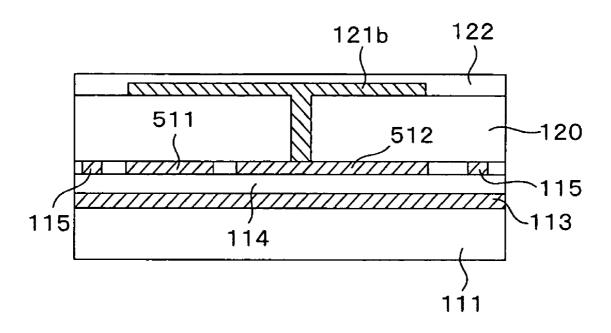

FIG. **45** is a plan view showing a liquid crystal display device according to the fifth embodiment.

FIG. **46** is a cross-sectional view taken along the XII-XII line in FIG. **45**.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Now, the present invention will be described further in detail.

Normally, image sticking on a liquid crystal display device is attributable to existence of direct-current voltage components in signals flowing on a gate bus line, a data bus line, and the like, and variation in CR values (values of a liquid crystal capacitance and a liquid crystal resistor) of a liquid crystal layer between a white display mode and a black display mode as a consequence. In the following, the reason why the image sticking occurs in a liquid crystal display device including a floating sub picture element electrode will be described.

FIG. 9 is a plan view showing one picture element in a liquid crystal display device including a floating sub picture element electrode. Meanwhile, FIG. 10A is a schematic cross-sectional view taken along the II-III line in FIG. 9, FIG. 10B is a schematic cross-sectional view taken along the III-III line in FIG. 9, FIG. 10C is a schematic cross-sectional view taken along the IV-IV line in FIG. 9, and FIG. 10D is a schematic cross-sectional view taken along the V-V line in FIG. 9.

In the liquid crystal display device shown in FIG. 9, it is possible to consider that  $C_{LC2}$  and  $R_{LC2}$  are connected in parallel between a sub picture element electrode (a floating sub picture element electrode)  $\mathbf{61}a$  and a common electrode  $\mathbf{73}$  as shown in FIG.  $\mathbf{10}A$ . Here, reference code  $C_{LC2}$  denotes a capacitance between the sub picture element electrode  $\mathbf{61}a$  and the common electrode  $\mathbf{73}$ , and reference code  $R_{LC2}$  denotes a resistance between the sub picture element electrode  $\mathbf{61}a$  and the common electrode  $\mathbf{73}$ .

Moreover, it is also possible to consider that  $C_{gpx2}$  and  $R_{goff}$  45 are connected in parallel between the sub picture element electrode  ${\bf 61}a$  and a gate bus line  ${\bf 52}$ . Here, reference code  $C_{gpx2}$  denotes a capacitance between the sub picture element electrode  ${\bf 61}a$  and the gate bus line  ${\bf 52}$ , and reference code  $R_{goff}$  denotes a resistance between the sub picture element electrode  ${\bf 61}a$  and the gate bus line  ${\bf 52}$ .

Meanwhile, it is also possible to consider that  $C_{LC1}$  and  $R_{LC1}$  are connected in parallel between a sub picture element electrode (a sub picture element electrode directly connected to a thin film transistor (TFT) **56**) **61**b and the common 55 electrode **73** as shown in FIG. **10**B. Here, reference code  $C_{LC1}$  denotes a capacitance between the sub picture element electrode **61**b and the common electrode **73**, and reference code  $R_{LC1}$  denotes a resistance between the sub picture element electrode **61**b and the common electrode **73**.

Moreover, it is also possible to consider that  $C_{gpx1}$  and  $R_{gpx1}$  are connected in parallel between the sub picture element electrode  $\mathbf{61}b$  and the gate bus line  $\mathbf{52}$ . Here, reference code  $C_{gpx1}$  denotes a capacitance between the sub picture element electrode  $\mathbf{61}b$  and the gate bus line  $\mathbf{52}$ , and reference code  $R_{gpx1}$  denotes a resistance between the sub picture element electrode  $\mathbf{61}b$  and the gate bus line  $\mathbf{52}$ .

12

To maintain the TFT 56 to an off state for most of time in one field period, a direct-current voltage ( $V_{\ensuremath{\textit{goff}}}$  ), which is lower by about -12 V than electric potential of the common electrode 73, is applied to the gate bus line 52. Electric charges corresponding to this direct-current voltage are accumulated in the sub picture element electrodes 61a and 61bthrough the capacitance  $C_{gpx2}$  and the resistance  $R_{goff}$ . However, the TFT **56** is normally turned on once in every field and the sub picture element electrode 61b is electrically connected to a data bus line 55. Accordingly, the electric charges charged in the sub picture element electrode 61b during the period when the TFT 56 is turned off will flow toward the data bus line 55, and the direct-current voltage component will not remain in the sub picture element electrode 61b. On the contrary, the electric charges charged in the sub picture element electrode **61***a* will be retained therein even if the TFT **56** is turned on. For this reason, the direct-current voltage component will remain in the sub picture element electrode 61a.

As shown in FIG. 10C, it is possible to consider that  $C_{dpx2}$  and  $R_{dpx2}$  are connected in parallel between the sub picture element electrode  $\bf 61a$  and the data bus line  $\bf 55$ . Here, reference code  $C_{dpx2}$  denotes a capacitance between the sub picture element electrode  $\bf 61a$  and the data bus line  $\bf 55$ , and reference code  $R_{dpx2}$  denotes a resistance between the sub picture element electrode  $\bf 61a$  and the data bus line  $\bf 55$ .

Moreover, as shown in FIG. 10D, it is also possible to consider that  $C_{dpx1}$  and  $R_{dpx1}$  are connected in parallel between the sub picture element electrode  $\mathbf{61}b$  and the data bus line 55. Here, reference code  $C_{dpx1}$  denotes a capacitance between the sub picture element electrode  $\mathbf{61}b$  and the data bus line 55, and reference code  $R_{dpx1}$  denotes a resistance between the sub picture element electrode  $\mathbf{61}b$  and the data bus line 55.

To compensate a feed through voltage, a direct-current voltage, which is higher by about 1 to 2 V than the electric potential of the common electrode **73**, is superposed with a display signal (an alternating-current signal) on the data bus line **55**. Electric charges corresponding to this direct-current voltage are also accumulated in the sub picture element electrode **61**a through the capacitance  $C_{dpx2}$  and the resistance  $R_{dpx2}$ .

$R_{dpx2}$ . However, as described above, the TFT **56** is turned on once in every field and the sub picture element electrode **61**b is electrically connected to the data bus line **55**. Accordingly, the electric charges charged in the sub picture element electrode **61**b during the period when the TFT **56** is turned off will flow toward the data bus line **55** when the TFT **56** is turned on. For this reason, the direct-current voltage component will not remain in the sub picture element electrode **61**b. On the contrary, the electric charges charged in the sub picture element electrode **61**a will be retained therein even if the TFT **56** is turned on. For this reason, the direct-current voltage component will remain in the sub picture element electrode **61**a.

As described above, while accumulation of the direct-current voltage component is hardly observed in the sub picture element electrode **61***b* directly connected to the TFT **56**, the electric charges are charged in the floating sub picture element electrode **61***a* and the direct-current voltage component remains therein.

Next, a relation between the electric charges charged in the floating sub picture element electrode and the image sticking will be described.

FIG. 11 is an equivalent circuit diagram showing a sub picture element electrode including a floating sub picture element electrode. Here, a direct-current voltage component between a control electrode and a common electrode will be defined as  $\Delta Vs$ , an amount of charges in the floating sub

picture element electrode will be defined as Q, an amount of charges in the common electrode will be defined as Q1, and an amount of charges in the control electrode will be defined as Q2. The values of Q1, Q2, and Q at a stationary state after termination of a transient state will be calculated by the following formulae (2a) to (2c):

$$QI = \frac{R_{LC2}}{R_{LC2} + R_C} \times \Delta Vs \times C_{LC2} \tag{2a} \label{eq:2a}$$

$$Q2 = \frac{R_C}{R_{LC2} + R_C} \times \Delta Vs \times C_C$$

(2b)

$$\begin{split} Q &= Q2 - QI \\ &= \frac{-((R_{LC2} \times C_{LC2}) - (R_C \times C_C))}{R_{LC2} + R_C} \times \Delta Vs \end{split} \tag{2c}$$

Even if the direct-current voltage component  $\Delta Vs$  is removed, a direct-current voltage component  $\Delta V_{LC2}$  as shown in the following formula (3) will remain in the liquid crystal layer:

$$\Delta V_{LC2} = -Q/Q_{LC2} \tag{3}$$

$$= \frac{((R_{LC2} \times C_{LC2}) - (R_C \times C_C)}{(R_{LC2} + R_C) \times C_{LC2}} \times \Delta Vs$$

Assuming that an area of a sub picture element electrode is 30 S and a cell thickness is d, the liquid crystal capacitance  $C_{LC2}$ will be expressed as  $C_{LC2} = \in (S/d)$ . Here,  $\in$  is a dielectric constant of the liquid crystal. Since a dielectric constant when liquid crystal molecules are aligned perpendicularly to surface of substrates is different from a dielectric constant when 35 the liquid crystal molecules are aligned horizontally, the values of the liquid crystal capacitance are different between a picture element displaying a white portion of a checker pattern and a picture element displaying a black portion thereof. As a result, the values of the direct-current voltage component 40  $\Delta V_{LC2}$  to be applied to the liquid crystal liquid layer are also different between these picture elements. When the checker pattern display is switched to a halftone display, the directcurrent voltage components remaining in the liquid crystal layer do not change immediately. Therefore, a picture ele-45 ment displaying white and a picture element displaying black have different voltages to be applied to the liquid crystal layer. For this reason, a light transmittance of the picture element displaying white is different from a light transmittance of the picture element displaying black, and the image sticking is thereby caused. Here, the image sticking occurring due to the above-described reason will be decreased within a period corresponding to a time constant between the sub picture element electrode and either the control electrode or the common electrode. However, it is necessary to reduce the image 55 sticking as much as possible in order to improve display

FIG. 12 is a graph showing a relation between  $\Delta V_s$  and  $\Delta V_{LC2}$  when a display voltage is applied to the liquid crystal layer (when the liquid crystal is turned on), and a relation 60 between  $\Delta V_s$  and  $\Delta V_{LC2}$  when the display voltage is not applied to the liquid crystal layer (when the liquid crystal is turned off), in which the lateral axis indicates the direct-current voltage component  $\Delta V_s$  between the control electrode and the common electrode and the longitudinal axis 65 indicates the direct-current voltage component  $\Delta V_{LC2}$  which remains in the liquid crystal layer. Here, it is to be noted that

14

figures in FIG. 12 are calculated on the basis of the liquid crystal display device having the structure shown in FIG. 9, in which a picture element pitch is set to  $125~\mu m$ , an area proportion between the sub picture element electrode 61a capacitively coupled to a control electrode 57 and the sub picture element electrode 61b directly connected to the TFT 56 is set to 3 to 7, and a ratio between a display voltage to be applied to the sub picture element electrode (the floating sub picture element electrode) 61a and a display voltage to be applied to the sub picture element electrode (the sub picture element electrode) 61a is set to 6.72

It is apparent from FIG. 12 that a voltage, which is several times higher than the direct-current voltage component  $\Delta Vs$  between the control electrode and the common electrode, is applied to the liquid crystal layer. For this reason, an effect to suppress image sticking is limited even if the direct-current voltage component  $\Delta Vs$  between the control electrode and the common electrode is reduced.

The inventors of the present invention considered that it was essential to apply any of the following countermeasures to prevent image sticking.

- (1) Accumulation of the electric charges in the floating sub picture element electrode is suppressed by electrically shielding between the bus line (such as the gate bus line or the data bus line), which allows the signal including the direct-current voltage component to flow thereon, and the floating sub picture element electrode.

- (2) The direct-current voltage component possessed by the signal flowing on the gate bus line has a reverse polarity as compared to the direct-current voltage component possessed by the signal flowing on the data bus line. Accordingly, the resistance between the floating sub picture element electrode and the gate bus line and the resistance between the floating sub picture element electrode and the data bus line are optimized so that the influences of these two direct-current voltage components cancel each other.

- (3) When the resistance between the floating sub picture element electrode and the control electrode is reduced, the direct-current voltage component remaining in the liquid crystal layer is also reduced. However, if the resistance between the floating sub picture element electrode and the control electrode is reduced excessively, it is not possible to obtain the effect to suppress wash out. Accordingly, the resistance between the floating sub picture element electrode and the control electrode is optimized so as not to cause wash out or image sticking.

- (4) The electric charges accumulated in the floating sub picture element electrode are discharged to the data bus line, the auxiliary capacitance bus line or the like at a constant frequency.

- (5) An auxiliary capacitance is formed in parallel to the capacitance (the liquid crystal capacitance) between the floating sub picture element electrode and the common electrode to reduce an influence of variation in the liquid crystal capacitance.

Now, liquid crystal display devices according to the preferred embodiments of the present invention provided with the aforementioned countermeasures will be described.

## First Embodiment

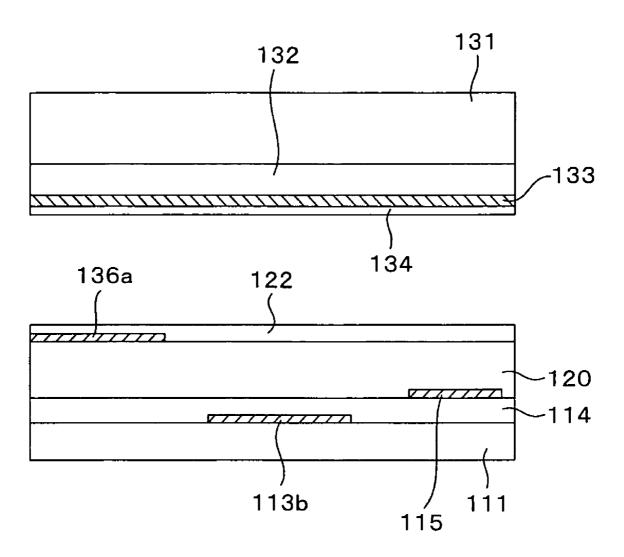

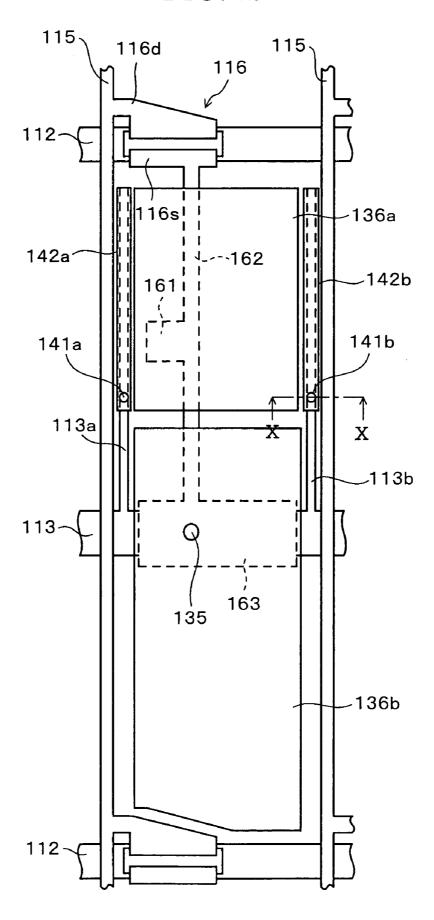

FIG. 13 is a plan view showing a liquid crystal display device according to a first embodiment of the present invention. Meanwhile, FIG. 14A is a cross-sectional view taken along the VI-VI line in FIG. 13, and FIG. 14B is a cross-sectional view taken along the VII-VII line in FIG. 13.

On a glass substrate 111 constituting a base of a TFT substrate, there are formed a plurality of gate bus lines 112 extending in a horizontal direction (an X direction) and a plurality of data bus lines 115 extending in a vertical direction (a Y direction). Each rectangular region defined by the gate 5 bus lines 112 and the data bus lines 115 constitutes a picture element region. Meanwhile, on the glass substrate 111, there are formed auxiliary capacitance bus lines 113 disposed parallel to the gate bus lines 112 and intersecting the center of the respective picture element regions.

15

A first insulating film 114, which is made of an insulative material such as SiN or SiO<sub>2</sub>, is formed in a space between each of the gate bus lines 112 and each of the data bus lines 115 and in a space between each of the auxiliary capacitance bus lines 113 and each of the data bus lines 115. By using this 15 first insulating film 114, the gate bus lines 112 and the data bus lines 115, and, the auxiliary capacitance bus lines 113 and the data bus lines 115 are electrically insulated, respectively.

ATFT 116, connection electrodes 117a and 117b, a control electrode 118, and sub picture element electrodes 121a to 20 121c made of a transparent material such as ITO are formed in each picture element region. The control electrode 118 constitutes an auxiliary capacitance electrode together with the auxiliary capacitance bus line 113 and the first insulating film 114. As shown in FIG. 13, the TFT 116 applies part of the 25 gate bus line 112 as a gate electrode. Moreover, as shown in FIG. 14A, a semiconductor film 116a constituting an active layer for the TFT 116 is formed above the gate bus line 112, and a channel protection film 116b is formed on this semiconductor film 116a.

A drain electrode **116***d* of the TFT **116** is connected to the data bus line 115, and a source electrode 116s thereof is disposed in a position opposed to the drain electrode 116d while sandwiching the gate bus line 112. Moreover, the control electrode 118 is formed in a position opposed to the 35 auxiliary capacitance bus line 113 while sandwiching the first insulating film 114. The connection electrode 117a is disposed below the sub picture element electrode 121a, and the connection electrode 117b is disposed below the sub picture element electrode 121c. The connection electrodes 117a and 40 the signal flowing on the gate bus line 112 is extremely small. 117b, as well as the control electrode 118 are connected to the source electrode 116s through a line 119.

The data bus lines 115, the TFT 116, the connection electrodes 117a and 117b, the control electrode 118, and the line 119 are covered with a second insulating film 120, which is 45 made of SiN, insulative resin or the like. Moreover, the sub picture element electrodes 121a to 121c are formed on this second insulating film 120. As shown in FIG. 13, the sub picture element electrode (the floating sub picture element electrode) 121b is disposed in the center of the picture ele- 50 ment region and is capacitively coupled to the control electrode 118. Meanwhile, the sub picture element electrode 121a is disposed between the sub picture element electrode 121b and the gate bus line 112 thereabove, and the sub picture element electrode 121c is disposed between the sub picture 55 element electrode 121b and the gate bus line 112 therebelow. These sub picture element electrodes 121a and 121c are electrically connected to the source electrode 116s of the TFT 116 through contact holes 120a and 120b, the connection electrodes 117a and 117b, and the line 119. Moreover, surfaces of 60 the sub picture element electrodes 121a to 121c are covered with an alignment film 122, which is made of polyimide, for

Here, the gate bus lines 112 and the auxiliary capacitance bus lines 113 are formed simultaneously by patterning a Cr 65 film or an Al-Ti lamination film in accordance with the photolithography method, for example. In the meantime, the

data bus lines 115, the source electrode 116s, the drain electrode 116d, and the control electrode 118 are formed simultaneously by patterning a Ti-Al-Ti lamination film in accordance with the photolithography method, for example.

16

Meanwhile, as shown in FIG. 14A and FIG. 14B, a counter substrate includes a color filter 132 formed on one of surfaces (which is on the lower side in FIG. 14A and FIG. 14B) of a glass substrate 131 constituting a base, a common electrode 133 formed on a surface of the color filter 132, and an alignment film 134 covering a surface of the common electrode 133. The common electrode 133 is made of a transparent conductive material such as ITO, and the alignment film 134 is made of polyimide, for example.

The TFT substrate and the counter electrode are disposed opposite to each other while placing the surfaces provided with the alignment films inward, and are joined together while sandwiching spacers. Then, liquid crystal 140 is sealed between the TFT substrate and the counter substrate.

In the liquid crystal display device of the first embodiment having the above-described configuration, the sub picture element electrodes 121a and 121c are electrically connected to the TFT 116, and are therefore connected to the data bus line 115 when the TFT 116 is turned on. For this reason, even if electric charges are accumulated in the sub picture element electrodes 121a and 121b due to the direct-current voltage component of the signal flowing on the gate bus line 112 in a period when the TFT 116 is turned off, the electric charges flow toward the data bus line 115 in a period when the TFT 116 is turned on and accumulation of the electric charges is thereby avoided. Accordingly, no image sticking occurs in these sub picture element electrodes 121a and 121b.

Meanwhile, the sub picture element electrode (the floating sub picture element electrode) 121b capacitively coupled to the control electrode 118 is remote from the gate bus line 112, and the sub picture element electrodes 121a and 121c are interposed between the sub picture element electrode 121b and the gate bus line 112. Accordingly, accumulation of the electric charges to the floating sub picture element electrode 121b attributable to the direct-current voltage component of In this way, it is possible to avoid occurrence of image sticking and to obtain favorable display quality.

## First Modified Example

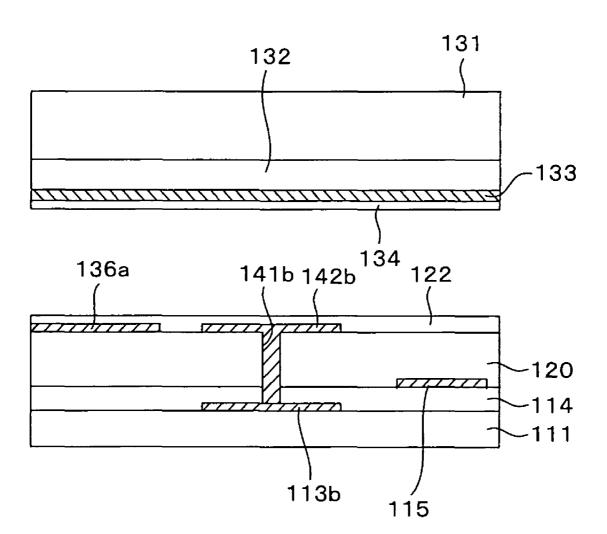

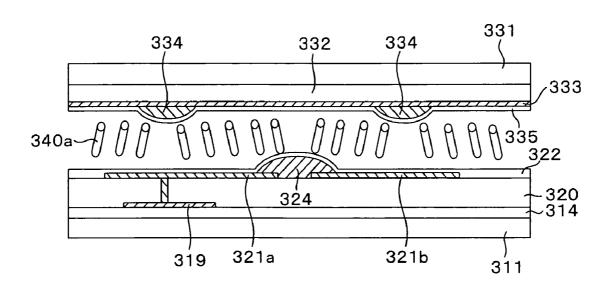

FIG. 15 is a plan view showing a liquid crystal display device according to a first modified example of the first embodiment, and FIG. 16 is a cross-sectional view taken along the VIII-VIII line in FIG. 15. In terms of FIG. 15 and FIG. 16, the same constituents as those illustrated in FIG. 13, FIG. 14A, and FIG. 14B are designated by the same reference numerals, and detailed description thereof will be omitted.

In the liquid crystal display device of the first modified example shown in FIG. 15 and FIG. 16, two sub picture element electrodes 136a and 136b are provided in one picture element. Moreover, a control electrode 161 is provided below the sub picture element electrode 136a while sandwiching the second insulating film 120 and the sub picture element electrode 136a is capacitively coupled to the control electrode

An auxiliary capacitance electrode 163 is provided above the auxiliary capacitance bus line 113 and this auxiliary capacitance electrode 163 is electrically connected to the sub picture element electrode 136b through a contact hole 135. Meanwhile, the auxiliary capacitance electrode 163 and the control electrode 161 are electrically connected to the source electrode 116s of the TFT 116 through a line 162.

In addition, shield patterns 113a and 113b extending from the auxiliary capacitance bus line 113 are disposed between the sub picture element electrode 136a and the data bus lines 115. The auxiliary capacitance bus line 113 is maintained either at the same electric potential as the electric potential of the common electrode 133 or at constant electric potential relative to the electric potential of the common electrode 133.

In the liquid crystal display device of this first modified example, the shield patterns 113a and 113b maintained at the same electric potential as the electric potential of the auxiliary capacitance bus line 113 are disposed between the floating sub picture element electrode 136a and the data bus lines 115. Accordingly, accumulation of the electric charges in the floating sub picture element electrode 136a attributable to the direct-current voltage component of the signal flowing on any 15 of the data bus lines 115 is suppressed. In this way, this liquid crystal display device exerts the effect to suppress image sticking.

## Second Modified Example

FIG. 17 is a plan view showing a liquid crystal display device according to a second modified example of the first embodiment, and FIG. 18 is a cross-sectional view taken along the IX-IX line in FIG. 17. In terms of FIG. 17 and FIG. 25 18, the same constituents as those illustrated in FIG. 15 and FIG. 16 are designated by the same reference numerals, and detailed description thereof will be omitted.

In the liquid crystal display device of the second modified example shown in FIG. 17 and FIG. 18, shield patterns 138a 30 and 138b which are formed on the same layer as the sub picture element electrode 136a are disposed between the floating sub picture element electrode 136a and the data bus lines 115. These shield patterns 138a and 138b are electrically connected to the auxiliary capacitance bus line 113 35 through contact holes 137a and 137b, which are formed on the first and second insulating films 114 and 120, respectively. The auxiliary capacitance bus line 113 is maintained either at the same electric potential as the electric potential of the common electrode 133 or at constant electric potential rela- 40 tive to the electric potential of the common electrode 133 as similar to the liquid crystal display device of the first modified example.

In the liquid crystal display device of the first modified example shown in FIG. 15 and FIG. 16, the shield patterns 45 113a and 113b are formed on a lower layer than the data bus lines 115 and the sub picture element electrode 136a. On the contrary, in the liquid crystal display device of the second modified example, the shield patterns 138a and 138b are formed on the same layer as the sub picture element electrode 50 136a. Accordingly, a resistance component of the first insulating film 114 disappears in the liquid crystal display device of the second modified example. For this reason, the liquid crystal display device of the second modified example has a from the data bus lines 115 as compared to the liquid crystal display device of the first modified example. In this way, the liquid crystal display device of the second modified example can avoid image sticking more reliably than the liquid crystal device of the first modified example.

## Third Modified Example

FIG. 19 is a plan view showing a liquid crystal display device according to a third modified example of the first 65 embodiment, and FIG. 20 is a cross-sectional view taken along the X-X line in FIG. 19. In terms of FIG. 19 and FIG.

18

20, the same constituents as those illustrated in FIG. 15 and FIG. 16 are designated by the same reference numerals, and detailed description thereof will be omitted.

In the liquid crystal display device of the third modified example shown in FIG. 19 and FIG. 20, the shield patterns 113a and 113b extending from the auxiliary capacitance bus line 113, and shield patterns 142a and 142b formed on the same layer as the sub picture element electrode 136a are disposed between the floating sub picture element electrode 136a and the data bus lines 115. The shield patterns 142a and 142b are electrically connected to the shield patterns 113a and 113b through contact holes 141a and 141b, which are formed on the first and second insulating films 114 and 120, respectively.

In the liquid crystal display device of the third modified example as well, the shield patterns 113a, 113b, 142a, and **142**b are formed between the floating sub picture element electrode 136a and the data bus lines 115. Accordingly, it is possible to suppress accumulation of the electric charges in 20 the floating sub picture element electrode **136***a* attributable to the direct-current voltage component flowing on any of the data bus lines 115 and thereby to avoid image sticking.

#### Fourth Modified Example

FIG. 21 is a plan view showing a liquid crystal display device according to a fourth modified example of the first embodiment. In terms of FIG. 21, the same constituents as those illustrated in FIG. 15 are designated by the same reference numerals, and detailed description thereof will be omitted.

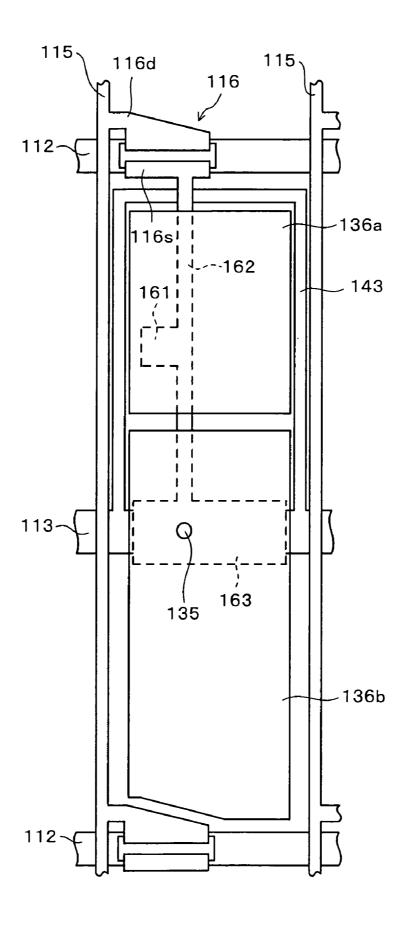

In the liquid crystal display device of the fourth modified example shown in FIG. 21, a shield pattern 143, which is formed on the same layer as the auxiliary capacitance bus line 113 and is connected to the auxiliary capacitance bus line 113, surrounds the floating sub picture element electrode 136a.

In the liquid crystal display device of the fourth modified example, it is possible to shield not only the direct-current voltage component included in the signal flowing on any of the data bus lines 115, but also the direct-current voltage component included in the signal flowing on any of the gate bus lines 112. In this way, this liquid crystal display device exerts the effect to avoid image sticking more reliably than the liquid crystal display device of the first modified example.

#### Fifth Modified Example

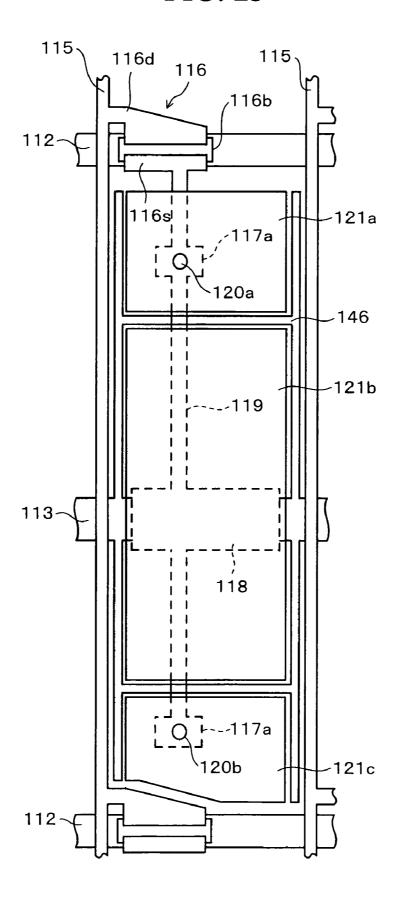

FIG. 22 is a plan view showing a liquid crystal display device according to a fifth modified example of the first embodiment. In terms of FIG. 22, the same constituents as those illustrated in FIG. 13 are designated by the same reference numerals, and detailed description thereof will be omit-

In the liquid crystal display device shown in FIG. 22, the larger effect to shield the sub picture element electrode 136a 55 sub picture element electrodes 121a and 121c are disposed between the floating sub picture element electrode 121b and the gate bus lines 112, which are indicated on an upper side and a lower side in FIG. 22. These sub picture element electrodes 121a and 121c are electrically connected to the TFT 60 116 through the contact holes 120a and 120b, and through the line 119. Meanwhile, shield patterns 145 respectively extending from the auxiliary capacitance bus line 113 are disposed between the floating sub picture element electrode 121b and the data bus lines 115 on the right side and the left side in FIG.

> In the liquid crystal display device of the fifth modified example, the floating sub picture element electrode 121b is

shielded from the gate bus lines 112 and the data bus lines 115 by the sub picture element electrodes 121a and 121c as well as the shield patterns 145. Accordingly, this liquid crystal display device exerts the effect to suppress accumulation of the electric charges attributable to the direct-current voltage 5 component of the signal flowing on any of the gate bus lines 112 and the data bus lines 115, and thereby to avoid image sticking effectively.

Moreover, in the liquid crystal display device of the fifth modified example, the shield patterns 145 are also disposed 10 between the sub picture element electrodes 121a and 121c, which are electrically connected to the TFT 116, and, the data bus lines 115. Accordingly, the liquid crystal display device also has the effect to suppress accumulation of the electric charges in the sub picture element electrodes 121a and 121c 15 attributable to the direct-current voltage component included in the signal flowing on any of the data bus lines 115.

#### Sixth Modified Example

FIG. 23 is a plan view showing a liquid crystal display device according to a sixth modified example of the first embodiment. In terms of FIG. 23, the same constituents as those illustrated in FIG. 22 are designated by the same reference numerals, and detailed description thereof will be omitted

In the liquid crystal display device of the sixth modified example shown in FIG. 23, the shield pattern 146, which is formed on the same layer as the auxiliary capacitance bus line 113 and connected to the auxiliary capacitance bus line 113, 30 is also disposed between the floating sub picture element electrode 121*b* and the sub picture element electrodes 121*a* and 121*c* directly connected to the TFT 116. In the liquid crystal display device of the sixth modified example as well, it is possible to suppress accumulation of the electric charges attributable to the direct-current voltage component of the signal flowing on any of the gate bus lines 112 and the data bus lines 115, and thereby to avoid image sticking effectively.

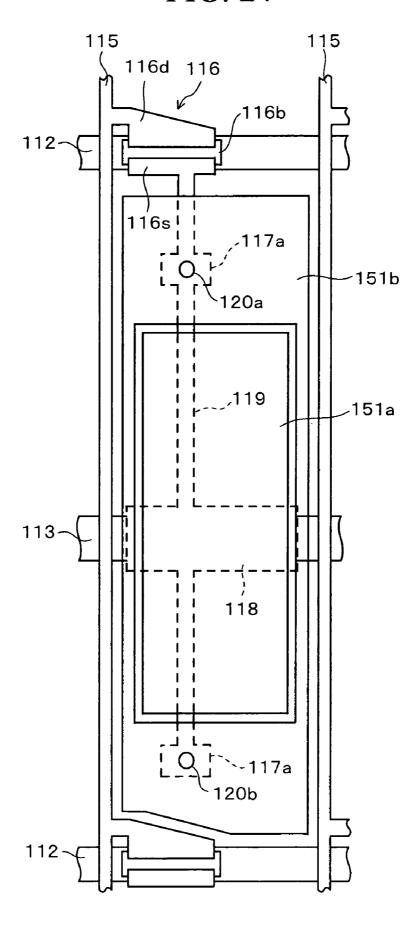

# Seventh Modified Example

FIG. 24 is a plan view showing a liquid crystal display device according to a seventh modified example of the first embodiment. In terms of FIG. 24, the same constituents as those illustrated in FIG. 13 are designated by the same reference numerals, and detailed description thereof will be omitted.

In the liquid crystal display device of the seventh modified example shown in FIG. **24**, a sub picture element electrode **151***b* surrounds a floating sub picture element electrode **151***a*. 50 This sub picture element electrode **151***b* is electrically connected to the source electrode **116***s* of the TFT **116** through the contact holes **120***a* and **120***b* as well as the line **119**.

In the liquid crystal display device of the seventh modified example as well, the floating sub picture element electrode 55 **151***a* is shielded from the gate bus lines **112** and from the data bus lines **115**. Accordingly, the liquid crystal display device exerts the effect to suppress accumulation of the electric charges attributable to the direct-current voltage component of the signal flowing on any of the gate bus lines **112** and the 60 data bus lines **115**, and thereby to avoid image sticking effectively.

### Second Embodiment

Now, a second embodiment of the present invention will be described.

20

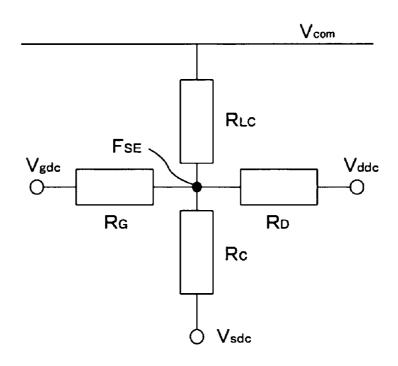

FIG. **25** is a view showing the principle of the second embodiment of the present invention. FIG. **25** shows an equivalent circuit involving a floating sub picture element electrode  $F_{SE}$ , a common electrode, a control electrode, a gate bus line, and a data bus line.

As shown in FIG. 25, it is possible to say that a resistance  $R_G$  exists between the floating sub picture element electrode  $F_{SE}$  and the gate bus line, that a resistance  $R_D$  exists between the floating sub picture element electrode  $F_{SE}$  and the data bus line, that a resistance  $R_C$  exists between the floating sub picture element electrode  $F_{SE}$  and the control electrode, and that a resistance (a liquid crystal resistance)  $R_{LC}$  exists between the floating sub picture element electrode  $F_{SE}$  and the common electrode. Here, electric potential of the control electrode will be defined as  $V_{sdc}$ , electric potential of the common electrode will be defined as  $V_{com}$ , a direct-current voltage component (central electric potential) of a signal flowing on the gate bus line will be defined as  $V_{gdc}$ , and a direct-current voltage component (central electric potential) of a signal flowing on the data bus line will be defined as  $V_{ddc}$ .

As described previously, a direct-current voltage, which is lower by about -12 V than the electric potential of the common electrode, is applied to the gate bus line to turn a TFT off. Meanwhile, a direct-current voltage, which is higher by about +2 V than the electric potential of the common electrode, is superposed with a display signal on the data bus line in order to compensate a feed through voltage. The direct-current voltage component applied to the signal flowing on the gate bus line has a reverse polarity as compared to the directcurrent voltage component applied to the signal flowing on the data bus line. Accordingly, by setting the values of  $V_{\it ddc}$ ,  $V_{gdc}$ ,  $R_G$ , and  $R_D$  so as to satisfy the following formula (4), it is possible to prevent accumulation of the electric charges in the floating sub picture element electrode attributable to the direct-current voltage components of the gate bus line and the data bus line, and eventually to prevent occurrence of image sticking.

$$V_{ddc} \times R_G - V_{gdc} \times R_D = 0 \qquad (4)$$