US 20020063666A1

(19) **United States**

(12) **Patent Application Publication**

Kang et al.

(10) **Pub. No.: US 2002/0063666 A1**

(43) **Pub. Date: May 30, 2002**

(54) **APPARATUS AND METHOD FOR CORRECTING GAMMA VOLTAGE AND VIDEO DATA IN LIQUID CRYSTAL DISPLAY**

**Publication Classification**

(51) **Int. Cl. 7** ..... G09G 3/36

(52) **U.S. Cl.** ..... 345/87

(76) Inventors: **Sin Ho Kang**, Kumi-shi (KR); **Kyeong Kun Jang**, Kumi-shi (KR); **Sang Tae Lee**, Kumi-shi (KR); **Jung Taeck Eu**, Kumi-shi (KR); **Kyu Ik Sohng**, Daegu-shi (KR); **Sang Hoon Lee**, Daegu-shi (KR); **Byung Joon Goo**, Daegu-shi (KR)

(57)

### ABSTRACT

A gamma voltage and video data correcting apparatus and method in a liquid crystal display that is capable of improving a display quality of the LCD, wherein gamma data for controlling the gamma voltage is stored for each of at least two modes. The gamma data for each mode is accessed in response to an instruction from a user to select any one of the gamma data for each mode. In response to the gamma data for the selected mode, n gamma voltages (wherein n is an integer), each having a different voltage level, indicated by the gamma data in the selected mode are generated. In the video data correcting method, a lookup table is provided in which a color temperature correction data for correcting a color temperature characteristic of an input image is set in correspondence with a gray level value of the input image. The lookup table is accessed in accordance with the gray level value of the input image to read out color temperature correction data corresponding to the gray level value of the input image. The data lines are driven by the color temperature correction data.

(21) Appl. No.: **09/892,997**

(22) Filed: **Jun. 28, 2001**

### (30) Foreign Application Priority Data

Jun. 28, 2000 (KR) ..... P2000-36213

Dec. 29, 2000 (KR) ..... P2000-85270

FIG. 1

CONVENTIONAL ART

FIG.2

CONVENTIONAL ART

**FIG.3**

**CONVENTIONAL ART**

FIG.4

CONVENTIONAL ART

FIG. 5

CONVENTIONAL ART

FIG. 7

CONVENTIONAL ART

FIG. 8

FIG. 10

FIG. 11

|   |    |    |    |    |    |    |    |    |   |   |   |    |    |    |    |    |    |

|---|----|----|----|----|----|----|----|----|---|---|---|----|----|----|----|----|----|

| S | A3 | A2 | A1 | A0 | SD | SC | SB | SA | A | X | X | D5 | D4 | D3 | D2 | D1 | D0 |

|---|----|----|----|----|----|----|----|----|---|---|---|----|----|----|----|----|----|

S=START CONDITION, A3~A0=ADDRESS BIT, SC~SA=SUBADDRESS BIT

A=HEADER BIT, D5~D0=DATA BIT

FIG. 12

FIG. 14

FIG. 16

FIG. 17

FIG.18

FIG.19

FIG. 20

FIG.21

- CHROMINANCE CO-ORDINATES OF INPUT IMAGE

- CHROMINANCE CO-ORDINATES OF LCD DISPLAY IMAGE

- CHROMINANCE CO-ORDINATES CORRECTED BY LOOKUP TABLE

## APPARATUS AND METHOD FOR CORRECTING GAMMA VOLTAGE AND VIDEO DATA IN LIQUID CRYSTAL DISPLAY

### BACKGROUND OF THE INVENTION

#### [0001] 1. Field of the Invention

[0002] This invention relates to a technique for driving a liquid crystal display, and more particularly to an apparatus and method for correcting a gamma voltage and a video data in a liquid crystal display that is capable of improving a display quality of the liquid crystal display.

#### [0003] 2. Description of the Related Art

[0004] Generally, an active matrix liquid crystal display (LCD) uses thin film transistors (TFTs) as switching devices to display a natural moving picture. Since such a LCD can be made into a smaller device in size than the existent Brown tube, it has been widely used for a monitor for a personal computer or a notebook computer as well as office automation equipment such as copy machines, etc. and portable equipment such as cellular phones and pagers, etc.

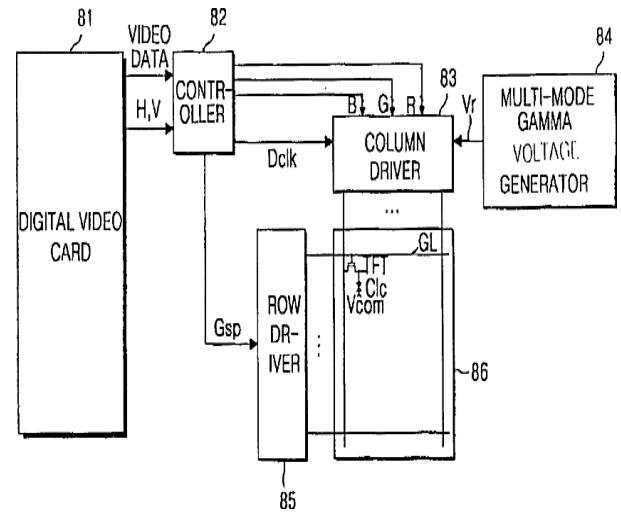

[0005] As shown in FIG. 1, a driving apparatus for the LCD includes a digital video card 1 for converting an analog signal into a digital video data, a column driver 3 for applying the video data to data lines DL of a liquid crystal panel 6, a row driver 5 for sequentially driving gate lines GL of the liquid crystal panel 6, a controller 2 for controlling the column driver 3 and the row driver 5, and a gamma voltage generator 4 for applying a gamma voltage to the column driver 3.

[0006] In the liquid crystal panel 6, liquid crystal is injected between two glass substrates, and the gate lines GL and the data lines DL are formed on the lower glass substrate in such a manner as to be perpendicular to each other. At each intersection between the gate lines GL and the data lines DL, a thin film transistor (TFT) for selectively applying an image input from the data lines DL to a liquid crystal cell Clc is provided. To this end, the TFT has a gate terminal connected to the gate line GL and a source terminal connected to the data line DL. The drain terminal of the TFT is connected to a pixel electrode of the liquid crystal cell Clc.

[0007] The digital video card 1 converts an analog input image signal into a digital image signal suitable for the liquid crystal panel 6 and detects a synchronous signal included in the image signal. The controller 2 applies red (R), green (G) and blue (B) digital video data from the digital video card 1 to the column driver 3. Also, the controller 2 generates a dot clock Dclk and a gate start pulse GSP using horizontal/vertical synchronizing signals H and V input from the digital video card 1 to provide a timing control of the column driver 3 and the row driver 5. The dot clock Dclk is applied to the column driver 3 while the gate start pulse GSP is applied to the row driver 5.

[0008] The row driver 5 includes a shift register for responding to the gate start pulse GSP input from the controller 2 to sequentially generate a scanning pulse, and a level shifter for shifting a voltage of the scanning pulse to a voltage level suitable for driving the liquid crystal cell. Video data at the data line DL is applied to a pixel electrode of the liquid crystal cell Clc by the TFT in response to the scanning pulse input from the row driver 5.

[0009] The dot clock Dclk, along with the R, G and B digital video data from the controller 2, is input to the column driver 3. The column driver 3 latches the R, G and B digital video data in synchronization with the dot clock Dclk and corrects the latched data in accordance with a gamma voltage V $\gamma$ . Then, the column driver 3 converts data corrected by the gamma voltage V $\gamma$  into analog data and supplies it to the data line DL for each line.

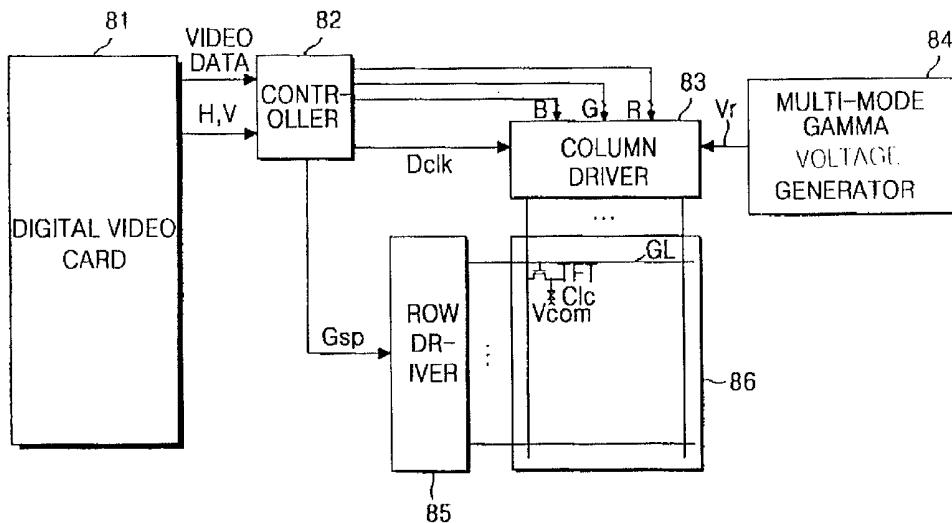

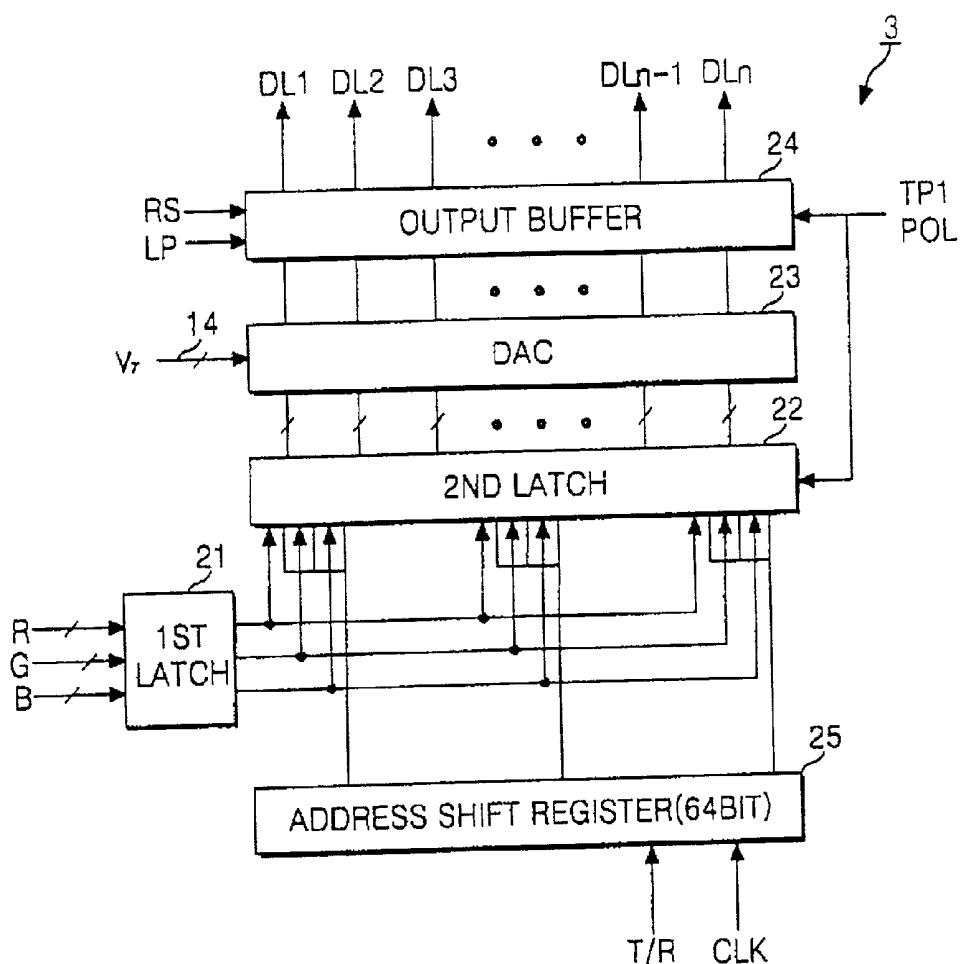

[0010] As shown in FIG. 2, the column driver 3 includes a first latch 21 to which R, G and B data are input, a second latch 22, a digital to analog converter (DAC) 23 and an output buffer 24 connected, in series, between the first latch 21 and the data lines DL1 to DLn, and an address shift register 25 for assigning an address of the second latch 25.

[0011] The first latch 21 temporarily stores the R, G and B data from the controller 2 and applies the stored data to the second latch 22 every horizontal period. The second latch 22 stores data from the first latch 21 in a location indicated by address information from the address shift register 25 and supplies the stored data for one line to the DAC 23.

[0012] The DAC 23 selects a gamma voltage V $\gamma$  corresponding to data from the second latch 22 and applies it to the data lines DL1 to DLn. A detailed description as to this DAC 23 will be made in conjunction with FIG. 6 later. The output buffer 24 consists of a voltage follower connected in series to the data line DL so as to buffer data from the DAC 23 and apply the buffered data to the data lines DL1 to DLn. The output buffer 24 and the second latch 22 receive a polarity inverting signal from the controller 2 for the purpose of inverting the polarity of the video data depending on an inversion driving system, such as a dot inversion system, a line (or column) inversion system, and a frame inversion system.

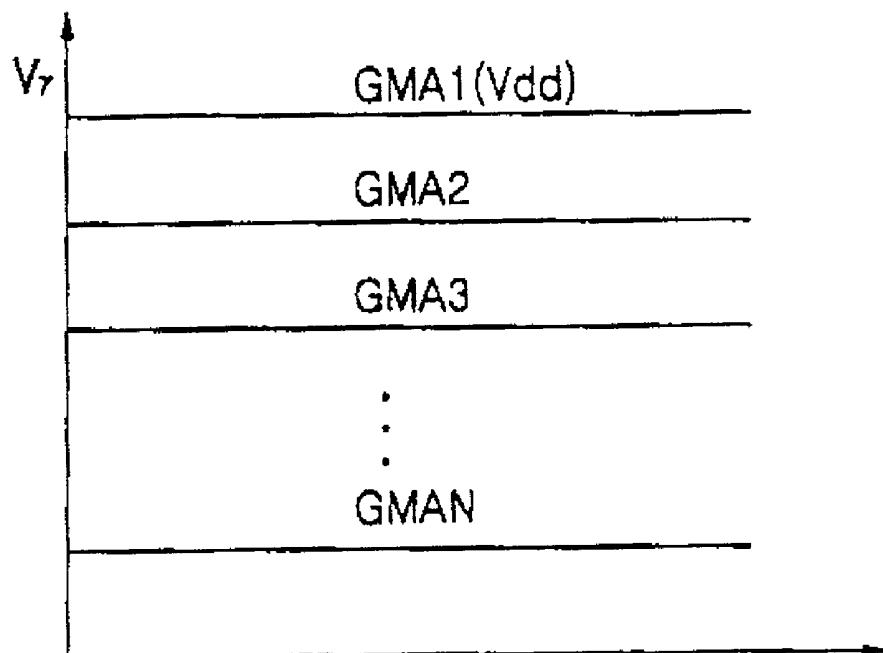

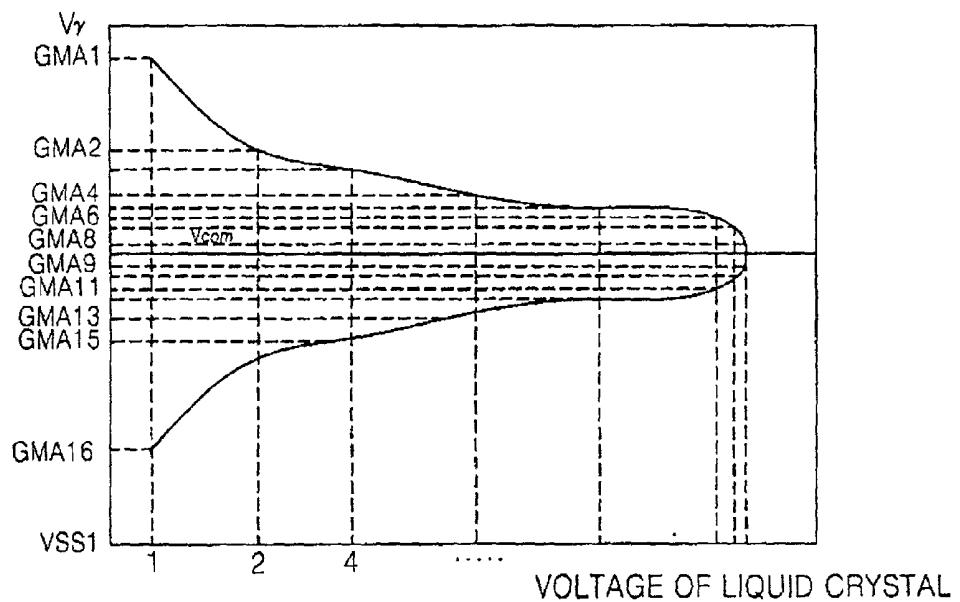

[0013] The address shift register 25 generates address information for the data stored in the second latch 22 to control the second latch 22. The gamma voltage generator 4 generates a gamma voltage V $\gamma$  corresponding to a gray level value of data, in consideration of an electro-optical characteristic of the liquid crystal panel 6, and applies it to the DAC 23. The gamma voltage V $\gamma$  from the gamma voltage generator 4 is set to have a different voltage magnitude in correspondence with a gray level value selected in an expressible range as shown in FIG. 3. In FIG. 3, in the normally white mode, data having the lowest brightness is GMA1, corresponding to a voltage Vdd, and data having a relatively higher brightness corresponds to GMA2, GMA3, . . . , GMAN.

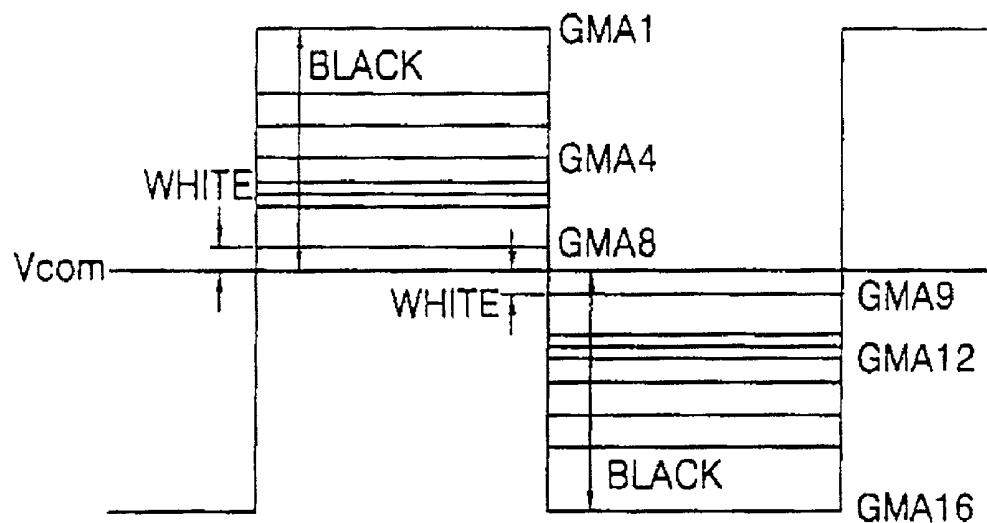

[0014] Each liquid crystal cell Clc expresses a gray level value having a specific brightness by a relative potential difference between the gamma voltage V $\gamma$  and a common voltage Vcom. More specifically, as shown in FIG. 4, an LCD with the normally white mode expresses an image at a brightness close to white when a potential difference between the gamma voltage V $\gamma$  and the common voltage Vcom is low, whereas it expresses an image at a brightness gradually closer to black as a potential difference between the gamma voltage V $\gamma$  and the common voltage Vcom becomes high. When a gamma voltage V $\gamma$  corresponding to an input image signal data expressed by a hexadecimal digit is selected, an analog voltage as shown in FIG. 5 is applied to the liquid crystal cell Clc of the liquid crystal panel 6. The gamma voltage generator 4 is classified into a positive part

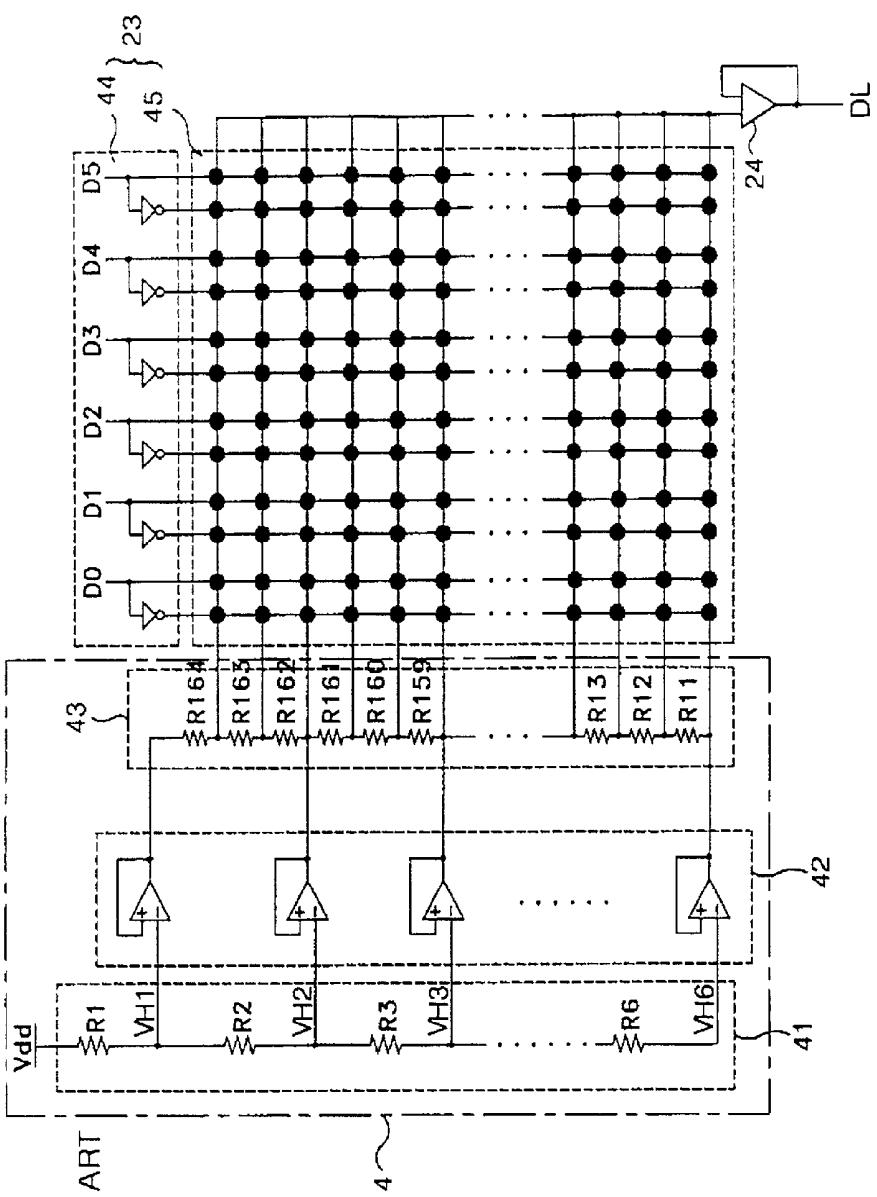

and a negative part to correspond to the inversion driving system. A configuration of the positive part is as shown in **FIG. 6**. The negative part has a configuration substantially identical to the positive part except for the polarity of a supplied voltage.

**[0015]** Referring to **FIG. 6**, the positive part type gamma voltage generator **4** includes: a reference voltage generator **41** for generating reference voltages **VH1** to **VH6** each having a different voltage level in accordance with a voltage-divided resistance ratio; a buffer unit **42** connected to an output terminal of the reference voltage generator **41**; and a gamma voltage output **43** connected between the buffer unit **42** and the DAC **23** to divide the reference voltage **VH1** to **VH6** and output gamma voltages **Vy** having different voltage levels.

**[0016]** The reference voltage generator **41** includes a serial connection of first to sixth resistors **R1** to **R6** to generate six reference voltages **VH1** to **VH6** in accordance with a voltage-divided resistance ratio, and to apply them to the buffer unit **42**. The buffer unit **42** consists of a voltage follower connected, in series, between an output terminal of the reference voltage generator **41** and the gamma voltage output **43**. The buffer unit **42** stabilizes the reference voltages **VH1** to **VH6** and applies them to the gamma voltage output **43**. The gamma voltage output **43** consists of a serial connection of **64** resistors **R11** to **R164**. The gamma voltage output **43** sub-divides the six reference voltages **VH1** to **VH6** into **64** gamma voltages and applies them to the DAC **23**.

**[0017]** The DAC **23** includes a data input **44** for receiving 6-bit data **D0** to **D5** from the second latch **22**, and a decoder **45** connected between the data input **44** and the gamma voltage output **43**. The data input **44** includes an inverter for inverting a logical value of each data bit to generate an inverted signal and a non-inverted signal of the data and to apply them to the decoder **45**. The decoder **45** consists of a plurality of logical elements in an array to select any one of the **64** gamma voltages **Vy** in accordance with the inverted and non-inverted data from the data input **44** and to apply the selected gamma voltage **Vy** to the output buffer **24**.

**[0018]** Nowadays, the LCD requires interchangeability with various peripheral equipment capable of displaying image signals input from a personal computer, a television, a player for an optical recording medium such as a compact disk (CD) or a digital versatile disk (DVD), or a camcorder, etc. However, the conventional driving apparatus for the LCD cannot correct a gamma voltage enough to be suitable for each image signal from the various peripheral equipment because the gamma voltage has been fixed by a predetermined voltage-divided resistance ratio. As a result in the case of displaying an image signal inputted from the peripheral equipment, the conventional LCD presents color distortion, etc., of a displayed image, depending on the type of the peripheral equipment to thereby cause a deterioration in quality of the displayed image.

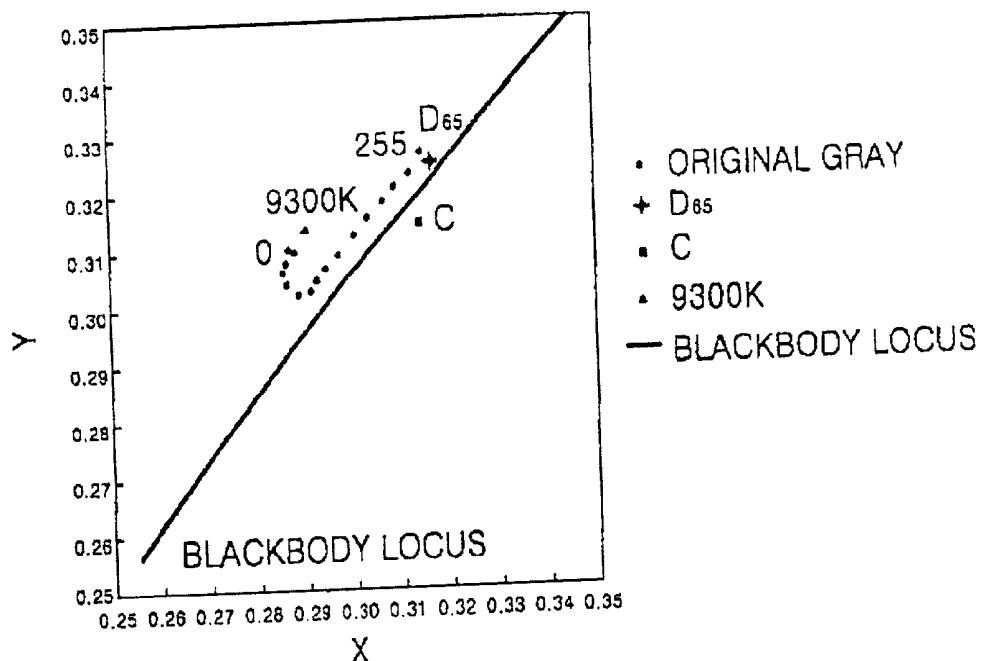

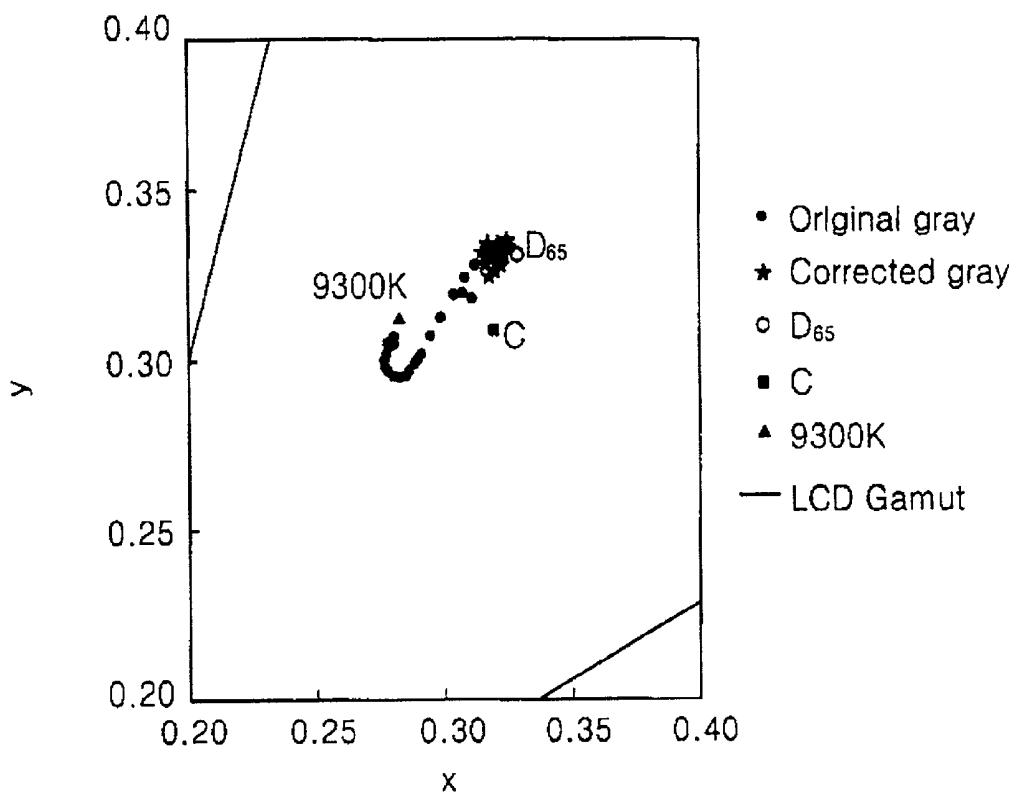

**[0019]** Also, the conventional LCD has a problem in that, since it has a poor correlative color temperature, it cannot obtain constant chrominance co-ordinates in accordance with a value of the input data. In other words, as can be seen from the color co-ordinates of **FIG. 7** that is indicated by the XYZ system defined by the Committee International Illumination (CIE), the LCD has a serious variation in a

correlative color temperature because it has a wide and irregular correlative color temperature distribution. If a variation in the correlative color temperature is serious, it becomes difficult to provide a color expression corresponding to a desired gray level value for a black and white image as well as for a color image and hence a displayed image becomes unnatural.

**[0020]** In **FIG. 7**, the horizontal axis and the vertical axis represent independent parameters **x** and **y**, respectively, when a color is displayed by the CIE co-ordinate system. The solid line indicates a color temperature of an ideal blackbody emitting a light identical to a light from a light source. In **FIG. 7**, “•” represents a correlative color temperature according to a gray level value of an input image. **D<sub>65</sub>** represents a standard light source corresponding to sunshine in broad daylight in which a correlative color temperature is 6504 K, whereas **C** represents a standard light source corresponding to average sunshine on a cloudy day in which a correlative color temperature is 6774 K. In reality, since only video data corresponding to the highest brightness in the LCD has an appropriate color temperature value, a real image is observed at a white level. However, a real image is observed at a blue color because a correlative color temperature is considerably high when a digit value of a video data is small, that is, when it is dark, whereas it is observed at a slight blue color in the case of a video data digit value having a middle brightness. As a result, since the screen is observed with a bluish color as a whole, it becomes difficult to provide a natural color display. This is caused by physical and optical characteristics of a liquid crystal. There is a limit in solving such a problem by a correction of the gamma voltage.

## SUMMARY OF THE INVENTION

**[0021]** Accordingly, it is an object of the present invention to provide a gamma voltage and video data correcting apparatus and method in a liquid crystal display that is capable of improving a display quality of the LCD.

**[0022]** In order to achieve these and other objects of the invention, a gamma voltage correcting apparatus for a liquid crystal display according to one aspect of the present invention includes memory means for storing a gamma data for controlling a gamma voltage for each of at least two modes; control means for accessing the gamma data for each mode in response to an instruction from a user; and multi-channel gamma voltage generator for responding to gamma data in a mode selected by the control means to generate **n** gamma voltages (wherein **n** is an integer) having a different voltage level indicating by the gamma data in the selected mode. The gamma voltage correcting apparatus further includes a column driver for correcting the video data using the gamma voltage from the multi-channel gamma voltage generator and supplying it to the data lines.

**[0023]** A video data correcting apparatus for a liquid crystal display according to another aspect of the present invention includes memory means for storing a lookup table in which a color temperature correction data for correcting a color temperature characteristic of an input image is set in correspondence with a gray level value of the input image; memory control means for accessing the lookup table of the memory means in accordance with the gray level value of the input image to read out a color temperature correction

data corresponding to the gray level value of the input image; and data driving means for driving the data lines using the color temperature correction data from the memory control means. The gamma voltage correcting apparatus further includes a row driver for sequentially applying a scanning pulse to the gate lines to drive the gate lines; and a timing controller for supplying the input image to the memory control means and for applying a desired timing control signal to the row driver.

[0024] A gamma voltage correcting method for a liquid crystal display according to still another aspect of the present invention the steps of storing a gamma data for controlling a gamma voltage for each of at least two modes; accessing the gamma data for each mode in response to an instruction from a user; selecting any one of the gamma data for each mode; and responding to a gamma data in the selected mode to generate  $n$  gamma voltages (wherein  $n$  is an integer) having a different voltage level indicating by the gamma data in the selected mode. The gamma is set differently in accordance with each mode set in correspondence with a peripheral equipment changeable with the liquid crystal display.

[0025] A gamma voltage correcting method for a liquid crystal display according to still another aspect of the present invention the steps of providing a lookup table in which a color temperature correction data for correcting a color temperature characteristic of an input image is set in correspondence with a gray level value of the input image; accessing the lookup table in accordance with the gray level value of the input image to read out a color temperature correction data corresponding to the gray level value of the input image; and driving the data lines using the color temperature correction data. The color temperature correction data is a data measured after controlling the input image such that a color temperature of a display image on the liquid crystal display maintains approximately 6500 K.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0026] These and other objects of the invention will be apparent from the following detailed description of the embodiments of the present invention with reference to the accompanying drawings, in which:

[0027] FIG. 1 is a block diagram showing a configuration of a conventional liquid crystal display;

[0028] FIG. 2 is a detailed block diagram of the column driver shown in FIG. 1;

[0029] FIG. 3 is a characteristic graph of a gamma voltage generated from the gamma voltage generator shown in FIG. 1;

[0030] FIG. 4 is a characteristic graph representing brightness corresponding to the gamma voltage;

[0031] FIG. 5 is a waveform diagram of a voltage applied to a liquid crystal cell by the gamma voltage;

[0032] FIG. 6 is a detailed circuit diagram of the gamma voltage generator and the column driver shown in FIG. 1;

[0033] FIG. 7 is a color co-ordinate graph for explaining a color distortion phenomenon in the conventional liquid crystal display;

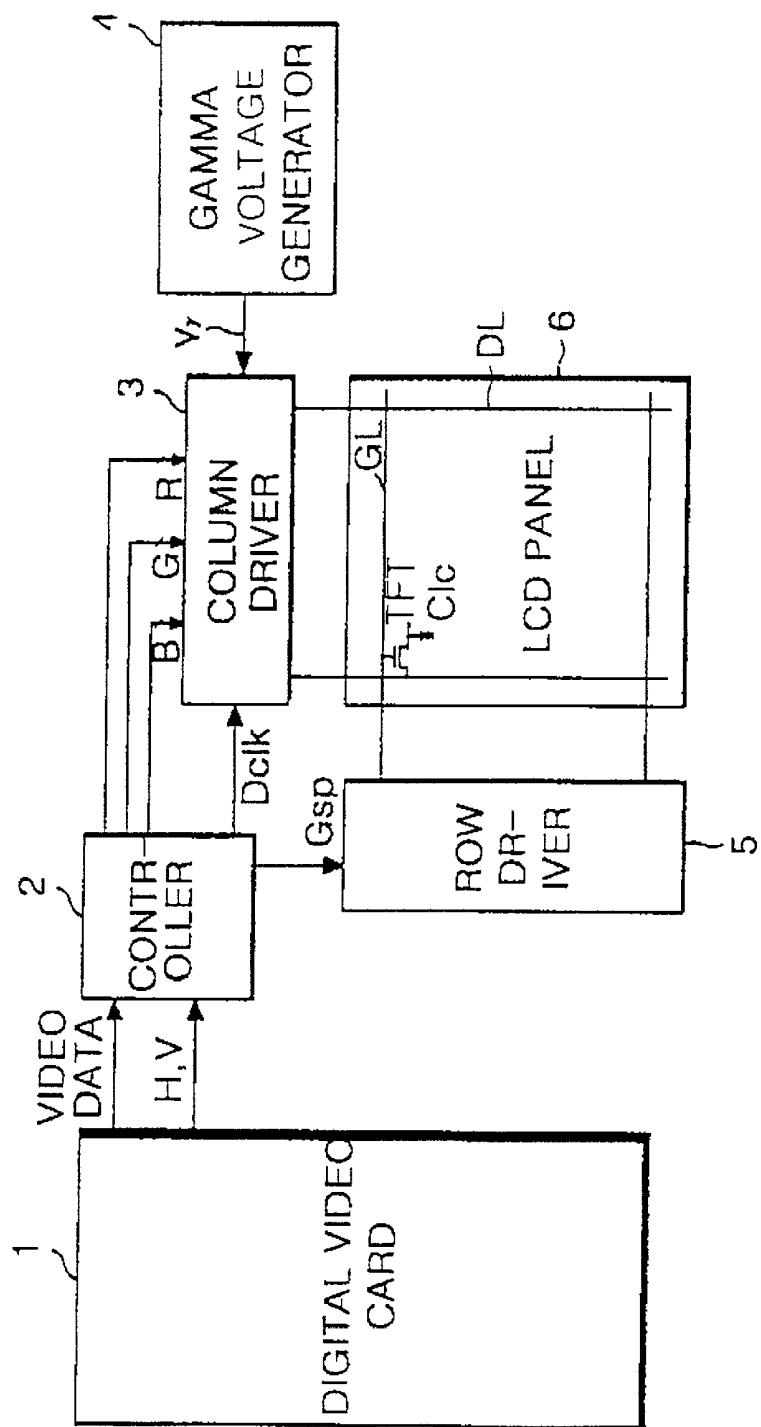

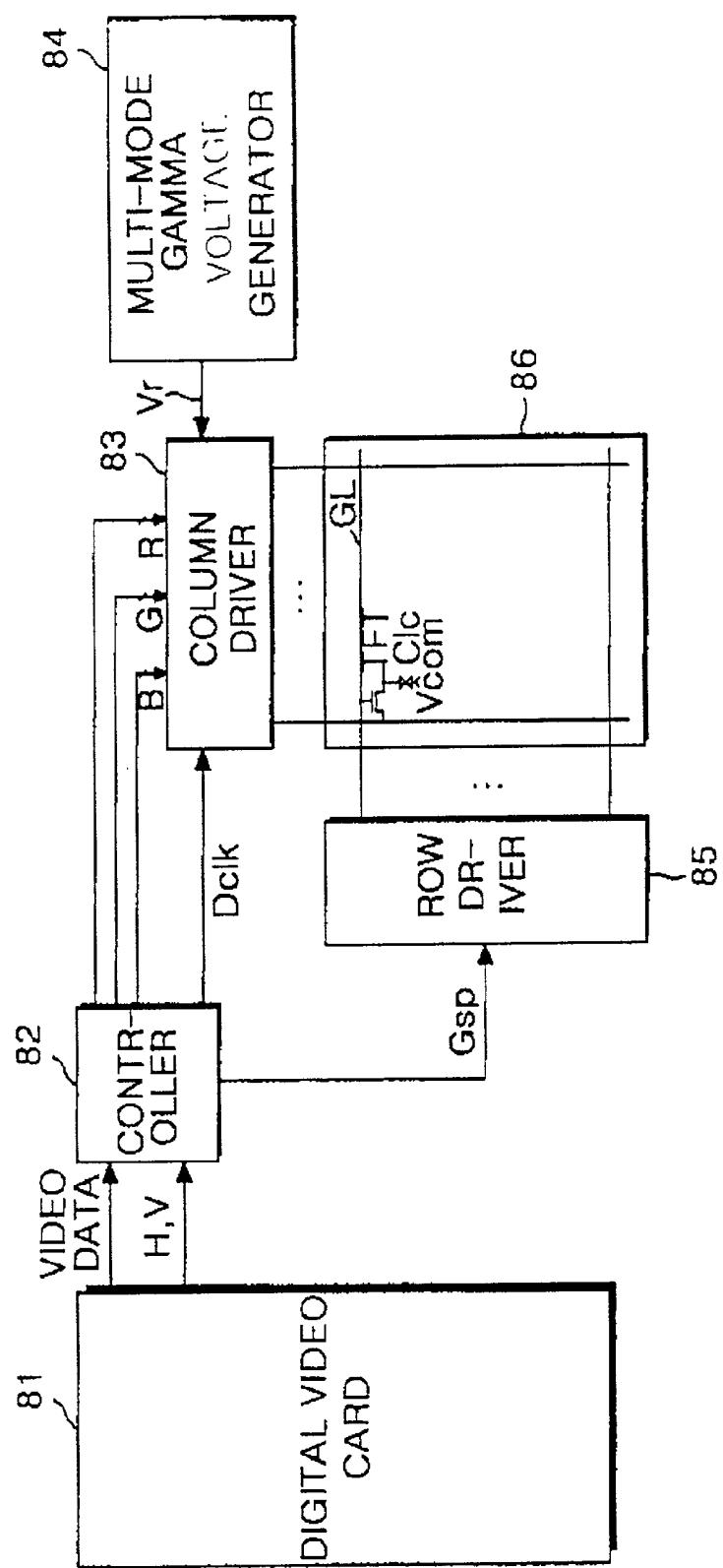

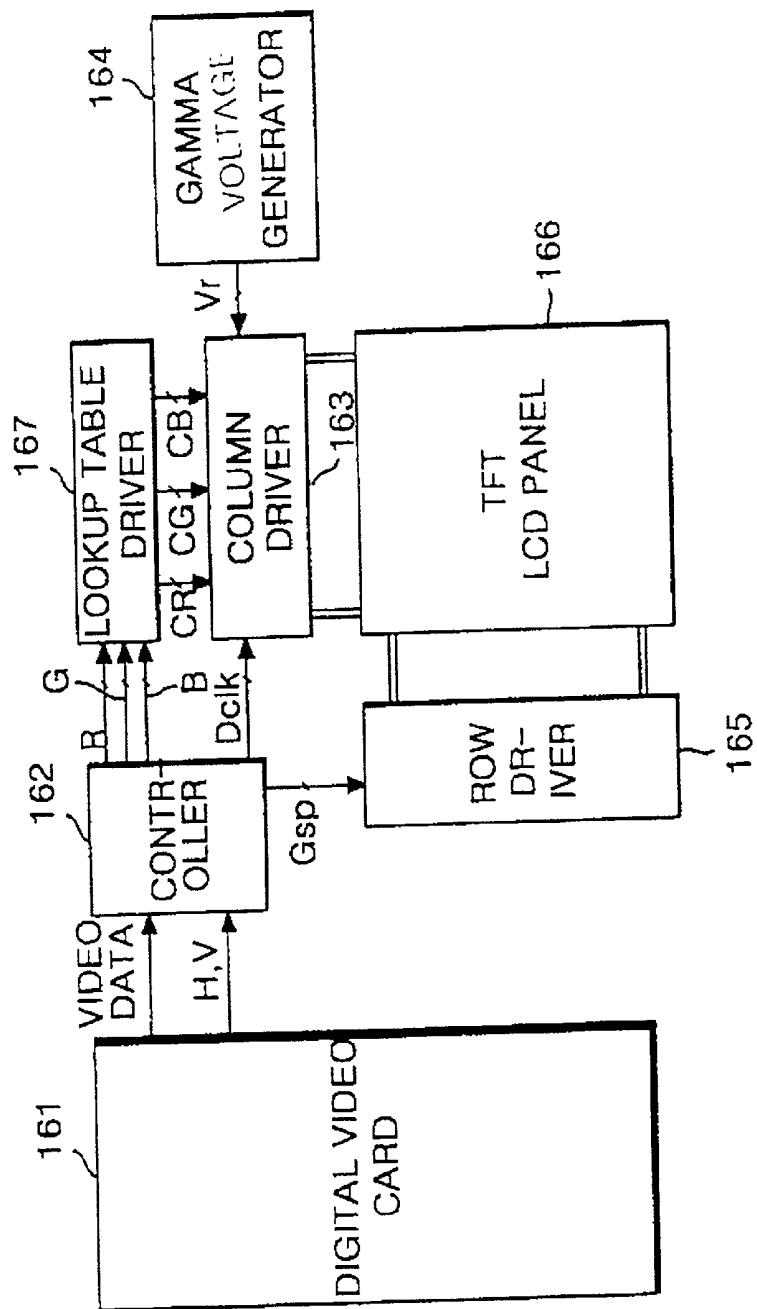

[0034] FIG. 8 is a block diagram showing a configuration of a liquid crystal display according to an embodiment of the present invention;

[0035] FIG. 9 is a detailed block circuit diagram of the multi-mode gamma voltage generator and the column driver shown in FIG. 8;

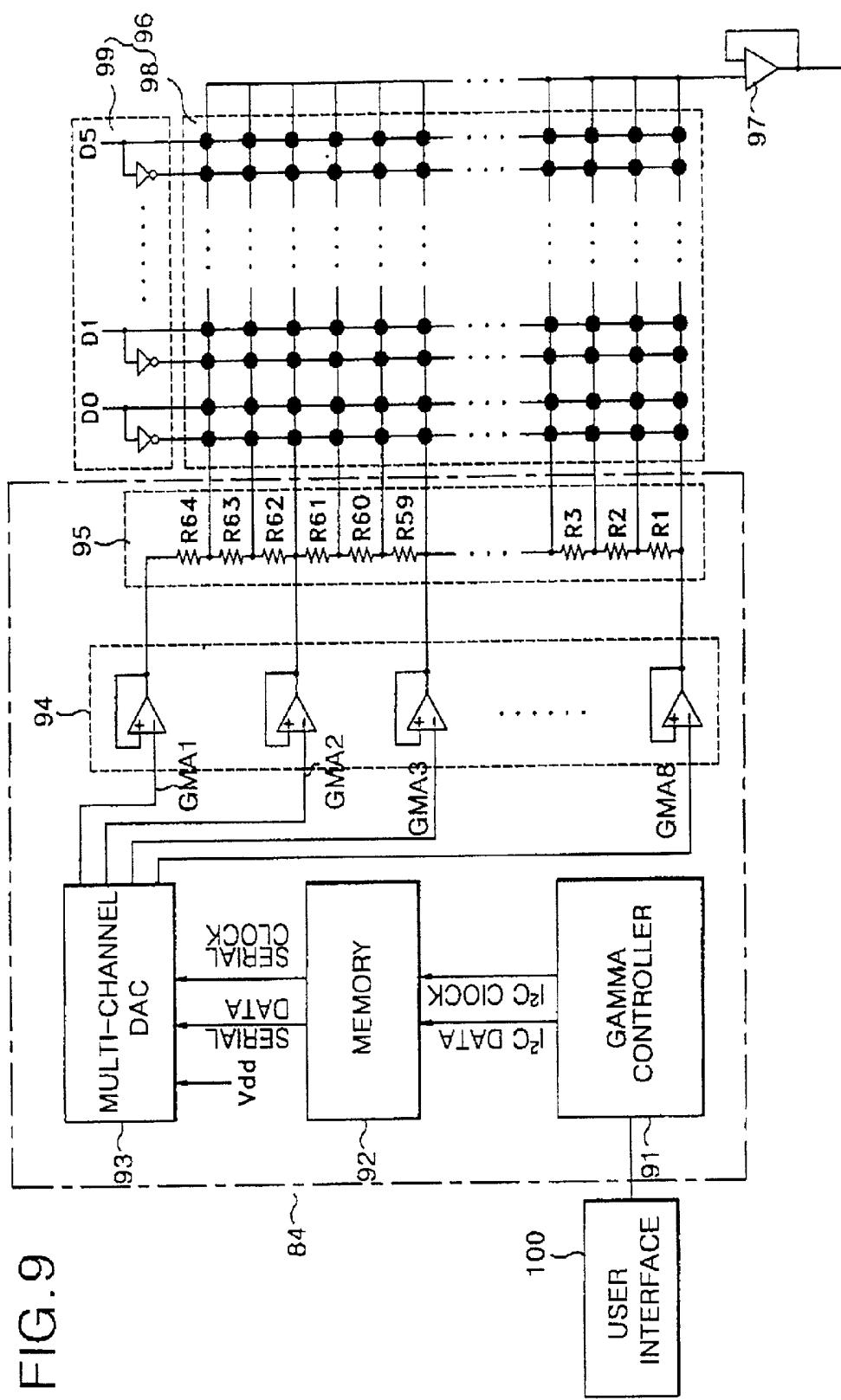

[0036] FIG. 10 is a detailed block diagram of the multi-channel digital to analog converter shown in FIG. 9;

[0037] FIG. 11 illustrates a signal format of gamma data generated from the multi-mode gamma voltage generator shown in FIG. 8;

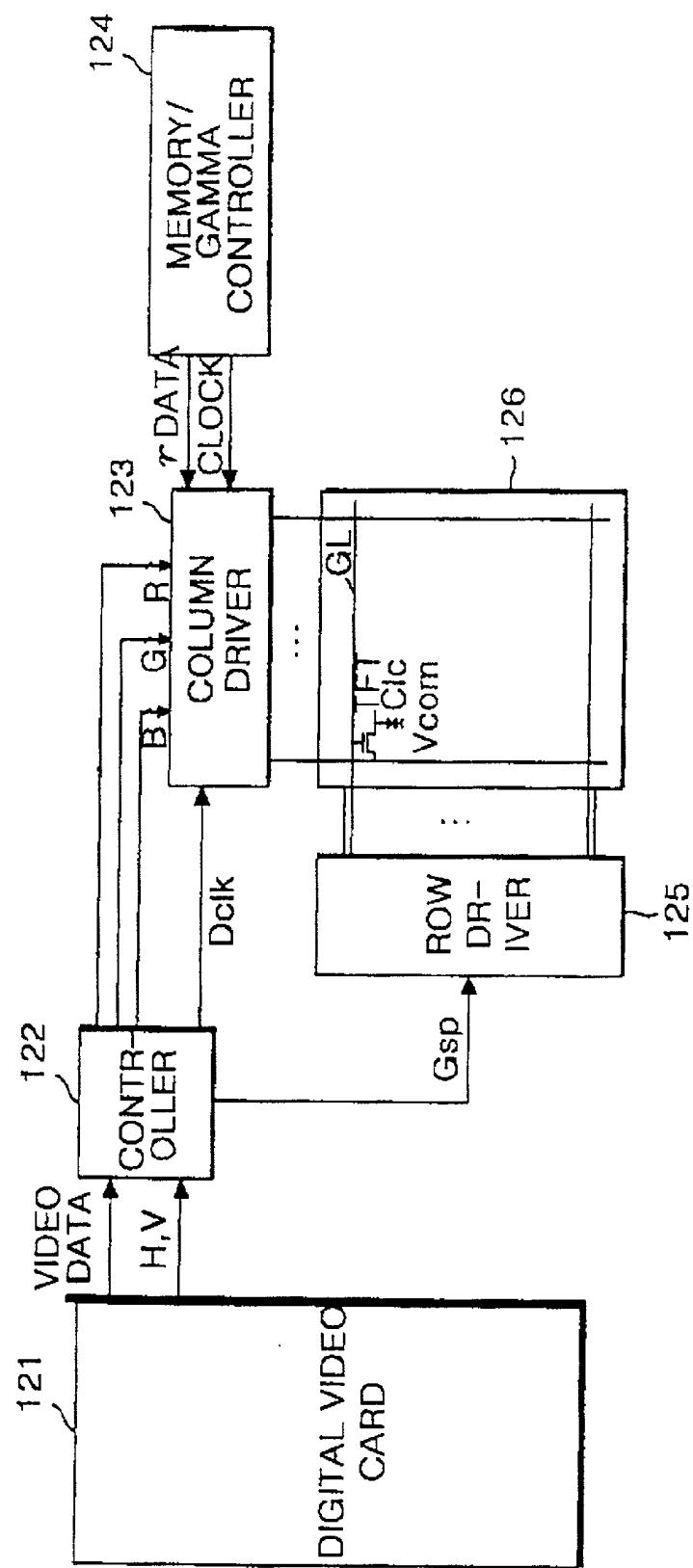

[0038] FIG. 12 is a block diagram showing a configuration of a liquid crystal display according to a second embodiment of the present invention;

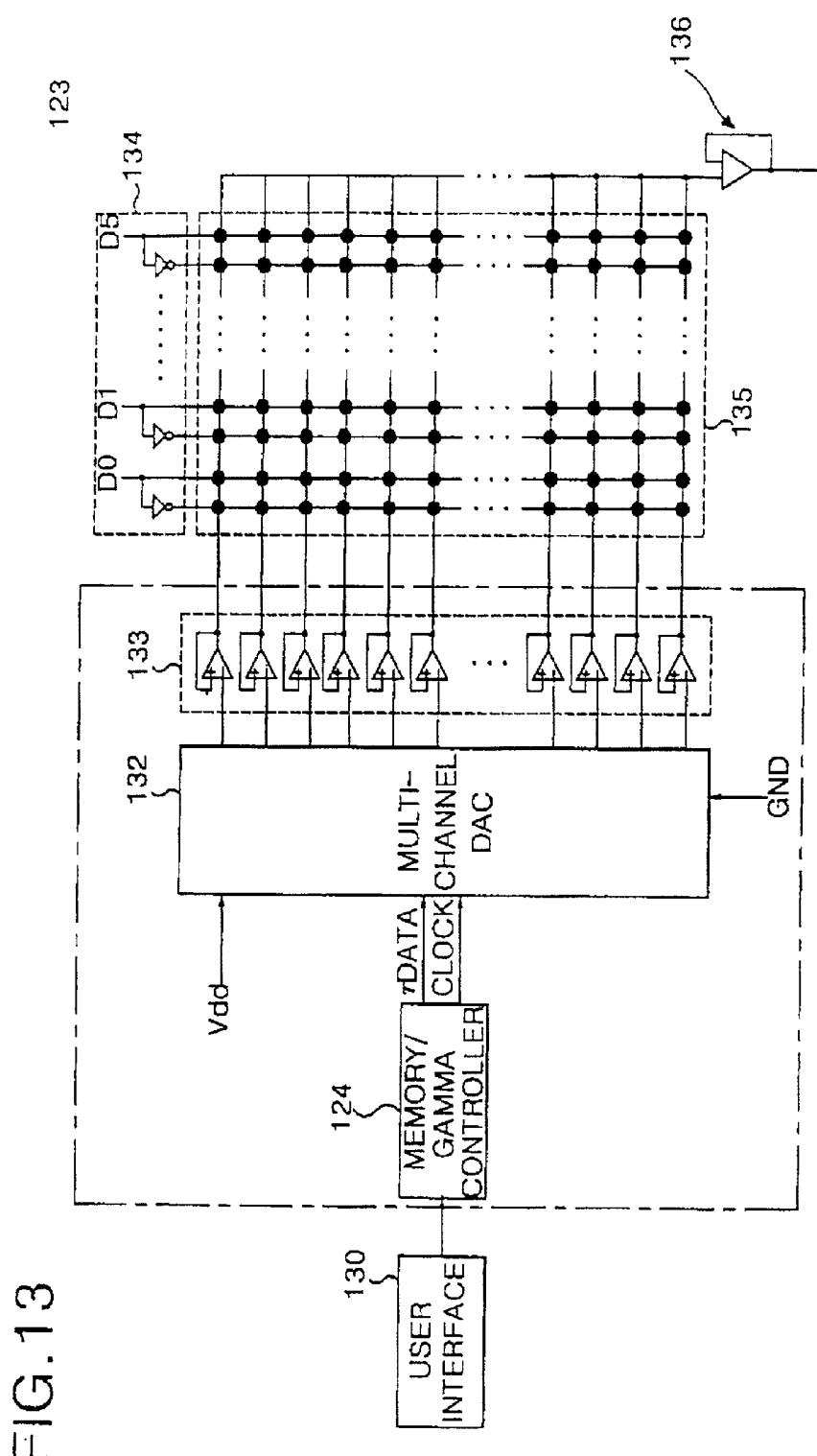

[0039] FIG. 13 is a detailed block circuit diagram of the memory/gamma controller and the column driver shown in FIG. 12;

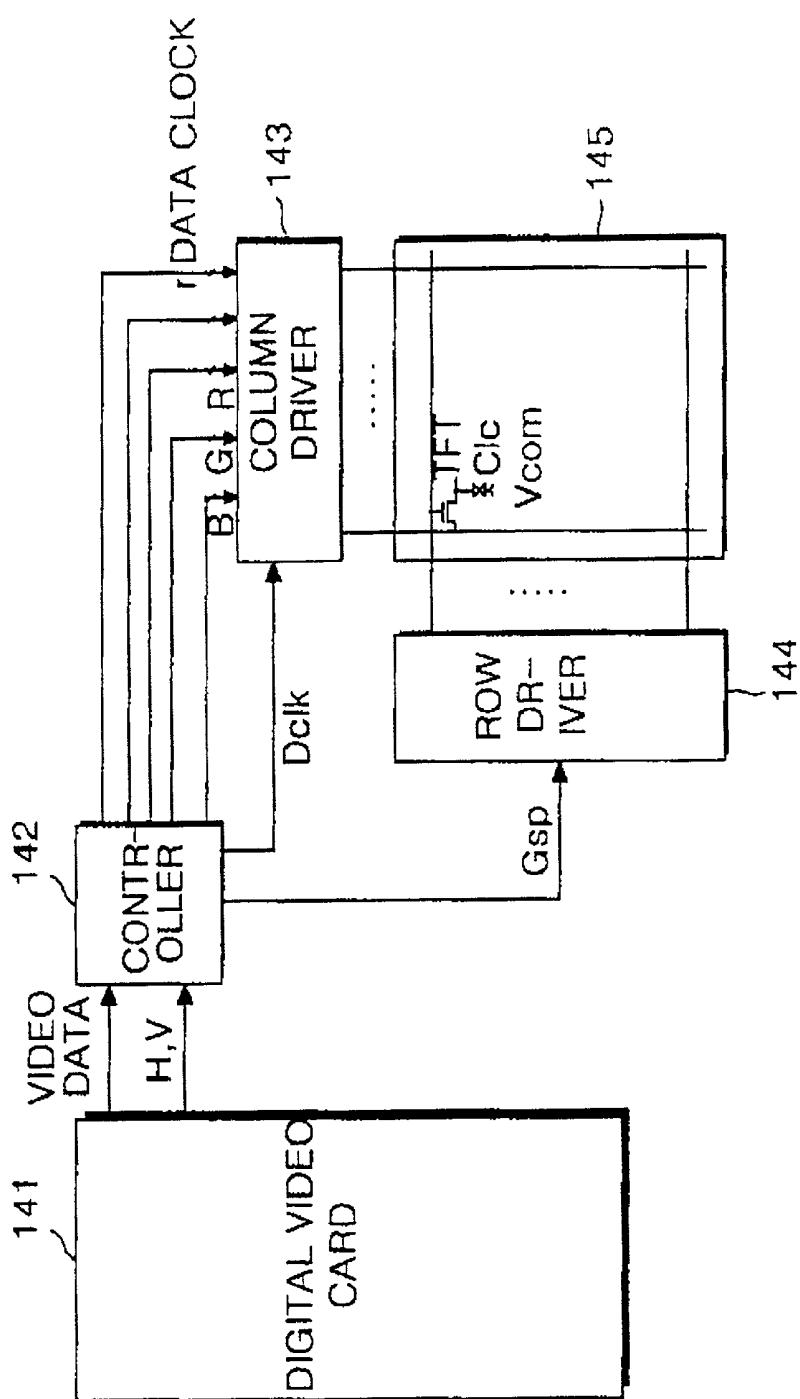

[0040] FIG. 14 is a block diagram showing a configuration of a liquid crystal display according to a third embodiment of the present invention;

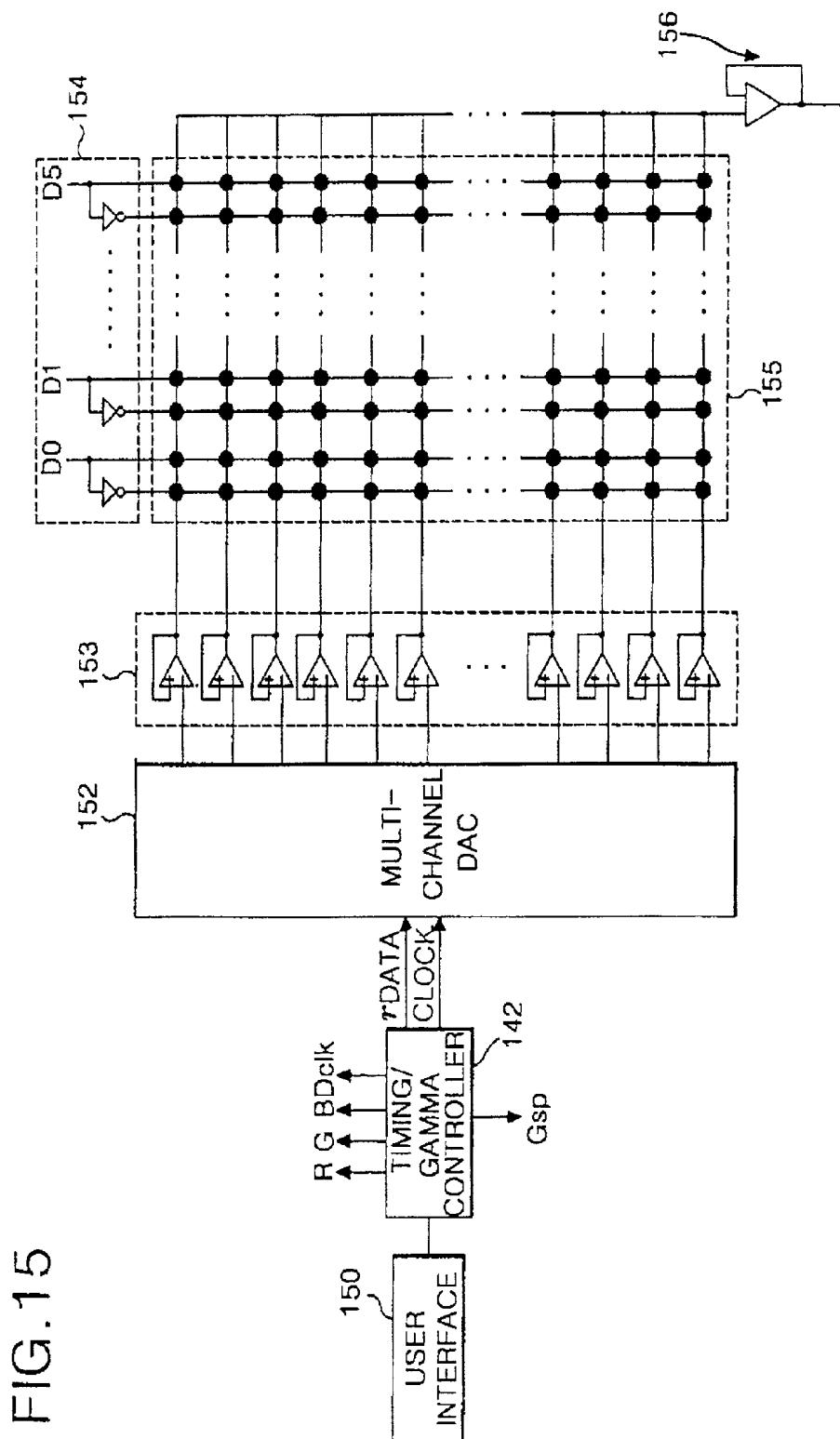

[0041] FIG. 15 is a detailed block circuit diagram of the timing/gamma controller and the column driver shown in FIG. 14;

[0042] FIG. 16 is a block diagram showing a configuration of a liquid crystal display according to a fourth embodiment of the present invention;

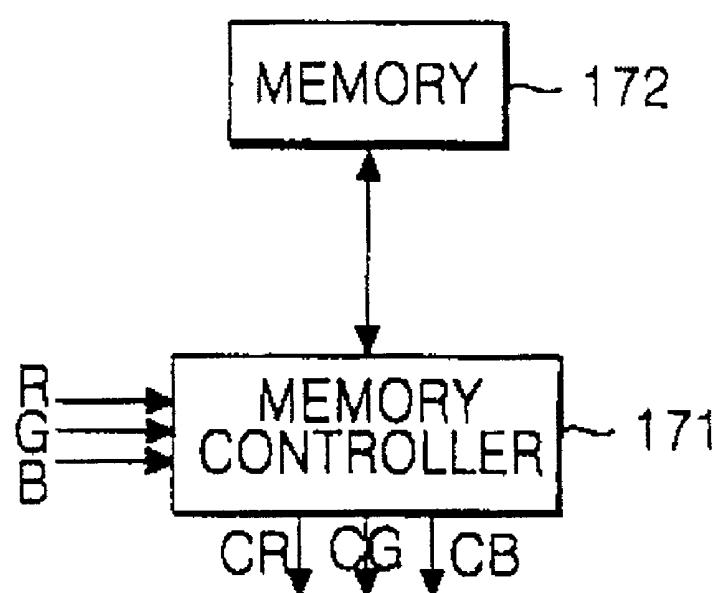

[0043] FIG. 17 is a detailed block diagram of the lookup table driver shown in FIG. 16;

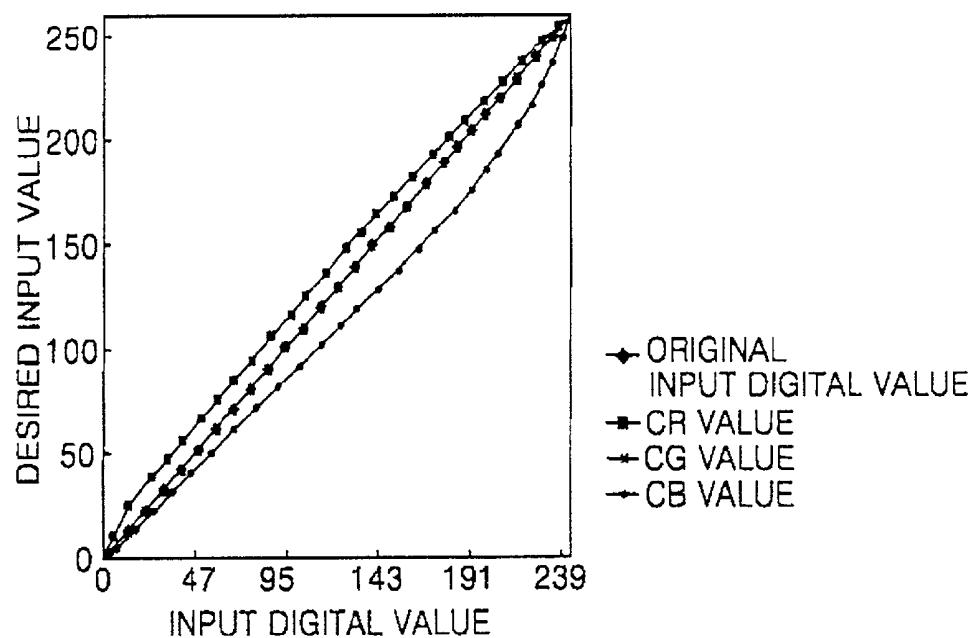

[0044] FIG. 18 is a characteristic graph representing gray levels of data having a color temperature corrected by means of the lookup table driver shown in FIG. 16 and an input digital video data;

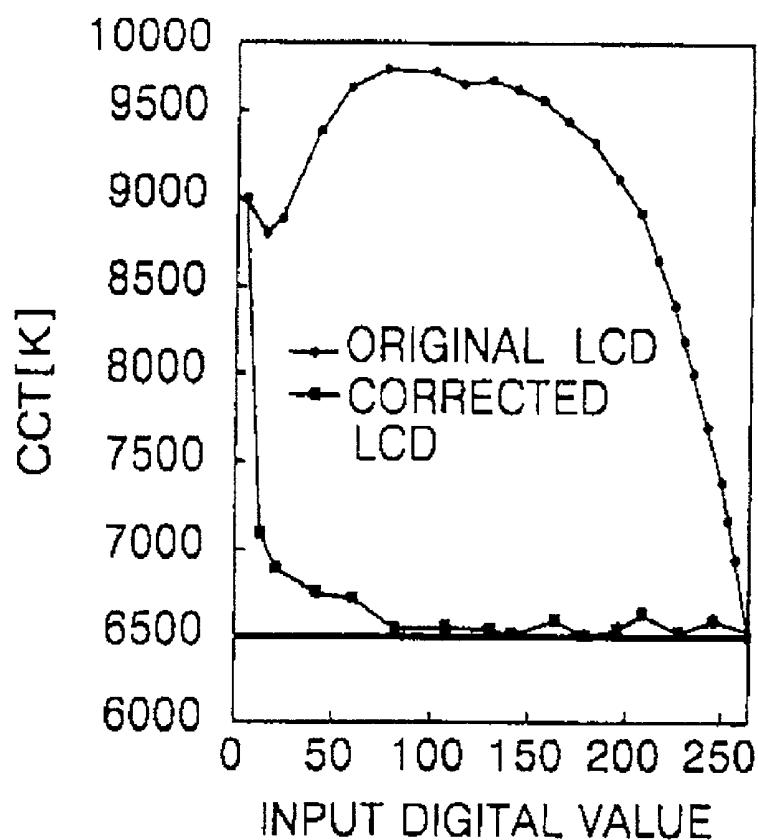

[0045] FIG. 19 is a characteristic diagram for comparing a corrected color temperature in the present liquid crystal panel with the color temperature in the conventional liquid crystal panel;

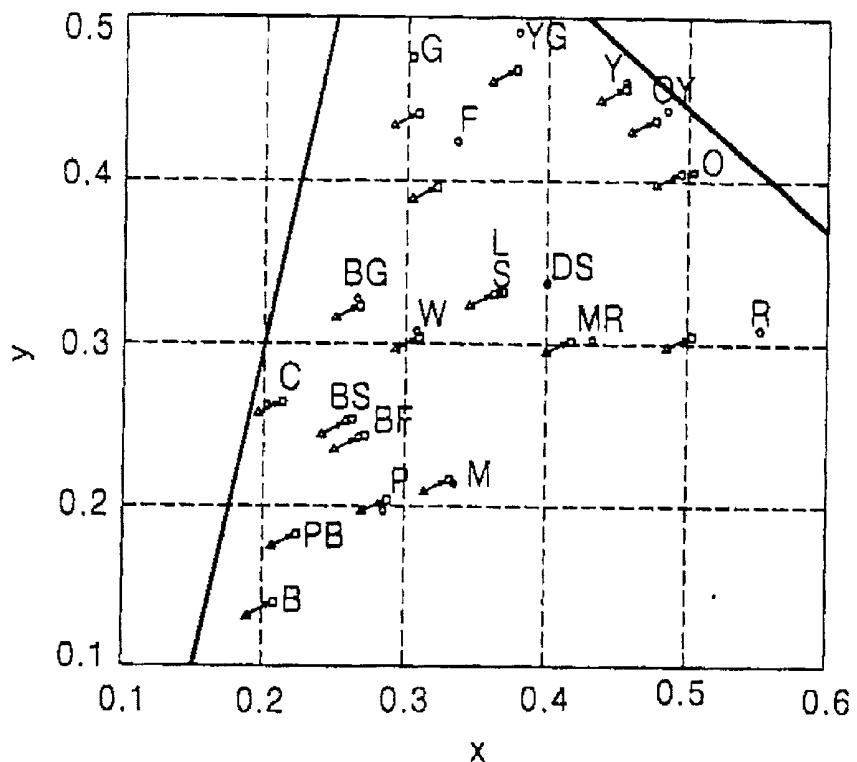

[0046] FIG. 20 is a characteristic graph representing a correlative color temperature of the liquid crystal panel having a corrected color temperature; and

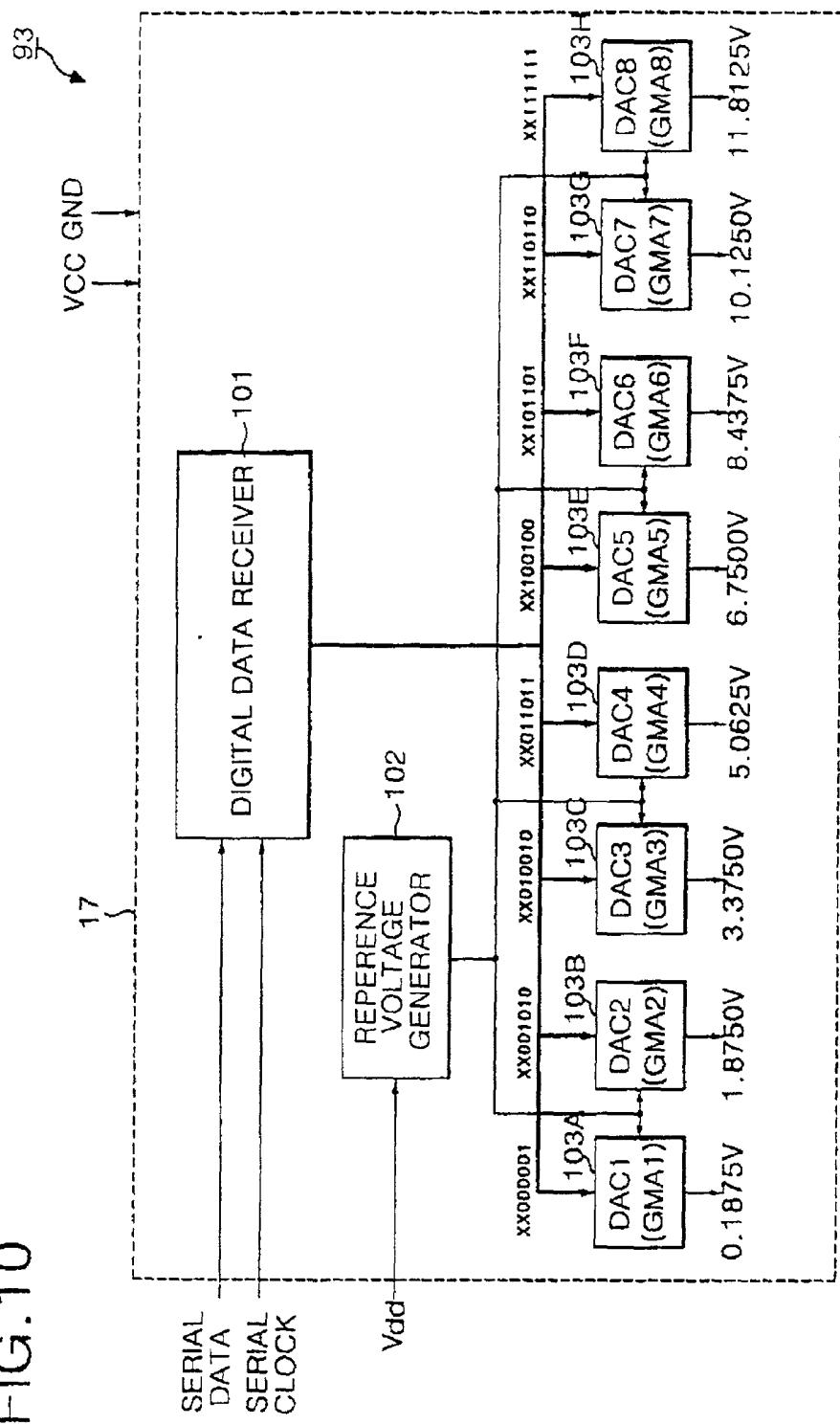

[0047] FIG. 21 is a characteristic graph comparing chrominance co-ordinates of an input image with those of a displayed image in the conventional liquid crystal panel so as to show a color reappearance effect according to a color temperature correction.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

[0048] Referring to FIG. 8, there is shown a liquid crystal display (LCD) according to a first embodiment. The LCD includes a digital video card 81 for converting an input image signal into digital video data, a multi-mode gamma voltage generator 84 for generating a gamma voltage using multi-mode gamma data set in advance in correspondence with various peripheral equipment, a column driver 83 for supplying data to data lines DL of a liquid crystal panel 86, a row driver 85 for sequentially driving gate lines GL of the

liquid crystal panel 86, and a controller 82 for controlling the column driver 83 and the row driver 85.

[0049] The multi-mode gamma voltage generator 84 stores therein gamma data in consideration of an electro-optical characteristic of a liquid crystal device so as to provide a natural display on the liquid crystal panel 86 of an original image input from the peripheral equipment, such as a personal computer, a television, an optical recording medium player or a camcorder. Also, the multi-mode gamma voltage generator 84 is connected to a user interface, for example, an on screen display key on a case, a remote control, a mouse, or a keyboard to select a specified mode gamma data in accordance with an instruction from a user. By utilizing the selected gamma data, the multi-mode gamma voltage generator 84 divides a gamma voltage into a gray level range to be displayed and applies it to the column driver 83.

[0050] A dot clock Dclk, along with red (R), green (G) and blue (B) digital video data, from the controller 82 is input to the column driver 83. The column driver 83 latches the R, G and B digital video data in synchronization with the dot clock Dclk and thereafter corrects the latched data in accordance with a gamma voltage  $V_g$  from the gamma voltage generator 84. Further, the column driver 83 converts the data corrected by the gamma voltage  $V_g$  into analog data to apply it to the data lines DL for each line. To this end, the column driver 83 includes a latch, a digital to analog converter (DAC), an output buffer and an address shift register.

[0051] Referring to FIG. 9, the multi-mode gamma voltage generator 84 includes a gamma controller 91 connected to a user interface 100, and a memory 92, a multi-channel DAC and a buffer unit 94 and a gamma voltage output 95 connected between the gamma controller 91 and a DAC 96 of the column driver 83.

[0052] The gamma controller 91 is connected between the user interface 100 and the memory 92 to control the memory 92 in accordance with a user instruction from the user interface 100. To this end, the gamma controller 91 is connected to the user interface 100 by a wire or wireless system and is connected, via an I<sup>2</sup>C (for example), to the memory 92 to thereby apply I<sup>2</sup>C data interpreting the user instruction and an I<sup>2</sup>C clock to the memory 92. The gamma controller 91 is preferably implemented with a microcomputer.

[0053] The memory 92 is changeable with peripheral equipment and stored therein is a multi-mode gamma data set in consideration of a liquid crystal display characteristic. The gamma data can be experimentally determined to provide a normal picture quality on the liquid crystal panel 86 after displaying signals from the changeable peripheral equipment. Such gamma data is input to the multi-channel DAC 93 as a desired bit (e.g., 6-bit) serial input data to indicate a gamma reference voltage for each mode. The memory 92 is preferably implemented with EEPROM or EPROM, etc.

[0054] The multi-channel DAC 93 is connected between the memory 92 and the buffer unit 94 to interpret serial gamma data inputted from the memory 92, thereby outputting eight gamma reference voltages GMA1 to GMA8 indicated by the serial gamma data. The buffer unit 94 consists of a voltage follower connected, in series, between

an output terminal of the multi-channel DAC 93 and the gamma voltage output 95. The buffer unit 94 stabilizes the eight gamma reference voltages GMA1 to GMA8 and applies them to the gamma voltage output 95. The inputs/outputs of the memory 92 and the multi-channel DAC 93 are synchronized with each other by clock signals, I<sup>2</sup>C clock and Serial Clock.

[0055] The gamma voltage output 95 consists of a serial connection of 64 resistors R1 to R64. The gamma voltage output 95 sub-divides the eight gamma reference voltages GMA1 to GMA8 into 64 gamma voltages and applies them to the DAC 96. The DAC 96 includes a data input 99 receiving 6-bit data D0 to D5 from a latch of the column driver (not shown), and a decoder 98 connected between the data input 99 and the gamma voltage output 95. The data input 99 includes an inverter for inverting a logical value of each data bit so as to generate an inverted signal and a non-inverted signal of the data and to apply them to the decoder 98. The decoder 98 consists of a plurality of logical elements in an array so as to select any one of the 64 gamma voltages  $V_g$  in accordance with the inverted and non-inverted data from the data input 99 and to apply the selected gamma voltage  $V_g$  to the output buffer 97.

[0056] Referring to FIG. 10, the multi-channel DAC 93 is supplied with a driving voltage Vcc and a ground voltage GND, and includes: a data receiver 101 to which a serial gamma data signal, Serial Data, and a clock signal, Serial Clock, are input from the memory 92; a reference voltage generator 102 to which a supply voltage Vdd is input; and a plurality of digital to analog converters (DACs) commonly connected to the data receiver 101 and the reference voltage generator 102.

[0057] The data receiver 101 applies gamma data from the memory 92 commonly to a plurality of DACs 103A to 103H. The reference voltage generator 102 divides the supply voltage Vdd to generate reference voltages having a different voltage level for each mode, and applies the reference voltages to the DACs 103A to 103H.

[0058] As shown in FIG. 11, the gamma data inputted to the DACs 103A to 103H is an 18-bit data packet including one start bit S, four address bits A0 to A3, four sub-address bits SA to SD, one data header bit A, and six gamma data bits D0 to D5. The start bit S indicates a start of the data packet. The address bits A0 to A3 assign each of the DACs 103A to 103H, while the sub-address bits SA to SD assign each address in the DACs 103A to 103H. The header bit A indicates an initiation of the gamma data bits D0 to D5. The DACs 103A to 103H interpret serial gamma data from the data receiver 101 and output eight gamma reference voltages GMA1 to GMA8 assigned by the gamma data.

[0059] An example of the gamma reference voltages GMA1 to GMA8 for each mode, Modes A to D, output from the DACs 103A to 103H is given by the following table:

TABLE 1

| Mode Gamma | Mode A | Mode B | Mode C | Mode D |

|------------|--------|--------|--------|--------|

| GMA 1      | 0.1875 | 0.3750 | 0.5625 | 0.7500 |

| GMA 2      | 1.8750 | 2.0625 | 2.2500 | 2.4375 |

| GMA 3      | 3.3750 | 3.5625 | 3.7500 | 3.9375 |

TABLE 1-continued

| Mode Gamma | Mode A  | Mode B  | Mode C  | Mode D  |

|------------|---------|---------|---------|---------|

| GMA 4      | 5.0625  | 5.2500  | 5.4375  | 5.6250  |

| GMA 5      | 6.7500  | 6.9375  | 7.1250  | 7.3125  |

| GMA 6      | 8.4375  | 8.6250  | 8.8125  | 9.0000  |

| GMA 7      | 10.1250 | 10.3125 | 10.5000 | 10.6875 |

| GMA 8      | 11.8125 | 11.6250 | 11.4375 | 11.2500 |

[0060] As seen from Table 1 and FIG. 10, the DACs 103A to 103H output specified mode gamma reference voltages GMA1 to GMA8 in accordance with a logical value of the gamma data. In the case of outputting a gamma reference voltage in the Mode A, the first DAC 103A responds to a gamma data '000001' to select 0.1 875 V in the reference voltages from the reference voltage generator 102 while the second to eighth DACs 103B to 103H output other gamma reference voltages GMA2 and GMA8 in the Mode A, respectively.

[0061] The gamma reference voltages GMA1 to GMA8 selected for each mode A to D in this manner are divided into 64 gamma voltages by means of the gamma voltage output 95. The gamma voltages in the Mode A are given by the following tables 2-1 and 2-2:

Table 2-1

| Gamma Data  | DAC Output | DAC Output(V) when Vref = 12 V |

|-------------|------------|--------------------------------|

| 0 0 0 0 0 0 | Vss        | 0.0000                         |

| 0 0 0 0 0 1 | Vref/64    | 0.1875                         |

| 0 0 0 0 1 0 | 2Vref/64   | 0.3750                         |

| 0 0 0 0 1 1 | 3Vref/64   | 0.5625                         |

| 0 0 0 1 0 0 | 4Vref/64   | 0.7500                         |

| 0 0 0 1 0 1 | 5Vref/64   | 0.9375                         |

| 0 0 0 1 1 0 | 6Vref/64   | 1.1250                         |

| 0 0 0 1 1 1 | 7Vref/64   | 1.3125                         |

| 0 0 1 0 0 0 | 8Vref/64   | 1.5000                         |

| 0 0 1 0 0 1 | 9Vref/64   | 1.6875                         |

| 0 0 1 0 1 0 | 10Vref/64  | 1.8750                         |

| 0 0 1 0 1 1 | 11Vref/64  | 2.0625                         |

| 0 0 1 1 0 0 | 12Vref/64  | 2.2500                         |

| 0 0 1 1 0 1 | 13Vref/64  | 2.4375                         |

| 0 0 1 1 1 0 | 14Vref/64  | 2.6250                         |

| 0 0 1 1 1 1 | 15Vref/64  | 2.8125                         |

| 0 1 0 0 0 0 | 16Vref/64  | 3.0000                         |

| 0 1 0 0 0 1 | 17Vref/64  | 3.1875                         |

| 0 1 0 0 1 0 | 18Vref/64  | 3.3750                         |

| 0 1 0 0 1 1 | 19Vref/64  | 3.5625                         |

| 0 1 0 1 0 0 | 20Vref/64  | 3.7500                         |

| 0 1 0 1 0 1 | 21Vref/64  | 3.9375                         |

| 0 1 0 1 1 0 | 22Vref/64  | 4.1250                         |

| 0 1 0 1 1 1 | 23Vref/64  | 4.3125                         |

| 0 1 1 0 0 0 | 24Vref/64  | 4.5000                         |

| 0 1 1 0 0 1 | 25Vref/64  | 4.6875                         |

| 0 1 1 0 1 0 | 26Vref/64  | 4.8750                         |

| 0 1 1 0 1 1 | 27Vref/64  | 5.0625                         |

| 0 1 1 1 0 0 | 28Vref/64  | 5.2500                         |

| 0 1 1 1 0 1 | 29Vref/64  | 5.4375                         |

| 0 1 1 1 1 0 | 30Vref/64  | 5.6250                         |

| 0 1 1 1 1 1 | 31Vref/64  | 5.8125                         |

| 1 0 0 0 0 0 | 32Vref/64  | 6.0000                         |

| 1 0 0 0 0 1 | 33Vref/64  | 6.1875                         |

| 1 0 0 0 1 0 | 34Vref/64  | 6.3750                         |

| 1 0 0 0 1 1 | 35Vref/64  | 6.5625                         |

| 1 0 0 1 0 0 | 36Vref/64  | 6.7500                         |

| 1 0 0 1 0 1 | 37Vref/64  | 6.9375                         |

| 1 0 0 1 1 0 | 38Vref/64  | 7.1250                         |

Table 2-1-continued

| Gamma Data  | DAC Output | DAC Output(V) when Vref = 12 V |

|-------------|------------|--------------------------------|

| 1 0 0 1 1 1 | 39Vref/64  | 7.3125                         |

| 1 0 1 0 0 0 | 40Vref/64  | 7.5000                         |

| 1 0 1 0 0 1 | 41Vref/64  | 7.6875                         |

| 1 0 1 0 1 0 | 42Vref/64  | 7.8750                         |

| 1 0 1 0 1 1 | 43Vref/64  | 8.0625                         |

| 1 0 1 1 0 0 | 44Vref/64  | 8.2500                         |

| 1 0 1 1 0 1 | 45Vref/64  | 8.4375                         |

| 1 0 1 1 1 0 | 46Vref/64  | 8.6250                         |

| 1 0 1 1 1 1 | 47Vref/64  | 8.8125                         |

| 1 1 0 0 0 0 | 48Vref/64  | 9.0000                         |

| 1 1 0 0 0 1 | 49Vref/64  | 9.1875                         |

| 1 1 0 0 1 0 | 50Vref/64  | 9.3750                         |

| 1 1 0 0 1 1 | 51Vref/64  | 9.5625                         |

| 1 1 0 1 0 0 | 52Vref/64  | 9.7500                         |

| 1 1 0 1 0 1 | 53Vref/64  | 9.9375                         |

| 1 1 0 1 1 0 | 54Vref/64  | 10.1250                        |

| 1 1 0 1 1 1 | 55Vref/64  | 10.3125                        |

| 1 1 1 0 0 0 | 56Vref/64  | 10.4500                        |

| 1 1 1 0 0 1 | 57Vref/64  | 10.6875                        |

| 1 1 1 0 1 0 | 58Vref/64  | 10.8750                        |

| 1 1 1 0 1 1 | 59Vref/64  | 11.0625                        |

| 1 1 1 1 0 0 | 60Vref/64  | 11.2500                        |

| 1 1 1 1 0 1 | 61Vref/64  | 11.4375                        |

| 1 1 1 1 1 0 | 62Vref/64  | 11.6250                        |

| 1 1 1 1 1 1 | 64Vref/64  | 11.8125                        |

[0062] Referring now to FIG. 12, there is shown an LCD according to a second embodiment. The LCD includes a digital video card 121 for converting an input image signal into a digital video data, a memory/gamma controller 124 for applying to a column driver 123 multi-mode gamma data "γData" preset in advance in correspondence with various peripheral equipment, a row driver 85 for sequentially driving gate lines GL of a liquid crystal panel 126, and a controller 122 for controlling the column driver 123 and the row driver 125.

[0063] The memory/gamma controller 124 is stored with multi-mode gamma data γ Data in consideration of an electro-optical characteristic of a liquid crystal device so as to provide a natural display of an original image inputted from the peripheral equipment, such as a personal computer, a television, an optical recording medium player or a camcorder, on the liquid crystal panel 126. Also, the memory/gamma controller 124 is connected to a user interface to select a specified mode gamma data γ Data in accordance with an instruction from a user. The gamma data γ Data selected in this manner is input to the column driver 123. The gamma data γ Data and a clock signal Clock are delivered, preferably via an I<sup>2</sup>C bus line, to the column driver 123.

[0064] The column driver 123 receives a dot clock Dclk, along with red (R), green (G) and blue (B) digital video data, from the controller 122 and, at the same time, receives the gamma data γ Data and the clock signal Clock from the memory/gamma controller 124. The column driver 123 latches the R, G and B digital video data in synchronization with the dot clock Dclk and thereafter generates a gamma voltage in the Mode A to D selected by the gamma data γ Data using the latched data. The gamma voltage generated from the column driver 123 is selected in accordance with a brightness of the video data to be applied to the data lines DL of the liquid crystal panel 126. To this end, the column driver

**123** includes a latch, a digital to analog converter (DAC), an output buffer and an address shift register to process data from the controller **122**. Further, the column driver includes a circuit for responding to the gamma data  $\gamma$  Data to generate a gamma voltage.

[0065] Referring to **FIG. 13**, the column driver **123** includes a multi-channel DAC **132** for receiving the gamma data  $\gamma$  Data and the clock signal Clock from the memory/gamma controller **124**, a data input **134** for receiving data from a latch (not shown), a buffer unit **133** and a decoder **135** connected between the data input **134** and the multi-channel DAC **132**, and an output buffer **136** connected between the decoder **135** and the data lines DL of the liquid crystal panel **126**.

[0066] The memory/gamma controller **124** is connected between a user interface **130** and the column driver **123** to output the gamma data  $\gamma$  Data in the specified modes, Mode A to Mode D, along with the clock signal Clock in accordance with a user instruction from the user interface **130**. To this end, the memory/gamma controller **124** is gamma data having logical values set in response to a plurality of modes corresponding to the peripheral equipment interchangeable with the LCD. The memory/gamma controller **124** is integrated into a single chip in which the gamma controller **91** in **FIG. 9** is integrated with the memory **92** in **FIG. 9**.

[0067] The multi-channel DAC **132** is provided with: a plurality of DACs for dividing a supply voltage Vdd to generate gamma reference voltages included in each mode, Mode A to D; DACs for selecting gamma reference voltages in accordance with a logical value of the gamma data  $\gamma$  Data; and DACs for dividing gamma reference voltages selected for each mode, Modes A to D, to generate 64 gamma voltages. Accordingly, since the multi-channel DAC **132** uses the above-mentioned DACs so as to generate gamma voltages selected for each mode, it does not require voltage-dividing resistors.

[0068] The buffer unit **133** consists of a voltage follower connected, in series, between an output terminal of the multi-channel DAC **132** and the decoder **135**. The buffer unit **133** stabilizes the 64 gamma voltages selected for each mode and applies them to the decoder **135**. The data input **134** includes an inverter for inverting a logical value of each data bit so as to generate an inverted signal and a non-inverted signal of the data and to apply them to the decoder **135**. The decoder **135** consists of a plurality of logical elements in an array so as to select any one of the 64 gamma voltages in accordance with the inverted and non-inverted data from the data input **99** and to apply the selected gamma voltage to the output buffer **136**. The multi-channel DAC **132** and the buffer unit **133** and the data input **134**, the decoder **135** and the output buffer are integrated into a single chip within the column driver **123**.

[0069] Referring to **FIG. 14**, there is shown an LCD according to a third embodiment. The LCD includes a digital video card **141** for converting an input image signal into digital video data, a timing/gamma controller **142** for applying multi-mode gamma data  $\gamma$  Data and R, G and B data preset in advance in correspondence with various peripheral equipment to a column driver **143**, and a row driver **144** for sequentially driving gate lines GL of a liquid crystal panel **145**.

[0070] The timing/gamma controller **142** supplies R, G and B digital video data from the digital video card **141** and

applies a gate start pulse GSP to the row driver **144**. Also, the timing/gamma controller **142** applies a timing signal generated by horizontal/vertical signals H and V input from the digital video card **141** to the column driver **143** and the row driver **144**. The timing/gamma controller **142** is stored with multi-mode gamma data “ $\gamma$  Data” in consideration of an electro-optical characteristic of a liquid crystal device so as to provide a natural display on the liquid crystal panel **126** of an original image input from the peripheral equipment, such as a personal computer, a television, an optical recording medium player or a camcorder. Further, the timing/gamma controller **142** is connected to a user interface to select a specified mode gamma data  $\gamma$  Data in accordance with an instruction from a user. The gamma data  $\gamma$  Data selected in this manner is input to the column driver **143**. The gamma data  $\gamma$  Data and clock signal Clock are delivered, preferably bus line, to the column driver **143**. To this end, the timing/gamma controller **142** is integrated into a single chip incorporating the gamma controller **91** and the memory **92** in **FIG. 9** and the controller **122** in **FIG. 12**.

[0071] The column driver **143** receives a dot clock Dclk, along with red (R), green (G) and blue (B) digital video data, from the timing/gamma controller **142** and, at the same time, receives the gamma data  $\gamma$  Data and the clock signal Clock from the timing/gamma controller **142**. The column driver **143** latches the R, G and B digital video data in synchronization with the dot clock Dclk and thereafter generates a gamma voltage in the Mode A to D selected by the gamma data  $\gamma$  Data using the latched data. The gamma voltage generated from the column driver **143** is selected in accordance with a brightness of the video data to be applied to the data lines DL of the liquid crystal panel **145**. To this end, the column driver **143** includes a latch, a digital to analog converter (DAC), an output buffer and an address shift register so as to process data from the timing/gamma controller **142**. Further, the column driver **143** includes a circuit for responding to the gamma data  $\gamma$  Data to generate a gamma voltage.

[0072] Referring to **FIG. 15**, the column driver **143** includes a multi-channel DAC **152** for receiving the gamma data  $\gamma$  Data and the clock signal Clock from the timing/gamma controller **142**, a data input **154** for receiving data from a latch (not shown), a buffer unit **153** and a decoder **155** connected between the data input **154** and the multi-channel DAC **152**, and an output buffer **156** connected between the decoder **155** and the data lines DL of the liquid crystal panel **145**.

[0073] The multi-channel DAC **152** of the column driver **143** is connected between the timing/gamma controller **142** and the buffer unit **153** to interpret the gamma data  $\gamma$  Data input from the timing/gamma controller **142**, thereby outputting 64 gamma voltages corresponding to the modes, Mode A to D, indicated by the gamma data  $\gamma$  Data. The multi-channel DAC **152** is provided with: a plurality of DACs for dividing a supply voltage Vdd to generate gamma reference voltages included in each mode, Mode A to D; DACs for selecting gamma reference voltages in accordance with a logical value of the gamma data  $\gamma$  Data, and DACs for dividing gamma reference voltages selected for each mode, Mode A to D, to generate 64 gamma voltages. Accordingly, since the multi-channel DAC **152** uses the above DACs so as to generate gamma voltages selected for each mode, it does not require voltage-dividing resistors.

[0074] The buffer unit 153 consists of a voltage follower connected, in series, between an output terminal of the multi-channel DAC 152 and the decoder 155. The buffer unit 153 stabilizes the 64 gamma voltages selected for each mode and applies them to the decoder 155. The data input 154 includes an inverter for inverting a logical value of each data bit so as to generate an inverted signal and a non-inverted signal of the data and to apply them to the decoder 155. The decoder 155 consists of a plurality of logical elements in an array so as to select any one of the 64 gamma voltages in accordance with the inverted and non-inverted data from the data input 154 and to apply the selected gamma voltage to the output buffer 156. The multi-channel DAC 152 and the buffer unit 153 and the data input 154, the decoder 155 and the output buffer 156 are integrated into a single chip within the column driver 143.

[0075] Referring to FIG. 16, there is shown an LCD according to a fourth embodiment. The LCD includes a digital video card 161 for converting an input image signal into digital video data, a column driver 163 for supplying data to data lines DL of a liquid crystal panel 166, a row driver 165 for sequentially driving gate lines GL of a liquid crystal panel 165, a multi-mode gamma voltage generator 164 for generating a gamma voltage, a lookup table driver 167 for correcting a color temperature of video data, and a controller 162 for controlling the column driver 163 and the row driver 165.

[0076] The digital video card 161 converts an analog input image signal into a digital image signal suitable for the liquid crystal panel 166 and detects a synchronous signal included in the image signal. The controller 162 supplies R, G and B digital video data from the digital video card 161 to the lookup table driver 167. The controller 162 generates a dot clock Dclk and a gate start pulse GSP using horizontal/vertical synchronizing signals H and V input from the digital video card 161 to perform a timing control of the column driver 163 and the row driver 165.

[0077] The column driver 163 is supplied with R, G and B data having color temperatures corrected by the lookup table driver 167. The column driver 163 corrects the color temperature correction data CR, CG and CB from the lookup table driver 167 by a gamma voltage  $V_g$  applied from the gamma voltage generator 164 and supplies the connected data to the data lines DL of the liquid crystal panel 166.

[0078] The row driver 165 includes a shift register for responding to the gate start pulse GSP input from the controller 162 to sequentially generate a scanning pulse, and a level shifter for shifting a voltage of the scanning pulse to a voltage level suitable for driving the liquid crystal cell. Video data at the data line DL is applied to a pixel electrode of the liquid crystal cell Clc by the TFT in response to the scanning pulse input from the row driver 165. The gamma voltage generator 164 generates a gamma voltage  $V_g$  set to have a different direct current level in accordance with a gray level value, in consideration of an electro-optical characteristic of the liquid crystal device to be applied to the column driver 163.

[0079] The lookup table driver 167 corrects a color temperature of the R, G and B video data from the controller 162 such that a correlative color temperature of data displayed on the liquid crystal panel 166 is identical to a  $D_{65}$  light source having approximately 6500 K. As shown in FIG. 17,

the lookup table driver 167 includes a memory 172 for storing the color temperature correction data CR, CG and CB, and a memory controller 171 for controlling the memory 172.

[0080] The color temperature correction data CR, CG and CB stored in the memory 172 is determined by a procedure to be described below. First, the conventional LCD having no lookup table driver is driven to measure gray level values of input digital video data R, G and B and a correlative color temperature of a display image according to the gray level values. The gray level values of the input video digital data R, G and B are adjusted such that color co-ordinates according to each gray level value of the input digital video data R, G and B becomes  $D_{65}$  and the brightness maintains the brightness values of the input digital video data R, G and B as they were before color correction. If a display image for this adjusted data is identical to color co-ordinates of the  $D_{65}$  light source and the brightness of the input digital video data R, G and B is maintained as-is, then the adjusted data is stored as color temperature correction data CR, CG and CB in the lookup table memory 172. The color temperature correction data CR, CG and CB other than the color temperature correction data CR, CG and CB, determined in this manner, is determined by a linear interpolation as shown in FIG. 18.

[0081] The memory controller 171 reads out from the memory 172 the color temperature correction data CR, CG and CB corresponding to gray level values of the video data R, G and B input from the timing controller 162 and supplies the data to the column driver 163.

[0082] Since the conventional LCD has a high correlative color temperature, it expresses a blue color mainly. On the other hand, in the LCD according to the present invention, a brightness value of the blue color temperature correction data CB reduced to be less than that of the input digital video data R, G and B as can be seen from FIG. 18. A brightness value of the red color temperature correction data CR is increased to be more than that of the input digital video data R, G and B. A brightness value of the green color temperature correction data CG is virtually unchanged and is almost identical to that of the input digital video data R, G and B. For instance, when brightness values of the red, green and blue digital video data R, G and B in the conventional LCD having no lookup table driver are 195, 195 and 195, respectively, a brightness value of a real display image is 111 cd/m<sup>2</sup>.

[0083] A brightness value of the red color temperature correction data CR correcting such input digital video data R, G and B is increased to 204, while a brightness value of the blue color temperature correction data CB is decreased into 180. A brightness value of the green color temperature correction data CG becomes 195, which is identical to that of the green input digital video data G. A real display image for the color temperature correction data CR, CG and CB after correcting the input digital video data in this manner has a brightness value of 111 cd/m<sup>2</sup>, which is equal to that of the input digital video data before the correction.

[0084] If a gray level range to be displayed is 0 to 255, then values close to 0 (i.e., a minimum value of the linear correction data CR, CG and CB) and 255 (i.e., a maximum value of the linear correction data CR, CG and CB) are not corrected to maintain the contrast ratio, and become iden-

tical to those of the input digital video data. Such non-correction of values close to a gray level value of 0 is caused by a fact that such correction almost does not make a color correction effect because a color perceiving ability of an observer is deteriorated in accordance with a reduction of the brightness in light of an observer's eyesight characteristic.

[0085] FIG. 19 shows the result of a modeling experiment for obtaining a color temperature characteristic of a real image displayed on the liquid crystal panel 166 after correcting data using the color temperature correction data CR, CG and CB.

[0086] Referring to FIG. 19, a color temperature of the conventional LCD varies over a range of approximately 8800 K to 9800 K with respect to a gray level range of the input digital video data corresponding to a range of 0 to 100, while it varies over a range of approximately 9800 K to 6500 K with respect to a gray level range of the input digital video data corresponding to a range of 100 to 255. The conventional LCD has a correlative color temperature characteristic distributed widely, whereas an LCD having corrected the input digital video data using the color temperature correction data CR, CG and CB maintains a color temperature of about 6500 K, equal to the D<sub>65</sub> light source, in all gray level values except a gray level range of 0 to 50. The LCD according to the present invention allows color co-ordinates for each gray level value to be almost constantly maintained as shown in FIG. 20.

[0087] As can be seen from FIG. 21, there is a large difference between chrominance coordinates of the input digital video data R, G and B and those of a real image displayed on the liquid crystal panel 166. On the other hand, the LCD of FIG. 16 displays data corrected by the color temperature correction data CR, CG and CB in the lookup table, thereby allowing chrominance co-ordinates of a real image on the liquid crystal panel 168 to be almost close to the input digital video data R, G and B so as to make a natural expression of a desired color.

[0088] In FIG. 20 and FIG. 21, the horizontal axis and the vertical axis represent independent parameters x and y, respectively, in the CIE co-ordinate system.

[0089] As described above, according to the present invention, gamma data is stored in the memory for each mode corresponding to various peripheral equipment interchangeable with the LCD, and a desired gamma voltage is generated according to gamma data having a specified mode selected by a user, using the gamma data for each mode stored in the memory. Further, a color temperature characteristic from the input digital video data is corrected in consideration of a color temperature characteristic of the liquid crystal panel. Such a color temperature characteristic correction maintains the brightness and contrast of an input image as-is, to thereby make a natural expression of a desired color on the liquid crystal panel. Accordingly, it becomes possible to improve a display quality of an image input from various peripheral equipment interchangeable with the LCD as well as to provide a better picture quality by a correction of a color temperature characteristic displayed on the liquid crystal panel.

[0090] Although the present invention has been explained by the embodiments shown in the drawings described above,

it should be understood to the ordinary skilled person in the art that the invention is not limited to the embodiments, but rather that various changes or modifications thereof are possible without departing from the spirit of the invention. Accordingly, the scope of the invention shall be determined only by the appended claims and their equivalents.

What is claimed is:

1. A gamma voltage correcting apparatus for a liquid crystal display wherein a liquid crystal pixel is arranged at each intersection between data lines and gate lines and video data is corrected by a preset gamma voltage to display an image, said apparatus comprising:

memory means for storing gamma data for controlling the gamma voltage for each of at least two modes;

control means for accessing the gamma data for each mode in response to an instruction from a user; and

a multi-channel gamma voltage generator for responding to the gamma data for a mode selected by the control means to generate n gamma voltages (wherein n is an integer) having a different voltage level indicated by the gamma data for the selected mode.

2. The gamma voltage correcting apparatus according to claim 1, further comprising a column driver for correcting the video data using the gamma voltage from the multi-channel gamma voltage generator and supplying the corrected video data to the data lines.

3. The gamma voltage correcting apparatus according to claim 2, further comprising a buffer unit for buffering a signal having the gamma voltage from the multi-channel gamma voltage generator to apply it to the column driver.

4. The gamma voltage correcting apparatus according to claim 1, further comprising a voltage-dividing resistor for dividing the n gamma voltages into m gamma voltages (wherein m is an integer larger than n) having a different voltage level.

5. The gamma voltage correcting apparatus according to claim 1, where in the multi-channel gamma voltage generator includes:

a data receiver for receiving the gamma data and a clock signal in the m mode selected by the control means;

a reference voltage generator for dividing an externally supplied supply voltage to generate the gamma voltages having a different voltage level; and

n gamma voltage selectors (wherein n is an integer) for interpreting the gamma data from the data receiver to select a reference voltage indicated by the gamma data for the gamma voltages from the reference voltage generator.

6. The gamma voltage correcting apparatus according to claim 1, wherein the memory means and the control means are integrated into a single integrated circuit.

7. The gamma voltage correcting apparatus according to claim 2, further comprising:

a row driver for sequentially applying a scanning pulse to the gate lines to drive the gate lines; and

a timing controller for supplying red, green and blue digital video data to the column driver and for applying a desired timing control signal to the row driver.

**8.** The gamma voltage correcting apparatus according to claim 7, wherein the memory means, the control means and the timing controller are integrated into a single integrated circuit.

**9.** A video data correcting apparatus for a liquid crystal display which includes a liquid crystal panel having a liquid crystal pixel arranged at each intersection between data lines and the gate lines, said apparatus comprising:

memory means for storing a lookup table in which color temperature correction data for correcting a color temperature characteristic of an input image is set in correspondence with a gray level value of the input image;

memory control means for accessing the lookup table of the memory means in accordance with the gray level value of the input image to read out the color temperature correction data corresponding to the gray level value of the input image; and

data driving means for driving the data lines using the color temperature correction data from the memory control means.

**10.** The gamma voltage correcting apparatus according to claim 9, further comprising:

a row driver for sequentially applying a scanning pulse to the gate lines to drive the gate lines; and

a timing controller for supplying the input image to the memory control means and for applying a desired timing control signal to the row driver.

**11.** The gamma voltage correcting apparatus according to claim 9, wherein the color temperature correction data is measured after controlling the input image such that a color temperature of a displayed image on the liquid crystal display maintains approximately 6500 K.

**12.** The gamma voltage correcting apparatus according to claim 9, wherein a displayed image of the liquid crystal display on which the color temperature correction data is displayed maintains a brightness and a contrast equal to the input image.

**13.** A method of correcting a gamma voltage in a liquid crystal display wherein a liquid crystal pixel is arranged at each intersection between data lines and gate lines and video data is corrected by a preset gamma voltage to display an image, said method comprising:

storing gamma data for controlling the gamma voltage for each of at least two modes;

accessing the gamma data for each mode in response to an instruction from a user;

selecting any one of the gamma data for each mode; and

responding to the gamma data for the selected mode to generate n gamma voltages (wherein n is an integer) having a different voltage level indicated by the gamma data in the selected mode.

**14.** The method according to claim 13, wherein the gamma data is set differently in accordance with each mode set in correspondence with peripheral equipment interchangeable with the liquid crystal display.

**15.** The method according to claim 13, wherein the gamma data is set differently in accordance with each mode

set in correspondence with an optical recording medium player, a television image signal display device, and a camcorder.

**16.** The method according to claim 13, further comprising the steps of:

dividing the n gamma voltages into m gamma voltages (wherein m is an integer larger than n) having a different voltage level; and

correcting the video data using the m gamma voltages and supplying the corrected video data to the data lines.

**17.** The method according to claim 16, further comprising:

buffering the m gamma voltages and applying the buffered m gamma voltages to the column driver.

**18.** A method of correcting video data in a liquid crystal display which includes a liquid crystal panel having a liquid crystal pixel arranged at each intersection between data lines and gate lines, said method comprising:

providing a lookup table in which color temperature correction data for correcting a color temperature characteristic of an input image is set in correspondence with a gray level value of the input image;

accessing the lookup table in accordance with the gray level value of the input image to read out color temperature correction data corresponding to the gray level value of the input image; and

driving the data lines using the color temperature correction data.

**19.** The method according to claim 18, wherein the color temperature correction data is data measured after controlling the input image such that a color temperature of a displayed image on the liquid crystal display maintains approximately 6500 K.

**20.** The method according to claim 18, wherein a displayed image of the liquid crystal display on which data corrected by the color temperature correction data is displayed maintains a brightness and a contrast equal to the input image.

**21.** A device for providing a desired gamma voltage for a liquid crystal display (LCD), said device comprising:

a memory for storing gamma data corresponding to a plurality of modes;

a controller for receiving an external mode signal and in response thereto selecting selected gamma data from the memory; and

means for generating a plurality of gamma reference voltages according to the selected gamma data.

**22.** The device of claim 21, wherein the means for generating the plurality of gamma reference voltages comprises a multi-channel digital-to-converter (DAC).

**23.** The device of claim 22 wherein the multi-channel digital-to-converter comprises:

a reference voltage generator for receiving a supply voltage and generating a plurality of reference voltages;

a data receiver for receiving the reference voltages and the selected gamma data and generating therefrom the plurality of gamma reference voltages.

**24.** The device of claim 21, further comprising:

a gamma voltage generator receiving the plurality of gamma reference voltages and generating therefrom a plurality of gamma voltages.

**25.** The device of claim 21, wherein the gamma voltage generator comprises a resistor divider network.

**26.** The device of claim 24, further comprising means for selecting the selected gamma voltage from the plurality of gamma voltages.

**27.** The device of claim 26, wherein the means for selecting the selected gamma voltage comprises a DAC.

**28.** The device of claim 21, wherein each of the plurality of modes corresponds to a different source video generator for providing video data to the LCD.

**29.** A method of providing a desired gamma voltage for a liquid crystal display, comprising:

storing gamma data corresponding to a plurality of modes in a memory device;

receiving an external mode signal and in response thereto selecting selected gamma data from the memory; and

generating a plurality of gamma reference voltages according to the selected gamma data.

**30.** The method of claim 29, wherein generating the plurality of gamma reference voltages comprises:

receiving a supply voltage and generating therefrom a plurality of reference voltages; and

generating the plurality of gamma reference voltages from the gamma data and the plurality of reference voltages.

**31.** The method of claim 29, further comprising generating a plurality of gamma voltages from the plurality of gamma reference voltages.

**32.** The method of claim 31, wherein generating the a plurality of gamma voltages comprises dividing the plurality of gamma reference voltages in a divider network.

**33.** The method of claim 31, further comprising selecting the selected gamma voltage from the plurality of gamma voltages.

\* \* \* \* \*

|                |                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于校正液晶显示器中的伽马电压和视频数据的装置和方法                                                                                                |         |            |

| 公开(公告)号        | <a href="#">US20020063666A1</a>                                                                                           | 公开(公告)日 | 2002-05-30 |

| 申请号            | US09/892997                                                                                                               | 申请日     | 2001-06-28 |

| [标]申请(专利权)人(译) | 康SIN HO<br>JANG KUN KYEONG<br>李相TAE<br>欧盟JUNG TAECK<br>SOHNG KYU IK<br>李尚勋<br>GOO BYUNG JOON                              |         |            |

| 申请(专利权)人(译)    | 康SIN HO<br>JANG KUN KYEONG<br>李相TAE<br>欧盟JUNG TAECK<br>SOHNG KYU IK<br>李尚勋<br>GOO BYUNG JOON                              |         |            |

| 当前申请(专利权)人(译)  | 康SIN HO<br>JANG KUN KYEONG<br>李相TAE<br>欧盟JUNG TAECK<br>SOHNG KYU IK<br>李尚勋<br>GOO BYUNG JOON                              |         |            |

| [标]发明人         | KANG SIN HO<br>JANG KYEONG KUN<br>LEE SANG TAE<br>EU JUNG TAECK<br>SOHNG KYU IK<br>LEE SANG HOON<br>GOO BYUNG JOON        |         |            |

| 发明人            | KANG, SIN HO<br>JANG, KYEONG KUN<br>LEE, SANG TAE<br>EU, JUNG TAECK<br>SOHNG, KYU IK<br>LEE, SANG HOON<br>GOO, BYUNG JOON |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H04N5/66                                                                                      |         |            |

| CPC分类号         | G09G3/2092 G09G3/3696 G09G2320/0666 G09G2320/0276 G09G2320/0606 G09G2310/027                                              |         |            |

| 优先权            | 1020000036213 2000-06-28 KR<br>1020000085270 2000-12-29 KR                                                                |         |            |

| 其他公开文献         | US7298352                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>                                                                           |         |            |

## 摘要(译)

一种液晶显示器中的伽马电压和视频数据校正装置和方法，其能够改善LCD的显示质量，其中，用于控制伽马电压的伽马数据被存储用于至少两种模式中的每一种。响应于来自用户的指令访问每个模式的伽马数据，以选择每个模式的任何一个伽马数据。响应于所选模式的伽马数据，产生n个伽马电压（其中n是整数），每个伽马电压具有由所选模式中的伽马数据指示的不同电压电平。在视频数据校正方法中，提供查找表，其中用于校正输入图像的色温特性的色温校正数据被设置为与输入图像的灰度级值相对应。根据输入图像的灰度值访问查找表，以读出与输入图像的灰度值对应的色温校正数据。数据线由色温校正数据驱动。