US 20020036609A1

(19) United States

(12) Patent Application Publication

Kajihara et al.

(10) Pub. No.: US 2002/0036609 A1

(43) Pub. Date: Mar. 28, 2002

(54) LIQUID CRYSTAL DRIVER AND LIQUID CRYSTAL DISPLAY INCORPORATING THE SAME

(76) Inventors: Noriyuki Kajihara, Nara-Shi (JP); Yoshinori Ogawa, Yamatotakada-Shi (JP)

Correspondence Address:

**BIRCH STEWART KOLASCH & BIRCH**

**PO BOX 747**

**FALLS CHURCH, VA 22040-0747 (US)**

(21) Appl. No.: 09/964,572

(22) Filed: Sep. 28, 2001

## (30) Foreign Application Priority Data

Sep. 28, 2000 (JP) ..... 2000-297529

Jul. 3, 2001 (JP) ..... 2001-202539

## Publication Classification

(51) Int. Cl.<sup>7</sup> ..... G09G 3/36

(52) U.S. Cl. ..... 345/87

## (57) ABSTRACT

The present invention includes:

standard voltage producing means for producing  $2^n$  tone display voltages from incoming first reference voltages in accordance with n-bit display data; and selecting means for selecting a voltage from the  $2^n$  tone display voltages in accordance with incoming display data, for transmission to a liquid crystal panel through a plurality of output terminals with no further processing,

wherein the standard voltage producing means includes:

generation means for generating a second reference voltage from adjacent two of the first reference voltages arranged in ascending or descending order, the second reference voltage having an intermediate level between those of the adjacent first reference voltages;

buffer means for impedance-converting the second reference voltage for output; and

voltage dividing means for producing a voltage having an intermediate level between those of the adjacent first reference voltages and of adjacent ones of the first and second reference voltages by voltage division, so as to produce the  $2^n$  tone display voltages.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG.13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

## LIQUID CRYSTAL DRIVER AND LIQUID CRYSTAL DISPLAY INCORPORATING THE SAME

### FIELD OF THE INVENTION

[0001] The present invention relates to liquid crystal drivers for driving a liquid crystal panel (liquid crystal display section) and liquid crystal displays including the driver, in particular to liquid crystal drivers that are small in size and low in power consumption and liquid crystal displays including the driver.

### BACKGROUND OF THE INVENTION

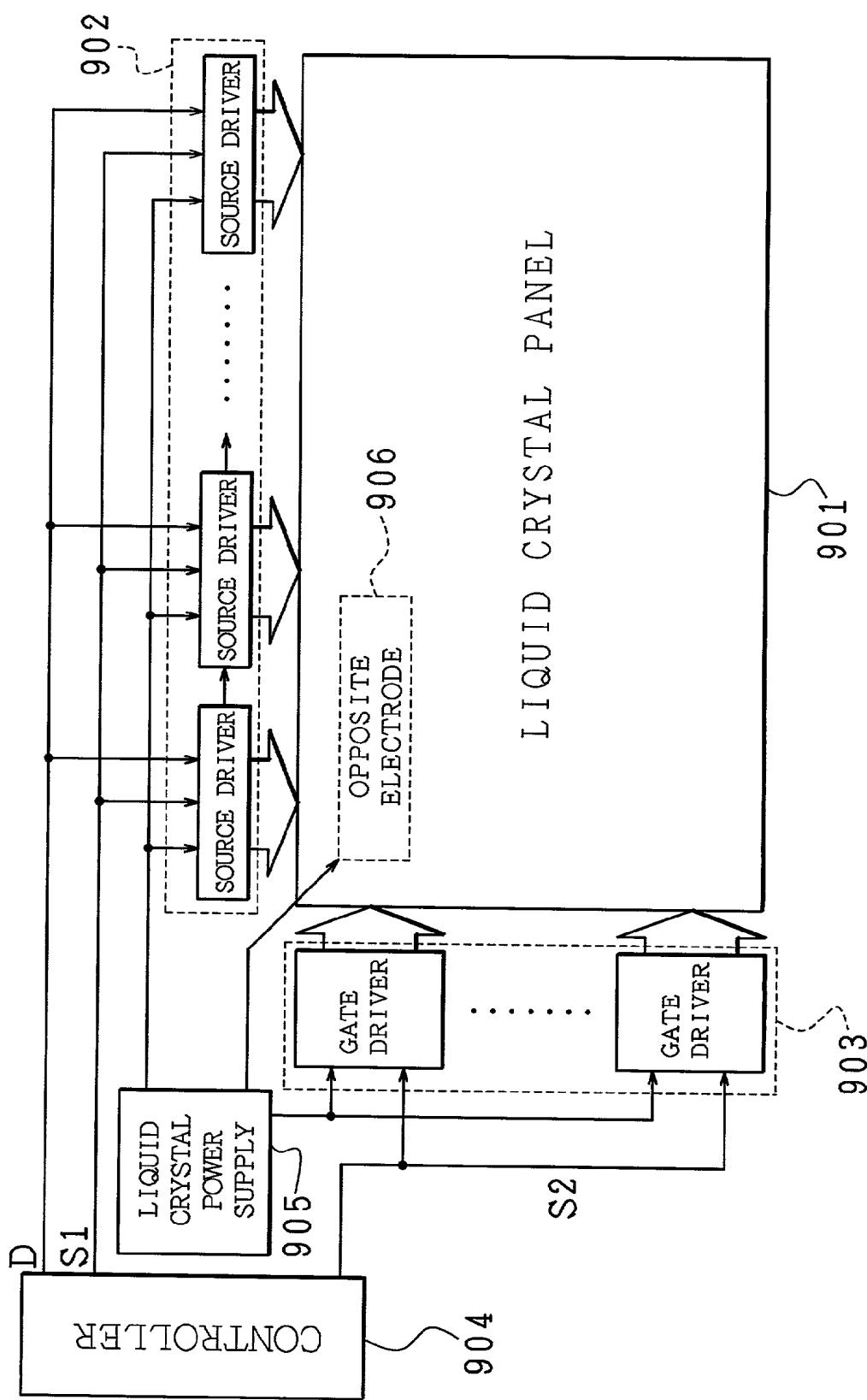

[0002] Referring to FIG. 9, a block diagram is shown depicting a thin film transistor (TFT) liquid crystal display, which is a typical example of active matrix liquid crystal displays.

[0003] The liquid crystal display includes a liquid crystal display section and a liquid crystal driver driving the display section. The liquid crystal display section is made based on a TFT liquid crystal panel 901 in which there are provided a liquid crystal display element (not shown) and an opposite electrode (common electrode) 906.

[0004] Meanwhile, the liquid crystal driver is formed by IC-based source drivers 902, IC-based gate drivers 903, a controller 904, and a liquid crystal power supply 905.

[0005] Each of the source drivers 902 and the gate drivers 903 is typically fabricated from an IC (Integrated Circuit) chip placed on a wired film, such as a tape carrier package (TCP). The mounting of the IC chip on a liquid crystal panel is done by connecting the IC chip to the ITO (Indium Tin Oxide) terminals of the liquid crystal panel or by direct thermocompression of the IC chip to the ITO terminals with an intervening anisotropic conductive film (ACF).

[0006] In some cases, the controller 904, liquid crystal power supply 905, source drivers 902, and gate drivers 903 are entirely or partly integrated on a single chip to fit in a reduced size of the liquid crystal display. FIG. 9 shows these components individually according to their functions.

[0007] The controller 904 supplies digitized display data (for example, RGB signals corresponding to red, green, and blue) and various control signals to the source drivers 902 and gate drivers 903. Major control signals supplied to the source drivers 902 include a horizontal synchronizing signal, a start pulse signal, and a source driver clock signal which are indicated as S1 in the diagram. Major control signals supplied to the gate drivers 903 include a vertical synchronizing signal and a gate driver clock signal which are indicated as S2 in the diagram. The power source to drive the ICs are omitted in the diagram.

[0008] The liquid crystal power supply 905 supplies a liquid crystal panel display voltage (more specifically, in the present invention, a reference voltage from which tone display voltages are produced) to the source drivers 902 and gate drivers 903.

[0009] The controller 904, receiving the display data from a member not shown in the diagram, transmits the data to the source drivers 902 in the form of a digital signal as the display data D. Each source driver 902 latches the incoming digital display data serially and subsequently converts the latched data from digital to analog based on the incoming

horizontal synchronizing signal (alternatively referred to as latch signal Ls as shown in FIG. 13). The source driver 902 then supplies the D/A converted data, i.e., the analog voltage for tone displays (tone display voltage), from its liquid crystal drive voltage output terminal over a later-detailed source signal line 1004 to an associated liquid crystal display element (not shown) in the liquid crystal panel 901.

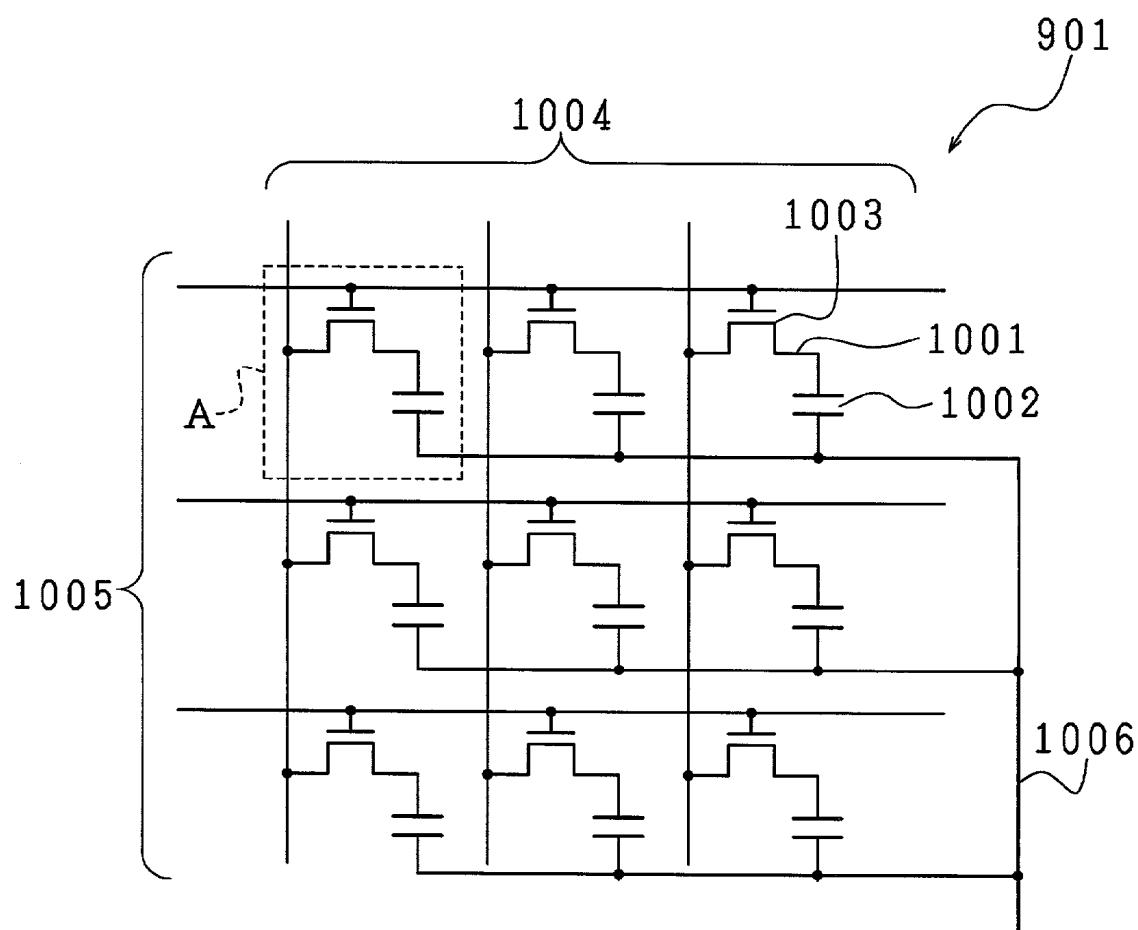

[0010] Now, the liquid crystal panel 901 will be described. FIG. 10 shows the structure of the liquid crystal panel 901. The liquid crystal panel 901 is provided with pixel electrodes 1001, pixel capacitors 1002, TFTs 1003 for turning on/off the application of voltages to the respective pixels, source signal lines 1004, gate signal lines 1005, and an opposite electrode 1006 (an equivalent to the opposite electrode 906 in FIG. 9). In the figure, the region identified as "A" encloses liquid crystal display elements for one pixel.

[0011] The source signal lines 1004 are fed from the source drivers 902 with tone display voltages according to the brightness of the pixels required for a display. The gate signal lines 1005 are fed from the gate drivers 903 with scan signals to sequentially turn on the TFTs 1003 row by row. As the scan signal turns on the TFT 1003, permitting a voltage to be applied through the source signal line 1004 to the pixel electrode 1001 connected to the drain of the TFT 1003, the pixel capacitor 1002 between the pixel electrode 1001 and the opposite electrode 1006 is charged. This changes the transmittance of the liquid crystal to visible light, effecting a display.

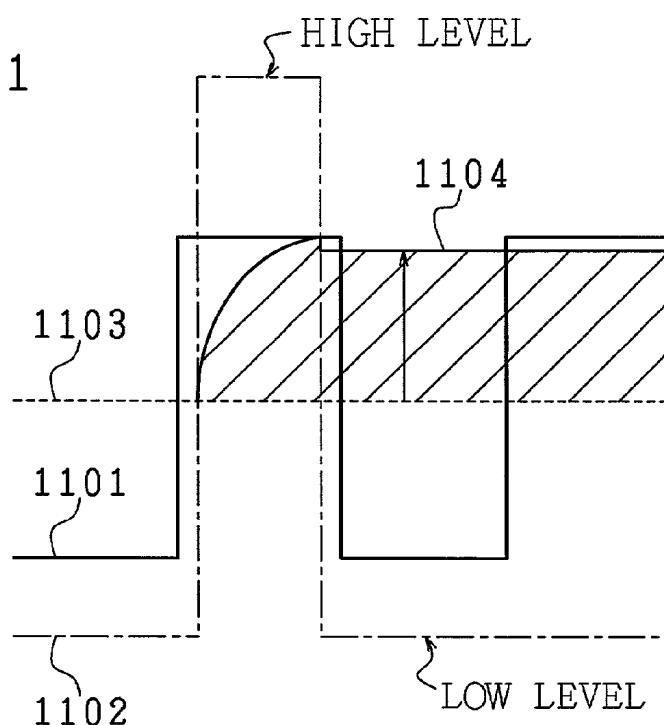

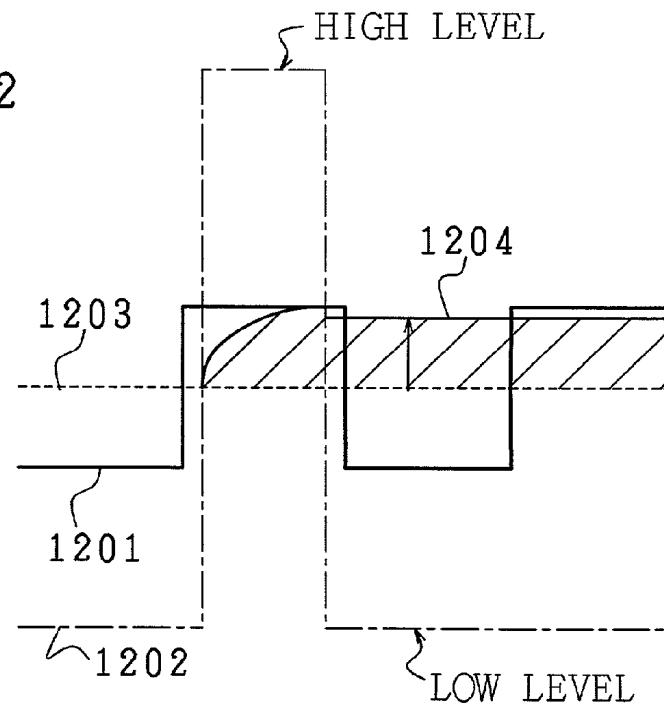

[0012] FIGS. 11 and 12 show an example of a liquid crystal drive waveform. In the figures, 1101 and 1201 identify a drive signal output from the source driver 902; 1102 and 1202 a drive signal output from the gate driver 903; 1103 and 1203 the potential of the opposite electrode 1006; and 1104 and 1204 the potential of the pixel electrode 1001. The voltage across the liquid crystal material is equal to the potential difference between the pixel electrode 1001 and the opposite electrode 1006, which is shown by slant lines in the figure.

[0013] For example, in FIG. 11, the TFT 1003 is on when the drive signal output 1102 from the gate driver 903 is high, causing the difference between the drive signal output 1101 from the source driver 902 and the potential 1103 of the opposite electrode 1006 to be applied to the pixel electrode 1001. The drive signal output 1102 from the gate driver 903 subsequently goes LOW. This turns off the TFT 1003, but does not change the foregoing voltage applied to the pixel due to the provision of the pixel capacitor 1002. The same description holds true with the case of FIG. 12.

[0014] FIGS. 11 and 12 show cases of different voltages being applied to the liquid crystal material. A higher voltage is applied in the case of FIG. 11 than in the case of FIG. 12. The voltage across the liquid crystal, when varied in an analog manner as above, causes the transmittance of the liquid crystal to light to vary in an analog manner; a tone display is thus produced. The number of displayed tones is determined by the number of analog voltages available for application to the liquid crystal.

[0015] The present invention is directed to standard voltage generator circuits and output circuits for use in tone display circuits that are very large in size and very high in power consumption. For these reasons, the following will describe the liquid crystal driver with a focus on the source drivers 902.

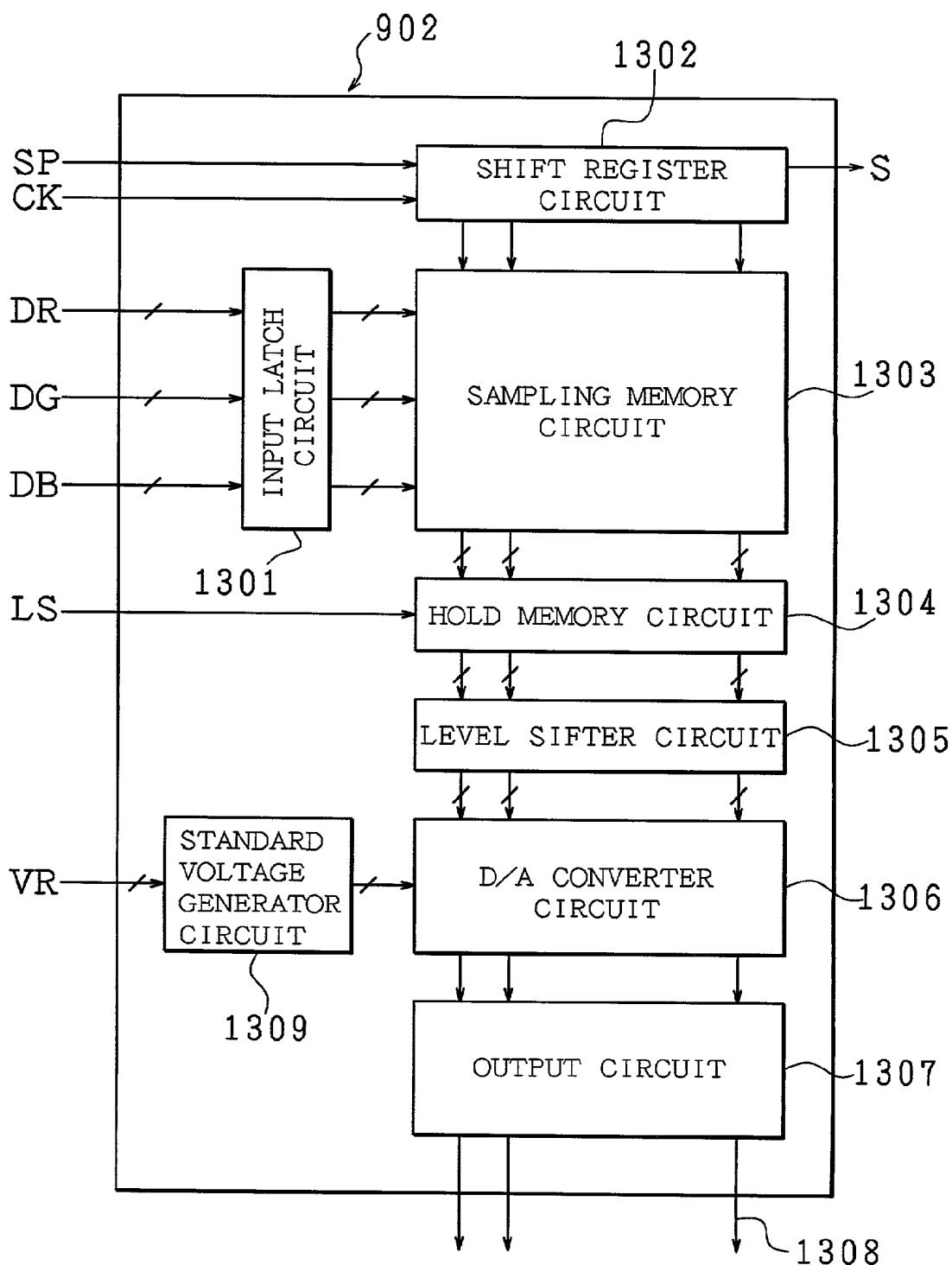

[0016] FIG. 13 is a block diagram of the source drivers 902. Description will be made below about major components only. Digital display data sets DR, DG, DB (for example, 6 bits), as transmitted from the controller 904, are temporarily latched by an input latch circuit 1301. The digital display data sets DR, DG, DB correspond to red, green, and blue respectively.

[0017] Meanwhile, a start pulse signal SP is shifted through a shift register circuit 1302 in synchronism with the clock signal CK and appears at the last stage of the shift register circuit 1302, from which the start pulse signal SP (cascade output signal S) is supplied to a next source driver.

[0018] The digital display data sets DR, DG, DB latched by the input latch circuit 1301 are temporarily stored serially in the sampling memory circuit 1303 in synchronism with output signals from a number of stages of the shift register circuit 1302 and transmitted to a hold memory circuit 1304 in the next stage.

[0019] As display data for one horizontal synchronization period is stored in the sampling memory circuit 1303, the hold memory circuit 1304 acquires an output signal from the sampling memory circuit 1303 based on the horizontal synchronizing signal (latch signal Ls) to supply to a level shifter circuit 1305 in the next stage and to retain the display data until an input of a succeeding horizontal synchronizing signal.

[0020] The level shifter circuit 1305 boosts or otherwise changes a signal level so that the signal is suitable to a D/A converter circuit 1306, in the next stage, which processes the level of a voltage applied to the liquid crystal panel. The standard voltage generator circuit 1309 produces analog voltages from a reference voltage VR fed from the aforementioned liquid crystal power supply 905 (see FIG. 9) for outputs to the D/A converter circuit 1306 to effect a tone display.

[0021] The D/A converter circuit 1306 chooses, from the analog voltages supplied from the standard voltage generator circuit 1309, an analog voltage suitable to the display data of which the level is shifted by the level shifter circuit 1305. The analog voltage representative of a display tone is transmitted to an output circuit 1307 from which the analog voltage leaves through liquid crystal drive voltage output terminals (hereinafter, output terminals) 1308 for source signal lines in the liquid crystal panel 901. The output circuit 1307 is basically a buffer circuit and is formed by, for example, a voltage follower circuit including a differential amplifier circuit.

[0022] Now, the standard voltage generator circuit 1309 and the D/A converter circuit 1306, which are the core of the present invention, will be described in more detail in terms of their circuit structure.

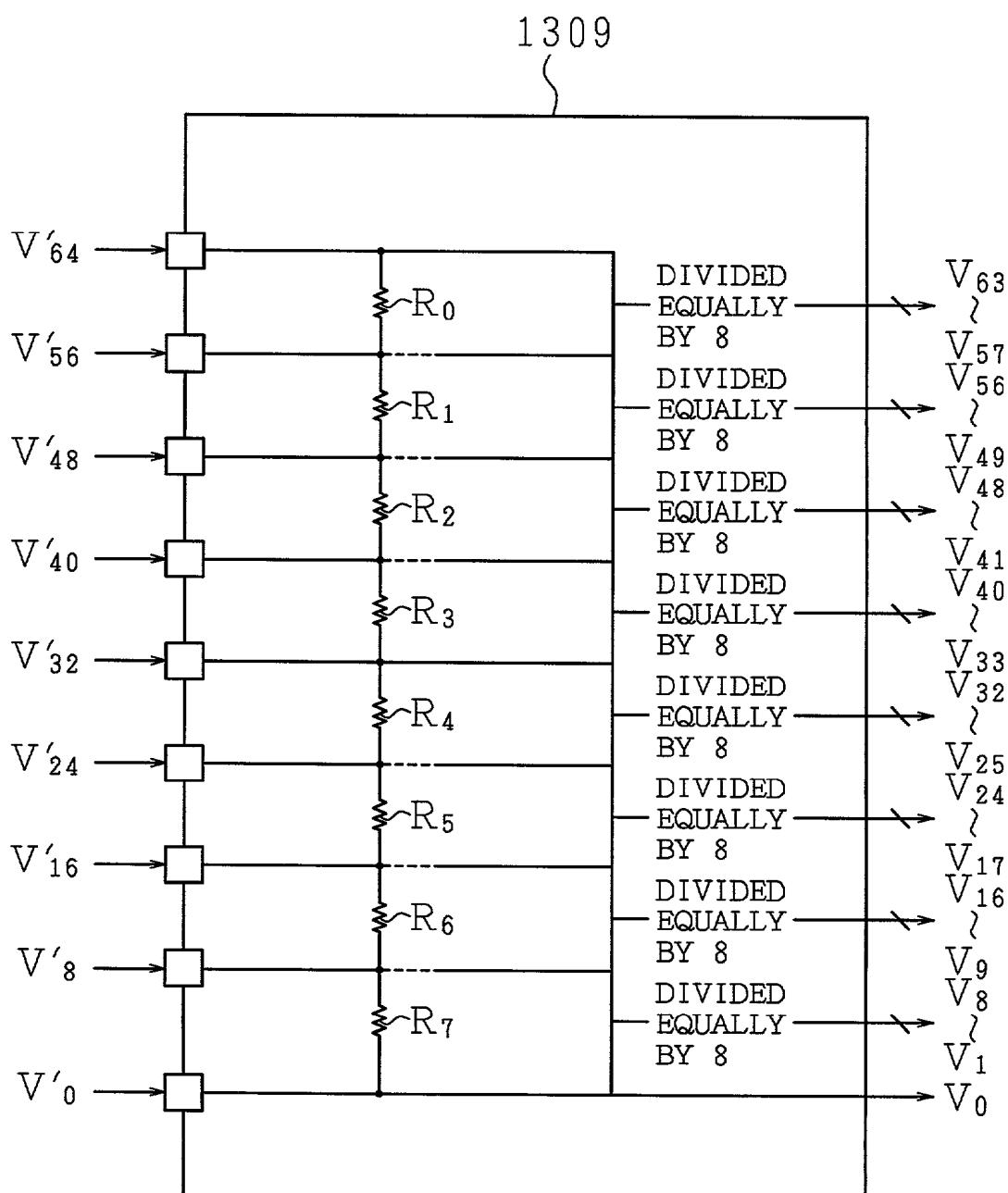

[0023] FIG. 14 shows, as an example, a circuit structure of the standard voltage generator circuit 1309. When each R, G, B digital display data set consists of, for example, 6 bits, the standard voltage generator circuit 1309 produces 64 analog voltages that correspond to  $2^6$  (=64) display tones for output. The structure is now described more specifically.

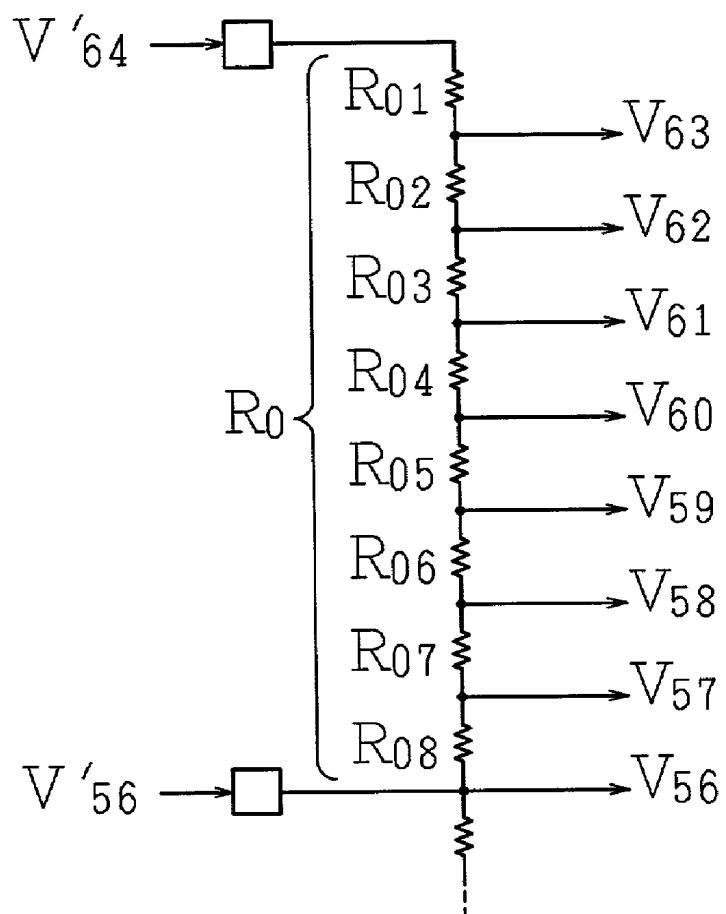

[0024] The standard voltage generator circuit 1309 includes a resistance divider circuit formed by resistors R<sub>0</sub>-R<sub>7</sub> connected in series, a very simple configuration. Each

resistor R<sub>0</sub>-R<sub>7</sub> is formed by eight resistor elements connected in series: for example, referring to FIG. 15, the resistor R<sub>0</sub> is formed by eight resistor elements R<sub>01</sub>, R<sub>02</sub>, ..., and R<sub>08</sub> connected in series. The remaining resistors R<sub>1</sub>-R<sub>7</sub> have an identical configuration to the resistor R<sub>0</sub>. So, the standard voltage generator circuit 1309 as a whole includes 64 resistor elements connected in series.

[0025] The standard voltage generator circuit 1309 has nine halftone voltage input terminals corresponding to the nine reference voltages V'<sub>0</sub>, V'<sub>8</sub>, ..., V'<sub>56</sub> and V'<sub>64</sub>. The resistor R<sub>0</sub> is connected at an end thereof to a halftone voltage input terminal for to the reference voltage V'<sub>64</sub> and at the other end, i.e., the contact of the resistors R<sub>0</sub> and R<sub>1</sub>, to a halftone voltage input terminal for the reference voltage V'<sub>56</sub>. Likewise, the contacts of the adjacent resistors R<sub>1</sub> and R<sub>2</sub>, R<sub>2</sub> and R<sub>3</sub>, ..., R<sub>6</sub> and R<sub>7</sub> are connected to respective halftone voltage input terminals corresponding to the reference voltages V'<sub>48</sub>, V'<sub>40</sub>, ..., V'<sub>8</sub>. A halftone voltage input terminal for the reference voltage V'<sub>0</sub> is connected to one of the ends of the resistor R<sub>7</sub> at which the resistor R<sub>6</sub> is not connected.

[0026] The configuration enables voltages V<sub>1</sub>-V<sub>63</sub> to be picked up at the contacts between the 64 resistor elements. The voltages V<sub>1</sub>-V<sub>63</sub>, plus a voltage V<sub>0</sub> coming straight from the reference voltage V'<sub>0</sub>, provide 64 different analog voltages (V<sub>0</sub>-V<sub>63</sub>) for a tone display. In short, if the standard voltage generator circuit 1309 is formed by the resistance divider circuit, the resistance ratios determines the analog voltages V<sub>0</sub>-V<sub>63</sub> for use to produce a tone display. The 64 analog voltages V<sub>0</sub>-V<sub>63</sub> are fed from the standard voltage generator circuit 1309 to the D/A converter circuit 1306.

[0027] Typically, the two reference voltages V'<sub>0</sub> and V'<sub>64</sub> derived at the ends are always coupled to the halftone voltage input terminals. The seven halftone voltage input terminals for the remaining voltages V'<sub>8</sub>-V'<sub>56</sub> are used for fine adjustment and may in some cases receive no voltages at all.

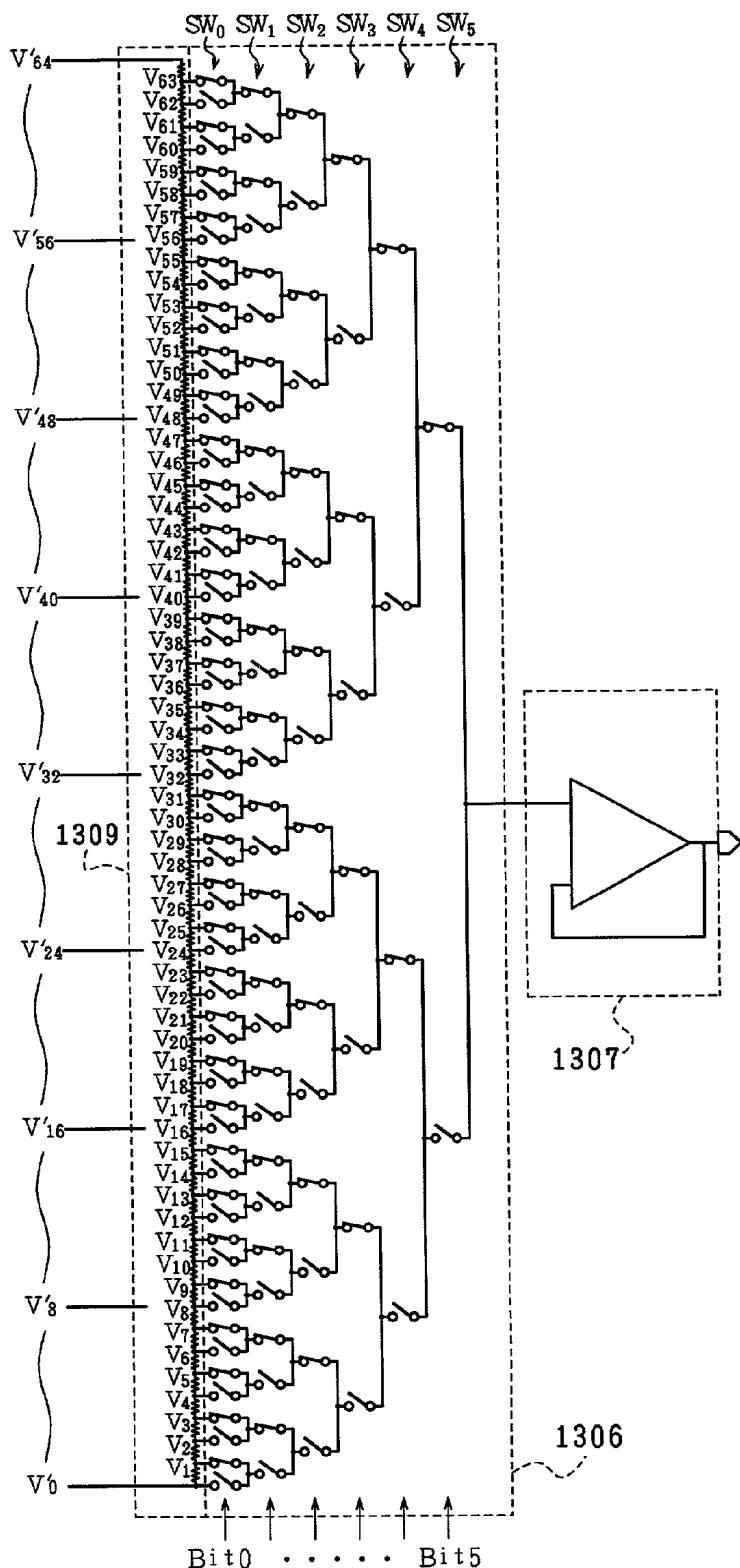

[0028] Now, the D/A converter circuit 1306 will be described. FIG. 16 shows the structure of the D/A converter circuit 1306 as an example. In the figure, 1307 is the structure (voltage follower circuit) of the output circuit described above.

[0029] MOS transistors and transmission gates are arranged as analog switches in the D/A converter circuit 1306 so that one of the 64 input voltages V<sub>0</sub>-V<sub>63</sub> is selected for output according to display data represented by a 6-bit digital signal, that is, the switches are turned on/off according to the display data (Bit 0 to Bit 5) represented by a 6-bit digital signal. As a result, a voltage is selected from the 64 input voltages for an output to the output circuit 1307. The process will be described in more detail below.

[0030] The 6-bit digital signal gives Bit 0 as the least significant bit (LSB) and Bit 5 as the most significant bit (MSB). The switches are arranged in pairs. 32 pairs of switches (or 64 switches) correspond to Bit 0 and 16 pairs of switches (or 32 switches) correspond to Bit 1. The number of (pairs of) switches halves for each subsequent bit. That leaves a single pair of switches (or two switch) corresponding to Bit 5. Thus, the D/A converter circuit 1306 includes  $2^5+2^4+2^3+2^2+2^1+1=63$  pairs of switches (or 126 switches).

[0031] An end of each switch for Bit 0 has a terminal to which one of the voltages V<sub>0</sub>-V<sub>63</sub> is coupled. The other end

is connected to an end of another switch, and the two ends are both connected together to an end of a switch for next Bit 1. The same arrangement is repeated for every switch corresponding to Bit 0 to Bit 5. That leaves a single line extended from the switch corresponding to Bit 5 and connected to the output circuit 1307.

[0032] The switches for Bit 0 to Bit 5 will be referred to as switch groups SW<sub>0</sub> to SW<sub>5</sub>. The switches in the switch groups SW<sub>0</sub> to SW<sub>5</sub> are controlled by 6-bit digital display data (Bit 0 to Bit 5) as will be described in the following.

[0033] The switch groups SW<sub>0</sub> to SW<sub>5</sub> behave so that one of the paired analog switches (the lower one of the paired switches in the diagram) is on when the corresponding bit is 0 (LOW) and the other of the paired analog switches (the upper one in the diagram) is on when the corresponding bit is 1 (HIGH). The diagram shows Bit 0 to Bit 5 (111111): the upper switch of every pair is on and the lower switch is off. In this situation, the D/A converter circuit 1306 supplies the voltage V<sub>63</sub> to the output circuit 1307.

[0034] Likewise, for example, when Bit 5 to Bit 0 are (111110), (000001), and (000000), the D/A converter circuit 1306 supplies the voltages V<sub>62</sub>, V<sub>1</sub>, and V<sub>0</sub> respectively to the output circuit 1307. A voltage is selected in this manner from the tone display analog voltages V<sub>0</sub>-V<sub>63</sub> in accordance with a digital display to produce a tone display.

[0035] Typically, each source driver IC includes only one standard voltage generator circuit 1309 for common use among the output terminals 1308. A D/A converter circuit 1306 and an output circuit 1307 are however provided to each output terminal 1308.

[0036] To produce a color display, different colors require different sets of output terminals 1308. In that situation, a D/A converter circuit 1306 and an output circuit 1307 are provided to each pixel and each color. In other words, suppose that the liquid crystal panel 901 has N pixels along the width, the liquid crystal panel 901 requires N output terminals 1308 for each color and hence includes 3N D/A converter circuits 1306 and 3N output circuits 1307 in all. The output terminals 1308 are denoted as R<sub>1</sub>, G<sub>1</sub>, B<sub>1</sub>; R<sub>2</sub>, G<sub>2</sub>, B<sub>2</sub>; . . . and; R<sub>N</sub>, G<sub>N</sub>, B<sub>N</sub>, where R, G, B stand for red, green, and blue, and the subscript n (n=1, 2, . . . , N) denotes each pixel.

[0037] In practical use, to produce a naturally looking tone image on a liquid crystal display, a gamma correction is carried out for adjustment of light transmission characteristics of the liquid crystal material in consideration of human vision. The gamma correction is implemented by the standard voltage generator circuit 1309 producing various tone display analog voltages through unequal division of the internal resistance, not through equal division thereof.

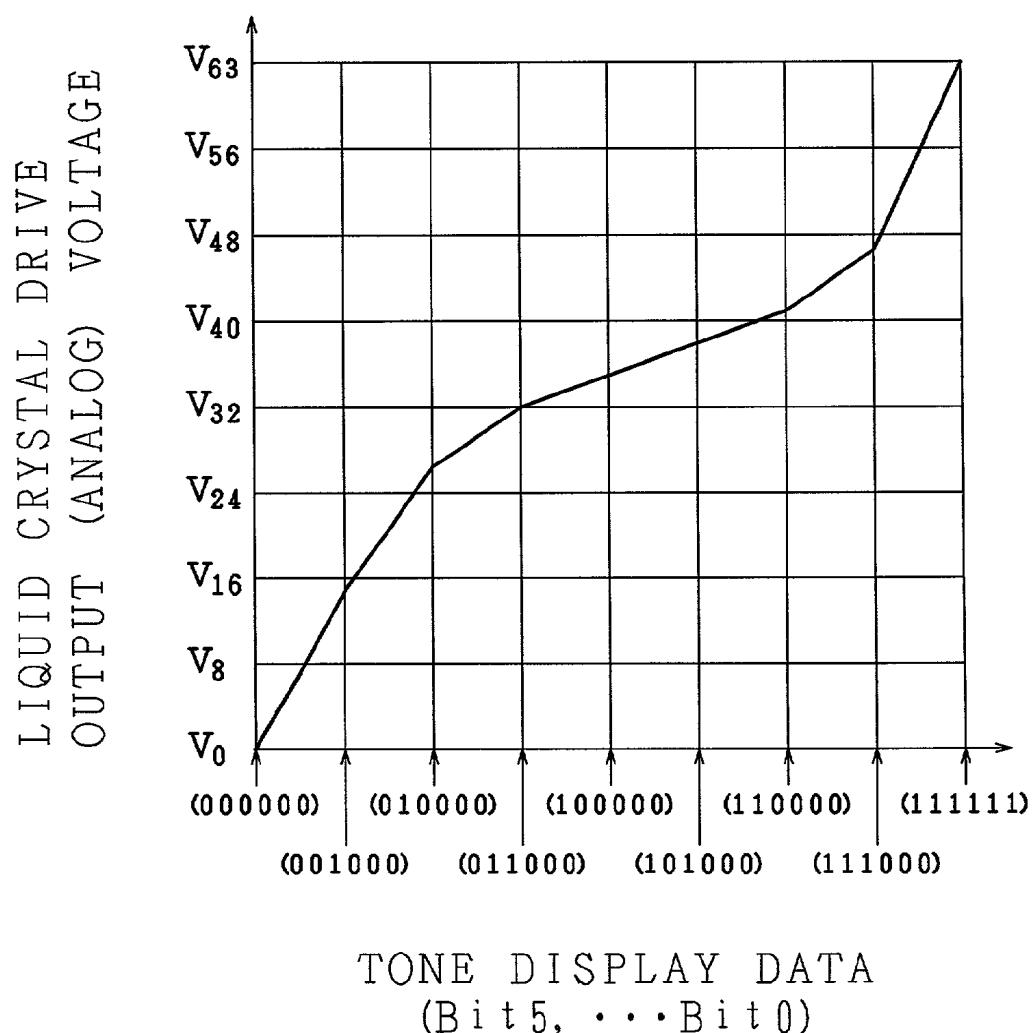

[0038] FIG. 17 shows the relationship between tone display data (digital display data) and a liquid crystal drive output voltage (tone display analog voltage) with gamma correction applied. As is observable in the figure, the tone display analog voltage is adapted so that the relationship thereof with digital display data is represented by a zigzag line.

[0039] To actually impart such properties to the tone display analog voltage, in the standard voltage generator circuit 1309 of FIG. 14, the resistors R<sub>0</sub>-R<sub>7</sub> are adapted to

exhibit such resistance values that can effect the gamma correction and each resistor R<sub>0</sub>-R<sub>7</sub> is divided to eight elements with an identical resistance. In other words, the eight resistor elements R<sub>01</sub>, R<sub>02</sub>, . . . R<sub>08</sub> connected in series (collectively termed "the resistor R<sub>0</sub>") have an identical resistance, and the resistors R<sub>0</sub>, R<sub>1</sub>, . . . R<sub>7</sub>, each of which is formed by eight series resistor elements, have a ratio of resistances that can effect the gamma correction. The gamma correction is effected this way.

[0040] The description above is made about drivers to produce a tone image on a TFT liquid crystal display.

[0041] Incidentally, research and development on liquid crystal displays were conventionally centered around demands to increase the screen size for application to television sets, computer displays, and the like. Conversely, today's demands are shifting to liquid crystal displays and liquid crystal drivers suited for application to portable displays in portable phones and other like devices that are creating a rapidly growing market.

[0042] The screen size suitable for adoption in portable devices is basically small. Accordingly, it is strongly required that the liquid crystal display and driver be small, lightweight, and energy efficient (because they rely on battery for operational power), and inexpensive.

[0043] Circuitry to produce the aforementioned, conventional tone display works in the following manner: A standard voltage generator circuit formed by resistor circuits connected in series generates number of analog voltages for output. The outputs are coupled to a D/A converter circuit including analog switch circuits where the analog switches select one of the incoming voltages according to digital display data. The output circuit (voltage follower circuit) then transmits the selected analog voltage as a tone display liquid crystal drive voltage. Among these components, the voltage follower circuit occupies a large portion of the circuit area and consumes a lot of electric power, because the circuit is an analog circuit including a differential amplifier circuit.

[0044] In a conventional display for large screens, source signal lines and pixels of the liquid crystal panel have large load capacity. A voltage follower circuit and other buffer circuits were therefore essential as part of an output circuit to charge and discharge the pixel and the source signal line capacitor and provide a predetermined drive voltage free from waveform distortion (rounding). For these reasons, each output terminal is provided with its own voltage follower circuit despite large current consumption.

[0045] The display of a portable device has a small screen size and pixel area, which does not require strict specifications on resolution. Therefore, medium to small size liquid crystal displays with about 560×240 pixels are often used, so the pixel and the source signal line have a small load capacity. This indicates that the output stage no longer must have much driving capability.

[0046] For these reasons, the highly current-consuming output circuit (voltage follower circuit) is omitted in the display for use in portable devices. Under these conditions, a standard voltage generator circuit formed by resistor circuits connected in series generates a number of analog voltages for output. The outputs are coupled to a D/A converter circuit including analog switch circuits where the

analog switches select one of the incoming voltages according to digital display data and directly transmit the selected analog voltage as a tone display liquid crystal drive voltage.

[0047] A problem arises from the fact that tone display analog voltages are supplied to the liquid crystal panel through resistors in the standard voltage generator circuit. A downside of this technique is that the liquid crystal drive voltage waveform is rounded at rises and falls, because of charging/discharging of the pixel and source signal line capacitor of the liquid crystal panel.

#### SUMMARY OF THE INVENTION

[0048] The present invention, in view of the foregoing problems, has an objective to offer a liquid crystal driver capable of preventing distortion of a drive waveform without providing an output circuit in each output terminal to the liquid crystal panel and thus reducing the size of the liquid crystal display sufficiently for use in a compact, low power consuming portable devices, and also to offer a liquid crystal display including such a liquid crystal driver.

[0049] In order to achieve the objective, a liquid crystal driver in accordance with the present invention is a liquid crystal driver including:

[0050] standard voltage producing means for producing  $2^n$  tone display voltages from incoming first reference voltages in accordance with n-bit display data; and

[0051] selecting means for selecting a voltage from the  $2^n$  tone display voltages in accordance with incoming display data, for transmission to a liquid crystal panel through a plurality of output terminals with no further processing, and is characterized in that the standard voltage producing means includes:

[0052] generation means for generating a second reference voltage from adjacent two of the first reference voltages arranged in ascending or descending order, the second reference voltage having an intermediate level between those of the adjacent first reference voltages;

[0053] buffer means for impedance-converting the second reference voltage for output; and

[0054] voltage dividing means for producing a voltage having an intermediate level between those of the adjacent first reference voltages and of adjacent ones of the first and second reference voltages by voltage division, so as to produce the  $2^n$  tone display voltages.

[0055] By adopting this arrangement, the selecting means selects, in accordance with incoming display data, a voltage from the  $2^n$  tone display voltage produced by the standard voltage producing means, for transmission to the liquid crystal panel through a plurality of output terminals with no further processing.

[0056] Here, in the standard voltage producing means, the generation means generates a second reference voltage from adjacent two of the incoming first reference voltages arranged in ascending or descending order, the second reference voltage having an intermediate level between those of the adjacent first reference voltages. The second

reference voltage is impedance-converted by the buffer means, and its waveform distortion is reduced as a result. The second reference voltage is supplied to the voltage dividing means with reduced waveform distortion. The voltage dividing means produces a voltage having an intermediate level between those of the adjacent first reference voltages and of adjacent ones of the first and second reference voltages by voltage division, so as to produce the  $2^n$  tone display voltages.

[0057] By disposing the buffer means in the preceding stage of the voltage dividing means, distortion is reduced in waveform of the voltage supplied to the voltage dividing means, and consequently, distortion is reduced in waveform of the tone display voltage outputs from the voltage dividing means. On account of this, display quality deterioration caused by output waveform distortion can be restrained even when the tone display voltages are supplied to the liquid crystal panel through the selecting means with no further processing. In other words, good display quality is ensured without providing, to each output terminal connected to the liquid crystal panel, an output circuit that occupies a large area and consumes large power as in a conventional example. Meanwhile, the buffer means provided to the standard voltage producing means is far smaller in layout area and power consumption than conventional configurations in which each output terminal has its own buffer means.

[0058] Therefore, with the structure, a small, energy efficient liquid crystal driver can be fabricated, and a small- to medium-sized liquid crystal display for use in small, energy efficient portable devices can be fabricated by applying the liquid crystal driver in the liquid crystal display.

[0059] In order to achieve the objective, a liquid crystal display in accordance with the present invention is characterized in that it includes the liquid crystal driver and a liquid crystal panel driven by the liquid crystal driver.

[0060] The forgoing liquid crystal driver is smaller and capable of running on lower power consumption, and still does not lose its good display quality. By arranging a liquid crystal display from the liquid crystal driver and the liquid crystal panel, for example, a small- to medium-sized liquid crystal display for use in small, energy efficient portable devices can be fabricated.

[0061] For a fuller understanding of the nature and advantages of the invention, reference should be made to the ensuing detailed description taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

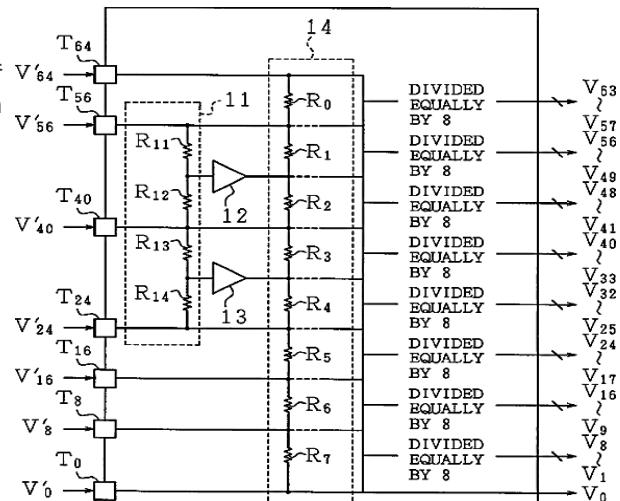

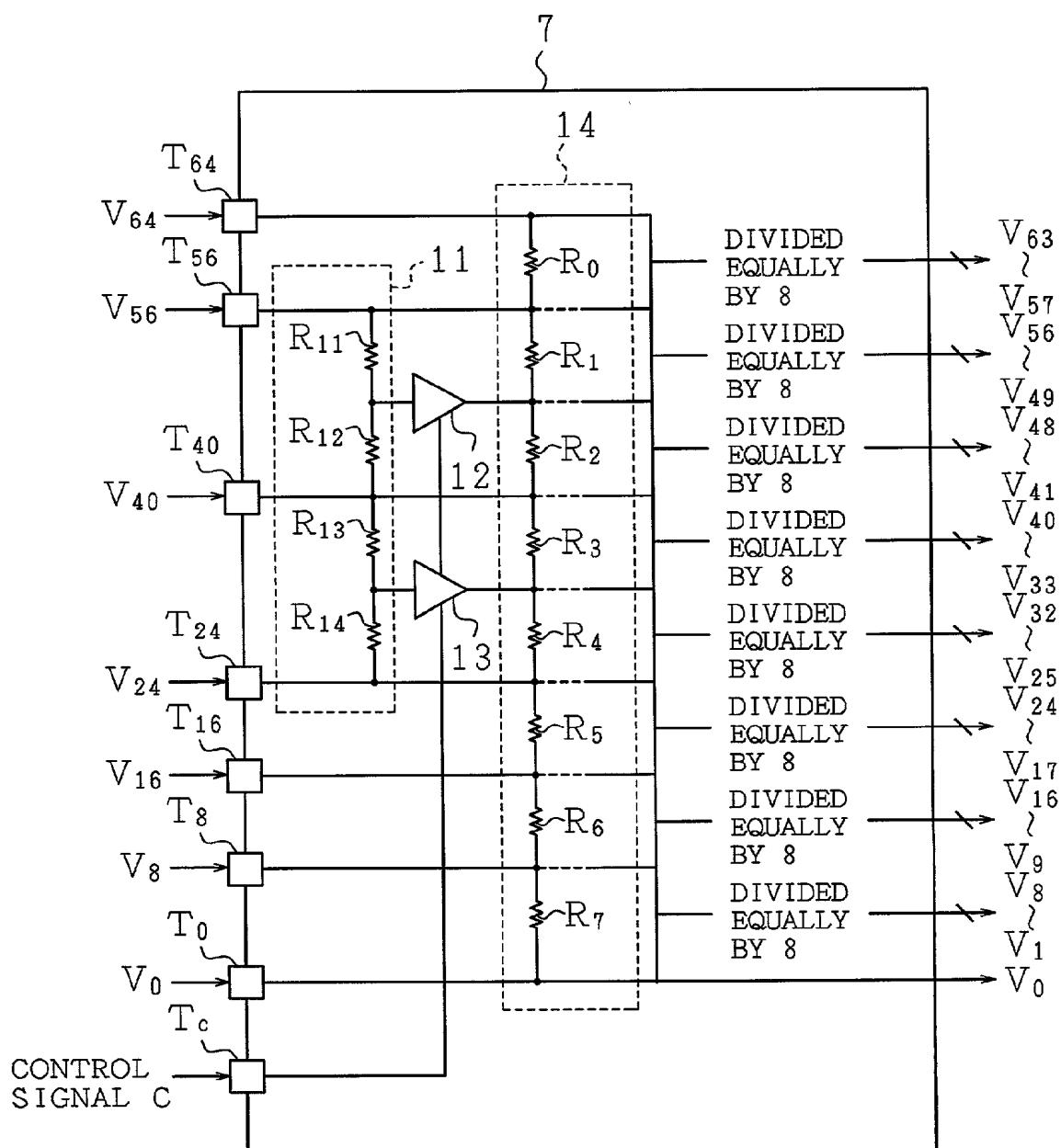

[0062] FIG. 1 is a diagram depicting a schematic structure of a standard voltage generator circuit in a source driver that is a liquid crystal driver of an embodiment in accordance with the present invention.

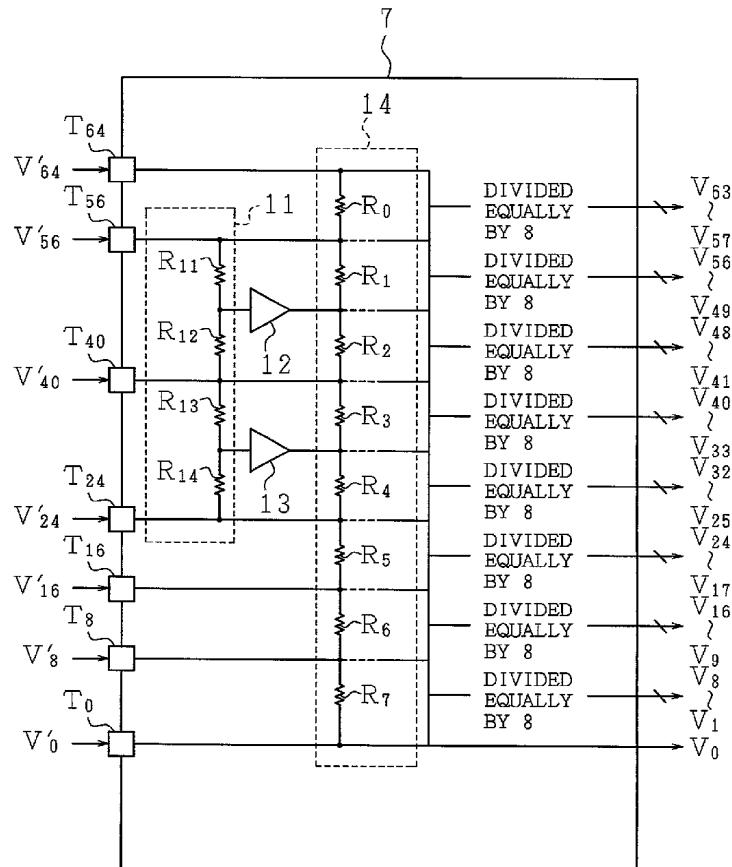

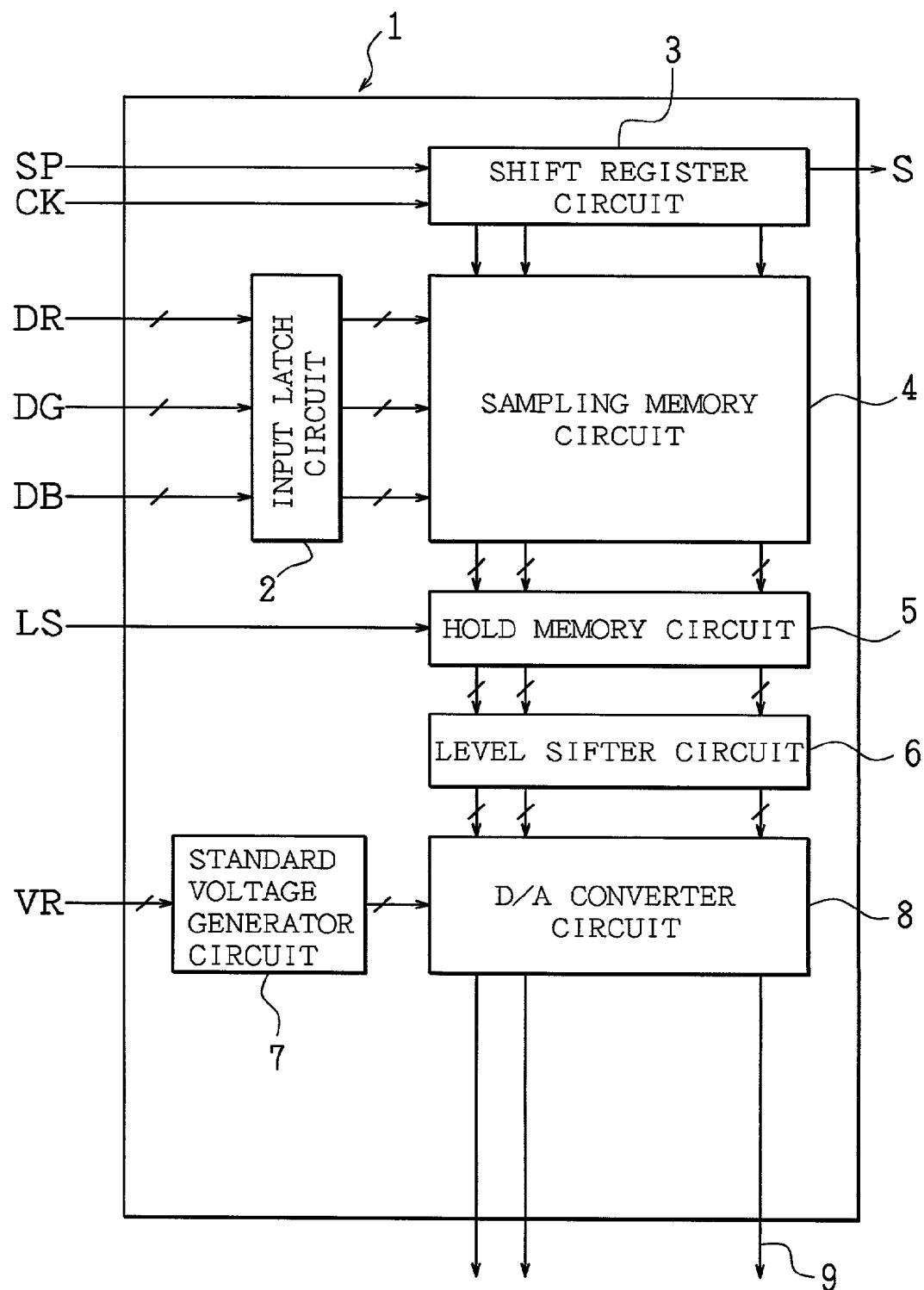

[0063] FIG. 2 is a block diagram showing a schematic structure of the source driver.

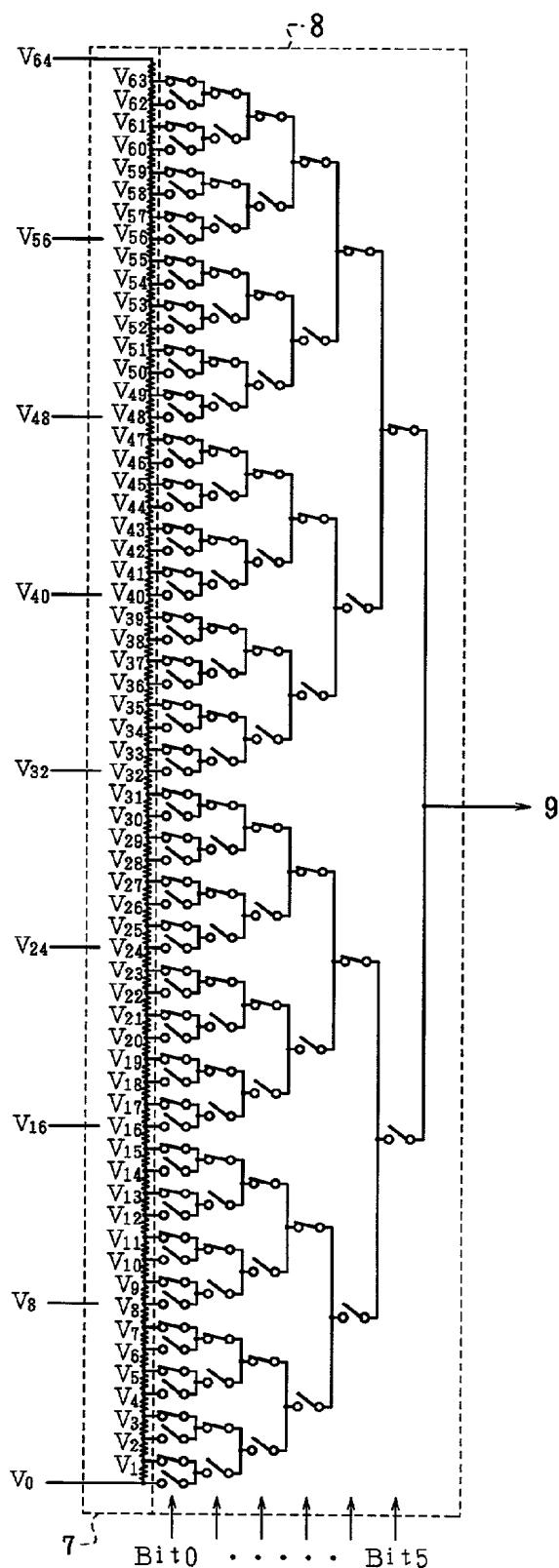

[0064] FIG. 3 is a diagram depicting a schematic structure of a D/A converter formed by the standard voltage generator circuit and a D/A converter circuit, in particular the structure of the D/A converter circuit.

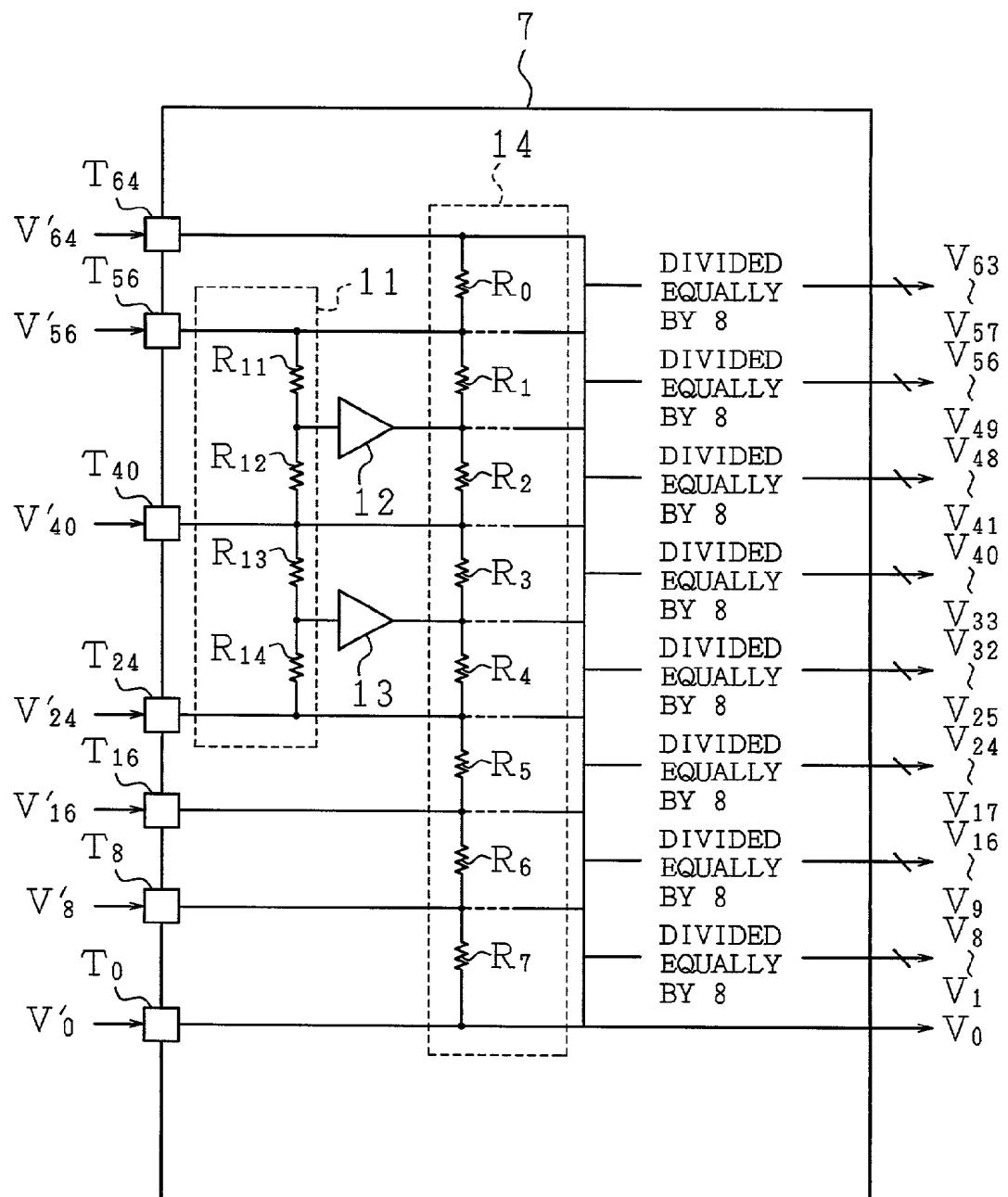

[0065] FIG. 4 is a diagram depicting a schematic structure of a standard voltage generator circuit in a source driver that is a liquid crystal drive circuit of another embodiment in accordance with the present invention.

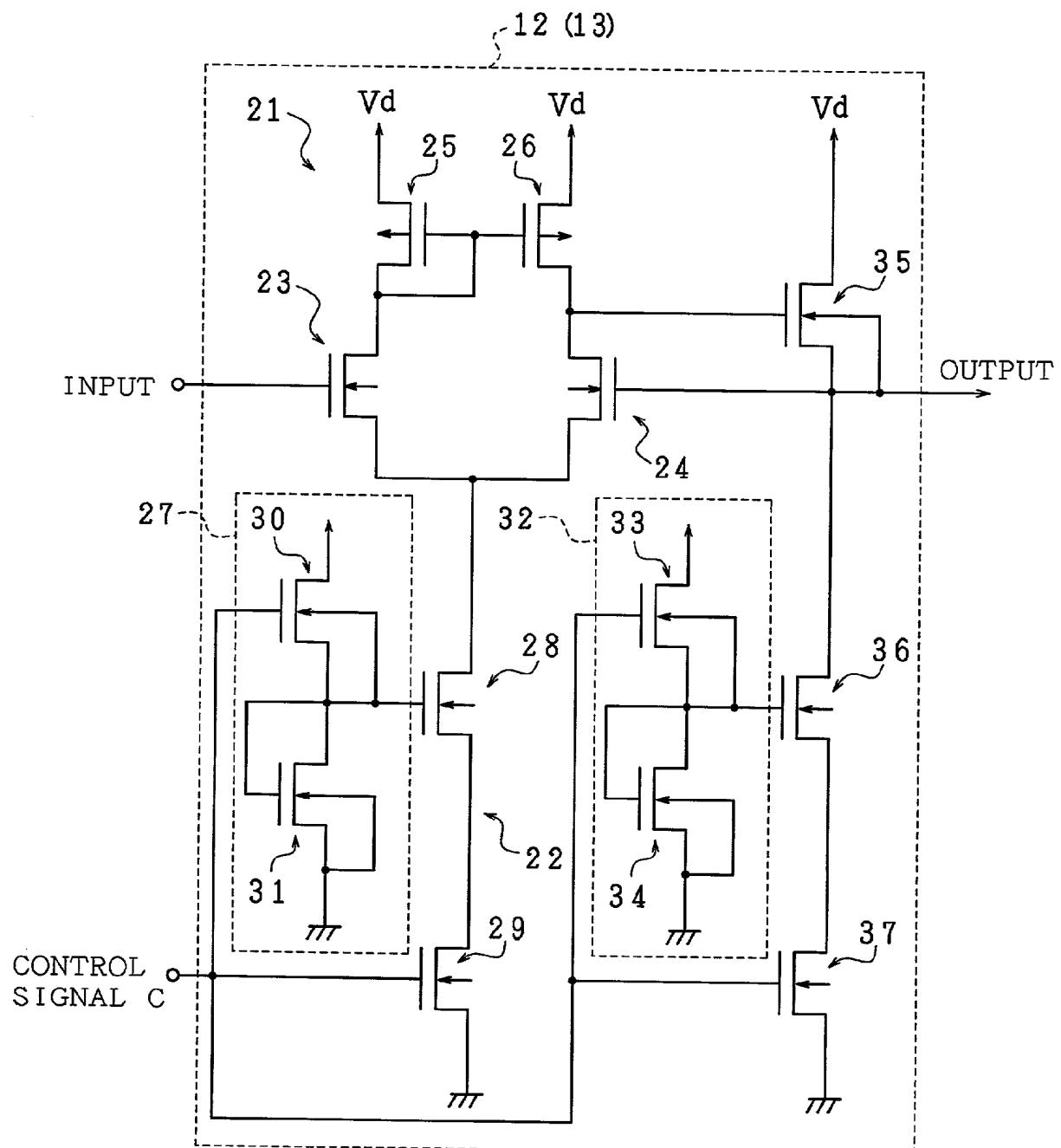

[0066] FIG. 5 is a circuit diagram depicting a schematic structure of a buffer circuit provided in the standard voltage generator circuit.

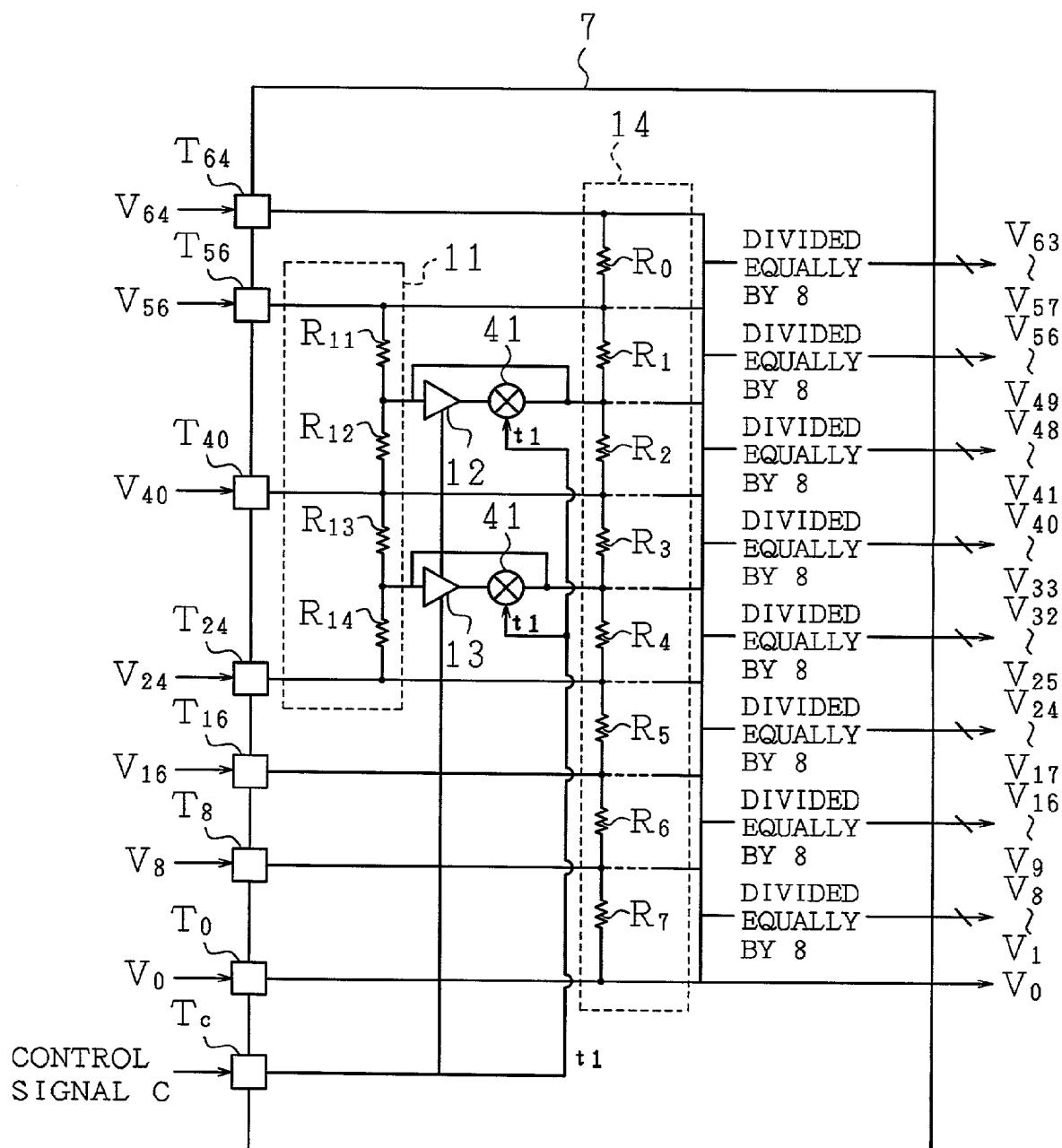

[0067] FIG. 6 is a diagram depicting a schematic structure of a standard voltage generator circuit in a source driver that is a liquid crystal drive circuit of a further embodiment in accordance with the present invention.

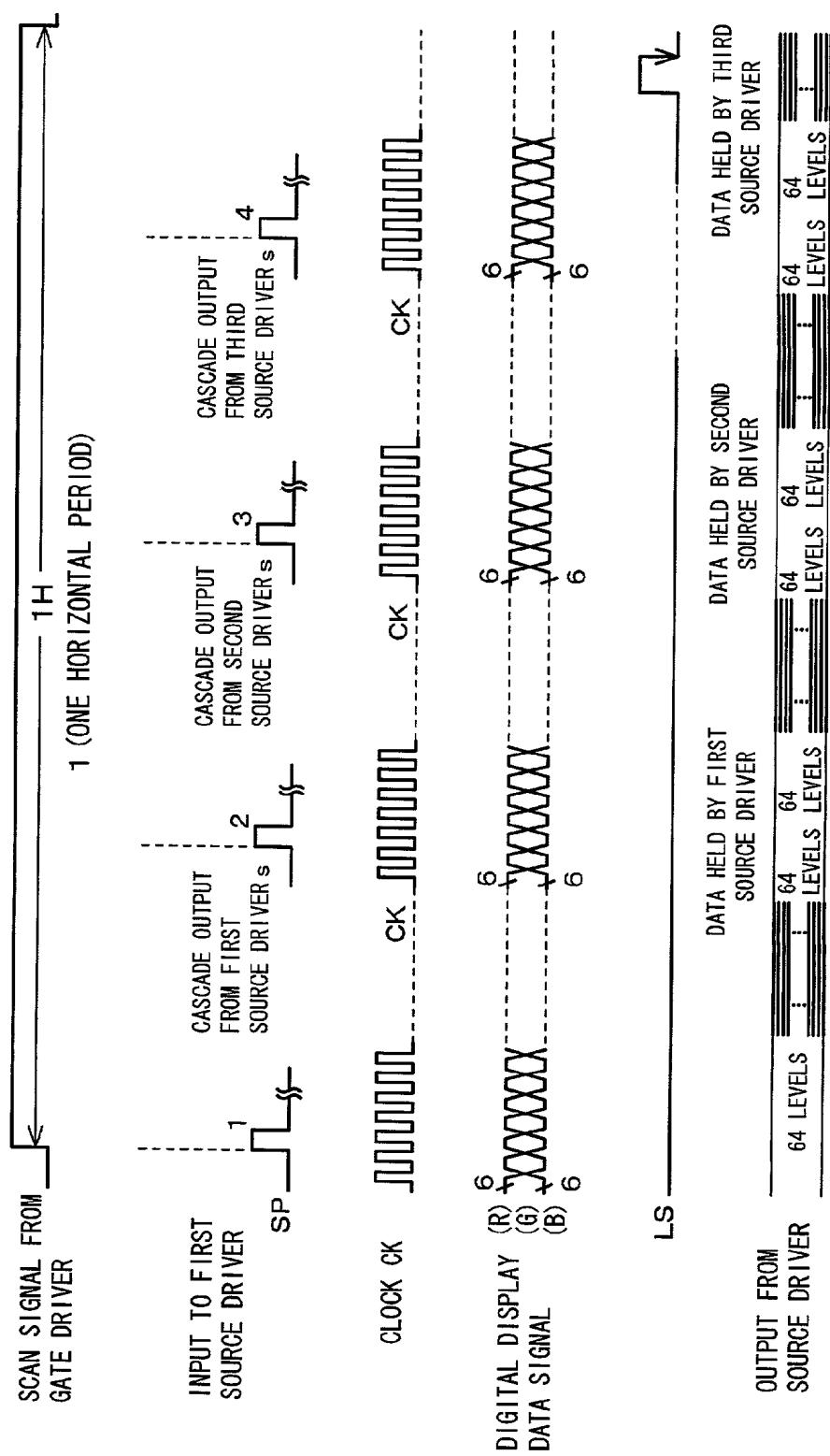

[0068] FIG. 7 is a timing chart showing input and output signals of the source driver.

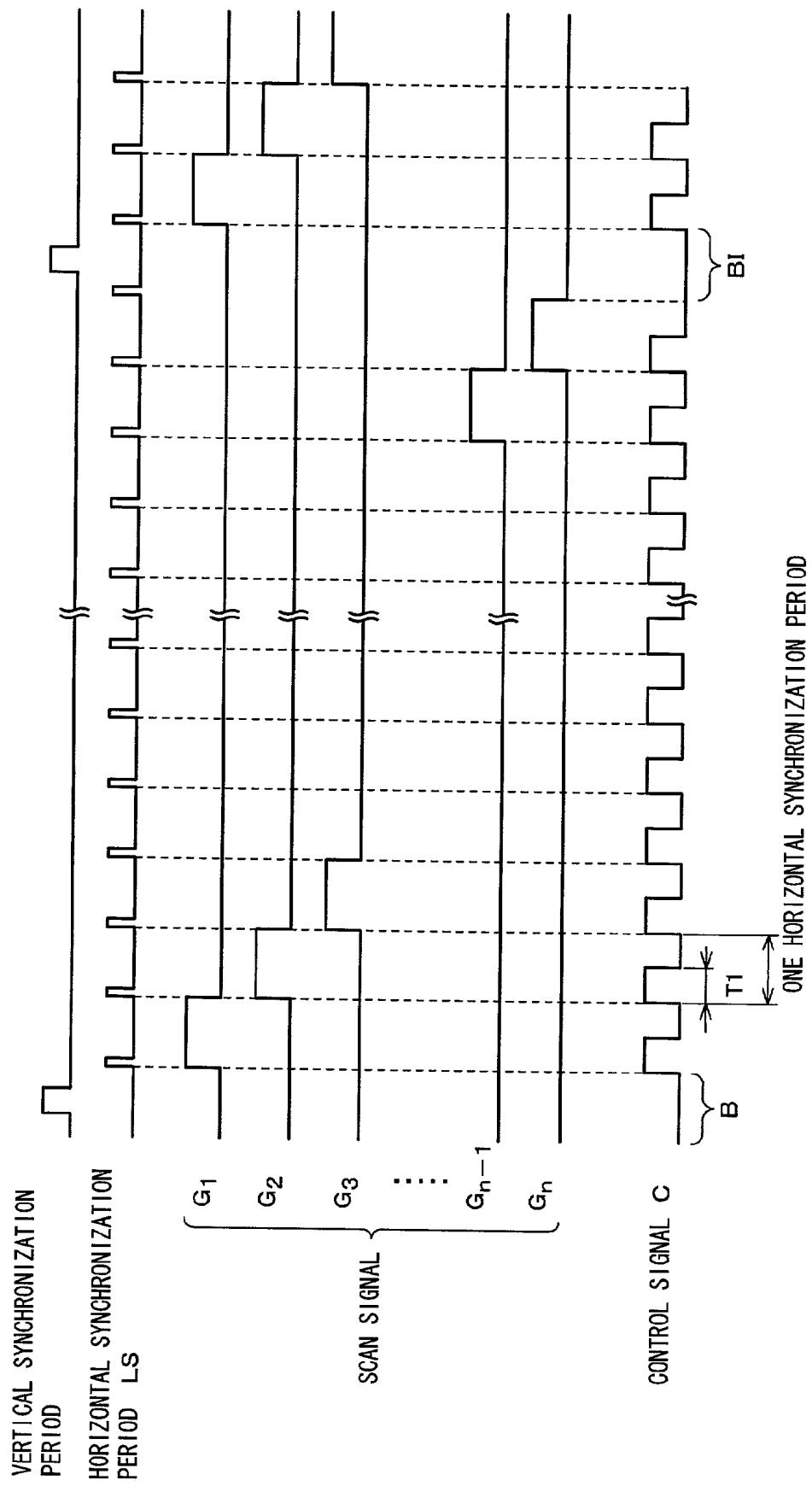

[0069] FIG. 8 is a timing chart showing timings to switch the source driver between a high impedance state and a low impedance state.

[0070] FIG. 9 is a block diagram depicting a schematic structure of a liquid crystal display including at least a liquid crystal driver and a liquid crystal panel.

[0071] FIG. 10 is a circuit diagram depicting a schematic structure of the liquid crystal panel.

[0072] FIG. 11 is a drawing showing an example of a liquid crystal drive waveform for the liquid crystal display.

[0073] FIG. 12 is a drawing showing another example of a liquid crystal drive waveform for the liquid crystal display.

[0074] FIG. 13 is a block diagram depicting a schematic structure of a conventional source driver.

[0075] FIG. 14 is a block diagram depicting a schematic structure of a standard voltage generator circuit provided in the source driver.

[0076] FIG. 15 is a circuit diagram depicting in detail a structure of resistors constituting a resistance divider circuit provided in the standard voltage generator circuit.

[0077] FIG. 16 is a diagram depicting a schematic structure of the standard voltage generator circuit, D/A converter circuit, and output circuit provided in the source driver.

[0078] FIG. 17 is a graph showing the relationship between tone display data and a liquid crystal drive output voltage when gamma correction is applied.

#### DESCRIPTION OF THE EMBODIMENTS

##### [0079] [Embodiment 1]

[0080] The following will describe an embodiment in accordance with the present invention in reference to figures.

[0081] The structure of the liquid crystal display including the liquid crystal driver detailed below, the structure of the liquid crystal panel in a liquid crystal display, and the liquid crystal drive waveforms are identical to those mentioned above in reference to FIGS. 9-12, and description thereof is omitted here. The following description will focus on liquid crystal drivers (source drivers), a feature of the present invention.

[0082] FIG. 2 depicts a schematic structure of a source driver 1 that is a liquid crystal driver in accordance with the present invention. The source driver 1 is formed by an input latch circuit 2, a shift register circuit 3, a sampling memory

circuit 4, a hold memory circuit 5, a level shifter circuit 6, a standard voltage generator circuit 7, and a D/A converter circuit 8.

[0083] Digital display data sets DR, DG, DE (for example, 6 bits) transmitted from a controller (not shown) are temporarily latched by the input latch circuit 2. The digital display data sets DR, DG, DE correspond to red, green, and blue respectively.

[0084] Meanwhile, a start pulse signal SP is shifted through the shift register circuit 3 in synchronism with a clock signal CK and appears at the last stage of the shift register circuit 3, from which the start pulse signal SP (cascade output signal S) is supplied to a next source driver.

[0085] The digital display data sets DR, DG, DE latched by the input latch circuit 2 are temporarily stored serially in the sampling memory circuit 4 in synchronism with output signals from a number of stages of the shift register circuit 3 and transmitted to a hold memory circuit 5 in the next stage.

[0086] As display data for one horizontal synchronization period is stored in the sampling memory circuit 4, the hold memory circuit 5 acquires an output signal from the sampling memory circuit 4 based on the horizontal synchronizing signal (latch signal Ls) to supply to a level shifter circuit 6 in the next stage and to retain the display data until an input of a succeeding horizontal synchronizing signal.

[0087] The level shifter circuit 6 boosts or otherwise changes a signal level so that the signal is suitable to a D/A converter circuit 8, in the next stage, which processes the level of a voltage applied to the liquid crystal panel. The standard voltage generator circuit 7 produces analog voltages from a reference voltage VR fed from the aforementioned liquid crystal power supply (not shown) for outputs to the D/A converter circuit 8 to effect a tone display.

[0088] The standard voltage generator circuit 7 has a different structure from conventional counterparts, which is a feature of the present invention. Detail will be given later.

[0089] The D/A converter circuit 8 chooses, from the analog voltages supplied from the standard voltage generator circuit 7, an analog voltage suitable to the display data of which the level is shifted by the level shifter circuit 6. The analog voltage representative of a tone display is transmitted from the D/A converter circuit 8 directly through the associated liquid crystal drive voltage output terminal (hereinafter, output terminal) 9 to one of the source signal lines of the liquid crystal panel.

[0090] Therefore, the source driver 1 is not provided with a circuit that is an equivalent to an output circuit conventionally provided corresponding to output terminals 9, but includes such a structure to directly supply the output from the D/A converter circuit 8 to the liquid crystal panel.

[0091] The standard voltage generator circuit 7 and the D/A converter circuit 8 forms a part of a D/A converter. In the liquid crystal display, it could also be said that the inclusion of the D/A converter as a part of the liquid crystal drive circuit (source driver) enables the D/A converter to convert the digital data (display data sets DR, DG, DB) to be displayed on the liquid crystal panel from digital to analog before applying the data set to the liquid crystal display elements.

[0092] FIG. 3 shows a schematic structure of the D/A converter. As is observable in the figure, the D/A converter circuit 8 has the same structure as a conventional equivalent of FIG. 16. The voltage follower circuit as an output circuit provided to each output terminal 9 is omitted from the figure. It would be understood that the tone display analog voltage selected by the D/A converter circuit (analog switch circuit) 8 in accordance with the digital display data is directly applied to a source signal line of the liquid crystal panel as the liquid crystal drive voltage as mentioned earlier.

[0093] Next, the standard voltage generator circuit 7, a feature of the present invention, will be described in detail. In the following description, it is assumed, as an example, that each digital display data set DR, DG, DB is 6 bits.

[0094] FIG. 1 shows details of the structure of the standard voltage generator circuit 7. The standard voltage generator circuit 7 produces  $2^n$  (here, 64) tone display voltages from two or more incoming reference voltages (first reference voltages) in accordance with n-bit (here, 6-bit) display data. It could there be said that the D/A converter circuit 8 forms selecting means for selecting a voltage from the  $2^n$  tone display voltages produced by the standard voltage generator circuit 7 in accordance with incoming display data and directly supplying the selected voltage to the liquid crystal panel through the output terminals.

[0095] Assume here that there exist seven reference voltages  $V'_0$ ,  $V'_8$ ,  $V'_{16}$ ,  $V'_{24}$ ,  $V'_{40}$ ,  $V'_{56}$ ,  $V'_{64}$ . The standard voltage generator circuit 7, as shown in the figure, has halftone voltage input terminals  $T_0$ ,  $T_8$ ,  $T_{16}$ ,  $T_{24}$ ,  $T_{40}$ ,  $T_{56}$ ,  $T_{64}$  for the seven reference voltages respectively. The standard voltage generator circuit 7 in accordance with the present embodiment differs from the conventional standard voltage generator circuit of FIG. 14 in that the former lacks halftone voltage input terminals for the reference voltages  $V'_{32}$ ,  $V'_{48}$ .

[0096] The standard voltage generator circuit 7 further includes a generation circuit (generation means) 11, buffer circuits (buffer means) 12, 13, and a resistance divider circuit (voltage dividing means, first resistance divider circuit) 14.

[0097] The generation circuit 11 produces anew a number of voltages from reference voltages that are adjacent when arranged in either ascending or descending order, the resultant voltage falling between those adjacent ones. The generation circuit 11 is formed by a resistance divider circuit (second resistance divider circuit) composed of the resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$  connected in series.

[0098] In the present embodiment, the resistors  $R_{11}$ ,  $R_{12}$  are connected in series correspondingly between the reference voltages  $V'_{40}$ ,  $V'_{56}$ , whereas the resistors  $R_{13}$ ,  $R_{14}$  are connected in series correspondingly between the reference voltages  $V'_{24}$ ,  $V'_{40}$ . Thus, a voltage with an intermediate level between the reference voltages  $V'_{40}$ ,  $V'_{56}$  can be derived from the contact of the resistors  $R_{11}$ ,  $R_{12}$  in accordance with the ratio of resistances of the resistors  $R_{11}$ ,  $R_{12}$ . Likewise, a voltage with an intermediate level between the reference voltages  $V'_{24}$ ,  $V'_{40}$  can be derived from the contact of the resistors  $R_{13}$ ,  $R_{14}$  in accordance with the ratio of resistances of the resistors  $R_{13}$ ,  $R_{14}$ .

[0099] Referring to the voltages newly produced in the generation circuit 11 as the second reference voltages, the

resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$  can be said to be provided correspondingly between an adjacent first reference voltage and a second reference voltage in the structure of the generation circuit 11. In the present embodiment, it would be correct to understand that the reference voltages  $V'_{32}$ ,  $V'_{48}$  are not externally supplied, but internally generated as the second reference voltages by the generation circuit 11.

[0100] In the resistance divider circuit 14, the ratio of the resistances of the resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$  is likewise specified to be equal to the ratio of the resistances (detailed later) of the resistors  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$  provided correspondingly between a first reference voltage and an adjacent second reference voltage.

[0101] Each buffer circuit 12, 13 is a circuit that convert the voltages newly produced by the generation circuit 11 in terms of impedance for output and is formed by, for example, a voltage follower circuit. The buffer circuit 12, 13 has a function to reduce distortion in the output waveform by means of the impedance conversion.

[0102] This indicates that the buffer circuit 12, 13 should be provided for such a voltage, among the 64 tone display voltages  $V'_0$ - $V'_{63}$ , that the rising or falling output waveform is distorted if the voltage is fed from the resistance divider circuit 14 to directly to the source signal lines of the liquid crystal panel through the D/A converter circuit 8 (see FIGS. 2, 3). This is reflected in the present embodiment in, for example, the provision of the buffer circuit 12 between the interconnection of the resistors  $R_{11}$ ,  $R_{12}$  in the generation circuit 11 and the interconnection of the resistors  $R_1$ ,  $R_2$  in the resistance divider circuit 14. The buffer circuit 13 is provided, for the same reasons, between the interconnection of the resistors  $R_{13}$ ,  $R_{14}$  in the generation circuit 11 and the interconnection of the resistors  $R_3$ ,  $R_4$  in the resistance divider circuit 14.

[0103] The resistance divider circuit 14 is a circuit that produces voltages of intermediate levels between those of adjacent first reference voltages and of adjacent first and second reference voltages by means of voltage dividing so as to produce the  $2^n$  tone display voltages, and is specifically configured in the following manner.

[0104] The resistance divider circuit 14 is formed by the resistors  $R_0$ - $R_7$  connected in series. Each resistor  $R_0$ - $R_7$  is formed by eight resistor elements connected in series. Taking the resistor  $R_0$  as an example, like the conventional example shown in FIG. 15, eight resistor elements  $R_{01}$ ,  $R_{02}$ , ...,  $R_{08}$  are connected in series to form the resistor  $R_0$ . The other resistors  $R_0$ - $R_7$  are configured in the same manner as the resistor  $R_0$ . The resistance divider circuit 14 is therefore formed by 64 resistor elements connected in series in all.

[0105] The resistor  $R_0$  is connected at an end thereof to a halftone voltage input terminal  $T_{64}$  for the reference voltage  $V'_{64}$  and at the other end, i.e., the contact of the resistors  $R_0$  and  $R_1$ , to a halftone voltage input terminal  $T_{56}$  for the reference voltage  $V'_{56}$ . Likewise, the contacts of the resistors  $R_2$ ,  $R_3$ ,  $R_4$ ,  $R_5$ ,  $R_6$ ,  $R_7$  are connected to respective halftone voltage input terminals  $T_{40}$ ,  $T_{24}$ ,  $T_{16}$ ,  $T_8$  for the reference voltages  $V'_{40}$ ,  $V'_{24}$ ,  $V'_{16}$ ,  $V'_8$ . A halftone voltage input terminal  $T_0$  for the reference voltage  $V'_0$  is connected to one of the ends of the resistor  $R_7$  at which the resistor  $R_6$  is not connected.

[0106] Meanwhile, the contact between the resistors  $R_1$ ,  $R_2$  is connected to the output from the buffer circuit 12,

whereas the contact between the resistors  $R_3$ ,  $R_4$  is connected to the output from the buffer circuit **13**.

[0107] The configuration enables the voltages  $V_1-V_{63}$  to be picked up at the contacts between the 64 resistor elements in the resistance divider circuit **14**. The voltages  $V_1-V_{63}$ , plus the voltage  $V_0$  coming straight from the reference voltage  $V'_0$ , provide 64 different analog voltages  $V_0-V_{63}$  as tone display voltages. Hence, the voltages  $V_0-V_{63}$  are determined by the ratio of resistances of the 64 resistor elements.

[0108] The ratio of the resistances of the resistors  $R_0-R_7$  is specified so as to effect a gamma correction for a naturally looking tone display, in consideration of differences between human vision and the actual light transmission characteristics of the liquid crystal material in the liquid crystal display. That is, the ratio of the resistances of the resistor  $R_0-R_7$  is specified so that the relationship between the tone display voltages and the tone display data can be represented by the zigzag line shown in **FIG. 17**. For this reason, the internal resistance of the resistance divider circuit **14** is not equally divided.

[0109] Note that in the present embodiment, each of the resistors  $R_0, \dots, R_7$  is divided into identical eight parts so that the eight resistor elements making up the resistor are all identical in resistance. The resistor elements may, however, have different resistances from each other in accordance with gamma characteristics. When this is the case, more detailed specifications become possible.

[0110] In the present embodiment, as mentioned above, locating the buffer circuit **12**, **13** immediately before the resistance divider circuit **14** where there occurs a large waveform distortion successfully reduces the distortion in the waveforms of the reference voltages  $V'_0-V'_{63}$  supplied to the resistance divider circuit **14** and in turn the distortion in the waveforms of the output tone display voltages  $V_0-V_{63}$  from the resistance divider circuit **14**. The structure is capable of preventing the load capacity from taking an extended period of time in charging and discharging due to distortion in output waveforms and effecting a display of satisfactory quality for practical use, even if the tone display voltages  $V_0-V_{63}$  produced by means of the resistors  $R_0-R_7$  of which the resistance ratio is specified to impart gamma characteristics are directly fed to the source signal lines of the liquid crystal panel through the D/A converter circuit **8** formed by analog switches.

[0111] This ensures good display quality without providing to each output terminal an analog output circuit that occupies a large area and consumes large power as in a conventional example. The resulting source driver **1** is therefore small in size and runs on low power consumption with no compromise on display quality. The source driver **1** of the present embodiment is therefore suitable for use with small- to medium-sized liquid crystal displays in portable and other similar devices.

[0112] The miniaturization and low power consumption feature of the source driver **1** facilitate the entire or partial integration of the source driver **1**, the controller, liquid crystal power supply, and gate drivers on a single chip, which in turn reduces the size and power consumption of the liquid crystal driver as a whole. The miniaturization of the liquid crystal driver as a whole can also lead to cost reductions.

[0113] The layout area and power consumption of the analog buffer circuits **12**, **13** are far smaller in the present embodiment where the buffer circuits **12**, **13** are provided in the standard voltage generator circuit **7** in each source driver **1** than a conventional example where an output circuit is provided to each output terminal **9**. Further, the reduced number of output circuits means a reduced output resistance compared to prior art; the transistors of the analog switches making up the D/A converter circuit **8** are increased in size by expanding the gate width thereof, for example, the reduction in the layout area owing to the omission of the analog output circuit in each output terminal **9** is by far larger.

[0114] An experimental liquid crystal driver to drive a liquid crystal panel with  $560 \times 240$  pixels for use in small- to medium-sized liquid crystal displays was fabricated including an only one buffer circuit provided correspondingly between the reference voltages  $V'_{24}$ ,  $V'_{40}$ , with only the halftone voltage input terminal  $T_{32}$  for the reference voltage  $V'_{32}$  omitted; it was confirmed that the experimental driver operated satisfactorily in display generation and would cause no problems in practical use.

[0115] Alternatively, the source driver **1** may include a buffer circuit provided correspondingly between other adjacent reference voltages (for example, the reference voltages  $V'_{16}$ ,  $V'_{24}$ ).

[0116] In the present embodiment, the input terminal is omitted to which the first reference voltages (for example, reference voltages  $V'_{32}$ ,  $V'_{48}$ ) that correspond to the second reference voltage produced by the generation circuit **11** is connected. This is because the provision of the generation circuit **11** makes it possible to obtain the second reference voltage replacing an external reference voltage and eliminates the need to provide a halftone voltage input terminal for the external reference voltage.

[0117] This omission of a halftone voltage input terminal for an external reference voltage makes it possible to reduce the number of wires required in the supply of reference voltages from the liquid crystal power supply to the source driver **1**, further reducing the size of the liquid crystal driver and hence the size of the liquid crystal display. Besides reducing the output circuits of the liquid crystal power supply, the less wires are also advantageous to a less power consumption and impermeable to noise over the wires. The layout design of the terminals of the source driver **1** is made easier, because the source driver **1** does not have as many terminals, including the output terminal **9**, as before.

[0118] In the present embodiment, the halftone voltage input terminals is reduced from nine to seven; the omitted input terminal is determined in accordance with the provision of a buffer circuit for such a voltage that the load capacity of the liquid crystal panel takes longer to charge and discharge as mentioned previously. There is no global criterion as to which terminal should be omitted.

[0119] As mentioned above, the ratio of the resistances of the resistor  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$  in the generation circuit **11** is specified to be equal to that of the resistance values of the resistor  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$  in the resistance divider circuit **14**. In other words, the resistors in the resistance divider circuit **14** are configured in such a resistance ratio that can effect a gamma correction. This allows the resistor in the generation

circuit 11 to be also configured in such a resistance ratio that can effect a gamma correction. The gamma correction, thus effected both in the generation circuit 11 and in the resistance divider circuit 14, ensures creation of a naturally looking tone display in accordance with human vision based on the 64 tone display voltages produced by the resistance divider circuit 14.

[0120] Further, the provision of the buffer circuits 12, 13 makes it possible to amplify the second reference voltages produced by the generation circuit 11 before supplied to the resistance divider circuit 14. In other words, the resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$  in the generation circuit 11 can be specified to a very high resistance values compared to the resistors  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ ; there are less restraints in the specifying the resistance values for the resistors  $R_{11}$ ,  $R_{12}$ ,  $R_{13}$ ,  $R_{14}$ .

[0121] Typically, the two reference voltages  $V'_0$  and  $V'_{64}$  that appear at the respective ends are always supplied to the standard voltage generator circuit 7, and the halftone voltage input terminals  $T_8-T_{56}$  are connected to the remaining reference voltages  $V'_8-V'_{56}$  and used for fine adjustment. In some cases, however, no voltage is applied to these terminals.

[0122] Therefore, the generation circuit 11 is preferably provided, as in the present embodiment, so that the circuit is capable of producing as the second reference voltage a voltage having a level either equal or close to a mid-level of the input range of a plurality of first reference voltages (a voltage other than the reference voltage  $V'_0$  which is the minimum in the input range and the reference voltage  $V'_{64}$  which is the maximum in the input range). The buffer circuits are preferably provided corresponding to the second reference voltages produced by the generation circuit 11. This ensures that even if no voltages are supplied which are far from the reference voltages  $V'_0$  and  $V'_{64}$  the 64 tone display voltages  $V_0-V_{63}$  are obtainable from the remaining, incoming first reference voltages and the second reference voltages produced by the generation circuit 11. The voltage with a level either equal or close to a mid-level of the input range of a plurality of first reference voltages may be any one of the remaining seven reference voltages  $V'_8$ ,  $V'_{16}$ ,  $V'_{24}$ ,  $V'_{40}$ ,  $V'_{48}$ ,  $V'_{56}$ .

[0123] The generation circuit 11, together with the buffer circuits, are preferably provided corresponding to a voltage of which the output waveform is too distorted to disregard due to high resistance when the ratio of the resistances of the resistors  $R_0-R_7$  in the resistance divider circuits 14 is changed to implement a gamma correction.

[0124] [Embodiment 2]

[0125] Referring to drawings, the following will describe another embodiment in accordance with the present invention. Here, for convenience, members of the present embodiment that have the same arrangement and function as members of embodiment 1, and that are mentioned in that embodiment are indicated by the same reference numerals and description thereof is omitted.

[0126] The present embodiment differs from embodiment 1 only in that the standard voltage generator circuit 7 of the present embodiment has an input terminal  $T_C$  (see FIG. 4) to which an external control signal  $C$  is coupled, for example, from a controller and that the buffer circuits 12, 13

each include a later-detailed control section 22 (see FIG. 5) that controls an operating current in the circuit based on the control signal  $C$ . The description below will therefore focus on this feature. Since the buffer circuits 12, 13 are identical, the buffer circuit 12 is taken as an example in the following.

[0127] FIG. 5 shows a schematic diagram showing a structure of the buffer circuit 12 that is formed by a voltage follower circuit 21 and a control section 22.

[0128] The voltage follower circuit 21 includes N-channel MOS (hereinafter, NMOS) transistors 23, 24 and P-channel MOS (hereinafter, PMOS) transistors 25, 26. The NMOS transistors 23, 24 form a differential pair. Meanwhile, the PMOS transistors 25, 26 form a current mirror circuit (active load circuit).

[0129] The gate of the NMOS transistor 23 is connected to an input terminal as an identical-phase input terminal. The NMOS transistors 23, 24 are interconnected through their sources which are in turn connected to the drain of the NMOS transistor 28 of the control section 22 (detailed later). The gate (inverse-phase input terminal) of the NMOS transistor 24 is connected to the source of the NMOS transistor 35 and the drain of the NMOS transistor 36 to form an output terminal. The gate of the NMOS transistor 35 is connected to the drain of the NMOS transistor 24. The source of the NMOS transistor 35 is connected to a power supply  $V_d$ .

[0130] The drain of the NMOS transistor 23 is connected to the drain of the PMOS transistor 25, and the source of the PMOS transistor 25 is connected to the power supply  $V_d$ . Meanwhile, the drain of the NMOS transistor 24 is connected to the drain of the PMOS transistor 26, and the source of the PMOS transistor 26 is connected to the power supply  $V_d$ .

[0131] Meanwhile, the control section 22 includes a bias voltage specification section 27 which determines an operating point for the differential amplifier section, a NMOS transistor 28 for transmitting an operating current for the differential section, a NMOS transistor 29 which serves as a switching element to turn on/off an operating current for the differential amplifier section, a bias voltage specification section 32 which determines an operating point for the output section, a NMOS transistor 36 for transmitting an operating current for the output section, and a NMOS transistor 37 which serves as a switching element to turn on/off an operating current for the output section.

[0132] The bias voltage specification section 27 is formed by NMOS transistors 30, 31. The gate of the NMOS transistor 30 receives the control signal  $C$ . The source of the NMOS transistor 30 is connected to the gate and drain of the NMOS transistor 31 and to the gate of the NMOS transistor 28. The gate of the NMOS transistor 28 therefore receives a bias voltage. The drain of the NMOS transistor 30 is connected to a power supply (not shown). The source of the NMOS transistor 31 is either grounded or connected to a standard potential.

[0133] Meanwhile, the bias voltage specification section 32 in the output section is formed by NMOS transistors 33, 34 and configured identically to the bias specification section 27 in the differential amplifier section. The gate of the NMOS transistor 33 receives the control signal  $C$  as does the gate of the NMOS transistor 37. The source of the NMOS transistor 33 is connected to the gate of the NMOS transistor

[0136] The source of the NMOS transistor **36** is connected to the drain of the NMOS transistor **37**. The source of the NMOS transistor **37** is grounded.

[0134] The source of the NMOS transistor **28** is connected to the drain of the NMOS transistor **29**. The source of the NMOS transistor **29** is grounded. The gate of the NMOS transistor **29** receives the control signal C.

[0135] With the buffer circuit **12** thus configured, the control signal C is set to a HIGH when a circuit must operate and to a LOW when the circuit must not operate. A LOW control signal C turns off the NMOS transistor **31** which determines an operating point for the differential amplifier circuit and the NMOS transistor **34** which determines an operating point for the output section, causing the NMOS transistors **28**, **36** for transmitting a bias current for the differential amplifier section and the output section respectively to not conduct. This causes the voltage follower circuit **21** to stop operating and consume no more current.

[0136] As detailed in the foregoing, the buffer circuit **12** of the present embodiment is adapted to set the output to a high output impedance through the control signal C and to cut off the operating current in the voltage follower circuit **21** which is a differential amplifier circuit when the circuit is not used. This ensures prevention of wasting electric power while the circuit is not being used and a large reduction of overall power consumption in the circuit.

[0137] Power consumption is reduced frequently if the control is carried out so as to stop the operation of the differential amplifier circuit when the liquid crystal display produces no display, as during blanking periods in a television system. Frequent reductions of power consumption are also possible in a portable device by stopping the operation of the differential amplifier circuit through the control signal C when the device has just been powered and the circuitry (including the circuitry other than the liquid crystal driver) has not reached a steady state yet.

[0138] [Embodiment 3]

[0139] Referring to drawings, the following will describe another embodiment in accordance with the present invention. Here, for convenience, members of the present embodiment that have the same arrangement and function as members of embodiments 1 and 2, and that are mentioned in those embodiments are indicated by the same reference numerals and description thereof is omitted.

[0140] The present embodiment differs from embodiment 2 only in that the buffer circuits **12**, **13** of the present embodiment each include a switch circuit **41** (see FIG. 6). The description below will therefore focus on this feature.

[0141] Referring to FIG. 6, the output of the buffer circuit (**12**, **13**) is connected to an end of an input/output terminal of the switch circuit **41**, whereas the other end of the input/output terminal of the switch circuit **41** is connected to the input terminal of the buffer circuit (**12**, **13**).

[0142] The switch circuit **41** can be formed by an analog switch, such as an MOS transistor or a transmission gate. In the present embodiment, an analog switch is used as the switch circuit **41**. The analog switch conducts (closes) when a control signal **t1** is HIGH and does not conduct (opens) when the control signal **t1** is LOW. Reasons why such switch circuits **41** are provided to the buffer circuits **12**, **13** will be detailed later.

[0143] The buffer circuits **12**, **13** have the same configuration as that described in embodiment 1 in reference to FIG. 5; detailed description thereof is omitted here.

[0144] The output of the buffer circuit **12** is connected to a contact between the resistors **R<sub>1</sub>**, **R<sub>2</sub>**. The output of the buffer circuit **13** is connected to a contact between the resistors **R<sub>3</sub>**, **R<sub>4</sub>**.

[0145] Here, the resistances of **R<sub>1</sub>**, **R<sub>2</sub>** and those of **R<sub>3</sub>**, **R<sub>4</sub>** are specified to satisfy  $R_1:R_2=R_{11}:R_{12}$ , and  $R_3:R_4=R_{13}:R_{14}$ . Reasons why the resistances are specified to such ratios will be detailed later.

[0146] The control terminal for controlling the opening/closing of the switch circuit **41** receives the control signal **t1** which is the same signal as the control signal C. By the use of identical control signals C and **t1**, the input terminal **T<sub>C</sub>** of the source driver **1** can be shared between the control signal C and the control signal **t1**, reducing the total number of terminals.

[0147] The standard voltage generator circuit **7** of the present embodiment, including the buffer circuits **12**, **13** configured as above, produces the tone display voltages  $V_0-V_{63}$  that correspond to the digital display data sets DR, DG, DB latched in accordance with a latch signal **Ls** for output to the source signal lines of the liquid crystal panel as does the standard voltage generator circuit **7** of embodiment 1.

[0148] The gate signal lines of the liquid crystal panel receive incoming HIGH scan signals from gate drivers so as to turn on the TFTs in the liquid crystal panel. The tone display voltages  $V_0-V_{63}$  are transmitted over the source signal lines and through the turned-on TFTs and applied to pixel capacitors connected to the drains of the TFTs to produce a display on the liquid crystal panel.

[0149] Referring to FIG. 7, the latched digital display data is stored in the hold memory circuit **5** until another latch signal **Ls** is received. In FIG. 7, the source drivers **1**, of which there are provided more than one in the liquid crystal display, are termed individually a first source driver, a second source driver, a third source driver, etc.

[0150] Therefore, upon reception of a latch signal **Ls**, the outputs of the source drivers are switched among tone display voltages  $V_0-V_{63}$  in accordance with the digital display data sets DR, DG, DB, and remain so until a next latch signal **Ls** is received. By retaining the outputs at one of the tone display voltages  $V_0-V_{63}$ , the pixel capacitors in the pixels in the liquid crystal panel are charged/discharged.

[0151] Now, the following will describe why a switch circuit **41** is provided to each buffer circuit **12**, **13**.

[0152] A current surge occurs in some cases in the standard voltage generator circuit **7** immediately after the tone display voltages  $V_0-V_{63}$  are applied to the pixel capacitor as in the foregoing. The surge subsides following a characteristic determined by a time constant of the capacitance of the pixel capacitors and the resistances, such as the TFT ON resistance, source signal line resistance, and source driver's output impedance. The current drops to substantially 0 with ignorable leak current, when the voltage applied to the pixel capacitor comes to a steady state at the predetermined value.

[0153] To produce a good quality display on the liquid crystal display, the surge current possibly occurring in the

standard voltage generator circuit 7 preferably come to a steady state at the desired tone display voltage  $V_0-V_{63}$  as soon as possible. To this end, the source driver 1 needs to have a low output impedance when the source driver 1 produces a new tone display voltage for output in response to the reception of a latch signal LS.

[0154] Besides, once the voltage applied to the pixel capacitor comes to a steady state at a predetermined value when a certain period of time TI (TI is set within a horizontal synchronization period) has elapsed, the display quality can be retained by applying a retainment voltage to retain the voltage at the predetermined steady-state value until the TFT turns off. While the retainment voltage is being applied, the source driver 1 may have a high output impedance.

[0155] As is illustrated above, the output impedance of the source driver 1 needs to be low in some cases and may be high in other cases even when an image is being displayed. Therefore, it is preferred if the source driver 1 can switch between a low output impedance state and a high output impedance state. A switch circuit 41 is provided to each buffer circuit 12, 13 in the present embodiment to enable the source driver 1 to switch the output impedance state.

[0156] A switching function of the switch circuit 41 between output impedance states are described in the following.

[0157] Referring to FIG. 6, when the switch circuits 41 conduct, the D/A converter circuit 8 receives two groups of currents: one through the buffer circuits 12, 13 and another through the resistors  $R_0-R_7$ .

[0158] The output of the buffer circuit 12, 13 is fed back to the input of the buffer circuit 12, 13 through the associated switch circuit 41. In other words, the buffer circuits 12, 13 are used as voltage followers and are capable of supplying large current in a low output impedance state.

[0159] Therefore, the current supply to the D/A converter circuit 8 is mainly made up of the current passing through the buffer circuits 12, 13. In other words, the output impedance of the standard voltage generator circuit 7 in relation to the D/A converter circuit 8 is low. The output impedance of the source driver 1 thus becomes low.

[0160] Meanwhile, when the switch circuit 41 does not conduct, no current flows through the buffer circuits 12, 13, which means that the current supply to the D/A converter circuit 8 is mainly made up of the current passing through the resistors  $R_0-R_7$ . The resistors  $R_0-R_7$  here have high resistances to reduce power consumption.

[0161] In other words, the output impedance of the standard voltage generator circuit 7 in relation to the D/A converter circuit 8 is high. This output impedance of the source driver 1 thus becomes high.

[0162] Now, the following will describe timings to switch the source driver 1 between a high output impedance state and a low output impedance state.

[0163] As shown in FIG. 8, for a predetermined time of TI after the input of a synchronizing signal LS, the control signal C (t1) is HIGH, activating the buffer circuits 12, 13 and causing the switch circuit 41 to conduct. The outputs from the buffer circuits 12, 13 are thereby supplied to the D/A converter circuit 8.

[0164] Consequently, the output from the source driver 1 is in a low output impedance state for a predetermined time of TI following the input of the synchronizing signal LS.

[0165] Meanwhile, after the predetermined time of TI elapses and the charging/discharging of the pixel capacitor is completed, the control signal C (t1) drops to a LOW level.

[0166] This deactivates the buffer circuits 12, 13 and causes the switch circuit 41 to not conduct. Consequently, the output of the source driver 1 in a high output impedance state.

[0167] In this situation, as mentioned above, since  $R_{11}:R_{12}=R_1:R_2$  (=1:1 in this case), the deactivation of the buffer circuits 12, 13 does not affect the levels of the tone display voltages  $V_0-V_{63}$ . In FIG. 8, period BI in the timing chart for the control signal C indicates that the buffer circuits 12, 13 are deactivated during a vertical synchronization blanking period.

[0168] The description above is based on an assumption that the control signal C is identical to the control signal t1. However, the two signals may be different and alternate between HIGH and LOW at different timings. The use of such two different signals eradicates switching noise that occurs in the output stage of the buffer circuits 12, 13 when the buffer circuits 12, 13 are activated and deactivated.

[0169] In this manner, in the source driver 1 of the present embodiment, the outputs of the buffer circuits 12, 13 are fed back to the inputs to the buffer circuits 12, 13.

[0170] Therefore the outputs of the buffer circuits 12, 13 are in a low output impedance state, and even if a large surge current occurs, for example, immediately after the liquid crystal panel is powered on, the tone display voltages  $V_0-V_{63}$  can come to a steady state more quickly, and a good quality image can be displayed.

[0171] Further, the ratio of the two resistors ( $R_{11}:R_{12}$ ) interposed between two adjacent first reference voltages  $V'_{56}$ ,  $V'_{40}$  in the generation circuit 11 to produce the second reference voltage is equal to the ratio of the two resistors ( $R_1:R_2$ ) interposed between the two first reference voltages  $V'_{56}$ ,  $V'_{40}$  in the resistance divider circuit 14.

[0172] In other words, the partial voltage level produced by the generation circuit 11 and fed to the buffer circuit 12 is always equal to the voltage level supplied from the buffer circuit 12 to the resistance divider circuit 14.

[0173] In other words, even if such control is done that no operating current flows in the buffer circuit 12, the second reference voltage is still retainable. Therefore, even if no internal current flows in the buffer circuit 12, the display quality of the liquid crystal panel can be maintained.

[0174] Further, even in a case when the operating current again flows in the buffer circuit, since the output of the buffer circuit 12 is fed back to the input of the buffer circuit 12, the tone display voltages  $V_0-V_{63}$  can come to a steady state more quickly.

[0175] Accordingly, even if the buffer circuit 12 is supplied with no operating current or conducts while an image display is being produced on the liquid crystal panel, effect on the quality of the image display on the liquid crystal panel is reduced.

[0176] On account of this, while a display is being produced on the liquid crystal panel, waste of electric power is again preventable and power consumption is further reduced when the buffer circuit 12 is not required to operate.

[0177] The source driver 1 includes: the switch circuits 41 passing or blocking the outputs from the buffer circuits 12, 13; and branch lines connecting the inputs of the buffer circuits 12, 13 to the outputs of the switch circuit 41.

[0178] In other words, when the switch circuit 41 conducts, the outputs of the buffer circuits 12, 13 are in a low output impedance state.

[0179] On account of this, even if a large surge current occurs, for example, immediately after the liquid crystal panel is powered on, the tone display voltages  $V_0-V_{63}$  can come to a steady state more quickly, and a good quality image can be displayed.

[0180] Meanwhile, while the switch circuit 41 is blocking the output from the buffer circuits 12, 13, the second reference voltage produced by the generation circuit 11 flows to the resistance divider circuit 14 through the path connecting the inputs of the buffer circuits 12, 13 to the output of the switch circuit 41.

[0181] On account of this, for example, after the display by the liquid crystal panel comes to a steady state, even if the internal currents of the buffer circuits 12, 13 are blocked, the display quality of the liquid crystal panel can be maintained.

[0182] On account of this, while a display is being produced on the liquid crystal panel, waste of electric power is again preventable and power consumption is further reduced when the buffer circuit 12 is not required to operate.

[0183] Moreover, in the source driver 1, the control signal C for the operating currents in the buffer circuits 12, 13 is identical to the control signal t1 for the switch circuits 41.

[0184] On account of this, the input terminal of the source driver 1 can be shared between the two control signals C, t1, reducing the total number of terminals.

[0185] Further, in the source driver 1, the operating currents in the buffer circuits 12, 13 are blocked when a predetermined time T1 elapses after the second reference voltage is received.

[0186] In other words, the operating currents in the buffer circuits 12, 13 are more frequently blocked while a display is being produced on the liquid crystal panel. On account of this, the power consumption in the source driver 1 is further reduced.

[0187] Japanese Laid-Open Patent Application No. 2000-47625 (Tokukai 2000-47625; published on Feb. 18, 2000) and other publications disclose a structure to supply the output of a selective circuit directly to a liquid crystal panel without going through a buffer circuit. The conventional structure is the same as the structure of the present invention in that both are intended to reduce the buffer circuits in number which are conventionally provided so that each output terminal has one buffer circuit. However, the structure disclosed in the Japanese Laid-Open Patent Application includes buffer circuits in a subsequent stage of a resistance divider circuit (bias voltage generator section) for generating a plurality of bias voltages, whereas the structure of the present invention includes buffer circuits 12, 13 in a pre-

ceding stage of the resistance divider circuit 14. The two structures are clearly different.

[0188] Suppose that buffer circuits are provided in a subsequent stage of a resistance divider circuit as in the Japanese Laid-Open Patent Application, the same number of buffer circuits as the tone display voltages need to be provided to use the buffer circuits in reducing distortion in waveforms of the tone display voltage outputs from the resistance divider circuit.

[0189] By contrast, in the present invention, for example, the resistor R<sub>2</sub> in the resistance divider circuit 14 derives tone display voltages  $V_{41}-V_{48}$  from the second reference voltage supplied from the buffer circuit 12. Under these circumstances, the buffer circuit 12 reduces distortion in the waveform of the second reference voltage. This can be interpreted to mean that the single buffer circuit 12 is capable of reducing distortion in the waveforms of the tone display voltages  $V_{41}-V_{48}$ , because these tone display voltages are obtained from the second reference voltage. In other words, in the present invention, since the buffer circuit 12 is located in the preceding stage of the resistance divider circuit 14, there is no need to provide the same number of buffer circuits 12 as the tone display voltages  $V_{41}-V_{48}$ .

[0190] Therefore, for the same number of derived tone display voltages, the present invention significantly reduces the number of buffer circuits provided in the standard voltage generator circuit 7 and ensures effects of the miniaturization of the device and the reduction in power consumption of the device, compared to the Japanese Laid-Open Patent Application.

[0191] Incidentally, a liquid crystal driver in accordance with the present invention may include: voltage dividing means formed by a first resistance divider circuit in which resistors are connected in series correspondingly between adjacent first reference voltages and adjacent first and second reference voltages; and generation means formed by a second resistance divider circuit in which resistors are connected in series correspondingly with adjacent first and second reference voltages, wherein the resistors constituting the first resistance divider circuit and those constituting the second resistance divider circuit are specified to have such a resistance ratio that gamma correction can be implemented on 2<sup>n</sup> tone display voltage by each group of resistors to produce a naturally looking tone display.

[0192] According to the arrangement, the resistors constituting the first resistance divider circuit in the voltage dividing means and those constituting the second resistance divider circuit in the generation means are specified to have such a resistance ratio that gamma correction can be implemented by each group of resistors. The gamma correction implemented by both the first resistance divider circuit and the second resistance divider circuit ensures that a tone display that look natural to the human eye is produced from the 2<sup>n</sup> tone display voltage produced by the first resistance divider circuit.

[0193] In a liquid crystal driver in accordance with the present invention, the generation means may be adapted so as to produce a voltage other than those equal to a maximum or a minimum in an input range of the first reference voltages as the second reference voltage.

[0194] It is ensured that the maximum and minimum in the input range of the first reference voltages are supplied to the

standard voltage producing means; however, other voltages in the input range are in some cases not supplied to standard voltage producing means, because they are used fine adjustment.

[0195] In the foregoing structure, the generation means produces a voltage other than those equal to the maximum or minimum as the second reference voltage; therefore, it is ensured that the voltage dividing means can produce the 2<sup>nd</sup> tone display voltages from remaining ones of the incoming first reference voltages and the second reference voltages produced by the generation means even when no voltage is supplied to the standard voltage producing means other than the maximum and minimum in the input range of the first reference voltages.