## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2005/0170592 A1

Aug. 4, 2005 (43) **Pub. Date:**

THIN FILM TRANSISTOR ARRAY PANELS FOR A LIQUID CRYSTAL DISPLAY AND A METHOD FOR MANUFACTURING THE **SAME**

Aug. 12, 1999 (KR)......1999-33091 Jul. 8, 1999

(76) Inventors: **Bum-Ki Baek**, Suwon-city (KR); Jang-Soo Kim, Suwon-city (KR); Sung-Wook Huh, Seoul (KR); Jong-Soo Yoon, Cheonan-city (KR);

### **Publication Classification**

Mun-Pyo Hong, Seongnam-city (KR); Dong-Gyu Kim, Suwon-city (KR)

| (51) | Int. Cl. <sup>7</sup> | H01L | 31/0376 |

|------|-----------------------|------|---------|

| (52) | U.S. Cl.              |      | 438/294 |

Correspondence Address: MCGUIREWOODS, LLP 1750 TYSONS BLVD

#### (57)ABSTRACT

**SUITE 1800** MCLEAN, VA 22102 (US) A conductive layer, including a lower layer made of refractory metal such as chromium, molybdenum, and molybdenum alloy and an upper layer made of aluminum or aluminum alloy, is deposited and patterned to form a gate wire including a gate line, a gate pad, and a gate electrode on a substrate. At this time, the upper layer of the gate pad is removed using a photoresist pattern having different thicknesses depending on position as etch mask. A gate insulating layer, a semiconductor layer, and an ohmic contact layer are sequentially formed. A conductive material is deposited and patterned to form a data wire including a data line, a source electrode, a drain electrode, and a data pad. Next, a passivation layer is deposited and patterned to form contact holes respectively exposing the drain electrode, the gate pad, and the data pad. At this time, the contact hole on the gate pad only exposes the lower layer of the gate pad, and the gate insulating layer and the passivation layer completely cover the upper layer of the gate pad. Next, indium tin oxide is deposited and patterned to form a pixel electrode, a redundant gate pad, and a redundant data pad respectively connected to the pixel electrode, the gate pad, and the data pad.

(21) Appl. No.: 11/080,612

(22) Filed:

## Mar. 16, 2005 Related U.S. Application Data

(63) Continuation of application No. 10/302,927, filed on Nov. 25, 2002, now Pat. No. 6,887,742, which is a continuation of application No. 09/545,891, filed on Apr. 7, 2000, now Pat. No. 6,524,876.

#### (30)Foreign Application Priority Data

Apr. 8, 1999 (KR)......1999-12287

FIG. 1

FIG.2

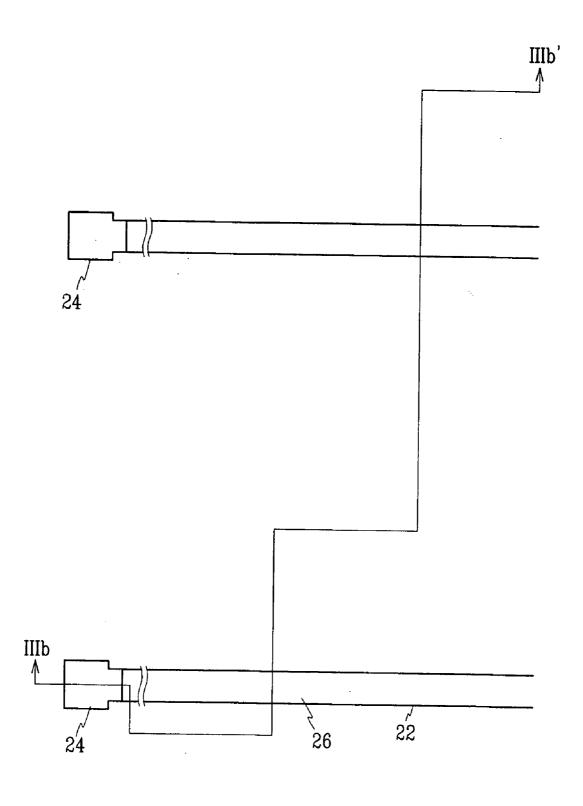

FIG. 3A

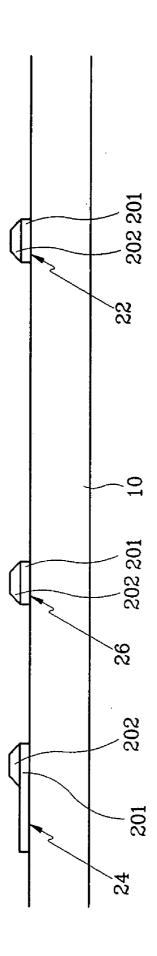

FIG.3B

FIG.3C

FIG. 4

FIG. 5

FIG. 6A

FIG. 6B

FIG. 7A

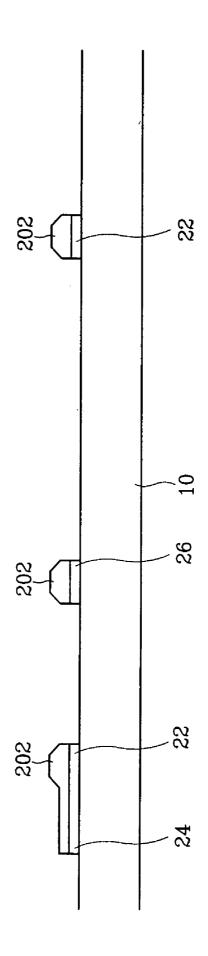

FIG. 7B

FIG. 8A

FIG.8B

FIG. 9

FIG. 10

FIG. 12A

FIG. 12B

FIG. 12C

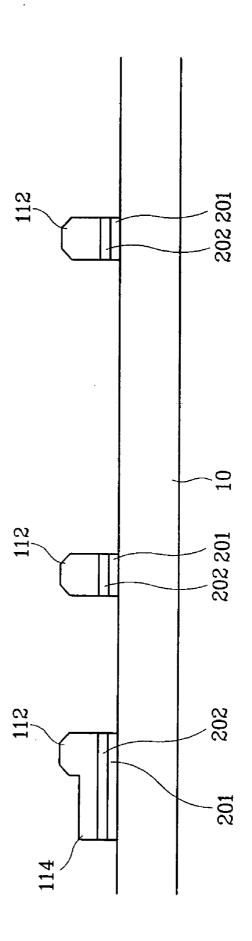

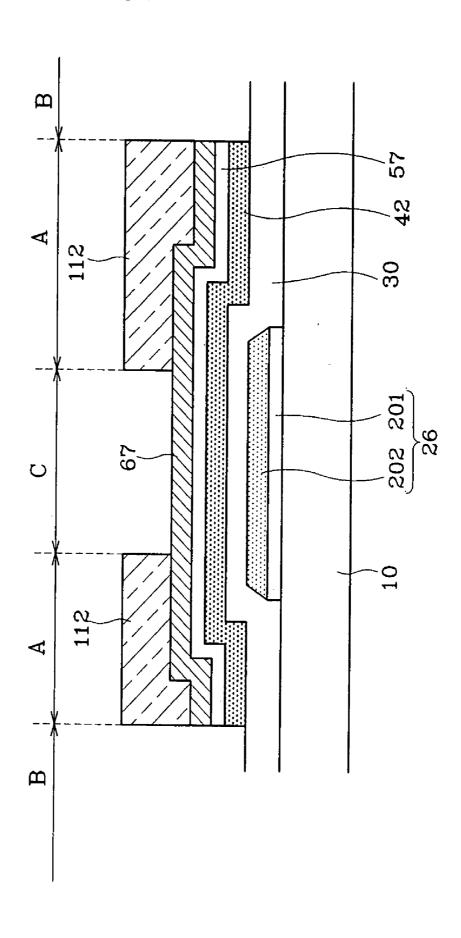

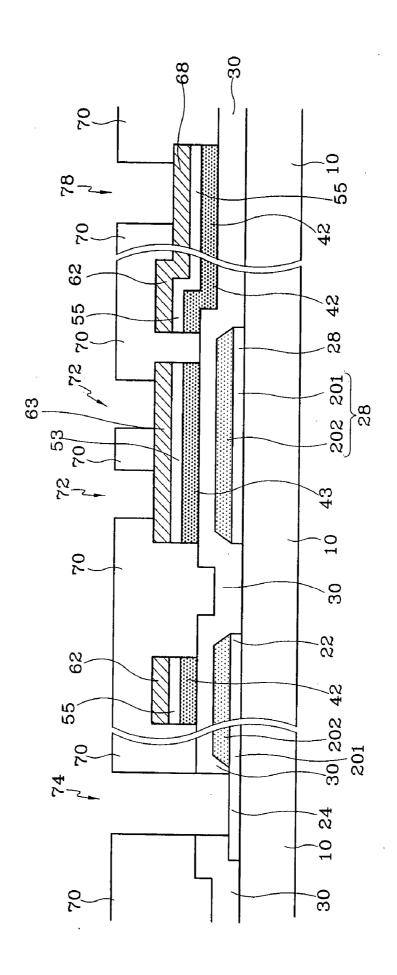

202 201 FIG. 13B

FIG. 14A

FIG. 14B

FIG. 14C

FIG. 15B

-67 -57 B 10 ¥ 42 67-57-В 202 201 ¥ 53 FIG. 16A 10 43~ 63~ М 42 30 な | 202 201  $\mathbf{B}$ 24 30

FIG. 17A

FIG. 17B

FIG. 18A

FIG. 18B

FIG. 19

FIG. 20

FIG.21

FIG.22

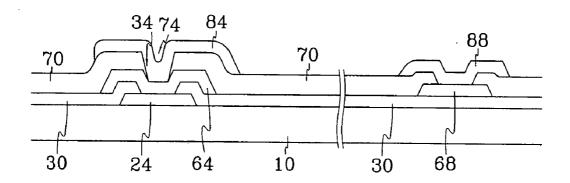

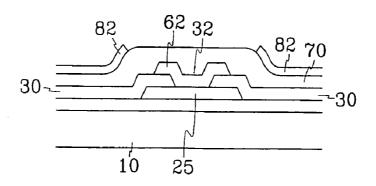

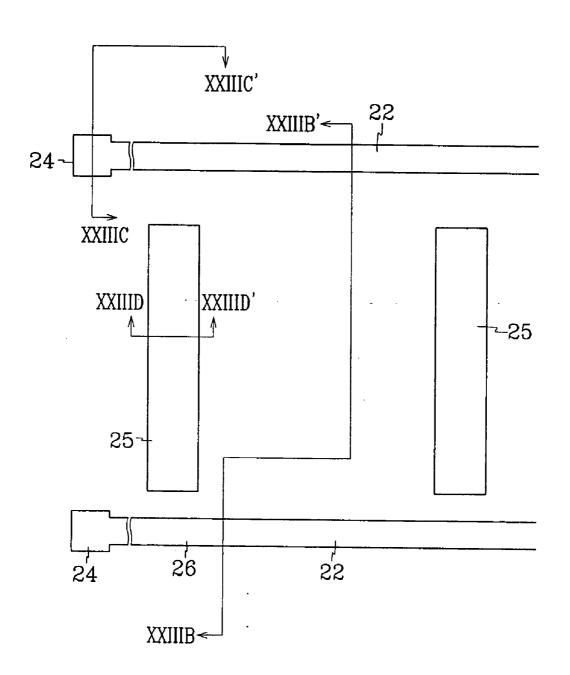

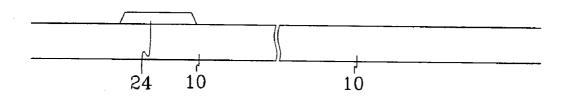

FIG. 23A

FIG. 23B

FIG.23C

FIG. 23D

FIG. 24A

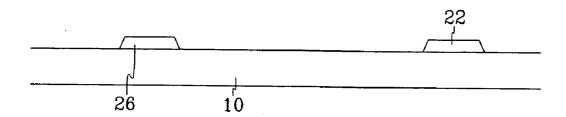

FIG.25A

FIG. 25B

FIG.25C

FIG. 26A

FIG. 26B

FIG.26C

FIG. 26D

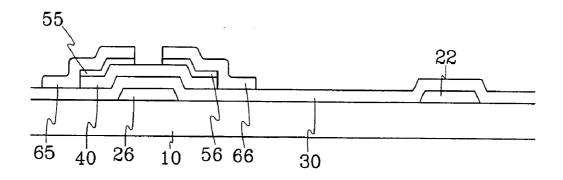

FIG. 27A

FIG. 27B

FIG. 27C

FIG. 27D

FIG. 28

## FIG.29

FIG. 30

FIG. 31

FIG. 32A

FIG. 32B

FIG. 32C

FIG. 32D

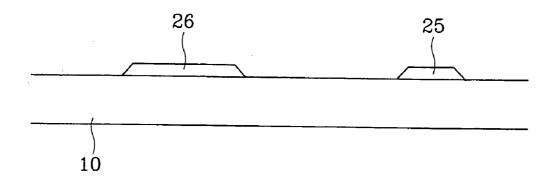

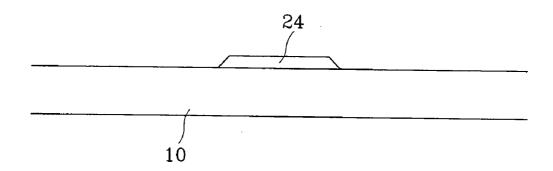

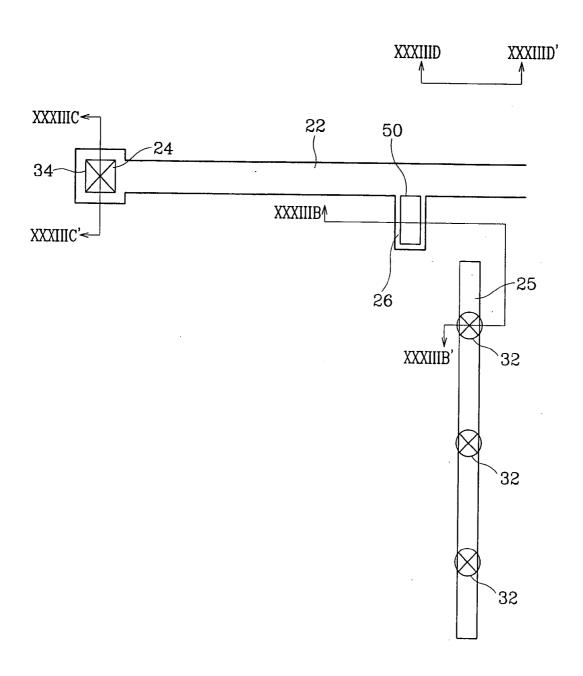

FIG. 33A

FIG. 33B

FIG. 33C

FIG. 33D

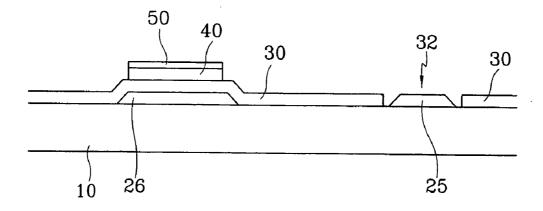

FIG. 34A

FIG. 34B

FIG. 34C

*FIG.34D*

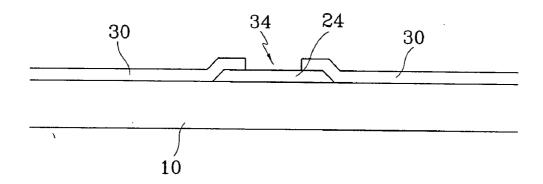

FIG. 35A

FIG. 35B

FIG. 35C

FIG. 35D

# THIN FILM TRANSISTOR ARRAY PANELS FOR A LIQUID CRYSTAL DISPLAY AND A METHOD FOR MANUFACTURING THE SAME

#### BACKGROUND OF THE INVENTION

[0001] (a) Field of the Invention

[0002] The present invention relates to a thin film transistor array panel and a method for manufacturing the same.

[0003] (b) Description of the Related Art

[0004] A liquid crystal display (LCD) is one of the most popular flat panel displays (FPD). The liquid crystal display has two panels having electrodes for generating electric fields and a liquid crystal layer interposed therebetween.

[0005] The transmittance of incident light is controlled by the intensity of the electric field applied to the liquid crystal layer.

[0006] In the most widely used liquid crystal display, the field-generating electrodes are provided at both of the panels, and one of the panels has switching elements such as thin film transistors.

[0007] In general, a thin film transistor array panel is manufactured by photolithography using a plurality of photomasks. Since the photolithography process is expensive, the number of the photolithography steps needs to be minimized.

[0008] In order to prevent the delay or distortion of signals applied to wires, materials having a low resistivity, such as aluminum or aluminum alloy, are generally used. However, because of the poor contact properties between aluminum or aluminum alloy and indium tin oxide (ITO), which is used as a transparent electrode in a pad portion of a liquid crystal display, the aluminum or aluminum alloy is removed to prevent the corrosion of aluminum and aluminum alloy and a different material is then inserted therebetween. Accordingly, the manufacturing process is complicated and production costs are increased.

[0009] Also, it is desirable that a data wire transmitting image signals is made of aluminum or aluminum alloy. However, since such a data wire is connected to an ITO pixel electrode, the data wire is made of material having good contact properties such as chromium and molybdenum. Unfortunately, because material such as chromium and molybdenum has a higher resistivity than aluminum or aluminum alloy, signals are often delayed or distorted in a large scale liquid crystal display.

[0010] Also, when combining a completed thin film transistor panel and a completed color filter panel in the manufacturing process, if there are conductive particles between the two panels, the pixel electrode or the data wire of the thin film transistor panel and a common electrode of the color filter panel may be shorted.

#### SUMMARY OF THE INVENTION

[0011] It is therefore an object of the present invention to simplify a method for manufacturing a thin film transistor array panel for a liquid crystal display.

[0012] It is another object of the present invention to provide a method for manufacturing a thin film transistor array panel for a liquid crystal display having a good contact structure.

[0013] It is still another object of the present invention to prevent the disconnection and corrosion of wires and to minimize the delay or distortion of signals in a large scale liquid crystal display.

[0014] It is still yet another object of the present invention to reduce defects of liquid crystal displays by preventing conductive particles from shorting two panels.

[0015] These and other objects are provided, according to the present invention, by forming at least two patterns through one photolithography process. A photoresist pattern has different thickness on various positions of an etch mask. Wires are formed by a conductive layer of aluminum or aluminum alloy. In this way, a layer of aluminum or aluminum alloy only on a pad portion may be removed by the photoresist pattern. A redundant line of aluminum or aluminum alloy may be laid on the layer different from the wire. A passivation layer may be formed after the wires and a pixel electrode are formed.

[0016] According to the present invention, a conductive layer of a multi-layered structure is deposited on an insulating substrate, and then patterned to form a gate wire including a gate line and a gate electrode connected to the gate line. A gate insulating layer covering the gate wire and a semiconductor layer on the gate insulating layer opposite to the gate electrode are sequentially formed. A data wire including a data line intersecting the gate line, a source electrode connected to the data line and neighboring the gate electrode, and a drain electrode separated from the source electrode and opposite to the source electrode with respect to the gate electrode is formed. Next, a passivation layer covering the data wire is formed, and a pixel electrode connected to the drain electrode is formed. At this time, the conductive layer is selectively patterned by partially exposing the lower layer located at the middle portion of its multi-layered structure.

[0017] It is desirable that the gate wire is formed through one photolithography step using a photoresist pattern having different thickness depending on positions. The photoresist pattern may have a first portion having a first thickness, a second portion having a second thickness larger than the first portion, and a third portion having a third thickness smaller than the first thickness.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0018] The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate an embodiment of the invention, and, together with the description, serve to explain the principle of the invention.

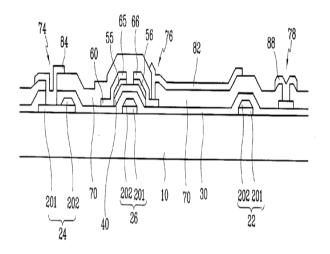

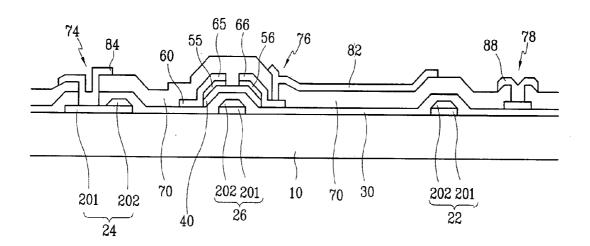

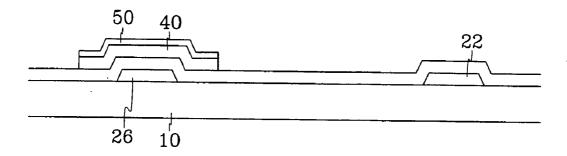

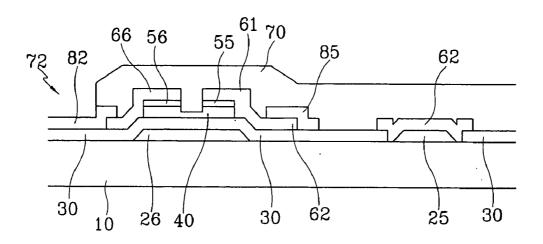

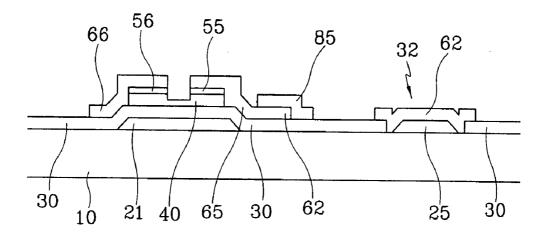

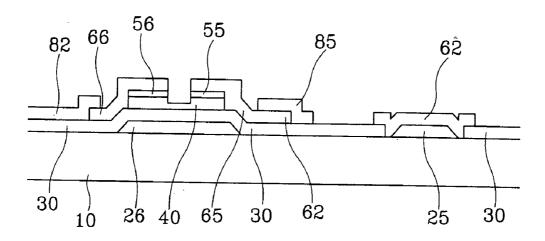

[0019] FIG. 1 is a layout view of a thin film transistor array panel for a liquid crystal display according to the first embodiment of the present invention.

[0020] FIG. 2 is cross-sectional view taken along lines II-II" of FIG. 1.

[0021] FIGS. 3A, 6A, 7A, and 8A are layout views of a thin film transistor array panel according to a first embodiment of the present invention showing manufacturing steps.

[0022] FIGS. 3B, 4, and 5 are cross-sectional views taken along the line IIIB-IIIB' of FIG. 3A.

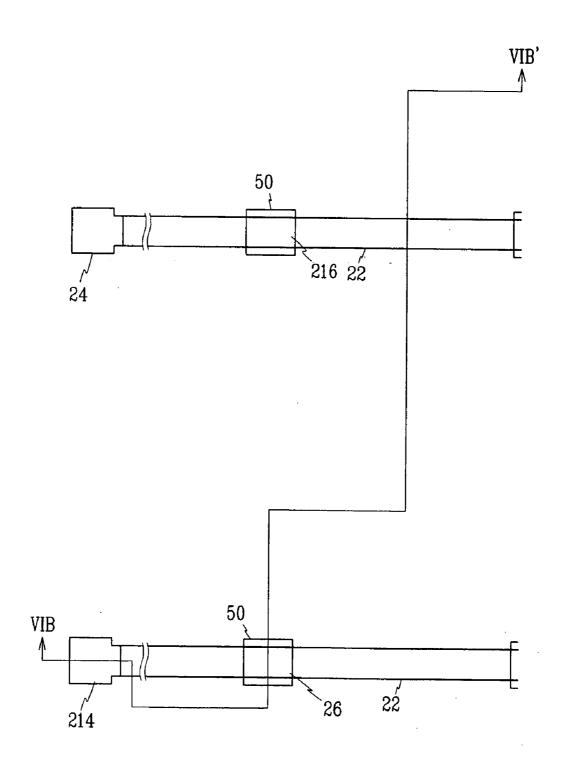

[0023] FIG. 6B is a cross-sectional view at the next step following FIG. 3B taken along the line VIB-VIB' of FIG. 6A.

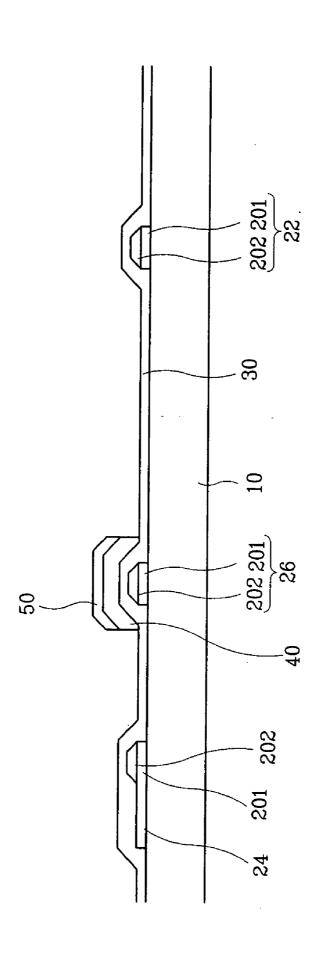

[0024] FIG. 7B is a cross-sectional view at the next step following FIG. 6B taken along the line VIIB-VIIB' of FIG. 7A.

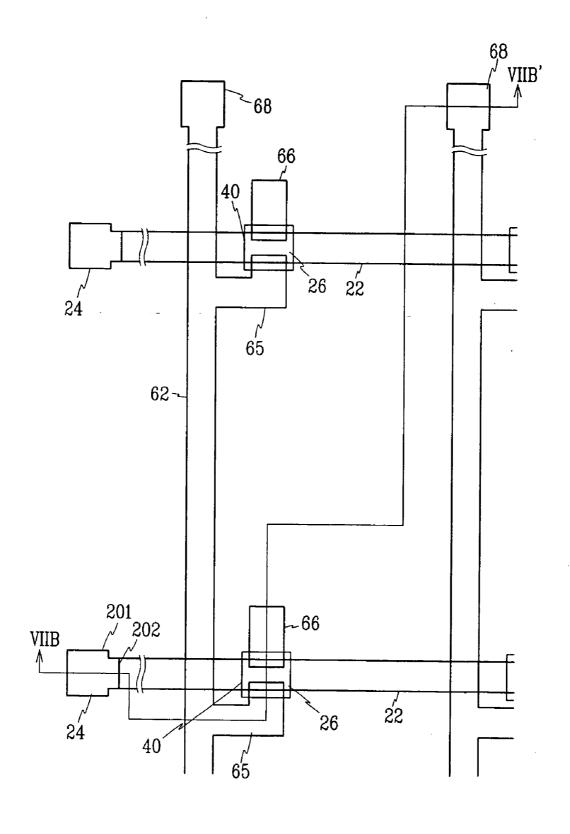

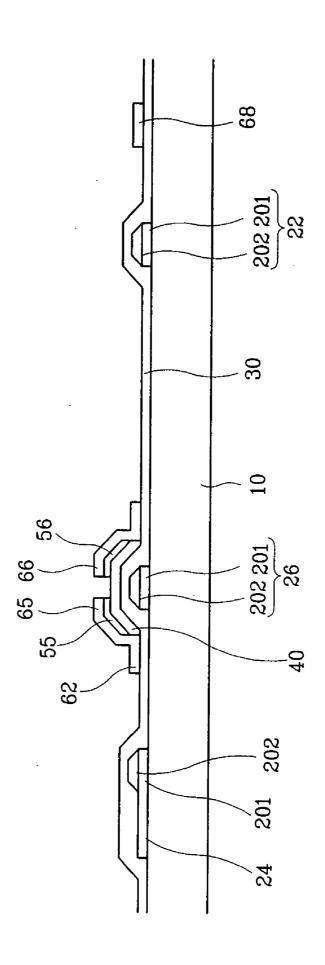

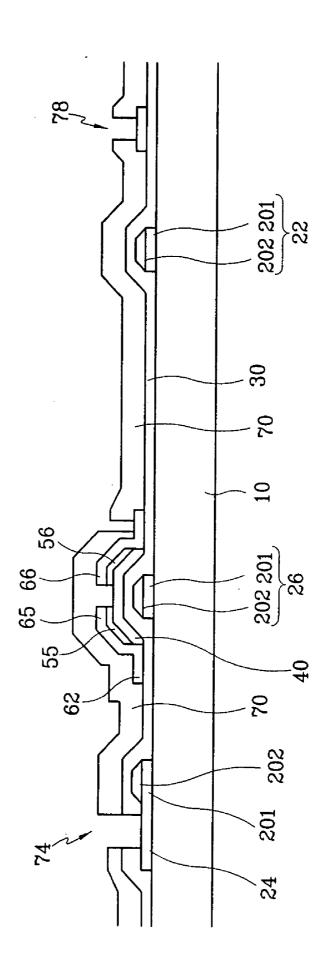

[0025] FIG. 8B is a cross-sectional view in the next step following FIG. 7B taken along the line VIIIB-VIIIB' of FIG. 8A.

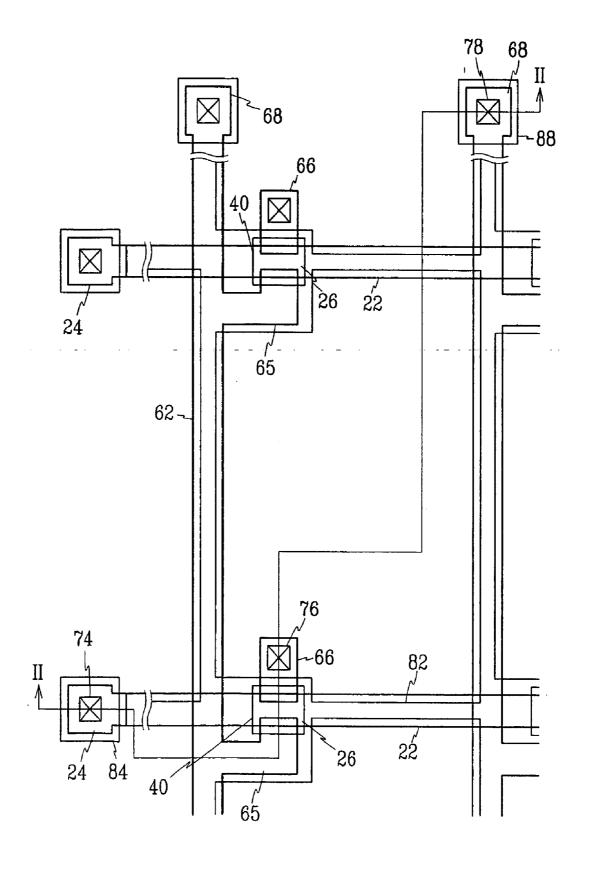

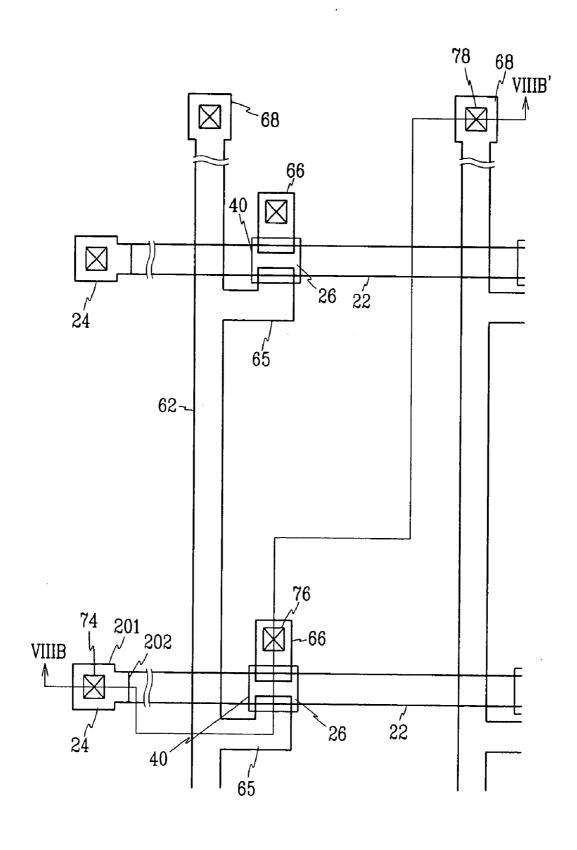

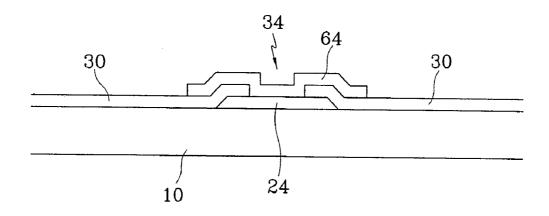

[0026] FIG. 9 is a layout view of a thin film transistor array panel for a liquid crystal display according to the second embodiment of the present invention.

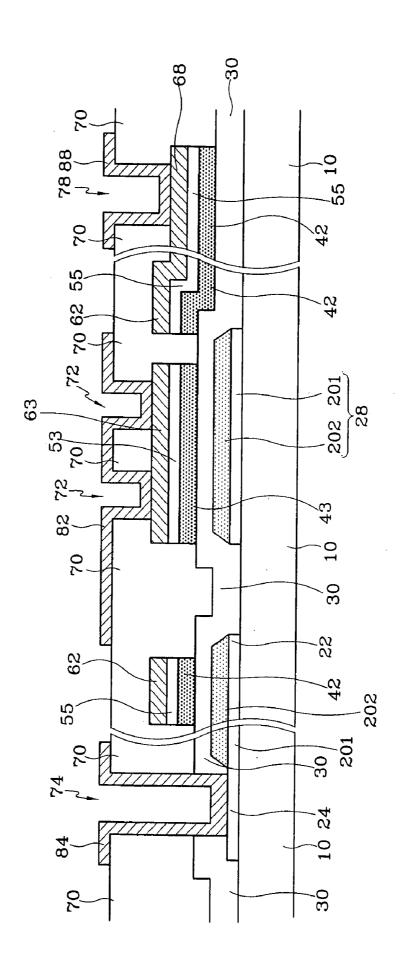

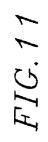

[0027] FIGS. 10 and 11 are cross-sectional views taken along lines X-X' and XI-XI' of FIG. 9, respectively.

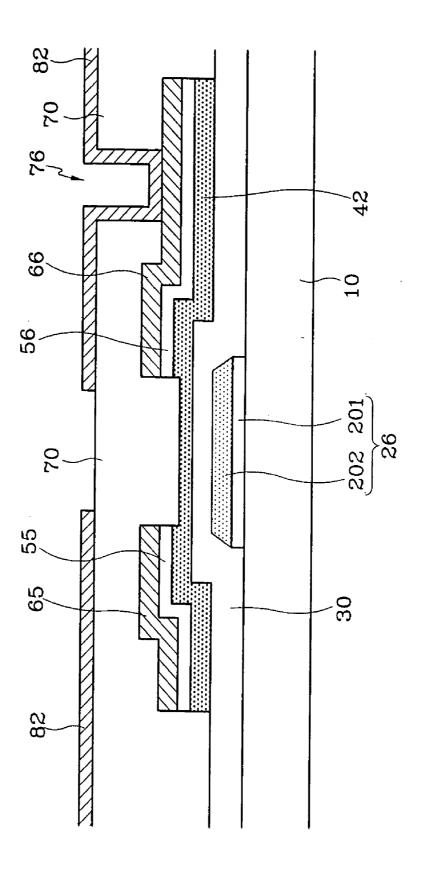

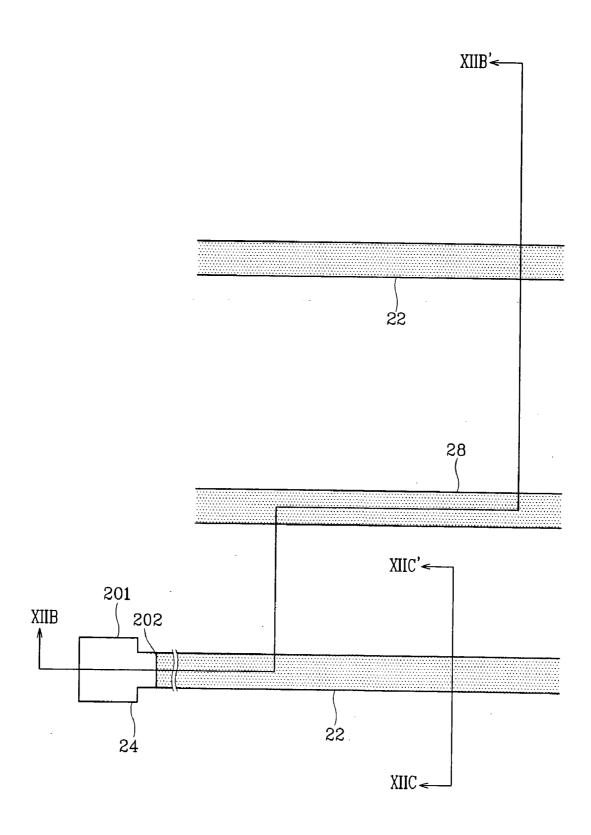

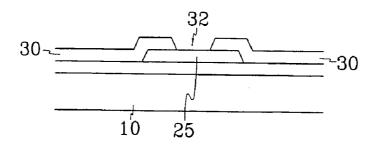

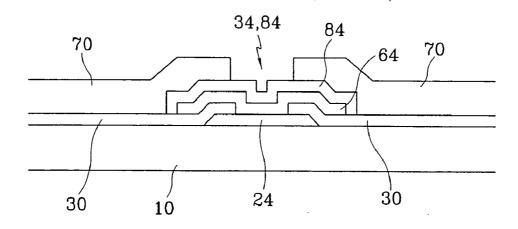

[0028] FIG. 12A is a layout view of the thin film transistor array panel according to the second embodiment of the present invention at a first manufacturing step.

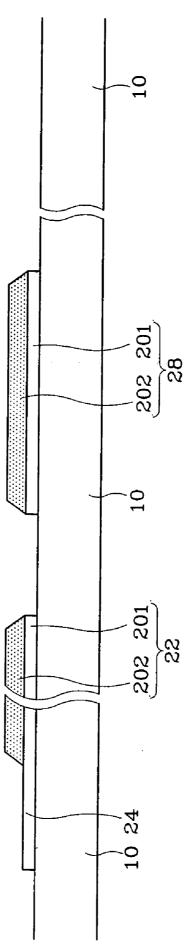

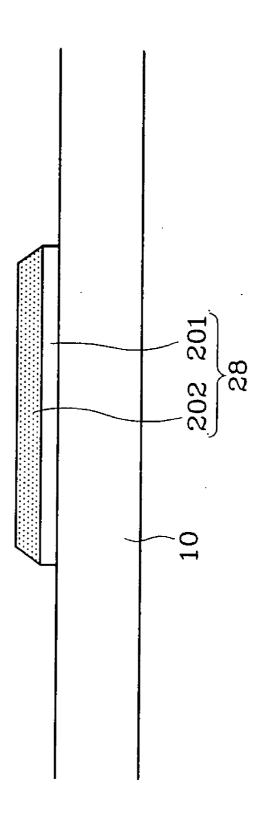

[0029] FIGS. 12B and 12C are cross-sectional views taken along the lines XIIB-XIIB' and XIIC-XIIC' of FIG. 12A.

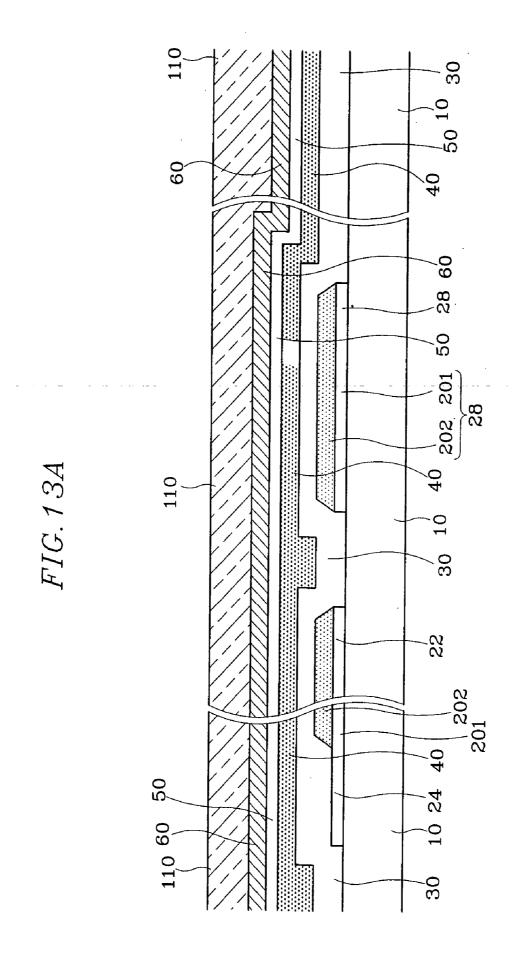

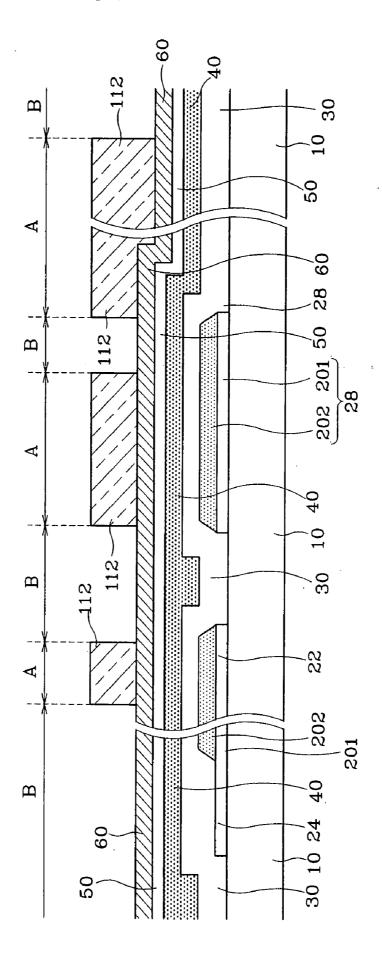

[0030] FIGS. 13A and 13B are cross-sectional views in the next step following FIGS. 12B and 12C taken along the lines XIIB-XIIB' and XIIC-XIIC' of FIG. 12A.

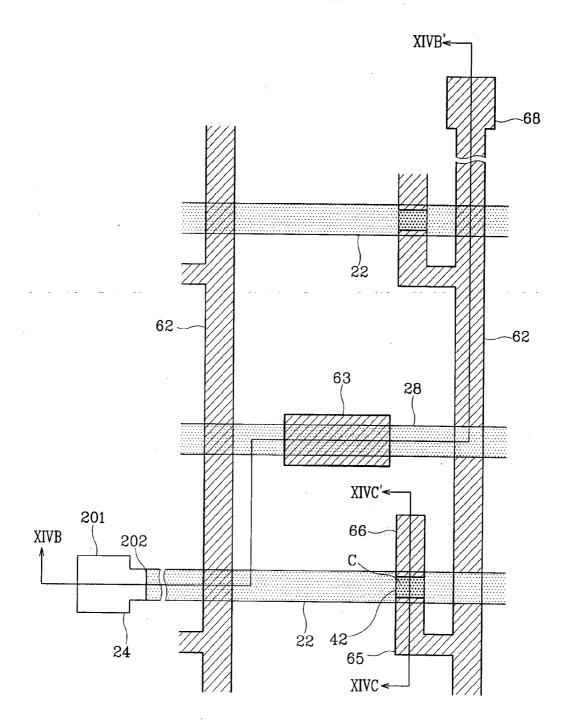

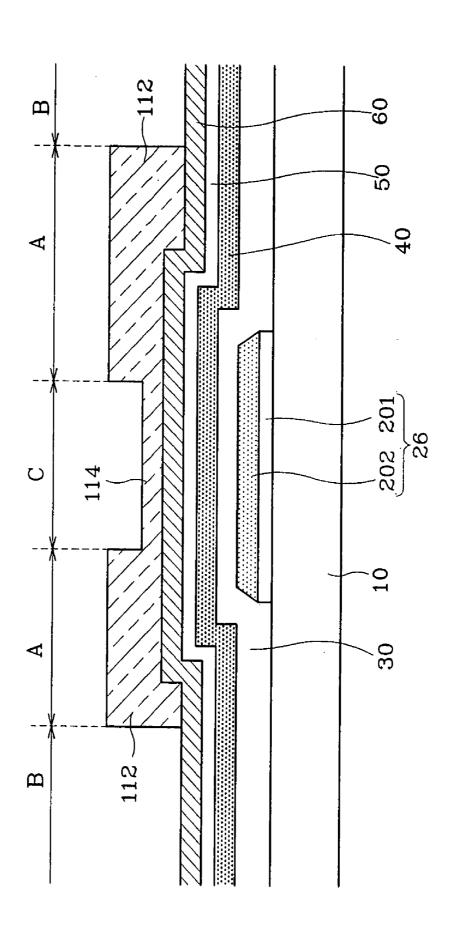

[0031] FIG. 14A is a layout view of thin film transistor array panel in the next step following FIGS. 13A and 13B.

[0032] FIGS. 14B and 14C are respectively cross-sectional views taken along the lines XIVB-XIVB' and XIVC-XIVC' of FIG. 14A.

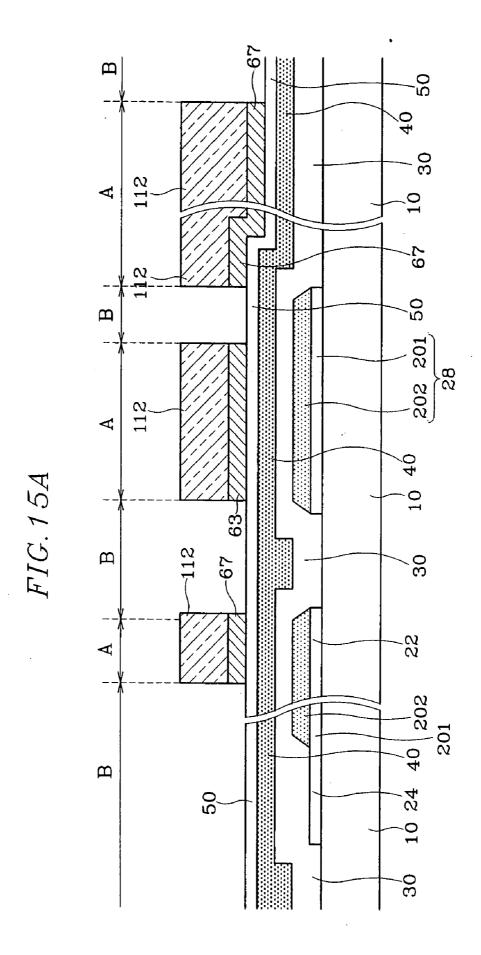

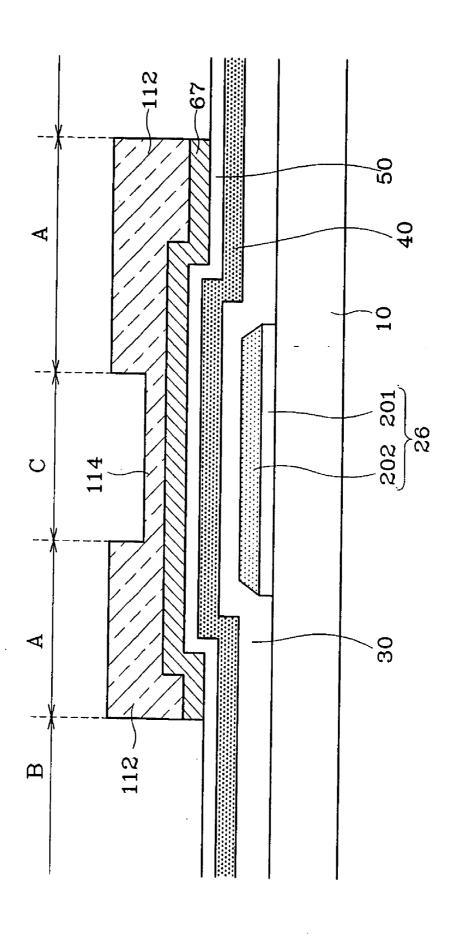

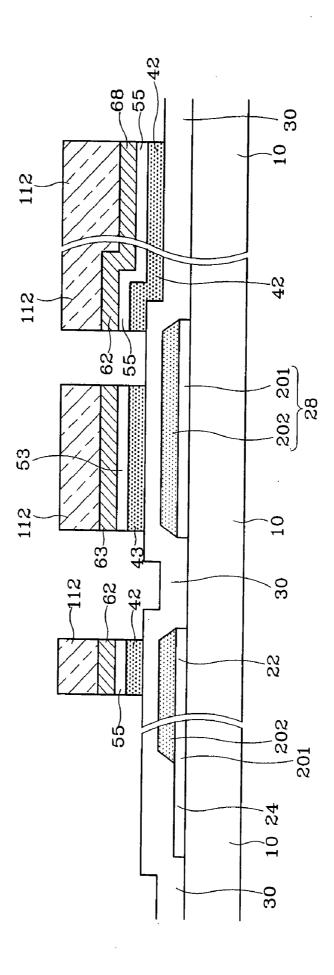

[0033] FIGS. 15A, 16A, and 17A are cross-sectional views in the next step following FIG. 14B taken along the line XIVB-XIVB' of FIG. 14A.

[0034] FIGS. 15B, 16B, and 17B are cross-sectional views in the next step following FIG. 14C taken along the line XIVC-XIVC' of FIG. 14A.

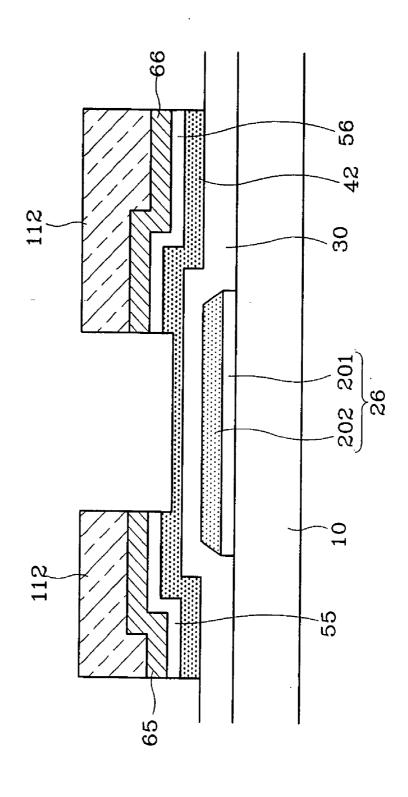

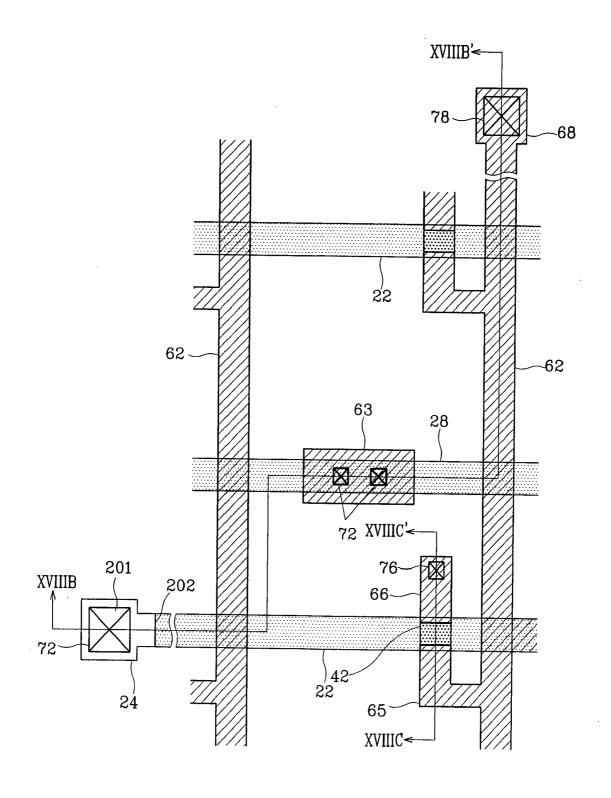

[0035] FIG. 18A is a layout view of a thin film transistor array panel in the next step following FIGS. 17A and 17B.

[0036] FIGS. 18B and 18C are the cross-sectional views taken along the lines XVIIIB-XVIIIB' and XVIIIC-XVIIIC' of FIG. 18A, respectively.

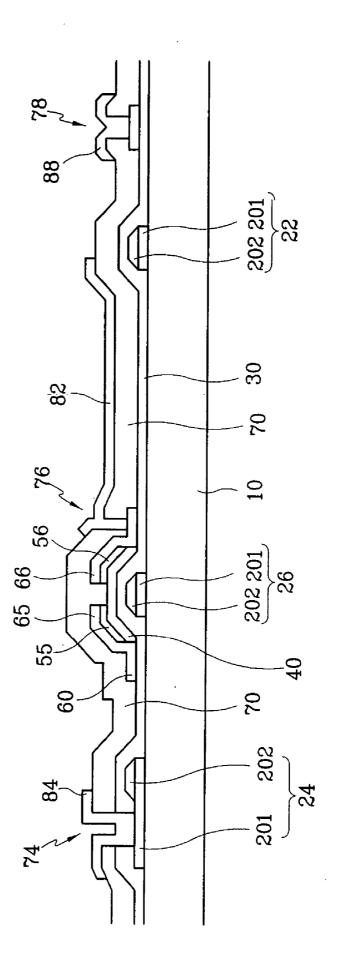

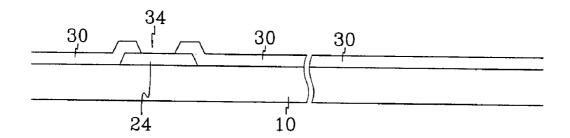

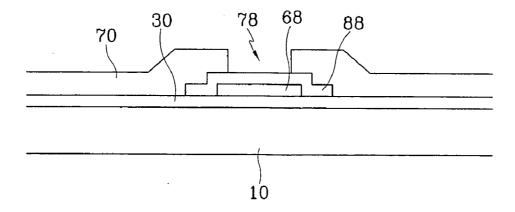

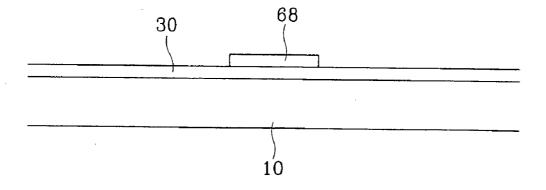

[0037] FIG. 19 is a layout view of a thin film transistor array panel for a liquid crystal display according to the third embodiment of the present invention.

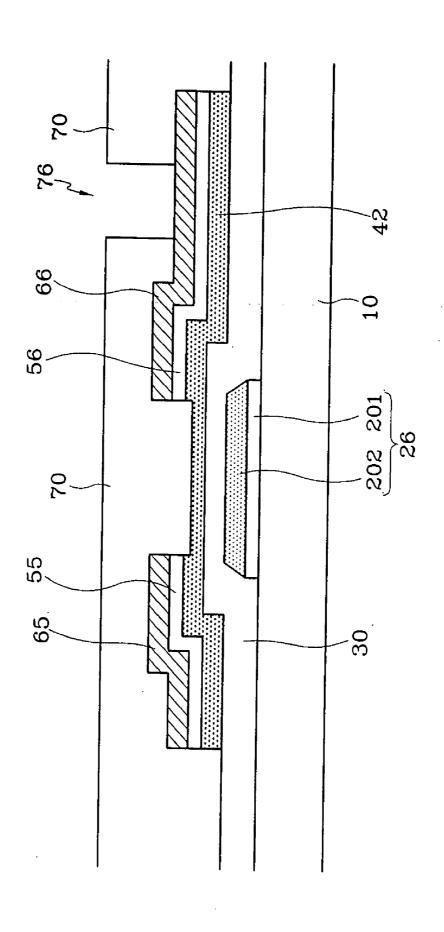

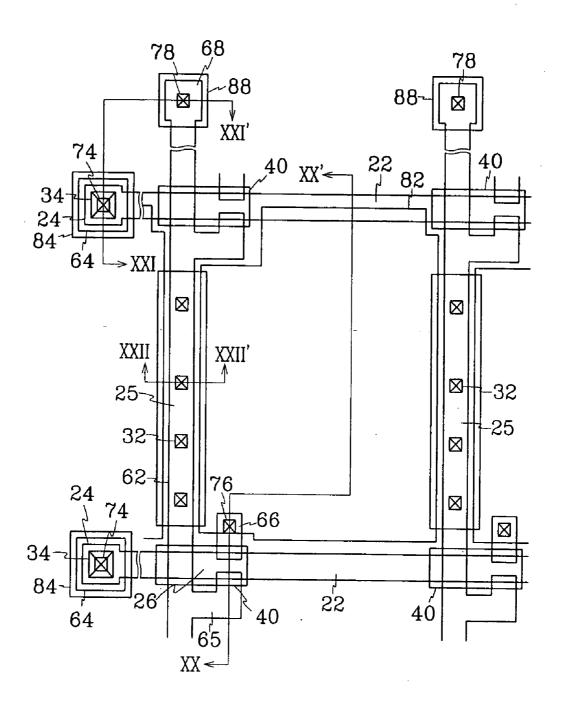

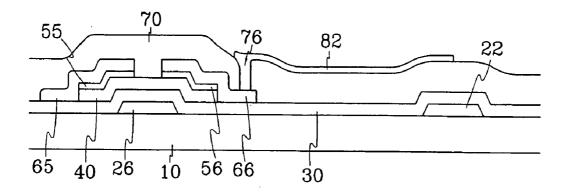

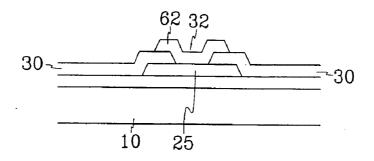

[0038] FIGS. 20, 21, and 22 are the cross-sectional view taken along the lines XX-XX', XXI-XXI', and XXII-XXII' of FIG. 19, respectively.

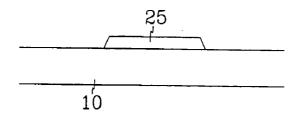

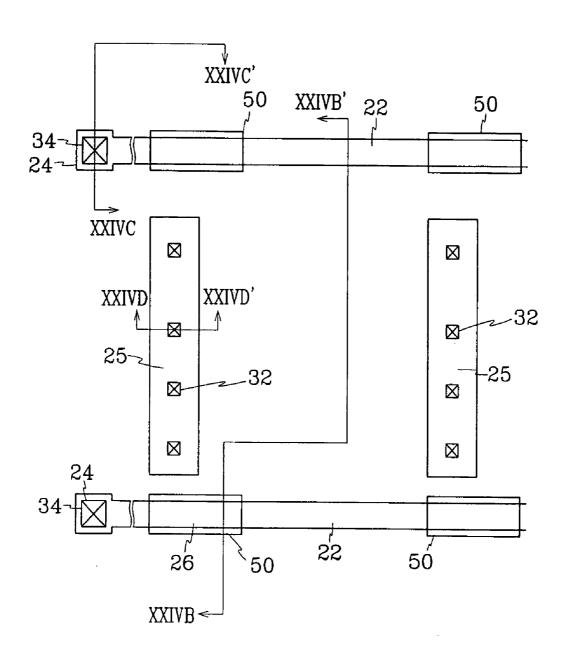

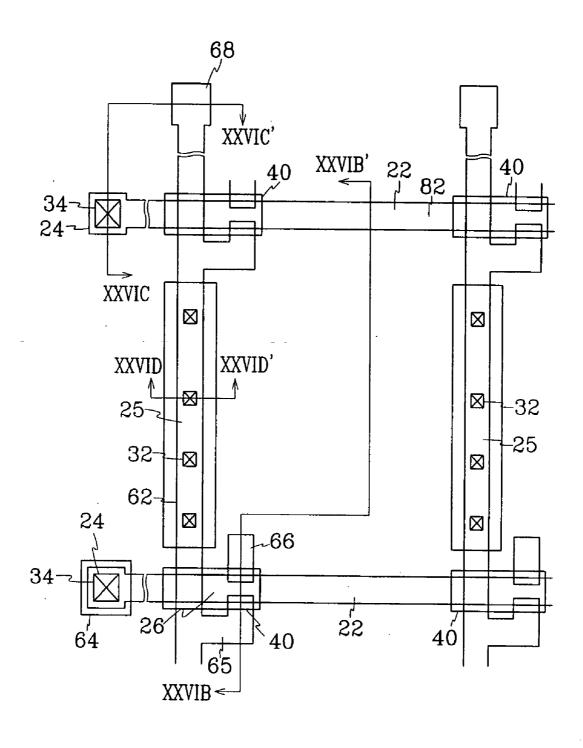

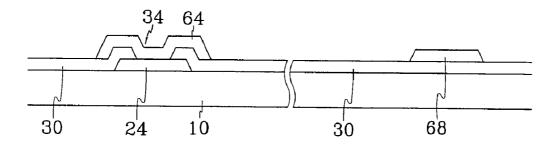

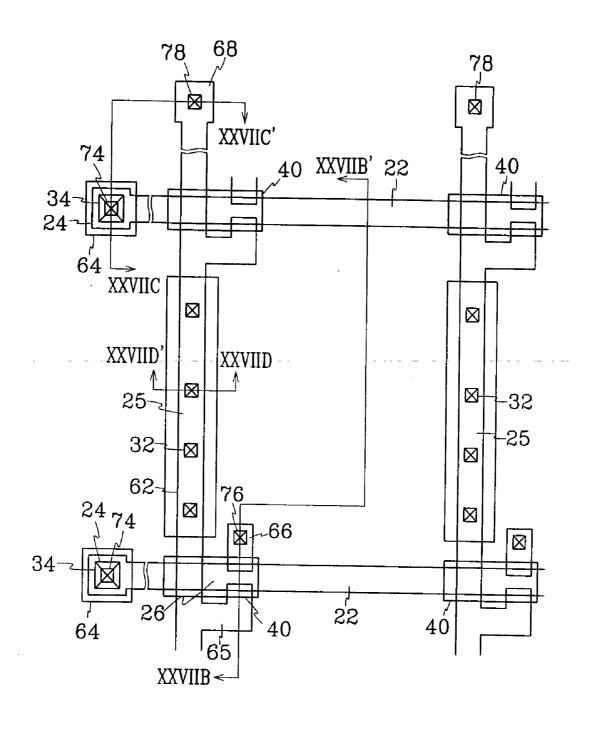

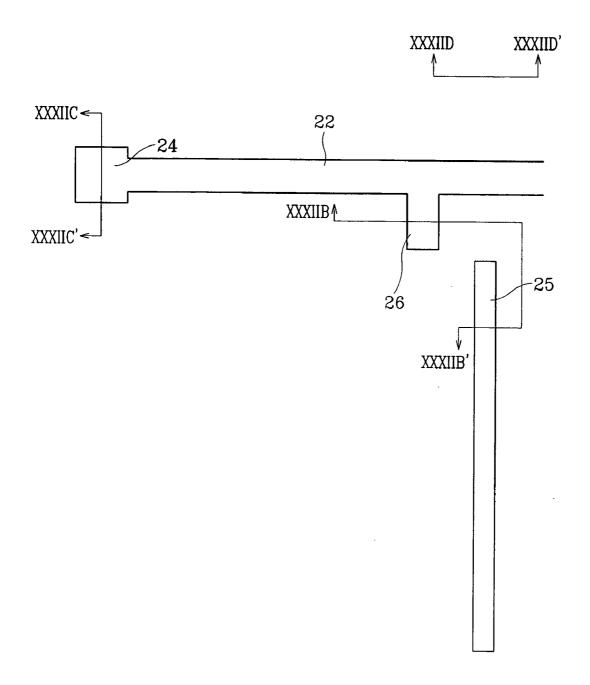

[0039] FIGS. 23A, 24A, 26A, and 27A are layout views of a thin film transistor array panel according to a third embodiment of the present invention showing manufacturing steps.

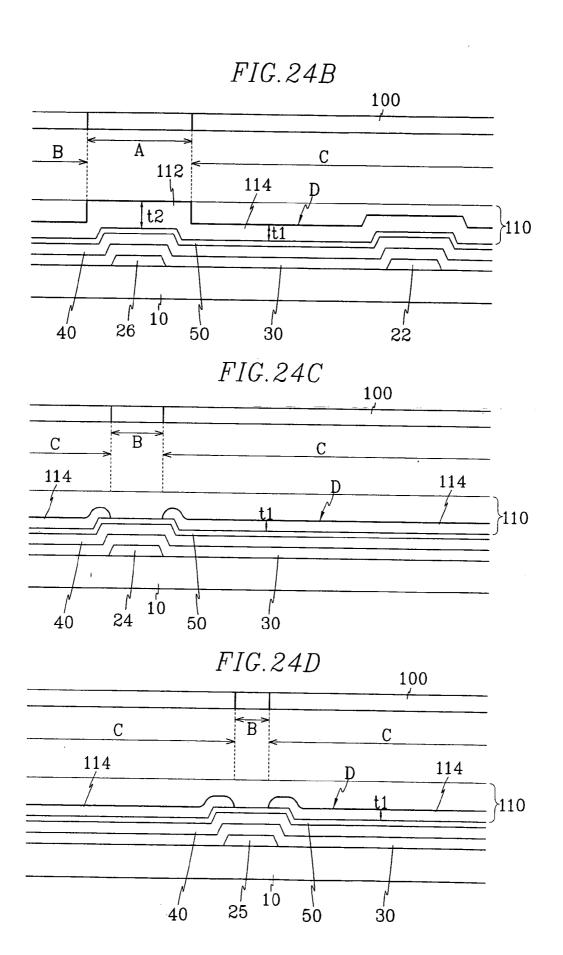

[0040] FIGS. 23B, 24B and 25A, 26B, and 27B are the cross-sectional views taken along the lines XXIIIB-XXIIIB', XXIVB-XXIVB', XXVIB-XXVIB', and XXVIIB-XXVIIB' of FIGS. 23A, 24A, 26A, and 27A, respectively.

[0041] FIGS. 23C, 24C and 25B, 26C, and 27C are the cross-sectional views taken along the lines XXIIIC-XXIIIC', XXIVC-XXIVC', XXVIC-XXVIC', and XXVIIC-XXVIIC' of FIGS. 23A, 24A, 26A, and 27A, respectively.

[0042] FIGS. 23D, 24D and 25C, 26D, and 27D are the cross-sectional views taken along the lines XXIIID-

XXIIID', XXIVD-XXIVD', XXVID-XXVID', and XXVIID-XXVIID' of FIGS. 23A, 24A, 26A, and 27A, respectively.

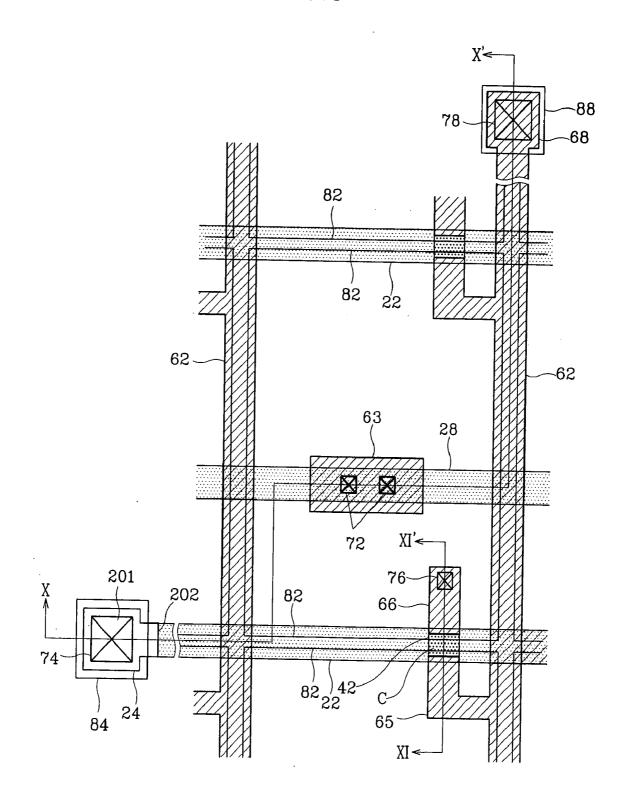

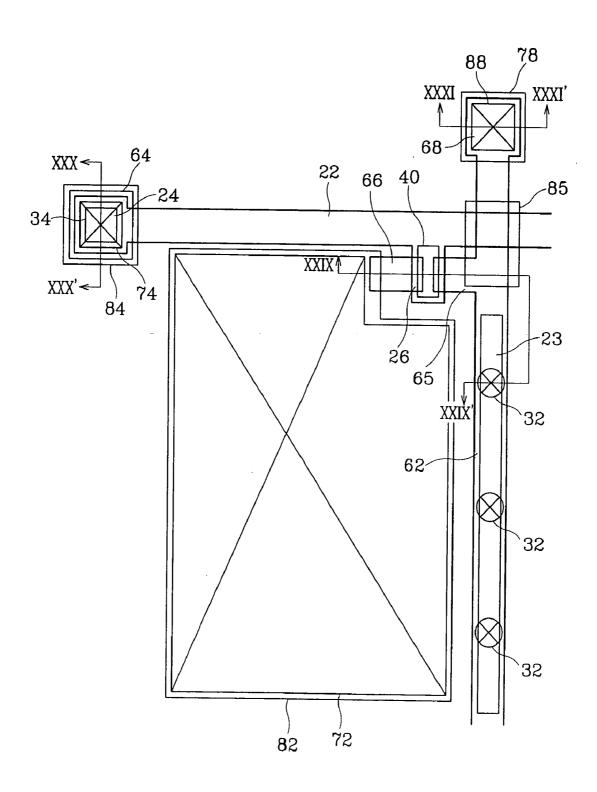

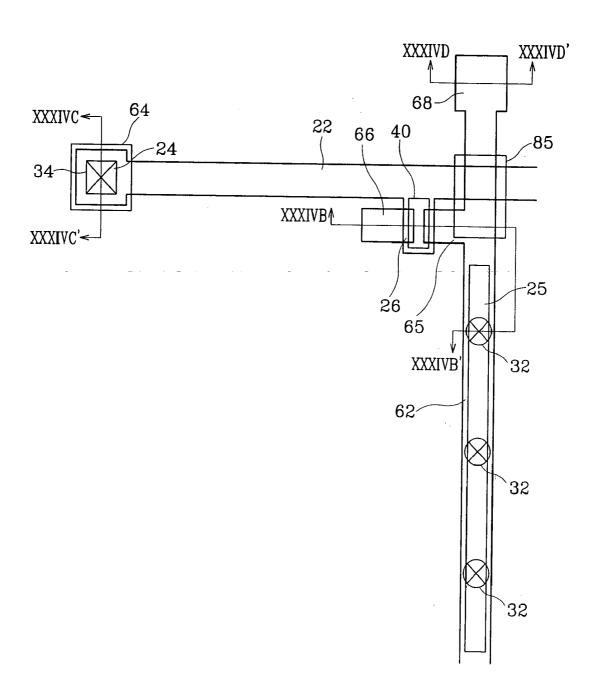

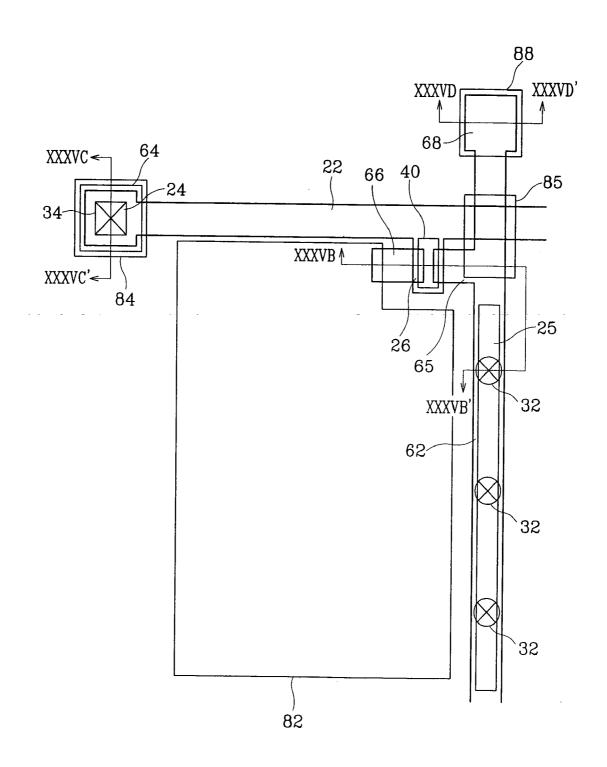

[0043] FIG. 28 is a layout view of a thin film transistor array panel for a liquid crystal display according to a fourth embodiment of the present invention.

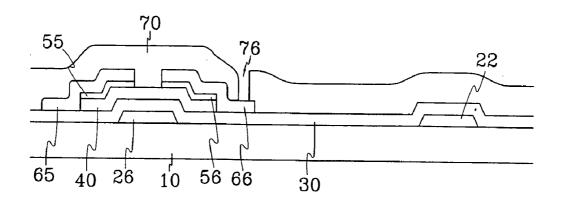

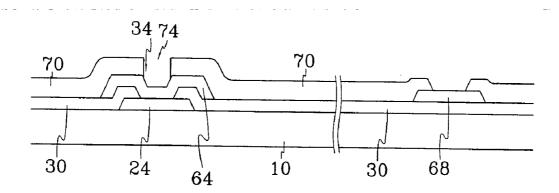

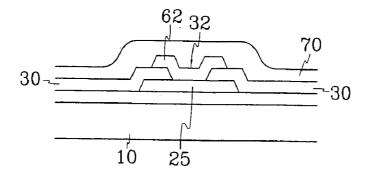

[0044] FIGS. 29, 30, and 31 are cross-sectional views taken along lines XXIX-XXIX', XXX-XXX', and XXXI-XXXI' of FIG. 28, respectively.

[0045] FIGS. 32A to 35D are cross-sectional views illustrating a manufacturing method of the thin film transistor array panel according to the fourth embodiment of the present invention.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0046] The present invention now will be described more fully hereinafter with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. This invention may, however, be embodied in many different forms and should not be construed as limited to the embodiments set forth herein. In the drawings, the thickness of layers and regions are exaggerated for clarity. Like numerals refer to like elements throughout. It will be understood that when an element such as a layer, region, or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may also be present. In contrast, when an element is referred to as being "directly on" another element, there are no intervening elements present.

[0047] First, the structure of the thin film transistor panel for a liquid crystal display (LCD) of the first embodiment according to the present invention will be described with reference to FIGS. 1 and 2.

[0048] FIG. 1 is a layout view of a thin film transistor array panel for a liquid crystal display according to the first embodiment of the present invention, and FIG. 2 is a cross-sectional view taken along line II-II' of FIG. 1.

[0049] Gate wires including a lower layer of conductive material having good contact properties with ITO, such as molybdenum (Mo) or molybdenum alloy (Mo alloy), and chromium (Cr), and an upper layer of conductive material having a low resistivity, such as aluminum (Al) or aluminum alloy (Al alloy), are formed on an insulating substrate 10. A gate wire includes a gate line (or scanning signal line) 22 extending in the horizontal direction in FIG. 1, a gate pad 24 that is connected to an end of the gate line 22 and transmits a scanning signal from an external circuit to the gate line 22, and a gate electrode 26 that is a part of a thin film transistor. At this time, the gate pad 24 is only formed of the lower layer 201.

[0050] A gate insulating layer 30 of silicon-nitride (SiNx) is formed on and covers the gate wire parts 22, 24, and 26. The gate insulating layer 30 has a contact hole 74 exposing the gate pad 24 along with a passivation layer 70, which will be formed later, and completely covers the upper layer 202 of the gate wires 22 and 26.

[0051] A semiconductor layer 40 such as hydrogenated amorphous silicon is formed in an island-like shape on the gate insulating layer 30 of the gate electrode 26. Ohmic

contact layers 55 and 56 (made of such materials as silicide or hydrogenated amorphous silicon heavily doped with impurities like phosphorus) are formed on the semiconductor layer 40.

[0052] A data wire made of conductive materials such as Mo or Mo alloy and Cr is formed on the ohmic contact layer patterns 55 and 56 and the gate insulating layer 30. The data wire has a data line 62 extending in the vertical direction in FIG. 1 and defining a pixel along with the gate line 22, a data pad 68 that is connected to an end of data line 62 and transmits image signals from an external circuit to the data line 62, a source electrode 65 of a thin film transistor that is connected to the data line 62 and is extended on the ohmic contact layer 55, and a drain electrode 66 of the thin film transistor that is formed on the ohmic contact layer 56 opposite the source electrode 65 with respect to the gate electrode 26 and is separated from the source electrode 65.

[0053] A passivation layer 70 is formed on the data wire parts 62, 65, 66, and 68, and the semiconductor layer 40 which is not covered by the data wire parts 62, 65, 66, and 68. The passivation layer 70 has contact holes 76 and 78 respectively exposing the drain electrode 66 and the data pad 68, and also has (along with the gate insulating layer 30) another contact hole 74 exposing the lower layer 201 of the gate pad 24. The passivation layer 70 can be made of an insulating material such as SiNx, acrylic organic material, other transparent photo-definable material, or other organic

[0054] The pixel electrode 82, which receives an image signal and generates an electric field with a common electrode of an upper panel is formed on the passivation layer 70 of the pixel. The pixel electrode 82 is connected to the drain electrode 66 both physically and electrically through the contact hole 76, and receives the image signal from the drain electrode 66. A redundant gate pad 84 and a redundant data pad 88, respectively connected to the lower layer 201 of the gate pad 24 and to the data pad 68 through the contact holes 74 and 78, are formed on the passivation layer 70.

[0055] Here, as shown in FIGS. 1 and 2, the pixel electrode 82 overlaps the gate lines 22 or the data lines 62 to make a storage capacitor. If this configuration does not generate enough storage capacitance, a storage wire may be formed with the same layer as the gate wire parts 22, 24, and 26.

[0056] A method for manufacturing a thin film transistor array panel according to a first embodiment of the present invention will now be described with reference to the FIGS. 3A to 8B and FIGS. 1 to 2.

[0057] At first, as shown in FIGS. 3A and 3B, a lower layer 201 of a conductive layer having good contact properties with ITO such as chromium, molybdenum, molybdenum alloy, and titanium, and an upper layer 202 of a conductive layer having a low resistivity such as aluminum or aluminum alloy are deposited on a substrate 10 by such methods as sputtering to a thickness of 500 Å to 2,500 Å. Then, gate wire parts including a gate line 22 and a gate electrode 26, which have the lower layer 201 and the upper layer 202, and a gate pad 24 made only of the lower layer 201 are formed by dry or wet etching through a photolithography process using a mask.

[0058] The lower layer 201 and the upper layer 202 that does not correspond to the gate wire parts 22, 24, and 26

must be all removed, while only the upper layer 202 must be removed on the portion corresponding to the gate pad 24. To achieve this, a photoresist pattern including at least three portions having different thicknesses must be used as etch mask in the photolithography process. A mask including at least three regions having different transmittance values may be used to form the photresist pattern and will be described with reference to FIGS. 4 and 5.

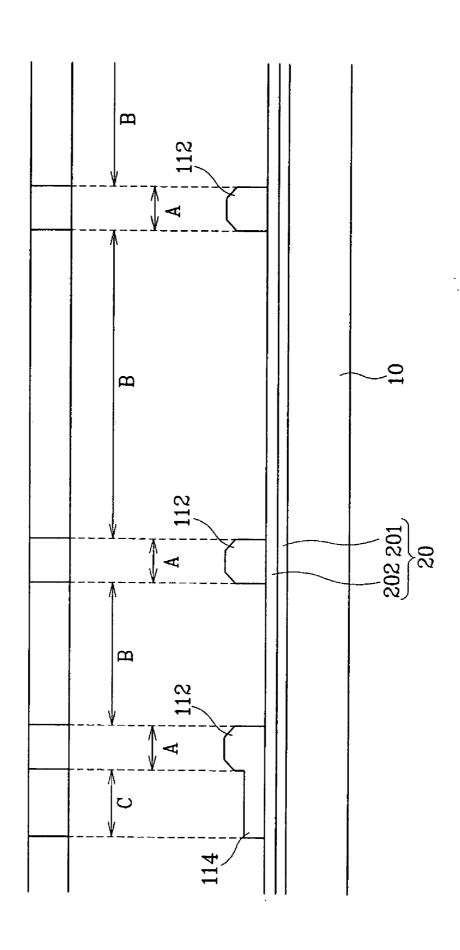

[0059] Firstly, as shown in FIG. 4, the lower and the upper layers 201 and 202 are sequentially deposited on the substrate 10, and a photoresist layer is coated on the upper layer 202. Next, the photoresist layer is exposed to light through a mask including three portions A, B, and C, which have different transmittance values, and developed to form photoresist pattern portions 112 and 114 that have different thickness. Here, positive or negative photoresist layers may be used, and it is desirable that the thickness of the photoresist layer is more than  $1.9 \,\mu m$ . Also, it is preferable that the thickness of the first portion 114 is equal to or less than half of the second portion 112.

[0060] There are many ways to make the thickness of the photoresist layer different depending on positions. A pattern, such as a slit or a lattice, or a partly-transparent layer, may be formed on the C portion of the mask to control the amount of incident light.

[0061] At this time, it is desirable that the widths and the intervals of the slit and the lattice are smaller than the resolution of the exposure device. When using a partly-transparent layer, the mask including a plurality of thin films having different transmittance values, or a thin film having different thickness depending on positions may be used to control the amount of incident light.

[0062] When the photoresist layer is exposed to light, the polymers of the photoresist layer are disintegrated by the light, and the exposing step is finished when the portion of polymers that is directly exposed to the light are completely disintegrated. At this time, the polymers of a photoresist layer, which are exposed through slit patterns or a partlytransparent layer, are not completely dissolved because the amount of incident light is less than that of the directly exposed portion. Hence, the polymers of the photoresist layer hidden by the opaque portions of the mask are hardly dissolved at all. The non-disintegrated part 112 of the photoresist pattern is left after developing the photoresist layer, and a thinner portion 114 of the photoresist pattern is left at the part that was exposed to less light than the parts that received full exposure. However, if the exposure time is too long, all the polymers of the photoresist layer are disintegrated. Therefore, such an overexposure should be

[0063] The second way to make the thickness of the photoresist layer different is reflowing. The photoresist layer is exposed to light through a mask having substantially transparent portions and substantially opaque portions. Then, the photoresist layer is developed to form a photoresist pattern having portions of zero and non-zero thicknesses. The photoresist pattern is allowed to reflow such that the photoresist flows into the zero thickness portions to form a photoresist pattern having the thinner portion 114.

[0064] Using these methods, the photoresist pattern having different thickness at different positions is obtained.

[0065] Next, as shown in FIG. 5, the upper layer 202 and the lower layer 201 are etched using the photoresist patterns 114 and 112. At this time, when the lower 201 and the upper layer 202 are respectively made of aluminum or aluminum alloy and chromium, wet etching is desirable.

[0066] The remaining photoresist layer 114 on the upper layer 202 is then removed by ashing, the upper layer 202 is etched using the photoresist layer 112 as an etch mask to form the gate electrode 24 of only the lower layer 201, and the remaining photoresist layer is removed. Here, it is preferable that the thickness of the photoresist layer 112 is about 2,000 Å after ashing. At this time, the edge of the upper layer 202 is tapered to have a sloping angle.

[0067] Next, as shown in FIGS. 6A and 6B, a gate insulating layer 30, an amorphous silicon semiconductor layer 40, and a doped amorphous silicon ohmic contact layer 50 are sequentially layered. Then, the semiconductor layer 40 and the ohmic contact layer 50, which are both island shaped, are formed on top of the gate electrode 26 and the opposing gate insulating layer 30 using a mask patterning process.

[0068] Then, as shown in FIGS. 7A and 7B, a conductor layer such as chromium, aluminum, or aluminum alloy is deposited by such methods as sputtering and patterned through a photolithography process using a mask to form a data wire including a data line 62 intersecting the gate line 22, a source electrode 65 connected to the data line 62 and extended over the gate electrode 26, a drain electrode 66 separated from the source electrode 65 and opposite the source electrode 65 with respect to the gate electrode 22, and a data pad 68 connected to the end of the data line 62.

[0069] Then, the ohmic contact layer 50 is etched by a plasma dry etch method using the data wires 62, 65, and 68 as a mask to divide the ohmic contact layer 50 at the center of the gate electrode 26, and to expose the central portion of the amorphous silicon layer 40 between the ohmic contact layers 55 and 56.

[0070] After forming data wire parts 62, 65, 66, and 68, a passivation layer 70 is coated with an organic insulator, as shown in FIGS. 8A and 8B. Then, contact holes 74, 76, and 78 respectively exposing the gate pad 24, the drain electrode 66, and the data pad 68 are formed by etching the passivation layer 70 and the gate insulating layer 30 at the same time with a third mask. At this time, the upper layer 202 of the gate wire parts 22 and 26 made of aluminum or aluminum alloy is completely covered by the gate insulating layer 30, and only the lower layer 201 of the gate pad 24 is exposed through the contact hole 74.

[0071] Next, as shown in FIGS. 1 to 2, an ITO layer is deposited and etched by photolithography using a mask to form a pixel electrode 82, a redundant gate pad 84 and a redundant data pad 88 connected to the drain electrode 66, the gate pad 24 and the data pad 68 through the contact holes 76, 74 and 78, respectively.

[0072] As described above in the first embodiment, with the use of a photoresist pattern having different thicknesses depending on positions, contacts between aluminum metals and ITO is prevented so that the additional step of removing aluminum or aluminum alloy from the pad portion may be omitted and the reliability of the pad portion may be enhanced. Because the upper layer 202 made of aluminum

alloy is completely covered by the insulating layer 30 and the passivation layer 70, corrosion of the gate wire may be prevented.

[0073] Furthermore, by forming the passivation layer 70 made of an organic insulator having a low dielectric constant, even though the pixel electrode 82 and the data line 62 are overlapped, the distortion of signals may be minimized and the aperture ratio may be increased.

[0074] In the first embodiment, the thin film transistor array panel is manufactured by a photolithography process using five photomasks, but a thin film transistor array panel may be manufactured by a photolithography process using four photomasks, and this will be described with reference to FIGS. 9 to 11.

[0075] FIG. 9 is a layout view of a thin film transistor array panel for a liquid crystal display according to the second embodiment of the present invention. FIGS. 10 and 11 are the cross-sectional views taken along lines X-X' and XI-XI' of FIG. 9.

[0076] Gate wires including a gate line (or scanning signal line) 22 and a gate electrode 26, which are made of a lower layer 201 and an upper layer 202, and a gate pad made only of the lower layer 201 are formed on an insulating substrate 10, as in the first embodiment. The gate wire further comprises a storage electrode 28 formed in parallel with the gate line 22 and supplied with a voltage such as a common voltage applied to a common electrode (not shown) on an upper panel of the liquid crystal display. The storage electrode 28 provides the storage capacitance along with a pixel electrode 82 that will be described later. The liquid crystal capacitor includes the pixel electrode 82 and the common electrode. The storage electrode 28 may not be necessary if the pixel electrode 82 and the gate line 22 generate sufficient storage capacitance.

[0077] A gate insulating layer 30 of silicon-nitride (SiNx) is formed on and covers the gate wire parts 22, 24, 26 and 28.

[0078] A semiconductor pattern 42 and 43 (made of semiconductor such as hydrogenated amorphous silicon) is formed on the gate insulating layer 30. An ohmic contact layer pattern 55, 56, and 53 (made of such materials as amorphous silicon heavily doped with impurities like phosphorus) is formed on the semiconductor patterns 42 and 43.

[0079] A data wire made of conductive materials such as Mo or MoW, Cr, Al or Al alloy, and Ta is formed on the ohmic contact layer patterns 55, 56 and 54. The data wire has data line parts including a data line 62 extending in the vertical direction on FIG. 9, a data pad 68 that is connected to an end of data line 62 and transmits image signals from an external circuit to the data line 62, and a source electrode 65 of a thin film transistor that is a branch of the data line 62. The data wire also includes a drain electrode 66 of the thin film transistor on the other side of the gate electrode 26 or the channel part C of a thin film transistor, as well as separate data line parts 62, 68, 65, and a conductor pattern 63 for a storage capacitor located on the storage electrode 28. When the storage electrode 28 is not provided, neither is the conductor pattern 63.

[0080] The data wire parts 62, 63, 65, 66, and 68 may have a multiple-layered structure like the gate wire parts 22, 24,

26, and 28. Of course, when the data wire has a multiplelayered structure, it is preferable that one layer is made of a material having a low resistivity and another is made of a material having good contacting properties with other materials

[0081] The ohmic contact layer patterns 55, 56, and 53 reduce the contact resistance between the semiconductor patterns 42 and 43 and the corresponding data wire parts 62, 63, 65, 66, and 68, and have the same layout as the data wire parts 62, 63, 65, 66, and 68. In other words, a first ohmic contact layer portion 55 under the data line part has the same shape as the data line parts 62, 68, and 65, a second ohmic contact layer portion 56 under the drain electrode part has the same shape as the drain electrode 66, and a third ohmic contact layer portion 53 under the conductor pattern 63 has the same shape as the conductor pattern 63 for the storage capacitor.

[0082] The semiconductor patterns 42 and 43 have the same layout as the corresponding data wire parts 62, 63, 65, 66, and 68 and the corresponding ohmic contact layer patterns 55 and 56, and except for the channel part C of the thin film transistor. Or, more concretely, the semiconductor portion 43, the conductor pattern 63, and the third ohmic contact layer portion 53 all have the same shape, but the semiconductor portion 42 has a shape different from the data wire and the ohmic contact layer pattern. In other words, the data line parts 62, 68, and 65, especially the source electrode 65 and the drain electrode 66 are separated from each other by the channel part C of the thin film transistor and the portions 55 and 56 of the ohmic contact layer pattern thereunder are also separated from each other. However the semiconductor portion 42 is not divided into two pieces so that it can traverse the channel of a thin film transistor.

[0083] A passivation layer 70 is formed on the data wire parts 62, 63, 65, 66, and 68. The passivation layer 70 has contact holes 76, 78, and 72 respectively exposing the drain electrode 66, the data pad 68, and the conductor pattern 63 for the storage capacitor, and also has (along with the gate insulating layer 30) another contact hole 74 exposing the gate pad 24. The passivation layer 70 can be made of an insulating material such as SiNx, acrylic organic material, other transparent photo-definable material, or other organic material.

[0084] The pixel electrode 82 that receives an image signal and generates an electric field with a common electrode of an upper panel is formed on the passivation layer 70. The pixel electrode 82 is made of a transparent conductive material such as indium tin oxide (ITO). The pixel electrode 82 is connected to the drain electrode 66 both physically and electrically through the contact hole 76, and receives the image signal from the drain electrode 66. Even though the aperture ratio is increased when the pixel electrode 82 overlaps the gate lines 22 or the adjacent data lines, these lines are not required to overlap the pixel electrode. The pixel electrode 82 is connected to the conductor pattern 63 for the storage capacitor through the contact hole 72 and transmits the image signal to the conductor pattern 63.

[0085] A redundant gate pad 84 and a redundant data pad 88 are formed on the gate pad 24 and the data pad 68 and are respectively connected to the gate pad 24 and the data pad 68 through the contact holes 74 and 78. These redundant pads 84 and 88 are optional as they protect the pads 24 and

68 from corrosion caused by the ambient air and strengthen the adhesion between an external circuit and the pads 24 and 68

[0086] In this embodiment, a transparent ITO layer is used as an example of the material of the pixel electrode 82, but an opaque-conductive material may also be used in a reflective type liquid crystal display.

[0087] A method for manufacturing a thin film transistor array panel according to an embodiment of the present invention will now be described with reference to the FIGS. 12A to 18C and FIGS. 9 to 11.

[0088] At first, as shown in FIGS. 12A to 12C, gate wire parts including a gate line 22, a gate pad 24, a gate electrode 26, and a storage electrode 28 are formed by dry or wet etching through a photolithography process using a first mask, as in the first embodiment.

[0089] The gate wire parts 22, 24, 26, and 28 may have a multiple-layered structure such as a double-layered structure. Also, in this case, it is desirable that a conductive layer made of aluminum or aluminum alloy of the gate pad 24 be removed by using a photoresist pattern having different thicknesses depending on positions.

[0090] Next, as shown in FIGS. 13A and 13B, a gate insulating layer 30, a semiconductor layer 40, and an ohmic contact layer 50 are sequentially deposited to thicknesses of 1,500 Å to 5,000 Å, 500 Å to 2,000 Å, and 300 Å to 600 Å, respectively, by such methods as chemical vapor deposition (CVD). Then, a conductor layer 60, such as a metal, is deposited to a thickness of 1,500 Å to 3,000 Å by such methods as sputtering, and a photoresist layer 110 having a thickness of 1 um to 2 um is coated on the conductive layer 60

[0091] Thereafter, the photoresist layer 110 is exposed to light through a second mask and developed to form photoresist patterns 112 and 114 as shown in FIGS. 14B and 14C. At this time, the first portion 114 of the photoresist pattern located between a source electrode 65 and a drain electrode 66, i.e., a thin film transistor channel part C as shown in FIG. 14C, is thinner than the second portion 112 of photoresist pattern located over the data wire portion A where a data wires 62, 63, 65, 66, and 68 will be formed, and the third portion, the remaining portion of the photoresist pattern located at portion B, is thinner than the first portion. The third portion may have a thickness determined according to an etching method. For example, the third portion has substantially zero thickness when using a wet etch, but the third portion may have a non-zero thickness when using a dry etch. At this time, the thickness ratio between the first portion 114 and the second portion 112 depends on the etch conditions that will be described later. However, it is preferable that the thickness of the first portion 114 is equal to or less than half of that of the second portion 112, or for example, less than 4,000 Å.

[0092] Next, the photoresist pattern 114 and the layers thereunder including the conductor layer 60, the ohmic contact layer 50, and the semiconductor layer 40 are subject to an etching process. After the etching process, a data wire and the underlying layers at the data wire part A, and only the semiconductor layer on the channel part C should remain. In addition, the three layers 60, 50, and 40 in the remaining part B are removed in order to expose the gate insulating layer 30.

[0093] As shown in FIGS. 15A and 15B, the ohmic contact layer 50 of the part B is exposed by removing the conductor layer 60 thereon. At this time, both wet and dry etch can be used, and it is preferable that the etch is performed under a condition that the conductor layer 60 is etched but the photoresist layers 112 and 114 are not etched. However, due to its etch selectivity, the dry etch method may also etch the photoresist patterns 112 and 114. In this case, the first portion 114 may be made thicker than in the wet etch case so that the conductor layer 60 is not exposed.

[0094] If the conductor layer 60 is made of Mo or MoW alloy, Al or Al alloy, or Ta, both dry or wet etch methods can be used. However, if the conductor layer 60 is made of Cr, wet etch is better because Cr is not easily removed by dry etching. CeNHO $_3$  can be used as a wet etchant for etching a Cr conductor layer 60. The gas mixture of CF $_4$  and HCl or the mixture of CF $_4$  and O $_2$  can be used for dry etching a Mo or MoW conductor layer 60. The mixture of CF $_4$  and O $_2$  shows similar etch rate on the photoresist layer and on the conductor layer 60.

[0095] Referring to FIGS. 15A and 15B, it leaves only the portions of the conductor 60 under the photoresist portions 112 and 114 at the channel part C and the data wire part A for the source/drain electrodes and a storage capacitor. And the remaining portion of the conductor layer 60 at part B is wholly removed to expose the underlying ohmic contact layer 50. At this time, the conductor pattern 67 and 63 has the same layout as the data wire parts 62, 63, 65, 66 and 68 except that the source electrode 65 and the drain electrode 66 are connected to each other. When dry etch is used, the photoresist layers 112 and 114 are also etched to some degrees.

[0096] Next, the exposed portions of the ohmic conductor layer 50 at part B and its underlying semiconductor layer 40 of FIGS. 16A and 16B are removed by dry etching along with the first portion 114 of the photoresist layer as shown in FIGS. 16A and 16B. The etch condition should be set to etch all the photoresist patterns 112 and 114, the ohmic contact layer 50, and the semiconductor layer 40 (the semiconductor layer and the ohmic contact layer have almost the same etch rate), but to leave the gate insulating layer 30 not etched. It is preferable that the etch rates of the photoresist patterns 112 and 114 and the semiconductor layer 40 are almost the same. The gas mixture of SF<sub>6</sub> and HCl or the mixture SF<sub>6</sub> and O<sub>2</sub> may meet such conditions. When the etch rates of the photoresist patterns 112 and 114 and the semiconductor layer 40 are almost the same, the thickness of the first portion 114 may be equal to or less than the sum of the thicknesses of the semiconductor 40 and the ohmic contact layer 50.

[0097] Then, as shown in FIGS. 16A and 16B, the conductor pattern 67 is exposed by removing the first portion 114 of the channel part C, and the gate insulating layer 30 is exposed by removing the ohmic contact layer 50 and the semiconductor layer 40 of the part B shown in FIG. 11B. At the same time, the thickness of the second portion 112 over the data wire part A is reduced by etching. This step completes the semiconductor pattern 42 and 43. The reference numerals 57 and 53 respectively represent the ohmic contact layer pattern under the conductor patterns 67 and 63 for the source/drain electrodes and the storage capacitor.

[0098] The remaining photoresist layer on the conductor pattern 67 is then removed by ashing or plasma etching.

[0099] Next, as shown in 17A and 17B, the conductor pattern 67 for source/drain electrodes at the channel part C and the ohmic contact layer pattern 57 for source/drain electrodes of FIG. 16B are removed by etching. At this time, it is possible either to etch both the conductor pattern 67 and the ohmic contact layer 57 by a dry etching method, or to etch the conductor pattern 67 by a wet etching method and the ohmic contact layer 57 by a dry etching method. The first method is preferable when etch conditions have a large etch selectivity between the conductor pattern 67 and the ohmic contact layer pattern 57. This is because if the etch selectivity is not large enough, it is hard to detect the end point of the etch and control the thickness of the semiconductor pattern 42 around the channel part C. A gas mixture of SF<sub>6</sub> and O<sub>2</sub> can bring such a result. When doing a wet etch and a dry etch sequentially, the lateral sides of the conductor pattern 67 exposed to the wet etchant are also etched but those of the ohmic contact layer pattern 57, which is dry etched, are hardly etched at all. Thereby, the profile of these two patterns 67 and 57 makes a step like form. The gas mixture of CF<sub>4</sub> and O<sub>2</sub> may be used for etching the ohmic contact layer pattern 57 and the semiconductor pattern 42. The semiconductor pattern 42 may also be formed to have a uniform thickness by etching with a gas mixture of CF<sub>4</sub> and O<sub>2</sub>. At this time, as shown in **FIG. 12B**, the thickness of the semiconductor pattern 42 may be reduced and the second portion 112 of photoresist pattern is also etched to a certain thickness. The etch conditions may also be set not to etch the gate insulating layer 30, and it is preferable to make the photoresist pattern thick enough not to expose the data wire parts 62, 63, 65, 66, and 68.

[0100] As a result, the source electrode 65 and the drain electrode 66 are divided, and the completed data wire parts 62, 63, 65, 66, and 68 and the completed contact layer pattern 55, 56, and 53 thereunder are obtained.

[0101] Next, the remaining second portion 112 of the photoresist layer on the data wire (Region A of FIG. 14C) is removed. However, the second portion 112 may be removed after removing the conductor pattern 67 for the source/drain electrodes on the channel part C of FIG. 16B and before removing the ohmic contact layer pattern 57 under the conductor pattern 67.

[0102] To summarize, this process can be done by using both wet etching and dry etching in turn, or by using only dry etching.

[0103] In the former case, the conductor layer of the part B is first removed by wet etching, and the ohmic contact layer and the underlying semiconductor layer are removed by dry etching. At this time, the photoresist layer of the part C is etched out to a certain thickness, and the part C may have or may not have any residual photoresist. It mainly depends on the initial thickness of the photoresist layer of the part C. When the part C has remaining photoresist, it is removed by ashing. Finally, the conductor layer of the part C is wet etched to separate the source and the drain electrodes, and the ohmic contact layer of the part C is removed by using dry etching.

[0104] In the latter case, the conductor layer, the ohmic contact layer and the semiconductor layer of the part B are removed by dry etching. As in the former case, the part C may have or may not have residual photoresist, and the residual photoresist is removed by ashing when the part C

has residual photoresist. Finally, the conductor layer of the part C is dry etched to separate the source electrode and the drain electrode, and the ohmic contact layer of the part C is removed by dry etching.

[0105] Also, if the data wire is etched, the semiconductor pattern, the contact layer pattern, and the data wire may be completed with a single step. That is to say, it is desirable that the photoresist pattern 114 of the part C and the underlying contact layer 50 are dry etched, and the portion of the photoresist pattern 112 of the part A is dry etched during the dry etching of the conductor layer, the ohmic contact layer, and the semiconductor layer of part B.

[0106] Since the latter process uses only one type of etching method, it is simpler although it is hard to control proper etching conditions. On the other hand, the former process may achieve proper etching condition, but it is a more complicated process.

[0107] After forming data wire parts 62, 63, 65, 66, and 68 by the above steps, a passivation layer 70 having the thickness of over 2,000 Å is formed by CVD of SiNx or by spin coating of organic insulator, as shown in FIG. 18A to FIG. 18C. Then, contact holes 76, 74, 78, and 72 respectively exposing the drain electrode 66, the gate pad 24, the data pad 68, and the conductor pattern 63 for the storage capacitor are formed by etching the passivation layer 70 and the gate insulating layer 30 at the same time by using a third mask

[0108] Next, as shown in FIGS. 9 to 11, an ITO layer is deposited to a thickness of 400 Å to 500 Å, and etched by using a fourth mask to form a pixel electrode 82, a redundant gate pad 84, and a redundant data pad 88.

[0109] As described above, the second embodiment is forming the data wires 62, 63, 65, 66, and 68, the ohmic contact patterns 55, 56, and 53, and the semiconductor patterns 42 and 43 by using one mask. Furthermore, by separating the source electrode 65 and the drain electrode 66 in this process, the second embodiment can achieve the structure of the first embodiment in a much simpler process.

[0110] A third embodiment-according to the present invention, in order to simplify a manufacturing process for a thin film transistor panel for LCD, exposes a gate pad portion when forming a semiconductor layer by using a photoresist layer of different thickness, and lays a redundant data line made of metal having a low resistivity.

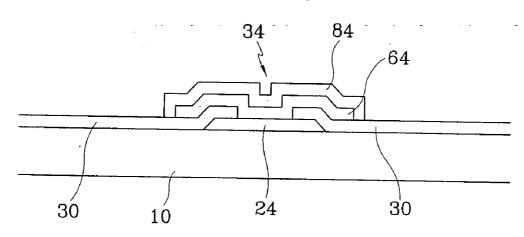

[0111] FIG. 19 is a layout view of a thin film transistor array panel for a liquid crystal display according to the third embodiment of the present invention, and FIGS. 20, 21, and 22 are the cross-sectional views taken along the lines XX-XX', XXI-XXI' and XXII-XXII' of FIG. 19, respectively.

[0112] As shown in FIGS. 19 to 22, gate wire parts 22, 24, and 26, and a redundant data line 25 extending in a vertical direction, which are all made of aluminum or aluminum alloy are formed on an insulating substrate 10. Furthermore, the gate wire parts 22, 24, and 26, and the redundant data line 25 may also be made of metals such as chromium, molybdenum, and molybdenum alloy.

[0113] A gate insulating layer pattern 30 of silicon-nitride (SiNx) is formed on the gate wire parts 22, 24, 26, and the

redundant data line 25. The gate insulating layer pattern 30 has contact holes 34 and 32 exposing the gate pad 24 and the redundant data line 25.

[0114] A semiconductor layer 40 and ohmic contact layers 55 and 56 are formed on the gate insulating layer 30 of the gate electrode 26 as in the first embodiment.

[0115] Data wire parts 62, 65, 66, and 68 are formed on the ohmic contact layer patterns 55 and 56, and the gate insulating layer 30. Here, the data line 62 overlaps the redundant data line 25 and is connected to the redundant data line 25 through the contact hole 32. A first redundant gate pad 64 is formed on the same layer as the data wire 62, 65, 66, and 68, is connected to the gate pad 24 through the contact hole 34, and completely covers the contact hole 34.

[0116] A passivation layer 70 is formed on the data wire parts 62, 65, 66, 68, the semiconductor layer 40 not covered by the data wire parts 62, 65, 66, and 68, and the first redundant gate pad 64. The passivation layer 70 has contact holes 76, 74, and 78 respectively exposing the drain electrode 66, the first redundant gate pad 64, and the data pad 68.

[0117] The pixel electrode 82 is formed on the passivation layer 70 of the pixel. The pixel electrode 82 is connected to the drain electrode 66 through the contact hole 76, and a redundant gate pad 84 and a redundant data pad 88 are respectively connected to the first redundant gate pad 24 and the data pad 68 through the contact holes 74 and 78 that are formed in the passivation layer 70.

[0118] A method for manufacturing a thin film transistor array panel according to a third embodiment of the present invention will now be described with reference to the FIGS. 23A to 27B and FIGS. 19 to 22.

[0119] FIGS. 23A, 24A, 26A, and 27A are layout views of a thin film transistor array panel according to the third embodiment of the present invention showing the manufacturing steps. FIGS. 23B, 24B and 25A, 26B, and 27B are cross-sectional views taken along lines XXIIIB-XXIIIB', XXIVB-XXIVB', XXVIB-XXVIB', and XXVIIB-XXVIIB' of FIGS. 23A, 24A, 26A, and 27A, respectively.

[0120] Furthermore, FIGS. 23C, 24C and 25B, 26C, and 27C are cross-sectional views taken along lines XXIIIC-XXIIIC', XXIVC-XXIVC', XXVIC-XXVIC', and XXVIIC-XXVIIC' of FIGS. 23A, 24A, 26A, and 27A, respectively. Additionally FIGS. 23D, 24D and 25C, 26D, and 27D are cross-sectional views taken along lines XXIIID-XXIIID', XXIVD-XXIVD', XXVID-XXVID', and XXVIID-XXVIID' of FIGS. 23A, 24A, 26A, and 27A, respectively.

[0121] At first, as shown in FIGS. 12A to 12C, a conductive material is deposited and gate wire parts, including a gate line 22, a gate pad 24, and a gate electrode 26, and a redundant data line 25 are formed by dry or wet etching through a photolithography step using a first mask. The gate wire parts 22, 24, and 26, and the redundant data line 25 may be made of aluminum or aluminum alloy, and may also have a multi-layered structure including chromium, molybdenum, or molybdenum alloy.

[0122] Next, as shown in FIGS. 24A, and 25A to 25C, a gate insulating layer 30, a semiconductor layer 40, and an ohmic contact layer 50 are respectively deposited sequentially by such methods as chemical vapor deposition (CVD), and are sequentially patterned through a photolithography

step using a second mask to form a gate insulating layer pattern having contact holes 34 and 32 exposing the gate pad 24 and the redundant data line 25. The semiconductor layer pattern 40 and an ohmic contact layer pattern 50, which both have an island-like shape, are located over the gate electrode 26. At this time, the gate insulating layer 30, the semiconductor layer 40 and the ohmic contact layer 50 must be all removed to form contact holes 32 and 34, and the semiconductor layer 40 and the ohmic contact layer 50 on the portions excluding the gate electrode 26 must be removed to form the semiconductor layer and the ohmic contact layer patterns 40 and 50 having an island-like shape. To obtain this object, as in the above embodiment, a photoresist pattern including at least three portions having different thickness must be used as etch mask, and a mask including at least three regions having these different transmittance values must be used to form such a photoresist pattern.

[0123] First, as shown in FIGS. 24B, 24C, and 24D, a positive photoresist layer 110 having a thickness of 1 um to 2 um is coated on the ohmic contact layer 50, exposed to light through a second mask, and developed to form photoresist patterns 112 and 114, which have different thicknesses indicated as t1 and t2, respectively. At this time, it is preferable that the transmittances of the regions of the mask 100 corresponding to portions A, C, and B are in the ranges of 0-3%, 20-60% (more preferably 25-40%), and more than 90%. A thick reference line D represents the thickness of the photoresist patterns 112 and 114. Here, the portion B may be of substantially zero thickness, but may also have a non-zero thickness. It is preferable that the thickness of the first portion 114 and the second portion 112 are respectively in the range of 2,000-4,000 Å (more preferably 3,000-4,000 Å) and more than 1  $\mu$ m. At this time, the thickness between the first portion 114 and the second portion 112 depends on the etch condition and on the etch method, which will be described later, as well as the thicknesses of the triple layers 30, 40, and 50. The transmittances of the portions A, B, and C may be different when a negative photoresist layer is used. Next, the underlying layers including the gate insulating layer 30, the ohmic contact layer 50, and the semiconductor layer 40 are etched by using the photoresist pattern 112 and 114. Then, the gate insulating pattern 30, the semiconductor layer 40, and the ohmic contact layer 50 can be formed.

[0124] Thus, in the third embodiment, the semiconductor pattern 40 and the ohmic contact layer pattern 50 are formed along with the gate insulating layer pattern 30 in one photolithography step using a photoresist pattern including at least three portions having different thickness. This simplifies the manufacturing steps.

[0125] At this time, it is preferable that the semiconductor pattern 40 is extended on the portions where it will intersect data line 62, which will be formed later, to prevent the disconnection of the data line 62 due to the step of the gate line 22.

[0126] As shown in FIGS. 26A to 26D, a conductive layer of metal such as molybdenum (Mo), MoW alloy layer, or chromium is deposited and patterned to form a data wire including a data line 62, a source electrode 65, a drain electrode 66, and a data pad 68, as well as a first redundant gate pad 64 by photolithography using a third mask. At this time, it is desirable that the first redundant gate pad 64 completely cover the contact hole 34.

[0127] Next, the amorphous silicon layer 50, that is not covered by the data wire 62, 65, 66, and 68, is etched out to form ohmic contact layers 55 and 56 and to expose the semiconductor pattern 40 between the ohmic contact layer patterns 55 and 56.

[0128] Next, as shown in FIGS. 27A to 27D, a passivation layer 70 of an organic insulator is formed by a spin coating, and is patterned to form contact holes 76, 74, and 78 respectively exposing the drain electrode 66, the first redundant gate pad 64, and the data pad 68, through a photolithography step using a fourth mask.

[0129] Next, as shown in FIGS. 19 to 22, an ITO layer is deposited and etched through a photolithography step using a fifth mask to form a pixel electrode 82, a second redundant gate pad 84, and a redundant data pad 88 respectively connecting to the drain electrode 66, a first redundant gate pad 64, and a data pad 68. At this time, the pixel electrode 82 overlaps the previous gate line 22 to make a storage capacitor. If the storage capacitance is not enough, a storage line may be added on the same layer as the gate line 22 to increase the storage capacitance.

[0130] In the third embodiment, by forming: a passivation layer 70 of an organic insulator with a low dielectric constant, even though the pixel electrode 82, and the data line 62, or the redundant data line 25 are overlapped, the distortion of signals may be minimized while increasing the aperture ratio.

[0131] Furthermore, by preventing contact between the aluminum or aluminum alloy of the gate pad 24 and the ITO of the second redundant gate pad 84 by using the first redundant gate pad 64, the gate wire made of a metal having a low resistivity such as aluminum or aluminum alloy may be formed when the first redundant gate pad 64 is formed of a material having good contact properties.

[0132] Also, by forming the redundant data line 25 of a metal having a low resistivity such as aluminum or aluminum alloy, the delay of signals may be minimized in large scale LCDs.

[0133] On the other hand, a pixel electrode may be formed before forming a passivation layer, and this will now be described with reference to drawings.

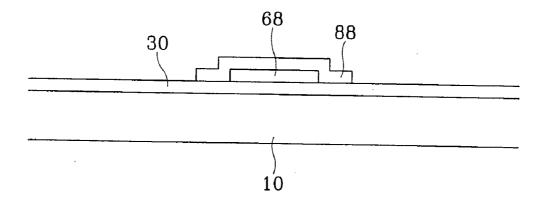

[0134] FIG. 28 is a layout view of a thin film transistor array panel for a liquid crystal display according to the fourth embodiment of the present invention, and FIGS. 29, 30, and 31 are cross-sectional views taken along line XXIX-XXIX', XXX-XXXI', and XXXI-XXXI' of FIG. 28, respectively.

[0135] Most of the structure according to the fourth embodiment is similar to the third embodiment.

[0136] However, a pixel electrode 82 of transparent conductive material such as ITO is formed on a gate insulating layer 30 of the pixel enclosed by a gate line 22 and a data line 62, and is connected to the drain electrode 66. A supporting data line 85 is formed on the data line 62 intersecting the gate line 22, and a second redundant gate pad 84 and a redundant data pad 88 are formed on the first redundant gate pad 24 and the data pad 68. The supporting data line 85 prevents the data line 62 from disconnecting due to the steps of the gate line 22.

[0137] A passivation layer 70 of silicon nitride or silicon oxide is formed on the entire insulating substrate 10. The passivation layer 70 has an opening 72 exposing the greater part of the pixel electrode 82, and has openings 74 and 78 respectively exposing the second redundant gate pad 84 and the data pad 68.

[0138] A method for manufacturing a thin film transistor array panel according to the fourth embodiment of the present invention will now be described with reference to the FIGS. 28 to 31 and FIGS. 32A to 35D.

[0139] FIGS. 32A to 35D are cross-sectional views illustrating the method for manufacturing the thin film transistor array panel according to the fourth embodiment of the present invention.

[0140] As shown in FIGS. 32A to 34D, gate wire parts 22, 24, and 26, a redundant data line 25, a gate insulating layer pattern 30 having contact holes 32 and 34, a semiconductor pattern 40, ohmic contact layer patterns 55 and 56, data wire parts 62, 65, 66, and 68, and a first redundant gate pad 64 are formed on an insulating substrate 10, as in the third embodiment

[0141] Next, as shown in FIGS. 35A to 35D, an ITO layer is deposited and etched through a photolithography step using a mask to form a pixel electrode 82 connected to the drain electrode 66, and to form a second redundant gate pad 84 and a redundant data pad 88 covering the first redundant gate pad 64 and the data pad 68.

[0142] Finally, as shown in FIGS. 28 to 31, a passivation layer 70 of silicon-nitride (SiNx) or silicon-oxide (SiOx) is formed and patterned to form opening 72 and contact holes 74 and 78 that respectively expose the second redundant gate pad 84 and the redundant data pad 88 through a photolithography step using a mask.

[0143] In the present invention, patterning at least two layers through one photolithography step and forming a gate wire of a single-layered structure simplify the manufacturing process of a thin film transistor panel for a liquid crystal display, and minimize manufacturing costs. Also, a pad portion of conductive material having good contact proper-

ties and a wire of aluminum and aluminum alloy make a reliable pad portion and minimize the delay and distortion of signals in a large scale LCD. Covering the wire with the gate insulating layer and the passivation layer prevents corrosion of a wire made of aluminum or aluminum alloy. The passivation layer as the upper most layer prevents a possible short between the data line or the pixel electrode and a common electrode of the upper panel due to conductive particles. Additionally, a supporting portion at the intersection of the gate line and the redundant data line prevents the data line from disconnecting.

[0144] In the drawings and specification, typical preferred embodiments of the present invention are disclosed. Although specific terms are employed, they are used in a generic and descriptive sense only and not for purposes of limitation, the scope of the invention being set forth in the following claims.

1-49. (canceled)

**50**. A method for manufacturing a thin film array panel, comprising steps of:

forming a gate line on a substrate;

sequentially forming a first insulating layer, a semiconductor layer and an ohmic contact layer;

simultaneously etching the ohmic contact layer, the semiconductor layer and the first insulating layer to form an ohmic contact pattern, a semiconductor pattern, and a gate insulation pattern;

forming a data line and a drain electrode connected to the data line on the ohmic contact layer;

removing a portion of the ohmic contact layer pattern not covered by the data line and the drain electrode;

forming a second insulating layer on the data line and the drain electrode; and

forming a pixel electrode electrically connected to the drain electrode.

\* \* \* \* \*

| 专利名称(译)        | 用于液晶显示器的薄膜晶体管阵列面板及其制造方法                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | US20050170592A1                                                                                                                                                                                       | 公开(公告)日 | 2005-08-04 |

| 申请号            | US11/080612                                                                                                                                                                                           | 申请日     | 2005-03-16 |

| [标]申请(专利权)人(译) | BAEK BUM KI<br>HONG MUN PYO<br>KIM JANG SOO<br>HUH SUNG旭<br>YOON JONG SOO<br>金东GYU                                                                                                                    |         |            |

| 申请(专利权)人(译)    | BAEK BUM-KI<br>HONG MUN杓<br>金章洙<br>HUH成旭<br>YOON JONG-SOO<br>金东GYU                                                                                                                                    |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO.,LTD.                                                                                                                                                                                    |         |            |

| [标]发明人         | BAEK BUM KI HONG MUN PYO KIM JANG SOO HUH SUNG WOOK YOON JONG SOO KIM DONG GYU                                                                                                                        |         |            |

| 发明人            | BAEK, BUM-KI HONG, MUN-PYO KIM, JANG-SOO HUH, SUNG-WOOK YOON, JONG-SOO KIM, DONG-GYU                                                                                                                  |         |            |

| IPC分类号         | G02F1/1362 H01L21/336 H01L21/77 H01L21/84 H01L27/12 H01L29/417 H01L29/423 H01L29/45 H01L29/49 H01L31/0376                                                                                             |         |            |

| CPC分类号         | G02F1/136227 H01L27/1288 G02F2001/136236 G02F2001/136272 G02F2001/13629 H01L27/12<br>H01L29/41733 H01L29/42384 H01L29/458 H01L29/4908 H01L29/66765 G02F1/13458 Y10S438/949<br>H01L27/124 G02F1/136286 |         |            |

| 优先权            | 1019990012287 1999-04-08 KR<br>1019990027550 1999-07-08 KR<br>1019990033091 1999-08-12 KR                                                                                                             |         |            |

| 其他公开文献         | US7176496                                                                                                                                                                                             |         |            |

| 外部链接           | Espacenet USPTO                                                                                                                                                                                       |         |            |

|                |                                                                                                                                                                                                       |         |            |

#### 摘要(译)

将包括由诸如铬,钼和钼合金的难熔金属制成的下层和由铝或铝合金制成的上层的导电层沉积并图案化以形成包括栅极线,栅极焊盘的栅极线,和基板上的栅电极。此时,使用具有不同厚度的光致抗蚀剂图案去除栅极焊盘的上层,该光致抗蚀剂图案取决于作为蚀刻掩模的位置。依次形成栅极绝缘层,半导体层和欧姆接触层。沉积并图案化导电材料以形成包括数据线,源电极,漏电极和数据焊盘的数据线。接下来,沉积并图案化钝化层以形成分别暴露漏电极,栅极焊盘和数据焊盘的接触孔。此时,栅极焊盘上的接触孔仅露出栅极焊盘的下层,栅极绝缘层和钝化层完全覆盖栅极焊盘的上层。接下来,沉积并图案化氧化铟锡以形成分别连接到像素

电极,栅极焊盘和数据焊盘的像素电极,冗余栅极焊盘和冗余数据焊盘。