#### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2004/0160563 A1

Ashizawa et al.

Aug. 19, 2004 (43) Pub. Date:

#### (54) LIQUID CRYSTAL DISPLAY DEVICE

Inventors: Keiichiro Ashizawa, Mobara-shi (JP); Masayuki Hikiba, Mobara-shi (JP);

Masuyuki Ohta, Mobara-shi (JP)

Correspondence Address:

ANTONELLI, TERRY, STOUT & KRAUS, 1300 NORTH SEVENTEENTH STREET **SUITE 1800** ARLINGTON, VA 22209-9889 (US)

10/779,794 (21) Appl. No.:

(22) Filed: Feb. 18, 2004

#### Related U.S. Application Data

Continuation of application No. 10/400,686, filed on Mar. 28, 2003, now Pat. No. 6,697,142, which is a continuation of application No. 10/038,599, filed on Jan. 8, 2002, now Pat. No. 6,545,736, which is a

continuation of application No. 09/234,494, filed on Jan. 21, 1999, now Pat. No. 6,341,003.

#### Foreign Application Priority Data (30)

(JP) ...... 10-11543 Jan. 23, 1998

#### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ...... G02F 1/1343

#### (57)**ABSTRACT**

A liquid crystal display device includes first and second substrates, a liquid crystal layer interposed therebetween, video signal lines, gate signal lines and counter signal lines formed on the first substrate, counter electrodes connected to one of the counter signal lines formed on the first substrate, pixel electrodes formed on the first substrate and pixel regions having at least a counter electrode and at least a pixel electrode. A distance between farthest apart edges of the counter electrodes in one of the pixel regions is longer than a distance between farthest apart edges of the pixel electrodes in the one of the pixel regions in a direction perpendicular to an extension direction of the video signal lines.

FIG. 1

(PRIOR ART)

### FIG. 2 (A) FIG. 2 (B) FIG. 2 (C)

F I G. 3

F I G. 5

### FIG. 6

### F I G. 7

FIG. 8

~SUB1 ~SUB1 -SUB1 g FIG. 10 (B) (C) ITO SPUTTER(g2) FIRST-PHOTO (AI) | SPUTTER(g1) SECOND PHOTO **ETCHING ETCHING** RESIST **9**0 ~SUB1 ~SUB1 ~SUB1 GТ GT AOF AOF

# FIG. 13

SIGNAL FLOW

Fig. 15

## FIG. 17 (A)

FIG. 17 (B)

## FIG. 20 (A)

FIG. 20 (B)

### FIG. 24 (A)

FIG. 24 (B)

<u>SUB</u>

Fig. 28  $C_5H_{11}$   $C_5H_{1$

Fig. 29(B) Fig. 29(A) 29C PS1H on High CL (High) 29C -Edge 1 PS1L 29B on Low **SUB** (High) (Low) Edge 2 Edge 2 Fig. 29(C) Growth Growth PS1H CT/CL **SUB** Fig. 29(D) Fig. 29(E) Edge 1 CL (High) CT Edge 1 (High) PS1H PS1L 29E on High on Low **SUB** (Low) Edge 2 Edge 2

Fig. 30(A)

Fig. 30(B)

Fig. 30(C)

Fig. 30(D)

Fig. 30(E)

Fig. 37

CL

e'

SUB

Fig. 39

hvout (Expected)

hvout (Observeed)

SUB2

OC

BM

FIL

LC

PS2

PX

PS1

SUB1

hvin

hvin

W

Fig. 40(B)

## LIQUID CRYSTAL DISPLAY DEVICE

# CROSS REFERENCE TO RELATED APPLICATION

[0001] This is a continuation of U.S. application Ser. No. 10/400,686, filed Mar. 28, 2003, which is a continuation of U.S. application Ser. No. 10/038,599, filed Jan. 8, 2002, now U.S. Pat. No. 6,545,736, which is a continuation of U.S. application Ser. No. 09/234,494, filed Jan. 21, 1999, now U.S. Pat. No. 6,341,003, the subject matter of which is incorporated by reference herein.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a liquid crystal display device and, more specifically, to a liquid crystal display device in which a pair of insulating substrates are opposed to each other via a predetermined gap that is maintained by spacers, a liquid crystal composition (a liquid crystal molecule) is held in the gap, and a storage capacitor portion is formed in each pixel region.

[0004] 2. Description of the Related Art

[0005] High-resolution liquid crystal display devices capable of color display for use in notebook-sized computers and computer monitors are now widely utilized.

[0006] Basically, in this type of liquid crystal display device, what is called a liquid crystal panel is formed by holding a layer of a liquid crystal composition between two insulating substrates (hereinafter also referred to simply as substrates) such as glass plates at least one of which is transparent. This type of liquid crystal display device is generally classified into a type (simple matrix type) in which an image is formed by changing the orientation directions of liquid crystal molecules of desired pixels by selectively applying voltages to various electrodes for pixel formation that are formed on the insulating substrates of the liquid crystal panel and a type (active matrix type) in which various electrodes for pixel formation and active elements for pixel selection are formed and an image is formed by changing the orientation directions of liquid crystal molecules of desired pixels by making selections from the active elements.

[0007] In general, the active matrix liquid crystal display device employs that is called a vertical electric field type in which electric fields are developed between electrodes formed on one substrate and an electrode formed on the other substrate.

[0008] On the other hand, the liquid crystal display device of what is called a lateral electric field type (also called as In-Plane Switching type, abbreviated as "IPS type" hereinafter) has been put into practical use in which the directions of electric fields that act on the liquid crystal layer are approximately parallel with the substrate surfaces. In an example of the lateral electric field type liquid crystal display device, a very wide viewing angle is obtained by forming comb-teeth electrodes for electric field formation on one of the two substrates.

[0009] In the lateral electric field liquid crystal display device, an active matrix substrate is provided with scanning signal lines and video signal lines, switching elements formed in the vicinity of the crossing points of the scanning

signal lines and the video signal lines, pixel electrodes to which drive voltages are applied via the respective switching elements, and counter electrodes that are formed in the same plane as the pixel electrodes. A color filter substrate is provided with a black matrix made of a resin composition and color filter layers formed for each pixel in an opening region of the black matrix. A liquid crystal panel is formed by holding a liquid crystal composition between the active matrix substrate and the color filter substrate. The liquid crystal display device is configured in such a manner that a backlight is disposed in the rear of the liquid crystal panel and a unified structure is obtained by using top and bottom cases.

[0010] Image display is performed by changing the light transmittance of the liquid crystal compound by electric field components that are formed between the pixel electrodes and the counter electrodes so as to extend approximately parallel with the substrate surfaces.

[0011] In contrast to the vertical electric field type one, the lateral electric field type liquid crystal display device is superior in viewing angle; that is, it allows a user to view a clear image even when he is located at a position that forms a large angle with the display screen.

[0012] The liquid crystal display device having the above configuration is disclosed in Japanese Unexamined Patent Publication No. Hei. 6-160878 and its counterpart U.S. Pat. No. 5,598,285, and 5,737,051, for example.

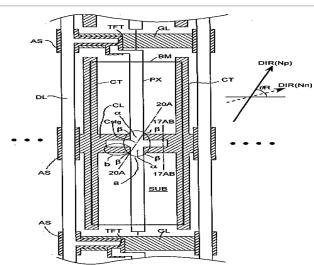

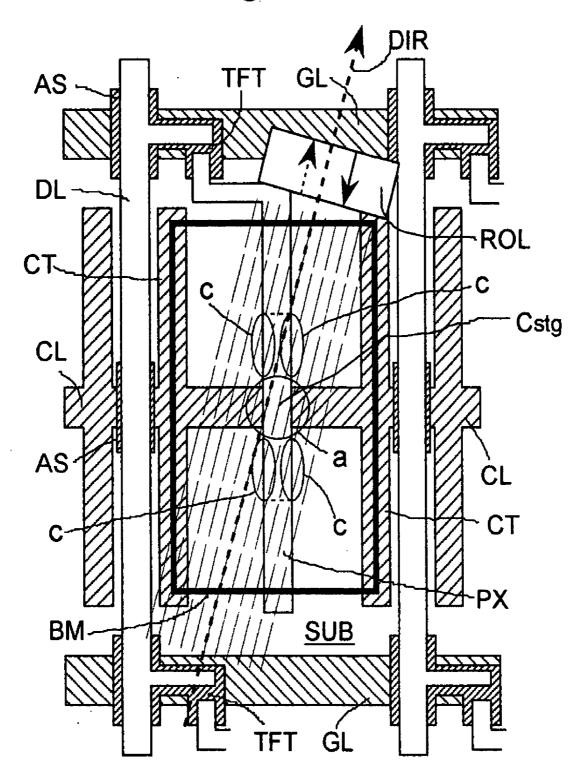

[0013] FIG. 1 is a plan view showing one pixel, a light shield region of a black matrix BM, and its vicinity of a conventional lateral electric field type liquid crystal display device.

[0014] As shown in FIG. 1, each pixel is provided in a region enclosed by four signal lines that cross each other, that is, a scanning signal line (gate signal line or horizontal signal line) GL, a counter voltage signal line CL, and two adjacent video signal lines (drain signal line or vertical signal line DL.

[0015] Each pixel includes a thin-film transistor TFT, a storage capacitor portion Cstg, a pixel electrode PX, and an counter electrode CT. In FIG. 1, a plurality of scanning signal lines GL and counter voltage signal lines CL are provided at the top and bottom of the pixel direction so as to extend in the right-left or horizontal direction. A plurality of video signal lines DL are provided at the right-left side of the pixel so as to extend in the top-bottom or vertical direction. The pixel electrode PX is connected to the thin-film transistor TFT, and the counter electrode CT is integral with the counter voltage signal line CL.

[0016] The pixel electrode PX and the counter electrode CT confront each other, and display is controlled by modulating transmission light or reflection light by controlling the orientation state of a layer of a liquid crystal composition LC (hereinafter also referred to simply as a liquid crystal or a liquid crystal layer) by means of an electric field developed between the pixel electrode PX and the counter electrode CT. Each of the pixel electrode PX and the counter electrode CT assumes a comb-teeth shape and has long and narrow portions extending in the top-bottom or vertical direction in FIG. 1.

[0017] The pixel electrode PX and the counter electrode CT are formed in such a manner that the number P of

comb-teeth portions of the pixel electrode PX and number C of comb-teeth portions of the counter electrode CT in one pixel necessarily satisfy a relationship C=P+1 (in FIG. 1, C=2 and P=1). The comb-teeth portions of the counter electrode CT and those of the pixel electrode PX are arranged alternately so as to have the comb-teeth portions of the counter electrode CT arranged adjacent to the video signal lines DL. With this structure, shielding from electric lines of force originating from the video signal lines DL can be effected by the counter electrode CT so that electric fields between the counter electrode CT and the pixel electrode PX are not influenced by the electric fields originating from the video signal lines.

[0018] The potential of the counter electrode CT is stable because it is always supplied with a potential externally via the counter voltage signal line CL. Therefore, the counter electrode CT has almost no potential variation even if it is adjacent to the video signal lines DL. Further, the above structure makes the geometrical position of the pixel electrode PX more distant from the video signal lines DL, whereby the parasitic capacitances between the pixel electrode PX and the video signal lines DL are greatly reduced and hence a variation of a pixel electrode potential Vs due to video signal voltages can be controlled.

[0019] As a result, vertically extending crosstalk lines (an image quality failure called vertical smears) can be prevented.

[0020] In a specific construction, widths Wp and Wc of the pixel electrode PX and the counter electrode CT, respectively, are set at 6  $\mu$ m, which is sufficiently larger than 4.5  $\mu$ m which is the maximum setting thickness of a liquid crystal layer (described later). It is desirable that the electrode widths Wp and Wc be sufficiently larger than 5.4 µm because it is preferable to provide a margin of 20% or more in view of processing variations in manufacture. As a result, electric field components parallel with the substrate surfaces that are applied to the liquid crystal layer become stronger than those perpendicular to the substrate surfaces, which prevents voltages for driving the liquid crystal to become unduly high. It is preferable that the maximum values of the electrode widths Wp and Wc be smaller than an interval L between the pixel electrode PX and the counter electrode CT. This is because it the interval between the electrodes is too short, electric lines of force are curved sharply and hence regions where electric field components parallel with the substrate surfaces are stronger than those perpendicular to the substrate surfaces are made larger, as a result of which the electric field components parallel with the substrate surfaces cannot be applied to the liquid crystal layer efficiently. To give a margin of 20% to the interval L between the pixel electrode PX and the counter electrode CT, it is necessary that the interval L be larger than 7.2  $\mu$ m. For example, in a case of constructing a liquid crystal display device having a diagonal size of about 14.5 cm (5.7 inches) and a resolution of 640×480 dots, an interval L that is larger than 7.2  $\mu$ m can be realized by setting the pixel pitch at about  $60 \mu m$  and dividing each pixel into two parts.

[0021] To avoid disconnection, the electrode width of the video signal lines DL is set at 8  $\mu$ m, which is somewhat larger than the widths of the pixel electrode PX and the counter electrode CT. To avoid short-circuiting, an interval of about 1  $\mu$ m is provided between the video signal lines DL

and the counter electrode CT. The video signal lines DL and the counter electrode CT are provided in different layers by forming the video signal lines DL and the counter electrode CT above and below a gate insulating film, respectively. On the other hand, the interval between the pixel electrode PX and the counter electrode CT is changed in accordance with the liquid crystal material used, for the following reason. The electric field intensity for attaining the maximum transmittance depends on the liquid crystal material. To obtain the maximum transmittance within the range of the maximum amplitude of a signal voltage that is set by the breakdown voltage of a video signal driver circuit (signalside driver) used, the electrode interval needs to be set in accordance with the liquid crystal material. The electrode interval becomes about 15  $\mu$ m when a liquid crystal material that will be described later is used.

[0022] In the example configuration being discussed, in a plan view of FIG. 1, a black matrix BM surrounds an opening of the pixel and is formed on the gate line GL, the counter voltage signal line CL, the thin-film transistor TFT, and the drain lines DL, and between the counter electrode CT and the drain lines DL. The storage capacitor portion Cstg is located outside the opening of the black matrix BM (i.e., outside the pixel region) and is composed of the pixel electrode PX, the counter voltage signal line CL, and an insulating film formed between them.

[0023] In the liquid crystal display device, an alignment film is applied after formation of the respective electrodes and electrode wiring lines, protective films, and insulating films and is given a liquid crystal alignment control ability by being subjected to a treatment called rubbing.

[0024] In the conventional lateral electric field type liquid crystal display device, since the storage capacitor portion Cstg is formed outside each pixel region, there is no large height change or steps in the pixel region and hence the alignment film in the pixel region can be given a uniform liquid crystal alignment control ability.

[0025] However, in recent years, liquid crystal display devices have been proposed in which the aperture ratio of the entire screen is increased by forming the storage capacitor portion Cstg in each pixel region. In those devices, the storage capacitor Cstg produces large steps in the pixel region and those steps may cause an alignment defect in a rubbing treatment. As a result, what is called a domain occurs and causes display unevenness.

[0026] In particular, alignment defects of the above kind occur frequently in a case where the multilayered film structure that constitutes the storage capacitor portion Cstg has steps extending perpendicularly or approximately perpendicularly to the alignment direction (rubbing direction) of the alignment film. When such an alignment defect occurs, the liquid crystal does not operate normally in the vicinity of the storage capacitor portion Cstg, to cause a domain. This results in a problem that the contrast is lowered and display unevenness occurs, which means a marked reduction in image quality.

### SUMMARY OF THE INVENTION

[0027] An object of the present invention is to provide a liquid crystal display device having good display quality by solving the above problems in the art, specifically by

decreasing the frequency of occurrence of alignment defects that result from the presence of steps of the storage capacitor portion Cstg formed in each pixel region and thereby preventing display failures such as a contrast reduction and display unevenness.

[0028] To attain the above object, in the invention, edge sectional shapes of steps of a multilayered film structure formed in each pixel region (actually each opening region of a black matrix), in particular steps of multilayered films such as electrode that constitute a storage capacitor portion, are made gentle.

[0029] Specifically, the invention provides a liquid crystal display device comprising an active matrix substrate comprising a plurality of scanning signal lines, a plurality of video signal lines, switching elements formed in the vicinity of respective crossing points of the scanning signal lines and the video signal lines, pixel electrodes to which drive voltages are applied via the respective switching elements, counter electrodes formed in a different plane than the pixel electrodes; a color filter substrate comprising a black matrix made of a resin composition, and color filter layers provided for respective pixels formed in respective opening regions of the black matrix; a liquid crystal composition held between the active matrix substrate and the color filter substrate; and storage capacitor portions located in the respective opening regions of the black matrix, each of the storage capacitor portions being composed of a counter voltage signal line for supplying a signal to an associated one of the counter electrodes, a pixel electrode, and an insulating film provided between the counter voltage signal line and the pixel electrode, wherein image display is performed by varying the light transmittance of the liquid crystal composition by electric field components that develop between the pixel electrodes and the counter electrodes so as to extend approximately parallel with the substrate surfaces, and wherein one of a portion of the counter voltage signal line and a portion of the pixel electrode which form the storage capacitor have an outline within that of the other of the portion of the counter voltage signal line and the portion of the pixel electrode.

[0030] With the above configuration, the angles of steps in the storage capacitor portions with respect to the surface of an alignment film become gentle, whereby rubbing defects can be prevented from occurring in the vicinity of the storage capacitor portions. As a result, it becomes possible to provide a liquid crystal display device having good display quality in which the frequency of occurrence of display failures such as a contrast reduction and display unevenness are greatly reduced.

[0031] In the above liquid crystal display device, most of a projected outline shape of the portion of one of the counter voltage signal line and the pixel electrode arranged in an upper layer may be located inside a projected outline shape of the portion of the other of the counter voltage signal line and the pixel electrode arranged in a lower layer.

[0032] In the above liquid crystal display device, most of a projected outline shape of the portion of one of the counter voltage signal line and the pixel electrode arranged in a lower layer may be located inside a projected outline shape of the portion of the other of the counter voltage signal line and the pixel electrode arranged in an upper layer.

[0033] With the above two features, the angles of steps of the electrode films constituting the storage capacitor por-

tions with respect to the surface of an alignment film become gentle, whereby rubbing defects can be prevented from occurring in the vicinity of the storage capacitor portions. As a result, it becomes possible to provide a liquid crystal display device having good display quality in which the frequency of occurrence of display failures such as a contrast reduction and display unevenness are greatly reduced.

[0034] These features can be not only applied to the pixel electrode and the pixel, but also to a pair of conductive layers extending in transverse directions and crossing one another in the pixel region and at least one of the conductive layers including the branch portion extending from the crossing in the direction of extension of the other of the conductive layers within the pixel region. The pixel region is defined as a region formed on the liquid crystal display substrate and transmitting light to be modulated by the liquid crystal layer.

[0035] Where multilayered films such as electrode films, insulating films, and protective films are formed in each pixel region, the invention is not limited to the case where the multilayered films are ones belonging to the storage capacitor portion.

[0036] The second object of the invention is to prevent the liquid crystal display device from display failures caused by the reduction of the voltage applied to its liquid crystal layer. This problem appears the liquid crystal display having such two kinds of conductive layers defined as first and second conductive layers as follows. The first and second conductive layers are formed above a main surface of one of substrates facing to the liquid crystal layer. The first conductive layer extends in first direction, and has a first voltage. The second conductive layer extends in second direction, and has a second voltage. Each of the first and second conductive layers has at least one portion therefrom in a different direction and joined thereto at a corner, and is covered with an insulating film.

[0037] When the first voltage differs from the second voltage, the display failures appear in the liquid crystal layer. Namely, applying the different electrical signals or voltages the first and second conductors induces this problem, even if the first and second conductive layers are isolated from one another by an insulating film, or are formed on the main surfaces of different substrates from one another.

[0038] To attain this object, the invention forms the corner with at least one of a curve and at least one obtuse.

[0039] Specifically, the invention provides following two structures for the liquid crystal display device having a pixel electrode, an counter electrode, and an counter voltage signal line for supplying a signal to the counter electrode formed between a liquid crystal layer and one of a pair of substrates sealing the liquid crystal layer therebetween.

[0040] One of the structures is described that the counter voltage signal line extending in one direction crosses the pixel electrode extending in a transverse direction, at least one of the counter voltage signal line and the pixel electrode has branch portions extending in the direction of extension of the other the counter voltage signal line and the pixel electrode, and edges of the counter voltage signal line and the pixel electrode with the branch portions thereof are connected with at least one of a curve and at least one obtuse angle.

[0041] The other of the structures is described that the counter voltage signal line extending in one direction is connected to the counter electrode extending in transverse direction to the one direction so as to connect their edges with at least one of a curve and at least one obtuse, and the counter voltage signal line and the pixel electrode cross one another.

[0042] In both of the inventions, the pixel electrode, the counter electrode, the counter voltage signal line, and the substrate on which these electrodes and the signal line are covered with an insulating layer, and preferably the insulating film formed on the pixel electrode is different from that formed on the counter electrode and the counter voltage signal line. The crossing region in accordance to an overlapping of the counter voltage signal line and the pixel electrode is formed in the light transmission region delimited by a light shielding material.

[0043] The detailed structures of this invention will be explained later.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0044] FIG. 1 is a plan view showing one pixel, a light shield region of a black matrix BM, and its vicinity of a conventional lateral electric field type liquid crystal display device:

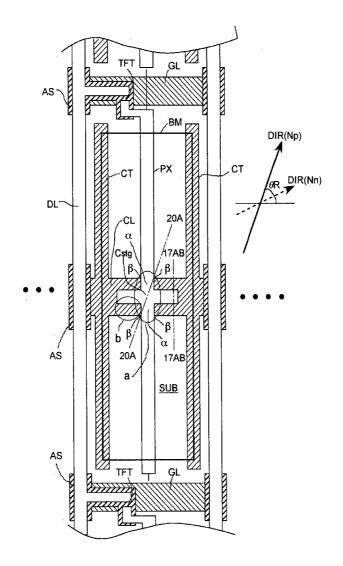

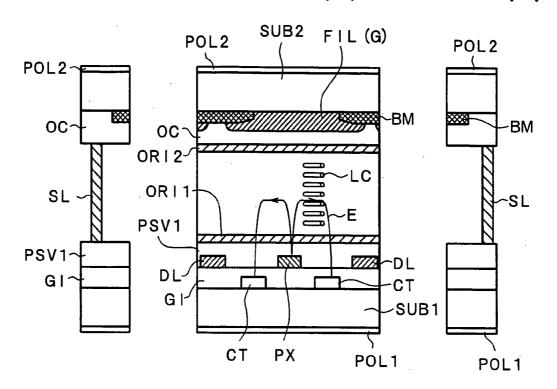

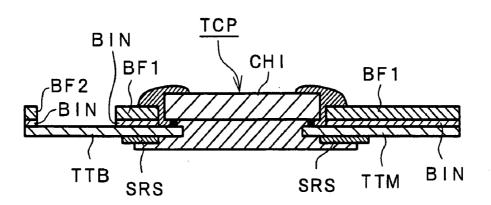

[0045] FIG. 2(A)-2(C) is a sectional view of electrodes for one pixel (FIG. 2(A)) and their vicinity (FIGS. 2(B), 2(C)) in an image display area and substrate peripheral portions of a liquid crystal panel that constitutes a lateral electric field type liquid crystal display device;

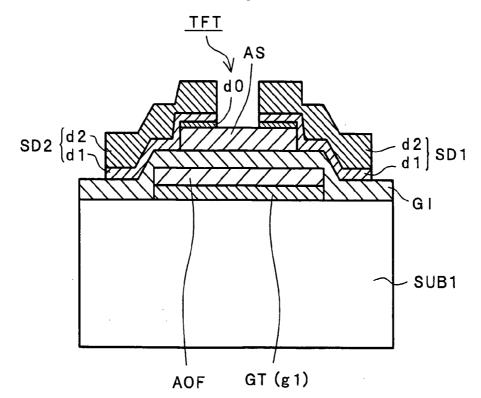

[0046] FIG. 3 is a sectional view of a thin-film transistor TFT;

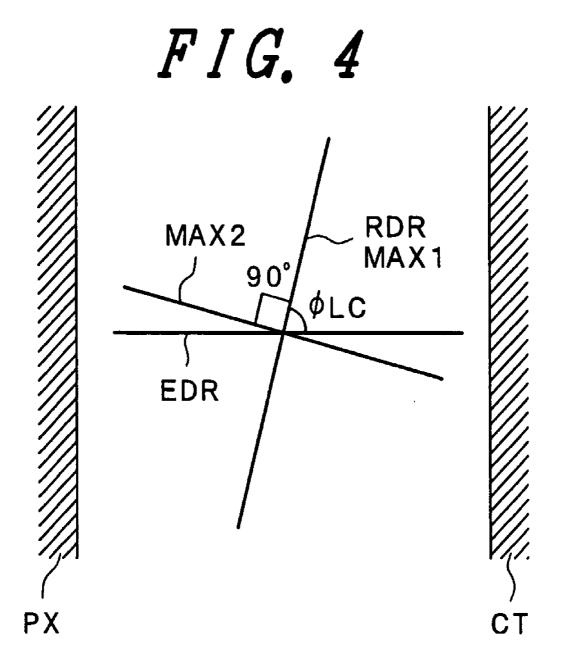

[0047] FIG. 4 illustrates an angular relationship between the rubbing direction RDR and the applied electric field direction EDR:

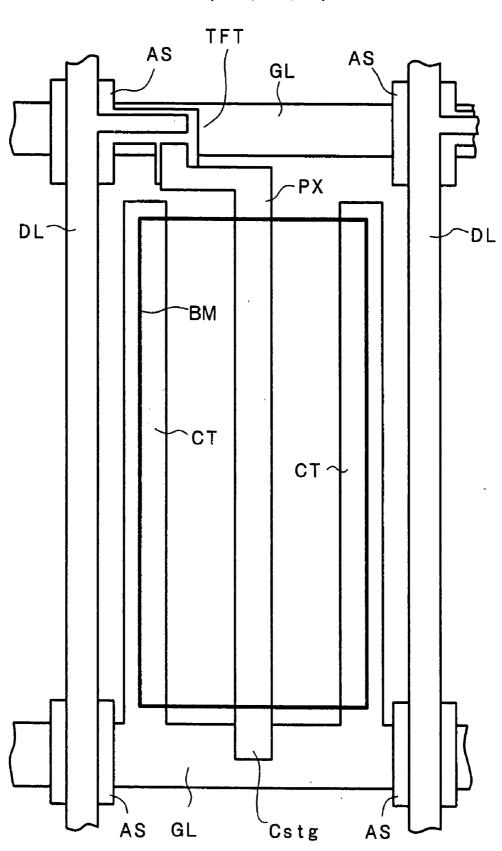

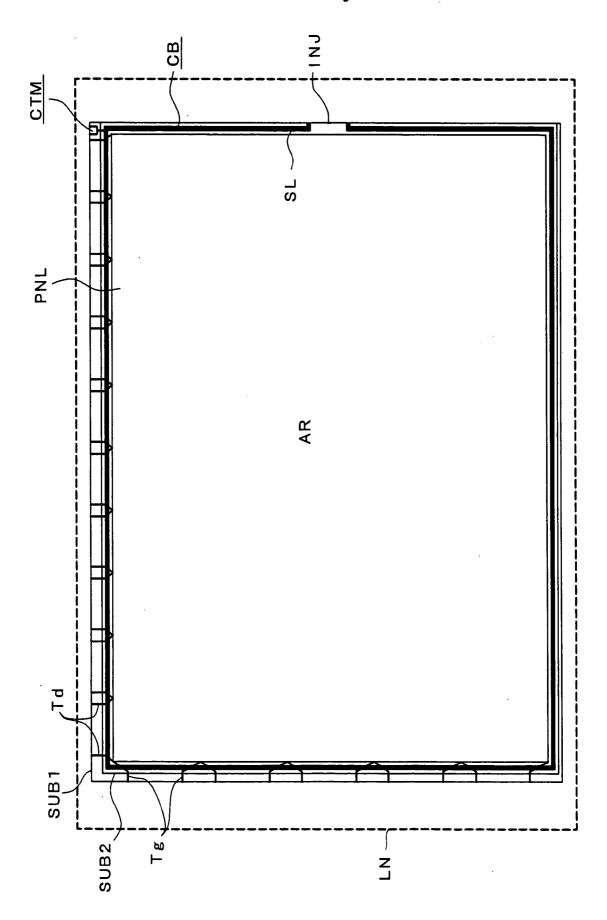

[0048] FIG. 5 is a plan view showing the main part of peripheral portions of a matrix (AR) of a display panel including top and bottom substrates;

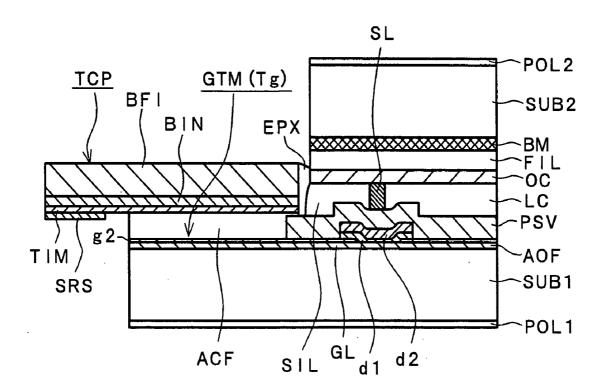

[0049] FIG. 6 is a sectional view of external connection terminals GTM to which a scanning circuit is connected from the left side and its vicinity;

[0050] FIG. 7 is a sectional view of a tape carrier package shown in FIG. 6;

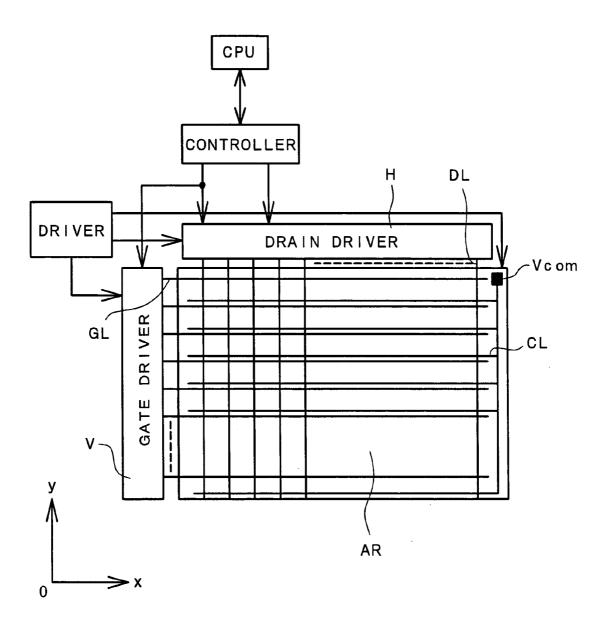

[0051] FIG. 8 is a general circuit diagram of an equivalent circuit of the liquid crystal display device according to the invention;

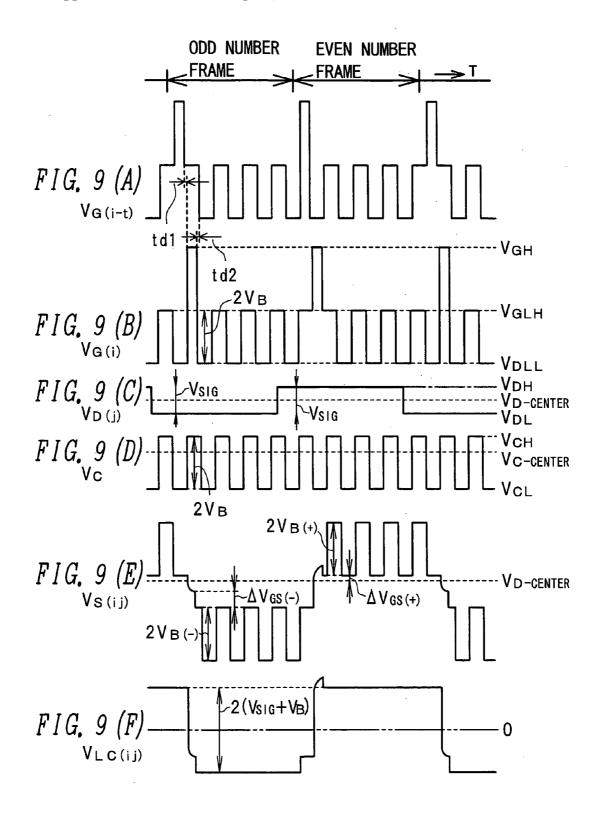

[0052] FIG. 9(A)-9(F) are a drive waveform diagram of the liquid crystal display device according to the invention;

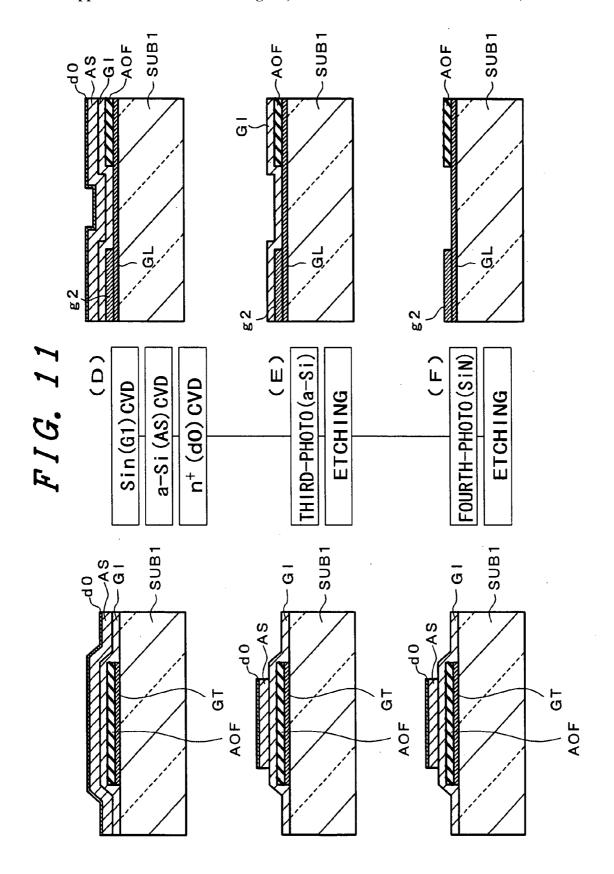

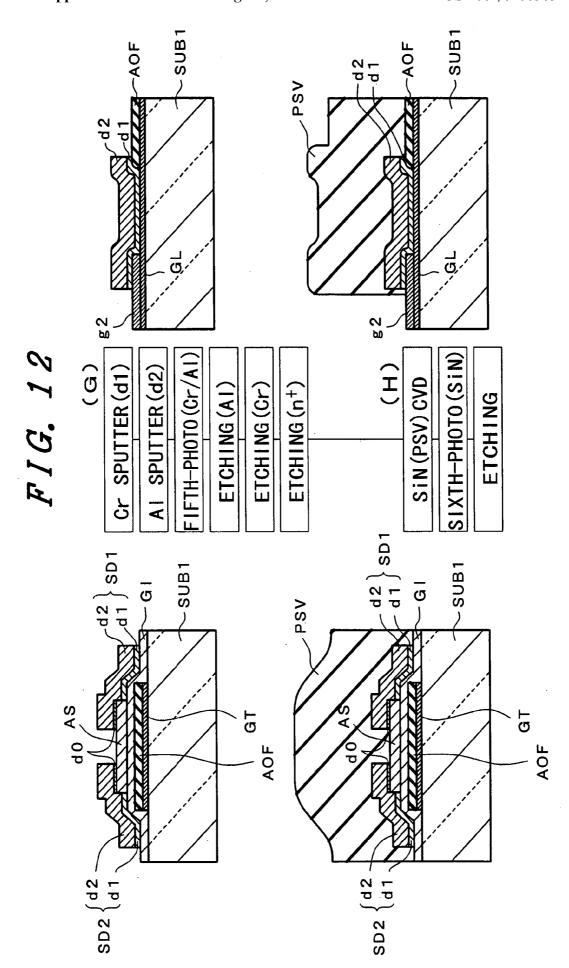

[0053] FIGS. 10 through 12 show a manufacturing process of a liquid crystal display device according to the invention;

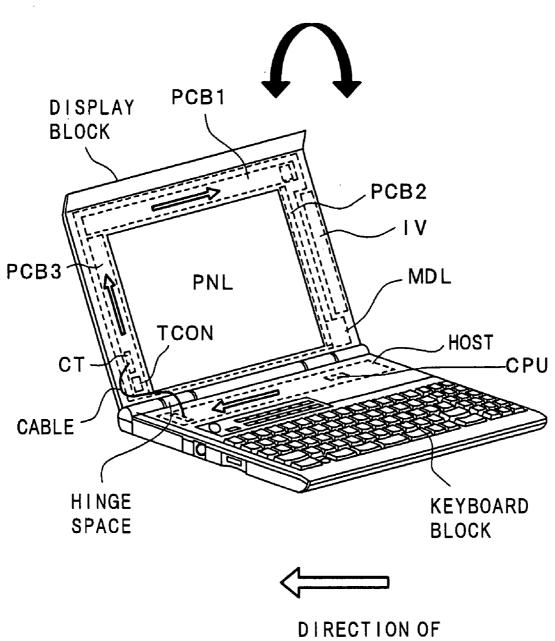

[0054] FIG. 13 shows a notebook-sized personal computer that is an example of an information apparatus in which a liquid crystal display device of the invention is incorporated;

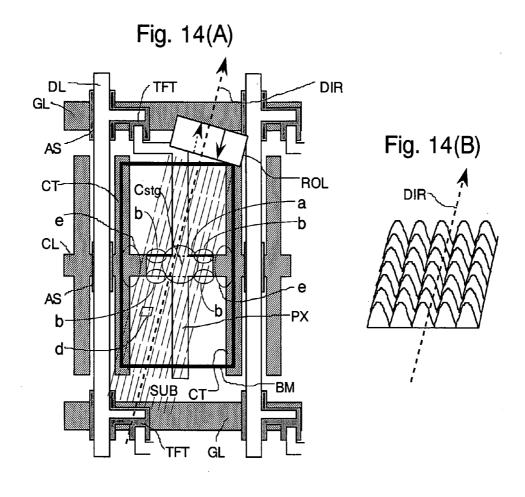

[0055] FIG. 14(A)-14(C) are a plan view of the electrode structure for obtaining larger storage capacitance Cstg, a

enlarged image of a part of its uppermost surface after rubbing treatment, and an image of the rubbing treatment around the storage capacitance, respectively;

[0056] FIG. 15 is the other plan view of the electrode structure for obtaining larger storage capacitance Cstg;

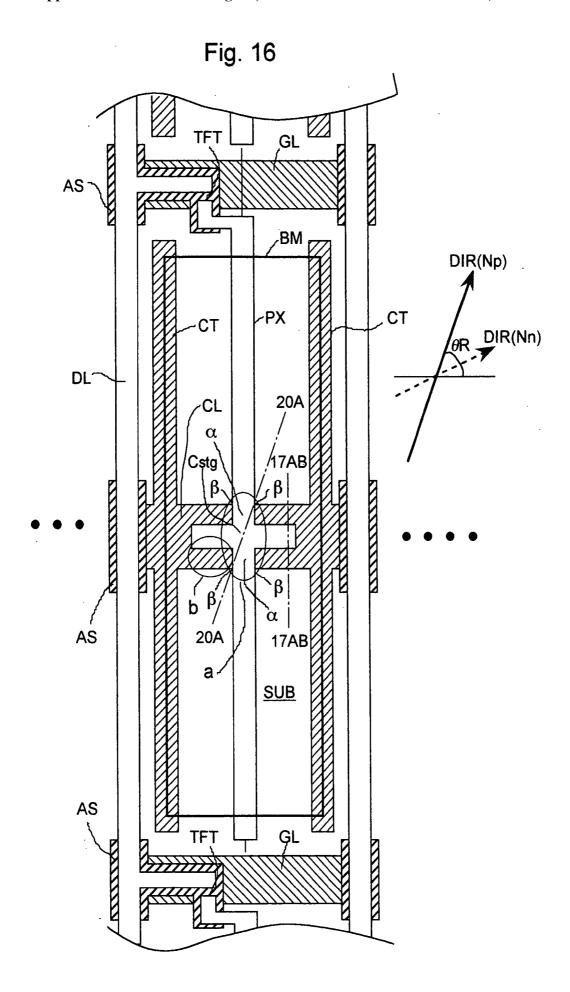

[0057] FIG. 16 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a first embodiment of the present invention;

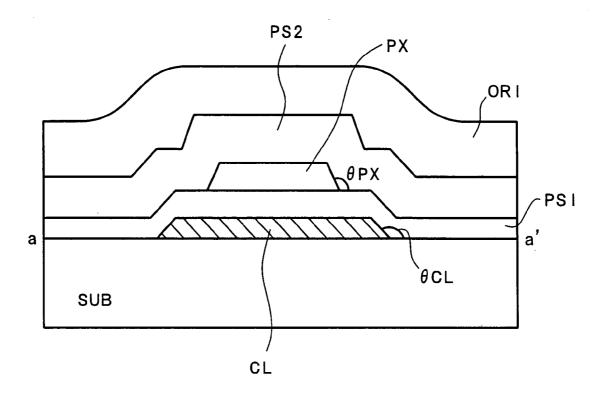

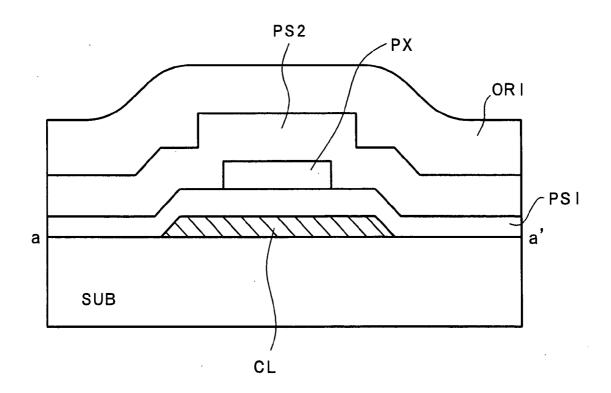

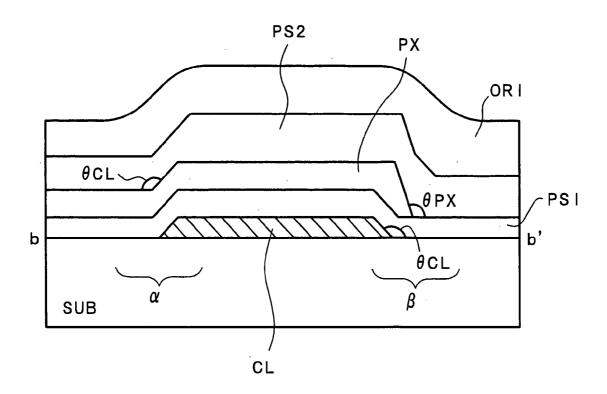

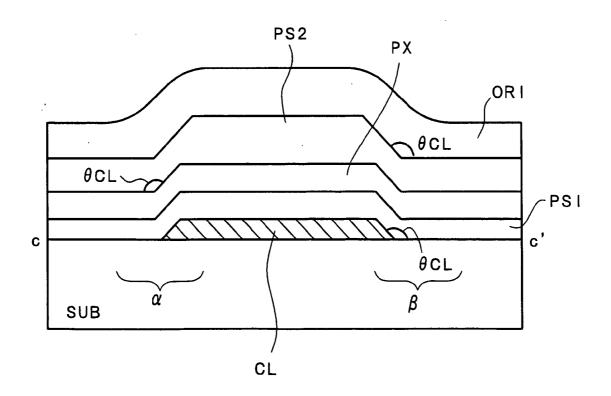

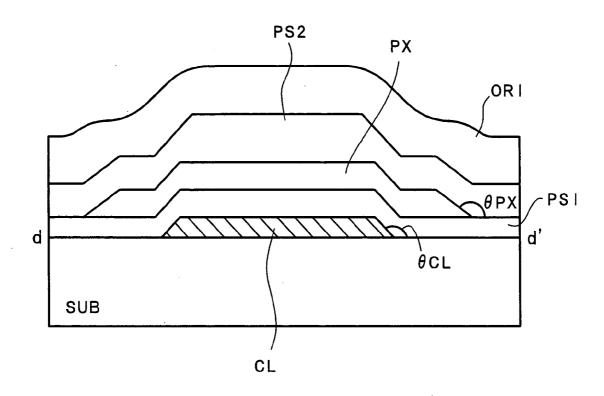

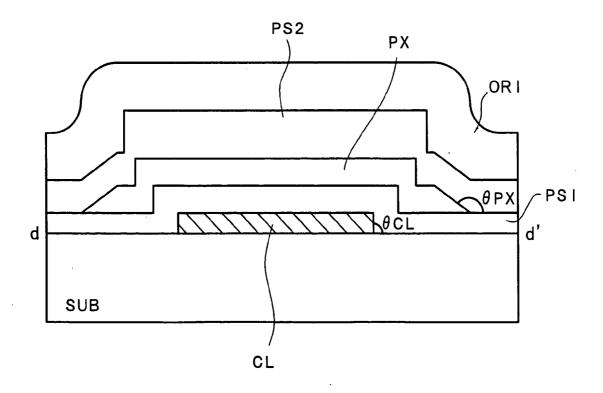

[0058] FIGS. 17(A) and 17(B) are sectional views of the storage capacitor portion Cstg taken along line a-a' in FIG. 1:

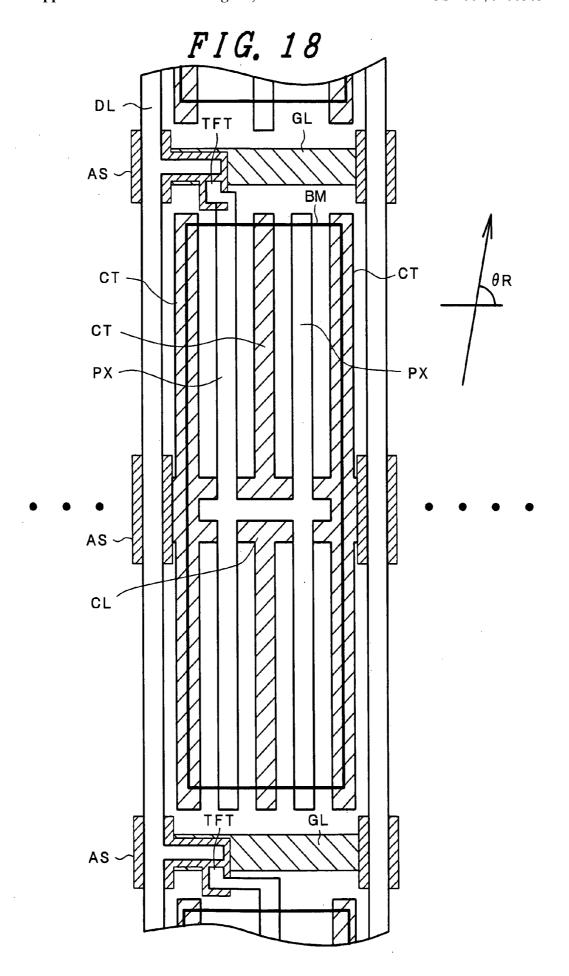

[0059] FIG. 18 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a second embodiment of the invention;

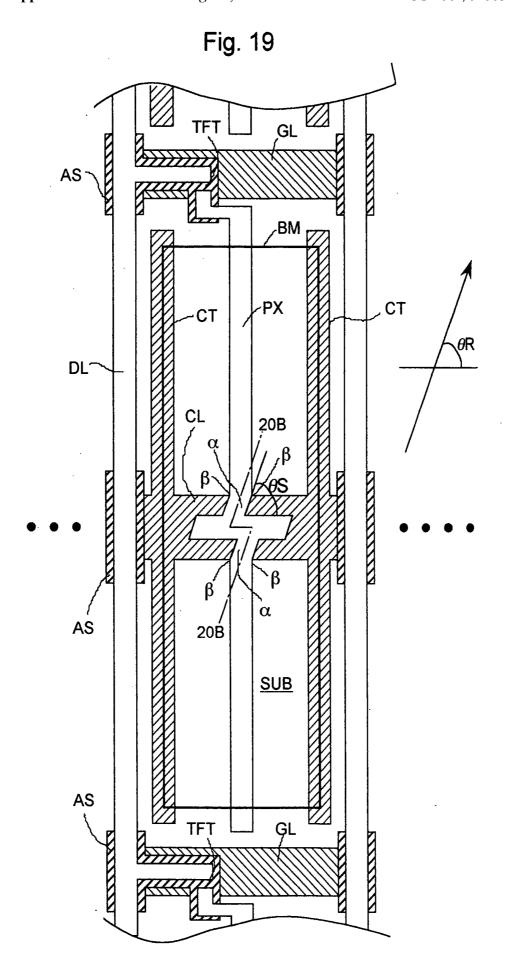

[0060] FIG. 19 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a third embodiment of the invention;

[0061] FIGS. 20(A) and 20 (B) are sectional views taken along line 20A-20A in FIG. 16 and line 20B-20B in FIG. 19, respectively;

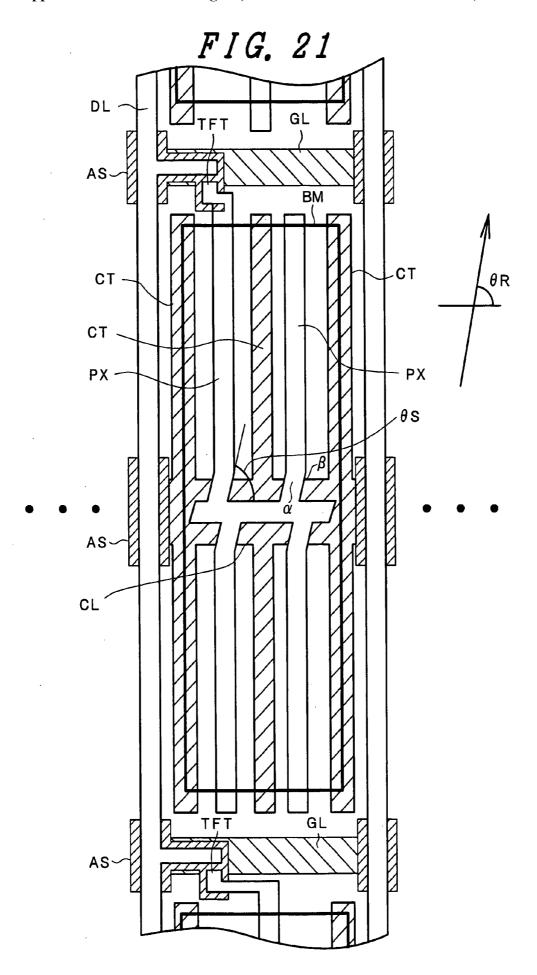

[0062] FIG. 21 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a fourth embodiment of the invention;

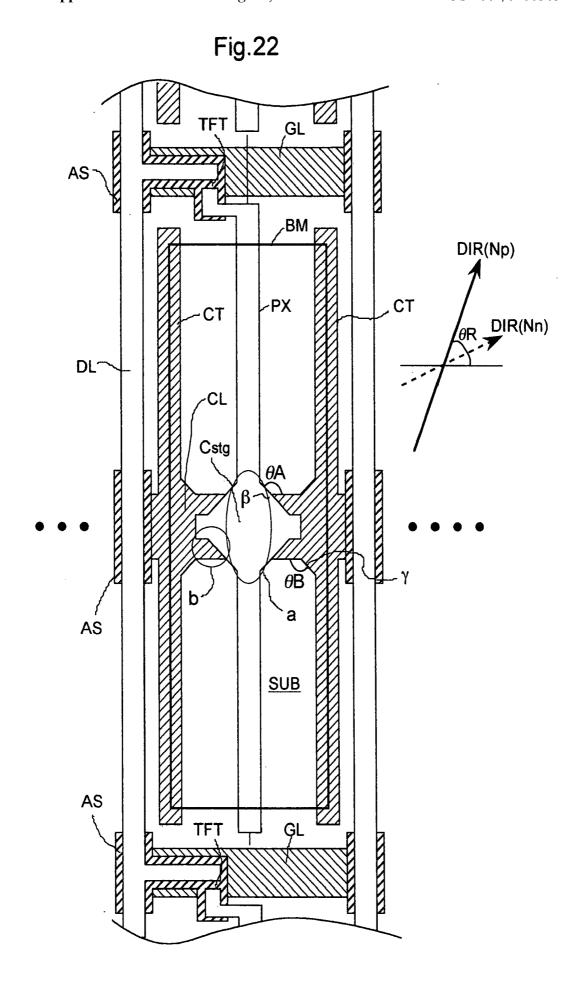

[0063] FIG. 22 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a fifth embodiment of the invention:

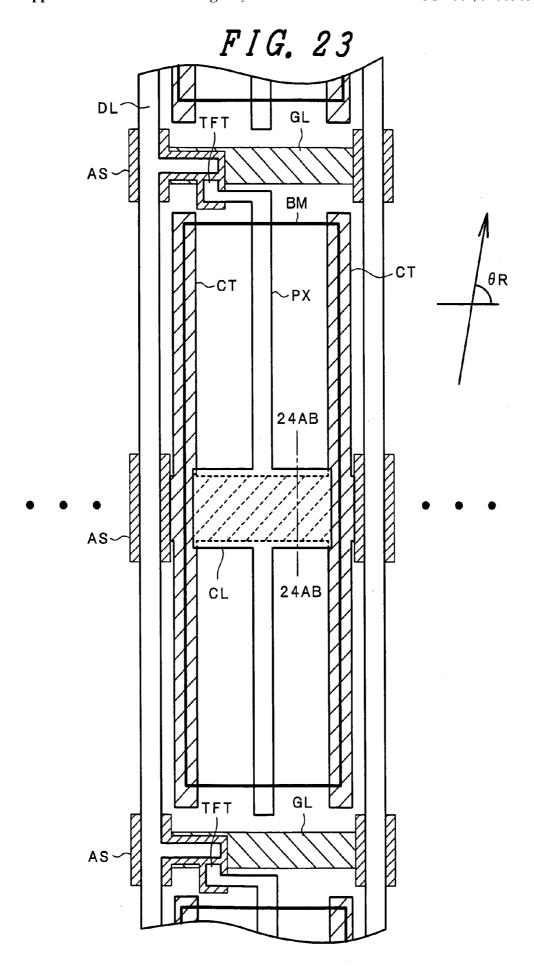

[0064] FIG. 23 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a sixth embodiment of the invention;

[0065] FIGS. 24(A) and 24(B) are sectional views taken along line 24AB-24AB in FIG. 23;

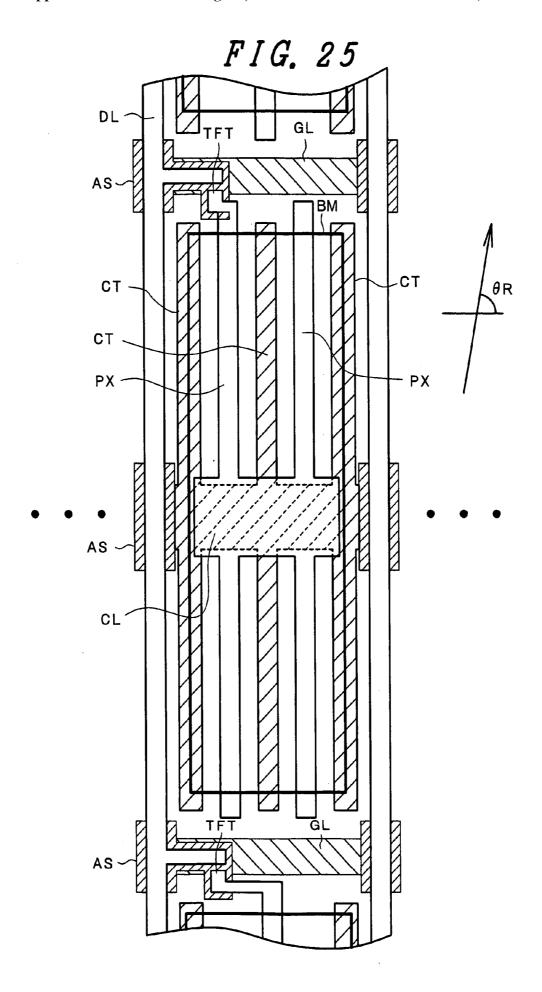

[0066] FIG. 25 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a seventh embodiment of the invention;

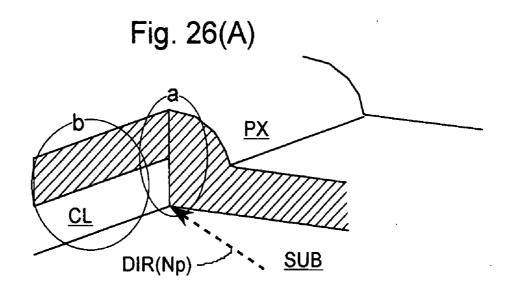

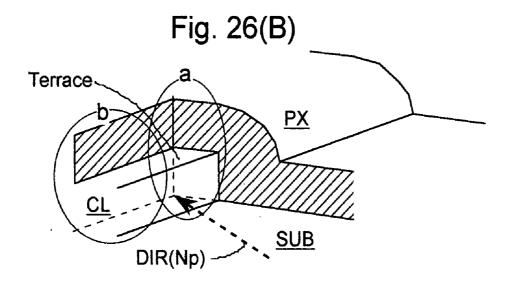

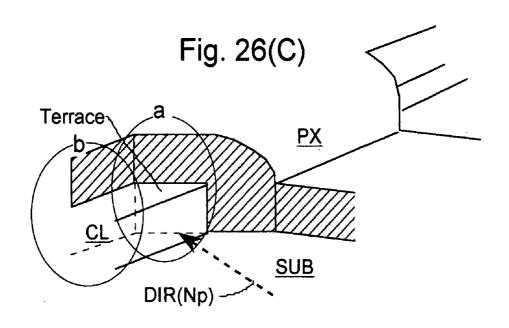

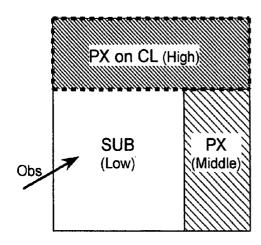

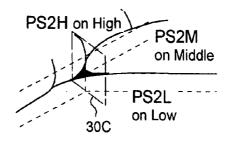

[0067] FIG. 26(A)-26(C) are sketches of circled portions "a" at each of which the pixel electrode gets over the counter voltage signal line CL, of FIGS. 14A, 16, 22, in this order;

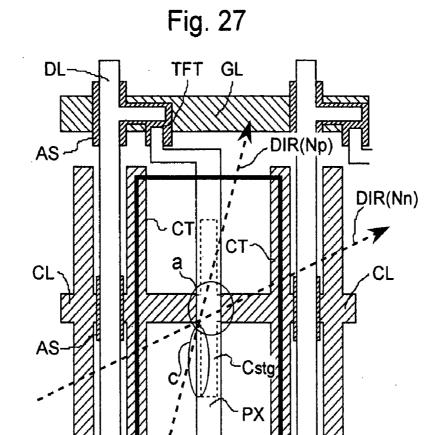

[0068] FIG. 27 is a plan view of another kind of the electrode structures for reducing the alignment defect during the rubbing treatment;

[0069] FIG. 28 is an explanatory figure showing relationship between one of actual liquid crystal molecules and its model used in this specification;

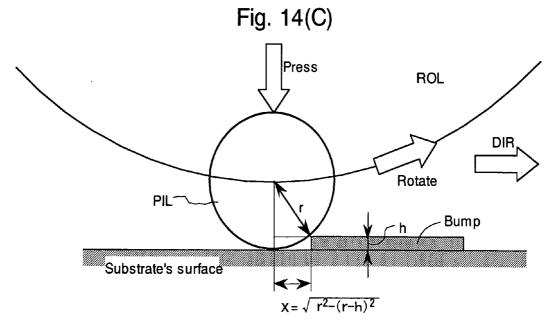

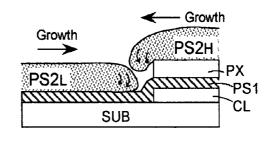

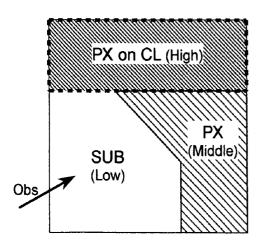

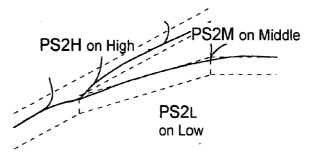

[0070] FIG. 29(A)-29(E) are explanatory figures showing the relationship between the electrode structure and a shape of a protective films formed thereon, FIGS. 29(A)-29(C) show the electrode structure and the protective film formed thereon in circled portion e of FIG. 14(A), and FIGS. 29(D) and 29(E) shows the improved electrode structure and the protective film formed thereon;

[0071] FIGS. 30(A)-30(E) are explanatory figures showing the relationship between the electrode structure and a shape of a protective films formed thereon, FIGS. 30(A)-30(C) show the electrode structure and the protective film formed thereon in circled portion a of FIG. 14(A), and FIGS. 30(D) and 30(E) shows the improved electrode structure and the protective film formed thereon;

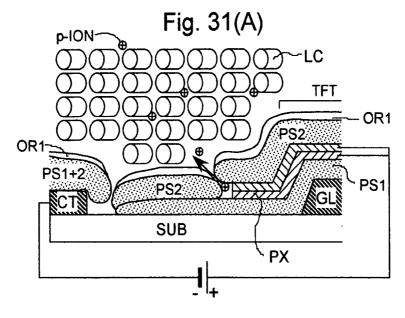

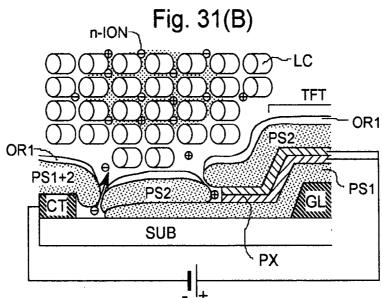

[0072] FIGS. 31A-31C are cross sectional images for explaining the progress of the contamination in the liquid crystal layer that reduces driving voltage applied to the liquid crystal molecules;

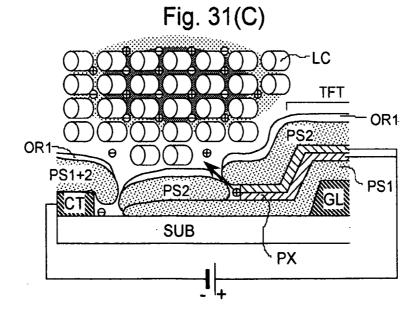

[0073] FIG. 32 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to an eighth embodiment of the invention;

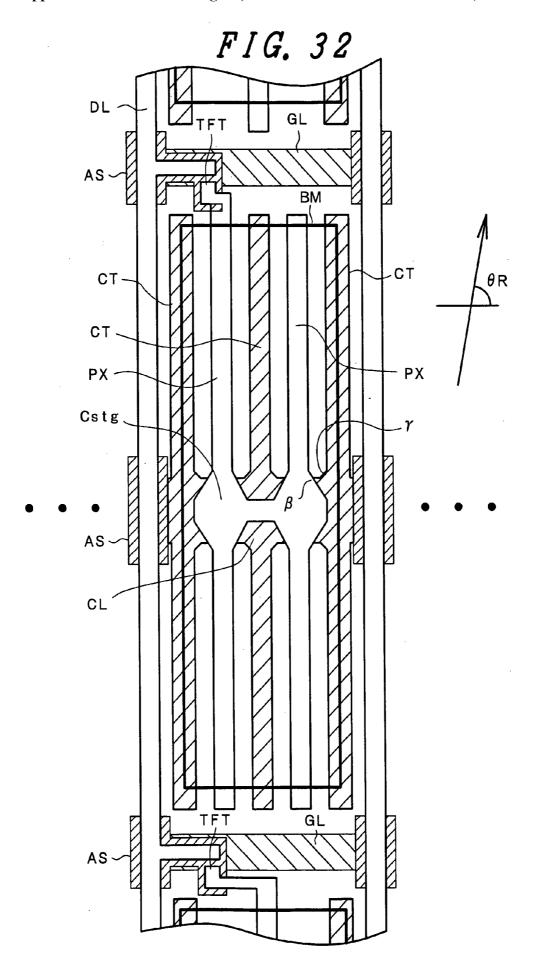

[0074] FIG. 33 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a ninth embodiment of the invention;

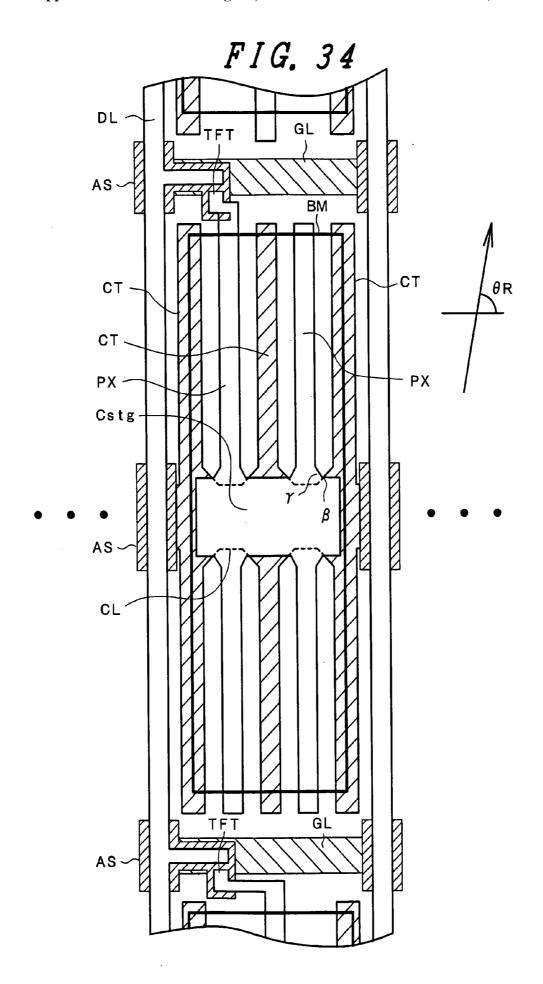

[0075] FIG. 34 is a schematic plan view of one pixel that is enclosed by a light shield film, that is, the main structure of a liquid crystal display device according to a 10th embodiment of the invention;

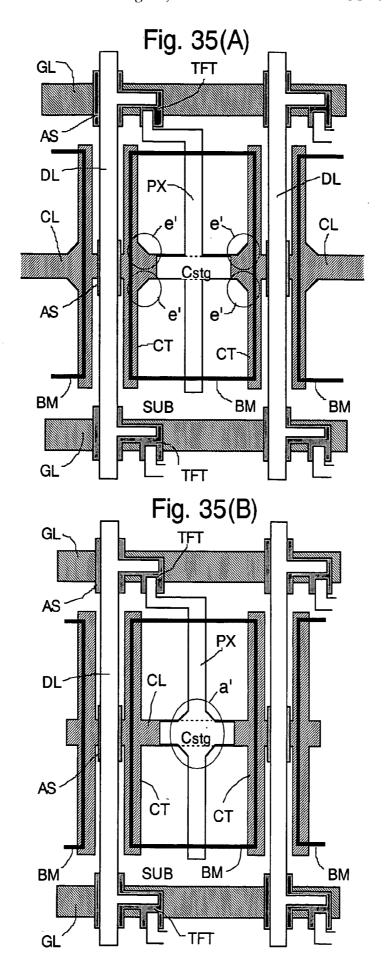

[0076] FIGS. 35(A) and 35(B) are plan views of two kinds of the electrode structure for solving the display failure caused by the reduction of the liquid crystal driving voltage;

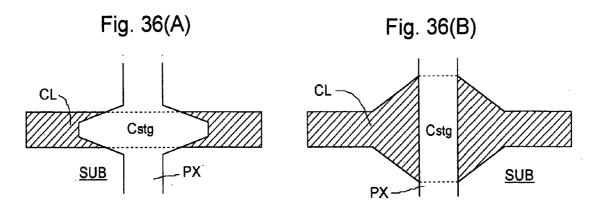

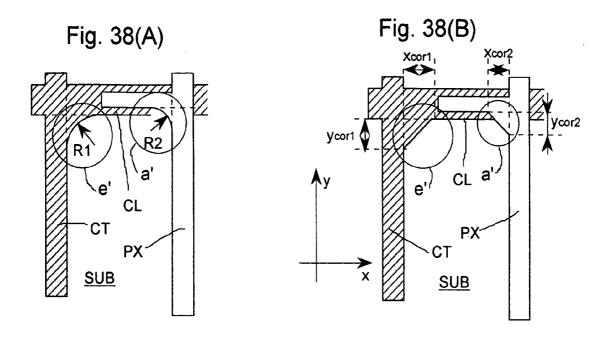

[0077] FIGS. 36 through 38 are partial plan views of the other electrode structures for solving the display failure caused by the reduction of the liquid crystal driving voltage;

[0078] FIG. 39 is a cross sectional image for explaining optical transmittance in the IPS-type liquid crystal display device; and

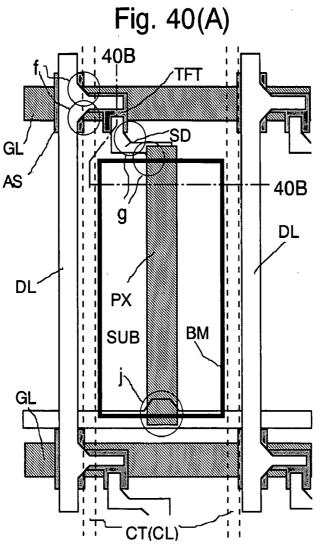

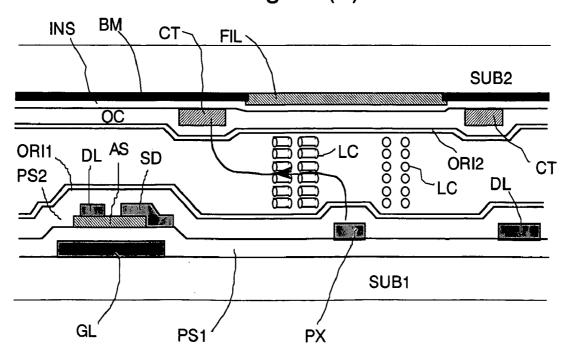

[0079] FIGS. 40(A) and 40(B) are a plan view and its cross sectional image showing further variation of the invented liquid crystal display device.

#### DETAILED DESCRIPTION

[0080] 1. Details of a Liquid Crystal Display Device

[0081] First of all, the details of the liquid crystal display device to which the inventions mentioned above are applied will be described with reference to FIGS. 2 to 12.

[0082] <Sectional Structure of Matrix Area (Pixel Portions)>

[0083] FIG. 2 is a sectional view of electrodes for one pixel (FIG. 2(A)) and left and right side sectional views (FIGS. 2(B) and 2(C)) in an image display area and substrate peripheral portions of a liquid crystal panel that constitutes a lateral electric field type liquid crystal display device. FIG. 3 is a sectional view of a thin-film transistor TFT. As shown in FIG. 2(A), in the lateral electric field type liquid crystal panel, a thin-film transistor TFT, a storage capacitor Cstg (not shown), and electrodes (a counter electrode CT, a pixel electrode PX, a video signal line DL, etc.) are formed on a bottom substrate (transparent glass substrate) SUB1. Color filters FIL and a pattern of a light shield black matrix BM are formed on a top substrate (transparent glass substrate) SUB2. It is possible to form a pattern of the light shield black matrix BM on the bottom transparent glass substrate

SUB1 as proposed in Japanese Patent Publication No. Hei. 8-806463. An alignment film ORI1 and an alignment film ORI2 for controlling the liquid crystal initial alignment are formed on the inside surfaces (i.e., the surfaces on the side of a liquid crystal LC) of the respective transparent glass substrates SUB1 and SUB2. Polarizing plates POL1 and POL2 are provided on the outside surfaces of the respective transparent glass substrates SUB1 and SUB2 so that their polarizing axes are perpendicular to each other (crossed Nicols arrangement).

[0084] TFT Substrate

[0085] Next, the components provided on the side of the bottom transparent glass substrate SUB1 (TFT substrate) will be described in detail.

[0086] <Thin-Film Transistor>

[0087] The thin-film transistor TFT operates in such a manner that the source-drain channel resistance of decreases when a positive bias is applied to a gate electrode GT and increases when no bias is applied. As shown in FIG. 3, the thin-film transistor TFT has the gate electrode GT, a gate insulating film GI, an i-type semiconductor layer AS made of an i-type (intrinsic; not intentionally doped with any conductivity type determining impurity) amorphous silicon (a-Si), and a source electrode SDI and a drain electrode SD2 that are paired. Essentially, the source and drain are determined depending on the polarity of a bias that is applied between them. It should be understood that the source and drain are interchanged because the bias polarity is changed during operation in the circuit of this liquid crystal display device. However, for convenience of description, the source and drain will be fixed in the following description.

[0088] Gate Electrode GT

[0089] The gate electrode GT is formed so as to be continuous with a scanning signal line GL; that is, part of the scanning signal line GL serves as the gate electrode GT. The gate electrode GT is so formed as to be larger than and hence cover completely the active region, that is, the i-type semiconductor layer AS, of the thin-film transistor TFT (when viewed from below). Therefore, the gate electrode GT plays not only its original role but also a role of preventing ambient light and back light from entering the i-type semiconductor layer AS. In this example, the gate electrode GT is a single-layer conductive film g1, which is a sputtered aluminum (Al) film, for instance. An Al anodic oxide film AOF is formed on the conductive film g1.

[0090] <Scanning Signal Line GL>

[0091] The scanning signal line GL is formed in the same manufacturing process as the gate conductive film g1 and is integral with it. A gate voltage Vg is supplied to the gate electrode GT from an external circuit via the scanning signal line GL. An Al anodic oxide film AOF is also formed on the scanning signal line GL. To decrease the probability of short-circuiting with the video signal line DL, the scanning signal line GL is made narrower at the position where it crosses the video signal line DL. Further, the scanning signal line GL is branched into two parts so that even if short-circuiting occurs the short-circuited line can be separated by laser trimming.

[0092] < Counter Electrode CT>

[0093] The counter electrode CT is a conductive film g1 that is in the same layer as the gate electrode GT and the scanning signal line GL. An Al anodic oxide film AOF is also formed on the counter electrode CT. Since the counter electrode CT is completely covered with the anodic oxide film AOF, it is not short-circuited with the video signal line DL even if it is made closer to the video signal line DL infinitely.

[0094] It is possible to cross the counter electrode CT and the video signal line DL with each other. A counter electrode voltage Vcom is applied to the counter electrode CT. In this embodiment, the counter electrode voltage Vcom is set at a potential which is lower than the middle DC potential of a minimum-level drive voltage Vdmin and a maximum-level drive voltage Vdmax that are applied to the video signal line DL by a feed-through voltage ΔVs that occurs when the thin-film transistor TFT is turned off. When it is desired to approximately reduce the power supply voltage of integrated circuits used in a video signal driver circuit by one half, an AC voltage may be applied to the counter electrode CT.

[0095] < Counter Voltage Signal Line CL>

[0096] The counter voltage signal line CL (see FIG. 1) is formed in the same manufacturing step as the conductive films g1 of the gate electrode GT, the scanning signal line GL, and the counter electrode CT, and is integral with the counter electrode CT. The counter electrode voltage Vcom is supplied to the counter electrode CT from an external circuit via the counter voltage signal line CL. An Al anodic oxide film AOF is also formed on the counter voltage signal line GL, to decrease the probability of short-circuiting with the video signal line DL, the counter voltage signal line GL is made narrower at the position where it crosses the video signal line DL. Further, the scanning signal line CL may be branched into two parts so that even if short-circuiting occurs the short-circuited line can be separated by laser trimming.

[0097] <Insulating Film GI>

[0098] In the thin-film transistor TFT, the insulating film GI serves as a gate insulating film for applying an electric field to the semiconductor layer AS in cooperation with the gate electrode GT. The insulating film GI is formed in a layer above the layer of the gate electrode GT and the scanning signal line GL. For example, the insulating film GI is a silicon nitride film formed at a thickness of 120-270 nm (in this embodiment, 240 nm) by plasma CVD. The gate insulating film GI is so formed as to surround the entire matrix portion AR. Peripheral portions of the insulating film GI are removed to expose external connection terminals DTM and GTM. The insulating film GI also contributes to electrically insulating the scanning signal line GL and the counter voltage signal line CL from the video signal line DL.

[0099] <i-type Semiconductor Layer AS>

[0100] The i-type semiconductor layer AS is formed with amorphous silicon at a thickness of 20-220 nm (in this embodiment, about 200 nm). Layers d0 are n+type amorphous silicon semiconductor layers for ohmic contact that are doped with phosphorus (P). The i-type semiconductor layer AS exists under the layers d0. The layers d0 are left only in areas where conductive films d1 (and d2) exist over the layers d0.

[0101] At the crossing portion of the scanning signal line GL and the video signal line DL and the crossing portion of the counter voltage signal line CL and the video signal line DL, i-type semiconductor layers AS are also provided between those lines. These i-type semiconductor layers AS decrease the possibility of short-circuiting between those lines at the crossing portions. <Source electrode SDI and drain electrode SD2>

[0102] Each of the source electrode SDI and the drain electrode SD2 is composed of the conductive film d1 that is in contact with the n+-type semiconductor layer d0 and the conductive film d2 that is formed on the conductive film d1. The conductive film d1 is a chromium (Cr) film formed at a thickness of 50-100 nm (in this embodiment, about 60 nm) by sputtering. The thickness of the Cr film should not exceed about 200 nm because the stress increases with the thickness. The Cr film serves to provide good adhesion with the n+-type semiconductor layer d0 and to prevent Al of the conductive film d2 from diffusing into the n+-type semiconductor layer d0; that is, the Cr film is used as what is called a barrier layer.

[0103] Other examples of the conductive film d1 are refractory metal films (Mo, Ti, Ta, and W) and refractory metal silicide films (MoSi<sub>2</sub>, TiSi<sub>2</sub>, TaSi<sub>2</sub>, and WSi<sub>2</sub>).

[0104] The conductive film d2 is formed at a thickness of 300-500 nm (in this embodiment, 400 nm) by sputtering Al. The Al film can be formed to have a large thickness because the stress in the Al film is smaller than in the Cr film. The Al film serves to decrease the resistance values of the source electrode SD1, the drain electrode SD2, and the video signal line DL and to facilitate covering the steps caused by the gate electrode GT and the i-type semiconductor layers AS (i.e., improve the step coverage).

[0105] After the conductive films d1 and d2 have been patterned by using the same mask pattern, part of a film for forming the n+-type semiconductor layer d0 is removed by using the same mask or using the conductive films d1 and d2 as a mask. That is, the portion of the film for forming the n+-type semiconductor layer d0 except the portions under the conductive films d1 and d2 is removed in a self-aligned manner. Since the etching is performed so as to remove the entire thickness of the film for forming the n+-type semiconductor layer d0, a slight surface portion of the i-type semiconductor layer AS is also etched. The degree of etching of the i-type semiconductor layer AS may be controlled by the etching time.

[0106] < Video Signal Line DL>

[0107] The video signal line DL is composed of a second conductive film d2 and a third conductive film d3 that are in the same layer as the source electrode SD1 and the drain electrode SD2. The video signal line DL is formed so as to be integral with the drain electrode SD2.

[0108] <Pixel Electrode PX>

[0109] The pixel electrode PX is composed of a second conductive film d2 and a third conductive film d3 that are in the same layer as the source electrode SD1 and the drain electrode SD2. The pixel electrode PX is formed so as to be integral with the source electrode SD1.

[0110] <Storage Capacitor Cstg>

[0111] The pixel electrode PX is so formed as to coextend with part of the counter voltage signal line CL at its end as shown in FIG. 1. This coextending structure provides the storage capacitor (capacitor element) Cstg having the pixel electrode PX as one electrode and the counter voltage signal line CL as the other electrode. The dielectric film of the storage capacitor Cstg is composed of the anodic oxide film AOF and the insulating film GI that is for example formed as the passivation film and used as the gate insulating film GI of the thin-film transistor TFT.

[0112] Color Filter Substrate

[0113] Next, the components provided on the side of the top transparent glass substrate SUB2 (color filter substrate) will be described in detail with reference to FIGS. 2(B), 2(C), and 6.

[0114] <Light Shield Film: Black Matrix BM>

[0115] The light shield film BM (what is called a black matrix) is formed on the transparent glass substrate SUB2 to prevent a reduction in contrast ratio or the like due to entrance to the display screen side of unnecessary transmission light coming from gaps other than the gaps between the pixel electrode PX and the counter electrode CT. The light shield film BM also serves to prevent ambient light or back light from entering the i-type semiconductor layer AS. That is, since the i-type semiconductor layer AS of the thin-film transistor TFT is sandwiched between the light shield film BM and the gate electrode GT that is larger than usual, ambient natural light or back light does not enter it.

[0116] The closed, rectangular outline of the black matrix BM shown in FIG. 1 indicates the opening in which the light shield film BM is not formed. The same indications as FIG. 1 are employed in the other plan-views of the pixel in this specification. The outline pattern shown in those figures is just an example.

[0117] In the lateral electric field type liquid crystal display device, the black matrix BM is generally made of a resin composition because its resistivity should be as high as possible. The Japanese Unexamined Patent Publication No. Hei. 9-43589 and its counterpart U.S. Pat. No. 5,831,701 discloses a proper range of the resistivity of the black matrix BM. According to this publication, the resistivity of the liquid crystal composition LC should be larger than  $10^N$   $\Omega$ ·cm and the resistivity of the black matrix BM should be larger than  $10^M$   $\Omega$ ·cm where  $N \ge 9$  and  $M \ge 6$ . It is desirable that N and M satisfy relationships N>13 and  $M \ge 7$ . Also for the purpose of reducing the surface reflection of the liquid crystal display device, it is desirable that the black matrix BM be made of a resin composition.

[0118] In contrast to a case where the black matrix BM is made of a metal film such as a Cr film, the use of a resin composition makes a metal film etching step unnecessary and hence can simplify a manufacturing process of the color filter substrate. Where a metal film is used, the manufacturing process includes 1) metal film formation, 2) resist application, 3) exposure, 4) development, and 5) resist peeling. On the other hand, where a resin is used, the manufacturing process includes 1) resist application, 2) exposure, and 3) development. Therefore, the process can greatly be shortened.

[0119] However, resin compositions have lower light shield performance than metal films. Although making a resin film thicker increases its light shield performance, it increases the thickness variation of the black matrix BM. For example, a thickness variation of 10% means a variation of  $\pm 0.1 \ \mu m$  when the thickness of the black matrix BM is 1.0  $\mu m$  and a variation of  $\pm 0.2 \ \mu m$  when it is  $2 \ \mu m$ .

[0120] Further, making the black matrix BM thicker increases the thickness variation of the color filter substrate, as a result of which it becomes difficult to increase the gap accuracy of the liquid crystal display panel. For the above reasons, it is desirable that the thickness of the resin film be  $2 \mu m$  or less.

[0121] To provide an OD value of about 4.0 or more with a film thickness of 1  $\mu$ m in a case where blackening is effected by, for instance, increasing the carbon content, the resistivity of the black matrix BM becomes lower than about  $10^6~\Omega$ ·CM. Such a black matrix BM cannot be used under the current technological situations. The OD value is defined as the light absorption coefficient multiplied by the film thickness.

[0122] In view of the above, in this embodiment, the light shield film BM is made of a resin composition in which a black inorganic pigment is mixed into a resist material, and is formed at a thickness of about  $1.3+0.1~\mu m$ . Examples of the inorganic pigment are palladium and nickel that is formed by non-electrolyte electrode plating. The resistivity and the OD value of the black matrix BM are set at about  $109~\Omega$ -cm and about 2.0, respectively.

[0123] A calculation result of a light transmission amount that will be obtained when a black matrix made of the above resin composition is used is as follows.

(OD value)=

$$log(100/Y)$$

(1)

$$Y = \int A(\lambda)B(\lambda)C(\lambda)d(\lambda)/\int A(\lambda)C(\lambda)d(\lambda)$$

(2)

[0124] where A is the luminous efficiency, B is the transmittance, C is the light source spectrum, and  $\lambda$  is the wavelength of incident light.

[0125] When light shielding is effected by using a film having an OD value 2.0, Y=1% is obtained from Equation (1). If it is assumed that the intensity of the incident light is  $4,000 \text{ cd/m}^2$ , a transmission light amount is calculated as about  $40 \text{ cd/m}^2$ . This light intensity can not satisfactorily be recognized visually by a human.

[0126] The light shield film BM is also formed in a peripheral area in frame-like form, and the peripheral pattern is made continuous with the pattern in the matrix area having a number of dot-like openings.

[0127] <Color Filters FIL>

[0128] Color filters FIL are formed as a repetition of red, green, and blue stripes at positions confronting the respective pixels. The color filters FIL are so formed as to be laid on the edge portions of the light shield film BM.

[0129] The invention relates to a projected layout of these overlap portions. The details will be described later.

[0130] For example, the color filters FIL can be formed in the following manner. First, a dyeing base member such as an acrylic resin is formed on the surface of the top transparent glass substrate SUB2, and its portions not located in

the red filters forming regions are removed by photolithography. Subsequently, red filters R are formed by dyeing the remaining portions of the dyeing base member with a red dye and then performing a fixing treatment. Then, green filters G and blue filters B are sequentially formed by executing similar steps.

[0131] <Overcoat Film OC>

[0132] An overcoat film OC is provided to prevent the dyes of the color filters FIL from leaking to the liquid crystal LC and to planarize the steps caused by the light shield film BM. The overcoat film OC is made of a transparent resin material such as an acrylic resin or an epoxy resin.

[0133] Liquid Crystal Layer and Polarizing Plates

[0134] Next, the liquid crystal layer, the alignment films, the polarizing plates, etc. will be described.

[0135] <Liquid Crystal Layer>

[0136] The liquid crystal LC is a nematic liquid crystal having a positive permittivity anisotropy value  $\Delta\epsilon$  (called as "a positive dielectric anisotropy", also) of 13.2 and a refractive index anisotropy value  $\Delta n$  of 0.081 (589 nm, 20° C.) and a nematic liquid crystal having a negative permittivity anisotropy value  $\Delta\epsilon$  of -7.3 and a refractive index anisotropy value  $\Delta n$  (also called "birefringence") of 0.053 (589 nm, 20° C.).

[0137] The thickness of the liquid crystal layer (i.e., the gap) is set larger than 2.8  $\mu m$  and smaller than 4.5  $\mu m$  when the permittivity anisotropy value  $\Delta \epsilon$  is positive. This is because a permittivity characteristic having almost no wavelength dependence in the visible range when the retardation  $\Delta \cdot n$  is larger than 0.25  $\mu m$  and smaller than 0.32  $\mu m$ , and that most of liquid crystals having a positive permittivity anisotropy value  $\Delta \epsilon$  have a refractive index anisotropy value  $\Delta n$  that is larger than 0.07 and smaller than 0.09.

[0138] On the other hand, when the permittivity anisotropy value  $\Delta \epsilon$  is negative, the thickness of the liquid crystal layer (i.e., the gap) is set larger than 4.2  $\mu$ m and smaller than 8.0  $\mu$ m. This is to make the retardation  $\Delta n$ -d larger than 0.25  $\mu$ m and smaller than 0.32  $\mu$ m, as in the case of liquid crystals having a positive permittivity anisotropy value  $\Delta \epsilon$ . Most of liquid crystals having a negative permittivity anisotropy value  $\Delta \epsilon$  have a refractive index anisotropy value  $\Delta n$  that is larger than 0.04 and smaller than 0.06.

[0139] In a state that the liquid crystal layer is combined with the alignment films and the polarizing plates, the maximum transmittance is obtained when liquid crystal molecules are turned by 45 from the rubbing direction toward the electric field direction. The thickness of the liquid crystal layer (i.e., the gap) is controlled by polymer beads.

[0140] The kind of liquid crystal LC is not restricted except that it should be a nematic liquid crystal.

[0141] A larger permittivity anisotropy value  $\Delta \epsilon$  makes it easier to set the drive voltage at a smaller value. A smaller refractive index anisotropy value  $\Delta n$  makes it easier to set the thickness of the liquid crystal layer (i.e., the gap) larger, whereby the liquid crystal sealing time can be shortened and the gap variation can be reduced.

[0142] <Alignment Films (Orientation Films)>

[0143] The alignment films ORI are made of polyimide. The rubbing directions RDR for the top and bottom substrates are set parallel with each other, and are set so as to form an angle \$\phi LC\$ of 75\circ\$ with the applied electric field direction EDR. This relationship is illustrated in FIG. 4.

[0144] The angle between the rubbing direction RDR and the applied electric field direction EDR may be set not smaller than 45° and smaller than 90° when the liquid crystal LC has a positive permittivity anisotropy value  $\Delta \epsilon$  and set larger than 0° and not larger than 45° when the liquid crystal LC has a negative permittivity anisotropy value  $\Delta \epsilon$ .

[0145] < Polarizing Plates>

[0146] The polarizing plates POL are G122DU (product name) of Nitto Denko Corp. A polarized light transmission axis MAX1 of the bottom polarizing plate POLL is set coincident with the rubbing direction RDR and a polarized light transmission axis MAX2 of the top polarizing plate POL2 is set perpendicular to the rubbing direction RDR.

[0147] This provides a normally closed characteristic in which the transmittance increases as the voltage applied to each pixel of the invention (i.e., the voltage applied between the pixel electrode and the counter electrode CT) is increased.

[0148] In the lateral electric field type liquid crystal display device to which the invention is directed, a display abnormality may occur when a high voltage of static electricity or the like is applied externally to the surface of the top substrate SUB2. Therefore, it is necessary to form a transparent conductive film layer having a sheet resistance of less than  $1\times10^8 \Omega/\Box$  above or on the surface of the top polarizing plate POL2, form a transparent conductive film layer of ITO or the like having a sheet resistance of less than  $1\times10^8 \Omega/\Box$  between the polarizing plate POL2 and the top transparent substrate SUB2, or mixing conductive particles of ITO, SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub>, or the like into an adhesive layer of the polarizing plate POL2 to thereby make its sheet resistance lower than  $1\times10^8 \Omega/\Box$ . As for this measure, The Japanese Unexamined Patent Publication No. Hei. 9-105918 discloses in detail a method of improving a shield function.

[0149] <Matrix Peripheral Structures>

[0150] FIG. 5 is a plan view showing the main part of peripheral portions of the matrix (AR) of the display panel PNL including the top and bottom glass substrates SUB1 and SUB2. FIG. 6 is a sectional view of external connection terminals GTM to which a scanning circuit is connected from the left side and its vicinity. FIG. 7 is a sectional view of a tape carrier package TCP shown in FIG. 6.

[0151] The display panel shown in FIG. 5 is manufactured as follows. In the case of a small-size panel, to increase the throughput, one glass substrate is divided after being subjected to processing for a plurality of devices. In the case of a large-size panel, to commonly use manufacturing facilities, a glass substrate whose size is standardized for all product types is processed and then reduced in size so as to be suitable for each product type. In either case, a glass plate is cut after being subjected to a series of steps.

[0152] FIGS. 5 and 6 correspond to the latter case, and show a state that both of the top and bottom substrates SUB1

and SUB2 have been cut. Symbol LN denotes edges of those substrates before cutting. In either case, in the completed state, the ends of the top substrate SUB2 is located inside the ends of the bottom substrate SUB1 in portions including external connection terminal groups Tg and Td or a terminal CTM (the top portion and the left portion in FIGS. 5) to expose those terminals.

[0153] Each of the terminal groups Tg and Td is a collection of a plurality of connection terminals GTM for a scanning circuit or connection terminals DTM for a video signal circuit and their lead-out wiring portions in which they are collected for each tape carrier package TCP (see FIGS. 6 and 7) on which an integrated circuit chip CHI is mounted

[0154] The lead-out lines of each terminal group extending from the matrix area to the external connection terminal portion are inclined as they approach the both ends to adapt the terminals DTM and GTM of the display panel PNL to the arrangement pitch of the packages TCP and the connection terminal pitch of each package TCP.

[0155] The counter electrode terminal CTM is a terminal for supplying a counter electrode voltage to the counter electrode CT externally. The counter voltage signal lines CL of the matrix area are lead out to the side (right side in FIG. 5) opposite to the terminals GTM for a scanning circuit and are together connected to a common bus line CB, which is in turn connected to the counter electrode terminal CTM.

[0156] A sealing pattern SL is formed between the transparent glass substrates SUB1 and SUB2 along their edges so as to seal the liquid crystal LC except for a liquid crystal injection inlet INJ. The sealing material is an epoxy resin, for instance.

[0157] The alignment films ORI1 and ORI2 are formed inside the sealing pattern SL. The polarizing plates POL1 and POL2 are provided on the outside surfaces of the bottom transparent glass substrates SUB1 and the top transparent glass substrates SUB2, respectively.

[0158] The liquid crystal LC is sealed in the region partitioned by the sealing pattern SL between the bottom alignment film ORI1 and the top alignment film ORI2 that set the alignment direction of liquid crystal molecules. The bottom alignment film ORI1 is formed on top of the protective film PSV1 that is formed on the bottom transparent glass substrate SUB1.

[0159] The liquid crystal display device is assembled as follows. First, various layers are laid separately on the bottom transparent glass substrate SUB1 and the top transparent glass substrate SUB2. After a sealing pattern SL is formed on the substrate SUB2, the substrates SUB1 and SUB2 are placed one on another. Subsequently, a liquid crystal LC is injected through an opening INJ of the sealing pattern SL and then the injection inlet INJ is sealed with an epoxy resin or the like. Finally, the substrates SUB1 and SUB2 are cut.

[0160] <Connection Structure of Tape Carrier Package TCP>

[0161] As mentioned above, FIG. 7 shows a sectional structure of a tape carrier package TCP in which an integrated circuit chip CHI of a scanning signal driver circuit V or a video signal driver circuit H is mounted on a flexible

wiring board and FIG. 6 is a sectional view showing the main part of a structure in which the tape carrier package TCP of FIG. 6 is connected to, in this case, the terminals GTM for a scanning signal circuit of the liquid crystal display panel PNL.

[0162] In FIGS. 6 and 7, an input terminals/wiring portion TTB of the integrated circuit CHI and an output terminals/wiring portion TTM of the integrated circuit CHI are made of Cu, for instance. Bonding pads PAD of the integrated circuit CHI are connected to inside tip portions (commonly called inner leads) of the portions TTB and TTM by what is called face-down bonding.

[0163] Outside tip portions (commonly called outer leads) of the portions TTB and TTM, which correspond to the inputs and outputs, respectively, of the integrated circuit chip CHI, are connected to a CRT/TFT conversion circuit/power supply circuit SUP by soldering or the like and to the liquid crystal display panel PNL via anisotropic conductive films ACF.

[0164] The package TCP is connected to the panel PNL so that its tip portion covers the protective film PSV1 of the panel PNL from which the connection terminals GTM are exposed. Since the protective film PSV1 is covered with one side portion of the package TCP, the external connection terminals GTM (or DTM) are resistant to galvanic corrosion.

[0165] Symbol BF1 denotes a base film that is made of polyimide or the like, and SRS denotes a solder resist film as a mask for preventing solver from sticking to an undesirable portion during soldering.

[0166] The gap between the top and bottom glass substrates SUB2 and SUB1 outside the sealing pattern SL is protected by an epoxy resin EPX or the like after cleaning. The space between the package TCP and the top substrate SUB2 is charged with a silicone resin SIL to effect multiple protection.

[0167] < Equivalent Circuit of Entire Display Device>

[0168] FIG. 8 is a general circuit diagram of an equivalent circuit of the liquid crystal display device according to the invention. In the liquid crystal display panel, the image display section is constituted of a set of a number of pixels that are arranged in matrix form. Each pixel is so configured as to be able to independently control, that is, modulate, transmission light that is emitted from a backlight provided in the rear of the liquid crystal display panel.

[0169] In the active matrix substrate which is one component of the liquid crystal display panel, the gate signal lines GL and the counter voltage signal lines CL that extend in the x-direction (row direction) and parallel arranged in the y-direction (column direction) and the video signal lines (drain signal lines) DL that are insulated from the signal lines GL and CL, extend in the y-direction, and parallel arranged in the x-direction are formed in the effective pixel area AR.

[0170] A unit pixel is formed in each rectangular region enclosed by a scanning signal line (gate signal line) GL, a counter voltage signal line CL, and drain signal lines DL.

[0171] The liquid crystal display panel is provided with the vertical scanning circuit V and the video signal driver circuit H as external circuits. Scanning signals (voltages) are sequentially supplied from the vertical scanning circuit V to the respective gate signal lines GL, and video signals (voltages) are supplied to the respective drain signal lines DL from the video signal driver circuit H with proper timing with respect to the scanning signals.

[0172] The vertical scanning circuit V and the video signal driver circuit H receive power supply voltages from a liquid crystal driving power supply circuit 3 as well as display data and control signals that are produced by a controller 2 by dividing image information that is supplied from a CPU 1.

[0173] < Driving Method>

[0174] FIGS. 9(A)-9(F) shows drive waveform diagrams of the liquid crystal display device according to the invention. A counter electrode voltage is an AC rectangular wave having two values VCH and VCL. The non-selection voltage of scanning signals VG(i-l) and VG(i) are varied between VGH and VGHL every scanning period in synchronism with the counter electrode voltage. The amplitude of the counter electrode voltage is set equal to that of the non-selection voltage.

[0175] A video signal voltage is a voltage that is desired to be applied to the liquid crystal layer minus ½ of the amplitude of the counter electrode voltage.

[0176] Although the counter electrode voltage may be a DC voltage, the use of an AC voltage can decrease the maximum amplitude of the video signal voltage and enables use of a video signal driver circuit (signal-side driver) that is low in breakdown voltage.

[0177] <Function of Storage Capacitor Portion Cstg>

[0178] The storage capacitor portion Cstg is provided to store video information that has been written to a pixel for a long time (after turning off of a thin-film transistor TFT).

[0179] In contrast to the type in which electric fields develop perpendicularly to the substrate surfaces, in the type employed by the invention in which electric fields develop parallel with the substrate surfaces, a pixel electrode and an counter electrode form almost no capacitance (what is called liquid crystal capacitance) and hence the storage capacitor portion Cstg is an indispensable component.

[0180] The storage capacitor portion Cstg also acts to reduce influence of a gate potential variation  $\Delta Vg$  on a gate electrode potential Vs when the thin-film transistor TFT is switched. This is expressed by the following formula:

$\Delta Vs = \big\{Cgs/\big(Cgs + Cstg + Cpix\big)\big\} \times \Delta Vg$

[0181] where Cgs is the parasitic capacitance formed between the gate electrode GT and the source electrode SD1 of the thin-film transistor TFT, Cpix is the capacitance formed between the pixel electrode PX and the counter electrode CT, and  $\Delta Vs$  is a variation of the pixel electrode potential Vs caused by  $\Delta Vg$ , that is, what is called a feed-through voltage.

[0182] The variation  $\Delta Vs$ , which may cause a DC component that is applied to the liquid crystal LC, can be reduced by increasing the storage capacitance Cstg. Reducing the DC component that is applied to the liquid crystal LC is effective in increasing the life of the liquid crystal LC and in decreasing the degree of what is called sticking, that is, a

phenomenon that a previous image remains on the liquid crystal display screen after switching is made to a new image.

[0183] Since the gate electrode GT is so formed as to completely cover the i-type semiconductor layer AS as described above, the overlap area between the gate electrode GT and each of the source electrode SD1 and the drain electrode SD2 increases accordingly and hence the parasitic capacitance Cgs increases, which results in a reverse effect that the pixel electrode potential is prone to be affected by the gate (scanning) signal Vg. However, this demerit can be eliminated by providing the storage capacitor portion Cstg.

[0184] <Manufacturing Method>

[0185] Next, a description will be made of a manufacturing method of the components on the side of the substrate SUB1 of the above-described liquid crystal display device.

[0186] FIGS. 10-12 show a manufacturing process of the liquid crystal display device according to the invention. In FIGS. 10-12, parenthesized characters at the central part are abbreviated names of steps, and sectional views of a thin-film transistor TFT portion and a gate electrode terminal and its vicinity both of which indicate a flow of the process are shown in the left part and the right part, respectively. Steps A, C in FIG. 10, B, C in FIG. 11, A and B in FIG. 12 correspond to respective photolithography processes and show a state that processing to be executed after the photolithography process has been finished and a photoresist has been removed.

[0187] In the invention, each of the photolithography processes means a series of operations including application of a photoresist, selected exposure using a mask, and development. Repeated descriptions of the photolithography processes will be avoided. Each of steps A-I will be described below.

[0188] Step A (FIG. 10):

[0189] A 300-nm-thick conductive film g1 of Al-Pd, Al-W, Al-Ta, Al-Ti-Ta, or the like is formed on a bottom transparent glass substrate SUB1 made of an AN635 glass (product name) by sputtering. After execution of a photolithography process, the conductive film g1 is etched selectively with a mixed liquid of phosphoric acid, nitric acid, and glacial acetic acid. As a result, gate electrodes GT, scanning signal lines GL, counter electrodes CT, counter voltage signal lines CL, electrodes PL1, gate terminals GTM, a first conductive layer of a counter electrode terminal CTM, anodized bus lines SHg (not shown) that are connected to the gate terminals GTM, and anodized pads (not shown) that are connected to the anodized bus lines SHg are formed.

[0190] Step B (FIG. 10):

[0191] After formation of an anodized mask AO by direct drawing, the substrate SUB1 is immersed in an anodization liquid obtained by diluting an ammonia solution of 3%-tartaric acid (pH is adjusted to 6.25±0.05) at a ratio of 1:9 with an ethylene glycol liquid and the forming current density is set at 0.5 mA/cm<sup>2</sup> (constant current forming).

[0192] Anodization is continued until the forming voltages reaches 125 V that is necessary to obtain an aluminum  $(Al_2O_3)$  film having a desired thickness. It is desirable that

this state be held for tens of minutes (constant voltage forming). This is important to obtain a uniform  $Al_2O_3$  film. As a result, the conductive films g1 are anodized and 180-nm-thick anodic oxide films AOF are formed on the gate electrode GT, the scanning signal lines GL, the counter electrodes CT, the counter voltage signal lines CL, and the electrodes PL1.

[0193] Step C (FIG. 10):

[0194] A 140-nm-thick ITO film as a transparent conductive film g2 is formed by sputtering. After execution of a photolithographic process, the transparent conductive film g2 is selectively etched with an etching liquid that is a mixed acid solution of hydrochloric acid and nitric acid. As a result, uppermost layers of the gate terminals GTM, drain terminals DTM, and a second conductive film of the counter electrode terminal CTM are formed. Step A (FIG. 11):

[0195] A 220-nm-thick silicon nitride film is formed by introducing an ammonia gas, a silane gas, and a nitrogen gas into a plasma CVD apparatus, and then a 200-nm-thick i-type amorphous silicon film is formed by introducing a silane gas and a hydrogen gas into the plasma CVD apparatus. Subsequently, a 30-nm-thick n+-type amorphous silicon film is formed by introducing a silane gas, a hydrogen gas, and a phosphine gas into the plasma CVD apparatus.

[0196] Step B (FIG. 11):

[0197] After execution of a photolithography process, island-like i-type semiconductor layers AS are formed by selectively etching the n+-type amorphous silicon film and the i-type amorphous silicon film by using  $SF_6$  as a dry etching gas.

[0198] Step C (FIG. 11):

[0199] After execution of a photolithography process, the silicon nitride film is selectively etched by using  $SF_6$  as a dry etching gas.

[0200] Step A (FIG. 12):

[0201] A 60-nm-thick conductive film d1 made of Cr is formed by sputtering, and then a 400-nm-thick conductive film d2 made of Al-Pd, Al-Si, Al-Ta, Al-Ti-Ta, or the like is formed by sputtering. After execution of a photolithography process, video signal lines DL, source electrodes SD1, drain electrodes SD2, pixel electrodes PX, electrodes PL2, second and third conductive layers of the common bus line CB, and bus lines SHd (not shown) that short-circuit drain terminals are formed by etching the conductive film d2 with a liquid similar to the liquid used in step A and etching the conductive film d1 with a solution of ceric ammonium nitrate.

[0202] Then, the portions of the n+-type semiconductor layer d0 located between the sources and the drains are removed selectively by etching the n+-type amorphous silicon film by introducing  $SF_6$  into a dry etching apparatus.

[0203] Step B (FIG. 12):

[0204] A 500-nm-thick silicon nitride film is formed by introducing an ammonia gas, a silane gas, and a nitrogen gas into the plasma CVD apparatus. After execution of a photolithography process, a protective film PSV1 is formed by selectively etching the silicon nitride film by using  $SF_6$  as a dry etching gas.

[0205] FIG. 13 shows a notebook-sized personal computer that is an example of an information apparatus in which a liquid crystal display device of the invention is incorporated.

[0206] In this personal computer, a keyboard section incorporating a host having a CPU and a display section incorporating a liquid crystal display device are joined to each other by means of a hinge. Display data generated by the host of the keyboard section are sent from a driver circuit board PCB3 that is mounted with TCON for performing CRT/TFT signal conversion and generating various timing signals to driver circuit boards PCB1 and PCB2 that is mounted with a pixel driver chip. As a result, an image is generated on a liquid crystal panel PNL.

[0207] It goes without saying that the liquid crystal display device of the invention can be used not only in the above type of notebook-sized personal computer but also other types of personal computers such as a desk-top type one and as other types of monitors.

[0208] 2. The Electrode Structure in the Pixel

[0209] The inventors considered a liquid crystal display device as disclosed in FIG. 15 of PCT gazette WO95/25291 corresponded to U.S. Pat. No. 5,786,876 and proposed a liquid crystal display device of IPS type having a pixel portion as shown in FIG. 14(A) in order to improve the above-mentioned storage capacitor portion Ctsg. FIG. 14(A) shows the layout of electrode formed on the substrate SUB corresponding to SUB1 in FIG. 2.

[0210] In contrast to the layout shown in FIG. 1, the proposed structure in FIG. 14(A) has a storage capacitance formed of the overlapping of the pixel electrode PX and a counter voltage signal line CL via insulating film (not shown) in the pixel region. The pixel region is defined by an opening of the black matrix which is a region within a thick-lined frame denoted as BM in FIG. 14(A). The structure is further characterized in that a cross-shaped pixel electrode has its branches extending from the crossing so as to overlap the counter voltage signal line. The pixel electrode PX and the counter electrode CT form an electric field with a component substantially parallel to the substrate on which the circuit shown in FIG. 14(A) is formed. The potential of the pixel electrode PX depends on an output of a switching device (transistor TFT, in FIG. 14(A)) controlled by a scanning signal provided by scanning signal line (gate signal line) GL. The potential of the counter electrode CT is determined by a counter voltage signal line CL electrically connected to each counter electrode of the pixels arranged along the scanning signal line GL.

[0211] The cross-shaped pixel electrode in FIG. 14A enlarges an area where the pixel electrode PX overlaps with the counter voltage signal line CT to attain higher capacitance for maintaining an electric field applied on a pixel region which determines the orientation of the liquid crystal molecules. Thus, the pixel having the electrodes with a layout of FIG. 14(A) can maintain its optical transmittance stable. Furthermore, as each of the pixel electrodes branches ends in the pixel region (not extending outside of the pixel region), electrical charges can go into or out from the pixel electrode PX over the counter voltage signal line CT easily and rapidly when the switching device TFT passes the charges therethrough. Therefore, the pixel can also respond to the scanning signal quickly.

[0212] In spite of these advantages by the structure of FIG. 14(A), unexpected failures are found in controlling the orientations of the liquid crystal molecules by applying the field. The inventors recognized that a probability of this failure depends on an intersecting angle defined between an extending direction of the branch of the pixel electrode PX and a rubbing direction described later.

[0213] As shown in FIG. 14(A) for illustration purposes and which is not drawn to scale, a rubbing treatment is a process to rub a rubbing roller ROL having fiber around its circumference against an uppermost surface of a substrate, which will face to a liquid crystal layer later. The uppermost surface to be treated is usually formed of an alignment film (also called, an orientation film). In this process, as the rubbing roller moves along the direction shown by an arrow DIR, piles of the fiber around the rubbing roller make dents extending in a predetermined direction shown as fine stripes on the uppermost surface.

[0214] Precisely speaking, the rubbing roller is considered to align the polymers forming the alignment film, and their alignments depend not only on the direction DIR but on the rotating direction of the rubbing roller as well. However, fine undulations (corrugations) as shown in FIG. 14(B) (enlarged portion d of FIG. 14(A)) can be observed on the uppermost surface by an atomic force microscope (AFM) after the rubbing treatment. Thus, the extending direction of the dents in the following description represent the alignment direction of the polymers, also. On the other hand, the rubbing direction DIR in the following descriptions may deviate from the direction to which the rubbing roller goes on

[0215] In a condition when an electric field is not applied to the liquid crystal layer or is so faint as to drive liquid crystal molecules therein for displaying purpose (called a non-field condition, expediently), liquid crystal molecules are oriented along extending directions of the dents (the alignment direction of the polymers, mentioned above). Therefore, a result of the rubbing treatment can be evaluated by orientating directions of liquid crystal molecules in the non-field condition or their variations according to applied fields. The above-mentioned orientating directions of liquid crystal molecules in the non-field condition are also called as "Initial orientating (alignment) direction".

[0216] The failures in controlling orientations of liquid crystal molecules mentioned before (called "alignment defects", hereinafter) occur in circled portions "a" and "b" of FIG. 14A where the rubbing roller rolls over the pixel electrode PX or its branches overlapping the counter voltage signal line CL as a result of a step or elevation thereat. The inventor also proposed another structure as shown in FIG. 15 forming branches of the counter voltage signal line CL extending up and down from its crossing with the pixel electrode PX instead of the branches of the pixel electrode PX as FIG. 14(A). Upper and lower ends of branches of the counter voltage signal line CL are shown by dotted lines in FIG. 15. An elevation or step as a result of an overlap of the counter voltage signal line CL and the pixel electrode PX extending from the main surface of the substrate SUB appears at circled portions c in FIG. 15 instead of circled portions b in FIG. 14(A). In this structure of FIG. 15, the alignment defects can be avoided at circled portions a and c looking like circled portions a and b in FIG. 14(A).

[0217] According to these results, the alignment defects are considered to be caused by a difference of elevation on a rubbing direction onto a surface of the substrate and an angle defined by an extending direction of the elevation and the rubbing direction.