US 20060125764A1

(19) **United States**

(12) **Patent Application Publication**

Furuhashi et al.

(10) Pub. No.: US 2006/0125764 A1

(43) Pub. Date: Jun. 15, 2006

(54) LIQUID CRYSTAL DISPLAY DRIVING METHOD/DRIVING CIRCUIT CAPABLE OF BEING DRIVEN WITH EQUAL VOLTAGES

(76) Inventors: **Tsutomu Furuhashi**, Yokohami-shi (JP); **Makiko Ikeda**, Yokohama-shi (JP); **Naruhiro Kasai**, Fujisawa-shi (JP); **Toshio Futami**, Mobara-shi (JP); **Tetsuya Suzuki**, Fujisawa-shi (JP)

continuation of application No. 08/948,032, filed on Oct. 9, 1997, now Pat. No. 6,127,995, which is a continuation of application No. 08/135,357, filed on Oct. 13, 1993, now Pat. No. 5,731,796.

(30) **Foreign Application Priority Data**

Oct. 15, 1992 (JP) ..... 04-276976

## Publication Classification

Correspondence Address:

**ANTONELLI, TERRY, STOUT & KRAUS,

LLP**

**1300 NORTH SEVENTEENTH STREET

SUITE 1800

ARLINGTON, VA 22209-3873 (US)**

(21) Appl. No.: 11/348,401

(22) Filed: **Feb. 7, 2006**

#### Related U.S. Application Data

(63) Continuation of application No. 10/139,266, filed on May 7, 2002, now Pat. No. 7,038,649, which is a continuation of application No. 09/669,446, filed on Sep. 25, 2000, now Pat. No. 6,384,807, which is a

(51) **Int. Cl.**

**G09G 3/36** (2006.01)

(52) U.S. Cl. .... 345/98

## ABSTRACT

A display apparatus comprising a plurality of pixel portions arranged in a matrix, a signal driver circuit which generates apply voltages corresponding to display data, and applies the apply voltages to the pixel portions, a scan driver circuit which applies a selecting voltage to selected ones of the pixel portions, and a level shifter circuit which converts a voltage level of the display data into a drive voltage level of the signal driver circuit, thereby producing level-shifted display data. The signal driver circuit generates the apply voltages based on the level-shifted display data.

FIG. 1

## F I G. 2

## F I G. 3

F I G. 4

## F I G. 5

F I G. 6

F I G. 7

F I G. 9

## F I G. 8

## F I G. 10

F I G. 11

F I G. 12

## F I G. 13

14

F - G. 15

F I G. 16

FIG. 17A

FIG. 17B

18 - G - F

FIG. 9

F I G. 20

F I G. 21

F 1 G. 22

F I G. 23

24

FIG. 25

F I G. 26

F I G. 27

28 - G.

FIG. 29

FIG. 30A

FIG. 30B

F I G. 31

F I G. 32

FIG. 33

F I G. 34

F I G. 35

F I G. 36

FIG. 37

F I G. 38

FIG. 39

F I G. 40A

F I G. 40B

F - G. 40C

FIG. 4IB

FIG. 4IA

F I G. 42A

F I G. 42B

F I G. 43A

F I G. 43B

F I G. 44

FIG. 45

F I G. 46

F I G. 47

F I G. 48

## LIQUID CRYSTAL DISPLAY DRIVING METHOD/DRIVING CIRCUIT CAPABLE OF BEING DRIVEN WITH EQUAL VOLTAGES

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This appln. is a cont. of application Ser. No. 10/139,266, filed May 7, 2002, which is a cont. of application Ser. No. 09/669,446, filed on Sep. 25, 2000 (now U.S. Pat. No. 6,384,807), which is a cont. of application Ser. No. 08/948,032 filed on Oct. 9, 1997 (now U.S. Pat. No. 6,127,995), which is a cont. of application Ser. No. 08/135,357, filed on Oct. 13, 1993 (now U.S. Pat. No. 5,731,796). The entire contents of which are incorporated herein by reference in their entirety.

### BACKGROUND OF THE INVENTION

[0002] The present invention generally relates to a driving method and a driving circuit of a liquid crystal display employed in an information processing apparatus such as a personal computer. More specifically, the present invention is directed to LCD (liquid crystal display) driving method/circuit capable of applying equal drive voltages to pixel elements on a horizontal line.

[0003] Conventionally, various LCD structures and LCD driving methods/circuits have been proposed. For instance, as to the structure/driving method of the TFT (thin-film transistor) liquid crystal panel, Flat Panel Display 1991 "Multi-Color Technique for TFT Color Liquid Crystal Display, from 4096 colors to 260 thousands or 15 more colors" published by Nikkei BP publisher, Nov. 26, 1990, pages 173 to 180 describes the LCD driving method with employment of the high withstanding voltage drain driver. Also, JP-A-57-49995 (1982) describes the method for converting common electrode voltages into AC voltages with employment of the low withstanding voltage drain driver. A high withstanding voltage drain driver implies a drain driver with such a withstanding voltage capable of producing voltages to obtain maximum luminance and minimum luminance having a positive polarity and a negative polarity with regard to one electrode voltage of a liquid crystal display. A low withstanding voltage drain driver implies a drain driver with one withstanding voltage capable of obtaining maximum luminance and minimum luminance having either a positive polarity or a negative polarity (namely, "a single polarity"), and also with the other withstanding voltage not capable of obtaining maximum luminance and minimum luminance having both positive/negative polarities.

[0004] The above-explained two typical conventional driving methods will now be described more in detail.

[0005] First, the LCD driving method with employment of the high withstanding voltage drain driver will now be explained with reference to FIG. 5 and FIGS. 24 to 27.

[0006] FIG. 24 schematically represents a system structural diagram of the conventional liquid crystal display apparatus with employment of the high withstanding voltage drain driver.

[0007] In FIG. 24, reference numeral 101 is a system bus for transferring digital display data and a synchronization (sync) signal. In this example, it should be noted that both the display data and the sync signal transferred in the system

bus 101 are such line sequential scanning signals similar to the display data and the sync signal transferred to be displayed on the CRT (cathode-ray tube) display apparatus. Reference numeral 102 denotes a liquid crystal controller for converting the digital display data and the sync signal transferred by the system bus 101 into digital LCD data and a timing signal for driving the liquid crystal display apparatus. Reference numerals 103, 104, 105 represent reference voltages in which 103 is a digital-low drive voltage  $V_{EE}$ , 104 is a digital-high drive voltage  $V_{CC}$ , and 105 is DC voltages having various LCD drive voltages. Reference numerals 106 and 107 denote signal drive circuit control buses for transferring both of the digital LCD data and the timing signal which have been converted for the signal drive circuit under control of the LCD controller 102. Reference numeral 108 is a scanning drive circuit control bus used to transfer a timing signal for a scanning drive circuit. Reference numeral 109 shows an LCD alternating signal which becomes a timing signal for alternating a polarity of a voltage applied to a liquid crystal display. Reference numerals 2401 and 2402 represent signal drive circuits for acquiring the digital LCD display data transferred via the respective signal drive circuit control buses in response to the timing signal and for converting the display data into LCD voltages corresponding to the LCD display data. Reference numerals 116 and 117 show signal lines for transferring the LCD apply voltages  $V_{DC}$ ,  $VDL$  produced in the respective signal drive circuits 2401 and 2402. Reference numeral 118 is a scanning drive circuit and reference numeral 119 is a scanning line. The scanning drive circuit 118 sequentially causes the scanning line 119 to be active in response to the timing signal transferred via the scanning drive circuit control bus 108. Reference numeral 120 is a liquid crystal display panel. Reference numeral 2403 is a reference DC voltage producing circuit for producing various DC reference voltages used to operate this LCD apparatus. Reference numeral 122 shows a DC voltage line used to the scanning drive circuit, for applying a DC voltage to the scanning drive circuit 118. Reference numeral 123 denotes a common (opposing) electrode line for transferring a DC common voltage  $V_{COM}$ . Reference numeral 2402 denotes a reference voltage line for transferring a high-level reference voltage  $V_{CC}$  for driving signal drive circuits 2401 and 2402, reference numeral 2405 is similarly a reference voltage line for transferring a low-level reference voltage  $V_{EE}$ , and reference numeral 2406 denotes a reference voltage line of a LCD drive unit, for transferring a LCD drive voltage  $V_{CCD}$  used to drive the LCD drive circuit unit among the signal drive circuits 2401 and 2402. Any of the reference voltages transferred via the reference voltage lines 2404, 2405, 2406 are DC voltages. Reference numeral 125 shows a DC LCD apply voltage for the signal drive circuit. Reference numeral 131 denotes an AC circuit. Reference numeral 132 is an LCD drive voltage line used to transfer the AC LCD drive voltage employed in the upper-sided signal drive circuit 2401, whereas reference numeral 133 is an LCO drive voltage line used to transfer the AC LCD drive voltage employed in the lower-sided signal drive circuit 2402.

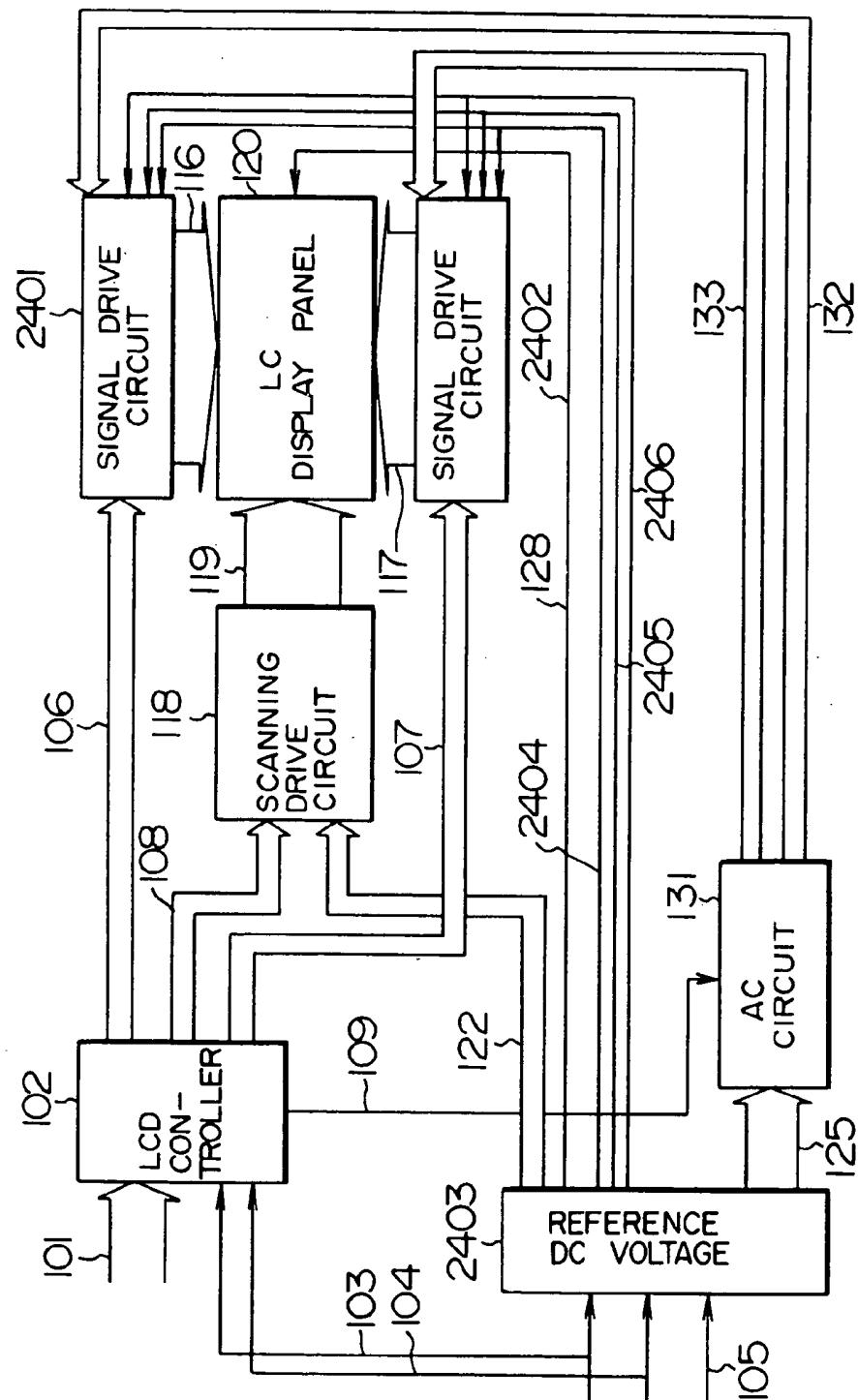

[0008] FIG. 25 is a schematic block diagram for showing an example of the signal drive circuit 2401 of FIG. 24. It should be noted that the signal drive circuit 2402 for the lower side of the LCD panel 120 has a similar arrangement to that of this signal drive circuit 2401.

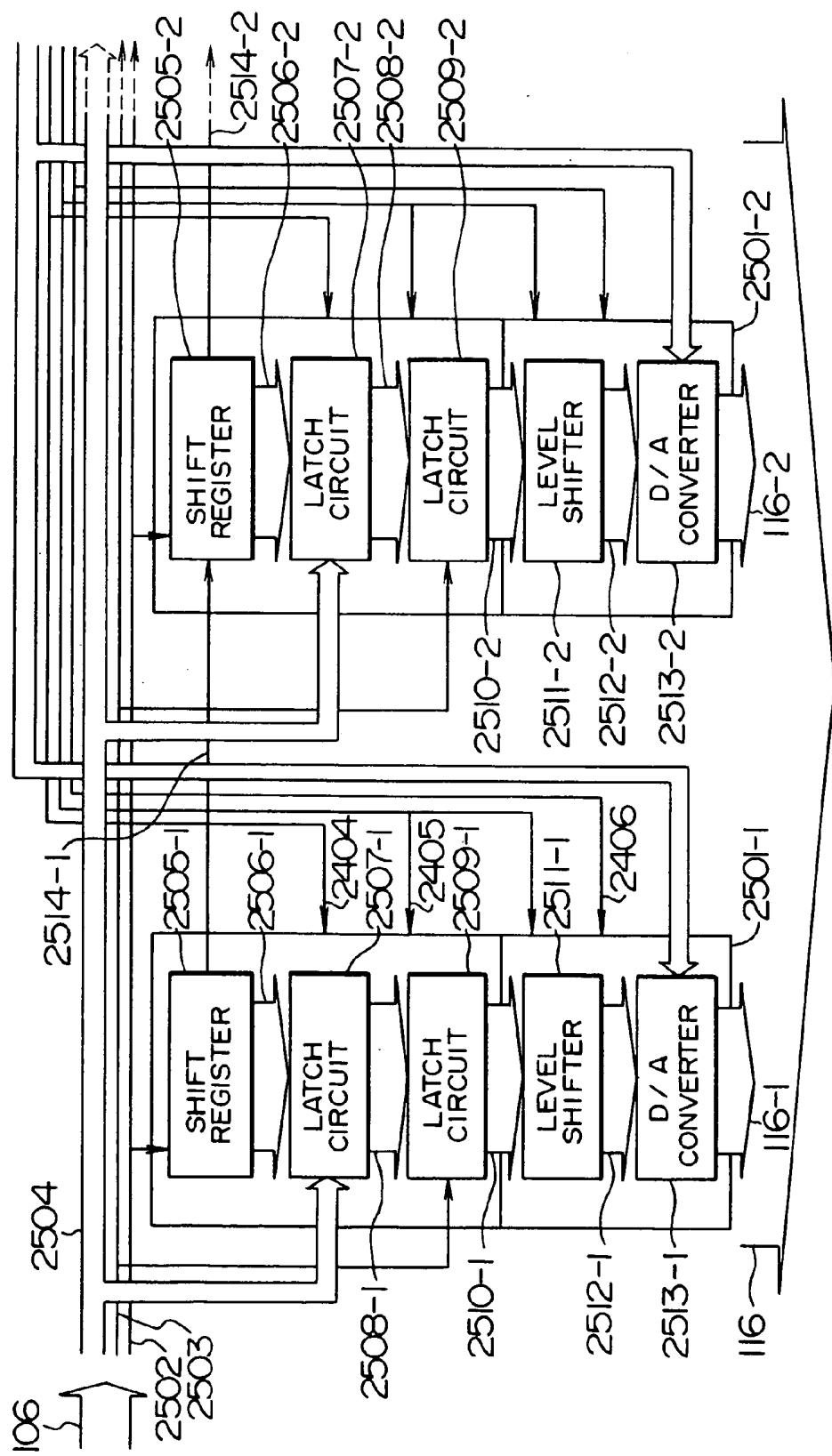

[0009] In FIG. 25, reference numerals 2501-1, 2501-2, - - denotes drain drivers, and the signal drive circuit 2401 is arranged by a plurality of drain drivers 2501. The drain driver 2501 is so arranged that the digital LCD display data is inputted and converted into a LCD apply voltage which will then be outputted. Among the signal drive circuit control bus 106, reference numeral 2502 is a shift clock, reference numeral 2503 is a latch clock, and reference numeral 2504 is an LCD display data bus. The shift clock 2502 is synchronized with the digital LCD display data transferred via the LCD display data bus 2504, whereas the latch clock 2503 becomes active after the digital LCD display data for 1 line has been transferred to the signal drive circuits 2401 and 2402. Reference numeral 2505 is a shift register and reference numeral 2506 is a latch signal. The shift register 2505 accepts the shift clock 2502 to perform the shift operation. The latch signal 2506 sequentially becomes active in response to this latch operation. Reference numeral 2507 shows a latch circuit for successively latches the digital LCD display data transferred via the LCD display data bus 2504. Reference numeral 2508 denotes a data bus for transferring data latched by a latch circuit 2507. Reference numeral 2509 represents a latch circuit for latching data transferred via the data bus 2508. Reference numeral 2510 is a data bus for transferring the data latched by the latch circuit 2509. Reference numeral 2511 is a level sifter for converting a voltage amplitude level of digital data transferred via the data bus 2510. Reference numeral 2513 is a digital-to-analog converting circuit for converting the digital data via the data bus 2512 into a liquid crystal apply voltage based on the AC voltage transferred via the AC LCD drive voltage line 132. Reference numeral 116 is a signal line for transferring the LCD apply voltage produced by the digital-to-analog converting circuit 2513. Reference numeral 2514 shows an enable signal corresponding to such a control signal that causes the shift register 2505 of the drain driver 2501 provided at the post stage when the latch circuit 2507 has latched the digital LCD display data, namely when the shift operation of the shift register 2505 has been accomplished, and that commences the acquisition operation of the digital LCD display data by the latch circuit 2507 of the drain driver 2501 provided at the post stage. In the drain driver 2501, the shift register 2505, the latch circuit 2507, and the digital 2509 are driven by the high-level reference voltage transferred via the reference voltage line 2404 and the low-level reference voltage transferred via the reference voltage line 2405. The level sifter 2511 and the analog circuit unit of the digital-to-analog converting circuit 2513 are driven by the LCD drive voltage transferred via the reference voltage line 2406.

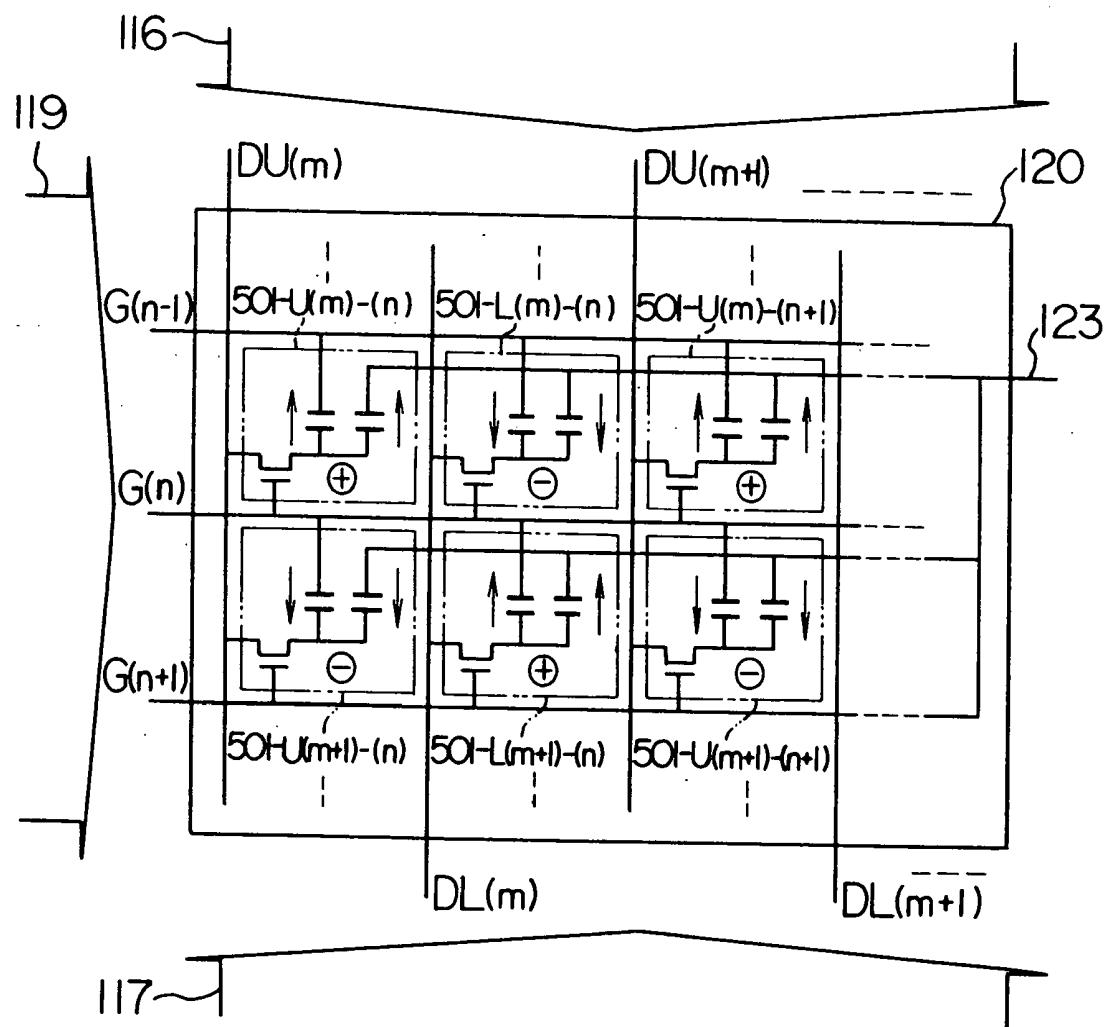

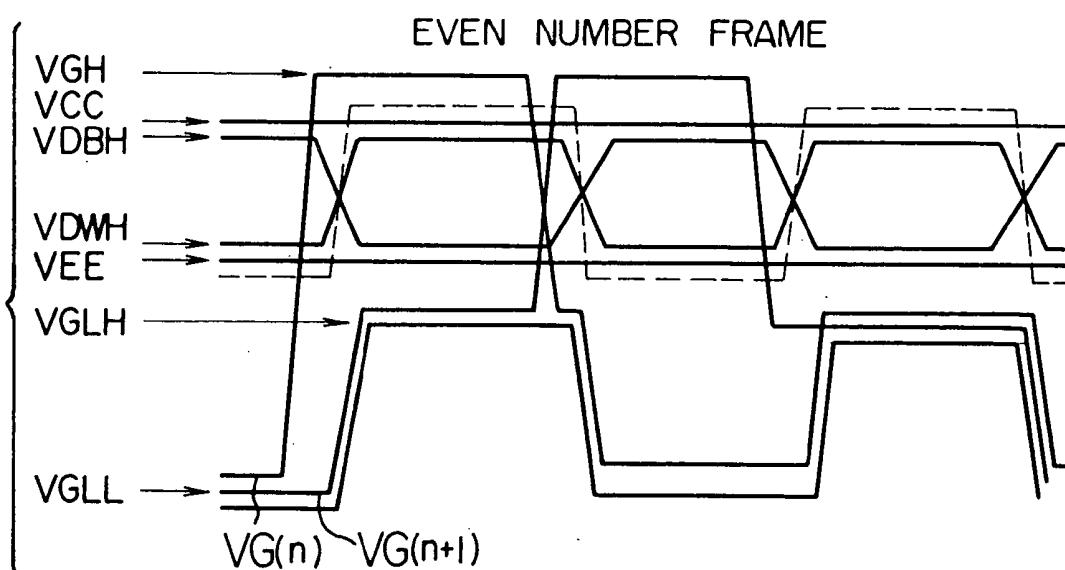

[0010] FIG. 5 is an equivalent circuit diagram of a liquid crystal display panel 120 shown in FIG. 1.

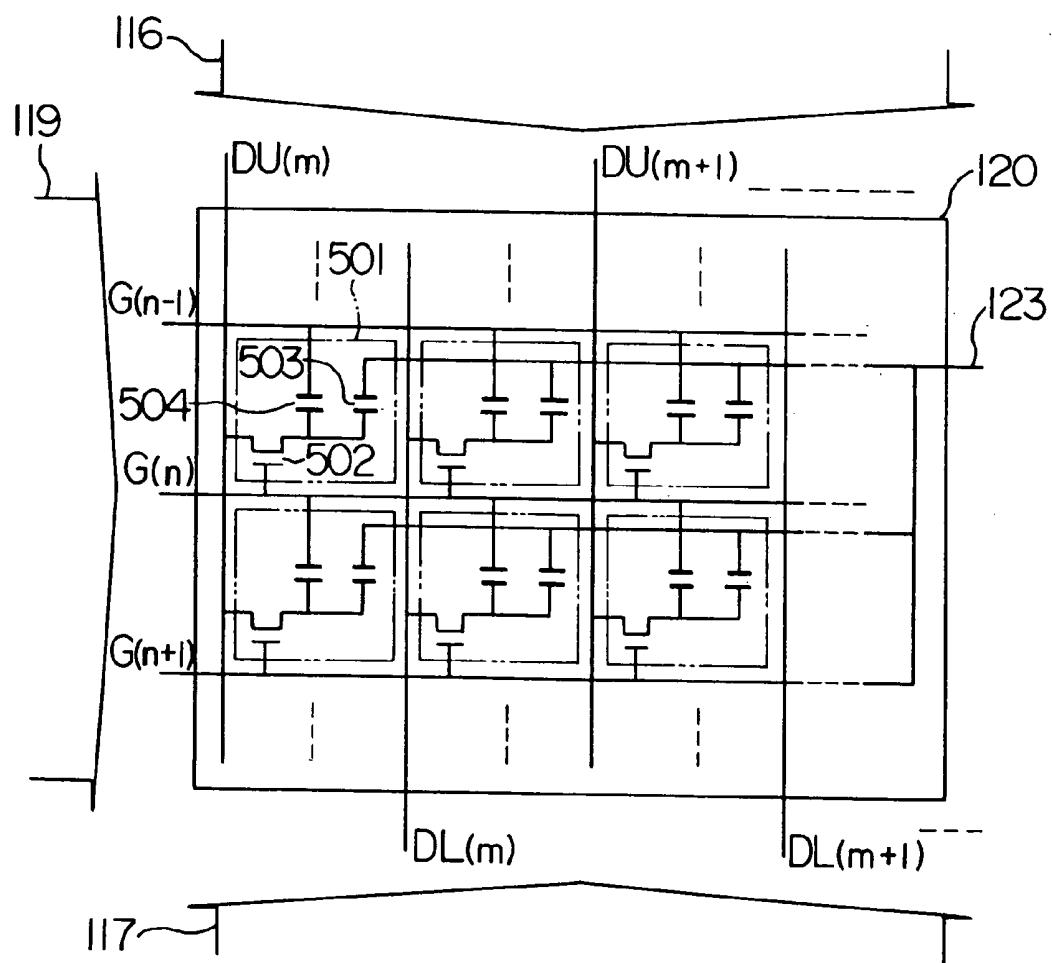

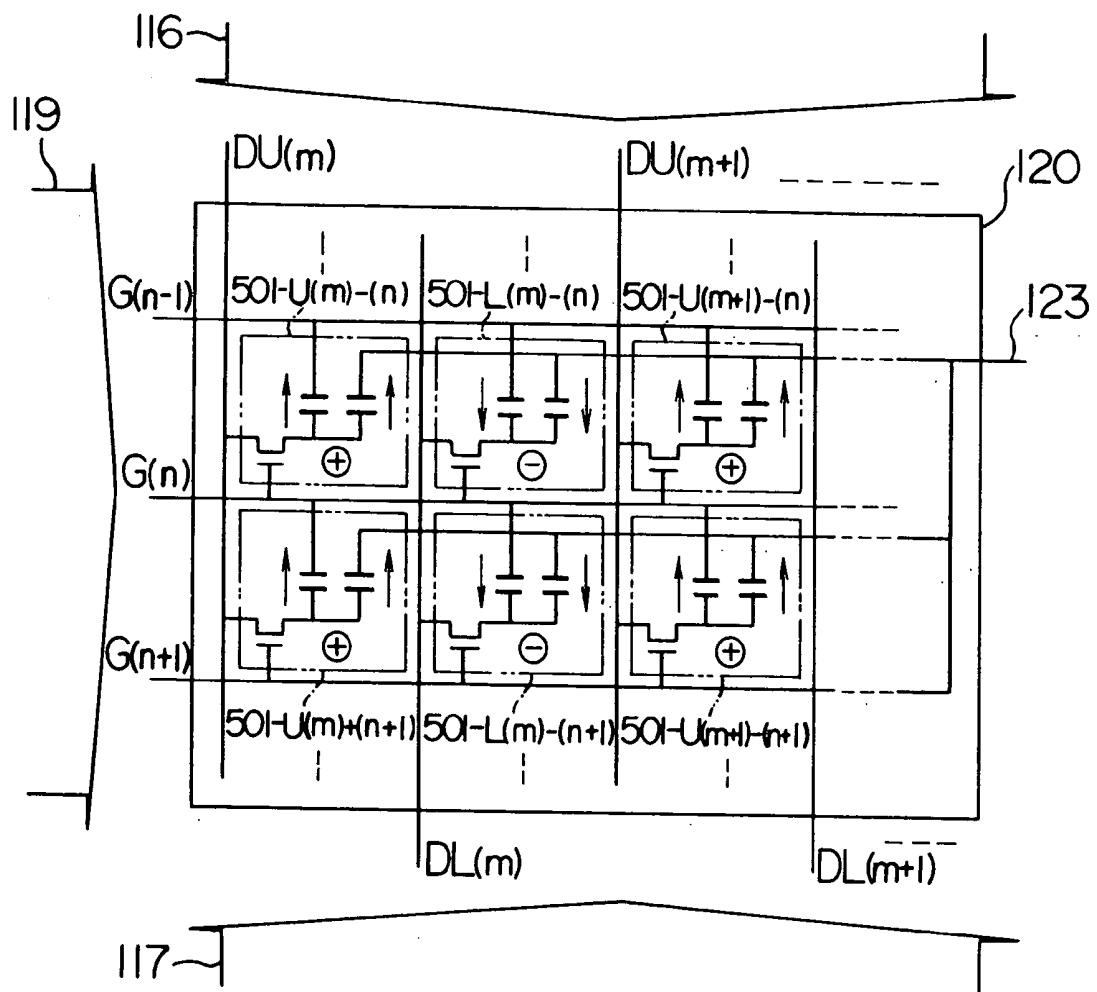

[0011] In FIG. 5, symbols DU(m), DU(m+1), DL(m) and DL(m+1) represent signal lines corresponding to pixel units for constituting signal lines 116 and 117. Symbols G(n-1), G(n), G(n+1) denote scanning lines corresponding to the respective pixel units for constituting a scanning line 119. Reference 501 shows a pixel unit. In the pixel unit 501, reference numeral 502 is a thin-film transistor (abbreviated as "TFT"), reference numeral 503 is a liquid crystal display, and reference numeral 504 is an added capacitance. A drain electrode of the TFT 502 is connected to the signal line 116, and a gate electrode thereof is connected to the scanning line 119. The drain electrodes of the TFTs 502 employed within

the respective pixel units 501 arranged along the vertical direction commonly use the signal line, for instance, DU(m). The gate electrodes of the TFTs 502 employed in the respective pixel units 502 arranged along the horizontal direction commonly use the scanning line, for example, G(n). Furthermore, the source electrodes of the TFTs 502 are connected to one electrode of each of the liquid crystal display 503 and the added capacitance 504. The other electrode of the liquid crystal display 503 is connected to a common electrode line 123, and all pixels thereof commonly utilize the common electrode line 123. One electrode of the added capacitance 504 is connected to the scanning line provided at the pre stage. For example, in case of the added capacitance 504 connected to the TFT 502 under control of the scanning line G(n), the electrode is connected to the scanning line G(n-1).

[0012] As described above, this LCD panel 120 is constructed of a matrix structure having a plurality of pixel units 501 along the horizontal direction and the vertical direction. For instance, when a screen with 640 pixels in horizontal resolution and 480 lines in vertical resolution is displayed, the horizontal resolution of 640 pixels can be realized by arranging 1920 pixels along the horizontal direction, and attaching red, green, blue color filters to three adjacent pixels to constitute 1 pixel. Furthermore, the 480 pixel arrangements as explained with regard to the horizontal direction are prepared for the vertical direction, thereby obtaining the vertical resolution of 480 lines.

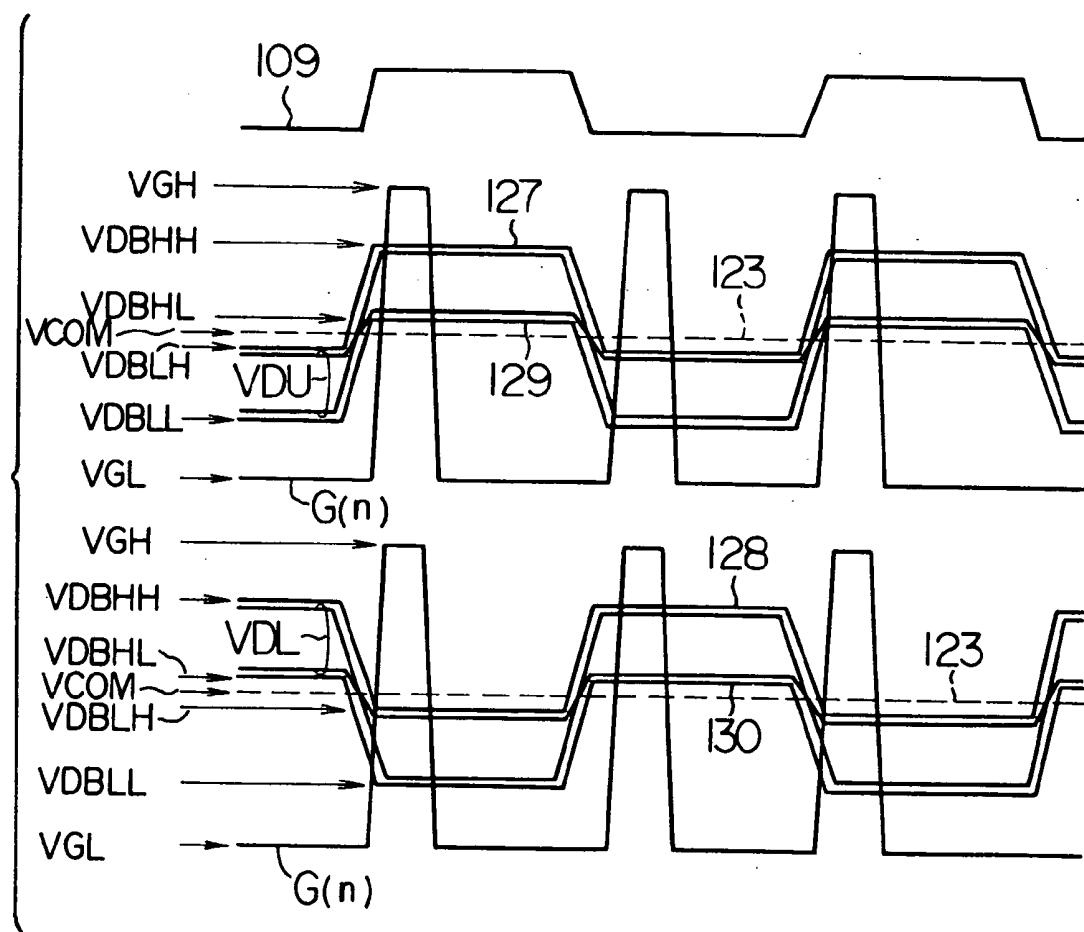

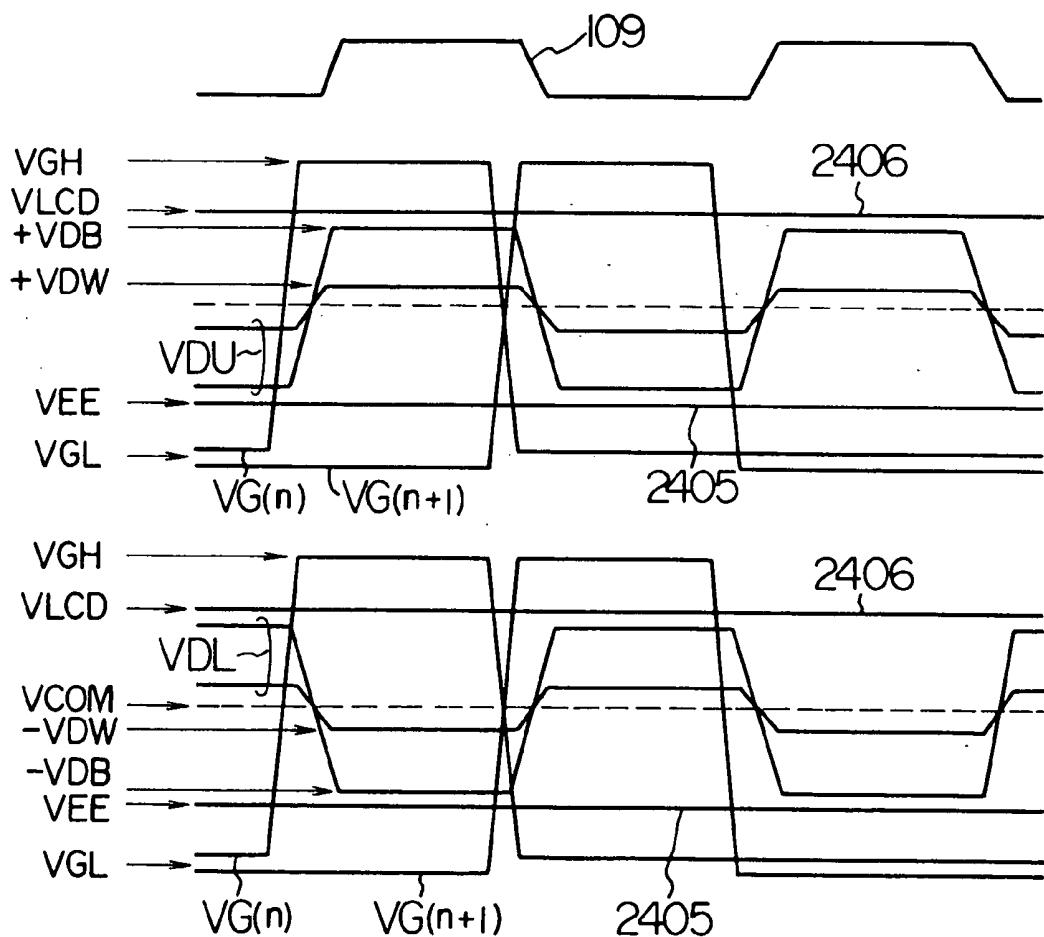

[0013] FIG. 26 represents voltage waveforms appearing when the conventional LCD display apparatus of FIG. 24 is driven. It should be noted that the voltage waveforms represent a line AC drive for alternately changing the polarity of voltage applied to the LCD for every line.

[0014] In FIG. 26, symbol VG(n) shows a voltage waveform of the scanning line G(n) shown in FIG. 5, and symbol VG(n+1) represents a voltage waveform of the scanning line G(n+1). Symbol VGH denotes a selective voltage level and VGL represents a non-selective voltage level. Symbol VCOM is a voltage value of a common electrode 123. A voltage level of the reference voltage line 2406 is VLCD, whereas a voltage level of the reference voltage line 2405 is VEE. Symbols VDU and VDL show drive waveforms of LCD apply voltages outputted from the respective signal lines 116 and 117 in this prior art.

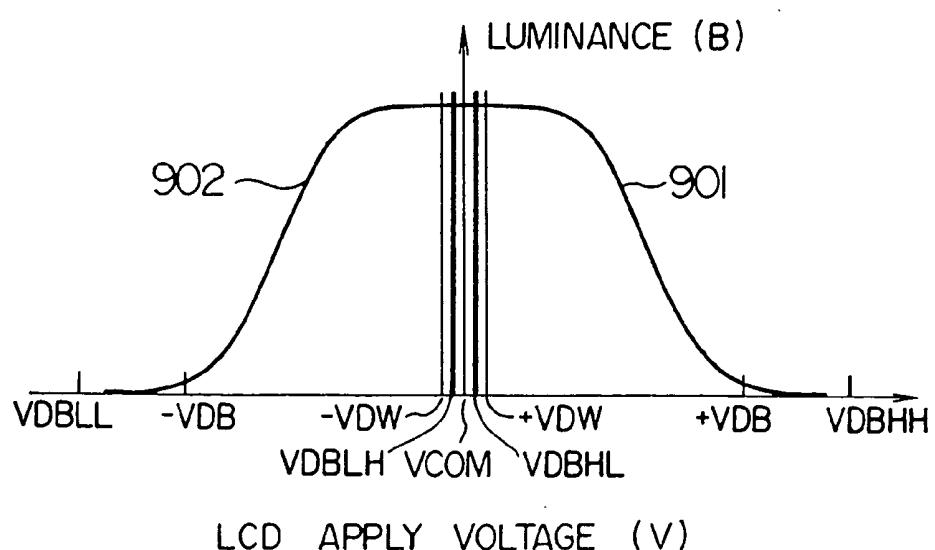

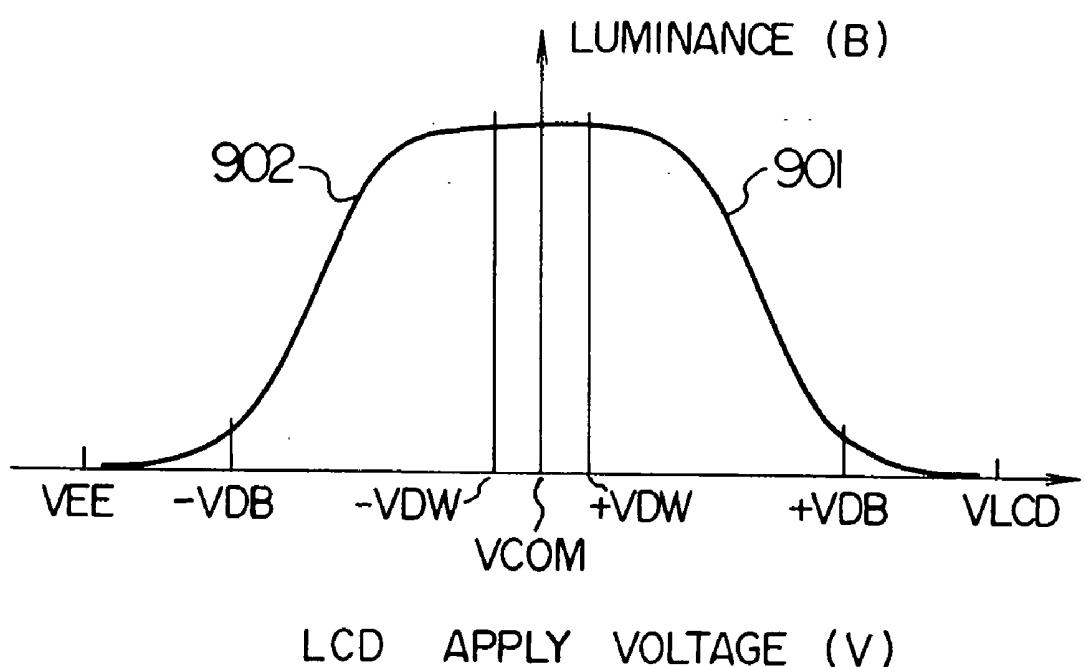

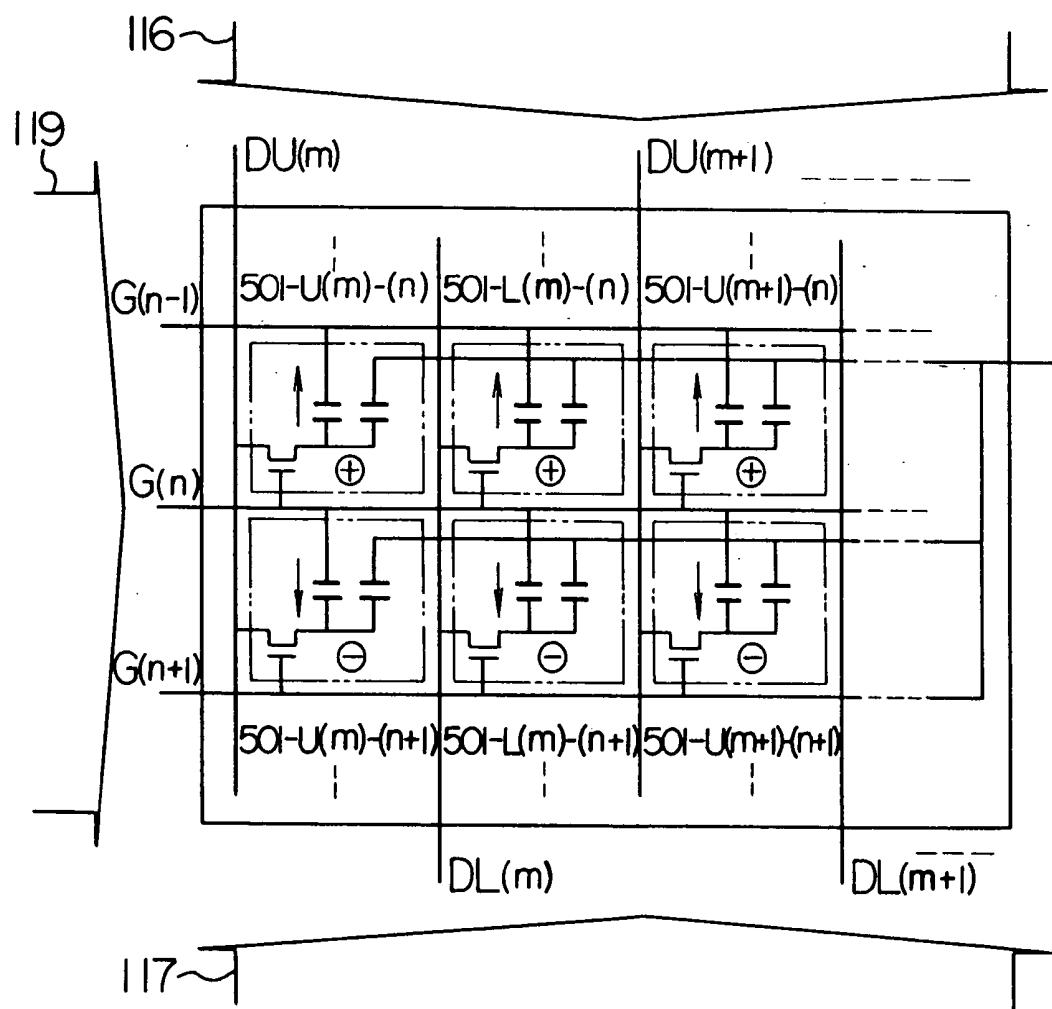

[0015] FIG. 27 is a graphic representation of a relationship between luminance and a voltage of the liquid crystal display employed in this prior art.

[0016] In FIG. 27, an ordinate indicates luminance and an abscissa shows an LCD apply voltage reference numeral 901 shows a luminance-voltage characteristic when a positive LCD voltage is applied, and reference numeral 902 shows a voltage-luminance characteristic when a negative LCD voltage is applied. As apparent from this drawing, the liquid crystal display owns such a characteristic that even when any of voltages having a positive polarity and a negative polarity with respect to the common electrode voltage VCOM are applied, if absolute values of these voltages are equal to each other, then similar luminance representations are realized. In this prior art, when the value of the LCD apply voltage is small, namely when the LCD apply voltage is approximated to the voltage value of the opposite electrode 123 (for instance, voltage +VDW and voltage -VDW),

there is such a characteristic that luminance is high, and this luminance may be lowered every time any of the positive apply voltage and the negative apply voltage are increased. It should be noted that the voltage VEE corresponds to the low-level reference voltage of the drain driver 2501 shown in **FIG. 25** and the voltage VLCD corresponds to the reference voltage of the LCD drive unit.

[0017] Again with reference to **FIGS. 5 and 24** to **27**, operation of the conventional LCD apparatus will now be described.

[0018] In **FIG. 24**, the digital LCD data transferred via the system bus 101 is converted through the LCD controller 102 and the signal drive circuits 2401, 2402 into the LCD apply voltage. The LCD apply voltage is outputted to the LCD panel 120 for display purposes. In the LCD controller 102, the digital display data inputted via the system bus 101 is converted into the sync signal in order to be fitted to the input interfaces of the signal drive circuits 2401 and 2402 and the pixel arrangement of the LCD panel 120, and then the sync signal is outputted via the signal drive circuit control buses 106 and 107. Both of the digital LCD display data and the timing signal supplied via the signal drive circuit control buses 106 and 107 are entered into the signal drive circuits 114 and 115 so as to be converted into the LCD apply voltages. The above-described operations will now be explained with reference to **FIG. 25**.

[0019] In **FIG. 25**, in response to the shift clock 2502, the shift register 2505-1 starts its operation and sequentially enables the latch signal 2506-1 in the drain driver 2501-1. The storage circuit in the latch circuit 2507-1, corresponding to the enable latch signal 2506-1, sequentially latches the digital LCD display data transferred via the display data bus 2504. The latches data are outputted to the data bus 2508-1. When the data acquisition operation by the storage circuit within the latch circuit 2507-1 is accomplished, namely when the shift operation of the shift register 2505-1 is completed, the shift register 2505-1 brings the enable signal 2514-1 into an active (enable) condition. When the enable signal 2514-1 become active, the shift operation of the shift register 2505-2 employed in the drain driver 2501-2 provided at the subsequent stage is commenced. Then, the latch circuit 2507-2 sequentially latches the data which have been latched by the latch circuit 2507-1 in the drain driver 2501-1. Furthermore, upon completion of the data acquisition operation by the storage circuit in the latch circuit 2507-2, the enable signal 2514-2 becomes active, and the drain driver 2501 at the next stage performs a similar operation to that of the drain driver 2501-1. Since the above operation are carried out by the respective drain drivers 2501 employed in the signal drive circuits 2401 and 2402, the LCD display data used for 1 horizontal line can be acquired.

[0020] After the LCD display data for 1 horizontal line have been acquired by the latch circuit 2507 in the respective drain drivers 2501, the latch clock 2503 becomes enabled, the data which are transferred via the data bus 2508 of the respective drain drivers 2501 and are stored in the latch circuit 2508, are latched for 1 horizontal line by the latch circuit 2509 at the same time. After the data have been stored by the latch circuit 2509, the shift register 2505 and the latch circuit 2507 of the respective drain drivers 2501 commence operations similar to the above-described operations in order to fetch the data for the subsequent line. It should be noted

that the drive voltage of the drain driver 2501 described in this prior art is different from the drive voltages for the shift register 2505, the latch circuit 2507, the digital circuit unit of the latch circuit 2509, and the digital-to-analog converting circuit 2513. The digital circuit unit is operated by the low-level reference voltage transferred via the reference voltage line 2405 and the high-level reference voltage transferred via the reference voltage line 2404. However, the digital-to-analog converting circuit 2513 is operated by the LCD drive voltage transferred via the reference voltage line 2406. Necessity of the LCD drive voltage transferred via the reference voltage line 2408 in the digital-to-analog converting circuit 2513 will now be explained with reference to **FIG. 26** and **FIG. 27**.

[0021] In the voltage-luminance characteristic diagram shown in **FIG. 27**, the liquid crystal display owns similar luminance displays to each other even when a positive-polarity voltage and a negative-polarity voltage are applied thereto with respect to the common electrode voltage VCOM, if absolute values thereof are equal to each other.

[0022] Furthermore, there is a problem that when a DC voltage is applied to the liquid crystal display, deterioration thereof may occur. Therefore, the DC voltage applied to the liquid crystal display must be alternately changed in a certain period. In addition, to display a structure of 1 frame, image deterioration caused by a flicker phenomenon is prevented by setting that the luminance display of the LCD driven by the DC voltage having the positive polarity is equal to the luminance display of the LCD driven by the DC voltage having the negative polarity. As a consequence, when the voltage having the negative polarity with respect to the common voltage is applied, the voltage of -VDW is applied to the liquid crystal display so as to achieve a high luminance display, whereas the voltage of -VDB is applied to it in order to achieve a low luminance display. Furthermore, when the voltage having the negative polarity with respect to the common voltage, the voltage of +VDW is applied to the liquid crystal display so as to achieve a high luminance display, whereas the voltage of +VDB is applied thereto in order to achieve a low luminance display.

[0023] Thus, since the digital-to-analog converting circuit 2513 of the prior art LCD can be so constructed as to produce the LCD apply voltages having the positive polarity and the negative polarity, the drive voltages thereof have such a relationship  $(VLCD-VEE) < (+VDB - (-VDB))$ . Although it depends upon luminance characteristics of liquid crystal display, since the drive voltage for the digital-to-analog converting circuit 2513 is different from the drive voltage for the digital circuit unit within the drain driver 2501, the level sifter 2511 for perform the voltage conversion is required between the digital circuit unit and the digital-to-analog converting circuit 2513.

[0024] The data stored in the latch circuit 2509 is processed via the data bus 2510 in the level sifter 2511 for the voltage conversion, and then the voltage-converted data is transferred via the data bus 2512 to the digital-to-analog converting circuit 2513. In the digital-to-analog converting circuit 2513, the LCD apply voltage corresponding to the digital data is generated in response to the LCD drive voltage transferred via the LCD drive voltage line 132, and then outputted via the signal line 116. Since the digital-to-analog converting circuit 2513 is driven by the LCD drive

unit reference voltage VLCD, and the low-level reference voltage VEE, the LCD apply voltage transferred via the signal line 116 is present within the operation range of the voltage-luminance characteristic shown in **FIG. 27**, and thus this LCD apply voltage becomes a voltage required to a luminance display.

**[0025]** Moreover, conditions under which a voltage is applied to the liquid crystal display panel 120 of **FIG. 24** will now be explained.

**[0026]** The display data transferred via the system bus 101 is converted into the LCD apply voltages by the signal drive circuits 2401, 2402 and the AC circuit 131 of **FIG. 24** to obtain the LCD apply voltages VDU and VDL represented in **FIG. 26**, which are outputted to the LCD panel 120. At this time, in the scanning drive circuit 118, the shift operation is carried out by the scanning drive circuit control bus 108. The scanning line 119 connected to the horizontal line for applying the LCD apply voltages derived from the signal drive circuits 114 and 115, becomes active.

**[0027]** The voltage VDU shown in the drive waveform chart of **FIG. 26** is applied from the signal drive circuit 2401 to the signal line 116. The voltage VDL shown in the drive waveform chart of **FIG. 26** is applied from the signal drive circuit 2402 to the signal line 117. The scanning line G(n) is operated in such a manner that the selective voltage VGH becomes active during 1 line period, and thereafter the non-selective voltage VGL becomes active during 1 frame period. When the selective voltage VGH of the scanning line G(n) becomes active, the TFT 502 of the pixel unit 501 connected to the scanning line G(n) shown in **FIG. 5** is brought into an ON state, and the voltages appearing on the signal lines 116 and 117 are stored via the TFT 502 into the liquid crystal display 503 and the load capacitance 504.

**[0028]** The drive voltages of the liquid crystal 503 must be converted into AC voltage with a certain time period so as to prevent deterioration. Also, as shown in **FIG. 27**, luminance may be varied, depending on the voltage accumulated in the liquid crystal 503. When the positive potential voltage with regard to the common electrode 123 is applied to the liquid crystal 503, this liquid crystal 503 owns the characteristic of the luminance-voltage curve 901, whereas when the negative potential voltage with respect to the common electrode 123 is applied to the liquid crystal 503, this liquid crystal 503 owns the characteristic of the luminance-voltage curve 902. As a result, since luminance of the liquid crystal can be controlled by the effective value of the applied voltage, irrelevant to the polarity of the applied voltage, the polarities of the apply voltage are alternately changed with respect to the common electrode voltage VCOM for each frame in order to prevent deterioration of the liquid crystal. Based on this alternating apply voltage, the crystal liquid display is performed.

**[0029]** Then, another conventional liquid crystal display apparatus with employment of the low-withstanding voltage drain driver will now be described with reference to FIGS. 28 to 32.

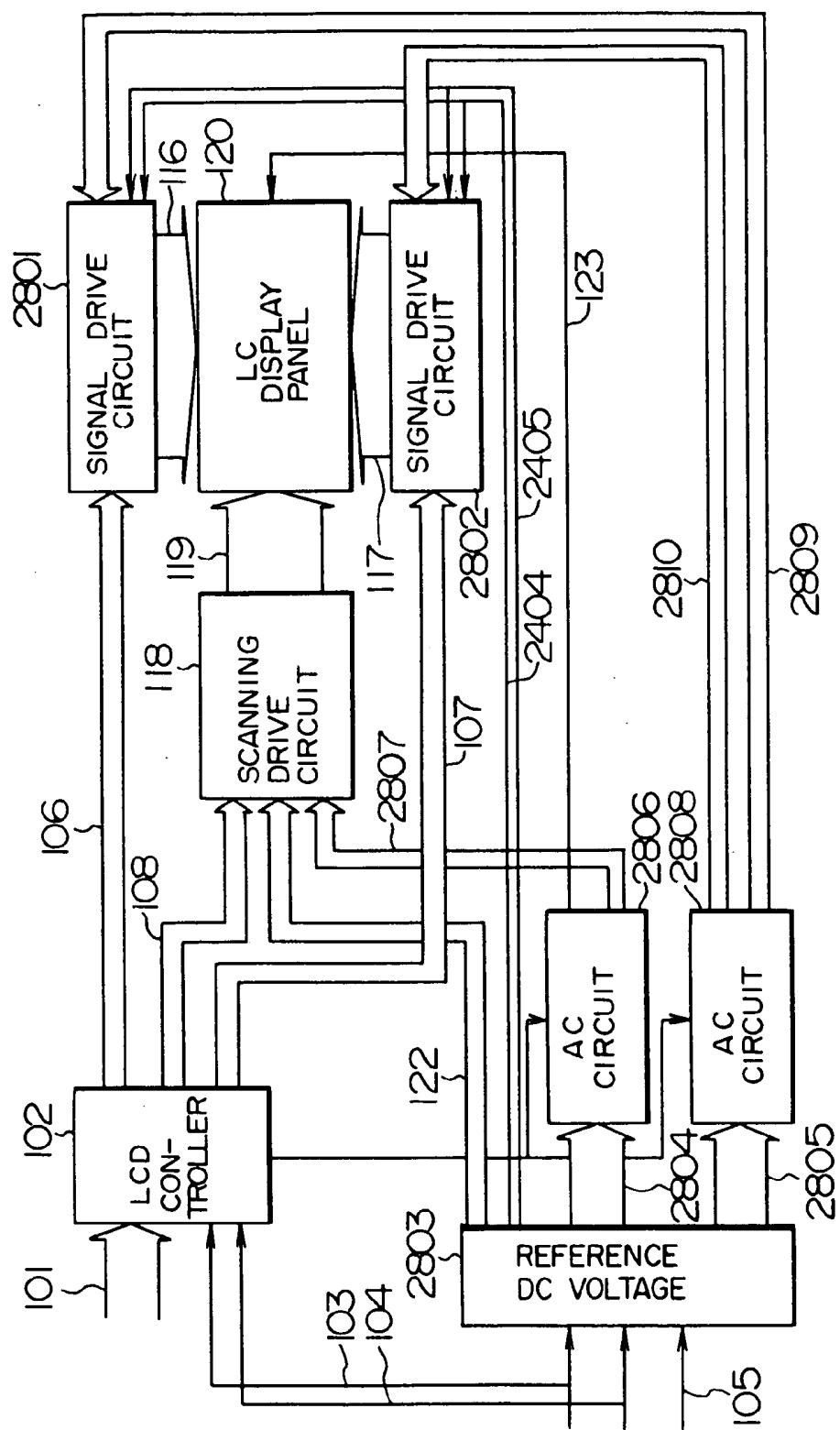

**[0030]** In **FIG. 28**, reference numeral 2801 and 2802 denote signal drive circuits which fetch digital LCD data transferred via the respective signal drive circuit control buses 106 and 107 in response to a timing signal, and converts the fetched data into the LCD apply voltages

corresponding to the LCD display data. Reference numerals 116 and 117 are signal lines used to transfer the LCD apply voltages generated in the respective signal drive circuits 114 and 115. Reference numeral 2803 denotes a reference DC voltage generating circuit for generating various sorts of DC voltages functioning as reference voltages to drive the LCD apparatus. Reference numeral 2804 denotes a DC voltage line. Reference numeral 2805 indicates a signal drive circuit DC voltage line. Reference numeral 2806 denotes an AC circuit. Reference numeral 2807 shows a reference voltage line for transferring an alternating non-selective voltage outputted from the scanning circuit 118. Reference numeral 123 indicates a common electrode line for transferring an alternating common electrode voltage. Further, reference numeral 2808 shows an AC circuit for producing alternating LCD drive voltages to be applied to the signal drive circuit 2801. Reference numeral 2809 denotes an LCD apply voltage line for transferring the alternating LCD apply voltage used in the upper-sided signal drive circuit 2802, and reference numeral 2810 shows an LCD apply voltage line for transferring the alternating LCD apply voltage employed in the lower-sided signal drive circuit 115.

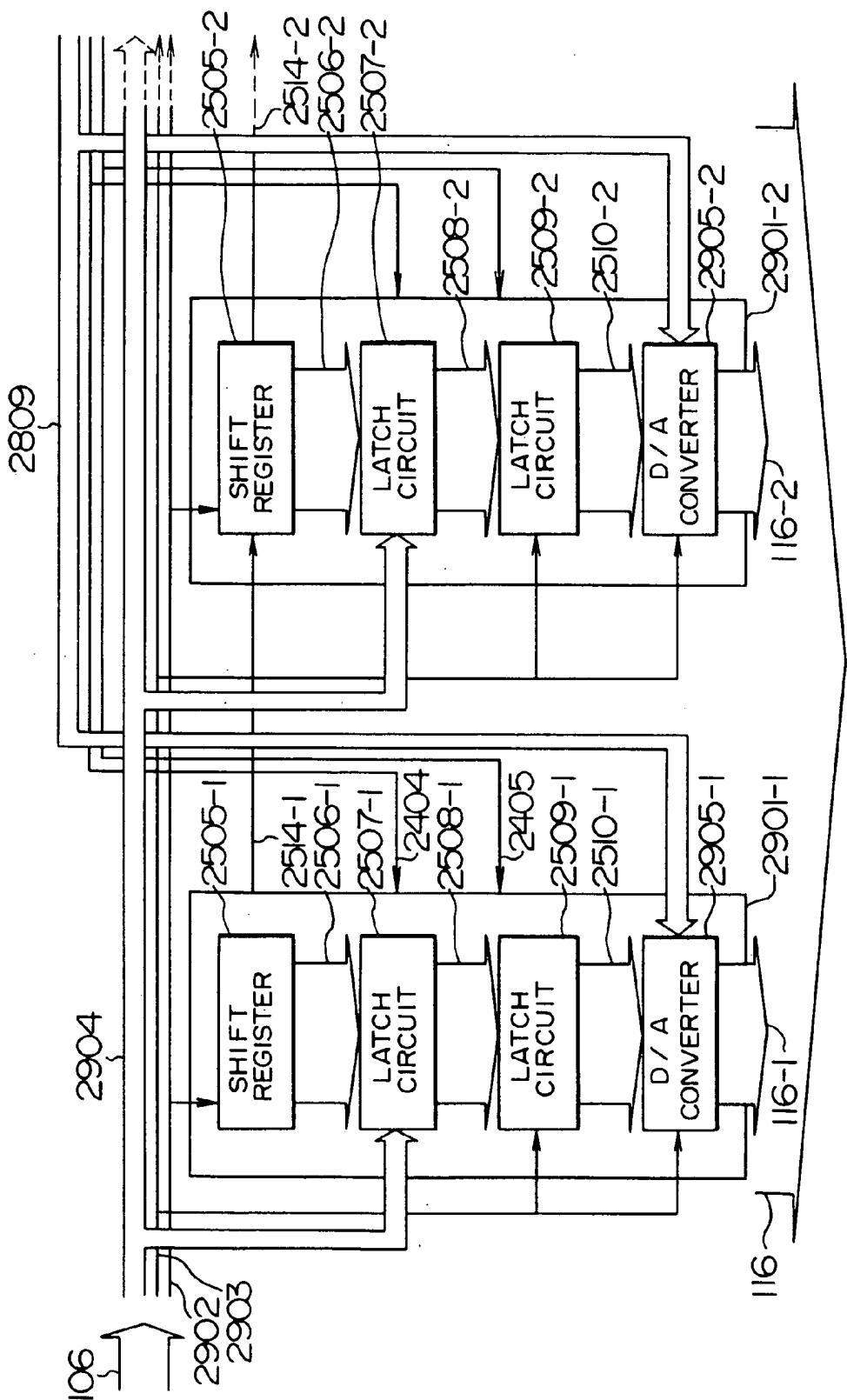

**[0031]** **FIG. 29** is a schematic block diagram for showing the signal drive circuit 2801 of **FIG. 28**.

**[0032]** In **FIG. 29**, reference numerals 2901-1, 2901-2, --, indicate drain drivers, and a signal drive circuit 2801 is arranged by a plurality of drain drivers 2901. The drain drivers receive the digital LCD display data to be converted into LCD apply voltages, and outputs the LCD apply voltages to the LCD panel 120. Among the signal drive circuit control bus 106, reference numeral 2904 is an LCD display data bus, reference numeral 2902 denotes a shift clock, and reference numeral 2903 is a latch clock. The shift clock 2902 is synchronized with the digital LCD display data transferred via the LCD display data bus 2904, and the latch clock 2903 becomes active after the digital LCD display data for 1 horizontal line have been transferred to the signal drive circuits 2801 and 2802. Reference numeral 2905 shows a digital-to-analog converting circuit for converting the digital data transferred via the data bus 2510 based on the LCD drive voltage transferred via the LCD-drive voltage line 2809 into the LCD apply voltages. Reference numeral 116 denotes a signal line for transferring the LCD apply voltages produced by the digital-to-analog converting circuit 409. The drain driver 2901 has such a different point from the drain driver 2501 shown in **FIG. 25** that any of the shift register 403, the latch circuit 405, the digital circuit unit of the latch circuit 407, and the digital-to-analog converting circuit 2905 are driven by the high-level reference voltage transferred via the reference voltage line 2404 and the low-level reference voltage transferred via the reference voltage line 2405.

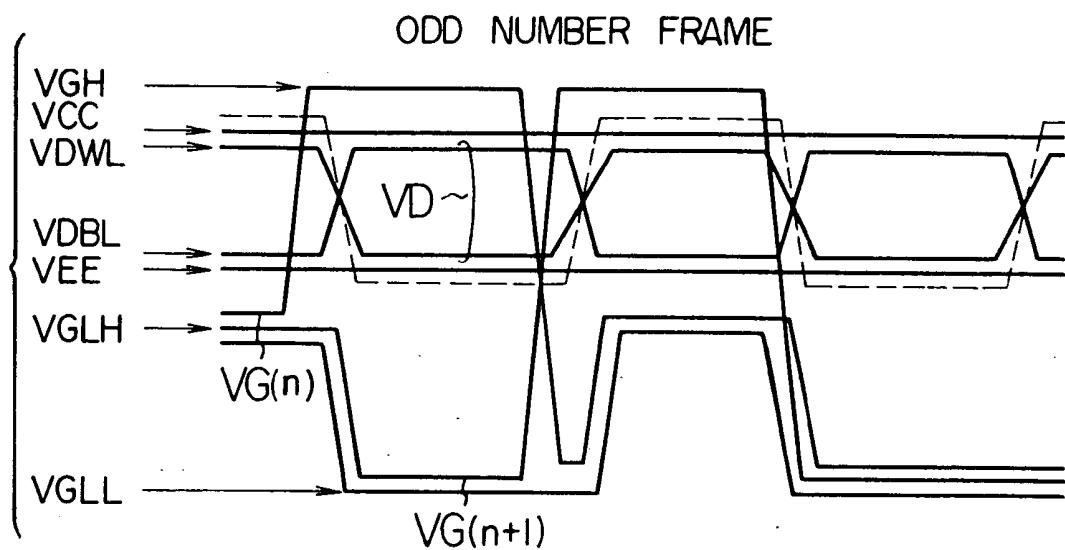

**[0033]** **FIG. 30** represents voltage waveforms produced when the LCD apparatus of **FIG. 29** is driven. It should be noted that the present voltage waveforms show line AC drives in which the polarity of the voltages applied to the liquid crystal are alternately switched for every line.

**[0034]** In **FIG. 30**, symbol VG(n) is a voltage waveform of the scanning line G(n) shown in **FIG. 5**, and symbol VG(n+1) is a voltage waveform of the scanning line G(n+1) indicated in **FIG. 5**. Symbol VGH denotes a selective voltage level of the scanning line 119, and symbols VGLH

and VGLL are non-selective voltage levels. Symbol VCOMH shows a high-level common electrode voltage value of the common electrode 123, and symbol VCOML represents a low-level common electrode voltage value of the common electrode 123.

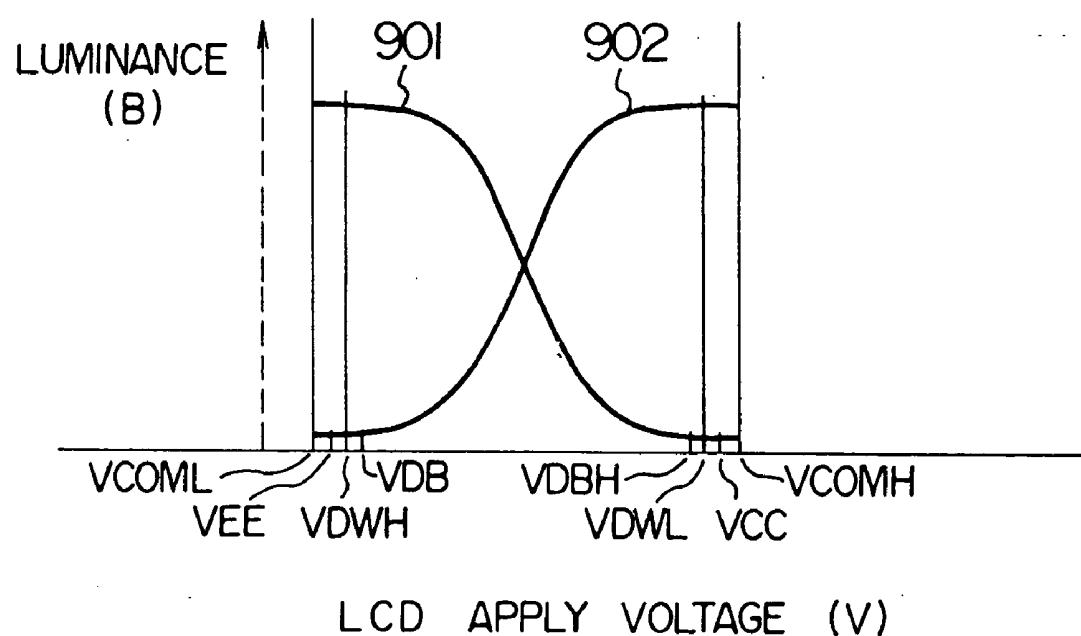

[0035] FIG. 31 explanatory shows such conditions that either a positive potential voltage, or a negative potential voltage is applied to the respective pixel units when the LCD display panel is driven at the timings of FIG. 29, and also directions of currents produced in the pixel units at this time.

[0036] In FIG. 31, symbol “+” represents an application of a voltage having a positive polarity with respect to the voltage of the common electrode 123, and symbol “-” show an application of a voltage having a negative polarity with regard to the voltage of the common electrode 123.

[0037] FIG. 32 is a graphic representation for indicating a relationship between a voltage and luminance of the liquid crystal display.

[0038] In FIG. 32, an abscissa indicates luminance, and an ordinate represents an LCD apply voltage. Reference numeral 901 denotes a luminance-voltage characteristic when the positive voltage is applied, and reference numeral 902 shows a luminance-voltage characteristic when the negative voltage is applied.

[0039] In this conventional LCD display apparatus, this LCD display apparatus owns such a characteristic that, when no voltage is applied to the liquid crystal signal, namely the apply voltage is 0V, the highest luminance is obtained, and the luminance is lowered when either the positive apply voltage, or the negative apply voltage is increased. As previously explained in the above-described prior art, since the liquid crystal represents the same luminance irrelevant to the polarities of the apply voltages if the absolute voltage values thereof with respect to the voltage of the common electrode 123, if two different common electrode voltages VCOMH and VCOML are provided, then the resultant voltage-luminance characteristic as shown in FIG. 32 is obtained.

[0040] Referring again to FIGS. 28 to 32, operations of this liquid crystal display apparatus will be described.

[0041] In FIG. 28, the digital display data transferred via the system bus 101 is converted through the LCD controller 102 and the signal drive circuits, 2801, 2802 into the LCD apply voltage, and this LCD apply voltage is outputted to the LCD panel 120 for display purposes. The LCD controller 102 converts the digital display data entered into the system bus 101 into the sync signal in conformity to the input interfaces of the signal drive circuits 2801, 2802 and the pixel arrangements of the LCD panel 120, and the sync signal is outputted via the signal drive circuit control buses 106 and 107. Although the operation of the drain driver 2901 shown in FIG. 29 is similar to that of the drain driver 2501 of FIG. 25, there is a different point that the digital-to-analog converting circuit 2908 is operated under a low voltage equal to the drive voltages for the respective digital circuit units of the shift register 2505, the latch circuit 2507, and the latch circuit 2509. Thus, in contradiction to the first-mentioned prior art LCD display apparatus shown in FIG. 24, since the withstand voltage of the LCD drive circuit unit is low, various efforts are made of establishing

the drive method for applying the proper voltage to the LCD panel in order to obtain necessary display luminance.

[0042] As illustrated in the voltage-luminance characteristic diagram of FIG. 32, two common voltages of VCOML and VCOMH are produced. In case that the voltage applied to the liquid crystal is a positive polarity voltage, the voltage-luminance characteristic curve 901 is utilized. The common electrode voltage VCOML is used, and the voltage applied to the liquid crystal is higher than the common electrode voltage VCOMH. For instance, in case of high luminance representation, the voltage VDWL is applied to the liquid crystal, whereas in case of low luminance representation, the voltage VDBL is applied to the liquid crystal. Furthermore, when the voltage applied to the liquid crystal corresponds to the negative polarity voltage, the voltage-luminance characteristic curve 902 is employed. The common electrode voltage VCOMH is used and the voltage applied to the liquid crystal is a voltage lower than the common electrode voltage VCOMH. For example, in case of high luminance representation, the voltage VDWL is applied to the liquid crystal, whereas in case of low luminance representation, the voltage VDBL is applied to the liquid crystal. Since these LCD apply voltages VDWL, VDBL, VDWL and VDBL can be produced within the voltage range of the reference voltage VCC-VEE which is being applied to the digital-to-analog converting circuit 2908 employed in the drain driver 2901 shown in FIG. 29, the display operation is available. As shown in the drive waveforms of FIG. 30, the common electrode voltage VCOM of the common electrode line 123 is required to be produced as an AC voltage for each line in synchronism with the LCD alternating signal. As a result, the LCD apply voltages produced in the signal drive circuits 2801 and 2802 become the waveform of “VD”, and if a potential difference between the LCD apply voltages and the common electrode voltage VCOM is small, the luminance of the LCD is increased in accordance with the voltage-luminance characteristic shown in FIG. 31. If a potential difference between them is large, the luminance of the LCD is lowered in accordance with the voltage-luminance characteristic shown in FIG. 31.

[0043] In addition, in the even frames and the odd frames, since the polarities of the voltages applied to the LCD are alternately changed, it is possible to prevent deterioration of the liquid crystal.

[0044] Now, a problem may be caused by the pixel arrangement of the LCD panel 120.

[0045] In this prior art, it is assumed that a capacitance of the liquid crystal 503 for constituting the respective pixel units 501 is  $C_{1c}$  and a capacitance of the added capacitance 504 is  $C_{add}$ . When the liquid crystal 503 is held under the common electrode voltage VCOML and the voltage  $V_{c1}$  with the positive polarity, if this common electrode voltage is changed into VCOMH, such a voltage variation  $C_{add}/(C_{1c}+C_{add}) \times (VCOMH-VCOML)$  happens to occur in the holding voltage of the liquid crystal 503. This is because one electrode of the added capacitance  $C_{add}$  is constructed of the scanning line 119 provided at the prestage, and the voltage at this electrode is constant, though the common electrode voltage VCOM is changed. This implies that the LCD apply voltage is varied during the holding period by alternately changing the common electrode voltage VCOM,

and display luminance of the liquid crystal **503** is also varied. To prevent the voltage variation in the LCD apply voltage during the holding period, the voltage appearing on the scanning line **119** at the prestage must be alternately changed only by the AC voltage value of the common electrode voltage VCOM. It should be noted that since the common electrode **123** functions as a common electrode at the respective pixel units **501** within the LCD panel **120**, the voltage of the scanning line **119** at the prestage is alternately changed in phase with that of the common electrode voltage.

[0046] Accordingly, it is determined that when the common electrode voltage is VCOML, the non-selective voltage level of the scanning line **119** is VGLL, whereas when the common electrode voltage VCOMH, the non-selective voltage level of the scanning line **119** is VGLH. It should be understood that when the following condition is satisfied ( $VGLH - VGLL = (VCOMH - VCOML)$ ), the voltages applied to the liquid crystal are not varied.

[0047] In this prior art, the non-selective voltage VGL is alternately changed by an AC circuit **2806** shown in **FIG. 28**.

[0048] In **FIG. 32**, there is shown polarities of the voltages applied to the pixel unit **501**. As previous mentioned, since the common electrode **123** is commonly used to the liquid crystal **503** within all pixel units **501**, when the common electrode voltage is VCOMH, all voltages applicable to the liquid crystal are voltages having negative polarities, whereas when the common electrode voltage is VCOML, all voltages applicable to the liquid crystal are voltages having positive polarities. Therefore, the polarities of the apply voltages become identical to each other in 1 horizontal line, and the polarities are reversed for every line.

[0049] In the pixel unit **501** to which the voltage with the positive polarity is being applied, a current is flown through the liquid crystal **503** into the common electrode line **123**, and then flown via the added capacitance **504** into the scanning line **119** at the prestage. In the pixel unit **501** to which the voltage with the negative polarity is being applied, a current is flown from the common electrode line **123** through the liquid crystal **503**, and then flown via the added capacitance **504** from the scanning line **119** at the prestage. Under the above described controls, the LCD display can be done with employment of the low-withstanding-voltage drain driver.

[0050] With respect to the prior art LCD display apparatus shown in **FIG. 24**, there is another problem that the signal drive circuits **2401** and **2402** cannot be manufactured at low cost. Since the drive voltage of the digital-to-analog converting circuit **2513** in the drain driver **2501** for constituting the signal drive circuits **2401**, **2402** is high, a high withstanding voltage process for LSI must be employed. The minimum dimension of the element for constituting the LSI manufactured under the high withstanding voltage process is 3 times to 5 times greater than a minimum dimension of an element for an LSI manufactured under the low withstanding voltage process, used in a digital circuit and the like. Accordingly, when the circuits having the same functions and characteristics except for the output voltage are arranged by the withstanding voltage process and the low withstanding voltage process, since the circuit area thereof becomes approximately the squared minimum dimension, a ratio of the circuit area constructed by the high withstanding voltage

process to that by the low withstanding voltage process is selected to be approximately 10 times to 20 times. Since the price of LSI depends upon the chip size, cost of the drain driver **2501** constructed by the high withstanding voltage process become expensive, as compared with that by the low withstanding voltage process.

[0051] Moreover, there is a trend that a quantity of display colors will be increased in order to manufacture an LCD display apparatus with high performance. To increase the quantity of display colors of the LCD display apparatus, since the circuit scale of the drain driver **2501** becomes large, such a high cost problem with the high withstanding voltage process will become more serious.

[0052] Then, it may be conceived use of the low withstanding voltage process for manufacturing the drain driver **2901** in order to manufacture the signal drive circuit at low cost.

[0053] In accordance with this prior art drain driver **2901**, low cost of the signal drive circuits **2801** and **2802** may be realized. Then, the conventional LCD display apparatuses have been manufactured as represented in **FIG. 28**. As in the conventional LCD display apparatus of **FIG. 28**, the polarities of the voltages applied to the respective pixel units **501** of the LCD panel **120** are illustrated in **FIG. 31** in accordance with such a drive method for alternately changing the common electrode voltage transferred by the common electrode **123**. As a result, the current flown into/from the scanning line **119** at the prestage and the common electrode line **123** is directed only one direction for each scanning line **109**. For instance, as to the scanning line  $G(n-1)$ , since the voltages applied to the pixel units **501-U(m)-(n)**, **501-L(m)-(n)**, **501-U(M+1)-(n)** are positive polarities, the currents flowing via the added capacitances **504** of the respective pixel units **501** are concentrated and flown into the scanning line  $G(n-1)$ . As to the scanning line  $G(n)$ , since the voltages applied to the pixel units **501-U(m)-(n+1)**, **501-L(m)-(n+1)**, **501-U(m+1)-(n+1)** are negative polarities, the currents flowing via the added capacitances **504** of the respective pixel units **501** are concentrated and flown from the scanning line  $G(n)$ . Since the scanning line **109** has a wiring resistance, voltages are produced on this scanning line **109** by the flowing in/out currents and the wiring resistance. In particular, when such LCD display apparatuses as in workstations and the like require high definition and a large number of pixels, the currents are increased, so that the resultant voltages are increased. Due to this voltage variation, the voltage values applied to the added capacitances **504** are also varied. In addition, voltage variations happen to occur also in the common electrode line **123** due to adverse influences caused by the concentrated currents. In response to the voltage variations, the apply voltage values to the liquid crystal **503** are also changed. If the voltage variations happen to occur in the liquid crystal **503** and the added capacitance **504**, the normal luminance representation for the display data cannot be achieved, resulting in deterioration of image quality.

[0054] A primary object of the present invention is to control with employment of a low withstanding voltage drain driver that both of a positive-polarity voltage and a negative-polarity voltage are applied to each of pixel units for a 1 horizontal line are applied, whereby a high image quality representation can be realized.

[0055] A secondary object of the present invention is to control that even when a plurality of drain drivers are provided at either an upper side, or a low side, a positive-polarity voltage and a negative-polarity voltage are equally applied to each of pixel units for 1 horizontal line, whereby a high image quality representation can be realized.

[0056] A third object of the present invention is to control with employment of a low withstanding voltage drain driver into which analog display data is entered, that both of a positive-polarity voltage and a negative-polarity voltage are applied to each of pixel units for 1 horizontal line.

[0057] A fourth object of the present invention is to reduce fluctuation in output voltages of a drain driver in order to realize a high image quality representation.

[0058] A fifth object of the present invention is to arrange an information processing apparatus by employing a liquid crystal display apparatus capable of a high image quality representation, while being driven by a low withstanding voltage drain driver.

#### SUMMARY OF THE INVENTION

[0059] To achieve the primary object, in accordance with the present invention, a liquid crystal panel is arranged by a plurality of matrix-formed pixel units; the pixel unit is arranged by either liquid crystal and a switching transistor, or liquid crystal, a switching transistor, and an added capacitance; one electrode of the liquid crystal is a DC common electrode voltage, the liquid crystal is so arranged as to control a light transmission amount by an apply voltage value with respect to the common electrode voltage, thereby perform a luminance representation; signal lines used to transfer voltages which are applied to the liquid crystal of the respective pixel units, are drawn from both of an upper side and a lower side of the liquid crystal panel, and are driven by signal drive circuits constructed of plural drain drivers; both of a reference voltage level and a liquid crystal drive voltage for the upper-sided signal drive circuit and the lower-sided signal drive circuit own phases opposite to a phase of the common electrode voltage in a certain time period; display data and a synchronization signal, which are transferred via a system bus, are converted into data suitable for the arrangements of the signal drive circuits and the liquid crystal display panel; the converted liquid crystal display data and a voltage level of a timing signal are shifted so as to be fitted to drive voltage levels of each of the upper-sided and lower-sided signal drive circuits; and both of the liquid crystal display data and the timing signal, whose voltage levels have been shifted, are inputted to the signal drive circuits.

[0060] To achieve the secondary object, in accordance with the present invention, a liquid crystal panel is arranged by a plurality of matrix-formed pixel units; the pixel unit is arranged by either liquid crystal and a switching transistor, or liquid crystal, a switching transistor, and an added capacitance; one electrode of the liquid crystal is a DC common electrode voltage, the liquid crystal is so arranged as to control a light transmission amount by an apply voltage value with respect to the common electrode voltage, thereby perform a luminance representation; signal lines used to transfer voltages which are applied to the liquid crystal of the respective pixel units, are drawn from both of an upper side and a "lower side of the liquid crystal panel, and are

driven by signal drive circuits constructed of plural drain drivers; both of a reference voltage level and a liquid crystal drive voltage owns phases opposite to a phase of the common electrode voltage in a certain time period within the drain driver of the signal drive circuit; display data and a synchronization signal, which are transferred via a system bus, are converted into data suitable for the arrangements of the signal drive circuits and the liquid crystal display panel; the converted liquid crystal display data and a voltage level of a timing signal are shifted so as to be fitted to a drive voltage levels of each of the upper-sided and lower-sided signal drive circuits; and both of the liquid crystal display data and the timing signal, whose voltage levels have been shifted, are inputted to the signal drive circuits.

[0061] To achieve the third object, in accordance with the present invention, a liquid crystal panel is arranged by a plurality of matrix-formed pixel units; the pixel unit is arranged by either liquid crystal and a switching transistor, or liquid crystal, a switching transistor, and an added capacitance; one electrode of the liquid crystal is a DC common electrode voltage, the liquid crystal is so arranged as to control a light transmission amount by an apply voltage value with respect to the common electrode voltage, thereby perform a luminance representation; signal lines used to transfer voltages which are applied to the liquid crystal of the respective pixel units, are drawn from both of an upper side and a lower side of the liquid crystal panel, and are driven by signal drive circuits constructed of plural drain drivers; a reference voltage level owns a phase opposite to a phase of the common electrode voltage in a certain time period in the drain driver of the signal drive circuit; both of analog display data and a synchronization signal, which are transferred via a system bus, are converted into data suitable for the arrangements of the signal drive circuits and the liquid crystal panel; a polarity of the analog liquid crystal display data suitably converted for the upper-sided signal drive circuit is opposite to a polarity of the analog liquid crystal display data suitably converted for the lower-sided signal drive circuit; the phase-shifted liquid crystal display data and a voltage level of a timing signal are shifted so as to be fitted to drive voltage levels of each of the upper-sided and lower-sided signal drive circuits; and both of the liquid crystal display data and the timing signal, whose voltage levels have been shifted, are inputted to the signal drive circuits.

[0062] To achieve the fourth object, in accordance with the present invention, a drain driver for producing a liquid crystal apply voltage is so arranged that a plurality of liquid crystal drive voltages are inputted from an external power supply circuit, a voltage corresponding to an upper bit of display data is selected, and the selected two-level voltages are subdivided, a voltage corresponding to a lower bit of the display data is selected from the subdivided voltage which will then be outputted. For a constant time period after the voltage selection, this drain driver outputs the voltage selected by the upper bit, and thereafter for another constant time period, outputs a liquid crystal apply voltage corresponding to the display data selected by the upper bit and the lower bit.

[0063] To achieve the fifth object, in accordance with the present invention, an information processing apparatus is arranged by a central processing unit, a system memory, a display memory for strong display data, a display controller

for controlling the display data to be written into/read from the display memory, and a liquid crystal display apparatus for displaying the display data read from the display memory.

[0064] In the means for achieving the primary object, even if the drain driver does not have a drive withstanding voltage function capable of simultaneously driving the positive-polarity voltage and the negative-polarity voltage with regard to the common electrode voltage of the liquid crystal, the upper-sided and lower-sided signal drive circuits can produce both of the liquid crystal apply voltages having the positive polarity and the negative polarity in a certain time period with regard to the common electrode voltage of the liquid crystal by alternately changing the reference voltage level and the liquid crystal drive voltage level with regard to the common electrode voltage, and also by shifting the voltage levels of the liquid crystal display data and the timing signal to the drive voltage levels of the signal drive circuits. Furthermore, the upper-sided and lower-sided signal drive circuits are driven in the opposite phase with regard to the phase of the common electrode voltage, so that the voltage having the positive polarity and the voltage having the negative polarity can be equally applied to the respective pixel units on 1 horizontal line.

[0065] In the means for achieving the secondary object, even if the drain driver does not have a drive withstanding voltage function capable of simultaneously driving the positive-polarity voltage and the negative-polarity voltage with regard to the common electrode voltage of the liquid crystal, the upper-sided or lower-sided signal drive circuit can produce both of the liquid crystal apply voltages having the positive polarity and the negative polarity in a certain time period with regard to the common electrode voltage of the liquid crystal by alternately changing the reference voltage level and the liquid crystal drive voltage level with regard to the common electrode voltage, and also by shifting the voltage levels of the liquid crystal display data and the timing signal to the drive voltage levels of the signal drive circuit. Furthermore, when some of the drain drivers employed in the signal drive circuit are driven by the voltage having the positive polarity with respect to that of the common electrode voltage, since the remaining drain drivers are driven by the drive voltage having the negative polarity with regard to that of the common electrode voltage, the positive-polarity voltage and the negative polarity voltage can be equally applied to the respective pixel units on 1 horizontal line.

[0066] In the means for achieving the third object, even if the drain driver does not have a drive withstanding voltage function capable of simultaneously driving the positive-polarity voltage and the negative-polarity voltage with regard to the common electrode voltage of the liquid crystal, the upper-sided and lower-sided signal drive circuits can produce both of the liquid crystal apply voltages having the positive polarity and the negative polarity in a certain time period with regard to the common electrode voltage of the liquid crystal by alternately changing the reference voltage level, reversing the polarity of the analog liquid crystal display data, and also shifting the analog liquid crystal display data and the timing signal to the drive voltage levels of the signal drive circuits. Furthermore, the upper-sided and lower-sided signal drive circuits are driven in the opposite phase with regard to the phase of the common electrode

voltage, so that the voltage having the positive polarity and the voltage having the negative polarity can be equally applied to the respective pixel units on 1 horizontal line.

[0067] In the means for achieving the fourth object, since the liquid crystal apply voltages produced by the drain drivers are produced from a plural levels of liquid crystal drive voltages inputted from the external power source circuit, the stable liquid crystal apply voltages can be obtained. Furthermore, for a constant time period, the liquid crystal apply voltages do not pass through the voltage dividing circuit, so that the current drivability may be increased, and the time during which the voltages are stored in the pixel units can be shortened.

[0068] In the means for achieving the fifth object, the contents of the display memory for storing the display content may be readily updated by the main memory for storing the program, the central processing unit, and the display controller, and the display content stored in the display memory may be easily displayed on the liquid crystal display apparatus by the display controller.

#### BRIEF DESCRIPTION OF THE DRAWINGS

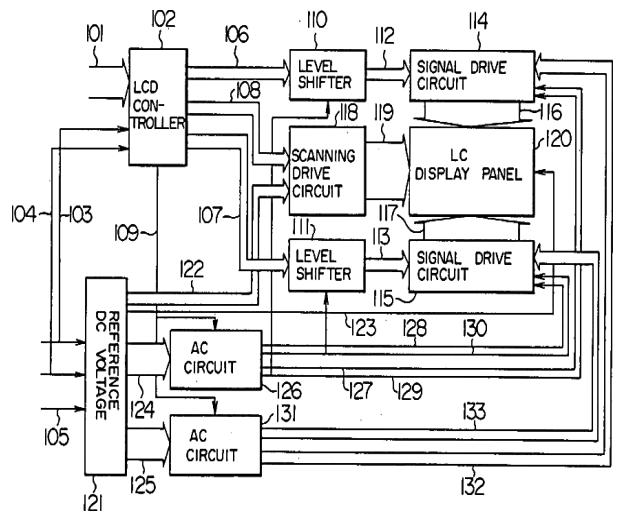

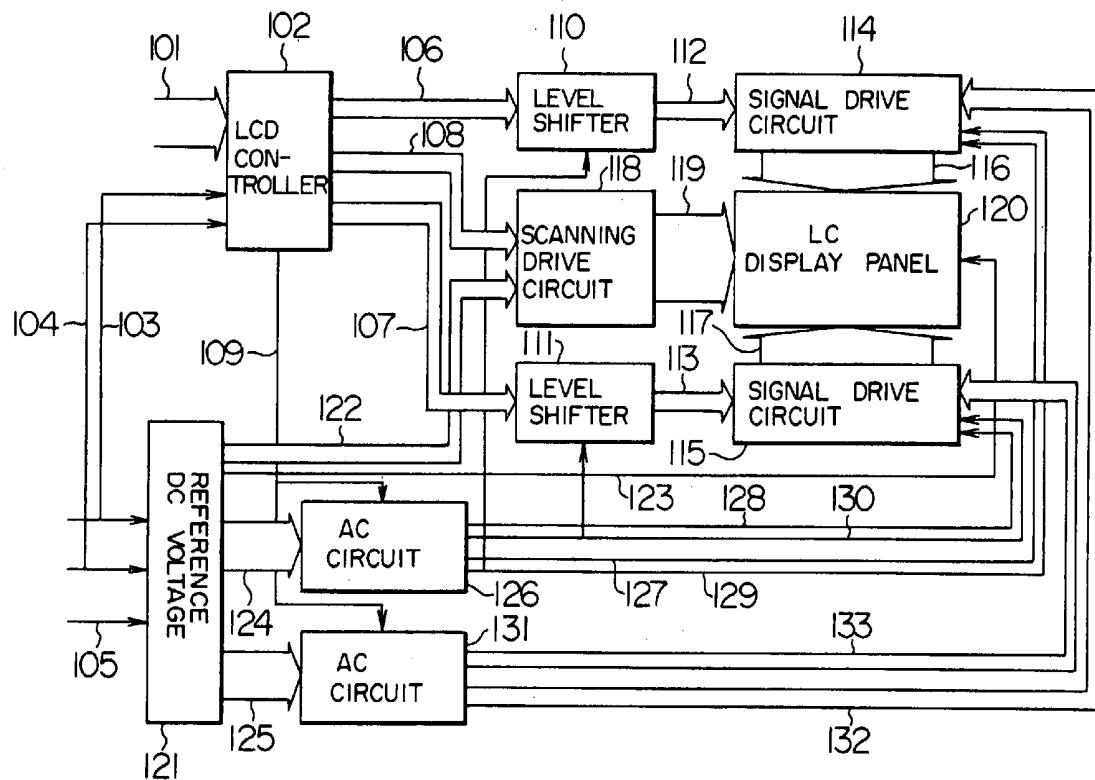

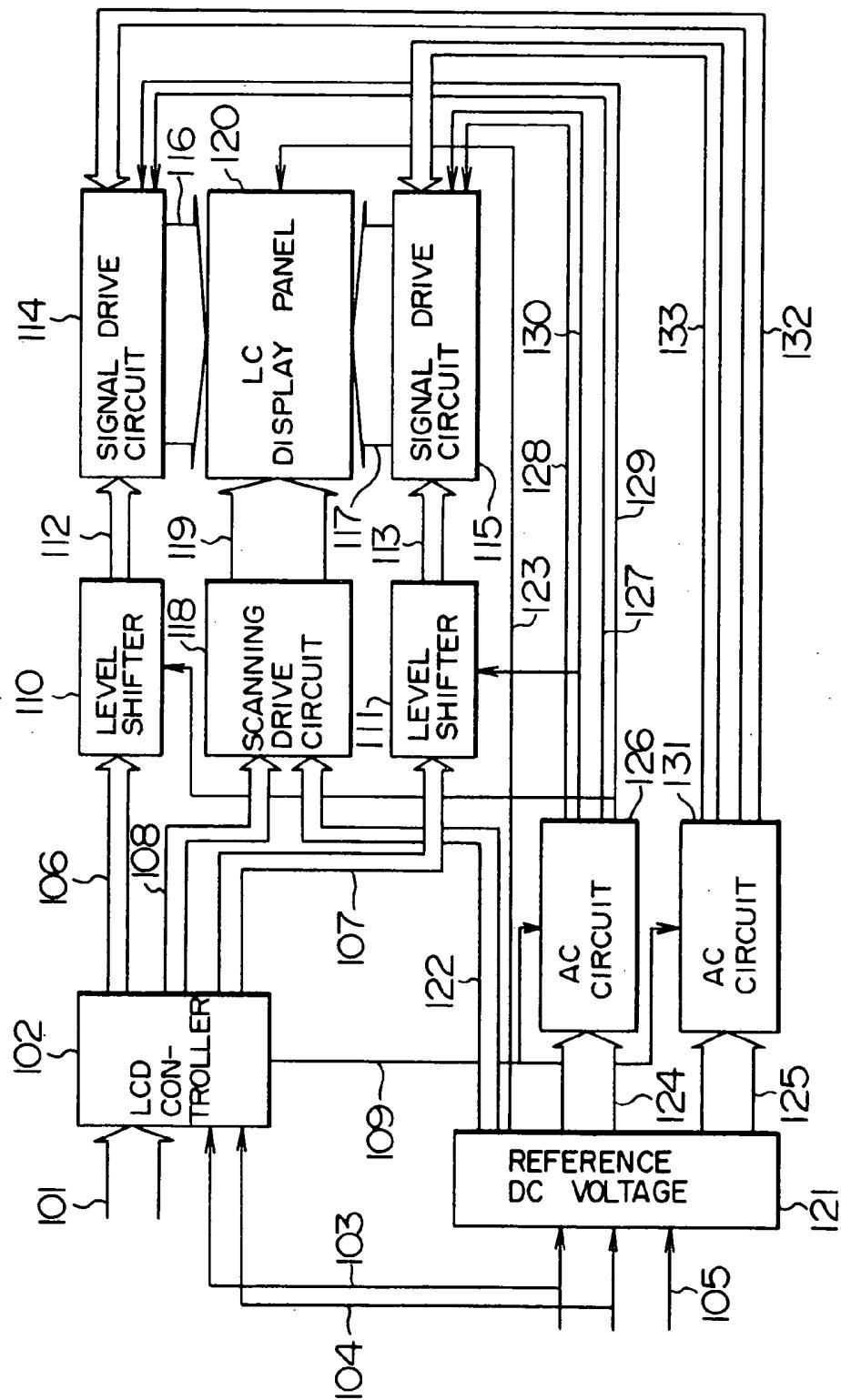

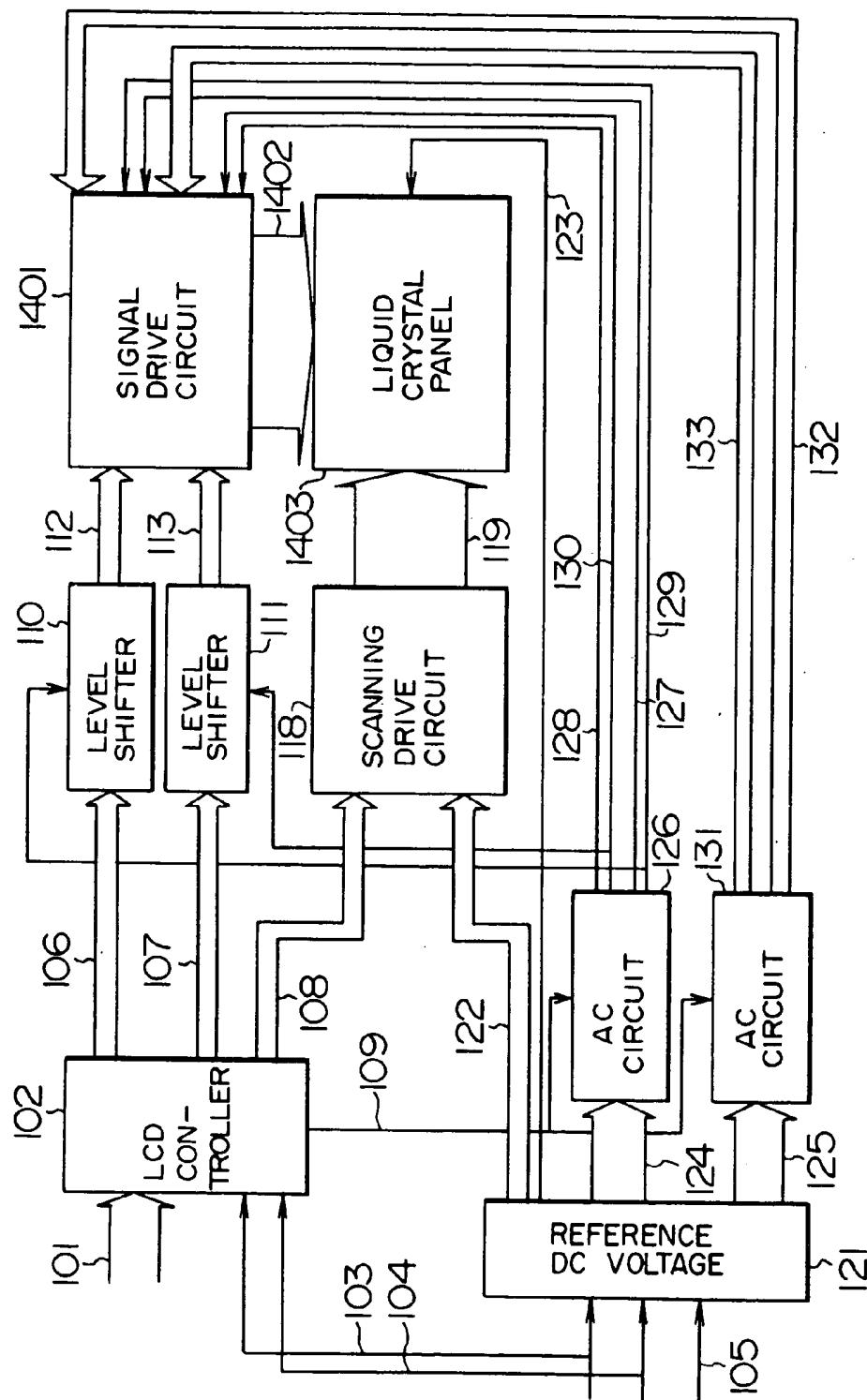

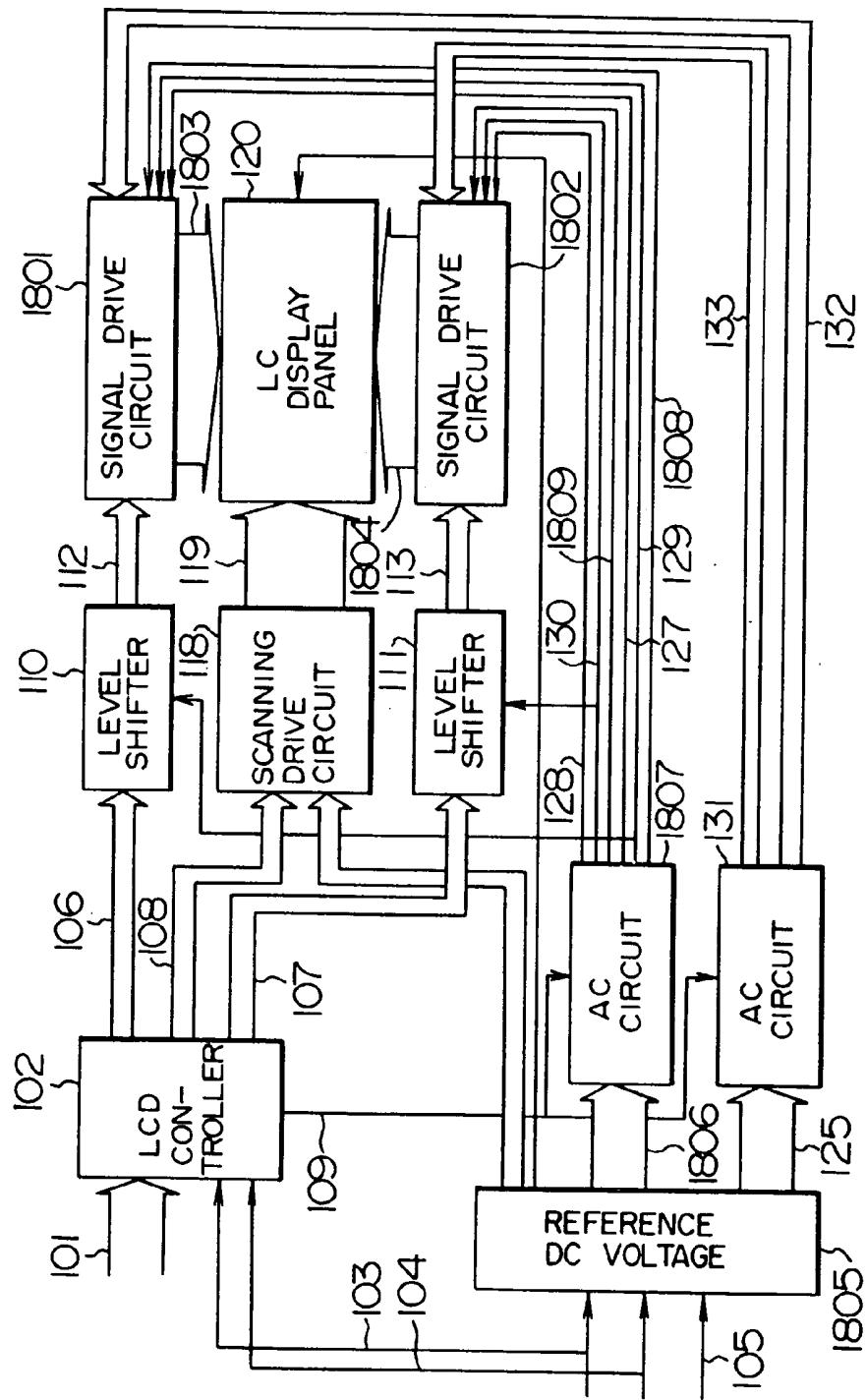

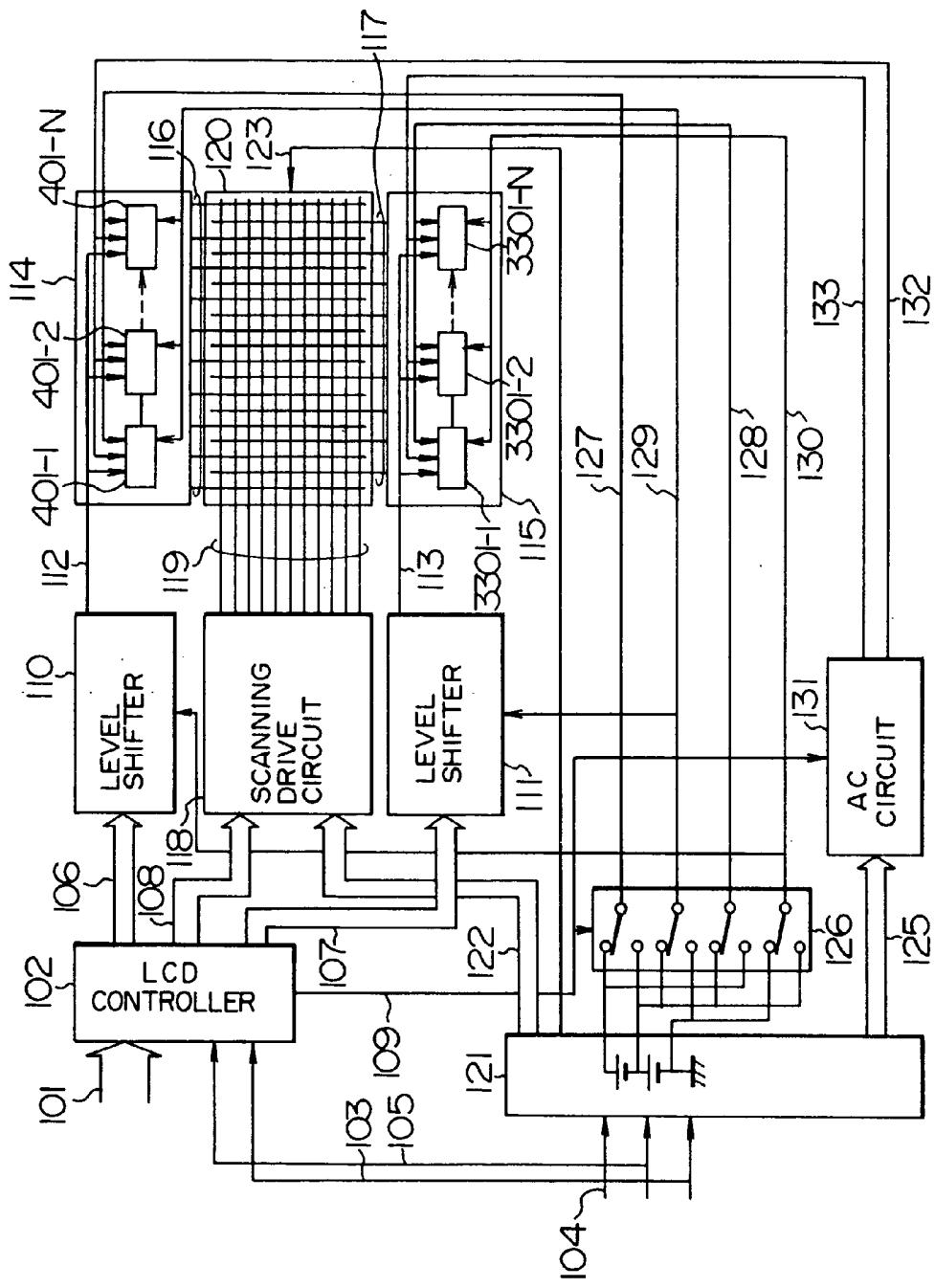

[0069] FIG. 1 schematically shows a system arrangement of a liquid crystal display apparatus according to an embodiment of the present invention;

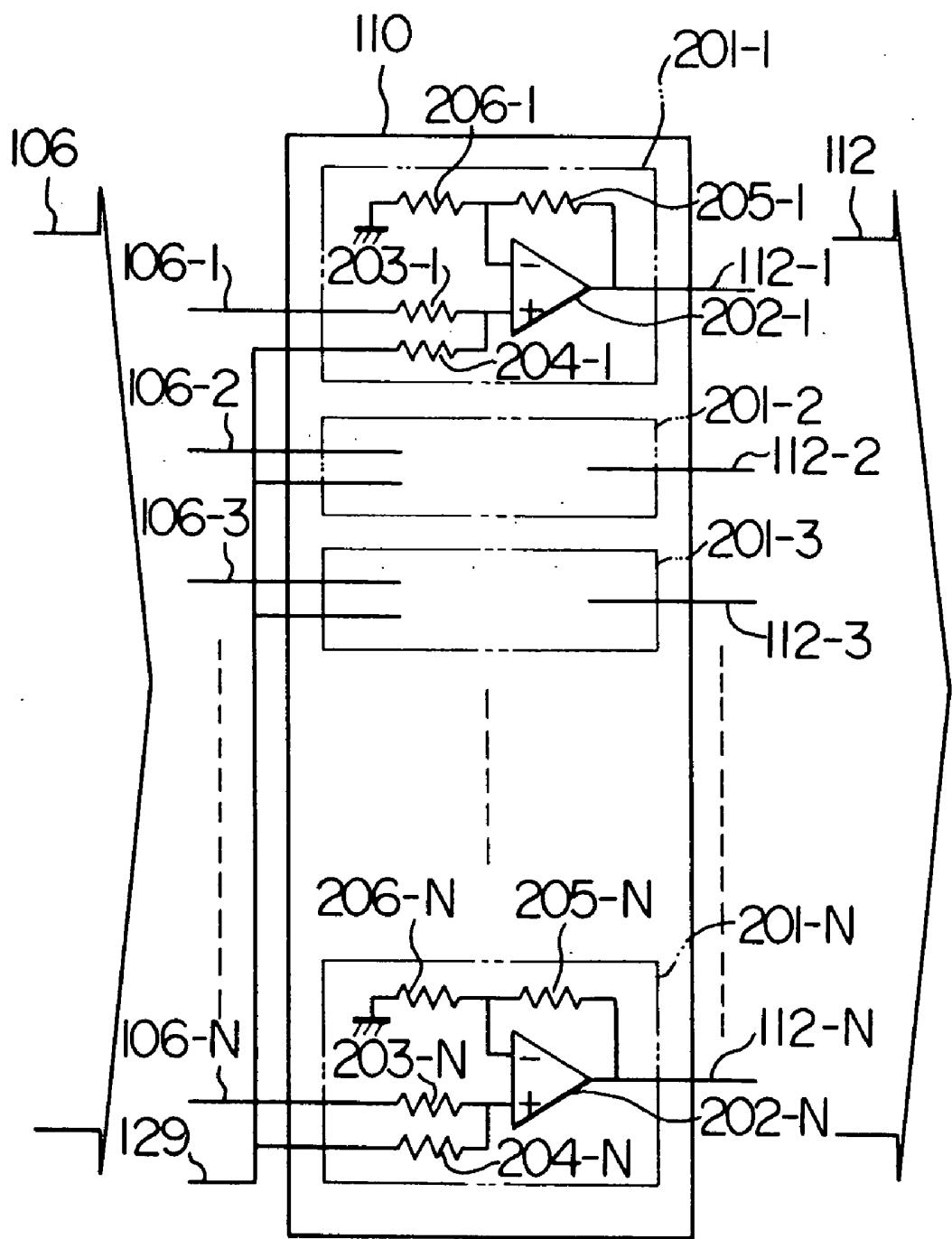

[0070] FIG. 2 schematically indicates an internal arrangement of a level sifter according to the present invention;

[0071] FIG. 3 is a timing circuit for indicating operation of the level sifter according to the present invention;

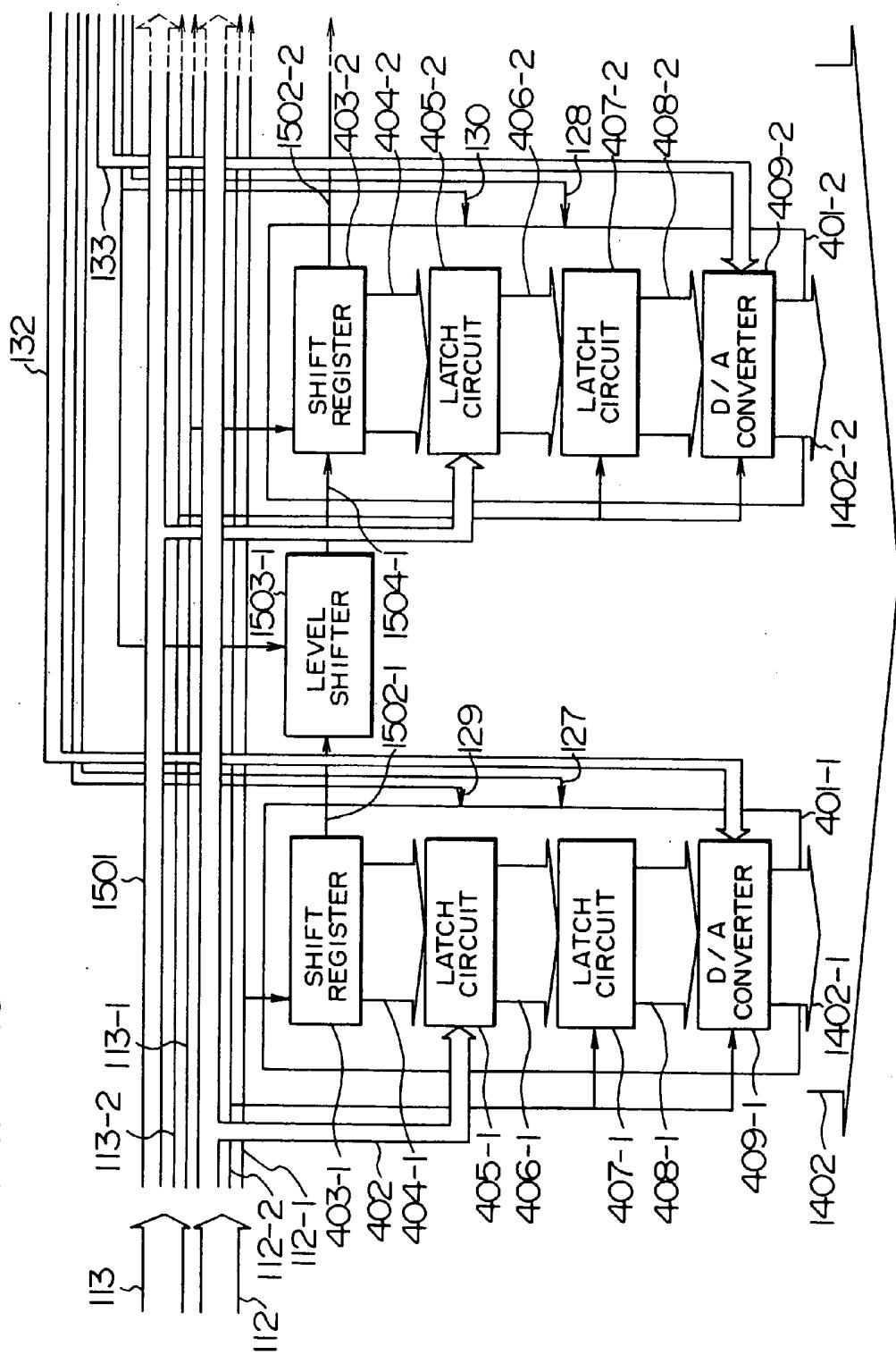

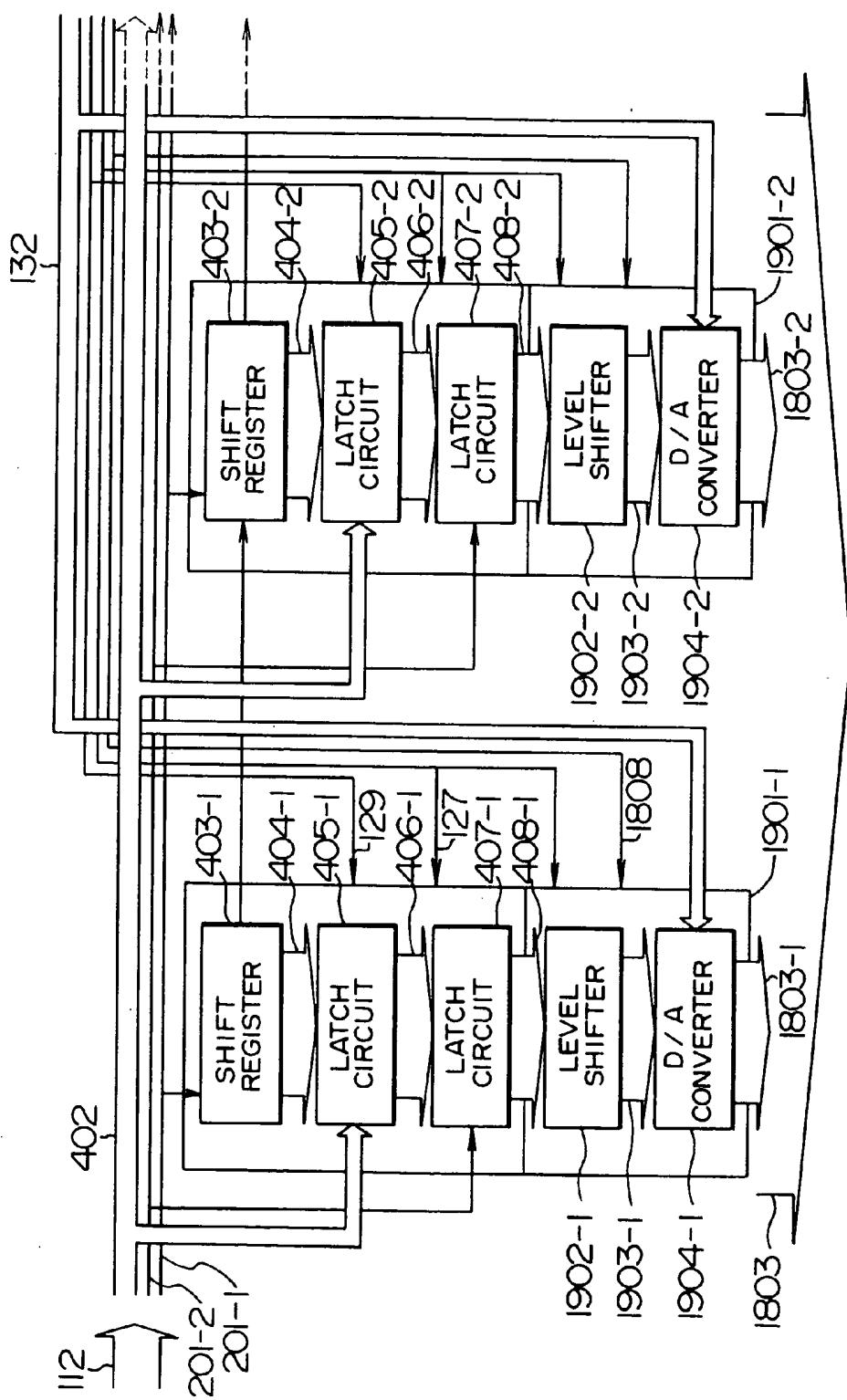

[0072] FIG. 4 is a schematic block diagram for showing a signal drive circuit according to an embodiment of the present invention;

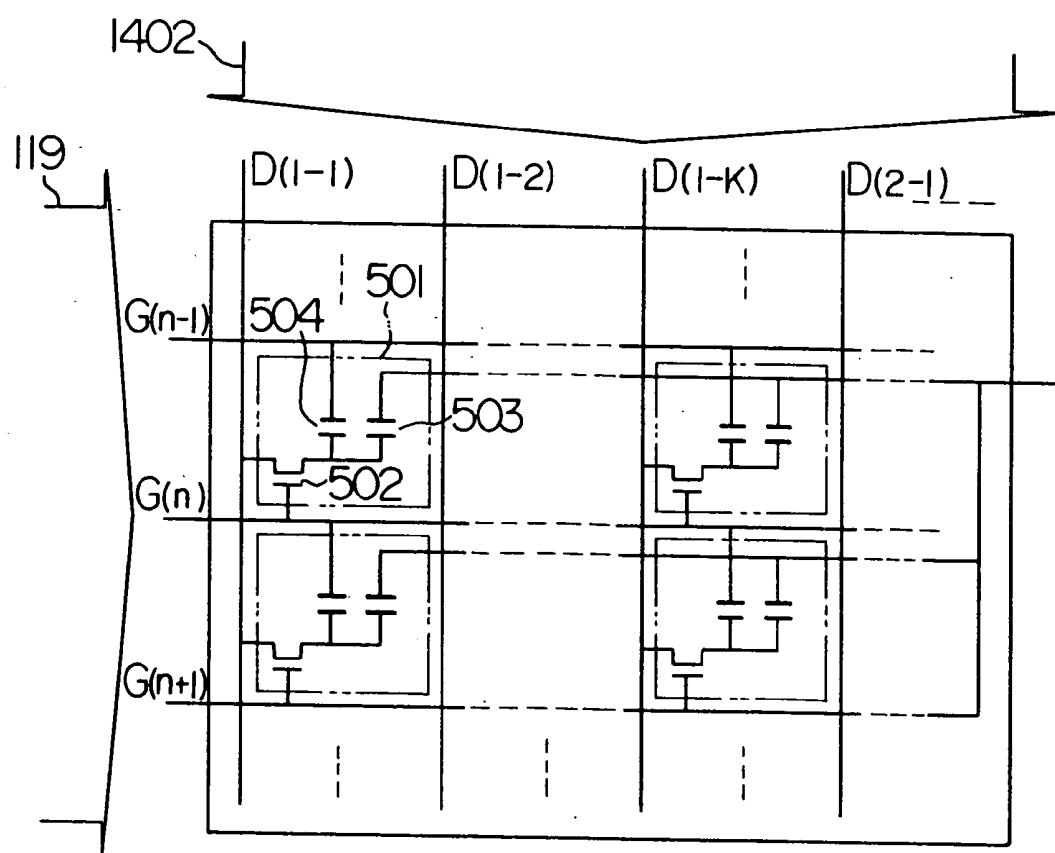

[0073] FIG. 5 shows an equivalent circuit of a liquid crystal display panel according to one embodiment of the present invention;

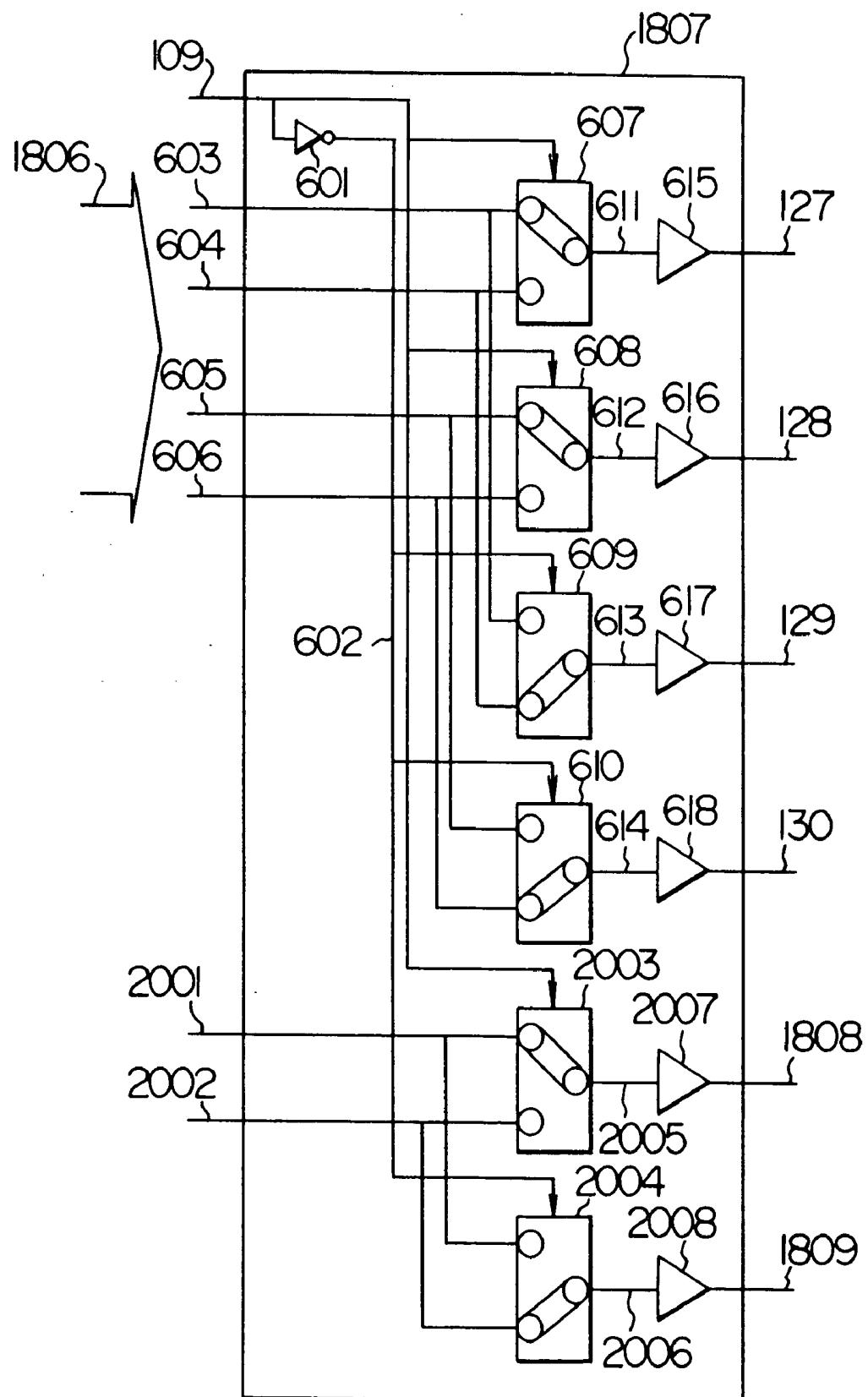

[0074] FIG. 6 is a schematic block diagram of an AC circuit according to one embodiment of the present invention;

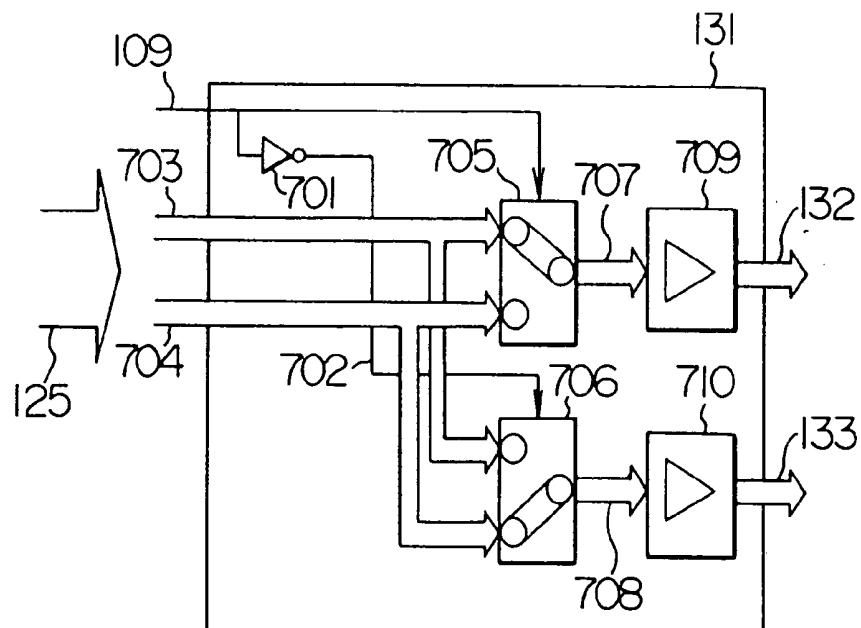

[0075] FIG. 7 is a schematic block diagram of an AC circuit according to an embodiment of the present invention;

[0076] FIG. 8 shows drive waveforms (frame AC) of the liquid crystal display apparatus according to the present invention;

[0077] FIG. 9 is a graphic representation of a voltage-luminance characteristic of a liquid crystal display;

[0078] FIG. 10 schematically shows an equivalent circuit of the liquid crystal panel according to the present invention, in which current directions are indicated;

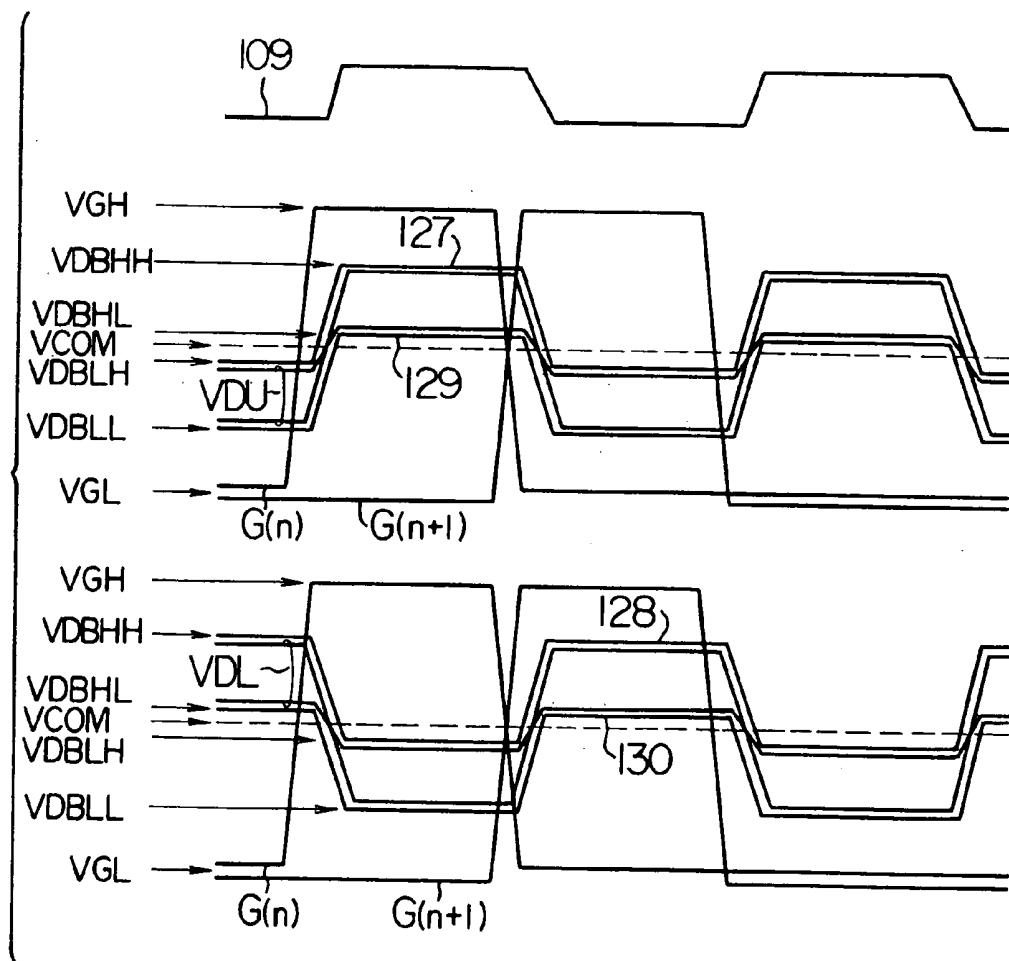

[0079] FIG. 11 shows a drive waveform (line AC) of the liquid crystal display apparatus according to the present invention;

[0080] FIG. 12 schematically shows an equivalent circuit of the liquid crystal panel according to the present invention, in which current directions are denoted;

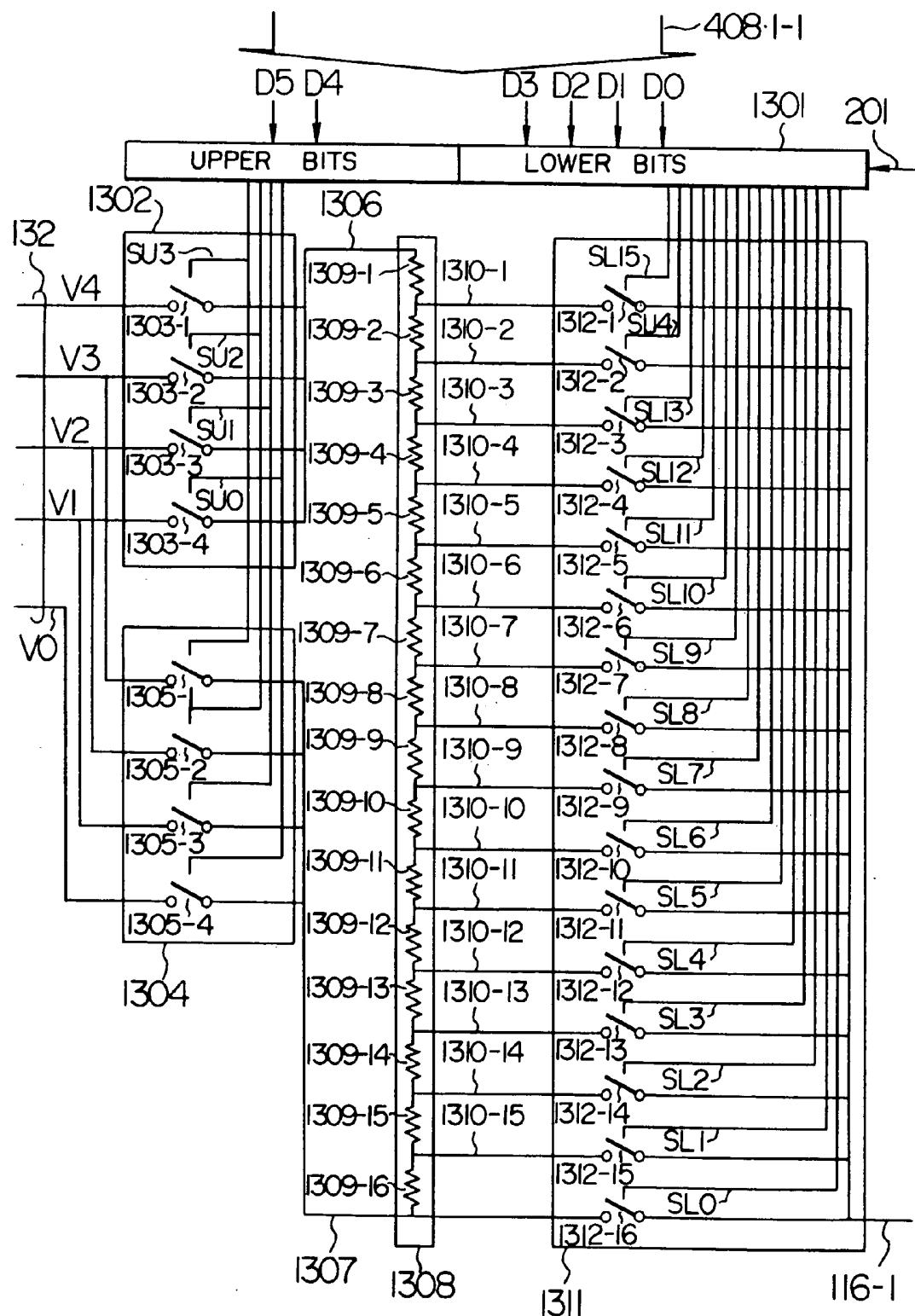

[0081] FIG. 13 is a schematic circuit diagram of a digital-to-analog converting circuit of a drain driver according to an embodiment of the present invention;

[0082] **FIG. 14** is a schematic block diagram for showing a system arrangement of a liquid crystal display apparatus according to another embodiment of the present invention;

[0083] **FIG. 15** is a schematic block diagram of a signal drive circuit according to another embodiment of the present invention;

[0084] **FIG. 16** is an equivalent surcoat of a liquid crystal panel according to another embodiment of the present invention;

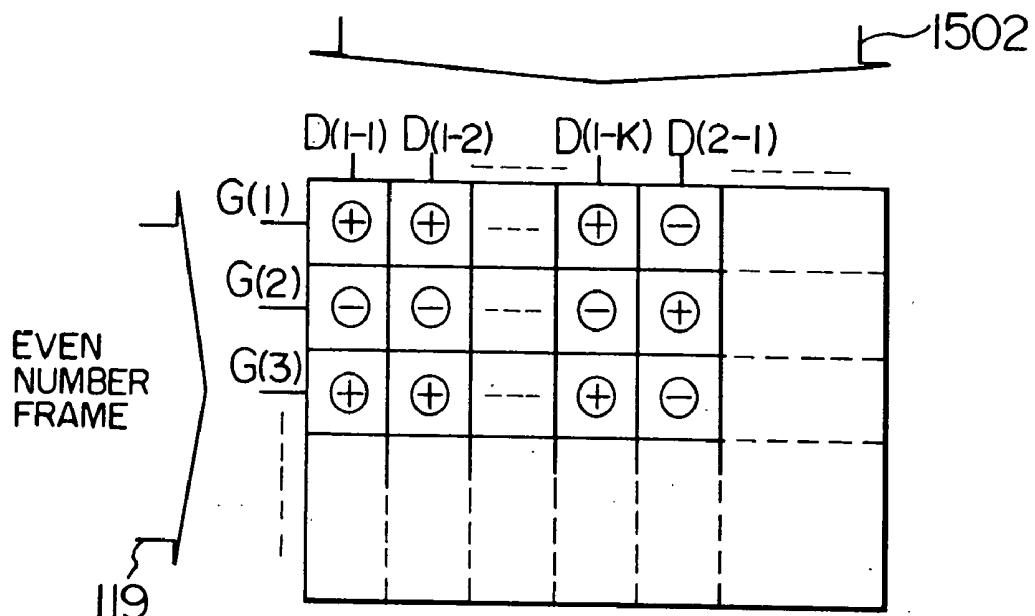

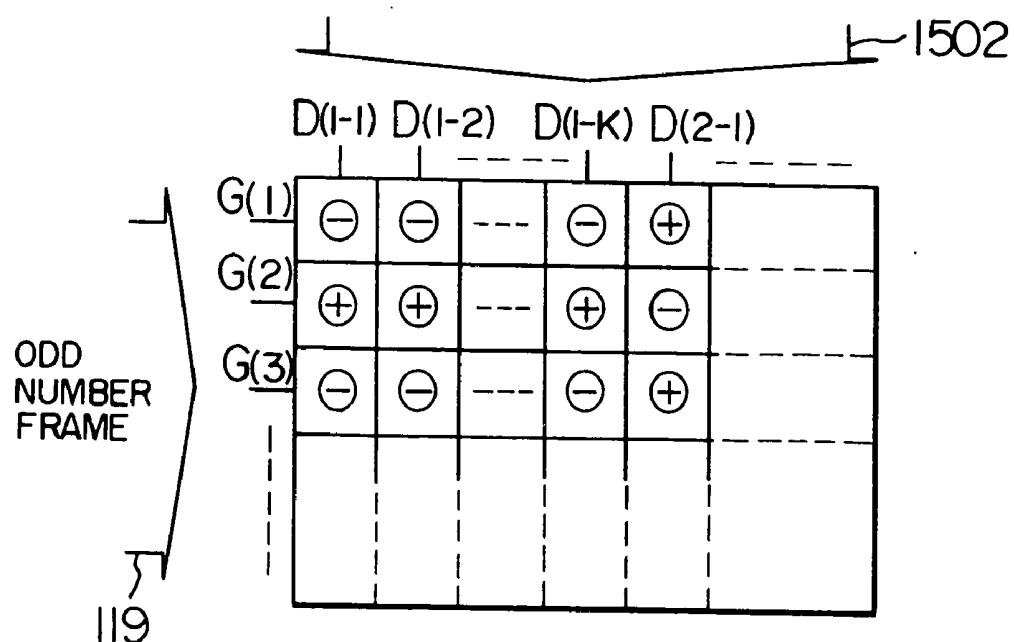

[0085] **FIG. 17** schematically indicates polarities of liquid crystal apply voltages with respect to that of the common electrode voltage in the equivalent circuit of the present invention;

[0086] **FIG. 18** schematically represents a system arrangement of a liquid crystal display apparatus according to a further embodiment of the present invention;

[0087] **FIG. 19** is a schematic block diagram of a signal drive circuit according to a further embodiment of the present invention;

[0088] **FIG. 20** is a schematic block diagram of an AC circuit according to a further embodiment of the present invention;

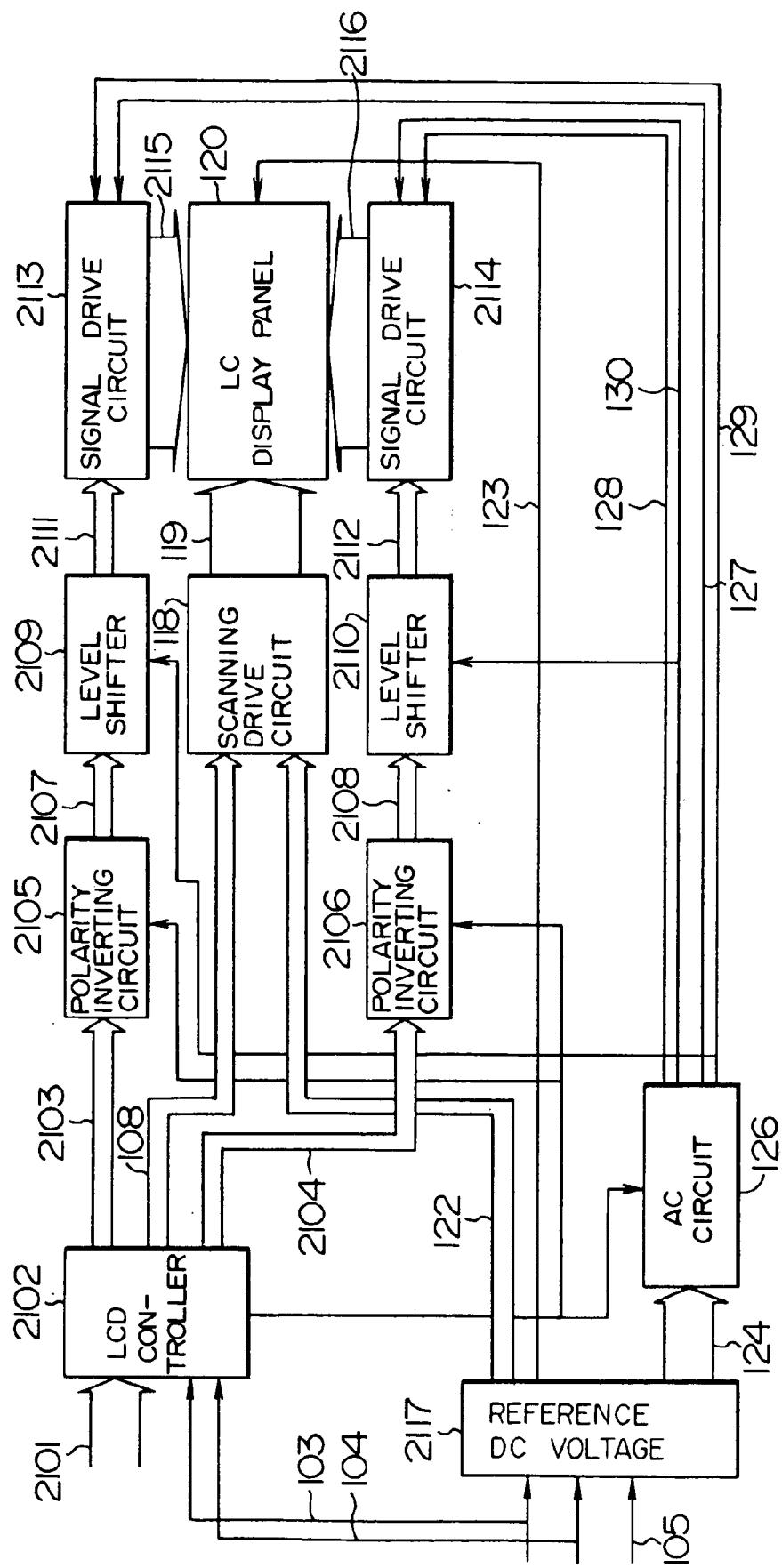

[0089] **FIG. 21** is a schematic block diagram for showing a system arrangement of a liquid crystal display apparatus according to a still further embodiment of the present invention;

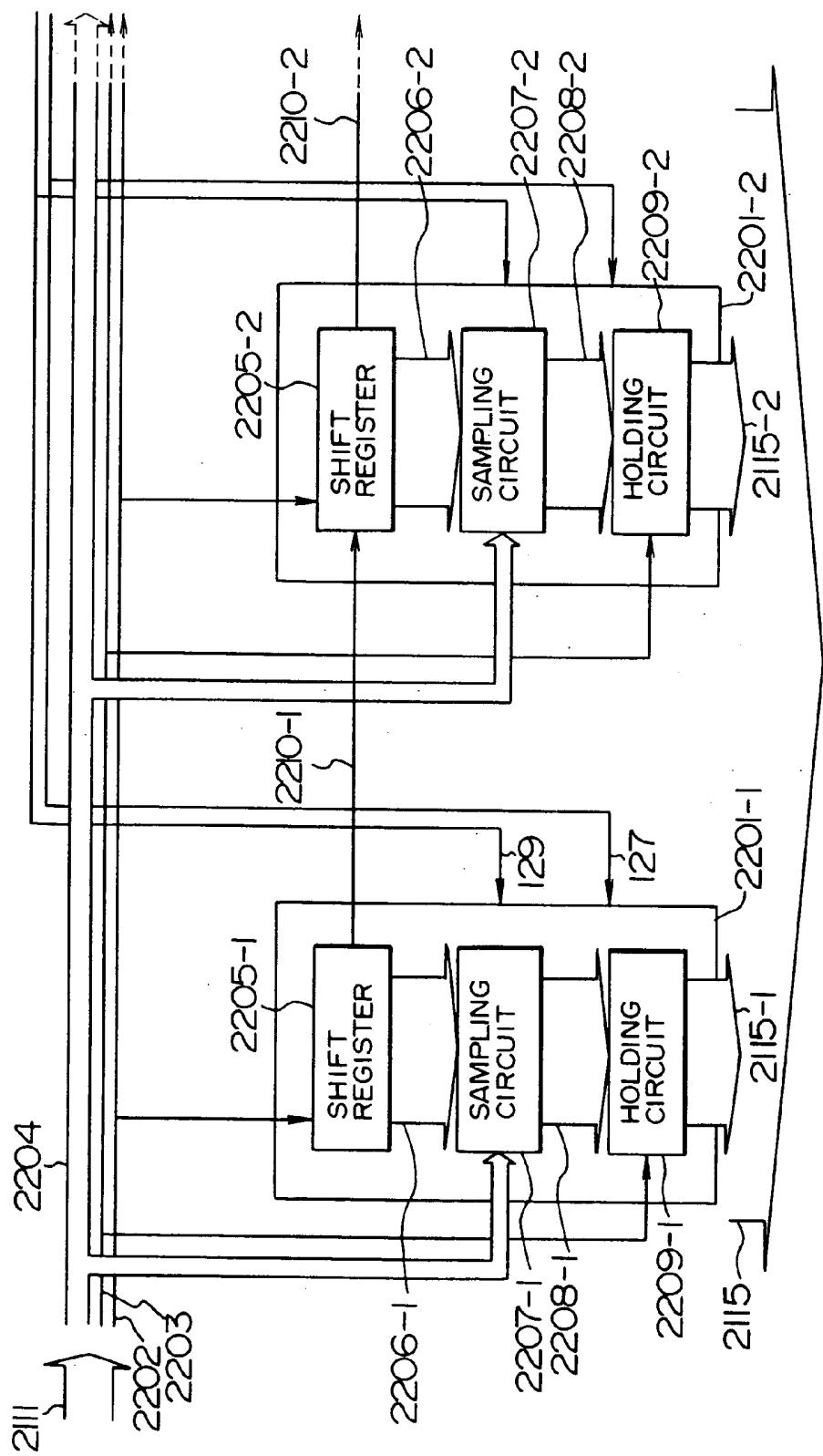

[0090] **FIG. 22** is a schematic block diagram for representing a signal drive circuit according to a still further embodiment of the present invention;

[0091] **FIG. 23** is a schematic block diagram for indicating an information processing apparatus according to one embodiment of the present invention;

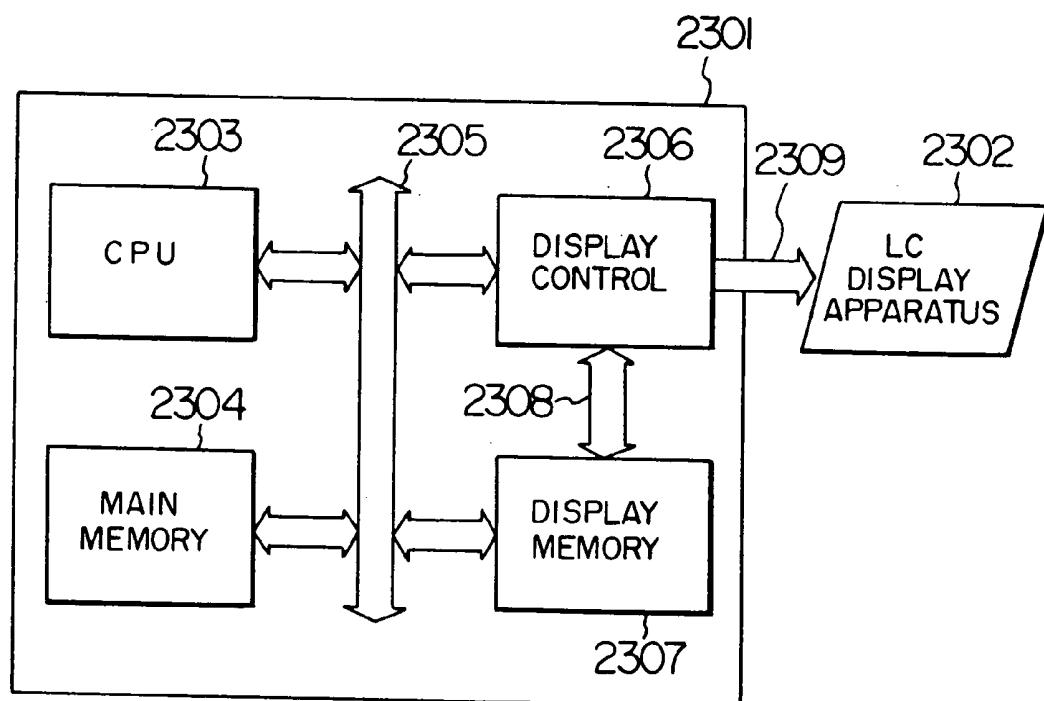

[0092] **FIG. 24** is a schematic block diagram for showing a system arrangement of the conventional liquid crystal display apparatus;

[0093] **FIG. 25** is a schematic block diagram of the conventional signal drive circuit as one example;

[0094] **FIG. 26** shows a drive waveform (line AC) of the conventional LCD display apparatus;

[0095] **FIG. 27** is a graphic representation for showing a voltage-luminance characteristic of liquid crystal;

[0096] **FIG. 28** schematically shows a system arrangement of the conventional LCD display apparatus as another example;

[0097] **FIG. 29** is a schematic block diagram for showing the conventional signal drive circuit as another example;

[0098] **FIG. 30** shows a drive waveform (line AC) of the conventional LCD display apparatus as a further embodiment;

[0099] **FIG. 31** shows an equivalent circuit of the conventional LCD panel in which current directions are represented;

[0100] **FIG. 32** is a graphic representation of a voltage-luminance characteristic of liquid crystal;

[0101] **FIG. 33** schematically denotes a system arrangement of a system arrangement of a liquid crystal display apparatus according to another embodiment of the present invention;

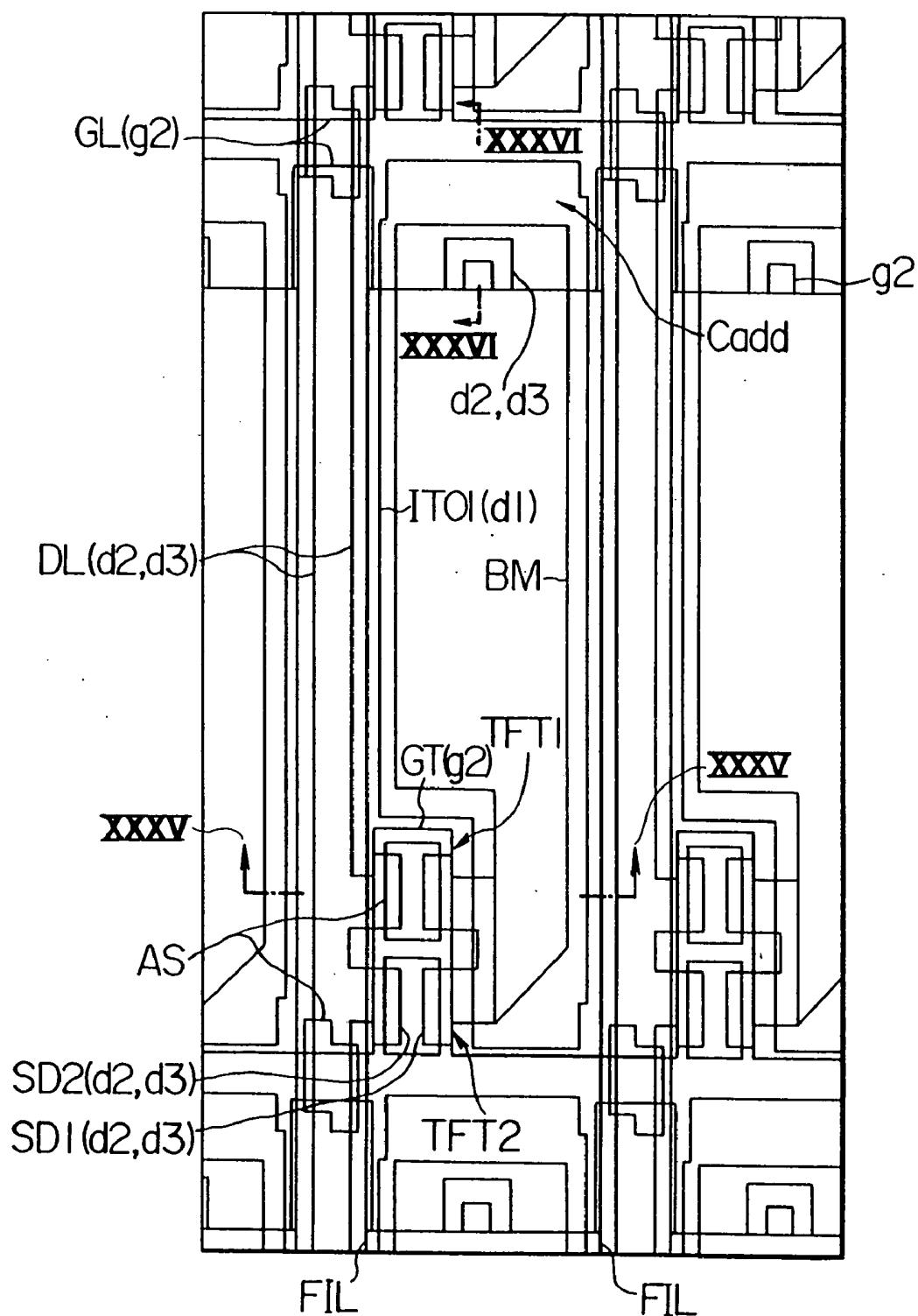

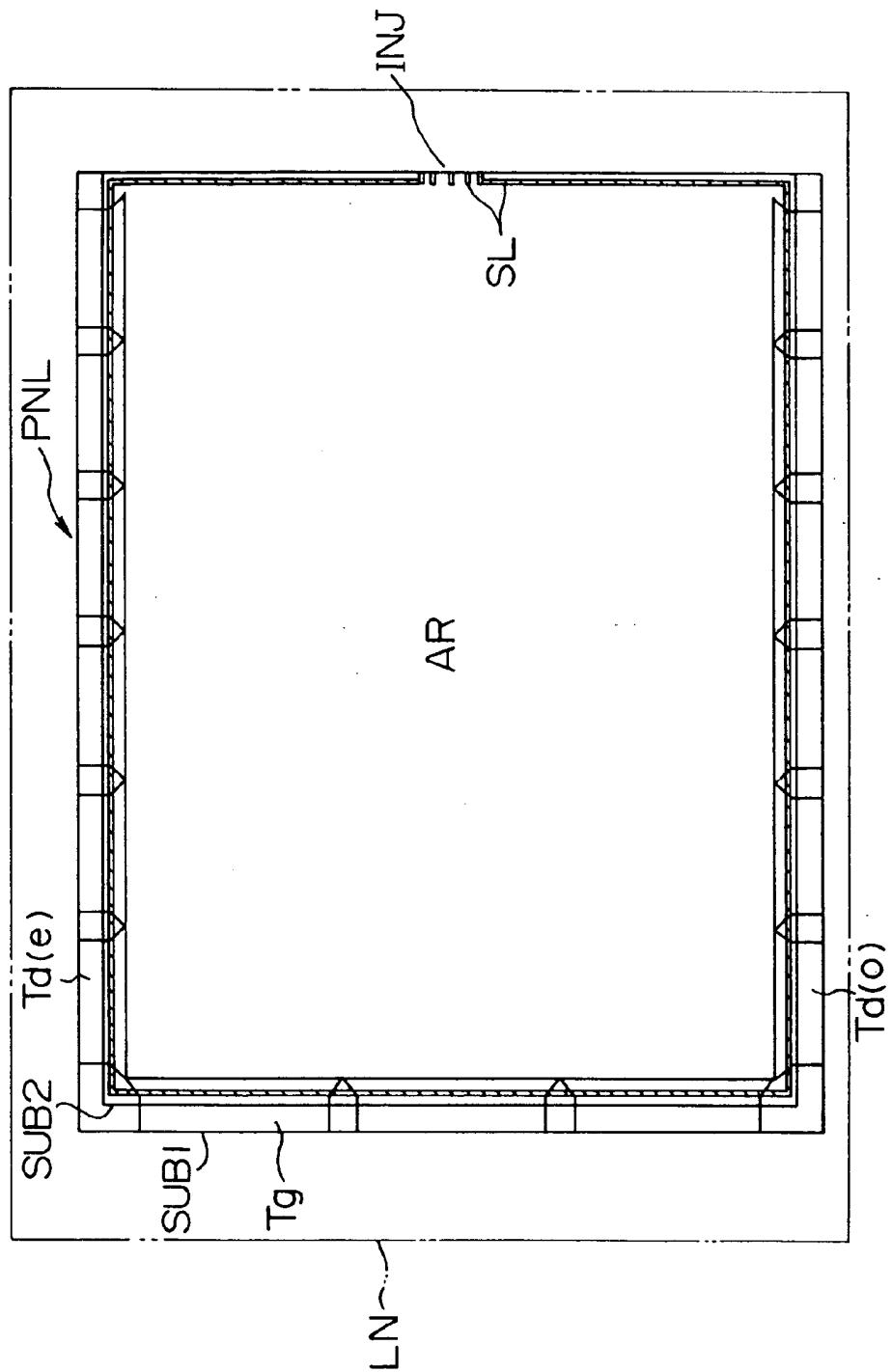

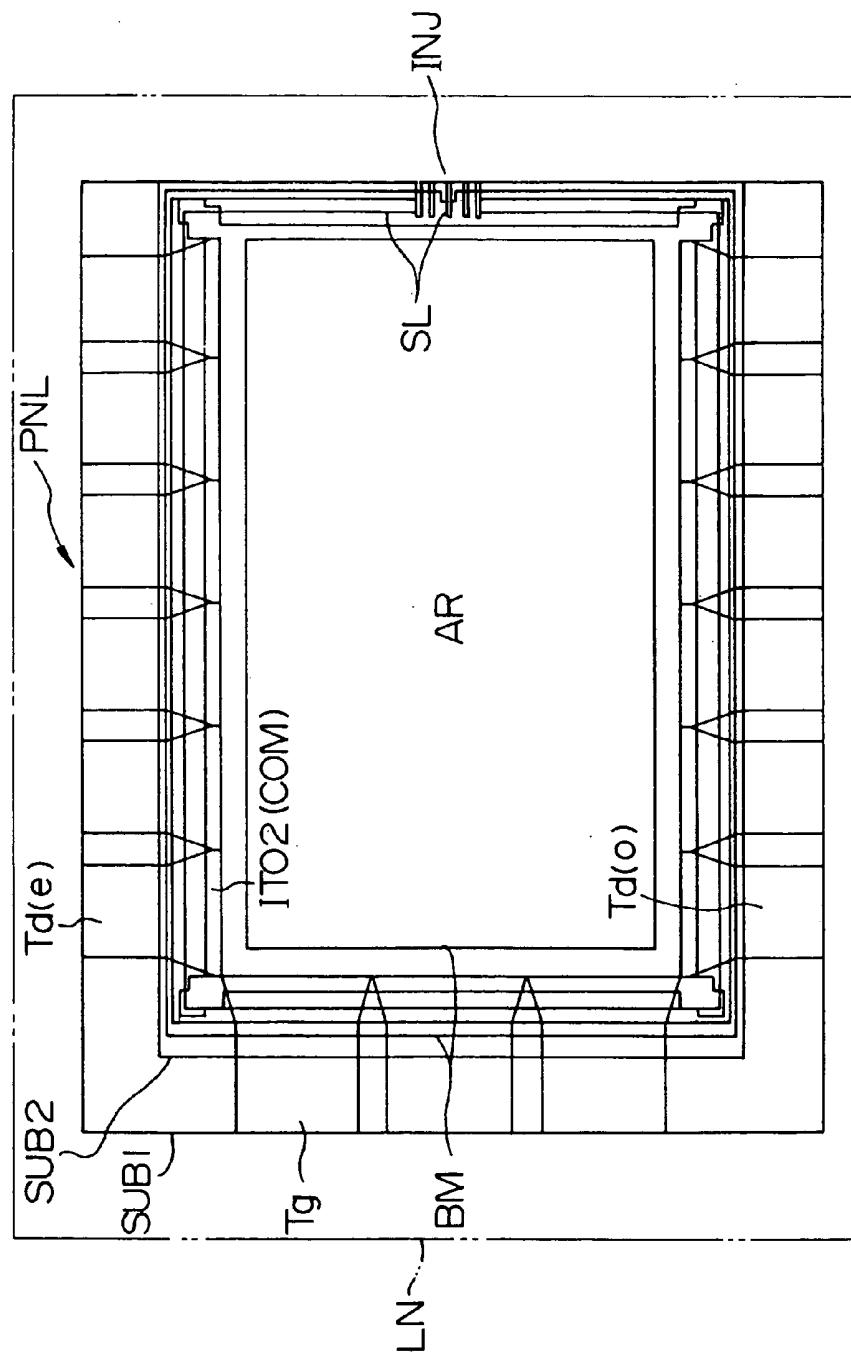

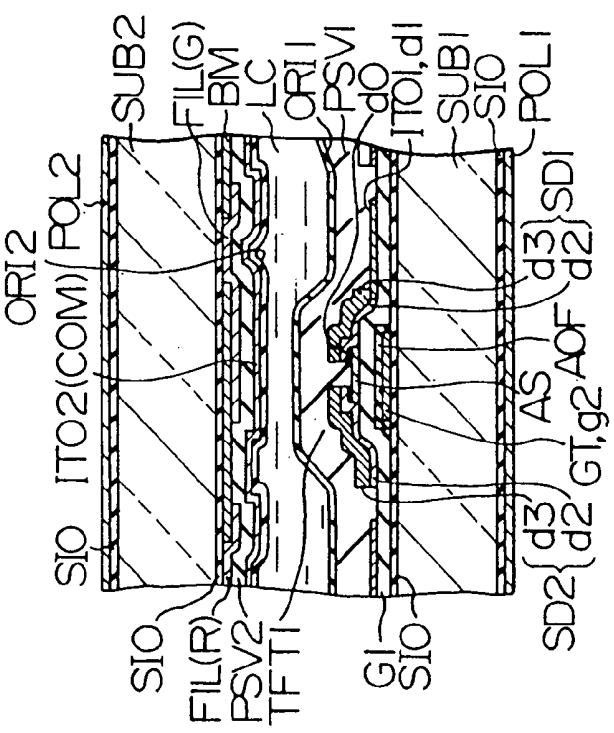

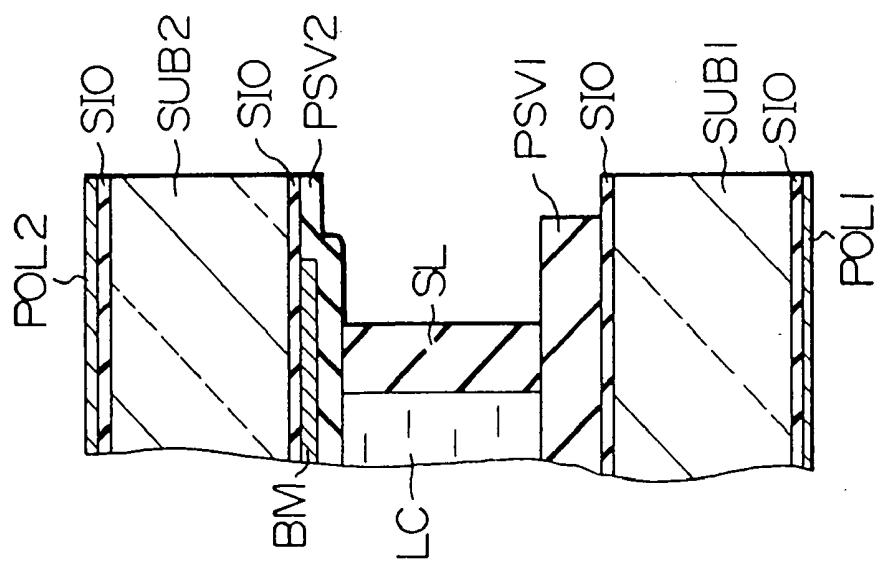

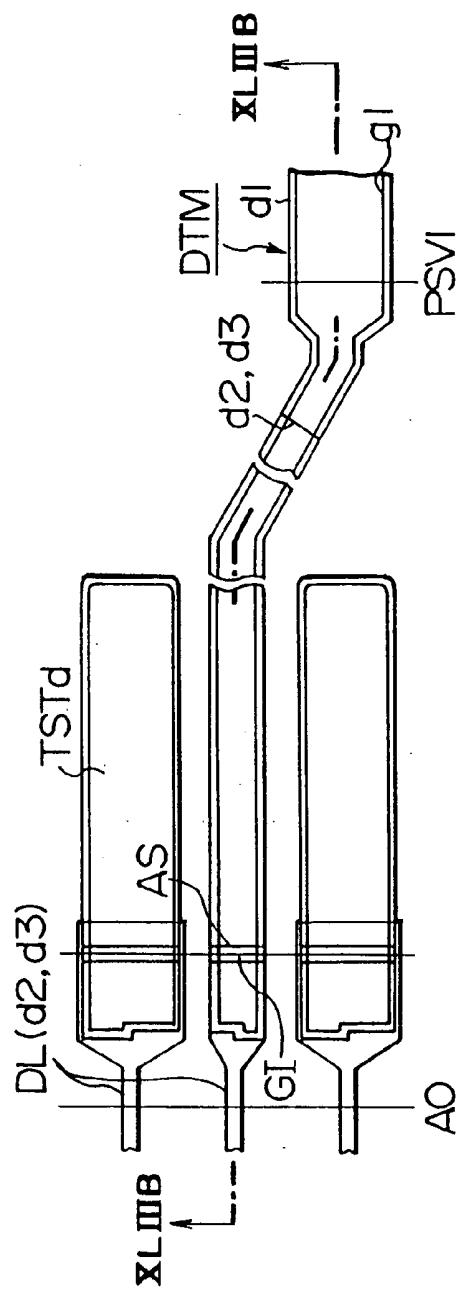

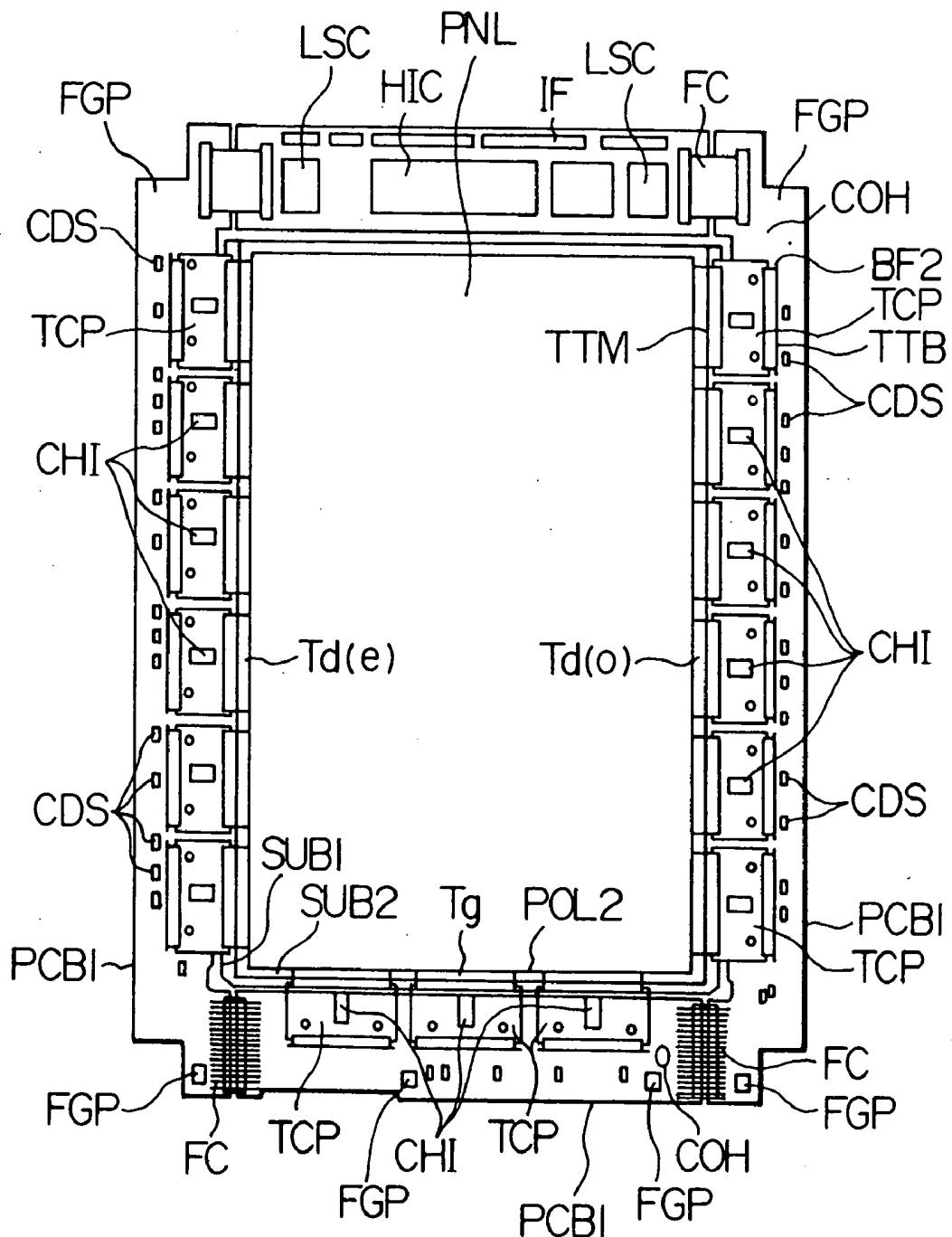

[0102] **FIG. 34** is a plan view of major portions of a pixel of a liquid crystal display unit for an active matrix type color LCD display apparatus, and of a peripheral portion thereof, to which the present invention is applied;

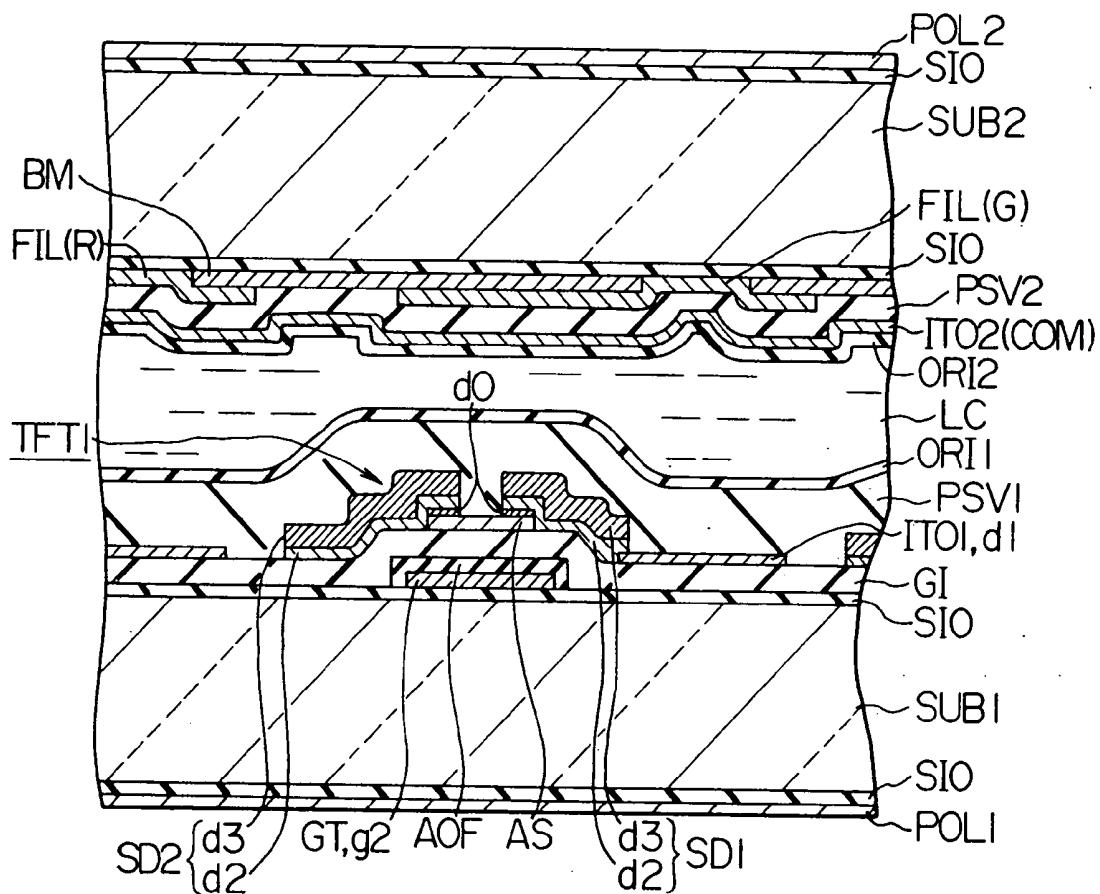

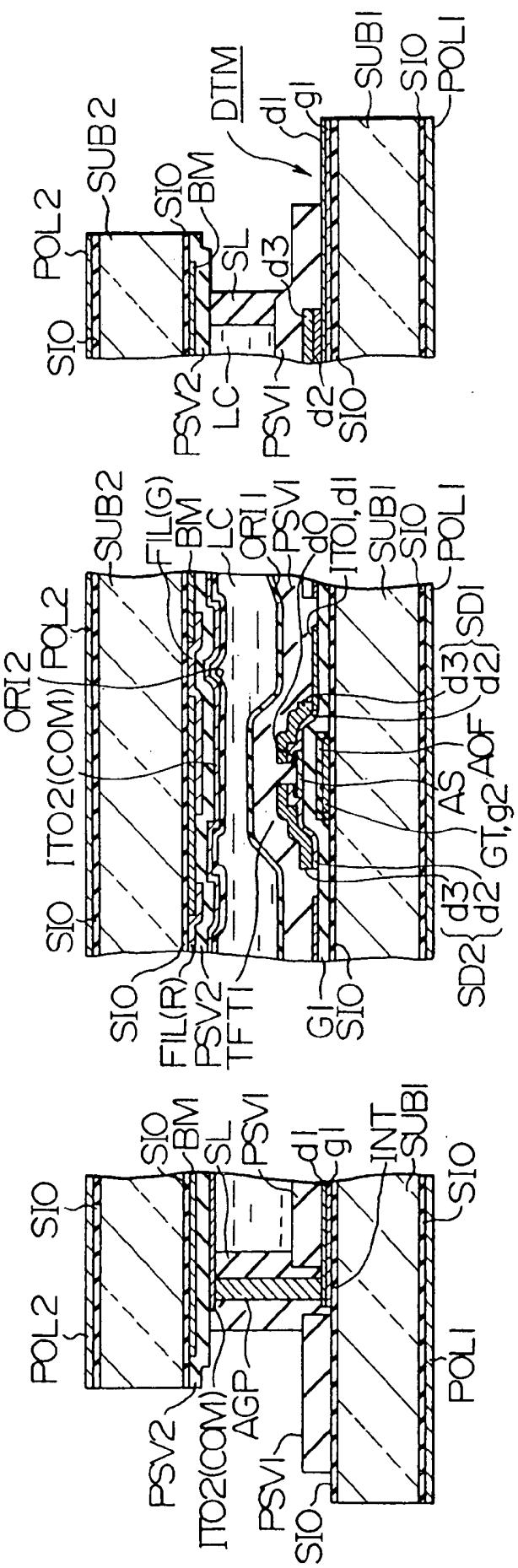

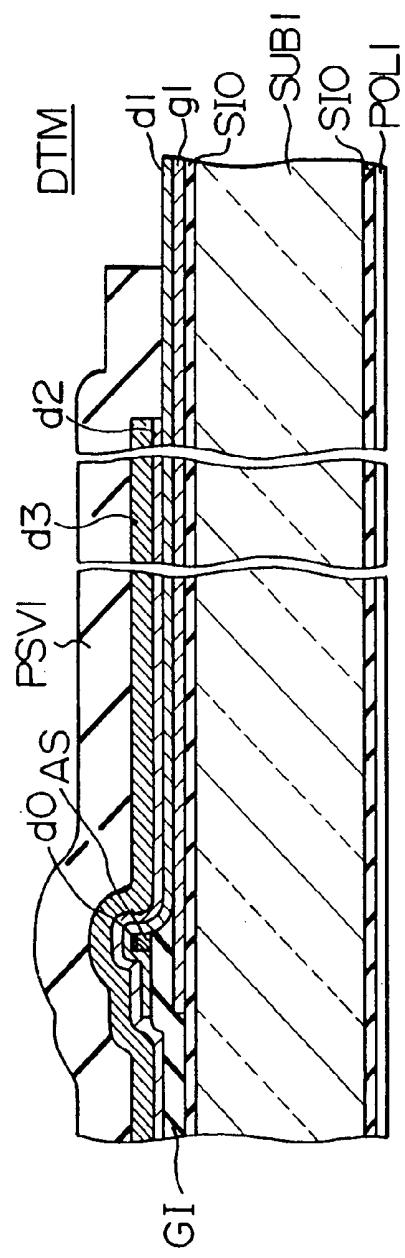

[0103] **FIG. 35** is a sectional view for indicating one pixel and the peripheral portion thereof, taken along a cutting line 3-3 of **FIG. 33**;

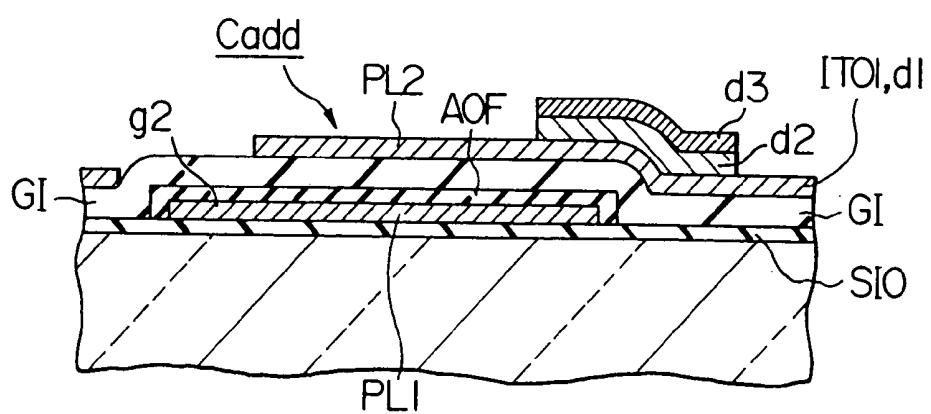

[0104] **FIG. 36** is a sectional view of an added capacitance Cadd, taken along a cutting line 4-4 of **FIG. 33**;

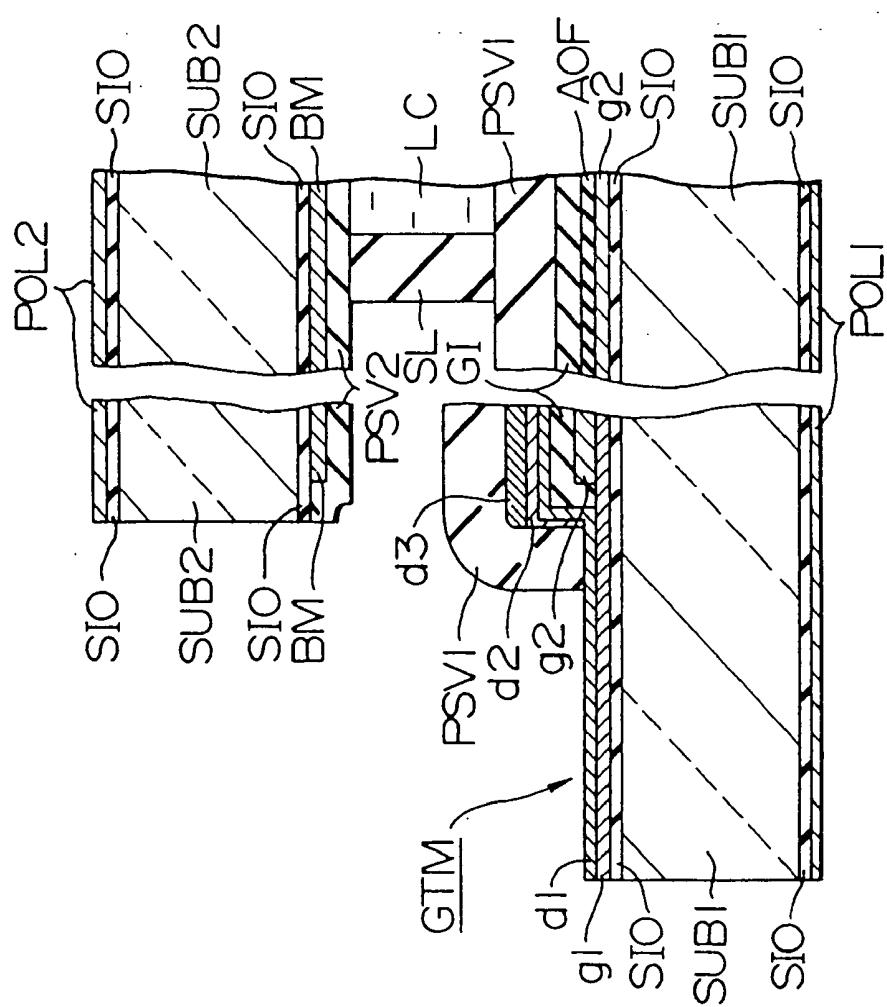

[0105] **FIG. 37** is a plan view for explaining a structure of a matrix peripheral portion of a display panel;

[0106] **FIG. 38** is another plan view for explaining the panel more concretely with an exaggerate peripheral portion of **FIG. 36**;

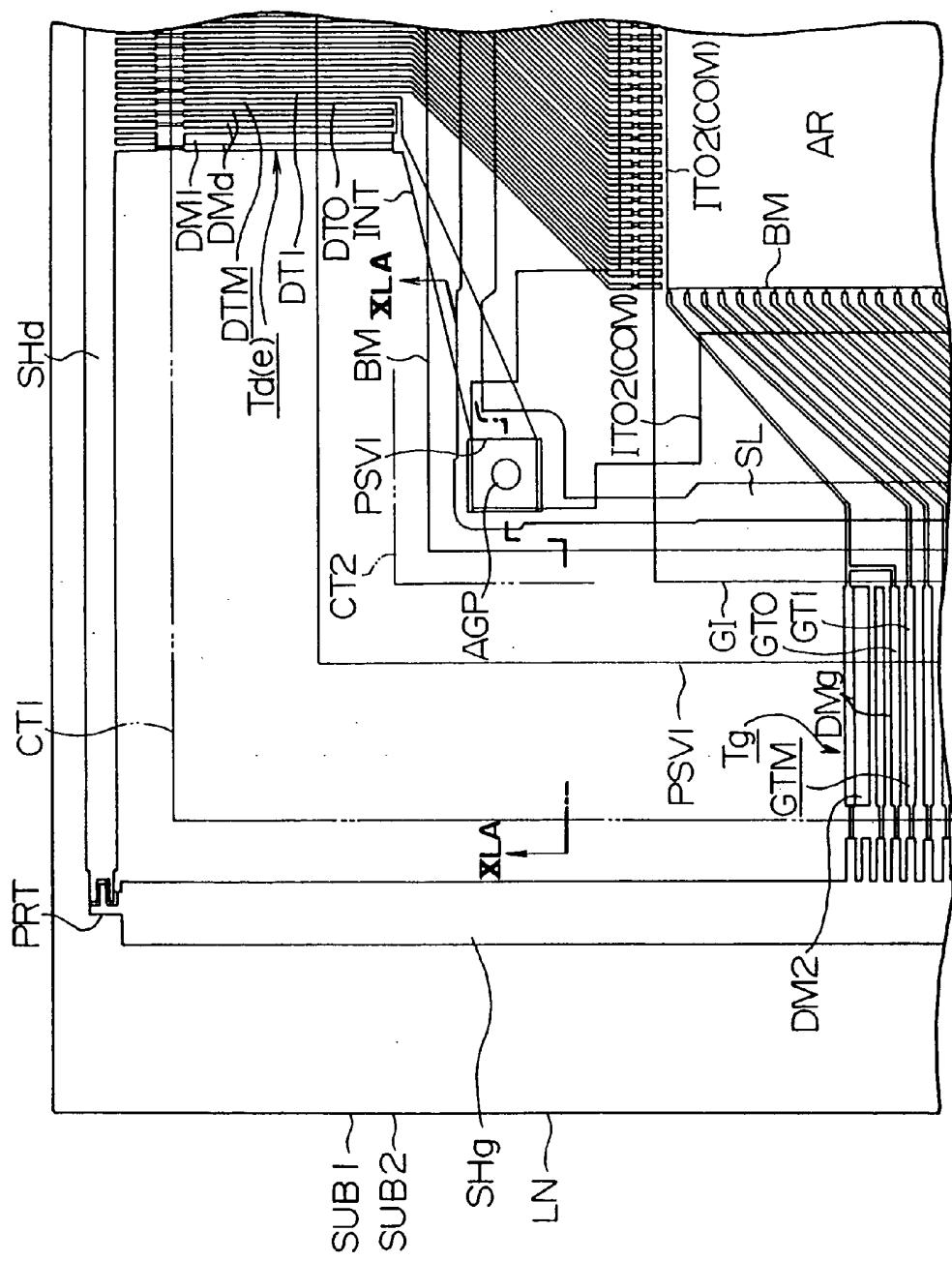

[0107] **FIG. 39** is an enlarged plan view of corners of the display panel containing electric connection units of upper/lower substrates;

[0108] **FIG. 40** is a sectional view for representing that the pixel unit of the matrix is positioned at a center, and both of panel corners and video signal terminals are located on both sides;

[0109] **FIG. 41** is a sectional view for showing that a scanning signal terminal is located at a left side and a panel edge portion having no external connection terminal is located at a right side;

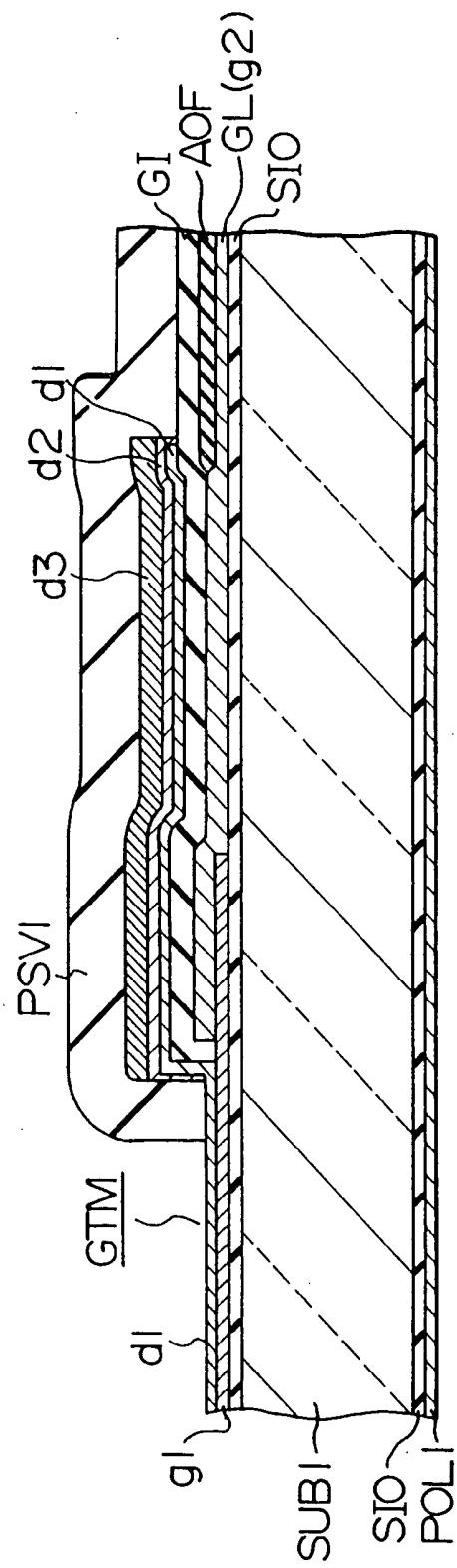

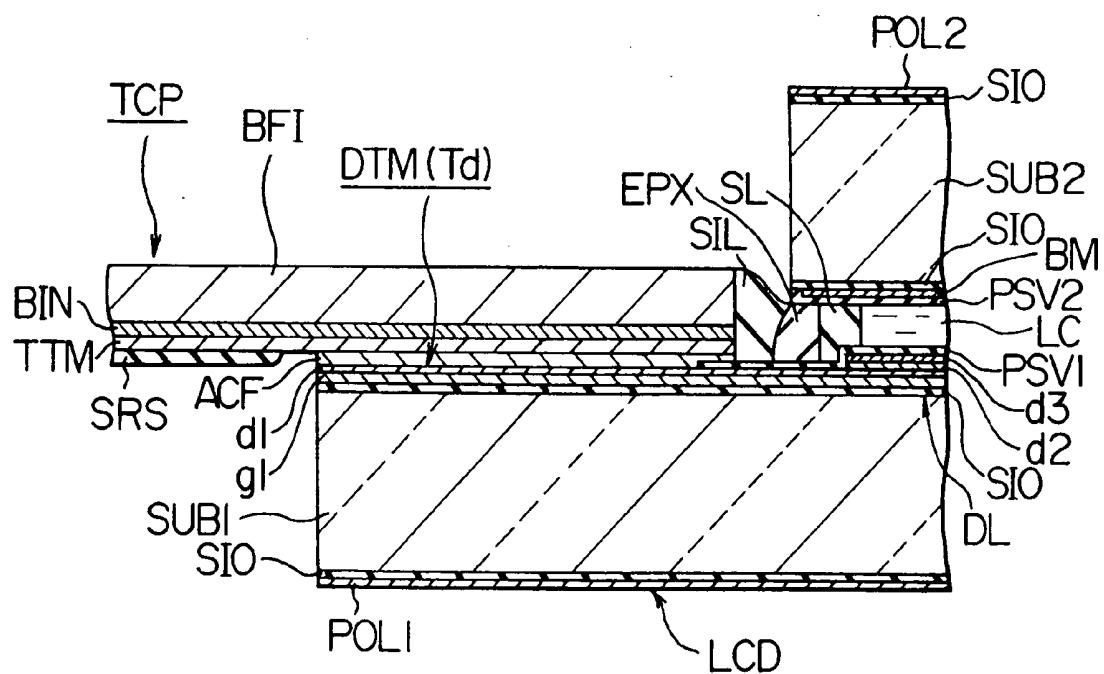

[0110] **FIGS. 42A and 42B** are plan view/sectional view for indicating a connection portion between a gate terminal GTM and a gate wiring GL;

[0111] **FIGS. 43A and 43B** are plan view/sectional view for representing a connection portion between a drain terminal DTM and a video signal line DL;

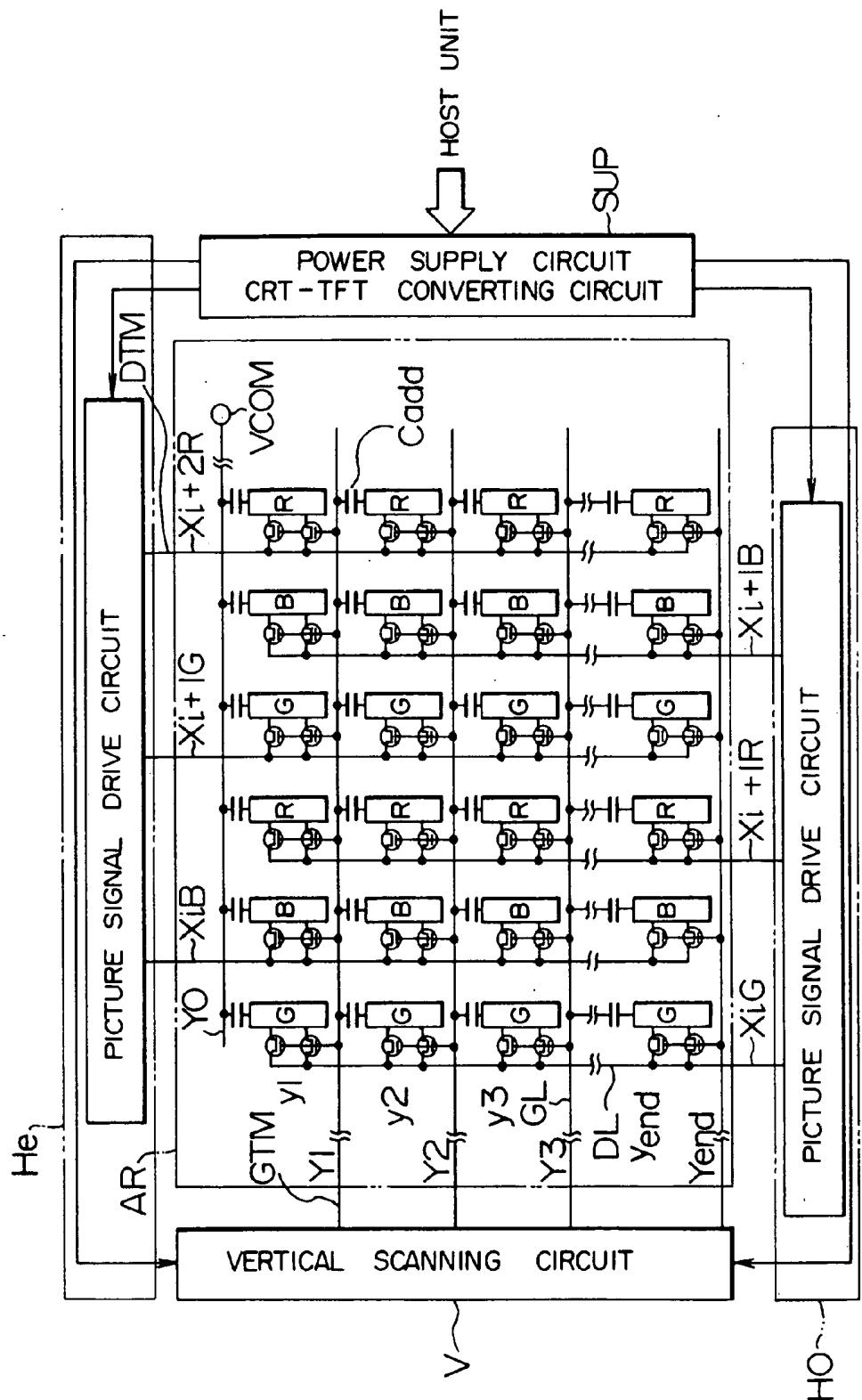

[0112] **FIG. 44** is a circuit diagram of a matrix unit and a peripheral portion thereof for the active matrix type color LCD display apparatus;

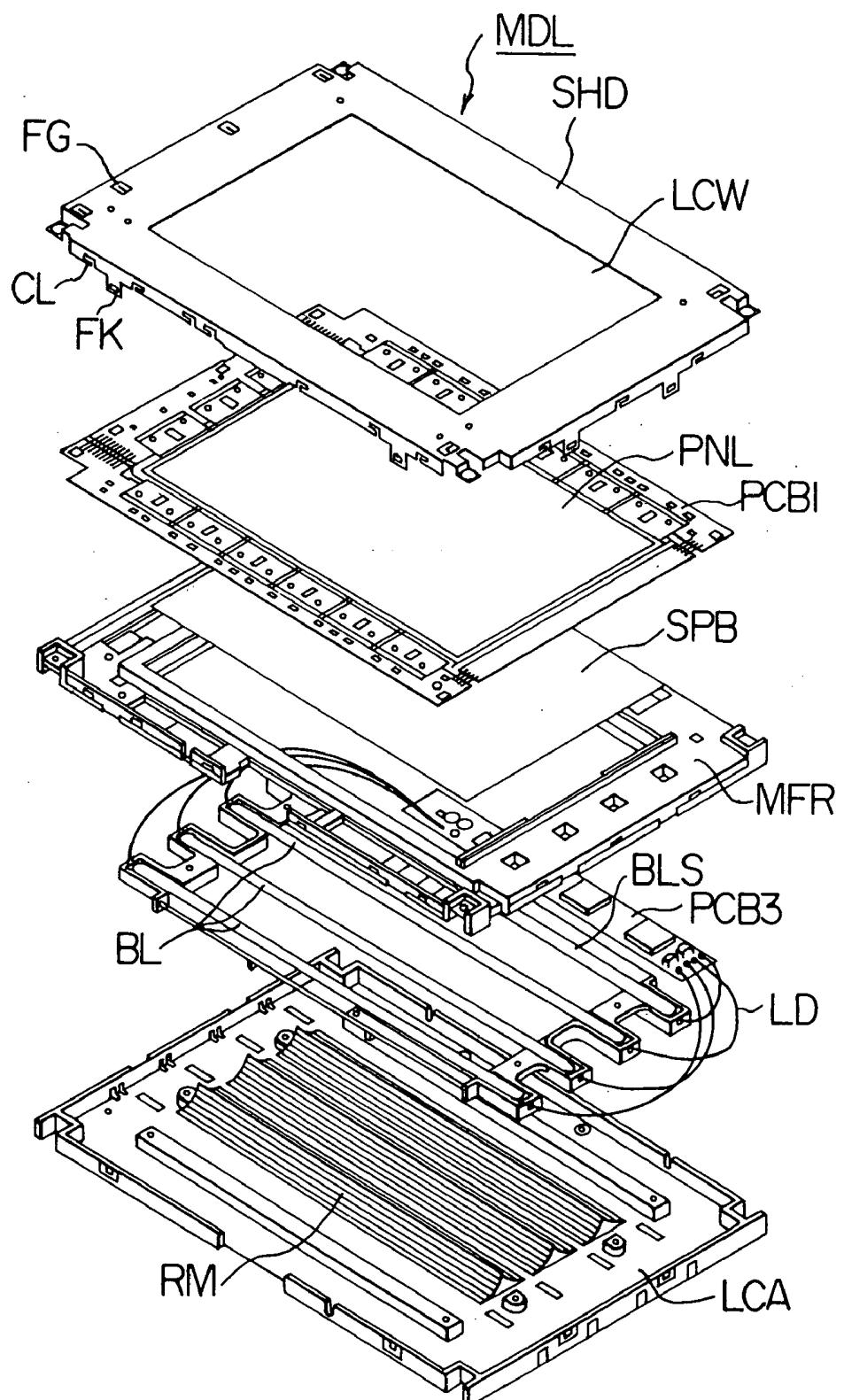

[0113] **FIG. 45** is a perspective view for showing a resolved LCD display module;

[0114] **FIG. 46** is a top view for representing such a condition that a peripheral drive circuit is actually mounted on the LCD display panel;

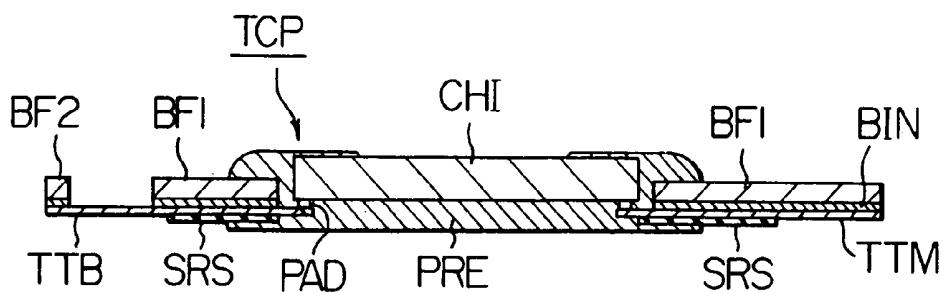

[0115] **FIG. 47** schematically shows a sectional structure of a tape carrier package TCP where an integrated circuit chip CH1 for constituting the drive circuit is mounted on a flexible wiring substrate; and

[0116] **FIG. 48** is a sectional view for indicating a major portion of such a condition that the tape carrier package TCP is connected to the video signal circuit terminal DTM of the LCD panel PNL.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0117] Referring to FIGS. 1 to 13 and a table 1, a liquid crystal display apparatus, according to an embodiment of the

present invention, arranged by employing signal drive circuits at an upper side of a liquid crystal panel and a lower side thereof. The signal drive circuits convert input digital display data into a liquid crystal apply voltage and supply the liquid crystal panel for representation purposes.

[0118] FIG. 1 schematically shows a system arrangement of the liquid crystal display apparatus according to this embodiment of the present invention.

[0119] In FIG. 1, reference numeral 101 is a system bus for transferring digital image data and a synchronization (sync) signal. In this embodiment, it should be noted that both the image data and the sync signal transferred via the system bus 101 are such line sequential scanning signals similar to the image data and the sync signal transferred to be displayed on the CRT (cathode-ray tube) display apparatus. Reference numeral 102 denotes a liquid crystal controller for converting the digital image data and the sync signal transferred via the system bus 101 into digital LCD image data and a timing signal for driving the liquid crystal display apparatus. Reference numerals 103, 104, 105 indicate reference voltage lines for transferring reference voltages, in which 103 is a digital drive voltage  $V_{EE}$ , 104 is a digital-high drive voltage  $V_{CC}$ , and 105 is DC voltages having various voltage levels of the LCD drive voltage  $VLCD1$ . Reference numerals 106 and 107 denote signal drive circuit control buses for transferring both of the digital LCD image data and the timing signal which have been converted for the signal drive circuit under control of the LCD controller 102. Reference numeral 108 is a scanning drive circuit control bus used to transfer a timing signal for a scanning drive circuit. Reference numeral 109 shows an LCD alternating signal which becomes a timing signal for alternating a polarity of a voltage applied to a liquid crystal display, and a drive voltage of the signal drive circuit. Reference numerals 110 and 111 are level sifters for converting voltage levels of the digital LCD image data and the timing signal which are transferred via the respective signal drive circuit control buses 106, 107, into drive voltage levels of the signal drive circuits. Reference numerals 112 and 113 are signal drive circuit control buses for transferring the digital LCD image data and the timing signal whose voltage levels have been shifted by the level sifters 110 and 111. Reference numerals 114 and 115 denote signal drive circuits which fetch the digital LCD image data transferred via the respective signal drive circuit control buses 112, 113 in response to the timing signal, and convert the fetched image data into LCD apply voltages corresponding to the digital LCD image data. Then, the LCD apply voltages are applied to the LCD panel.

[0120] Reference numerals 116 and 117 show signal line for transferring the LCD apply voltages produced in the respective signal drive circuits 114 and 115. Reference numeral 118 is a scanning drive circuit and reference numeral 119 is a scanning line. The scanning drive circuit 118 sequentially causes the scanning line 119 to be active in response to the timing signal transferred via the scanning drive circuit control bus 108. Reference numeral 120 is a liquid crystal display panel. Reference numeral 121 is a reference DC voltage producing circuit for producing various DC reference voltages used to operate this LCD apparatus. Reference numeral 122 shows a DC voltage line used to the scanning drive circuit, for applying the DC voltages to the scanning drive circuit 118. Reference numeral 123

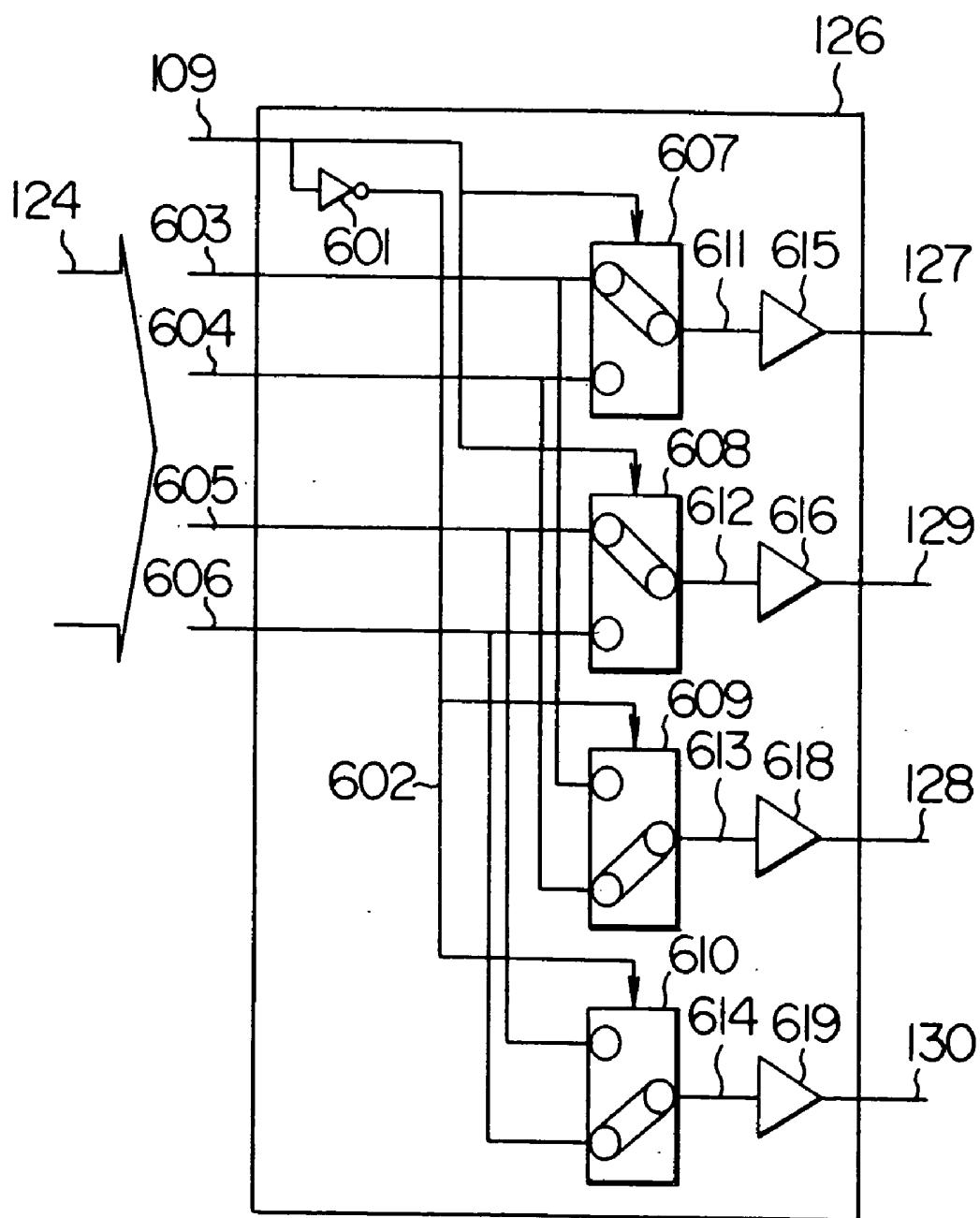

denotes a common (opposing) electrode line for transferring a DC common voltage. Reference numeral 124 is a reference DC voltage line for signal drive circuit, and reference numeral 125 is another reference DC voltage line for signal drive circuit. Reference numeral 126 shows an AC circuit. Reference numeral 127 indicates a reference voltage line for transferring a high-level reference voltage used to drive the upper-sided signal drive circuit 114, and similarly reference numeral 128 is a reference voltage line for transferring a high-level reference voltage used to drive the lower-sided signal drive circuit 115. Reference numeral 129 shows a reference voltage line for transferring a low-level reference voltage used to drive the upper-sided signal drive circuit 114, and similarly reference numeral 130 indicates a reference voltage line for transferring a low-level reference voltage used to drive the lower-sided signal drive circuit 115. It should be understood that any of the reference voltages transferred via the reference voltage lines 129 and 130 become reference voltages for the level sifters 110 and 111. Reference numeral 131 denotes an AC circuit. Reference numeral 132 is an LCD drive voltage line used to transfer the AC LCD drive voltage employed in the upper-sided signal drive circuit 114, whereas reference numeral 133 is an LCD drive voltage line used to transfer the AC LCD drive voltage employed in the lower-sided signal drive circuit.

[0121] FIG. 2 is a schematic block diagram of the level sifter 110 shown in FIG. 1, according to an embodiment of the present invention.

[0122] In FIG. 2, reference numerals 201-1 to 201-N indicate adder circuits for constituting the level sifter 110. The level sifter 110 owns the adder circuits 201-1 to 201-N, the number of which is equal to that of the signal lines for the signal drive circuit control bus 106. In this embodiment, two adder circuits 201-1 to 201-2 are prepared for the sync signals, and (N-2) adder circuits 201-3 to 201-N are prepared for the digital LCD image data. It should be noted that the level sifter 111 has a similar circuit arrangement to that of this level sifter 110. Reference numeral 202-1 indicates an amplifier and reference numerals 203-1, 204-1, 205-1, 206-1 show resistors. Among the signal drive circuit control bus 106, the control bus 106-1 is to transfer the shift clock, the control bus 106-2 is to transfer the latch clock, and reference numerals 106-3 to 106-N are LCD image data buses transferring the digital LCD image data. A bus 112-1 is to transfer a latch clock after being level-shifted, a bus 112-2 is to transfer a latch clock after being level-shifted, and reference numerals 112-3 to 112-N indicate LCD image data buses for transferring the digital LCD image data after being level-shifted. The voltage levels of the signals outputted from the adder circuits 201-1 to 201-N are equal to voltage values obtained by adding the reference voltage transferred via the reference voltage line 129 to the voltage levels of the input signals. As a result, the amplitudes of the voltage values of the signals representative of "1" and "0", outputted from the adder circuits 201-1 to 201-N are equal to those of the voltage values of the signals indicative of "1" and "0" inputted to the adder circuits 201-1 to 201-N.

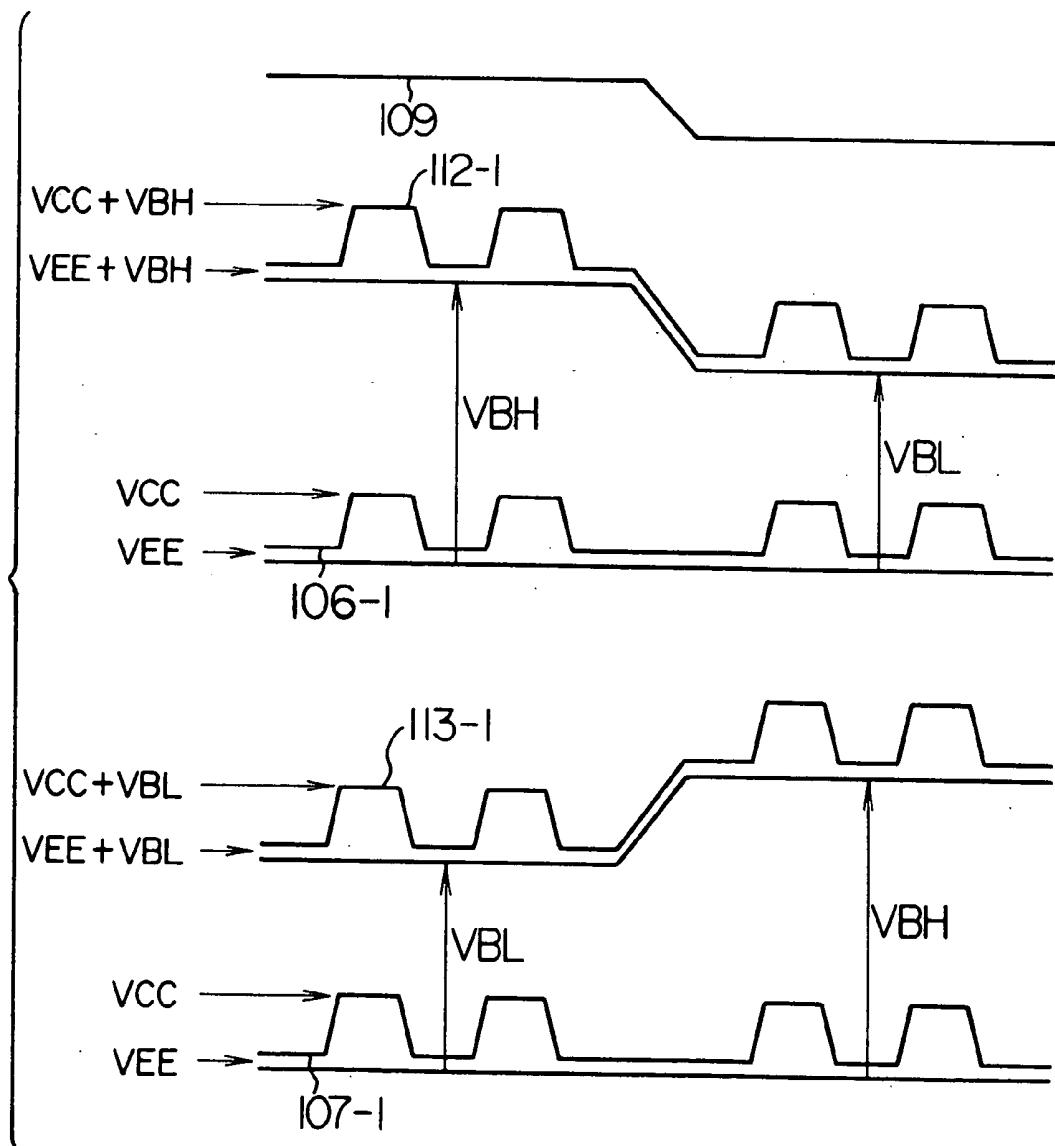

[0123] In FIG. 3, there is shown such a condition that the voltage levels are converted by the level sifters 110 and 111. It is assumed that voltage values indicative of "1" of the latch clocks 106-1 and 107-1 are "VCC", and voltage values representative of "0" thereof are "VEE". In other words, a

low-level voltage transferred via the reference voltage line 103 is VEE, and a digital high level transferred via the reference voltage 104, namely a voltage of a digital drive level is VCC. Also, high-potential voltage values of the reference voltage lines 129 and 130 are VBH with respect to VEE, and low-potential voltage values thereof are VBL with regard to VEE.

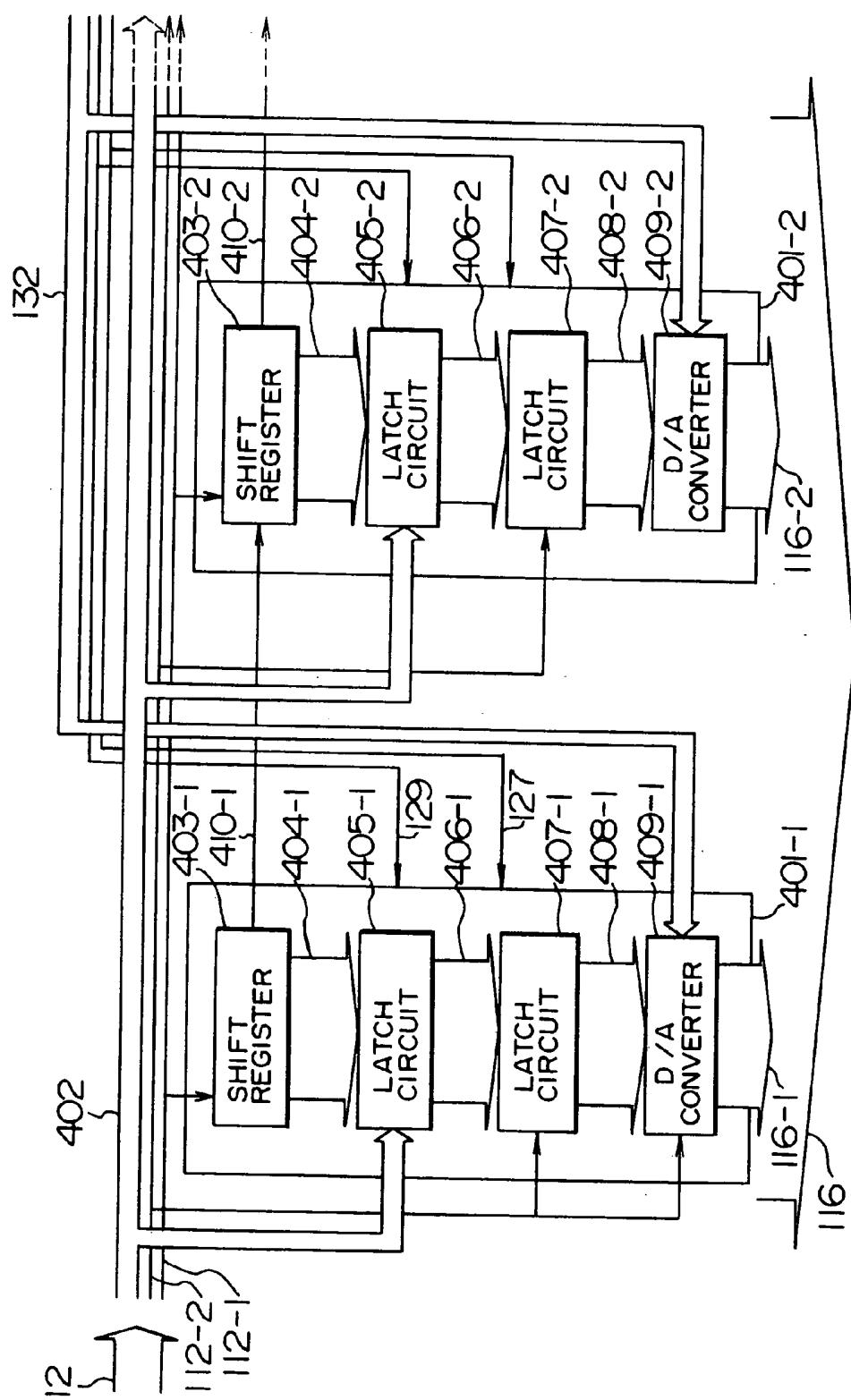

[0124] FIG. 4 is a schematic block diagram for showing an internal circuit arrangement of the signal drive circuit 114 of FIG. 1 according to one embodiment of the present invention. It should be understood that the signal drive circuit 115 provided at the low side of the LCD panel 120 has a similar circuit arrangement to that of this signal drive circuit 114.

[0125] In FIG. 4, reference numerals 401-1, 401-2, . . . , denote drain drivers, and the signal drive circuit 114 is constructed of a plurality of drain drivers 401. It should also be noted that the signal drive circuit 115 provided at the lower side of the LCD panel 120 shown in FIG. 1 is similarly arranged by a plurality of drain drivers. The drain driver 401 has a function such that the digital LCD image data is inputted and converted into the LCD apply voltage which will then be outputted to the LCD panel 120. In the signal drive circuit control bus 112, reference numeral 402 is an LCD image data bus, and a generic name for representing the LCD image data buses 201-2 to 201-N shown in FIG. 2. Furthermore, reference numeral 112-1 is a shift clock, and reference numeral 112-2 is a latch clock. The shift clock 112-1 is synchronized with the digital LCD image data transferred via the LCD image data bus 402. The latch clock 112-2 becomes active after the digital LCD image data for 1 horizontal line have been transferred to the signal drive circuits 114 and 115. Reference numeral 403 indicates a shift register, and reference numeral 404 represents a latch signal. In response to the shift clock 112-1, the shift register 403 performs the shift operation. In accordance with this shift operation, the latch signals 404 are sequentially valid. Reference numeral 405 is a latch circuit which sequentially latches the digital LCD image data transferred via the LCD image data bus 402 in response to the latch signal 404. Reference numeral 406 is a data bus for transferring the data latched by the latch circuit 405. Reference numeral 407 is a latch circuit for latching the data transferred via the data bus 406 in response to the latch clock 112-2. Reference numeral 408 is a data bus for transferring the data latched by the latch circuit 407. Reference 409 denotes a digital-to-analog converting circuit for converting the digital data transferred via the data bus 408 into the LCD apply voltage based on the LCD drive voltage transferred via the LCD drive voltage line 132. Reference numeral 116 is a signal line used to transfer the LCD apply voltage produced by the D/A converting circuit 409. Reference numeral 410 is an enable signal which corresponds to such a control signal that when the fetching operation of the digital LCD image data by the latch circuit 403 has been accomplished, namely when the shift operation by the shift register 403 has been completed, the shift register 403 of the drain driver 401 at the subsequent stage is operated so as to commence the fetching operation of the digital LCD image data by the latch circuit 405 of the drain driver 401 at the subsequent stage.

[0126] In the drain driver 401, any of the digital circuit units for the shift register 403, the latch circuit 405 and the latch circuit 407, and also the D/A converting circuit 409 are

driven under the high-level reference voltage transferred via the reference voltage line 127 and the low-level reference voltage transferred via the reference voltage line 129.

[0127] FIG. 5 shows an equivalent circuit diagram of the liquid crystal display panel 120 shown in FIG. 1.

[0128] In FIG. 5, symbols DU(m), DU(m+1), DL(m) and DL(m+1) represent signal lines corresponding to pixel units for constituting signal lines 116 and 117. Symbols G(n-1), G(n), G(n+1) denote scanning lines corresponding to the respective pixel units for constituting a scanning line 119. Reference 501 shows a pixel unit. In the pixel unit 501, reference numeral 502 is a thin-film transistor (abbreviated as "TFT"), reference numeral 503 is a liquid crystal display, and reference numeral 504 is an added capacitance. A drain electrode of the TFT 502 is connected to the signal line 116, and a gate electrode thereof is connected to the scanning line 119. The drain electrodes of the TFTs 502 employed within the respective pixel units 501 arranged along the vertical direction commonly use the signal line, for instance, DU(m). The gate electrodes of the TFTs 502 employed in the respective pixel units 502 arranged along the horizontal direction commonly use the scanning line, for example, G(n). Furthermore, the source electrodes of the TFTs 502 are connected to one electrode of each of the liquid crystal display 503 and the added capacitance 504. The other electrode of the liquid crystal display 503 is connected to a common electrode line 123, and all pixels thereof commonly utilize the common electrode line 123. One electrode of the added capacitance 504 is connected to the scanning line provided at the pre stage. For example, in case of the added capacitance 504 connected to the TFT 502 under control of the scanning line G(n), the electrode is connected to the scanning line G(n-1).

[0129] Even if another electrode of the added capacitance 504 is connected to a newly employed electrode line (not shown in this embodiment), other circuits and the drive conditions shown in FIG. 1 are the same as those above except that a voltage applied to the newly provided electrode line is selected to be equal to the common electrode voltage applied to the common electrode line 123. Furthermore, even when no added capacitance 504 is provided in the pixel unit 501, other circuits and the drive conditions shown in FIG. 1 are the same as those above.

[0130] As described above, this LCD panel 120 is constructed of a matrix structure having a plurality of pixel units 501 along the horizontal direction and the vertical direction. For instance, when a screen with 640 pixels in horizontal resolution and 480 lines in vertical resolution is displayed, the horizontal resolution of 640 pixels can be realized by arranging 1920 pixels along the horizontal direction, and attaching red, green, blue color filters to three adjacent pixels to constitute 1 pixel. Furthermore, the 480 pixel arrangements as explained with regard to the horizontal direction are prepared for the vertical direction, thereby obtaining the vertical resolution of 480 lines. In this embodiment, the LCD panel 120 is so arranged that the signal lines of the adjacent pixel units 501 are alternately drawn as a signal line 116 and a signal line 117. It should be noted that even when the signal line 116 and the signal line 117 are alternately drawn in a pixel alternating form, the LCD controller 102 shown in FIG. 1 merely performs the data conversion in conformity to this pixel alternating form, but

other circuit arrangements and the drive conditions are similar to those of this embodiment.

[0131] **FIG. 6** is a schematic block diagram for showing an internal circuit of the AC circuit 126 shown in **FIG. 1**, according to one embodiment of the present invention.