US 20050003640A1

(19) **United States**

(12) **Patent Application Publication**

Ushiyama et al.

(10) **Pub. No.: US 2005/0003640 A1**

(43) **Pub. Date: Jan. 6, 2005**

(54) **METHOD FOR FABRICATING THIN FILM PATTERN, DEVICE AND FABRICATING METHOD THEREFOR, METHOD FOR FABRICATING LIQUID CRYSTAL DISPLAY, LIQUID CRYSTAL DISPLAY, METHOD FOR FABRICATING ACTIVE MATRIX SUBSTRATE, ELECTRO-OPTICAL APPARATUS, AND ELECTRICAL APPARATUS**

(75) Inventors: **Toshihiro Ushiyama**, Chino-shi (JP); **Toshimitsu Hirai**, Chino-shi (JP); **Toshiaki Mikoshiba**, Suwa-shi (JP); **Hirosi Kiguchi**, Suwa-shi (JP); **Hironori Hasei**, Okaya-shi (JP)

Correspondence Address:

**OLIFF & BERRIDGE, PLC**

**P.O. BOX 19928**

**ALEXANDRIA, VA 22320 (US)**

(73) Assignee: **SEIKO EPSON CORPORATION**,

Tokyo (JP)

(21) Appl. No.: **10/854,668**

(22) Filed: **May 27, 2004**

(30) **Foreign Application Priority Data**

May 30, 2003 (JP) ..... 2003-155858

May 30, 2003 (JP) ..... 2003-155865

May 30, 2003 (JP) ..... 2003-155866

May 30, 2003 (JP) ..... 2003-155867

Mar. 31, 2004 (JP) ..... 2004-103418

**Publication Classification**

(51) **Int. Cl.<sup>7</sup>** ..... **C30B 1/00**

(52) **U.S. Cl.** ..... **438/502**

(57) **ABSTRACT**

A method for fabricating a thin film pattern on a substrate, includes the steps of: forming a concave part on the substrate that conforms to the thin film pattern; and applying a function liquid into the concave part.

FIG. 1

FIG.2

FIG.3A

FIG.3B

FIG.3C

FIG.4D

FIG.4E

FIG.4F

FIG.5

FIG.6

FIG.7

FIG.8

FIG.9

FIG.10

FIG.11

FIG.12

FIG.13

FIG.14

FIG.15

FIG.16

FIG.17

FIG.18

FIG.19A

FIG.19B

FIG.20

FIG.21

FIG.22

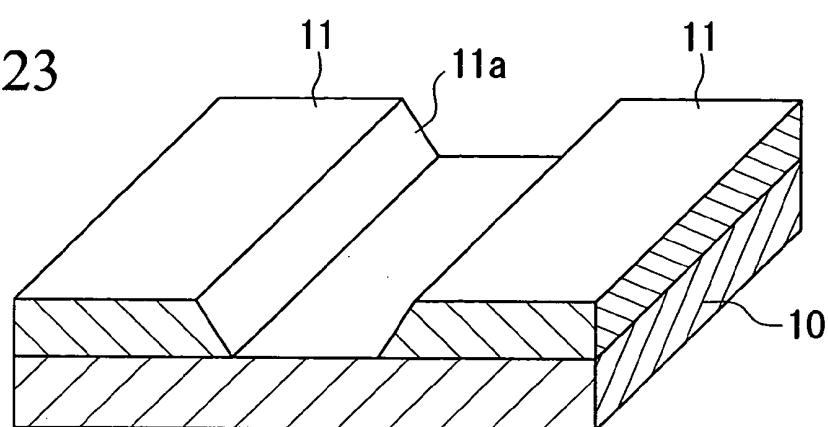

FIG.23

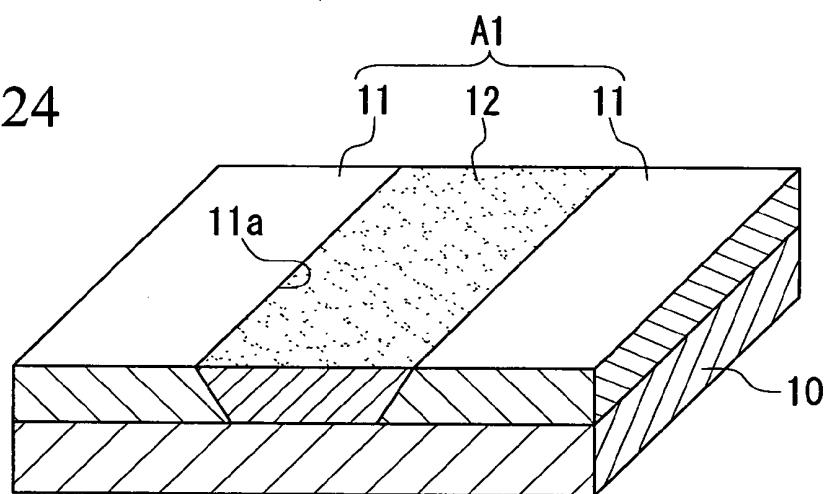

FIG.24

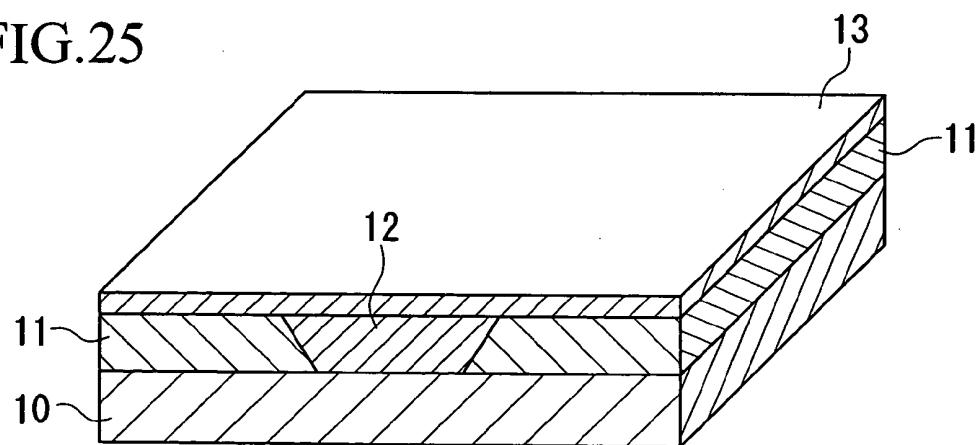

FIG.25

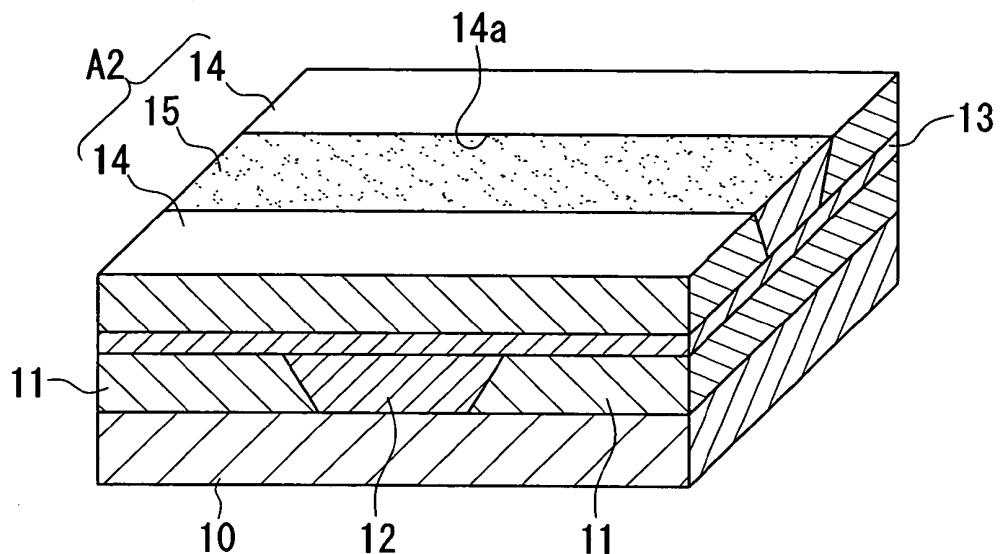

FIG.26

FIG.27

FIG.28

FIG.29

FIG.30

FIG.31

FIG.32

FIG.33

FIG.34

FIG.35

FIG.36

FIG.37

FIG.38

FIG.39

FIG.40

FIG.41

FIG.42

FIG.43

FIG. 44

FIG.45

FIG.46

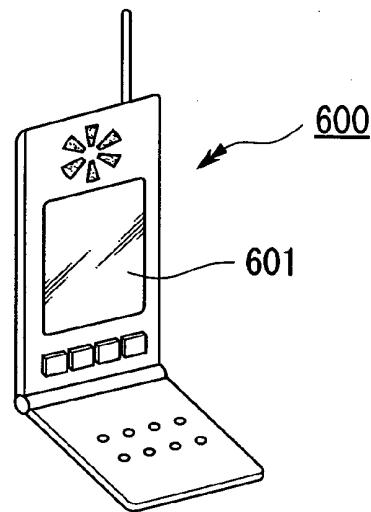

FIG.47A

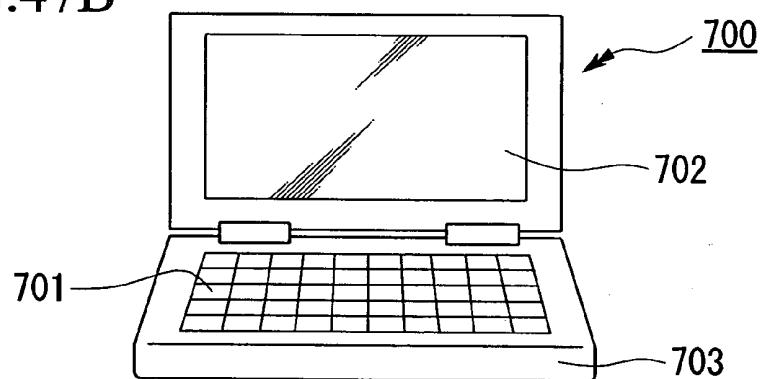

FIG.47B

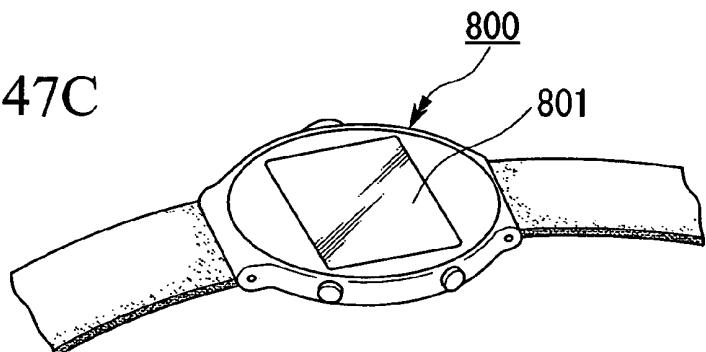

FIG.47C

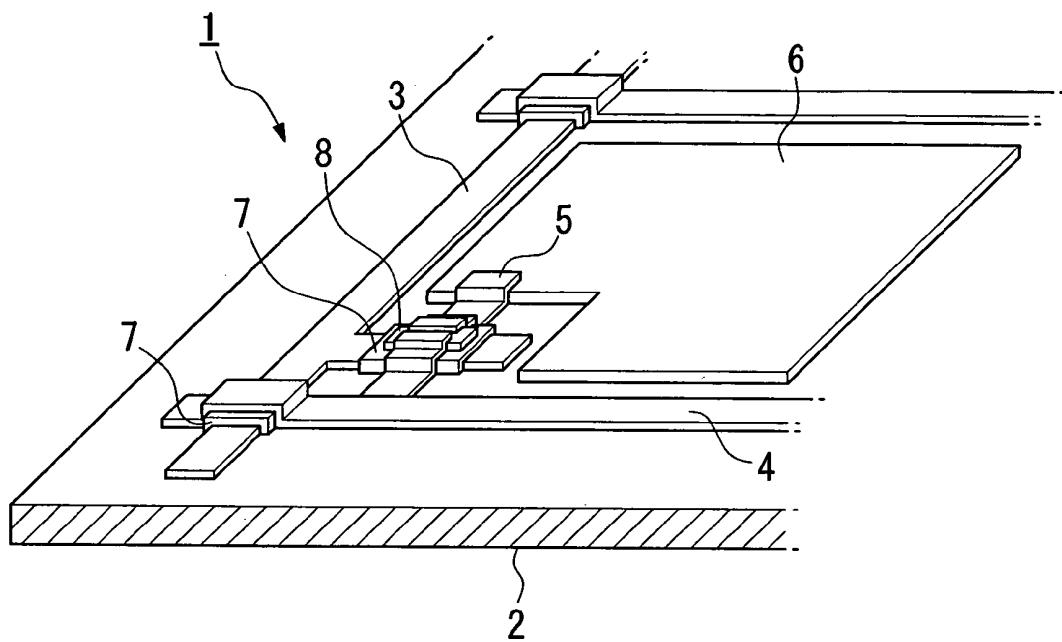

FIG.48

**METHOD FOR FABRICATING THIN FILM PATTERN, DEVICE AND FABRICATING METHOD THEREFOR, METHOD FOR FABRICATING LIQUID CRYSTAL DISPLAY, LIQUID CRYSTAL DISPLAY, METHOD FOR FABRICATING ACTIVE MATRIX SUBSTRATE, ELECTRO-OPTICAL APPARATUS, AND ELECTRICAL APPARATUS**

**BACKGROUND OF THE INVENTION**

**[0001] 1. Field of the Invention**

**[0002]** The present invention relates to a method for fabricating a thin film pattern, a device and fabricating method therefor, a method for fabricating a liquid crystal display, a liquid crystal display, a method for fabricating an active matrix substrate, an electro-optical apparatus, and an electrical apparatus.

**[0003]** Priority is claimed on Japanese Patent Application No. 2003-155858, filed May, 2003, Japanese Patent Application No. 2003-155865, filed May, 2003, Japanese Patent Application No. 2003-155866, filed May, 2003, Japanese Patent Application No. 2003-155867, filed May, 2003, Japanese Patent Application No. 2004-103418, filed March, 2004, the contents of which are incorporated herein by reference.

**[0004] 2. Description of Related Art**

**[0005]** To fabricate a device having wiring used for electronic circuits or integrated circuits, a photolithographic method, for example, is used. This photolithographic method forms a wiring pattern on a thin film by applying a photosensitive material called a resist to a substrate that has had a conducting film applied thereto in advance, the circuit pattern is developed by being irradiated, and the conducting film is etched that conforms to the resist pattern. This photolithographic method requires large-scale equipment and complicated steps. In addition, the material use efficiency is only a few percent, most of the product must be discarded, and thus the fabrication cost is high.

**[0006]** In contrast, U.S. Pat. No. 5,132,248 proposes a method wherein a wiring pattern is formed on a substrate by using an ink ejection method in which a liquid material is ejected in a droplet form from a liquid discharge head, also known as an inkjet method. In this method, a wiring pattern ink, which is a function liquid having conductive particles such as gold particles dispersed therein, is applied directly to a substrate, and subsequently this ink is converted to a thin film conducting film pattern by heat treatment and laser irradiation. According to this method, there are the merits that photolithography becomes unnecessary, the process can be greatly simplified, and the amount of raw materials used becomes small.

**[0007]** At the same time, with the popularization of mobile devices such as mobile telephones, thin and light liquid crystal displays have become widely used. This type of liquid crystal display has a liquid crystal interposed between an upper substrate and a lower substrate.

**[0008]** An example of the lower substrate is shown in FIG. 48. As shown in this figure, the lower substrate 1 is formed by providing a glass substrate 2, a gate scanning line electrode and a source electrode 4 that are laid out so as to intersect each other on this glass substrate 1, a drain elec-

trode 5 similarly laid out on the glass substrate 2, an image electrode (ITO) 6 connected to this drain electrode 5, an insulating layer 7 interposed between the gate scanning line electrode 3 and the source electrode 4, and a TFT (thin film transistor) consisting of a thin film semiconductor.

**[0009]** In the formation of each of the metal wires on the substrate 1, conventionally a method in which, for example, a dry process and photoetching are combined is used, but the dry process has the drawbacks that the fabrication cost is high and adapting it to increasingly larger substrate sizes is difficult. Thus, a method in which the metal wiring is formed on the glass substrate by using an inkjet method is being used (refer, for example, to Japanese Unexamined Patent Application, First Publication No. 2002-164635).

**[0010]** However, the conventional technology described above has the following problems.

**[0011]** Because the wiring patterns are formed by conductive particles applied to the surface of the substrate, the films that consist of the conductive particles protrude from the substrate surface, and this is a cause of obstructing the thin formation of the device.

**[0012]** In addition, there is a concern this may hinder the increasing integration even for devices having a wiring pattern formed over several layers on the substrate.

**[0013]** In addition, in other methods as well, as shown in FIG. 48, many irregularities remain on the surface of the completed product. If these irregularities become comparatively large, there is a concern that display distortions will occur when the liquid crystal display is assembled.

**[0014]** Specifically, a rubbing treatment will be carried out on the upper surface of this lower substrate 1 after formation of the orientation film. However, there is a concern that differences will occur in the results of the rubbing at the concave and convex parts. When such unevenness in the rubbing treatment occurs, differences in the orientation force of the liquid crystal will occur between parts thereof, and display distortions occur as a result.

**[0015]** In consideration of the problems described above, objects of the present invention are to provide method for fabricating a thin film pattern that can realize increased thinness, a device and fabricating method for the same, an electro-optical apparatus, and electrical apparatus.

**SUMMARY OF THE INVENTION**

**[0016]** In order to achieve the objects described above, the present invention provides a method for fabricating a thin film pattern on a substrate, including the steps of: forming a concave part on the substrate that conforms to the thin film pattern; and applying a function liquid into the concave part. The method may further include the steps of: building up banks on the substrate that conform to the thin film pattern; forming the concave part on the substrate between the banks; and removing the banks after applying the function liquid.

**[0017]** Therefore, in the present invention, because the thin film pattern can be formed in the concave part of the substrate, it becomes possible to carry out wiring without the wires projecting from the substrate surface, and devices that use this substrate can be made thinner. At the same time, it becomes possible to increase the integration when laminat-

ing the wiring pattern (thin film pattern). In addition, after building up the banks, when the function liquid is ejected (applied) to the concave part formed on the substrate between the banks, the drops of the function liquid do not readily spatter over the surroundings, and it becomes possible to carry out patterning in a predetermined profile. In addition, it is possible to prevent thickening of the substrate if the banks are removed after the function liquid has been applied.

[0018] Note that when banks have been built up, preferably a concave part is formed by etching, for example, using the banks as a mask.

[0019] Thereby, it becomes possible to fabricate a separate mask, the work of setting the mask on the substrate becomes unnecessary, and the productivity can be improved.

[0020] In addition, when the banks have been built up, preferably a step in which the banks have imparted a liquid repellency that is stronger than that of the concave part.

[0021] Thereby, even if a part of the ejected droplet falls on a bank, the droplet is repelled from the bank because the bank surface has been made liquid repelling, and it flows down into the concave part between banks. Therefore, the ejected function liquid spreads in the concave part on the substrate and can fill the concave part more evenly.

[0022] Note that when conductive particles are included in the function liquid, the thin film pattern can be used as the wiring pattern, and application to any type of device becomes possible. In addition, besides conductive particles, by using a phosphorescent element formation material such as an organic EL or an RGB ink material, application to fabrication, for example, of liquid crystal displays having color filters becomes possible. Furthermore, it is possible to select a function liquid that exhibits conductivity due to heat processing such as heating or due to light processing such as light irradiation.

[0023] The present invention provides a method for fabricating a device having a substrate, including a step of forming a thin film pattern on the substrate using the above-mentioned method for fabricating a thin film pattern.

[0024] Thereby, in the present invention, it is possible to obtain a device that is thin and can be highly integrated.

[0025] In particular, it is possible to obtain a highly integrated thin switching element when forming a part of a switching element such as a TFT (thin film transistor) having a thin film pattern formed on the substrate.

[0026] In addition, the present invention provides an electro-optical apparatus including a device that is manufactured by using the device fabricating method described above.

[0027] In addition, the present invention provides an electrical apparatus including the electro-optical apparatus described above.

[0028] Thereby, in the present invention, it becomes possible to obtain a thin film electro-optical apparatus and electrical apparatus.

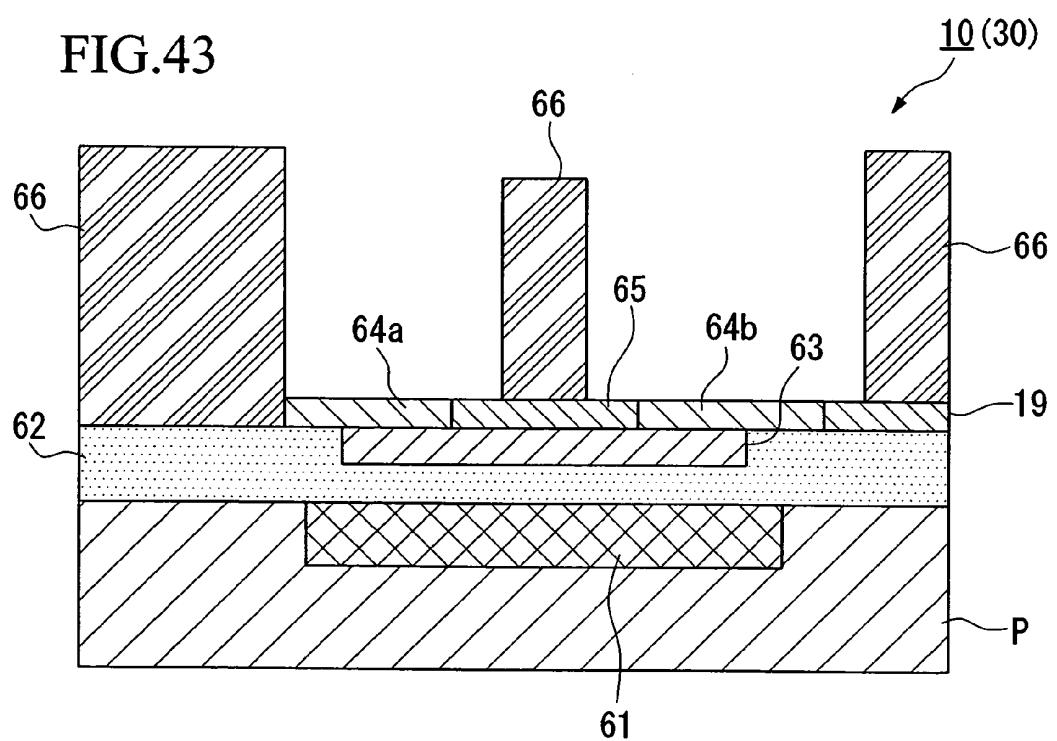

[0029] In addition, the present invention provides a device including: a substrate; a concave part formed on the substrate; and a thin film pattern disposed in the concave part, wherein the concave part is formed so as to conform to the thin film pattern.

[0030] Thereby, in the present invention, because the thin film pattern can be formed in the concave part of the substrate, it becomes possible to carry out wiring without the wires protruding from the substrate surface, and devices that use this substrate can be made thinner. At the same time, it becomes possible to increase the integration when laminating the wiring pattern (thin film pattern).

[0031] Preferably, the thin film pattern is formed so as not to protrude from the surface of the substrate.

[0032] Thereby, in the present invention, decreasing the thinness becomes possible, and at the same time, in addition to being able to decrease the thinness, the surface flatness is improved when the surface of the thin film pattern and the substrate surface are made flush, and post-processing such as forming an insulating film become easy.

[0033] In addition, preferably, the concave part is formed having a reverse taper whose cross-section gradually widens towards a bottom thereof.

[0034] Thereby, in the present invention, the thin film pattern formed in the concave part becomes difficult to strip from the substrate, and it becomes possible to prevent deterioration in the quality of the device.

[0035] Note that when the thin film pattern is formed by a conducting film, the thin film pattern can serve as the wiring pattern, and application to any type of device becomes possible.

[0036] In addition, the present invention provides a method for fabricating a liquid crystal display, including: a substrate groove formation step of forming a substrate groove on a substrate; a liquid repellent part formation step of forming a liquid repellent part so as to define the substrate groove; a first conduction pattern formation step of forming a first conductive pattern by ejecting droplets that include a conducting material into the substrate groove; a first insulating layer formation step of forming a first insulating layer so as to cover at least the first conductive pattern; a bank formation step of forming first banks that provide a thin film transistor comprising a thin film semiconductor and transparent first banks on the first insulating layer; a second conductive pattern formation step forming a second conductive pattern by ejecting droplets that include a conducting material into the formation region defined by the banks; and a second insulating layer formation step of forming a second insulating layer so as to cover at least the first banks and the second conductive pattern.

[0037] According to the fabricating method for this liquid crystal display, the substrate before the first insulation film formation step is formed such that the first conductive pattern is embedded in the substrate groove, and thus has a flat surface profile. Because a first insulating layer is formed on a flat substrate, it is possible to form a flat first insulating layer by the first insulating layer formation step. Furthermore, in the second conductive pattern formation step, one flat layer is formed on this flat first insulating layer in which the first banks and the second conductive pattern are integrally formed.

[0038] In the second insulating layer formation step, the second insulating layer is formed on this flat layer, and thus it is possible to form a flat second insulating layer. Specifically, the first banks that would usually have been removed

are left in place to form the second insulating layer, and thus a surface profile having less irregularity than a conventional one can be guaranteed.

[0039] As explained above, it is possible to guarantee that after completion of all steps, the substrate will have a flat surface profile. Thereby, when carrying out a rubbing treatment on the substrate, irregularities in the result occur with difficulty, and thus it becomes possible to prevent display distortions by improving the liquid crystal orientation force.

[0040] In addition, the first conductive pattern formed by the first conductive pattern formation step is formed so as to be embedded in the substrate groove, and thus, in comparison to the case in which the first conductive pattern formed on a substrate without a substrate groove, the thickness dimension of the substrate after completion can be made thin.

[0041] Furthermore, in the fabricating method of the liquid crystal display described above, in the liquid repelling part formation step, the liquid repelling part can be formed by forming second banks that define the substrate groove, and the second banks can be removed before the first insulating layer formation step.

[0042] In this case, by forming the second banks, it is possible to form reliably a fine first conduction pattern by the first conductive pattern formation step described above. In addition, because the second banks are removed after the first conductive pattern formation step, the substrate after completion can be made thin.

[0043] In addition, in order to solve the problems described above, the present invention provides a liquid crystal display including: two substrates, one of which includes substrate grooves formed thereon and a first conductive pattern formed in the substrate grooves; a liquid crystal layer interposed between the substrates; an insulating layer that is formed so as to cover at least the first conductive pattern; a thin film transistor comprising a thin film semiconductor and disposed on the insulating layer; transparent banks disposed on the insulating layer; and a second conductive pattern defined by the transparent banks and disposed on the insulating layer.

[0044] According to this liquid crystal display, because one substrate is formed so that the first conductive pattern is embedded in the substrate grooves, it has a flat surface. Thus, it is possible to impart a flat surface to the insulating layer formed on this flat surface as well. Furthermore, it is possible to impart a flat surface to the thin film transistors, banks, and second conductive pattern formed on this flat insulating layer. Specifically, a surface profile having fewer irregularities than a conventional one can be guaranteed because the banks that would usually have been removed are left in place.

[0045] In this manner, because each surface is flat, the liquid crystal alignment resistance force increases because irregularities in the rubbing treatment are prevented. Therefore, the liquid crystal display can prevent display distortions.

[0046] In addition, the first conductive pattern formed by the first conductive pattern formation step is formed so as to be embedded in the substrate groove, and thus, in comparison to the case in which the first conductive pattern formed

on a substrate without a substrate groove, the thickness dimension of the substrate after completion can be made thin.

[0047] Furthermore, to solve the problems described above, the present invention provides a method for fabricating a liquid crystal display, including: a substrate groove formation step of forming a substrate groove in a substrate; a first bank formation step of forming first banks within the substrate groove; and a first conductive pattern formation step of forming a first conductive pattern in the substrate groove by ejecting droplets that include a conducting material into a region defined by the first banks.

[0048] According to this fabricating method for a liquid crystal display, because the wiring formation is carried out by filling the concave substrate groove with the first banks and the first conductive pattern, it is possible to guarantee a flat surface having fewer irregularities than a conventional one. Thereby, when carrying out a rubbing treatment on the substrate, irregularities in the result occur with difficulty, and thus it becomes possible to prevent display distortions by improving the liquid crystal orientation force.

[0049] In addition, by embedding the first banks and the first conductive pattern in the substrate groove, it becomes possible to make the thickness dimension of the substrate after completion thin in comparison to the case of forming the first conductive pattern without providing the substrate groove.

[0050] Furthermore, the method for fabricating a liquid crystal display described above may further include a first insulating layer formation step of covering at least the first conductive pattern and the first banks by an insulating layer; a second bank formation step of forming a thin film transistor comprising a thin film semiconductor and second banks in the substrate groove; and a second conductive pattern formation step of forming a second conductive pattern in the substrate groove by ejecting droplets that include a conducting material into a region defined by the second banks.

[0051] In this case, because an insulating layer, a thin film transistor, second banks, and a second conductive pattern region also accommodated in the substrate groove, it is possible to guarantee an even more flat surface profile. Thereby, it is possible to increase further the evenness of the rubbing treatment even more, and it becomes possible to prevent display irregularity by increasing the liquid crystal alignment resistance force. In addition, it is possible to make the thickness dimension of the substrate after completion even thinner.

[0052] In addition, in order to solve the problems described above, the present invention provides a liquid crystal display including: two substrates, one of which includes substrate grooves formed thereon; a liquid crystal layer interposed between the substrates; and at least one layer comprising banks and conductive pattern formed in a region defined by the banks is provided in the substrate groove.

[0053] According to this liquid crystal display, because wiring formation is carried out in the substrate groove such that the banks and the conductive pattern are embedded in the substrate groove, it is possible to guarantee a flat surface profile having fewer irregularities than a conventional one.

Due to such increased flatness, the liquid crystal alignment resistance force is increased by preventing irregularities in the rubbing treatment. Therefore, the liquid crystal display can prevent display distortions.

[0054] In addition, because the banks and conductive pattern are embedded in the substrate groove so as to form wirings, it is possible to make the thickness dimension of the substrate thin in comparison to a conventional one in which the conductive pattern is formed on a substrate surface that does not have substrate grooves.

[0055] In order to solve the problems described above, the present invention provides a method for fabricating a liquid crystal display, including: a bank formation step of forming transparent banks on an upper surface of a substrate; a conductive pattern formation step of forming a first conductive pattern by ejecting droplets that include a conducting material into a formation region defined by the banks; and an insulating layer formation step of forming a thin film transistor comprising a thin film semiconductor and an insulating layer so as to cover at least the banks and the first conductive pattern.

[0056] According to the fabricating method of this liquid crystal display, the substrate before the insulating layer formation step forms one flat layer in which the banks and first conductive pattern are integrally formed. By forming the insulating layer on this flat layer, it is possible to form a flat insulating layer.

[0057] In this manner, because the insulating layer is formed by leaving in place the banks that would be usually be removed, it is possible to guarantee a surface profile that has fewer irregularities than a conventional one. Thereby, when carrying out the rubbing treatment, because irregularities in the result occur with difficulty, it is possible to prevent display distortions by increasing the liquid crystal alignment resistance force.

[0058] Furthermore, in the fabricating method for the liquid crystal display described above, it is possible to carry out a bank formation step, a conductive pattern formation step, and an insulating layer formation step on the insulating layer, and form a second conductive pattern that intersects the first conductive pattern.

[0059] In this case as well, the substrate before repeating the insulating layer formation step forms one flat surface on which the banks and second conductive pattern formed by the repeated conductive pattern formation step are integrally formed. By forming the insulating layer again on this flat surface, it is possible to form a flat insulating layer.

[0060] Therefore, in the case, for example, that, in a planar view, the traversing gate scanning line electrode, the capacity line, the source electrode, and the drain electrode are formed by the conductive pattern, an insulating layer is formed in which the banks for forming these electrodes remains in place, and thus it is possible to guarantee a surface profile that has fewer irregularities than a conventional one, and it becomes possible to increase the liquid crystal alignment resistance force by making the result of the rubbing treatment uniform.

[0061] Furthermore, in the fabricating method for the liquid crystal display described above, the gate scanning line electrode, the source electrode, the drain electrode, and the

pixel electrode can be formed by a metal wiring formation step that includes the conductive pattern formation step.

[0062] In this case, because the gate wiring, the source wiring, the drain wiring, and the pixel electrode are formed by the ejection of a droplet that includes a conducting material, it is possible to reduce material used in the metal wiring formation step.

[0063] In addition, in order to solve the problems described above, the present invention provides a liquid crystal display including: two substrates; a liquid crystal layer interposed between the substrates; a first conductive layer comprising transparent first banks provided on one of the substrates, and a first conductive pattern provided in a region defined by the first banks; and a first insulating layer provided on the first conductive layer.

[0064] According to this liquid crystal display, one flat first conductive layer is formed in the one substrate in which the banks and first conductive pattern are integrally formed. Therefore, it is also possible to impart a flat surface profile to the first insulating layer formed on this flat first conductive layer.

[0065] In this manner, because the first insulating layer is formed with the banks that would usually be removed remaining in place, it is possible to guarantee a surface profile having fewer irregularities than a conventional one. Due to this flatness, because the liquid crystal alignment resistance force is increased because irregularities in the rubbing treatment are prevented, the liquid crystal display can prevent display distortions.

[0066] Furthermore, in the liquid crystal display described above, it is possible to provide a second conductive layer consisting of second banks provided on the first insulating layer and a second conductive pattern, and a second insulating layer provided on the second conductive layer.

[0067] In this case, one flat second conductive layer is formed in which the second banks and the second conductive pattern are integrally formed. In addition, it is also possible to impart a flat surface profile to the second insulating layer provided on this flat second conductive layer.

[0068] Therefore, in the case, for example, that the traversing conductive pattern on this flat surface serves as the gate scanning line electrode and the source electrode, the banks for forming these electrodes remains in place, and thus it is possible to guarantee a surface profile having fewer irregularities than a conventional one, and it becomes possible to increase the liquid crystal alignment resistance force by making the result of the rubbing treatment uniform.

[0069] In addition, the present invention provides an electrical apparatus including a liquid crystal display fabricated by using the method for fabricating a liquid crystal display described above, or including the liquid crystal display described above.

[0070] According to this electronic device, because a liquid crystal display having a superior liquid crystal alignment resistance force is provided, it becomes possible to provide an electronic device providing a visually superior display unit that does not have display distortions.

[0071] In addition, the present invention provides a method for fabricating an active matrix substrate including:

a first step of forming gate wiring on a substrate; a second step of forming a gate insulating layer on the gate wiring; a third step of laminating a semiconductor layer over the gate insulating layer; a fourth step of forming a source electrode and a drain electrode on the gate insulating layer; a fifth step of disposing an insulating material on the source electrode and the drain electrode; a sixth step of forming a pixel electrode that is electrically connected to the drain electrode, wherein at least one of the first step, the fourth step, and the sixth step comprises a step of forming a concave part that conforms to the formation pattern and a material disposition step of disposing a function liquid in the concave part by ejection using a droplet ejection device.

[0072] According to the present invention, it becomes possible to carry out wiring formation in which the gate wiring, the source electrode, the drain electrode, and the pixel electrode do not protrude from the substrate surface, the device using this substrate can be made thin, and it is possible to increase integration when laminating a wiring pattern (thin film pattern).

#### BRIEF DESCRIPTION OF THE DRAWINGS

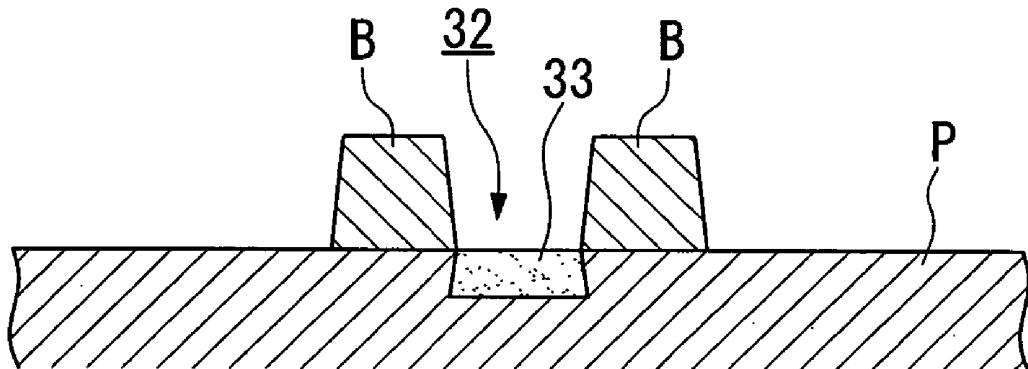

[0073] FIG. 1 is a schematic perspective drawing of the droplet ejecting device.

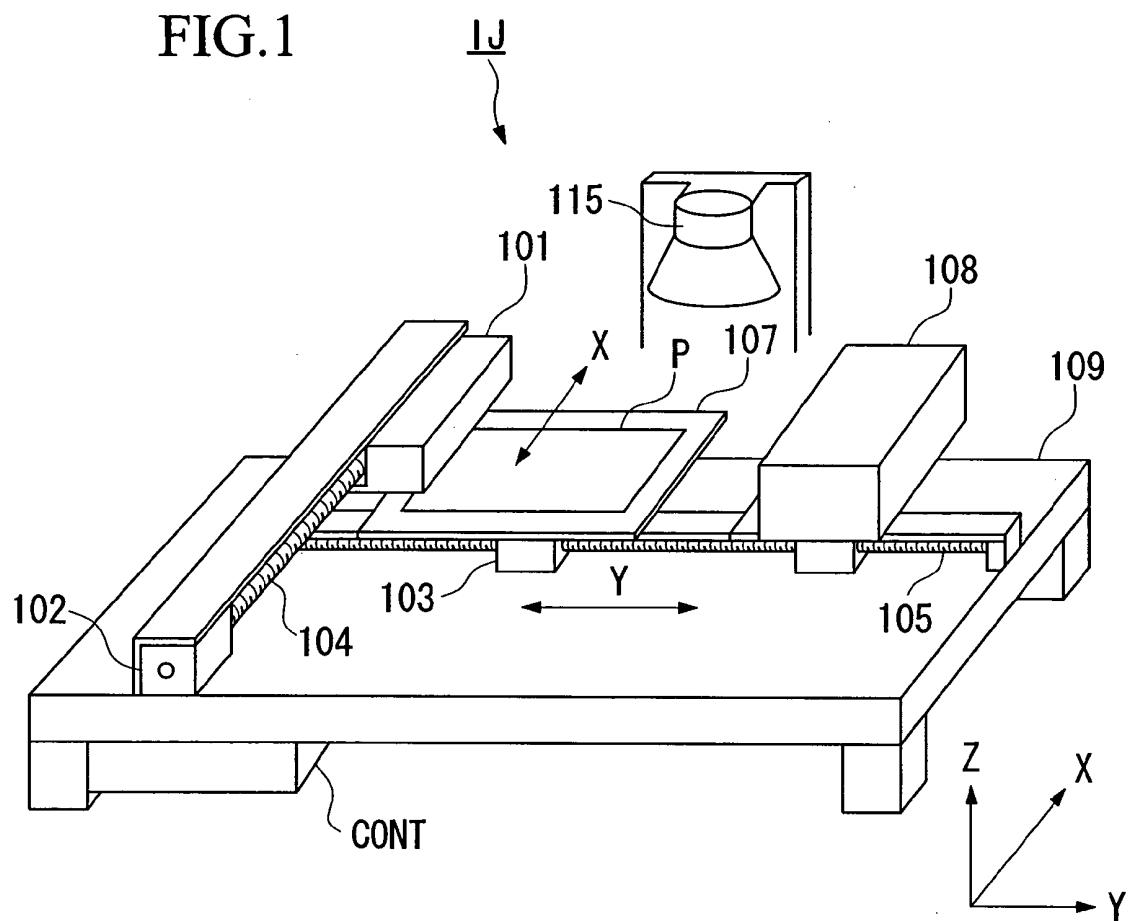

[0074] FIG. 2 is a drawing for explaining the ejection principle of the liquid body according to the piezoelectric method.

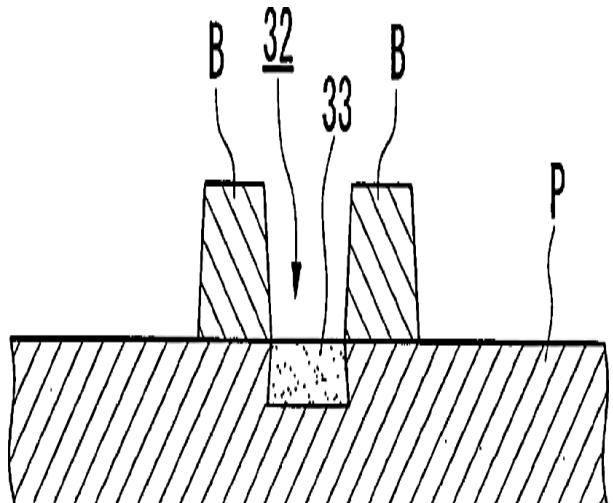

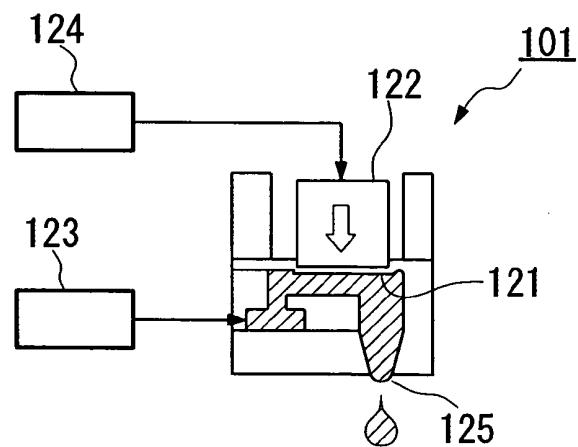

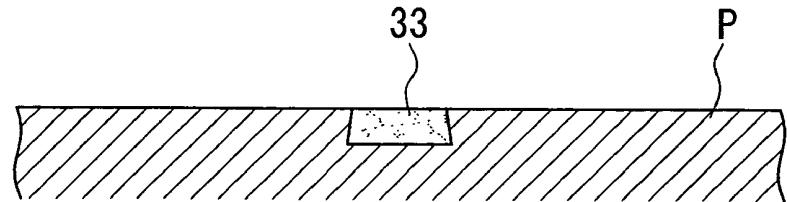

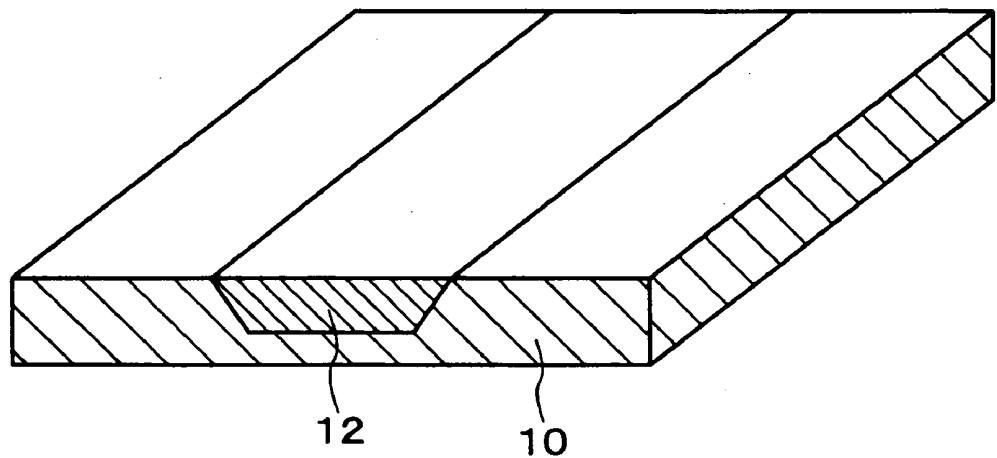

[0075] FIG. 3A to 3C are drawings showing the wiring pattern formation sequence.

[0076] FIG. 4D to 4F are drawings showing the wiring pattern formation sequence.

[0077] FIG. 5 is a drawing showing an embodiment of the fabricating method for the liquid crystal display of the present invention.

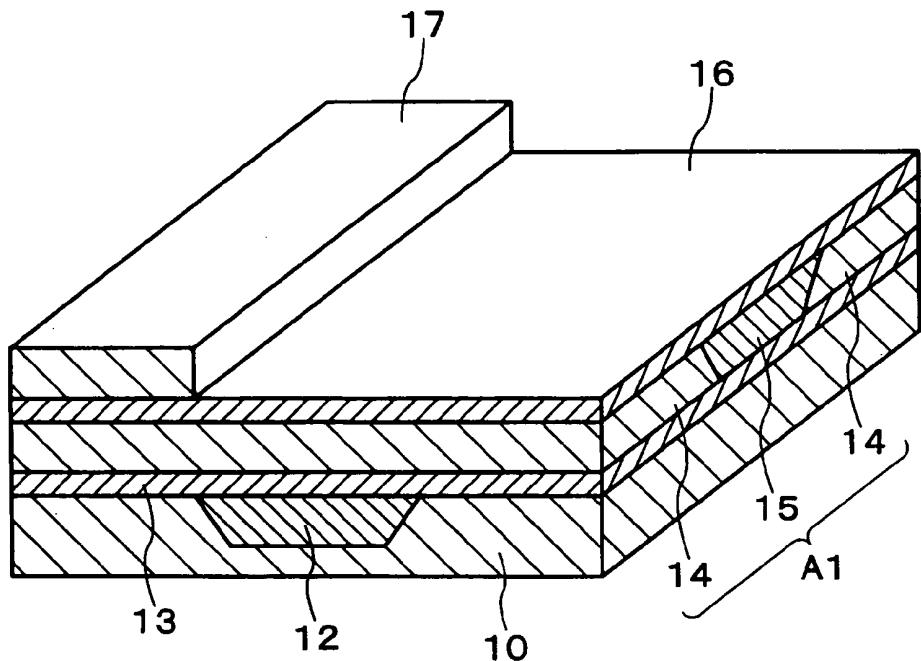

[0078] FIG. 6 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the banks are formed.

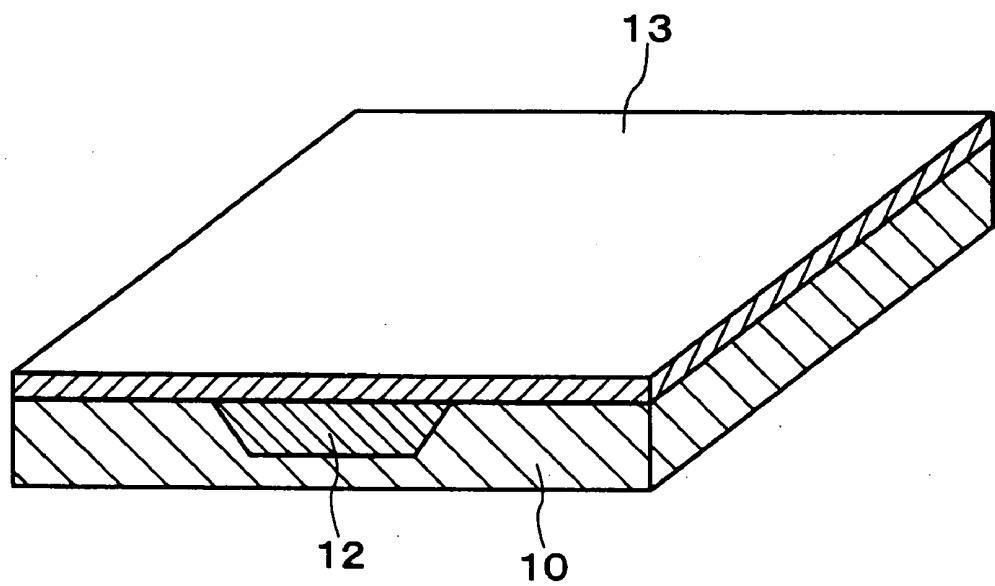

[0079] FIG. 7 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the gate scanning line electrode is formed.

[0080] FIG. 8 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the banks are removed.

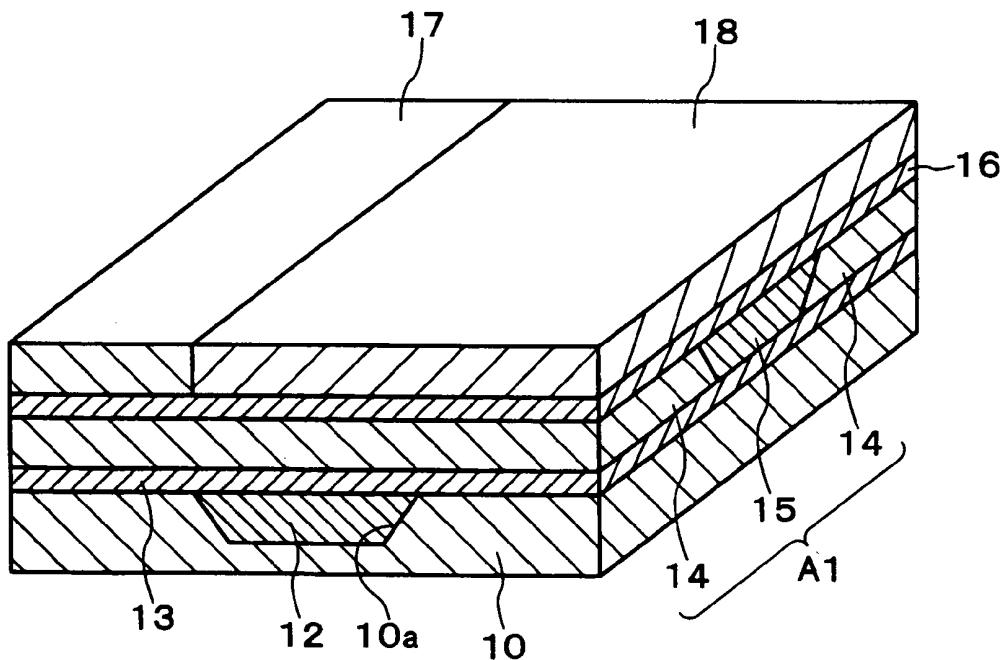

[0081] FIG. 9 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the gate scanning line electrode is formed.

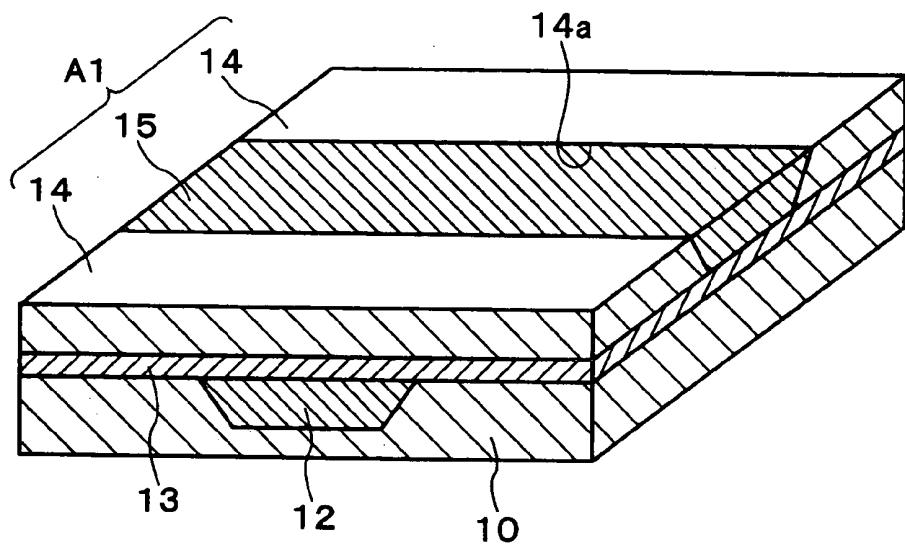

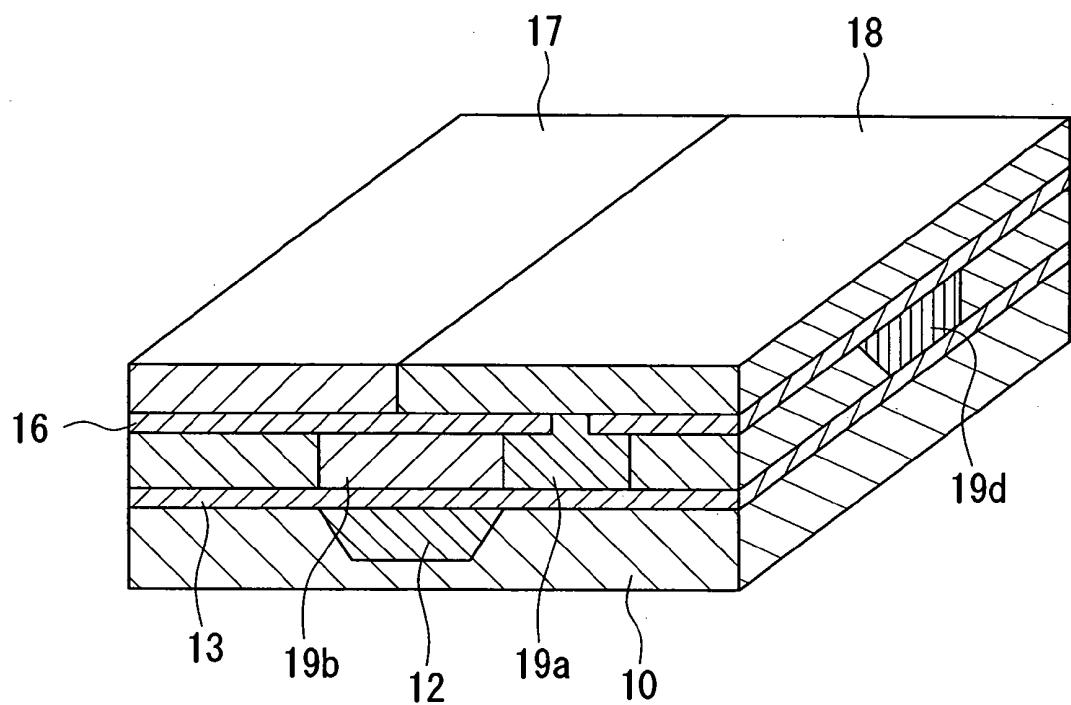

[0082] FIG. 10 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the banks and source electrode are formed.

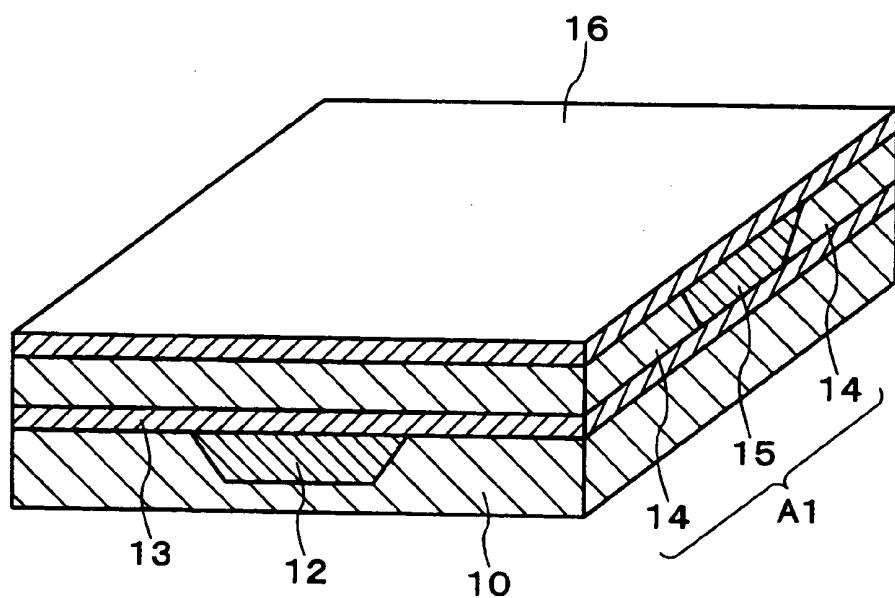

[0083] FIG. 11 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the source line insulation film is formed.

[0084] FIG. 12 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing step in which the banks are formed.

[0085] FIG. 13 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the pixel electrode is formed.

[0086] FIG. 14 is a partial perspective drawing showing an  $\alpha$ -Si TFT device, which is another part formed by the fabricating method.

[0087] FIG. 15 is a drawing showing an embodiment of the fabricating method for the liquid crystal display of the present invention, and is a drawing of a longitudinal section showing the step in which the substrate groove is formed in the substrate.

[0088] FIG. 16 is a drawing showing the continuation of the same fabricating method, and is a drawing of a longitudinal section showing the step in which the substrate grooves are formed in the substrate.

[0089] FIG. 17 is a drawing showing the continuation of the same fabricating method, and is a drawing of a longitudinal section showing the step in which the gate scanning line electrode and the gate scanning line insulating film are formed.

[0090] FIG. 18 is a drawing showing the continuation of the same fabricating method, and is a drawing of a longitudinal section showing the step in which the banks are formed on the gate scanning line insulating film.

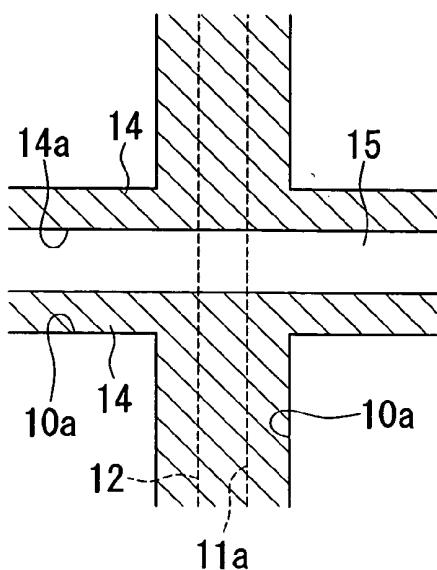

[0091] FIG. 19A is a drawing for explaining the fabricating method, and is a cross-sectional drawing along the line A-A in FIG. 21, and FIG. 19B is a drawing for explaining the fabricating method, and is a cross-sectional drawing along the line C-C in FIG. 21.

[0092] FIG. 20 is a drawing showing the continuation of the same fabricating method, and is a drawing of a longitudinal section showing the step in which the source electrode and the scanning line insulating film are formed.

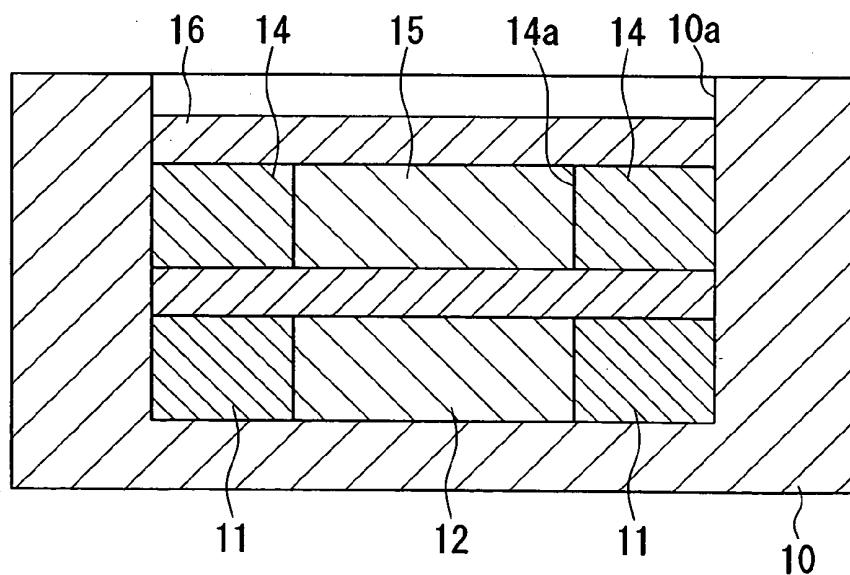

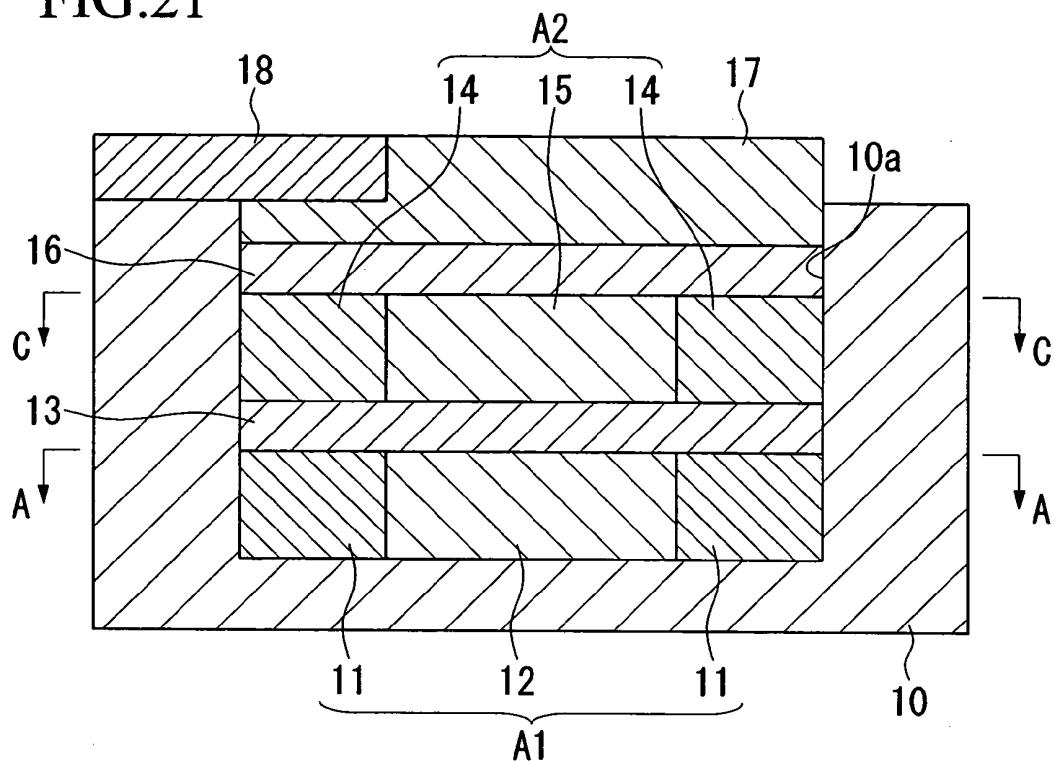

[0093] FIG. 21 is a drawing showing the continuation of the same fabricating method, and is a drawing of a longitudinal section showing the step in which the banks and pixel electrode are formed.

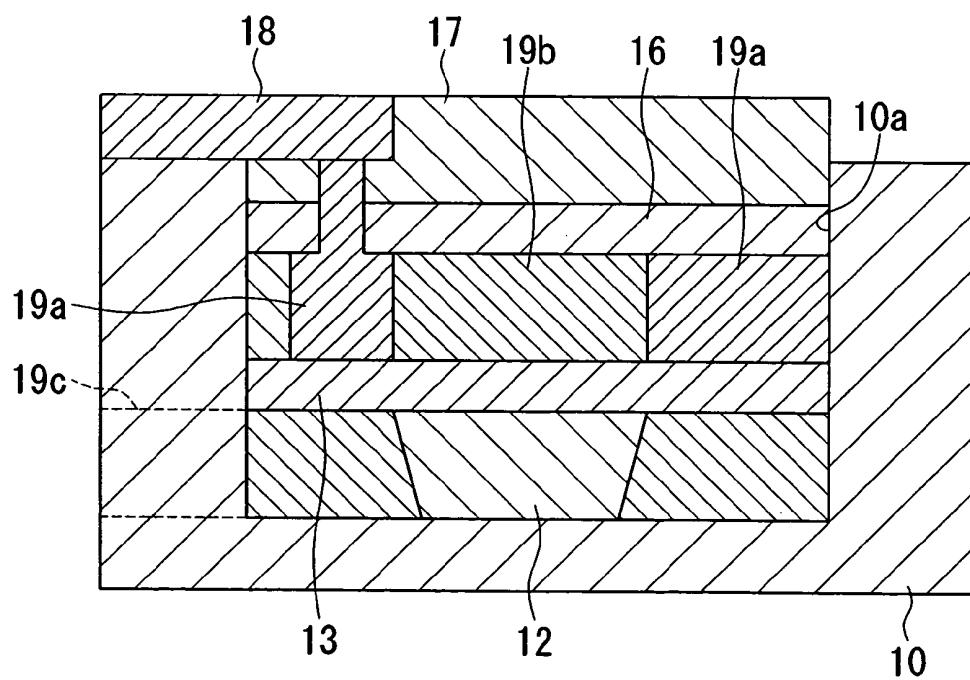

[0094] FIG. 22 is a partial perspective drawing showing an  $\alpha$ -Si TFT device, which is another part formed by the fabricating method.

[0095] FIG. 23 is a drawing showing an embodiment of the fabricating method for the liquid crystal display of the present invention, and is a partial perspective drawing showing the step in which the first layer banks are formed on the lower substrate.

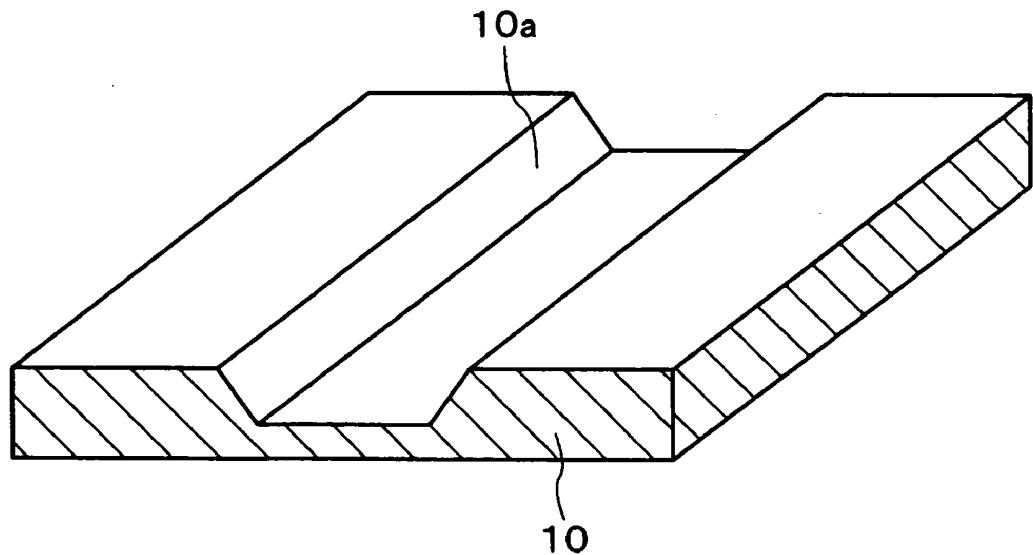

[0096] FIG. 24 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the gate scanning line electrode is formed.

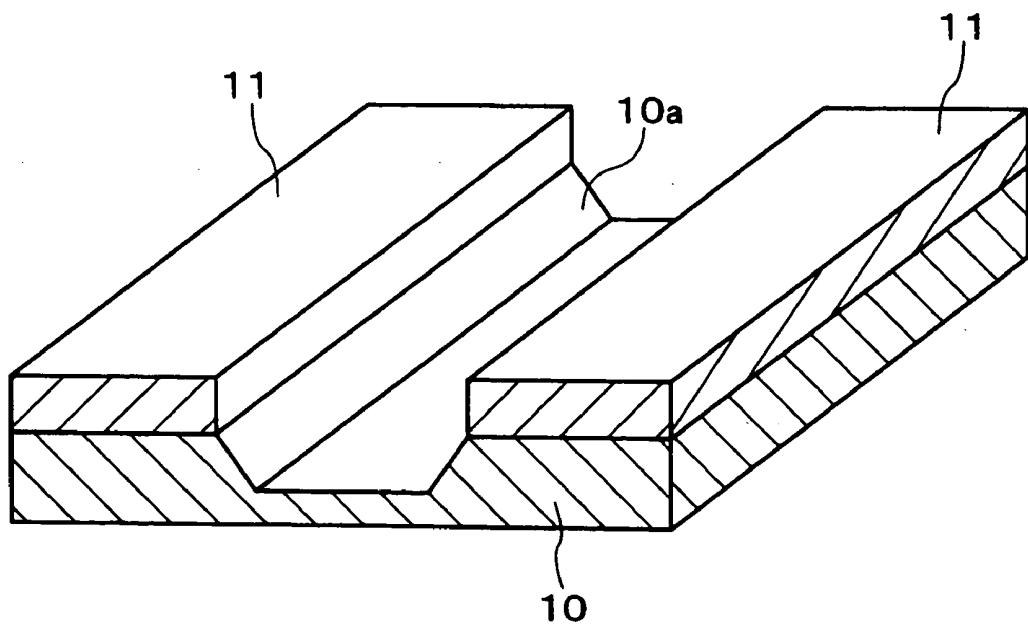

[0097] FIG. 25 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the first insulating layer is formed.

[0098] FIG. 26 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the second banks and source electrode are formed.

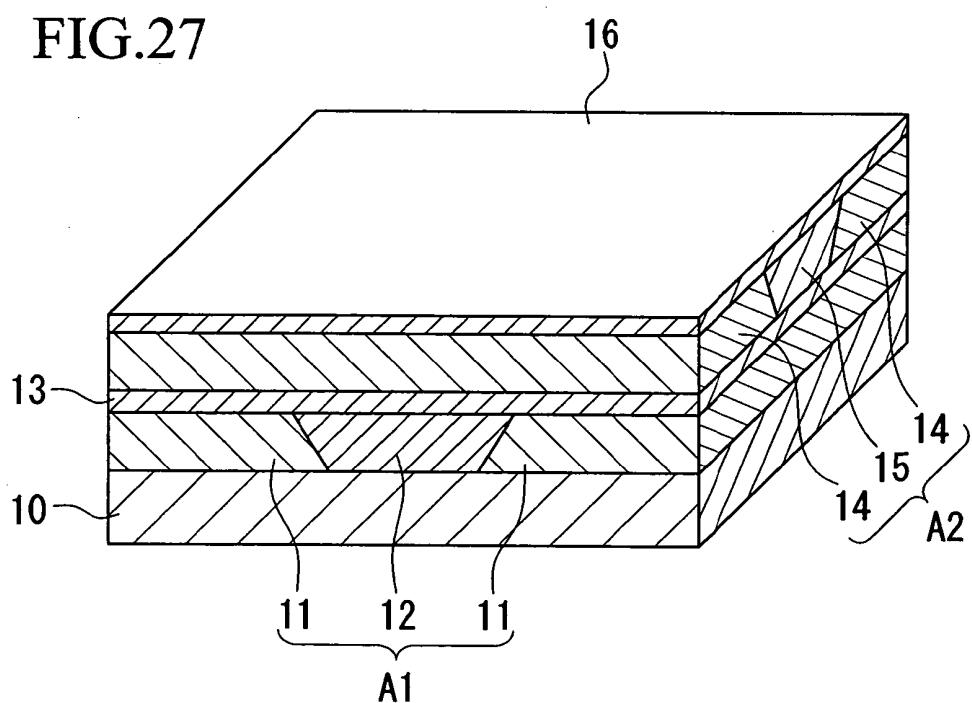

[0099] FIG. 27 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the second insulating layer is formed.

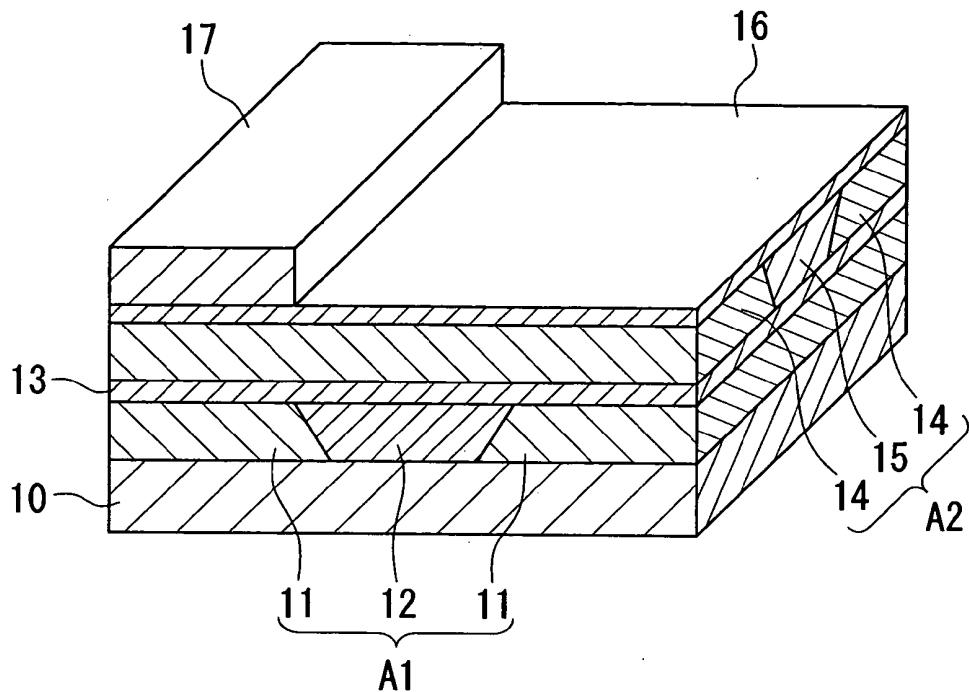

[0100] FIG. 28 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the third banks are formed.

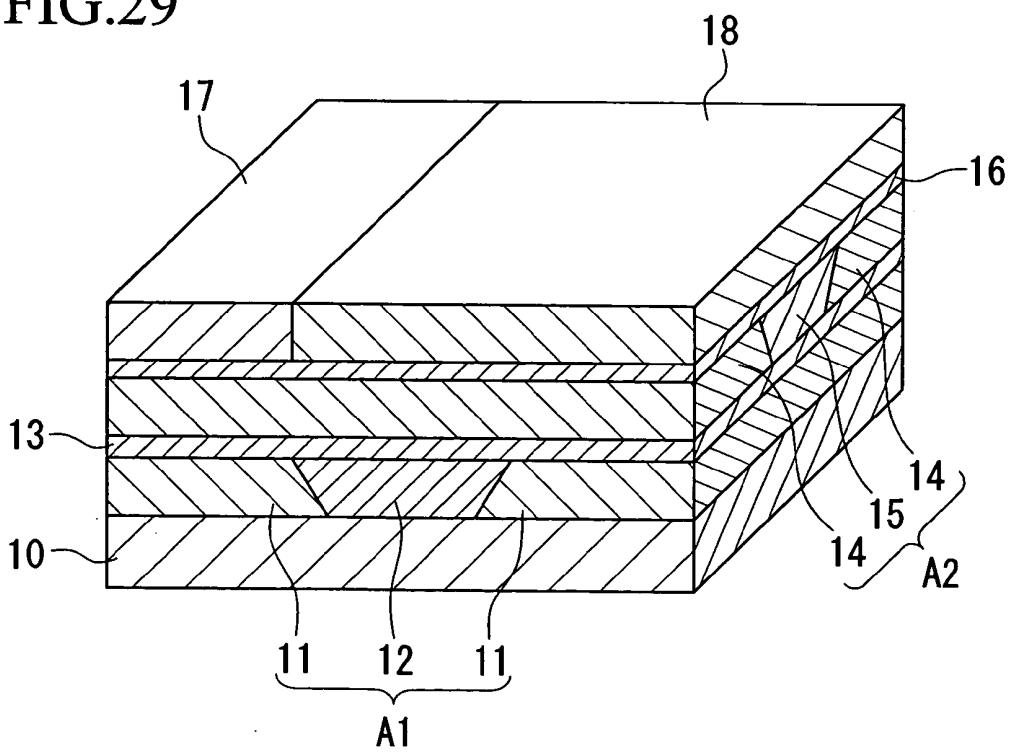

[0101] FIG. 29 is a drawing showing the continuation of the same fabricating method, and is a partial perspective drawing showing the step in which the pixel electrode is formed.

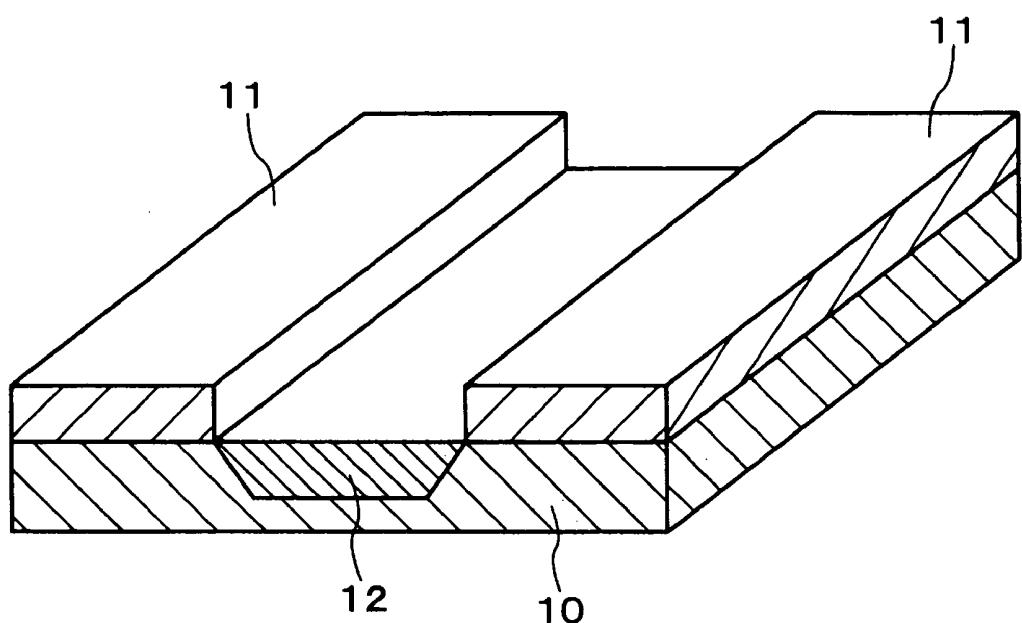

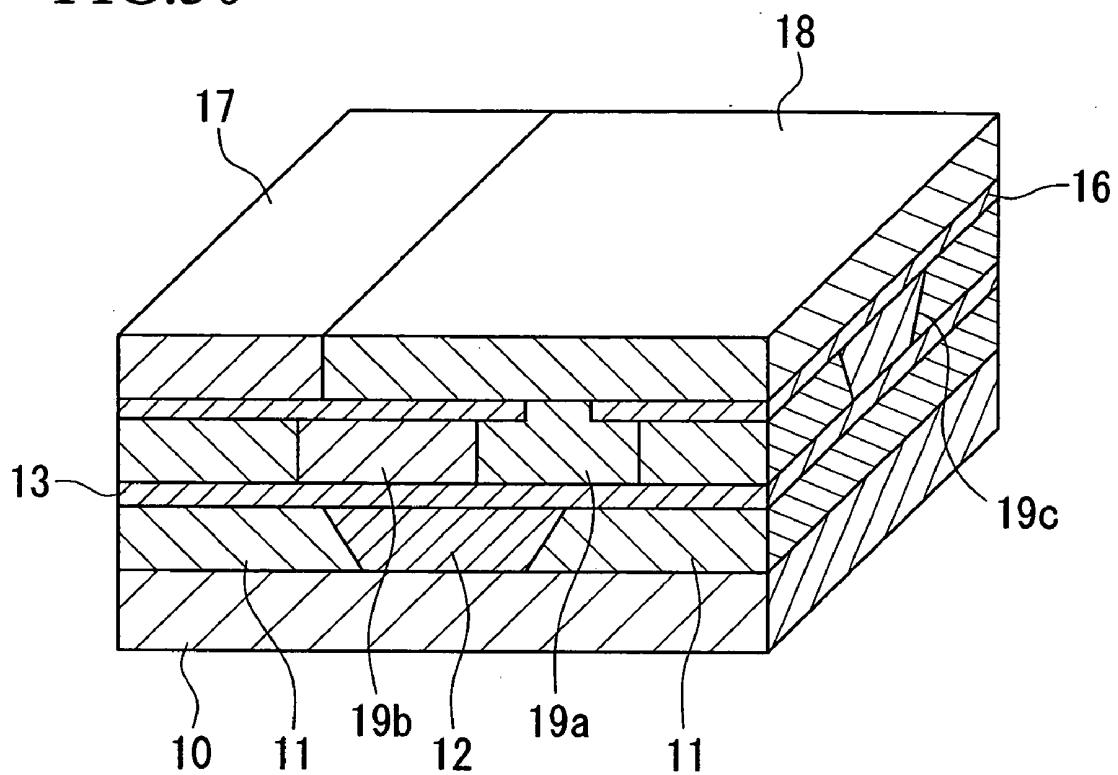

[0102] FIG. 30 is a partial perspective drawing showing an c-Si TFT device, which is another part formed by the fabricating method.

[0103] FIG. 31 is a drawing for explaining the step in which the thin film transistor is formed.

[0104] FIG. 32 is a drawing for explaining the step in which the thin film transistor is formed.

[0105] FIG. 33 is a drawing for explaining the step in which the thin film transistor is formed.

[0106] FIG. 34 is a drawing for explaining the step in which the thin film transistor is formed.

[0107] FIG. 35 is a drawing for explaining the step in which the thin film transistor is formed.

[0108] FIG. 36 is a drawing for explaining the step in which the thin film transistor is formed.

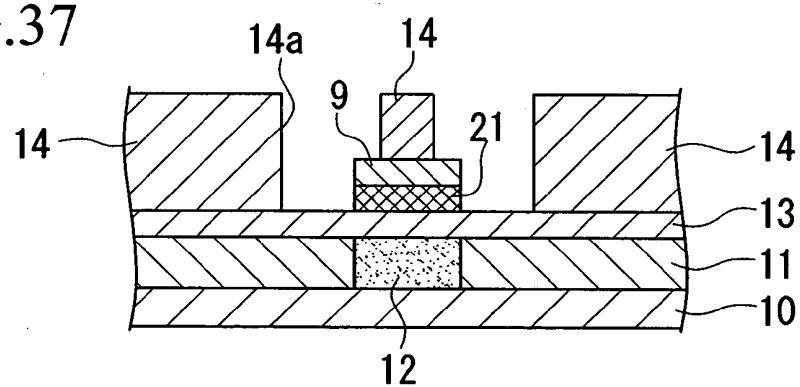

[0109] FIG. 37 is a drawing for explaining the step in which the thin film transistor is formed.

[0110] FIG. 38 is a drawing for explaining the step in which the thin film transistor is formed.

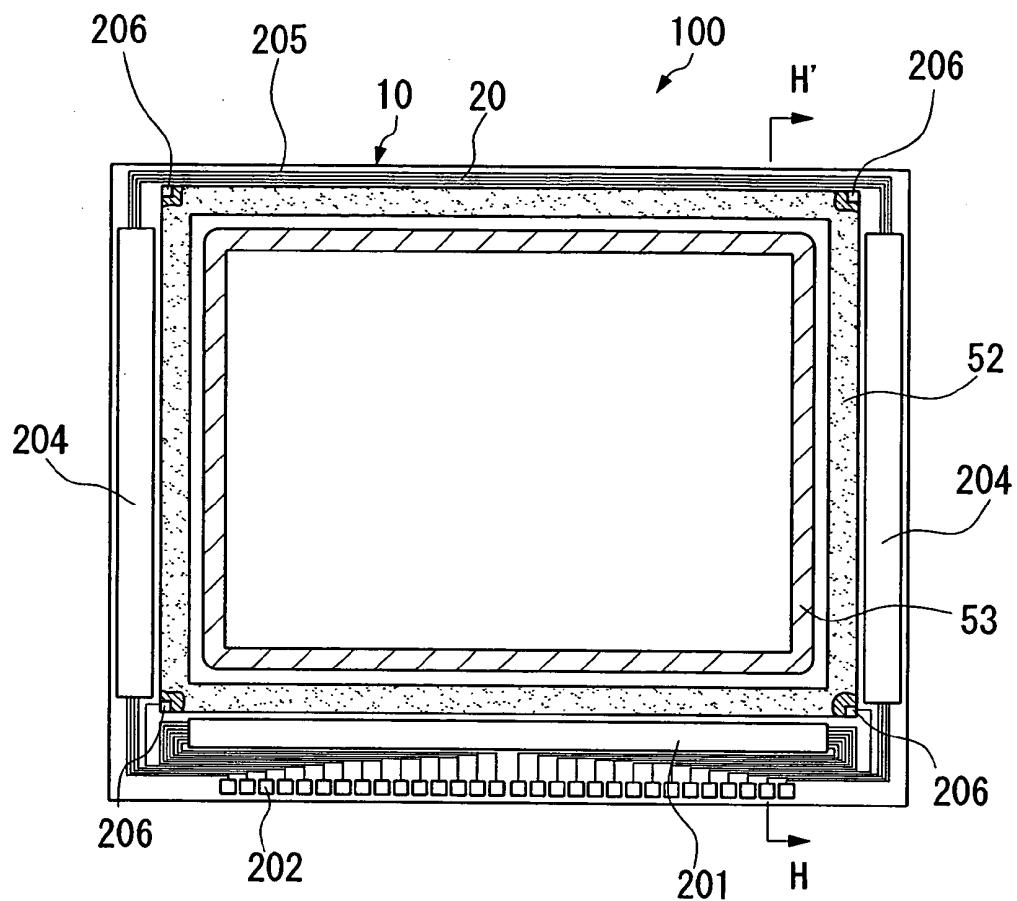

[0111] FIG. 39 is a plane drawing viewing the liquid crystal display from the side of the opposed substrate.

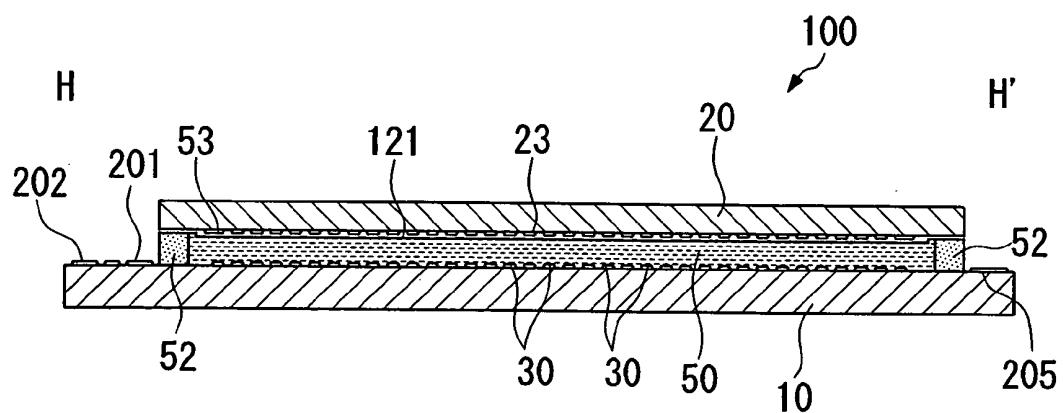

[0112] FIG. 40 is a cross-sectional drawing taken along the line H-H' in FIG. 39.

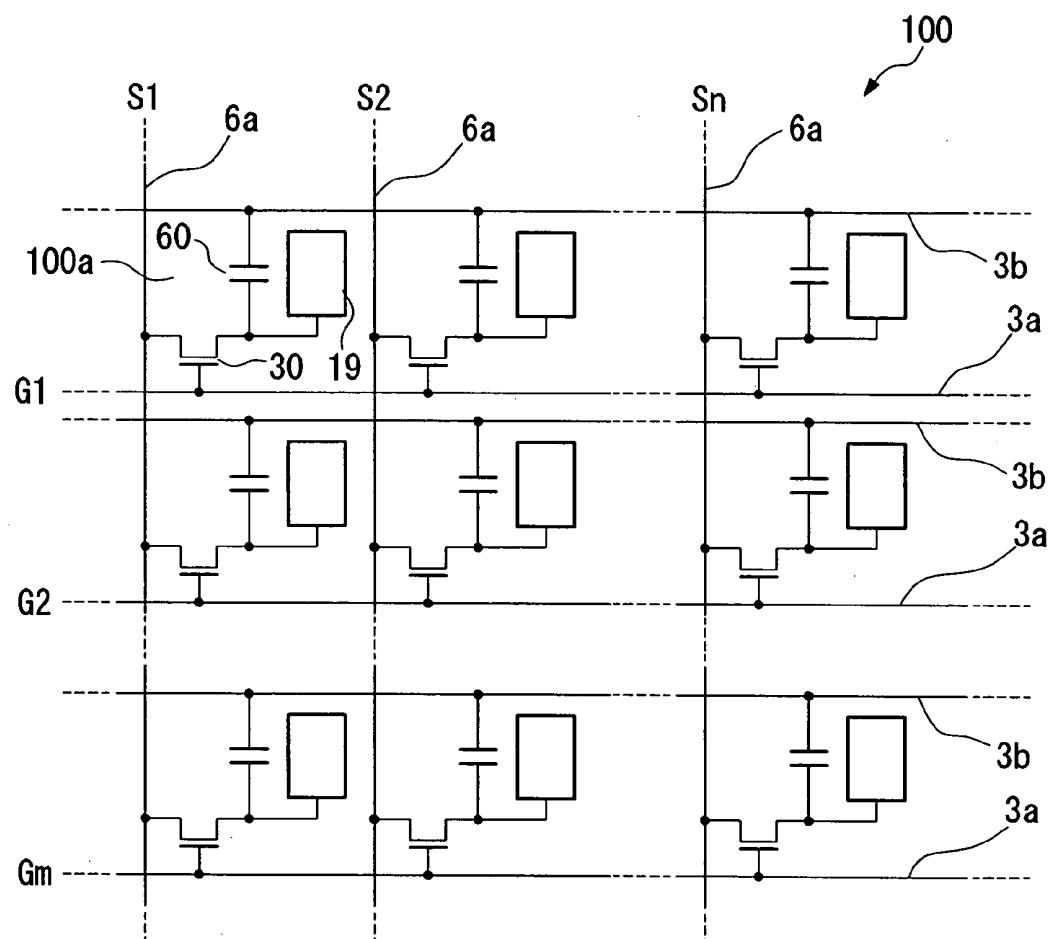

[0113] FIG. 41 is an equalizing circuit diagram for the liquid crystal display.

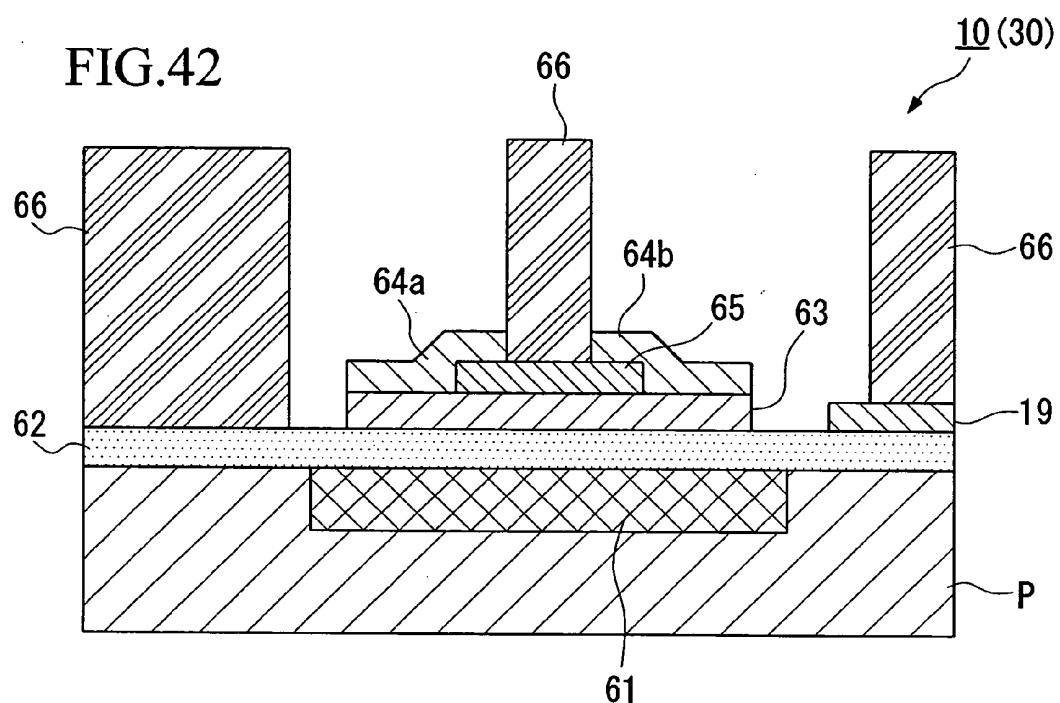

[0114] FIG. 42 is a partial enlarged cross-sectional drawing of the same liquid crystal display.

[0115] FIG. 43 is a partial enlarged cross-sectional drawing of another embodiment of the liquid crystal display.

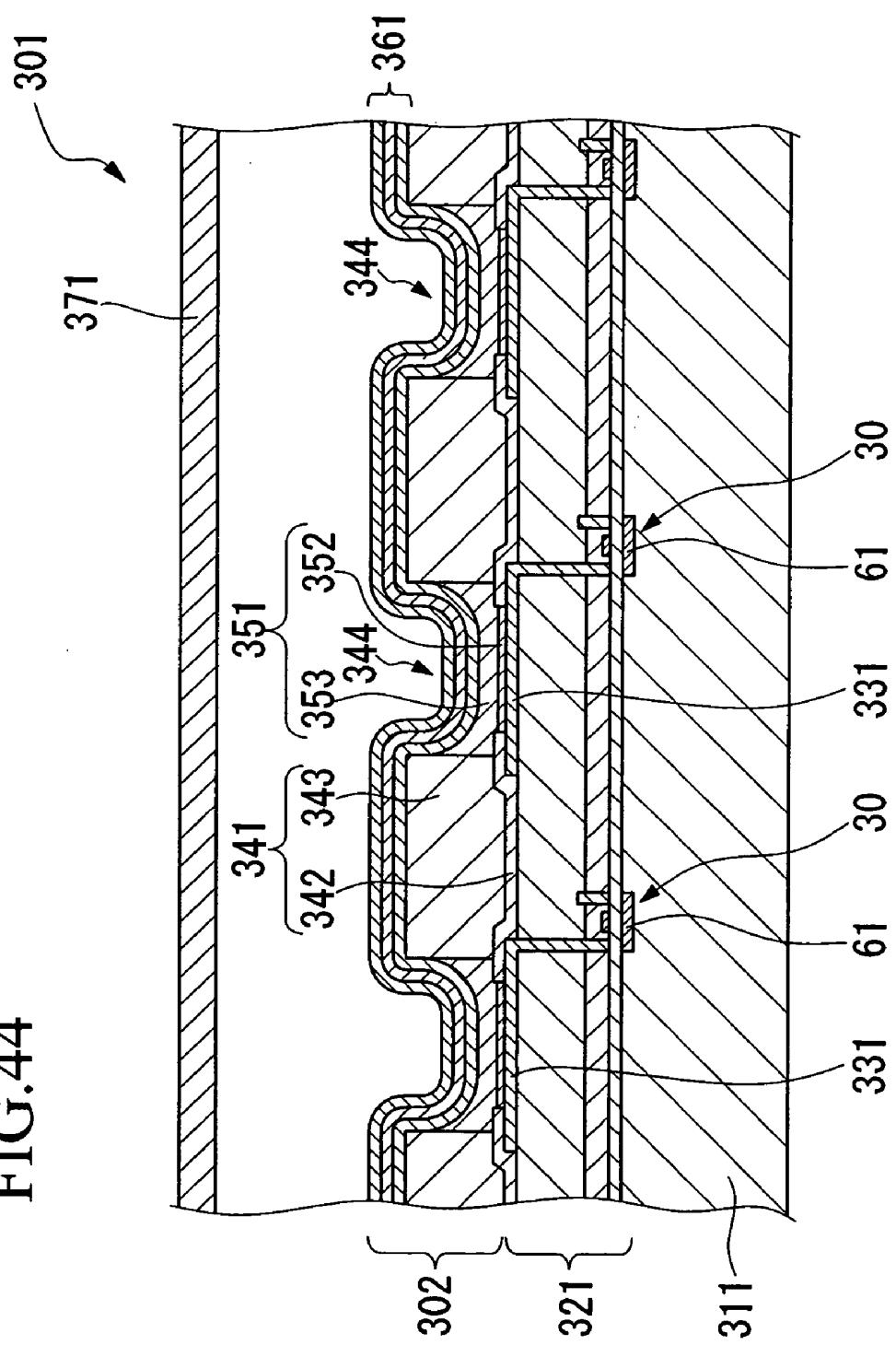

[0116] FIG. 44 is a partial enlarged cross-sectional drawing of an organic EL device.

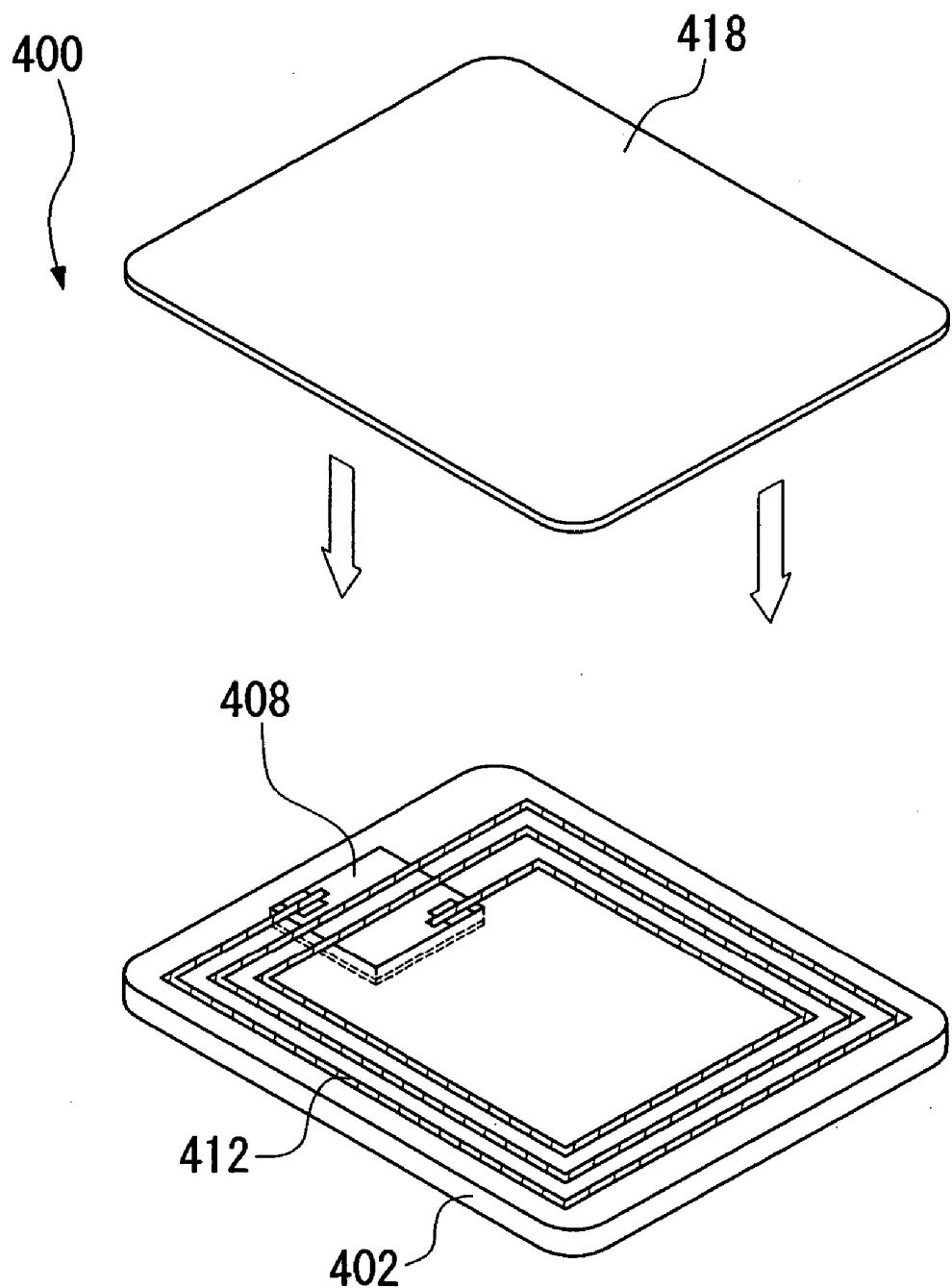

[0117] FIG. 45 is a drawing showing another embodiment of the liquid crystal display.

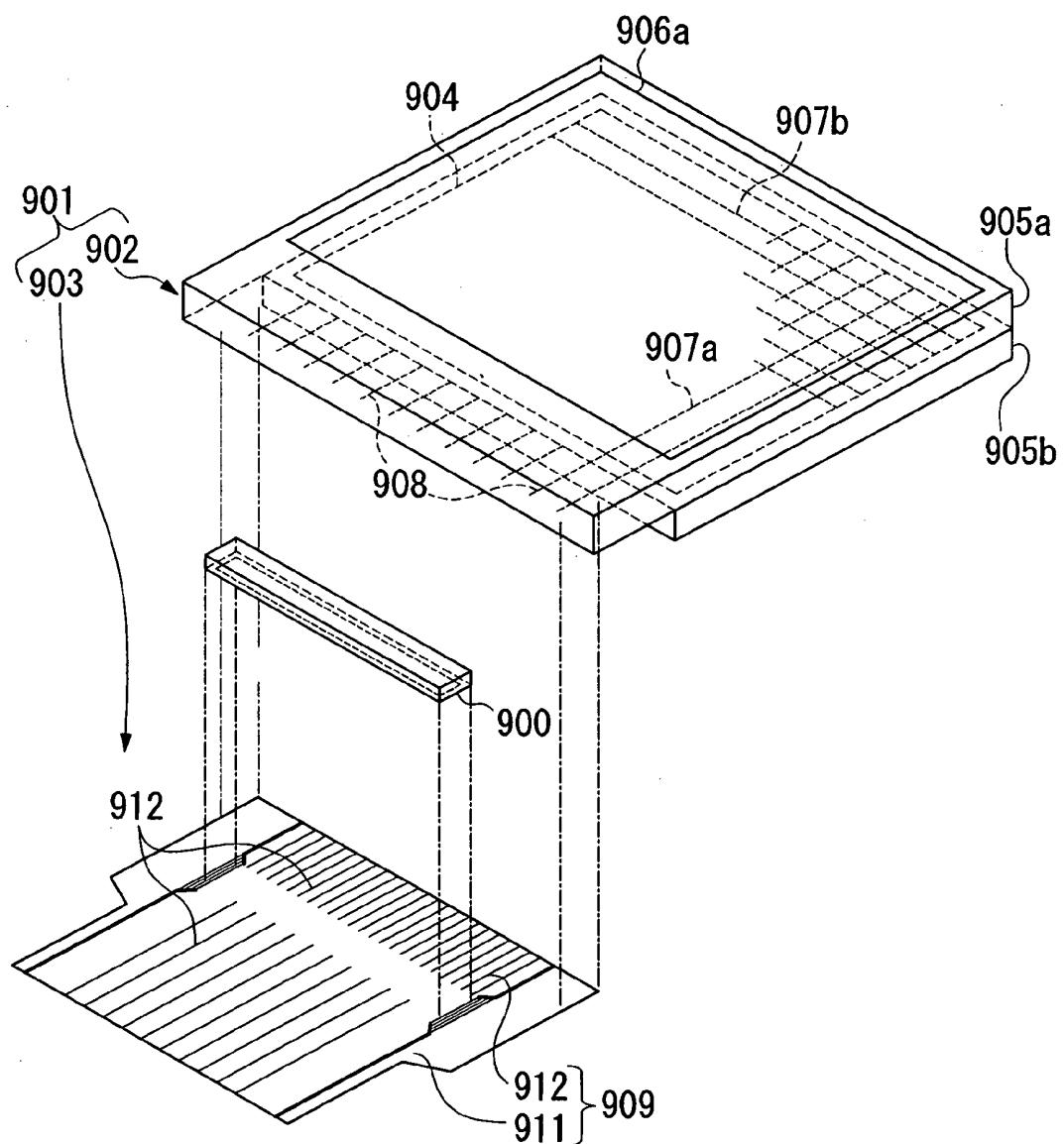

[0118] FIG. 46 is an exploded perspective drawing of the non-contact card medium.

[0119] FIG. 47A to 47C are drawings showing concrete examples of the electronic device of the present invention.

[0120] FIG. 48 is a partial enlarged perspective drawing showing one pixel on the lower substrate in a conventional liquid crystal display.

## DETAILED DESCRIPTION OF THE INVENTION

[0121] Below, embodiments of the thin film pattern fabricating method, a device and a fabricating method for the same, a fabricating method for a liquid crystal display, a liquid crystal display, a method for fabricating an active matrix substrate, an electro-optical apparatus, and an electronic device of the present invention are explained with reference to FIG. 1 through FIG. 48.

### FIRST EMBODIMENT

[0122] In the present embodiment, an example is explained for the case in which a wiring pattern (thin film pattern) ink (function liquid) that includes conductive particles is ejected as a droplet from the nozzle of a droplet ejection head using a droplet ejection method, and a wiring pattern formed by the conducting film is formed on the substrate.

[0123] The wiring pattern ink consists of a dispersant that disperses conductive particles into a dispersing medium, organic silver compounds, and a solvent that disperses silver oxide nanoparticles in a medium (dispersion medium).

[0124] In the present embodiment, in addition to using metal particles including any one among, for example, gold, silver, copper, palladium, and nickel as the conductive particles, the oxides thereof, along with conducting polymers and superconductive particles can be used.

[0125] These conductive particles can be used after the surface has been coated with organic substances in order to improve the dispersibility.

[0126] The diameters of the conductive particles are preferably equal to or greater than 1 nm and equal to or less than 0.1  $\mu\text{m}$ . When the diameter is larger than 0.1  $\mu\text{m}$ , there is a concern that they will plug the nozzle of the liquid ejection head described below. In addition, when the diameter is smaller than 1 nm, the volume ratio of the coating material to the conductive particle becomes large, and the proportion of the organic material in the obtained film becomes excessive.

[0127] The dispersant is not particularly limited as long as the conductive particles described above can be dispersed and they do not flocculate.

[0128] For example, besides water, alcohols such as methanol, ethanol, propanol, butanol, or the like; hydrocarbon compounds such as n-heptane, n-octane, decane, dodecane, tetradecane, toluene, xylene, cymene, durene, indene, dipentene, tetrahydronaphthalene, decahydronaphthalene, cyclohexylbenzene; ether compounds such as ethylene glycol dimethylether, ethylene glycol diethylether, ethylene glycol methylether, diethylene glycol dimethylether, diethylene glycol diethylether, diethylene glycol methylether-ether, 1, 2-demethoxyethane, bis(2-methoxyethyl) ether, p-dioxane; and further, polar compounds such as propylene carbonate,  $\gamma$ -butyrolactone, N-methyl-2-pyrolidone, dimethylformamide, dimethylsulfoxide, cyclohexanone. Among these, in terms of the dispersibility of the particles, stability of the dispersion liquid, and ease of application to the droplet ejection method (ink jet method), water, alcohols, hydrocarbon compounds, and ether compounds are prefer-

able, and as a dispersion medium, water and hydrocarbon compounds are more preferable.

[0129] The surface tension of the dispersing liquid for the conductive particles described above is preferably within a range equal to or greater than 0.02 N/m and equal to or less than 0.07 N/m. When ejecting the liquid in an ink jet method, when the surface tension is less than 0.02 N/m, the curvature of the ejection path occurs easily because wettability of the ink compound with respect to the nozzle surface increases. When the surface tension exceeds 0.07 N/m, the control of the amount of the ejection and the ejection timing becomes difficult because the contour of the meniscus at the distal end of the nozzle is unstable. In order to adjust the surface tension, in the dispersing liquid, fluoride, silicone, or nonionic surface tension modifier can be added in small amounts within a range in which the contact angle with the substrate does not decrease greatly. A nonionic surface tension modifier increases the wettability of the liquid with respect to the substrate, improves the leveling of the film, and contributes to preventing occurrences of fine irregularities in the film. As necessary, the surface tension modifier described above can also include organic compounds such as alcohol, ether, ester, ketone and the like.

[0130] The viscosity of the dispersing liquid is preferably equal to or greater than 1 mPa.s and equal to or less than 50 mPa.s. During the ejection of the liquid material as a droplet by using an ink jet method, when the viscosity is smaller than 1 mPa.s, the vicinity of the nozzle easily becomes contaminated due to flowing out of the ink, and when the viscosity is larger than 50 mPa.s, the frequency of clogging of the nozzle hole becomes high and flat ejection of the droplets becomes difficult.

[0131] Any type of glass, silicon glass, Si wafers, plastic films, metal plates, or the like can be used as the substrate on which the wiring pattern is formed. In addition, semiconductor films, metal films, dielectric films, organic films or the like can be formed as under layers on the surface of any type of these material substrates.

[0132] The electrification control method, the pressure oscillation method, the electromechanical conversion method, the electro-thermal conversion method, and the electrostatic attraction method can be used as ejection technology for the droplet ejection method. The electrification control method imparts an electric charge to the material by using an electrification electrode, and controls the trajectory of the material by using a deflecting electrode to eject the material from the nozzle. In addition, a pressure oscillation method ejects the material to the distal end of the nozzle by applying an ultrahigh pressure of about 30 kg/cm<sup>2</sup> to the material. When a control voltage is not applied, the material is propelled forward to be ejected from the nozzle, and when the control voltage is applied, the electrostatic reaction within the material occurs, the material is scattered and does not eject from the nozzle. In addition, the electromechanical conversion method uses the characteristic that a piezoelectric element deforms upon receiving a pulsed electrical signal. A pressure is applied to the space accommodating the material via a flexible substance due to the deformation of the piezoelectric element, the material is pushed out of this space, and is ejected from the nozzle.

[0133] Next, a device fabrication apparatus used when fabricating the device according to the present invention will be explained.

[0134] A droplet ejection device (inkjet device) that fabricates a device by ejecting a droplet from a droplet ejection head to a substrate can be used as the device fabrication apparatus.

[0135] FIG. 1 is a perspective drawing showing the schematic configuration of the droplet ejection apparatus.

[0136] The droplet ejection apparatus IJ provides a droplet ejection head 101, an X-axis direction drive axle 104, a Y-axis direction guide axle 105, a control device CONT, a stage 107, a cleaning mechanism 108, a platform 109, and a heater 115.

[0137] The stage 107 supports the substrate P to which the ink (fluid material) is applied by this droplet ejection apparatus IJ, and provides a fastening mechanism (not illustrated) that fastens the substrate P at a standard position.

[0138] The droplet ejection apparatus 101 is a multi-nozzle type droplet ejection head that provides a plurality of nozzles, and the longitudinal direction and the X-axis direction are made to coincide. The plurality of ejection nozzles are provided at a regular interval arranged in the Y-axis direction on the lower surface of the droplet ejection head 101. Ink that includes the conductive particles described above is ejected from the ejection nozzles 101 towards the substrate P supported by the stage 107.

[0139] An X-axis direction drive motor 102 is connected at the X-axis direction drive axle 104. The X-axis direction drive motor 102 is a stepping motor or the like, and when an X-direction drive signal is supplied from the control device CONT, the X-axis direction drive axle 104 rotates. When the X-axis direction drive axle 104 rotates, the droplet ejection head 101 is moved in the X-axis direction.

[0140] The Y-axis direction guide axle 105 is fastened so as not to move with respect to the platform 109. The stage 107 provides a Y-axis direction drive motor 103. The Y-axis direction drive motor 103 is a stepping motor or the like, and when a Y-axis direction drive signal is supplied from the control device CONT, the stage 107 is moved in the Y-axis direction.

[0141] The control device CONT supplies a voltage for the discharge control of the droplet to the droplet ejection head 101. In addition, a drive pulse signal that controls the movement of the droplet ejection head 101 in the X-axis direction is supplied to the X-axis direction drive motor 102, and a drive pulse signal that controls the movement of the stage 107 in the Y-axis direction is supplied to the Y-axis direction drive motor 103.

[0142] The cleaning mechanism 108 cleans the droplet ejection head 101. A Y-axis direction drive motor (not illustrated) is provided in the cleaning mechanism 108. Due to the drive of the Y-axis direction drive motor, the cleaning mechanism 108 moves along the Y-axis direction guide axle 105. The movement of the cleaning mechanism 108 is controlled by the control device CONT.

[0143] The heater 115 is a device that heat treats the substrate P by lamp annealing, and carries out vaporization and drying of the medium that contains the liquid material that is applied to the substrate P.

[0144] The droplet ejection device IJ ejects the droplet to the substrate P while scanning relative to the droplet ejection

head 101 and the stage 107 that supports the substrate P. Here, in the following explanation, the X-axis direction is the scanning direction and the Y-axis direction perpendicular to the X-axis direction is the non-scanning direction. Therefore, the ejection nozzle of the droplet ejection heads 101 are provided arranged at regular intervals in the Y-axis direction, which is the non-scanning direction. Note that in FIG. 1, the droplet ejection head 101 is disposed at a right angle with respect to the forward direction of the substrate P, but it is also possible to adjust the angle of the droplet ejection head 101 so that the droplet ejection heads 101 intersects in the forward direction of the substrate P. In this manner, by adjusting the angle of the droplet ejection head 101, it is possible to adjust the pitch between the nozzles. In addition, it is also possible to adjust arbitrarily the distance between the substrate P and the nozzle surface.

[0145] FIG. 2 is a drawing for explaining the ejection principle of the fluid material according to the piezoelectric method.

[0146] In FIG. 2, a piezoelectric element 122 is disposed adjacent to a fluid chamber 121 that accommodates a liquid material (wiring pattern ink, function liquid). The fluid material is supplied to the fluid chamber 121 via a fluid material supply system 123 that includes a material tank that accommodates the fluid material. The piezoelectric element 122 is connected to a drive circuit 124, a voltage is applied to the piezoelectric element 122 via the drive circuit 124 causing the piezoelectric element 122 to be deformed. Thereby, the fluid chamber 121 is deformed and thereby the fluid material is ejected from the nozzle 125. In this case, the deformation amount of the piezoelectric element 122 can be controlled by changing the value of the applied voltage. Thus, there is the advantage that the composition of the material is difficult to influence because the droplet ejection by the piezoelectric method does not apply heat to the material.

[0147] Next, as an example of an embodiment of the wiring pattern formation method of the present invention, the method in which the conducting film wiring is formed on a substrate will be explained with reference to FIGS. 3A to 3C. The wiring pattern formation method according to the present embodiment disposes ink for the wiring pattern on the substrate, and forms the conducting film pattern for the wiring on this substrate. The wire pattern formation method generally consists of a bank formation step, a concave part formation step, a residue treatment step, a liquid repelling treatment step, a material disposition step and intermediate drying step, a baking step, and a bank removal step.

[0148] Below, each of the steps will be explained in detail.

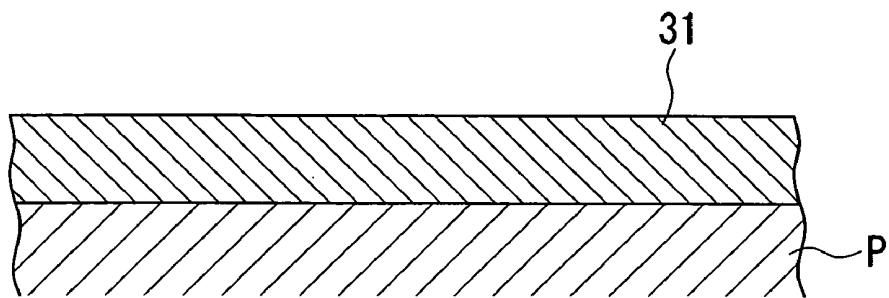

#### [0149] Bank Formation Step

[0150] A bank is a member that functions as a defining member, and the formation of a bank can be carried out by any arbitrary method, such as a lithographic method or a printing method. For example, in the case of using lithographic method, as shown in FIG. 3A, an organic photo-sensitive material 31 is applied in alignment with the height of the banks on the substrate P by using a predetermined method such as spin coating, spray coating, roll coating, die coating, dip coating or the like, and a resist layer is applied thereto. In addition, in conformity with the bank profile (the wiring pattern), masking is carried out, the resist is exposed

and developed, and thereby a resist remains that conforms to the bank profile. Finally, etching is carried out, and bank material in parts that are outside the mask is removed. In addition, a bank (convex part) can be formed using two layers, where the lower layer is material consisting of an organic or inorganic substance and has liquid-affinity with respect to the function liquid, and the upper layer is a material consisting of an organic substance and is water-repelling.

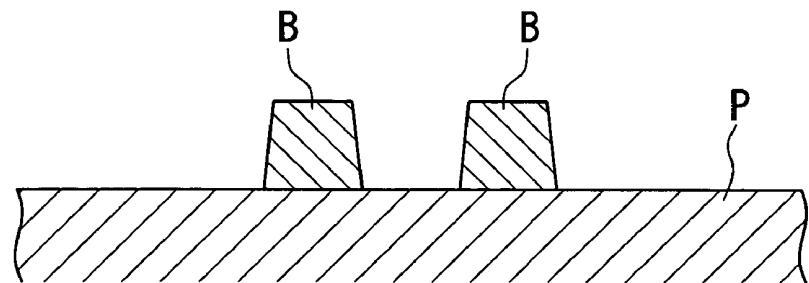

[0151] Thereby, as shown in FIG. 3B, banks B and B are built up, for example, at a 10  $\mu\text{m}$ , so as to surround the vicinity of the region in which the wiring pattern is to be formed.

[0152] Note that with respect to the substrate P, as a surface improvement treatment before the organic material application, HMDS treatment can be carried out (a method in which  $(\text{CH}_3)_3\text{SiNHSi}(\text{CH}_3)_3$  is applied by vaporization), but in FIG. 3, the illustration thereof is omitted.

[0153] A material that exhibits a liquid repellency with respect to the fluid material can be used as the organic material to form the banks, and as will be described below, an insulating organic material that can impart a liquid repellency (Teflon (registered trademark)) by using a plasma treatment, has a good adhesiveness to the lower substrate, allows easy patterning using photolithography can be used. For example, it is possible to use a high molecular material such as an acryl resin, a polyimide resin, an olefin resin, a melanin resin or the like.

#### [0154] Concave Part Formation Step

[0155] When the banks B and B have been formed on the substrate P next, as shown in FIG. 3C, a concave part 32 is formed on the substrate P between the banks B and B. Concretely, the banks serve as the mask with respect to the substrate P on which banks B and B have been formed, and the concave part 32 is formed by etching by using, for example, SF6. At this time, using the etching time as a parameter, the depth of the concave part 32 is adjusted to a predetermined value (for example, 2  $\mu\text{m}$ ). Thereby, the substrate P is etched, and as shown in the figure, a concave part 32 having a reverse-taper cross-sectional profile, which gradually widens towards the base, is formed.

#### [0156] Residue Treatment Step (Liquid-Affinity Treatment Step)

[0157] Next, the substrate P undergoes residue treatment in order to remove the resist (organic material) residue from bank formation.

[0158] As a residue treatment, it is possible to select an ultraviolet (UV) irradiation treatment that carried out the residue treatment by irradiation with ultraviolet light, an O<sub>2</sub> plasma treatment in which oxygen in the atmosphere serves as the treatment gas, and the like. Here, O<sub>2</sub> plasma treatment is carried out.

[0159] Concretely, this is carried out by irradiating the substrate P with oxygen plasma from a plasma discharge electrode. The conditions for the O<sub>2</sub> plasma treatment are, for example, a plasma power between 50 to 1000 W, an oxygen gas flow rate of 50 to 100 mm/sec, a conveyance speed for the substrate P of 0.5 to 10 mm/sec, and a substrate temperature of 70 to 90° C. Note that in the case in which the substrate P is a glass substrate, the surface thereof has

liquid-affinity with respect to the wire pattern formation material, but like the present embodiment, it is possible to increase the liquid-affinity of the concave part 32 by carrying out O<sub>2</sub> plasma treatment and ultraviolet light irradiation treatment for the residue treatment.

**[0160] Liquid-Repelling Treatment Step**

**[0161]** Next, a liquid-repelling treatment is carried out on the banks B and B, and water-resistance is imparted to the surface thereof. It is possible to use a plasma treatment method (CF<sub>4</sub> plasma treatment method) in the atmosphere, in which tetrafluoromethane is used as the treatment gas. The conditions for the CF<sub>4</sub> plasma treatment are, for example, a plasma power between 50 to 1000 W, an CF<sub>4</sub> flow rate of 50 to 100 ml/min, a substrate conveyance speed of 0.5 to 1020 mm/sec, and a substrate temperature of 70 to 90° C.

**[0162]** Note that the treatment gas is not limited to CF<sub>4</sub>, by other fluorocarbon type gases can be used.

**[0163]** By carrying out this type of liquid-repelling treatment, a fluorine group is introduced into the resin that forms the banks B and B, and a high water-resistance is imparted to the concave part 32. Note that the O<sub>2</sub> plasma treatment used as a liquid-affinity treatment can be carried out before formation of the banks B. However, because acrylic resins, polyimide resins and the like have the property that fluoridating is easier when pretreatment using an O<sub>2</sub> plasma is carried out, preferably the O<sub>2</sub> plasma treatment is carried out after the bank B has been formed.

**[0164]** Note that although there is a small influence on the substrate P surface that has undergone the liquid-affinity treatment first due to the liquid-affinity treatment of the banks B and B. In particular, in the case in which the substrate P consists of glass or the like, the introduction of the fluoride group occurs with difficulty due to the liquid-repelling treatment, and thus, the liquid-affinity, i.e., the wettability, of the substrate P is not substantially lost.

**[0165]** In addition, the liquid-repelling treatment for the banks B and B can be omitted by forming them with a material (for example, a resin material having a fluorine group) that is water-repelling.

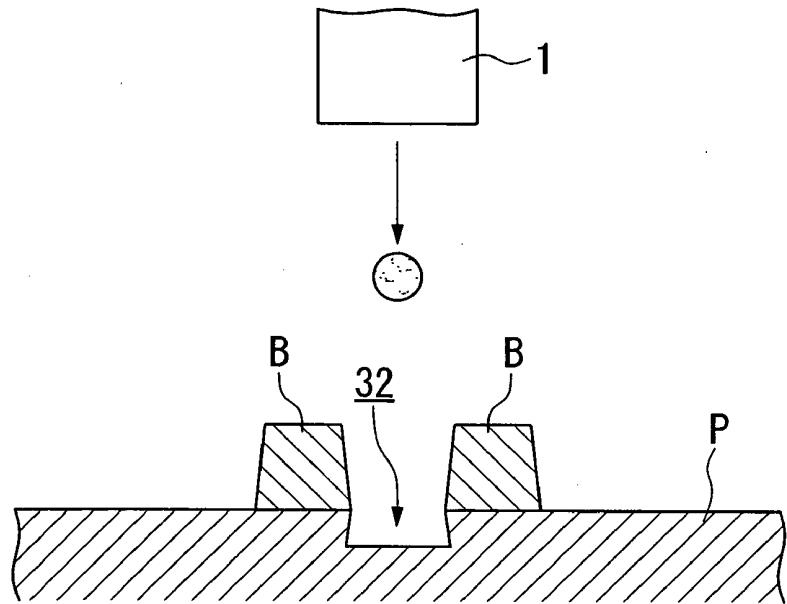

**[0166] Material Disposition Step and Intermediate Drying Step**

**[0167]** Next, using a droplet ejection method employing the droplet ejection device II, the wiring pattern formation material is applied to the concave part 32 on the substrate P. Note that here an ink is ejected in which silver is used as the conductive particle, and diethylene glycol diethylether is used as the medium (dispersion medium).

**[0168]** Specifically, in the material disposition step, as shown in FIG. 4D, the fluid material that includes a wiring pattern formation material is formed into a droplet and ejected from the droplet ejection head 101, and this droplet is disposed in the concave part 32 on the substrate P. Conditions for the droplet ejection are an ink weight of 4 ng/dot, and an ink speed (ejection speed) of 5 to 7 m/sec.

**[0169]** At this time, because the concave part 32 is surrounded by the banks B and B, it is possible to prevent the liquid from spreading beyond the predetermined position. In addition, because the banks B and B have had water resis-

tance imparted, even if a part of the ejected drop lands on the bank B, it will be repelled from the bank B, and flow down into the concave part 32 between the banks. Furthermore, because a liquid-affinity has been imparted to the concave part 32, the ejected fluid spreads easily within the concave part 32, and thereby the fluid can fill the concave part 32 evenly within a predetermined location.

**[0170] Intermediate Drying Step**

**[0171]** After ejecting the droplet onto the substrate P, a drying treatment is carried out as necessary in order to remove the dispersion medium. The drying treatment can be carried out by a heating treatment that uses, for example, a normal hotplate or electric furnace that heats the substrate P. In the present embodiment, for example, the step is carried out at 180° C. for about 60 minutes. This heating can be carried out in an N<sub>2</sub> atmosphere or the like, and it is not always necessary to carry it out in the atmosphere.

**[0172]** In addition, this drying treatment can be carried out by lamp annealing. While not particularly limited, the light source for the light used in the lamp annealing can be an infrared lamp, a xenon lamp, a YAG laser, argon laser, a carbon gas laser, or an excimer laser such as XeF, XeCl, XeBr, KrF, KrCl, ArF, or ArCl. These light sources are generally used within an output range equal to or greater than 10 W and equal to or less than 5000 W, but in the present embodiment, a range equal to or greater than 100 W and equal to or less than 5000 W is sufficient.

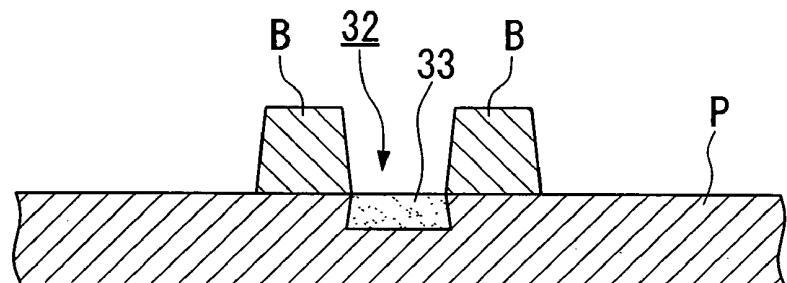

**[0173]** By repeatedly carrying out the intermediate drying step and the material disposition step described above, as shown in FIG. 4E, the thin film of the wiring pattern (thin film pattern) 33 is formed so as not to protrude from the surface (preferably substantially flush to the surface) of the substrate P.

**[0174] Baking Step**

**[0175]** The dry film after the ejection step is to improve the electrical connection between particles, and the dispersing medium must be completely removed. In addition, in the case in which the surface of the conductive particles is coated with coating material such as an organic substance in order to improve the dispersibility, it is necessary to remove the coating material. Thus, heat treatment and/or light irradiation treatment is carried out on the substrate after the ejection step.

**[0176]** The heat treatment and/or light irradiation treatment are normally carried out in the atmosphere, but depending on necessity, the treatments can also be carried out in an inert gas atmosphere such as nitrogen, argon, or helium. The treatment temperature during the heat treatment and/or light irradiation treatment is suitably set taking into account the boiling point (vapor pressure) of the diffusion medium, the type and pressure of the atmosphere gas, the thermal behavior of the dispersibility and oxidizing properties of the particles, the presence or absence of the coating material and the amount thereof if present, the heat resistance temperature of the substrate, and the like.

**[0177]** For example, in order to remove a coating material consisting of an organic substance, baking must be carried out at approximately 300° C. In addition, in the case in which a substrate such as plastic is used, preferably the temperature is greater than or equal to room temperature and equal to or less than 100° C.

[0178] Due to the above steps, the electrical contact between the particles in the dry film after the ejection step is guaranteed, and the film is converted into a conducting film.

[0179] **Bank Removal Step**

[0180] In this step, the banks B and B that are present around the concave part 32 are removed by an ashing separation treatment. Plasma ashing, ozone ashing, or the like can be used as the ashing treatment.

[0181] In plasma ashing, a gas such as a plasma oxygen gas and the banks (resist) are reacted, and the banks are stripped and removed by vaporization. The banks are solid materials formed from carbon, oxygen, and hydrogen, and by chemically reacting these with an oxygen plasma,  $\text{CO}_2$ ,  $\text{H}_2\text{O}$ , and  $\text{O}_2$  are generated, and it is possible to strip all of a bank as a vapor.

[0182] At the same time, the fundamental principle of ozone ashing is the same as plasma ashing.  $\text{O}_3$  (ozone) is decomposed and converted into the reaction gas  $\text{O}^+$  (oxygen radical), and this  $\text{O}^+$  and the banks react together. A bank that has reacted with the  $\text{O}^+$  is converted to  $\text{CO}_2$ ,  $\text{H}_2\text{O}$ , and  $\text{O}_2$ , and the entire bank is stripped as vapor.

[0183] By carrying out the ashing stripping treatment on the substrate P, as shown in FIG. 4F, the banks are removed from the substrate P.

[0184] In the above manner, in the present embodiment, the concave part 32 is formed in the substrate P and a droplet of a function liquid is ejected into this concave part 32. Thereby, it is possible to form a wiring pattern 33 that does not protrude from the substrate P, it becomes possible to make the devices formed by the wiring pattern in the substrate thin, and furthermore, it becomes possible to realize increased integration when laminating the wiring pattern across a plurality of surfaces on the substrate. In addition, in the present embodiment, the wiring pattern 33 is formed so as not to protrude from the surface of the substrate P, and thus the flatness is improved, and it becomes possible to carry out easily the subsequent steps such as forming the insulating film.

[0185] Furthermore, when forming the concave part 32 in the present embodiment, the banks B and B are used as masks, and thus the fabrication of special use masks and the setting of the masks on the substrate become unnecessary, and thereby it is possible to improve the productivity. Furthermore, in the present embodiment, a liquid repellency is imparted to the banks B and B, and thus even if a part of an ejected droplet lands on a bank B, the ink flows down into the concave part 32, and thereby it is possible to apply the liquid more evenly, and it becomes possible to obtain a wiring pattern 33 having a uniform film thickness.

[0186] In addition, in the present embodiment, because the concave part 32 is formed so as to have a reverse taper cross-section, the wiring pattern 33 becomes difficult to strip off after baking, and it becomes possible to improve the device quality.

## SECOND EMBODIMENT

[0187] Next, the fabricating method for the liquid crystal device of the present invention and the liquid crystal display fabricated by using this manufacturing method are explained

below with reference to the figures. First, the fabricating method of the liquid crystal display of the present embodiment will be explained with reference to FIG. 5 to FIG. 14.

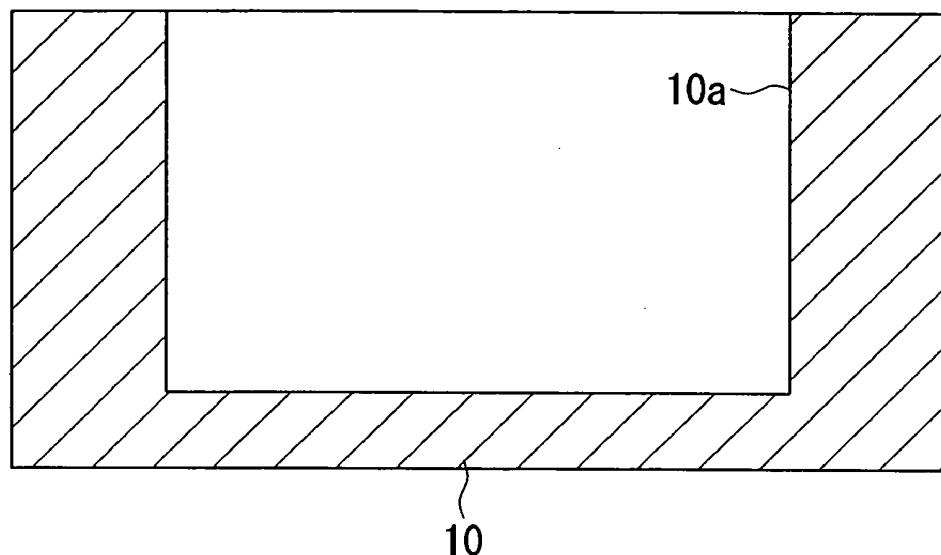

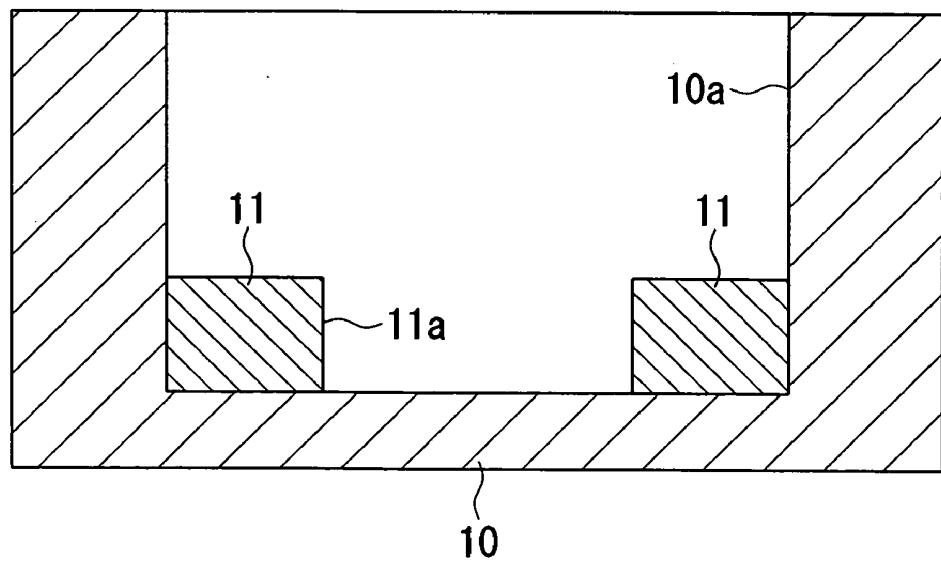

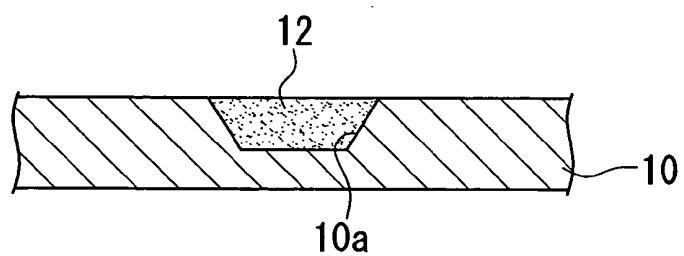

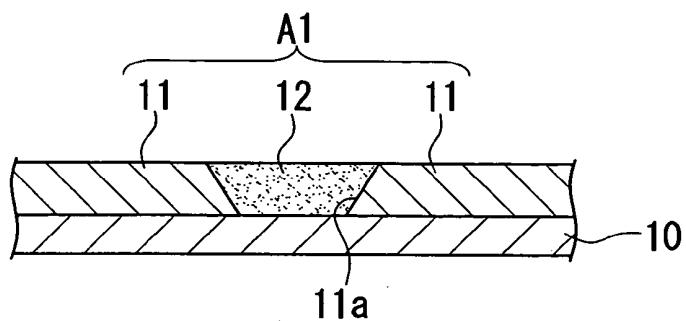

[0188] As shown in FIG. 5, in the substrate groove formation step, in the upper surface of a cleaned glass substrate 10, substrate grooves 10a having groove width of  $\frac{1}{20}$  to  $\frac{1}{10}$  that of the pitch of one pixel are applied by photoetching. Preferably, as shown in the figure, a forward-taper (a tapered profile that opens toward the ejection source) is used. Thereby, it becomes possible for the ejected droplet to fill the grooves down to the bottom.

[0189] Next, as shown in FIG. 6, in the liquid repelling part formation step, banks 11 are formed by lithography as a liquid repelling part that partitions the substrate groove 10a. These banks must be provided with a liquid repellency, and a high molecular material such as acryl resin, polyimide resin, olefin resin, melamin resin or the like can be suitable used as this material.

[0190] In order to provide a liquid repellency to the banks 11 after formation, it is necessary to carry out  $\text{CF}_4$  plasma treatment (plasma treatment in which a gas incorporating a fluoride component is used), but instead, the material of the banks 11 itself can include a liquid repelling material (a fluorine group or the like) in advance. In this case, the  $\text{CF}_4$  plasma treatment can be omitted.

[0191] The contact angle of the liquid repelling banks 11 with respect to the ejected ink is preferably guaranteed to be  $40^\circ$  or greater. Specifically, as a result of experimental confirmation by the inventors, a after treatment contact angle of  $66.20$  ( $10^\circ$  or less when untreated) with respect to, for example, an organic silver compound (a diethylene glycol dimethyl ether solvent) can be guaranteed when using an organic material as the material for the banks 11, and an angle of  $49.0^\circ$  ( $10^\circ$  or less when untreated) can be guaranteed when an inorganic material is used. Note that these contact angles are obtained under treatment conditions in which the plasma power is  $550$  W and the tetrafluoromethane gas is supplied at  $0.11$  ml/min.

[0192] In addition, as a result of experimental confirmation by the inventors, a contact angle of  $104.1^\circ$  ( $10^\circ$  or less when untreated) after treatment with respect to pure water can be guaranteed when using an organic material as the material for the banks 11, and a contact angle of  $96.3^\circ$  ( $10^\circ$  or less when untreated) can be guaranteed when an inorganic material is used.

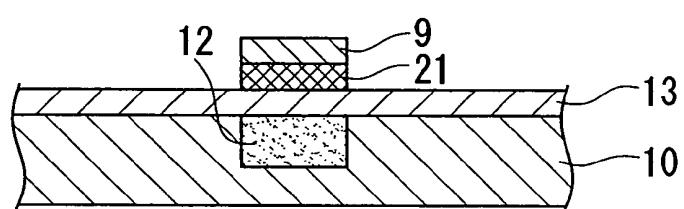

[0193] In the gate scanning line electrode formation step (the first conductive pattern formation step) that follows the liquid repelling part formation step described above, as shown in FIG. 7, a gate scanning line electrode 12 is formed by ejecting droplets that include a conducting material using an ink jet so as to fill the substrate groove 10a, which is the formation region defined by the banks 11. Ag, Al, Au, Cu, palladium, Ni, W—Si, conducting polymers and the like can be used as the conducting material here. The gate scanning line electrode 12 formed in this matter can impart a sufficient liquid repellency to the banks 11, and thus it is possible to form a fine wiring pattern that does not protrude from the substrate groove 10a.

[0194] In the bank removal step (liquid repelling part removal step) that follows the gate scanning line electrode formation step, as shown in FIG. 8, all of the banks 11 are

removed from the upper surface of the glass substrate **10**. Thereby, the upper surface of the glass substrate **10** acquires a flat surface profile in which the substrate groove **10a** is filled with the gate scanning line electrode **12**.

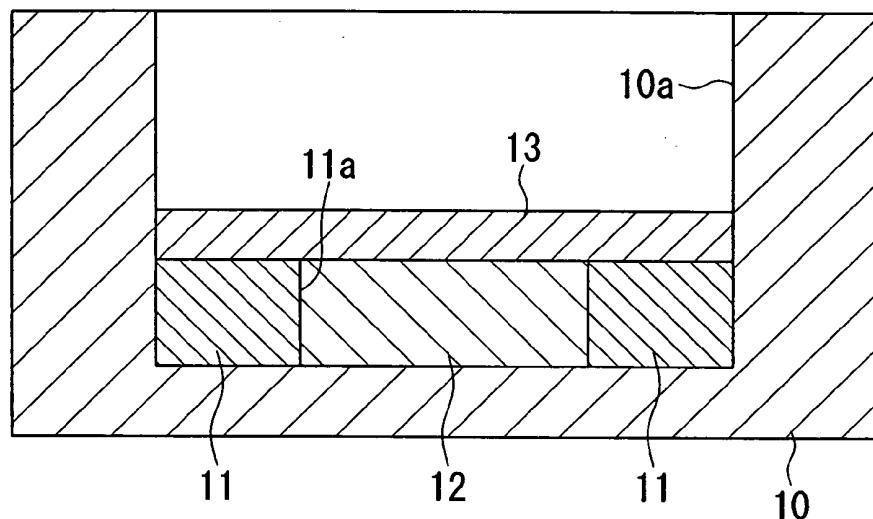

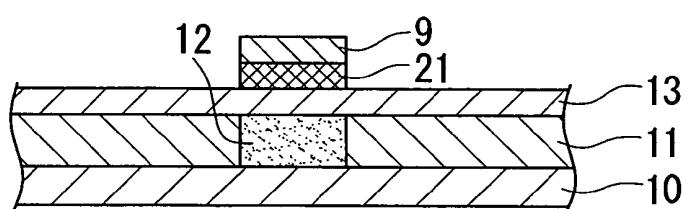

[0195] In the insulating layer formation step (the first insulating layer formation step) that follows the removal step described above, as shown in **FIG. 9**, a TFT (thin film transistor) consisting of a thin film semiconductor and a gate scanning line insulating layer (insulating layer) **13** are formed so as to cover the upper surface of the gate scanning line electrode **12**.  $\text{SiO}_2$ ,  $\text{SiNe}$ , BPSG, NSG and the like can be used as the material for this gate scanning line insulating layer **13**.

[0196] Note that in the case in which  $\text{SiNe}$  is formed by a CVD method, a thermal history of  $300^\circ \text{C}$ . to  $350^\circ \text{C}$ . is necessary, but by using an inorganic material in the banks, it is possible to avoid problems related to transparency and heat resistance.

[0197] The gate scanning line insulating layer **13** formed in this manner is formed on a flat glass substrate **10**, and thus provides a flat surface.

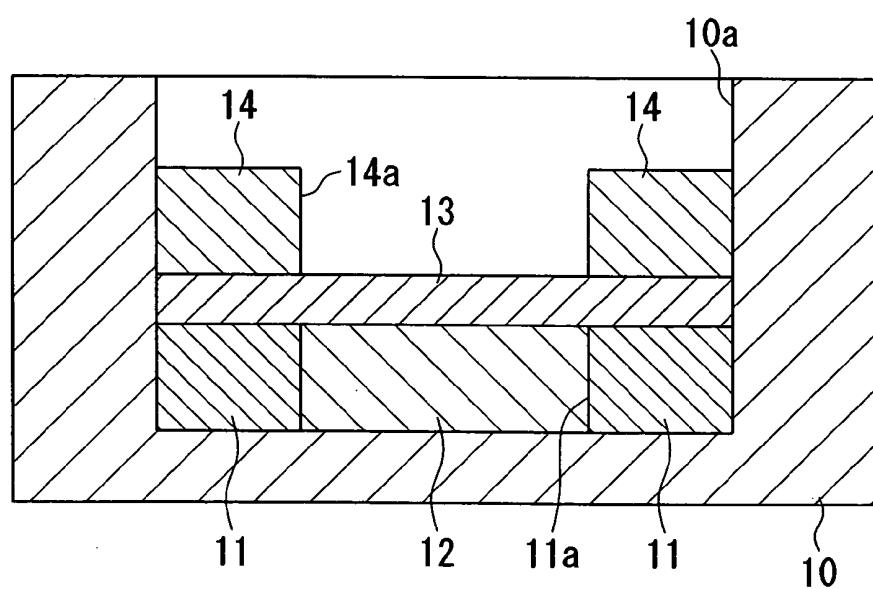

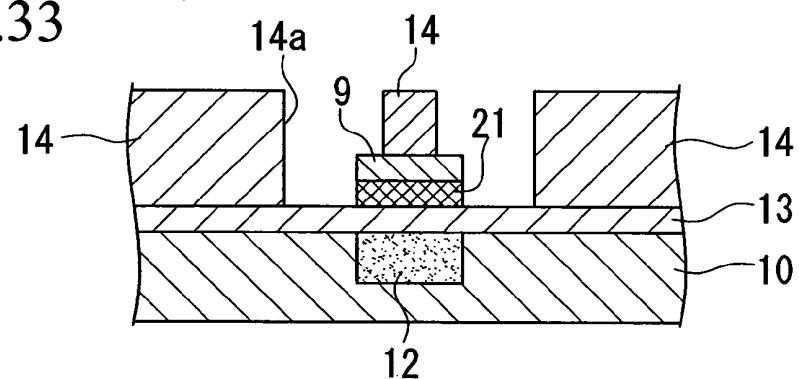

[0198] In the second bank formation step (bank formation step) that follows the first insulating layer formation step described above, as shown in **FIG. 10**, banks **14** are formed by lithography. These banks are for providing a groove **14a** that is  $\frac{1}{20}$  to  $\frac{1}{10}$  the pitch of one pixel and intersects the substrate groove **10a**. Transparency and a liquid repellency must be provided to the banks **14** after formation, and thus a high molecular material such as an acryl resin, a polyimide resin, an olefin resin, a melanin resin or the like can be appropriately used as this material.

[0199] In order to provide a liquid repellency to the banks **14** after formation, it is necessary to carry out a  $\text{CF}_4$  plasma treatment (a plasma treatment in which a has having a fluoride component has been used), but instead, the material of the banks **14** itself can include a liquid repelling material (a fluorine group or the like) in advance. In this case, the  $\text{CF}_4$  plasma treatment can be omitted.

[0200] Thereby, the contact angle of the liquid repelling banks **14** with respect to the ejected ink is preferably guaranteed to be equal to or greater than  $40^\circ$ .

[0201] In the source electrode formation step (second conductive pattern formation step) that follows the second bank formation step described above, as shown in the same **FIG. 10**, a droplet that includes a conducting material is ejected by an ink jet so as to fill the groove **14a**, which is the formation region defined by the banks **14**. Thereby, a source electrode **15** is formed that intersects the gate scanning line electrode **12**. Ag, Al, Au, C, palladium, Ni, W—Si, a conductive polymer or the like can be suitably used here as the conductive material. Because a sufficient liquid repellency to the banks **14** in advance, it is possible for the source electrode **15** to form a fine wiring pattern that does not protrude from the groove **14a**.

[0202] By the step described above, a conductive layer Al is formed that provides a flat upper surface consisting of banks **14** and a source electrode **15** on the substrate **10**.

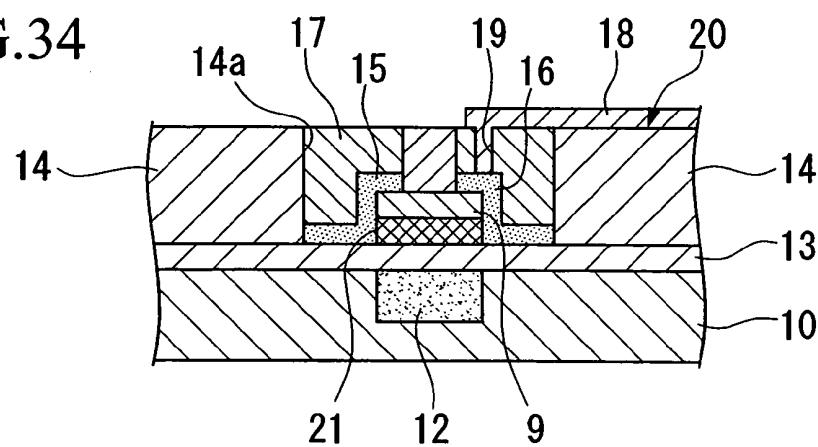

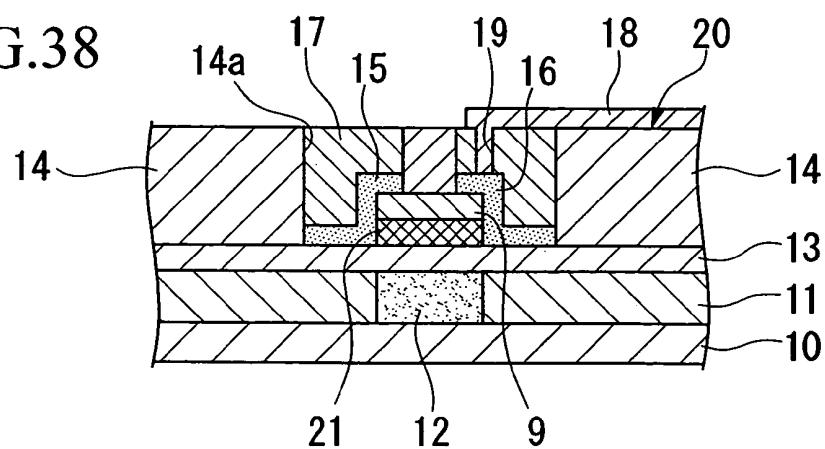

[0203] In the second insulating layer formation step (second insulating layer formation step) that follows the source electrode formation step described above, as shown in **FIG.**

**11**, a source line insulating film (second insulating layer) **16** is formed so as to cover the upper surface of the banks **14** and the source electrode **15**.  $\text{SiO}_2$ ,  $\text{SiNe}$ , BPSG, NSG or the like can be used as the material for this source line insulating film **16**.

[0204] Because the source line insulating film **16** formed in this manner is formed on the flat conductive layer Al, a flat upper surface can be provided.

[0205] In the third bank formation step following the second insulating film formation step, as shown in **FIG. 12**, except for the patterning region for the pixel electrode (ITO), a bank **17** is formed by photolithography on the upper surface of the source line insulating film **16**. A high molecular material such as an acryl resin, a polyimide resin, an olefin resin, a melanin resin or the like can be appropriately used as the material for the bank **17**.

[0206] In the pixel electrode formation step that follows the third bank formation step, as shown in **FIG. 13**, a droplet that is the material for the pixel electrode is ejected by an ink jet into the region defined by the bank **17**, and thereby the pixel electrode **18** is formed. The pixel electrode **18** formed in this manner is formed on the flat source line insulating film **16**, and thus a flat surface is provided. Because the pixel electrode **18** and the bank **17** formed in this manner are formed on the flat source line insulating film **16**, a flat upper surface can be provided.

[0207] Note that an  $\alpha$ -si TFT device portion formed via each of the steps described above is shown in **FIG. 14**. In this figure, reference numeral **19a** denotes the drain electrode and reference numeral **19a** denotes the channel region ( $\alpha$ -si).

[0208] In addition, after the pixel electrode formation step, the lower substrate is completed by carrying out baking, orientation film formation, and rubbing treatment. In addition, by forming a liquid crystal layer between the lower substrate and the upper substrate fabricated separately, the liquid crystal display is completed (not illustrated).

[0209] According to the fabricating method for the liquid crystal display of the present embodiment described above, because the source line insulating film **16** is formed by leaving in place the banks **14** that would be usually be removed, it is possible to guarantee a surface profile that has fewer irregularities than a conventional one.

[0210] As explained above, after all the steps, the glass substrate **10** can guarantee a flat surface profile. Thereby, when implementing the rubbing treatment on the glass substrate **10**, irregularities in the result occur with difficulty, and thereby it is possible to improve the liquid crystal orientation force and thus prevent display distortions. Thereby, it is possible to fabricate a liquid crystal display having few display distortions.

[0211] In addition, because the gate scanning line electrode **12** is formed so as to be embedded in the substrate groove **10a** of the glass substrate **10**, compared to the case in which the gate scanning line electrode **12** is formed on a glass substrate on which a substrate groove **10a** is not formed, it is possible to make the thickness dimension of the substrate after completion thin.

[0212] Furthermore, because an ink jet is used in the formation of the gate scanning line electrode **12** and the

capacity line **19d** (refer to **FIG. 14**), the source electrode **15** and the drain electrode **19a**, the pixel electrode **18**, and the like, it is possible to eliminate needless waste material, and thus it is possible to reduce material costs.

### THIRD EMBODIMENT

[0213] Next, a fabricating method for a liquid crystal display of the present invention and the liquid crystal display fabricated by using this fabricating method will be explained below with reference to **FIG. 15** to **FIG. 22**. Note that in these figures, essential elements identical to those in **FIG. 5** through **FIG. 14** shown in the second embodiment have identical reference numerals, and thus the explanation thereof is omitted.

[0214] As shown in **FIG. 15**, in the substrate groove formation step, in the upper surface of a cleaned glass substrate **10**, substrate grooves **10a** having groove width of  $\frac{1}{20}$  to  $\frac{1}{10}$  that of the pitch of one pixel are applied by photoetching. As shown in **FIG. 19A** and **FIG. 19B**, the substrate groove **10a** is a groove in which the alternately traversing gate scanning line electrode **12**, the capacity line **19c** (explained below with reference to **FIG. 22**), the source electrode **15**, and the drain electrode **19a** (explained below with reference to **FIG. 22**) are embedded, and an island shape is formed in which two grooves alternately intersect each other separately to form a cross shape.

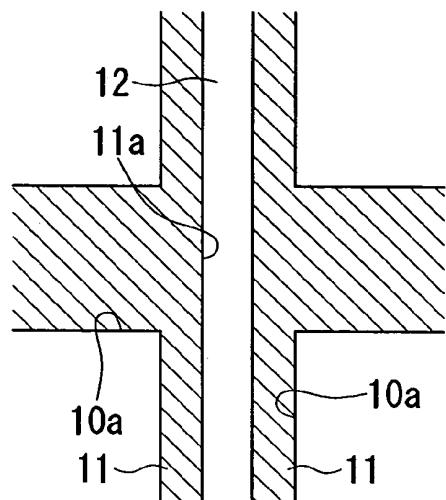

[0215] In the first bank formation step (first bank formation step) following this substrate groove formation step, as shown in **FIG. 16** and **FIG. 19A**, on the bottom of the substrate groove **10a**, the banks **11** are formed by photolithography. These banks **11** define the groove **11a** that demarks the gate scanning line electrode and the capacity line. These banks **11** must be provided with a liquid repellency, and a high molecular material such as an acryl resin, a polyimide resin, an olefin resin, a melanin resin, or the like can be suitably used as this material.

[0216] In order to provide a liquid repellency to the banks **11** after formation, it is necessary to carry out  $\text{CF}_4$  plasma treatment (plasma treatment in which a gas incorporating a fluoride component is used), but instead, like the second embodiment, the material of the banks **11** itself can include a liquid repelling material (a fluorine group or the like) in advance.

[0217] In addition, in order to obtain an advantageous ejection result in the groove **11a** between the banks **11**, preferably a forward-taper (a tapered profile that opens toward the ejection source) is used as the profile of this groove **11a**. Thereby, it becomes possible for the ejected droplet to fill the grooves down to the bottom.

[0218] In the gate scanning line electrode formation step (first conductive pattern formation step) that follows the first bank formation step described above, as shown in **FIG. 17** and **FIG. 19A**, the gate scanning line electrode **12** is formed by ejecting a liquid that includes a conductive material by using an ink jet such that the groove **11a**, which is the formation region defined by the banks **11**, is filled. Ag, Al, Au, Cu, palladium, Ni, W—Si, conducting polymers and the like can be appropriately used as the conducting material here. The gate scanning line electrode **12** formed in this manner imparts in advance a sufficient liquid repellency to the banks **11**, and thus it becomes possible to form a fine wiring pattern that does not project from the groove **11a**.