US008044902B2

(12) **United States Patent**

**Hashimoto**

(10) **Patent No.:** **US 8,044,902 B2**

(b4) **Date of Patent:** **Oct. 25, 2011**

(54) **METHOD OF DRIVING A COLOR LIQUID CRYSTAL DISPLAY AND DRIVER CIRCUIT FOR DRIVING THE DISPLAY AS WELL AS PORTABLE ELECTRONIC DEVICE WITH THE DRIVER CIRCUIT**

6,384,807 B1 5/2002 Furuhashi et al.

6,452,579 B1 9/2002 Itoh et al.

6,563,482 B1 5/2003 Yamazaki et al.

(75) Inventor: **Yoshiharu Hashimoto**, Tokyo (JP)

FOREIGN PATENT DOCUMENTS

(73) Assignee: **Renesas Electronics Corporation**, Kanagawa (JP)

|    |              |         |

|----|--------------|---------|

| EP | 0 479 304 A2 | 4/1992  |

| JP | 4-165329     | 6/1992  |

| JP | 6-161392     | 6/1994  |

| JP | 7-325556     | 12/1995 |

| JP | 8-76726      | 3/1996  |

| JP | 2695981      | 9/1997  |

| JP | 10-187106    | 7/1998  |

| JP | 11-95729     | 4/1999  |

| JP | 11-282421    | 10/1999 |

| JP | 2000-250494  | 9/2000  |

| JP | 2001-188499  | 7/2001  |

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1052 days.

(21) Appl. No.: **11/407,803**

(22) Filed: **Apr. 20, 2006**

(65) **Prior Publication Data**

US 2006/0187163 A1 Aug. 24, 2006

**Related U.S. Application Data**

(63) Continuation of application No. 10/051,567, filed on Jan. 18, 2002, now abandoned.

(30) **Foreign Application Priority Data**

Jan. 19, 2001 (JP) ..... 2001-012540

(51) **Int. Cl.**

**G09G 3/36** (2006.01)

(52) **U.S. Cl.** ..... 345/88; 345/87

(58) **Field of Classification Search** ..... 345/87-111,

345/204-215, 690-699

See application file for complete search history.

(56) **References Cited**

U.S. PATENT DOCUMENTS

5,414,443 A 5/1995 Kanatani et al.

5,886,689 A 3/1999 Chee et al.

6,166,725 A 12/2000 Isami et al.

6,340,970 B1 \* 1/2002 Furuhashi et al. ..... 345/213

U.S. Office Action dated Mar. 3, 2011 from U.S. Appl. No. 12/050,832.

\* cited by examiner

*Primary Examiner* — Srilakshmi K Kumar

(74) *Attorney, Agent, or Firm* — Scully, Scott, Murphy & Presser, P.C.

(57) **ABSTRACT**

The present invention provides a method and a circuit for driving a color liquid crystal display in a normal driving mode and a power saving mode, wherein in the normal driving mode, voltages corresponding to image display data are applied to data electrodes of the color liquid crystal display, and wherein in the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as display data signals to the data electrodes.

**3 Claims, 23 Drawing Sheets**

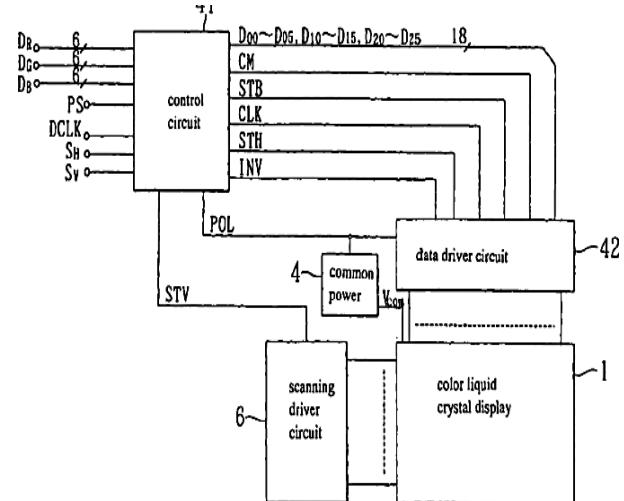

FIG. 1 prior art

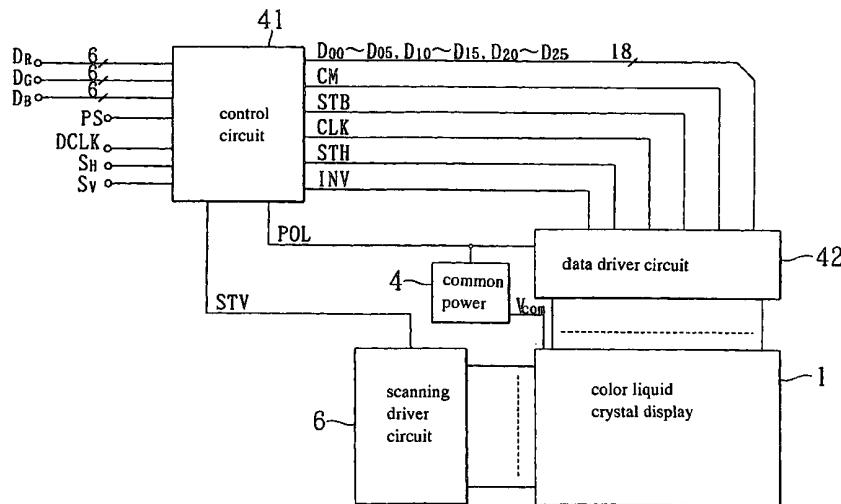

FIG. 2 prior art

3

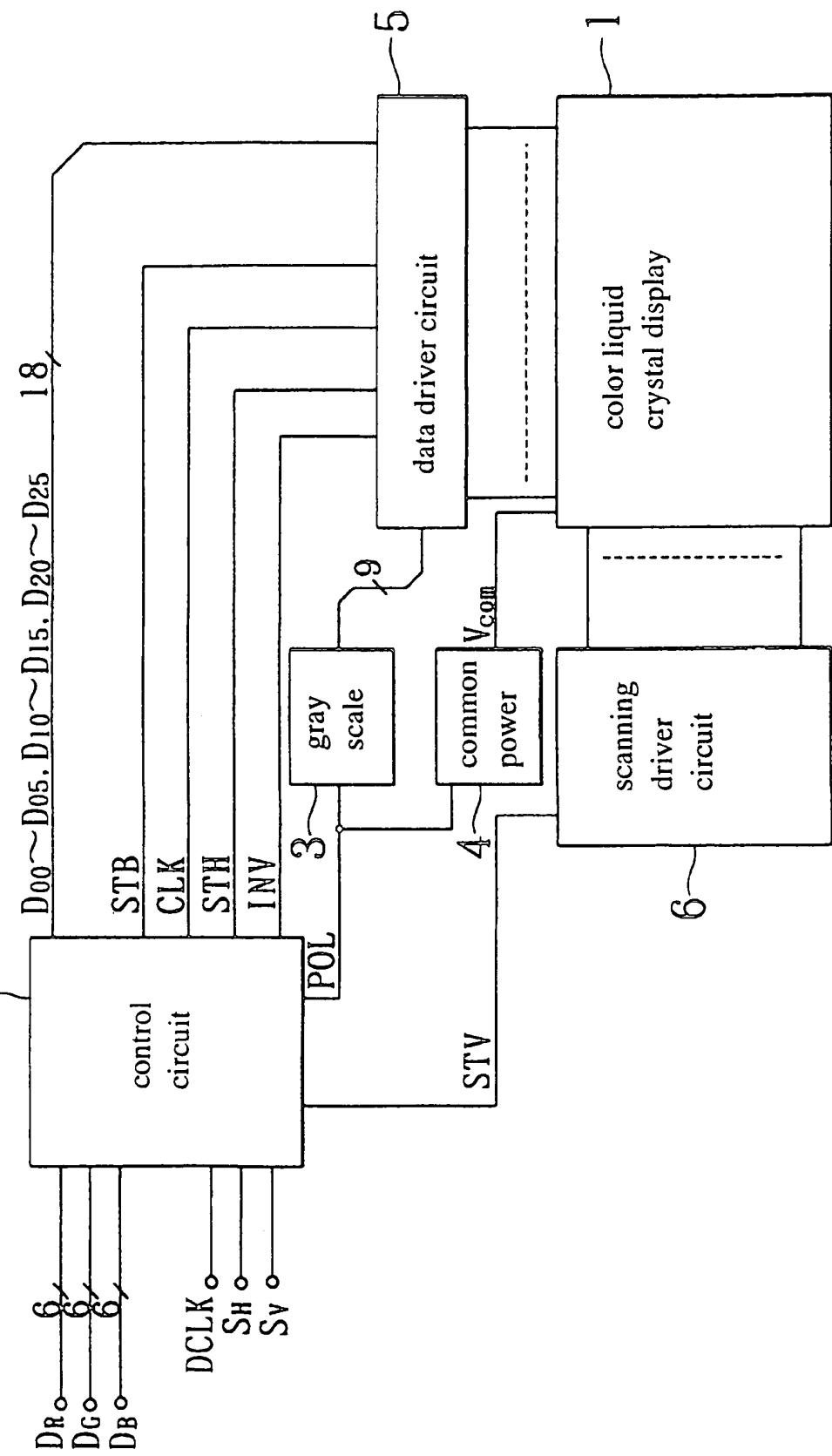

FIG. 3 prior art

5

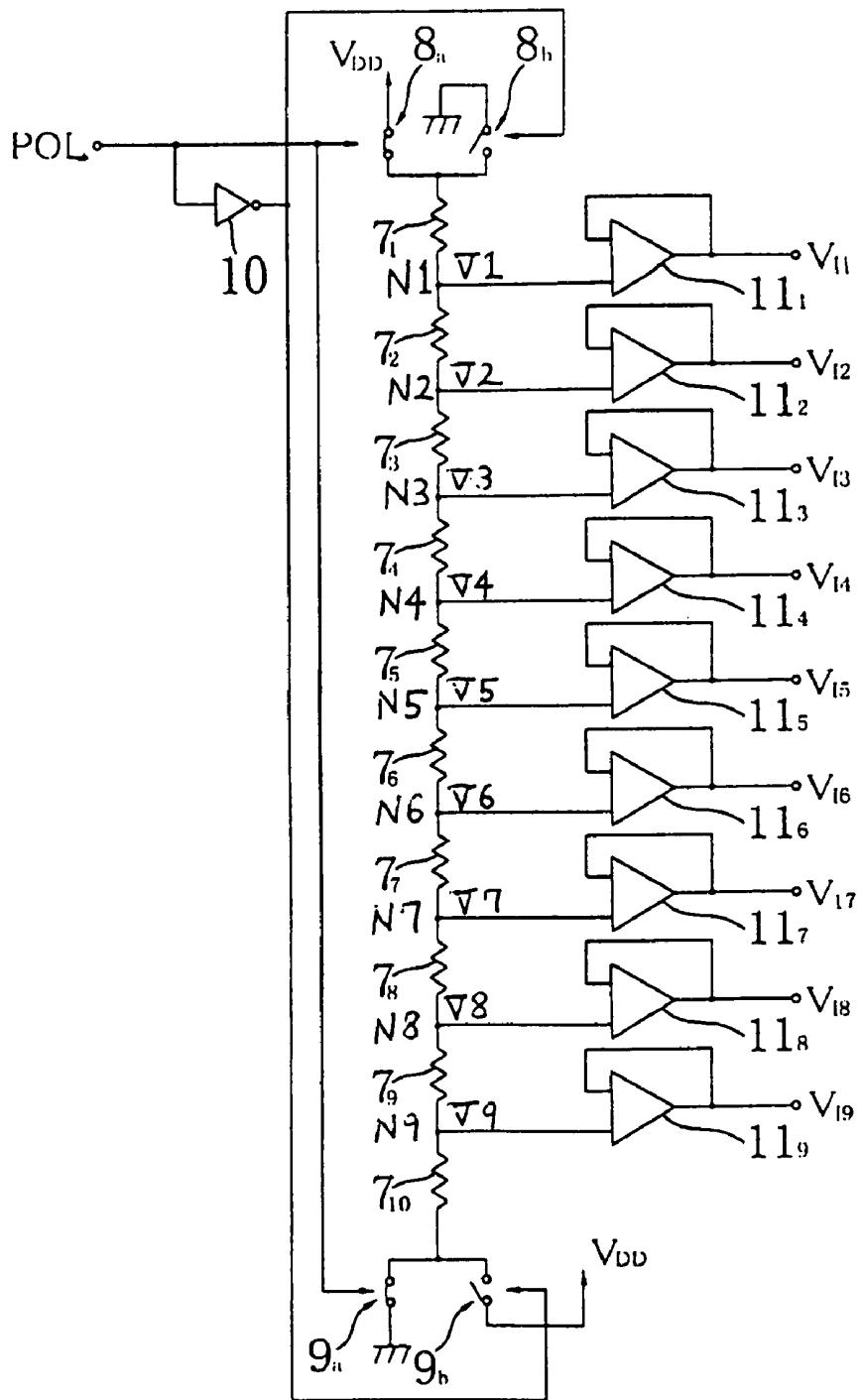

FIG. 4 prior art

FIG. 5 prior art

17

FIG. 6 prior art

FIG. 7 prior art

FIG. 8 prior art

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

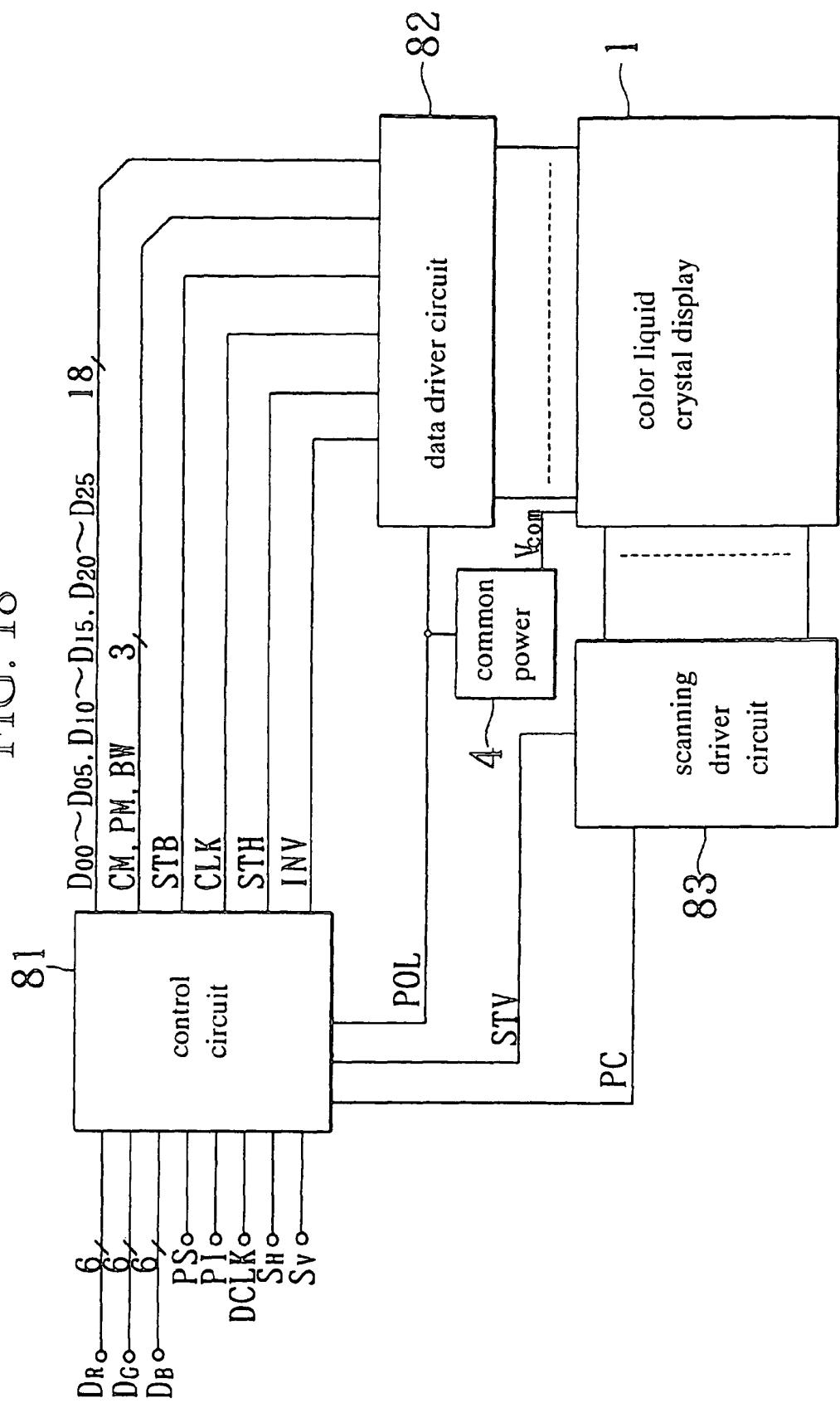

82

FIG. 20

FIG. 21

FIG. 22

## FIG. 23

CMa

CMb

CMc

CMd

**METHOD OF DRIVING A COLOR LIQUID CRYSTAL DISPLAY AND DRIVER CIRCUIT FOR DRIVING THE DISPLAY AS WELL AS PORTABLE ELECTRONIC DEVICE WITH THE DRIVER CIRCUIT**

**CROSS REFERENCE TO RELATED APPLICATION**

The present application is a continuation application of Ser. No. 10/051,567 dated Jan. 18, 2002 now abandoned.

**BACKGROUND OF THE INVENTION**

**1. Field of the Invention**

The present invention relates to a method of driving a liquid crystal display and a driver circuit for driving the liquid crystal display as well as an electronic device with the driver circuit, and more particularly to an improvement of the driver circuit and the driving method for driving a color liquid crystal display with a relatively small display screen in a line inversion driving system or in a frame inversion driving system at a reduced power consumption.

**2. Description of the Related Art**

The liquid crystal display has been applied to various electronic devices such as note-type computers, palm-type computers, pocket-type computers, mobile terminals such as personal digital assistants, mobile phones, and personal handyphone systems. The advanced liquid crystal display is a color liquid crystal display.

FIG. 1 is a block diagram illustrative of a first conventional driver circuit for driving a color liquid crystal display. A color liquid crystal display 1 may be driven by an active matrix driving system using thin film transistors as switching devices. The color liquid crystal display 1 includes a plurality of scanning lines or gate lines which extend parallel to each other in a column direction at a constant pitch, and a plurality of data lines or source lines which extend parallel to each other in a row direction at another constant pitch, as well as a two-dimensional matrix array of pixels, each of which is positioned in an area defined by adjacent two of the scanning lines and adjacent two of the data lines.

Each of the pixels further includes a liquid crystal cell as an equivalent capacitive load, a common electrode, a thin film transistor for driving the liquid crystal cell, and a data electrode for storing data charge in a vertical synchronizing term. A gate electrode of the thin film transistor is connected to the scanning line. The gate electrode of the thin film transistor serves as a scanning electrode.

The color liquid crystal display 1 may be driven as follows. The common electrode is applied with a common potential  $V_{com}$ . The data electrode is applied with data signals, wherein the data signals may include data red signals, data green signals and data blue signals, which have been generated from red data  $D_R$ , green data  $D_G$ , and blue data  $D_B$  as digital image data. The scanning electrode is applied with a scanning signal which has been generated from a horizontal synchronizing signal  $S_H$  and a vertical synchronizing signal  $S_V$ .

The following description with reference to FIG. 1 will be made assuming that the color liquid crystal display 1 is a normally white type color liquid crystal display which is high in transmittivity under no voltage application.

The driver circuit for driving the color liquid crystal display 1 mainly includes a control circuit 2, a gray scale power supply 3, a common power supply 4, a data electrode driver circuit 5, and a scanning electrode driver circuit 6.

The control circuit 2 may, for example, comprise an application specific integrated circuit (ASIC). The control circuit 2 receives parallel inputs of red data  $D_R$  of 6-bits, green data  $D_G$  of 6-bits and blue data  $D_B$  of 6-bits. The control circuit 2 converts the red data  $D_R$ , green data  $D_G$  and blue data  $D_B$  into 18-bits display data D00-D05, D10-D15 and D20-D25 respectively, and outputs the 18-bits display data. The, 18-bits display data outputted from the control circuit 2 are supplied to the data electrode driver circuit 5.

The control circuit 2 also receives further inputs of a dot-clock signal DCLK, a horizontal synchronizing signal  $S_H$ , and a vertical synchronizing signal  $S_V$ , so that the control circuit 2 generates a strobe signal STB, a clock signal CLK, a horizontal start pulse signal STH, a vertical start pulse signal STV, a polarity signal POL, a data inversion signal INV from the dot-clock signal DCLK, the horizontal synchronizing signal  $S_H$ , and the vertical synchronizing signal  $S_V$ . The strobe signal STB, the clock signal CLK, the horizontal start pulse signal STH and the data inversion signal INV are supplied to the data electrode driver circuit 5. The polarity signal POL is supplied to the gray scale power supply 3 and the common power supply 4. The vertical start pulse signal STV is supplied to the scanning electrode driver circuit 6.

The strobe signal STB has the same cycle as the horizontal synchronizing signal  $S_H$ . The clock signal CLK may be either identical with or different in frequency from the dot-clock signal DCLK. The clock signal CLK may be used for allowing shift registers in the data electrode driver circuit 5 to generate sampling pulse signals SP1-SP176 from the horizontal start pulse signal STH.

The horizontal start pulse signal STH is identical in cycle to the horizontal synchronizing signal  $S_H$ , and delayed from the strobe signal STB by a time corresponding to a few pulses of the clock signal CLK. The polarity signal POL is inverted in a single line unit or in a single horizontal synchronizing cycle for alternating current driving of the color liquid crystal display 1. The vertical start pulse signal STV has the same cycle as the vertical synchronizing signal  $S_V$ .

The data inversion signal INV is used for the purpose of reducing the power which is consumed by the control circuit 2. If the current 18-bits display data D00-D05, D10-D15 and D20-D25 has at least 10-inverted bits from the previous 18-bits display data, the data inversion signal INV is inverted in synchronizing with the clock signal CLK, instead of inversions of the current 18-bits display data D00-D05, D10-D15 and D20-D25 for the following reasons.

It is general that the control circuit 2 and the gray scale power supply 3 are integrated over a printed board whilst the data electrode driver circuit 5 is mounted as a tape carrier package (TCP) over a film tape carrier which provides an electrical connection between the printed board and the color liquid crystal display 1. The printed board is mounted at an upper portion on a back face of a back light which is attached to the color liquid crystal display 1.

18-signal lines are provided on the film carrier tape for transmitting the 18-bits display data D00-D05, D10-D15 and D20-D25 from the control circuit 2 to the data electrode driver circuit 5. The 18-signal lines have a line capacitance. In addition, the data electrode driver circuit 5 has an input capacitance of about 20 pF from the control circuit 2. A sufficient current for charging and discharging the line capacitance and the input capacitance would be needed if the polarity of the 18-bits display data D00-D05, D10-D15 and D20-D25 are inverted and supplied to the data electrode driver circuit 5 from the control circuit 2. For reducing the necessary charge and discharge currents to the line capacitance and the input capacitance, it is effective that the data

inversion signal INV is inverted, instead of inversions of the 18-bits display data D00-D05, D10-D15 and D20-D25. The reduction of the charge and discharge currents results in a reduction in the power consumed by the control circuit 2.

FIG. 2 is a circuit diagram illustrative of a circuit configuration of a gray scale power supply in the driver circuit shown in FIG. 1. The gray scale power supply 3 includes a series connection of resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, a first pair of switches 8-a and 8-b, a second pair of switches 9-a and 9-b, a single inverter 10, and voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8, and 11-9 as well as gray scale voltage input ports which receive gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9. The gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 have been set for gamma-control.

The gray scale power supply 3 amplifies the gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 and supplies the amplified gray scale voltages to the data electrode driver circuit 5. The polarity inversions of the gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 between positive and negative potentials with reference to the common voltage Vcom applied to the common electrode-are made based on the polarity signal POL in the single line unit.

The resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10 are different in resistance values from each other. The switch 8-a has a first terminal applied with a power voltage VDD and a second terminal connected to a first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, wherein the resistance 7-1 is connected directly to the second terminal of the switch 8-a. The switch 8-a also has a control terminal applied with the polarity signal POL. If the polarity signal POL is low level "L", then the switch 8-a is in OFF-state. If the polarity signal POL is high level "H", then the switch 8-a is in ON-state, whereby the power voltage VDD is applied to the first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10.

The inverter 10 receives the polarity signal POL and generates an inverted polarity signal /POL. The switch 8-b has a first terminal grounded and a second terminal connected to the first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, wherein the resistance 7-1 is connected directly to the second terminal of the switch 8-b. The switch 8-b also has a control terminal connected to an output from the inverter 10 for receiving the inverted polarity signal /POL from the inverter 10. If the inverted polarity signal /POL is low level "L", then the switch 8-b is in OFF-state. If the inverted polarity signal /POL is high level "H", then the switch 8-b is in ON-state, whereby the ground potential GND is applied to the first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10.

The switch 9-a has a first terminal grounded and a second terminal connected to a second end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, wherein the resistance 7-10 is connected directly to the second terminal of the switch 9-a. The switch 9-a also has a control terminal applied with the polarity signal POL. If the polarity signal POL is low level "L", then the switch 9-a is in OFF-state. If the polarity signal POL is high level "H", then the switch 9-a is in ON-state, whereby the ground potential GND is applied to the second end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10.

The switch 9-b has a first terminal applied with the power voltage VDD and a second terminal connected to the second end of the series connection of the resistances 7-1, 7-2, 7-3,

7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, wherein the resistance 7-10 is connected directly to the second terminal of the switch 9-b. The switch 9-b also has a control terminal connected to the output from the inverter 10 for receiving the inverted polarity signal /POL from the inverter 10. If the inverted polarity signal /POL is low level "L", then the switch 9-b is in OFF-state. If the inverted polarity signal /POL is high level "H", then the switch 9-b is in ON-state, whereby the ground potential GND is applied to the second end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10.

The series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10 has first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9, at which divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are generated respectively if the first and second ends of the series connection are biased. The first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9 are connected to inputs of the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively, whereby the divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are amplified by the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively.

If the polarity signal POL is the high level "H", then the first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10 is applied with the power voltage VDD, whilst the second end thereof is applied with the ground voltage, whereby positive-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are generated at the first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9 respectively in accordance with respective ratios of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, provided that  $VDD > V1 > V2 > V3 > V4 > V5 > V6 > V7 > V8 > V9 > GND$ . The positive-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are then amplified by the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively to generate the first to ninth positive-polarity gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 which will subsequently be supplied to the data electrode driver circuit 5, provided that  $VI1 > VI2 > VI3 > VI4 > VI5 > VI6 > VI7 > VI8 > VI9$ .

If the polarity signal POL is the low level "L", then the first end of the series connection of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10 is applied with the ground voltage, whilst the second end thereof is applied with the power voltage VDD, whereby negative-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are generated at the first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9 respectively in accordance with respective ratios of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, provided that  $VDD < V1 < V2 < V3 < V4 < V5 < V6 < V7 < V8 < V9 < GND$ . The negative-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are then amplified by the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively to generate the first to ninth negative-polarity gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 which will subsequently be supplied to the data electrode driver circuit 5, provided that  $VI1 < VI2 < VI3 < VI4 < VI5 < VI6 < VI7 < VI8 < VI9$ .

The common power supply 4 receives an input of the polarity signal "POL" from the control circuit 2 and supplies the common potential Vcom to the common electrode of the color liquid crystal display 1. If the polarity signal "POL" is in the high level "H", then the common power supply 4 sets the common potential Vcom at the ground level GND. If the

polarity signal "POL" is in the low level "L", then the common power supply **4** sets the common potential  $V_{COM}$  at the power voltage level  $V_{DD}$ .

The data electrode driver circuit **5** receives the strobe signal  $STB$ , the clock signal  $CLK$ , the horizontal start pulse signal  $STH$  and the data inversion signal  $INV$  in addition to the 18-bits display data  $D00-D05$ ,  $D10-D15$  and  $D20-D25$  from the control circuit **2**. The data electrode driver circuit **5** selects the gray scale voltages based on the 18-bits display data  $D00-D05$ ,  $D10-D15$  and  $D20-D25$  under the controls by the strobe signal  $STB$ , the clock signal  $CLK$ , the horizontal start pulse signal  $STH$  and the data inversion signal  $INV$ . The data electrode driver circuit **5** applies the selected gray scale voltages to the data electrodes of the color liquid crystal display **1**.

The scanning electrode driver circuit **6** receives the vertical start pulse signal  $STV$  from the control circuit **2**, so that the scanning electrode driver circuit **6** generates, in sequence, the scanning signals and applies the scanning signals to the scanning electrodes of the color liquid crystal display **1**.

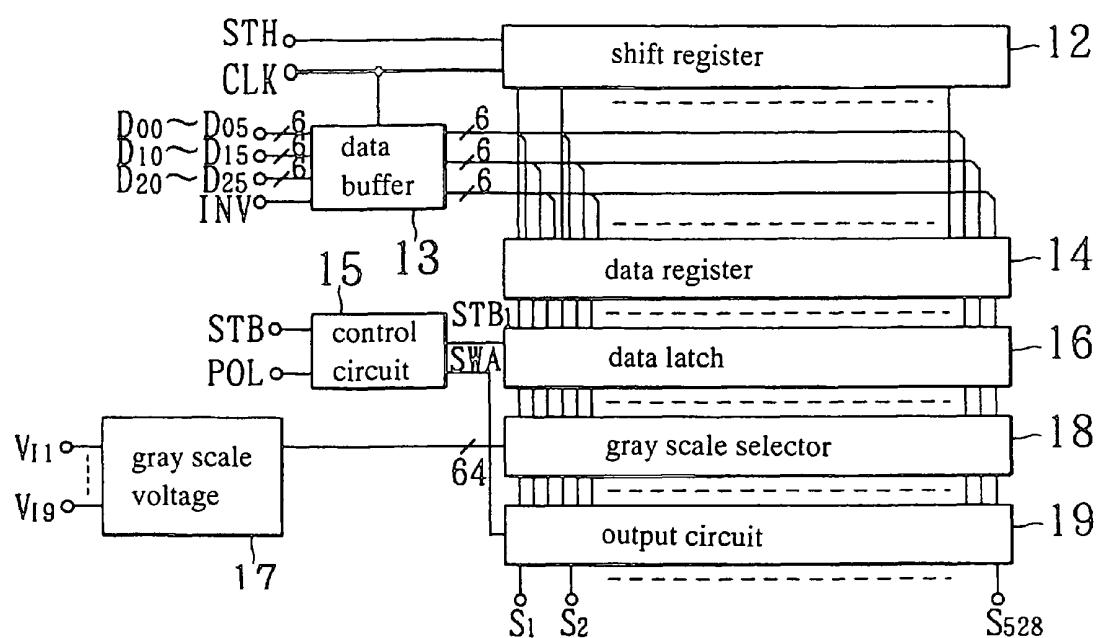

FIG. 3 is a block diagram illustrative of the data electrode driver circuit shown in FIG. 1. It is assumed that a resolution of the color liquid crystal display **1** is defined by  $176 \times 220$  pixels. Since each pixel comprises three-dots of red (R), green (G) and blue (B), then the color liquid crystal display **1** has a  $528 \times 220$  dot-pixels.

The data electrode driver circuit **5** includes a shift register **12**, a data buffer **13**, a data register **14**, a control circuit **15**, a data latch **16**, a gray scale voltage generating circuit **17**, a gray scale voltage selecting circuit **18**, and an output circuit **19**.

The shift register **12** is a serial in parallel-out shift register which comprises **176** delay-flip-flops. The shift register **12** receives the clock signal  $CLK$  and the horizontal start pulse signal  $STH$  from the control circuit **2**, so that the shift register **12** shifts the horizontal start pulse signal  $STH$  in synchronizing with the clock signal  $CLK$ , and generates sampling pulses  $SP1, SP2, \dots, SP176$  which comprise a 176-bits parallel-out signal. The data buffer **13** receives the 18-bits display data  $D00-D05$ ,  $D10-D15$  and  $D20-D25$  and the data inversion signal  $INV$  from the control circuit **2**, so that the data buffer **13** performs an inversion operation of the 18-bits display data in accordance with the data inversion signal  $INV$ , so that the data buffer **13** outputs 18-bits display data  $D'00-D'05$ ,  $D'10-D'15$  and  $D'20-D'25$ .

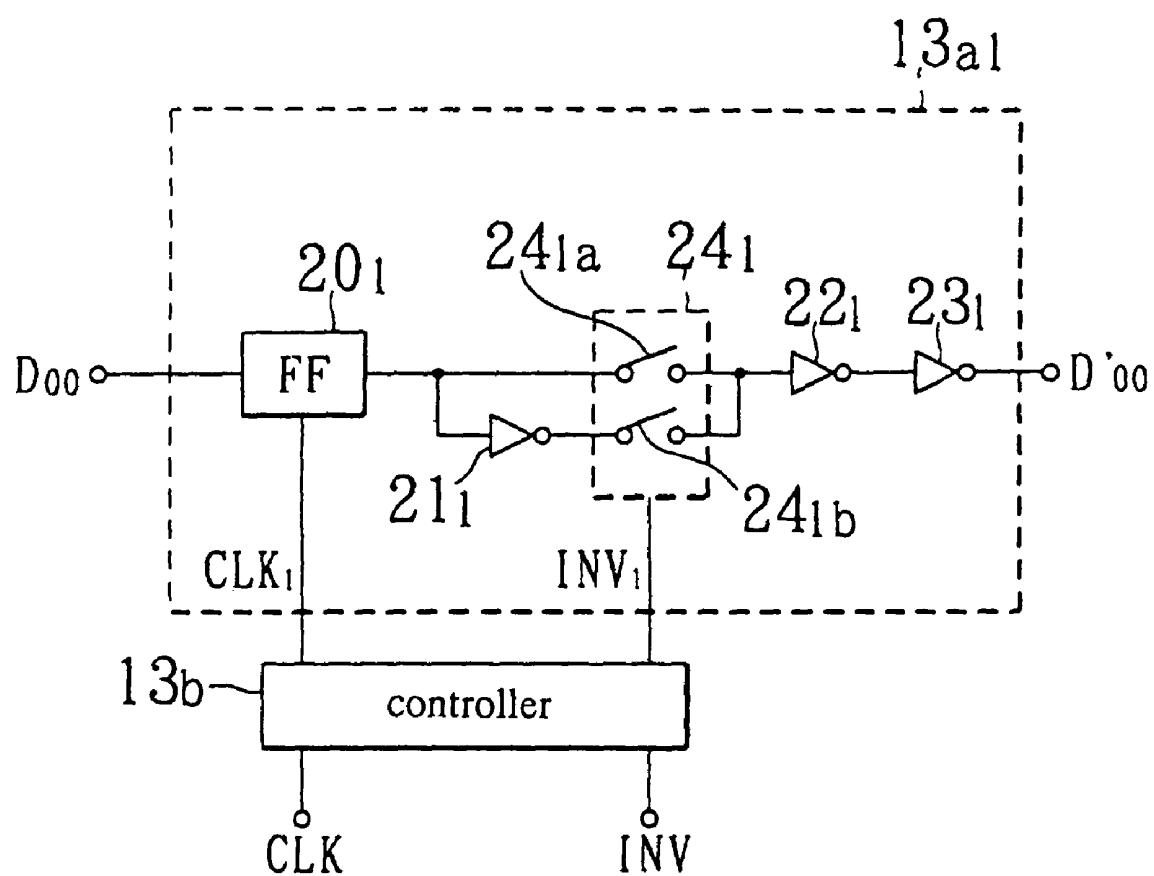

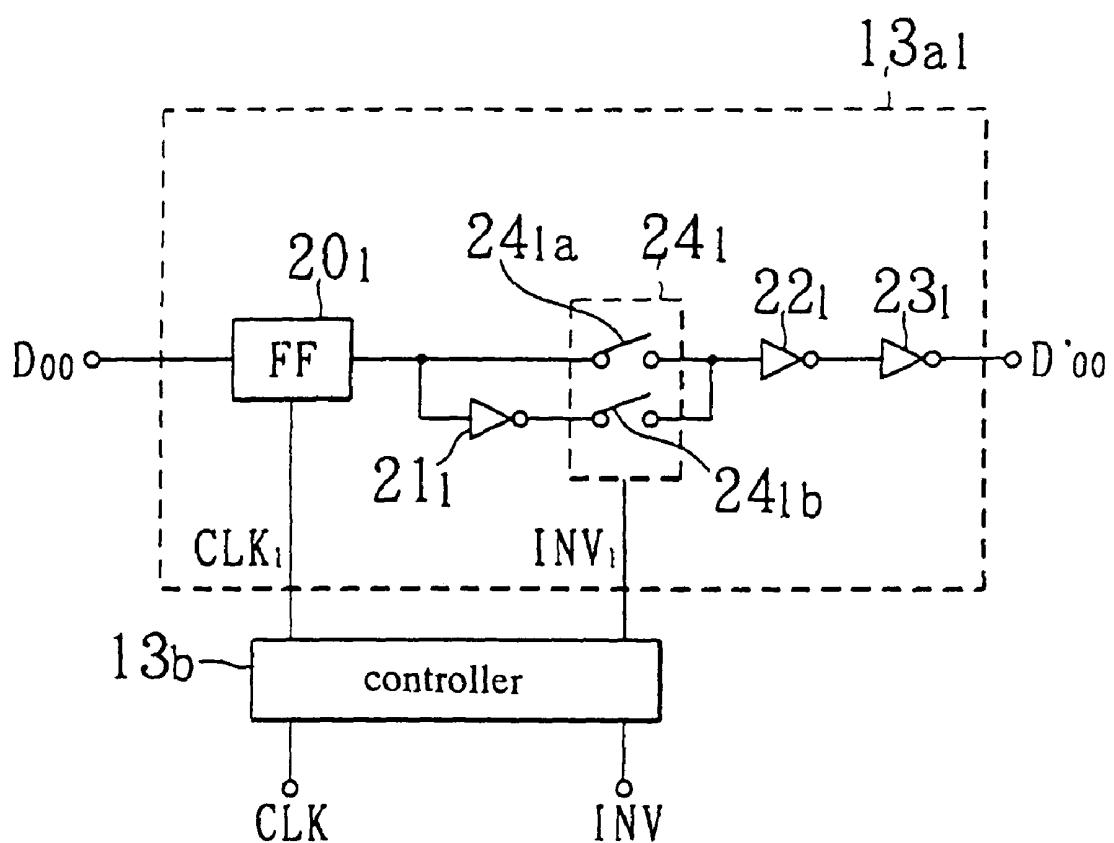

FIG. 4 is a partial circuit diagram illustrative of a part of the circuit configuration of the data buffer shown in FIG. 3. The data buffer **13** comprises first to eighteenth data buffer circuits **13a1**, **13a2**, **13a3**, **13a4**, **13a5**, **13a6**, **13a7**, **13a8**, and a single control unit **13b**. The control unit **13b** includes two series connections of plural inverters. The two series connections of plural inverters in the control unit **13b** receive the data inversion signal  $INV$  and the clock signal  $CLK$  from the control circuit **2** respectively, so that the control unit **13b** delays the data inversion signal  $INV$  and the clock signal  $CLK$  from the control circuit **2** by predetermined delay times respectively, whereby the control unit **13b** supplies a delayed clock signal  $CLK1$  and a delayed data inversion signal  $INV1$  to the first data buffer circuit **13a1**.

The control unit **13b** also supplies other delayed clock signals  $CLK2, CLK3, \dots, CLK18$  and other delayed data inversion signals  $INV2, INV3, \dots, INV18$  to the remaining second to eighteenth data buffer circuits **13a2**, **13a3**, **13a4**, **13a5**, **13a6**, **13a7**, **13a8**, respectively. The first to eighteenth data buffer circuits **13a1**, **13a2**, **13a3**, **13a4**, **13a5**, **13a6**, **13a7**, **13a8** have the same circuit configuration and perform the same operations, for which reason the following description will focus on the first data buffer circuit **13a1** only.

The first data buffer circuit **13a1** includes a D-flip-flop **20-1**, inverters **21-1**, **22-1** and **23-1**, and a switching circuit

**24-1**. The switching circuit **24-1** comprises two parallel switches **24-1a** and **24-1b**. The control unit **13b** supplies the delayed clock signal  $CLK1$  to the D-flip-flop **20-1** and the delayed data inversion signal  $INV1$  to the switching circuit **24-1**.

The D-flip-flop **20-1** latches a single bit display data  $D00$  in synchronizing with the clock signal  $CLK1$  for a term corresponding to the single pulse width of the clock signal  $CLK1$ , and outputs the single bit display data  $D00$ . The inverter **21-1** inverts the single bit display data  $D00$ , so that the inverted bit display data  $D00$  is supplied to the switch **24-1b**. The non-inverted bit display data  $D00$  outputted from the D-flip-flop **20-1** is also directly supplied to the switch **24-1a**.

If the delayed data inversion signal  $INV1$  from the control unit **13b** is high level "H", then the switching circuit **24-1a** is placed in the ON-state, whilst the switching circuit **24-1b** is placed in the OFF-state, whereby the non-inverted bit display data  $D00$  is transmitted through the series connection of the inverters **22-1** and **23-1** to an output terminal as the output bit display data  $D'00$ .

If the delayed data inversion signal  $INV1$  from the control unit **13b** is low level "L", then the switching circuit **24-1a** is placed in the OFF-state, whilst the switching circuit **24-1b** is placed in the ON-state, whereby the inverted bit display data  $D00$  is transmitted through the series connection of the inverters **22-1** and **23-1** to the output terminal as the output single bit display data  $D'00$ .

With reference again to FIG. 3, the data register **14** receives the 18-bits display data  $D'00-D'05$ ,  $D'10-D'15$  and  $D'20-D'25$  from the data buffer **13** and also receives the sampling pulses  $SP1, SP2, \dots, SP176$  from the shift register **12**. In synchronizing with the sampling pulses  $SP1, SP2, \dots, SP176$ , the data register **14** accepts the inputs of the 18-bits display data  $D'00-D'05$ ,  $D'10-D'15$  and  $D'20-D'25$  and transmits display data  $PD1, PD2, PD3, \dots, PD528$  to the data latch **16**.

The control circuit **15** comprises a series connection of plural inverters. The control circuit **15** receives the strobe signal  $STB$  from the control circuit **2**, so that the control circuit **15** generates a delayed strobe signal  $STB1$  which has a predetermined delay time from the strobe signal  $STB$  as well as generates a switch control signal  $SWA$  which is opposite in phase to the delayed strobe signal  $STB1$ . The control circuit **15** transmits the delayed strobe signal  $STB1$  to the data latch **16** and also transmits the switch control signal  $SWA$  to the output circuit **19**.

The data latch **16** accepts the inputs of the display data  $PD1, PD2, PD3, \dots, PD528$  in synchronizing with a rising edge of the displayed strobe signal  $STB1$  and holds the display data  $PD1, PD2, PD3, \dots, PD528$  for a time period of the next vertical synchronizing term. In synchronizing with the next rising edge of the delayed strobe signal  $STB1$ , the data latch **16** transmits the display data  $PD1, PD2, PD3, \dots, PD528$  to the gray scale voltage selecting circuit **18**.

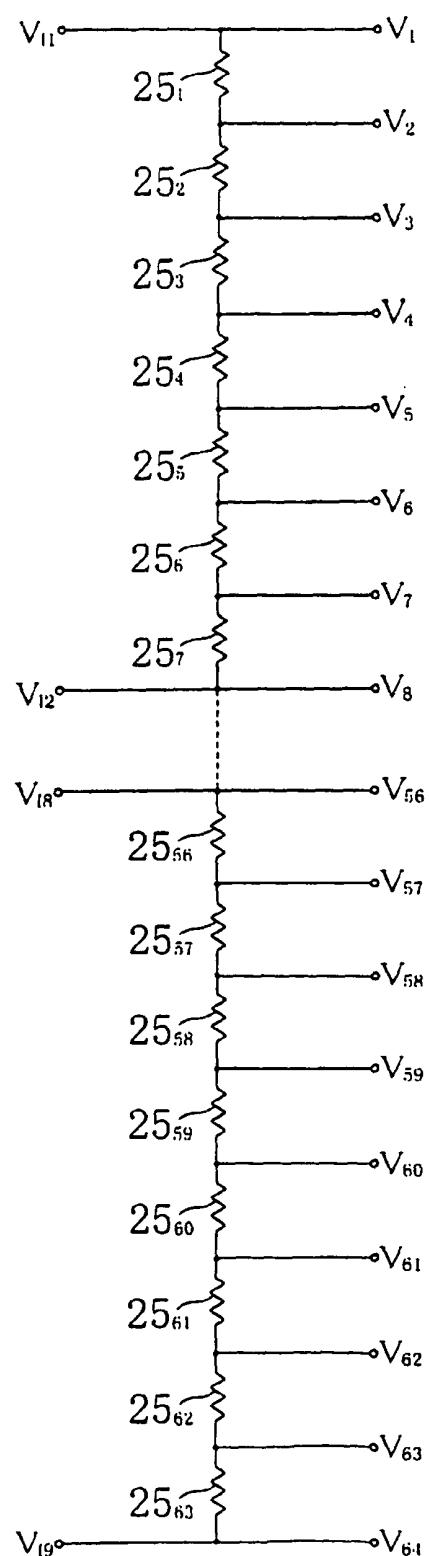

FIG. 5 is a circuit diagram illustrative of the gray scale voltage generating circuit shown in FIG. 3. The gray scale voltage generating circuit **17** comprises a single series connection of first to sixty third resistances **25-1**, **25-2**, **25-3**, **25-4**, **25-5**, **25-6**, **25-7**, **25-8**, **25-9**, **25-10**, **25-11**, **25-12**, **25-13**, **25-14**, **25-15**, **25-16**, **25-17**, **25-18**, **25-19**, **25-20**, **25-21**, **25-22**, **25-23**, **25-24**, **25-25**, **25-26**, **25-27**, **25-28**, **25-29**, **25-30**, **25-31**, **25-32**, **25-33**. The first to sixty third resistances **25-1**, **25-2**, **25-3**, **25-4**, **25-5**, **25-6**, **25-7**, **25-8**, **25-9**, **25-10**, **25-11**, **25-12**, **25-13**, **25-14**, **25-15**, **25-16**, **25-17**, **25-18**, **25-19**, **25-20**, **25-21**, **25-22**, **25-23**, **25-24**, **25-25**, **25-26**, **25-27**, **25-28**, **25-29**, **25-30**, **25-31**, **25-32**, **25-33** have respective resistance values which are adjusted to applied voltage to-transmittivity characteristic of the color liquid crystal display **1**. The gray scale voltage generating circuit **17** receives first to ninth gray scale voltages  $VI1, VI2, VI3, \dots, VI9$  from the gray scale power supply **3**.

The first gray scale voltage  $VI1$  is supplied to a first node of the first side of the first resistance **25-1**. The second gray scale voltage  $VI2$  is supplied to an eighth node between the seventh

resistance 257 and the eighth resistance 25-8. The third gray scale voltage V13 is supplied to a sixteenth node between the fifteenth resistance 25-15 and the sixteenth resistance 25-16. The fourth gray scale voltage V14 is supplied to a twenty fourth node between the twenty third resistance 25-23 and the twenty fourth resistance 25-24. The fifth gray scale voltage V15 is supplied to a thirty second node between the thirty first resistance 25-31 and the thirty second resistance 25-32. The sixth gray scale voltage V16 is supplied to a fortieth node between the thirty ninth resistance 25-39 and the fortieth resistance 25-40. The seventh gray scale voltage V17 is supplied to a forty eighth node between the forty seventh resistance 25-47 and the forty eighth resistance 25-48. The eighth gray scale voltage V18 is supplied to a fifty sixth node between the fifty fifth resistance 25-55 and the fifty sixth resistance 25-56. The ninth gray scale voltage V19 is supplied to a sixty fourth node of a second side of the sixty third resistance 25-63.

The gray scale voltage generating circuit 17 generates first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 at the first to sixty fourth nodes respectively, wherein the generated first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 depend on the first to ninth gray scale voltages V11, V12, V13, - - - V19 from the gray scale power supply 3 and also on the respective resistance values of the first to sixty third resistances 25-1, 25-2, 25-3, - - - 25-63. Each of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 may individually be inverted between positive-polarity and negative-polarity with reference to the common potential Vcom.

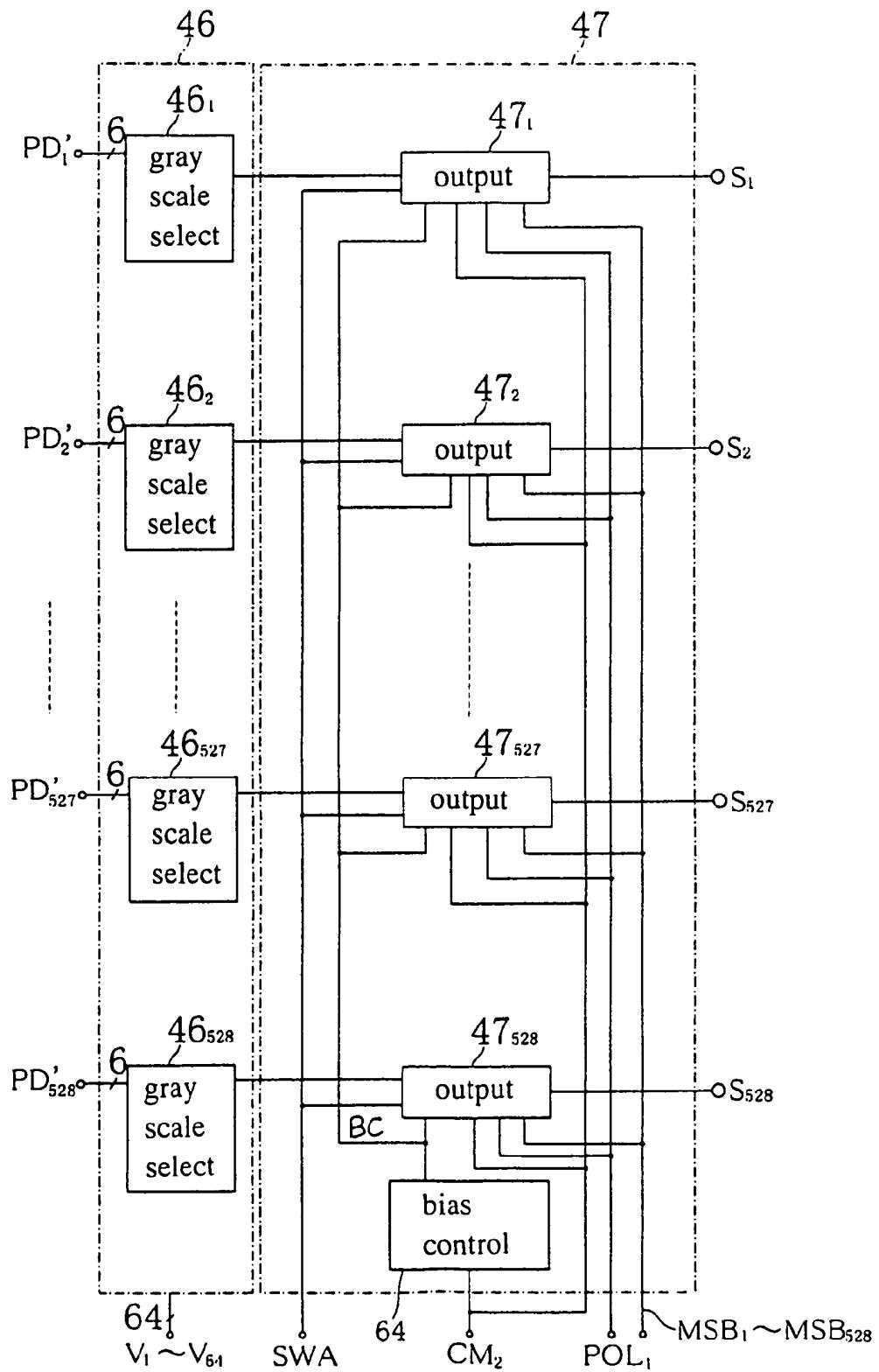

With reference back to FIG. 3, the generated first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 are supplied to the gray scale voltage selecting circuit 18. Namely, a gray scale signal of 64 bits is supplied from the gray scale voltage generating circuit 17 to the gray scale voltage selecting circuit 18.

The gray scale voltage selecting circuit 18 comprise first to five hundred twenty eighth gray scale voltage selecting mits 18-1, 18-2, 18-3, - - - , 18-528. Each of the first to five hundred twenty eighth gray scale voltage selecting units 18-1, 18-2, 18-3, - - - , 18-528 receives corresponding one of 6-bits display data PD1, PD2, - - - PD528, so as to select one of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 based on the corresponding one of 6-bits display data PD1, PD2, - - - PD528, whereby the selected one gray scale voltage is supplied to the output circuit 19. For example, the first gray scale voltage selecting unit 18-1 receives the 6-bits display data PD1 to select one of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 based on the 6-bits display data PD1, whereby the selected one gray scale voltage is supplied to the output circuit 19.

The first to five hundred twenty eighth gray scale voltage selecting units 18-1, 18-2, 18-3, - - - , 18-528 have the same circuit configuration, for which reason the following description will focus only on the first gray scale voltage selecting unit 18-1. The output circuit 19 comprises first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - , 19-528 which are connected to the first to five hundred twenty eighth gray scale voltage selecting units 18-1, 18-2, 18-3, - - - , 18-528 respectively. The first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - , 19-528 have the same circuit configuration, for which reason the following description will focus only on the first output unit 19-1.

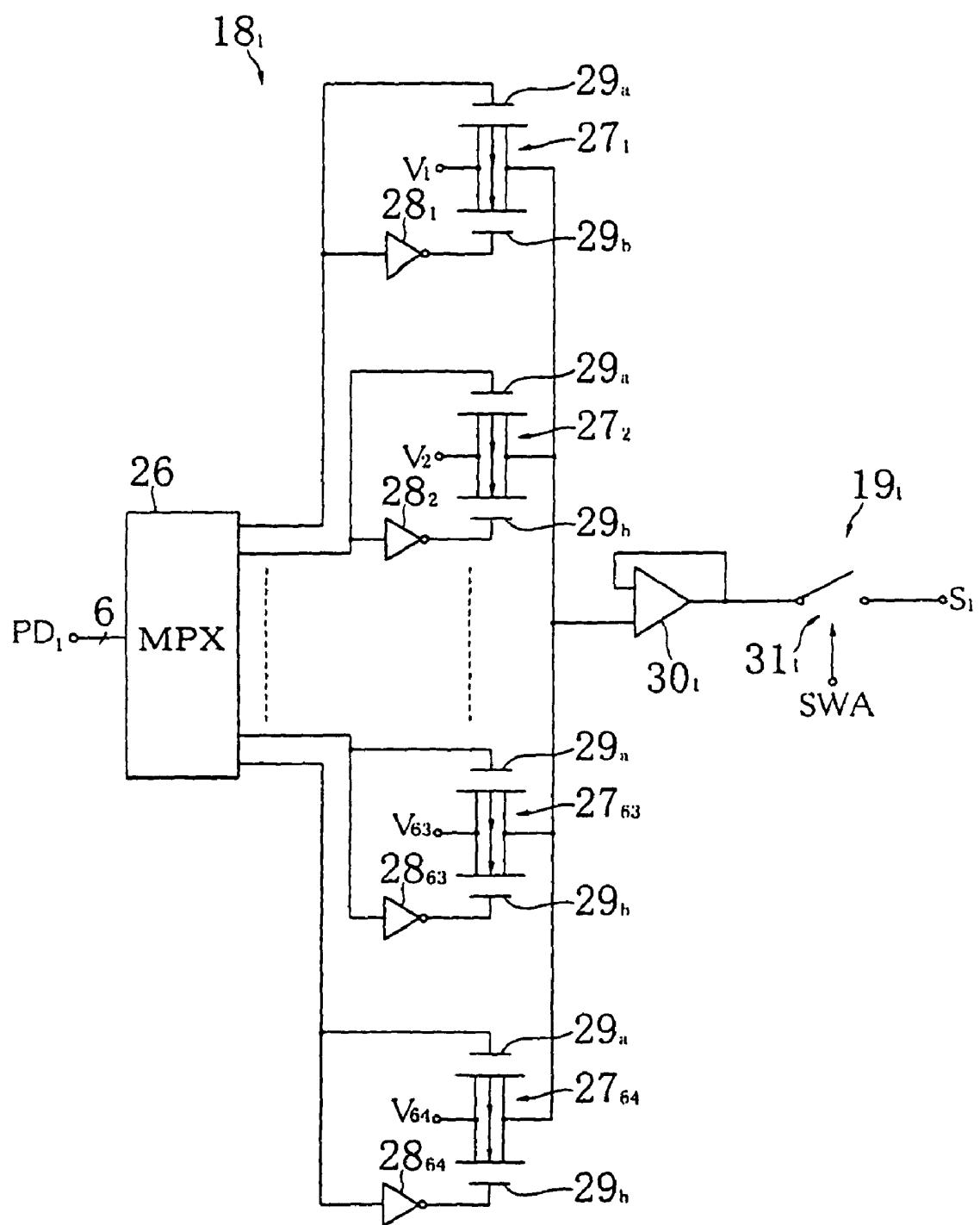

FIG. 6 is a circuit diagram illustrative of the first gray scale voltage selecting unit included in the gray scale voltage selecting circuit and a first output unit included in the output circuit of FIG. 3. The first gray scale voltage selecting unit 18-1 comprises a single multiplexer 26, first to sixty fourth

transfer gates 27-1, 27-2, 27-3, - - - 27-64, and first to sixty fourth inverters 28-1, 28-2, 28-3, - - - 28-64. Each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 comprises a pair of p-channel MOS field effect transistor 29a and an n-channel MOS field effect transistor 29b.

A gate of the p-channel MOS field effect transistor 29a of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives the display data PD1 from the multiplexer 26. A gate of the n-channel MOS field effect transistor 29b of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives inverted display data /PD1 through the corresponding one of the first to sixty fourth inverters 28-1, 28-2, 28-3, - - - 28-64 from the multiplexer 26.

The first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 also receive the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 from the gray scale voltage generating circuit 17 respectively. For example, the first transfer gate 27-1 receives the first gray scale voltage V1. The single multiplexer 26 receives the 6-bits display data PD1 from the data latch 16 for selecting one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 based on the received 6-bits display data PD1, whereby the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 turns ON, and the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 outputs the corresponding one of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 as a data red signal, a data green signal or a data blue signal.

The first output unit 19-1 is connected to the first gray scale voltage selecting unit 18-1. The first output unit 19-1 comprises a first amplifier 30-1, and a first switch 31-1. The first amplifier 30-1 receives the data red signal, a data green signal or a data blue signal as the gray scale voltage from the first gray scale voltage selecting unit 18-1 for amplifying the received signal. Each of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 also receives a switch control signal SWA from the control circuit 15. The first to five hundred twenty eighth switches 31-1, 31-2, 31-3, - - - 31-528 of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 receive the switch control signal SWA from the control circuit 15.

If the first switch 31-1 of the first output unit 19-1 turns ON based on the switch control signal SWA from the control circuit 15, then the amplified data red, green or blue signal S 1 is outputted from the first output unit 19-1. As shown in FIG. 3, the output circuit 19 outputs the first to five hundred twenty eighth data red, green and blue signals S1, S2, S3, - - - S528 which are then supplied to the data electrodes of the color liquid crystal display 1.

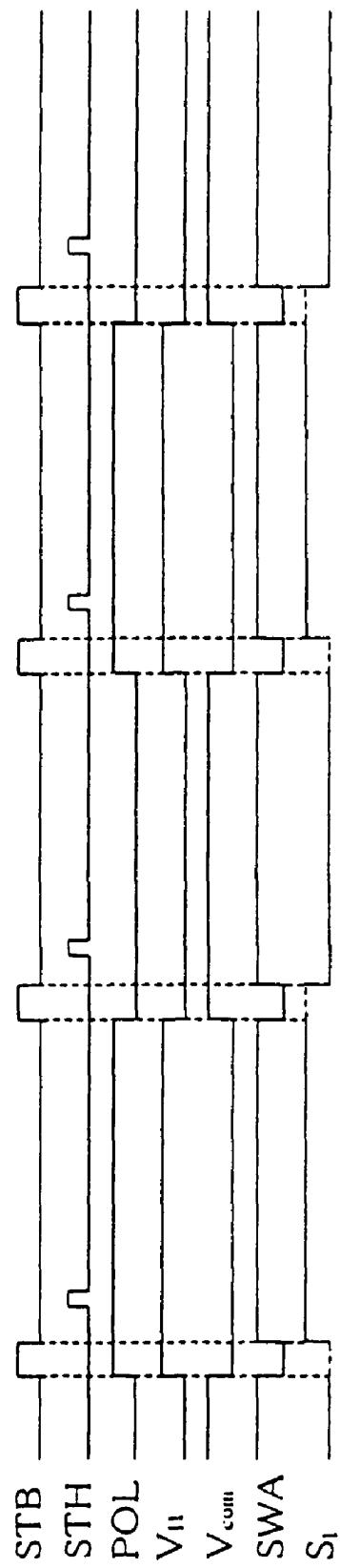

FIG. 7 is a timing chart illustrative of operations of the control circuit, the gray scale power supply 3, the common power supply 4 and the data electrode driver circuit 5 in FIG. 1. The control circuit 2 supplies the data electrode driver circuit 5 with the strobe signal STB, the clock signal CLK, the horizontal start pulse signal STH delayed by a few clock pulses of the clock signal CLK from the strobe signal STB, and the polarity signal POL. The shift register 12 in the data electrode driver circuit 5 shifts the horizontal start pulse signal STH and outputs the sampling pulse signals SP1-SP176 of 176 bits in synchronizing with the clock signal CLK.

The control circuit 2 also converts the red data  $D_R$ , green data  $D_G$ , and blue data  $D_B$ , into the 18-bits display data D00-D05, D10-D15 and D20-D25 which are then supplied to the data electrode driver circuit 5. The data buffer 13 in the data electrode driver circuit 5 receives the 18-bits display data D00-D05, D10-D15 and D20-D25 from the control circuit 2

and holds the 18-bits display data D00-D05, D10-D15 and D20-D25 for a time period corresponding a single pulse width of the clock signal CLK in synchronizing with the clock signal CLK, before the data buffer 13 supplies the data register 14 with the 18-bits display data D'00-D'05, D'10-D'15 and D'20-D'25.

The data register 14 in the data electrode driver circuit 5 accepts serious inputs of the 18-bits display data D'00-D'05, D'10-D'15 and D'20-D'25 as the 6-bits display data PD1, PD2, - - - PD528 in synchronizing with the sampling pulse signals SP1- SP 176. The data latch 16 accepts simultaneous inputs of the 6-bits display data PD1, PD2, - - - PD528 in synchronizing with a rising edge of the strobe signal STB and latches the 6-bits display data PD1, PD2, - - - PD528 for a single horizontal time period.

The gray scale power supply 3 shown in FIG. 2 receives the polarity signal POL. If the polarity signal POL is high level "H", then the switches 8a and 9a turn ON as well as the switches 8b and 9b turn OFF, whereby the first side of the first resistance 7-1 is applied with the power voltage VDD whilst the second side of the tenth resistance 7-10 is applied with the ground voltage GND, so that the series connection of the first to tenth resistances 7-1, 7-2, 7-3, - - - 7-10 is biased between the power voltage VDD and the ground voltage GND. As a result, positive-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are generated at the first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9 respectively in accordance with respective ratios of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, provided that VDD>V1>V2>V3>V4>V5>V6>V7>V8>V9>GND. The positive-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are then amplified by the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively to generate the first to ninth positive-polarity gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 which will subsequently be supplied to the gray scale voltage generating circuit 17 in the data electrode driver circuit 5, provided that the VI1>VI2>VI3>VI4>VI5>VI6>VI7>VI8>VI9.

The gray scale voltage generating circuit 17 generates first to sixty fourth positive-polarity gray scale voltages V1, V2, V3, - - - V64 at the first to sixty fourth nodes respectively, wherein the generated first to sixty fourth positive-polarity gray scale voltages V1, V2, V3, - - - V64 depend on the first to ninth gray scale voltages VI1, VI2, VI3, - - - VI9, wherein VI1>V2>V3> - - - >V64. The first to sixty fourth positive polarity gray scale voltages V1, V2, V3, - - - V64 are then supplied to the gray scale voltage selecting circuit 18 in the data electrode driver circuit 5.

Each of the first to five hundred twenty eighth gray scale voltage selecting units 18-1, 18-2, 18-3, - - - , 18-528 receives corresponding one of 6-bits display data PD1, PD2, - - - PD528.

A gate of the p-channel MOS field effect transistor 29a of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives the display data PD from the multiplexer 26. A gate of the n-channel MOS field effect transistor 29b of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives inverted display data /PD through the corresponding one of the first to sixty fourth inverters 28-1, 28-2, 28-3, - - - 28-64 from the multiplexer 26. The first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 also receive the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 from the gray scale voltage generating circuit 17 respectively. The single multiplexer 26 receives the 6-bits display data PD1 from the data latch 16 for selecting one of the first to sixty fourth transfer gates 27-1, 27-2,

27-3, - - - 27-64 based on the received 6-bits display data PD1, whereby the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 turns ON, and the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 outputs the corresponding one of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 as a data red signal, a data green signal or a data blue signal.

The first amplifier 30-1 receives the data red signal, a data green signal or a data blue signal as the gray scale voltage from the first gray scale voltage selecting unit 18-1 for amplifying the received signal. Each of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 also receives a switch control signal SWA from the control circuit 15. The first to five hundred twenty eighth switches 31-1, 31-2, 31-3, - - - 31-528 of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 receive the switch control signal SWA from the control circuit 15, wherein the switch control signal SWA rises at the timing of falling edge of the strobe signal STB. The output circuit 19 outputs the first to five hundred twenty eighth data red, green and blue signals S1, S2, S3, - - - S528 which are then supplied to the data electrodes of the color liquid crystal display 1.

In FIG. 7, shown is the signal S1 which is the data red signal, in case that the display data PD1 is "000000". In this case, the transfer gate 27-1 in the first gray scale voltage selecting unit 18-1 turns ON based on the display data PD1 "000000", whereby the positive-polarity gray scale voltage V1 is outputted as the data red signal S1. The data red signal S1 is represented by a broken line when the strobe signal "STB" is high level because the switch 31-1 is in the OFF and the signal S1 applied to the data electrode of the color liquid crystal display 1 is in the high impedance state.

The common power supply 4 supplies the ground level GND to the common electrode of the color liquid crystal display 1 based on the polarity signal POL of high level "H", wherein the common potential of the common electrode of the color liquid crystal display 1 becomes the ground level GND. The pixel corresponding to the data electrode shows black, assuming that the color liquid crystal display 1 is of the normally white type.

If the polarity signal POL is low level "L", then the switches 8a and 9a turn OFF as well as the switches 8b and 9b turn ON, whereby the first side of the first resistance 7-1 is applied with the ground voltage GND whilst the second side of the tenth resistance 7-10 is applied with the power voltage VDD, so that the series connection of the first to tenth resistances 7-1, 7-2, 7-3, - - - 7-10 is biased between the power voltage VDD and the ground voltage GND. As a result, negative-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are generated at the first to ninth nodes N1, N2, N3, N4, N5, N6, N7, N8 and N9 respectively in accordance with respective ratios of the resistances 7-1, 7-2, 7-3, 7-4, 7-5, 7-6, 7-7, 7-8, 7-9, and 7-10, provided that VDD<V1<V2<V3<V4<V5<V6<V7<V8<V9<GND. The negative-polarity divided voltages V1, V2, V3, V4, V5, V6, V7, V8 and V9 are then amplified by the voltage followers 11-1, 11-2, 11-3, 11-4, 11-5, 11-6, 11-7, 11-8 and 11-9 respectively to generate the first to ninth negative-polarity gray scale voltages VI1, VI2, VI3, VI4, VI5, VI6, VI7, VI8 and VI9 which will subsequently be supplied to the gray scale voltage generating circuit 17 in the data electrode driver circuit 5, provided that VI1<VI2<VI3<VI4<VI5<VI6<VI7<VI8<VI9.

The gray scale voltage generating circuit 17 generates first to sixty fourth negative-polarity gray scale voltages V1, V2, V3, - - - V64 at the first to sixty fourth nodes respectively, wherein the generated first to sixty fourth negative-polarity gray scale voltages V1, V2, V3, - - - V64 depend on the first to

ninth gray scale voltages V11, V12, V13, - - - V19, wherein V1<V2<V3< - - - <V64. The first to sixty fourth negative polarity gray scale voltages V1, V2, V3, - - - V64 are then supplied to the gray scale voltage selecting circuit 18 in the data electrode driver circuit 5.

Each of the first to five hundred twenty eighth gray scale voltage selecting units 18-1, 18-2, 18-3, - - - 18-528 receives corresponding one of 6-bits display data PD1, PD2, - - - PD528.

A gate of the p-channel MOS field effect transistor 29a of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives the display data PD from the multiplexer 26. A gate of the n-channel MOS field effect transistor 29b of each of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 receives inverted display data /PD through the corresponding one of the first to sixty fourth inverters 28-1, 28-2, 28-3, - - - 28-64 from the multiplexer 26. The first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 also receive the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 from the gray scale voltage generating circuit 17 respectively. The single multiplexer 26 receives the 6-bits display data PD 1 from the data latch 16 for selecting one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 based on the received 6-bits display data PD1, whereby the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 turns ON, and the selected one of the first to sixty fourth transfer gates 27-1, 27-2, 27-3, - - - 27-64 outputs the corresponding one of the first to sixty fourth gray scale voltages V1, V2, V3, - - - V64 as a data red signal, a data green signal or a data blue signal.

The first amplifier 30-1 receives the data red signal, a data green signal or a data blue signal as the gray scale voltage from the first gray scale voltage selecting unit 18-1 for amplifying the received signal. Each of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 also receives a switch control signal SWA from the control circuit 15. The first to five hundred twenty eighth switches 31-1, 31-2, 31-3, - - - 31-528 of the first to five hundred twenty eighth output units 19-1, 19-2, 19-3, - - - 19-528 receive the switch-control signal SWA from the control circuit 15, wherein the switch control signal SWA rises at the timing of falling edge of the strobe signal STB. The output circuit 19 outputs the first to five hundred twenty eighth data red, green and blue signals S1, S2, S3, - - - S528 which are then supplied to the data electrodes of the color liquid crystal display 1.

In FIG. 7, shown is the signal S1 which is the data red signal, in case that the display data PD1 is "000000". In this case, the transfer gate 27-1 in the first gray scale voltage selecting unit 18-1 turns ON based on the display data PD1 "000000", whereby the positive-polarity gray scale voltage V1 is outputted as the data red signal S1. The data red signal S1 is represented by a broken line when the strobe signal "STB" is high level because the switch 31-1 is in the OFF and the signal S1 applied to the data electrode of the color liquid crystal display 1 is in the high impedance state.

The common power supply 4 supplies the power voltage level VDD to the common electrode of the color liquid crystal display 1 based on the polarity signal POL of low level "L", wherein the common potential of the common electrode of the color liquid crystal display 1 becomes the power voltage level VDD. The pixel corresponding to the data electrode shows black, assuming that the color liquid crystal display 1 is of the normally white type.

The above-described driving system is so called to as a line-inversion driving system, wherein the data signals applied to the data electrodes are opposite to each other in polarity with reference to corresponding common potentials

Vcom between adjacent two of the data lines, provided that the common potentials Vcom are respectively inverted between ground and power voltage levels for every data lines.

The line-inversion driving system has been utilized for the following two reasons. The first reason is that the applications of the same or uniform polarity voltages to the liquid crystal cells shorten the life-time of the color liquid crystal display. The second reason is that the transmittivity of the liquid crystal cells is almost independent from the polarity of the applied voltage to the liquid crystal display.

The above described line-inversion driving system, however, has the following disadvantages particularly in case of the mobile phones and personal handy-phone systems. In a stand-by mode, the power ON-state is maintained without, however, any operations by the users, and a predetermined stand-by display is displayed in full-colors on the color liquid crystal display screen, even the users are unlikely to view the display screen. The driver circuit of the color liquid crystal display is driven in the same manner as in the normal mode. This means that, in the stand-by mode, the driver circuit consumes the same power as in the normal mode. It is desirable to suppress the power consumption by the driver circuit in the stand-by mode as many as possible.

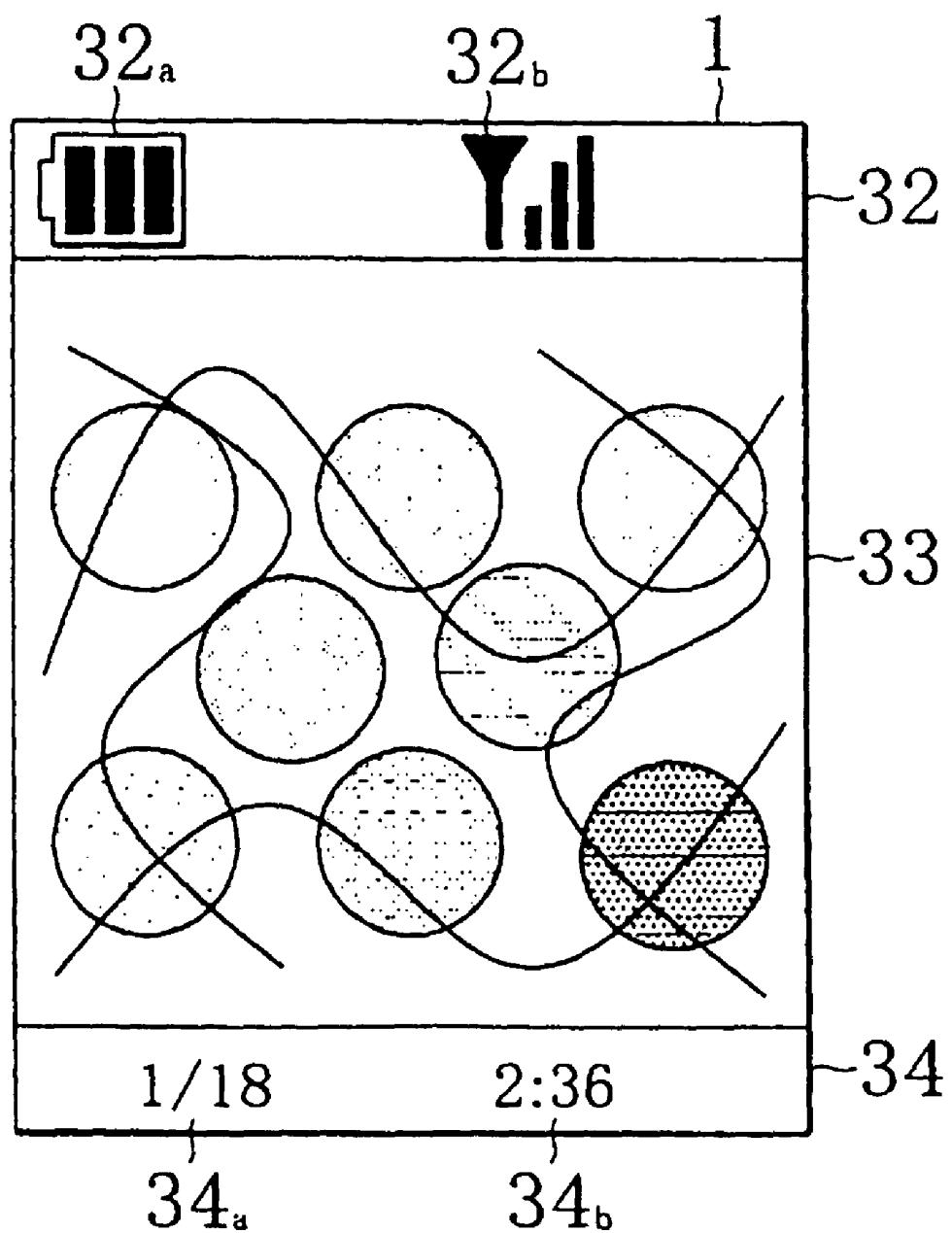

FIG. 8 is a view illustrative of a display screen of the mobile phone or the personal handyphone system. A display screen 1 of the mobile phone or the personal handyphone system includes a top display region 32, a center display region 33 and a bottom display region 34. The top display region 32 displays a battery mark 32a and an antenna mark 32b. The battery mark 32a indicates a charge-level of a battery accommodated in the mobile phone or the personal handy-phone system. The antenna mark 32b indicates whether the position of the mobile phone or the personal handy-phone system is in a service area of a wireless phone service on a mobile communication network.

The center display region 33 displays images of the contents attached to e-mails and provided from World Wide Web servers. The bottom display region 34 displays month-and-day information 34a and clock-time information 34b. The center display region 33 shows the full color display. The top and bottom display regions 32 and 34 show monochrome or 8-colors displays.

For performing the monochrome or 8-colors display on the top and bottom display regions 32 and 34, the conventional driver circuit of the color liquid crystal display 1 operates the data electrode driver circuit 5 in the same manners as performing the full-color display on the center display region 33. This causes unnecessary power consumption by the conventional driver circuit. It is thus desirable to suppress the power consumption for displaying the top and bottom display regions 32 and 34.

Another driving system, for example, the frame inversion system also has the same disadvantages as described above. In the frame inversion system, the data signals applied to the data electrodes are opposite to each other in polarity with reference to corresponding common potentials Vcom between adjacent two frames, provided that the common potentials Vcom are respectively inverted between ground and power voltage levels for every frames.

The above described disadvantages of the line inversion driving system and the frame-inversion driving system are also common to other portable or mobile electric devices than the mobile phones and the personal handy-phone systems, for example, various electronic devices such as note-type computers, palm-type computers, pocket-type computers, mobile terminals such as personal digital assistants.

In the above circumstances, the developments of a novel method of driving a liquid crystal display and of a drive circuit for driving the liquid crystal display as well as of an electronic device with the driver circuit are desirable.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide a novel method of driving a liquid crystal display free from the above problems.

It is a further object of the present invention to provide a novel line-inversion driving method of driving a color liquid crystal display, wherein the method is suitable for reducing the power consumption.

It is a still further object of the present invention to provide a novel frame-inversion driving method of driving a color liquid crystal display, wherein the method is suitable for reducing the power consumption.

It is yet a further object of the present invention to provide a novel driver circuit for driving a liquid crystal display free from the above problems.

It is further more object of the present invention to provide a novel driver circuit for driving a liquid crystal display in a line inversion driving, wherein the driver circuit is suitable for reducing the power consumption.

It is moreover object of the present invention to provide a novel driver circuit for driving a liquid crystal display in a frame inversion driving, wherein the driver circuit is suitable for reducing the power consumption.

It is yet more object of the present invention to provide a novel electronic device with an improved driver circuit driver circuit for driving a liquid crystal display free from the above problems.

It is another object of the present invention to provide a novel electronic device with an improved driver circuit for driving a liquid crystal display in a line-inversion driving, wherein the driver circuit is suitable for reducing the power consumption.

It is still another object of the present invention to provide a novel electronic device with an improved driver circuit for driving a liquid crystal display in a frame-inversion driving, wherein the driver circuit is suitable for reducing the power consumption.

The present invention provides a method and a circuit for driving a color liquid crystal display in a normal driving mode and -a power saving mode, wherein in the normal driving mode, voltages corresponding to image display data are applied to data electrodes of the color liquid crystal display, and wherein in the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as display data signals to the data electrodes.

The above and other objects, features and advantages of the present invention will be apparent from the following descriptions.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Preferred embodiments according to the present invention will be described in detail with reference to the accompanying drawings.

FIG. 1 is a block diagram illustrative of a first conventional driver circuit for driving a color liquid crystal display.

FIG. 2 is a circuit diagram illustrative of a circuit configuration of a gray scale power supply in the driver circuit shown in FIG. 1.

FIG. 3 is a block diagram illustrative of the data electrode driver circuit shown in FIG. 1.

FIG. 4 is a partial circuit diagram illustrative of a part of the circuit configuration of the data buffer shown in FIG. 3.

FIG. 5 is a circuit diagram illustrative of the gray scale voltage generating circuit shown in FIG. 3.

FIG. 6 is a circuit diagram illustrative of the first gray scale voltage selecting unit included in the gray scale voltage selecting circuit and a first output unit included in the output circuit of FIG. 3.

FIG. 7 is a timing chart illustrative of operations of the control circuit, the gray scale power supply, the common power supply and the data electrode driver circuit in FIG. 1.

FIG. 8 is a view illustrative of a display screen of the mobile phone or the personal handy-phone system.

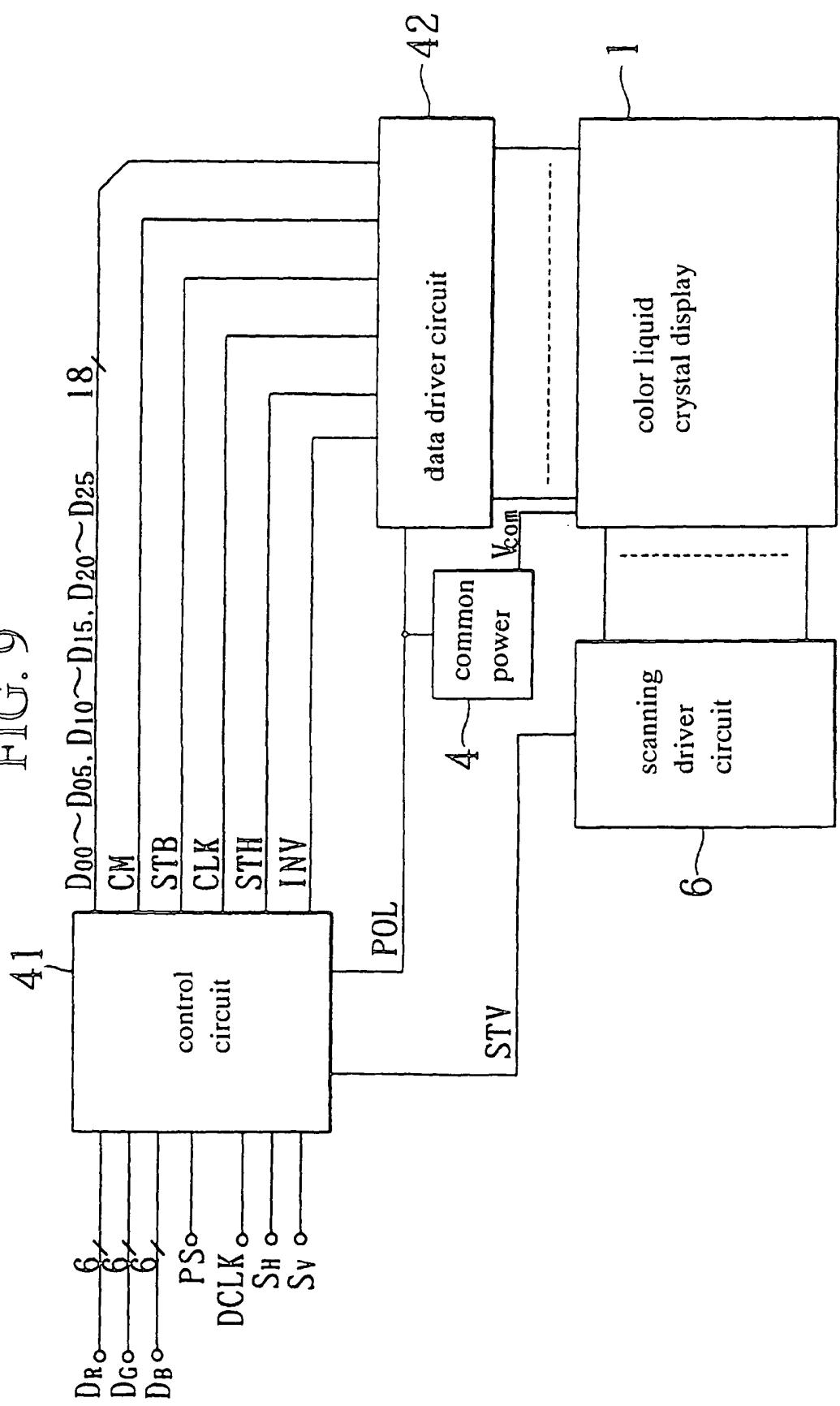

FIG. 9 is a block diagram illustrative of a first novel driver circuit for driving a color liquid crystal display in a first embodiment in accordance with the present invention.

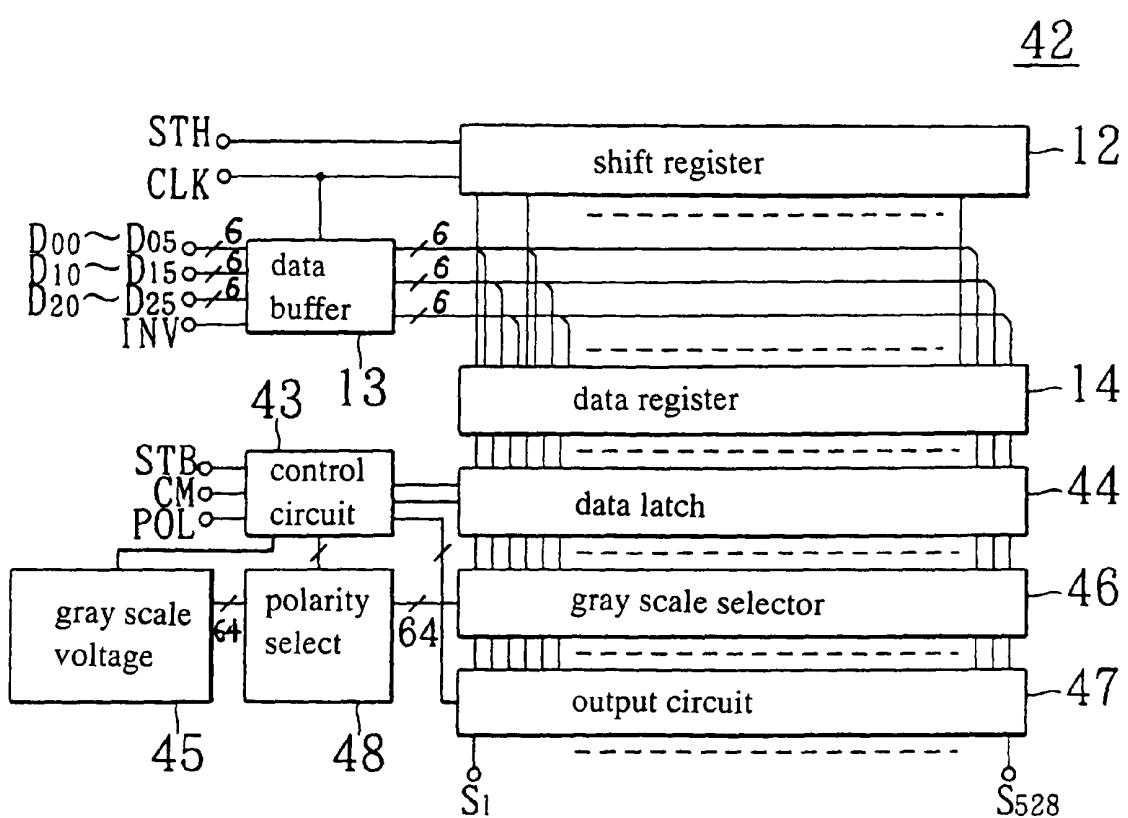

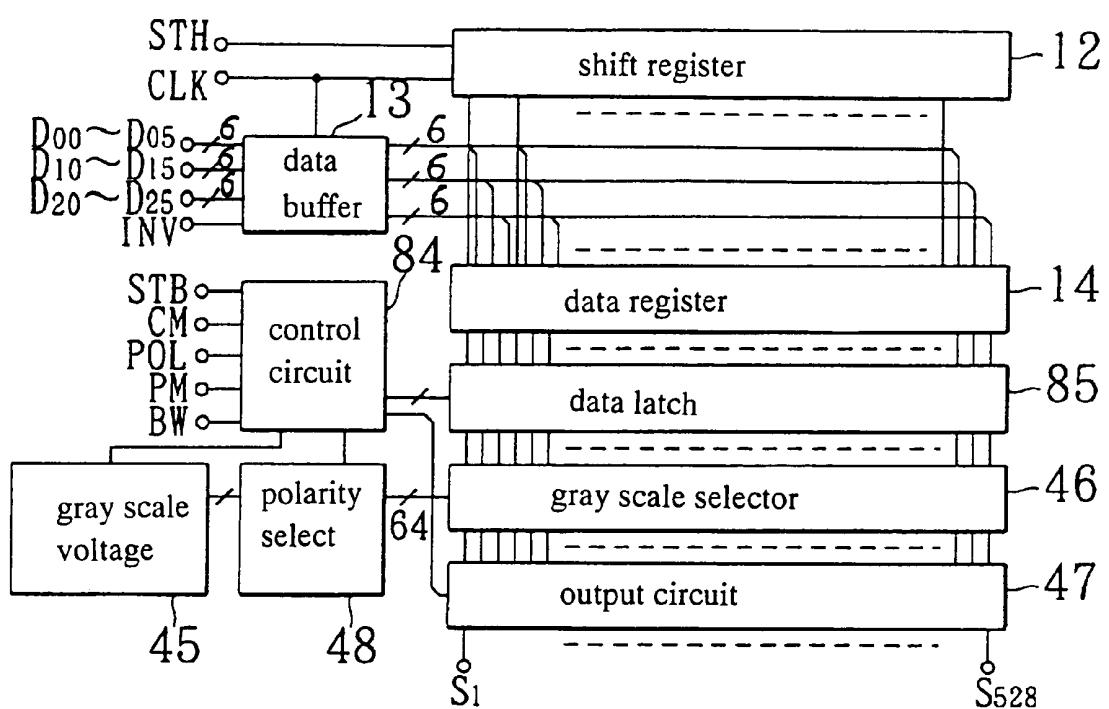

FIG. 10 is a block diagram illustrative of the data electrode driver circuit shown in FIG. 9.

FIG. 11 is a partial circuit diagram illustrative of a part of the circuit configuration of the data buffer shown in FIG. 10.

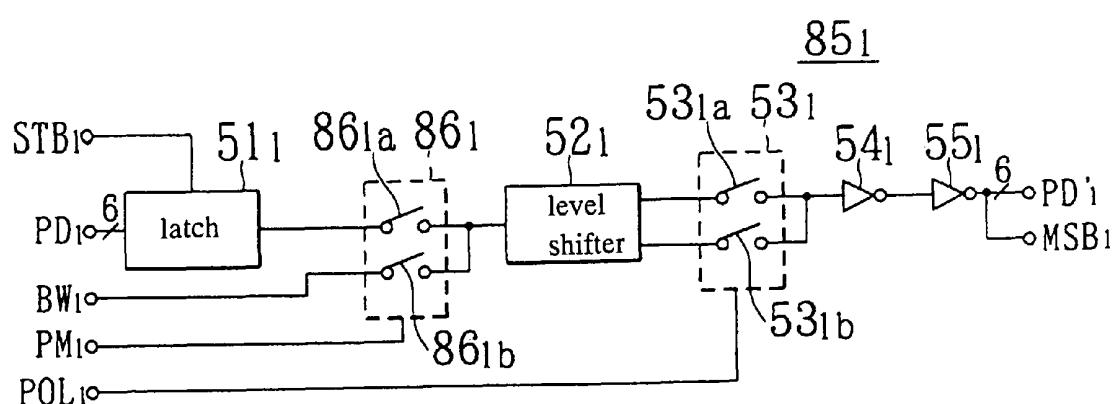

FIG. 12 is a diagram illustrative of the first data latch unit included in the data latch of the data electrode driver circuit shown in FIG. 10.

FIG. 13 is a circuit diagram illustrative of the gray scale voltage generating circuit and the polarity selecting circuit shown in FIG. 10.

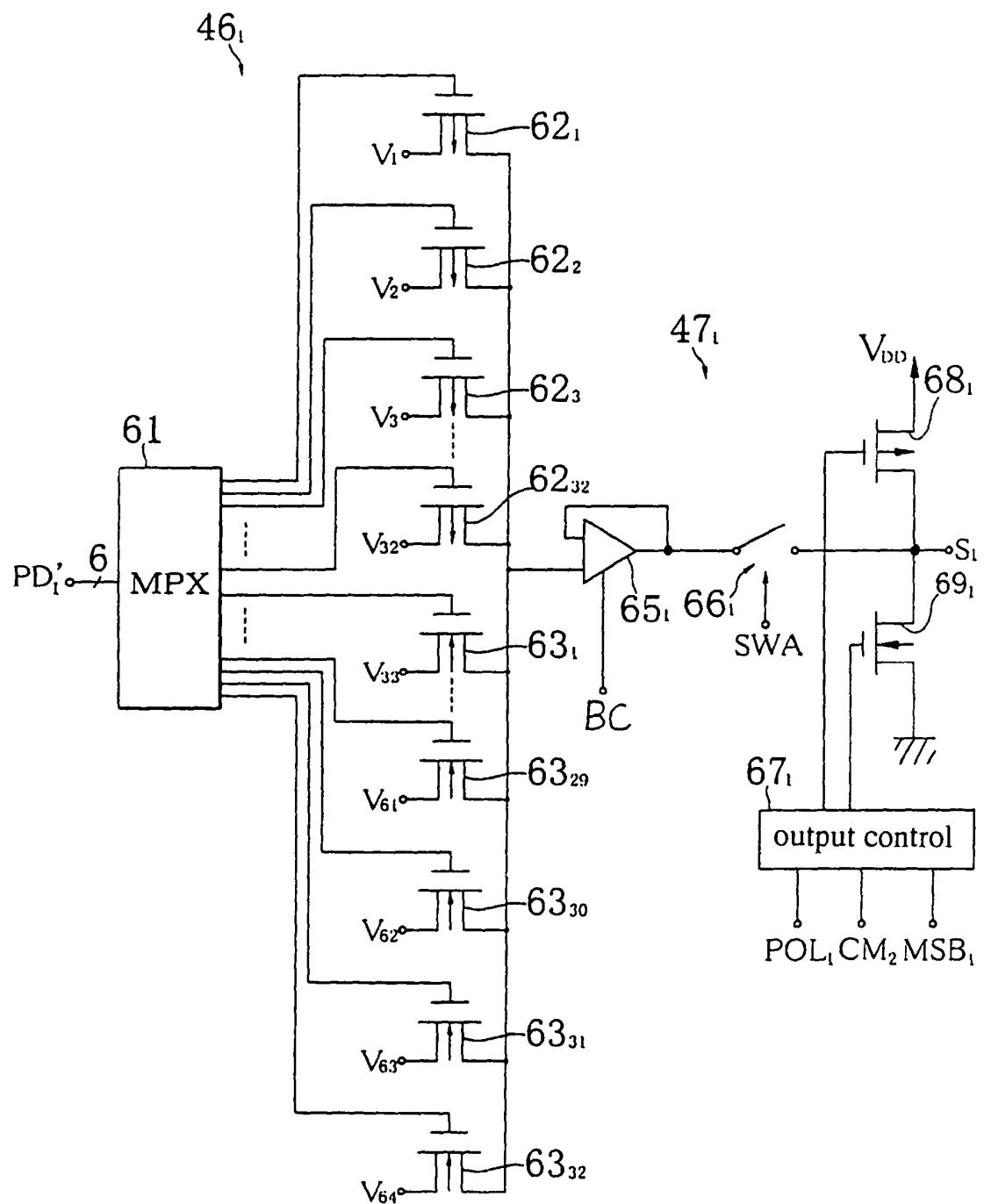

FIG. 14 is a block diagram illustrative of the gray scale voltage selecting circuit and the output circuit shown in FIG. 10.

FIG. 15 is a circuit diagram illustrative of the first gray scale voltage selecting unit included in the gray scale voltage selecting circuit and the first output unit included in the output circuit shown in FIG. 14.

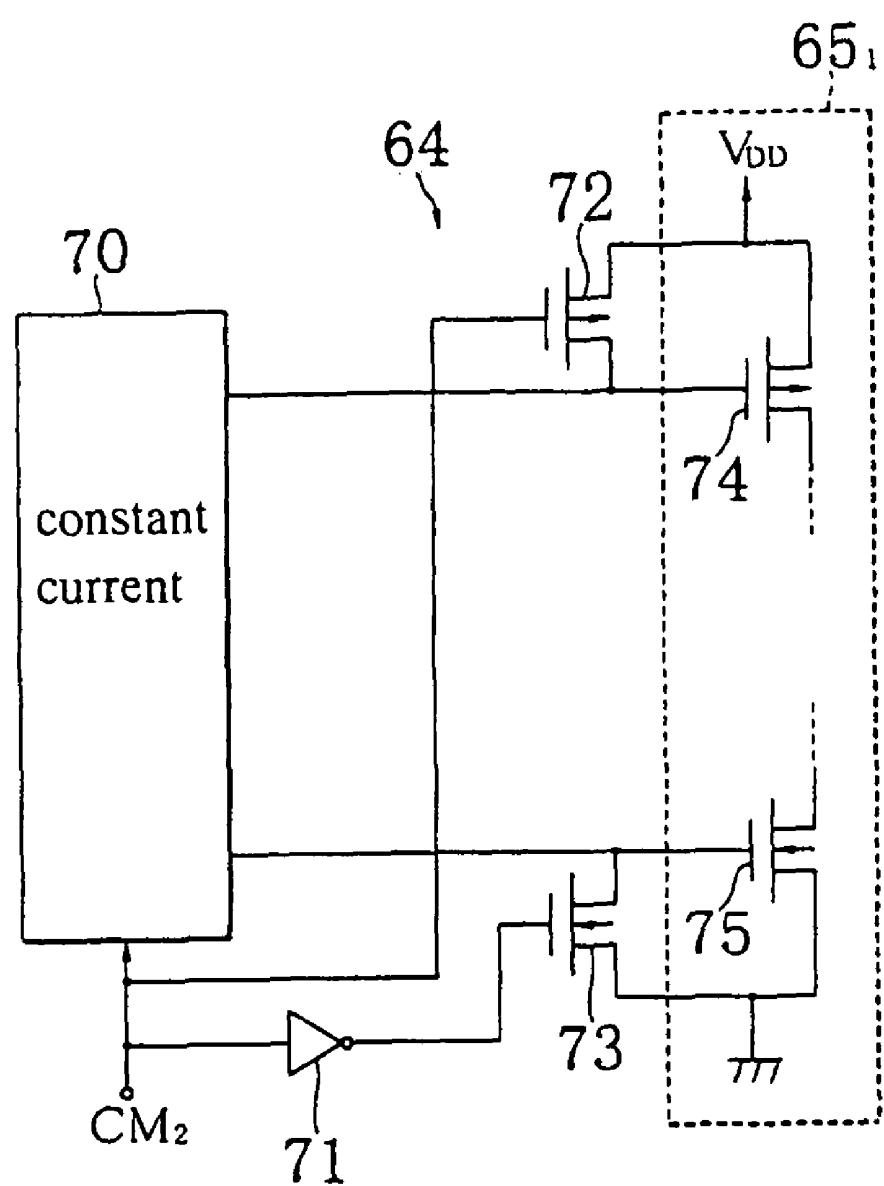

FIG. 16 is a circuit diagram illustrative of the bias current control circuit included in the output circuit shown in FIG. 14 as well as of a part of the amplifier included in the first output unit shown in FIG. 15.

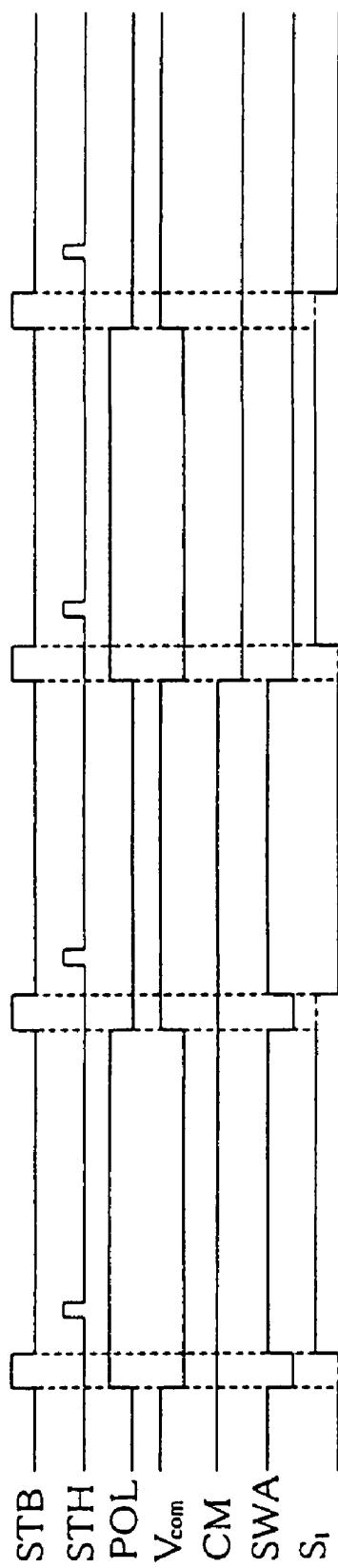

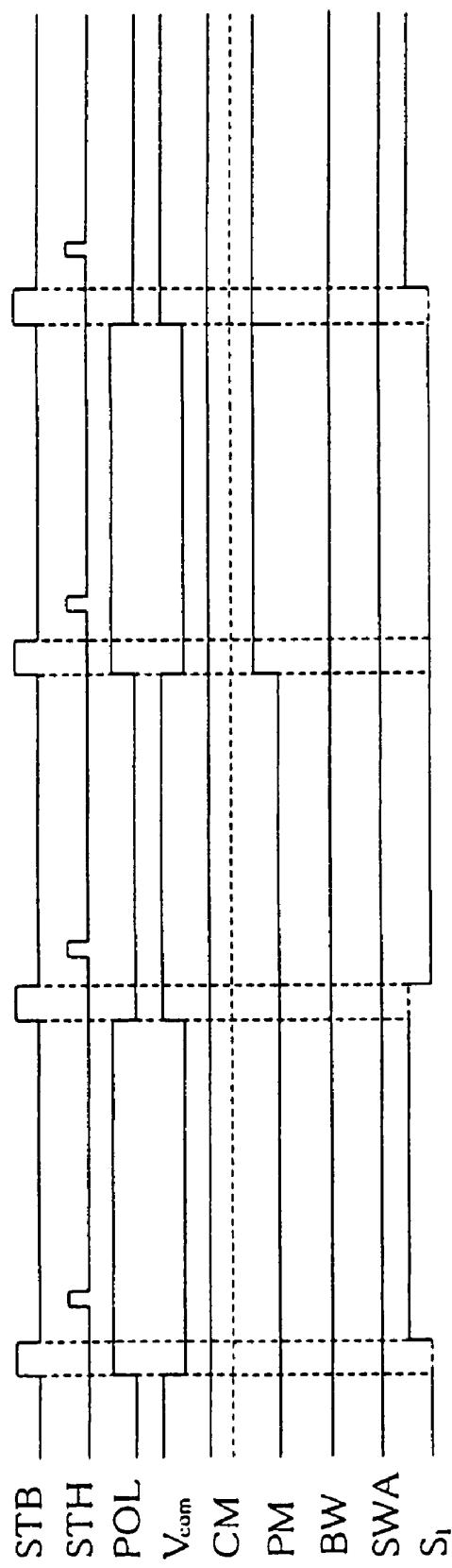

FIG. 17 is a timing chart illustrative of operations of the control circuit, the common power supply and the data electrode driver circuit included in the driver circuit shown in FIG. 9.

FIG. 18 is a block diagram illustrative of a second novel driver circuit for driving a color liquid crystal display in a second embodiment in accordance with the present invention.

FIG. 19 is a block diagram illustrative of the data electrode driver circuit shown in FIG. 18.

FIG. 20 is a diagram illustrative of the first data latch unit included in the data latch of the data electrode driver circuit shown in FIG. 18.

FIG. 21 is a timing chart illustrative of operations of the control circuit, the common power supply and the data electrode driver circuit included in the driver circuit shown in FIG. 18.

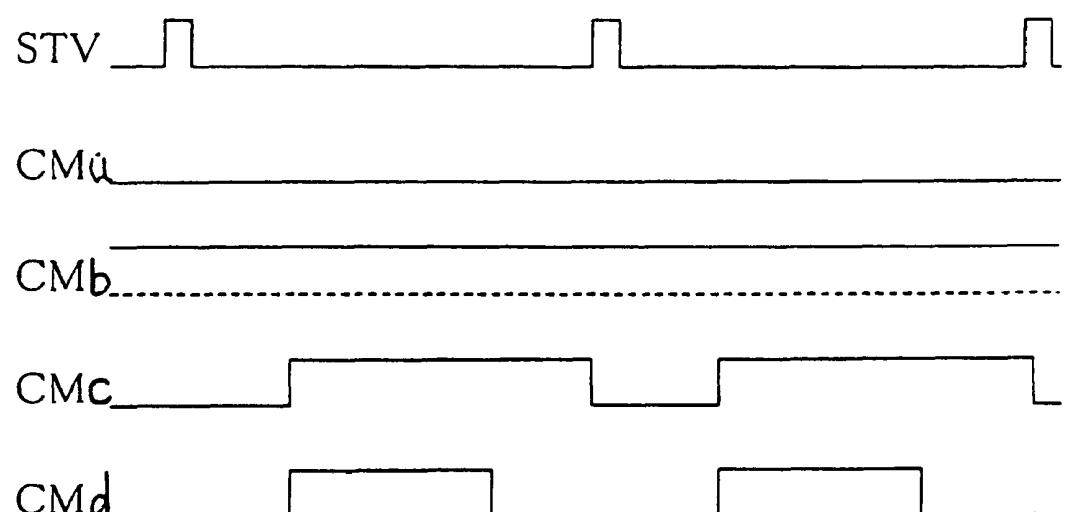

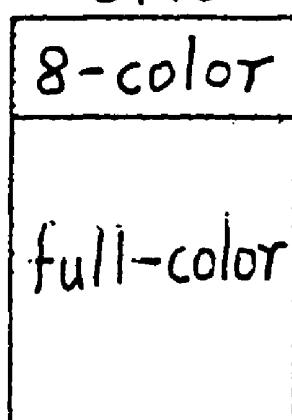

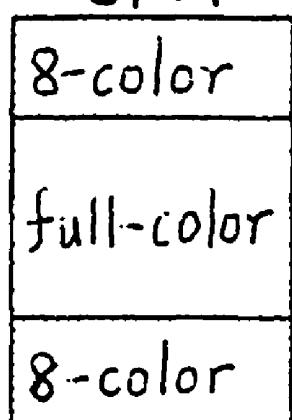

FIG. 22 is a timing chart illustrative of four possible modifications to waveforms of the four color mode signals CMa, CMb, CMc and CMd with reference to the vertical start pulse signal STV.

FIG. 23 is a view illustrative of corresponding four display states of the display screen to the four color mode signals CMa, CMb, CMc and CMd shown in FIG. 22.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

A first aspect of the present invention is a method of driving a color liquid crystal display in a normal driving mode and a power saving mode, wherein in the normal driving mode,

voltages corresponding to image display data are applied to data electrodes of the color liquid crystal display, and wherein in the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as display data signals to the data electrodes. In the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as the display data signals to the data electrodes of the color liquid crystal display, in order to reduce the power consumption in the line-inversion driving system or the frame inversion driving system.

It is possible that the power saving mode includes an essential information display mode, where a predetermined uniform voltage level, which corresponds to a predetermined color and which is independent from the image display data, is uniformly applied to all data electrodes on other region than at least a designated region for displaying the essential information.

It is further possible that the color liquid crystal display is of normally white type, and the predetermined color is white.

It is also possible that the color liquid crystal display is of normally black type, and the predetermined color is black.

It is also possible that a uniform scanning signal is simultaneously applied to all scanning electrodes on other region than the at least designated region for displaying the essential information.

It is also possible that at least a full color display region in the color liquid crystal display is displayed in the normal driving mode, and that at least a partial color display region in the color liquid crystal display is displayed in the power saving mode.

It is also possible that the power saving mode further inactivates a gray scale voltage generating circuit, a polarity selecting circuit, and an output circuit included in a driver circuit for driving the color liquid crystal display.

A second aspect of the present invention is a circuit for driving a color liquid crystal display. The circuit comprises: a data latch for selectively inverting image display data based on a polarity signal; a gray scale voltage generating circuit for generating a first set of plural positive-polarity gray scale voltages and a second set of plural negative-polarity gray scale voltages; a polarity selecting circuit for selecting one of the first set of the plural positive-polarity gray scale voltages and the second set of the plural negative-polarity gray scale voltages based on the polarity signal; a gray scale voltage selecting circuit for selecting a single gray scale voltage from the selected plural gray scale voltages based on the image display data supplied from the data latch; an output circuit for supplying the selected single gray scale voltage to a corresponding data electrode of the color liquid crystal display; and a control circuit for inactivating the gray scale voltage generating circuit, the polarity selecting circuit and the output circuit in a power saving mode, and also for applying voltages corresponding to highly significant bit signals of the image display data as display data signals to the data electrodes in the power saving mode. In the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as the display data signals to the data electrodes of the color liquid crystal display, in order to reduce the power consumption in the line-inversion driving system or the frame inversion driving system.

It is possible that the polarity signal is selectively inverted for every horizontal synchronizing time periods or for every vertical synchronizing time periods.

It is also possible that the plural positive-polarity gray scale voltages are predetermined to adjust to a positive voltage to transmittivity characteristic of the color liquid crystal display,

and the plural negative-polarity gray scale voltages are also predetermined to adjust to a negative voltage to transmittivity characteristic of the color liquid crystal display.

It is also possible that the power saving mode includes an essential information display mode, where the control circuit controls the data latch so that a predetermined uniform voltage level, which corresponds to a predetermined color and which is independent from the image display data, is uniformly applied to all data electrodes on other region than at least a designated region for displaying the essential information.

It is further possible that the color liquid crystal display is of normally white type, and the predetermined color is white.

It is also possible that the color liquid crystal display is of normally black type, and the predetermined color is black.

It is also possible to further comprise a scanning electrode driving circuit, wherein the control circuit controls the scanning electrode driving circuit for simultaneously applying a uniform scanning signal to all scanning electrodes on other region than the at least designated region for displaying the essential information.

It is also possible that at least a full color display region in the color liquid crystal display is displayed in the normal driving mode, and that at least a partial color display region in the color liquid crystal display is displayed in the power saving mode.

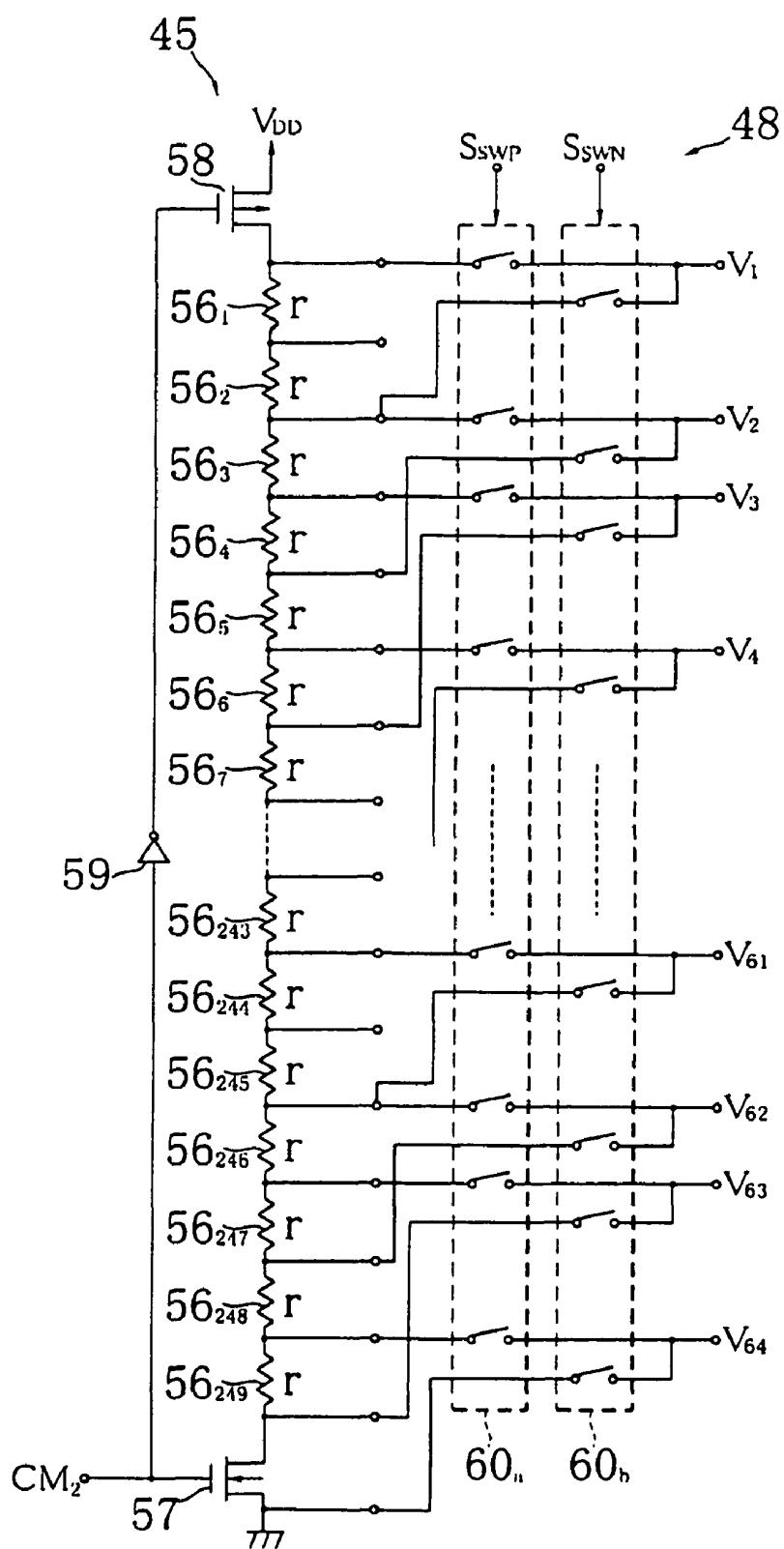

It is also possible that the gray scale voltage generating circuit further comprises: a divided-voltage generating circuit for generating plural divided-voltages different in voltage level from each other in a normal driving mode and also for generating no divided-voltages in the power saving modes.

It is further possible that the divided-voltage generating circuit further comprises: a series connection of plural resistances having a uniform resistance value; a high voltage side switch for applying a high voltage to a first side of the series connection of plural resistances in the normal driving mode and for applying a voltage to the first side in the power saving mode; and a low voltage side switch for applying a low voltage to a second side of the series connection of plural resistances in the normal driving mode and for applying no voltage to the second side in the power saving mode.

It is also possible that the polarity selecting circuit further comprises: a first switching group including plural switches for selecting the plural positive-polarity gray scale voltages based on a positive switching signal; and a second switching group including plural switches for selecting the plural negative-polarity gray scale voltages based on a negative switching signal.

It is also possible that the gray scale voltage selecting circuit selects either first one of the plural positive-polarity gray scale voltages or second one of the plural negative-polarity gray scale voltages based on the image display data.

It is further possible that the output circuit generates an output signal based on the selected gray scale voltage supplied from the gray scale voltage selecting circuit in the normal driving mode, and also the output circuit generates either one of predetermined high and low voltage levels which are independent from the selected gray scale voltage in the power saving mode.

It is further possible that the output circuit further comprises: an amplifying circuit for amplifying the selected gray scale voltage in the normal driving mode, and also the amplifying circuit being inactivated in the power saving mode; and a selecting circuit for selecting the amplified gray scale voltage supplied from the amplifying circuit in the normal driving mode, and also selecting either one of the predetermined high

and low voltage levels which are independent from the selected gray scale voltage in the power saving mode.

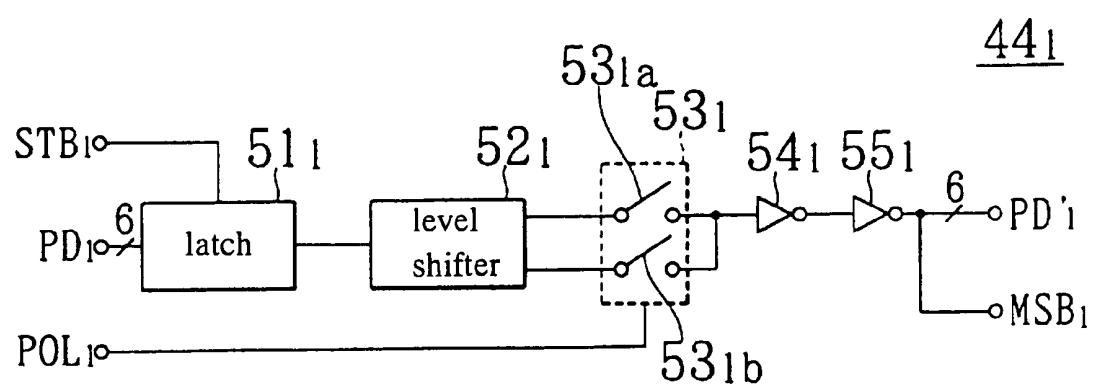

It is also possible that the data latch comprises: a latch circuit for accepting input of the image display data in synchronizing with a strobe signal having the same cycle as a horizontal synchronizing signal and the latch circuit subsequently holding the image display data for a single horizontal synchronizing time period; a level shifter for shifting a voltage level of the image display data supplied from the latch circuit and also inverting the image display data to generate both non-inverted image display data and inverted image display data; and a selector for selecting, based on the polarity signal, the non-inverted image display data or the inverted image display data supplied from the level shifter.

It is also possible that the data latch comprises: a latch circuit for accepting input of the image display data in synchronizing with a strobe signal having the same cycle as a horizontal synchronizing signal and the latch circuit subsequently holding the image display data for a single horizontal synchronizing time period; a first selector for selecting, based on a partial display signal supplied from the control circuit, either monochrome display data supplied from the control circuit or the image display data supplied from the latch circuit; a level shifter for shifting a voltage level of the selected monochrome display data or the image display data supplied from the latch circuit and also inverting the display data to generate either a first pair of non-inverted image display data and inverted image display data or a second pair of non-inverted monochrome display data and inverted monochrome display data; and a second selector for selecting, based on the polarity signal, one of the non-inverted image display data and the inverted image display data or of the non-inverted monochrome display data and the inverted monochrome display data supplied from the level shifter.

A third aspect of the present invention is a portable device including a color liquid crystal display and a driver circuit for driving the color liquid crystal display with a battery power. The driver circuit comprises: a data latch for selectively inverting image display data based on a polarity signal; a gray scale voltage generating circuit for generating a first set of plural positive-polarity gray scale voltages and a second set of plural negative-polarity gray scale voltages; a polarity selecting circuit for selecting one of the first set of the plural positive-polarity gray scale voltages and the second set of the plural negative-polarity gray scale voltages based on the polarity signal; a gray scale voltage selecting circuit for selecting a single gray scale voltage from the selected plural gray scale voltages based on the image display data supplied from the data latch; an output circuit for supplying the selected single gray scale voltage to a corresponding data electrode of the color liquid crystal display; and a control circuit for inactivating the gray scale voltage generating circuit, the polarity selecting circuit, and the output circuit in a power saving mode, and also for applying voltages corresponding to highly significant bit signals of the image display data as display data signals to the data electrodes in the power saving mode. In the power saving mode, voltages corresponding to highly significant bit signals of the image display data are applied as the display data signals to the data electrodes of the color liquid crystal display, in order to reduce the power consumption in the line-inversion driving system or the frame inversion driving system.

It is possible that the polarity signal is selectively inverted for every horizontal synchronizing time periods or for every vertical synchronizing time periods.

It is also possible that the plural positive-polarity gray scale voltages are predetermined to adjust to a positive voltage to

transmittivity characteristic of the color liquid crystal display, and the plural negative-polarity gray scale voltages are also predetermined to adjust to a negative voltage to transmittivity characteristic of the color liquid crystal display.

It is also possible that the power saving mode includes an essential information display mode, where the control circuit controls the data latch so that a predetermined uniform voltage level, which corresponds to a predetermined color and which is independent from the image display data, is uniformly applied to all data electrodes on other region than at least a designated region for displaying the essential information.

It is further possible that the color liquid crystal display is of normally white type, and the predetermined color is white.

It is also possible that the color liquid crystal display is of normally black type, and the predetermined color is black.

It is also possible to further comprise a scanning electrode driving circuit, wherein the control circuit controls the scanning electrode driving circuit for simultaneously applying a uniform scanning signal to all scanning electrodes on other region than the at least designated region for displaying the essential information.

It is also possible that at least a full color display region in the color liquid crystal display is displayed in the normal driving mode, and that at least a partial color display region in the color liquid crystal display is displayed in the power saving mode.

It is also possible that the gray scale voltage generating circuit further comprises: a divided-voltage generating circuit for generating plural divided-voltages different in voltage level from each other in a normal driving mode and also for generating no divided-voltages in the power saving modes.

It is further possible that the divided voltage generating circuit further comprises: a series connection of plural resistances having a uniform resistance value; a high voltage side switch for applying a high voltage to a first side of the series connection of plural resistances in the normal driving mode and for applying no voltage to the first side in the power saving mode; and a low voltage side switch for applying a low voltage to a second side of the series connection of plural resistances in the normal driving mode and for applying no voltage to the second side in the power saving mode.

It is also possible that the polarity selecting circuit further comprises: a first switching group including plural switches for selecting the plural positive-polarity gray scale voltages based on a positive switching signal; and a second switching group including plural switches for selecting the plural negative-polarity gray scale voltages based on a negative switching signal.

It is also possible that the gray scale voltage selecting circuit selects either first one of the plural positive-polarity gray scale voltages or second one of the plural negative-polarity gray scale voltages based on the image display data.

It is further possible that the output circuit generates an output signal based on the selected gray scale voltage supplied from the gray scale voltage selecting circuit in the normal driving mode, and also the output circuit generates either one of predetermined high and low voltage levels which are independent from the selected gray scale voltage in the power saving mode.

It is further possible that the output circuit further comprises: an amplifying circuit for amplifying the selected gray scale voltage in the normal driving mode, and also the amplifying circuit being inactivated in the power saving mode; and a selecting circuit for selecting the amplified gray scale voltage supplied from the amplifying circuit in the normal driving mode, and also selecting either one of the predetermined high

and low voltage levels which are independent from the selected gray scale voltage in the power saving mode.

It is also possible that the data latch comprises: a latch circuit for accepting input of the image display data in synchronizing with a strobe signal having the same cycle as a horizontal synchronizing signal and the latch circuit subsequently holding the image display data for a single horizontal synchronizing time period; a level shifter for shifting a voltage level of the image display data supplied from the latch circuit and also inverting the image display data to generate both non-inverted image display data and inverted image display data; and a selector for selecting, based on the polarity signal, the non-inverted image display data or the inverted image display data supplied from the level shifter.

It is also possible that the data latch comprises: a latch circuit for accepting input of the image display data in synchronizing with a strobe signal having the same cycle as a horizontal synchronizing signal and the latch circuit subsequently holding the image display data for a single horizontal synchronizing time period; a first selector for selecting, based on a partial display signal supplied from the control circuit, either monochrome display data supplied from the control circuit or the image display data supplied from the latch circuit; a level shifter for shifting a voltage level of the selected monochrome display data or the image display data supplied from the latch circuit and also inverting the display data to generate either a first pair of non-inverted image display data and inverted image display data or a second pair of non-inverted monochrome display data and inverted monochrome display data; and a second selector for selecting, based on the polarity signal, one of the non-inverted image display data and the inverted image display data or of the non-inverted monochrome display data and the inverted monochrome display data supplied from the level shifter.

#### First Embodiment

A first embodiment according to the present invention will be described in detail with reference to the drawings. FIG. 9 is a block diagram illustrative of a first novel driver circuit for driving a color liquid crystal display in a first embodiment in accordance with the present invention.

A color liquid crystal display 1 may be driven by an active matrix driving system using thin film transistors as switching devices. The color liquid crystal display 1 includes a plurality of scanning lines or data lines which extend parallel to each other in a column direction at a constant pitch, and a plurality of data lines or source lines which extend parallel to each other in a row direction at another constant pitch, as well as a two-dimensional matrix array of pixels, each of which is positioned in an area defined by adjacent two of the scanning lines and adjacent two of the data lines.

Each of the pixels further includes a liquid crystal cell as an equivalent capacitive load, a common electrode, a thin film transistor for driving the liquid crystal cell, and a data electrode for storing data charge in a vertical synchronizing term. A gate electrode of the thin film transistor is connected to the scanning line. The gate electrode of the thin film transistor serves as a scanning electrode.

The color liquid crystal display 1 may be driven as follows. The common electrode is applied with a common potential  $V_{com}$ . The data electrode is applied with data signals, wherein the data signals may include data red signals, data green signals and data blue signals, which have been generated from red data  $D_R$ , green data  $D_G$ , and blue data  $D_B$  as digital image data. The scanning electrode is applied with a

scanning signal which has been generated from a horizontal synchronizing signal  $S_H$  and a vertical synchronizing signal  $S_V$ .

The following description with reference to FIG. 9 will be made assuming that the color liquid crystal display 1 is a normally white type color liquid crystal display which is high in transmittivity under no voltage application.

The driver circuit for driving the color liquid crystal display 1 mainly includes a control circuit 41, a common power supply 4, a data electrode driver circuit 42, and a scanning electrode driver circuit 6.

The control circuit 41 may, for example, comprise an application specific integrated circuit (ASIC). The control circuit 41 receives parallel inputs of red data  $D_R$  of 6-bits, green data  $D_G$  of 6-bits and blue data  $D_B$  of 6-bits. The control circuit 41 converts the red data  $D_R$ , green data  $D_G$  and blue data  $D_B$  into 18-bits display data D00-DOS, D10-D15 and D20-D25 respectively, and outputs the 18-bits display data. The 18-bits display data outputted from the control circuit 41 are supplied to the data electrode driver circuit 42.