US008395716B2

(12) **United States Patent**

Ishitani et al.

(10) **Patent No.:** US 8,395,716 B2

(45) **Date of Patent:** Mar. 12, 2013

(54) **LIQUID CRYSTAL DISPLAY DEVICE**(75) Inventors: **Tetsuji Ishitani**, Isehara (JP); **Daisuke Kubota**, Isehara (JP)(73) Assignee: **Semiconductor Energy Laboratory Co., Ltd.**, Atsugi-shi, Kanagawa-ken (JP)

(\* ) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 552 days.

(21) Appl. No.: **12/627,187**(22) Filed: **Nov. 30, 2009**(65) **Prior Publication Data**

US 2010/0134710 A1 Jun. 3, 2010

(30) **Foreign Application Priority Data**

Dec. 3, 2008 (JP) ..... 2008-308787

(51) **Int. Cl.****G02F 1/136** (2006.01)

**G02F 1/1335** (2006.01)

**G02F 1/1343** (2006.01)(52) **U.S. Cl.** ..... 349/46; 349/106; 349/141(58) **Field of Classification Search** ..... 349/46, 349/106, 141

See application file for complete search history.(56) **References Cited**

## U.S. PATENT DOCUMENTS

5,530,265 A 6/1996 Takemura

5,696,011 A 12/1997 Yamazaki et al.

5,701,167 A 12/1997 Yamazaki

5,744,864 A 4/1998 Cillessen et al.

5,847,410 A 12/1998 Nakajima

6,191,835 B1 2/2001 Choi6,294,274 B1 9/2001 Kawazoe et al.

6,532,045 B2 3/2003 Chung et al.

6,563,174 B2 5/2003 Kawasaki et al.

6,586,346 B1 7/2003 Yamazaki et al.

6,674,136 B1 1/2004 Ohtani

6,727,522 B1 4/2004 Kawasaki et al.

6,852,998 B2 2/2005 Sung et al.

(Continued)

## FOREIGN PATENT DOCUMENTS

EP 1 033 755 9/2000

EP 1 134 811 9/2001

(Continued)

## OTHER PUBLICATIONS

Dembo.H et al., "RFCPUS on Glass and Plastic Substrates Fabricated by TFT Transfer Technology", IEDM 05: Technical Digest of International Electron Devices Meeting, Dec. 5, 2005, pp. 1067-1069.

(Continued)

Primary Examiner — Huyen Ngo

(74) Attorney, Agent, or Firm — Eric J. Robinson; Robinson Intellectual Property Law Office, P.C.

(57) **ABSTRACT**

A liquid crystal display device is provided, which includes a thin film transistor including an oxide semiconductor layer, a first electrode layer, a second electrode layer having an opening, a light-transmitting chromatic-color resin layer between the thin film transistor and the second electrode layer, and a liquid crystal layer. One of the first electrode layer and the second electrode layer is a pixel electrode layer which is electrically connected to the thin film transistor, and the other of the first electrode layer and the second electrode layer is a common electrode layer. The light-transmitting chromatic-color resin layer is overlapped with the pixel electrode layer and the oxide semiconductor layer of the thin film transistor.

24 Claims, 17 Drawing Sheets

## U.S. PATENT DOCUMENTS

|              |      |         |                 |              |    |         |                       |

|--------------|------|---------|-----------------|--------------|----|---------|-----------------------|

| 6,900,461    | B2   | 5/2005  | Inoue et al.    | 2008/0006877 | A1 | 1/2008  | Mardilovich et al.    |

| 6,960,812    | B2   | 11/2005 | Yamazaki et al. | 2008/0038882 | A1 | 2/2008  | Takechi et al.        |

| 7,009,204    | B2   | 3/2006  | Tsai et al.     | 2008/0038929 | A1 | 2/2008  | Chang                 |

| 7,049,190    | B2   | 5/2006  | Takeda et al.   | 2008/0050595 | A1 | 2/2008  | Nakagawara et al.     |

| 7,061,014    | B2   | 6/2006  | Hosono et al.   | 2008/0068359 | A1 | 3/2008  | Yoshida et al.        |

| 7,064,346    | B2   | 6/2006  | Kawasaki et al. | 2008/0073653 | A1 | 3/2008  | Iwasaki               |

| 7,075,614    | B2   | 7/2006  | Izumi et al.    | 2008/0083950 | A1 | 4/2008  | Pan et al.            |

| 7,105,868    | B2   | 9/2006  | Nause et al.    | 2008/0106191 | A1 | 5/2008  | Kawase                |

| 7,211,825    | B2   | 5/2007  | Shih et al.     | 2008/0128689 | A1 | 6/2008  | Lee et al.            |

| 7,282,782    | B2   | 10/2007 | Hoffman et al.  | 2008/0129195 | A1 | 6/2008  | Ishizaki et al.       |

| 7,297,977    | B2   | 11/2007 | Hoffman et al.  | 2008/0166834 | A1 | 7/2008  | Kim et al.            |

| 7,301,211    | B2   | 11/2007 | Yamazaki et al. | 2008/0182358 | A1 | 7/2008  | Cowdery-Corvan et al. |

| 7,323,356    | B2   | 1/2008  | Hosono et al.   | 2008/0198108 | A1 | 8/2008  | Aoki                  |

| 7,402,506    | B2   | 7/2008  | Levy et al.     | 2008/0203387 | A1 | 8/2008  | Kang et al.           |

| 7,411,209    | B2 * | 8/2008  | Endo et al.     | 2008/0224133 | A1 | 9/2008  | Park et al.           |

| 7,453,065    | B2   | 11/2008 | Saito et al.    | 2008/0254569 | A1 | 10/2008 | Hoffman et al.        |

| 7,453,087    | B2 * | 11/2008 | Iwasaki         | 2008/0258139 | A1 | 10/2008 | Ito et al.            |

| 7,462,862    | B2   | 12/2008 | Hoffman et al.  | 2008/0258140 | A1 | 10/2008 | Lee et al.            |

| 7,468,304    | B2 * | 12/2008 | Kaji et al.     | 2008/0258141 | A1 | 10/2008 | Park et al.           |

| 7,501,293    | B2   | 3/2009  | Ito et al.      | 2008/0258143 | A1 | 10/2008 | Kim et al.            |

| 7,674,650    | B2   | 3/2010  | Akimoto et al.  | 2008/0296568 | A1 | 12/2008 | Ryu et al.            |

| 7,687,808    | B2   | 3/2010  | Umezaki         | 2008/0308796 | A1 | 12/2008 | Akimoto et al.        |

| 7,964,876    | B2   | 6/2011  | Umezaki         | 2008/0308797 | A1 | 12/2008 | Akimoto et al.        |

| 7,978,274    | B2   | 7/2011  | Umezaki et al.  | 2008/0308804 | A1 | 12/2008 | Akimoto et al.        |

| 8,054,279    | B2   | 11/2011 | Umezaki et al.  | 2008/0308805 | A1 | 12/2008 | Akimoto et al.        |

| 2001/0046027 | A1   | 11/2001 | Tai et al.      | 2009/0008639 | A1 | 1/2009  | Akimoto et al.        |

| 2002/0056838 | A1   | 5/2002  | Ogawa           | 2009/0065771 | A1 | 3/2009  | Iwasaki et al.        |

| 2002/0109796 | A1   | 8/2002  | Lin et al.      | 2009/0073325 | A1 | 3/2009  | Kuwabara et al.       |

| 2002/0132454 | A1   | 9/2002  | Ohtsu et al.    | 2009/0114910 | A1 | 5/2009  | Chang                 |

| 2003/0189401 | A1   | 10/2003 | Kido et al.     | 2009/0114911 | A1 | 5/2009  | Maekawa et al.        |

| 2004/0038446 | A1   | 2/2004  | Takeda et al.   | 2009/0134399 | A1 | 5/2009  | Sakakura et al.       |

| 2004/0127038 | A1   | 7/2004  | Carcia et al.   | 2009/0152541 | A1 | 6/2009  | Maekawa et al.        |

| 2004/0132293 | A1   | 7/2004  | Takayama et al. | 2009/0153762 | A1 | 6/2009  | Kuwabara et al.       |

| 2004/0263752 | A1   | 12/2004 | Kim             | 2009/0186437 | A1 | 7/2009  | Akimoto               |

| 2005/0199959 | A1   | 9/2005  | Chiang et al.   | 2009/0186445 | A1 | 7/2009  | Akimoto               |

| 2005/0259206 | A1   | 11/2005 | Son             | 2009/0189155 | A1 | 7/2009  | Akimoto               |

| 2005/0275038 | A1   | 12/2005 | Shih et al.     | 2009/0189156 | A1 | 7/2009  | Akimoto               |

| 2006/0035452 | A1   | 2/2006  | Carcia et al.   | 2009/0239335 | A1 | 9/2009  | Akimoto et al.        |

| 2006/0086933 | A1   | 4/2006  | Iechi et al.    | 2011/0227066 | A1 | 9/2011  | Umezaki               |

| 2006/0091793 | A1   | 5/2006  | Baudé et al.    | 2011/0260169 | A1 | 10/2011 | Umezaki et al.        |

| 2006/0108529 | A1   | 5/2006  | Saito et al.    | 2012/0049184 | A1 | 3/2012  | Umezaki et al.        |

| 2006/0108636 | A1   | 5/2006  | Sano et al.     | 2012/0056860 | A1 | 3/2012  | Umezaki et al.        |

| 2006/0110867 | A1   | 5/2006  | Yabuta et al.   |              |    |         |                       |

| 2006/0113536 | A1   | 6/2006  | Kumomi et al.   |              |    |         |                       |

| 2006/0113539 | A1   | 6/2006  | Sano et al.     |              |    |         |                       |

| 2006/0113549 | A1   | 6/2006  | Den et al.      |              |    |         |                       |

| 2006/0113565 | A1   | 6/2006  | Abe et al.      |              |    |         |                       |

| 2006/0163743 | A1   | 7/2006  | Kuwabara et al. |              |    |         |                       |

| 2006/0169973 | A1   | 8/2006  | Isa et al.      |              |    |         |                       |

| 2006/0170067 | A1   | 8/2006  | Maekawa et al.  |              |    |         |                       |

| 2006/0170111 | A1   | 8/2006  | Isa et al.      |              |    |         |                       |

| 2006/0197092 | A1   | 9/2006  | Hoffman et al.  |              |    |         |                       |

| 2006/0208977 | A1   | 9/2006  | Kimura          |              |    |         |                       |

| 2006/0228974 | A1   | 10/2006 | Theless et al.  |              |    |         |                       |

| 2006/0231882 | A1   | 10/2006 | Kim et al.      |              |    |         |                       |

| 2006/0238135 | A1   | 10/2006 | Kimura          |              |    |         |                       |

| 2006/0243979 | A1   | 11/2006 | Park et al.     |              |    |         |                       |

| 2006/0244107 | A1   | 11/2006 | Sugihara et al. |              |    |         |                       |

| 2006/0284171 | A1   | 12/2006 | Levy et al.     |              |    |         |                       |

| 2006/0284172 | A1   | 12/2006 | Ishii           |              |    |         |                       |

| 2006/0286737 | A1   | 12/2006 | Levy et al.     |              |    |         |                       |

| 2006/0292777 | A1   | 12/2006 | Dunbar          |              |    |         |                       |

| 2007/0024187 | A1   | 2/2007  | Shin et al.     |              |    |         |                       |

| 2007/0046191 | A1   | 3/2007  | Saito           |              |    |         |                       |

| 2007/0052025 | A1   | 3/2007  | Yabuta          |              |    |         |                       |

| 2007/0054507 | A1   | 3/2007  | Kaji et al.     |              |    |         |                       |

| 2007/0072439 | A1   | 3/2007  | Akimoto et al.  |              |    |         |                       |

| 2007/0090365 | A1   | 4/2007  | Hayashi et al.  |              |    |         |                       |

| 2007/0108446 | A1   | 5/2007  | Akimoto         |              |    |         |                       |

| 2007/0158652 | A1   | 7/2007  | Lee et al.      |              |    |         |                       |

| 2007/0172591 | A1   | 7/2007  | Seo et al.      |              |    |         |                       |

| 2007/0187678 | A1   | 8/2007  | Hirao et al.    |              |    |         |                       |

| 2007/0187760 | A1   | 8/2007  | Furuta et al.   |              |    |         |                       |

| 2007/0194379 | A1   | 8/2007  | Hosono et al.   |              |    |         |                       |

| 2007/0252928 | A1   | 11/2007 | Ito et al.      |              |    |         |                       |

| 2007/0272922 | A1   | 11/2007 | Kim et al.      |              |    |         |                       |

| 2007/0284627 | A1   | 12/2007 | Kimura          |              |    |         |                       |

| 2007/0287296 | A1   | 12/2007 | Chang           |              |    |         |                       |

## FOREIGN PATENT DOCUMENTS

|    |                |         |

|----|----------------|---------|

| EP | 1 396 881      | 3/2004  |

| JP | 60-170972      | 9/1985  |

| JP | 02-226729      | 9/1990  |

| JP | 03-231472 A    | 10/1991 |

| JP | 05-251705      | 9/1993  |

| JP | 05-251705 A    | 9/1993  |

| JP | 06-088972      | 3/1994  |

| JP | 08-264794 A    | 10/1996 |

| JP | 11-505377      | 5/1999  |

| JP | 2000-044236    | 2/2000  |

| JP | 2000-150900 A  | 5/2000  |

| JP | 2002-076356    | 3/2002  |

| JP | 2002-289859    | 10/2002 |

| JP | 2003-086000 A  | 3/2003  |

| JP | 2003-086808 A  | 3/2003  |

| JP | 2004-103957 A  | 4/2004  |

| JP | 2004-273732    | 9/2004  |

| JP | 2004-273732 A  | 9/2004  |

| JP | 2006-190923    | 7/2006  |

| JP | 2007-096055    | 4/2007  |

| JP | 2007-123861    | 5/2007  |

| JP | 2007-250983 A  | 9/2007  |

| JP | 2008-130689 A  | 6/2008  |

| WO | WO-2004/114391 | 12/2004 |

| WO | WO-2007/119386 | 10/2007 |

## OTHER PUBLICATIONS

Ikeda.T et al., "Full-Functional System Liquid Crystal Display Using CG-Silicon Technology", SID Digest '04 : SID International Symposium Digest of Technical Papers, 2004, vol. 35, pp. 860-863.

Takahashi.M et al., "Theoretical Analysis of IGZO Transparent Amorphous Oxide Semiconductor", IDW '08 : Proceedings of the

15th International Display Workshops, Dec. 3, 2008, pp. 1637-1640.

Prins.M et al., "A Ferroelectric Transparent Thin-Film Transistor", Appl. Phys. Lett. (Applied Physics Letters), Jun. 17, 1996, vol. 68, No. 25, pp. 3650-3652.

Nakamura.M et al., "The phase relations in the  $In_2O_3$ - $Ga_2ZnO_4$ - $ZnO$  system at 1350°C", Journal of Solid State Chemistry, Aug. 1, 1991, vol. 93, No. 2, pp. 298-315.

Kimizuka.N et al., "Syntheses and Single-Crystal Data of Homologous Compounds,  $In_2O_3(ZnO)_m$  (m = 3, 4, and 5),  $InGaO_3(ZnO)_3$ , and  $Ga_2O_3(ZnO)_m$  (m = 7, 8, 9, and 16) in the  $In_2O_3$ - $ZnGa<sub>2</sub>O<sub>4</sub>$ - $ZnO$  System.", Journal of Solid State Chemistry, Apr. 1, 1995, vol. 116, No. 1, pp. 170-178.

Osada.T et al., "15.2: Development of Driver-Integrated Panel using Amorphous In-Ga-Oxide TFT", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 184-187.

Lee.J et al., "World's Largest (15-Inch) XGA AMLCD Panel Using IGZO Oxide TFT", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 625-628.

Nowatari.H et al., "60.2: Intermediate Connector With Suppressed Voltage Loss for White Tandem OLEDs", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 899-902.

Kanno.H et al., "White Stacked Electrophosphorecent Organic Light-Emitting Device Employing  $MoO_3$  as a Change-Generation Layer", Adv. Mater. (Advanced Materials), 2006, vol. 18, No. 3, pp. 339-342.

Tsuda.K et al., "Ultra Low Power Consumption Technologies for Mobile TFT-LCDs", IDW '02 : Proceedings of the 9th International Display Workshops, Dec. 4, 2002, pp. 295-298.

Jeong.J et al., "3.1: Distinguished Paper: 12.1-Inch WXGA AMOLED Display Driven by Indium-Gallium-Zinc Oxide TFTs Array", SID Digest '08 : SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, No. 1, pp. 1-4.

Kurokawa.Y et al., "UHF RFCPUS on Flexible and Glass Substrates for Secure RFID Systems", Journal of Solid-State Circuits, 2008, vol. 43, No. 1, pp. 292-299.

Ohara.H et al., "Amorphous In-Ga-Zn-Oxide TFTs with Suppressed Variation for 4.0 inch QVGA AMOLED Display", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 227-230, The Japan Society of Applied Physics.

Coates.D et al., "Optical Studies of the Amorphous Liquid-Cholesteric Liquid Crystal Transition: The "Blue Phase", Physics Letters, Sep. 10, 1973, vol. 45A, No. 2, pp. 115-116.

Cho.D et al., "21.2: AL and SN-Doped Zinc Indium Oxide Thin Film Transistors for AMOLED Back-Plane", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 280-283.

Lee.M et al., "15.4: Excellent Performance of Indium-Oxide-Based Thin-Film Transistors by DC Sputtering", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 191-193.

Jin.D et al., "65.2: Distinguished Paper: World-Largest (6.5") Flexible Full Color Top Emission AMOLED Display on Plastic Film and its Bending Properties", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 983-985.

Sakata.J et al., "Development of 4.0-In. AMOLED Display With Driver Circuit Using Amorphous In-Ga-Zn-Oxide TFTs", IDW '09 : Proceedings of the 16th International Display Workshops, 2009, pp. 689-692.

Park.J et al., "Amorphous Indium-Gallium-Zinc Oxide TFTs and Their Application for Large Size AMOLED", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 275-277.

Park.S et al., "Challenge to Future Displays: Transparent AM-OLED Driven by Peal'd Grown  $ZnO$  TFT", IMID '07 Digest, 2007, p. 1249-1252.

Godó.H et al., "Temperature Dependence of Characteristics and Electronic Structure for Amorphous In-Ga-Zn-Oxide TFT", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 41-44.

Osada.T et al., "Development of Driver-Integrated Panel Using Amorphous In-Ga-Zn-Oxide TFT", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 33-36.

Hirao.T et al., "Novel Top-Gate Zinc Oxide Thin-Film Transistors (ZNO TFTs) for AMLCDS", Journal of the SID, 2007, vol. 15, No. 1, pp. 17-22.

Hosono.H, "68.3: Invited Paper: Transparent Amorphous Oxide Semiconductors for High Performance TFT", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1830-1833.

Godó.H et al., "P-9: Numerical Analysis on Temperature Dependence of Characteristics of Amorphous In-Ga-Zn-Oxide TFT", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 1110-1112.

Ohara.H et al., "21.3: 4.0 In. QVGA Amoled Display Using In-Ga-Zn-Oxide TFTs with a Novel Passivation Layer", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 284-287.

Miyasaka.M, "58.2 Invited Paper: Softla Flexible Microelectronics on Their Way to Business", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1673-1676.

Chern.H et al., "An Analytical Model for the Above-Threshold Characteristics of Polysilicon Thin-Film Transistors", IEEE Transactions of Electron Devices, Jul. 1, 1995, vol. 42, No. 7, pp. 1240-1246.

Kikuchi.H et al., "39.1: Invited Paper: Optically Isotropic NANO-Structured Liquid Crystal Composites for Display Applications", SID Digest '09 : SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 578-581.

Asaoka.Y et al., "29.1: Polarizer-Free Reflective LCD Combined with Ultra Low-Power Driving Technology", SID Digest '09 : SID International Symposium Digest of Technical Papers, 2009, pp. 395-398.

Lee.H et al., "Current Status of, Challenges to, and Perspective View of AM-OLED", IDW '06 : Proceedings of the 13th International Display Workshops, Dec. 7, 2006, pp. 663-666.

Kikuchi.H et al., "62.2: Invited Paper: Fast Electro-Optical Switching in Polymer-Stabilized Liquid Crystalline Blue Phases for Display Application", SID Digest '07 : SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1737-1740.

Kikuchi.H et al., "Polymer-Stabilized Liquid Crystal Blue Phases", Nature Materials, Sep. 1, 2002, vol. 1, pp. 64-68.

Kimizuka.N et al., "Spinel,  $YbFe_2O_4$ , and  $Yb_2Fe_3O_7$  Types of Structures for Compounds in the  $In_2O_3$  and  $Sc_2O_3A_2O_3$ -Bo Systems [A: Fe, Ga, or Al; B: Mg, Mn, Fe, Ni, Cu or Zn] at Temperatures Over 1000°C", Journal of Solid State Chemistry, 1985, vol. 60, pp. 382-384.

Kitzerow.H et al., "Observation of Blue Phases in Chiral Networks", Liquid Crystals, 1993, vol. 14, No. 3, pp. 911-916.

Costello.M et al., "Electron Microscopy of a Cholesteric Liquid Crystal and its Blue Phase", Phys. Rev. A (Physical Review A), May 1, 1984, vol. 29, No. 5, pp. 2957-2959.

Meiboom.S et al., "Theory of the Blue Phase of Cholesteric Liquid Crystals", Phys. Rev. Lett. (Physical Review Letters), May 4, 1981, vol. 46, No. 18, pp. 1216-1219.

Park.J et al., "Amorphous Indium-Gallium-Zinc Oxide TFTs and Their Application for Large Size AMOLED", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 275-278.

Fortunato et al., "Wide-Bandgap High-Mobility  $ZnO$  Thin-Film Transistors Produced at Room Temperature", Appl. Phys. Lett. (Applied Physics Letters), Sep. 27, 2004, vol. 85, No. 13, pp. 2541-2543.

Nomura et al., "Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors", Nature, Nov. 25, 2004, vol. 432, pp. 488-492.

Nomura et al., "Thin-Film Transistor Fabricated in Single-Crystalline Transparent Oxide Semiconductor", SCIENCE, May 23, 2003, vol. 300, pp. 1269-1272.

Masuda et al., "Transparent thin film transistors using  $ZnO$  as an active channel layer and their electrical properties", J. Appl. Phys. (Journal of Applied Physics), Feb. 1, 2003, vol. 93, No. 3, pp. 1624-1630.

Asakuma et al., "Crystallization and Reduction of Sol-Gel-Derived Zinc Oxide Films by Irradiation with Ultraviolet Lamp," Journal of Sol-Gel Science and Technology, 2003, vol. 26, pp. 181-184.

Nomura et al., "Carrier transport in transparent oxide semiconductor with intrinsic structural randomness probed using single-crystalline  $\text{InGaO}_3(\text{ZnO})_5$  films," Appl. Phys. Lett. (Applied Physics Letters), Sep. 13, 2004, vol. 85, No. 11, pp. 1993-1995.

Kamiya et al., "1a-F-5 Room temperature fabrication and carrier transport of amorphous semiconductor exhibiting large electron Hall mobilities  $> 10 \text{ cm}^2 \text{ Vs}$ ," (The 65<sup>th</sup> Autumn Meeting, 2004) The Japan Society of Applied Physics, Sep. 2004, No. 2, p. 791.

Nomura et al., "31a-ZA-6 Carrier Transport in Transparent Amorphous Oxide Semiconductor  $\text{InGaZnO}_4$ ," (The 51st Spring Meeting, 2004); The Japan Society of Applied Physics and Related Societies, Mar. 2004, No. 2, p. 669.

Li et al., "Modulated Structures of Homologous Compounds  $\text{InMO}_3(\text{ZnO})_m$  (M=In, Ga; m=Integer) Described by Four-Dimensional Superspace Group," Journal of Solid State Chemistry, 1998, vol. 139, pp. 347-355.

\* cited by examiner

FIG. 1A

FIG. 1B

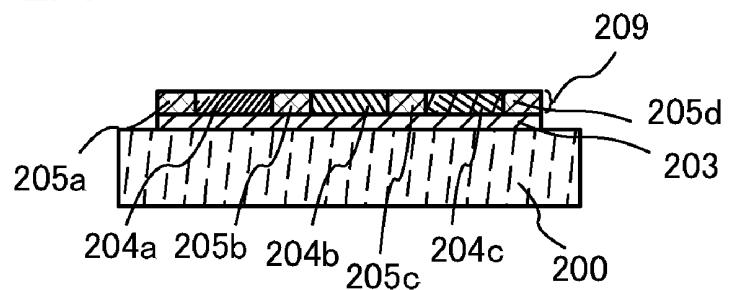

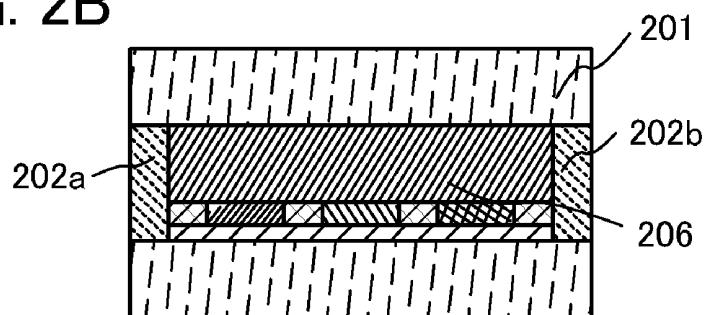

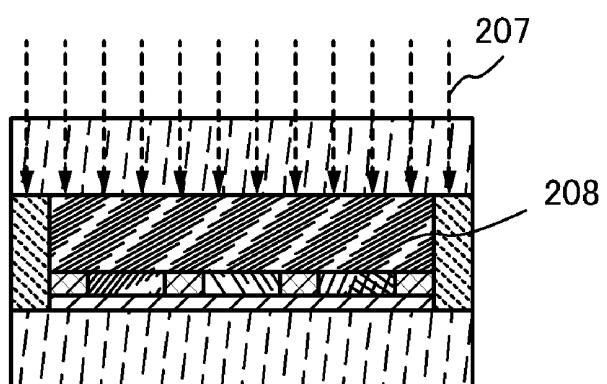

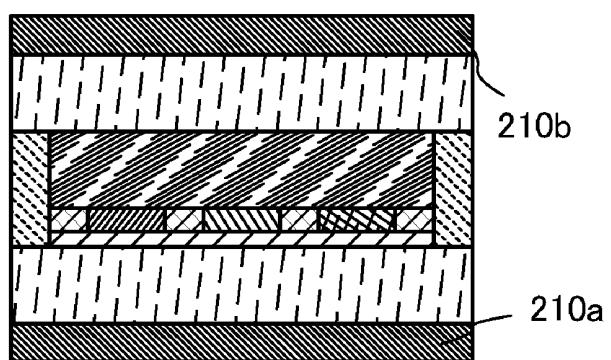

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 8A

FIG. 8B

FIG. 8C

FIG. 8D

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 11A

FIG. 11B

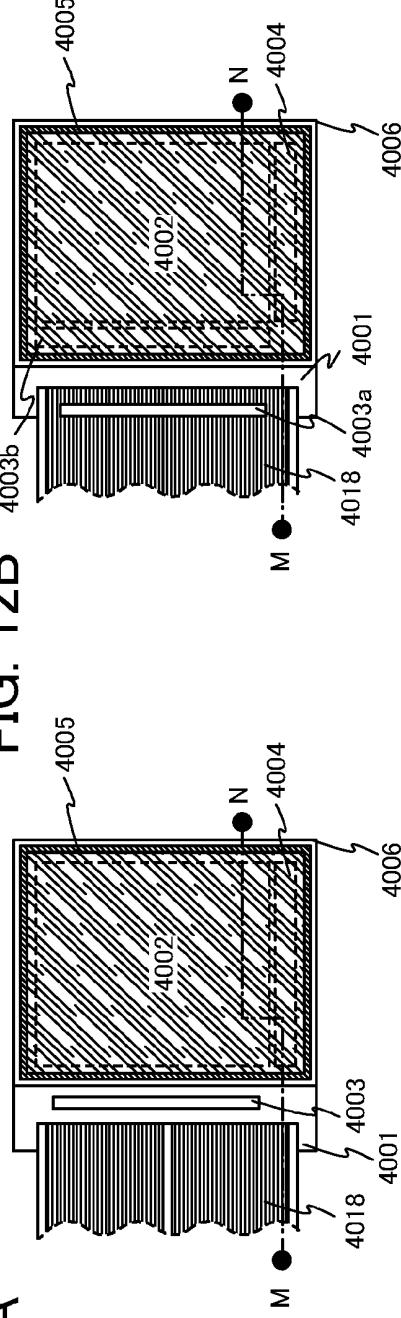

FIG. 12A

FIG. 12B

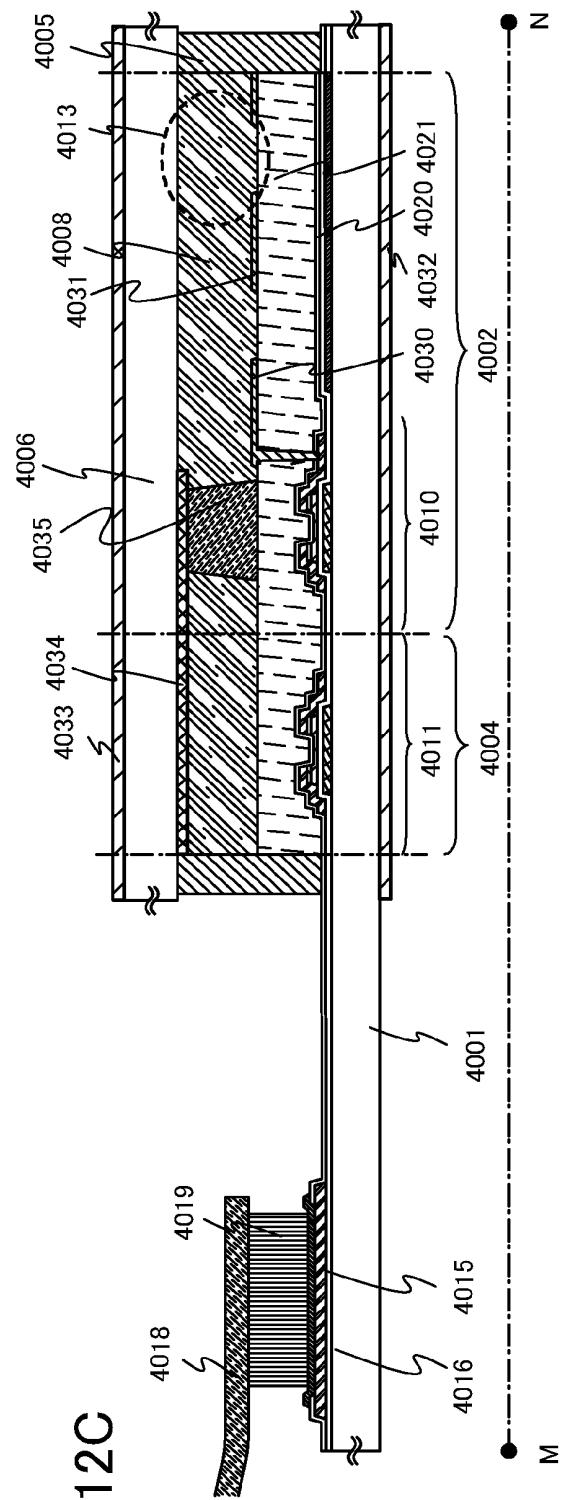

FIG. 12C

FIG. 13A

FIG. 13B

FIG. 14A

FIG. 14B

FIG. 15A

FIG. 15B

FIG. 16

FIG. 17A

FIG. 17B

## LIQUID CRYSTAL DISPLAY DEVICE

## BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates to a liquid crystal display device using an oxide semiconductor and a method for manufacturing the same.

## 2. Description of the Related Art

As typically seen in a liquid crystal display device, a thin film transistor formed over a flat plate such as a glass substrate is manufactured using amorphous silicon or polycrystalline silicon. A thin film transistor manufactured using amorphous silicon has low field effect mobility, but can be formed over a larger glass substrate. In contrast, a thin film transistor manufactured using polycrystalline silicon has high field effect mobility, but needs a crystallization step such as laser annealing and is not always suitable for a larger glass substrate.

In view of the foregoing, attention has been drawn to a technique for manufacturing a thin film transistor using an oxide semiconductor and applying the thin film transistor to an electronic device or an optical device. For example, Patent Document 1 and Patent Document 2 disclose a technique by which a thin film transistor is manufactured using zinc oxide or an In—Ga—Zn—O-based oxide semiconductor for an oxide semiconductor film and such a transistor is used as a switching element or the like of an image display device.

The thin film transistor in which a channel formation region is formed using an oxide semiconductor has higher field effect mobility than a thin film transistor using amorphous silicon. The oxide semiconductor film can be formed by a sputtering method or the like at a temperature 300°C. or lower. Its manufacturing process is easier than that of a thin film transistor using polycrystalline silicon.

The oxide semiconductor is a transparent semiconductor which transmits light in a visible wavelength range; thus, it is said that use of the oxide semiconductor for a pixel of a display device makes it possible to provide a high aperture ratio.

Such an oxide semiconductor is expected to be used for forming a thin film transistor on a glass substrate, a plastic substrate, or the like, and to be applied to a display device.

## REFERENCE

[Patent Document 1] Japanese Published Patent Application No. 2007-123861

[Patent Document 2] Japanese Published Patent Application No. 2007-096055

## SUMMARY OF THE INVENTION

Thus, it is an object to provide a liquid crystal display device which is suitable for a thin film transistor using an oxide semiconductor.

In a liquid crystal display device including thin film transistors each including an oxide semiconductor layer, a film having a function of attenuating the intensity of transmitting visible light is used for an interlayer film which covers at least the oxide semiconductor layer. The film having a function of attenuating the intensity of transmitting visible light is a film having a transmittance of visible light lower than the oxide semiconductor layer. As the film having a function of attenuating the intensity of transmitting visible light, a coloring layer can be used, and a light-transmitting chromatic-color resin layer is preferable. Alternatively, in the interlayer film including a light-transmitting chromatic-color resin layer and

a light-blocking layer, the light-blocking layer may be used as a film having a function of attenuating the intensity of transmitting visible light.

When a coloring layer which is a light-transmitting chromatic-color resin layer is used as the interlayer film provided over a thin film transistor, the intensity of incident light on a semiconductor layer of the thin film transistor can be attenuated without reduction in an aperture ratio of a pixel. Accordingly, electric characteristics of the thin film transistor can be prevented from being varied due to photosensitivity of the oxide semiconductor and can be stabilized. Further, the light-transmitting chromatic-color resin layer can function as a color filter layer. In the case of providing a color filter layer on the counter substrate side, precise positional alignment of a pixel region with an element substrate over which a thin film transistor is formed is difficult and accordingly there is a possibility that image quality is degraded. Here, since the interlayer film is formed as the color filter layer directly on the element substrate side, the formation region can be controlled more precisely and this structure is adjustable to a pixel with a fine pattern. In addition, one insulating layer can serve as both the interlayer film and the color filter layer, whereby the process can be simplified and a liquid crystal display device can be manufactured at low cost.

As a technique for realizing a wide viewing angle, a method is used in which a gray scale is controlled by generating an electric field approximately parallel (i.e., in a lateral direction) to a substrate to move liquid crystal molecules in a plane parallel to the substrate. In such a method, an electrode structure used in a fringe field switching (FFS) mode can be used.

In a horizontal electric field mode such as an FFS mode, a first electrode layer in a flat-plate shape (e.g., a pixel electrode layer with which voltage is controlled per pixel) and a second electrode layer having an opening pattern (e.g., a common electrode layer with which common voltage is applied to all pixels) are located below a liquid crystal layer such that the second electrode layer is provided above the first electrode layer so as to overlap the first electrode layer. By applying an electric field between the pixel electrode layer and the common electrode layer, liquid crystal is controlled. An electric field in a lateral direction is applied to the liquid crystal, so that liquid crystal molecules can be controlled using the electric field. That is, since the liquid crystal molecules can be controlled in a direction parallel to the substrates, a wide viewing angle can be obtained. Accordingly, a liquid crystal display device with improved viewing angle characteristics and higher image quality can be provided.

Chromatic colors are colors except achromatic colors such as black, gray, and white. The light-transmitting chromatic-color resin layer is formed using a material which transmits only light of a chromatic color which the material is colored in so as to function as a color filter. As a chromatic color, red, green, blue, or the like can be used. Alternatively, cyan, magenta, yellow, or the like may be used. "Transmitting only light of a chromatic color which a material is colored in" means that light transmitted through the light-transmitting chromatic-color resin layer has a peak at the wavelength of the chromatic color light.

The thickness of the light-transmitting chromatic-color resin layer is preferably controlled as appropriate in consideration of a relation between the concentration of the coloring material to be contained and light transmittance, in order to make the light-transmitting chromatic-color resin layer function as a color filter layer. In the case of forming the interlayer film by stacking a plurality of thin films, if at least one of the

thin films is a light-transmitting chromatic-color resin layer, the interlayer film can function as a color filter.

In the case where the thickness varies depending on the chromatic colors or in the case where there is surface unevenness due to a thin film transistor, an insulating layer which transmits light in a visible wavelength range (so-called colorless and transparent insulating layer) may be stacked for planarization of the surface of the interlayer film. Improvement in planarization of the interlayer film allows favorable coverage with a pixel electrode layer or a common electrode layer to be formed thereover and uniform gap (thickness) of a liquid crystal layer, whereby the visibility of the liquid crystal display device is increased and higher image quality can be achieved.

When a light-blocking layer (black matrix) is used in the interlayer film provided over the thin film transistor, the light-blocking layer can block incident light on the semiconductor layer of the thin film transistor. Thus, electric characteristics of the thin film transistor can be prevented from being varied due to photosensitivity of the oxide semiconductor and can be stabilized. Further, the light-blocking layer can prevent light leakage to an adjacent pixel, which enables higher contrast and higher definition display. Therefore, high definition and high reliability of the liquid crystal display device can be achieved.

Accordingly, an element layer, a pixel electrode layer, a common electrode layer, and an interlayer film (the light-transmitting chromatic-color resin layer) are formed over the same substrate and sealed with a counter substrate which is opposite to the substrate with the liquid crystal layer interposed therebetween. The pixel electrode layer and the common electrode layer are located so as to be stacked with an insulating film (or the interlayer film) interposed therebetween. One of the pixel electrode layer and the common electrode layer is formed in a lower part (a position far from the liquid crystal layer) and has a plate shape. On the other hand, the other electrode layer is formed in an upper part (a position close to the liquid crystal layer) and has various opening patterns such as a pattern with a bend portion or a comb-like shape. In this specification, the electrode layer formed in a lower layer far from the liquid crystal layer (close to the element substrate) is referred to as a first electrode layer, and the first electrode layer has a flat-plate shape. On the hand, the electrode layer formed in an upper layer closed to the liquid crystal layer (far from the element substrate) is referred to as a second electrode layer, and the second electrode layer has an opening pattern (slit). In order to generate an electric field between the pixel electrode layer and the common electrode layer, the electrode layers are located such that the first electrode layer in a flat-plate shape and the opening pattern (slit) of the second electrode layer overlap with each other.

In this specification, the opening pattern (slit) of the pixel electrode layer or the common electrode layer includes a pattern of a comb-like shape which has a partly-opened portion, in addition to a pattern which has an opening in a closed space.

In this specification, a substrate over which a thin film transistor, a pixel electrode layer, a common electrode layer, and an interlayer film are formed is referred to as an element substrate (a first substrate), and a substrate which is positioned opposite from the element substrate with a liquid crystal layer interposed therebetween is referred to as a counter substrate (a second substrate).

The light-blocking layer can be formed on either the counter substrate side or the element substrate side of the liquid crystal display device. Accordingly, improvement in

contrast and stabilization of the thin film transistor can be achieved. When the light-blocking layer is formed in a region corresponding to the thin film transistor (at least in a region which overlaps with a semiconductor layer of the thin film transistor), electric characteristics of the thin film transistor can be prevented from being varied due to incident light from the counter substrate. In the case where the light-blocking layer is formed on the counter substrate side, the light-blocking layer may be formed in a region corresponding to the thin film transistor (at least in a region which covers the semiconductor layer of the thin film transistor) with a liquid crystal layer interposed therebetween. In the case where the light-blocking layer is formed on the element substrate side, the light-blocking layer may be formed directly over the thin film transistor (at least in a region which covers the semiconductor layer of the thin film transistor) or formed over the thin film transistor with an insulating layer interposed therebetween.

In the case where the light-blocking layer is also provided on the counter substrate side, there is a case where light from the element substrate and light from the counter substrate toward the semiconductor layer of the thin film transistor can be blocked by a light-blocking wiring layer, electrode layer, or the like. Thus, the light-blocking layer need not always be formed to cover the thin film transistor.

An embodiment of the invention disclosed in this specification includes a thin film transistor in which an oxide semiconductor layer overlapping with a gate electrode layer is a channel formation region, a first electrode layer in a flat-plate shape, a second electrode layer having an opening pattern, an interlayer film provided between the thin film transistor and the second electrode layer, and a liquid crystal layer over the interlayer film, the first electrode layer, and the second electrode layer. One of the first electrode layer and the second electrode layer is a pixel electrode layer which is electrically connected to the thin film transistor, and the other electrode layer is a common electrode. The interlayer film is a light-transmitting chromatic-color resin layer having light transmittance lower than the oxide semiconductor layer. The light-transmitting chromatic-color resin layer is provided so as to overlap with the pixel electrode layer and cover the oxide semiconductor layer.

Another embodiment of the invention disclosed in this specification includes a thin film transistor in which an oxide semiconductor layer overlapping with a gate electrode layer is a channel formation region, a first electrode layer in a flat-plate shape, a second electrode layer having an opening pattern, an interlayer film provided between the thin film transistor and the second electrode layer, and a liquid crystal layer over the interlayer film, the first electrode layer, and the second electrode layer. One of the first electrode layer and the second electrode layer is a pixel electrode layer which is electrically connected to the thin film transistor, and the other electrode layer is a common electrode layer. The interlayer film includes a light-blocking layer and a light-transmitting chromatic-color resin layer having light transmittance lower than the oxide semiconductor layer. The light-blocking layer is provided to cover the oxide semiconductor layer. The light-transmitting chromatic-color resin layer is provided to overlap with the pixel electrode layer.

In this specification, in the case where a liquid crystal display device is a light-transmitting liquid crystal display device (or a semi-transmissive liquid crystal display device) which performs display by transmitting light from a light source, light is needed to be transmitted at least in the pixel region. Thus, all components provided in the pixel region through which light is transmitted: the first substrate; the second substrate; and thin films included in an element layer,

such as the pixel electrode layer, the common electrode layer, the insulating film, and the conductive film, have a property of transmitting light in a visible wavelength range.

Note that the ordinal numbers such as "first" and "second" in this specification are used for convenience and do not denote the order of steps and the stacking order of layers. In addition, the ordinal numbers in this specification do not denote particular names which specify the invention.

In this specification, a semiconductor device refers to all types of devices which can function by using semiconductor characteristics. An electro-optical device, a semiconductor circuit, and an electronic device are included in the category of all semiconductor devices.

In a liquid crystal display device which includes a thin film transistor formed by using an oxide semiconductor layer for a channel, an interlayer film which covers at least the oxide semiconductor layer is formed using a material which attenuates the intensity of transmitting visible light. Accordingly, operation characteristics of the thin film transistor can be stabilized without reduction in an aperture ratio.

Further, viewing angle characteristics are improved; thus, a liquid crystal display device with higher image quality can be provided.

#### BRIEF DESCRIPTION OF THE DRAWINGS

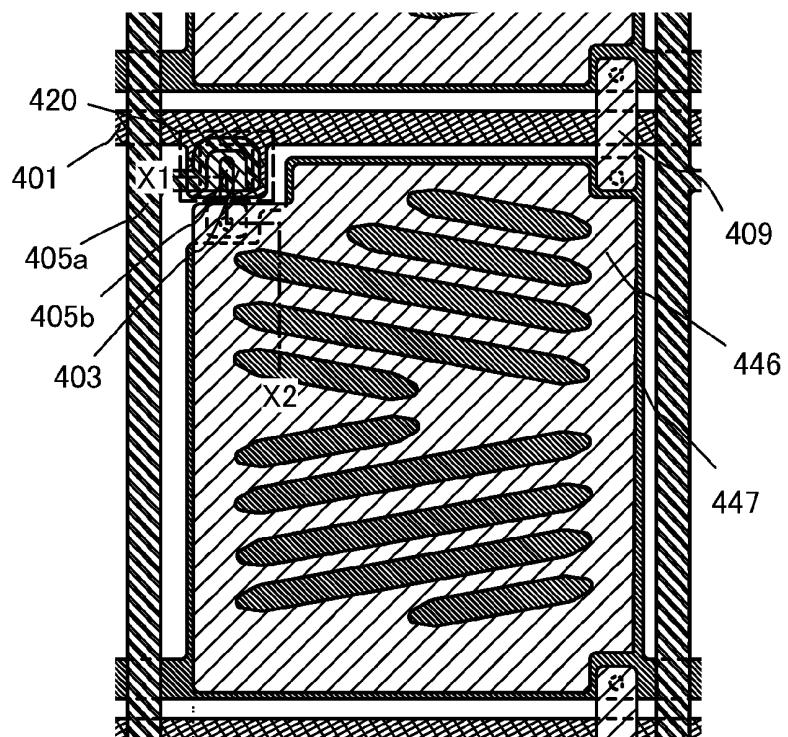

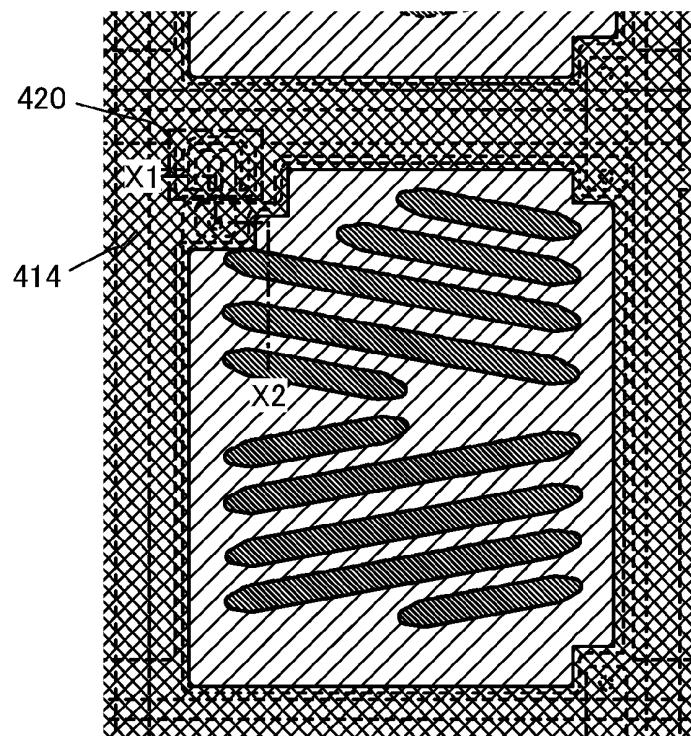

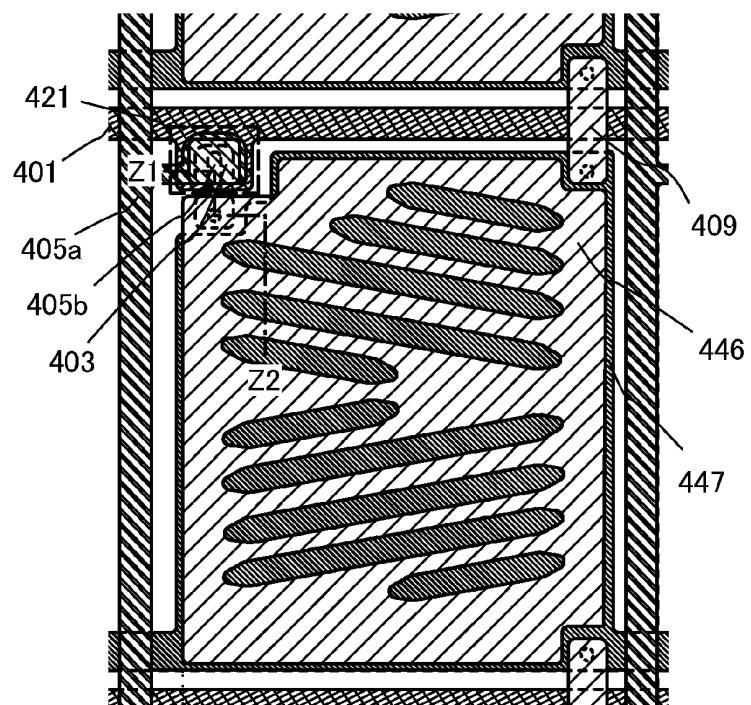

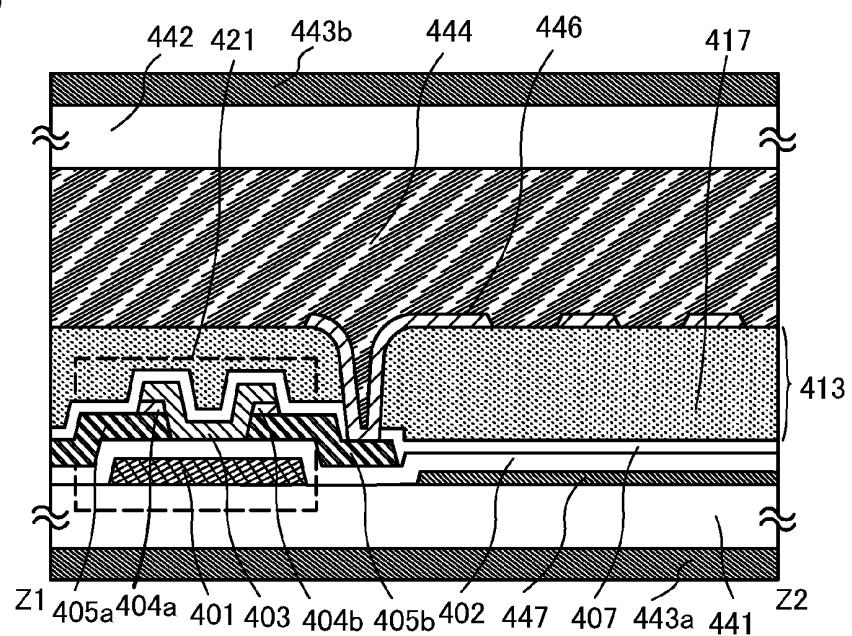

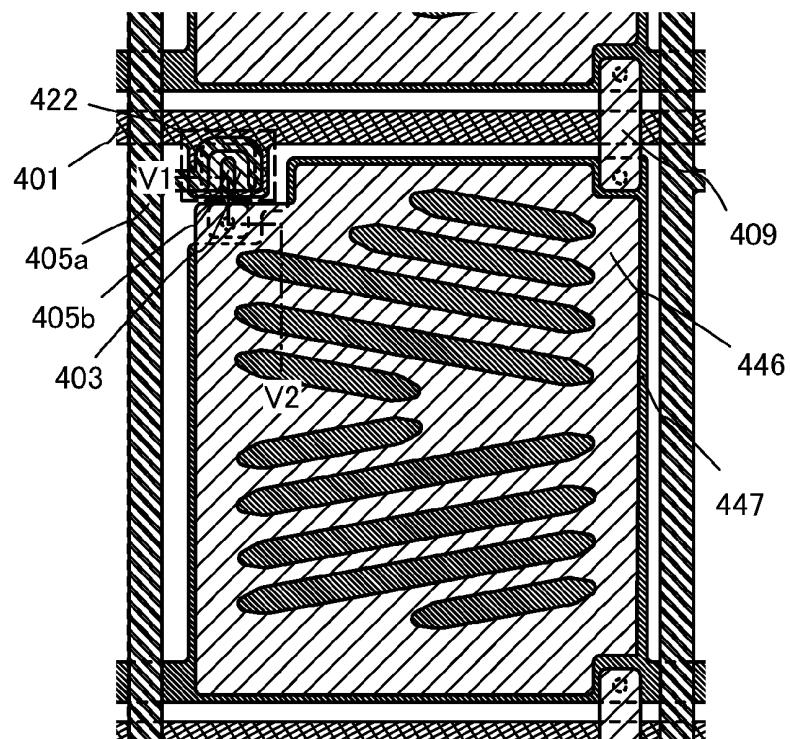

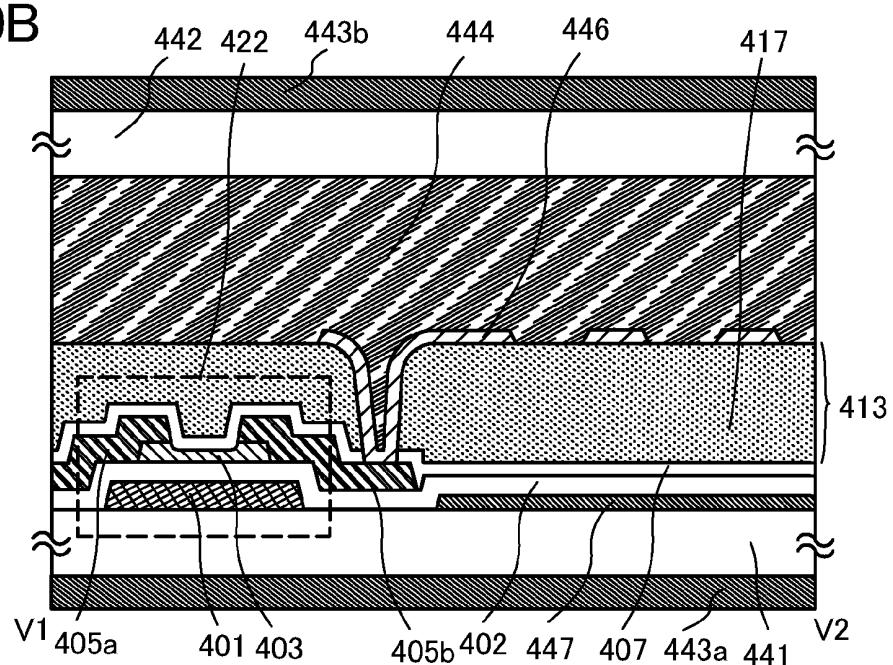

FIGS. 1A and 1B illustrate a liquid crystal display device.

FIGS. 2A to 2D illustrate a method for manufacturing a liquid crystal display device.

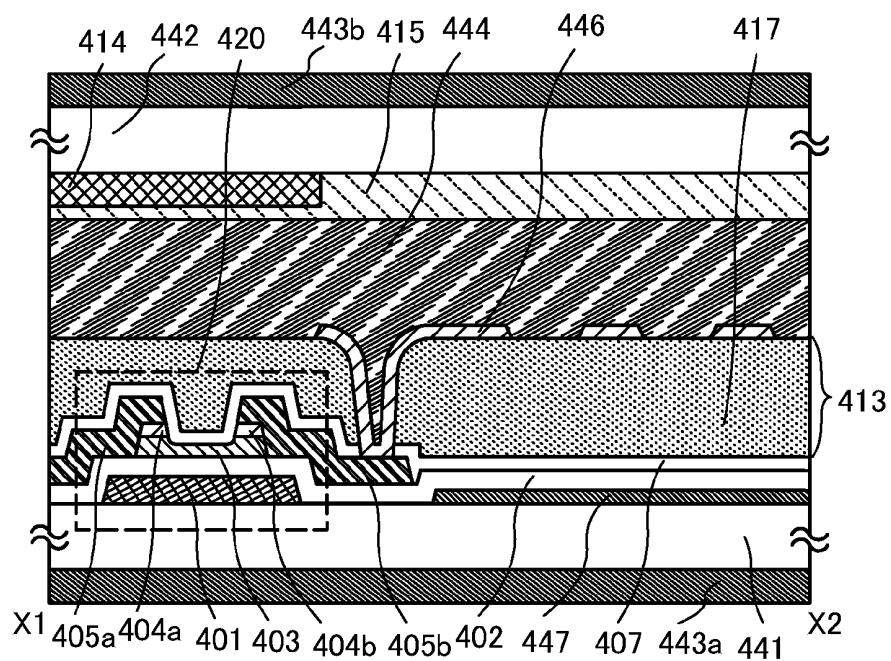

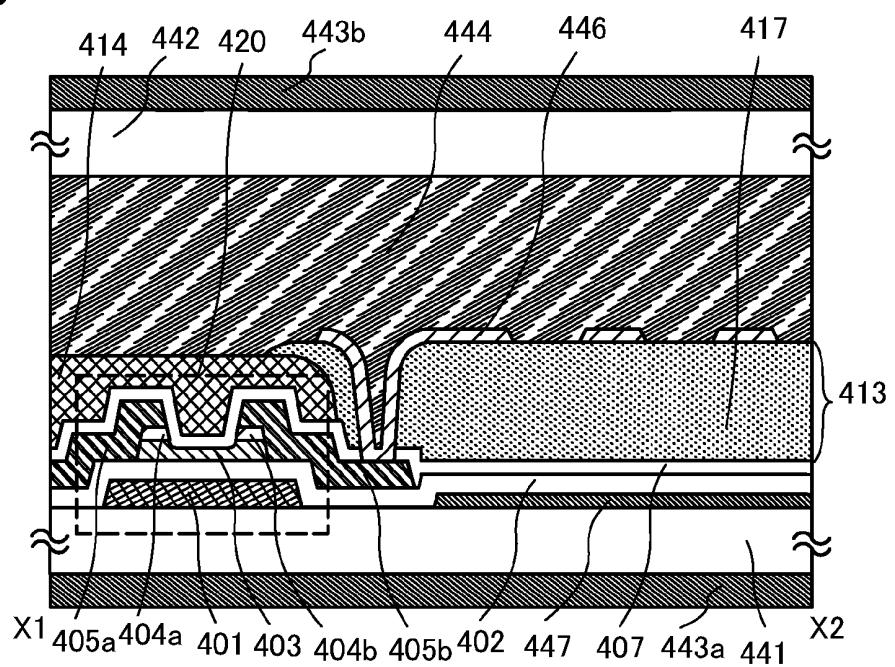

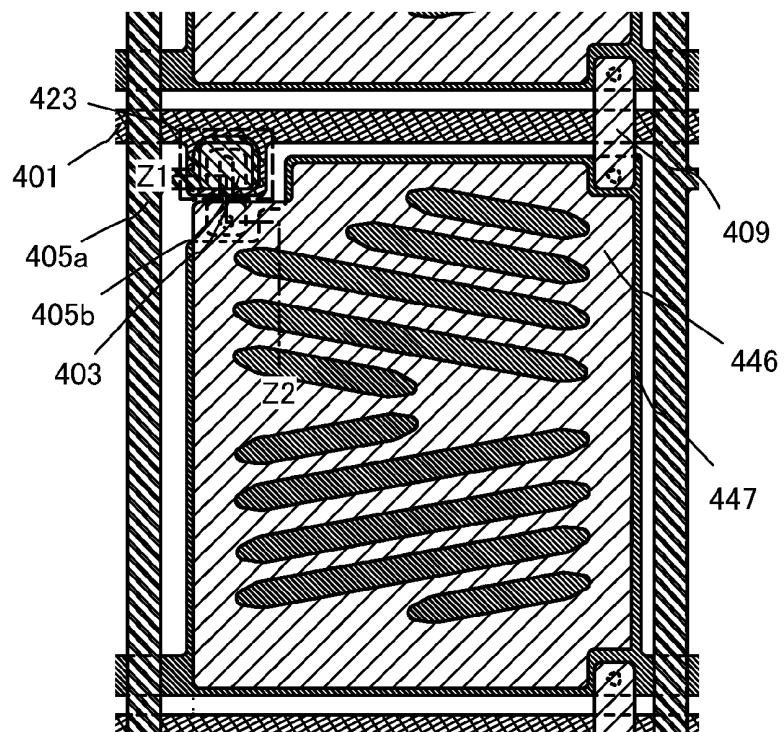

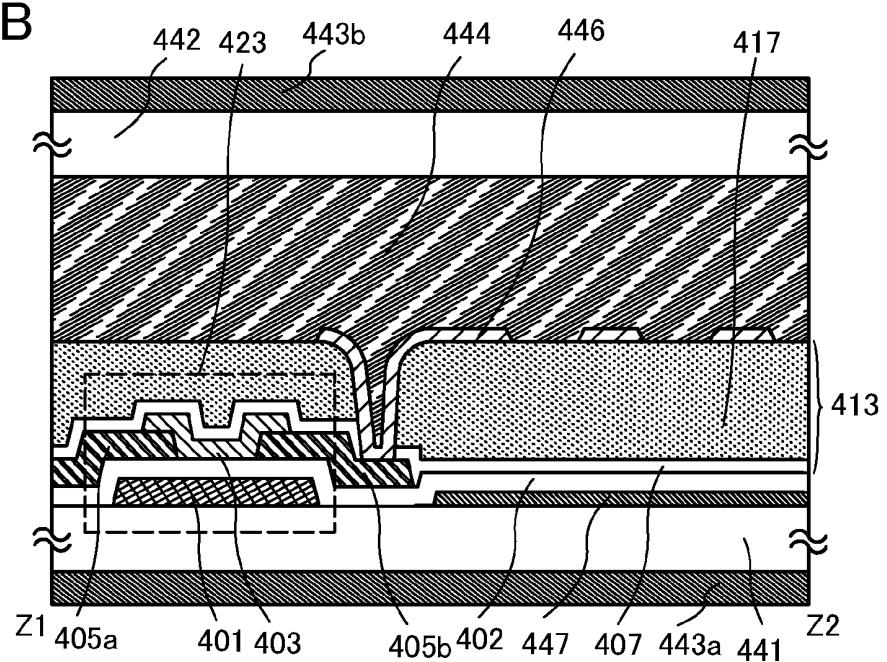

FIGS. 3A and 3B illustrate a liquid crystal display device.

FIGS. 4A and 4B illustrate a liquid crystal display device.

FIGS. 5A and 5B illustrate a liquid crystal display device.

FIGS. 6A and 6B illustrate a liquid crystal display device.

FIGS. 7A and 7B illustrate a liquid crystal display device.

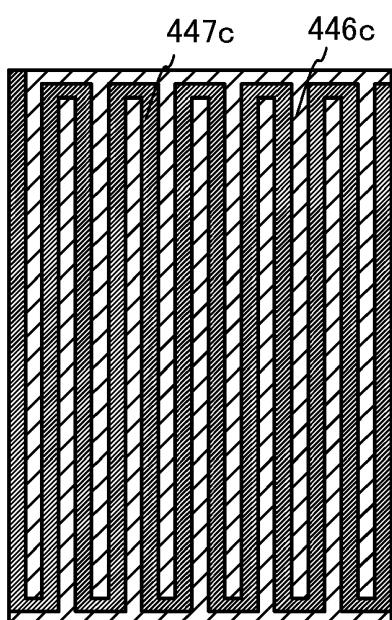

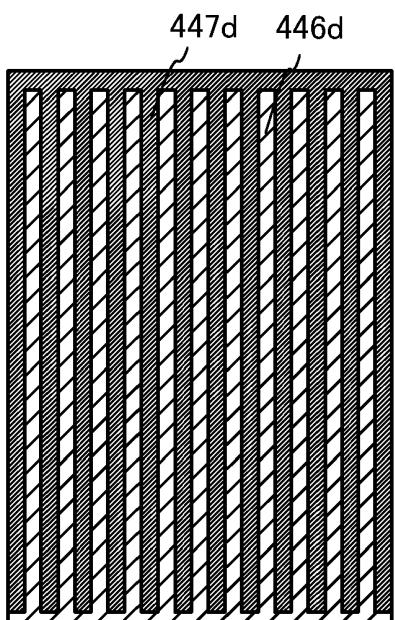

FIGS. 8A to 8D illustrate electrode layers of a liquid crystal display device.

FIGS. 9A and 9B illustrate a liquid crystal display device.

FIGS. 10A and 10B illustrate a liquid crystal display device.

FIGS. 11A and 11B illustrate a liquid crystal display device.

FIGS. 12A to 12C illustrate a liquid crystal display device.

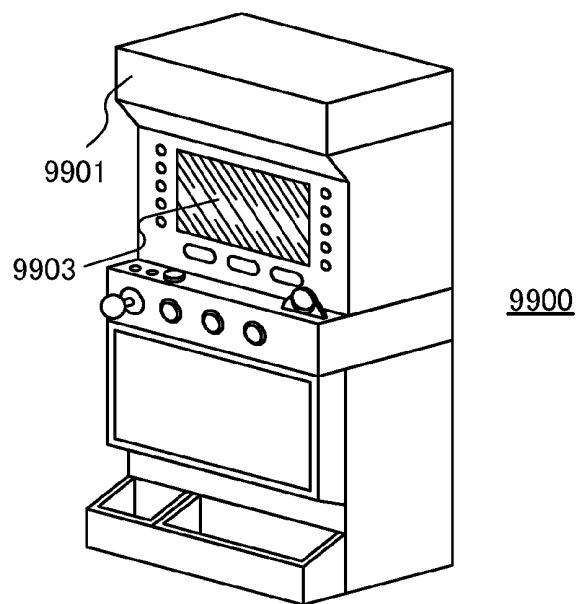

FIG. 13A is an external view illustrating an example of a television device and

FIG. 13B is an external view illustrating an example of a digital photo frame.

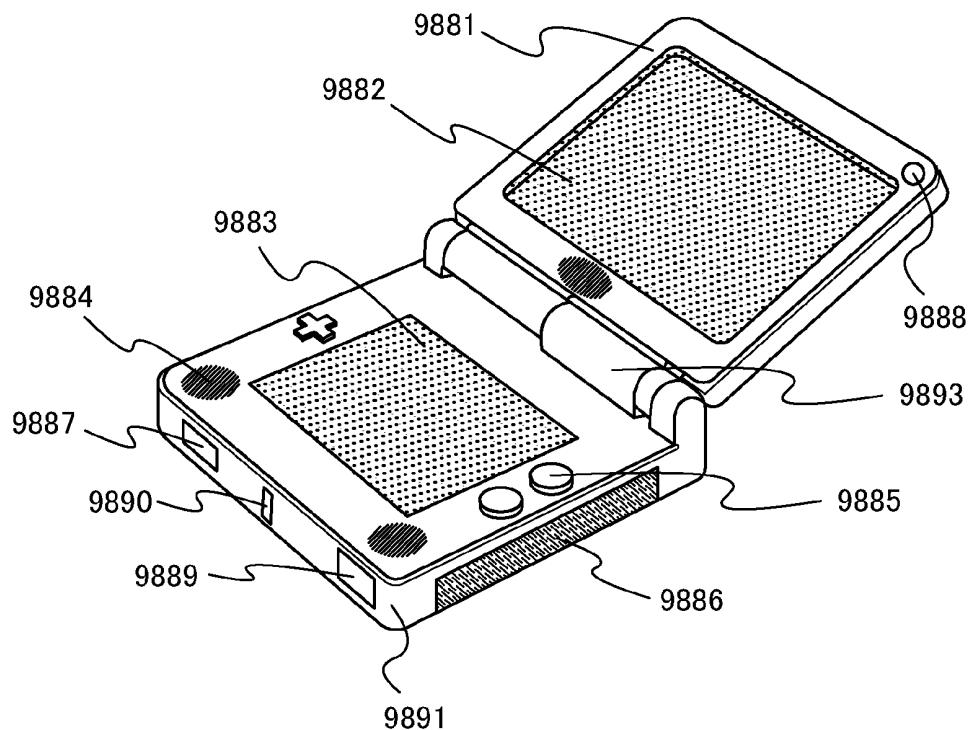

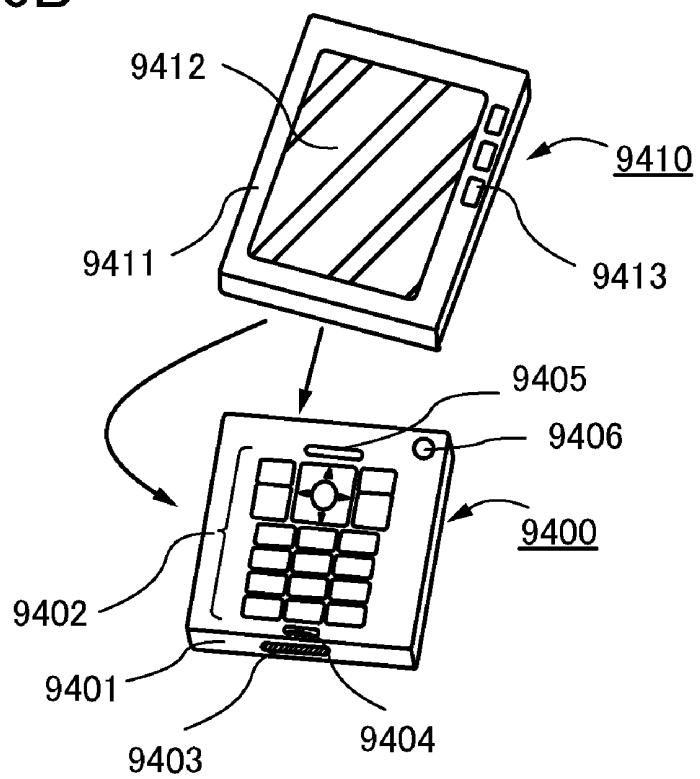

FIGS. 14A and 14B are external views illustrating examples of game machines.

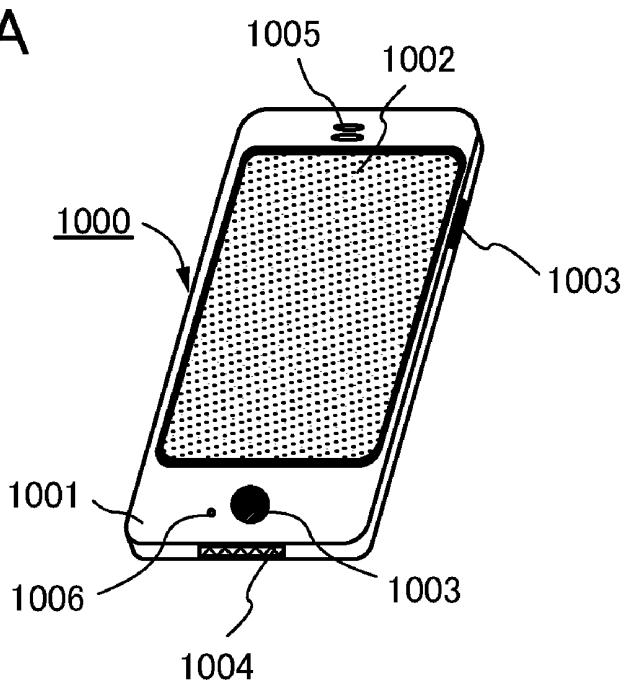

FIGS. 15A and 15B are external views illustrating examples of mobile phones.

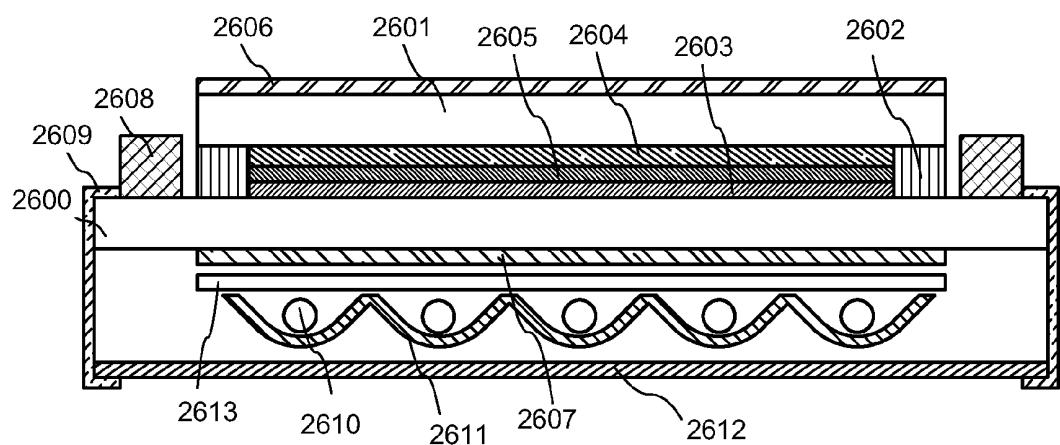

FIG. 16 illustrates a liquid crystal display module.

FIGS. 17A and 17B illustrate a liquid crystal display device.

#### DETAILED DESCRIPTION OF THE INVENTION

Embodiments will be described with reference to the accompanying drawings. However, the present invention is not limited to the following description, and it will be easily understood by those skilled in the art that various changes and modifications can be made in modes and details without departing from the spirit and scope of the present invention. Therefore, the present invention should not be construed as being limited to the description of the following embodiments. Note that a common reference numeral refers to the

same part or a part having a similar function throughout the drawings in the structures described below, and the description thereof is omitted.

#### Embodiment 1

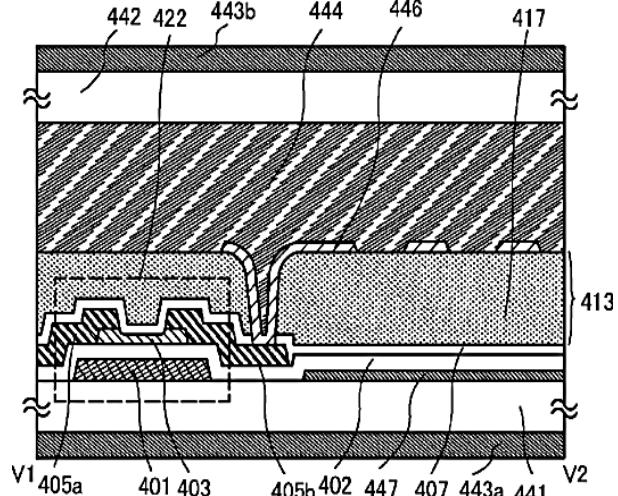

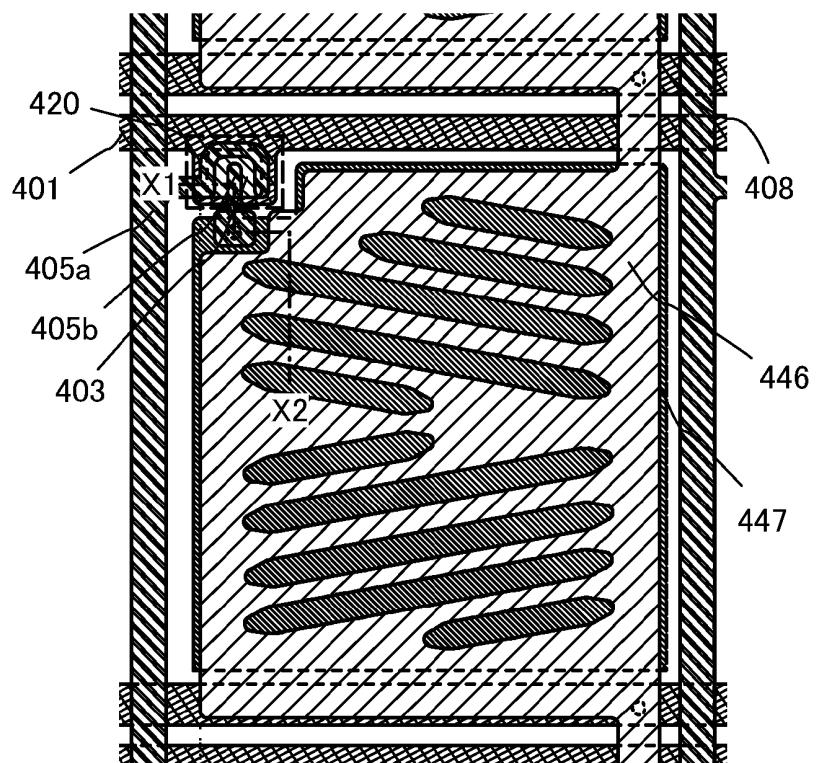

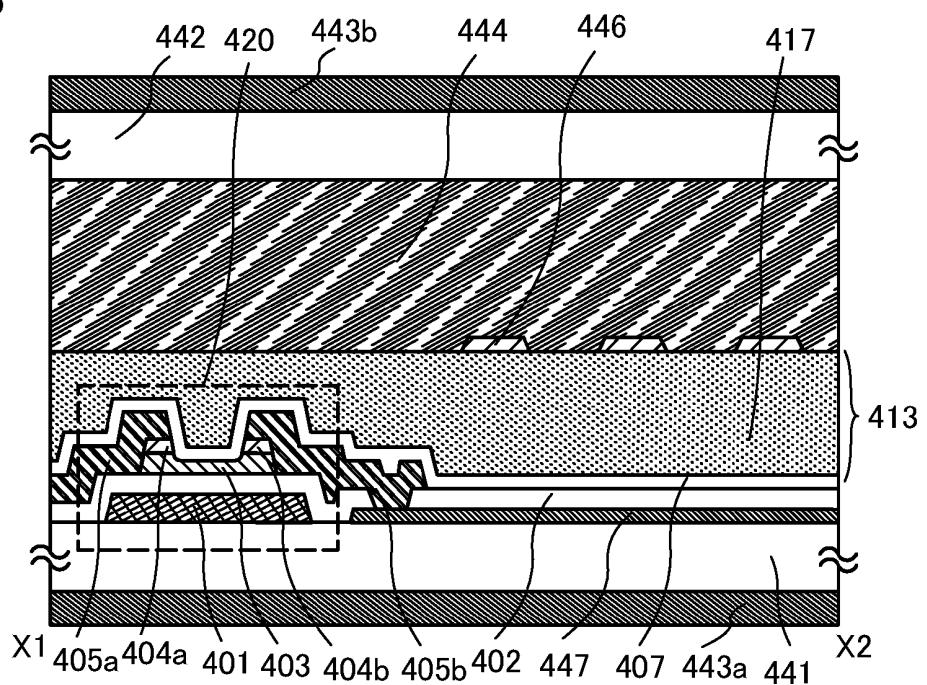

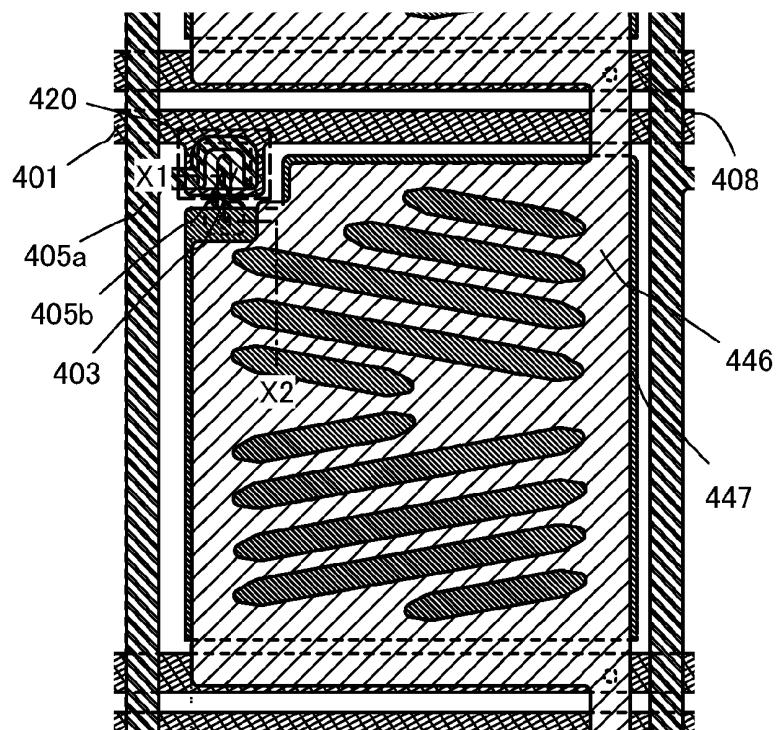

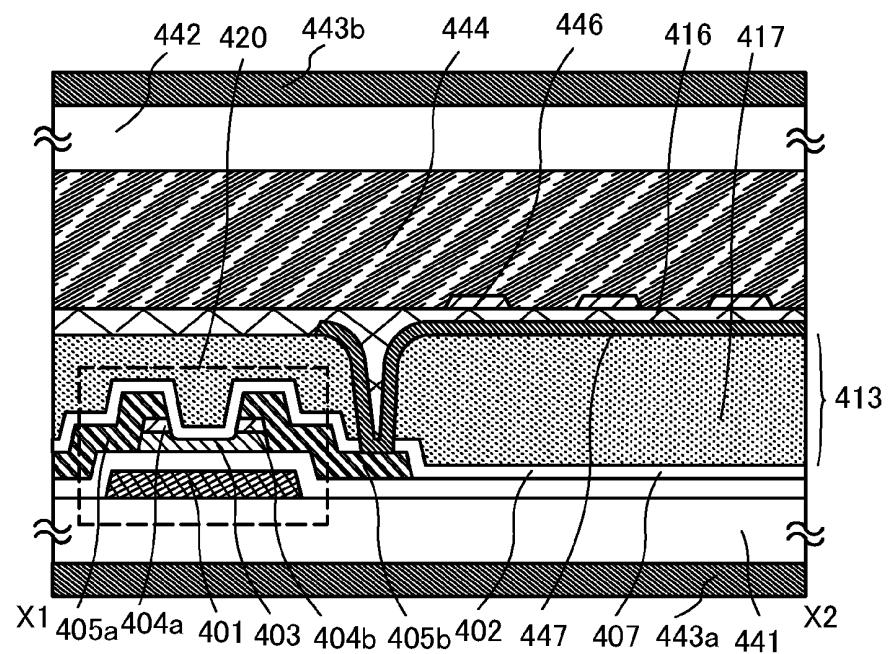

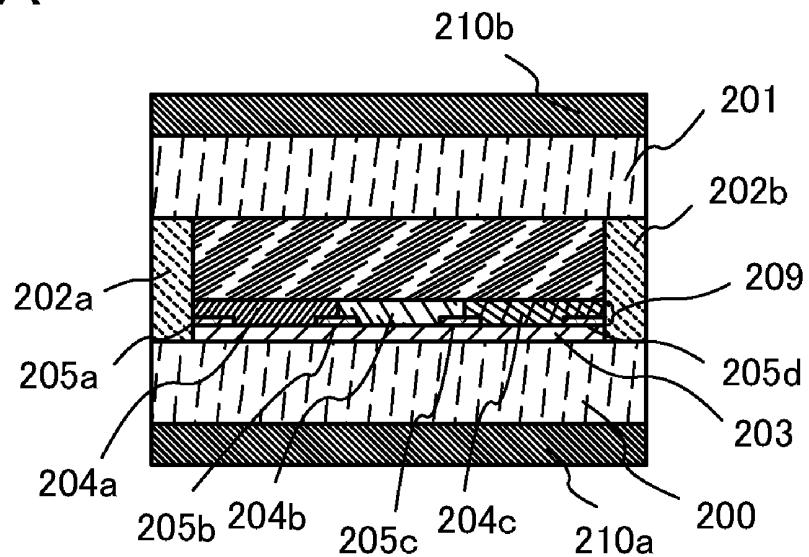

A liquid crystal display device is described with reference to FIGS. 1A and 1B.

FIG. 1A is a plan view of a liquid crystal display device and illustrates one pixel thereof. FIG. 1B is a cross-sectional view along line X1 to X2 in FIG. 1A.

In FIG. 1A, a plurality of source wiring layers (including a wiring layer 405a) are provided to be in parallel to each other (extended in a vertical direction in the drawing) and apart from each other. A plurality of gate wiring layers (including a gate electrode layer 401) are provided to be extended in a direction generally perpendicular to the source wiring layers (the horizontal direction in the drawing) and apart from each other. Common wiring layers (common electrode layers) are provided adjacent to the respective plurality of gate wiring layers and extended in a direction generally parallel to the gate wiring layers, that is, in a direction generally perpendicular to the source wiring layers (the horizontal direction in the drawing). A roughly rectangular space is surrounded by the source wiring layers, the common wiring layers (common electrode layers), and the gate wiring layers. In this space, a pixel electrode layer and the common electrode layer of the liquid crystal display device are provided. A thin film transistor 420 driving the pixel electrode layer is provided at the upper left corner in the drawing. A plurality of pixel electrode layers and thin film transistors are provided in matrix.

In the liquid crystal display device of FIGS. 1A and 1B, a second electrode layer 446 electrically connected to the thin film transistor 420 functions as a pixel electrode layer, and a first electrode layer 447 electrically connected to the common wiring layer functions as a common electrode layer. Note that as shown in FIGS. 1A and 1B, the first electrode layer 447 also serves as the common wiring layer in the pixel; thus, adjacent pixels are electrically connected to each other with a common electrode layer 409. Note that a capacitor is formed with the pixel electrode layer and the common electrode layer. Although the common electrode layer can operate in a floating state (an electrically isolated state), the potential of the common electrode layer may be set to a fixed potential, preferably to a potential around a common potential (an intermediate potential of an image signal which is transmitted as data) in such a level as not to generate flickers.

A method in which the gray scale is controlled by generating an electric field generally parallel (i.e., in a horizontal direction) to a substrate to move liquid crystal molecules in a plane parallel to the substrate can be used. For such a method, an electrode structure used in an FFS mode illustrated in FIGS. 1A and 1B can be employed.

In a horizontal electric field mode as an FFS mode, the first electrode layer in a flat-plate shape (e.g., a pixel electrode layer with which voltage is controlled per pixel) and the second electrode layer having an opening pattern (e.g., a common electrode layer with which common voltage is applied to all pixels) are located below the liquid crystal layer, such that the second electrode layer is provided above the first electrode layer so as to overlap the first electrode layer. Thus, over a first substrate 441, the first electrode layer and the second electrode layer, one of which is a pixel electrode layer and the other of which is a common electrode layer, are formed, and the pixel electrode layer and the common electrode layer are provided so as to be stacked with an insulating film (or an interlayer insulating film) interposed therebe-

tween. One of the pixel electrode layer and the common electrode layer is formed below the other one and has a flat-plate shape, and the other electrode layer is formed above the one and has various opening patterns such as a pattern with a bend portion or a comb-like shape. The first electrode layer 447 and the second electrode layer 446 do not have the same shape or do not overlap with each other in order to generate an electric field between the electrodes.

In this specification, the electrode layer formed in a lower layer far from the liquid crystal layer (close to the element substrate) is a first electrode layer, and the first electrode layer has a flat-plate shape. On the other hand, the electrode layer formed in an upper layer close to the liquid crystal layer (far from the element substrate) is a second electrode layer, and the second electrode layer has an opening pattern (slit). The first electrode layer in a flat-plate shape and the opening pattern (slit) of the second electrode layer overlap with each other in order to generate an electric field between the pixel electrode layer and the common electrode layer.

An electric field is added between the pixel electrode layer and the common electrode layer, so that liquid crystal is controlled. An electric field in a horizontal direction is applied to the liquid crystal, so that liquid crystal molecules can be controlled using the electric field. That is, the liquid crystal molecules aligned in parallel to the substrate can be controlled in a direction parallel to the substrate, whereby a wide viewing angle is obtained.

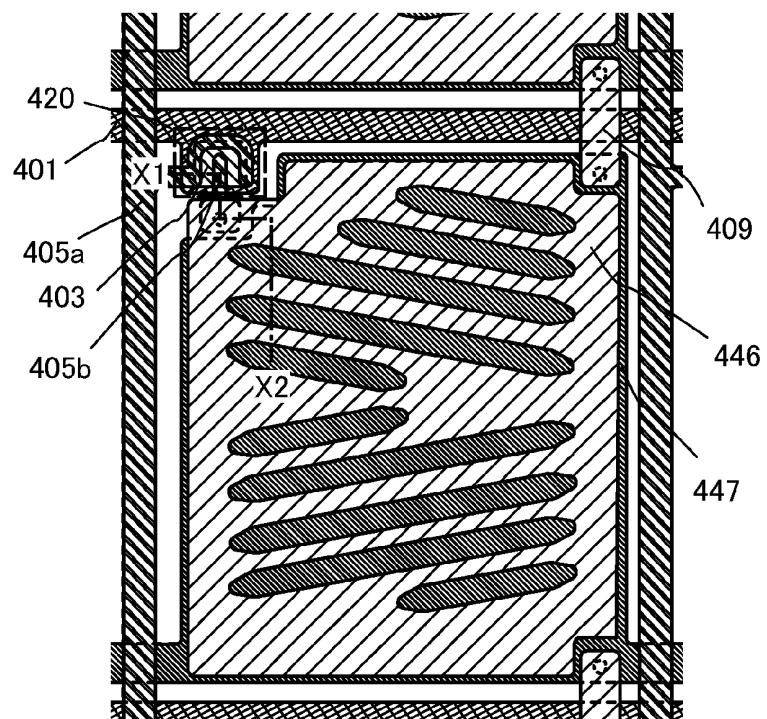

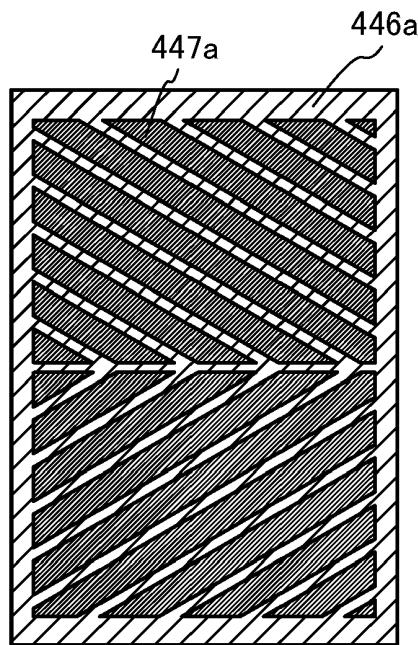

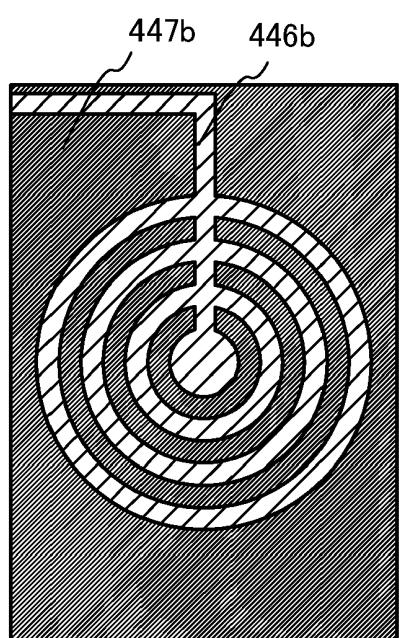

Examples of the first electrode layers 447 and the second electrode layers 446 are illustrated in FIGS. 8A to 8D. As shown in FIGS. 8A to 8D, first electrode layers 447a to 447d and second electrode layers 446a to 446d are disposed so as to overlap with each other, and insulating films are formed between the first electrode layers 447a to 447d and the second electrode layers 446a to 446d, so that the first electrode layers 447a to 447d and the second electrode layers 446a to 446d are formed over different films.

As illustrated in top views of FIGS. 8A to 8D, the second electrode layers 446a to 446d patterned in various shapes are formed over the first electrode layers 447a to 447d. In FIG. 8A, the second electrode layer 446a over the first electrode layer 447a has a V-like shape. In FIG. 8B, the second electrode layer 446b over the first electrode layer 447b has a concentric circular shape. In FIG. 8C, the second electrode layer 446c over the first electrode layer 447c has a comb-like shape such that the electrodes are engaged with each other. In FIG. 8D, the second electrode layer 446d over the first electrode layer 447d has a comb-like shape.

The thin film transistor 420 is an inverted staggered thin film transistor which includes, over the first substrate 441 having an insulating surface, the gate electrode layer 401, a gate insulating layer 402, a semiconductor layer 403, n<sup>+</sup> layers 404a and 404b serving as source and drain regions, and the wiring layers 405a and 405b serving as source and drain electrode layers. The first electrode layer 447 is formed in the same layer as the gate electrode layer 401 over the first substrate 441 and is a flat-shaped electrode layer in the pixel.

An insulating film 407 which covers the thin film transistor 420 and is in contact with the semiconductor layer 403 is provided. An interlayer film 413 is provided over the insulating film 407, and over the interlayer film 413, the second electrode layer 446 having an opening pattern is formed. Thus, the first electrode layer 447 and the second electrode layer 446 are provided to overlap with each other with the gate insulating layer 402, the insulating film 407, and the interlayer film 413 interposed therebetween.

As for the interlayer film 413 in the liquid crystal display device of FIGS. 1A and 1B, a light-transmitting chromatic-

color resin layer 417 which is a film having a function of attenuating the intensity of transmittance visible light. The light-transmitting chromatic-color resin layer 417 has transmittance of visible light lower than the semiconductor layer 403 which is an oxide semiconductor layer.

When a coloring layer which is the light-transmitting chromatic-color resin layer 417 is used as the interlayer film 413 provided over the thin film transistor 420, the intensity of incident light on the semiconductor layer 403 of the thin film transistor 420 can be attenuated without reduction in an aperture ratio of a pixel. Accordingly, electric characteristics of the thin film transistor 420 can be prevented from being varied due to photosensitivity of the oxide semiconductor and can be stabilized. Further, the light-transmitting chromatic-color resin layer 417 can function as a color filter layer. In the case of providing the color filter layer on the counter substrate side, precise positional alignment of a pixel region with an element substrate over which the thin film transistor is formed is difficult, and accordingly there is a possibility that image quality is degraded. Here, since the interlayer film is formed as the color filter layer directly on the element substrate side, the formation region can be controlled more precisely and this structure is adjustable to a pixel with a fine pattern. In addition, one insulating layer serves as both the interlayer film and the color filter layer, whereby the process can be simplified and a liquid crystal display device can be manufactured at low cost.

Chromatic colors are colors except achromatic colors such as black, gray, and white. The coloring layer is formed using a material which transmits only light of a chromatic color which the material is colored in so as to function as the color filter. As chromatic color, red, green, blue, or the like can be used. Alternatively, cyan, magenta, yellow, or the like may also be used. "Transmitting only light of a chromatic color which a material is colored in" means that light transmitted through the coloring layer has a peak at the wavelength of the chromatic color light.

The thickness of the light-transmitting chromatic-color resin layer is preferably controlled as appropriate in consideration of a relation between the concentration of the coloring material to be contained and light transmittance, in order to make the light-transmitting chromatic-color resin layer function as a color filter layer. In the case of forming the interlayer film by stacking a plurality of thin films, if at least one of the thin films is a light-transmitting chromatic-color resin layer, the interlayer film can function as a color filter.

In the case where the thickness of the light-transmitting chromatic-color resin layer differs in accordance with the chromatic colors or in the case where there is surface unevenness due to a light-blocking layer or the thin film transistor, an insulating layer which transmits light in a visible wavelength range (so-called colorless and transparent insulating layer) may be stacked for planarization of the surface of the interlayer film. Improvement in planarization of the interlayer film allows favorable coverage with the pixel electrode layer or the common electrode layer to be formed thereover and uniform gap (thickness) of the liquid crystal layer, whereby the visibility of the liquid crystal display device is increased and higher image quality can be achieved.

As formation of the light-transmitting chromatic-color resin layer 417, a light-transmitting organic resin, a chromatic pigment, or a dye can be used, and an organic resin in which a pigment, a dye, or the like is mixed may be used. As the light-transmitting organic resin, a photosensitive or non-photosensitive resin can be used. Use of the photosensitive organic resin layer makes it possible to reduce the number of resist masks; thus, the steps are simplified, which is prefer-

able. In addition, since a contact hole formed in the interlayer film has an opening shape with a curvature, coverage with a film such as an electrode layer formed in the contact hole can be improved.

There is no particular limitation on the formation method of the interlayer film 413 (the light-transmitting chromatic-color resin layer 417). In accordance with the material, a wet method such as spin coating, dip coating, spray coating, or droplet discharging (e.g., ink jetting, screen printing, or offset printing) may be performed, and the formed film may be patterned into a desired shape by an etching method (dry etching or wet etching method) if necessary.

A liquid crystal layer 444 is provided over the first electrode layer 447 and the second electrode layer 446 and sealed with a second substrate 442 which is a counter substrate.

The first substrate 441 and the second substrate 442 are light-transmitting substrates and are provided with a polarizing plate 443a and a polarizing plate 443b respectively on their outer sides (the sides opposite from the side where the liquid crystal layer 444 is provided).

The first electrode layer 447 and the second electrode layer 446 can be formed using a light-transmitting conductive material such as indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium tin oxide (hereinafter referred to as ITO), indium zinc oxide, or indium tin oxide to which silicon oxide is added.

A conductive composition containing a conductive high molecule (also referred to as a conductive polymer) can be used to form the first electrode layer 447 and the second electrode layer 446. The pixel electrode formed using the conductive composition preferably has a sheet resistance of 10000  $\Omega$ /square or less and a transmittance of 70% or more at a wavelength of 550 nm. Furthermore, the resistivity of the conductive high molecule contained in the conductive composition is preferably 0.1  $\Omega\cdot\text{cm}$  or less.

As the conductive high molecule, a so-called  $\pi$ -electron conjugated conductive polymer can be used. For example, it is possible to use polyaniline or a derivative thereof, polypyrrole or a derivative thereof, polythiophene or a derivative thereof, or a copolymer of two or more kinds of them.

An insulating film serving as a base film may be provided between the first substrate 441, and the gate electrode layer 401 and the first electrode layer 447. The base film functions to prevent diffusion of an impurity element from the first substrate 441 and can be formed using one film or stacked films selected from a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and a silicon oxynitride film. The gate electrode layer 401 can be formed to have a single-layer structure or a stacked structure using a metal material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, or scandium or an alloy material which contains any of these materials as its main component. By using a light-blocking conductive film as the gate electrode layer 401, light from a backlight (light emitted through the first substrate 441) can be prevented from entering the semiconductor layer 403.

For example, as a two-layer structure of the gate electrode layer 401, the following structures are preferable: a two-layer structure of an aluminum layer and a molybdenum layer stacked thereover; a two-layer structure of a copper layer and a molybdenum layer stacked thereover; a two-layer structure of a copper layer and a titanium nitride layer or a tantalum nitride layer stacked thereover, and a two-layer structure of a titanium nitride layer and a molybdenum layer. As a three-layer structure, a stack of a tungsten layer or a tungsten nitride

layer, a layer of an alloy of aluminum and silicon or an alloy of aluminum and titanium, and a titanium nitride layer or a titanium layer is preferable.

The gate insulating layer 402 can be formed to have a single-layer structure or a stacked structure using a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer, or a silicon nitride oxide layer by a plasma CVD method, a sputtering method, or the like. Alternatively, the gate insulating layer 402 can be formed using a silicon oxide layer by a CVD method using an organosilane gas. As the organosilane gas, a silicon-containing compound such as tetraethoxysilane (TEOS: chemical formula,  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ), tetramethylsilane (TMS: chemical formula,  $\text{Si}(\text{CH}_3)_4$ ), tetramethylcyclotetrasiloxane (TMCTS), octamethylcyclotetrasiloxane (OM-CTS), hexamethyldisilazane (HMDS), triethoxysilane ( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ), or trisdimethylaminosilane ( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ) can be used.

It is preferable that reverse sputtering in which an argon gas is introduced to generate plasma be performed before the formation of the oxide semiconductor film used as the semiconductor layer 403 in order to remove dust attached to a surface of the gate insulating layer. Note that instead of an argon atmosphere, a nitrogen atmosphere, a helium atmosphere, or the like may be used. Alternatively, an argon atmosphere to which oxygen, hydrogen,  $\text{N}_2\text{O}$ , or the like is added may be used. Further alternatively, an argon atmosphere to which  $\text{Cl}_2$ ,  $\text{CF}_4$ , or the like is added may be used.

In this specification, a thin film represented by  $\text{InMO}_3(\text{ZnO})_m$  ( $m>0$ ) is preferably used as an oxide semiconductor. In the thin film transistor 420, a thin film represented by  $\text{InMO}_3(\text{ZnO})_m$  ( $m>0$ ) is formed, and the thin film is used as the semiconductor layer 403. Note that M denotes one or more of metal elements selected from gallium (Ga), iron (Fe), nickel (Ni), manganese (Mn), and cobalt (Co). In addition to a case where only Ga is contained as M, there is a case where Ga and the above metal elements other than Ga are contained as M, for example, M contains Ga and Ni or Ga and Fe. Moreover, in the oxide semiconductor, in some cases, a transition metal element such as Fe or Ni or an oxide of the transition metal is contained as an impurity element in addition to a metal element contained as M. For example, an In—Ga—Zn—O-based non-single-crystal film can be used.

In the case where M is gallium (Ga) in the  $\text{InMO}_3(\text{ZnO})_m$  ( $m>0$ ) film (layer), this thin film is referred to as an In—Ga—Zn—O-based non-single-crystal film in this specification. Even in the case where after film formation by sputtering using a target of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO}=1:1:1$ , the In—Ga—Zn—O-based non-single-crystal film is subjected to heat treatment at 200°C. to 500°C., typically 300°C. to 400°C. for 10 minutes to 100 minutes, an amorphous structure is observed in the In—Ga—Zn—O-based non-single-crystal film by X-ray diffraction (XRD) spectrometry. Further, a thin film transistor having electric characteristics such as an on/off ratio of 10<sup>9</sup> or higher and mobility of 10 or higher at a gate voltage of  $\pm 20$  V can be manufactured. In addition, the In—Ga—Zn—O-based non-single-crystal film formed by sputtering has photosensitivity at a wavelength of 450 nm or less.

The semiconductor layer 403 and the n<sup>+</sup> layers 404a and 404b serving as source and drain regions can be formed using an In—Ga—Zn—O-based non-single-crystal film. The n<sup>+</sup> layers 404a and 404b are oxide semiconductor layers having a resistance lower than the semiconductor layer 403. For example, the n<sup>+</sup> layers 404a and 404b have n-type conductivity and an activation energy ( $\Delta E$ ) of from 0.01 eV to 0.1 eV inclusive. The n<sup>+</sup> layers 404a and 404b are In—Ga—Zn—O-based non-single-crystal films and include at least an amor-

phous component. The n<sup>+</sup> layers 404a and 404b may include crystal grains (nanocrystals) in an amorphous structure. These crystal grains (nanocrystals) in the n<sup>+</sup> layers 404a and 404b each have a diameter of 1 nm to 10 nm, typically about 2 nm to 4 nm.

Provision of the n<sup>+</sup> layers 404a and 404b can make a good junction between the wiring layers 405a and 405b which are metal layers and the semiconductor layer 403 which is an oxide semiconductor layer, which allows higher thermal stability than in the case of providing Schottky junction. In addition, willing provision of the n<sup>+</sup> layer is effective in supplying carriers to the channel (on the source side), stably absorbing carriers from the channel (on the drain side), or preventing a resistance component from being formed at an interface between the wiring layer and the semiconductor layer. Moreover, since resistance is reduced, high mobility can be ensured even with a high drain voltage.

A first In—Ga—Zn—O-based non-single-crystal film used as the semiconductor layer 403 is formed under deposition conditions different from those for formation of a second In—Ga—Zn—O based non-single-crystal film which is used as the n<sup>+</sup> layers 404a and 404b. For example, a flow rate ratio of an oxygen gas to an argon gas in formation condition of the first In—Ga—Zn—O-based non-single-crystal film is made higher than a flow rate ratio of an oxygen gas to an argon gas in formation condition of the second In—Ga—Zn—O-based non-single-crystal film. Specifically, the second In—Ga—Zn—O-based non-single-crystal film is formed in a rare gas (e.g., argon or helium) atmosphere (or an atmosphere containing an oxygen gas of 10% or lower and an argon gas containing 90% or higher), and the first In—Ga—Zn—O-based non-single-crystal film is formed in an oxygen atmosphere (or an atmosphere in which a flow rate of oxygen gas is equal to or higher than a flow rate of argon gas).

For example, the first In—Ga—Zn—O-based non-single-crystal film used as the semiconductor layer 403 is formed under the conditions where the oxide semiconductor target including In, Ga, and Zn (composition ratio is In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1) with a diameter of 8 inches is used, the distance between the substrate and the target is set at 170 mm, the pressure is set at 0.4 Pa, and the direct current (DC) power supply is set at 0.5 kW. Note that a pulse direct current (DC) power supply is preferable because dust can be reduced and the film thickness can be uniform. The thickness of the first In—Ga—Zn—O-based non-single-crystal film is set to 5 nm to 200 nm.

On the other hand, the second In—Ga—Zn—O-based non-single-crystal film used as the n<sup>+</sup> layers 404a and 404b is formed by a sputtering method using the target (In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1), under the conditions where the pressure is set at 0.4 Pa, the power is 500 W, the deposition temperature is room temperature, and an argon gas is introduced at a flow rate of 40 sccm. An In—Ga—Zn—O based non-single-crystal film including crystal grains with a size of 1 nm to 10 nm immediately after the film formation is formed in some cases. Note that it can be said that the presence or absence of crystal grains or the density of crystal grains can be adjusted and the diameter size can be adjusted within the range of 1 nm to 10 nm by appropriate adjustment of the reactive sputtering deposition conditions such as the composition ratio in the target, the film deposition pressure (0.1 to 2.0 Pa), the power (250 W to 3000 W: 8 inches φ), the temperature (room temperature to 100° C.), or the like. The second In—Ga—Zn—O-based non-single-crystal film has a thickness of 5 nm to 20 nm. Needless to say, when the film includes crystal grains, the size

of the crystal grains does not exceed the thickness of the film. The thickness of the second In—Ga—Zn—O-based non-single-crystal film is 5 nm.

Examples of a sputtering method include an RF sputtering method in which a high-frequency power source is used as a sputtering power source, a DC sputtering method, and a pulsed DC sputtering method in which a bias is applied in a pulsed manner. An RF sputtering method is mainly used in the case where an insulating film is formed, and a DC sputtering method is mainly used in the case where a metal film is formed.

In addition, there is also a multi-source sputtering apparatus in which a plurality of targets of different materials can be set. With the multi-source sputtering apparatus, films of different materials can be formed to be stacked in the same chamber, or a film of plural kinds of materials can be formed by electric discharge at the same time in the same chamber.

Further, as a sputtering apparatus, there are a sputtering apparatus provided with a magnet system inside the chamber and used for a magnetron sputtering method, and a sputtering apparatus used for an ECR sputtering method in which plasma is generated with the use of not glow discharge but microwaves is used.

In addition, as a film formation method by sputtering, there are also a reactive sputtering method in which a target substance and a sputtering gas component are chemically reacted with each other during film formation to form a thin compound film thereof, and a bias sputtering method in which voltage is also applied to a substrate during film formation.

In the manufacturing process of the semiconductor layer, the n<sup>+</sup> layers, and the wiring layers, an etching step is used to process thin films into desired shapes. Dry etching or wet etching can be used for the etching step.

As an etching gas used for dry etching, a gas containing chlorine (a chlorine-based gas such as chlorine (Cl<sub>2</sub>), boron chloride (BCl<sub>3</sub>), silicon chloride (SiCl<sub>4</sub>), or carbon tetrachloride (CCl<sub>4</sub>)) is preferably used.

Alternatively, a gas containing fluorine (a fluorine-based gas such as carbon tetrafluoride (CF<sub>4</sub>), sulfur fluoride (SF<sub>6</sub>), nitrogen fluoride (NF<sub>3</sub>), or trifluoromethane (CHF<sub>3</sub>)), hydrogen bromide (HBr), oxygen (O<sub>2</sub>), any of these gases to which a rare gas such as helium (He) or argon (Ar) is added, or the like can be used.

As an etching apparatus used for dry etching, an etching apparatus that uses reactive ion etching (RIE), or a dry etching apparatus that uses a high-density plasma source such as an electron cyclotron resonance (ECR) source or an inductively coupled plasma (ICP) source can be used. As such a dry etching apparatus with which uniform discharge can be easily obtained over a large area as compared to an ICP etching apparatus, there is an enhanced capacitively coupled plasma (ECCP) mode etching apparatus in which an upper electrode is grounded, a high-frequency power source of 13.56 MHz is connected to a lower electrode, and further a low-frequency power source of 3.2 MHz is connected to the lower electrode. This ECCP mode etching apparatus can be used even in the case where a substrate having the size exceeding 3 meters of the tenth generation is used, for example.

In order to etch the films into desired shapes, etching conditions (e.g., the amount of electric power applied to a coiled electrode, the amount of electric power applied to an electrode on a substrate side, or the electrode temperature on the substrate side) are controlled as appropriate.

As an etchant used for wet etching, a mixed solution of phosphoric acid, acetic acid, and nitric acid, an ammonia peroxide mixture (hydrogen peroxide:ammonia:water=5:2:

2), or the like can be used. Alternatively, ITO-07N (produced by Kanto Chemical Co., Inc.) may be used.

The etchant after the wet etching is removed by cleaning, together with the etched material. The waste liquid of the etchant including the etched material may be purified so that the included material is reused. If a material such as indium included in the oxide semiconductor layer is collected from the waste liquid of the etching and reused, resources can be used effectively and cost can be reduced.

In order to etch the films into desired shapes, etching conditions (e.g., etchant, etching time, temperature, or the like) are controlled as appropriate in accordance with the material.

As a material of the wiring layers **405a** and **405b**, an element selected from Al, Cr, Ta, Ti, Mo, and W, an alloy containing any of the elements as its component, an alloy containing any of the elements in combination, and the like can be given. Further, in the case of performing heat treatment at 200°C. to 600°C., the conductive film preferably has heat resistance against such heat treatment. Since Al itself has disadvantages such as low heat resistance and a tendency to be corroded, it is used in combination with a conductive material having heat resistance. As a conductive material having heat resistance which is combined with Al, an element selected from titanium (Ti), tantalum (Ta), tungsten (W), molybdenum (Mo), chromium (Cr), neodymium (Nd), or scandium (Sc), or an alloy including any of the elements, an alloy film including a combination of such elements, or a nitride film including any of the elements can be used.

The gate insulating layer **402**, the semiconductor layer **403**, the n<sup>+</sup> layers **404a** and **404b**, and the wiring layers **405a** and **405b** may be formed in succession without being exposed to air. By successive formation without exposure to air, each interface between the stacked layers can be formed without being contaminated by atmospheric components or contaminating impurities contained in air; therefore, variation in characteristics of the thin film transistor can be reduced.

Note that the semiconductor layer **403** is partly etched so as to have a groove (a depressed portion).

The semiconductor layer **403** and the n<sup>+</sup> layers **404a** and **404b** are preferably subjected to heat treatment at 200°C. to 600°C., typically 300°C. to 500°C. For example, heat treatment is performed for 1 hour at 350°C. in a nitrogen atmosphere. By this heat treatment, rearrangement at the atomic level is caused in the In—Ga—Zn—O based oxide semiconductor which forms the semiconductor layer **403** and the n<sup>+</sup> layers **404a** and **404b**. This heat treatment (also including photo-annealing or the like) is important in that the distortion that interrupts carrier transfer in the semiconductor layer **403** and the n<sup>+</sup> layers **404a** and **404b** can be reduced. Note that there is no particular limitation on when to perform the heat treatment, as long as it is performed after the semiconductor layer **403** and the n<sup>+</sup> layers **404a** and **404b** are formed.

In addition, oxygen radical treatment may be performed on the exposed depression portion of the semiconductor layer **403**. The radical treatment is preferably performed in an atmosphere of O<sub>2</sub> or N<sub>2</sub>O, or an atmosphere of N<sub>2</sub>, He, Ar, or the like which includes oxygen. Alternatively, an atmosphere obtained by adding Cl<sub>2</sub> or CF<sub>4</sub> to the above atmosphere may be used. Note that the radical treatment is preferably performed with no bias voltage applied to the first substrate **441** side.

Note that there is no particular limitation on a structure of the thin film transistor formed in the liquid crystal display device. The thin film transistor may have a single-gate structure in which one channel formation region is formed, a double-gate structure in which two channel formation regions

are formed, or a triple-gate structure in which three channel formation regions are formed. In addition, the transistor in the peripheral driver circuit region may also have a single-gate structure, a double-gate structure, or a triple-gate structure.

The thin film transistor may have a top-gate structure (e.g., a staggered structure or a coplanar structure), a bottom-gate structure (e.g., an inverted-staggered structure or an inverted-coplanar structure), a dual-gate structure including two gate electrode layers provided above and below a channel region each with a gate insulating film interposed therebetween, or other structures.

An alignment film or an optical film such as a polarizing plate, a retardation plate, or an anti-reflection film is provided as appropriate. For example, circular polarization by the polarizing plate and the retardation plate may be used. In addition, a backlight, a side light, or the like may be used as a light source.

The insulating film **407** covering the thin film transistor **420** can be formed using an inorganic insulating film or organic insulating film formed by a wet method or a dry method. For example, the insulating film **407** can be formed by a CVD method, a sputtering method, or the like, using a silicon nitride film, a silicon oxide film, a silicon oxynitride film, an aluminum oxide film, a tantalum oxide film, or the like. Alternatively, an organic material such as acrylic, polyimide, benzocyclobutene, polyamide, or an epoxy resin can be used. Other than such organic materials, it is also possible to use a low-dielectric constant material (a low-k material), a siloxane-based resin, PSG (phosphosilicate glass), BPSG (borophosphosilicate glass), or the like.

Note that a siloxane-based resin is a resin formed from a siloxane-based material as a starting material and having the bond of Si—O—Si. A siloxane-based resin may include, as a substituent, an organic group (e.g., an alkyl group, and an aryl group) or a fluoro group. The organic group may include a fluoro group. A siloxane-based resin is applied by a coating method and baked; thus, the insulating film **407** can be formed.

Alternatively, the insulating film **407** may be formed by stacking plural insulating films formed using any of these materials. For example, the insulating film **407** may have such a structure that an organic resin film is stacked over an inorganic insulating film.

As a liquid crystal material of the liquid crystal layer **444**, various kinds of liquid crystal can be used, and lyotropic liquid crystal, thermotropic liquid crystal, low molecular liquid crystal, high molecular liquid crystal, discotic liquid crystal, ferroelectric liquid crystal, anti-ferroelectric liquid crystal, or the like may be selected as appropriate to be used.

In this specification, in the case where a liquid crystal display device is a light-transmitting liquid crystal display device (or a semi-transmissive liquid crystal display device) which performs display by transmitting light from a light source, light is needed to be transmitted at least in the pixel region. Thus, all components provided in the pixel region through which light is transmitted: the first substrate; the second substrate; and thin films included in an element layer, such as the pixel electrode layer, the common electrode layer, the insulating film, and the conductive film have a property of transmitting light in a visible wavelength range.

As for the first substrate **441** and the second substrate **442**, a glass substrate of barium borosilicate glass, aluminoborosilicate glass, or the like; a quartz substrate; a plastic substrate; or the like can be used.

Further, by use of a resist mask having regions with plural thicknesses (typically, two different thicknesses) which is

formed using a multi-tone mask, the number of resist masks can be reduced, resulting in simplified process and lower costs.

Improvement in contrast and viewing angle characteristics enables a liquid crystal display device with higher image quality to be supplied. Further, such a liquid crystal display device can be manufactured at low cost with high productivity.

Further, characteristics of the thin film transistor can be stabilized; thus, reliability of the liquid crystal display device can be improved.

### Embodiment 2

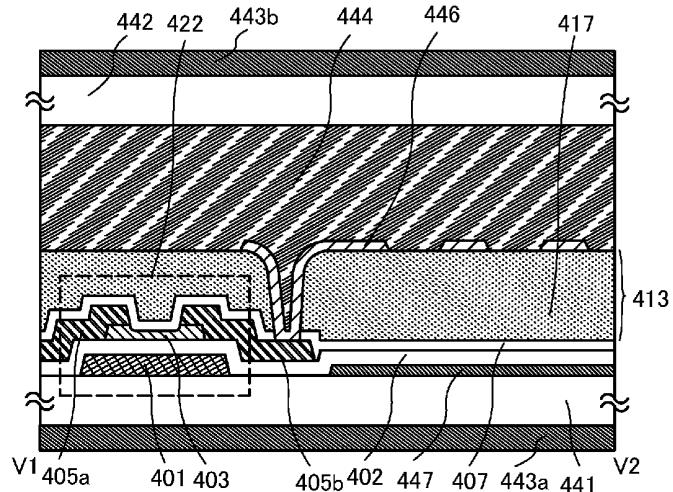

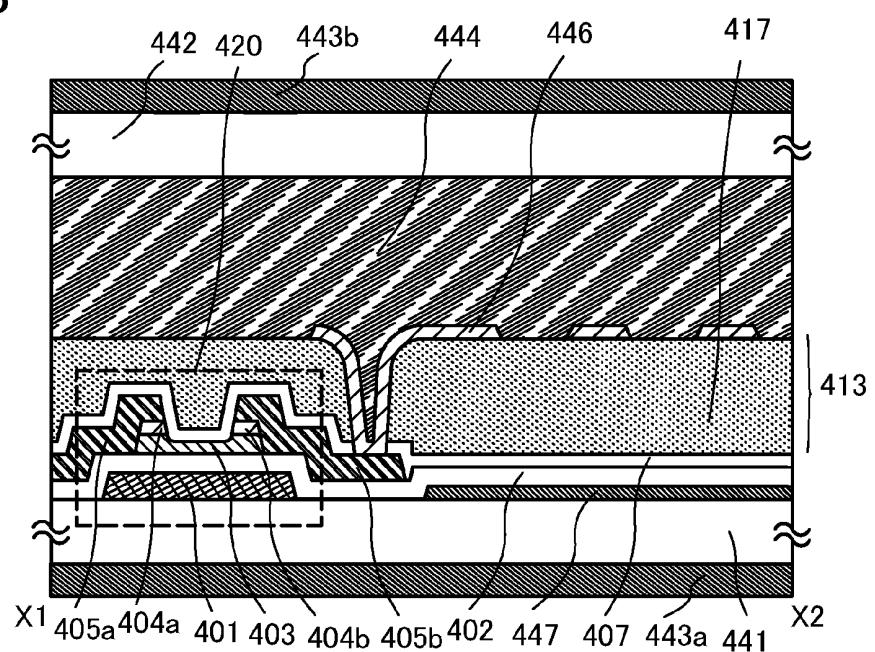

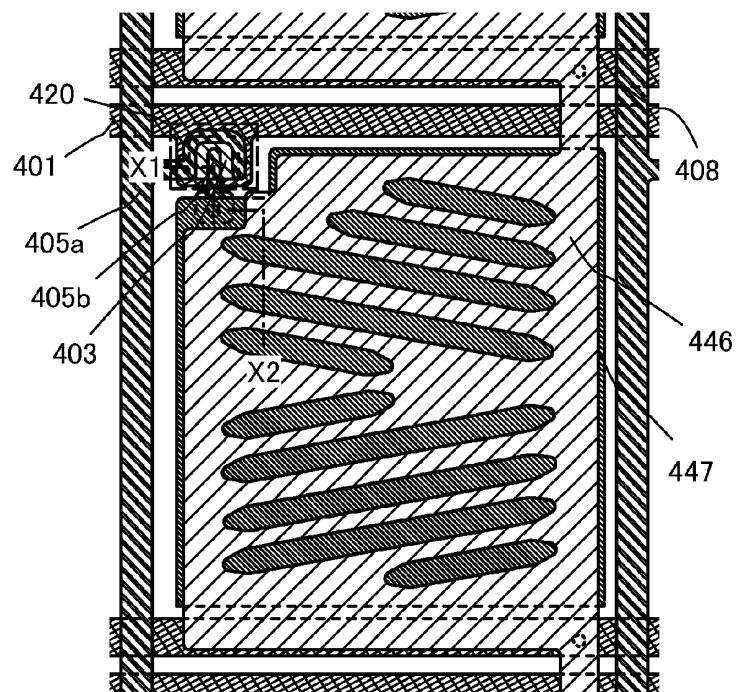

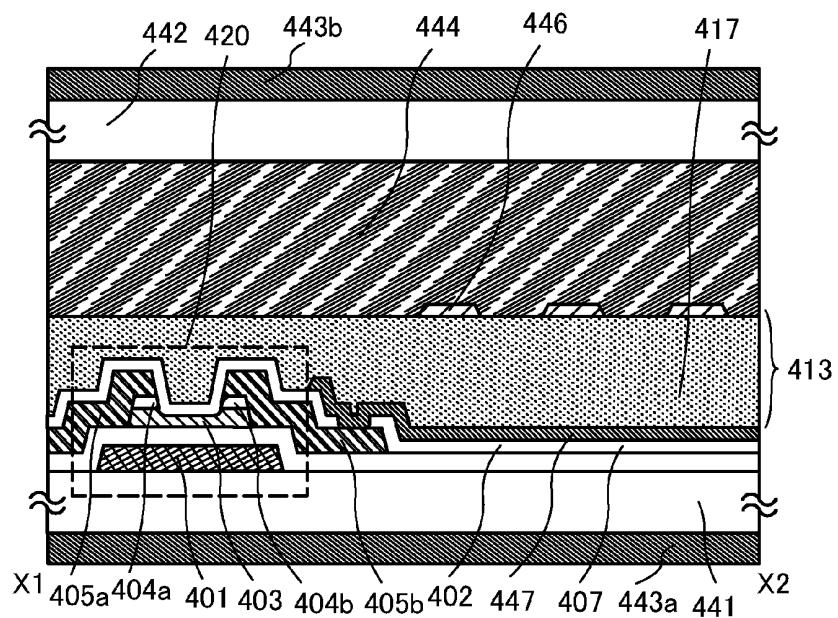

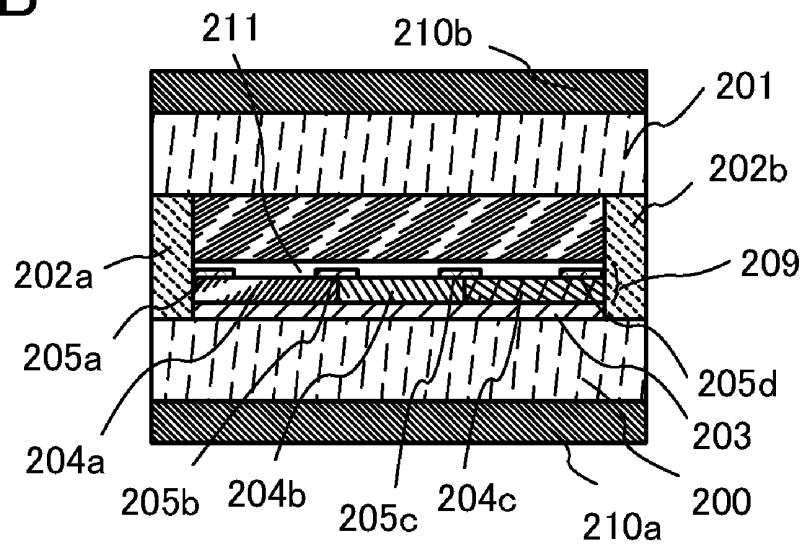

Another mode of a liquid crystal display device is illustrated in FIGS. 3A and 3B. Specifically, an example of a liquid crystal display device is described, in which a first electrode layer in a flat-plate shape formed in a lower layer is used as a pixel electrode layer, and a second electrode layer having an opening pattern formed in an upper layer is used as a common electrode layer. Note that components in common with those in Embodiment 1 can be formed using the similar material and the similar manufacturing method, and detailed description of the same portions and portions which have similar functions is omitted.

FIG. 3A is a plan view of a liquid crystal display device and illustrates one pixel thereof. FIG. 3B is a cross-sectional view along line X1 to X2 in FIG. 3A.

In FIG. 3A, a plurality of source wiring layers (including the wiring layer 405a) are provided in parallel to each other (extended in a vertical direction in the drawing) and apart from each other. A plurality of gate wiring layers (including the gate electrode layer 401) are provided apart from each other and extended in a direction generally perpendicular to the source wiring layers (a horizontal direction in the drawing). Common wiring layers 408 are provided adjacent to the respective plurality of gate wiring layers and extended in a direction generally parallel to the gate wiring layers, that is, in a direction generally perpendicular to the source wiring layers (a horizontal direction in the drawing). A roughly rectangular space is surrounded by the source wiring layers, the common wiring layers 408, and the gate wiring layers. In this space, a pixel electrode layer and a common electrode layer of the liquid crystal display device are provided. The thin film transistor 420 for driving the pixel electrode layer is provided at the upper left corner in the drawing. A plurality of pixel electrode layers and thin film transistors are provided in matrix.