US 20070229749 A1

(19) **United States**

(12) **Patent Application Publication** (10) **Pub. No.: US 2007/0229749 A1**

Kaneko et al.

(43) **Pub. Date:** **Oct. 4, 2007**

(54) **FFS MODE LIQUID CRYSTAL DISPLAY PANEL**

(75) Inventors: **Hideki Kaneko**, Tottori (JP); **Masahiro Horiguchi**, Tottori (JP)

Correspondence Address:

**WESTERMAN, HATTORI, DANIELS & ADRIAN, LLP**

**1250 CONNECTICUT AVENUE, NW, SUITE 700**

**WASHINGTON, DC 20036**

(73) Assignee: **EPSON IMAGING DEVICES CORP.**, Azumino-shi (JP)

(21) Appl. No.: **11/727,005**

(22) Filed: **Mar. 23, 2007**

(30) **Foreign Application Priority Data**

Mar. 28, 2006 (JP) ..... 2006-088208

**Publication Classification**

(51) **Int. Cl.**

**G02F 1/1343** (2006.01)

(52) **U.S. Cl.** ..... **349/141**

(57) **ABSTRACT**

The present invention provides a fringe field switching (FFS) mode liquid crystal display panel including a plurality of scanning lines 12 and common lines 13 provided in parallel, a plurality of signal lines 14 provided in a crank manner in a direction perpendicular to the scanning lines 12, and pixel electrodes 18<sub>1</sub> and 18<sub>2</sub> each formed between the plurality of scanning lines 12 and signal lines 14 in a delta arrangement. Each of the pixel electrodes 18<sub>1</sub> and 18<sub>2</sub> has a plurality of slits 17<sub>1</sub> and 17<sub>2</sub>, respectively, inclined in different directions to each other with respect to an axis x parallel to the scanning lines 12 and positioned between adjacent scanning lines 12. The pixel electrodes 18<sub>1</sub> in odd-numbered rows and the pixel electrodes 18<sub>2</sub> in even-numbered rows are inverted to each other with respect to another axis perpendicular to the axis x. With such features, the FFS mode liquid crystal display panel provides symmetrical viewing angle generating no spots in a transverse direction, a wide viewing angle, a bright display with high transmittance and excellent display quality.

FIG:1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

FIG.8

FIG.9

FIG.10

FIG.11

FIG.12

FIG.13

FIG.14

70A

FIG.15

FIG.16

FIG.17

70D

## FFS MODE LIQUID CRYSTAL DISPLAY PANEL

### BACKGROUND

[0001] 1. Technical Field

[0002] The present invention relates to a fringe field switching (hereinafter, referred to as "FFS") mode liquid crystal display (LCD) panel. More particularly, the present invention relates to an FFS mode LCD panel in a dual-domain structure in which pixels are arranged in a delta arrangement.

[0003] 2. Related Art

[0004] In recent years, LCD panels are widely used not only for information and communication devices but also for electrical devices in general. Typical LCD panels include one pair of substrates made of glass and the like formed with electrodes and the like on their surfaces, and a liquid crystal layer formed between the pair of substrates. By applying a voltage to the electrodes on both substrates to change transmittance of light by rearranging liquid crystal molecules, various images are displayed. This is a so-called longitudinal electric field mode. There are a twisted nematic (TN) mode and a vertical alignment (VA) mode in a longitudinal electric field mode LCD panel. But, as there is a problem of a narrow viewing angle, various improved longitudinal electric field mode LCD panels such as a multidomain vertical alignment (MVA) mode have been developed.

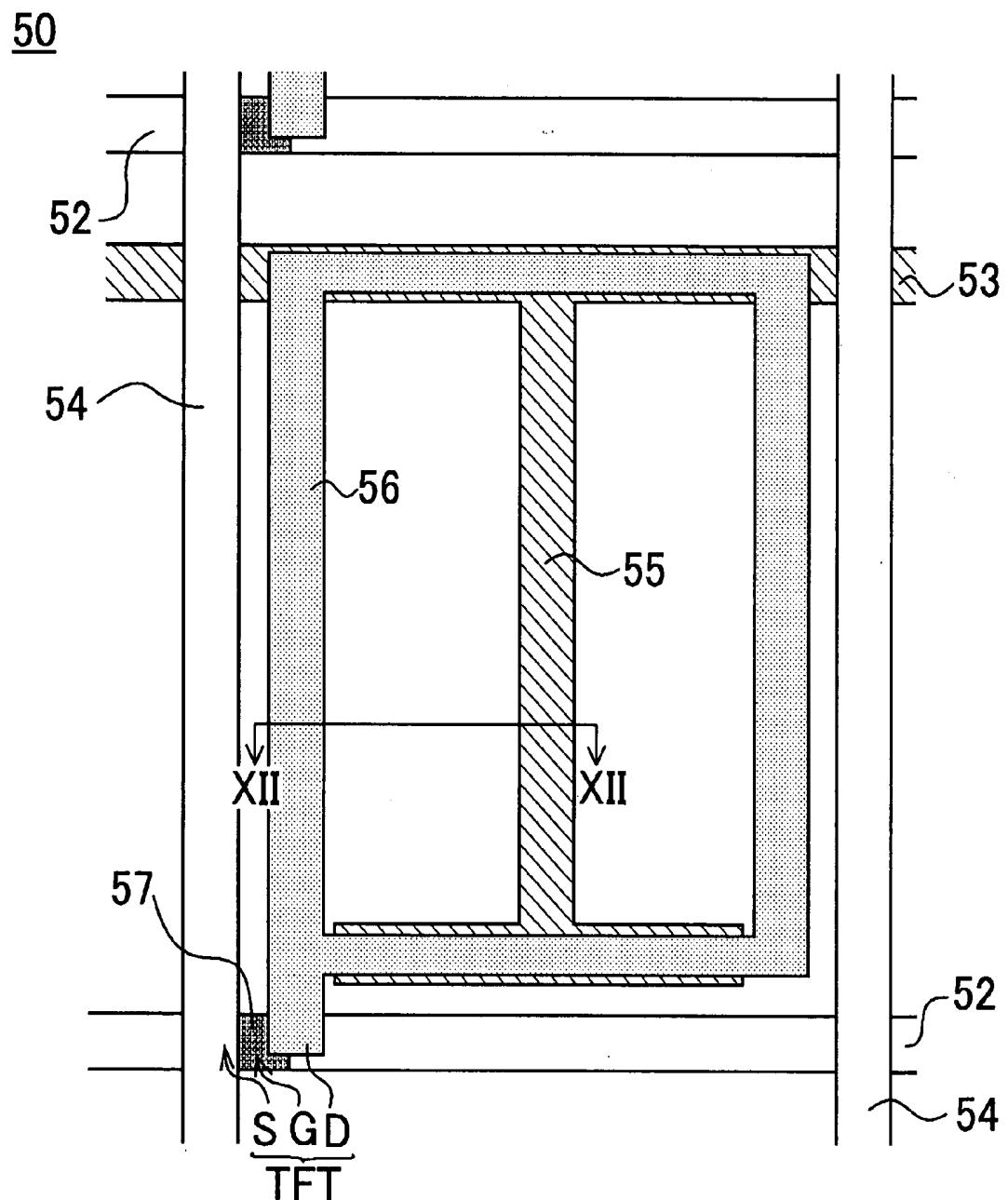

[0005] Unlike the above longitudinal electric field mode LCD panel, an LCD panel including electrodes only on one of the substrates, which may be called a transverse electric field mode, is known as an in-plane switching (IPS) mode LCD panel (refer to JP-A-2005-338256). An operational principle of the IPS mode LCD panel will be described with reference to FIGS. 11 and 12. FIG. 11 is a schematic plan view of one pixel of the IPS mode LCD panel, and FIG. 12 is a schematic sectional view taken along the line XII-XII of FIG. 11.

[0006] An IPS mode LCD panel 50 includes an array substrate AR and a color filter substrate CF. The array substrate AR is provided with a plurality of scanning lines 52 and common lines 53 in parallel on a surface of a first transparent substrate 51. A plurality of signal lines 54 are provided in a direction perpendicular to the scanning lines 52 and the common lines 53. In a central part of each pixel, a strip of common electrode 55 is provided from the common line 53, in an inverted T-shape as in FIG. 11. A pixel electrode 56 is provided so as to surround the periphery of the common electrode 55.

[0007] A thin film transistor (TFT) serving as a switching element is formed between the scanning line 52 and the signal line 54. The TFT is disposed with a semiconductor layer 57 between the scanning line 52 and the signal line 54. A portion of the signal line on the semiconductor layer 57 forms a source electrode S, a portion of the scanning line under the semiconductor layer 57 forms a gate electrode G, and a portion of the pixel electrode 56 overlapping with a part of the semiconductor layer 57 forms a drain electrode D.

[0008] The color filter substrate CF includes a color filter layer 59 on a surface of a second transparent substrate 58. The array substrate AR is disposed to face the color filter substrate CF, so as the pixel electrode 56 and the common electrode 55 of the array substrate AR, and the color filter layer 59 of the color filter substrate CF are opposed to each

other. A liquid crystal LC is sealed therebetween. By respectively disposing polarizers 60 and 61 at outer sides of both substrates, so that their polarizing directions are perpendicular to each other, the IPS mode LCD panel 50 is formed.

[0009] According to the IPS mode LCD panel 50, as shown in FIG. 12, when an electric field is formed between the pixel electrode 56 and the common electrode 55, liquid crystal molecules aligned in a horizontal direction revolve in a horizontal direction. This enables the amount of transmitting light entering from a backlight to be controlled. The IPS mode LCD panel 50 has a wide viewing angle and high contrast. Furthermore, because the pixel electrode 56 and the common electrode 55 are disposed with a relatively narrow space therebetween, it has an advantage of secondarily generating a storage capacitance. But, because the common electrode 55 is formed of the same metal material as the common line 53, there are problems of a low aperture ratio and a low transmittance, and color changes depending on viewing angle.

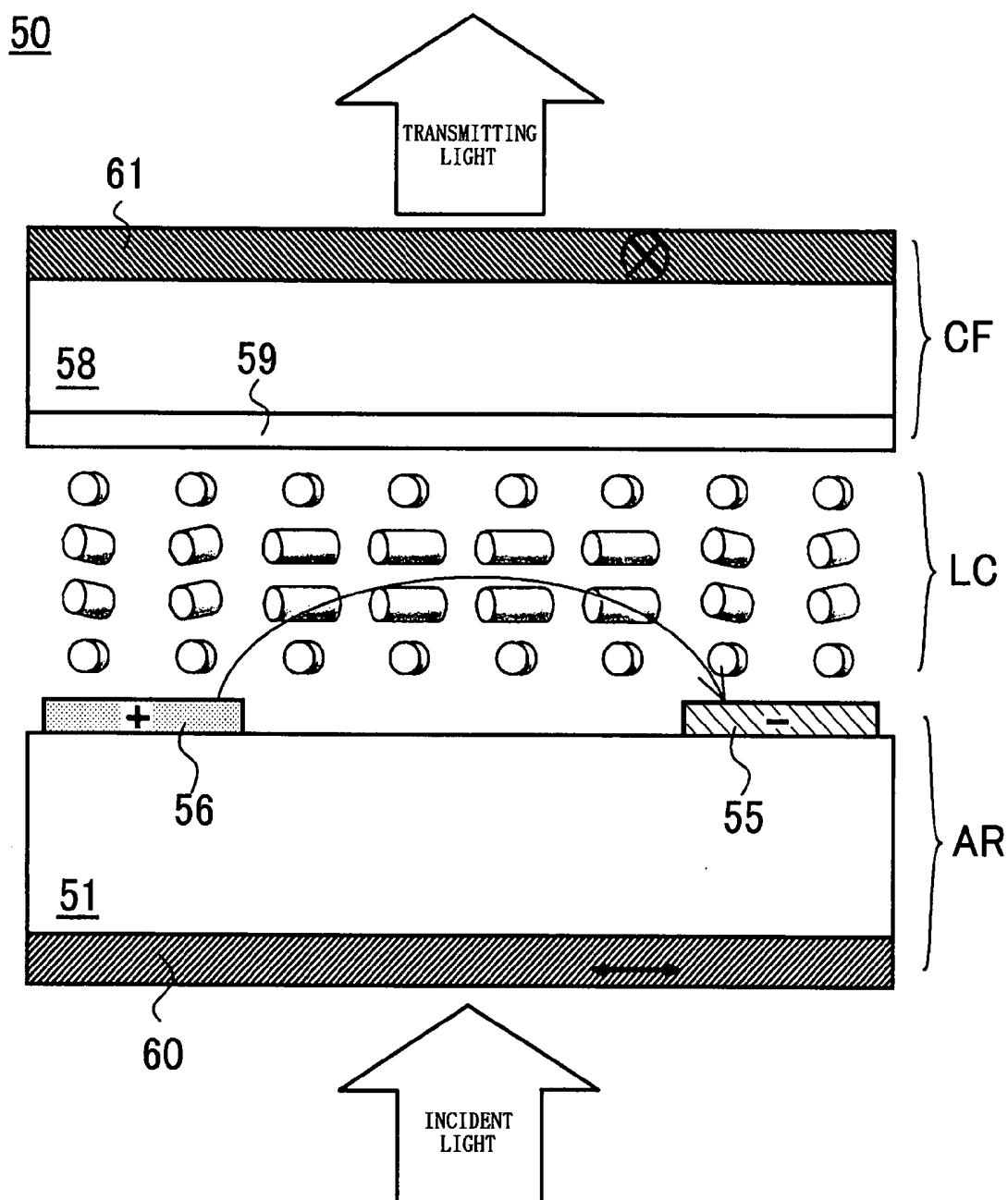

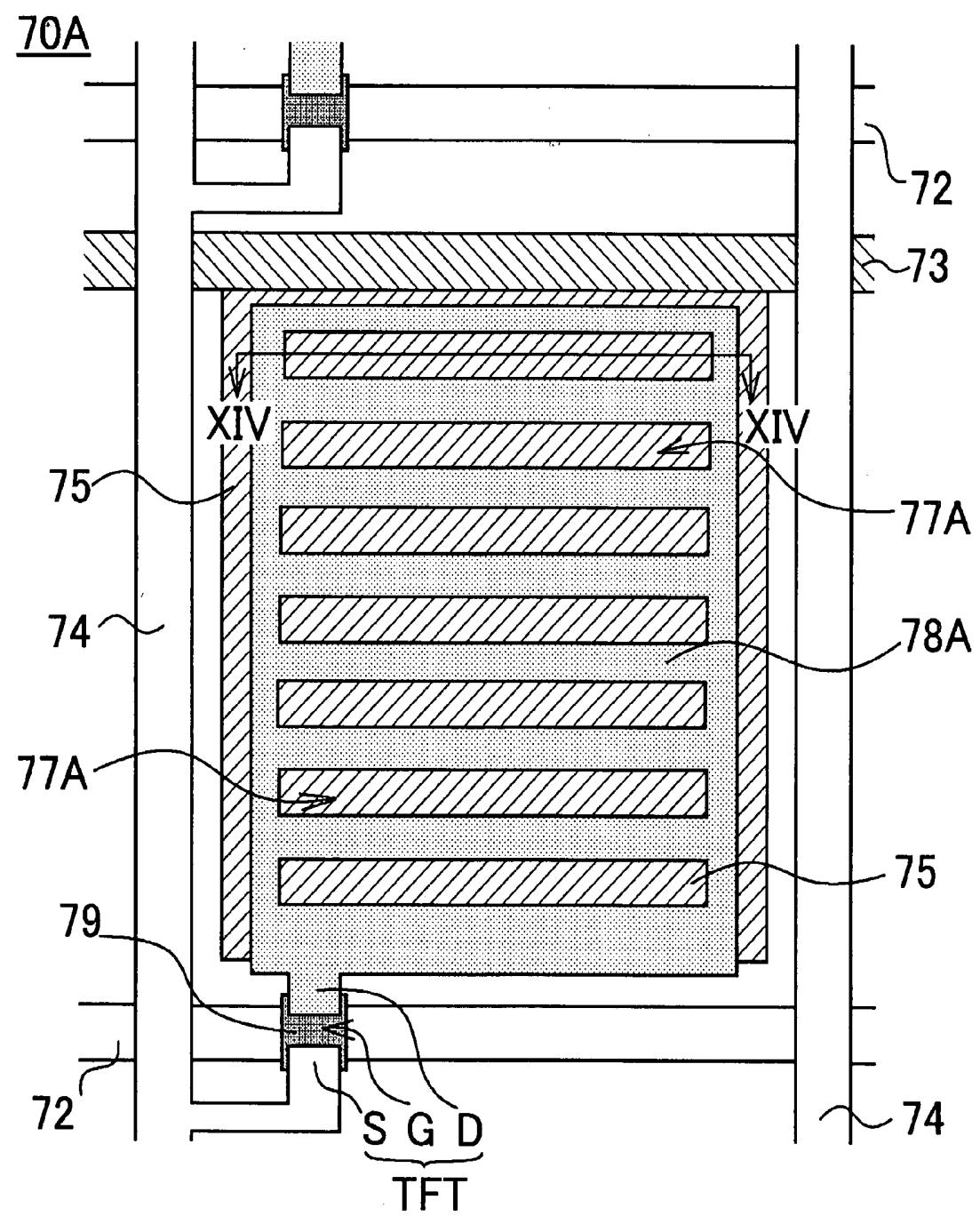

[0010] In order to solve the problems of the low aperture ratio and the low transmittance of the IPS mode LCD panel, an FFS mode LCD device which may be called an inclined electric field system has been developed (refer to JP-A-2000-131720, JP-A-2002-14363 and JP-A-2002-244158). An operational principle of such a FFS mode LCD panel will be described with reference to FIGS. 13 and 14. FIG. 13 is a schematic plan view of one pixel of an FFS mode LCD panel, and FIG. 14 is a schematic sectional view taken along the line XIV-XIV of FIG. 13.

[0011] An FFS mode LCD panel 70A includes an array substrate AR and a color filter substrate CF. The array substrate AR is provided with a plurality of scanning lines 72 and common lines 73 in parallel on a surface of a first transparent substrate 71. A plurality of signal lines 74 are provided in a direction perpendicular to the scanning lines 72 and the common lines 73. A common electrode 75 made of a transparent material such as indium tin oxide (ITO), which is connected to the common line 73, is provided so as to cover an entire surface of each pixel. A pixel electrode 78A made of a transparent material such as ITO, which is formed with a plurality of slits 77A in stripes, is provided on a surface of the common electrode 75 with an insulating film 76 therebetween.

[0012] A TFT serving as a switching element is formed near an intersection of the scanning line 72 and the signal line 74. The TFT is disposed with a semiconductor layer 79 on a surface of the scanning line 72. A part of the signal line 74 is extended to cover a part of a surface of the semiconductor layer 79, thereby forming a source electrode S of the TFT. A portion of the scanning line under the semiconductor layer 79 forms a gate electrode G, and a portion of the pixel electrode 78A overlapping with a part of the semiconductor layer 79 forms a drain electrode D.

[0013] The color filter substrate CF includes a color filter layer 81 on a surface of a second transparent substrate 80. The array substrate AR is disposed to face the color filter substrate CF, so as the pixel electrode 78A and the common electrode 75 of the array substrate AR, and the color filter layer 81 of the color filter substrate CF are opposed to each other. A liquid crystal LC is sealed therebetween. By respectively disposing polarizers 82 and 83 at outer sides of both substrates, so that their polarizing directions are perpendicular to each other, the FFS mode LCD panel 70A is formed.

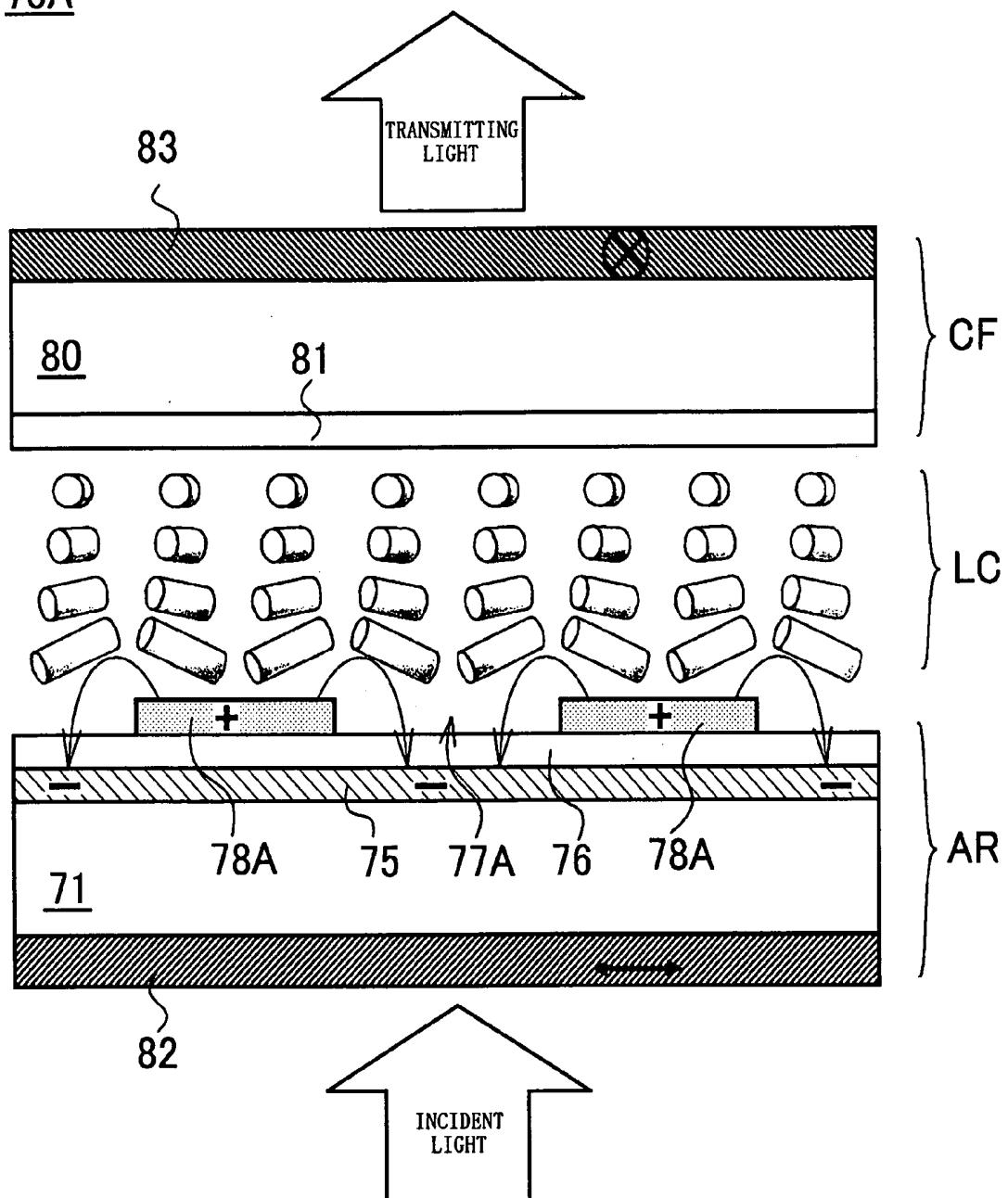

[0014] According to the FFS mode LCD panel 70A, when an electric field is formed between the pixel electrode 78A and the common electrode 75, as shown in FIG. 14, the electric field moves toward the common electrode 75 from both sides of the pixel electrodes 78A. This allows not only liquid crystal molecules existing between the pixel electrodes 78A but also liquid crystal molecules existing above the pixel electrodes 78A to move. Therefore, the FFS mode LCD panel 70A has a wider viewing angle and higher contrast than the IPS mode LCD panel 50, and allows a bright display because of its high transmittance. In addition, the FFS mode LCD panel 70A has an advantage of secondarily generating a larger storage capacitance, because the overlapping area between the pixel electrode 78A and the common electrode 75 is larger than that in the IPS mode LCD panel 50 in plan view, thereby eliminating a need to provide an auxiliary capacitor line separately.

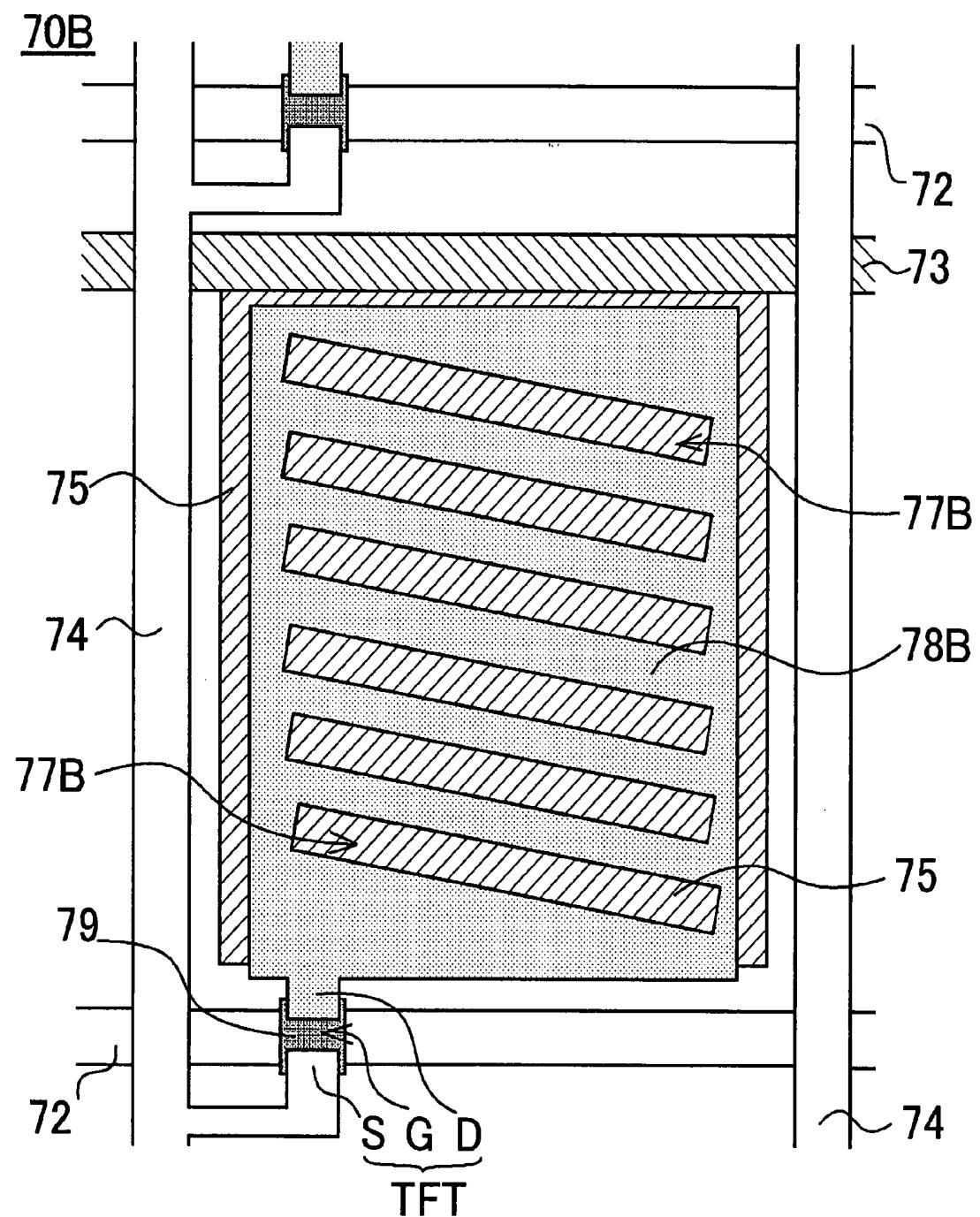

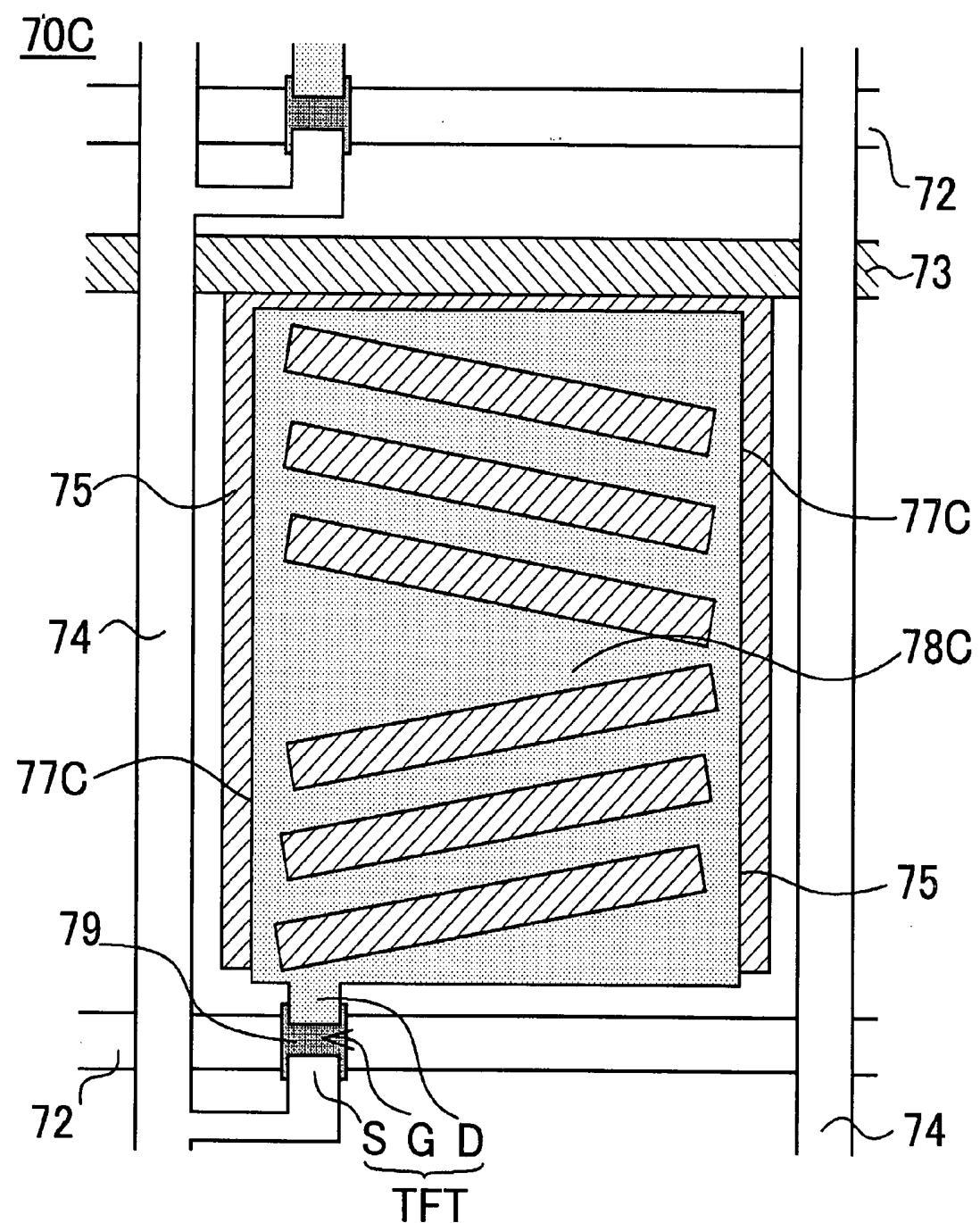

[0015] According to the FFS mode LCD panel, in the same manner as the IPS mode LCD panel disclosed in JP-A-2005-338256, due to its display characteristics, a rubbing direction is preferably perpendicular to the signal lines, and a minimum inclined angle is preferably provided between the pixel electrodes and the rubbing direction. Therefore, as an FFS mode LCD panel 70B shown in FIG. 15, slits 77B in stripes provided to a pixel electrode 78B are inclined toward the scanning line 72 or the common line 73. Similarly, in order to eliminate changes in color depending on viewing angle, as an FFS mode LCD panel 70C shown in FIG. 16, a dual-domain approach has been adopted by disposing slits 77C in stripes provided to a pixel electrode 78C in a V-shape. The only difference between the FFS mode LCD panels 70B and 70C shown in FIGS. 15 and 16, and the FFS mode LCD panel 70A shown in FIG. 13, is the inclination of the slits 77B or 77C provided to the pixel electrode 78B or 78C. The same components of the panels 70B and 70C as in the panel 70A shown in FIG. 13 are denoted by the same reference numerals, and descriptions thereof are omitted.

[0016] As described above, FFS mode LCD panels have a wider viewing angle and higher contrast than IPS mode LCD panels, and allow a bright display because of their high transmittance. As they can operate at low voltage and secondarily generate a larger storage capacitance, their display quality is excellent even when an auxiliary capacitor line is not provided separately. In the FFS mode LCD panels disclosed in JP-A-2000-131720, JP-A-2002-14363 and JP-A-2002-244158, pixels are aligned in a row direction and a column direction, and generally used in combination with color filters arranged in stripes or color filters arranged in diagonal rows. When they are used mainly for displaying images taken by a digital still camera and the like, a delta arrangement (also referred to as "triangle arrangement"), in which pixels are arranged alternatively, may be used.

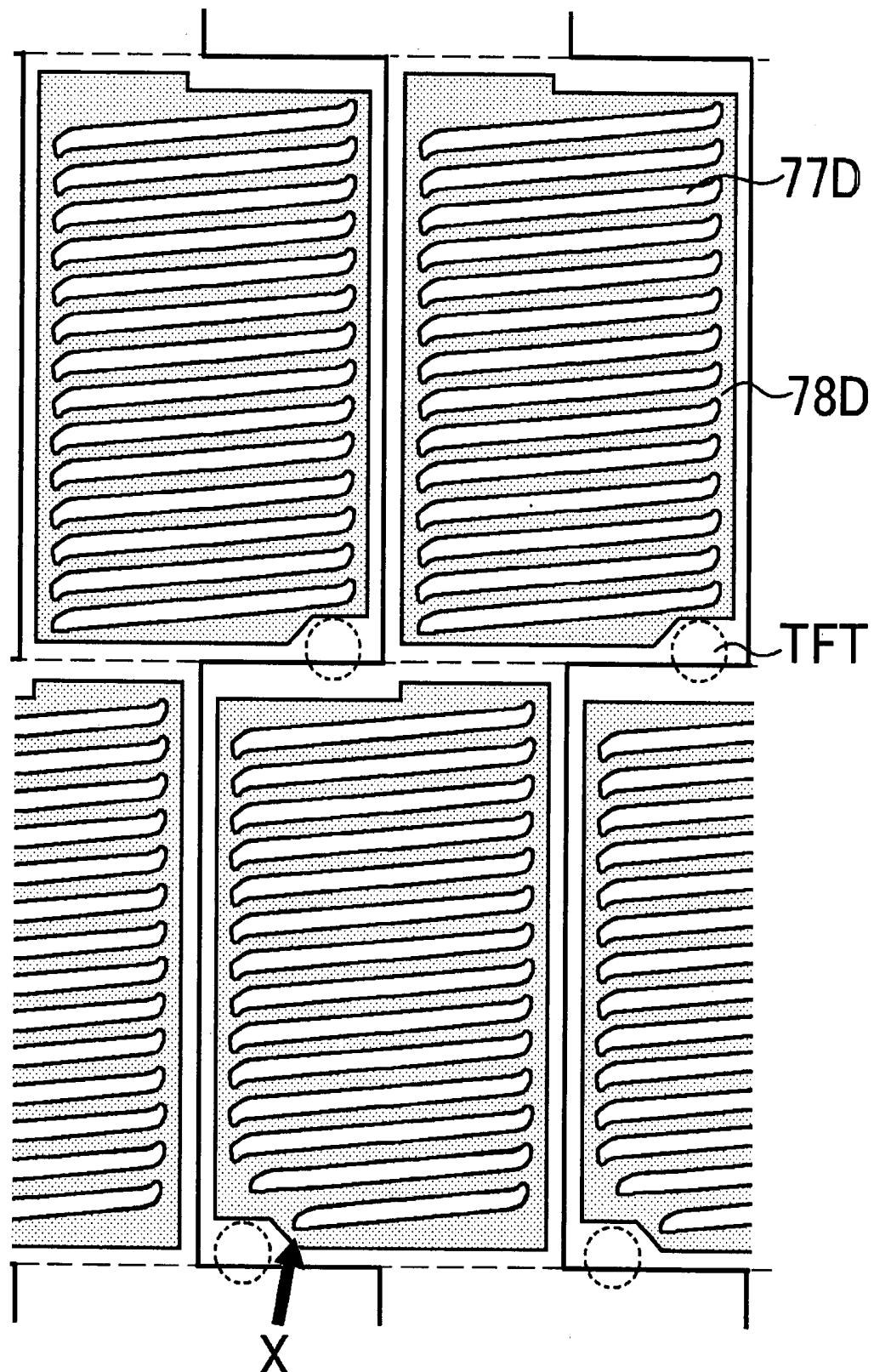

[0017] According to these FFS mode LCD panels in which pixels are arranged in the delta arrangement, the shape of the slits is preferably formed in the same shape at every pixel electrode in order to reduce display unevenness. However, the signal lines need to be arranged in a direction perpendicular to the scanning lines, although in a crank manner, by shortening the wiring length. As a result, the TFTs are positioned differently depending on whether they are in odd-numbered or even-numbered rows. Such a state will be described with reference to FIG. 17. FIG. 17 is a schematic plan view of several pixels of an FFS mode LCD panel 70D

in which pixels are arranged in a delta arrangement. The view shows a pixel electrode 78D and slits 77D provided at the pixel electrode 78D only, omitting other specific features. In FIG. 17, broken lines between the pixels show a boundary of each pixel, and solid lines show a path of the signal line. A portion enclosed within a broken line circle shows a position where the TFT of each pixel is provided.

[0018] In the FFS mode LCD panel 70D shown in FIG. 17, the TFTs of the pixels in odd-numbered rows are positioned at the lower right-hand side of the view, while the TFTs of the pixels in even-numbered rows are positioned at the lower left-hand side of the view, whereby the signal lines can be arranged linearly in a longitudinal direction, although in a crank manner, with a short wiring length. In the FFS mode LCD panel 70D, the shape of slits provided to each pixel electrode of the pixels in odd-numbered row are formed in an optimum shape to utilize a display opening effectively. But, the shape of the slits provided to each pixel electrode in even-numbered rows at a position shown by the X-mark in the view is different from that of odd-numbered rows. As they cannot form into the same shape, a symmetrical viewing angle cannot be obtained. As a result, when the FFS mode LCD panel 70D displays an image, spots are generated in a transverse direction. On the other hand, when the shape of the slits of the pixel electrode of each pixel is made into the same shape both in odd-numbered and even-numbered rows, the display opening cannot be effectively utilized. The same phenomenon occurs to FFS mode LCD panels having slits provided to the pixel electrodes in a dual-domain structure and pixels provided in a delta arrangement.

## SUMMARY

[0019] In consideration of the problems with FFS mode LCD panels having slits provided to pixel electrodes in a dual-domain structure and pixels provided in a delta arrangement as described above, the present invention provides an FFS mode LCD panel having symmetrical viewing angle without generating spots in a transverse direction. It also has a wide viewing angle, allows a bright display with its high transmittance and excellent display quality.

[0020] To obtain the above advantage, an FFS mode LCD panel of the present invention includes a plurality of scanning lines and common lines provided in parallel, a plurality of signal lines provided in a crank manner in a direction perpendicular to the scanning lines, and a plurality of pixel electrodes each formed between the plurality of scanning lines and signal lines in a delta arrangement. Each of the plurality of pixel electrodes includes portions defining a plurality of slits inclined in different directions to each other with respect to an axis parallel to the scanning lines and positioned between adjacent scanning lines. Among the pixel electrodes, pixel electrodes in odd-numbered rows and pixel electrodes in even-numbered rows are inverted to each other with respect to an axis perpendicular to the scanning lines.

[0021] In the above FFS mode LCD panel, the slits provided at both sides of the axis parallel to the scanning lines may be the same in number on both sides.

[0022] In the above FFS mode LCD panel, the common lines may be provided under the pixel electrodes with respect to the axis parallel to the scanning lines.

[0023] In the above FFS mode LCD panel, ends of the slits that are on both sides of and closest to the axis parallel to the scanning lines may be coupled on the axis parallel to the scanning lines.

[0024] By providing the features stated above, the present invention offers beneficial advantages as described below. With the above FFS mode LCD panel, while switching elements, such as TFTs to operate the pixel electrodes are positioned differently depending on whether they are in odd-numbered or even-numbered rows, the length of the signal lines can be shortened. Further, the slits provided at the pixel electrodes of each pixel are symmetric with respect to an axis parallel to the scanning lines, while keeping dead space at a minimum. Furthermore, the slits are symmetric by each row with respect to another axis perpendicular to the scanning lines. This makes it possible to maintain symmetrical viewing angle in both directions parallel and perpendicular to the scanning lines, utilizing a display opening. Also, no spots are generated in a transverse direction as in the related art, and an FFS mode LCD panel with a bright display can be obtained.

[0025] Furthermore, as the slits of the pixel electrodes provided at both sides of the axis parallel to the scanning lines are the same in number, the shape of the pixel electrodes is near-perfectly symmetric with respect to the axis parallel to the scanning lines within one pixel. This enhances symmetrical viewing angle in a direction perpendicular to the scanning lines, whereby an FFS mode LCD panel with a wider viewing angle and excellent display quality can be obtained.

[0026] Furthermore, as the common lines are not transparent as they are generally made of the same conductive material as the scanning lines, the common lines can shield a disclination portion generated at a position where the slits inclined in different directions are adjacent to each other. Therefore, an FFS mode LCD panel with excellent display quality can be obtained.

[0027] Furthermore, by coupling ends of the slits that are on both sides of and closest to the axis parallel to the scanning lines, an area of each pixel electrode can be utilized effectively. As the generation of disclination near the coupling point of both slits is suppressed, an FFS mode LCD panel with excellent display quality can be obtained.

#### BRIEF DESCRIPTION OF THE DRAWINGS

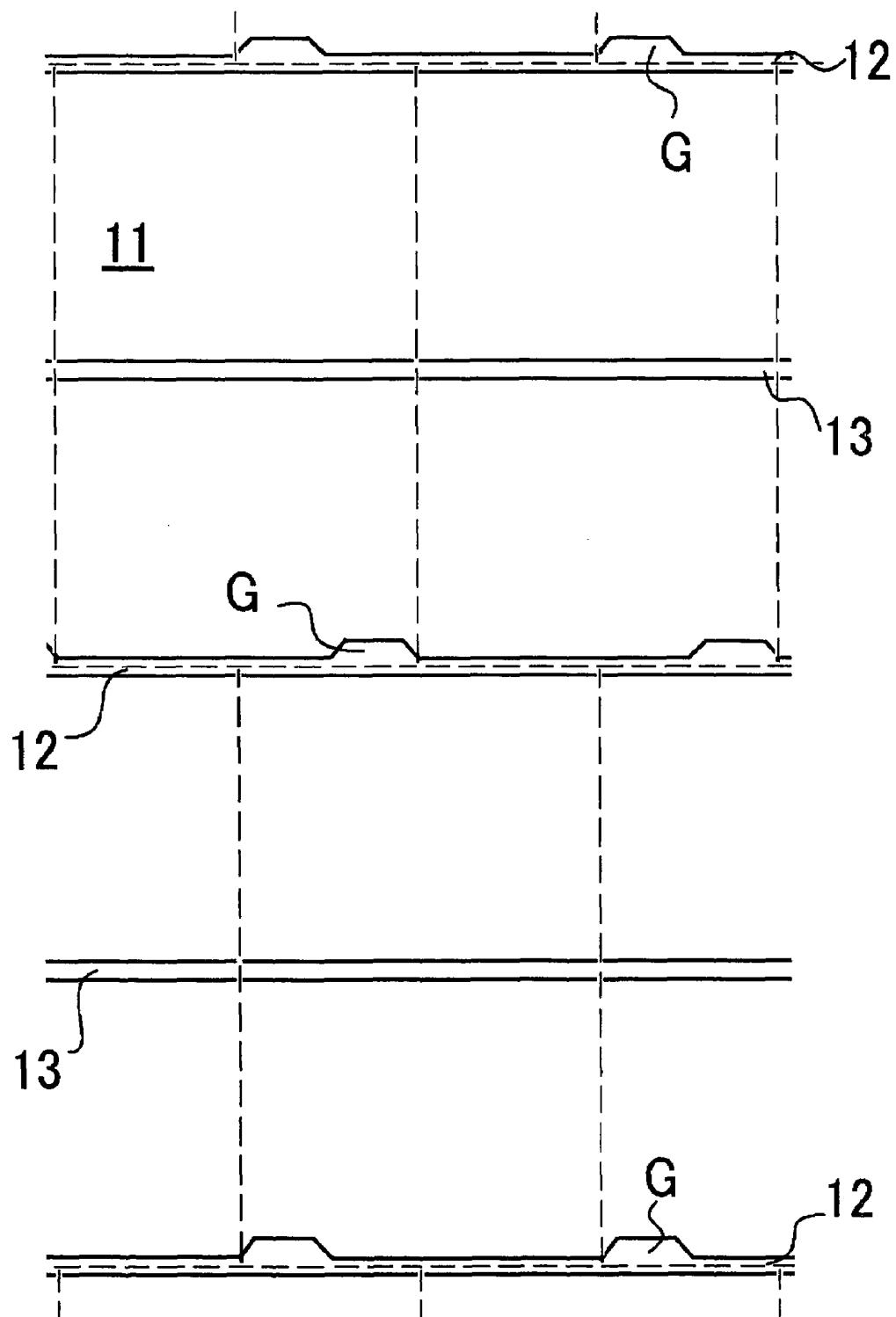

[0028] FIG. 1 is a diagram showing a pattern of scanning lines and common lines formed by a scanning line and common line forming process.

[0029] FIG. 2 is a diagram showing a pattern of common electrodes formed by a common electrode forming process.

[0030] FIG. 3 is a diagram showing a pattern of semiconductor layers formed by a semiconductor layer forming process.

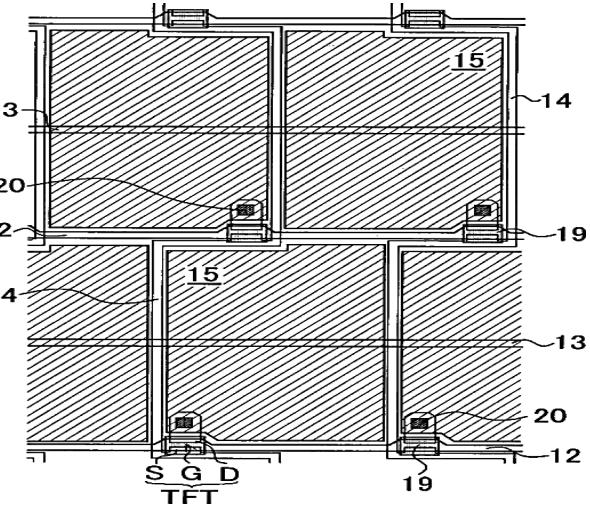

[0031] FIG. 4 is a diagram showing a pattern of signal lines and drain electrodes formed by a signal line and drain electrode forming process.

[0032] FIG. 5 is a diagram showing a pattern of contact holes formed by a contact hole forming process.

[0033] FIG. 6 is a plan view showing all the patterns of FIGS. 1 to 5 overlapping with each other without taking their vertical positional relationship into consideration.

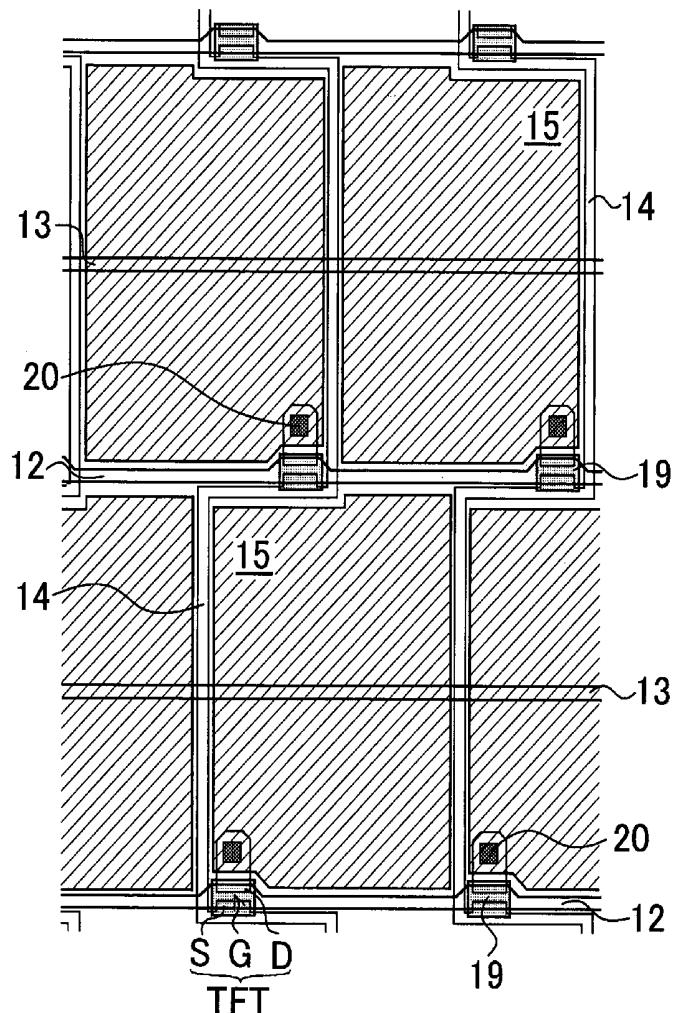

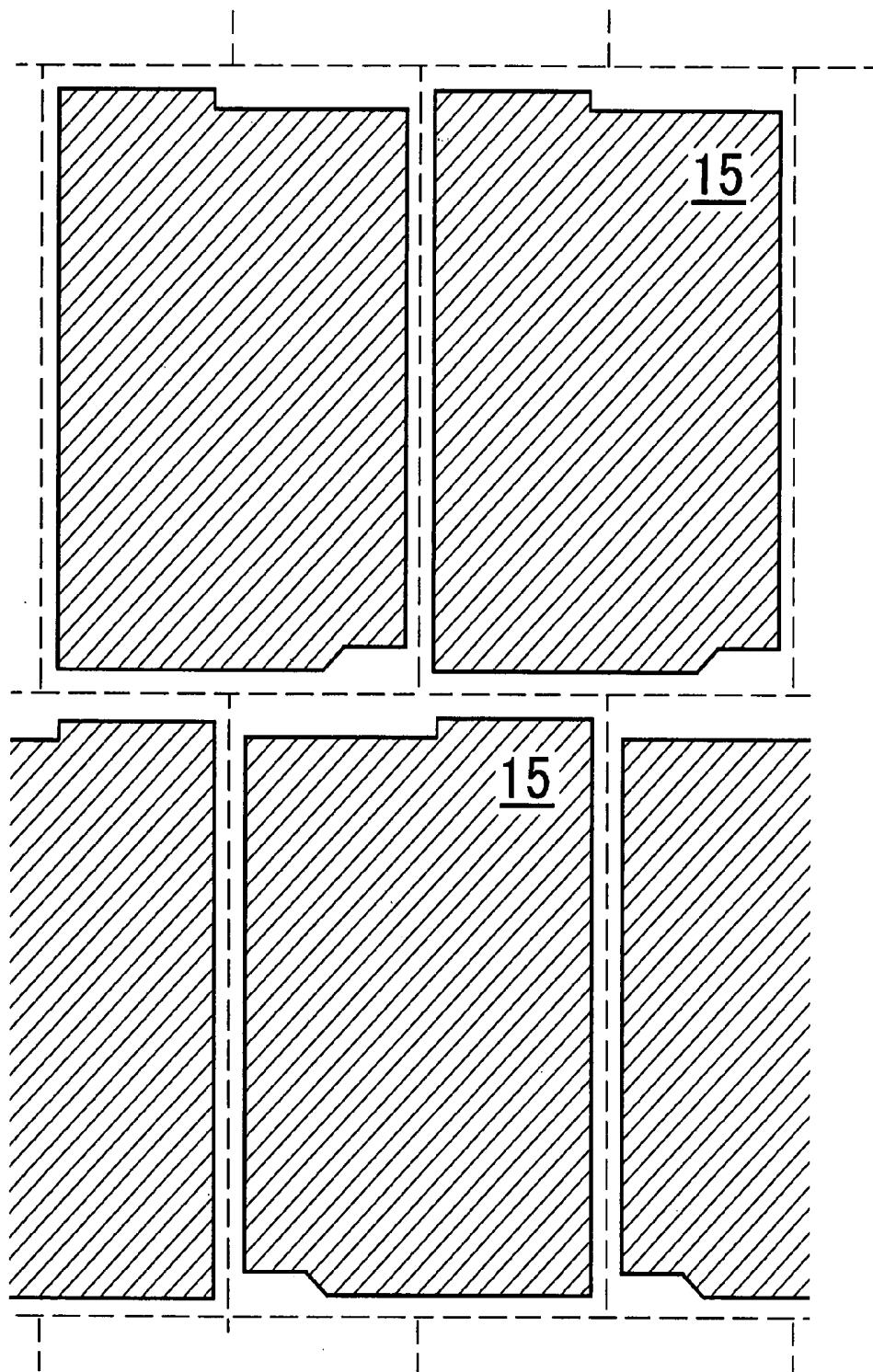

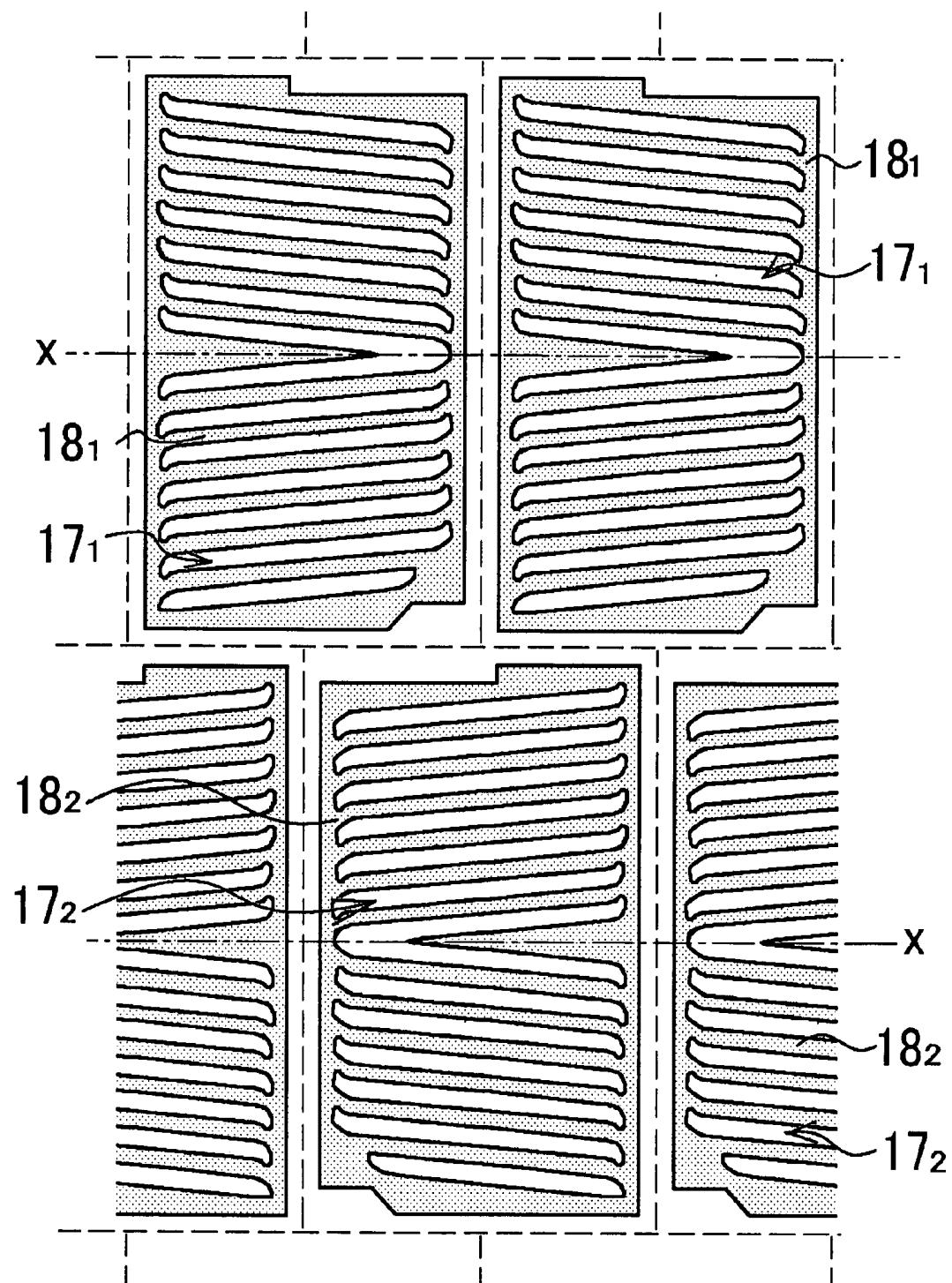

[0034] FIG. 7 is a diagram showing pixel electrodes formed by a pixel electrode forming process.

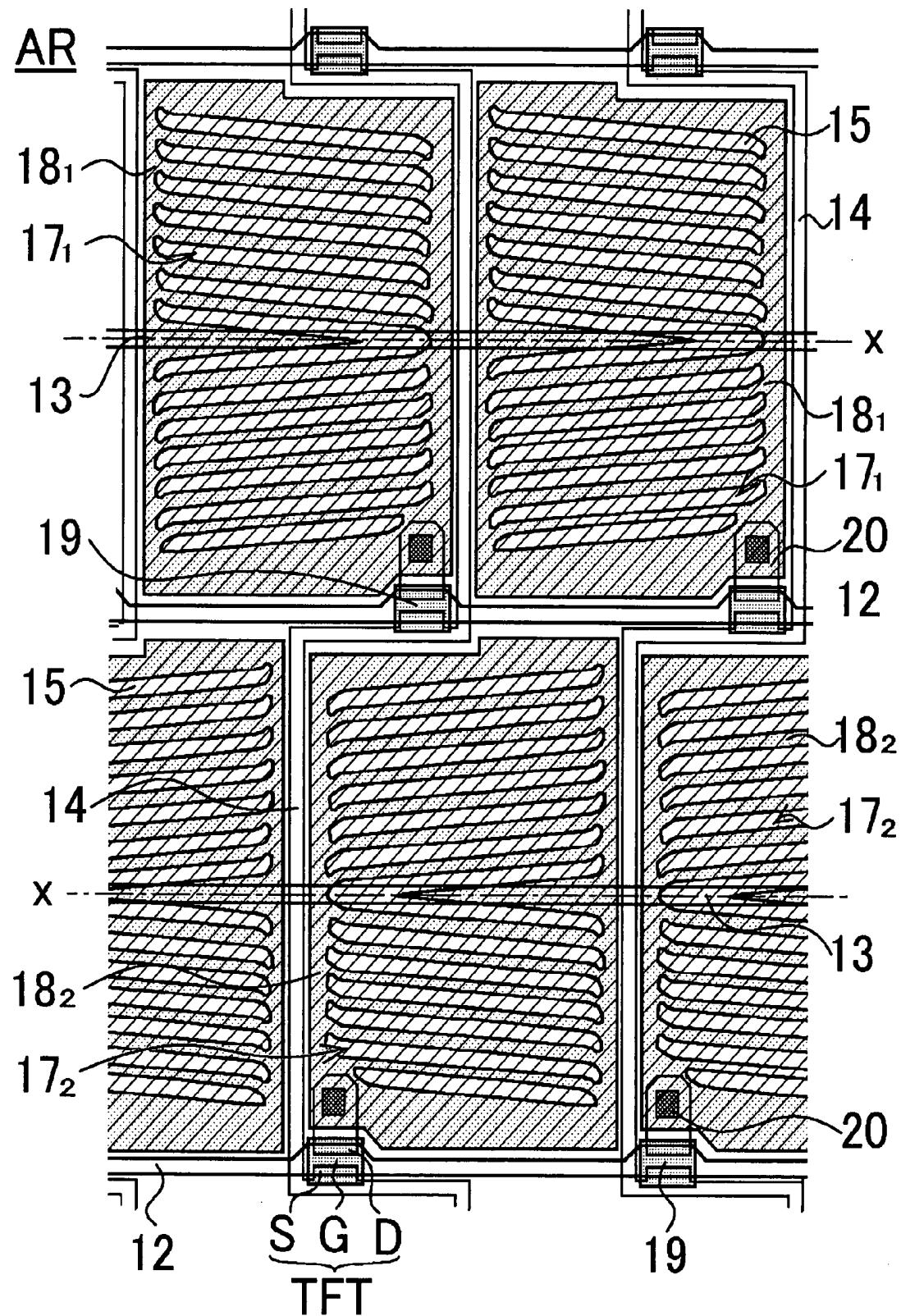

[0035] FIG. 8 is a plan view showing the patterns of FIGS. 6 and 7 overlapping with each other without taking their vertical positional relationship into consideration.

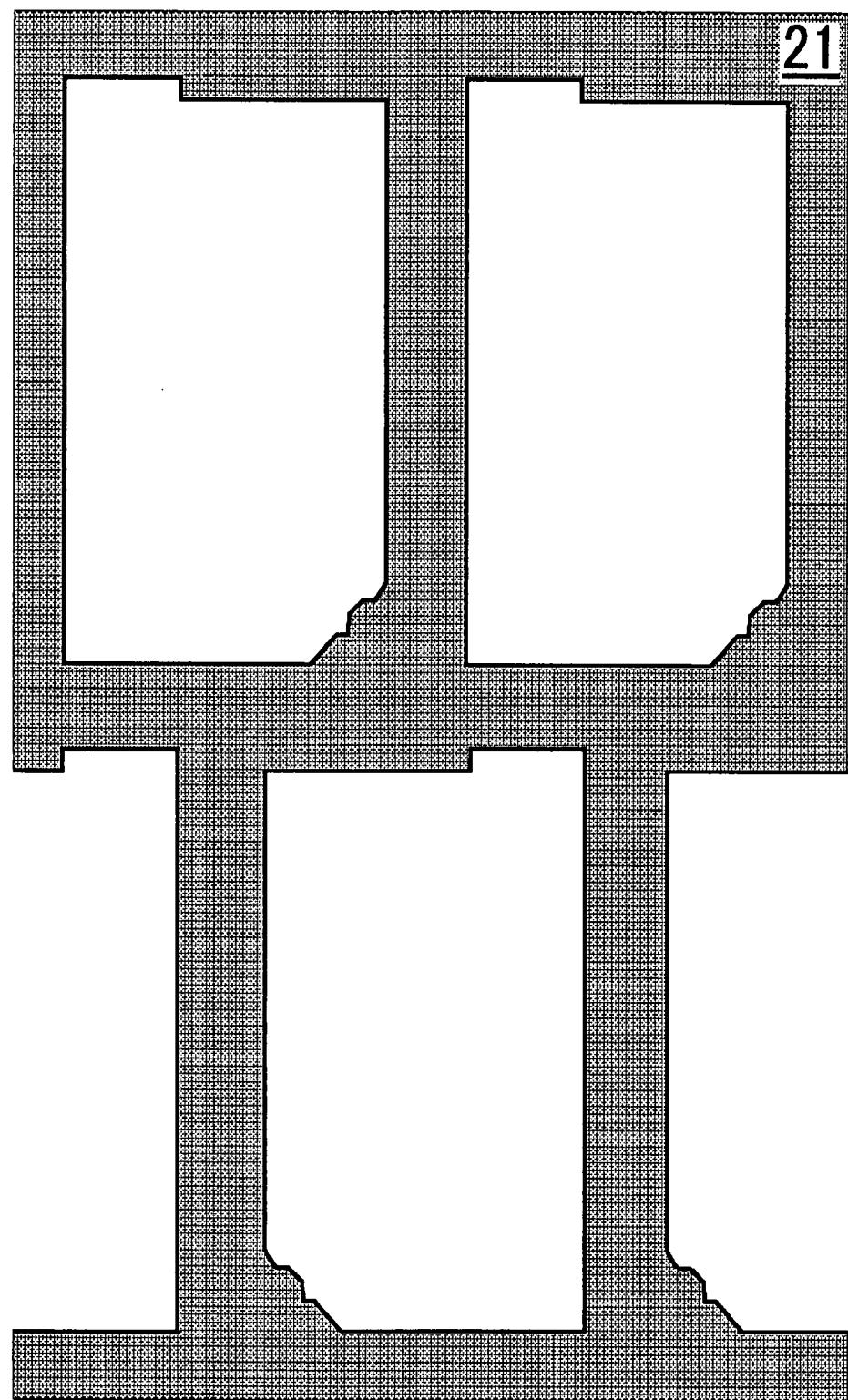

[0036] FIG. 9 is a diagram showing a pattern of a black matrix provided on a color filter substrate.

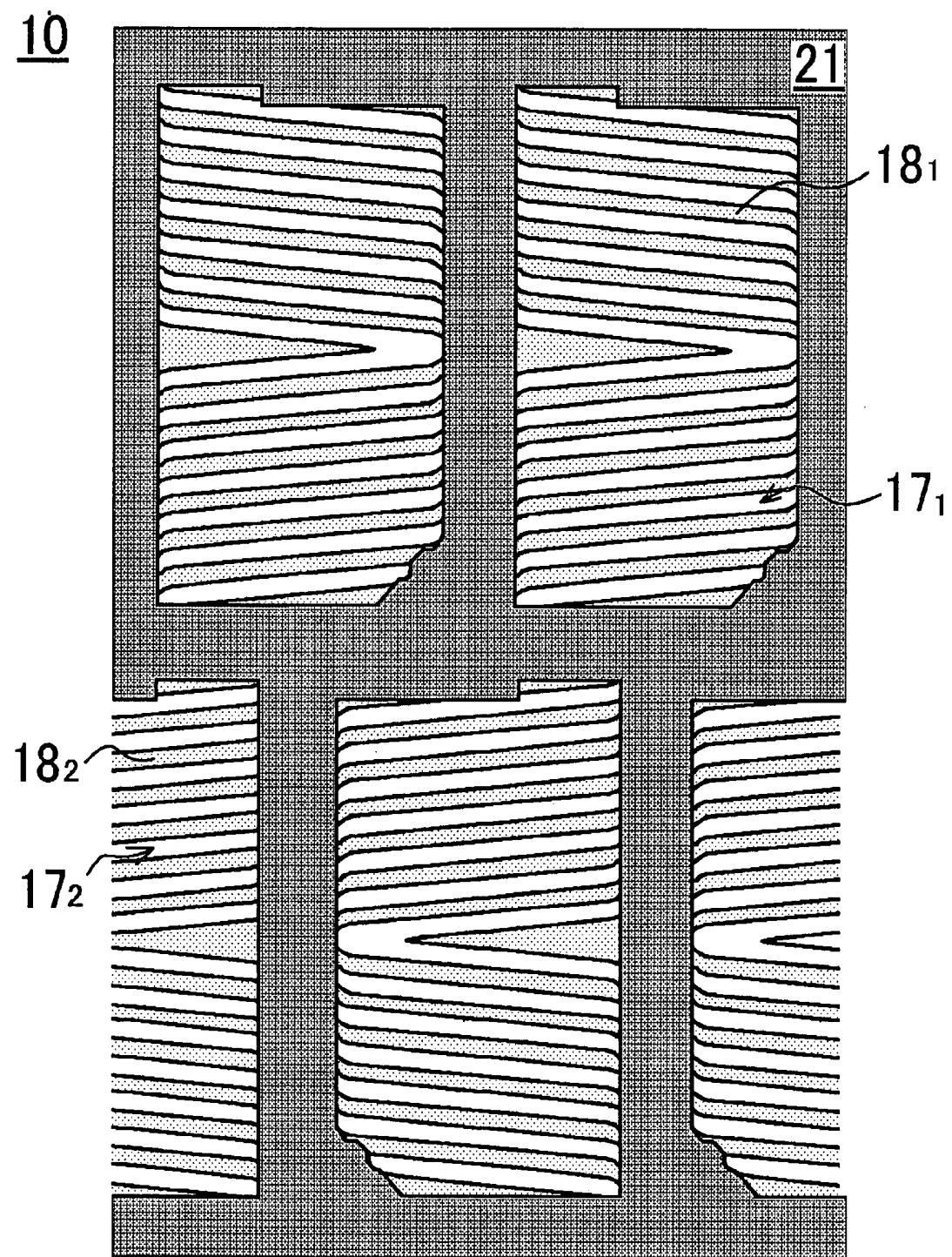

[0037] FIG. 10 is a diagram showing the pattern of FIG. 9 overlapped on the pattern of FIG. 7.

[0038] FIG. 11 is a schematic plan view of one pixel of an IPS mode LCD panel.

[0039] FIG. 12 is a schematic sectional view taken along the line XII-XII of FIG. 11.

[0040] FIG. 13 is a schematic plan view of one pixel of an FFS mode LCD panel.

[0041] FIG. 14 is a schematic sectional view taken along the line XIV-XIV of FIG. 13.

[0042] FIG. 15 is a plan view of one pixel of an FFS mode LCD panel with inclined slits.

[0043] FIG. 16 is a plan view of one pixel of an FFS mode LCD panel in a dual-domain structure.

[0044] FIG. 17 is a schematic plan view of several pixels of an FFS mode LCD panel 70D in which pixels are provided in a delta arrangement.

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0045] Hereinafter, preferred embodiments of the present invention will be described with reference to the drawings. The following embodiments are examples to show features of an FFS mode LCD panel, in order of manufacturing steps, to embody the concept of the present invention. The present invention is not intended to be specified to this FFS mode LCD panel, and may be equally applied to other embodiments not departing from the spirit and scope of the appended claims.

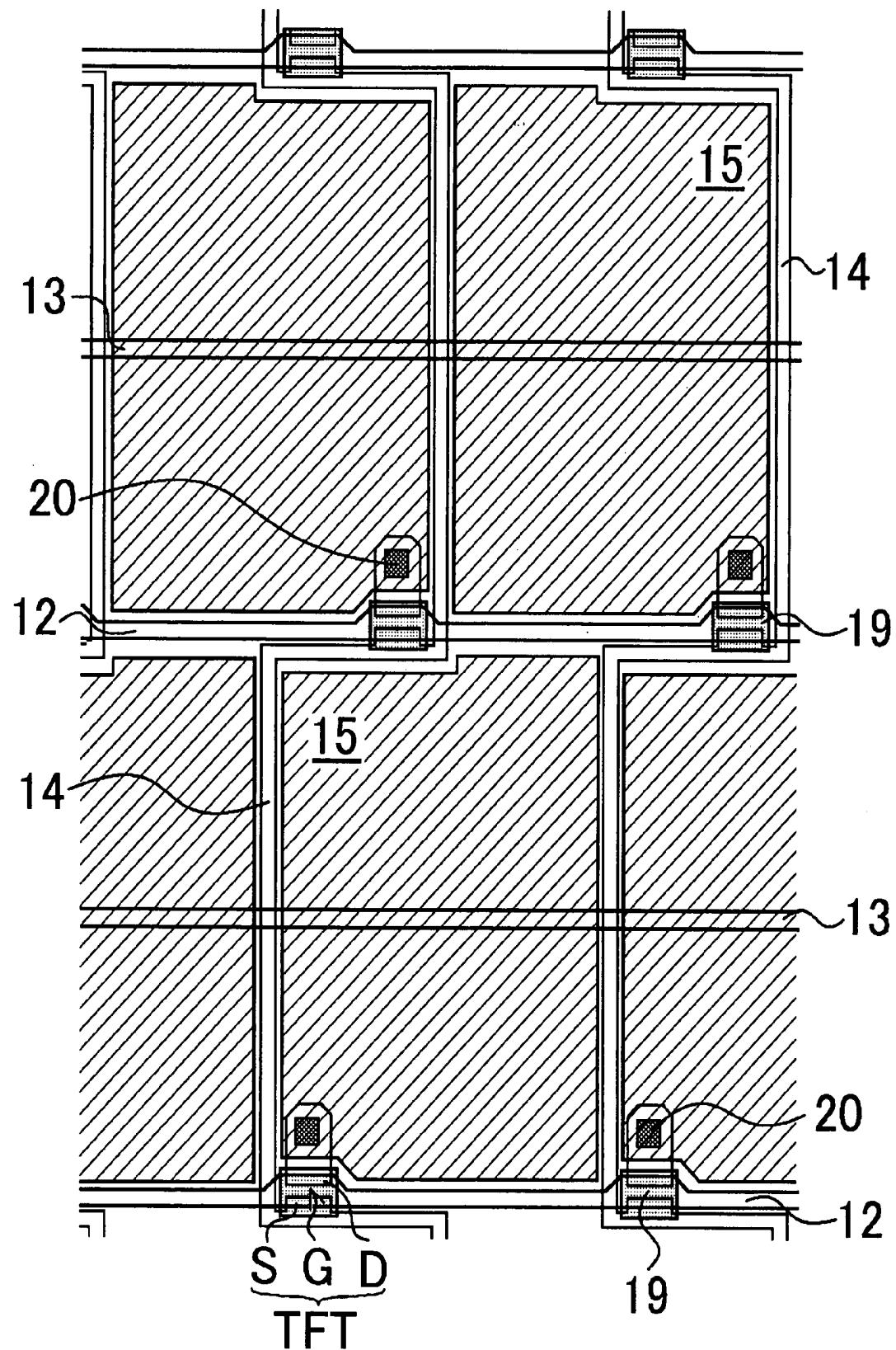

[0046] FIG. 1 is a diagram showing a pattern of scanning lines and common lines formed by a scanning line and common line forming process. FIG. 2 is a diagram showing a pattern of common electrodes formed by a common electrode forming process. FIG. 3 is a diagram showing a pattern of semiconductor layers formed by a semiconductor forming process. FIG. 4 is a diagram showing a pattern of signal lines and drain electrodes formed by a signal line and drain electrode forming process. FIG. 5 is a diagram showing a pattern of contact holes formed by a contact hole forming process. FIG. 6 is a plan view showing all the patterns of FIGS. 1 to 5 overlapping with each other without taking their vertical positional relationship into consideration.

[0047] FIG. 7 is a diagram showing a pattern of pixel electrodes formed by a pixel electrode forming process. FIG. 8 is a plan view of the patterns of FIGS. 6 and 7 overlapping with each other without taking their vertical positional relationship into consideration. FIG. 9 is a diagram showing a pattern of a black matrix provided on a color filter substrate. FIG. 10 is a diagram showing the pattern of FIG. 9 overlapped on the pattern of FIG. 7.

[0048] A manufacturing process of an FFS mode liquid crystal display (LCD) panel 10 of a first embodiment of the

invention will be described in separated processes for manufacturing an array substrate and manufacturing a color filter substrate.

#### Array Substrate Manufacturing Process

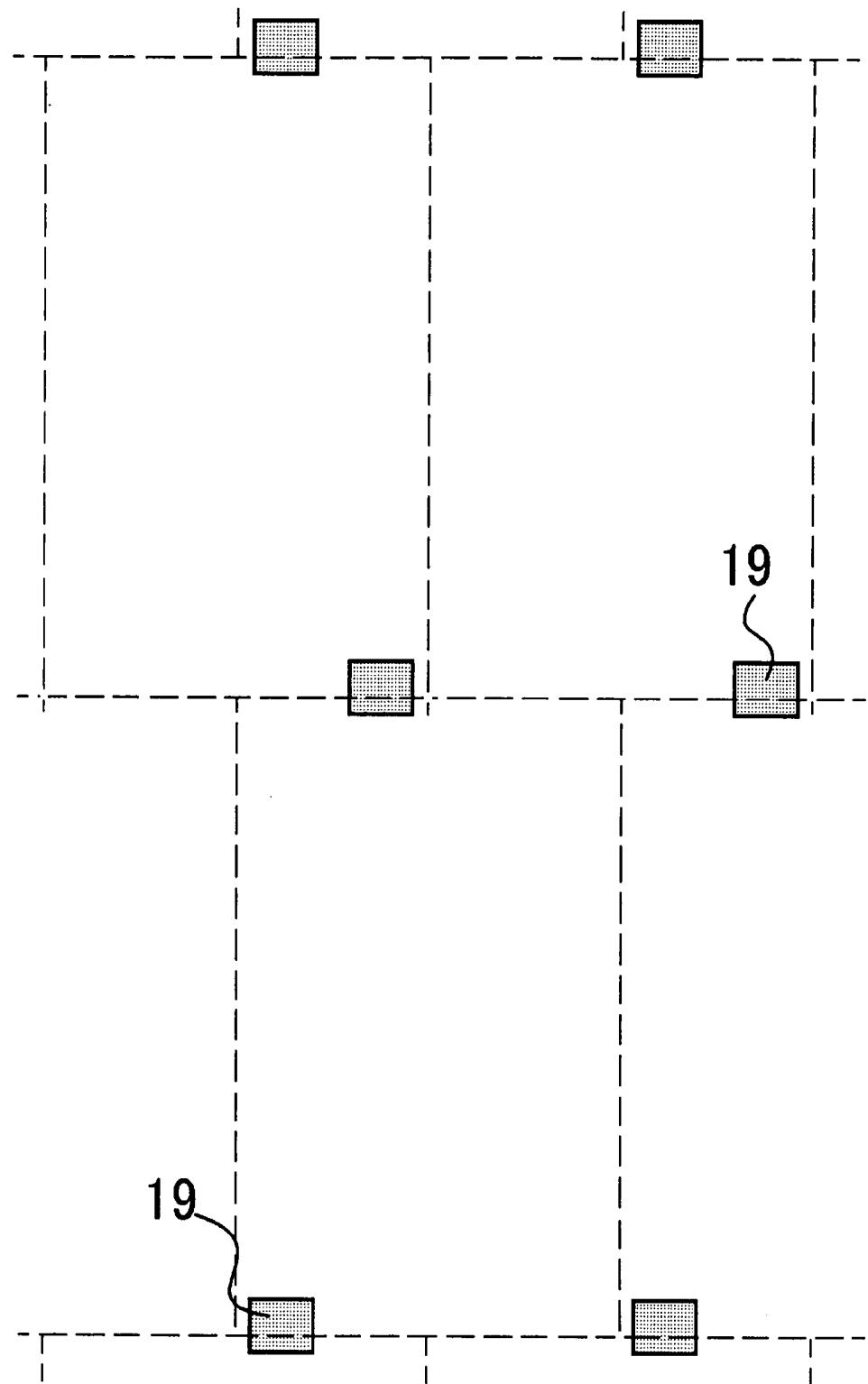

##### (1) Scanning Line and Common Line Forming Process

**[0049]** First, a two-layered film whose lower part is made of Al metal and surface is made of Mo metal is deposited over an entire surface of a transparent substrate **11** such as a glass substrate. Then, using a photolithography technology and an etching technology, a plurality of scanning lines **12** and a plurality of common lines **13** each made of the Mo—Al two-layered film are formed in parallel with each other, as in a pattern shown in FIG. 1. Here, a part of each scanning line **12** is protruded to be a gate electrode **G** of each TFT. Each of the common lines **13** is provided between adjacent scanning lines **12**. In FIG. 1, a broken line portion shows a boundary of each pixel (hereinafter, the same applies to other drawings).

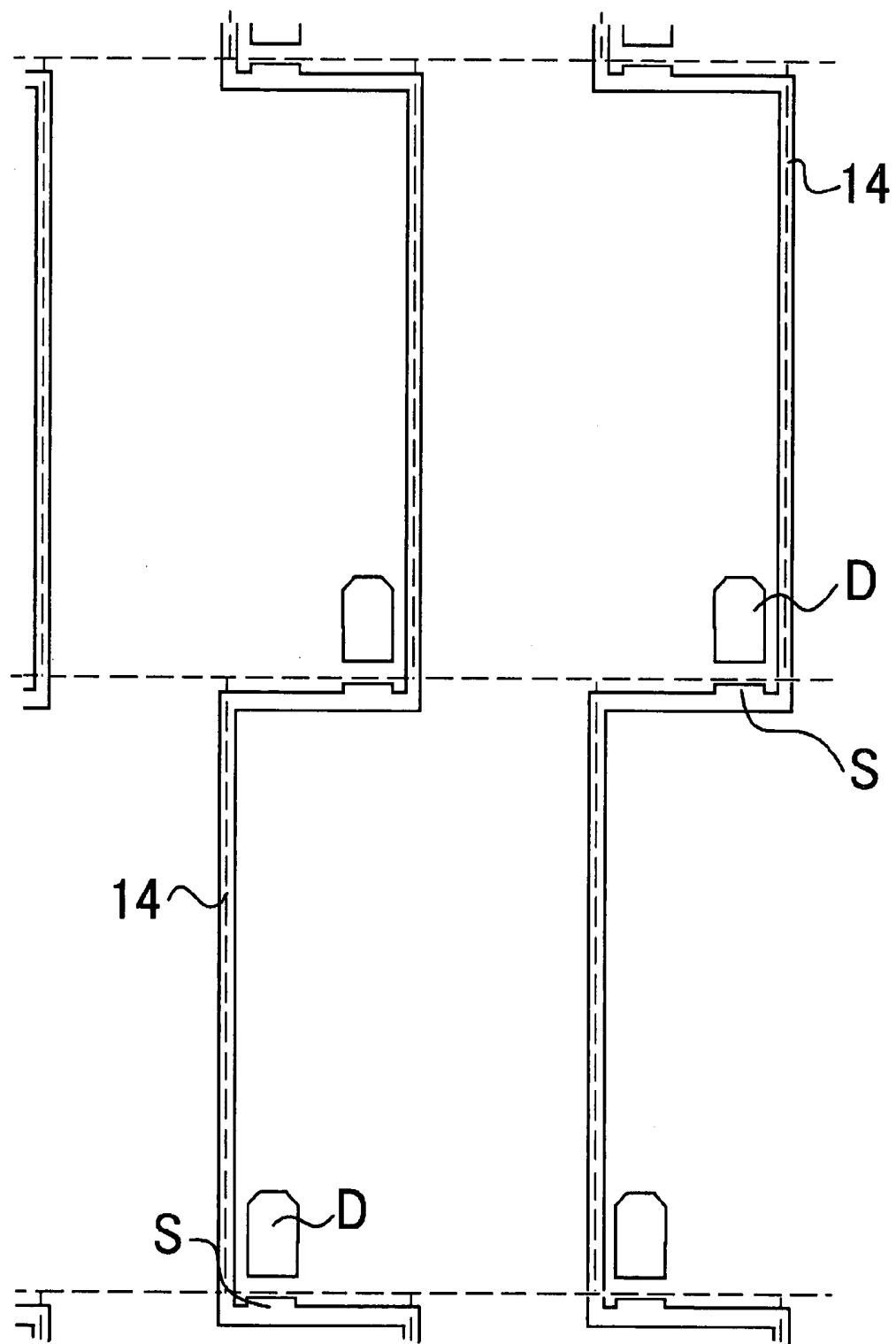

##### (2) Common Electrode Forming Process

**[0050]** A transparent conductive layer made of ITO is deposited over an entire surface of the transparent substrate **11** with which the scanning line and common line forming process (1) has been carried out. Using the photolithography technology and the etching technology, common electrodes **15** are formed as in a pattern shown in FIG. 2. The common electrodes **15** are electrically connected to the common lines **13**, but not connected to the scanning lines **12** or the gate electrodes **G**.

##### (3) Insulating Film Forming Process

**[0051]** An insulating film made of silicon nitride or silicon oxide is deposited over an entire surface of the transparent substrate **11** with which the common electrode forming process (2) has been carried out.

##### (4) Semiconductor Layer Forming Process

**[0052]** Using a chemical vapor deposition (CVD) method, an amorphous silicon (hereinafter, referred to as “a-Si”) layer is deposited over an entire surface of the transparent substrate **11** with which the insulating film forming process (3) has been carried out. Using the photolithography technology and the etching technology, a semiconductor layer **19** made of a-Si layer is formed above each gate electrode **G** as in a pattern shown in FIG. 3.

##### (5) Signal Line and Drain Electrode Forming Process

**[0053]** A conductive layer having a three-layered structure of Mo—Al—Mo is deposited over an entire surface of the transparent substrate **11** with which the semiconductor layer forming process (4) has been carried out. Using the photolithography technology and the etching technology, signal lines **14** and drain electrodes **D** are formed as in a pattern shown in FIG. 4. Portions serving as the source electrode **S**

and the drain electrode **D** included in the signal lines **14** overlap partially with the surface of the semiconductor layer **19**.

#### (6) Passivation Film Forming Process

**[0054]** A passivation film made of silicon nitride is deposited over an entire surface of the transparent substrate **11** with which the signal line and drain electrode forming process (5) has been carried out.

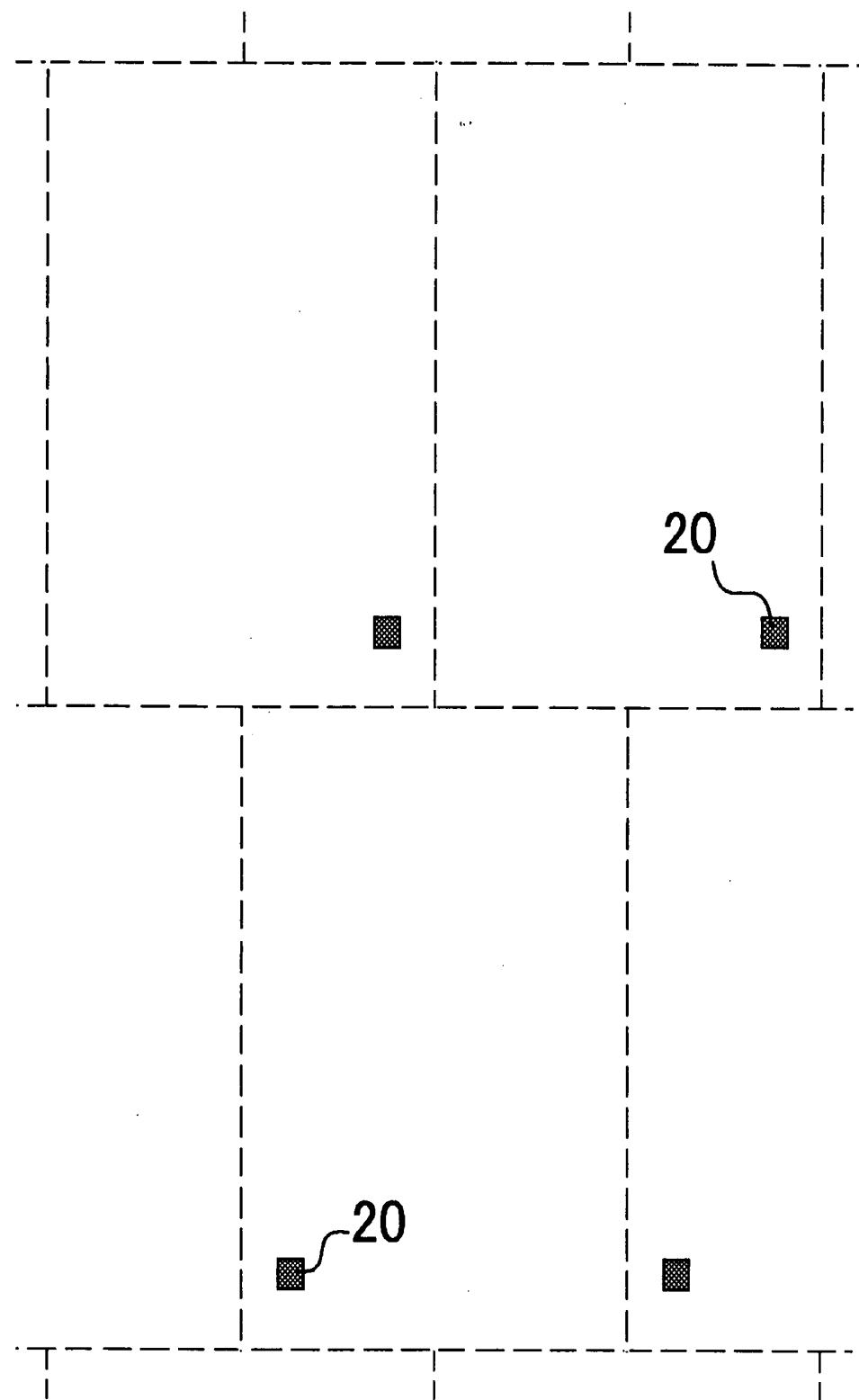

#### (7) Contact Hole Forming Process

**[0055]** To the transparent substrate **11** with which the passivation film forming process (6) has been carried out, a contact hole **20** is formed at a predetermined position of the passivation film to expose a part of the drain electrode **D**, using the photolithography technology and the etching technology. FIG. 6 is a plan view of the transparent substrate **11** with which the contact hole forming process has been carried out perspective without taking the vertical positional relationship of each layer into consideration.

#### (8) Pixel Electrode Forming Process

**[0056]** A transparent conductive layer made of ITO is deposited over an entire surface of the transparent substrate **11** with which the contact hole forming process (7) has been carried out. Using the photolithography technology and the etching technology, pixel electrodes **18<sub>1</sub>** of odd-numbered rows each having slits **17<sub>1</sub>** and pixel electrodes **18<sub>2</sub>** of even-numbered rows each having slits **17<sub>2</sub>** are formed in a pattern shown in FIG. 7. The pixel electrodes **18<sub>1</sub>** and **18<sub>2</sub>** are both electrically connected to the drain electrodes **D** via the contact holes **20**. FIG. 8 is a plan view of the transparent substrate **11** with which the pixel electrode forming process has been carried out perspective without taking the vertical positional relationship of each layer into consideration. By depositing a predetermined alignment layer (not shown) over an entire surface, the array substrate **AR** is completed. The shape and the like of the slits **17<sub>1</sub>** and **17<sub>2</sub>** provided to the pixel electrodes **18<sub>1</sub>** and **18<sub>2</sub>** are described later.

#### Color Filter Substrate Manufacturing Process

**[0057]** A color filter substrate is provided as follows. A layer of a black matrix material such as a photosensitive resin is deposited on an entire surface of a transparent substrate made of glass substrate and the like, which is not shown. Using a photolithography technology, a black matrix **21** having a pattern as shown in FIG. 9 is formed. A color filter layer of three primary colors of RGB, for example, is formed at a position corresponding to each pixel. Next, an overcoat layer is deposited on a surface of the color filter layer so as to planarize the surface. Then by forming a predetermined alignment layer on a surface of the overcoat layer and forming a spacer at a predetermined position, the color filter substrate is completed.

**[0058]** The array substrate **AR** is disposed to face the color filter substrate. By sealing the circumference with a sealing material and injecting a liquid crystal between both substrates, an FFS mode LCD panel **10** according to the embodiment is obtained. The dispositional relationship between the pixel electrodes **18<sub>1</sub>** and **18<sub>2</sub>** and the black matrix **21** of the FFS mode LCD panel according to the present embodiment is as shown in FIG. 10, when viewed from the side of the black matrix **21**.

[0059] Hereinafter, the shape of slits  $17_1$  and  $17_2$  provided respectively at the pixel electrodes  $18_1$  and  $18_2$  of the FFS mode LCD panel  $10$  according to the present embodiment will be described with reference to FIGS. 7, 8 and 10. The plurality of slits  $17_1$  provided to the pixel electrodes  $18_1$  in odd-numbered rows are in a state that are inclined toward the upper left-hand side or the lower left-hand side with respect to an axis  $x$  (see FIGS. 7 and 8) which is parallel to the scanning lines  $12$ . The axis  $x$  corresponds to a section where each common line  $13$  is positioned between adjacent scanning lines  $12$ . The same number of slits are arranged in line symmetry with respect to the axis  $x$ . Similarly, the plurality of slits  $17_2$  provided at the pixel electrodes  $18_2$  in even-numbered rows are in a state that are inclined toward the upper right-hand side or the lower right-hand side with respect to an axis  $x$ . The same number of slits are arranged in line symmetry with respect to the axis  $x$ . In the FFS mode LCD panel  $10$  according to the present embodiment, all the pixel electrodes of the pixels are in symmetry with respect to the axis  $x$  parallel to the scanning lines  $12$  by each pixel electrode. This results in reducing viewing angle dependence in display quality in a direction perpendicular to the scanning lines  $12$ . The number of slits provided on both sides of the axis  $x$  may be different from each other, but as there is no merit in making them different in numbers, it is preferable to provide the same number in order to secure the symmetrical viewing angle.

[0060] In the FFS mode LCD panel  $10$  according to the present embodiment, the plurality of slits  $17_1$  provided at the pixel electrodes  $18_1$  in odd-numbered rows and the plurality of slits  $17_2$  provided at the pixel electrodes  $18_2$  in even-numbered rows are inverted to each other with respect to the axis perpendicular to the scanning lines  $12$ . This means that the pixel electrodes  $18_2$  in the even-numbered rows can be manufactured by inverting (turn over) a manufacturing mask of the pixel electrodes  $18_1$  in the odd-numbered rows. Therefore, with the FFS mode LCD panel  $10$  according to the present embodiment, each row is in symmetry with respect to the axis perpendicular to the scanning lines, thereby reducing the viewing angle dependence in display quality also in a direction along the scanning lines  $12$ . In the FFS mode LCD panel  $10$  according to the present embodiment, the symmetrical viewing angle is maintained in directions both perpendicular to the scanning lines and along the scanning lines, utilizing a display opening. No spots are generated in a transverse direction as in the related art. Therefore, the FFS mode LCD panel with a bright display can be obtained.

[0061] In the FFS mode LCD panel  $10$  according to the present embodiment, the common lines  $13$  are made of a Mo—Al two-layered wiring which is the same material as the scanning lines  $12$ , thereby shielding light. The ends of slits that are on both sides and closest to the axis  $x$  parallel to the scanning lines  $12$  are coupled on the axis  $x$ , in other words, above the common lines  $13$ , and the slits form a V shape. As inclination directions of the slits that are on both sides and closest to the axis  $x$  parallel to the scanning line  $12$  are different, alignment directions from the axis  $x$  of liquid crystal molecules are different. Therefore, although a disclination is generated along the axis  $x$ , a portion where the disclination appears is shielded from light by the common lines  $13$ . As the generated disclination is difficult to view from outside, the display quality improves.

1. A fringe field switching mode liquid crystal display panel, comprising:

a plurality of scanning lines and common lines provided in parallel;

a plurality of signal lines provided in a crank manner in a direction perpendicular to said scanning lines; and a plurality of pixel electrodes each formed between said plurality of scanning lines and signal lines in a delta arrangement,

each of said plurality of pixel electrodes including portions defining a plurality of slits inclined in different directions to each other with respect to an axis parallel to said scanning lines and positioned between adjacent scanning lines, and

among said pixel electrodes, pixel electrodes in odd-numbered rows and pixel electrode in even-numbered rows being inverted to each other with respect to an axis perpendicular to said scanning lines.

2. The fringe field switching mode liquid crystal display panel according to claim 1, wherein said slits provided at both sides of said axis parallel to said scanning lines are same in number on both sides.

3. The fringe field switching mode liquid crystal display panel according to claim 1, wherein said common lines are provided under said pixel electrodes with respect to said axis parallel to said scanning lines.

4. The fringe field switching mode liquid crystal display panel according to claim 1, wherein ends of said slits that are on both sides of and closest to said axis parallel to said scanning lines are coupled on said axis parallel to said scanning lines.

\* \* \* \* \*

|                |                                                                    |         |            |

|----------------|--------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | FFS模式液晶显示面板                                                        |         |            |

| 公开(公告)号        | <a href="#">US20070229749A1</a>                                    | 公开(公告)日 | 2007-10-04 |

| 申请号            | US11/727005                                                        | 申请日     | 2007-03-23 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                       |         |            |

| 申请(专利权)人(译)    | 爱普生影像设备CORP.                                                       |         |            |

| 当前申请(专利权)人(译)  | 日本展示WEST INC.                                                      |         |            |

| [标]发明人         | KANEKO HIDEKI<br>HORIGUCHI MASAHIRO                                |         |            |

| 发明人            | KANEKO, HIDEKI<br>HORIGUCHI, MASAHIRO                              |         |            |

| IPC分类号         | G02F1/1343                                                         |         |            |

| CPC分类号         | G02F1/133707 G02F1/134363 G02F2201/40 G02F2201/128 G02F2001/134372 |         |            |

| 优先权            | 2006088208 2006-03-28 JP                                           |         |            |

| 其他公开文献         | US8711311                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>                    |         |            |

#### 摘要(译)

本发明提供一种边缘场切换 ( FFS ) 模式液晶显示面板，包括多条平行设置的扫描线12和公共线13，多条信号线14在垂直于扫描线的方向上以曲柄方式设置如图12所示，像素电极181和182分别以三角形排列形成在多条扫描线12和信号线14之间。每个像素电极181和182分别具有多个狭缝171和172，它们相对于与扫描线12平行并位于相邻扫描线12之间的轴x在彼此不同的方向上倾斜。像素电极181奇数行中的像素电极182和偶数行中的像素电极182相对于垂直于轴x的另一轴彼此反转。利用这些特征，FFS模式液晶显示面板提供对称视角，在横向不产生斑点，宽视角，具有高透射率的明亮显示和优异的显示质量。