## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2001/0000439 A1 Ohta et al.

### Apr. 26, 2001 (43) Pub. Date:

### (54) LIQUID CRYSTAL DISPLAY DEVICE WITH WIDE VIEWING ANGLE **CHARACTERISTICS**

(76) Inventors: Masuyuki Ohta, Mobara-shi (JP); Kazuhiko Yanagawa, Mobara-shi (JP); Keiichiro Ashizawa, Mobara-shi (JP); Yasuyuki Mishima, Mobara-shi (JP); Kazuhiro Ogawa, Mobara-shi (JP); Masahito Ohe, Mobara-shi (JP); Masahiro Yanai, Mobara-shi (JP);

Katsumi Kondo, Hitachinaka-shi (JP)

Correspondence Address: ANTONELLI TERRY STOUT AND KRAUS **SUITE 1800** 1300 NORTH SEVENTEENTH STREET **ARLINGTON, VA 22209**

(21) Appl. No.: 09/734,208

(22) Filed: Dec. 12, 2000

### Related U.S. Application Data

Continuation of application No. 09/443,305, filed on Nov. 19, 1999, now Pat. No. 6,201,590, which is a continuation of application No. 09/079,359, filed on May 15, 1998, now Pat. No. 6,064,460, which is a

continuation of application No. 08/610,340, filed on Mar. 4, 1996, now Pat. No. 5,754,266.

#### (30)Foreign Application Priority Data

| Mar. 17, 1995 | (JP) | 07-58874  |

|---------------|------|-----------|

| Apr. 28, 1995 | (JP) | 07-105862 |

|               |      | 07-191341 |

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |         |

|------|-----------------------|---------|

| (52) | U.S. Cl.              | <b></b> |

#### (57)ABSTRACT

A panel of a liquid crystal display, having a transparent insulating substrate, a gate line which is formed on the substrate, has a double-layered structure including a bottom metal layer and a top indium tin oxide layer, and extends to form a gate pad. A plurality of common electrodes which are formed on the substrate, connected to each other and separated from the gate line. An insulating layer covering the gate line and the common electrodes. A plurality of pixel electrodes which are formed on the insulating layer and are arranged between two of the common electrodes. A data line which is formed on the insulating layer and extends to form a data pad and a switching element having a gate connected to the gate line, a source connected to the data line and a drain connected to the pixel electrode.

FIG.2

FIG.3

FIG.4

FIG.5

•

FIG.6

FIG.7

FIG.8

FIG.9

FIG.11

Ω FIG.12A **A**0 g2 Ω

FIG.14A

# FIG.18

FIG.19

**FIG.20**

## FIG.21

## FIG.22

FIG.23

FIG.24

FIG.26

FIG.27

FIG.28

FIG.29

FIG.30A

FIG.30C

FIG.30B

## FIG.31A

FIG.31B

## FIG.32A

FIG.32B

FIG.34

FIG.35

FIG.36C

# FIG.37A

## FIG.38A

## FIG.38B

FIG.39

### LIQUID CRYSTAL DISPLAY DEVICE WITH WIDE VIEWING ANGLE CHARACTERISTICS

## CROSS REFERENCE TO RELATED APPLICATION

[0001] This is a continuation of U.S. application Ser. No. 09/443,305, filed Nov. 19, 1999, which is a continuation of U.S. application Ser. No. 09/079,359, filed May 15, 1998, now U.S. Pat. No. 6,064,460, which is a continuation of U.S. application Ser. No. 08/610,340, filed Mar. 4, 1996, now U.S. Pat. No. 5,754,266, the subject matter which is incorporated by reference herein. The application is also related to U.S. application Ser. No. 09/079,360, filed May 15, 1998, now U.S. Pat. No. 5,929,958, U.S. application Ser. No. 09/079,547, filed May 15, 1998, now U.S. Pat. No. 5,956, 111, and U.S. application Ser. No. 09/079,549, filed May 15, 1998, now U.S. Pat. No. 5,978,059, all of which are continuation applications of U.S. application Ser. No. 08/610, 340, filed Mar. 4, 1996, now U.S. Pat. No. 5,754,266.

#### BACKGROUND OF THE INVENTION

[0002] (1) Field of the Invention

[0003] The present invention relates to a liquid crystal display device and, more particularly, to a liquid crystal display device with wide viewing angle characteristics of the active matrix system using thin-film transistors.

[0004] (2) Description of the Prior Art

[0005] Active matrix liquid crystal display devices using active elements as represented by thin-film transistors (TFT) have now been widely used as display terminals of OA equipment since they are light in weight and have a high picture quality equivalent to that of cathode-ray tubes.

[0006] The display system of the liquid crystal display devices can be roughly divided into two. One is a system in which liquid crystals are sandwiched by two substrates having transparent electrodes and are driven by a voltage applied to the transparent electrodes, and light incident upon the liquid crystals and transmitted through the transparent electrode is modulated to achieve display. All of the products that are now available are based upon this system. Another one is a system in which liquid crystals are driven by an electric field which is nearly in parallel with the surface of a substrate between two electrodes that are formed on the same substrate, and light incident upon the liquid crystals through a gap between the two electrodes is modulated to provide display. Though no product which is based upon this system has yet been provided, it has a feature of a very wide viewing angle and a promising art in connection with active matrix liquid crystal display devices.

[0007] Features of the latter system have been disclosed in, for example, Japanese Patent Laid-Open No. 505247/1993, Japanese Patent Publication No. 21907/1988 and Japanese Patent Laid-Open No. 160878/1994.

#### SUMMARY OF THE INVENTION

[0008] A first problem that is to be solved by the present invention will be described below.

[0009] In a conventional liquid crystal display device of the latter system, an electric field which is substantially in parallel with the surface of the substrate is generated via thin-film electrodes having thicknesses of about several thousand angstroms, making it difficult to effectively generate the electric field in the liquid crystal layer compared with the former system.

[0010] Therefore, an electric field stronger than that of the former-system must be generated between the electrodes, resulting in an increase in consumption of electric power and making it necessary to employ, as a driver unit, an LSI having an increased breakdown voltage.

[0011] A second problem is that in the former system, a metal material having good light-shielding property has been used as a black matrix (light-shielding film) that covers the portions where undesired light passes through. When this metal material is used for the latter system, however, the electric field between the electrodes is absorbed by the black matrix, making it difficult to generate an effective electric field between the electrodes.

[0012] A third problem is that in the former system, the electric field from a video signal line is absorbed by a counter electrode that is formed on nearly the whole surface of a substrate opposed to the substrate on which the video signal line is formed, and the electric field formed by the video signal line does not affect the electric field established between the electrodes. In the latter system in which no electrode exists on the substrate opposed to the substrate on which the video signal line is formed, however, the electric field formed by the video signal line affects the electric field established between the electrodes, giving rise to the occurrence of crosstalk (particularly in the vertical direction of the screen) in which video information of other rows affect the display and, hence, appearance of striped image called vertical smear.

[0013] A fourth problem is that in the latter system in which the counter electrode can be formed linearly, the resistance of the counter electrode from the input end to the other end thereof becomes very larger than that of when the counter electrode is formed in a planar shape in the former system. Therefore, the counter voltage is not sufficiently fed to the terminal pixels, and the counter voltage is distorted by the video signals due to the capacitance at a portion where the counter voltage signal line intersects the video signal line, resulting in the occurrence of crosstalk (particularly, in the horizontal direction of the screen) and appearance of striped image called lateral smear.

[0014] A fifth problem is that in the latter conventional system in which the pixel electrode PX and the counter electrode CT are arranged on the same substrate, the opening area that contributes to the display decreases by the amount corresponding to the arrangement of the counter voltage signal line CL compared with that of the former conventional system.

[0015] Moreover, an increase in the number of intersecting points of the wirings arranged in the form of a matrix results in increased chances of short-circuiting among the wirings and in an increase in the parasitic capacitance among the signal lines, hindering smooth transfer of signals.

[0016] Besides, while the pixel electrode PX in the former system has a planar shape, the pixel electrode PX of the latter system has a narrow strip shape or a line shape, often causing pixels to become defective due to disconnection of the line.

[0017] A sixth problem is that the latter conventional system may employ an AC driving method to apply an AC voltage to the liquid crystal layer, e.g., an AC driving method which inverts a drive voltage applied to the liquid crystal layer after every horizontal scanning interval. In this case, when a pulse voltage is applied to the counter voltage signal line CL having a resistance R and a capacitance C, the pulse voltage is distorted. Hereinafter, the sixth problem will be described with reference to FIGS. 25 and 26.

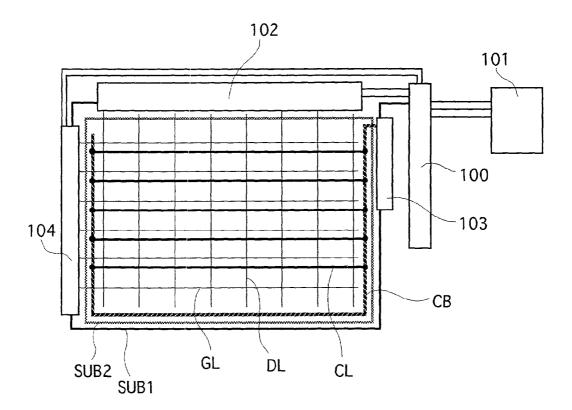

[0018] FIG. 25 is a diagram of an equivalent circuit of a transmission passage for transmitting a drive voltage applied to the counter voltage signal line CL in a liquid crystal display device of the latter system, and FIG. 26 is a diagram showing waveforms of a drive voltage applied to the counter electrode CT at each of the points.

[0019] The transmission passage for transmitting a drive voltage applied to the counter electrode CT includes chiefly resistors 50 of the counter voltage signal line CL, a resistor 51 of a common bus line CB between a common voltage driver unit 52 and the counter voltage signal line CL, and storage capacitors 53 in the pixels. Therefore, when a liquid crystal layer is driven by an AC drive voltage, the waveform of the drive voltage (pulse voltage) fed to the counter electrode CT from the common voltage driver unit 52 of a common voltage generator and driver unit 103 is distorted.

[0020] As will be understood from a counter voltage waveform 54 at point D, a counter voltage waveform 55 at point E, a counter voltage waveform 56 at point F and a counter voltage waveform 57 at point G shown in FIG. 26, the distortion of waveform of the drive voltage fed to the counter electrode CT increases with an increase in the distance, from point D, to point G.

[0021] As a result, the electric field between the pixel electrode PX and the counter electrode CT in the pixels differs, irregular brightness (irregular display) occurs along the counter voltage signal line CL, and the display quality of the liquid crystal display panel is impaired.

[0022] This becomes a serious problem particularly when there is employed an AC drive system which inverts the drive voltage applied to the liquid crystal layer after every horizontal scanning interval.

[0023] When the counter voltage signal line CL is broken even at one place, furthermore, it is impossible to drive the liquid crystals since the drive voltage is no longer fed to the counter electrode CT of the pixels after the broken portion, impairing the display quality of the liquid crystal display panel.

[0024] According to the constitution of the prior art, furthermore, the thickness differs by a thickness of the signal line depending upon the portions where the video signal line DL and the scanning signal line GL are led out and the portions where such signal lines are not led out. Therefore, the gap becomes irregular in the whole panel impairing the display quality of the liquid crystal display panel.

[0025] The object of the present invention is to provide a liquid crystal display device of high picture quality that can be efficiently fabricated, that is powered on a low voltage and consumes small amounts of electric power, and has wide viewing characteristics as a result of solving the abovementioned problems inherent in the prior art.

[0026] Description of representatives of the invention disclosed in this specification is as follows.

[0027] Means for solving the above-mentioned first to fourth problems will be described below.

[0028] Means 1.

[0029] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a pixel electrode and a counter electrode formed between one of the substrates and the liquid crystal layer, in order to change the light transmission factor or the light reflection factor of the liquid crystals by use of an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the one substrate, wherein the dielectric constant anisotropy  $\Delta \epsilon$  and the effective thickness deff of the liquid crystal layer, the width Wp of the pixel electrode in the lateral direction, the width Wc of the counter electrode in the lateral direction, and the gap L between the pixel electrode and the counter electrode satisfy the following relationships,

[0030]  $\Delta \epsilon > 0$ , 2.8  $\mu$ m < deff < 4.5  $\mu$ m,

[0031] 1.2×deff<Wp<L/1.2, and 1.2×deff<Wc<L/1.2

[0032] Means 2.

[0033] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a pixel electrode and a counter electrode formed between the one of the substrates and the liquid crystal layer, in order to change the light transmission factor or the light reflection factor of the liquid crystals by use of an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the one substrate, wherein the dielectric constant anisotropy  $\Delta \varepsilon$  and the effective thickness deff of the liquid crystal layer, the width Wp of the pixel electrode in the lateral direction, the width Wc of the counter electrode in the lateral direction, and the gap L between the pixel electrode and the counter electrode satisfy the following relationships,

[0034]  $\Delta \epsilon < 0$ , 4.2  $\mu$ m<deff<8.0  $\mu$ m

[0035] 1.2×deff<Wp<L/1.2, and 1.2×deff<Wc<L/1.2

[0036] Means 3.

[0037] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a pixel electrode and a counter electrode formed between one of the substrates and the liquid crystal layer, whereby pixels are formed such that the light transmission factor or the light reflection factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the one substrate, and forming a black matrix surrounding the pixels on a plane, wherein the black matrix is made of an insulating material.

[0038] Means 4.

[0039] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is

applied a video signal from the video signal line via the drain electrode and a thin film transistor, and a counter electrode, that are formed between one of the substrates and the liquid crystal layer, whereby pixels are formed such that the light transmission factor or the light reflection factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the one substrate, wherein the counter electrodes of adjacent pixels are positioned on both sides of the video signal line, and the widths of the counter electrodes are not smaller than one-half the width of the video signal line.

[0040] Means 5.

[0041] In the means 4, the counter electrode is made of an anodizable metal, and a self-anodized film of this metal covers the counter electrode.

[0042] Means 6.

[0043] In the means 5, the counter electrode is made of aluminum.

[**0044**] Means 7.

[0045] In the means 5, the counter electrode is formed simultaneously with the gate signal line which is made of a metal layer having anodized surface.

[0046] Means 8.

[0047] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is applied a video signal from the video signal line via the drain electrode and a thin film transistor, a gate signal line connected to a gate electrode which turns the thin film transistor on, and a counter electrode to which a counter voltage is applied via a counter voltage signal line, which are formed between one of the substrates and the liquid crystal layer, whereby pixels are formed such that the light transmission factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the surface of the one substrate, wherein the gate signal line is made of a metal layer having anodized surface, and the counter voltage signal line is made of the same material as that of the gate signal line.

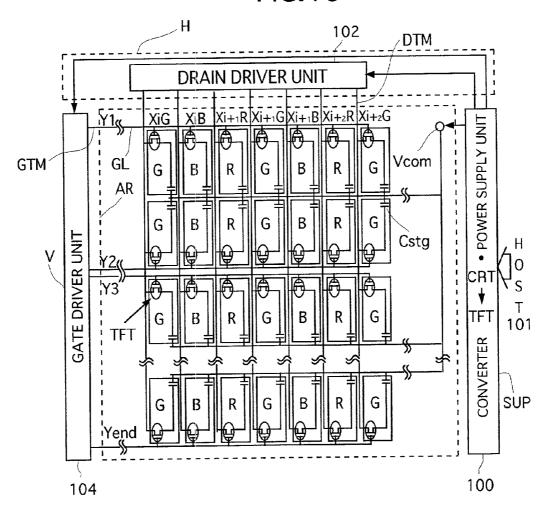

[0048] Means 9.

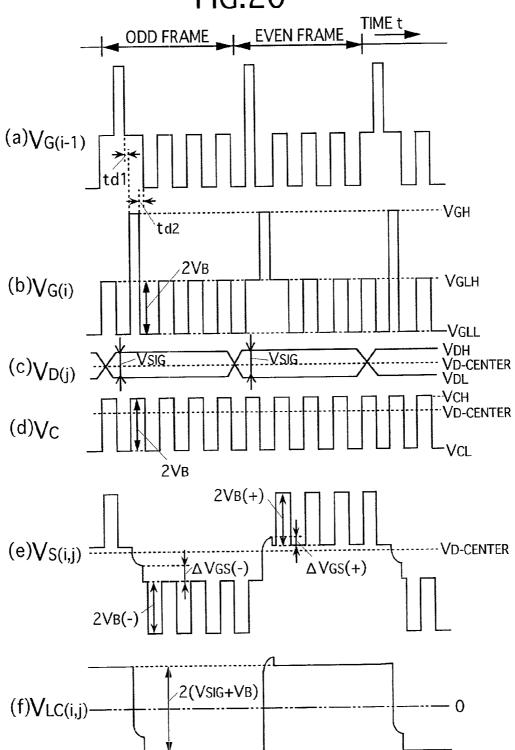

[0049] In the means 8, the counter voltage signal line is made of aluminum.

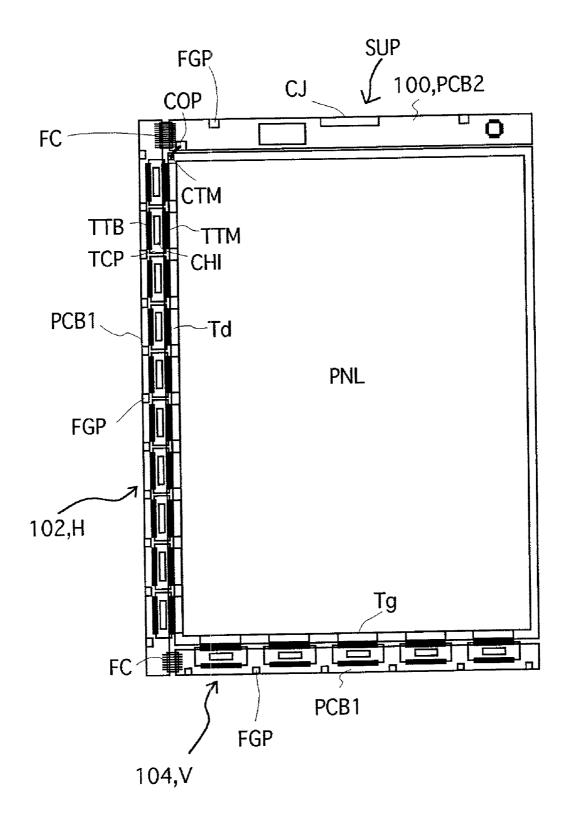

[0050] Means 10.

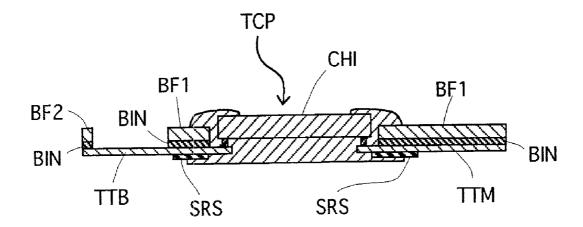

[0051] In the means 8, the counter voltage signal line and the gate signal line are formed through the same step.

[0052] Means 11.

[0053] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is applied a video signal from the video signal line via the drain electrode and a thin film transistor, a gate electrode for turning the thin film transistor on, a counter electrode to which a counter voltage is applied via a counter voltage

signal line, and a storage capacitor formed by superposing part of the pixel electrode on part of the counter voltage signal line via an interlayer insulating film, which are formed between one of the substrate and the liquid crystal layer, whereby pixels are formed such that the light transmission factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the surface of the substrate, wherein the counter voltage signal line is made of aluminum having anodized surface.

[0054] Means 12.

[0055] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is applied a video signal from the video signal line via the drain electrode and a thin film transistor, a gate electrode for turning the thin film transistor on, and a counter electrode to which a counter voltage is applied via a counter voltage signal line, which are formed between the one substrate and the liquid crystal layer, whereby pixels are formed such that the light transmission factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the substrate, wherein a common bus line is provided to connect in common the counter voltage signal lines of the plurality of pixels, and the common bus line has a multilayer structure of two or more conductive layers.

[0056] Means 13.

[0057] In the means 12, the common bus line is made up of a conductive layer of the same material as that of the gate electrode and a conductive layer of the same material as that of the video signal line, and these conductive layers are formed simultaneously with the formation of the gate electrode and the video signal line.

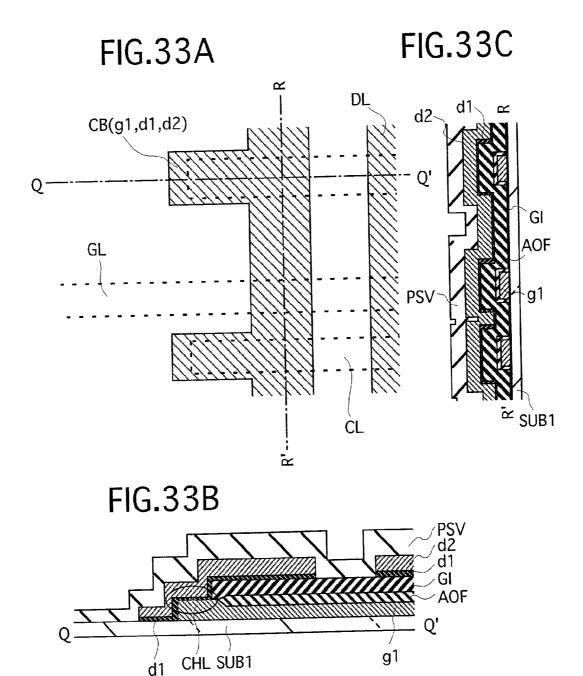

[0058] In order to solve the above-mentioned fifth problem according to the present invention, the counter voltage signal line and the drain electrode are used in common by two pixels adjacent to each other in the direction of column, and the storage capacitor is formed in a part of the counter voltage signal line.

[0059] Means 14.

[0060] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is applied a video signal from the video signal line via the drain electrode and a thin film transistor, a gate electrode for turning the thin film transistor on, a counter electrode to which a counter voltage is applied via a counter voltage signal line, and a storage capacitor formed by superposing part of the pixel electrode on part of the counter voltage signal line via an interlayer insulating film, which are formed between the one of the substrates and the liquid crystal layer, whereby pixels are formed such that the light transmission factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the substrate, wherein the scanning signal lines connected to the gate electrodes and the counter voltage signal lines connected to the counter electrodes are arranged

in parallel in a first direction of the plurality of pixels that are arranged in the form of a matrix, and the video signals connected to the drain electrodes are arranged in parallel in a second direction, and wherein the counter voltage signal line is used in common by two pixels adjacent to each other in the second direction.

[0061] Means 15.

[0062] In the means 14, the gate electrodes, scanning signal lines and thin-film transistor elements of the two pixels adjacent to each other in the direction of column are so arranged as to be opposed to each other, the drain electrodes are used in common by the -two pixels, and the wirings from the drain electrodes to the video signal lines are arranged between the opposing scanning signal lines.

[0063] Means 16.

[0064] In the means 15, the thin-film transistors are formed along the scanning signal line in such a way that the plurality of the thin-film transistors are connected to the pixel electrodes in a pixel;

[0065] Means for solving the above-mentioned sixth problem will be described below.

[0066] Means 17.

[0067] A liquid crystal display device having a pair of substrates at least one of which is transparent, a liquid crystal layer sandwiched by the pair of substrates, a video signal line, a drain electrode, a pixel electrode to which is applied a video signal from the video signal line via the drain electrode and a thin film transistor, a gate signal line connected to a gate electrode for turning the thin film transistor on, and a counter electrode to which a counter voltage is applied via a counter voltage signal line, which are formed between one of the substrates and the liquid crystal layer, whereby pixels are formed such that the light transmission factor of the liquid crystals is changed by an electric field which is established between the pixel electrode and the counter electrode and has a component in parallel with the substrate, wherein the ends on both sides of the counter voltage signal line are connected to a common bus line and are, further, connected to a common voltage generating and driving means.

[0068] Means 18.

[0069] In the means 17, thickness adjustment patterns are provided on the non-display area of one of the substrates, and the thickness adjustment patterns are made of the same material and have the same thickness as that of the common bus line.

[0070] Means 19.

[0071] In the means 17 or 18, a thickness adjustment film made of the same material and having the same thickness as that of the gate electrode is provided over or under the common bus line in the non-intersecting areas except the areas where the common bus line intersects the gate signal line or the video signal line and except the areas where the common bus line is connected to the counter voltage signal line.

[0072] Means 20.

[0073] In the means 17 or 18, a thickness adjustment film made of the same material and having the same thickness as

that of the drain electrode is provided over or under the common bus line in the non-intersecting areas except the areas where the common bus line intersects the gate signal line or the video signal line and except the areas where the common bus line is connected to the counter voltage signal line.

[0074] According to the constitution of means 1, when a liquid crystal composition having positive dielectric constant anisotropy is used, it is possible to obtain a transmission characteristic little depending upon the wavelength in the birefringence mode, i.e., to obtain good white display, and to apply an electric field component to the liquid crystal layer in parallel with the substrate, which is much stronger than the component of the electric field in the direction perpendicular to the substrate. It is therefore possible to utilize the most efficient transmission state enabling the voltage between the pixel electrode and the counter electrode to be efficiently converted into the component in the direction in parallel with the substrate without raising the voltage for driving the liquid crystal.

[0075] According to the constitution of means 2, when a liquid crystal composition having negative dielectric constant anisotropy is used, it is possible to obtain a transmission characteristic little depending upon the wavelength in the birefringence mode, i.e., to obtain good white display, and to apply an electric field component to the liquid crystal layer in parallel with the substrate, which is much stronger than an electric field component in the direction perpendicular to the substrate. It is therefore possible to utilize the most efficient transmission state enabling the voltage between the pixel electrode and the counter electrode to be efficiently converted into the one in the direction in parallel with the substrate without raising the voltage for driving the liquid crystal.

[0076] According to the constitution of means 3, it is possible to eliminate the effect upon the electric field between the pixel electrode and the counter electrode because the black matrix is constituted by an insulating material. The black matrix cuts off the effect upon the electric field between the pixel electrode and the counter electrode enabling the distance to be decreased among the electrodes. It is therefore allowed to increase the aperture ratio, and to effectively apply an electric field component in parallel with the surface of the substrate to the liquid crystal layer without raising the voltage for driving the liquid crystals.

[0077] According to the constitution of means 4, the lines of electric force from the video signal line can be absorbed by the counter electrodes that are located on both sides thereof, making it possible to prevent the occurrence of so-called crosstalk. In this case, the lines of electric force from the video signal line are equally divided by the counter electrodes on both sides each by 50%; i.e., 100% of the lines of electric force are absorbed in total.

[0078] According to the constitution of means 5, short-circuiting is prevented from occurring even when the counter electrodes on both sides are brought as close to each other as possible or even when they are arranged to intersect with the video signal line. This makes it possible to increase the aperture ratio.

[0079] According to the constitution of means 6, the counter electrodes have a small resistance. Therefore, a

nearly uniform and stable current flows through the counter electrodes, and the counter voltage is sufficiently transmitted even to the pixels at the terminals, making it possible to further heighten the effect of means 4.

[0080] According to the constitution of means 7, it is possible to obtain the effect of means 5 without increasing the number of steps of production.

[0081] According to the constitution of means 8, it is possible to decrease the probability of short-circuiting at the areas where the counter voltage signal line intersects the video signal line.

[0082] According to the constitution of means 9, the counter voltage signal line has a small resistance and a nearly uniform and stable current flows through each of the counter electrodes. Therefore, a counter voltage is sufficiently transmitted to the pixels even at the terminals making it possible to achieve uniform pixel display.

[0083] According to the constitution of means 10, the effect of means 7 is gained without increasing the number of production steps.

[0084] According to the constitution of means 11, the electrode of the lower side formed via an interlayer insulating film is made of aluminum having an anodized surface, making it possible to form a storage capacitor little permitting the occurrence of troubles that are caused by point defects due to so-called whiskers.

[0085] According to the constitution of means 12, it is possible to decrease the resistance without increasing the width of the common bus line and to apply a sufficiently large voltage up to the ends of the counter electrodes. This makes it possible to decrease crosstalk (particularly, crosstalk in the horizontal direction of the screen) that is caused by distortion of the counter voltage according to the video signals.

[0086] According to the constitution of means 13, it is possible to obtain the effect of means 12 without increasing the number of steps of production.

[0087] According to the constitution of means 14, the gate signal lines GL connected to the gate electrodes GT and the counter voltage signal lines CL connected to the counter electrodes CT are arranged in parallel in the direction of row of a plurality of pixels arranged in the form of a matrix, the counter voltage signal line CL is used in common by the two pixels adjacent to each other in the direction of column, and the video signal lines DL connected to the drain electrodes SD2 are arranged in parallel in the direction of column, in order to decrease the parasitic capacitance among the wirings, to increase the production yield, to ensure the openings in the pixels and to decrease the resistances of the counter voltage signal lines CL.

[0088] According to the constitution of means 15, the gate electrodes GT, gate signal lines GL and thin-film transistor elements of two pixels adjacent to each other in the direction of column in the constitution of means 14 are so arranged as to be opposed to each other, the drain electrode SD2 is used in common by the two pixels, and the wiring from the drain electrode SD2 to the video signal line DL is arranged between the opposing gate signal lines GL, in order to decrease the parasitic capacitance among the wirings, to

increase the production yield, to ensure the openings in the pixels and to decrease the resistances of the counter voltage signal lines CL.

[0089] According to the constitution of means 16, the thin-film transistors are formed along the gate signal line GL in such a way that the plurality of thin-film transistors are connected to the pixel electrodes PX in one pixel of the constitution of means 15, in order to decrease the parasitic capacitances among the wirings, to increase the production yield, to ensure the openings in the pixels and to decrease the resistances of the counter voltage signal lines CL.

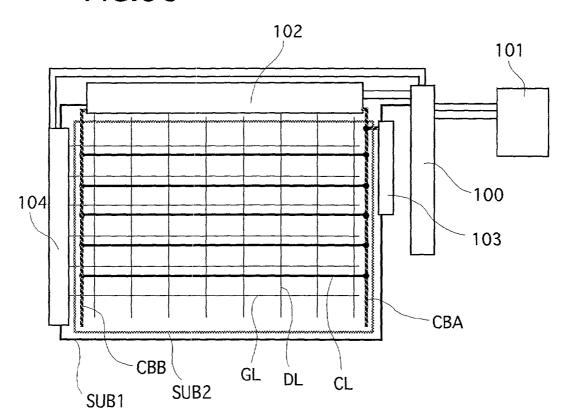

[0090] According to the constitution of means 17 to 20, both ends of the counter voltage signal lines CL are connected to the common bus line CB which has a resistance smaller than the resistances of the counter voltage signal lines CL. It is therefore possible to decrease distortion in the waveform of the drive voltage applied to the counter electrodes CT from the common voltage driver unit 52, to uniformalize the electric field intensity between the pixel electrode PX and the counter electrode CT in each pixel in the panel, and to decrease irregularity in the brightness that occurs along the counter voltage signal line CL.

[0091] Even in case the counter voltage signal line CL is broken at a portion, the common voltage is supplied from both ends of the counter voltage signal line CL to drive liquid crystal of the pixels. Unlike the prior art, therefore, the liquid crystal of pixels after the broken portion can be driven, and the quality of display is not impaired.

[0092] Furthermore, the area where the common bus line CB is arranged has the same cross-sectional structure as that of an area where the common bus line CB intersects the gate signal line GL or the video signal line DL, making it possible to decrease irregularity in the film thickness at the edges of the substrate where the common bus line CB is formed, to uniform the gap length between two substrates, and to decrease gap irregularity of the liquid crystal display device.

[0093] The foregoing and other objects, advantages, manner of operation and novel features of the present invention will be understood from the following detailed description when read in connection with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0094] FIG. 1 is a diagram schematically illustrating a pixel for explaining the basic operation of a liquid crystal display element of the present invention;

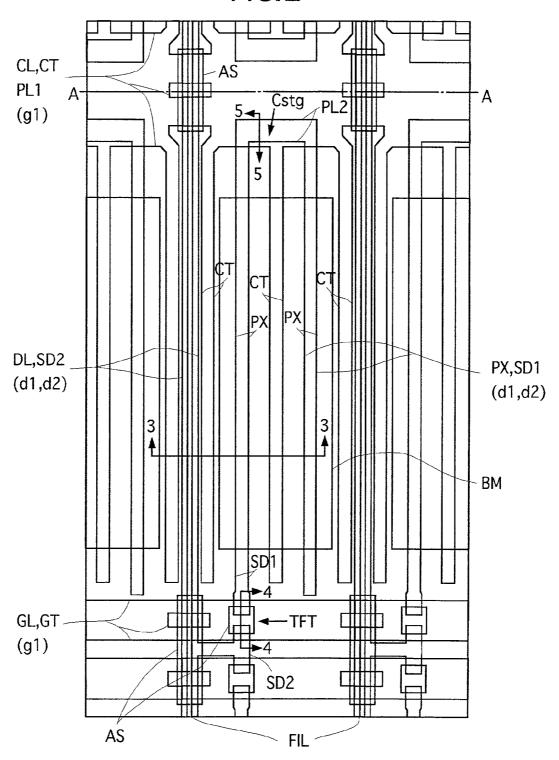

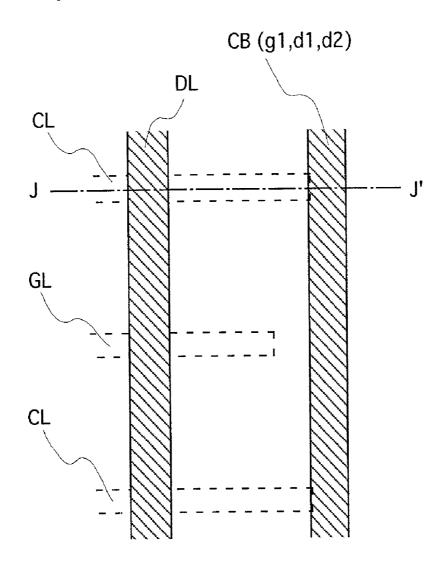

[0095] FIG. 2 is a plan view of essential portions illustrating a pixel and peripheries thereof in a liquid crystal display unit of an active matrix-type color liquid crystal display device of an embodiment 1;

[0096] FIG. 3 is a diagram illustrating a pattern of a black matrix of embodiment 1;

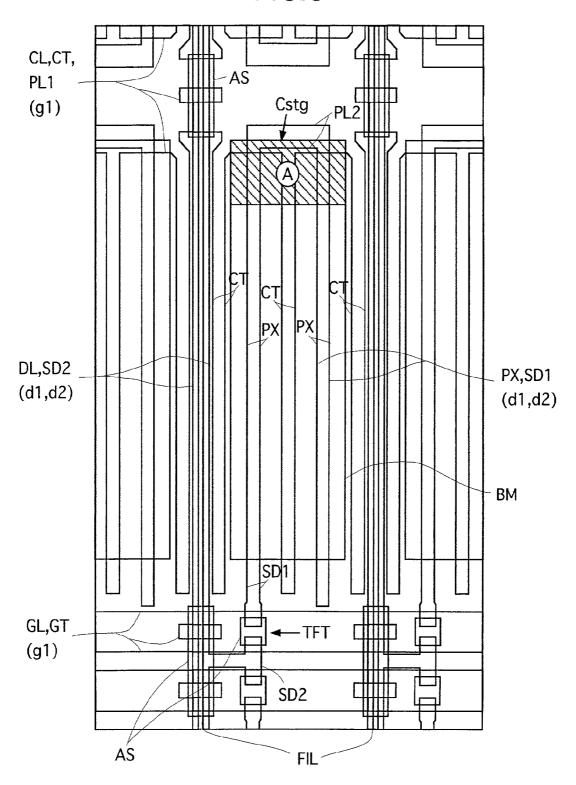

[0097] FIG. 4 is a plan view of essential portions illustrating a pixel and peripheries thereof in a liquid crystal display unit of an active matrix-type color liquid crystal display device of embodiment 2;

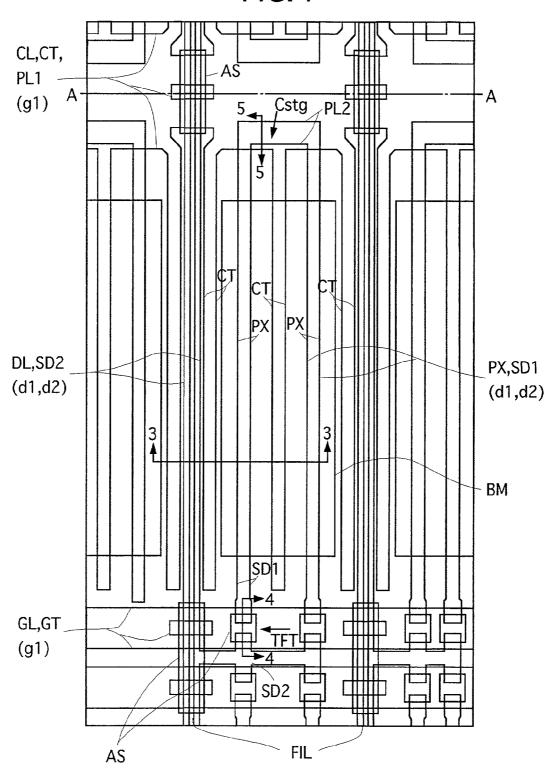

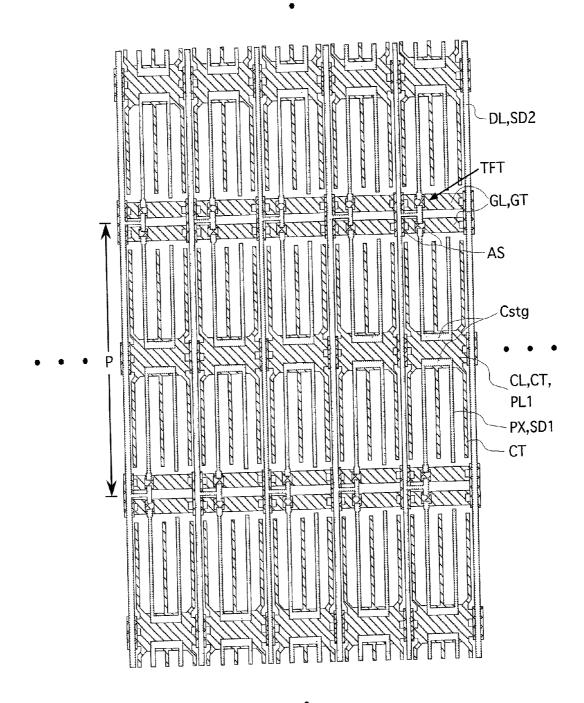

[0098] FIG. 5 is ea plan view of a plurality of pixels on a liquid crystal display panel formed by arranging the pixels of embodiment 1;

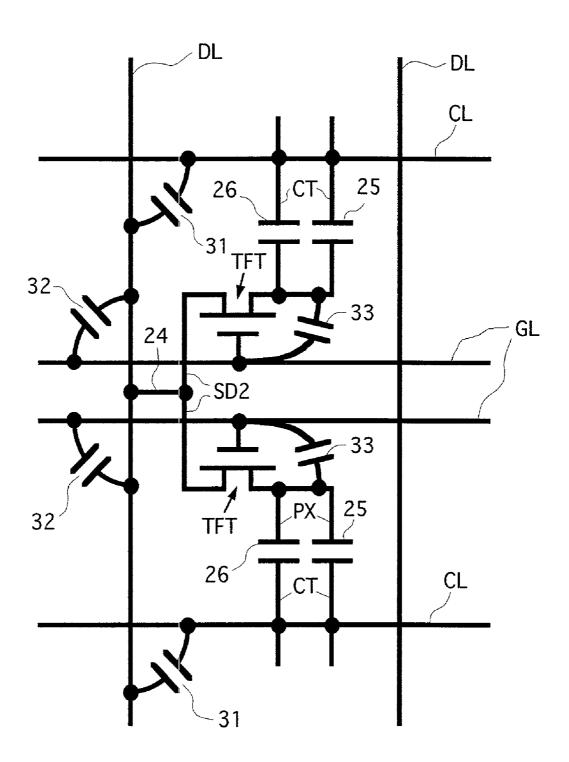

- [0099] FIG. 6 is a diagram of an electrically equivalent circuit of two pixels adjacent to each other in the direction of column of embodiment 1;

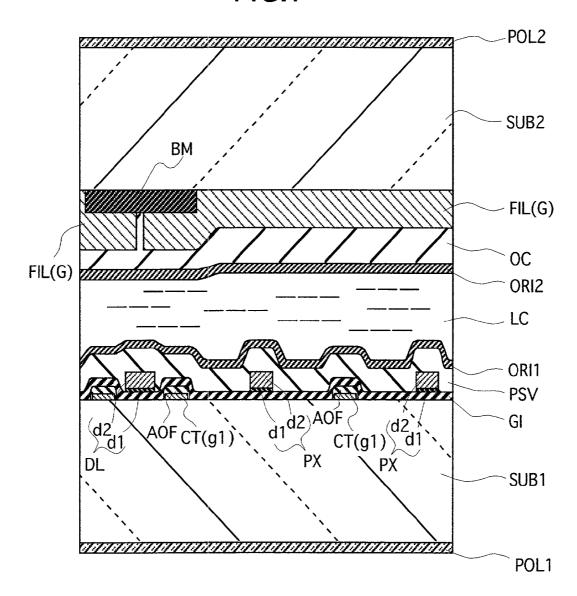

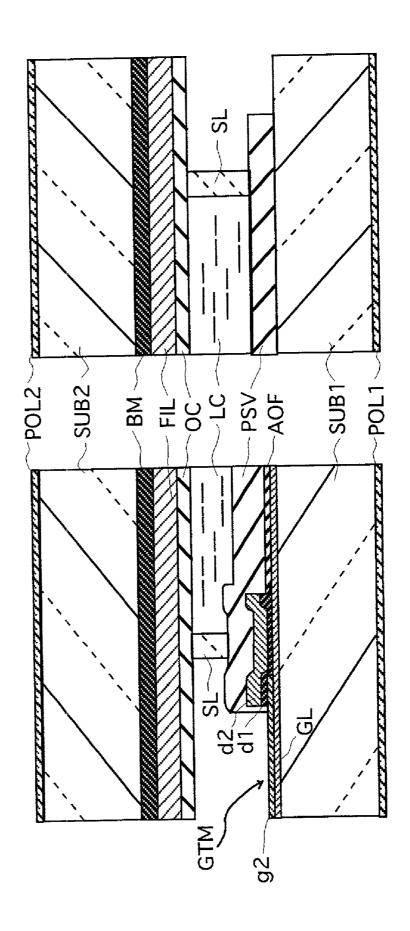

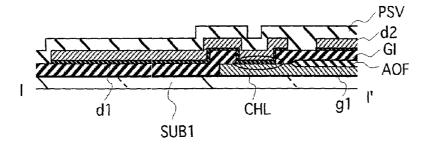

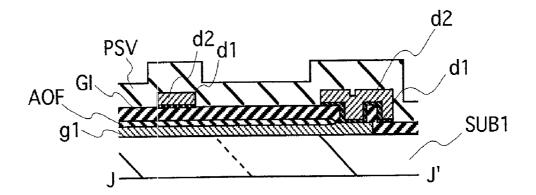

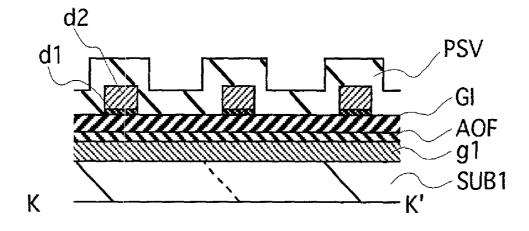

- [0100] FIG. 7 is a sectional view of a pixel cut along the line 3-3 in. FIG. 2;

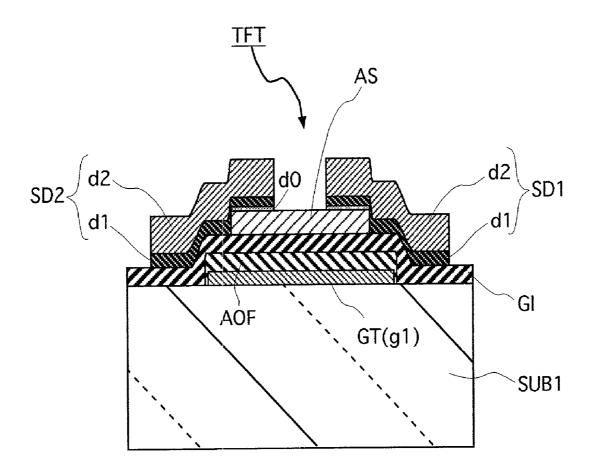

- [0101] FIG. 8 is a sectional view of a thin-film transistor element TFT cut along the line 4-4 in FIG. 2;

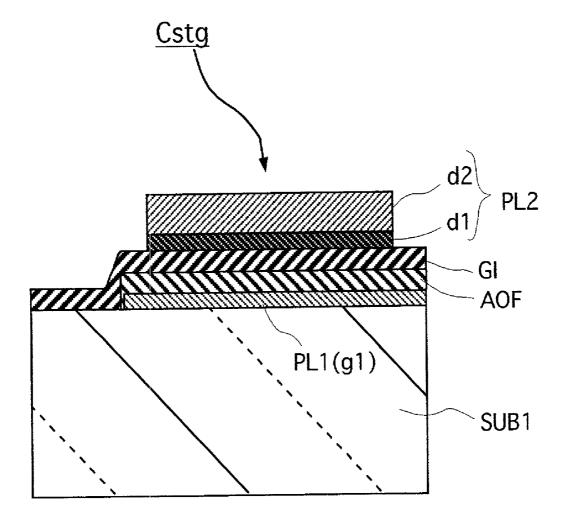

- [0102] FIG. 9 is a sectional view of a storage capacitor Cstg cut along the line 5-5 in FIG. 2;

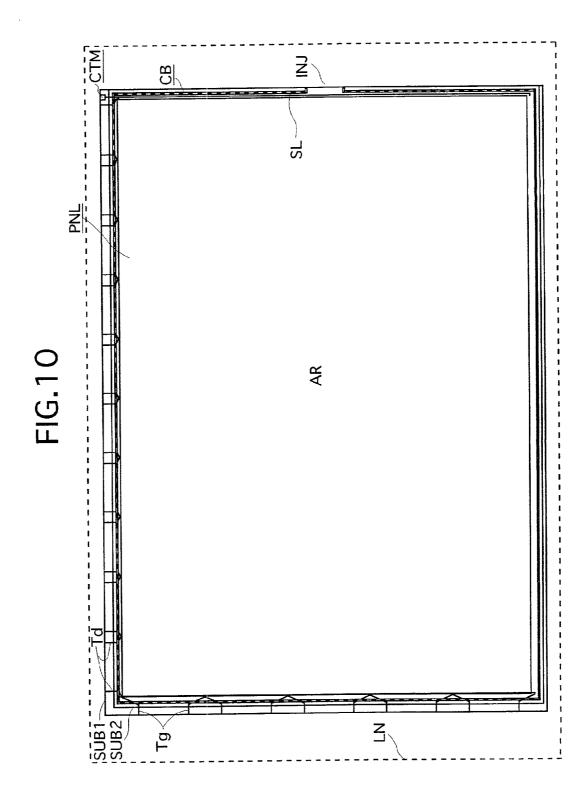

- [0103] FIG. 10 is a plan view for explaining the constitution of the peripheries of a matrix of the display panel;

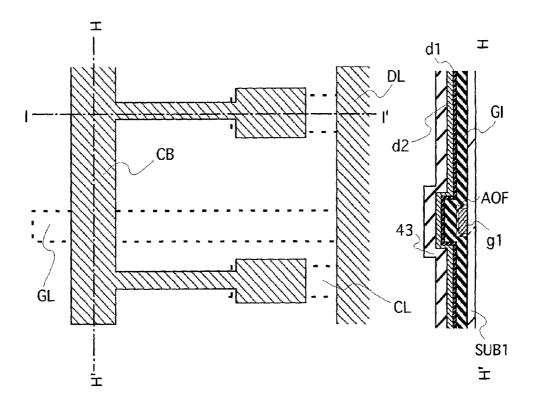

- [0104] FIG. 11 is a sectional view illustrating panel edge portions with gate signal terminals on the left side but without external connection terminals on the right side;

- [0105] FIGS. 12A and 12B are a plan view and a sectional view illustrating the area where a gate terminal GTM is connected to a gate wiring GL;

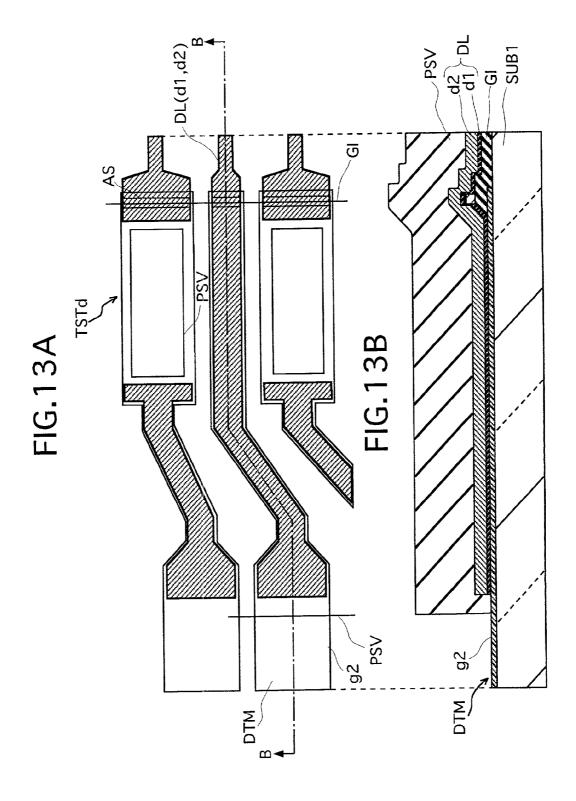

- [0106] FIGS. 13A and 13B are a plan view and a sectional view illustrating the area where a drain terminal DTM is connected to a video signal line DL;

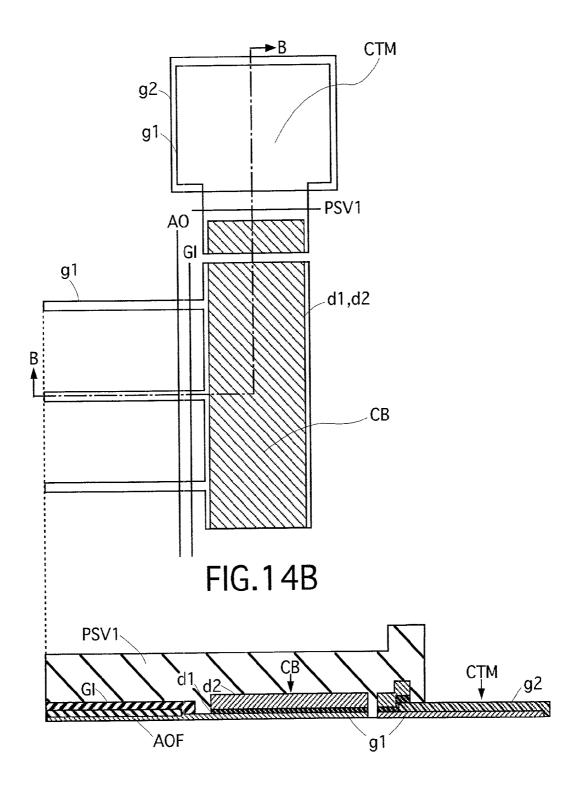

- [0107] FIGS. 14A and 14B are a plan view and a sectional view illustrating the area where a common electrode terminal CTM, a common bus line CB and a common voltage signal line CL are connected together;

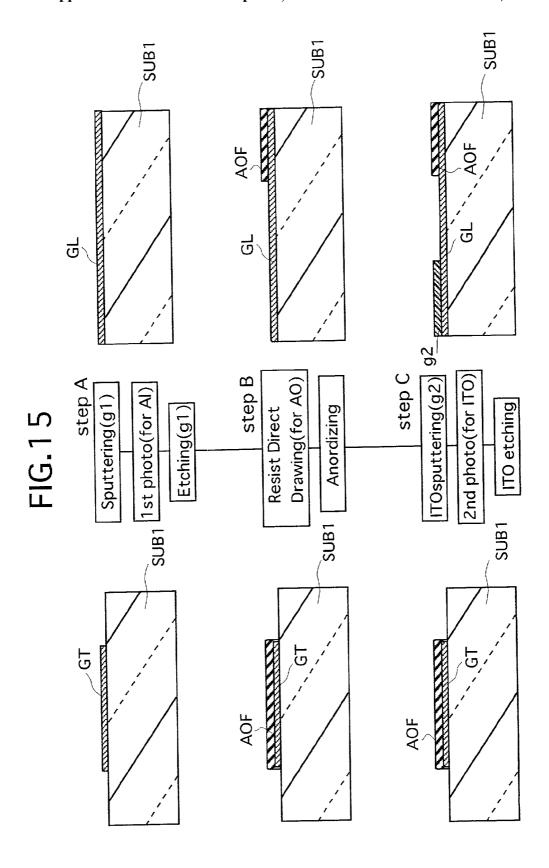

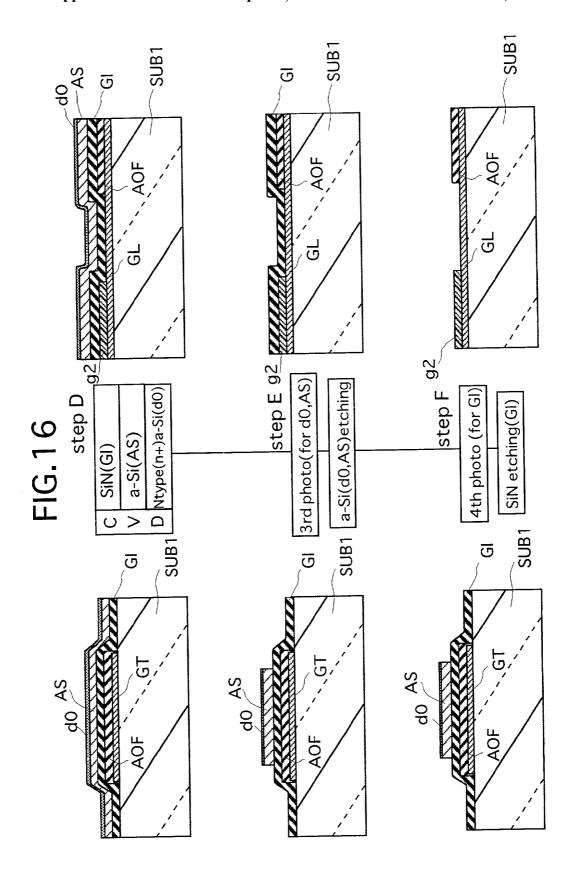

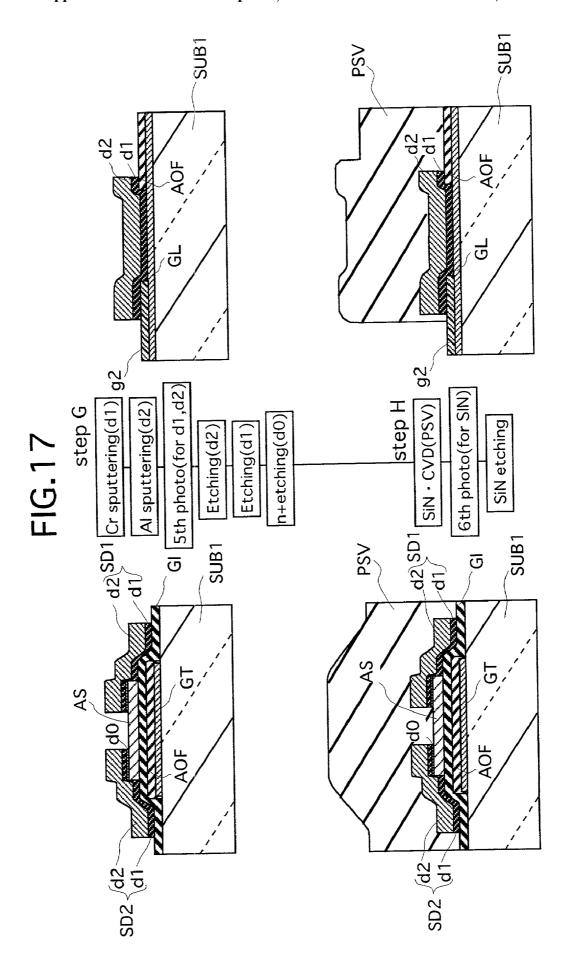

- [0108] FIG. 15 is a flow chart of a sectional view of a pixel and a gate terminal illustrating the steps A to C of fabricating a substrate SUB1;

- [0109] FIG. 16 is a flow chart of a sectional view of the pixel and the gate terminal illustrating the steps D to F of fabricating the substrate SUB1;

- [0110] FIG. 17 is a flow chart of a sectional view of the pixel and the gate terminal, illustrating the steps G to H of fabricating the substrate SUB1;

- [0111] FIG. 18 is a diagram illustrating the relationships among the direction in which the electric field is applied, the direction of rubbing and the transmission axis of a polarizer plate;

- [0112] FIG. 19 is a diagram of a circuit illustrating a matrix unit and the peripheries thereof of a active matrix-type color liquid crystal display device of the present invention;

- [0113] FIG. 20 is a diagram illustrating waveforms for driving the active matrix-type color liquid crystal display device of the present invention;

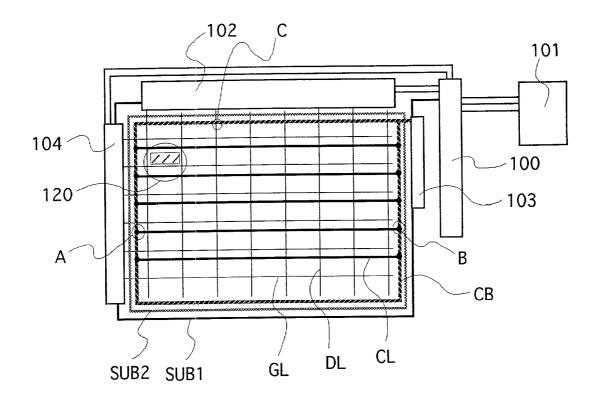

- [0114] FIG. 21 is a top view illustrating the state where the peripheral driver units are mounted on a liquid crystal display panel;

- [0115] FIG. 22 is a diagram illustrating, in cross section, the structure of a tape carrier package TCP in which an integrated circuit chip CHI constituting the driver unit is mounted on a flexible wiring substrate;

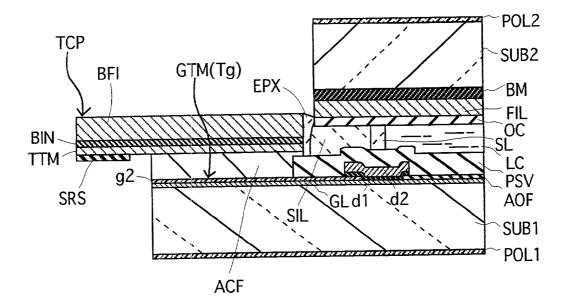

- [0116] FIG. 23 is a sectional view illustrating essential portions in a state where the tape carrier package TCP is connected to a terminal GTM for a gate signal circuit in the liquid crystal display panel PNL;

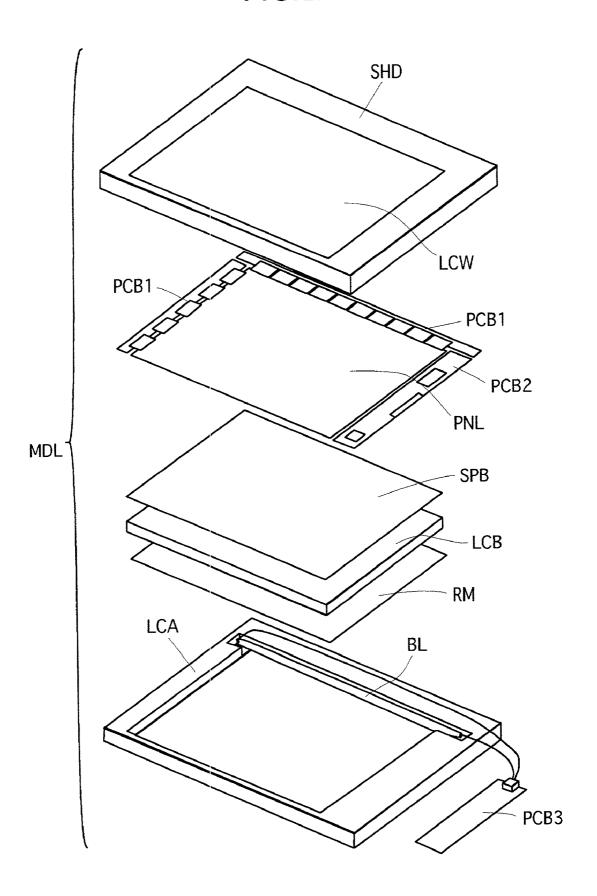

- [0117] FIG. 24 is an exploded perspective view illustrating a liquid crystal display module;

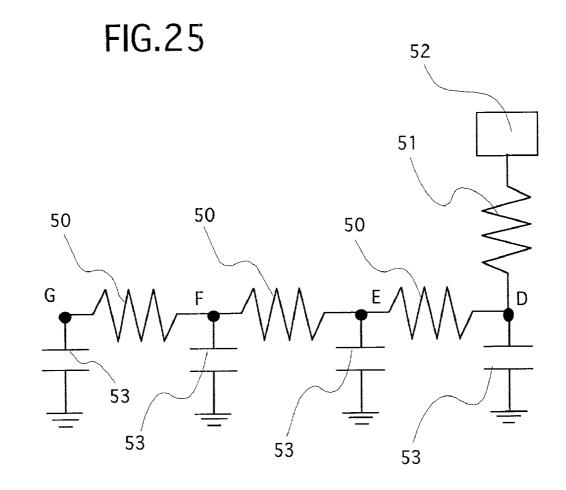

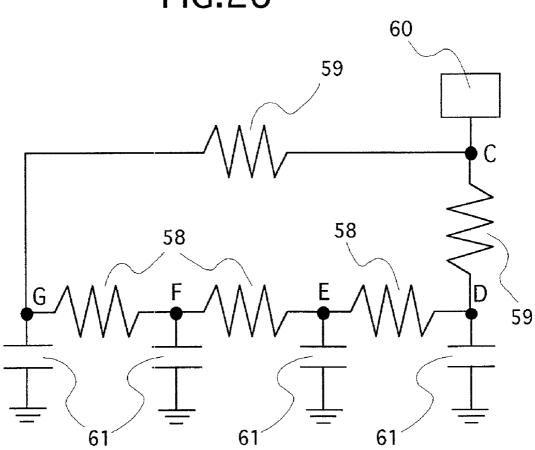

- [0118] FIG. 25 is a diagram illustrating an equivalent circuit of a passage for transmitting a drive voltage to the counter electrodes CT in the liquid crystal display device of FIG. 19;

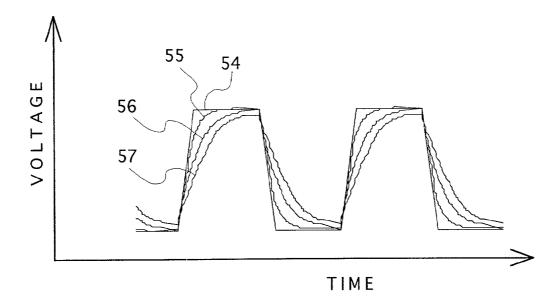

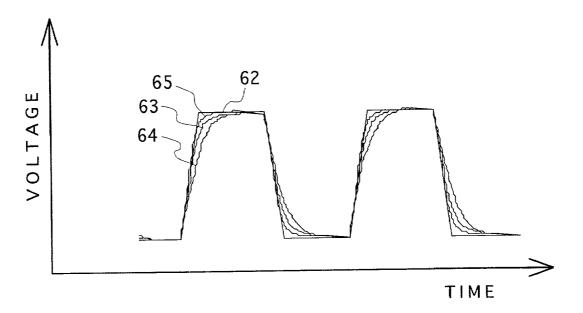

- [0119] FIG. 26 is a diagram of characteristics illustrating waveforms of the drive voltage at each of the points shown in FIG. 25;

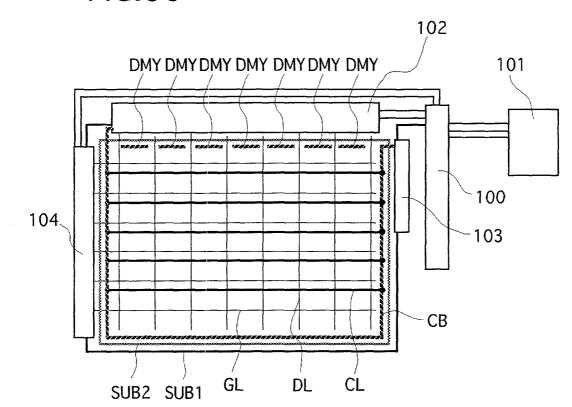

- [0120] FIG. 27 is a block diagram schematically illustrating the constitution of the liquid crystal display device of embodiment 3;

- [0121] FIG. 28 is a diagram illustrating an equivalent circuit of a passage for transmitting a drive voltage to the counter electrodes CT in the liquid crystal display device of embodiment 3;

- [0122] FIG. 29 is a diagram of characteristics illustrating waveforms of the drive voltage at each of the points shown in FIG. 28;

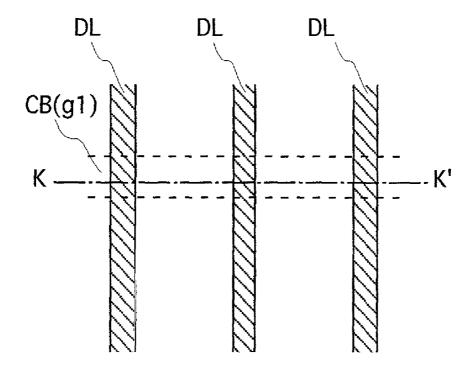

- [0123] FIGS. 30A to 30C are a plan view and sectional views illustrating the connection of the counter voltage signal line CL and the common bus line CB at point A on the matrix substrate of FIG. 27;

- [0124] FIGS. 31A and 31B are a plan view and a sectional view illustrating the connection of the counter voltage signal line CL and the common bus line CB at point B on the matrix substrate of FIG. 27;

- [0125] FIGS. 32A and 32B are a plan view and a sectional view illustrating the intersection of the video signal line DL and the common bus line CB at point C on the matrix substrate of FIG. 27;

- [0126] FIGS. 33A to 33C are a plan view and sectional views illustrating another example of connection of the counter voltage signal line CL and the common bus line CB at point A on the matrix substrate of FIG. 27;

- [0127] FIG. 34 is a plan view illustrating another arrangement of the common bus line CB of embodiment 3;

- [0128] FIG. 35 is a plan view illustrating a further arrangement of the common bus line CB of embodiment 3;

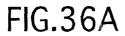

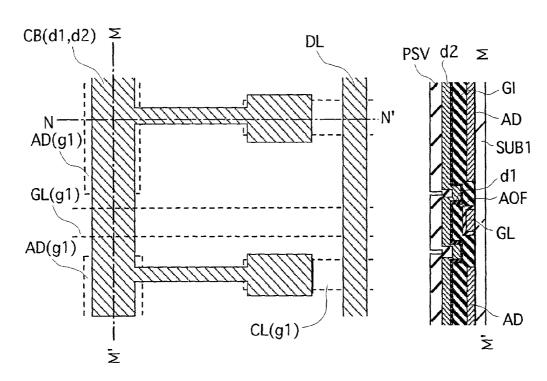

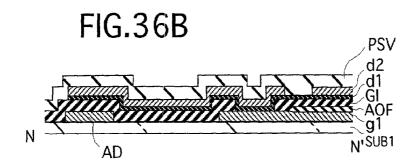

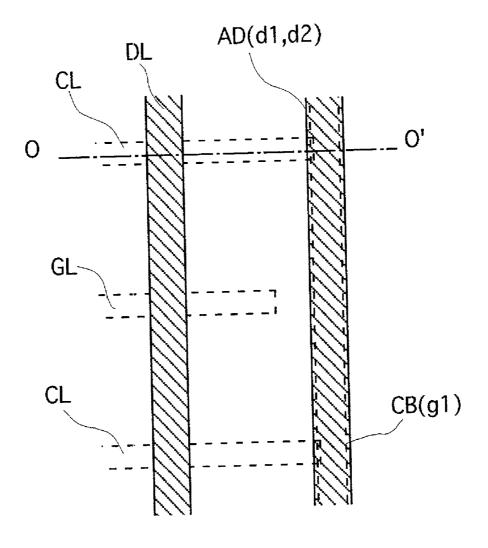

- [0129] FIGS. 36A to 36C are a plan view and sectional views illustrating the connection of the counter voltage signal line CL and the common bus line CB at a point corresponding to point A on the matrix substrate of FIG. 27 in the liquid crystal display device of embodiment 4;

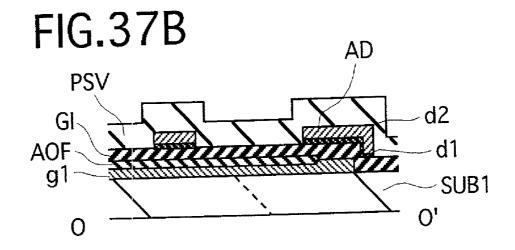

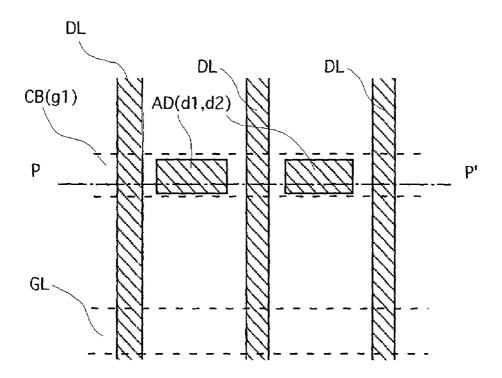

- [0130] FIGS. 37A and 37B are a plan view and a sectional view illustrating the connection of the counter voltage signal line CL and the common bus line CB at a point corresponding to point B on the matrix substrate of FIG. 27 in the liquid crystal display device of embodiment 4;

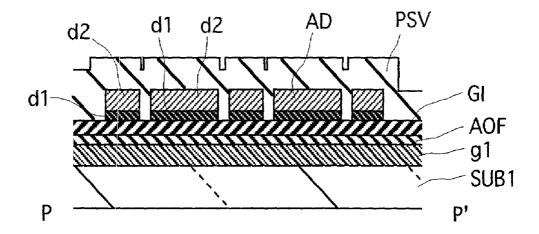

- [0131] FIGS. 38A and 38B are a plan view and a sectional view illustrating the intersection of the video signal line DL and the common bus line CB at a point corresponding to point C of the matrix substrate of FIG. 27 in the liquid crystal display device of embodiment 4; and

- [0132] FIG. 39 is a plan view illustrating another arrangement of the common bus line CB of embodiment 4.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0133] Further objects and features of the present invention will become obvious from the following description in conjunction with the drawings.

[0134] [Active matrix Liquid crystal display device]

[0135] An embodiment in which the present invention is adapted to a color liquid crystal display device of the active matrix system will be described below. In the drawings, those portions having the same functions are denoted by the same reference numerals and their description will not be repeated.

[0136] First, prior to illustrating embodiments of the present invention, the basic operation of the liquid crystal display element to which the present invention is applied will be explained.

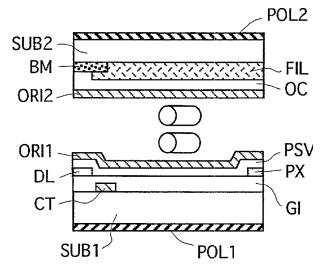

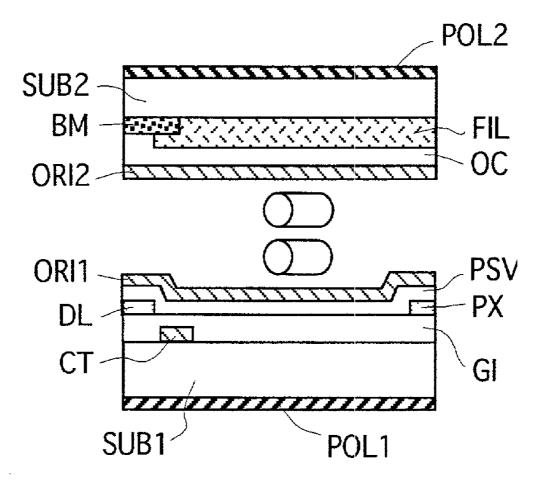

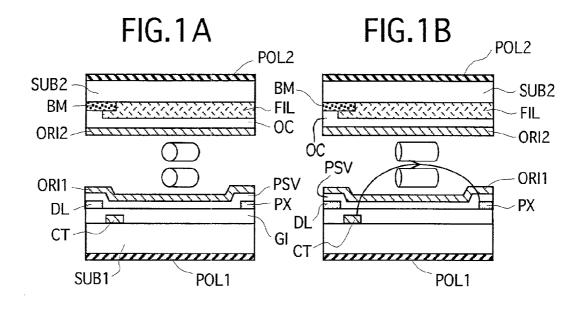

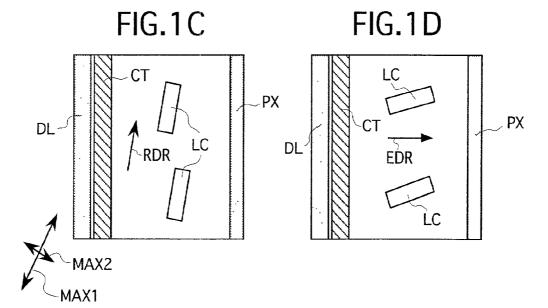

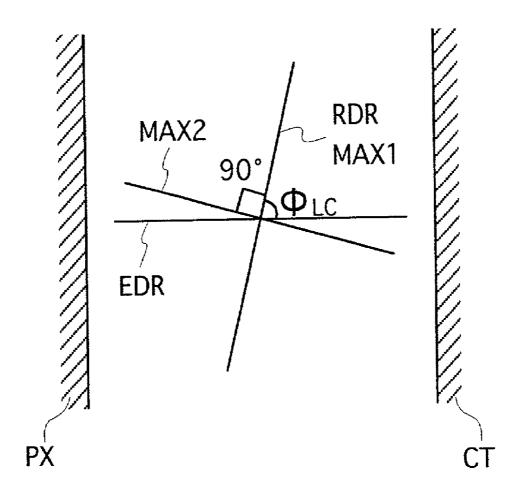

[0137] FIGS. 1A to 1D are schematic diagrams of a pixel for explaining the operation of a liquid crystal display element to which the present invention is applied, wherein FIG. 1A is a sectional view of when no voltage is applied, FIG. 1B is a sectional view of when a voltage is applied, FIG. 1C is a plan view of when no voltage is applied, and FIG. 1D is a plan view of when a voltage is applied. In these drawings, SUB1 and SUB2 denote transparent glass substrates (hereinafter often referred to simply as substrates), CT denotes a counter electrode, GI denotes an insulating film, DL denotes a video signal line, PX denotes a pixel electrode, POL1 and POL2 denote polarizer plates, MAX1 denotes the polarizing axis of the lower polarizer plate, MAX2 denotes the polarizing axis of the upper polarizer plate, RDR denotes the initial orientation of liquid crystal molecules, EDR denotes the direction of electric field, BM denotes a black matrix, FIL denotes a color filter, OC denotes a flattening film, ORI1 and ORI2 denote orientation films, and LC denotes liquid crystals (rod-like liquid crystal molecules).

[0138] In the liquid crystal display element, the polarizer plate POL2, light-shielding black matrix BM, color filter FIL, protective film OC and orientation film ORI2 are formed on one substrate SUB2 of the two transparent glass substrates SUB1 and SUB2. On the other substrate SUB1, via the liquid crystals LC, are formed the polarizer plate POL1, orientation film ORI1, drain electrode SD2, pixel electrode PX, counter electrode CT, wirings and thin-film transistor. These drawings do not show wirings and thin-film transistors.

[0139] Referring to FIGS. 1A and 1C, liquid crystals LC have been oriented in advance by the orientation films ORI1 and ORI2 in the orientation RDR that is substantially in parallel with the surface of the substrate SUB1. In this state, the initial orientation RDR of the liquid crystals LC is nearly in agreement with the polarizing axis MAX1 of the polarizing plate POL1, the polarizing axis MAX1 and the polarizing axis MAX2 of the other polarizing plate POL2 intersect at right angles, and the pixel is in a non-display state.

[0140] Next, referring to FIGS. 1B and 1D, when a voltage is applied between the counter electrode CT and the pixel electrode PX formed on the glass substrate SUB1 in order to create an electric field (having a direction EDR) substantially in parallel with the surface of the substrate

SUB1, the liquid crystal molecules LC are twisted on a plane substantially in parallel with the surface of the substrate SUB1. Then, the pixel becomes a display state. A large number of pixels are arranged to constitute a display panel.

[0141] [Planar constitution of a matrix unit (pixel unit)]

[0142] FIG. 2 is a plan view illustrating a pixel and peripheries thereof in the active matrix-type color liquid crystal display device of a first embodiment of the present invention.

[0143] Referring to FIG. 2, each pixel is provided in a region (surrounded by four signal lines) where the gate signal line (gate signal line or horizontal signal line) GL, counter voltage signal line (counter electrode wiring) CL and two adjacent video signal lines (drain signal lines or vertical signal lines) DL intersect. Each pixel includes a thin-film transistor TFT, a storage capacitor Cstg, a pixel electrode PX and a counter electrode CT. The gate signal lines GL and the counter voltage signal lines CL extend in the right-and-left direction in the drawing and are arranged in a plural number in the up-and-down direction. The video signal lines DL extend in the up-and-down direction and are arranged in a plural number in the right-and-left direction. The pixel electrode PX is connected to the thin-film transistor TFT, and the counter electrode CT is formed integrally with the counter voltage signal line CL.

[0144] The two adjacent pixels along the video signal line DL have a planar constitution such that they have the same size and pattern. The reason is that the counter voltage signal line CL is used in common by the two vertically adjacent pixels along the video signal line DL, the width of the counter voltage signal line CL is increased and, hence, the resistance of the counter voltage signal line CL is decreased. This makes it easy to sufficiently feed a counter voltage to the counter electrodes CT of the pixels arranged in the right-and-left direction from an external circuit.

[0145] The pixel electrode PX and the counter electrode CT are opposed to each other, and the optical state of the liquid crystals LC is controlled by an electric field between each pixel electrode PX and the counter electrode CT, thereby to control the display. The pixel electrodes PX and the counter electrodes CT are formed like comb teeth, and extend in a slender form in the up-and-down direction.

[0146] When the pixel electrodes PX and the counter electrodes CT are arranged on the surface of the same substrate, the liquid crystal display element of this embodiment makes it possible to increase the area of the opening portion of the pixel that transmits light and to increase the width of the counter voltage signal line CL compared with the wiring constitution in which the counter voltage signal line CL is not used in common by the two pixels adjacent to each other in the direction of column.

[0147] As a result, the counter voltage signal line CL has a decreased resistance, the common signals are smoothly propagated, the picture quality is improved, and the common signal generator unit consumes a reduced amount of electric power.

[0148] By commonly using the counter voltage signal line CL, furthermore, the number of portions where the video signal line DL intersects the counter voltage signal line CL is decreased by about 25% compared with that of the

conventional structure, and probability of short-circuiting between the video signal line DL and the counter voltage signal line CL decreases.

[0149] FIG. 6 is a diagram of an electric equivalent circuit of two pixels adjacent to each other in the direction of column, constituting the liquid crystal display element of a lateral electric field system of the embodiment.

[0150] In FIG. 6, reference numeral 24 denotes a wiring from the video signal line DL to the drain electrode SD2, 31 denotes the interline capacitance between the counter voltage signal line CL and the video signal line DL, 32 denotes the interline capacitance between the gate signal line GL and the video signal line DL, and 33 denotes the interline capacitance between the gate electrode GT and the pixel electrode PX.

[0151] The constitution of embodiment 1, as shown in the drawings, makes it possible to decrease the parasitic capacitance 31 between the video signal line DL and the counter voltage signal line CL, and to smoothly propagate liquid crystal drive signals to the drain electrodes SD2 and to the counter electrodes CT through the active filter wiring.

[0152] According to this embodiment as described above, it is possible to improve the picture quality and to decrease the consumption of electric power by the signal generator unit

[0153] As shown in FIG. 2, furthermore, the gate electrodes GT, gate signal lines GL and thin-film transistors TFT are devided by the two pixels adjacent to each other in the direction of column, the drain electrode SD2 is used in common, and the wiring 24 from the commonly used drain electrode SD2 to the video signal line DL is provided between the opposing gate signal lines GL. The constitution of this embodiment makes it possible to decrease the area where the drain electrode SD2 intersects the gate signal line GL and to decrease the probability of short-circuiting between the drain electrode SD2 and the gate signal line GL.

[0154] Referring to the equivalent circuit of FIG. 6, the parasitic capacitance (interline capacitance) 32 decreases between the drain electrode SD2 and the gate signal line GL, signals can be smoothly propagated to the gate electrodes GT, the picture quality is improved, and a decreased amount of electric power is consumed by the signal generator unit.

[0155] The constitution of this embodiment in which the counter voltage signal line CL is used in common and the drain electrode SD2 is used in common by the two pixels adjacent to each other in the direction of column, can be further applied to a conventional liquid crystal display panel of vertical electric field system.

[0156] The position of the thin-film transistor TFT can be moved on the gate signal line GL without increasing the area of intersection of the drain electrode SD2 and the gate electrode GT.

[0157] Here, the pixel electrode PX in the liquid crystal display element according to the present invention is of a narrow linear form, which may cause the pixel to become defective when it is broken.

[0158] FIG. 4 is a plan view illustrating the structure of a pixel constituting a liquid crystal display element of a second embodiment according to the present invention. As

shown in FIG. 2, the thin-film transistors TFT are so provided that the plurality of thin-film transistors TFT are connected to the number of the pixel electrodes PX while utilizing the features of the first embodiment, the drain electrode SD2 is used in common, and the wiring from the drain electrode SD2 to the video signal line DL is formed between the opposing gate signal lines GL. Hence the display of pixel is in an almost normal state even in case one of the pixel electrodes PX is broken at a portion.

[0159] When any one of the thin-film transistors becomes defective, furthermore, the pixel electrode PX connected to the defective thin-film transistor is cut by using a laser correction means or the like, and the image is displayed using other normal thin-film transistors.

[0160] According to the second embodiment as described above, it is possible to obtain an active matrix-type liquid crystal display element having a high picture quality and fabricated efficiently.

[0161] FIG. 5 is a plan view illustrating a plurality of pixels in a liquid crystal display panel of in-plane electric field system formed by arranging the pixels of the first embodiment. In FIG. 5, the counter voltage signal line CL is used in common by the two pixels adjacent to each other in the direction of column indicated by arrow P.

[0162] The number O of counter electrodes CT (number of comb teeth) in a pixel is so selected as to always maintain the relationship O=P+1 with respect to the number P of pixel electrodes PX (number of comb teeth) (O=3, P=2 in this embodiment). The reason is that the counter electrode CT and the pixel electrode PX are alternately arranged and the counter electrodes CT are provided on both sides of the video signal line DL on a plane. This makes it possible to shield the lines of electric force from the video signal line DL with the counter electrodes CT, so that the electric field between the counter electrode CT and the pixel electrode PX is not affected by the electric field generated by the video signal line DL. The counter electrode CT is fed with a potential at all times from an external unit, i.e., from a counter voltage signal line CL that will be described later, and takes a stable potential. Therefore, the potential of the counter electrode CT changes very little even when it is laid close to the video signal line DL. This further causes the pixel electrode PX to be located geometrically away from the video signal line DL. Therefore, the parasitic capacitance between the pixel electrode PX and the video signal line DL, greatly decreases, making it possible to suppress fluctuation in the pixel electrode potential Vs caused by the video signal voltage. Therefore, crosstalk (image defect called vertical smear) that occurs in the up-and-down direction is suppressed.

[0163] The pixel electrode PX and the counter electrode CT have widths Wp and Wc which are 6  $\mu$ m, respectively, and are very larger than a maximum predetermined thickness of 4.5  $\mu$ m of a liquid crystal layer that will be described later. By taking variation during the production into consideration, it is desired that a margin of not smaller than 20% is maintained. Desirably, therefore, these electrodes should have widths of much larger than 5.4  $\mu$ m. Therefore, the electric field component which is applied to the liquid crystal layer and is in parallel with the surface of the substrate becomes larger than the electric field component in

the direction perpendicular to the surface of the substrate,, making it possible to lower the voltage for driving liquid crystals.

[0164] It is further desirable that the maximum widths Wp and Wc of the pixel electrode PX and the counter electrode CT are smaller than the gap L between the pixel electrode PX and the counter electrode CT. The reason is that when the gap between the electrodes is too small, the lines of electric force are greatly curved whereby the area increases where the electric field component perpendicular to the surface of the substrate becomes greater than the electric-field component in parallel with the surface of the substrate, making it difficult to efficiently apply the electric field component in parallel with the surface of the substrate to the liquid crystal layer. Therefore, when the margin is 20%, the gap L between the pixel electrode PX and the counter electrode CT must be greater than 7.2  $\mu$ m.

[0165] The embodiments 1 and 2 have a resolution of 640×480 dots, a diagonal of 10.4 inches, and a pixel pitch of 110  $\mu$ m. By dividing the pixels by four, the gap L becomes greater than 7.2  $\mu$ m. That is, by dividing the pixels by not more than eight, a gap L> 7.2  $\mu$ m is satisfied. When the pixels are divided by 10 or a larger number, however, the gap L becomes smaller than 7  $\mu$ m, which does not satisfy the required condition.

[0166] Furthermore, the video signal line DL has a width of 8  $\mu$ m so that it will not be broken, which is slightly larger than that of the pixel electrode PX and the counter electrode CT. In order to prevent short-circuiting, a gap of 1  $\mu$ m is formed between the video signal line DL and the counter electrode CT. Here, the video signal line DL has a width which is not larger than twice the width of the counter electrodes CT that are located on both sides thereof. Or, when the width of the video signal line DL is determined based on the production yield, the width of the counter electrodes CT located on both sides of the video signal line DL is determined to be not smaller than one-half the width of the video signal line DL. The reason is that the lines of electric force generated from the video signal line DL is absorbed by the counter electrodes CT on both sides thereof. To absorb the lines of electric force generated from the signal line having a given width, the lines that absorb the lines of electric force must have a width which is not smaller than the width of the line generating the lines of electric

[0167] Therefore, the lines of electric force generated from half (4 µm each) the width of the video signal line DL need to be absorbed by the counter electrodes CT on both sides thereof, respectively. For this purpose, the counter electrodes CT located on both sides of the video signal line DL has a width of not smaller than one-half thereof. This makes it possible to prevent crosstalk (particularly, crosstalk in the up-and-down (vertical) direction) caused by video signals.

[0168] The gate signal line GL has a width that satisfies a resistance capable of applying a sufficient gate voltage to the gate electrodes GT of pixels at the terminals (on the side opposite to the gate electrode terminals GTM that will be described later). Furthermore, the counter voltage signal line CL has a width, i.e., has a resistance capable of applying a sufficient counter voltage to the counter electrodes CT of pixels at the terminals (on the side opposite to the common bus line CB that will be described later).

[0169] On the other hand, the gap between the pixel electrode PX and the counter electrode CT is changed according to the liquid crystal material that is used. The reason is that the electric field intensity for accomplishing a maximum transmission factor differs with the liquid crystal material. Therefore, the gap between the electrodes is determined depending upon the liquid crystal material, such that a maximum transmission factor is obtained within a range of maximum amplitude of a signal voltage that is determined depending upon the breakdown voltage of the video signal driver unit (driver of the signal side) that is used. The gap between the electrodes becomes 16 µm when a liquid crystal material described later will be used.

[0170] [Cross-sectional constitution of the matrix unit (pixel unit)]

[0171] FIG. 7 is a sectional view cut along the line 3-3 in FIG. 2, FIG. 8 is a sectional view of a thin-film transistor element TFT cut along the line 4-4 in FIG. 2, and FIG. 9 is a sectional view of a storage capacitor Cstg cut along the line 5-5 in FIG. 2. As shown in FIGS. 7 to 9, on the side of the lower transparent glass substrate SUB1 are formed a thin-film transistor TFT, a storage capacitor Cstg and a group of electrodes, and on the side of the upper transparent glass substrate SUB2 are formed a color filter FIL and a black matrix pattern BM for blocking light, with respect to a liquid crystal layer LC.

[0172] Furthermore, orientation films ORI1 and ORI2 for controlling the initial orientation of liquid crystals are provided on the inside surfaces (liquid crystal LC side) of the transparent glass substrates SUB1 and SUB2, and polarizer plates are provided with their polarizing axes intersecting at right angles (cross-nicol arrangement) on the outside surfaces of the transparent glass substrates SUB1 and SUB2.

[0173] [TFT substrate]

[0174] Constitution of the lower transparent glass substrate SUB1 (TFT substrate) will now be described in detail.

[0175] [Thin-film transistor TFT]

[0176] The thin-film transistor TFT so operates that the channel resistance decreases between the source and the drain when a positive bias is applied to the gate electrode GT thereof, and that the channel resistance increases when a zero bias is applied thereto.

[0177] Referring to FIG. 8, the thin-film transistor TFT includes the gate electrode GT, a gate insulating film GI, an i-type semiconductor layer AS made of i-type amorphous silicon (a-Si)(without doped with intrinsic conductivity-type-determining impurities), a pair of source electrode SD1 and drain electrode SD2. The source and drain are usually determined by the bias polarity therebetween. In the circuit of the liquid crystal display device, the polarity is inverted during the operation. It should therefore be noted that the source and drain are interchanged during the operation. In the following description, however, either of them is fixedly expressed as a source and the other as a drain only for convenience of description.

[0178] [Gate electrode GT]

[0179] The gate electrode GT is continuous to the gate signal line GL, and is formed by part of the region of the gate signal line GL. The gate electrode GT is a portion which

extends over the active region of the thin-film transistor TFT, and is so formed as to completely cover the i-type semiconductor layer AS (as viewed from below). Therefore, in addition to its role, the gate electrode GT works to shield the i-type semiconductor layer AS from external light or backlight. In this embodiment, the gate electrode GT is composed of a single conductive film gl. As the conductive film gl, there can be used an aluminum film formed by, for example, sputtering and an anodically oxidized film AOF of aluminum is formed thereon.

[0180] [Scanning (gate) signal line GL]

[0181] The scanning (gate) signal line GL is constituted by a conductive film gl. The conductive film g1 forming the scanning signal line GL is formed through the same step as that of forming the conductive film g1 of the gate electrode GT and as a unitary structure. Through the scanning signal line GL, the gate voltage Vg is fed to the gate electrode GT from an external circuit. On the scanning signal line GL is formed an anodically oxidized film AOF of aluminum, too. A portion that intersects the video signal line DL is formed narrow to decrease the probability of short-circuiting relative to the video signal line, and is branched into two so that it can be separated by laser trimming in case it has short-circuited.

#### [0182] [Counter electrode CT]

[0183] The counter electrode CT is constituted by the conductive film g1 of the same layer as the gate electrode GT and the scanning signal line GL. On the counter electrode CT is formed an anodically oxidized film AOF of aluminum, too. The counter electrode CT is completely covered with the anodically oxidized film AOF and prevents short-circuit even when it is laid as close to the video signal line as possible. Moreover, they can be so arranged as to intersect. A counter voltage Vcom is applied to the counter electrode CT. In this embodiment, the counter voltage Vcom is set to a potential which is lower than an intermediate potential between a drive voltage Vdmin of a minimum level applied to the video signal line DL and a drive voltage Vdmax of a maximum level by a field-through voltage  $\Delta Vs$  that generates when the thin-film transistor element TFT is turned off. When it is necessary to nearly halve the power source voltage of the integrated circuit used in the video signal driver unit, an AC voltage should be applied.

#### [0184] [Counter voltage signal line CL]

[0185] The counter voltage signal line CL is constituted by a conductive film g1. The conductive film g1 forming the counter voltage signal line CL is formed through the same step as that of forming the conductive film g1 of the gate electrode GT, scanning signal line GL and counter electrode CT, and as a unitary structure. Through the counter voltage signal line CL, the counter voltage Vcom is fed to the counter electrode CT from an external circuit. On the counter voltage signal line CL is formed an anodically oxidized film AOF of aluminum, too. A portion that intersects the video signal line DL is formed narrow to decrease the probability of short-circuiting relative to the video signal line like the case of the scanning signal line GL, and is branched into two so that it can be separated by laser trimming in case it has short-circuited.

[0186] [Insulating film GI]

[0187] The insulating film GI is used as a gate insulating film for imparting an electric field to the gate electrode GT and to the semiconductor layer AS in the thin-film transistor TFT. The gate insulating film GI is formed on the gate electrode GT and on the scanning signal line GL. As the gate insulating film GI, a silicon nitride film formed by, for example, plasma CVD having a thickness of 1200 to 2700 Å (about 2400 Å in this embodiment) is used. The gate insulating film GI is so formed as to surround the whole matrix unit AR, and the periphery is removed so that external connection terminals DTM, GTM are exposed. The insulating film GI contributes to electrically insulating the scanning signal line GL, counter voltage signal line CL and video signal line DL.

[0188] [i-Type semiconductor layer AS]

[0189] The i-type semiconductor layer AS is made of amorphous silicon and has a thickness of from 200 to 2200 Å (about 2000 Å in this-embodiment). A layer d0 is an N(+)-type amorphous silicon semiconductor layer doped with phosphorus (P) for ohmic contact, and is left only on a portion where the i-type semiconductor layer AS exists thereunder and conductive layers d1 (d2) exist thereover.

[0190] The i-type semiconductor layer AS is also provided at the portions (cross-over portion) where the scanning signal line GL, the counter voltage signal line CL and the video signal line DL intersect. The i-type semiconductor layer AS at the intersecting portion decreases the probability of short-circuiting at the portions where the scanning signal line GL, the counter voltage signal line CL and the video signal line DL intersect.

[0191] [Source electrode SD1, drain electrode SD2]

[0192] The source electrode SD1 and the drain electrode SD2 are, respectively, composed of the conductive film d1 that is in contact with the N(+)-type semiconductor layer d0 and the conductive film d2 formed thereon.

[0193] The conductive film d1 is composed of a chromium (Cr) film formed by sputtering and has a thickness of 500 to 1000 Å (about 600 Å in this embodiment). The Cr film is so formed as to have a thickness of not larger than about 2000 Å, since stress is produced as its thickness increases. The Cr film is used in order to improve the adhesiveness to the N(+)-type semiconductor layer d0 and to prevent aluminum conductive film d2 from diffusing into the N(+)-type semiconductor layer d0 (i.e., used as a so-called barrier layer). As the conductive film d1, there may be used a film of a high-melting metal (Mo, Ti, Ta or W) and a film of a high-melting metal silicide (MoSi<sub>2</sub>, TiSi<sub>2</sub>, TaSi<sub>2</sub> or WSi<sub>2</sub>) in addition to Cr film.

[0194] The conductive film d2 having a thickness of 3000 to 5000 Å (about 4000 Å in this embodiment) is formed by Al sputtering. The Al film causes less stress than Cr film and can, hence, be so formed as to have a large thickness, in order to decrease the resistances of the source electrode SD1, drain electrode SD2 and video signal line DL, and to reliably extend over the steps caused by the gate electrode GT and the i-type semiconductor layer AS (to improve step coverage).

[0195] After the conductive films d1 and d2 are patterned using the same mask pattern, the N(+)-type semiconductor

layer  $d\mathbf{0}$  is removed by using the same mask or by using the conductive films  $d\mathbf{1}$  and  $d\mathbf{2}$  as masks. That is, the N(+)-type semiconductor layer  $d\mathbf{0}$  remaining on the i-type semiconductor layer AS is removed in a self-alignment manner except the portions of the conductive films  $d\mathbf{1}$  and  $d\mathbf{2}$ . In this case, the N(+)-type semiconductor layer  $d\mathbf{0}$  is removed by etching and, hence, the surface of the i-type semiconductor layer AS is etched to some extent, which, however, can be controlled by changing the etching time.

[0196] [Video signal line DL]

[0197] The video signal line DL is constituted by the first conductive film d1 and the second conductive film d2 of the same layers as the source electrode SD1 and the drain electrode SD2. Moreover, the video signal line DL is formed integrally with the drain electrode SD2.

[0198] [Pixel electrode PX]

[0199] The pixel electrode PX is constituted by the first conductive film d1 and the second conductive film d2 of the same layers as the source electrode SD1 and the drain electrode SD2. Moreover, the pixel electrode PX is formed integrally with the source electrode SD1.

[0200] [Storage capacitor Cstg]

[0201] The pixel electrode PX is so formed as to be superposed on the counter voltage signal line CL at an end on the side opposite to the end that is connected to the thin-film transistor TFT. As will be obvious from FIG. 9, this superposition constitutes a storage capacitor (capacitance element) Cstg having the pixel electrode PX as one electrode PL2 and having the counter voltage signal line CL as the other electrode PL1. The dielectric film of this storage capacitor Cstg is composed of the insulating film GT that is used as the gate insulating film of the thin-film transistor TFT and the anodically oxidized film AOF.

[0202] As shown in FIG. 2, the storage capacitor Cstg is formed, when viewed from above, on an expanded portion of the conductive film g1 of the counter voltage signal line GI

[0203] In this case, the electrode located under the insulative film GI of the storage capacitor Cstg is made of aluminum having anodized surface. Therefore, the storage capacitor hardly causes defect (short-circuiting to the electrode of the upper side) that is caused by so-called whiskers of aluminum.

[0204] [Protective film PSV1]

[0205] A protective film PSV1 is provided on the thin-film transistor TFT. The protective film PSV1 is formed chiefly for protecting the thin-film transistor TFT from moisture and the like and must have a high transparency and a good resistance against humidity. The protective film PSV1 is composed of, for example, a silicon oxide film or a silicon nitride film formed by a plasma CVD device, and has a thickness of about 1  $\mu$ m.

[0206] The protective film PSV1 is so formed as to surround the whole matrix unit AR, and its periphery is removed so that the external connection terminals DTM and GTM are exposed. As for the thicknesses of the protective film PSV1 and the gate insulative film GI, the former film is formed so as to have a large thickness in consideration of the effect of protection and the latter film is formed so as to have

a small thickness in consideration of the mutual conductance gm to the transistor. Therefore, the protective film PSV1 that exhibits a high protection effect is formed in a size larger than the gate insulative film GI in order to protect even the peripheral portions as wide as possible.

[0207] [Color filter substrate]

[0208] Referring to FIGS. 2 and 7 again, the constitution of the upper transparent glass substrate SUB2 (color filter substrate) will now be described in detail.

[0209] [Light-shielding film BM]

[0210] On the upper transparent glass substrate SUB2 is formed a light-shielding BM (so-called black matrix), so that undesired light transmitted through the gaps (gaps other than the gap between the pixel electrode PX and the counter electrode CT) does not go to the side of the display Surface to deteriorate the contrast and the like. The light-shielding film BM also serves to prevent external light or backlight from falling on the i-type semiconductor layer AS. That is, the i-type semiconductor layer AS of the thin-film transistor TFT is sandwiched by the light-shielding film BM and the gate electrode GT of a large size located on the upper and lower sides, and so does not receive natural light or backlight from the external side.

[0211] A polygonal contour line of the light-shielding film BM shown in FIG. 2 represents an opening inside which no light-shielding film BM is formed. This is only an example of the contour line. The pattern may be the one shown in FIG. 3 when it is desirable to form a large opening portion. In the region A of FIG. 3, the direction of the electric field is disordered and the display of this portion corresponds to the video data in the pixel in such a 1-to-1 manner that the display is black when this portion is black, and is white when this portion is white. Therefore, this portion can be utilized as part of the display. Furthermore, the boundary in the up-and-down direction of the drawing is determined by the precision of registration of the upper and lower substrates. When the precision registration is better than the width of the counter electrodes CT located on both sides of the video signal line DL, the opening portion can be widened by setting the boundary line within-the width of the counter electrode.

[0212] The light-shielding film BM has light-shielding property against light, and is composed of a highly insulating film so as not to affect the electric field between the pixel electrode PX and the counter electrode CT. This enables the electric field component in parallel with the surface of the substrate to be effectively applied to the liquid crystal layer, and makes it possible to lower the voltage for driving liquid crystals. The light-shielding film BM is made of a material obtained by mixing a black pigment into a resist material, and has a thickness of about 1.2  $\mu$ m. As another embodiment, there can be used a material obtained by mixing palladium and electroless-plated nickel into the resist material

[0213] In this case, the gap can be increased to some extent between the pixel electrode PX and the counter electrode CT, making it possible to increase the aperture ratio.

[0214] The light-shielding film BM is formed like a lattice surrounding the pixels. The lattice partitions the effective

display area of each pixel. Therefore, the contour of each pixel is clearly shown by the light-shielding film BM. That is, the light-shielding film BM has the two functions, i.e., a black matrix and shielding against light that falls on the i-type semiconductor layer AS.

[0215] The light-shielding film BM is formed like a frame even on the peripheral portions, and has a pattern that is continuous to the pattern of the matrix unit that has a plurality of dot-like openings. The light-shielding film BM on the peripheral portions outwardly extends over the sealing portion SL to prevent the leakage of light such as light reflected by a device on which the display is mounted, such as a personal computer, from entering the matrix unit. The light-shielding film BM is short of the edges of the substrate SUB2 by about 0.3 to 1.0 mm, and does not extend to the cut regions of the substrate SUB2.

[0216] [Color filter FIL]

[0217] The color filter FIL forms stripes of a repetition of red, green and blue lines at positions facing the pixels. The color filter FIL is so formed as to be superposed on the edge portions of the light-shielding film BM.

[0218] The color filter FIL is formed as described below. First, a dyeable member such as acrylic resin is formed on the surface of the upper transparent glass substrate SUB2, and is then removed by photolithographic technology, leaving it on the red filter-forming regions. Then, the dyeable member is dyed with a red dye and is fixed to form a red filter R. Next, a green filter G and a blue filter B are formed successively through the same steps.

[0219] [Overcoat film OC]

[0220] The overcoat film OC is provided to prevent the dye of the color filter FIL from leaking to the liquid crystals LC and to flatten the steps produced by the color filter FIL and light-shielding film BM. The overcoat film OC is formed by using a transparent resin material such as acrylic resin, epoxy resin or the like resins.

[0221] [Liquid crystal layer and polarizer plate]

[0222] The liquid crystal layer, orientation film and polarizer plate will be described below.

[0223] [Liquid crystal layer]

[0224] As the liquid crystal materials LC, there are used nematic liquid crystals having a positive dielectric constant anisotropy  $\Delta\epsilon$  of 13.2 and a refractive index anisotropy  $\Delta$ n of 0.081 (589 nm at 20° C.), and nematic liquid crystals having a negative dielectric constant anisotropy  $\Delta\epsilon$  of -7.3 and a refractive index anisotropy  $\Delta$ n of 0.053 (589 nm at 20°). The liquid crystal layer has a thickness (gap) of not smaller than 2.8  $\mu$ m but not larger than 4.5  $\mu$ m when it has a positive dielectric constant anisotropy  $\Delta\epsilon$ .

[0225] In this case, there is obtained a transmission factor that does not almost change with the wavelengths within a range of visible light when the retardation  $\Delta n \cdot d$  is not smaller than 0.25  $\mu m$  but is not larger than 0.32  $\mu m$ , and most of the liquid crystals having a positive dielectric constant anisotropy  $\Delta \epsilon$  have a birefringence anisotropy  $\Delta n$  which is not smaller than 0.07 but is not larger than 0.09.

[0226] On the other hand, the liquid crystal layer has a thickness (gap) which is not smaller than 4.2  $\mu$ m but is not

larger than 8.0  $\mu m$  when it has a negative dielectric constant anisotropy  $\Delta \varepsilon$ . The reason is that it is necessary to determine the retardation  $\Delta n$ -d within a range of not smaller than 0.25  $\mu m$  but not larger than 0.32  $\mu m$ , like the case of the liquid crystals having a positive dielectric constant anisotropy  $\Delta \varepsilon$ . In this case, most of the liquid crystals having a negative dielectric constant anisotropy  $\Delta \varepsilon$  have a birefringence anisotropy  $\Delta n$  of not smaller than 0.04 but not larger than 0.06.

[0227] A combination of the orientation films and the polarizer plates that will be described later makes it possible to obtain a maximum transmission factor when the liquid crystal molecules are turned by about 45° toward the direction of the electric field EDR from the rubbing direction RDR

[0228] The thickness (gap) of the liquid crystal layer is controlled by using polymer beads.

[0229] There is no particular limitation on the liquid crystal material LC so long as it is a nematic liquid crystal material. The drive voltage can be decreased with an increase in the value of the dielectric constant anisotropy  $\Delta \varepsilon$ . The thickness (gap) of the liquid crystal layer can be increased with a decrease in the refractive index anisotropy  $\Delta n$ , in order to shorten the time to pour the liquid crystals and to decrease variation in the gap.

[0230] [Orientation film]