US 20030076289A1

(19) **United States**

(12) **Patent Application Publication**

Tokonami et al.

(10) **Pub. No.: US 2003/0076289 A1**

(43) **Pub. Date: Apr. 24, 2003**

(54) **LIQUID CRYSTAL DISPLAY APPARATUS

AND DRIVING METHOD THEREFOR**

**Related U.S. Application Data**

(75) Inventors: **Susumu Tokonami**, Kikuchi-Gun (JP);

**Susumu Shibata**, Kikuchi-Gun (JP);

**Hironori Aoki**, Kikuchi-Gun (JP);

**Shingo Nagano**, Kikuchi-Gun (JP)

(62) Division of application No. 09/353,833, filed on Jul. 15, 1999, now Pat. No. 6,515,646.

**Foreign Application Priority Data**

Jul. 17, 1998 (JP) ..... 10-203726

Correspondence Address:

**OBLON, SPIVAK, MCCLELLAND, MAIER &

NEUSTADT, P.C.**

1940 DUKE STREET

ALEXANDRIA, VA 22314 (US)

(51) **Int. Cl. 7** ..... G09G 3/36

(52) **U.S. Cl.** ..... 345/100

(73) Assignee: **ADVANCED DISPLAY INC.**, Kikuchi-gu (JP)

(21) Appl. No.: **10/307,434**

(22) Filed: **Dec. 2, 2002**

**Publication Classification**

(57) **ABSTRACT**

The present invention is directed to a liquid crystal display apparatus including: a timing circuit for operating a shift register within a timing circuit during a vertical blanking period such that a common signal that has been alternated at a cycle of a Single Horizontal period is applied on counter electrodes during the vertical blanking period and such that a storage electrode signal is applied on storage electrodes having a frequency, phase and amplitude identical to those of the common signal.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

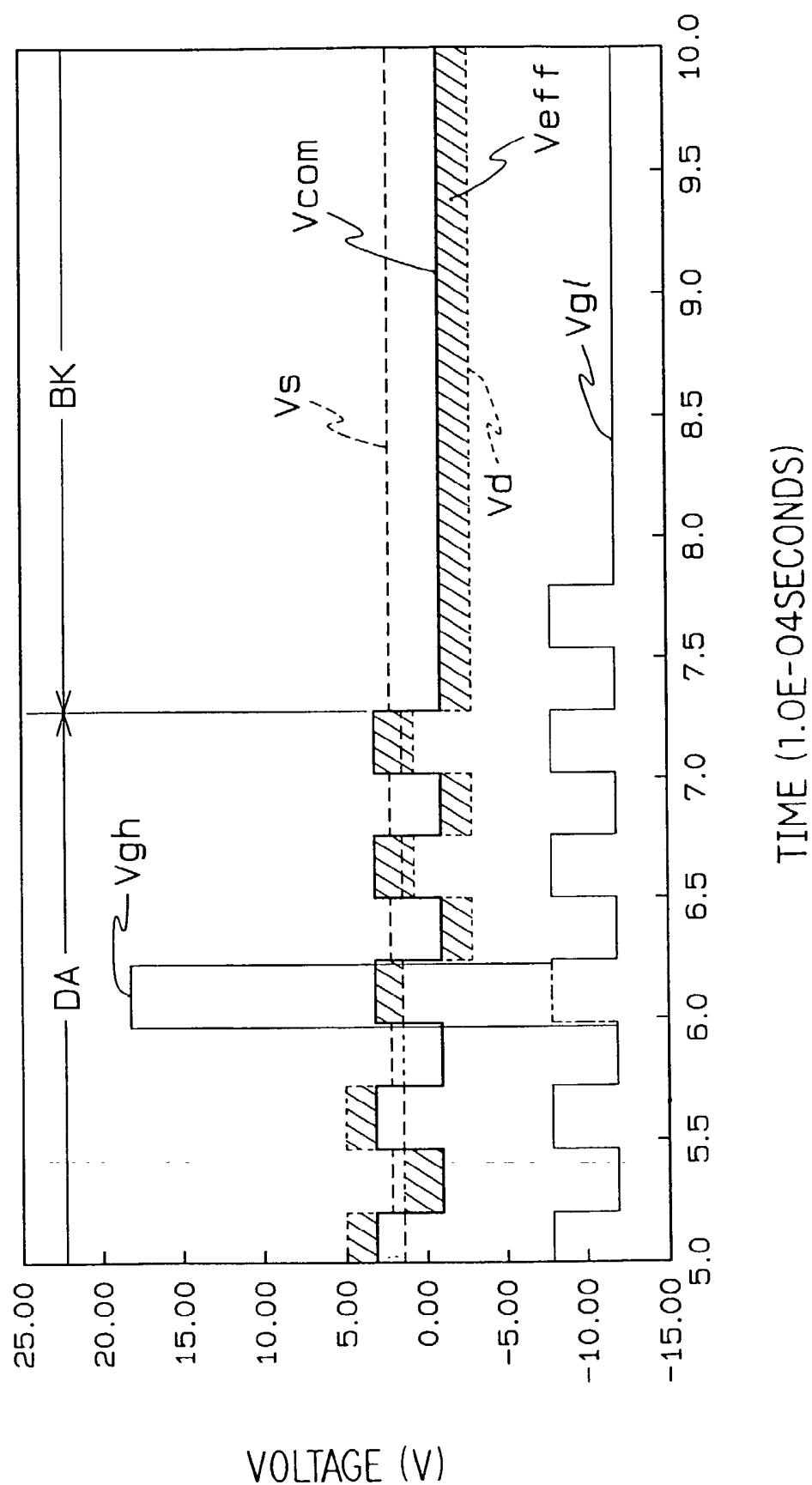

FIG. 8(a)

FIG. 8(b)

FIG. 8(c)

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

## LIQUID CRYSTAL DISPLAY APPARATUS AND DRIVING METHOD THEREFOR

### BACKGROUND OF THE INVENTION

[0001] The present invention relates to a liquid crystal display apparatus of active matrix type and a driving method therefor.

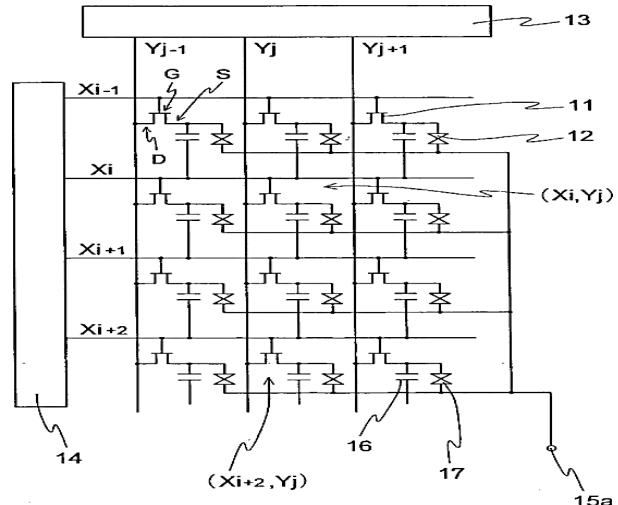

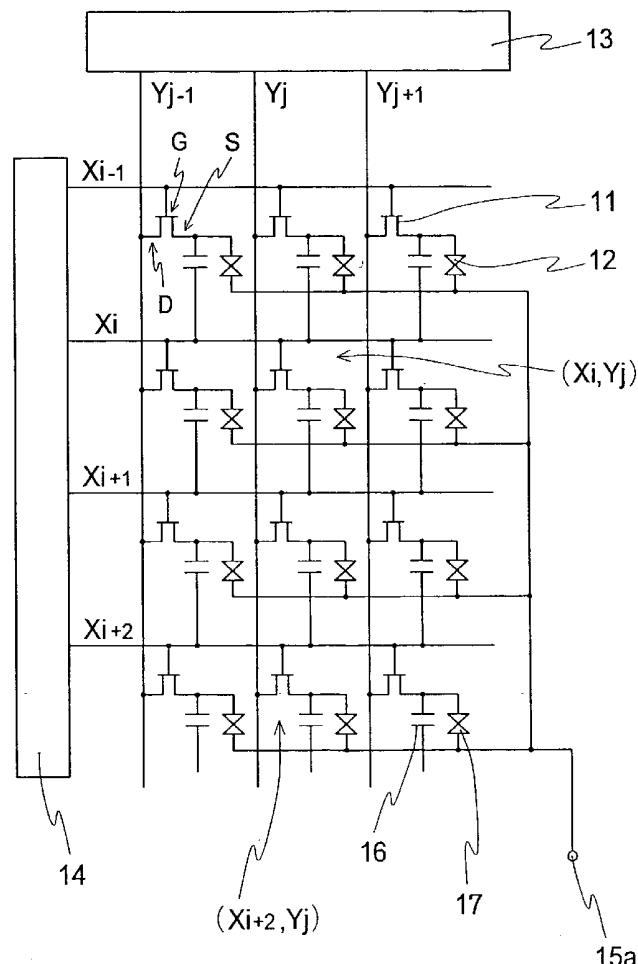

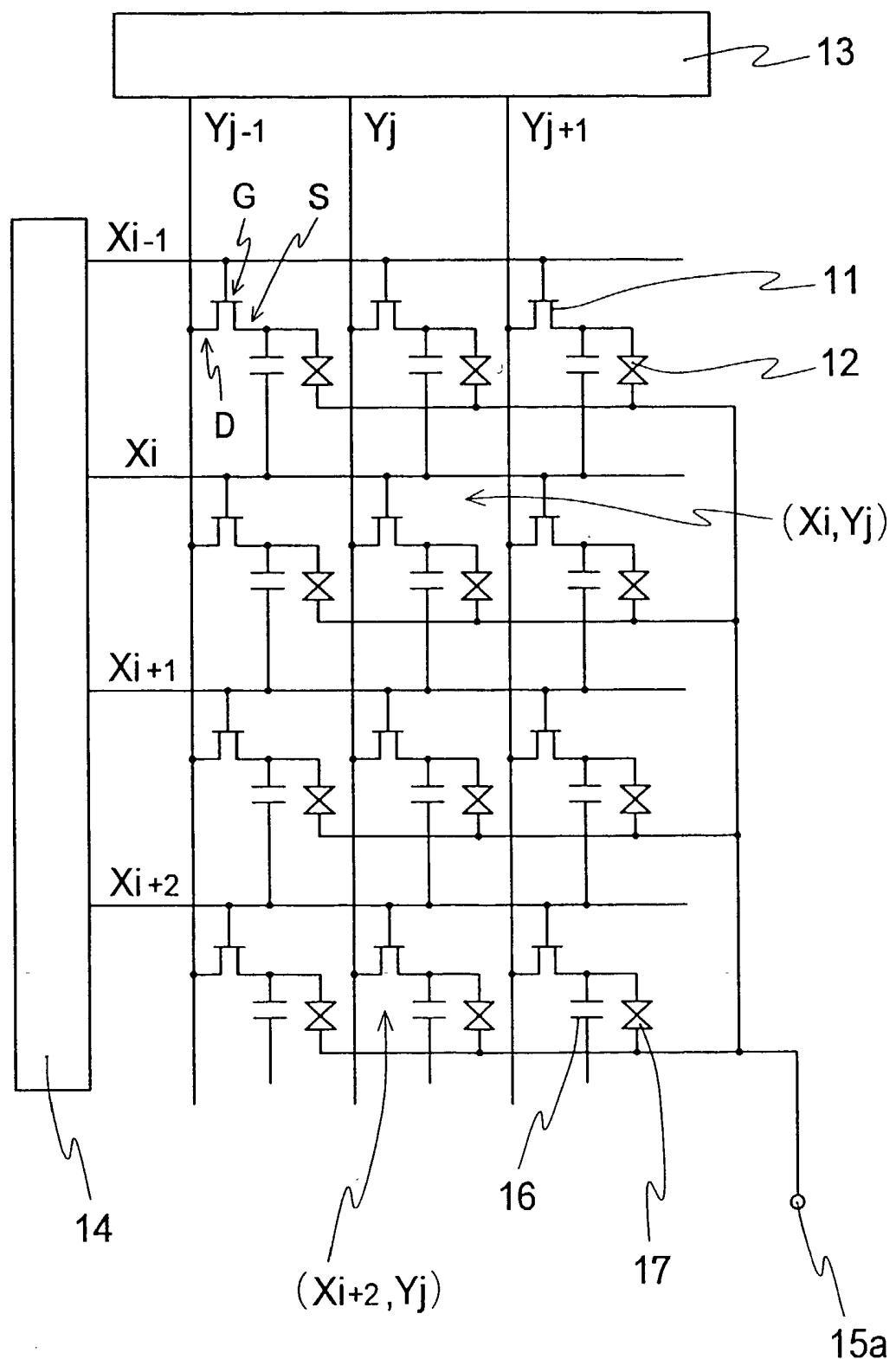

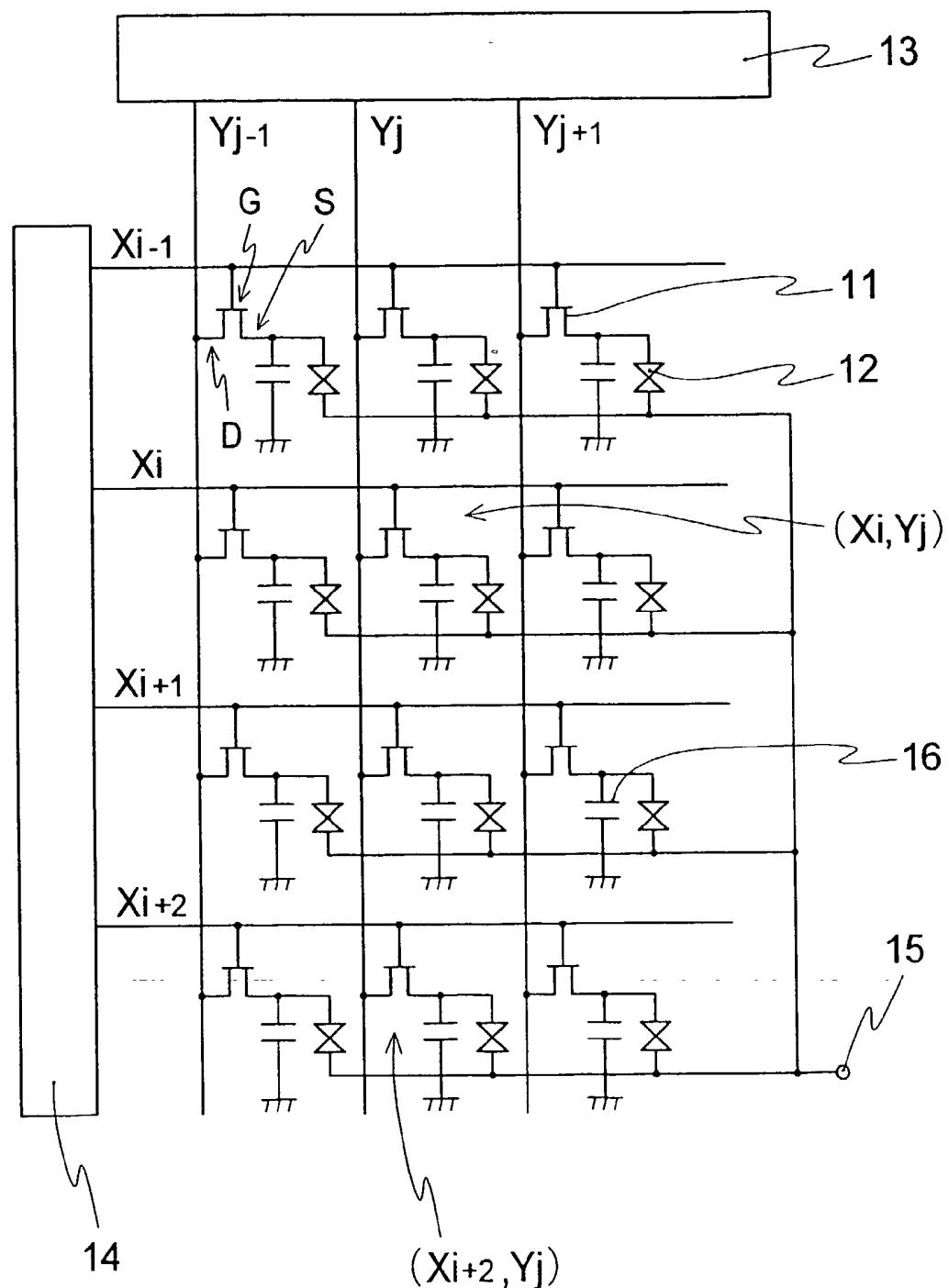

[0002] FIG. 13 is a diagram of a driving circuit of a conventional active matrix type liquid crystal display apparatus as described in Japanese Unexamined Patent Publication No. 313607/1993. In this diagram, a plurality of X electrode lines ( $X_{i-1}, X_i, X_{i+1} \dots$ ) and Y electrode lines ( $Y_{j-1}, Y_j, Y_{j+1} \dots$ ) are arranged in a form of a matrix, and active elements 11 and liquid crystal elements 12 such as TFT (thin film transistors) are formed on intersections of each of the X electrode lines and Y electrode lines. The Y electrode lines are also called data lines and are connected to a display signal circuit 13 for outputting display data signals for each of the liquid crystal display elements 12. Further, the X electrode lines are also called scanning signal lines and are connected to a scanning signal circuit 14 for outputting scanning signals.

[0003] The counter side of the liquid crystal display elements 12 are connected to a common electrode 15. The driving of the active elements 11 is performed in that the active elements 11 on the X electrode lines are set to at ON conditions (active conditions) synchronously with the scanning of the X electrode lines, in that display data signals are output from the display signal circuit 13, and in that data signals are written into corresponding liquid crystal display elements 12 via the active elements 11 in ON conditions. It should be noted that there have also been taken measures in which storage capacitances 16 are provided, upon requirement, for the liquid crystal display elements 12 in order to improve storage characteristics of electrical charge of the liquid crystal display elements 12.

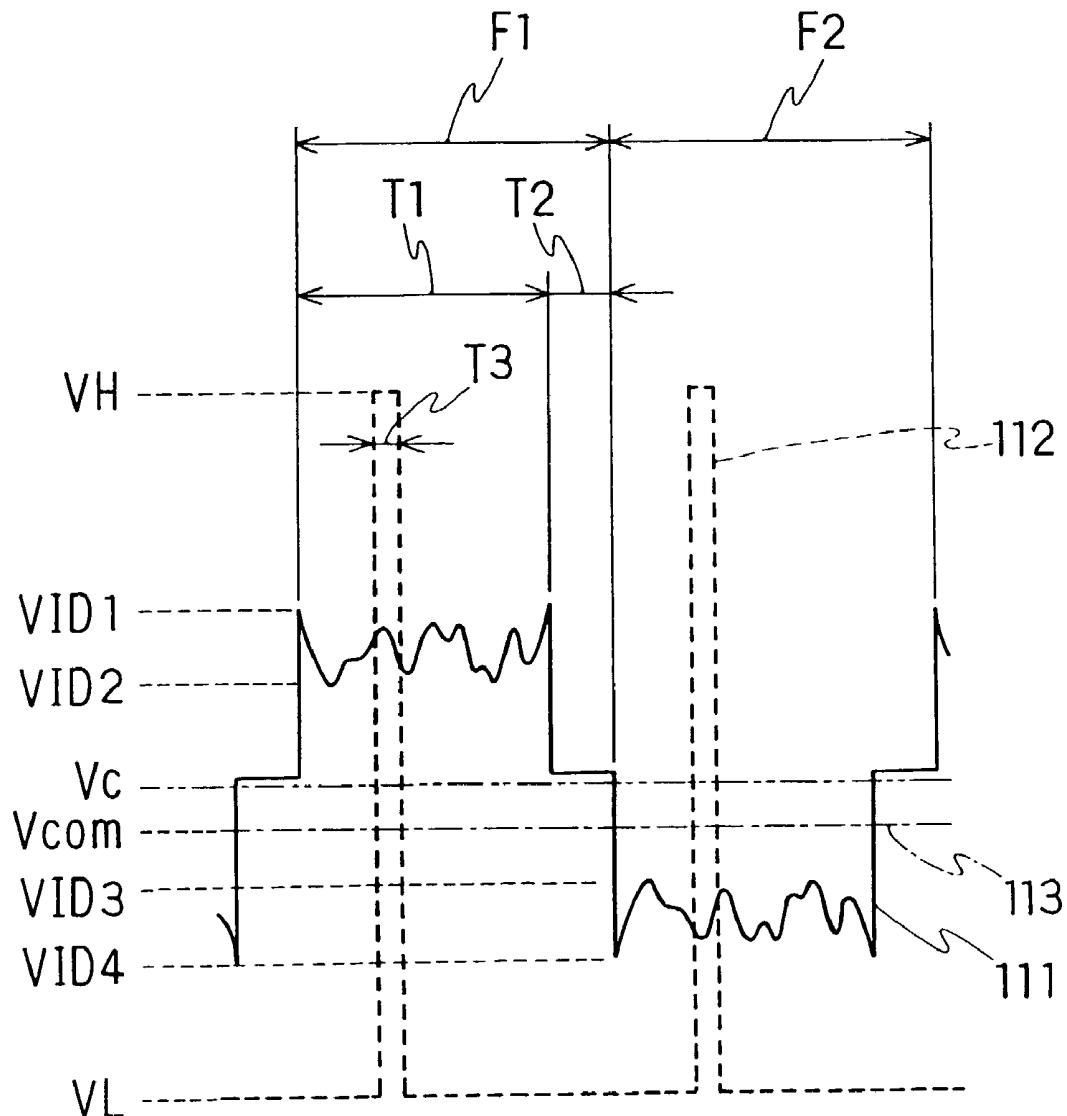

[0004] An example of a conventional driving method for an active matrix type liquid crystal display apparatus is disclosed in Japanese Unexamined Patent Publication No. 141269/1994, and FIG. 14 is a view showing an example of a timing chart for indicating the driving method. As known, liquid crystal need to be driven through alternating-current, whereby an electric potential 111 of the signal line is made to be an image signal performing alternating-current inversion with a certain electric potential  $V_c$  being the center. During vertical scanning period  $T_1$ , an electric potential 112 of a scanning line becomes high-leveled by a single scanning period  $T_3$ . Such a scanning pulse is sequentially applied from above the screen per scanning line.  $T_2$  denotes a vertical blanking period (hereinafter also referred to as mere "blanking period") in which usually no image signals are applied. An electric potential of a counter electrode 113 is set to be lower than the central electric potential  $V_c$  of the image signal in case of N channel TFTs.

[0005] It will now be explained for a line common inversion driving method that is one of the objects of the present invention as a driving method for the above liquid crystal display apparatus. In a line common inversion driving method, two adjacent pixels are driven through alternating-current to be of opposite polarity, and this method is advantaged in that a driving IC of low cost may be employed and the power consumption can be decreased.

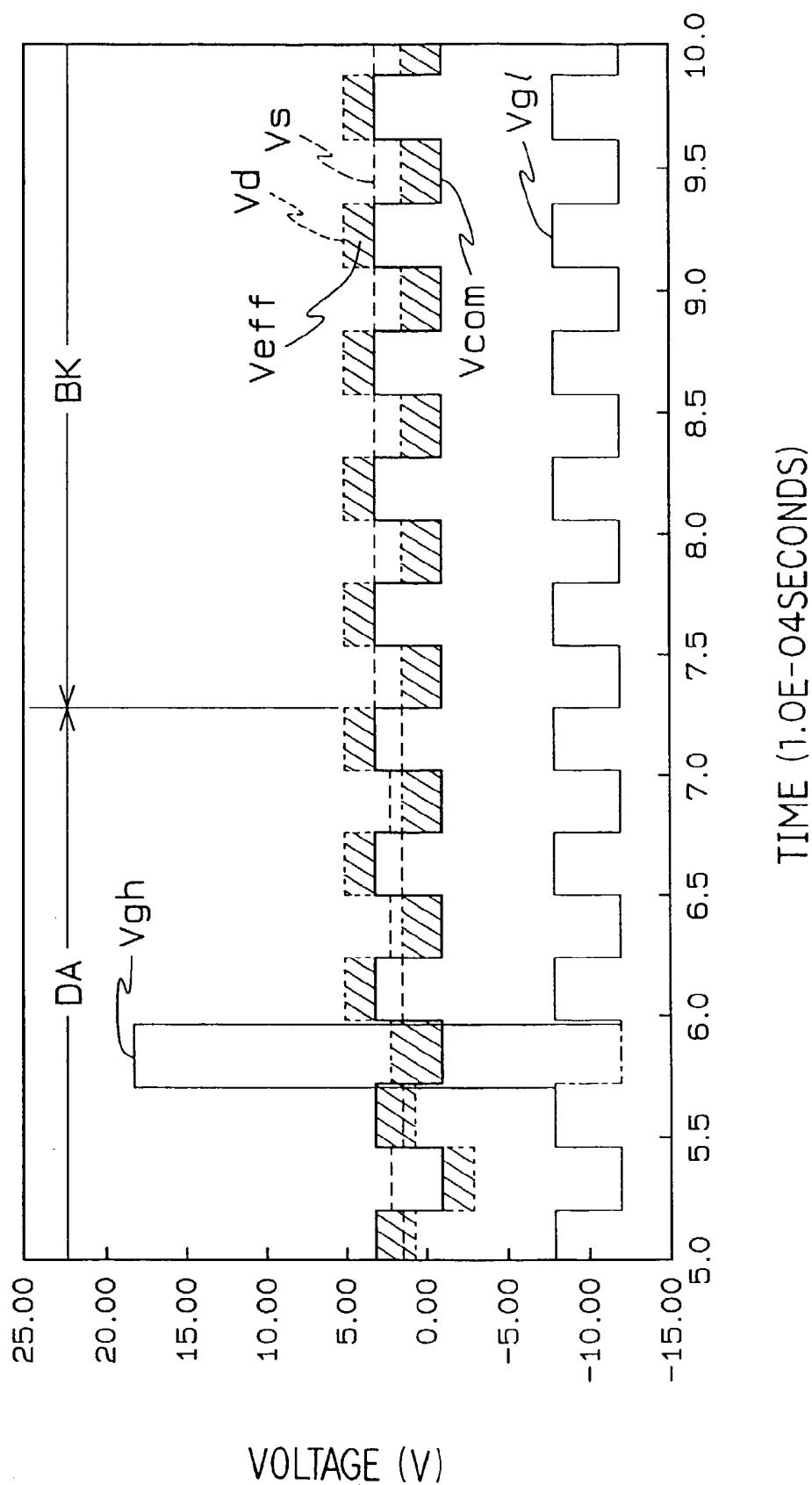

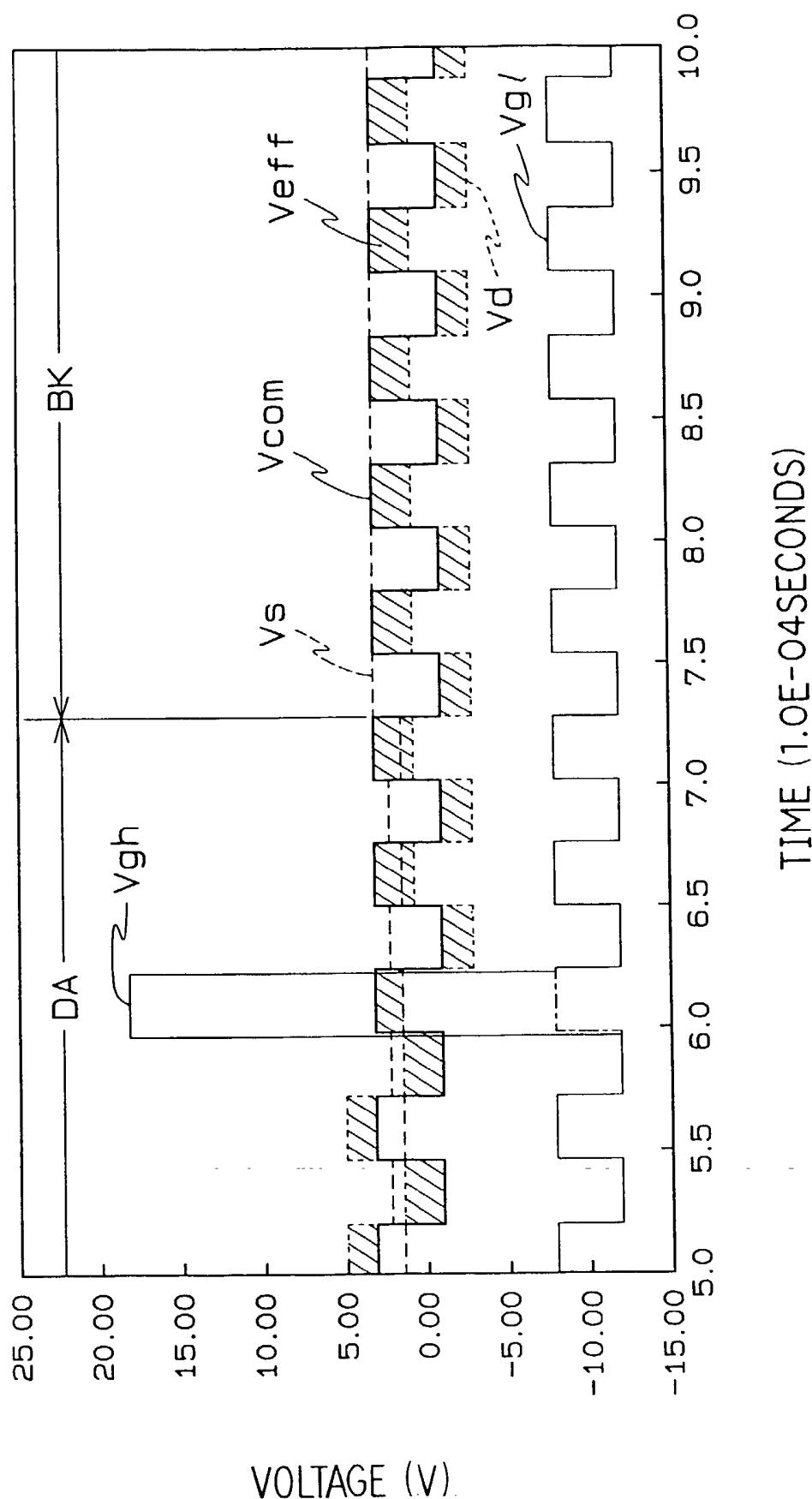

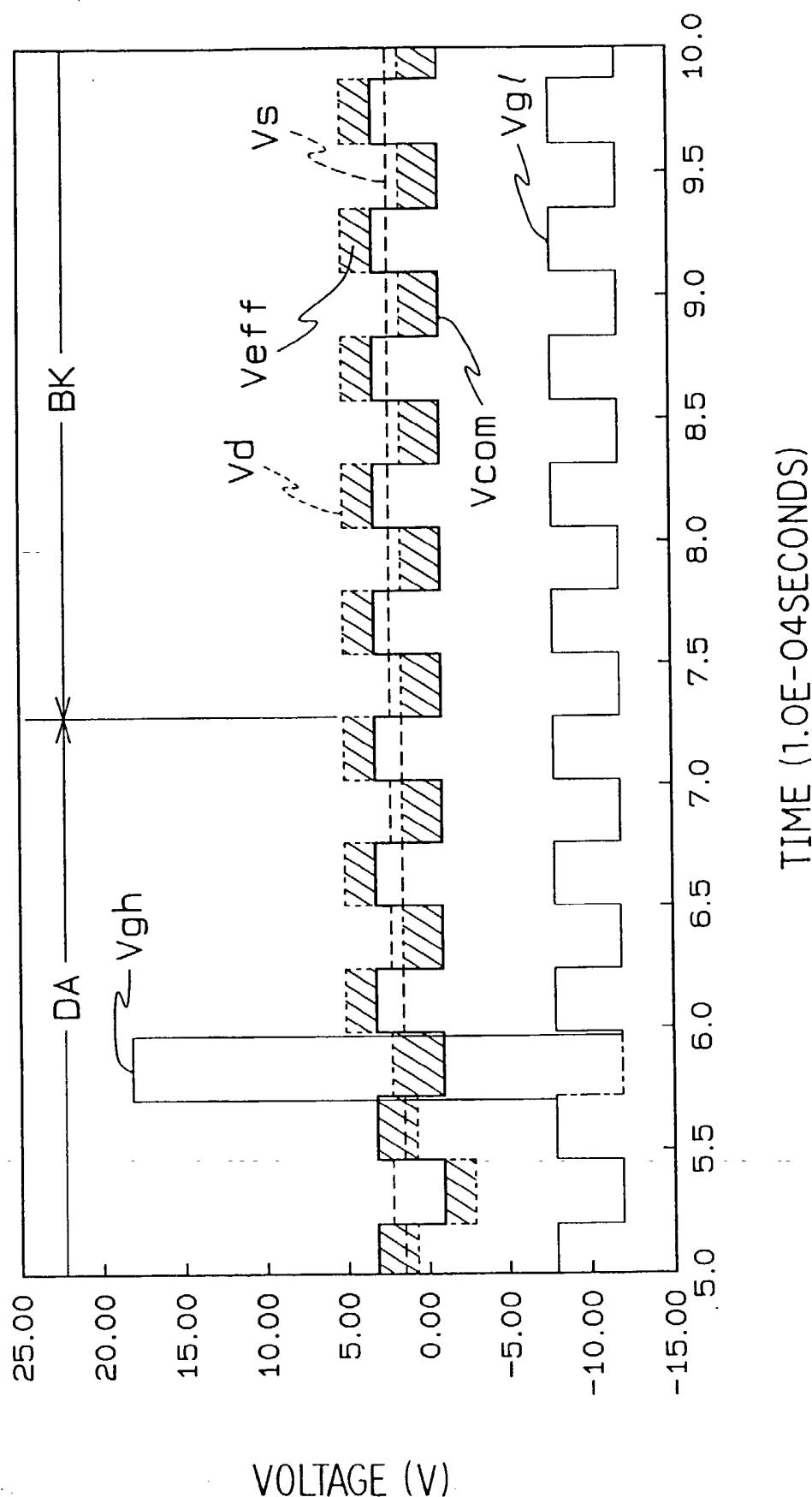

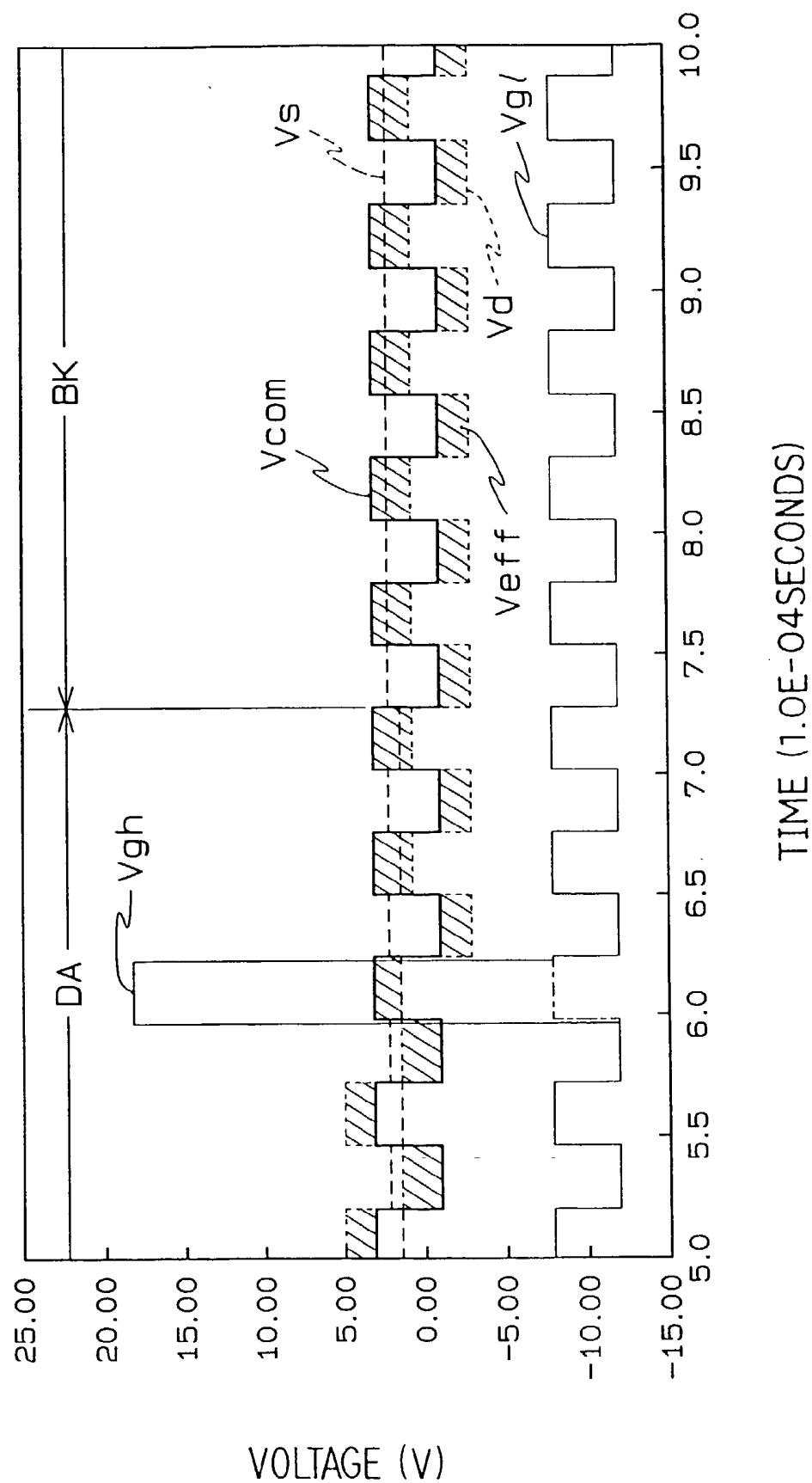

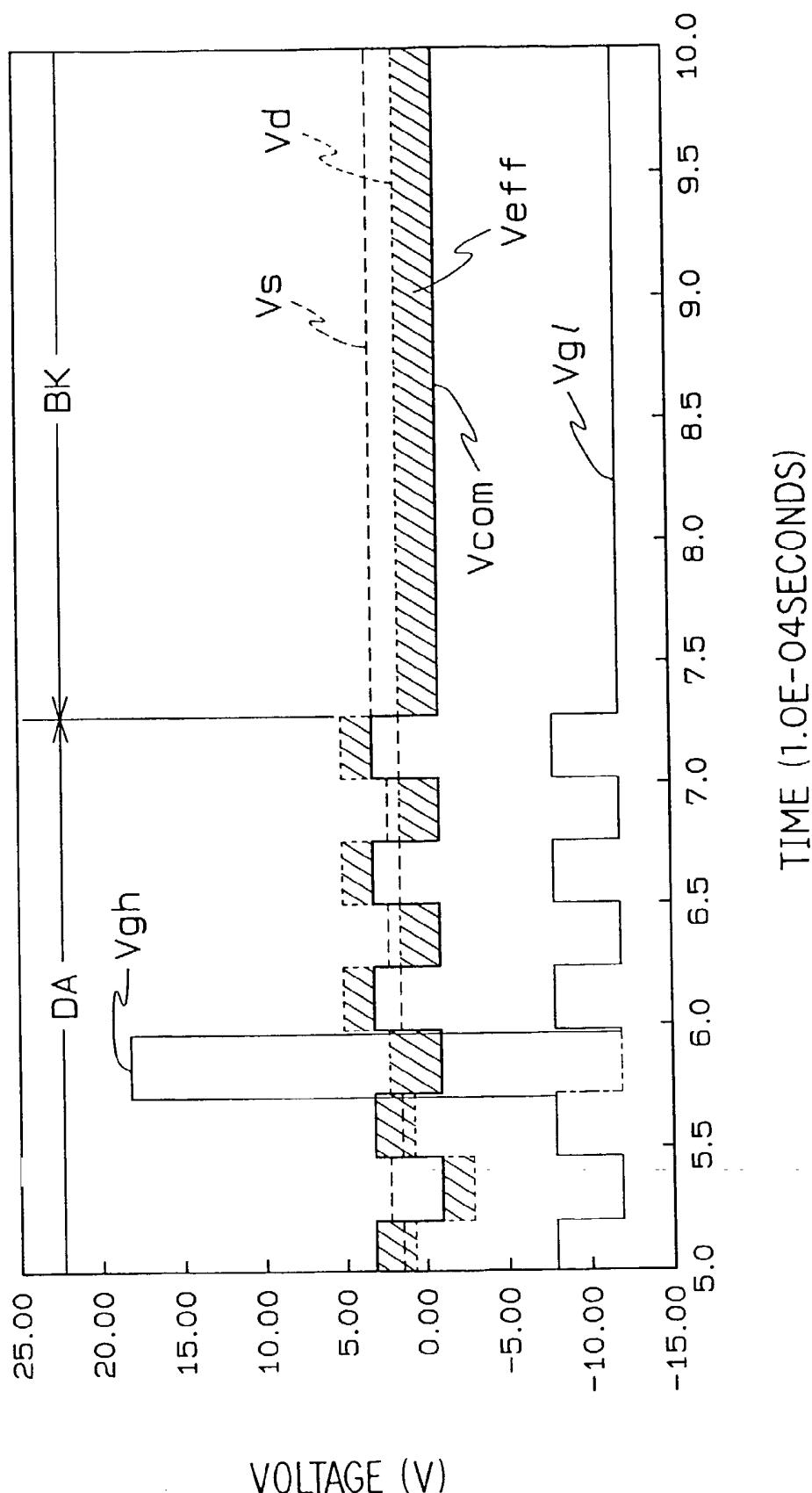

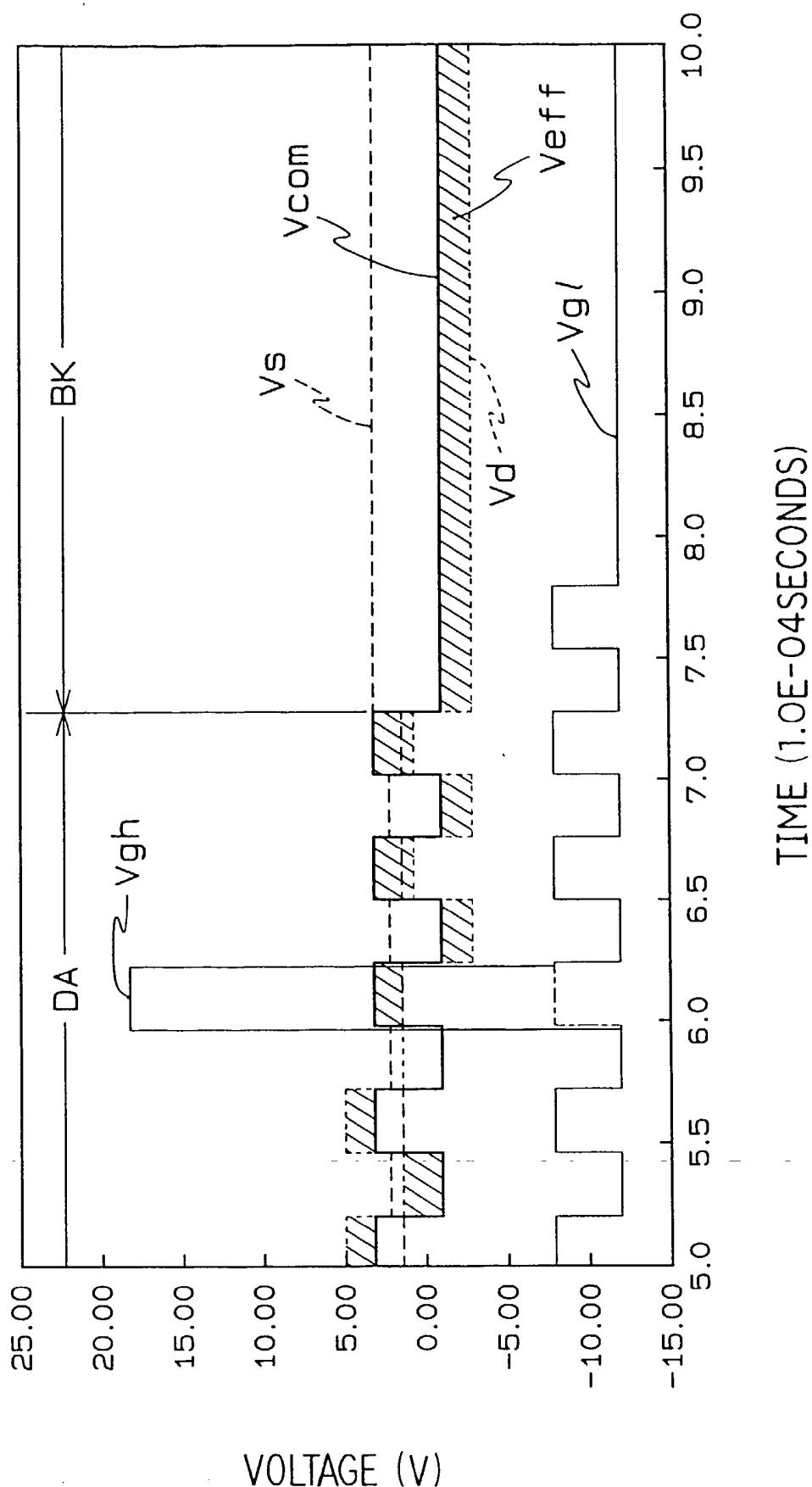

[0006] Driving waveforms of a conventional TFT-LCD employing the line common inversion method is shown in FIG. 15 and FIG. 16. FIG. 15 is a view of driving waveforms of odd-numbered lines and FIG. 16 of driving waveforms of even-numbered lines, respectively. In FIGS. 15 and 16,  $V_d$  denotes electric potentials of drain electrodes (broken line of short pitches),  $V_{com}$  electric potentials of the counter electrodes (thin real line),  $V_{eff}$  voltage applied onto the liquid crystal (potential differences between  $V_d$  and  $V_{com}$  are shown by the hatching),  $V_g$  electric potentials of the gate lines including voltage at the time of gate OFF  $V_{gl}$  and voltage at the time of gate ON  $V_{gh}$ .  $V_s$  denotes electric potentials of source lines (broken line of long pitches). In case the reference marks  $V_{com}$ ,  $V_g$ ,  $V_s$  are indicated in connection with the word "signal" such as "V<sub>com</sub> signal", these represent signals having electric potentials of counter electrodes. Further, DA denotes data period, and BK blanking period, respectively. The effective voltage  $V_{eff}$  that is applied on the liquid crystal corresponds to a root-mean-square of a single frame period of an electric potential difference between  $V_d$  and  $V_{com}$ . The  $V_d$  varies per Single Horizontal period (1H) depending on the  $V_{com}$ ,  $V_g$  and  $V_s$  signals.

[0007] In alternating-current driving based on a line common inversion method,  $V_g$  is controlled by the scanning signal circuit,  $V_s$  by the display signal circuit,  $V_{com}$  by a timing control circuit and a power source circuit (not shown), while  $V_d$  is determined by the  $V_g$ ,  $V_s$  and  $V_{com}$ . A Single Horizontal period (1H) is approximately 32  $\mu$ s in case of VGA, approximately 26  $\mu$ s in case of SVGA, and 20  $\mu$ s in case of XGA, and a value for each of the electric potentials  $V_{gh}$  is set to be a voltage with which charge/discharge of electric charge of the drain electrodes can be completed within 1H, that for  $V_{gl}$  to be a voltage with which the electric charge of the drain electrodes can be sufficiently held during a single frame period, and those for  $V_s$  and  $V_{com}$  to be a voltage with which display can be performed at a desired luminance.

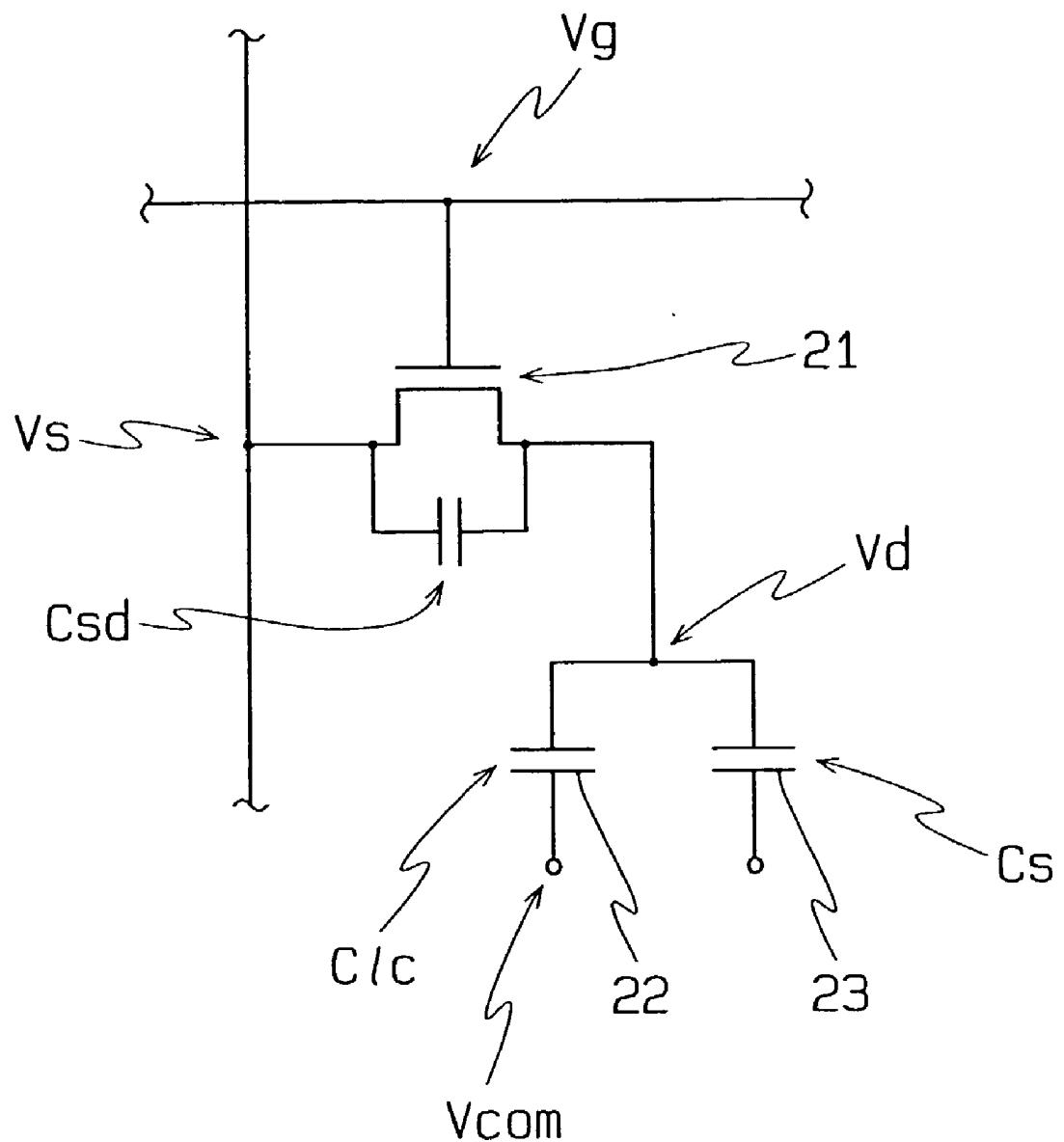

[0008] Since this variation is repeated per 1H during the data display period, the  $V_{eff}$  of the odd-numbered lines and even-numbered lines can be set to be identical by optimizing the central value for the  $V_{com}$ . However, since the  $V_{com}$ ,  $V_{gl}$  and  $V_s$  signal are usually not varied but remain fixed during the blanking period, the drain variation at the start of the blanking period is maintained during the blanking period whereby luminance differences are generated line by line owing to the different values for the  $V_{eff}$  of the odd-numbered lines and even-numbered lines during the blanking period as shown in FIG. 15 and FIG. 16. The relationship between  $V_d$  and  $V_{com}$  will now be explained. As shown in FIG. 17, the electric potential  $V_d$  of the pixel electrodes (drain electrodes) changes owing to effects of variations in (1) electric potential  $V_{com}$  of the counter electrodes 22, (2) electric potential of a storage electrodes 23, and (3) electric potential  $V_s$  of the source electrodes in a holding condition of the TFTs 21. However, the electric potential of the storage electrode is determined by the  $V_g$ ,  $V_{com}$  and other factors, and a signal identical in amplitude and polarity with those of the  $V_{com}$  (while the DC values may be different) is applied. In this manner, since the alternation of (1) to (3) is terminated during the blanking period, it may happen that the luminance differences of brightness between odd-numbered lines and even-numbered lines are generated.

[0009] The present invention has been made to solve such problems, and it is an object thereof to provide a liquid crystal display apparatus and a driving method therefor in which TFT driving signals during blanking periods are optimized to compensate for effective voltage differences during vertical blanking periods between odd-numbered lines and even-numbered lines and to decrease luminance differences per gate line.

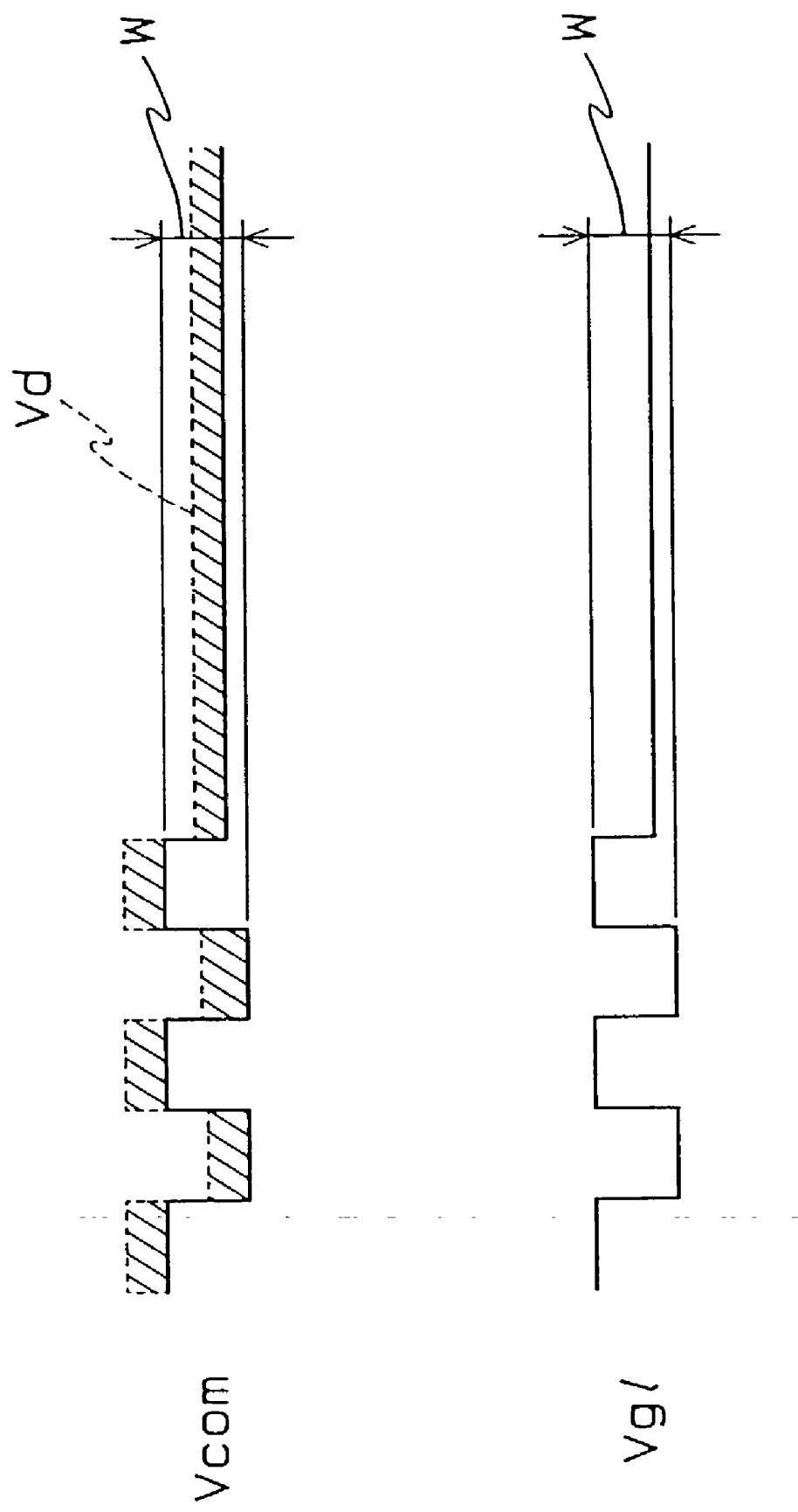

[0010] In order to compensate for effective voltage differences during the afore-mentioned vertical blanking period, the present invention employs a means to perform alternation of the afore-mentioned (1) electric potential Vcom of counter electrodes 22, (2) electric potential of storage electrodes 23, and (3) electric potential Vs of source electrodes also during the blanking period as it is similarly performed during the data period. However, it is also possible to perform alternation of only one of (1), (2) and (3) during the blanking period or to combine some of these. It will now be shown that variations in the Vcom and Cs electrodes are corresponding in a set with respect to each other. Variations in the Vd in case of TFT-OFF conditions are dominated by the coupling of signals that are transmitted through three capacitance Clc, Cs, Csd as shown in FIG. 16 whereby it is desirable to set the conditions of signal coupling for these to be identical with those of the data period. Since the Vd is floating during the TFT-OFF condition, the electric potential of the Cs electrode needs to vary similarly to Vcom in order to maintain a voltage that is applied on the Clc with respect to the Vcom that is to be alternated constant (note that the DC values may be different). Therefore, variations in the Vcom and Cs electrodes are always in subordinate relations and should be considered as a set.

[0011] Japanese Unexamined Patent Publication No. 141269/1994 suggests a method in which an alternating-current voltage exceeding a threshold for liquid crystal is applied on signal lines or scanning lines in order to solve such problems during the vertical blanking period. However, the technique disclosed in this publication is merely directed to the subject of coping with display deficiencies owing to defects caused by shorting of signal lines and pixel electrodes which stand out during the vertical blanking period in which no voltage is applied, and it is not suitable to achieve the purpose of the present invention to decrease luminance differences per line.

#### SUMMARY OF THE INVENTION

[0012] In order to achieve the afore-mentioned purpose of the present invention, the liquid crystal display apparatus according to one embodiment of the present invention comprises a timing circuit for operating a shift register within a timing circuit during a vertical blanking period such that a common signal that has been alternated at a cycle of a Single Horizontal period is applied on counter electrodes during the vertical blanking period and such that a storage electrode signal is applied on storage electrodes having a frequency, phase and amplitude identical to those of the common signal.

[0013] The liquid crystal display apparatus comprises either an array substrate having a wiring arrangement in which gate lines concurrently serve as storage capacitances or an array substrate having a wiring arrangement in which common lines concurrently serve as storage capacitances.

[0014] The liquid crystal display apparatus comprises a timing circuit for operating a shift register within the timing circuit during a vertical blanking period such that a source signal that has been alternated at a cycle of a Single Horizontal period is applied on source lines during the vertical blanking period.

[0015] The liquid crystal display apparatus according to another embodiment of the present invention comprises a timing circuit in which a polarity inverting signal is at least one inverted during a vertical blanking period such that a variable common signal, which voltage is at least once varied during the vertical blanking period, is generated and applied on counter electrodes, and such that a variable storage electrode signal, which is varied to assume a polarity identical with the variable common signal and by an identical amplitude synchronously with the variable common signal, is generated and applied on storage electrodes.

[0016] The liquid crystal display apparatus according to still another embodiment of the present invention comprises a timing circuit in which a polarity inverting is at least one inverted during a vertical blanking period such that a signal a variable source signal, which voltage is at least once varied during the vertical blanking period, is generated, and such that the variable source signal is applied on the source lines.

[0017] The liquid crystal display apparatus according to another embodiment of the present invention comprises a timing circuit in which Gray level data are generated as data for a line following a last line, and wherein a Gray level source signal is applied on source lines during the vertical blanking period.

[0018] According to the liquid crystal display apparatus according to another embodiment of the present invention, the liquid crystal display apparatus (a) comprising a timing circuit in which a common signal and a storage electrode signal having a frequency, phase and amplitude identical to those of the common signal are generated to be of same polarity by fixing a polarity inverting signal either to H or L during each of the vertical blanking periods, and

[0019] (b) wherein a common signal of same polarity is applied on counter electrodes during each of the vertical blanking periods and the storage electrode signal is applied on storage electrodes.

[0020] According to the liquid crystal display apparatus according to another embodiment of the present invention, the liquid crystal display apparatus (a) comprising a circuit in which a common signal and storage electrode signal of a frequency, phase and amplitude identical to those of the common signal are generated by amplifying a polarity inverting signal, wherein an intermediate electric potential common signal having a potential that is between a maximum peak value and minimum peak value for an amplitude during a data period is generated by setting an amplifying rate to zero, and wherein an intermediate electric potential storage electrode signal having an intermediate electric potential that is between a maximum peak value and a minimum peak value for the amplitude during the data period synchronously with the intermediate electric potential common signal is generated, and

[0021] (b) wherein the intermediate potential common signal is applied on counter electrodes during the vertical blanking period and the intermediate

potential storage electrode signal is applied on storage electrodes during the vertical blanking period.

[0022] In the driving method for a liquid crystal display apparatus according to one embodiment of the present invention, a common signal is alternated at a cycle of a Single Horizontal period and applied on counter electrodes, and a storage electrode signal having a frequency, phase and amplitude identical to those of the common signal is applied on storage electrodes during the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0023] In the driving method for a liquid crystal display apparatus according to another embodiment of the present invention, a source signal that has been alternated at a cycle of a Single Horizontal period is applied on source lines during a vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0024] In the driving method for a liquid crystal display apparatus according to another embodiment of the present invention, a variable common signal, which voltage is at least once varied during a vertical blanking period, is generated and applied on counter electrodes, and a variable storage electrode signal, which is varied to assume a polarity identical with the variable common signal and by an identical amplitude synchronously with the variable common signal, is generated and applied on storage electrodes for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0025] In the driving method for a liquid crystal display apparatus according to still another embodiment of the present invention, a voltage for a source signal is at least once varied during a vertical blanking period and applied on source lines for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0026] In the driving method for a liquid crystal display apparatus according to another embodiment of the present invention, a source signal having a Gray level electric potential is applied on source lines during a vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0027] In the driving method for a liquid crystal display apparatus according to still another embodiment of the present invention, a common signal and storage electrode signal are set to be of same polarity, wherein the common signal is applied on counter electrodes and the storage electrode signal on storage electrodes during each of the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0028] In the driving method for a liquid crystal display apparatus according to another embodiment of the present invention, a common signal having an intermediate electric potential that is between a maximum peak value and minimum peak value for an amplitude during a data period is

applied on counter electrodes during a vertical blanking period, and a storage electrode signal having an intermediate electric potential that is between a maximum peak value and minimum peak value for the amplitude during the data period is applied, synchronous with the common signal, to storage electrodes during the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

[0029] Embodiments of the present invention will now be discussed in details with reference to the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0030] FIG. 1 is an explanatory view showing an equivalent circuit relative to the liquid crystal display apparatus of the present invention;

[0031] FIG. 2 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 1;

[0032] FIG. 3 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 1;

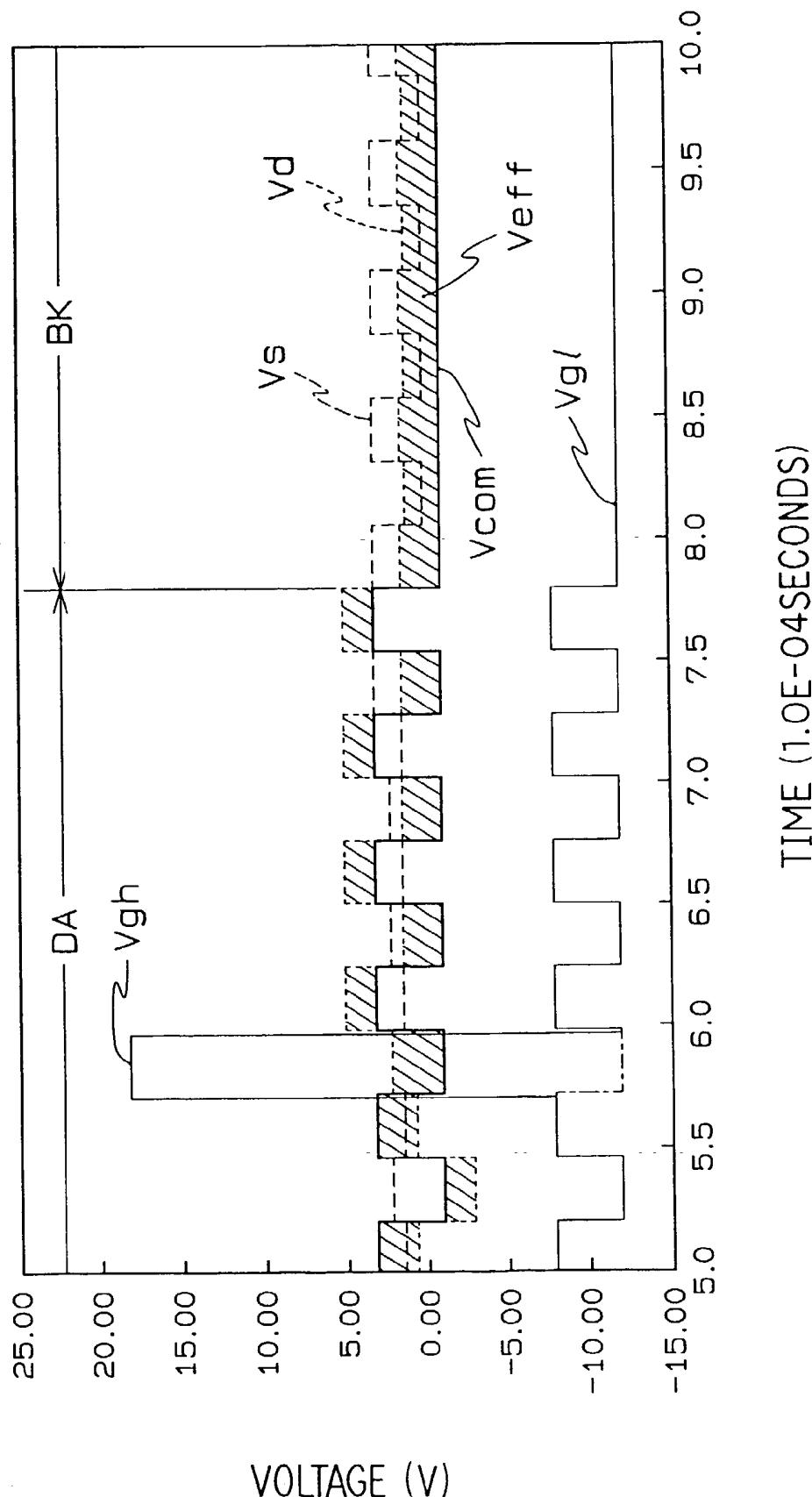

[0033] FIG. 4 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 2;

[0034] FIG. 5 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 2;

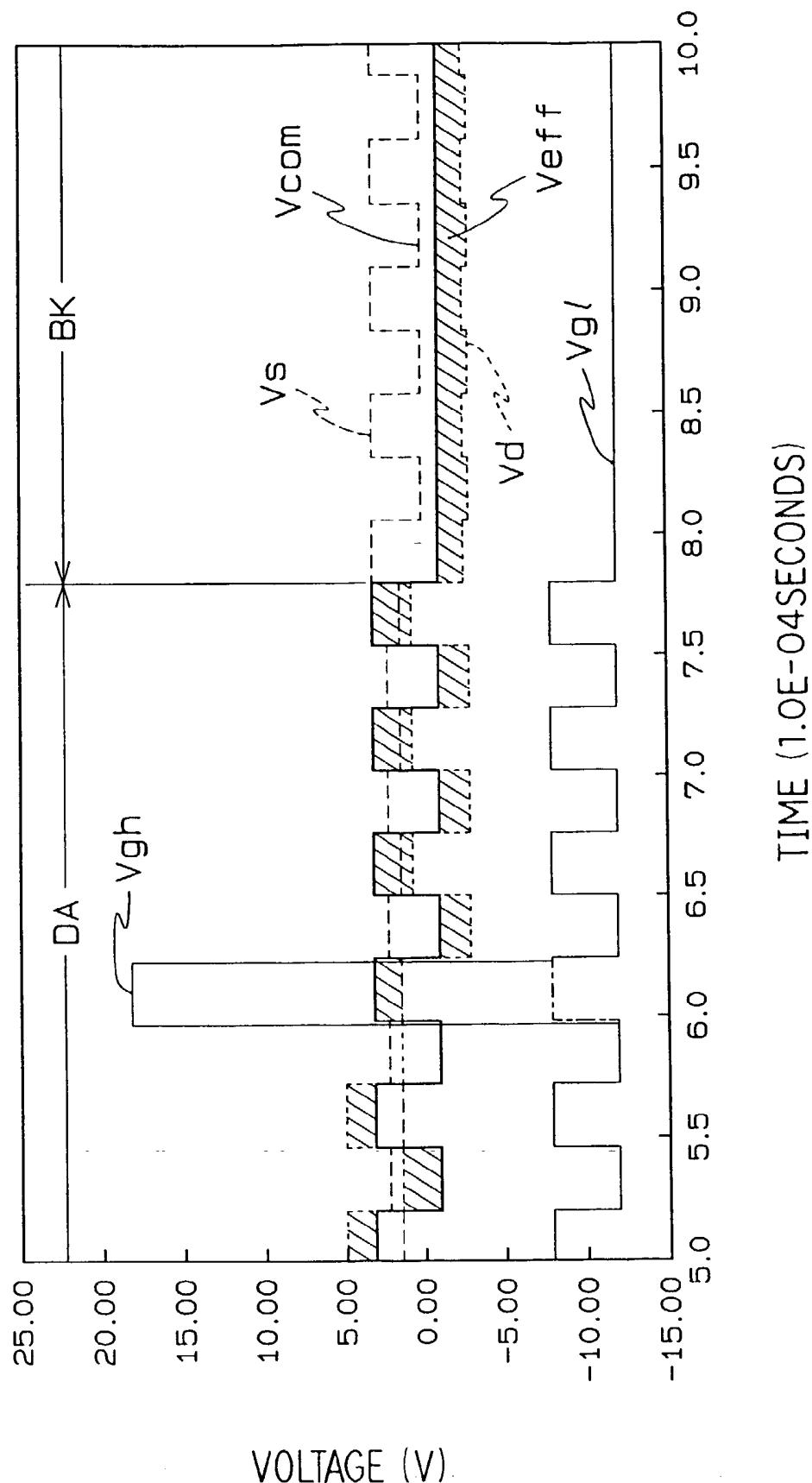

[0035] FIG. 6 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 4;

[0036] FIG. 7 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 4;

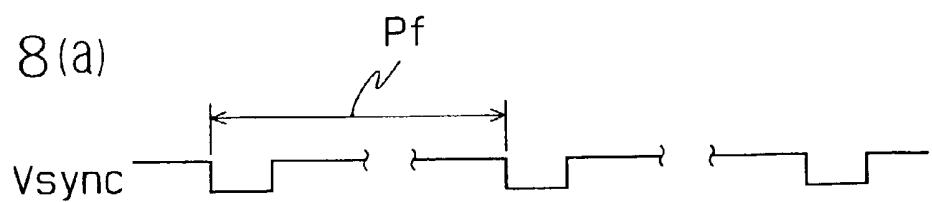

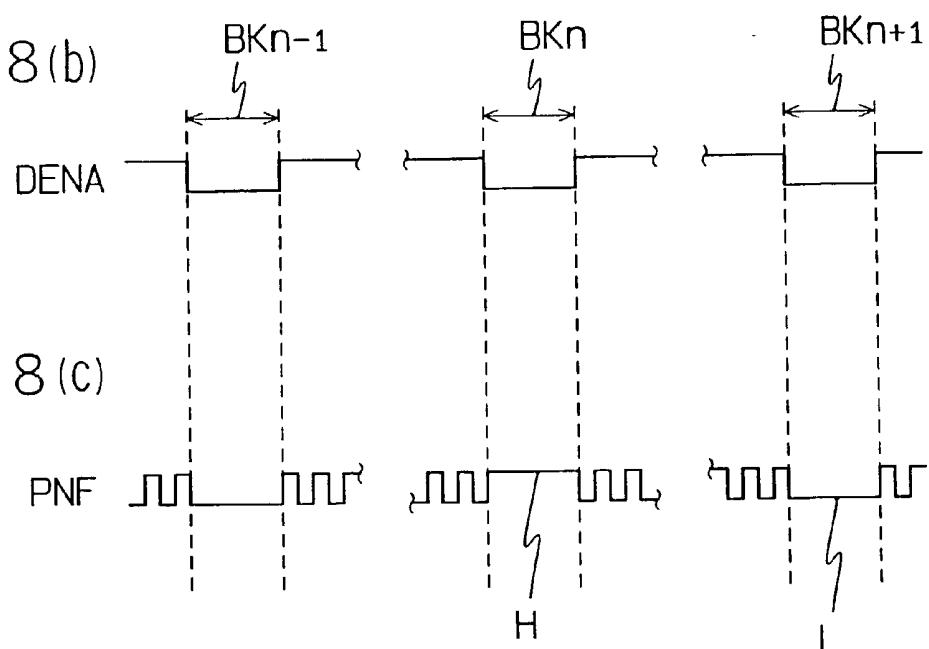

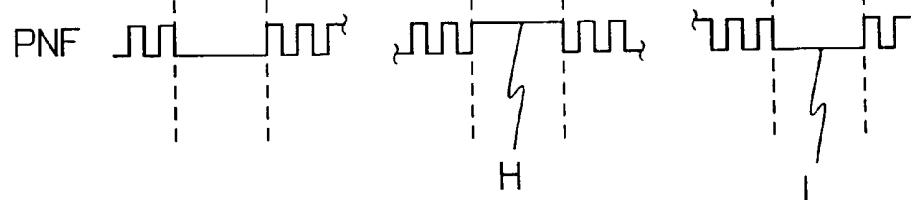

[0037] FIG. 8 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 5;

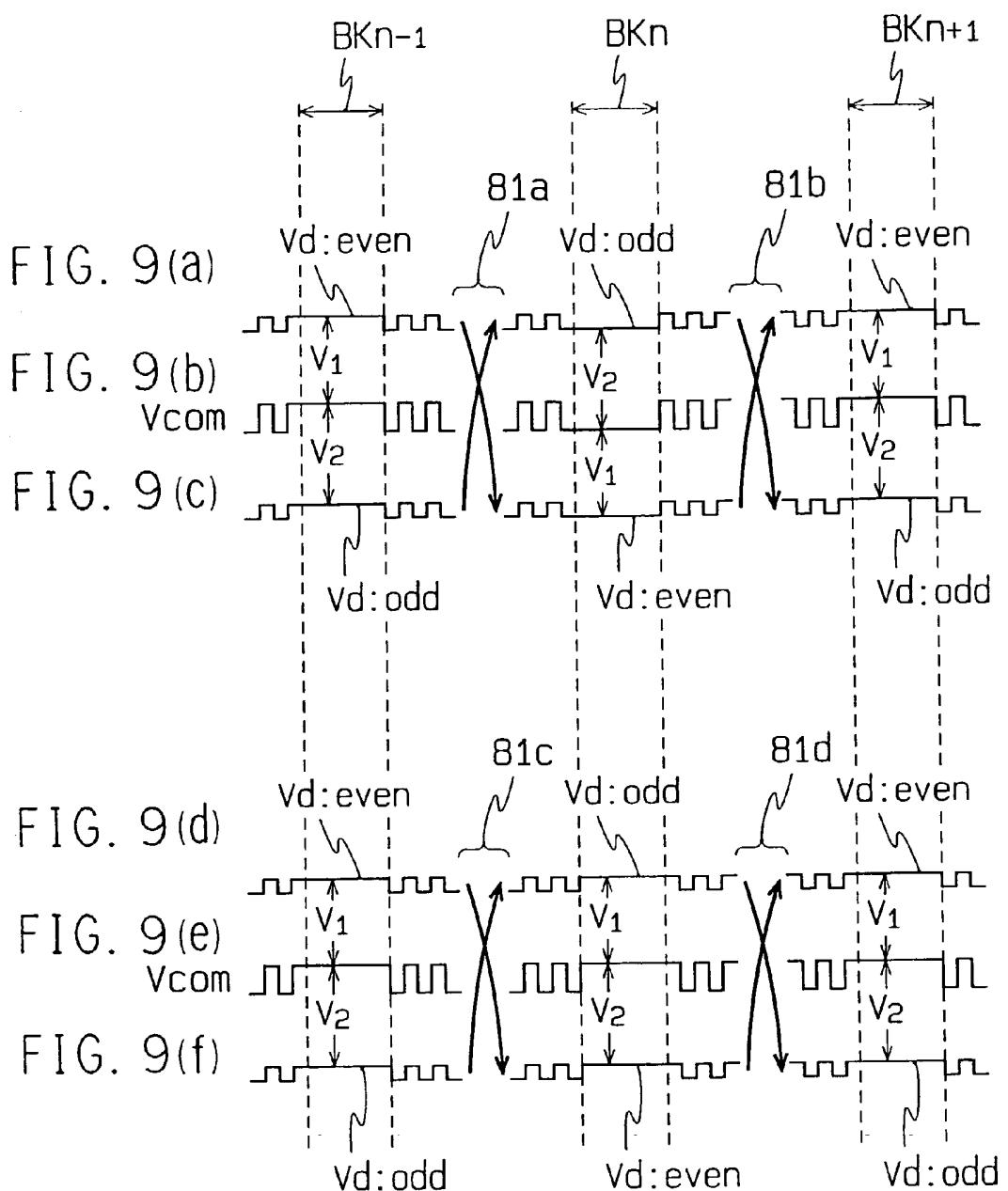

[0038] FIG. 9 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 5;

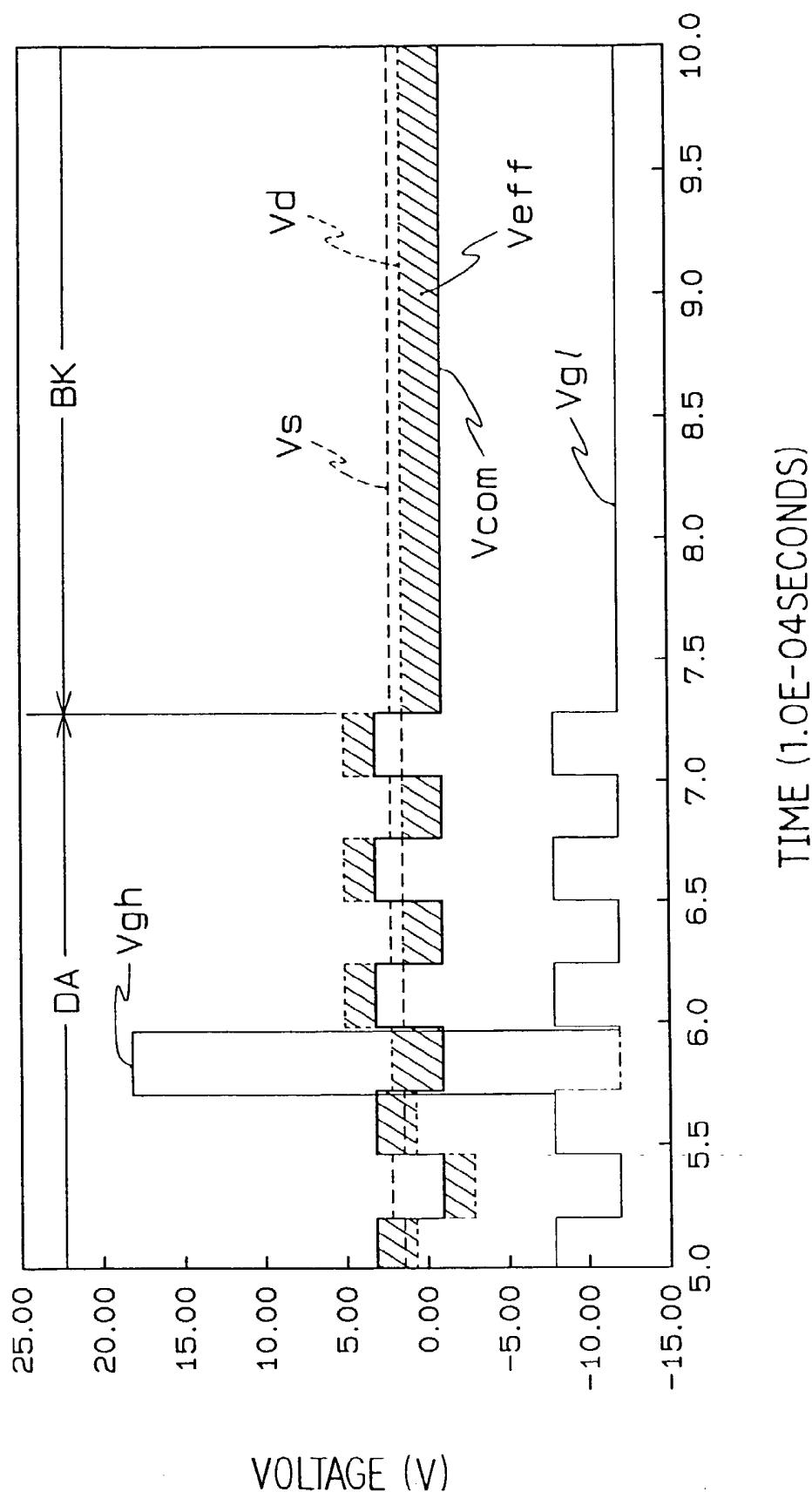

[0039] FIG. 10 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 6;

[0040] FIG. 11 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 7;

[0041] FIG. 12 is an explanatory view showing a driving waveform of the liquid crystal display apparatus of EMBODIMENT 7;

[0042] FIG. 13 is an explanatory view showing a driving waveform of the conventional liquid crystal display apparatus;

[0043] FIG. 14 is an explanatory view showing a driving waveform of the conventional liquid crystal display apparatus;

[0044] FIG. 15 is an explanatory view showing a driving waveform of the conventional liquid crystal display apparatus;

[0045] FIG. 16 is an explanatory view showing a driving waveform of the conventional liquid crystal display apparatus; and

[0046] FIG. 17 is an explanatory view showing a driving waveform of the conventional liquid crystal display apparatus.

common line 15a, and by applying a gate OFF signal having a frequency, phase and amplitude identical with those of the common signal on the gate lines, a storage electrode signal was applied on the storage electrodes 16. There are indicated in Table 1 effective voltage differences  $dV_{lc}$  between  $G_n$  and  $G_{n+1}$  ( $n$ -th line and  $n+1$ -th line of the gate) wherein  $dV_{lc}$  values of a conventional liquid crystal display apparatus and  $dV_{lc}$  values of the liquid crystal display apparatus according to the present invention have been compared (it should be noted that in the display condition, all pixel Gray level were displayed).

TABLE 1

| dV <sub>lc</sub> [V] at<br>Blanking Period         |                                                                 | V <sub>com</sub> , V <sub>gl</sub> |                                                                                   |

|----------------------------------------------------|-----------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------|

| Vs<br>(Black level)<br>(in case of normally white) | DC                                                              | DC                                 | AC<br>(in case of varying every<br>Single<br>Horizontal period)                   |

|                                                    | AC<br>(in case of varying<br>every Single<br>Horizontal period) | EMBODIMENT 2<br>0.280              | EMBODIMENT 1<br>0.199<br>combination of EMBODIMENT 1<br>and EMBODIMENT 2<br>0.043 |

| Vs<br>(Gray level)                                 | DC                                                              | EMBODIMENT 4<br>0.374              | combination of EMBODIMENT 1<br>and EMBODIMENT 4<br>0.021                          |

|                                                    | AC<br>(in case of varying<br>every Single<br>Horizontal period) | EMBODIMENT 2<br>0.317              | combination of EMBODIMENT 1,<br>EMBODIMENT 2 and EMBODIMENT 4<br>0.000            |

## DETAILED DESCRIPTION

## Embodiment 1

[0047] This embodiment will be explained based on a case in which a liquid crystal display apparatus of line common inversion method was used employing a panel having a wiring arrangement in which gate lines concurrently served as storage capacitances (hereinafter referred to as “Cs on Gate arrangement”), wherein the Vs remained as conventional ones and V<sub>com</sub> and V<sub>gl</sub> were AC converted during the blanking period. Through this arrangement, signals applied on the gate lines were also applied on the storage capacitance electrodes (also called “storage electrodes”). FIG. 1 is a view of an equivalent circuit of an active matrix type liquid crystal display apparatus having a “Cs on Gate arrangement” according to the present invention. Further explanations will be eliminated since the same arrangement is employed in each of the following embodiments. FIG. 2 is an explanatory view of driving waveforms of odd-numbered lines ( $G_{n+1}$  and  $n$  are even natural numbers) and FIG. 3 an explanatory view of driving waveforms of even-numbered lines ( $G_n$ ), respectively. In these drawings, elements that are identical with those of FIGS. 13 to 17 are indicated by identical reference numerals or marks. Similarly to the data display period, V<sub>com</sub> and V<sub>gl</sub> were varied per Single Horizontal period (1H) whereby effective voltage differences between odd-numbered lines and even-numbered lines can be decreased. For this purpose, the common signal was AC converted, applied on the counter electrodes 17 via

[0048] It can be understood from Table 1 that the effective voltage difference  $dV_{lc}$  between odd-numbered lines and even-numbered lines was 0.524V in a conventional liquid crystal display apparatus while it was 0.199V in EMBODIMENT 1.

[0049] Methods for applying such V<sub>com</sub> and V<sub>gl</sub> that have been alternated at a cycle of a Single Horizontal period onto the common lines and gate lines also during the blanking period will now be explained. As for the V<sub>com</sub> and V<sub>gl</sub> during the data period, alternation is performed by generating polarity inversion signals PNF in the timing circuit based on signals such as HD (horizontal synchronous signal) or DENA (display data enabling signal) and respectively amplifying these. The amplified V<sub>com</sub> is inputted into the counter electrodes in the original form, and the V<sub>gl</sub> is inputted into a scanning electrode driving circuit. In the scanning electrode driving circuit, the V<sub>gh</sub> is selected for each single line and this V<sub>gl</sub> is maintained also in the blanking period but except for the charging/discharging period. Conventionally, this PNF had been given as a DC voltage in the blanking period, while in this embodiment, the PNF is AC converted also in this period to obtain V<sub>com</sub> and V<sub>gl</sub>. For performing AC conversion of the PNF (signal for determining the polarity of V<sub>com</sub> and V<sub>gl</sub>) also during the blanking period, the shift register in the timing circuit is operated also during the blanking period. Therefore, alternation can be performed without the necessity of any particular means.

[0050] It should be noted that the common signal is AC converted and applied on the counter electrodes and the storage electrode signal having a frequency, phase and amplitude identical to those of the common signal is applied

on the storage electrodes similarly to the above described embodiment also in case a panel other than of the aforementioned “Cs on Gate arrangement” is employed.

### Embodiment 2

[0051] The present embodiment will now be explained in which the Vcom and Vgl remained as conventional ones and only the Vs was AC converted during the blanking period in a liquid crystal display apparatus of line common inversion method employing a panel of Cs on Gate arrangement, similarly to EMBODIMENT 1 (reference should be made to **FIG. 4** and **FIG. 5**). By performing AC conversion, effective voltage differences between odd-numbered lines and even-numbered lines were decreased. As it can be seen from Table 1, the effective voltage difference dVlc between odd-numbered lines and even-numbered lines was decreased to 0.280V in EMBODIMENT 2 while it was 0.524V in a conventional liquid crystal display apparatus. In case the AC amplitude was fixed to Gray level in this embodiment, the dVlc was 0.317V.

[0052] In order to apply the Vs that has been alternated at a cycle of a Single Horizontal period onto source lines also during the blanking period, Vs that has been alternated at a cycle of a Single Horizontal period in a timing circuit in which a shift register within the timing circuit is operated during the vertical blanking period was generated during the blanking period and applied on the source lines, similarly to EMBODIMENT 1.

### Embodiment 3

[0053] Concerning the AC conversion of Vcom and Vgl in EMBODIMENT 1 and the AC conversion of Vs in EMBODIMENT 2, it was set in EMBODIMENT 1 and EMBODIMENT 2 that these were varied during the blanking period per 1H. However, by applying Vcom, Vgl and Vs signals which voltages have been varied for more than once during the blanking period without particularly relying on frequency, effective voltage differences can be decreased. For this reason, a variable common signal was applied on counter electrodes and Vgl was generated as a variable storage electrode signal that varies synchronously with the variable common signal to be of same polarity as the common signal and by an identical amplitude and is applied on the gate lines. However, in this embodiment, Vcom (variable common signal), Vgl (variable gate OFF signal) and Vs (variable source signal) which voltages were varied at least once during the blanking period were generated by a timing circuit in which a polarity inverting signal was inverted at least once during the blanking period.

### Embodiment 4

[0054] The present embodiment will now be explained in which the Vcom and Vgl remained as conventional ones and the DC level of the Vs was set to be at Gray level during the blanking period in a liquid crystal display apparatus of line common inversion method employing a panel of Cs on Gate arrangement, similarly to EMBODIMENT 1 to EMBODIMENT 3 (reference should be made to **FIG. 6** and **FIG. 7**). Since the Vs is usually fixed to a black (in case of normally white mode) DC level having large amplitudes, differences between Veff of odd-numbered and even-numbered lines owing to signal coupling is large. In this embodiment, the Vs

has been fixed to a Gray level in which the amplitude was smaller than that of a black level whereby the effective voltage difference dVlc between odd-numbered lines and even-numbered lines could be decreased to 0.374V than compared to 0.524V in a conventional liquid crystal display apparatus as it is shown in Table 1. Generating a Vs which DC level is a Gray level is performed as follows:

[0055] Since an output corresponding to a last gate line is usually maintained for the Vs during the blanking period, data for the Gray level are generated in the timing circuit as data for a line following the last line and are input into the display signal circuit, whereby the source signal during the blanking period is maintained at a DC voltage of Gray level, and a Gray level source signal is generated. Generation of other signals and control were performed through similar methods using the same driving circuit as described in the afore-mentioned EMBODIMENT 1 or EMBODIMENT 2.

### Embodiment 5

[0056] **FIG. 8** and **FIG. 9** are diagrams showing, in details, comparison between generation of signals wherein Vcom of a n-th blanking period BKn and that of a n+1-th blanking period BKn+1 are set to be of same polarity (FIGS. 9(d) to (f)) and a conventional one (FIGS. (a) to (c)), wherein BKn and BKn+1 are of opposite polarity), wherein Pf denotes a single frame (50 to 70 Hz), Vsync a vertical synchronizing signal (or VD), DENA a display data enabling signal, PNF a signal for determining the polarity of Vcom and Vgl, Vd:odd an electric potential of an arbitrary drain electrode among the odd-numbered lines of the gate, Vd:even an electric potential of an arbitrary drain electrode among the even-numbered lines of the gate, and 81a, 81b, 81c and 81d recharge, respectively. Further, V<sub>1</sub> denotes a case in which the effective voltage Veff becomes small and V<sub>2</sub> in which the effective voltage Veff becomes large, wherein V<sub>1</sub> indicates that the luminance is “bright” and V<sub>2</sub> that the luminance is “dark”. It can be understood from the drawings that the gate even-numbered lines became both “bright” in luminance in BKn and BKn+1 in case the Vcom of BKn and that of BKn+1 are of opposite polarity (while the odd-numbered lines were all “dark”) while the gate even-numbered lines became “bright” at BKn and “dark” at BKn+1 (while the odd-numbered lines were “dark” at BKn and “bright” at BKn+1) in case the Vcom were of same polarity as in the present embodiment.

[0057] In a liquid crystal display apparatus of line common inverting method, voltage levels of Vcom and Vgl of blanking periods BKn and BKn+1 were conventionally determined by an electric potential of a last stage during the data period as shown in FIGS. 9(a) to 9(c) whereby the polarity during the blanking period became opposite at BKn and BKn+1. In this embodiment, effective voltage differences between odd-numbered lines and even-numbered lines could be decreased by making the polarity of BKn and BKn+1 identical and thus to achieve effects similar to those of EMBODIMENT 1 to EMBODIMENT 4. Therefore, a common signal as well as a gate OFF signal having a frequency, phase and amplitude identical to those of the common signal were generated to be of same polarity by fixing the polarity inverting signal either to H or L during each of the vertical blanking period, and the common signal of same polarity was applied on the counter electrodes and the gate OFF signal on the gate lines, respectively, during the

vertical blanking period. At this time, the polarity of  $B_{Kn}$  and  $B_{Kn+1}$  were made identical by fixing the PNF during the blanking period to either H or L in the timing generating circuit. Generation of other signals and control were performed through similar methods using the same driving circuit as described in the afore-mentioned EMBODIMENT 1 to EMBODIMENT 3 or that of EMBODIMENT 4.

#### Embodiment 6

[0058] In the liquid crystal display apparatus of line common inverting method employing a panel of Cs on Gate arrangement, it is also possible to use Vs as conventional ones and to apply  $V_{com}$  and  $V_{gl}$  as signals having intermediate electric potentials of amplitude W (reference should be made to **FIG. 10**) during the blanking period. By fixing the  $V_{com}$  and  $V_{gl}$  during the blanking period to assume intermediate electric potentials of amplitudes, effective voltage differences between odd-numbered lines and even-numbered lines could be decreased and similar effects as those of EMBODIMENT 1 to EMBODIMENT 5 could be achieved. In this case, the intermediate electric potential may be an electric potential between a maximum peak value and a minimum peak value of the amplitude of each of the signals during the data period.  $V_{com}$  and  $V_{gl}$  are respectively set to be at an intermediate electric potential of the amplitude by setting an amplification rate to zero in a circuit for generating  $V_{com}$  and  $V_{gl}$  by amplifying PNF. Generation of other signals and control were performed through similar methods using the same driving circuit as described in the afore-mentioned EMBODIMENT 1 to EMBODIMENT 3 or that of EMBODIMENT 4.

#### Embodiment 7

[0059] In EMBODIMENT 7 (references should be made to **FIG. 11** and **FIG. 12**), EMBODIMENT 1 and EMBODIMENT 4 were combined, that is,  $V_{com}$  and  $V_{gl}$  were AC converted and the DC level of Vs was set to Gray level. In this case, the effective voltage difference  $dV_{LIC}$  between odd-numbered lines and even-numbered lines was decreased to 0.021V as can be seen from Table 1. In case EMBODIMENT 1 and EMBODIMENT 2 are combined, the effective voltage difference  $dV_{LIC}$  between odd-numbered lines and even-numbered lines became 0.043V as can be seen from Table 1, and further, in case of combining EMBODIMENT 1, EMBODIMENT 2 and EMBODIMENT 4 for performing AC conversion of Vs at Gray level and AC conversion of  $V_{com}$  and  $V_{gl}$ , the same value is decreased to 0.000V (in the display condition, all pixels displayed Gray level). In this manner, from among liquid crystal display apparatuses of line common inverting method employing a panel of Cs on Gate arrangement, a liquid crystal display apparatus embodying combinations of a plurality of embodiments selected from EMBODIMENT 1, EMBODIMENT 2 and EMBODIMENT 4 as shown in Table 1 (e.g. EMBODIMENT 1 and EMBODIMENT 2, EMBODIMENT 1 and EMBODIMENT 4 or EMBODIMENT 1, EMBODIMENT 2 and EMBODIMENT 4) was capable of decreasing the effective voltage difference between odd-numbered lines and even-numbered lines to achieve effects similar to those of EMBODIMENT 1 to EMBODIMENT 6.

#### Embodiment 8

[0060] Similarly to EMBODIMENT 7, the effective voltage difference between odd-numbered lines and even-numbered lines could also be decreased by combining at least two of EMBODIMENT 1 to EMBODIMENT 6 (e.g. EMBODIMENT 2 and EMBODIMENT 5, EMBODIMENT 2 and EMBODIMENT 4, EMBODIMENT 2 and EMBODIMENT 6 or EMBODIMENT 4 and EMBODIMENT 6).

#### Embodiment 9

[0061] In a line common inverting method having an array arrangement which is a common Cs arrangement in which storage capacitances are provided by the common lines, the storage capacitance (Cs) electrodes are of same electric potential as those of the  $V_{com}$ . Therefore, by making  $V_{com}$  correspond instead of  $V_{gl}$  in EMBODIMENT 1 to EMBODIMENT 8, similar effects as those of EMBODIMENT 1 to EMBODIMENT 8 can be achieved.

[0062] According to the present invention, luminance differences that are generated per each line of gate lines can be decreased in a liquid crystal display apparatus of line common inverting method.

#### What is claimed is:

1. A liquid crystal display apparatus comprising:

- a timing circuit for operating a shift register within a timing circuit during a vertical blanking period such that a common signal that has been alternated at a cycle of a Single Horizontal period is applied on counter electrodes during the vertical blanking period and such that a storage electrode signal is applied on storage electrodes having a frequency, phase and amplitude identical to those of the common signal.

- 2. The liquid crystal display apparatus of claim 1, including either an array substrate having a wiring arrangement in which gate lines concurrently serve as storage capacitances or an array substrate having a wiring arrangement in which common lines concurrently serve as storage capacitances.

- 3. A liquid crystal display apparatus comprises a timing circuit for operating a shift register within the timing circuit during a vertical blanking period such that a source signal that has been alternated at a cycle of a Single Horizontal period is applied on source lines during the vertical blanking period.

- 4. A liquid crystal display apparatus comprising a timing circuit in which a polarity inverting signal is at least one inverted during a vertical blanking period such that a variable common signal, which voltage is at least once varied during the vertical blanking period, is generated and applied on counter electrodes, and such that a variable storage electrode signal, which is varied to assume a polarity identical with the variable common signal and by an identical amplitude synchronously with the variable common signal, is generated and applied on storage electrodes.

- 5. A liquid crystal display apparatus comprising a timing circuit in which a polarity inverting is at least one inverted during a vertical blanking period such that a signal a variable source signal, which voltage is at least once varied during the vertical blanking period, is generated, and such that the variable source signal is applied on the source lines.

- 6. A liquid crystal display apparatus comprising a timing circuit in which Gray level data are generated as data for a line following a last line, and wherein a Gray level source signal is applied on source lines during the vertical blanking period.

## 7. A liquid crystal display apparatus comprising:

- (a) a timing circuit in which a common signal and a storage electrode signal having a frequency, phase and amplitude identical to those of the common signal are generated to be of same polarity by fixing a polarity inverting signal either to H or L during each of the vertical blanking periods, and

- (b) wherein a common signal of same polarity is applied on counter electrodes during each of the vertical blanking periods and the storage electrode signal is applied on storage electrodes.

## 8. A liquid crystal display apparatus comprising:

- (a) a circuit in which a common signal and storage electrode signal of a frequency, phase and amplitude identical to those of the common signal are generated by amplifying a polarity inverting signal, wherein an intermediate electric potential common signal having a potential that is between a maximum peak value and minimum peak value for an amplitude during a data period is generated by setting an amplifying rate to zero, and wherein an intermediate electric potential storage electrode signal having an intermediate electric potential that is between a maximum peak value and a minimum peak value for the amplitude during the data period synchronously with the intermediate electric potential common signal is generated, and

- (b) wherein the intermediate potential common signal is applied on counter electrodes during the vertical blanking period and the intermediate potential storage electrode signal is applied on storage electrodes during the vertical blanking period.

## 9. Method for driving a liquid crystal display apparatus comprising steps of:

alternating a common signal at a cycle of a Single Horizontal period and applied on counter electrodes, and

applying a storage electrode signal having a frequency, phase and amplitude identical to those of the common signal on storage electrodes during the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 10. Method for driving a liquid crystal display apparatus comprising steps of:

applying a source signal that has been alternated at a cycle of a Single Horizontal period on source lines during a vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 11. Method for driving a liquid crystal display apparatus comprising steps of:

generating a variable common signal, which voltage is at least once varied during a vertical blanking period,

applying said variable common signals on counter electrodes,

generating variable storage electrode signal, which is varied to assume a polarity identical with the variable common signal and an identical amplitude by synchronizing said variable storage electrode signal with the variable common signal, and

applying said variable storage electrode signal on storage electrodes for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 12. Method for driving a liquid crystal display apparatus comprising steps of:

varying a voltage for a source signal at least once varied during a vertical blanking periods and applying said voltage on source lines for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 13. Method for driving a liquid crystal display apparatus comprising steps of:

applying a source signal having a Gray level electric potential on source lines during a vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 14. Method for driving a liquid crystal display apparatus comprising steps of:

setting a common signal and storage electrode signal to be of same polarity, wherein the common signal is on counter electrodes and the storage electrode signal on storage electrodes during each of the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line.

## 15. Method for driving a liquid crystal display apparatus comprising steps of:

applying a common signal having an intermediate electric potential that is between a maximum peak value and minimum peak value for an amplitude during a data period on counter electrodes during a vertical blanking period, and

applying a storage electrode signal having an intermediate electric potential that is between a maximum peak value and minimum peak value for the amplitude during the data period to storage electrodes during the vertical blanking period for decreasing effective voltage differences between odd-numbered lines and even-numbered lines and for decreasing luminance differences per gate line, by synchronizing said storage electrode signal with the common signal.

\* \* \* \* \*

|               |                                                                         |         |            |

|---------------|-------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 液晶显示装置及其驱动方法                                                            |         |            |

| 公开(公告)号       | <a href="#">US20030076289A1</a>                                         | 公开(公告)日 | 2003-04-24 |

| 申请号           | US10/307434                                                             | 申请日     | 2002-12-02 |

| 申请(专利权)人(译)   | 高级显示INC.                                                                |         |            |

| 当前申请(专利权)人(译) | 三菱电机株式会社                                                                |         |            |

| [标]发明人        | TOKONAMI SUSUMU<br>SHIBATA SUSUMU<br>AOKI HIRONORI<br>NAGANO SHINGO     |         |            |

| 发明人           | TOKONAMI, SUSUMU<br>SHIBATA, SUSUMU<br>AOKI, HIRONORI<br>NAGANO, SHINGO |         |            |

| IPC分类号        | G02F1/133 G09G3/36                                                      |         |            |

| CPC分类号        | G09G3/3614 G09G2320/0233 G09G3/3659 G09G3/3655                          |         |            |

| 优先权           | 1998203726 1998-07-17 JP                                                |         |            |

| 其他公开文献        | US6876351                                                               |         |            |

| 外部链接          | <a href="#">Espacenet</a> <a href="#">USPTO</a>                         |         |            |

## 摘要(译)

本发明涉及一种液晶显示装置，包括：定时电路，用于在垂直消隐期间操作定时电路内的移位寄存器，使得在单个水平周期的周期交替的公共信号被施加到在垂直消隐期间反电极，使得存储电极信号施加在具有与公共信号相同的频率，相位和幅度的存储电极上。