US 20050082528A1

(19) **United States**

(12) **Patent Application Publication**

**Kobayashi et al.**

(10) **Pub. No.: US 2005/0082528 A1**

(43) **Pub. Date: Apr. 21, 2005**

(54) **LIQUID CRYSTAL DISPLAY**

**Related U.S. Application Data**

(75) Inventors: **Kazuhiro Kobayashi**, Kikuchi-gun (JP); **Nobuhiro Nakamura**, Kikuchi-gun (JP); **Ken Nakashima**, Kikuchi-gun (JP); **Yuichi Masutani**, Kikuchi-gun (JP)

(62) Division of application No. 09/805,039, filed on Mar. 14, 2001, now Pat. No. 6,838,696.

(30) **Foreign Application Priority Data**

Mar. 15, 2000 (JP) ..... 2000-072766

Mar. 23, 2000 (JP) ..... 2000-082141

Mar. 23, 2000 (JP) ..... 2000-082142

Correspondence Address:

**OBLON, SPIVAK, MCCLELLAND, MAIER & NEUSTADT, P.C.**

**1940 DUKE STREET**

**ALEXANDRIA, VA 22314 (US)**

**Publication Classification**

(51) **Int. Cl. 7** ..... **H01L 29/04**

(52) **U.S. Cl.** ..... **257/57**

(57) **ABSTRACT**

A thin film transistor array substrate including an insulating substrate, a first metallic pattern formed on the insulating substrate, and an insulating film provided on the first metallic pattern. A semiconductor pattern is provided on the insulating film, and a second metallic pattern is provided on the semiconductor pattern. The second metallic pattern is surrounded by the semiconductor pattern.

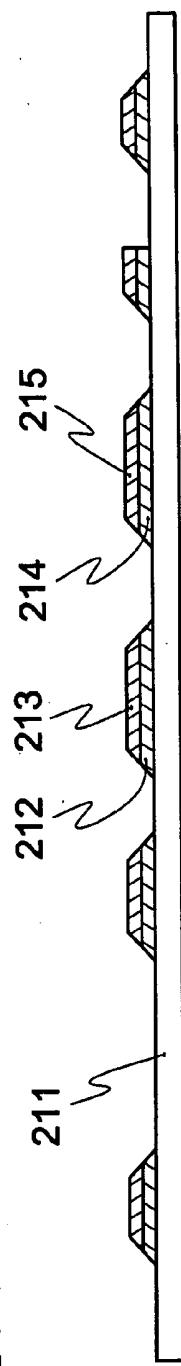

FIG. 1

FIG. 2(a)

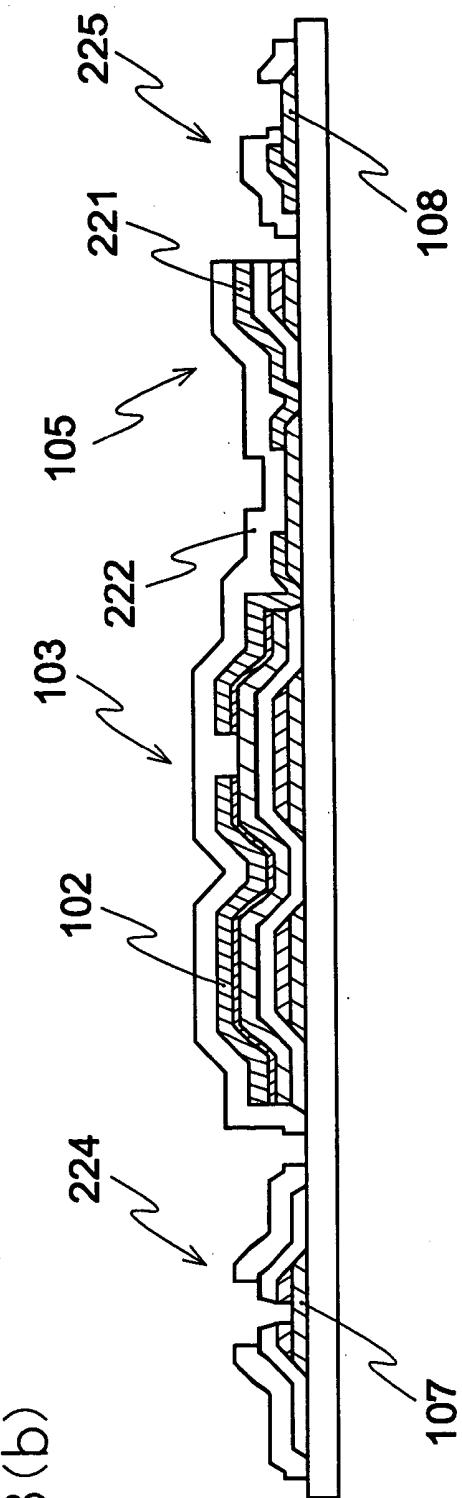

FIG. 2(b)

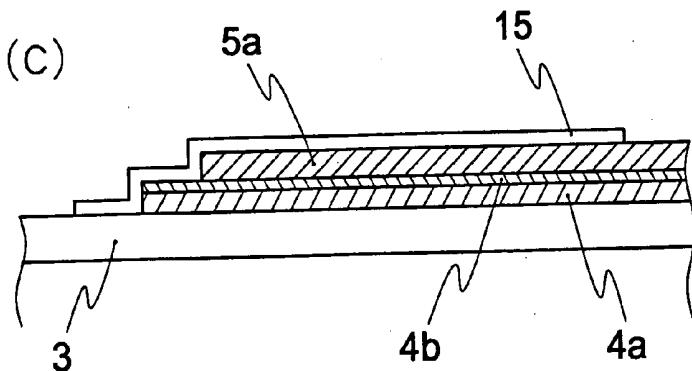

FIG. 2(c)

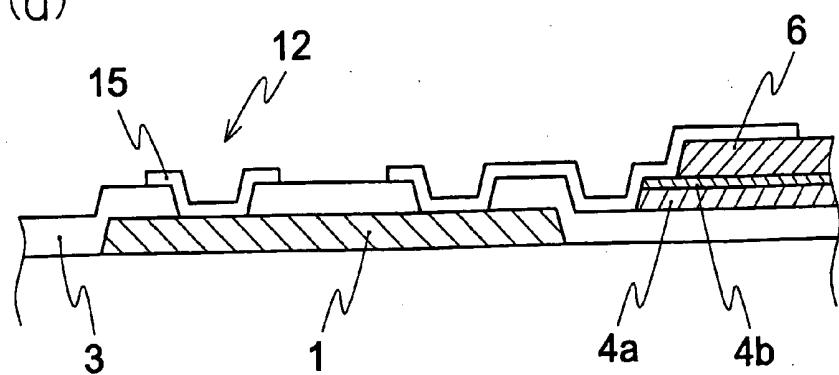

FIG. 2(d)

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

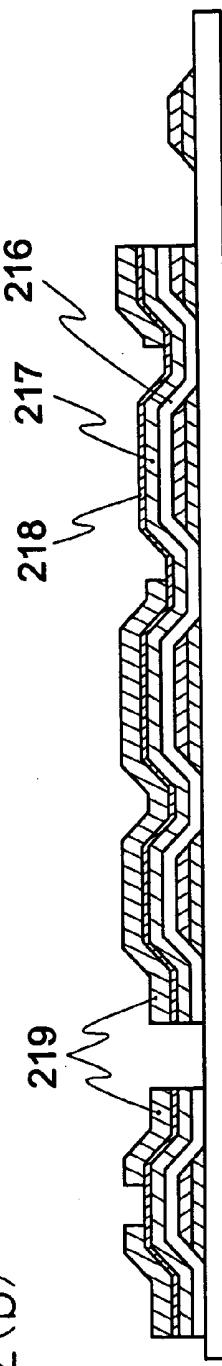

FIG. 29(a)

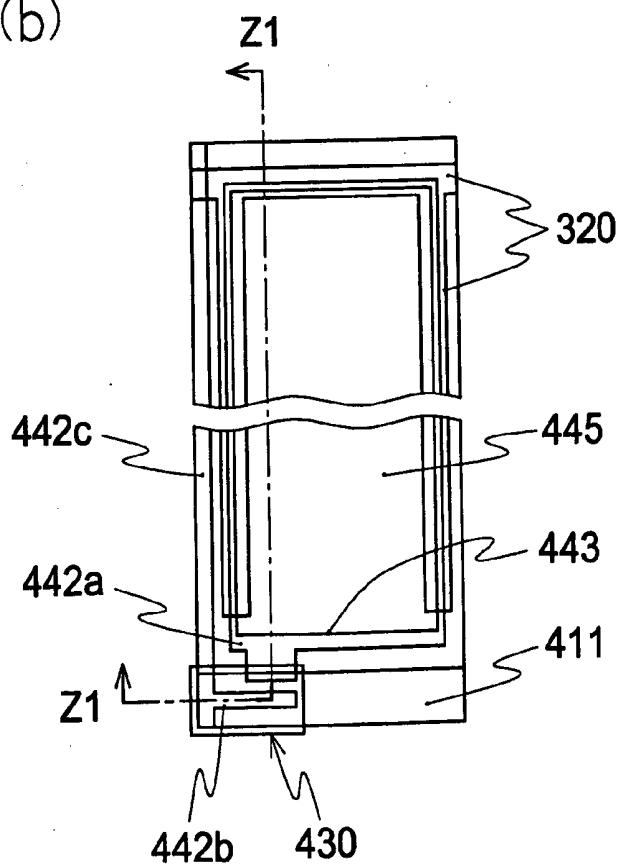

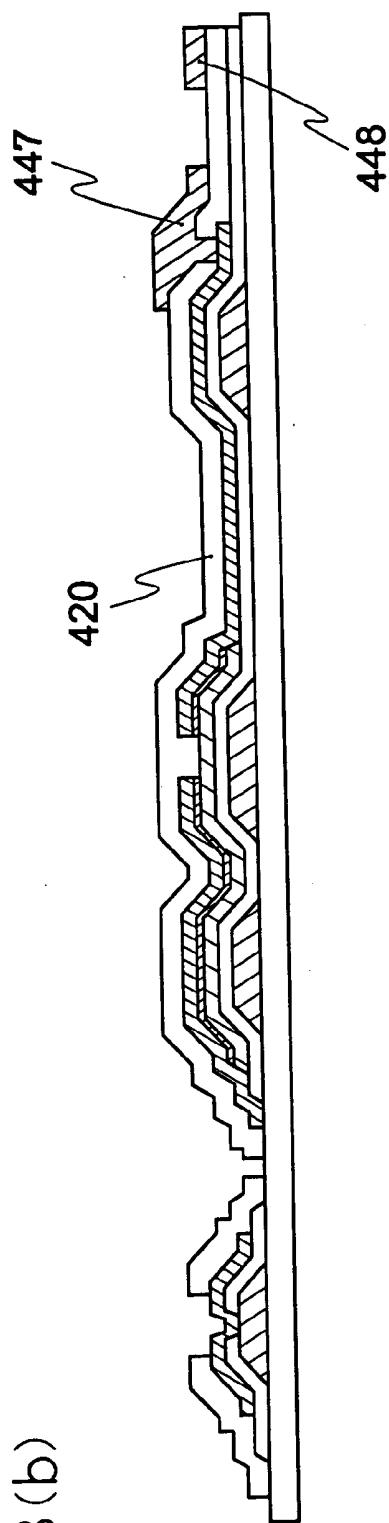

FIG. 29(b)

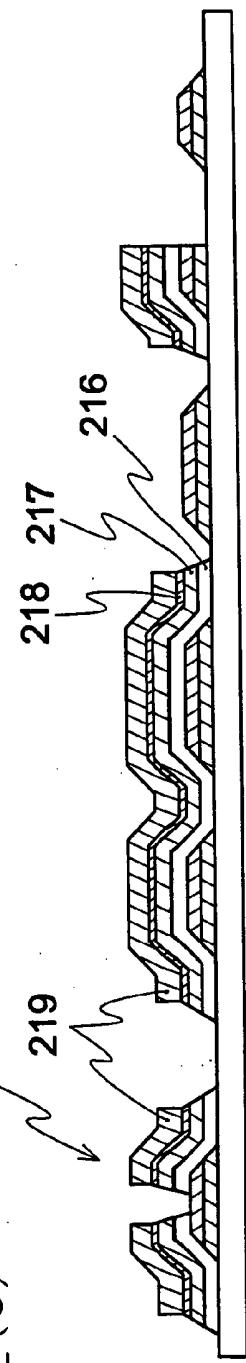

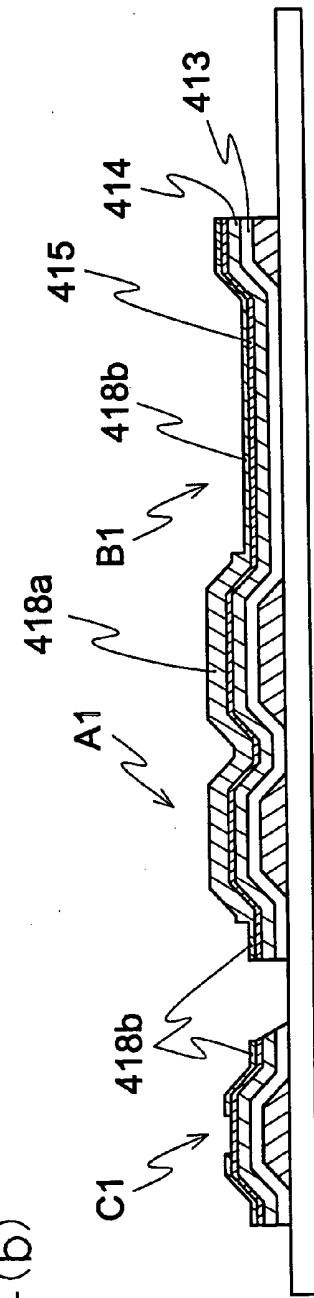

FIG. 31(a)

FIG. 31(b)

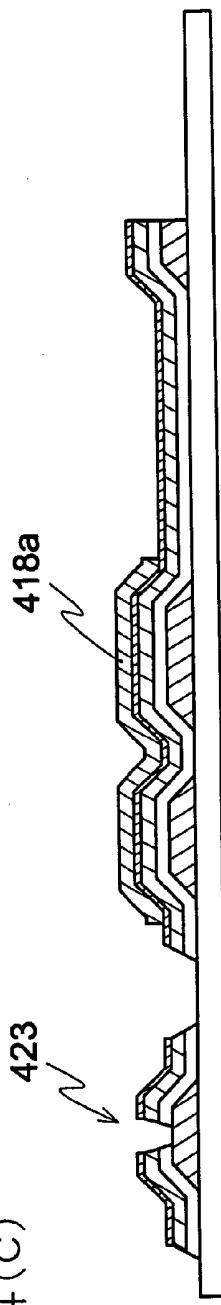

FIG. 31(c)

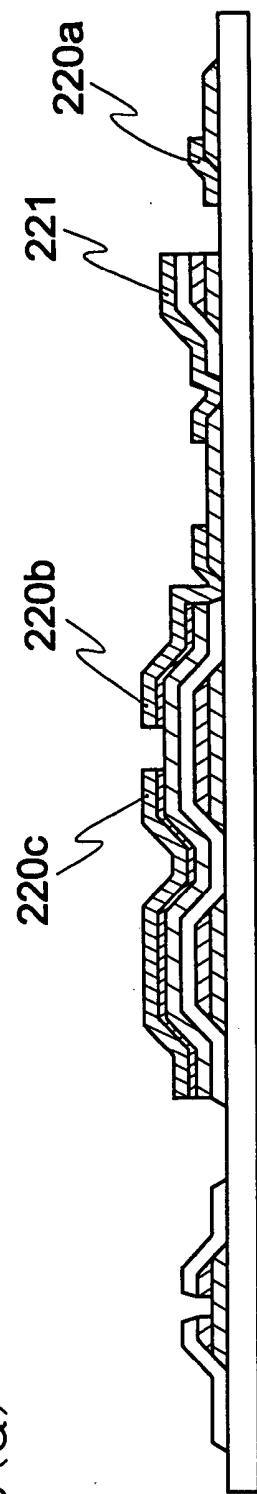

FIG. 32(a)

FIG. 32(b)

FIG. 32(c)

FIG. 32(d)

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37(a)

FIG. 37(b)

FIG. 37(c)

FIG. 37(d)

FIG. 38

FIG. 39

FIG. 40

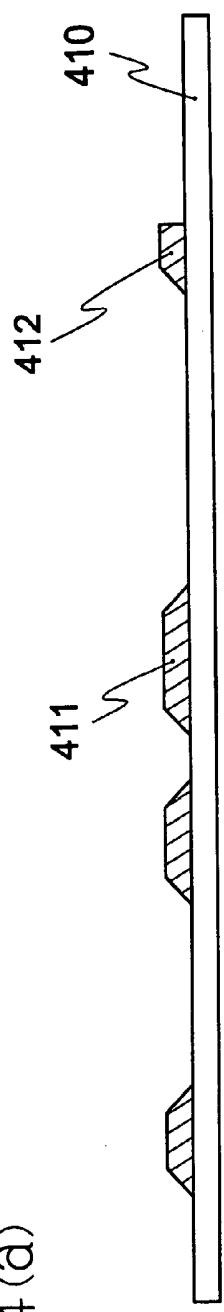

FIG. 41(a)

FIG. 41(b)

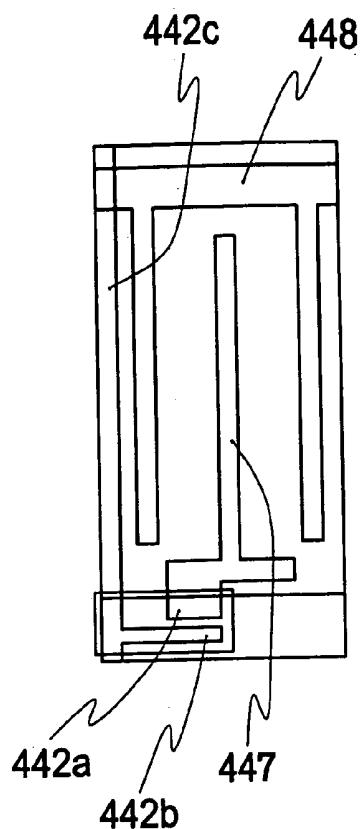

FIG. 42 (a)

FIG. 42 (b)

FIG. 42 (c)

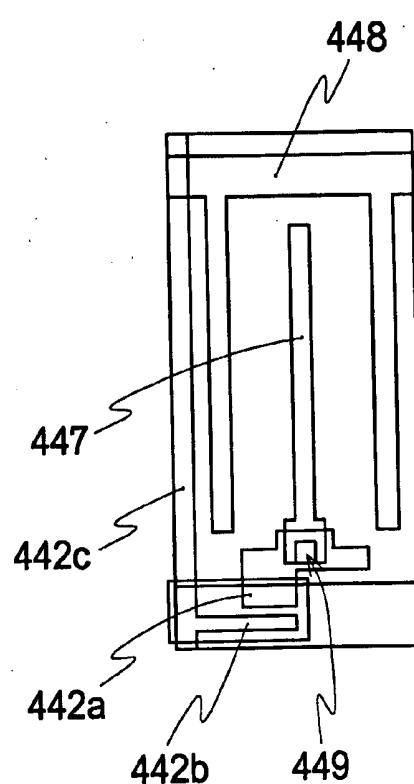

FIG. 43(a)

FIG. 43(b)

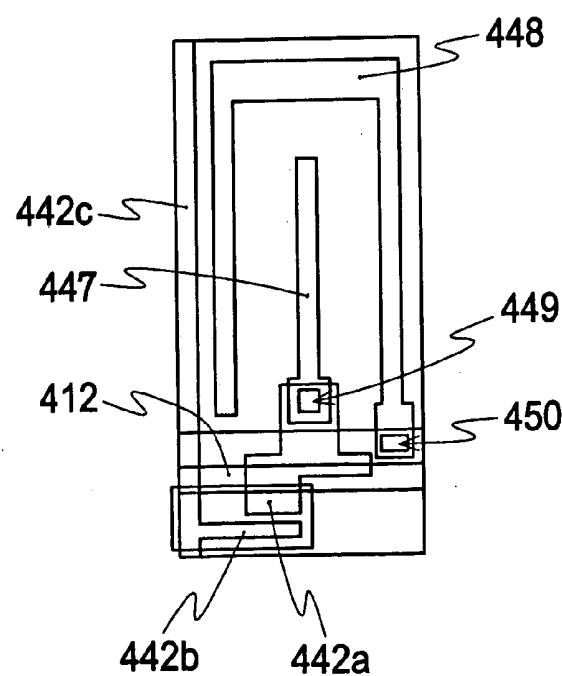

FIG. 44 (a)

FIG. 44 (b)

FIG. 44 (c)

FIG. 45(a)

FIG. 45(b)

FIG. 45(c)

FIG. 46(a)

FIG. 46(b)

FIG. 46(c)

FIG. 47(a)

FIG. 47(b)

FIG. 48

FIG. 49

FIG. 50

FIG. 51

FIG. 52(a)

FIG. 52(b)

FIG. 52(c)

FIG. 53(a)

FIG. 53(b)

FIG. 54

FIG. 55

FIG. 56

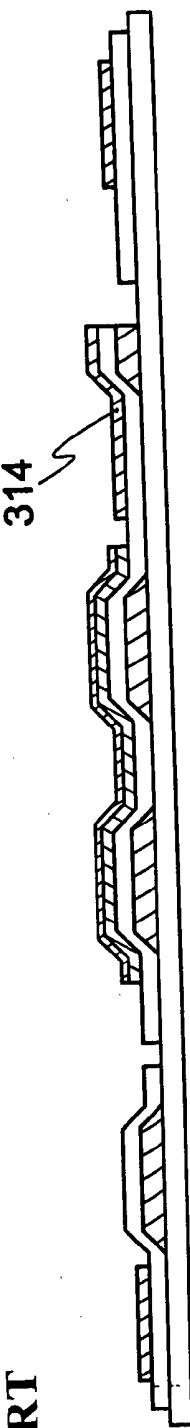

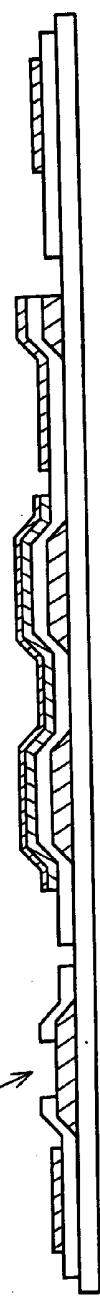

FIG. 57 PRIOR ART

FIG. 58 PRIOR ART

FIG. 59(a)

PRIOR ART

FIG. 59(b)

PRIOR ART

FIG. 59(c)

PRIOR ART

FIG. 60(a)

PRIOR ART

FIG. 60(b)

PRIOR ART

FIG. 60(c)

PRIOR ART

FIG. 61(a)

FIG. 61(b)

FIG. 61(c)

FIG. 61(d)

FIG. 62(a)

FIG. 62(b)

FIG. 62(c)

FIG. 63(a)

FIG. 63(b)

FIG. 64

FIG. 65(a)

FIG. 65(b)

FIG. 65(c)

FIG. 65(d)

FIG. 66

FIG. 67

FIG. 68

FIG. 69

FIG. 70

FIG. 71

FIG. 72

FIG. 73

FIG. 74

## LIQUID CRYSTAL DISPLAY

### BACKGROUND OF THE INVENTION

**[0001]** The present invention relates to a thin film transistor array substrate and a method of manufacturing the same. More particularly, the present invention relates to a method of manufacturing a thin film transistor array substrate having less point defect and line defect and capable of reducing a leakage current of a thin film transistor (TFT) by carrying out a photolithographic process four times, and enhances the display characteristic and productivity of a TFT-LCD.

**[0002]** An electro-optic element using a liquid crystal has been vigorously applied to a display. The electro-optic element using the liquid crystal generally has such a structure that the liquid crystal interposed between two substrates including electrodes in a vertical direction and a polarizing plate is provided in the vertical direction. In a transmission type, a back light is provided on a back face. The surfaces of the upper and lower electrode substrates are subjected to a so-called orientation processing, and a director to be an average direction of a liquid crystal molecule is controlled to be brought into a desirable initial state. The liquid crystal has a double refracting property, and a light incident through the polarizing plate from the back light is changed into an elliptically polarized light through the double refraction and is then incident on the polarizing plate on the opposite side. When a voltage is applied to the upper and lower electrodes in this state, the state of array of the director is changed so that a double refractive index of a liquid crystal layer is changed and the state of the elliptically polarized light incident on the polarizing plate on the opposite side. Accordingly, an intensity of the light transmitted through the electro-optic element and a spectrum thereof are varied. The electro-optic effect is varied depending on the type of a liquid crystal layer, an initial orientation state, the direction of an polarizing axis of the polarizing plate, a thickness of the liquid crystal layer or a color filter provided in the middle of a light transmission path or various interference films, which has been reported in detail by well-known papers or the like. In general, a structure referred to as TN or STN using a nematic liquid crystal layer is used.

**[0003]** Examples of an electro-optic element for a display using a liquid crystal include a simple matrix type and a TFT-LCD using a thin film transistor (TFT) as a switching element. The TFT-LCD having more characteristics than those of a CRT and a simple matrix type liquid crystal display in respect of portability and display quality has been widely put into practical use for a notebook type personal computer. The TFT-LCD generally has such a structure that a liquid crystal is interposed between a TFT array substrate having a TFT formed like an array and an opposed substrate having a color filter which is provided with a common electrode, a polarizing plate is provided above and under the structure, and furthermore, a back light is provided on the back. With such a structure, excellent color display can be obtained.

**[0004]** In order to apply a voltage to the liquid crystal in the TFT-LCD, the TFT is turned ON within a gate line selection time and electric charges are caused to flow from a source line to a pixel electrode and a pixel potential is set to be equal to the electric potential of the source line. Then, when a gate is brought into a non-selection state, the TFT is

turned OFF so that the electric charges of a pixel are held. Actually, the amount of the electric charges of the pixels is decreased by the TFT and the leakage current in the liquid crystal. As a result, the electric potential of the pixel is reduced. In order to prevent the electric potential of the pixel from fluctuating, an auxiliary capacitor is usually provided to reduce the amount of a change in the electric potential of the pixel for a change in a unit charge amount is reduced. Moreover, a trial to decrease the number of FTF array manufacturing steps has been made to enhance the productivity of the TFT-LCD. A trial to eliminate a photolithographic step has been disclosed in Japanese Unexamined Patent Publication No. 202153/1994, Japanese Unexamined Patent Publication No. 328040/1996 and Japanese Unexamined Patent Publication No. 50308/1996.

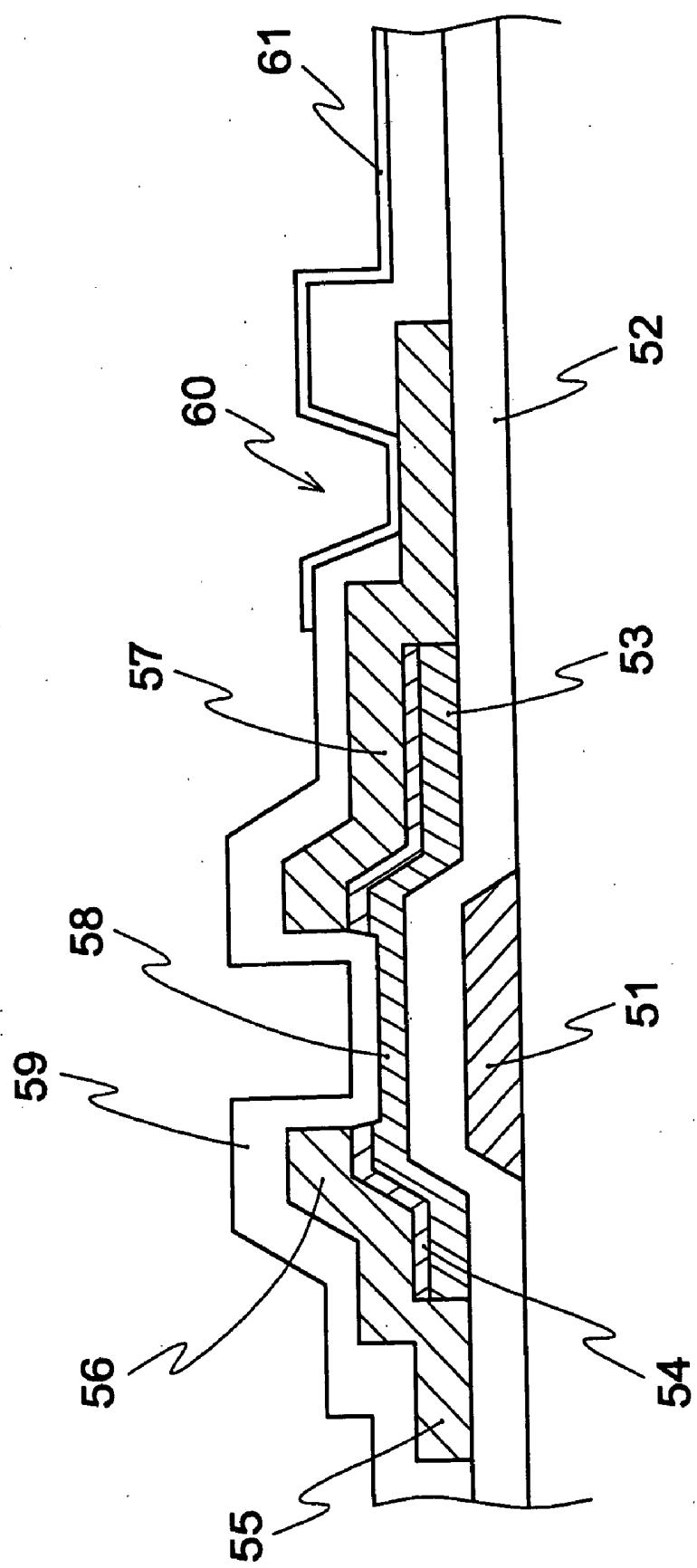

**[0005]** FIG. 57 is a sectional view showing a pixel portion of a TFT array substrate manufactured at a five-time photolithographic step disclosed in a seventh embodiment of the Japanese Unexamined Patent Publication No. 50308/1996. In the conventional example, first of all, a first conductive metallic thin film such as Cr, Ta, Mo or Al is formed in a thickness of approximately 100 nm on a transparent substrate. Next, the first conductive metallic thin film is subjected to patterning at a first photolithographic step, thereby forming a gate electrode 51. At this time, if the first conductive metallic thin film is Cr, a wet etching treatment is carried out by using a  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution, for example. Then, a  $\text{SiN}_x$  film, an a-Si film and an  $n^+a\text{-Si}$  film are provided in thicknesses of approximately 300 nm, 100 nm and 20 nm as a first insulating film 52, a semiconductor active film 53 and an ohmic contact film 54, respectively. At a second photolithographic step, next, the semiconductor active film 53 and the ohmic contact film 54 are subjected to patterning like an island in a state in which a semiconductor portion is isolated from other portions above a gate electrode. At this time, the semiconductor active film and the ohmic contact film are subjected to dry etching with  $\text{SF}_6+\text{HCl}+\text{He}$ , for example.

**[0006]** Next, a second metallic thin film such as Ti is formed in a thickness of approximately 300 nm. Then, the second metallic thin film and the ohmic contact film are subjected to patterning at a third photolithographic step so that a source line 55, a source electrode 56, a drain electrode 57 and a semiconductor active layer 58 of a thin film transistor are formed. Subsequently, an interlayer insulating film (passivation film) 59 is formed in a thickness of approximately 400 nm by a method such as plasma CVD. Next, the passivation film is subjected to the patterning at a fourth photolithographic step so that a contact hole 60 communicating with the drain electrode 57, a contact hole communicating with a gate line and a contact hole communicating with a source line are formed. At this time, the passivation film is subjected to the etching through dry etching using  $\text{SF}_6+\text{O}_2$  or the like, for example. Then, a transparent conductive film comprising ITO is formed in a thickness of approximately 150 nm. Thereafter, the transparent conductive film is subjected to the patterning at a fifth photolithographic step to form a transparent pixel electrode 61, a terminal portion for source line connection and a terminal portion for gate line connection. At this time, the ITO film is subjected to wet etching by using an  $\text{HCl}+\text{HNO}_3+\text{H}_2\text{O}$  solution, for example.

[0007] In the conventional art, thus, the method of manufacturing a TFT array at five photolithographic steps has been disclosed. The following effects have been described. More specifically, the five photolithographic steps are enough, resulting in an enhancement in yield and a reduction in cost. In addition, since the passivation film is not provided on the transparent pixel electrode, a voltage can be applied efficiently to the liquid crystal. Furthermore, since the transparent pixel electrode, the source line and the gate line are isolated from each other through an insulating film, there is no possibility that the source lines or the gate lines might be short-circuited due to the defective formation of the transparent pixel electrode. As the effects of the conventional art, moreover, the following has been described. More specifically, in the case in which a multilayered film of a metallic thin film and a barrier film made of a material oxidized or a material solidified as a conductive oxide to the transparent conductive film is used for a first conductive metallic thin film, the barrier film further produces antioxidant effects to maintain contact property of these films with the transparent conductive film. Therefore, a signal delay is caused signal delay with difficulty. Furthermore, Al or Ta having high conductive property is used as a metallic thin film to reduce a thickness of the metallic thin film. Consequently, a step coverage of the whole TFT element can be enhanced and yield can be improved. In the TFT array structure, the gate line, the source line and the pixel electrode are isolated from each other through the insulating film. Therefore, there is also an advantage that a short-circuit is generated with difficulty and the yield can easily be enhanced.

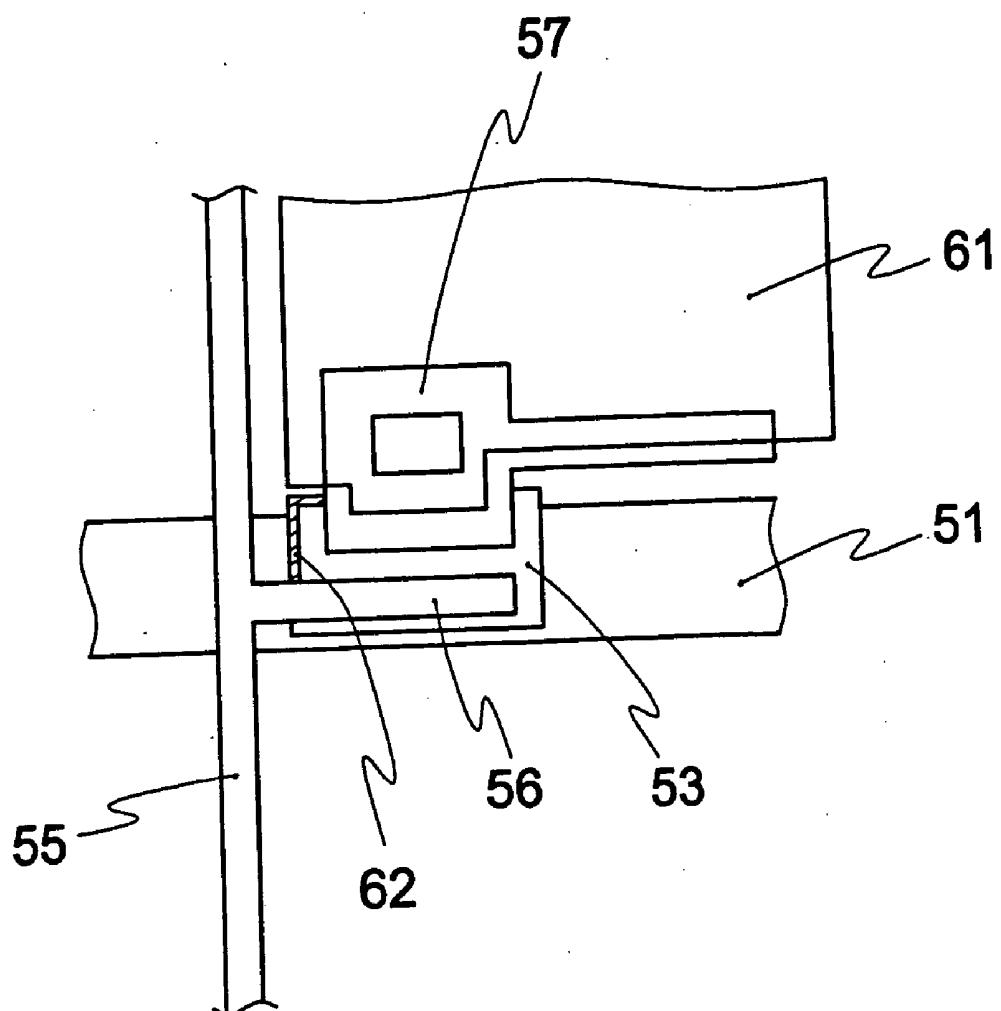

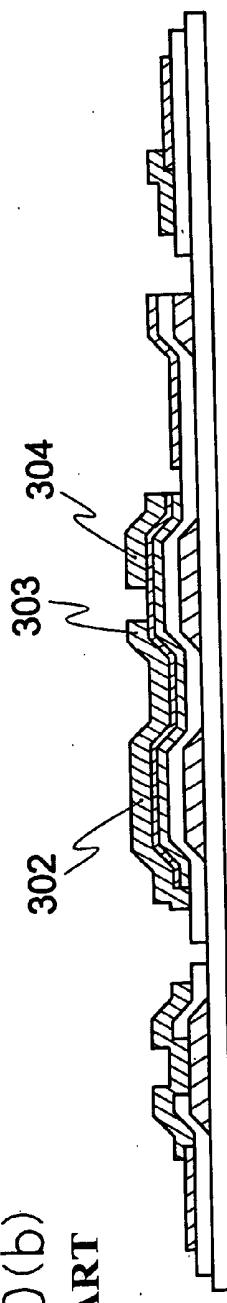

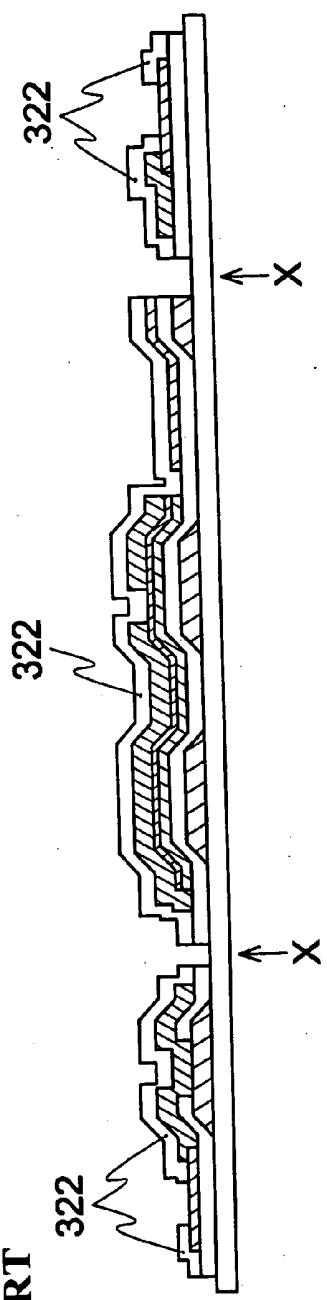

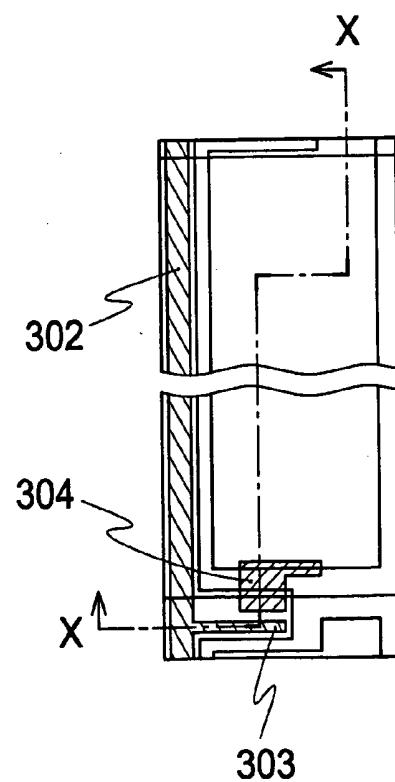

[0008] FIGS. 59(a) to 59(c), 60(a) to 60(c) and 61(a) to 61(d) show an example of the TFT array structure to be used for a conventional active matrix type liquid crystal display (AMLCD). FIGS. 59(a) to 59(c) and 60(a) to 60(c) are an example of sectional views, FIG. 61(a) to 61(d) is a plan view, and FIGS. 59(a) to 59(c) and 60(a) to 60(c) show sectional structures of X-X in FIG. 61 (a) to 61(d) and a gate-source terminal portion.

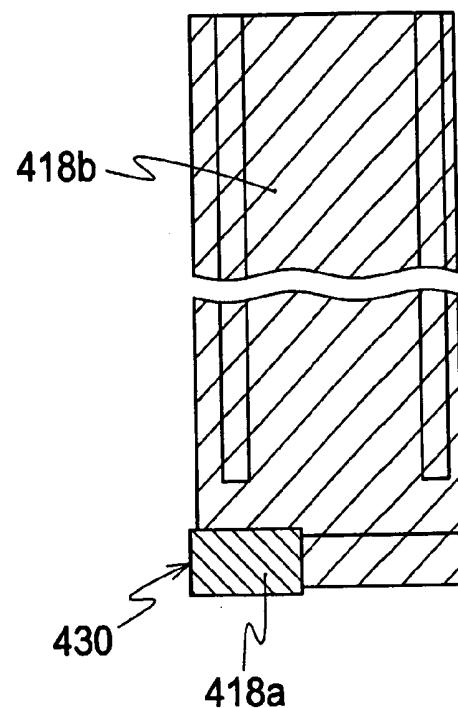

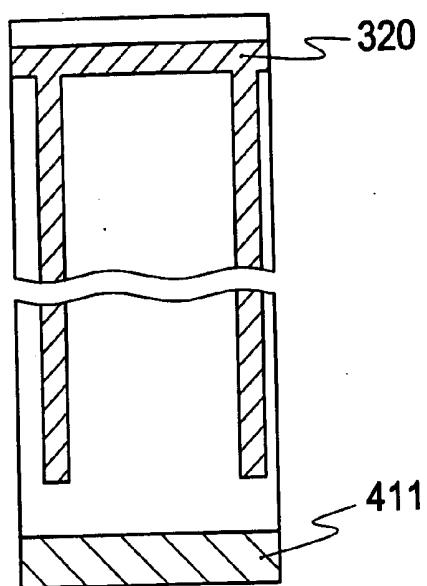

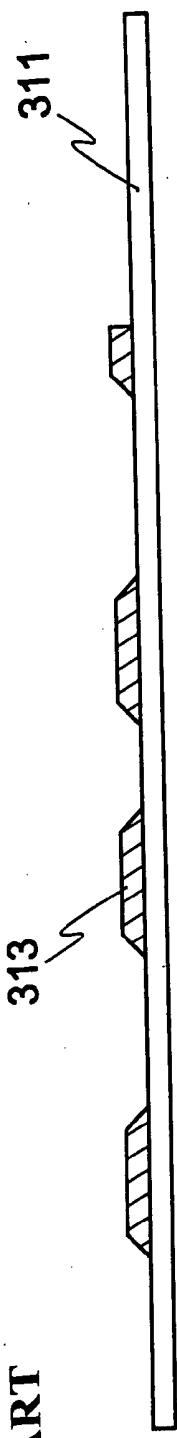

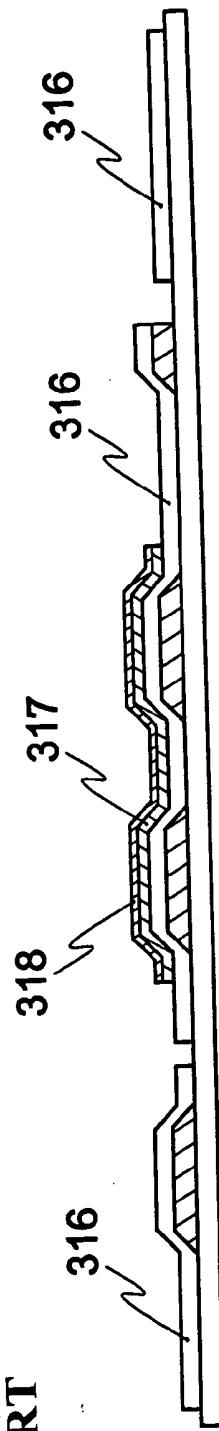

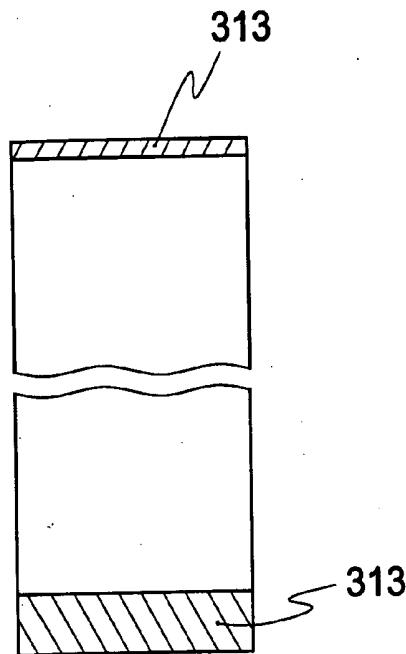

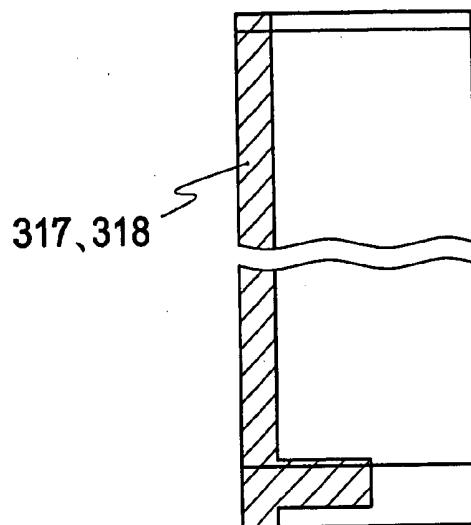

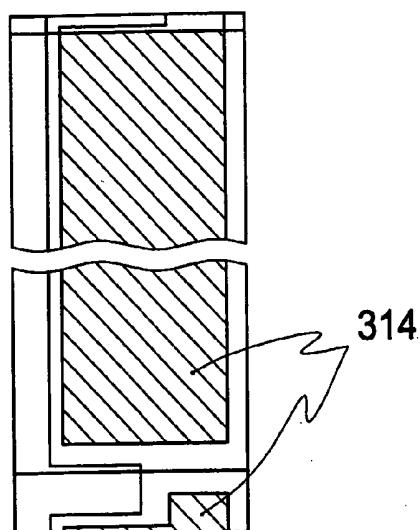

[0009] In FIGS. 59(a) to 59(c), 60(a) to 60(c) and 61(a) to 61(d), the reference numeral 311 denotes an insulating substrate, the reference numeral 313 denotes a gate electrode and a gate line, the reference numeral 314 denotes a pixel electrode formed of a transparent conductive film, the reference numeral 316 denotes a gate insulating film, the reference numeral 317 denotes a semiconductor layer (active layer), the reference numeral 318 denotes a semiconductor layer (ohmic contact layer) containing an impurity such as P or B, the reference numeral 322 denotes an insulating film such as SiN<sub>4</sub>, the reference numeral 330 denotes a contact hole, the reference numeral 302 denotes a source line, the reference numeral 303 denotes a source electrode, and the reference numeral 304 denotes a drain electrode.

[0010] Description will be given to a method of manufacturing a TFT array substrate to be used for a conventional active matrix liquid crystal display (AMLCD). A layer of a substance comprising a metal such as Cr, Al or Mo, an alloy having them as a main component, a metal having them multilayered or the like is formed on the insulating substrate 311 by sputtering or the like. Next, a gate electrode, a gate line pattern 313 and the like are formed by using a photoresist or the like through photolithography and succeeding etching or the like (FIGS. 59(a) and 61(a)).

[0011] Next, an insulating film 316 comprising Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub> or the like to be a gate insulating film formed by various CVD methods such as plasma CVD, sputtering, evaporation, coating or the like, a semiconductor layer 317 comprising an a-Si:H film (amorphous silicon hydride film), and an ohmic contact layer 318 comprising an n<sup>+</sup>a-Si: H film or a micro-crystal n<sup>+</sup>Si layer to be a semiconductor layer formed by the plasma CVD or sputtering and doped with an impurity such as phosphorus, antimony boron in order to take a contact with a metal are continuously formed. Then, a semiconductor layer (active layer) 317 is used as a TFT portion, a gate line—source line cross section and the like and a semiconductor layer (ohmic contact layer) 318 containing an impurity such as P or B are formed by photolithography and succeeding etching or the like using a photoresist or the like (FIGS. 59(b) and 61(b)).

[0012] Then, a transparent conductive layer formed of a transparent conductive material such as ITO (Indium Tin Oxide) is provided by sputtering, evaporation, a sol-gel method and the like. Thereafter, a pixel electrode 314, a terminal electrode and the like are formed by photolithography and succeeding etching or the like by using the photoresist or the like (FIGS. 59(c) and 61(c)).

[0013] Subsequently, a pattern is formed such that a contact hole can be provided in a gate terminal portion or the like by the photolithography using the photoresist or the like. Then, the gate insulating film 316 is removed by dry etching or the like using a CF<sub>4</sub> based gas or the like. Thereafter, the photoresist is removed to form a contact hole 330 (see FIG. 60(a)).

[0014] Next, a layer of a substance comprising a metal such as Cr, Al or Mo, an alloy comprising them as a main component or a metal having them multilayered is formed by the sputtering or the like. Then, a source line 302, a source electrode 303 and a drain electrode 304 are formed by using the photoresist or the like through the photolithography and succeeding etching or the like (FIGS. 60(b) and 61(d)).

[0015] Thereafter, an insulating film 322 such as Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub> or their multilayered layer, that is, Si<sub>3</sub>N<sub>4</sub> to act as a gate insulating film is formed by various CVD methods such as plasma CVD, sputtering, evaporation, coating and the like. Next, a photoresist or the like is used to remove an insulating film in a terminal portion or the like through the photolithography and succeeding dry etching using a CF<sub>4</sub> based gas or the like such that a signal can be input from an external TCP or the like to each wiring. Consequently, a TFT array is formed (FIG. 60(c)).

[0016] Subsequently, an orientation film is formed on the TFT array and counter electrodes are opposed and a liquid crystal is interposed therebetween. Thus, an active matrix type liquid crystal display is formed.

[0017] In the seventh embodiment of the Japanese Unexamined Patent Publication No. 50308/1996, there has been disclosed a technique in which the semiconductor layer 53 is isolated like an island. In the case in which a source line is formed of a single metal layer and is patterned by wet etching, etching liquid enters a metal and semiconductor interface from a step portion of the semiconductor layer to cause a disconnection if a source metal has poor adhesion in the step portion. As disclosed in Japanese Unexamined

Patent Publication No. 268353/1998, it is preferable that a semiconductor pattern should be extended under the source line. **FIG. 58** is a plan view showing a thin film transistor in which the semiconductor layer **53** is isolated. In general, a leakage current easily flows to a semiconductor end face. With such a structure, therefore, an end face leak path **62** provided from a source electrode **56** to a drain electrode **57** is present to increase a leakage current of the thin film transistor. Consequently, the display quality of a display is greatly affected, for example, a contrast is reduced, a luminescent spot is increased during use at a high temperature (in the case of normally white).

**[0018]** On the other hand, there has been disclosed a technique in which the photolithographic process is carried out five times in the state in which the gate line, the source line and the pixel electrode are isolated. However, a technique in which the photolithographic process is reduced has not been disclosed. It is an object of the present invention to carry out the photolithographic step four times while maintaining the above-mentioned structure, to have no semiconductor layer step under a source electrode or a source line and to efficiently prevent display defects from being caused by the end face leakage of the semiconductor layer, thereby maintaining display quality and yield, and furthermore, enhancing productivity.

**[0019]** Moreover, in the case in which the TFT array is to be formed by using a conventional manufacturing method, the photolithographic step should be carried out at least five times. Therefore, a manufacturing process is prolonged. In particular, there is a problem in that an exposing step having a high operation cost for production equipment is often used. For this reason, the cost of the TFT array to be fabricated is necessarily increased.

**[0020]** The present invention has been made to solve the above-mentioned problems of the conventional art, and has an object to decrease the number of photolithographic steps required for manufacturing the TFT array, and furthermore, to reduce the number of masks, thereby improving productivity and reducing a cost.

**[0021]** In the case in which the TFT array is to be fabricated by using a conventional manufacturing method, the photolithographic step should be carried out at least five times. Therefore, the manufacturing process is prolonged. In particular, there is a problem in that an exposing step having a high operation cost for production equipment is often used. For this reason, the cost of the TFT array to be fabricated is necessarily increased.

**[0022]** It is an object of the present invention to reduce the number of photolithographic steps (the number of masks) required for manufacturing the TFT array in order to enhance the productivity of an active matrix type liquid crystal display or to reduce a cost thereof.

#### SUMMARY OF THE INVENTION

**[0023]** A first aspect of the present invention is directed to a thin film transistor array substrate comprising an insulating substrate, a first metal pattern formed on the insulating substrate, an insulating film on the first metal pattern, a semiconductor pattern formed on the insulating film, and a second metal pattern formed on the semiconductor pattern, the semiconductor pattern including the second metal pattern.

**[0024]** A second aspect of the present invention is directed to a thin film transistor array substrate comprising an insulating substrate, a gate line formed on the substrate, a gate insulating film formed on the gate line, a semiconductor layer formed on the gate insulating film, a source line formed on the semiconductor layer, a source electrode, a drain electrode, an interlayer insulating film formed on the source line, the source electrode and the drain electrode, and a pixel electrode formed on the interlayer insulating film, the semiconductor pattern including the source line, the source electrode and the drain electrode and having a first contact hole penetrating through the interlayer insulating film and reaching the drain electrode, a second contact hole reaching the source line and a third contact hole penetrating the gate insulating film and the interlayer insulating film and reaching the gate line, the first to third contact holes being covered with a pattern of a pixel electrode material.

**[0025]** A third aspect of the present invention is directed to a method of manufacturing a thin film transistor array substrate comprising the steps of forming a first metallic thin film on an insulating substrate, forming a gate line at a first photolithographic step and an etching step, forming a gate insulating film, a semiconductor film and an ohmic film, and a second metal film, forming a resist pattern in corresponding portions of a source line, a source electrode, a drain electrode and a semiconductor active layer of a thin film transistor at a second photolithographic step such that a thickness of the resist in the corresponding portion of the semiconductor active layer is smaller than that in other portions, etching the second metal film to form the source line, the source electrode and the drain electrode, etching the ohmic contact film and the semiconductor film, reducing the thickness of the resist, removing the resist in the corresponding portion of the active layer of the thin film transistor, etching the second metal film to remove the second metal film on the corresponding portion of the semiconductor active layer, removing the ohmic film on the corresponding portion of the semiconductor active layer, forming an interlayer insulating film, patterning the gate insulating film and the interlayer insulating film at a third photolithographic step and an etching step, forming a first contact hole reaching the drain electrode, a second contact hole reaching the source line and a third contact hole reaching the gate line, forming a conductive film, forming a pixel electrode to be connected to the drain electrode through the first contact hole at a fourth photolithographic step and an etching step, forming a source terminal to be connected to the source line through the second contact hole, and forming a gate terminal to be connected to the gate line through the third contact hole.

**[0026]** In order to reduce the number of photolithographic steps, a fourth aspect of the present invention is directed to a method comprising the steps of forming a gate electrode and a gate line to be upper layers of a transparent conductive layer with such a structure that the gate electrode and gate line and a pixel electrode are constituted by at least two layers of the transparent conductive layer and a metal layer and simultaneously patterning them to form respective predetermined patterns, forming a region X in which a thickness of a photoresist is greater in a portion leaving a semiconductor layer, a region Z in which the photoresist in such a portion as to expose at least the pixel electrode is removed, and a region Y in which the thickness of the photoresist in other portions is smaller than that of a semiconductor layer portion, etching the semiconductor layer

and a gate insulating layer with the same pattern by using the photoresist, thereby exposing the pixel electrode, removing, through etching, a layer from an upper metal in a two-layered structure including a gate line material and a transparent conductive material which are formed of a metal in the exposed pixel electrode, removing the photoresist from the region Y while leaving the photoresist in the region X, and removing the semiconductor layer in portions other than the region X. Thus, the number of photolithographic steps can be reduced.

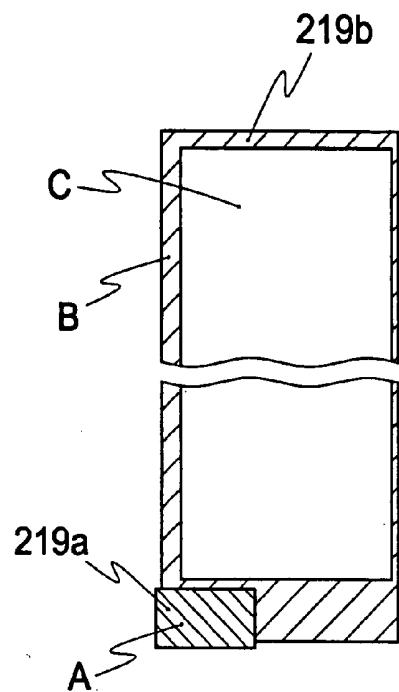

[0027] In order to reduce the number of photolithographic steps, a fifth aspect of the present invention is directed to a method comprising the steps of forming a gate insulating film and a semiconductor layer on a gate electrode and a gate line, forming a region A in which a thickness of a photoresist is greater in a portion leaving a semiconductor layer, a region C in which the photoresist is removed to etch at least the gate insulating film and the semiconductor layer and to expose a part of the gate electrode and the gate line and a region B in which the thickness of the photoresist in other portions is smaller than that of the semiconductor layer portion, etching the semiconductor layer and a gate insulating layer with the same pattern by using the photoresist, thereby exposing at least a part of the gate line, removing the photoresist from the region B while leaving the photoresist in the region A, and removing the semiconductor layer in portions other than the region A, and furthermore, comprising the steps of forming two layers including a transparent electrode and a metal film provided thereon, forming a source/drain electrode wiring and a pixel electrode by using a photoresist pattern simultaneously forming the source/drain electrode wiring and the pixel electrode, forming a protective film thereon, removing at least a portion on the pixel electrode where light is transmitted and a protective film on a connecting part in a terminal portion of a source/gate line, and removing a metal layer provided to form the source/drain electrode wiring in that portion. Consequently, the number of photolithographic steps can be reduced to four.

#### BRIEF DESCRIPTION OF THE DRAWINGS

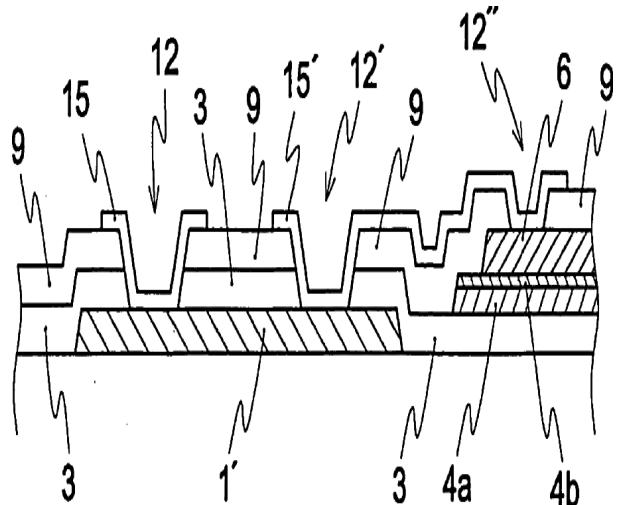

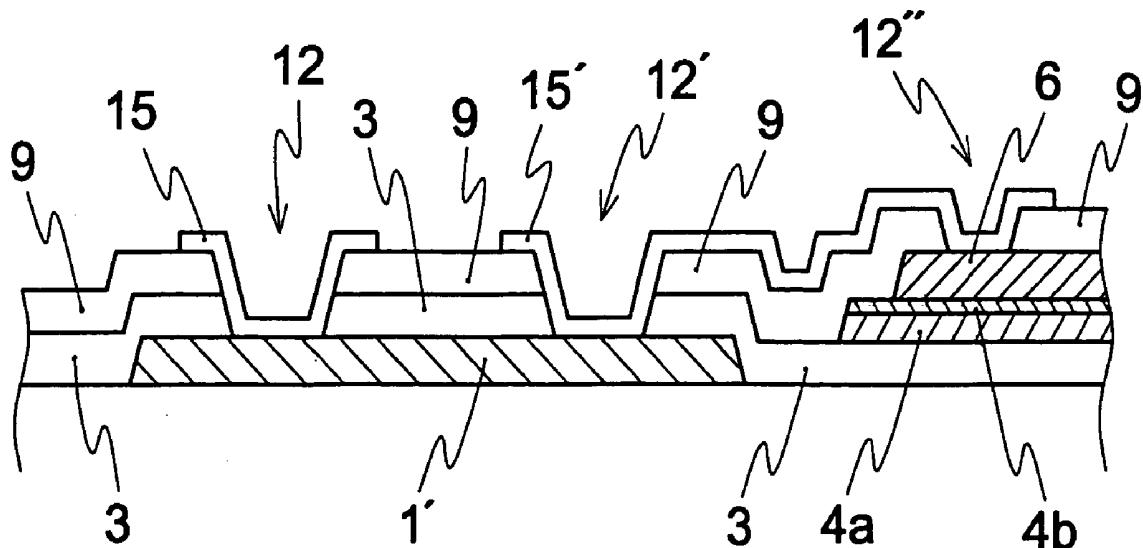

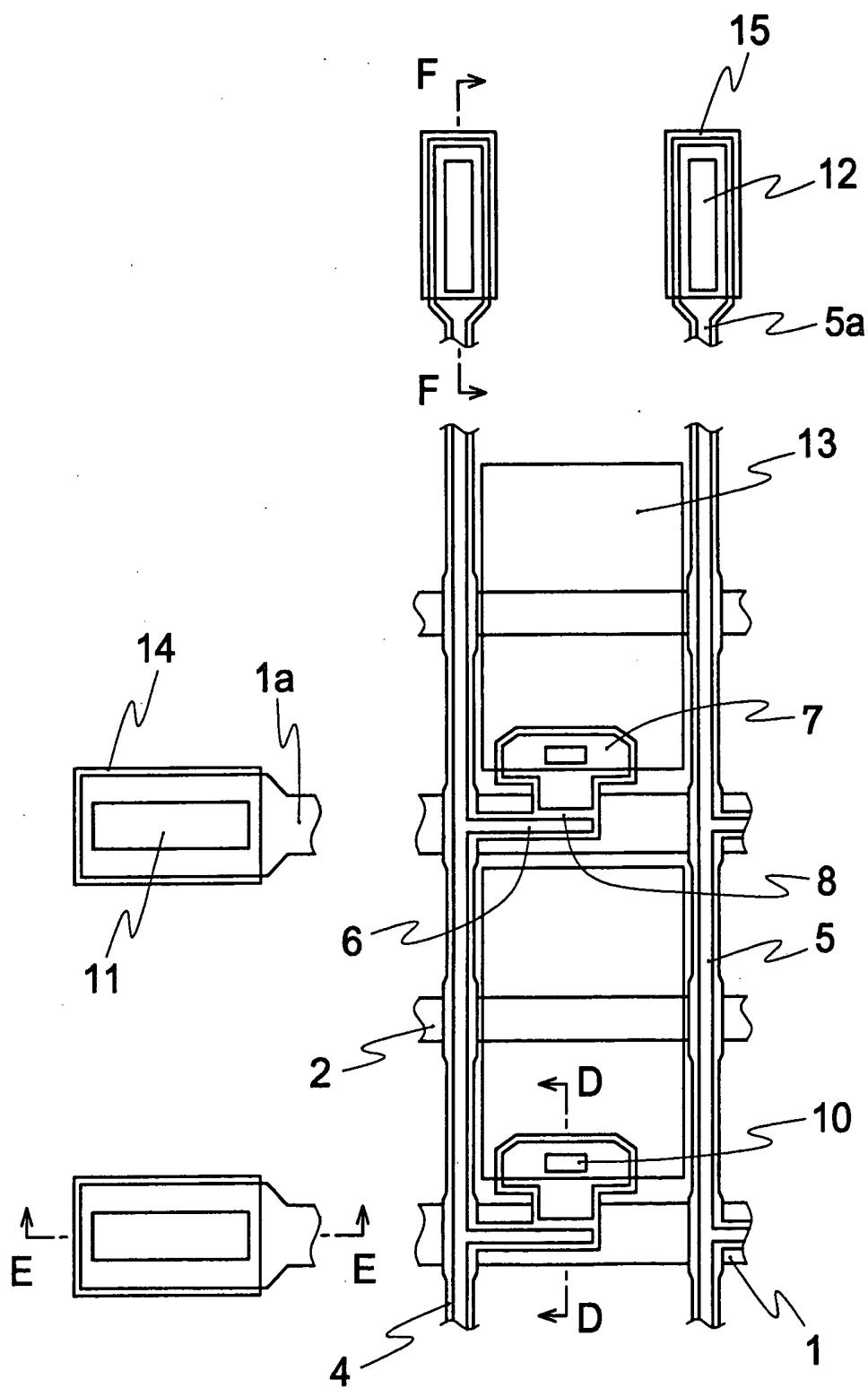

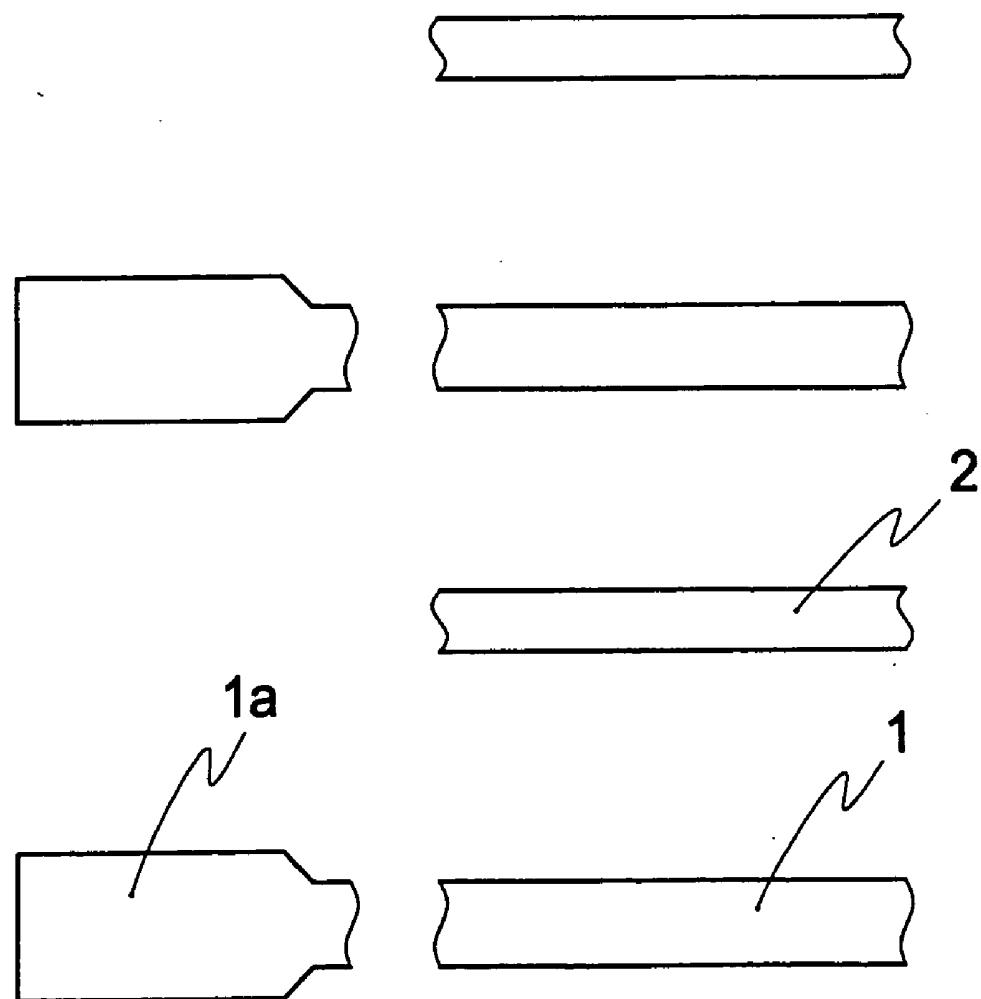

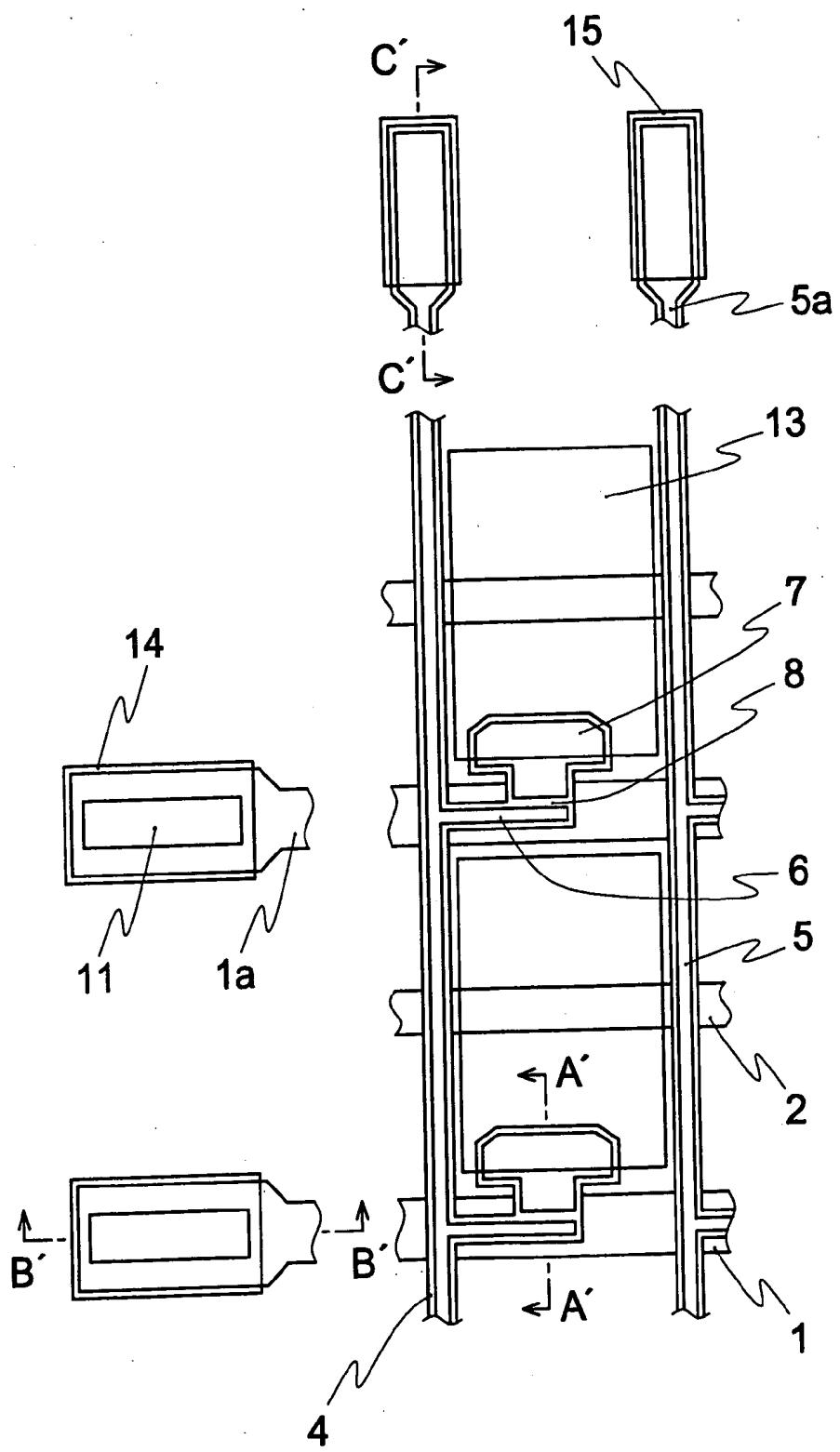

[0028] FIG. 1 is a plan view showing a thin film transistor array according to a first embodiment of the present invention;

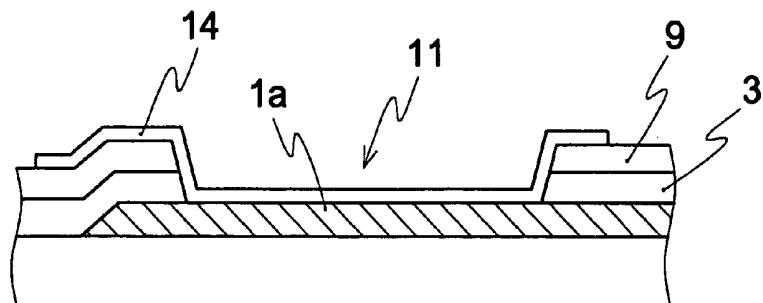

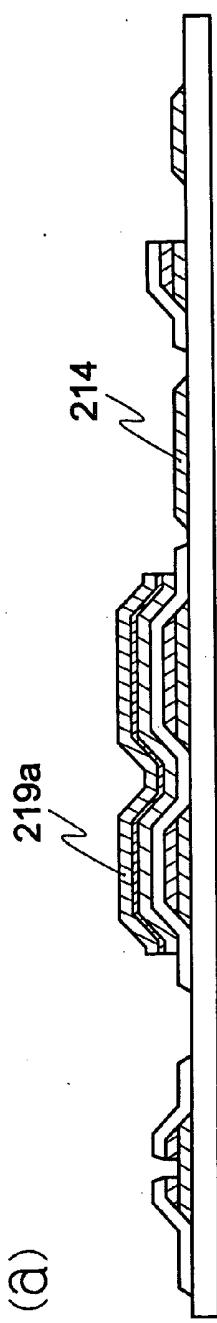

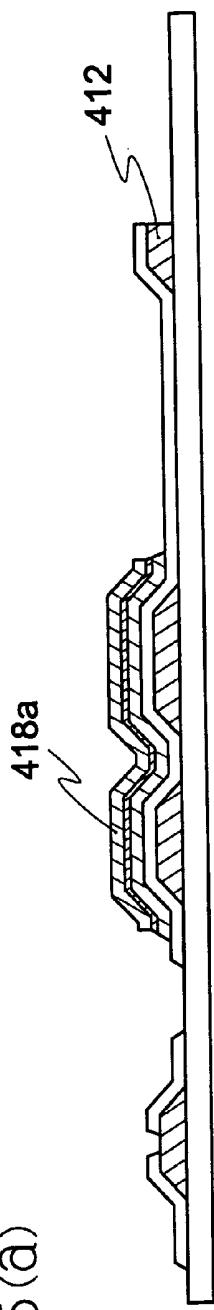

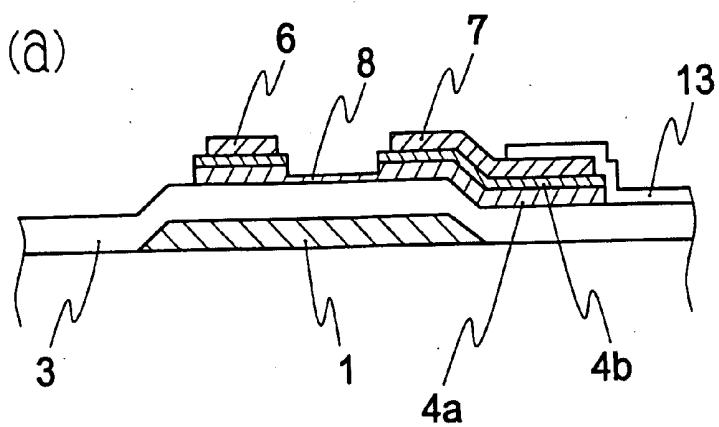

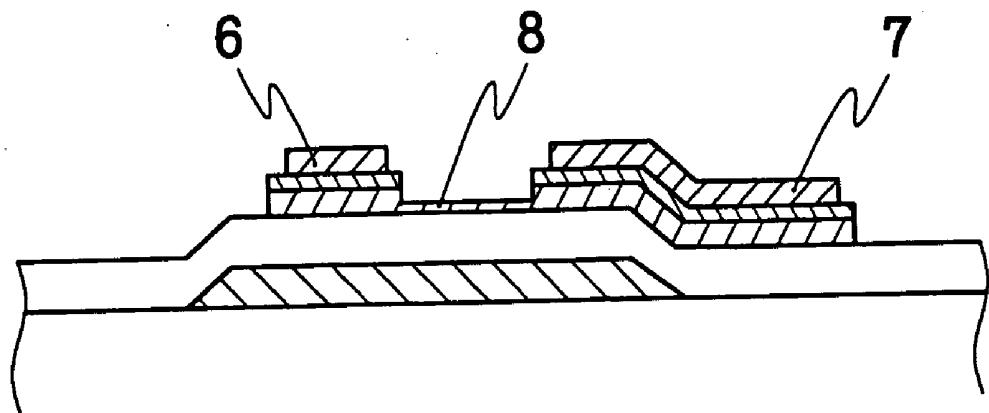

[0029] FIG. 2(a) is a sectional view taken along the line A-A in FIG. 1, FIG. 2(b) is a sectional view taken along the line B-B in FIG. 1, and FIG. 2(c) is a sectional view taken along the line C-C in FIG. 1;

[0030] FIG. 3 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0031] FIG. 4 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0032] FIG. 5 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0033] FIG. 6 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0034] FIG. 7 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

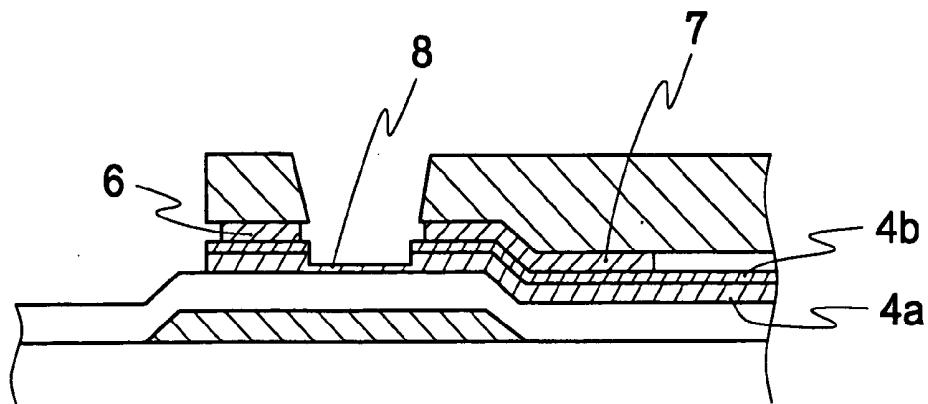

[0035] FIG. 8 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0036] FIG. 9 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0037] FIG. 10 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0038] FIG. 11 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0039] FIG. 12 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0040] FIG. 13 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0041] FIG. 14 is a sectional view taken along the line A-A in FIG. 1 at each step according to EMBODIMENT 1 of the present invention;

[0042] FIG. 15 is a plan view showing a thin film transistor array according to EMBODIMENT 2 of the present invention;

[0043] FIG. 16 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0044] FIG. 17 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0045] FIG. 18 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0046] FIG. 19 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0047] FIG. 20 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0048] FIG. 21 is a view showing a TFT portion pattern of a mask to be used for second photolithography according to EMBODIMENT 2 of the present invention;

[0049] FIG. 22 is a plan view showing a thin film transistor array according to EMBODIMENT 3 of the present invention;

[0050] FIG. 23 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0051] FIG. 24 is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0052] **FIG. 25** is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0053] **FIG. 26** is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

[0054] **FIG. 27** is a plan view showing the thin film transistor array at each step according to EMBODIMENT 1 of the present invention;

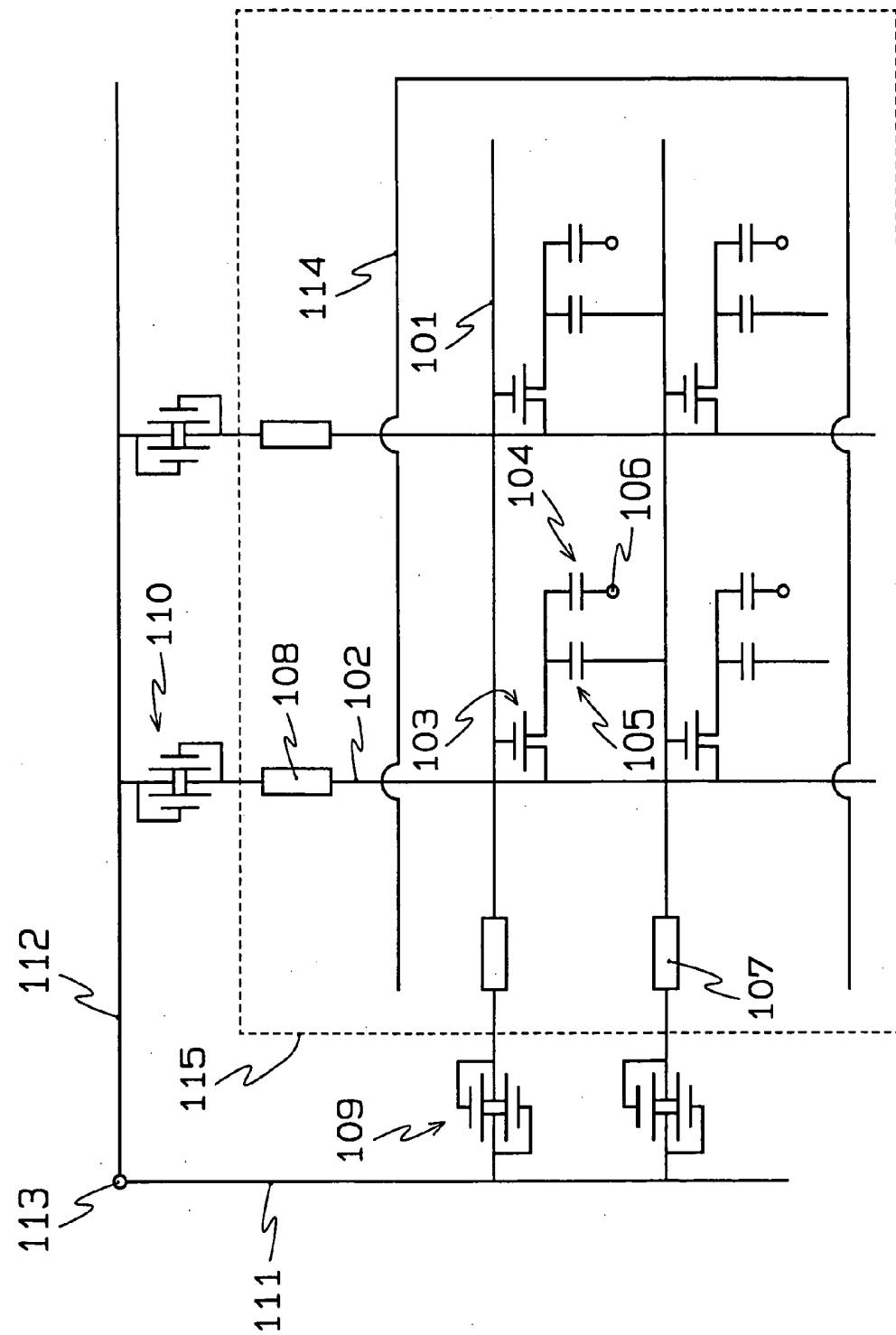

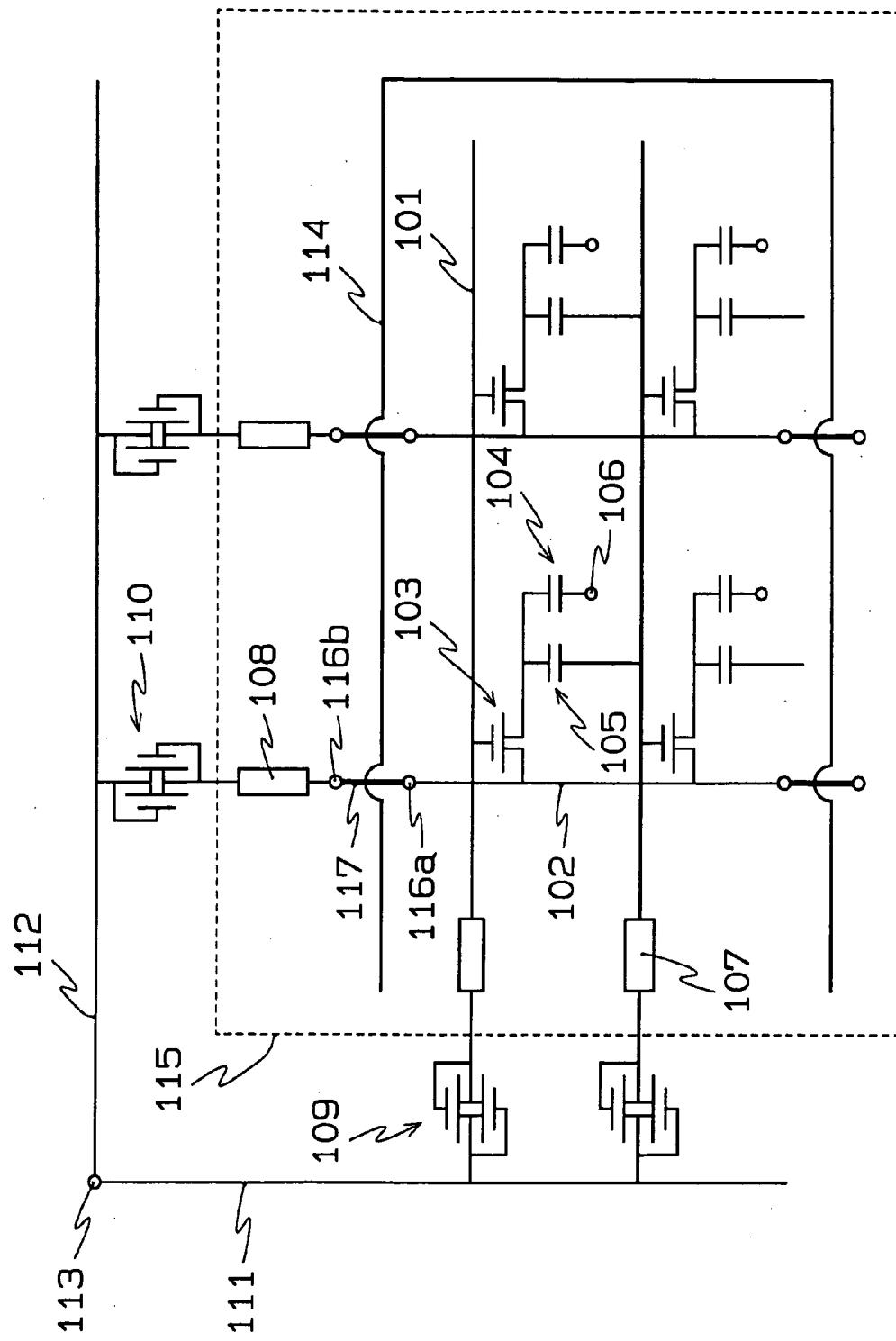

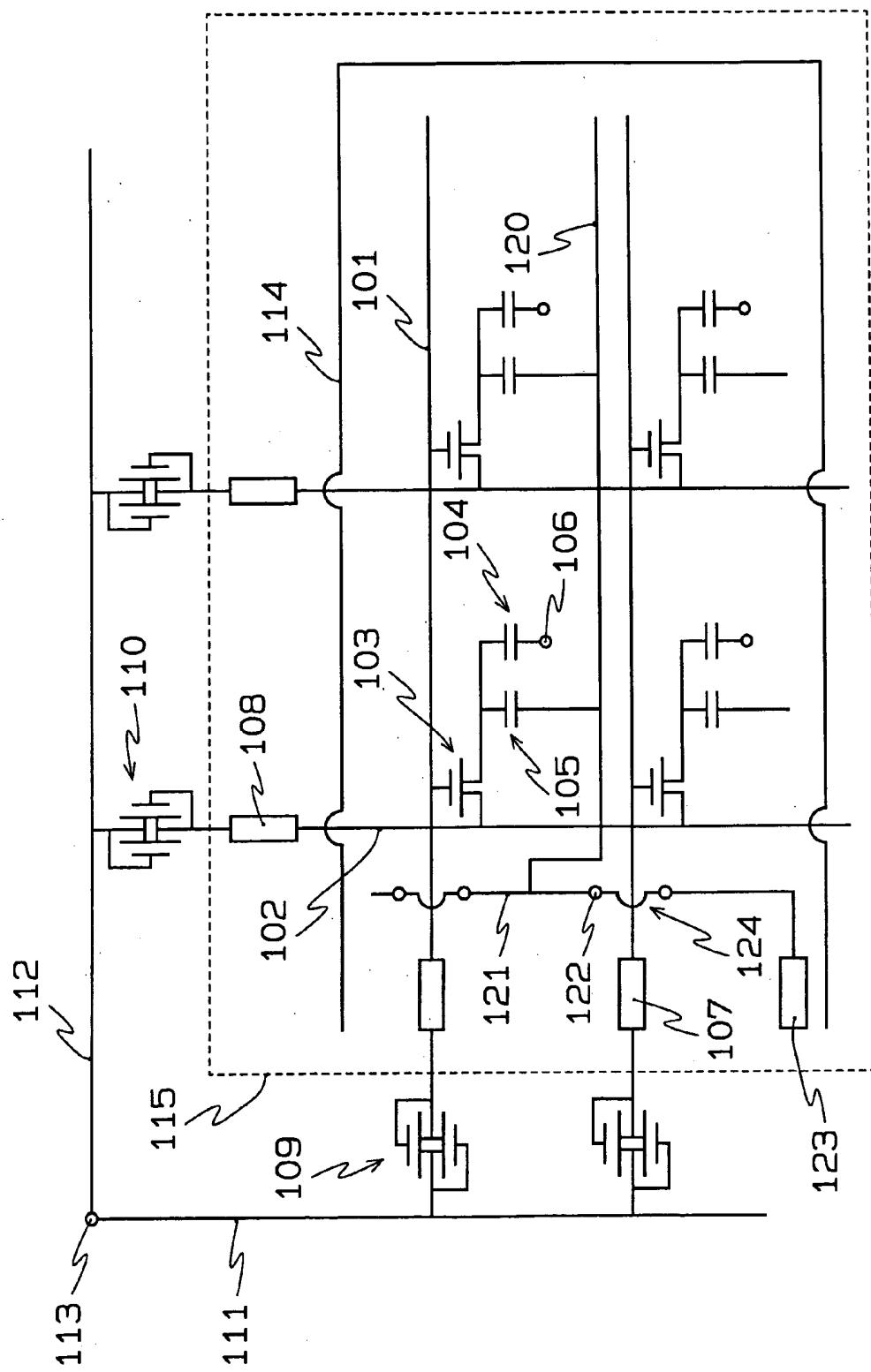

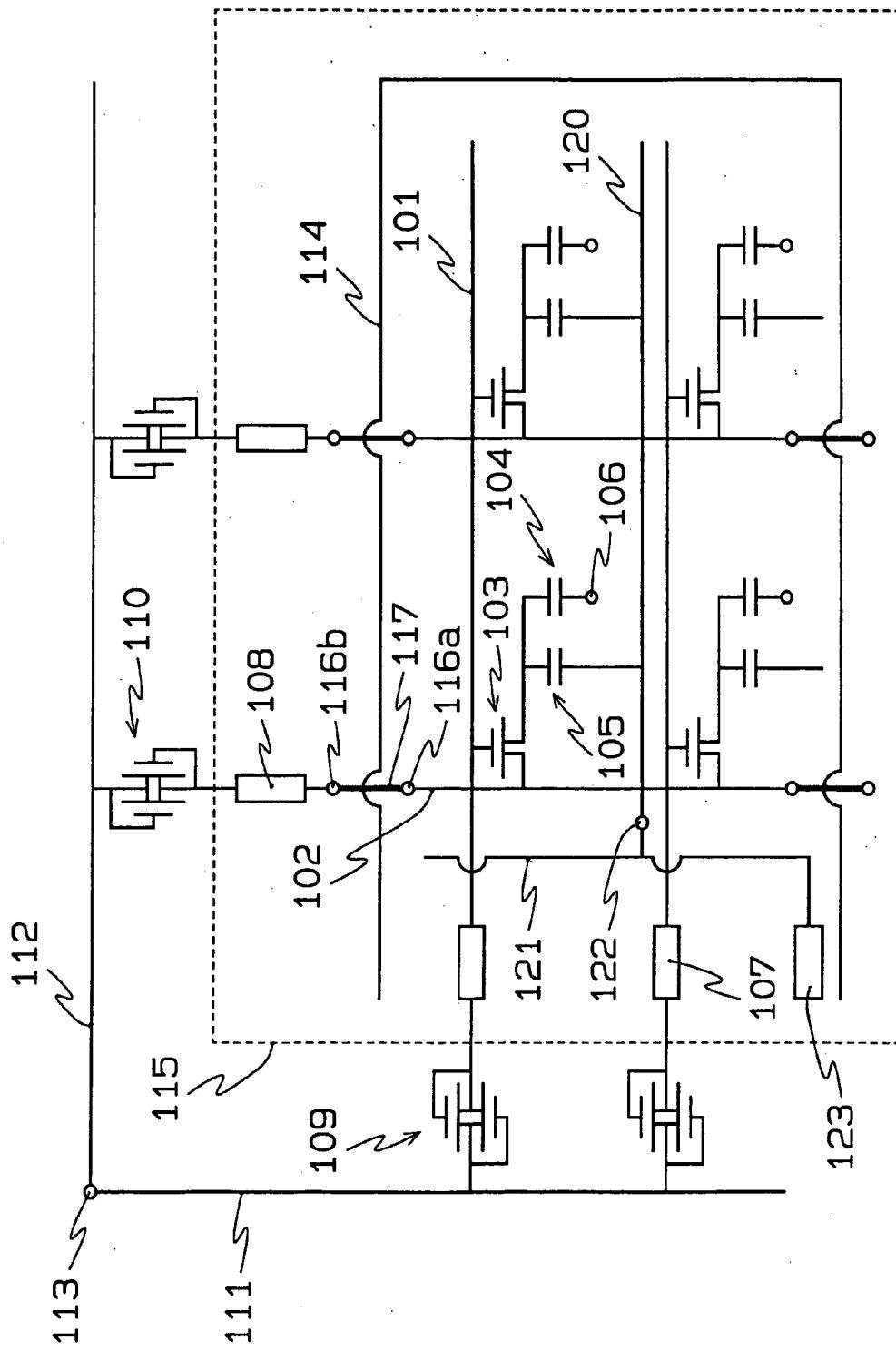

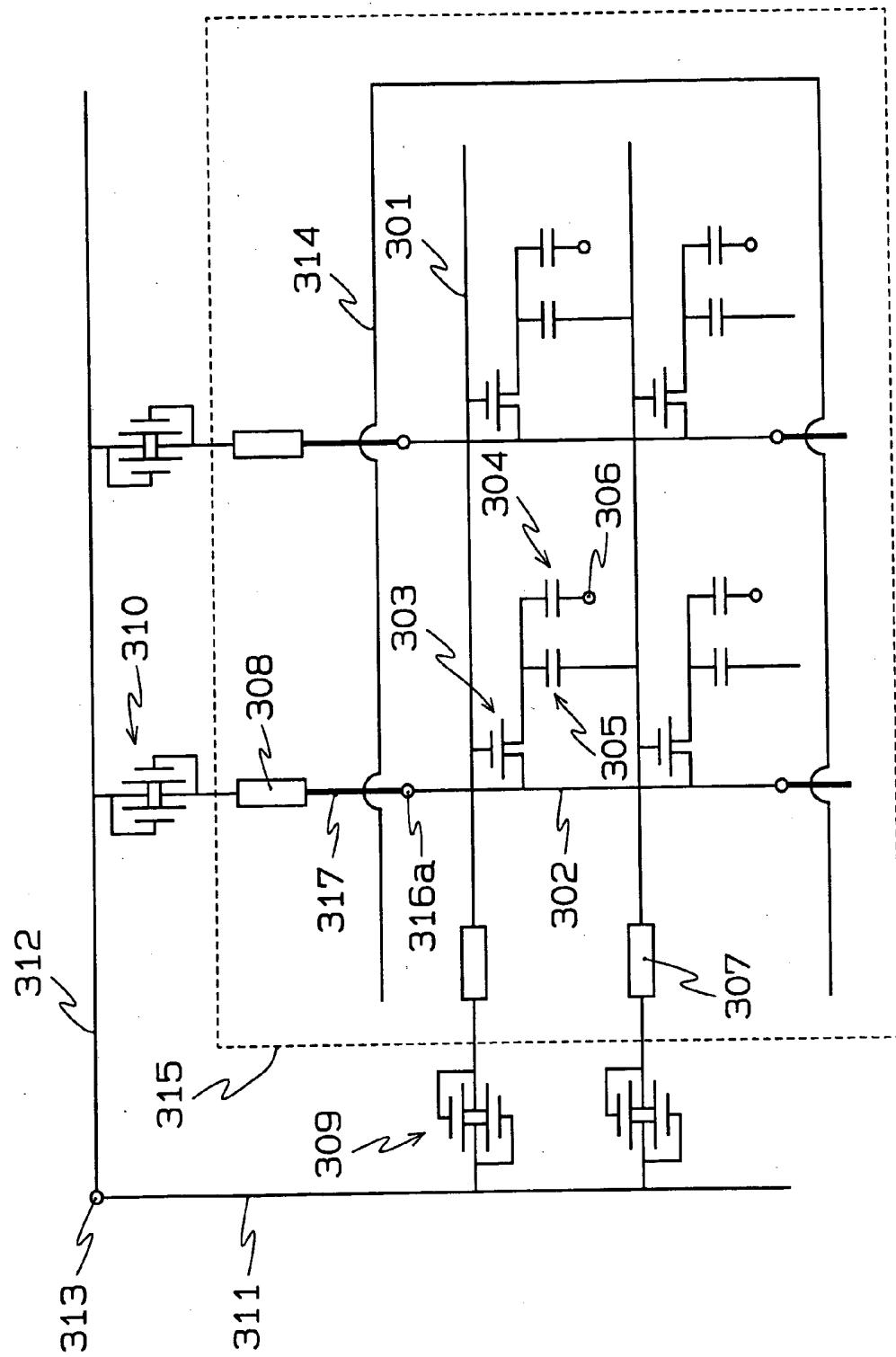

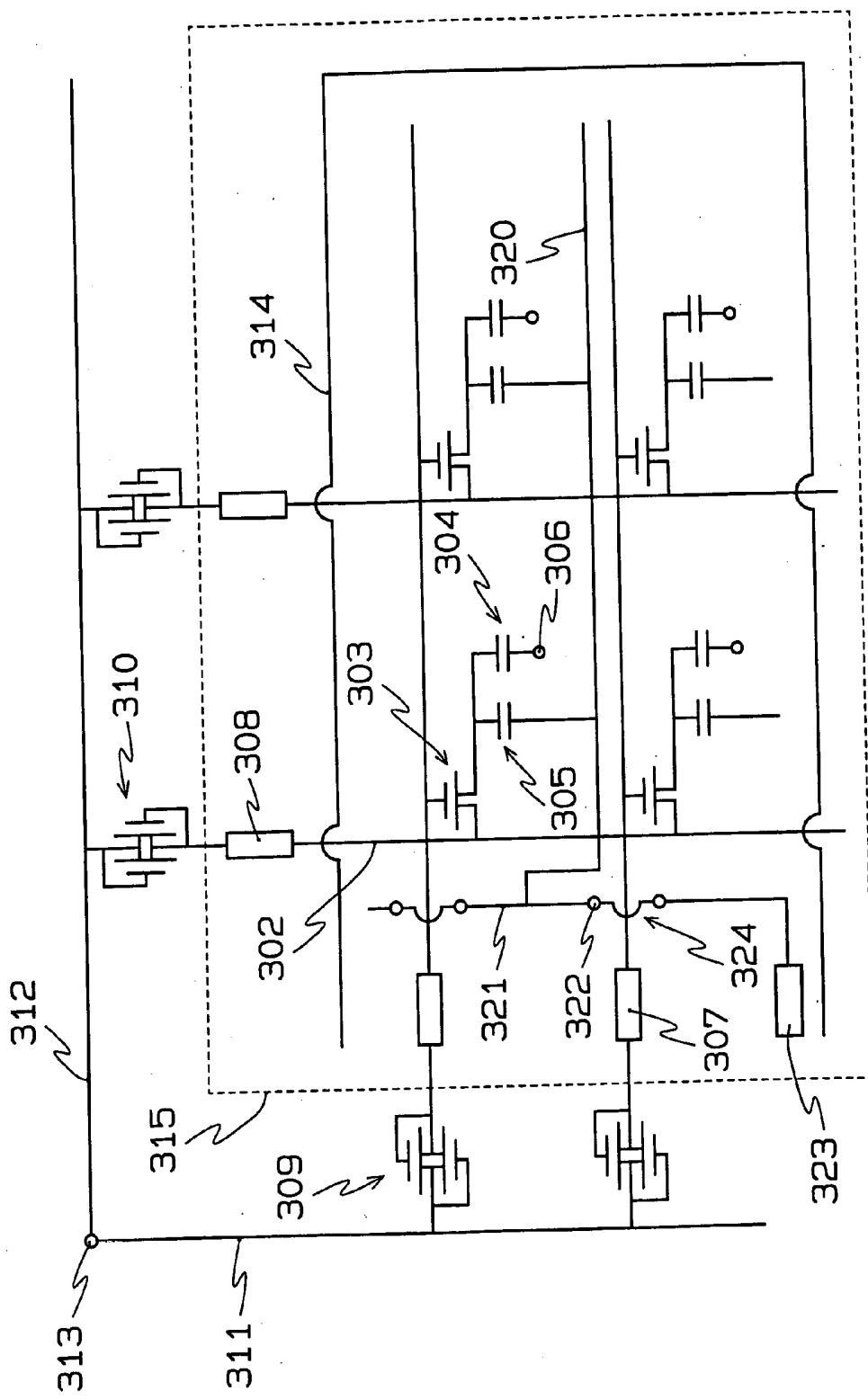

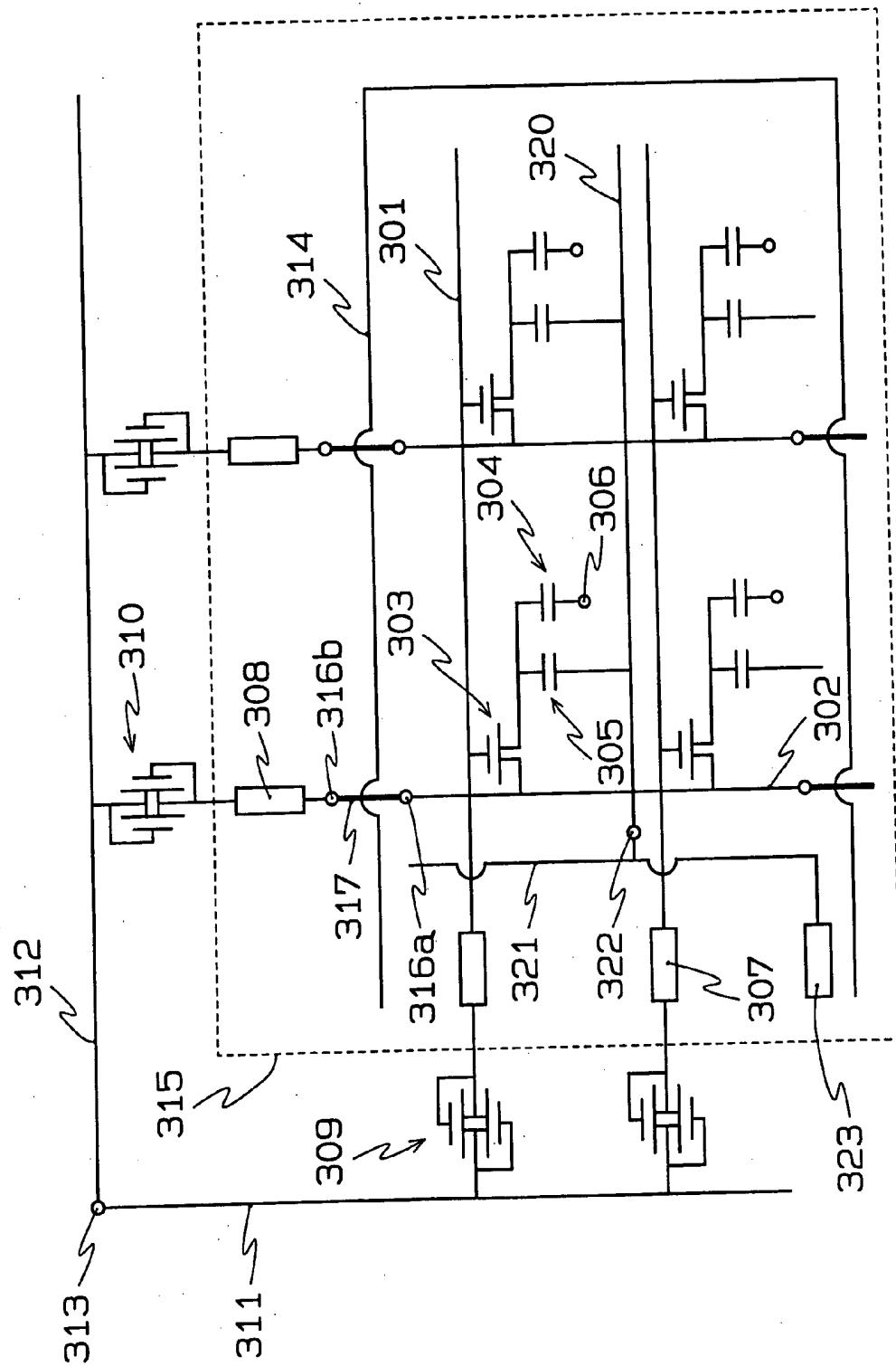

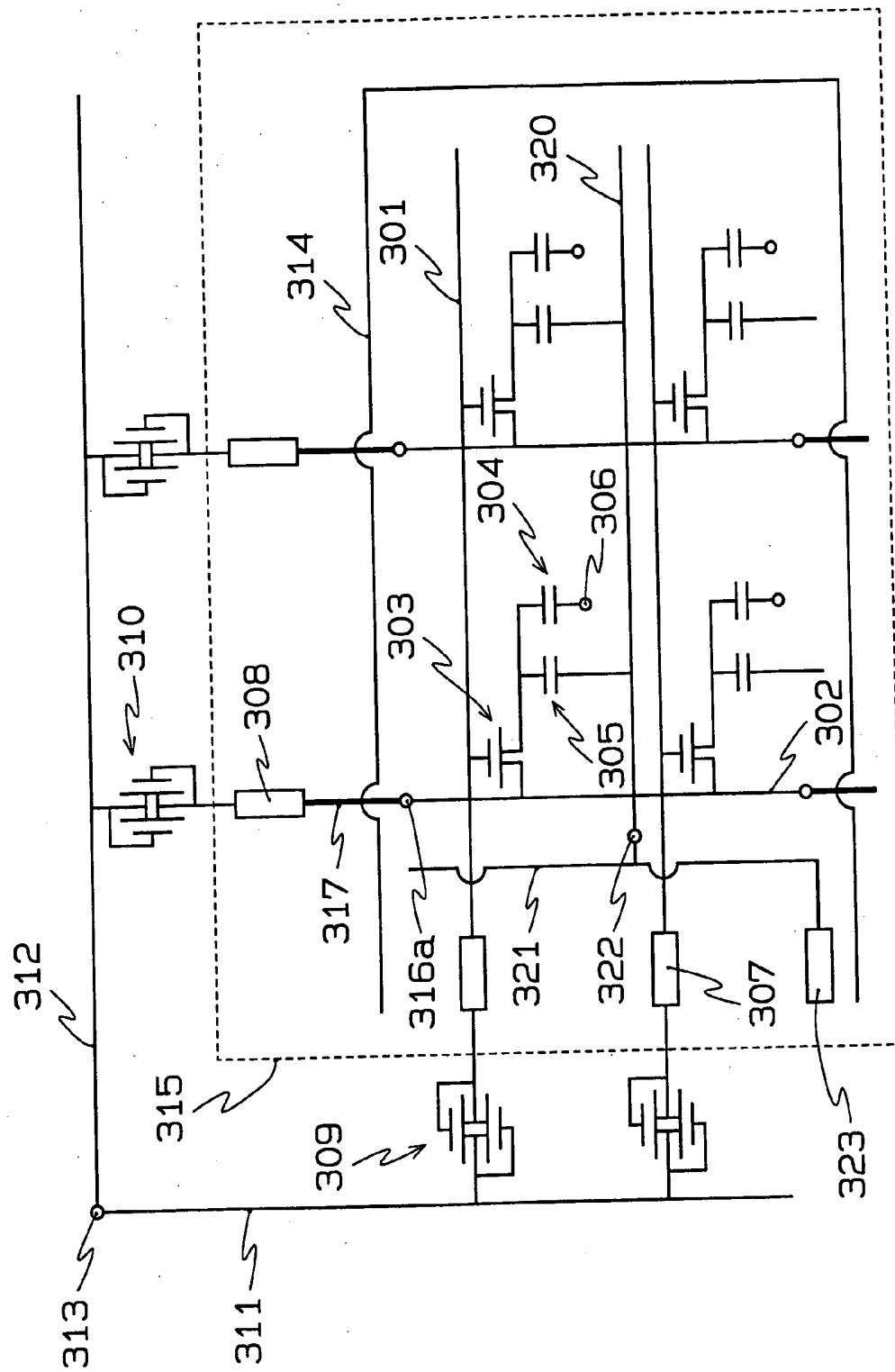

[0055] **FIG. 28** is a circuit diagram showing a TFT array substrate of an active matrix type liquid crystal display to which the present invention is applied;

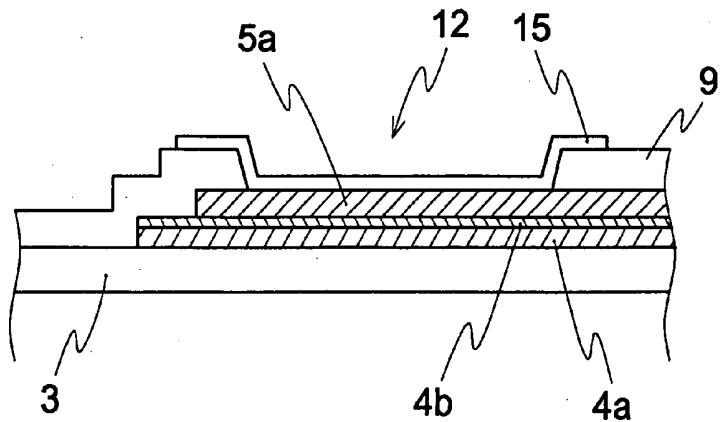

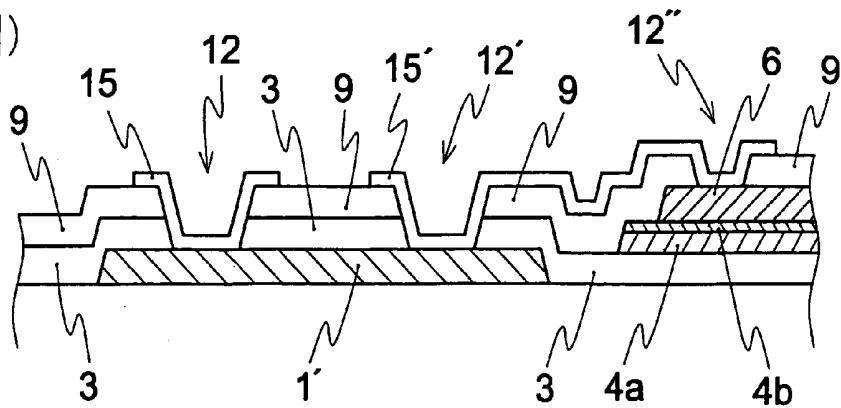

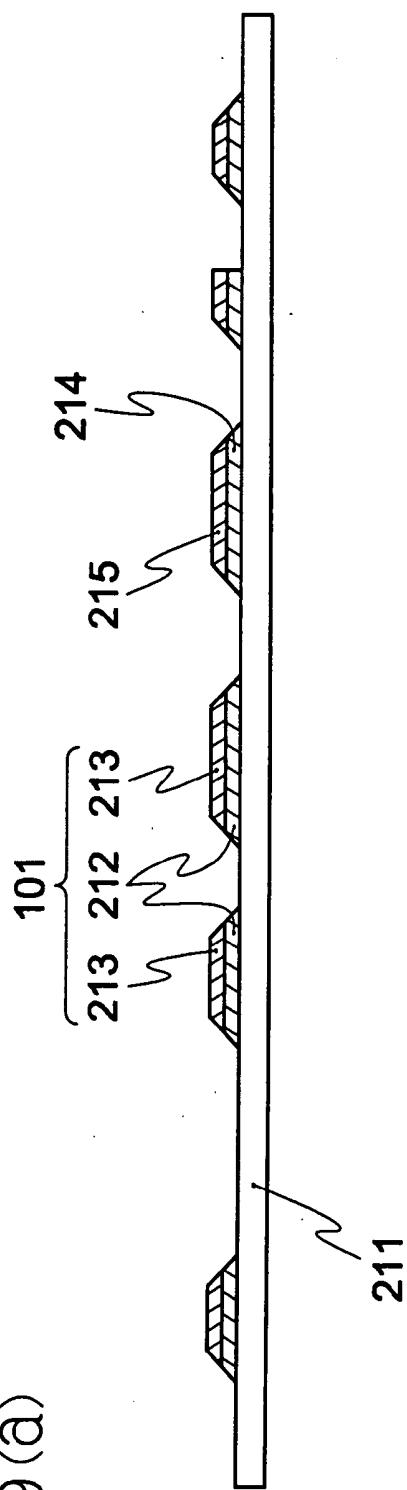

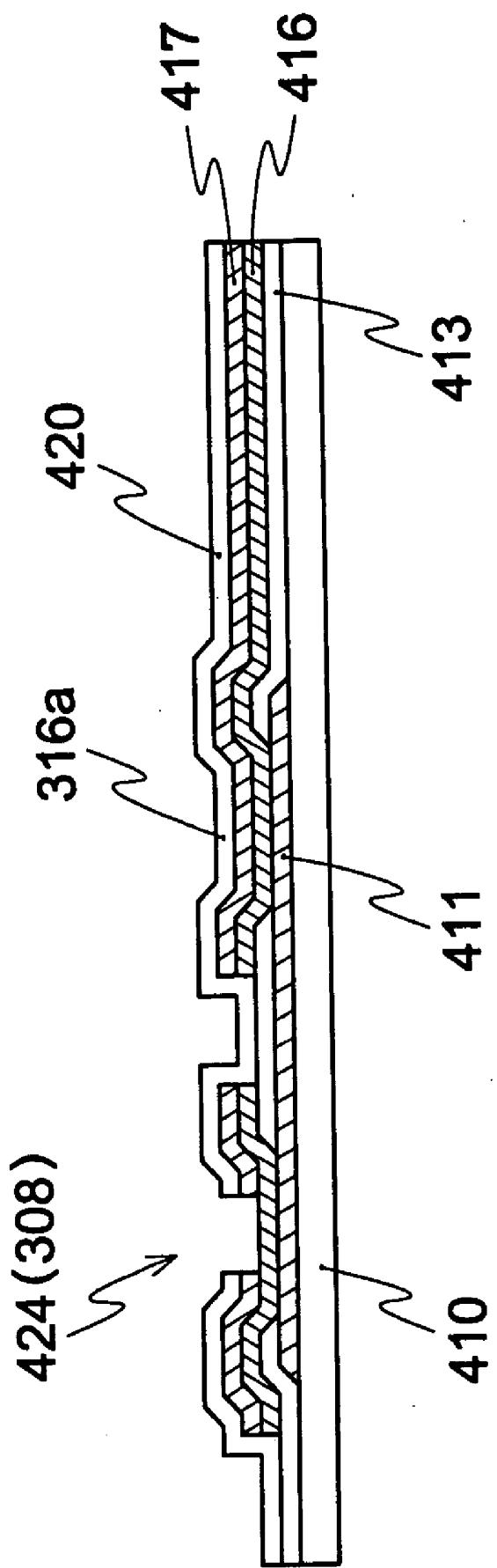

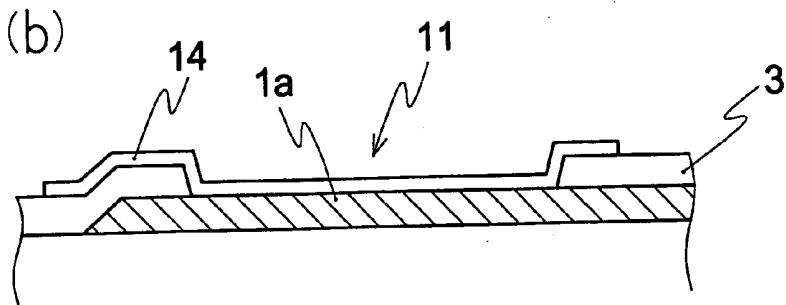

[0056] FIGS. 29(a) and 29(b) are sectional views showing a manufacturing process of the TFT array substrate according to the present invention;

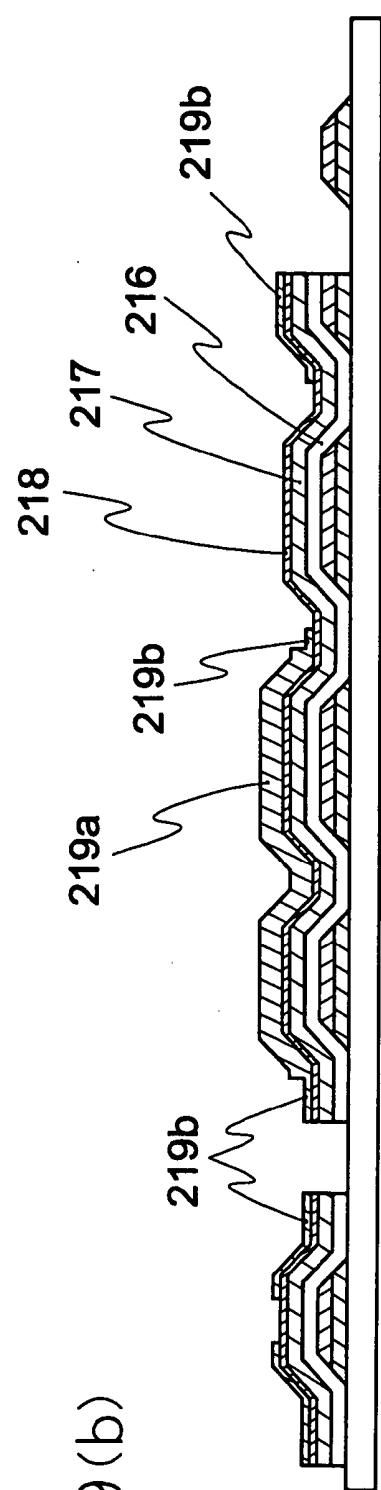

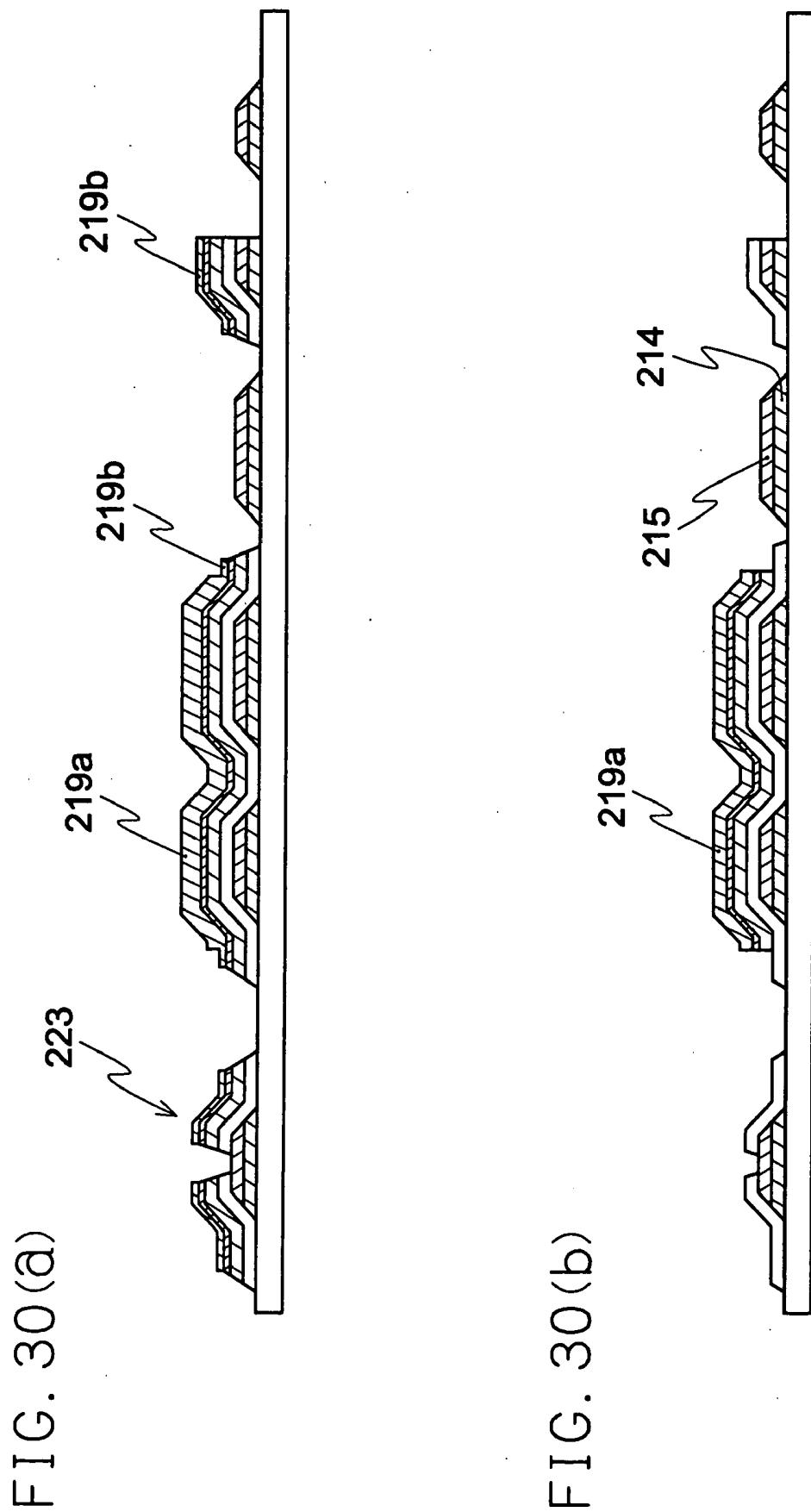

[0057] FIGS. 30(a) and 30(b) are sectional views showing the manufacturing process of the TFT array substrate according to the present invention;

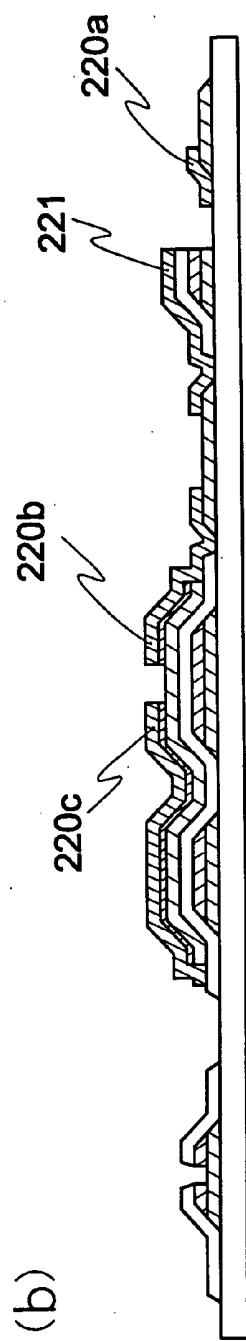

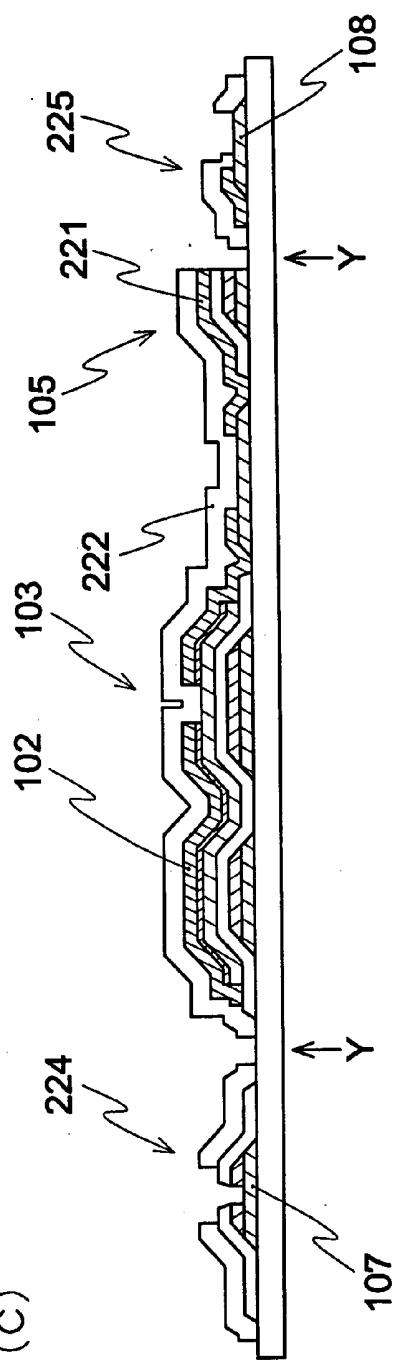

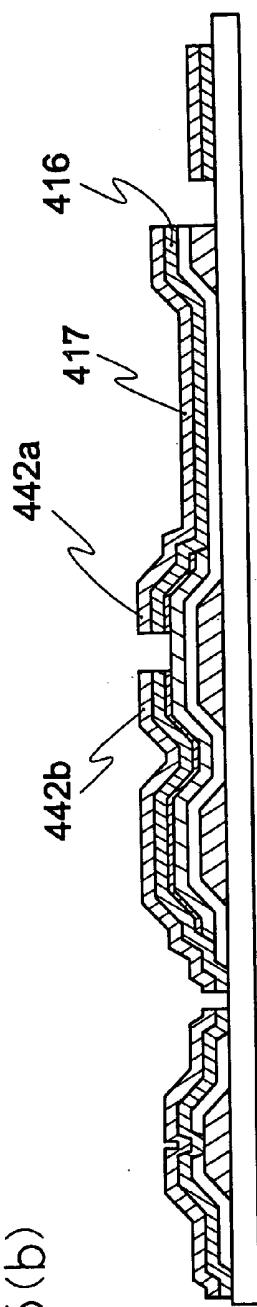

[0058] FIGS. 31(a) to 31(c) are sectional views showing the manufacturing process of the TFT array substrate according to the present invention;

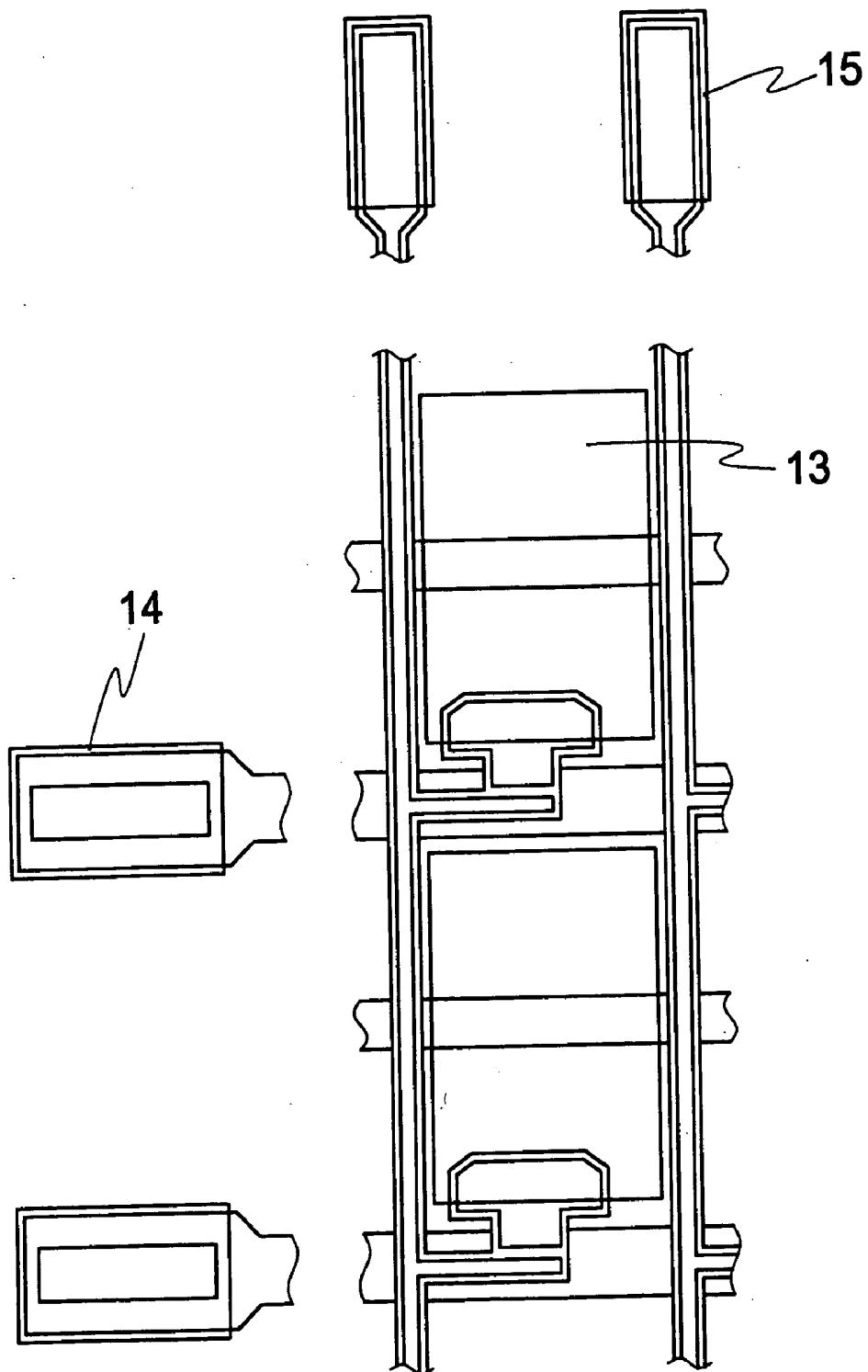

[0059] FIGS. 32(a) to 32(d) are plan views corresponding to FIGS. 29, 30 and 31;

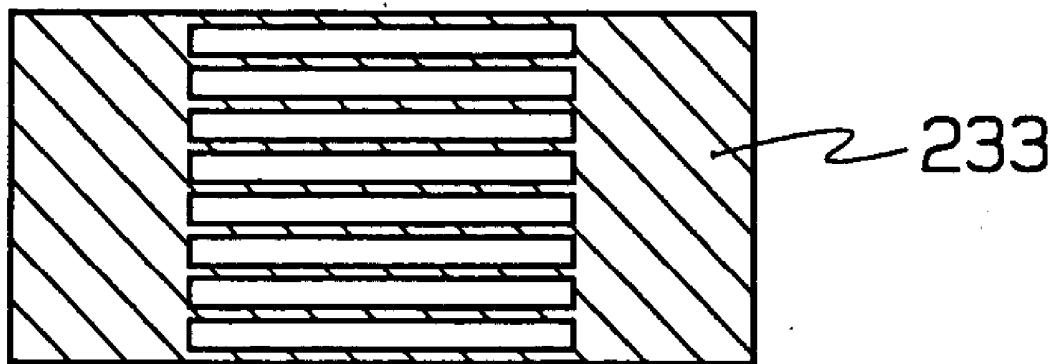

[0060] **FIG. 33** is a view showing an example of a pattern of a half tone mask;

[0061] **FIG. 34** is a circuit diagram showing an example of a cross portion of a source line and a repair line;

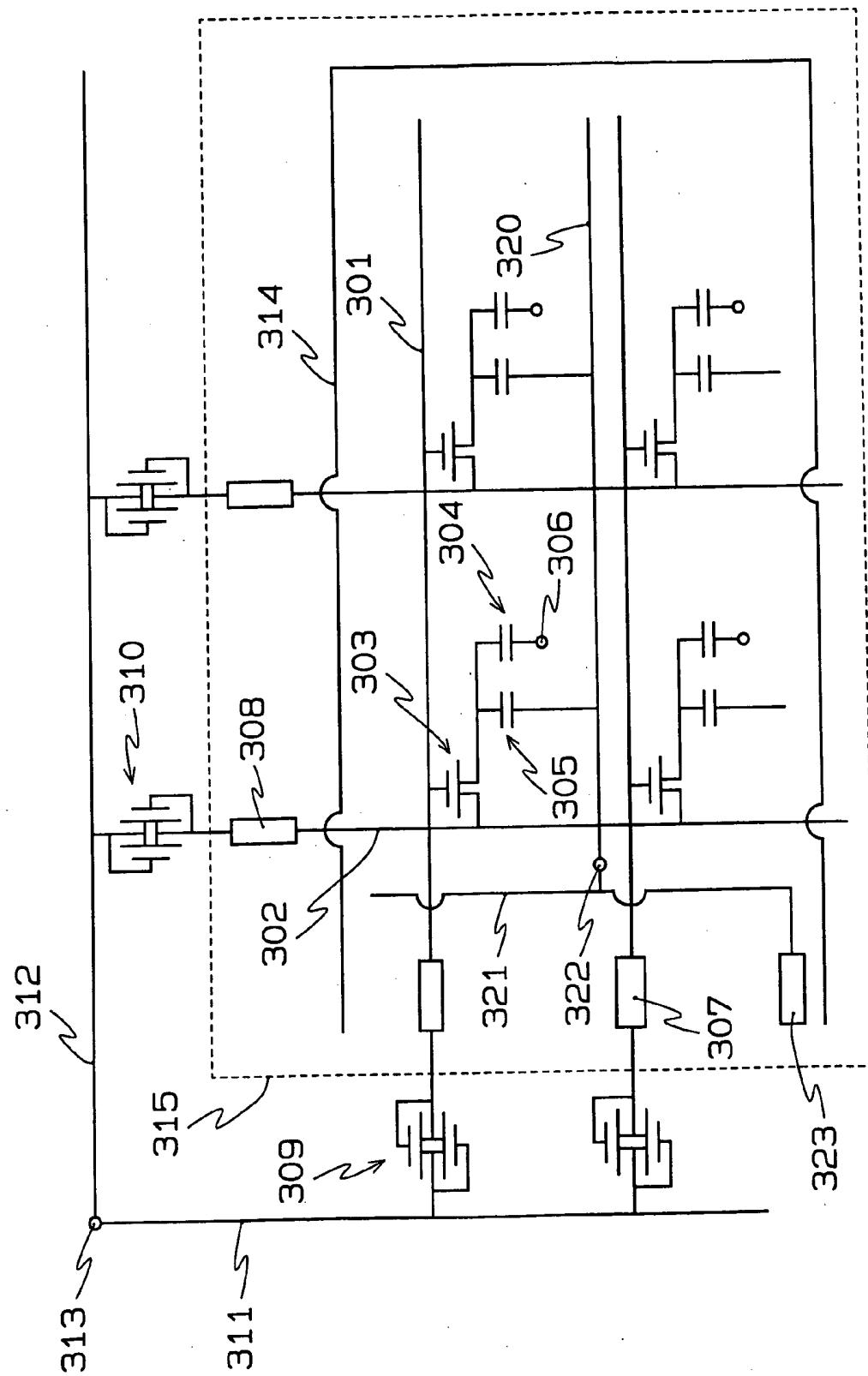

[0062] **FIG. 35** is a circuit diagram showing a common line method in which a retaining capacitance line is provided separately from a gate line;

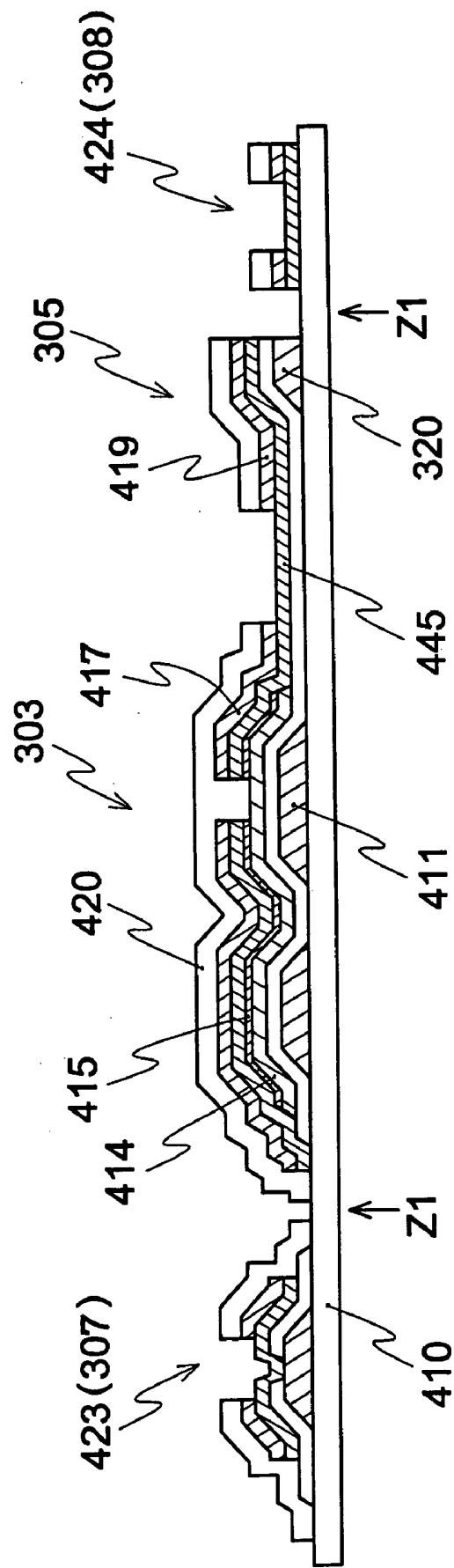

[0063] **FIG. 36** is a sectional view showing a structure of the common line method;

[0064] FIGS. 37(a) to 37(d) are plan views corresponding to FIG. 9;

[0065] **FIG. 38** is a plan view showing another example of the common line method;

[0066] **FIG. 39** is a circuit diagram showing a cross portion of a source line and a repair wiring in the common line method;

[0067] **FIG. 40** is a plan view showing an example of plane arrangement in which a shielding pattern is formed around a pixel electrode;

[0068] FIGS. 41(a) and 41(b) are plan views showing an example of plane arrangement of an IPS mode;

[0069] FIGS. 42(a) to 42(c) are sectional views showing another method of manufacturing a TFT array substrate according to the present invention;

[0070] FIGS. 43(a) and 43(b) are sectional views showing a further method of manufacturing a TFT array substrate according to the present invention;

[0071] FIGS. 44(a) to 44(c) are sectional views showing a process for manufacturing a TFT array substrate according to the present invention;

[0072] FIGS. 45(a) to 45(c) are sectional views showing the process for manufacturing a TFT array substrate according to the present invention;

[0073] FIGS. 46(a) to 46(c) are plan views corresponding to FIGS. 44(a) to 44(c) and FIGS. 45(a) to 45(c);

[0074] FIGS. 47(a) and 47(b) plan views corresponding to FIGS. 44(a) to 44(c) and FIGS. 45(a) to 45(c);

[0075] **FIG. 48** is a circuit diagram showing a TFT array substrate of an active matrix type liquid crystal display to which the present invention is applied;

[0076] **FIG. 49** is a sectional view showing an example of a source terminal portion;

[0077] **FIG. 50** is a circuit diagram showing a common line retaining capacitance;

[0078] **FIG. 51** is a sectional view showing a sectional structure of the TFT array substrate according to the present invention;

[0079] FIGS. 52(a) to 52(c) are plan views corresponding to FIG. 51;

[0080] FIGS. 53(a) and 53(b) are plan views corresponding to FIGS. 51;

[0081] **FIG. 54** is a circuit diagram showing the common line method of the retaining capacitance;

[0082] **FIG. 55** is a circuit diagram showing the common line method of the retaining capacitance;

[0083] **FIG. 56** is a circuit diagram showing the common line method of the retaining capacitance;

[0084] **FIG. 57** is a sectional view showing a thin film transistor portion according to a conventional structure;

[0085] **FIG. 58** is a plan view showing the thin film transistor portion according to the conventional structure;

[0086] FIGS. 59(a) to 59(c) are sectional views showing a process for manufacturing a TFT array substrate of a conventional active matrix type liquid crystal display;

[0087] FIGS. 60(a) to 60(c) are sectional views showing the process for manufacturing a TFT array substrate of the conventional active matrix type liquid crystal display;

[0088] FIGS. 61(a) to 61(d) are plan views showing the TFT array substrate of the conventional active matrix type liquid crystal display;

[0089] FIGS. 62(a) to 62(c) are plan views showing a TFT array substrate for a transverse field effect;

[0090] FIGS. 63(a) and 63(b) are sectional views showing a manufacturing process corresponding to FIG. 62(c);

[0091] **FIG. 64** is a plan view corresponding to FIG. 1;

[0092] FIGS. 65(a) to 65(d) are explanatory views respectively corresponding to FIGS. 2(a) to 2(d);

[0093] **FIG. 66** is an explanatory view showing additional step added to the manufacturing steps shown in FIGS. 3 to 5;

[0094] **FIG. 67** is an explanatory view showing manufacturing step of another embodiment corresponding to the embodiment shown in FIG. 13;

[0095] **FIG. 68** is an explanatory view showing manufacturing step of still another embodiment corresponding to the embodiment shown in **FIG. 14**;

[0096] **FIG. 69** is a plan view showing another embodiment corresponding to the embodiment shown in **FIG. 15**;

[0097] **FIG. 70** is an explanatory view showing additional step added to the manufacturing steps shown in FIGS. 16 to 18;

[0098] **FIG. 71** is a plan view showing another embodiment corresponding to the embodiment shown in **FIG. 22**;

[0099] **FIG. 72** is an explanatory view showing a manufacturing step added to the steps shown in FIGS. 23 to 25;

[0100] **FIG. 73** is an explanatory view showing a semiconductor region of another embodiment corresponding to the embodiment shown **FIG. 32(d)**; and

[0101] **FIG. 74** is an explanatory view showing a semiconductor region of still another embodiment corresponding to the embodiment shown **FIG. 32(d)**.

## DETAILED DESCRIPTION

### EMBODIMENT 1

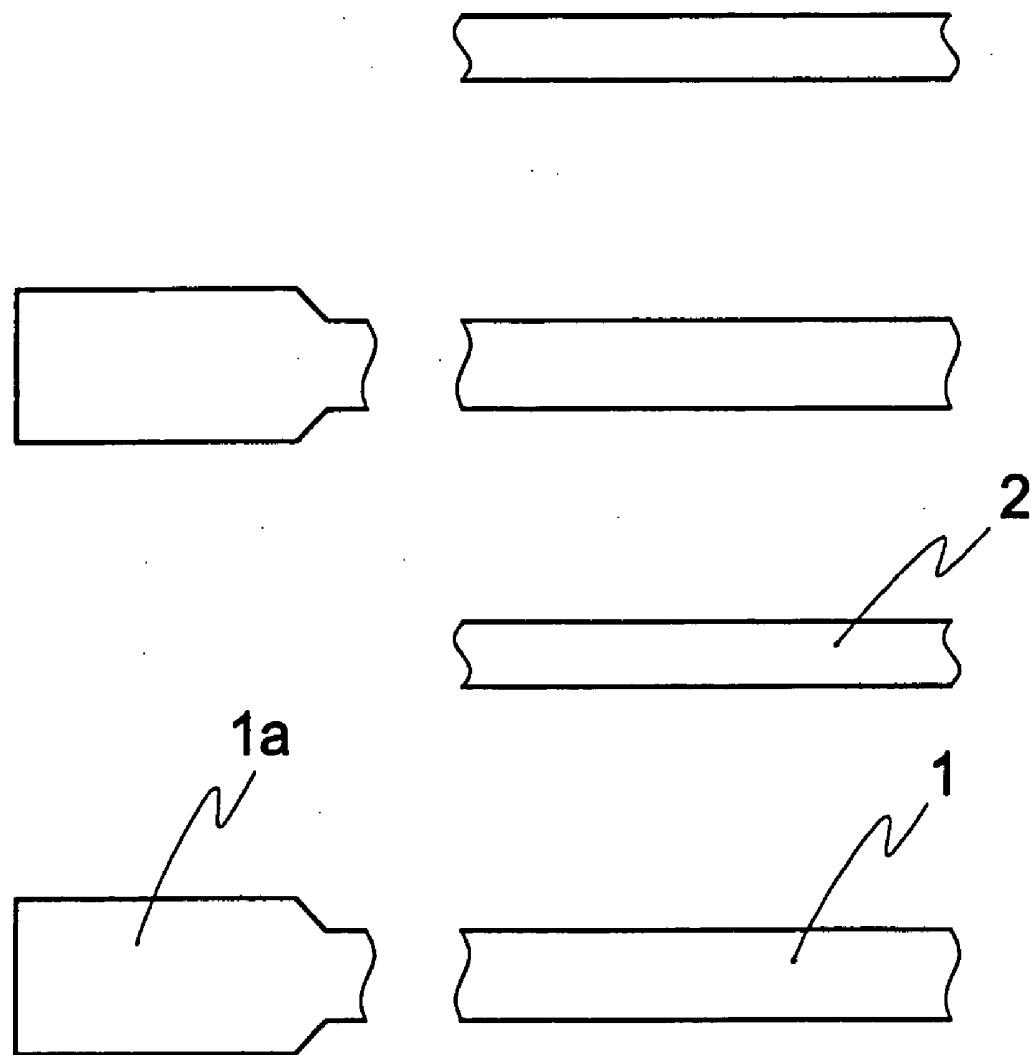

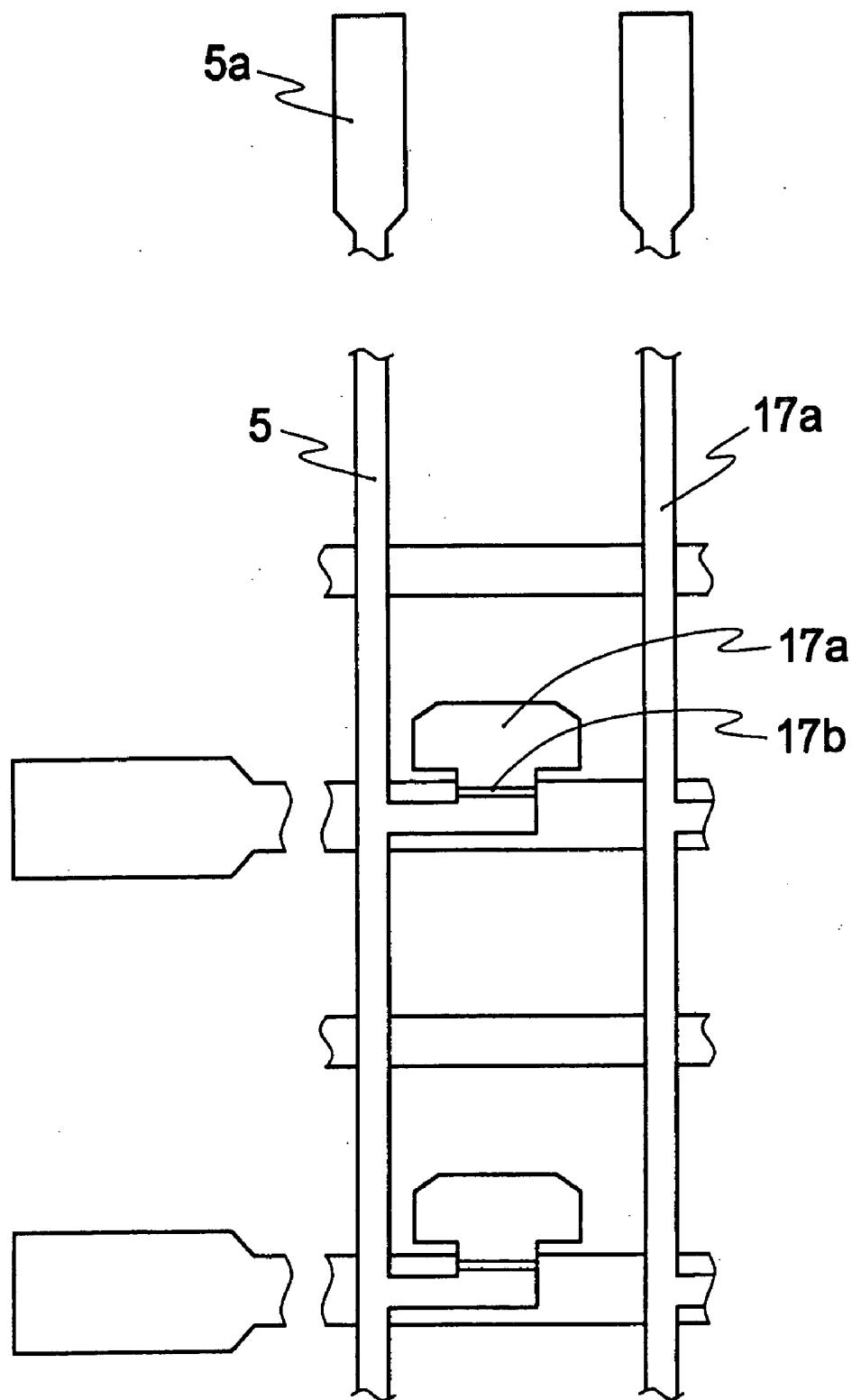

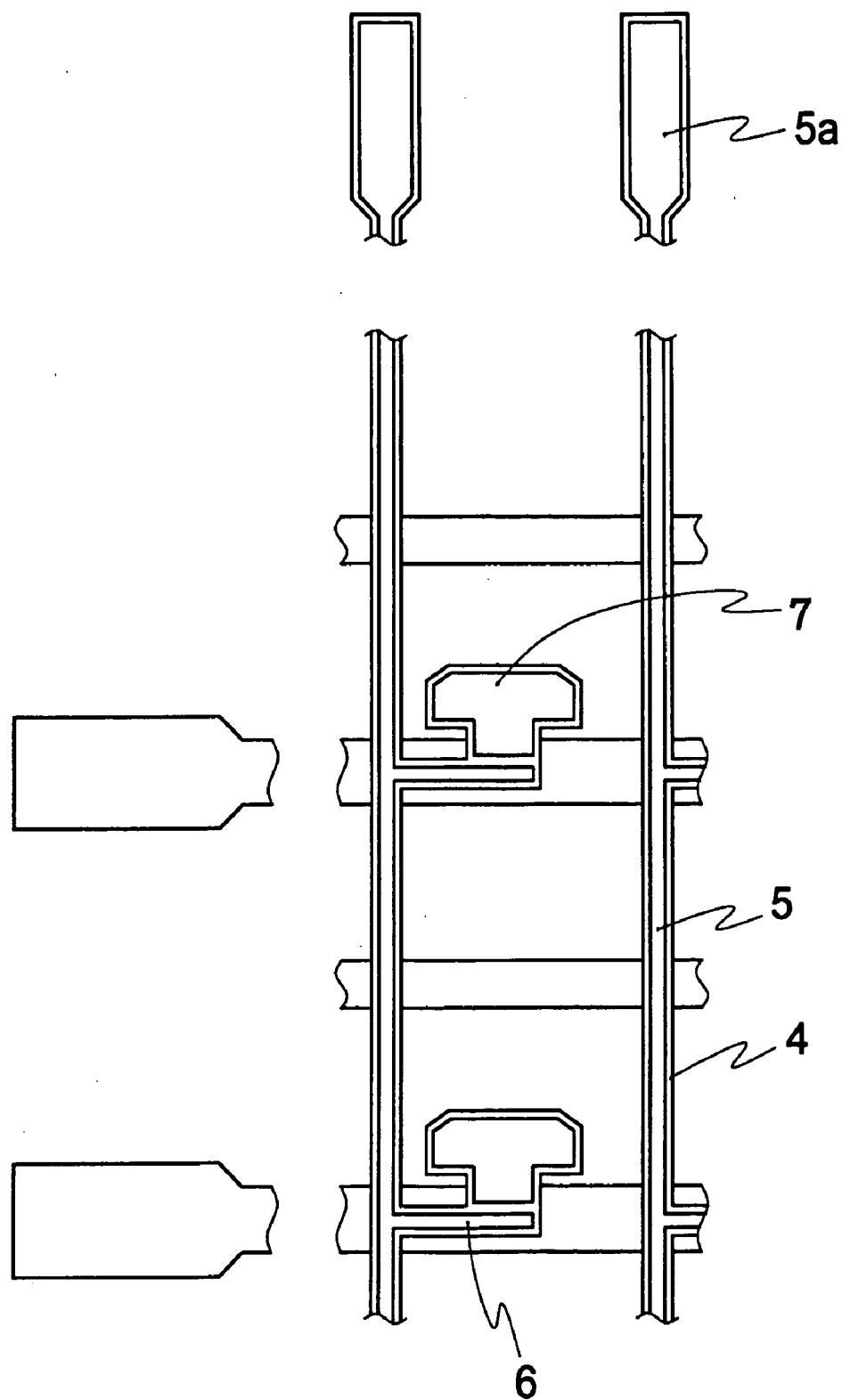

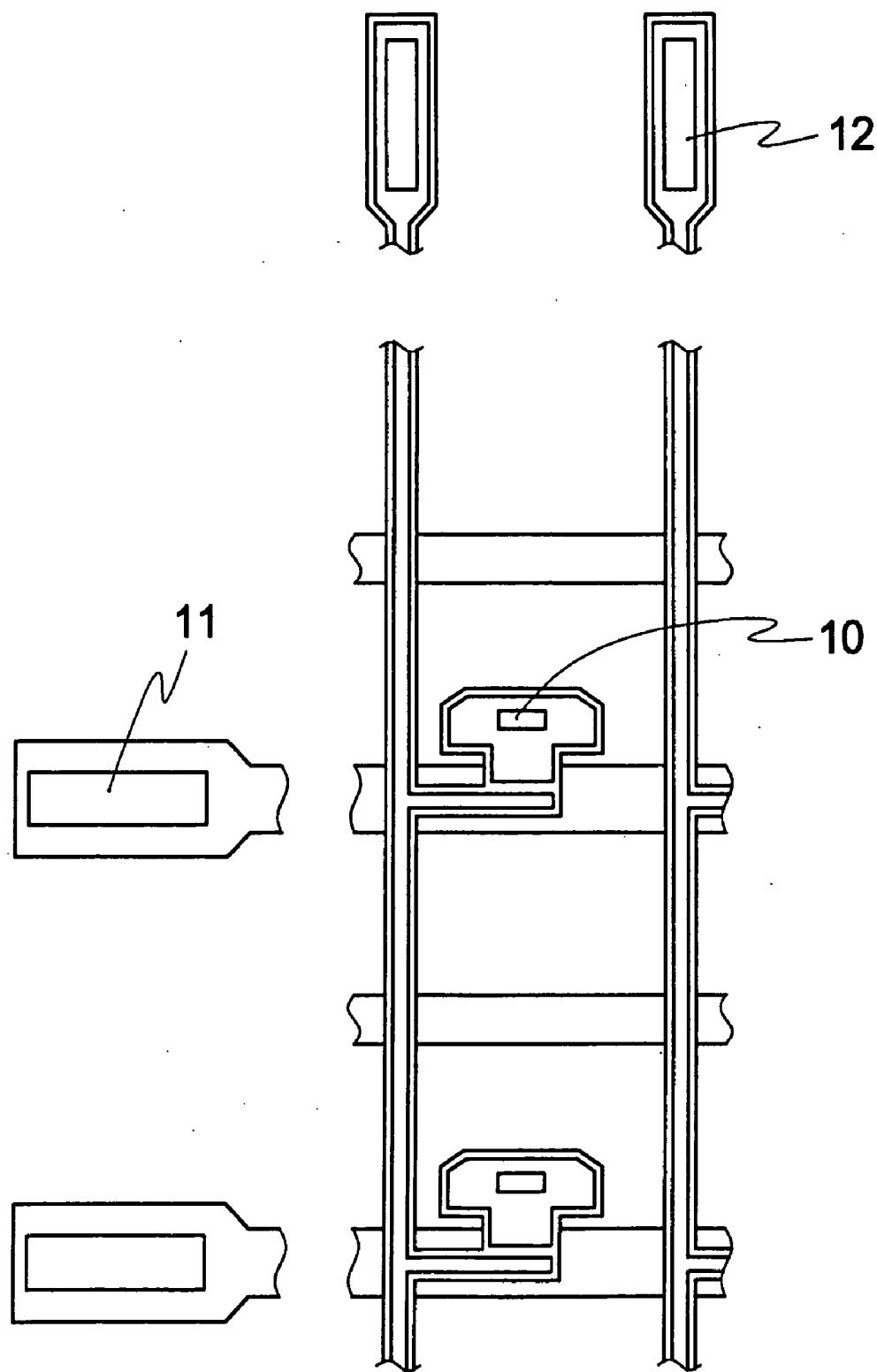

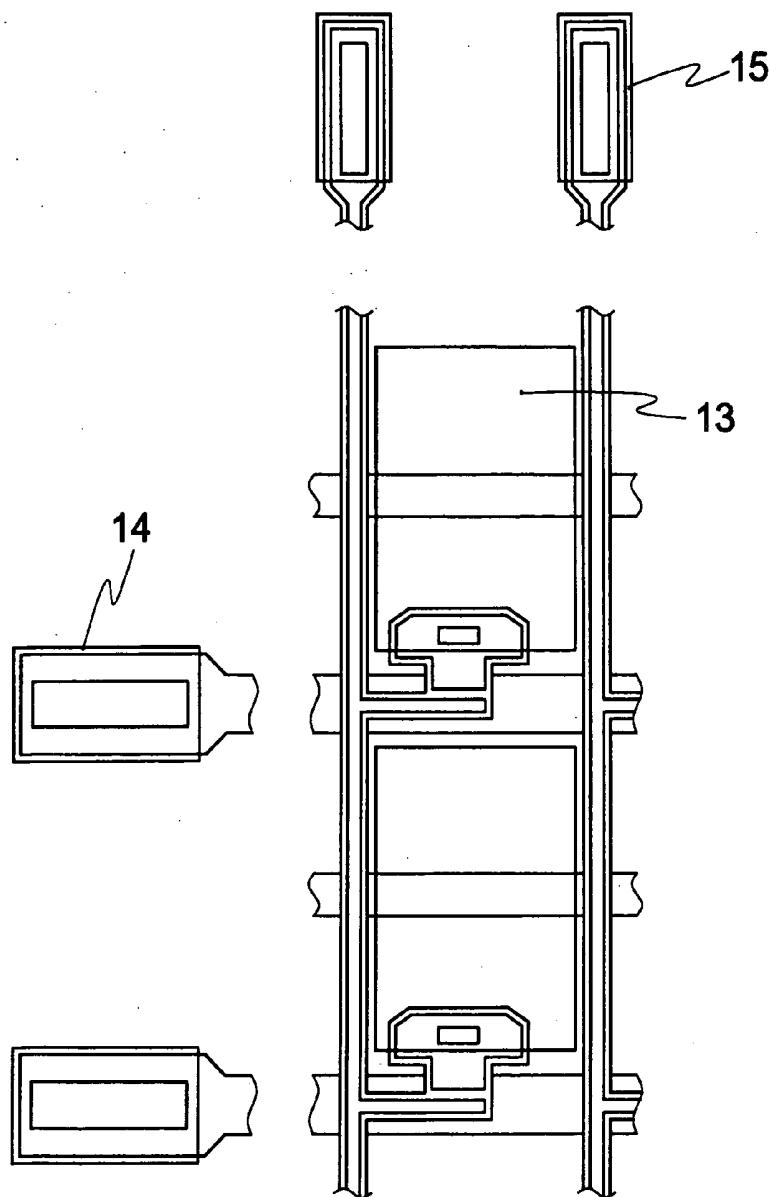

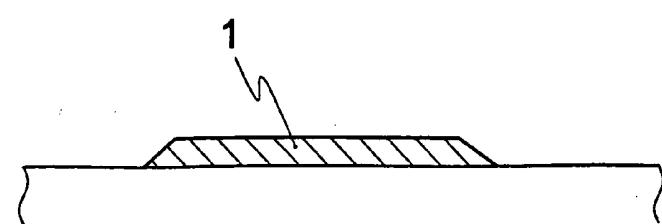

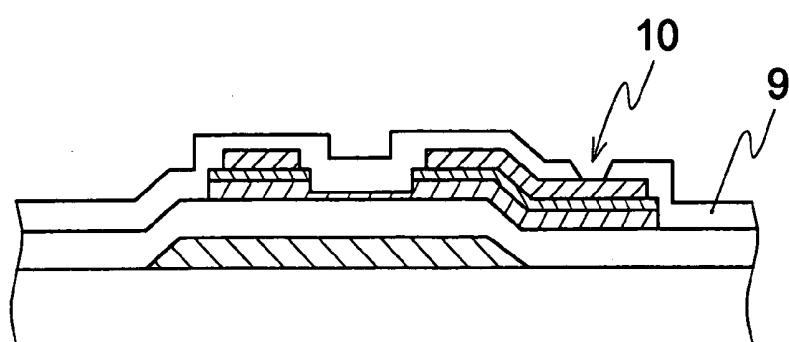

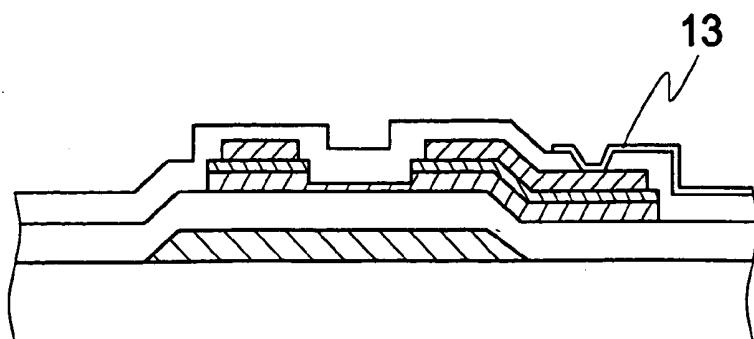

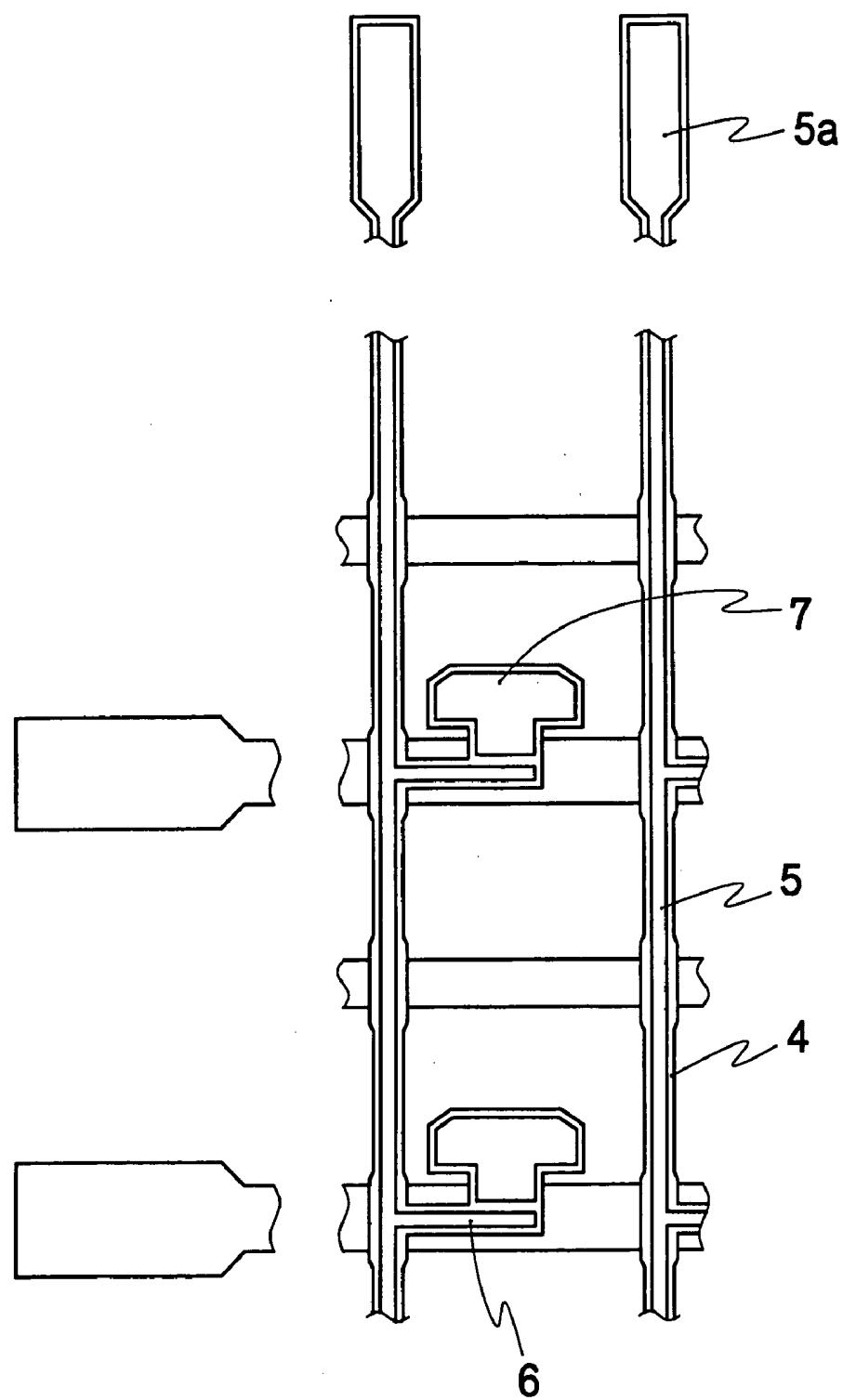

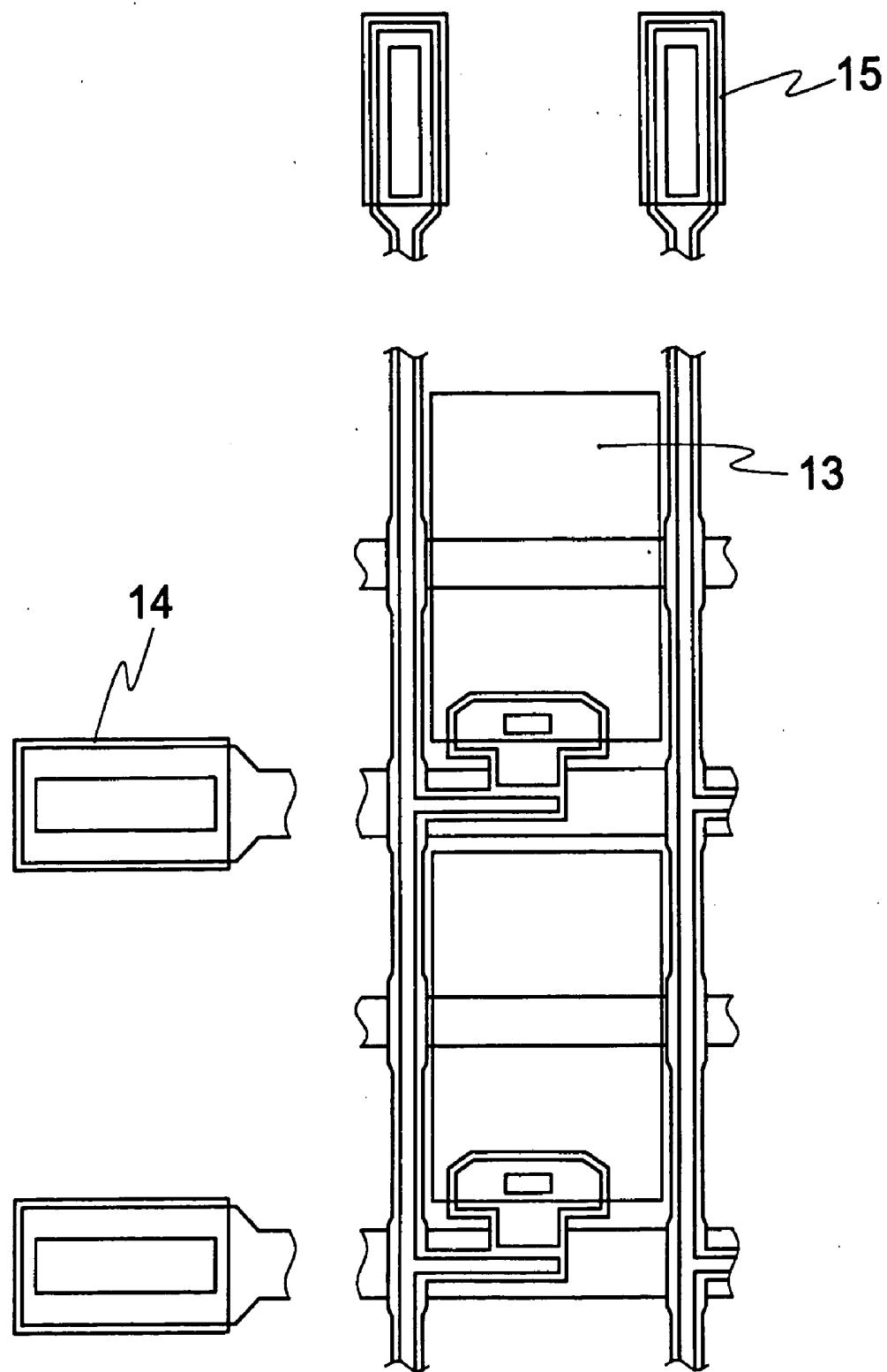

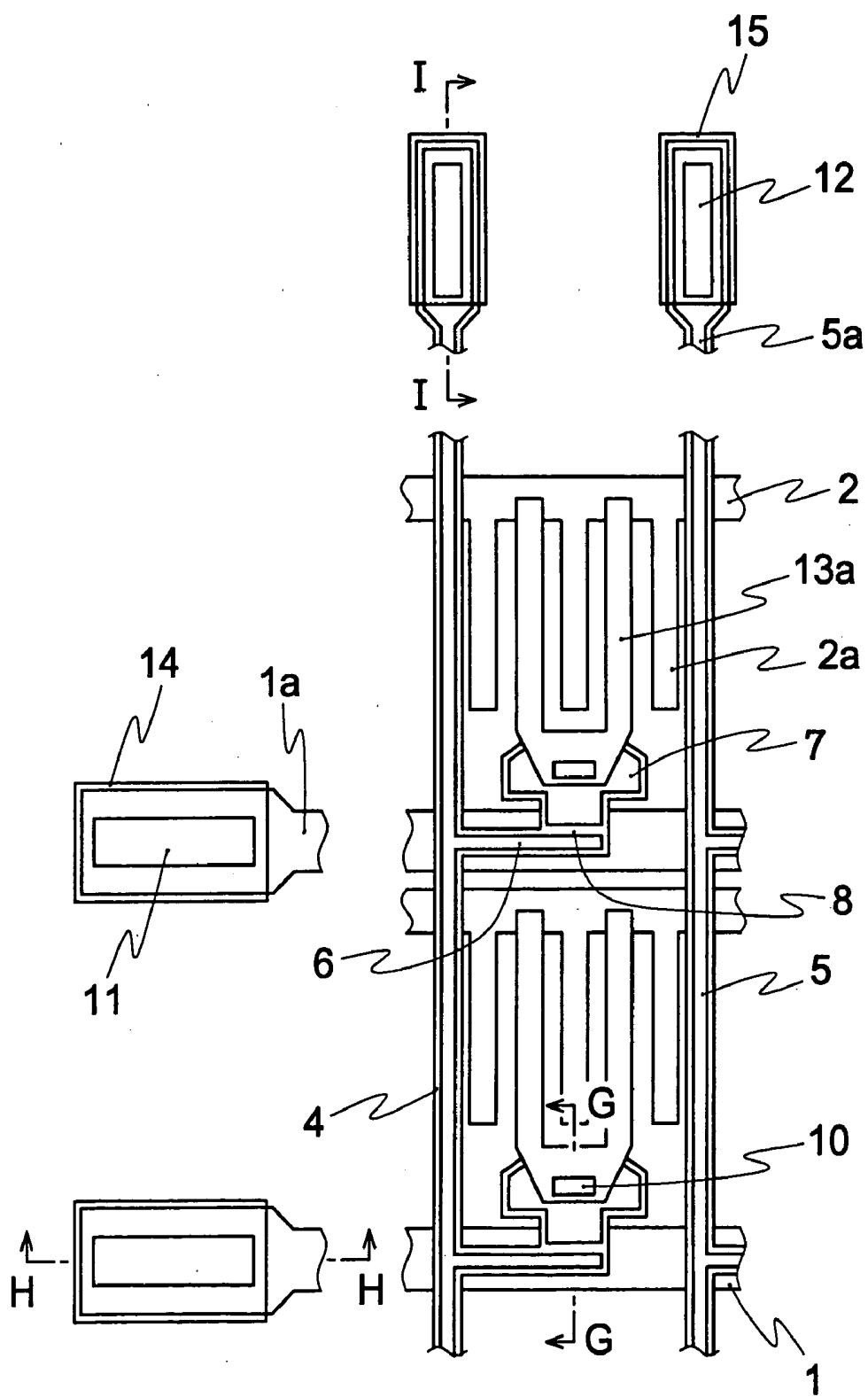

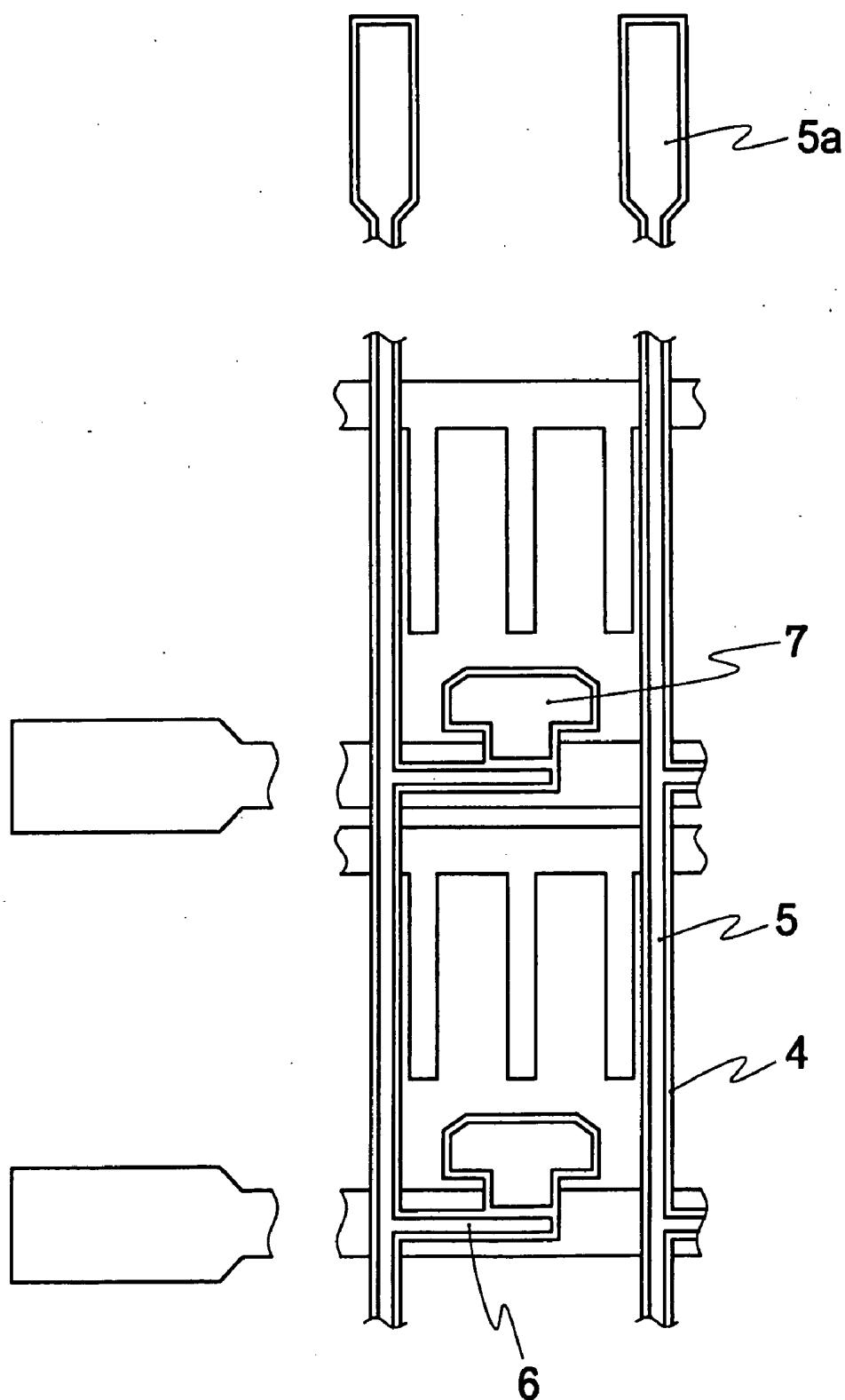

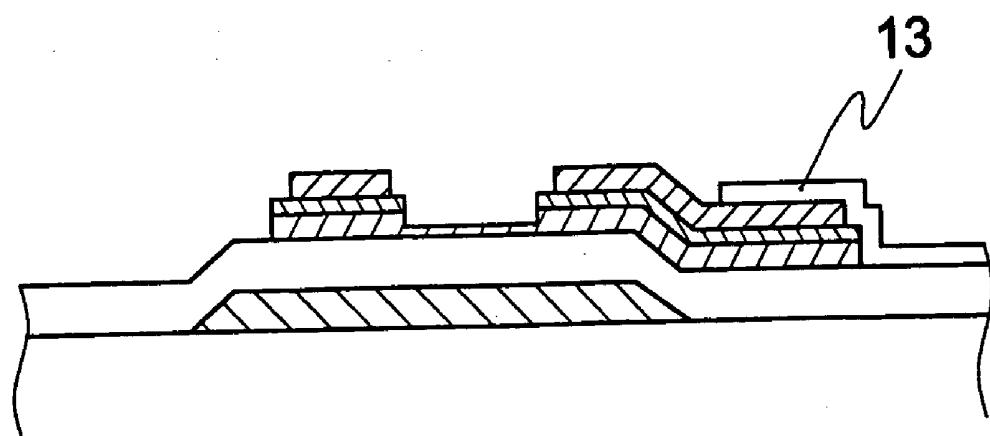

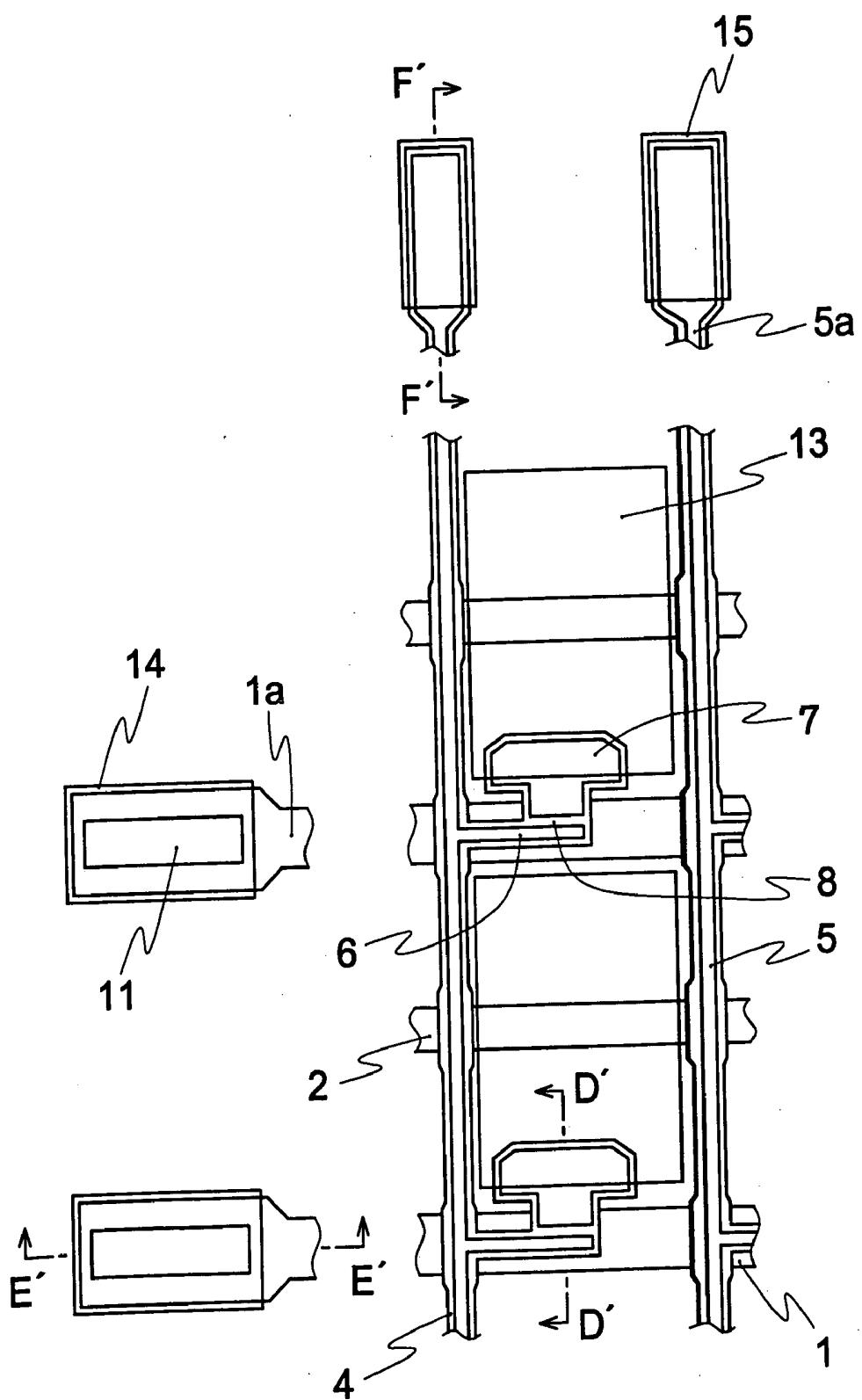

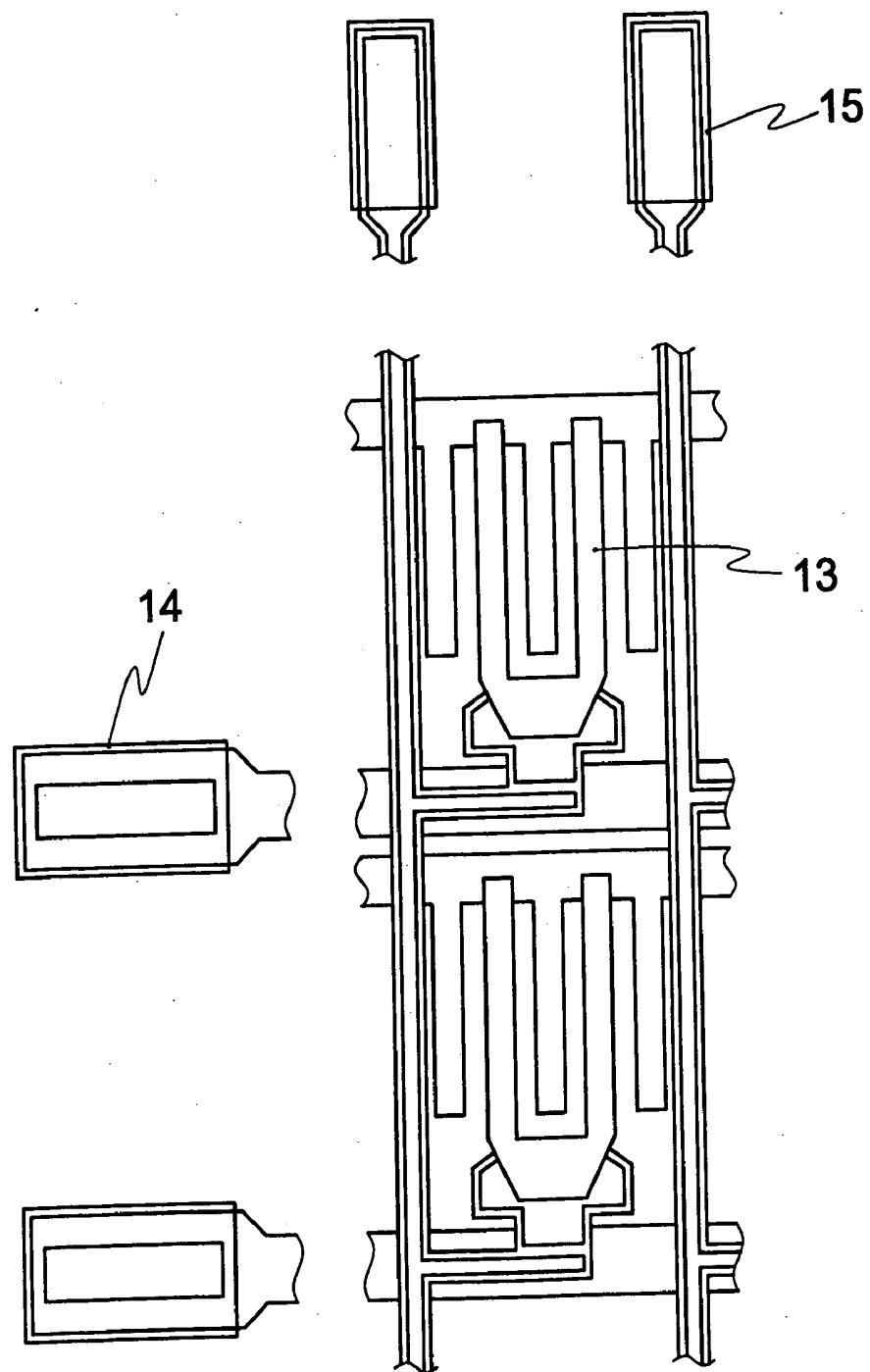

[0102] FIGS. 1 and 2(a) to 2(c) show a thin film transistor array substrate according to embodiment 1 of the present invention. **FIG. 1** is a plan view, **FIG. 2(a)** is a sectional view taken along the line A-A in **FIG. 1**, **FIG. 2(b)** is a sectional view taken along the line B-B in **FIG. 1**, and **FIG. 2(c)** is a sectional view taken along the line C-C in **FIG. 1**. In FIGS. 1 and 2(a) to 2(c), the reference numeral 1 denotes a gate line, the reference numeral 1a denotes a gate terminal portion metal pad, the reference numeral 2 denotes an auxiliary capacity wiring, the reference numeral 3 denotes a gate insulating film, the reference numeral 4 denotes a semiconductor pattern, the reference numeral 4a denotes a semiconductor layer (semiconductor active film), the reference numeral 4b denotes an ohmic layer (ohmic contact layer), the reference numeral 5 denotes a source line, the reference numeral 5a denotes source terminal portion metal pad, the reference numeral 6 denotes a source electrode, the reference numeral 7 denotes a drain electrode, the reference numeral 8 denotes a semiconductor active layer of a thin film transistor, the reference numeral 9 denotes an interlayer insulating film, the reference numeral 10 denotes a drain electrode contact hole, the reference numeral 11 denotes a gate terminal portion contact hole, the reference numeral 12 denotes a source terminal portion contact hole, the reference numeral 13 denotes a pixel electrode, the reference numeral 14 denotes a gate terminal connecting pad, and the reference numeral 15 denotes a source terminal connecting pad.

[0103] Next, a manufacturing method will be described. FIGS. 3 to 7 are plan views showing each step, and FIGS. 8 to 14 are sectional views taken along the line A-A in **FIG. 1** at each step. First of all, a first conductive metallic thin film such as Cr, Ta, Mo or Al is formed in a thickness of approximately 400 nm on a transparent substrate. Then, the first conductive metallic thin film is subjected to patterning at a first photolithographic step. As shown in FIGS. 3 and 8, the gate line 1, the gate terminal portion metal pad 1a and the auxiliary capacitance line 2 are formed. At this time, in the case in which the first conductive metallic thin film is Cr,

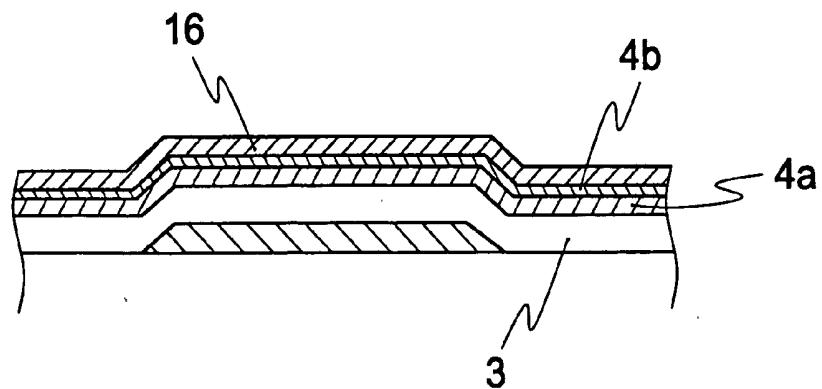

wet etching is carried out with an  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  solution, for example. As shown in **FIG. 9**, next, a  $\text{SiN}_x$  film, an a-Si film, an  $n^+$ a-Si film and Cr are provided as a gate insulating film 3, a semiconductor active film 4a, an ohmic contact film 4b and a second metal film 16 in thicknesses of approximately 400 nm, 150 nm, 30 nm and 400 nm, respectively. The  $\text{SiN}_x$  film, the a-Si film and the  $n^+$ a-Si film are formed by using a plasma CVD device, and  $\text{PH}_3$  is doped to form  $n^+$ a-Si during the formation of the ohmic layer. The Cr film is formed by using a DC magnetron type sputtering device.

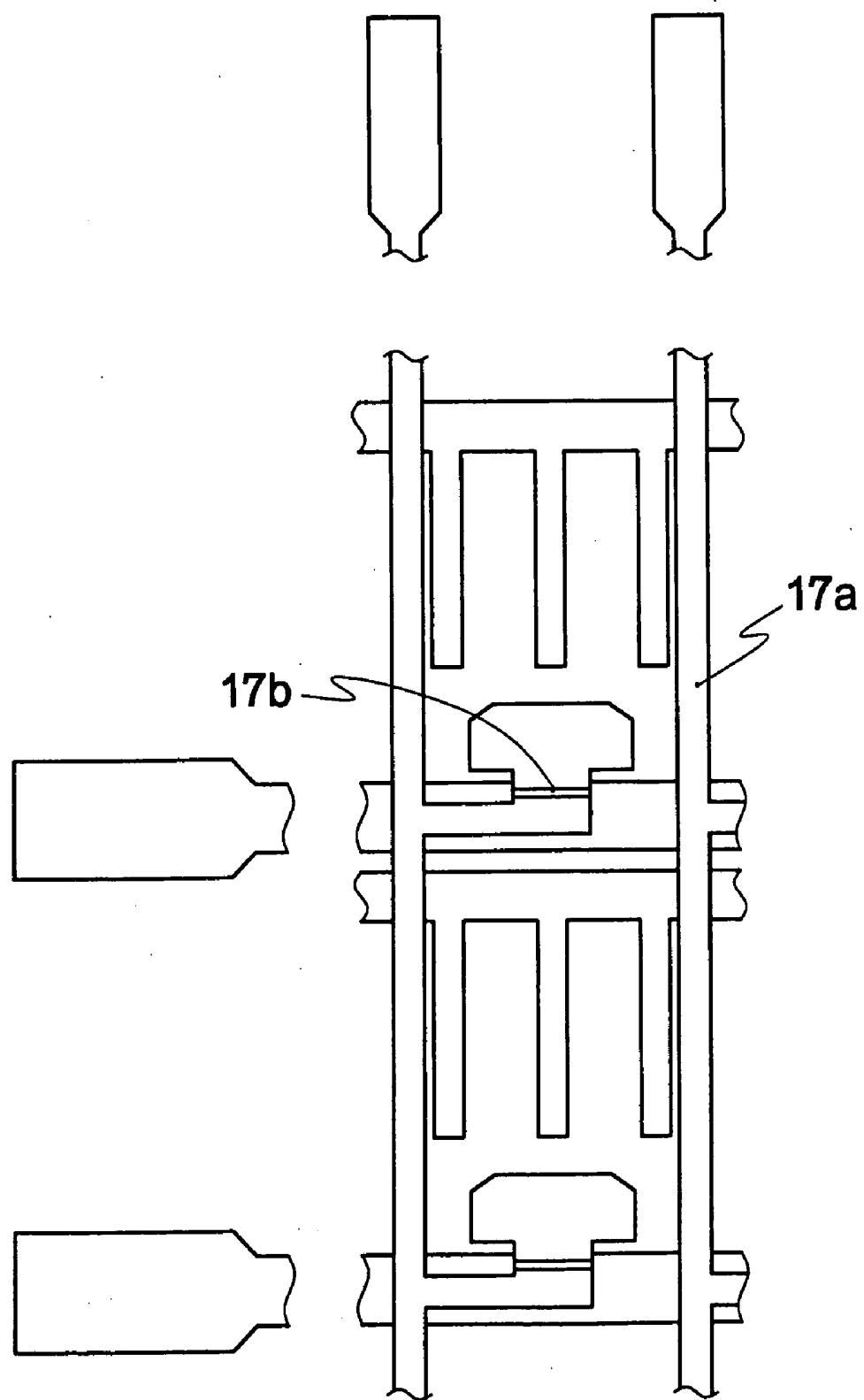

[0104] Next, a resist pattern 17a having an ordinary thickness for forming the source line 5, the source terminal portion metal pad 5a and the drain electrode 7 and a thin film resist pattern 17b for forming the semiconductor active layer 8 of the thin film transistor are provided at a second photolithographic step as shown in **FIG. 4**. A novolak resin based positive resist is used and the resist is coated in a thickness of 1.5  $\mu\text{m}$  by a spin coater. After the resist is coated, prebaking is carried out for 90 seconds at a temperature of 120° C. Then, exposure is carried out for 1000 milliseconds by using a mask pattern including the resist pattern 17a and the resist pattern 17b. Thereafter, additional exposure is carried out for 400 milliseconds by using a mask pattern capable of exposing only the resist pattern 17b in a semiconductor active layer portion. By carrying out the exposure in two stages, the resist pattern 17a having an ordinary thickness and the thin film resist pattern 17b have different thicknesses. An exposing machine is of a stepper or mirror projection type, and g rays and h rays of a high pressure mercury are used for a light source. Subsequently, development is carried out by using an organic alkali based developing solution and postbaking is then carried out for 180 seconds at a temperature of 100° C. to 120° C. consequently, a solvent in the resist is volatilized and the adhesion of the resist and Cr is increased. By these processes, the resist of the thin film transistor portion has a shape shown in **FIG. 10**. A thickness of the resist film of the resist pattern 17a having an ordinary thickness is approximately 1.4  $\mu\text{m}$  and a thickness of the resist of the thin film resist pattern 17b is approximately 0.4  $\mu\text{m}$ .

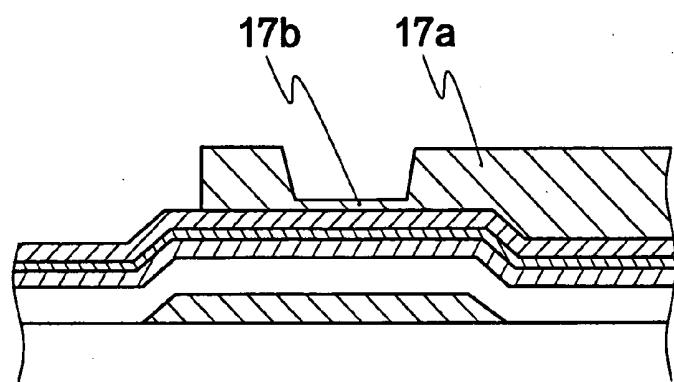

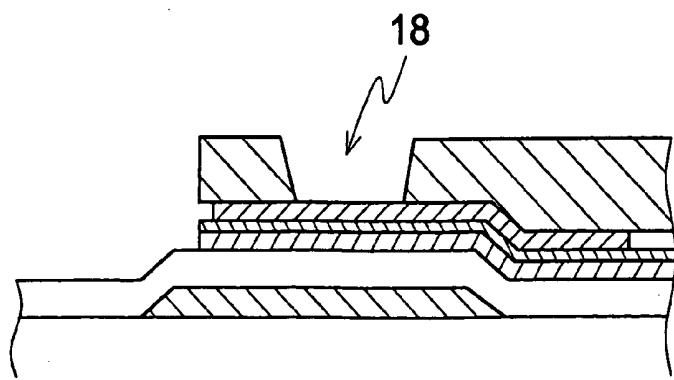

[0105] Then, oven baking is further carried out at a temperature of 120° C. to 130° C. Thus, the adhesion of the resist and Cr is further increased. At this time, if a baking temperature is too high, a resist end face becomes inactive, to which care should be given. Thereafter, the Cr film 16 is etched with the  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  solution. Thereafter, the ohmic film 4b and the semiconductor film 4a are etched with an  $\text{HCl} + \text{SF}_6 + \text{He}$  gas. Subsequently, the resist is subjected to ashing through oxygen plasma and the thin film resist pattern 17b is removed so that the Cr film of the corresponding portion of the thin film transistor active layer 8 is exposed as shown in **FIG. 11**. The ashing is carried out at a pressure of 40 Pa for 60 seconds. During the ashing, the size of a resist opening indicated as 18 in **FIG. 11** can be controlled in a RIE mode more easily than in PE mode.

[0106] Then, the oven baking is carried out at a temperature of 130° C. to 140° C. Thereafter, the Cr film 16 in the opening 18 is etched with the  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6] + \text{HNO}_3 + \text{H}_2\text{O}$  solution. At this time, the whole Cr pattern is subjected to side etching. Therefore, the Cr pattern is made thinner by approximately 1.5 to 2  $\mu\text{m}$  than an a-Si pattern (the inner side of the a-Si Pattern). Consequently, it is possible to

suppress a leakage current from flowing through an a-Si pattern end face from the source electrode to the drain electrode. For the Cr etching, overetching is required to some extent. It is desirable that the amount of the overetching should be approximately 50%. As shown in **FIG. 12**, subsequently, the ohmic layer **4b** and the semiconductor layer **4a** in the corresponding portion of the semiconductor active layer **8** are partially etched by approximately 100 nm in total by using  $SF_6+HCl$ . Then, when the resist is removed, the semiconductor pattern **4**, the source line **5**, the source electrode **6**, the drain electrode **7** and the source terminal portion metal pad **5a** are formed as shown in **FIG. 5**.

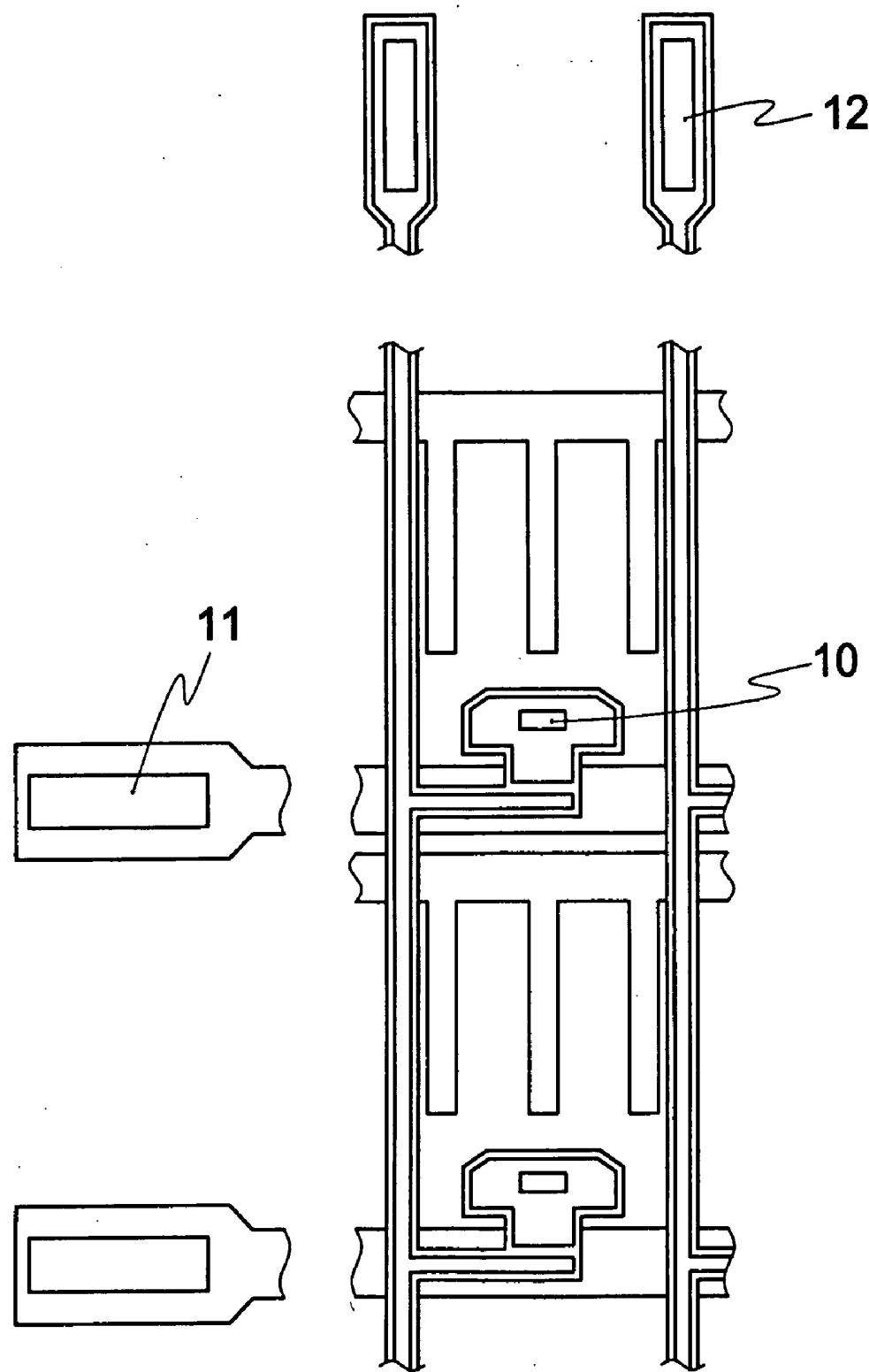

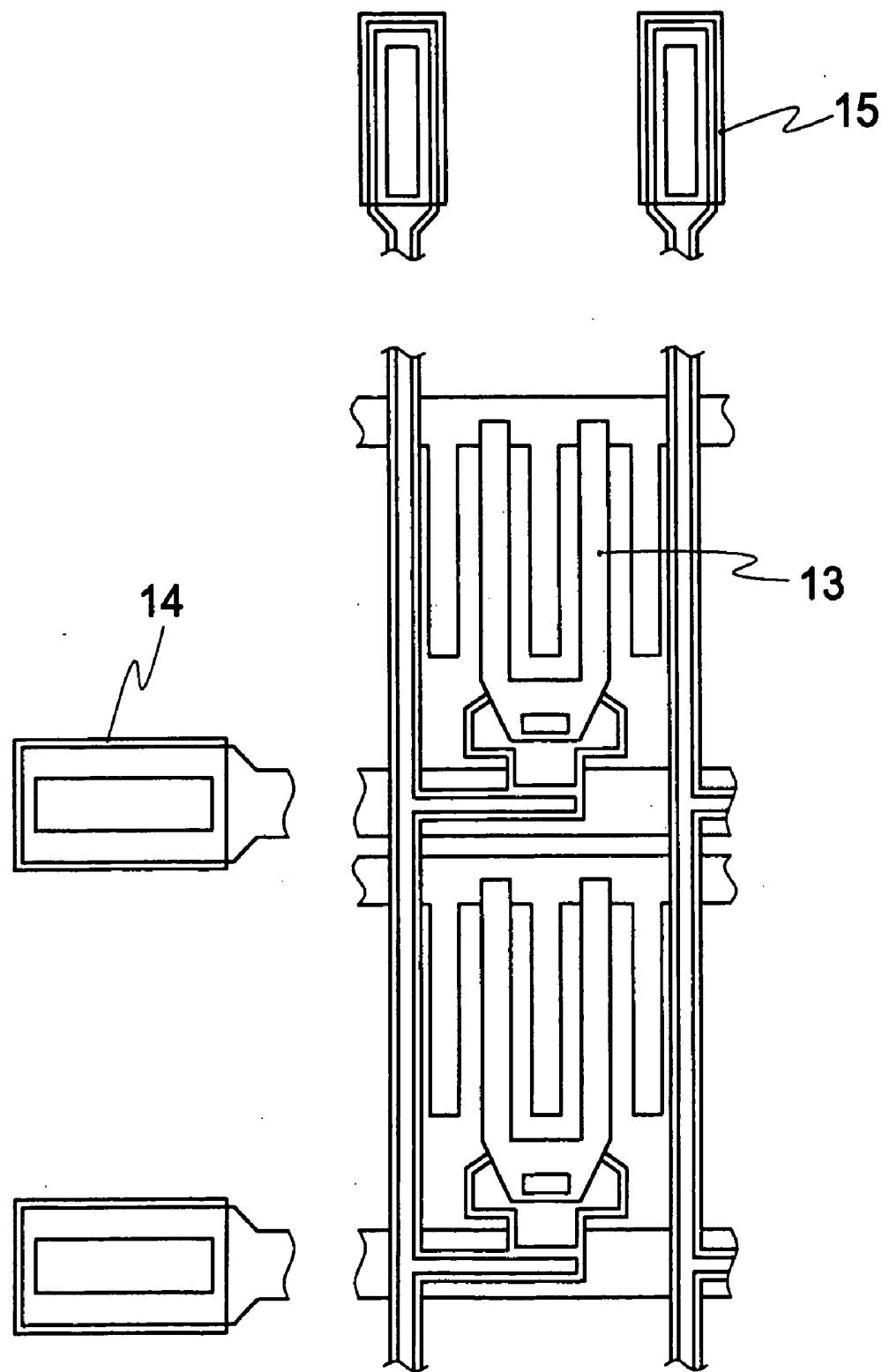

**[0107]** As shown in **FIGS. 6 and 13**, next,  $SiN_x$  to be the inter-layer insulating film is formed in a thickness of 300 nm by using a PCVD device, and is subjected to patterning at a third photolithographic step. Consequently, a contact hole **10** communicating with the drain electrode **7**, a contact hole **11** communicating with the gate terminal portion metal pad **1a** and a contact hole **12** communicating the source terminal portion metal pad **15** shown in **FIGS. 2(a), 2(b), 2(c), 6 and 13** are formed through dry etching using  $CF_4+O_2$ . As shown in **FIGS. 7 and 14**, subsequently, a transparent conductive film comprising ITO is formed in a thickness of approximately 100 nm by using a DC magnetron type sputtering device as shown in **FIGS. 7 and 14**. Then, the ITO is subjected to patterning at a fourth photolithographic step to form the transparent pixel electrode **13**, the gate terminal portion pad **14** and the source terminal portion pad **15**. At this time, the ITO film is subjected wet etching by using the  $HCl+HNO_3+H_2O$  solution, for example.

**[0108]** The thin film transistor array substrate thus manufactured is created at the fourth photolithographic step and a semiconductor step is not present under the source line. Therefore, a source disconnection is generated with difficulty, and the patterns of the source electrode and the drain electrode are included in the semiconductor pattern and do not cross each other. Therefore, a leakage current in the thin film transistor portion can be reduced. Moreover, the second metal film **16** is formed of a single metal. Consequently, it is sufficient that the second metal film **16** is etched twice. Furthermore, Cr is used for the metal. Therefore, when the pixel is to be formed of the ITO, it is possible to prevent a source line or the like from being corroded with an etchant through a pinhole provided in the interlayer insulating film **9**.

**[0109]** **FIG. 2(a)** is a sectional view of a TFT portion, **FIG. 2(b)** is a sectional view of a gate terminal portion, **FIGS. 2(c) and 2(d)** are sectional views each source terminal portion. The source terminal may be formed of source line layer **5a** as shown in **FIG. 2(c)**. Alternatively, the source terminal may be formed of the material of the gate line **1**, into which source line layer **5a** is converted at an intervening part of source terminal as shown in **FIG. 2(d)**. The intervening part where the source line layer **5a** is converted into the gate line **1** is situated under a repair line for the source line, where the repair line is formed of a material of the source line, or in the vicinity of a seal portion or liquid crystal portion. By virtue of converting the material of the source line into the material of the gate line, the source line can be prevented from being corroded in the vicinity of the source terminal portion, so that disconnection of the source line can be avoided.

**[0110]** **FIG. 2(a)** is a sectional view of the TFT, **FIG. 2(b)** of the gate terminal and **FIG. 2(c), (d)** of the source terminal. Source terminal may be formed using the source line layer **5a** connected to a transparent conductive film **15** thereon, preferably converted to the gate line material **1** in a point of its route. The point converting the material of source terminal (line) may be under a repair line serving for source lines (in this case, the repair line is formed of source line layer material) or a vicinity of sealing portion of pairing substrates or in a region of liquid crystal. Conversion of the source terminal (line) material saves from anticipated cut off of the source line by a corrosion in the vicinity of the source terminal.

**[0111]** Source terminal structure in case of converting the material of the source line to the material of the gate line **1** is illustrated in **FIG. 2(d)**. In the process of forming the gate line pattern, a conversion line for source line **1'** is formed.

**[0112]** Although an interlayer film **9** is used in this embodiment, it is not needed in some case. In this case, a plan view **FIG. 1** corresponds to **FIG. 64**. Sectional views **FIGS. 2(a), (b), (c), (d)** illustrating a manufacturing process correspond to **FIGS. 65(a), (b), (c), (d)**. In connection to plan views **FIGS. 3 through 7**, manufacturing processes indicated in **FIGS. 3 through 5** are similar to said processes above, and next process is shown in a plan view **FIG. 66**.

## EMBODIMENT 2

**[0113]** **FIG. 15** shows a thin film transistor substrate according to embodiment 2 of the present invention. D-D, E-E and F-F sections in **FIG. 15** are the same as those in embodiment 1 and are shown in **FIGS. 2(a), 2(b) and 2(c)** respectively. The reference numeral **1** denotes a gate line, the reference numeral **1a** denotes a gate terminal portion metal pad, the reference numeral **2** denotes an auxiliary capacitance line, the reference numeral **3** denotes a gate insulating film, the reference numeral **4** denotes a semiconductor pattern, the reference numeral **4a** denotes a semiconductor layer, the reference numeral **4b** denotes an ohmic layer, the reference numeral **5** denotes a source line, the reference numeral **5a** denotes source terminal portion metal pad, the reference numeral **6** denotes a source electrode, the reference numeral **7** denotes a drain electrode, the reference numeral **8** denotes a semiconductor active layer of a thin film transistor, the reference numeral **9** denotes an inter-layer insulating film, the reference numeral **10** denotes a drain electrode contact hole, the reference numeral **11** denotes a gate terminal portion contact hole, the reference numeral **12** denotes a source terminal portion contact hole, the reference numeral **13** denotes a pixel electrode, the reference numeral **14** denotes a gate terminal connecting pad, and the reference numeral **15** denotes a source terminal connecting pad.

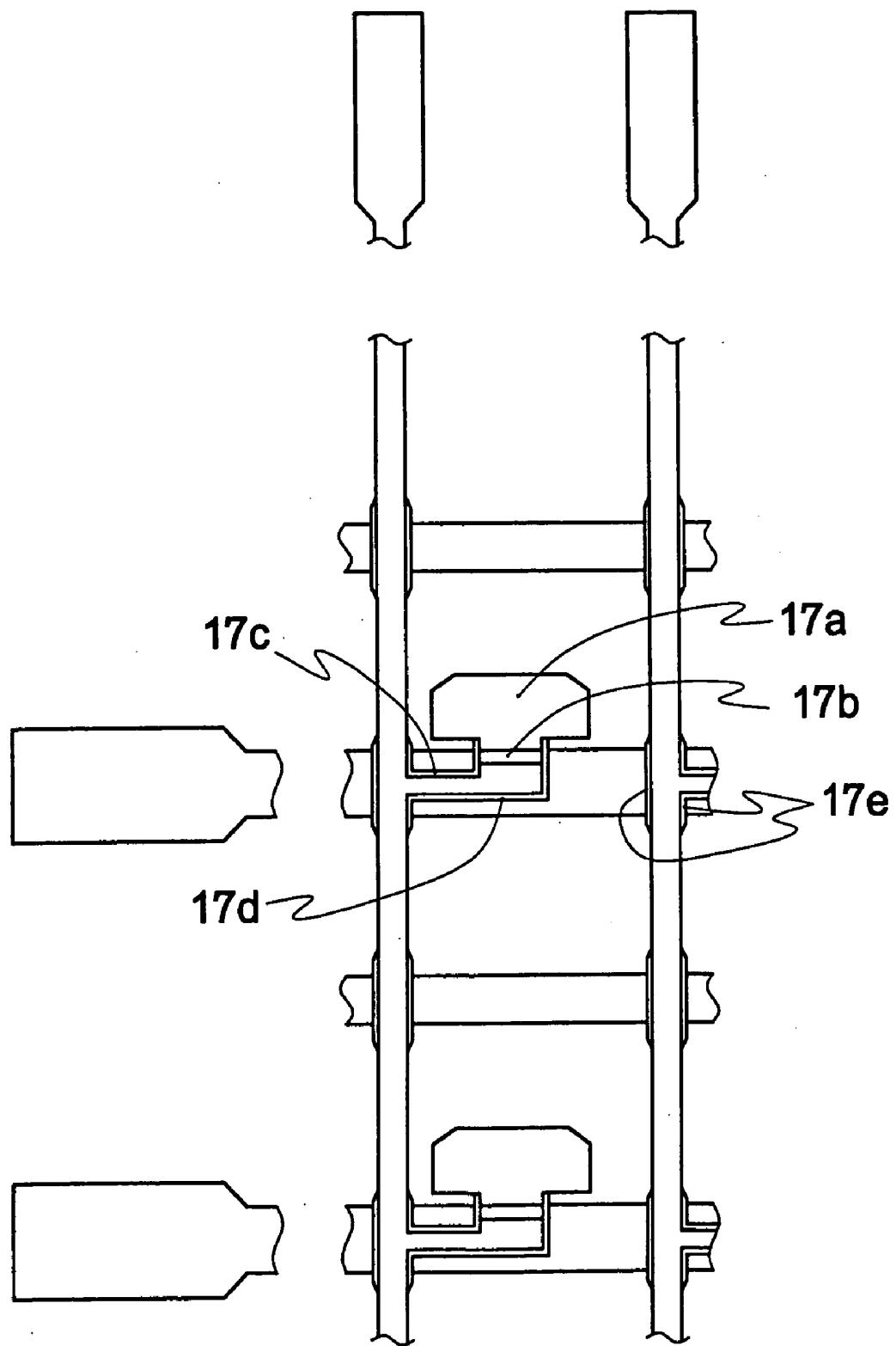

**[0114]** Next, a manufacturing method will be described. **FIGS. 16 to 20** are plan views showing each step, and **FIGS. 8 to 14** are sectional views taken along the line D-D in **FIG. 15** at each step in the same manner as in embodiment 1.

**[0115]** First of all, a first conductive metallic thin film such as Cr, Ta, Mo or Al is formed in a thickness of approximately 400 nm on a transparent substrate. Then, the first conductive metallic thin film is subjected to patterning at a first photolithographic step. As shown in **FIGS. 16 and 8**, the gate line **1**, the gate terminal portion metal pad **1a** and the auxiliary capacity wiring **2** are formed. At this time, in the case in

which the first conductive metallic thin film is Cr, wet etching is carried out with an  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution, for example. As shown in **FIG. 9**, next, a  $\text{SiN}_x$  film, an a-Si film, an  $n^+$ a-Si film and Cr are provided as a gate insulating film **3**, a semiconductor active film **4a**, an ohmic contact film **4b** and a second metal film **16** in thicknesses of approximately 400 nm, 105 nm, 30 nm and 400 nm, respectively. The  $\text{SiN}_x$  film, the a-Si film and the  $n^+$ a-Si film are formed by using a plasma CVD device, and  $\text{PH}_3$  is doped to form  $n^+$ a-Si during the formation of the ohmic layer. The Cr film is formed by using a DC magnetron type sputtering device.

**[0116]** Next, a resist pattern **17a** for forming the source line, the source terminal portion metal pad and the drain electrode, a resist pattern **17b** for forming the semiconductor active layer **8** of the thin film transistor, resist patterns **17c** and **17d** for preventing the leakage of a semiconductor end face, and a resist pattern **17e** for preventing a short-circuit between the gate-source lines are provided at a second photolithographic step as shown in **FIG. 17**. A novolak resin based positive resist is used and the resist is coated in a thickness of 1.5  $\mu\text{m}$  by a spin coater. After the resist is coated, prebaking is carried out for 90 seconds at a temperature of 120° C. Then, the resist pattern **17a** is exposed by using an ordinary Cr whole surface mask pattern and the resist patterns **17b**, **17c**, **17d** and **17e** are exposed by using a mask pattern having a Cr stripe shape of line/space=1.5  $\mu\text{m}/1.5\text{ }\mu\text{m}$  for 1000 milliseconds. The stripe mask pattern is shown in **FIG. 21**. An exposing machine is of an ordinary stepper or mirror projection type, and g rays and h rays of a high pressure mercury are used for a light source. At this time, the stripe pattern is finer than a resolution limit of an exposing device. Therefore, the resist is not exposed like a stripe but the amount of the exposure is uniformly smaller than that in other exposed portion.

**[0117]** Subsequently, development is carried out by using an organic alkali based developing solution and postbaking is then carried out for 180 seconds at a temperature of 100° C. to 120° C. Consequently, a solvent in the resist is volatilized and the adhesion of the resist and Cr is increased. By these processes, the resist of the thin film transistor portion has a shape shown in **FIG. 10**. A thickness of the resist film of the resist pattern **17a** having an ordinary thickness is approximately 1.4  $\mu\text{m}$  and thicknesses of the resist patterns **17b**, **17c**, **17d** and **17e** are approximately 0.4  $\mu\text{m}$  to 0.6  $\mu\text{m}$ . Then, oven baking is further carried out at a temperature of 120° C. to 130° C. Thus, the adhesion of the resist and Cr is further increased. At this time, if a baking temperature is too high, a resist end face becomes inactive, to which care should be given. Thereafter, the Cr film **16** is etched with the  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution.

**[0118]** Next, the ohmic film **4b** and the semiconductor film **4a** are etched with an  $\text{HCl}+\text{SF}_6$  gas. Subsequently, the resist is subjected to ashing through oxygen plasma such that the Cr film in the resist patterns **17b**, **17c**, **17d** and **17e** portions is exposed. The ashing is carried out at a pressure of 40 Pa for 60 seconds. During the ashing, the size of a resist opening indicated as **18** in **FIG. 11** can be controlled in a RIE mode more easily than in PE mode.

**[0119]** Then, the oven baking is carried out at a temperature of 130° C. to 140° C. Thereafter, the Cr film **16** in the resist patterns **17b**, **17c**, **17d** and **17e** is etched with the

$(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution. In the present patterns, semiconductor patterns in the vicinity of the source electrode and the drain electrode are provided more apart from each other. As compared with the first embodiment, therefore, the effect of suppressing the generation of the semiconductor end face leakage and a Cr overetching margin can be increased still more. In the case of this pattern, approximately 20% to 50% of Cr overetching can be carried out. In this case, however, care should be given to the following. In the case in which the a-Si pattern formed by the resist pattern **17c** continuously gets out of an outer edge of the gate line, a gate off bias is not applied to this portion in a hold state and this portion is not shielded by a gate pattern. Therefore, a leakage current is increased. Accordingly, at least a part of the outer edge of the semiconductor pattern including the source line and the drain electrode should enter the inside from the outer edge of the gate line as shown in **FIG. 17**. In other word, on a route of semiconductor pattern which extend from a region surrounding the TFT to a region surrounding the source line, both outside edge of the semiconductor pattern should intersect the outside edge of the gate line. Semiconductor pattern edge **17d** intersects the gate line edge automatically because of the disposition of the TFT. As for **17c**, it is preferable to have it intersect the gate line intentionally. Then, the ohmic layer **4b** and the semiconductor layer **4a** corresponding to the resist patterns **17b**, **17c**, **17d** and **17e** portions are partially etched by approximately 100 nm in total with  $\text{SF}_6+\text{HCl}$  as shown in **FIG. 12**. Then, when the resist is removed, the semiconductor pattern **4**, the source line **5**, the source electrode **6**, the drain electrode **7** and the source terminal portion metal pad **5a** are formed as shown in **FIG. 18**.

**[0120]** Next,  $\text{SiN}_x$  to be the inter-layer insulating film is formed in a thickness of 300 nm by using a PCVD device, and is subjected to patterning at a third photolithographic step. Consequently, a contact hole **10** communicating with the drain electrode **7**, a contact hole **11** communicating with the gate terminal portion metal pad **1a** and a contact hole **12** communicating the source terminal portion metal pad **15** shown in **FIGS. 2(a), 2(b), 2(c), 13** and **19** are formed through dry etching using  $\text{CF}_4+\text{O}_2$ . Subsequently, a transparent conductive film comprising ITO is formed in a thickness of approximately 100 nm by using a DC magnetron type sputtering device. Then, the ITO is subjected to patterning at a fourth photolithographic step to form the transparent pixel electrode **13**, the gate terminal portion pad **14** and the source terminal portion pad **15** as shown in **FIGS. 2(a), 2(b), 2(c), 14** and **20**. At this time, the ITO film is subjected wet etching by using the  $\text{HCl}+\text{HNO}_3+\text{H}_2\text{O}$  solution, for example.

**[0121]** The thin film transistor array thus manufactured is created at the fourth photolithographic step and a semiconductor step is not present under the source line. Therefore, a source disconnection is generated with difficulty, and the patterns of the source electrode and the drain electrode do not cross each other. In addition, a space between the semiconductor pattern end face of the thin film transistor and the source electrode and drain electrode is increased. Therefore, a leakage current can also be reduced still more. Moreover, at least a part of the outer edge of the semiconductor pattern including the source line and the drain electrode enter the inner side from the outer edge of the gate line. Consequently, it is possible to prevent a leakage current from being increased due to light leakage or the like.

[0122] Although an interlayer film 9 is used in this embodiment, it is not needed in some case. In this case, a plan view FIG. 15 corresponds to FIG. 69. In connection to plan views FIG. 16 through FIG. 20, manufacturing processes indicated in FIG. 16 through FIG. 18 are similar to said processes above, and next process is shown in a plan view FIG. 70.

[0123] In this embodiment, there is formed a transparent conductive film (pixel electrode 13) as a gate terminal pad 14 and a source terminal pad 15. In some case where there is no need of the transparent conductive film 13 on the gate terminal and source terminal, the transparent conductive film 13 may not be formed there and the first metallic layer (1a: gate line layer) and the second metallic layer (5a: source line layer) may be left uncovered at their contact holes 11 and 12.

### EMBODIMENT 3

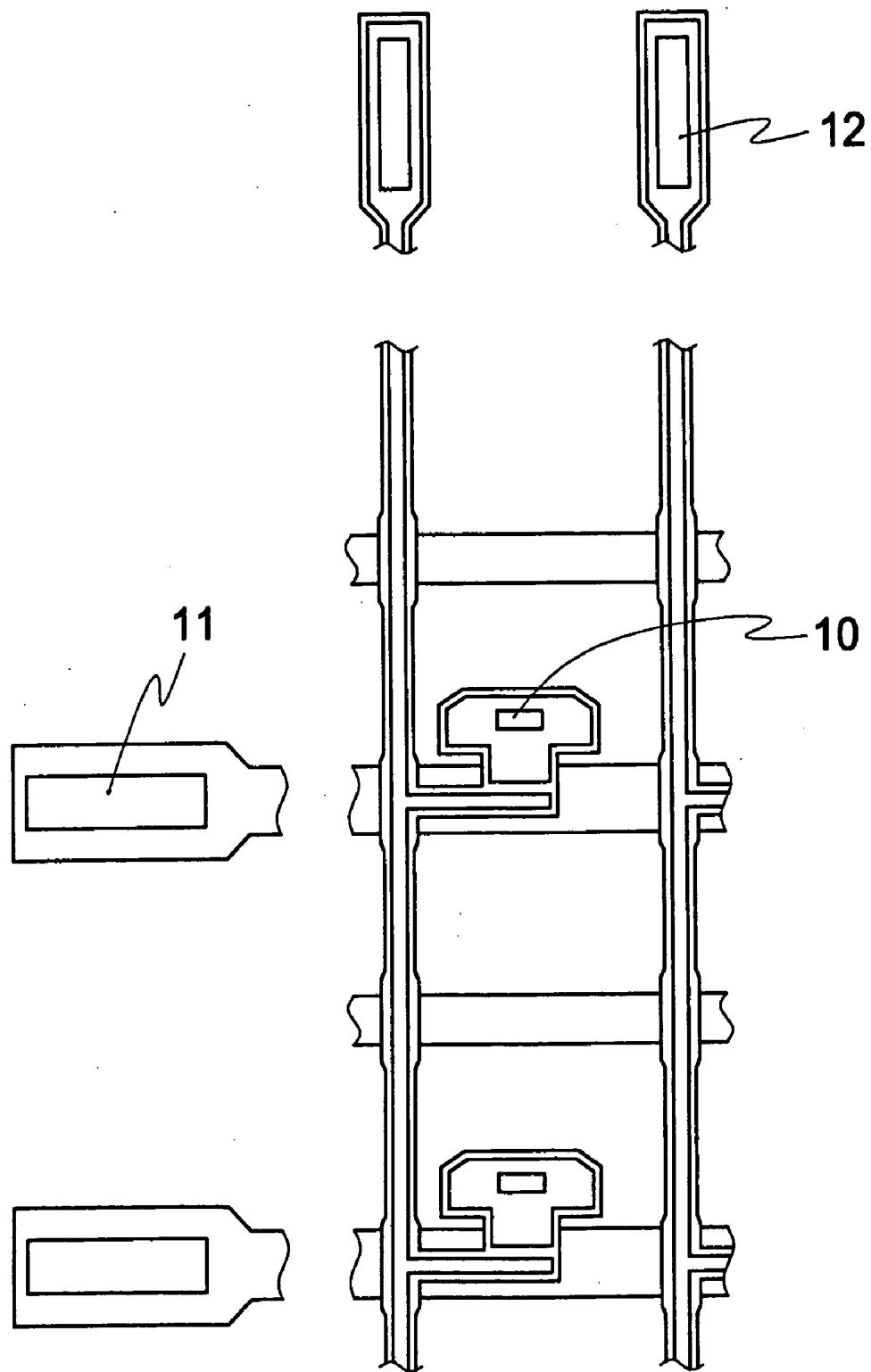

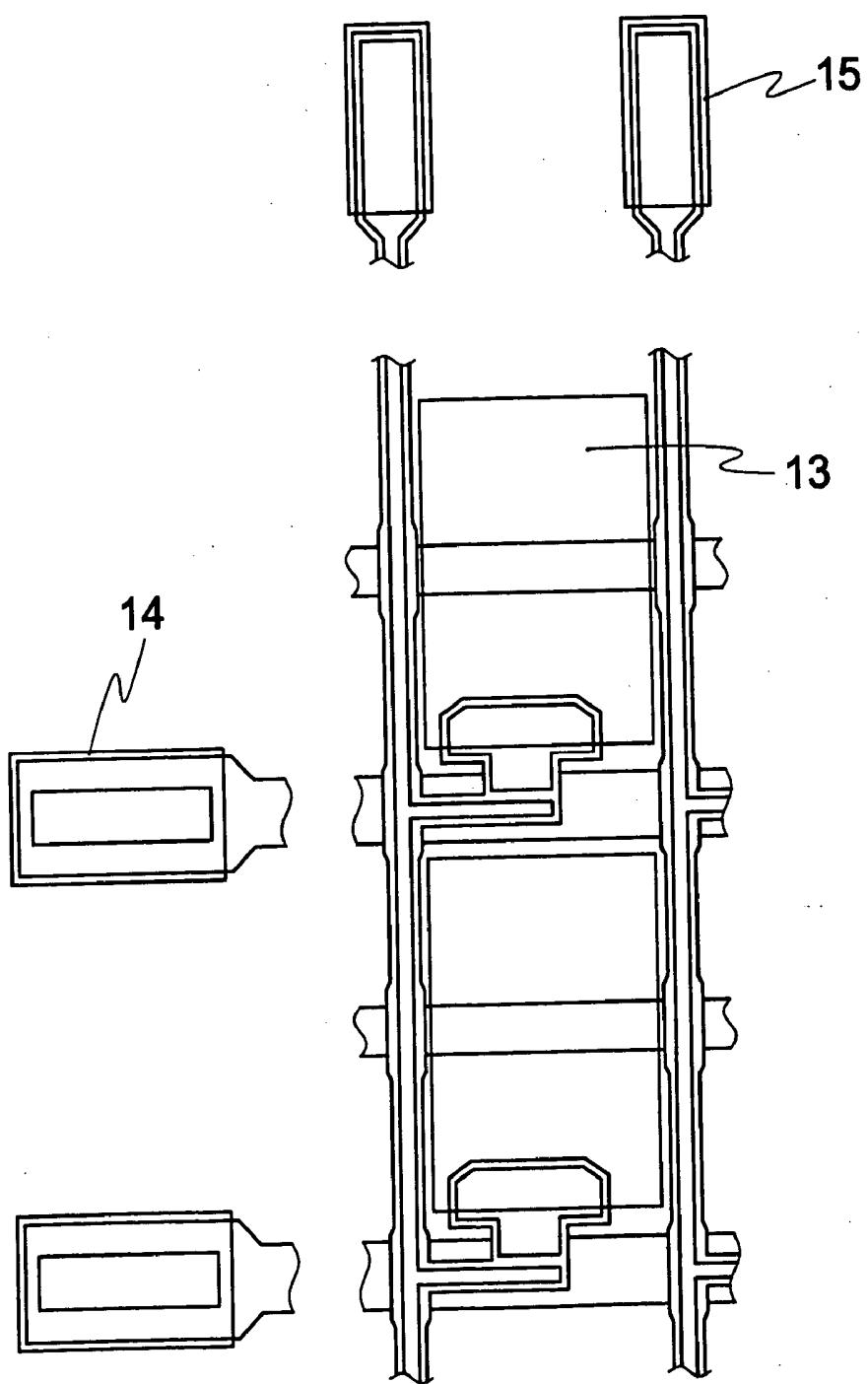

[0124] FIG. 22 shows a thin film transistor substrate according to embodiment 3 of the present invention. G-G, H-H and I-I sections are the same as those in embodiment 1 and are shown in FIGS. 2(a), 2(b) and 2(c) respectively. The reference numeral 1 denotes a gate line, the reference numeral 1a denotes a gate terminal portion metal pad, the reference numeral 2 denotes an auxiliary capacitance line, the reference numeral 2a denotes an IPS counter electrode, the reference numeral 3 denotes a gate insulating film, the reference numeral 4 denotes a semiconductor pattern, the reference numeral 4a denotes a semiconductor layer, the reference numeral 4b denotes an ohmic layer, the reference numeral 5 denotes a source line, the reference numeral 5a denotes source terminal portion metal pad, the reference numeral 6 denotes a source electrode, the reference numeral 7 denotes a drain electrode, the reference numeral 8 denotes a semiconductor active layer of a thin film transistor, the reference numeral 9 denotes an inter-layer insulating film, the reference numeral 10 denotes a drain electrode contact hole, the reference numeral 11 denotes a gate terminal portion contact hole, the reference numeral 12 denotes a source terminal portion contact hole, the reference numeral 13a denotes an IPS electrode, the reference numeral 14 denotes a gate terminal connecting pad, and the reference numeral 15 denotes a source terminal connecting pad.

[0125] Next, a manufacturing method will be described. FIGS. 23 to 27 are plan views showing each step, and FIGS. 8 to 14 are sectional views taken along the line G-G in FIG. 22 at each step in the same manner as in embodiment 1.

[0126] First of all, a first conductive metallic thin film such as Cr, Ta, Mo or Al is formed in a thickness of approximately 400 nm on a transparent substrate. Then, the first conductive metallic thin film is subjected to patterning at a first photolithographic step. As shown in FIGS. 23 and 8, the gate line 1, the gate terminal portion metal pad 1a, the auxiliary capacitance line 2 and the IPS counter electrode 2a are formed. At this time, in the case in which the first conductive metallic thin film is Cr, wet etching is carried out with an  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution, for example. As shown in FIG. 9, next, a SiNx film, an a-Si film, an n<sup>+</sup>a-Si film and Cr are provided as a gate insulating film 3, a semiconductor active film 4a, an ohmic contact film 4b and a second metal film 16 in thicknesses of approximately 400 nm, 150 nm, 30 nm and 400 nm, respectively.

[0127] The SiNx film, the a-Si film and the n<sup>+</sup>a-Si film are formed by using a plasma CVD device, and PH<sub>3</sub> is doped to form n<sup>+</sup>a-Si during the formation of the ohmic layer. The Cr film is formed by using a DC magnetron type sputtering device.

[0128] Next, a resist pattern 17a for forming the source line, the source terminal portion metal pad and the drain electrode and a resist pattern 17b for forming the semiconductor active layer 8 of the thin film transistor are provided at a second photolithographic step as shown in FIG. 24. A novolak resin based positive resist is used and the resist is coated in a thickness of 1.5  $\mu\text{m}$  by a spin coater. After the resist is coated, prebaking is carried out for 90 seconds at a temperature of 120° C. Then, exposure is carried out for 1000 milliseconds by using a mask pattern including the resist pattern 17a and the resist pattern 17b. Thereafter, additional exposure is carried out for 400 msec by using a mask pattern capable of exposing only the resist pattern 17b in a semiconductor active layer portion. An exposing machine is of a stepper or mirror projection type, and g rays and h rays of a high pressure mercury are used for a light source.

[0129] Subsequently, development is carried out by using an organic alkali based developing solution and postbaking is then carried out for 180 seconds at a temperature of 100° C. to 120° C. Consequently, a solvent in the resist is volatilized and the adhesion of the resist and Cr is increased. By these processes, the resist of the thin film transistor portion has a shape shown in FIG. 10. A thickness of the resist film of the resist pattern 17a having an ordinary thickness is approximately 1.4  $\mu\text{m}$  and a thickness of the resist of the resist pattern 17b is approximately 0.4  $\mu\text{m}$ .

[0130] Then, oven baking is further carried out at a temperature of 120° C. to 130° C. Thus, the adhesion of the resist and Cr is further increased. At this time, if a baking temperature is too high, a resist end face is becomes inactive, to which care should be given.

[0131] Thereafter, the Cr film 16 is etched with the  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution. Next, the ohmic film 4b and the semiconductor film 4a are etched with an  $\text{HCl}+\text{SF}_6+\text{He}$  gas. Subsequently, the resist is subjected to ashing through oxygen plasma and the thin film resist pattern 17b is removed so that the Cr film of the corresponding portion of the semiconductor active layer 8 is exposed as shown in FIG. 11. The ashing is carried out at a pressure of 40 Pa for 60 seconds. During the ashing, the size of a resist opening indicated as 18 in FIG. 11 can be controlled in a RIE mode more easily than in PE mode.

[0132] Then, the oven baking is carried out at a temperature of 130° C. to 140° C. Thereafter, the Cr film 16 in the opening 18 is etched with the  $(\text{NH}_4)_2[\text{Ce}(\text{NO}_3)_6]+\text{HNO}_3+\text{H}_2\text{O}$  solution. At this time, the whole Cr pattern is subjected to side etching. Therefore, the Cr pattern is made thinner by approximately 1.5 to 2  $\mu\text{m}$  than an a-Si pattern. Consequently, it is possible to suppress a leakage current from flowing through an a-Si pattern end face from the source electrode to the drain electrode. For the Cr etching, overetching is required to some extent. It is desirable that the amount of the overetching should be approximately 50%.

[0133] As shown in FIG. 12, subsequently, the ohmic film 4b and the semiconductor layer 4a in the corresponding

portion of the semiconductor active layer **8** are partially etched by approximately 100 nm in total by using  $SF_6+HCl$  as shown in **FIG. 12**. Then, when the resist is removed, the semiconductor pattern **4**, the source line **5**, the source electrode **6**, the drain electrode **7** and the source terminal portion metal pad **5a** are formed as shown in **FIG. 5**. As shown in **FIGS. 6 and 13**, next,  $SiN_x$  to be the interlayer insulating film is formed in a thickness of 300 nm by using a PCVD device, and is subjected to patterning at a third photolithographic step. Consequently, a contact hole **10** communicating with the drain electrode **7**, a contact hole **11** communicating with the gate terminal portion metal pad **1a** and a contact hole **12** communicating the source terminal portion metal pad **15** shown in **FIGS. 26, 2(a), 2(b) and 2(c)** are formed through dry etching using  $CF_4+O_2$ .

**[0134]** As shown in **FIGS. 27 and 14**, subsequently, a conductive film comprising Cr is formed in a thickness of approximately 100 nm by using a DC magnetron type sputtering device as shown in **FIGS. 7 and 14**. Then, the Cr is subjected to patterning at a fourth photolithographic step to form the IPS electrode **3a**, the gate terminal portion pad **14** and the source terminal portion pad **15**. At this time, the Cr film is subjected wet etching by using  $(NH_4)_2[Ce(NO_3)_6]+HNO_3+H_2O$  solution, for example.

**[0135]** The thin film transistor array thus manufactured is created at the fourth photolithographic step and a semiconductor step is not present under the source line. Therefore, a source disconnection is generated with difficulty, and the patterns of the source electrode and the drain electrode are included in the semiconductor pattern and do not cross each other. Therefore, a leakage current can be also reduced.

**[0136]** Moreover, the IPS electrode provided on the uppermost layer is formed of the Cr. Therefore, also in the case in which brush washing is to be carried out at a step after a panel assembling step, it is possible to prevent a disorder of the pattern such as a damage from being generated.

**[0137]** Although an interlayer film **9** is used in this embodiment, it is not needed in some case. In this case, a plan view **FIG. 22** corresponds to **FIG. 71**. In connection to plan views **FIG. 23** through **FIG. 27**, manufacturing processes indicated in **FIG. 23** through **FIG. 5** are similar to said processes above, and next process is shown in a plan view **FIG. 72**.

#### EMBODIMENT 4

**[0138]** **FIG. 28** is an example of a circuit diagram showing a TFT array substrate of an active matrix type liquid crystal display (AMLCD) to which the present invention is applied. The circuit structure shown in **FIG. 28** is referred to as a Cs on gate type in which a retaining capacitance Cs is formed by a pixel electrode and a gate line. The reference numeral **101** denotes a gate line for supplying a scan voltage, the reference numeral **102** denotes a source line for supplying a signal voltage, the reference numeral **103** denotes a thin film transistor (TFT) to be used as a switching element when applying a voltage is to be applied to a liquid crystal, the reference numeral **104** denotes a liquid crystal for switching transmission/non-transmission of light through a capacity on an equivalent circuit basis, the reference numeral **105** denotes a retaining capacitance Cs provided in parallel with the liquid crystal **104** and serving to reduce the influence of a parasitic capacitance of the TFT, the reference numeral **106**

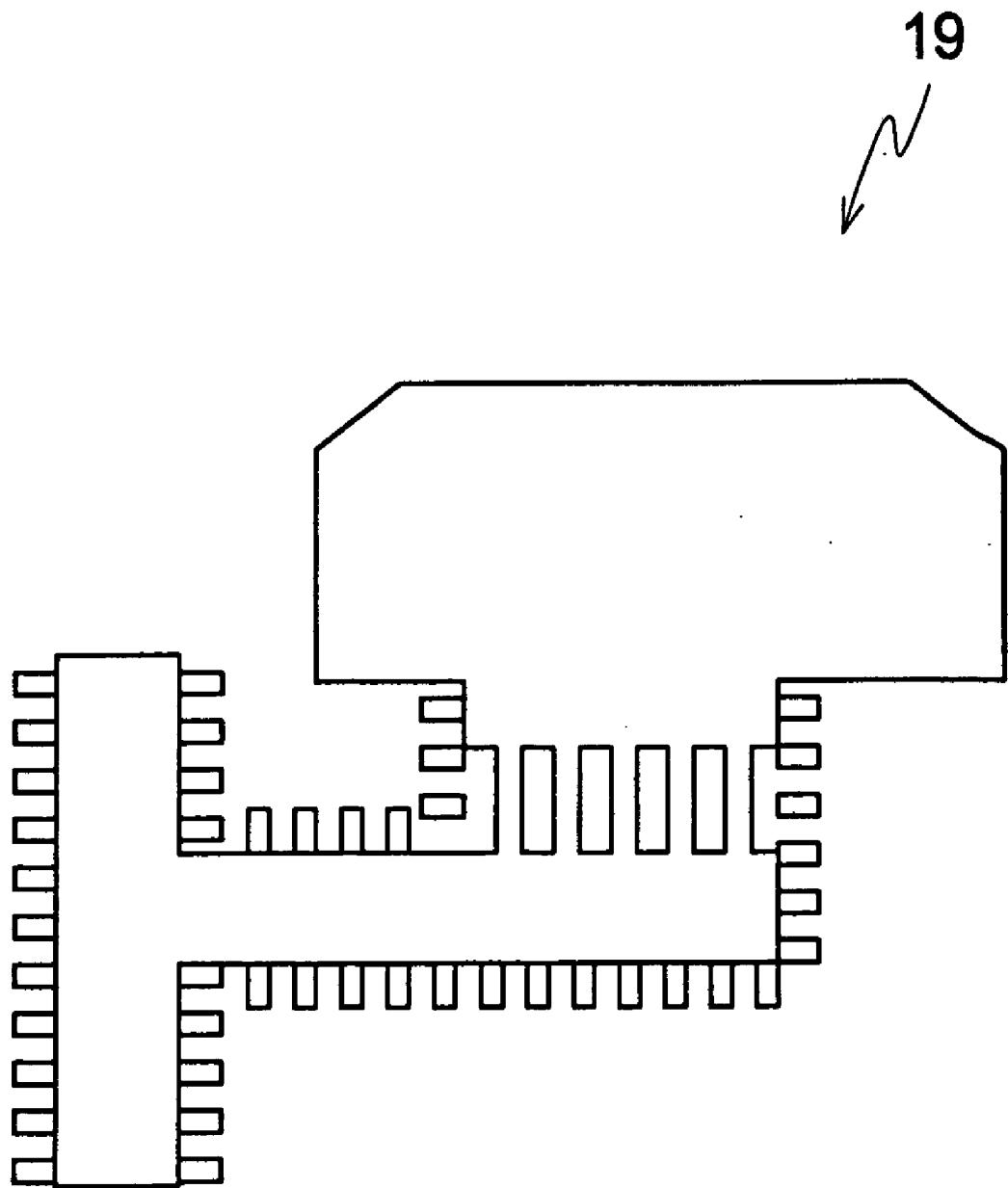

denotes a common electrode for connecting an electrode on one of sides of the liquid crystal **104** to a common voltage, the reference numeral **107** denotes a gate terminal for connecting a gate side external circuit to the gate line **101** through a TCP or the like, the reference numeral **108** denotes a source terminal for connecting the source side external circuit to the source line **102** through the TCP or the like, the reference numerals **109** and **110** denote a high resistance element formed of a TFT or a linear or non-linear element having a high resistance and serving to electrically isolate the gate terminal **107** and the source terminal **108** during signal application and to electrically couple them when static electricity having a high voltage is applied, the reference numeral **111** denotes a line A connected to the gate line **101** through the high resistance element **109**, the reference numeral **112** denotes a line B connected to the source line **102** through the high resistance element **110**, and the reference numeral **113** denotes a connecting portion for connecting the line A **(111)** and the line B **(112)** for taking countermeasures against the static electricity. The reference numeral **114** denotes a repair line to be used when the source line has an open failure or the like. A counter substrate provided with a color filter opposite to the TFT array substrate is combined, a liquid crystal is injected. Then, the outside of a region **115** shown in a dotted line of **FIG. 28** is cut away. Thus, an LCD (liquid crystal display) panel is obtained.

**[0139]** Moreover, it is not necessary to form at least a part of a portion outside the region **115** shown in the dotted line during the formation of the TFT array in some cases.

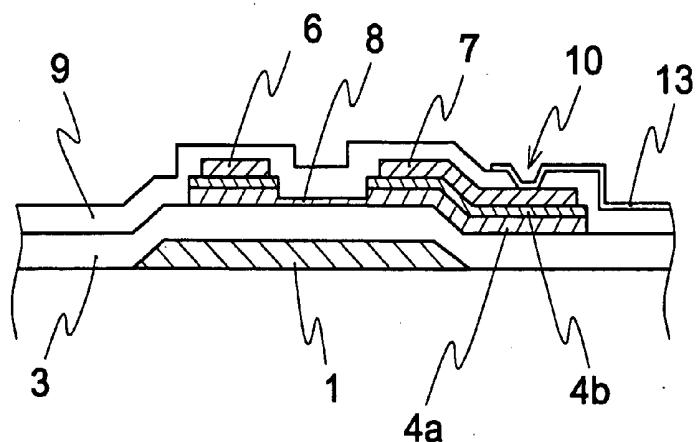

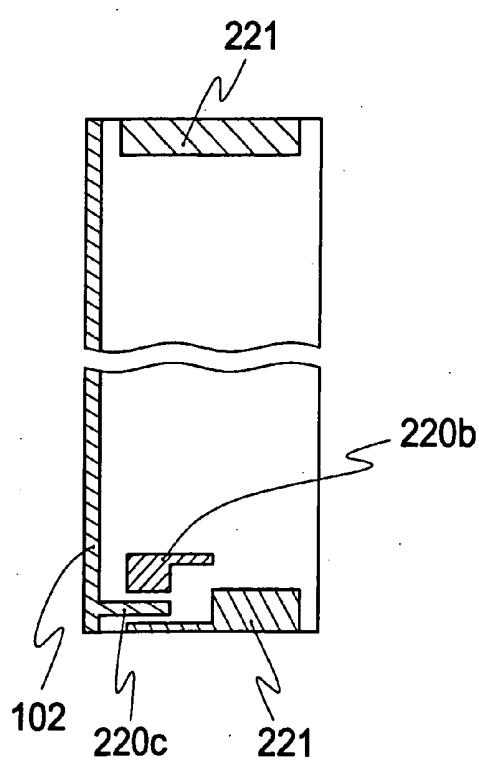

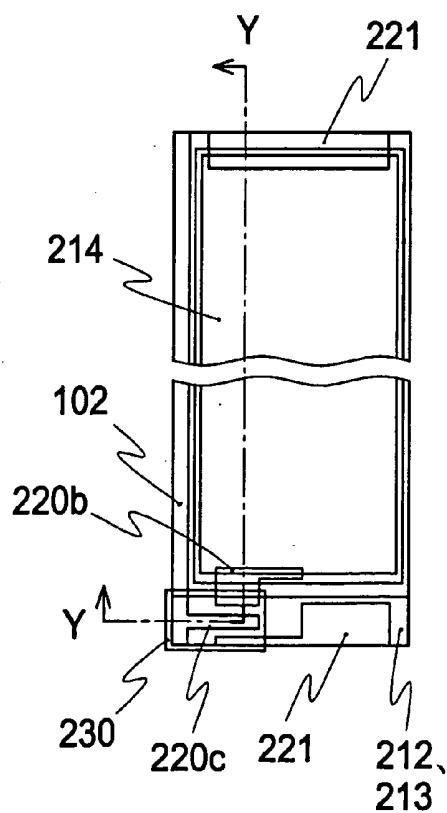

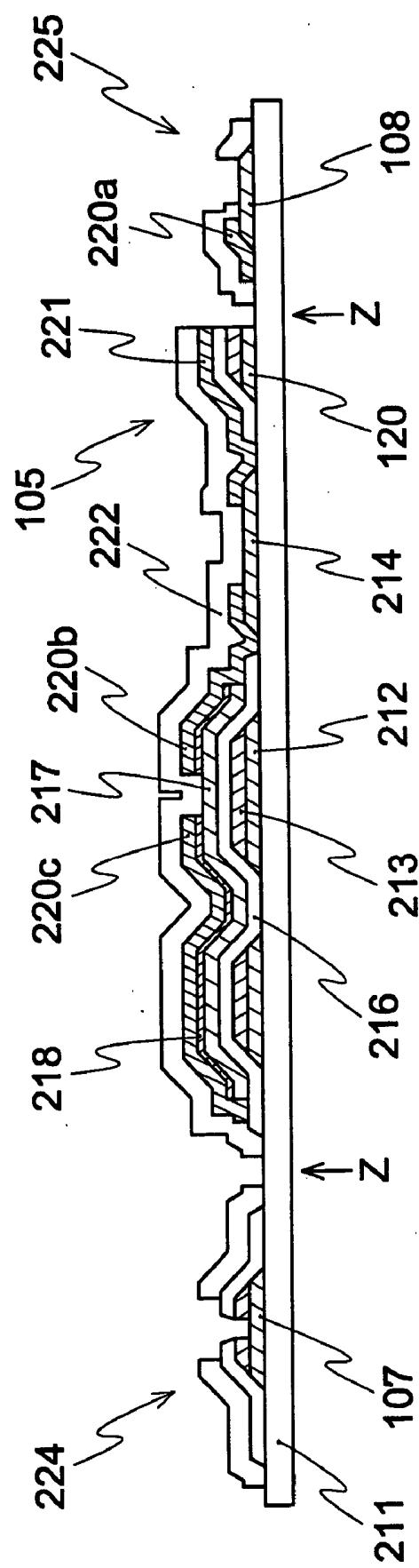

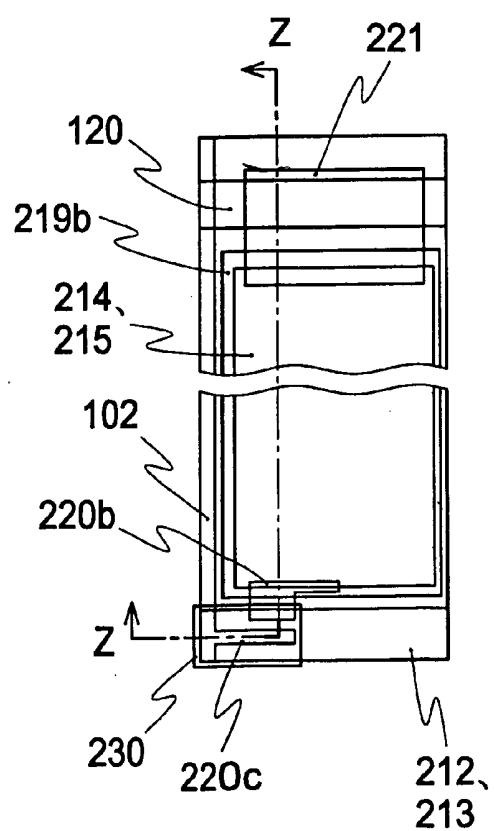

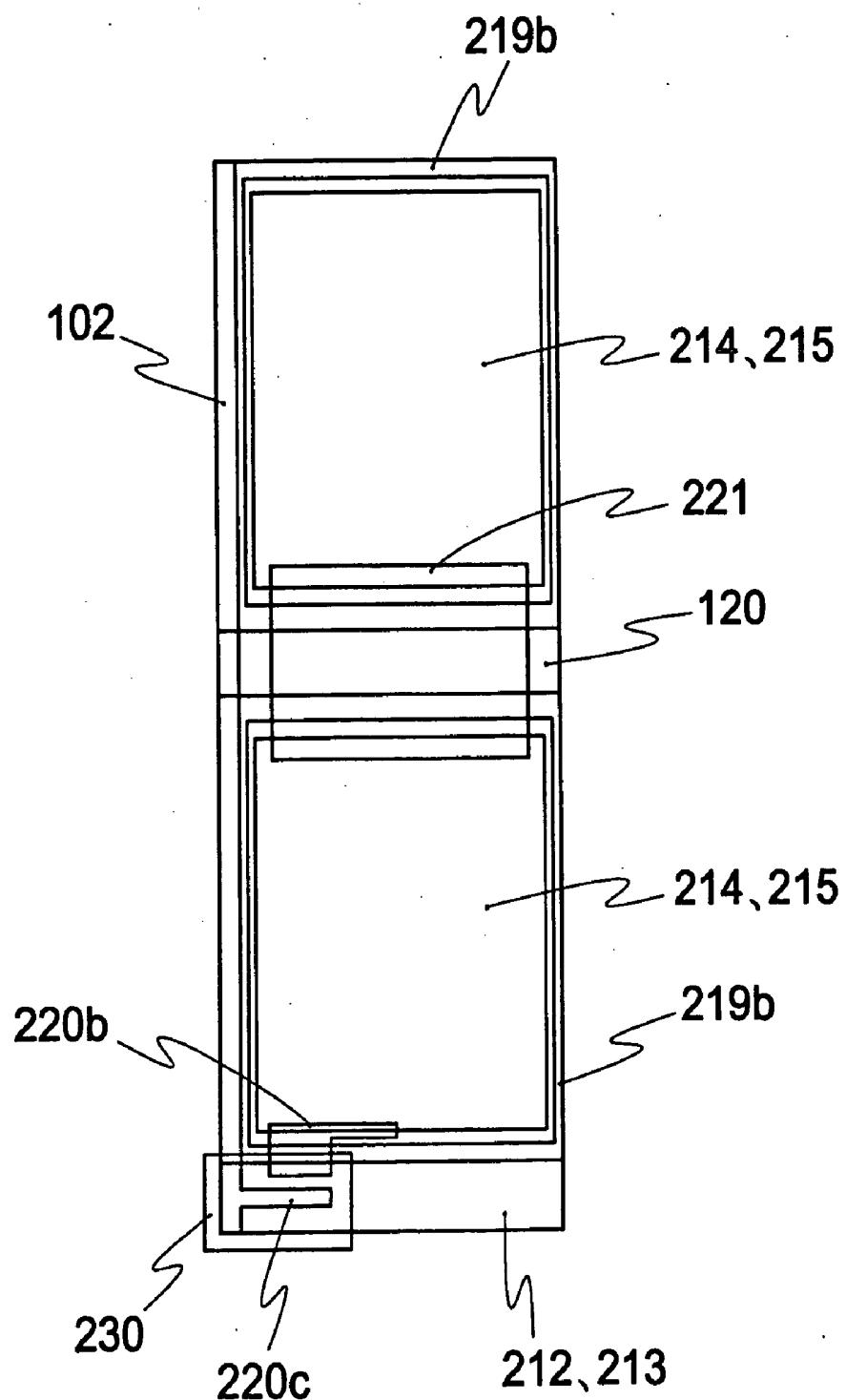

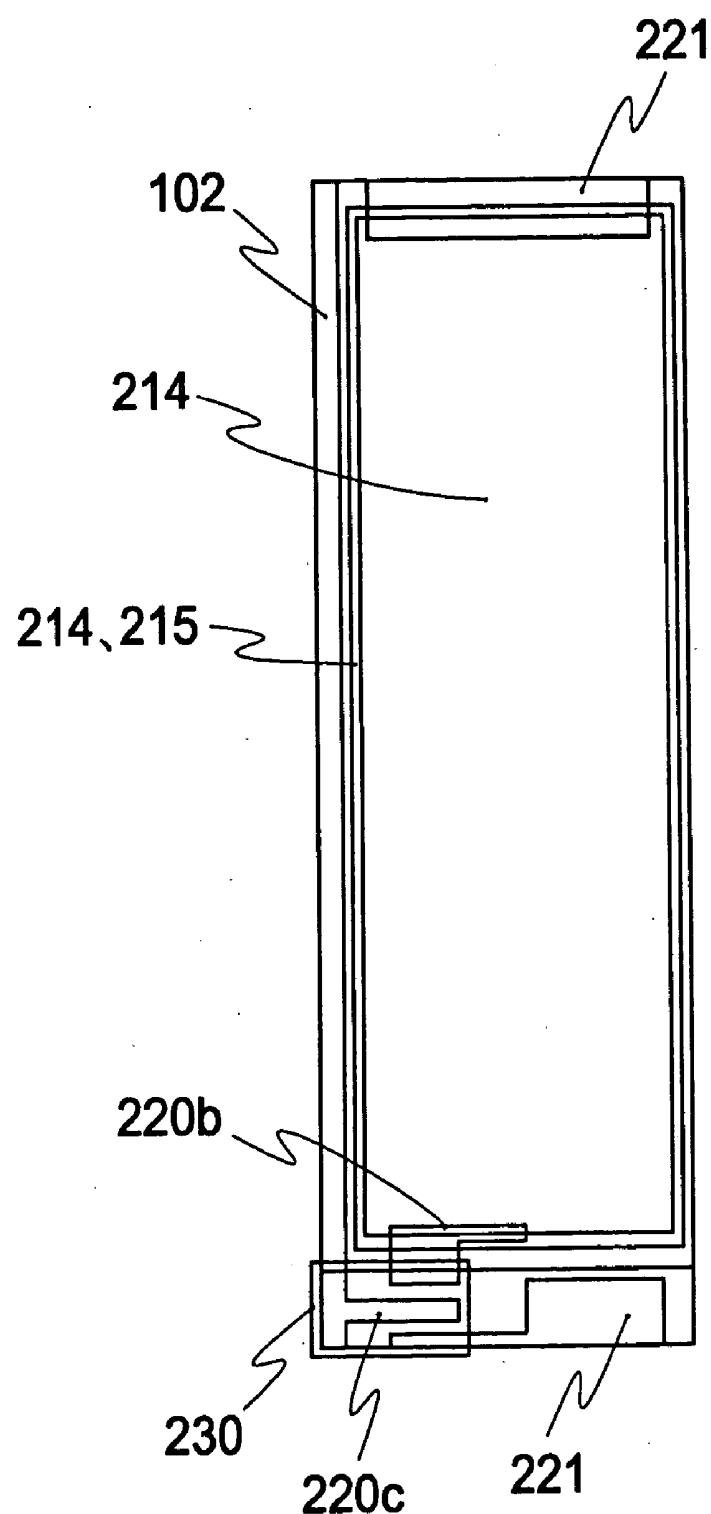

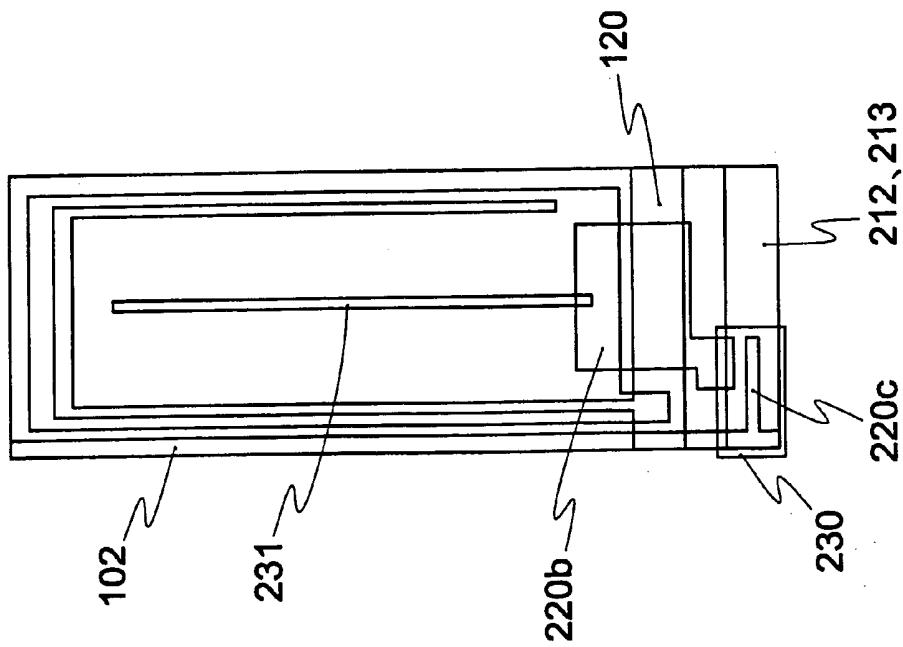

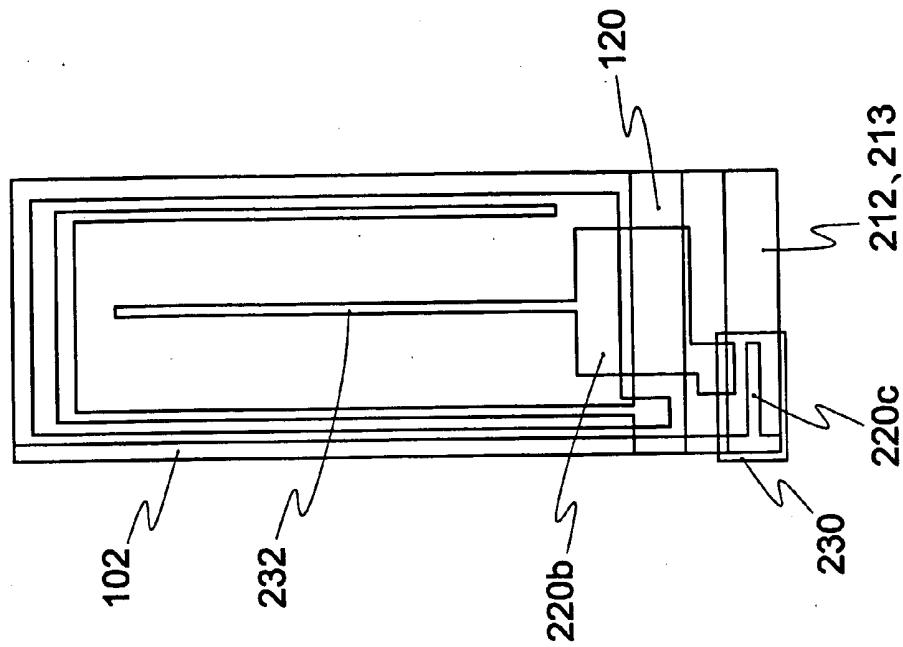

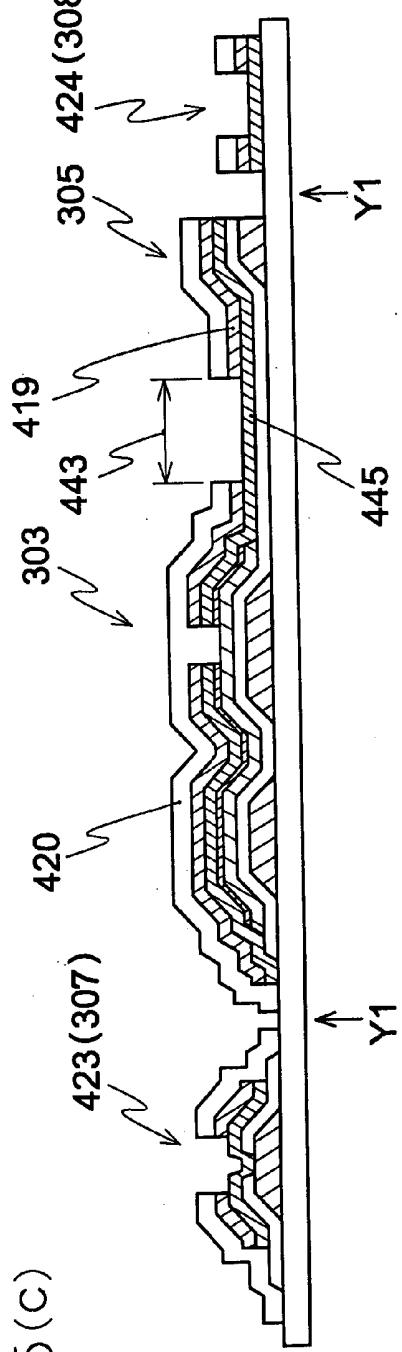

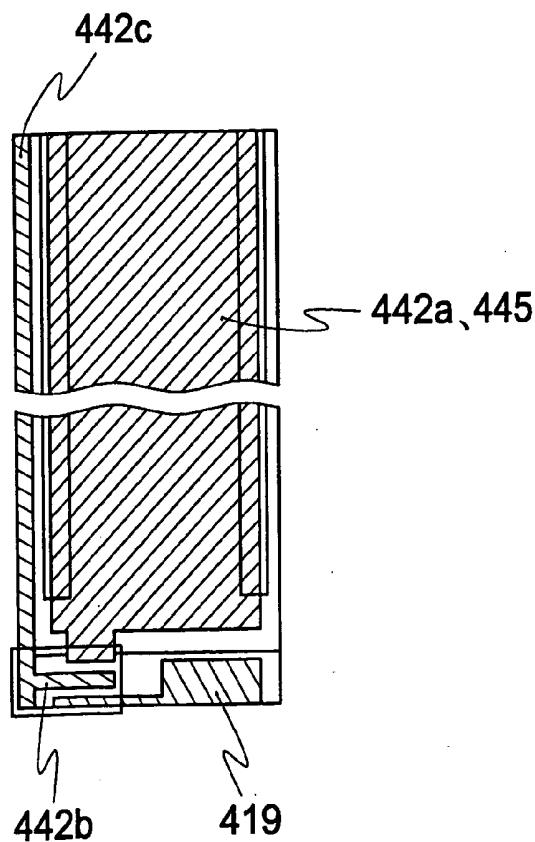

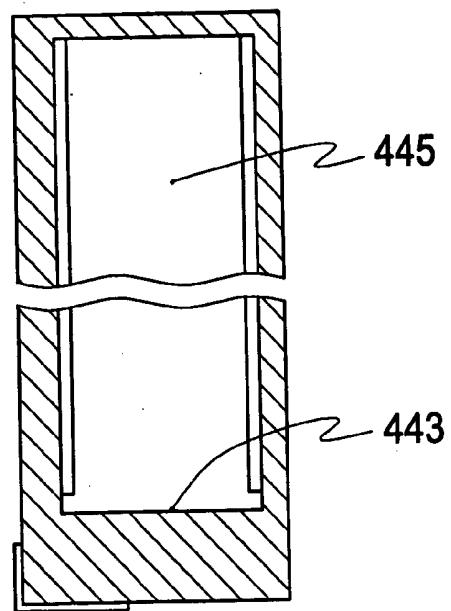

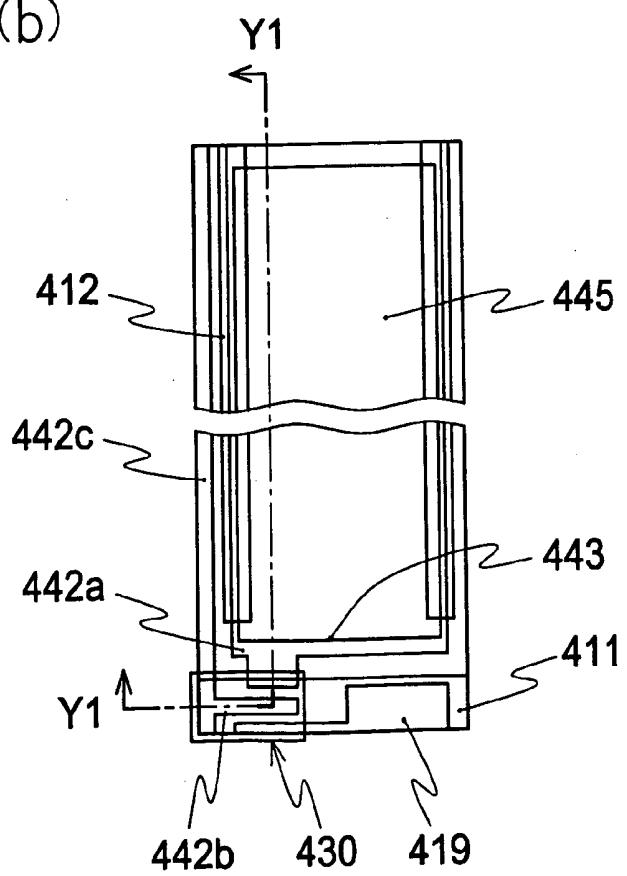

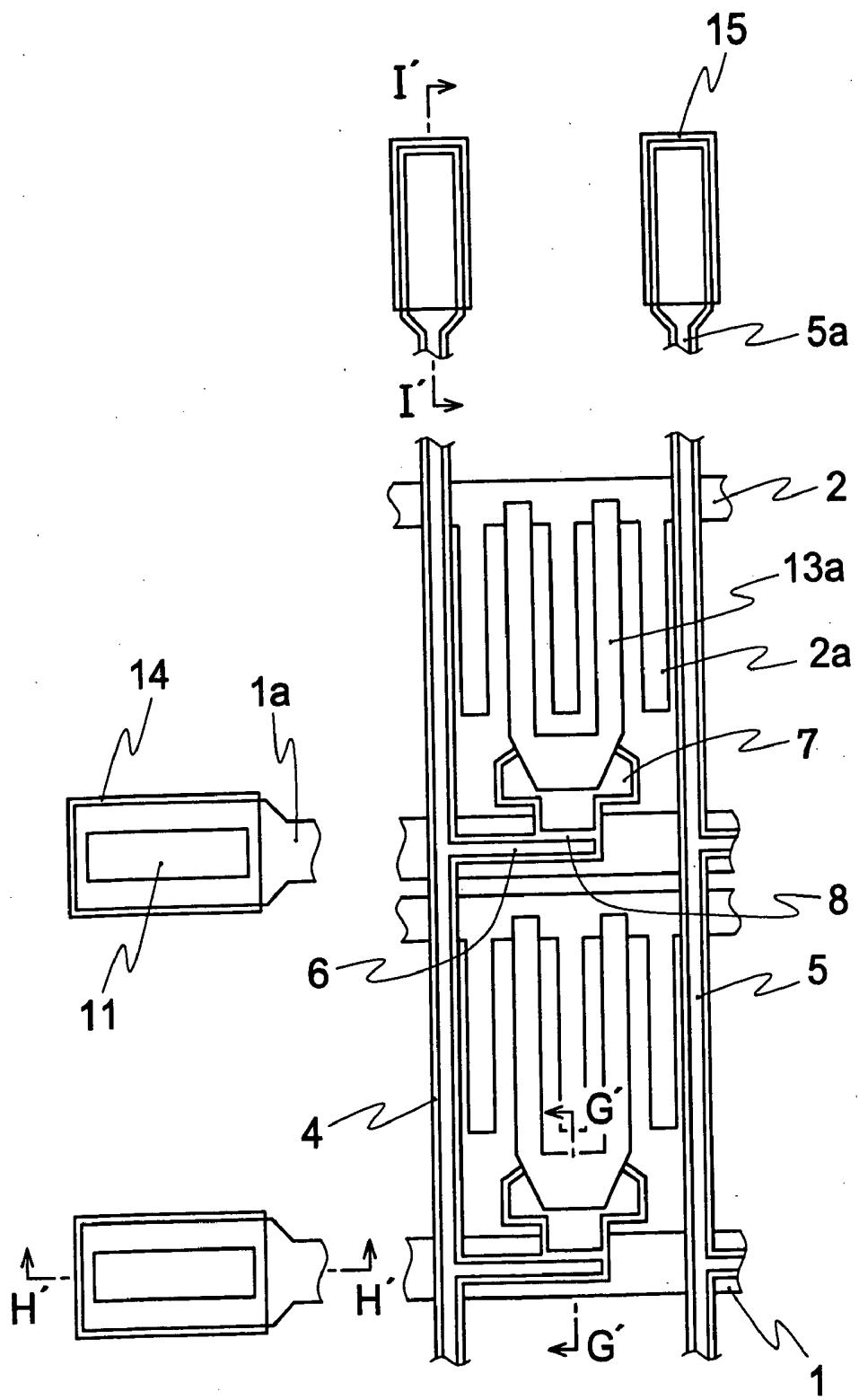

**[0140]** **FIGS. 29, 30 and 31** are sectional views showing a process for manufacturing the TFT array substrate in which the number of photolithographic steps (the number of masks) according to the present invention is reduced, illustrating the manufacturing process implementing a circuit of the TFT array substrate shown in **FIG. 28**. **FIG. 32** is a plan view corresponding to **FIGS. 29, 30 and 31**, and **FIGS. 29, 30 and 31** show a section taken along the line Y-Y in **FIG. 32** and the sectional structure of a gate-source terminal portion.

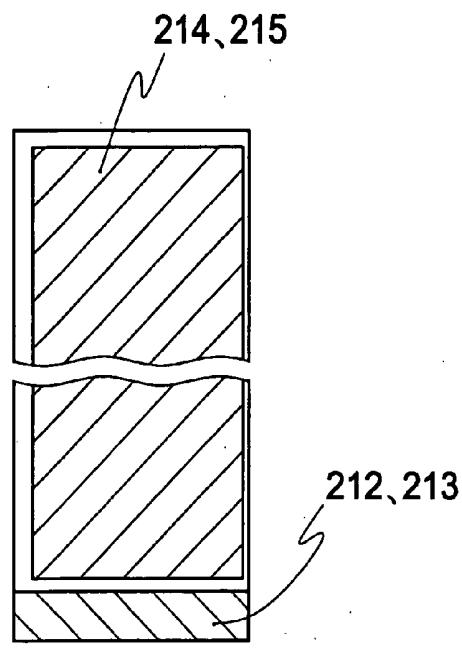

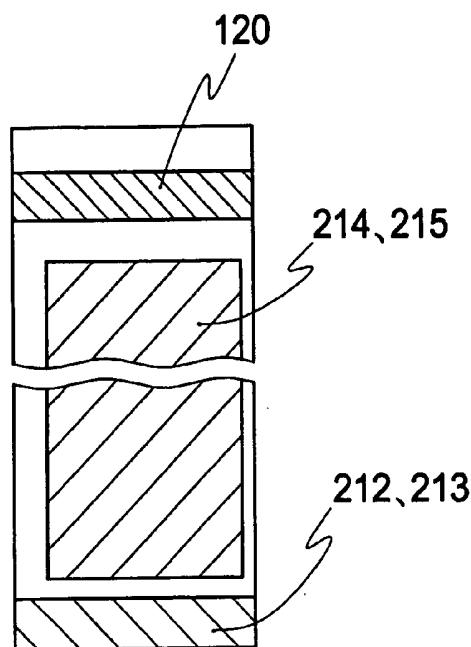

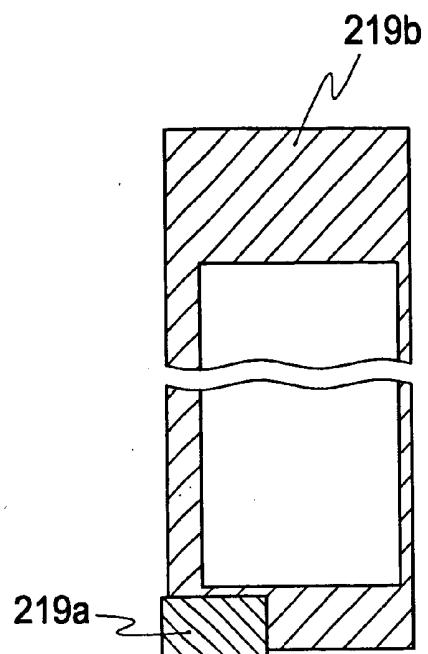

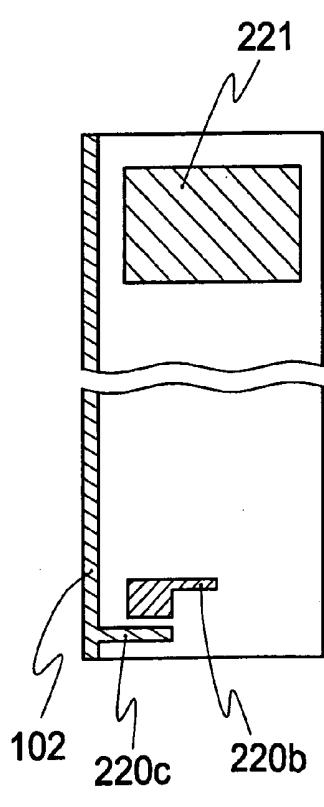

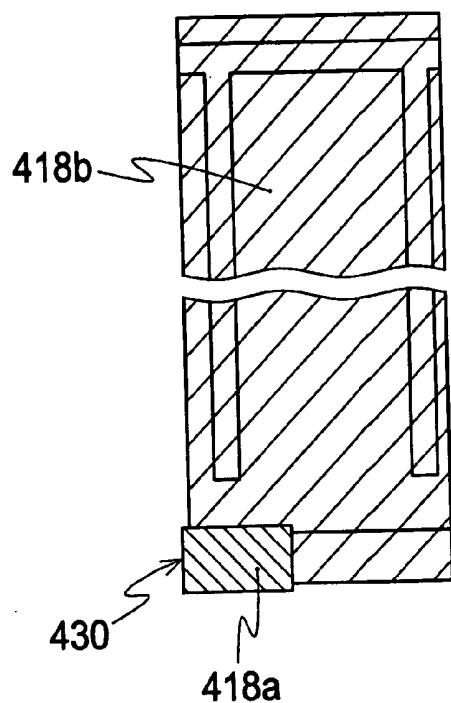

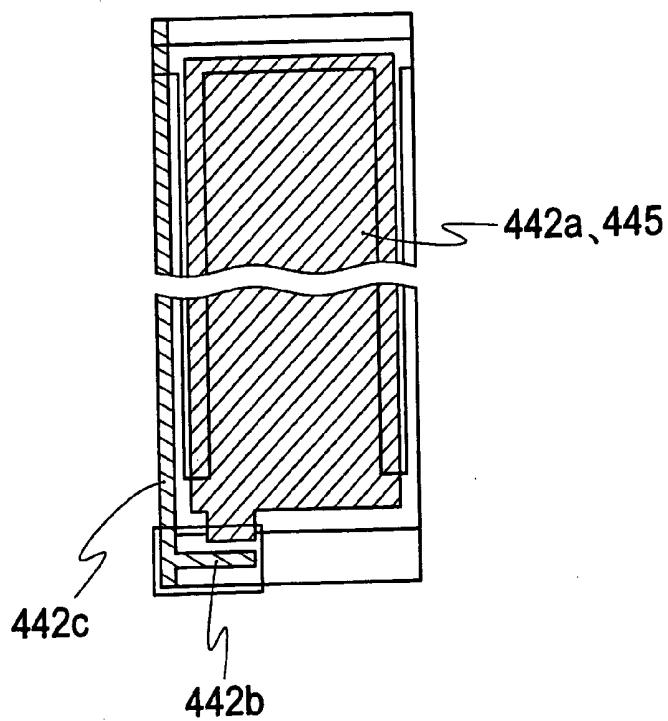

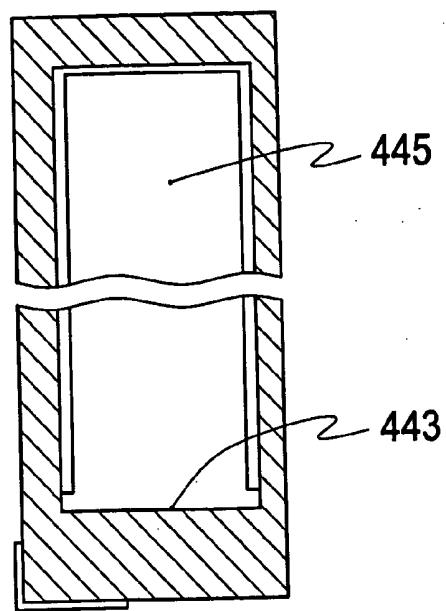

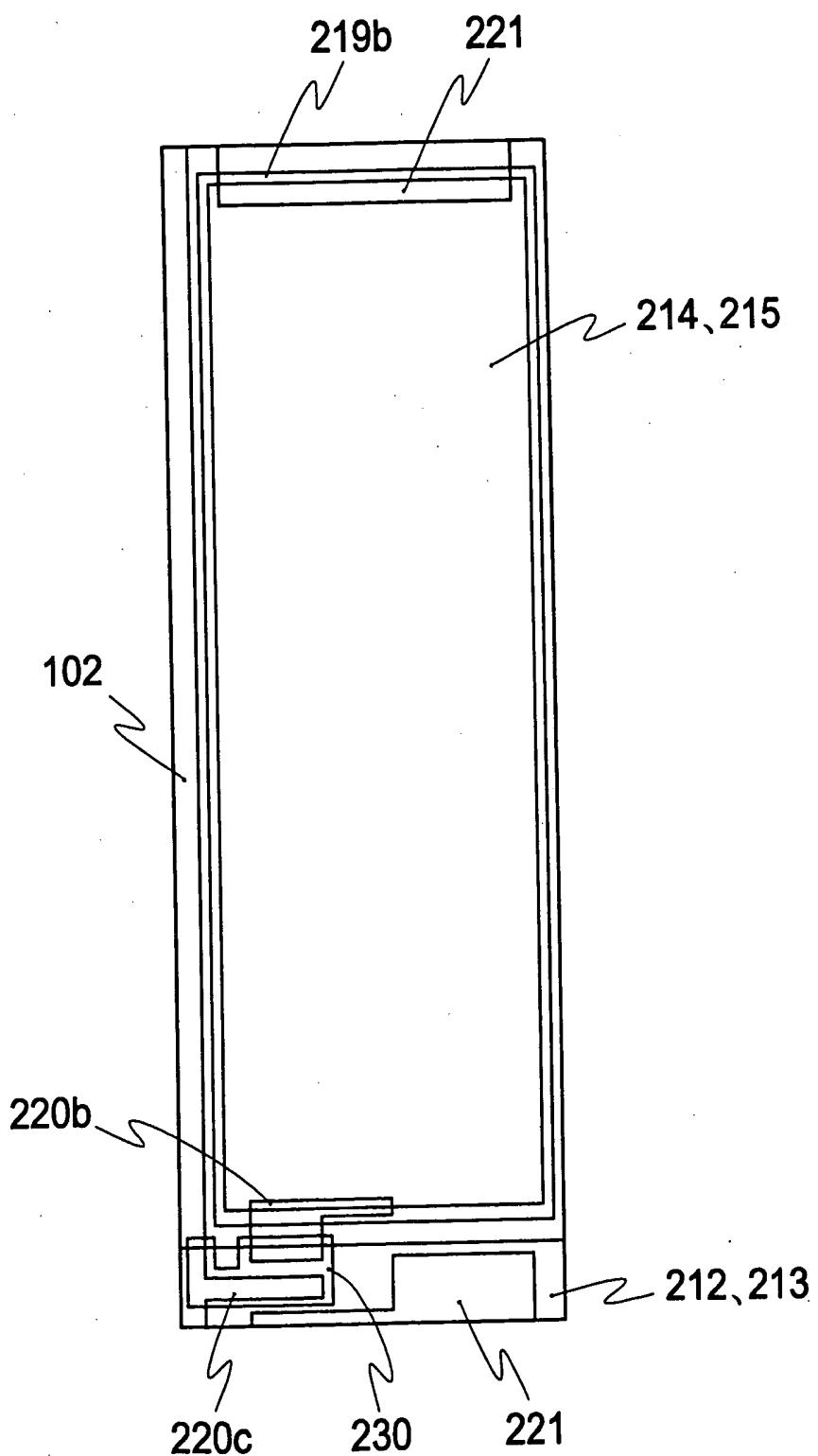

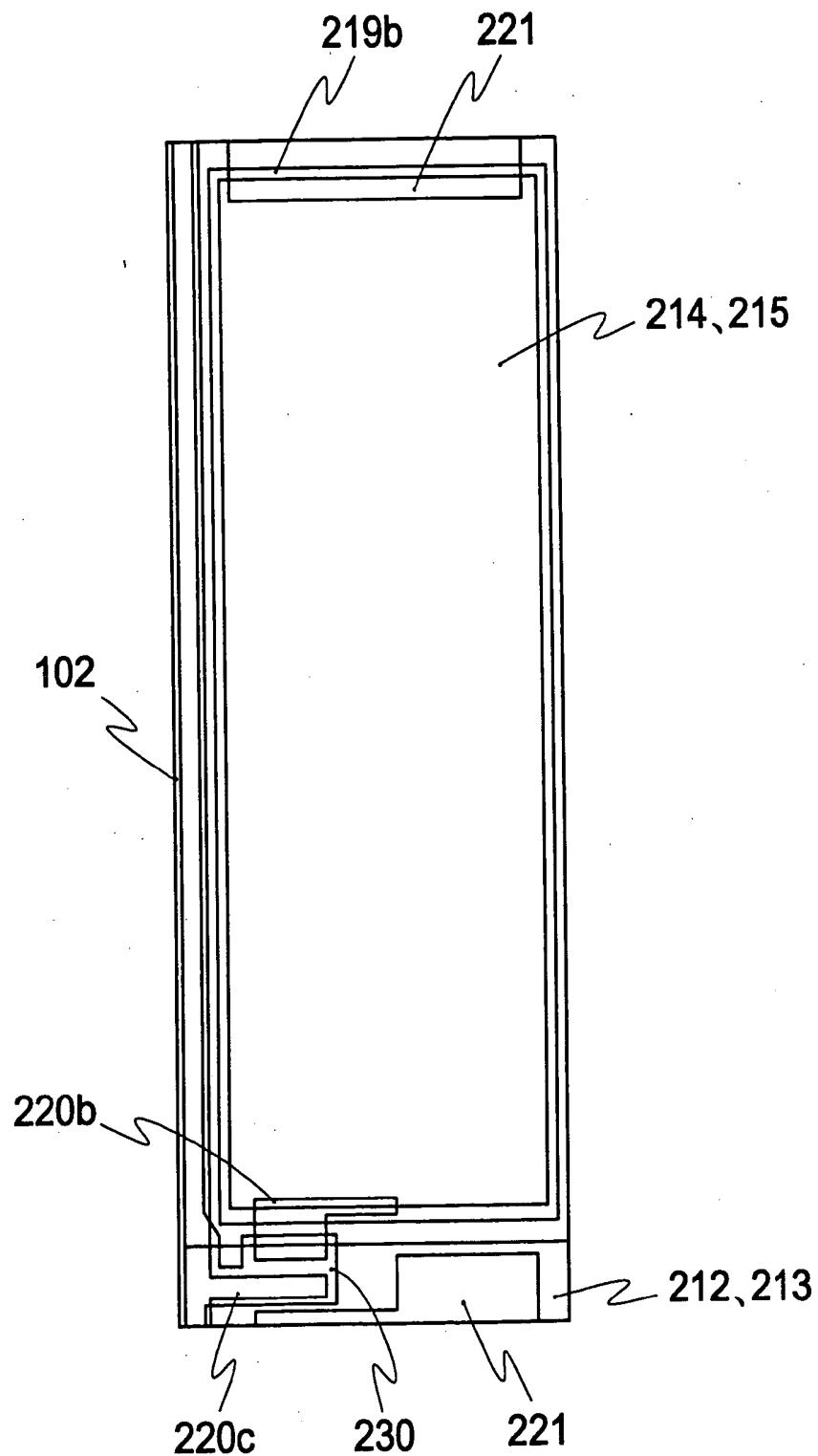

**[0141]** In **FIGS. 29, 30 and 31**, the reference numeral **211** denotes an insulating substrate, the reference numeral **212** denotes a gate electrode and a gate line which are formed of a transparent conductive layer, and the reference numeral **213** denotes a gate electrode and a gate line which are formed of a metallic layer. The reference numerals **212** and **213** form the gate line **101**. The reference numeral **204** denotes a pixel electrode formed of a transparent conductive layer, the reference numeral **215** denotes a pixel electrode formed of a metallic layer, the reference numeral **216** denotes a gate insulating film, the reference numeral **217** denotes a semiconductor layer (active layer), the reference numeral **218** denotes a semiconductor layer (contact layer) containing an impurity such as P or B with a high concentration, the reference numeral **219** (**219a** and **219b**) denotes a photosensitive organic resin capable of being used as a photoresist, the reference numeral **220** (**220a**, **220b** and **220c**) denotes a conductor layer to be a source electrode and a drain electrode, the reference numeral **102** denotes a source line, the reference numeral **103** denotes a thin film transistor (TFT) portion, the reference numeral **221** denotes a retaining capacitance electrode, the reference numeral **222**

denotes an insulating film such as  $\text{Si}_3\text{N}_4$  or the like, and the reference numeral 230 denotes a semiconductor region in the plan view (FIG. 32).

[0142] The reference numerals used in FIG. 32 which are the same numerals shown in FIG. 28 to FIG. 31 denotes the same contents.

[0143] Next, the manufacturing method according to the present invention will be described.

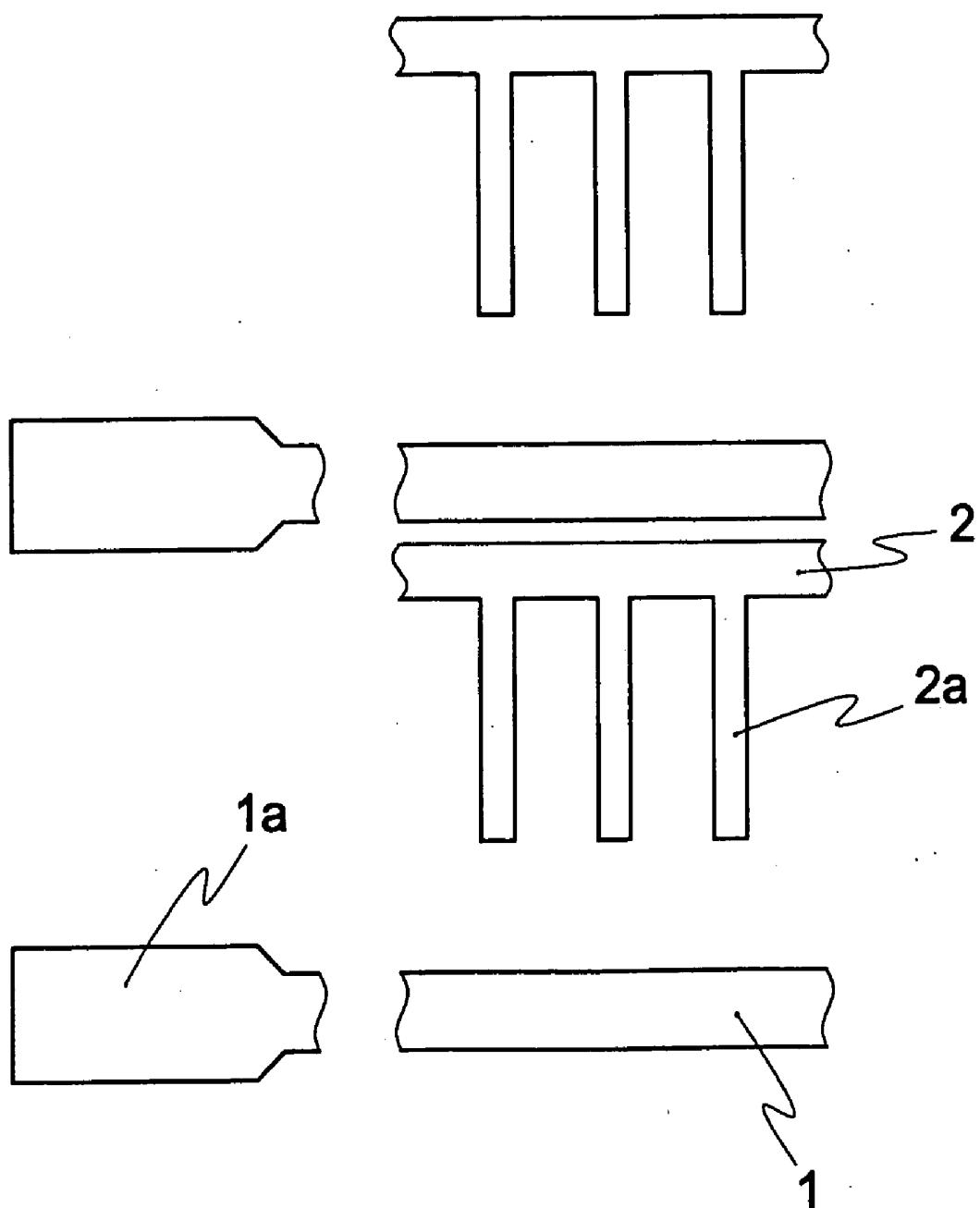

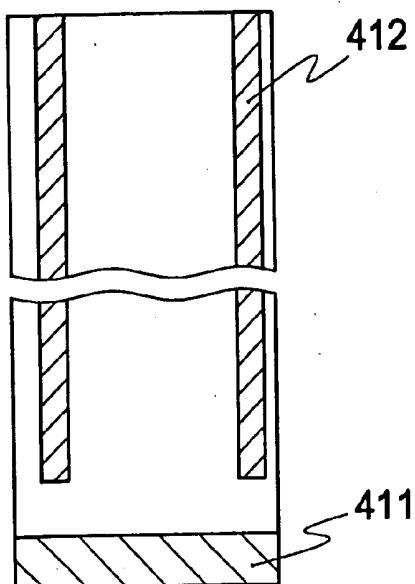

[0144] A transparent conductive layer such as IOT (Indium Tin Oxide),  $\text{SnO}_2$  or  $\text{InZnO}$  or a transparent conductive layer comprising their multilayer or mixed layer is formed on the insulating substrate 211 by a method such as sputtering, evaporation, coating, CVD, printing or a sol-gel method. Subsequently, a layer of a substance formed of a metal such as Cr, Al, Mo, W, Ti, Cu, Ag, Au or Ta, an alloy comprising them as a main component or a metal having them multilayered and having a lower resistance than that of the transparent conductive layer is provided on the transparent conductive layer by the method such as sputtering, evaporation, CVD or printing. Consequently, it is possible to obtain a line structure in which a low resistance layer formed of at least one metal is provided on the transparent conductive layer. Next, the gate electrodes and the gate line patterns 212 and 213 comprising the transparent conductive layer and the low resistance layer such as a metal are formed by photolithography using a photoresist or the like and succeeding etching. At this time, pixel electrode patterns 214 and 215 are simultaneously formed with a layer structure comprising the transparent conductive layer having the same material and structure as those of the gate line and the low resistance layer such as a metal (FIGS. 29(a) and 32(a)).

[0145] In general, a polycrystalline silicon is also used for the transparent conductive layer such as the ITO. In this case, a substance containing ferric chloride or HCl and nitric acid as a main component is used as an etchant for the ITO or the like, for example.

[0146] However, if the ITO layer 214 is formed to be amorphous and the metallic layer 215 is formed thereon at such a temperature that the ITO is crystallized or less, for example, the ITO can be etched with comparatively weak acid such as oxalic acid because it is in an amorphous state. In the case in which Al or the like is used for a metallic layer, the metal such as Al is rarely etched during the etching of the ITO. For structure formation, the ITO may be maintained to be amorphous until the metal is completely etched. For this reason, it is desirable that the metal such as Al should be formed at a temperature 160°C. or less at which the ITO is not crystallized.

[0147] Moreover, the ITO may be etched by using a gas such as HCl, HBr or HI.

[0148] Subsequently, there are consecutively provided an insulating film 216 comprising  $\text{Si}_3\text{N}_4$ ,  $\text{SiOxNy}$ ,  $\text{SiO}_2$ ,  $\text{Ta}_2\text{O}_5$  or  $\text{Al}_2\text{O}_5$ , a substance slightly deviated their stoichiometric composition or their ultiplayer which is to be formed as a gate insulating film by various CVD methods such as plasma CVD, sputtering, evaporation or coating, an a-Si:H film (hydrate amorphous silicon film) 217 to be used as a semiconductor layer (active layer) for a channel which is formed by the plasma CVD or the sputtering, for example, and is intentionally doped with no impurity to be a dopant or is intentionally doped with the impurity and has a

concentration of the impurity reduced to be approximately 50 ppm or less or a dopant impurity reduced to such that a leakage current does not exceed 50 pA in the dark on the actual usage voltage conditions of the TFT, and an  $n^+\text{a-Si:H}$  film or a microcrystal  $n^+\text{Si}$  film 218 to be a semiconductor layer (contact layer) which is formed by the plasma CVD or the sputtering to take a contact with a metal and is doped with an impurity with a high concentration in which an impurity such as phosphorus, antimony or boron is present in the film at an atom ratio of 0.05% or more, for example.

[0149] Next, the whole surface is first coated with a photoresist. Then, a photoresist pattern is formed by exposure using a photomask. The shape of the photoresist pattern is obtained in the following manner. First of all, the photoresist is not formed in at least a part of a portion to be a pixel electrode and a contact hole portion as shown in FIG. 29(b) or FIG. 32(b) (region C). A photoresist having a thickness A is formed in a portion formed of the a-Si:H film and leaving the semiconductor layer (region A, 219a). For example, only the a-Si:H film 217 and the  $n^+\text{a-Si:H}$  film 218 are etched and a photoresist having a thickness B is formed in a region where the gate insulating film 216 is to remain (region B, 219b). The thickness of the photoresist of the region A (219a) is set to be greater than that of the photoresist (219b) of the region B. It is desirable that the region B (219b) should be formed between adjacent source lines on the gate line, for example, the a-Si:H film 217 and the  $n^+\text{a-Si:H}$  film 218 in that portion should be removed and a portion between the adjacent source lines should be brought into an electrically insulation state. Moreover, at least a part of the source line may leave the semiconductor layers 217 and 218 on a lower layer as the region A on a lower layer such that the disconnection of the source line can be prevented.

[0150] Such a difference in the thickness of the photoresist depending on a place is made in the following manner. A positive photoresist will be described. A negative photoresist pattern is also formed basically in the same manner.