US 20040164943A1

(19) United States

(12) Patent Application Publication (10) Pub. No.: US 2004/0164943 A1

Ogawa et al.

(43) Pub. Date: Aug. 26, 2004

(54) LIQUID CRYSTAL DISPLAY DEVICE AND

DRIVING METHOD THEREOF

(52) U.S. Cl. ..... 345/92

(76) Inventors: Yoshinori Ogawa, Nara (JP); Shigeki

Tanaka, Kyoto (JP)

## (57) ABSTRACT

Correspondence Address:

**HARNESS, DICKEY & PIERCE, P.L.C.**

**P.O. BOX 8910**

**RESTON, VA 20195 (US)**

(21) Appl. No.: 10/727,645

(22) Filed: Dec. 5, 2003

## (30) Foreign Application Priority Data

Dec. 10, 2002 (JP) ..... 2002-358429

## Publication Classification

(51) Int. Cl.<sup>7</sup> ..... G09G 3/36

The liquid crystal display device includes: a plurality of scanning lines; a plurality of signal lines provided so as to cross the scanning signals; pixel capacitors, having pixel electrodes and counter electrodes (common electrodes), and corresponding to a liquid crystal layer, which are respectively formed on pixels corresponding to intersections of the scanning lines and the signal lines. The liquid crystal layer has liquid crystal molecules, aligned in random directions throughout a liquid crystal panel, each of which has a substantially fixed twist angle in a direction perpendicular to substrates for sandwiching the liquid crystal layer. In the liquid crystal display device, there is provided a Vcom adjustment circuit which supplies common electrode voltages to the counter electrodes (common electrodes) and is capable of adjusting the common electrode voltages. As a result, it is possible to display an image which can be viewed at a wider visual angle.

FIG. 1

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8 (a)

FIG. 8 (b)

**FIG. 10****FIG. 11**

FIG. 12

|    | R | G | B | R | G | B |

|----|---|---|---|---|---|---|

| C1 | + | - | + | - | + | - |

| C2 | - | + | - | + | - | + |

|    | + | - | + | - | + | - |

|    | - | + | - | + | - | + |

| C3 | + | - | + | - | + | - |

|    | - | + | - | + | - | + |

FIG. 13

|         | R | G | B | R | G | B |

|---------|---|---|---|---|---|---|

| C1      | + | - | + | - | + | - |

| n FRAME | - | + | - | + | - | + |

| C2      | + | - | + | - | + | - |

|         | - | + | - | + | - | + |

| C3      | + | - | + | - | + | - |

|         | - | + | - | + | - | + |

|           | R | G | B | R | G | B |

|-----------|---|---|---|---|---|---|

| C3        | - | + | - | + | - | + |

| n+1 FRAME | + | - | + | - | + | - |

| C1        | + | - | + | - | + | - |

|           | - | + | - | + | - | + |

| C2        | + | - | + | - | + | - |

|           | - | + | - | + | - | + |

FIG. 14

FIG. 15

FIG. 16

**FIG. 18**

FIG. 19

FIG. 20

FIG. 21 (a)

FIG. 21 (b)

FIG. 22

FIG. 23

FIG. 24

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_1$ | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

| $\gamma_2$ | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

$\gamma_1$        $\gamma_2$

FIG. 25

$n$  FRAME

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_1$ | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

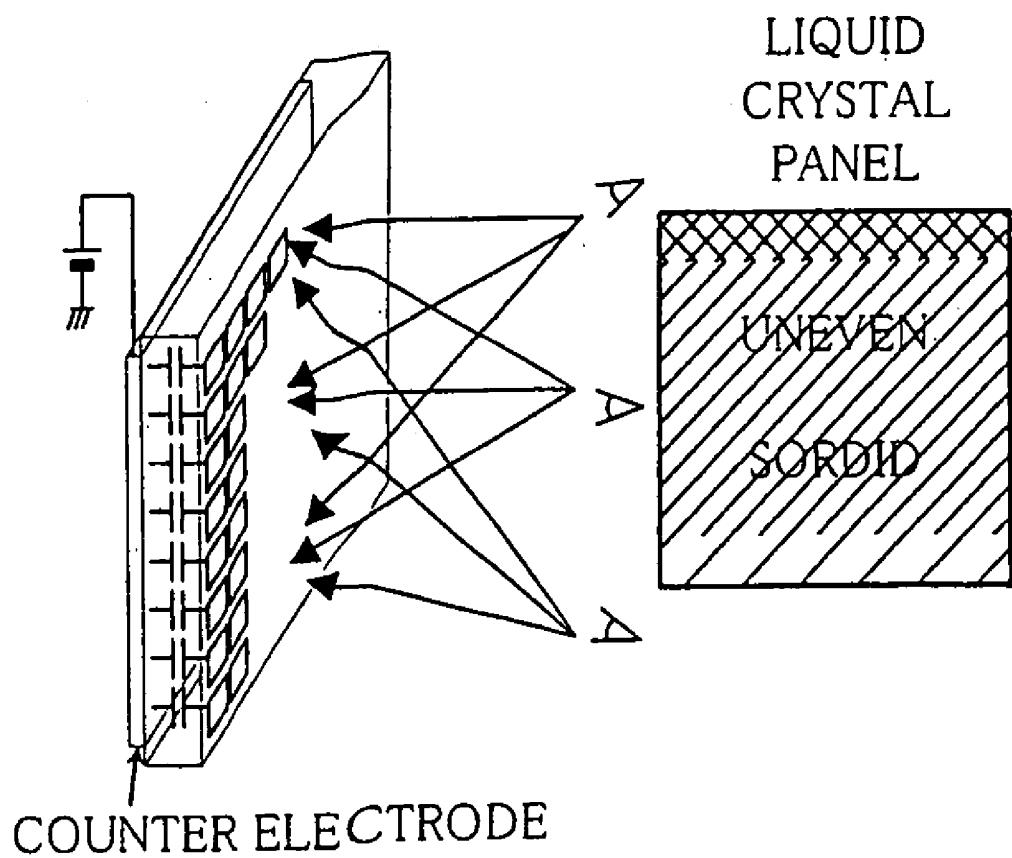

|            | + | - | + | - | + | - |

| $\gamma_2$ | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

$\gamma_1$   $\gamma_2$   $n+1$  FRAME

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_1$ | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

| $\gamma_2$ | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

# FIG. 26

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_2$ | + | - | + | - | + | - |

| $\gamma_1$ | - | + | - | + | - | + |

| $\gamma_3$ | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

Legend:

- $\gamma_1$ : Empty square

- $\gamma_2$ : Square with diagonal lines from top-left to bottom-right

- $\gamma_3$ : Square with diagonal lines from top-right to bottom-left

FIG. 27

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_2$ | + | - | + | - | + | - |

| n FRAME    | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

| $\gamma_3$ | - | + | - | + | - | + |

|            | R | G | B | R | G | B |

|------------|---|---|---|---|---|---|

| $\gamma_3$ | - | + | - | + | - | + |

| n+1 FRAME  | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

|            | - | + | - | + | - | + |

|            | + | - | + | - | + | - |

FIG. 28

FIG. 29

GRAPH SHOWING A RELATIONSHIP BETWEEN LUMINANCE OF A SINGLE PIXEL OF A LIQUID CRYSTAL PANEL AND AN ANGULAR POSITION IN VIEWING

FIG. 30 (a)

FIG. 30 (b)

SOURCE DRIVER (V<sub>com</sub> CONTROL

CIRCUIT IS PROVIDED THEREIN)

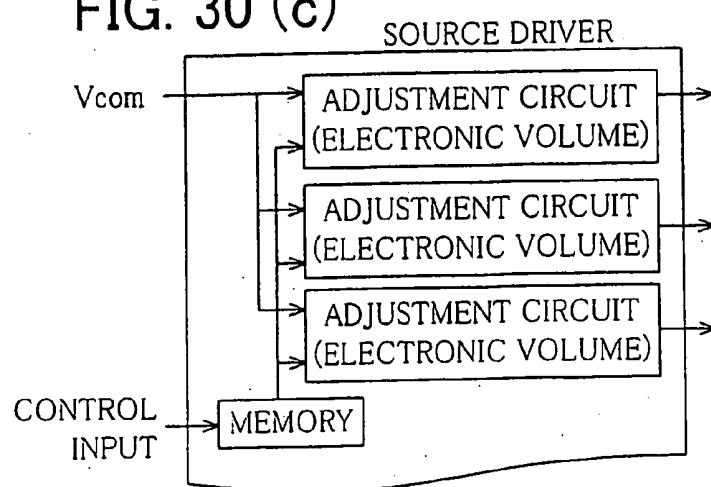

FIG. 30 (c)

# FIG. 31

FIG. 32 (a)

FIG. 32 (b)

FIG. 33 (a)

FIG. 33 (b)

# FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 38 (a)

FIG. 38 (b)

FIG. 39

**FIG. 40**

FIG. 41

FIG. 42 (a)

FIG. 42 (b)

LIQUID CRYSTAL ALIGNMENT (UPPER SURFACE)

FIG. 42 (c)

LIQUID CRYSTAL ALIGNMENT

(UPPER SURFACE)

FIG. 42 (d)

LIQUID CRYSTAL ALIGNMENT

(UPPER SURFACE)

FIG. 43

## LIQUID CRYSTAL DISPLAY DEVICE AND DRIVING METHOD THEREOF

[0001] This Nonprovisional application claims priority under 35 U.S.C. § 119(a) on Patent Application No. 2002/358429 filed in Japan on Dec. 10, 2002, the entire contents of which are hereby incorporated by reference.

### FIELD OF THE INVENTION

[0002] The present invention relates to a liquid crystal display device and a driving method thereof, and particularly to a structure for enlarging a visual angle.

### BACKGROUND OF THE INVENTION

[0003] The demand for a liquid crystal display (LCD) is increasing due to its characteristic such as a compact body and low power consumption. Further, the LCD is being developed as a product which realizes a larger screen, higher definition, and higher gradation in terms of a function.

[0004] However, there is such a technical problem that: in the LCD, a visual angle, particularly a visual angle in an up-and-down direction, is narrower than in CRT and the like. The problem is explained as follows.

[0005] For example, currently, in a normally-white transmissive TN (twist nematic) type LCD which is often used for OA (Office Automation), a voltage applied to liquid crystal is varied so as to control its luminance. That is, the liquid crystal is sandwiched by two polarizing plates which are disposed so that a polarization axis crosses the polarizing plates in an orthogonal manner, and a voltage applied to the liquid crystal is varied so as to vary a condition under which liquid crystal molecules are aligned, so that light that has been linearly polarized by the polarizing plate positioned on the incident side is elliptically polarized, thereby transmitting only light, positioned on the outgoing side, which is projected in a direction of the polarization axis. As a result, the luminance is controlled.

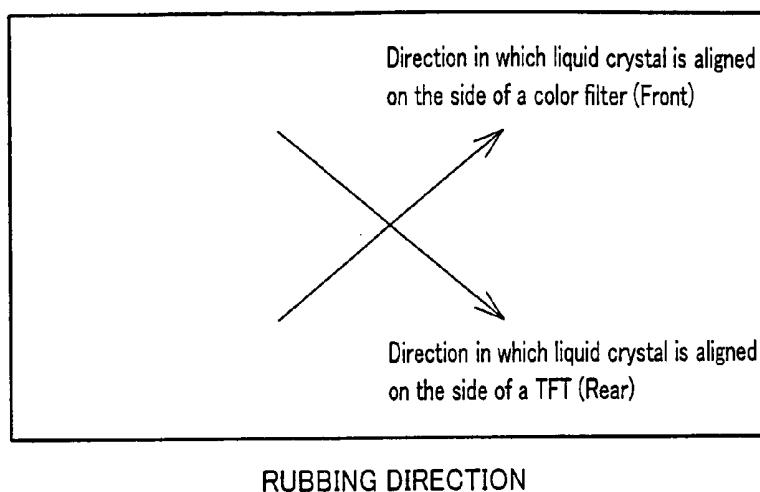

[0006] Further, in the LCD for OA, a rubbing process is performed with respect to an alignment film so that a portion on the side of a thin film transistor (TFT) and a portion on the side of a color filter (CF) are respectively rubbed in directions shown in FIG. 42(a), thereby aligning liquid crystal molecules in the foregoing directions.

[0007] When the voltage is not applied to the liquid crystal, the liquid crystal molecules are aligned in a twisted manner under such condition that the liquid crystal molecules lie down. When, the voltage is applied to the liquid crystal, the liquid crystal molecules are aligned in a vertical direction. Further, the liquid crystal molecule has a refraction which differs in a major axis direction and in a minor axis direction. Thus, when the liquid crystal molecule lies down, the refraction is anisotropic on a surface through which light passes, and when the liquid crystal molecule stands up, the refraction is isotropic on the surface through which light passes. Thus, rotation of the polarization differs depending on the voltage applied to the liquid crystal. The rotational amount of the polarization is defined by multiplying (a) refraction anisotropy of the liquid crystal molecule (reflection in a major axis direction-reflection in a minor axis direction) by a gap of liquid crystal cells (this condition is referred to as "retardation").

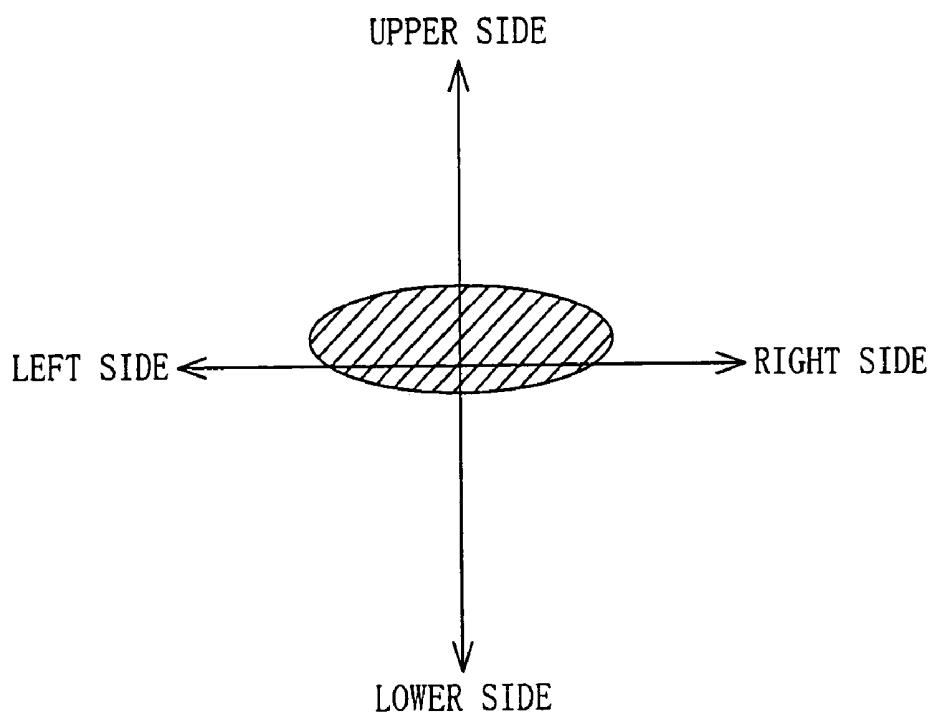

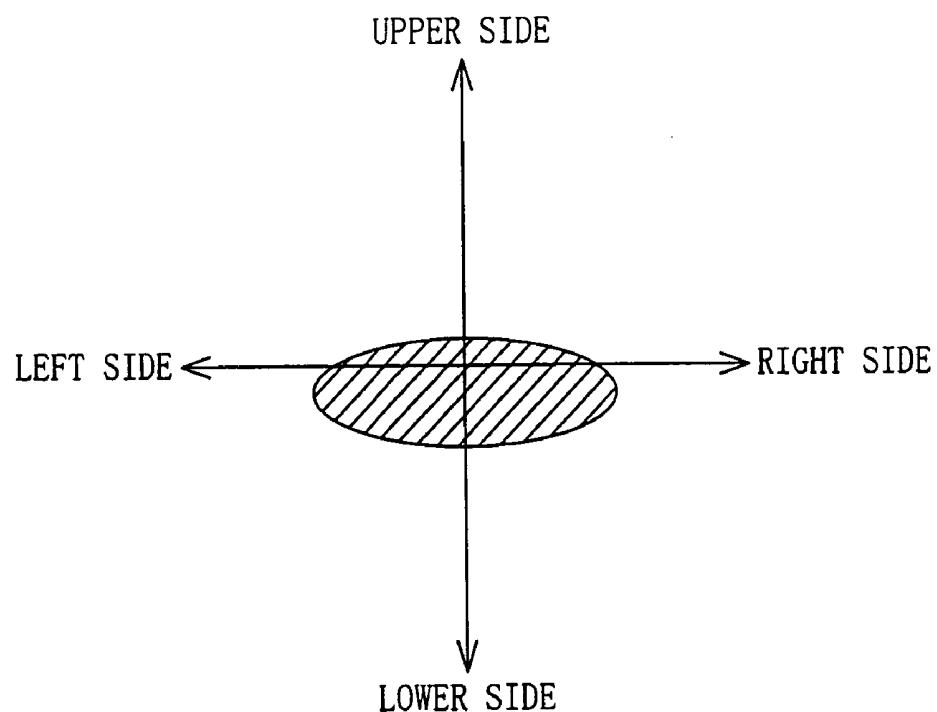

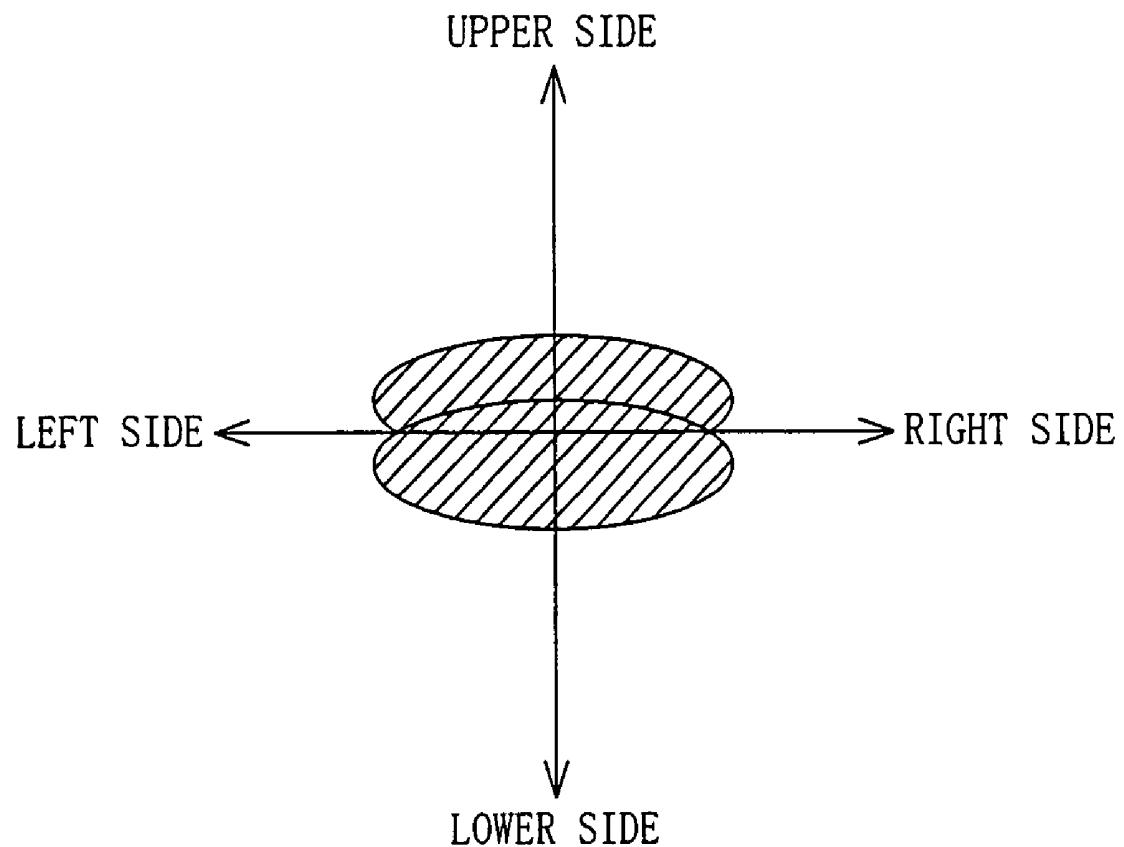

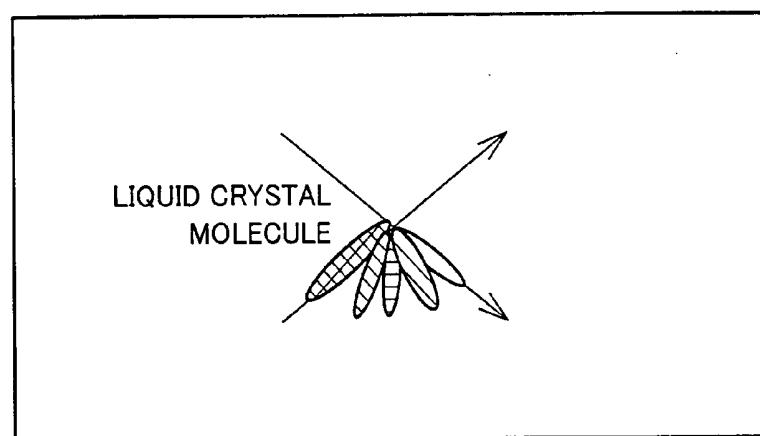

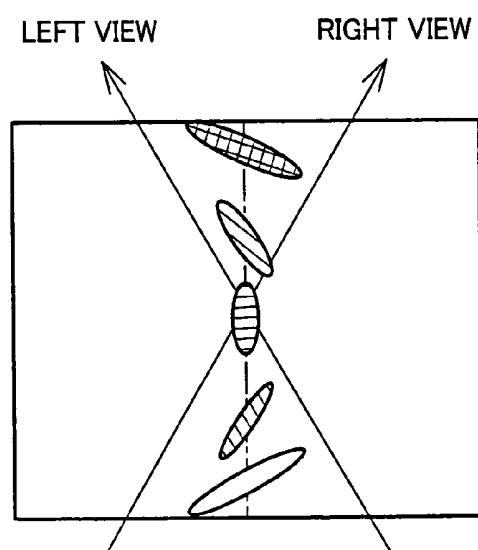

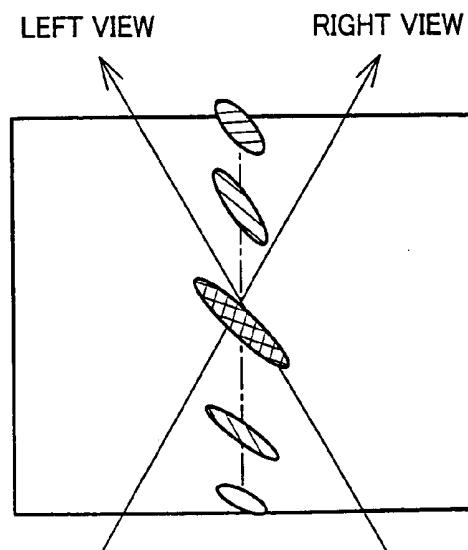

[0008] When the liquid crystal molecules are aligned in a direction shown in FIG. 42(a), the liquid crystal molecules are aligned with them twisted as shown in FIG. 42(b), so that the anisotropy caused by the retardation occurs. In this case, as shown in FIG. 42(c), the liquid crystal molecules are comparatively symmetrically aligned in a right-and-left direction, so that a visual angle is comparatively wider. In contrast, as shown in FIG. 42(d), the liquid crystal molecules are so asymmetrically aligned in an up-and-down direction, so that the visual angle is comparatively narrower. That is, when viewed from the upper side, the liquid crystal molecules seem to lie down, and when viewed from a lower side, the liquid crystal molecules seem to stand up. As a result, a black state is so conspicuous when viewed from an upper angular position in viewing ( $\theta < 0^\circ$ ), and gradation reversal occurs as shown in FIG. 43 when viewed from a lower angular position in viewing ( $\theta > 0^\circ$ ). This problem is particularly seen in a full-color LCD in which halftone is frequently used.

[0009] In order to widen the visual angle in a conventional LCD, it is necessary to be careful in managing the step of forming a TFT and the step of manufacturing a liquid crystal panel, and it is necessary to perform complicate manufacturing step, so that this raises such problem that the yield drops and the manufacturing cost increases.

[0010] As a method for solving the foregoing problem, Japanese Unexamined Patent Publication No. 194655/1994 (Tokukaihei 6-194655)(Publication date: Jul. 15, 1994) discloses a manufacturing method of a liquid crystal display device in which a rubbing process and an alignment film are not required.

[0011] In the manufacturing method, by using a multi-domain liquid crystal constituted of microdomains which are minute and are respectively aligned in random directions throughout a cell, it is possible to cause whole the display screen to display an image which is uniformed and does not vary depending on the visual angle.

[0012] However, according to the foregoing arrangement, by using a multi-domain liquid crystal constituted of micro-domains which are minute and are respectively aligned in random directions throughout a cell, it is possible to cause whole the display screen to display an image which is uniformed and does not vary depending on the visual angle, but it is difficult to completely guarantee the alignment which realizes such display condition in whole the multi-domain liquid crystal.

### SUMMARY OF THE INVENTION

[0013] The object of the present invention is to provide a liquid crystal display device and a driving method thereof by which it is possible to appropriately display an image which can be viewed at a wider visual angle.

[0014] In order to achieve the foregoing object, the liquid crystal display device according to the present invention includes: a plurality of scanning lines; a plurality of signal lines provided so as to cross the scanning signals; pixel capacitors, having pixel electrodes and common electrodes, and corresponding to a liquid crystal layer, which are respectively formed on pixels corresponding to intersections of the scanning lines and the signal lines, wherein the liquid crystal layer has liquid crystal molecules, aligned in random

directions throughout a liquid crystal panel, each of which has a substantially fixed twist angle in a direction perpendicular to substrates for sandwiching the liquid crystal layer, said liquid crystal display device including a common electrode voltage supplying circuit for supplying common electrode voltages to the common electrodes so that the common electrode voltages are adjustable.

[0015] Further, the method of the present invention is to drive the liquid crystal display device which includes: a plurality of scanning lines; a plurality of signal lines provided so as to cross the scanning signals; pixel capacitors, having pixel electrodes and common electrodes, and corresponding to a liquid crystal layer, which are respectively formed on pixels corresponding to intersections of the scanning lines and the signal lines, wherein the liquid crystal layer has liquid crystal molecules, aligned in random directions throughout a liquid crystal panel, each of which has a substantially fixed twist angle in a direction perpendicular to substrates for sandwiching the liquid crystal layer, and the method includes the step of supplying common electrode voltages and adjusting the common electrode voltages.

[0016] According to the foregoing arrangement, by adjusting the common electrode voltages supplied to the common electrodes as required, it is possible to adjust luminance of pixels and to correct color variation so as to widen a visual angle at which an observer views a display image from an arbitrary position. Thus, it is possible to appropriately display an image which can be viewed at a wider visual angle.

[0017] Further, as described above, the luminance of the pixels is adjusted and the color variation is corrected by adjusting the common electrode voltages supplied to the common electrodes, so that it is not necessary to adopt a complicate step of manufacturing the TFT or to remake a driving circuit. Thus, it is possible to obtain a high-performance liquid crystal display device at lower cost. Further, it is possible to easily correct the color variation, caused by viewing from different angular positions in viewing, in accordance with a material for the liquid crystal and a characteristic of the liquid crystal display device, so that this arrangement is applicable to various kinds of liquid crystal display devices which are different from each other in terms of the characteristic.

[0018] The liquid crystal display device may be arranged so that: the common electrodes of the pixels are divided into a plurality of groups, and the common electrode voltage supplying circuit is capable of respectively adjusting the common electrode voltages so that the common electrode voltages are adjusted independently every groups.

[0019] Further, the method for driving the liquid crystal display device may be arranged so that: the common electrodes of the pixels are divided into a plurality of groups, and the common electrode voltages are respectively adjusted so as to be adjusted independently every groups.

[0020] According to the foregoing arrangement, for example in the liquid crystal display device having such a characteristic that the visual angle varies depending on a position at which the observer views an image in an up-and-down direction, the common electrodes are divided into a plurality of groups each of which corresponds to each of the pixels, and each of the common electrode voltages is adjusted for each of the groups, so that it is possible to

appropriately adjust the visual angle, at the position where the observer views the image in an up-and-down direction for example.

[0021] The liquid crystal display device may be arranged so that: at least first pixel capacitors and second pixel capacitors are provided on each of the pixels as the pixel capacitors, and the common electrode voltage supplying circuit is capable of respectively independently adjusting a common electrode voltage supplied to common electrodes corresponding to the first pixel capacitors and common electrode voltages supplied to common electrodes corresponding to the second pixel capacitors.

[0022] Thus, it is possible to appropriately adjust the common electrode voltage in the multi-domain liquid crystal display device which includes, as the pixel capacitor, at least the first pixel capacitor and the second pixel capacitor that are provided in each pixel.

[0023] The liquid crystal display device may be arranged so that: the common electrodes corresponding to the second pixel capacitors are divided into a plurality of groups, and the common electrode voltage supplying circuit supplies the common electrode voltage of an equal value to each other to the common electrodes corresponding to the first pixel capacitors, and is capable of respectively adjusting the common electrode voltages supplied to the common electrodes corresponding to the second pixel capacitors independently every groups.

[0024] Thus, with a simple structure, it is possible to adjust the common electrode voltages supplied to the common electrodes of the multi-domain liquid crystal display device which includes, as the pixel capacitor, at least the first pixel capacitor and the second pixel capacitor that are provided in each pixel.

[0025] The liquid crystal display device may be arranged so that: the common electrodes corresponding to the first pixel capacitors are divided into a plurality of groups, and the common electrode corresponding to the second pixel capacitors are divided into a plurality of groups, and the common electrode voltage supplying circuit is capable of respectively adjusting the common electrode voltage supplied to the common electrodes corresponding to the first pixel capacitor independently every groups and is capable of respectively adjusting the common electrode voltages supplied to the common electrodes corresponding to the second pixel capacitors independently every groups.

[0026] Thus, it is possible to delicately control the common electrode voltages supplied to the common electrodes of the multi-domain liquid crystal display device which includes, as the pixel capacitor, at least the first pixel capacitor and the second pixel capacitor that are provided in each pixel, that is, it is possible to delicately control a display condition of the pixels.

[0027] The liquid crystal display device may be arranged so that: the common electrodes are grouped for n lines of the scanning lines (n includes one), where n is a positive integer.

[0028] The liquid crystal display device may be arranged so that: the common electrode voltage supplying circuit supplies a common electrode voltage which functions as a reference common electrode voltage to a first group corresponding to a scanning line centered in a direction in which

the scanning lines are disposed, and the common electrode voltage supplying circuit supplies a common electrode voltage which is higher than the reference common electrode voltage to a second group corresponding to a scanning line positioned on the one side in the direction in which the scanning lines are disposed, and the common electrode voltage supplying circuit supplies a common electrode voltage which is lower than the reference common electrode voltage to a third group corresponding to a scanning line positioned on the other side in the direction in which the scanning lines are disposed.

[0029] According to the foregoing arrangement, it is possible to perform appropriate adjustment required in widening the visual angle in a liquid crystal display device whose display characteristic differs in the first group corresponding to the scanning lines centered in the direction in which the scanning signals are disposed, the second group corresponding to the scanning lines positioned on one side in the direction in which the scanning signals are disposed, and the third group corresponding to the scanning lines positioned on the other side in the direction in which the scanning signals are disposed. In other words, it is possible to perform appropriate adjustment required in widening the visual angle in a liquid crystal display device whose display characteristic differs in three areas divided in a direction, in which the scanning lines are disposed, such as an up-and-down direction with respect to the image for example.

[0030] The liquid crystal display device may be arranged so as to include a signal line driving circuit for supplying a display signal voltage to each of the signal lines, wherein the common electrode voltage supplying circuit is provided in the signal line driving circuit.

[0031] The liquid crystal display device may be arranged so that: the common electrode voltage supplying circuit adjusts the common electrode voltages supplied to the groups so that luminance of the pixels gradually varies so as to be monotonously darker or so as to be monotonously brighter from one end side to a center of the scanning lines in a direction in which the scanning lines are disposed.

[0032] According to the foregoing arrangement, it is possible to perform appropriate adjustment required in widening the visual angle in a liquid crystal display device which has such characteristic that: luminance of the pixels gradually varies so as to be darker or brighter while moving from one side to a central in a direction, in which the scanning lines are disposed, such as an up-and-down direction with respect to the image for example.

[0033] The liquid crystal display device may be arranged so that: the common electrode voltage supplying circuit includes an input operation circuit which allows adjustment amounts of the common electrode voltages to be inputted.

[0034] According to the foregoing arrangement, it is possible more easily adjust the common electrode voltages by providing a pinch or the like (input operation circuit) on the liquid crystal display device.

[0035] The liquid crystal display device may be arranged so as to include: a scanning line driving circuit for driving the scanning lines; and a reference voltage generating circuit for generating reference voltages, having plural levels different from each other, which are supplied to the scanning line driving circuit so as to make gradation display in

accordance with a display signal, said reference voltage generating circuit being capable of adjusting the reference voltages.

[0036] Further, the method for driving the liquid crystal display device may be arranged so as to include the step of generating reference voltages, having plural levels, which cause gradation display to be made in accordance with a display signal, and adjusting the reference voltages.

[0037] According to the foregoing arrangement, reference voltages, having plural levels, which cause gradation display to be made in accordance with a display signal is generated, and the reference voltages are adjusted, so that it is possible to simplify a circuit for gradation display by making the circuit rationalized and shared unlike an arrangement in which a large number of resistance elements and switches generate a large number of gradation voltages.

[0038] The liquid crystal display device may be arranged so that: the reference voltage generating circuit adjusts the reference voltages so that a predetermined gamma characteristic is obtained in an arbitrary line of lines each of which is constituted of the pixels provided in a direction in which the scanning lines are disposed.

[0039] The method for driving the liquid crystal display device may be arranged so that: the reference voltages are adjusted so that a predetermined gamma characteristic is obtained in an arbitrary line of lines each of which is constituted of the pixels provided in a direction in which the scanning lines are disposed.

[0040] According to the foregoing arrangement, it is possible to obtain not only the luminance of the pixels but also a predetermined gamma characteristic in a line constituted of the pixels disposed in a direction in which the scanning lines are disposed, so that it is possible to realize more preferable display.

[0041] The liquid crystal display device may be arranged so as to include a correction information storage circuit for storing adjustment amounts of the reference voltages, wherein the reference voltage generating circuit adjusts the reference voltages in accordance with the adjustment amounts stored in the correction information storage circuit.

[0042] According to the foregoing arrangement, it is possible to easily adjust the gamma characteristic by rewriting the adjustment amount stored in the correction information storage circuit.

[0043] The liquid crystal display device may be arranged so that: the reference voltage generating circuit adjusts the reference voltages so that a gamma characteristic is obtained in a line, constituted of the pixels, which is positioned on the one side in a direction in which the scanning lines are disposed and another gamma characteristic is obtained in a line, constituted of the pixels, which is positioned on the other side in the direction in which the scanning lines are disposed, said gamma characteristics being different from each other.

[0044] According to the foregoing arrangement, it is possible to adjust the reference voltages so that a gamma characteristic is obtained in a line, constituted of the pixels, which is positioned on one side in a direction in which the scanning lines are disposed and another gamma characteristic is obtained in a line, constituted of the pixels, which is

positioned on other side in the direction in which the scanning lines are disposed, said gamma characteristics being different from each other, so that it is possible to more delicately adjust a display condition.

[0045] The liquid crystal display device may be arranged so that: the reference voltage generating circuit adjusts the reference voltages so as to obtain gamma characteristics different from each other in a first line constituted of the pixels provided on the one side in a direction in which the scanning lines are disposed, a second line constituted of the pixels provided on the other side in the direction in which the scanning lines are disposed, and a third line constituted of the pixels provided between the first line and the second line so that the gamma characteristic obtained in the third line is intermediate between the gamma characteristic obtained in the first line and the gamma characteristic obtained in the second line.

[0046] Thus, it is possible to appropriately adjust the gamma characteristic in a direction, in which the scanning lines are disposed, such as an up-and-down direction with respect to the display image, so that it is possible to realize more preferable display.

[0047] For a fuller understanding of the nature and advantages of the invention, reference should be made to the ensuing detailed description taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

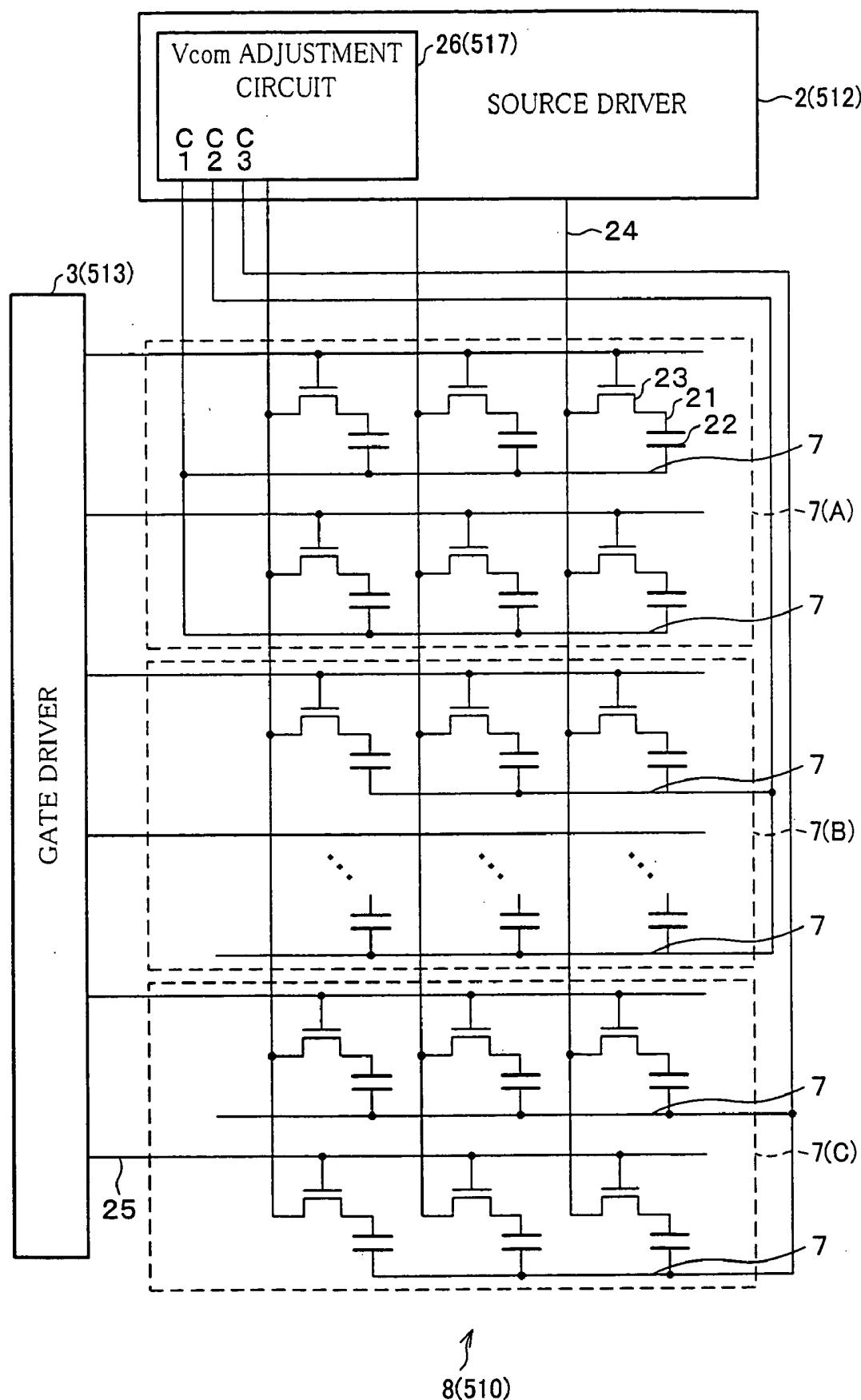

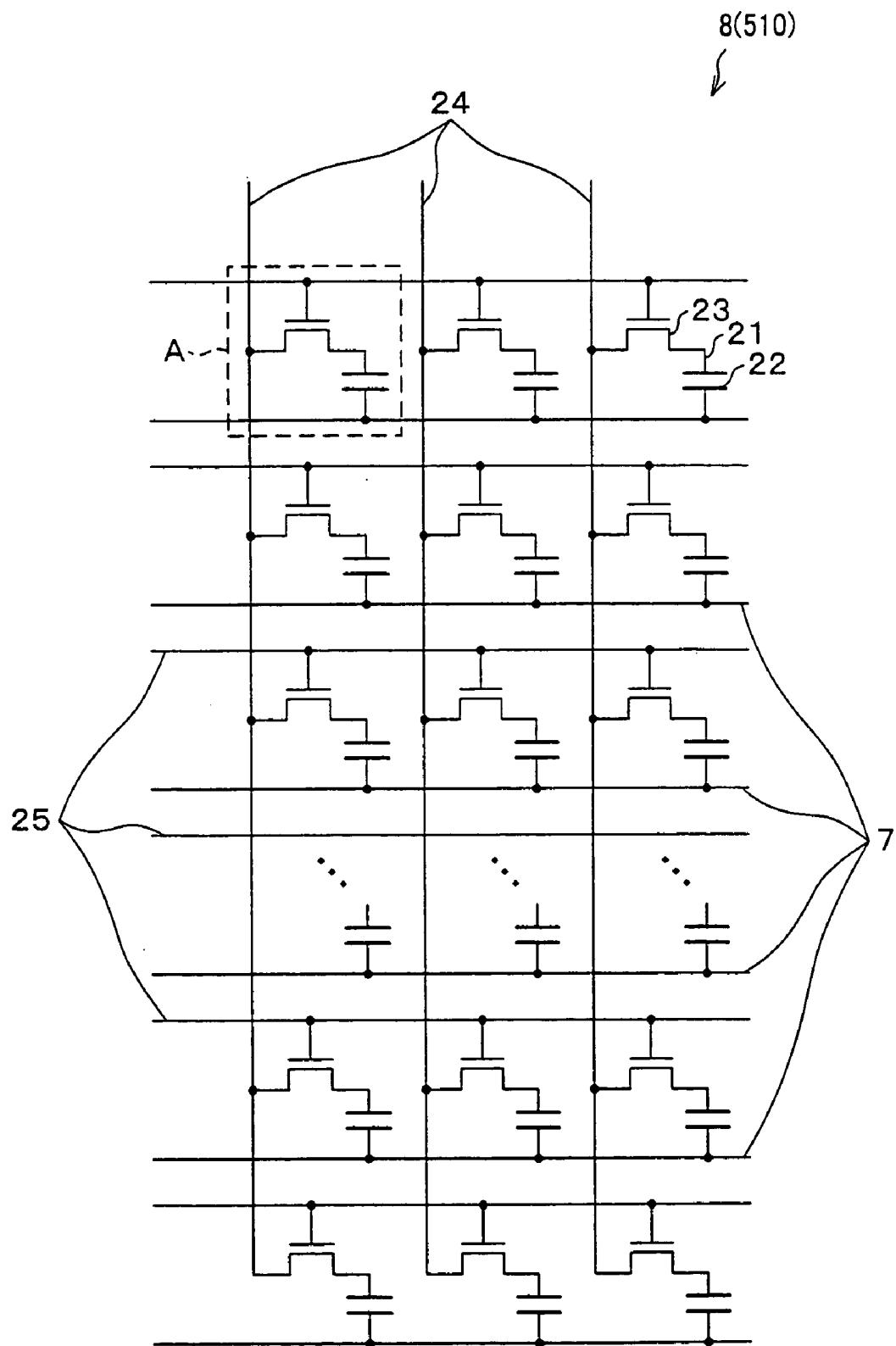

[0048] FIG. 1 is a circuit diagram showing a structure of a TFT-type liquid crystal panel in one embodiment of the present invention.

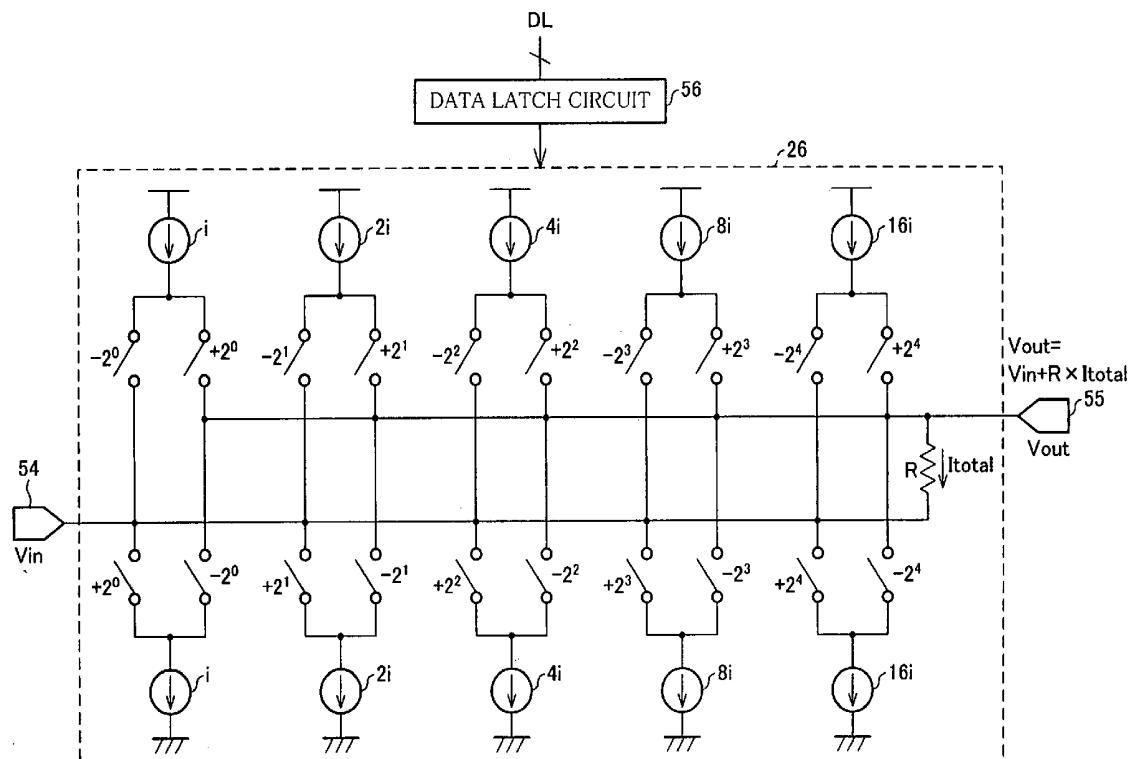

[0049] FIG. 2 is a block diagram showing a structure of a liquid crystal display device provided with the liquid crystal panel shown in FIG. 1.

[0050] FIG. 3 is a circuit diagram showing the liquid crystal panel of FIG. 1 except for a driver.

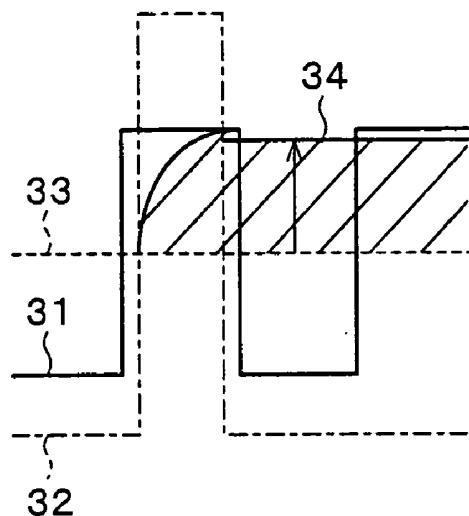

[0051] FIG. 4 is a waveform schematic showing an example of a general liquid crystal driving waveform.

[0052] FIG. 5 is a waveform schematic showing another example of the liquid crystal driving waveform shown in FIG. 4, and shows a case where a voltage applied to a liquid crystal layer is lower than a voltage in a case of FIG. 4.

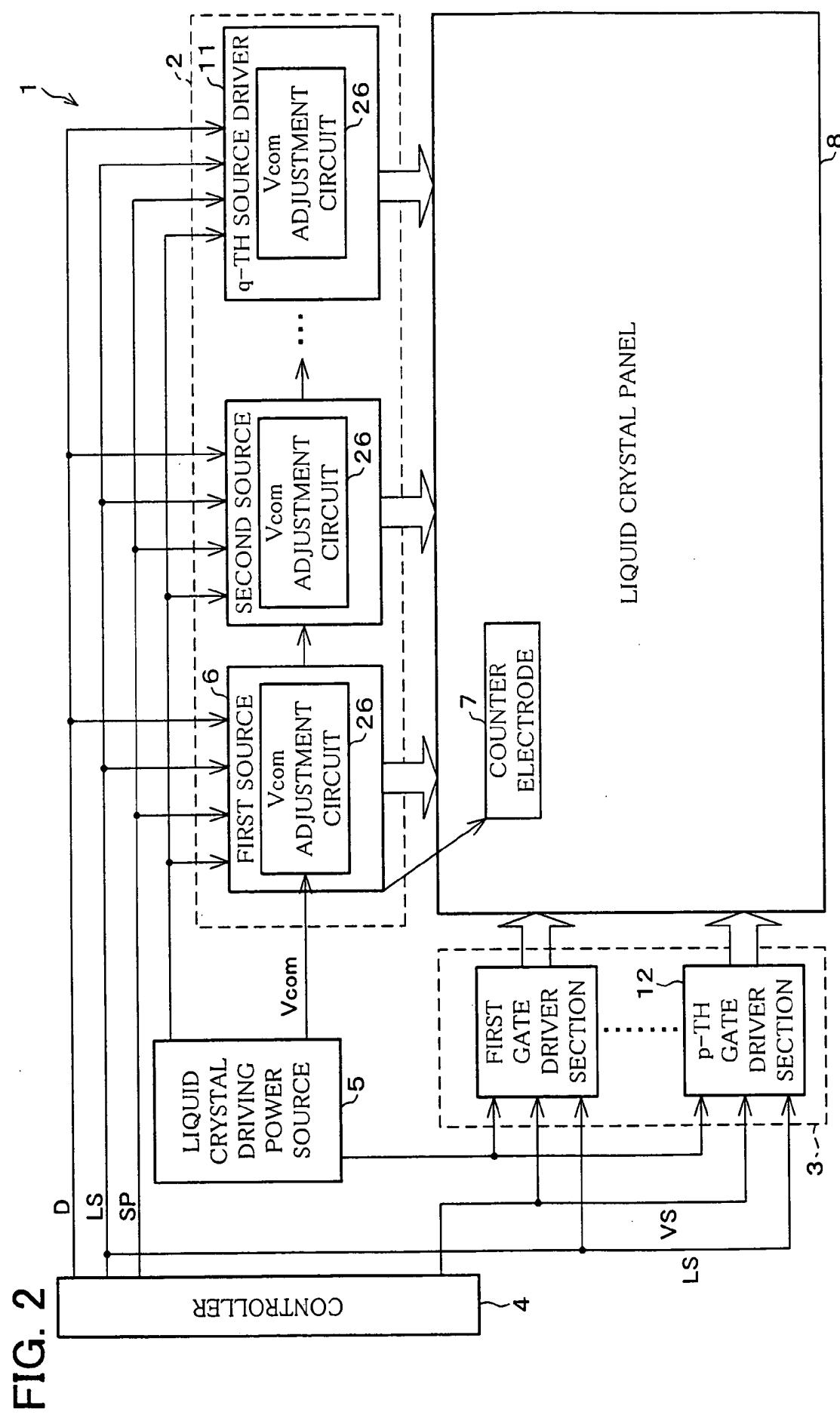

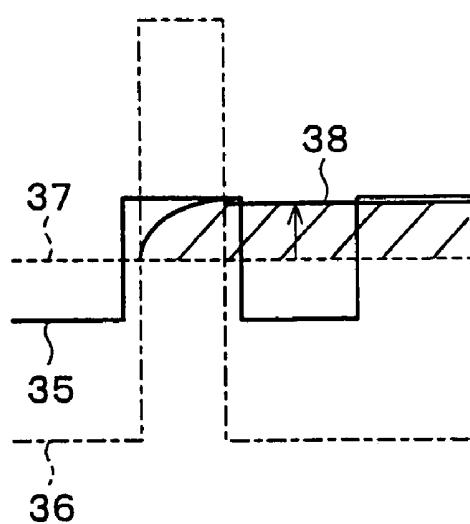

[0053] FIG. 6 is a block diagram showing a structure of a source driver section provided with a source driver of the liquid crystal display device shown in FIG. 2.

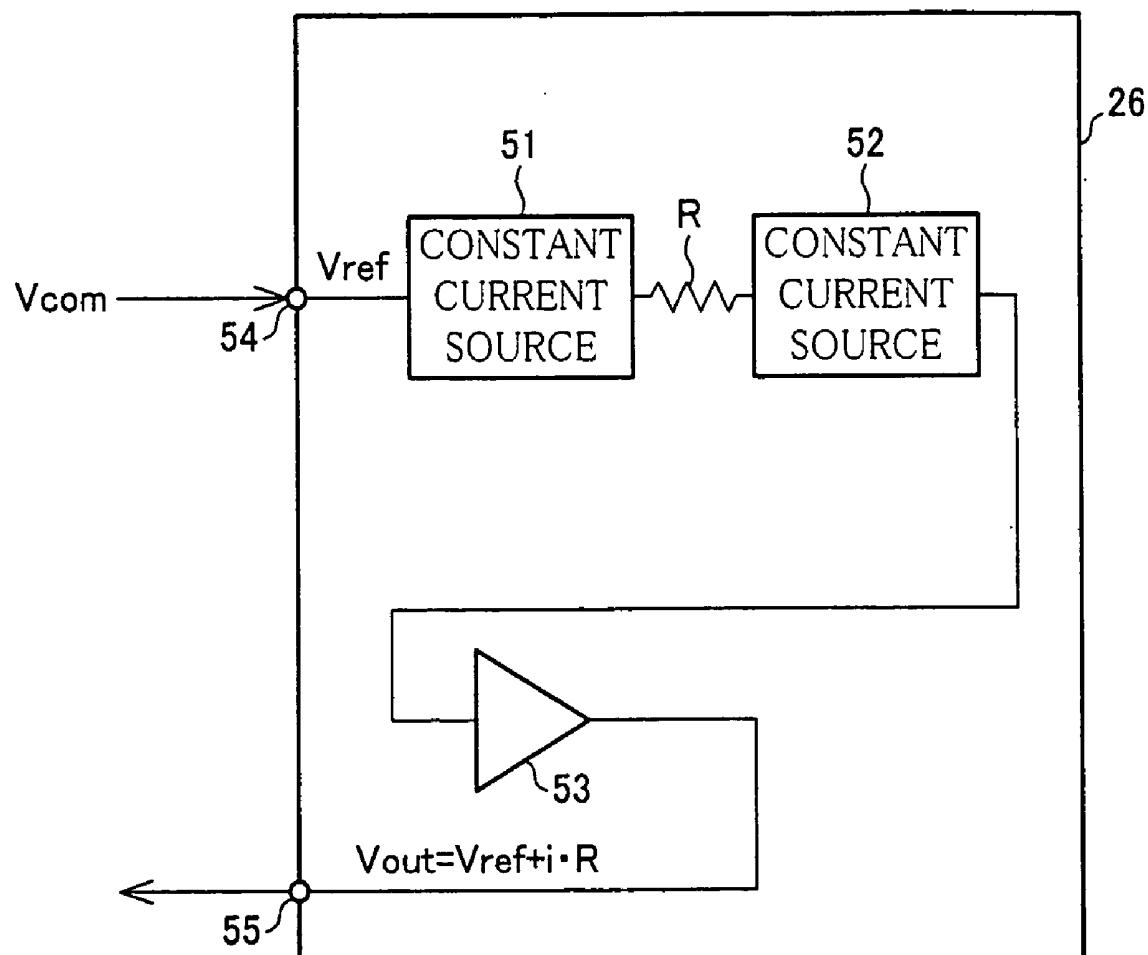

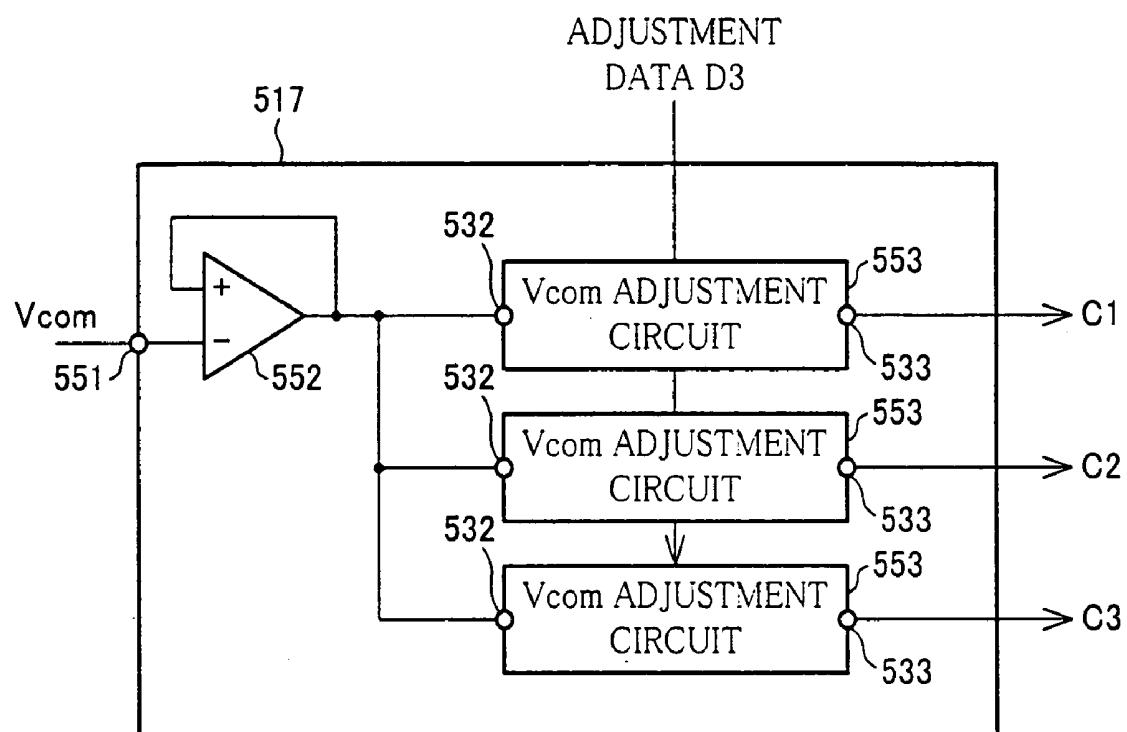

[0054] FIG. 7 is a block diagram schematically showing a structure of a Vcom adjustment circuit shown in FIG. 1.

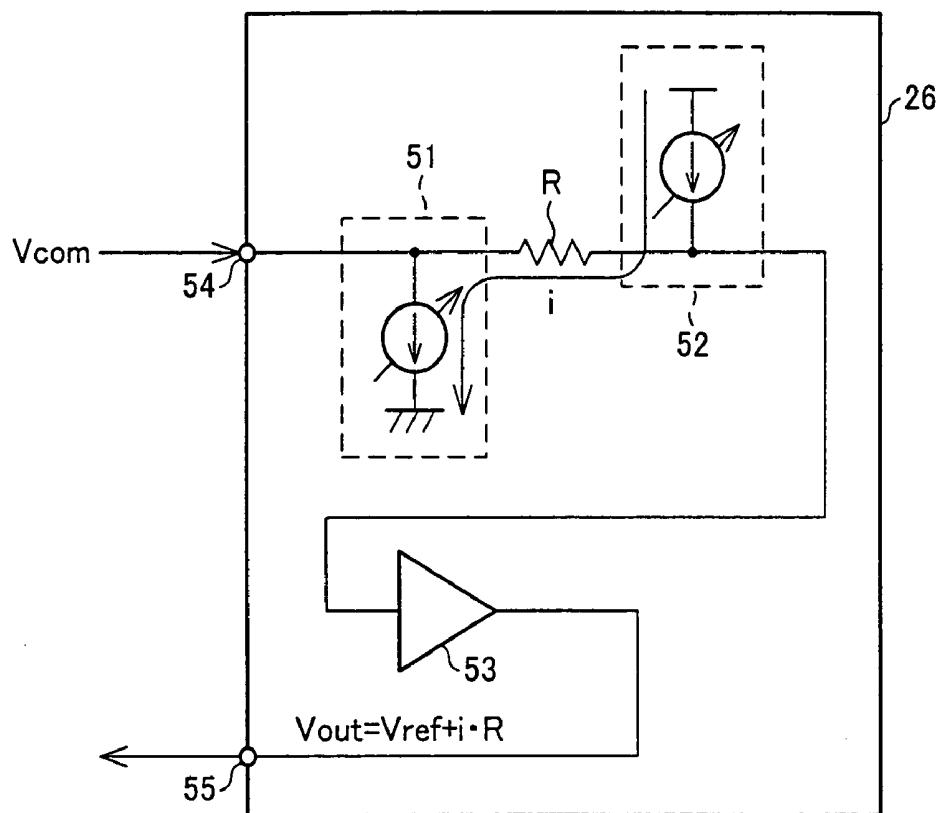

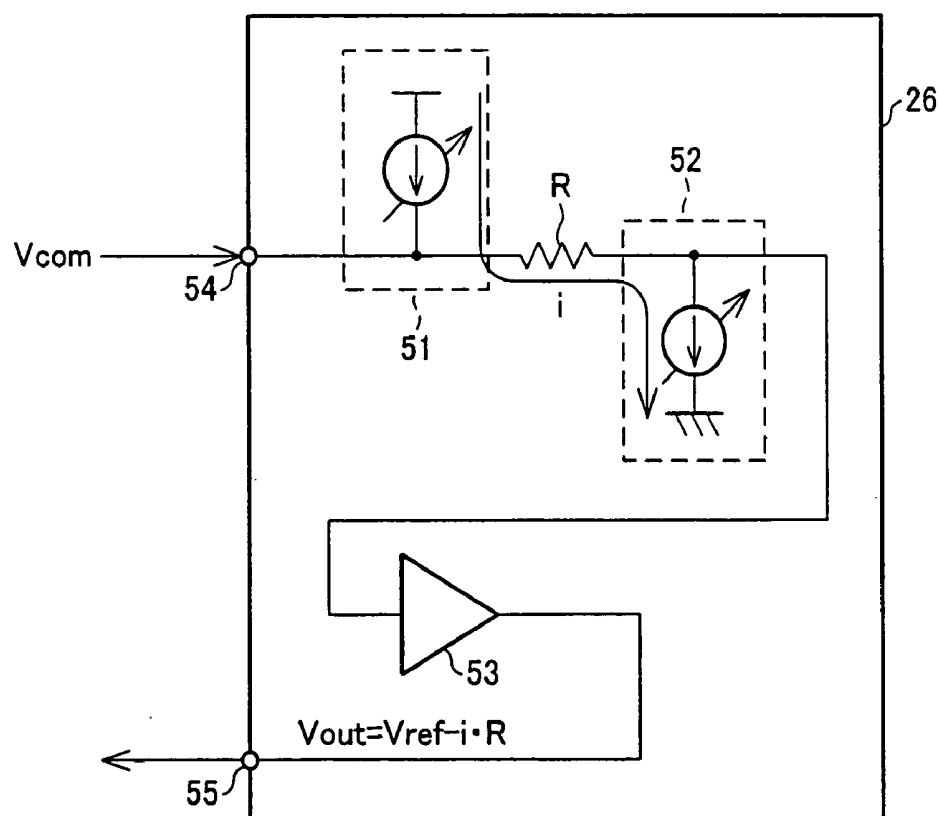

[0055] FIG. 8(a) shows how a constant current source in the Vcom adjustment circuit of FIG. 7 operates, and illustrates a case of obtaining an output voltage higher than a reference voltage, and FIG. 8(b) illustrates a case of obtaining an output voltage lower than the reference voltage.

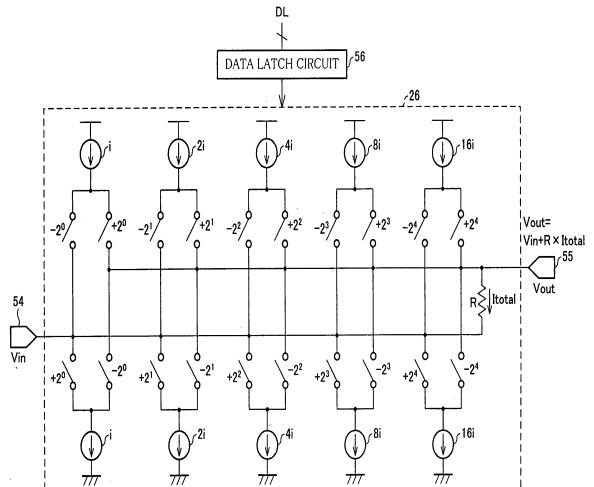

[0056] FIG. 9 is a circuit diagram showing a structure of the constant current source shown in FIG. 7.

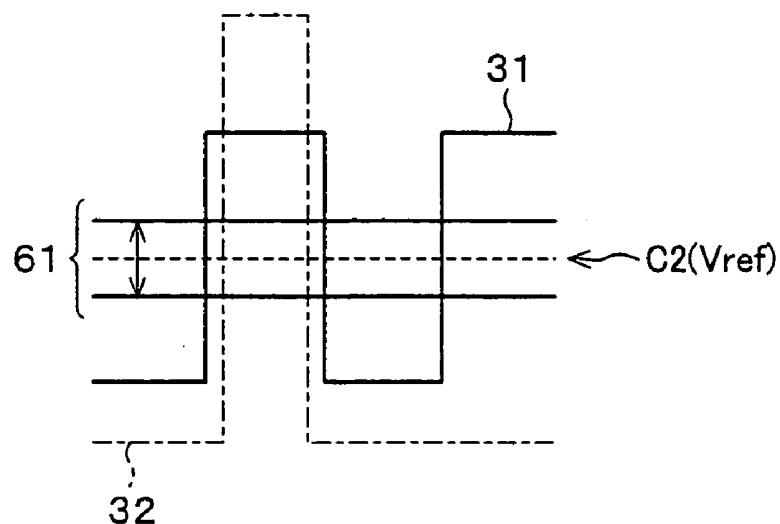

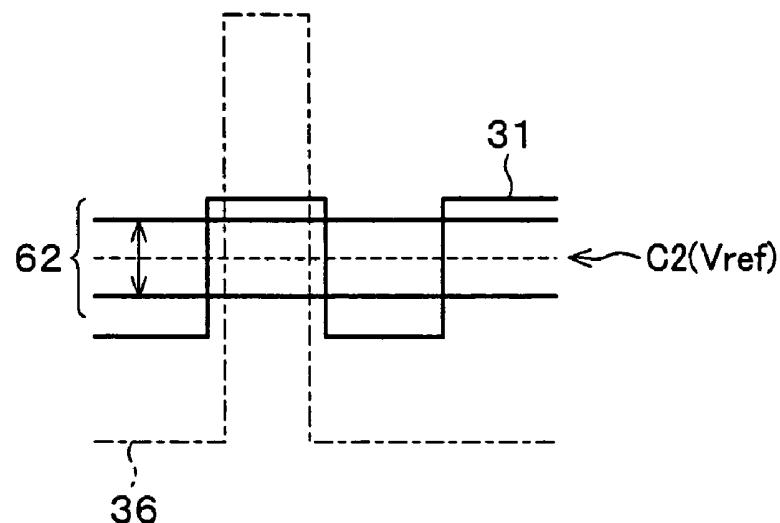

[0057] FIG. 10 is a waveform schematic showing an example of a liquid crystal driving waveform in the liquid crystal display device shown in FIG. 2.

[0058] FIG. 11 is a waveform schematic showing another example of the liquid crystal driving waveform shown in FIG. 10, and illustrates a case where the voltage applied to the liquid crystal layer is lower than a voltage in a case of FIG. 10.

[0059] FIG. 12 is a schematic showing a condition under which a counter electrode voltage is applied from the Vcom adjustment circuit of FIG. 1 to the liquid crystal panel.

[0060] FIG. 13 is a schematic showing a condition under which the counter electrode voltage is applied from the Vcom adjustment circuit of FIG. 1 to the liquid crystal panel in two sequential frames.

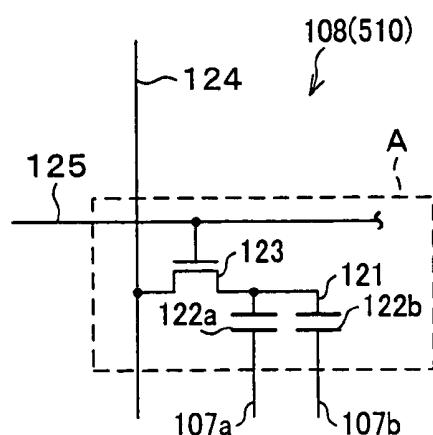

[0061] FIG. 14 is a circuit diagram showing a structure of a liquid crystal display element corresponding to a single pixel of a multi-domain liquid crystal panel.

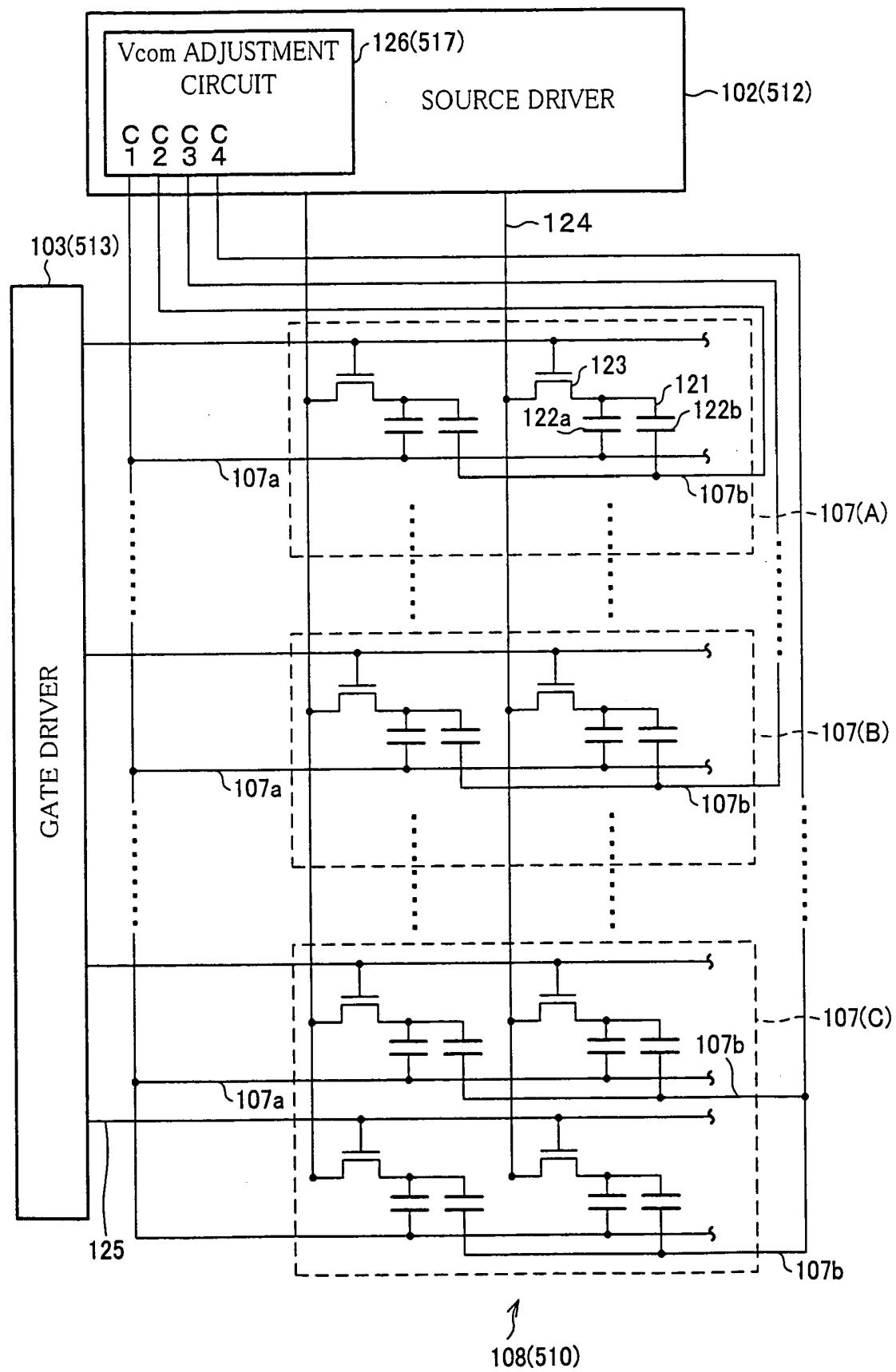

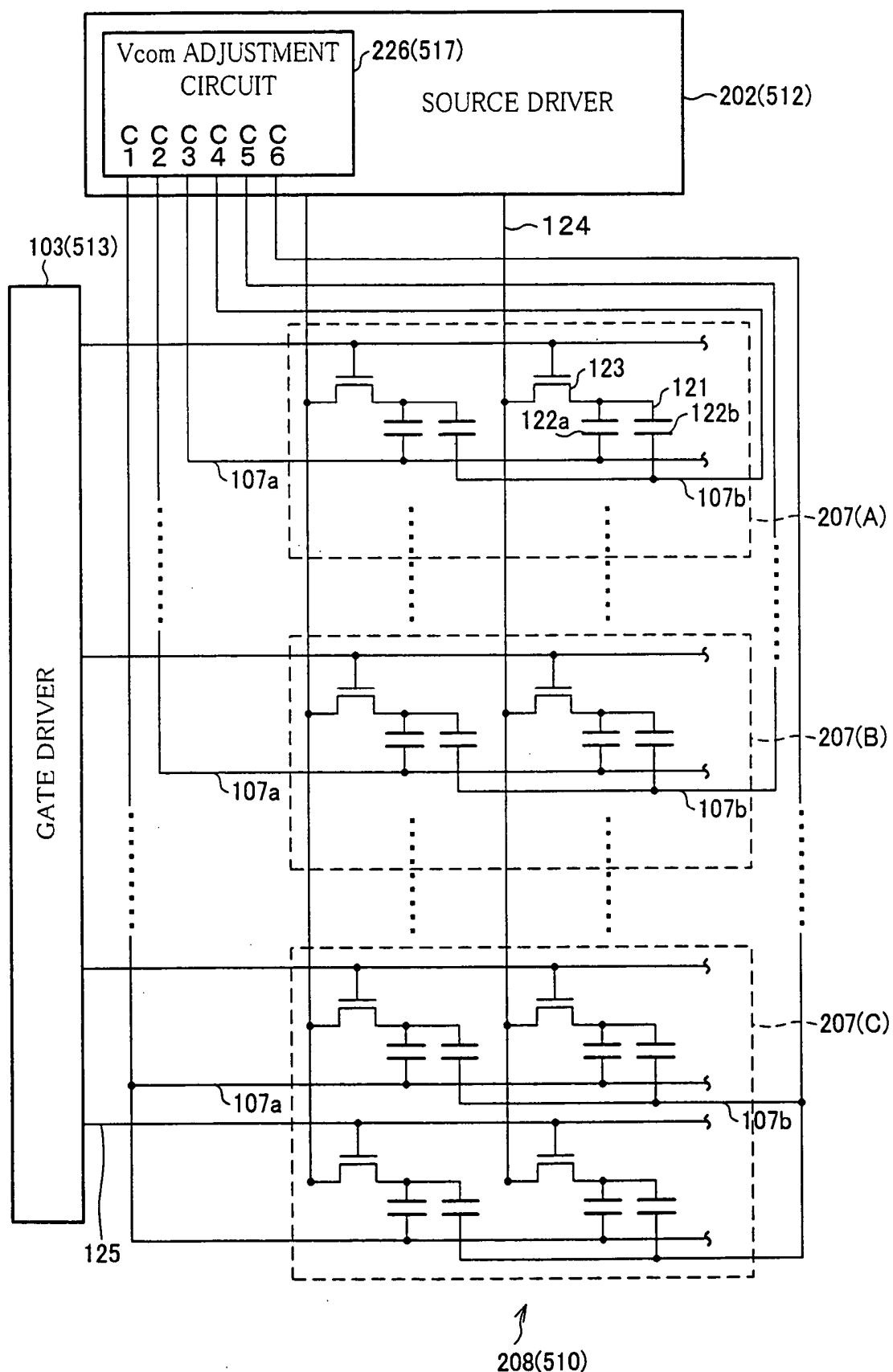

[0062] FIG. 15 is a circuit diagram showing a condition under which the structure of the liquid crystal panel of FIG. 1 is applied to the multi-domain liquid crystal panel.

[0063] FIG. 16 is a circuit diagram showing another example of the structure of the liquid crystal panel that is shown in FIG. 15.

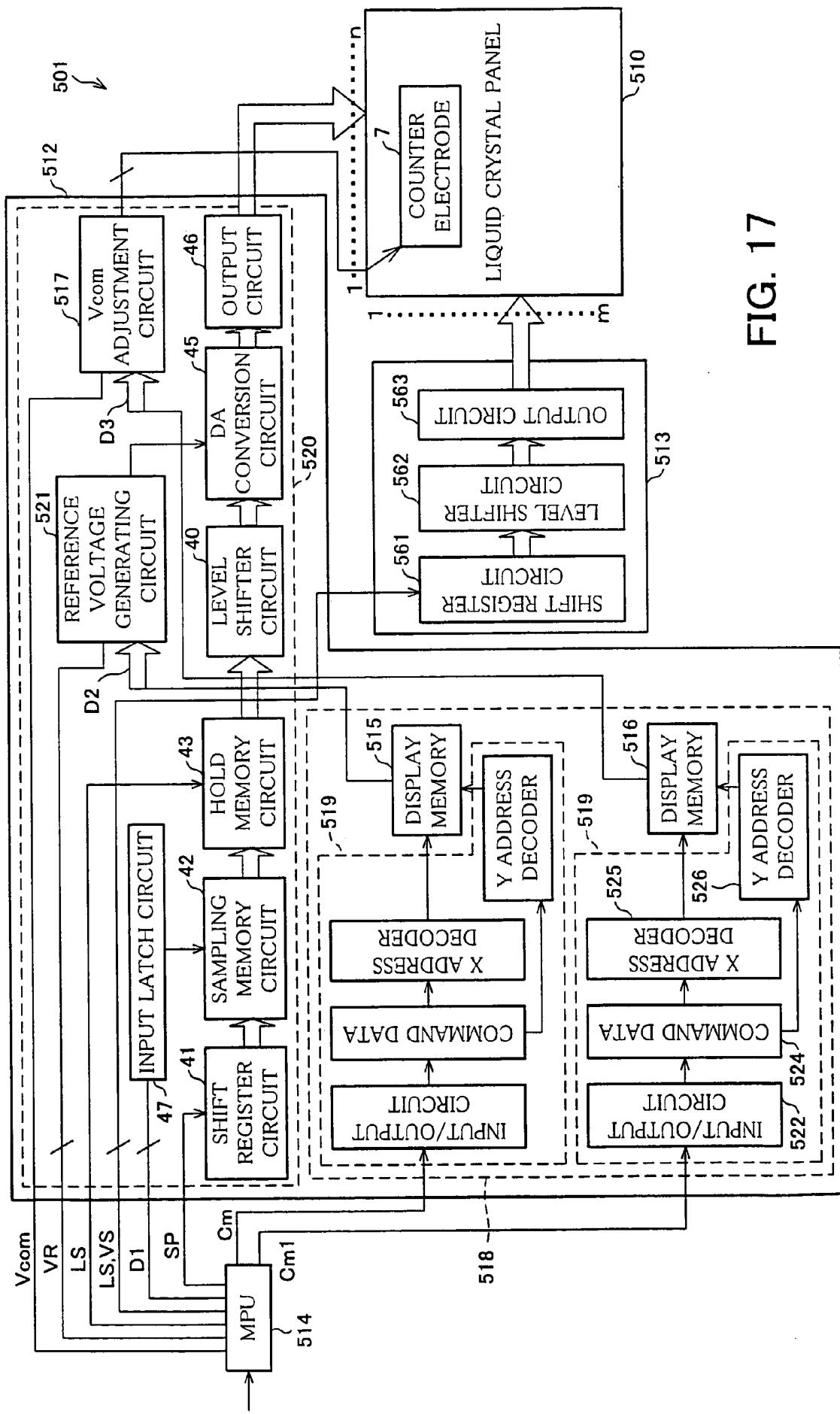

[0064] FIG. 17 is a block diagram showing a structure of a TFT-type liquid crystal display device in another embodiment of the present invention.

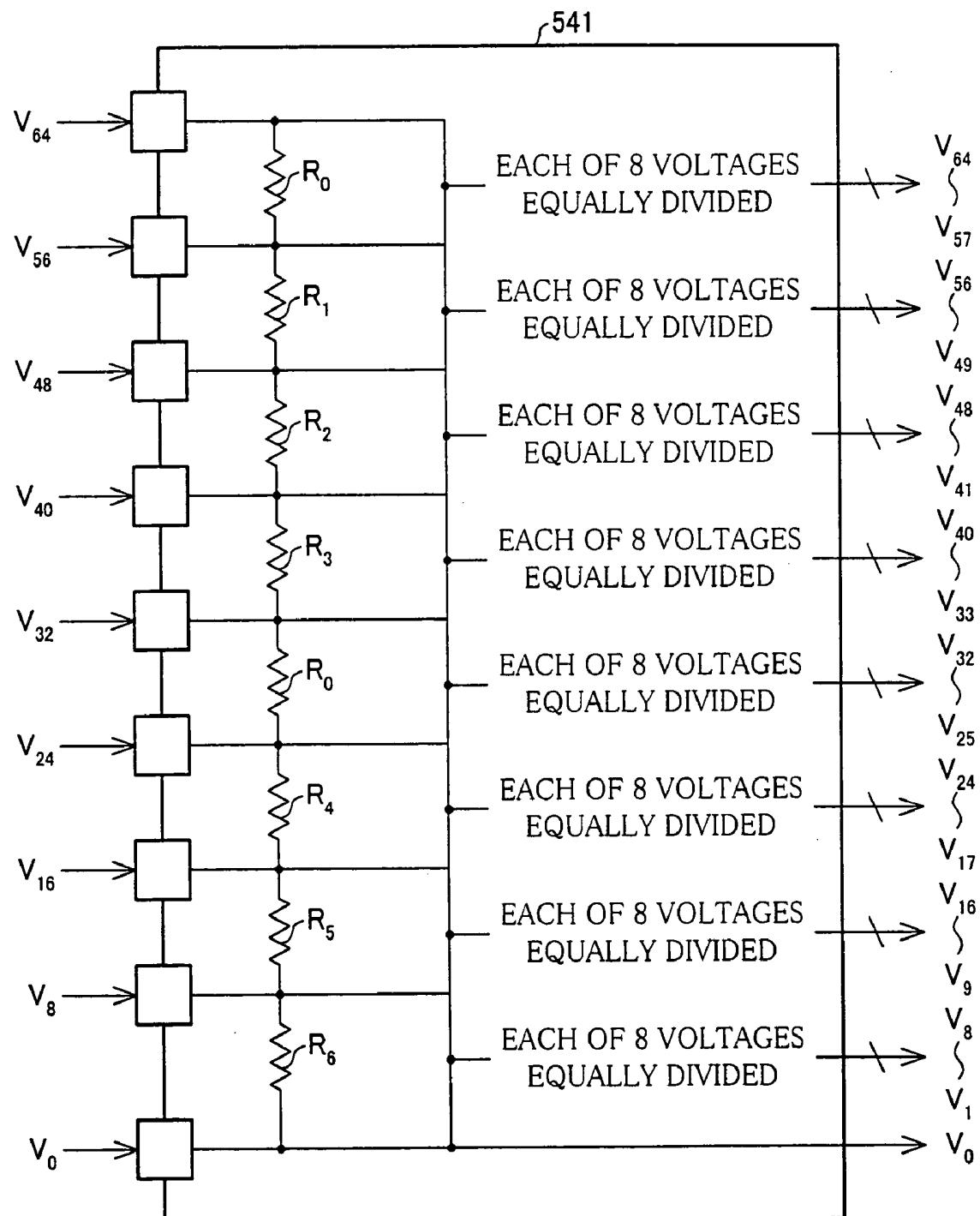

[0065] FIG. 18 is a block diagram schematically showing a structure of a reference voltage generating circuit shown in FIG. 17.

[0066] FIG. 19 is a block diagram schematically showing a structure of a conventional reference voltage generating circuit compared with the reference voltage generating circuit of FIG. 18.

[0067] FIG. 20 is a block diagram showing a structure of a  $\gamma$  correction adjustment circuit shown in FIG. 18.

[0068] FIG. 21(a) shows how a constant current source of the  $\gamma$  correction adjustment circuit of FIG. 20 operates, and illustrates a case of obtaining an output voltage higher than a reference voltage, and FIG. 21(b) illustrates a case of obtaining an output voltage lower than the reference voltage.

[0069] FIG. 22 is a circuit diagram showing a structure of the constant current source shown in FIG. 20.

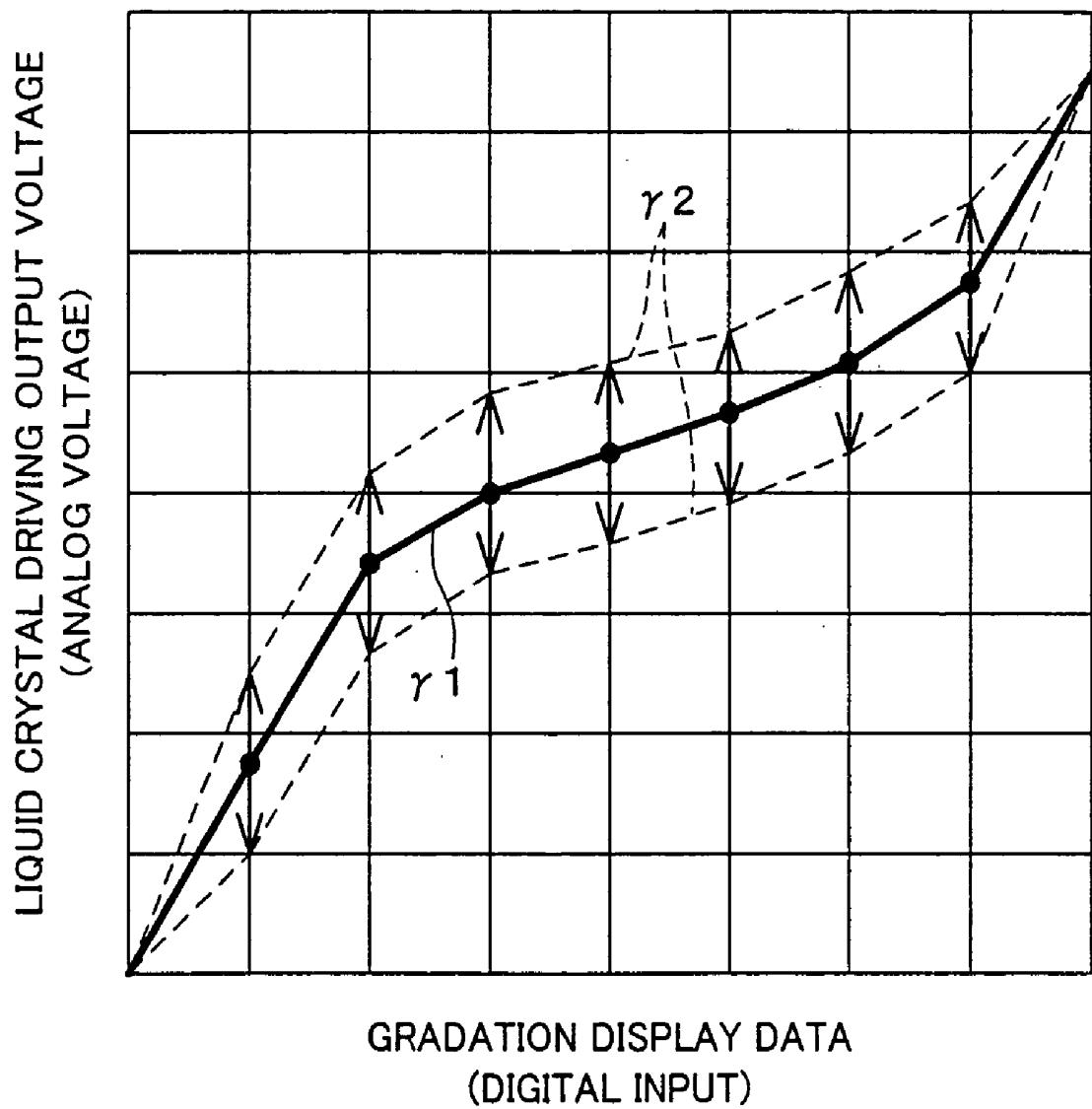

[0070] FIG. 23 is a graph showing a relationship ( $\gamma$  correction characteristic) between gradation display data (digital input) and a liquid crystal driving output voltage (analog voltage) in a reference voltage generating circuit shown in FIG. 21(a) and FIG. 21(b).

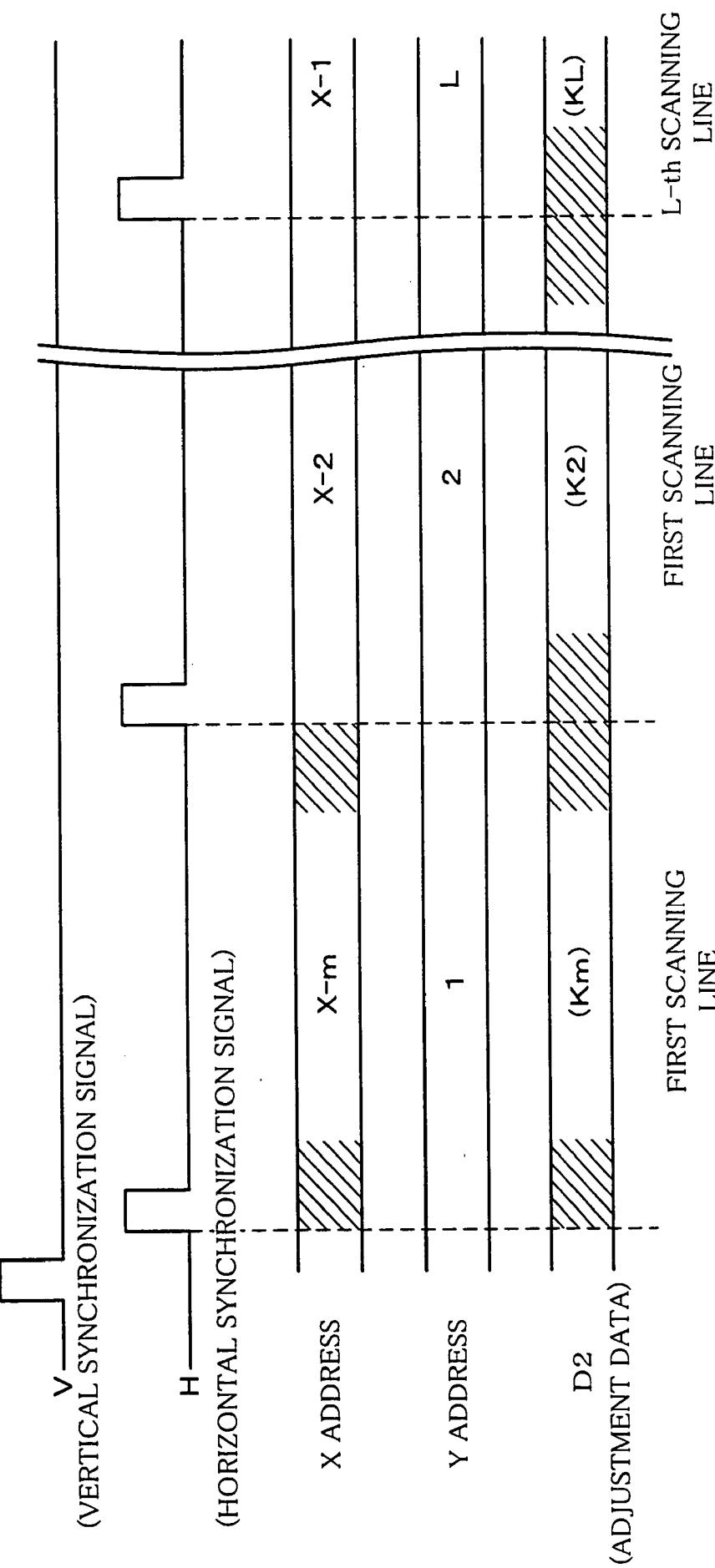

[0071] FIG. 24 is a schematic showing a condition under which  $\gamma$  correction characteristics  $\gamma_1$  and  $\gamma_2$  that are shown in FIG. 23 are applied to each pixel of the liquid crystal panel.

[0072] FIG. 25 is a schematic showing a condition under which the  $\gamma$  correction characteristics  $\gamma_1$  and  $\gamma_2$  that are shown in FIG. 23 are applied to each pixel of the liquid crystal panel in two sequential frames.

[0073] FIG. 26 is a schematic showing another example of the process shown in FIG. 24, and shows a condition under which  $\gamma$  correction characteristics  $\gamma_1$ ,  $\gamma_2$ , and  $\gamma_3$  are applied to each pixel.

[0074] FIG. 27 is a schematic showing how a condition of the liquid crystal panel varies in two sequential frames when using the  $\gamma$  correction characteristics  $\gamma_1$ ,  $\gamma_2$ , and  $\gamma_3$  that are shown in FIG. 26.

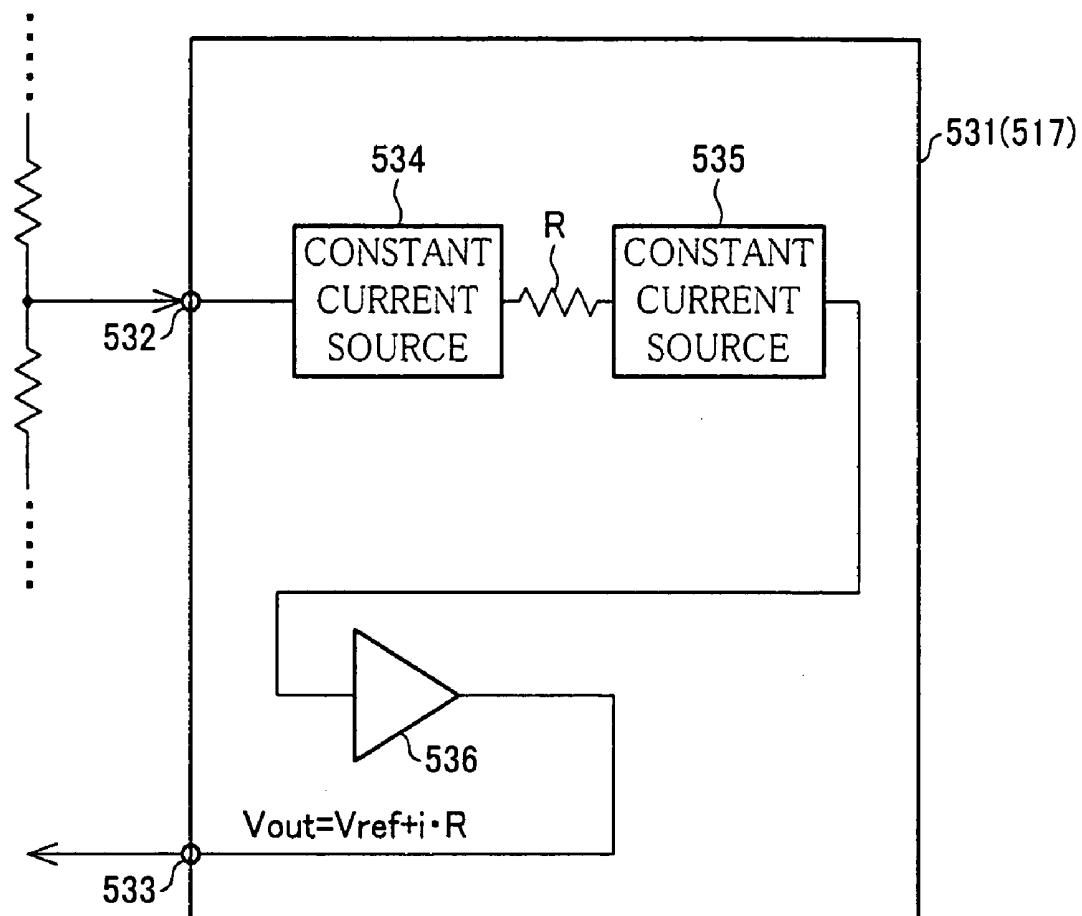

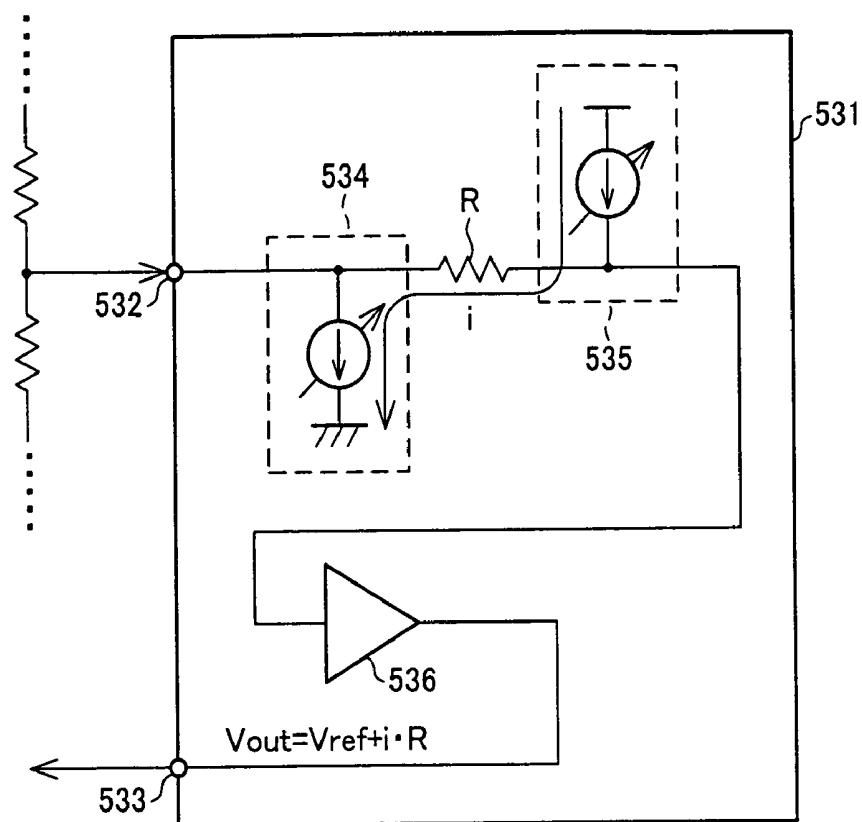

[0075] FIG. 28 is a block diagram schematically showing a structure of the Vcom adjustment circuit shown in FIG. 17.

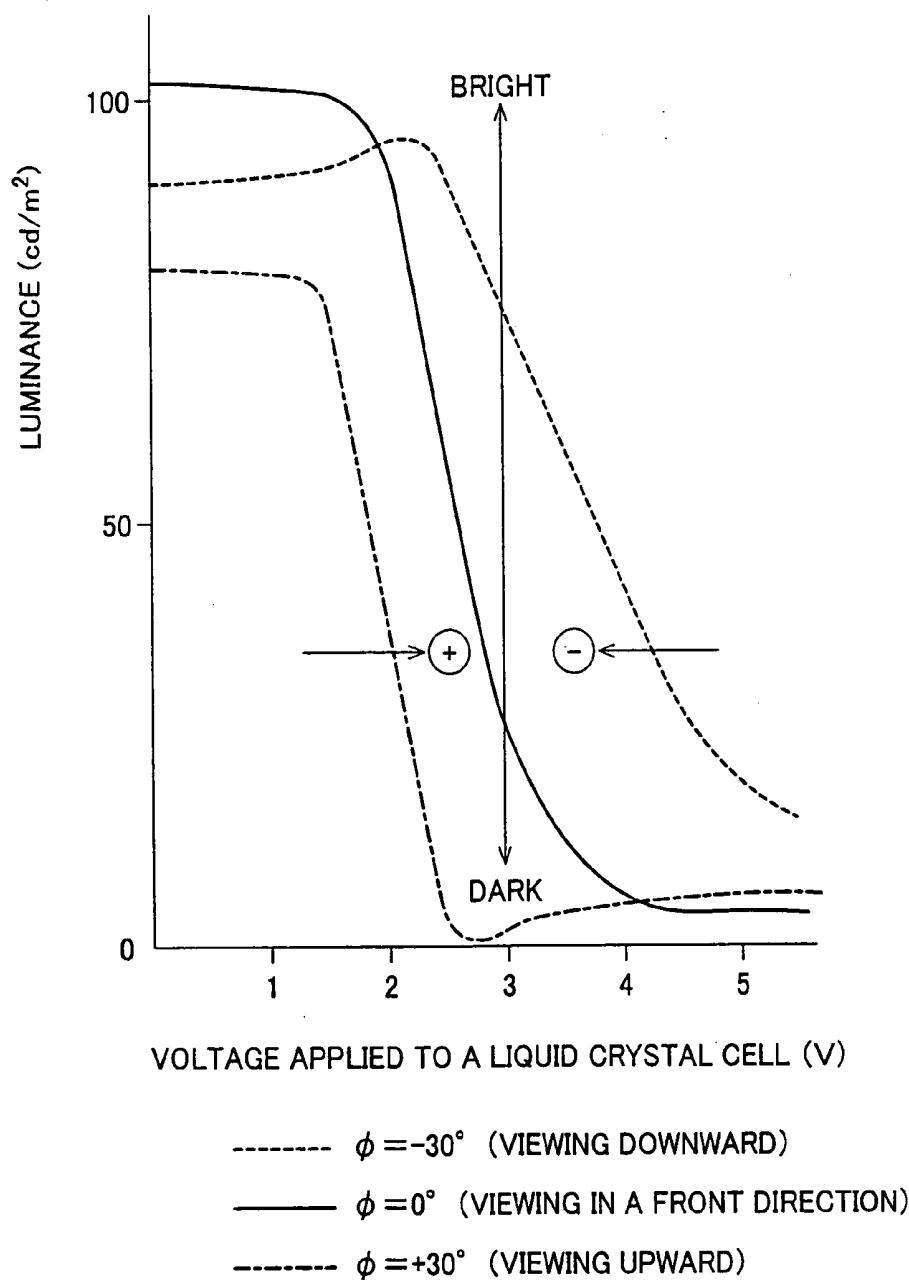

[0076] FIG. 29 is a graph showing a relationship between a voltage applied to the liquid crystal cell and luminance (transmittance) of a single pixel when the liquid crystal panel is viewed from each angular position in viewing  $\Phi$ .

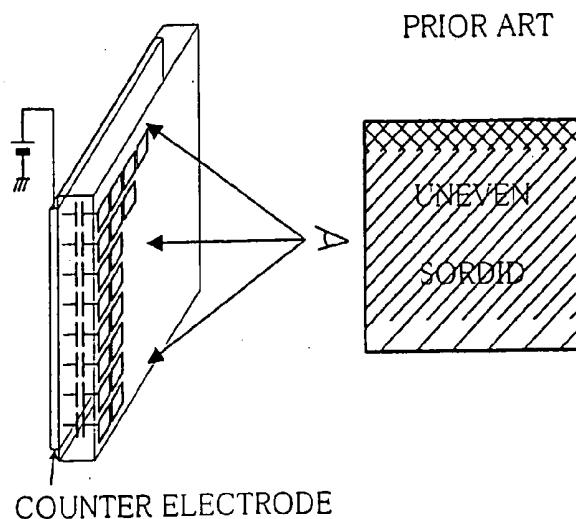

[0077] FIG. 30(a) illustrates a condition under which an upper portion and a lower portion of the liquid crystal panel are different from each other in terms of a visual angle, and FIG. 30(b) illustrates a liquid crystal display device of the present invention which solves the condition of FIG. 30(a), and FIG. 30(c) is a block diagram schematically showing a structure of a source driver used to solve the condition of FIG. 30(a).

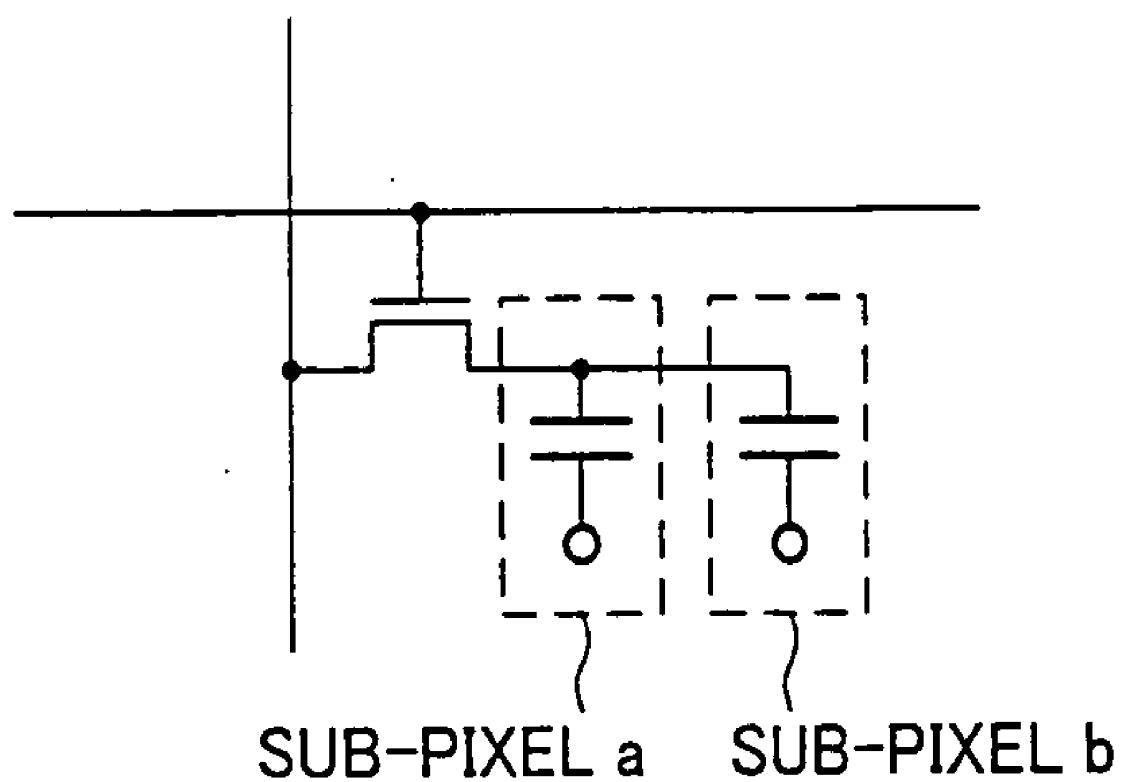

[0078] FIG. 31 is a circuit diagram showing a structure of a single pixel, having two sub-pixels, which is provided in the liquid crystal panel.

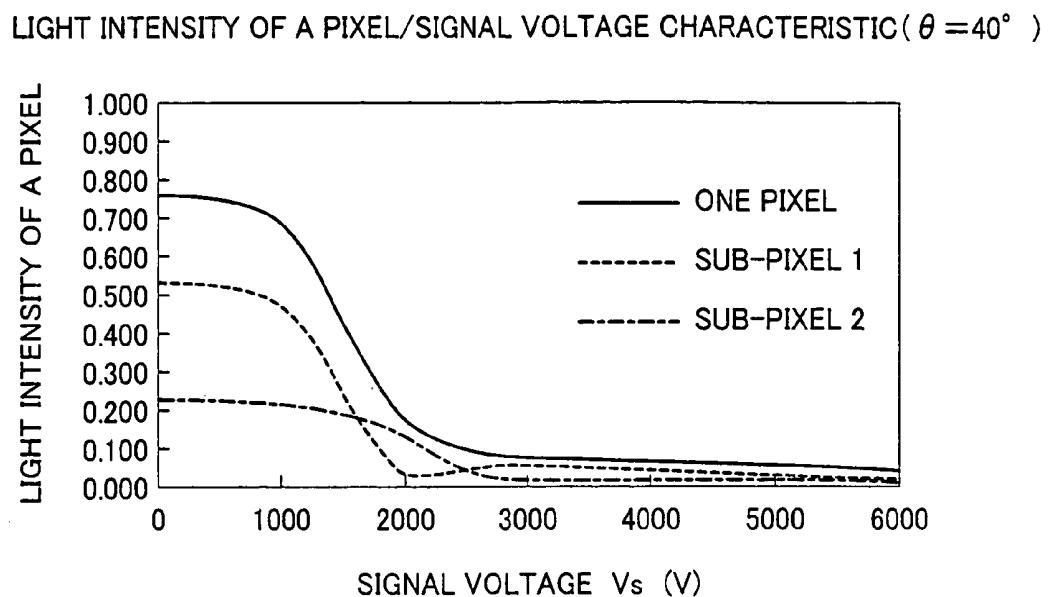

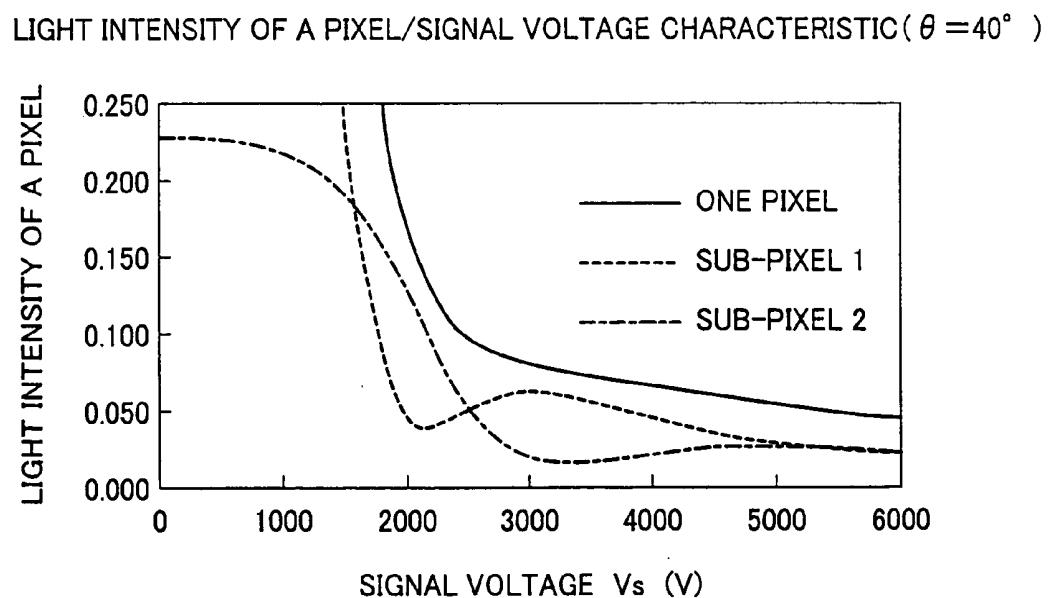

[0079] FIG. 32(a) is a graph showing a relationship between a signal voltage in the pixel shown in FIG. 31 and light intensity of the pixel, and FIG. 32(b) is a graph obtained by partially enlarging a range of the light intensity of the pixel that is shown in FIG. 32(a).

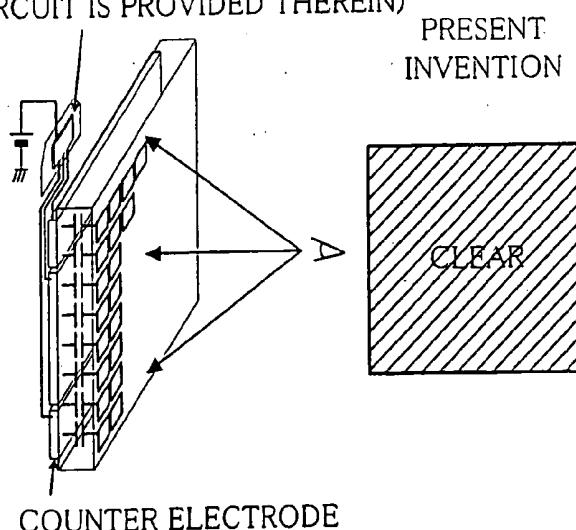

[0080] FIG. 33(a) shows a case where a visual angle distribution of the liquid crystal display device is adjusted into a predetermined condition, and illustrates a case of setting an image to be clearly observed when viewed from the upper side of the image, and FIG. 33(b) illustrates a case of setting the image to be clearly observed when viewed from the lower side of the image.

[0081] FIG. 34 illustrates an example of a visual angle distribution of the present invention that can be obtained by adjusting both the visual angle distributions shown in FIG. 33(a) and FIG. 33(b).

[0082] FIG. 35 illustrates a condition under which a visual angle characteristic varies depending on whether an image is viewed from the upper side or lower side in a conventional liquid crystal display device with a large screen.

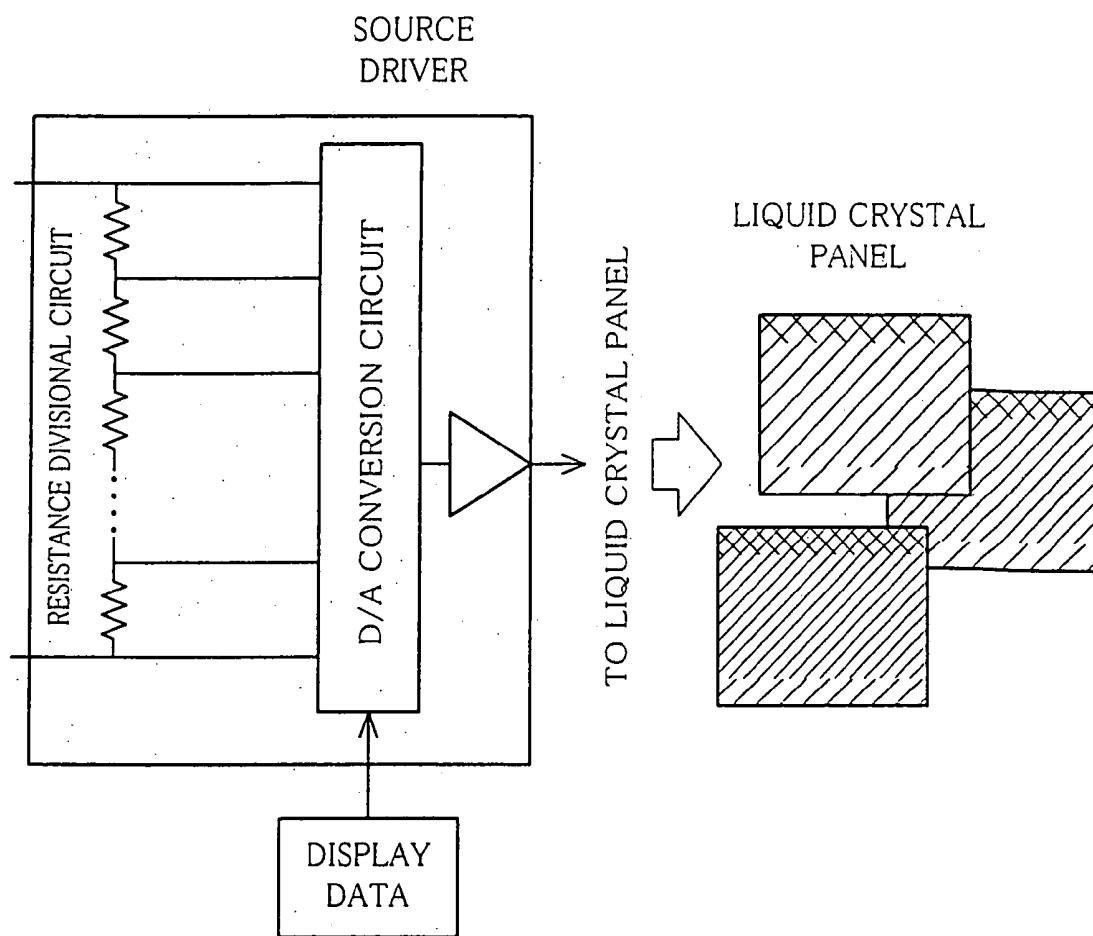

[0083] FIG. 36 illustrates a structure of a conventional source driver for generating a voltage applied to the liquid crystal panel by using each of voltages divided by a resistance dividing circuit, and a condition under which the liquid crystal panel displays an image by means of the source driver.

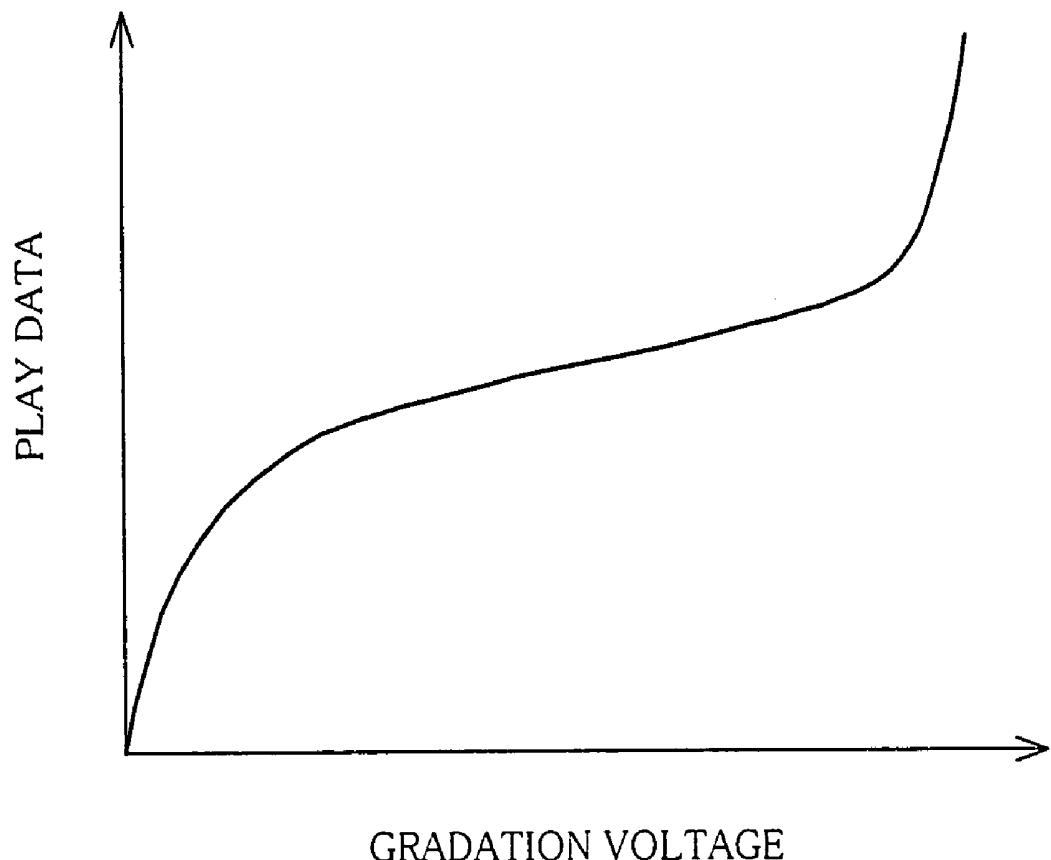

[0084] FIG. 37 is a graph showing a  $\gamma$  characteristic fixed by the structure shown in FIG. 36.

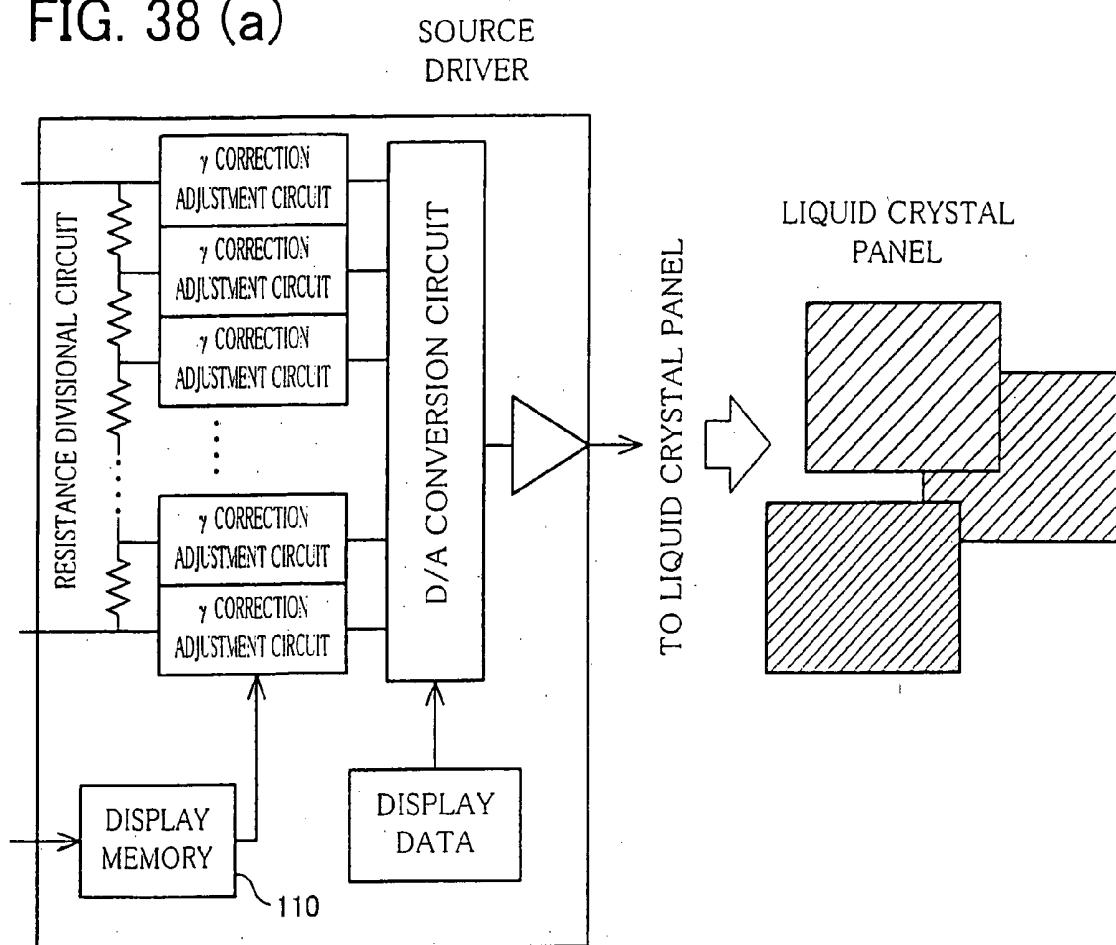

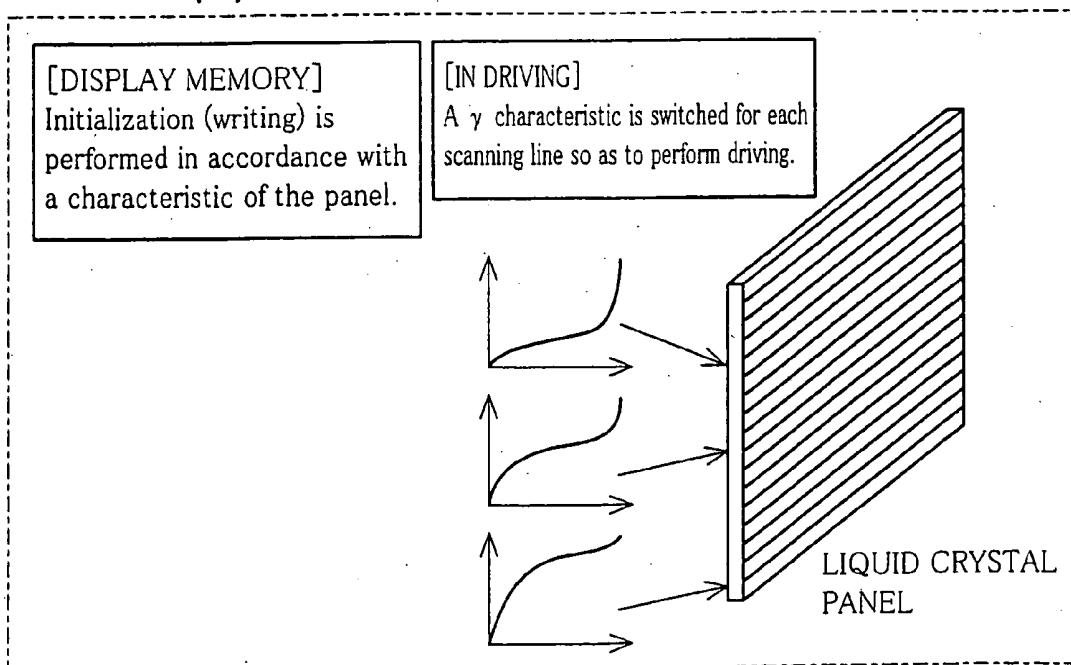

[0085] FIG. 38(a) illustrates a structure of a source driver of an embodiment of the present invention which source driver generates a voltage applied to the liquid crystal panel, and a condition under which the crystal panel displays an image by means of the source driver, and FIG. 38(b) illustrates a condition under which a voltage subjected to  $\gamma$  correction by means of the source driver is applied to the liquid crystal panel.

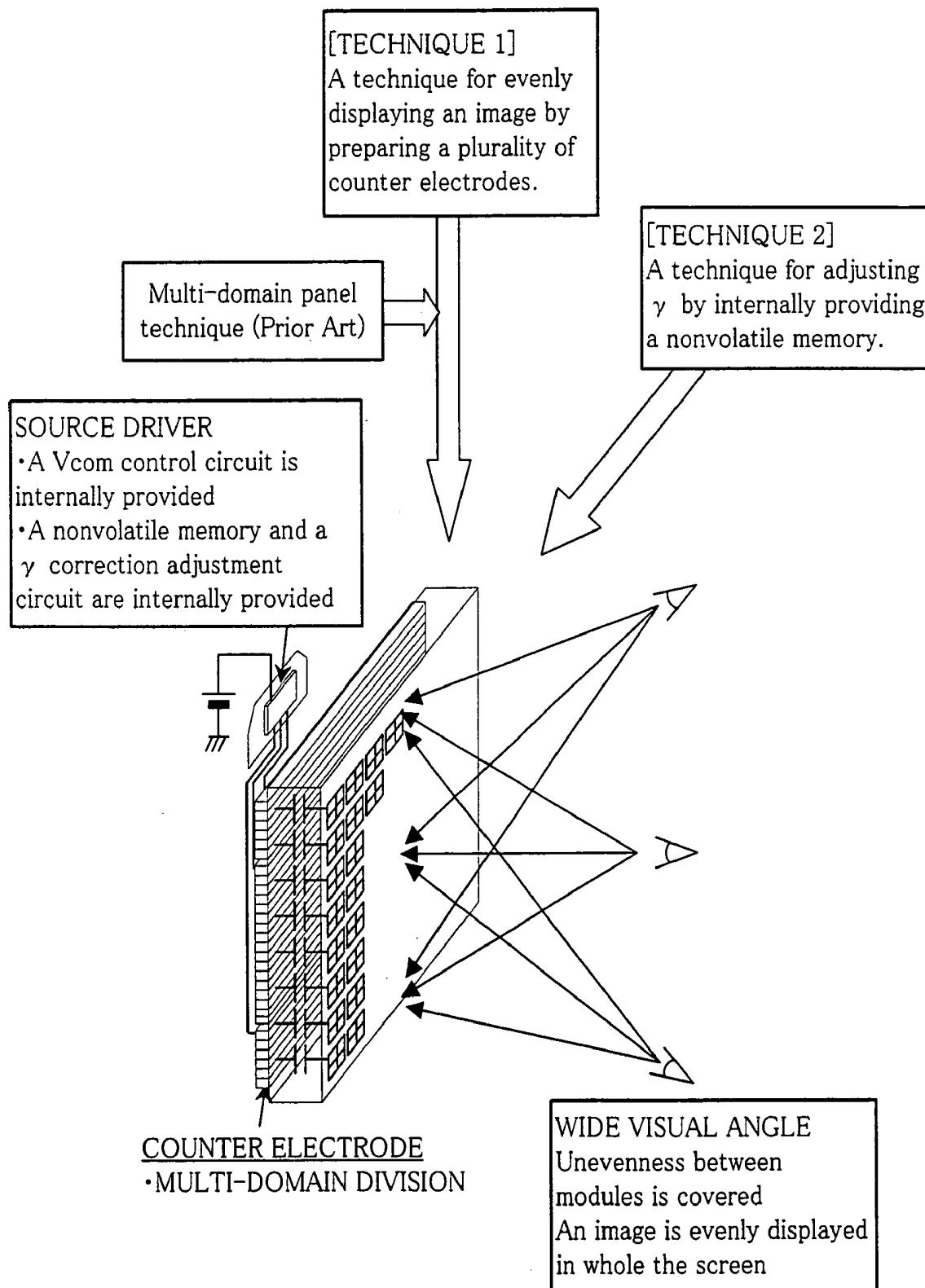

[0086] FIG. 39 illustrates a condition under which a uniformly displaying technique based on division of the counter electrodes and a  $\gamma$  adjustment technique based on a non-volatile memory internally provided are adopted with respect to the liquid crystal display device of the embodiment of the present invention.

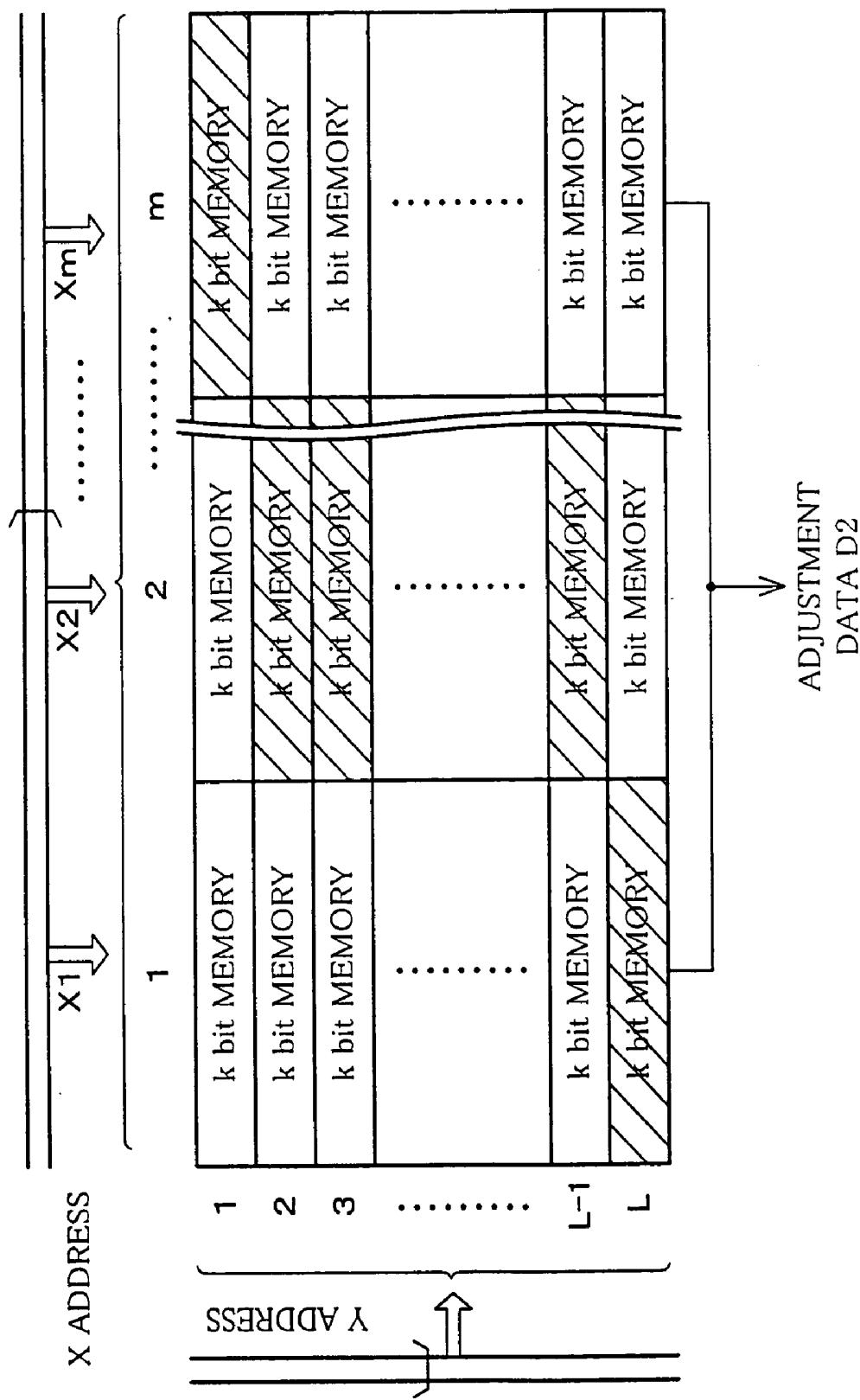

[0087] FIG. 40 illustrates a structure of a display memory provided in the liquid crystal display device of the embodiment of the present invention.

[0088] FIG. 41 is a timing chart showing how the display memory shown in FIG. 40 operates.

[0089] FIG. 42(a) illustrates a direction in which a liquid crystal molecule is aligned in a front side of the liquid crystal panel and a direction in which the liquid crystal molecule is aligned in a rear side of the liquid crystal panel, FIG. 42(b) illustrates a condition under which the liquid crystal molecule is aligned when viewed from an upper direction upon setting the alignment directions as shown in FIG. 42(a), and FIG. 42(c) illustrates a condition under which the liquid crystal molecule is aligned when viewed from a right-and-left direction upon setting the alignment directions as shown in FIG. 42(a), and FIG. 42(d) illustrates a condition under which the liquid crystal molecule is aligned when viewed from an up-and-down direction upon setting the alignment directions as shown in FIG. 42(a).

[0090] FIG. 43 is a graph showing a relationship between a voltage applied to the liquid crystal and luminance in the case where the liquid crystal panel is viewed from a front direction and from an up-and-down direction upon setting the alignment directions as shown in FIG. 42(a).

#### DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0091] [Embodiment 1]

[0092] The following description will explain one embodiment of the present invention with reference to the drawings.

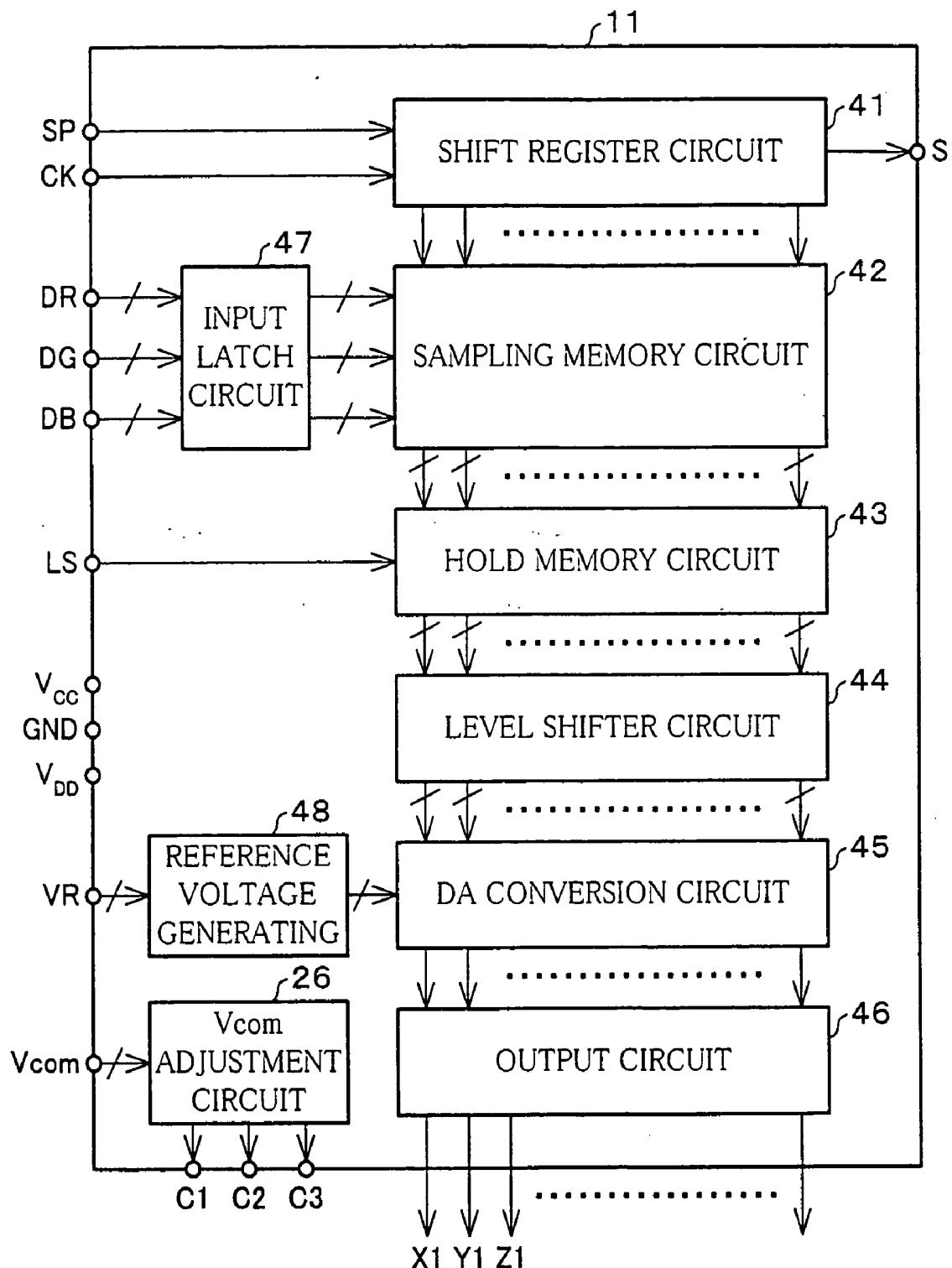

[0093] FIG. 2 is a block diagram showing a structure of a liquid crystal display device (TFT liquid crystal module) of the present embodiment.

[0094] The liquid crystal display device 1 is constituted of a liquid crystal display section for displaying an image and a liquid crystal driving section (liquid crystal driving circuit) for driving the liquid crystal display section in terms of a function. The liquid crystal display section includes a TFT-system liquid crystal panel 8. The liquid crystal panel 8 has a liquid crystal display element (not shown) and one or more counter electrodes 7 described later.

[0095] The liquid crystal driving circuit includes a source driver (signal line driving means) 2, a gate driver (scanning line driving means) 3, a controller 4, and a liquid crystal driving power source 5. The source driver 2 has a plurality of source driver sections 11 each of which is constituted of an IC (Integrated Circuit), that is, first to n-th source drivers. Likewise, the gate driver 3 includes a plurality of gate driver sections 12 each of which is constituted of an IC, that is, first to m-th gate drivers.

[0096] Each of the source driver 2 and the gate driver 3 is generally constituted, for example, of a TCP (Tape Carrier

Package) in which the IC chip is provided on a film having wirings. The TCP is provided on an ITO (Indium Tin Oxide) terminal of the liquid crystal panel 8 so as to be connected to the liquid crystal panel 8. Alternatively, the IC chip is provided directly on the ITO terminal of the liquid crystal panel 8 via an ACF (Anisotropic Conductive Film) in accordance with thermal pressure so as to be connected to the liquid crystal panel 8.

[0097] The controller 4 inputs display data D and a control signal (start pulse SP or the like) to the source driver 2, and inputs a vertical synchronization signal VS to the gate driver 3. Further, the controller 4 inputs a horizontal synchronization signal LS to the source driver 2 and the gate driver 3.

[0098] FIG. 3 shows a structure of the liquid crystal panel 8. The liquid crystal panel 8 includes a pixel electrode 21, a pixel capacitor 22, a TFT 23 for controlling whether or not to apply a voltage to a pixel electrode 21, a source line (signal line) 24, a gate line (scanning line) 25, and the counter electrode 7 (common electrode). Here, the pixel electrode 21, the pixel capacitor 22, and the TFT 23 constitute a liquid crystal display element A corresponding to a single pixel.

[0099] As shown in FIG. 1, the counter electrodes 7 are sequentially allocated to one or e gate lines 25 (e is a positive integer) as each group. Alternatively, the counter electrodes 7 are allocated to a plurality of gate lines 25 adjacent to each other as each group. A Vcom adjustment circuit (common electrode voltage supplying means) provided in the source driver 2 supplies counter electrode voltages C respectively to the counter electrodes 7 of each group.

[0100] For example, in a case where all the counter electrodes 7 of the liquid crystal panel 8 are divided into a first group 7(A), a second group 7(B), and a third group 7(C), the Vcom adjustment circuit 26 supplies counter electrode voltages C1, C2, and C3 to the counter electrodes 7 of these first to third groups.

[0101] As to the foregoing structure, a display operation of the liquid crystal display device 1 is described as follows.

[0102] Display data inputted from the outside is inputted to the source driver 2 via the controller 4 as the display data D which is a digital signal. The source driver 2 divides the inputted display data D in terms of time so as to latch the display data D to first to n-th source drivers. Thereafter, the source driver 2 performs DA conversion in synchronism with the horizontal synchronization signal LS inputted from the controller 4. Further, an analog voltage (hereinafter, referred to as gradation display voltage) for gradation display caused by performing the DA conversion with respect to the display data D divided in terms of time is outputted via the source line 24 to a corresponding liquid crystal display element of the liquid crystal panel 8.

[0103] The source driver 2 supplies the gradation display voltage, according to brightness of a target display pixel, to the source line 24. While, the gate driver 3 supplies a scanning signal, causing TFTs 23 to sequentially turn ON in a row direction, to the gate line 25. Further, the gradation display voltage of the source line 24 is applied via the TFT 23 turned ON to the counter electrode 7 connected to the drain of the TFT 23, and is stored in the pixel capacitor 22 positioned between the counter electrode 7 and the pixel electrode 21. In this manner, optical transmittance of the

liquid crystal is varied according to the gradation display voltage so as to display an image. Further, in the present embodiment, the Vcom adjustment circuit 26 provided in the source driver supplies the counter electrode voltages C1, C2, and C3 respectively to three groups of the counter electrode 7: the first group 7(A), the second group 7(B), and the third group 7(C).

[0104] FIG. 4 and FIG. 5 show an example of a general liquid crystal driving waveform. In FIG. 4 and FIG. 5, 31 and 35 indicate a driving waveform of an output from the source driver 2, and 32 and 26 indicate a driving waveform of an output from the gate driver 3. Further, 33 and 37 indicate a potential of the counter electrode 7, and 34 and 38 indicate a voltage waveform of a voltage of the pixel electrode 21. Note that, a voltage applied to a liquid crystal layer is a potential difference between the pixel electrode 21 and the counter electrode 7, and is indicated by a shaded area in FIG. 4 and FIG. 5.

[0105] For example, in the case of FIG. 4, the TFT 23 is ON only at a period in which a level of the driving waveform 32 of the gate driver 4 is high, so that a voltage corresponding to a difference between the driving waveform 31 of the source driver 3 and the potential 33 of the counter electrode 7 is applied to the pixel electrode 21. Thereafter, a level of the driving waveform 32 of the gate driver 4 is low, so that the TFT 23 is OFF. In this case, the pixel capacitor 22 exists in the pixel, so that the aforementioned voltage is kept.

[0106] An operation indicated in FIG. 5 is substantially the same as in FIG. 4. However, FIG. 5 is different from FIG. 4 in terms of the voltage applied to the liquid crystal layer. In the case of FIG. 4, the applied voltage is higher than that of FIG. 5.

[0107] In the liquid crystal display device 1, the voltage applied to the liquid crystal layer is varied as the analog voltage in this manner, so that the optical transmittance of the liquid crystal is varied in an analog manner, thereby realizing multiple tone display.

[0108] Further, the liquid crystal display device 1 is to solve the following problem: liquid crystal is aligned asymmetrically particularly in an up-and-down direction, so that a visual angle is narrowed. In order to solve such problem, the liquid crystal display device 1 is arranged so that: as described above, the counter electrodes 7 are divided into a plurality of groups (7(A), 7(B), 7(C), . . . ), and different counter electrode voltages C1, C2, C3, are applied from the Vcom adjustment circuit 26 of the source driver 2 to the counter electrodes 7 of the groups respectively. Thus, it is possible to vary the luminance characteristic so as to obtain a most appropriate view at each angular position in viewing, so that it is possible to correct color variation caused by the difference in the angular position in viewing. Note that, in the present embodiment, "angular position in viewing" means an angle between a visual line (visual axis) and a normal line of the display image. Further, "most appropriate view" means a view which causes an image to seem uniformed in a direction of a visual line of an observer.

[0109] FIG. 6 is a block diagram showing an example of a structure of a source driver section (n-th source driver) 11 of the source driver shown in FIG. 2.

[0110] FIG. 6 shows a condition of the source driver section 11 in which the display data D (DR, DG, and DB)

required in displaying an image are inputted in a serial manner, and the display data D are temporarily latched by an input latch circuit 47. Thereafter, in the sampling memory circuit 42, the display data D that have been transmitted in a time-divisional manner are sampled in accordance with an output signal at each stage of the shift register circuit 41. Then, the sampled display data D are outputted to a corresponding hold memory circuit 43 at the next stage. S is a cascade output.

[0111] The hold memory circuit 43 corresponds respectively to the first to n-th pixels, i.e., the first to n-th source lines 24 contained in the respective rows of the liquid crystal panel 8.

[0112] The display data D inputted to the hold memory circuit 43 are latched in accordance with the horizontal synchronization signal LS. Thus, until the next horizontal synchronization signal LS is inputted, the display data D outputted from the hold memory circuit 43 are fixed.

[0113] The level shifter circuit 44 performs level conversion, such as pressurization, with respect to the display data D outputted from the hold memory circuit 43 so as to correspond to a signal processing level of a DA conversion circuit 45 positioned at the next stage, and the display data D are inputted to the DA conversion circuit 45.

[0114] A reference voltage generating circuit 48 generates a reference voltage of each level in accordance with an original voltage VR. Specifically, when a potential that should be given to the pixel is inputted from the power source circuit (not shown), the potential is internally divided so as to generate 64 types of gradation display potentials in a case of 64-gradation display for example, and the gradation display potentials are outputted to the DA conversion circuit 45. The DA conversion circuit 45 selects a single gradation display potential, corresponding to the display data D outputted from the level shifter circuit 44, out of 64 types of the gradation display potentials for each pixel, and outputs the single gradation display potential to an output circuit 46.

[0115] The output circuit 46 is a low impedance conversion section constituted of a differential amplifier and the like, and gives the gradation display potential selected by the DA conversion circuit 45 to the respective first to n-th source lines 24 of the liquid crystal panel 8. The gradation display potential is maintained in one period of the horizontal synchronization signal LS, i.e., one horizontal synchronization period, and a gradation display potential corresponding to new display data D is outputted at the next horizontal synchronization period.

[0116] While, the gate driver 3 includes a shift register circuit, a level shifter circuit, and an output circuit. In the gate driver 3, the horizontal synchronization signal LS and the vertical synchronization signal VS are inputted to the shift register circuit, and the horizontal synchronization signal LS is used as a clock so as to cause respective stages in the shift register circuit to sequentially output the vertical synchronization signals VS.

[0117] Outputs from the respective stages of the shift register circuit respectively correspond to first to m-th pixels, i.e., first to m-th gate lines 25 included in the respective rows of the liquid crystal panel 8. The outputs from the respective stages of the shift register circuit are subjected to level conversion performed by the level shifter

circuit, so that the outputs are pressurized to a voltage which can control a gate of the TFT 23 of each pixel. Further, the outputs are subjected to low impedance conversion by means of the output circuit, and are outputted from the output circuit to respective first to m-th gate lines 25 of the liquid crystal panel 8. Each of the outputs from the gate driver 3 is a scanning signal, and ON/OFF of the gate of the TFT 23 in each pixel of the liquid crystal panel 8 is controlled in accordance with the scanning signal.

[0118] Operations of the source driver section 11 of the liquid crystal display device 1 are described as follows.

[0119] Each of the display data D (DR, DB, and DG) transmitted from a controller 4 is 6 bits, and is temporarily latched by an input latch circuit 47.

[0120] The shift register circuit 41 is a circuit for shifting, that is, forwarding a start pulse signal SP from the controller 4. The start pulse signal SP is outputted from a terminal of the controller 4, and is shifted by the shift register circuit 41 in accordance with a clock signal CK.

[0121] When eight source driver sections 11 are used for example, the start pulse signal SP shifted by the shift register circuit 41 is forwarded sequentially to the shift register circuit 41 of the eighth source driver section 11 positioned at the eighth stage.

[0122] Note that, each of blocks (each of the shift register circuit 41 to the output circuit 46) is constituted of n stages so as to correspond to first to n-th source electrodes of the liquid crystal panel 8. In synchronism with outputs from each stage of the shift register circuit 41, the display data D latched by the input latch circuit 47 are temporarily stored in a corresponding stage of a sampling memory circuit 42, and is outputted to a corresponding stage of the next hold memory circuit 43.

[0123] When n-sets of display data D are inputted from the sampling memory circuit 42 in one horizontal synchronization period, the hold memory circuit 43 fetches the display data D from the sampling memory circuit 42 in accordance with the horizontal synchronization signal LS (also referred to as a latch signal) from the controller 4, so as to output the display data D to a next hold memory circuit 43. Further, the hold memory circuit maintains the display data D until a next horizontal synchronization signal LS is inputted. Operations thereafter are as described above.

[0124] Note that, the controller 4 repeatedly transmits the display data D to the input latch circuit 47. Thus, a potential corresponding to the display data D is periodically written on the liquid crystal panel 8, so that display made in the liquid crystal panel 8 is maintained.

[0125] As described later, the reference voltage generating circuit 48 generates 64 patterns of reference voltages with respect to liquid crystal driving voltage terminals of red, green, and blue, so as to generate intermediate voltages for gradation display. A voltage VR inputted to the circuit 48 is supplied from an external liquid crystal driving power source.

[0126] The DA conversion circuit 45 converts each of 6-bit display data signals (digital signals) of RGB, outputted from the hold memory circuit 43, that have been converted by the level shifter circuit 4, into an analog signal in

accordance with 64 patterns of the intermediate voltages, so as to output the display data signals to the output circuit 46.

[0127] The output circuit 46 amplifies the analog signal of 64 levels so as to output the amplified analog signal to the liquid crystal panel 8 as a gradation display voltage.

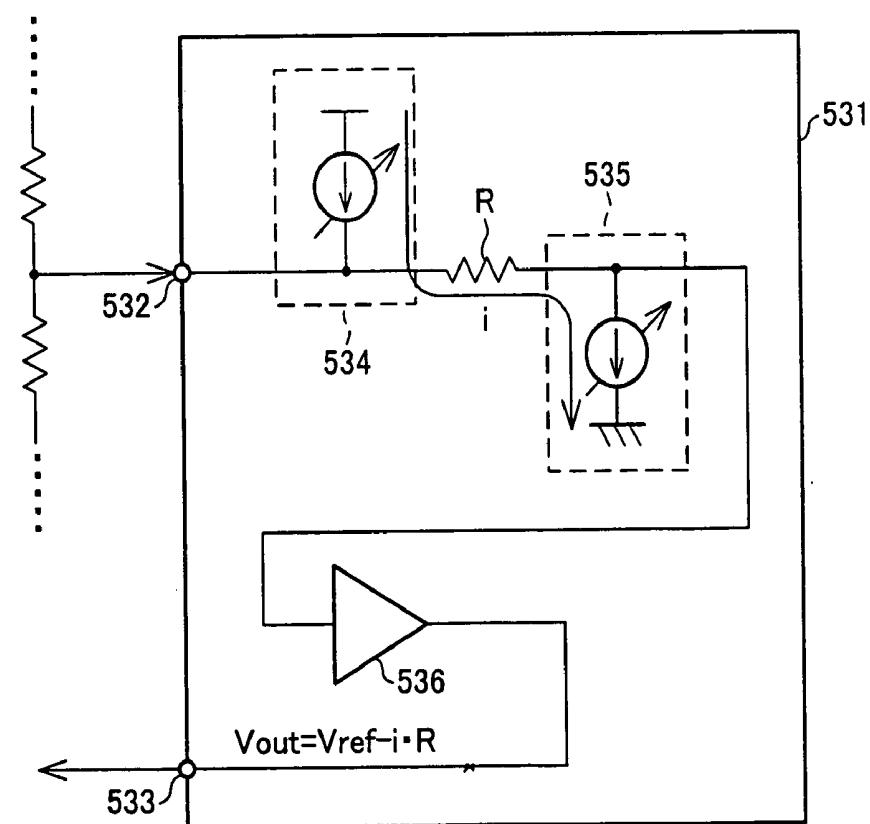

[0128] FIG. 7 is a block diagram schematically showing an example of how the Vcom adjustment circuit 26 of each source driver section 11 is arranged. The Vcom adjustment circuit 26 includes a single resistance element R for causing a voltage to drop, two constant current sources 51 and 52, and a buffer amplifier 53. Making use of the voltage drop caused by applying a current to the resistance element R, the Vcom adjustment circuit 26 shifts the inputted voltage up or down merely by a constant voltage, thereby adjusting a Vcom voltage. The Vcom adjustment circuit 26 arranged in this manner operates as follows.

[0129] To an input terminal 54 of the Vcom adjustment circuit 26, for example, a voltage Vcom (Vref) which functions as a reference voltage is supplied. Further, in a case of obtaining an output voltage higher or lower than the reference voltage Vcom (Vref), a current that the constant current sources 51 and 52 cause to flow to the resistance element R is varied. Making use of the voltage drop caused by the resistance element R, the output terminal 55 outputs a voltage Vout obtained by shifting the inputted voltage up or down corresponding to the voltage drop caused by the resistance element R.

[0130] That is, in the case of obtaining the output voltage Vout higher than the reference voltage Vcom (Vref), the voltage is adjusted so that  $Vout = Vref + i \cdot R$ , or in the case of obtaining the output voltage Vout lower than the reference voltage Vcom (Vref), the voltage is adjusted so that  $Vout = Vref - i \cdot R$ .

[0131] FIG. 8(a) and FIG. 8(b) show how a voltage the constant current sources 51 and 52 cause to flow in the resistance element R varies in the case of obtaining the output voltage Vout higher than the reference voltage Vcom (Vref) (FIG. 8(a)) and in the case of obtaining the output voltage Vout lower than the reference voltage Vcom (Vref) (FIG. 8(b)).

[0132] In this case, as shown in FIG. 8(a), the constant current source 51 positioned nearer to the input terminal 54 than the resistance element R is grounded, and the constant current source 52 positioned nearer to the output terminal 55 than the resistance element R is connected to a power source, so that the resistance element R allows a current i to flow from the constant current source 52 to the constant current source 51 in a forward direction. As a result, the output voltage Vout outputted from the output terminal 55, in the case where the reference voltage Vcom (Vref) is inputted from the input terminal 54, becomes a voltage, higher than the reference voltage Vcom (Vref) so as to correspond to the voltage drop caused by the resistance element R, which is such that  $Vout = Vref + i \cdot R$ .

[0133] While, as shown in FIG. 8(b), the constant current source 51 is connected to the power source, and the constant current source 52 is grounded, so that the resistance element R allows a current i to flow from the constant current source 51 to the constant current source 52 in a backward direction. As a result, the output voltage Vout outputted from the output terminal 55, in the case where the reference voltage

Vcom (Vref) is inputted from the input terminal 54, becomes a voltage, lower than the reference voltage Vcom (Vref) so as to correspond to the voltage drop caused by the resistance element R, which is such that  $Vout = Vref - i \cdot R$ .

[0134] In each Vcom adjustment circuit 26, the current value is switchable into plural values in the constant current sources 51 and 52, and the connection is switchable so as to be grounded or to be connected to the power source. Thus, by controlling the switching operations in accordance with the adjustment data (DL), it is possible to finely adjust the counter electrode voltages.

[0135] Note that, the adjustment data is inputted from the outside to a data latch circuit 56 (see FIG. 9) of the Vcom adjustment circuit 26 so as to be latched. The data latch circuit 56 may be constituted of a nonvolatile memory such as a flash memory and FRAM.

[0136] FIG. 9 shows a circuit arrangement of a constant current source section, corresponding to the constant current sources 51 and 52 of the Vcom adjustment circuit 26 (not only the constant current sources but also the resistance element R), which can switch the current value and can switch so as to be grounded or be connected to the power source.

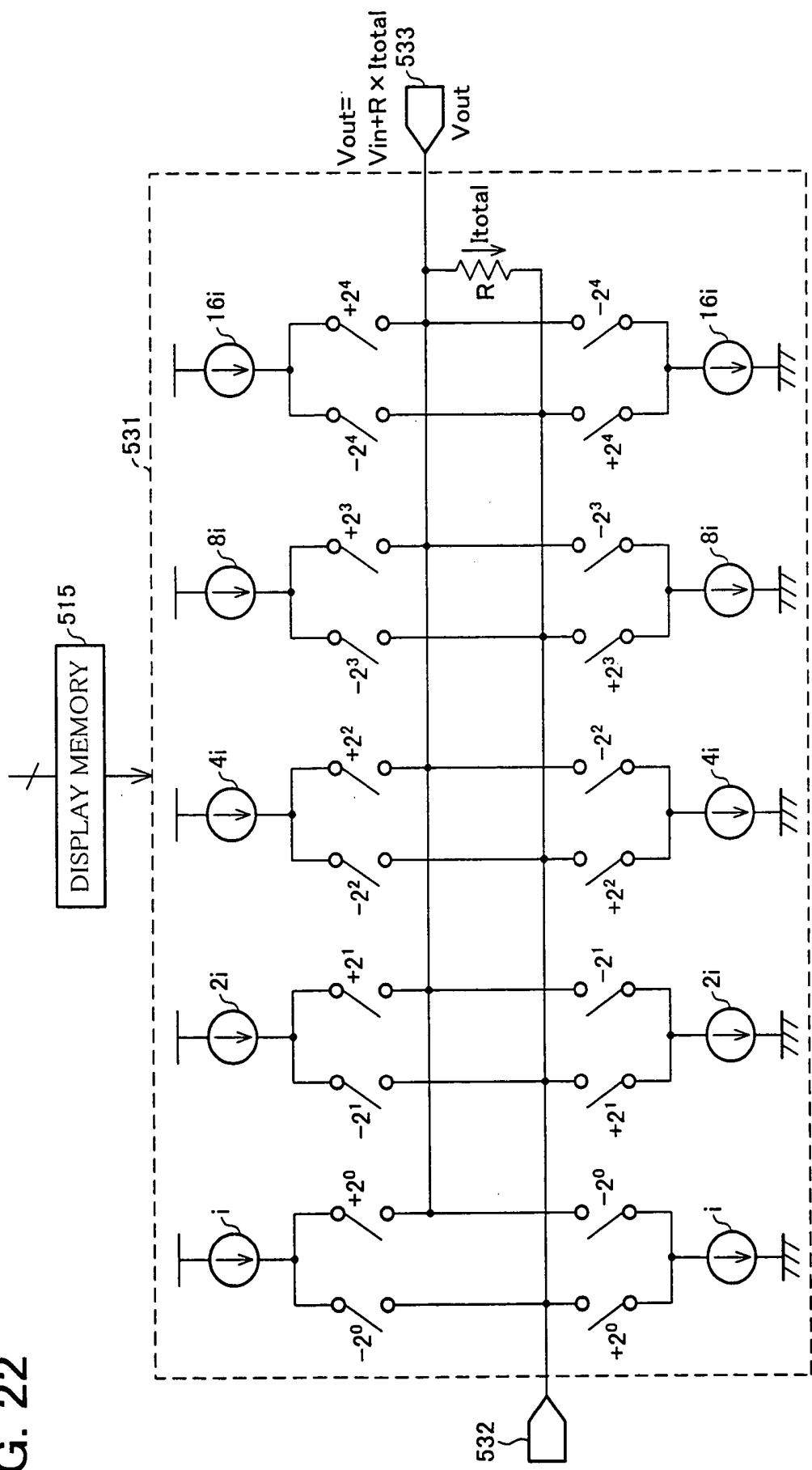

[0137] The constant current source section is connected to the power source, and includes five constant current sources  $i, 2i, 4i, 8i$ , and  $16i$ , each of which generates a current  $2^{(n-1)}i$  weighted by  $2^{(n-1)}$  where n is a positive integer. Further, each constant current source  $2^{(n-1)}i$  is connected to the one end of the resistance element R and the output terminal 55 via a switch- $+2^{(n-1)}$  which is turned ON by a control signal of  $+2^{(n-1)}$ . Further, the constant current source  $2^{(n-1)}i$  is connected to the other end of the resistance element R and the input terminal 54 via a switch- $-2^{(n-1)}$  which is turned ON by a control signal of  $-2^{(n-1)}$ .

[0138] Further, the constant current source is grounded, likewise, and includes five constant current sources  $i, 2i, 4i, 8i$ , and  $16i$ , each of which generates a current  $2^{(n-1)}i$  weighted by  $2^{(n-1)}$  where n is a positive integer. Further, each constant current source  $2^{(n-1)}i$  is connected to the other end of the resistance element R and the input terminal 54 via the switch- $+2^{(n-1)}$  which is turned ON by the control signal of  $+2^{(n-1)}$ . Further, the constant current source  $2^{(n-1)}i$  is connected to the one end of the resistance element R and the output terminal 55 via the switch- $-2^{(n-1)}$  which is turned ON by a control signal of  $-2^{(n-1)}$ .

[0139] That is, in the constant current source section, the constant current source  $2^{(n-1)}i$  which is connected to the input terminal 54 via the switch  $+2^{(n-1)}$  or the switch  $-2^{(n-1)}$  functions as the constant current source 51 of FIG. 8(a) and FIG. 8(b), and the constant current source  $2^{(n-1)}i$  which is connected to the output terminal 55 via the switch  $+2^{(n-1)}$  or the switch  $-2^{(n-1)}$  functions as the constant current source 52 of FIG. 8(a) and FIG. 8(b). Further, in accordance with the adjustment data, i.e., multi-bit digital data of signed binary, latched by the data latch circuit 56, which is expressed in terms of a complementary expression based on 2, ON/OFF of each switch  $+2^{(n-1)}$  and ON/OFF of each switch  $-2^{(n-1)}$  are controlled, so that it is possible to switch the voltage value concerning the constant current sources 51 and 52, and to switch the connection of constant current sources 51 and 52 so as to be connected to the power source or be grounded.

[0140] According to the foregoing arrangement, it is possible to vary a value and a direction of the current flowing in the resistance element R, so that it is possible to output the voltage Vout obtained by shifting the input voltage Vin up or down by several stages so as to correspond to the drop of the voltage flowing in the resistance element R. This function is exemplified as follows.

[0141] The following description will be made on the assumption that the adjustment data (DL) is 6-bit data. In accordance with the adjustment data indicated by 6 bits in this manner, it is possible to perform adjustment with 64 levels ranging from -32 to +31 levels.

[0142] In FIG. 9, the constant current sources i, 2i, 4i, 8i, and 16i respectively generate the current values i, 2i, 4i, 8i, and 16i, each of which is weighted by  $2^{(n-1)}$ . Further, the switch  $+2^{(n-1)}$  and the switch  $-2^{(n-1)}$  are turned ON/OFF in accordance with the adjustment data (DL). The following description will explain how the Vcom adjustment circuit 26 operates on the basis of the 6-bit adjustment data.

[0143] A case where the adjustment data (DL) is "+1;(000001)" is described as a first case. In this case, merely two switches  $+2^0$  are turned ON, and all the other switches are turned OFF. This condition is shown in FIG. 8(a).

[0144] That is, a current "I total" which flows to the resistance element R is the same as in the constant current source i, and flows in a forward direction. Thus, the output voltage Vout becomes higher than the inputted reference voltage Vin so as to correspond to the voltage drop caused by the resistance element R, so that it is possible to obtain such an output voltage that  $Vout=Vin+i\times R$ . This is a voltage higher than the inputted reference voltage Vin by  $(i\times R)$ .

[0145] Further, a case where the adjustment data (DL) is "-9;(101001)"—is described as another case. In this case, four switches: two switches  $-2^3$  and two switches  $-2^0$  are turned ON, and all the other switches are turned OFF. This condition is shown in FIG. 8(b).

[0146] That is, a current "I total" which flows to the resistance element R becomes  $9i$  which is a total of (i) a current of the constant current source i and (ii) a current of the constant current source  $8i$ , and flows in a backward direction. Thus, the output voltage Vout becomes lower than the inputted reference voltage Vin so as to correspond to the voltage drop caused by the resistance element R, so that it is possible to obtain such an output voltage that  $Vout=Vin-9i\times R$ . This is a voltage lower than the input reference voltage Vin by 9 times of  $(i\times R)$ .

[0147] That is, by using multi-bit digital data of signed binary expressed in terms of a complementary expression based on 2 as the adjustment data, it is possible to cause (i) a bit number n and (ii) a weight (scale factor)  $2^{(n-1)}$  of a value of a current flowing to the resistance element R to correspond to each other via the switches  $+2^{(n-1)}$  and  $-2^{(n-1)}$ . Thus, it is possible to obtain an adjustment amount whose scale factor corresponds to the adjustment data (DL). That is, it is possible to easily designate the adjustment amount of the reference value in accordance with the adjustment data (DL).

[0148] Further, the liquid crystal display device 1 of the present embodiment solves such a problem that: liquid

crystal is aligned so asymmetrically particularly in an up-and-down direction in the liquid crystal panel, so that a view angle is narrowed. Thus, in the liquid crystal display device 1, the counter electrodes 7 are divided into a plurality of groups, and the counter electrode voltages C1, C2, C3, ... outputted by the Vcom adjustment circuit 26 provided in the source driver are applied to arbitrary lines of the counter electrodes 7. Thus, it is possible to vary a luminance characteristic so as to obtain a most appropriate view at each angular position in viewing, so that it is possible to correct color variation caused by difference in the angular position in viewing.

[0149] FIG. 10 and FIG. 11 show an example of a liquid crystal driving waveform. In FIG. 10 and FIG. 11, as in the case shown in FIG. 4 and FIG. 5, each of 31 and 35 is a driving waveform of an output from the source driver 2, and each of 32 and 36 is a driving waveform of an output from the gate driver 3.

[0150] Further, each of 61 and 62 is a polarity driving potential (counter electrode voltage C) applied to the counter electrode 7, and the counter electrode voltages C1 to C3 outputted from the Vcom adjustment circuit 26 are applied to the counter electrodes 7 of three groups: the first group 7(A) to the third group 7(C). That is, the counter electrode voltage C1 is applied to the counter electrodes 7 of the first group 7(A), and the counter electrode voltage C2 is applied to the counter electrodes 7 of the second group 7(B), and the counter electrode voltage C3 is applied to the counter electrodes 7 of the third group 7(C).

[0151] The counter electrode voltage C2 (Vref) which functions as a standard voltage is applied to the second group 7(B). Further, as to the counter electrode voltage C1 applied to the first group 7(A) and the counter electrode voltage C3 applied to the third group 7(C), the one is set to be higher than the counter electrode voltage C2 (Vref) which functions as a standard voltage, and the other is set to be lower than the counter electrode voltage C2. Thus, in the up-and-down direction with respect to the liquid crystal panel 8, it is possible to widely vary the view angle characteristic. Note that, each of the counter electrode driving potentials 61 and 62 shown in FIG. 10 and FIG. 11 is described as a potential having a predetermined width so as to correspond to the counter electrode voltages C1 to C3.

[0152] Here, the following description explains comparison between the aforementioned case of the liquid crystal driving waveform shown in FIG. 4 and the aforementioned case of the liquid crystal driving waveform shown in FIG. 10 for example.

[0153] In the case of the liquid crystal driving waveform shown in FIG. 4, the TFT 23 is ON merely at a period in which a level of the driving waveform 32 of the gate driver 4 is high, so that a voltage difference between the driving waveform 31 of the source driver 3 and the potential 33 of the counter electrode 7 is applied to the pixel electrode 21. Thereafter, a level of the driving waveform 32 of the gate driver 4 becomes low, so that the TFT 23 is turned OFF. In this case, the pixel capacitor 22 exists in the pixel, so that the foregoing voltage is maintained.

[0154] In the case of the liquid crystal driving waveform shown in FIG. 10, basic operations such as ON/OFF of the TFT 23 are the same. However, the same potential is not

given to all the counter electrodes 7, but different potentials are applied to different groups of the counter electrode 7 for example, so that the case of **FIG. 10** is different from the case of **FIG. 4** in terms of a display condition of the liquid crystal panel 8.

**[0155]** **FIG. 12** shows an example of a condition of a potential in each pixel dot in the case where different counter electrode voltages C1 to C3 are applied from the Vcom adjustment circuit 26 to the counter electrodes 7 of the first group 7(A) to the third group 7(C).

**[0156]** In **FIG. 12**, the counter electrode voltage C2 which functions as a standard voltage is supplied to the pixel dots that are not positioned in a shaded area (pixel dots exist in four rows between an uppermost row and a lowermost row in **FIG. 12**), and the counter electrode voltages C1 and C3 that are different from the counter electrode voltage C2 are supplied to pixel dots that are positioned in the shaded area (pixel dots positioned in the uppermost row and the lowermost row in **FIG. 12**). Note that, + and - in **FIG. 12** show that the polarities of the voltages applied to the pixel dots are inverted by a dot inversion process. Further, a single square represents a single pixel dot.

**[0157]** Further, **FIG. 13** shows an example of the pixel dots corresponding to two sequential frames (frame n, frame n+1) in the driving condition of **FIG. 12**, and shows a case where the counter electrode voltage C is varied for each frame.

**[0158]** The liquid crystal display device 1 is controlled so that the counter electrode voltage C is varied for each group of the counter electrodes 7 as described above, so that it is possible to display an image which can be appropriately viewed at a wide visual angle in the up-and-down direction with respect to the liquid crystal panel 8.

**[0159]** In the foregoing example, two types of counter electrode voltages C whose potentials are different from that of the counter electrode voltage C functioning as a standard voltage are applied to arbitrary lines of the counter electrodes 7 within one frame, so that the visual angle is widened in the up-and-down direction with respect to the liquid crystal panel 8. However, it may be so arranged that three or more types of counter electrode voltages C are applied to arbitrary lines of the counter electrodes 7 with a single counter electrode voltage C being regarded as a standard voltage.

**[0160]** Next, the following description shows an example where the arrangement of the present invention is applied to a multi-domain liquid crystal panel.

**[0161]** As shown in **FIG. 14**, in a multi-domain liquid crystal panel 108, a source line 124, a gate line 125, and a TFT 123 are disposed in the same manner as the source line 24, the gate line 25, and the TFT 23. However, the multi-domain liquid crystal panel 108 includes two pixel capacitors 122a and 122b, and a pixel electrode 121 connected to the pixel capacitors 122a and 122b is connected to a drain of the TFT 123. Note that, the pixel electrode 121, the pixel capacitors 122a and 122b, and the TFT 123 constitute a liquid crystal display element A corresponding to a single pixel.

**[0162]** The multi-domain liquid crystal panel 108 is arranged so that: in a single liquid crystal display element A,

counter electrodes are divided into (i) a counter electrode 107a corresponding to the pixel capacitor 122a and (ii) a counter electrode 107b corresponding to the pixel capacitor 122b, and these counter electrodes are respectively controlled.

**[0163]** **FIG. 15** shows an example of how the multi-domain liquid crystal panel 108 is arranged. In the multi-domain liquid crystal panel 108, as in the liquid crystal panel 8, the counter electrodes 107a and 107b are sequentially grouped for one or e gate lines 125 (e is a positive integer). Alternatively, the counter electrodes 107a and 107b are grouped for a plurality of gate lines 125 adjacent to each other. Here, as in the case of the liquid crystal panel 8, the counter electrodes 107a and 107b are divided into a first group 107(A), a second group 107(B), and a third group 107(C) for example.

**[0164]** Further, the multi-domain liquid crystal panel 108 includes a source driver 102 corresponding to the source driver 2 and a gate driver 103 corresponding to the gate driver 3, and the source driver 102 has a Vcom adjustment circuit 126. The Vcom adjustment circuit 126 is arranged so as to correspond to the Vcom adjustment circuit 26, and can output at least counter electrode voltages C1 to C4. The Vcom adjustment circuit 126 can adjust values of the outputted counter electrode voltages C1 to C4 as in the Vcom adjustment circuit 26.

**[0165]** In the multi-domain liquid crystal panel 108, the counter electrode voltage C1 is supplied from the Vcom adjustment circuit 126 so as to be shared by the counter electrodes 107a of the respective groups. Further, the Vcom adjustment circuit 126 supplies the counter electrode voltage C2 to the counter electrode 107b of the first group 107(A), and supplies the counter electrode voltage C3 to the counter electrode 107b of the second group 107(B), and supplies the counter electrode voltage C4 to the counter electrode 107b of the third group 107(C).

**[0166]** In this manner, the multi-domain liquid crystal panel 108 is arranged so that the counter electrode voltages C applied to the counter electrodes 107b are respectively controlled. Thus, as in the liquid crystal panel 8, it is possible to widen the visual angle in the up-and-down direction with respect to the multi-domain liquid crystal panel 108.

**[0167]** **FIG. 16** shows a multi-domain liquid crystal panel 208 arranged so that: the counter electrodes 107a and 107b are sequentially grouped for one or e gate lines 125 (e is a positive integer), and the counter electrode voltages C applied to the counter electrode 107a and the counter electrodes 107b are respectively controlled for each group.

**[0168]** In this case, a Vcom adjustment circuit 226 of a source driver 202 is arranged so as to correspond to the Vcom adjustment circuit 26, and can output at least counter electrode voltages C1 to C6. The Vcom adjustment circuit 226 can adjust values of the counter electrode voltages C1 to C6.

**[0169]** In the multi-domain liquid crystal panel 208, the counter electrodes 107a and 107b are divided into a first group 207(A), a second group 207(B), and a third group 207(C) for example. In the multi-domain liquid crystal panel 208, the Vcom adjustment circuit 226 supplies the counter electrode voltage C3 to the counter electrode 107a of the first group 207(A), and supplies the counter electrode volt-

age C2 to the counter electrode **107a** of the second group **207(B)**, and supplies the counter electrode voltage C1 to the counter electrode **107a** of the third group **207(C)**. Further, the Vcom adjustment circuit **226** supplies the counter electrode voltage C4 to the counter electrode **107b** of the first group **207(A)**, and supplies the counter electrode voltage C5 to the counter electrode **107b** of the second group **207(B)**, and supplies the counter electrode voltage C6 to the counter electrode **107b** of the third group **207(C)**.

[0170] In this manner, the multi-domain liquid crystal panel **208** is arranged so that the counter electrode voltages C applied to the counter electrodes **107a** and **107b** are respectively controlled for each group. Thus, as in the liquid crystal panel **8**, it is possible to widen the visual angle in the up-and-down direction with respect to the multi-domain liquid crystal panel **208**.

[0171] [Embodiment 2]

[0172] The following description will explain another embodiment of the present invention with reference to drawings.

[0173] FIG. 17 is a block diagram showing a structure of a liquid crystal display device (TFT liquid crystal module) **501** of the present embodiment. Note that, FIG. 17 shows merely main components and signal paths, and does not show a power source circuit and paths of partial signals such as a clock signal, a reset signal, and a selection signal.

[0174] The liquid crystal display device **501** includes a liquid crystal panel **510** (having a counter electrode **7**), a source driver **512**, a gate driver **513**, and an MPU (micro processor unit) **514** which functions as a control circuit.

[0175] The liquid crystal panel **510** includes a TFT-type pixel in which n source lines **24** and m gate lines **25** are formed so that (horizontal direction n pixels)×(vertical direction m pixels).

[0176] Note that, a single line in which pixels are disposed in a horizontal direction is referred to as "column", and a single line in which pixels are disposed in a vertical direction is referred to as "row". Here, n=1028×RGB and m=900, and an image based on 64 gradation (6 bits) ranging from 0 gradation to 63 gradation is displayed in each pixel. Note that, in each column, pixels respectively displaying colors of R (red), G (green), and B (blue) are repeatedly disposed.

[0177] The liquid crystal panel **510** is arranged as shown in FIG. 3 for example, and the counter electrodes **7** are sequentially grouped for one or e gate lines **25** (e is a positive integer)(groups: a first group **7(A)**, a second group **7(B)**, and a third group **7(C)**) as described above.

[0178] In this case, the Vcom adjustment circuit **517** is arranged so as to correspond to the Vcom adjustment circuit **26**. The Vcom adjustment circuit **517** supplies counter electrode voltages C respectively to the counter electrodes **7** of the groups. That is, as shown in FIG. 1, the counter electrode voltage C1 is supplied to the first group **7(A)**, and the counter electrode voltage C2 is supplied to the second group **7(B)**, and the counter electrode voltage C3 is supplied to the third group **7(C)**. Thus, it is possible to widen the visual angle in the up-and-down direction with respect to the liquid crystal panel **510** as in the foregoing arrangements.

[0179] Further, the liquid crystal panel **510** may be arranged in the same manner as in the multi-domain liquid

crystal panel **108** shown in FIG. 14 and FIG. 15. In this case, the Vcom adjustment circuit **517** is arranged so as to correspond to the Vcom adjustment circuit **126**.

[0180] In such arrangement, as in the multi-domain liquid crystal panel **108**, the counter electrodes **107a** and **107b** are divided into a first group **107(A)**, a second group **107(B)**, and a third group **107(C)**, and the Vcom adjustment circuit **517** supplies the counter electrode voltage C3 so as to be shared by the counter electrodes **107a** of the respective groups. Further, the Vcom adjustment circuit **517** supplies the counter electrode voltage C4 to the counter electrode **107b** of the first group **107(A)**, and supplies the counter electrode voltage C5 to the counter electrode **107b** of the second group **107(B)**, and supplies the counter electrode voltage C6 to the counter electrode **107b** of the third group **107(C)**. Thus, it is possible to widen the visual angle in the up-and-down direction with respect to the liquid crystal panel **510** as in the foregoing arrangements.

[0181] Further, the liquid crystal panel **510** may be arranged in the same manner as in the multi-domain liquid crystal panel **208**. In this case, the Vcom adjustment circuit **517** is arranged so as to correspond to the Vcom adjustment circuit **226**.